System and Method for Efficiently Passing Information Between Compiler and Post-Compile-Time Software

a compiler and information technology, applied in the field of program optimization, can solve the problems that the execution of software programs optimized for an old computer architecture will not generally run as quickly on a computer system with a new architecture, face the challenge of analyzing low-level programs, etc., and achieve the effect of efficiently passing compiler information, and eliminating time overhead for analysis

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Reference will now be made in detail to the description of the invention as illustrated in the drawings. Although the invention will be described in connection with these drawings, there is no intent to limit it to the embodiment or embodiments disclosed therein. On the contrary, the intent is to include all alternatives, modifications, and equivalents included within the scope of the invention as defined by the appended claims.

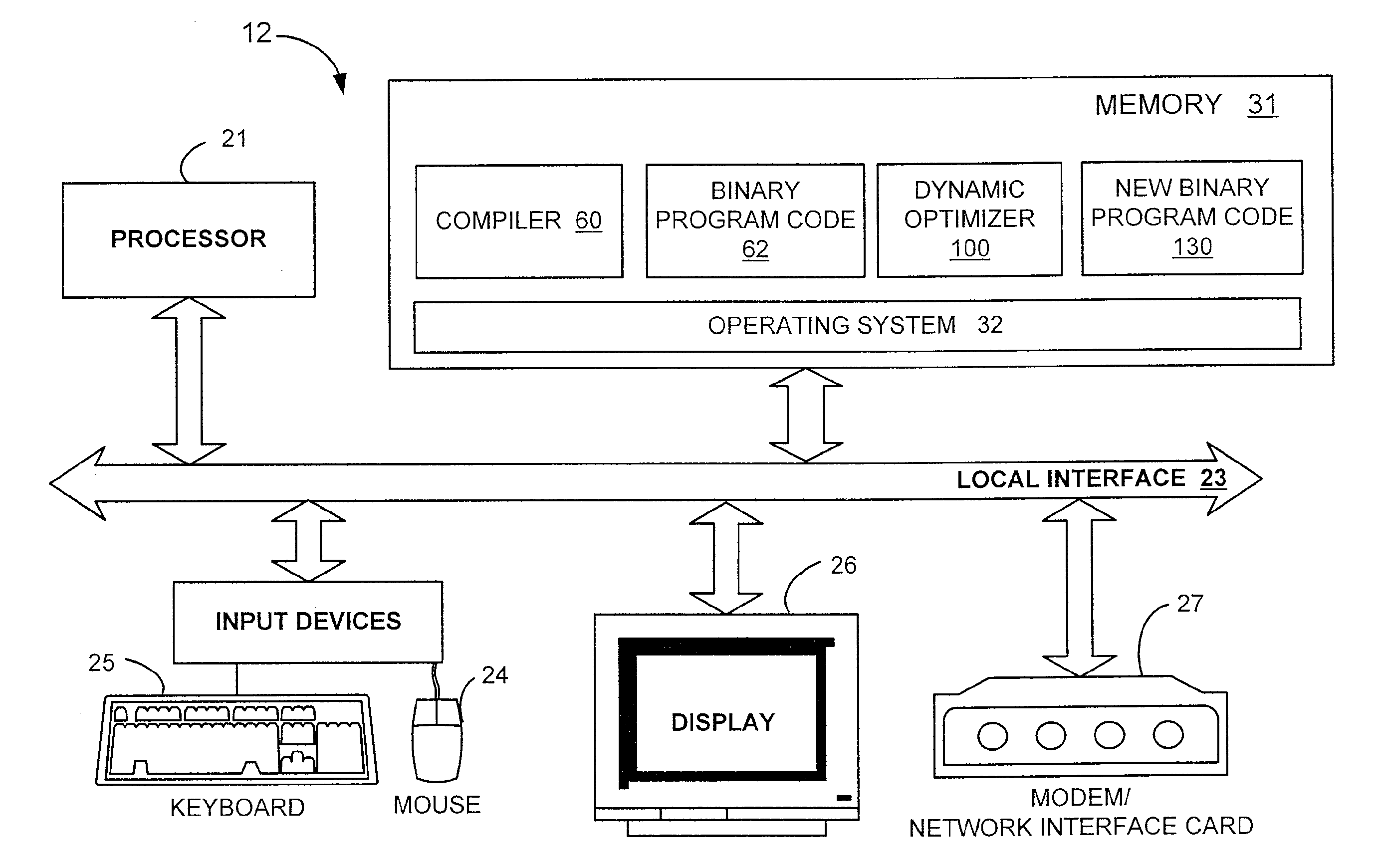

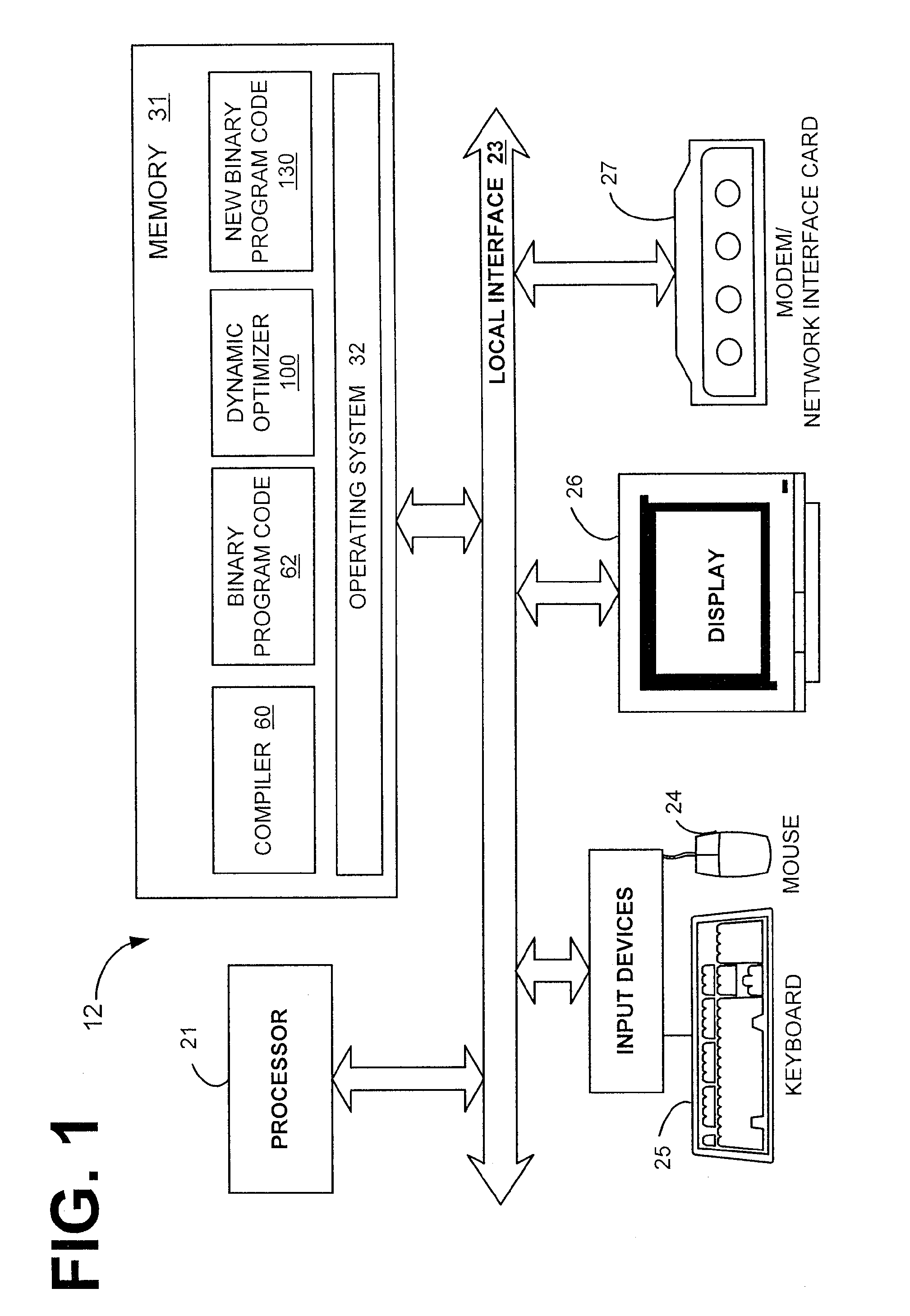

[0030] As illustrated in FIG. 1A, computer system 12 today generally comprises a processor 21 and memory 31 (e.g., RAM, ROM, hard disk, CD-ROM, etc.) including an operating system 32. The processor 21 accepts binary program code 62 and data from the memory 31 over the local interface 23, for example, a bus(es). Direction from the user can be signaled by using input devices, for example but not limited to, a mouse 24 and a keyboard 25. The actions input and result output are displayed on the display terminal 26.

[0031] Also shown is the compiler 60, bi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More