Instruction processing method of network processor and network processor

A network processor and instruction technology, applied in the direction of electrical digital data processing, address formation of the next instruction, instruments, etc., can solve the problems of reducing the performance of the main line process and prolonging the instruction execution cycle, so as to save the execution cycle, reduce the impact, easy-to-achieve effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

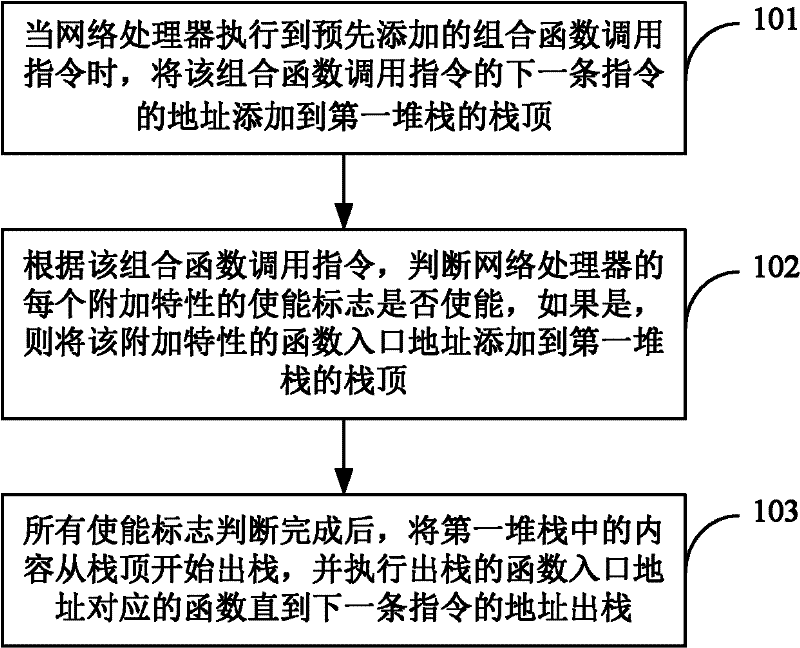

[0026] see figure 1 , this embodiment provides a network processor instruction processing method, including:

[0027] 101: When the network processor executes the pre-added combination function call instruction, add the address of the next instruction of the combination function call instruction to the stack top of the first stack; wherein, the first stack is preset for combination stack of function calls;

[0028] 102: Determine whether the enable flag of each additional feature of the network processor is enabled according to the combined function call instruction, and if the enable flag of the additional feature is enabled, add the function entry address corresponding to the additional feature to the top of the first stack;

[0029] 103: After the judgment of the enable flags of all additional features is completed, the function entry address added to the first stack is popped from the top of the stack, and the function corresponding to the popped function entry address i...

Embodiment 2

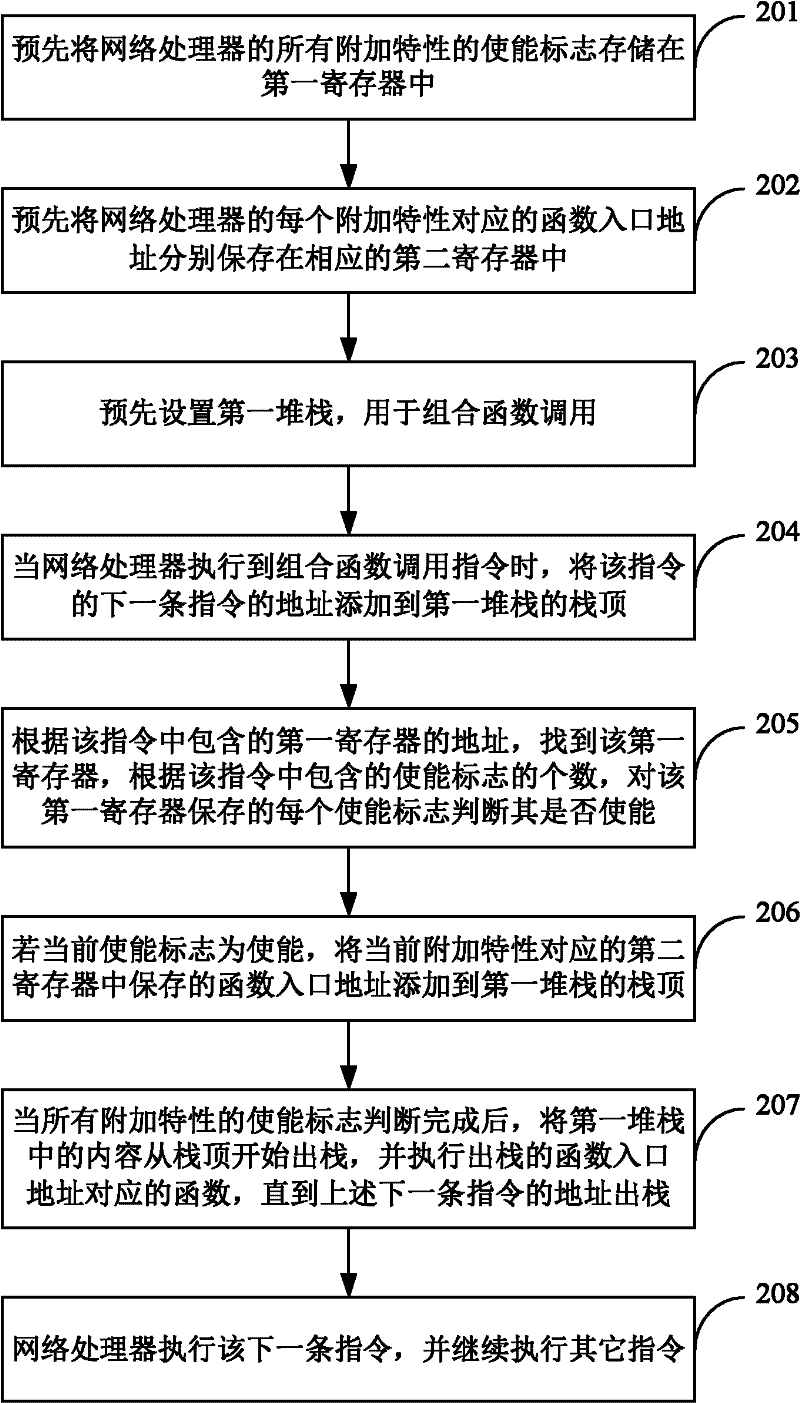

[0032] see figure 2 , this embodiment provides a network processor instruction processing method, including:

[0033] 201: Store enable flags of all additional features of the network processor in the first register in advance.

[0034] In this embodiment, there may be one or more additional features of the network processor, and generally there are more than one. When there are multiple additional features, they may be all enabled, partially enabled, or not enabled at all, which is not specifically limited in this embodiment of the present invention.

[0035]The enable flag of the additional feature is usually a 1-bit flag with two value ranges, representing enable and disable respectively. For example, when the value is 1, it means enabled, and when the value is 0, it means disabled. The embodiment of the present invention does not limit the specific value of the enable flag.

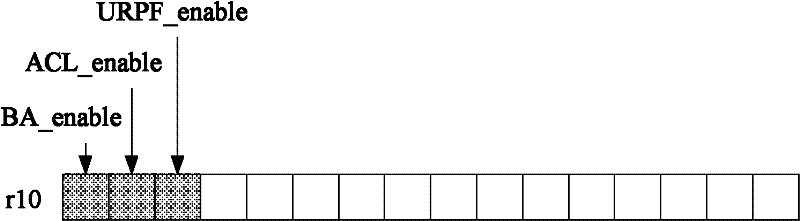

[0036] The first register in this embodiment may be a general-purpose register with a length ...

Embodiment 3

[0064] see Figure 7 , this embodiment provides a network processor, including:

[0065]The first processing module 701 is used to add the address of the next instruction of the combined function call instruction to the stack top of the first stack when the network processor executes the pre-added combined function call instruction; according to the combined function call instruction, judge Whether the enable flag of each additional feature of the network processor is enabled, if the enable flag corresponding to the additional feature is enabled, the function entry address corresponding to the additional feature is added to the stack top of the first stack; wherein, The first stack is a preset stack used for combining function calls;

[0066] The second processing module 702 is used to pop the function entry address added to the first stack from the top of the stack after the judgment of the enable flags of all additional features is completed, and execute the function corres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More