Patents

Literature

344 results about "Dual-ported RAM" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Dual-ported RAM (DPRAM) is a type of random-access memory that allows multiple reads or writes to occur at the same time, or nearly the same time, unlike single-ported RAM which allows only one access at a time.

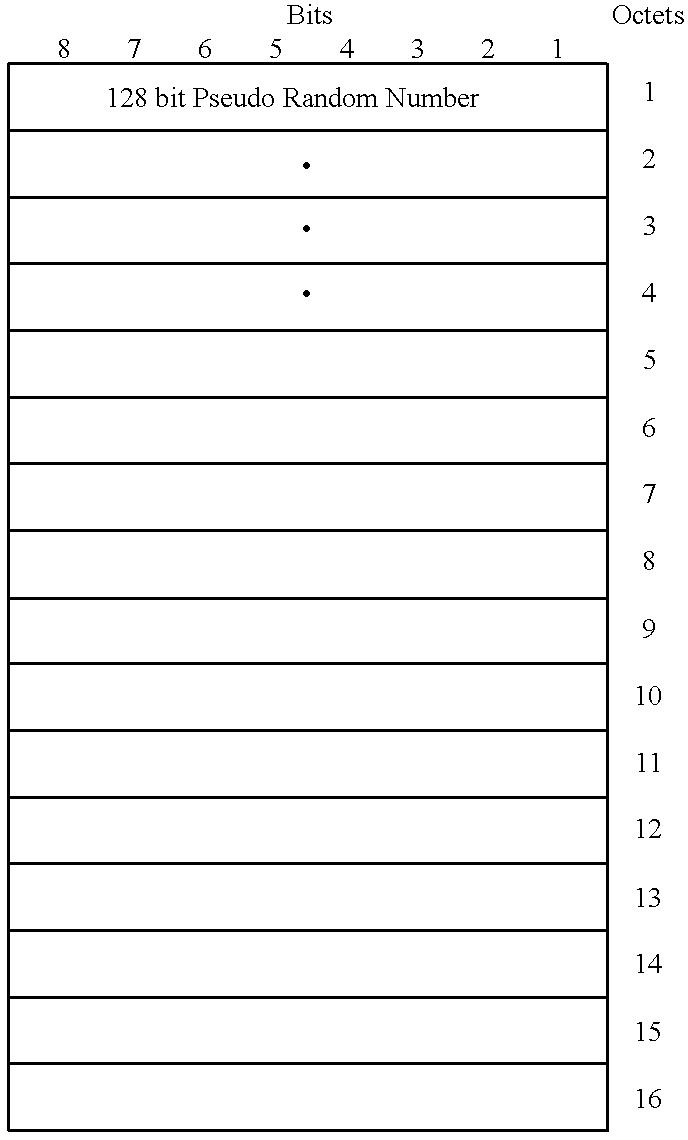

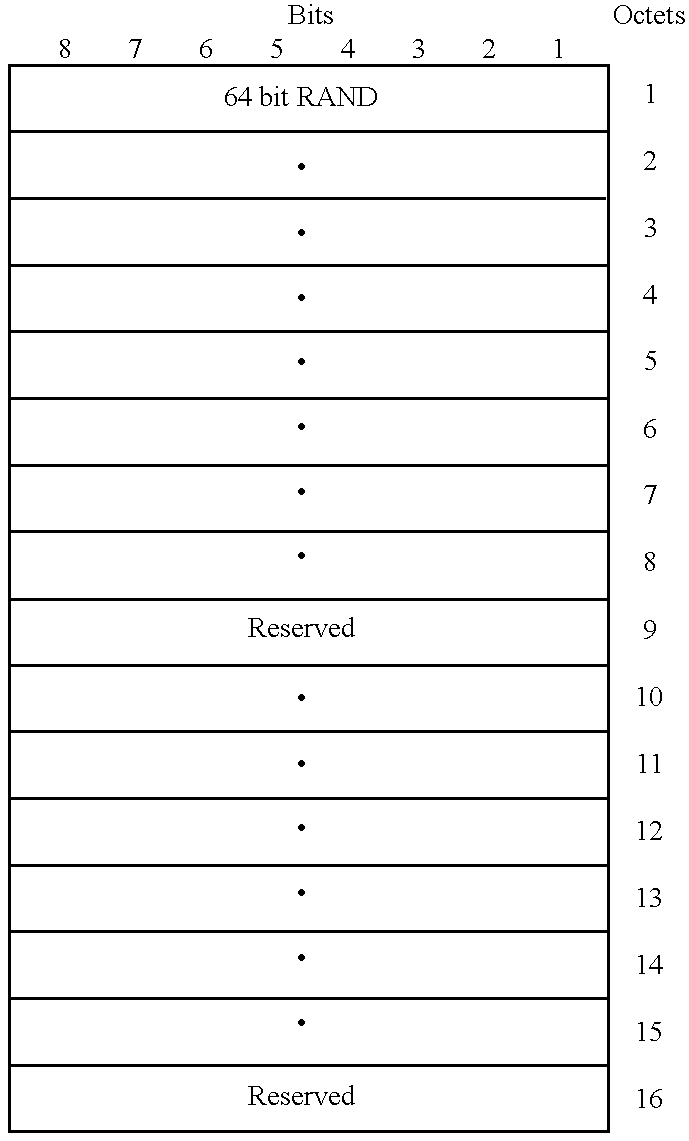

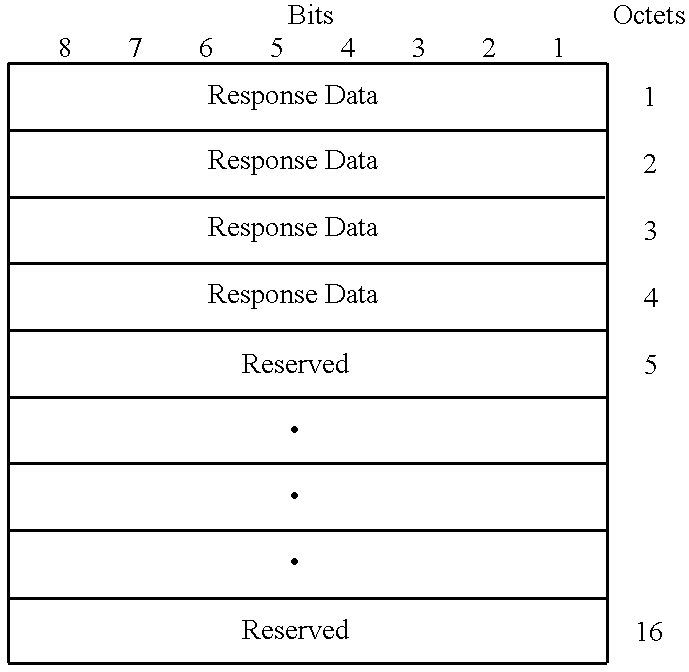

Method and system for transferring information within a mobile communication system

InactiveUS6434137B1Spatial transmit diversityError detection/prevention using signal quality detectorTransceiverCommunications system

Owner:INTEL CORP

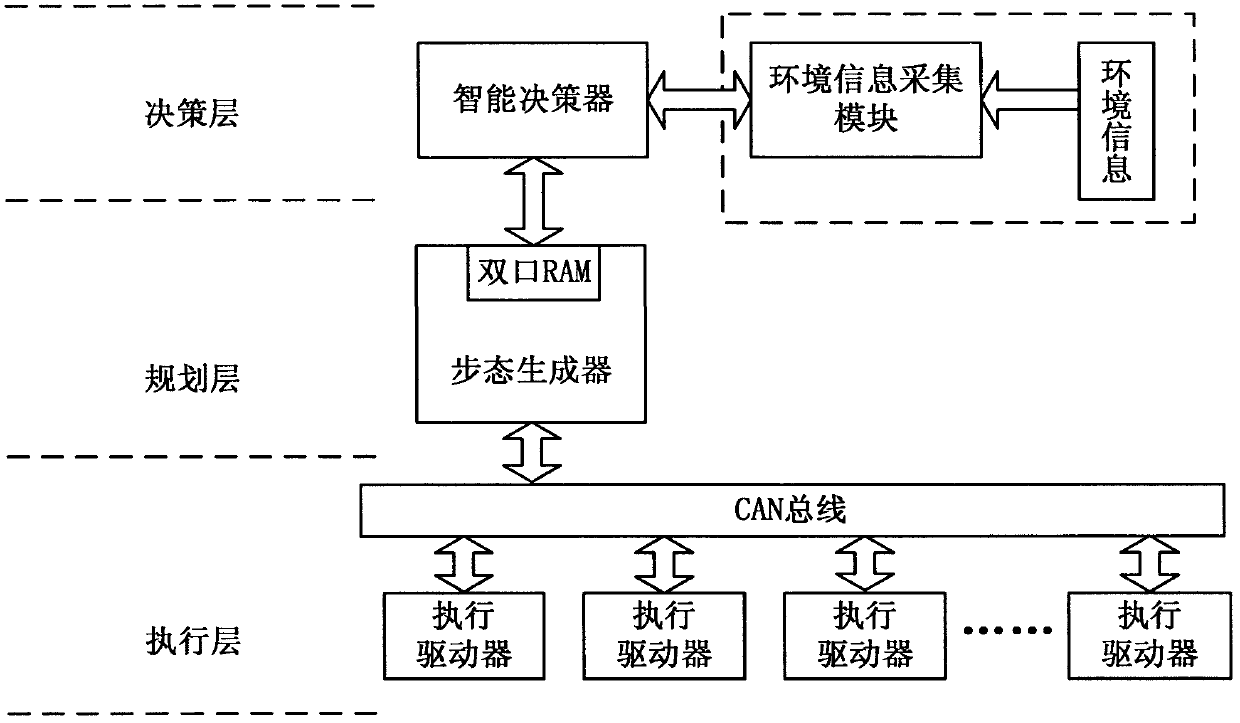

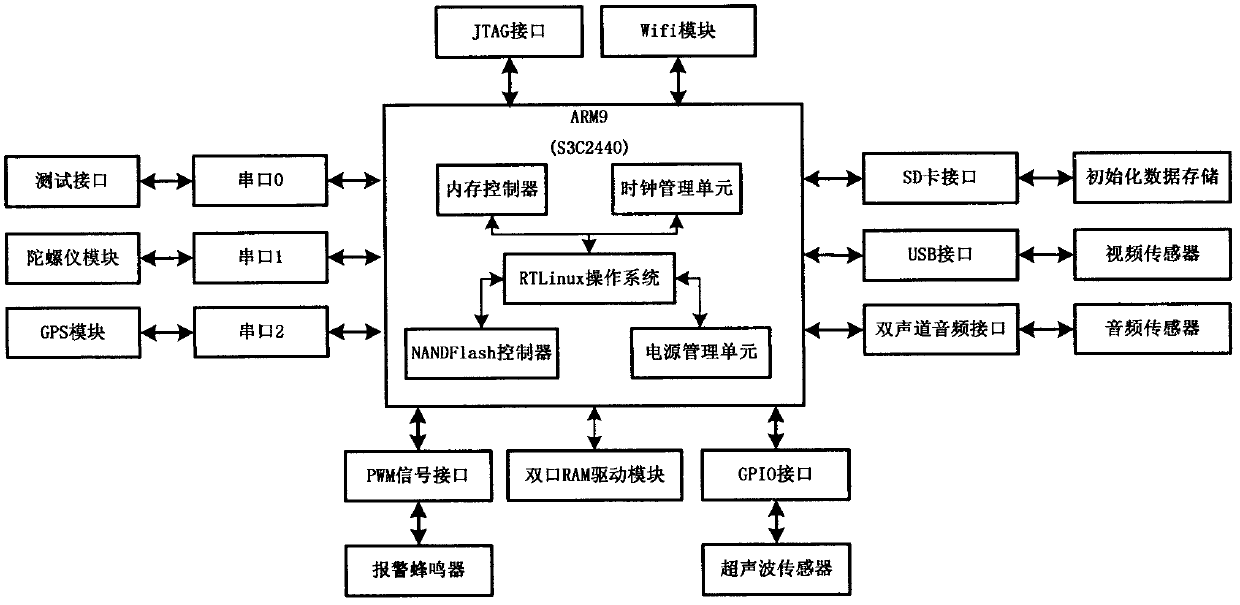

Combined type bionic quadruped robot controller

InactiveCN102637036AIntegrity guaranteedImprove adaptabilityPosition/course control in two dimensionsOperational systemNervous system

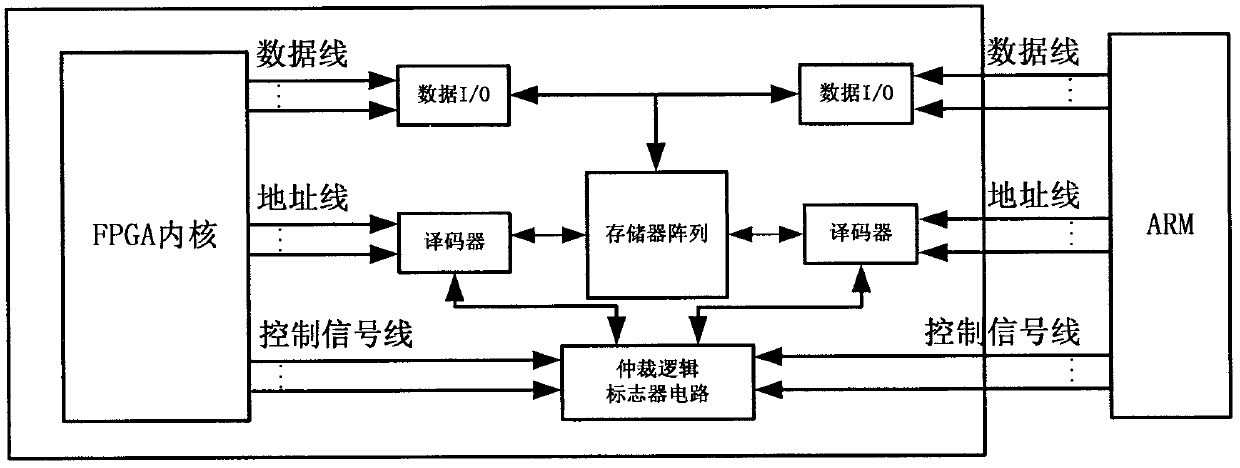

The invention relates to a combined type bionic quadruped robot controller, which is in a structure similar to a vertebrate nervous system, wherein the controller is divided into a decision layer, a planning layer and an execution layer which respectively correspond to a higher nervous center, a lower nervous center and a motor nerve of an animal. The decision layer for realizing that the robot senses the working environment and generates corresponding motion decision instructions consists of an ARM9 (advanced RISC (reduced instruction-set computer) machine 9) and an environmental information acquisition system, and a real-time operating system is embedded in the ARM9. The core of the planning layer is a walking pattern generator, and is used for planning and solving the motion parameters of each joint according to the decision instructions from the upper layer. The execution layer for controlling the current, the position and the speed of a driving motor in three closed loops consists of a motor controller using a digital signal processor as the core. Data can be effectively transmitted among the three layers in real time through a dual-port RAM (random-access memory) and a CAN (controller area network) bus network. The combined type bionic quadruped robot controller disclosed by the invention has the characteristics of high reliability, high flexibility, extension easiness and maintenance easiness, and has a broad application prospect in the technical field of bionic legged robots.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

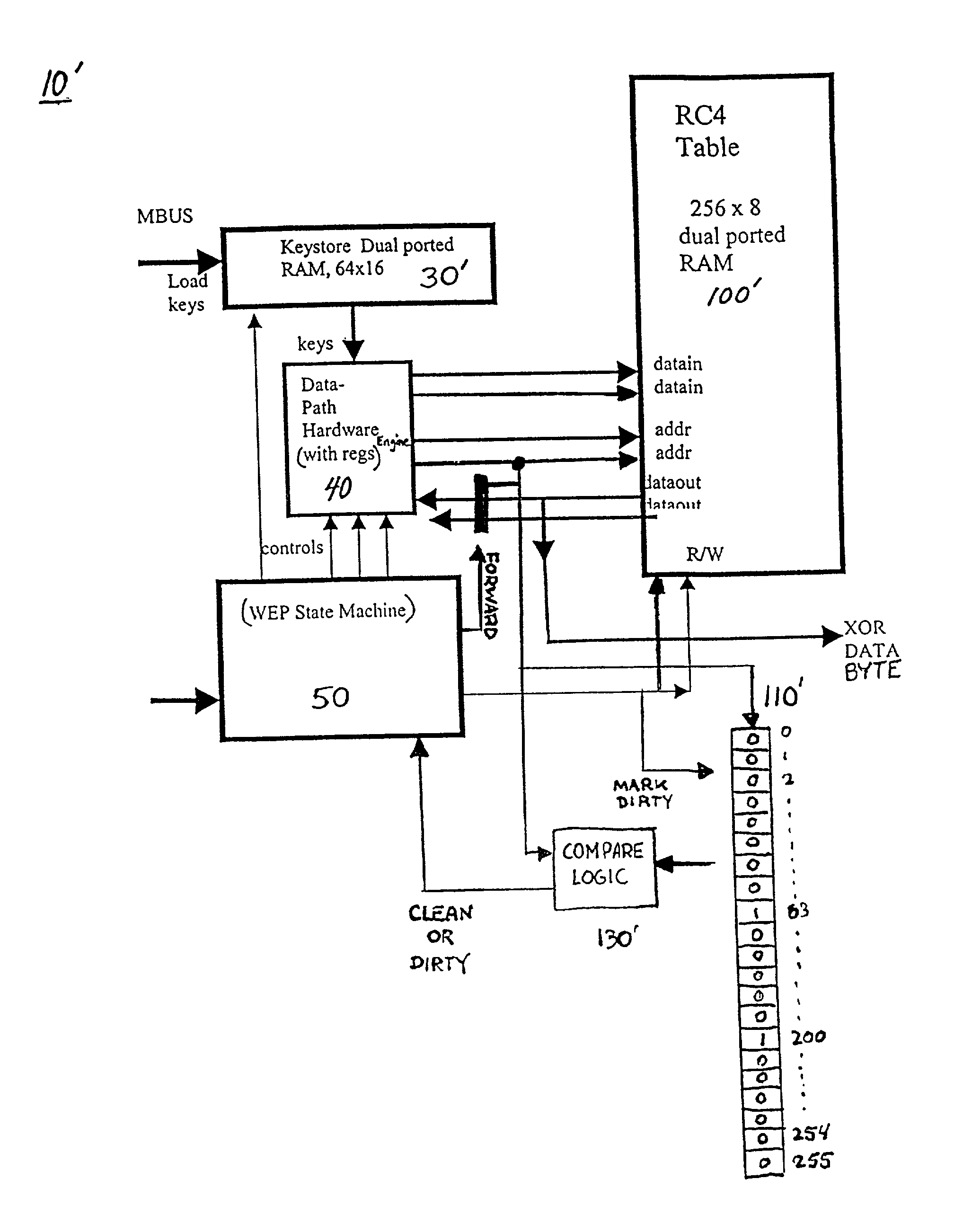

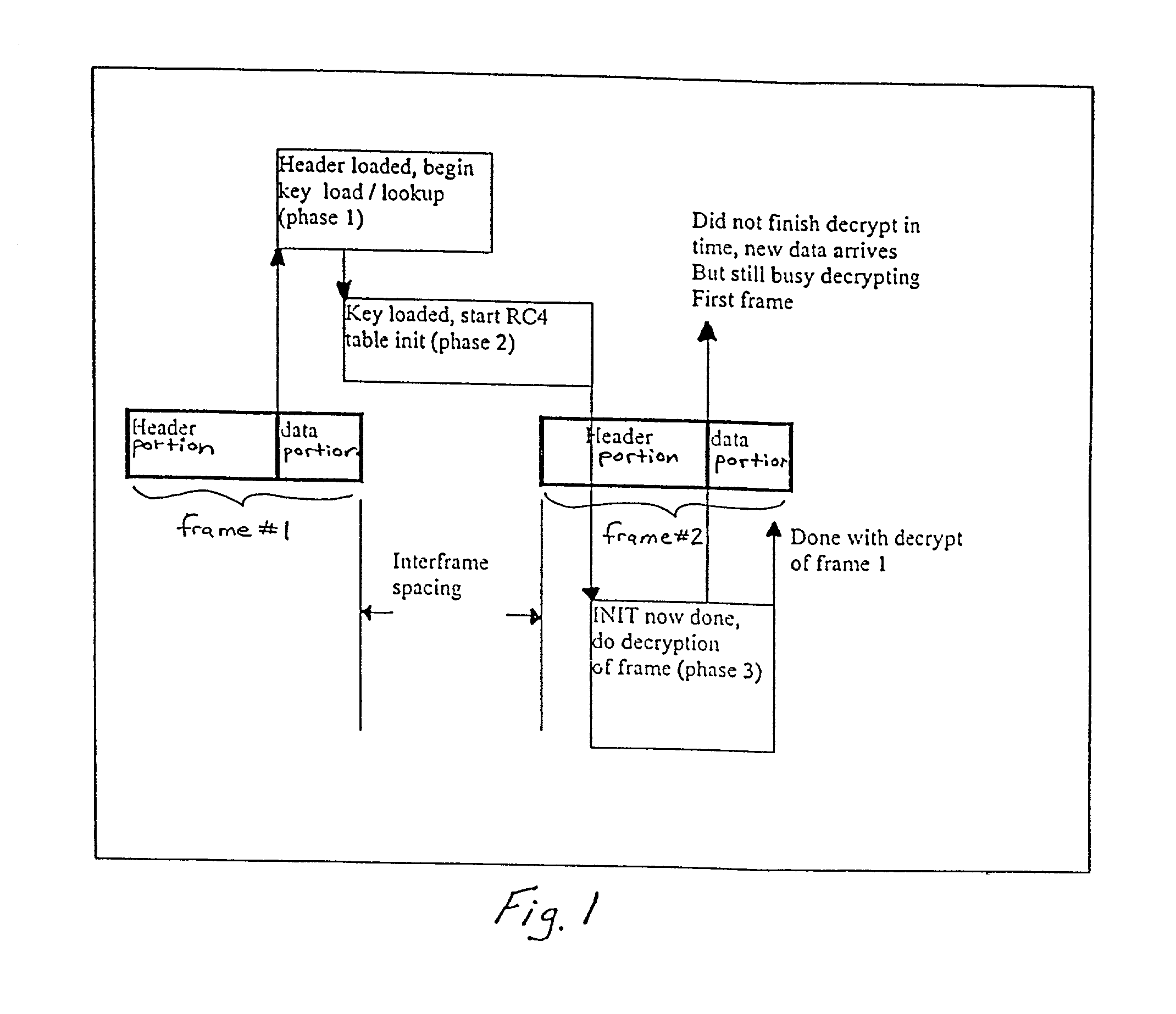

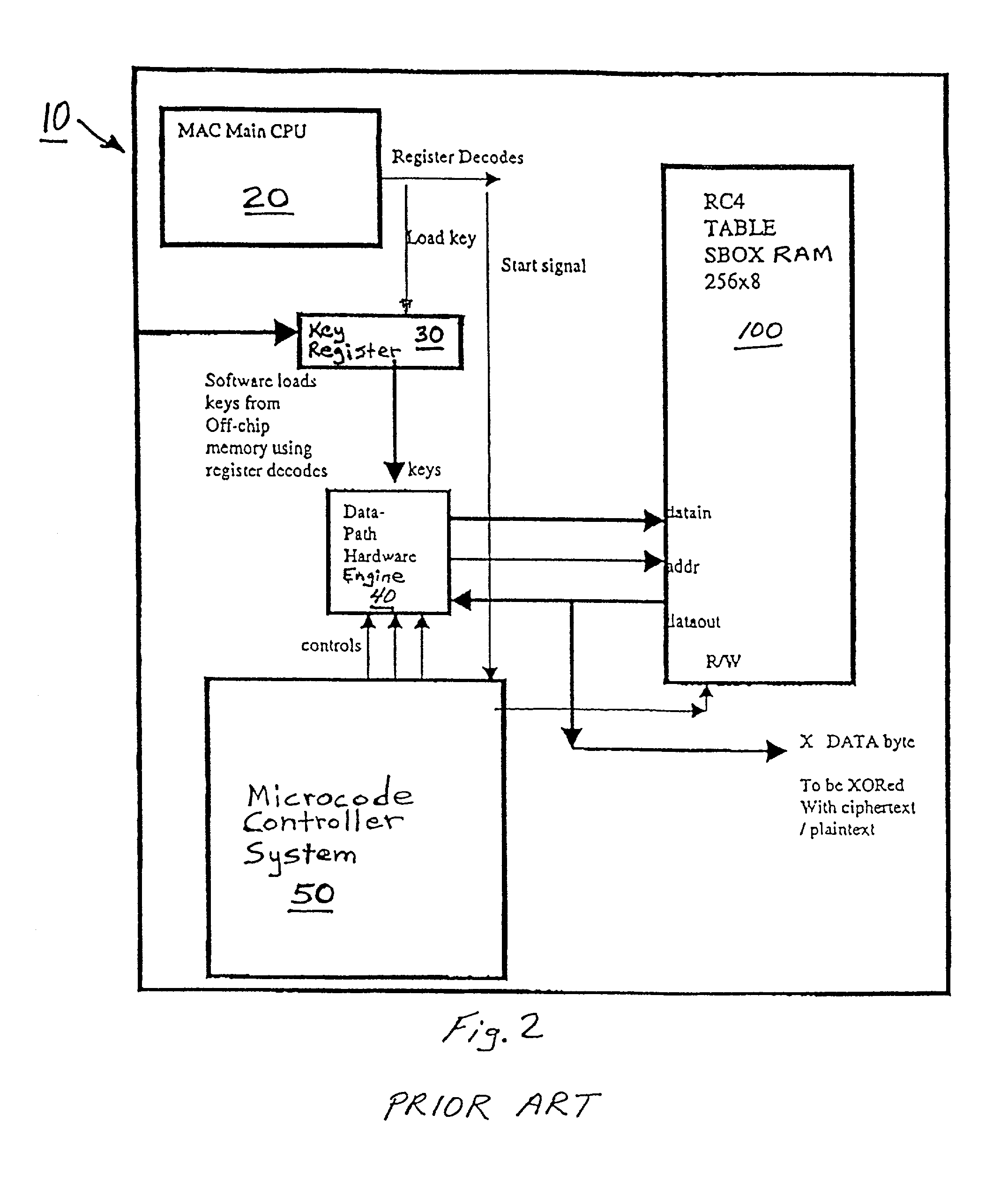

Hardware-based encryption/decryption employing dual ported memory and fast table initialization

ActiveUS6980649B1Faster and zero cost executionFaster and efficient executionData stream serial/continuous modificationSecret communicationData operationsDual-ported RAM

A system for the encryption and decryption of data employing dual ported RAM to accelerate data processing operations during the computation of the encryption and decryption algorithm. The system includes logic to track data changes in the dual ported memory for fast table initialization; a means to accelerate operations by performing read / write operations in different iterations of the algorithm to separate ports on the dual ported RAM in the same clock cycle; and a means to resolve data manipulation conflicts between out of order read / write operations so that the system correctly computes the desired algorithm.

Owner:CISCO TECH INC

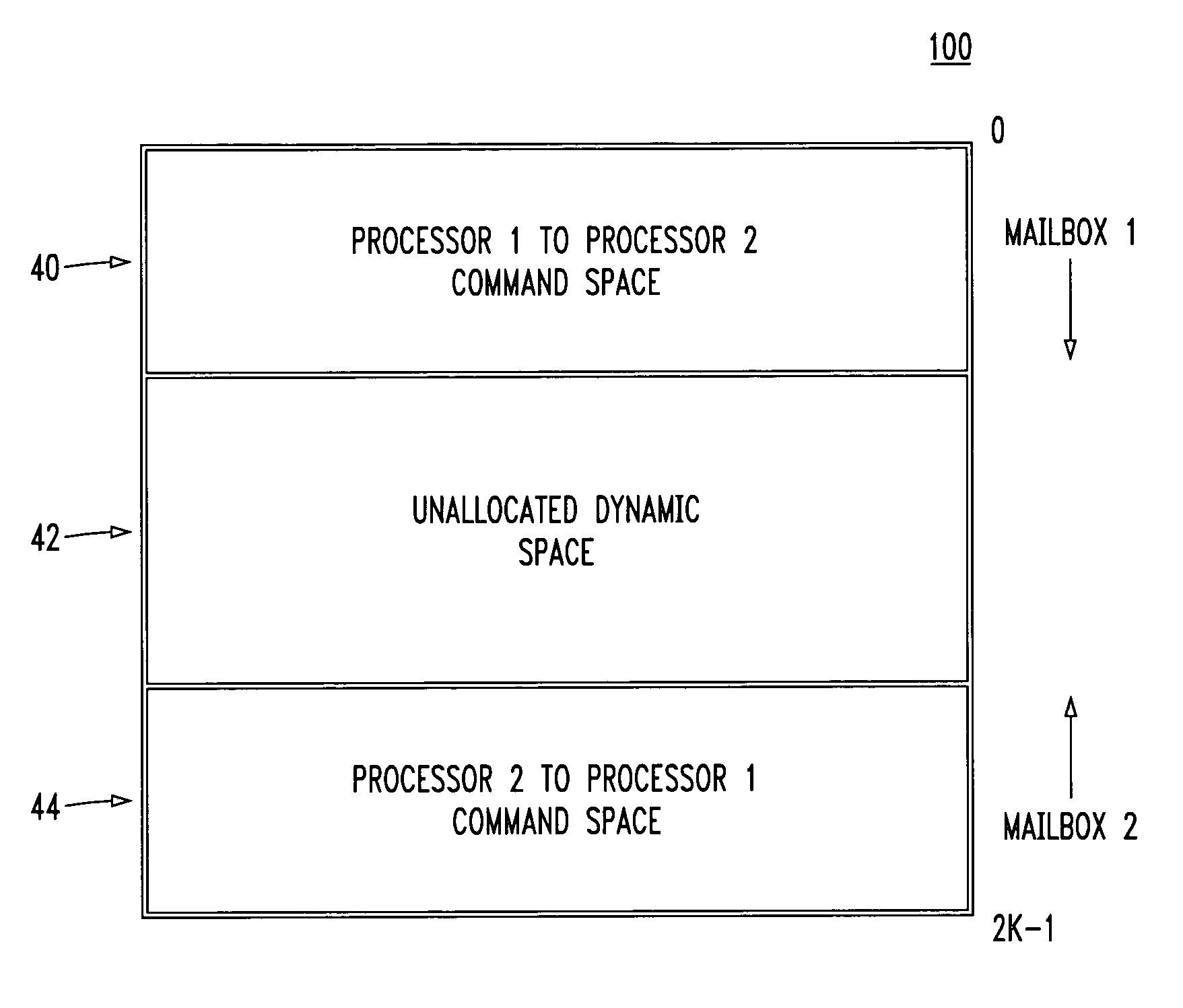

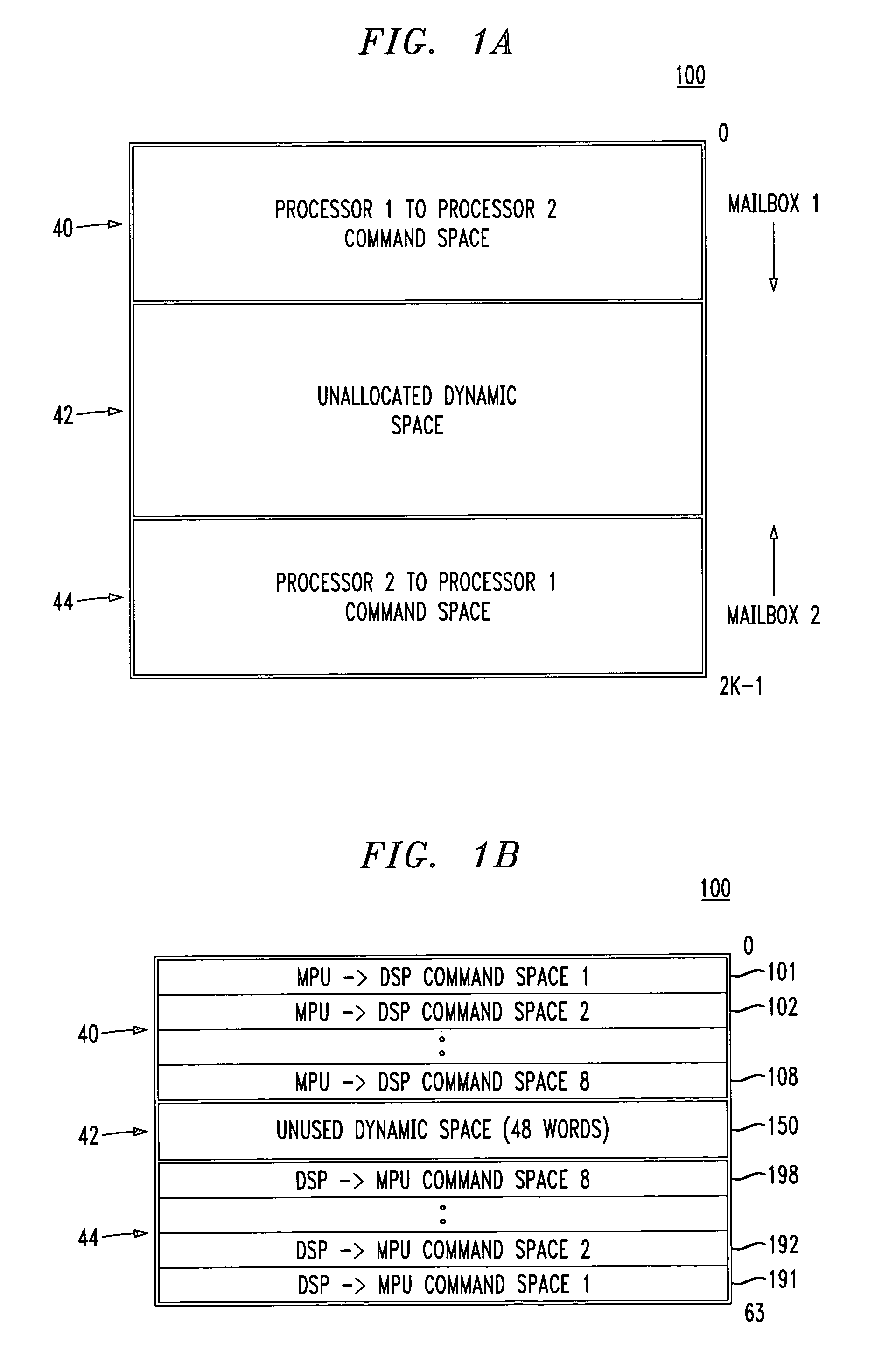

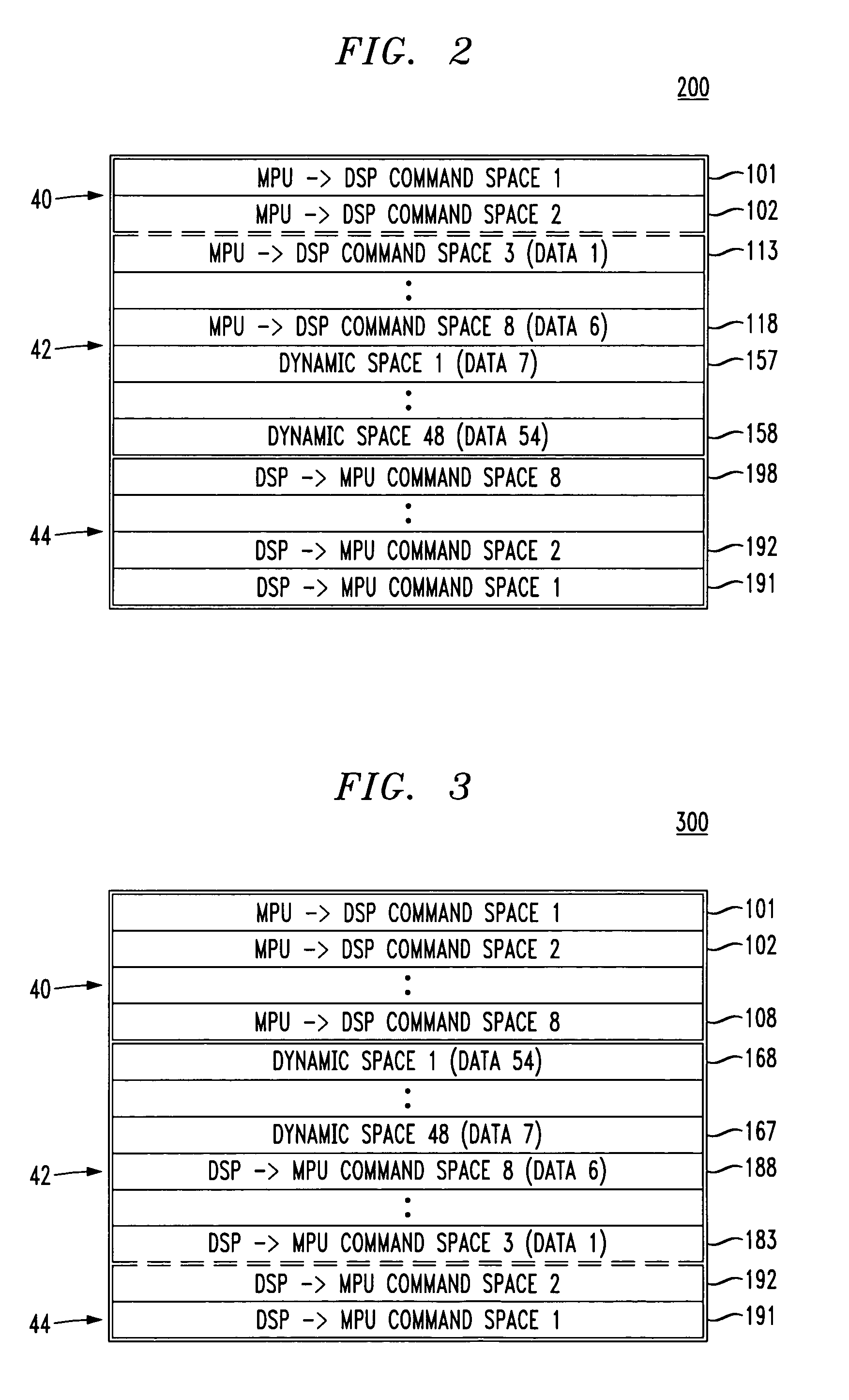

Maximized data space in shared memory between processors

A technique and apparatus for efficiently and flexibly utilizing shared memory as a full duplex mailbox for both data and payload information. The invention allows payload messages of varying lengths to be passed in contiguous memory space, allowing an interrupt service routine (ISR) or other process to easily and quickly read or cache the passed payload data. In a disclosed embodiment, a processor-to-processor mailbox is formed using a shared memory (e.g., a dual port RAM). The shared memory is separated into three main portions: a processor 1 to processor 2 fixed portion, a processor 2 to processor 1 fixed portion, and an unallocated dynamic portion. Importantly, the other direction of the mailbox is located starting at the highest address of the shared memory, and works toward the lowest address of the shared memory. Preferably, write access for payload messages and other generally longer messages are dynamically allocated in the unallocated dynamic portion for use in either mailbox. For messages passed in mailbox 1, i.e., from processor 1 to processor 2, the memory in the unallocated dynamic portion is allocated in a lowest to highest address direction. Conversely, for messages passed in mailbox 2, i.e., from processor 2 to processor 1, the memory in the unallocated dynamic portion is allocated in a highest to lowest address direction.

Owner:LUCENT TECH INC

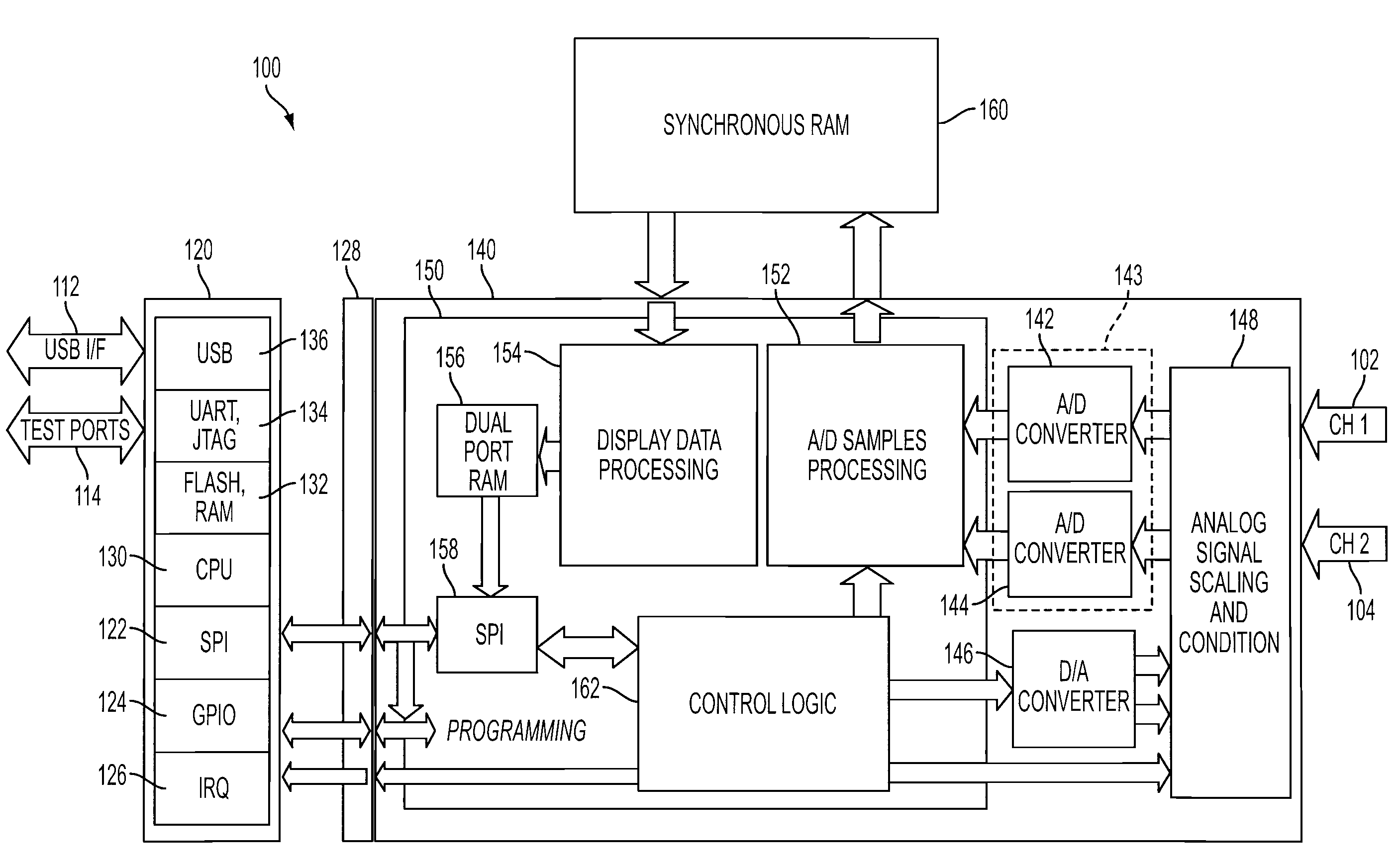

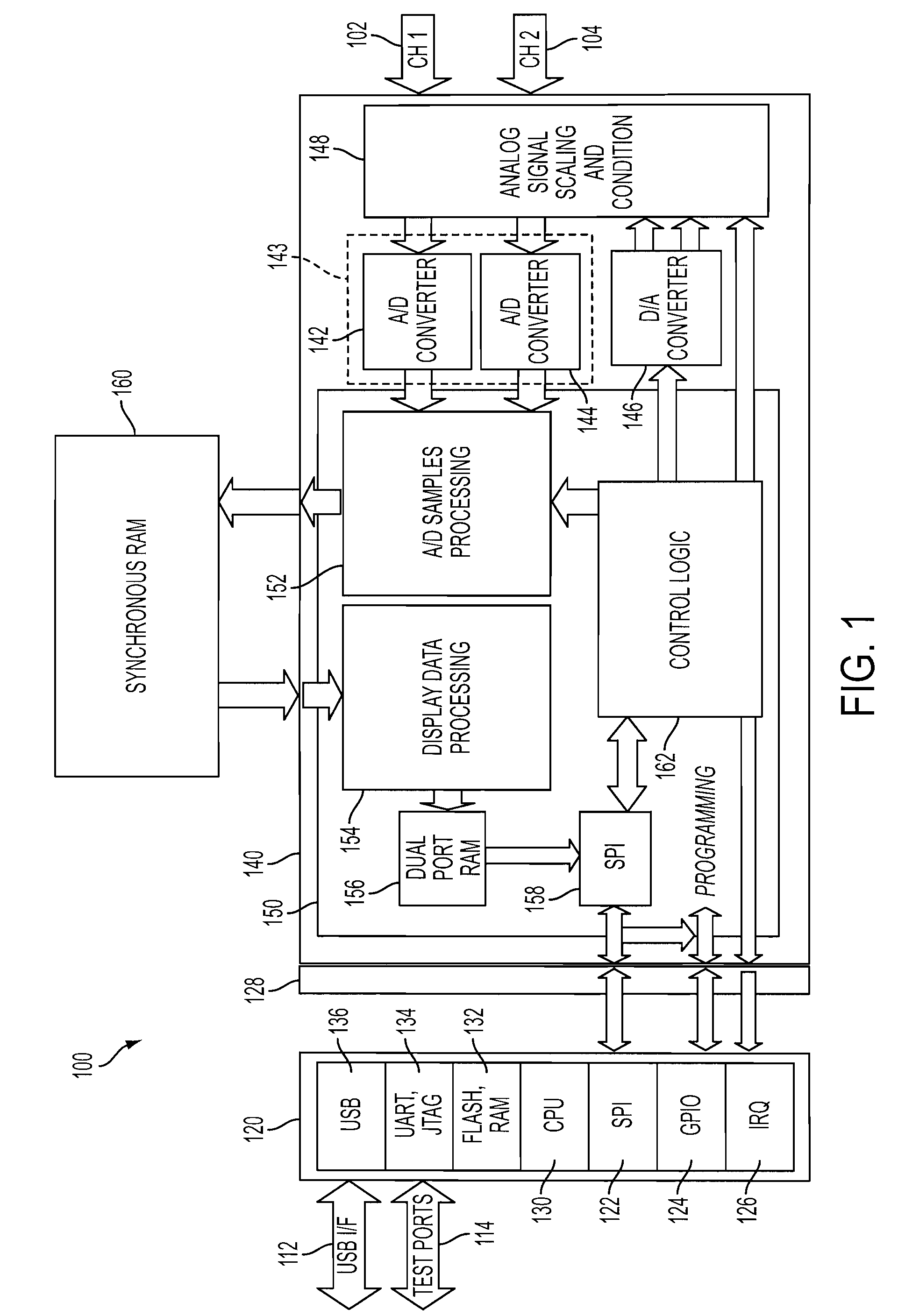

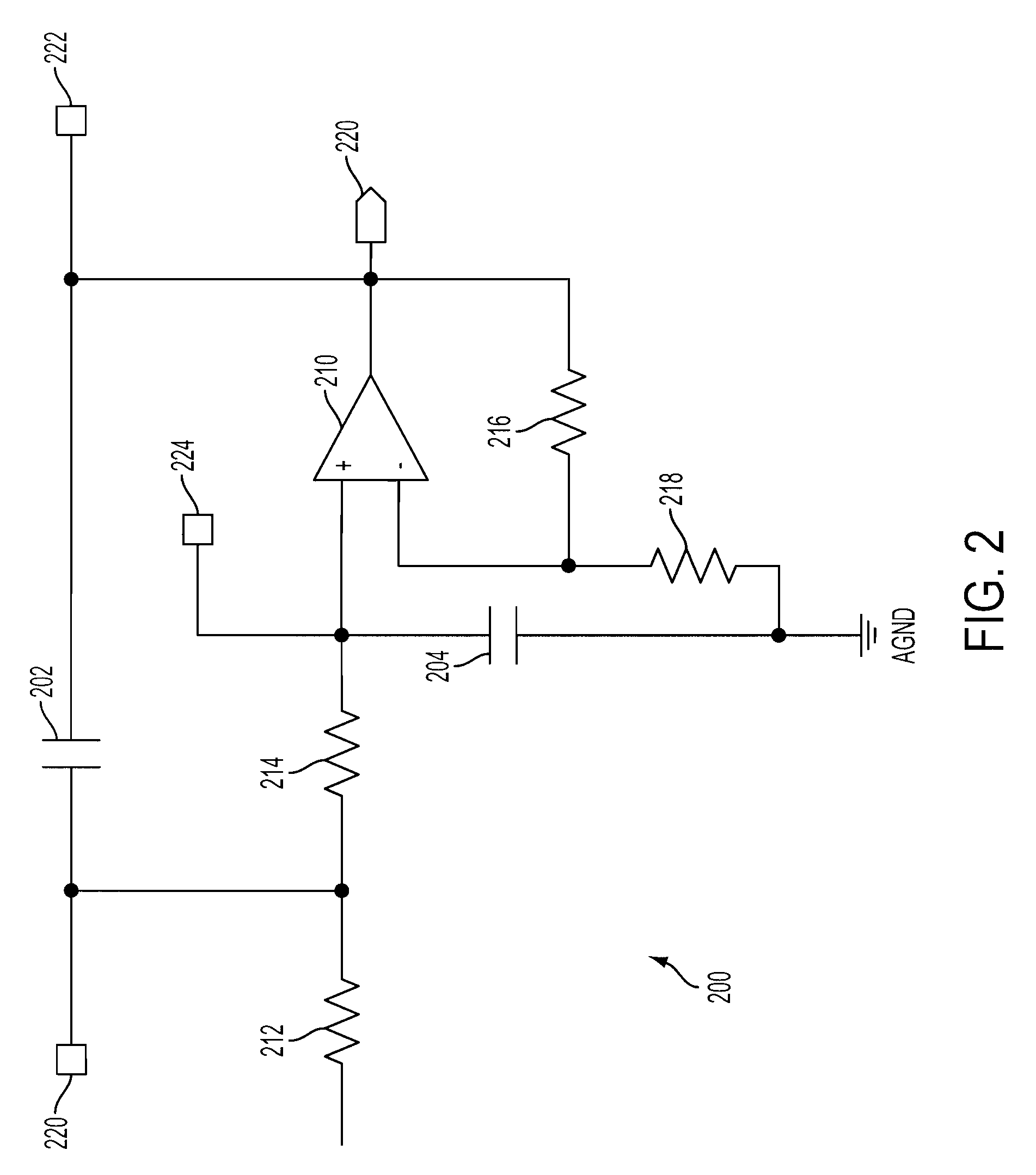

Digital Oscilloscope Module with Glitch Detection

ActiveUS20100052653A1Digital variable displayAmplifier modifications to reduce noise influenceDigital signal processingCommunication interface

The present invention provides a digital oscilloscope with glitch detection, including a synchronous random access memory (RAM), a digital signal processing unit, coupled to the synchronous RAM, and a master control unit coupled to the digital signal processing unit. The digital signal processing unit includes an analog-to-digital (A / D) converter to digitize an analog signal and a digital signal processor. The digital signal processor includes a dual-port RAM, a plurality of processing blocks to process the digitized analog signal data, detect glitches in the digitized analog signal data, store the processed signal data in the synchronous RAM, create display data from the stored signal data, and store the display data in the dual-port RAM, and a communications interface to transmit the stored display data. The master control unit includes an internal communications interface coupled to the digital signal processor communications interface, an external communications interface, and a central processing unit to receive the display data over the internal communications interface and transmit the display data over the external communications interface.

Owner:BOSCH AUTOMOTIVE SERVICE SOLUTIONS

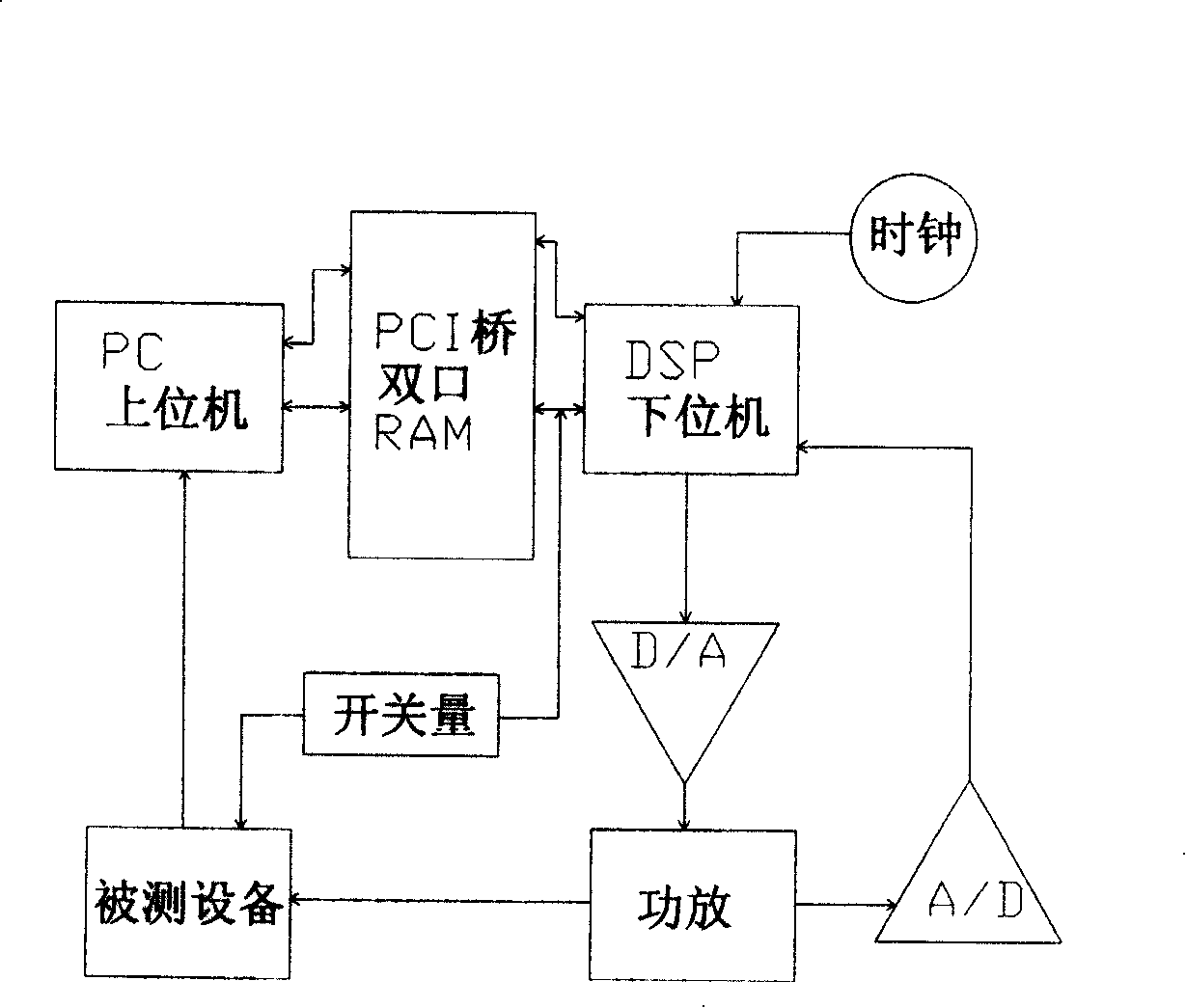

Electric power apparatus integrated automated detection system

InactiveCN101241155ARealize transmissionEasy to upgradeCircuit arrangementsElectrical testingElectric power systemElectric power equipment

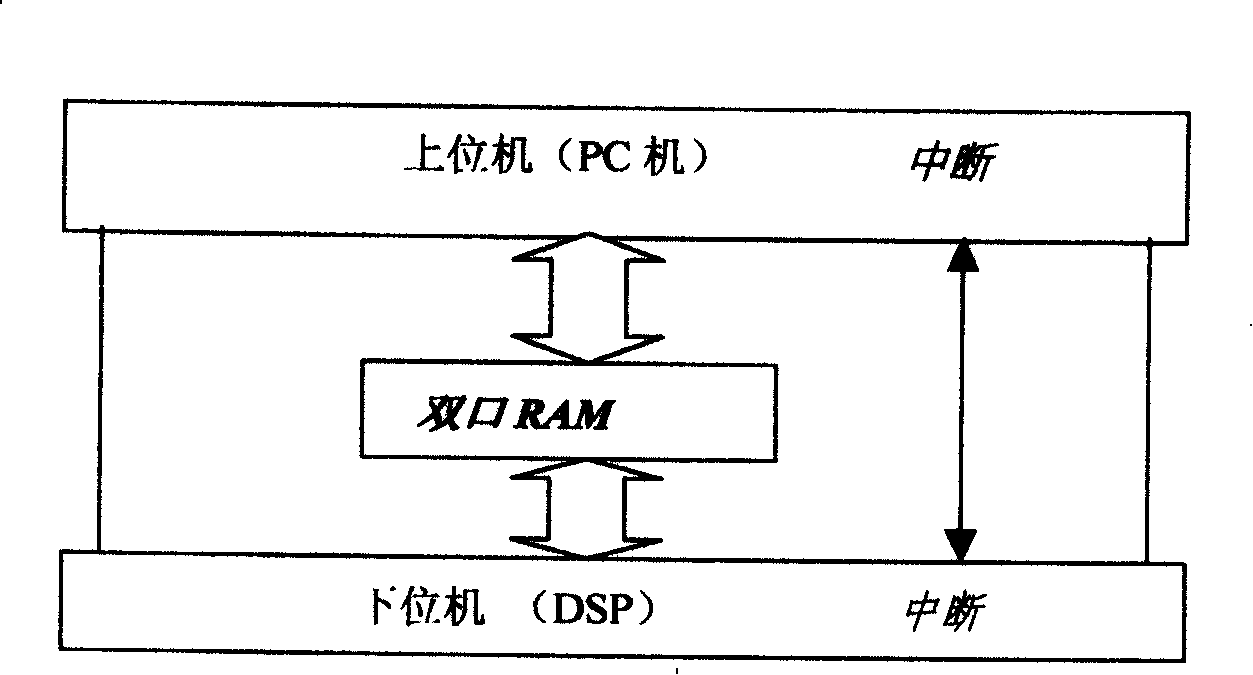

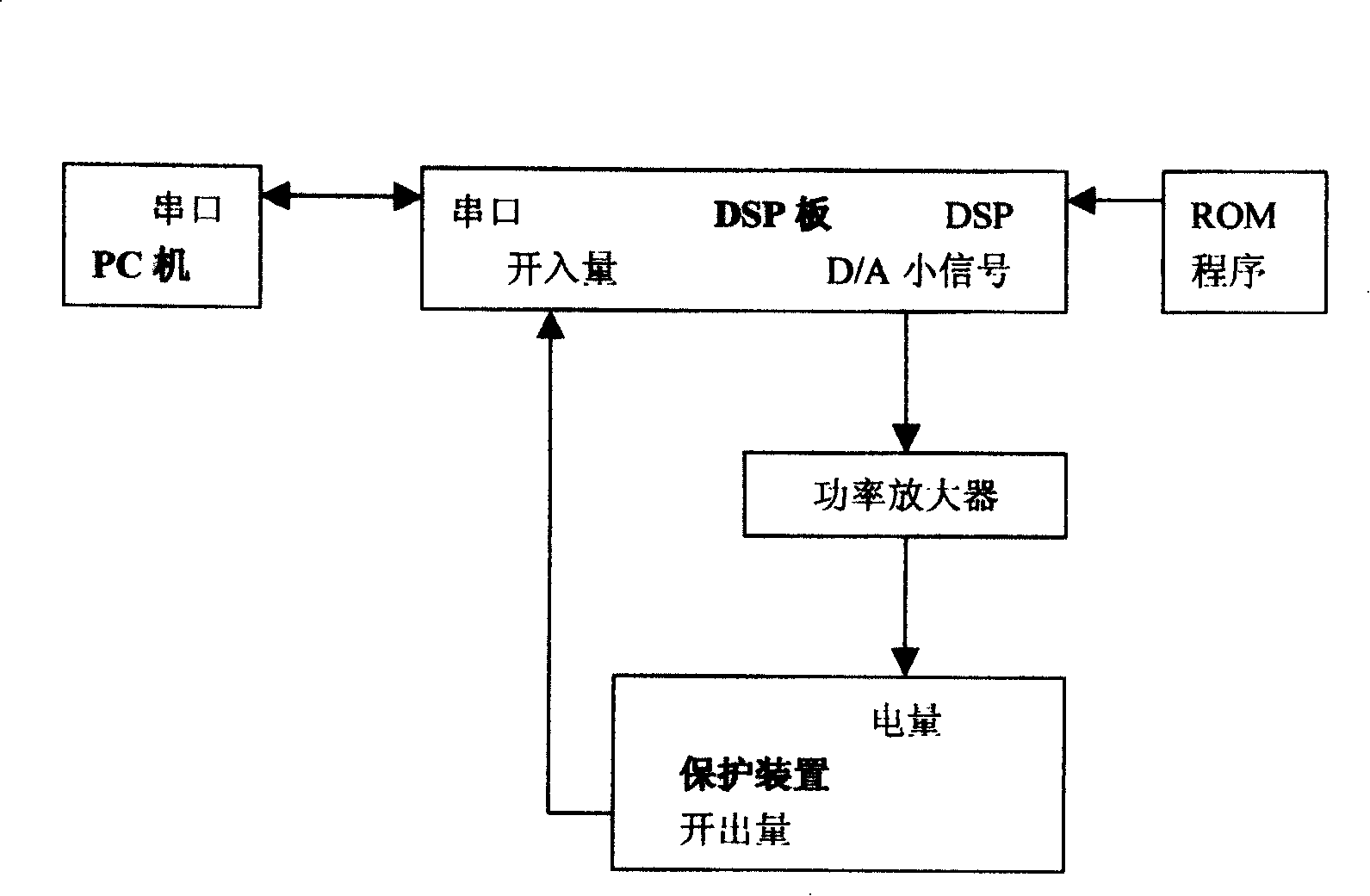

The present invention provides an integration automatization examining system of electric power equipment which relates to fields of integration automatization examining of electric power system, which comprises of host computer PC, lower computer DSP, power amplifier. A PCI bridge with dual-port RAM is connected between host computer PC and lower computer DSP, a sampling circuit connected with analog-to-digital converter in series is placed between power amplifier and lower computer DSP. Parameters and orders are input to host computer PC, selected program downloaded by PC is transferred to DSP, data current is passed through memorizer of DSP, and examining task is carried by DSP. The present invention changes former mode of customization examining device and realizes a multi-use machine, makes the upgrade operation of program convenient, can transfer large current data, and has high precision. The present invention can finish all kinds of protection functional testing of remote control, remote examining, remote signaling of on-line examining and inspection, can communicate with device to be measured, and display testing result on testing report automatically. The report employs Word document, so it's convenient operation by users.

Owner:扬州奥瑞科技有限公司

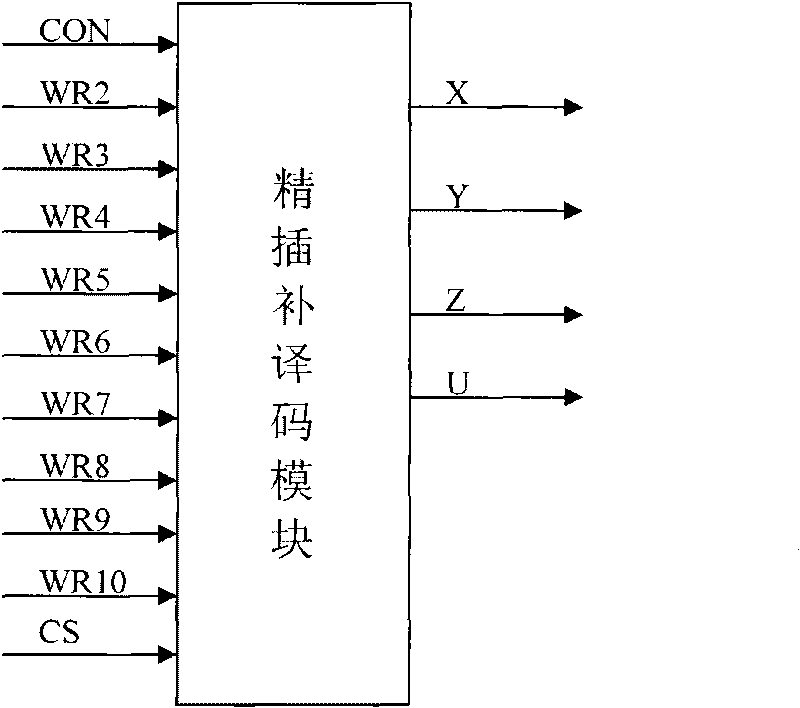

NC system fine interpolator and control method thereof based on SOPC

ActiveCN101751009AImprove confidentialityEasy to integrateProgramme controlComputer controlInternal memorySystems design

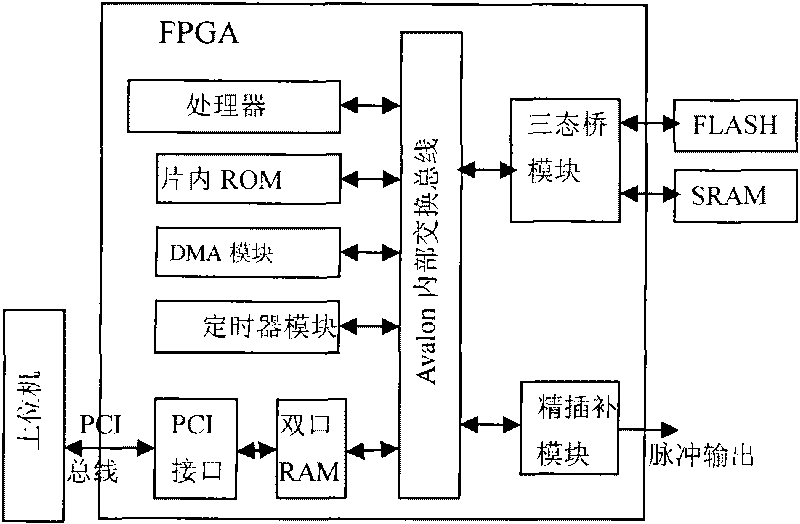

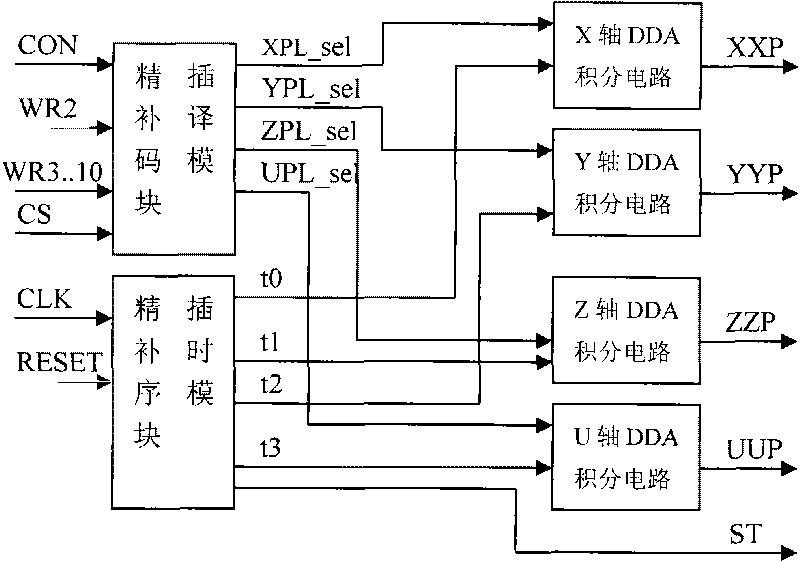

The invention relates to a NC system fine interpolator and a control method thereof based on SOPC; the fine interpolator is based on the FPGA structure, a processor is connected with a fine interpolation module, a tri-state bridge, a dual-port RAM, a DMA module, a timer module and a chip-interior ROM; wherein, the fine interpolation module is used for receiving the control signal of the processor and is controlled by the processor to output a fine interpolation pulse signal according to the thick interpolation command transmitted by the dual-port RAM; the processor is connected with a FLASH and SRAM on the exterior of the FPGA through the tri-state bridge; the dual-port RAM is connected with the microprocessor of an upper computer through a PCI interface module; the timer module outputs base frequency to the fine interpolation module for generating pulse signals; the DMA module copies the fine interpolation control program stored in the FLASH to the internal memory of the processor' and the internal switching bus module provides internal connection bus for each module. The invention adopts the FPGA-based on-chip system design to improve the confidentiality and integration of the fine interpolator, the processing stability and speed of the fine interpolator, and reduce the data throughput of the upper computer.

Owner:中国科学院沈阳计算技术研究所有限公司

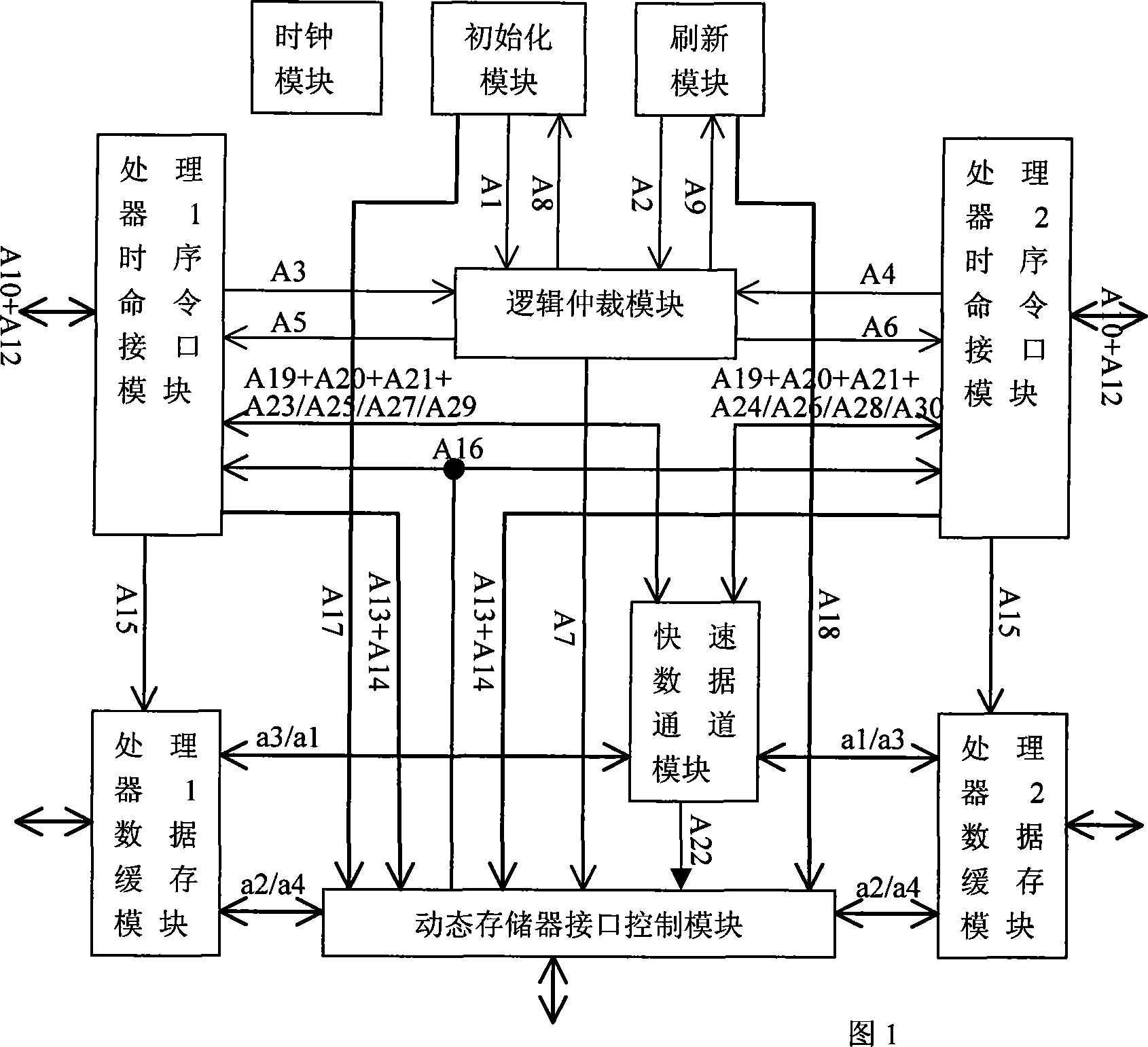

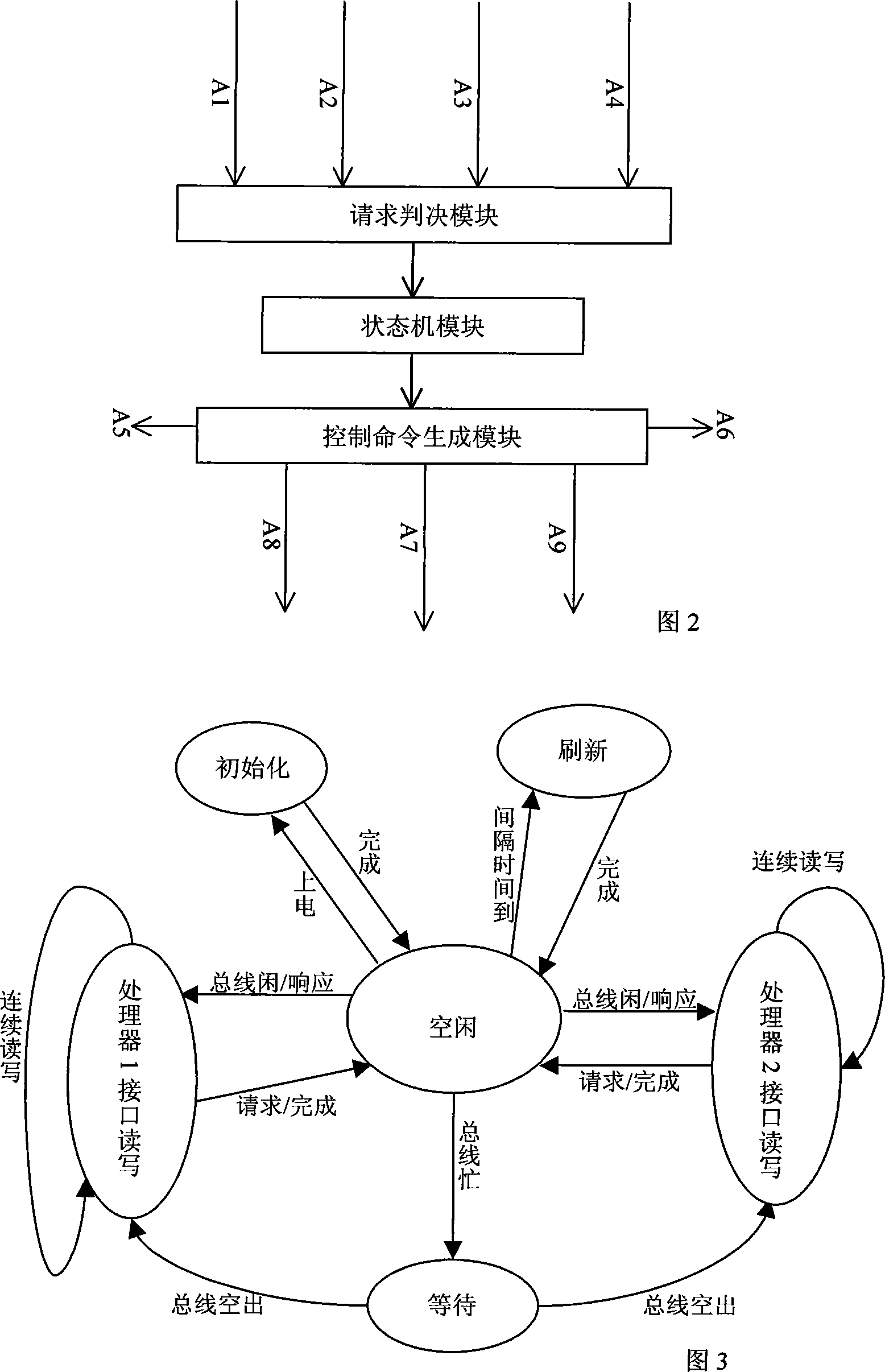

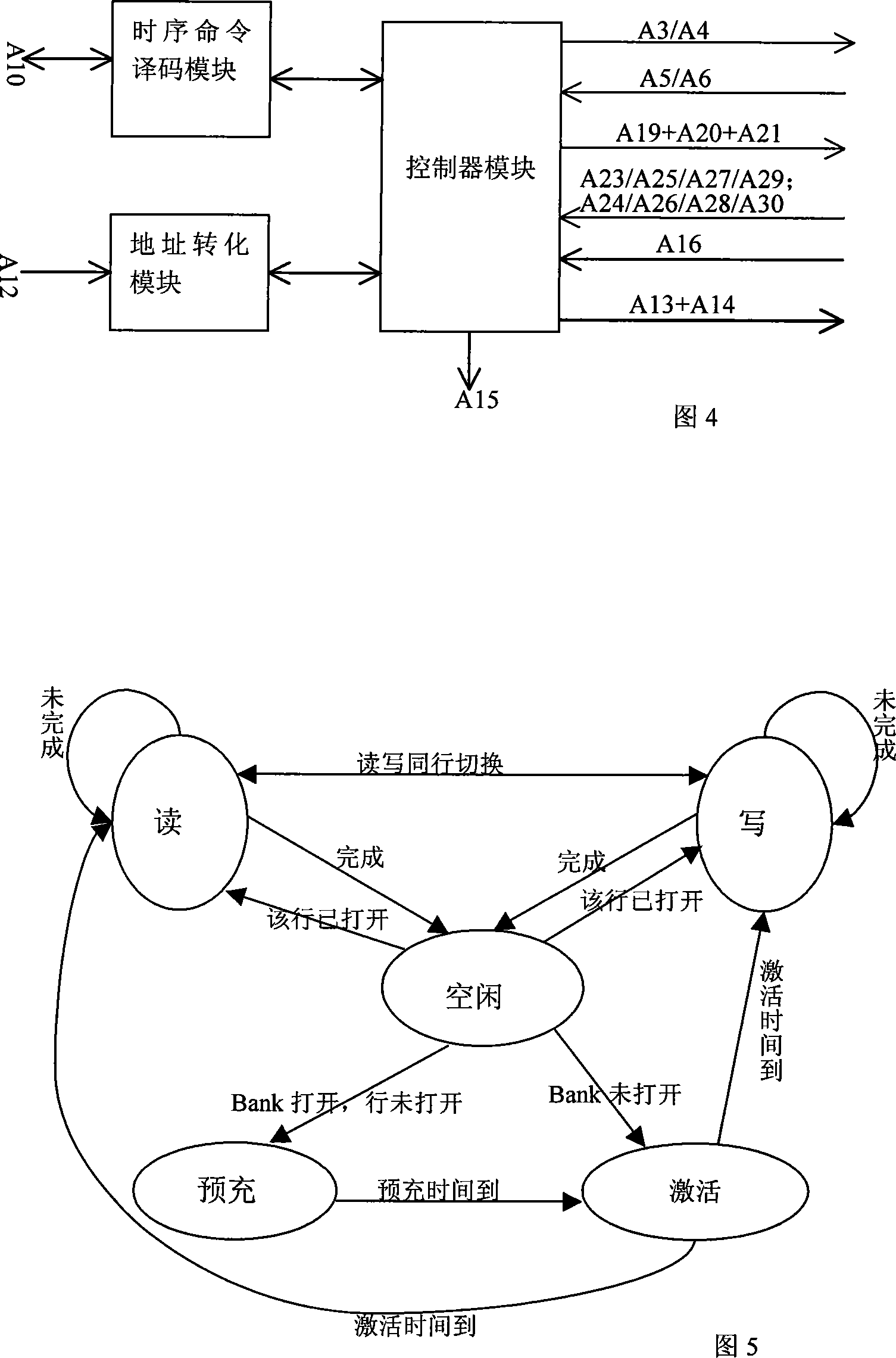

Double-port access single dynamic memory interface

InactiveCN101196856AIncrease capacityLarge capacityInput/output to record carriersDigital computer detailsMultiplexingMemory interface

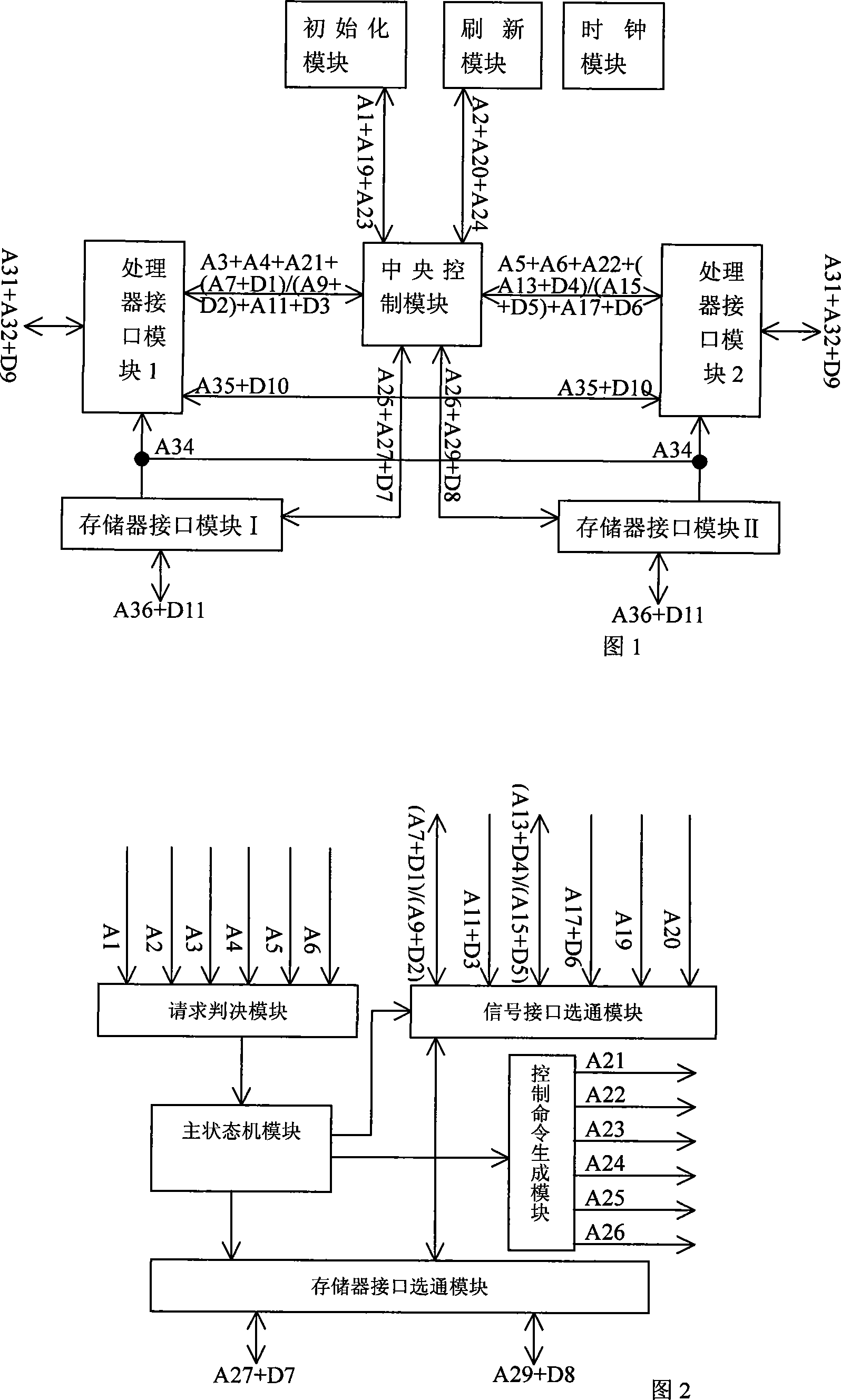

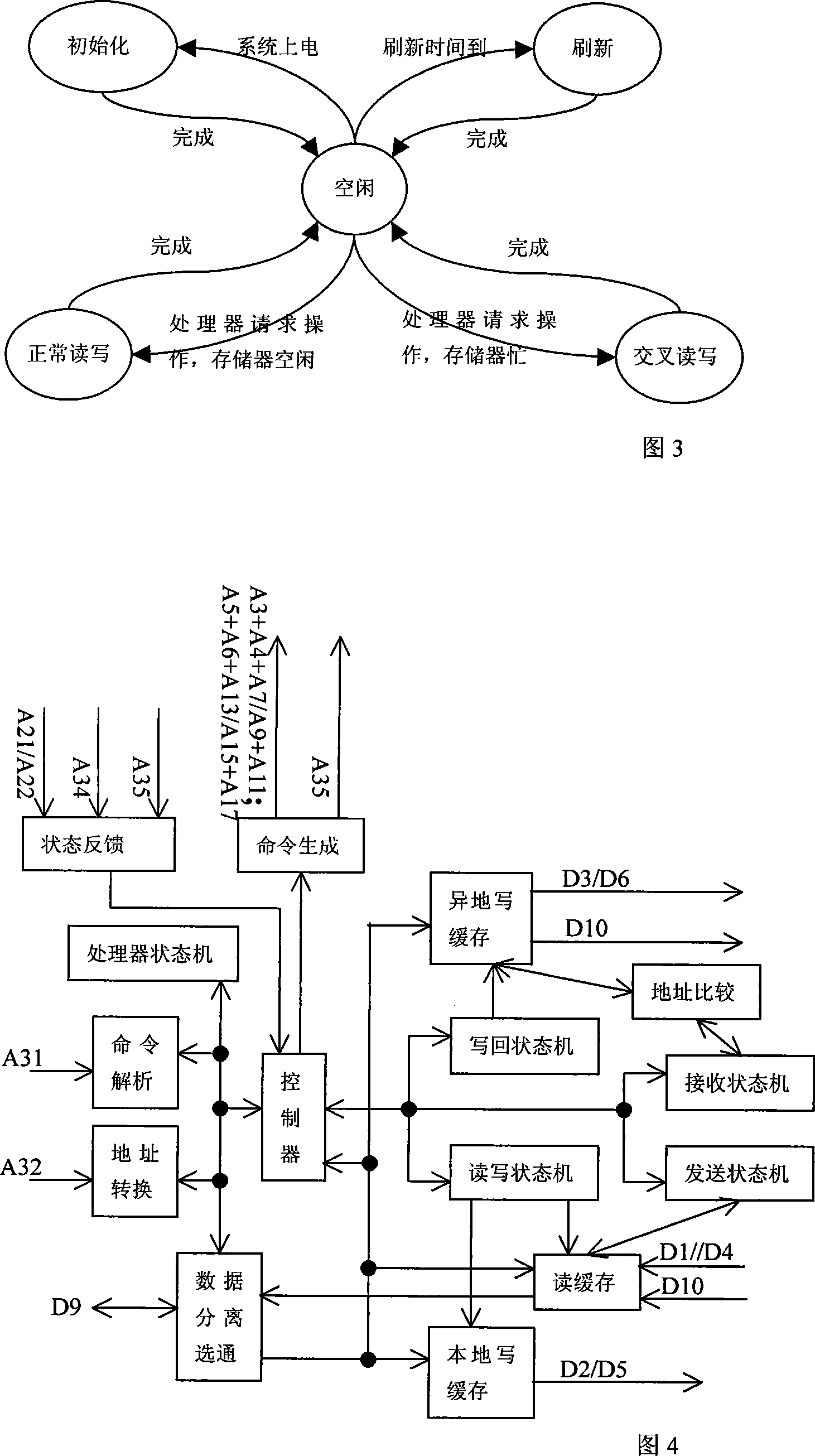

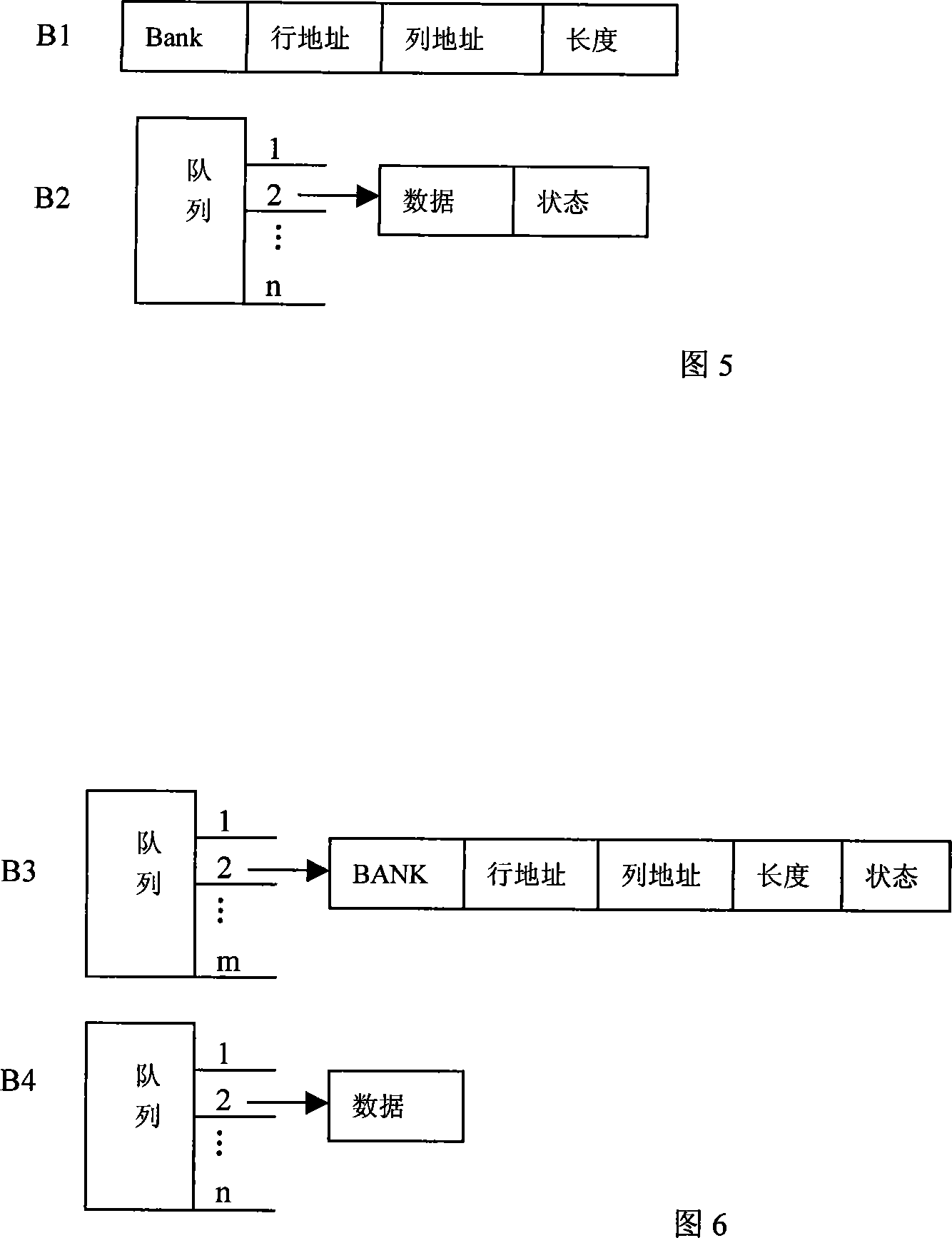

The invention relates to a computer interface, in particular to an interface of a single dynamic memory with dual ports access. The invention eliminates the defects in the aspects of cost, memory capacity, system performance, usability, etc. existing in adopting dual port RAM device as a share memory and adopting time-sharing multiplexing technology of a bus to access to the share memory. The invention comprises a logic arbitration module, a sequence command interface module of a processor 1, a data caching module of the processor 1, a sequence command interface module of a processor 2, a data caching module of the processor 2, an interface control module of the dynamic memory, an initialization module and a refreshing module. The interface facilitates two or more processors simultaneously access to the dynamic memory in parallel; when one processor accesses to the share dynamic memory, another processor can begin access to the same dynamic memory without waiting the present processor to finish the access to the memory; the time required by the response of the memory to the access of the processor is further reduced, thereby enhancing the system performance.

Owner:TAIYUAN UNIV OF TECH

Double-port access symmetrical dynamic memory interface

InactiveCN101196857AImprove performanceIncrease capacityInput/output to record carriersDigital computer detailsMultiplexingMemory interface

The invention relates to a computer interface, in particular to an interface of symmetrical dynamic memory with dual ports access. The invention eliminates the defects in the aspects of cost, memory capacity, system performance, usability, etc. existing in adopting dual port RAM device as a share memory and adopting time-sharing multiplexing technology of a bus to access to the share memory. The invention comprises a central control module, two processor interface modules, two memory interface modules, a refreshing module and an initialization module. The interface of the invention connects two dynamic memories with the same model and mirrored with each other as a share memory of the two processors, which realize that the two processors simultaneously access to the share memory without conflict through the interface under the requirements of high system performance and high speed processors.

Owner:TAIYUAN UNIV OF TECH

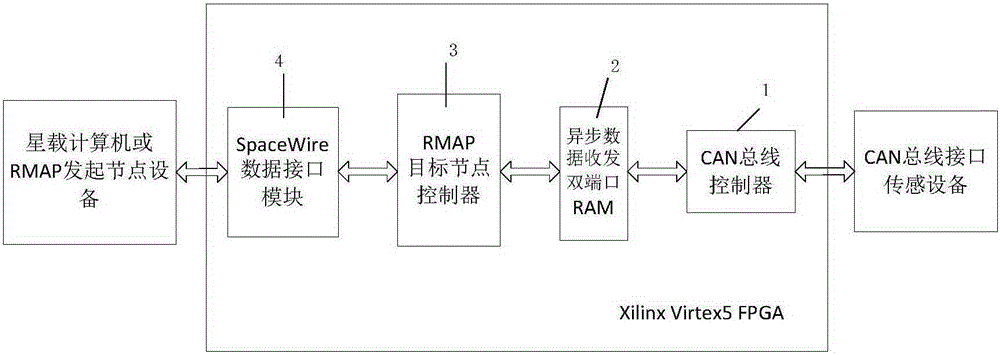

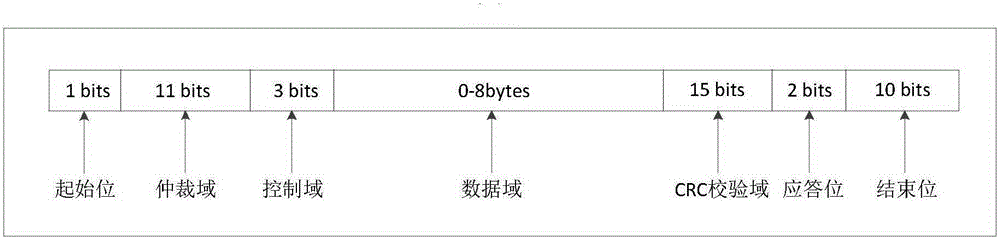

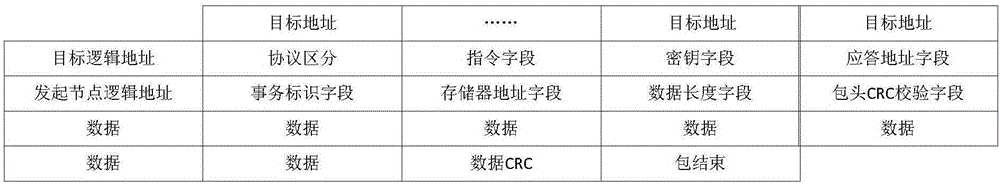

Device utilizing RMAP protocol to realize plug-and-play function of CAN bus equipment

InactiveCN105187227AShorten the timeImprove reliabilityForward error control useBus networksSource Data VerificationSpaceWire

The invention discloses a device utilizing an RMAP protocol to realize the plug-and-play function of CAN bus equipment. The device comprises an RMAP object node controller, a CAN bus controller, a SpaceWire data interface module and an asynchronous data transceiving dual-port RAM, wherein external CAN bus interface sensing equipment is connected with the CAN bus controller, the asynchronous data transceiving dual-port RAM, the RMAP object node controller and the SpaceWire data interface module, the RMAP object node controller comprises an object command packet decoding module, a verification control module and an object node controller module, a DMA module, an object response packet coding module and a CRC data verification module, and the SpaceWire data interface module is connected with a satellite-borne computer and the RMAP object node controller. The device is advantaged in that, the RMAP object node controller is realized through an IP soft core, data conversion efficiency and data transmission timeliness are improved, and design complexity is effectively reduced.

Owner:BEIHANG UNIV

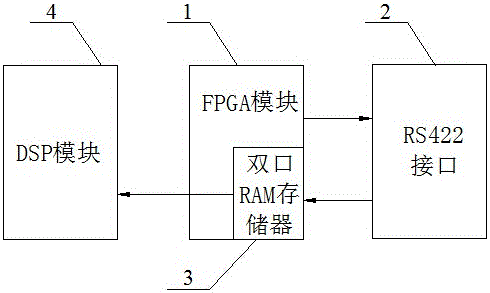

FPGA-based BiSS-C communication protocol method

Provided is an FPGA-based BiSS-C communication protocol method. The invention belongs to the technical field of transmission and communication between a sensor and a control card. The method comprises the following steps: step 1, clock signal MAs of an FPGA module are sent to a clock input end of an external grating sensor via an RS422 interface; step 2, the rising edges of the clock signal MAs trigger the external grating sensor to send data signals; step 3, the FPGA module judges whether the start position is at high level and the '0' position is at low level for each frame of data signal, the FPGA module waits for next frame of data if the start position is not at high level and the '0' position is not at low level for each frame of data signal, and the rising edge serial port of each clock MA receives one bit of data if the start position is at high level and the '0' position is at low level for each frame of data signal; step 4, a complete frame of data is stored in a dual-port RAM memory of the FPGA module; and step 5, the data in the dual-port RAM memory is transmitted to a DSP module in real time. The method belongs to the field of hardware decoding. Through FPGA decoding, two functions, namely, data communication and register, can be achieved. Communication can be completed, and data can be stored. The stored data is used to process other programs.

Owner:HARBIN INST OF TECH

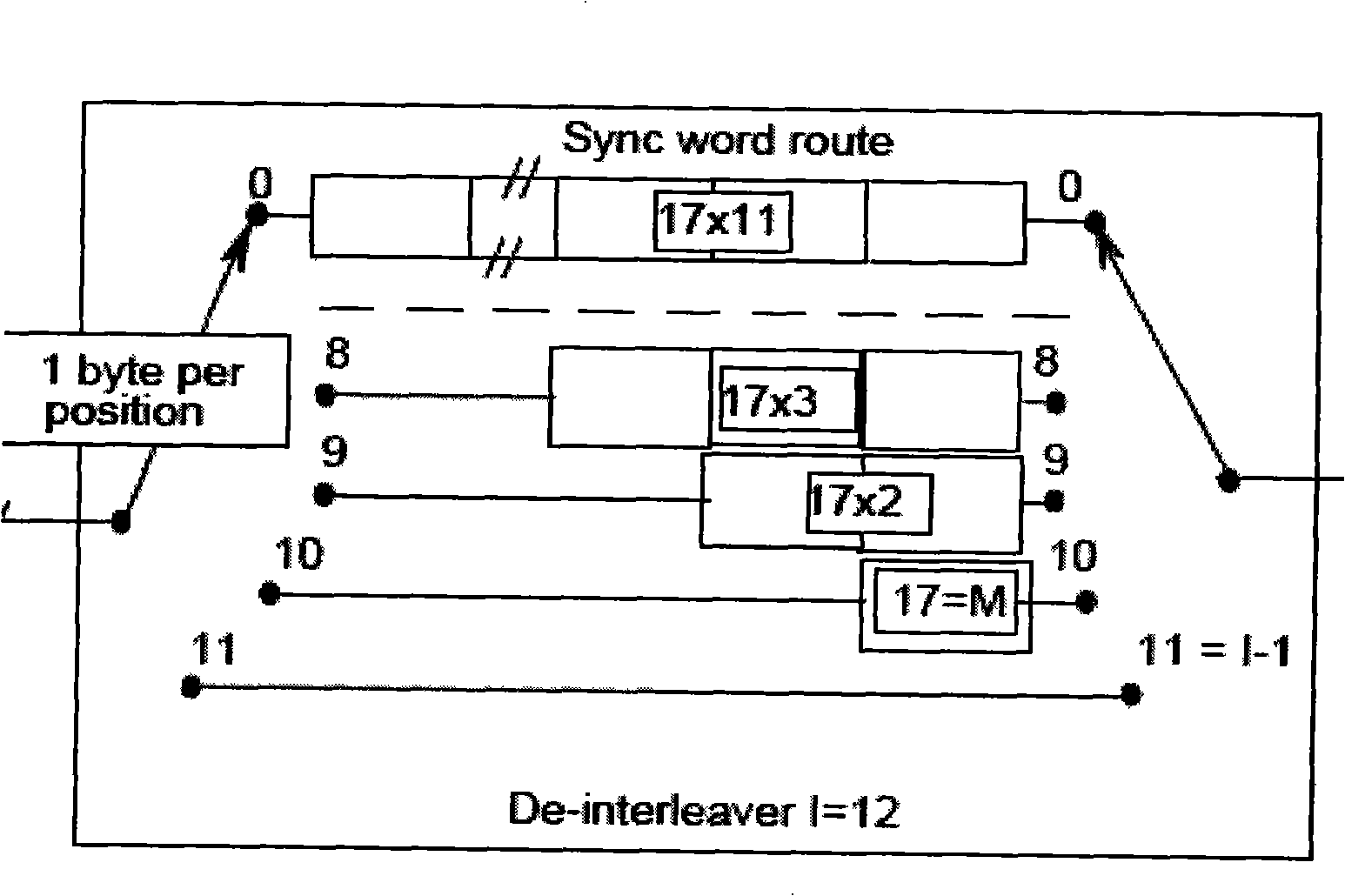

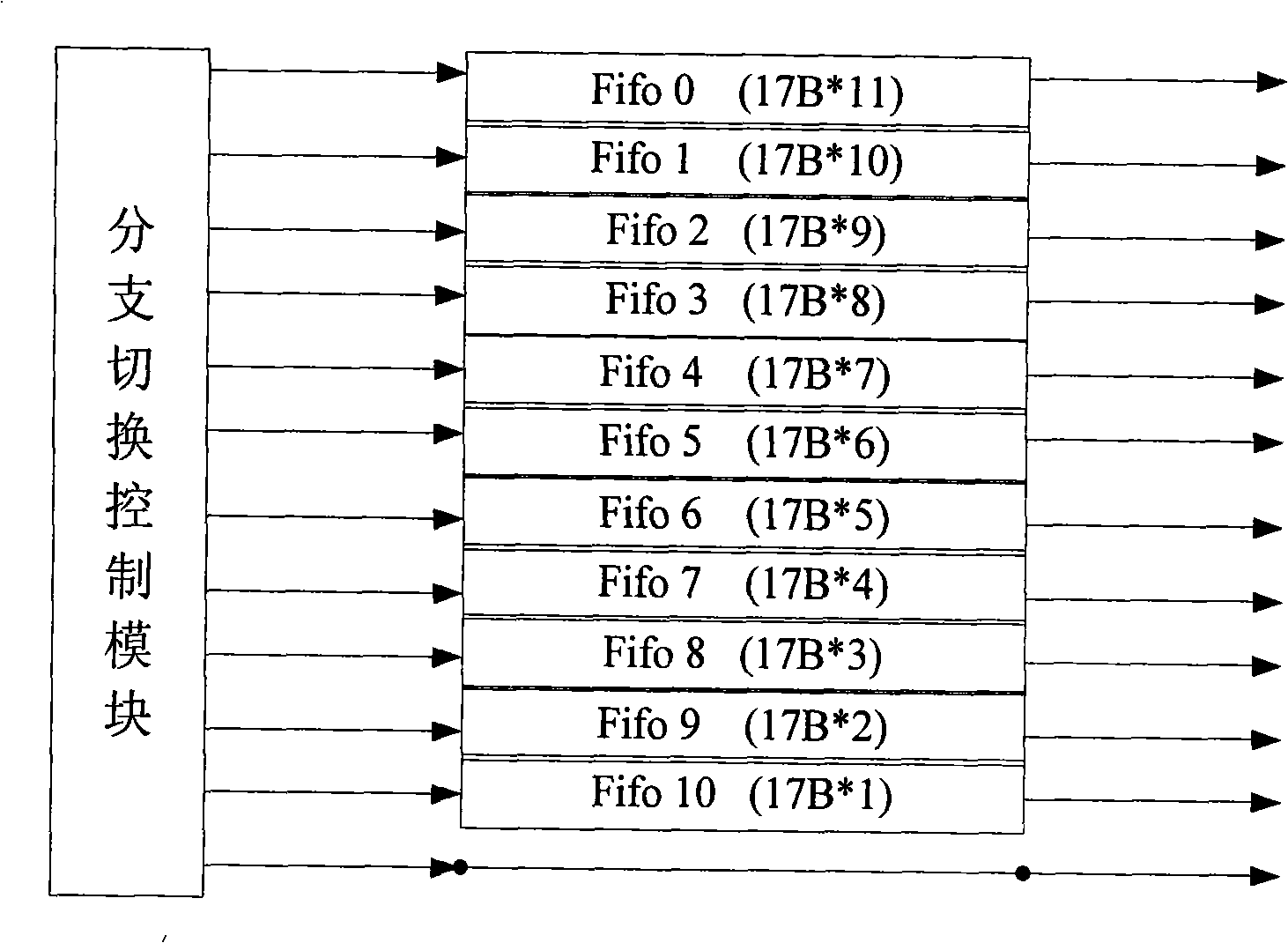

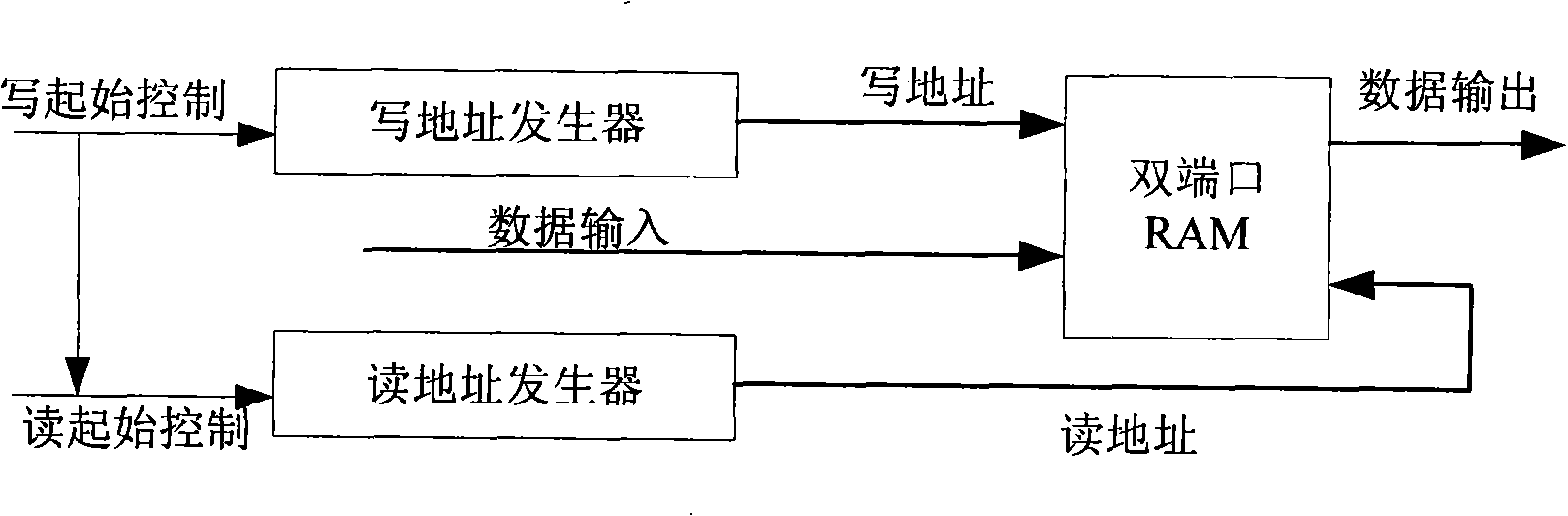

Deconvolution interweave machine and method realized based on FPGA

InactiveCN101257313AReduce areaImprove efficiencyError correction/detection using convolutional codesError correction/detection using interleaving techniquesShift registerFpga implementations

The invention discloses a deconvolution interleaver based on FPGA and a deconvolution interleaving method. The deconvolution interleaver comprises two dual-port RAMs, two read-write address generators, and a controller, wherein the dual-port RAM has the memory deepness of power of 2,and each of the dual-port RAMs is used in a plurality of shift registers with continuous branch; each of the read-write address generators is connected with a dual-port RAM; the controller is respectively connected with the dual-port RAMs and the read-write address generators, outputs a selecting and controlling signal, and selects one of the read-write address generators to produce the output of read address and write address. The controller also outputs a selecting signal to select the dual-port RAM corresponding to the read address and write address, writes the input data in the memory space corresponding to the read address in the dual-port RAM, or reads and outputs the data in the memory space corresponding to the read address in the dual-port RAM. The invention has the characters of high utility rate of memory space and fast working speed.

Owner:SHENZHEN COSHIP ELECTRONICS CO LTD

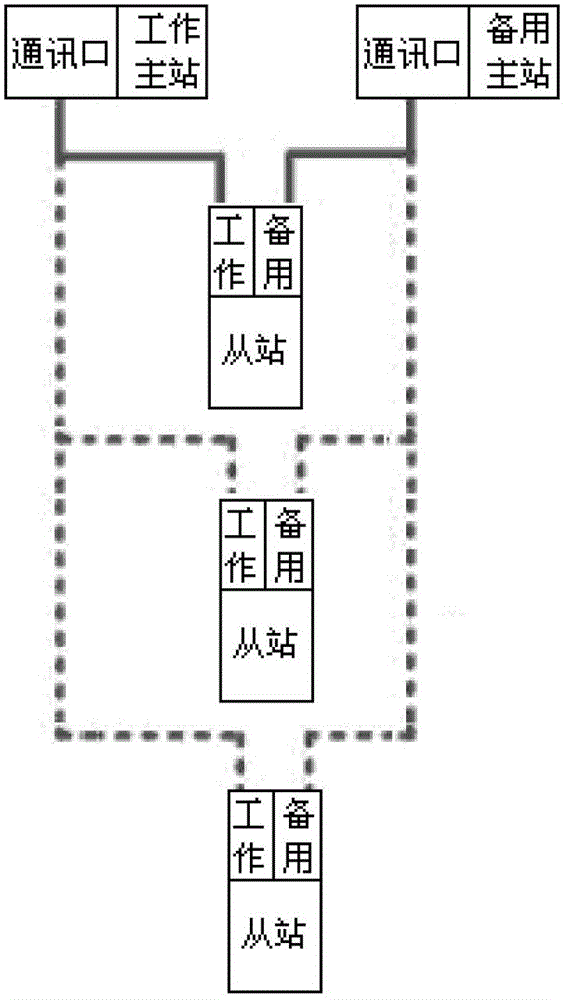

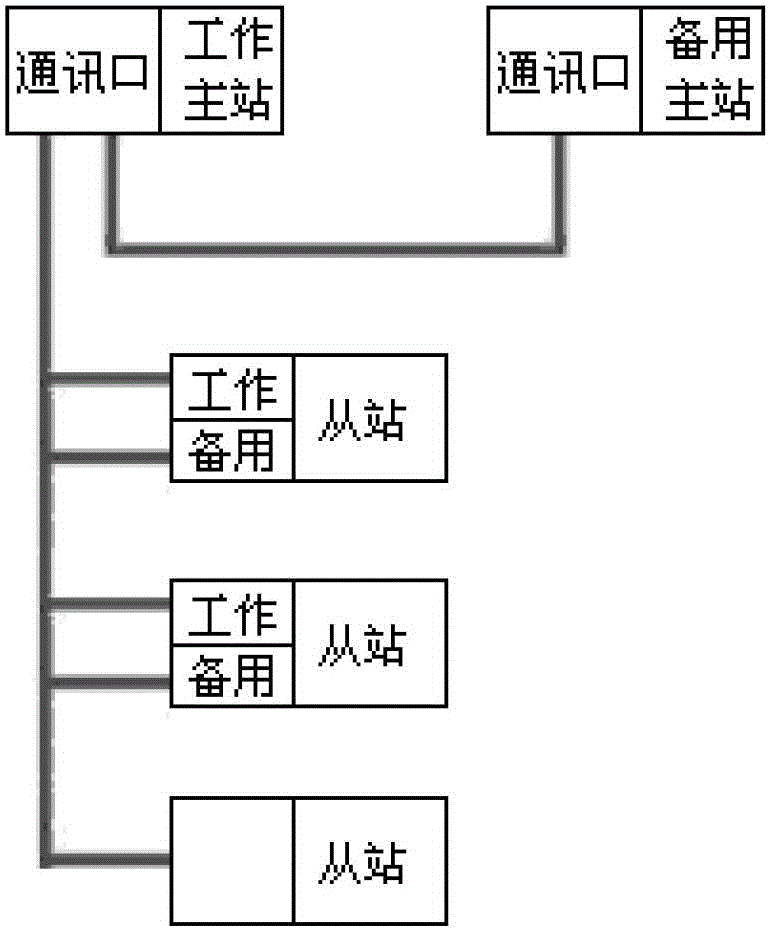

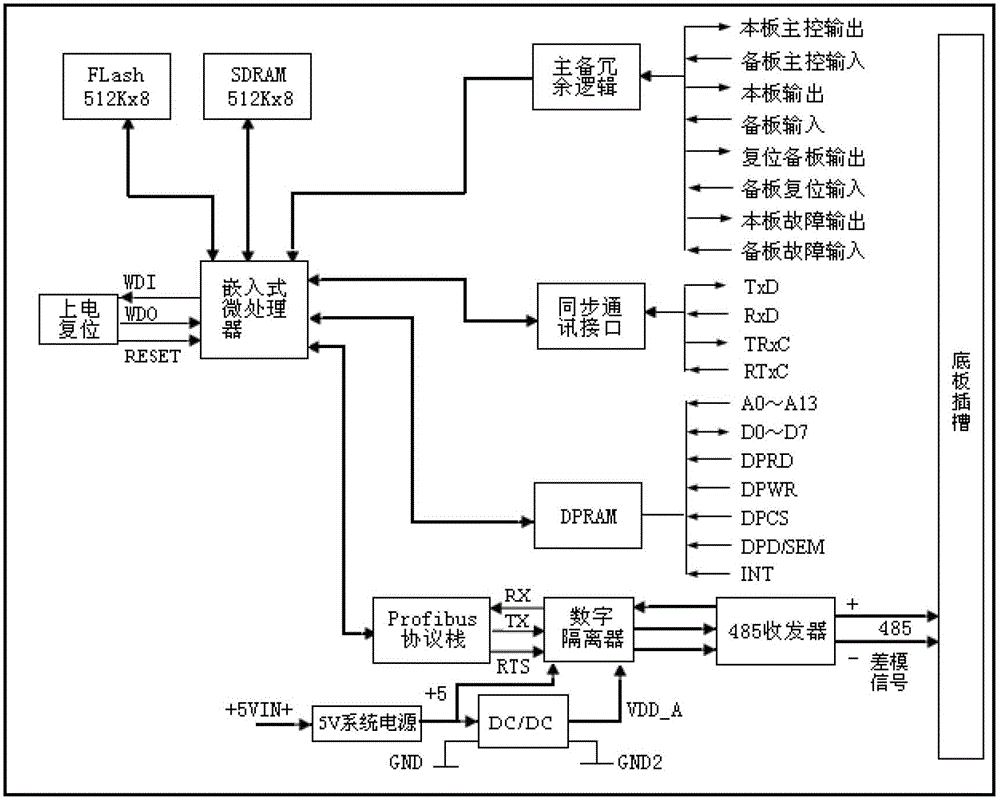

Profibus-DP communication protocol redundancy master station

InactiveCN102724092AAchieve interference-free switchingFor trouble-free data communicationBus networksMaster CardNetwork Communication Protocols

The invention discloses a profibus-DP communication protocol redundancy master station which comprises a master station communication card and a master station backup card; the master station communication card is in a working state, exchanges data with a slave station through a display port (DP) interface circuit, and exchanges data with a central processing card piece through a dual port RAM (DPRAM) interface circuit; the master card communication card periodically backs up the parameter set of the master station communication card and the real-time input / output (I / O) data of the slave station to the master station backup card; and the master station backup card is in a heat backup waiting state, takes over the work of the master station communication card when the master station communication card fails to work, and periodically receives the parameter set of the master station communication card sent by the master station communication card and the real-time I / O data of the slave station. According to the Profibus-DP communication protocol redundancy master station, a working master station is not required to work together with a backup master station, can be connected with a DP slave station or directly connected with the redundancy master station products of the DP slave station; and the defects caused by the redundancy method of an existing master station that the selection of master station products is greatly restricted and the cost is increased after the single-DP slave station is connected in are overcome.

Owner:XIAN THERMAL POWER RES INST CO LTD

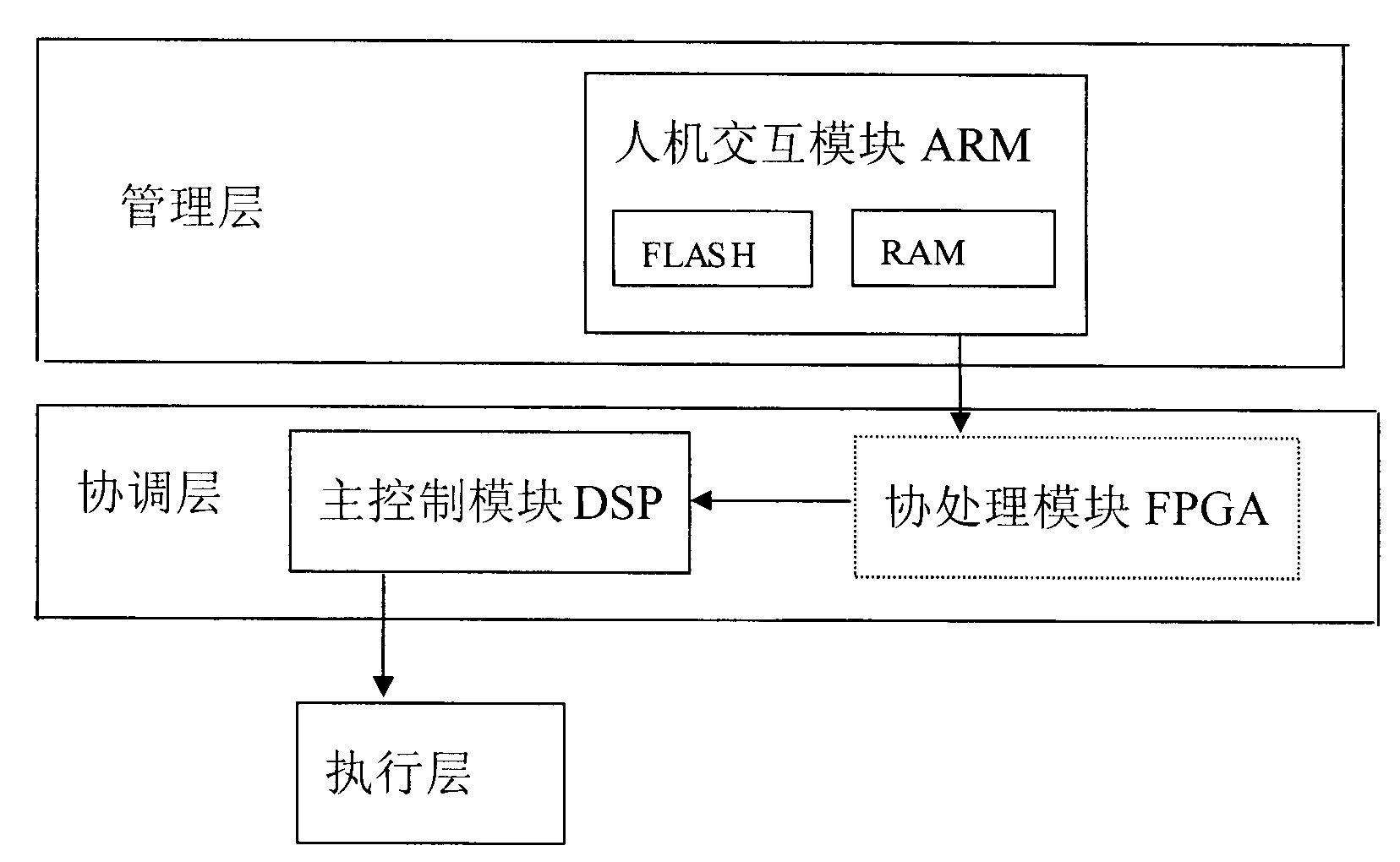

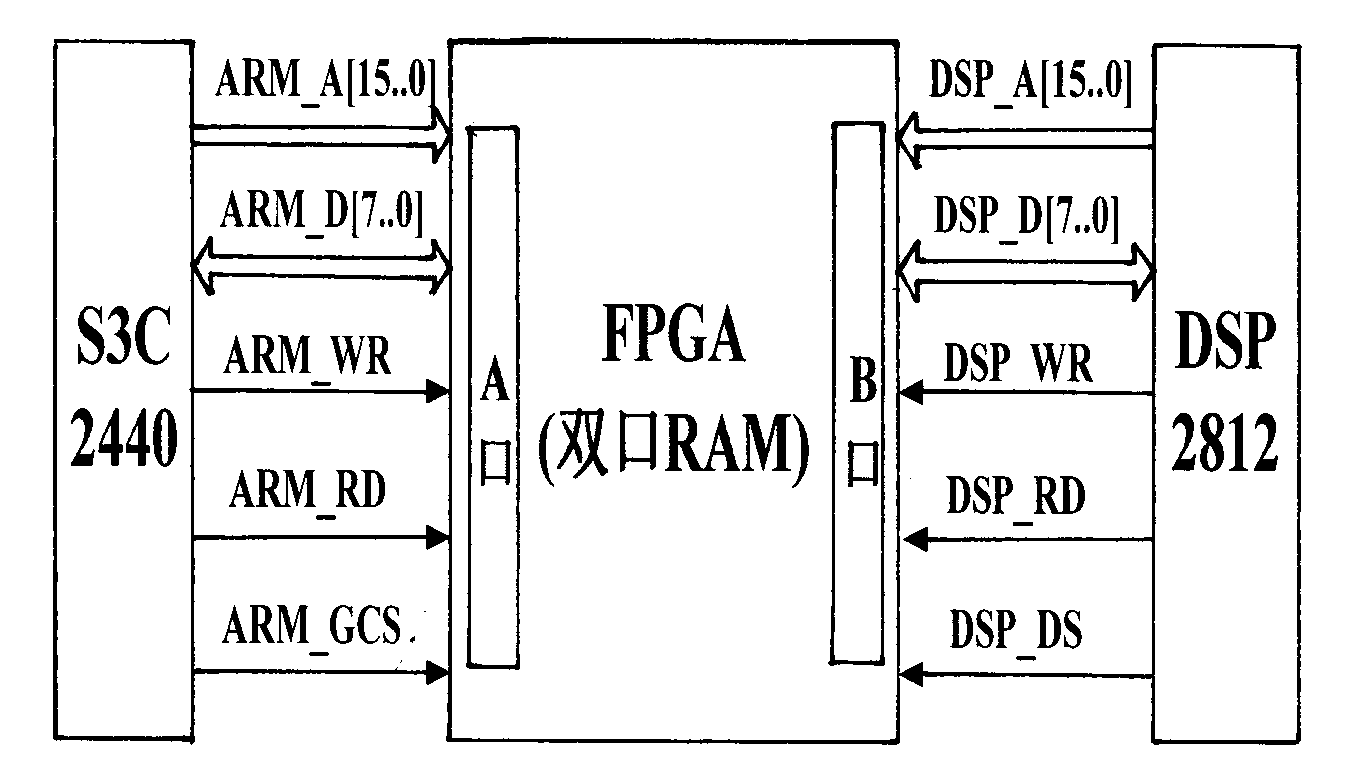

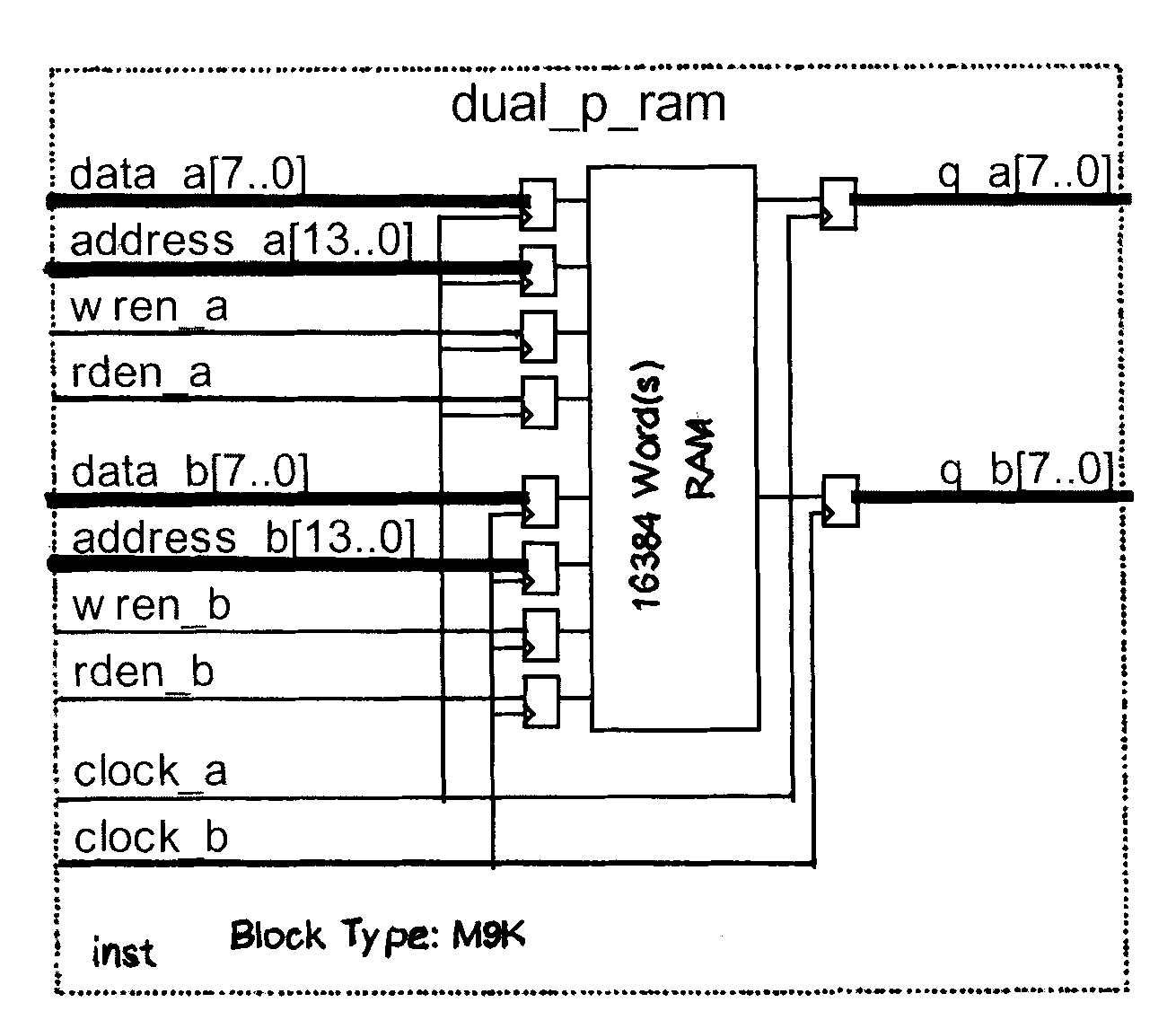

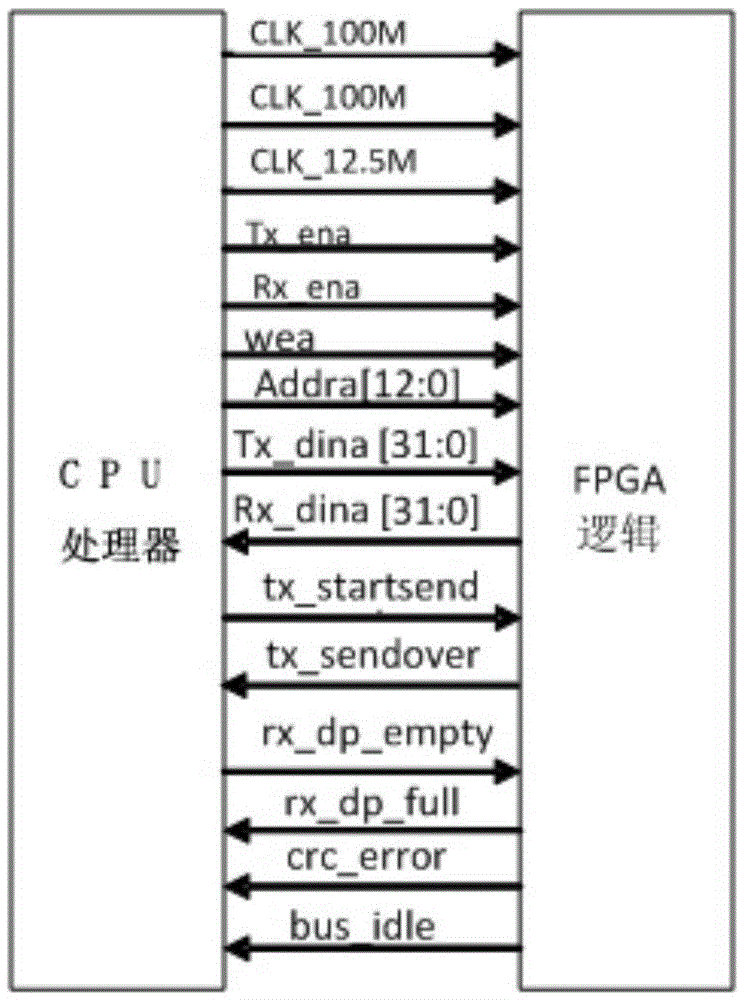

Flat machine numerical control system based on field programmable gate array (FPGA) high-speed communication method

InactiveCN101968642AHighly integratedImprove stabilityNumerical controlControl systemCoordination layer

The invention relates to a flat machine numerical control system based on a field programmable gate array (FPGA) high-speed communication method. The flat machine numerical control system comprises a management layer with an ARM module, a coordination layer with a DSP module and an FPGA module and an execution layer, and is characterized in that a dual-port RAM high-speed communication module is arranged between the ARM module and the FPGA module and is provided with independent valid read / write pins. The invention has the following obvious substantive characteristics: the dual-port RAM high-speed communication module is arranged and is provided with the independent read / write pins, so that signals of each layer are matched and are prevented from holding time and conflicting; and the data communication efficiency between the management layer and the coordination layer is improved by a method of adopting abundant logical resources in the FPGA module to realize dual-port RAM high-speed communication in a software programming mode, thus the weaving efficiency is improved. By adopting the control method of the control system, the communication speed is improved, and the control system has the characteristics of strong anti-interference performance, good generality and the like.

Owner:ZHEJIANG SCI-TECH UNIV +1

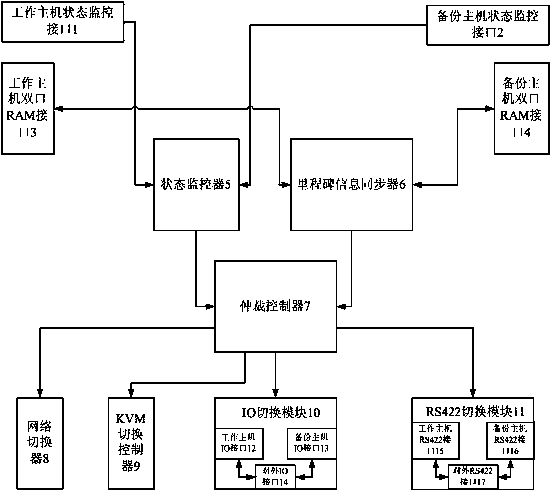

Arbitration device for double computer redundancy hot backup computer

InactiveCN104111881ARealize the arbitration functionMeet the control abilityRedundant hardware error correctionData synchronizationSynchronizer

The invention discloses an arbitration device for a double computer redundancy hot backup computer. The arbitration device for the double computer redundancy hot backup computer comprises an arbitration controller (7), a state control monitor (5) and a network switcher (8), and further comprises a milestone information synchronizer (6), an IO switching module (10), an RS422 switching module (11), a KVM switching controller (9), a work host computer dual port RAM interface (3) and a backup host computer dual port RAM interface. In the initial phase of booting the double computer redundancy hot backup computer, the arbitration device firstly confirms a host computer on duty between a work host computer and a backup host computer, and secondly performs booting synchronization. In the running process after booting the double computer redundancy hot backup computer, the arbitration device firstly performs task synchronization and data synchronization on the work host computer and the backup host computer, and secondly performs switching operation so as to obtain a work shift between the work host computer and the backup host computer. The arbitration device for the double computer redundancy hot backup computer meets the requirements of a display and control platform of a modern naval ship auxiliary device for manipulation ability and timeliness of the double computer redundancy hot backup computer.

Owner:706 INST SECOND RES INST OF CHINAAEROSPACE SCI & IND

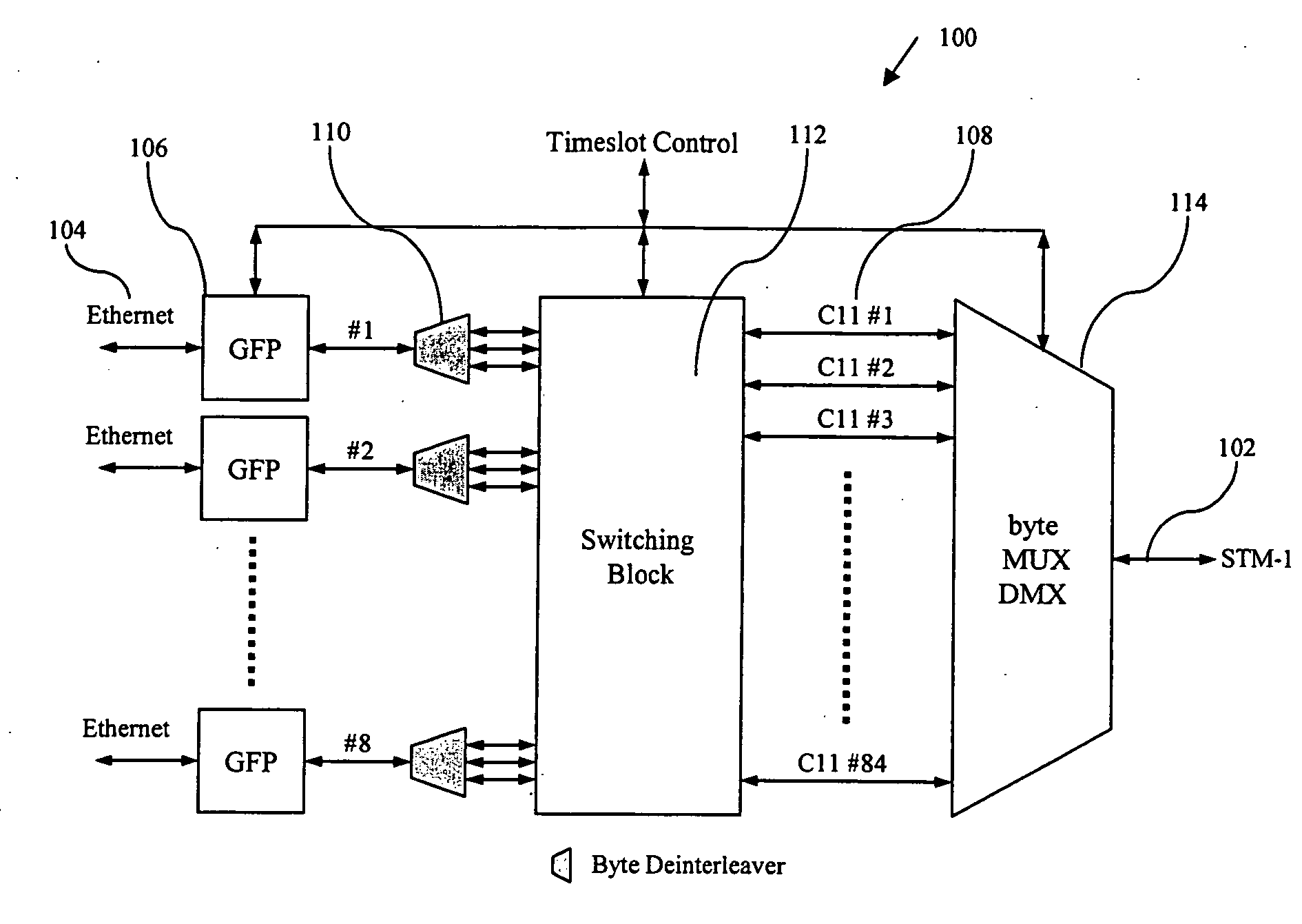

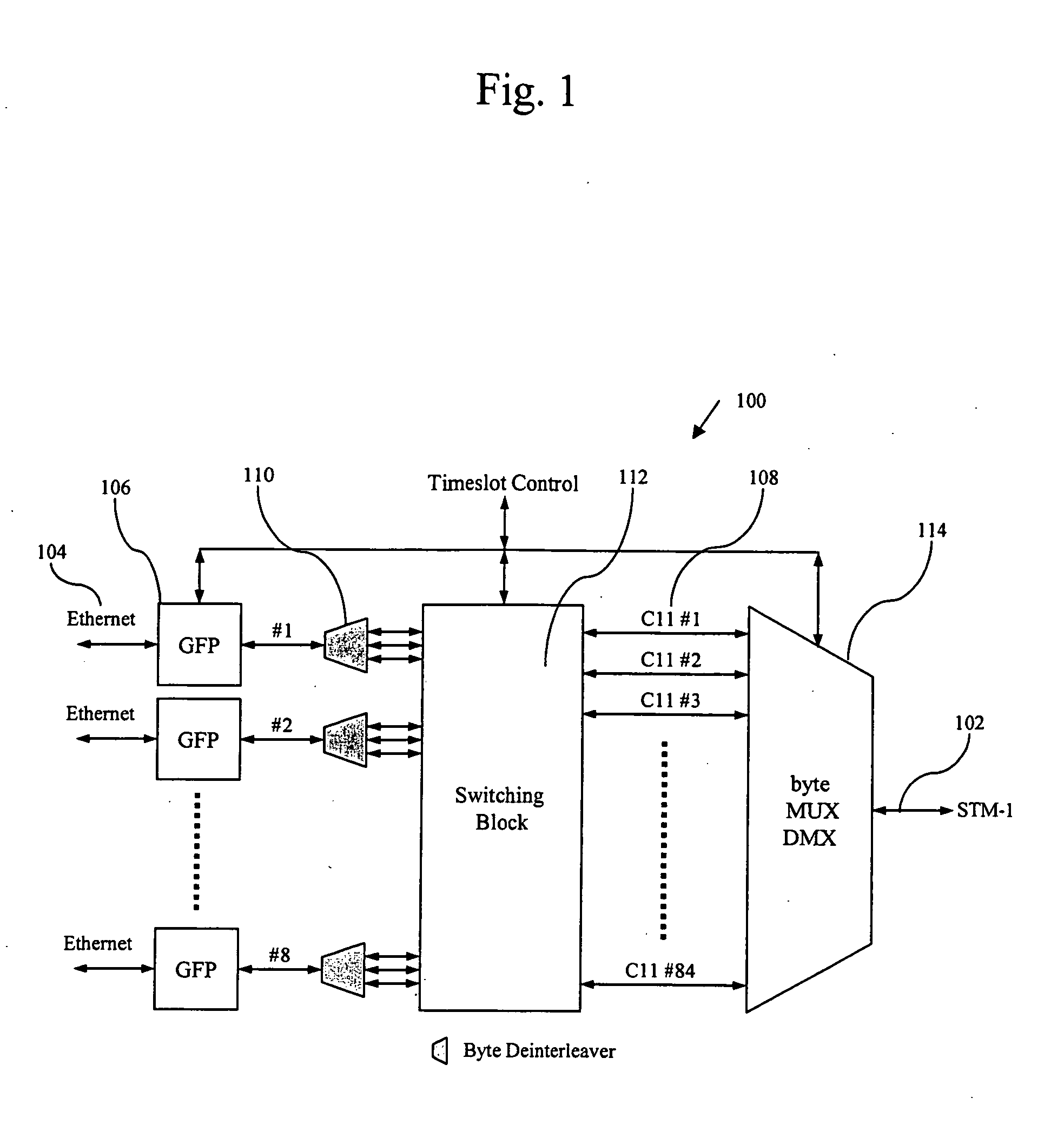

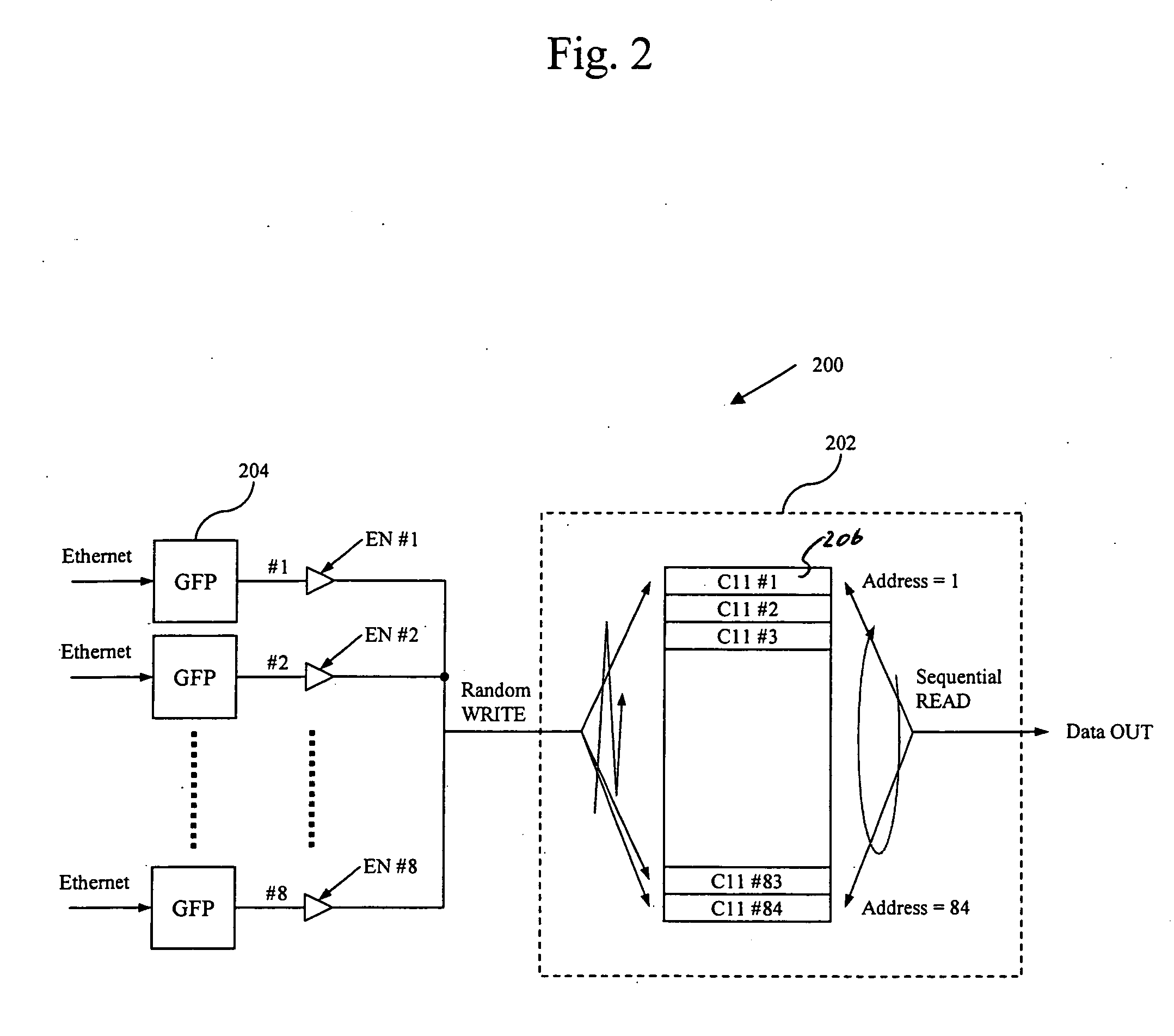

Mapping system of virtual concatenation group signals

InactiveUS20060126641A1Efficient mappingSmall sizeTime-division multiplexWide area networksFiberStorage area network

An interface system is capable of transmitting packet data or non-continuous data through a network that is adapted to transmit continuous data. In particular, the interface system is directed to transmitting data from Ethernet, Storage Area Network (SAN), and / or Digital Video Broadcasting (DVB) signals through a SONET fiber optics system. The interface system uses a Virtual Concatenation Group (VCG) signal to match the transmitting signal's bandwidth and effectively map it on to SONET / SDH frame. The interface system applies VCG mapping related to low order virtual container signals, VC-11 and VC-12 and higher order virtual container signals, VC-3 and VC-4. Likewise, the interface system may allow packet data to be transmitted through SDH configured network. The interface system may also use DPRAM (dual-port RAM) as the basic element of VCG mapping for the physical embodiment of VCG to reduce the size of the circuit. The interface system may also use two or more memories to prevent read / write collision that may occur when the input and output addresses are the same.

Owner:PONTUSYS

Multichannel FILO data buffer storage devices

InactiveCN1439966ASave resourcesSimplify complexityMemory adressing/allocation/relocationData storingFpga design

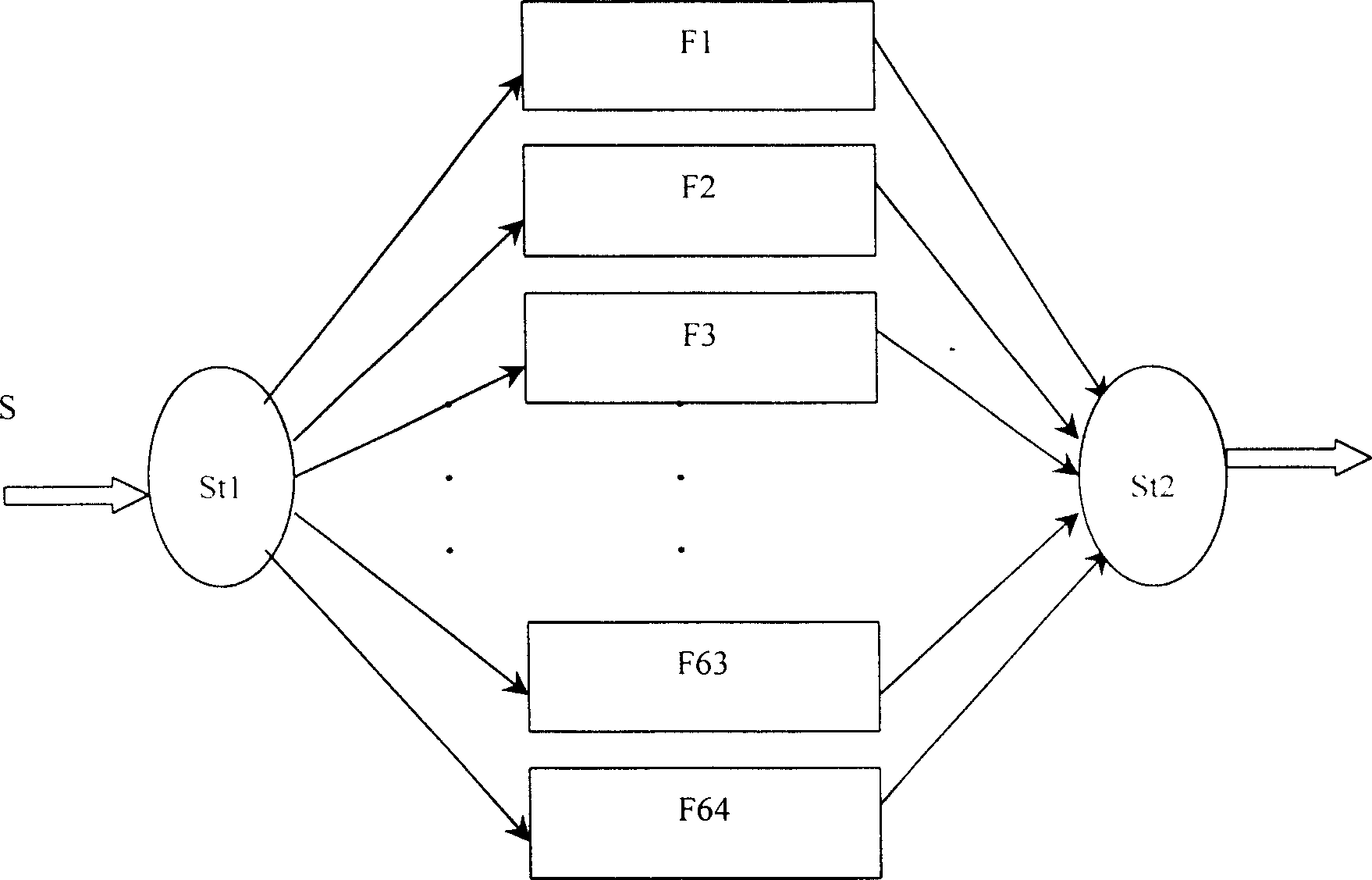

A data buffer storing device of first in first out with multichannel, used for carrying on FIFO data buffering for each of buffering data coming from the multichannel includes data storing unit, read / write pointer control unit and state labelling unit, of which the data storing unit only applies a dual port RAM (R1) and the read / write pointer control for each channel is also integrated separately into one read / write pointer control unit so as to decrease the resources for a large number of read / write pointer counter as well as to simplify the complicacy of interface logic.

Owner:HUAWEI TECH CO LTD

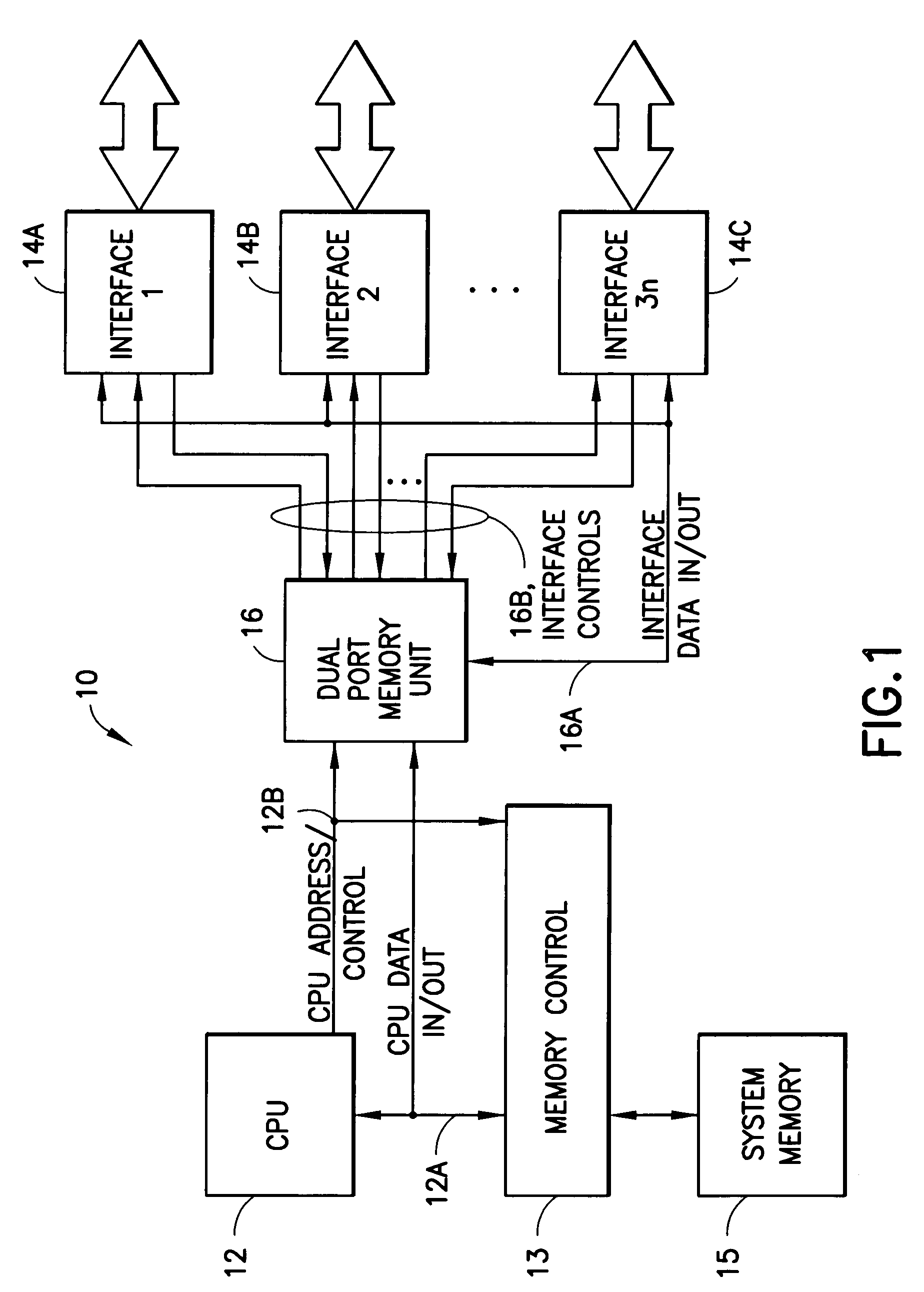

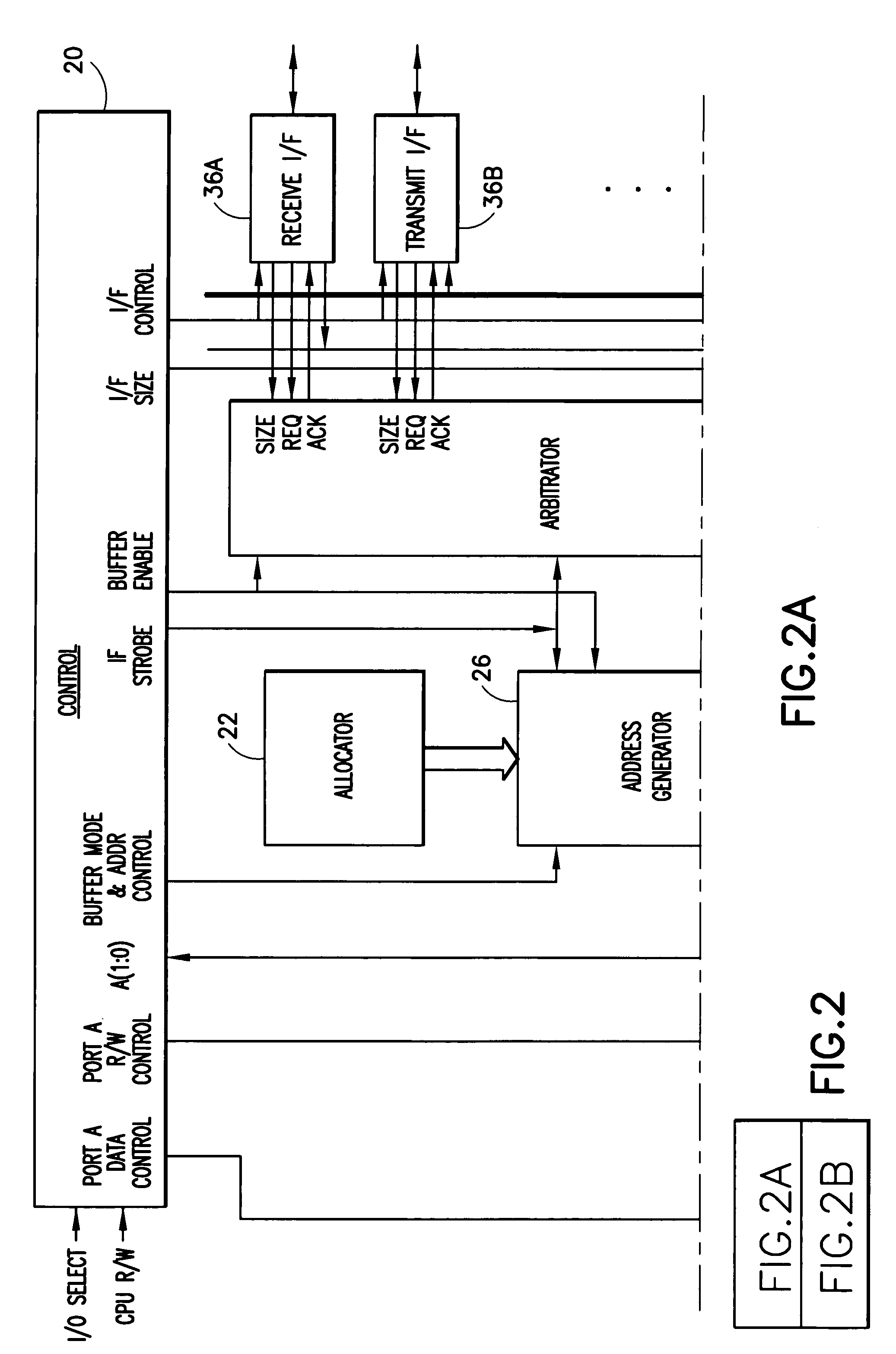

Programmable CPU/interface buffer structure using dual port RAM

InactiveUS7054986B2Selectively enablingUnauthorized memory use protectionInput/output processes for data processingChannel dataMemory address

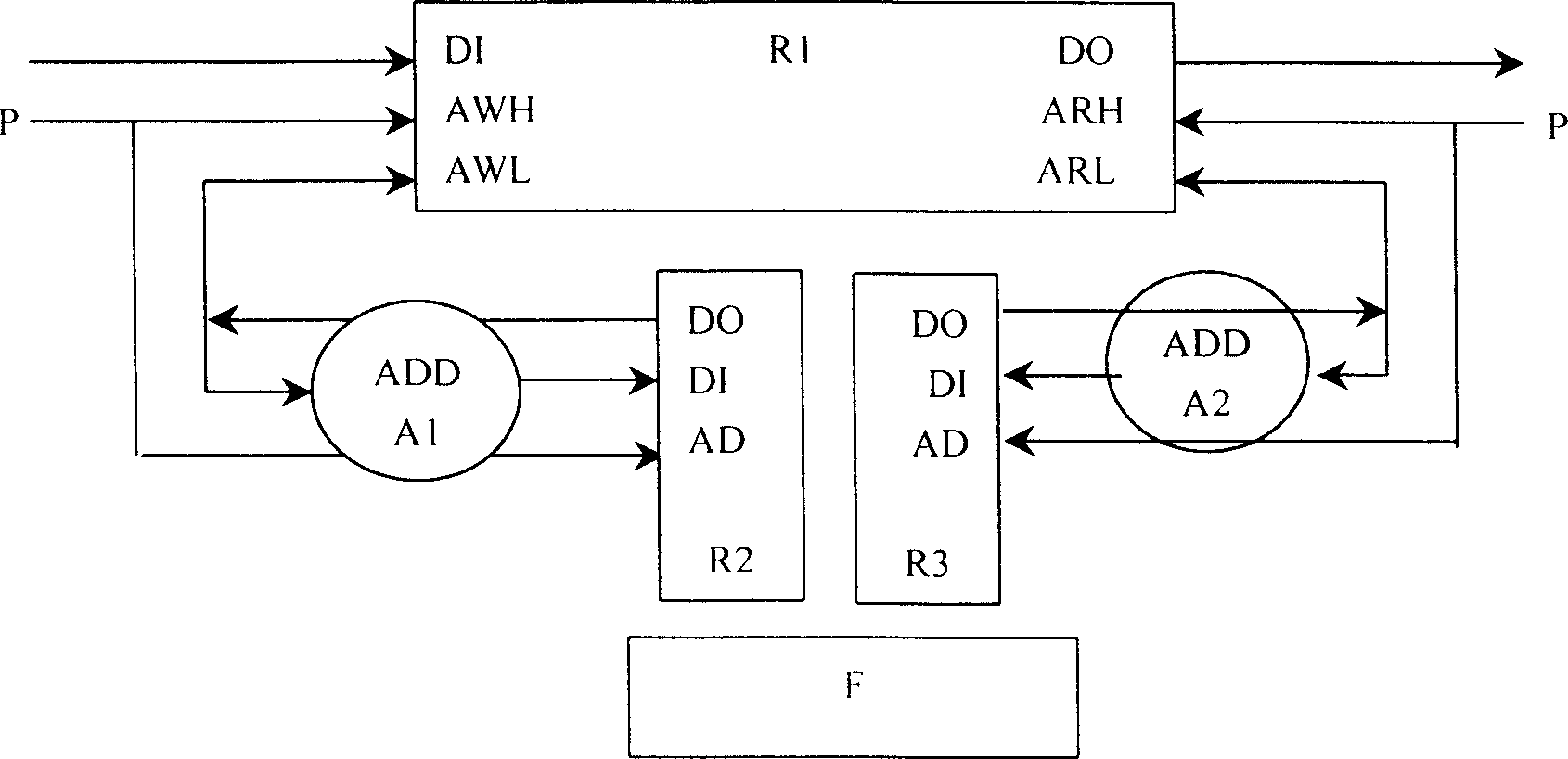

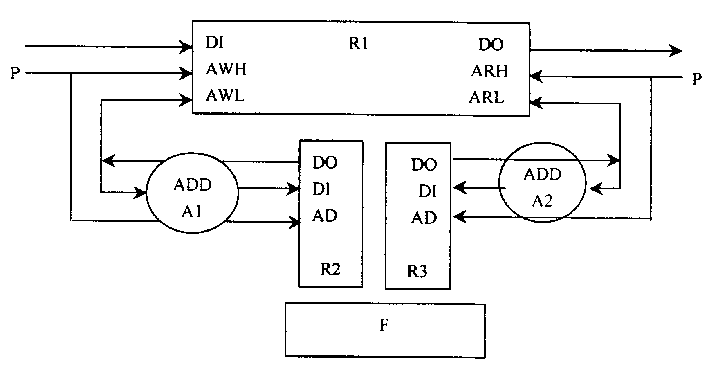

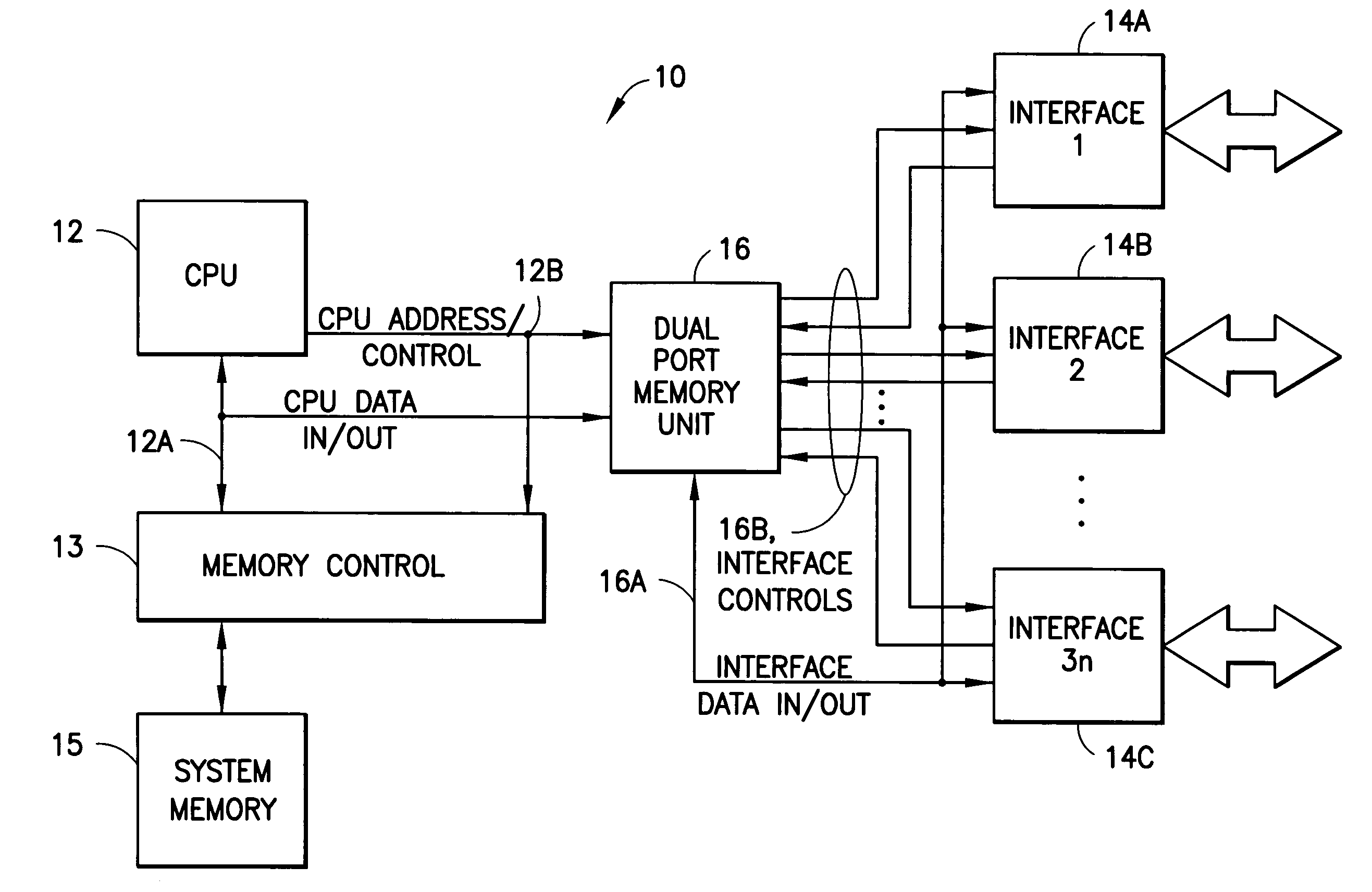

Disclosed is a programmable buffer circuit (16) for interfacing a CPU (12) to a plurality of channel interfaces (14). The buffer circuit includes a dual port memory (18) having a first port coupled to a CPU data bus and a second port coupled to a channel data bus that serves the plurality of channel interfaces. The buffer circuit further includes an arbitrator (24) for arbitrating access to the dual port memory by individual ones of the channel interfaces over the channel data bus; an address generator (26) for generating dual port memory addresses for reading and writing data using the CPU data bus and the channel data bus; and a control unit (20) and allocator (22) that are programmable by the CPU for specifying individual ones of buffer locations and sizes within the dual port memory for individual ones of the channel interfaces, and for enabling and disabling individual ones of the buffers.

Owner:NOKIA MOBILE PHONES LTD +1

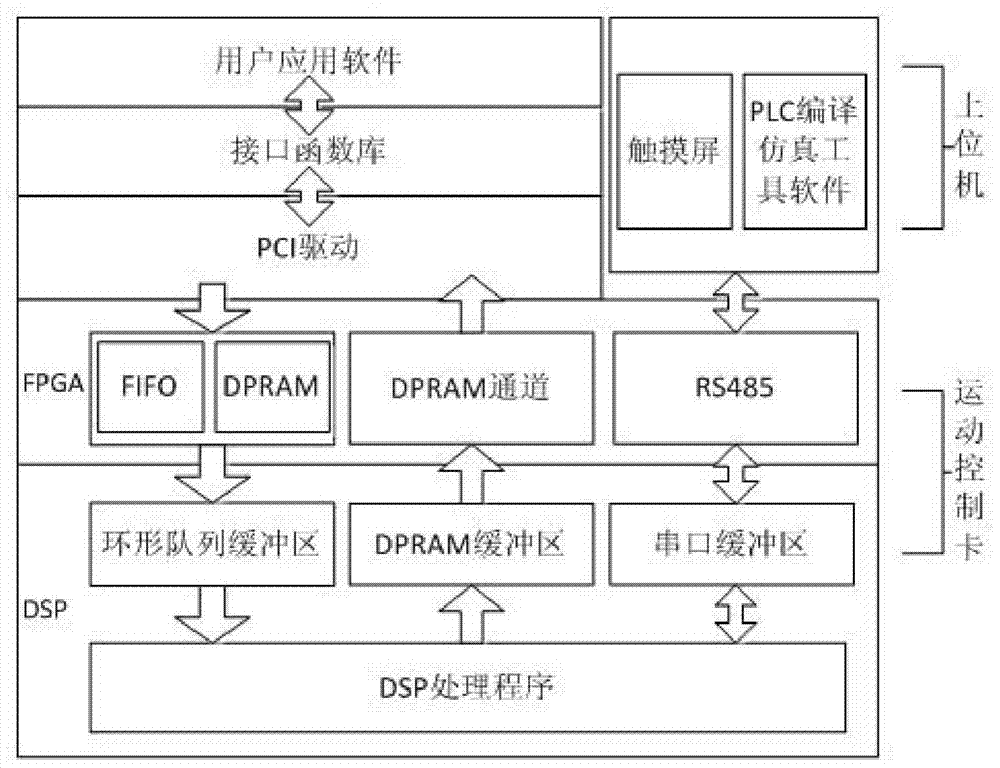

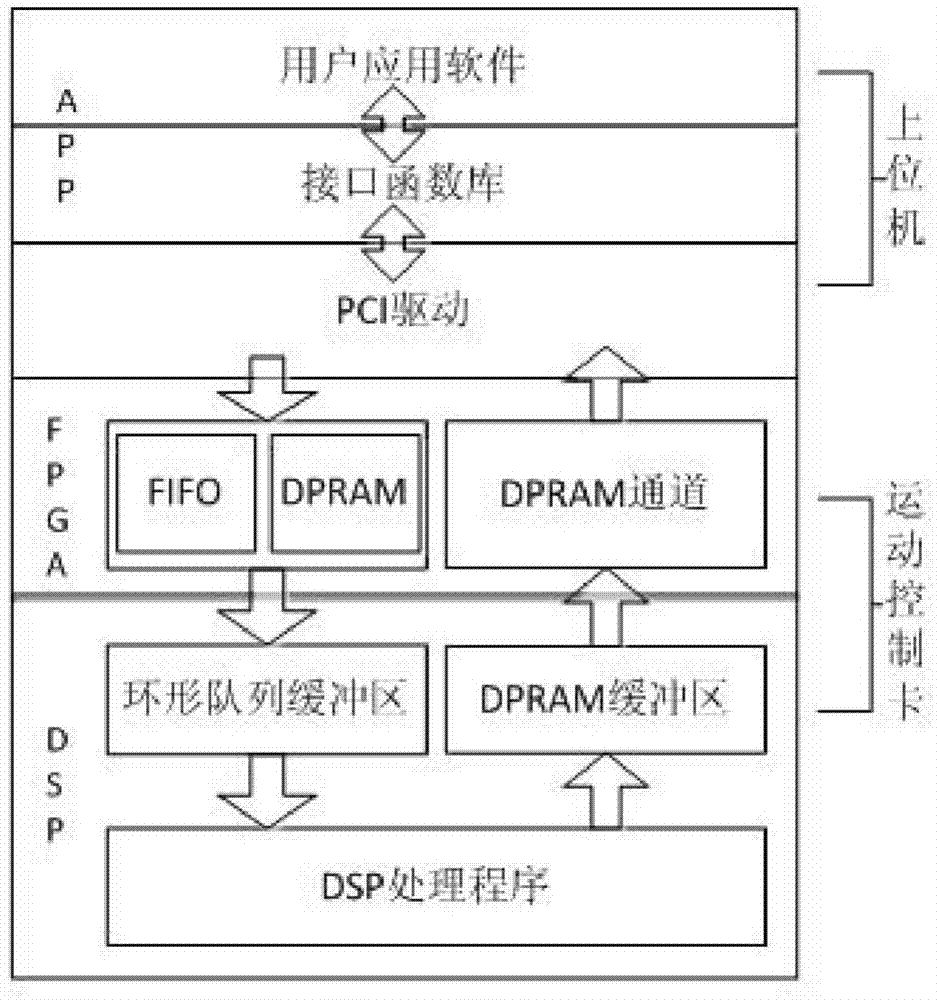

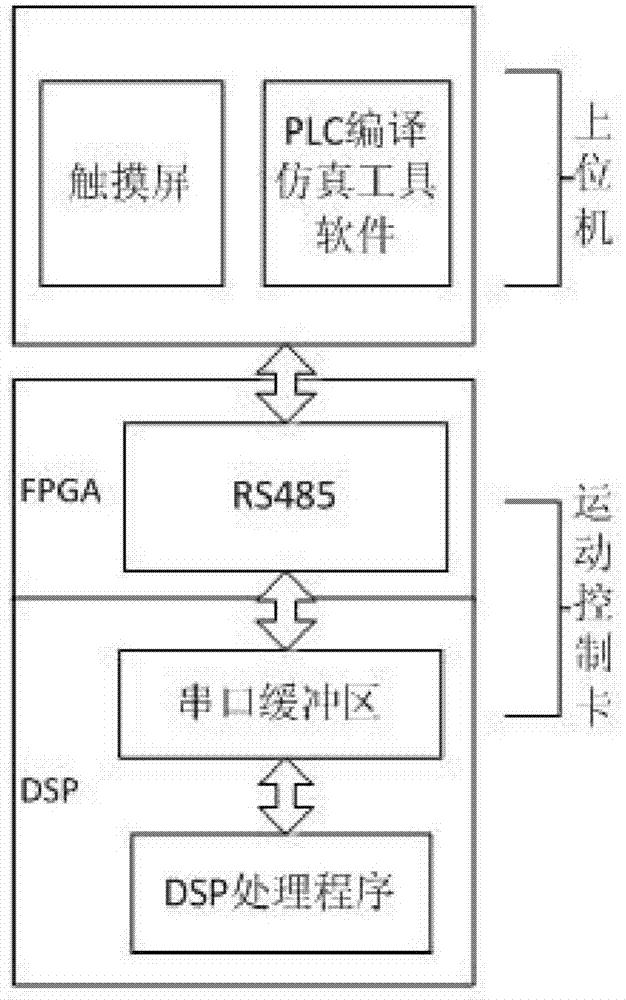

Multi-axis motion control system and control method thereof

InactiveCN103941648AHighly integratedRealize classification transmissionNumerical controlPci interfaceControl system

The invention discloses a multi-axis motion control system and a control method of the multi-axis motion control system, and relates to the field of mechanical design and the automation technology of the mechanical design. The control system comprises an upper computer, a multi-axis motion control card and an execution mechanism. The upper computer is used for issuing motion commands and receiving and displaying state information of the motion control card. The multi-axis motion control card is used for receiving the motion commands issued by the upper computer and achieving interface communication, pulse output, I / O state management, axis trajectory planning and PLC calculation execution according to the commands. The execution mechanism is used for receiving pulse signals output by the multi-axis motion control card and driving multi-axis motion according to the pulse signals. By the adoption of the system and the method of the system, the programmable characteristic of an FPGA in the motion control card is fully utilized, and PCI interface chip IP cores are integrated; due to the fact that a buffer module with an FIFO channel and dual-port RAM channels is provided, the integration level of the motion control card is increased, and data classification transmission is achieved.

Owner:东莞市升力智能科技有限公司

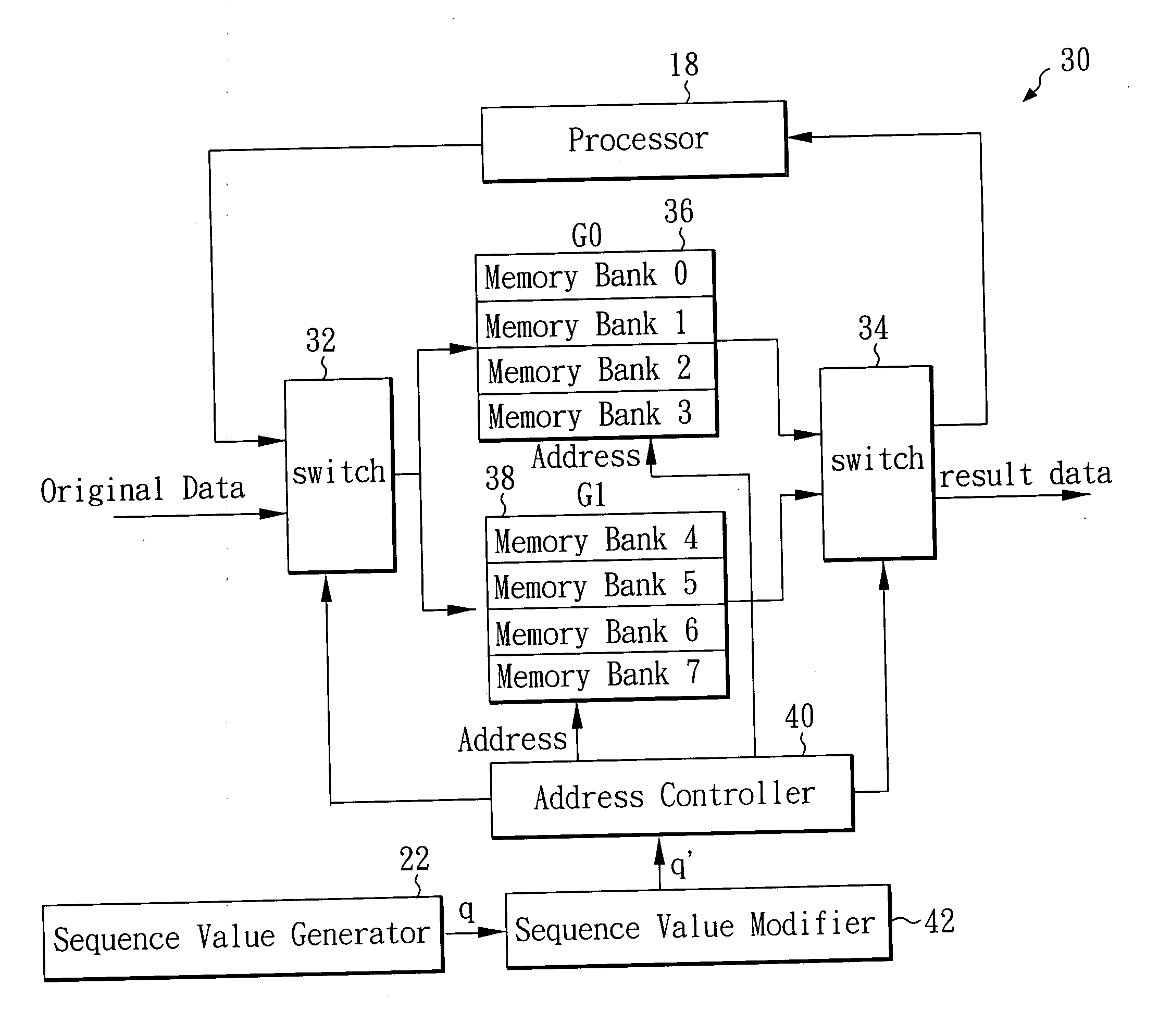

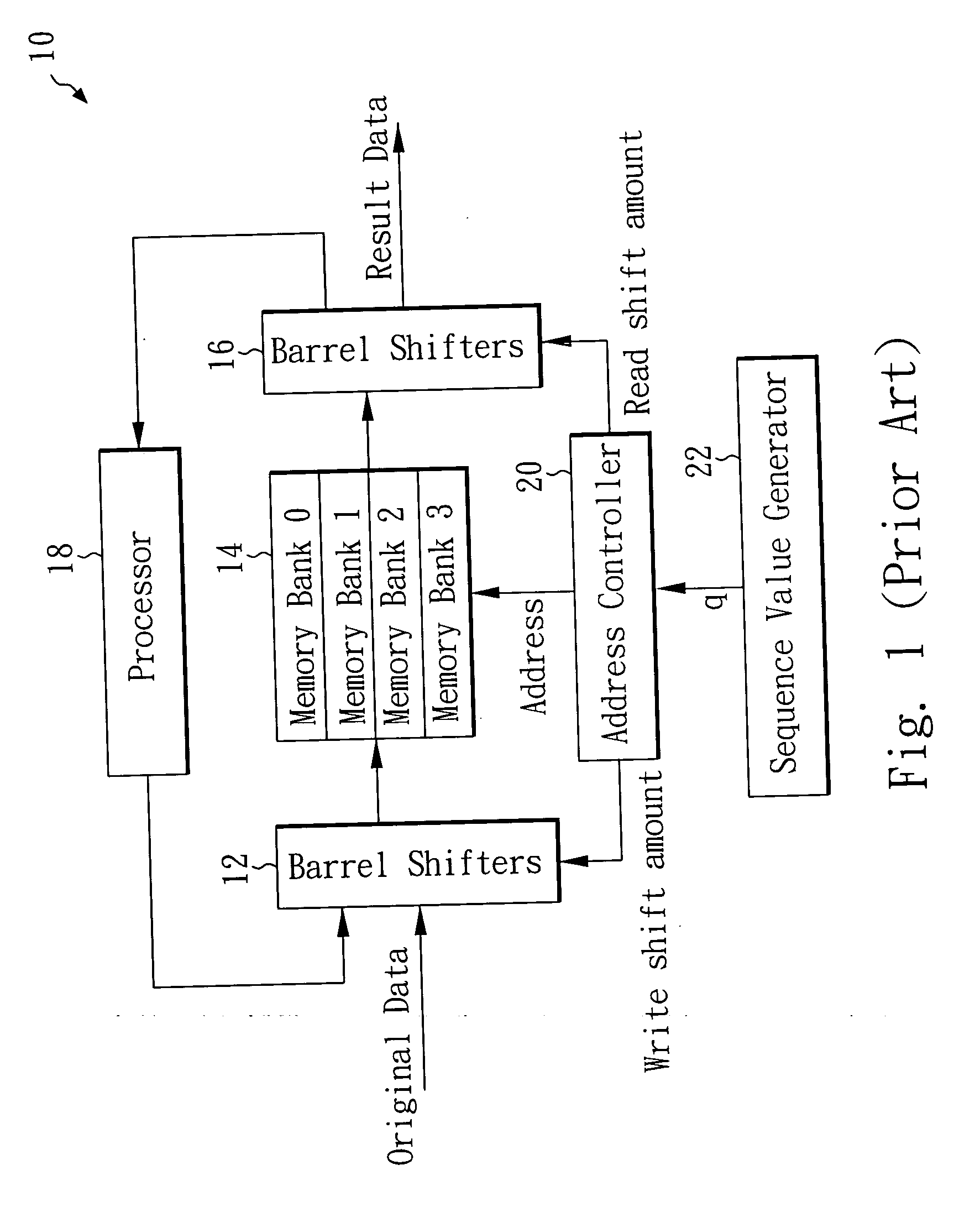

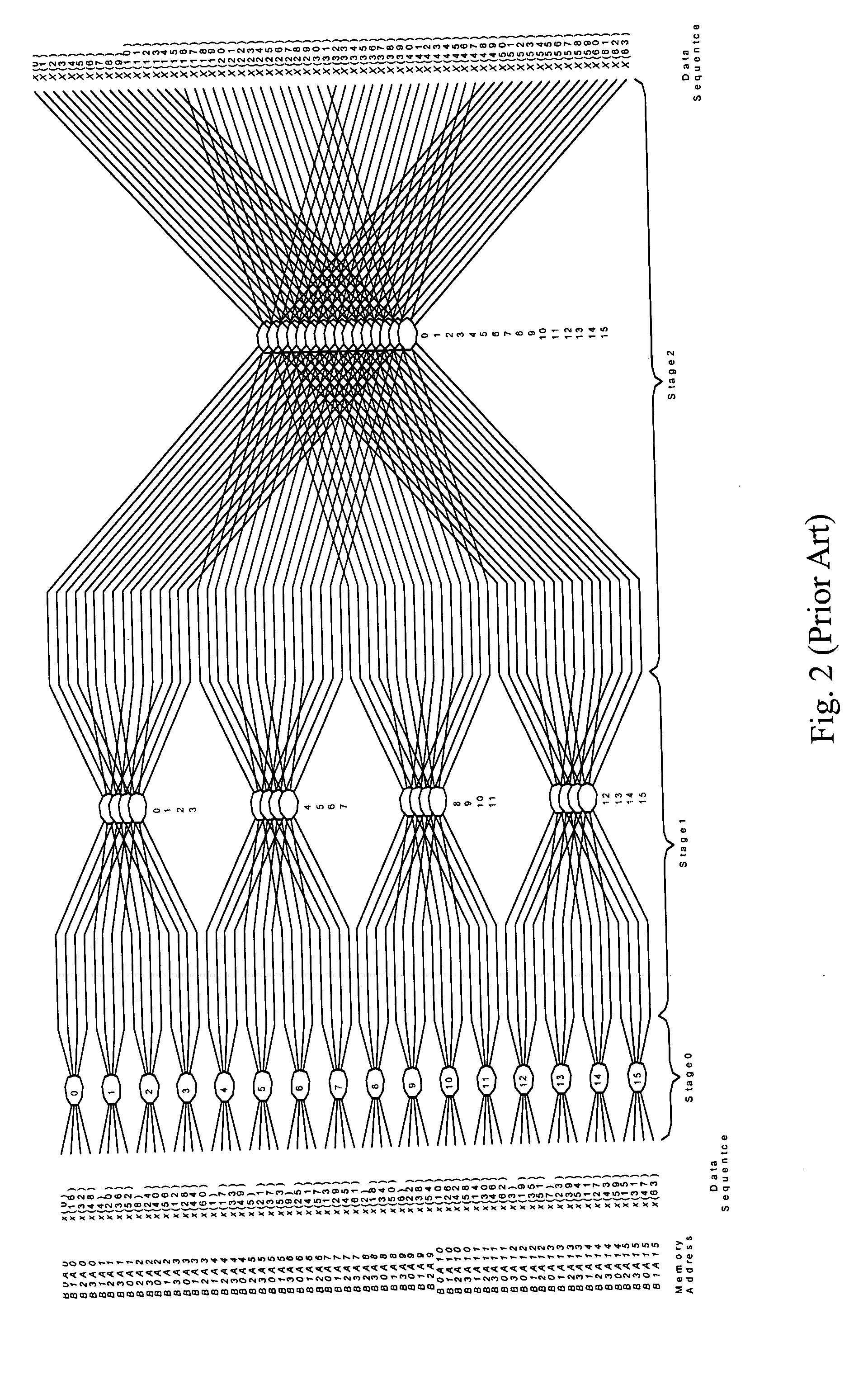

Memory-based Fast Fourier Transform device

InactiveUS20060253514A1Reduce circuit areaMemory adressing/allocation/relocationDigital computer detailsFast Fourier transformTransformer

A memory-based Fast Fourier Transform device is provided, which adopts single-port random access memory (RAM), rather than dual-port RAM, as a storage, and the circuit area of the FFT device is therefore reduced. In order to enhance the access efficiency of the memory and the use efficiency of a processor, the transformer adopts a modified in-place conflict-free addressing to achieve similar performance of a traditional Fast Fourier Transform device.

Owner:IND TECH RES INST

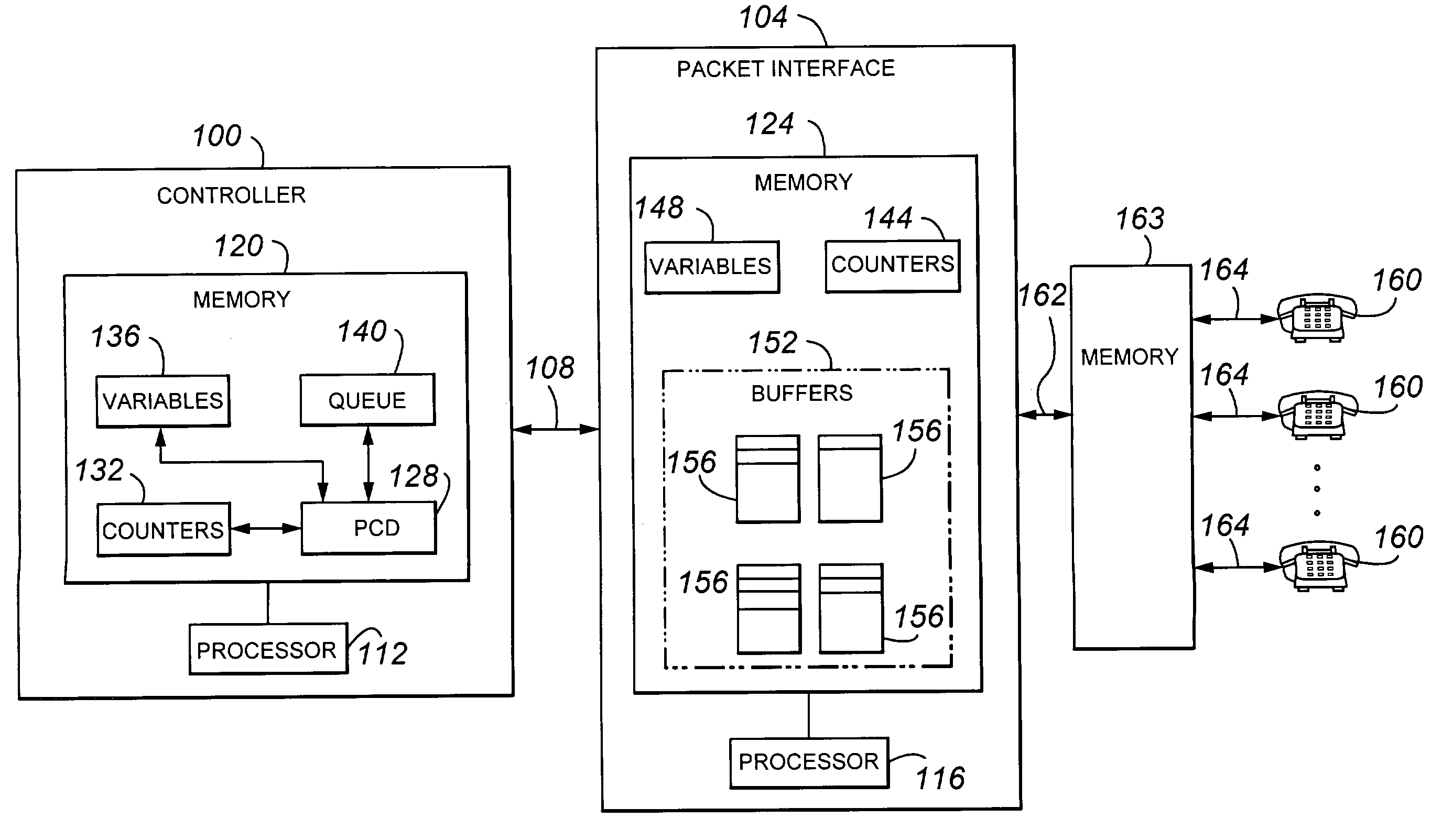

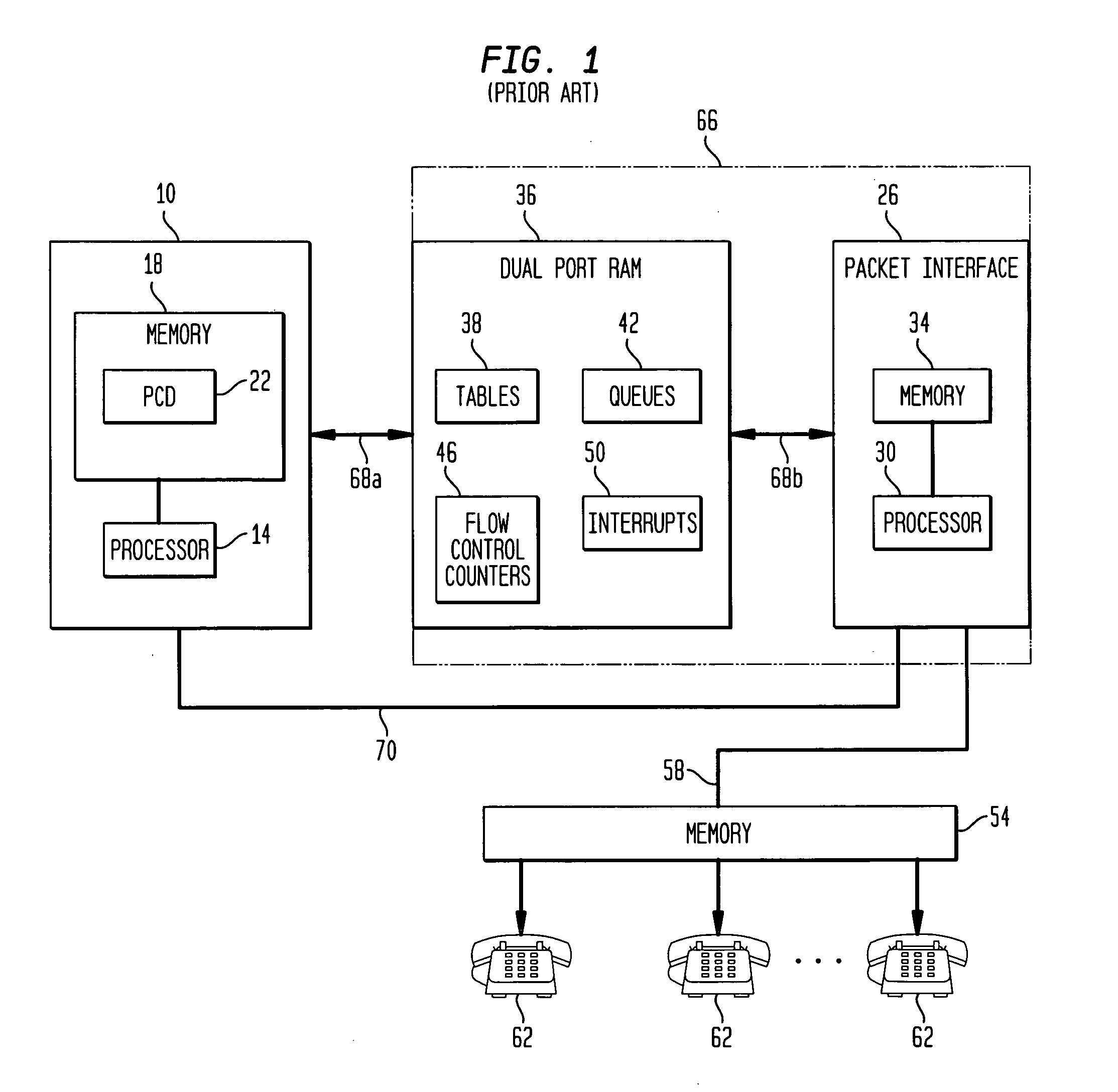

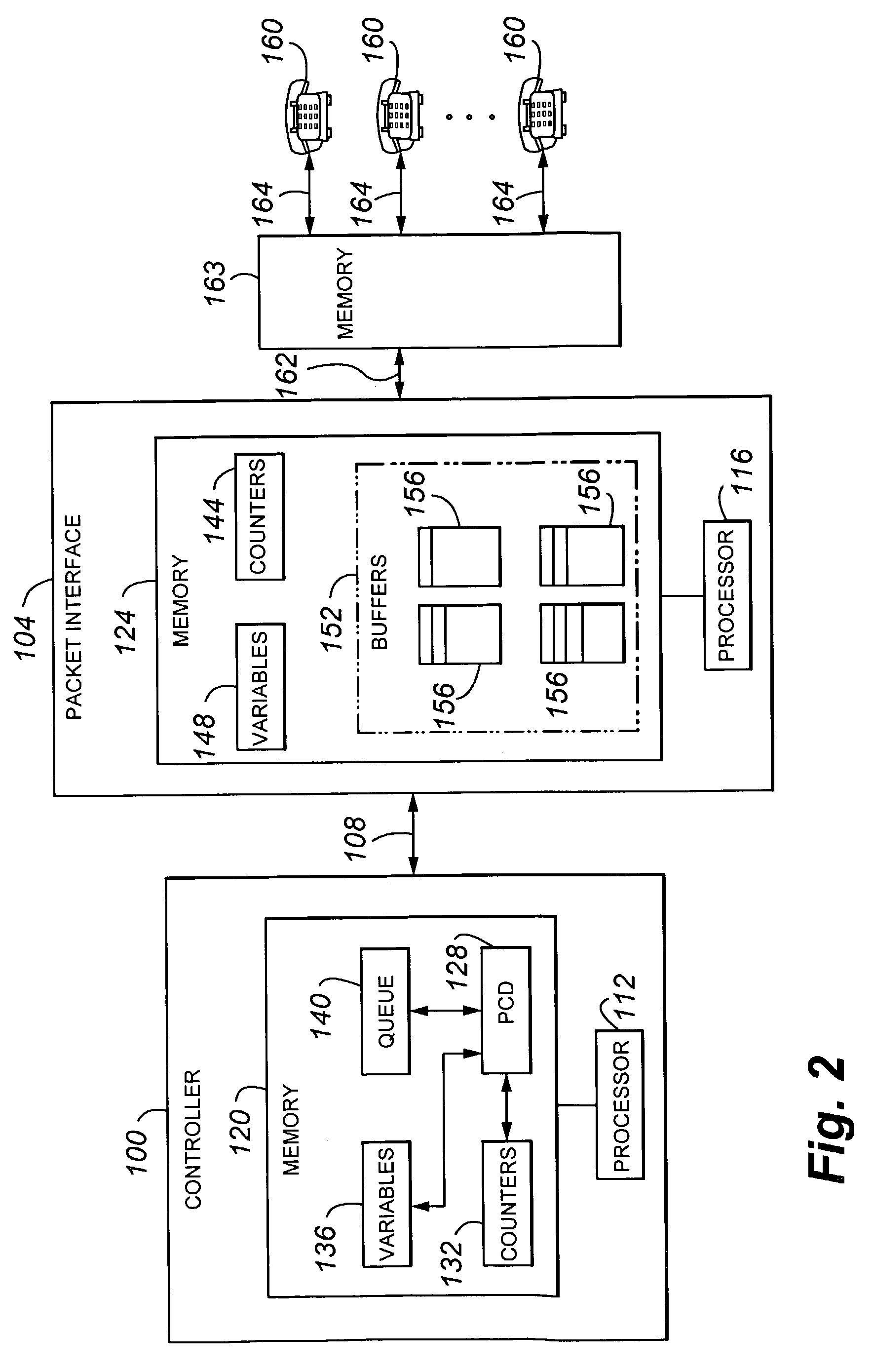

Message format and flow control for replacement of the packet control driver/packet interface dual port RAM communication

InactiveUS6944129B1Removing hardware dependencyLow costEnergy efficient ICTError preventionTraffic capacityCommunication endpoint

The architecture of the present invention provides a new message set and / or flow control mechanism and a networked architecture for managing telecommunication devices such as telephones, fax, voicemail, e-mail, and other communication endpoints. The new message set and flow control mechanism maps to existing (conventional) dual port RAM queues, tables, interrupts, and other memory locations, thus removing hardware dependency on the packet control driver / packet interface communications and allowing control of LAPD links to be remoted.

Owner:AVAYA INC

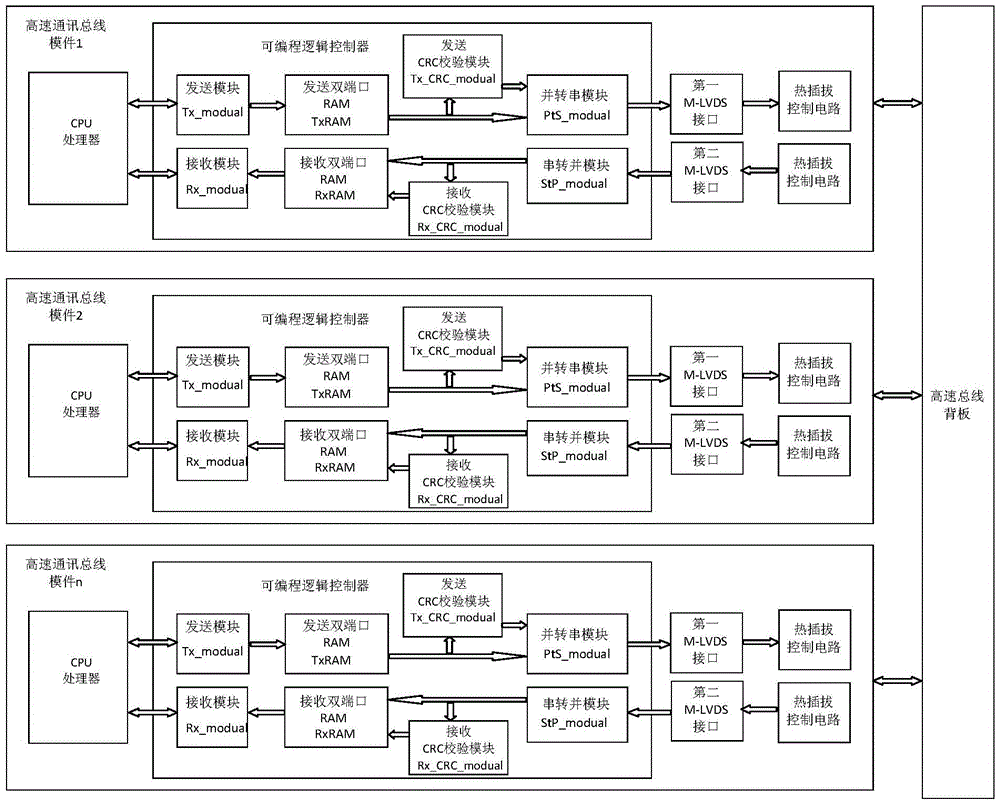

High speed backboard bus communication control device and method

InactiveCN105573239AWon't impactImprove utilization efficiencyProgramme control in sequence/logic controllersProgrammable logic controllerSerial module

The invention discloses a high speed backboard bus communication control device. The high speed backboard bus communication control device comprises a CPU, a programmable logic controller (PLC), a first M-LVDS (Multipoint low Voltage Differential Signaling) interface, a second M-LVDS interface, a first hot swap control circuit and a second hot swap control circuit, wherein the PLC includes a transmission module, a transmission dual-port RAM, a transmission CRC verification module, a parallel-to-serial module, a serial-to-parallel module, a reception CRC verification module, a reception dual-port RAM and a reception module. The high speed backboard bus communication control device and method utilize an M-LVDS as the transmission level, so that a communication rate more than 100Mbps and even higher can be realized. And at the same time, when a module performs hot swap, a power supply hot swap circuit guarantees that hot swap of the module does not cause impact of the power supply for the module and other on-line modules so as to guarantee normal working of the system; and hot swap for the bus can be automatically identified, so that different bus scanning flows can be started and the utilization efficiency of the bus can be improved.

Owner:NANJING NARI GROUP CORP +1

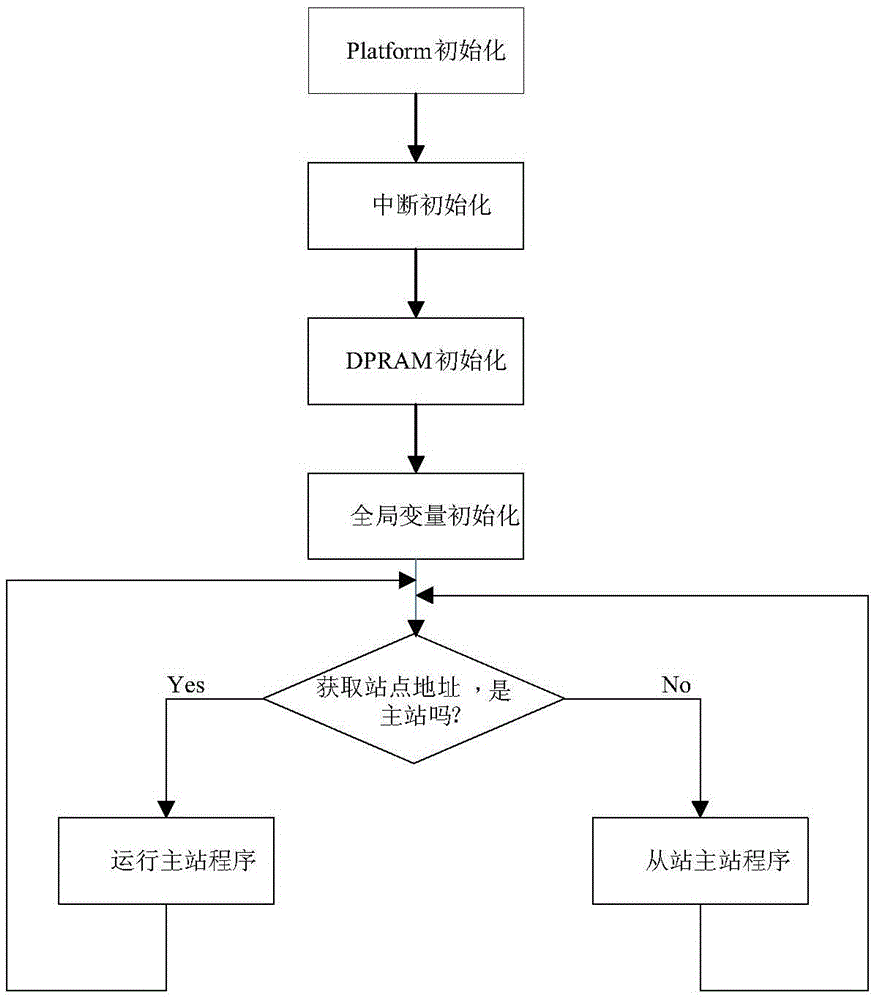

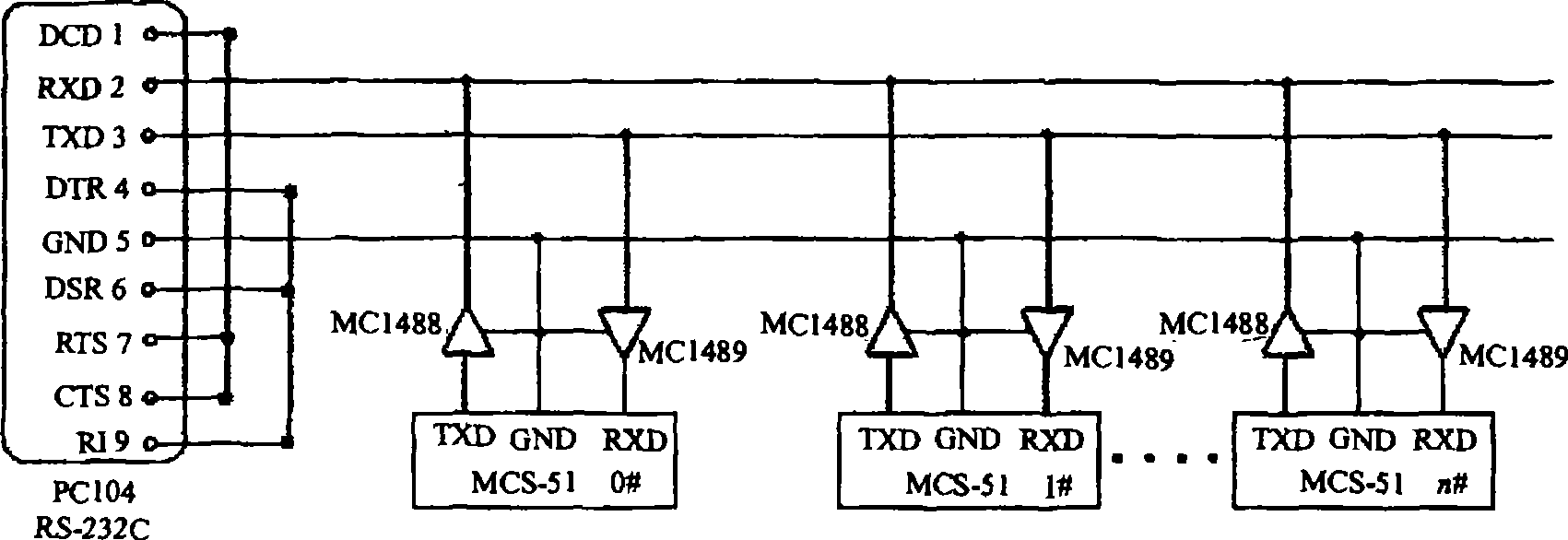

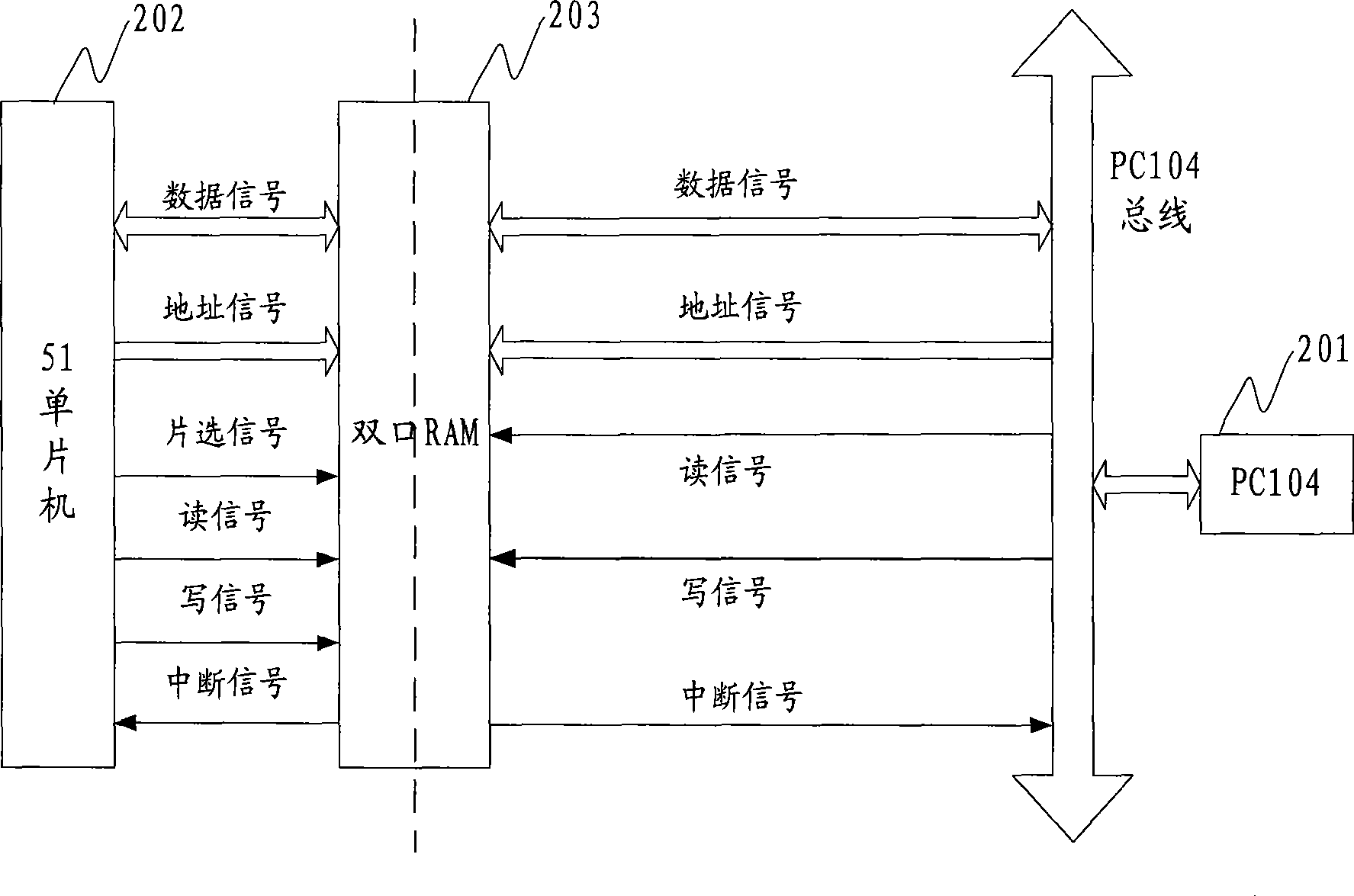

Master-salve distributed system and parallel communication method applying the same

InactiveCN101414291AEfficient accessA large amount of data is transferredDigital computer detailsTotal factory controlMicrocomputer systemProgrammable logic device

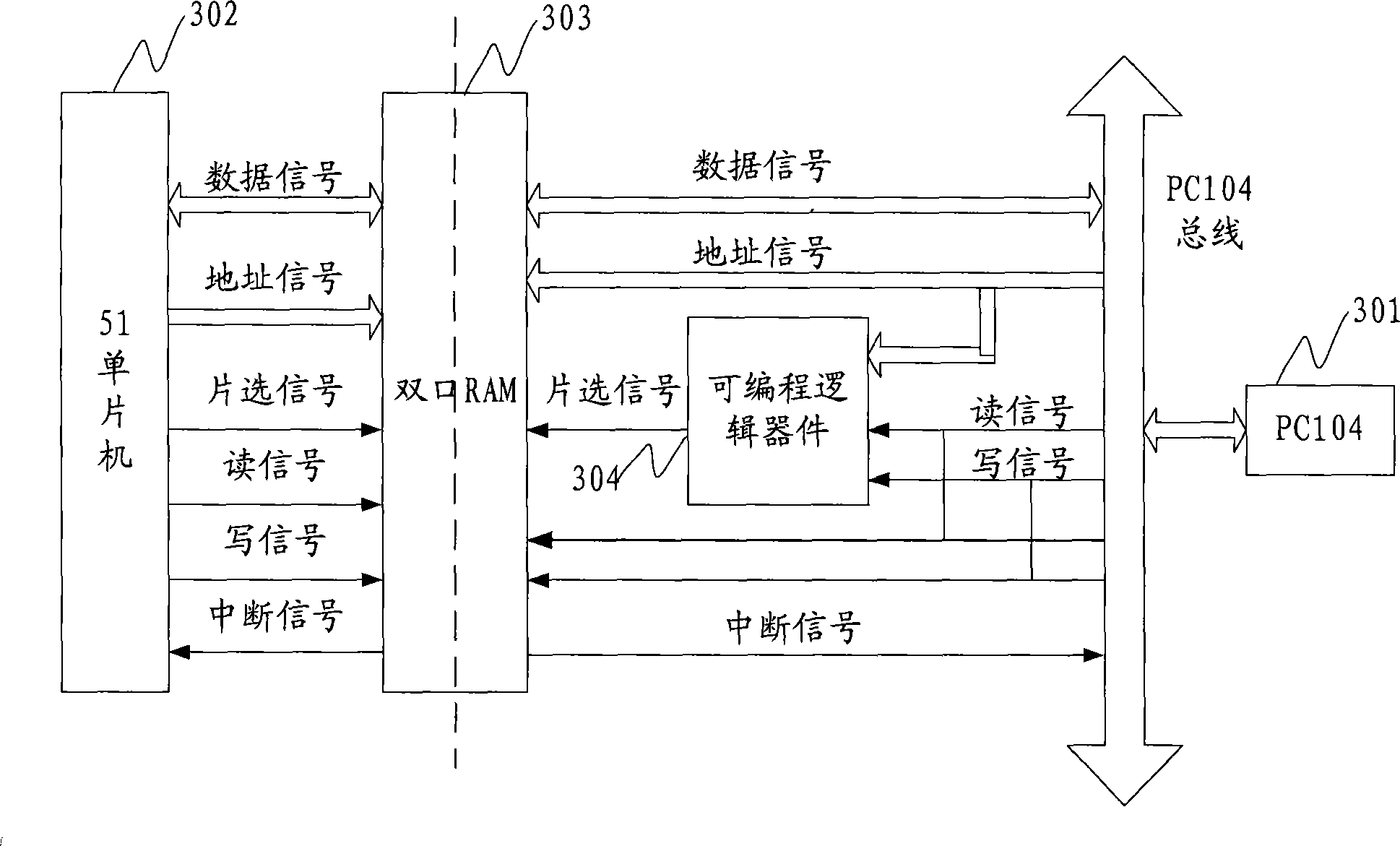

The invention provides a master-slave distributed system which comprises a master system consisting of PC104 modules, and slave systems consisting of a plurality of 51 single-chip microcomputers. A dual-port RAM is taken as a buffer area for data interaction between the master system consisting of the PC104 modules and the slave systems consisting of a plurality of 51 single-chip microcomputers. The system further comprises a programmable logic device. The system has the advantages of high transmission speed, good real-time characteristic, high reliability and simple circuit. Parallel communication between the PC104 and a plurality of 51 single-chip microcomputer systems can be achieved without address access conflict by combining the application of the programmable logic device. The invention also provides a parallel communication method which is applied to the master-slave distributed system.

Owner:ZHUZHOU CSR TIMES ELECTRIC CO LTD

System for data acquisition and signal treatment of testing flat wheel

InactiveCN101206162AHigh precisionHigh speedRailway vehicle testingInput/output processes for data processingProgrammable logic deviceData acquisition

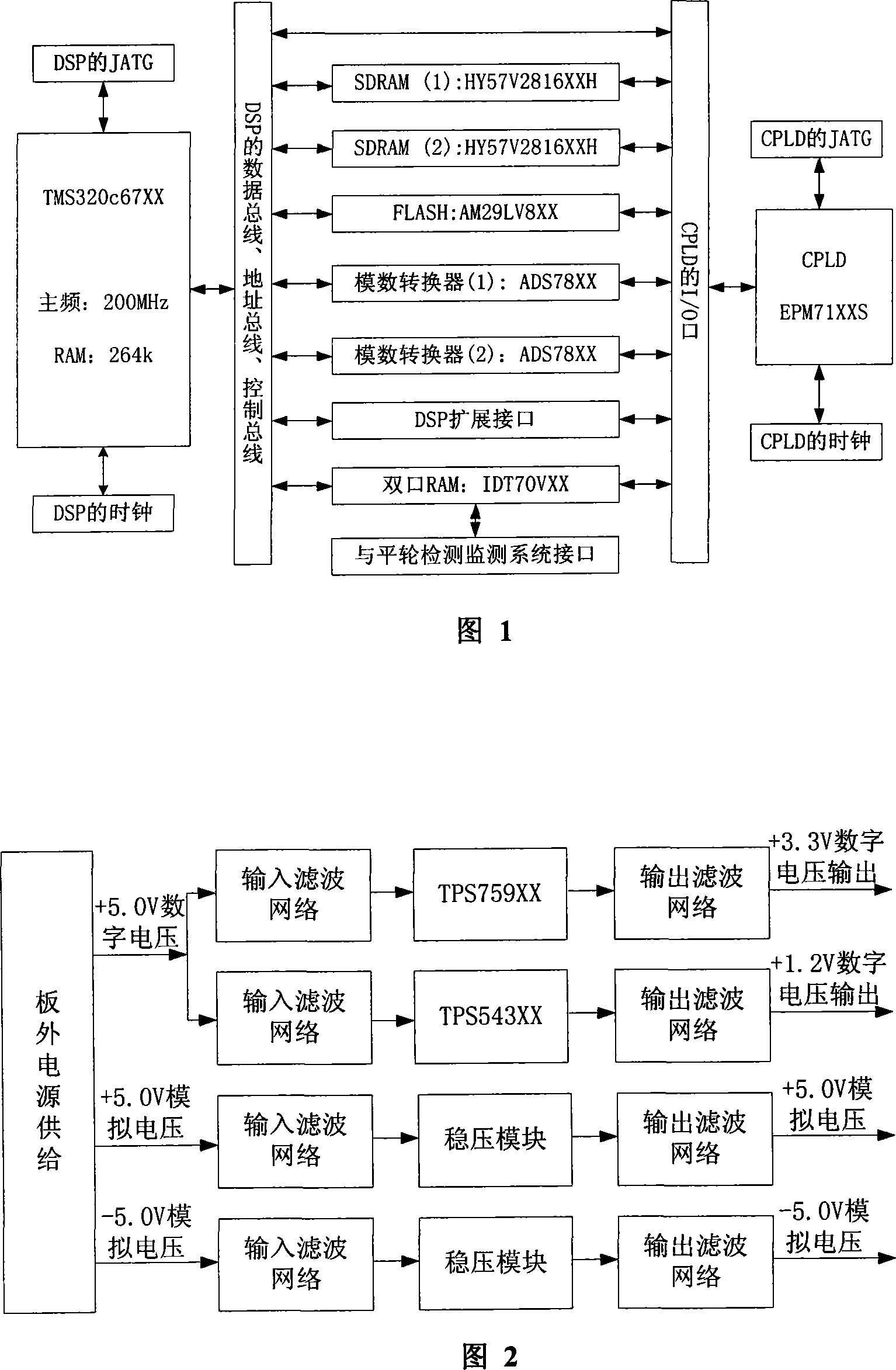

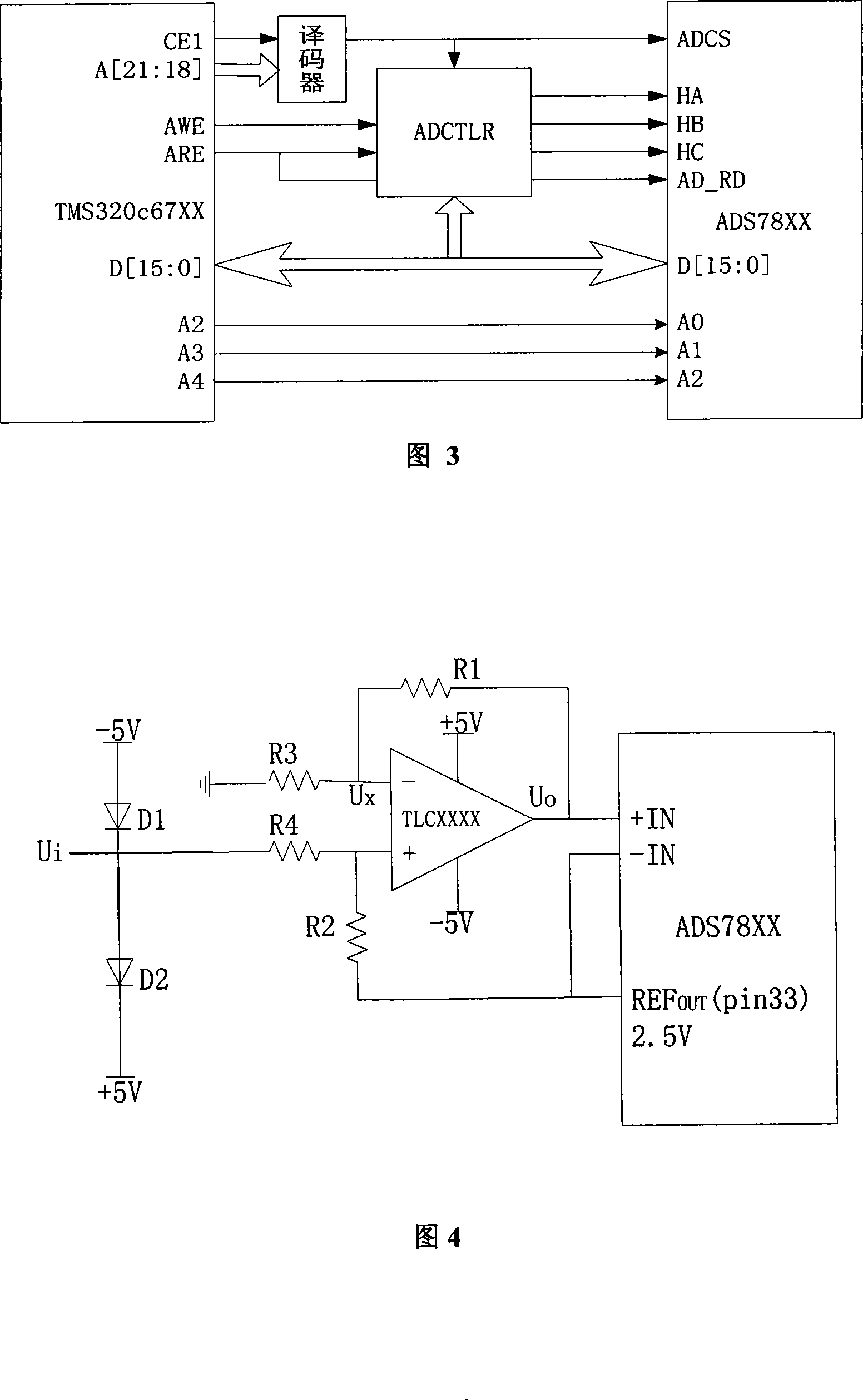

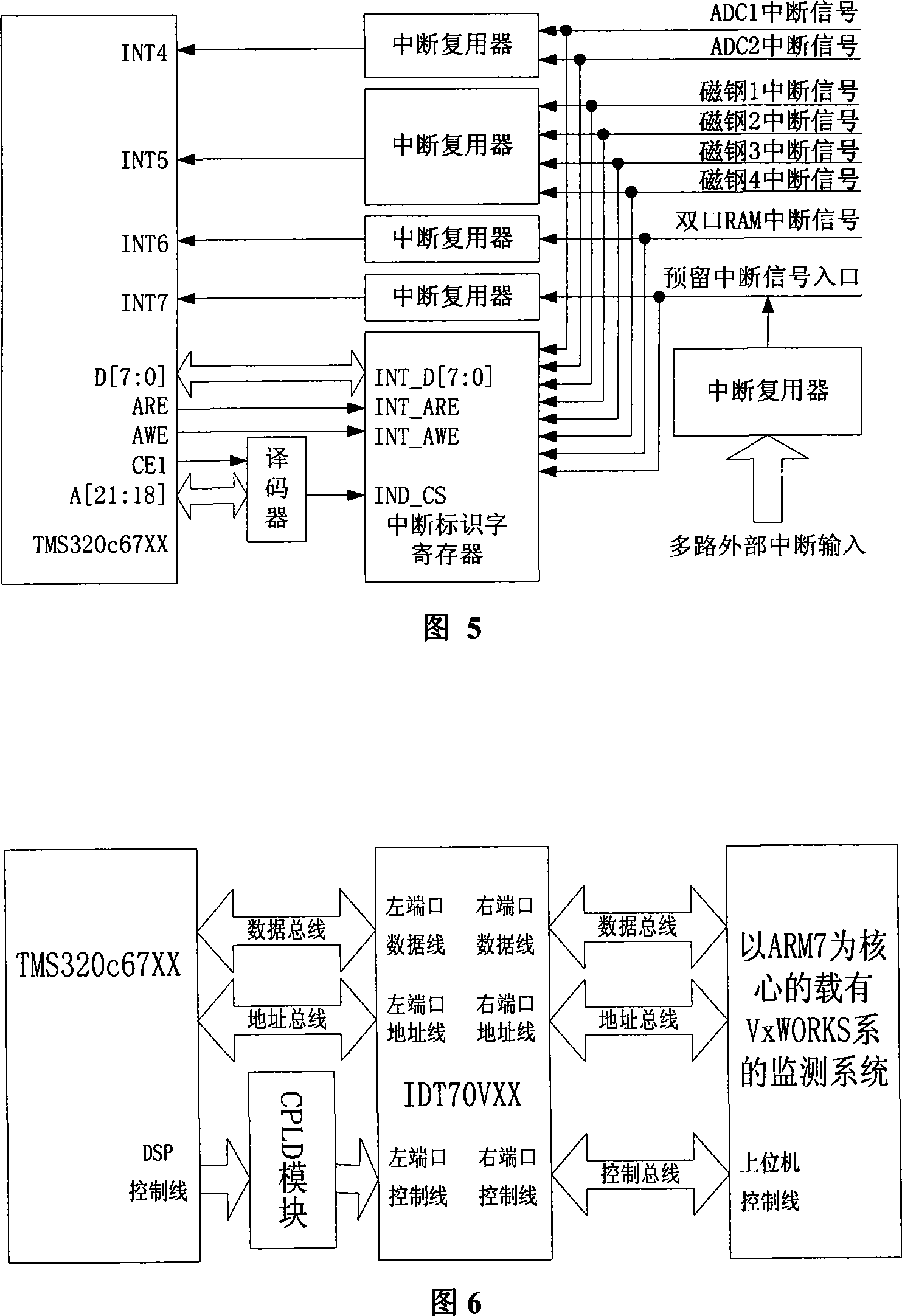

The invention provides a flat wheel detection data acquisition and signal processing system, which consists of seven parts, namely a power module, an AD sampling input front end conditioning module, an AD sampling conversion module, a data program memory module, an interruption management module, a high speed communication module and a reset module. The invention applies a high speed floating point DSP chip, a high speed low consumption double 12-bit parallel A / D converter, a dual-ported RAM chip and a complicated programmable logic device to the flat wheel detection data acquisition and signal processing system, develops a data acquisition and processing system taking the high speed floating point DSP as a core processor, and improves the speed, accuracy and stability of flat wheel detection data acquisition and processing (in addition, the system control, communication and monitoring is handled by ARM-VxWORK, and communication takes a form of network card.), thereby improving the performance index of the whole flat wheel detection system.

Owner:HARBIN ENG UNIV

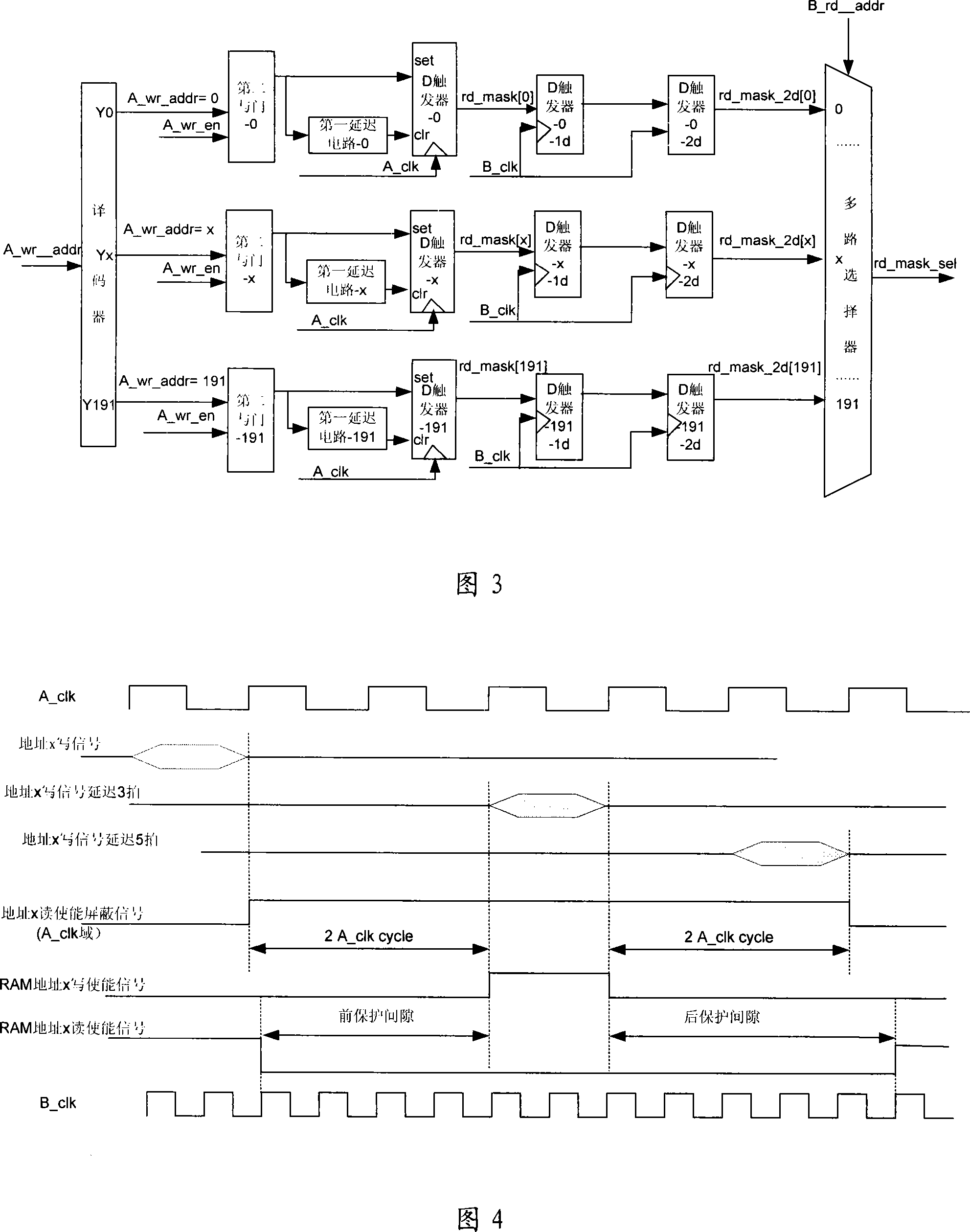

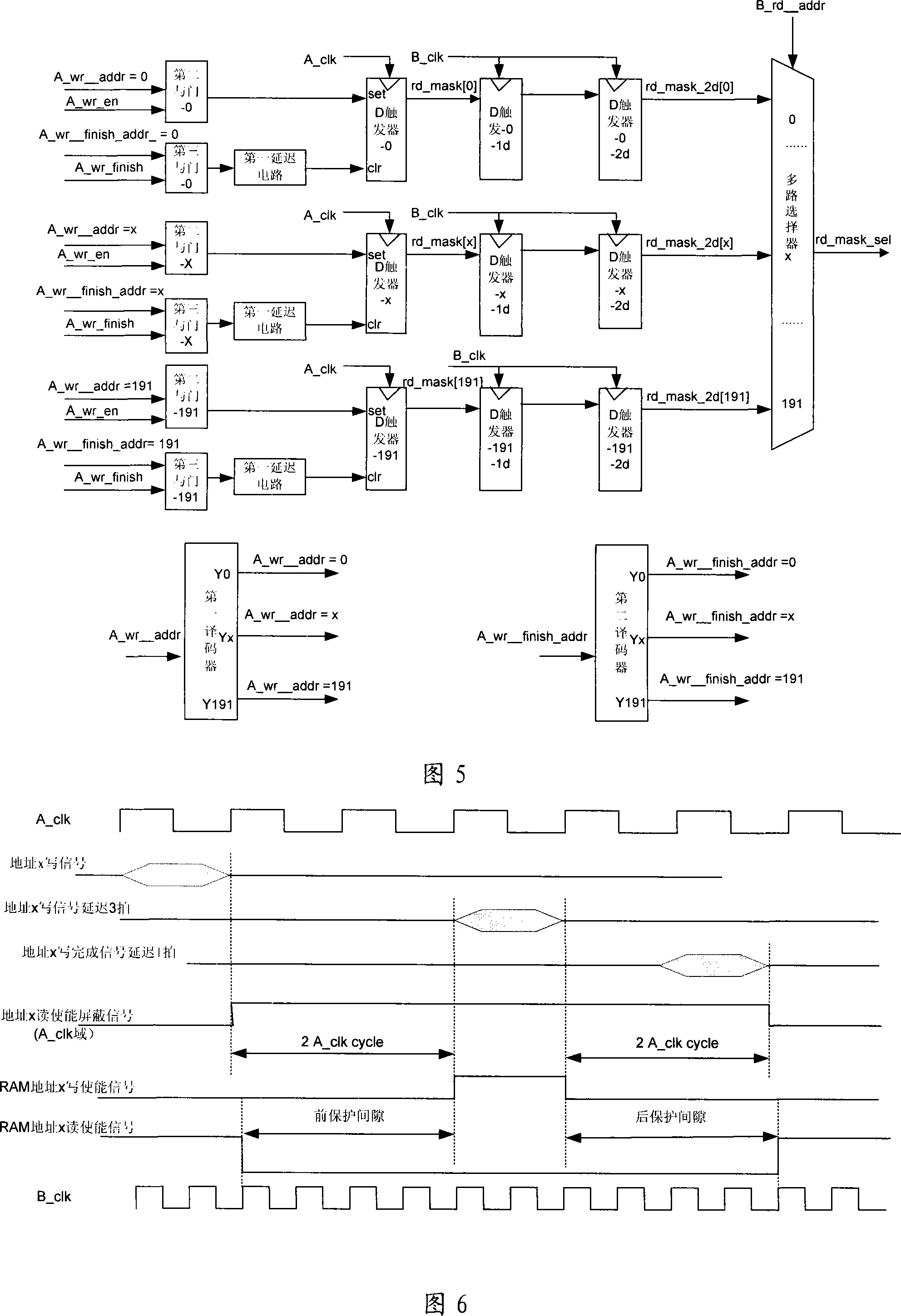

Read-write control circuit, method and apparatus for two-port RAM

ActiveCN101226767AAvoid reading and writing conflictsDoes not take up resourcesDigital storageControl circuitDual-ported RAM

The practical example of the invention discloses a read write control circuit with a dual-port RAM, a device and a method thereof, relating to the technical field of storage, and the invention is invented for evading read write conflict problem of the dual-port RAM. The circuit comprises a comparison circuit, a negation gate and a first coincidence gate, wherein the comparison circuit is used to output read screen signals of a storage unit corresponding with bus signals of a second port address, the negation gate is used to inverse the read screen signals of the storage unit which are corresponding with the bus signals of the second port address, one input end of the first coincidence gate receives the read screen signals of the storage unit which are corresponding with the bus signals of the second port address after being inversed, the other input end of the first coincidence gate receives the read enable signals of a second port, and the output end of the first coincidence gate is connected with the read enable end of the second port. The practical example of the invention can be used in chip circuit designing.

Owner:HONOR DEVICE CO LTD

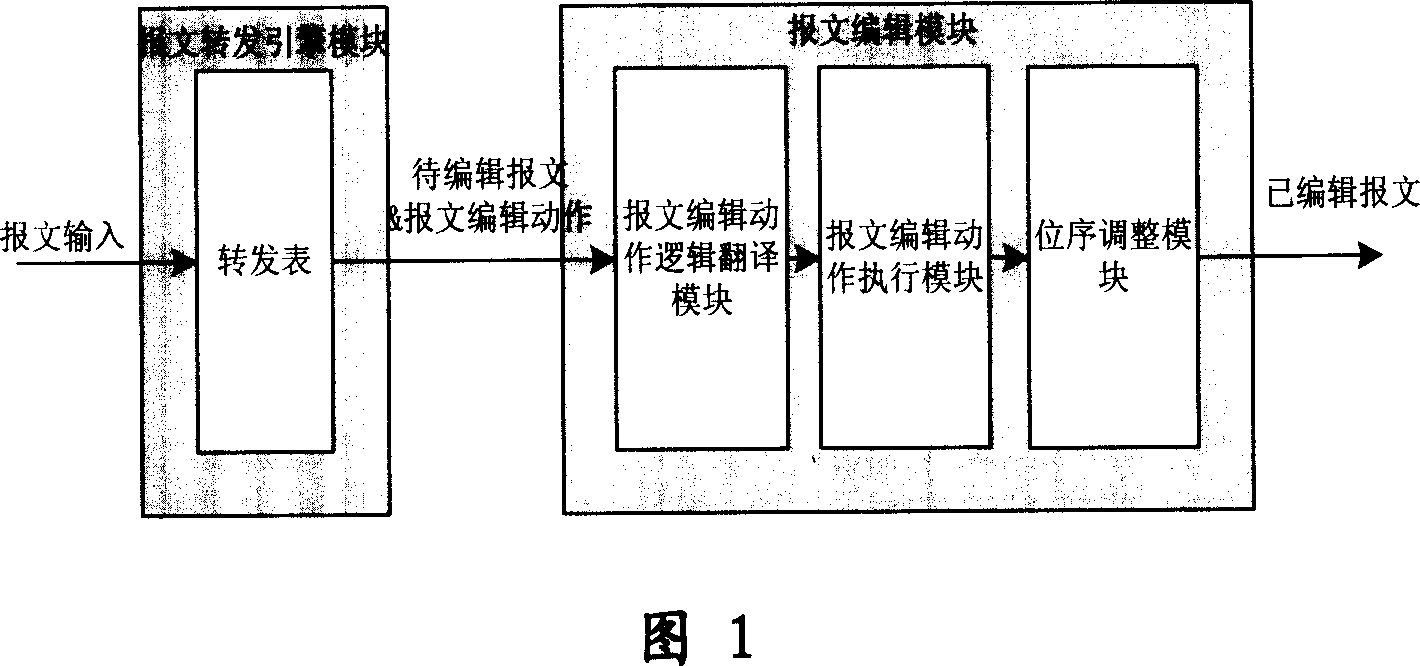

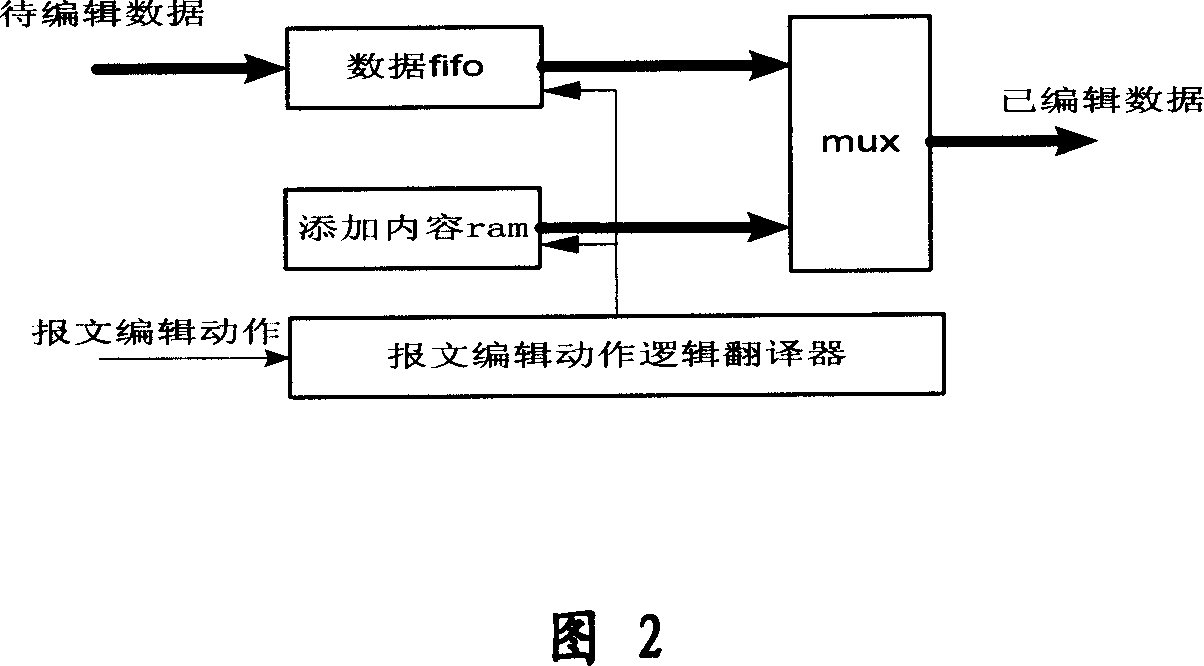

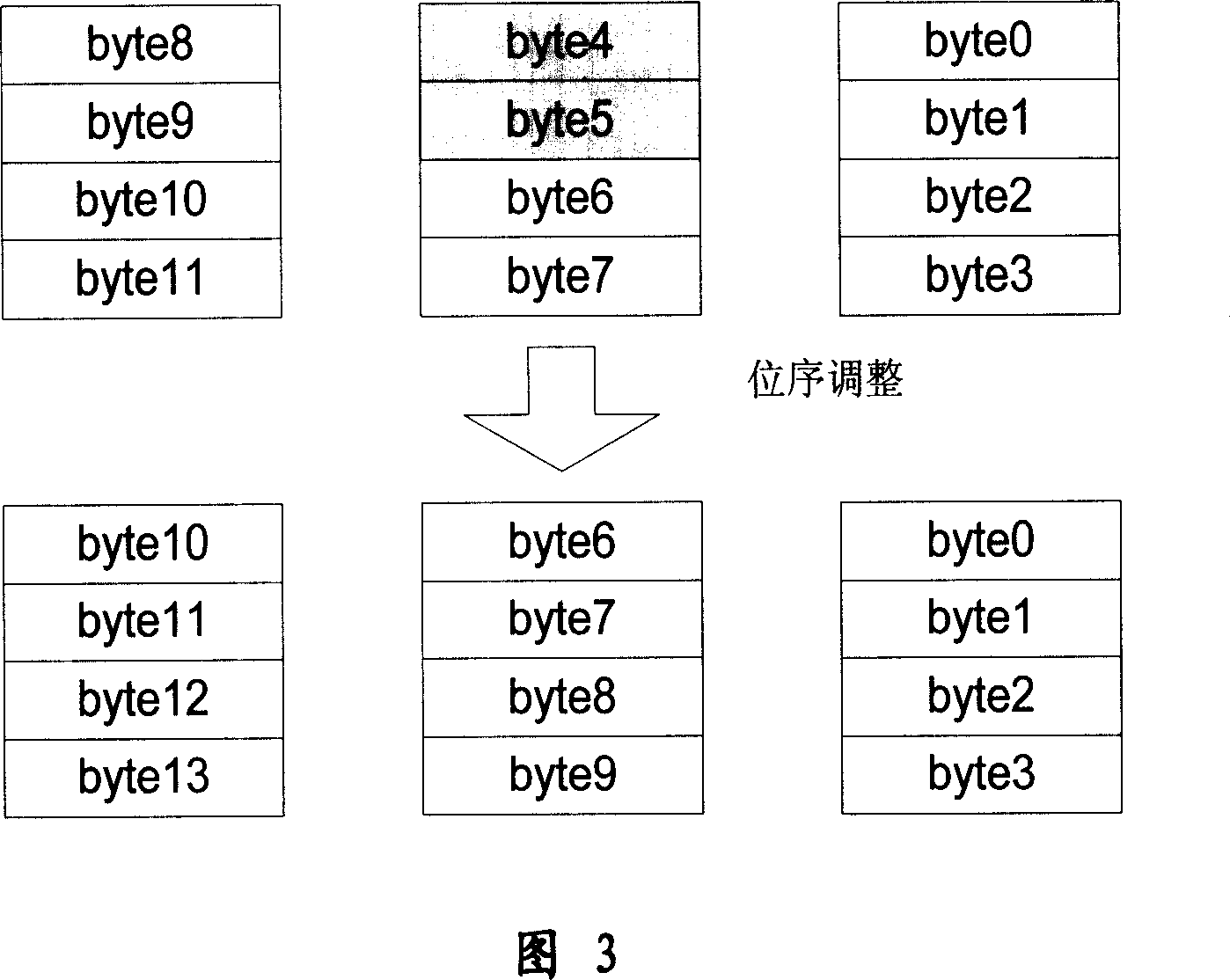

Text edition circuit and method

InactiveCN1949736AImprove editing speedAchieve translationData switching networksExtensibilityDual-ported RAM

The invention relates to a message editing circuit, comprising message input end, message transmission engine module, message editing module and message output end, connected in sequence, where message editing instruction set is constructed in the message transmission engine module, and a look-up table is constructed in the message editing module. And the invention also relates to a message editing method, where input message firstly enters a transmission engine and is transmitted by transmission table, it uses the message editing instruction set to analyze and generate message editing instructions, and the message editing module makes message editing instruction translation in contrast with the lool-up table and executes message editing action and makes bit sequence regulation and then outputs the edited message. And the look-up table can be implemented by dual port RAM, the contents of the look-up table is configured by CPU, and the look-up table can also be implemented by ROM and is updated, regularly. And the invention simplifies message editing action, and can save large numbers of required resources for logic determination and implement programmable message editing, and has good extensibility.

Owner:HUAWEI TECH CO LTD

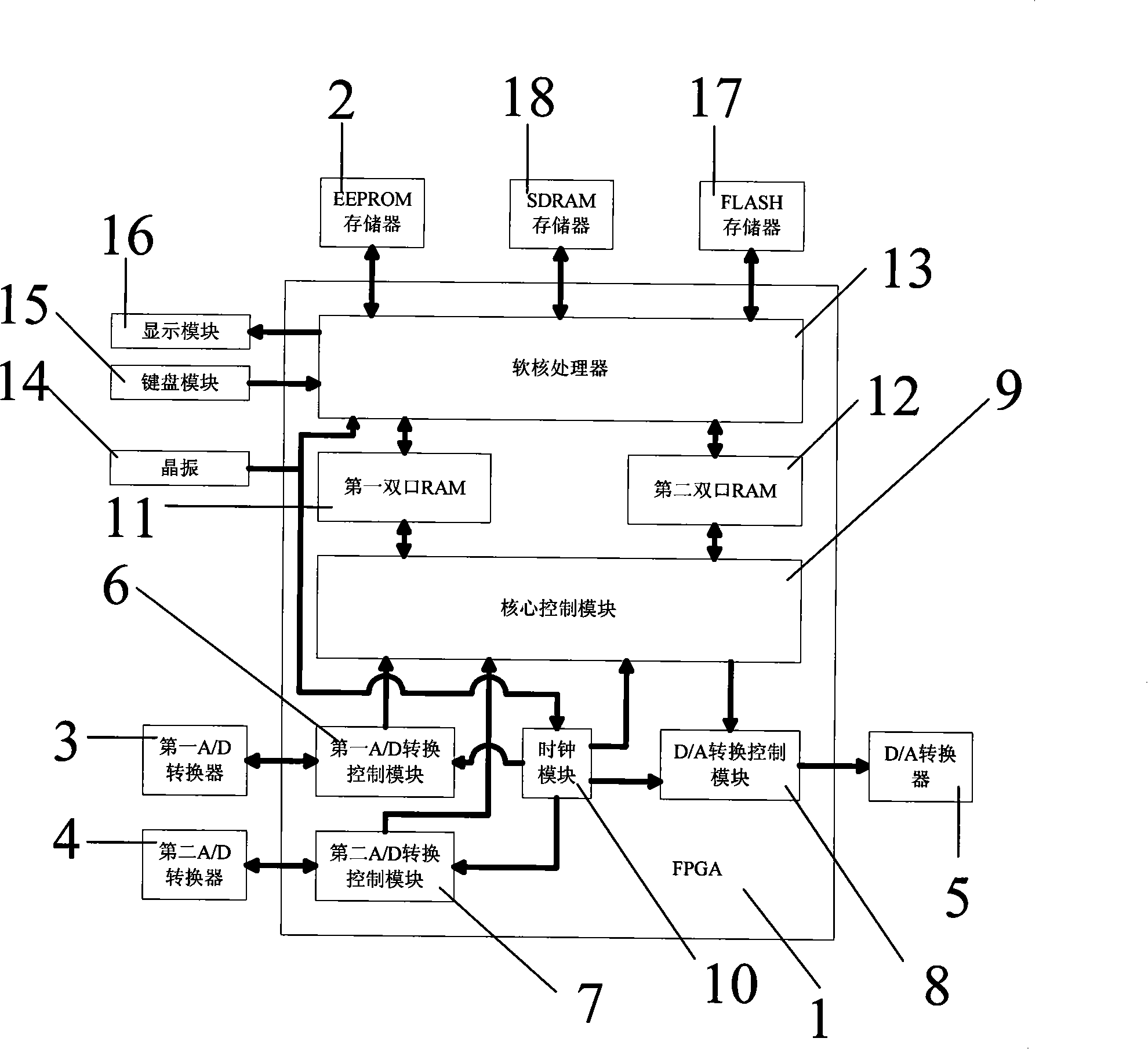

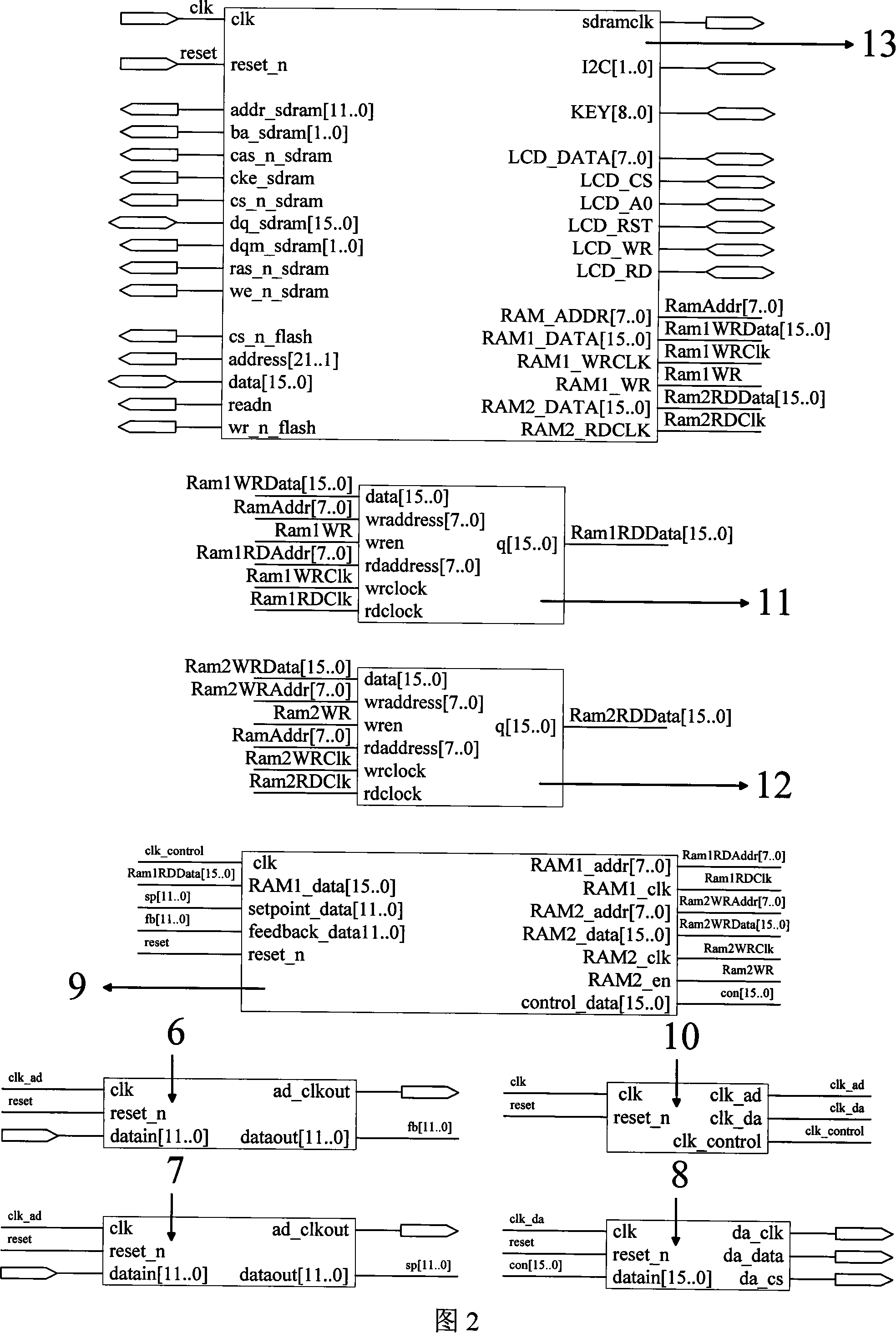

High speed servo controller with parallel processing structure based on FPGA

InactiveCN101251753AFast operationIncrease flexibilityNumerical controlParallel processingComputer science

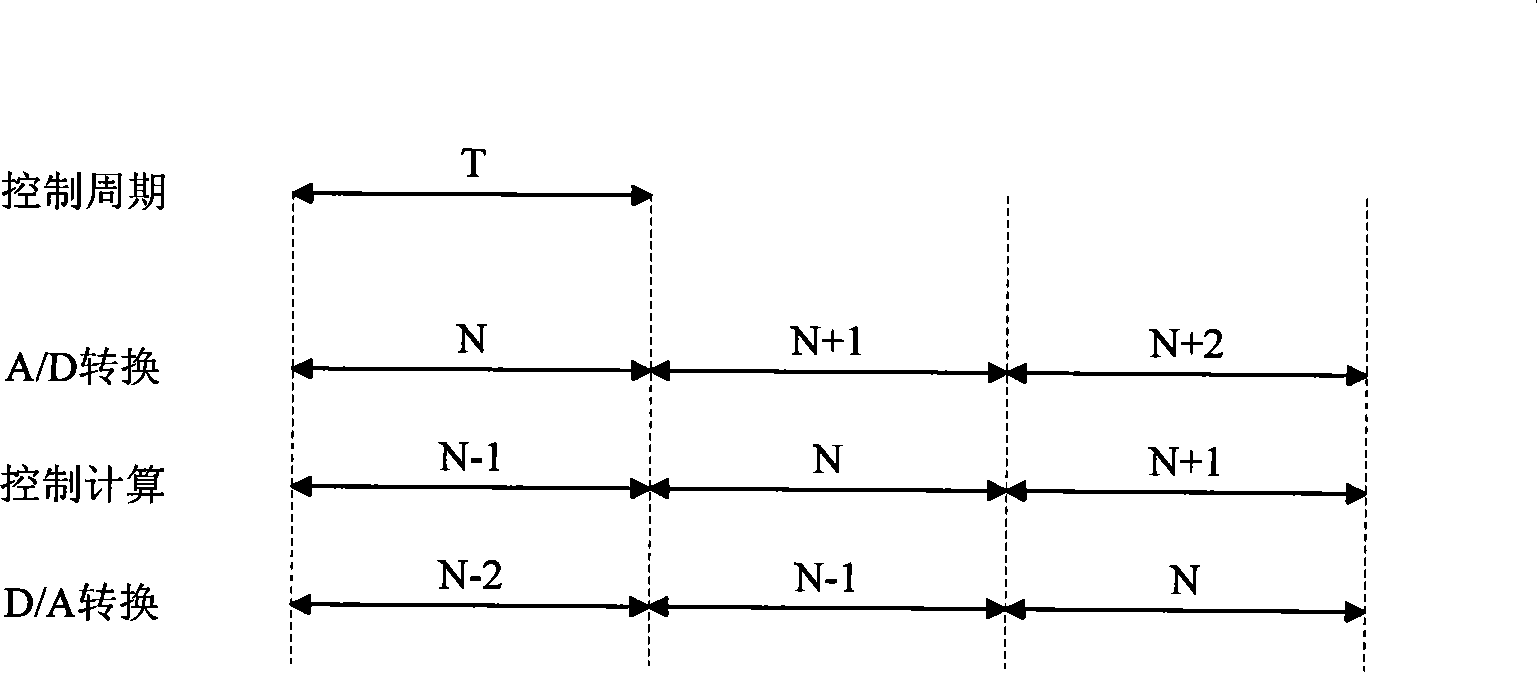

The present invention discloses a high-speed servo controller which is based on FPGA and has a parallel processing structure. The present invention comprises a field programmable gate array (FPGA), two A / D converters, a D / A converter, a crystal oscillator, a keyboard module, a display module, a FLASH memory, an SDRAM memory and an EEPROM memory, wherein the field programmable gate array comprises two A / D conversion control modules, a D / A conversion control module, a kernel control module for controlling calculation, a clock module, two dual-port RAMs and a soft-core processor. The servo controller can realize that the hardware realization of PID control calculation, as well as the pipeline realization parallel processing of A / D conversion, control calculation and D / A conversion, remarkably shortens control period, realizes the monitoring of the soft-core processor to the kernel control module as well as man-computer interaction, has extremely fast computing speed and high flexibility, can be widely applied to servo control systems in the industrial automation field, and is wide in application scope.

Owner:ZHEJIANG UNIV

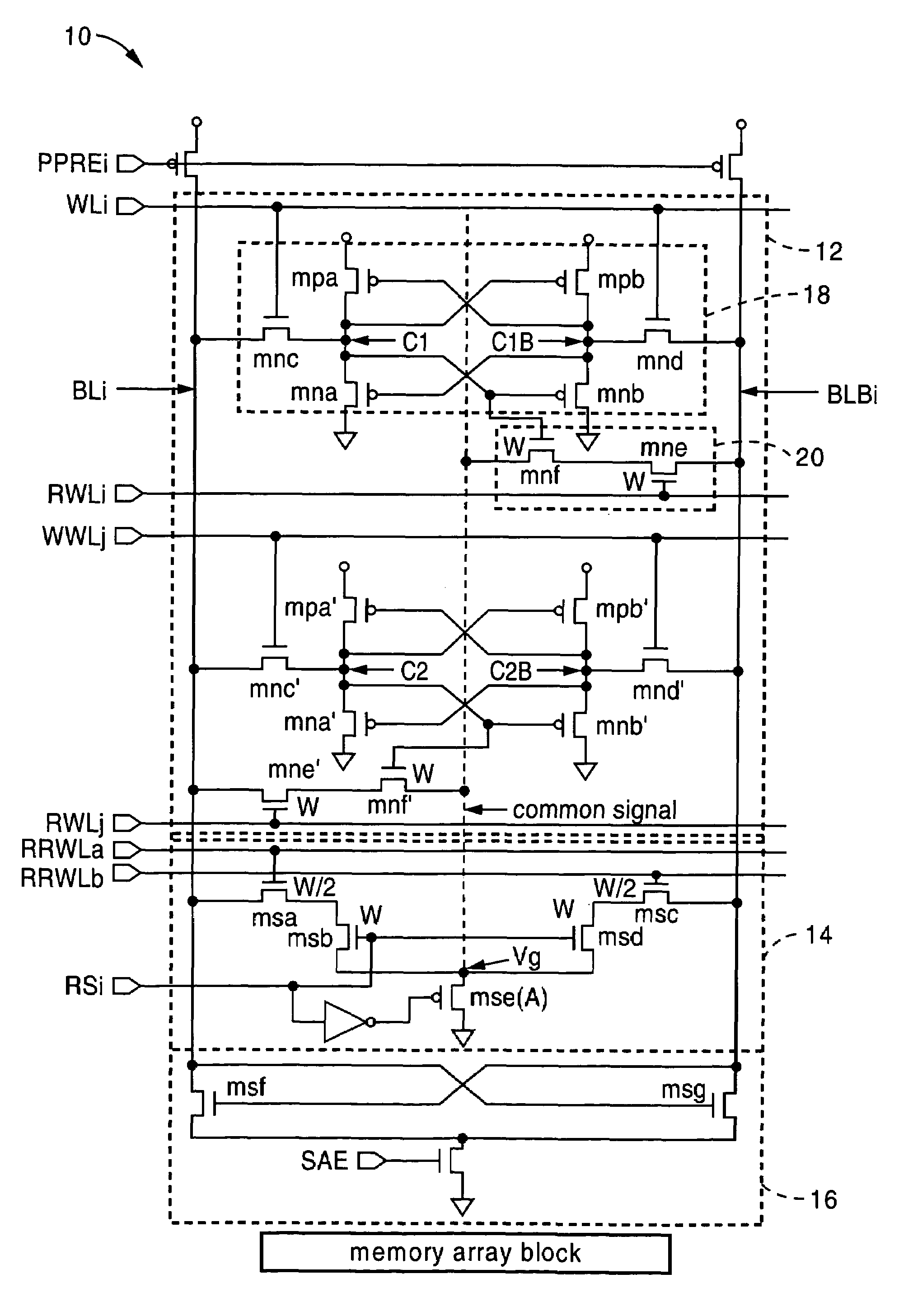

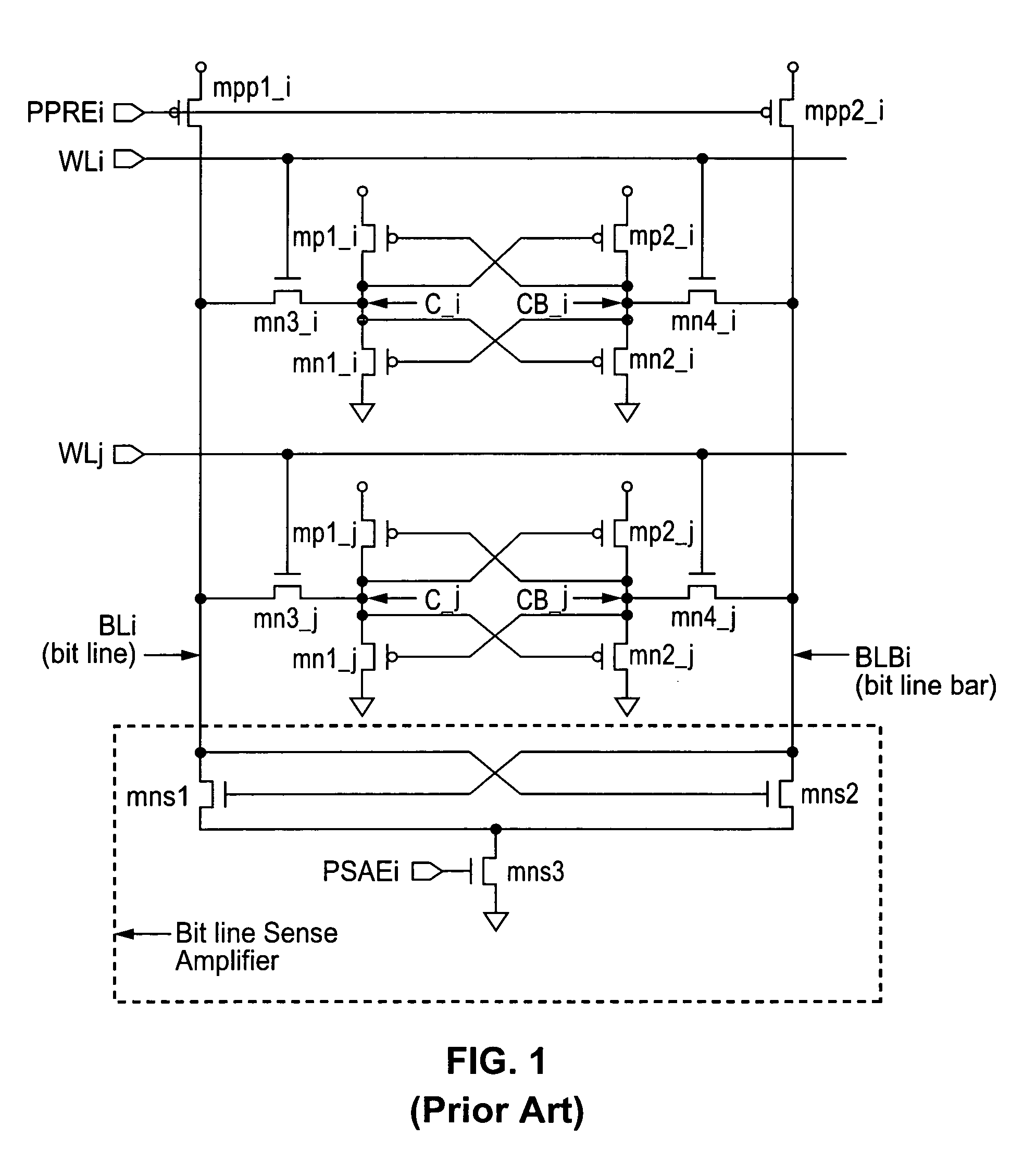

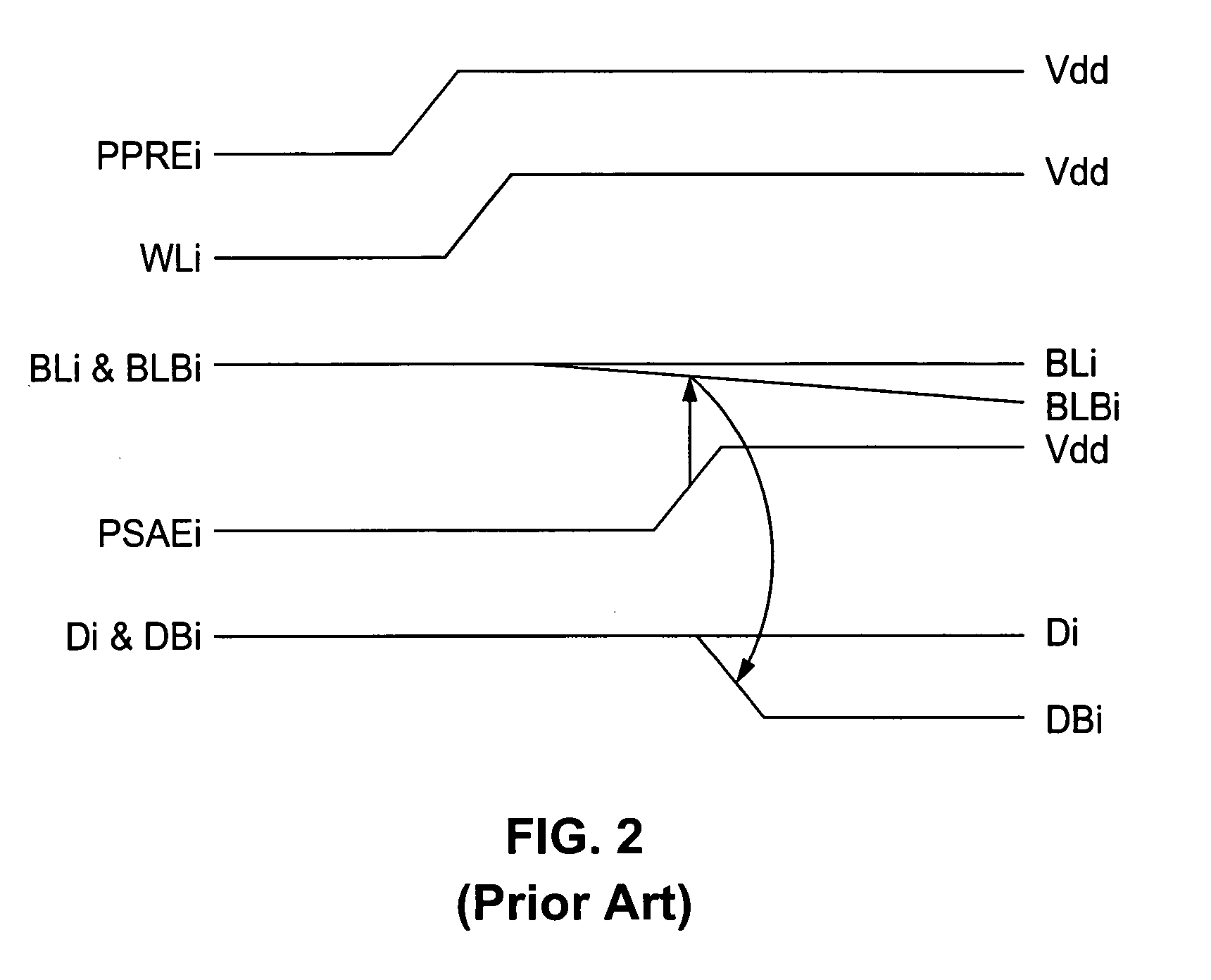

SRAM cell structure and circuits

An SRAM circuit structure and method for reducing leakage currents and / or increasing the speed of the devices. Various forms of SRAM devices may be fabricated utilizing the techniques, such as single port and dual port RAM devices. By way of example the SRAM structure utilizes separate write and read lines, splits the circuit into portions which can benefit from having differing threshold levels, and can allow splitting read path transistors for connection to a first terminal and a virtual node connected to a source transistor. The structure is particularly well suited for forming transistors in a combination of NMOS and PMOS, or solely in NMOS. Memory arrays may be organized according to the invention in a number of different distributed or lumped arrangements with the reference read paths and sense blocks being either shared or dedicated.

Owner:ZMOS TECH

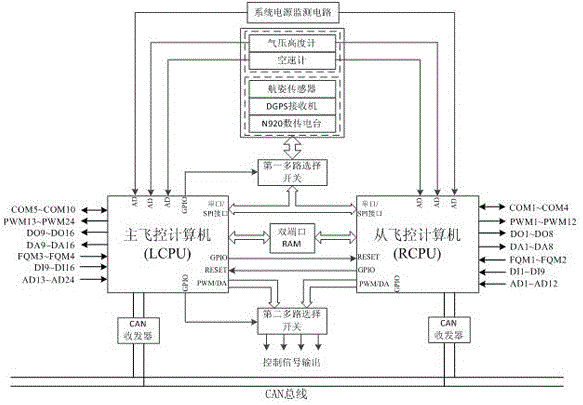

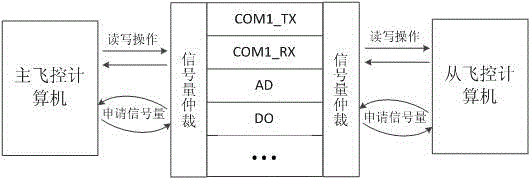

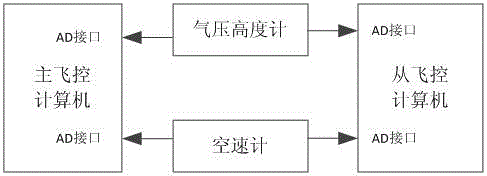

Universal small unmanned aerial vehicle dual-core flight control computer and control method

InactiveCN105867418AReduce loadImprove stabilityPosition/course control in three dimensionsWireless controlControl signal

The invention discloses a universal small unmanned aerial vehicle dual-core flight control computer and a control method. The computer comprises an airborne sensor system, a wireless communication module, master and slave flight control computer bodies, a dual-port RAM, a first multiplexer switch and a second multiplexer switch, wherein the master and slave flight control computer bodies send heartbeat detection signals to each other through a CAN bus to judge whether failures exist, the first multiplexer switch is controlled to connect the airborne sensor system and the wireless communication module to the master or slave flight control computer body according to a judgment result, and a control signal is obtained through calculation according to received and decoded unmanned aerial vehicle state information and a wireless control instruction by the master or slave flight control computer body; the second multiplexer switch is controlled according to a judgment result to output the control signal of the master or slave flight control computer body, so that the computer is made to work in the master-slave load sharing mode or independent sharing mode. The dual-core flight control computer is high in operation speed, large in data throughput and capable of guaranteeing continuous operation of a system.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

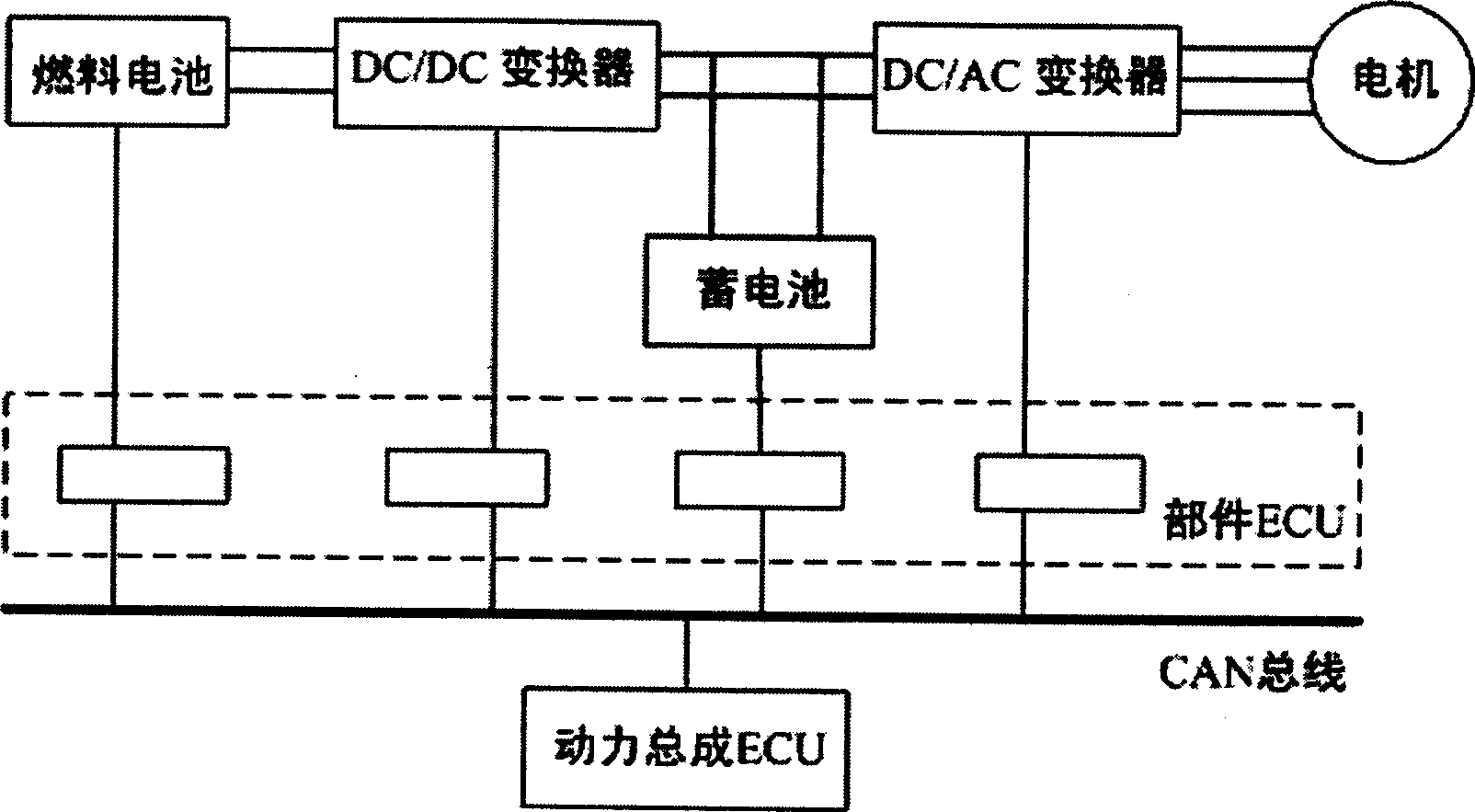

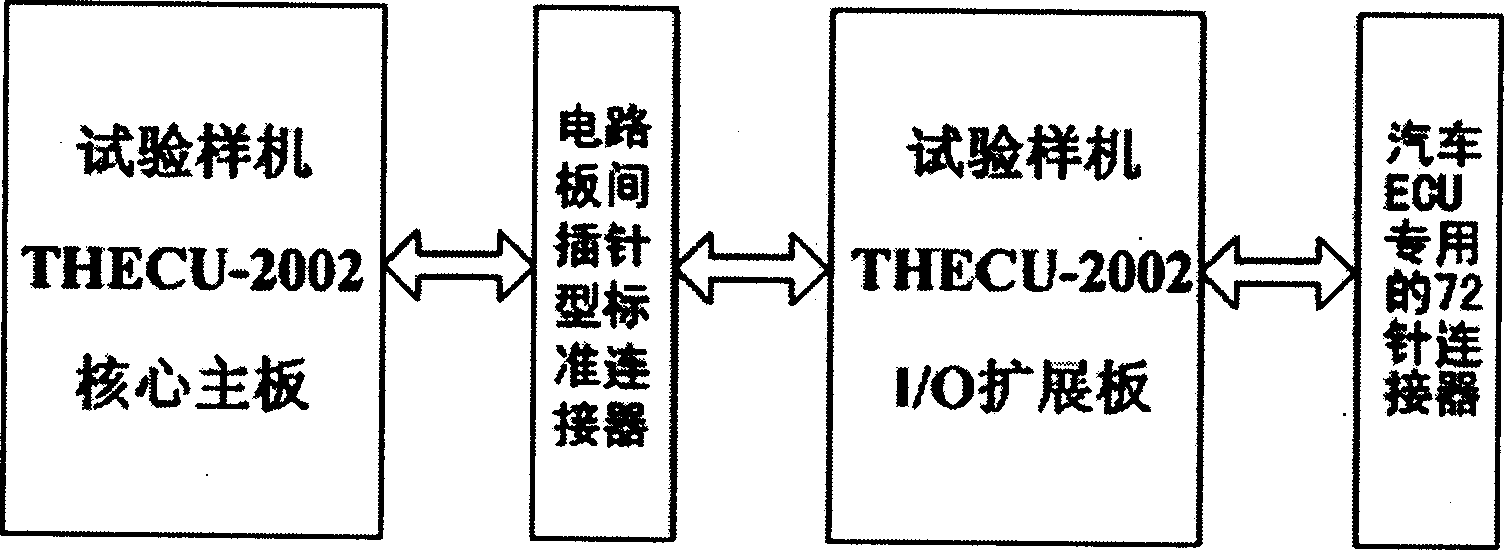

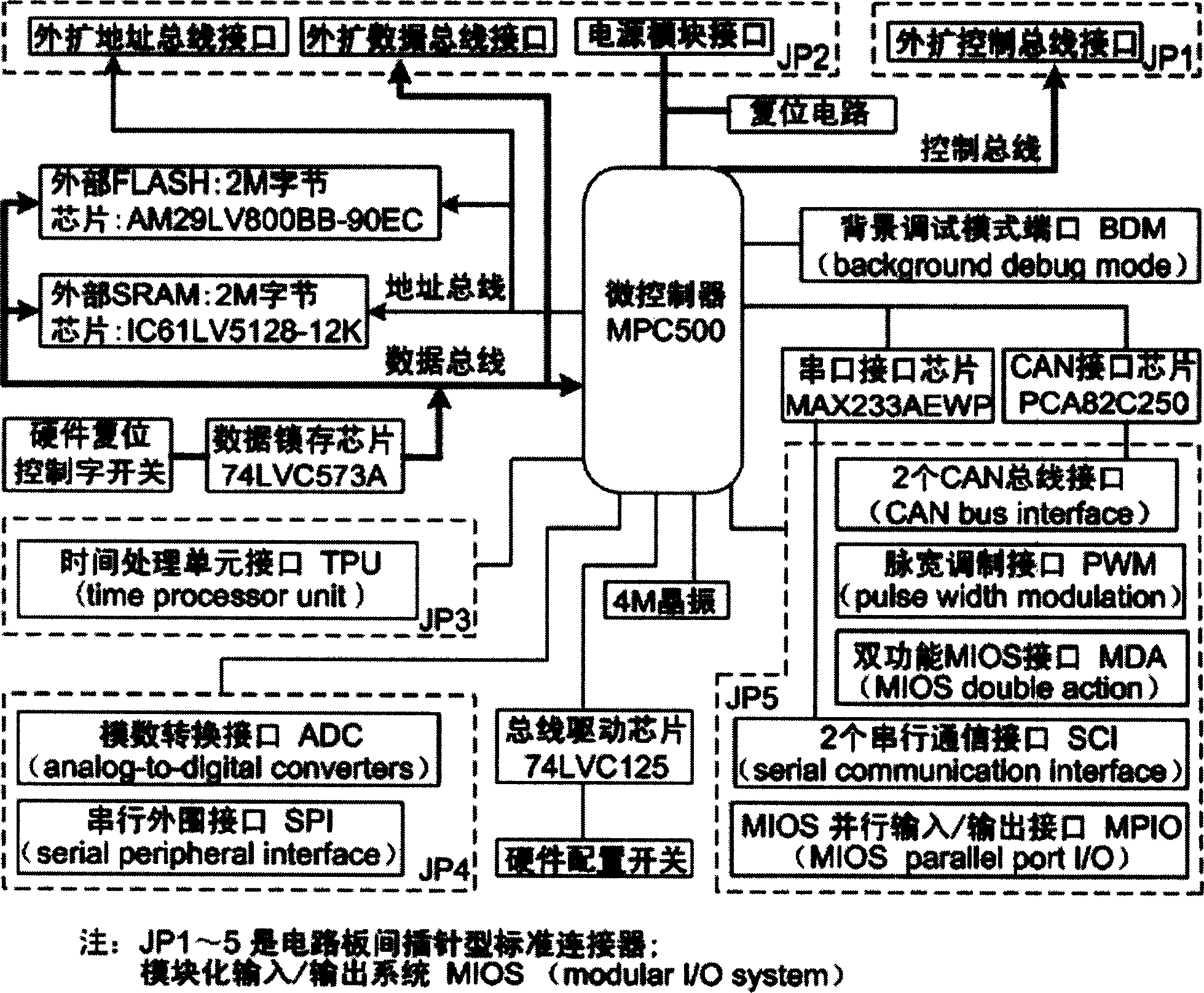

MPC500 process type electric car multi-energy power assembly control device

InactiveCN1528614AHighly integratedImprove reliabilitySpeed controllerPropulsion by capacitorsControl busElectron

The invention is a MPC500 processor-type electric car multi-energy source power assembly control device, using 32-bit car special embedded microprocessor as kernel hardware, designing pair control bus, address / data bus extended interface, serial communication interface, BDM debugging port and various I / O signal interfaces to compose kernel mainboard, which is connected with the I / O extended board with dual-port RAM interface through board to board pin-type standard linker so as to compose the hardware platform, thus heightening system integrity, vehicle carrying reliability and system technical performance, and making the control device able to ECU of each component of electric car multi-energy source power system through the CAN bus interface and the dual-port RAM interface, heightening application flexibility and transplantability. It only need change necessary soft module, thus able to be applied to various electric cars.

Owner:TSINGHUA UNIV