Deconvolution interweave machine and method realized based on FPGA

A deconvolution and interleaver technology, applied in the field of deconvolution and interleaving, can solve the problems of high power consumption, low storage space usage efficiency, idle storage units, etc., and achieve the goal of increasing working speed, improving usage efficiency, and high application value Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

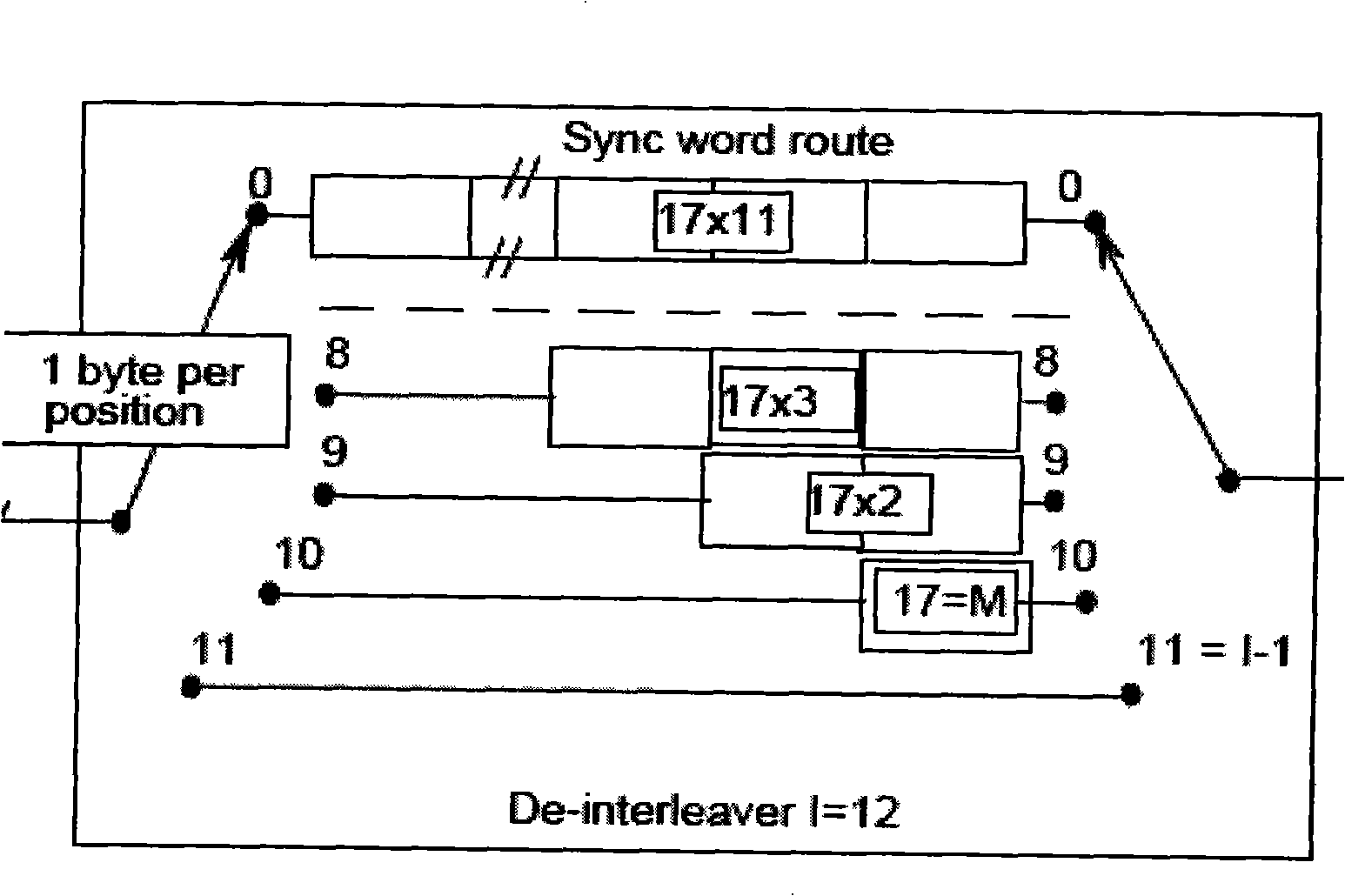

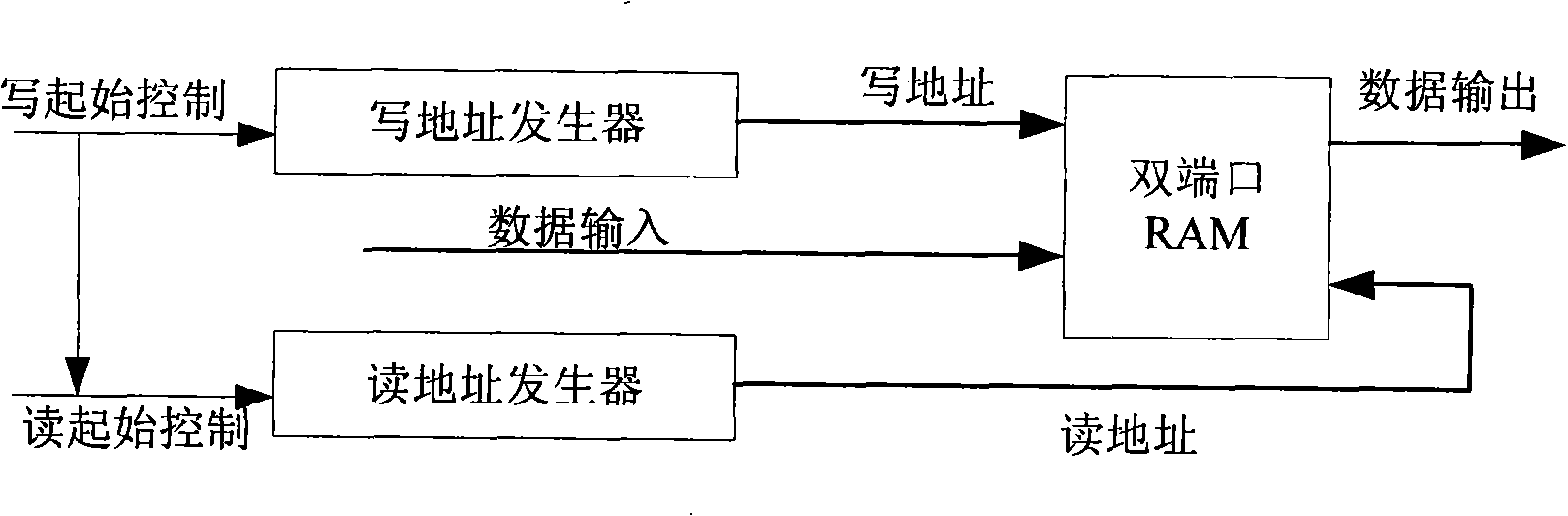

[0041] Please refer to Figure 4 As shown, it is a schematic structural diagram of a specific embodiment of the deconvolution interleaver implemented based on FPGA in the present invention. This embodiment is a simulation implementation figure 1 The deconvolutional interleaver shown. The deconvolution interleaver in this embodiment includes: two read-write address generators 11 and 12 , dual-port RAMs 21 and 22 with 1024*8 and 256*8 respectively, and a controller 30 .

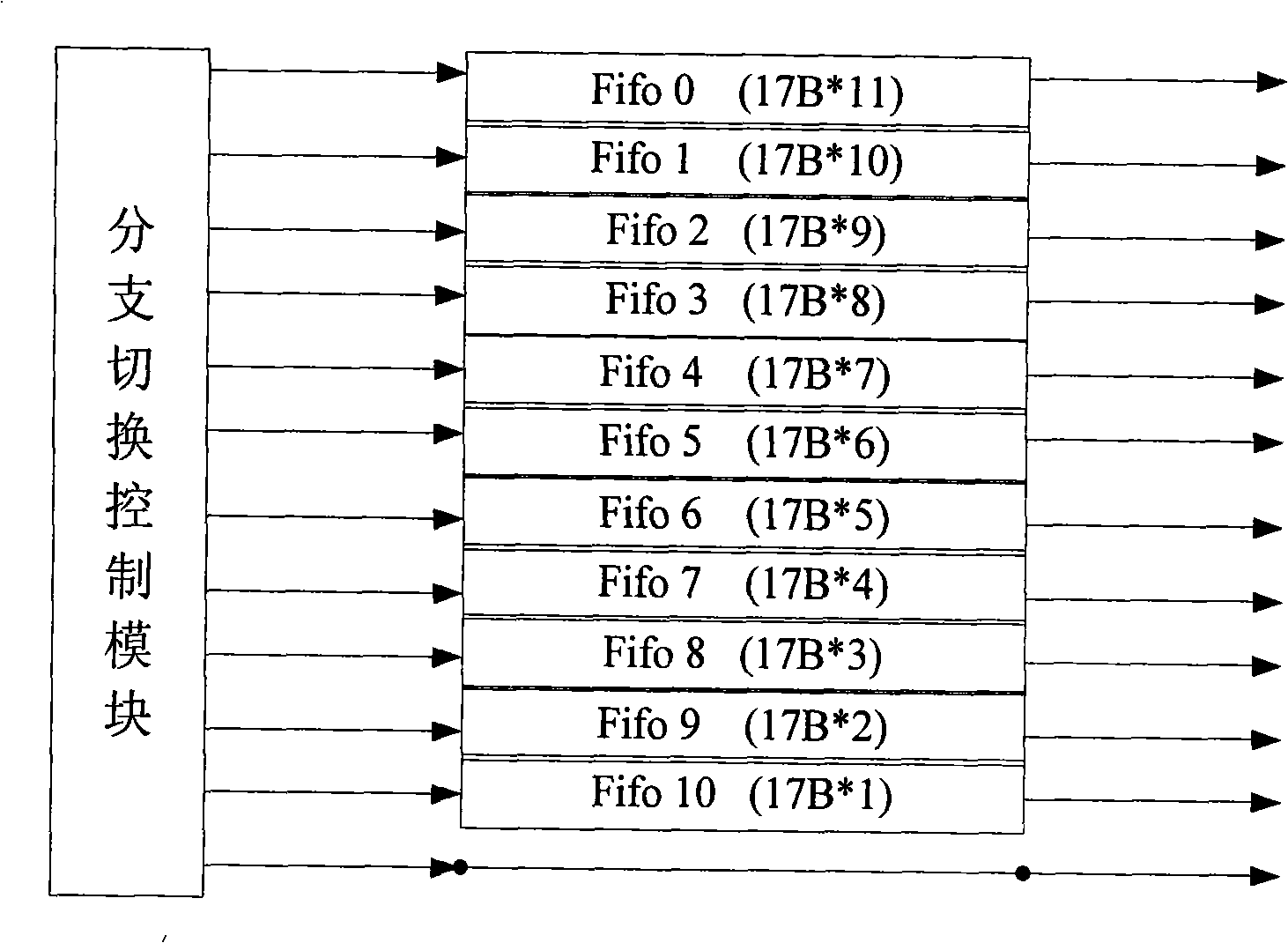

[0042] Since the FPGA only supports storage memory blocks (registers) with a power-of-two depth, although the interleaver only needs 1122*8 bits, it must be implemented with a power-of-two register. Therefore, in the deconvolution interleaver of the present embodiment: the dual-port RAM 21 of 1024*8 bits is an analog figure 1 The shift register of branches 0 to 6 shown; the dual-port RAM 22 of 256*8bits is analog figure 1Branches 7 to 11 of the shift register are shown. The part of the output (Out) has a s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More