Double-port access single dynamic memory interface

A dynamic memory and dual-port technology, applied in instruments, electrical digital data processing, computers, etc., can solve problems such as unfavorable applications, and achieve the effects of ease of use, increased capacity, and improved overall performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

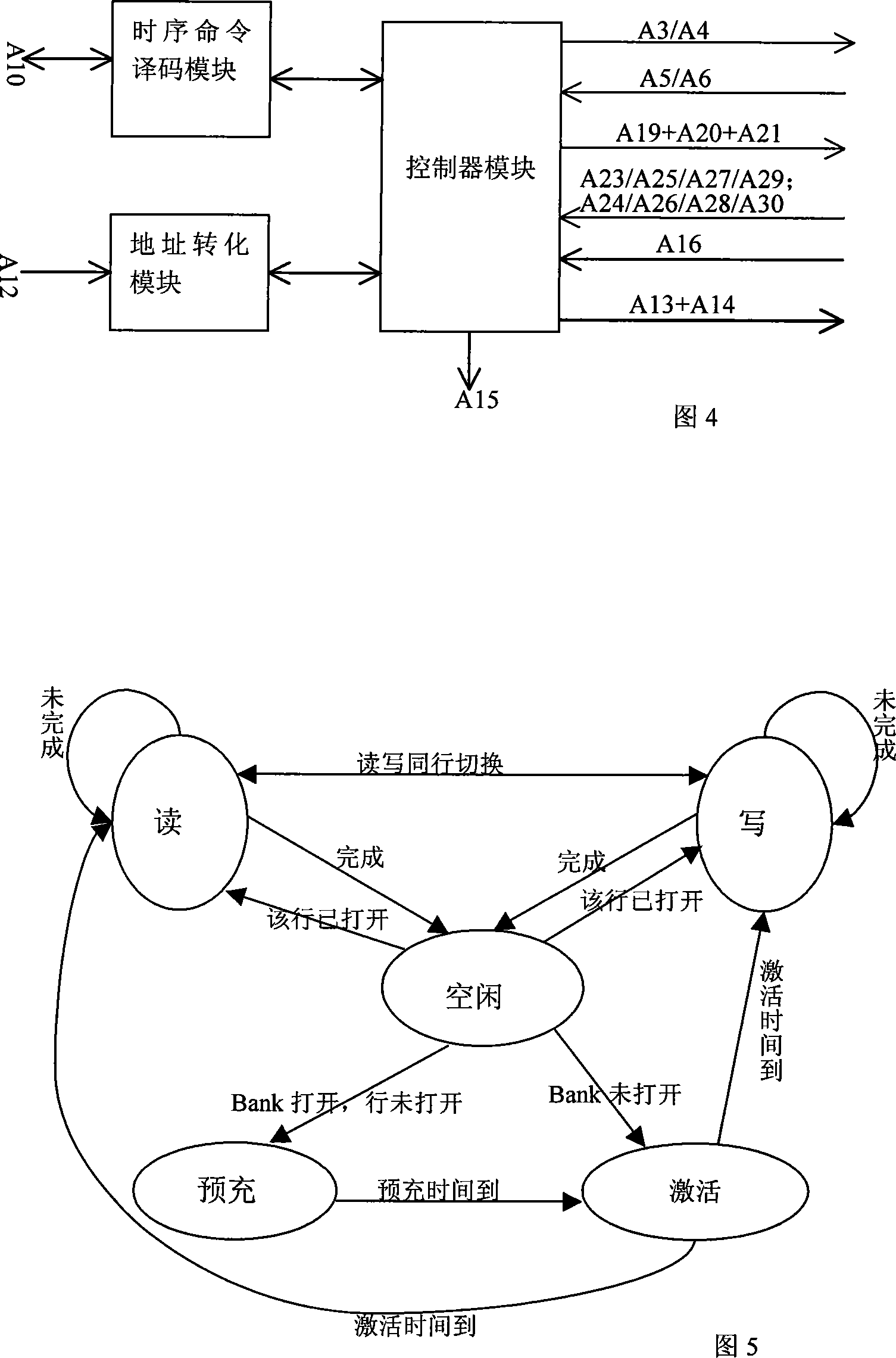

[0027] Compared with ASIC, FPGA device has the advantage of field programmable, and mature logic realized by FPGA can also be easily converted into ASIC. This embodiment provides a dual-port memory access interface implemented on FPGA. In this example, DDR SDRAM is selected for the dynamic memory, and the access timing of the two processors are respectively selected for the access timing of the SDRAM memory and the access timing of the asynchronous memory.

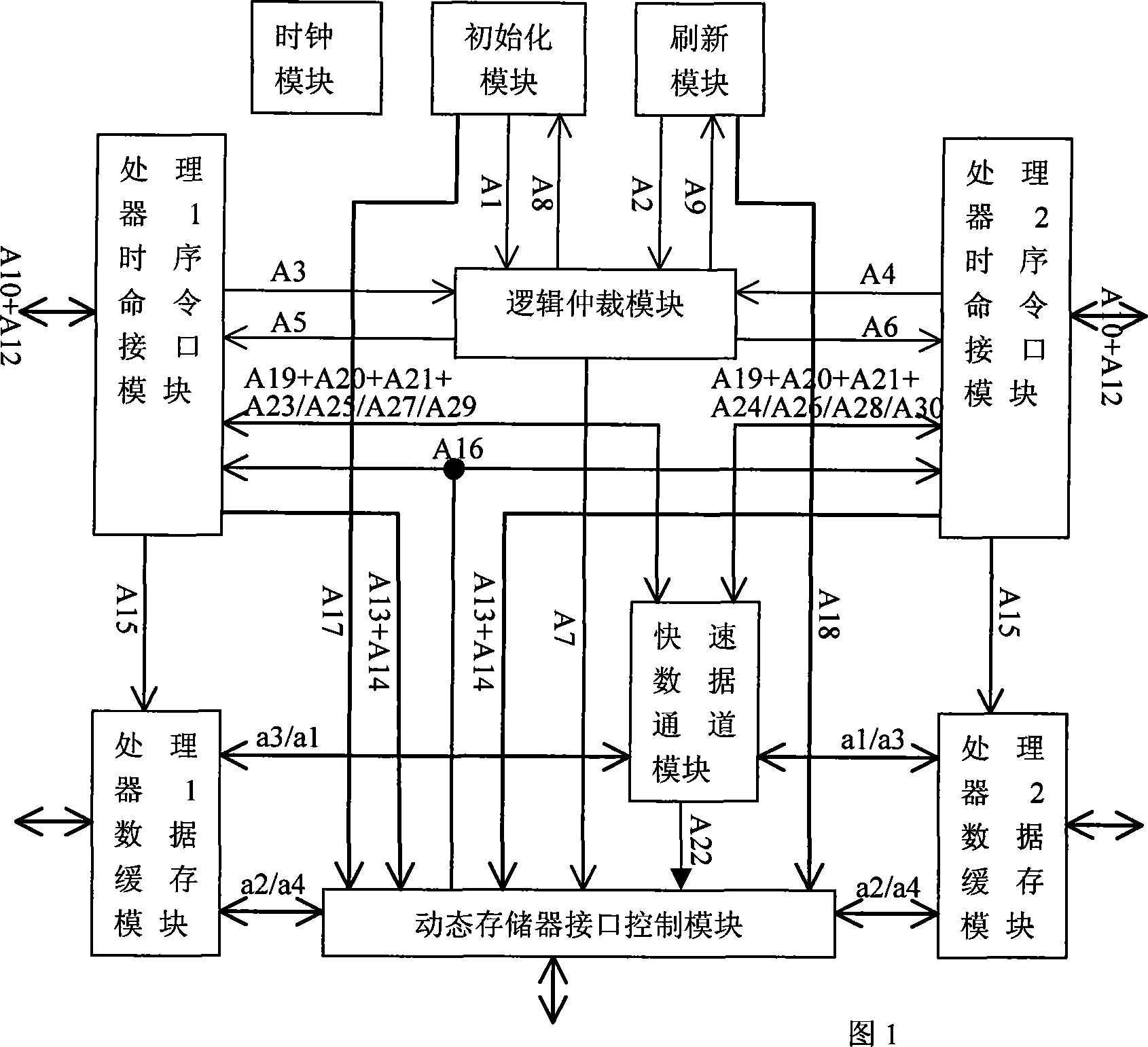

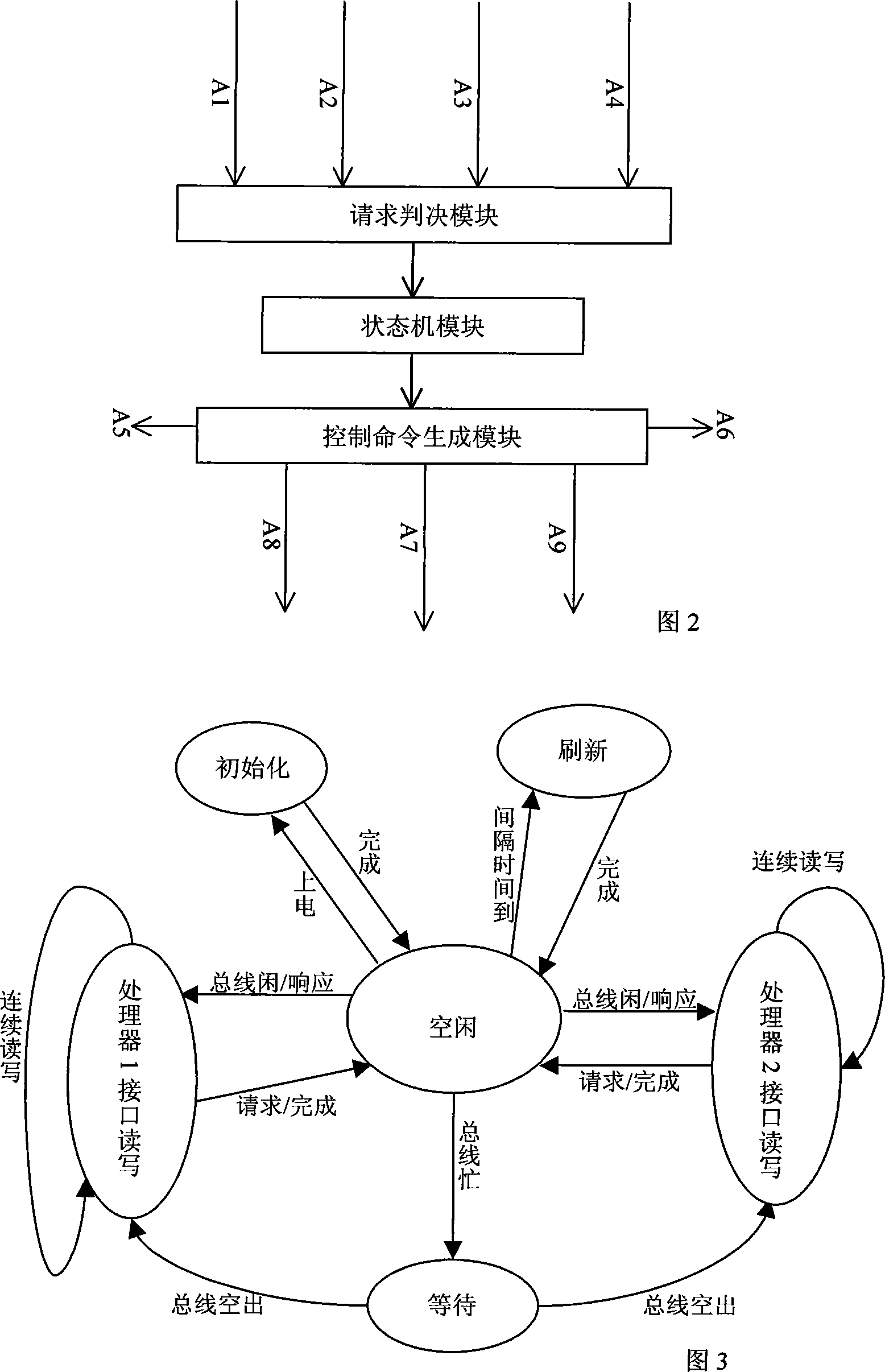

[0028] Dual port access to a single dynamic memory interface, including logic arbitration module, processor 1 timing command interface module, processor 1 data cache module, processor 2 timing command interface module, processor 2 data cache module, dynamic memory interface control module, Initialization module, refresh module (as shown in Figure 1); in this specific implementation, DDRSDRAM is selected as the dynamic memory. Like other existing interfaces, this interface also includes a clock module, which transforms the inpu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More