Patents

Literature

53results about How to "Avoid reading and writing conflicts" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

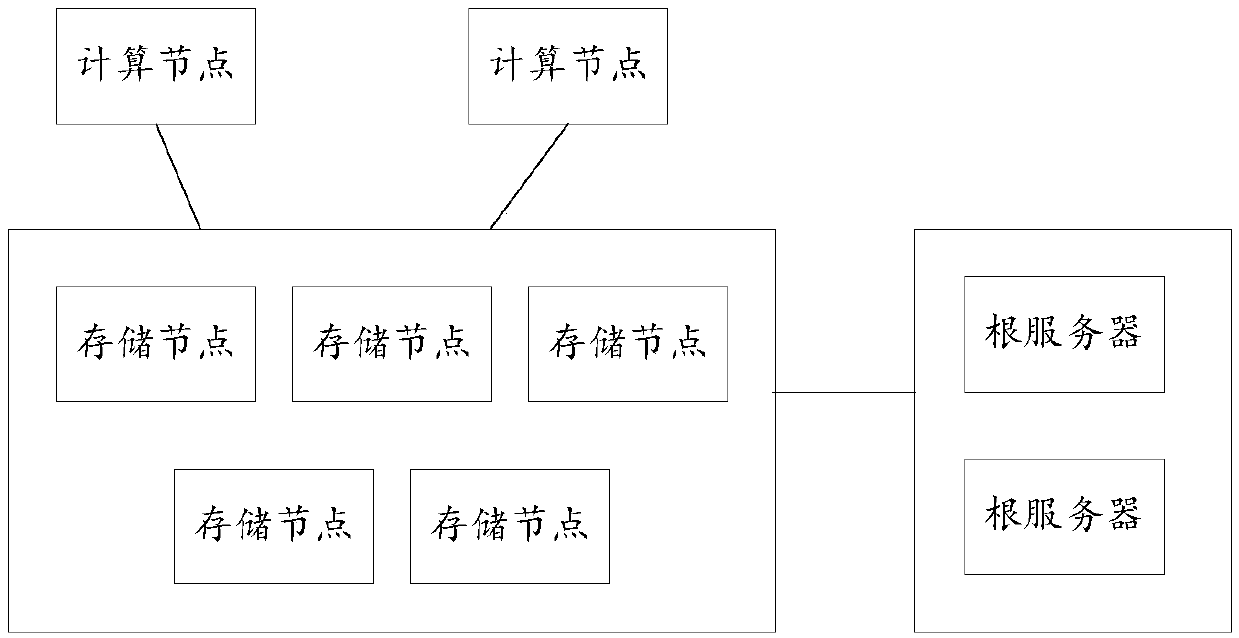

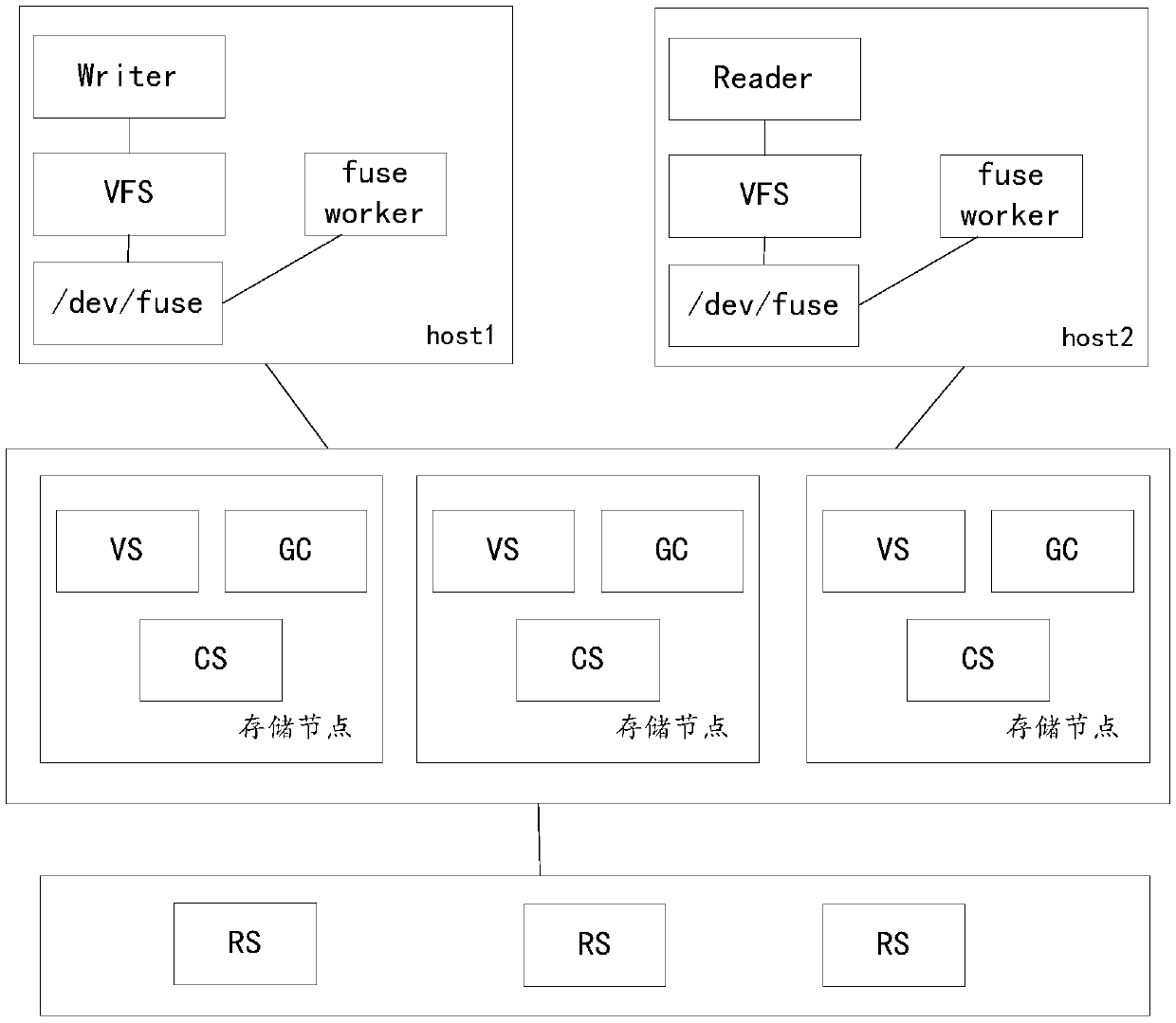

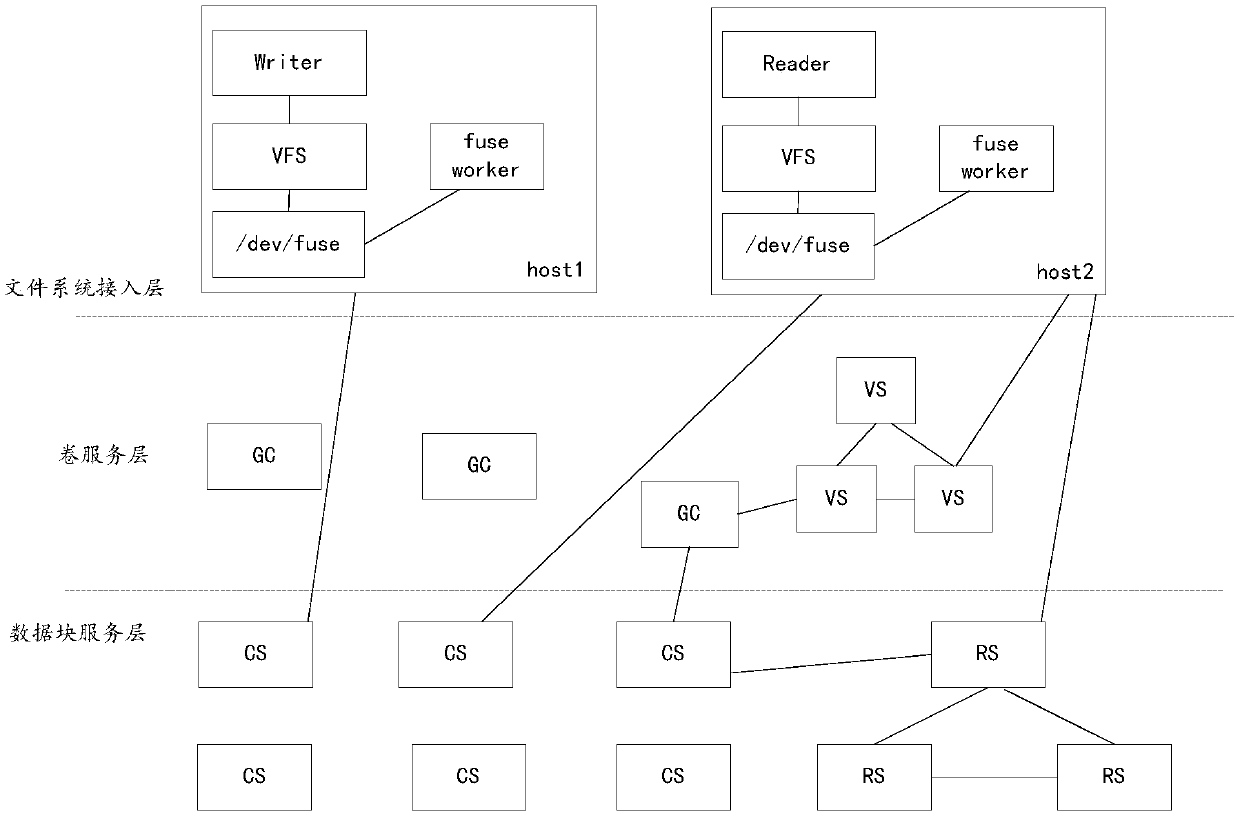

File system data access method and file system

ActiveCN110554834AGood read and write consistencyAvoid reading and writing conflictsInput/output to record carriersFile access structuresAccess methodCheck point

The embodiment of the invention provides a file system data access method and a file system, the file system comprises at least one computing node and a plurality of storage nodes, and the method comprises the following steps: the computing node sends a mounting request triggered for a target logical volume to a target storage node; the computing node receives a log segment corresponding to the target logical volume and check point storage position information sent by the target storage node; the computing node reads log metadata of the log segment and the check point according to the log segment and check point storage position information so as to recover the data state of the target logical volume; and the computing node performs data access processing based on the data state of the target logical volume. When the plurality of computing nodes access the target logical volume, the plurality of computing nodes can keep good read-write consistency based on the log information of the target logical volume maintained in each storage node, and read-write can be synchronously carried out, so that read-write conflicts are avoided.

Owner:ALIBABA GRP HLDG LTD

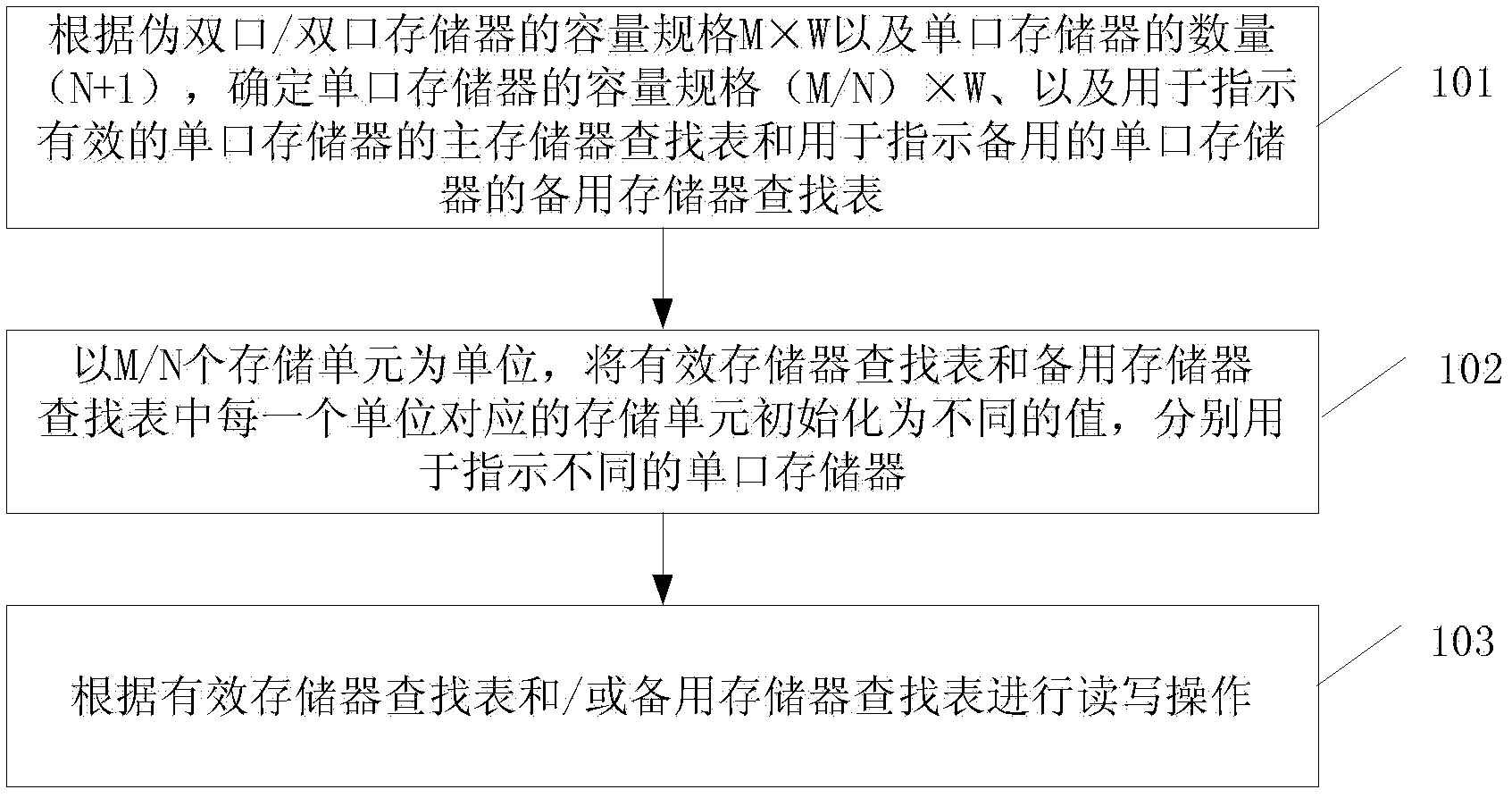

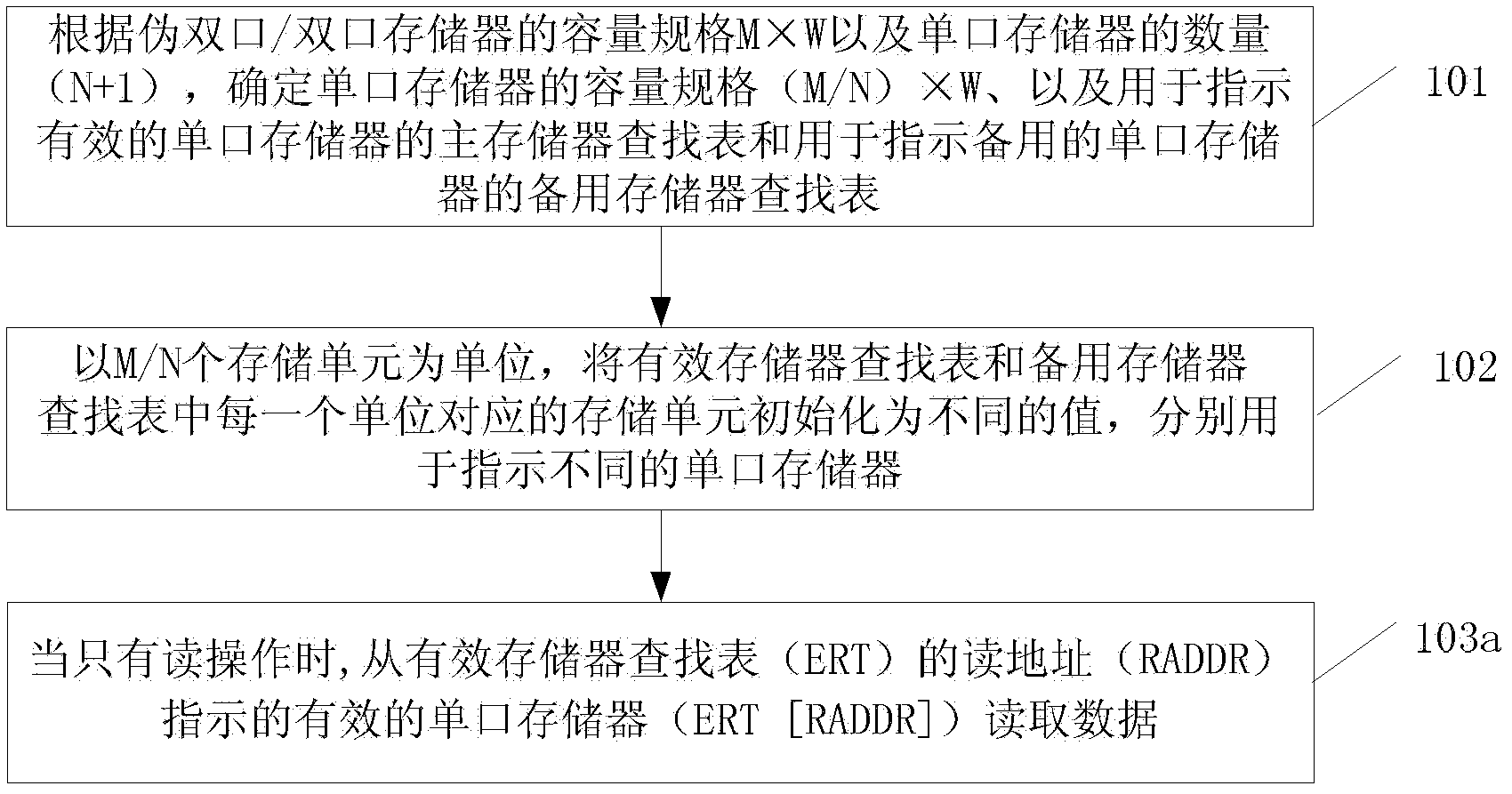

Data read-write method and storage device

InactiveCN102436427AReduce areaAvoid reading and writing conflictsMemory architecture accessing/allocationMemory adressing/allocation/relocationStorage cellOperating system

Owner:HUAWEI TECH CO LTD

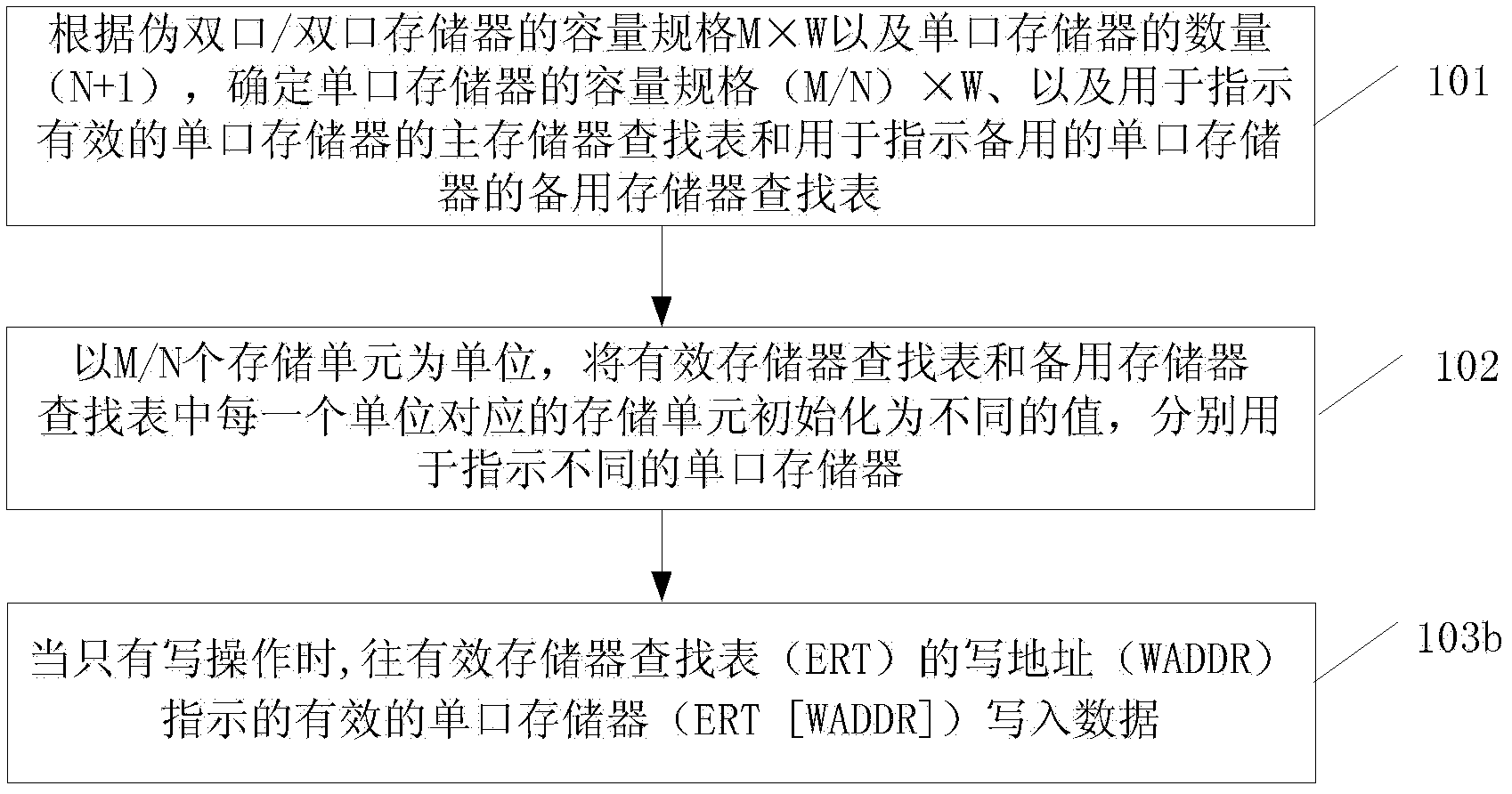

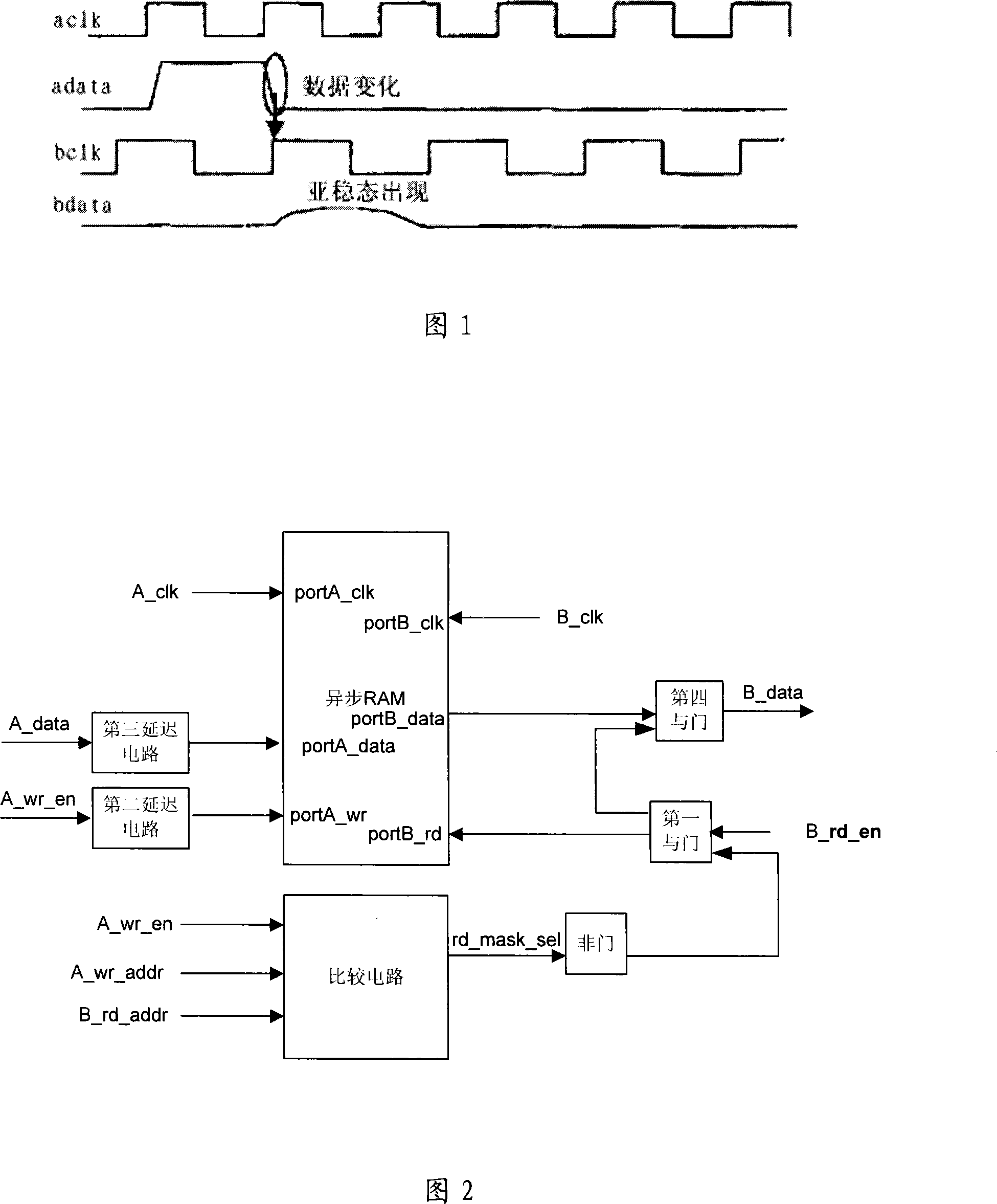

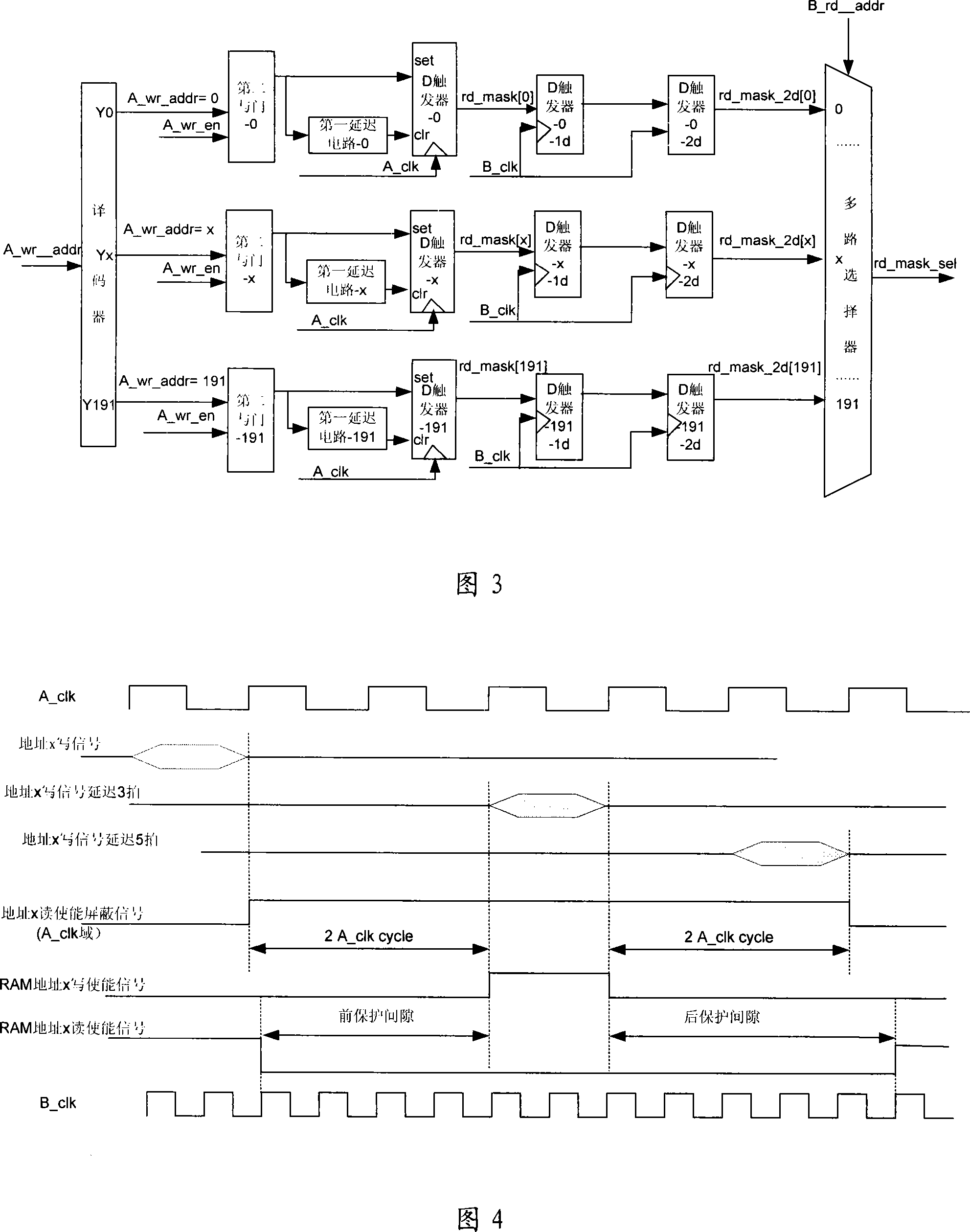

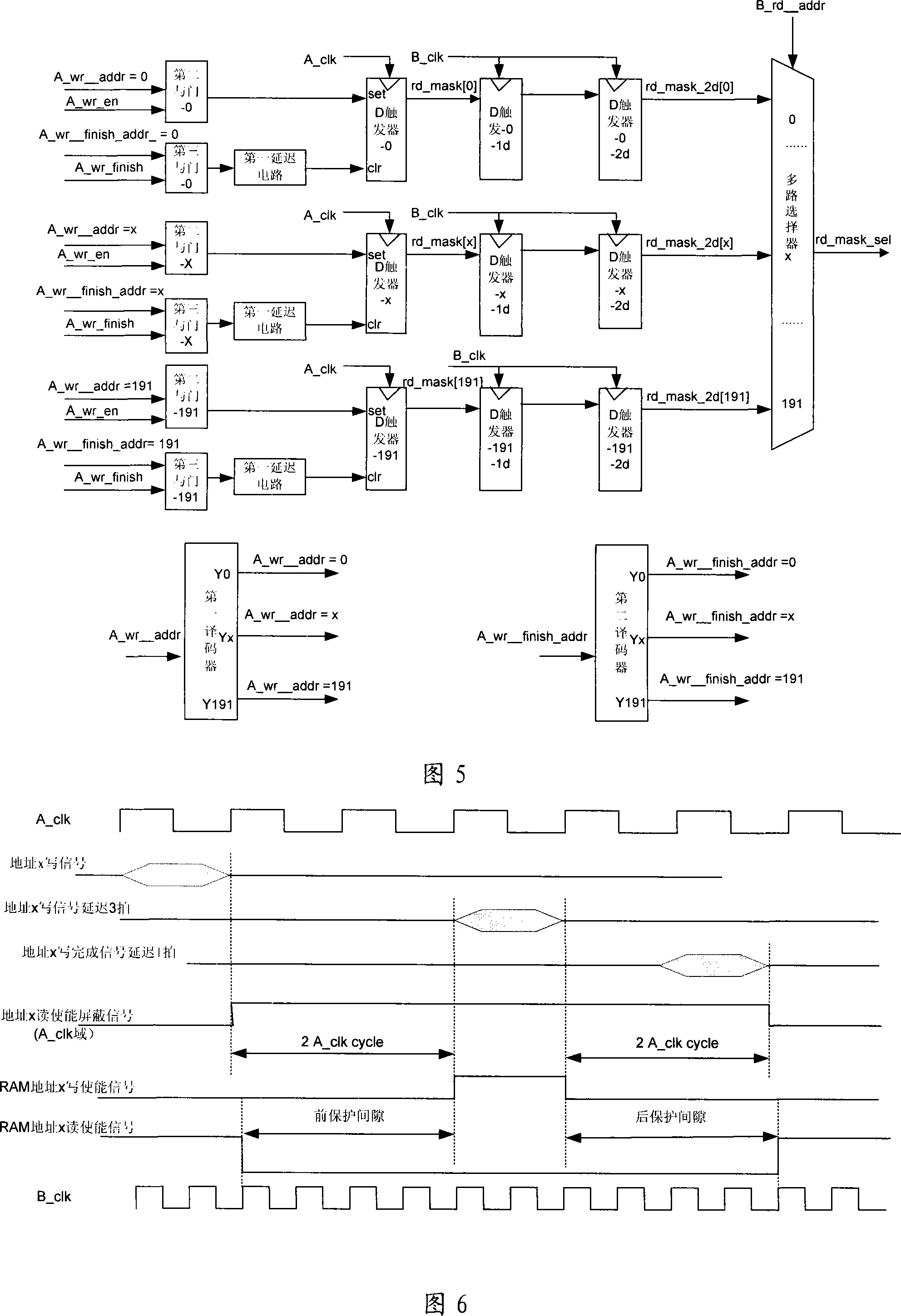

Read-write control circuit, method and apparatus for two-port RAM

ActiveCN101226767AAvoid reading and writing conflictsDoes not take up resourcesDigital storageControl circuitDual-ported RAM

The practical example of the invention discloses a read write control circuit with a dual-port RAM, a device and a method thereof, relating to the technical field of storage, and the invention is invented for evading read write conflict problem of the dual-port RAM. The circuit comprises a comparison circuit, a negation gate and a first coincidence gate, wherein the comparison circuit is used to output read screen signals of a storage unit corresponding with bus signals of a second port address, the negation gate is used to inverse the read screen signals of the storage unit which are corresponding with the bus signals of the second port address, one input end of the first coincidence gate receives the read screen signals of the storage unit which are corresponding with the bus signals of the second port address after being inversed, the other input end of the first coincidence gate receives the read enable signals of a second port, and the output end of the first coincidence gate is connected with the read enable end of the second port. The practical example of the invention can be used in chip circuit designing.

Owner:HONOR DEVICE CO LTD

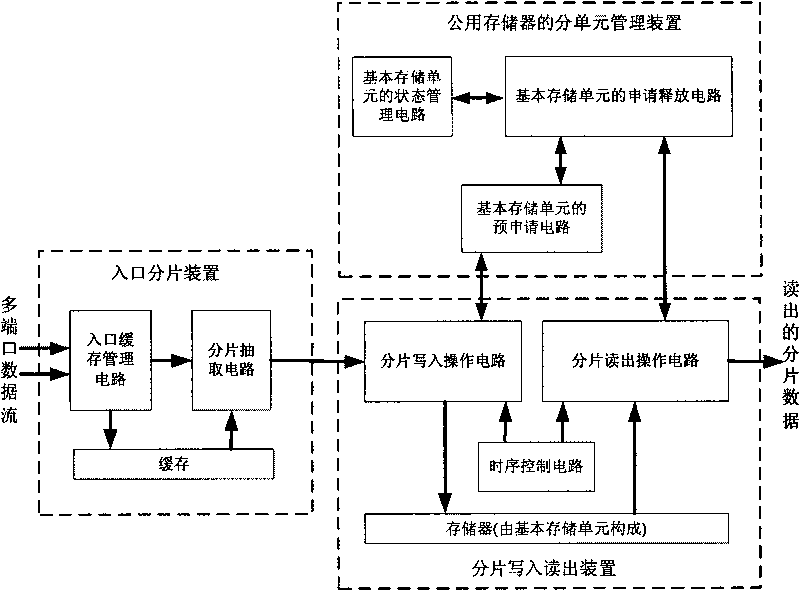

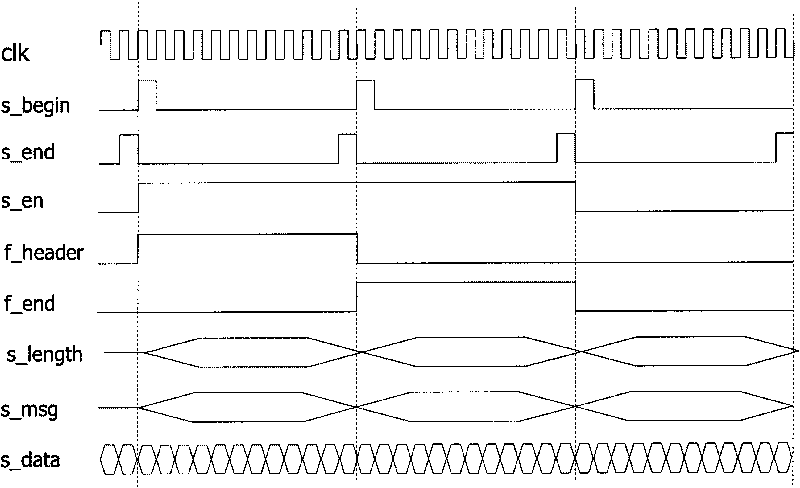

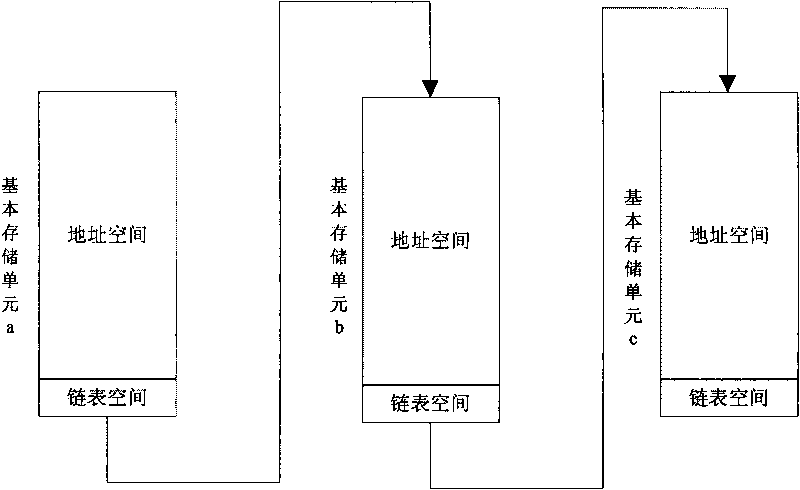

Data frame storage management device

InactiveCN101692655AAvoid reading and writing conflictsSimple circuit implementationData switching networksWhole systemsSequence signal

The invention discloses a data frame storage management device, and relates to data frame processing technology. The data frame storage management device comprises three parts, namely an inlet fragmentation device, a fragmentation write and read device and a sub-unit management device of a public storage, wherein the inlet fragmentation device caches a data stream, extracts the data stream in a fragmentation mode into fragmented data and sends the fragmented data to the fragmentation write and read device; the fragmentation write and read device writes the fragmented data into the storage according to sequence signals of a timing control circuit, or reads the fragmented data from the storage; and the sub-unit management device of the public storage controls the read-write operation of the fragmentation write-in and read-out device. The data frame storage management device divides the storage into a plurality of basic storage units which serve as basic units for storage, can be allocated with addresses based on a source port and also can be allocated with addresses in a sharing way, the independent use of the addresses is achieved by applying for a release mechanism, the write and read of the data are completed by adopting a sequence isolation method, and the conflict between the read and write is avoided, so the circuits of the whole system are realized simply.

Owner:FENGHUO COMM SCI & TECH CO LTD

Real-time timepiece chip interface circuit control method and real-time timepiece control circuit

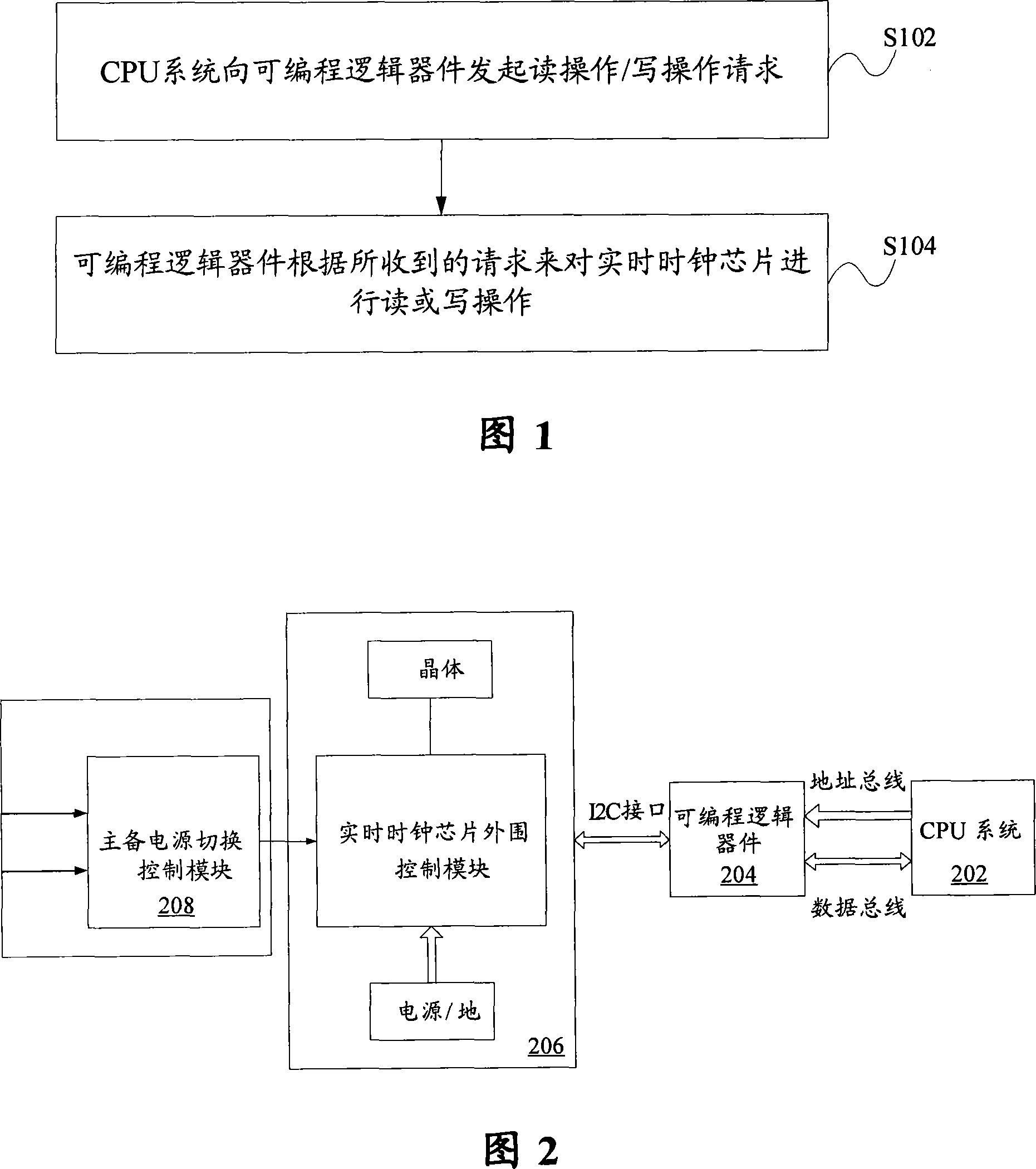

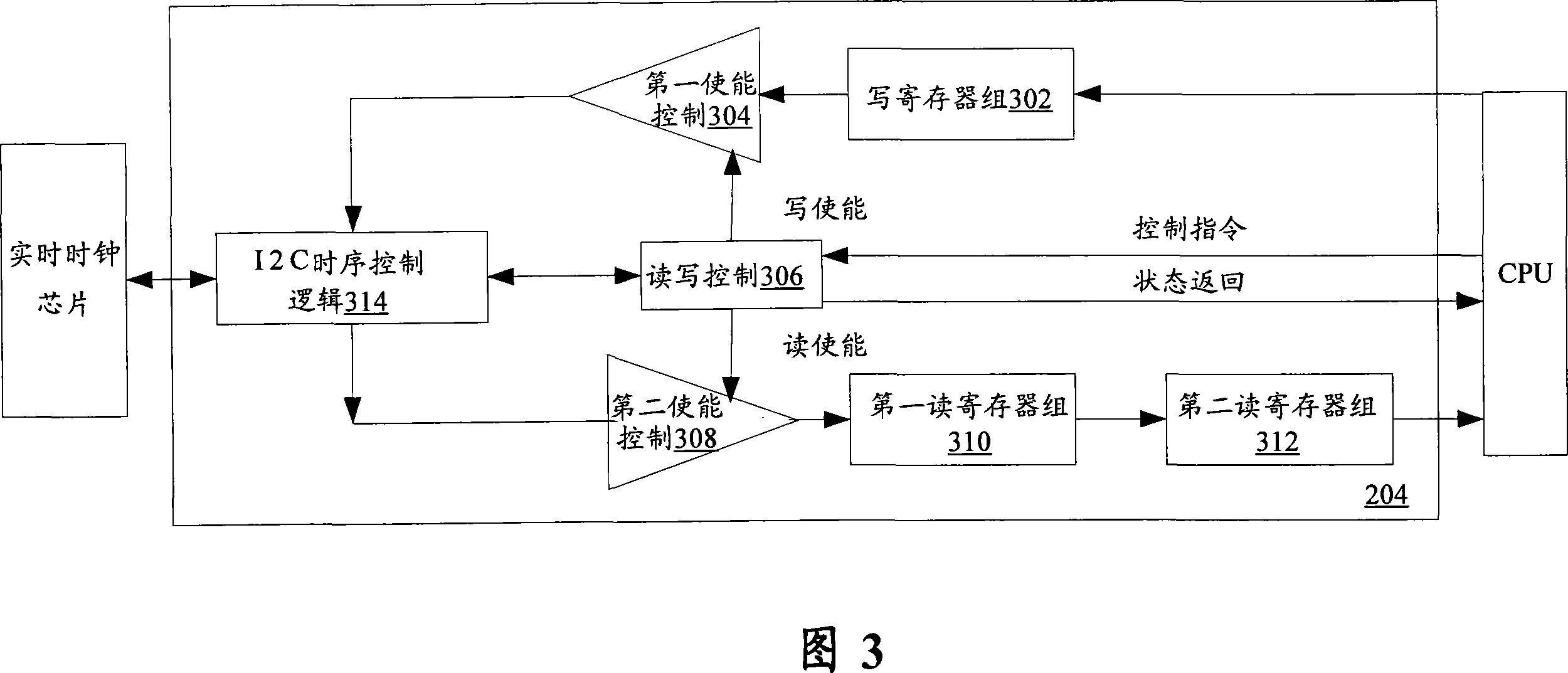

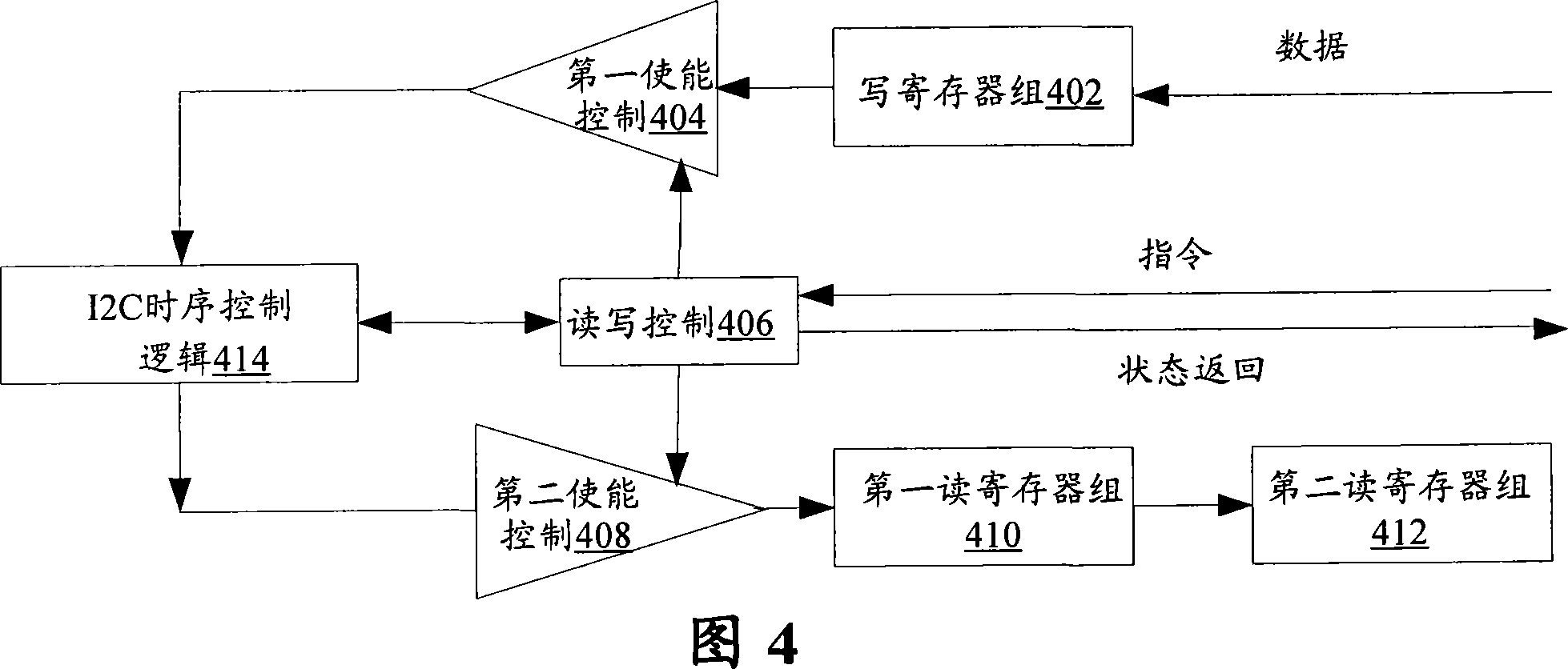

InactiveCN101169673ARelieve pressureShorten the timeGenerating/distributing signalsReal-time clockProgrammable logic device

The invention discloses a control method for a real-time clock chip interface circuit, a real-time clock circuit and a programmable logical circuit for the control of the real-time clock chip, wherein, the control method for the real-time clock chip interface circuit comprises the following procedures: procedure S102, wherein, a CPU system sends out the requests of reading / writing operation to a programmable logical device; and procedure S104, wherein, the programmable logical device performs reading or writing operation on the real-time clock chip according to requests received. Therefore, the invention significantly reduces the stress of CPU and saves a huge amount of time through a hardware-realizing mode, thereby not only improving the real-time performance of processing but also avoiding reading-writing conflicts.

Owner:WUXI POWER SUPPLY JIANGSU PROVINCE ELECTRIC POWER

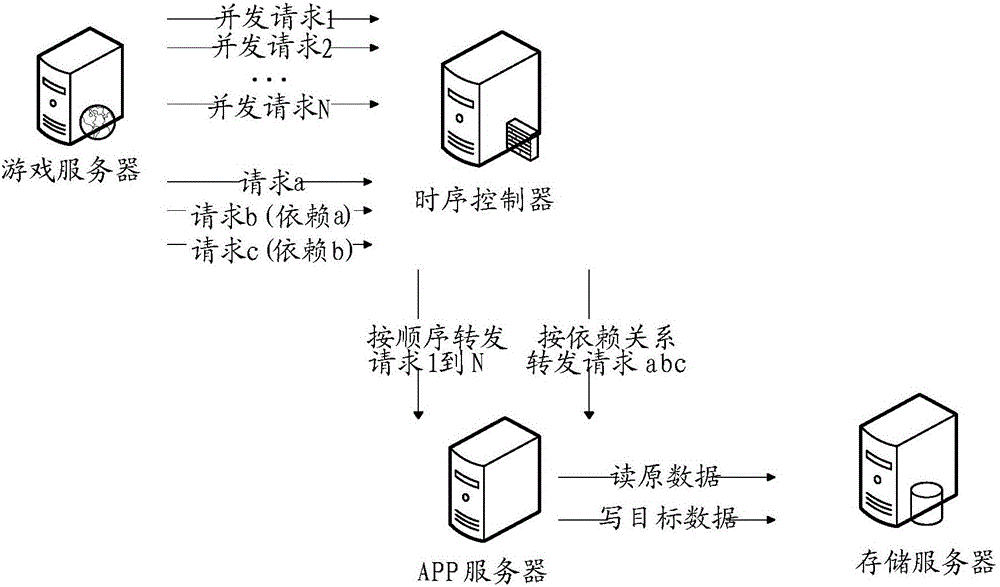

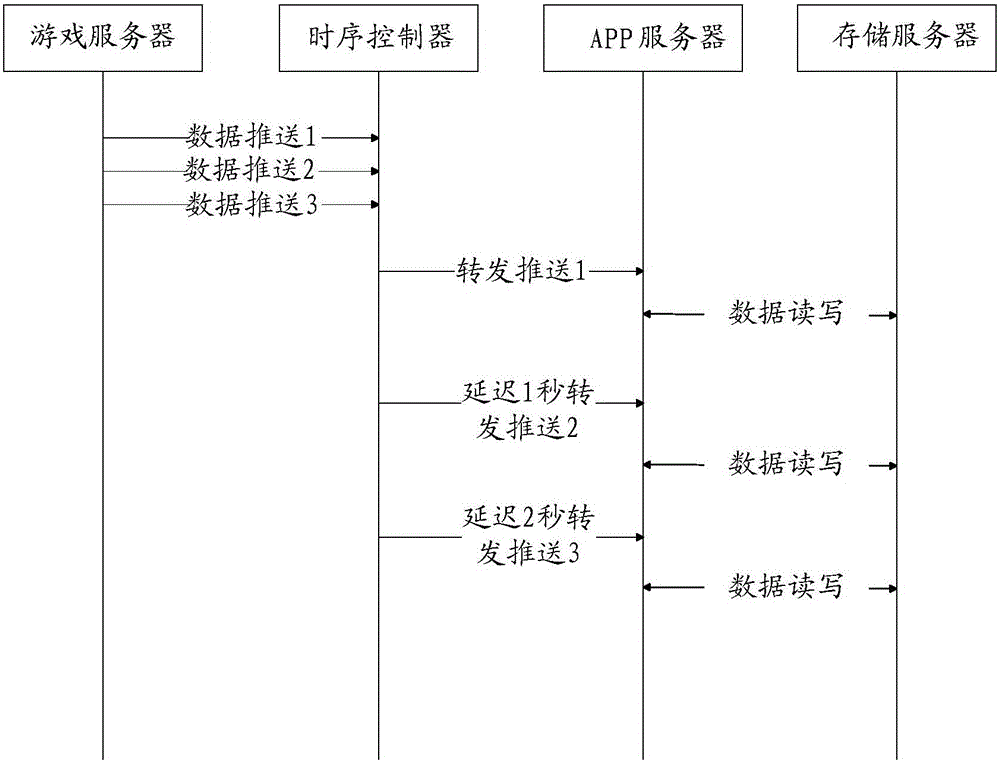

Data push method, time schedule controller and data push system

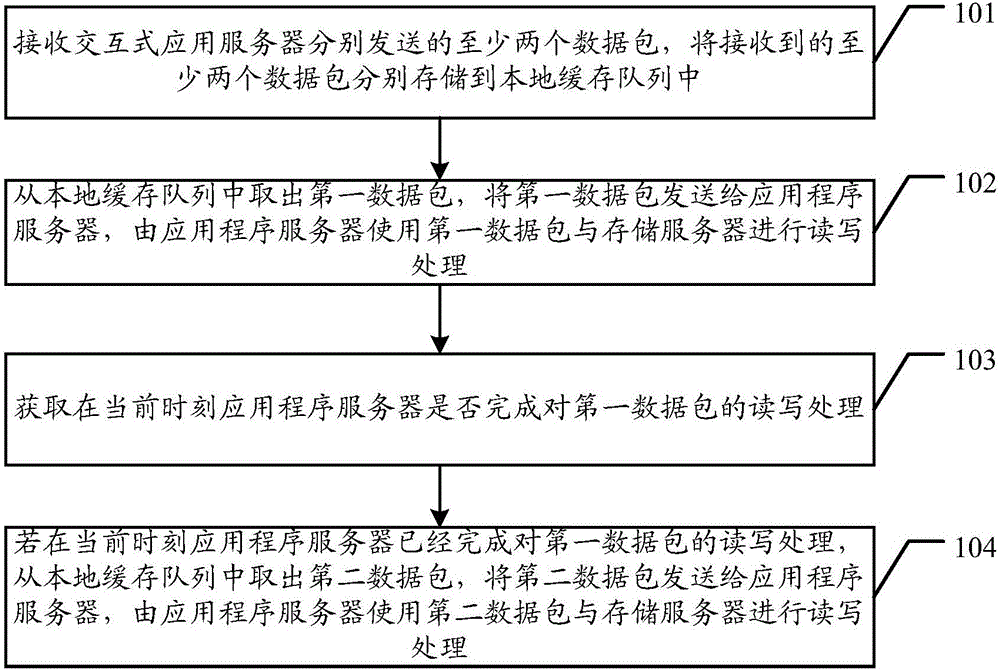

ActiveCN106375329AAlleviate read and write conflictsReduce processing loadTransmissionTime scheduleApplication server

The invention discloses a data push method, a time schedule controller and a data push system for improving the data read-write efficiency of an application server. The embodiments of the invention provide the data push method, which comprises the following steps of receiving at least two data packets which are respectively sent by an interactive application server, and respectively storing the at least two received data packets into a local buffer queue; taking a first data packet from the local buffer queue, sending the first data packet to the application server and making the application server use the first data packet and a storage server to carry out read-write processing; obtaining whether the application server completes read-write processing of the first data packet at the current moment; and if the application server completes read-write processing of the first data packet at the current moment, taking a second data packet from the local buffer queue, sending the second data packet to the application server and making the application server use the second data packet and the storage server to carry out read-write processing.

Owner:TENCENT TECH (SHENZHEN) CO LTD

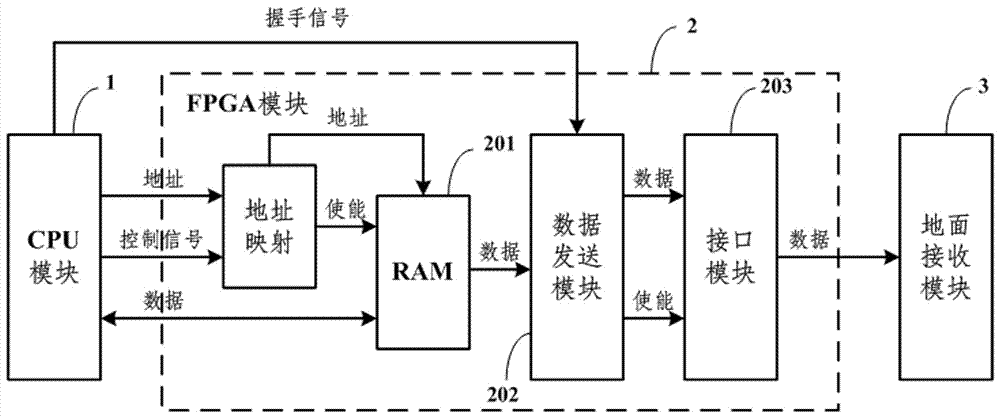

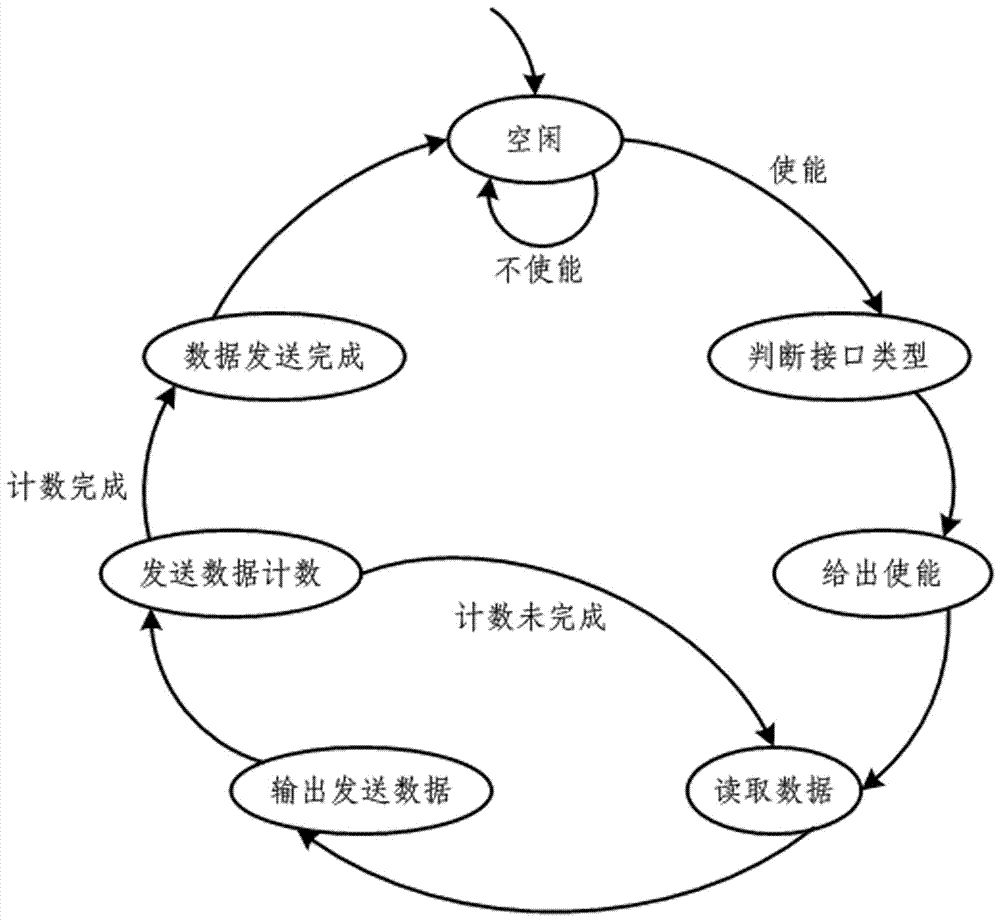

Star sensor software online fault monitoring system and monitoring method thereof

ActiveCN106933740AImplement cachingAvoid reading and writing conflictsMeasurement devicesSoftware testing/debuggingVisibilityMonitoring system

The invention discloses a star sensor software online fault monitoring system and a monitoring method thereof. The method comprises the following steps of: writing to-be-transmitted star sensor software key data into an FPGA module by a CPU module by utilizing an address mapping manner; after the FPGA module detects that the electric level state of a handshake signal sent by the CPU module changes, sending the star sensor software key data to ground reception equipment by the FPGA module; and analyzing and displaying star sensor software operation condition by the ground reception equipment in real time, and monitoring software faults online. According to the Star sensor software online fault monitoring system and monitoring method thereof, real-time online monitoring is carried out on star sensor software, the fault problems in the software operation process can be timely positioned, so that the visibility of the star sensor software faults is increased and the troubleshooting efficiency of the star sensor software faults is improved.

Owner:SHANGHAI AEROSPACE CONTROL TECH INST

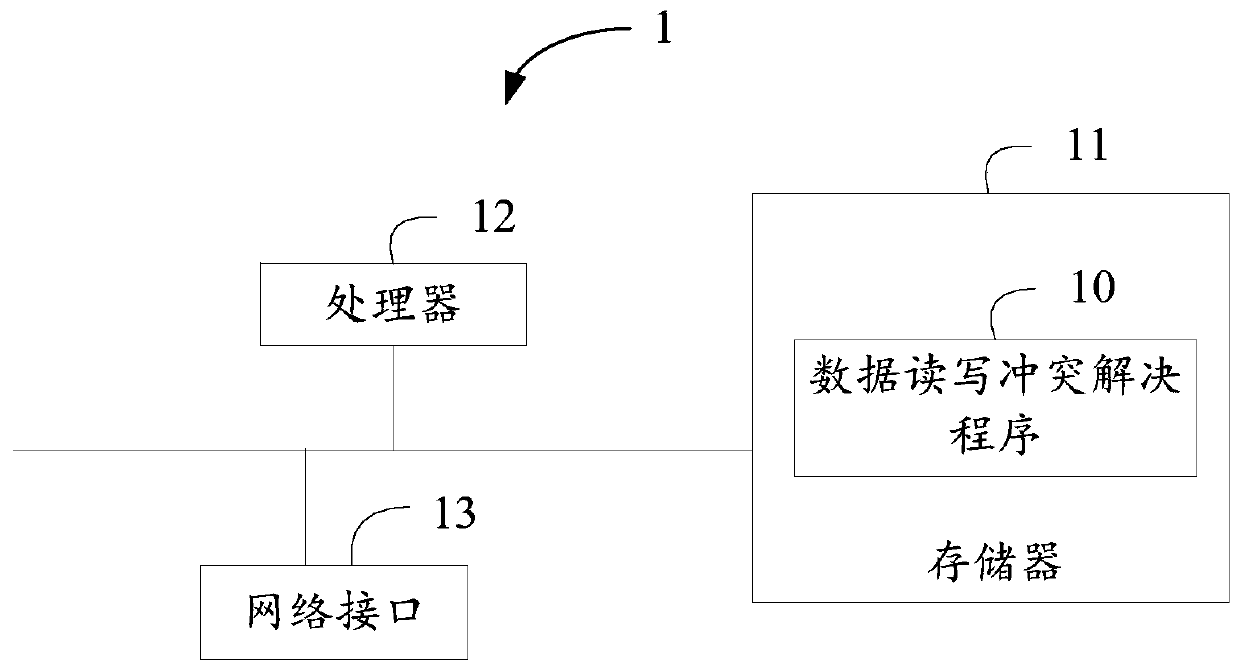

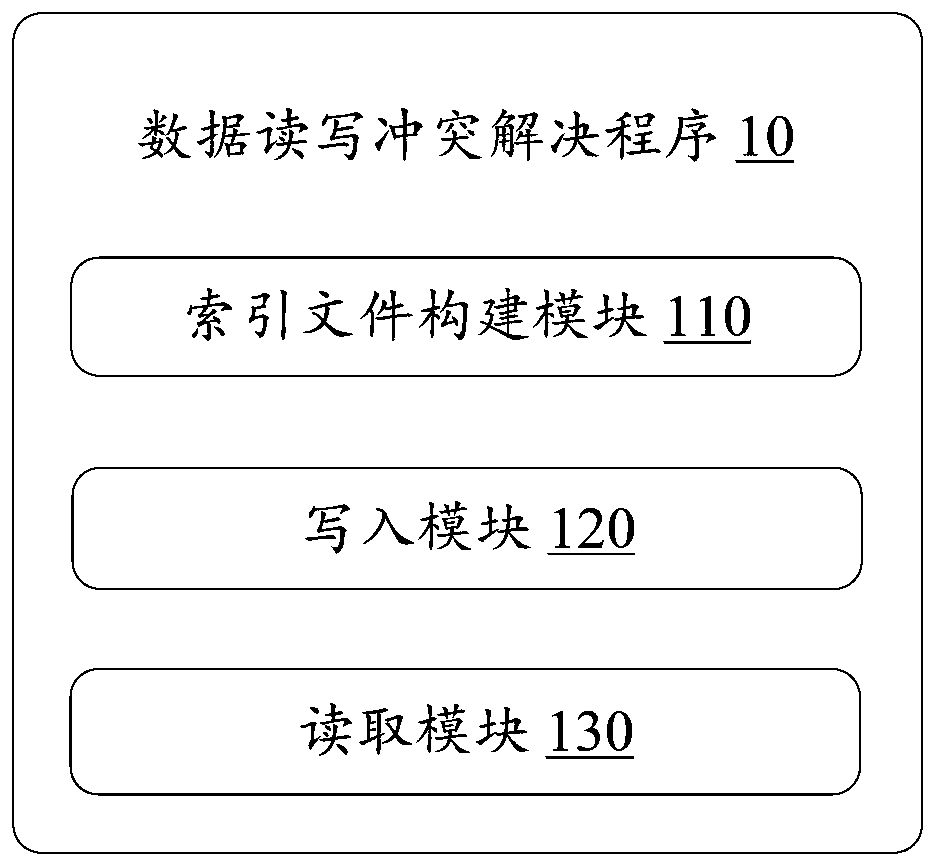

B + tree-based read-write conflict resolution method and device and storage medium

PendingCN110162525AImprove experienceAvoid reading and writing conflictsDatabase updatingInput/output to record carriersTree basedWrite–read conflict

The invention relates to a data processing technology, and provides a B+ tree-based read-write conflict resolution method and device and a storage medium. The method comprises the following steps: constructing an index file for a target data set, wherein the index file adopts a B+ tree structure and records the root node address of a B+ tree twice at the head of the file; when a write operation isexecuted on a target data set, adding a data identifier, a storage address or a deletion identifier corresponding to the write operation to a tail node of the B+ tree, then creating replica father nodes of all layers for the tail node, and after recording child node addresses, sequentially modifying a root node address of the file header by the replica father nodes of all layers; executing a reading operation on a target data set; judging whether the root node addresses of the file header are the same or not, if yes, accessing the root node by any one or default root node address, and accessing the corresponding sub-nodes layer by layer to complete the reading operation, and if not, respectively utilizing the root node address to complete the reading operation by the available root node address.

Owner:PING AN TECH (SHENZHEN) CO LTD

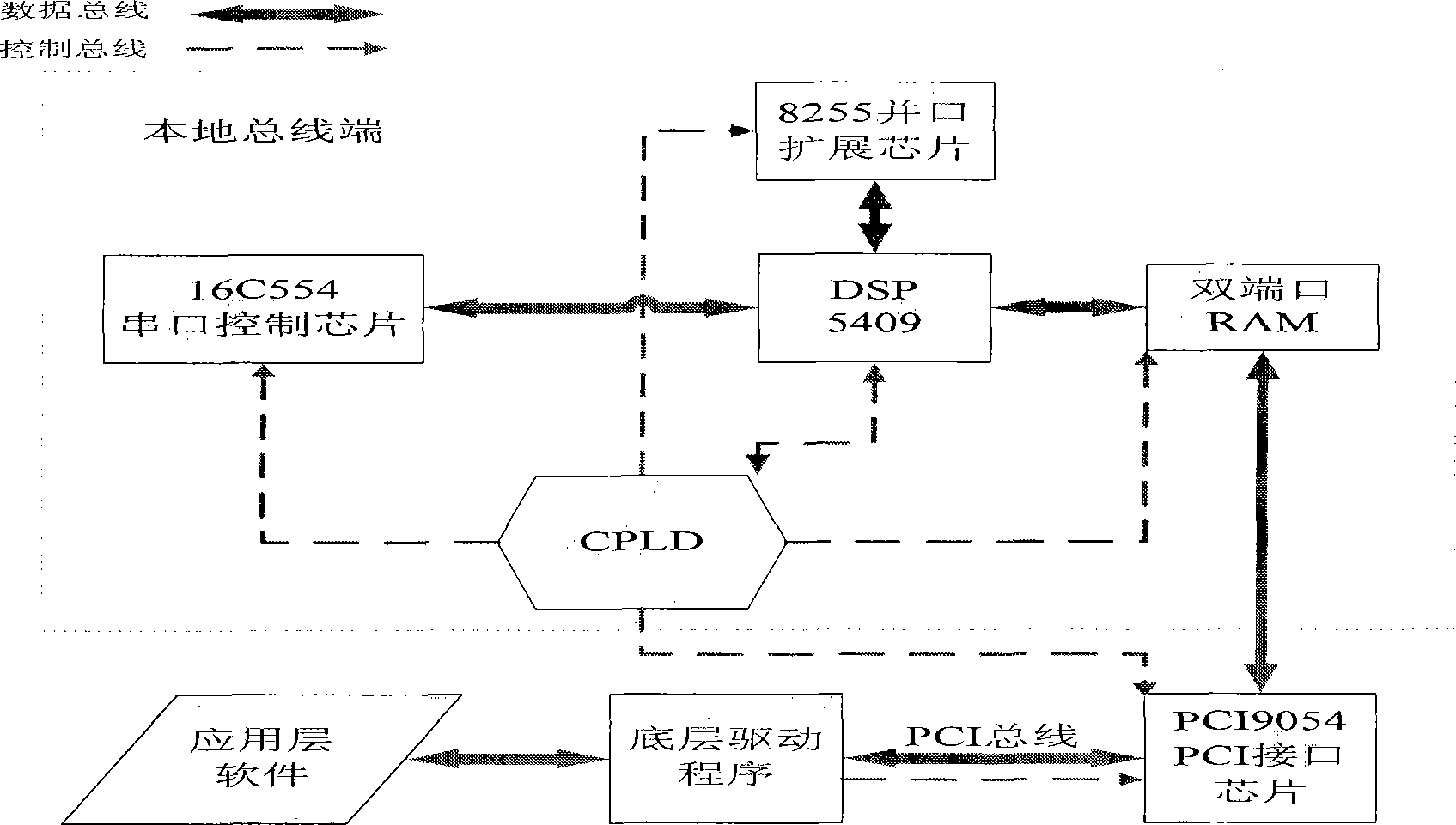

CompactPCI communication card

InactiveCN101452439AEasy to read and writeAvoid reading and writing conflictsElectric digital data processingImaging processingPci interface

The invention discloses a CompactPCI communication board used for fields such as industrial control, data transmission, signal acquisition and image processing, which comprises a DSP, a CPLD, a dual-port RAM, and a PCI interface chip, wherein the DSP is used as a central processing unit of a local end, the CPLD is used for finishing local address assignment, bus control and interruption arbitration work, and the PCI interface chip is utilized to convert a PCI electrical communication protocol into a protocol which can be used for the reading of a device of the local end; a data bus at one end of the dual-port RAM is connected with a data bus of the DSP; an address bus and a control bus of the DSP are accessed into the CPLD, a data bus and an address bus of the local end of the PCI interface chip are connected with the other end of the dual-port RAM, and a control bus of the local end of the PCI interface chip is accessed into the CPLD; and data, address and control pins of a PCI end of the PCI interface chip are accessed to a PCI bus. The CompactPCI communication board has the advantages of simple structure and strong universality.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

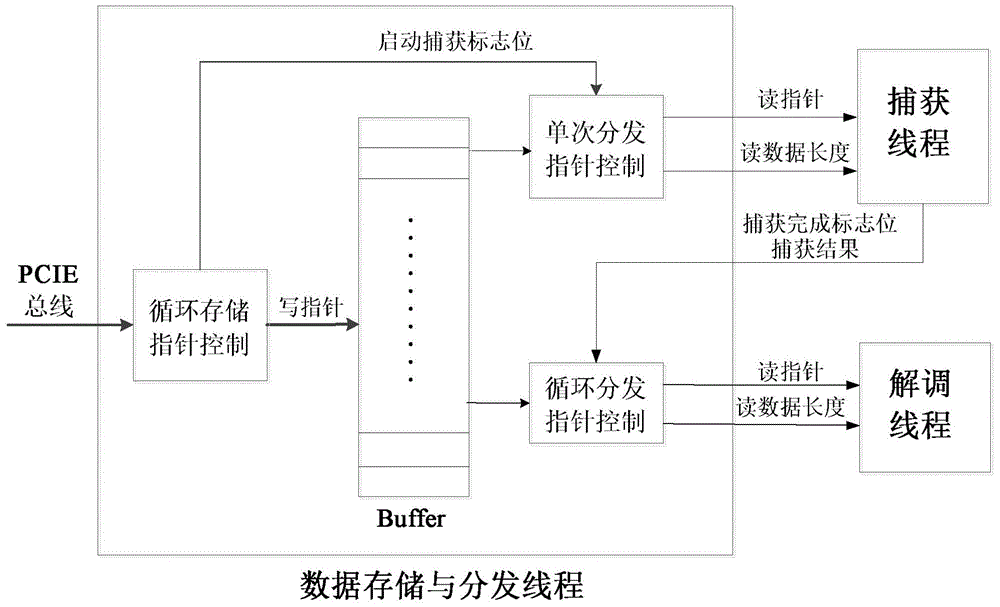

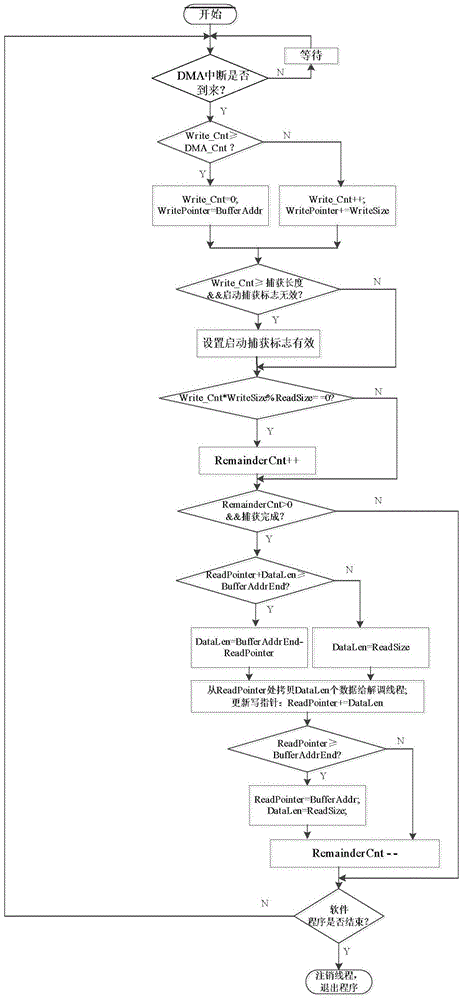

Collected data cyclic storage and distribution method in real-time software receiver

ActiveCN105676689AAvoid reading and writing conflictsMeet distribution needsSatellite radio beaconingProgramme control in sequence/logic controllersDistribution methodComputer module

The invention discloses a collected data cyclic storage and distribution method in a real-time software receiver, and aims to provide a data cyclic storage and distribution method which can perform real-time cyclic storage of measurement and control communication signals of different systems and speeds and is controllable in distribution speed. According to the technical scheme, the method comprises the following steps: after collected data are reported to a computer through a PCIE bus, the data are written into a buffer under the control of a cyclic storage pointer control module; when a capturing starting sign is valid, a distribution address pointer and a distribution data length are transmitted to a capturing thread by a one-time distribution pointer control module; after capturing is accomplished, a cyclic distribution pointer control module carries out cyclic data distribution operation; when the distribution address pointer reaches the end of the buffer, the distribution data length equals the data length between the distribution address pointer at the moment of distribution and the end of the buffer. After data distribution is completed, the cyclic distribution pointer control module updates the cyclic distribution pointer to the head address of the buffer.

Owner:10TH RES INST OF CETC

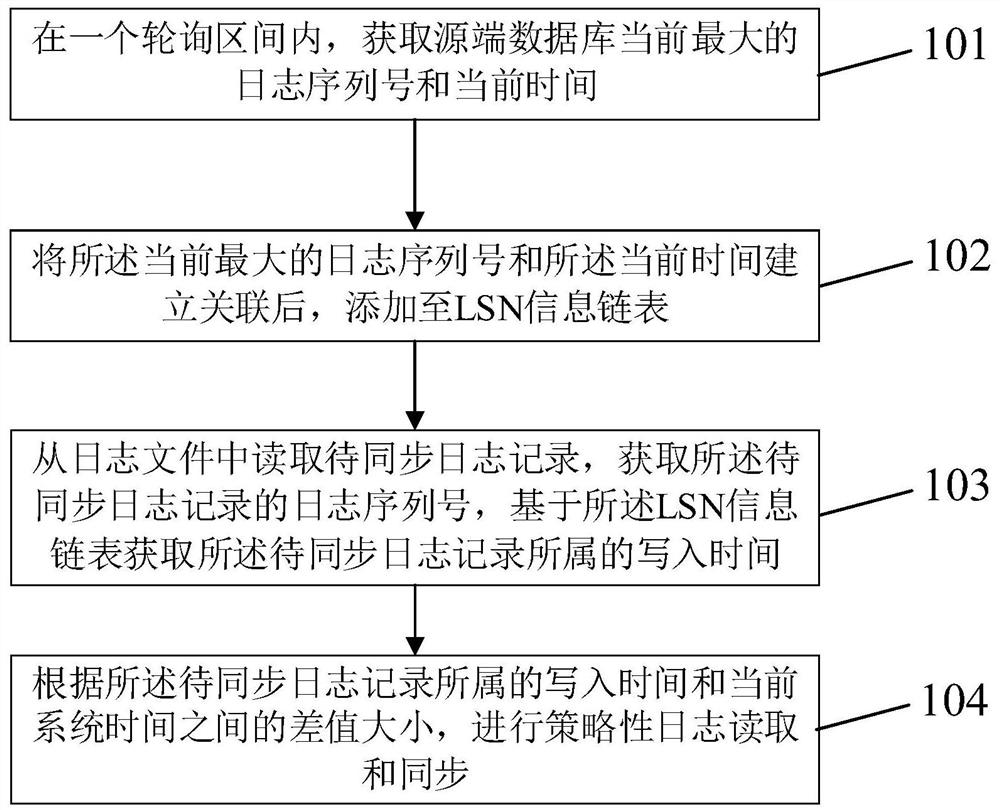

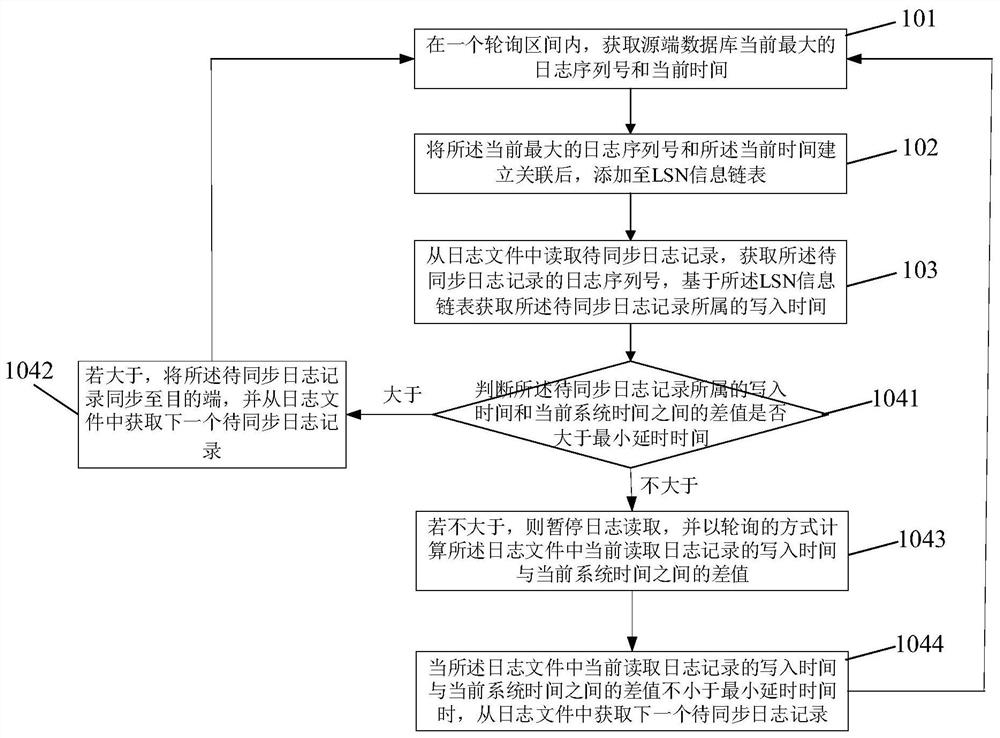

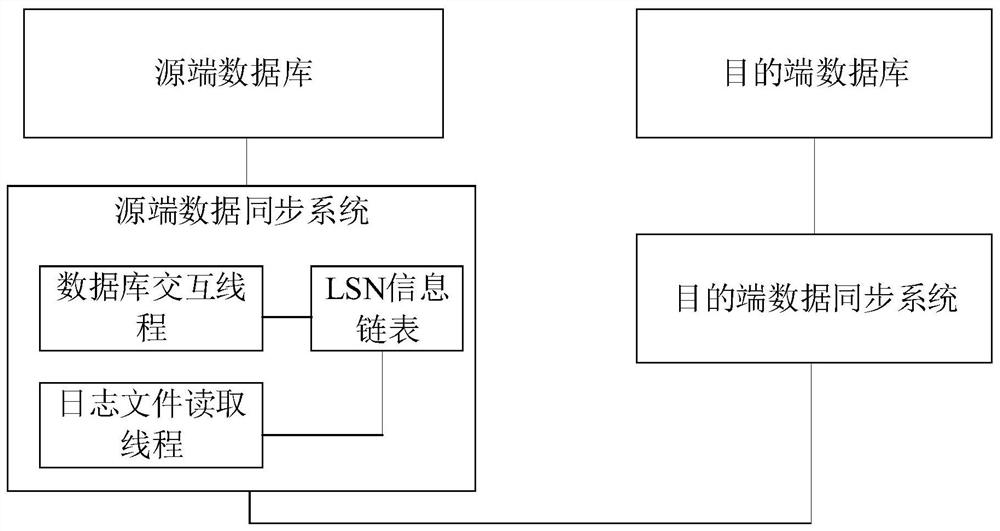

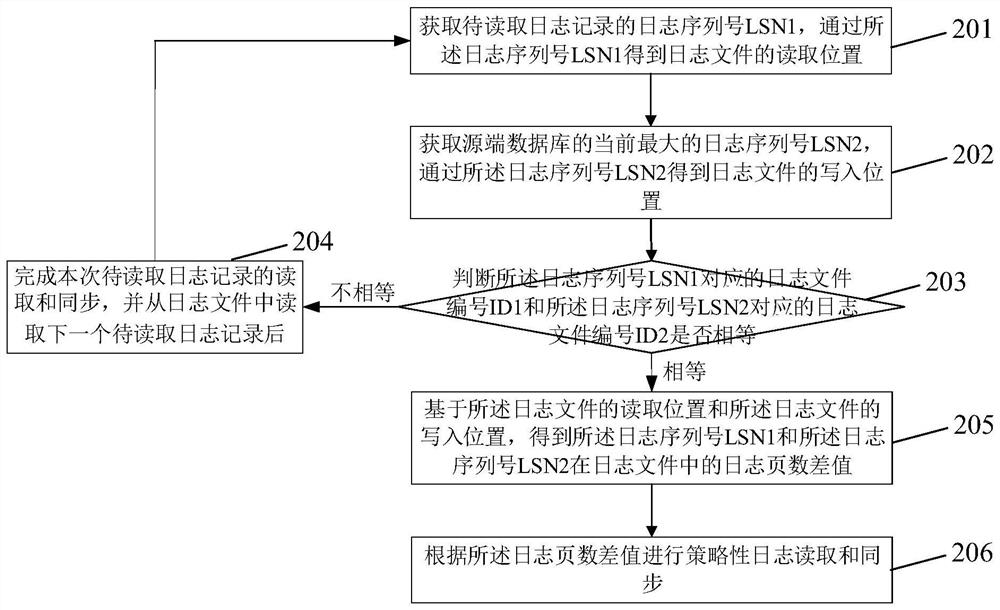

Log reading method based on log analysis synchronization and data synchronization system

ActiveCN111858501AAvoid reading and writing conflictsAvoid confictDatabase updatingDatabase distribution/replicationData synchronizationData mining

The invention discloses a log reading method based on log analysis synchronization and a data synchronization system, and the log reading method comprises the steps of obtaining the current maximum log serial number and current time of a source end database in a polling interval; establishing association between the current maximum log serial number and the current time, and adding the associationto an LSN information chain table; reading a to-be-synchronized log record from a log file, obtaining a log serial number of the to-be-synchronized log record, and obtaining writing time to which theto-be-synchronized log record belongs based on the LSN information chain table; performing strategy log reading and synchronization according to the difference value between the writing time to whichthe log record to be synchronized belongs and the current system time. According to the invention, the log file access positions of the data synchronization process and the database process are staggered through the time difference, and therefore read-write conflicts can be effectively prevented.

Owner:WUHAN DAMENG DATABASE

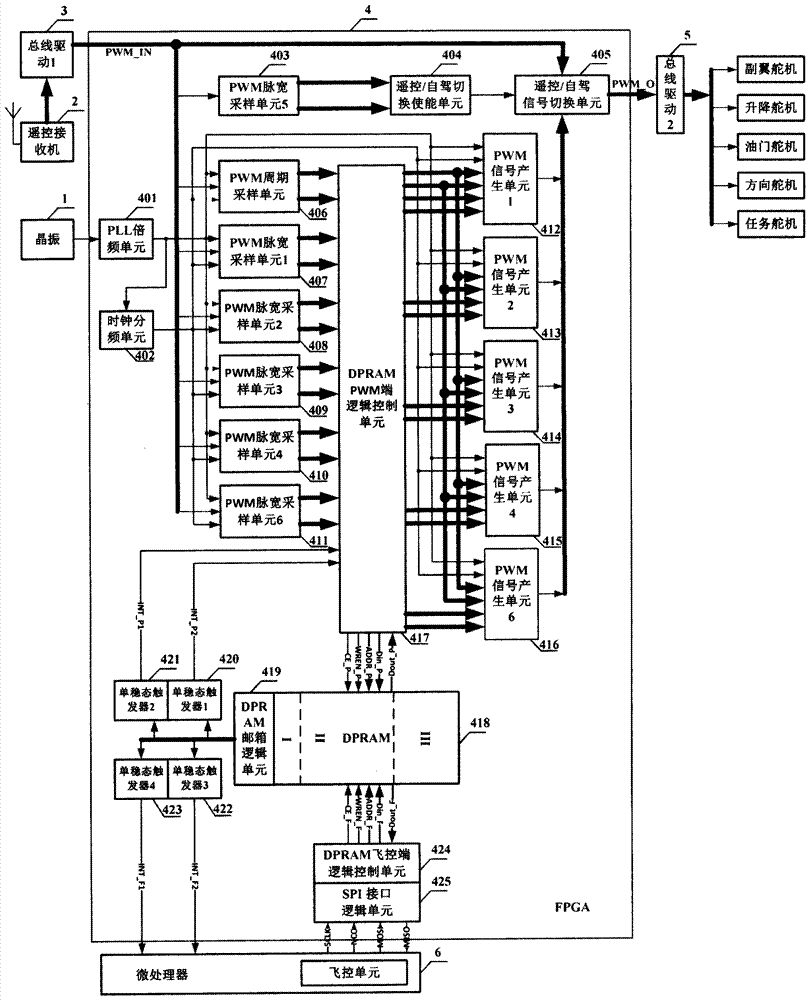

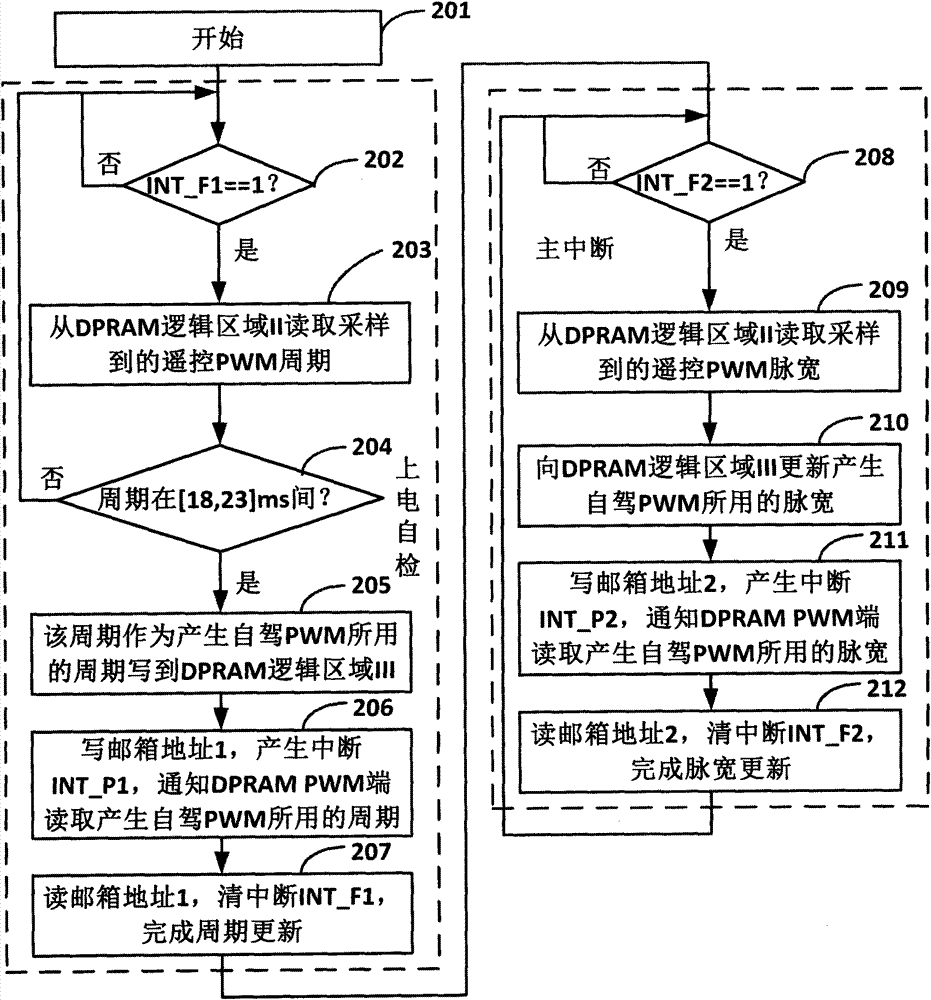

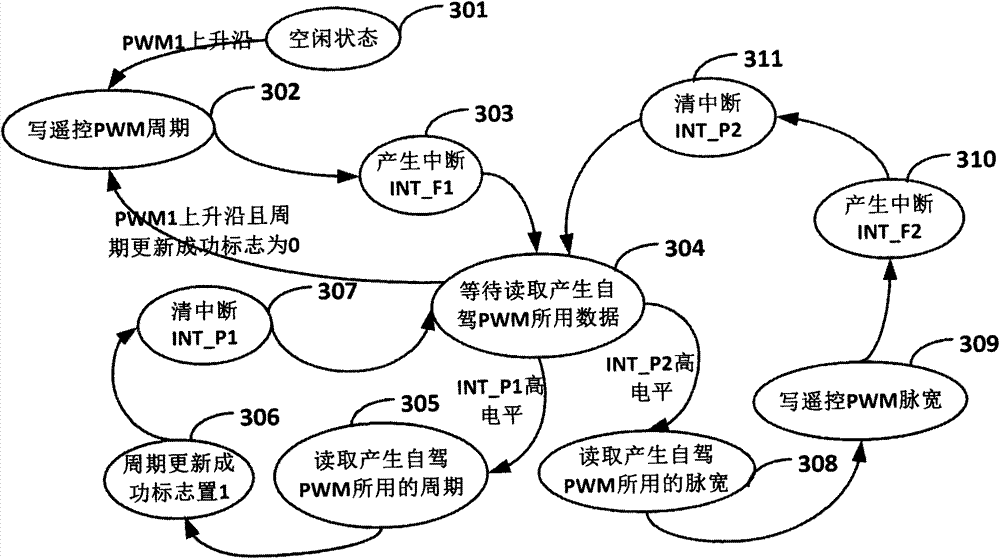

Airborne PWM signal conversion device and method

InactiveCN104300943AImprove versatilityImprove sampling accuracyPulse duration/width modulationPwm signalsField-programmable gate array

The invention provides an airborne PWM signal conversion device and a method. The precision in sampling and generating PWM signals is improved by using a method of combining coarse counting and fine counting; and data communication is carried out by using a DPRAM with dual mailboxes, and the rapidity, the stability and the reliability of data exchange between a flight control unit and a PWM terminal are improved. The device provided by the invention is realized in an FPGA (field programmable gate array), can be applied to different models of remote controllers and different types of unmanned aerial vehicles, and realizes multi-task expansion.

Owner:丑武胜 +1

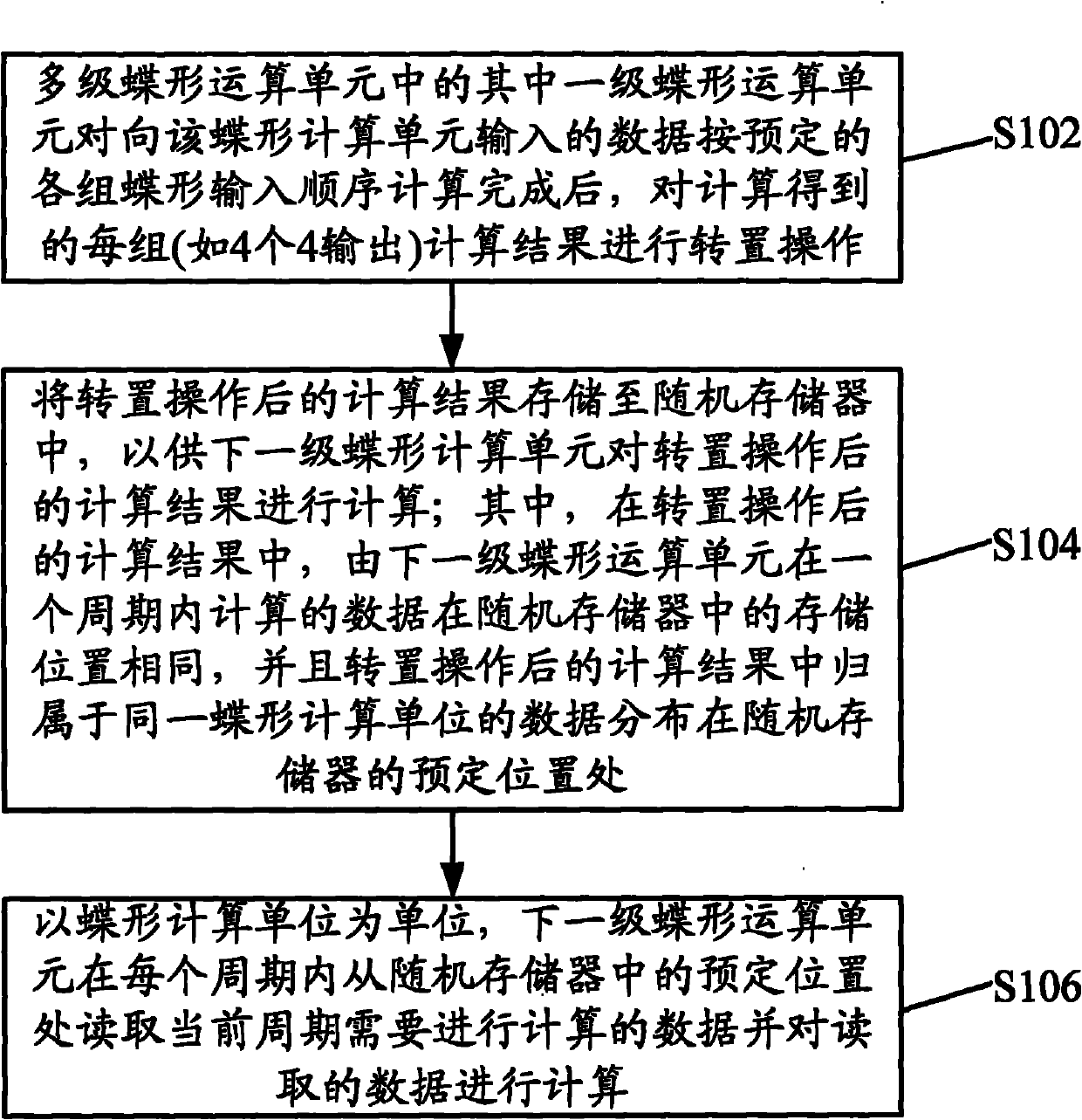

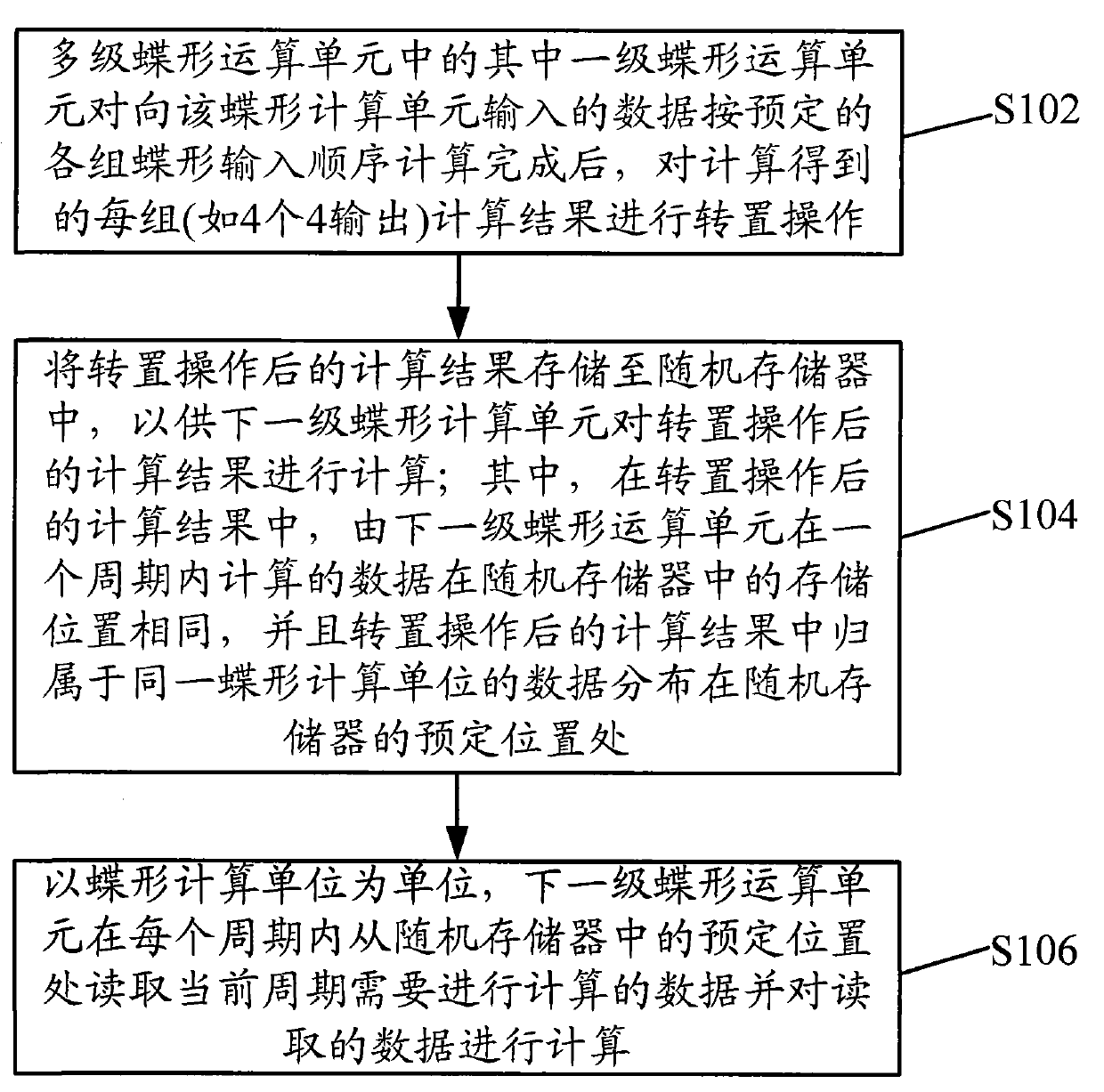

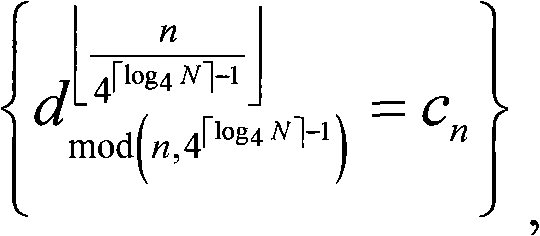

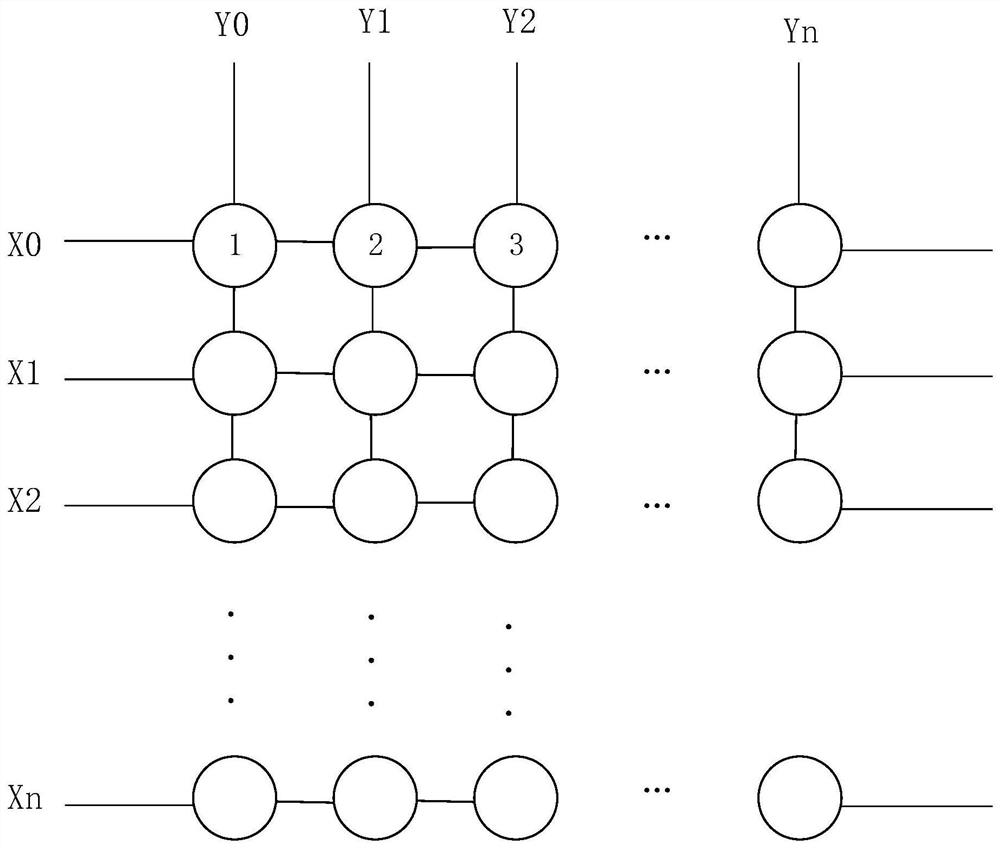

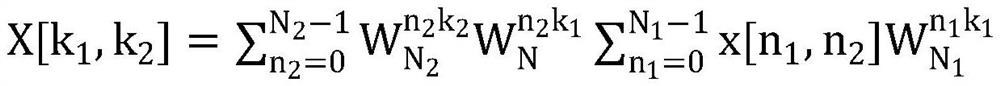

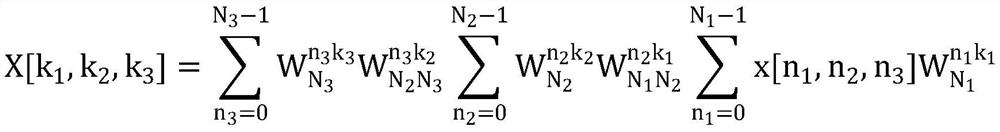

Method and device for realizing Fourier transform

InactiveCN102087640AEasy to readImprove efficiencyComplex mathematical operationsFast Fourier transformPartition of unity

The invention discloses a method and device for realizing Fourier transform. The method comprises the following steps of: calculating data input to a butterfly calculation unit in multi-level butterfly calculation units and carrying out transposition operation on a calculation result acquired through calculation; storing a calculation result after transposition operation to an RAM (Random Access Memory) for the next butterfly calculation unit of the butterfly calculation unit to calculate the calculation result after transposition operation; storing data calculated by the next butterfly calculation unit in a cycle in the same storage position in the RAM in the calculation result after transposition operation and distributing the data attributing to the same butterfly calculation unit in the calculation result after transposition operation in the preset position of the RAM; reading data needed to be calculated in the current cycle from the preset position of each RAM and calculating the read data by the next butterfly calculation unit in each cycle by using the butterfly calculation unit as a unit.

Owner:ZTE CORP

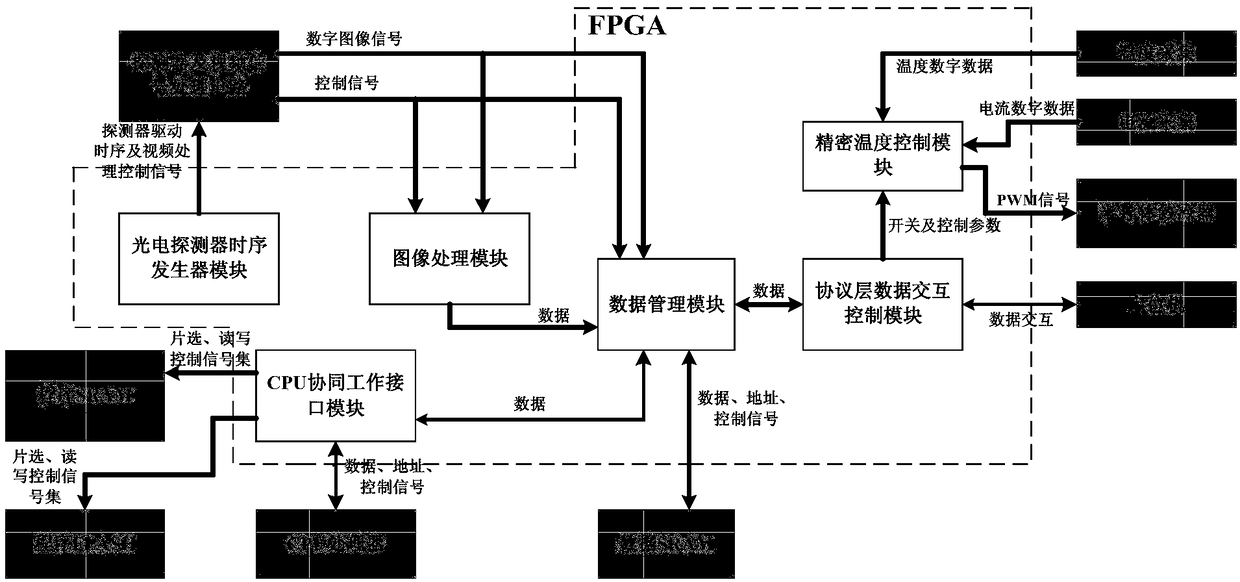

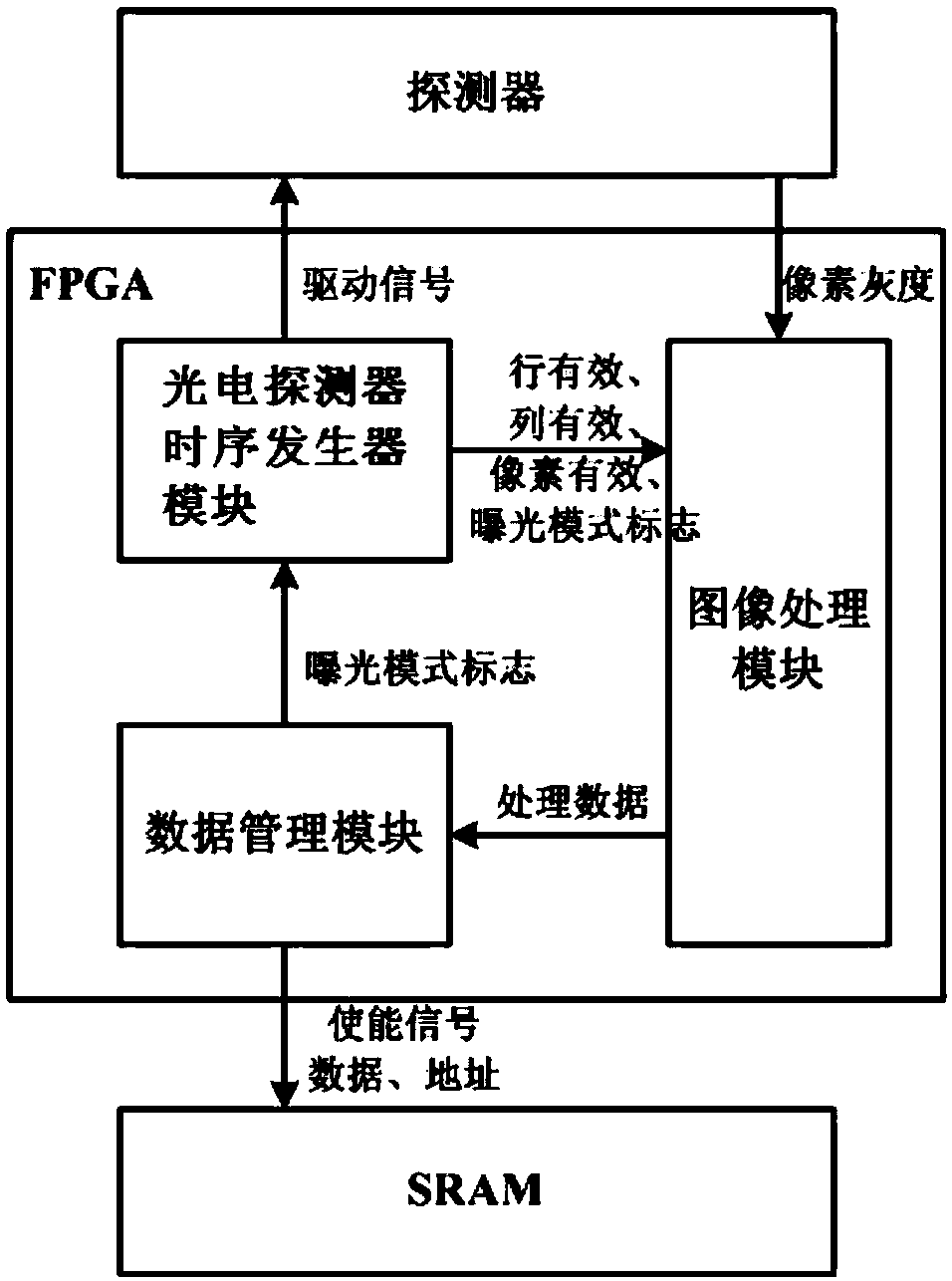

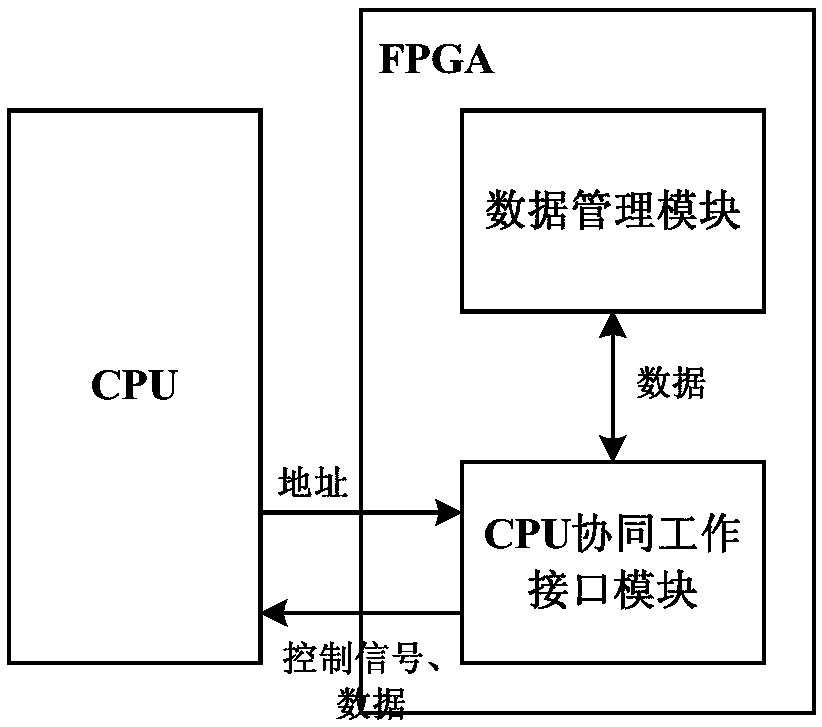

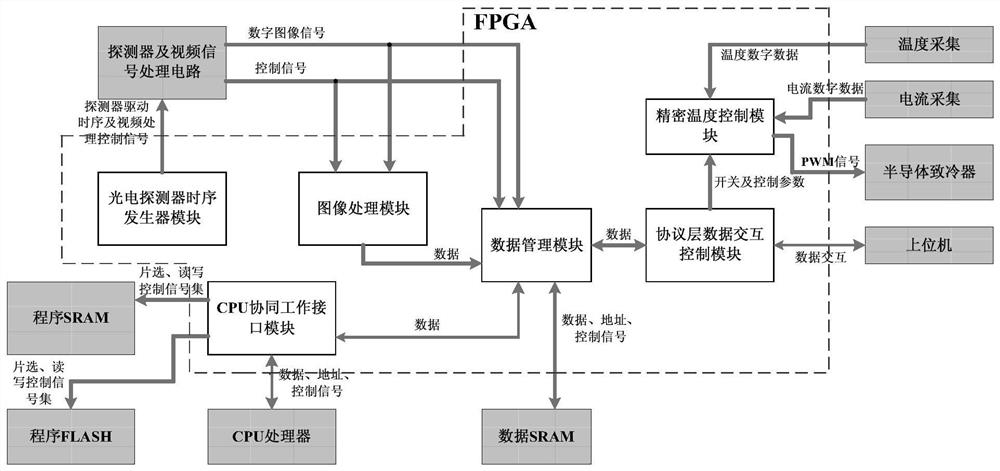

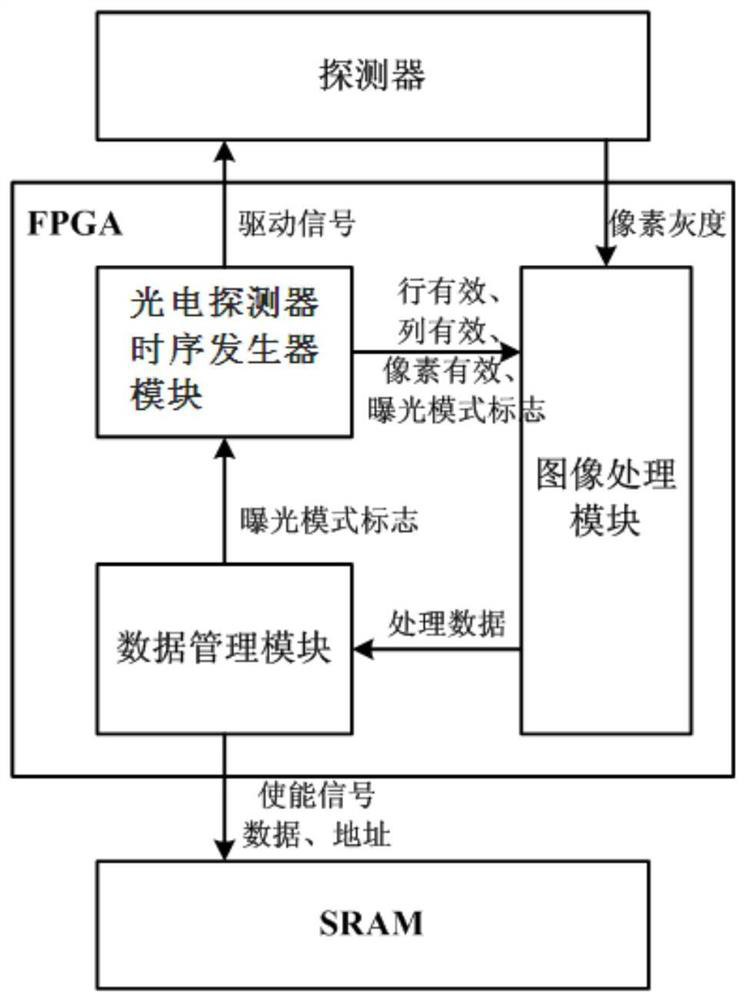

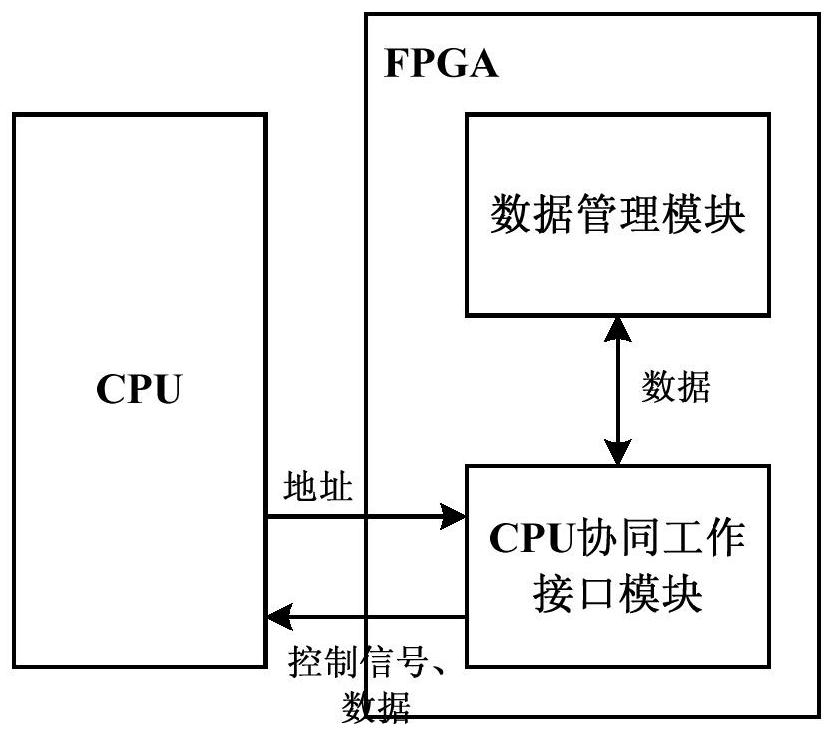

High-precision information processing system for star sensor

ActiveCN108871317AImprove data update rateImprove anti-stray light abilityProgramme controlComputer controlInformation processingMeasurement precision

The invention discloses a high-precision information processing system for a star sensor. According to the high-precision information processing system, a FPGA module comprises a photoelectric detector time sequence generator module, an image processing module, a protocol layer data interaction control module, a CPU collaborative working interface module, a data management module and a precision temperature control module, wherein the photoelectric detector time sequence generator module is used for transmitting a detector driving signal, the image processing module is used for receiving and processing star map data output by a detector, the protocol layer data interaction control module is used for carrying out protocol interaction with external equipment, the CPU collaborative working interface module is connected to an external CPU processor, and the data management module is used for managing various data packages. The high-precision information processing system has the advantagesthat the calculation load of a CPU is shared, and the parallel information processing capability is remarkably improved; the time sequence control, image background estimation and star point mass center extraction of the photoelectric detector are completed in real time, so that the requirements of real-time image processing and anti-stray-light high-reliability image processing strategies are met; and the temperature of the detector is acquired in real time, a precision temperature control technology for a semiconductor refrigerator is achieved, the integration degree of a circuit system isimproved, the cost is conveniently lowered, the product miniaturization is facilitated, and the measurement precision of the star sensor is improved.

Owner:SHANGHAI AEROSPACE CONTROL TECH INST

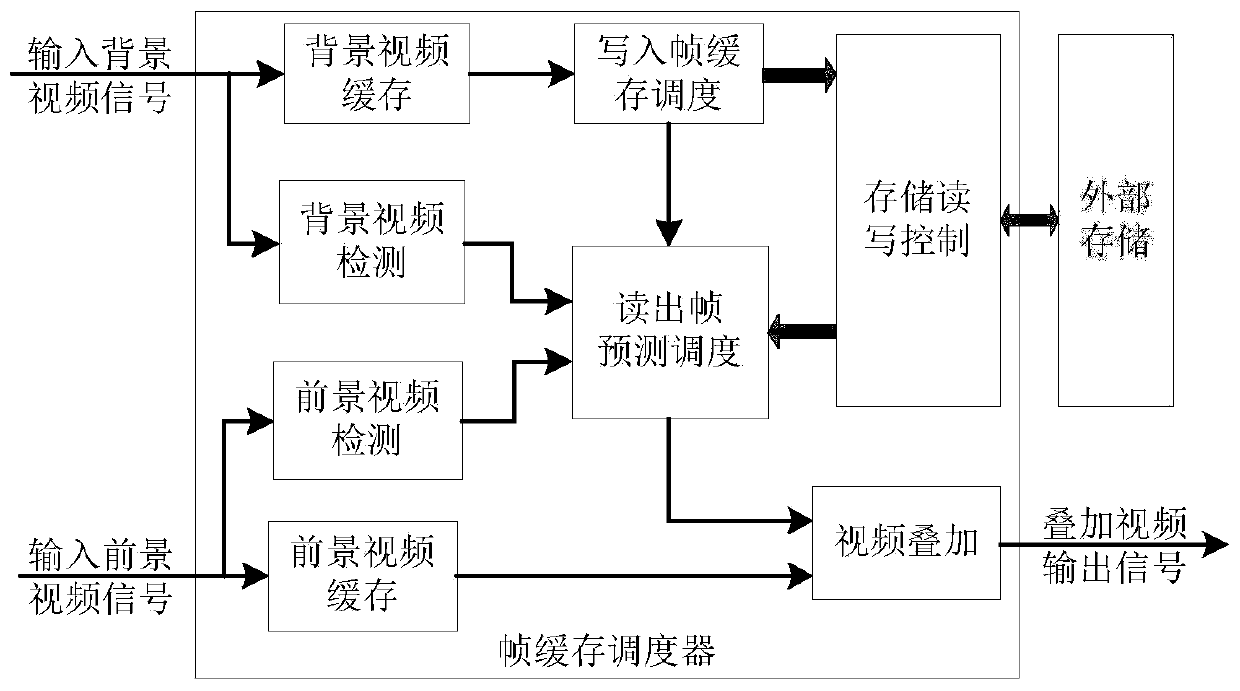

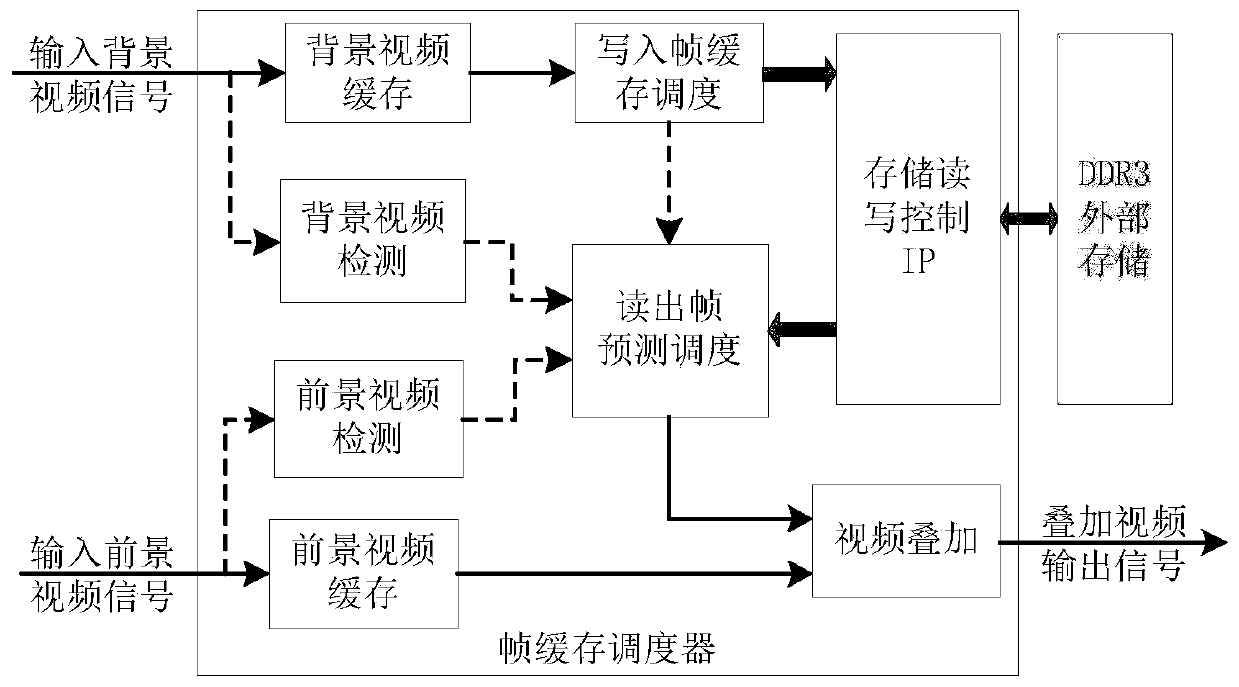

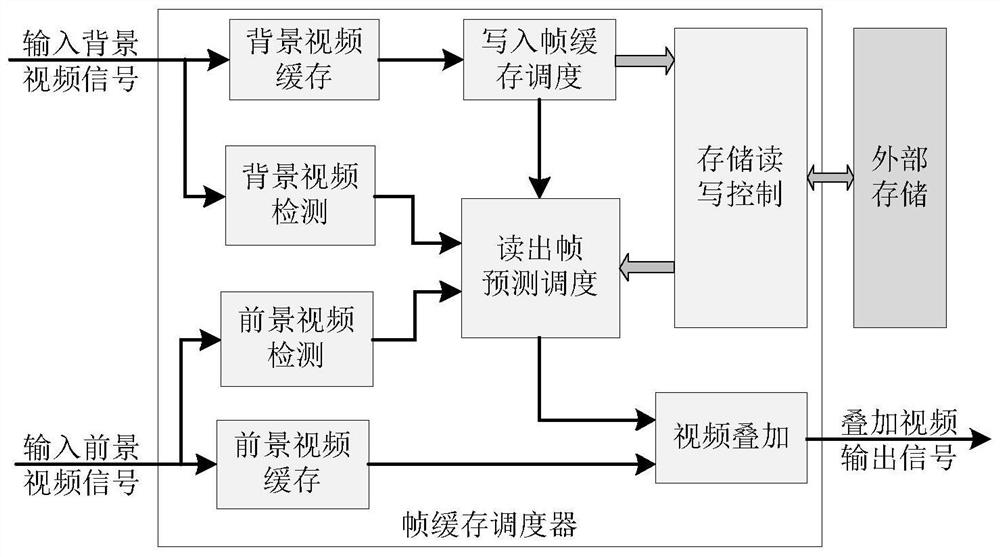

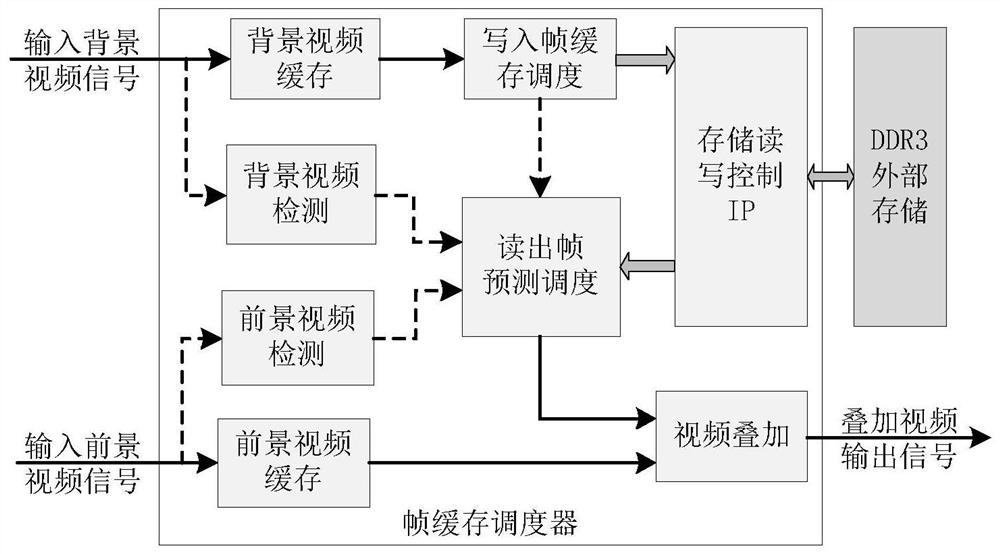

Prediction-based low-latency video overlay frame buffer scheduler

ActiveCN110855907AAvoid reading and writing conflictsAvoid tearingTelevision system detailsColor television detailsComputer hardwarePrediction algorithms

The invention relates to a prediction-based low-delay video superposition frame buffer scheduler, and belongs to the technical field of character video image processing in display equipment. Accordingto the invention, a frame buffer scheduler is constructed on an FPGA; the frame buffer scheduler adopts technologies of full parallelism, pipeline calculation and the like, adopts a reusable modulardesign method, and mainly comprises a background video buffer unit, a write-in frame buffer scheduling unit, a storage read-write control unit, a background video detection unit, a read-out frame prediction scheduling unit, a foreground video detection unit, a foreground video buffer unit, a video superposition unit and the like. The read-out frame prediction scheduling unit further shortens superposition delay while avoiding frame buffer read-write conflicts through a certain prediction algorithm according to the state information of the write-in frame buffer scheduling unit, the background video detection unit and the foreground video detection unit. The superimposed frame buffer scheduler has the characteristics that superimposed frame tearing is prevented, prediction algorithm parameters can be adjusted and configured on line, superimposed delay is less than 18 milliseconds and the like.

Owner:LUOYANG INST OF ELECTRO OPTICAL EQUIP OF AVIC

Video interface expansion device and method based on FPGA

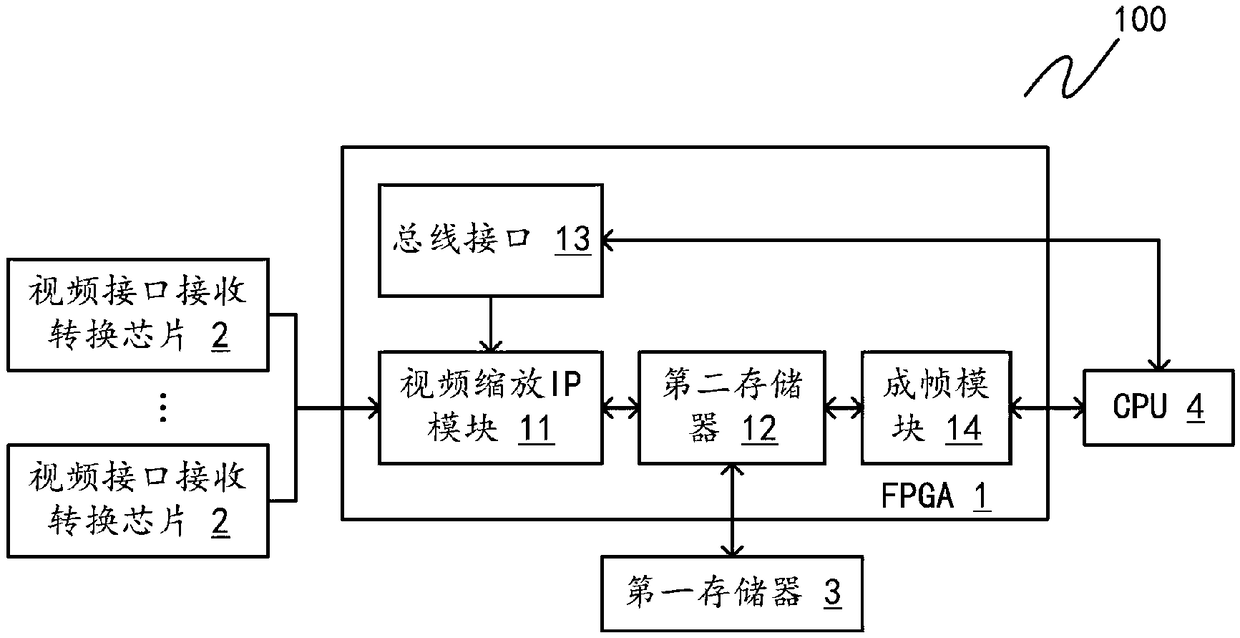

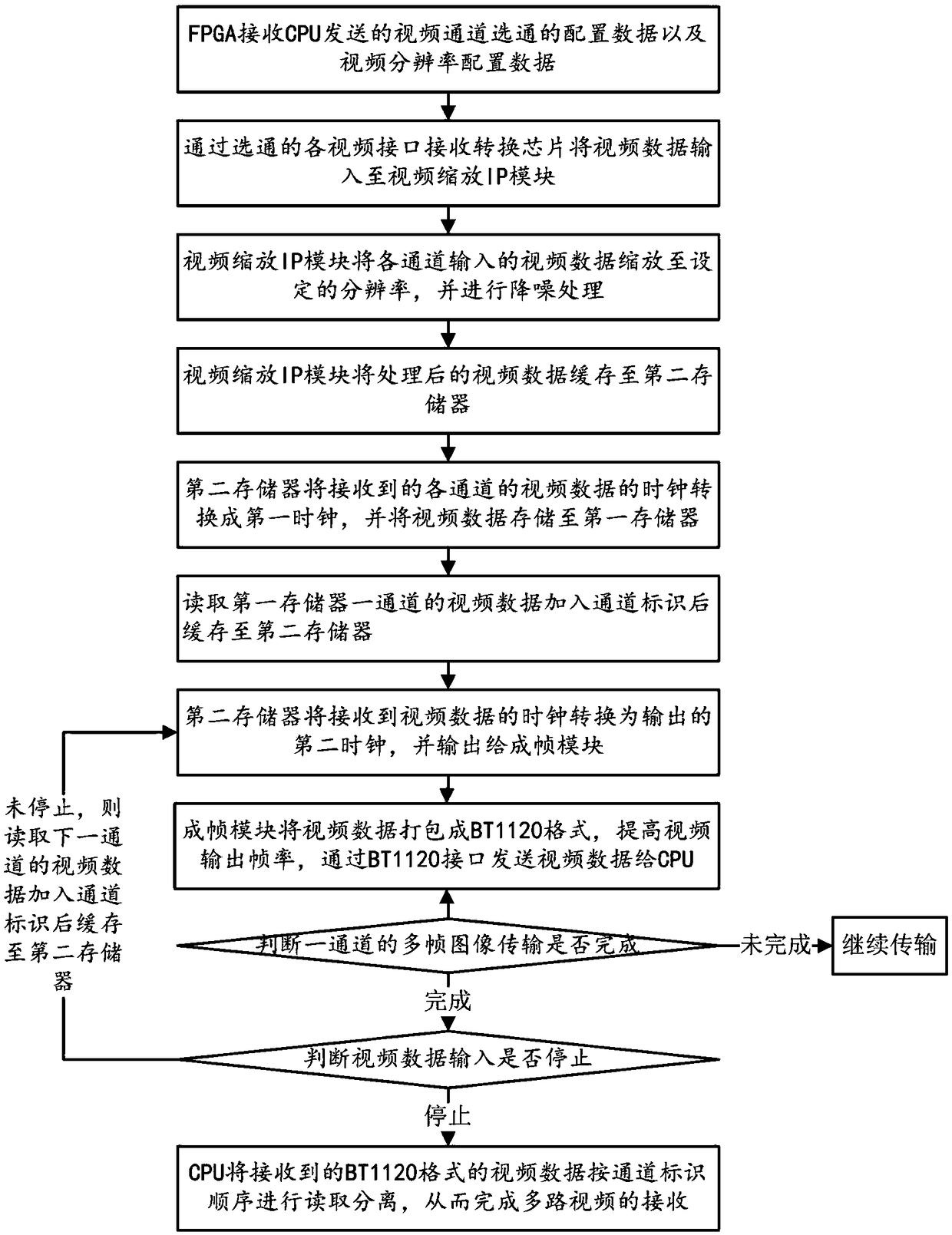

PendingCN109361894ASolve the problem that the CPU interface is not enoughLow costTelevision system detailsTelevision conference systemsExtension methodComputer hardware

The invention provides a video interface expansion device based on an FPGA. The device comprises the FPGA, a plurality of video interface receiving conversion chips, a first memory, and a CPU. The output end of each video interface receiving conversion chip is connected to the input end of the FPGA. The first memory is connected to the FPGA. The FPGA is connected to the CPU. The invention furtherprovides a video interface expansion method based on the FPGA. The device and the method have the advantages that a video interface can be expanded at a low cost, and the multi-channel video is simultaneously input.

Owner:FUJIAN STAR NET WISDOM TECH CO LTD

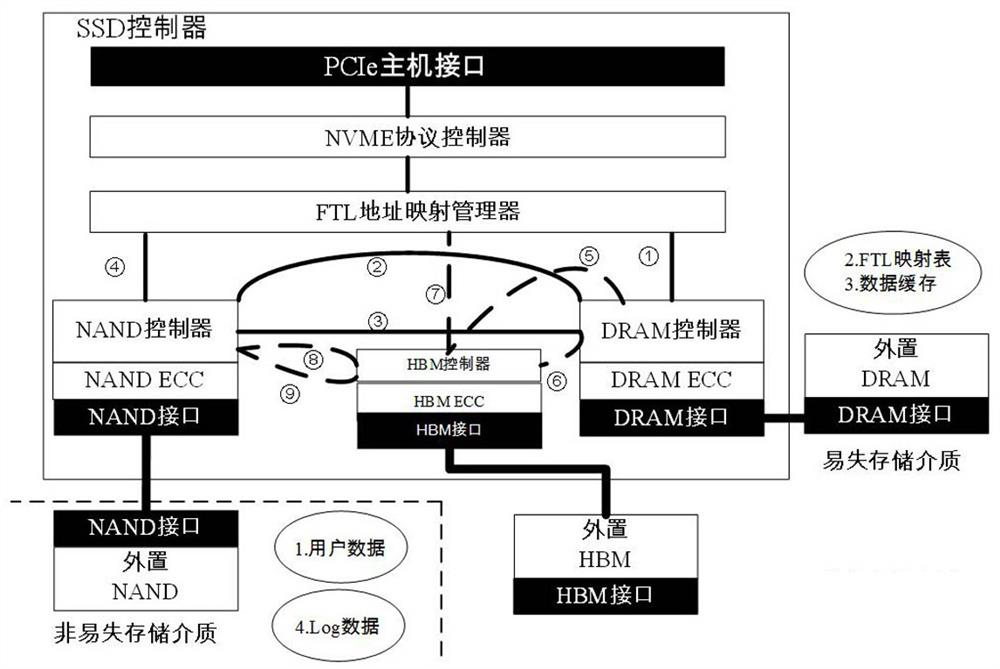

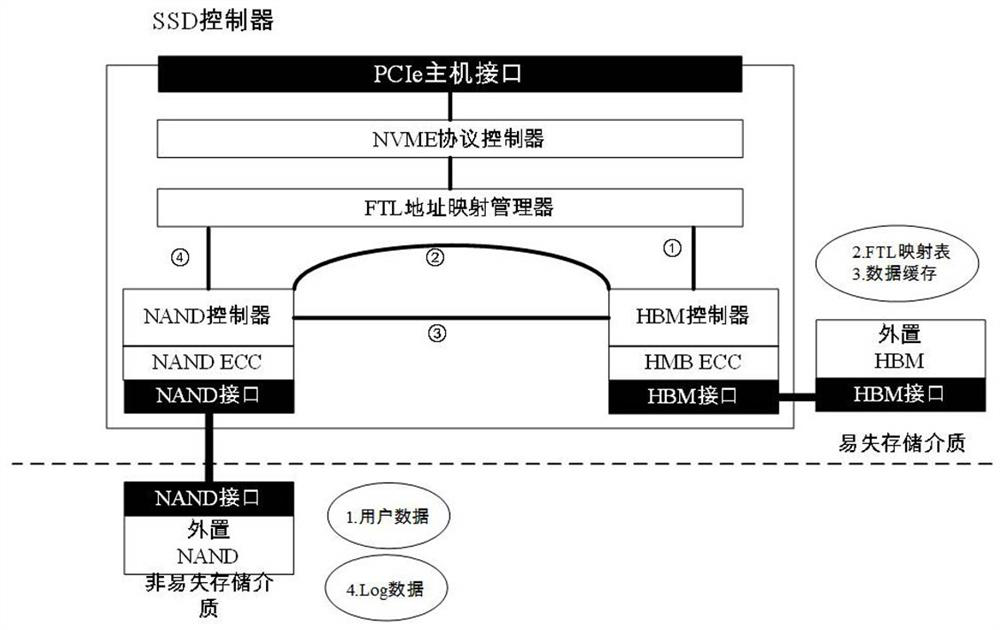

SSD based on HBM cache

PendingCN113760796AReduce visit frequencyReduce interruptionsMemory adressing/allocation/relocationEnergy efficient computingWrite amplificationComputer architecture

The invention relates to an SSD based on an HBM cache, and the SSD comprises an SSD based on the HBM and DRAM hybrid cache and an SSD based on the HBM cache; the SSD based on the HBM and DRAM hybrid cache mixedly uses the HBM and the DRAM as the cache, the DRAM stores an FTL (File Transfer Layer) mapping table, and the HBM provides a cache function. According to the SSD based on the HBM cache, the HBM is used for replacing a DRAM, and the HBM has the functions of caching data and storing an FTL mapping table. According to the method, the constant read-write bandwidth is ensured in the process of processing write amplification and garbage collection, the read-write time delay is reduced, and the high-concurrency multi-channel video data access efficiency is ensured to a greater extent.

Owner:SHANDONG SINOCHIP SEMICON

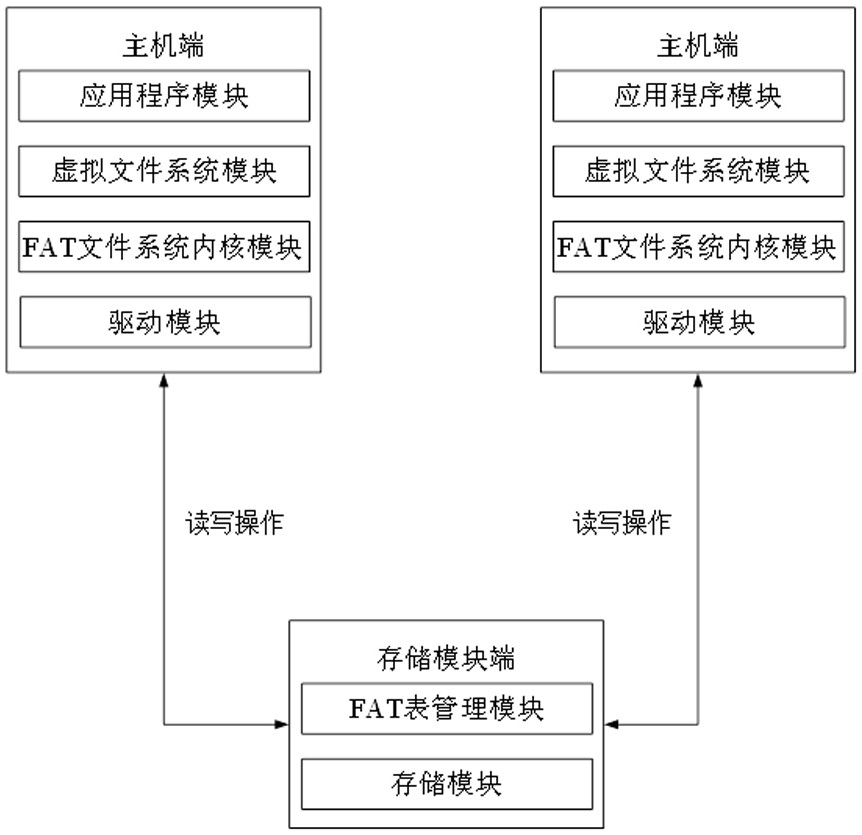

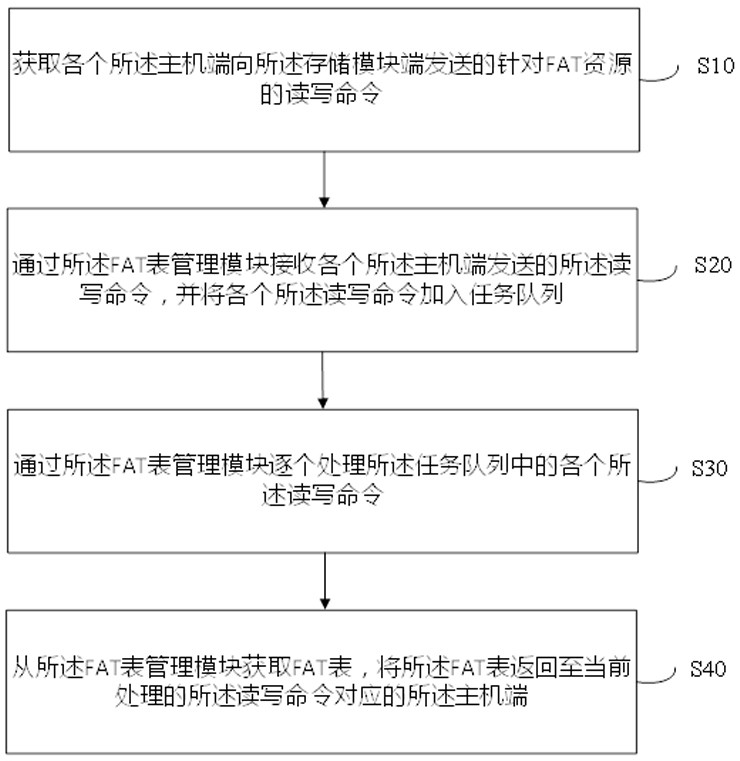

FAT sharing system and sharing method for multi-host FAT file system

ActiveCN112069147AAvoid data overwritingAchieve sharingInput/output to record carriersDigital data information retrievalFile systemComputer engineering

The invention discloses an FAT sharing system and sharing method for a multi-host FAT file system. The system comprises a storage module end and a plurality of host ends, wherein each host end is in communication connection with the storage module end, and each host end is used for sending a read-write command for FAT resources to the storage module end; the storage module end comprises an FAT management module and a storage module; the FAT management module is used for adding the received read-write commands sent by the host ends into a task queue so as to process the read-write commands in the task queue one by one, obtaining the FAT from the storage module, returning the FAT to the host end corresponding to the currently processed read-write commands, and sending the FAT to the host endcorresponding to the currently processed read-write commands. The actual read-write address of the FAT file is stored in the FAT table. According to the technical scheme, the problem that an FAT filesystem does not support multi-host requests is solved.

Owner:RUNCORE HIGH TECH

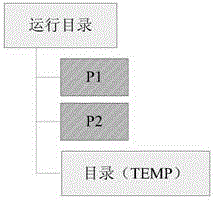

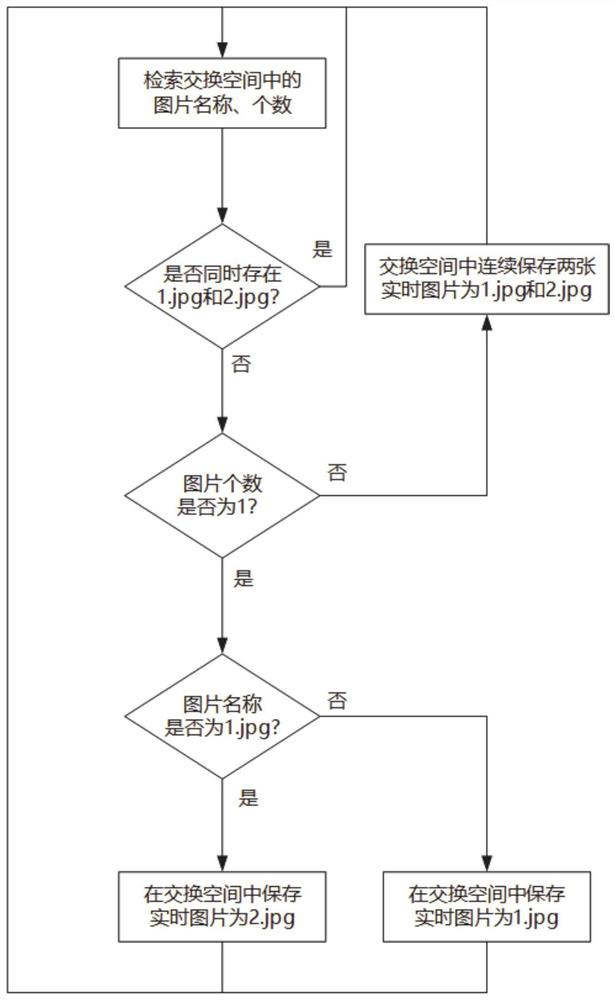

Isomerization program interaction method based on file names in Windows system

ActiveCN104572312AIncrease success rateAvoid reading and writing conflictsInterprogram communicationSpecial data processing applicationsIsomerizationWindow system

The invention belongs to the technical field of isomerization program interaction methods in a Windows system, and particularly relates to an isomerization program interaction method based on file names in the Windows system. By the isomerization program interaction method based on the file names in the Windows system, reading and writing conflict is avoided, and correct interaction is guaranteed. Basic programs involved in the system comprise an interface program (1.1), a computing program (1.2) and an isomerization program (1.3). The file names have a naming rule. The isomerization program interaction method based on the file names in the Windows system comprises the following steps of (1) determining an isomerization program document folder catalog; (2) setting interaction information of isomerization programs; (3) receiving N pieces of information by using an isomerization program P1; and (4) transmitting M pieces of information by using the isomerization program P1. The isomerization program P1 equals to an isomerization program P2, and the information of the isomerization program P2 and the information of the isomerization program P1 are transmitted and received by the isomerization program interaction method based on the file names in the Windows system. Compared with the traditional interaction mode, the isomerization program interaction method based on the file names in the Windows system has the advantages that isomerization program interaction success rate is greatly improved, and the isomerization programs can coordinate with each other and can be carried out correctly.

Owner:BEIJING LINJIN SPACE AIRCRAFT SYST ENG INST +1

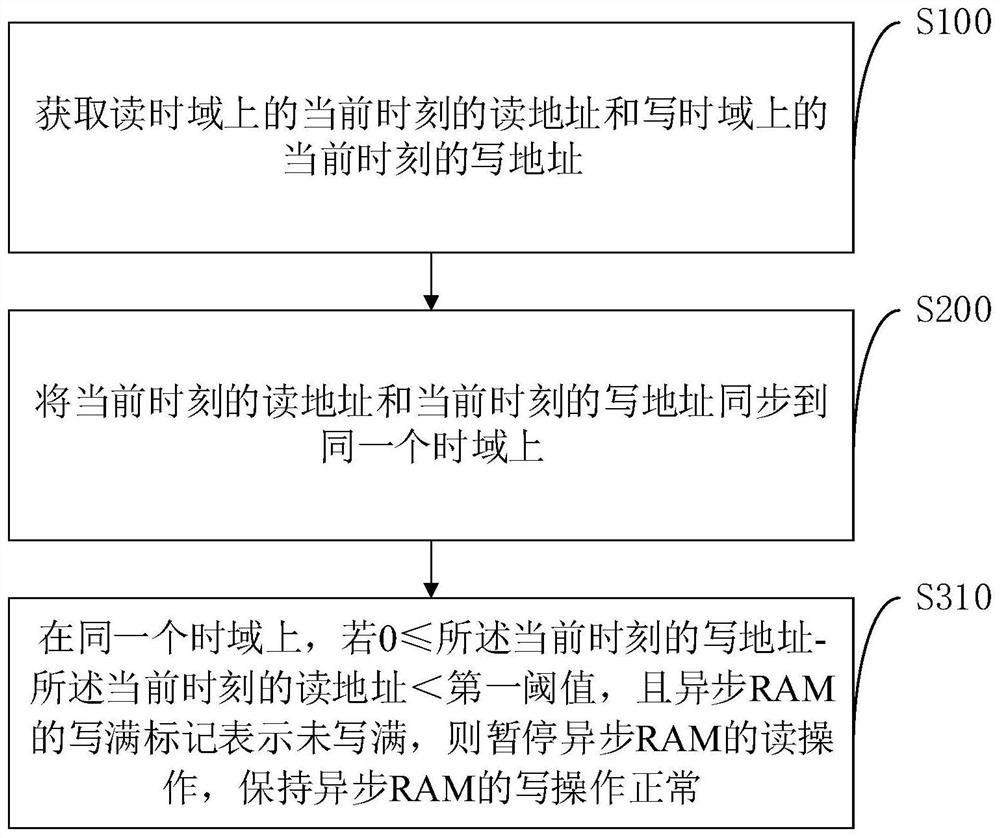

Asynchronous RAM read-write method and device, terminal equipment and readable storage medium

PendingCN112992220ARead and write operations are normalGuaranteed normal writeDigital storageData conversionEngineeringTerminal equipment

The embodiment of the invention discloses an asynchronous RAM (Random Access Memory) read-write method and device, terminal equipment and a readable storage medium. Therefore, the asynchronous RAM can ensure that the read operation of the asynchronous RAM is paused (namely, the position of a read pointer Rdr is kept unchanged) under different read-write frequencies under the conditions that the write address at the current moment minus the read address at the current moment is less than a first threshold value and equal to or greater than 0, and the full-write mark of the asynchronous RAM indicates that the asynchronous RAM is not full, the write operation of the asynchronous RAM is kept normal (namely, the write pointer Wdr moves normally). According to the method and the device, the data is ensured to be normally written into the address with empty data, and the distance between the write pointer Wdr and the read pointer Rdr is increased to avoid read-write conflicts, so that the asynchronous RAM can stably read and write the data, and the stability of the storage process is ensured.

Owner:SHENZHEN YSPRING TECH

Method for simultaneously reading and writing memory and data acquisition unit

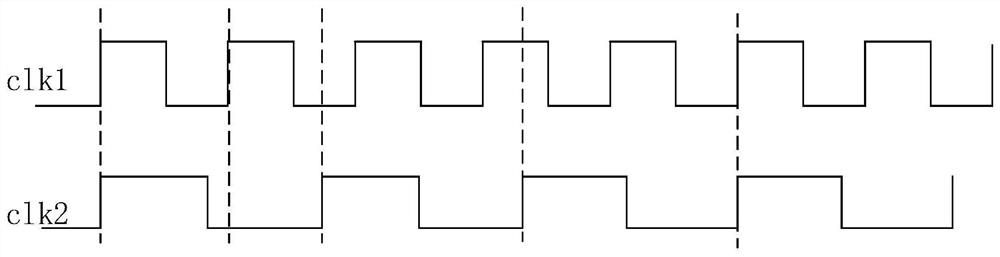

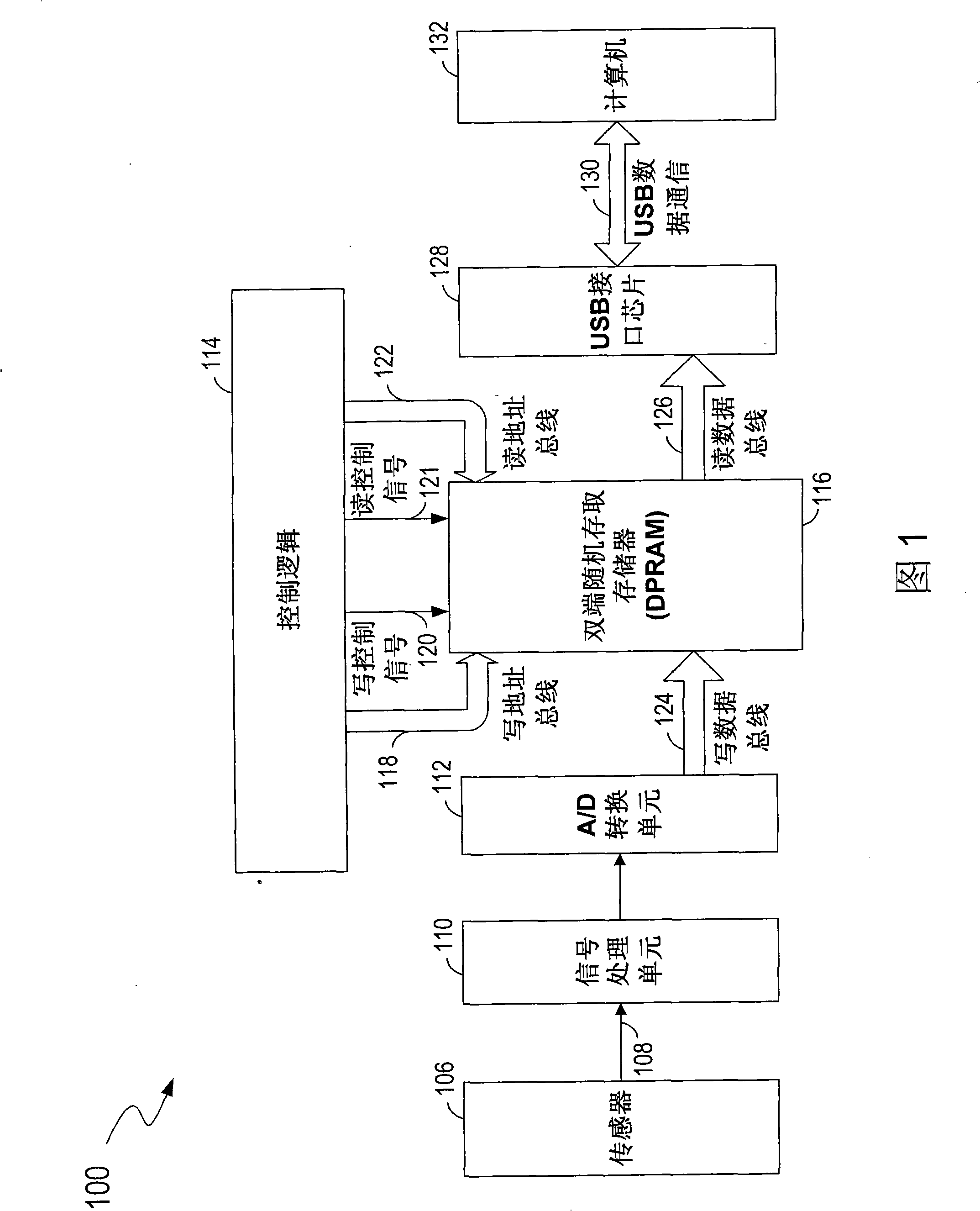

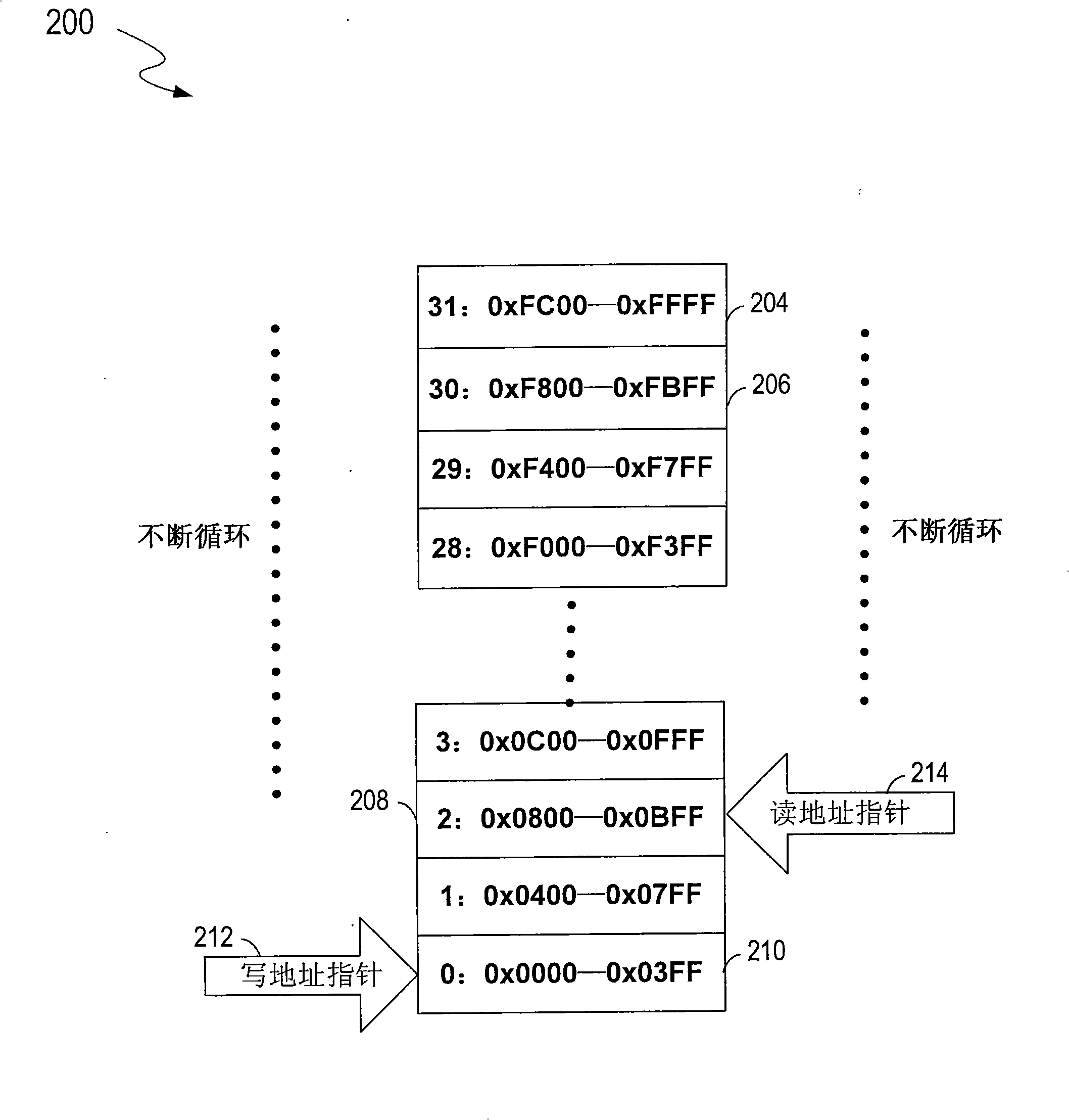

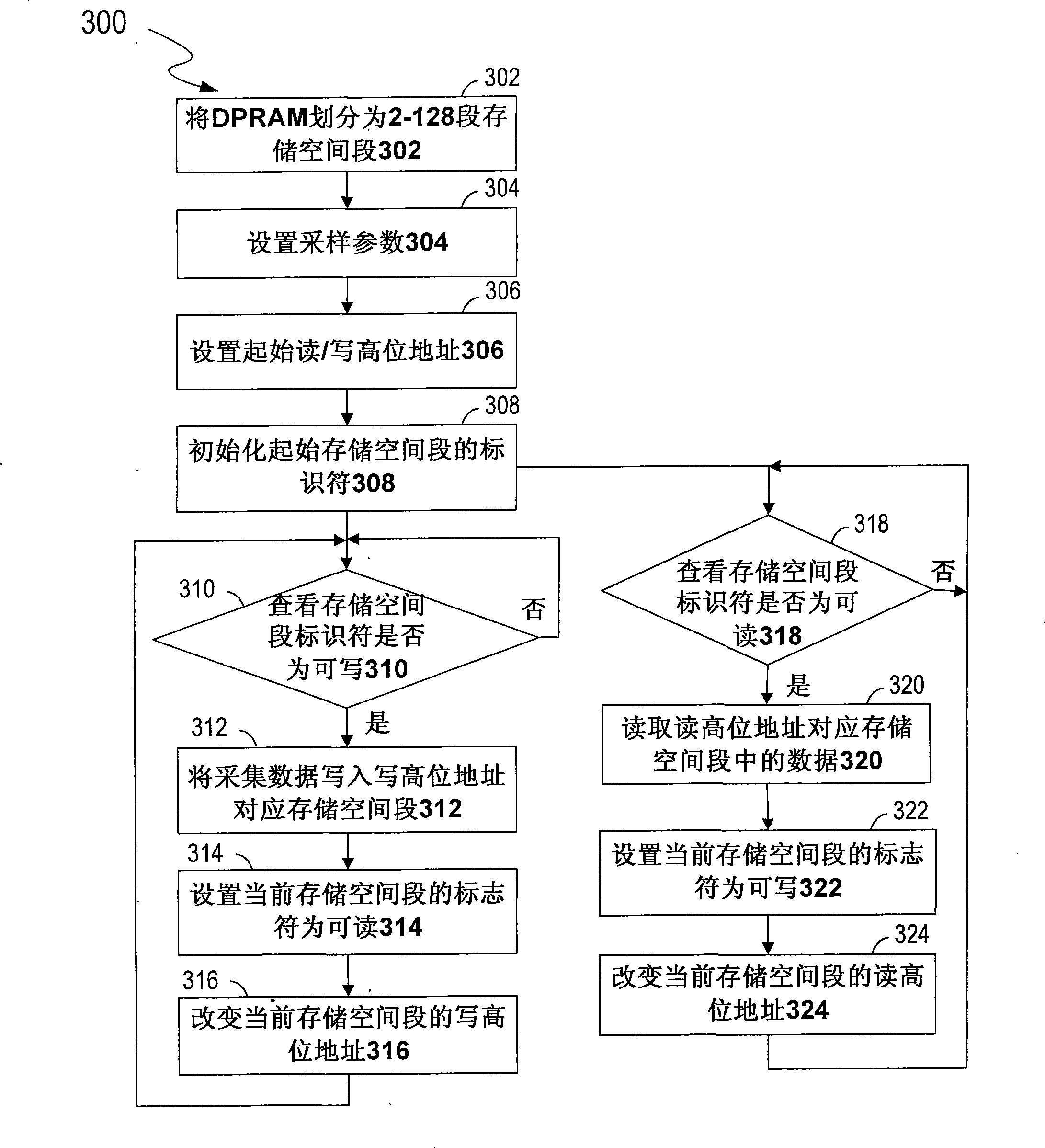

ActiveCN101493755BHigh speedAvoid reading and writing conflictsInput/output to record carriersConverting sensor outputComputer architectureData acquisition

The invention discloses a method for simultaneously reading and writing a memory and a data acquisition device thereof. The method comprises the following steps of: dividing the memory into 2-128 segment memory space sections; setting sampling parameters and starting read / write high bit address; writing acquired data into the memory space section corresponding to the current write high bit address; setting the identifier of the memory space section readable after the acquisition is completed; changing the write high bit address of the current memory section; reading data in the memory space section corresponding to the read high bit address; setting the identifier of the memory space section writable after the reading is completed; and changing the read high bit address of the current memory space section. The device comprises a sensor, a double-end random access memory, a signal processing unit, an A / D converting unit, a control logic, and an USB interface chip. With the segmented buffer storage, the invention can read data while storing data, avoids the read / write conflict on the memory, thereby reducing the time of reading and writing data and improving the speed of data acquiring of the device.

Owner:武汉中岩科技股份有限公司

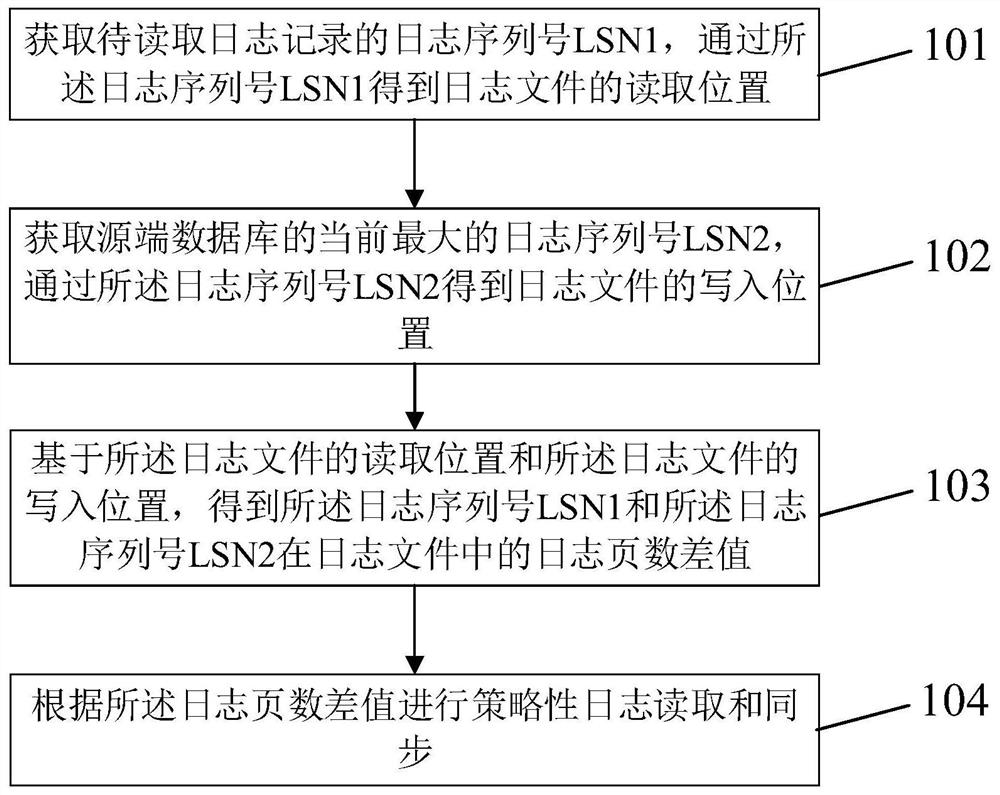

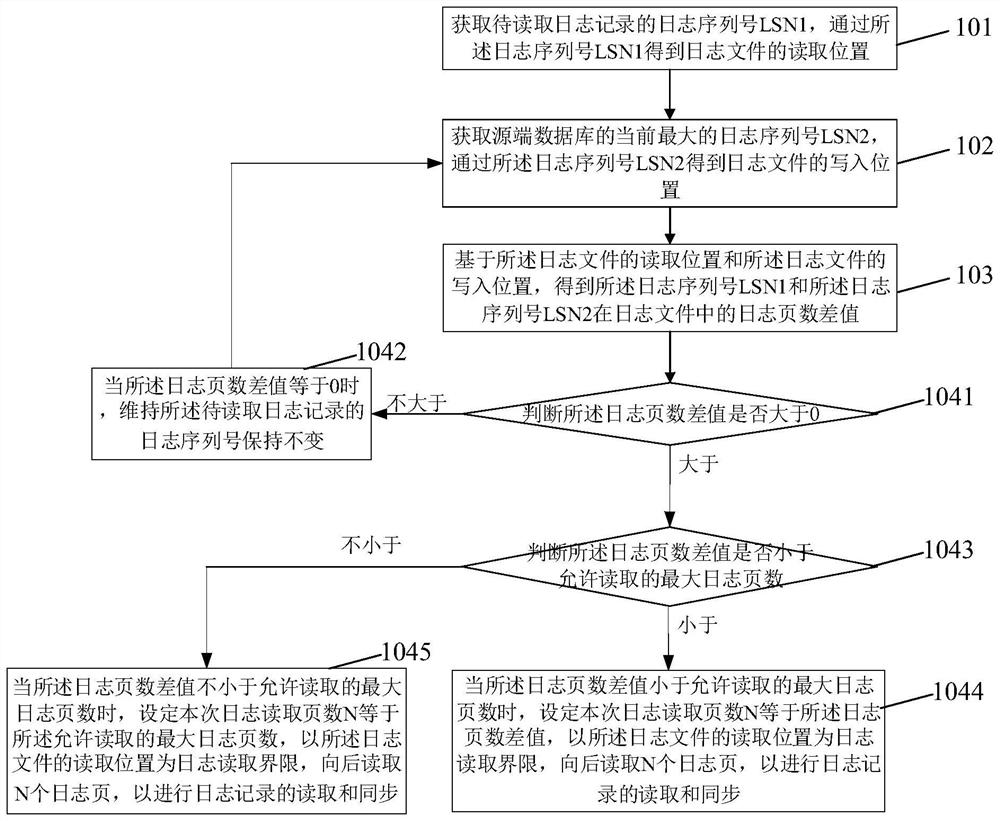

Log reading method based on log analysis synchronization and synchronization system

PendingCN111858502AAvoid reading and writing conflictsDatabase updatingDatabase distribution/replicationAlgorithmSynchronization system

The invention discloses a log reading method based on log analysis synchronization and a synchronization system, and the method comprises the steps of obtaining a log sequence number LSN1 of a to-be-read log record, and obtaining the reading position of a log file through the log sequence number LSN1; obtaining the current maximum log sequence number LSN2 of the source end database, and obtainingthe writing position of the log file through the log sequence number LSN2; obtaining a log page number difference value of the log serial number LSN1 and the log serial number LSN2 in the log file based on the reading position of the log file and the writing position of the log file; and performing strategic log reading and synchronization according to the log page number difference. According tothe invention, by calculating the distance between the log sequence number of the log record to be read and the current maximum log sequence number in the database system, the number of log pages readwhen the log file is read can be dynamically adjusted, strategic log reading and synchronization are carried out, and log reading and writing conflicts are prevented.

Owner:WUHAN DAMENG DATABASE

A High Precision Star Sensor Information Processing System

ActiveCN108871317BImprove data update rateImprove anti-stray light abilityProgramme controlComputer controlData packInformation processing

Owner:SHANGHAI AEROSPACE CONTROL TECH INST

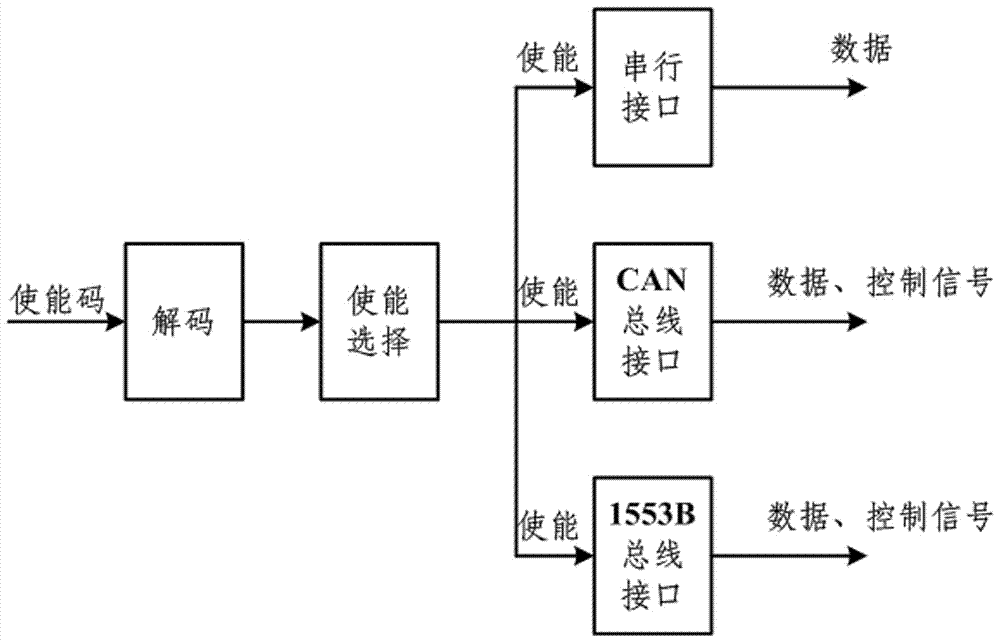

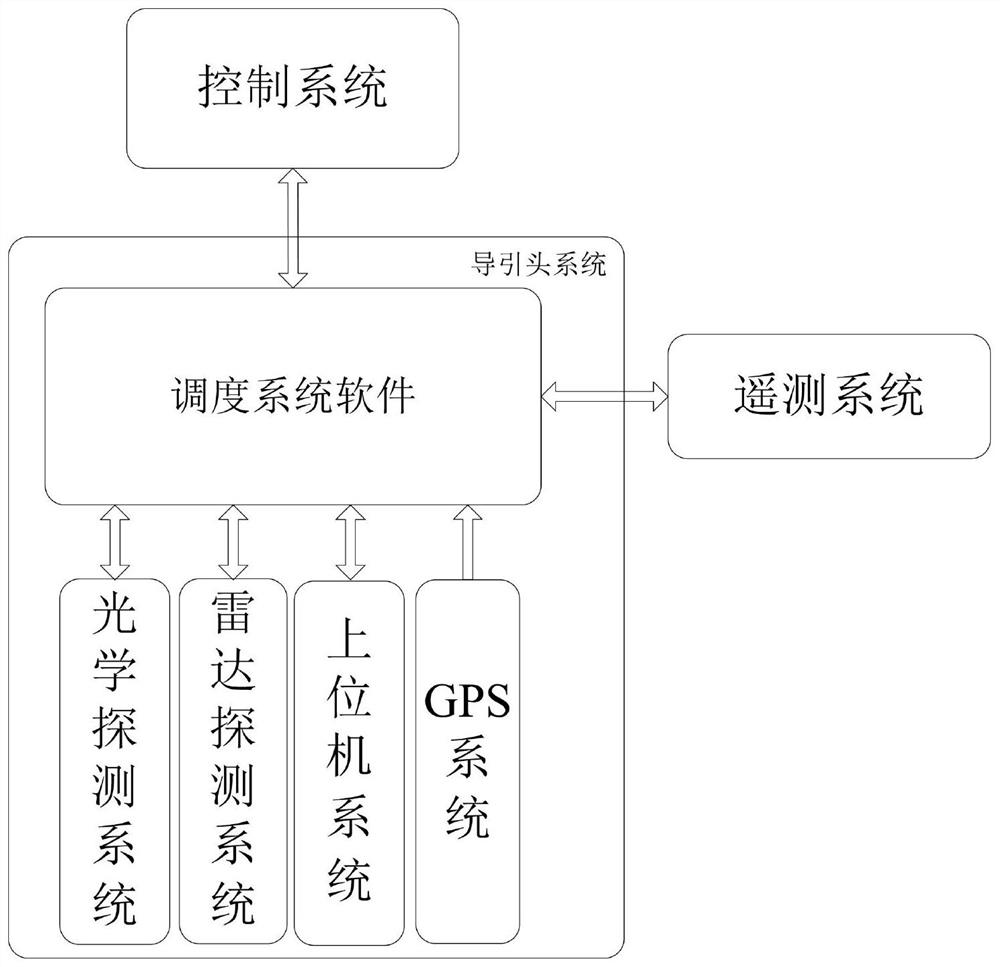

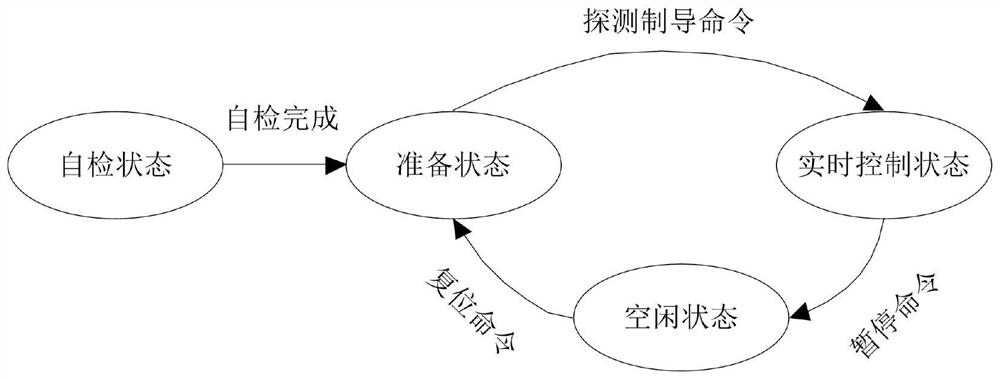

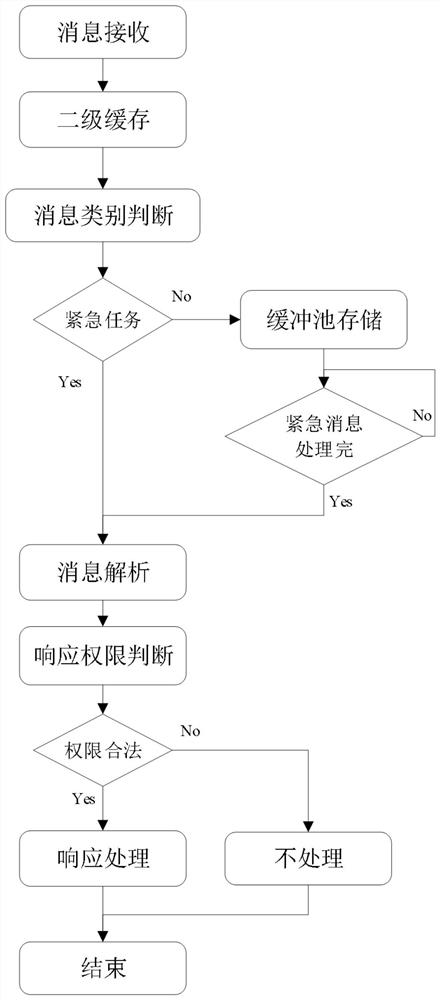

A DSP communication task scheduling system and method

ActiveCN109710399BMeet the requirements of engineering application environmentReduce resource usageResource allocationTransmissionTime delaysEmbedded system

The invention discloses a DSP communication task scheduling system and method, which relate to the field of missile-borne application platforms, including S1, classifying communication tasks according to communication task functions and sub-modules of the DSP communication task scheduling system, and classifying each type of communication task Set the priority; S2, set the task scheduling system running state machine, and control the permission bit of the communication command of each communication task processing process; S3, when the task scheduling system receives the message, perform secondary Cache, set message classification and message response authority. The DSP communication task scheduling system of the present invention, through the improved design of the internal task system architecture, occupies less hardware resources and lower processing time delay than the existing communication task scheduling system, and can well meet the engineering application environment requirements of the missile-borne embedded platform .

Owner:THE GENERAL DESIGNING INST OF HUBEI SPACE TECH ACAD

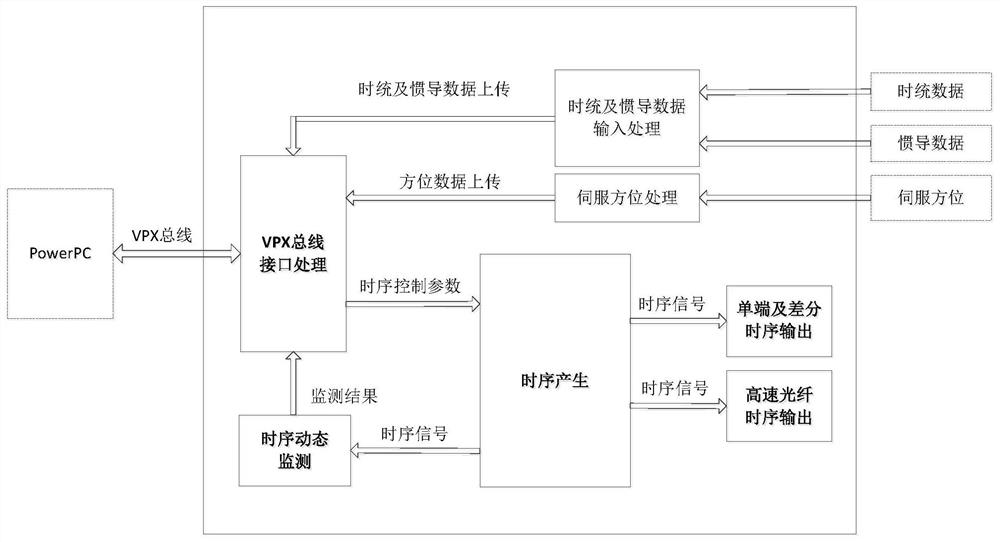

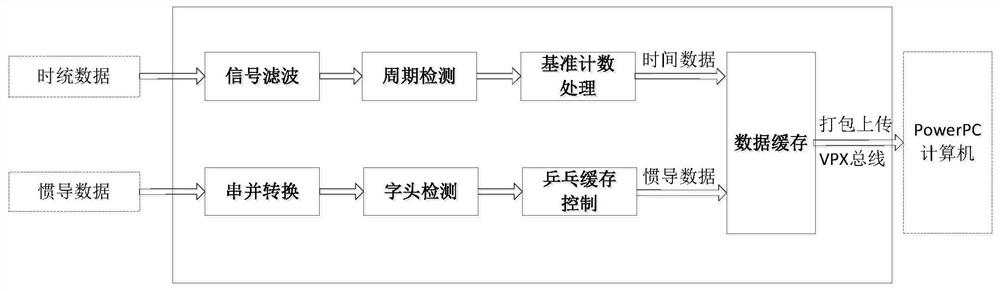

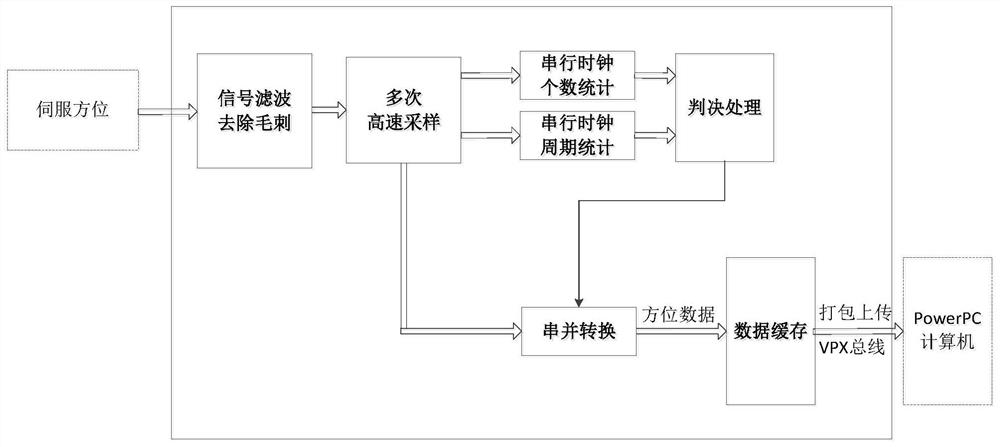

Vehicle-mounted radar time sequence generation system and method based on VPX bus

PendingCN111999704AAvoid reading and writing conflictsImprove transmission stabilityElectric digital data processingRadio wave reradiation/reflectionIn vehicleEmbedded system

The invention discloses a vehicle-mounted radar time sequence generation system and method based on a VPX bus, and belongs to the technical field of radar data processing. The system comprises a timing system and inertial navigation data input processing module, a servo azimuth input processing module, a VPX bus interface processing module, a time sequence generation module, a time sequence dynamic monitoring module and a time sequence output module, wherein the VPX bus interface processing module is respectively connected with the timing system and inertial navigation data input processing module, the servo azimuth input processing module, the time sequence generation module and the upper computer; the time sequence dynamic monitoring module is respectively connected with the VPX bus interface processing module and the time sequence generation module, and the time sequence output module is connected with the time sequence generation module. The system has the advantages that the timesequence generation method is universal, time sequence signals are stable and reliable, time sequence output interfaces are flexible and diverse, the system can be applied to development of various types of vehicle-mounted radars, and the research and development efficiency and reliability of the whole radar are effectively improved.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

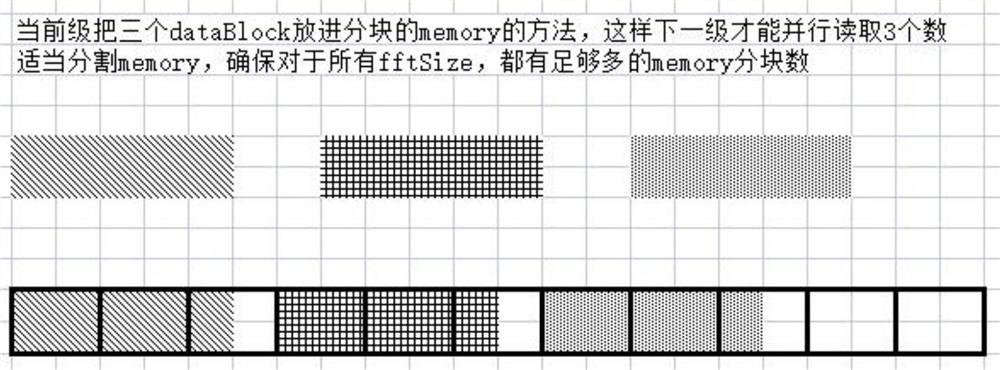

Fast Fourier transform twiddle factor calculation system and method

PendingCN113569190AMeet needsAvoid reading and writing conflictsComplex mathematical operationsFast Fourier transformCommunications system

The invention discloses a fast Fourier transform twiddle factor calculation system and method in the field of communication systems, and aims to solve the technical problem that under different fftSizes, the same memory is in the same clk, and read-write conflicts easily exist. The invention relates to a fast Fourier transform twiddle factor calculation method, which comprises the following steps: segmenting a memory into a plurality of blocks through a memory segmentation method, distributing different datablocks into different memory blocks, and calculating a twiddle factor required for carrying out stack operation on the datablocks through a twiddle factor parallel construction method, wherein the memory is a device for temporarily storing each level of data, and the datablock is a data block. Segmentation modes of FFT scenes of various fftSize of an NR system can be met, a corresponding read-write method is provided, verification is carried out in various scenes, and the conflict of read-write memory can be completely avoided. Besides, only one group of twiddle factors is stored, and a plurality of twiddle factors can be constructed in parallel through another auxiliary small table, so that the storage space can be saved, and the requirements of a parallel algorithm can be met.

Owner:星思连接上海半导体有限公司

A low-latency video overlay frame buffer scheduler based on prediction

ActiveCN110855907BAvoid reading and writing conflictsAvoid tearingTelevision system detailsColor television detailsComputer hardwarePrediction algorithms

The invention relates to a prediction-based low-latency video superimposition frame buffer scheduler, which belongs to the technical field of character video image processing in display devices. The present invention constructs a frame buffer scheduler on the FPGA. The frame buffer scheduler adopts technologies such as full parallelism and pipeline computing, and can reuse a modular design method, mainly including background video buffer, write frame buffer schedule, storage read and write Units for control, background video detection, readout frame prediction scheduling, foreground video detection, foreground video caching, and video overlay. The readout frame prediction scheduling unit further shortens the overlay delay while avoiding frame buffer read and write conflicts through a certain prediction algorithm according to the state information of the three units of writing frame buffer scheduling, background video detection and foreground video detection. The superimposed frame buffer scheduler of the present invention has the characteristics of preventing tearing of the superimposed picture, predictive algorithm parameters can be adjusted and configured online, superimposed delay less than 18 milliseconds, and the like.

Owner:LUOYANG INST OF ELECTRO OPTICAL EQUIP OF AVIC

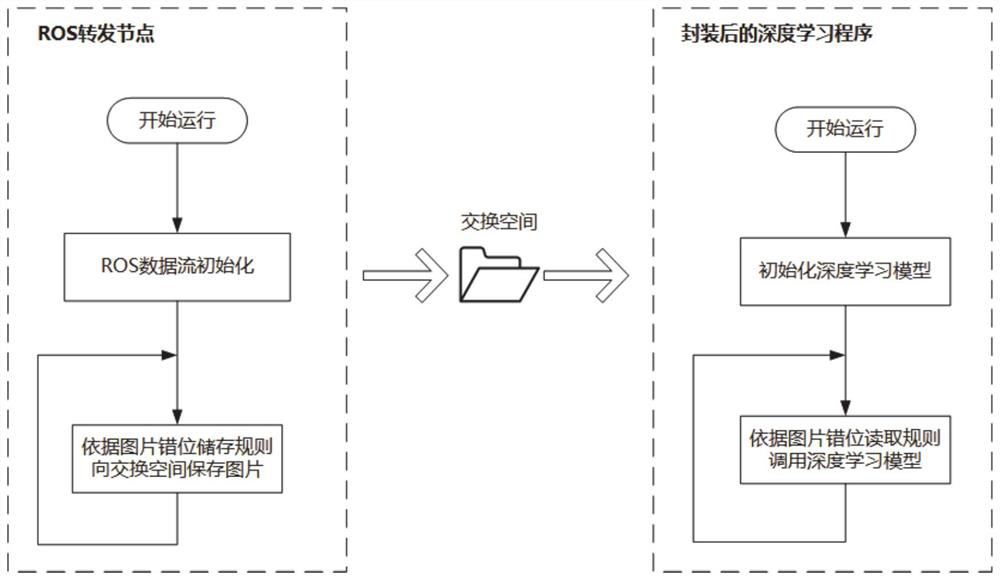

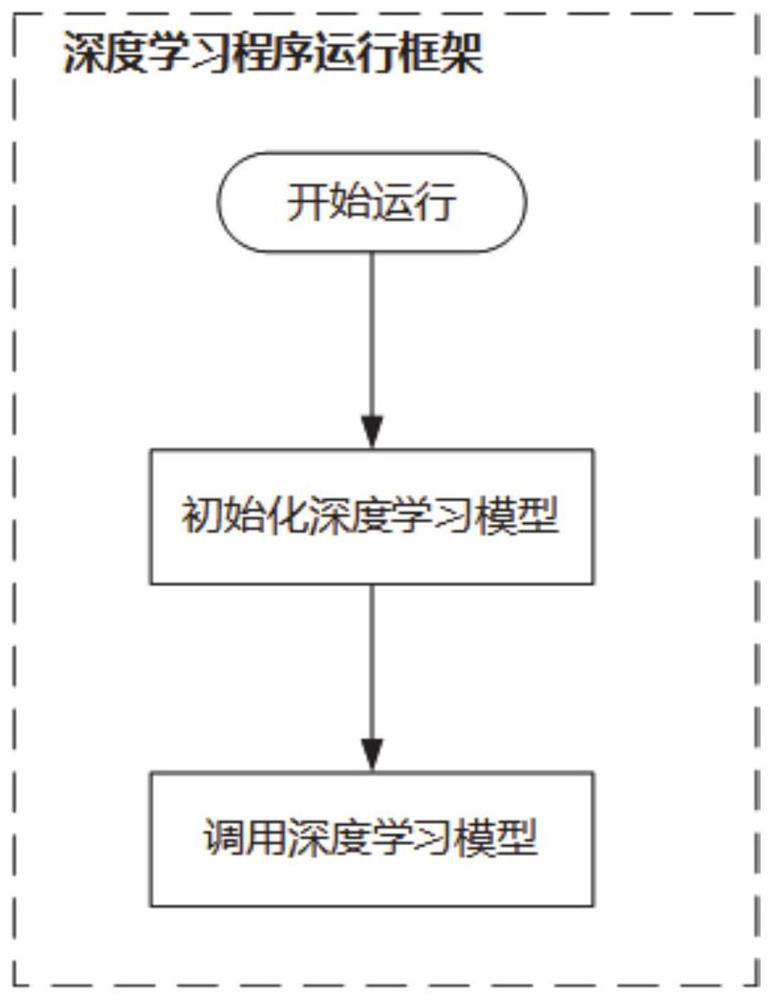

Cross-terminal picture transmission method and system

ActiveCN113157953AAvoid reading and writing conflictsLow latency transmissionStill image data indexingNeural architecturesData streamOperational system

The invention provides a cross-terminal picture transmission method and system, which are applied to a first terminal and a second terminal, wherein the first terminal carries a robot operation system, and the second terminal carries a preset deep learning network model. Comprising the following steps: a data forwarding node on a second terminal stores a picture from a data stream of a robot operating system to an exchange space in real time according to a picture dislocation storage mode, and a deep learning program of a preset deep learning network model reads and processes the picture from the exchange space according to a picture dislocation reading mode. According to the invention, a picture dislocation storage mode and a picture dislocation reading mode are provided, file read-write conflicts in the high-speed data transmission process can be avoided, and file read and write are operated in parallel in different processes, so that final low-delay transmission is ensured.

Owner:SHANDONG UNIV

Data updating and reading method, device and equipment and storage medium

ActiveCN109976675AAvoid reading and writing conflictsGuaranteed uptimeInput/output to record carriersOperating system

Owner:BIGO TECH PTE LTD

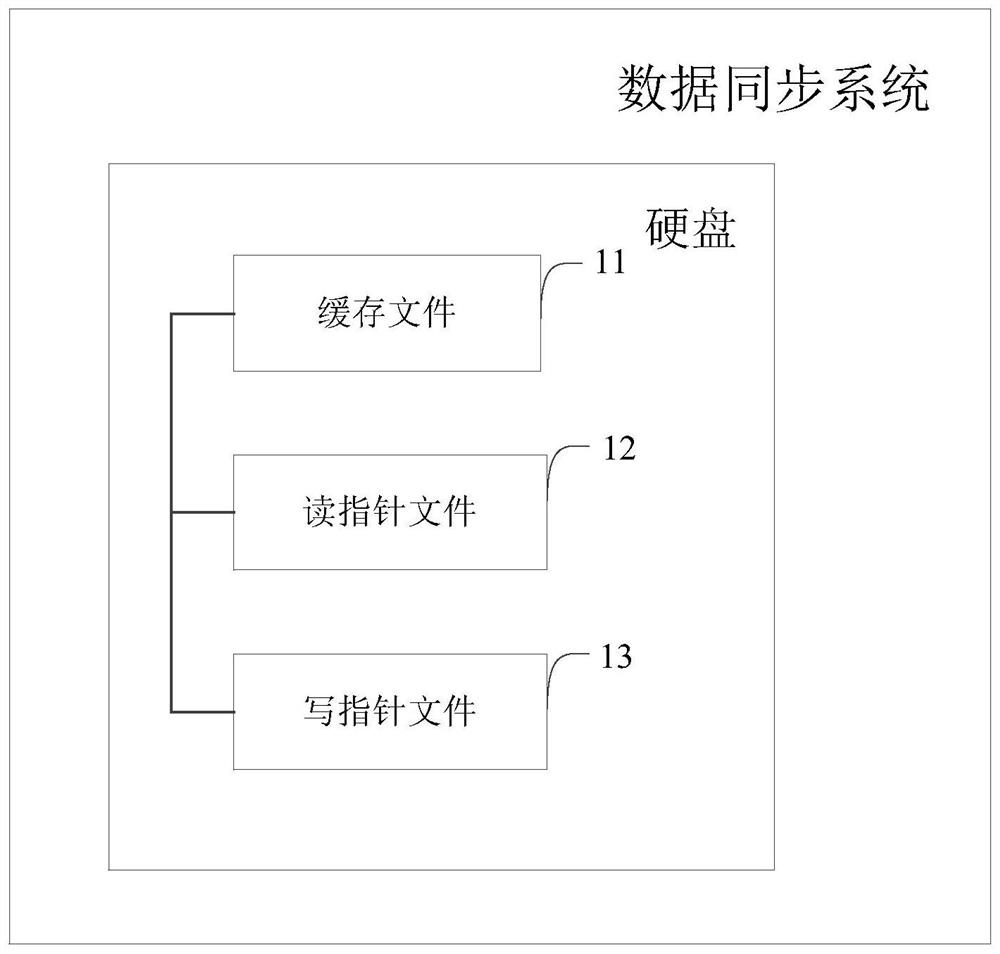

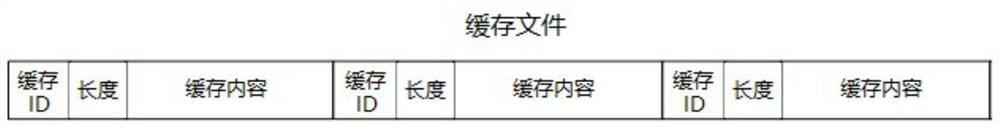

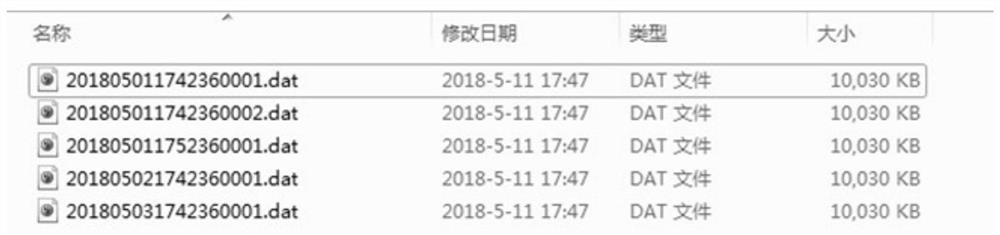

A data synchronization system and method

ActiveCN109299146BAvoid reading and writing conflictsData synchronization efficiencyDatabase distribution/replicationSpecial data processing applicationsComputer hardwareData synchronization

The invention provides a data synchronization system and a data synchronization method. The system comprises a cache file, a reading pointer file and a writing pointer file, arranged on a hard disk. The cache file is used for storing the data to be cached; A read pointer file for storing a read position of cache data to be synchronized at present; A write pointer file for storing a write positionof cache data to be added at present; When data synchronization is carried out, the system reads the reading pointer file, obtains the reading position of the cache data to be synchronized, and readsthe data to the corresponding cache file according to the reading position to complete data synchronization. When adding new cache data, the system reads the write pointer file, obtains the write position of the cache data to be added, and writes the new cache data to the corresponding cache file according to the write position. The invention can ensure that the read and write of the cached file are not in the same position, thus avoiding the read-write conflict.

Owner:TRAFFIC CONTROL TECH CO LTD