SSD based on HBM cache

A solid-state disk and cache technology, applied in the direction of memory system, memory address/allocation/relocation, instrument, etc., can solve the problem of not greatly improving SSD data access capability, reducing SSD performance degradation, and unable to reduce read and write time delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

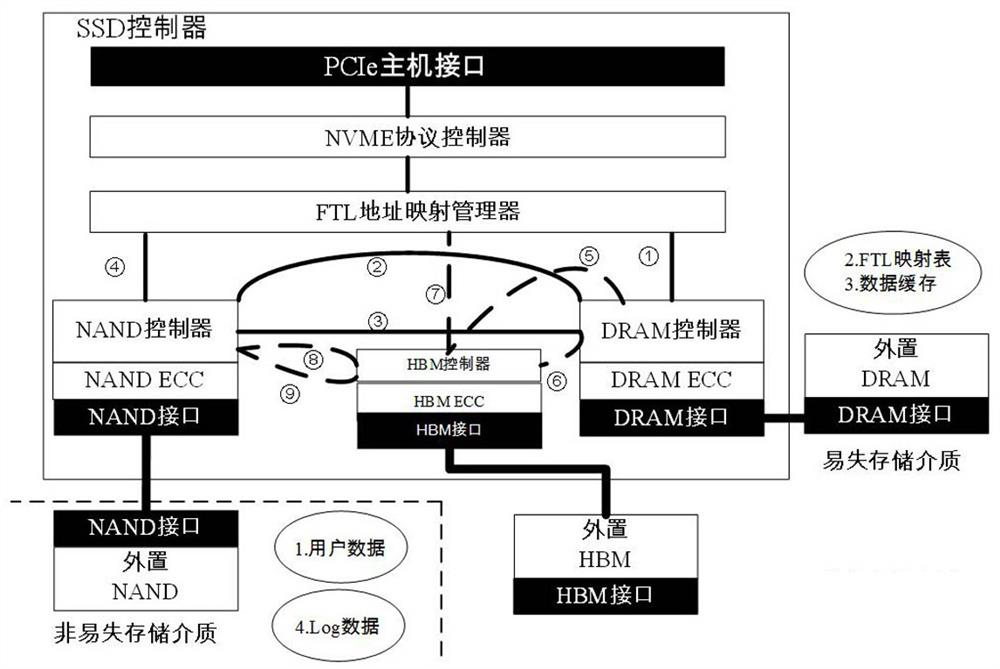

[0038] The SSD solid-state disk based on the HBM and DRAM hybrid cache described in Embodiment 1 uses DRAM to process FTL address mapping table information, uses large-capacity, high-speed HBM cache to process application data, and performs data garbage collection operations during continuous writing. Reduce the reading and writing pressure of DRAM, ensure the update efficiency of FTL address data, improve the processing efficiency of application data at the same time, speed up the data relocation speed in the garbage collection process, and reduce the impact of write amplification on the performance of the entire disk. Compared with traditional SSD solid state disk has a more powerful ability to receive data. Taking 8TB SSD as an example, the required cache capacity for FTL is 8GB, and a DDR cache chip is used as the storage space for its FTL address mapping table; at the same time, a large-capacity HBM2E cache (capacity 16GB~64GB) is configured, and one HBM2E chip is enough ...

Embodiment 2

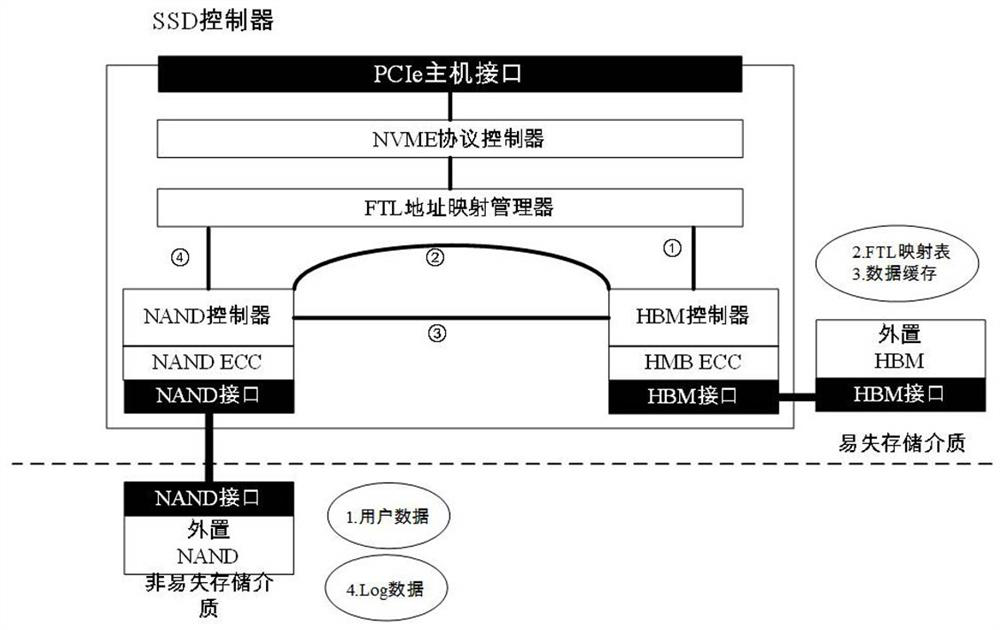

[0039] The SSD solid state disk based on the HBM cache described in Embodiment 2 has a stronger ability to receive data than ordinary SSD solid state disks. Taking an 8TB SSD as an example, the required cache capacity for FTL is 8GB. With a DDR4.0 cache chip, 4 DRAM chips need to be pasted; if HBM2E with a single-chip maximum capacity of 16GB is used, 1 HBM2E chip can meet the capacity And performance requirements, when increased to 4 slices, the total cache capacity reaches 64GB, and the excess cache capacity can bear the data writing or reading "margin" of more than 8s ((64GB-8GB) / 7GB / s = 8s) , which greatly improves the data receiving capability of the SSD solid state disk, and can shield the read and write delay of the NAND flash memory.

[0040] Example 1

[0041] This embodiment discloses an SSD solid state disk based on HBM and DRAM hybrid cache, such as figure 1 As shown, including SSD controller, DRAM cache controller, HBM cache controller and NAND controller, DRAM ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More