Patents

Literature

123 results about "Multicore architecture" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Multicore refers to an architecture in which a single physical processor incorporates the core logic of more than one processor. A single integrated circuit is used to package or hold these processors.

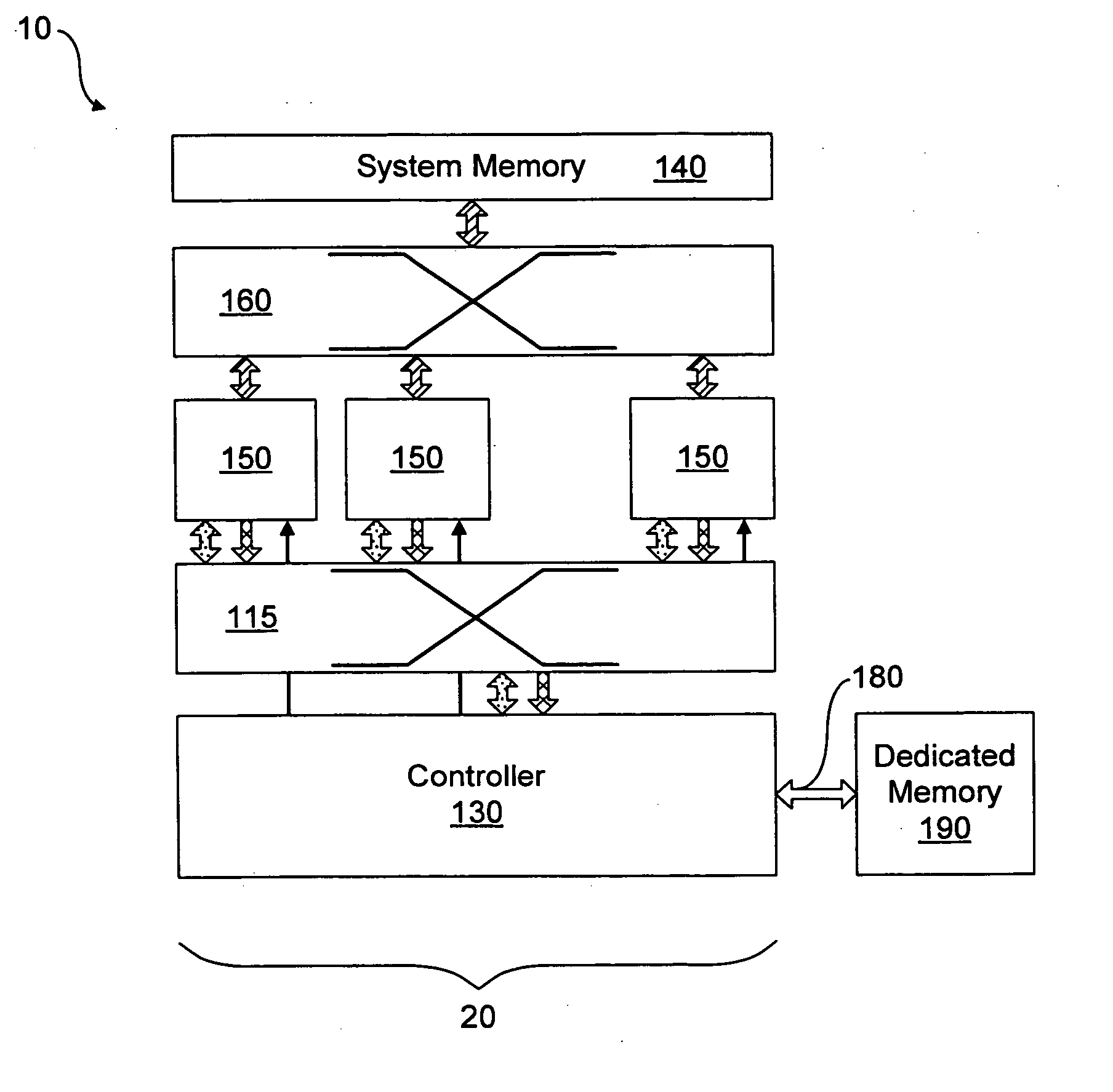

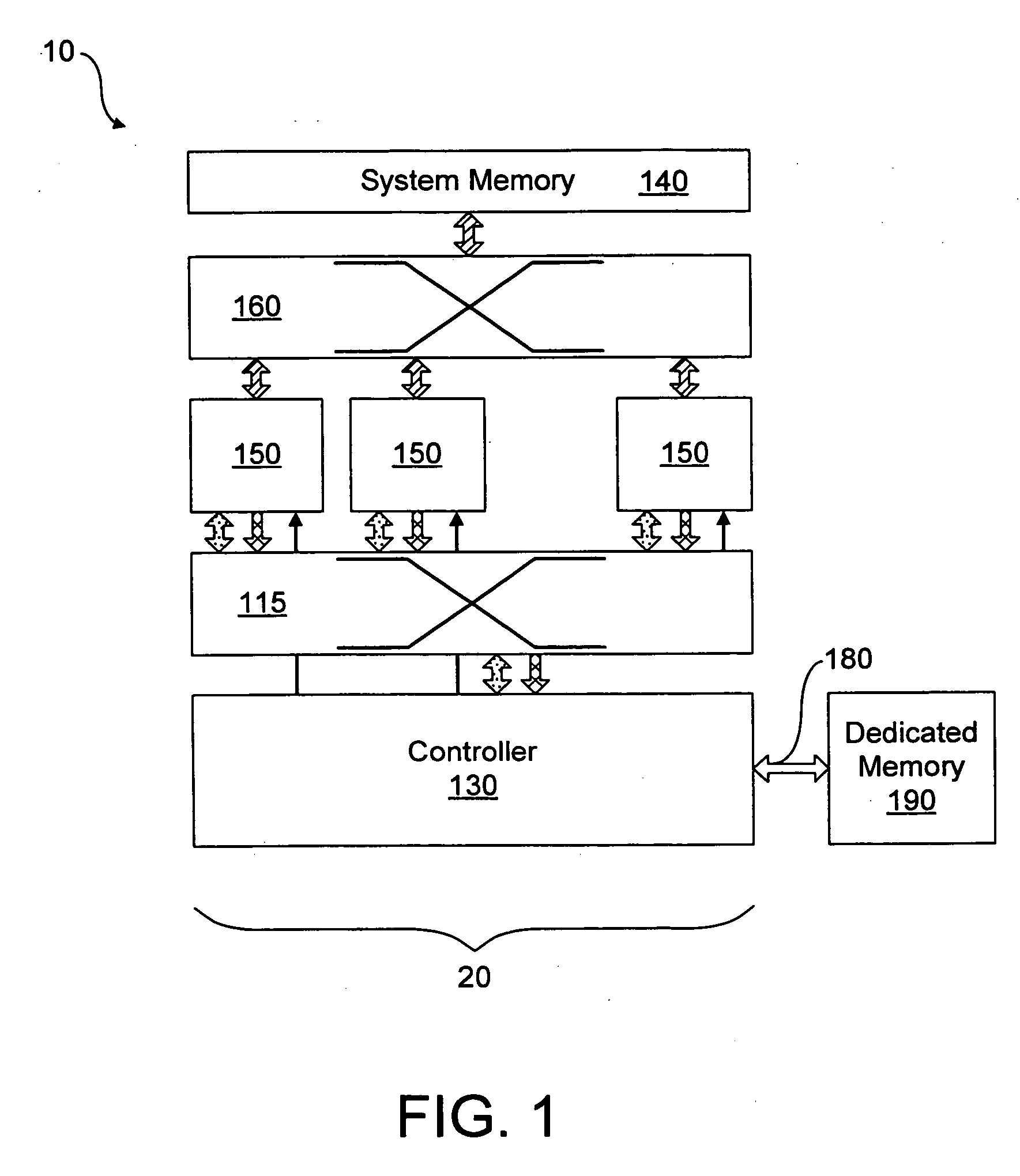

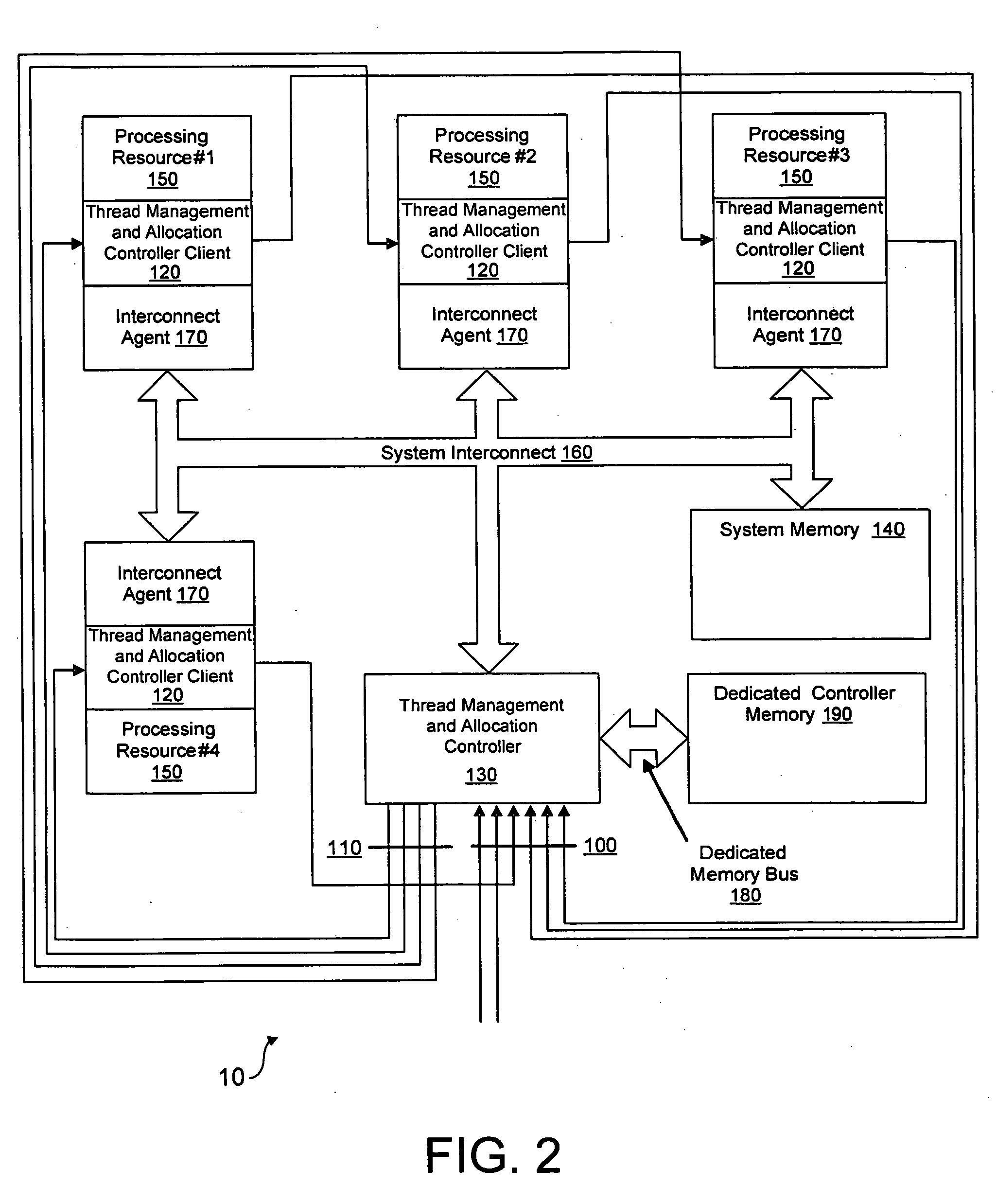

Resource management in a multicore architecture

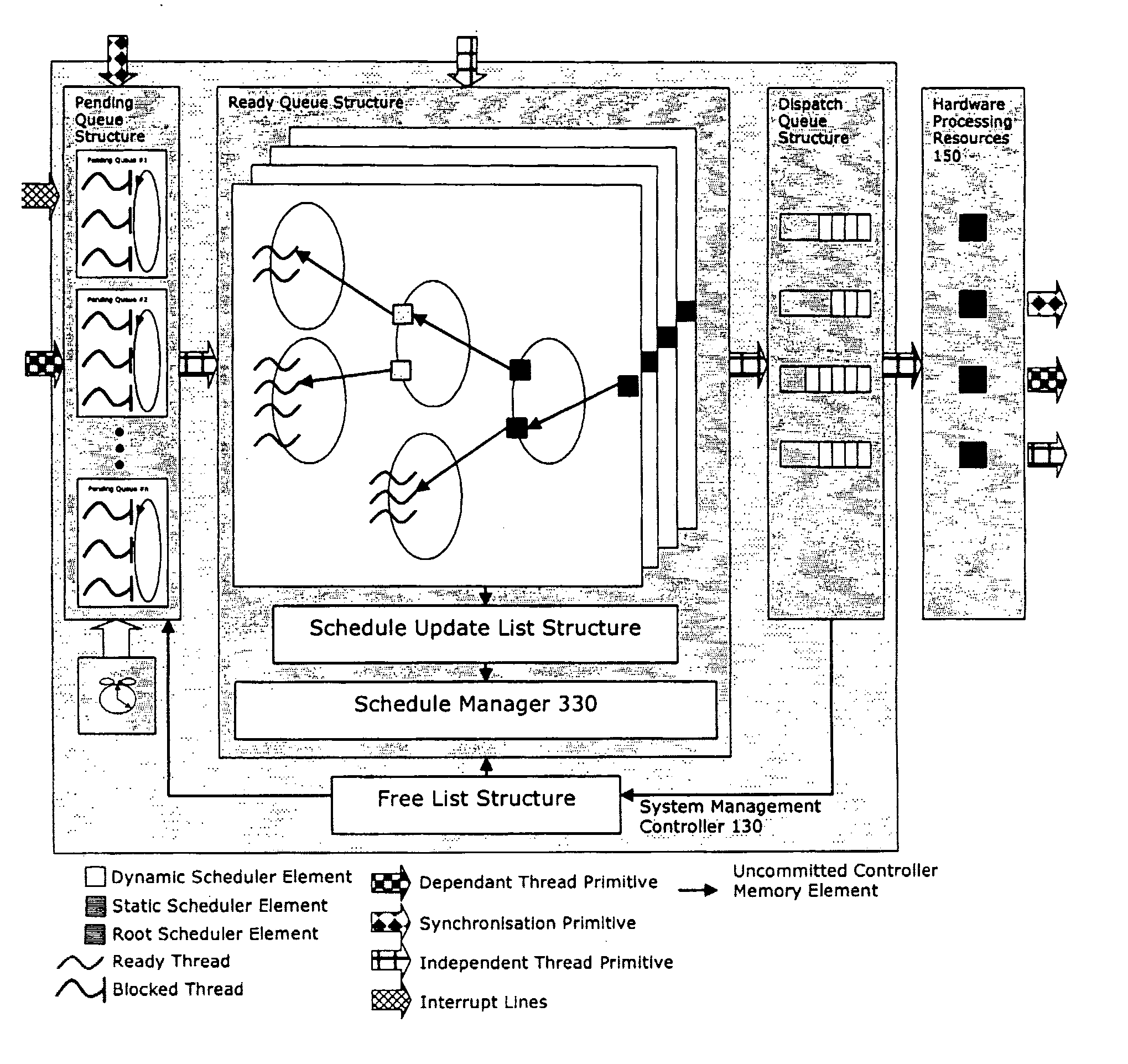

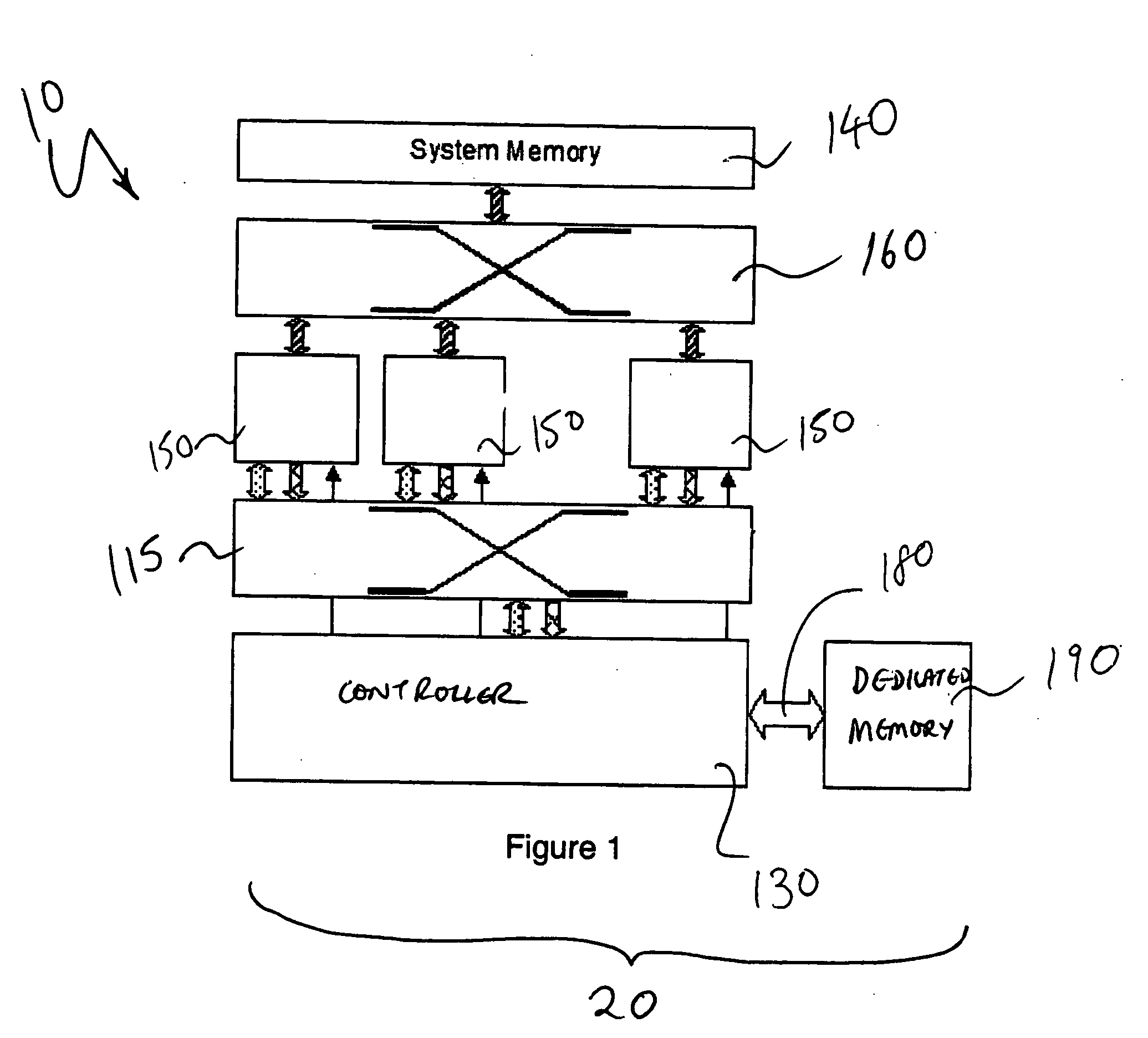

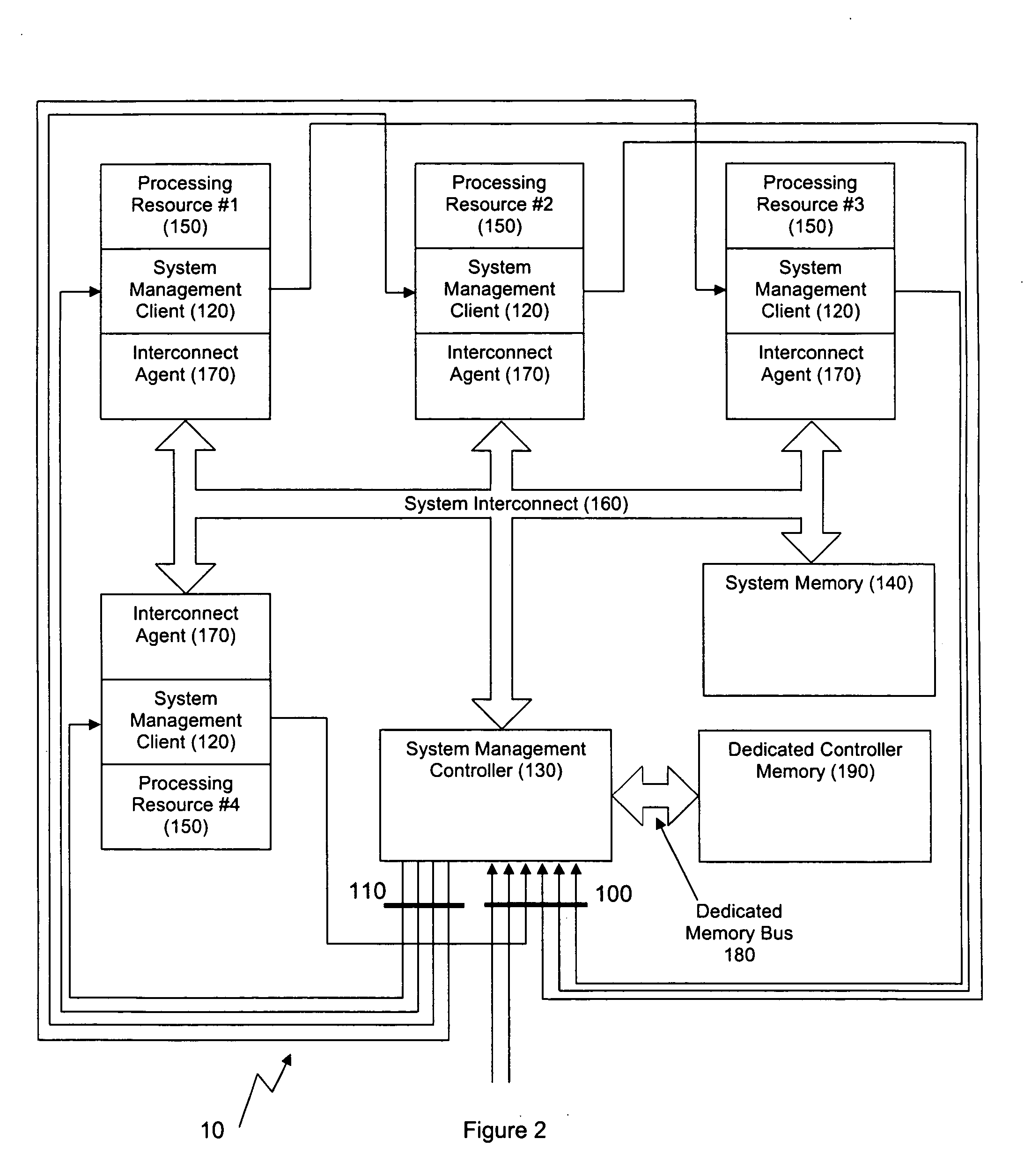

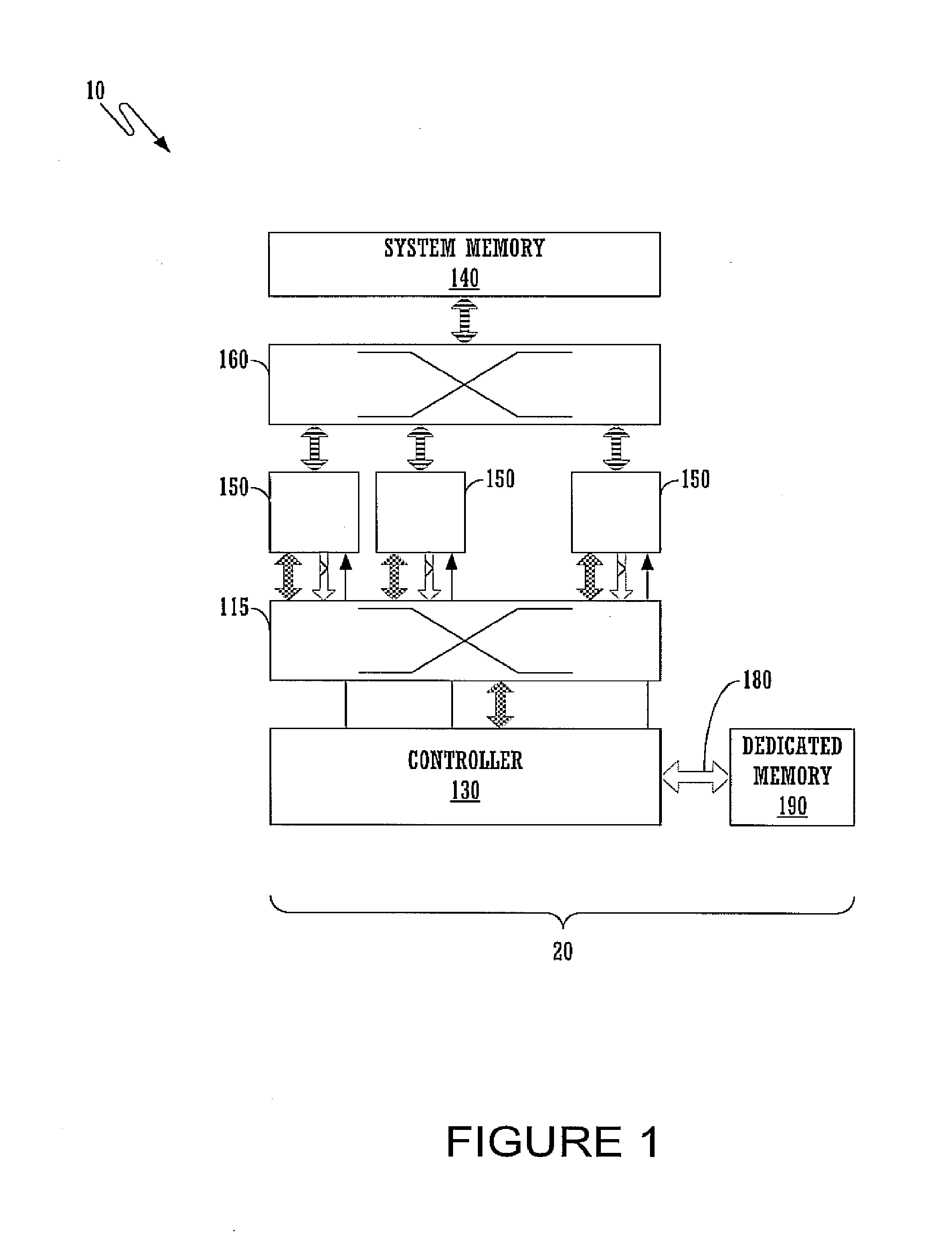

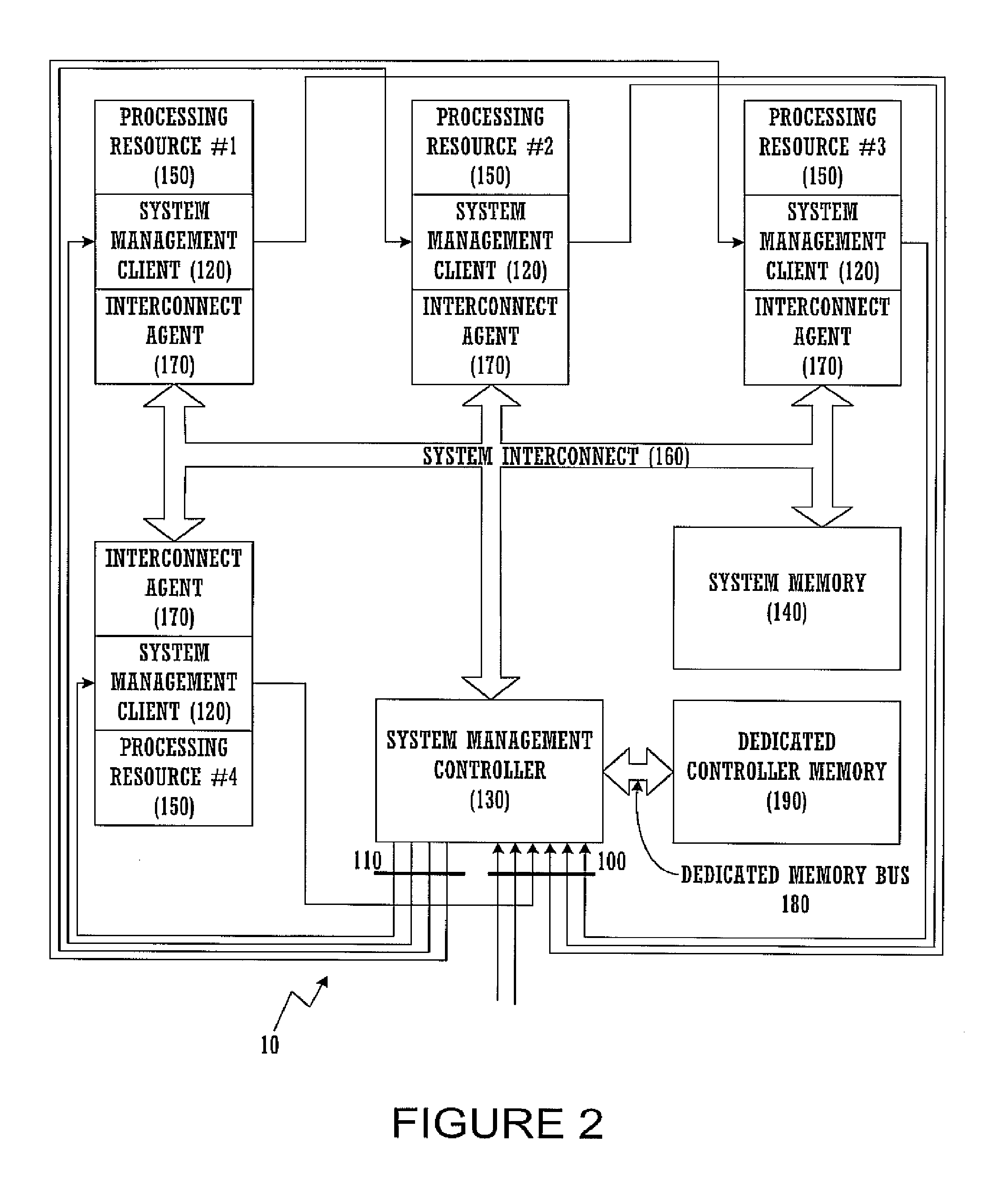

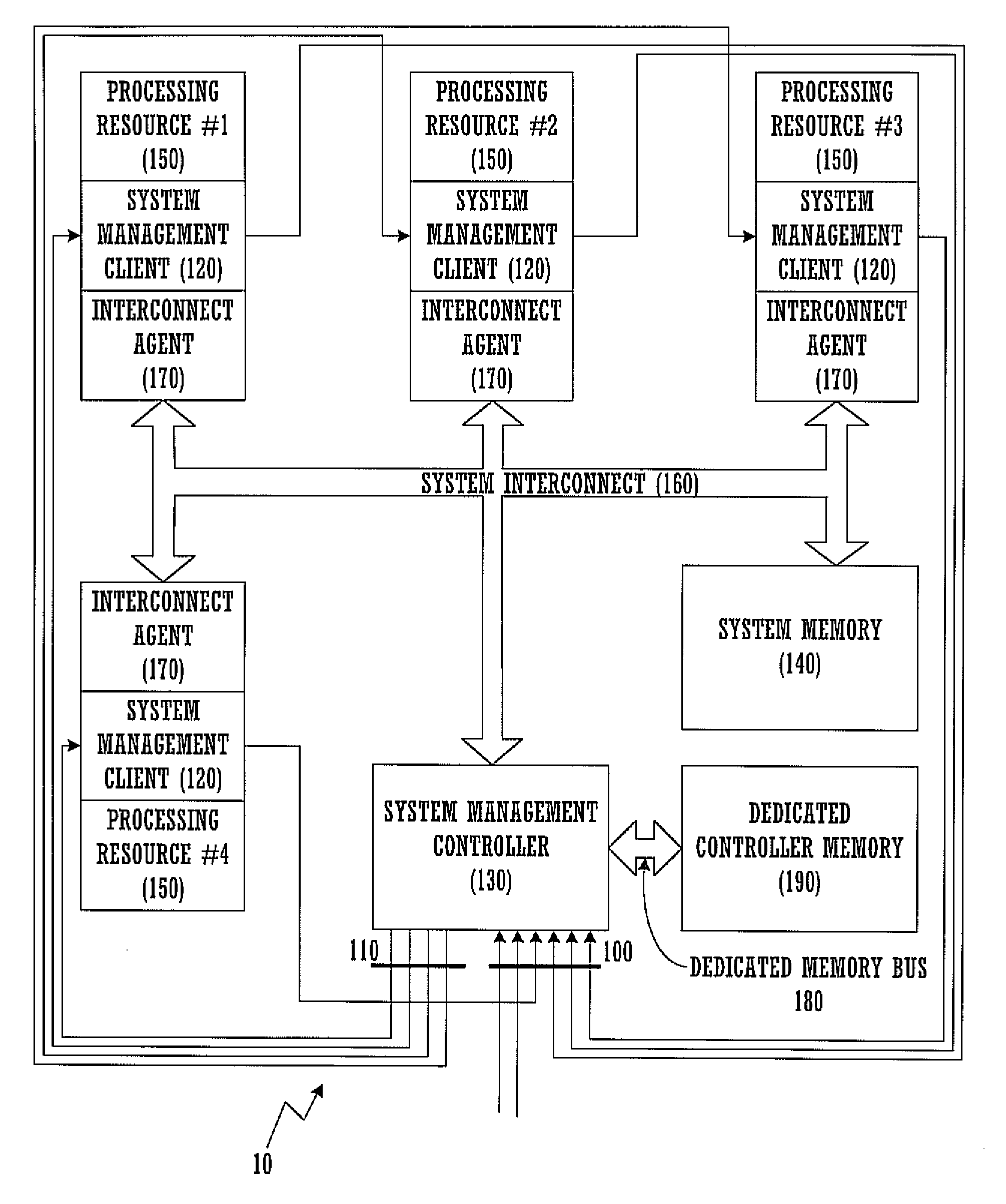

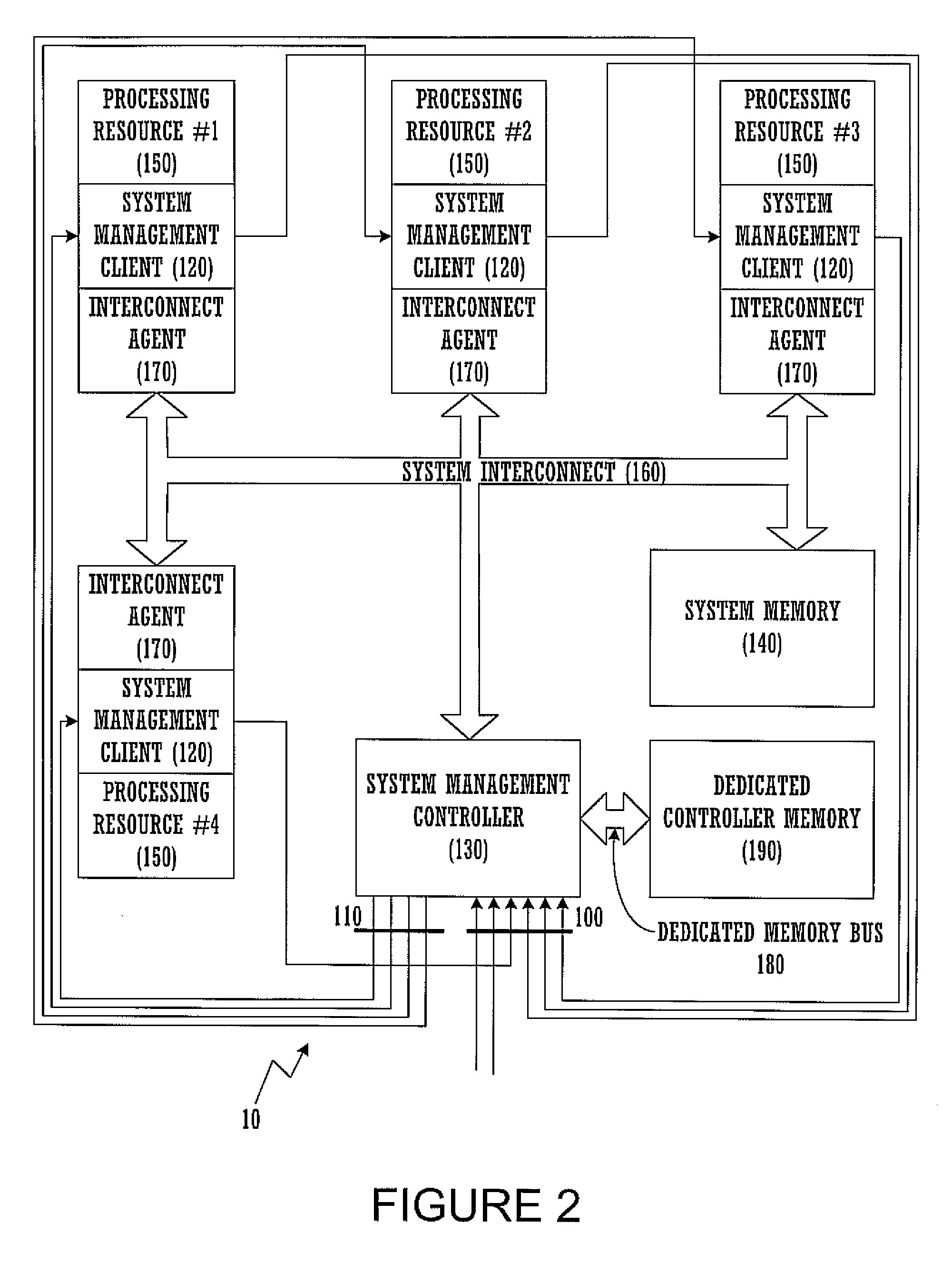

ActiveUS20050223382A1Effective distributionConfiguration highResource allocationGeneral purpose stored program computerMulticore architectureSystems management

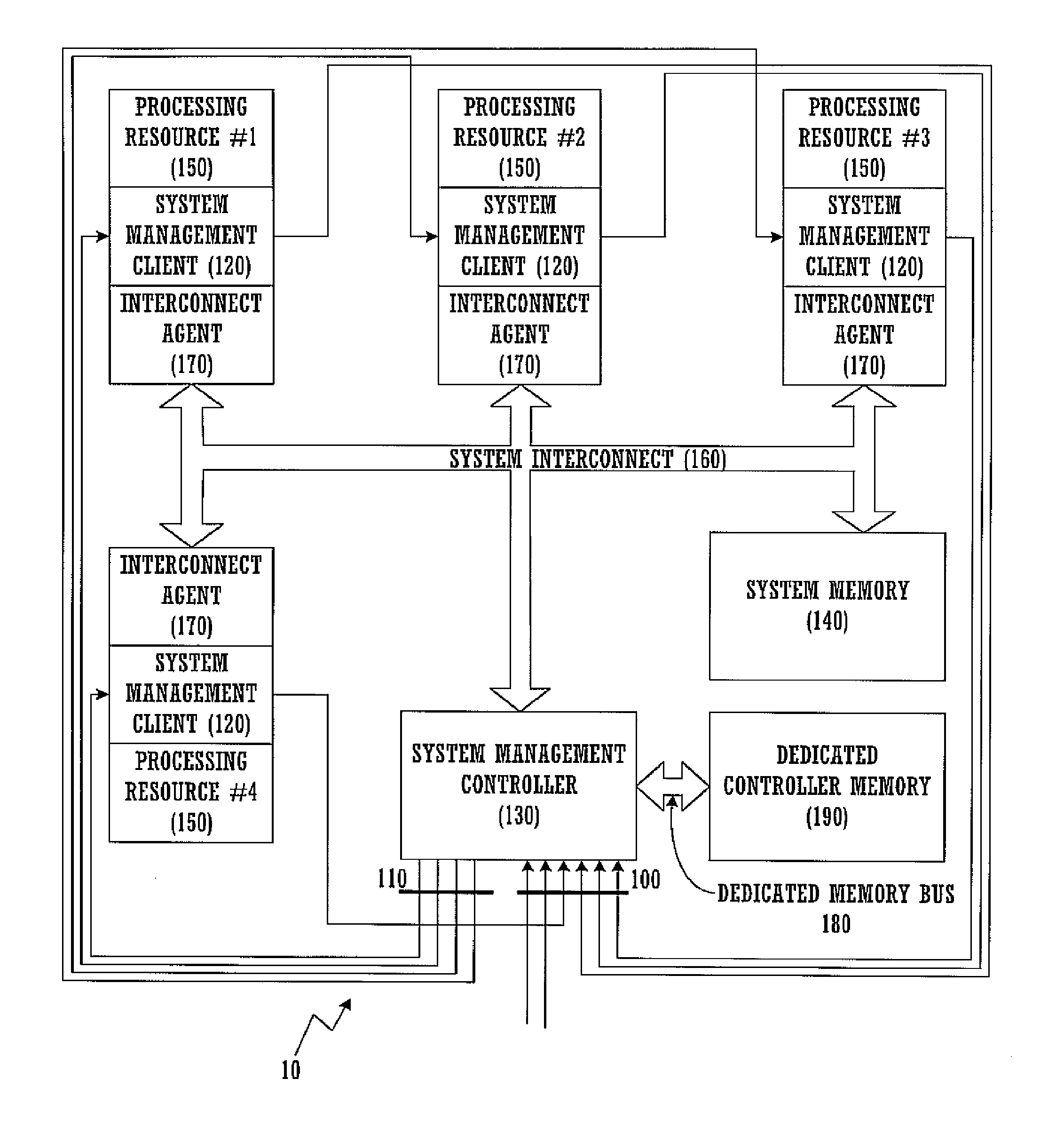

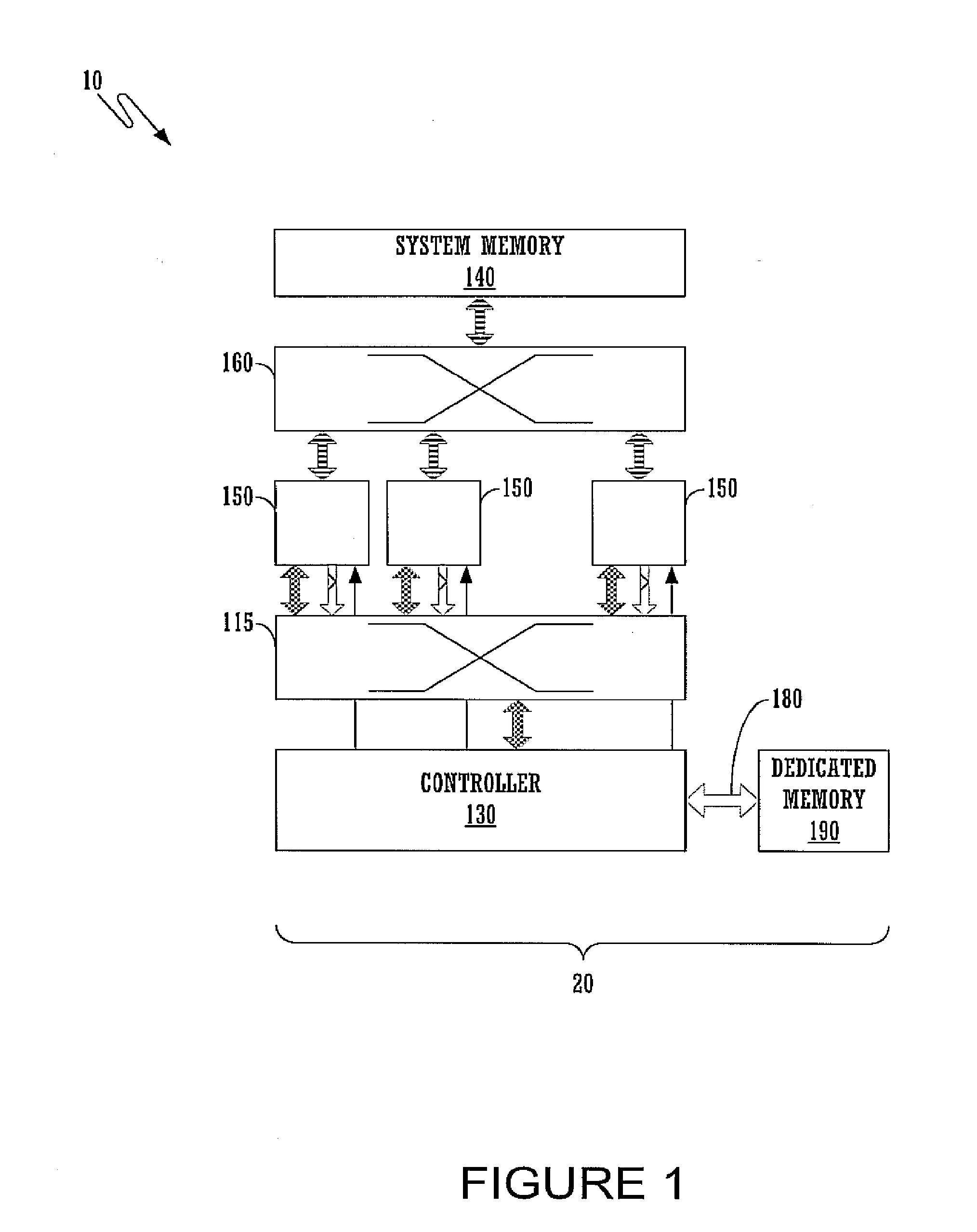

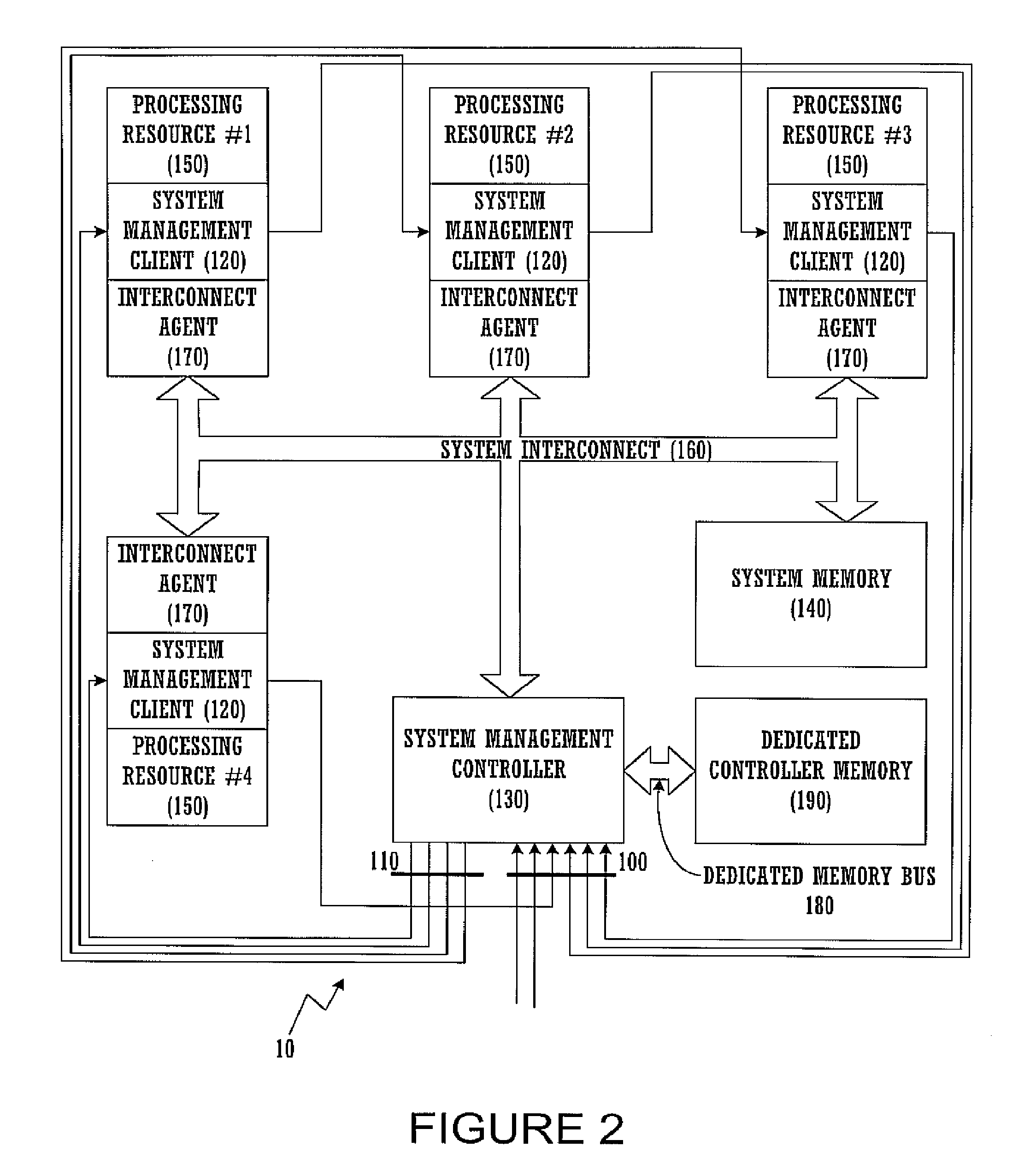

A method and apparatus for resource management in a multicore processor is disclosed. A system management controller (130) provides omnipresent scheduling, synchronisation, load balancing, and power and memory management services to each processing resource (150) within in a multicore processor (10), via a plurality of system management clients (120) implemented in hardware or software. The controller (130) allocates the tasks executing in each processing resource (150) by means of interrupt control signals, which interact directly with the system management clients (120), enabling processing resources (150) to autonomously create, execute and distribute tasks around a parallel system architecture whilst monitoring and policing the use of shared system resources (140).

Owner:FUJITSU SEMICON LTD +1

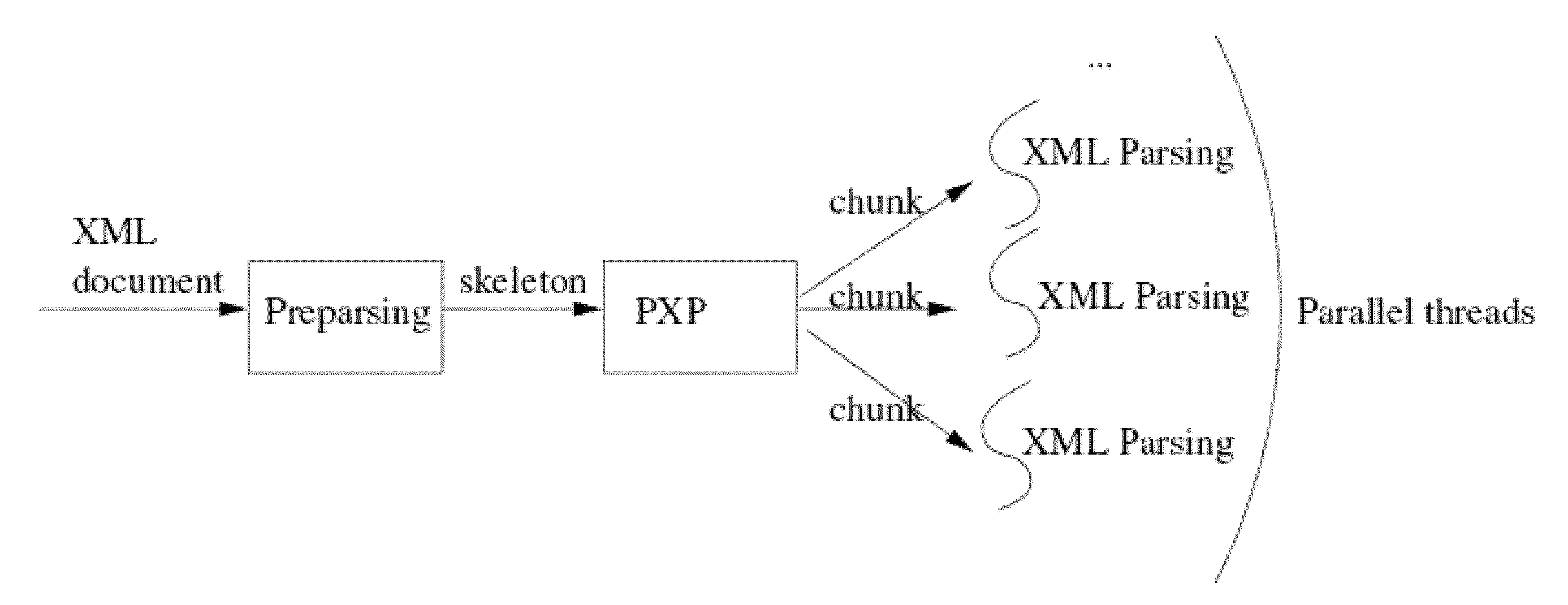

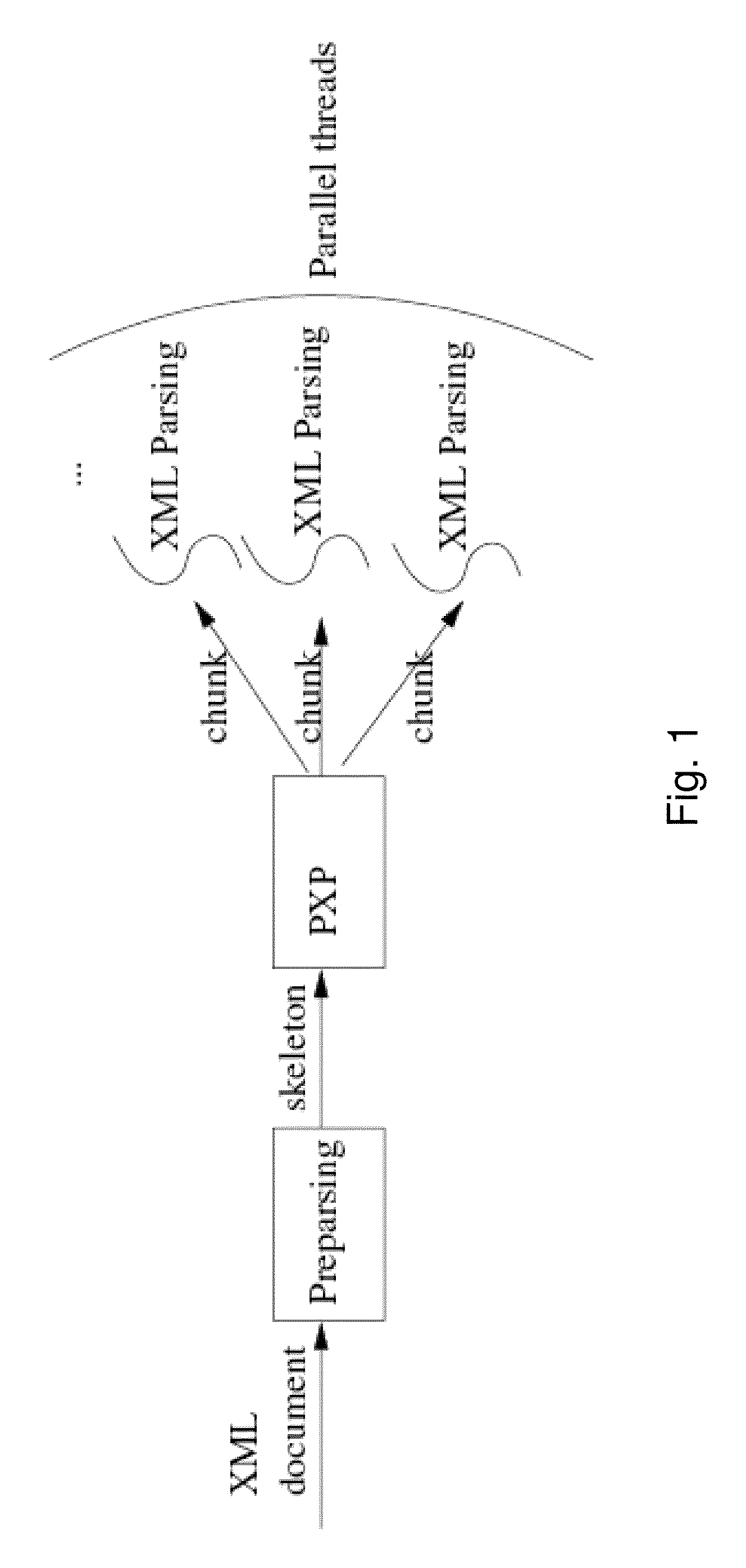

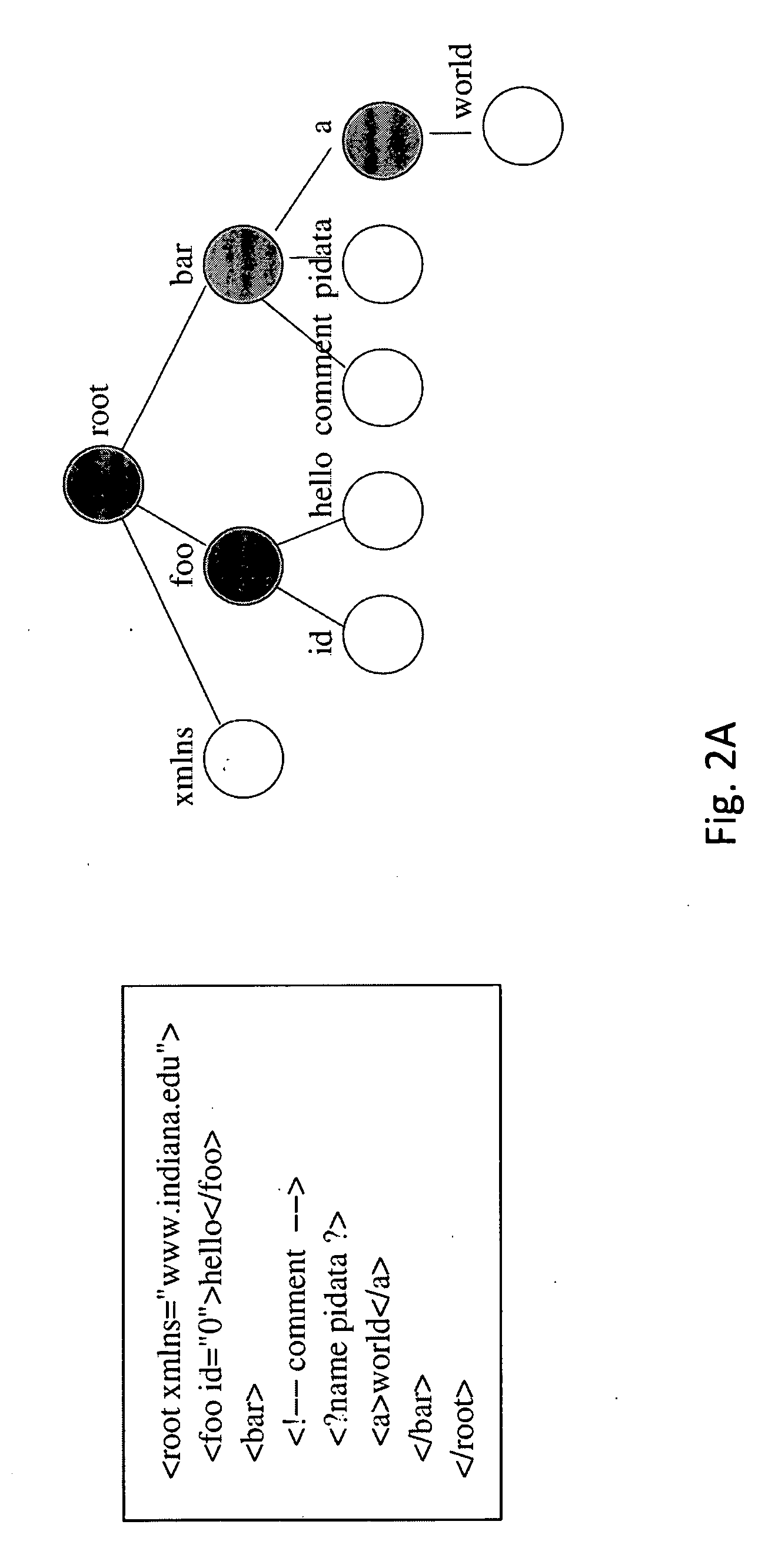

Parallel approach to XML parsing

InactiveUS20090089658A1Flexible performanceImprove readabilityNatural language data processingSpecial data processing applicationsMulticore architectureSchema for Object-Oriented XML

A language for semi-structured documents, XML has emerged as the core of the web services architecture, and is playing crucial roles in messaging systems, databases, and document processing. However, the processing of XML documents has a reputation for poor performance, and a number of optimizations have been developed to address this performance problem from different perspectives, none of which have been entirely satisfactory. Parallel XML parsing leverages the growing prevalence of multicore architectures in all sectors of the computer market, and yields significant performance improvements. The design consists of an initial preparsing phase to determine the structure of the XML document (or other data document), followed by a full, parallel parse. The results of the preparsing phase are used to help partition the XML document for data parallel processing. The parallel parsing phase is, for example, a modification of the libxml2 XML parser, which demonstrates that the approach applies to real-world, production quality parsers. Empirical study shows the parallel XML parsing algorithm can improve the XML parsing performance significantly and scales well.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK

Debug in a multicore architecture

According to a first aspect of the present invention, there is provided a method of monitoring thread execution within a multicore processor architecture which comprises a plurality of interconnected processor elements for processing the threads, the method comprising receiving a plurality of thread parameter indicators indicative of one or more parameters relating to the function and / or identity of a thread or threads comparing at least some of the thread parameter indicators with a first plurality of predefined criteria each representative of an indicator of interest and generating an output consequential upon thread parameter indicators which have been identified to be of interest as a result of the said comparison.

Owner:FUJITSU SEMICON LTD +1

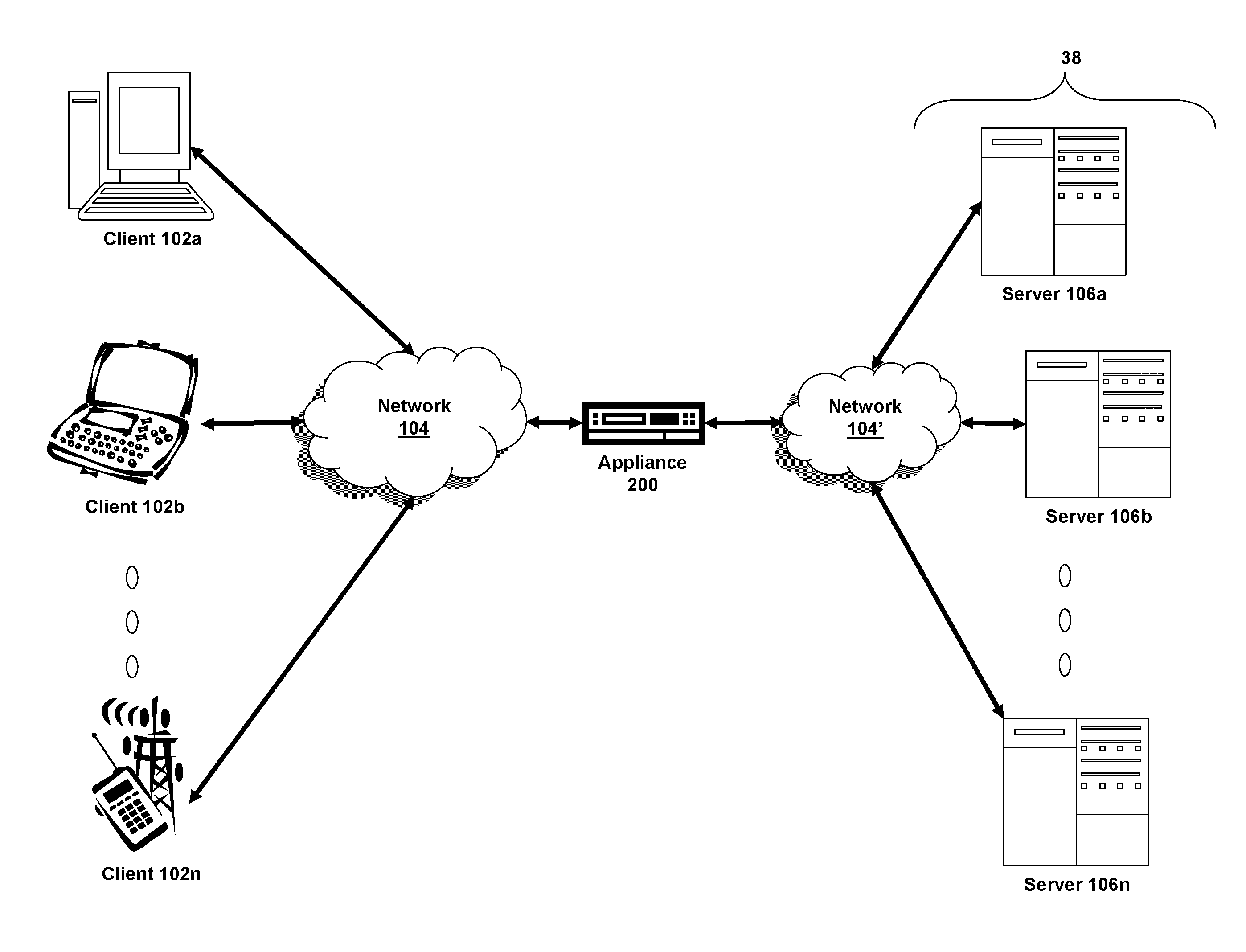

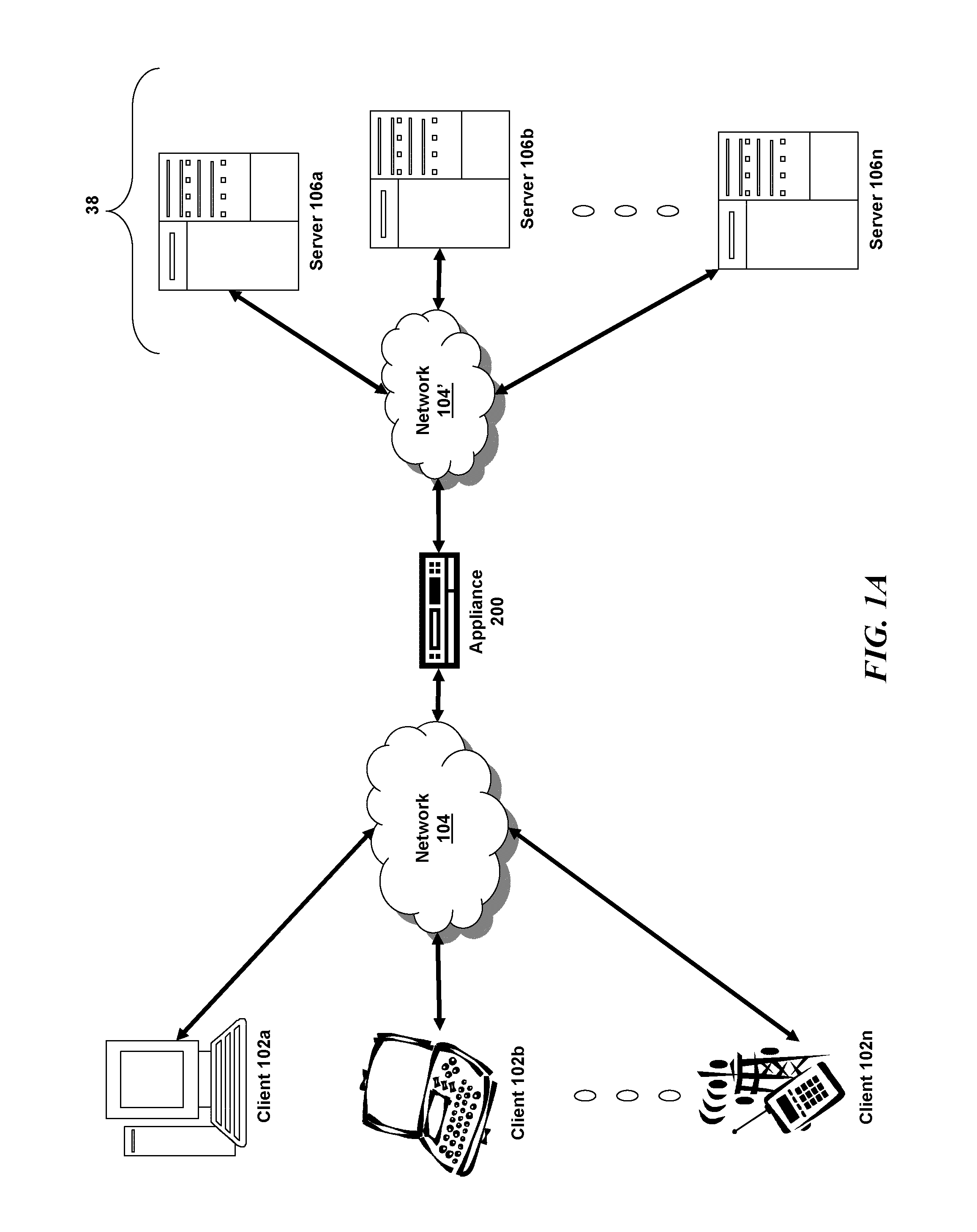

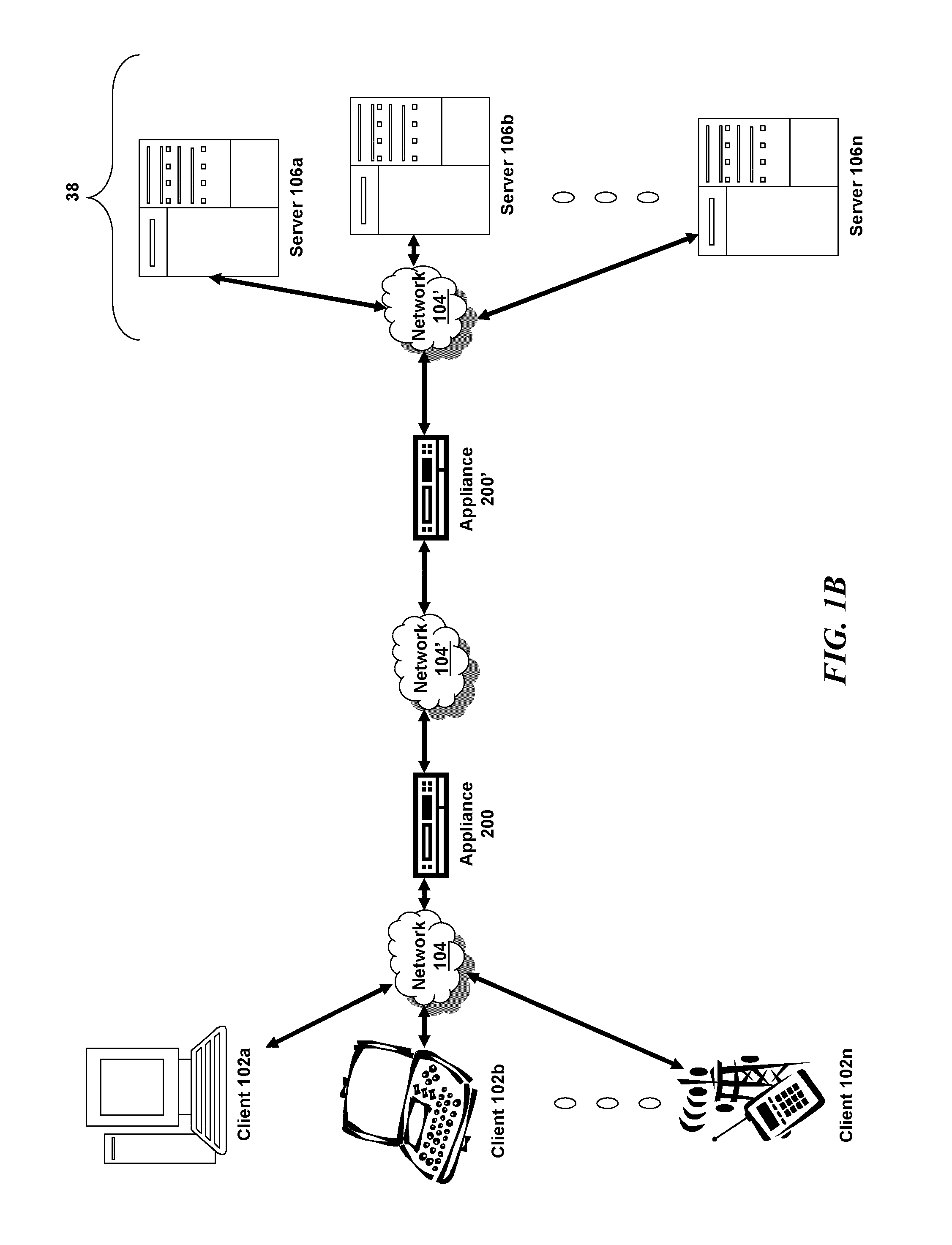

Systems and method for transaction stall detection and propagating the result in a multi-core architecture

ActiveUS20100325495A1Multiple digital computer combinationsNon-redundant fault processingEmbedded systemMulticore architecture

The present invention is directed towards systems and methods for determining failure in and controlling access to a shared resource in a multi-core system. In some embodiments of a multi-core system, individual cores may share the same resource. Additionally, the resource may occasionally fail or need to be reset, and the period during which the resource is being reset may be non-instantaneous. In an embodiment without coordination between the cores, one core experiencing a failure may reset the resource. During the period in which the resource is resetting, another core may interpret the reset as a failure and reset the resource. As more cores interpret the resets as failures, they will trigger resets, quickly resulting in the resource being constantly reset and unavailable. Thus, in some embodiments, a coordination system may be utilized to determine failure of a shared resource and control resets and access to the shared resource.

Owner:CITRIX SYST INC

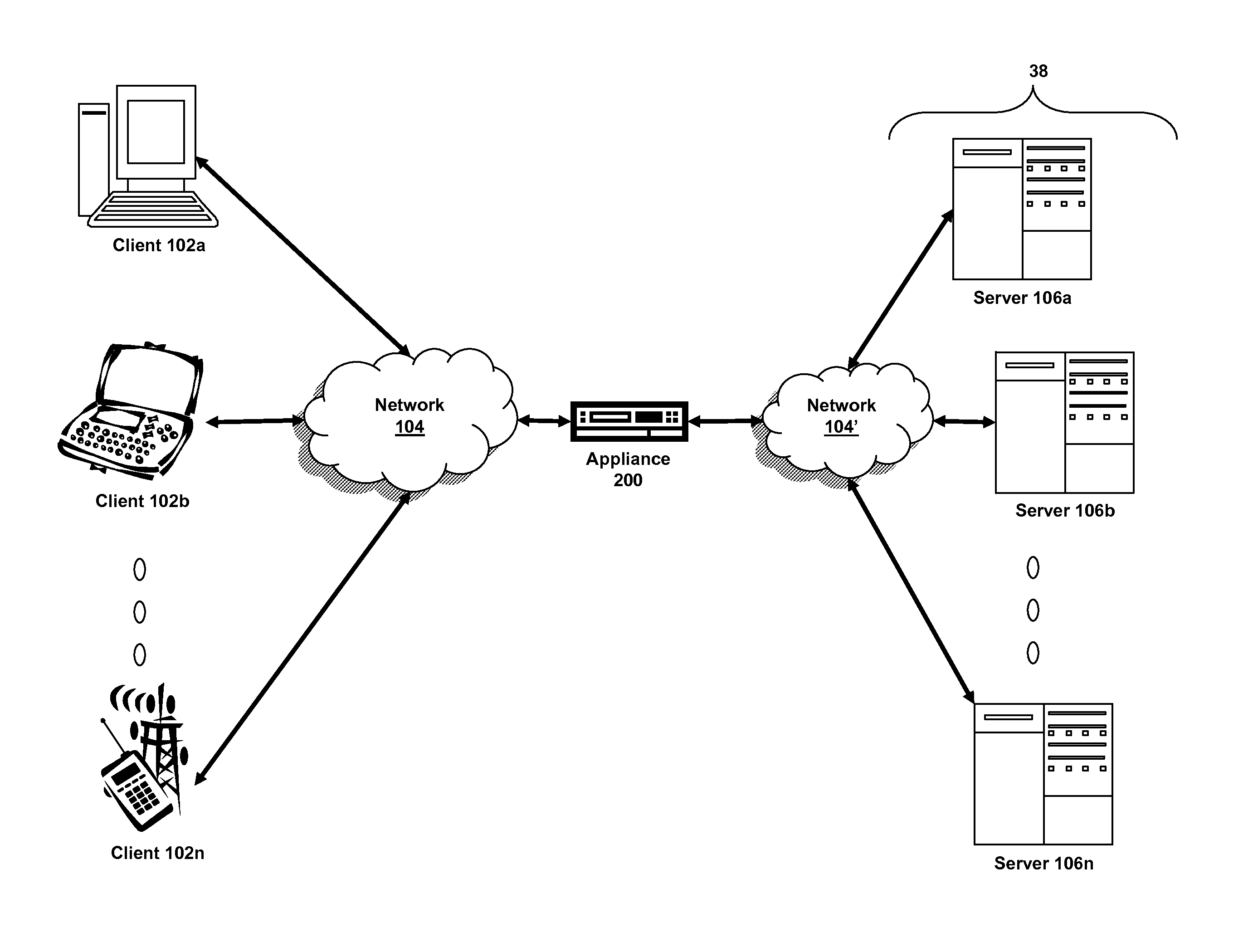

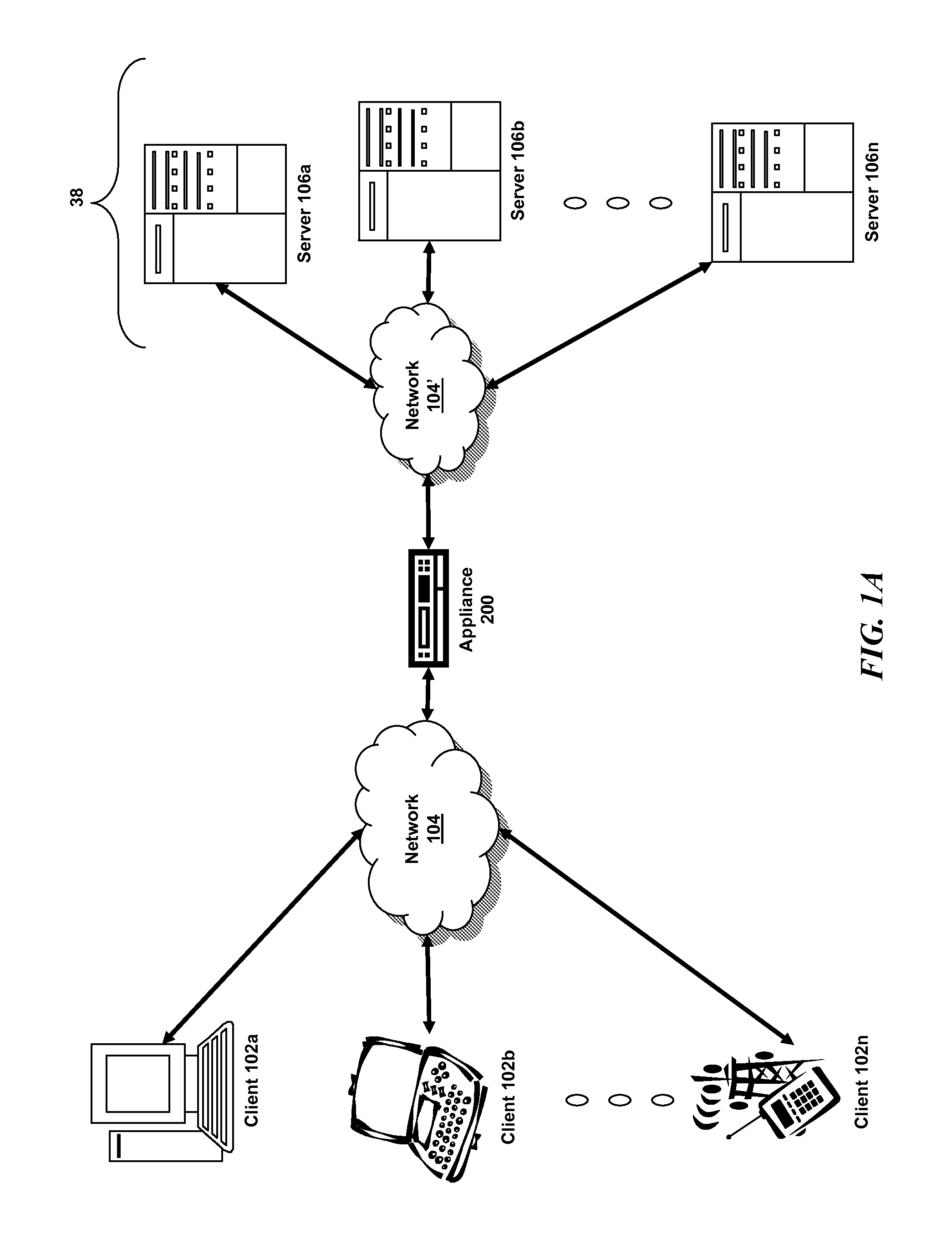

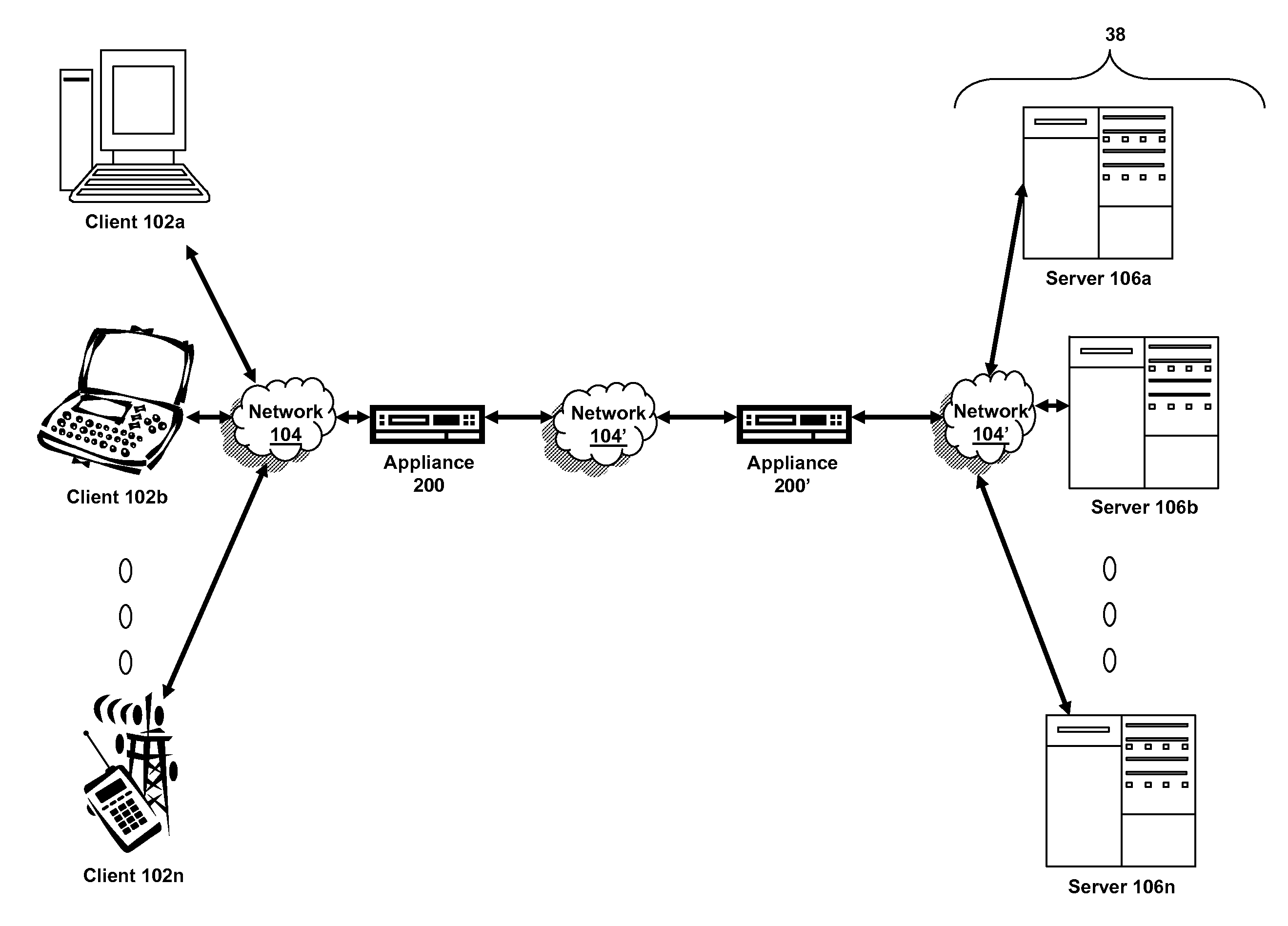

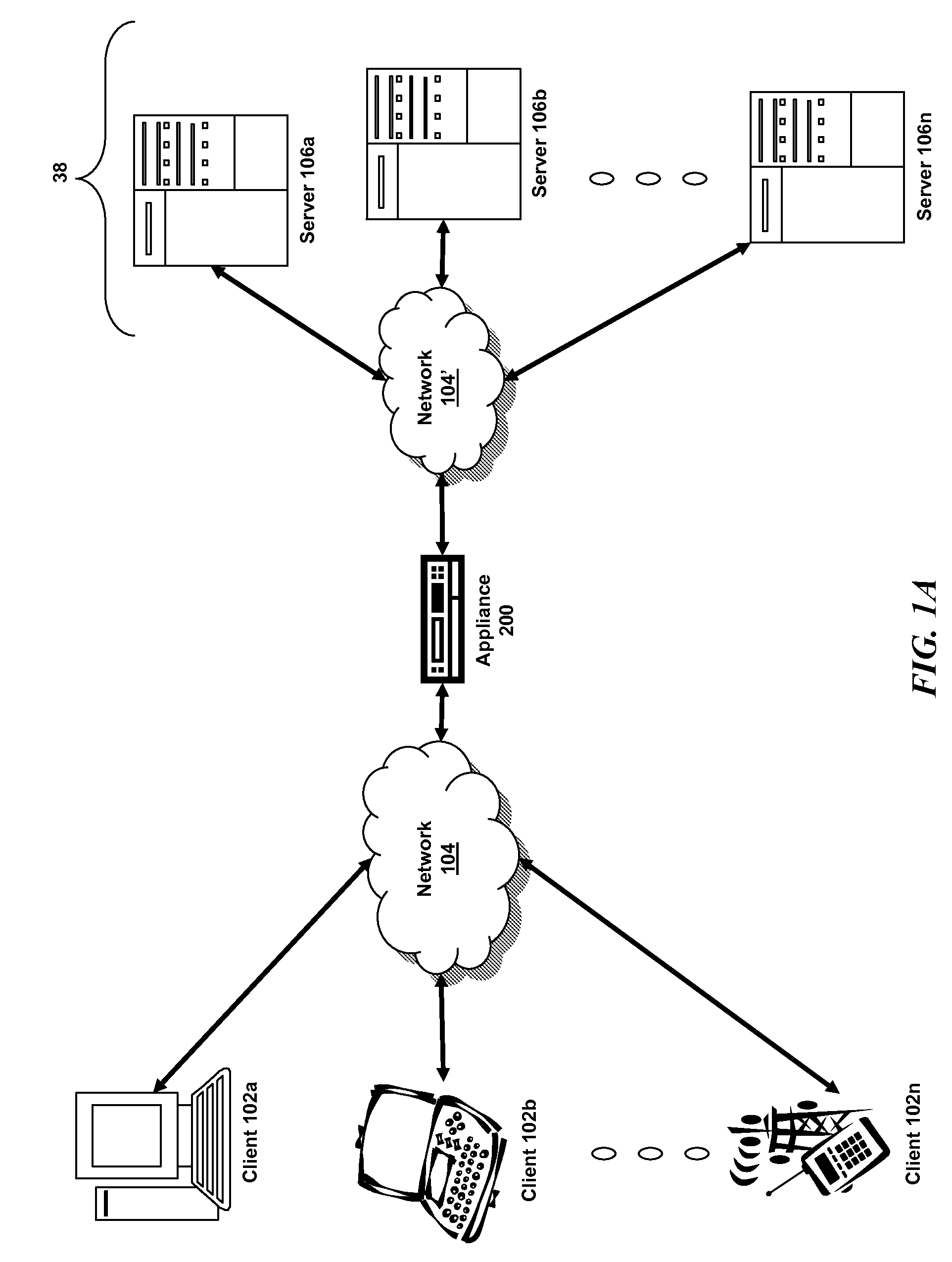

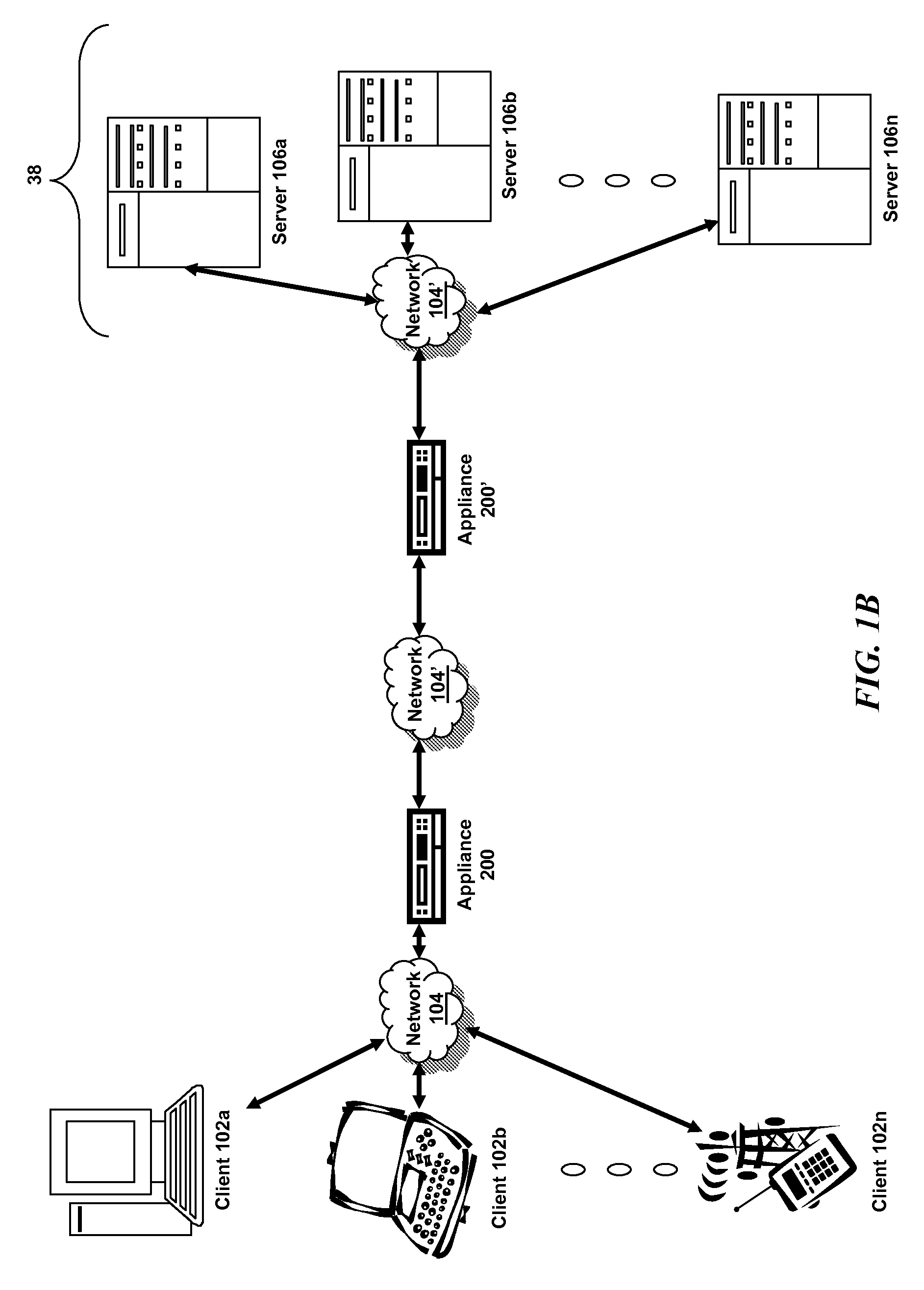

Systems and methods for receive and transmission queue processing in a multi-core architecture

Described herein is a method and system for directing outgoing data packets from packet engines to a transmit queue of a NIC in a multi-core system, and a method and system for directing incoming data packets from a receive queue of the NIC to the packet engines. Packet engines store outgoing traffic in logical transmit queues in the packet engines. An interface module obtains the outgoing traffic and stores it in a transmit queue of the NIC, after which the NIC transmits the traffic from the multi-core system over a network. The NIC receives incoming traffic and stores it in a NIC receive queue. The interface module obtains the incoming traffic and applies a hash to a tuple of each obtained data packet. The interface module then stores each data packet in the logical receive queue of a packet engine on the core identified by the result of the hash.

Owner:CITRIX SYST INC

Finite element methods and systems

ActiveUS20150120261A1Address limitationsComputation using non-denominational number representationDesign optimisation/simulationMulticore architectureCpu architecture

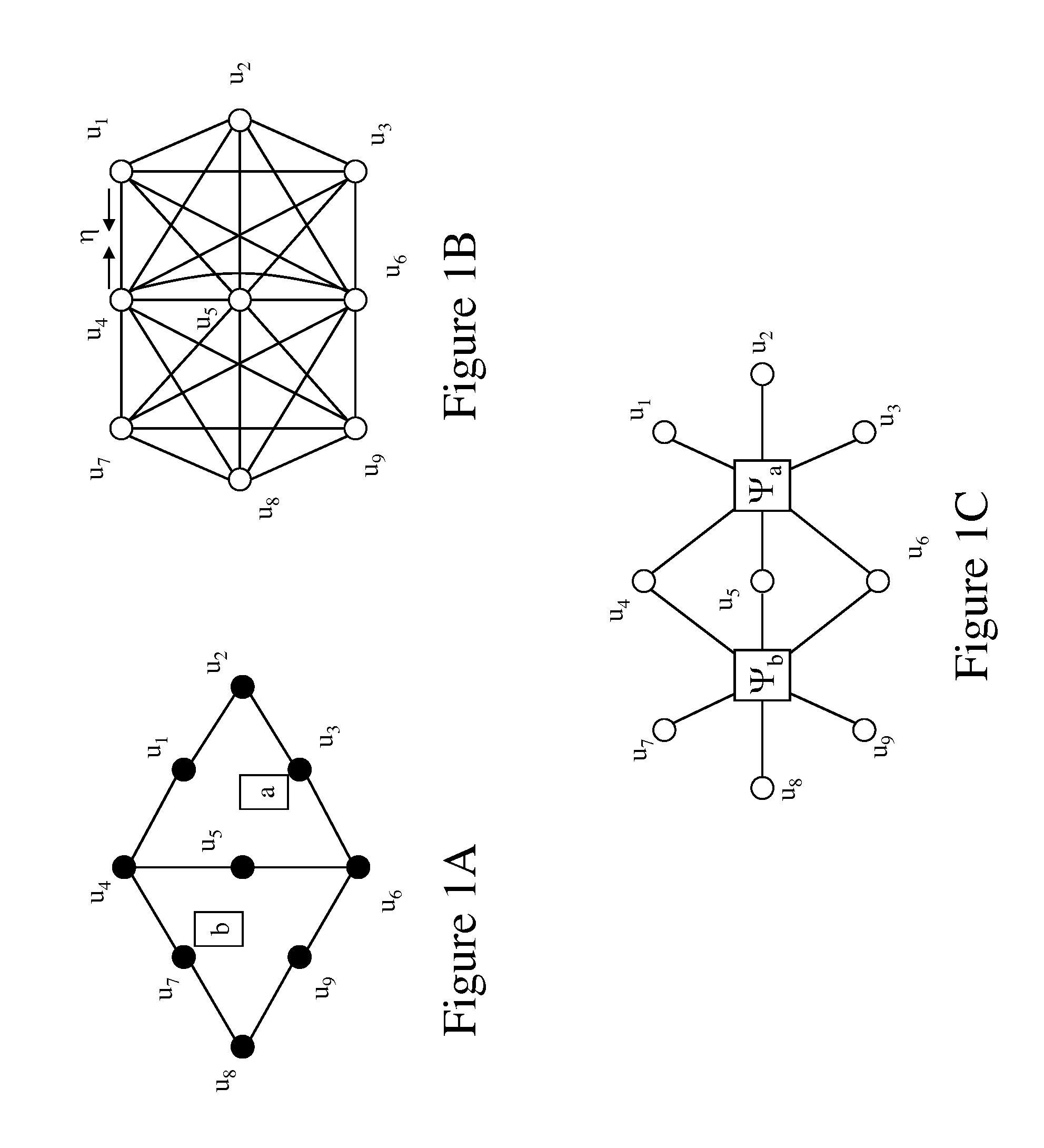

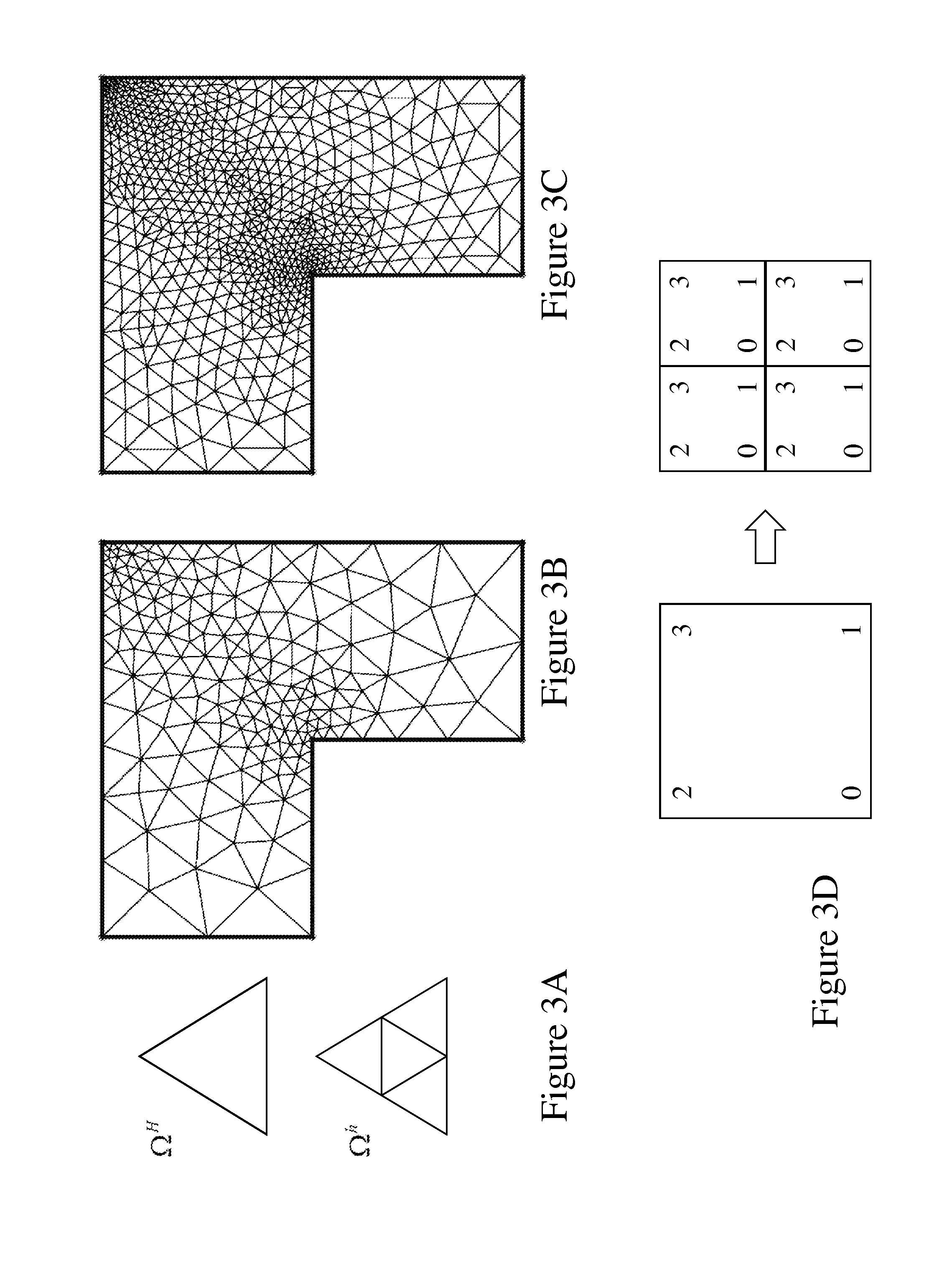

The computational efficiency of Finite Element Methods (FEM) on parallel architectures is typically severely limited by sparse iterative solvers. Standard iterative solvers are based on sequential steps of global algebraic operations, which limit their parallel efficiency, and prior art techniques exploit sophisticated programming techniques tailored to specific CPU architectures to improve performance. The inventors present a FEM Multigrid Gaussian Belief Propagation (FMGaBP) technique that eliminates global algebraic operations and sparse data-structures based upon reformulating the variational FEM into a probabilistic inference problem based upon graphical models. Further, the inventors present new formulations for FMGaBP, which further enhance its computation and communication complexities where the parallel features of FMGaBP are leveraged to multicore architectures.

Owner:MCGILL UNIV

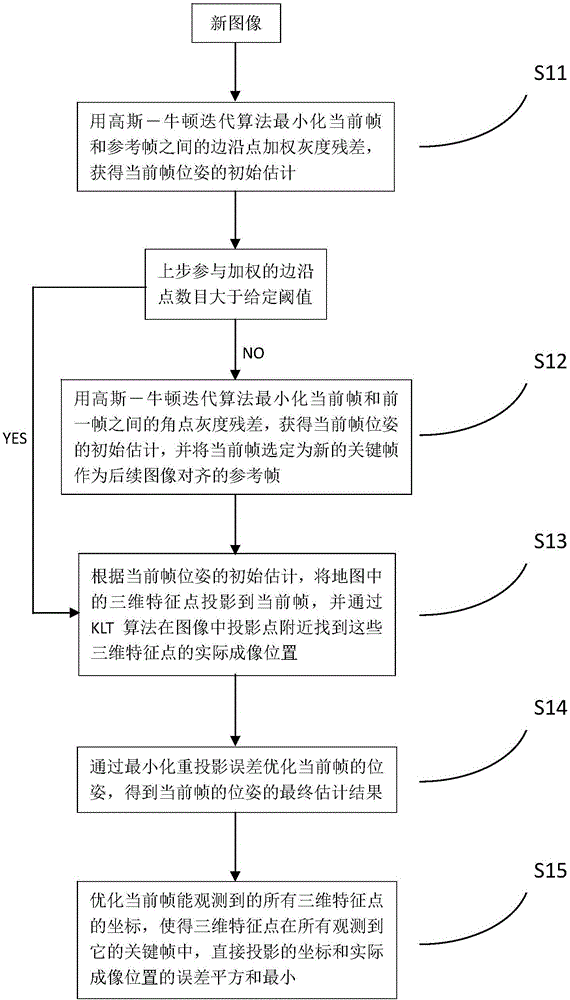

Monocular vision ranging method based on edge point information in image

ActiveCN105809687AImprove efficiencyImprove environmental adaptabilityImage analysisNavigational calculation instrumentsPattern recognitionMulticore architecture

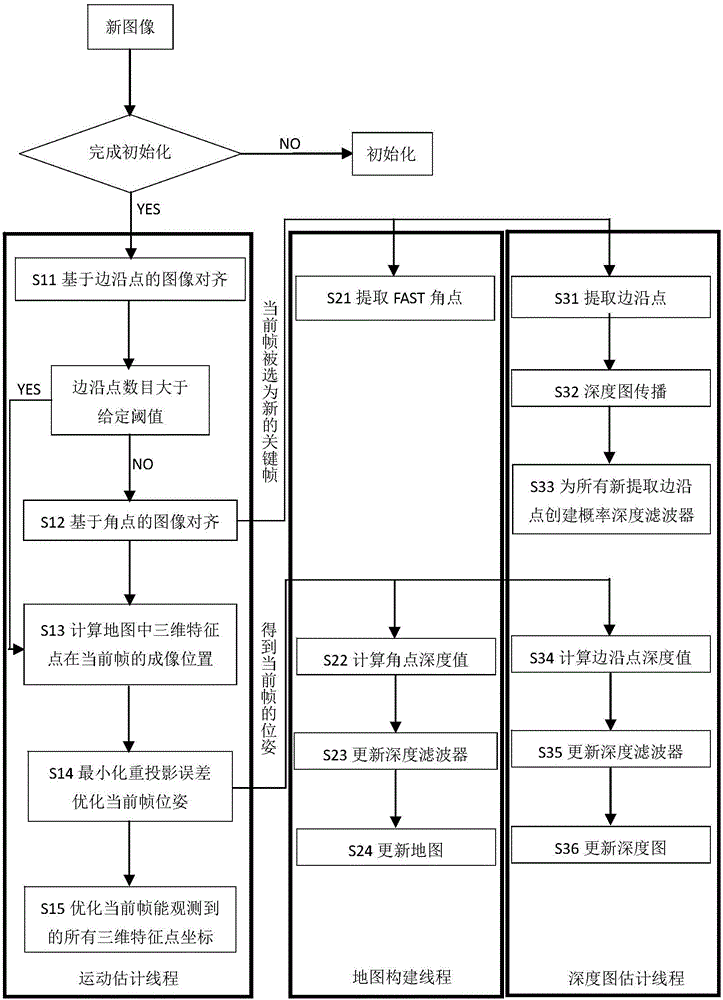

The invention relates to a monocular vision ranging method based on edge point information in an image and belongs to the unmanned aerial vehicle navigation and positioning technical field. The method includes the following steps that: two frames of images are selected from an image sequence captured by a downward-looking monocular camera fixedly connected with an unmanned aerial vehicle so as be adopted to construct an initial map and an initial depth graph, a first frame is adopted as a first key frame in the map, and a camera coordinate system corresponding to the first frame is adopted as a world coordinate system, and initialization is completed; and three threads, namely, a motion estimation thread, a map construction thread and a depth graph estimation thread are carried out parallelly, wherein the motion estimation thread aligns known map and depth graph information with a current frame so as to obtain a ranging result, and optimizes the existing map information according to the ranging result, and the map construction thread and the depth graph estimation thread operate simultaneously so as to maintain the map and depth graph information. According to the method of the invention, the multi-core architecture of a modern processor is fully utilized, and the edge point information in the image can be effectively utilized, and based on corner point information, the efficiency of the algorithm is improved. The method has higher adaptability.

Owner:TSINGHUA UNIV

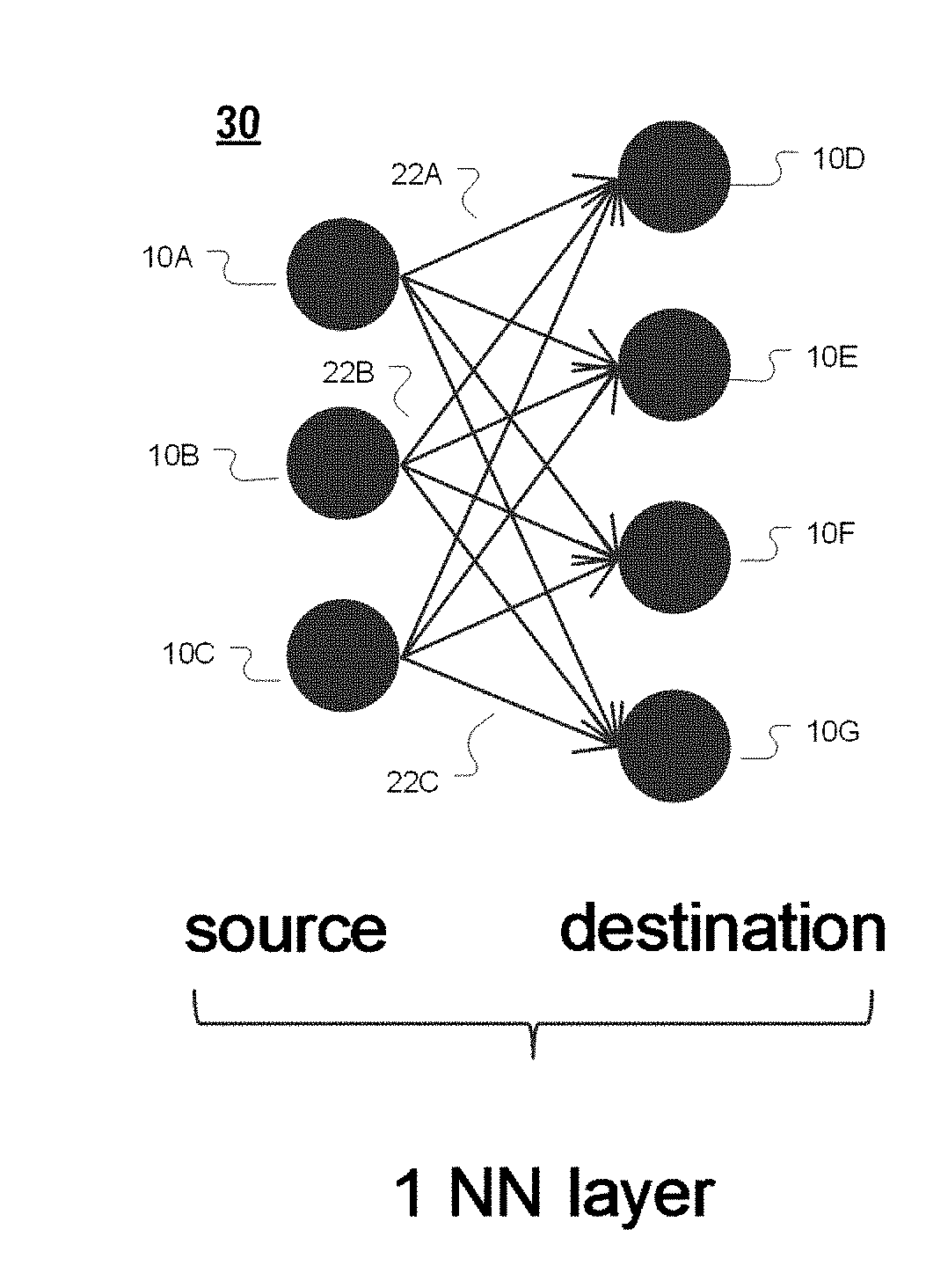

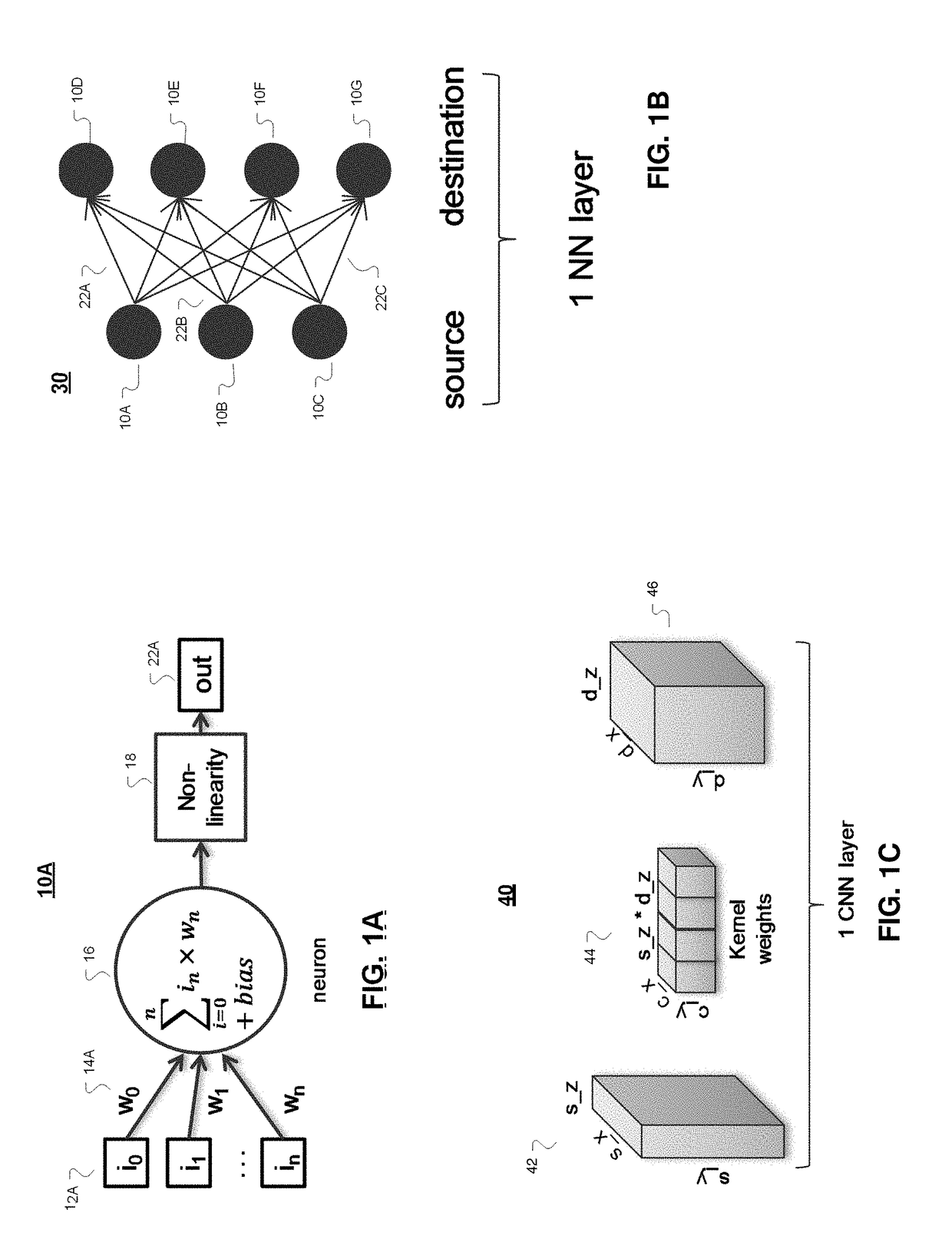

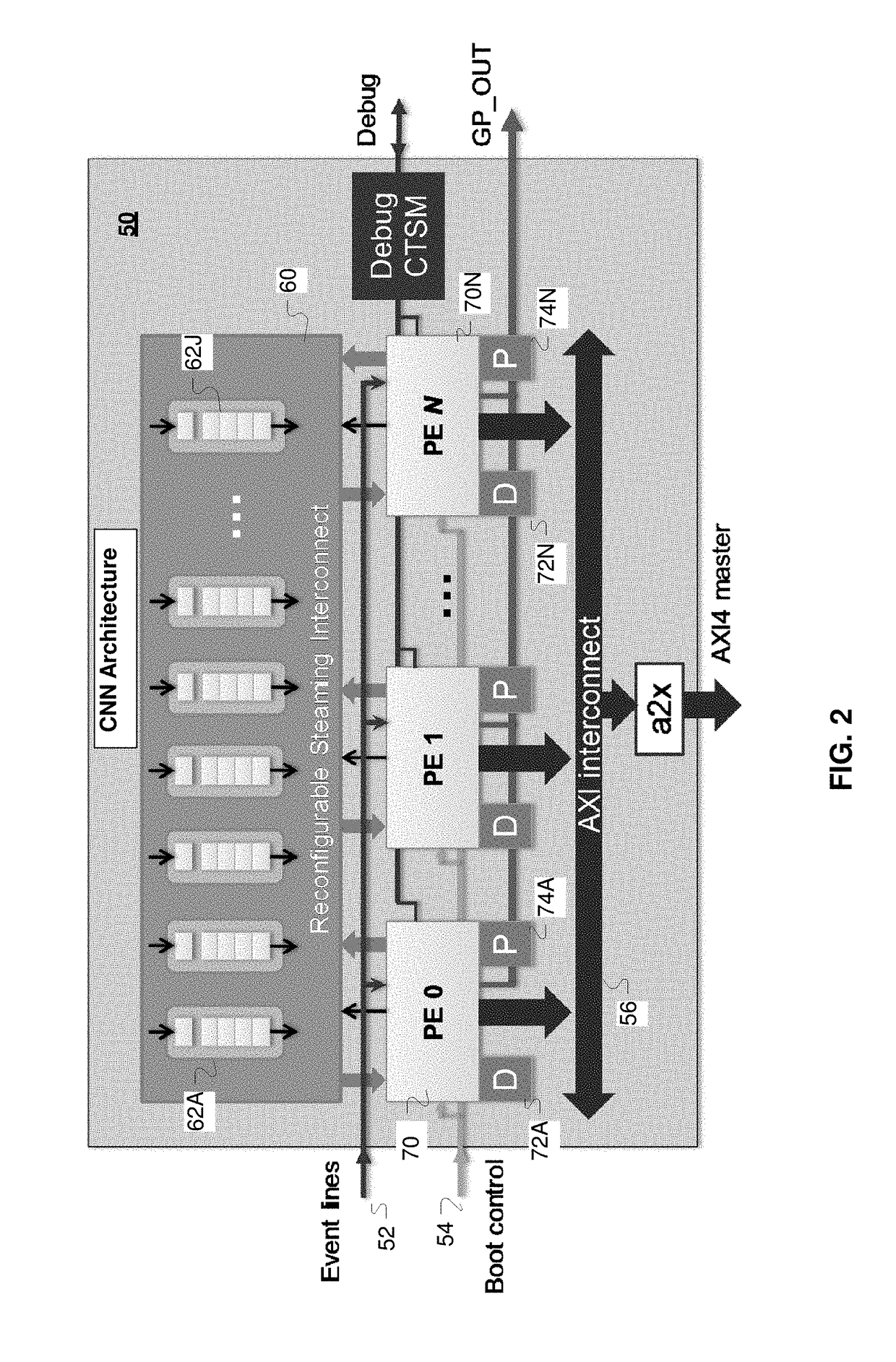

Configurable and Programmable Multi-Core Architecture with a Specialized Instruction Set for Embedded Application Based on Neural Networks

A programmable architecture specialized for convolutional neural networks (CNNs) processing such that different applications of CNNs may be supported by the presently disclosed method and apparatus by reprogramming the processing elements therein. The architecture may include an optimized architecture that provides a low-area or footprint and low-power solution desired for embedded applications while still providing the computational capabilities required for CNN applications that may computationally intensive, requiring a huge number of convolution operations per seconds to process inputs such as video streams in real time.

Owner:SYNOPSYS INC

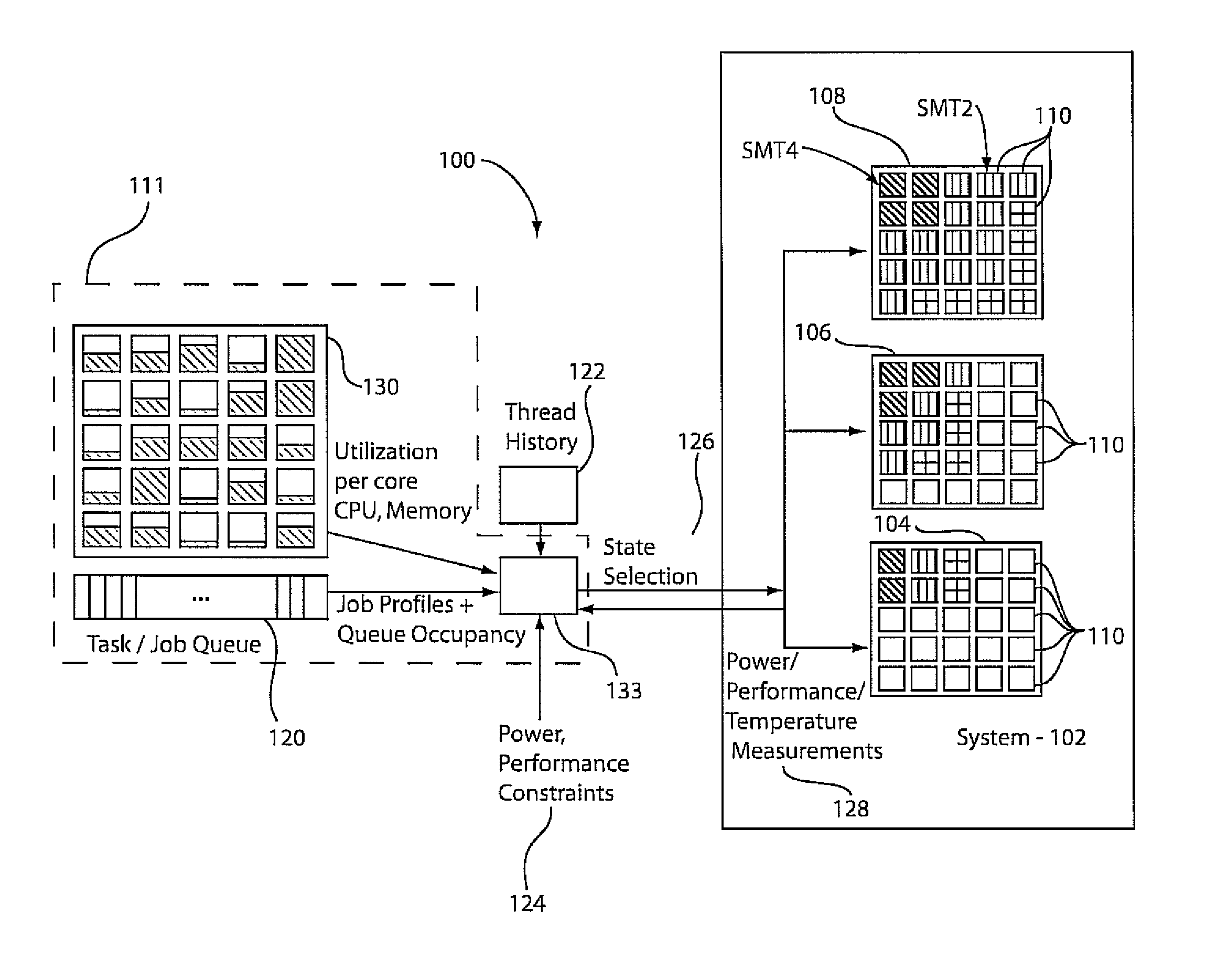

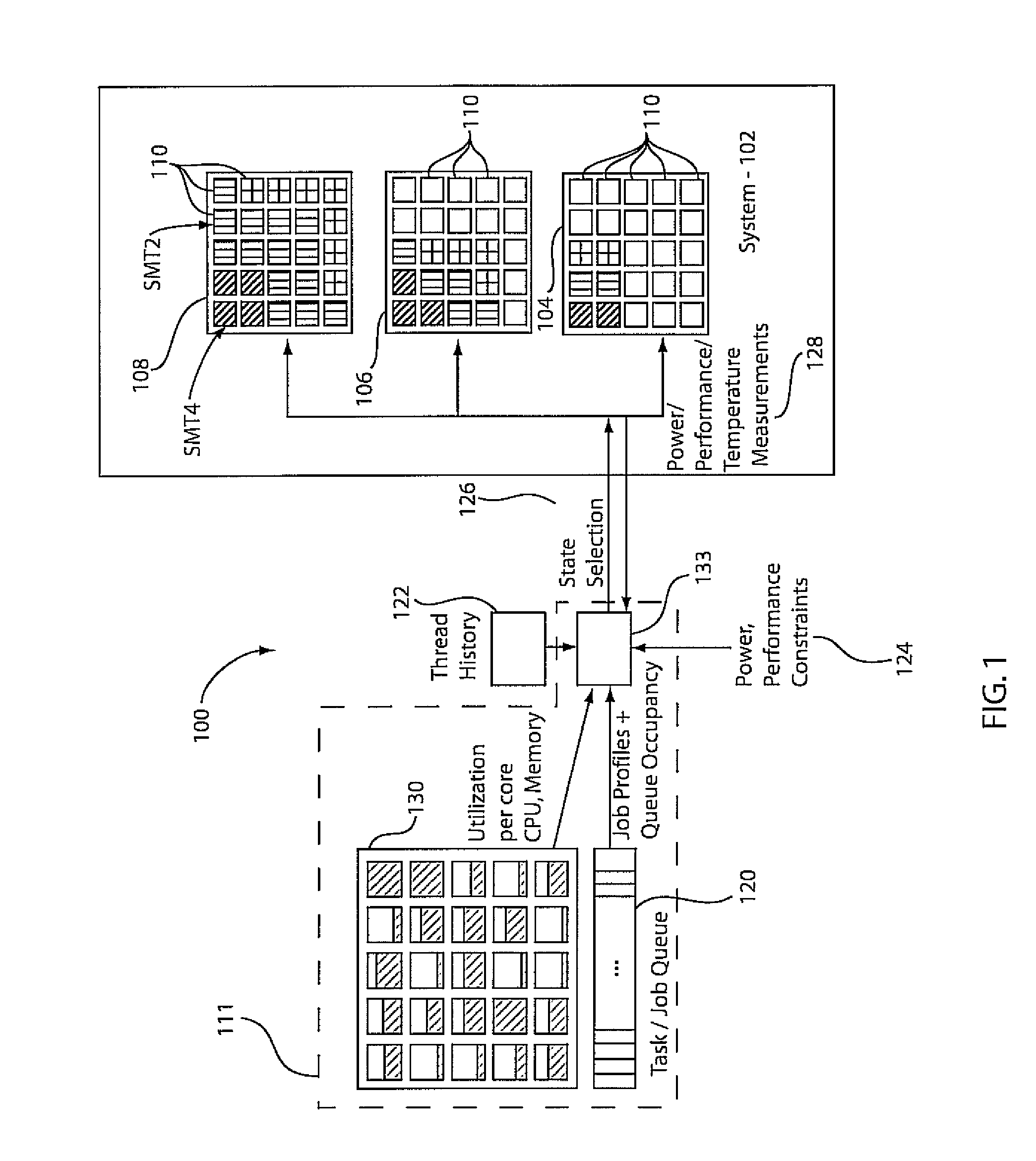

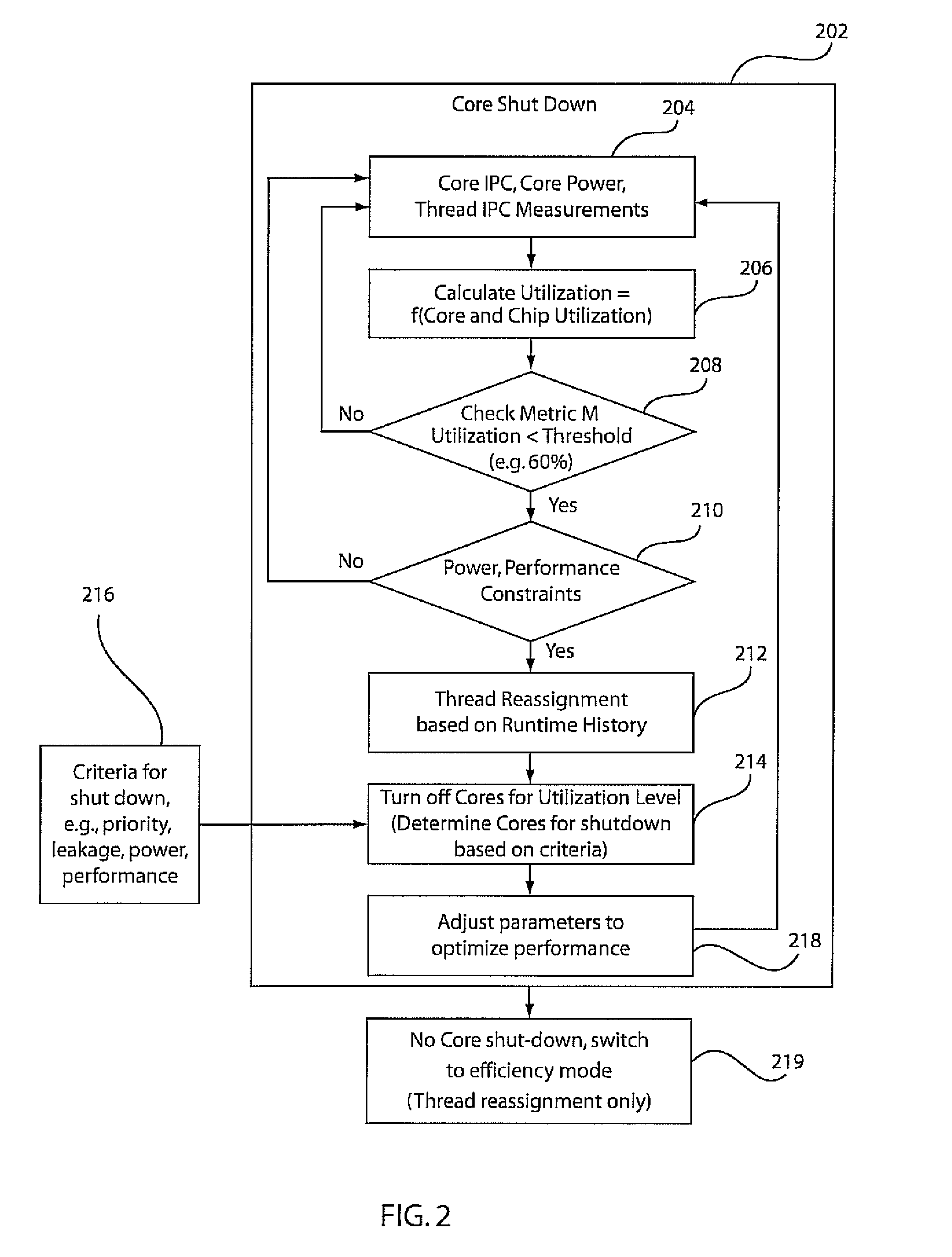

Systems and methods for thread assignment and core turn-off for integrated circuit energy efficiency and high-performance

InactiveUS8296773B2Improve efficiencyImprove performanceEnergy efficient ICTDigital data processing detailsMulticore architectureParallel computing

A system and method for improving efficiency of a multi-core architecture includes, in accordance with a workload, determining a number of cores to shut down based upon a metric that combines parameters to represent operational efficiency. Threads of the workload are reassigned to cores remaining active by assigning threads based on priority constraints and thread execution history to improve the operational efficiency of the multi-core architecture.

Owner:IBM CORP

Resource management in a multicore architecture

ActiveUS20140026141A1Configuration highEffective distributionResource allocationMemory systemsMain processing unitProcessor element

A resource management and task allocation controller for installation in a multicore processor having a plurality of interconnected processor elements providing resources for processing executable transactions, at least one of said elements being a master processing unit, the controller being adapted to communicate, when installed, with each of the processor elements including the master processing unit, and comprising control logic for allocating executable transactions within the multicore processor to particular processor elements in accordance with pre-defined allocation parameters.

Owner:SYNOPSYS INC +1

Method for realizing virtual execution environment of central processing unit (CPU)/graphics processing unit (GPU) heterogeneous platform

ActiveCN101963918AMultiple digital computer combinationsSoftware simulation/interpretation/emulationData streamMulticore architecture

The invention relates to a method for realizing a virtual execution environment of a central processing unit (CPU) / graphics processing unit (GPU) heterogeneous platform, which belongs to the technical field of telecommunication. In the method, programs can be run on an X86CPU and NVIDIA GPU hybrid architecture by a dynamic binary translation technique; static information and dynamic information of the programs are acquired by the dynamic binary translation technique; program execution nested loops, a dependency relationship among the loops and data streams of inlet and outlet hot blocks are searched through the information; and the execution is implemented by two steps of: 1, acquiring information, optimizing the hot blocks and storing the hot blocks into files; 2, and generating a hybridprogram comprising a serial instruction and a parallel instruction and executing the program comprising the hybrid instructions. The method has the advantages that: the traditional serial programs can be run a CPU / GPU heterogeneous multi-core architecture by the dynamic binary translation technique, without modifying program source codes; and the execution of the programs can be accelerated by the GPU.

Owner:SHANGHAI JIAO TONG UNIV

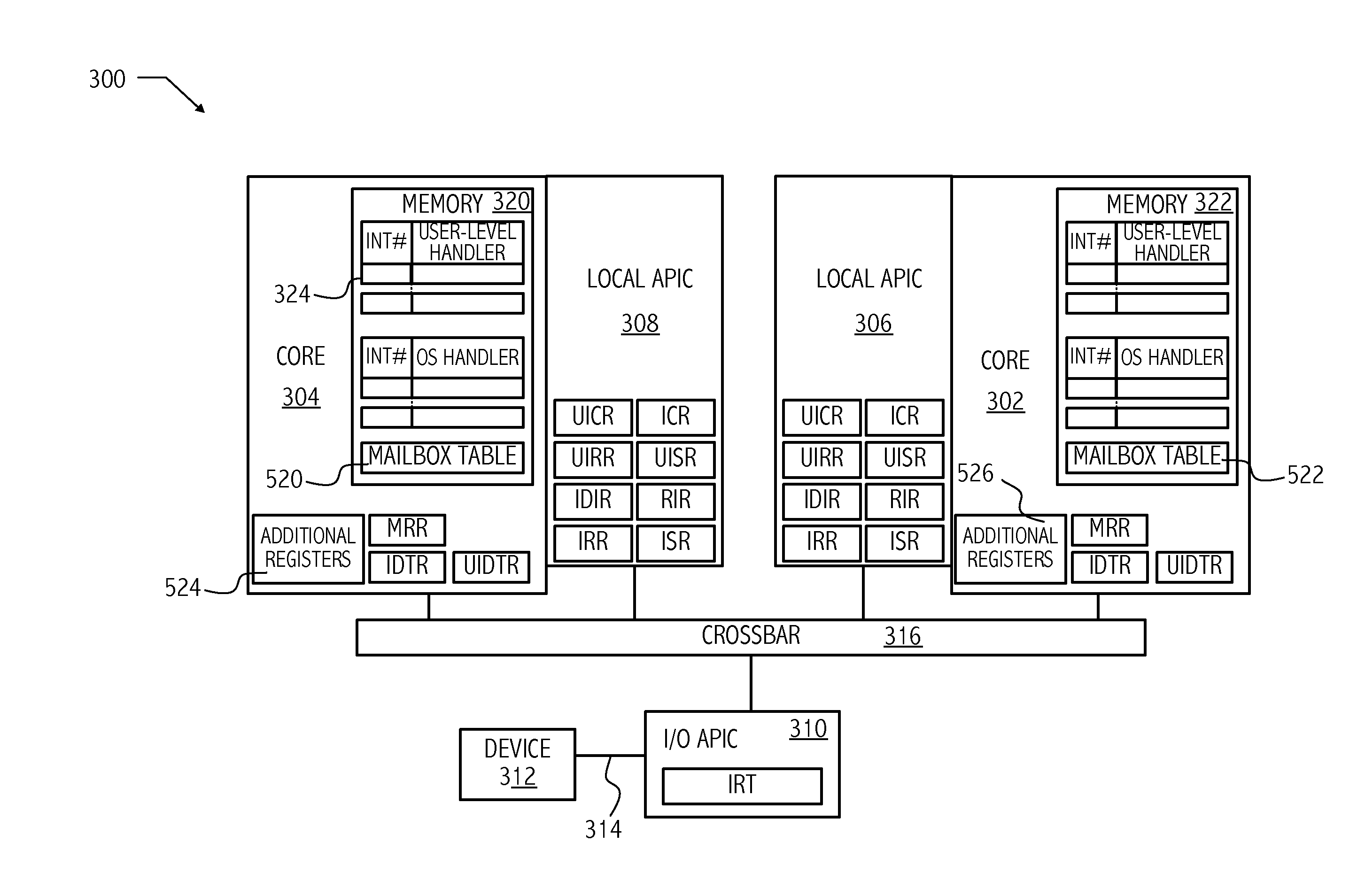

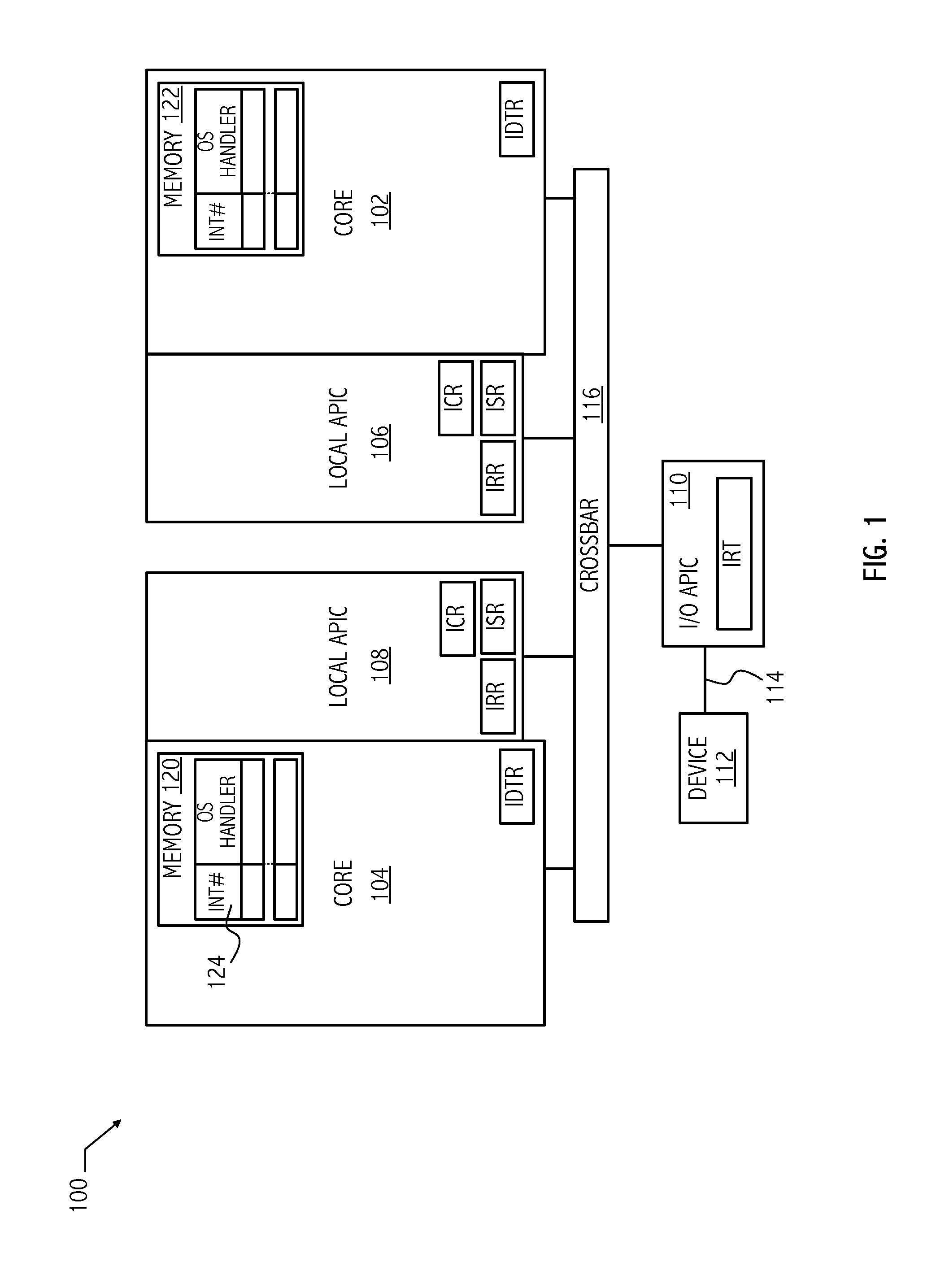

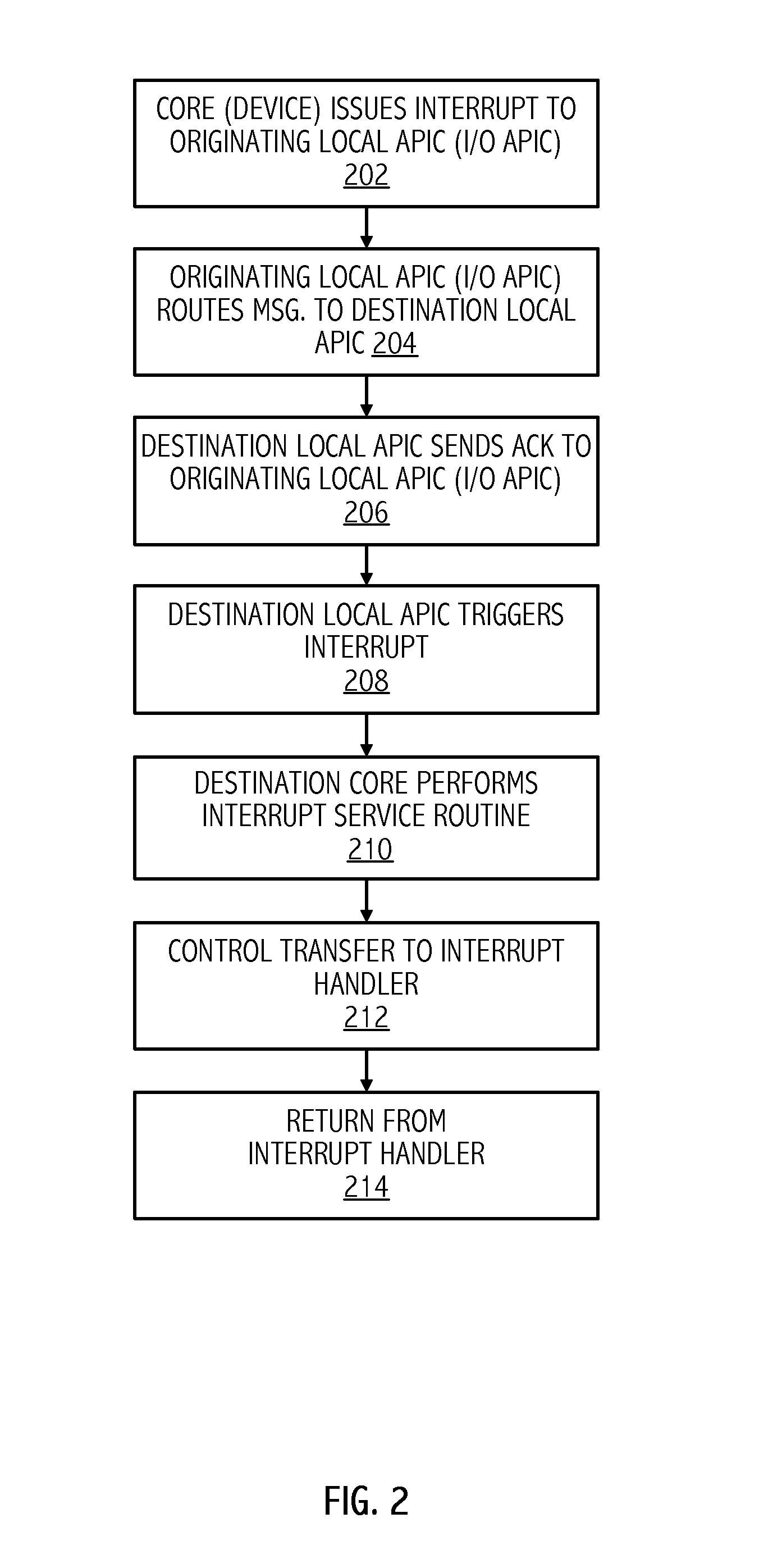

User-level interrupt mechanism for multi-core architectures

ActiveUS20110040913A1Program initiation/switchingData switching networksMulticore architectureMulticore systems

A method includes accepting for a first processor core of a plurality of processor cores in a multi-core system, a user-level interrupt indicated by a user-level interrupt message when an interrupt domain of an application thread executing on the first processor core and a recipient identifier of the application thread executing on the first processor core match corresponding fields in the user-level interrupt message.

Owner:ADVANCED MICRO DEVICES INC

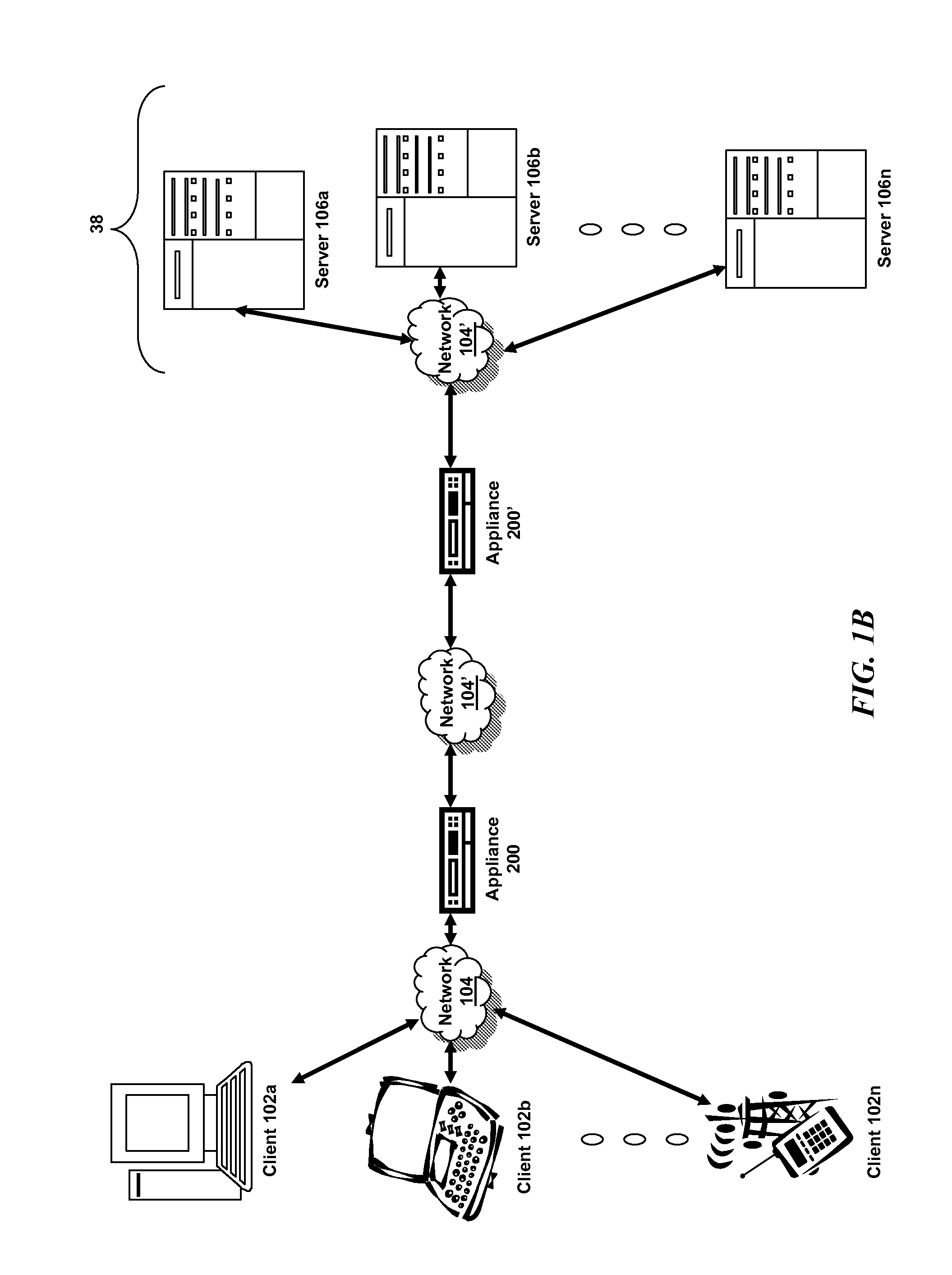

Systems and methods for packet steering in a multi-core architecture

InactiveUS8009682B2Reduces unnecessary copying and cachingSpeed up the flowError preventionTransmission systemsMulticore architectureNetwork packet

Described herein is a method and system for distributing whole and fragmented requests and responses across a multi-core system. Each core executes a packet engine that further processes data packets and data packet fragments allocated to that core. A flow distributor executing within the multi-core system forwards client requests to a packet engine on a core that is selected based on a value generated when a hash is applied to a tuple comprising a client IP address, a client port, a server IP address and a server port identified in the request. The packet engine maintains each element of the tuple and forwards the request to the selected core. The packet engine can also process data packet fragments by assembling the fragments prior to transmitting them to the selected core, or by transmitting the data packet fragments to the selected core.

Owner:CITRIX SYST INC

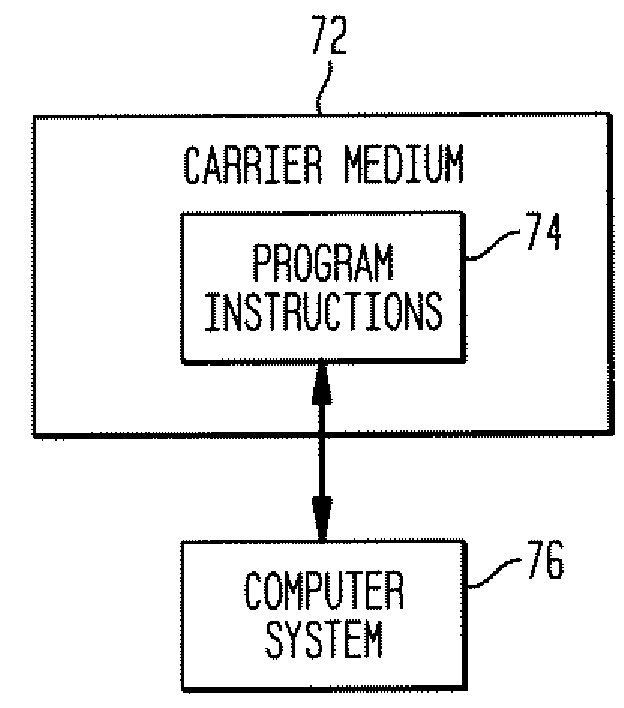

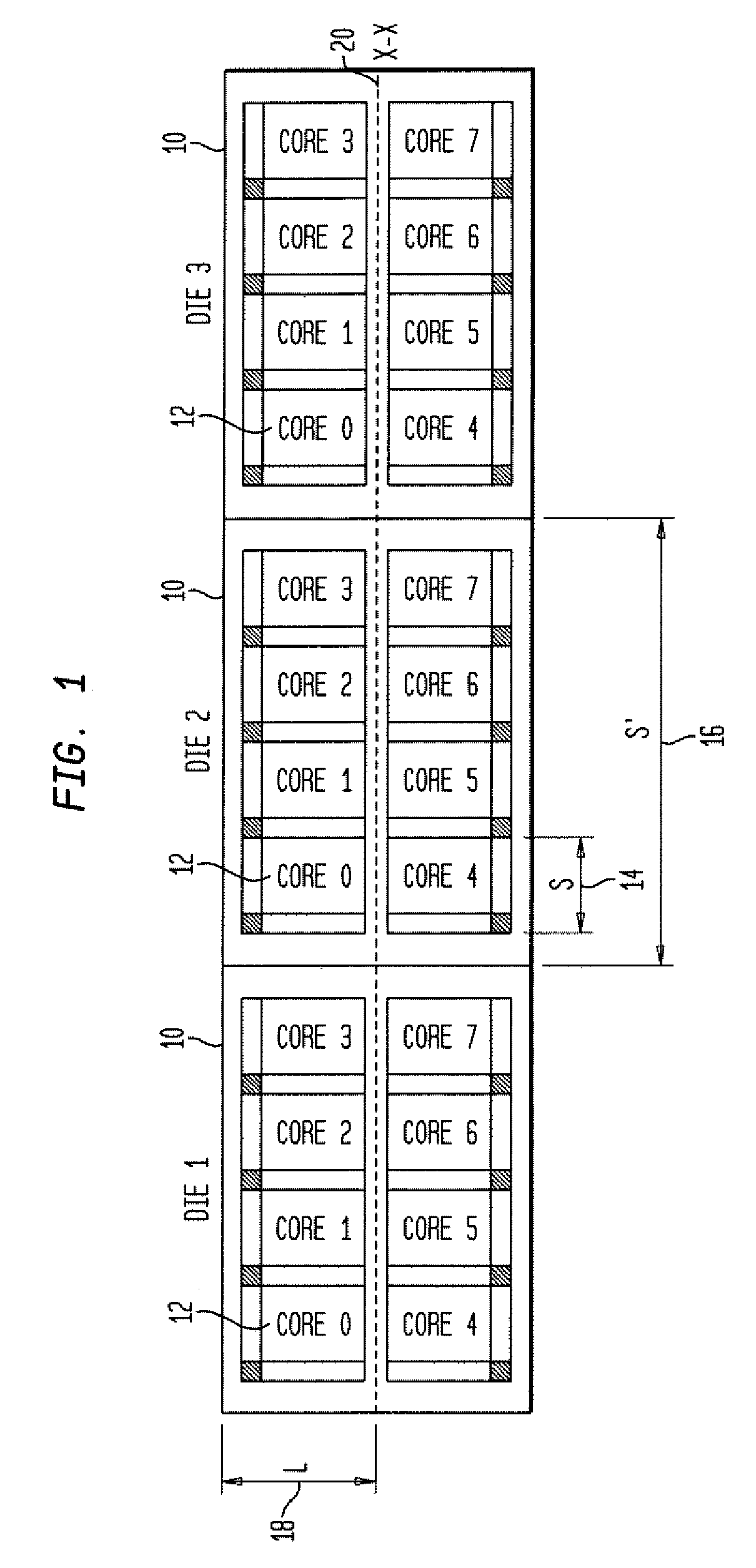

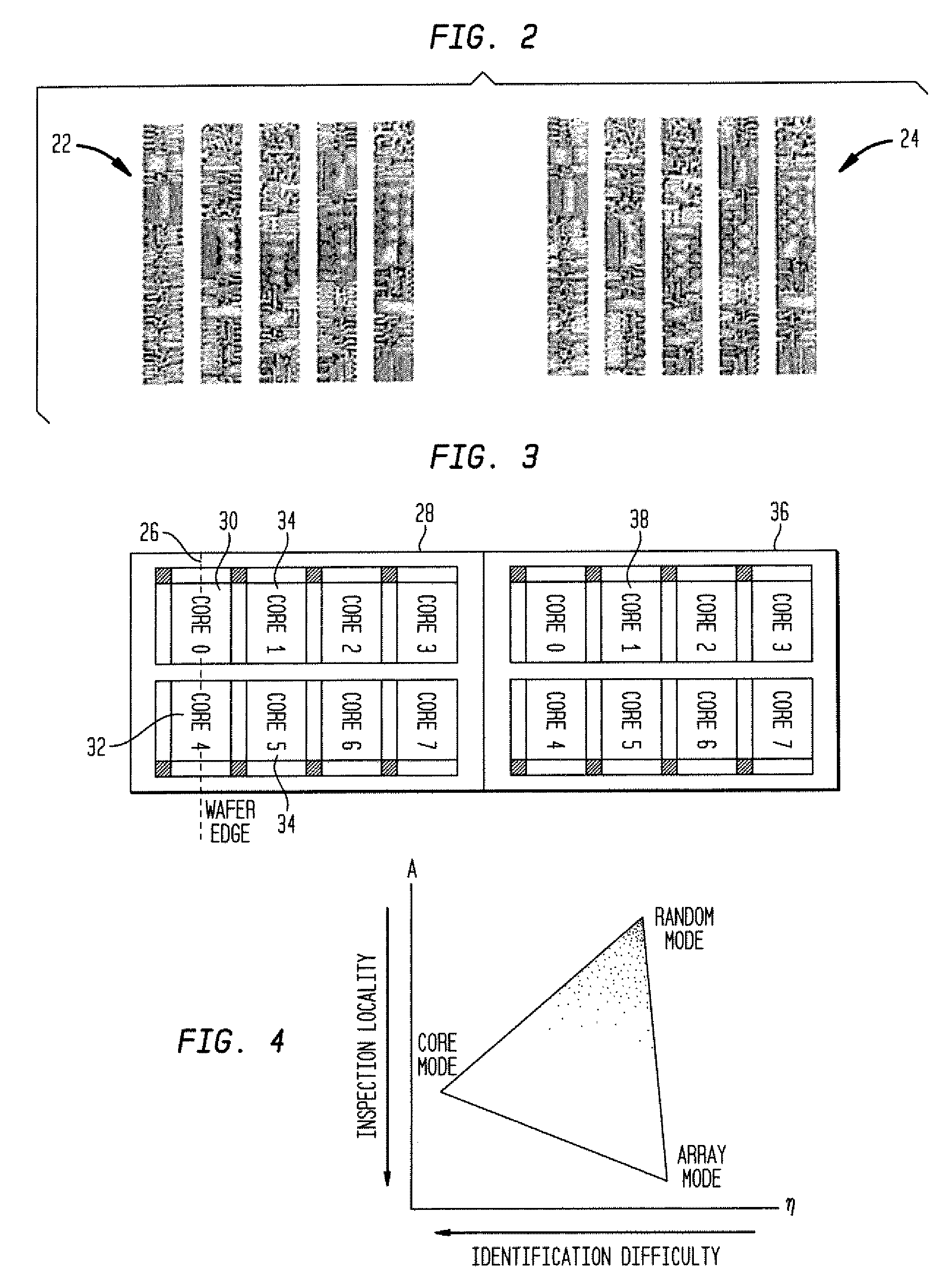

Computer-implemented methods, carrier media, and systems for detecting defects on a wafer based on multi-core architecture

ActiveUS20080306701A1Photometry using reference valueImage analysisMulticore architectureEngineering

Computer-implemented methods, carrier media, and systems for detecting defects on a wafer based on multi-core architecture are provided. One computer-implemented method for detecting defects on a wafer includes acquiring output for the wafer generated by an inspection system. Dies are formed on the wafer, and multiple cores are formed in the dies. The method also includes detecting defects on the wafer by comparing the output for a first of the multiple cores to the output for a second of the multiple cores. The first and second of the multiple cores are formed in the same die, different dies, or the same die and different dies.

Owner:KLA TENCOR TECH CORP

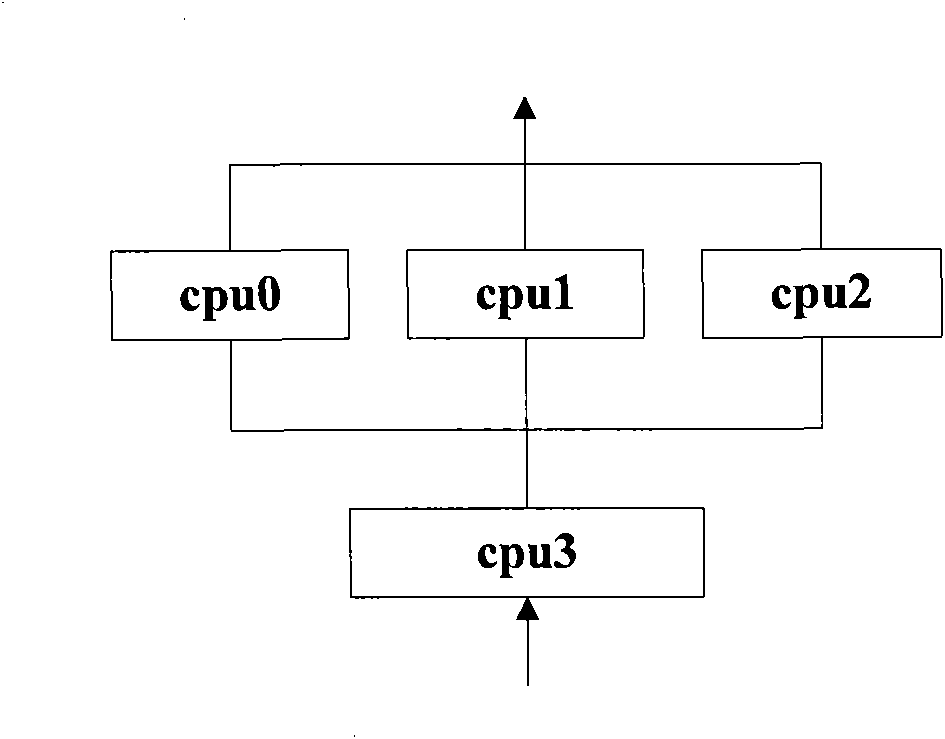

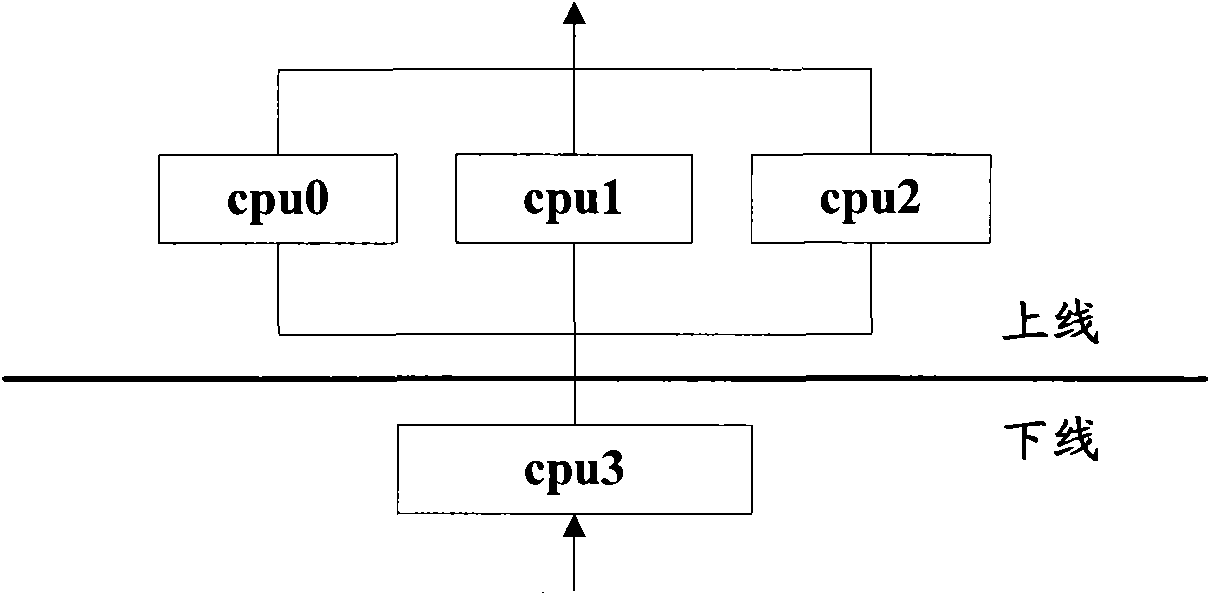

Method for building multi-core operating environment

ActiveCN101770401ARealize comprehensive utilizationEfficient wayResource allocationData switching networksData streamMulticore architecture

The invention provides a method for a building multi-core operating environment, which is characterized in that: a plurality of pieces of cpu are divided into two groups in advance, wherein one group is on-line cpu which operates a standard Linux operating system for checking message content, and the other group is an off-line cpu for operating a specified target code; when all cpu relevant resource finishes initializing, parts of on-line cpu become the off-line cpu; the off-line cpu operates one endless loop function cpu_idle so as to embed the code inlet function of a specified target into the endless loop function cpu_idle; the off-line cpu operates the specified target code to classify and distribute received network message to the corresponding on-line cpu according to data flow. Theinvention can solve the problem that cpu cost sharp increases along with the increase of cpu amount under the Linux environment and provides a new efficient path for multi-core framework development.

Owner:BEIJING TOPSEC NETWORK SECURITY TECH

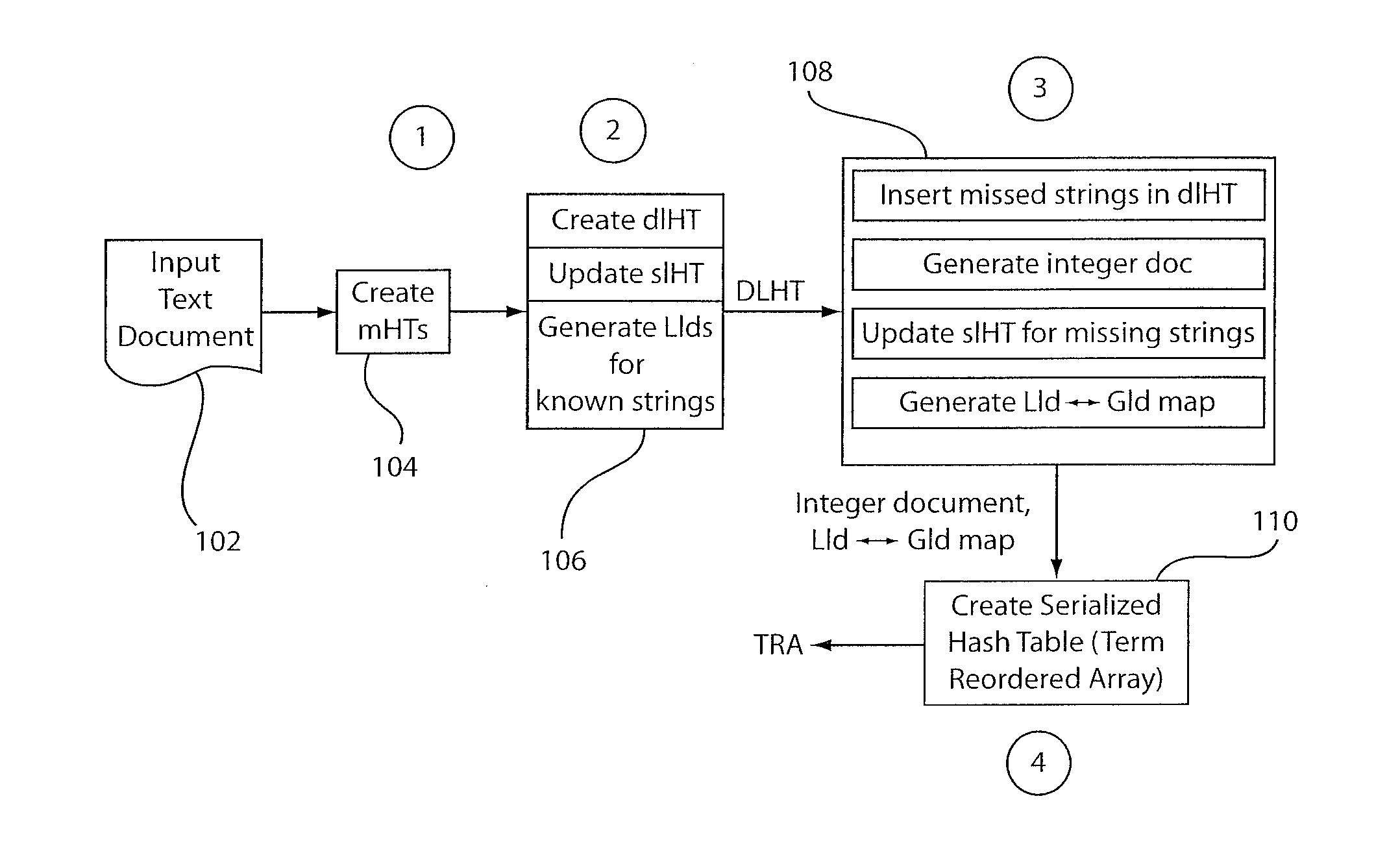

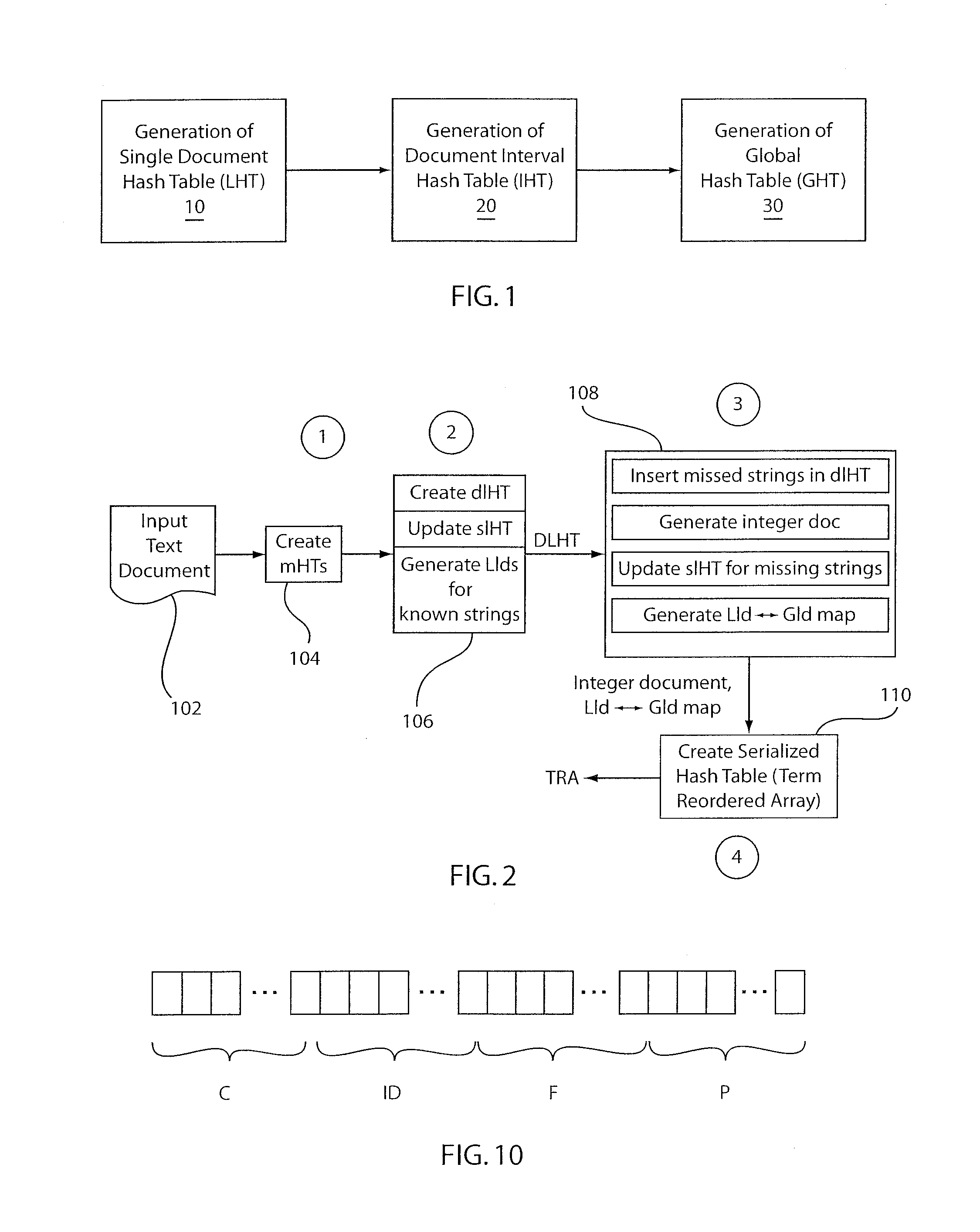

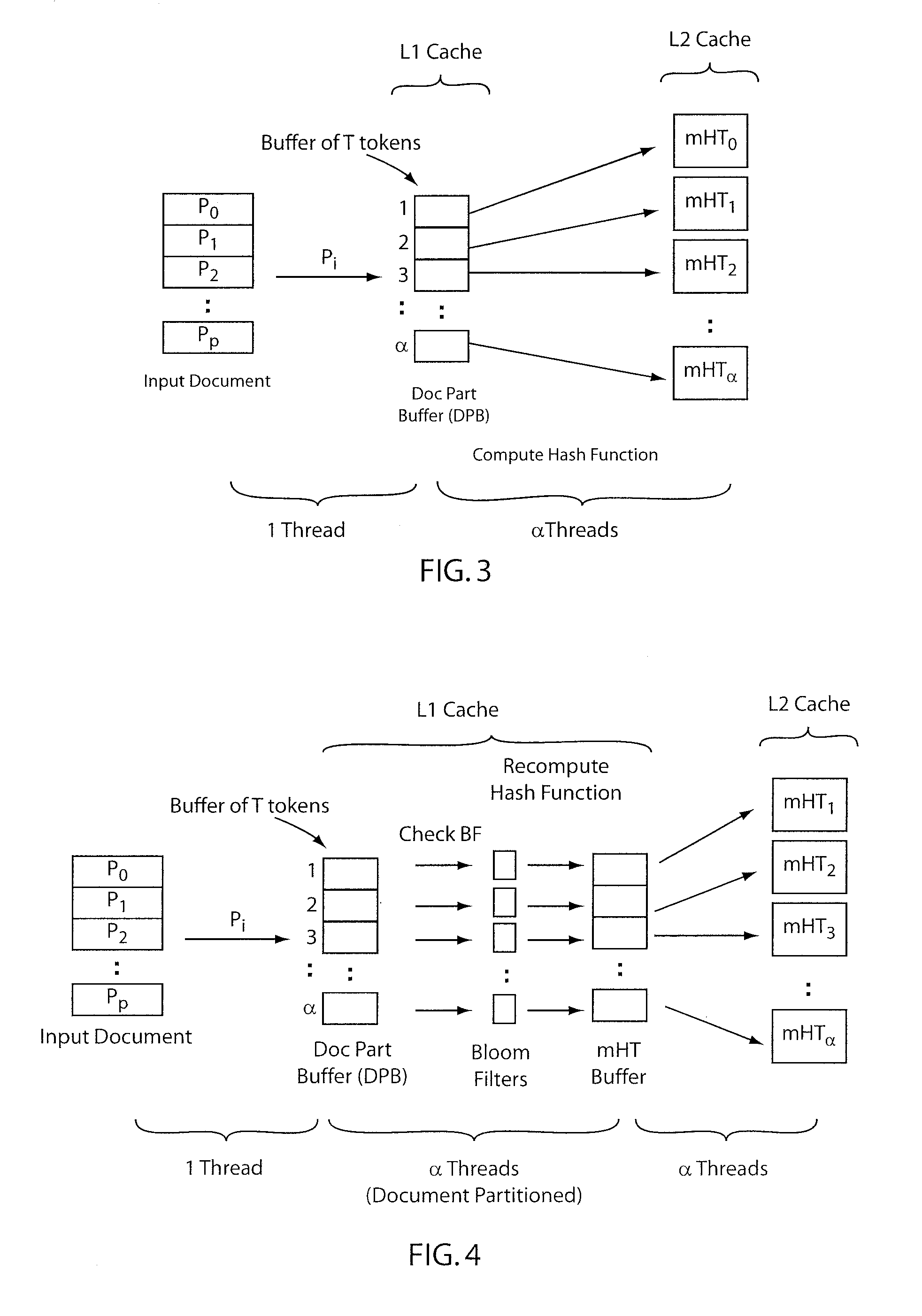

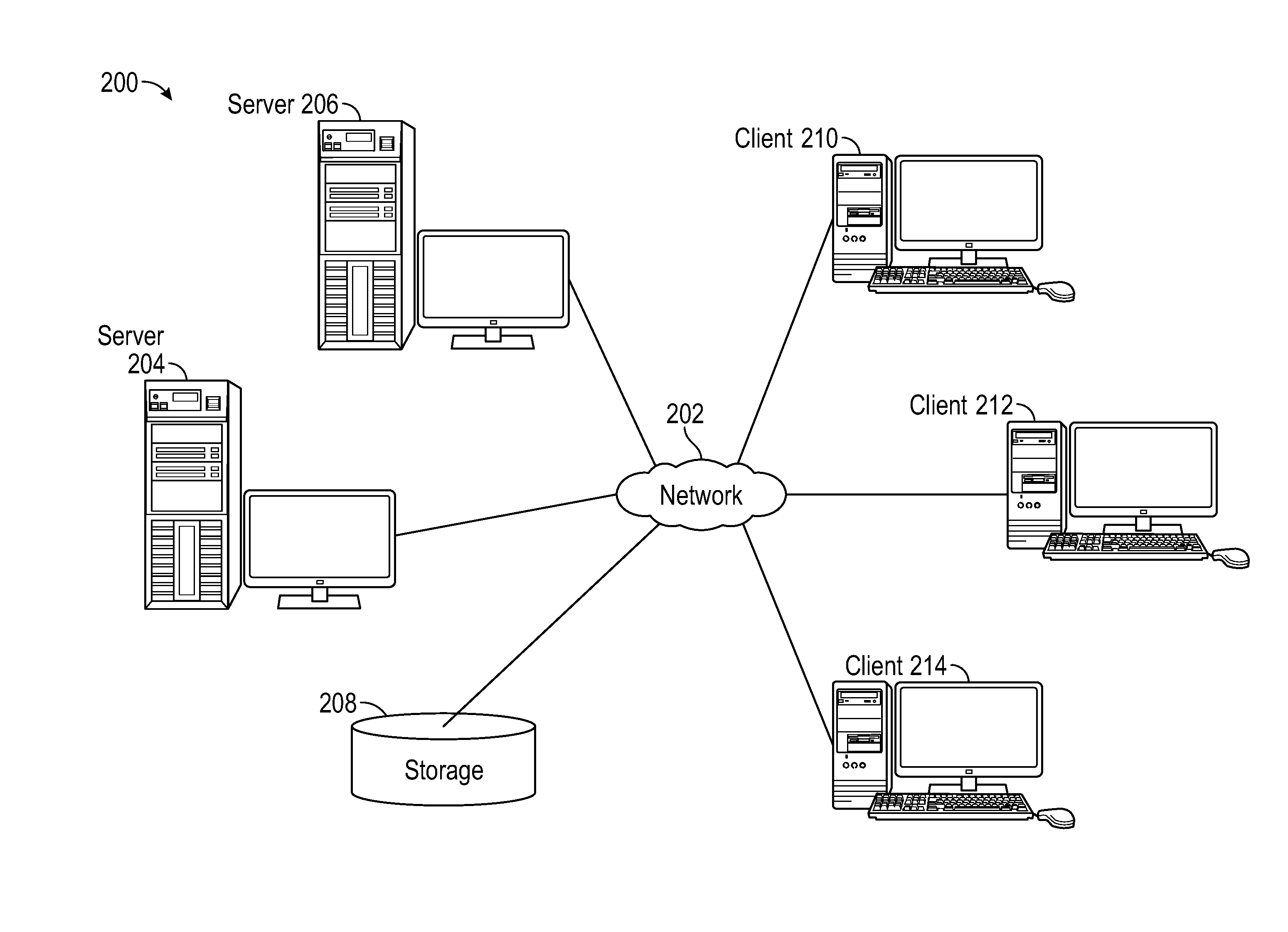

System and method for multithreaded text indexing for next generation multi-core architectures

InactiveUS20110252033A1Cutting synchronizationDigital data information retrievalDigital data processing detailsArray data structureDocumentation

A system and method for indexing documents in a data storage system includes generating a single document hash table in storage memory for a single document using an index construction in a multithreaded and scalable configuration wherein multiple threads are each assigned work to reduce synchronization between threads. The single document hash table includes partitioning the single document and indexing strings of partitioned portions of the single document to create a minor hash table for each document sub-part; generating a document level hash table from the minor hash tables; updating a stream level hash table for the strings which maps every string to a global identifier; and generating a term reordered array from the document level hash table.

Owner:IBM CORP

Packet capture engine for commodity network interface cards in high-speed networks

ActiveUS20160127276A1Better able to addressDigital computer detailsData switching networksZero-copyMulticore architecture

A method, systems for a packet capture engine for commodity network interface cards (NICs) in high-speed networks that provides lossless zero-copy packet capture and delivery services by exploiting multi-queue NICs and multicore architectures. The methods, systems include a ring-buffer-pool mechanism and a buddy-group based offloading mechanism.

Owner:FERMI RESEARCH ALLIANCE LLC

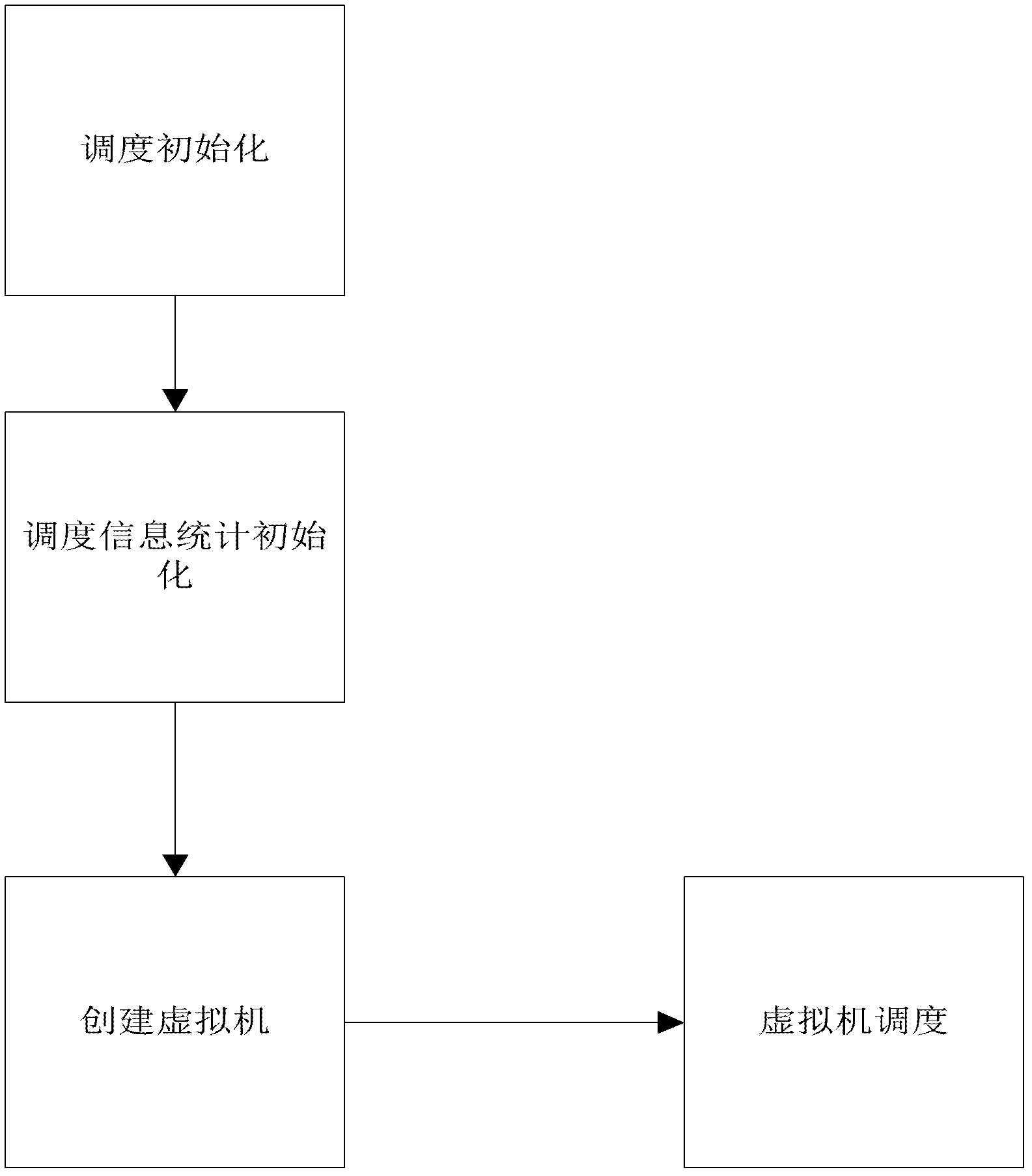

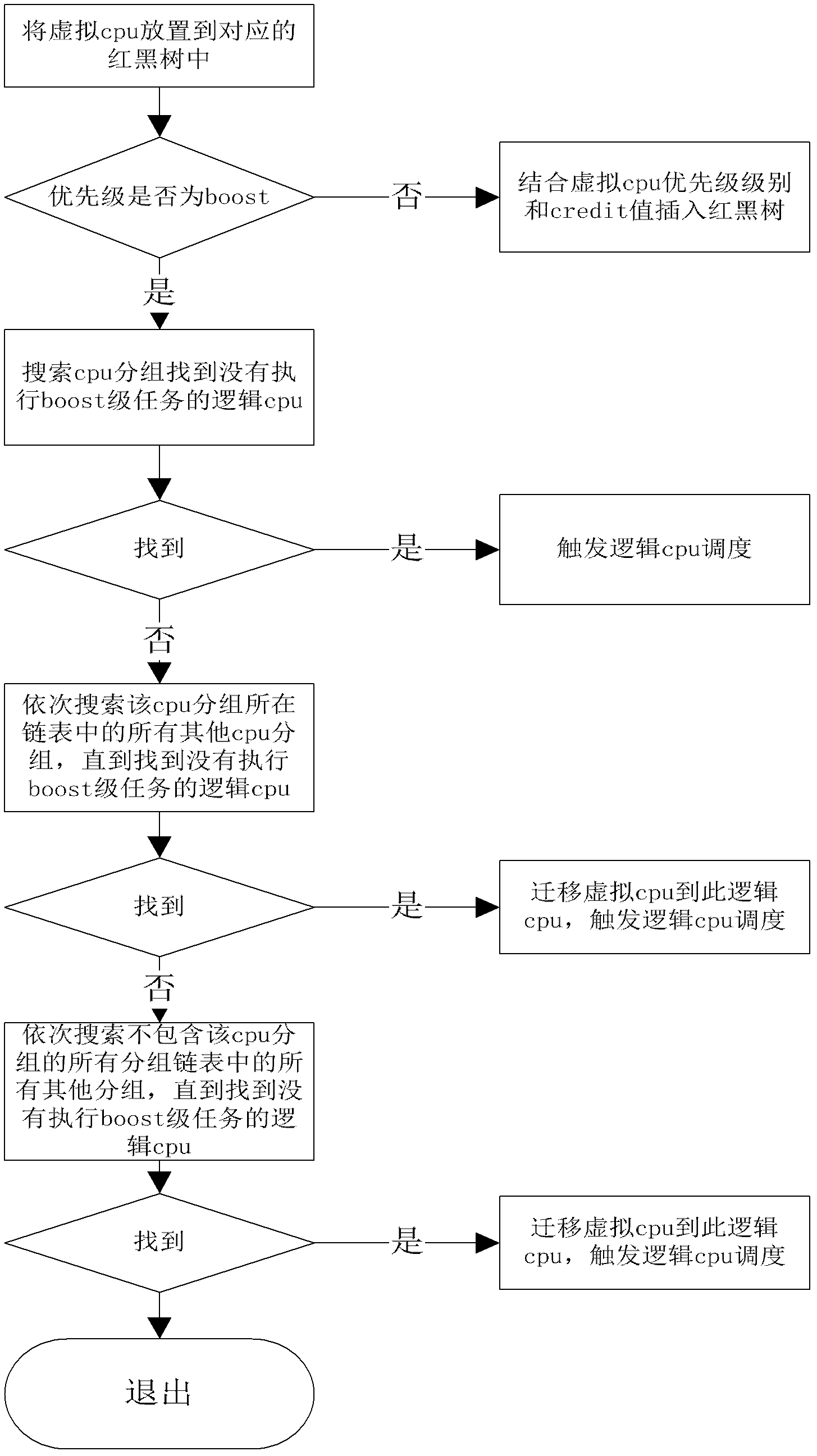

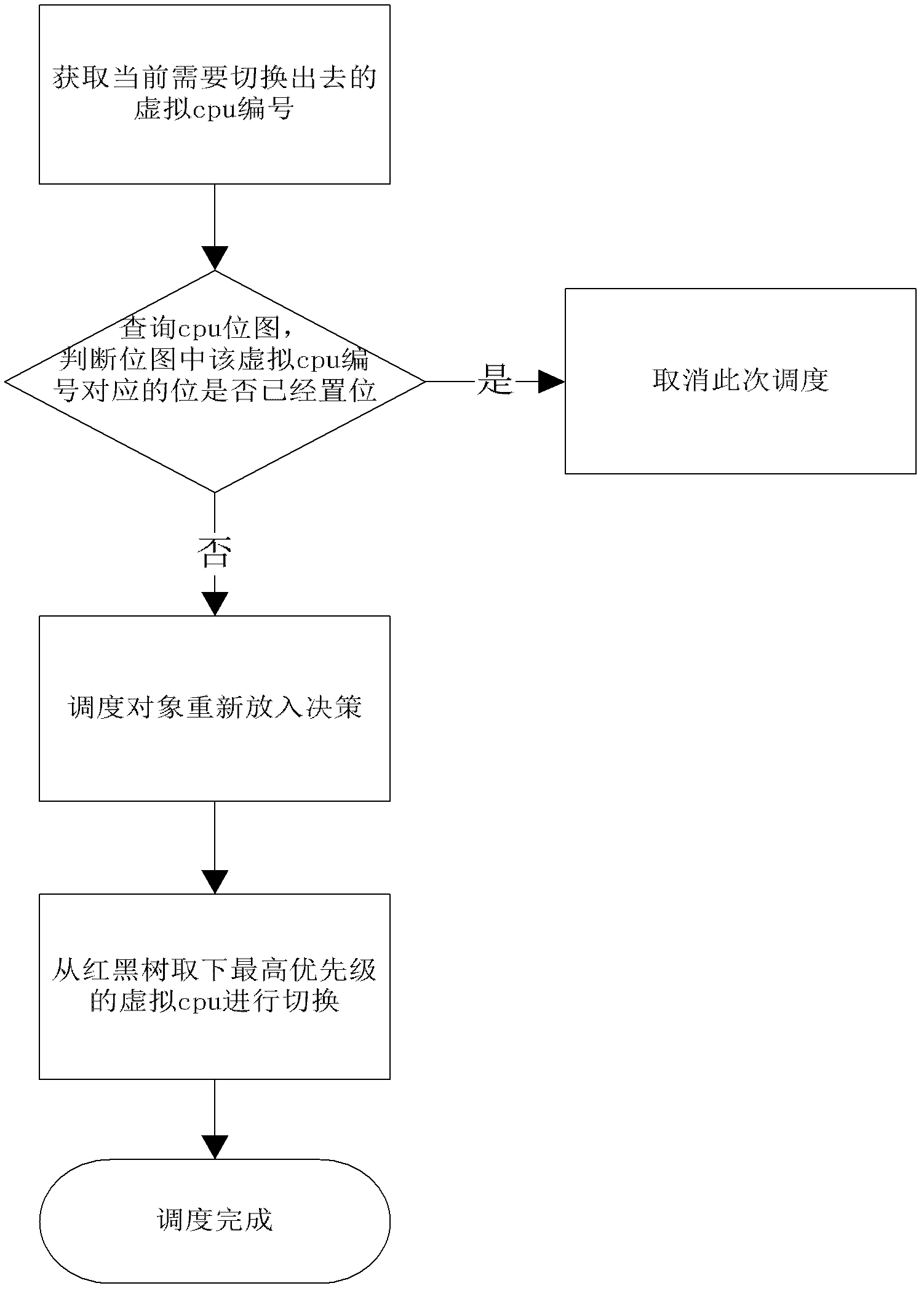

Xen virtual machine scheduling control method in multi-core environment

ActiveCN102253857AFast executionImprove performanceResource allocationSoftware simulation/interpretation/emulationMulticore architectureRed–black tree

The invention provides an Xen virtual machine scheduling control method in multi-core environment. The method comprises the following steps: (I) carrying out scheduling initialization; (II) carrying out initialization of scheduling information statistics, namely monitoring the virtual CPU (central processing unit) in a management domain 0, and sending the monitoring result to a VMM (virtual machine monitor) in real time; (III) creating a virtual machine, allocating the virtual CPU, storing the virtual CPU to a red black tree of a corresponding CPU group according to the priority level and a credit value, and starting all timers set in the initialization stage; and (IV) scheduling the virtual machine. According to the invention, the time slice executed by a logic CPU in the group can be dynamically adjusted, the time consumed by the scheduling method in the execution process is effectively reduced, relatively short response time for the IO (input / output) task is realized, and the method adapts to any type with relatively high requirement on time.

Owner:HUAZHONG UNIV OF SCI & TECH

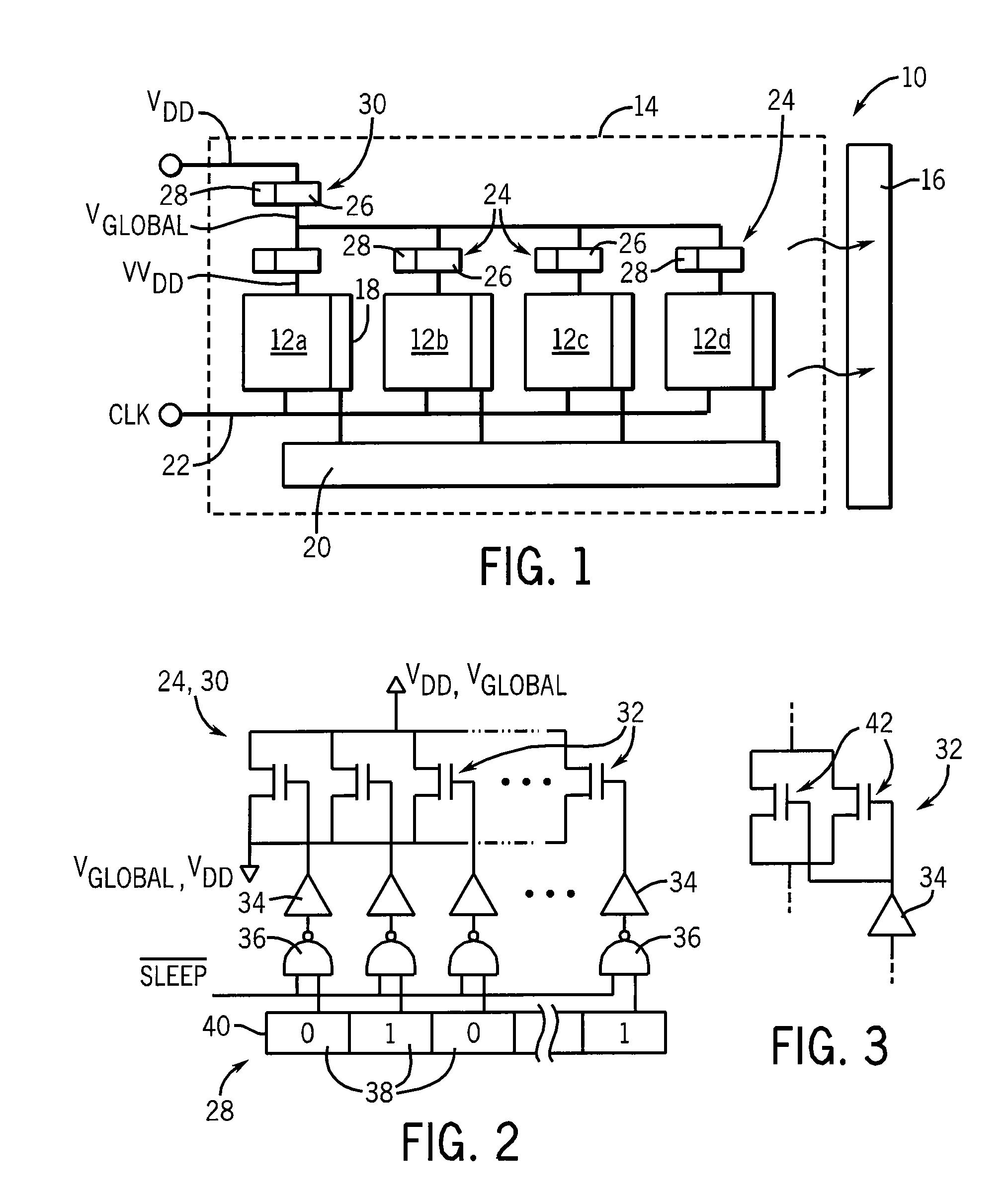

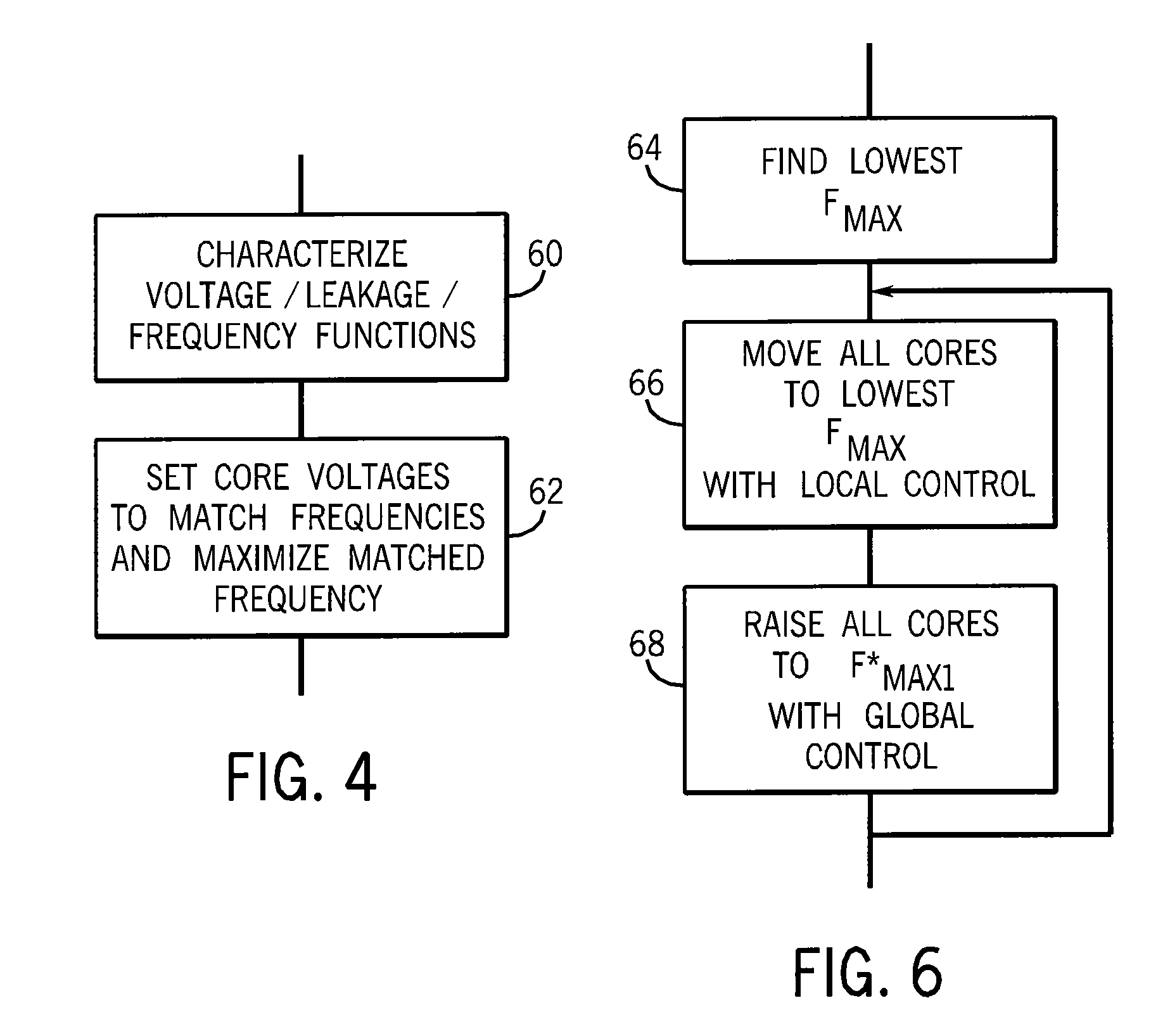

Method and Apparatus for Optimizing Clock Speed and Power Dissipation in Multicore Architectures

ActiveUS20120042176A1Reduce voltageHigh voltageEnergy efficient ICTVolume/mass flow measurementMulticore architectureEngineering

A multicore processor provides for local power control at each of the cores which is used to lower the maximum operating frequency of cores by any amount above of the maximum operating frequency of the slowest core. This power savings is then used to increase the maximum operating frequency of the frequency balanced cores within a power constraint.

Owner:WISCONSIN ALUMNI RES FOUND

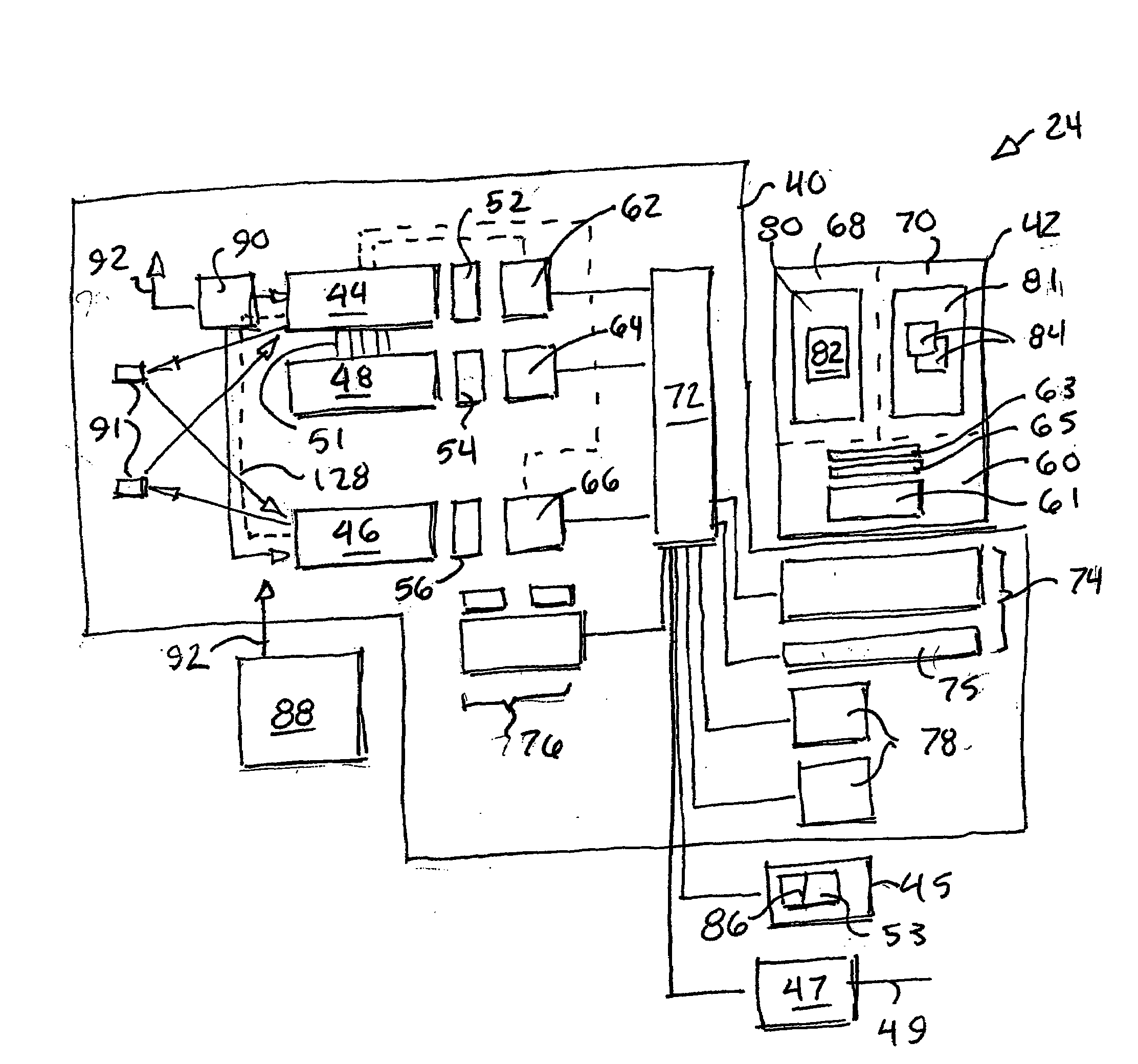

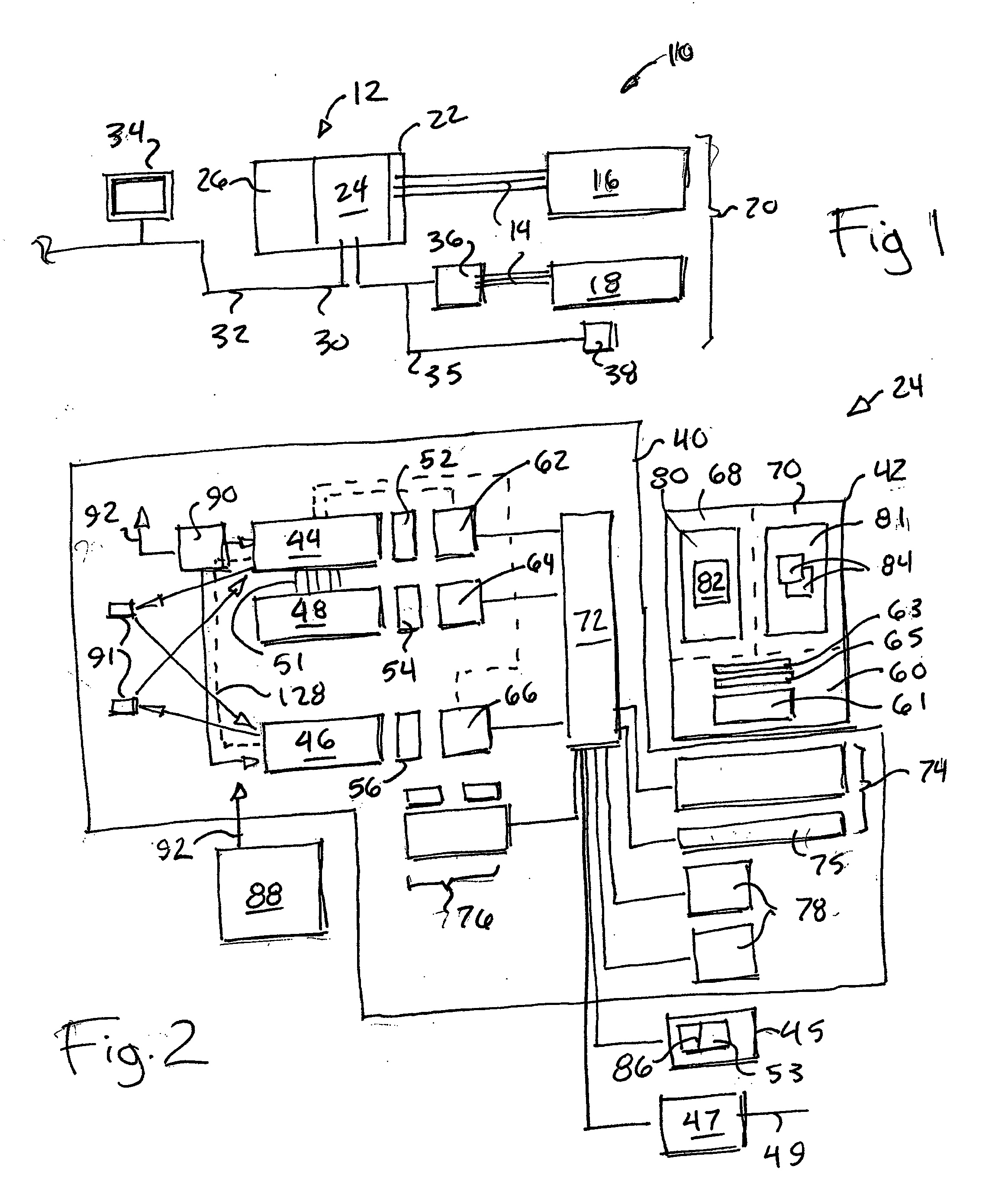

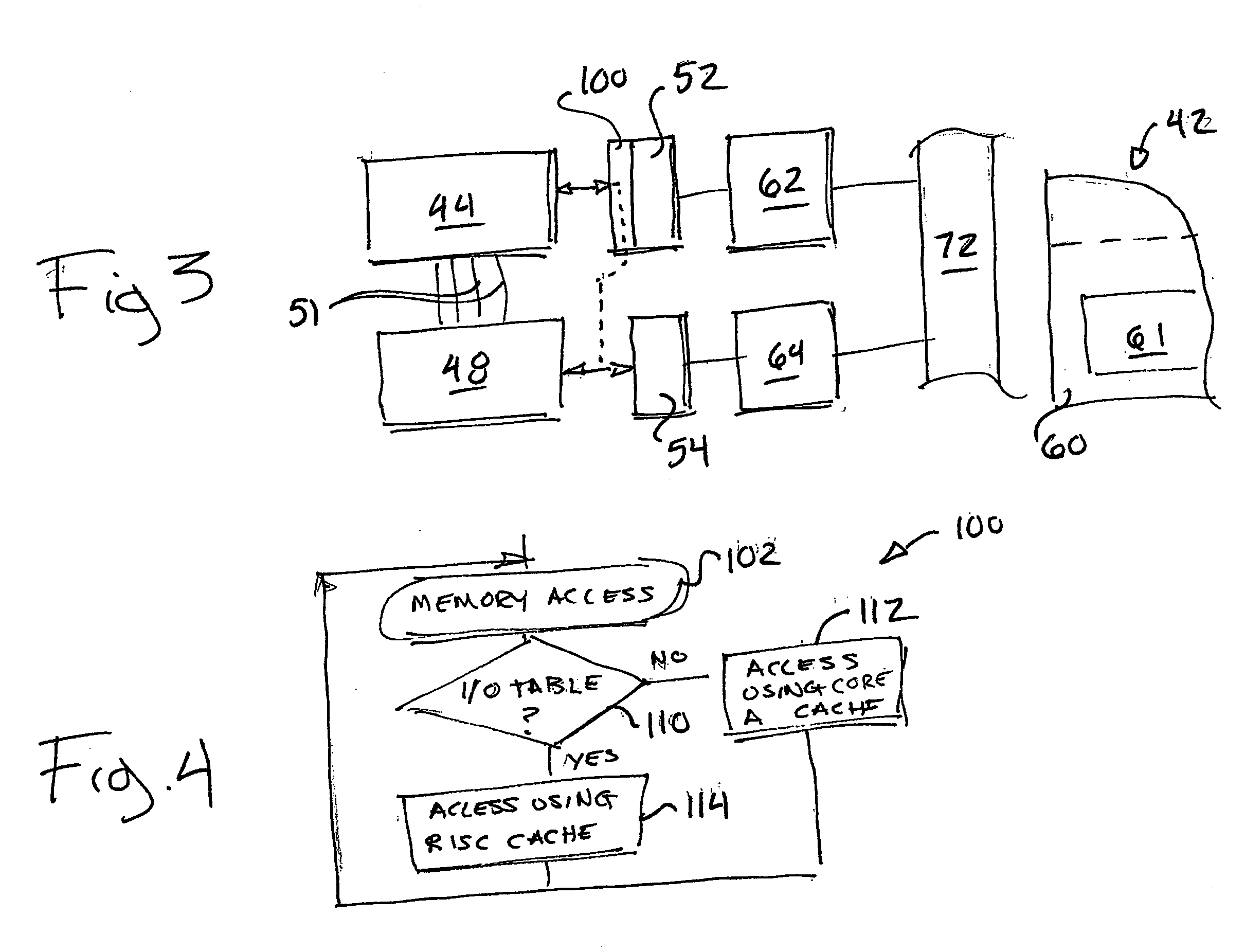

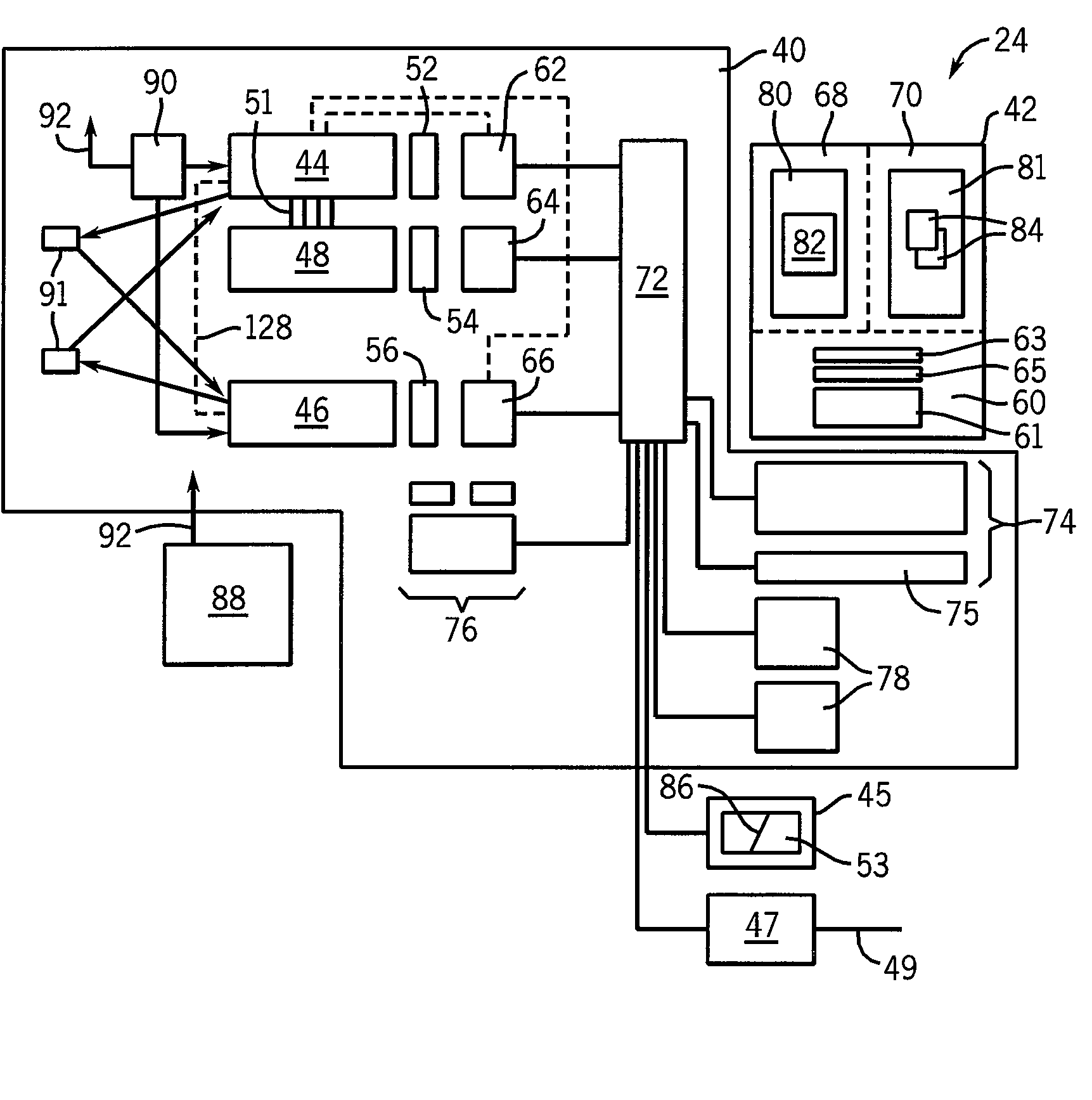

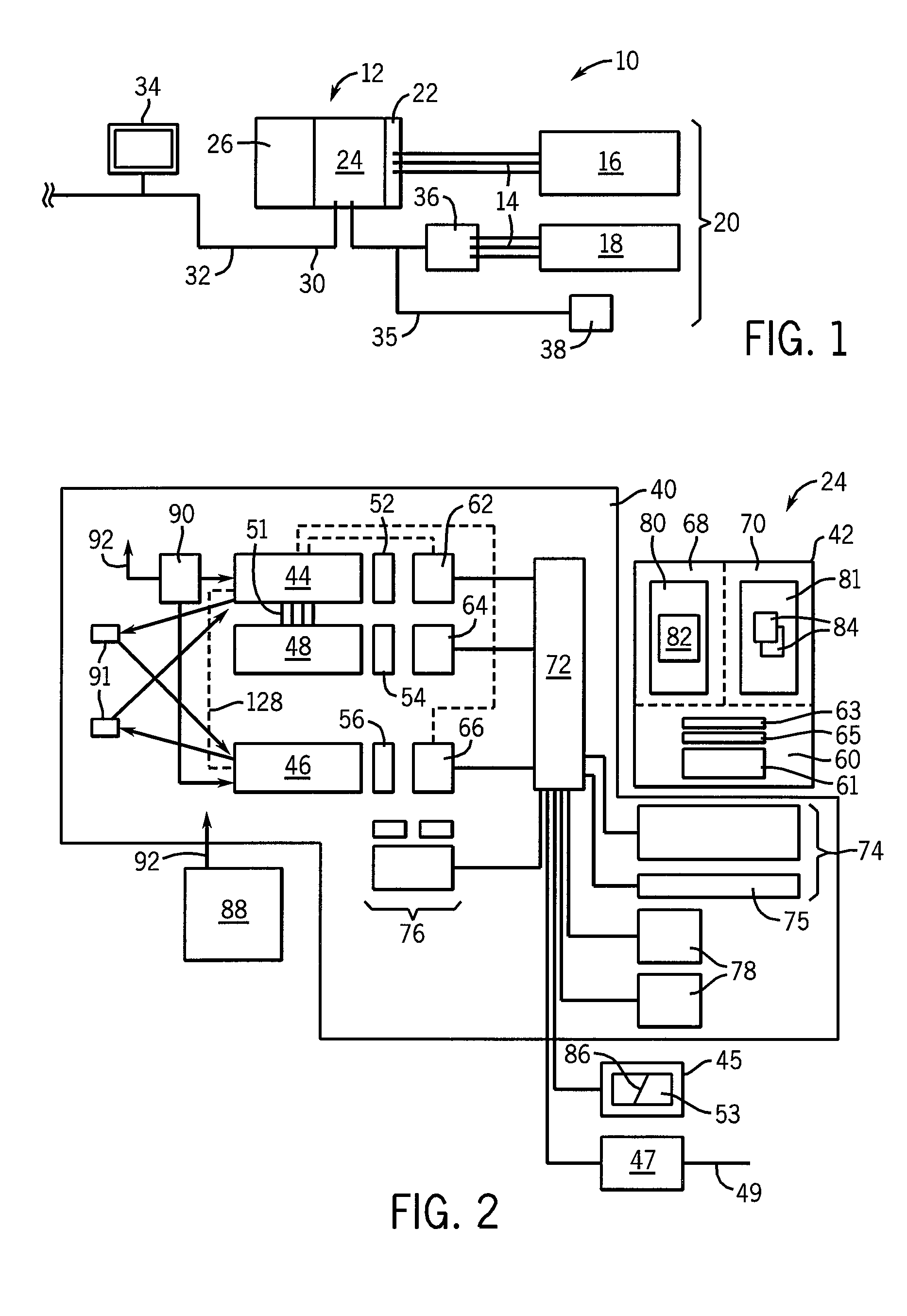

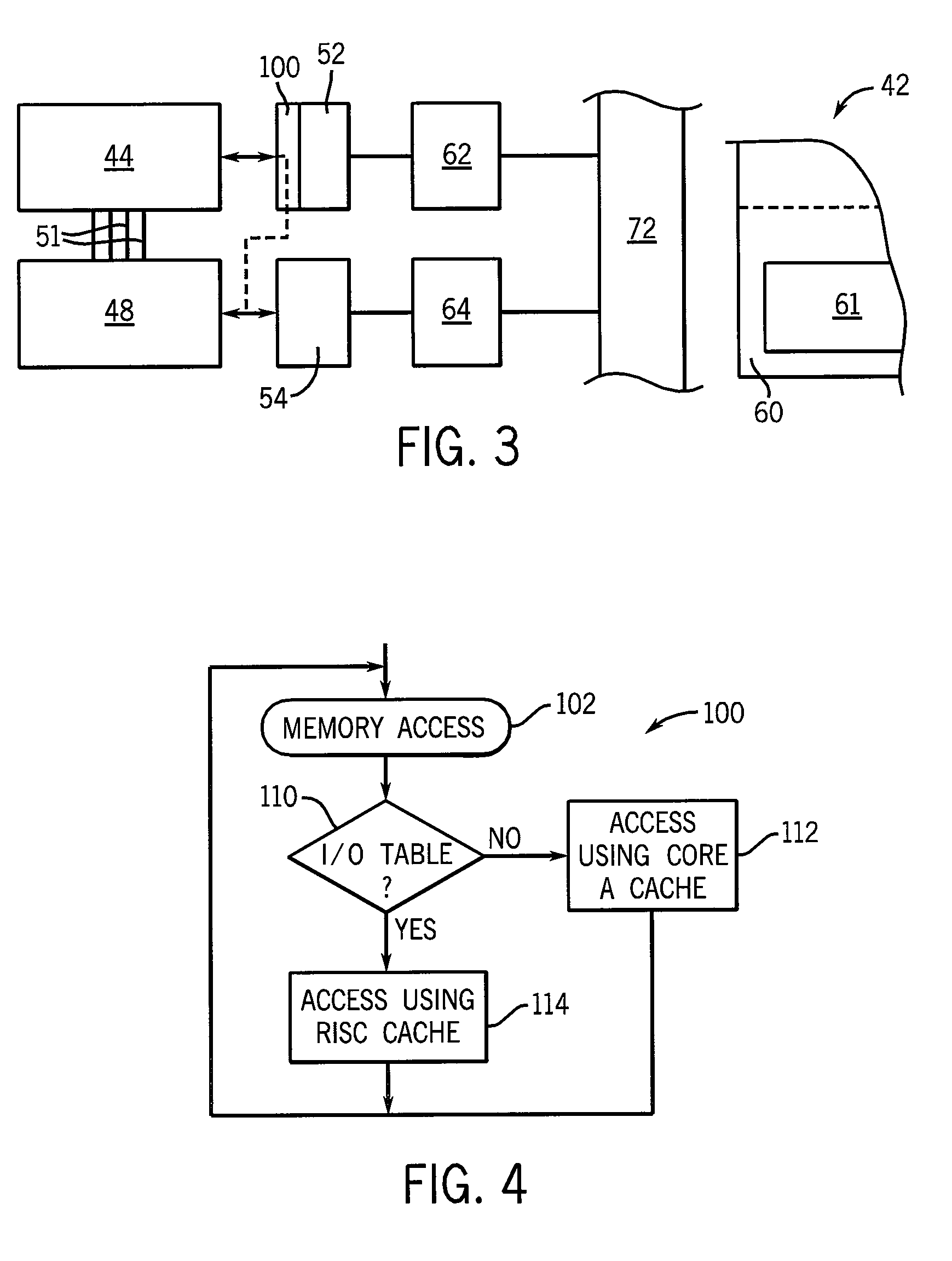

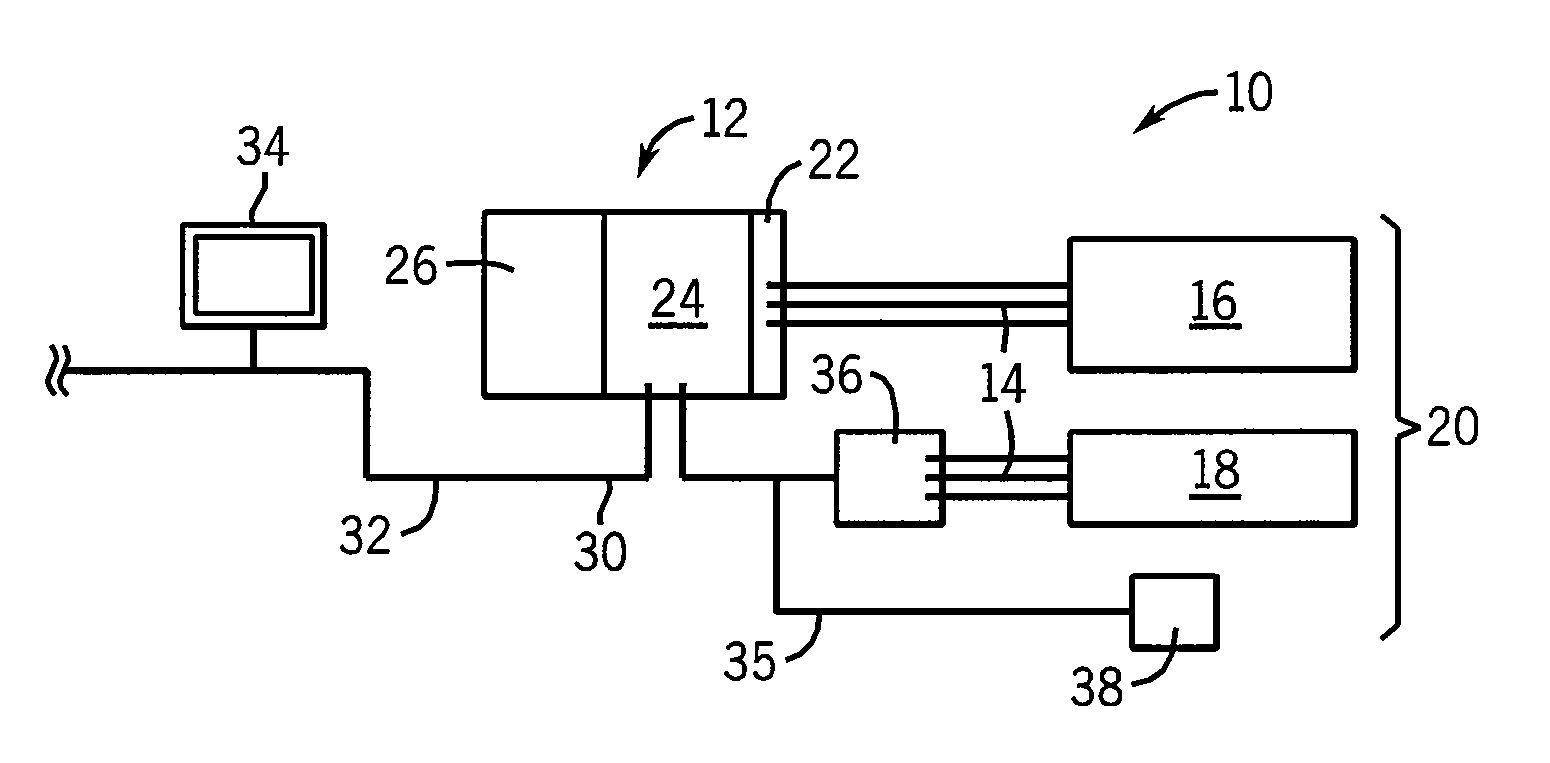

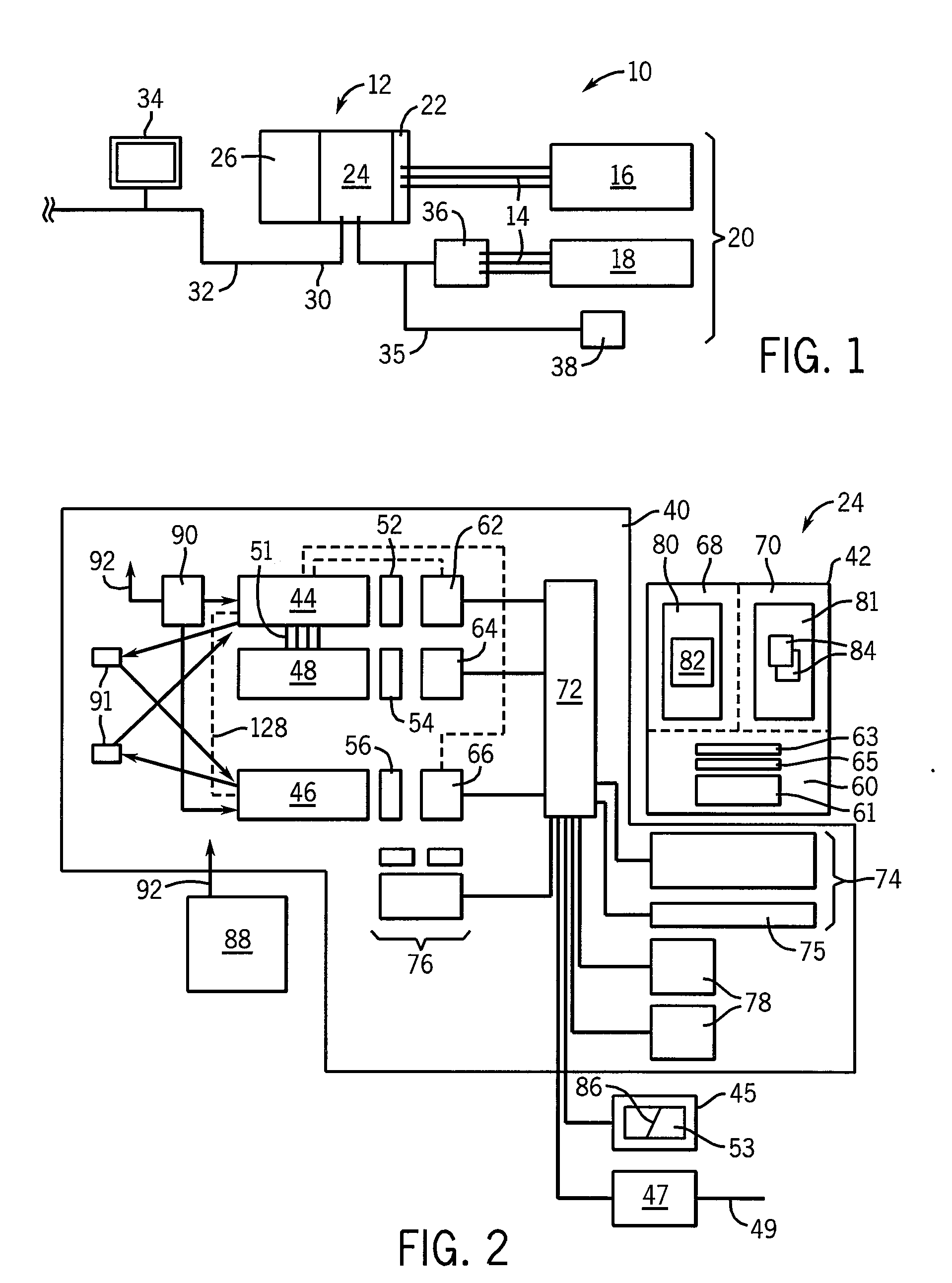

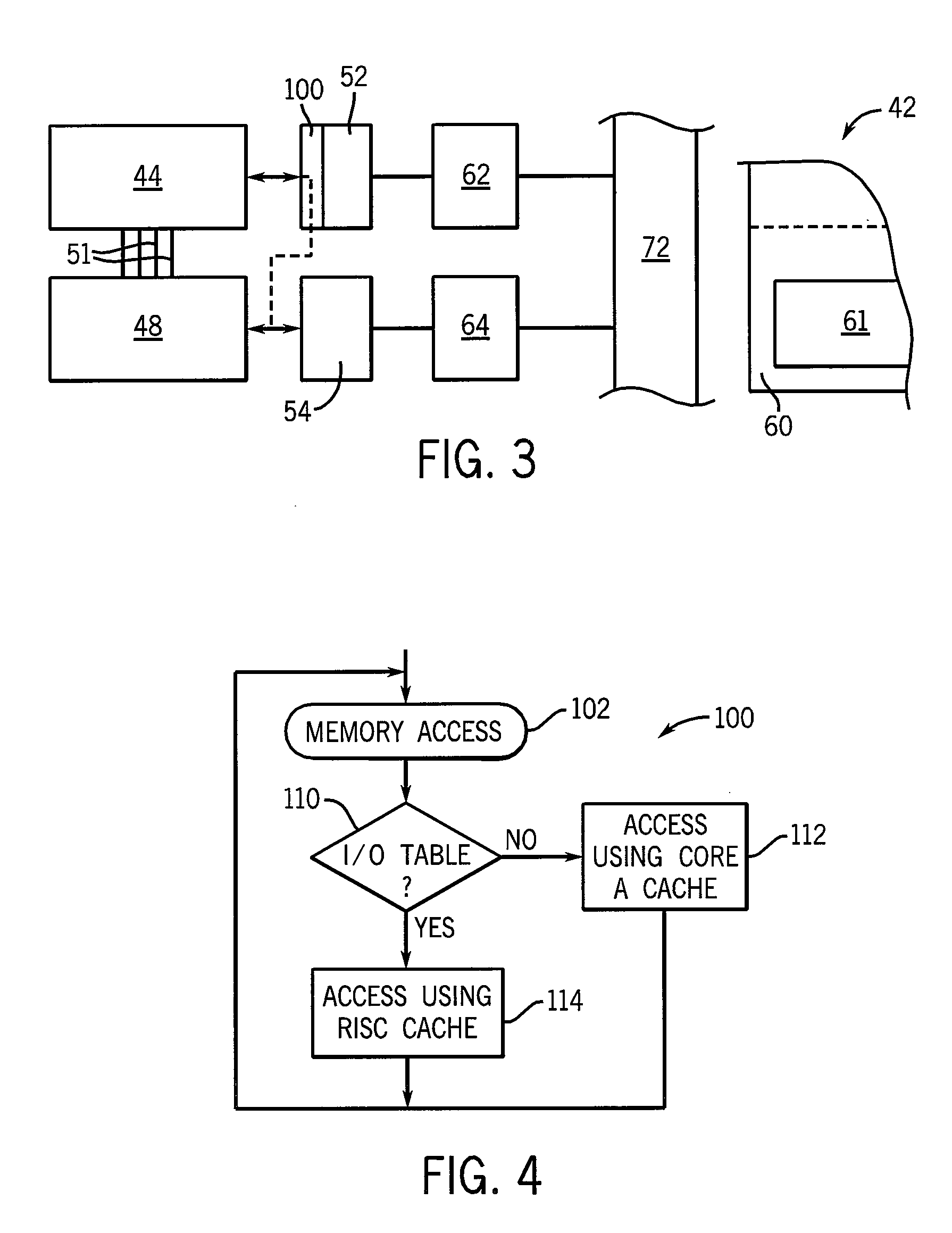

Industrial controller using shared memory multicore architecture

A multicore processor for industrial control provides for the execution of separate operating systems on the cores under control of one of the cores to tailor the operating system to optimum execution of different applications of industrial control and communication. One core may provide for a reduced instruction set for execution of industrial control programs with the remaining cores providing a general-purpose instruction set.

Owner:ROCKWELL AUTOMATION TECH

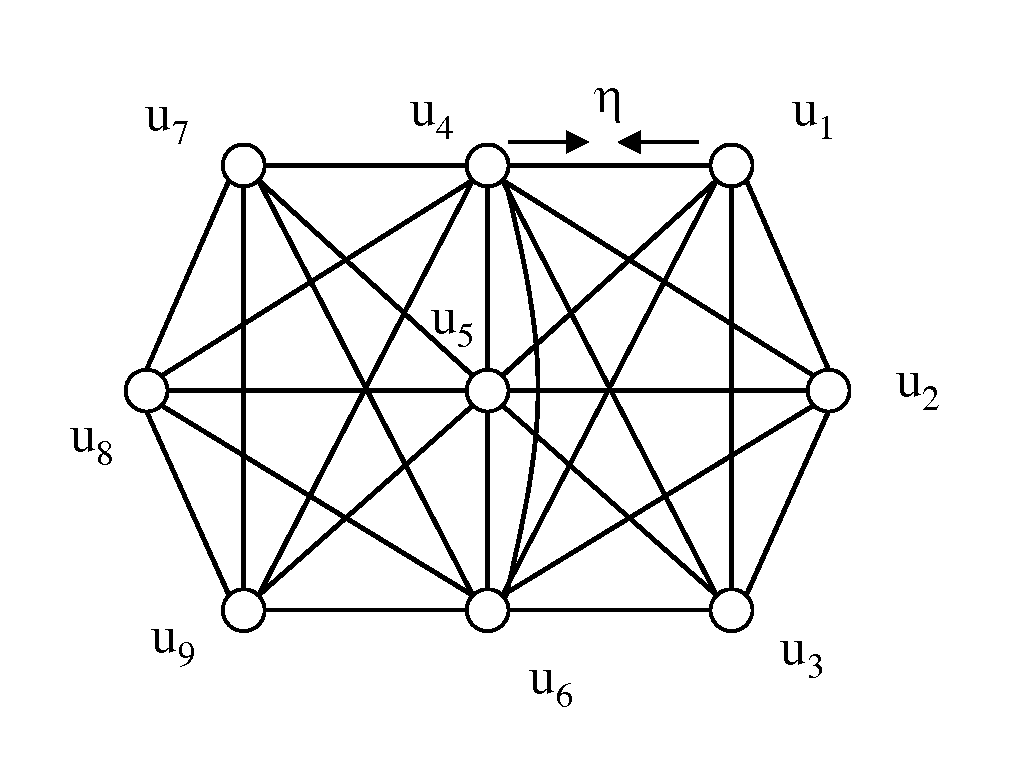

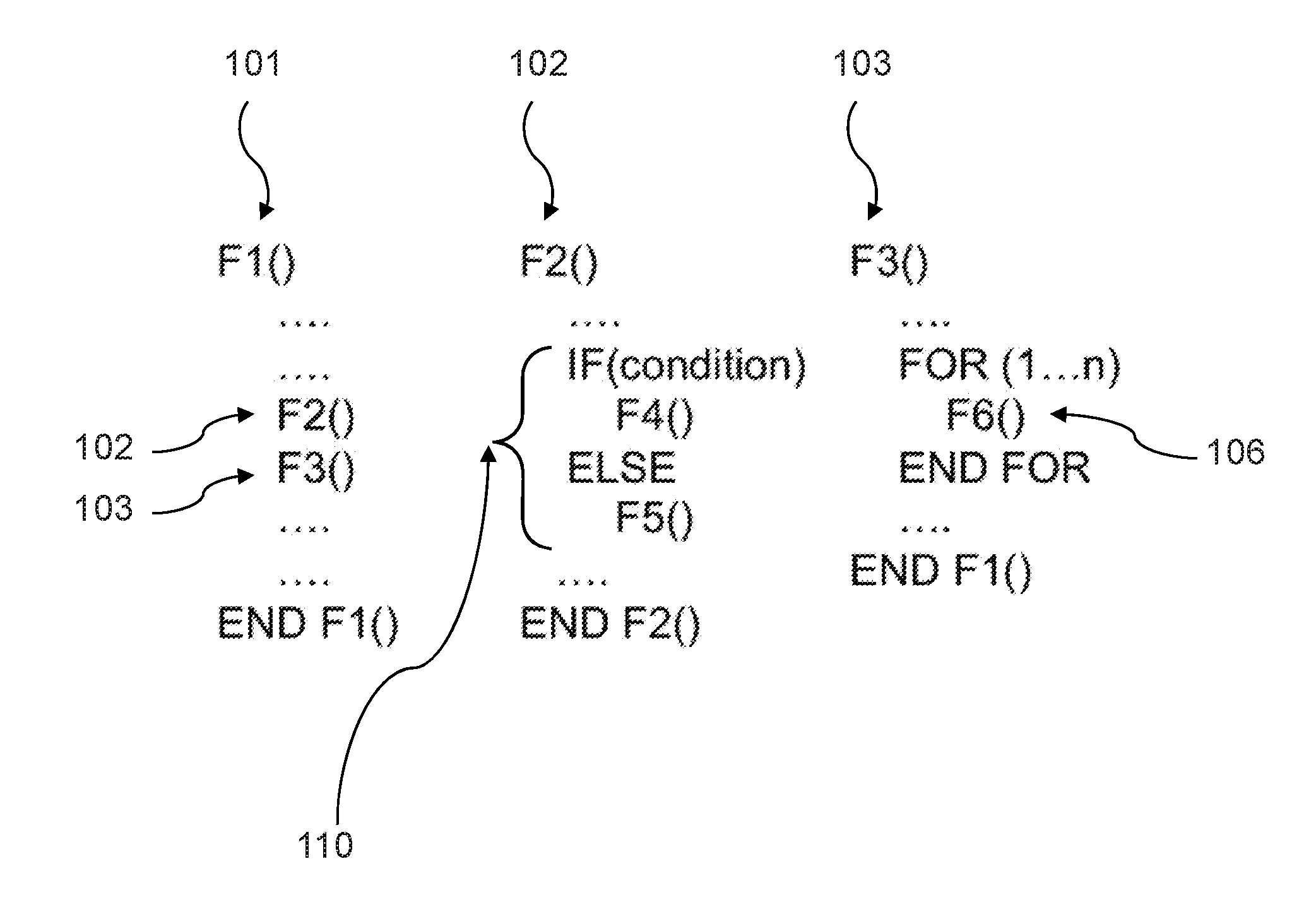

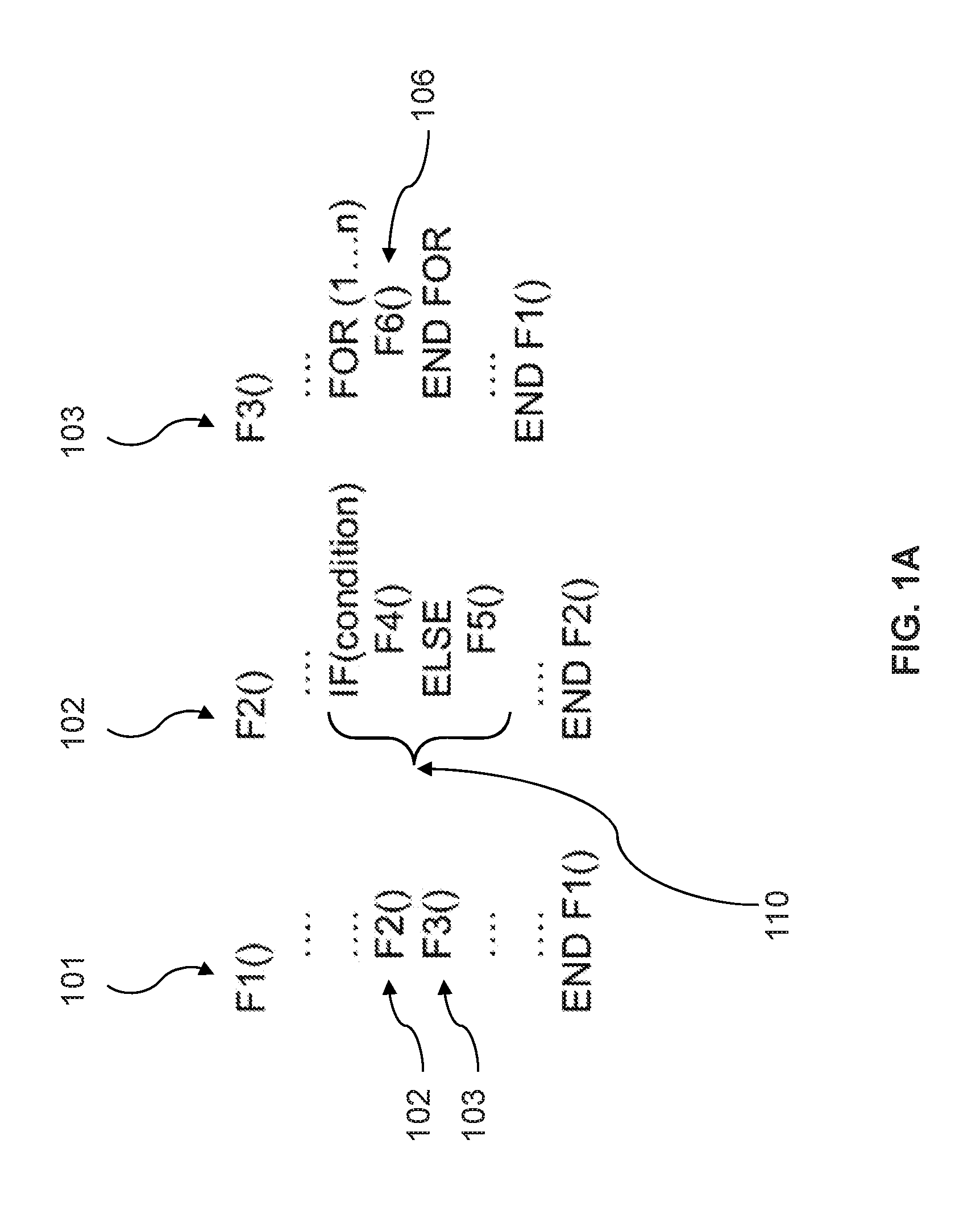

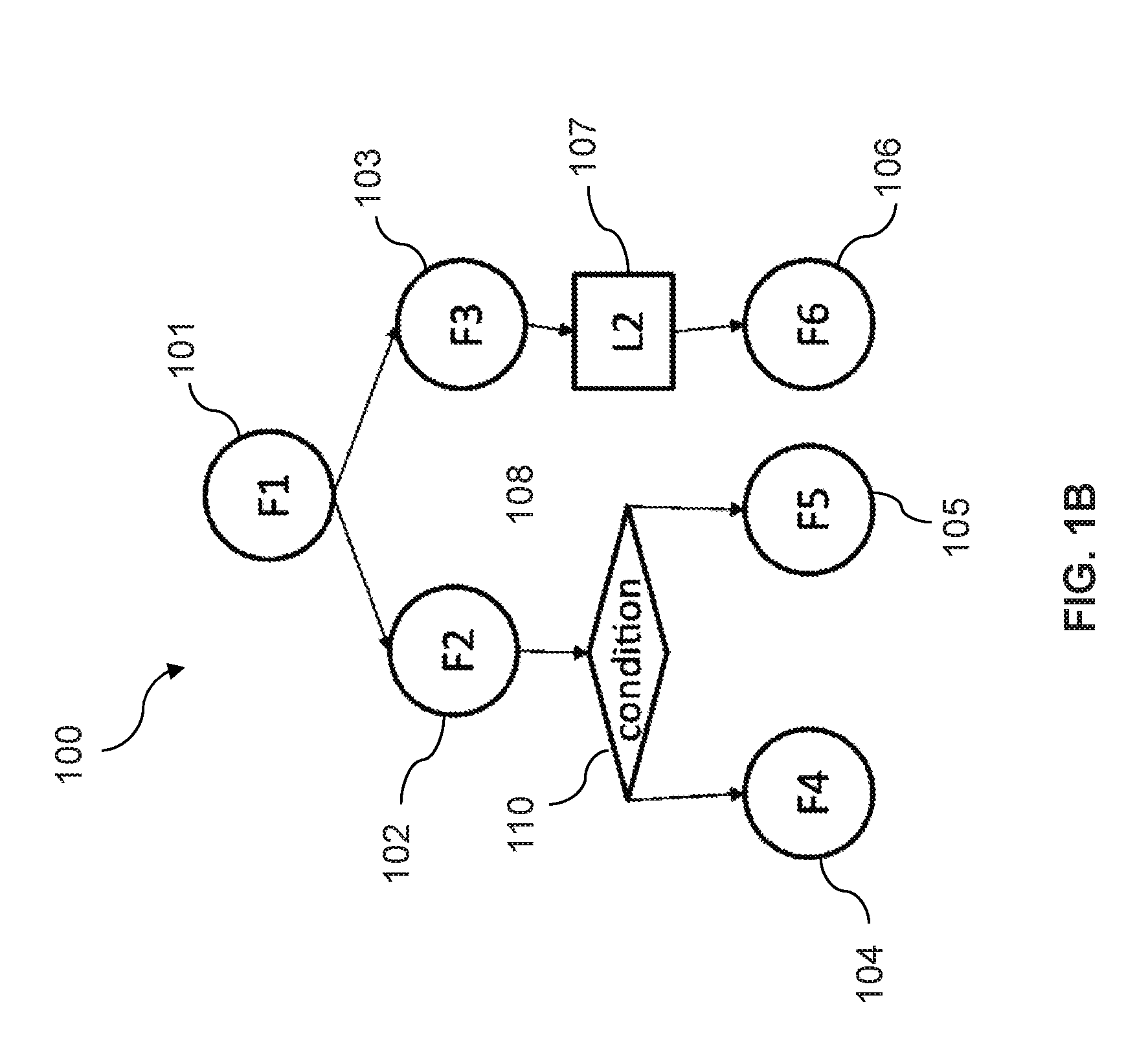

Global call control flow graph for optimizing software managed manycore architectures

InactiveUS20160170725A1Easy to useEfficient implementationSoftware engineeringProgram controlControl flowGraphics

Software Managed Manycore (SMM) architectures with scratch pad memory for reach core are a promising solution for scaling memory. In these architectures the code and data of the tasks mapped to the cores is explicitly managed by the compiler and often require inter-procedural information and analysis. But, a call graph of the program does not have enough information, and the Global CFG has too much information. Most new techniques informally define and use GCCFG (Global Call Control Flow Graph)—a whole program representation that succinctly captures the control-flow and function call information—to perform inter-procedural analysis. Constructing GCCFGs for several cases in common applications. The present disclosure provides unique graph transformations to formally and correctly construct GCCFGs for optimal compiler management of manycore systems.

Owner:ARIZONA STATE UNIVERSITY

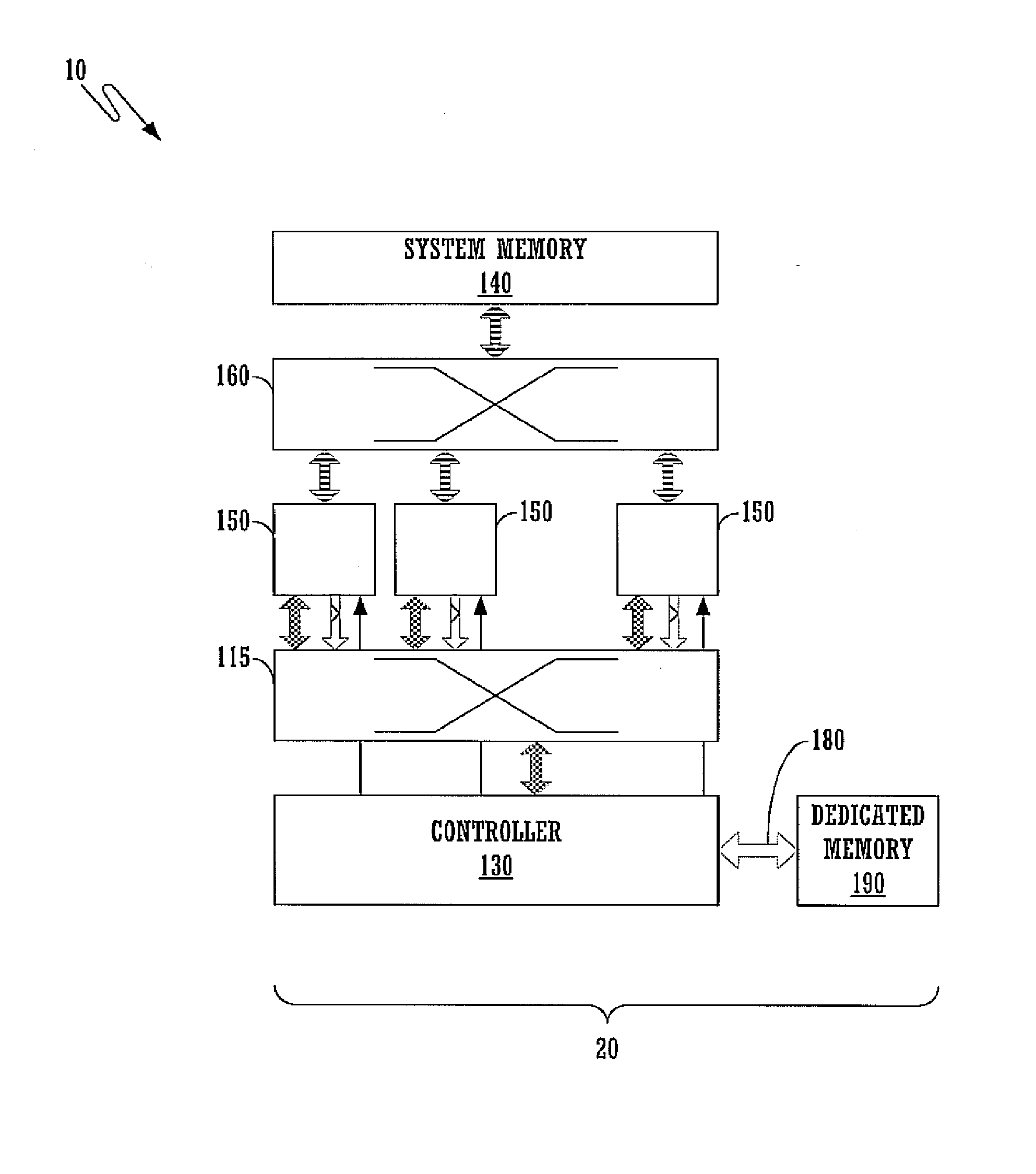

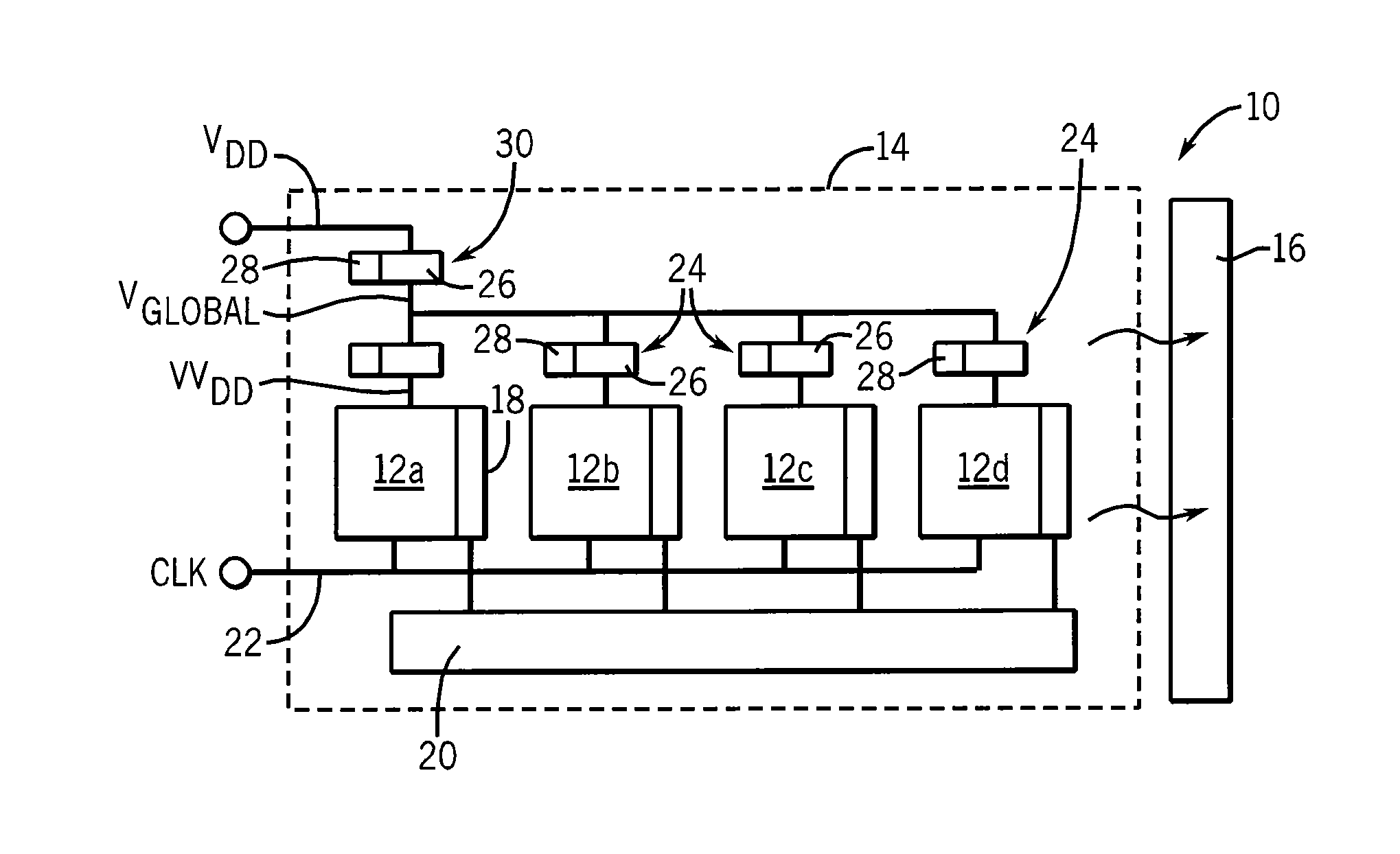

Resource management in a multicore architecture

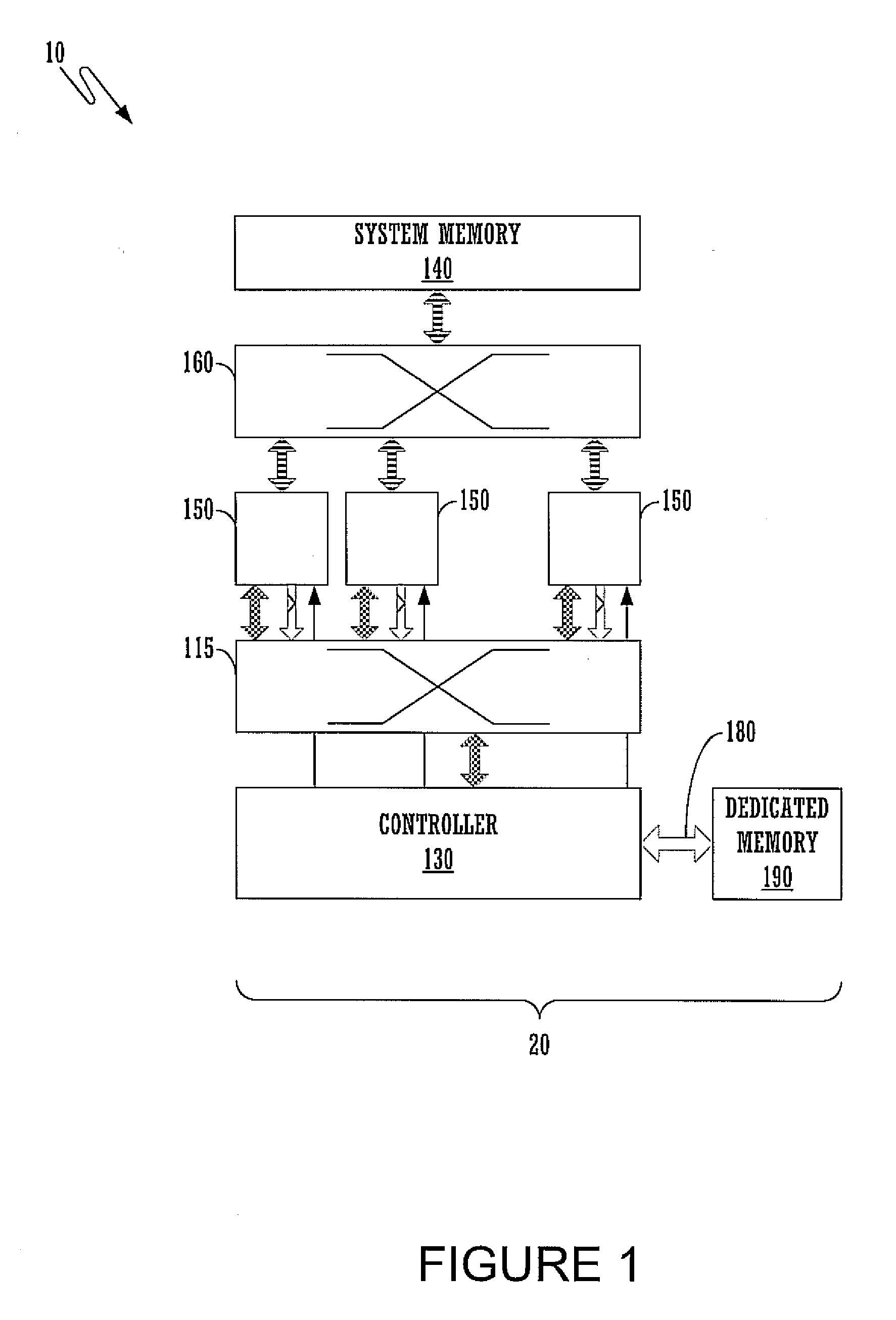

ActiveUS8533716B2Configuration highEffective distributionResource allocationGeneral purpose stored program computerMulticore architectureSystems management

A method and apparatus for resource management in a multicore processor is disclosed. A system management controller (130) provides omnipresent scheduling, synchronization, load balancing, and power and memory management services to each processing resource (150) within in a multicore processor (10), via a plurality of system management clients (120) implemented in hardware or software. The controller (130) allocates the tasks executing in each processing resource (150) by means of interrupt control signals, which interact directly with the system management clients (120), enabling processing resources (150) to autonomously create, execute and distribute tasks around a parallel system architecture whilst monitoring and policing the use of shared system resources (140).

Owner:FUJITSU SEMICON LTD +1

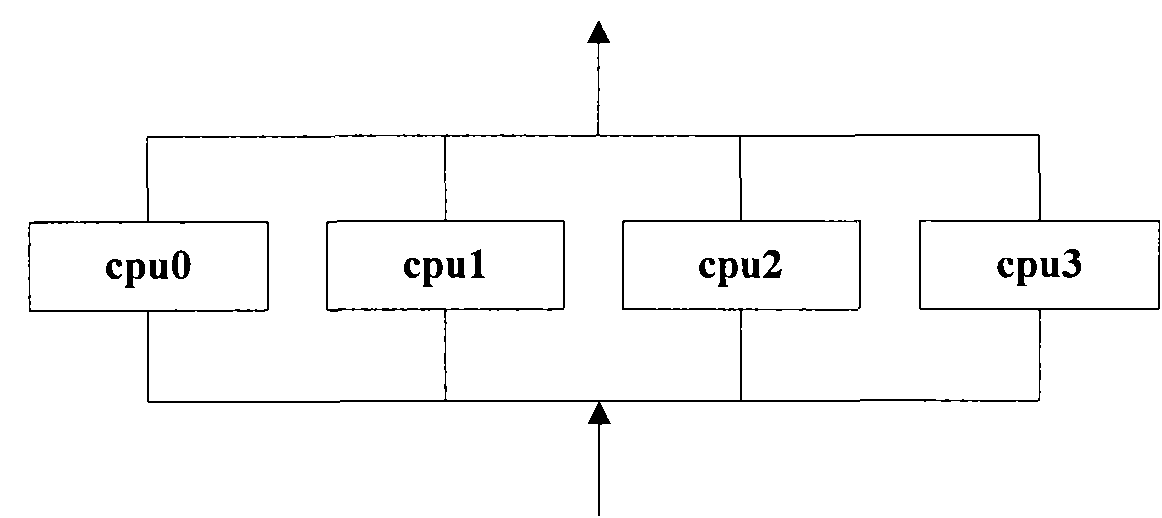

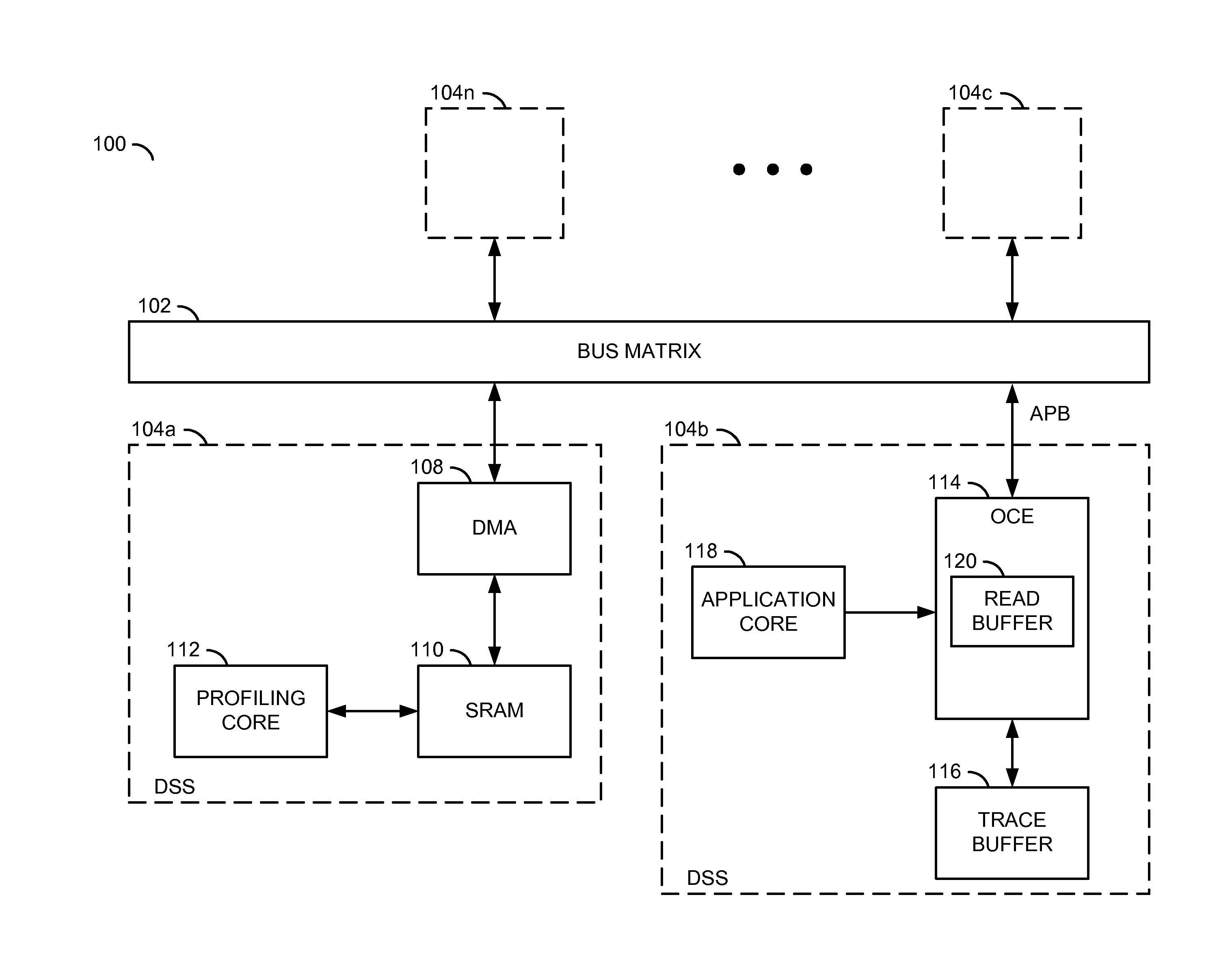

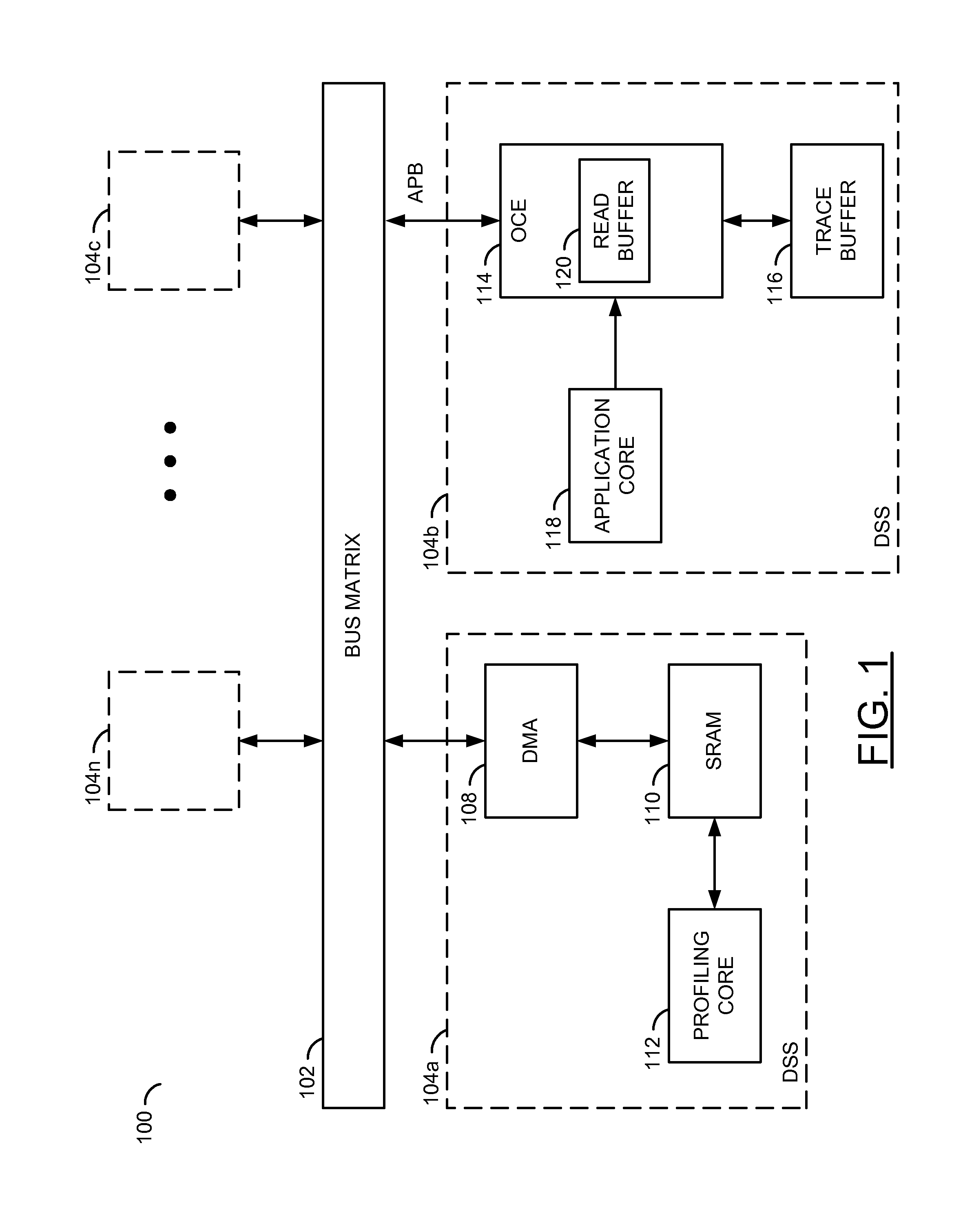

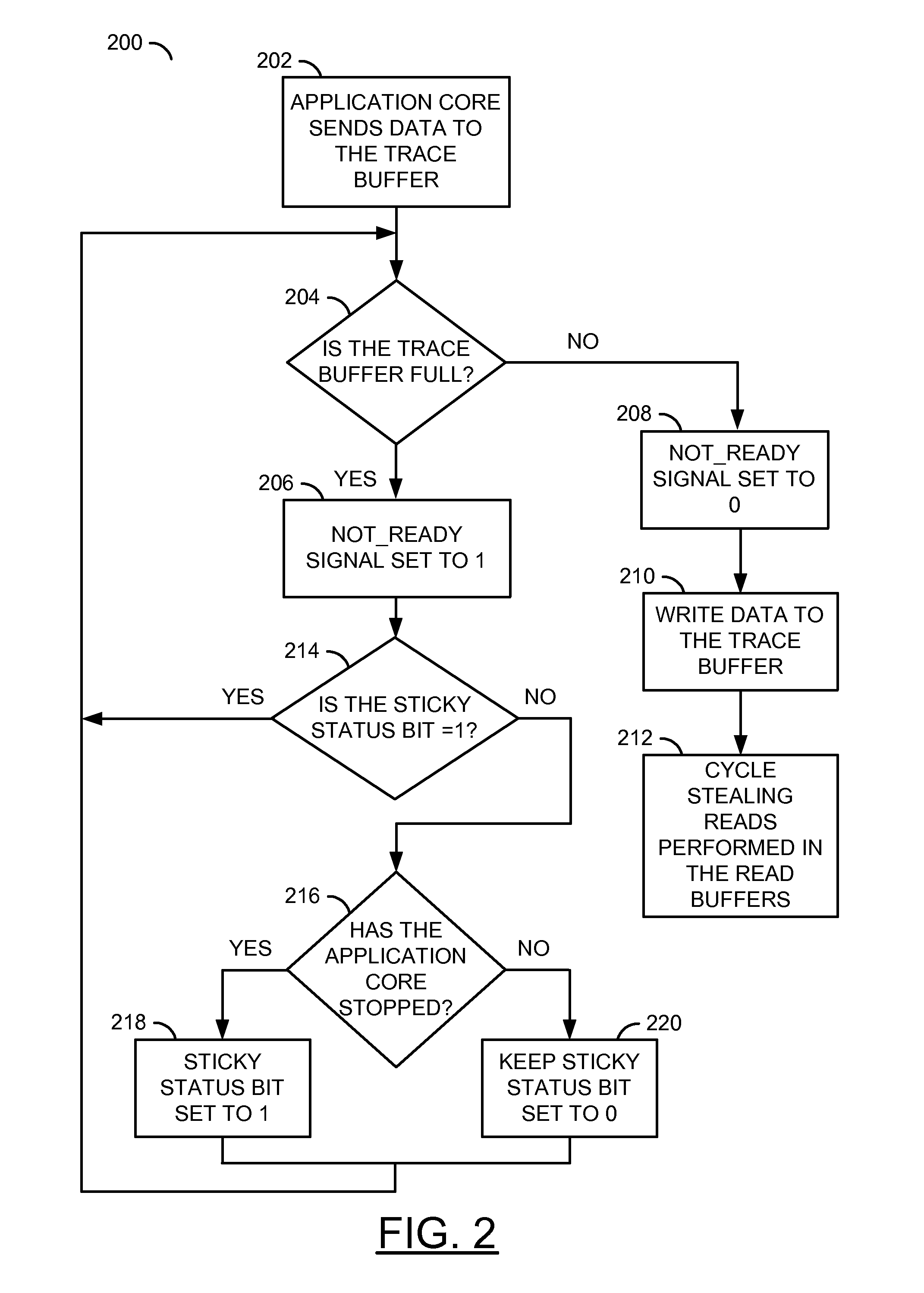

Real-time profiling in a multi-core architecture

ActiveUS20110302560A1Error detection/correctionSpecific program execution arrangementsComputer architectureMulticore architecture

An apparatus comprising a first core of a multi-core processor, a second core of a multi-core processor and a bus matrix. The first core may be configured to communicate through a first input / output port. The first core may also be configured to initiate a testing application. The second core may be configured to communicate through a second input / output port. The second core may also be configured to respond to the testing application. The bus matrix may be connected to the first input / output port and the second input / output port. The bus matrix may transfer data between the first core and the second core. The testing application may generate real-time statistics related to the execution of instructions by the second core.

Owner:AVAGO TECH INT SALES PTE LTD

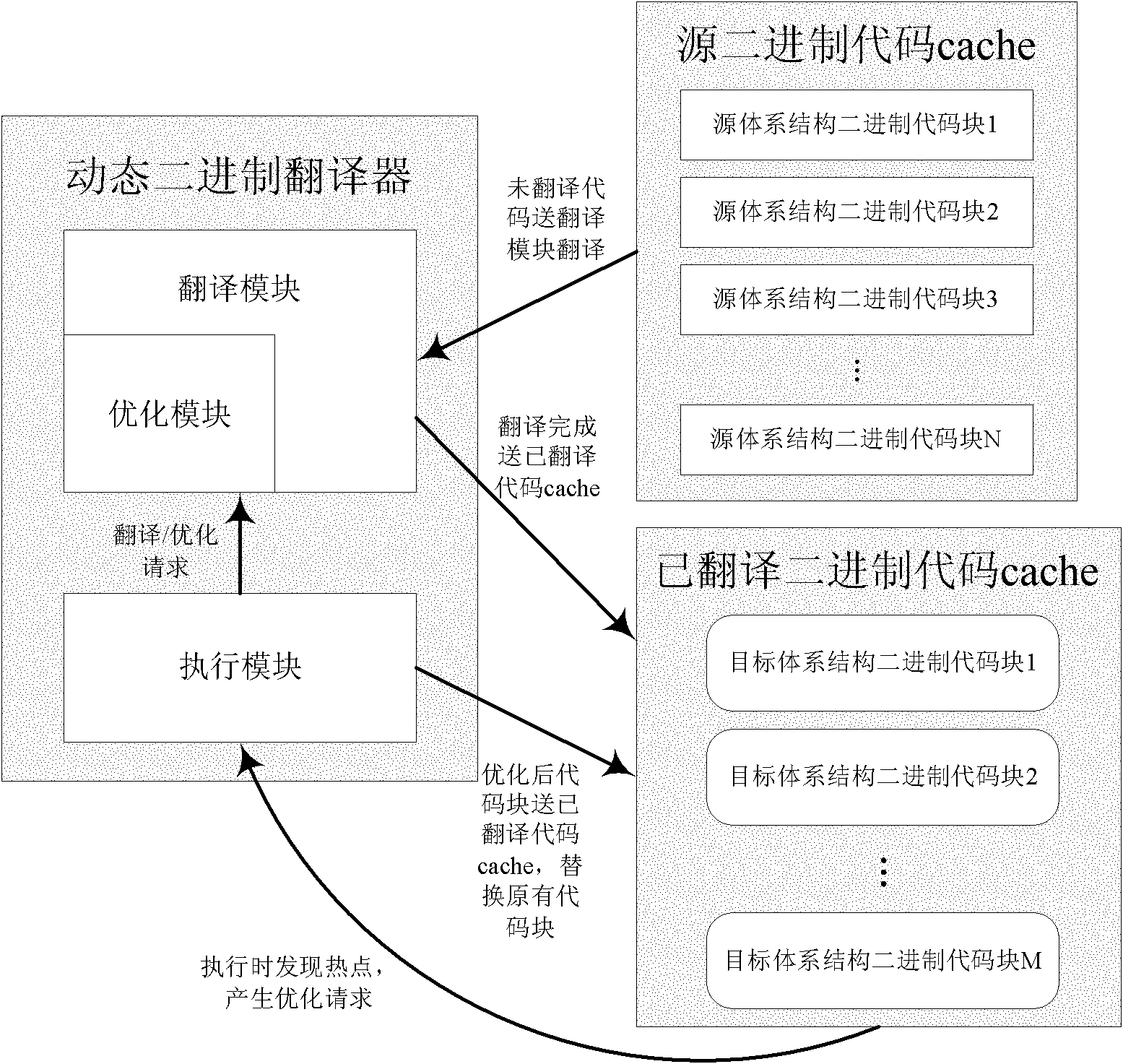

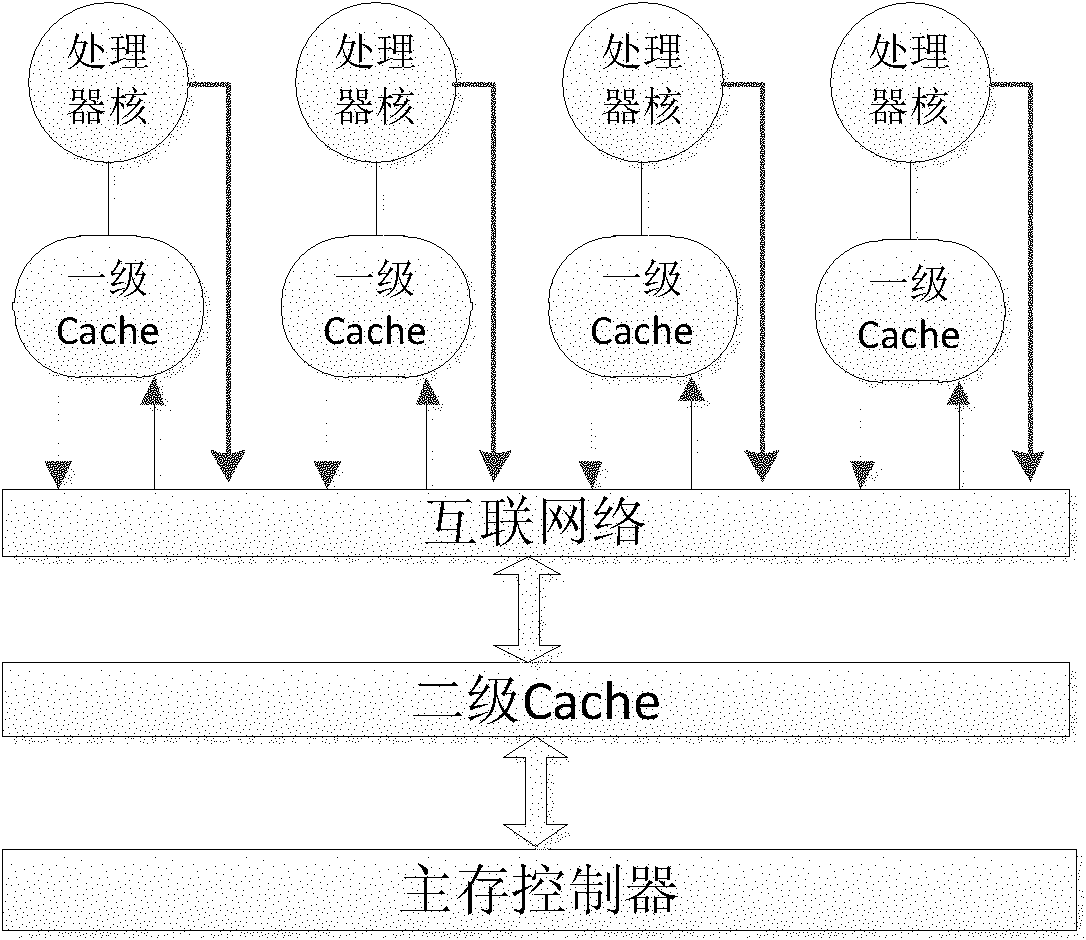

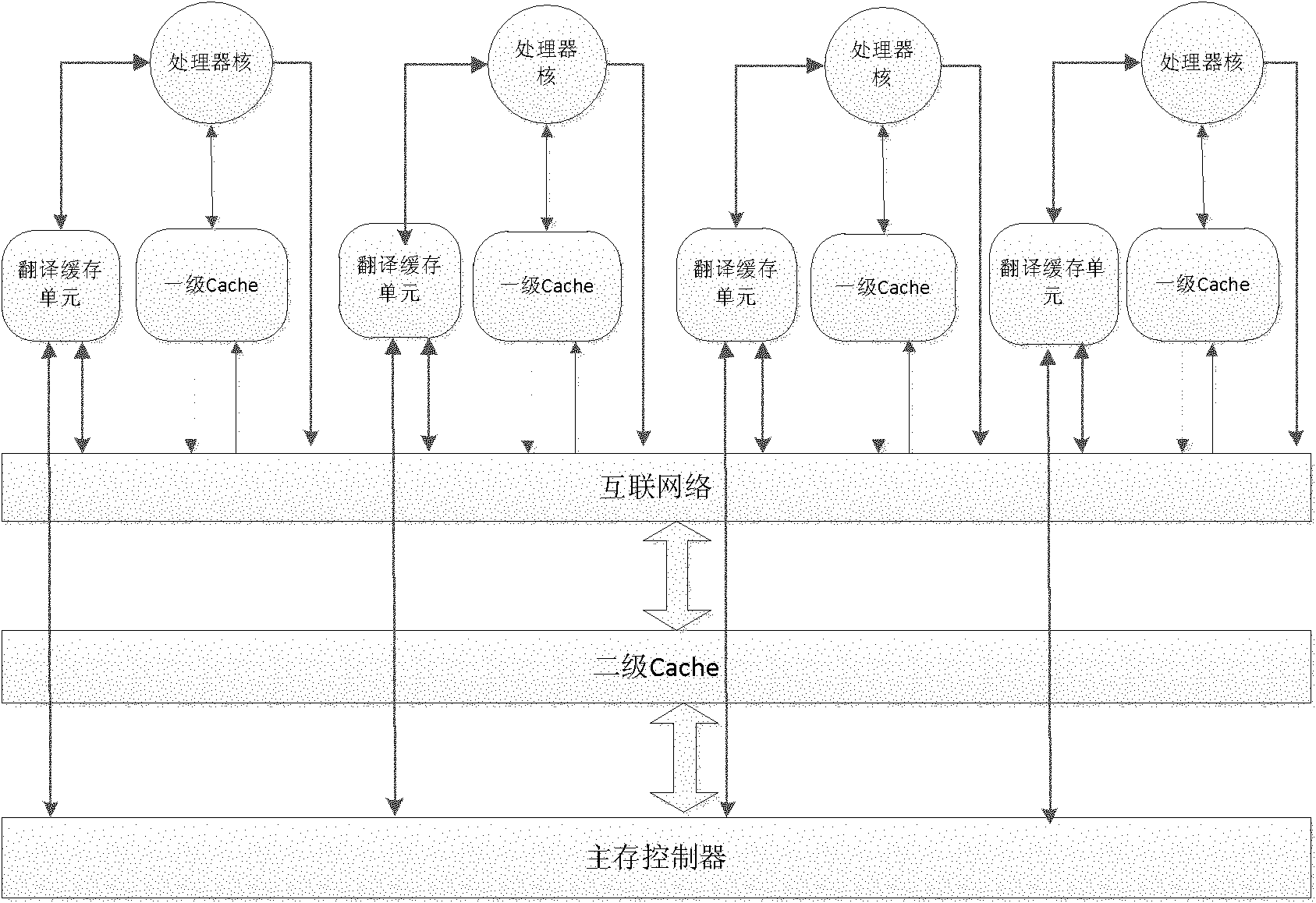

Multicore architecture supporting dynamic binary translation

InactiveCN102073533AReduce overheadReduce page access latencyMemory adressing/allocation/relocationMultiple digital computer combinationsMulticore architectureParallel computing

The invention discloses a multicore architecture supporting dynamic binary translation, aiming to solve the problems of Cache access conflict, main memory conflict and the like during dynamic binary translation. The multicore architecture comprises a plurality of processor cores, a plurality of primary Caches, a plurality of translation cache units, a secondary Cache and a main memory controller,wherein the primary Caches and the translation cache units are private for each processor core; the secondary Cache and the main memory controller are shared by all the processor cores; each translation cache unit comprises a communication control unit, a cache management unit and a data memory unit; the communication control unit comprises a multi-channel selector, a communication control unit controller, a transmission bus and three registers; the cache management unit comprises a page replacement component and a cache management control component; and the data memory unit comprises a source architecture binary code cache area, a target architecture binary code cache area and a page mapping table. The multicore architecture has the following technical effects: the data access latency isreduced, the translation throughput is high and the Cache access conflict is less.

Owner:NAT UNIV OF DEFENSE TECH

Industrial controller using shared memory multicore architecture

ActiveUS20090210070A1Sampled-variable control systemsComputer controlGeneral purposeMulticore architecture

A multicore processor for industrial control provides for the execution of separate operating systems on the cores under control of one of the cores to tailor the operating system to optimum execution of different applications of industrial control and communication. One core may provide for a reduced instruction set for execution of industrial control programs with the remaining cores providing a general-purpose instruction set.

Owner:ROCKWELL AUTOMATION TECH

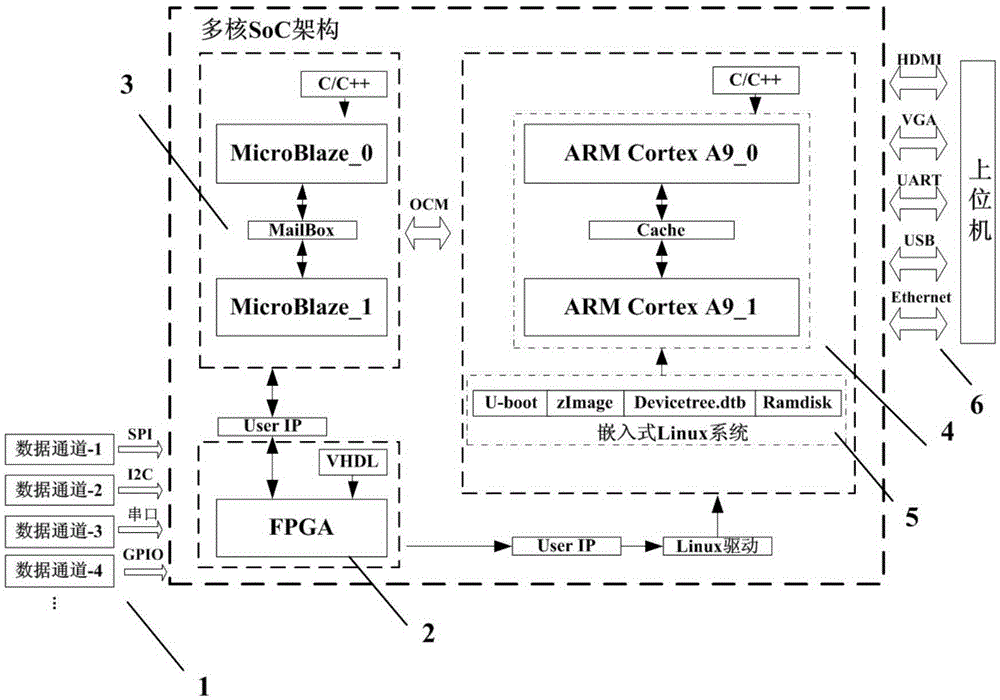

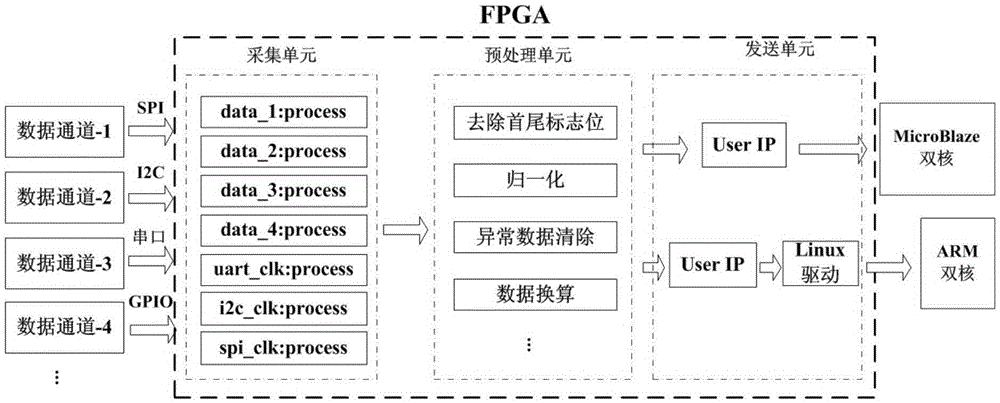

Multi-core SoC architecture design method supporting multi-task parallel execution

InactiveCN105260164AImprove execution efficiencyImprove collection efficiencyMultiple digital computer combinationsConcurrent instruction executionChannel dataComputer architecture

The invention relates to a multi-core SoC architecture design method supporting multi-task parallel execution. The method mainly comprises: establishing a MicroBlaze dual-core module and an ARM dual-core module; designing a multi-core multi-thread based multi-task parallel execution module based on the established MicroBlaze dual-core module and the ARM dual-core module; and meanwhile, designing a hardware acceleration module based on an FPGA. According to the multi-core SoC architecture design method, external multi-channel data are collected simultaneously through the FPGA, and then multi-channel data are transmitted to different cores for parallel execution, wherein the FPGA is designed in a mode that the FPGA interacts with MicroBlaze dual cores through User-IP, the FPGA interacts with ARM dual cores through the User-IP and a Linux driving module, the MicroBlaze dual cores interact through MailBox, the ARM dual cores interact through Cache, and the MicroBlaze dual cores and the ARM dual cores interact through OCM; and by establishing a multi-core SoC architecture, the parallel execution of multiple tasks on multiple cores can be realized, so that the executing efficiency of the multiple tasks is greatly improved.

Owner:BEIHANG UNIV

Industrial controller using shared memory multicore architecture

A multicore processor for industrial control provides for the execution of separate operating systems on the cores under control of one of the cores to tailor the operating system to optimum execution of different applications of industrial control and communication. One core may provide for a reduced instruction set for execution of industrial control programs with the remaining cores providing a general-purpose instruction set.

Owner:ROCKWELL AUTOMATION TECH

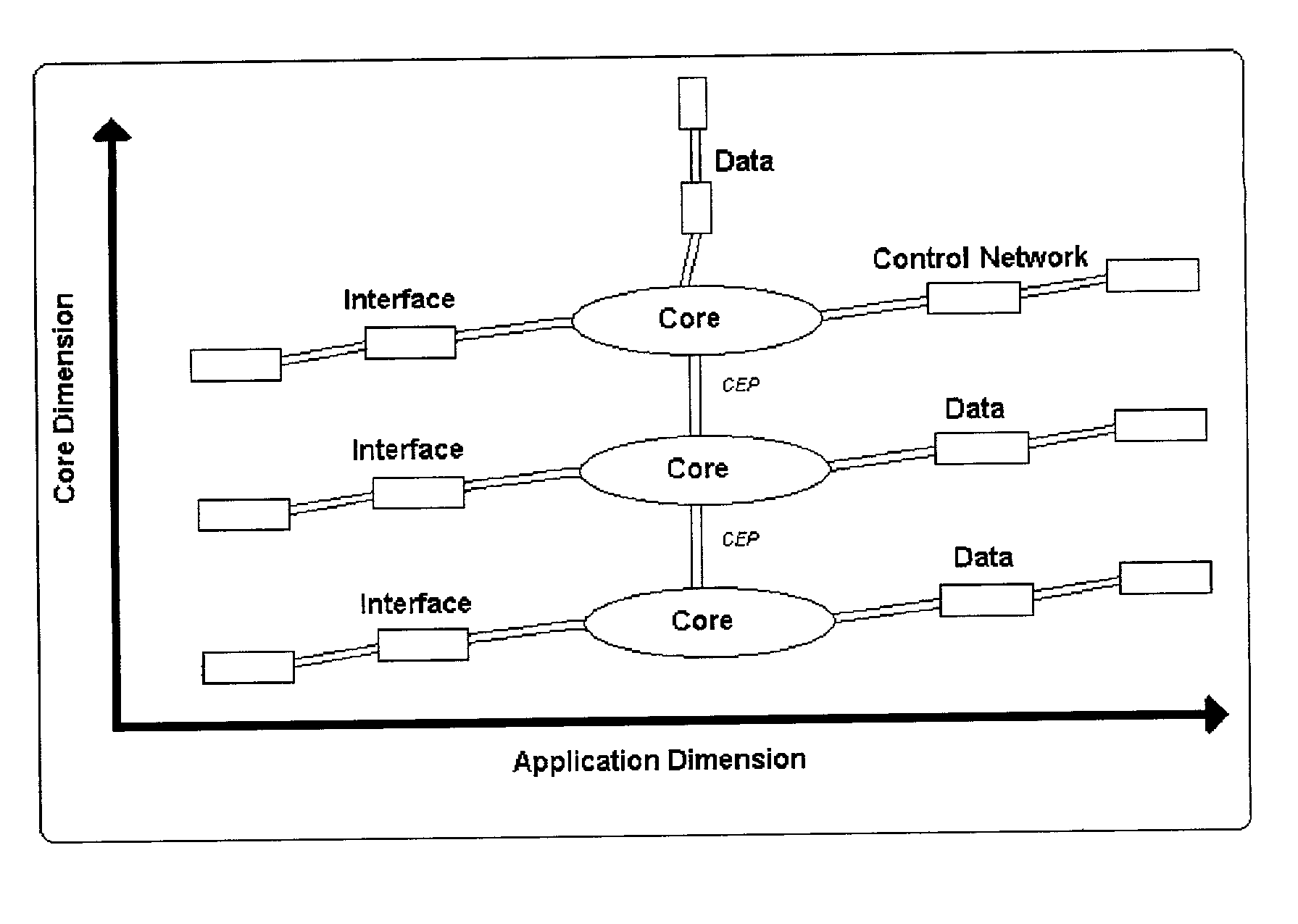

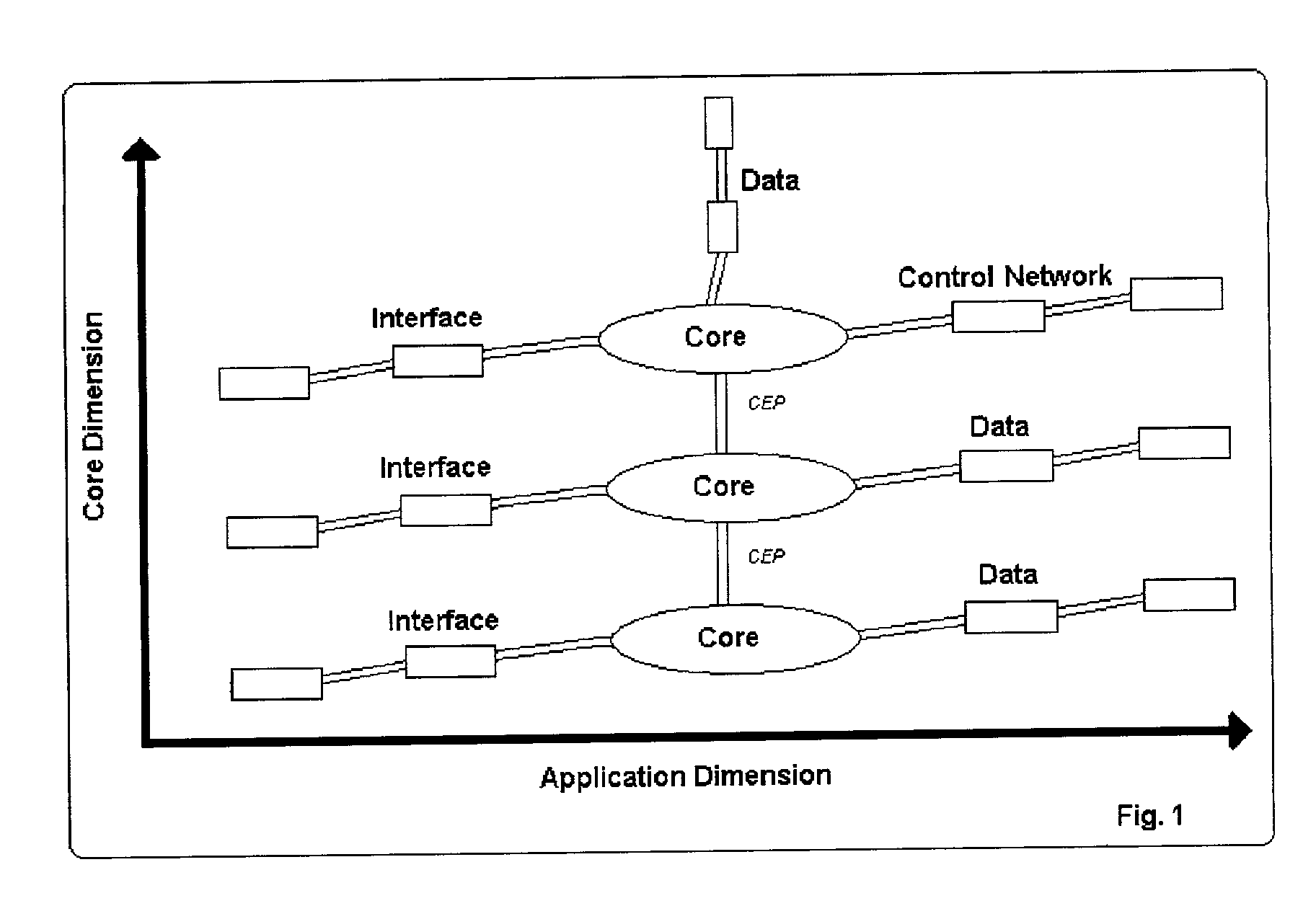

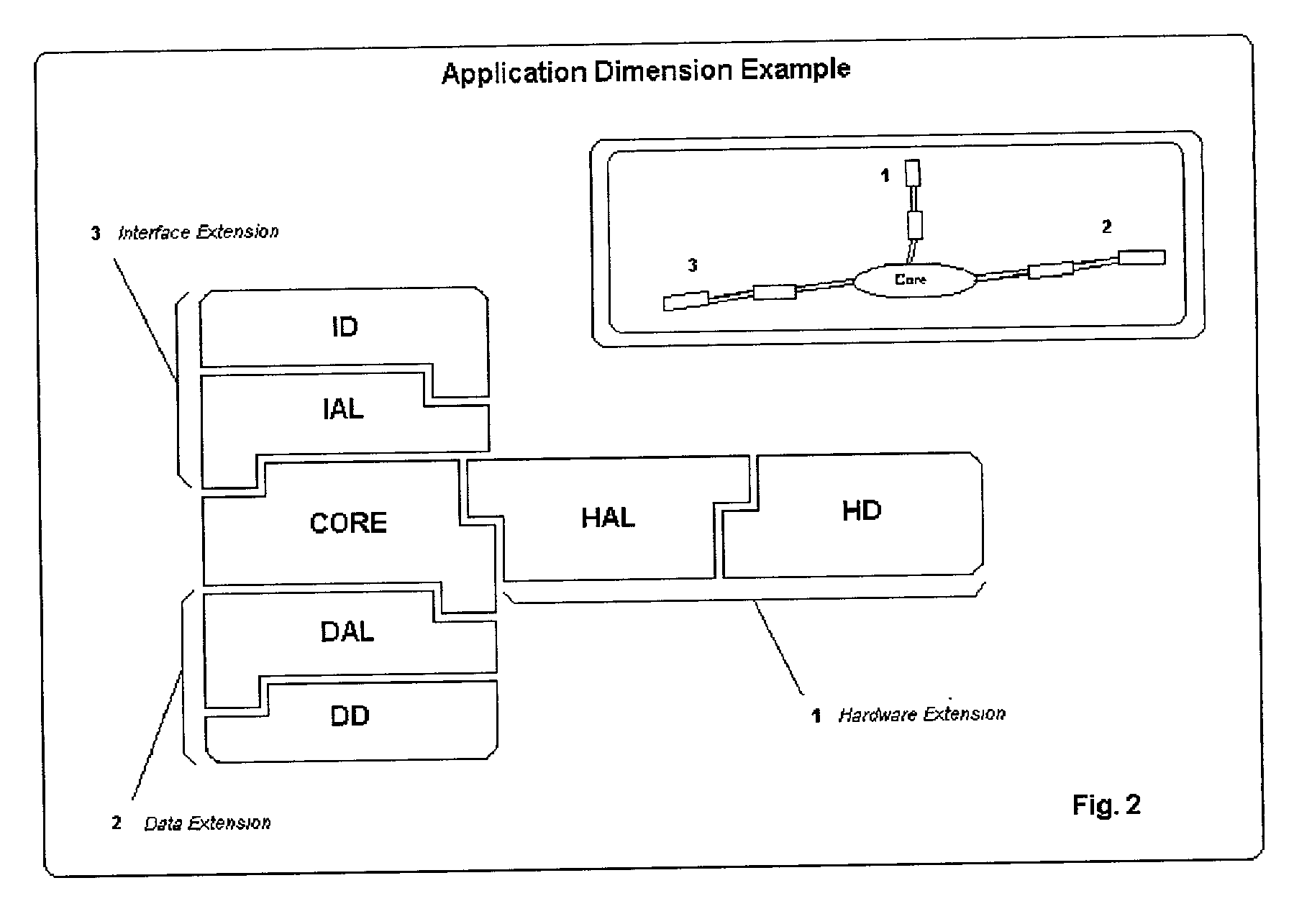

Multidimensional advanced adaptive software architecture

InactiveUS20030014560A1Improve versatilityImprove performanceMultiprogramming arrangementsSoftware designAbstraction layerMulticore architecture

The present invention is a software architecture that provides high versatility and performance. This architecture is composed of two dimensions: the first one belongs in the application level, and the second in the multicore dimension. The application dimension is related to the different applications based in the conceptual model of abstractions exposed in this patent. The multicore dimension is related to the applications dimension instantiated several times in the same computer (multiple processors) or in several computers. All the cores within the multicore dimension are related in order to share information and integrate all the architecture's applications. The multicore architecture avoids bottlenecks in the simultaneous execution of multiple applications on the same computer by means of a large virtual core composed of small interconnected cores. The conceptual model of abstractions is composed of various drivers, abstraction layers and a unique core that provides support by playing a referee role between different extensions of an application.

Owner:SMARTMATIC

Resource management in a multicore architecture

ActiveUS20140025857A1Configuration highEffective distributionResource allocationMain processing unitProcessor element

A resource management and task allocation controller for installation in a multicore processor having a plurality of interconnected processor elements providing resources for processing executable transactions, at least one of said elements being a master processing unit, the controller being adapted to communicate, when installed, with each of the processor elements including the master processing unit, and comprising control logic for allocating executable transactions within the multicore processor to particular processor elements in accordance with pre-defined allocation parameters.

Owner:SYNOPSYS INC +1

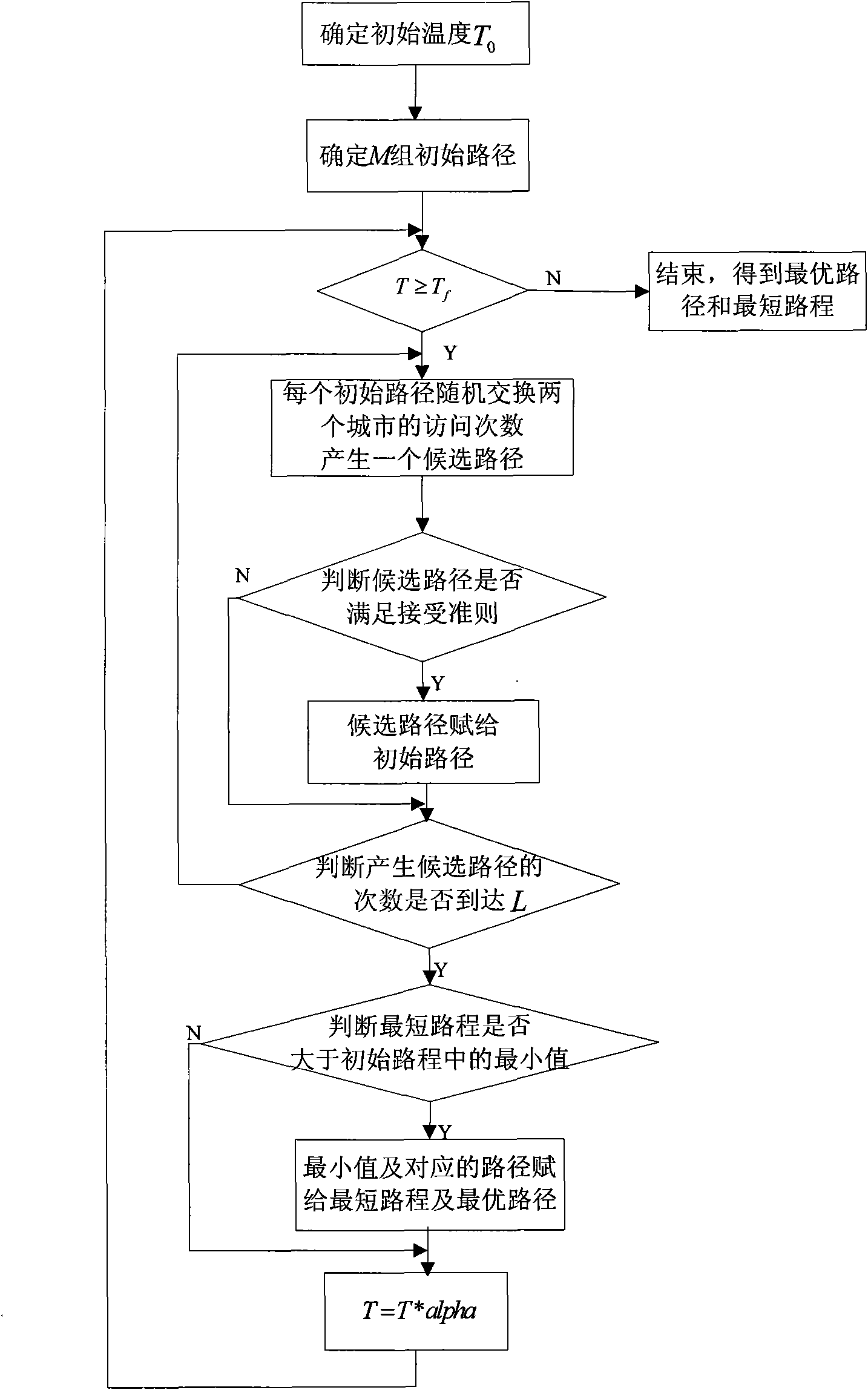

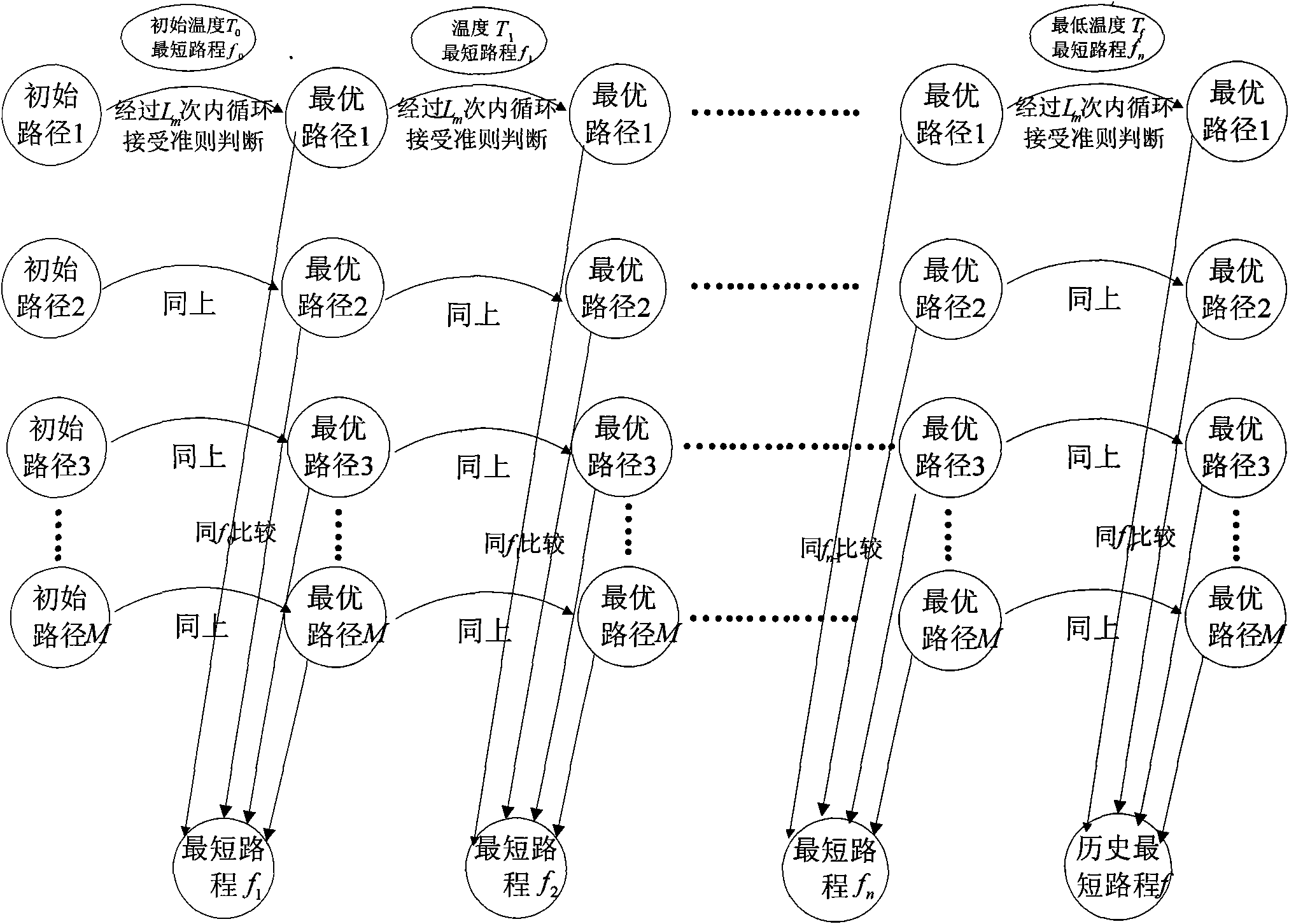

Multi-core parallel simulated annealing method based on thread constructing module

InactiveCN101593132AImprove operational efficiencyReduce running timeResource allocationConcurrent instruction executionMulticore architectureMulti processor

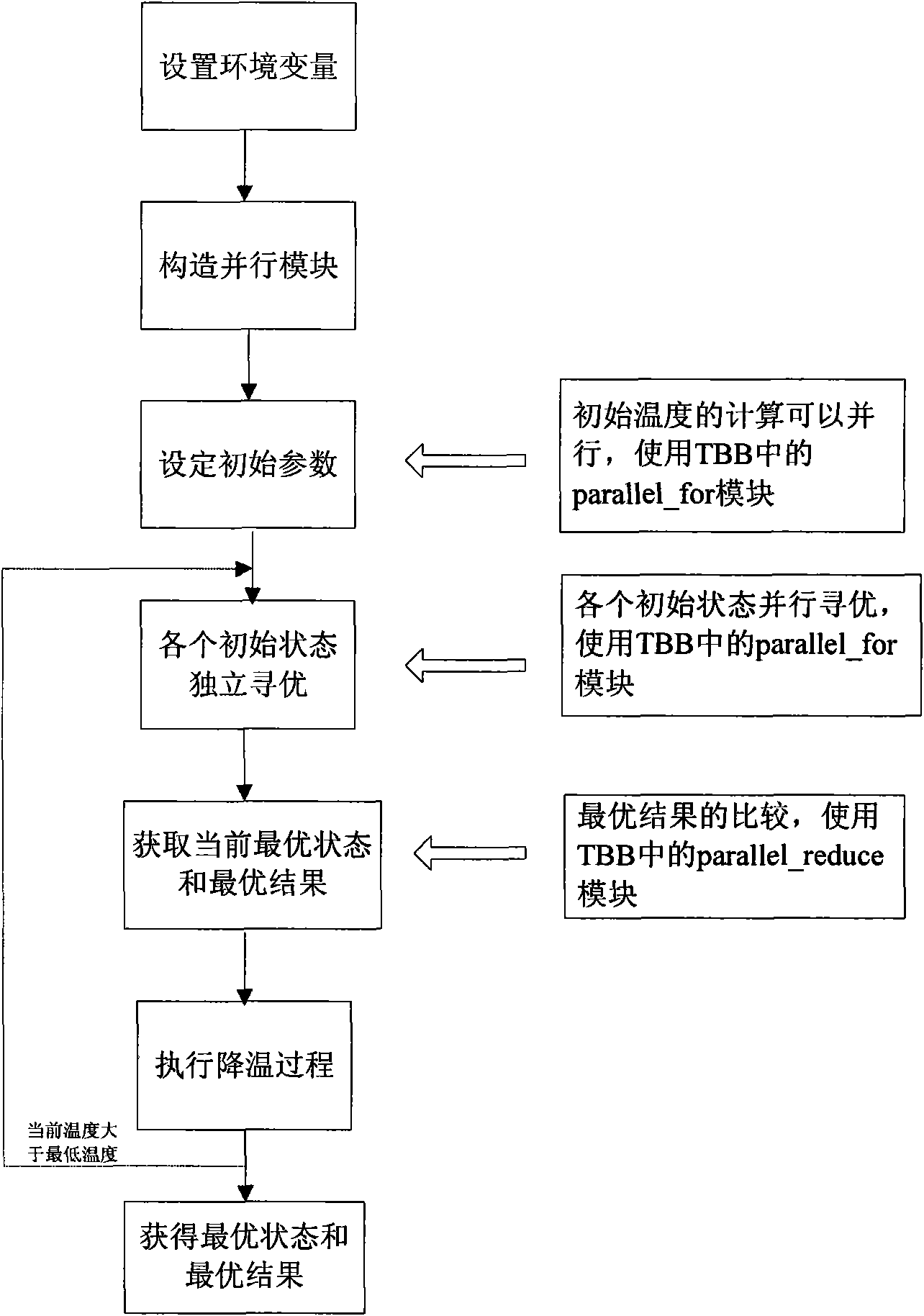

The invention discloses a multi-core parallel simulated annealing method based on a thread constructing module, which mainly solves the problem of the operating efficiency of a simulated annealing algorithm in large-scale engineering application and the problem of the utilization of computer multi-core resources. The method uses the advantage that the thread constructing module supports multi-core processor parallel algorithm and supports the expanded thread nesting parallel, and introduces a group optimization mechanism construction parallel algorithm of various groups on the basis of the former serial simulated annealing algorithm. The method comprises the following steps: firstly, setting environmental variables; secondly, constructing a parallel module; thirdly, setting initial parameters; fourthly, performing independent optimization on each initial state; fifthly, acquiring the current optimal state and the current optimal result; sixthly, executing temperature reducing process; and finally, obtaining the optimal state and the optimal result. The multi-core parallel simulated annealing method has simple and flexible processes, is easy for expansion, accords with the trend that computers are developed to have multi-processors and multi-core architectures, and is a convenient and quick parallel simulated annealing design method with strong practicability.

Owner:BEIHANG UNIV