Patents

Literature

340 results about "Multicore systems" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

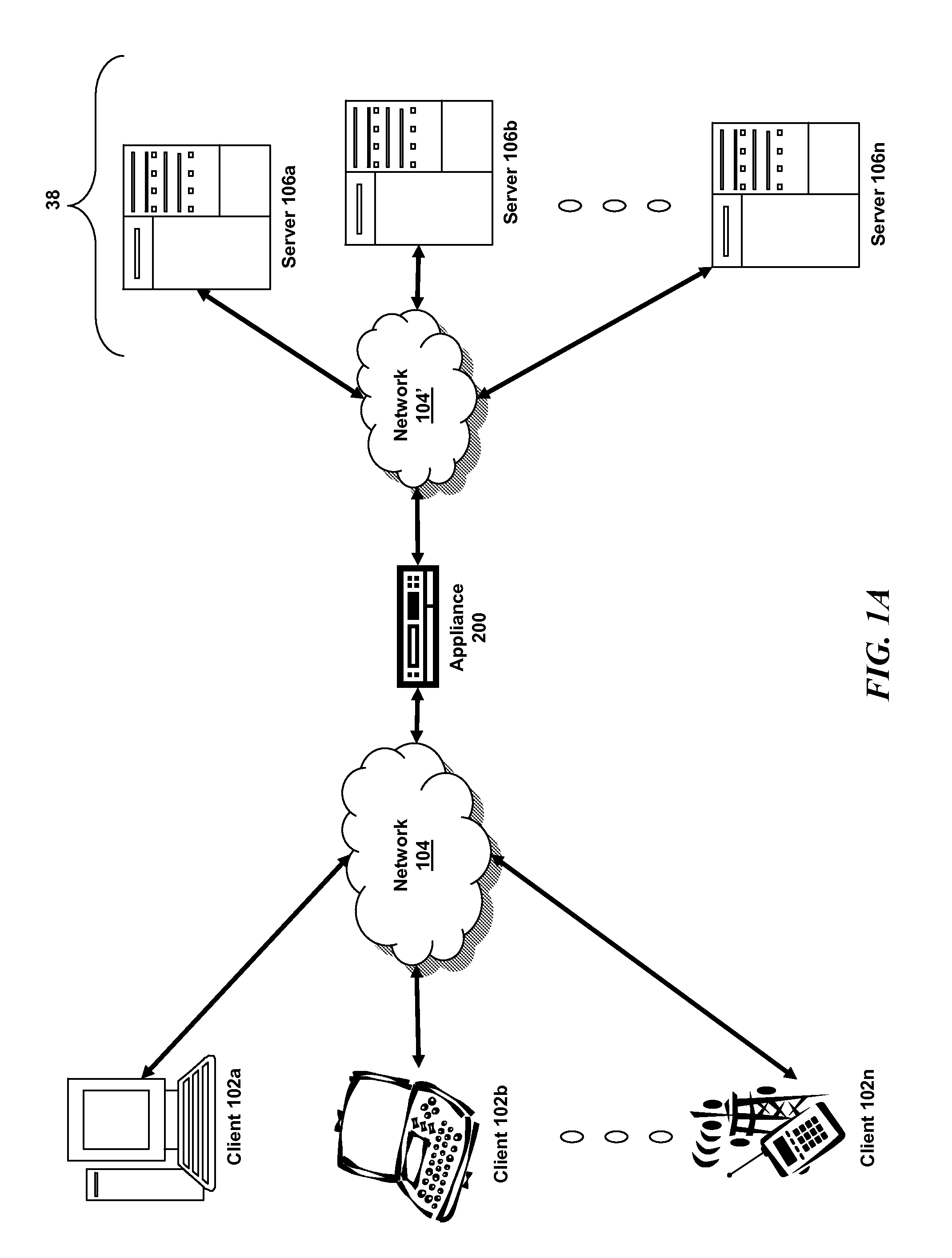

Multicore System. A Multi-core processor is a single computing component that has two or more independent cores or processing units. These cores are the ones that read and perform your program’s instructions on your CPU.

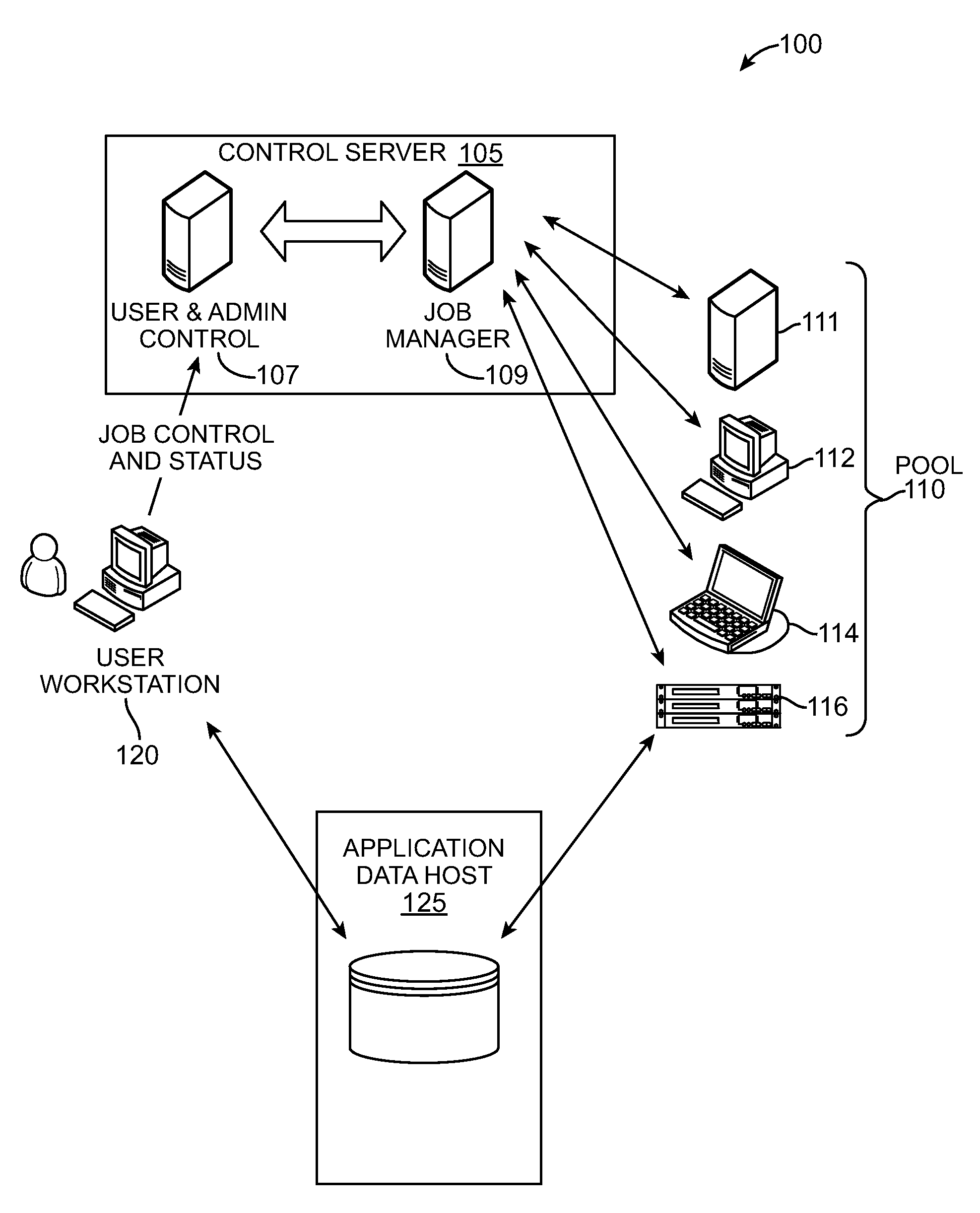

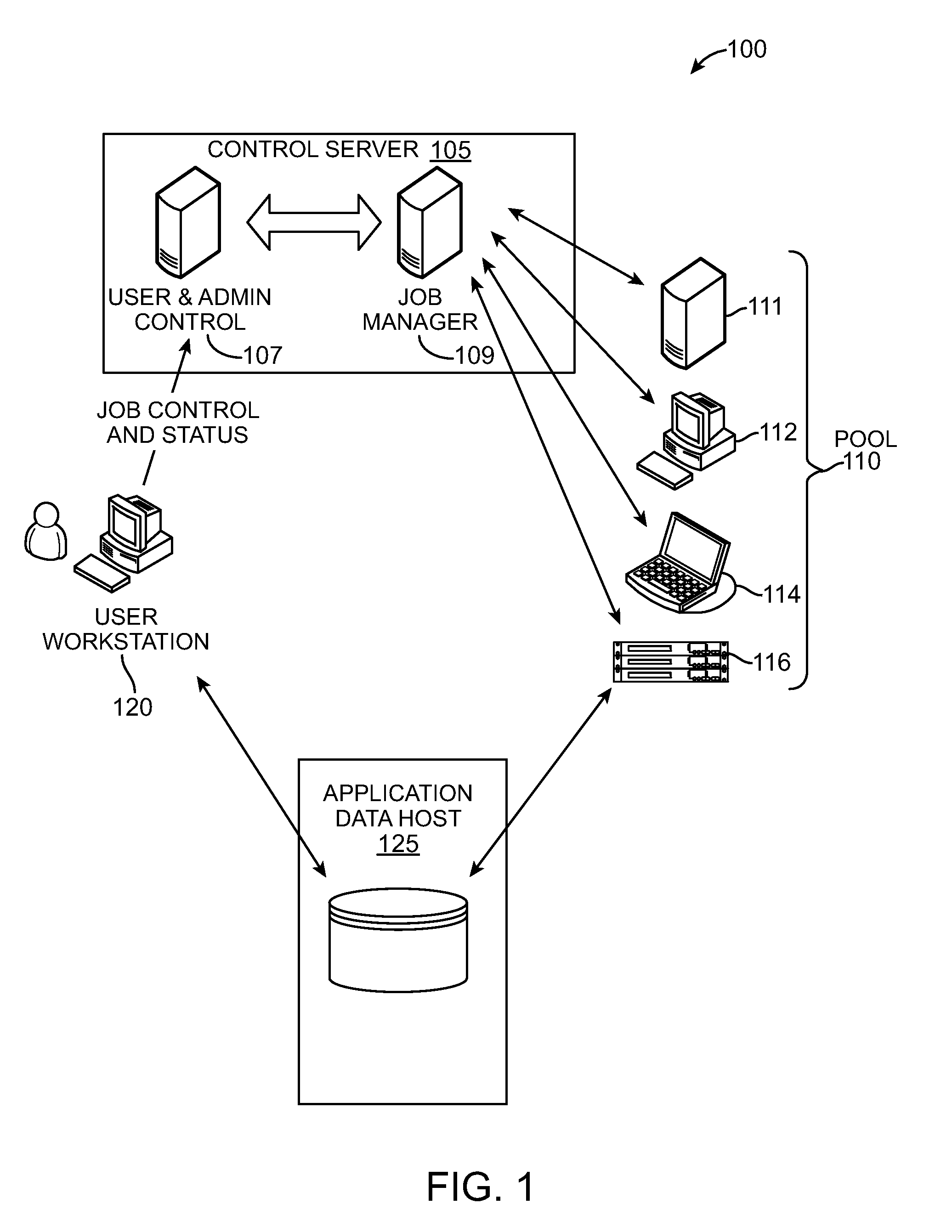

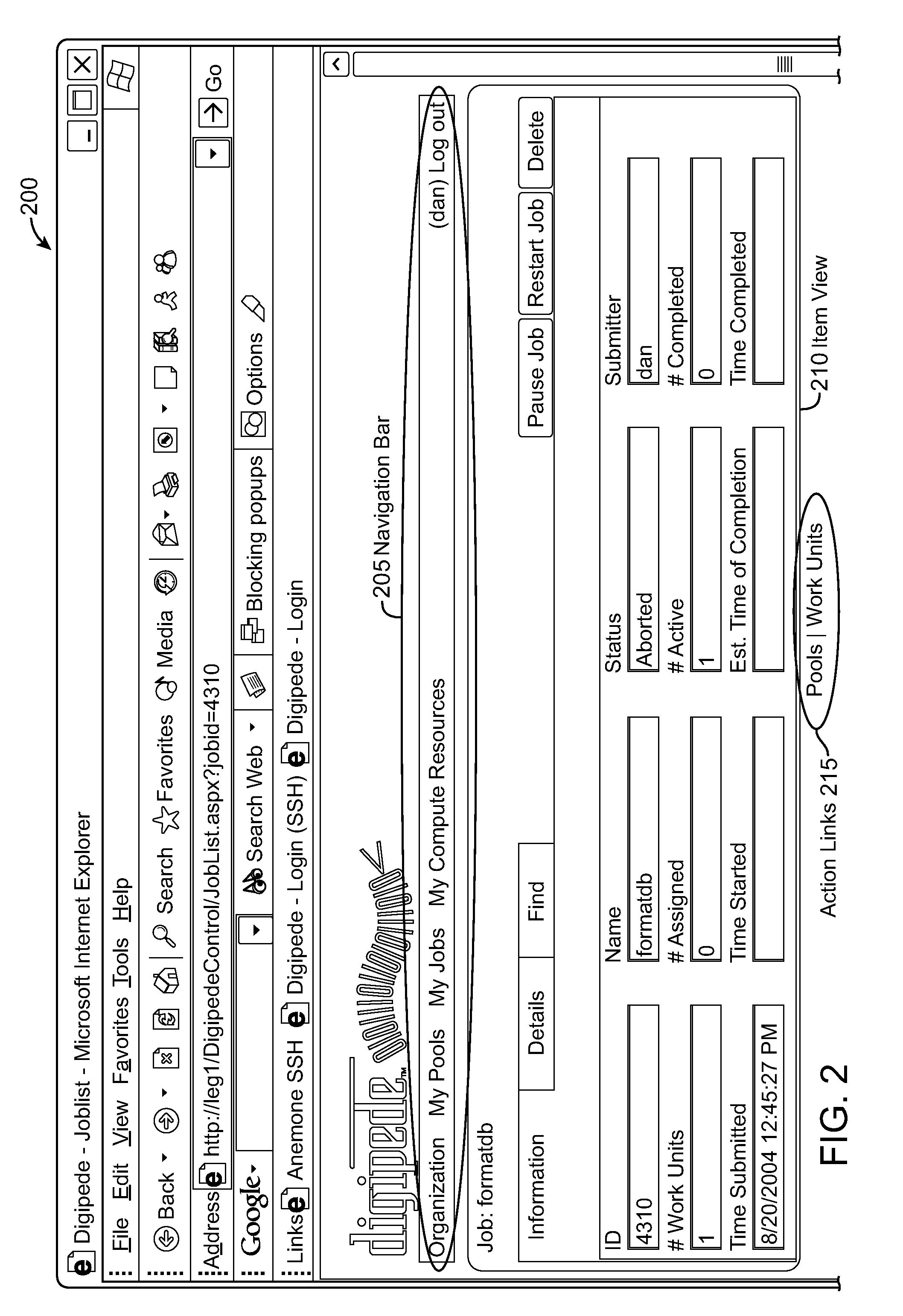

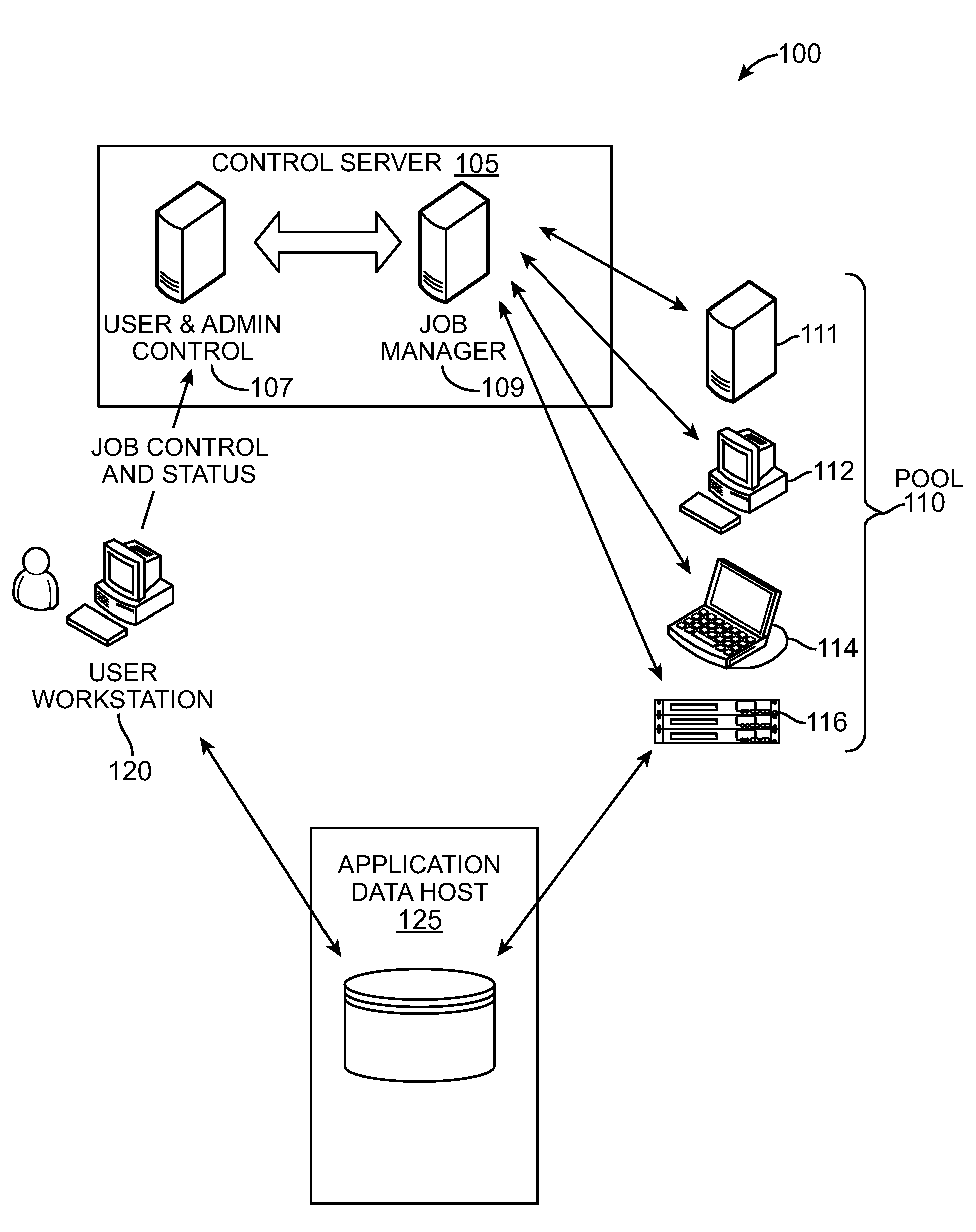

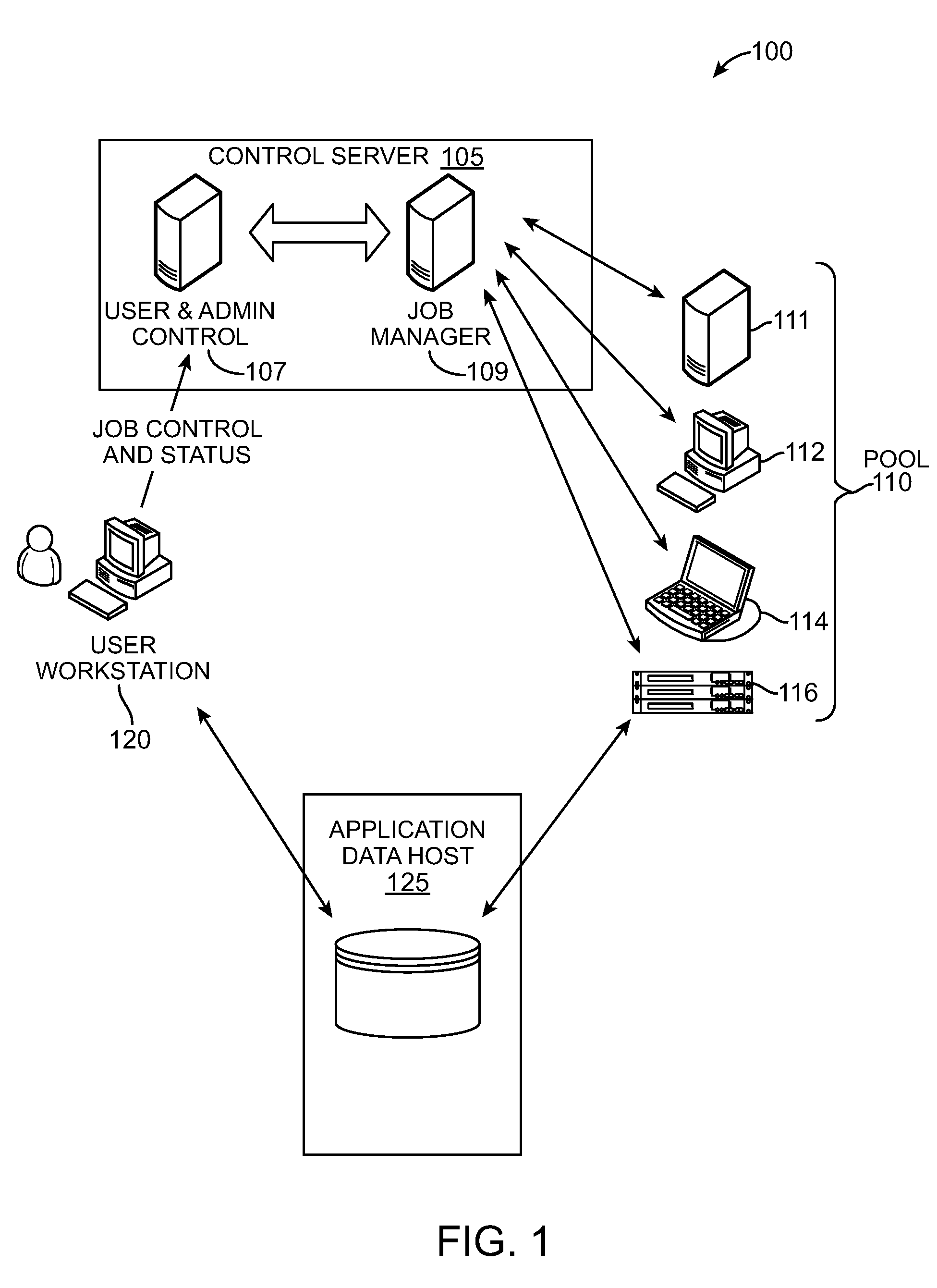

Multicore Distributed Processing System

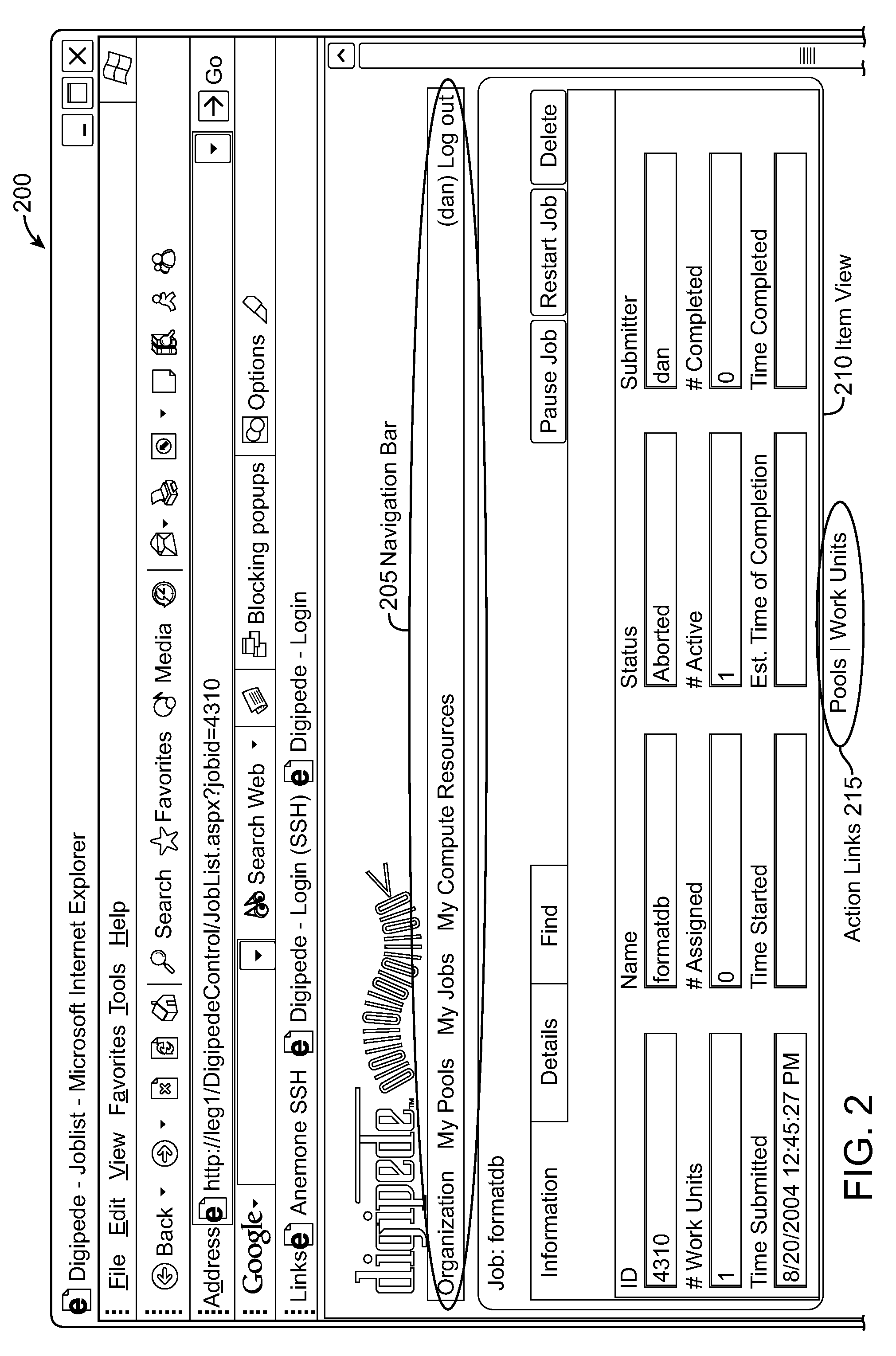

ActiveUS20090049443A1Improve application performanceFaster and relatively lightweightGeneral purpose stored program computerMultiprogramming arrangementsMulti processorWork unit

A distributed processing system delegates the allocation and control of computing work units to agent applications running on computing resources including multi-processor and multi-core systems. The distributed processing system includes at least one agent associated with at least one computing resource. The distributed processing system creates work units corresponding with execution phases of applications. Work units can be associated with concurrency data that specifies how applications are executed on multiple processors and / or processor cores. The agent collects information about its associated computing resources and requests work units from the server using this information and the concurrency data. An agent can monitor the performance of executing work units to better select subsequent work units. The distributed processing system may also be implemented within a single computing resource to improve processor core utilization of applications. Additional computing resources can augment the single computing resource and execute pending work units at any time.

Owner:DIGIPEDE TECH LLC

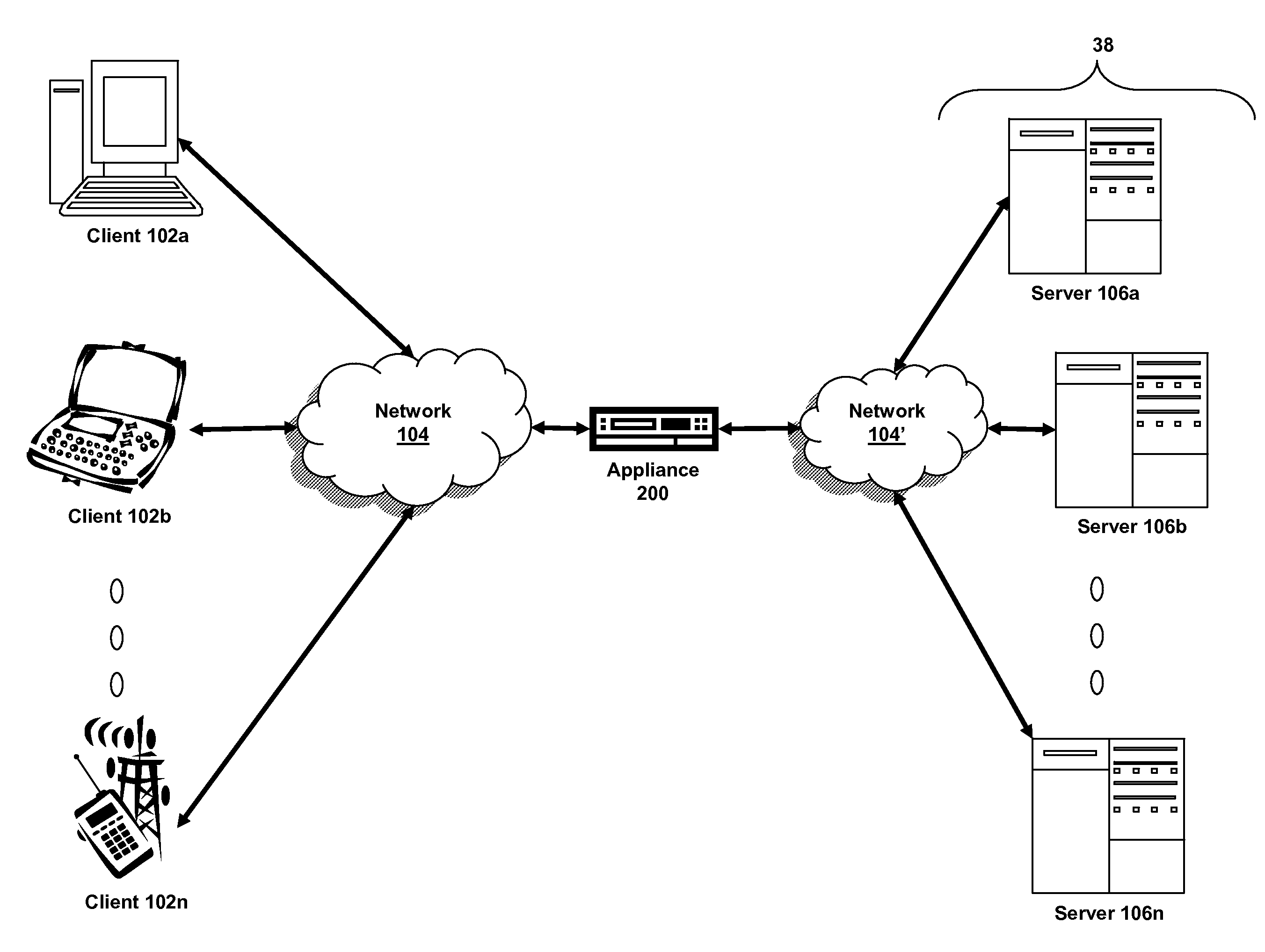

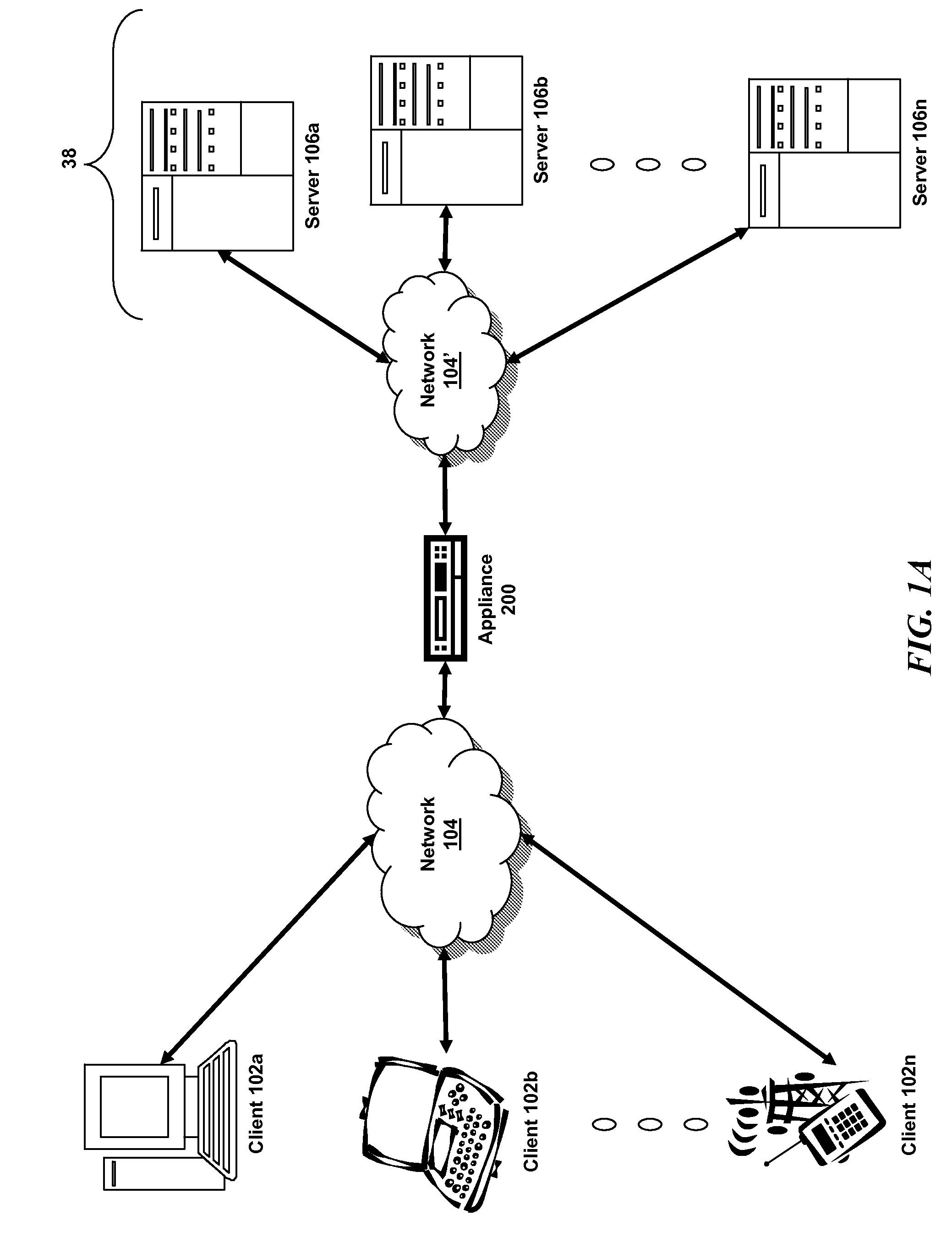

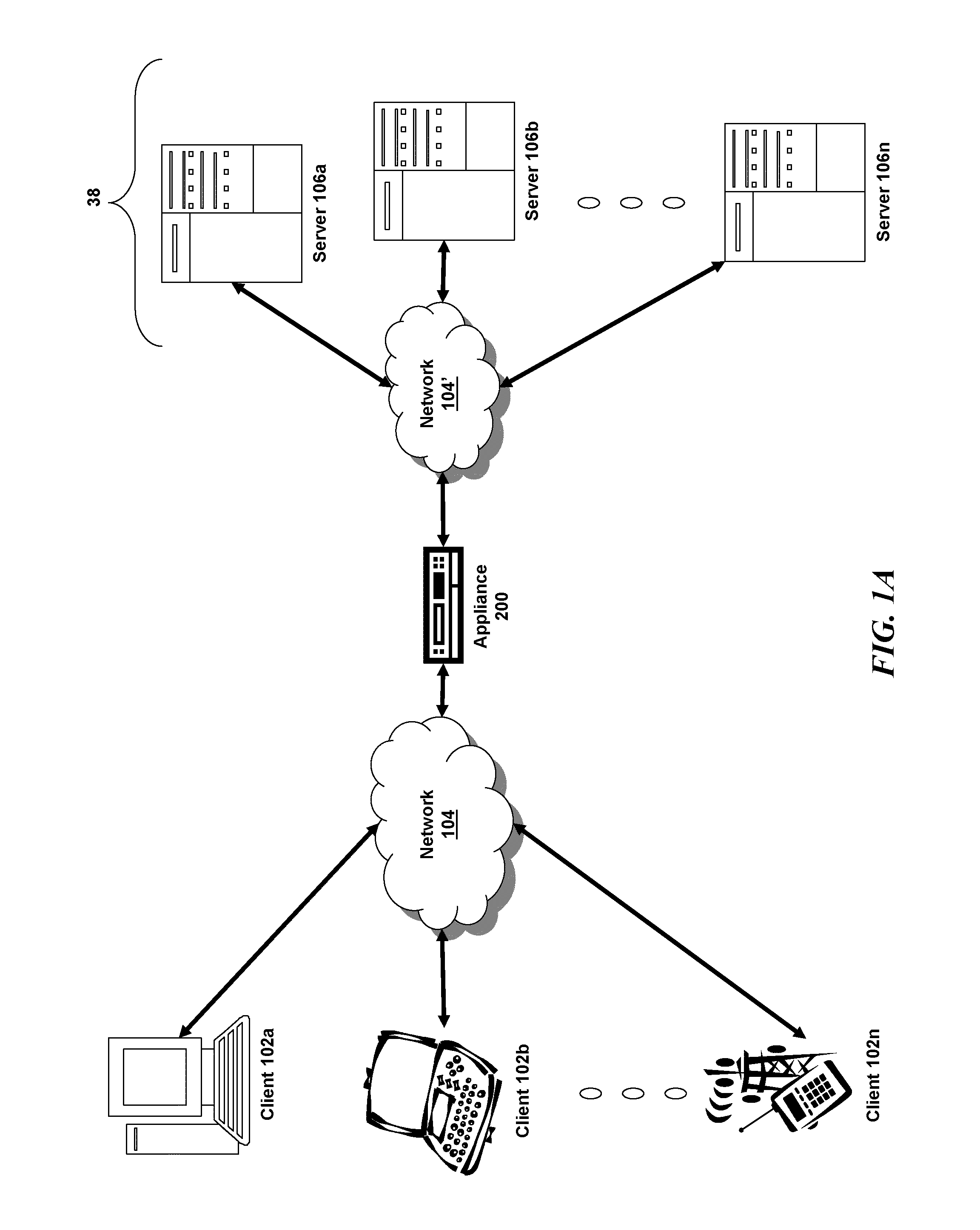

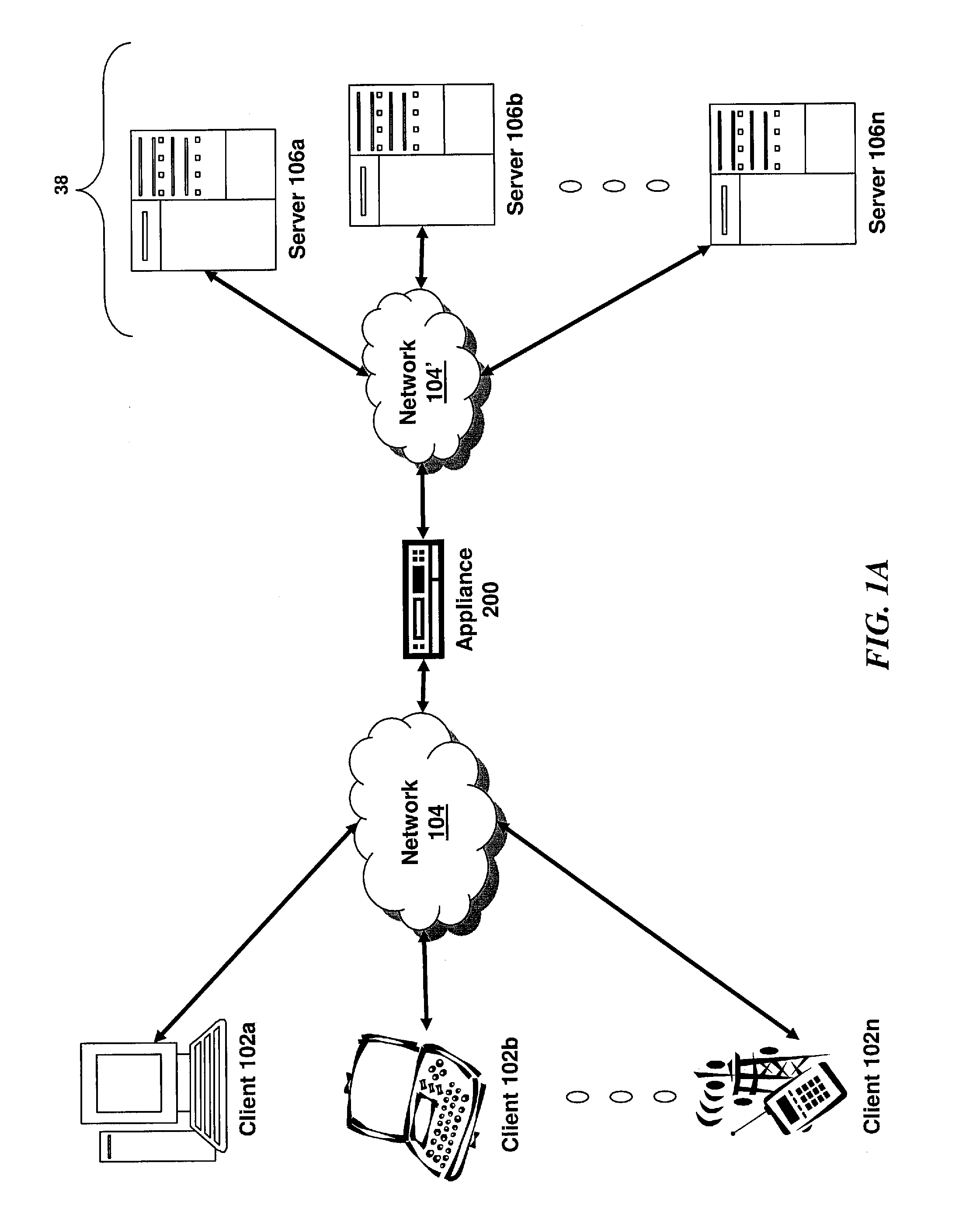

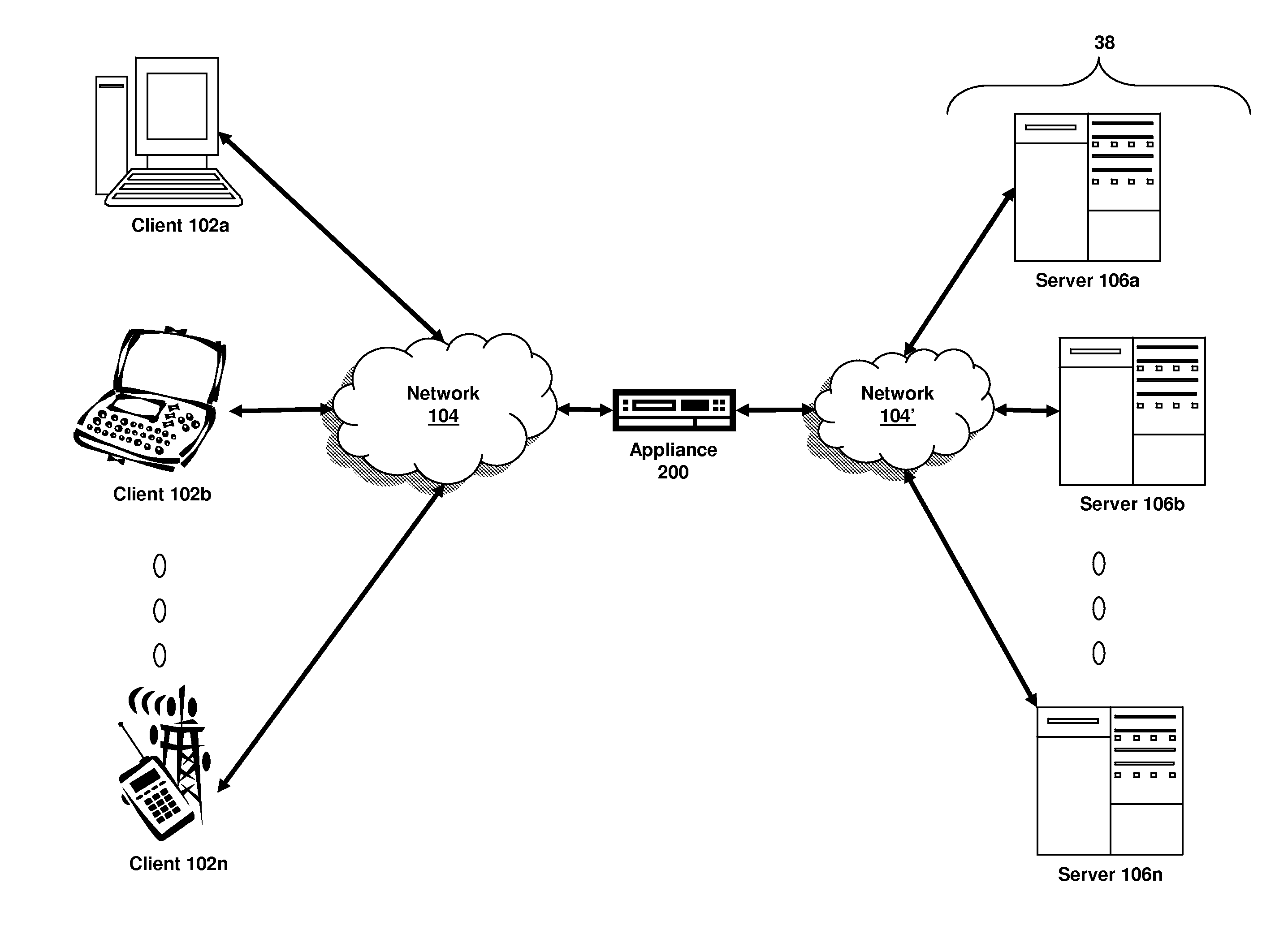

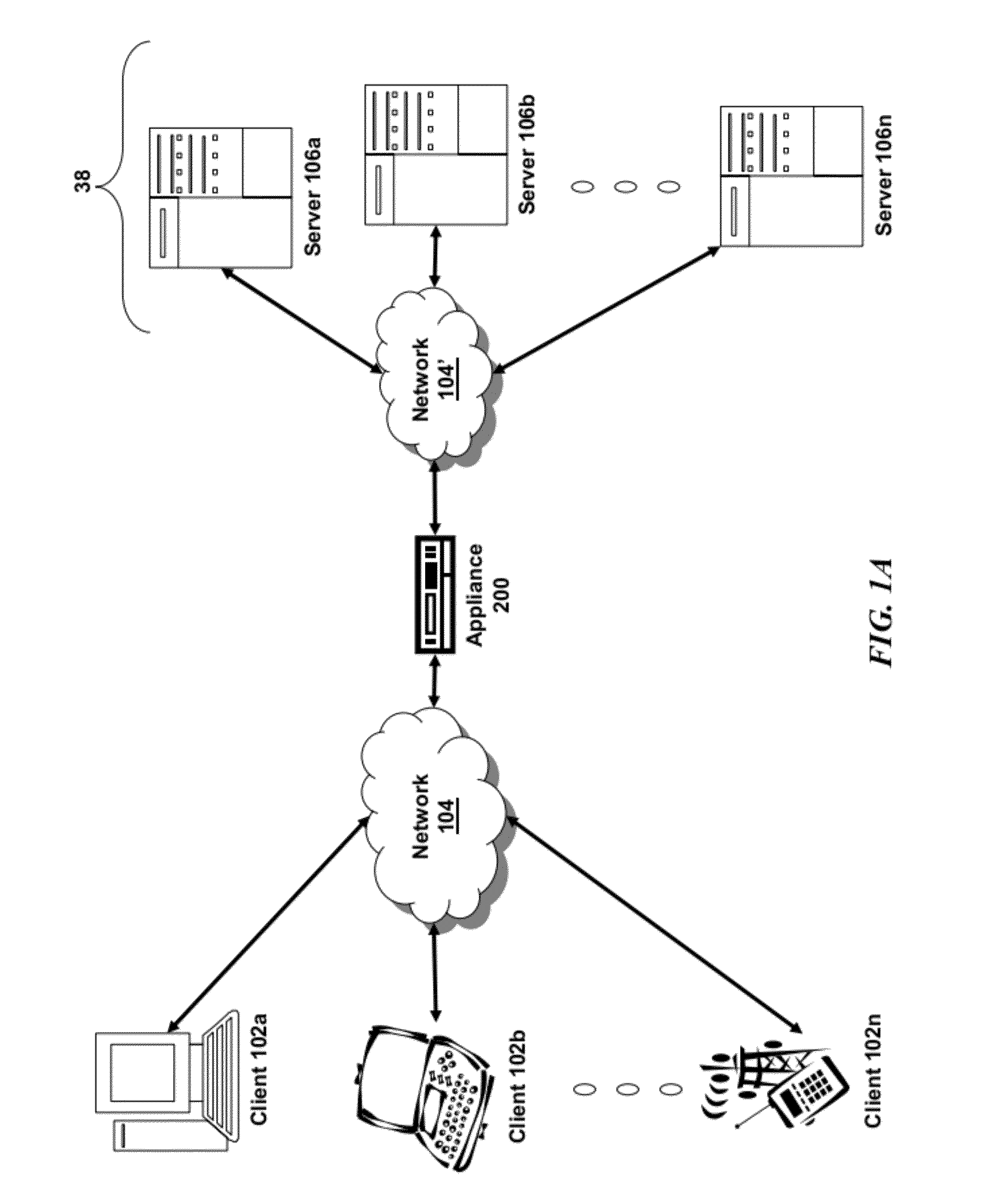

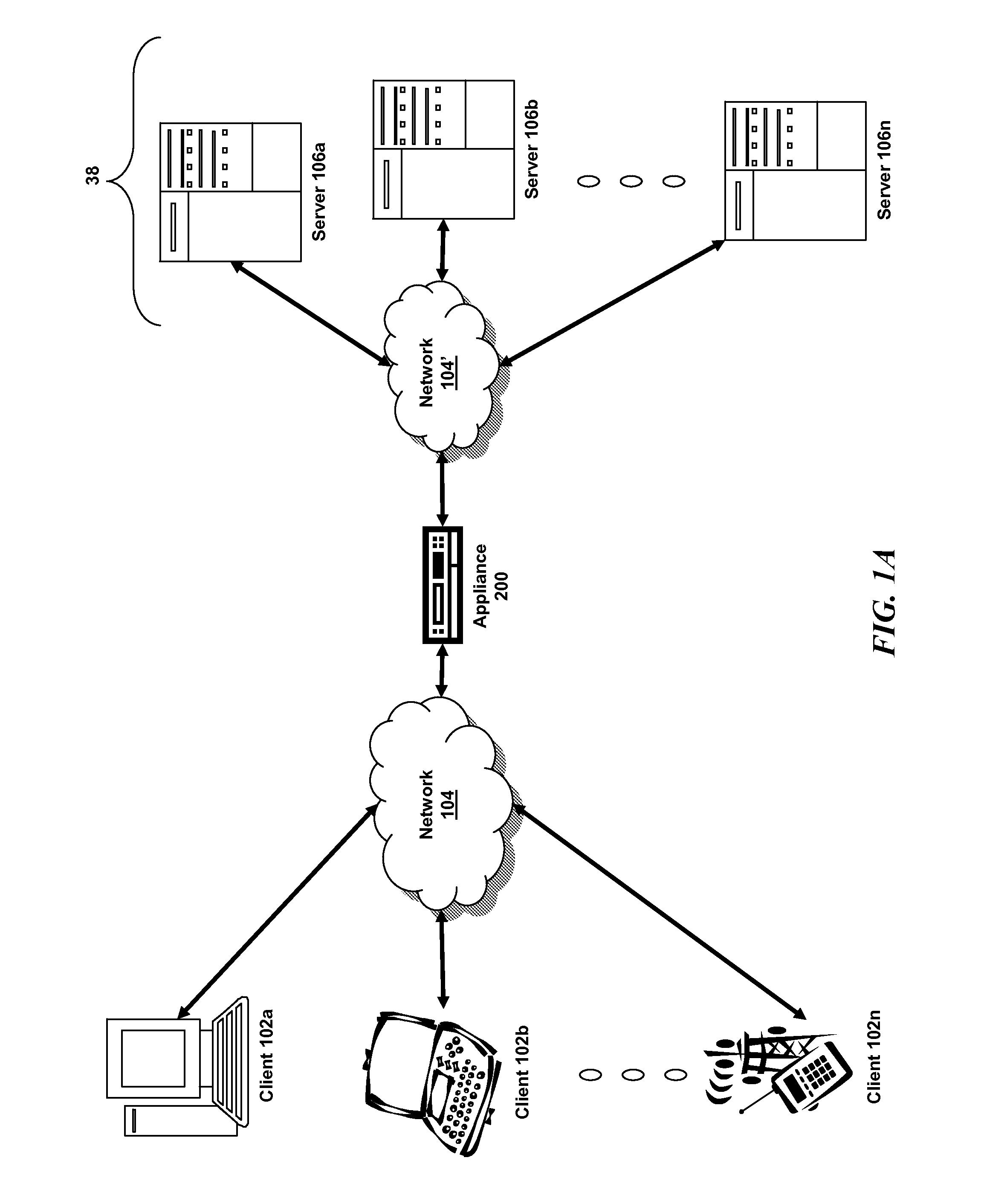

Systems and methods for object rate limiting in multi-core system

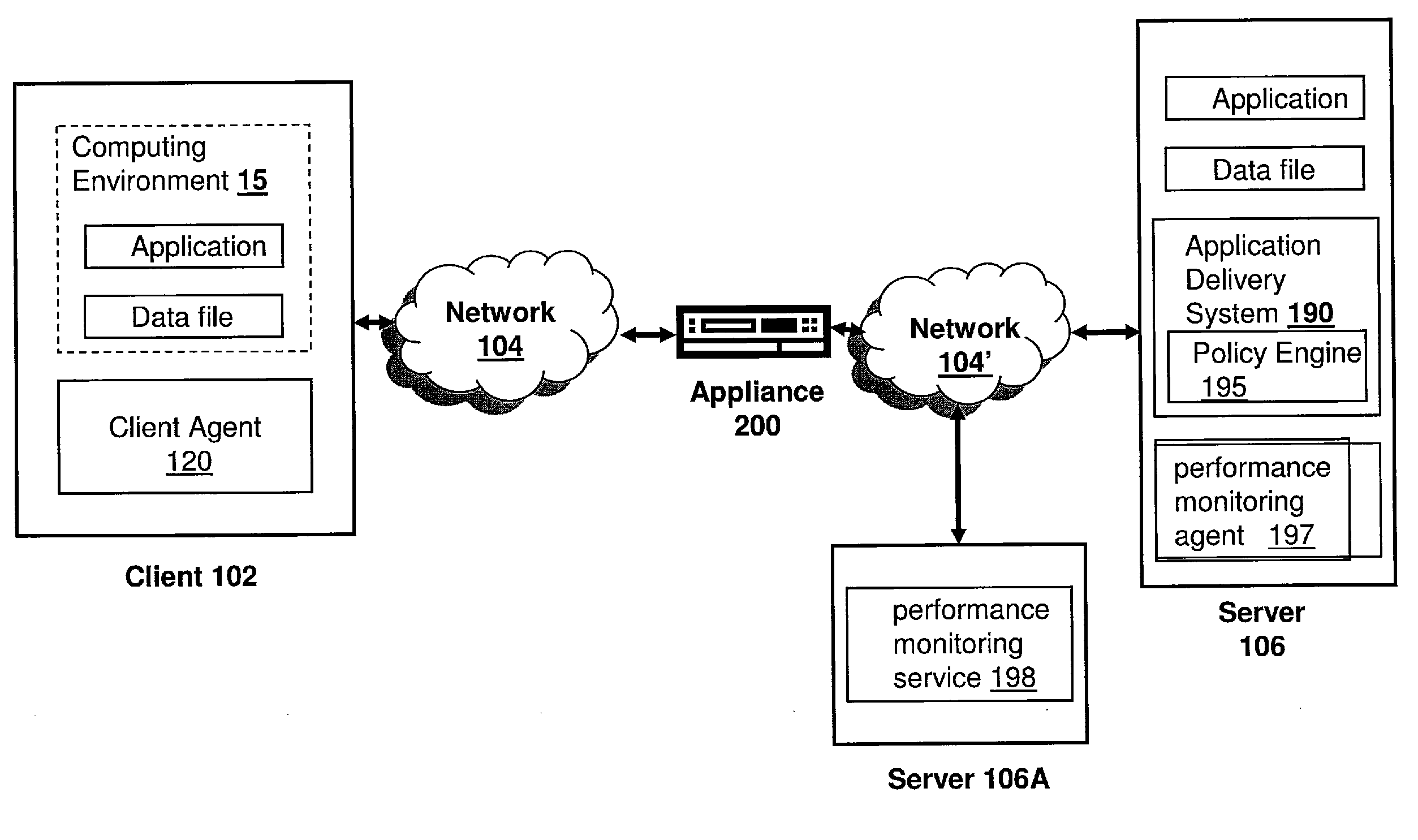

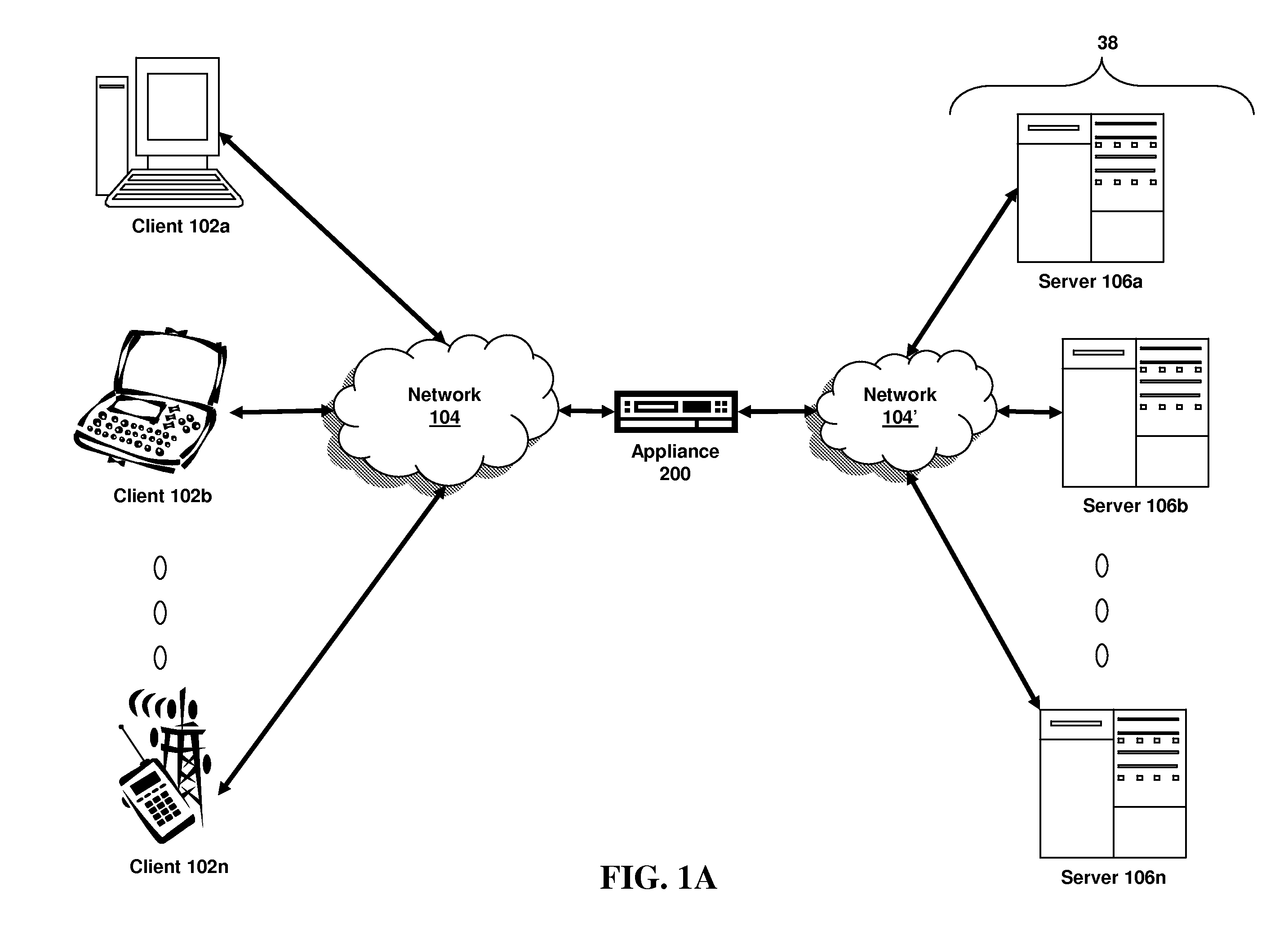

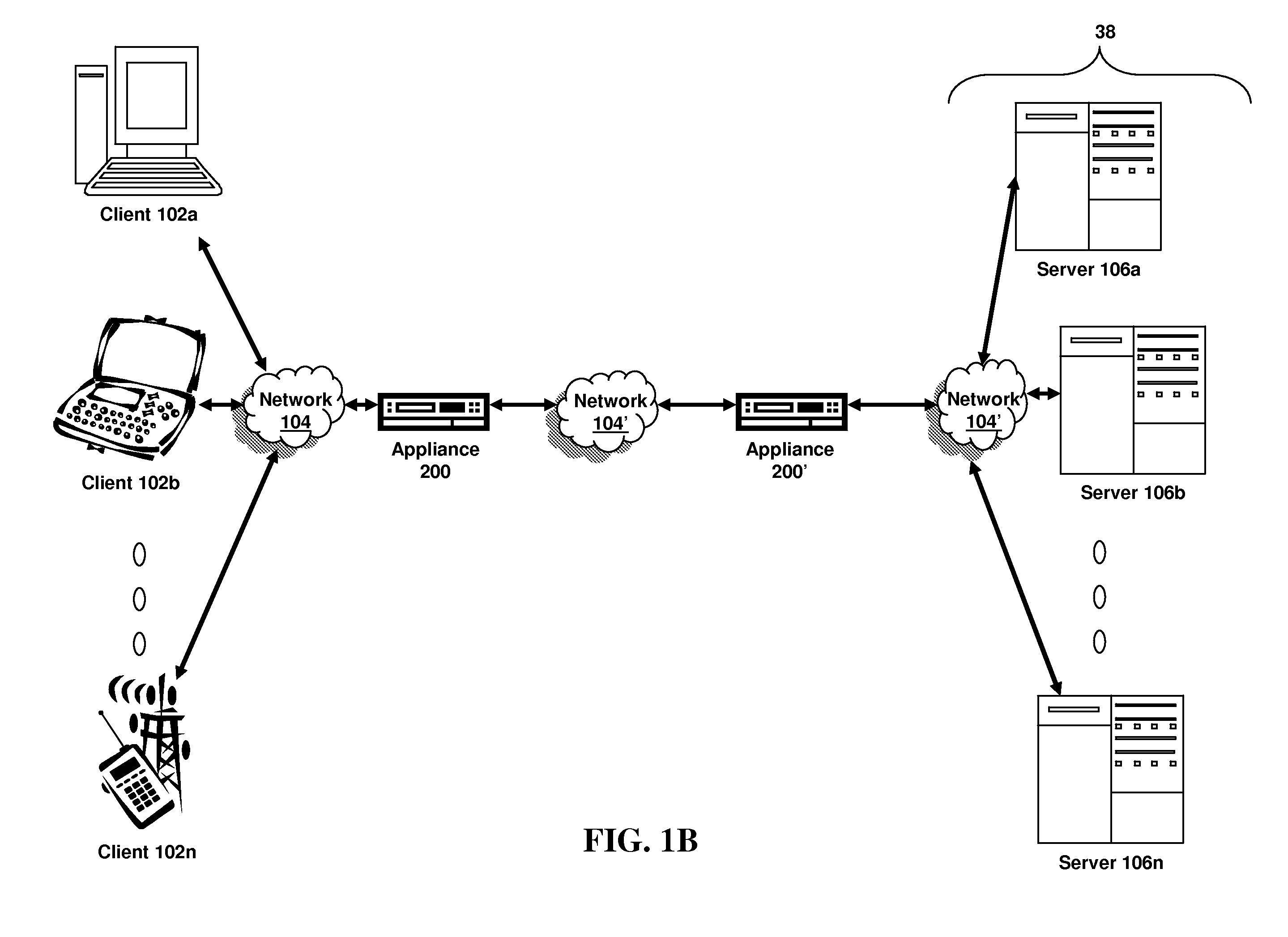

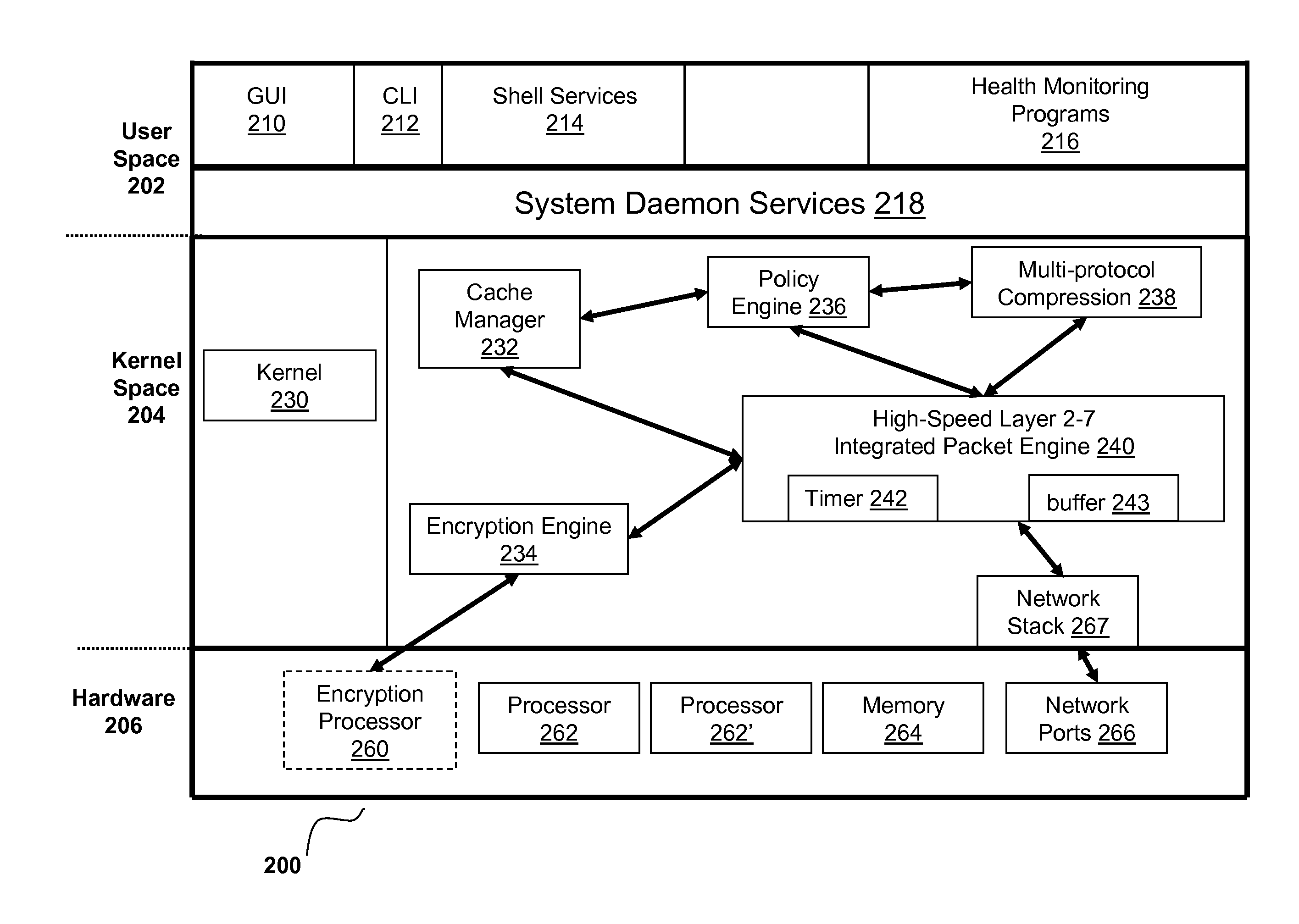

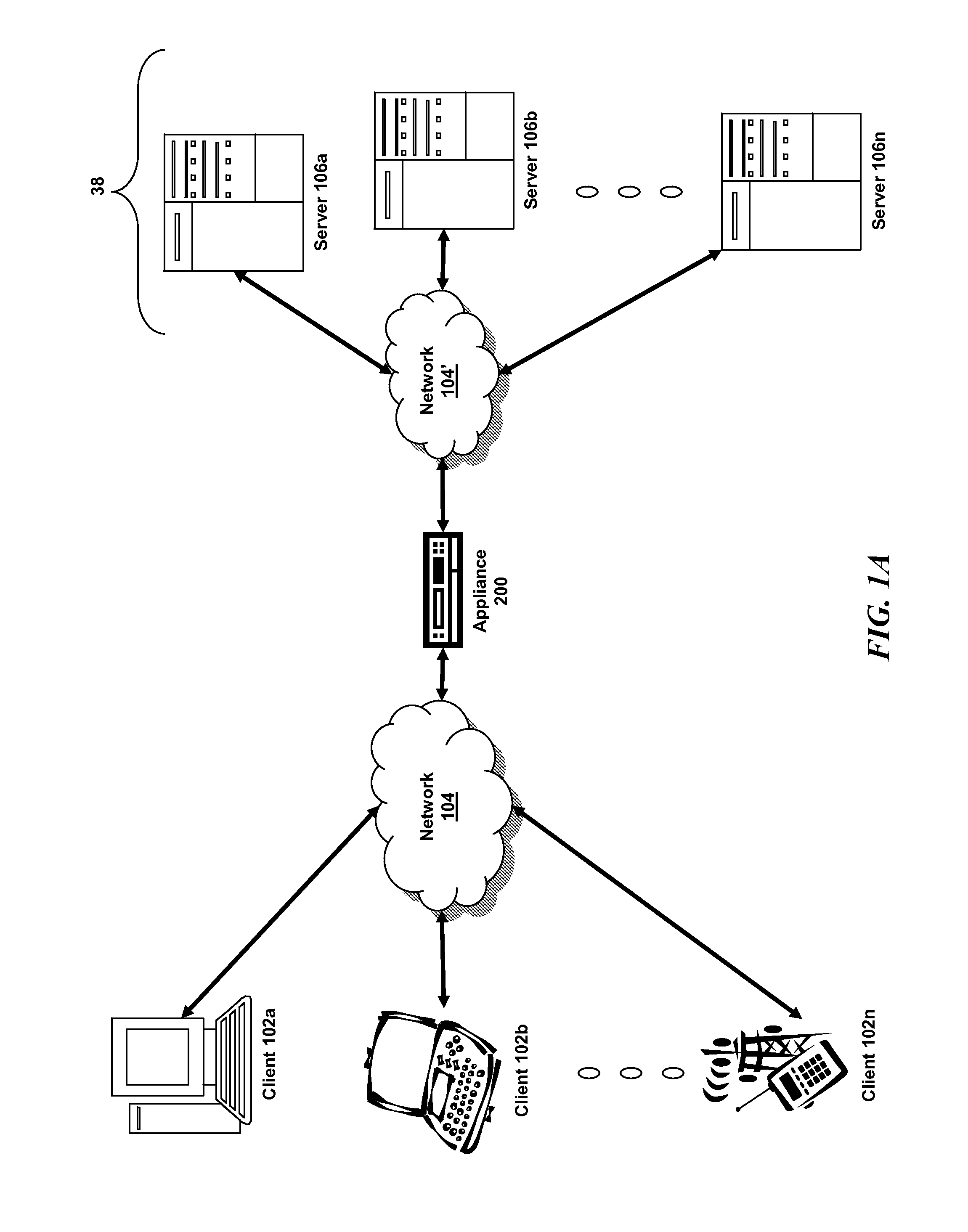

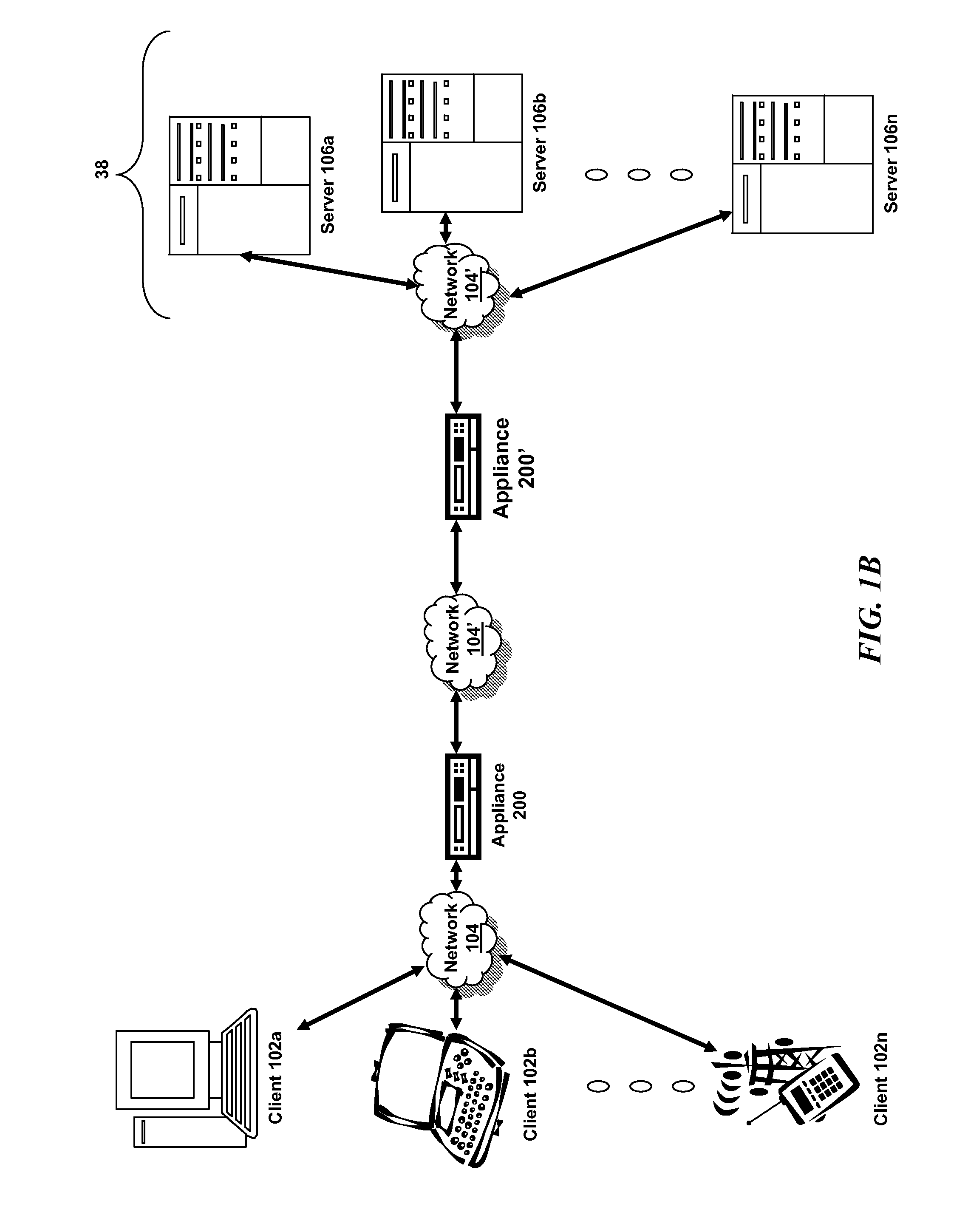

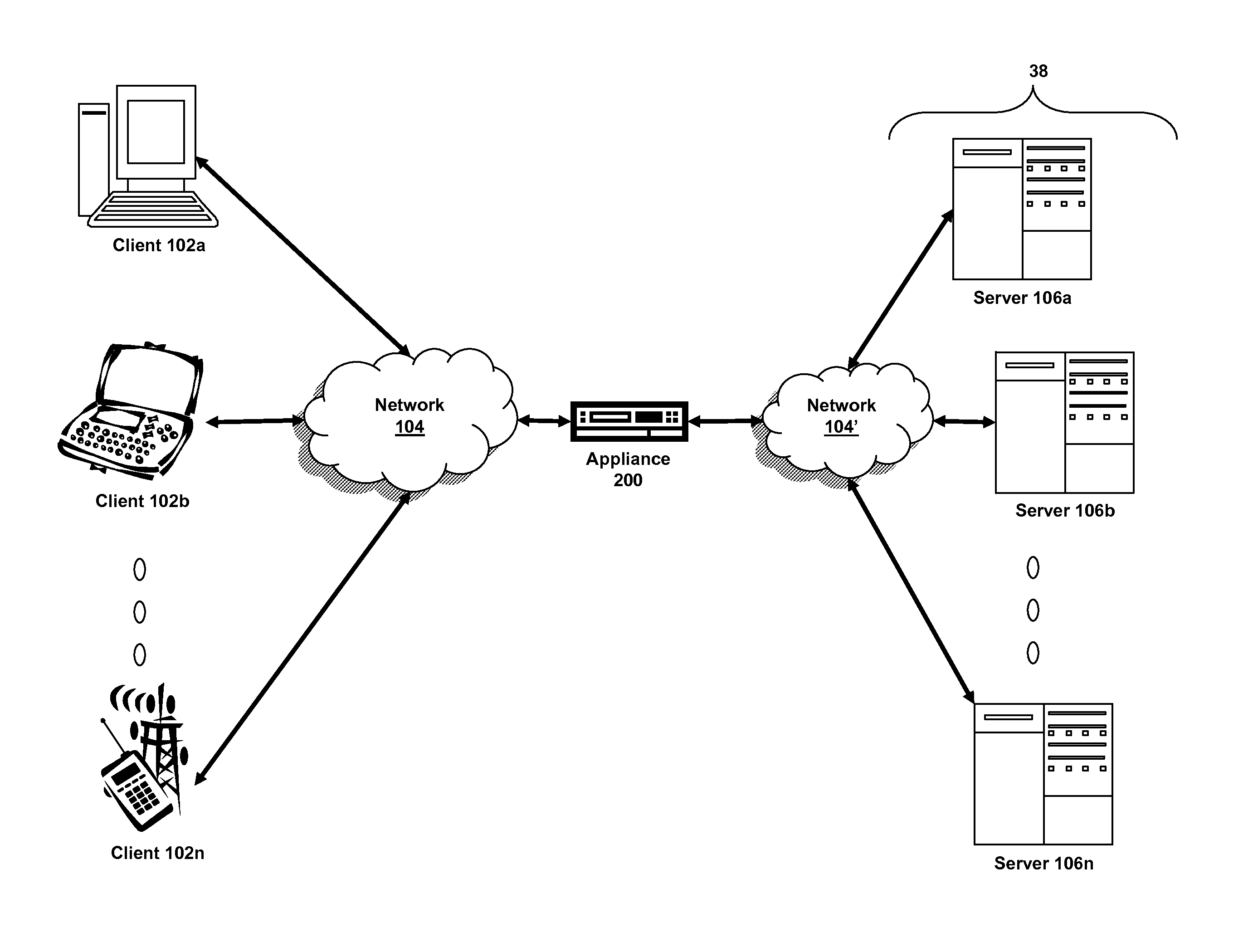

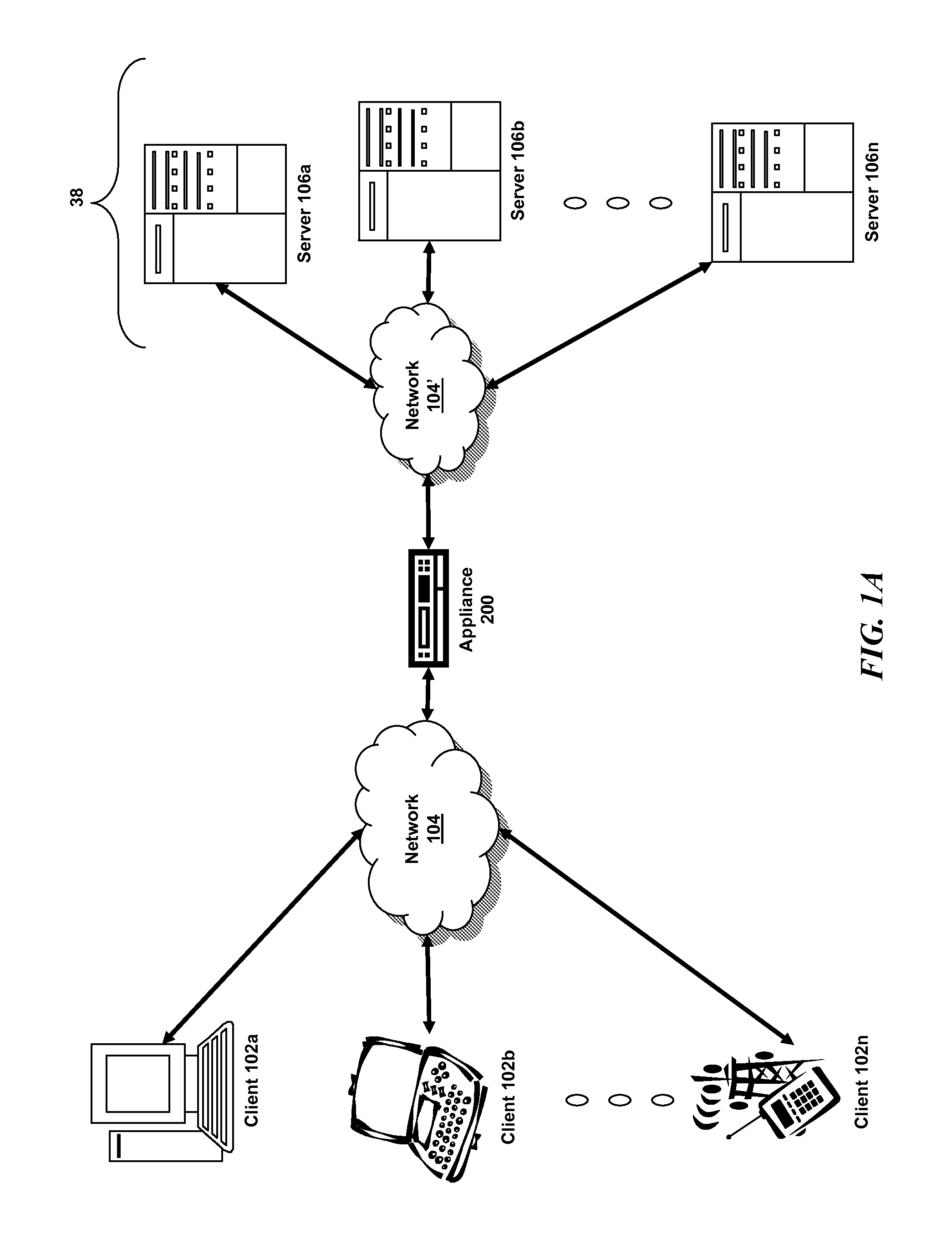

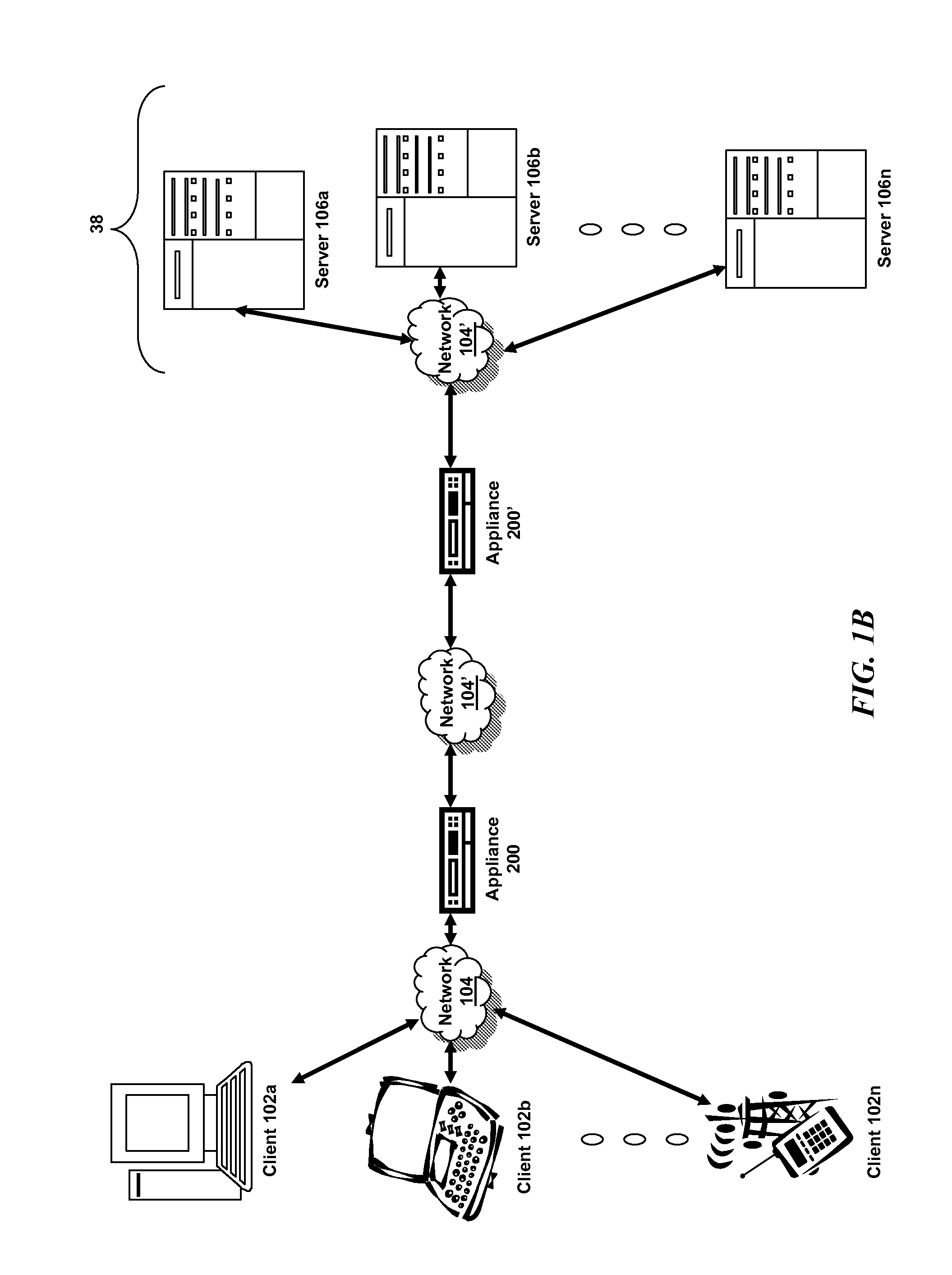

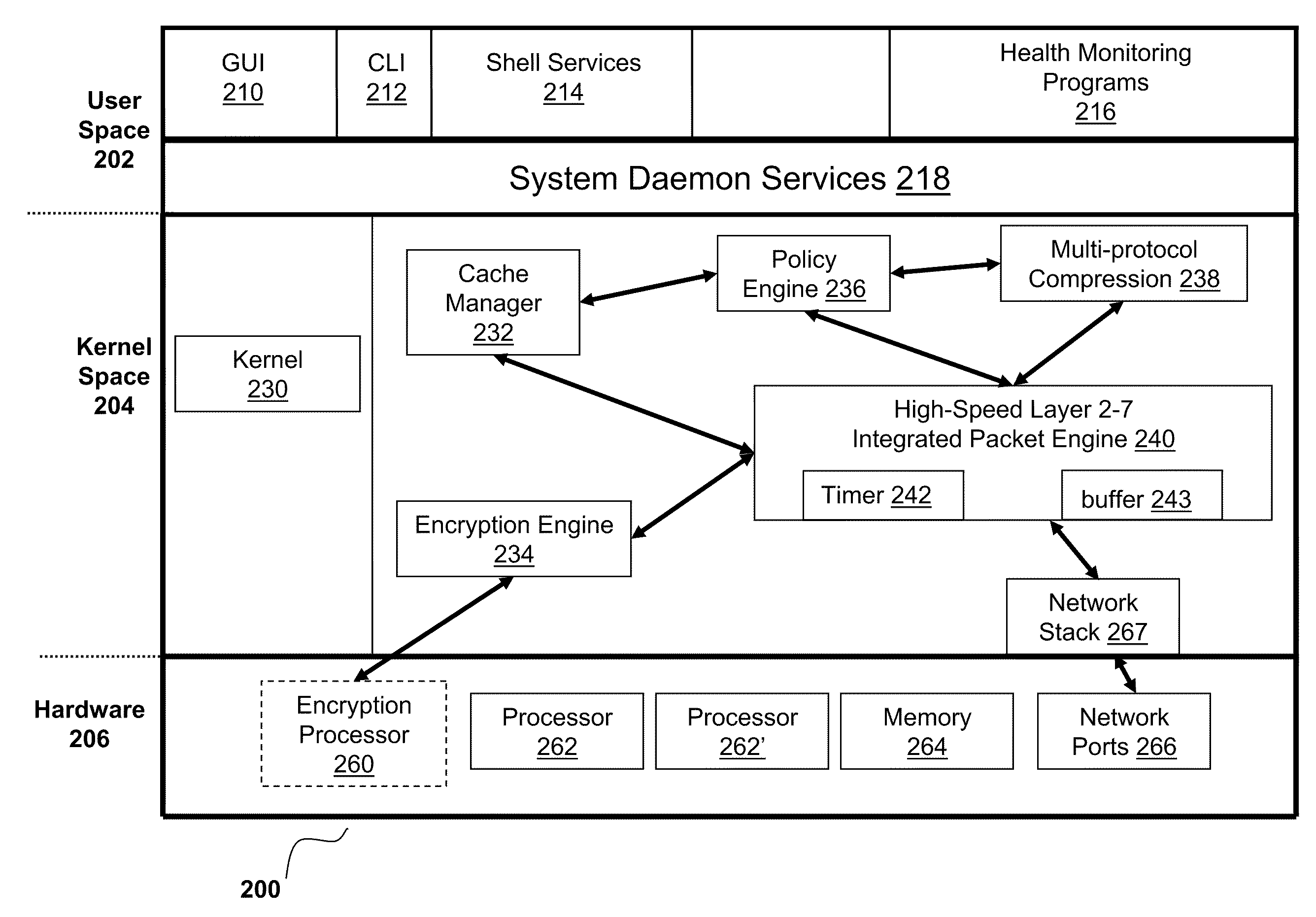

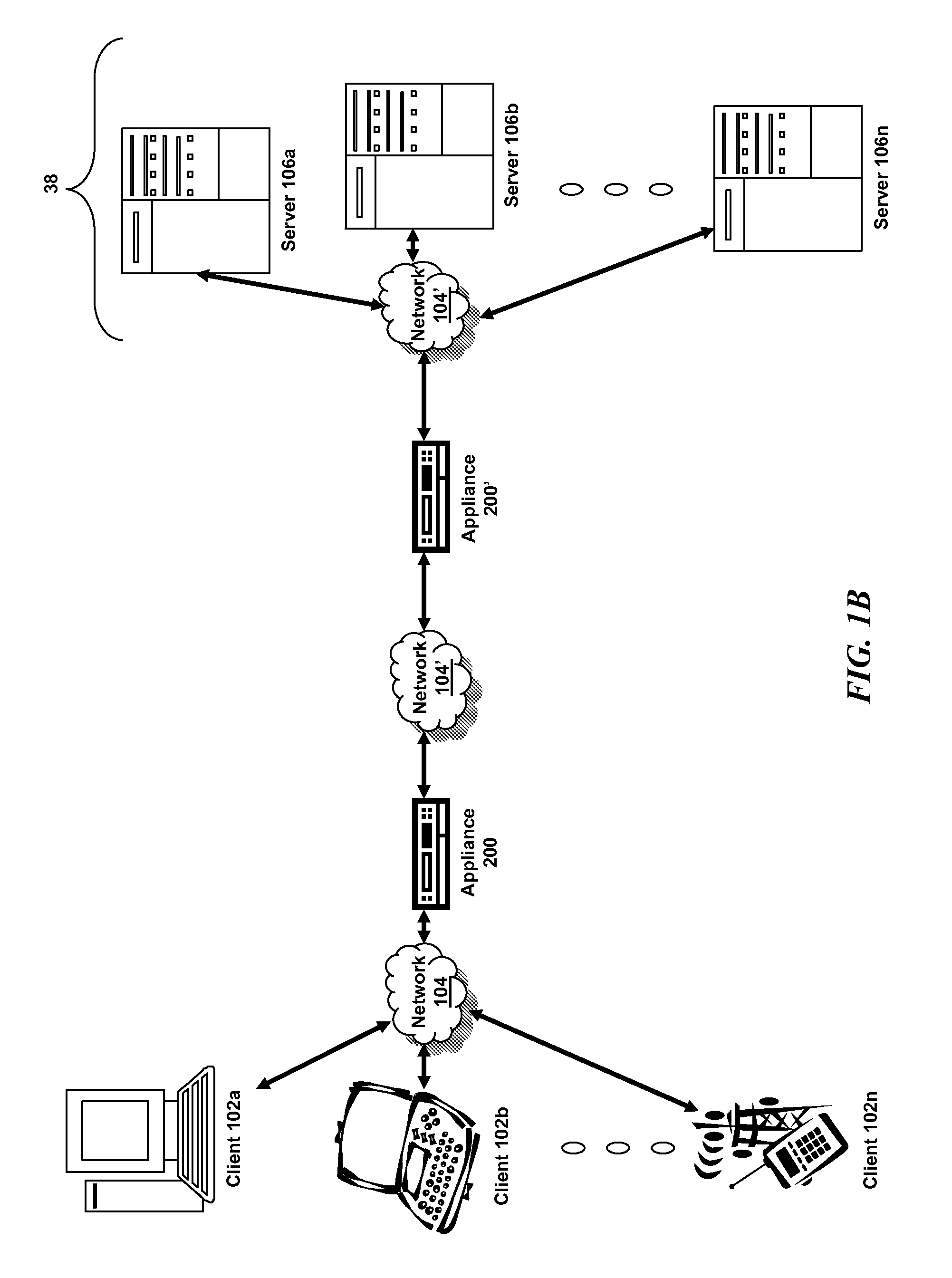

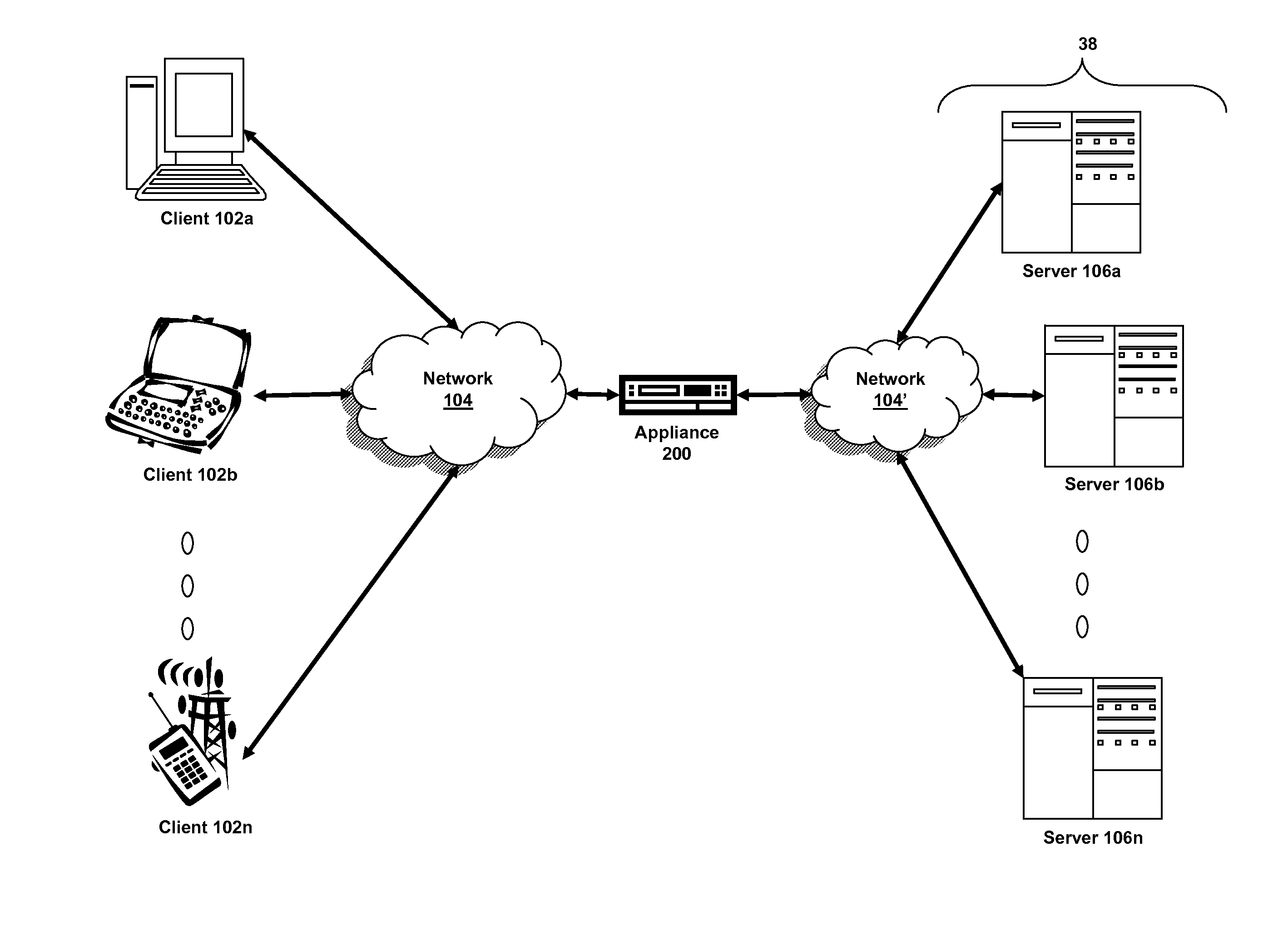

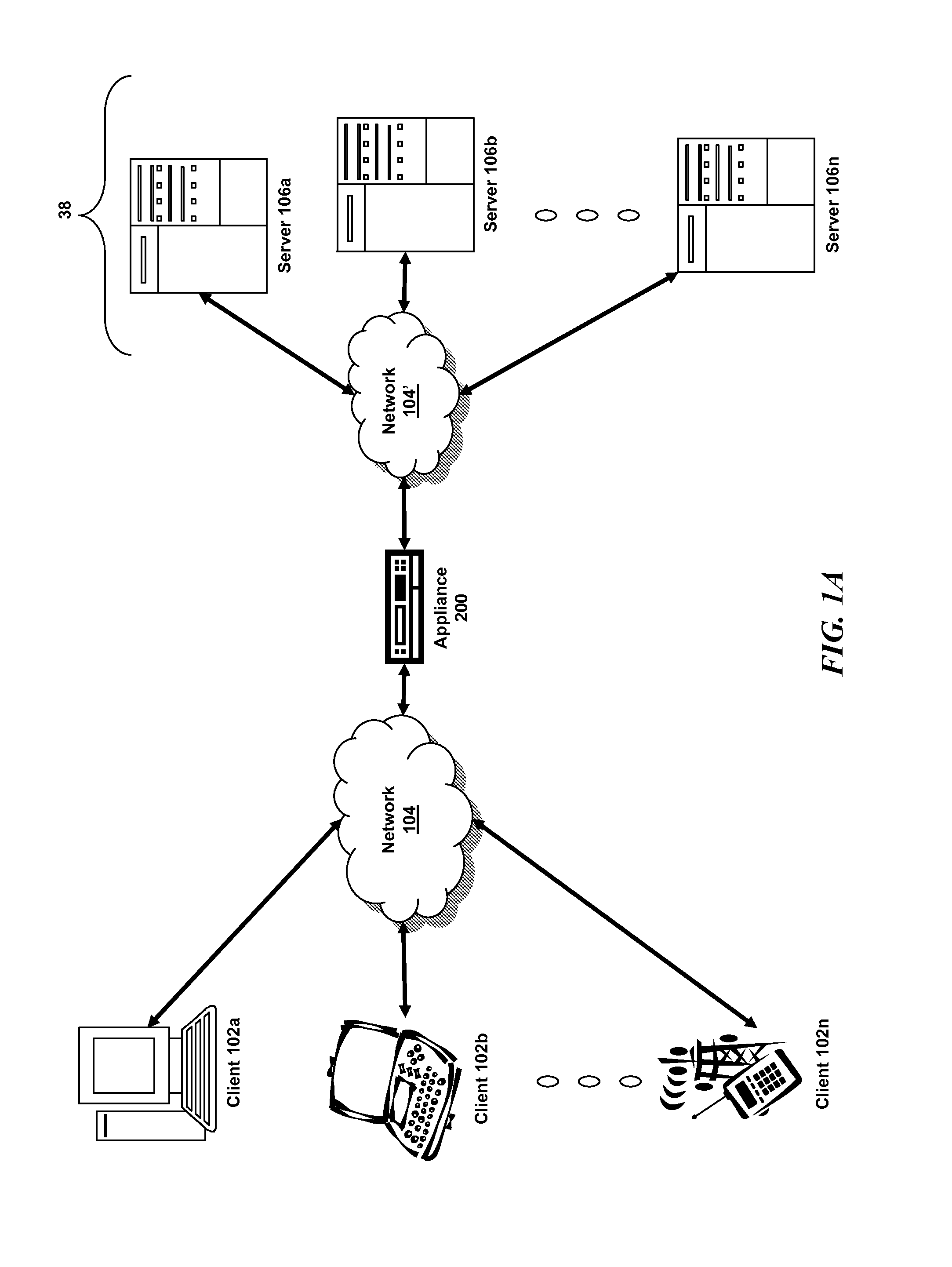

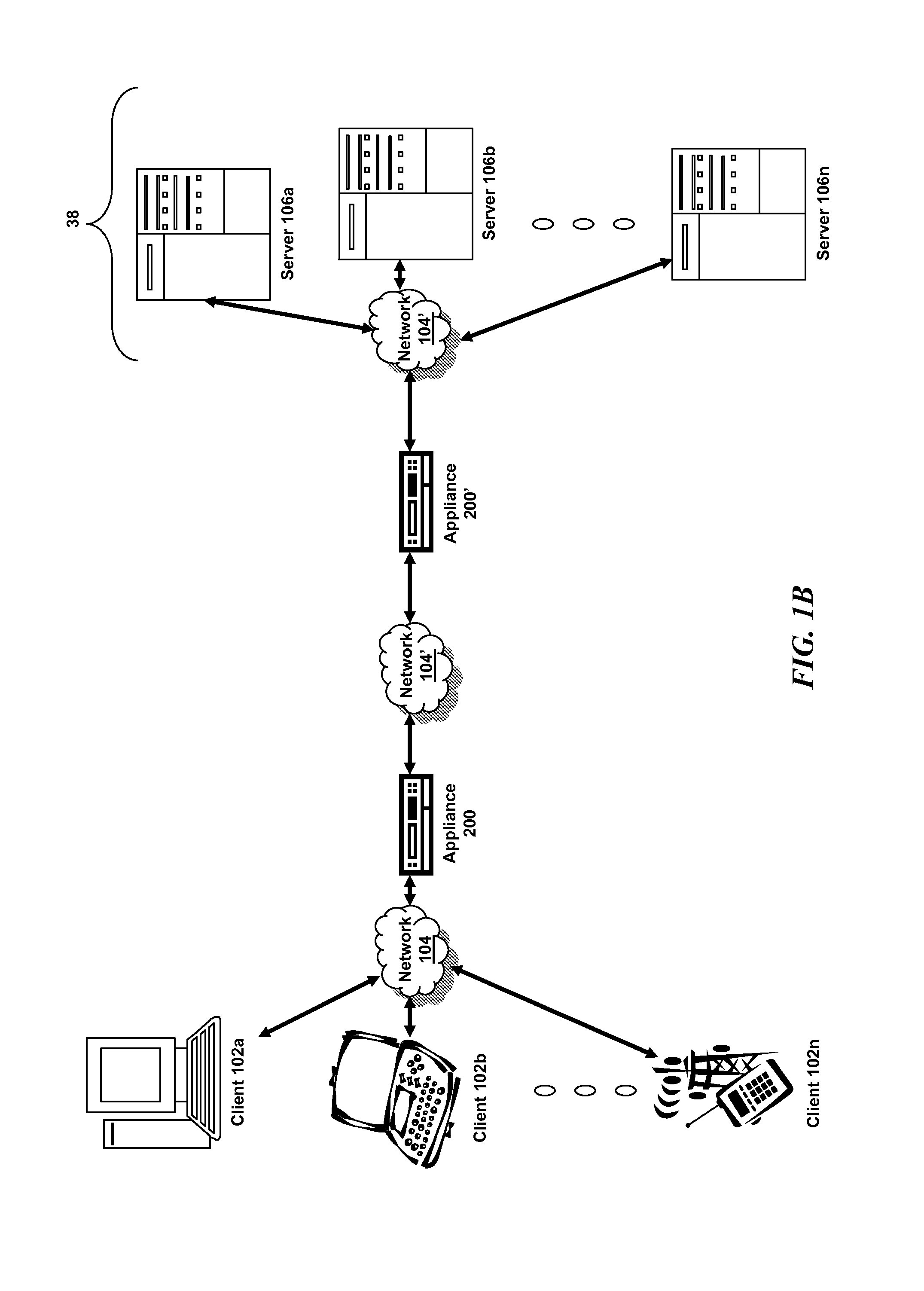

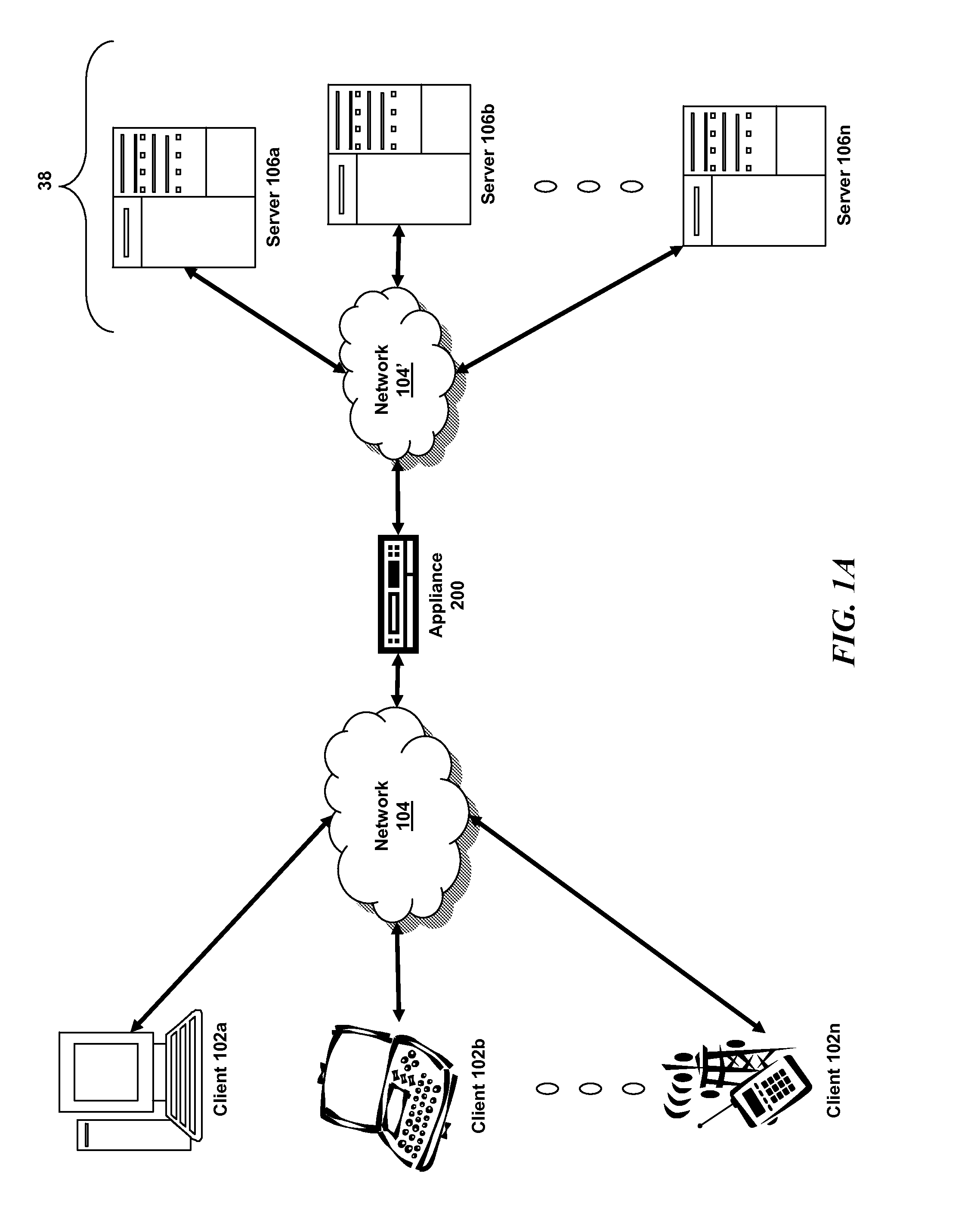

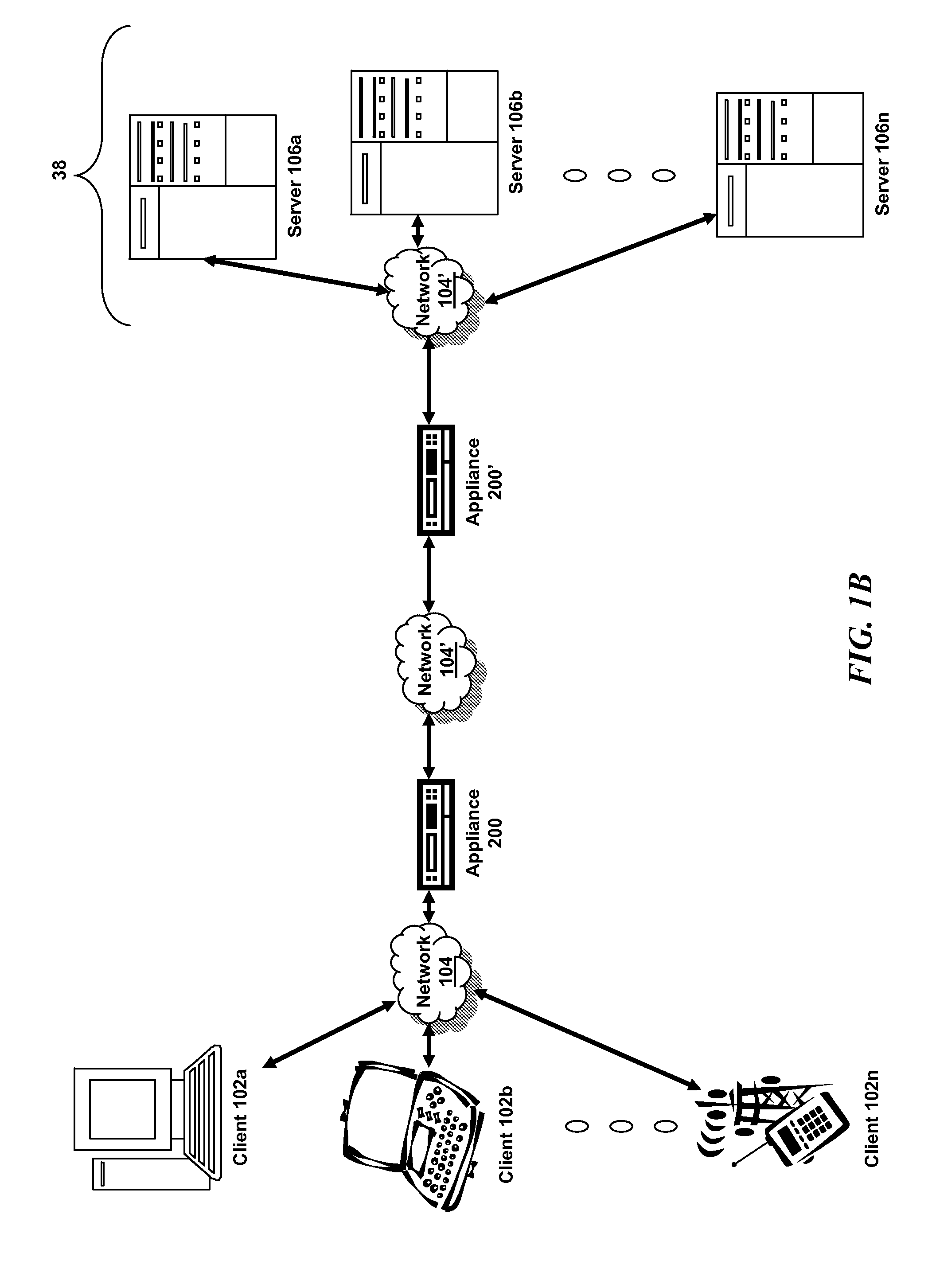

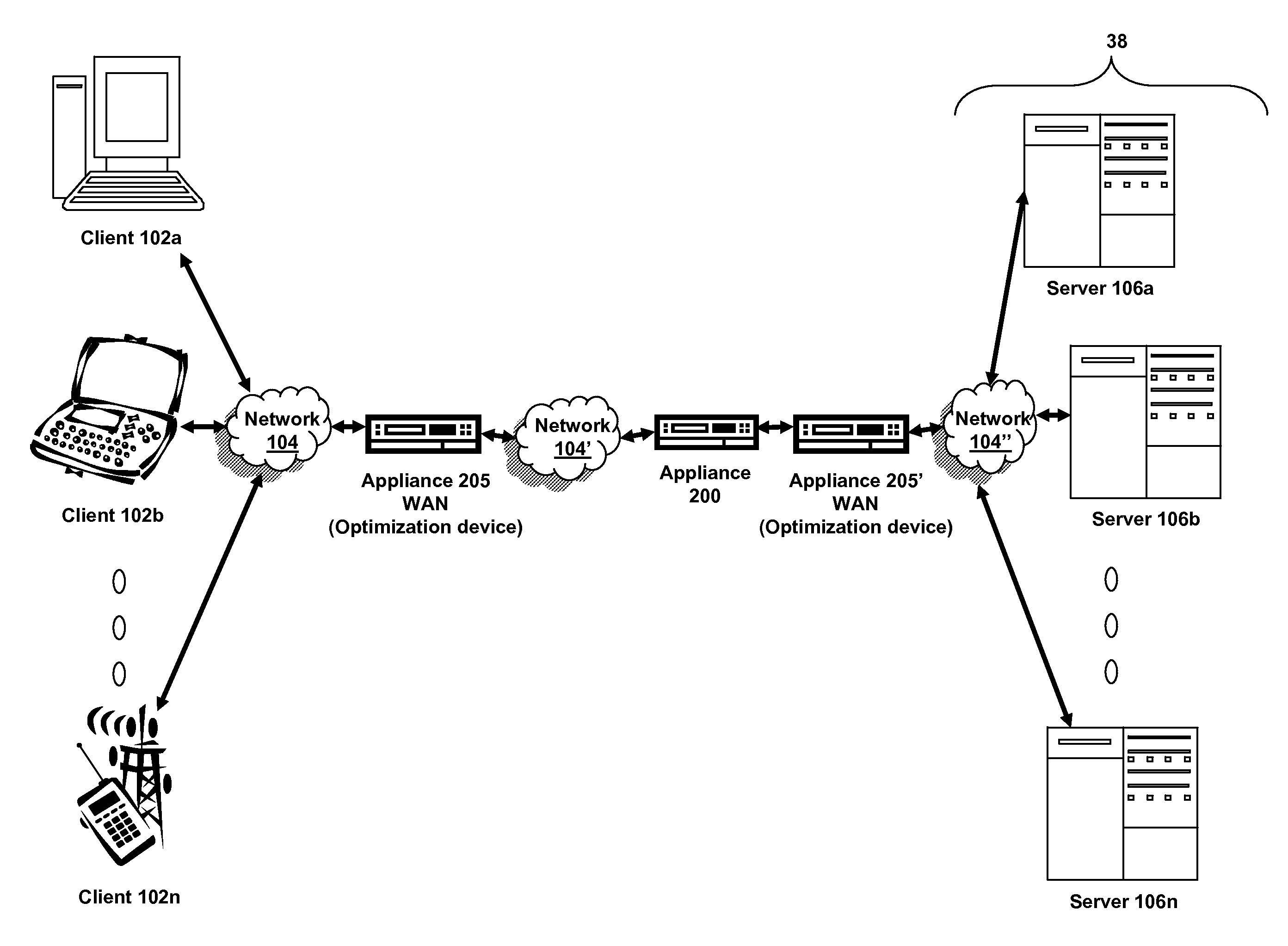

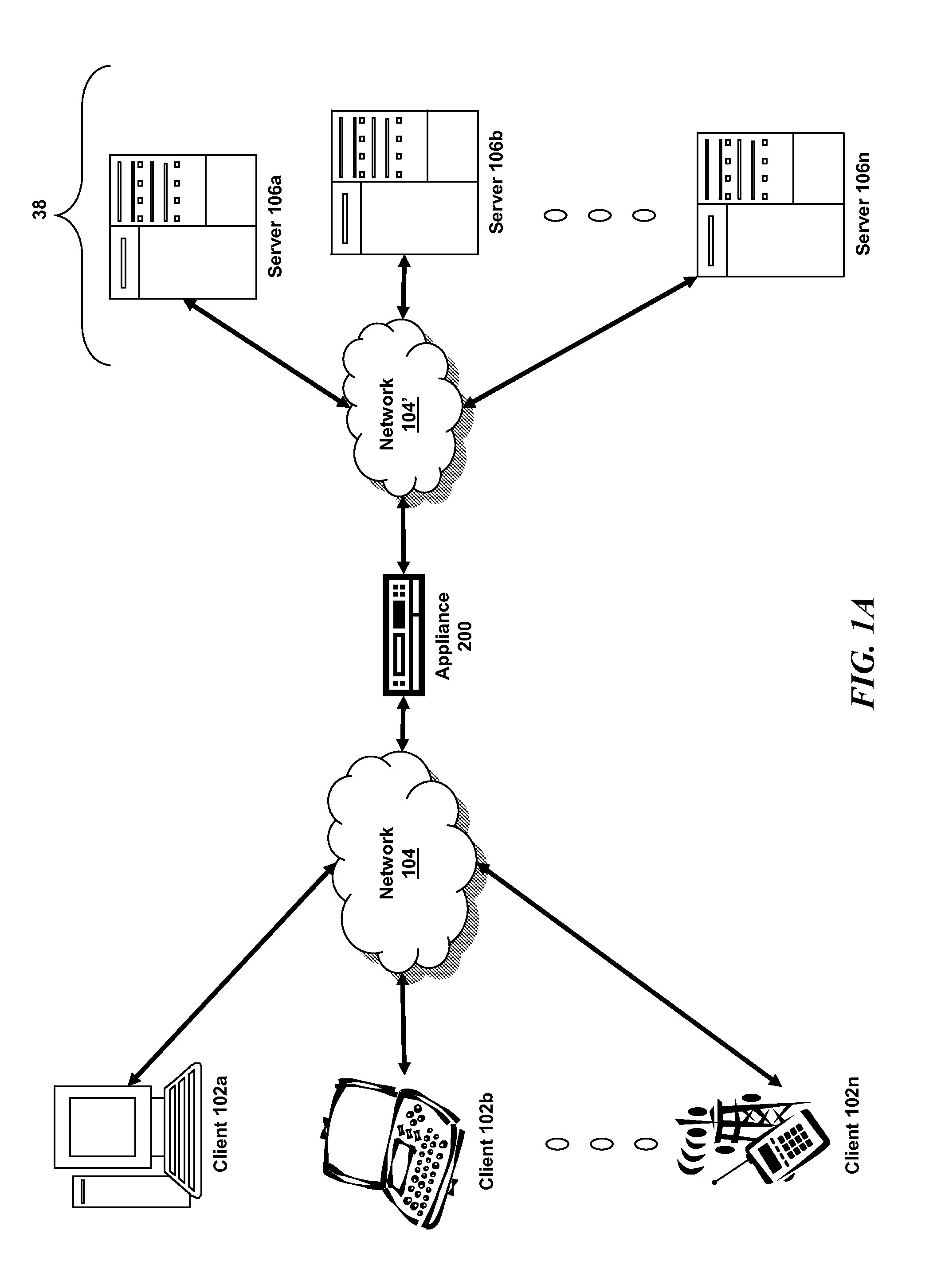

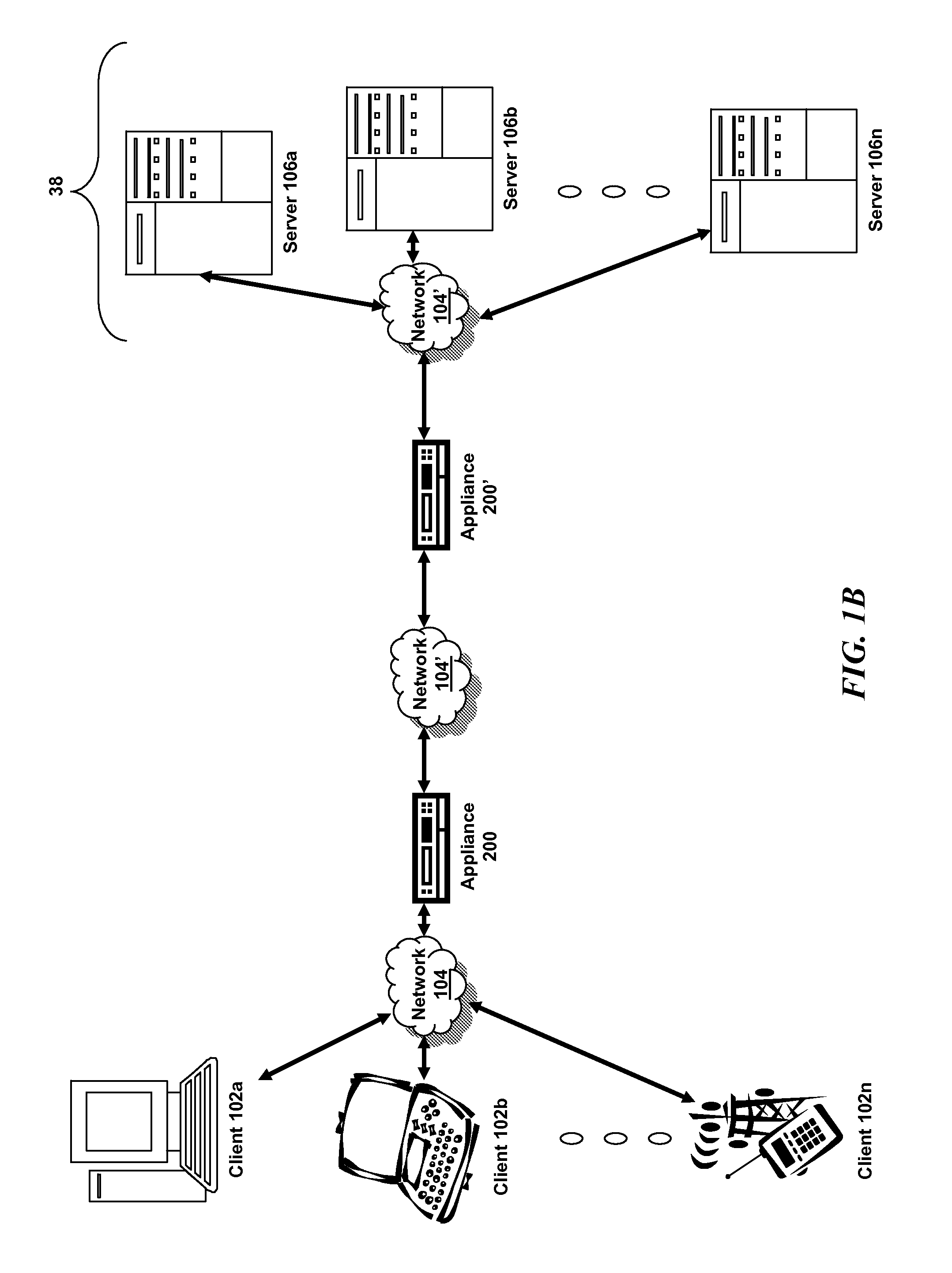

The present invention is directed towards systems and methods for managing a rate of request for an object transmitted between a server and one or more clients via a multi-core intermediary device. A first core of the intermediary device can receive a request for an object and assume ownership of the object. The first core can store the object in shared memory along with a rate-related counter for the object and generate a hash to the object and counter. Other cores can obtain the hash from the first core and access the object and counter in shared memory. Policy engines and throttlers in operation on each core can control the rate of access to the stored object.

Owner:CITRIX SYST INC

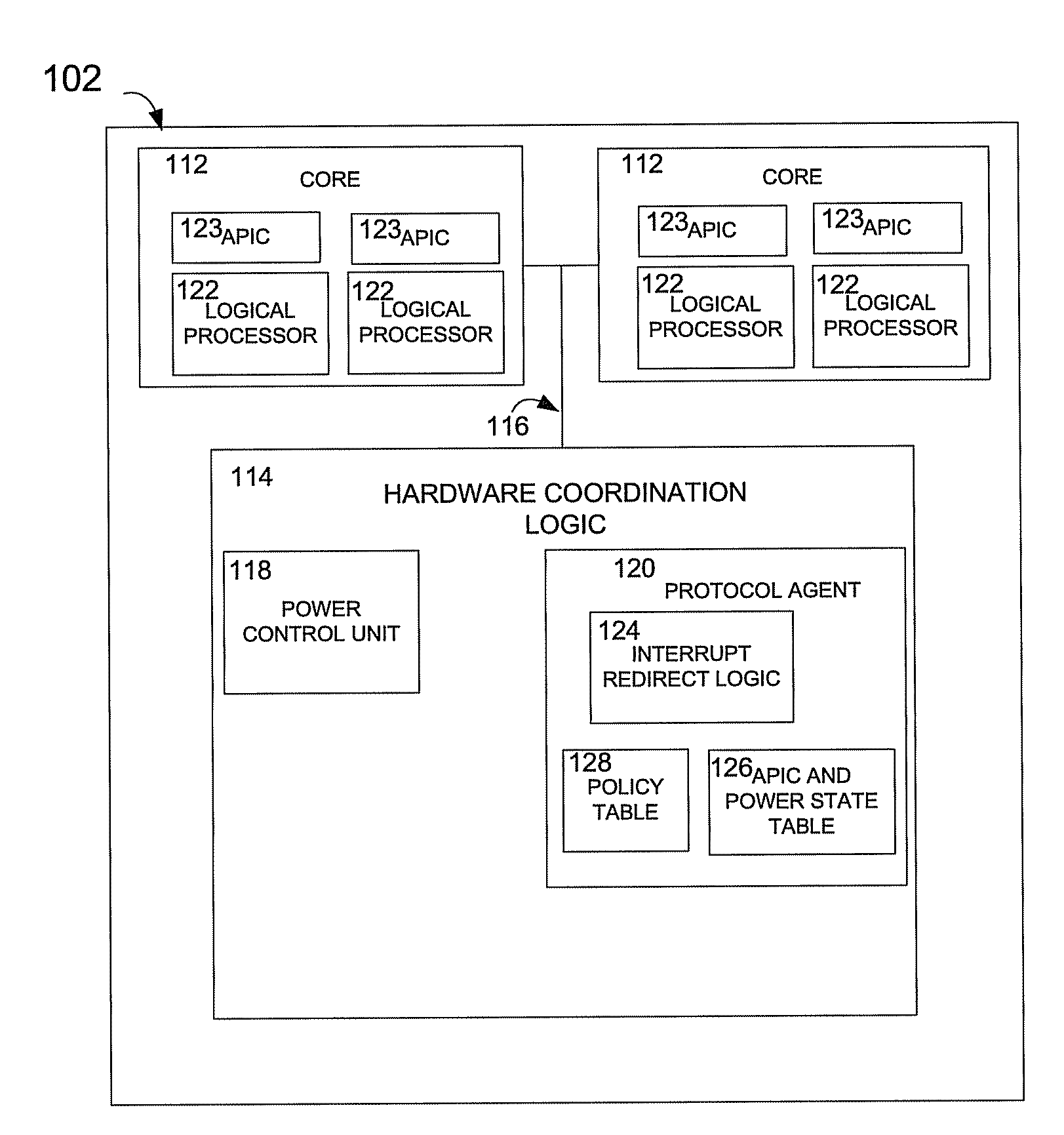

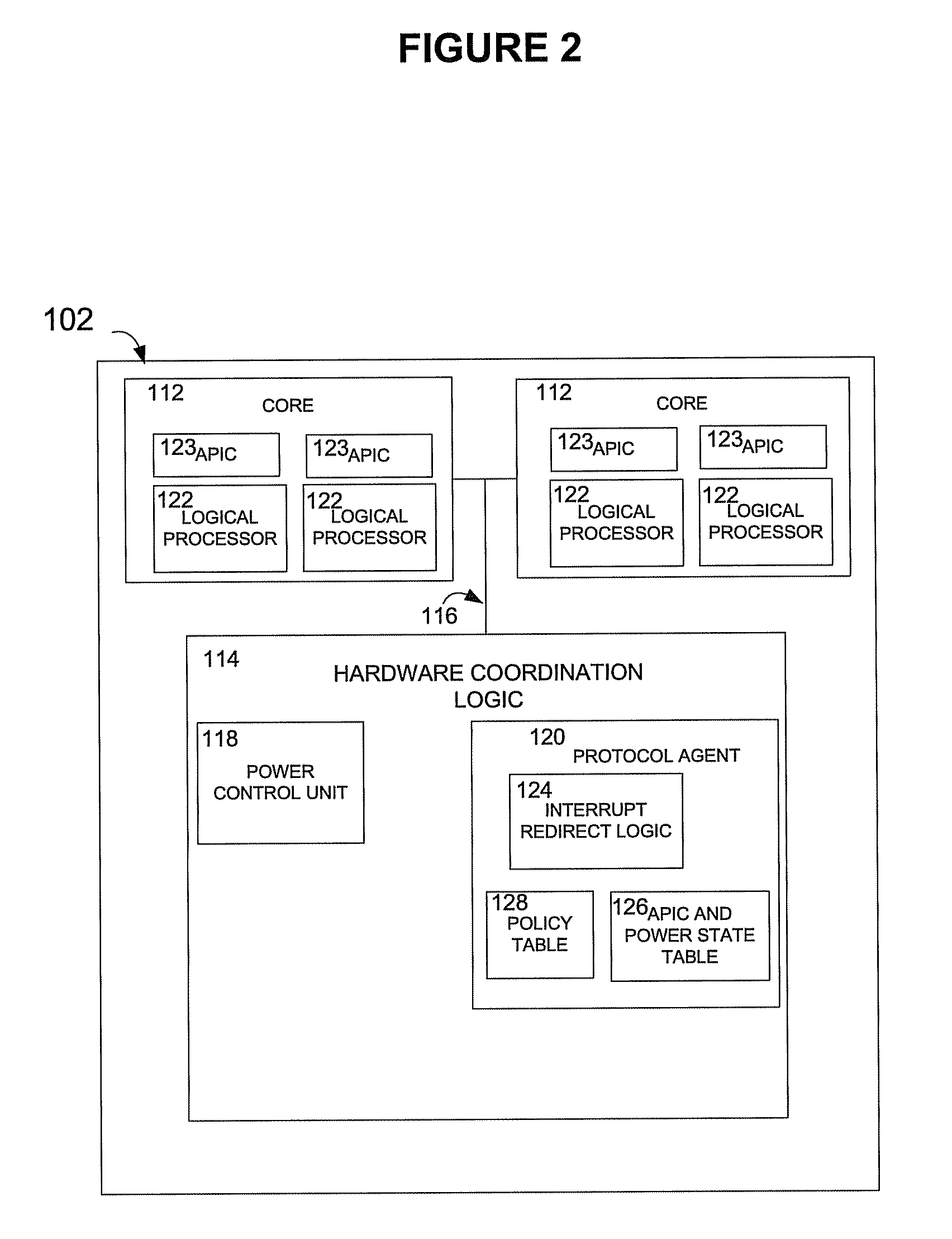

Method, system, and apparatus for rerouting interrupts in a multi-core processor

InactiveUS20090172423A1Energy efficient ICTDigital data processing detailsMulticore systemsEmbedded system

A method, system, and apparatus may route an interrupt to a first core of a plurality of cores of a multi-core system. If the first core is in an idle or low power state, or operating in a power state at or below a threshold power state, a core in a least idle state may be found. The interrupt may be rerouted to and processed by the core in the least idle state. Cores in a multi-core system may be rated based on for example, power states or other characteristics, and interrupts may be assigned based on these ratings. Other embodiments are described and claimed.

Owner:INTEL CORP

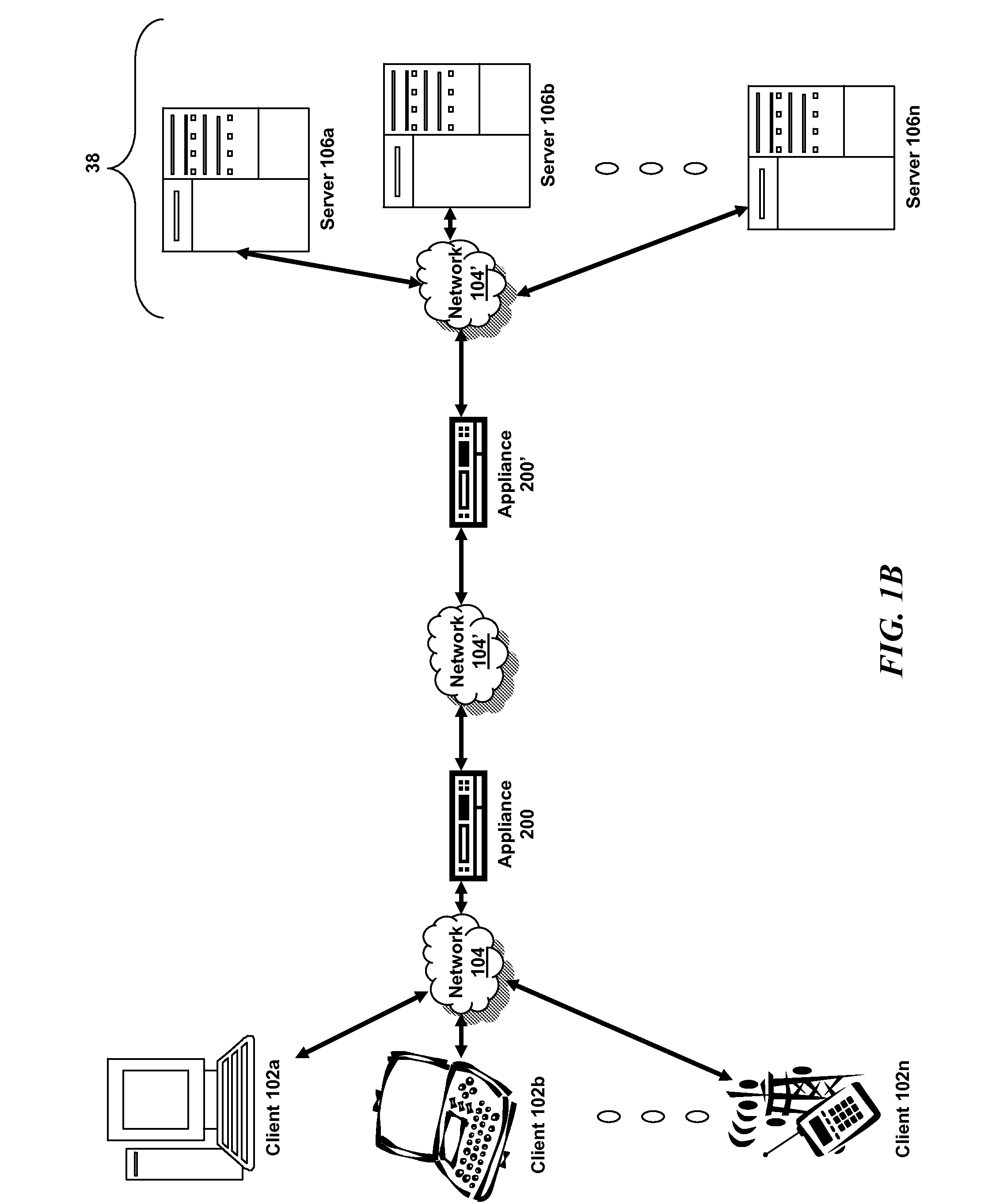

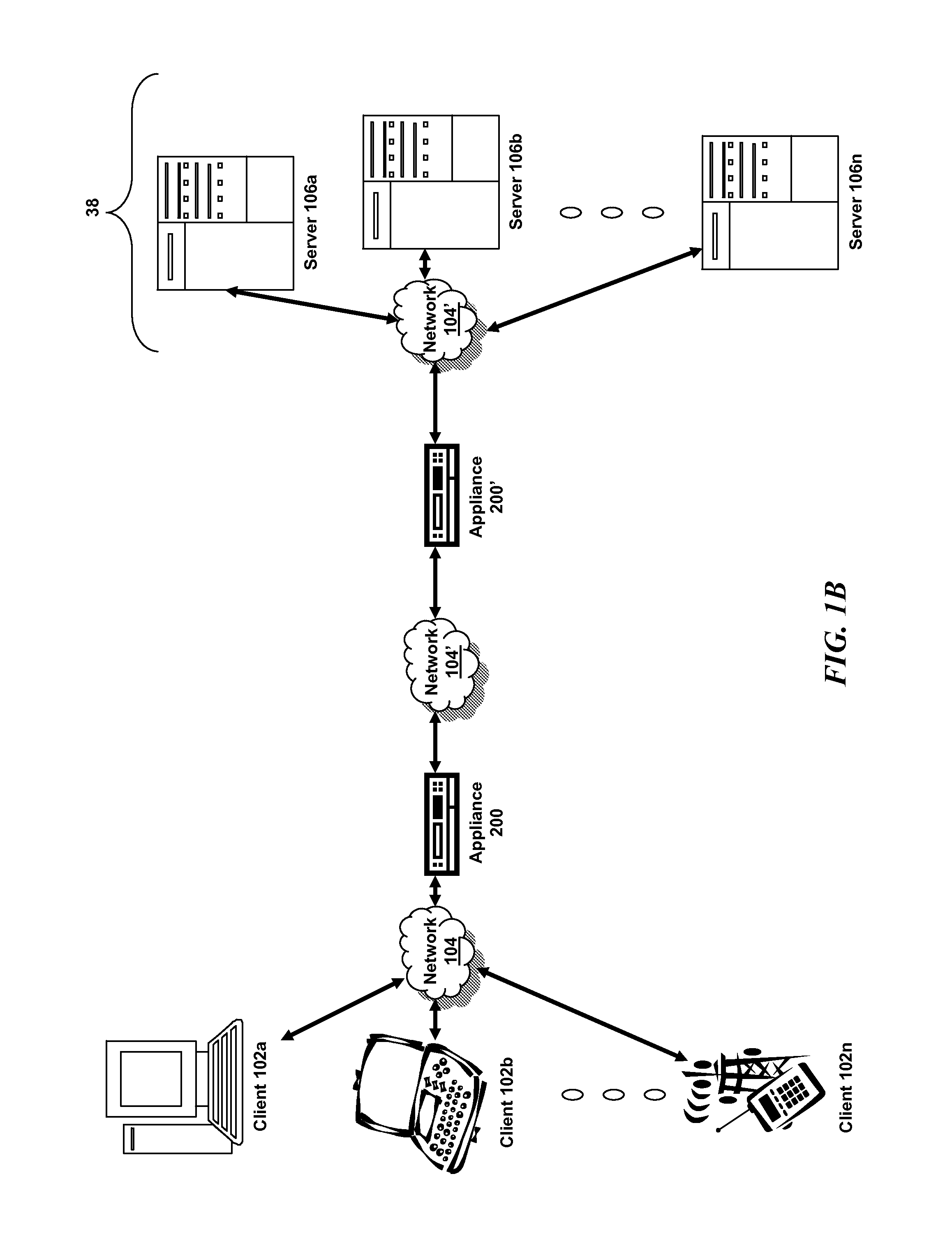

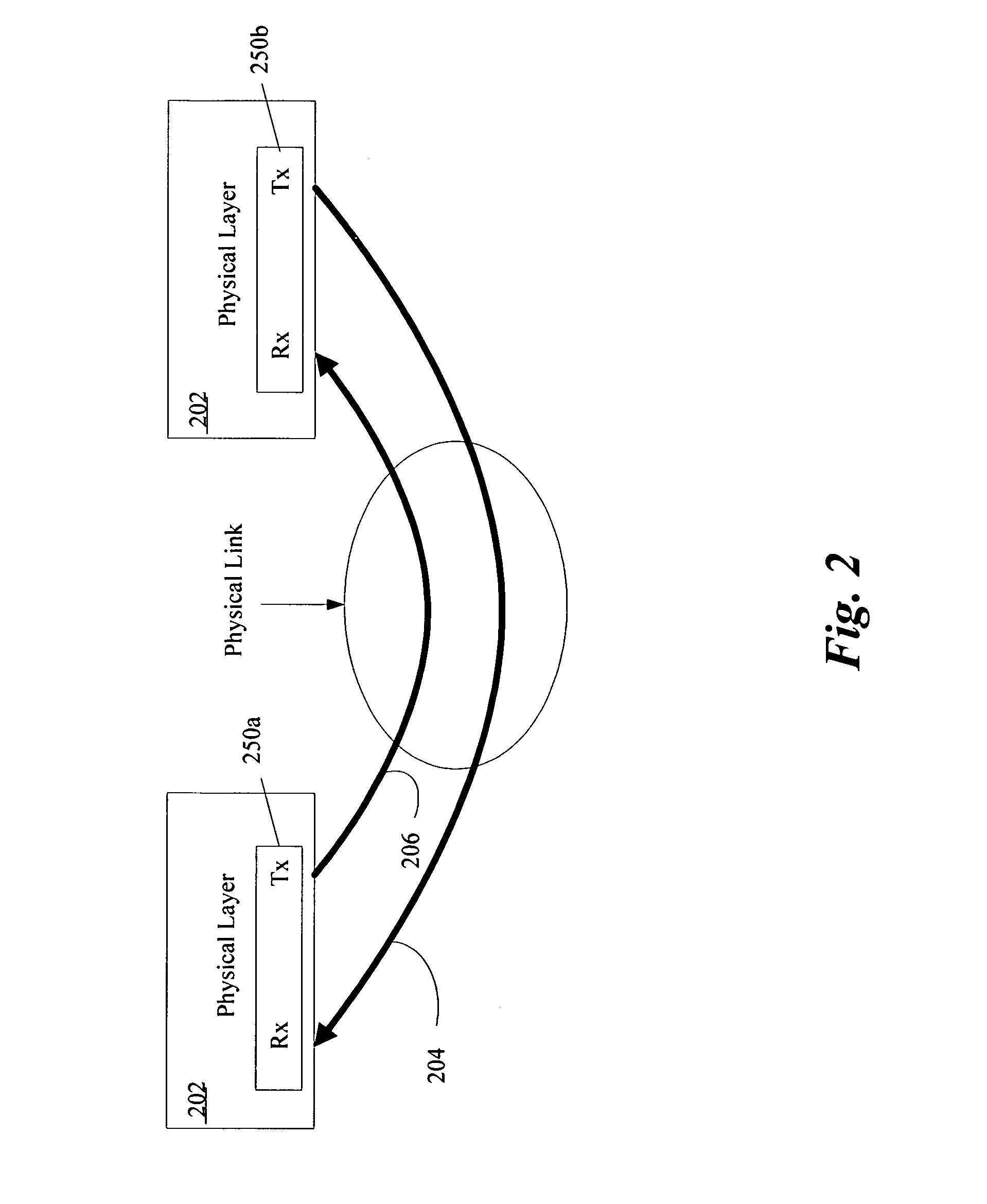

Systems and methods for providing link management in a multi-core system

The present application is directed towards systems and methods for providing link management in a multi-core system. In some embodiments, the present application describes solutions for managing address resolution in IPv4 networks in a multi-core system. In other embodiments, the present application describes solutions for managing neighbor discovery in IPv6 networks in a multi-core system. In still other embodiments, the present application describes solutions for managing network bridging in a multi-core system. In yet other embodiments, the present application describes solutions for managing link aggregation in a multi-core system. And in still other embodiments, the present application describes solutions for managing virtual routers in a multi-core system.

Owner:CITRIX SYST INC

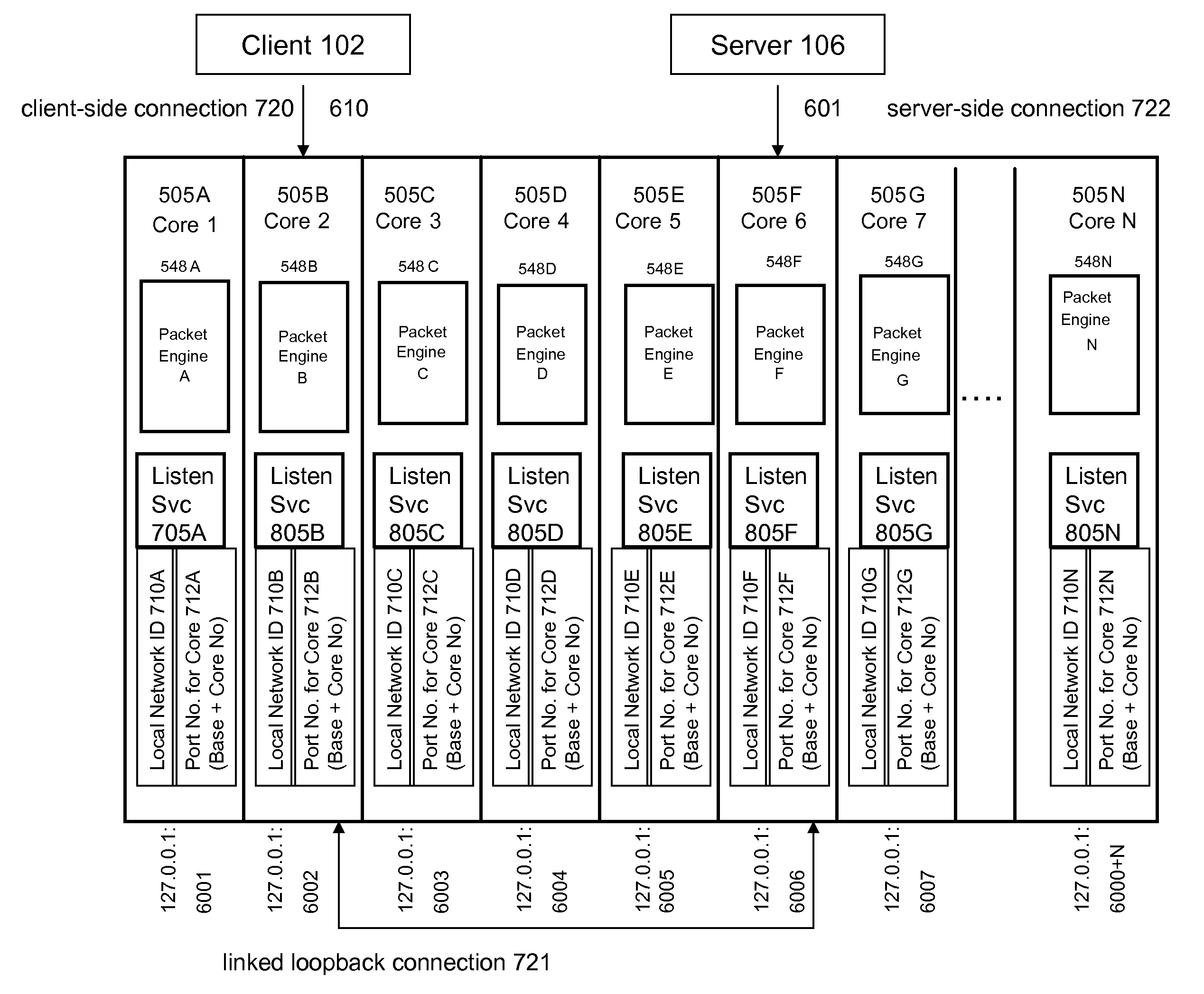

Systems and methods for identifying a processor from a plurality of processors to provide symmetrical request and response processing

ActiveUS20100287227A1Reduces unnecessary copying and cachingSpeed up the flowMultiple digital computer combinationsProgram controlIp addressNetwork packet

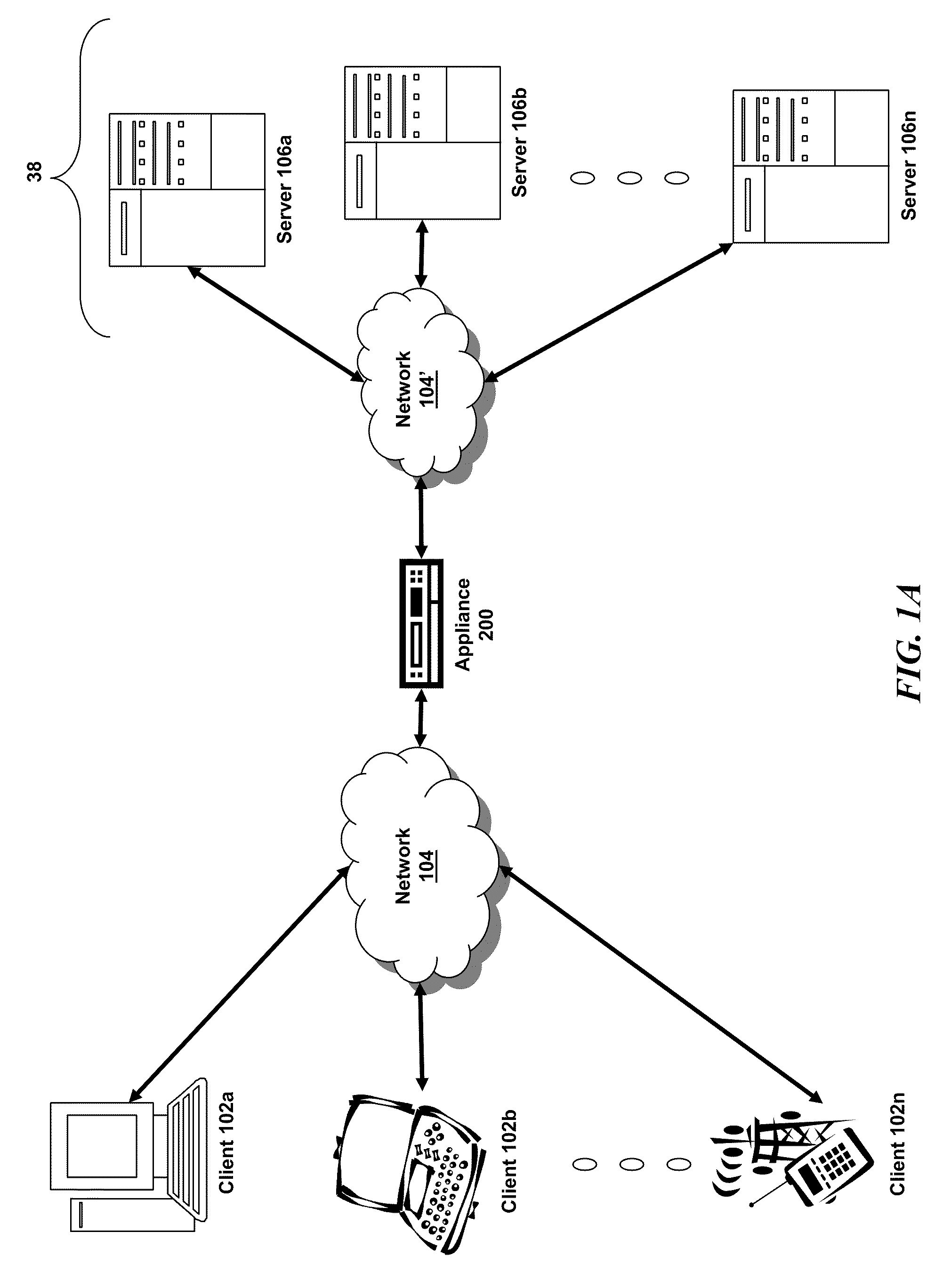

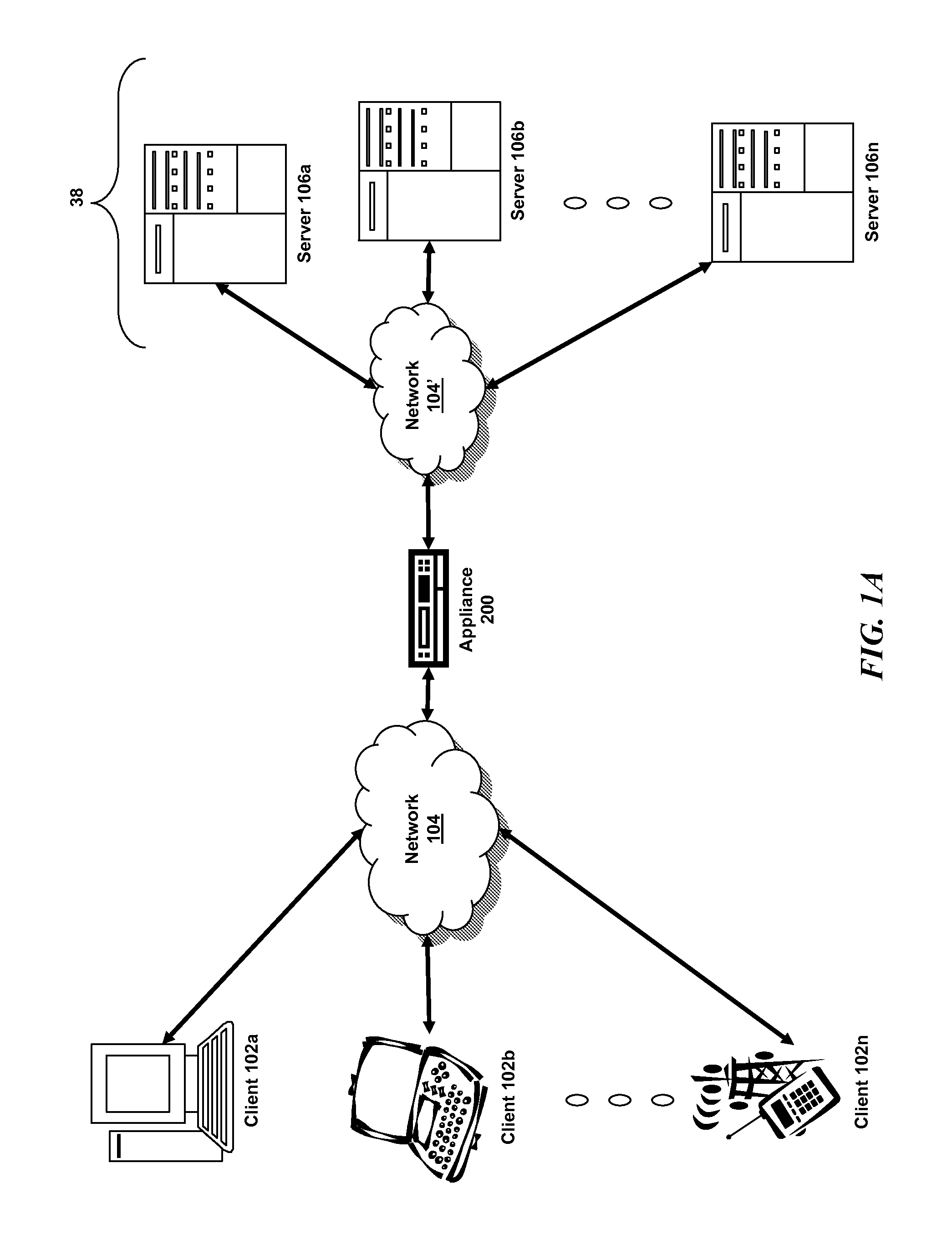

Described herein is a method and system for distributing request and responses across a multi-core system. Each core executes a packet engine that further processes data packets allocated to that core. A flow distributor executing within the multi-core system forwards client requests to a packet engine on a core that is selected based on a value generated when a hash is applied to a tuple comprising a client IP address, a client port, a server IP address and a server port identified in the request. The packet engine selects a first IP address and a first port of the core, and determines whether a hash of a tuple comprising those values identifies the selected core. A modification is then made to the client request so that the client request includes a tuple comprising the first IP address, the server IP address, the first port and the server port.

Owner:CITRIX SYST INC

Systems and methods for cookie proxy jar management across cores in a multi-core system

ActiveUS20120036178A1Improving cookie operationImprove performanceDigital data processing detailsMultiple digital computer combinationsClient-sideMulticore systems

The present solution is directed towards systems and methods for managing cookies by a multi-core device. The device is intermediary to a client and one or more servers. A first core of a multi-core device receives a response from a server to a request of the client through a user session. The response comprises a cookie. The first core removes the cookie from the response and stores the cookie in a corresponding storage for the session. The first core forwards the response without the cookie to the client. A second core then receives via a session, a second request from the client. The second core determines the identification of the first core as owner of the session from the second request. The second core then communicates to the first core a third request for cookie information for the session.

Owner:CITRIX SYST INC

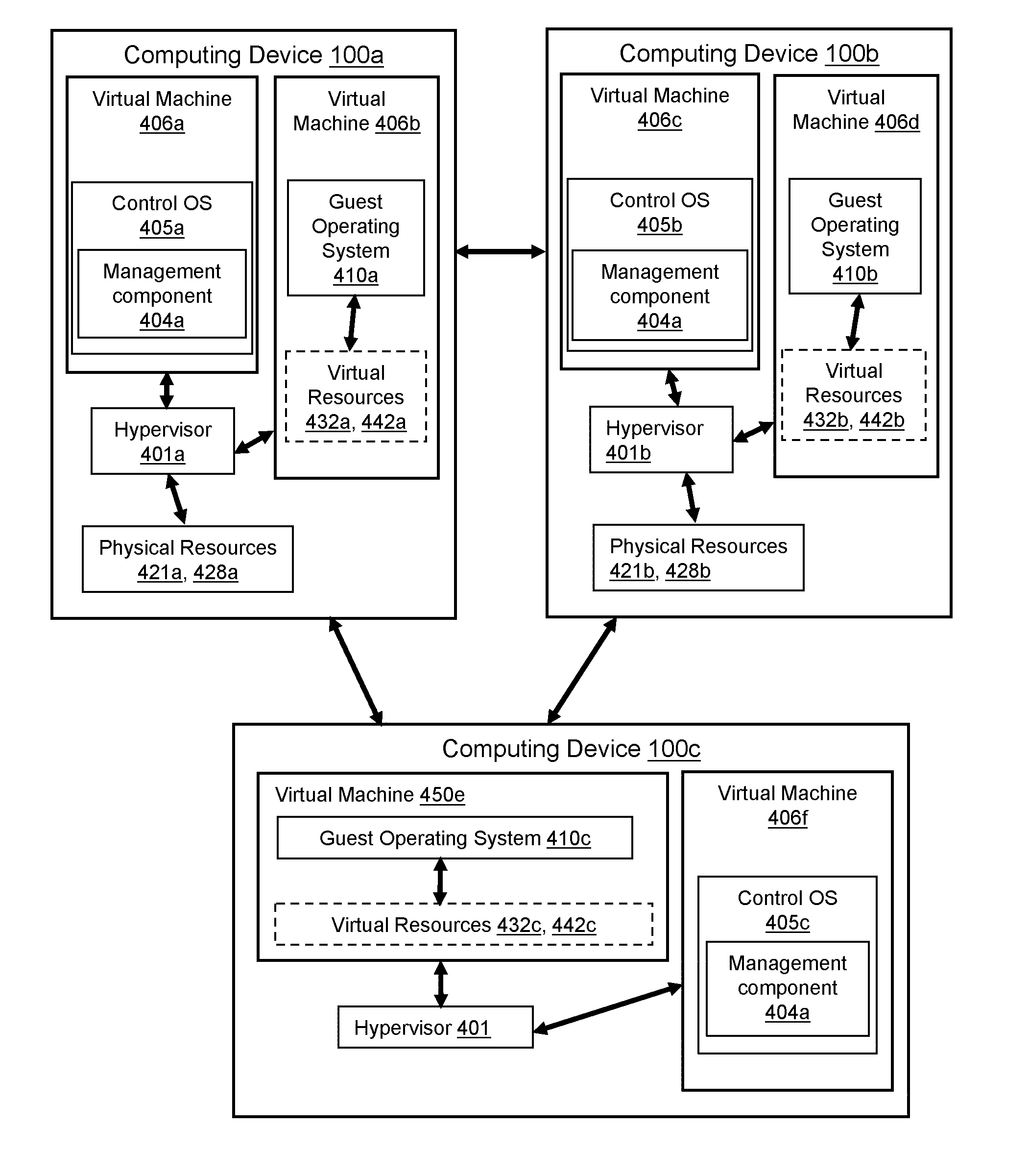

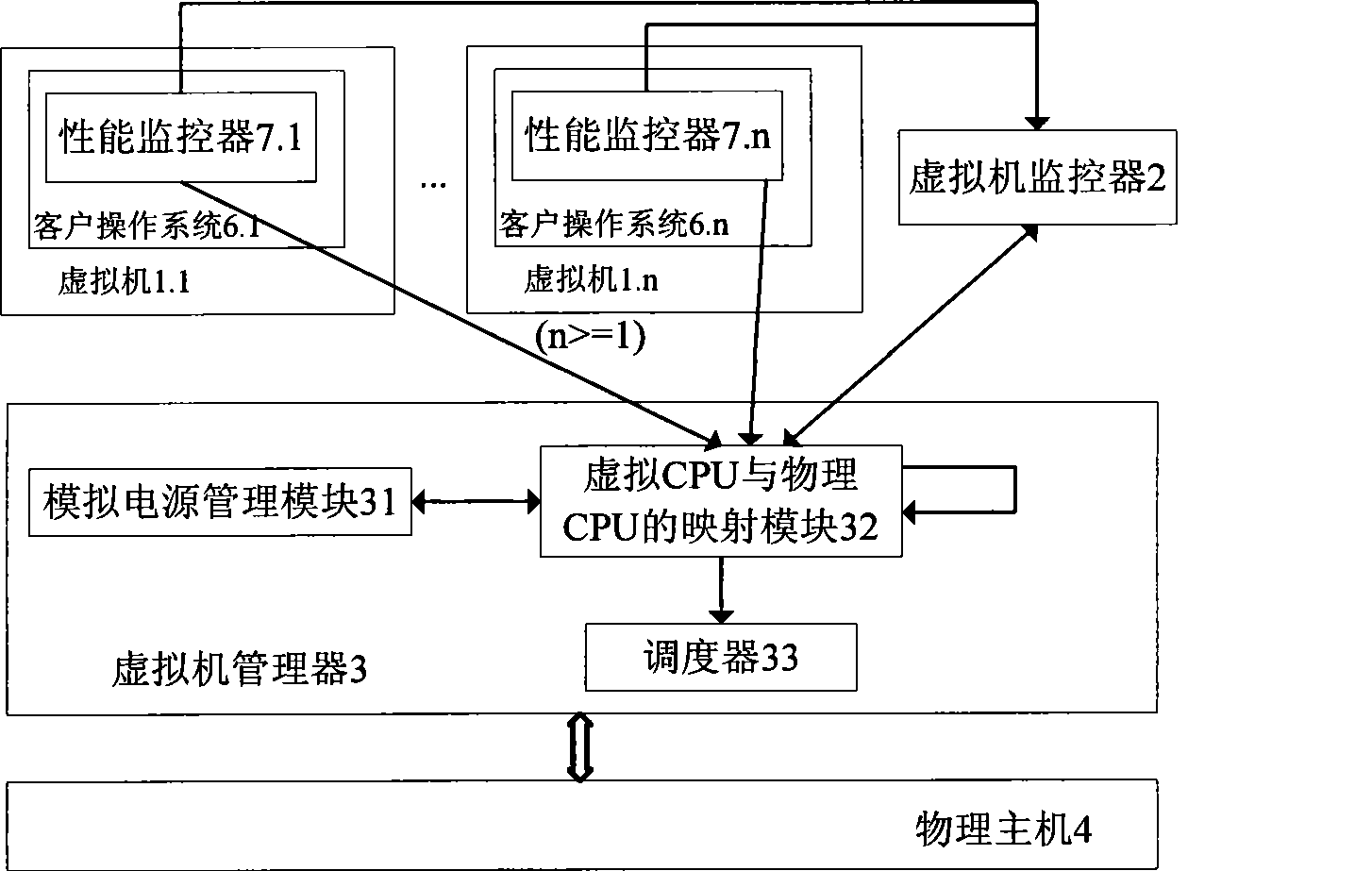

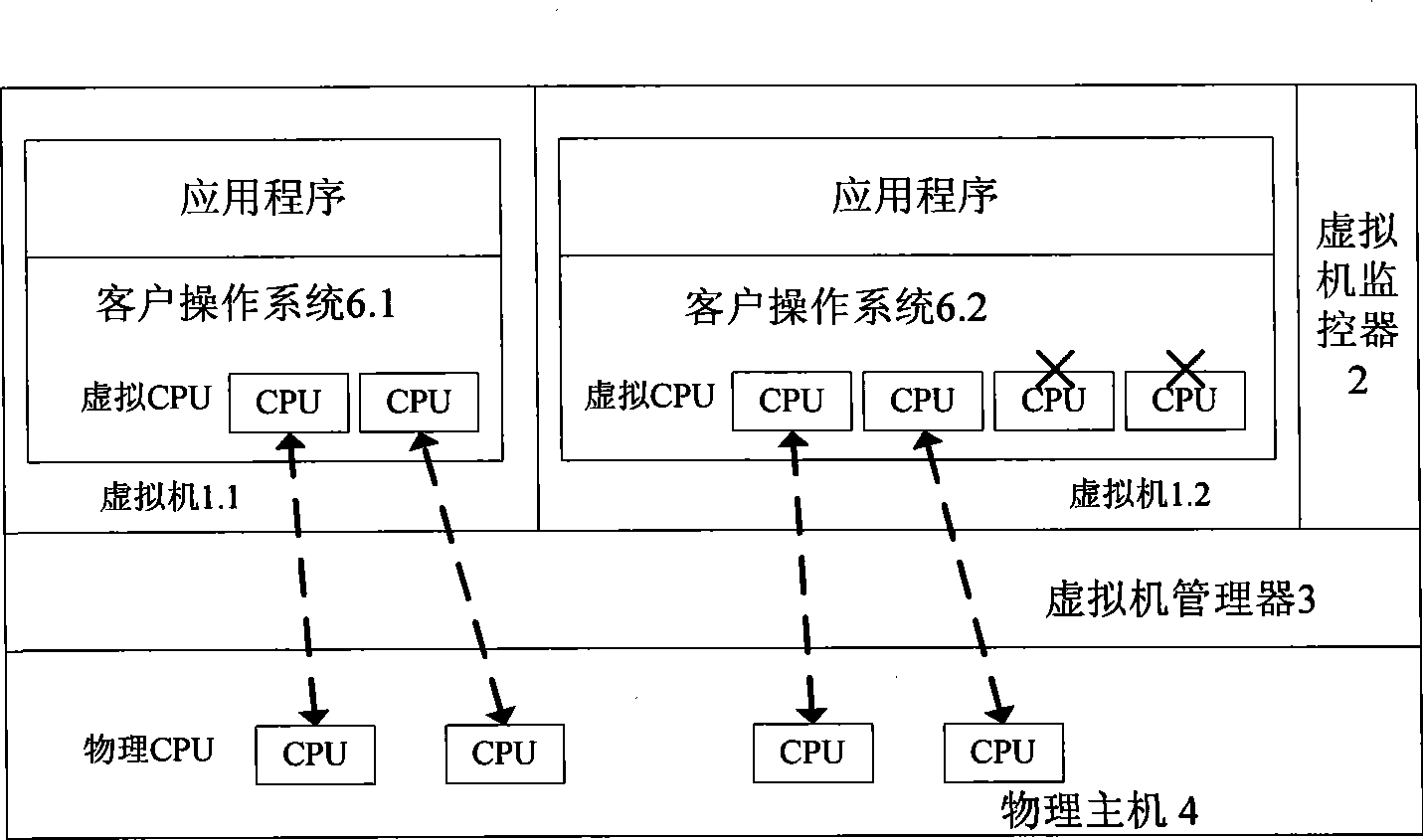

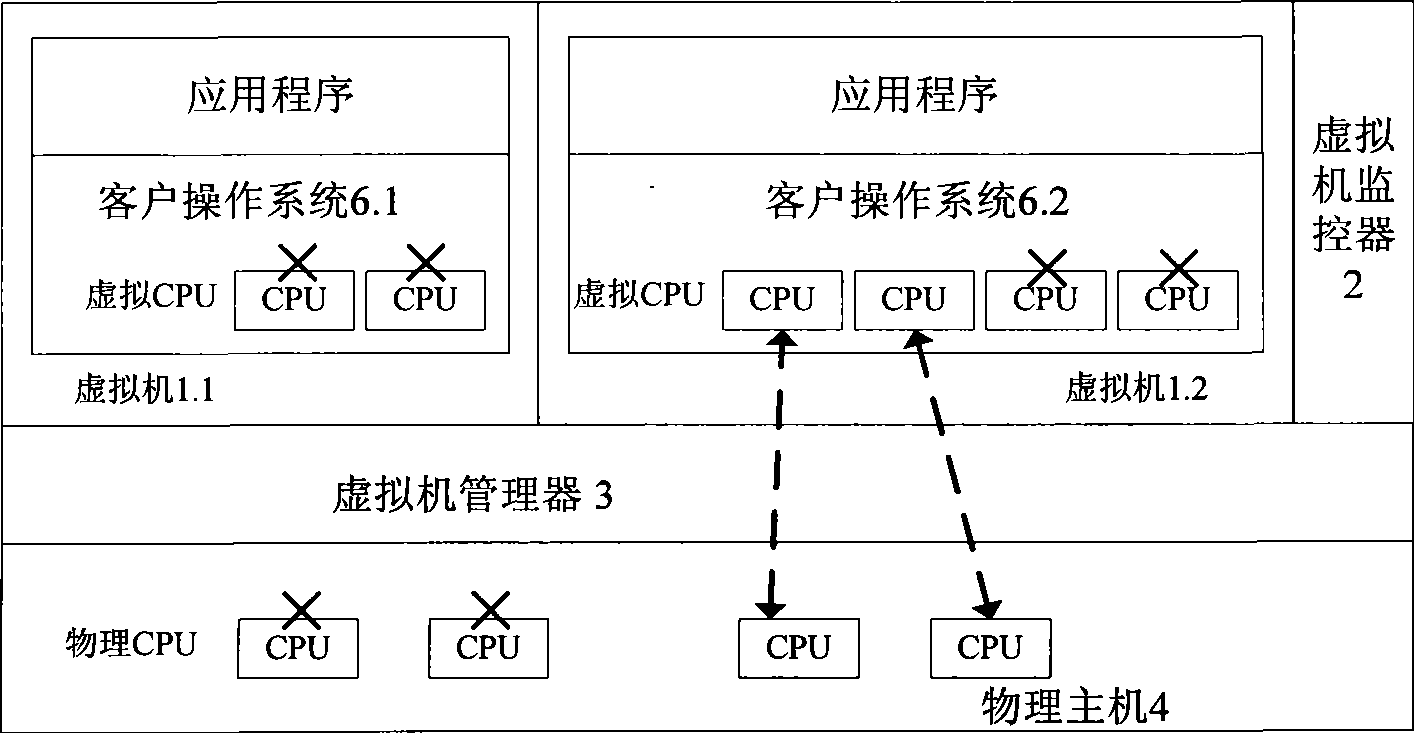

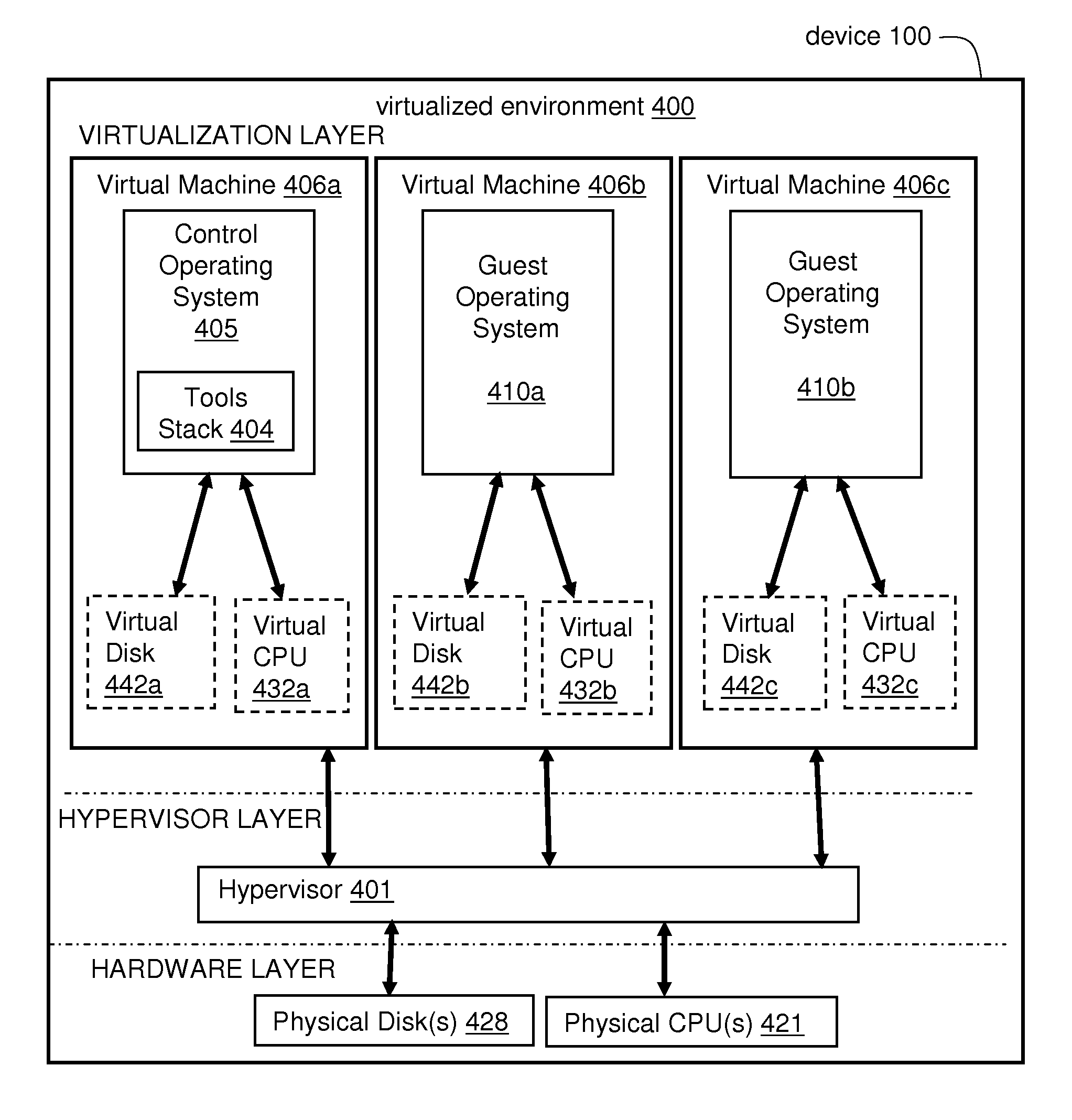

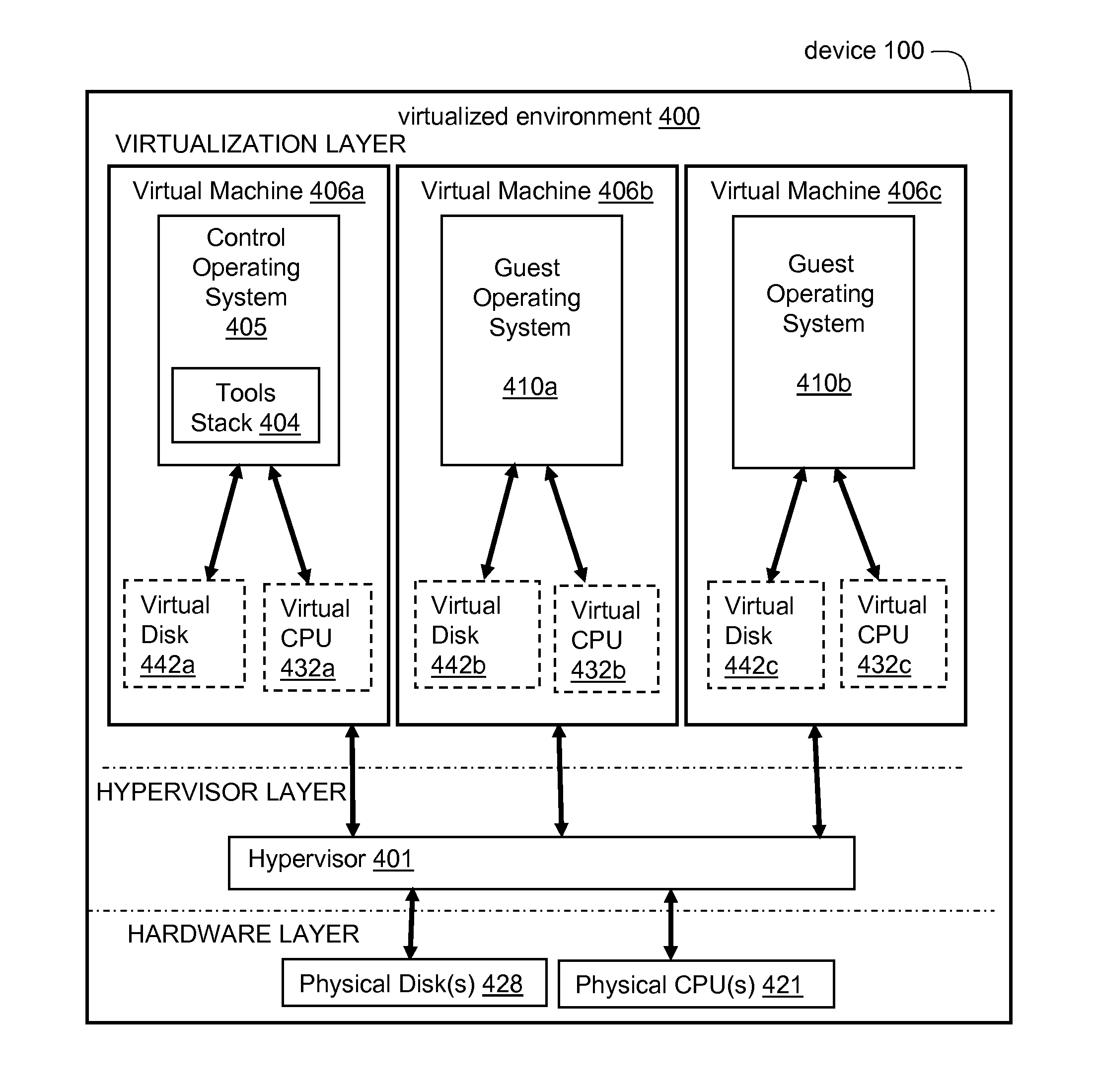

Multi-core computing resource management system based on virtual computing technology

InactiveCN101488098AReasonable distributionImprove management abilityEnergy efficient ICTResource allocationMulti core computingResource Management System

The invention relates to a multi-core system computer resource management system based on a virtual computer technology. The system comprises a plurality of virtual machines, a virtual machine monitor and a virtual machine manager. The virtual machine monitor monitors the load condition and the operation state of the virtual machine at real time. The virtual machine manager is a bond for communication between a virtual machine and a physical host. The virtual machine operates on the virtual machine manager and provides the user with a virtual platform. At the same time, the invention divides the virtual machine into three general categories, and different resource adjusting strategies are adopted for each category of the virtual machine respectively. The invention provides a practical and feasible way for the dynamic adjusting and distributing problem of multi-core computer resource and realizes the maximization of energy saving and resource utilization.

Owner:HUAZHONG UNIV OF SCI & TECH

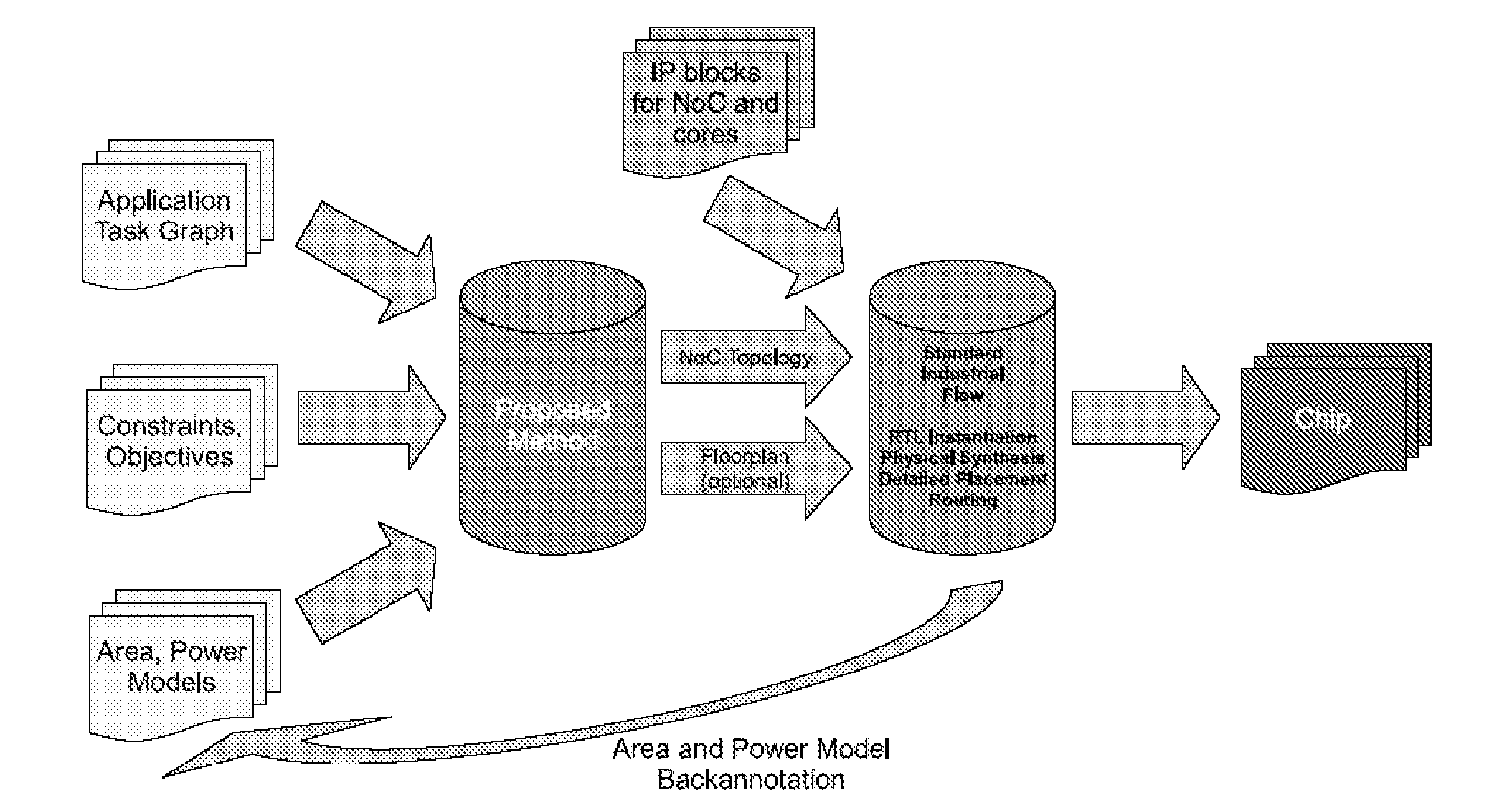

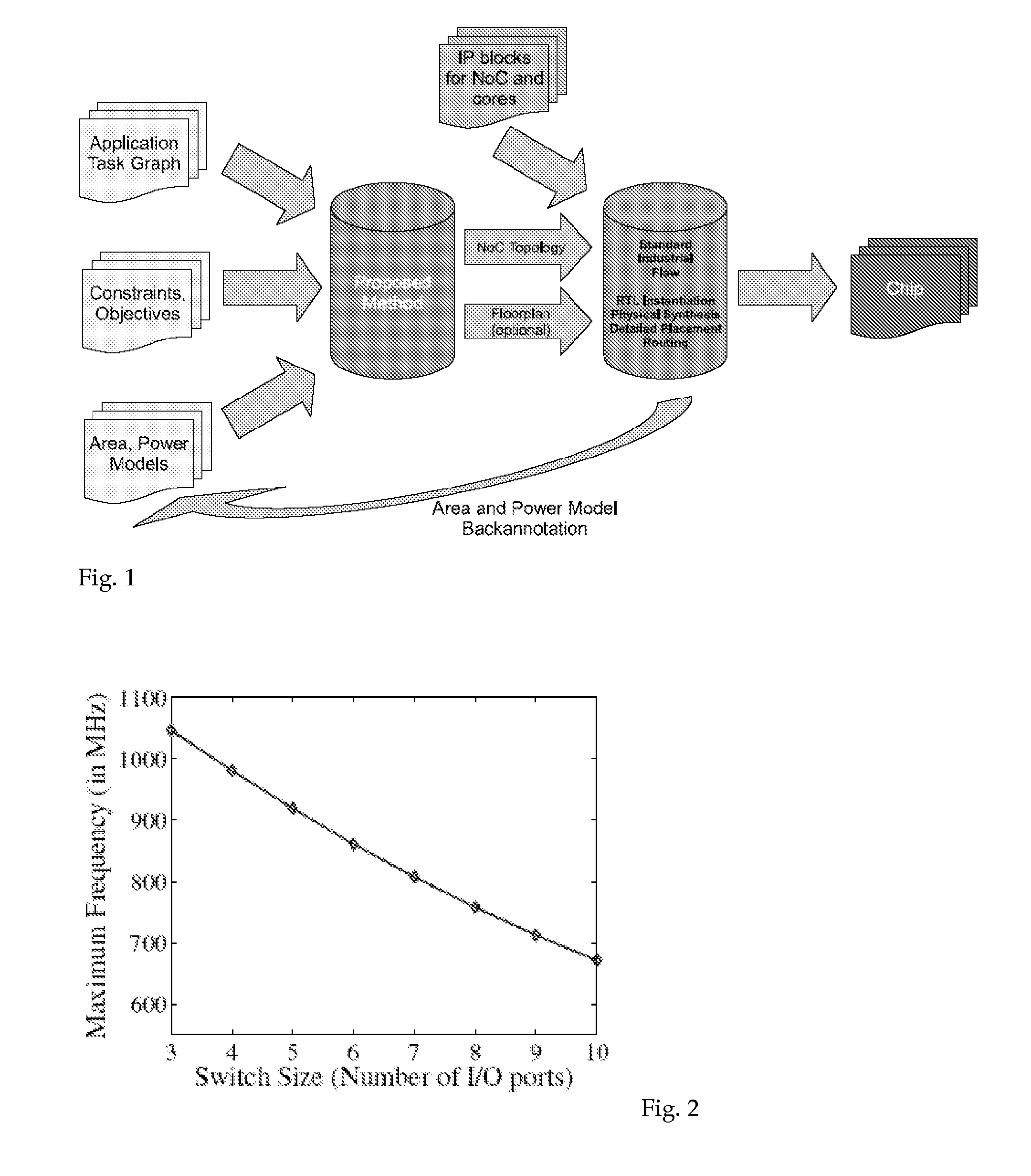

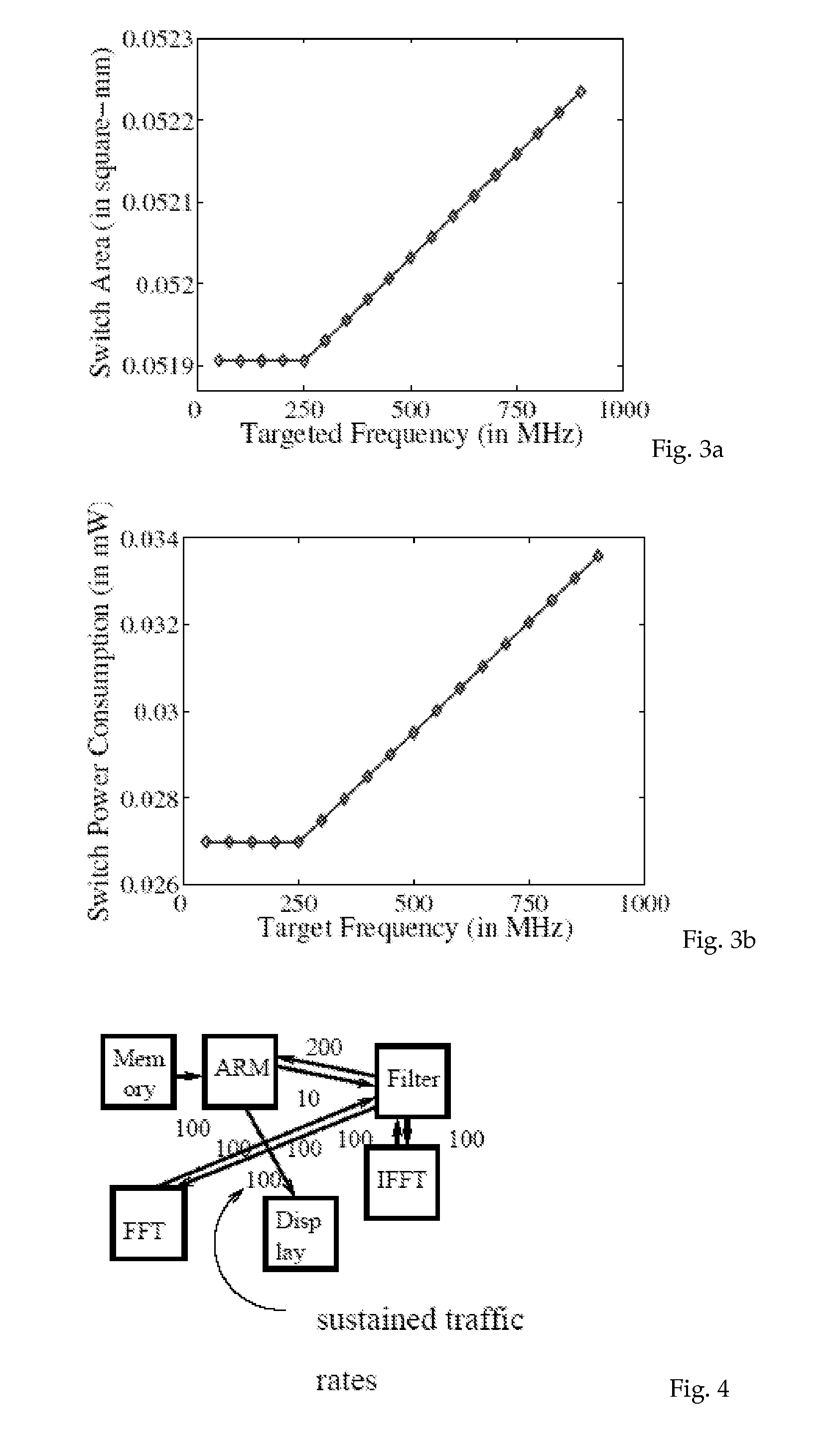

Method to design network-on-chip (NOC) - based communication systems

ActiveUS20090313592A1Error preventionFrequency-division multiplex detailsCommunications systemEngineering

A method to design a Networks on Chips (NoCs)-based communication system for connecting on-chip components in a multicore system, said system comprising several elements communicating through the communication system, said communication system comprising at least switches, said method comprising the steps of modelling the applications running on the multicore system, establishing the number and configuration of switches to connect the elements, establishing physical connectivity between the elements and the switches, for each two pairs of communicating elements: (a) a defining a communication path, (b) calculating metrics as affected by the need to render said path into physical connectivity, taking into account any previously defined physical connectivity, (c) iterating the steps a and b for a plurality of possible paths, (d) choosing the path having the optimal metrics, and (e) establishing any missing physical connectivity between the switches so that the selected optimal path occurs across physically connected switches.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

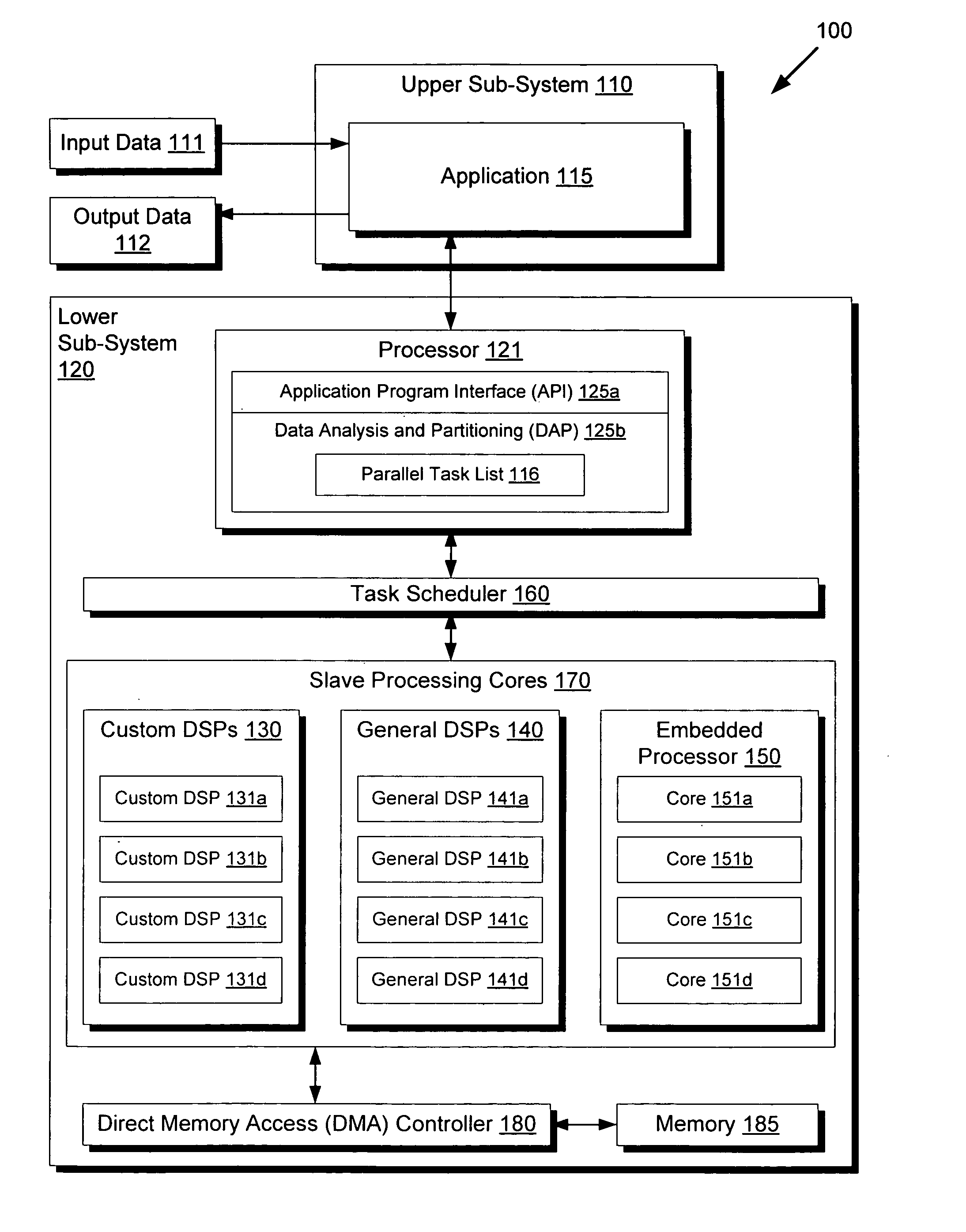

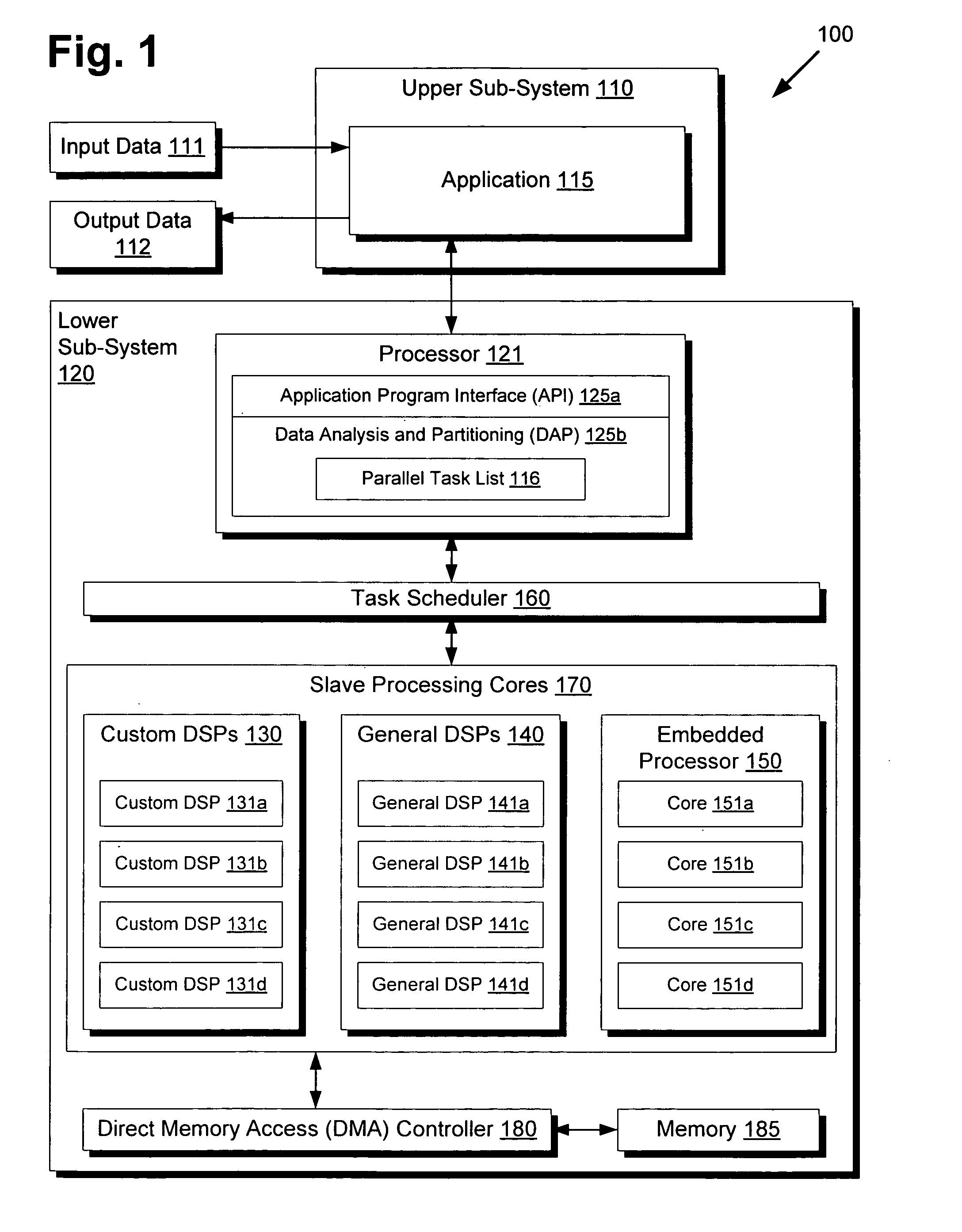

Highly distributed parallel processing on multi-core device

InactiveUS20100131955A1Multiprogramming arrangementsMemory systemsSystem requirementsSoftware development

There is provided a highly distributed multi-core system with an adaptive scheduler. By resolving data dependencies in a given list of parallel tasks and selecting a subset of tasks to execute based on provided software priorities, applications can be executed in a highly distributed manner across several types of slave processing cores. Moreover, by overriding provided priorities as necessary to adapt to hardware or other system requirements, the task scheduler may provide for low-level hardware optimizations that enable the timely completion of time-sensitive workloads, which may be of particular interest for real-time applications. Through this modularization of software development and hardware optimization, the conventional demand on application programmers to micromanage multi-core processing for optimal performance is thus avoided, thereby streamlining development and providing a higher quality end product.

Owner:MINDSPEED TECH LLC

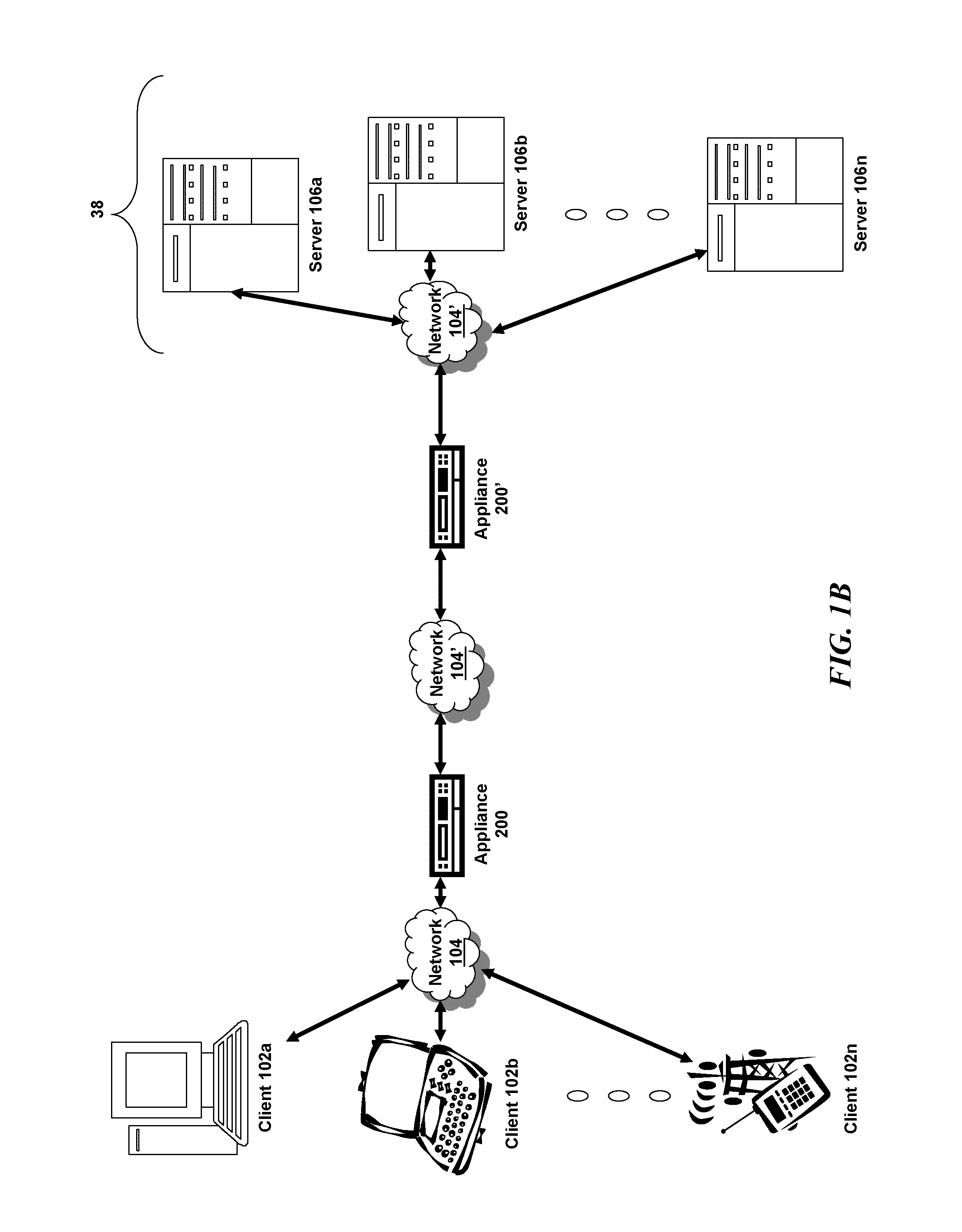

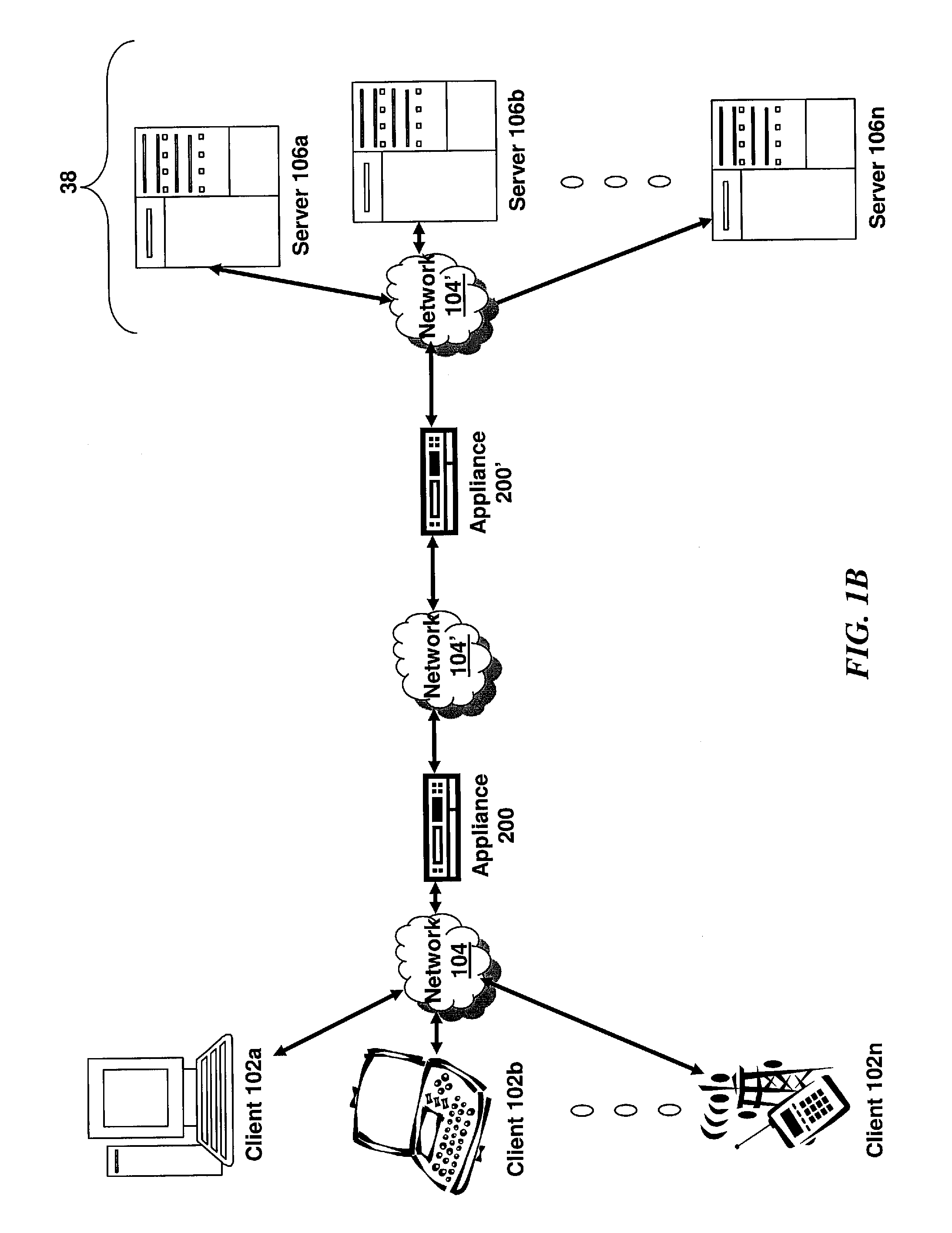

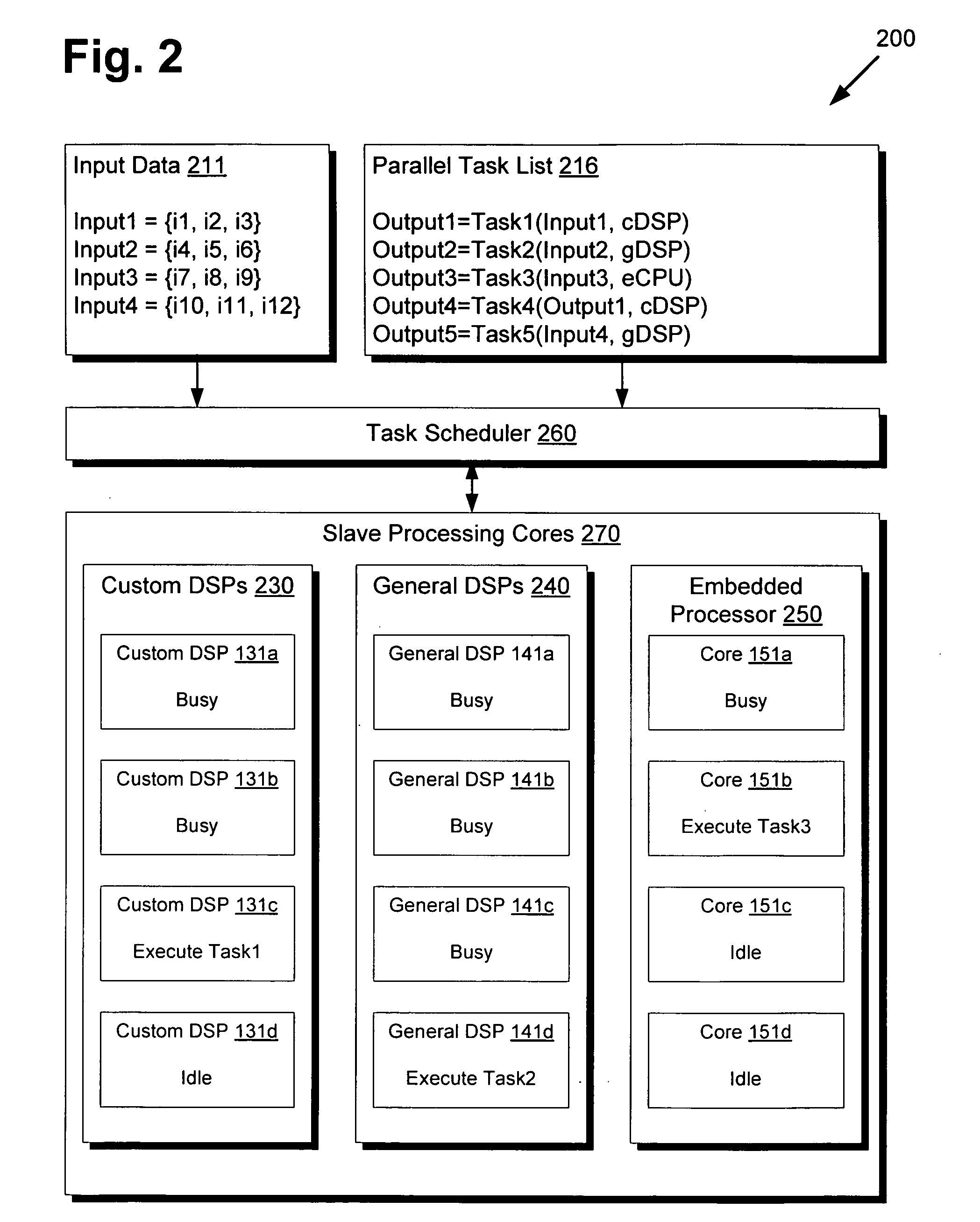

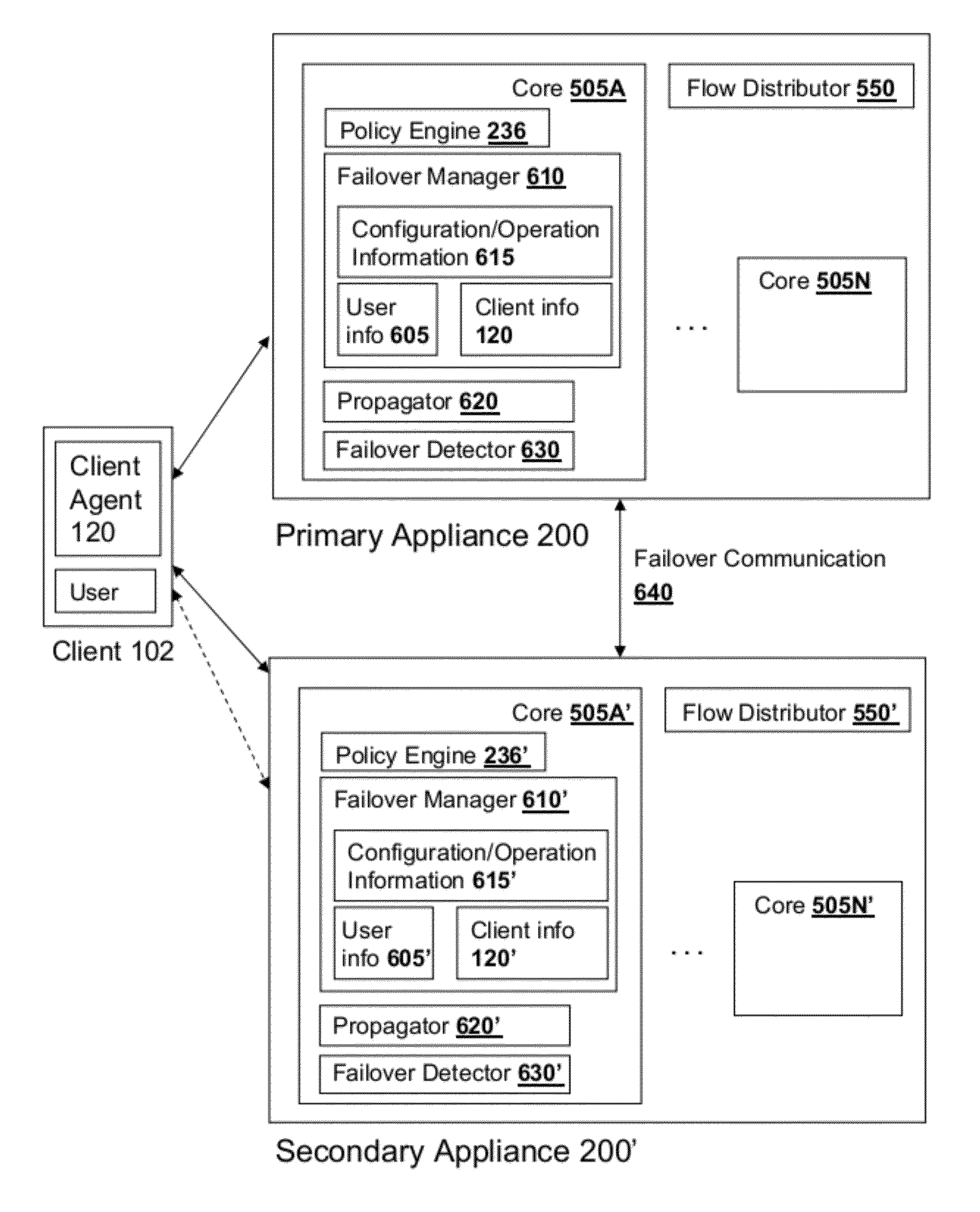

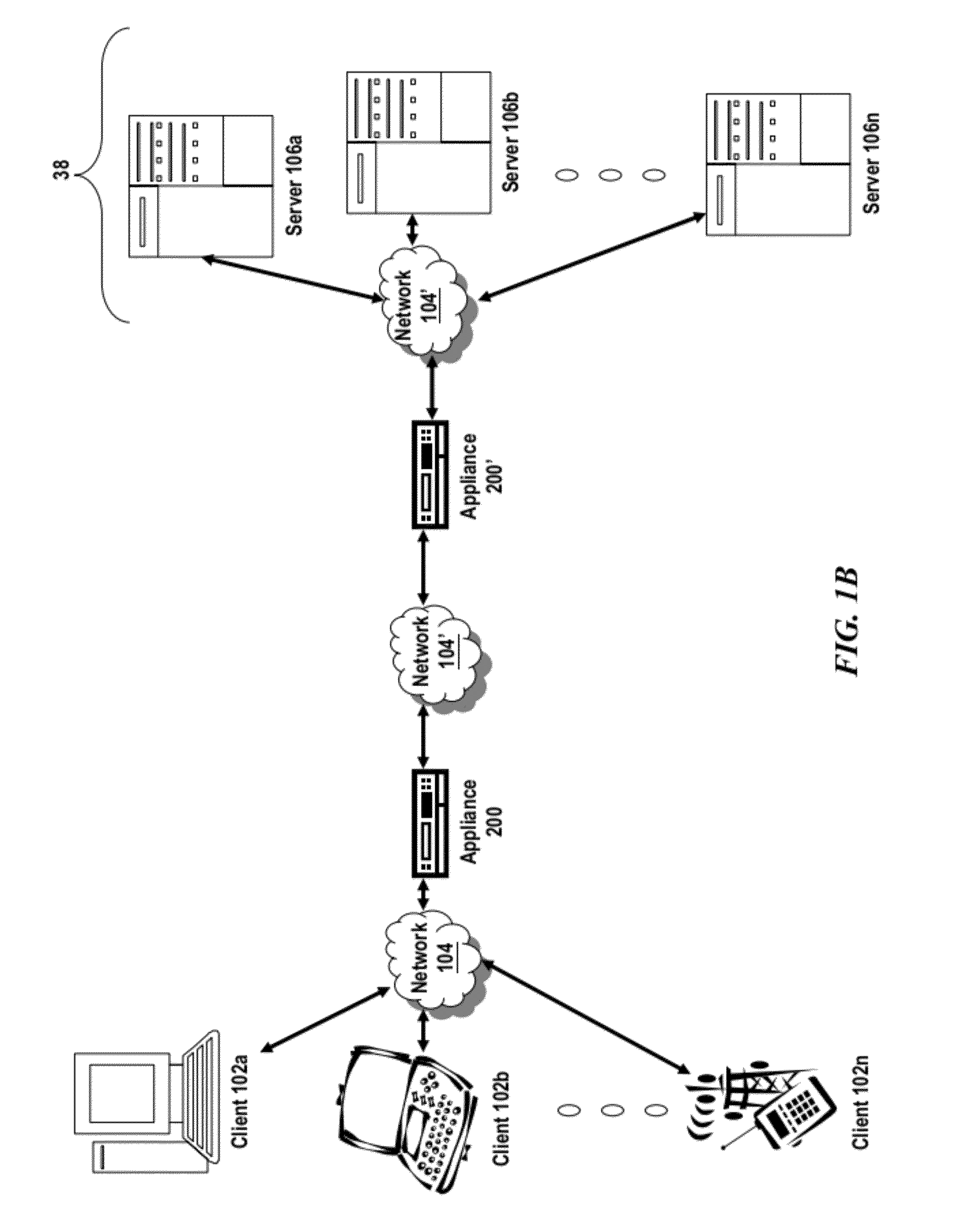

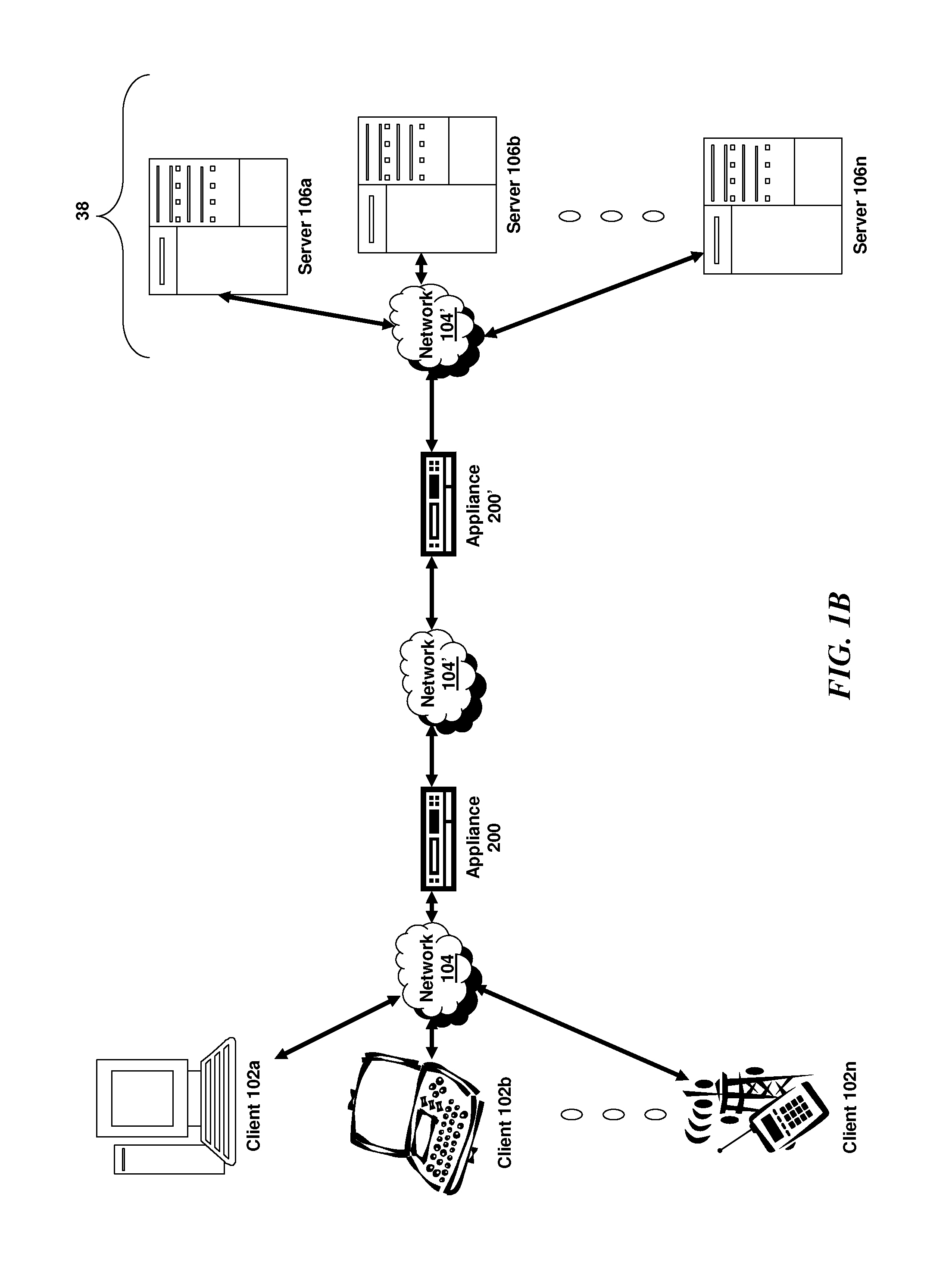

Systems and Methods for Implementing Connection Mirroring in a Multi-Core System

ActiveUS20120159235A1Easy to set upTransmissionRedundant hardware error correctionFailoverMulticore systems

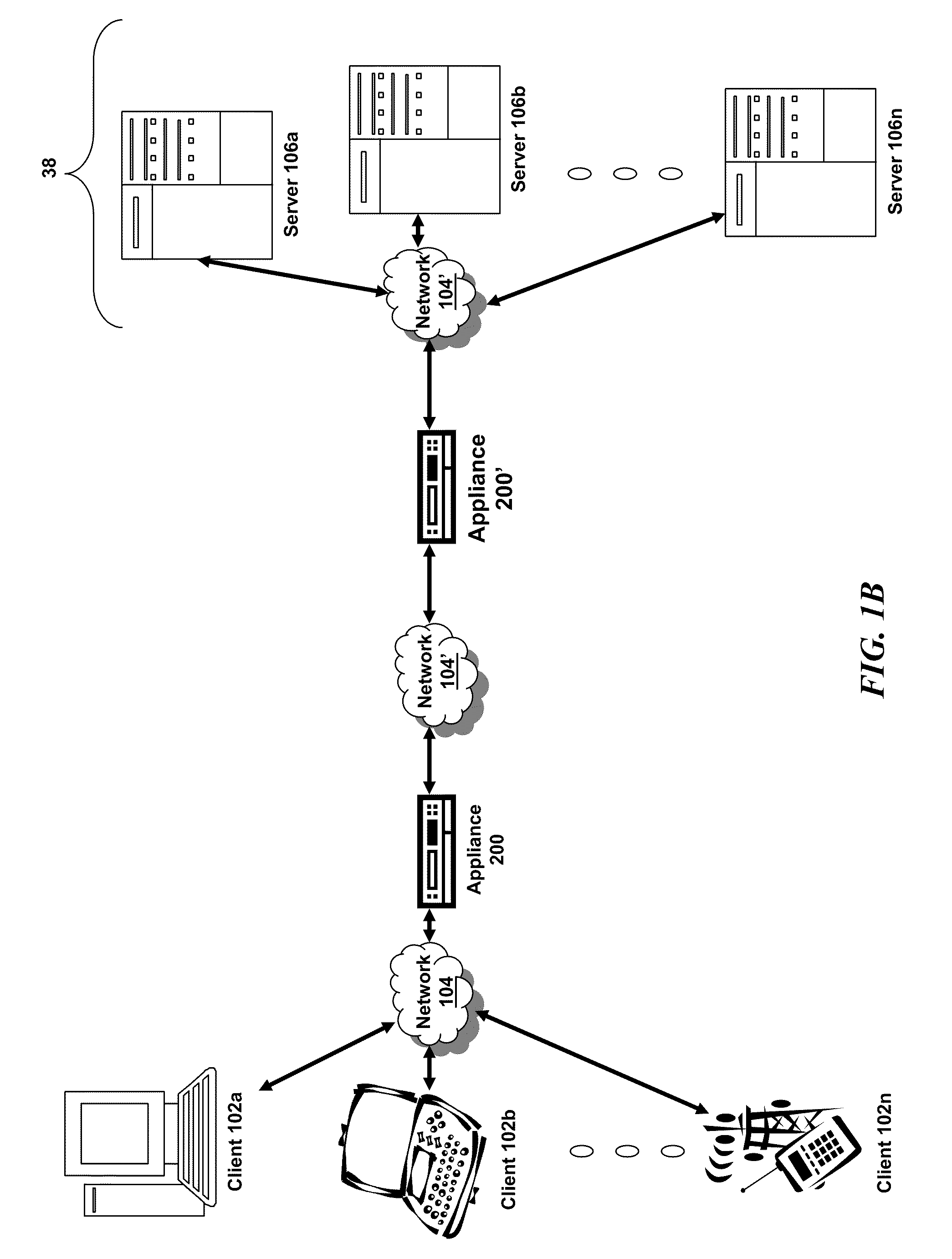

The present application is directed to systems and methods for providing failover connection mirroring between two or more multi-core devices intermediary between a client and a server. A first multi-core device may receive a hash key of a second multi-core device for mapping packets to cores of the second multi-core device. The first device may identify a core of the second device using (i) the hash key of the second device and (ii) tuple information corresponding to a connection between the client and the server via the first device. The first device may determine that the identified core is not a desired core for providing a failover connection. The first device may modify the tuple information so as to identify the desired core when used with the hash key of the second device. The first device may use the modified tuple information to establish the failover connection.

Owner:CITRIX SYST INC

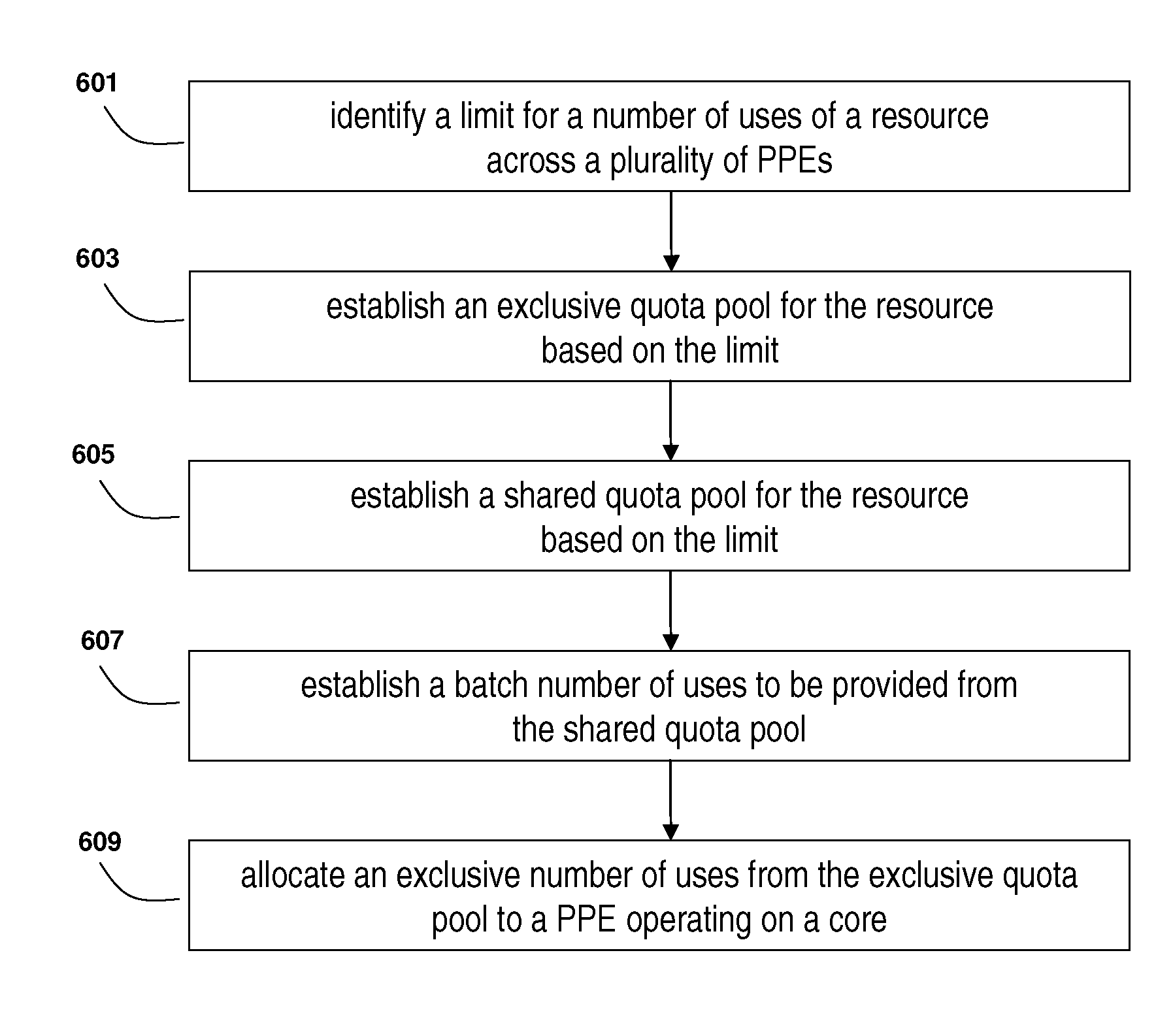

Systems and methods for handling limit parameters for a multi-core system

The present invention is directed towards systems and methods for handling limit parameters for multi-core systems. A pool manager divides the limited number of uses of a resource into an exclusive quota pool and a shared quota pool. Each packet processing engine operating on a core is allocated an exclusive number of uses of the resource from the exclusive quota pool. If a packet processing engine wishes to use the resource beyond its exclusive number, the packet processing engine must borrow from the shared quota pool.

Owner:CITRIX SYST INC

Systems and methods for managing large cache services in a multi-core system

InactiveUS20110153953A1Memory architecture accessing/allocationMemory adressing/allocation/relocationParallel computingMulticore systems

A multi-core system that includes a 64-bit cache storage and a 32-bit memory storage that stores a 32-bit cache object directory. One or more cache engines execute on cores of the multi-core system to retrieve objects from the 64-bit cache, create cache directory objects, insert the created cache directory object into the cache object directory, and search for cache directory objects in the cache object directory. When an object is stored in the 64-bit cache, a cache engine can create a cache directory object that corresponds to the cached object and can insert the created cache directory object into an instance of a cache object directory. A second cache engine can receive a request to access the cached object and can identify a cache directory object in the instance of the cache object directory, using a hash key calculated based on one or more attributes of the cached object.

Owner:CITRIX SYST INC

Systems and methods for managing preferred client connectivity to servers via multi-core system

The present application is directed towards systems and methods for providing a cookie by an intermediary device comprising a plurality of packet processing engines executing on a corresponding plurality of cores, the cookie identifying a session of a user that was redirected responsive to a service exceeding a response time limit. The cookie may be generated with identifiers based off a name of a virtual server managing a service of a server, and a name of a policy associated with the virtual server. Each packet processing engine of the plurality of packet processing engines may interpret cookies generated by other packet processing engines due to the name of the virtual server and name of the policy, and may provide preferred client connectivity based on cookies included in requests for access to a service.

Owner:CITRIX SYST INC

Systems and methods for monitoring and maintaining consistency of a configuration

ActiveUS20110238792A1Hinders its propagationPrevent further spreadDigital computer detailsProgram controlMulticore systemsOperating system

The present application is directed towards systems and methods for monitoring and maintaining consistency of a configuration across a plurality of cores or packet engines in a multi-core system. A configuration manager handles communication of configuration commands to a plurality of cores or packet engines. If a command executes successfully on a first packet engine but fails on a second packet engine, the configuration manager may communicate an undo command to the first packet engine. Successful execution of the undo command may restore the packet engines to a consistent configuration.

Owner:CITRIX SYST INC

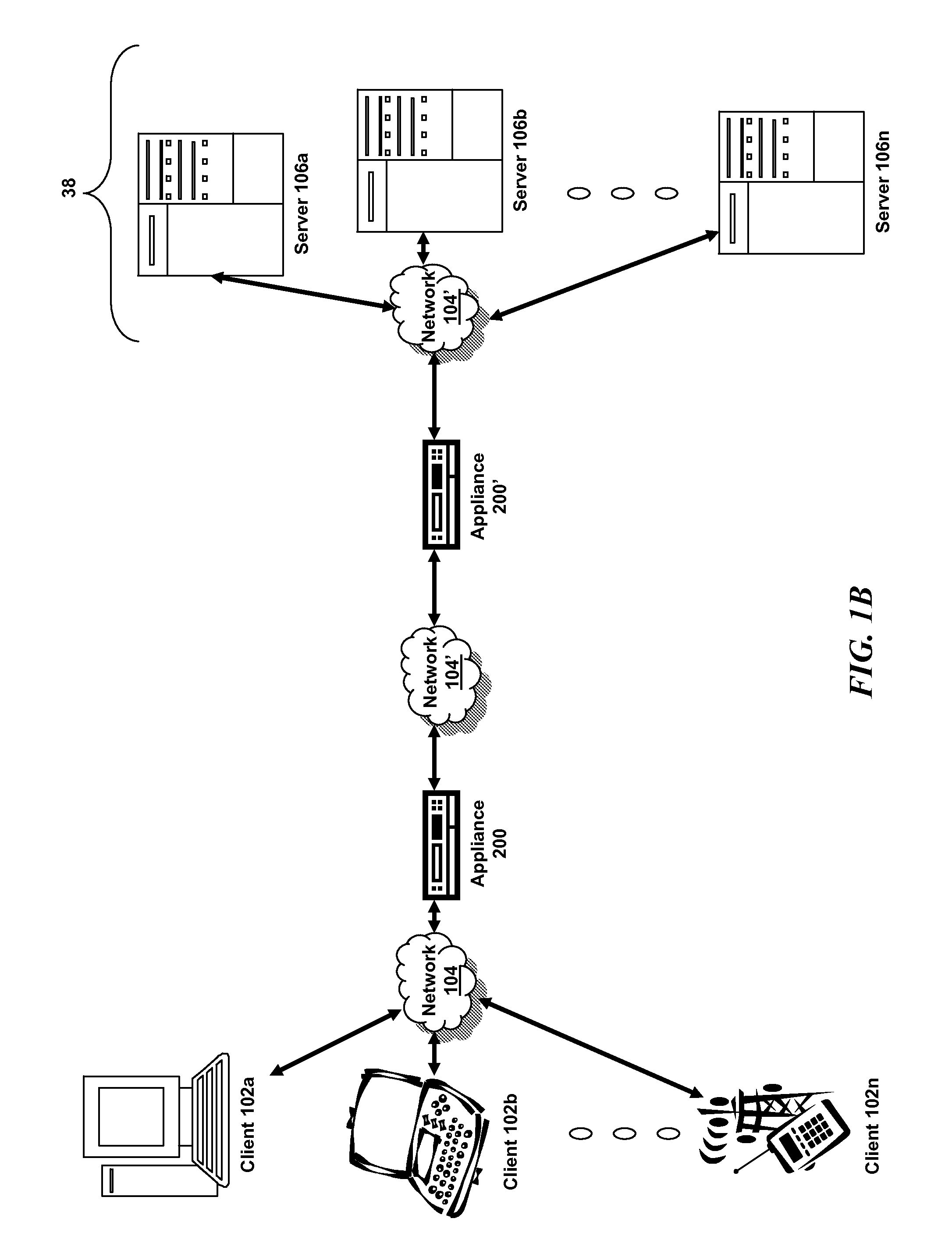

Systems and methods for server initiated connection management in a multi-core system

ActiveUS20120036231A1Multiple digital computer combinationsTransmissionConnection managementClient-side

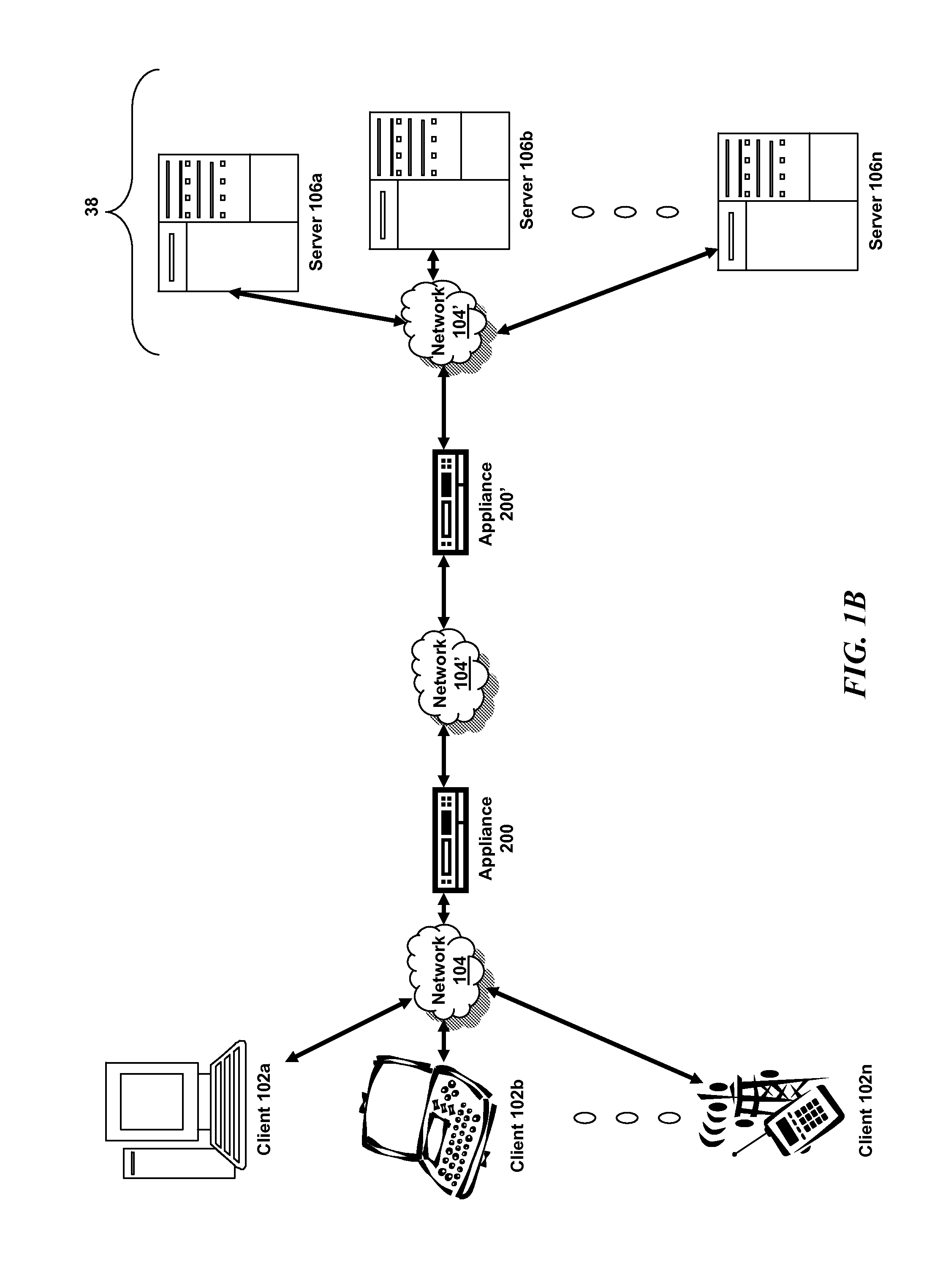

The present application is directed towards systems and methods for managing server initiated connections via a multi-core system that provides VPN access between clients and servers. The solution described herein provides a mechanism by which server and client communications via the multi-core system for a server initiated connection may be received on different cores and for the system to manage these communications across different cores to provide an end-to-end connectivity between the client and the server.

Owner:CITRIX SYST INC

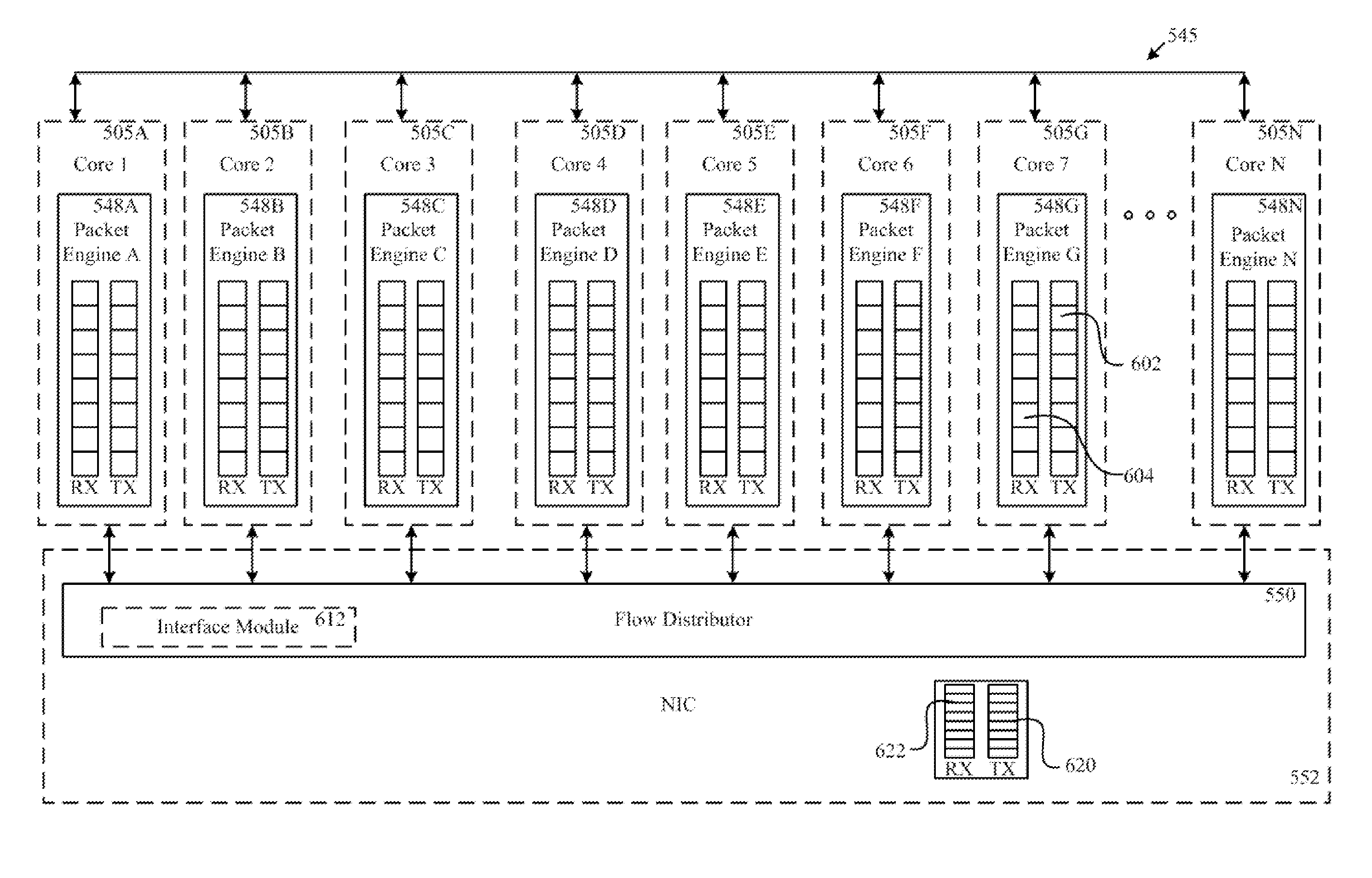

Systems and methods for receive and transmission queue processing in a multi-core architecture

Described herein is a method and system for directing outgoing data packets from packet engines to a transmit queue of a NIC in a multi-core system, and a method and system for directing incoming data packets from a receive queue of the NIC to the packet engines. Packet engines store outgoing traffic in logical transmit queues in the packet engines. An interface module obtains the outgoing traffic and stores it in a transmit queue of the NIC, after which the NIC transmits the traffic from the multi-core system over a network. The NIC receives incoming traffic and stores it in a NIC receive queue. The interface module obtains the incoming traffic and applies a hash to a tuple of each obtained data packet. The interface module then stores each data packet in the logical receive queue of a packet engine on the core identified by the result of the hash.

Owner:CITRIX SYST INC

Systems and methods for web logging of trace data in a multi-core system

A method and system for generating a web log that includes transaction entries from transaction queues of one or more cores of a multi-core system. A transaction queue is maintained for each core so that either a packet engine or web logging client executing on the core can write transaction entries to the transaction queue. In some embodiments, a timestamp value obtained from a synchronized timestamp variable can be assigned to the transaction entries. When a new transaction entry is added to the transaction queue, the earliest transaction entry is removed from the transaction queue and added to a heap. Periodically the earliest entry in the heap is removed from the heap and written to a web log. When an entry is removed from the heap, the earliest entry in a transaction queue corresponding to the removed entry is removed from the transaction queue and added to the heap.

Owner:CITRIX SYST INC

Systems and methods for receive and transmission queue processing in a multi-core architecture

Described herein is a method and system for directing outgoing data packets from packet engines to a transmit queue of a NIC in a multi-core system, and a method and system for directing incoming data packets from a receive queue of the NIC to the packet engines. Packet engines store outgoing traffic in logical transmit queues in the packet engines. An interface module obtains the outgoing traffic and stores it in a transmit queue of the NIC, after which the NIC transmits the traffic from the multi-core system over a network. The NIC receives incoming traffic and stores it in a NIC receive queue. The interface module obtains the incoming traffic and applies a hash to a tuple of each obtained data packet. The interface module then stores each data packet in the logical receive queue of a packet engine on the core identified by the result of the hash.

Owner:CITRIX SYST INC

Systems and methods for retaining source IP in a load balancing multi-core environment

ActiveUS20100322076A1Reduces unnecessary copying and cachingSpeed up the flowError preventionTransmission systemsNetwork packetIp address

Described herein is a method and system for distributing requests and responses across a multi-core system. Each core executes a packet engine that further processes data packets allocated to that core. A flow distributor executing within the multi-core system forwards client requests to a packet engine on a core that is selected based on a value generated when a hash is applied to a tuple comprising a client IP address, a client port, a server IP address and a server port identified in the request. The packet engine maintains the client IP address, selects a first port of the core, and determines whether a hash of a tuple comprising those values identifies the selected core. A modification is then made to the client request so that the client request includes a tuple comprising the client IP address, the server IP address, the first port and the server port.

Owner:CITRIX SYST INC

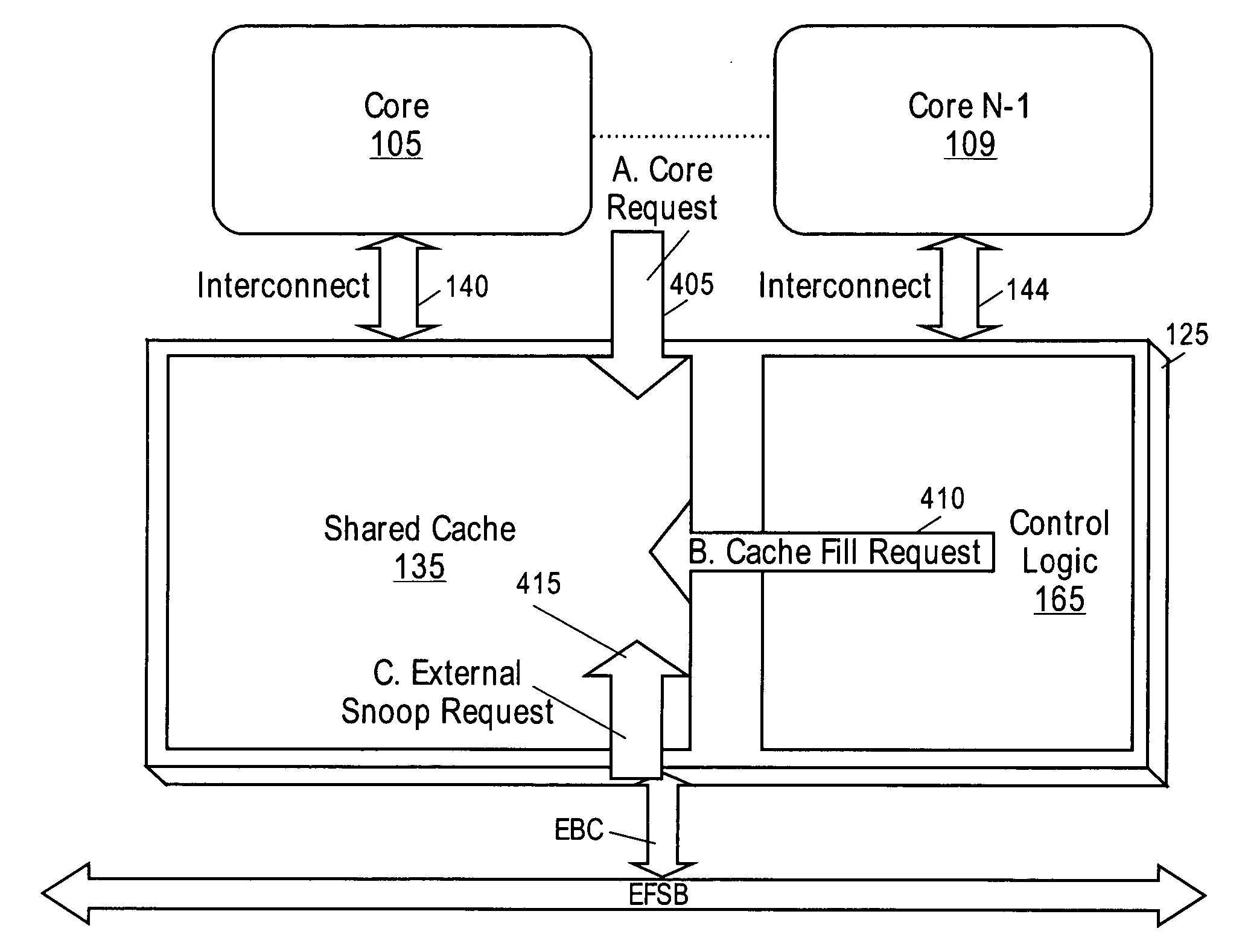

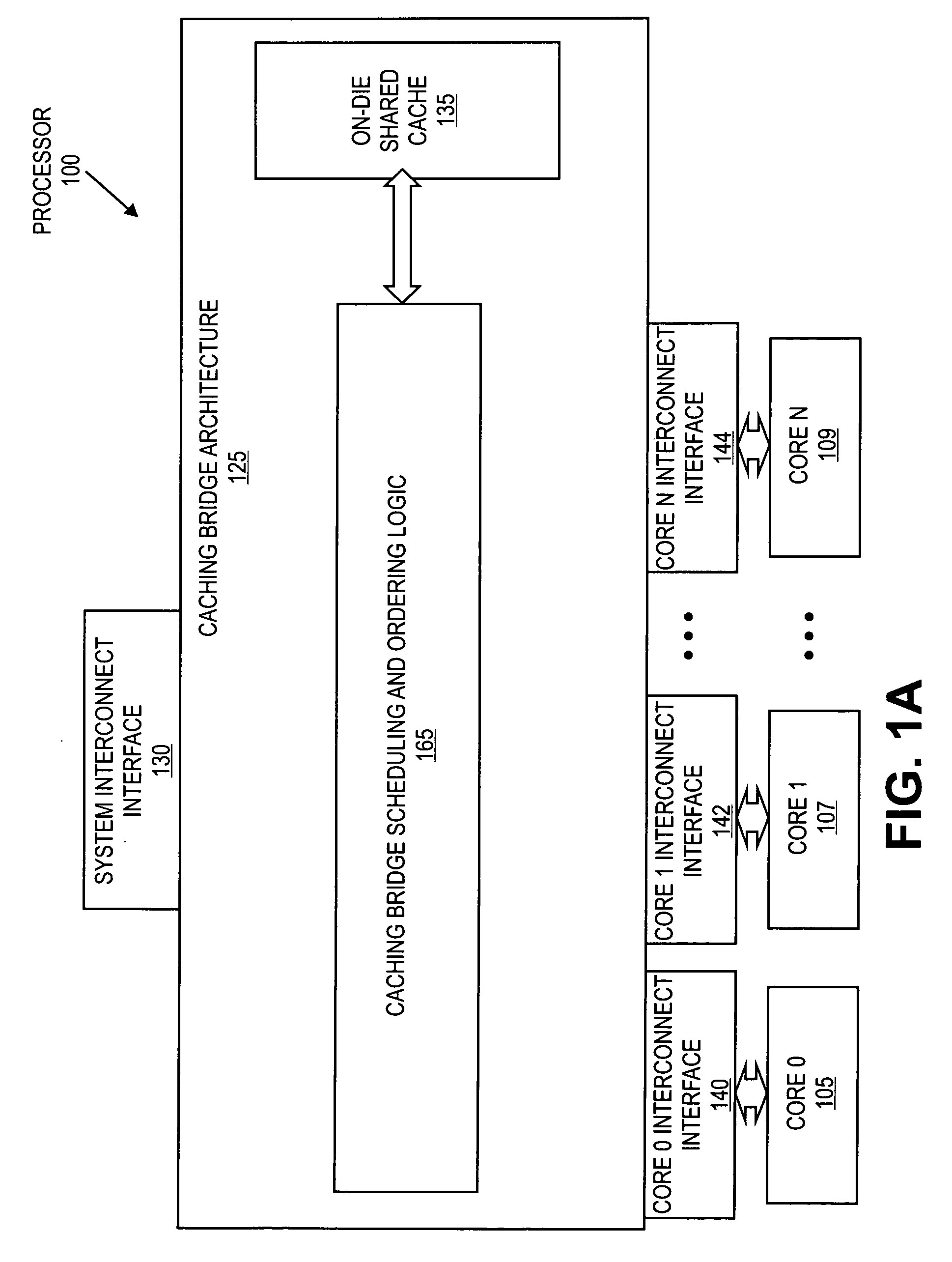

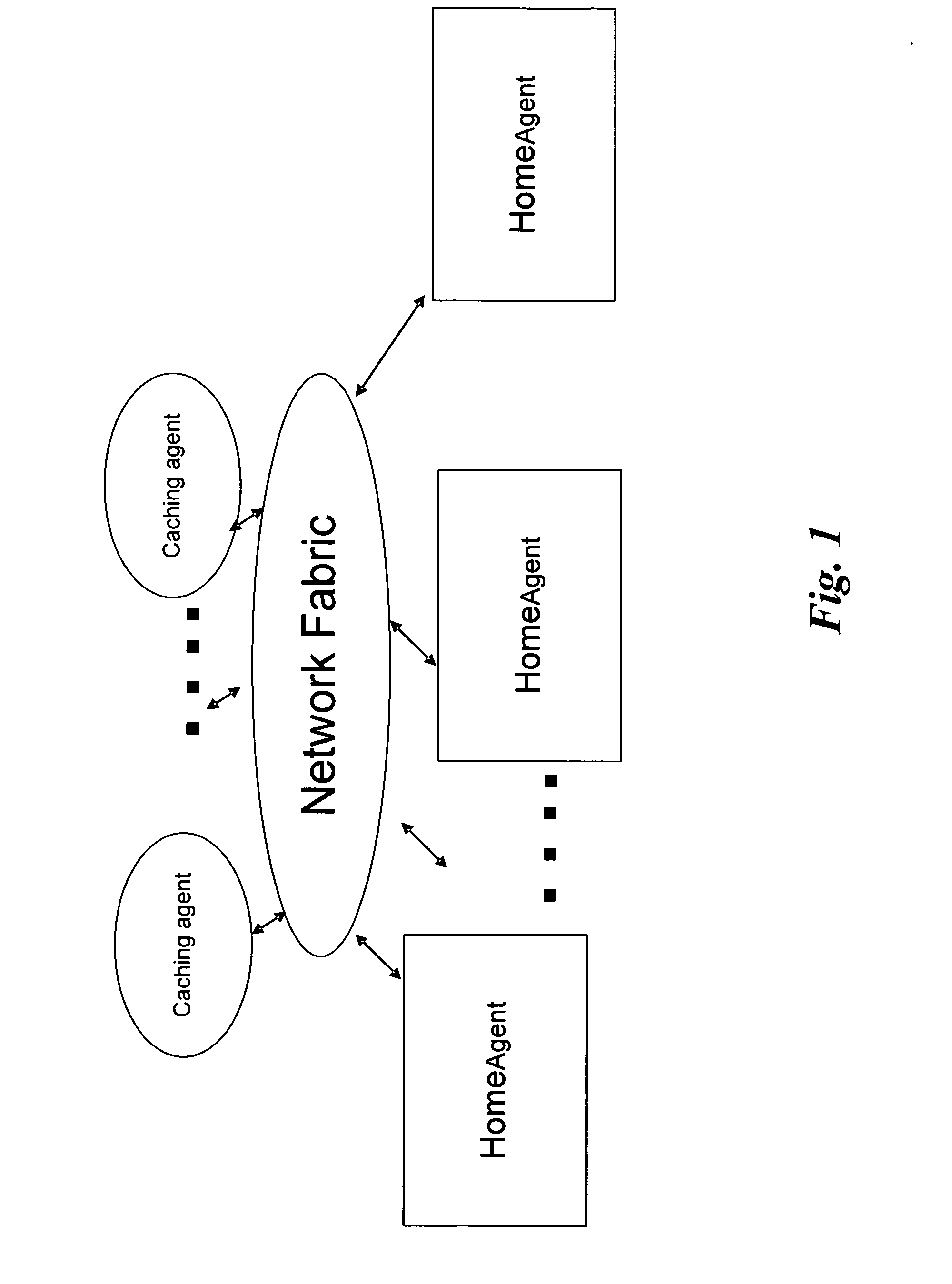

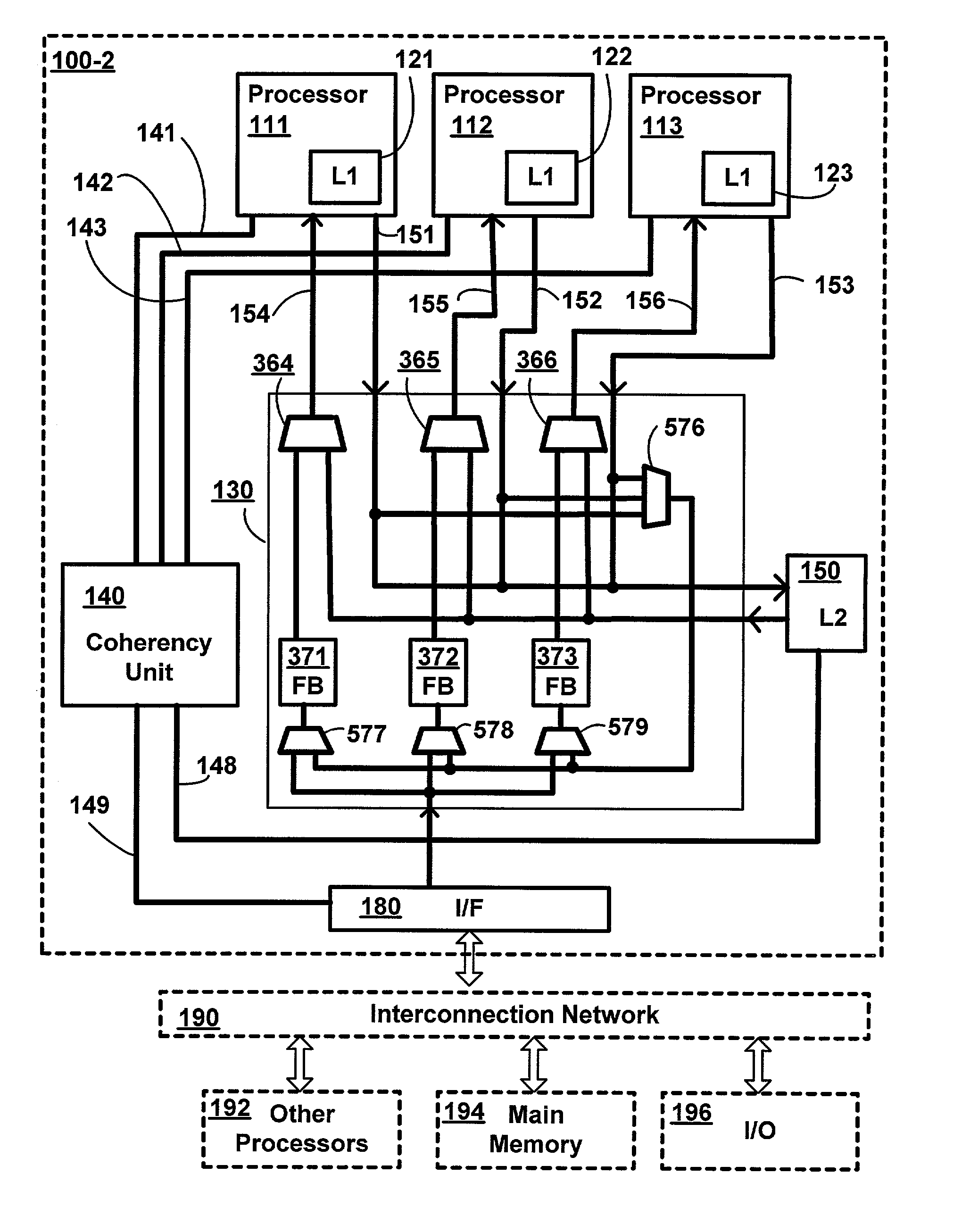

Cache coherency sequencing implementation and adaptive LLC access priority control for CMP

InactiveUS20070005909A1Memory architecture accessing/allocationMemory systemsCache accessParallel computing

A method and apparatus for cache coherency sequencing implementation and an adaptive LLC access priority control is disclosed. One embodiment provides mechanisms to resolve last level cache access priority among multiple internal CMP cores, internal snoops and external snoops. Another embodiment provides mechanisms for implementing cache coherency in multi-core CMP system.

Owner:INTEL CORP

Systems and methods for spillover in a multi-core system

The present invention is directed towards systems and methods for spillover threshold management in a multi-core system. A pool manager divides the spillover threshold limit of connections for vServers into an exclusive quota pool and a shared quota pool. Each vServer operating on a core is allocated an exclusive number of connections from the exclusive quota pool. If a vServer wishes to create connections beyond its exclusive number, the vServer can borrow from the shared quota pool. When the vServers are using at least a first predetermined threshold of their exclusive number of connections and the number of available connections in the shared quota pool has reached a second predetermined threshold, the multi-core system establishes a backup vServer.

Owner:CITRIX SYST INC

Multicore distributed processing system using selection of available workunits based on the comparison of concurrency attributes with the parallel processing characteristics

ActiveUS8230426B2Improve application performanceFast communicationGeneral purpose stored program computerMultiprogramming arrangementsMulti processorWork unit

Owner:DIGIPEDE TECH LLC

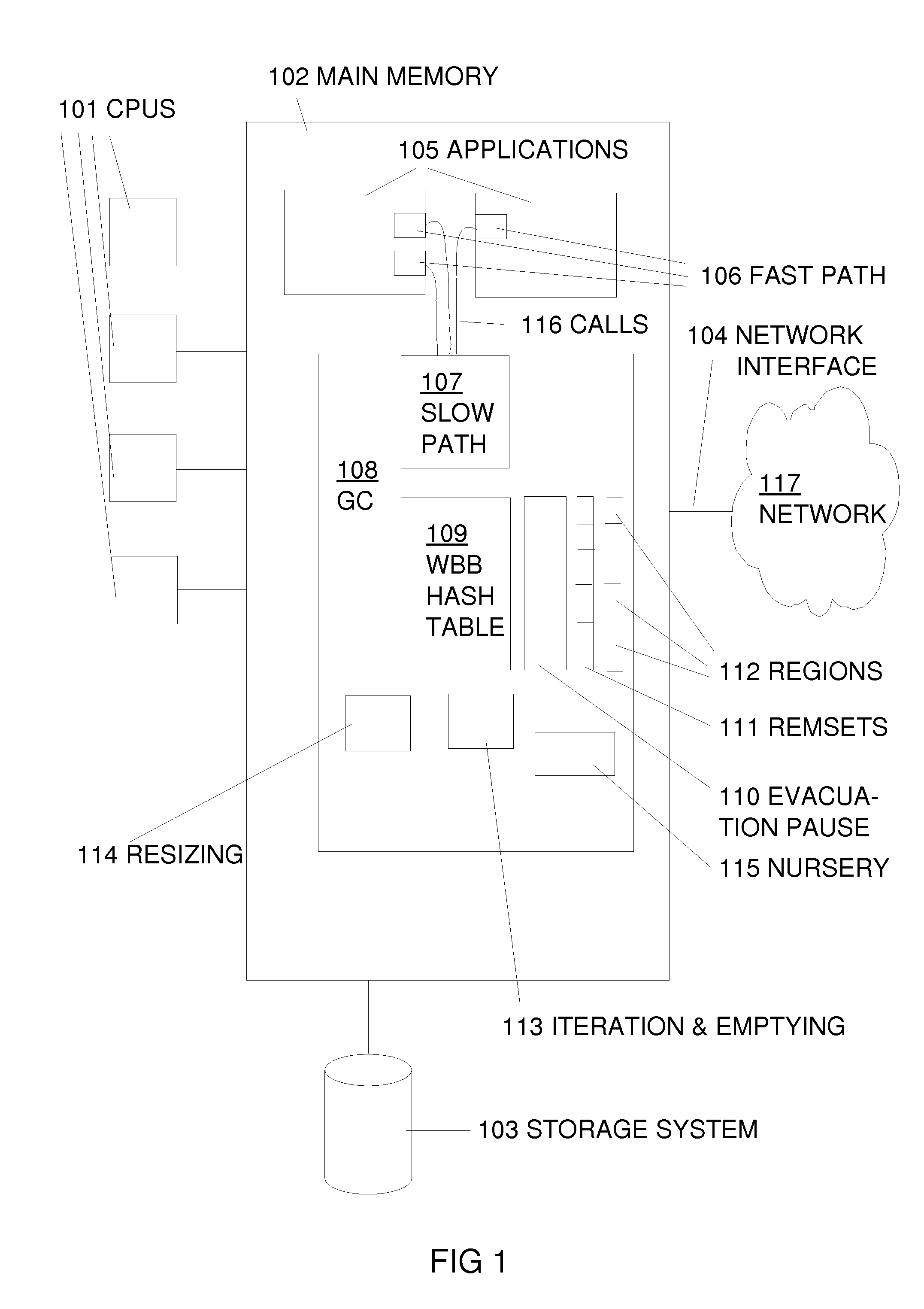

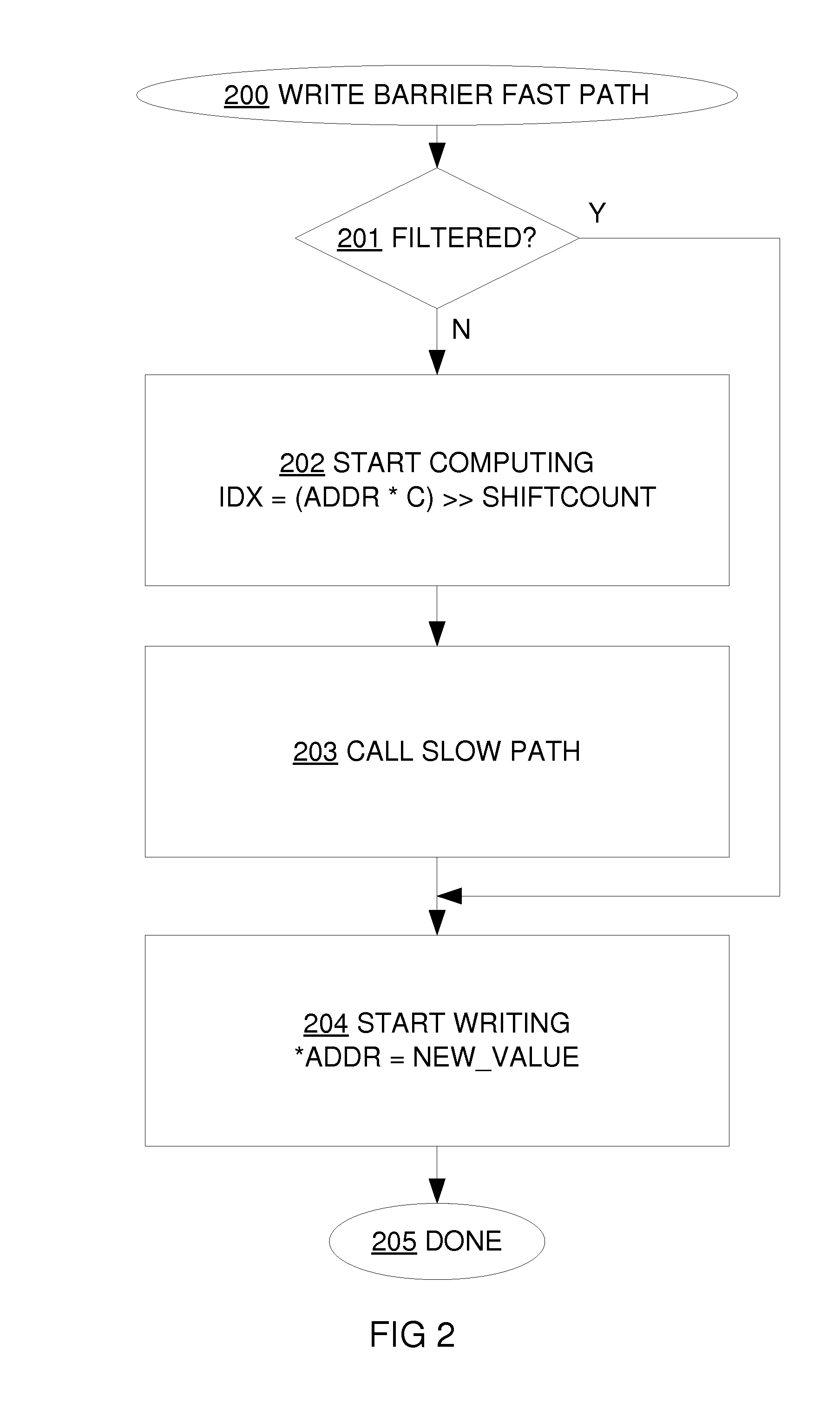

Lock-free hash table based write barrier buffer for large memory multiprocessor garbage collectors

InactiveUS20100185703A1Shorten pause timeReadily availableSpecial data processing applicationsMemory systemsMulti processorHash table

A lock-free write barrier buffer is used to combine multiple writes to identical locations and save old values of written memory locations and to reduce TLB misses compared to card marking. The old value of a written location as well as the address of the header of the written object can be saved, which is not possible with card marking. Scanning the card table and marked pages are eliminated. The method is lock-free, scaling to highly concurrent multiprocessors and multi-core systems.

Owner:CLAUSAL COMPUTING

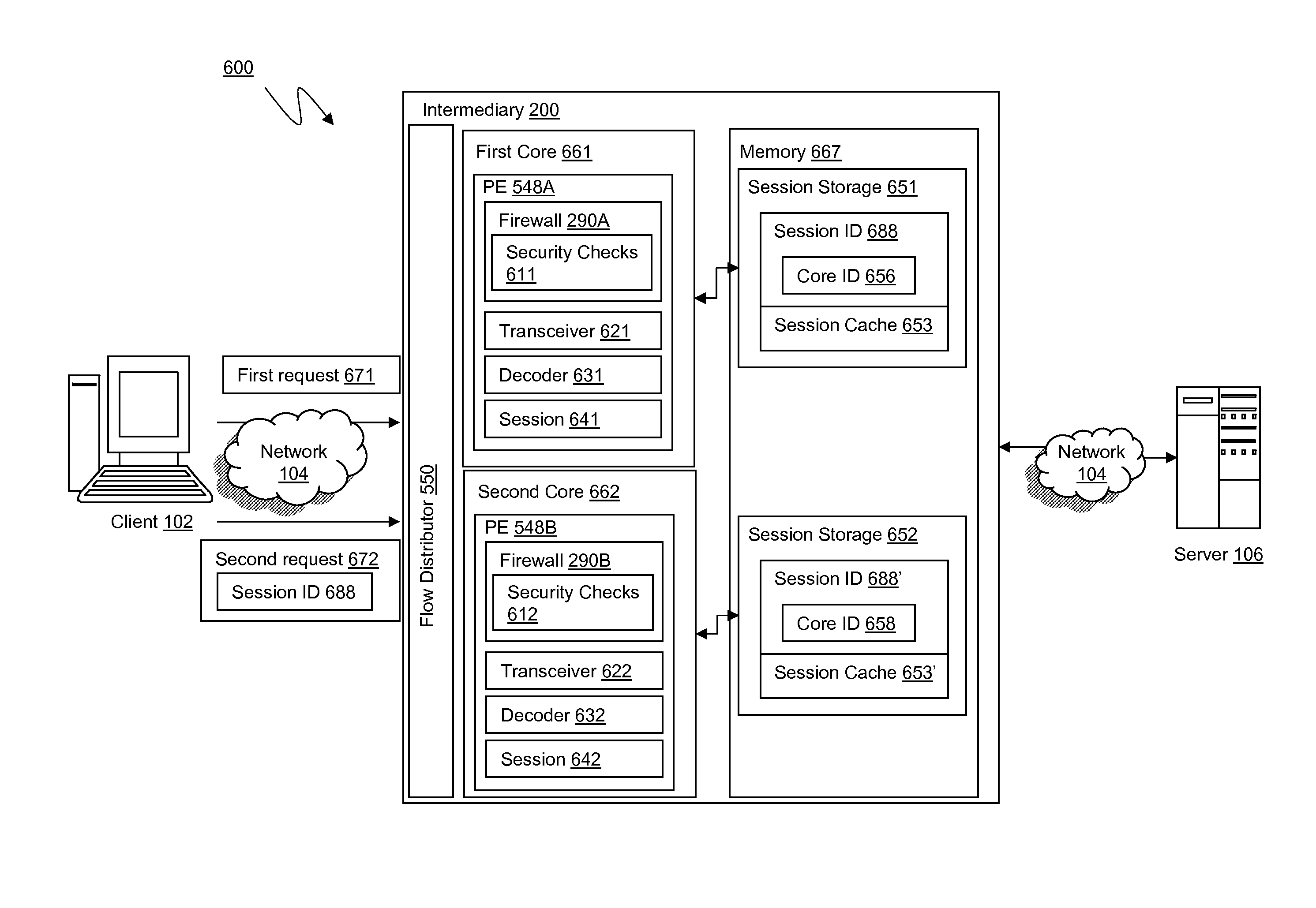

Systems and methods for processing application firewall session information on owner core in multiple core system

ActiveUS20110154471A1Improve computing powerInterprogram communicationMultiple digital computer combinationsComputer networkSecurity check

The present invention is directed towards systems and methods for sharing session data among cores in a multi-core system. A first application firewall module executes on a core of a multi-core intermediary device which establishes a user session. The first application firewall module stores application firewall session data to memory accessible by the first core. A second application firewall module executes on a second core of the multi-core intermediary device. The second application firewall module receives a request from the user via the established user session. The request includes a session identifier identifying that the user session was established by the first core. The second application firewall module determines to perform one or more security checks on the request and communicates a portion of the request the first core. The second application firewall module receives and processes the security check results and instructions from the first core.

Owner:CITRIX SYST INC

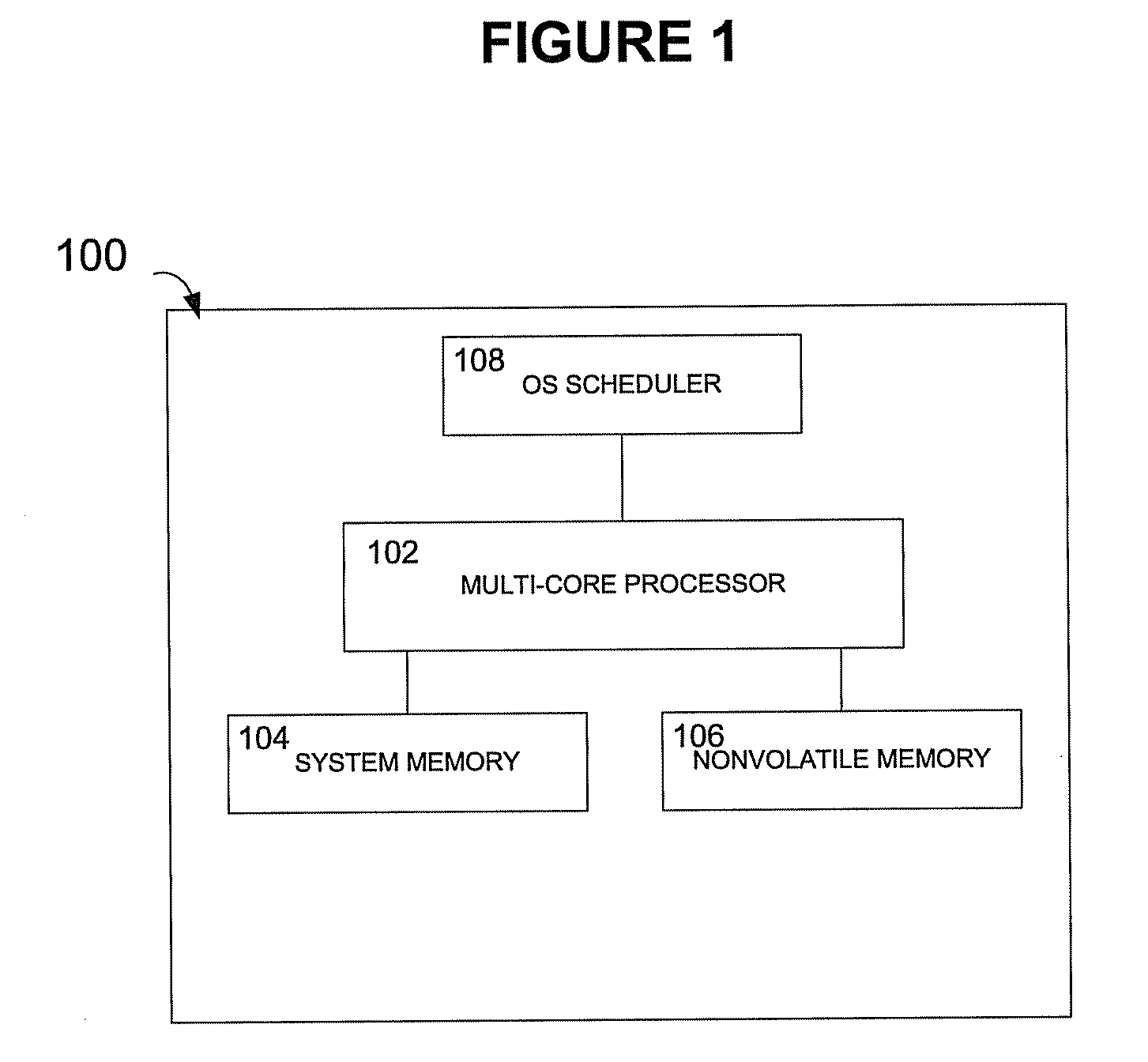

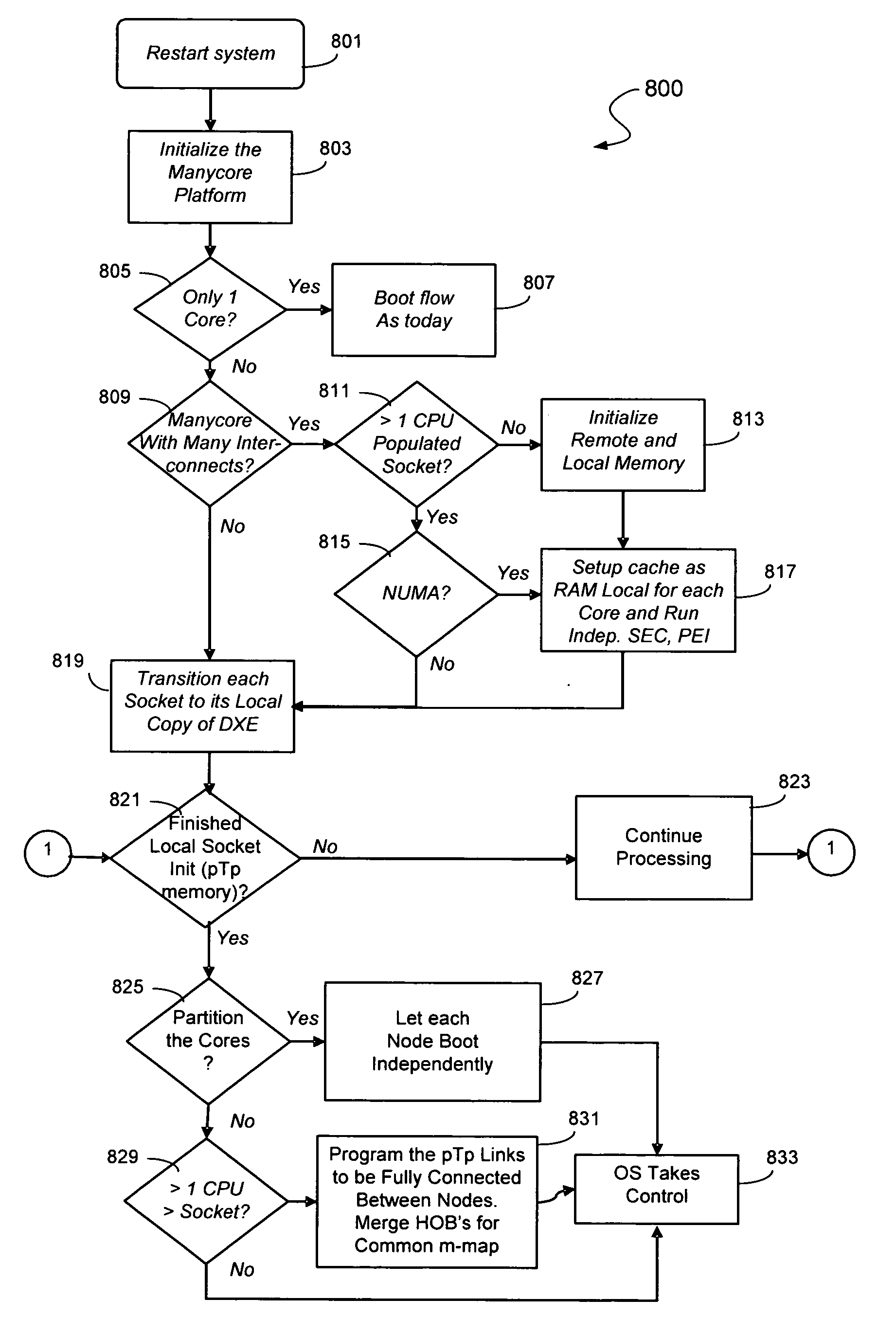

Multi-socket boot

In some embodiments, the invention involves a system and method to provide maximal boot-time parallelism for future multi-core, multi-node, and many-core systems. In an embodiment, the security (SEC), pre-EFI initialization (PEI), and then driver execution environment (DXE) phases are executed in parallel on multiple compute nodes (sockets) of a platform. Once the SEC / PEI / DXE phases are executed on all compute nodes having a processor, the boot device select (BDS) phase completes the boot by merging or partitioning the compute nodes based on a platform policy. Partitioned compute nodes each run their own instance of EFI. A common memory map may be generated prior to operating system (OS) launch when compute nodes are to be merged. Other embodiments are described and claimed.

Owner:INTEL CORP

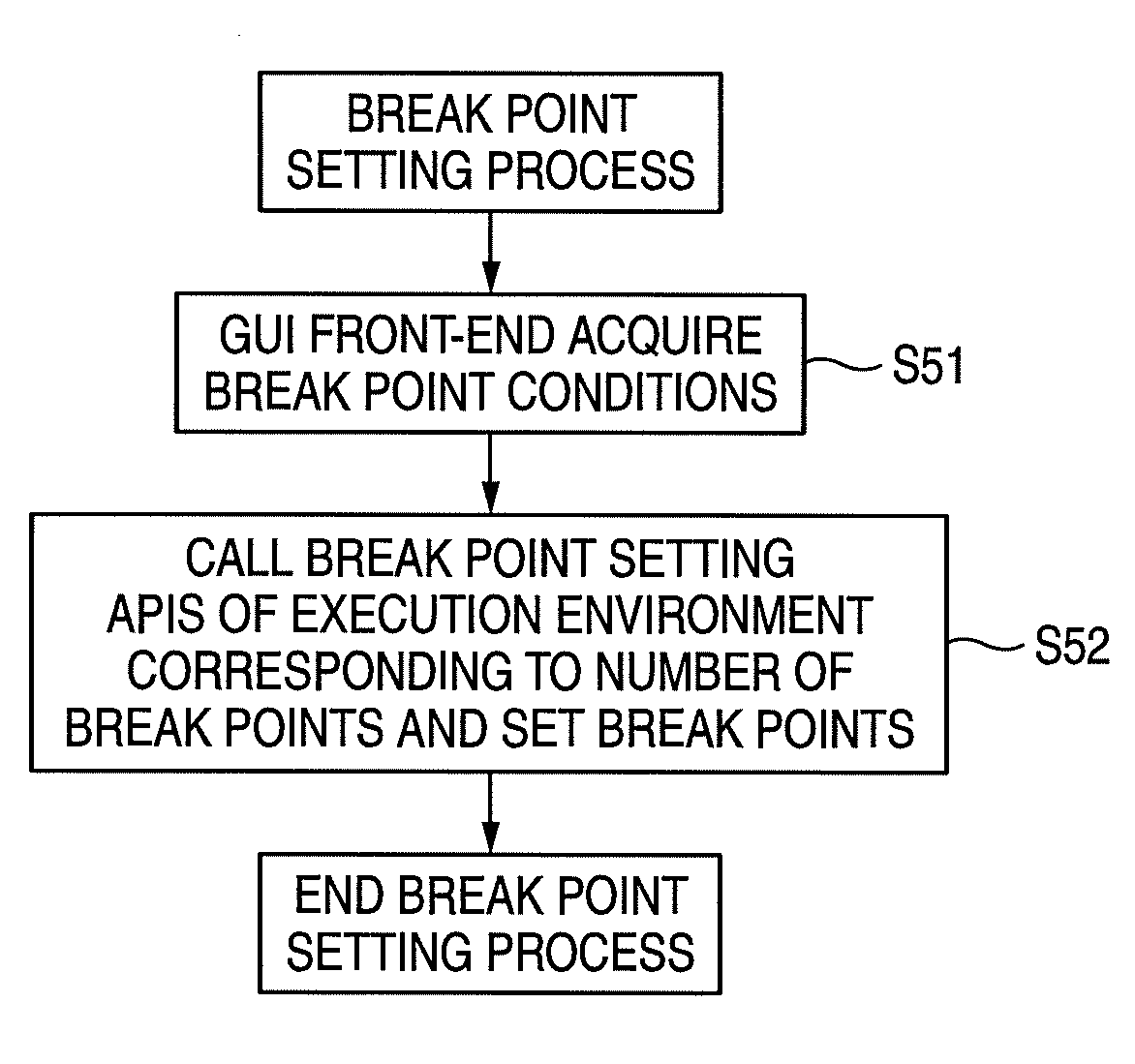

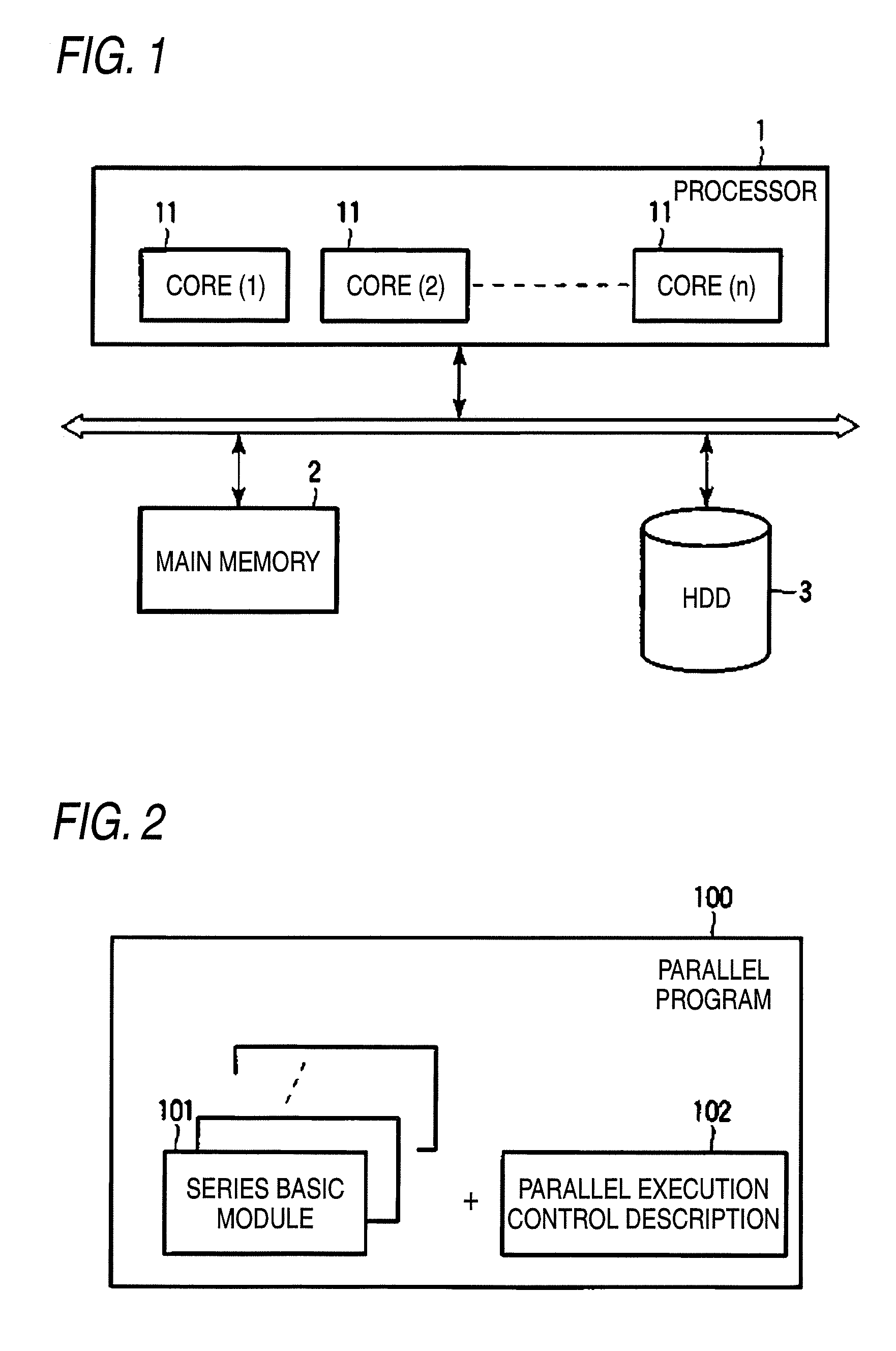

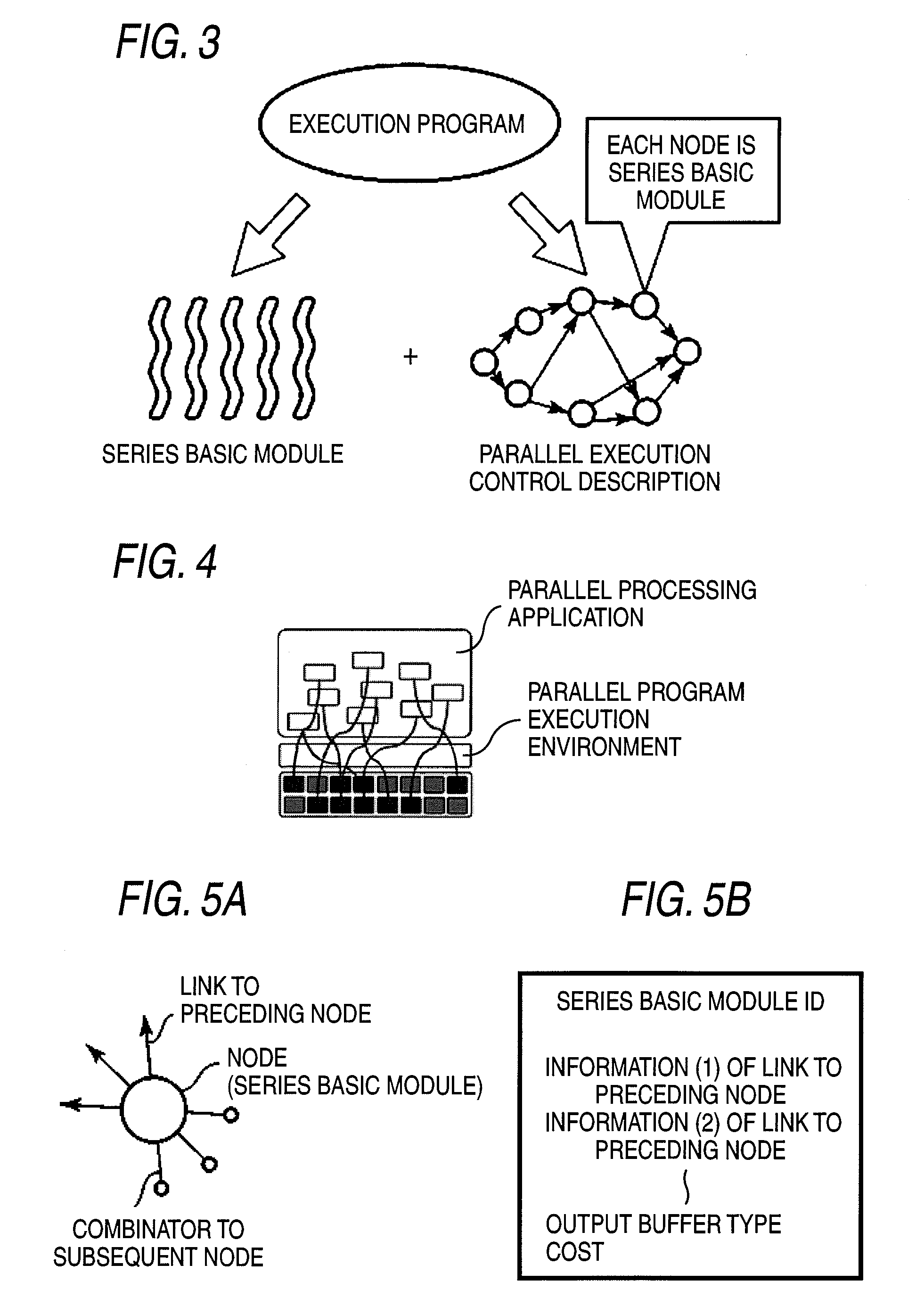

Debugger for Multicore System

A debugger includes: a plurality of processor cores; and a scheduler configured to control an allocation of a plurality of basic modules to the processor cores based on an execution rule for enabling parallel execution of a program that is divided into the basic modules that are executable asynchronously with one another, the program being defined with the execution rule of the basic modules for executing the basic modules in time series, wherein the scheduler includes a break point setting module configured to set a group of break points that are designated through a graphical user interface.

Owner:KK TOSHIBA

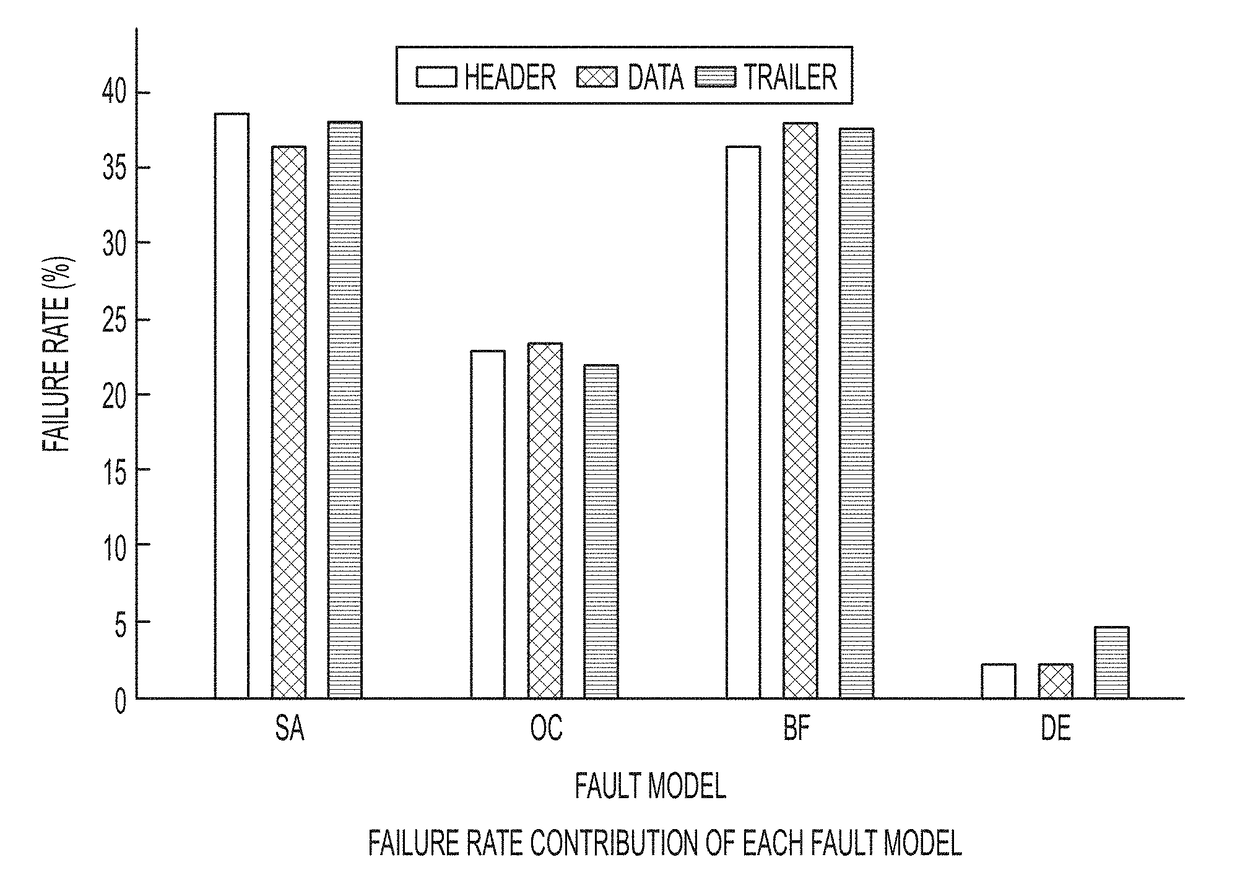

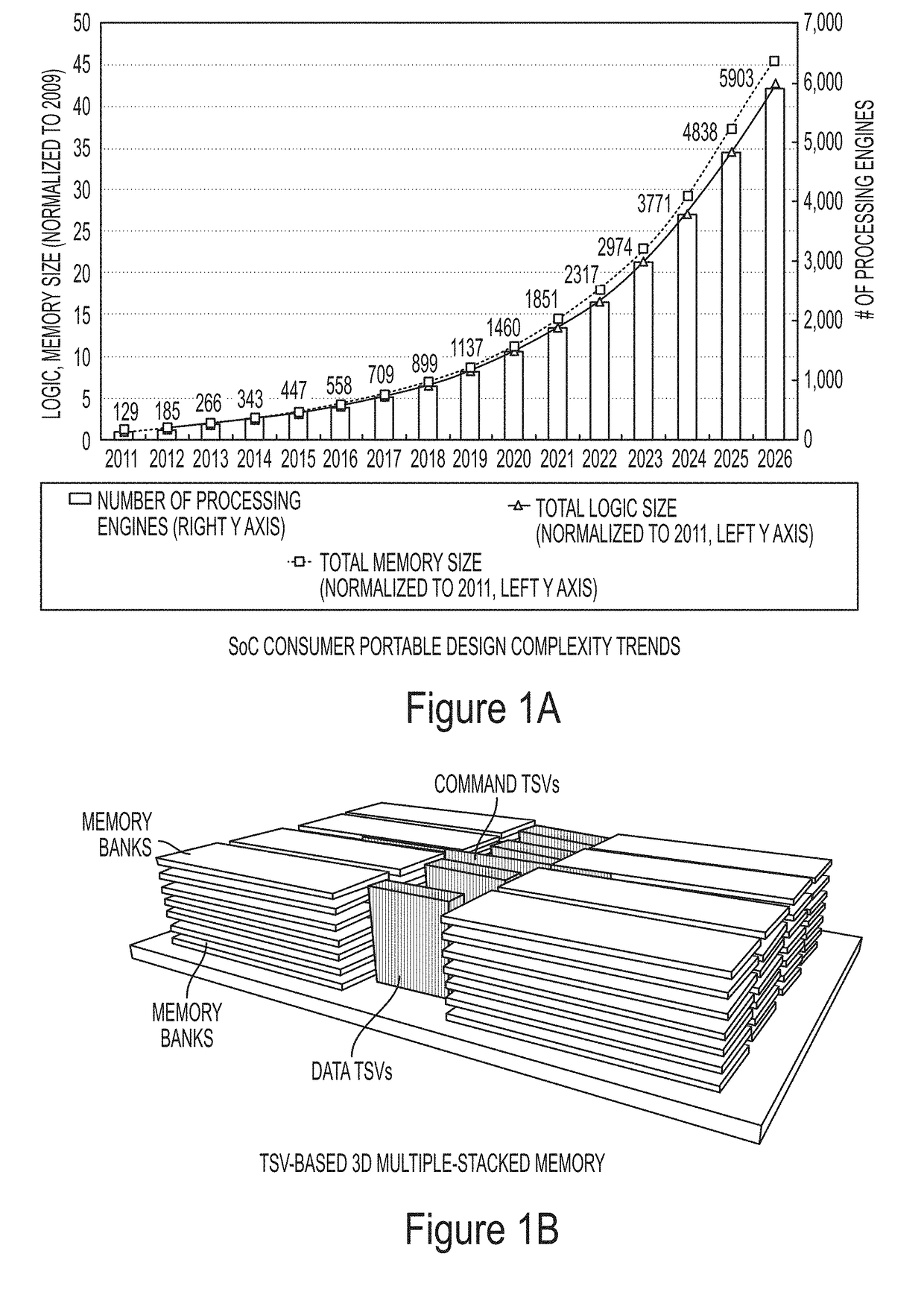

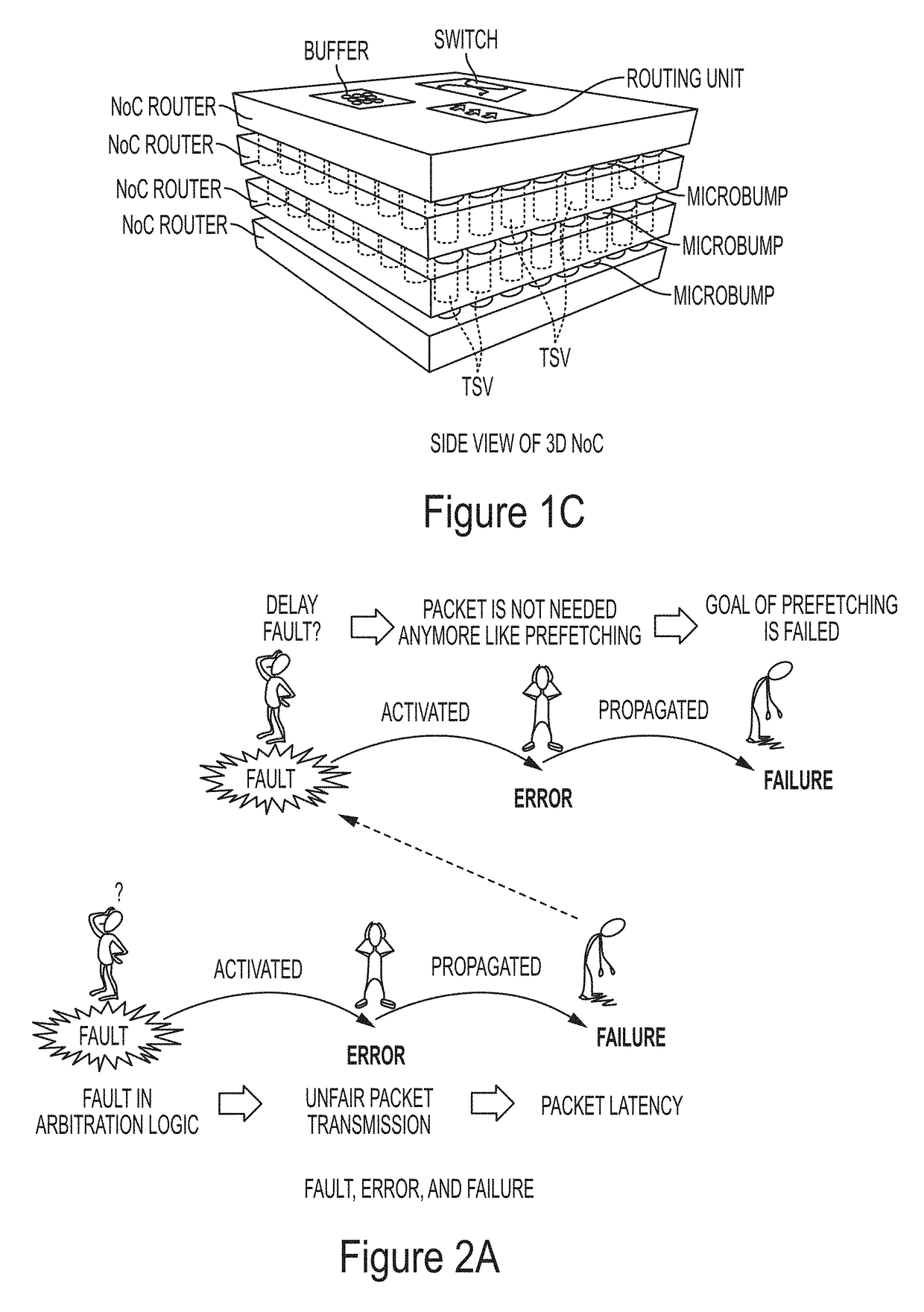

THREE-DIMENSIONAL NoC RELIABILITY EVALUATION

Methods, storage mediums, and apparatuses for evaluating the reliability of Three-Dimensional (3D) Network-on-Chip (NoC) designs are described. The described embodiments provide a 3D NoC specific fault-injector tool which is able to model logic-level fault models of 3D NoC specific physical faults in 3D-NoC platform. These embodiments automate the whole process of static and dynamic fault injection base on the user preference and reports the specific reliability metrics for 3D NoC platform as a single tool. The described embodiments can be used for the reliability evaluation and effectiveness of fault-tolerant designs in any of the 3D-many core designs such as manycore systems in different ranges of application from embedded systems in cellphones to larger systems which can be used in next generation of autonomous cars or hypercube memory cells.

Owner:SYNOPSYS INC

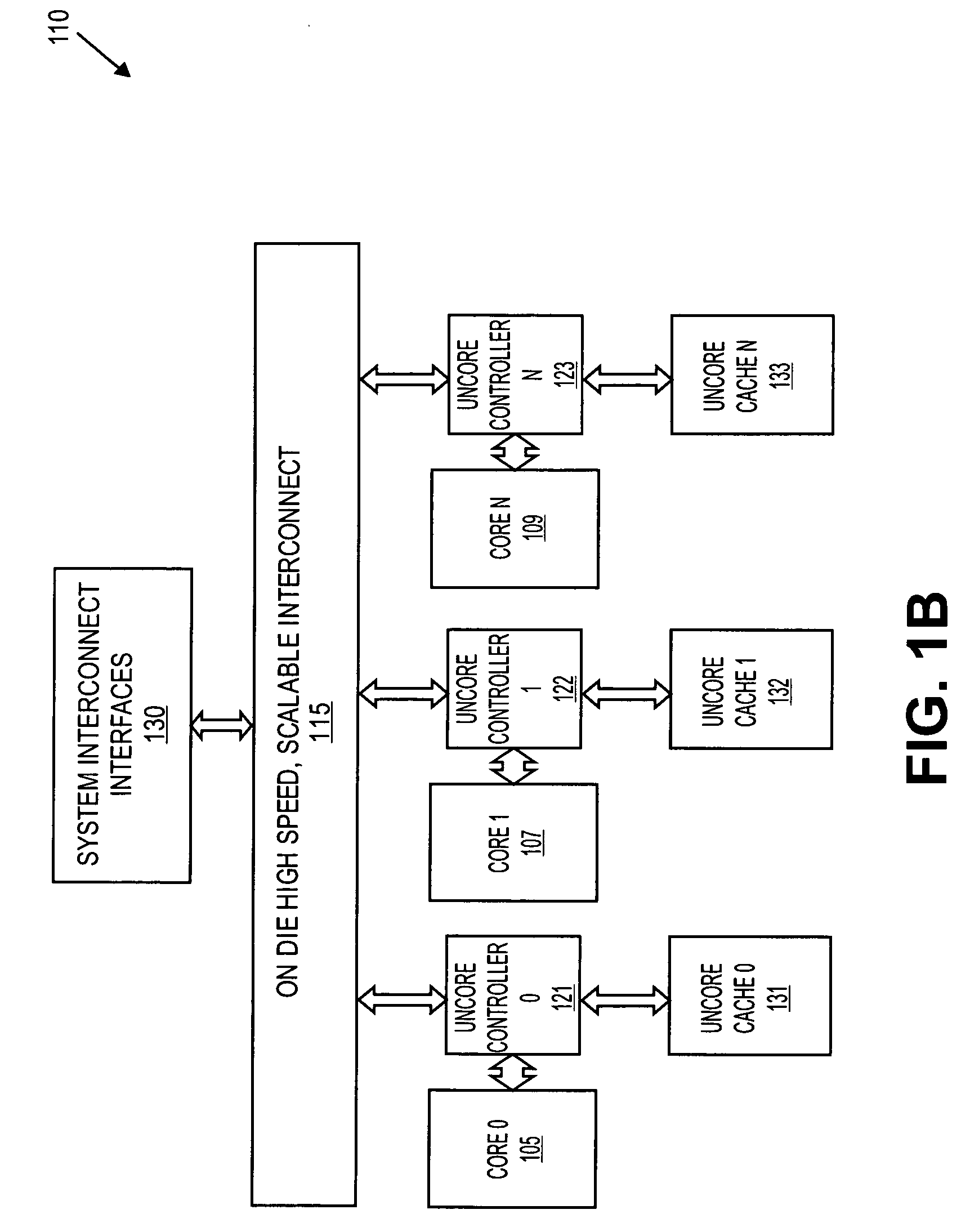

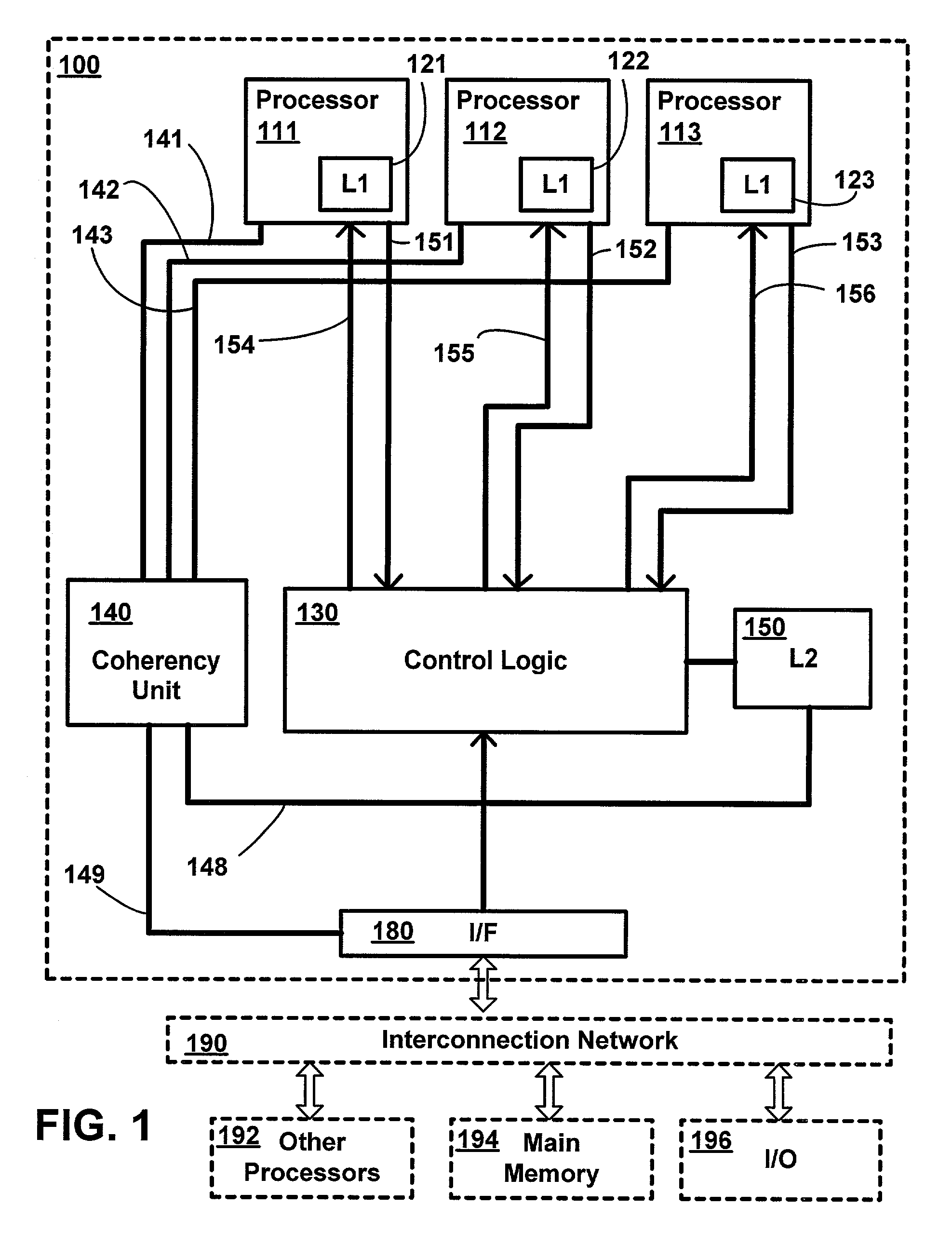

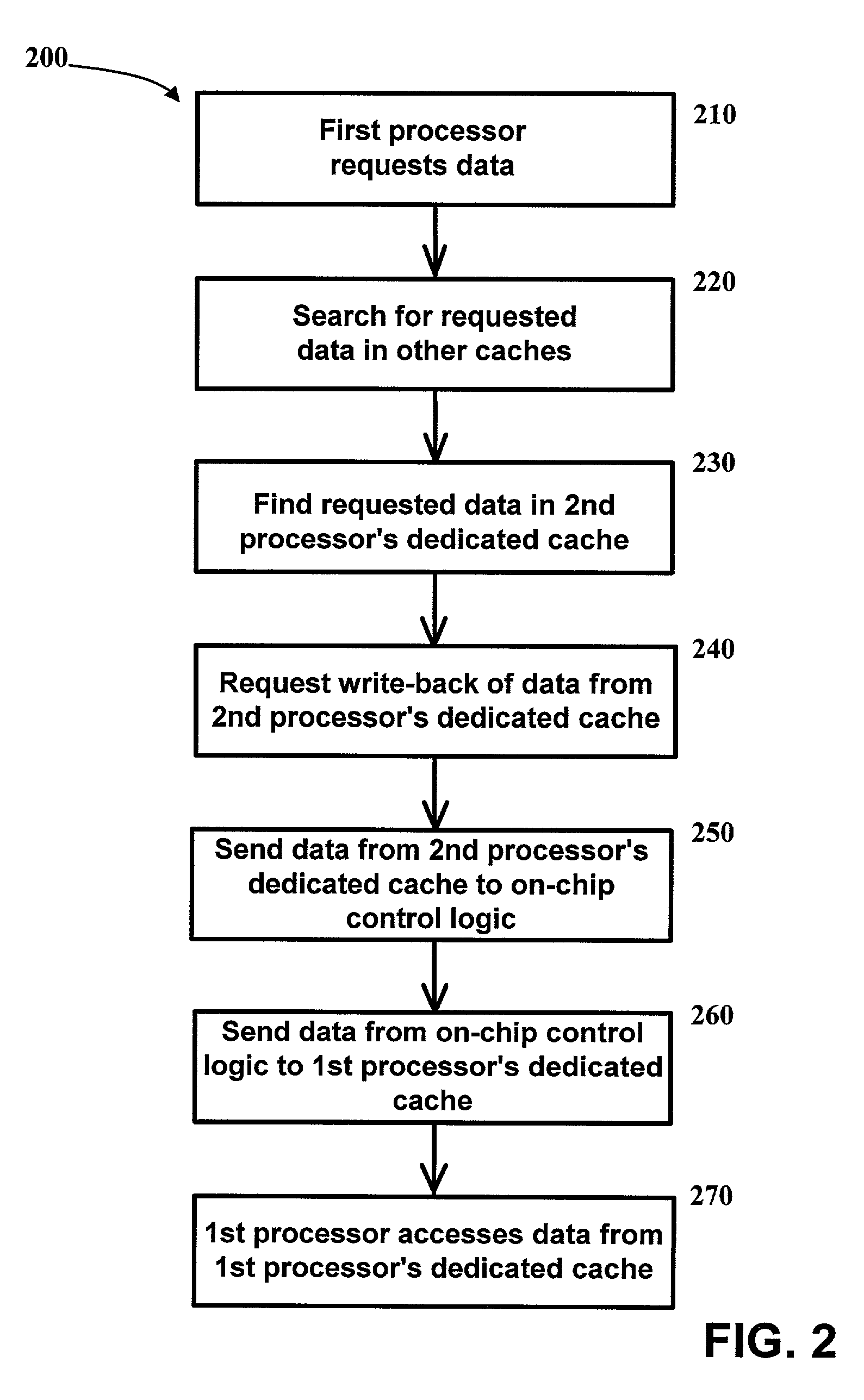

Transfer of cache lines on-chip between processing cores in a multi-core system

Cache coherency is maintained between the dedicated caches of a chip multiprocessor by writing back data from one dedicated cache to another without routing the data off-chip. Various specific embodiments are described, using write buffers, fill buffers, and multiplexers, respectively, to achieve the on-chip transfer of data between dedicated caches.

Owner:INTEL CORP

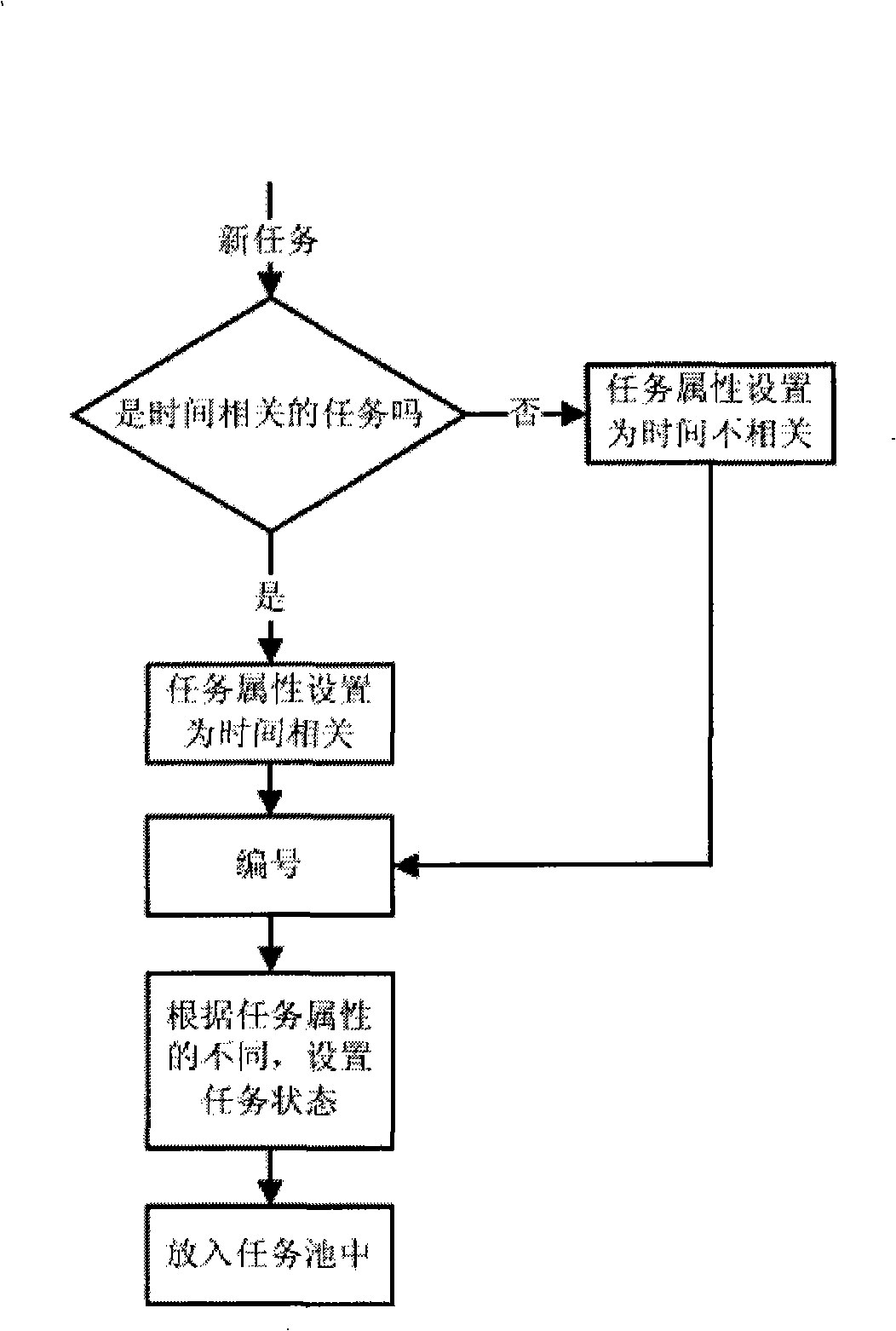

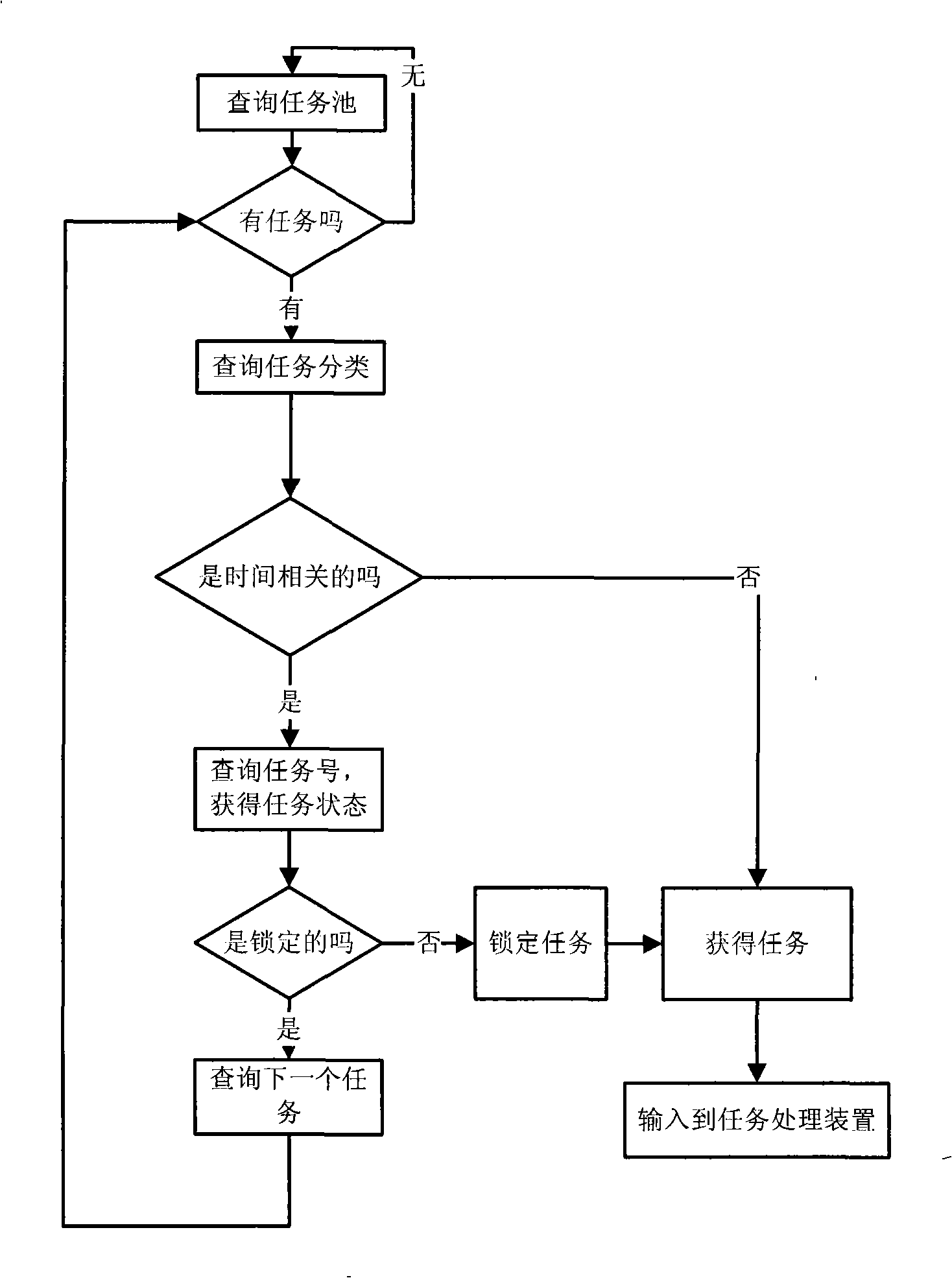

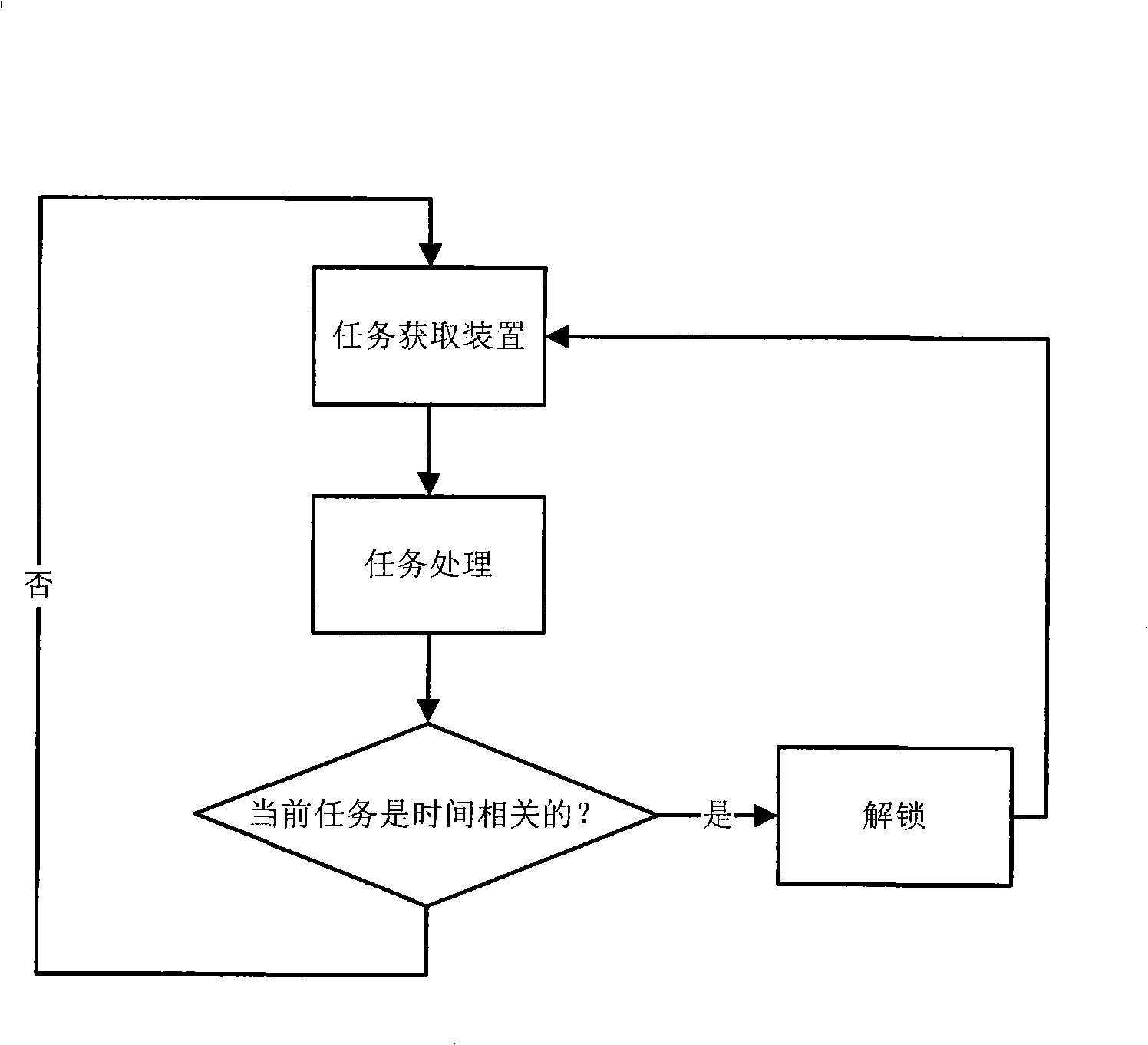

Multi- nuclear DSP system self-adapting task scheduling method

InactiveCN101261591ATo achieve load balancingReal-time processingProgram initiation/switchingIdle timeComputer architecture

The invention relates to a task scheduling method in a multi-core DSP system. A shared task pool is established in a shared memory in the multi-core DSP system, tasks are input into the task pool, the tasks are firstly classified into two categories of time-related and non-time-related, then each task is carried out the numbering, the time-related tasks have the same serial number, the non-time-related tasks are independently carried out the numbering, the initial states of the tasks with the different serial numbers are set as the non-locked states; and a task obtaining device of each idle slave core carries out the inquiry to the shared task pool and carries out the processing of the task after obtaining the task. The task scheduling method changes the technical proposal of using a main core for distributing tasks by the traditional multi-core DSP system and adopts the method of using the slave cores to actively obtain the tasks during the idle time, which can effectively reduce the requirements on the reliability of priori knowledge and reduce the load balance of the multi-core system.

Owner:AVONACO COMM SYST SUZHOU

Systems and methods for iip address sharing across cores in a multi-core system

In a multi-core system, multiple packet engines across corresponding cores may be working concurrently processing data packets from data flows of SSL VPN sessions. For example, a first core may establish a SSL VPN session with a client. Any one of the other cores, such as a second core, may received packets related to the session owned by the first core. Embodiments of the systems and method described below provide management of IIP addresses for the multi-core / multi-packet engine approach to providing SSL VPN service. In some embodiments, the approach to managing IIP addresses is to have one packet engine on a core act as a master or controller of the IIPs for the remaining packet engines and cores. The packet engines / cores use a protocol for communications regarding IIP management.

Owner:CITRIX SYST INC