Patents

Literature

270 results about "Many core" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and apparatus for embedding chat functions in a web page

InactiveUS7263526B1Special service provision for substationMultiple digital computer combinationsWriting messagesApplication software

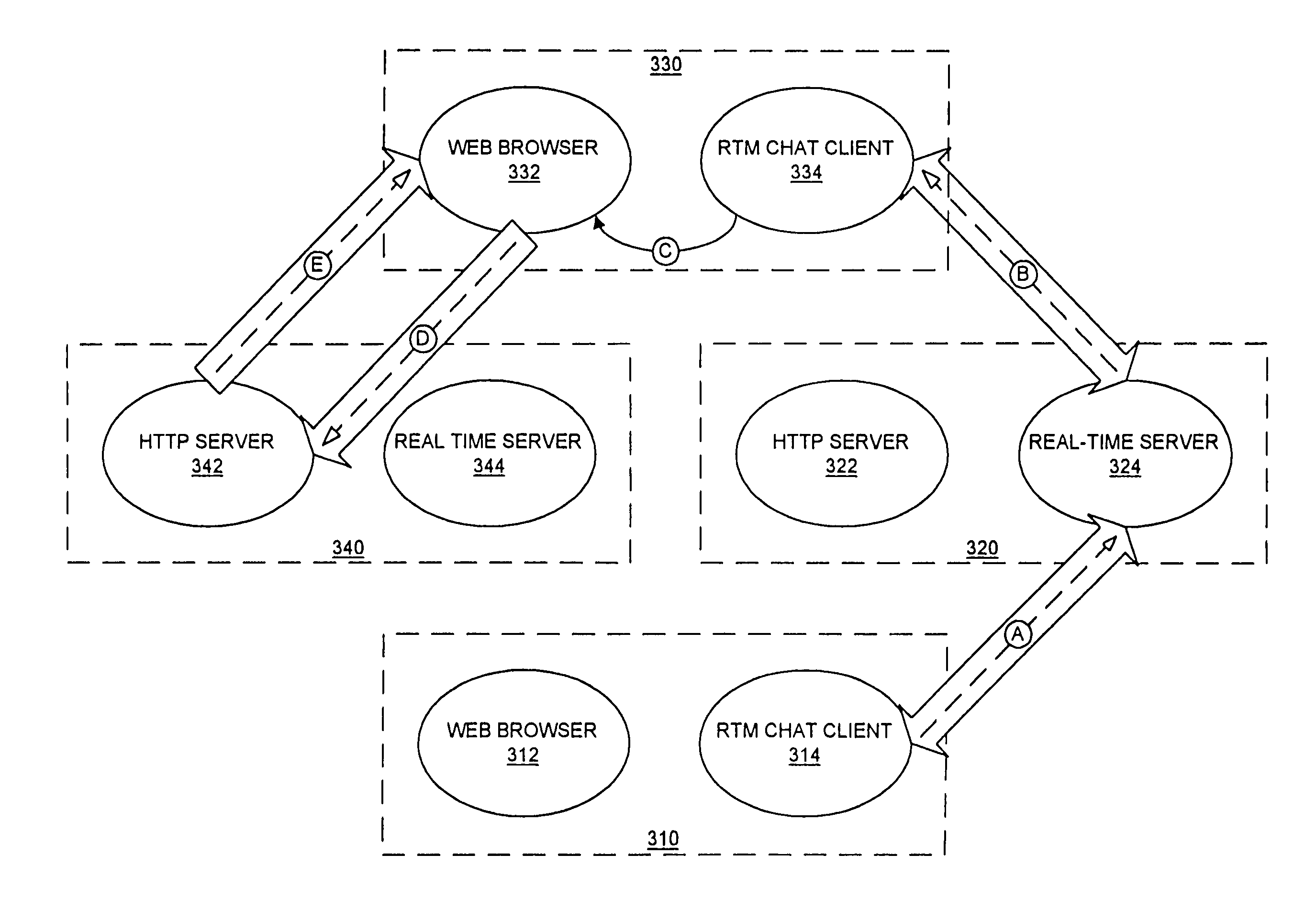

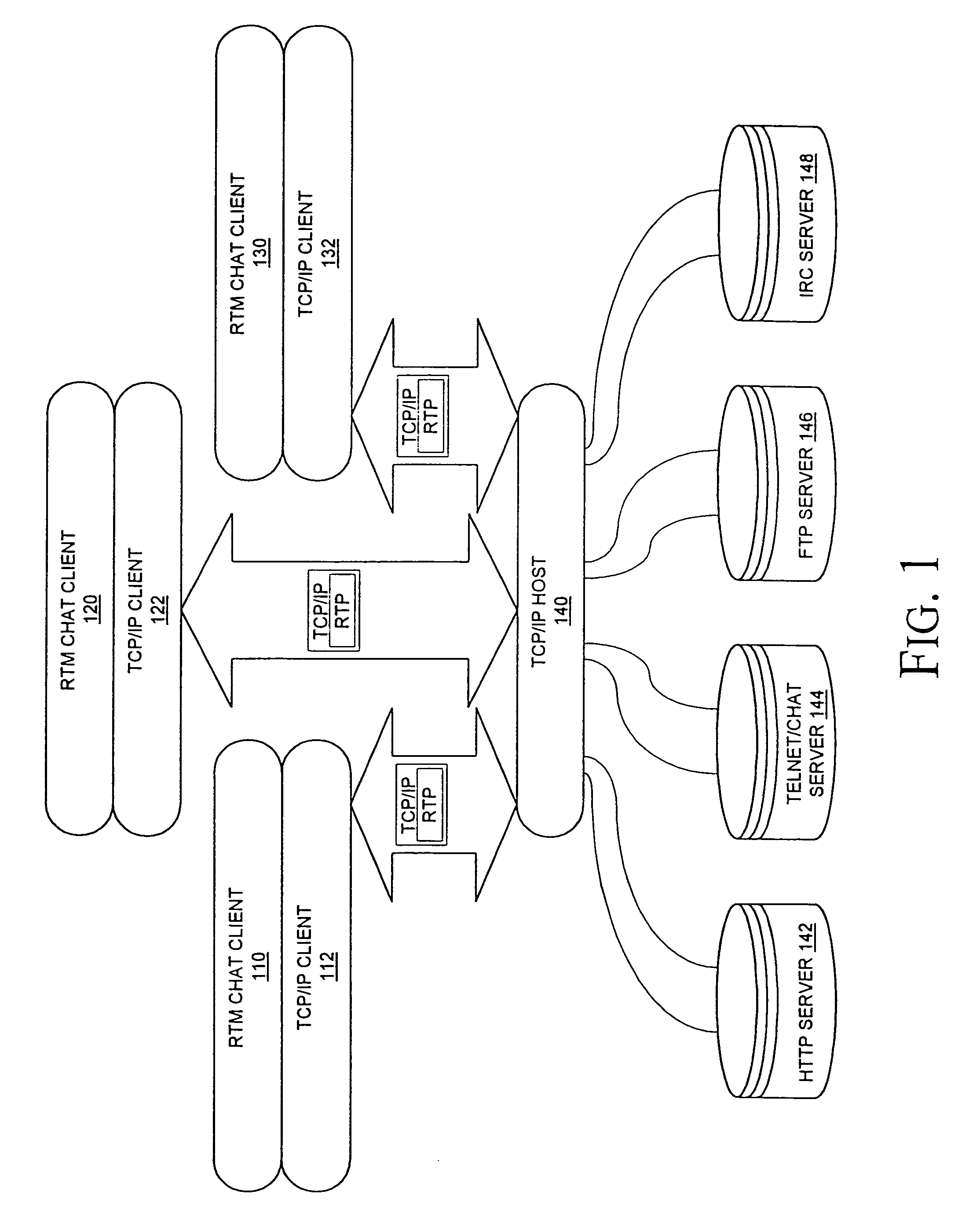

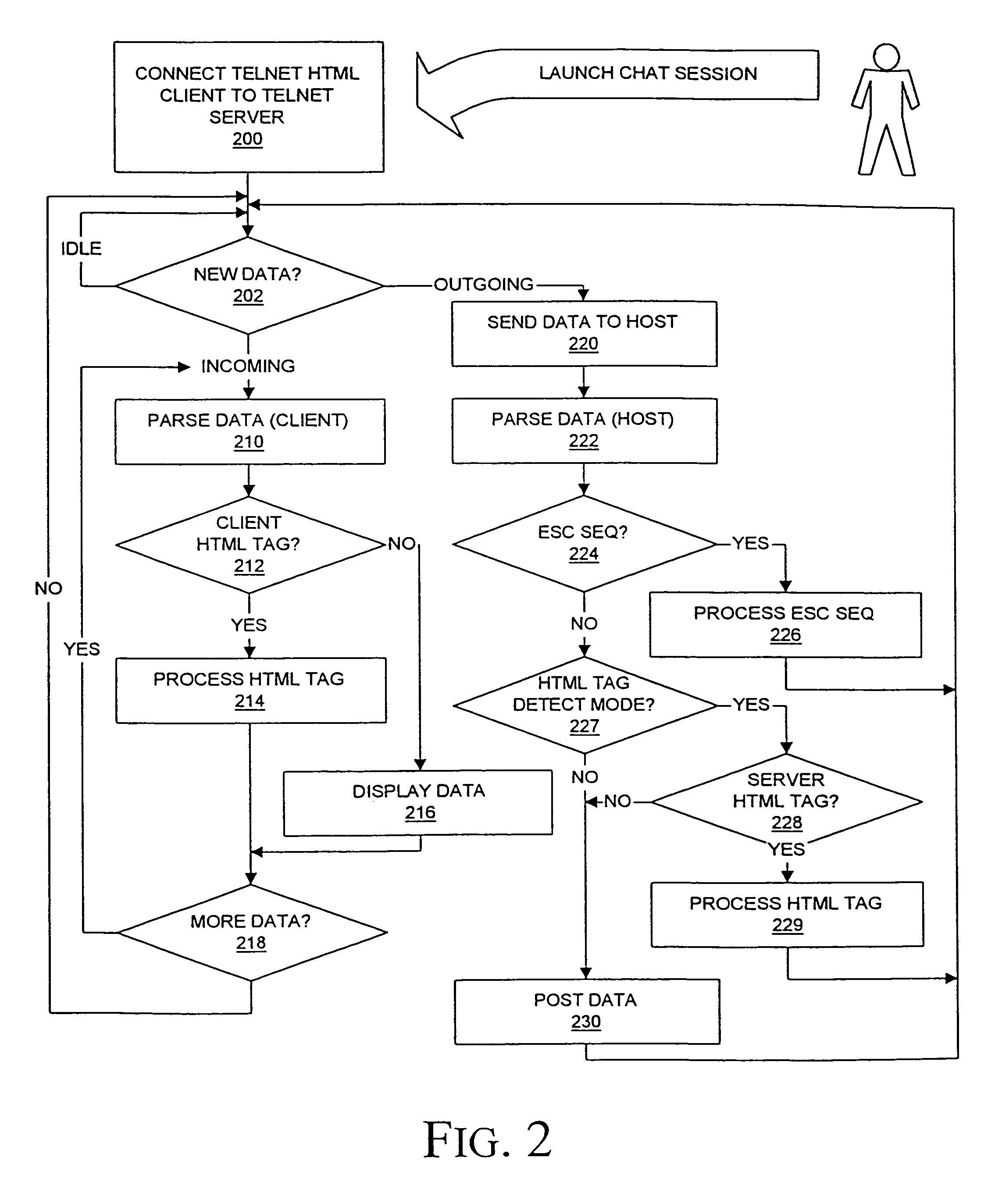

A real time chat server (610) not only maintains the chat session but also synchronizes the browse and chat functions by dynamically linking the browser and chat applications to allow the contents of the browser window and the chat window to change in a coordinated manner. The chat server is built from a number of core software objects, namely user objects (616, 618), connection objects, and room objects (612, 614). In this way, multiple users' browsers may be connected into one powerful distributed chat / HTTP server and all such users are able to fully interact with one another in a coordinated manner via type-written messages, HTML web documents, and file transfers. The usefulness of chat is enhanced by embedding the chat functions into the browser window.

Owner:NYTELL SOFTWARE LLC

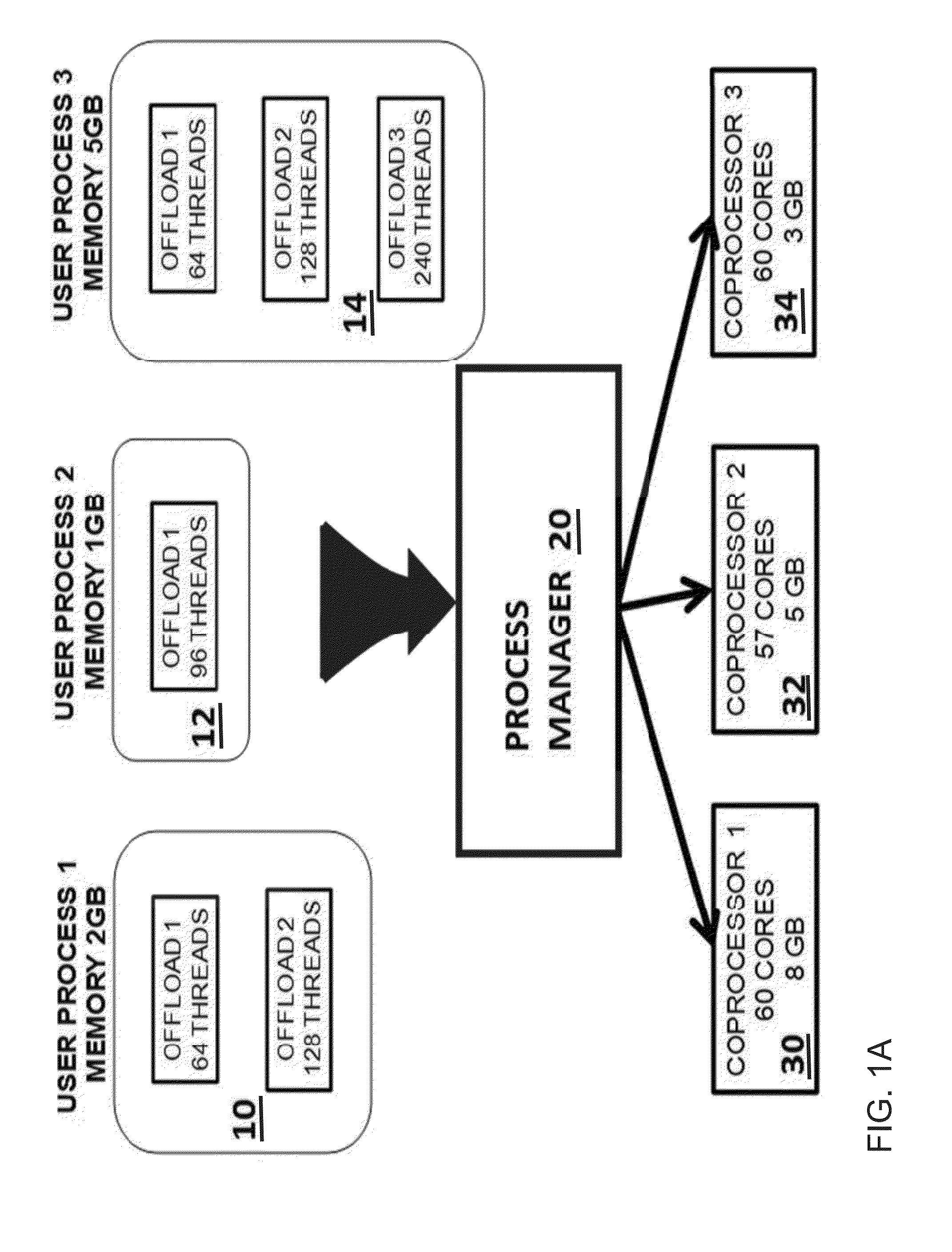

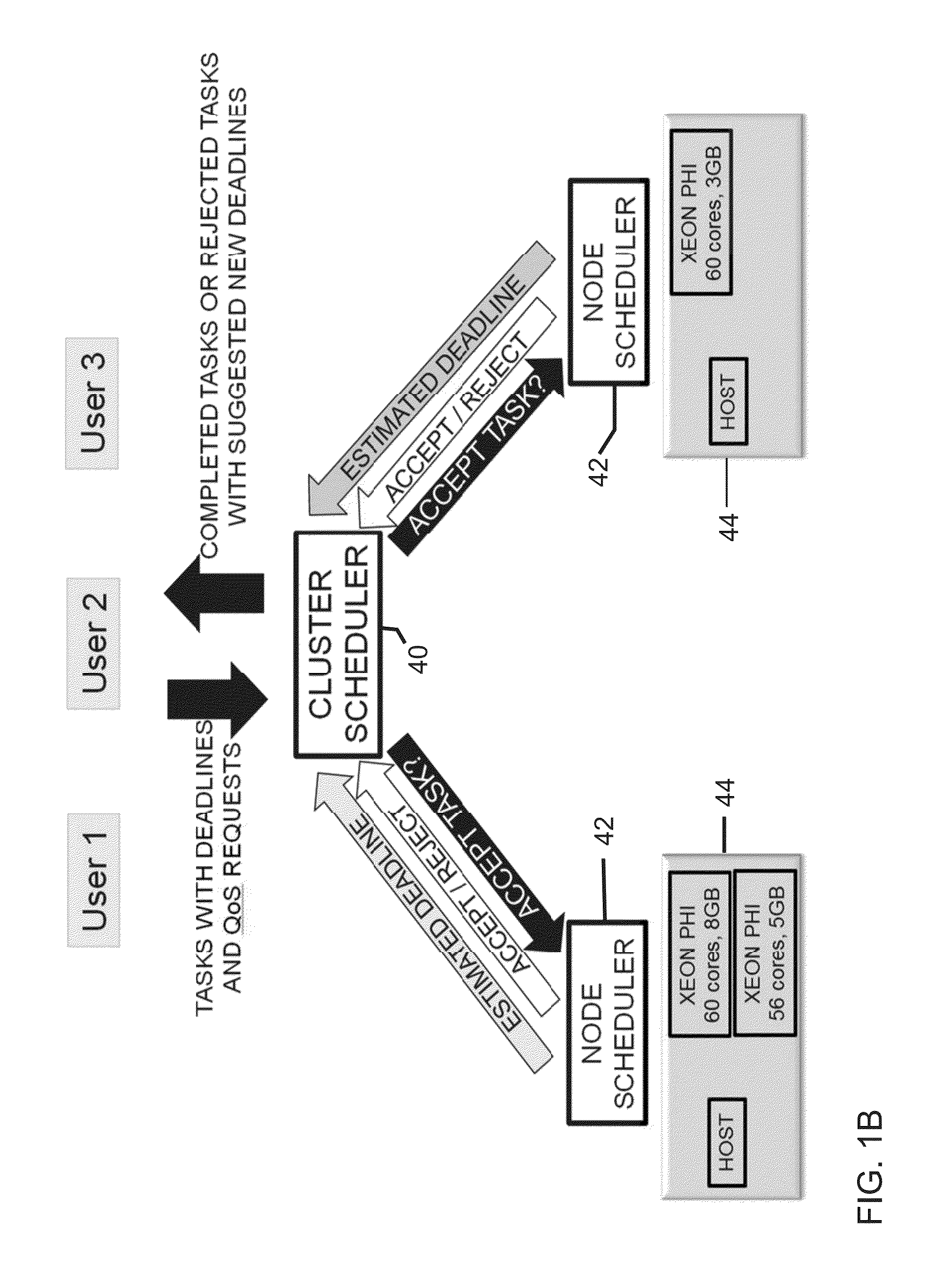

Simultaneous scheduling of processes and offloading computation on many-core coprocessors

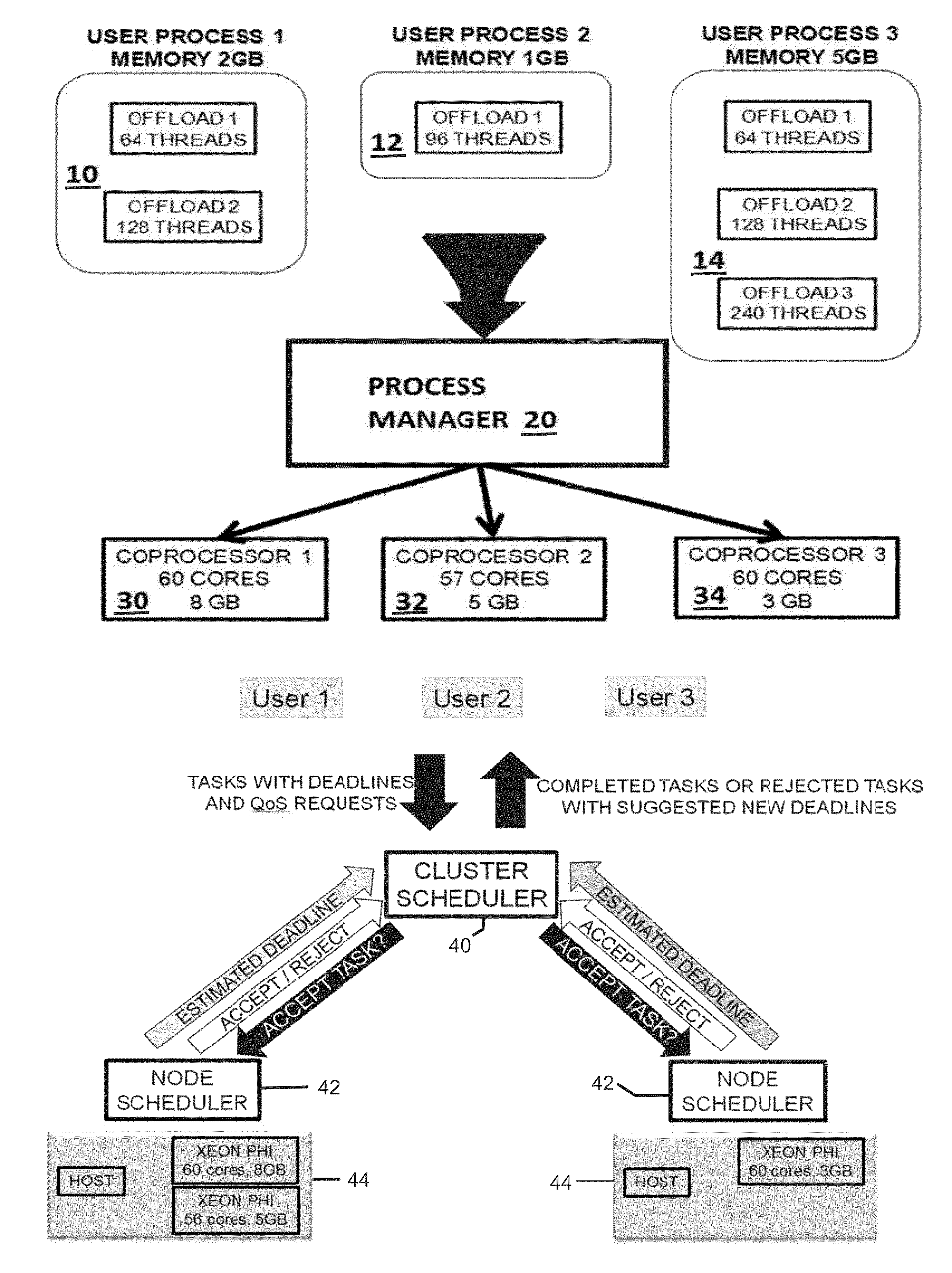

Methods and systems for scheduling jobs to manycore nodes in a cluster include selecting a job to run according to the job's wait time and the job's expected execution time; sending job requirements to all nodes in a cluster, where each node includes a manycore processor; determining at each node whether said node has sufficient resources to ever satisfy the job requirements and, if no node has sufficient resources, deleting the job; creating a list of nodes that have sufficient free resources at a present time to satisfy the job requirements; and assigning the job to a node, based on a difference between an expected execution time and associated confidence value for each node and a hypothetical fastest execution time and associated hypothetical maximum confidence value.

Owner:NEC CORP

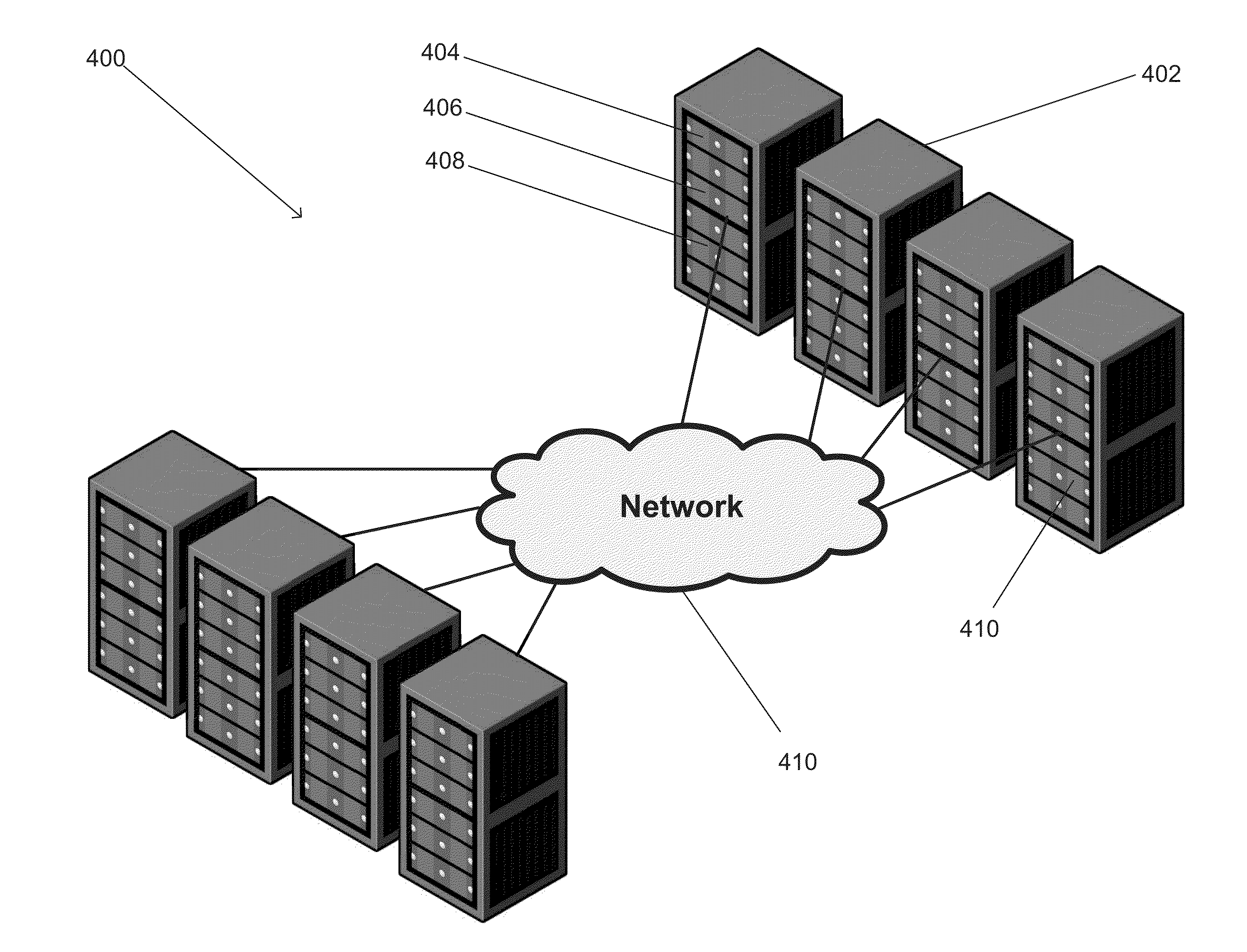

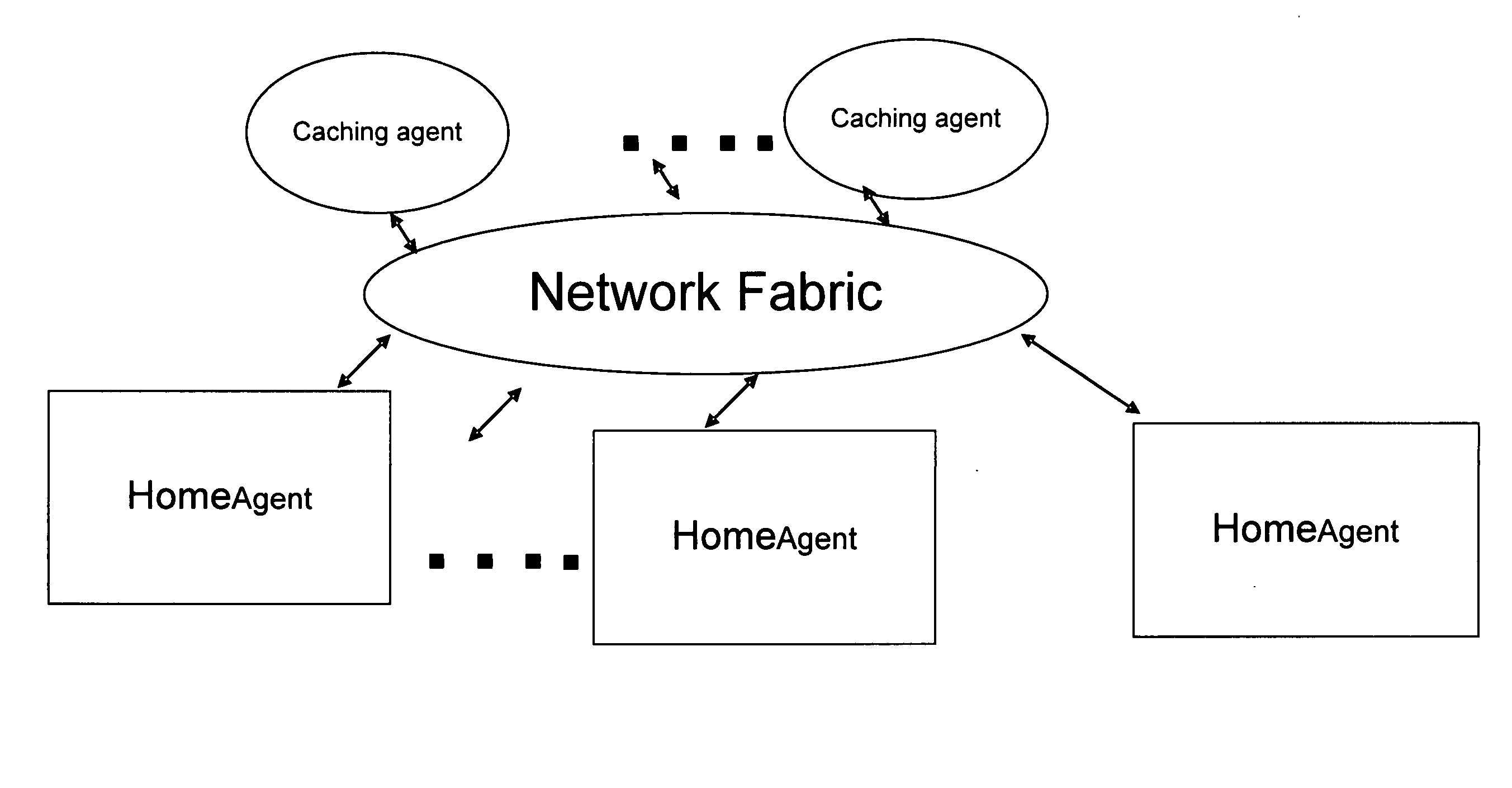

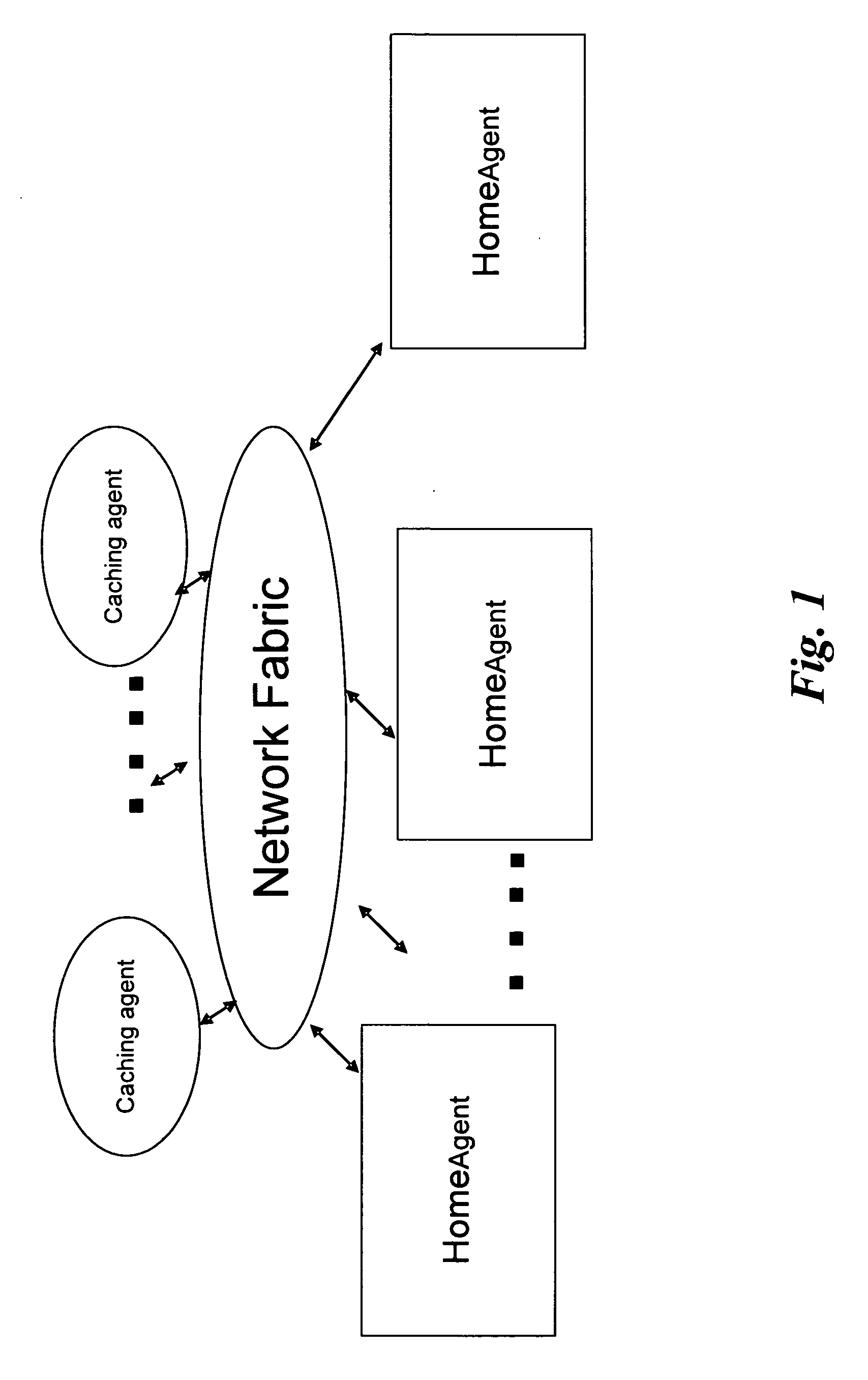

Systems and methods for implementing distributed databases using many-core processors

InactiveUS20140280375A1Rapid and low power retrievalDigital data processing detailsSpecial data processing applicationsSolid-state driveDistributed database

A distributed database, comprising a plurality of server racks, and one or more many-core processor servers in each of the plurality of server racks, wherein each of the one or more many-core processor servers comprises a many-core processor configured to store and access data on one or more solid state drives in the distributed database, where the one or more solid state drives are configured to enable retrieval of data through one or more text-searchable indexes. The one or more many-core processor servers are configured to communicate within the plurality of server racks via a network, and the data is configured as one or more tables distributed to the one or more many-core processor servers for storage in the one or more solid state drives.

Owner:WANDISCO

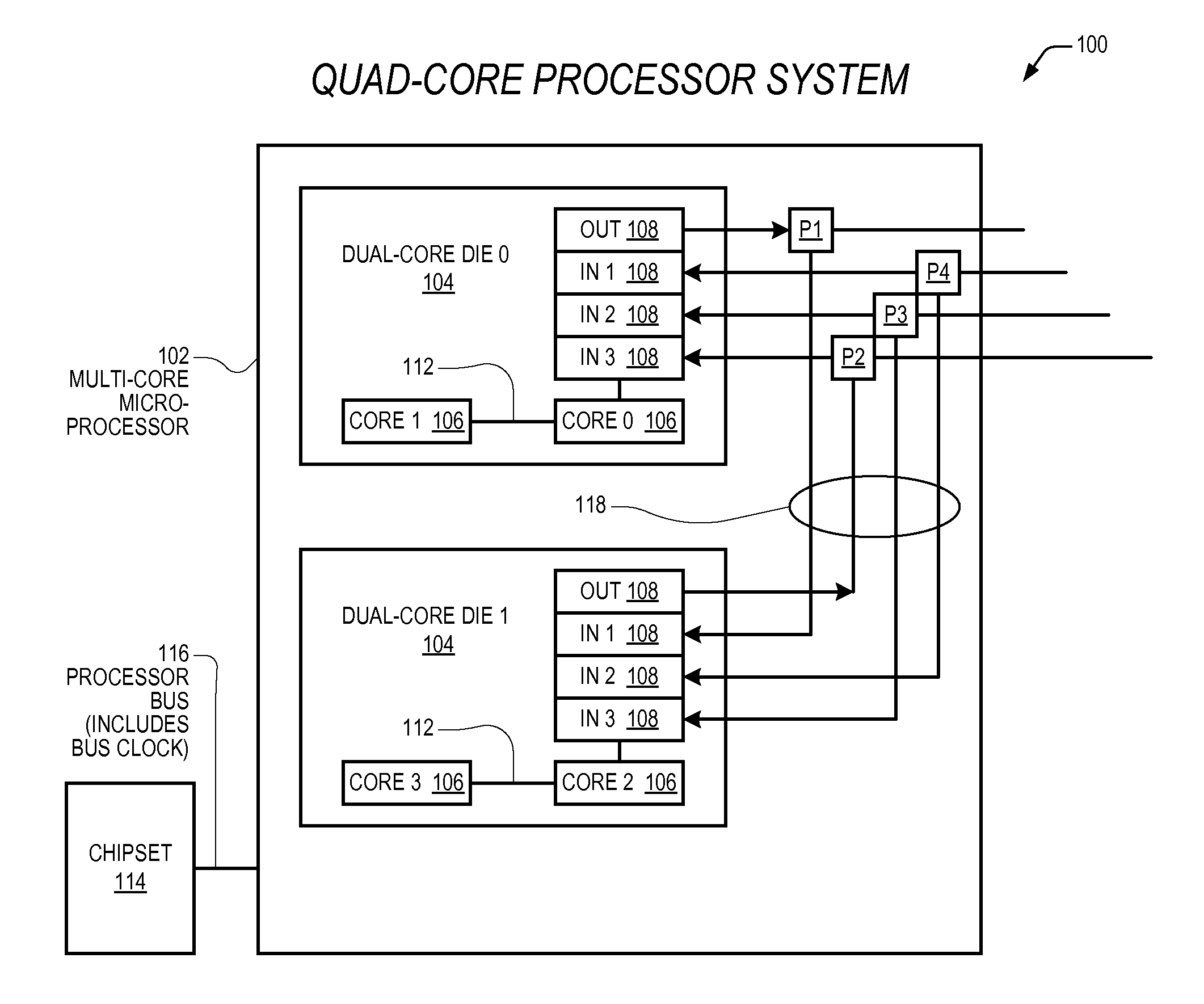

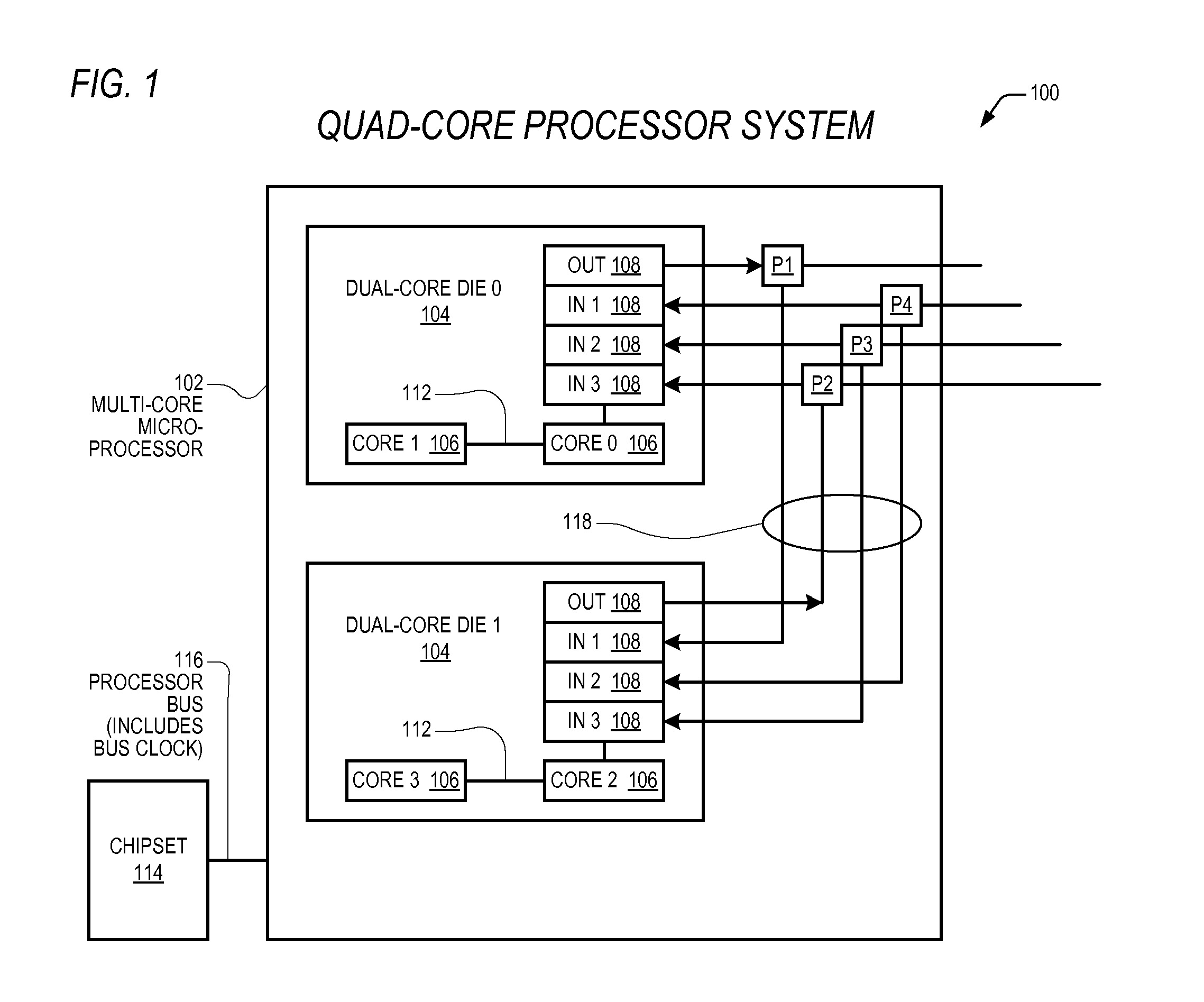

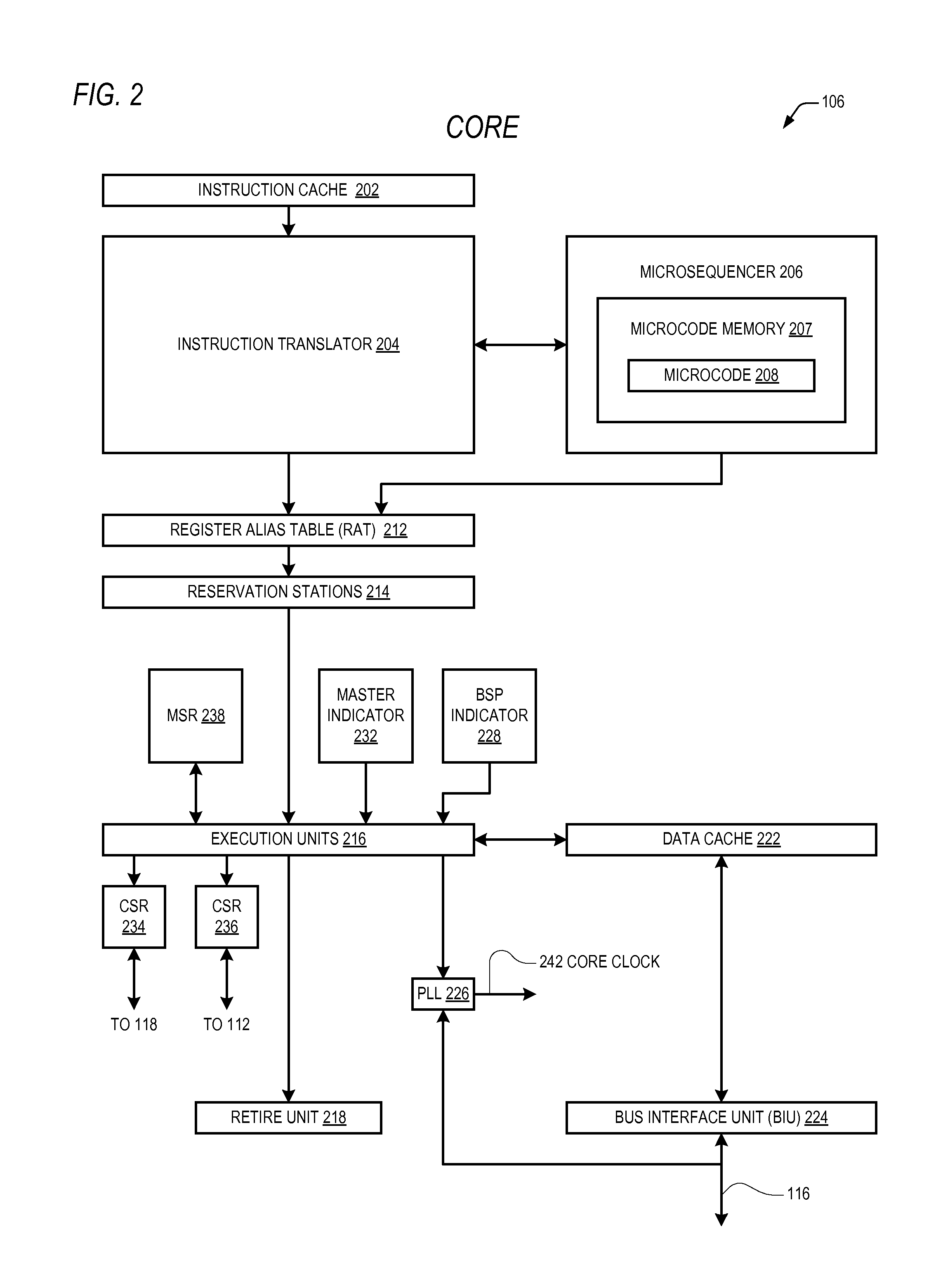

Power state synchronization in a multi-core processor

ActiveUS20120166845A1Energy efficient ICTVolume/mass flow measurementComputer architectureStructure of Management Information

A multi-core processor includes microcode distributed in each core enabling each core to participate in a de-centralized inter-core state discovery process. In a related microcode-implemented method, states of a multi-core processor are discovered by at least two cores participating in a de-centralized inter-core state discovery process. The inter-core state discovery process is carried out through a combination of microcode executing on each participating core and signals exchanged between the cores through sideband non-system-bus communication wires. The discovery process is unmediated by any centralized non-core logic. Applicable discoverable states include target and composite power states, whether and how many cores are enabled, the availability and distribution of various resources, and hierarchical structures and coordination systems for the cores. The inter-core state discovery process may be carried out in accordance with various hierarchical coordination systems involving chained inter-core communications.

Owner:VIA TECH INC

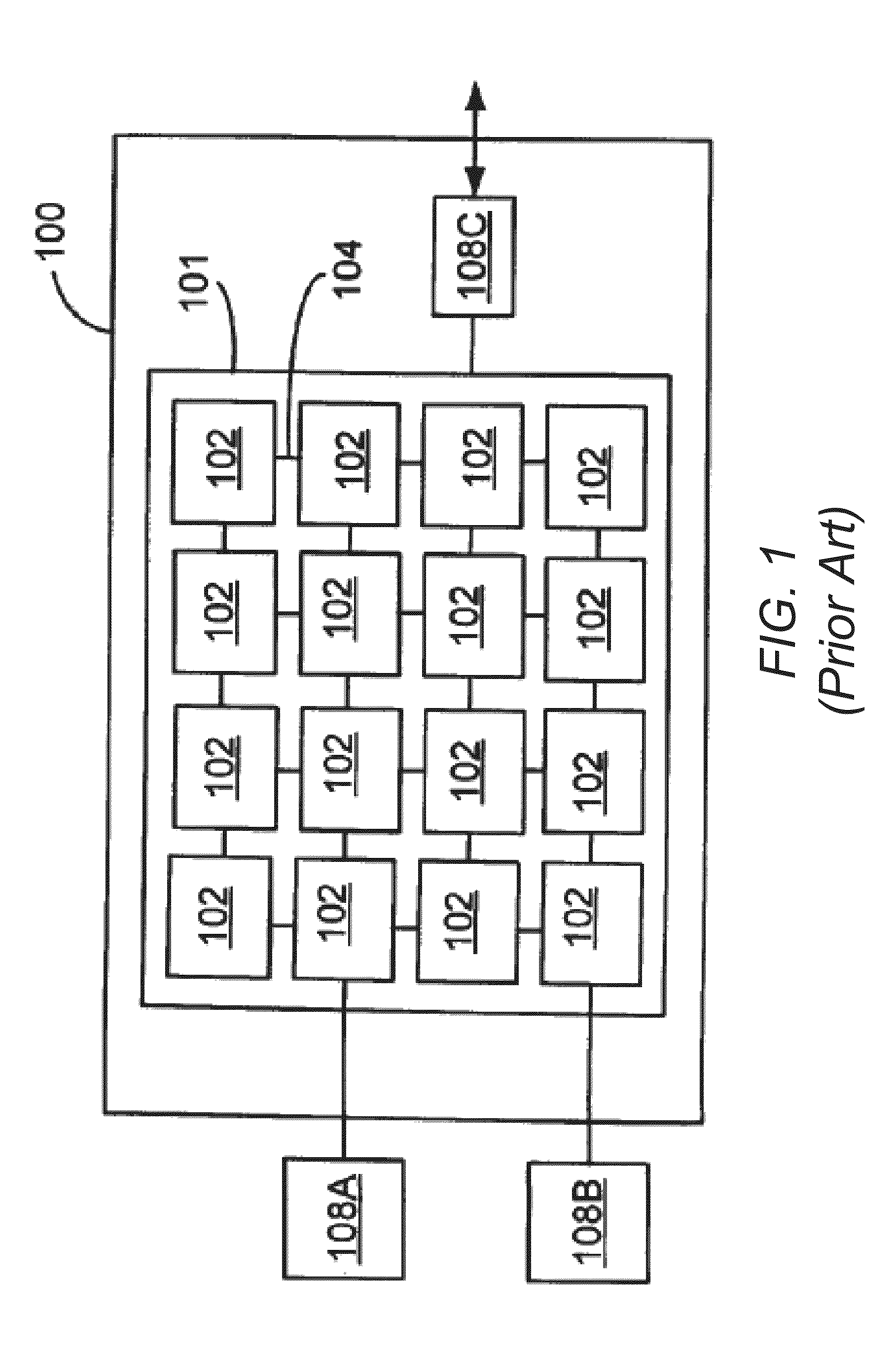

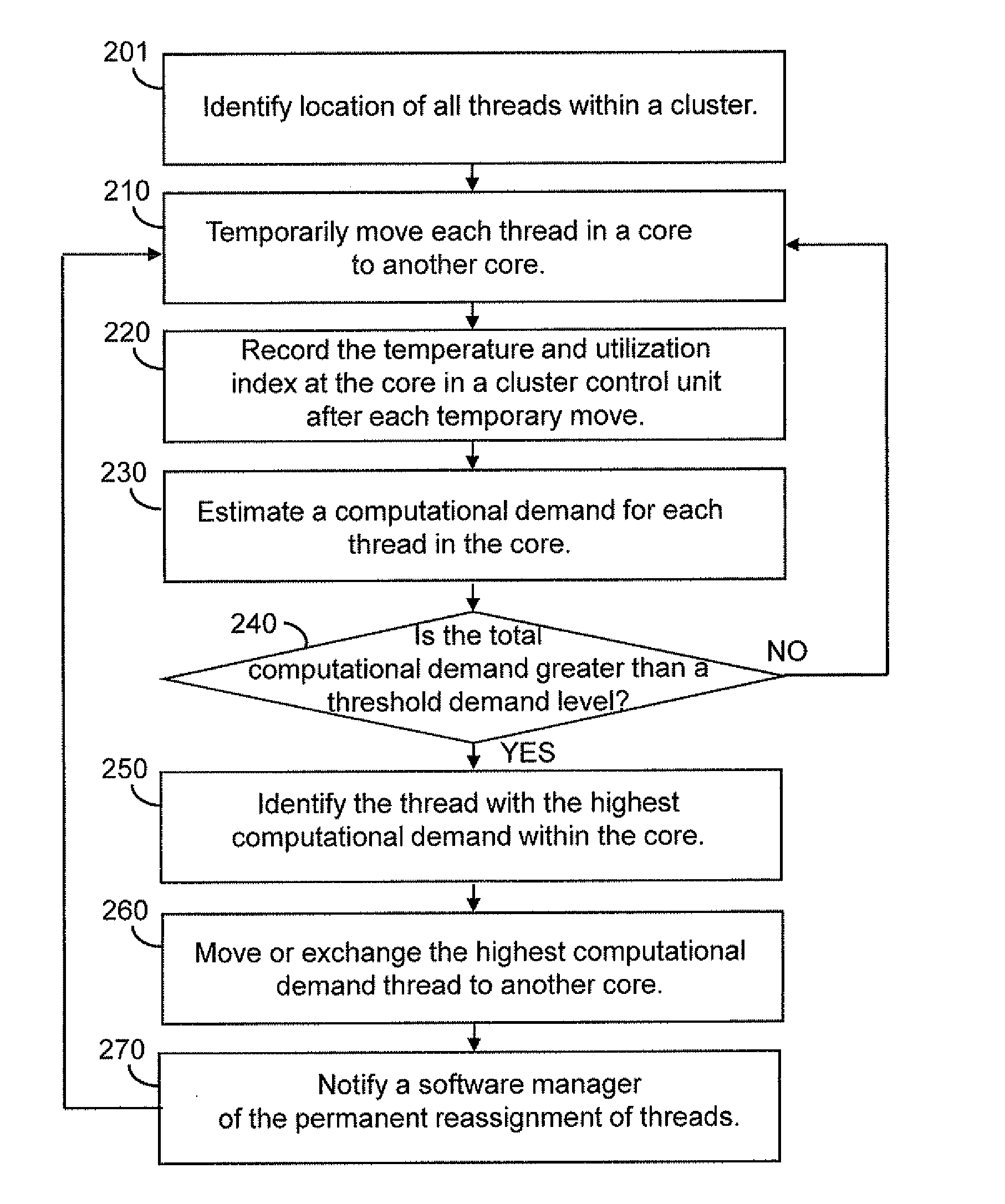

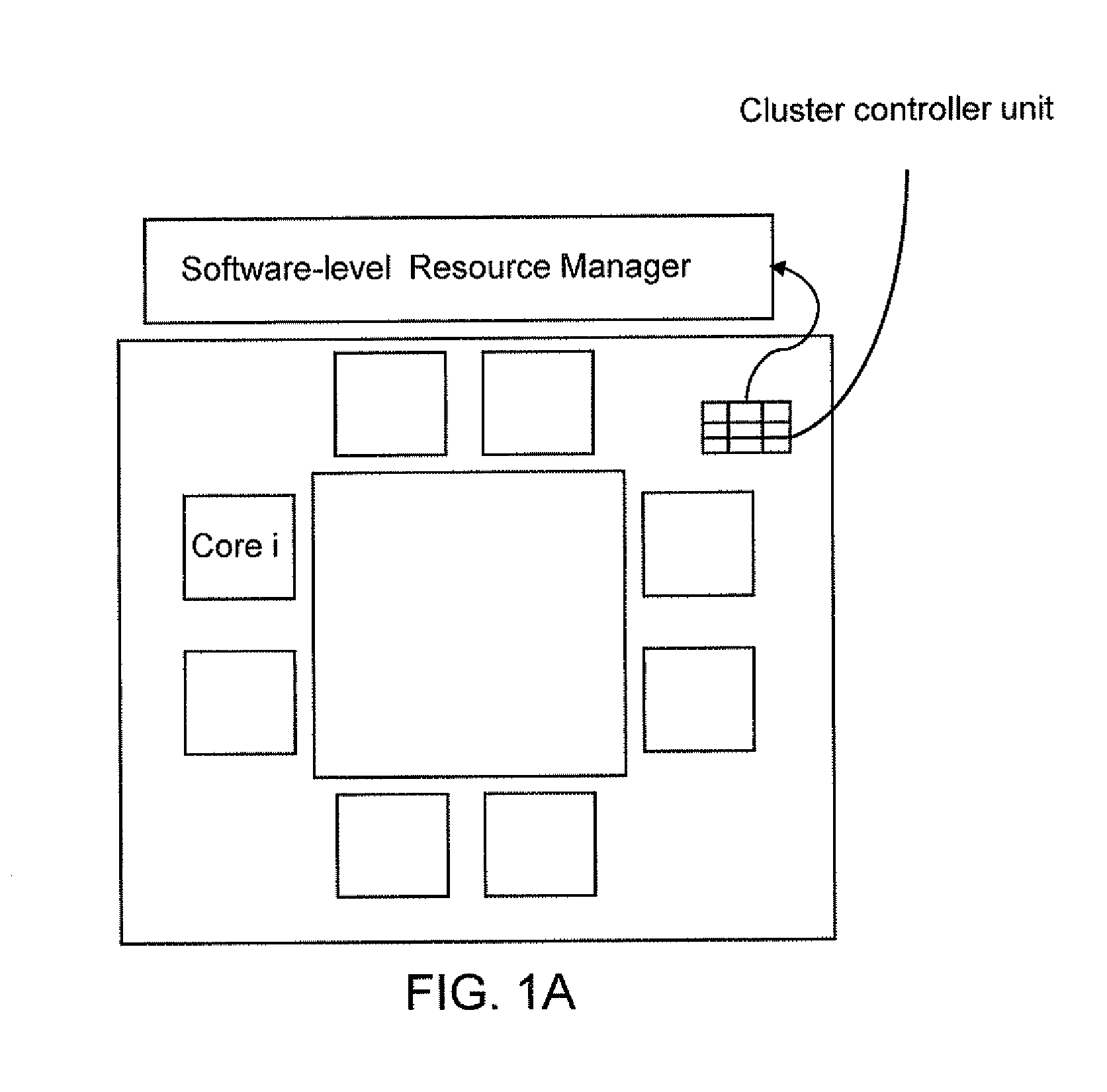

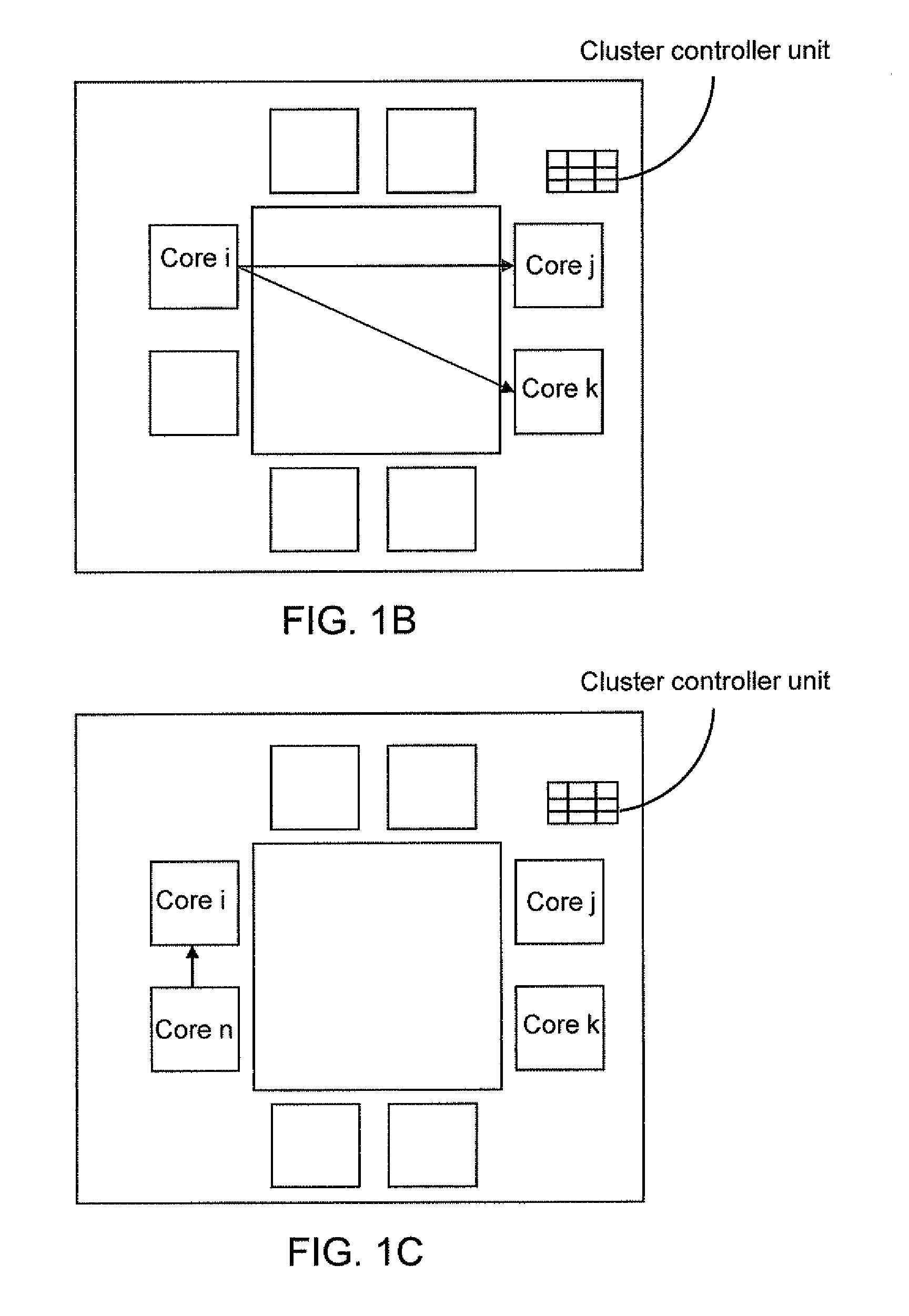

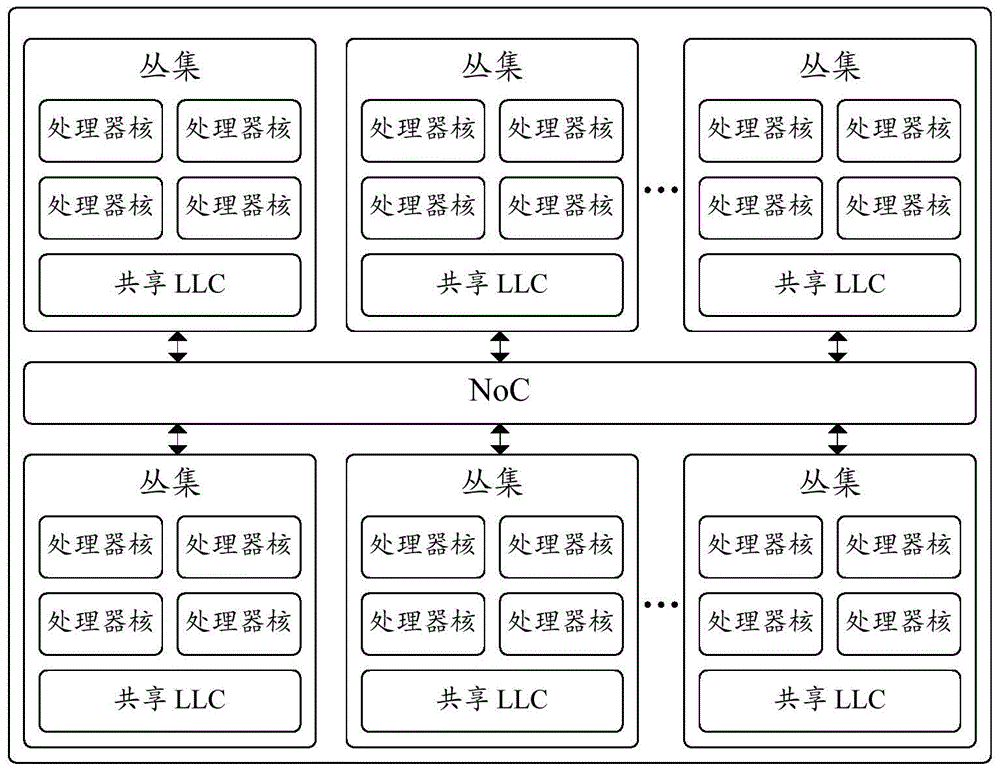

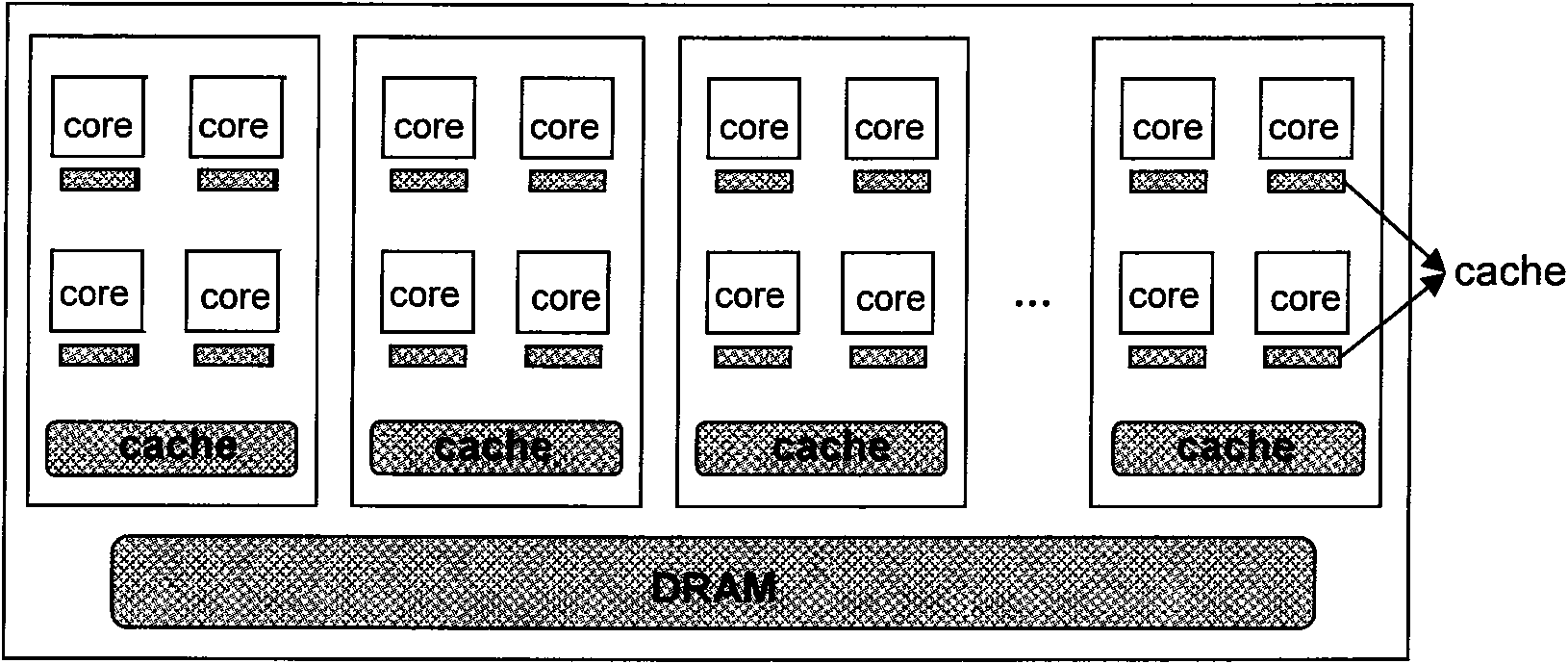

Low overhead dynamic thermal management in many-core cluster architecture

InactiveUS20110191776A1Digital data processing detailsMultiprogramming arrangementsSemiconductor chipEngineering

A semiconductor chip includes a plurality of multi-core clusters each including a plurality of cores and a cluster controller unit. Each cluster controller unit is configured to control thread assignment within the multi-core cluster to which it belongs. The cluster controller unit monitors various parameters measured in the plurality of cores within the multi-core cluster to estimate the computational demand of each thread that runs in the cores. The cluster controller unit may reassign the threads within the multi-core cluster based on the estimated computational demand of the threads and transmit a signal to an upper-level software manager that controls the thread assignment across the semiconductor chip. When an acceptable solution to thread assignment cannot be achieved by shuffling of threads within the multi-core cluster, the cluster controller unit may also report inability to solve thread assignment to the upper-level software manager to request a system level solution.

Owner:IBM CORP

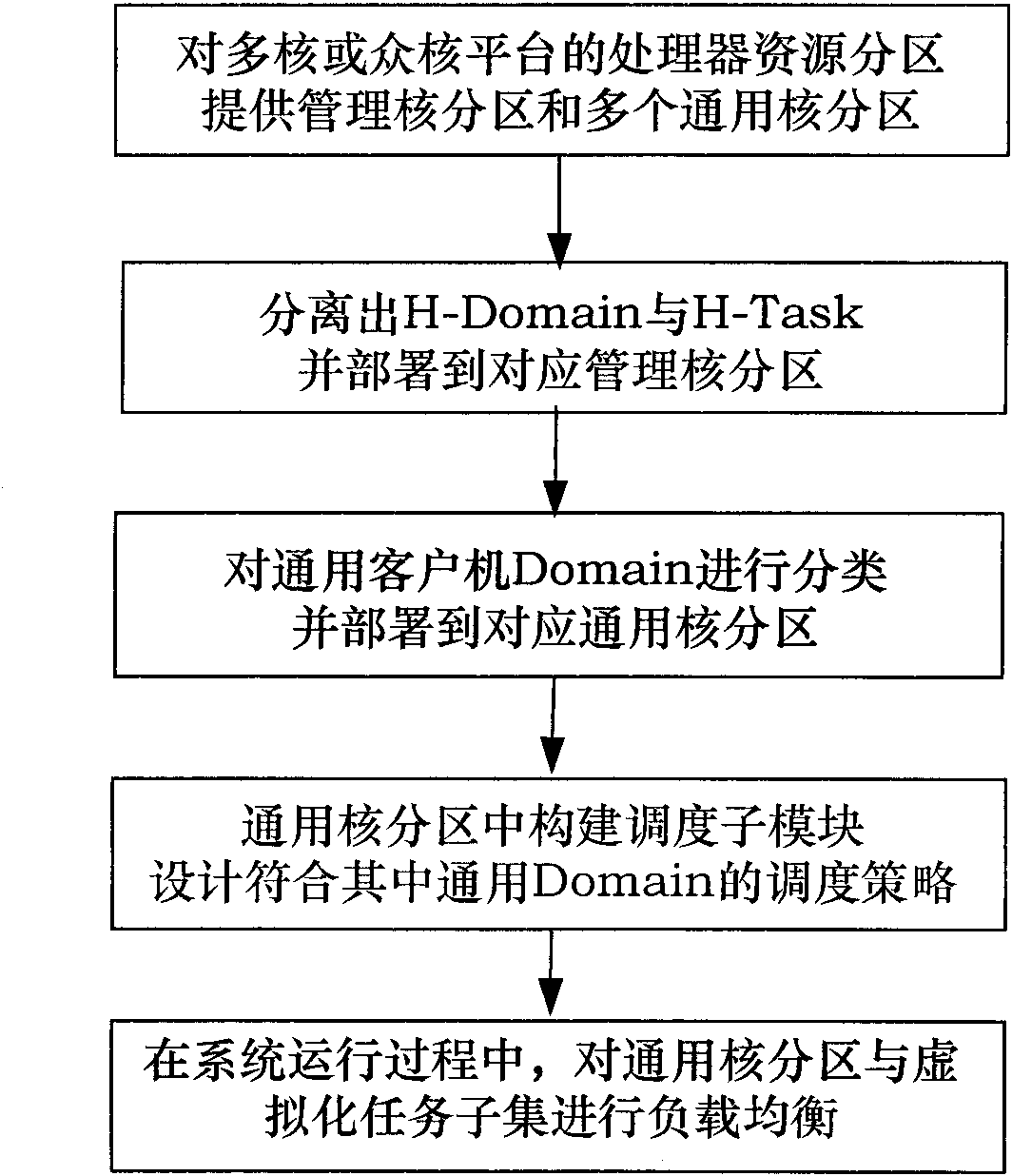

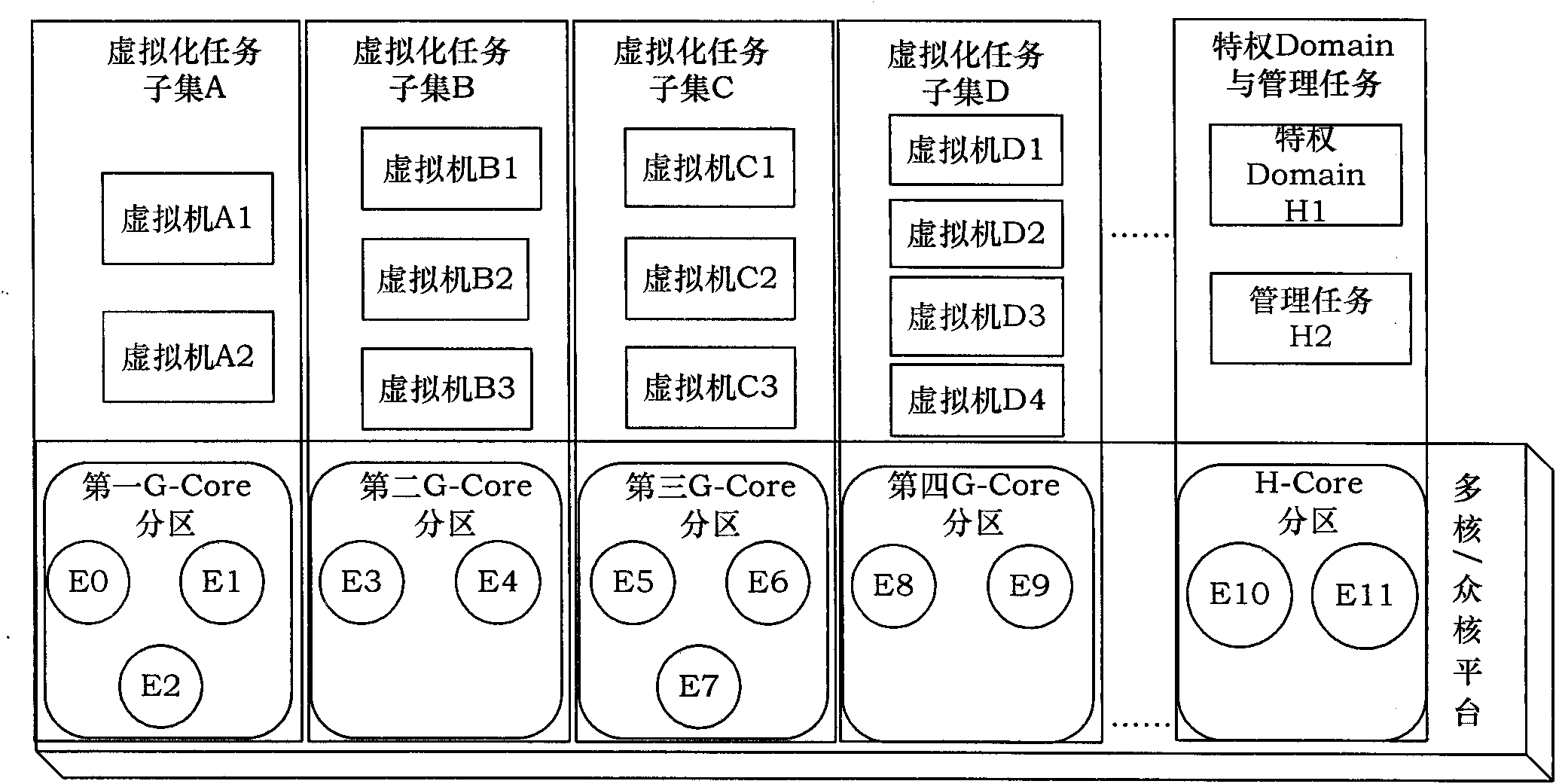

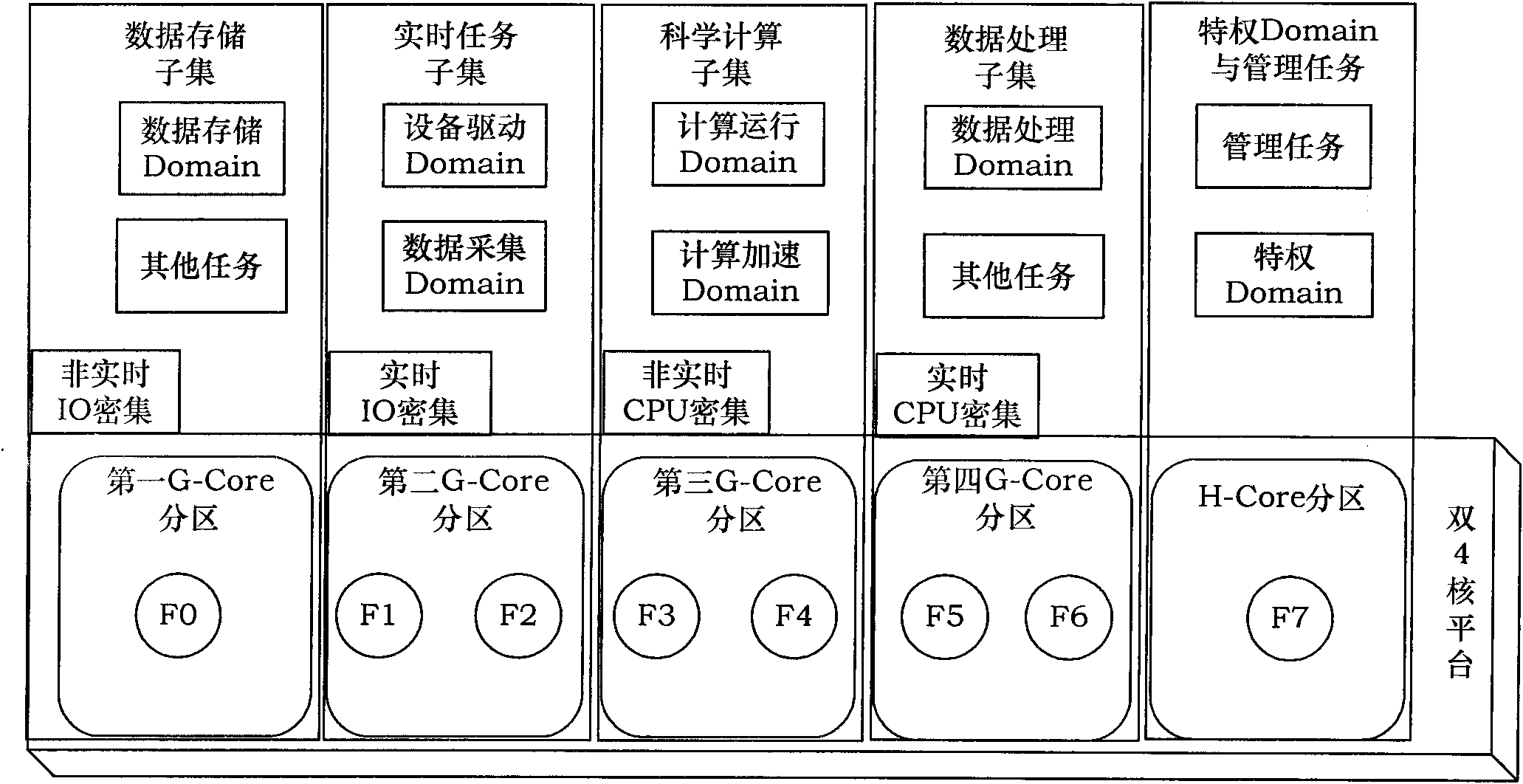

CPU virtualization method based on processor partitioning technology

InactiveCN101788920ADifficulty of SimplificationHigh computational complexityResource allocationSoftware simulation/interpretation/emulationVirtualizationResource allocation

The invention provides a CPU virtualization method based on processor partitioning technology, which comprises the following steps: aiming at a multi-core or many-core platform, firstly, dividing a CPU core into a management core (H-Core) partition and a plurality of general core (G-Core) partitions; then, allocating management tasks and privileged domains in a VMM into the H-Core partition for operating; dividing general client domains operating on the VMM into different virtualization task subsets according to individual characteristics; and allocating the virtualization task subsets into the corresponding G-Core partitions for operating. Different scheduling policies and resource allocation policies can be realized aiming at different types of virtualization tasks in different CPU partitions. The CPU virtualization method of the invention improves the safety and the reliability of the virtualization system on the multi-core or many-core platform, reduces the complexity of CPU virtualization, simultaneously simplifies the complexity of overall resource allocation and scheduling, improves the capacity of the VMM for allocating and scheduling computing resources, and has the advantages of safety, reliability, high efficiency and high performance.

Owner:BEIHANG UNIV

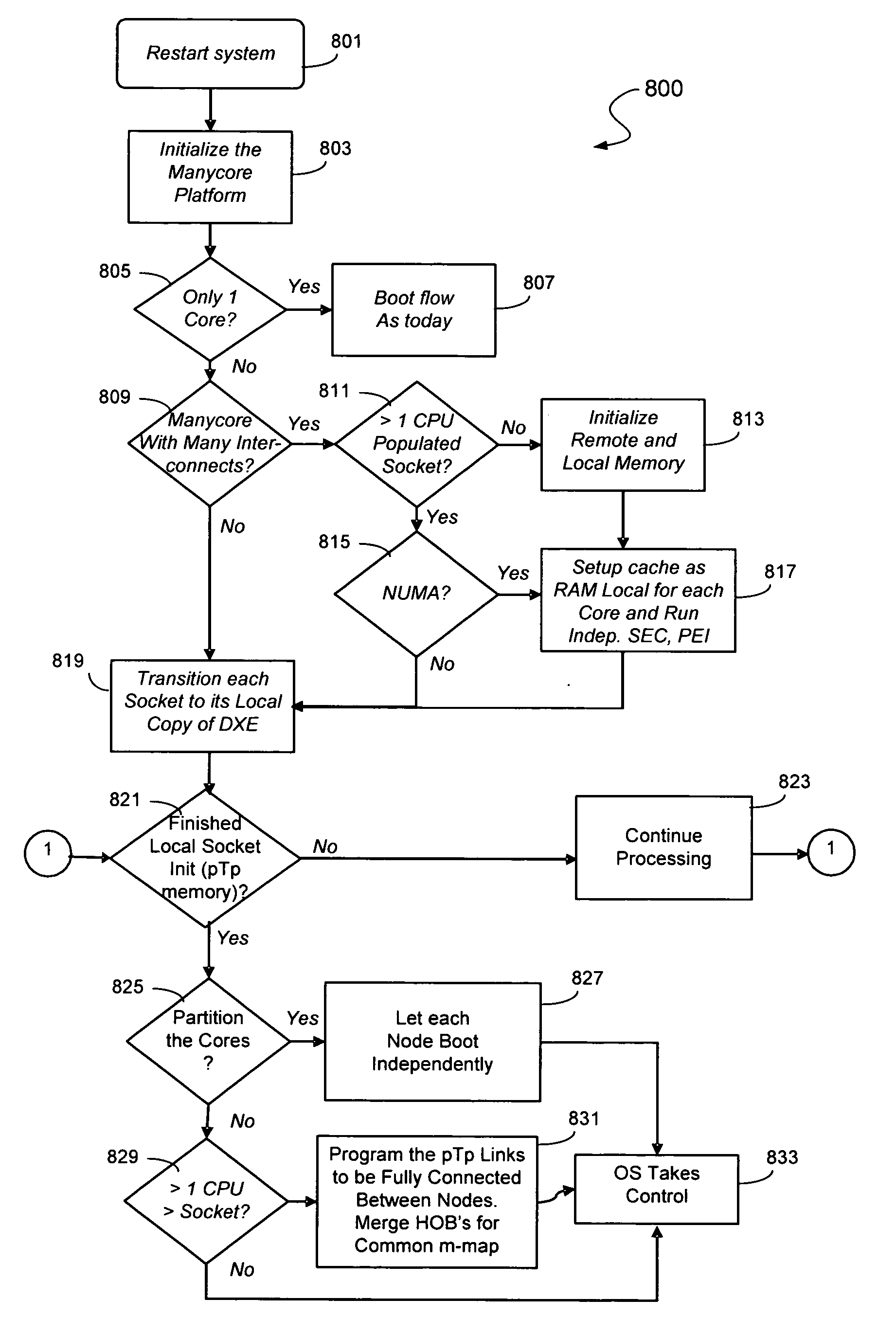

Multi-socket boot

In some embodiments, the invention involves a system and method to provide maximal boot-time parallelism for future multi-core, multi-node, and many-core systems. In an embodiment, the security (SEC), pre-EFI initialization (PEI), and then driver execution environment (DXE) phases are executed in parallel on multiple compute nodes (sockets) of a platform. Once the SEC / PEI / DXE phases are executed on all compute nodes having a processor, the boot device select (BDS) phase completes the boot by merging or partitioning the compute nodes based on a platform policy. Partitioned compute nodes each run their own instance of EFI. A common memory map may be generated prior to operating system (OS) launch when compute nodes are to be merged. Other embodiments are described and claimed.

Owner:INTEL CORP

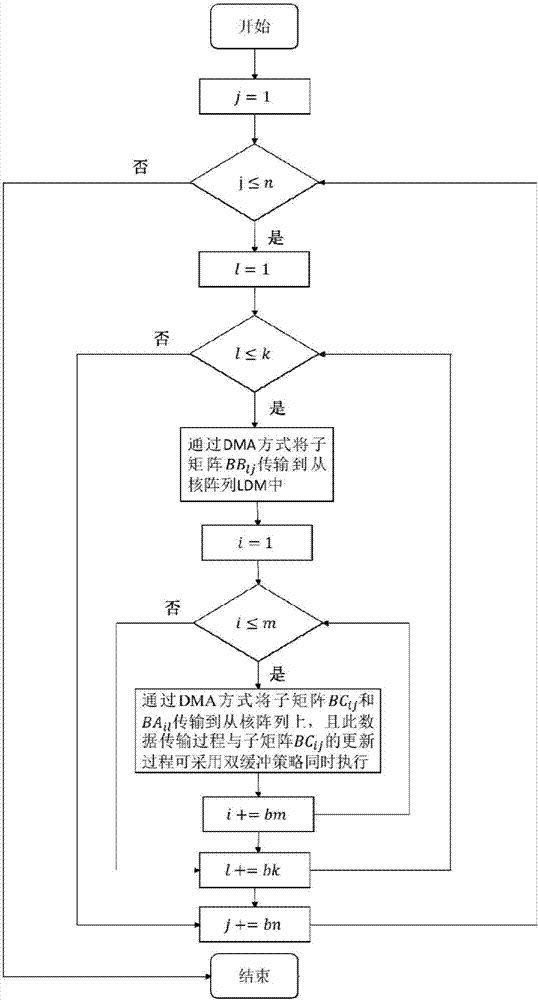

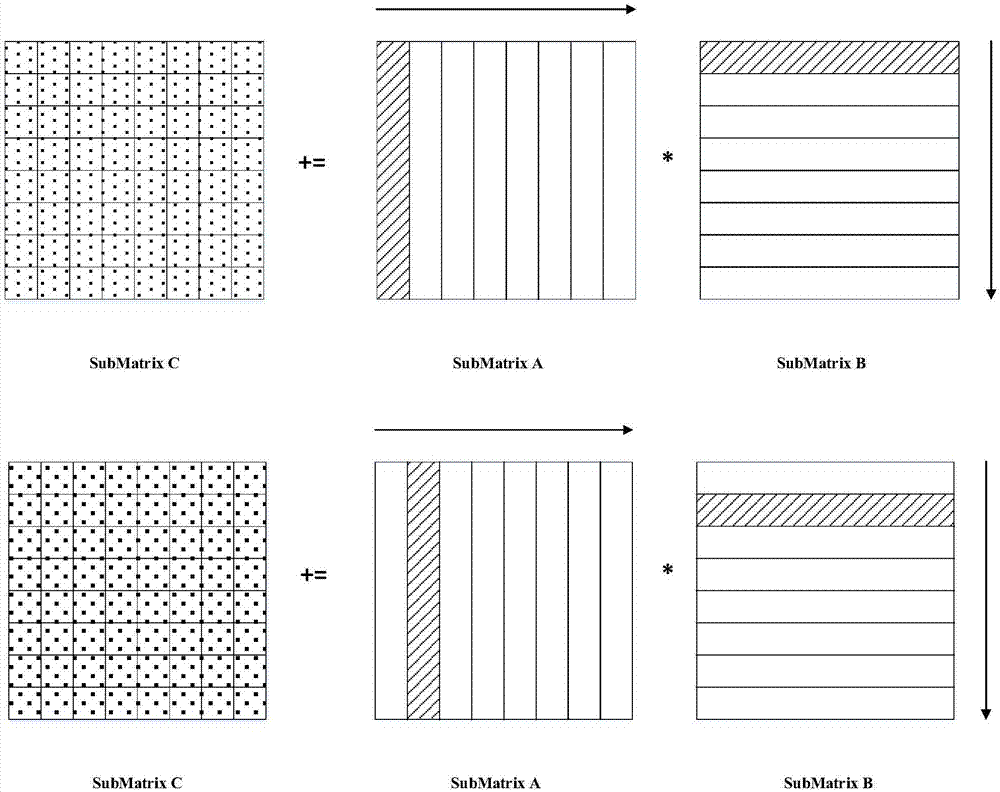

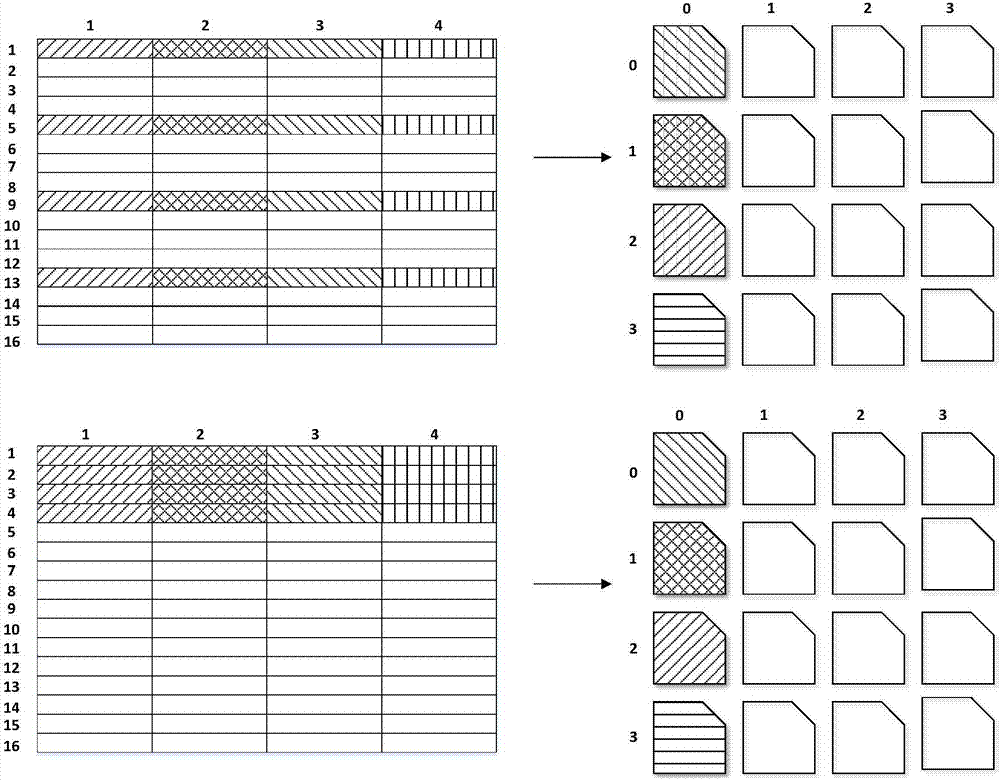

A GEMM (general matrix-matrix multiplication) high-performance realization method based on a domestic SW 26010 many-core CPU

ActiveCN107168683ASolve the problem that the computing power of slave cores cannot be fully utilizedImprove performanceRegister arrangementsConcurrent instruction executionFunction optimizationAssembly line

The invention provides a GEMM (general matrix-matrix multiplication) high-performance realization method based on a domestic SW 26010 many-core CPU. For a domestic SW many-core processor 26010, based on the platform characteristics of storage structures, memory access, hardware assembly lines and register level communication mechanisms, a matrix partitioning and inter-core data mapping method is optimized and a top-down there-level partitioning parallel block matrix multiplication algorithm is designed; a slave core computing resource data sharing method is designed based on the register level communication mechanisms, and a computing and memory access overlap double buffering strategy is designed by using a master-slave core asynchronous DMA data transmission mechanism; for a single slave core, a loop unrolling strategy and a software assembly line arrangement method are designed; function optimization is achieved by using a highly-efficient register partitioning mode and an SIMD vectoring and multiplication and addition instruction. Compared with a single-core open-source BLAS math library GotoBLAS, the function performance of the high-performance GEMM has an average speed-up ratio of 227. 94 and a highest speed-up ratio of 296.93.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI +1

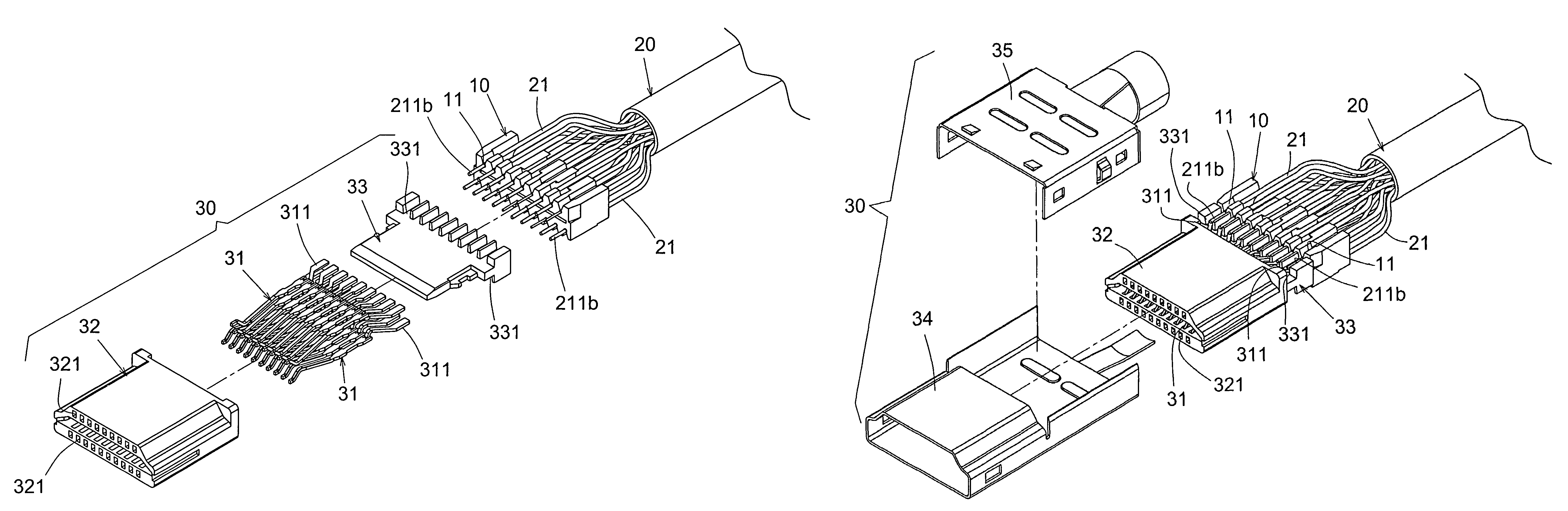

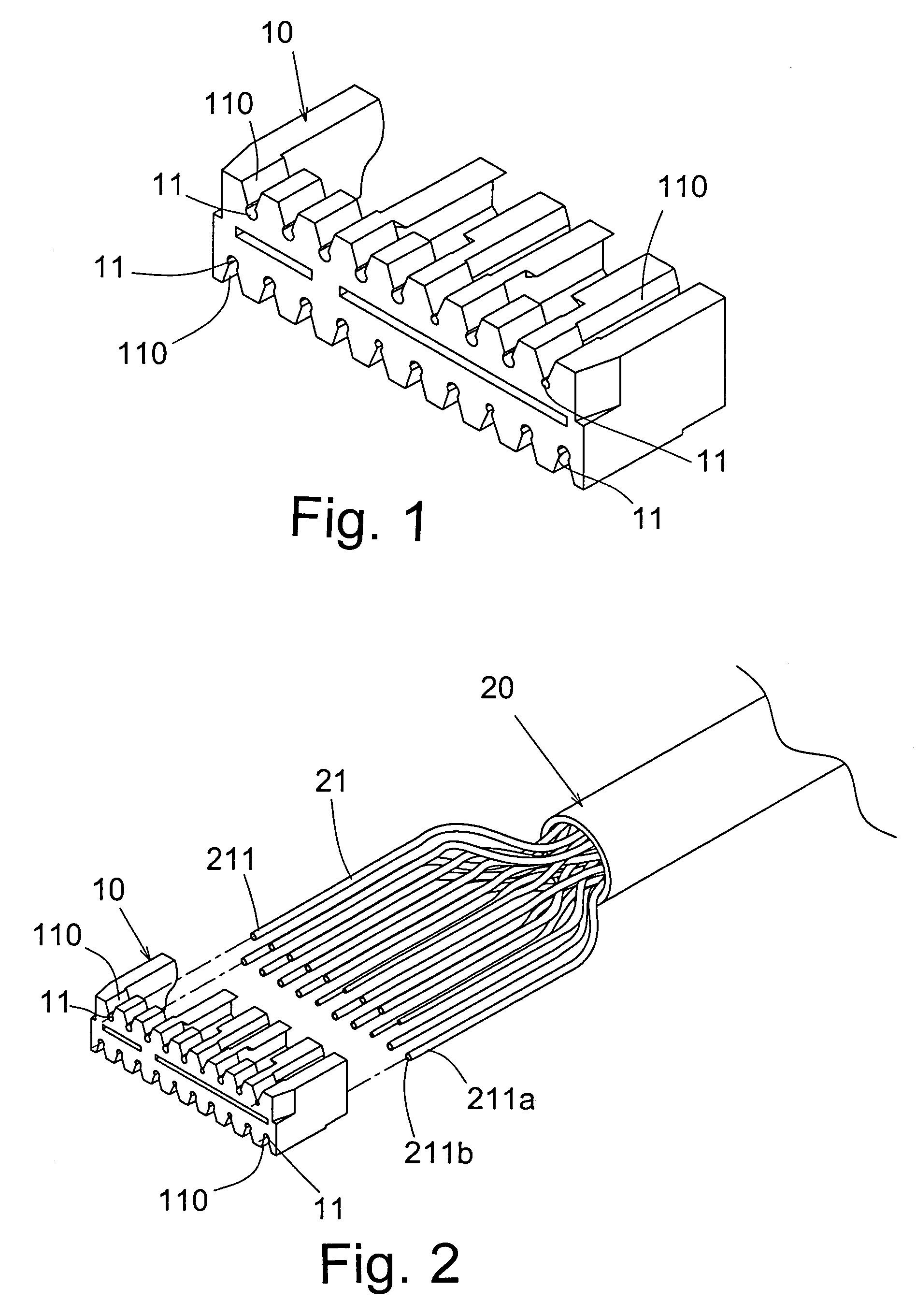

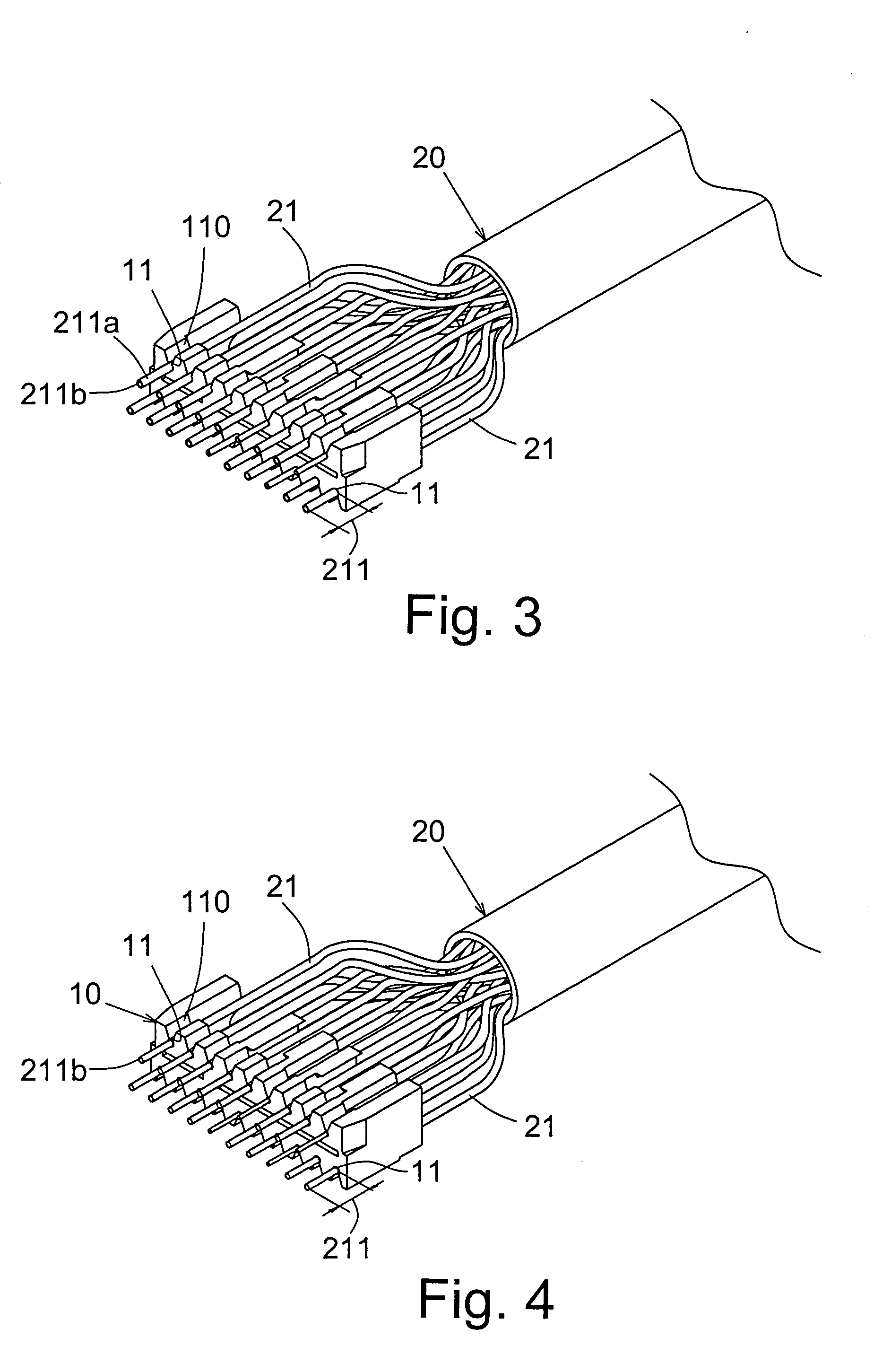

Cable cord locating element

InactiveUS7270571B1Reduce labor costsReduce time costLine/current collector detailsElectrically conductive connectionsSolderingElectrical connector

A cable core locating element includes a base formed of a plurality of clamping slots for clamping one of many cores of a cable each, with a free end of the core projected from a front side of the base. When the free ends of the forward projected cores are stripped and the base is assembled to an electronic connector, the stripped free end of each of the cores is lapped over and soldered to a wire soldering section of one of many terminals of the electronic connector, so as to electrically connect the electronic connector to the cable.

Owner:JOINSOON ELECTRONICS MFG

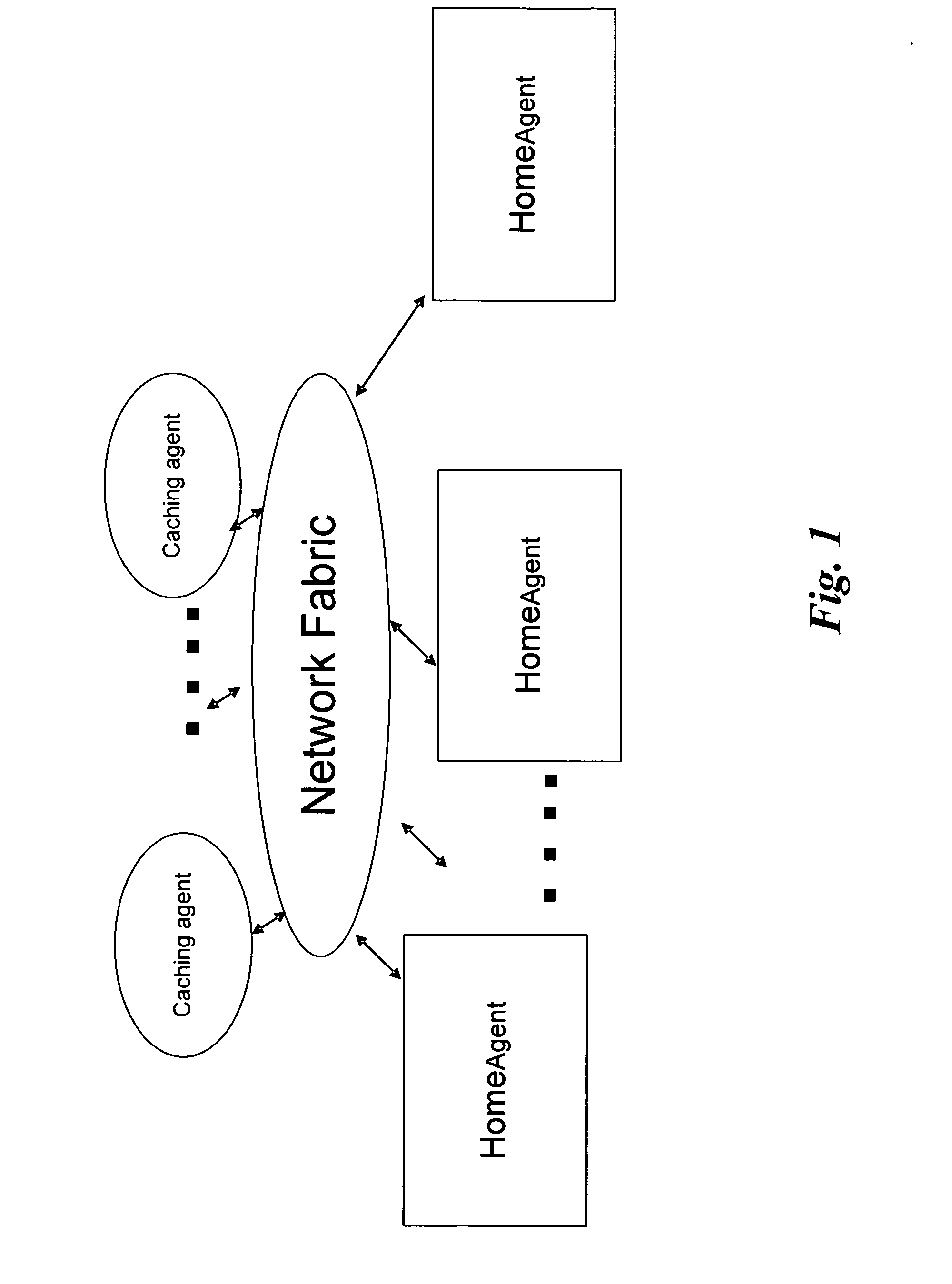

Heterogeneous multiprocessing

InactiveUS20080162873A1General purpose stored program computerProgram controlOperational systemMemory map

In some embodiments, the invention involves a system and method to provide maximal boot-time parallelism for future multi-core, multi-node, and many-core systems. In an embodiment, the security (SEC), pre-EFI initialization (PEI), and then driver execution environment (DXE) phases are executed in parallel on multiple compute nodes (sockets) of a platform. Once the SEC / PEI / DXE phases are executed on all compute nodes having a processor, the boot device select (BDS) phase completes the boot by merging or partitioning the compute nodes based on a platform policy. Partitioned compute nodes each run their own instance of EFI. A common memory map may be generated prior to operating system (OS) launch when compute nodes are to be merged. Other embodiments are described and claimed.

Owner:ZIMMER VINCENT J +3

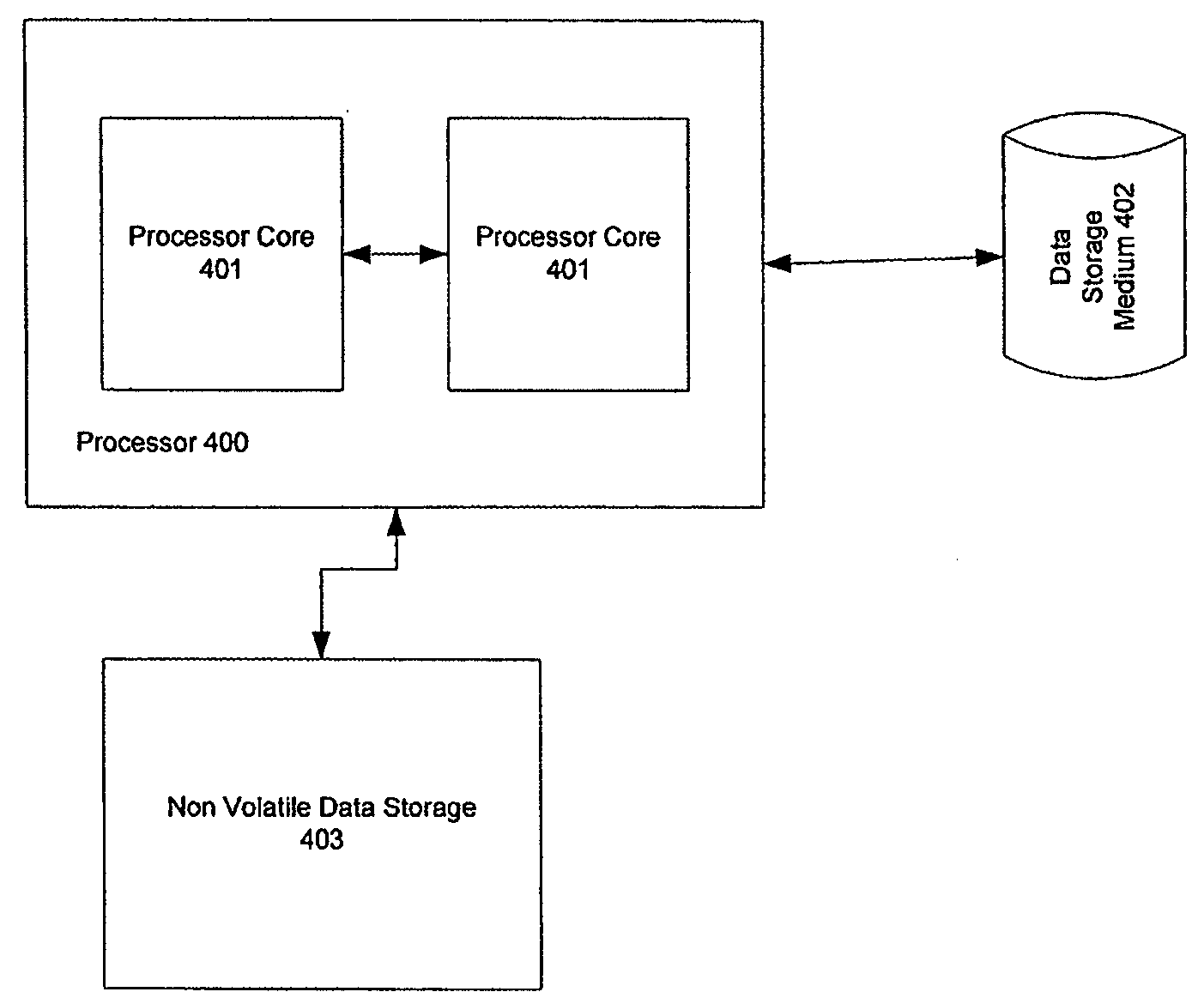

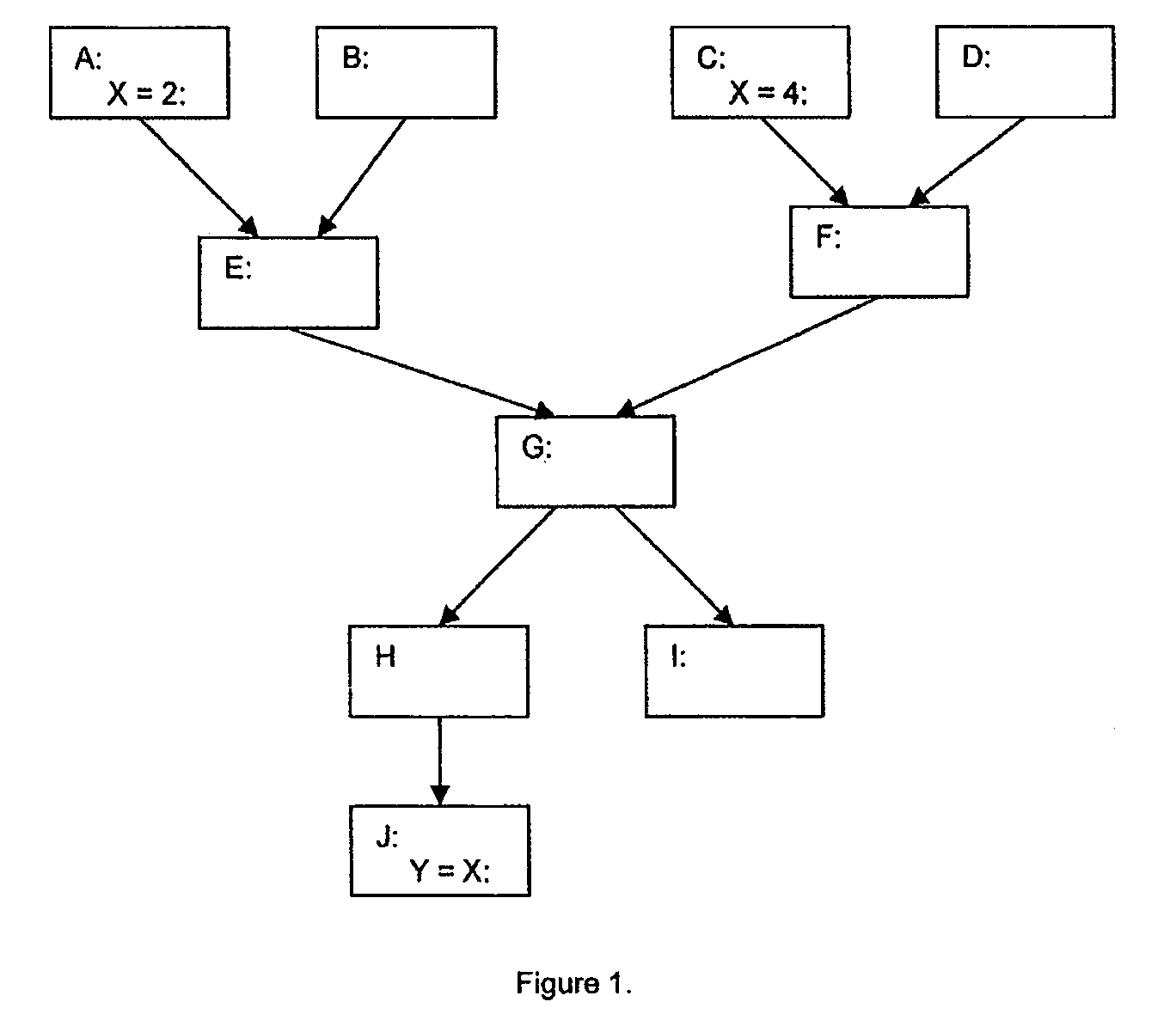

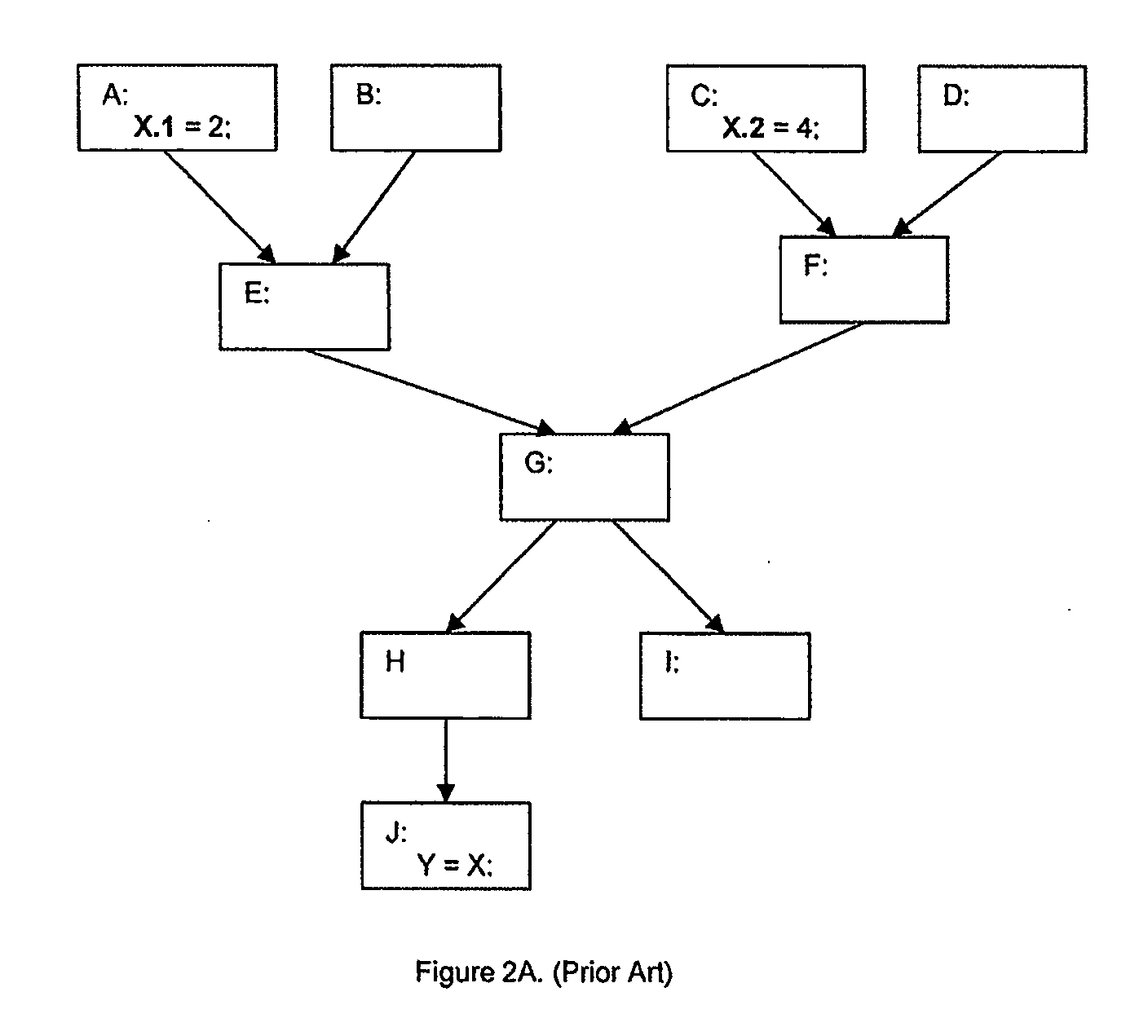

Highly scalable parallel static single assignment for dynamic optimization on many core architectures

A method, system, and computer readable medium for converting a series of computer executable instructions in control flow graph form into an intermediate representation, of a type similar to Static Single Assignment (SSA), used in the compiler arts. The indeterminate representation may facilitate compilation optimizations such as constant propagation, sparse conditional constant propagation, dead code elimination, global value numbering, partial redundancy elimination, strength reduction, and register allocation. The method, system, and computer readable medium are capable of operating on the control flow graph to construct an SSA representation in parallel, thus exploiting recent advances in multi-core processing and massively parallel computing systems. Other embodiments may be employed, and other embodiments are described and claimed.

Owner:INTEL CORP

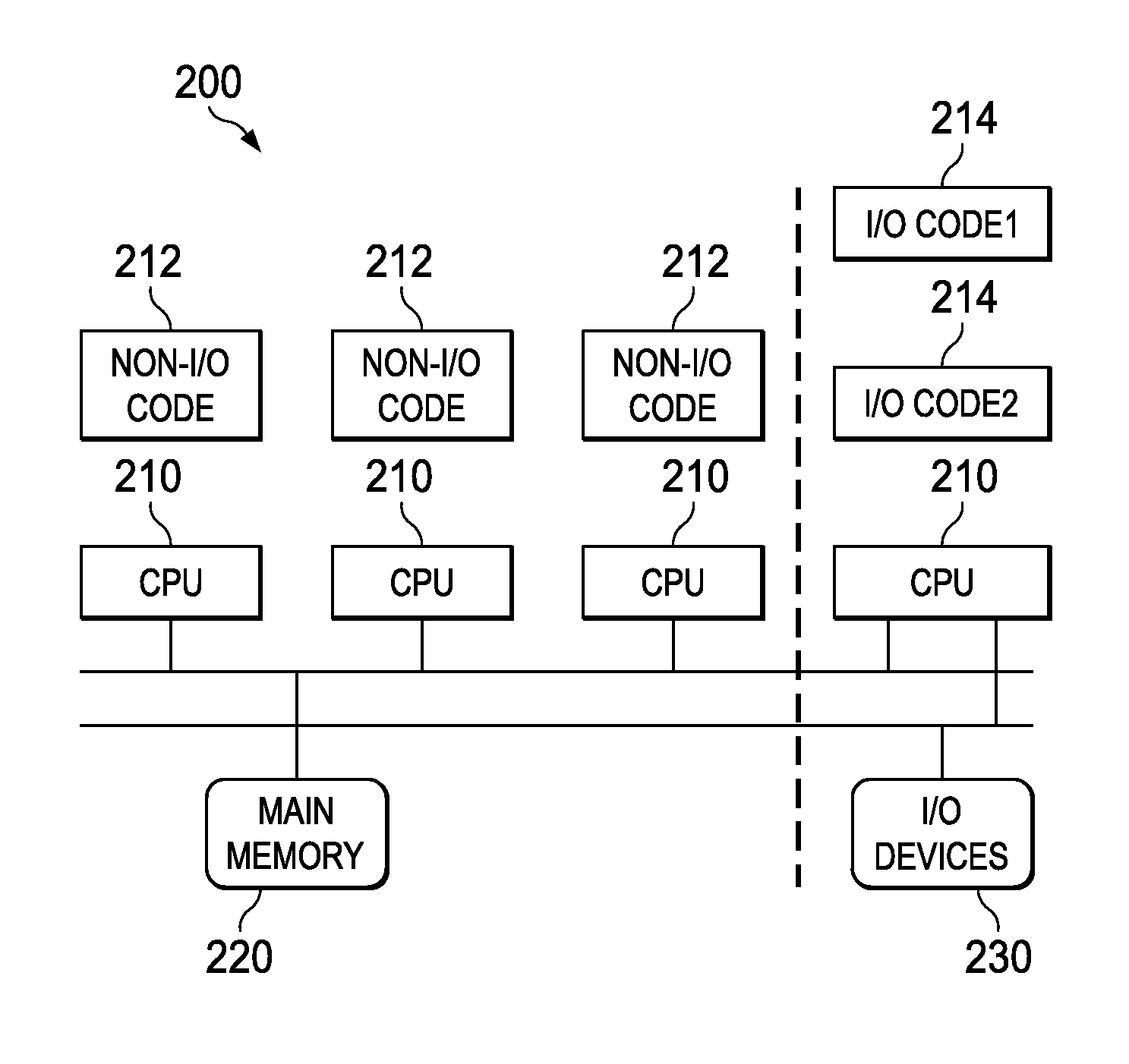

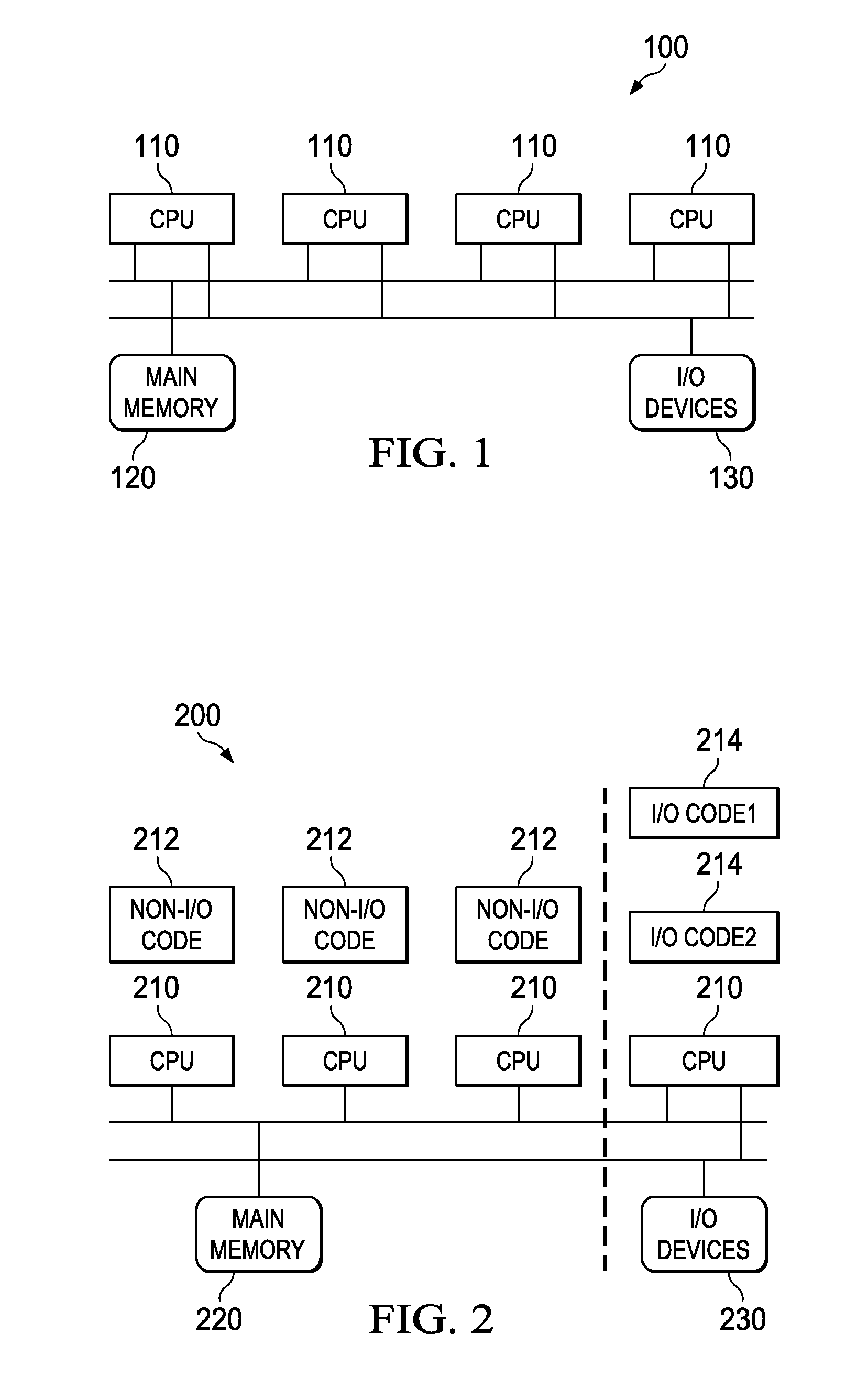

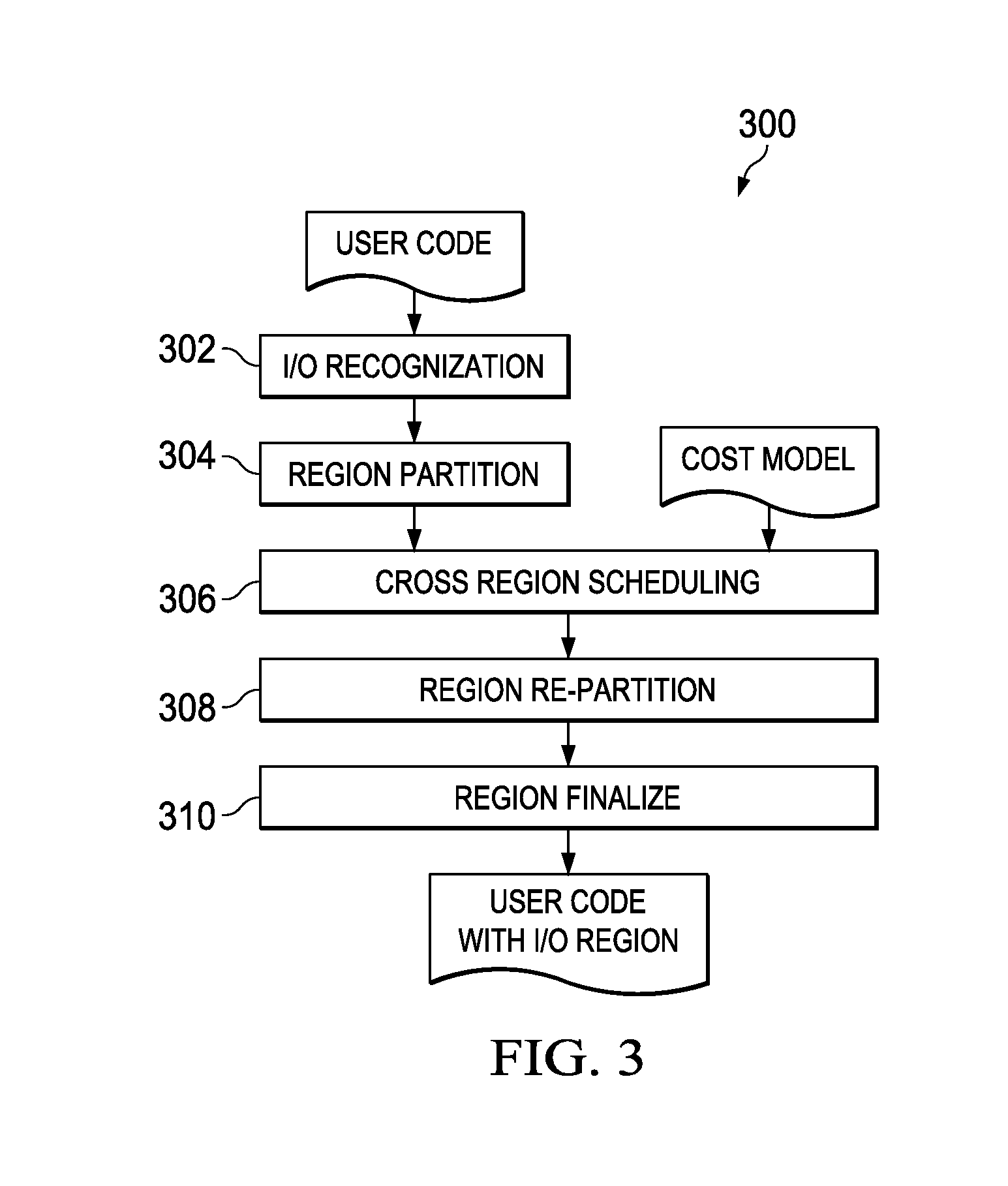

System and Method for Isolating I/O Execution via Compiler and OS Support

ActiveUS20150234640A1Easy to useProgram controlEnergy efficient computingOperational systemSource code

Embodiments are provided for isolating Input / Output (I / O) execution by combining compiler and Operating System (OS) techniques. The embodiments include dedicating selected cores, in multicore or many-core processors, as I / O execution cores, and applying compiler-based analysis to classify I / O regions of program source codes so that the OS can schedule such regions onto the designated I / O cores. During the compilation of a program source code, each I / O operation region of the program source code is identified. During the execution of the compiled program source code, each I / O operation region is scheduled for execution on a preselected I / O core. The other regions of the compiled program source code are scheduled for execution on other cores.

Owner:FUTUREWEI TECH INC

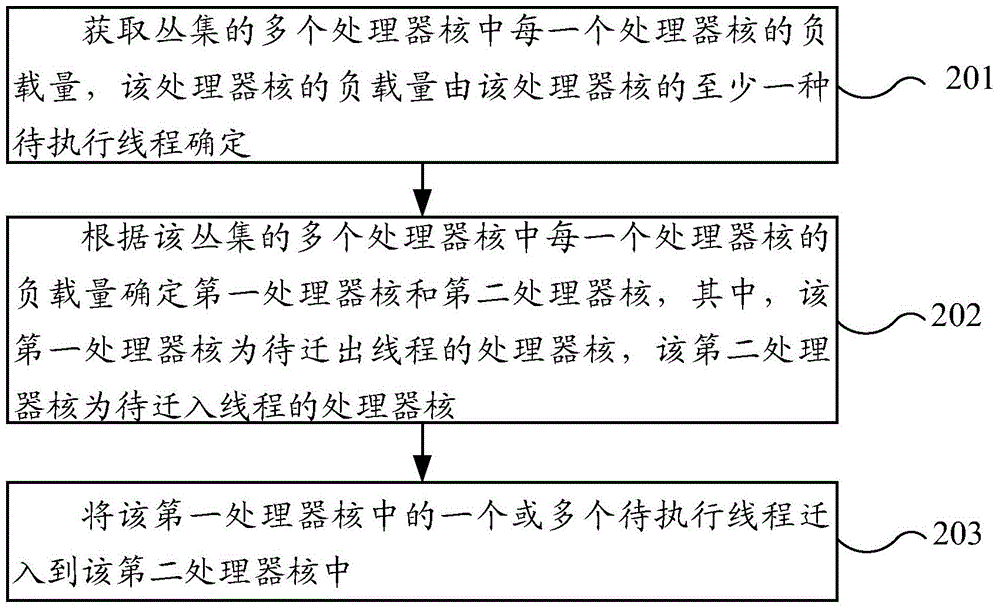

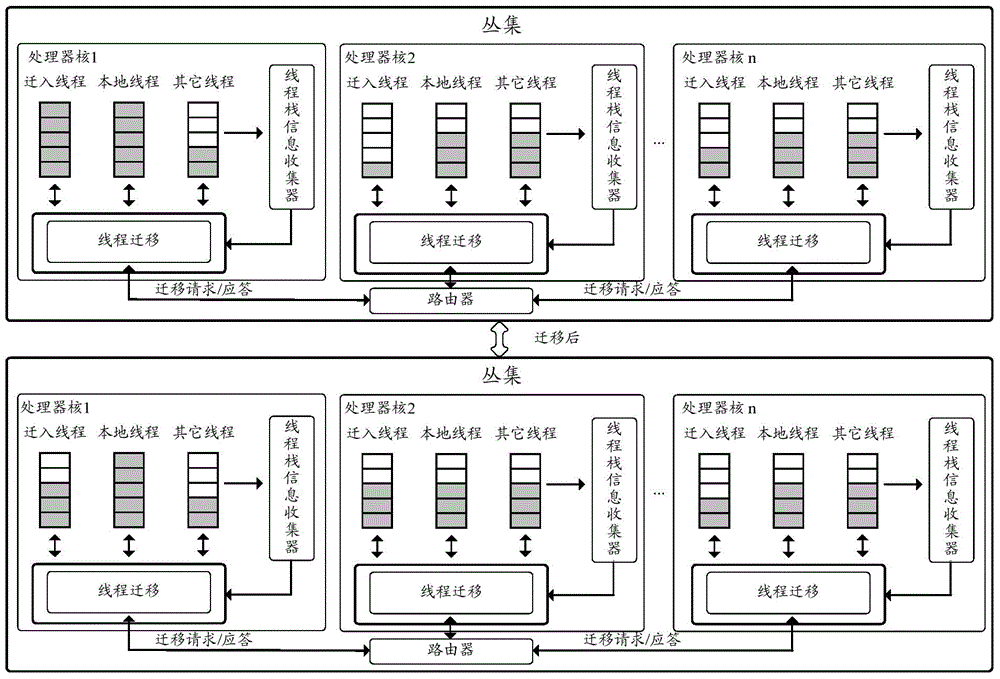

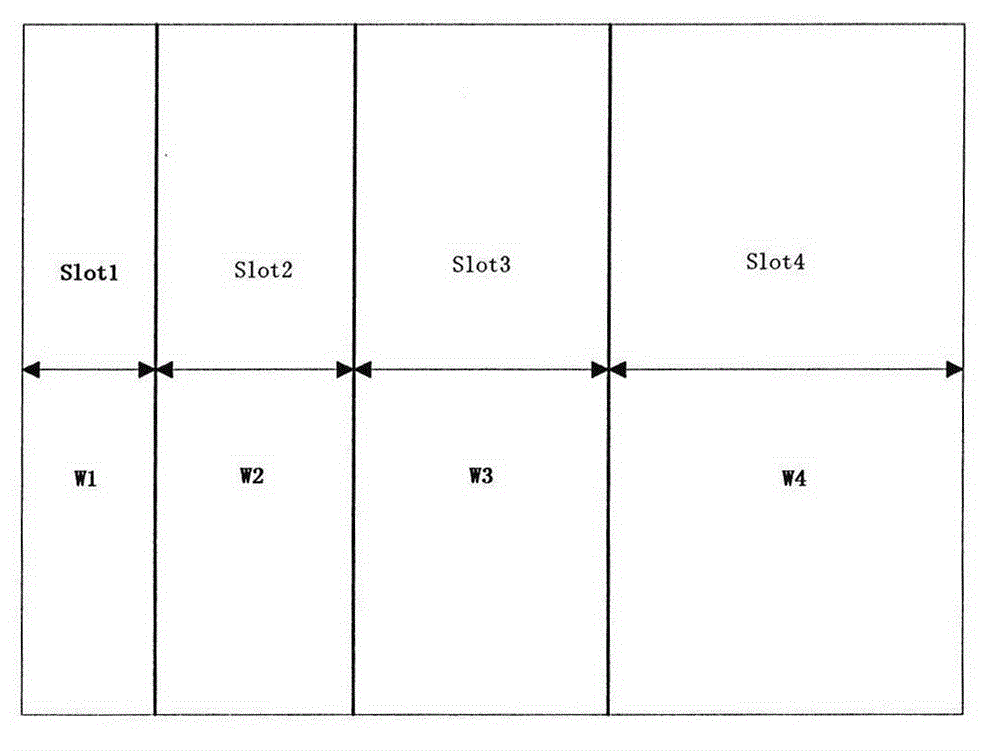

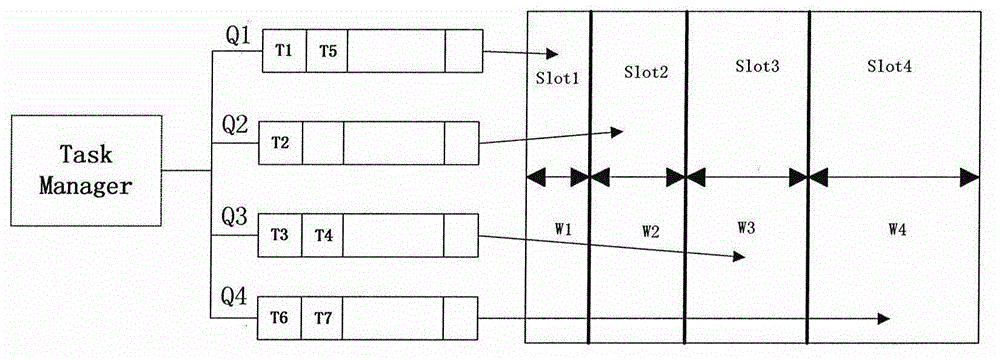

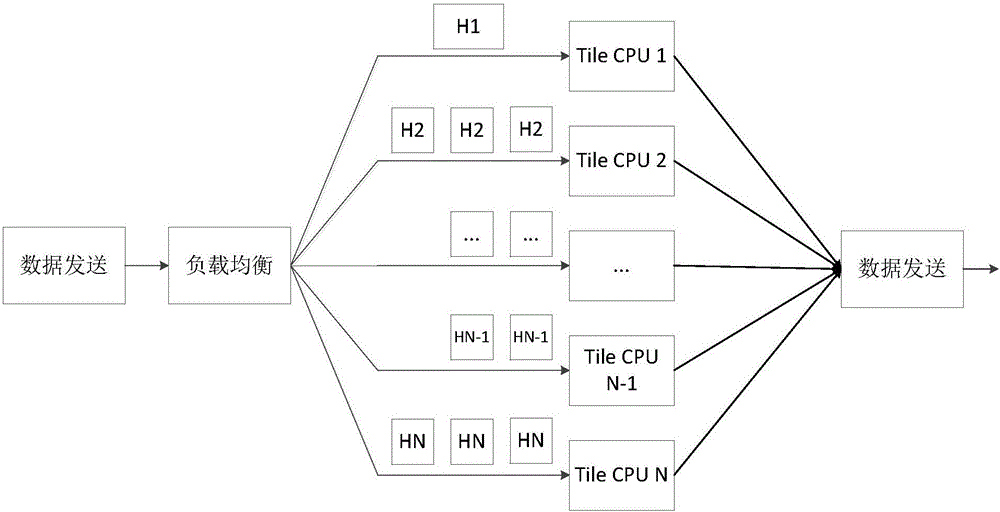

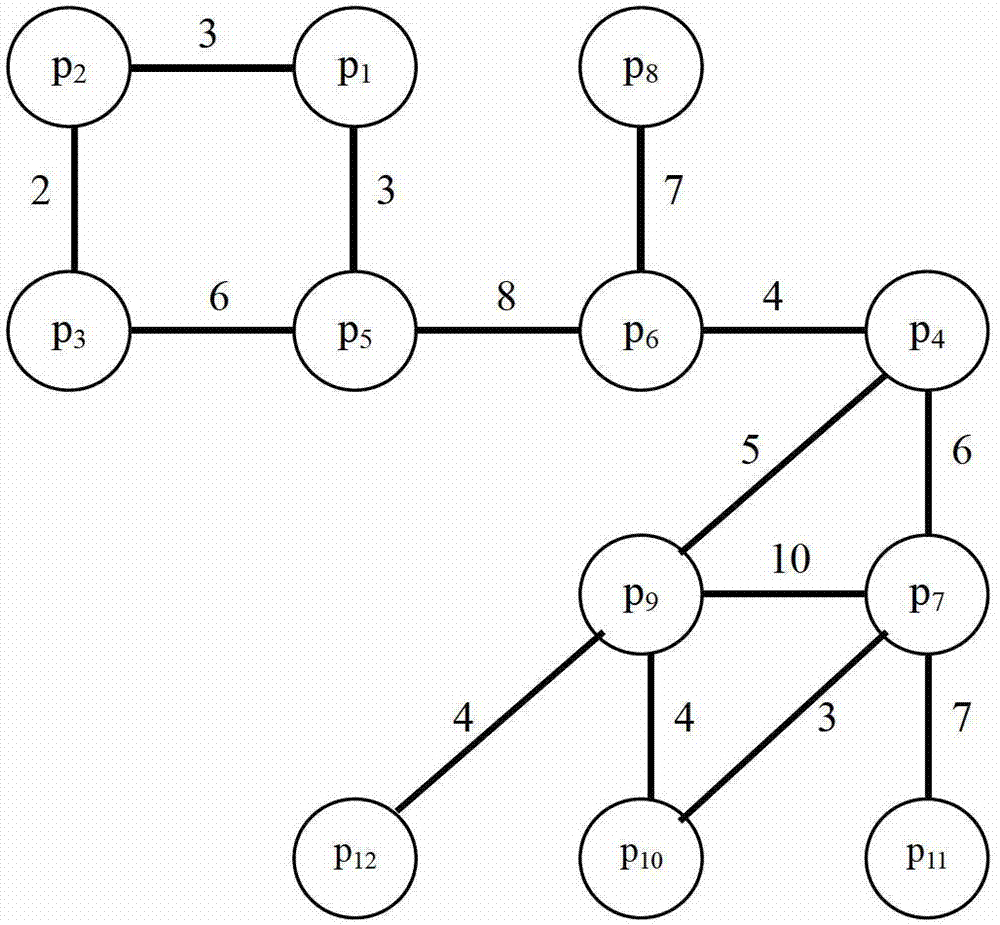

Load balancing method and device, cluster and many-core processor

InactiveCN105528330ALower average wait timeImprove parallelismResource allocationGeneral purpose stored program computerMulti-core processorMany core

Owner:HANGZHOU HUAWEI DIGITAL TECH

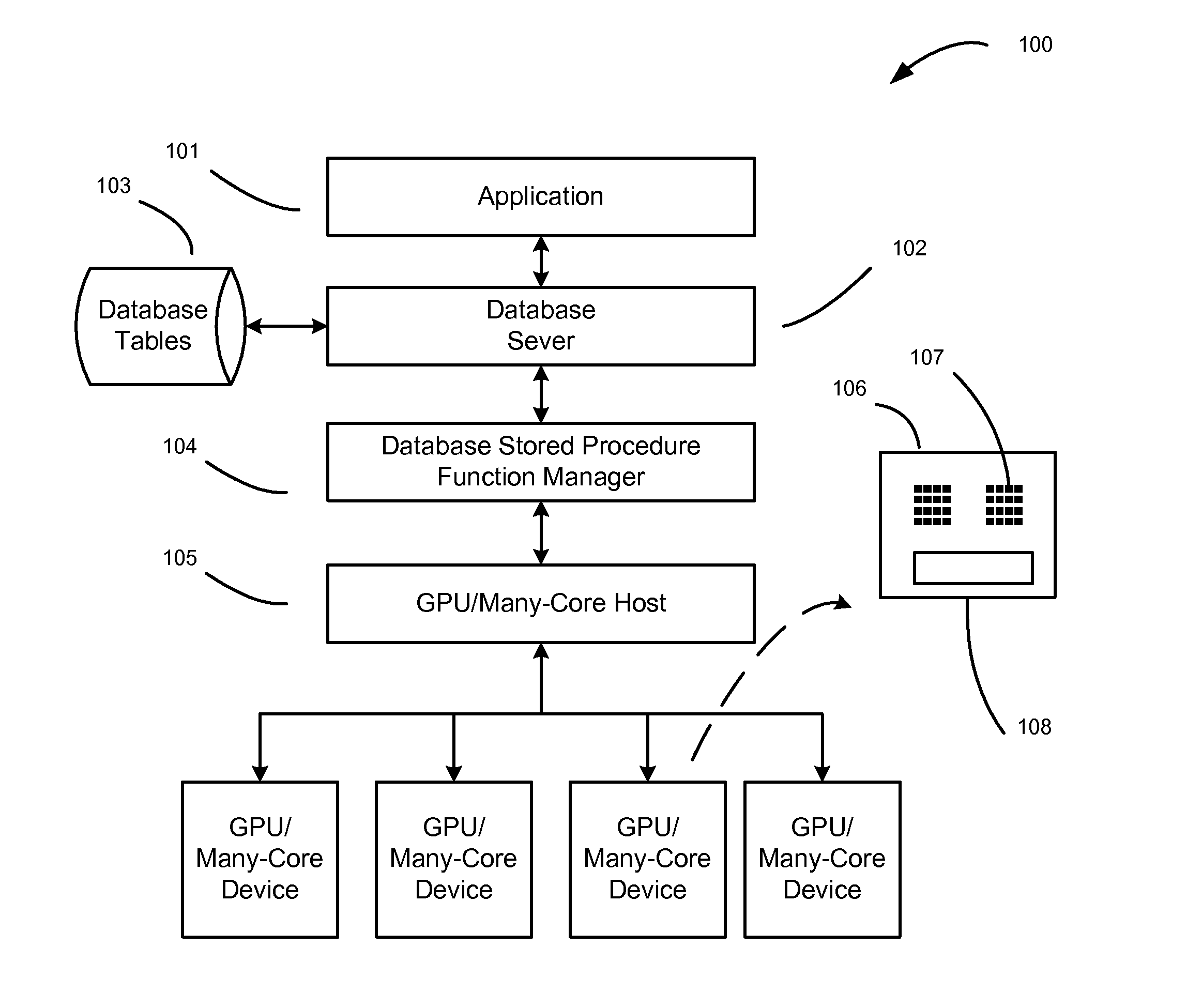

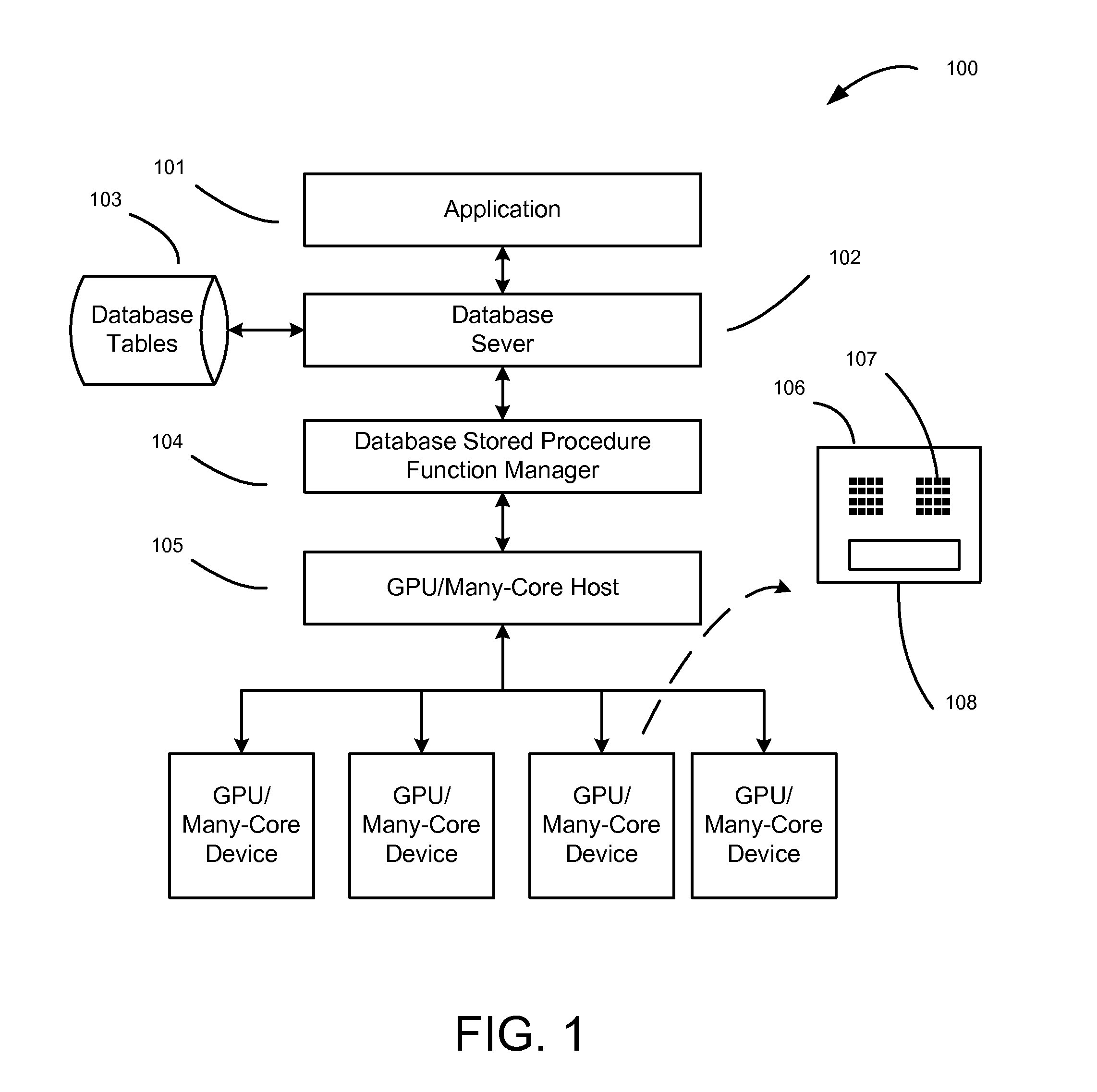

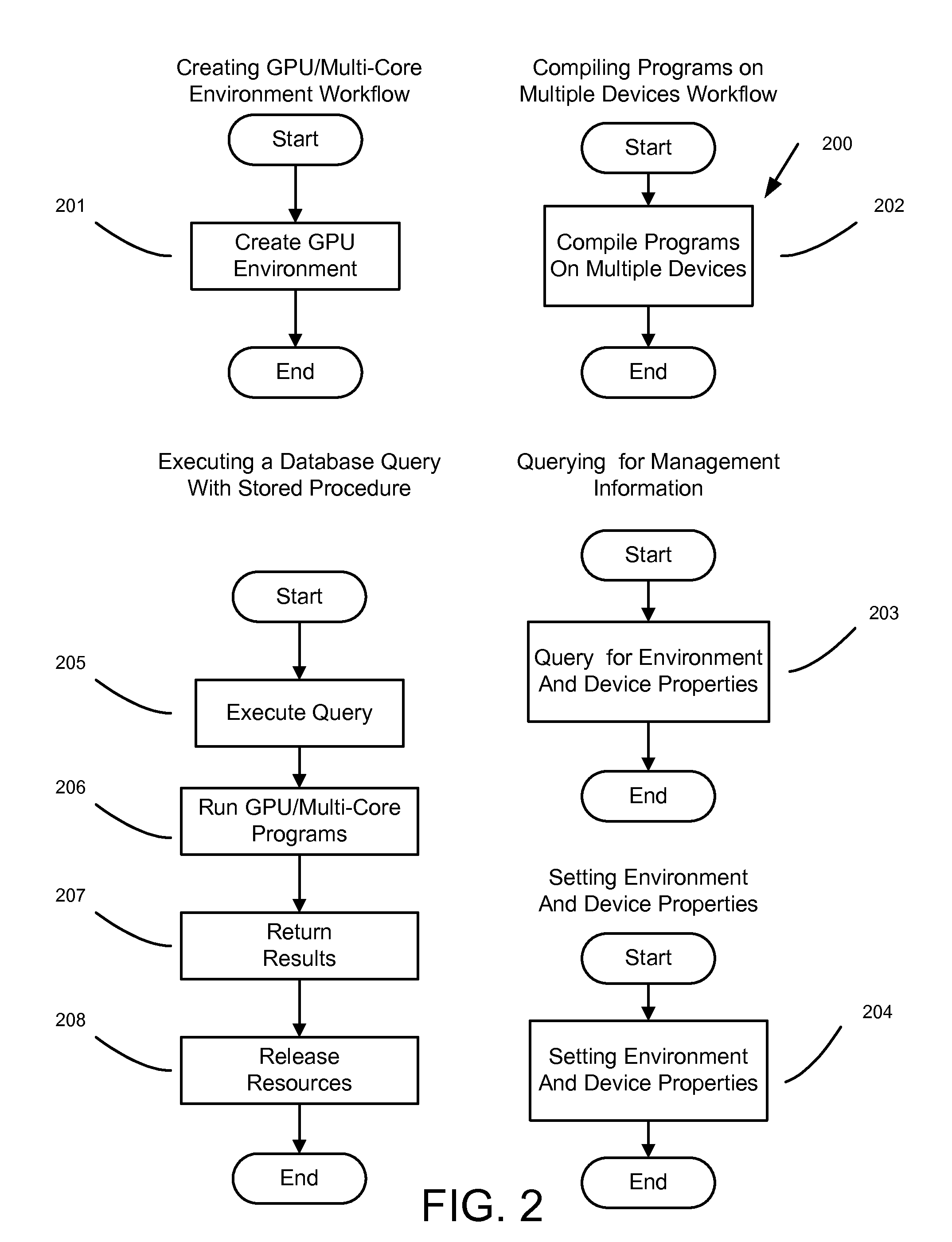

Database acceleration using GPU and multicore CPU systems and methods

InactiveUS20120259843A1Improve performanceHighly mannerDigital data information retrievalDigital data processing detailsDatabase serverMulticore cpu

A computer-implemented method for GPU acceleration of a database system, the method includes a) executing a parallelized query against a database using a database server, the parallelized query including an operation using a particular stored procedure available to the database server that includes a GPU / Many-Core Kernel executable; and b) executing the particular stored procedure on one or more GPU / Many-Core devices.

Owner:CHILD TIMOTHY

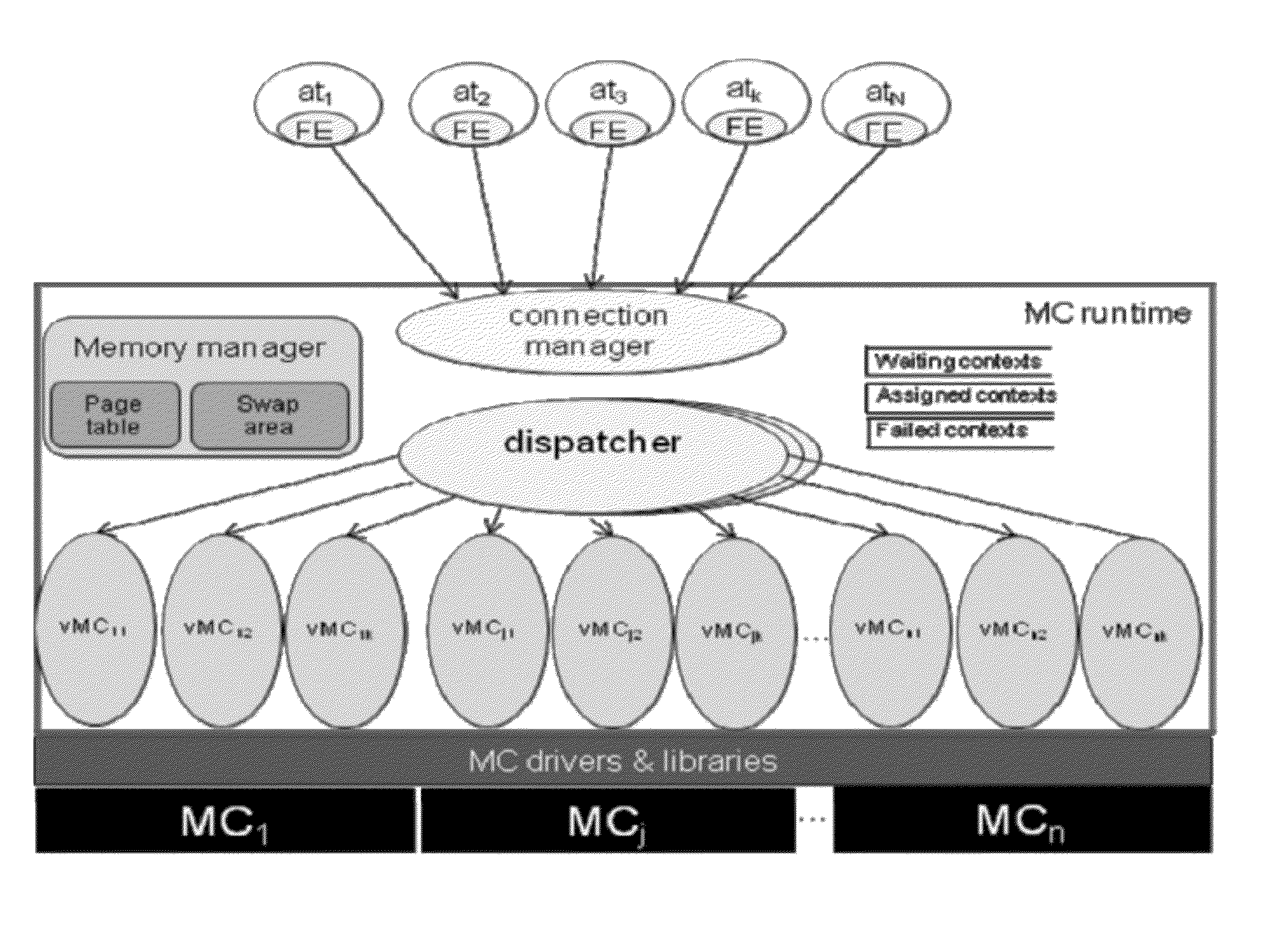

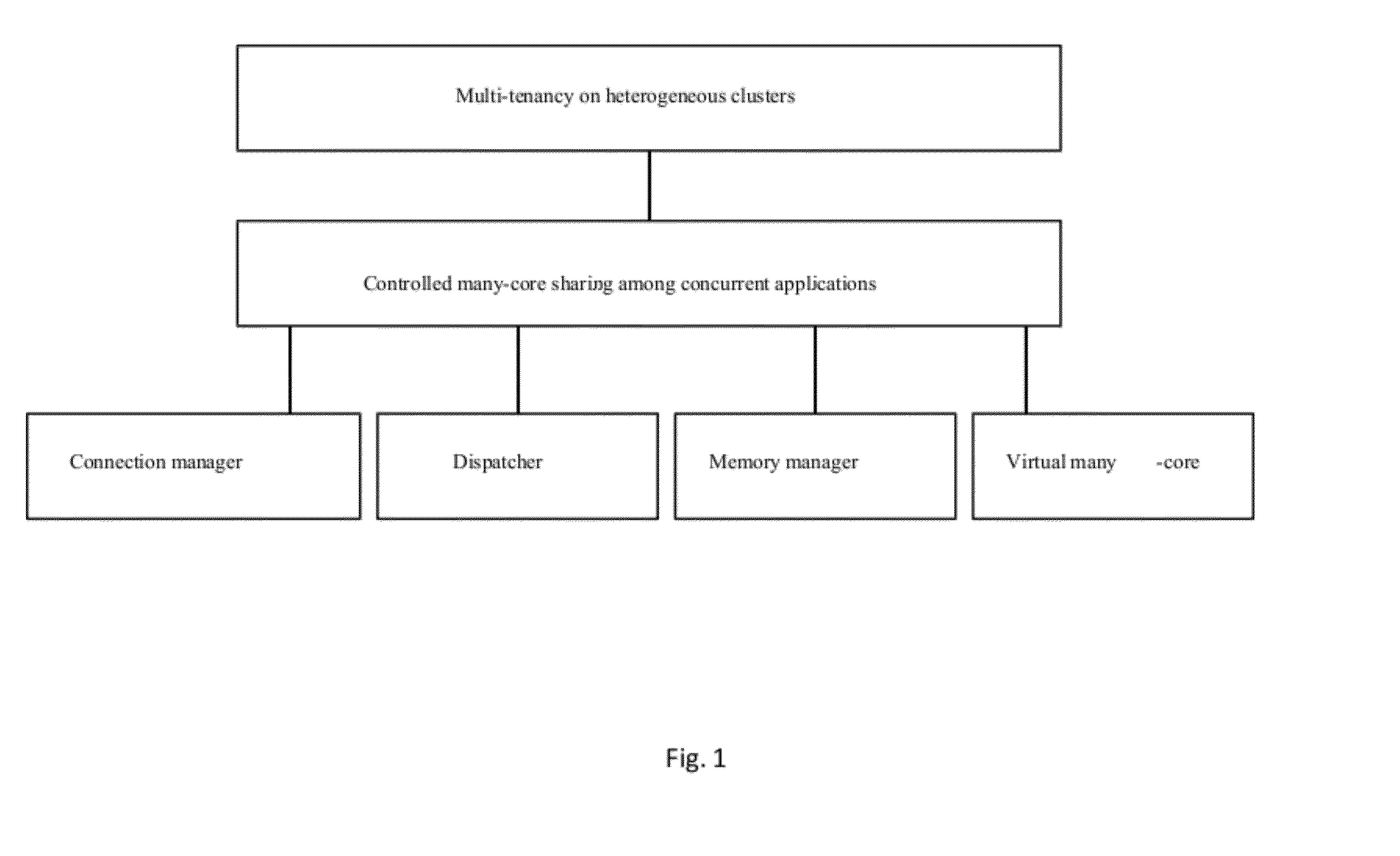

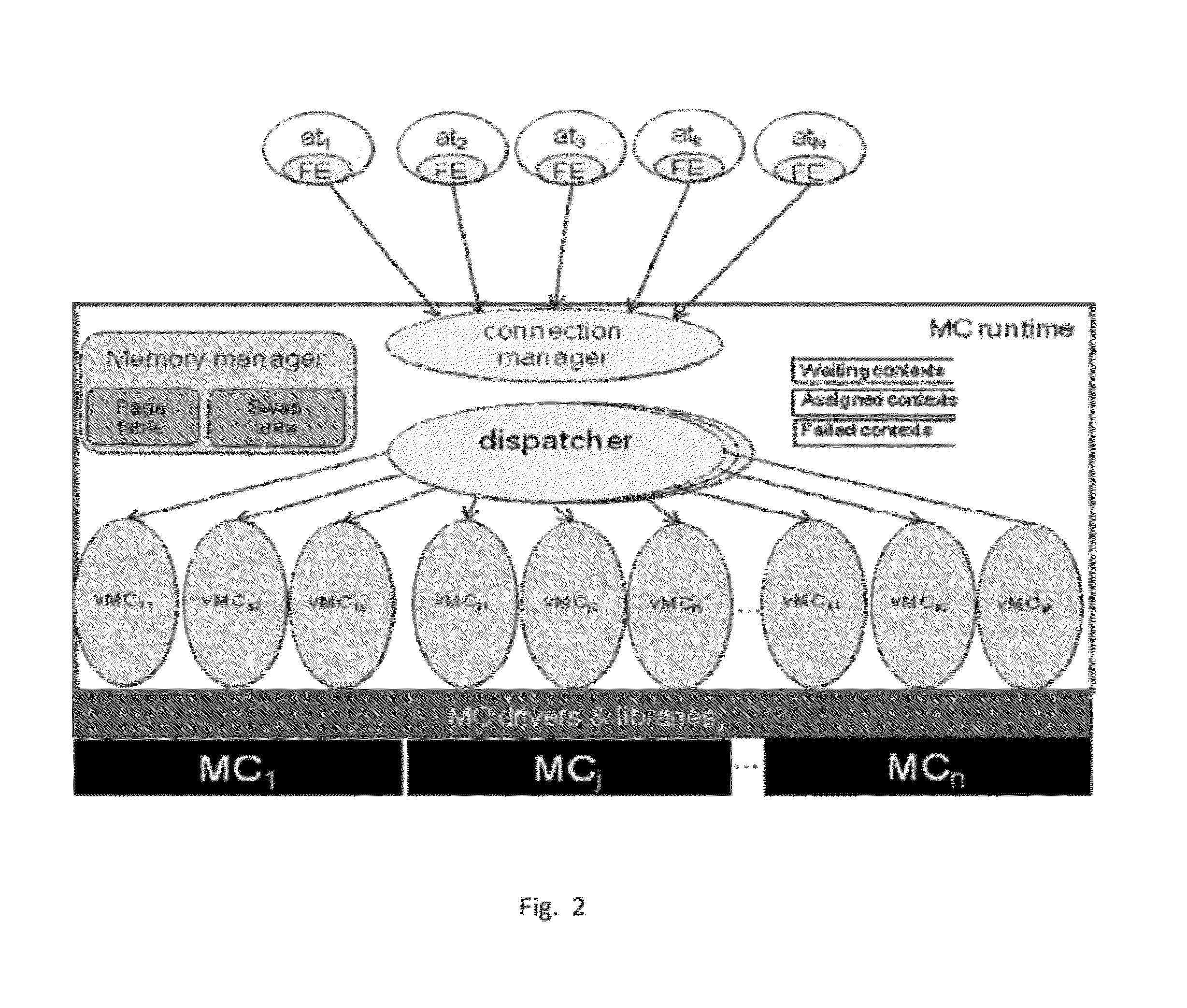

Method and System for Memory Aware Runtime to Support Multitenancy in Heterogeneous Clusters

ActiveUS20120192198A1Limited amountImage memory managementMultiprogramming arrangementsHeterogeneous clusterTime-sharing

Owner:NEC CORP

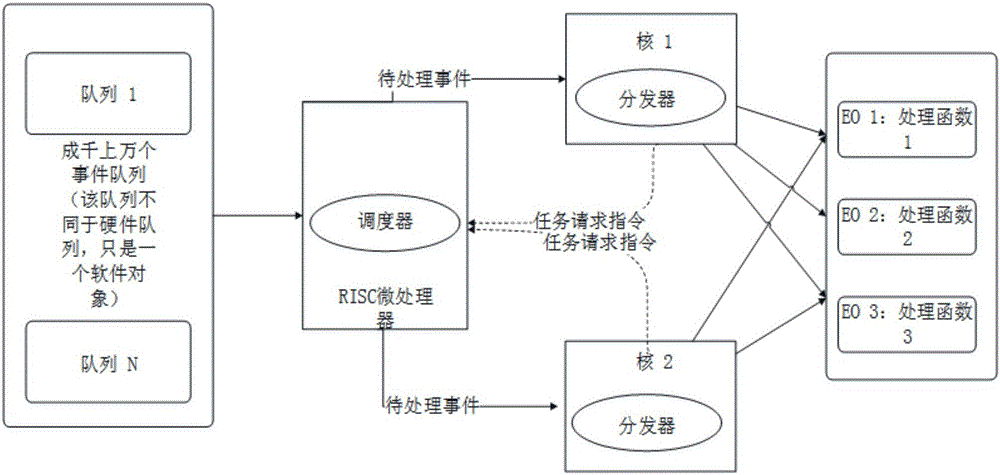

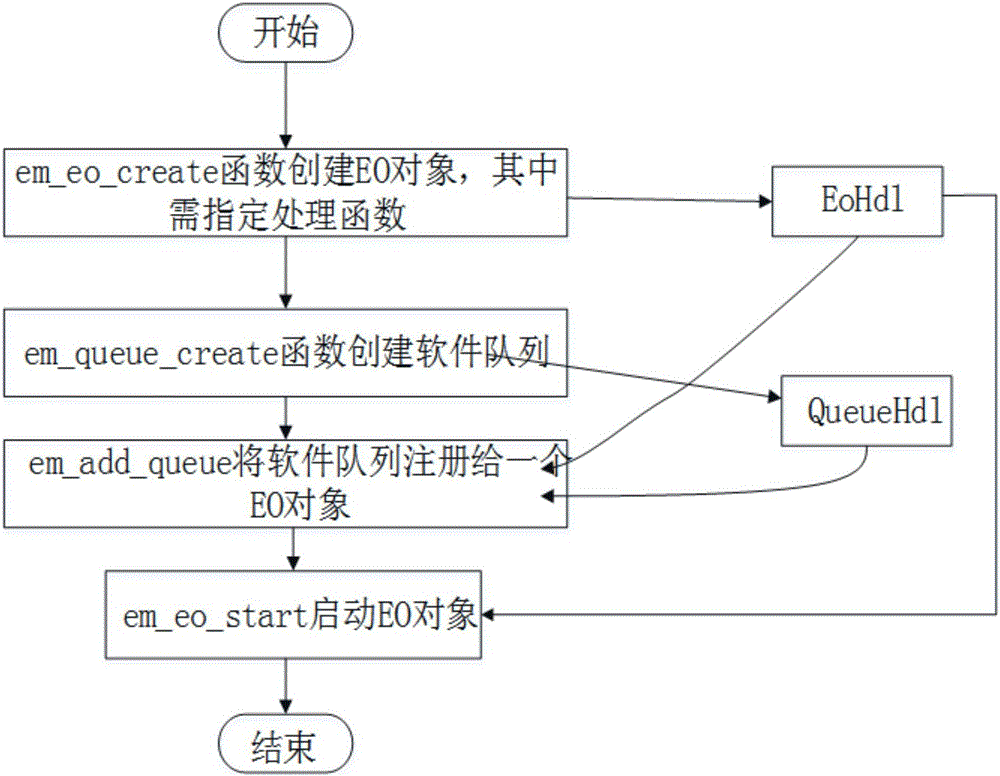

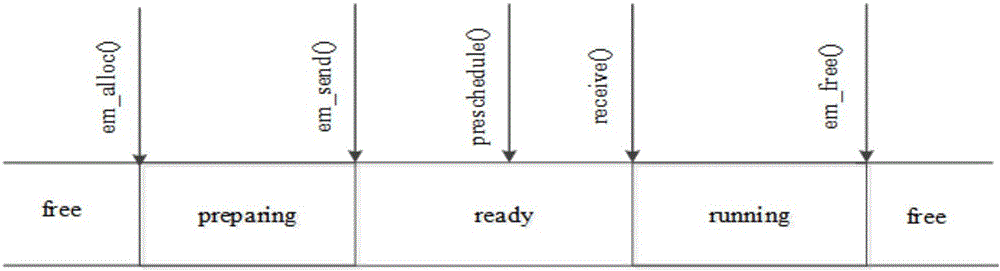

Method for realizing dynamic dispatching distribution of task by multi-core embedded DSP (Data Structure Processor)

ActiveCN105045658AImprove scalabilityMeet the application requirements of dynamic load balancingProgram initiation/switchingResource allocationComputer architectureOperational system

The invention discloses a method for realizing the dynamic dispatching distribution of a task by a multicore embedded DSP (Data Structure Processor). A KeyStone platform brought out by TI (Texas Instruments) provides a multicore runtime system library OpenEM (Event Machine) capable of realizing the dynamic dispatching distribution of the task on the basis of Multicore Navigator, the dynamic dispatching distribution of the task can be realized through the multicore runtime system library OpenEM, and multicore load balance is realized, wherein the multicore runtime system library OpenEM is independent of an operating system. A DSP core of a multicore embedded processor based on a KeyStone architecture is divided into a main core and slave cores, wherein the main core finishes the global initialization of a programming model, and all cores finish local initialization. The programming model consists of a main core generation event, an event driver, an OpenEM dispatching distribution event and a slave core processing event. The invention provides a uniform parallel programming model of the multicore embedded DSP on the basis of the OpenEM for embedded software developers. The implementation method is high in expansibility, can be suitable for the majority of multicore or many-core embedded processors based on a KeyStone architecture and can meet the application requirement of the dispatching distribution of the task under a multicore environment and realize the dynamic load balance.

Owner:杭州普锐视科技有限公司

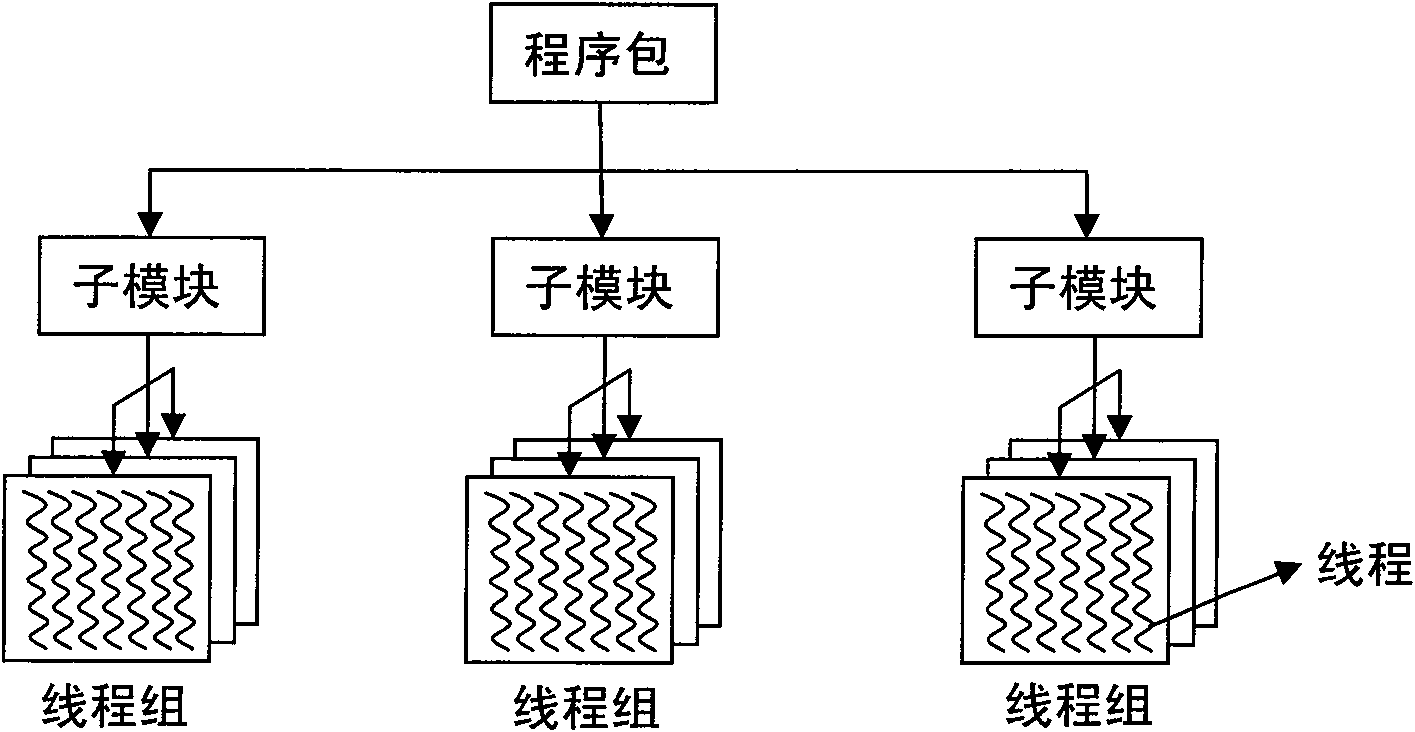

Large-scale data parallel computation method with many-core structure

InactiveCN101556534AImprove computing efficiencySpeed upMultiprogramming arrangementsConcurrent instruction executionBatch processingLarge scale data

The invention provides a computation method which utilizes a parallel processing chip with an isomorphic many-core to carry out large-scale data parallel processing, and the method utilizes a parallel processor with an isomorphic many-core structure to carry out parallel computation processing for large-scale data without logical relationship. Modules in an application sequentially run on an isomorphic many-core microprocessor, wherein each module is operated repeatedly, processes sub-modules with different data every time and is separated into a function which a plurality of threads executing on a many-core. The threads which correspond to each function are organized into a thread group according to a certain rule; the thread group is batch processing for the threads derived from the function; all the threads which are derived from the same function can access a global shared memory space on the many-core microprocessor; the accessing of each thread to a thread group shared memory space and the global shared memory space comprises reading data on the thread group memory space and the global shared memory space and writing an operation result in; and the threads which correspond to each function process different data simultaneously so as to achieve high parallelization.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

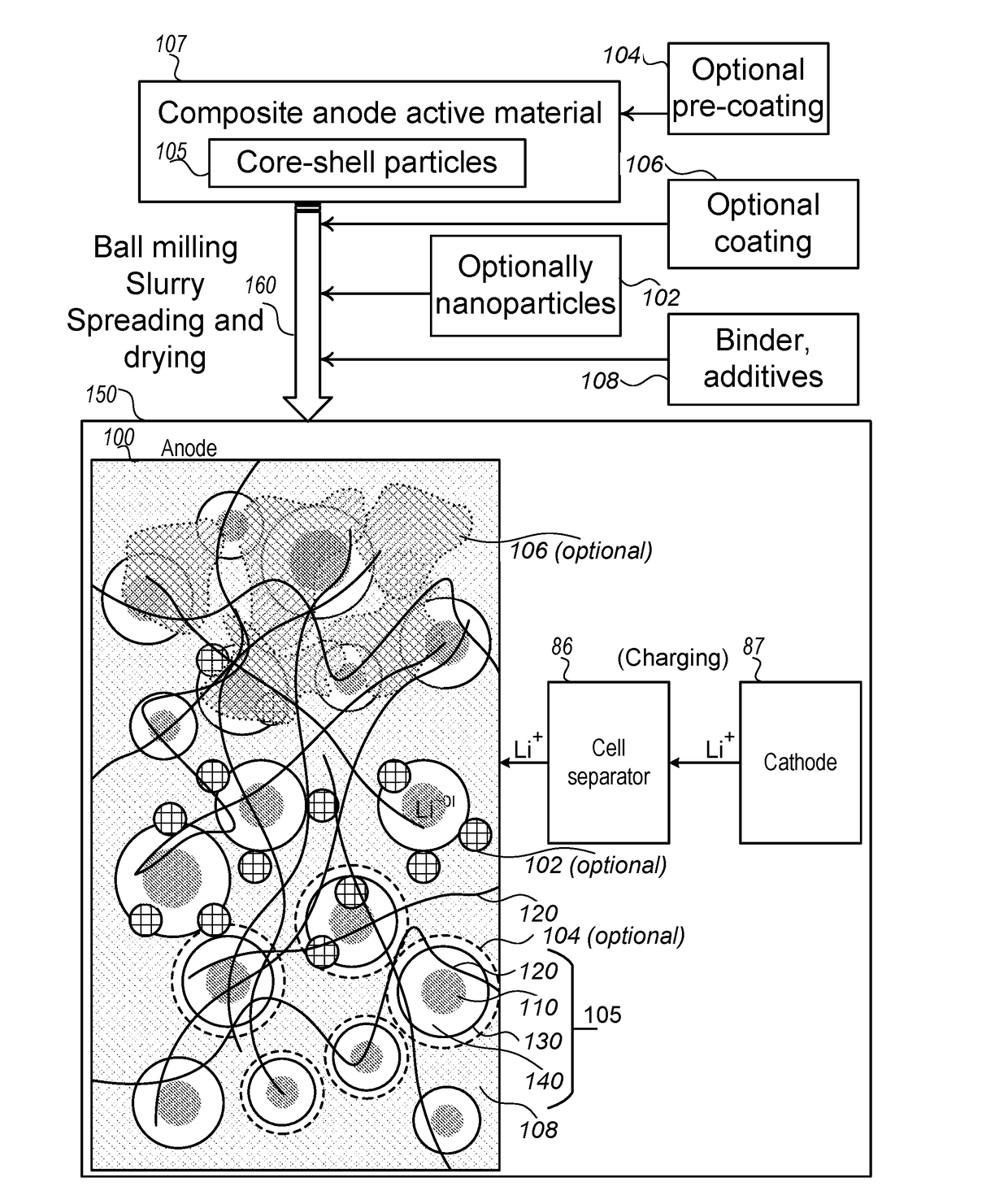

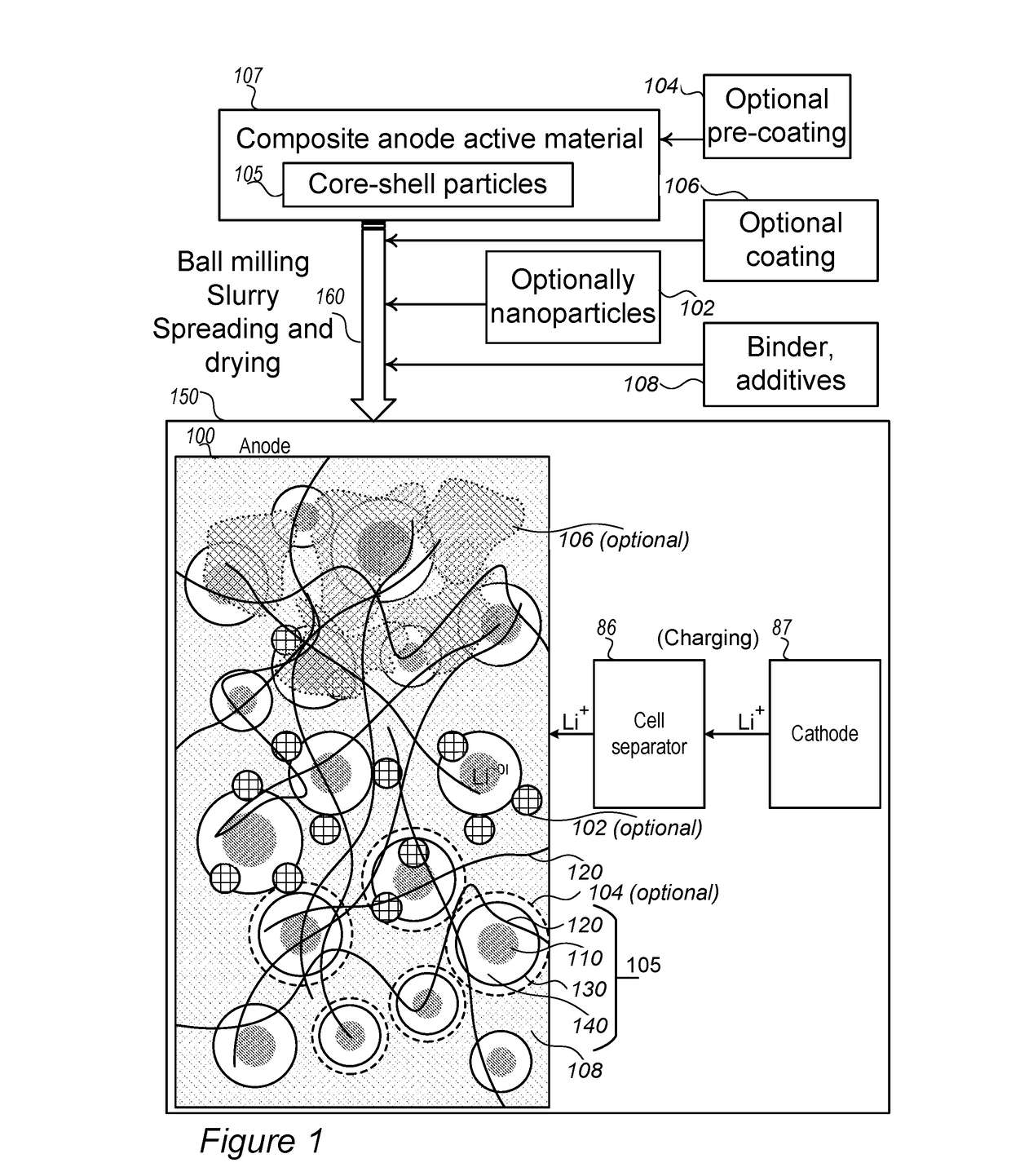

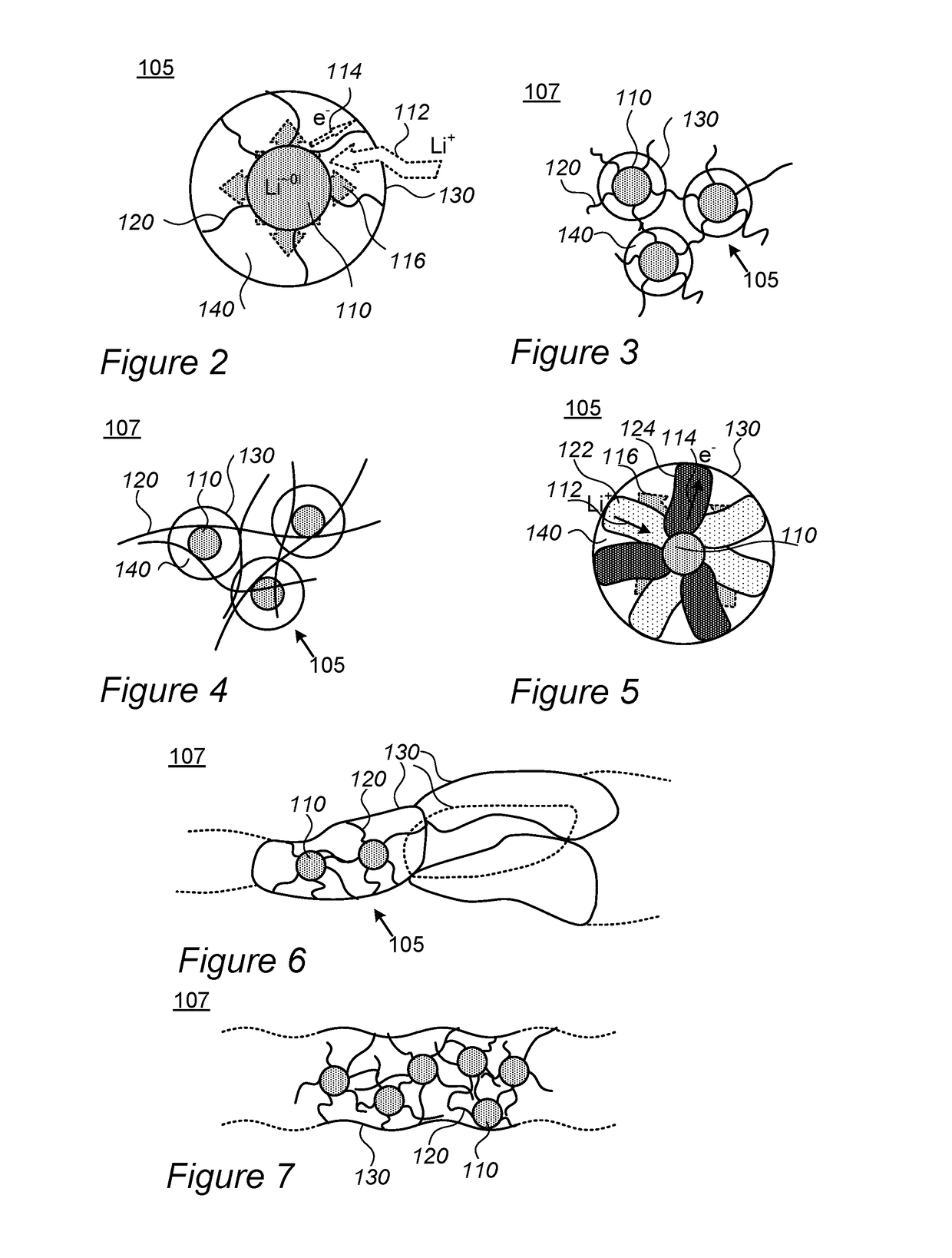

Composite anode material made of core-shell particles

Core-shell particles, composite anode material, anodes made therefrom, lithium ion cells and methods are provided, which enable production of fast charging lithium ion batteries. The composite anode material has core-shell particles which are configured to receive and release lithium ions at their cores and to have shells that are configured to allow for core expansion upon lithiation. The cores of the core-shell particles are connected to the respective shells by conductive material such as carbon fibers, which may form a network throughout the anode material and possibly interconnect cores of many core-shell particles to enhance the electrical conductivity of the anode. Ionic conductive material and possibly mechanical elements may be incorporated in the core-shell particles to enhance ionic conductivity and mechanical robustness toward expansion and contraction of the cores during lithiation and de-lithiation.

Owner:STOREDOT

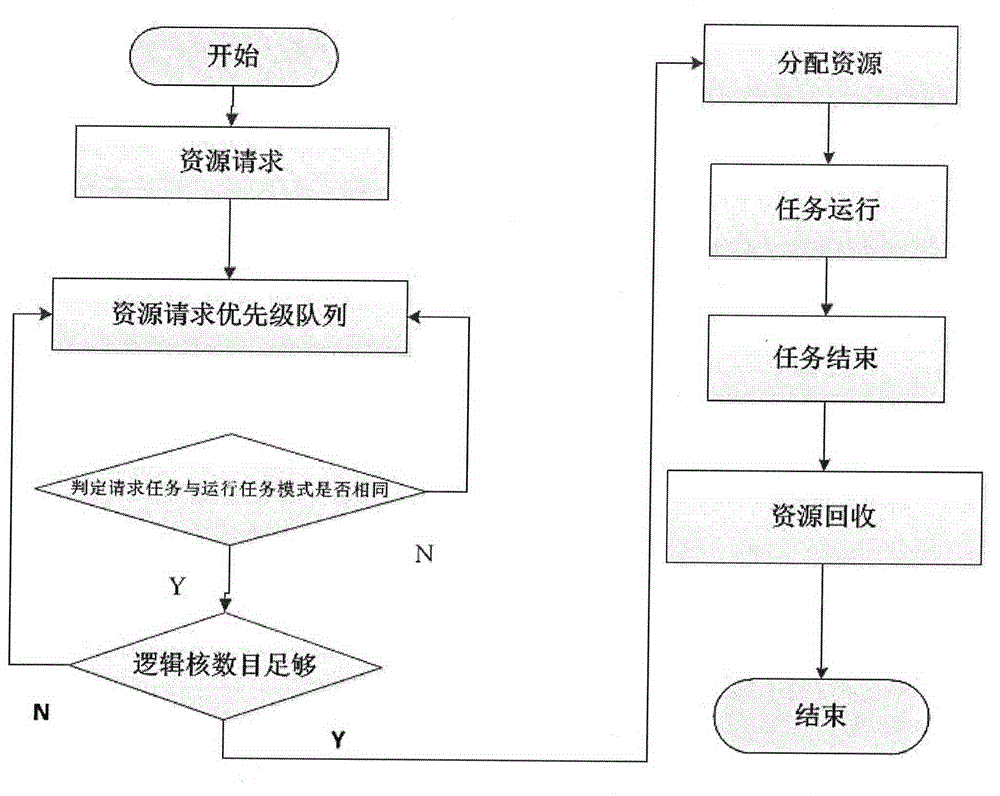

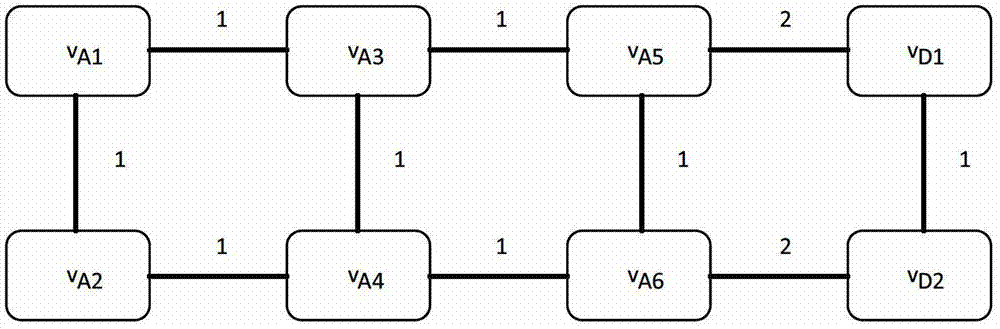

Mapping method for multimode real-time tasks and multimode computing resources

InactiveCN104834556ADynamic and Efficient MappingImprove computing powerMultiprogramming arrangementsCritical levelResource utilization

The invention discloses a mapping method for multimode real-time tasks and multimode computing resources. The mapping method comprises the steps of judging modes of upper mode management and task attribute decision services according to respectively periodic operation; updating a global task queue; updating task attributes which are changed in the global task queue; determining task priorities according to deadlines of tasks and task critical levels and performing uniquifying on the task priorities; searching a computing resource carrier set available for the tasks according to a task computing pattern; trying to allocate the tasks to the computing resources with the best task processing performance one by one according to priorities of elements in the computing resource carrier set from high to low, and determining the computing resource carrier attributes of the tasks; adding the tasks in a PPC task queue through a PPC processor according to an EDF scheduling method; inserting the tasks to proper positions of a many-core task queue through a many-core processor according to a scheduling algorithm. The mapping method for multimode real-time tasks and multimode computing resources can be used for effectively improving the operating performance of the system, the success rate of multimode task scheduling and the utilization rate of resources.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

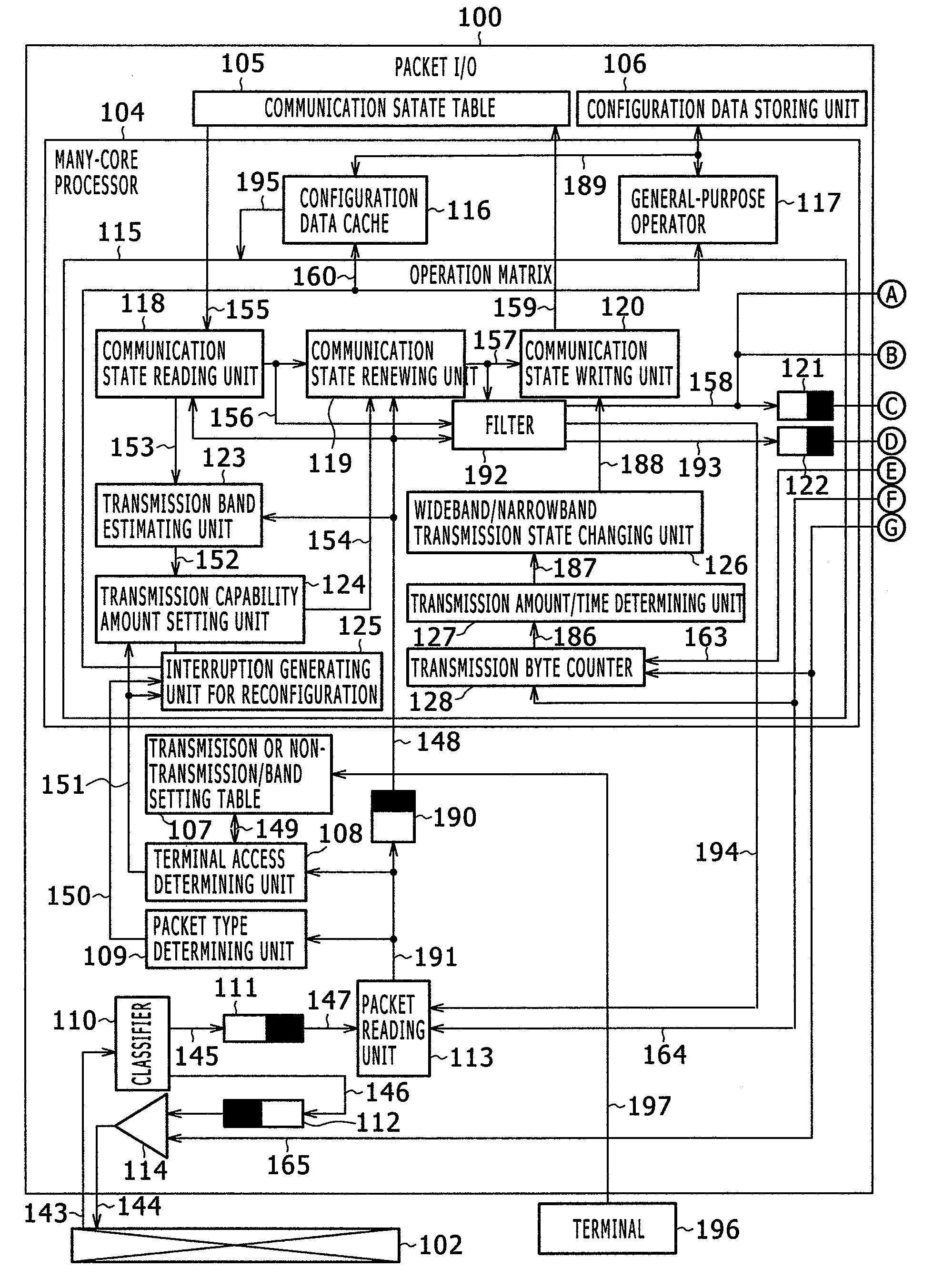

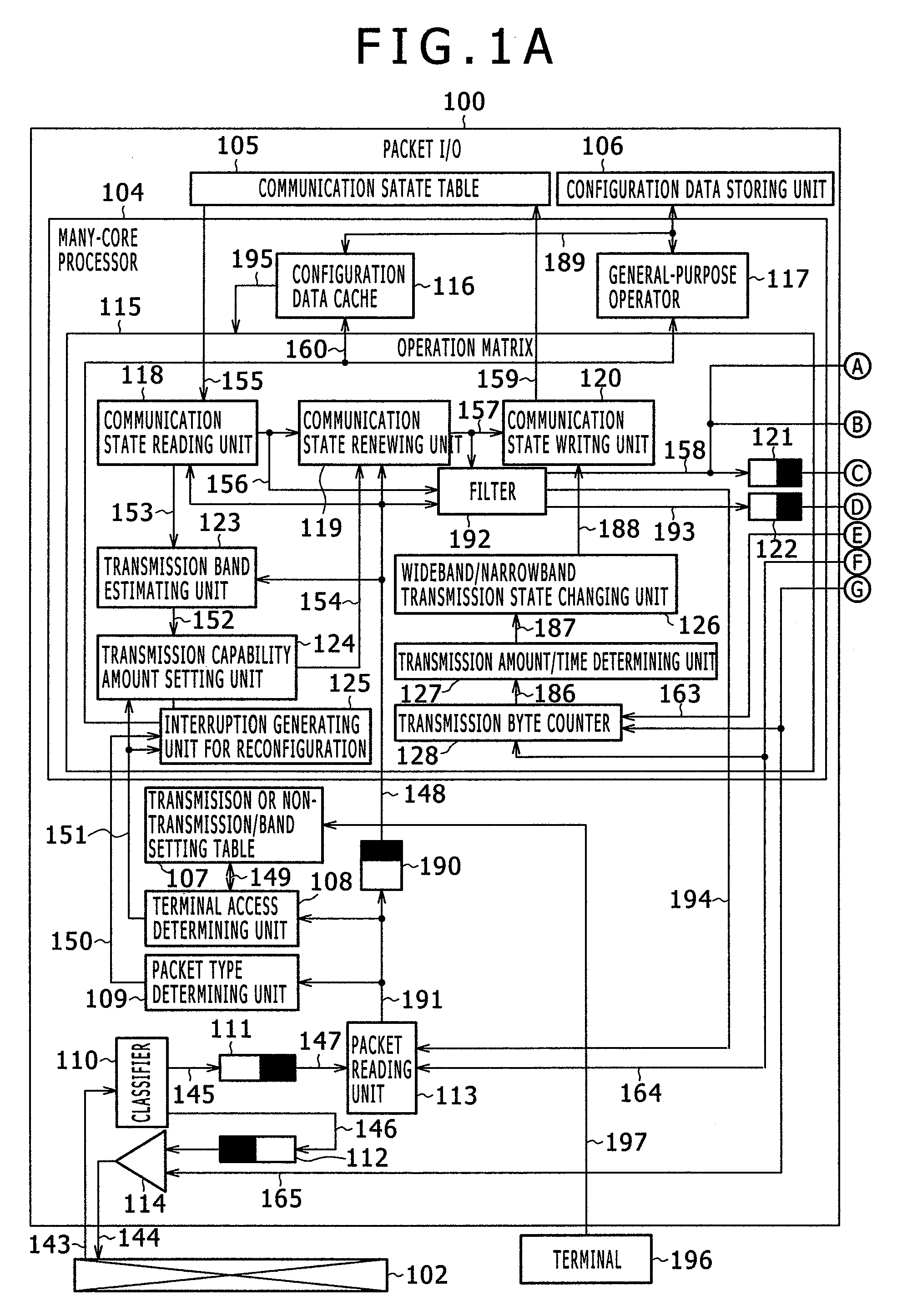

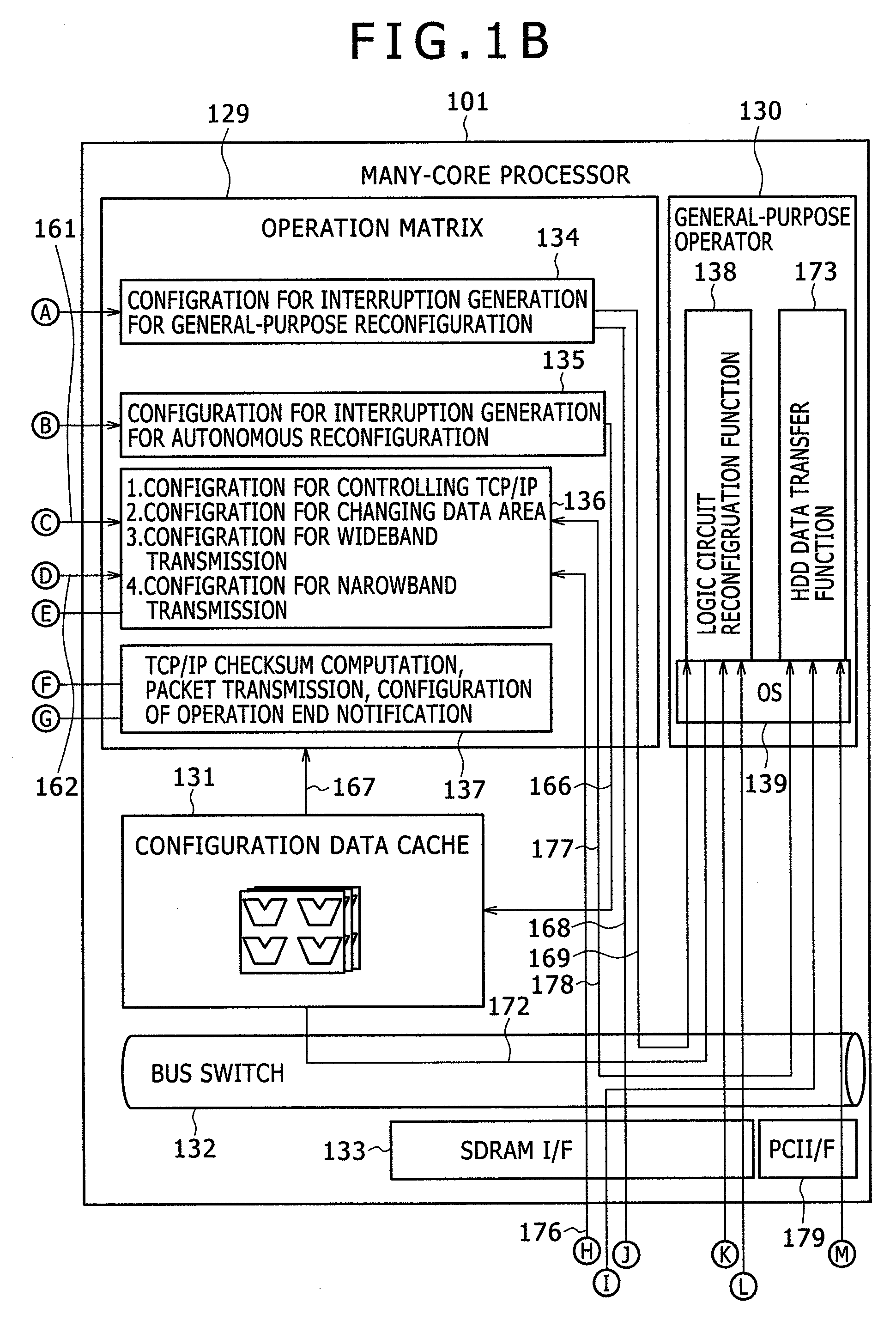

Information processing apparatus and information processing system

InactiveUS20090094353A1High speed responseQuick changeTwo-way working systemsTransmissionInformation processingBroadband transmission

It is an object of the present invention to provide an information processing apparatus equipped with a many-core processor providing a VOD service having a fast playing response speed with a small size and power saving and an information processing system. In the information processing apparatus equipped with a many-core processor configuring an operation matrix that performs a reconfiguration for each packet based on a communication state, the functions and wirings of the operation matrix are reconfigured so that data is transmitted in a wideband transmission process when a transmitted data amount is smaller than a preset threshold value and the data is transmitted in a narrowband transmission process when the transmitted data amount is larger than the threshold value by comparing the transmitted data amount obtained by counting a transmission data amount of a transmission byte counter with the threshold value in a transmission amount / time determining unit and changing a communication state in a wideband / narrowband transmission state changing unit according to the comparison result.

Owner:HITACHI LTD

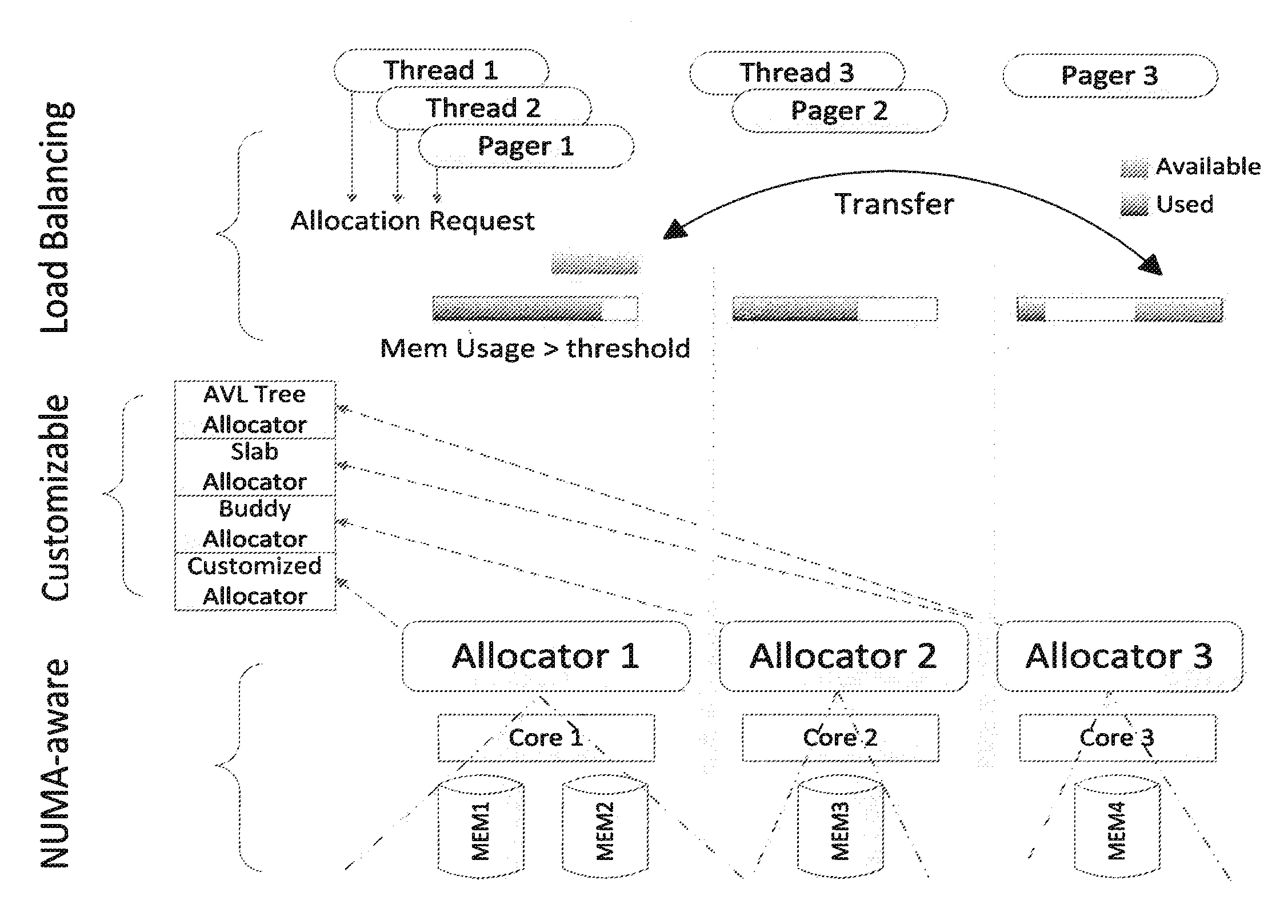

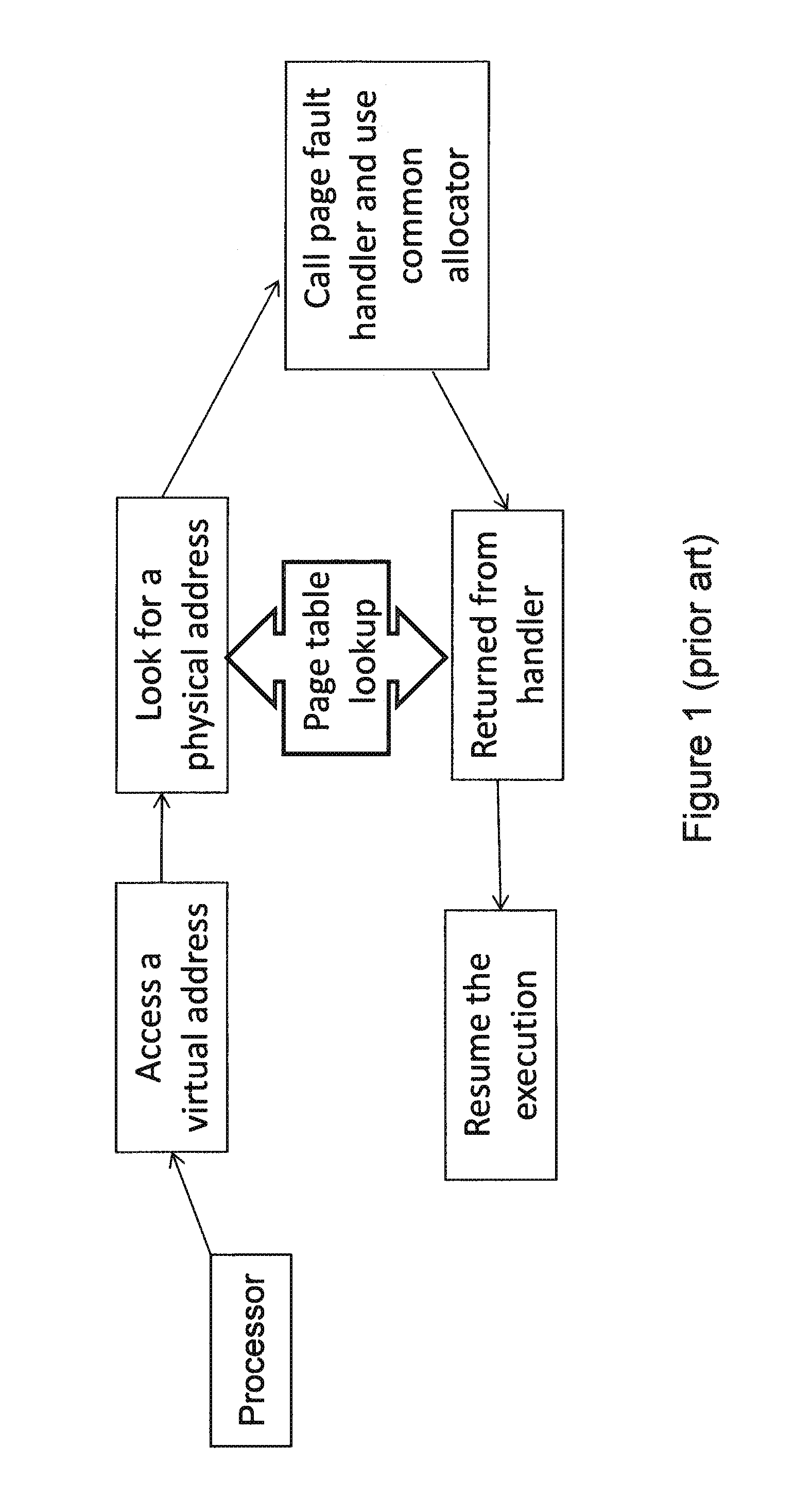

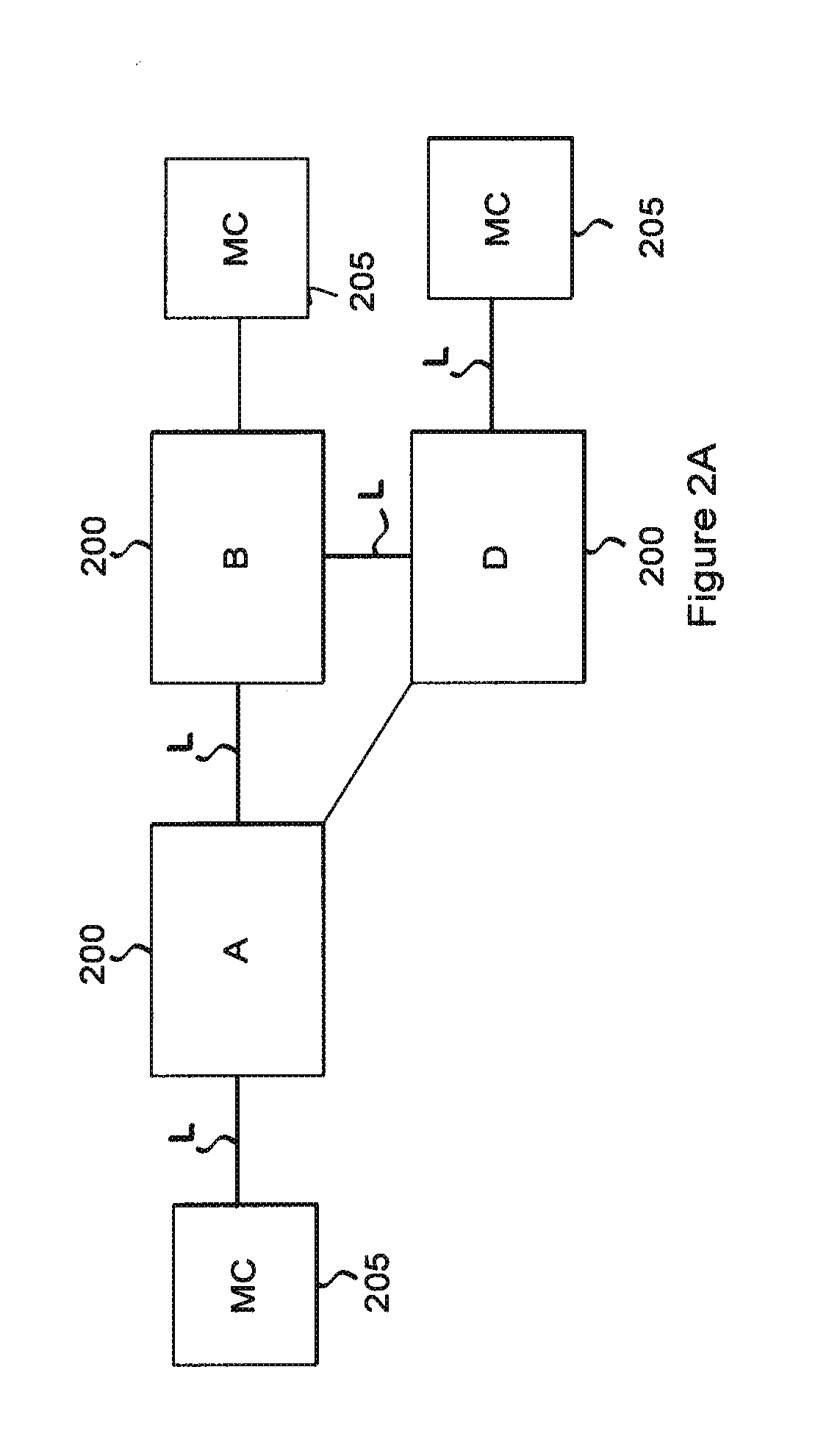

Scalable, customizable, and load-balancing physical memory management scheme

InactiveUS20130232315A1Improve scalabilityResource allocationMemory adressing/allocation/relocationLoad SheddingPager

A physical memory management scheme for handling page faults in a multi-core or many-core processor environment is disclosed. A plurality of memory allocators is provided. Each memory allocator may have a customizable allocation policy. A plurality of pagers is provided. Individual threads of execution are assigned a pager to handle page faults. A pager, in turn, is bound to a physical memory allocator. Load balancing may also be provided to distribute physical memory resources across allocators. Allocations may also be NUMA-aware.

Owner:SAMSUNG ELECTRONICS CO LTD

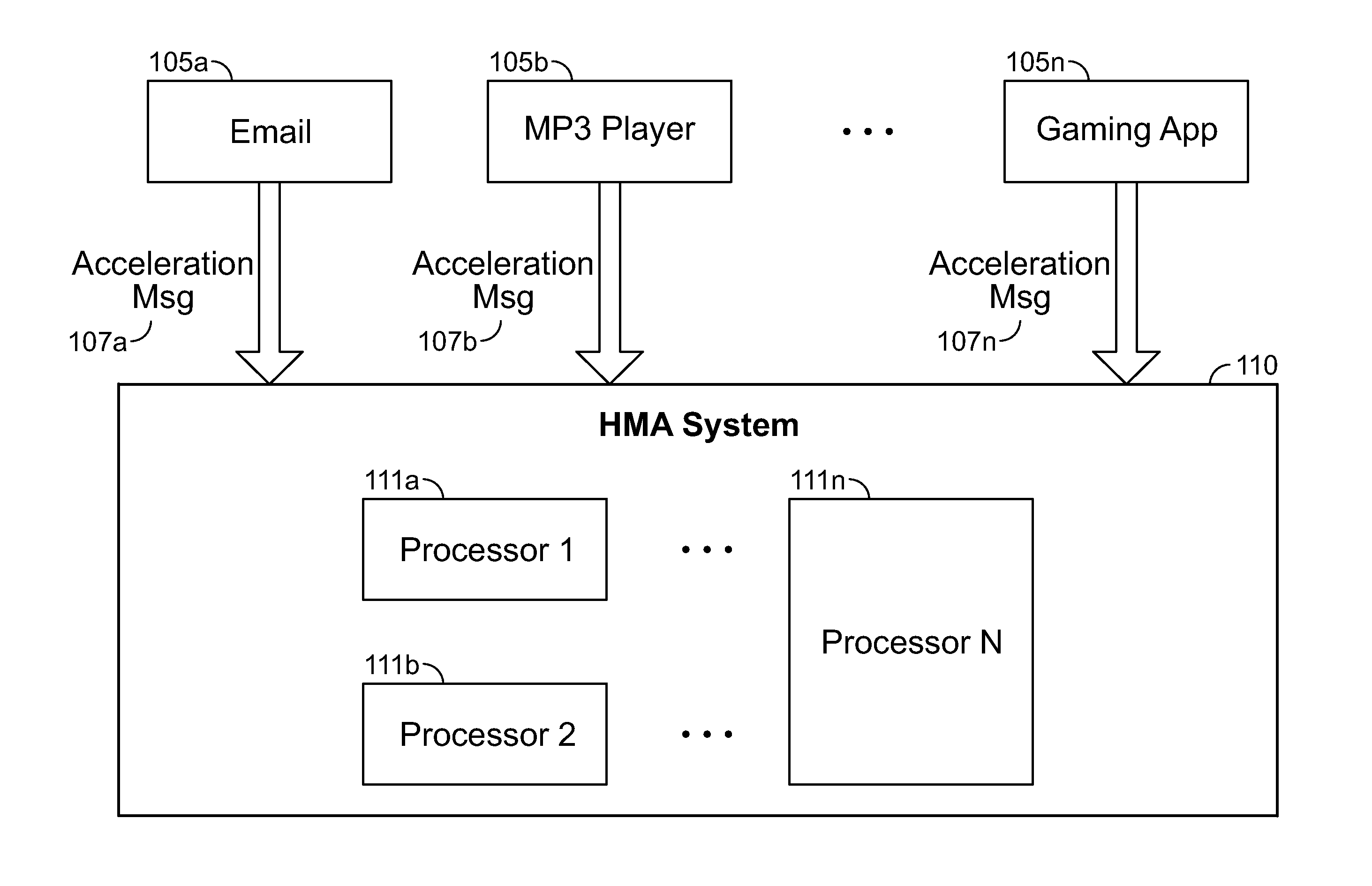

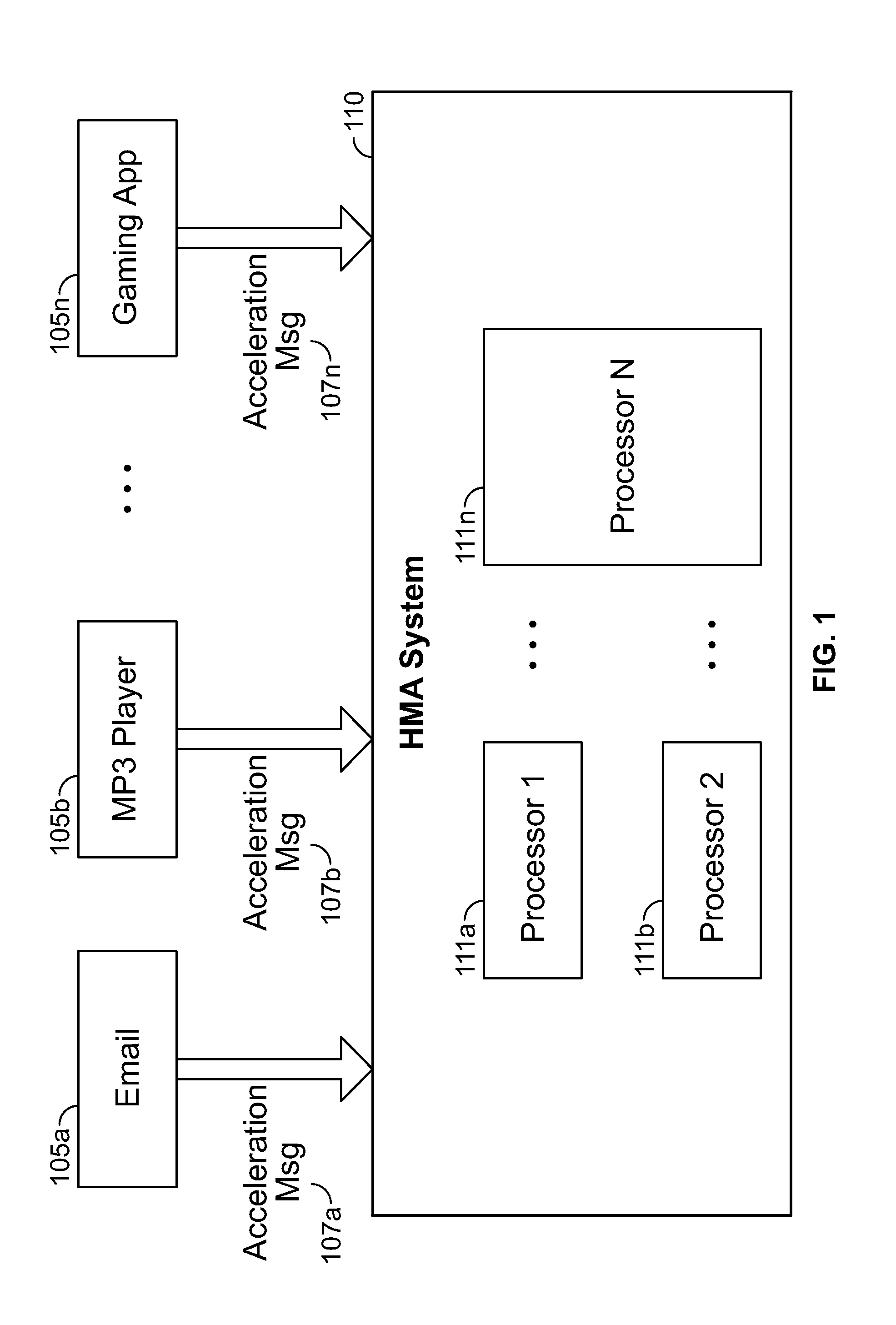

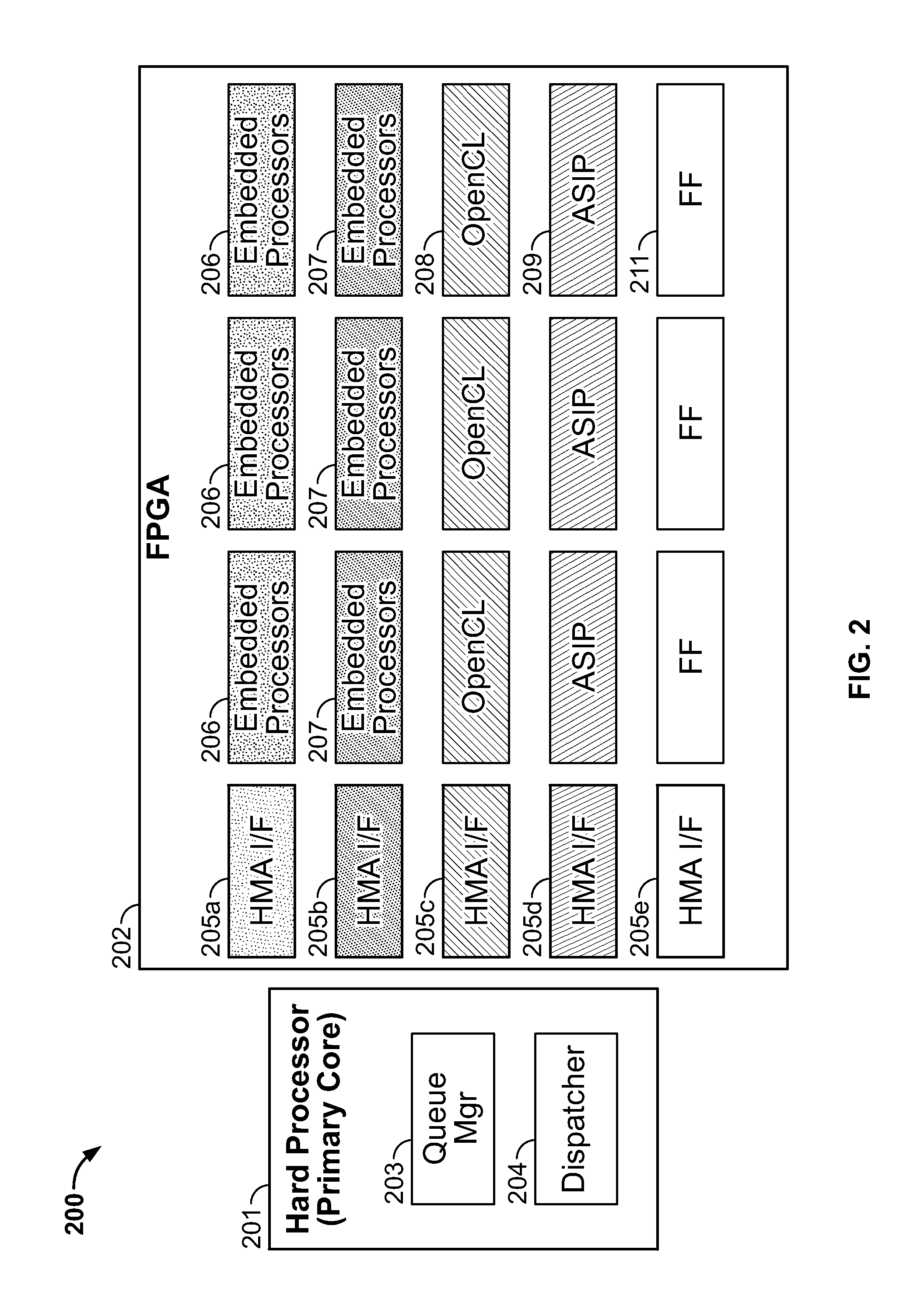

Application-based dynamic heterogeneous many-core systems and methods

ActiveUS20170046179A1Resource allocationMultiple digital computer combinationsApplication softwareOperating system

A method for dynamically configuring multiple processors based on needs of applications includes receiving, from an application, an acceleration request message including a task to be accelerated. The method further includes determining a type of the task and searching a database of available accelerators to dynamically select a first accelerator based on the type of the task. The method further includes sending the acceleration request message to a first acceleration interface located at a configurable processing circuit. The first acceleration interface sends the acceleration request message to a first accelerator, and the first accelerator accelerates the task upon receipt of the acceleration request message.

Owner:ALTERA CORP

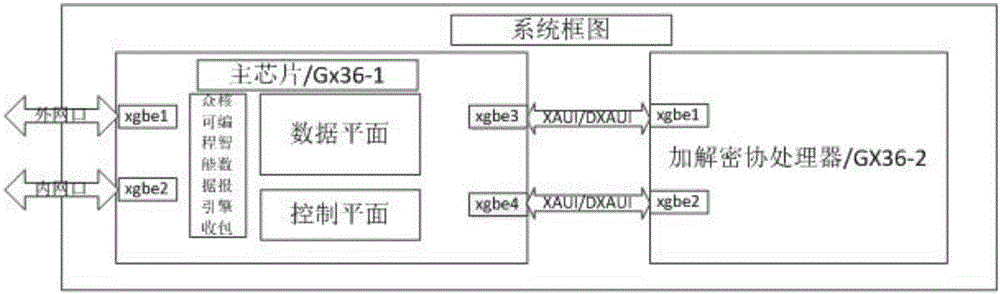

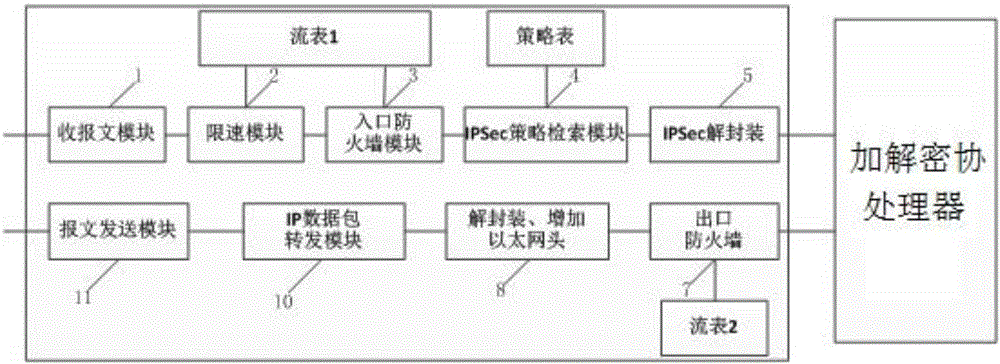

IPSec VPN system based on many-core processor and encryption and decryption processing method

InactiveCN106341404AMeet real-time online processing capabilitiesData transmission securityTransmissionSecure transmissionIPsec

The invention discloses an IPSec VPN system based on a many-core processor. The system comprises an encryption system and a decryption system. A message receiving module, a speed limit module, an inlet firewall module, an IPSec strategy retrieval module, an IPSec plus packaging module, an encryption module, a decryption module, an outlet firewall, a decapsulation and Ethernet head adding module, a repackaging module, an IP data packet forwarding module, a message sending module and the like are included. The invention also discloses an encryption method and a decryption method which adopt an IPSec VPN encryption and decryption system. By using the IPSec VPN system, safety of data transmission between connected users can be guaranteed and a real-time on-line processing capability of a high speed network flow can be satisfied. An identification system of the invention can be applied to various kinds of many-core processors and a purpose of safely transmitting the high speed network flow can be realized.

Owner:XI'AN POLYTECHNIC UNIVERSITY

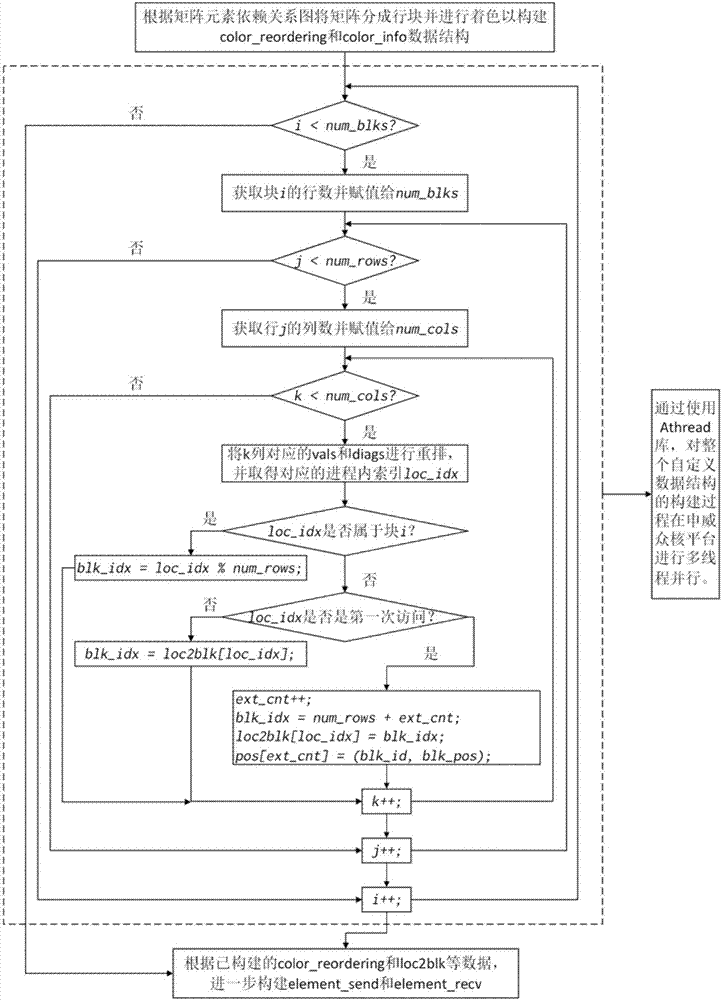

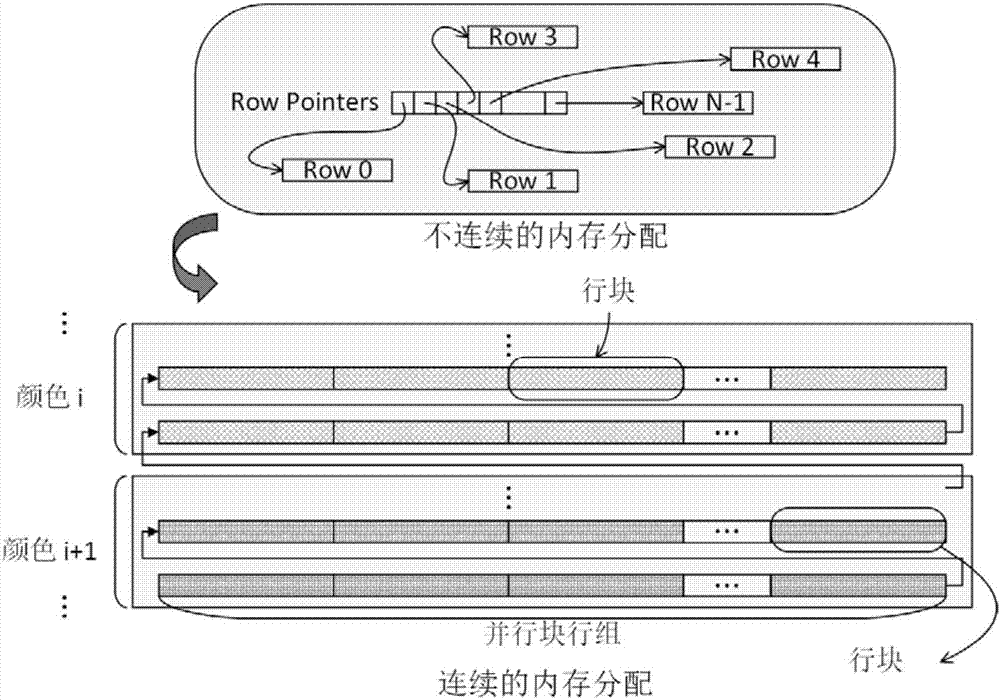

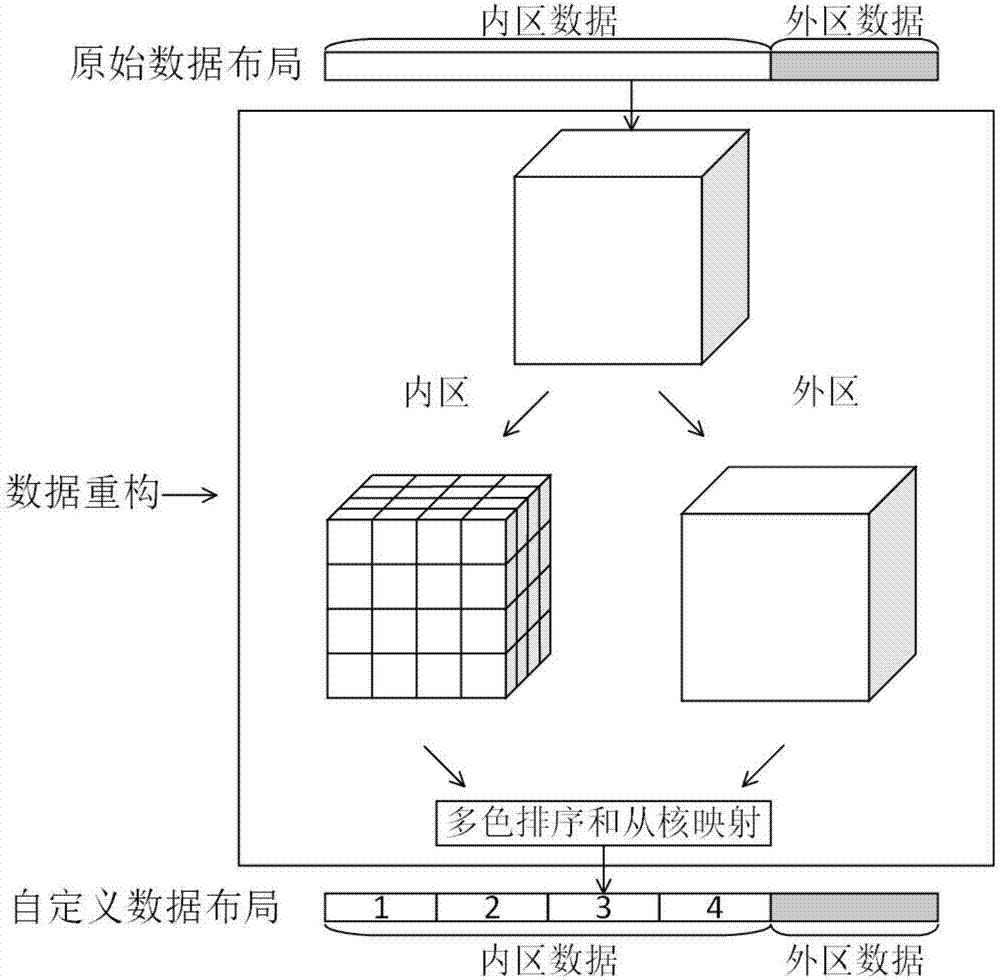

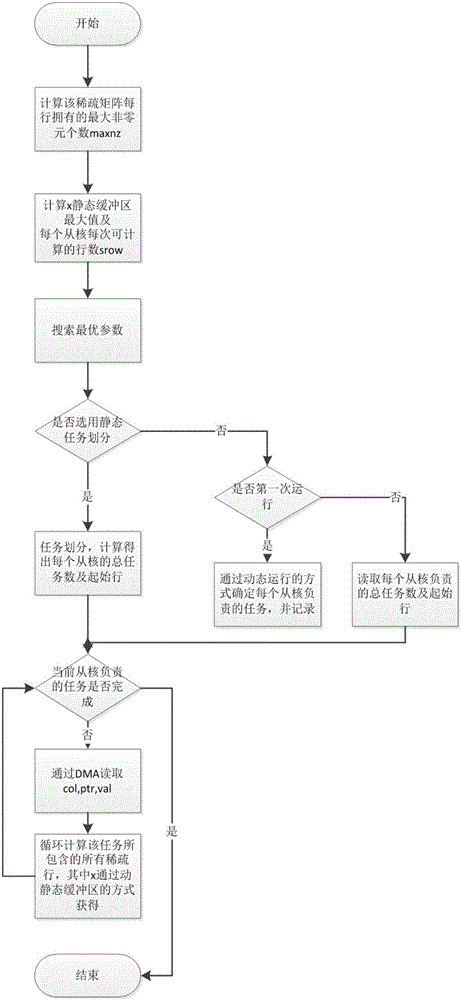

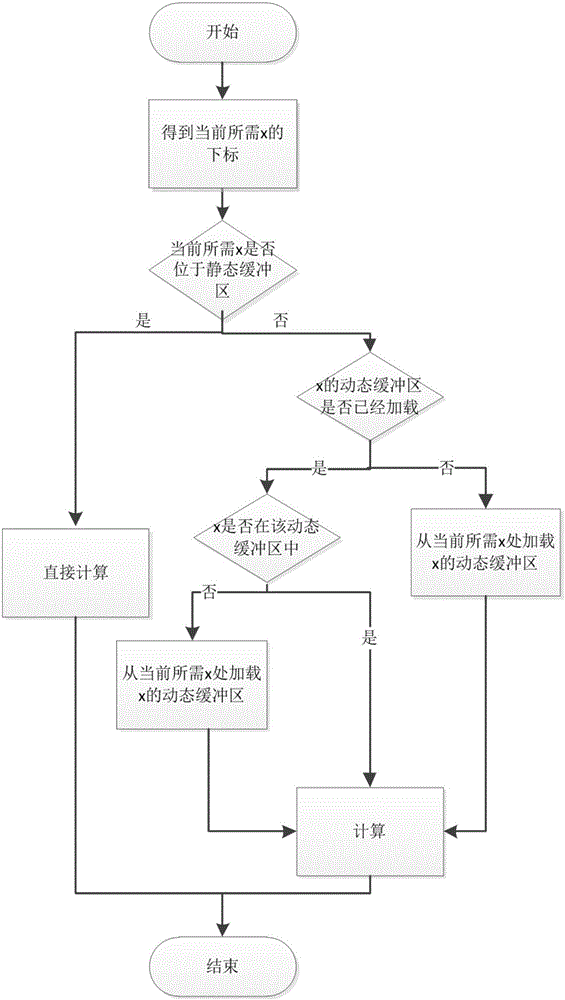

Data structure suitable for HPCG (High Performance Conjugate Gradients) optimization on "Sunway TaihuLight", and efficient implementation method thereof

ActiveCN107273094AImprove performanceReduce movementNext instruction address formationConcurrent instruction executionHigh bandwidthOriginal data

The invention discloses a data structure suitable for HPCG (High Performance Conjugate Gradients) optimization on "Sunway TaihuLight", and an efficient implementation method thereof. On the basis of the structural characteristics of a Sunway many-core processor system on the "Sunway TaihuLight" and HPCG algorithm optimization requirements, a data structure of an improved ELL (ELLPACK) format is used to replacing an original data structure, wherein the data structure includes the own data structure of matrix data and also supports the data structures related to blocking coloring, index conversion, process communication, vector position mapping and the like; in an intermediate treatment process, and an Athread multi-thread library provided by the Sunway many-core platform is adopted to carry out parallel so as to be finally applied to the kernel function SpMV and SymGS optimization processes of the HPCG algorithm; and corresponding performance and a bandwidth percentage obtain a consistent speed-up ratio, and the highest corresponding performance and the highest bandwidth percentage are independently 18.2 and 17.6.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI +1

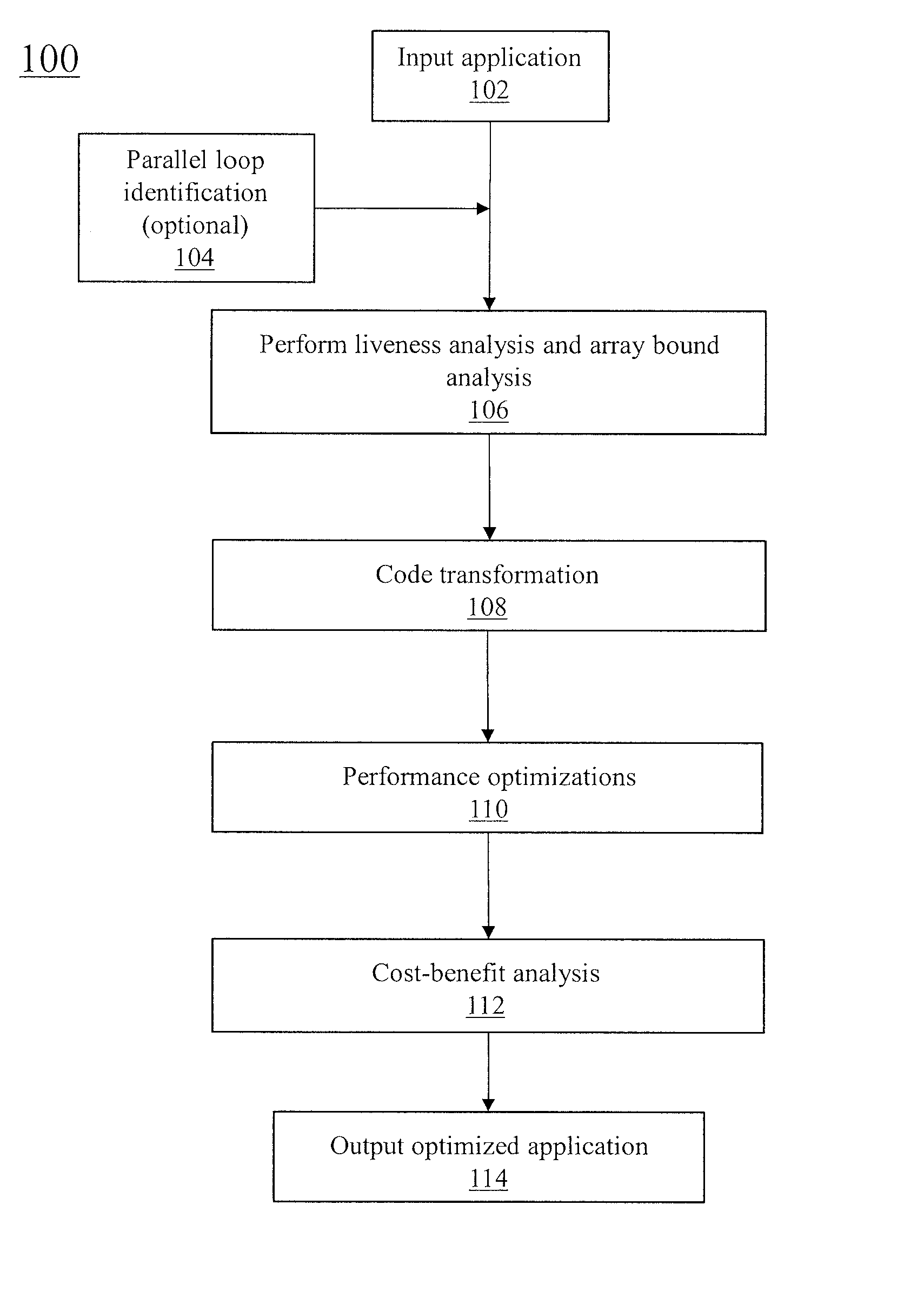

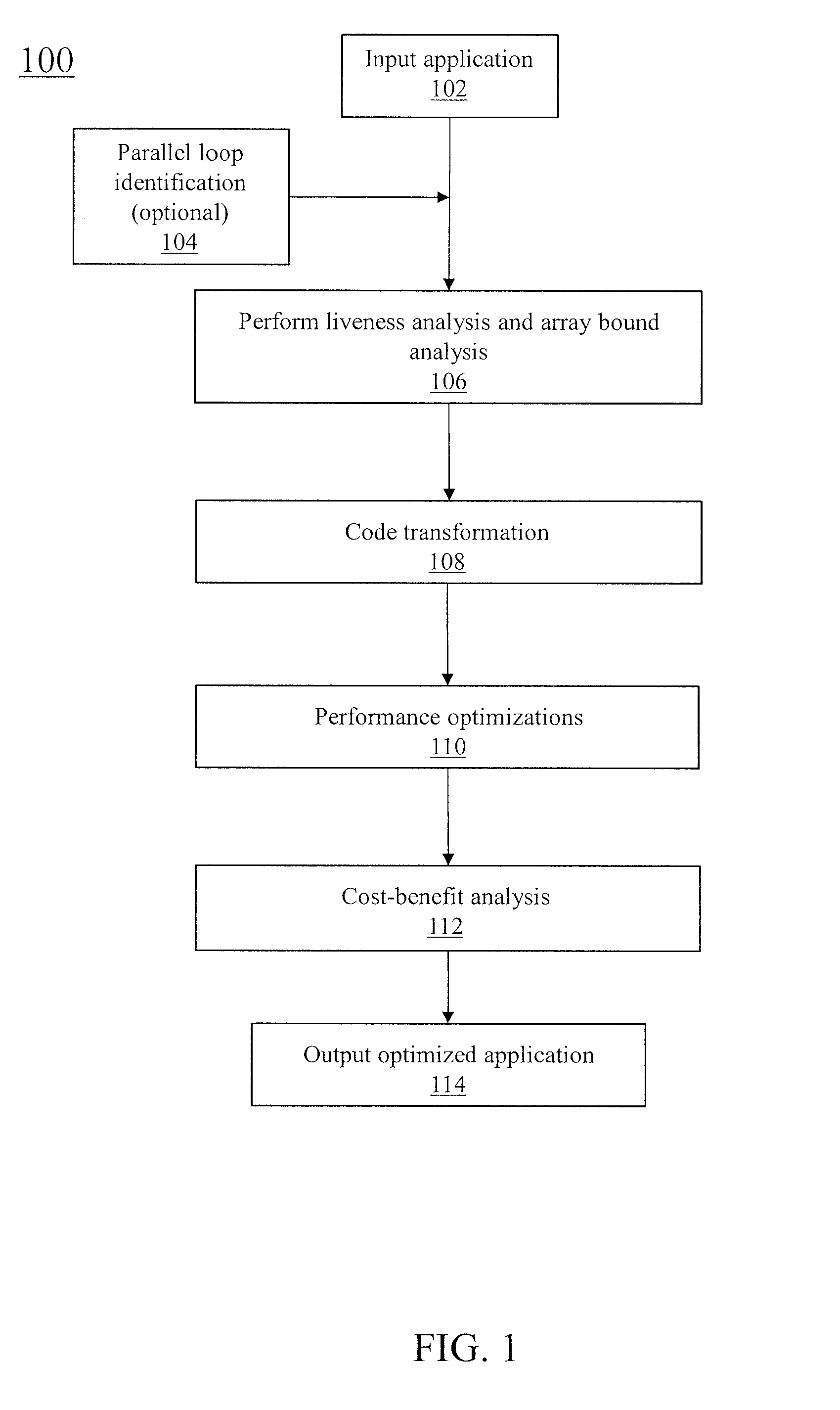

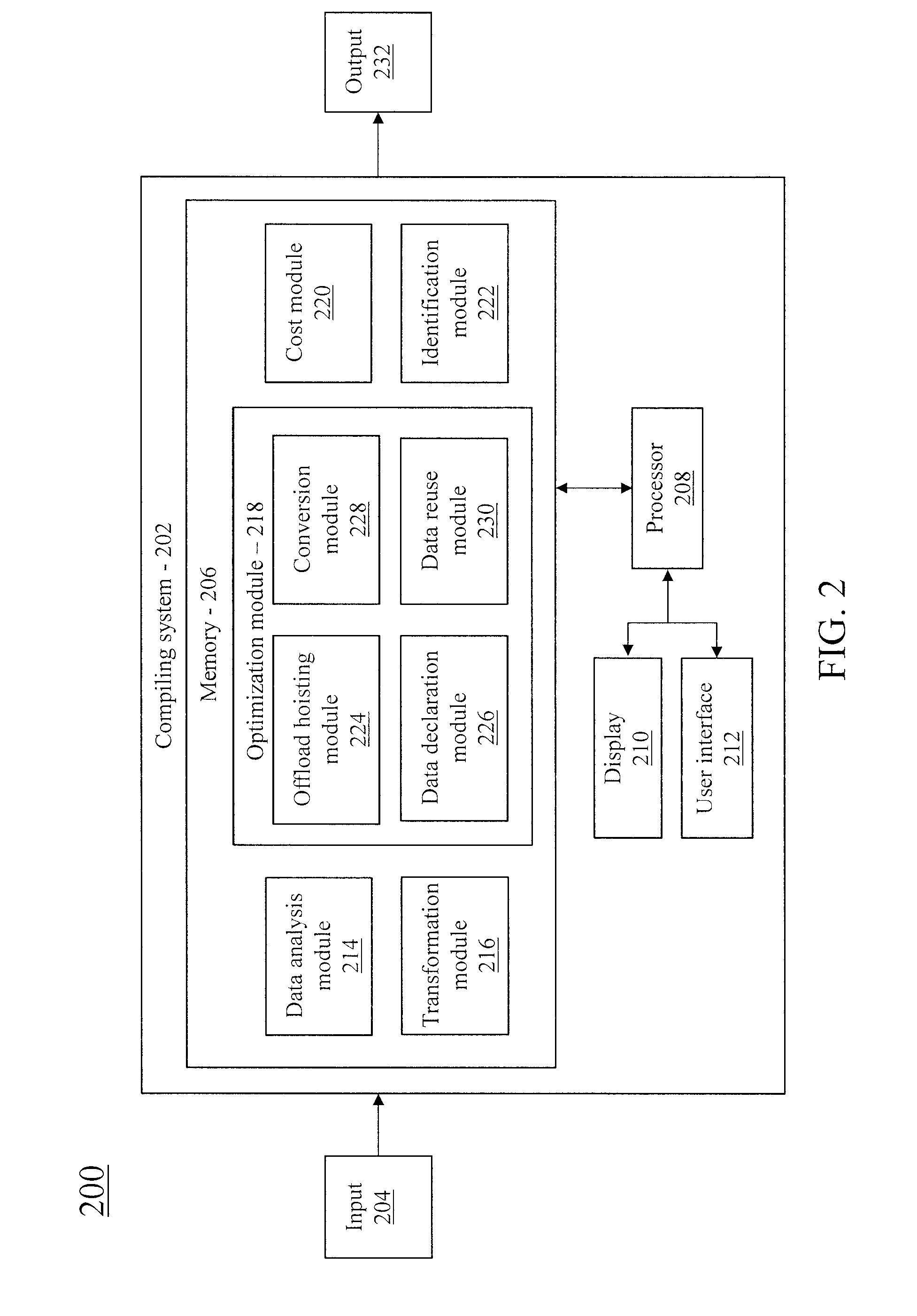

Compiler for x86-based many-core coprocessors

A system and method for compiling includes, for a parallelizable code portion of an application stored on a computer readable storage medium, determining one or more variables that are to be transferred to and / or from a coprocessor if the parallelizable code portion were to be offloaded. A start location and an end location are determined for at least one of the one or more variables as a size in memory. The parallelizable code portion is transformed by inserting an offload construct around the parallelizable code portion and passing the one or more variables and the size as arguments of the offload construct such that the parallelizable code portion is offloaded to a coprocessor at runtime.

Owner:NEC CORP

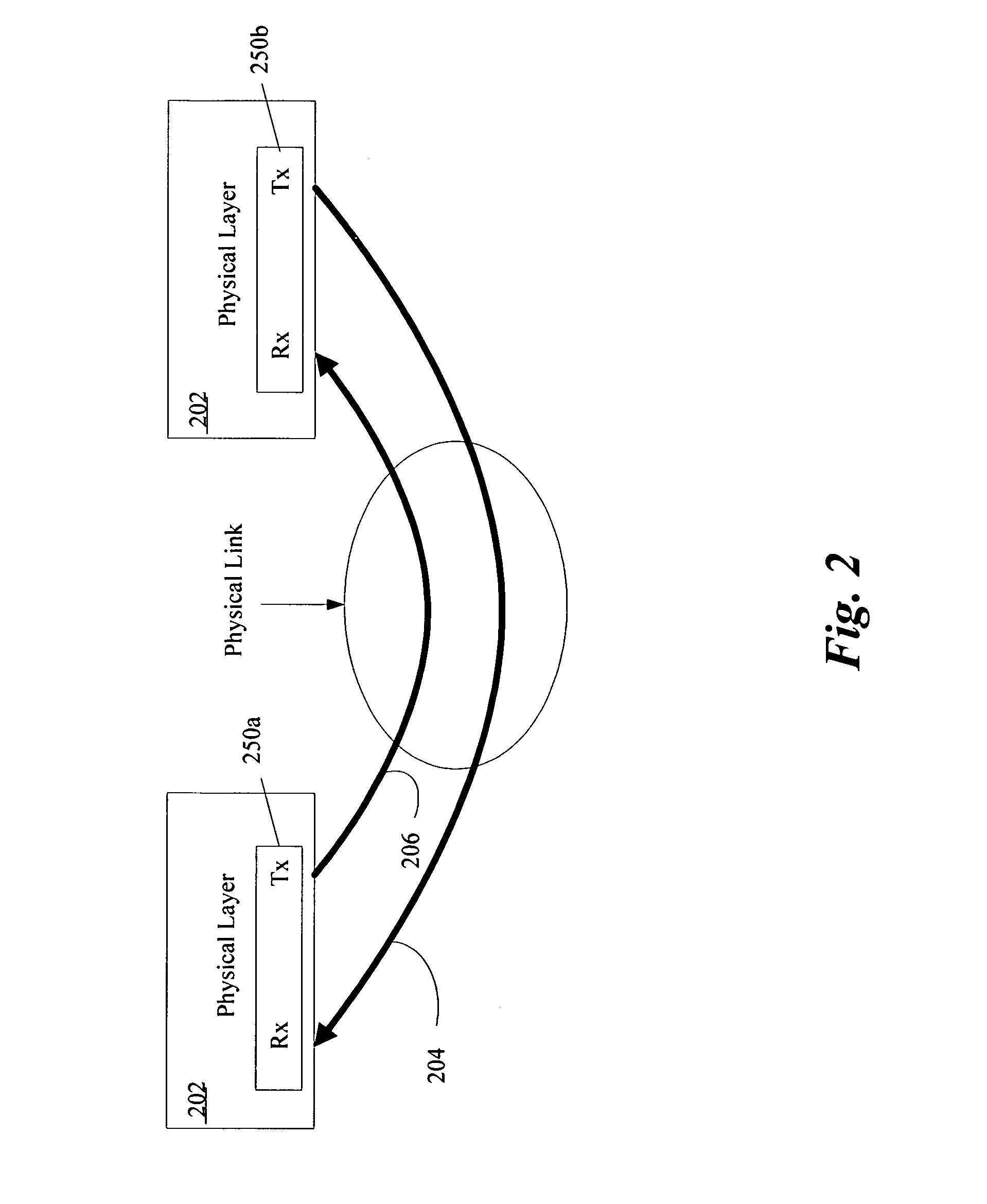

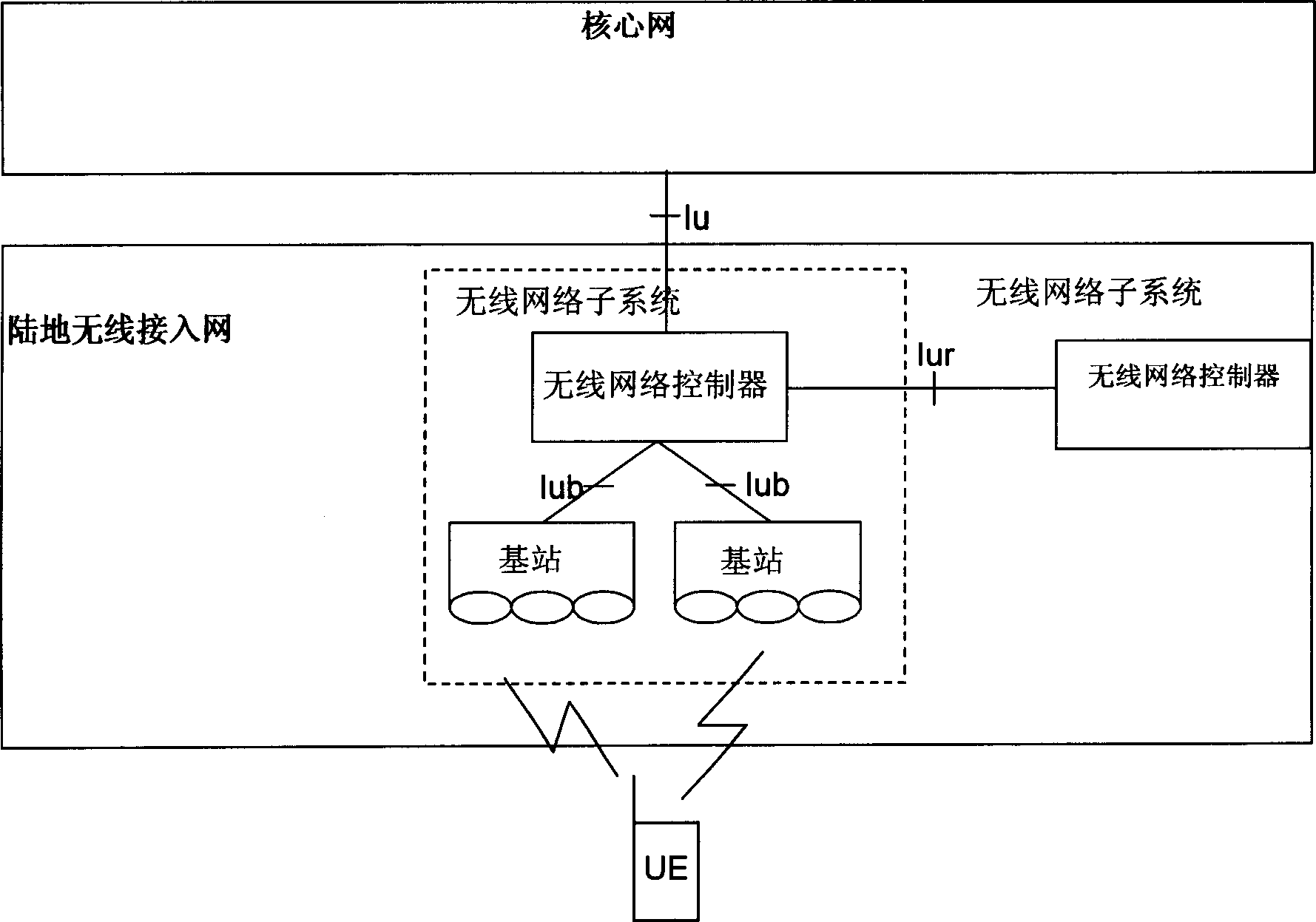

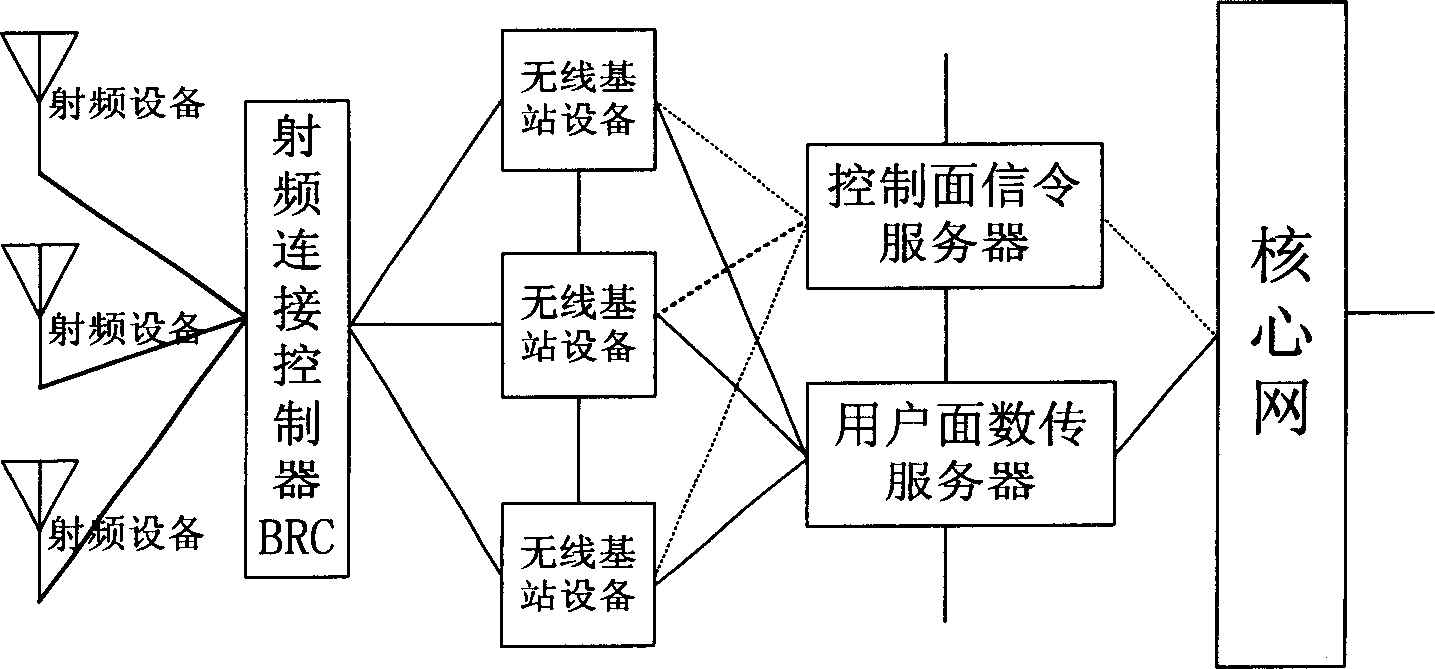

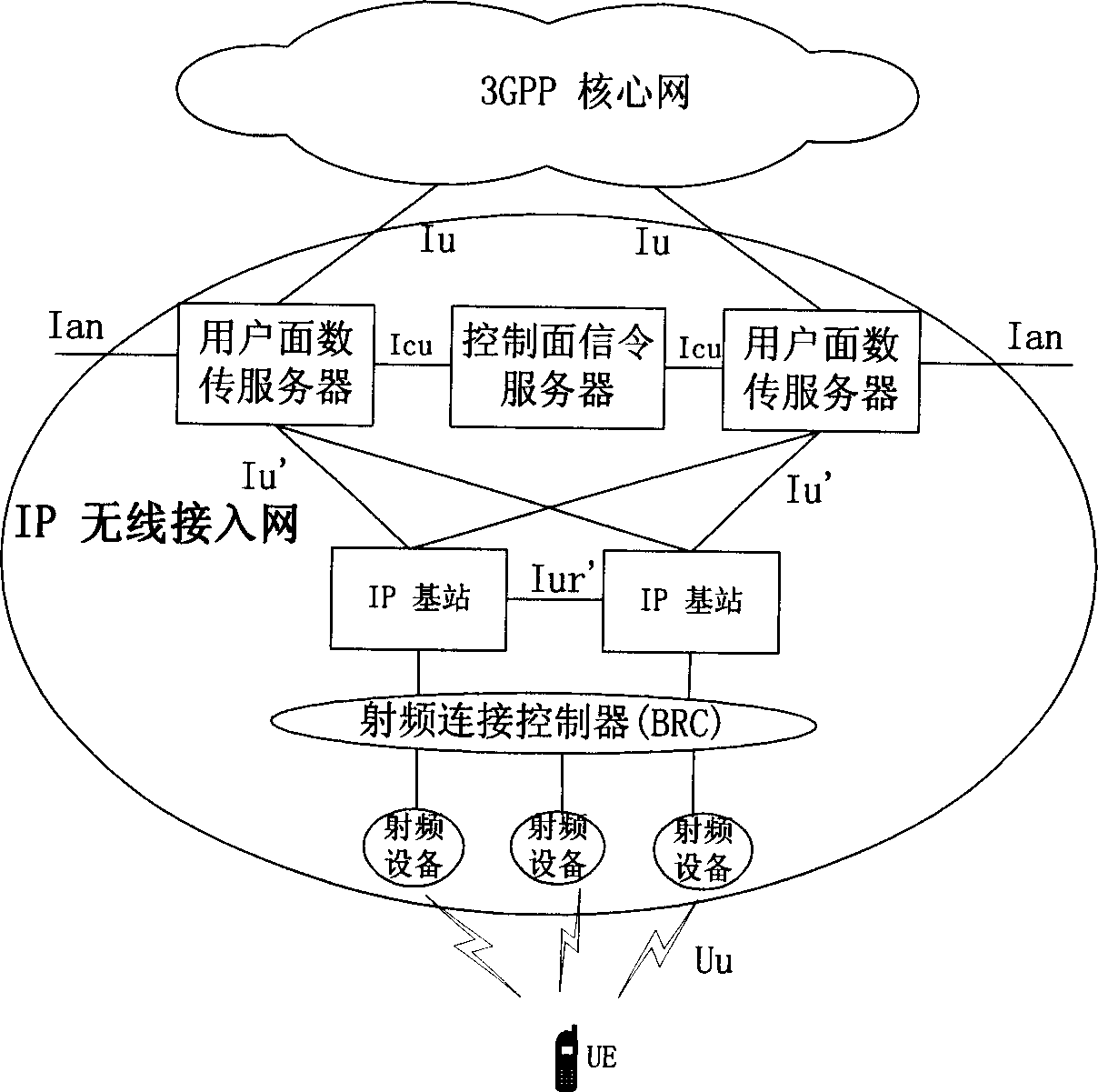

Wireless access network and wireless access system and method

InactiveCN1863344AGood for load sharingLittle impact on serviceabilityNetwork traffic/resource managementNetwork topologiesAccess networkAccess method

This invention relates to a radio access network, a system and a method, in which, the network includes: a signaling server of the control side, a data transmission server of the user side, a radio base station device, a RF connection controller and a RF device, the access system includes one or multiple radio access networks and one or many core networks, the access method includes: the RF device receives the access request signals of the radio terminal and its connection controller transmits them to the radio base station device, which transfers the data of the signaling side to the signaling server of the control side and transfers the data to the data transfer server to be processed and transmitted to the core network to be processed, then the signals received by the core network are sent to the user terminal by a counter process.

Owner:HUAWEI TECH CO LTD

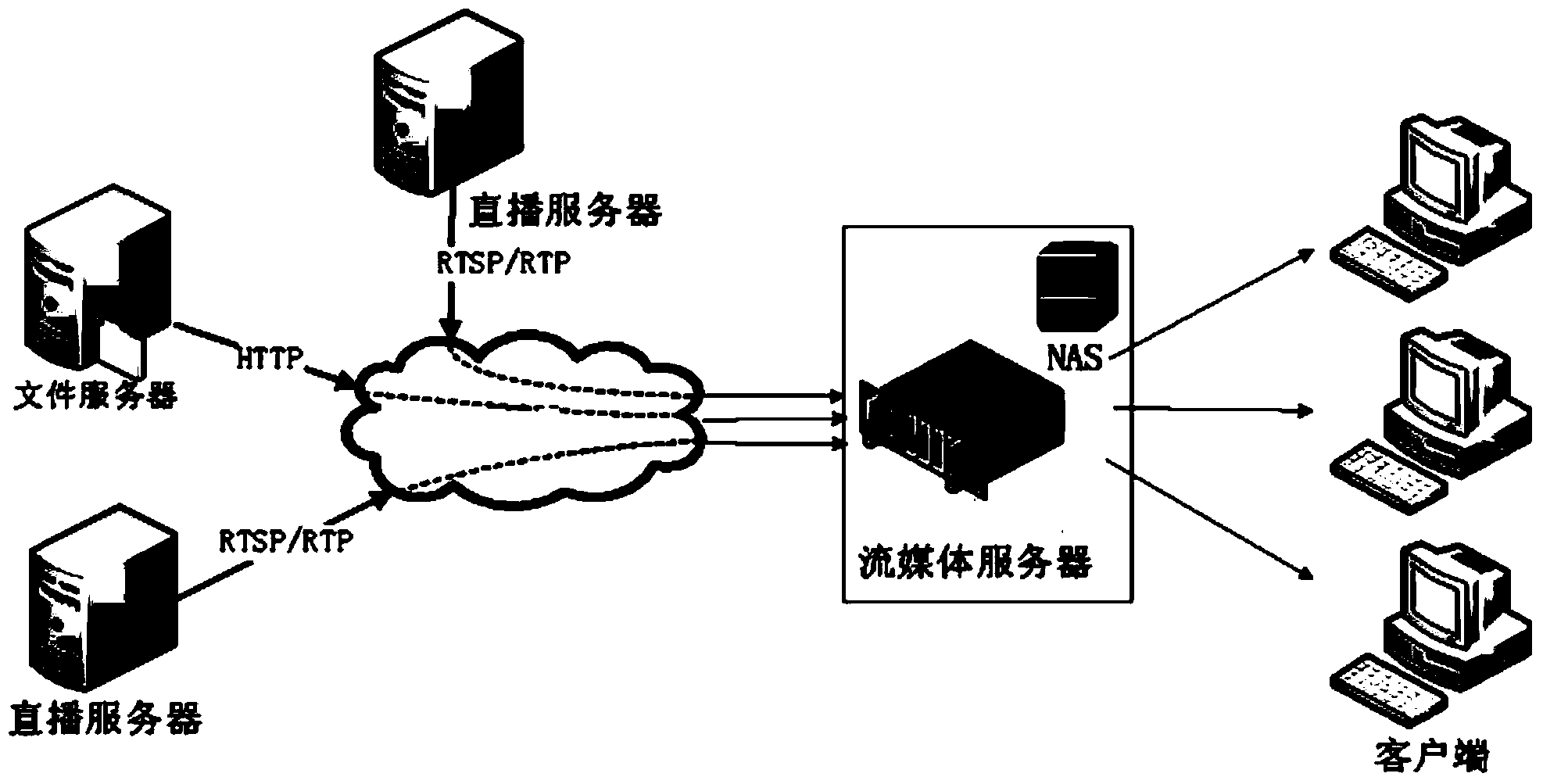

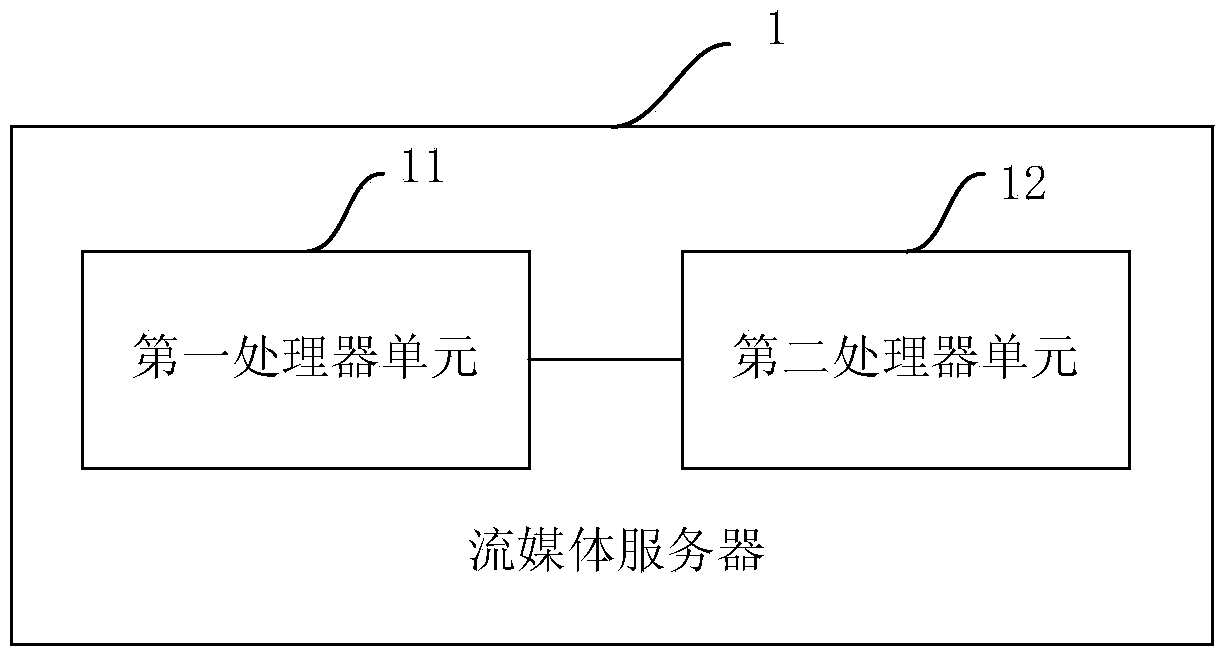

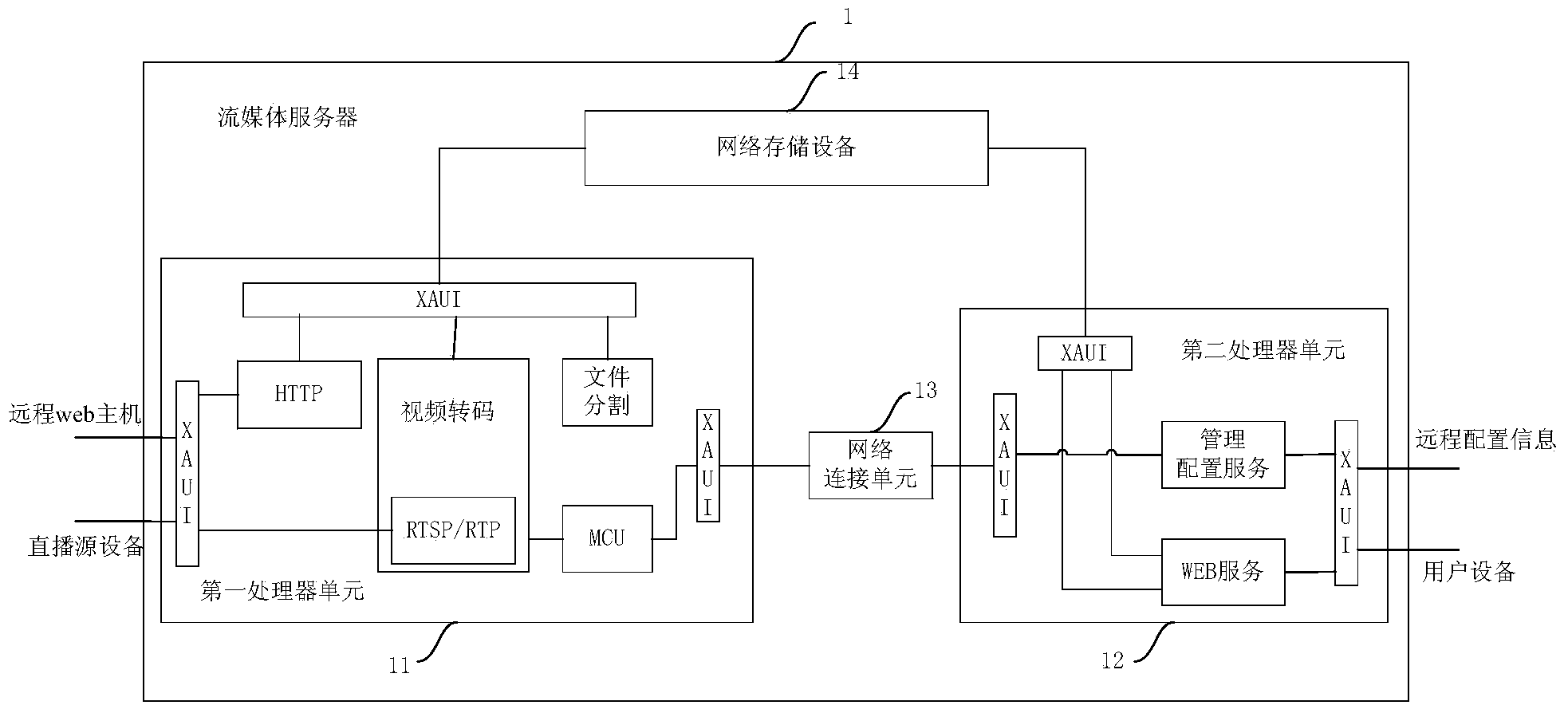

Streaming media server with multi-code-rate transcoding function based on many-core processor

InactiveCN103957428ALow transcoding latencyMeet business needsSelective content distributionTranscodingMedia server

The invention provides a streaming media server with a multi-code-rate transcoding function based on a many-core processor. The streaming media server at least comprises a first processor unit and a second processor unit connected with the first processor unit, wherein the first processor unit is used for conducting processing including multi-code-rate transcoding and slicing on video demand source information and / or live source information based on configuration information from the second processor unit and outputting a processing result; the second processor unit is used for providing a live and video demand service based the information output by the first processor unit and the web technology and providing a human-machine interaction interface through which configuration personnel input the configuration information; the requirement for a live or video demand service is met; meanwhile, cloud transcoding with extremely low delay further can be achieved.

Owner:SHANGHAI ADVANCED RES INST CHINESE ACADEMY OF SCI

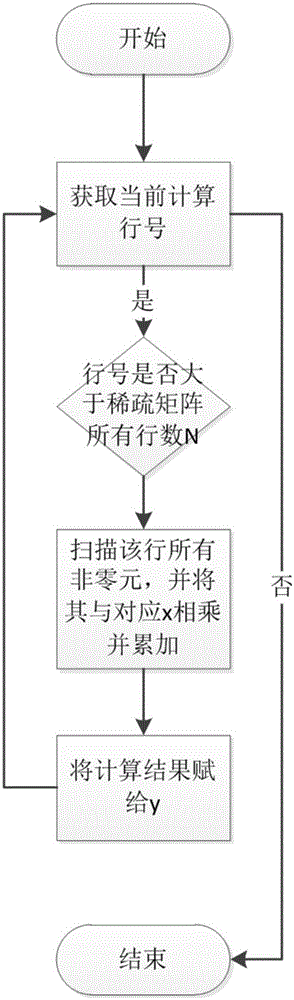

Method for realizing heterogeneous many-core of sparse matrix-vector multiplication based on domestic SW26010 processors

ActiveCN106775594AImprove performanceReduce the total memory accessMachine execution arrangementsSparse matrix vectorEuclidean vector

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI

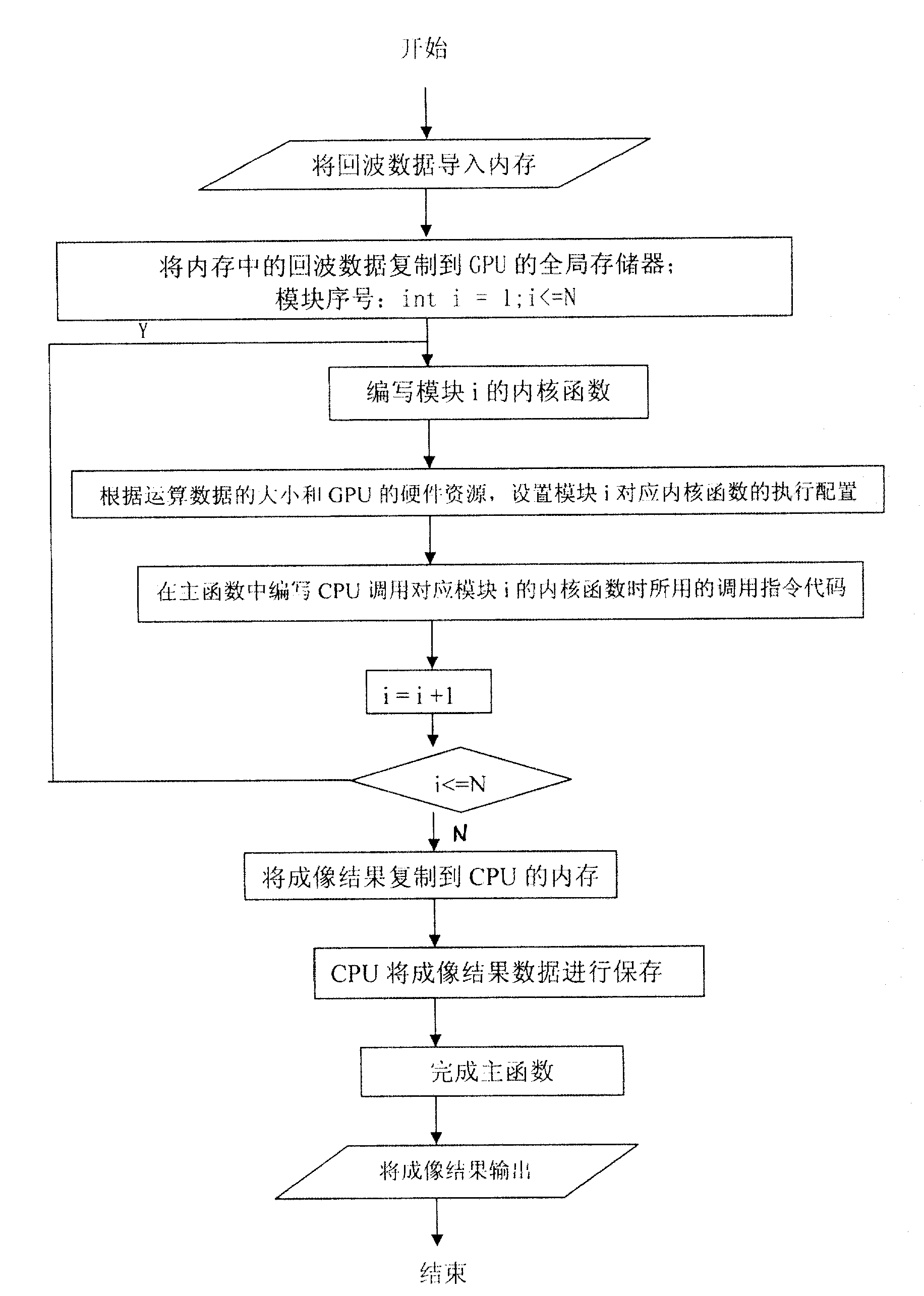

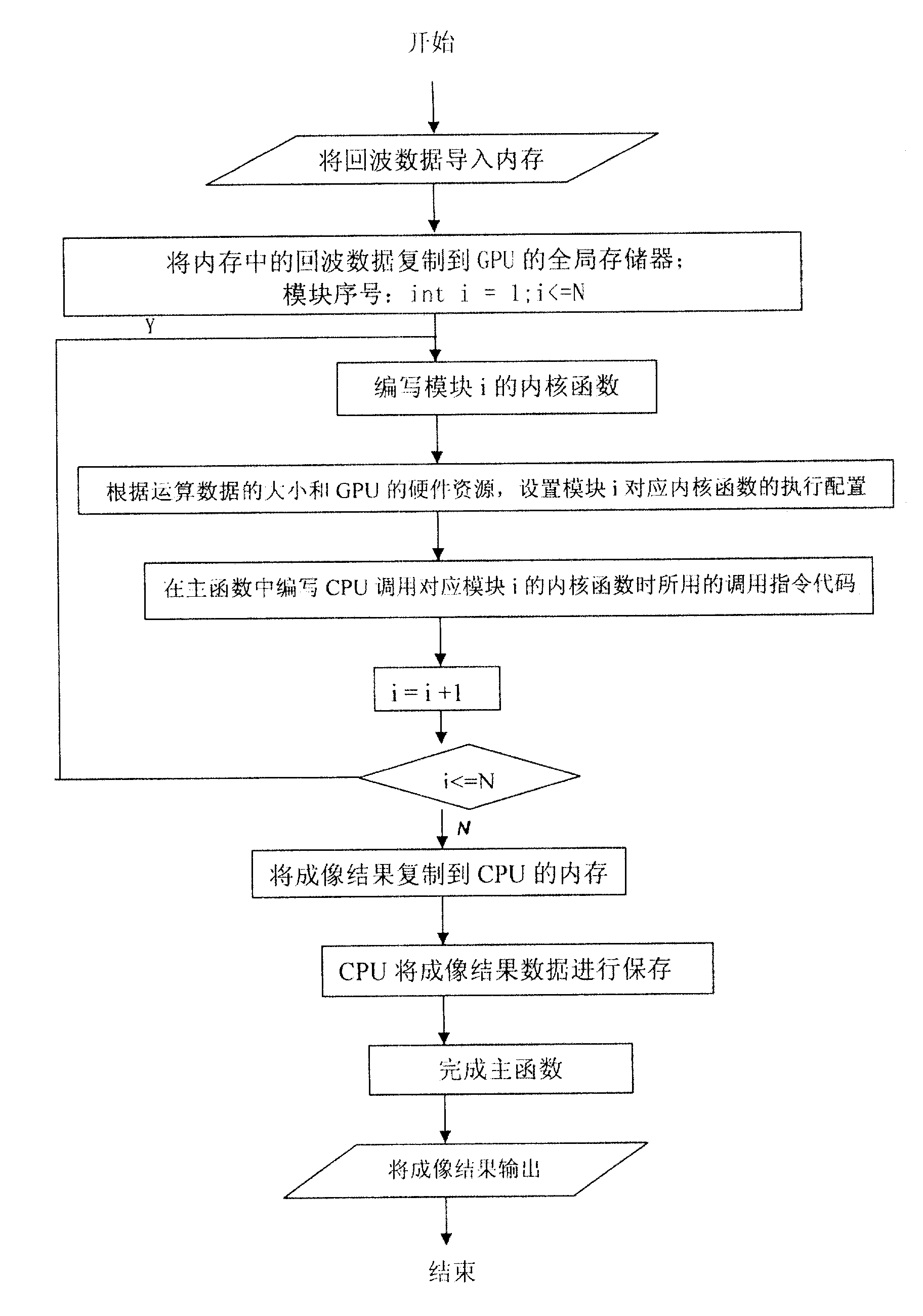

GPU (Graphic Processing Unit) many-core platform based parallel imaging method of synthetic aperture radar

InactiveCN101937082AImprove parallelismEnables parallel imagingConcurrent instruction executionRadio wave reradiation/reflectionSynthetic aperture sonarRadar

The invention discloses a GPU (Graphic Processing Unit) many-core platform based parallel imaging method of a synthetic aperture radar, which comprises the following steps of: firstly, leading original echo data into the global storage of a GPU, then initiating an operation request by a CPU (Central Processing Unit), finishing operation by the GPU, computing according to the mode until the imaging result of an SAR (Synthetic Aperture Radar) is obtained, then leading result data back to a memory, and finishing result preservation by the CPU. The invention realizes the parallel imaging of the SAR on the GPU through parallel programming and improves the parallel degree of programs, so that the operating efficiency is greatly improved, and the operation time is greatly reduced; and in the whole processing process, all the operations are finished and realized in parallel through the GPU except the leading-in and the leading-out of the data, the strong computational capability of the GPU is fully utilized, and the parallel degree is furthest improved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

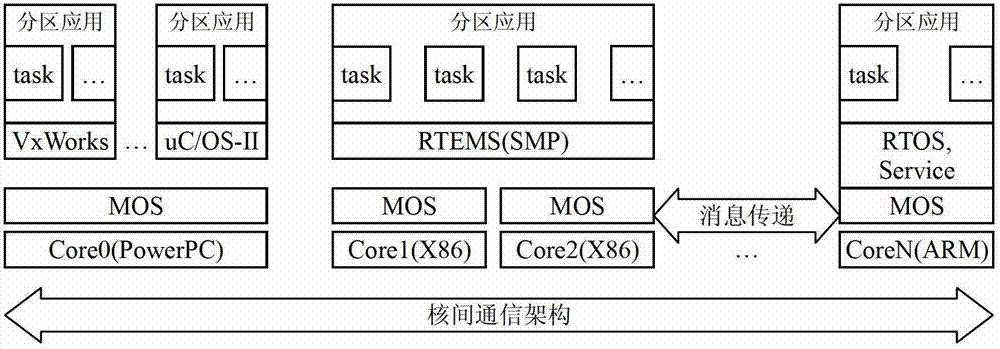

Method for establishing partition system based on multi-kernel MOS (Module Operating System)

InactiveCN103207782AEliminate data sharingGuaranteed certaintySpecific program execution arrangementsExtensibilityOperational system

The invention relates to a method for establishing a partition system based on a multi-kernel MOS (Module Operating System). The method is applicable to multi-core / many-core heterogeneous processor platforms. According to the principle of load balance and minimum communication latency, system partitions are mapped to proper processor cores respectively; an MOS kernel matching with ISA (Instruction Set Architecture) of the corresponding processor core is started to run on the processor core, a communication channel and an accessory management data structure are established and initialized for the partition mapped to the processor core, and the partitions are communicated by means of messaging; the MOS kernel starts operating systems and tasks inside the partitions mapped to the processor cores where the MOS kernel is located. The method allows the processor cores in varieties of ISAs to run in the same partition system, and timeliness and accuracy in program running are guaranteed to the maximum extent while system efficacy and extensibility are improved effectively.

Owner:BEIHANG UNIV