Patents

Literature

67 results about "Group memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

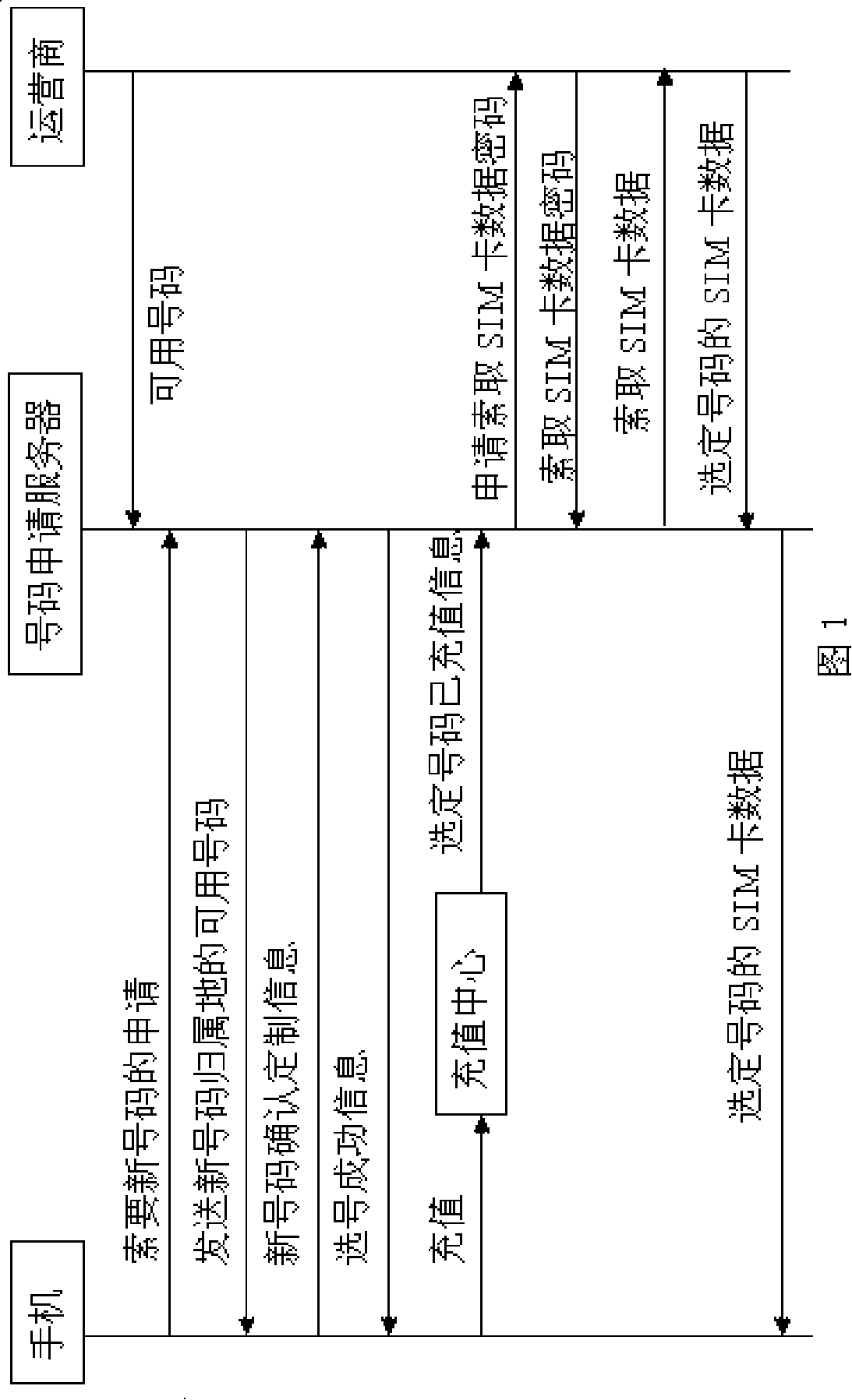

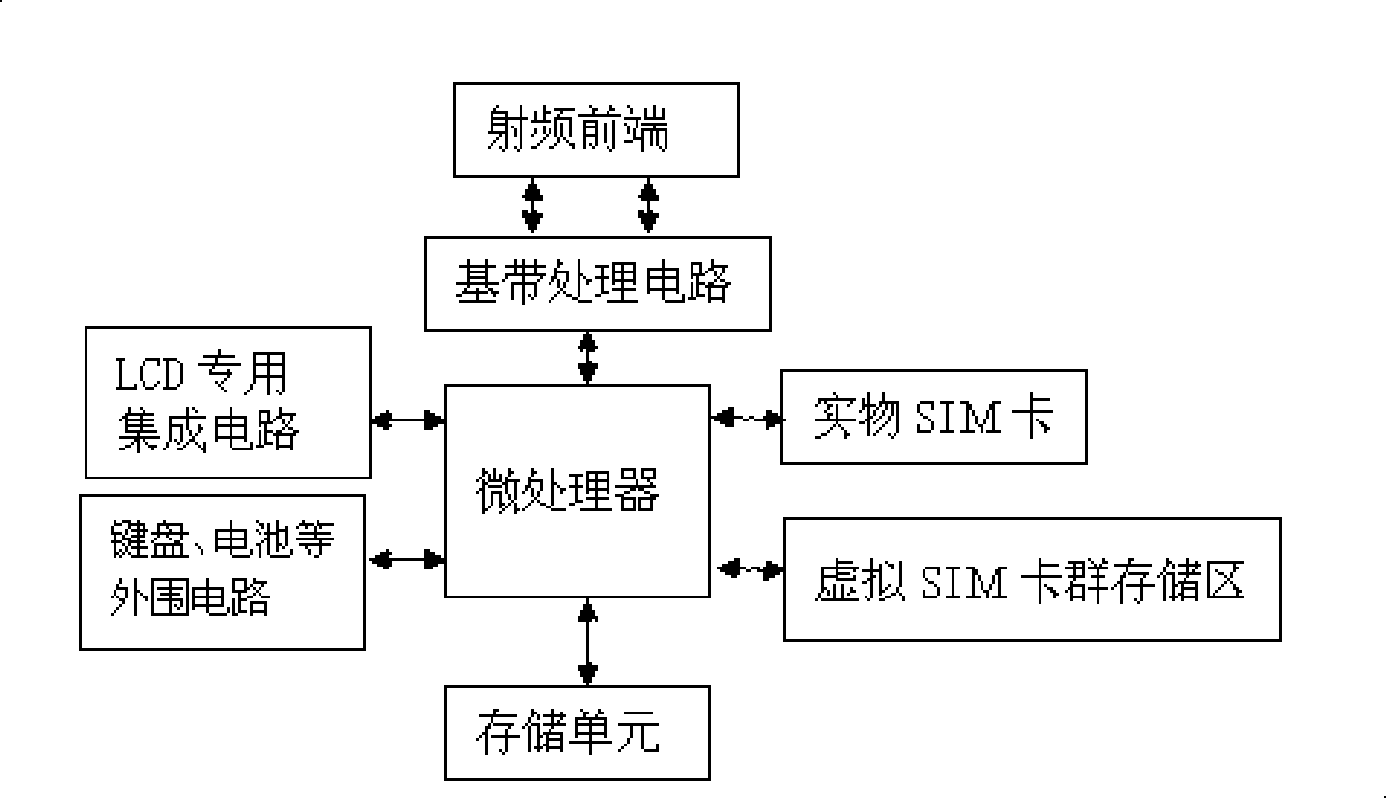

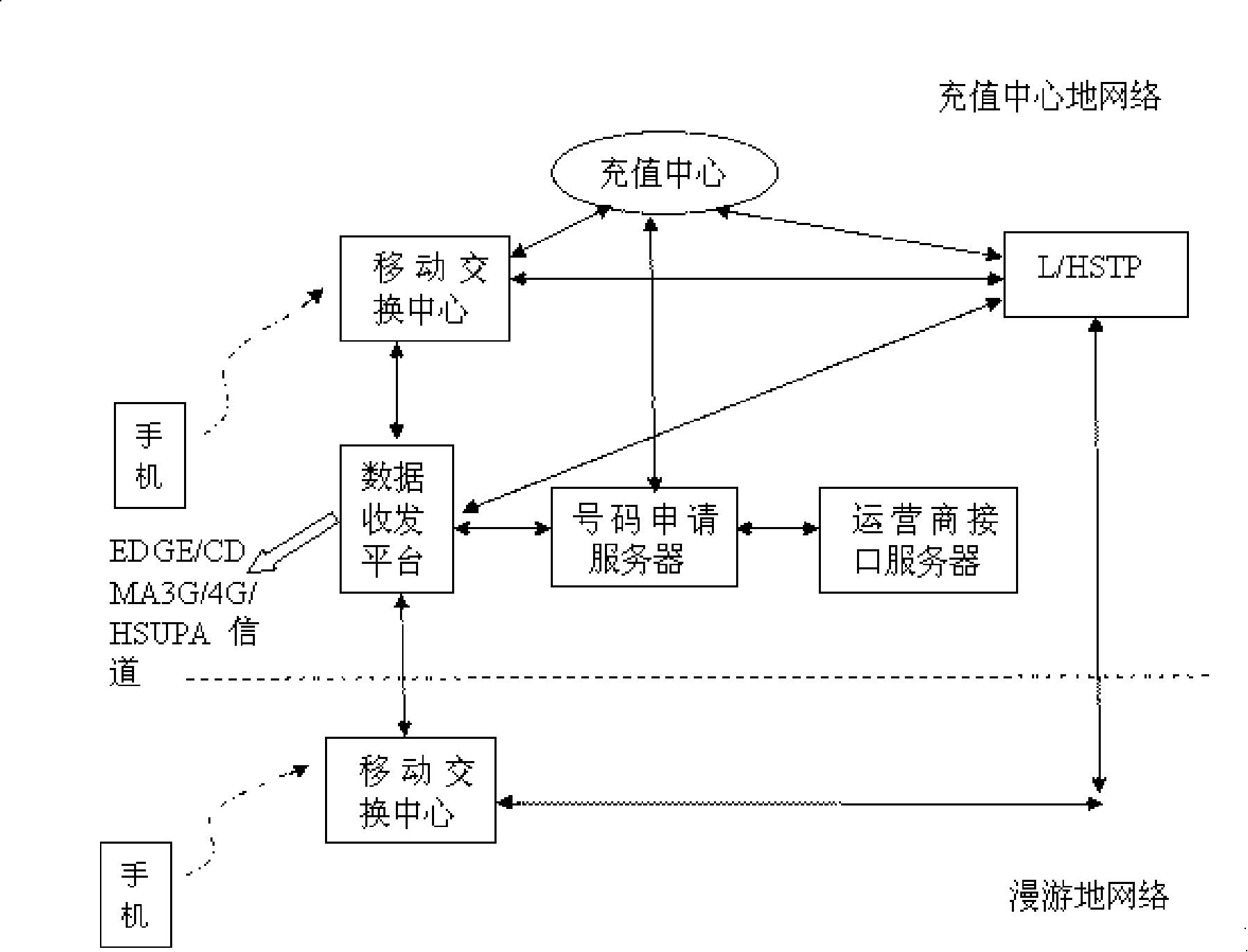

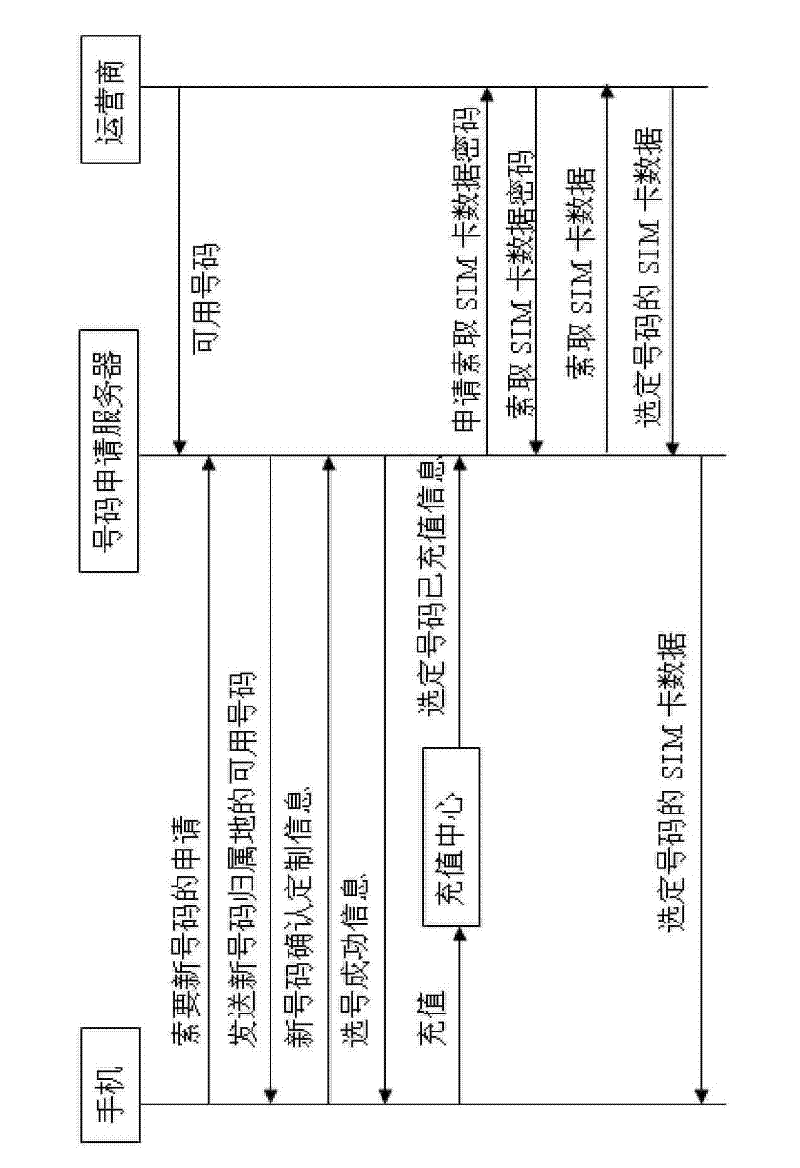

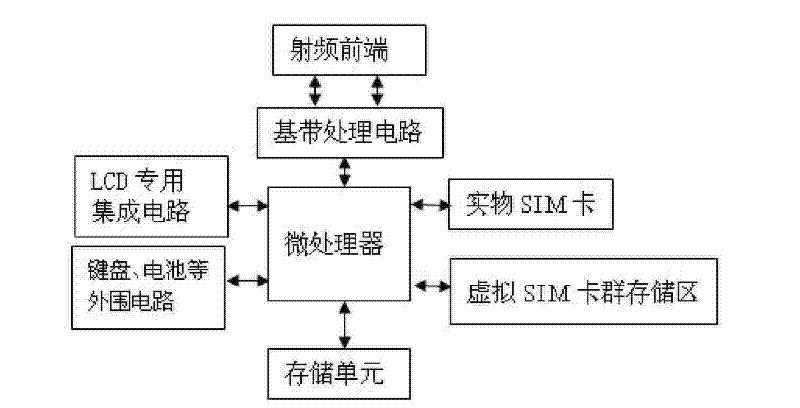

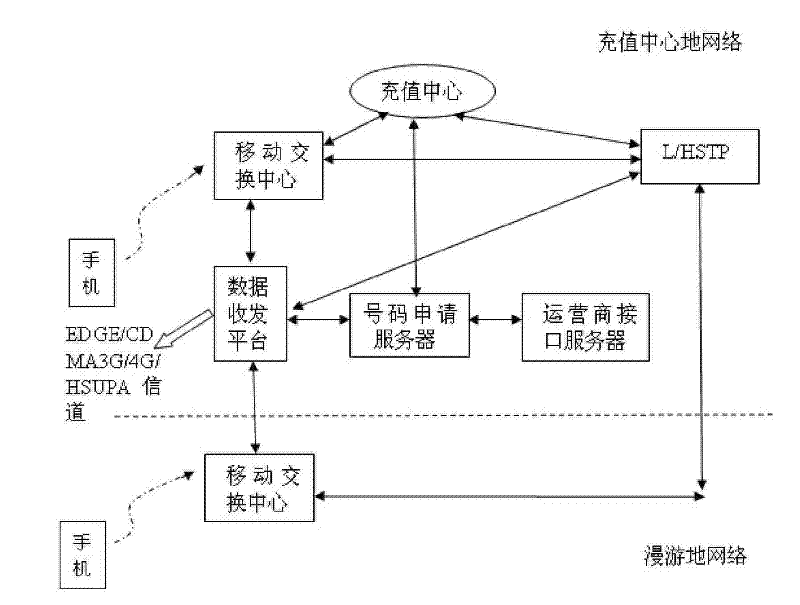

Virtual SIM card multi-number single/double module mobile phone, its implementing method and system

ActiveCN101222723ALow costHuge profitsRadio/inductive link selection arrangementsComputer hardwareCommunications system

The invention relates to the mobile communication technology. The technical problem to be solved by the invention is to provide a realization method for a virtual SIM card multiple number mobile phone, which makes a user not need to insert other SIM cards besides a home SIM card in the mobile phone and simultaneously have multiple numbers. Correspondingly, the invention also provides a virtual SIM card multiple number single / double mode mobile phone, a number application server and a communication system for realizing the virtual SIM card multiple number mobile phone. The technical proposal adopted by the invention is that: the number application server sends SIM card data corresponding to new numbers to the mobile phone through data channels such as short messages, GPRS / EGPRS, HSDPA / HSUPA, CDMA-nX, WiFi / Wimax or 3G / 4G and so on; the mobile phone receives the SIM card data and stores the SIM card data in a virtual SIM card group memory area. The invention is applied to the application spreading range of the prior single / double mode and double-card / double-duration mobile phone; multiple numbers in the mobile phone can follow the user to do free roaming when the mobile phone which is inserted with the prior home SIM card communicates with others.

Owner:HUAWEI TECH CO LTD

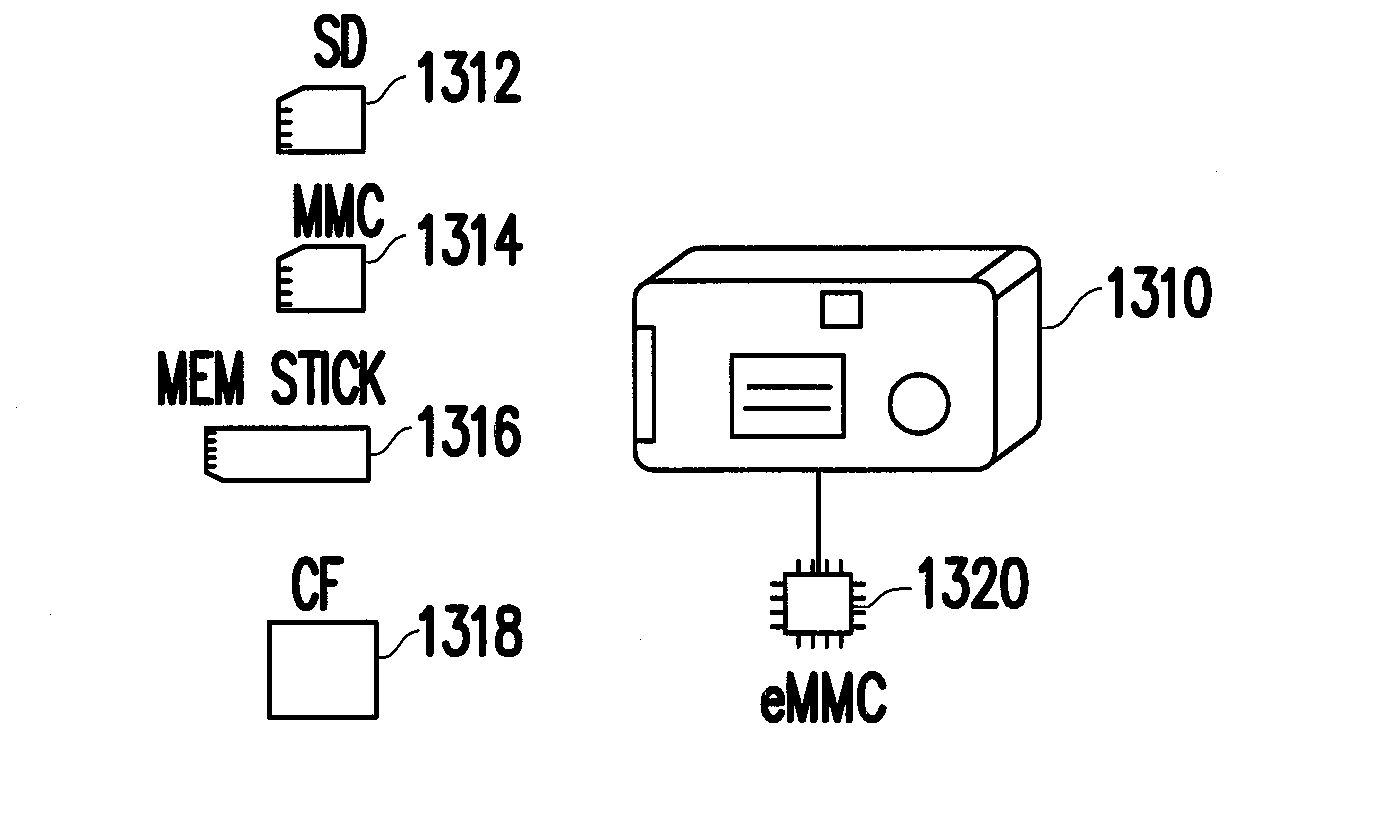

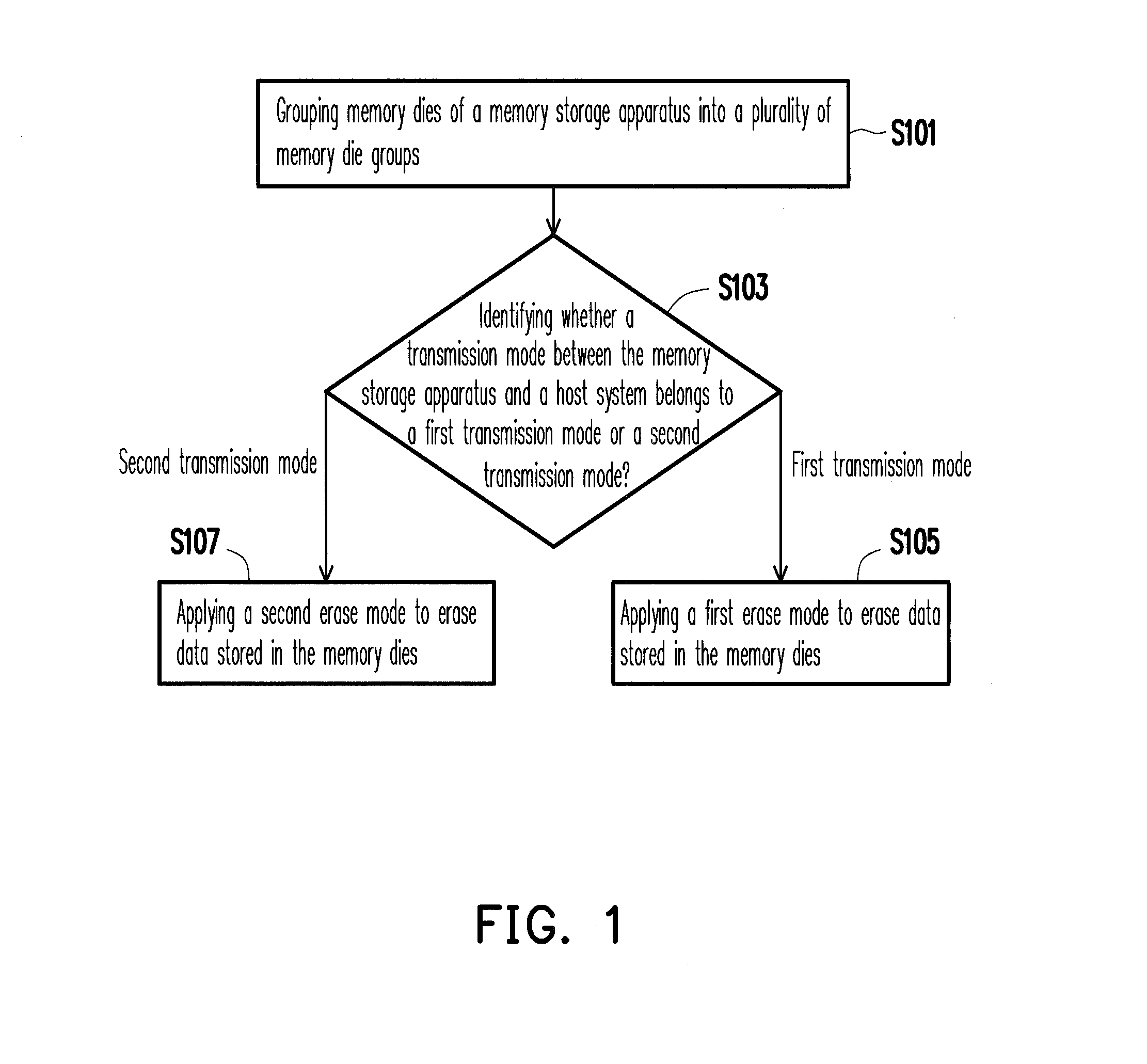

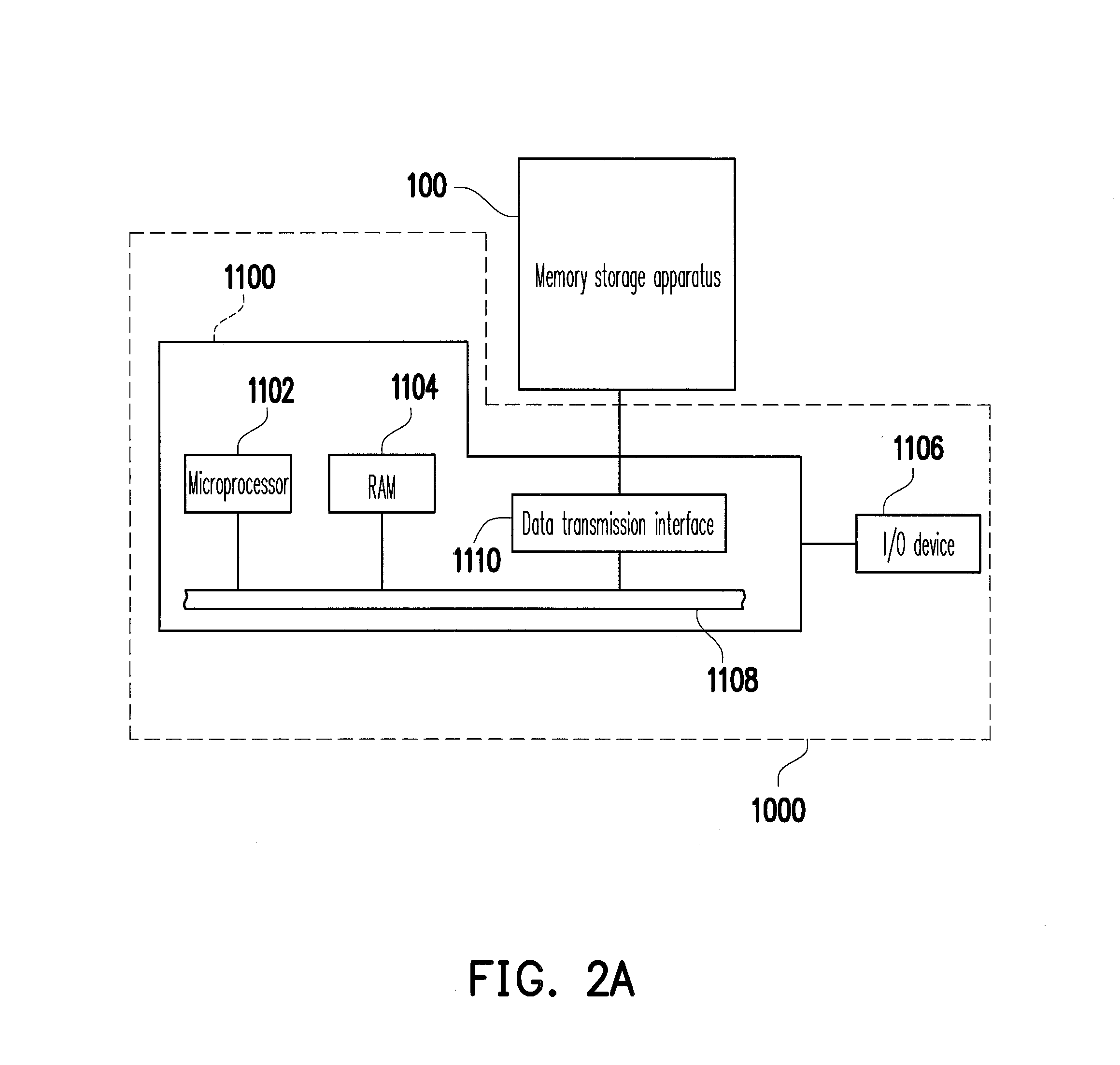

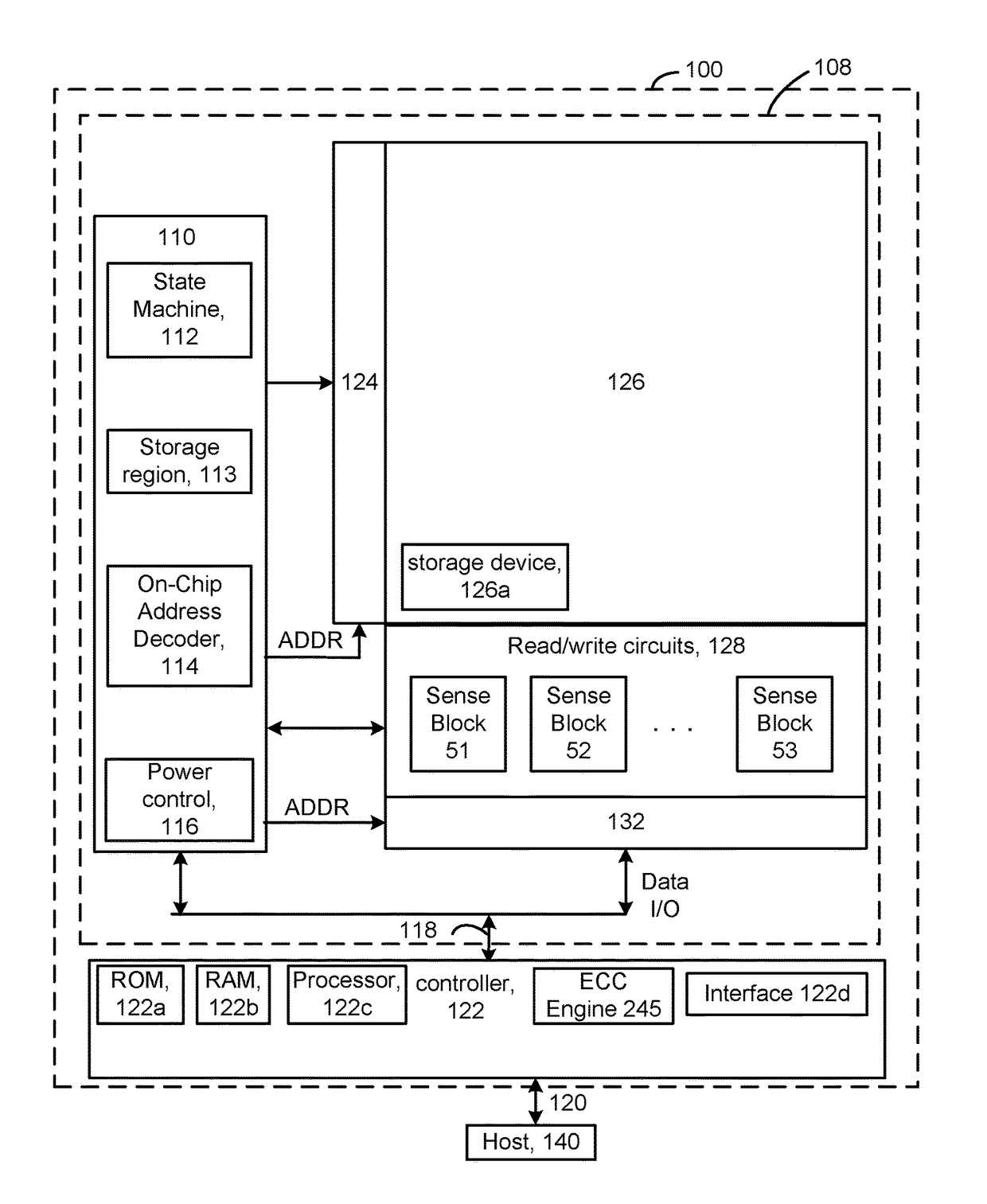

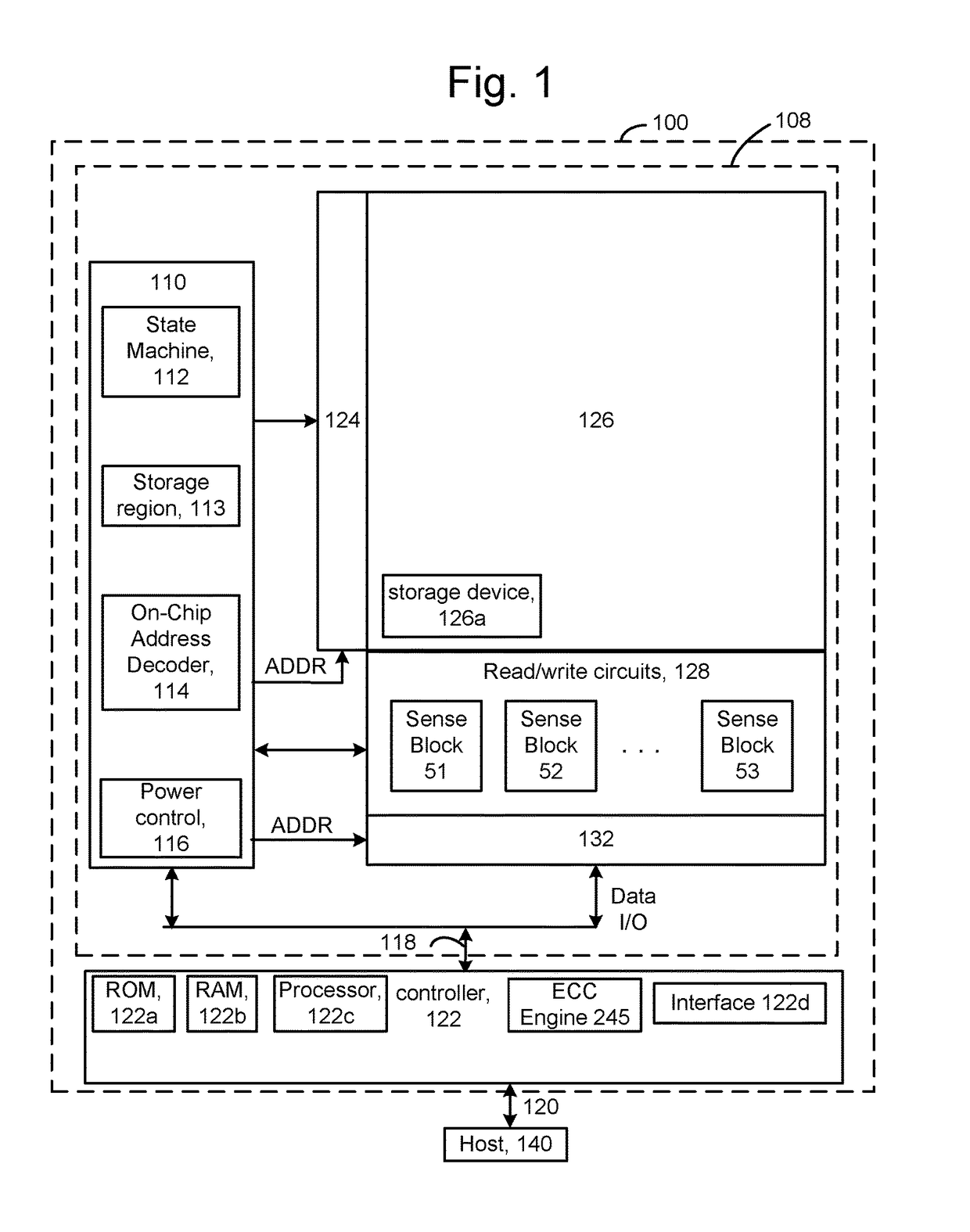

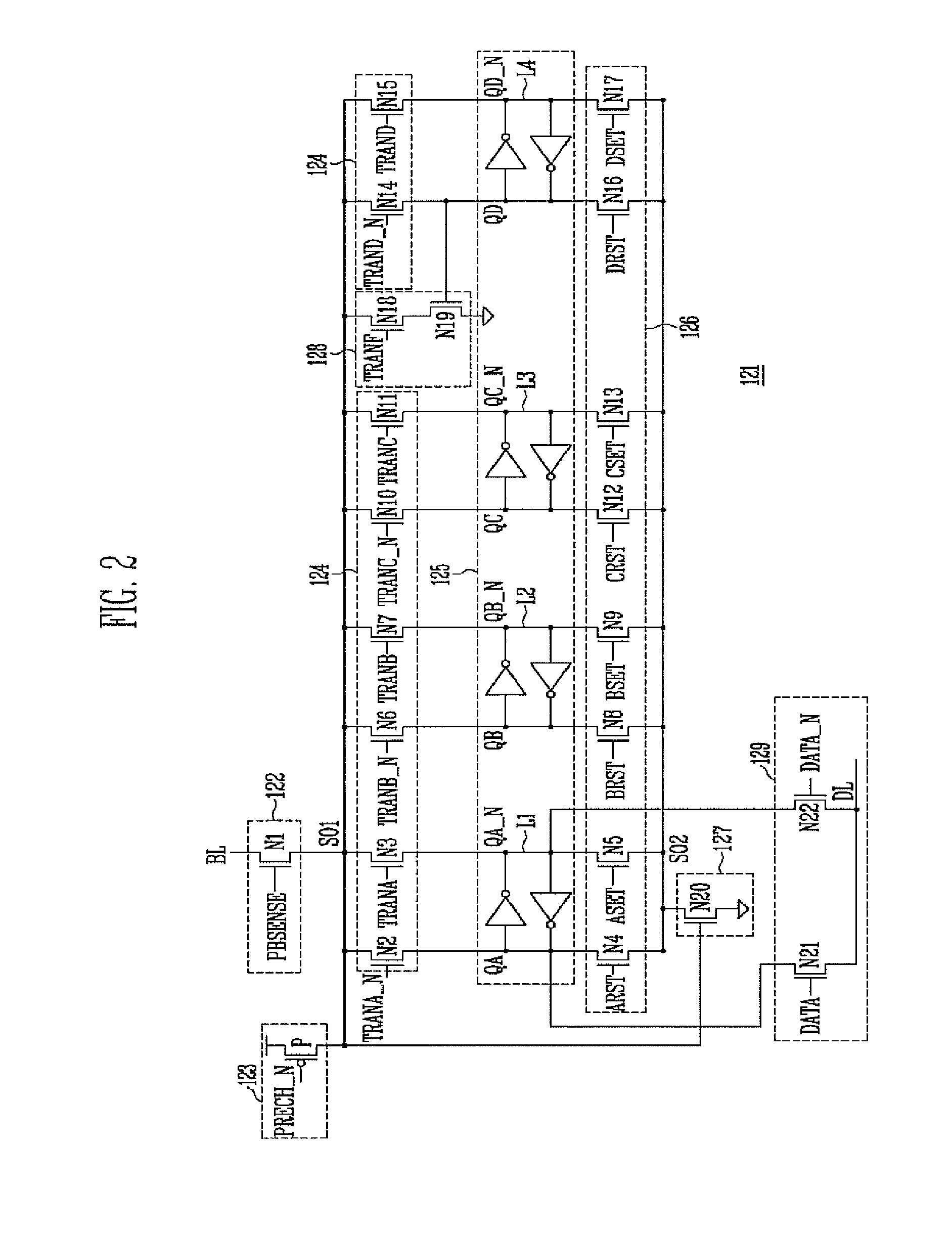

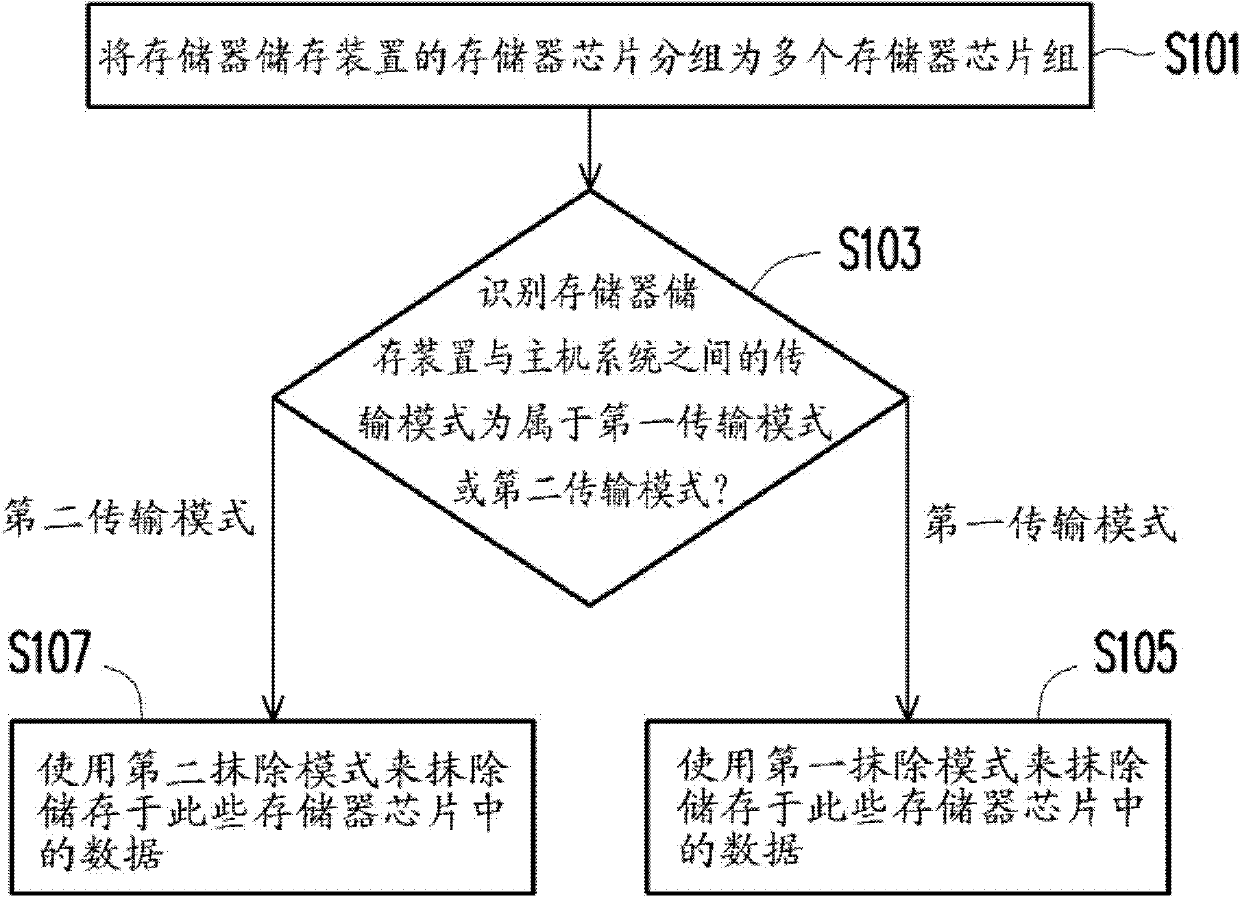

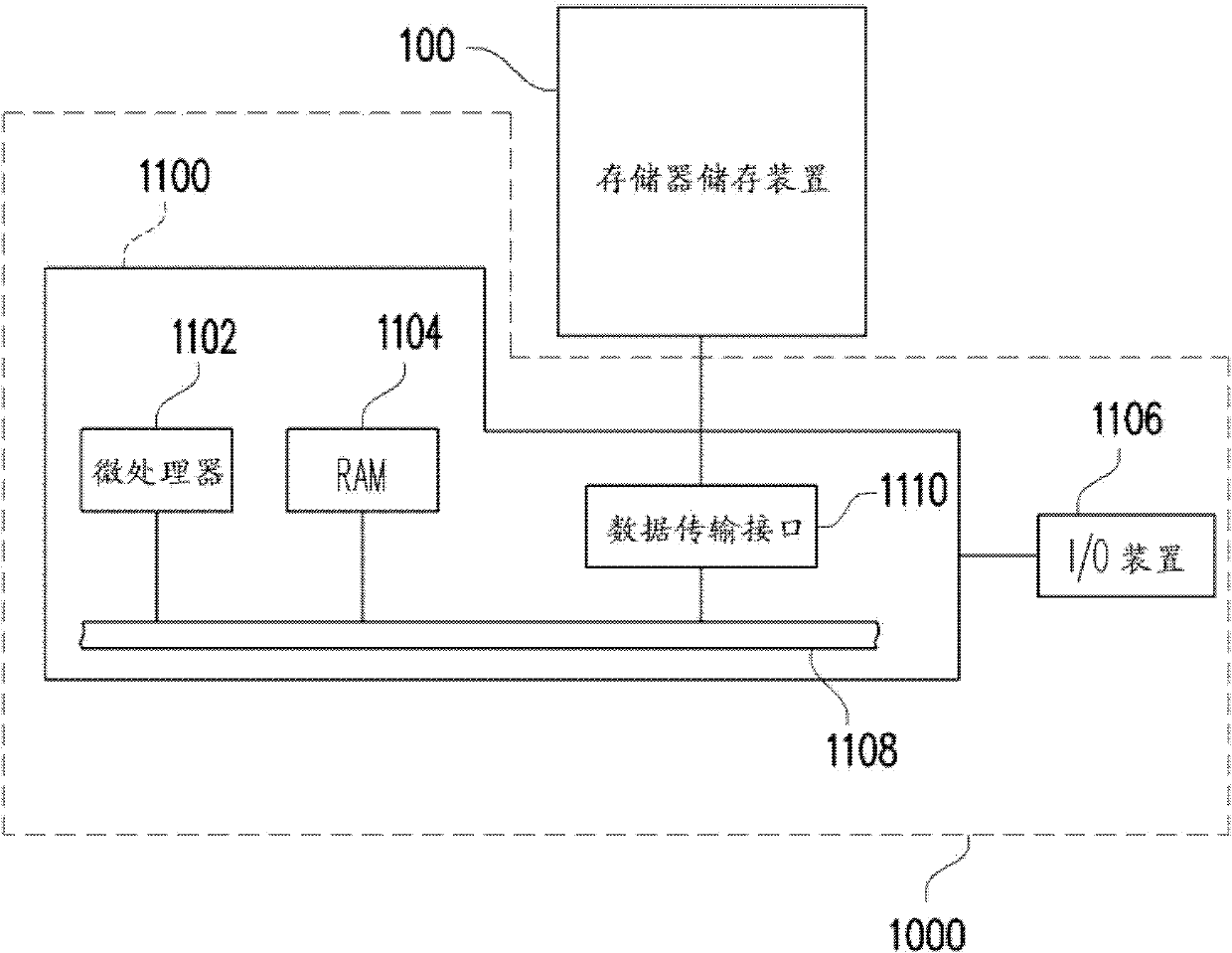

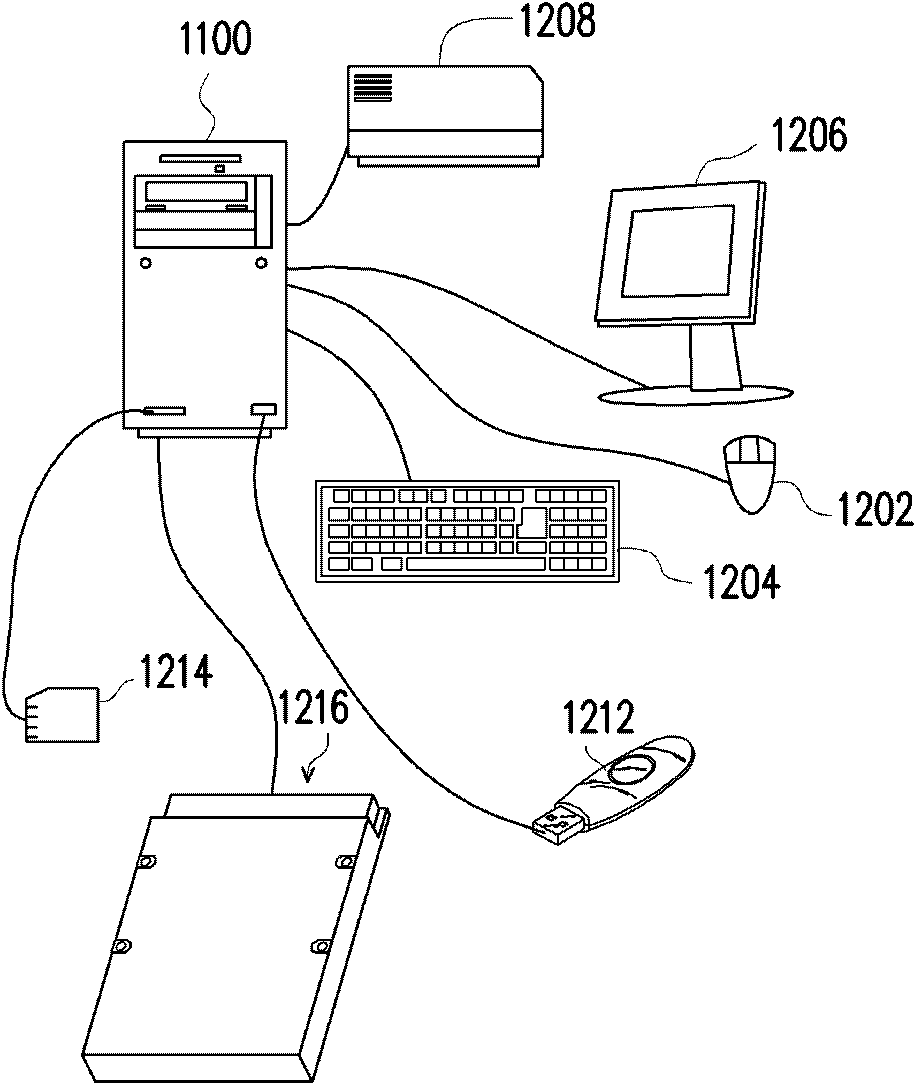

Memory controlling method, memory controller and memory storage apparatus

ActiveUS20130013852A1Avoid instabilityRead-only memoriesDigital storageTransfer modeMemory controller

A memory controlling method, a memory controller and a memory storage apparatus are provided. The method includes identifying whether a transmission mode between the memory storage apparatus and a host system belongs to a first transmission mode or a second transmission mode and grouping memory dies of the memory storage apparatus into a plurality of memory die groups. The method also includes applying a first erasing mode to erase data stored in the memory dies when the transmission mode belongs to the first transmission mode and applying a second erasing mode to erase the data stored in the memory dies when the transmission mode belongs to the second transmission mode, wherein at least a part of the memory die groups are enabled simultaneously in the first erasing mode and any two of the memory die groups are not enabled simultaneously in the second erasing mode.

Owner:PHISON ELECTRONICS

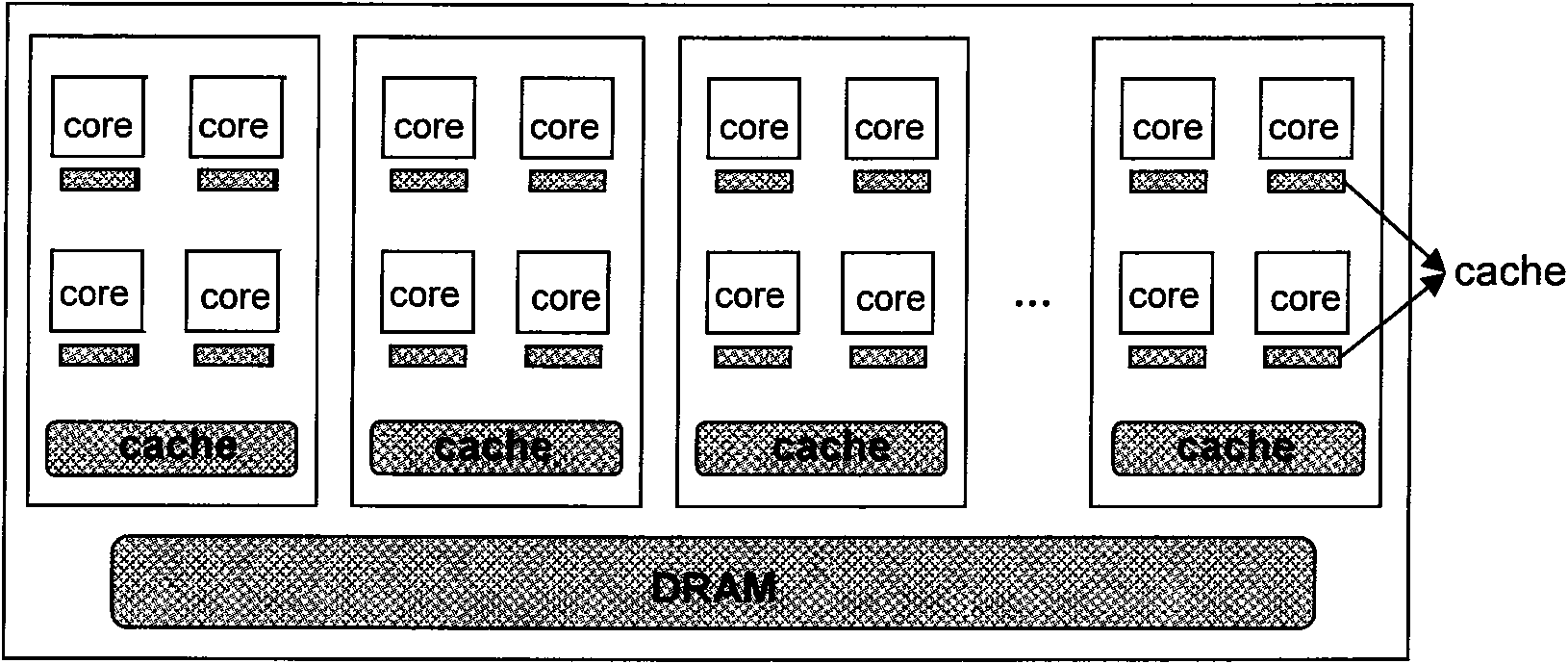

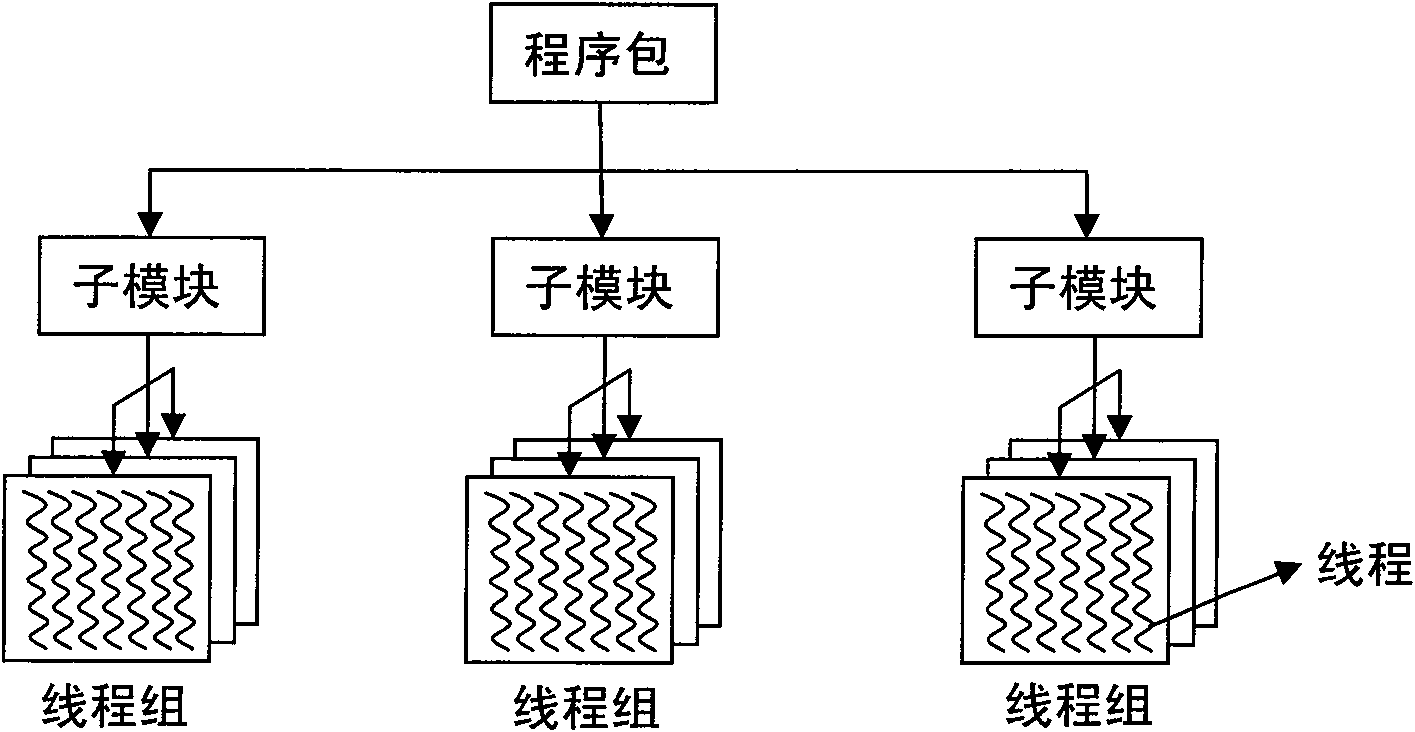

Large-scale data parallel computation method with many-core structure

InactiveCN101556534AImprove computing efficiencySpeed upMultiprogramming arrangementsConcurrent instruction executionBatch processingLarge scale data

The invention provides a computation method which utilizes a parallel processing chip with an isomorphic many-core to carry out large-scale data parallel processing, and the method utilizes a parallel processor with an isomorphic many-core structure to carry out parallel computation processing for large-scale data without logical relationship. Modules in an application sequentially run on an isomorphic many-core microprocessor, wherein each module is operated repeatedly, processes sub-modules with different data every time and is separated into a function which a plurality of threads executing on a many-core. The threads which correspond to each function are organized into a thread group according to a certain rule; the thread group is batch processing for the threads derived from the function; all the threads which are derived from the same function can access a global shared memory space on the many-core microprocessor; the accessing of each thread to a thread group shared memory space and the global shared memory space comprises reading data on the thread group memory space and the global shared memory space and writing an operation result in; and the threads which correspond to each function process different data simultaneously so as to achieve high parallelization.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

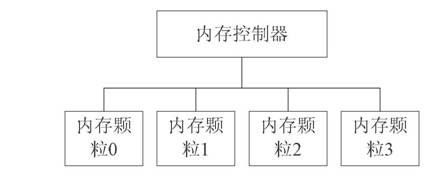

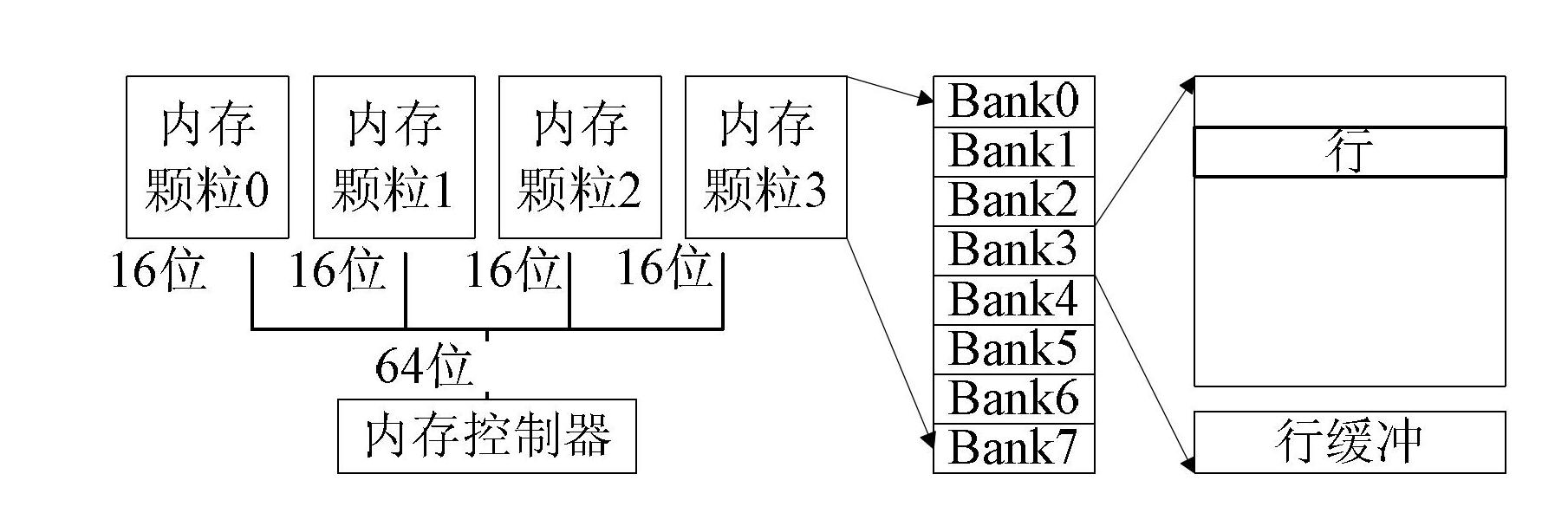

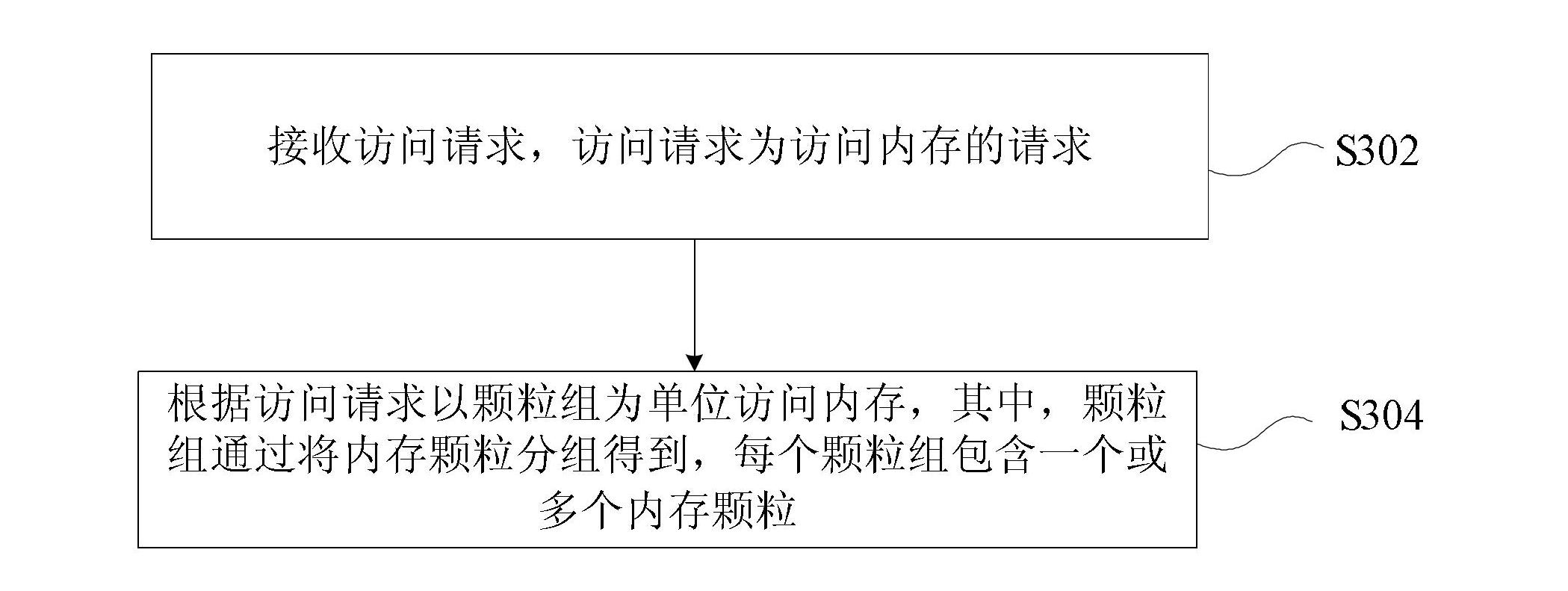

Memory access method and device

ActiveCN102681946AReduce conflictImprove performanceEnergy efficient ICTMemory adressing/allocation/relocationAccess methodGroup memory

The invention discloses a memory access method and device. The method comprises the following steps: receiving an access request which is a request for accessing a memory; and according to the access request, accessing the memory by taking a grain group as a unit, wherein the grain group is obtained by grouping memory grains, and each grain group comprises one or a plurality of memory grains. According to the memory access method and device, the problem in the relevant technique that high power consumption is caused because all memory grains at the same Rank need to open and close a page when page conflict happens in the memory accessing process is solved, the effect of reducing memory power consumption is achieved, and furthermore, the performance of a memory system is improved.

Owner:LOONGSON TECH CORP

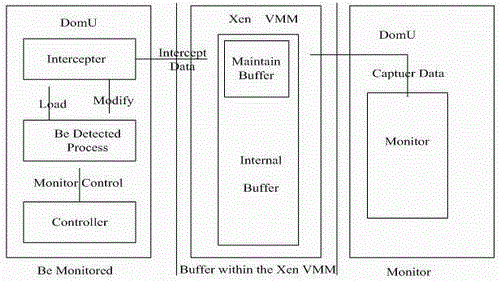

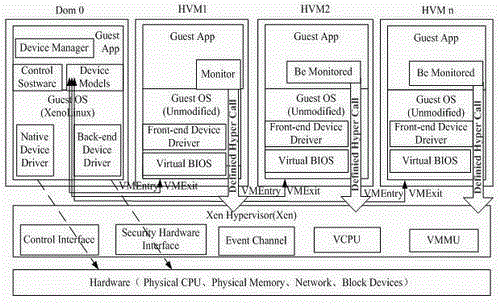

Memory leak detection method facing Xen environment during operation and implement system thereof

ActiveCN103064784ANo loss of efficiencyEfficient detectionSoftware testing/debuggingOperational systemParallel computing

The invention relates to a method and system for detecting memory leak facing Xen virtualization environment during operation. The method for memory leak under Xen virtualization calculating environment during operation is provided. The method mainly includes: (1) performing dynamic analysis on memory usage action of a monitored program, grouping memory objects, and maintaining and updating related information on the memory objects; (2) detecting potential memory leak based on objected behavior characteristics; (3) and performing memory leak judgment according to related rules. Compared with the prior art, the method and system can detect the memory leak during operation in cross-operating system platform and cross-language development environment mode, is wide in application range, has good performance, can improve quality and development efficiency of a software development industry especially software products with limited memory, shortens period of software development, saves development cost directly, and can bring good economic benefit and social benefit.

Owner:FUJIAN NORMAL UNIV

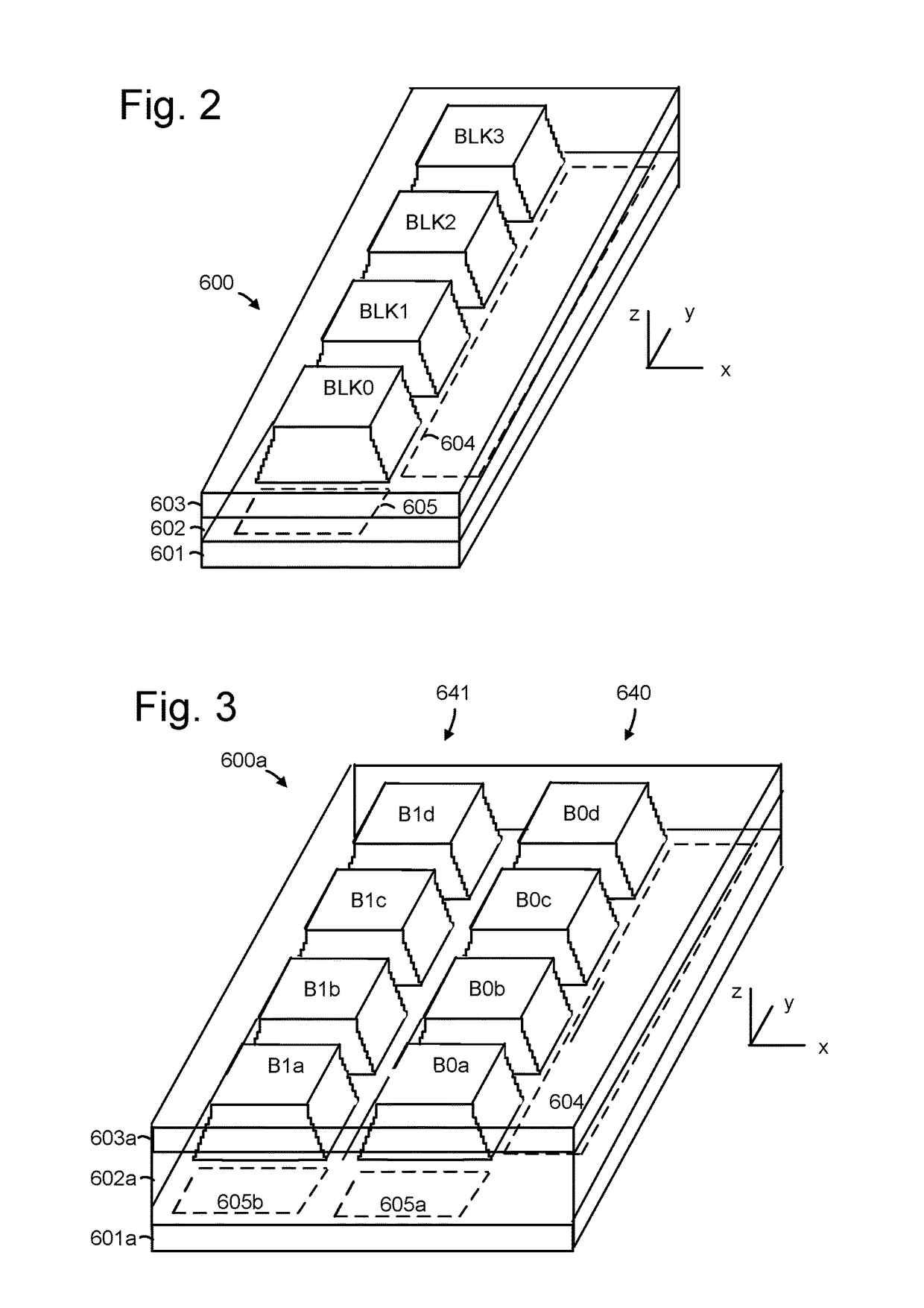

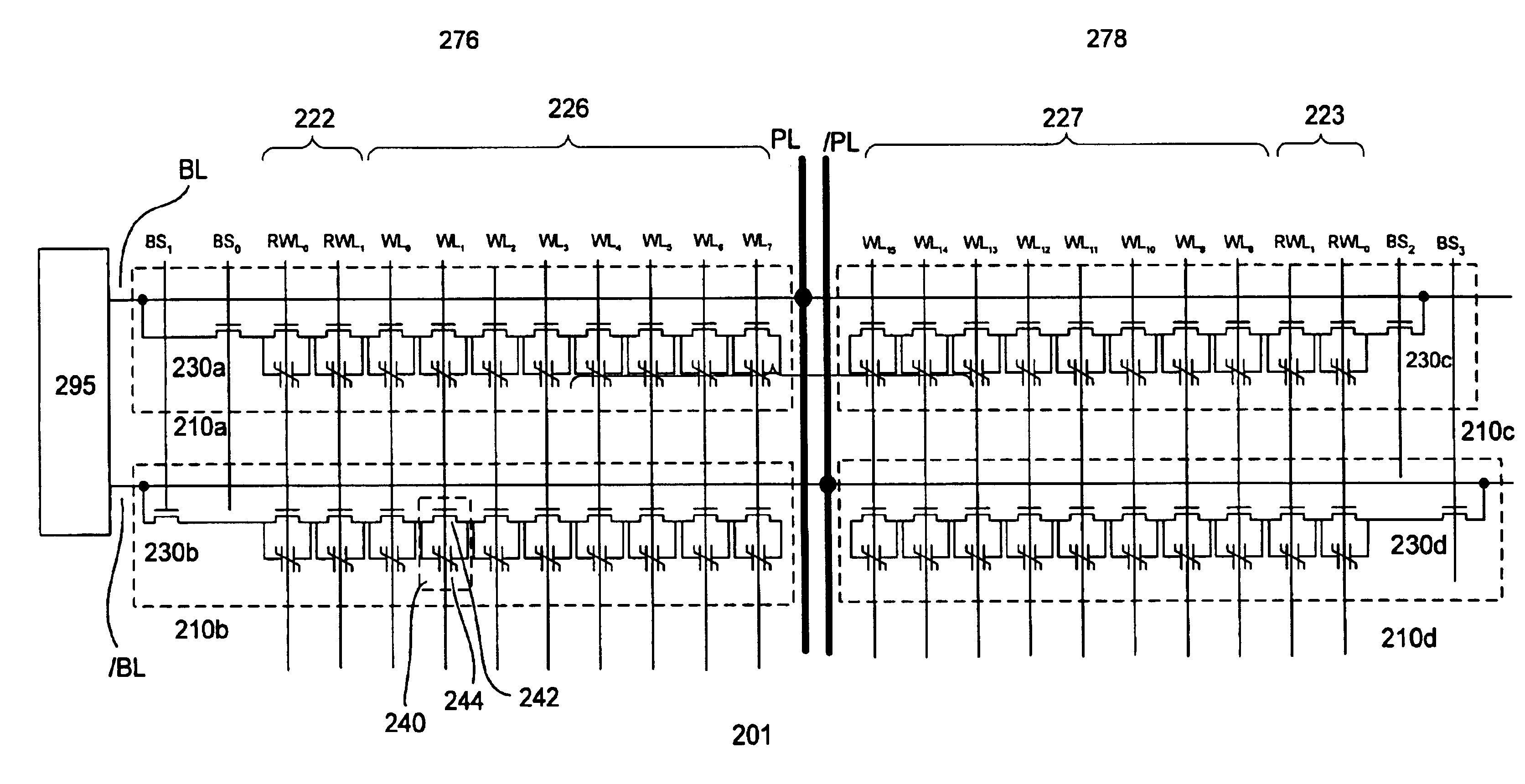

Grouping memory cells into sub-blocks for program speed uniformity

A three-dimensional stacked memory device is configured to provide uniform programming speeds of different sets of memory strings formed in memory holes. In a process for removing sacrificial material from word line layers, a block oxide layer in the memory holes is etched away relatively more when the memory hole is relatively closer to an edge of the word line layers where an etchant is introduced. A thinner block oxide layer is associated with a faster programming speed. To compensate, memory strings at the edges of the word line layers are programmed together, separate from the programming of interior memory strings. A program operation can use a higher initial program voltage for programming the interior memory strings compared to the edge memory strings.

Owner:SANDISK TECH LLC

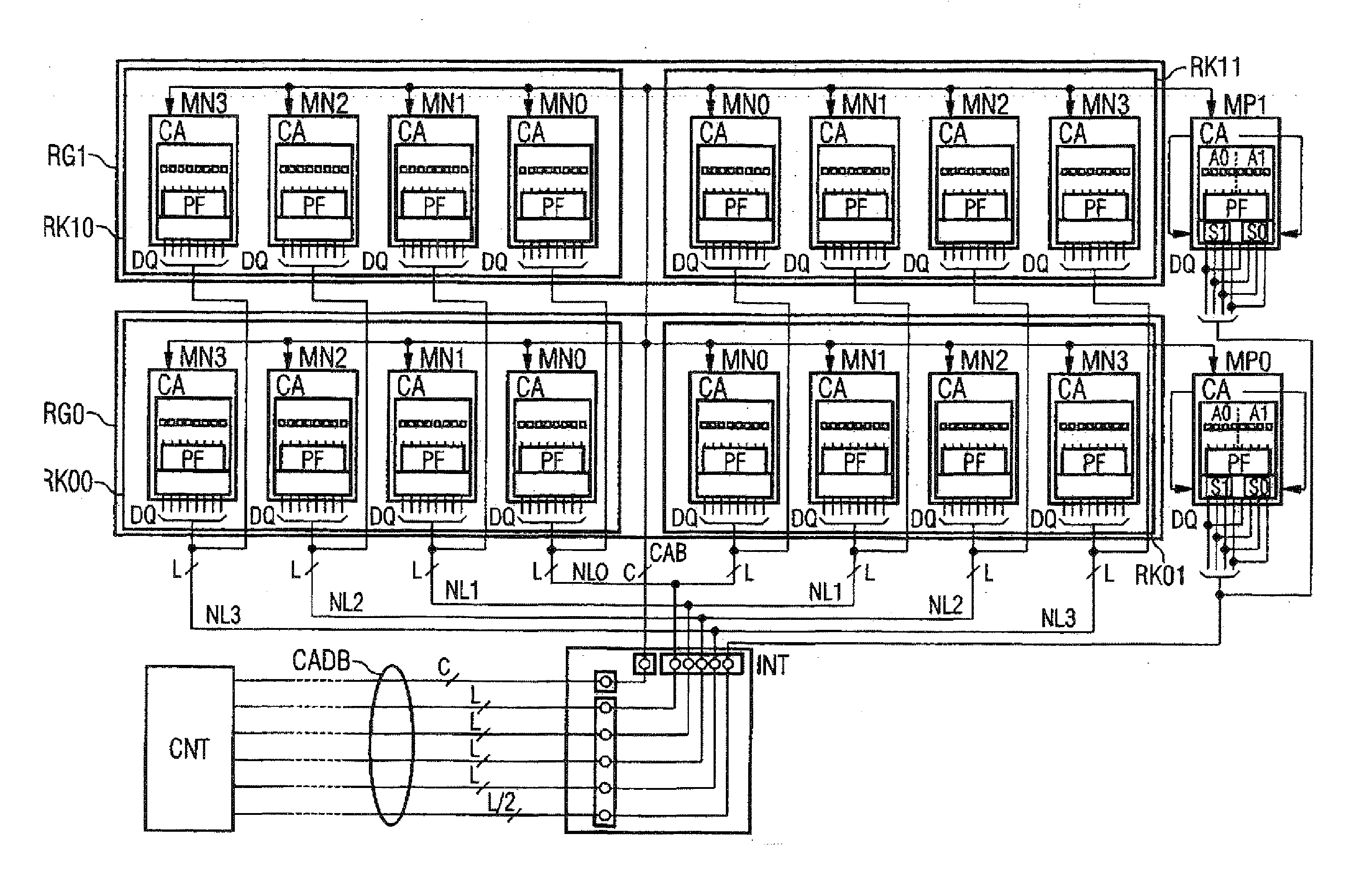

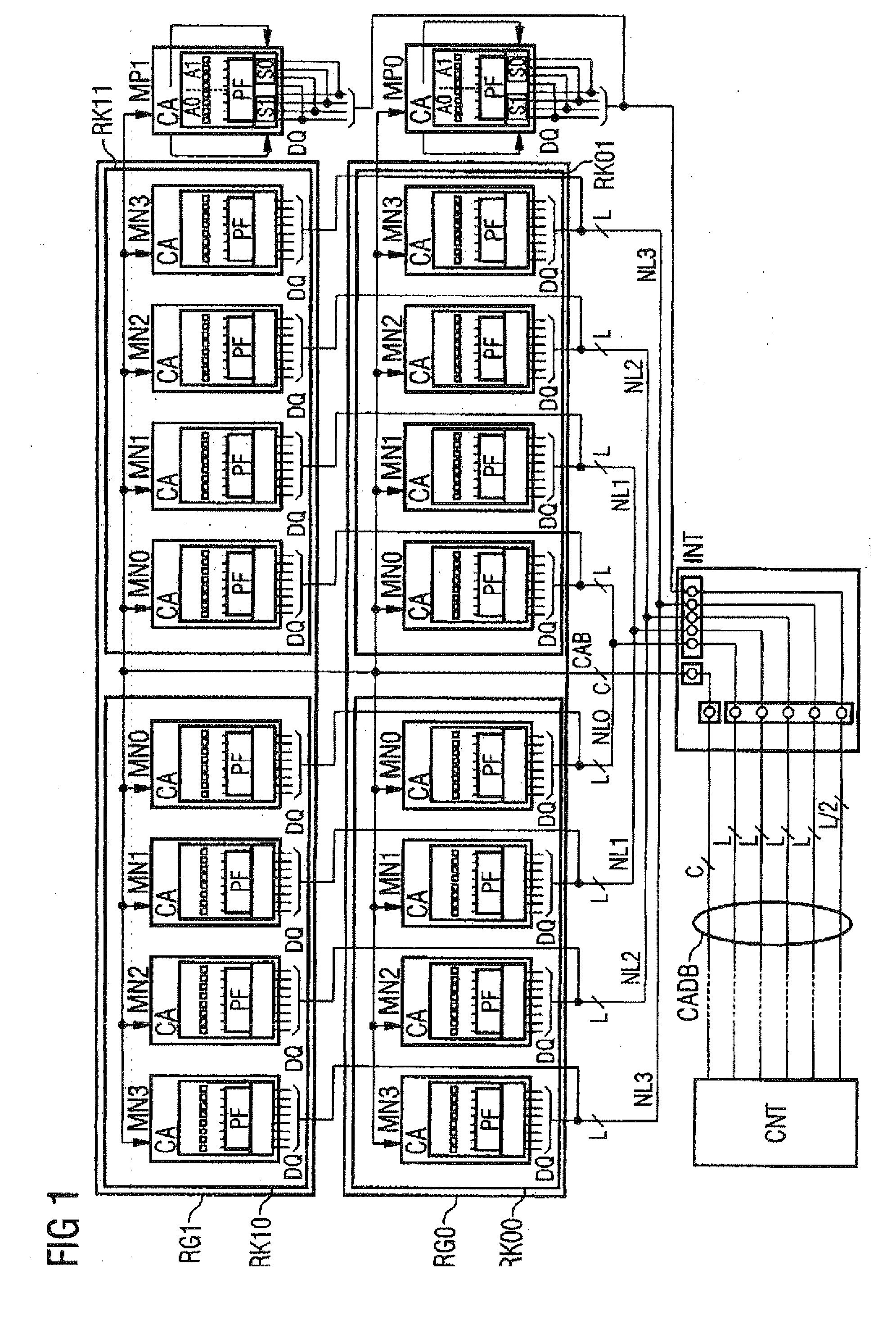

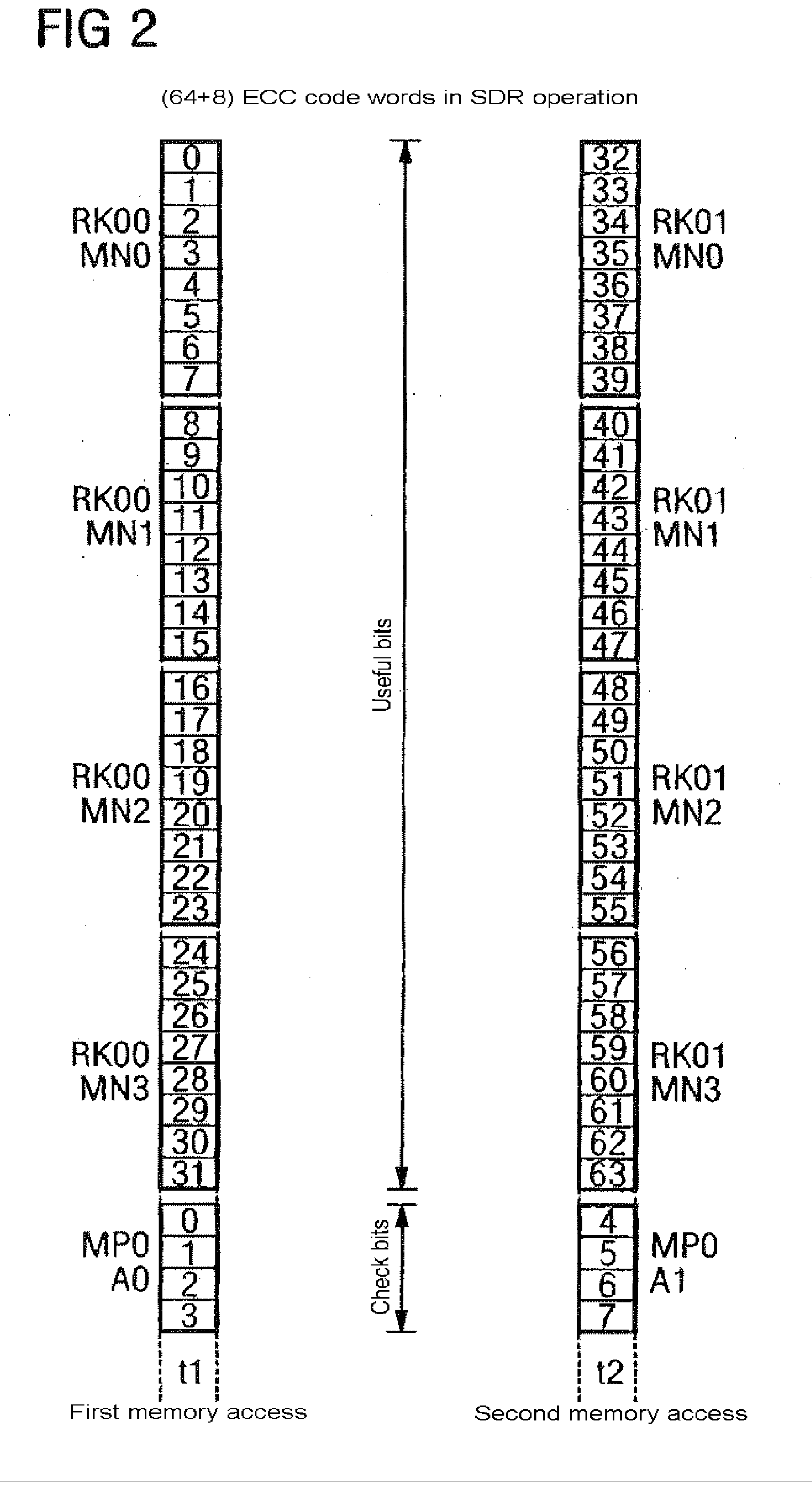

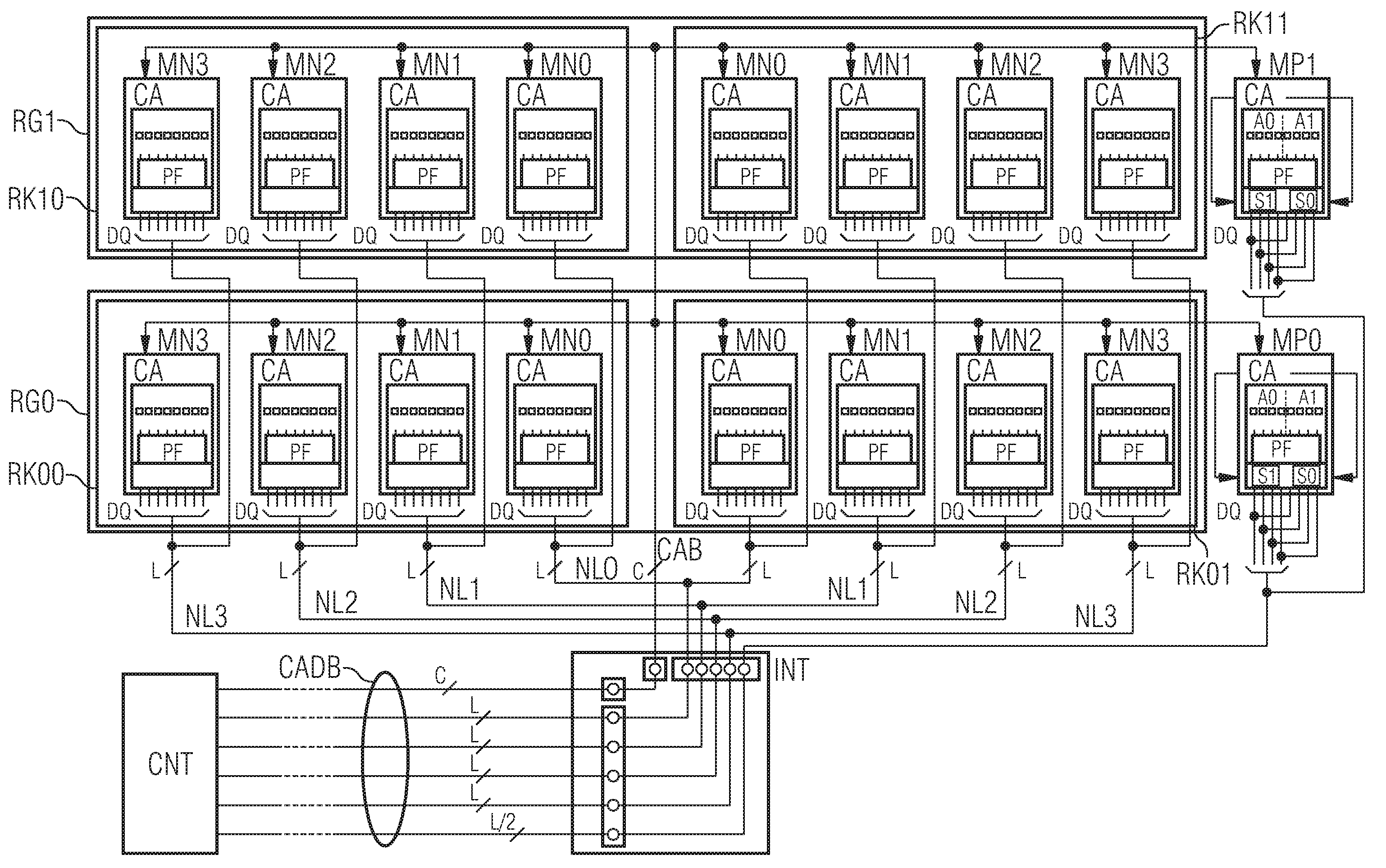

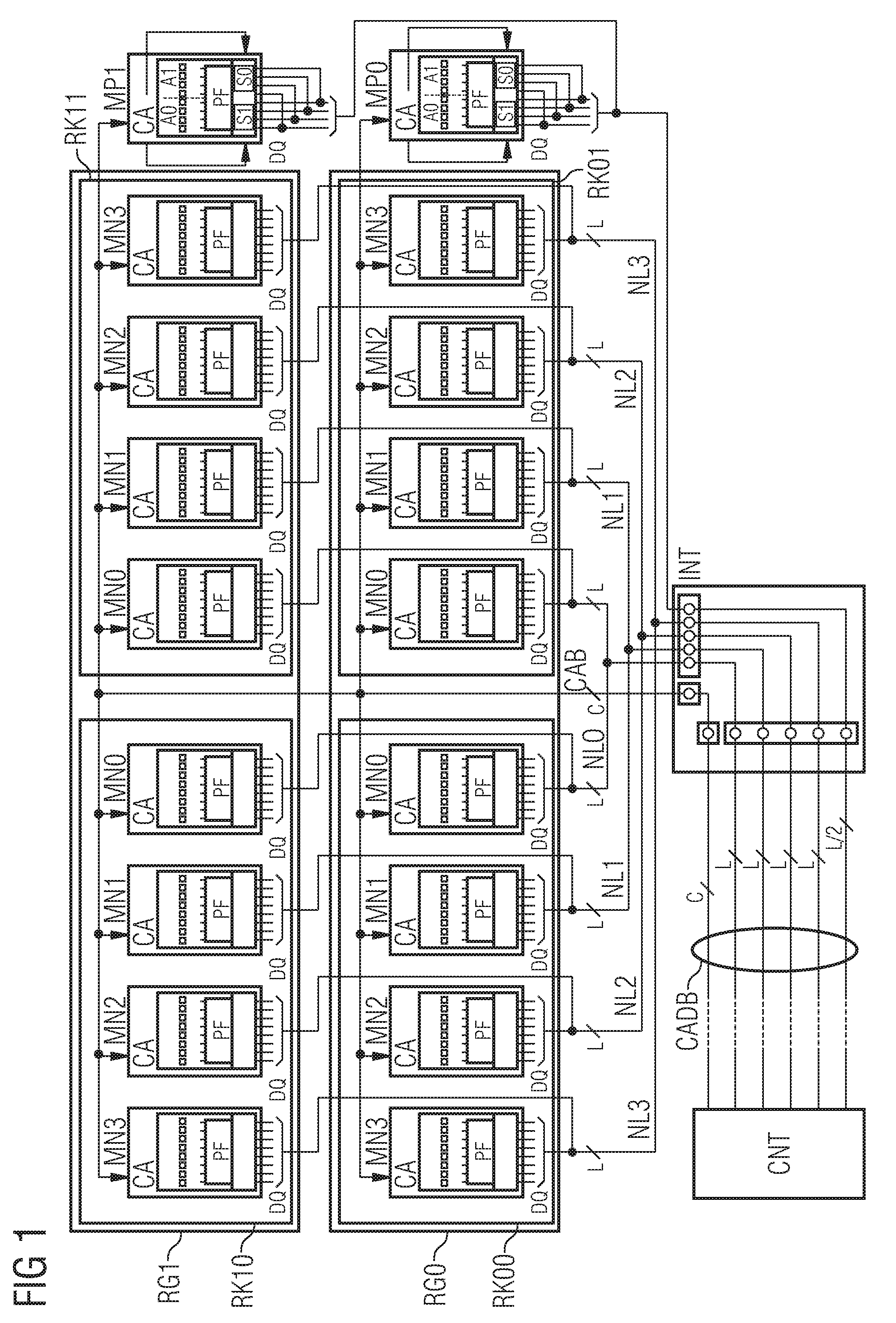

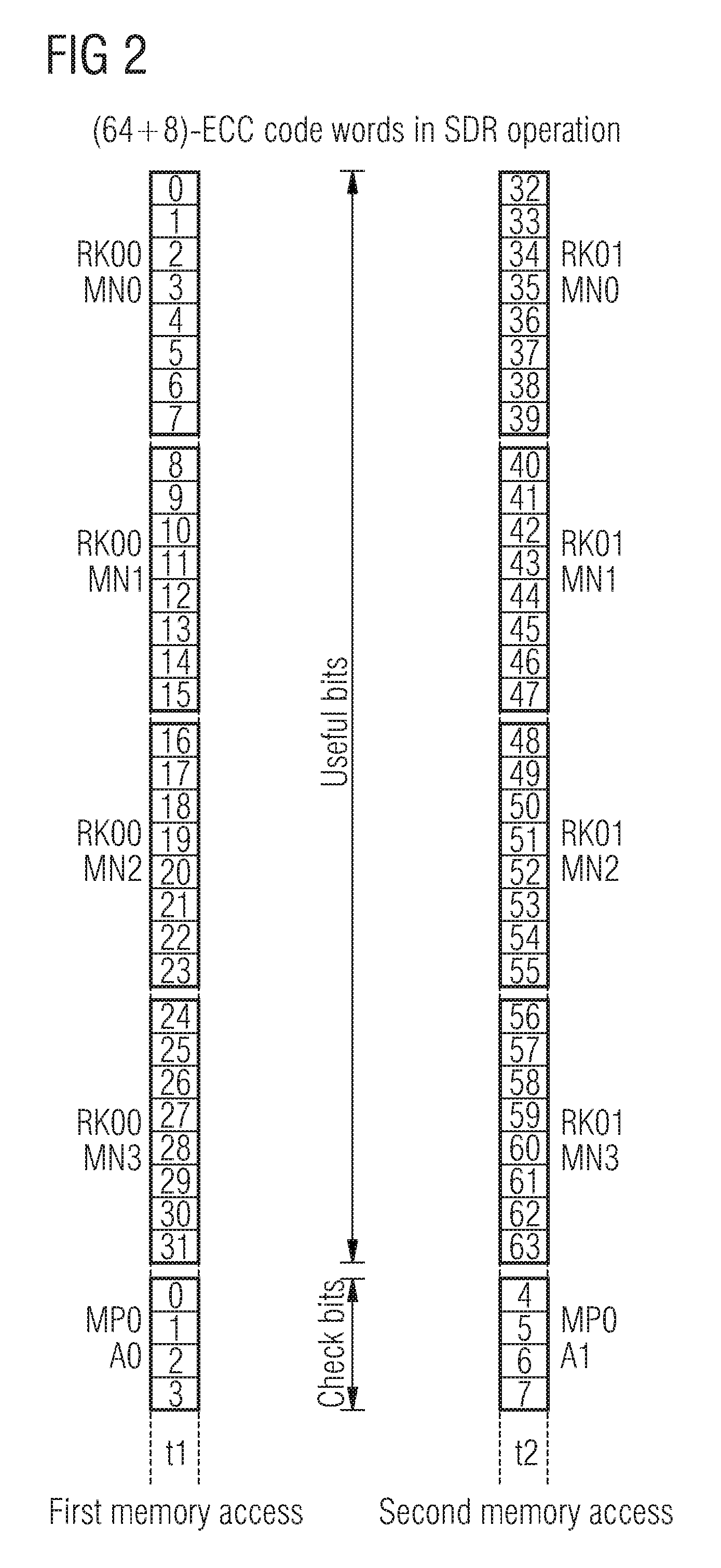

Memory module comprising a plurality of memory devices

InactiveUS20070150792A1Error detection/correctionMemory adressing/allocation/relocationDevice formGroup memory

A memory module stores data in the form of code words, each code word comprising useful bits and check bits for error correction. The memory module contains a first group of the memory devices including check bits and a second group of the memory devices including useful bits, the second group memory devices forming ranks, each rank being addressed as a whole, the ranks forming rank groups, each rank group including at least two ranks and a first group memory device. The memory module further contains a connecting device transferring bit packets each containing useful bits and check bits in the parallel format between an interface of the memory module and the memory devices of a selected rank group

Owner:POLARIS INNOVATIONS

Memory module comprising a plurality of memory devices

InactiveUS7650457B2Error detection/correctionMemory adressing/allocation/relocationDevice formComputer module

A memory module stores data in the form of code words, each code word comprising useful bits and check bits for error correction. The memory module contains a first group of the memory devices including check bits and a second group of the memory devices including useful bits, the second group memory devices forming ranks, each rank being addressed as a whole, the ranks forming rank groups, each rank group including at least two ranks and a first group memory device. The memory module further contains a connecting device transferring bit packets each containing useful bits and check bits in the parallel format between an interface of the memory module and the memory devices of a selected rank group.

Owner:POLARIS INNOVATIONS LTD

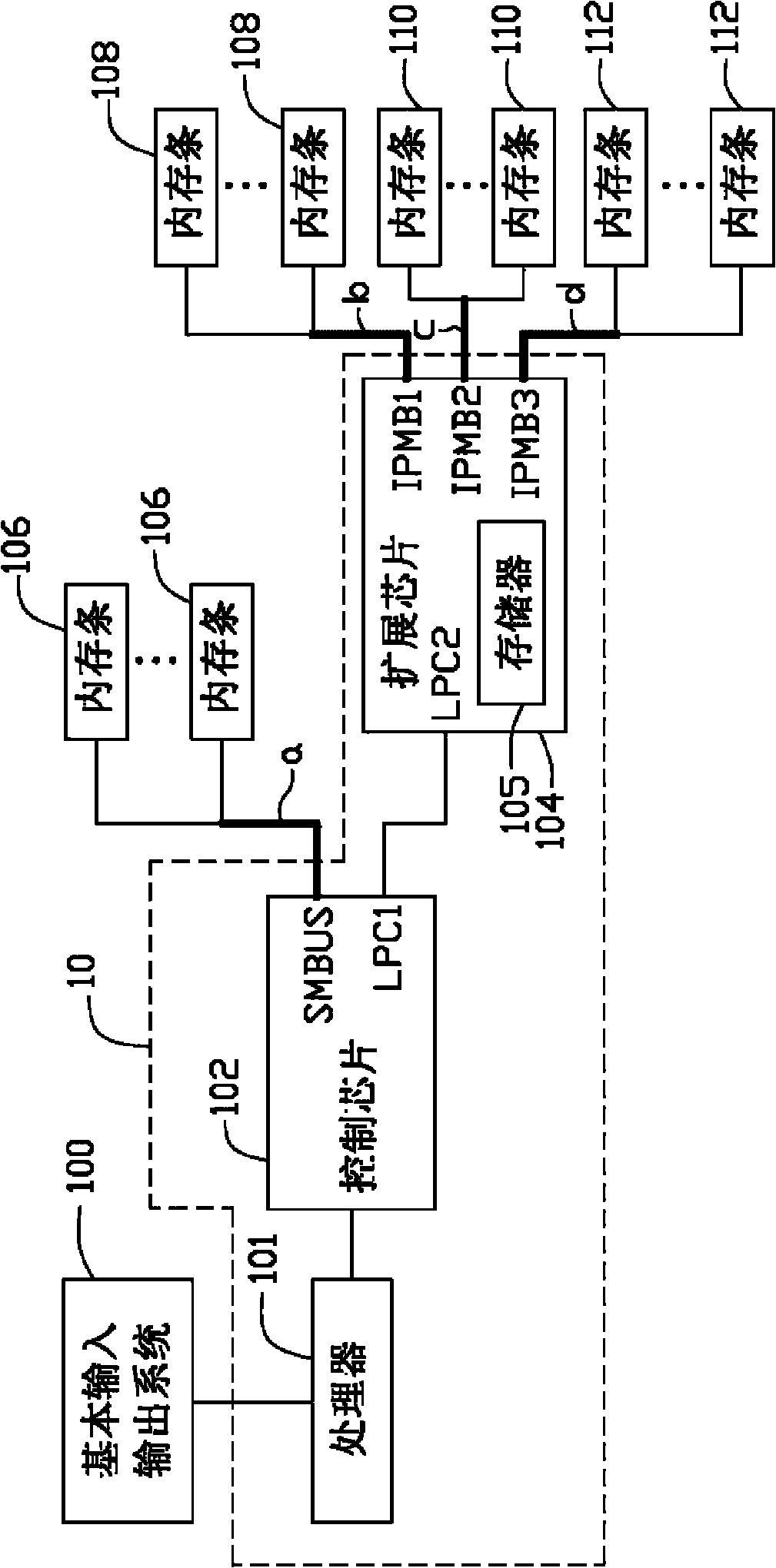

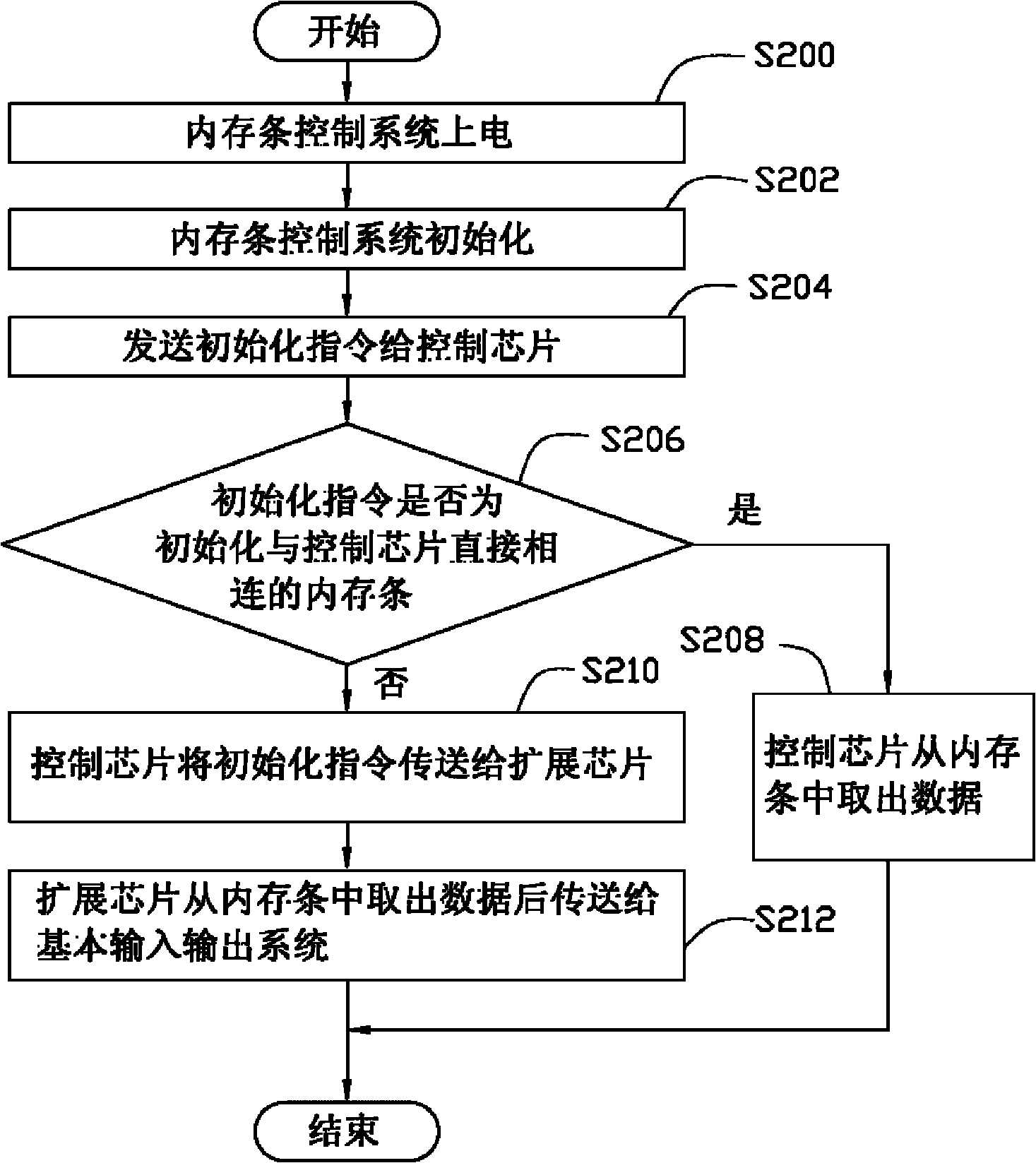

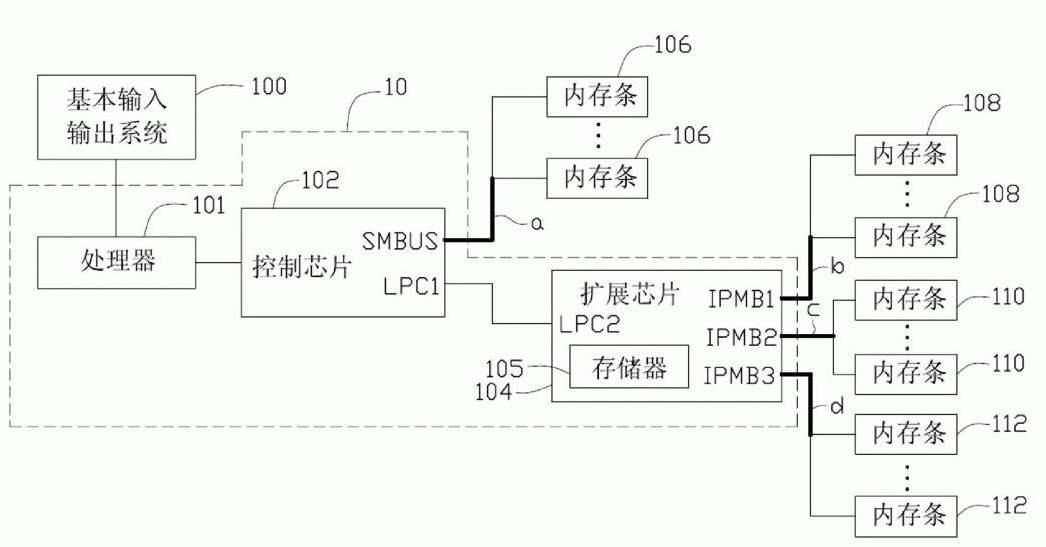

Memory bar control system and control method thereof

InactiveCN101872308AEasy to controlImplement initializationBootstrappingProgram loading/initiatingControl systemGroup memory

The invention relates to a memory bar control system comprising a processor, a control chip and an expansion chip; the processor is respectively connected with a basic input and output system and the control chip; the control chip is connected with multiple memory bars and the expansion chip; and the expansion chip is connected with multi-group memory bars. The invention also provides a memory bar control method. The memory bar control system and the control method thereof of the invention can be used for connecting multiple memory bars and controlling multiple memory bars.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

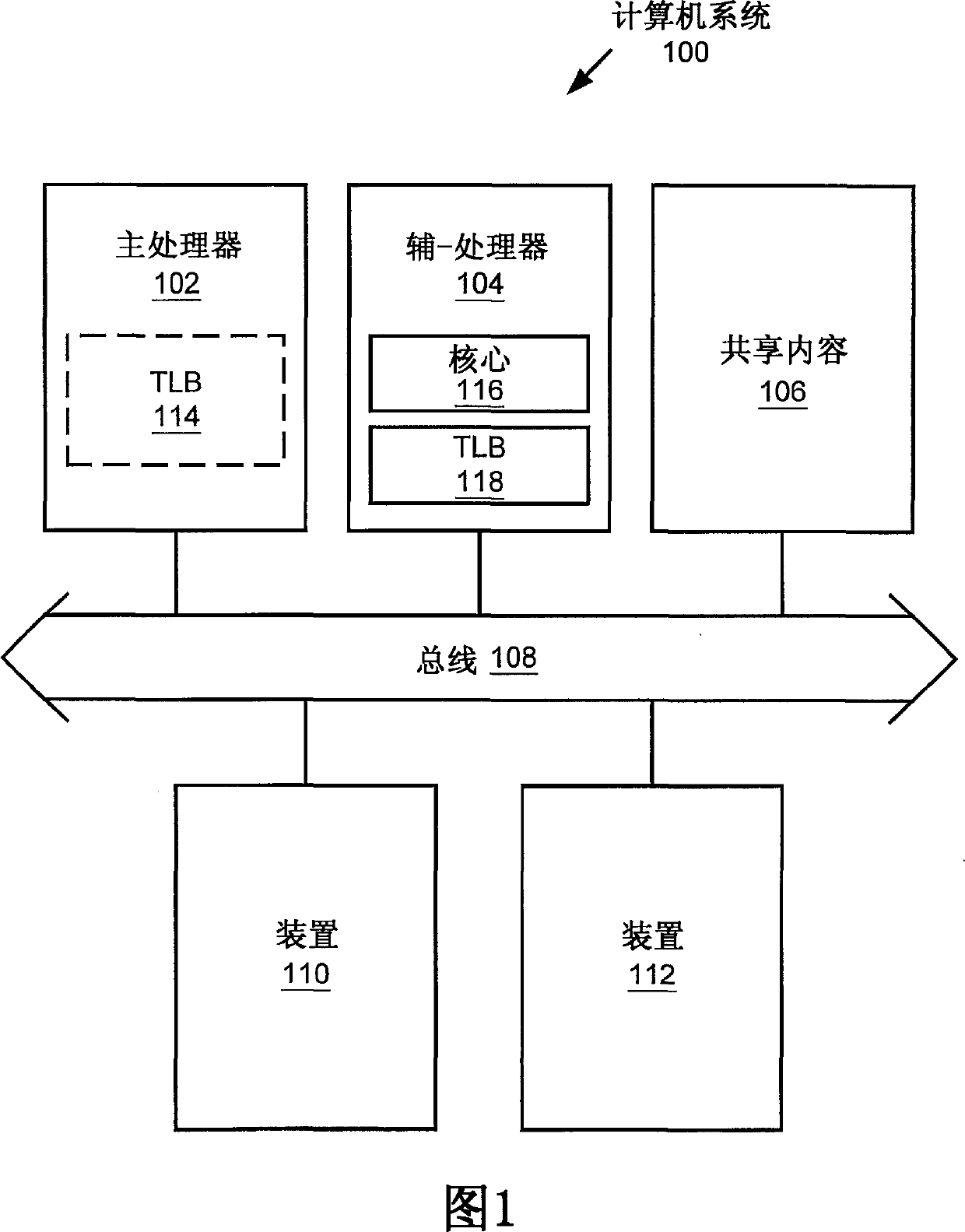

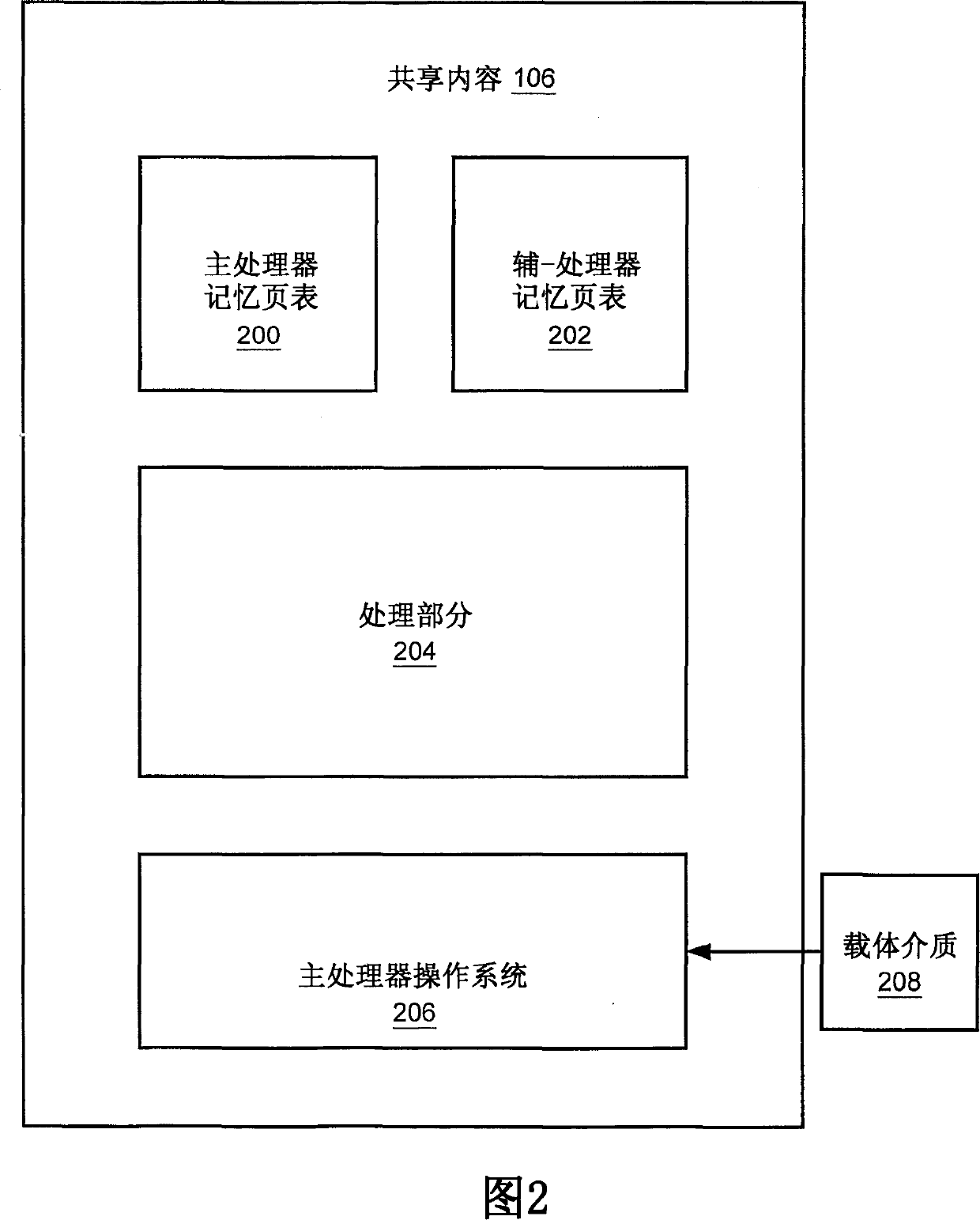

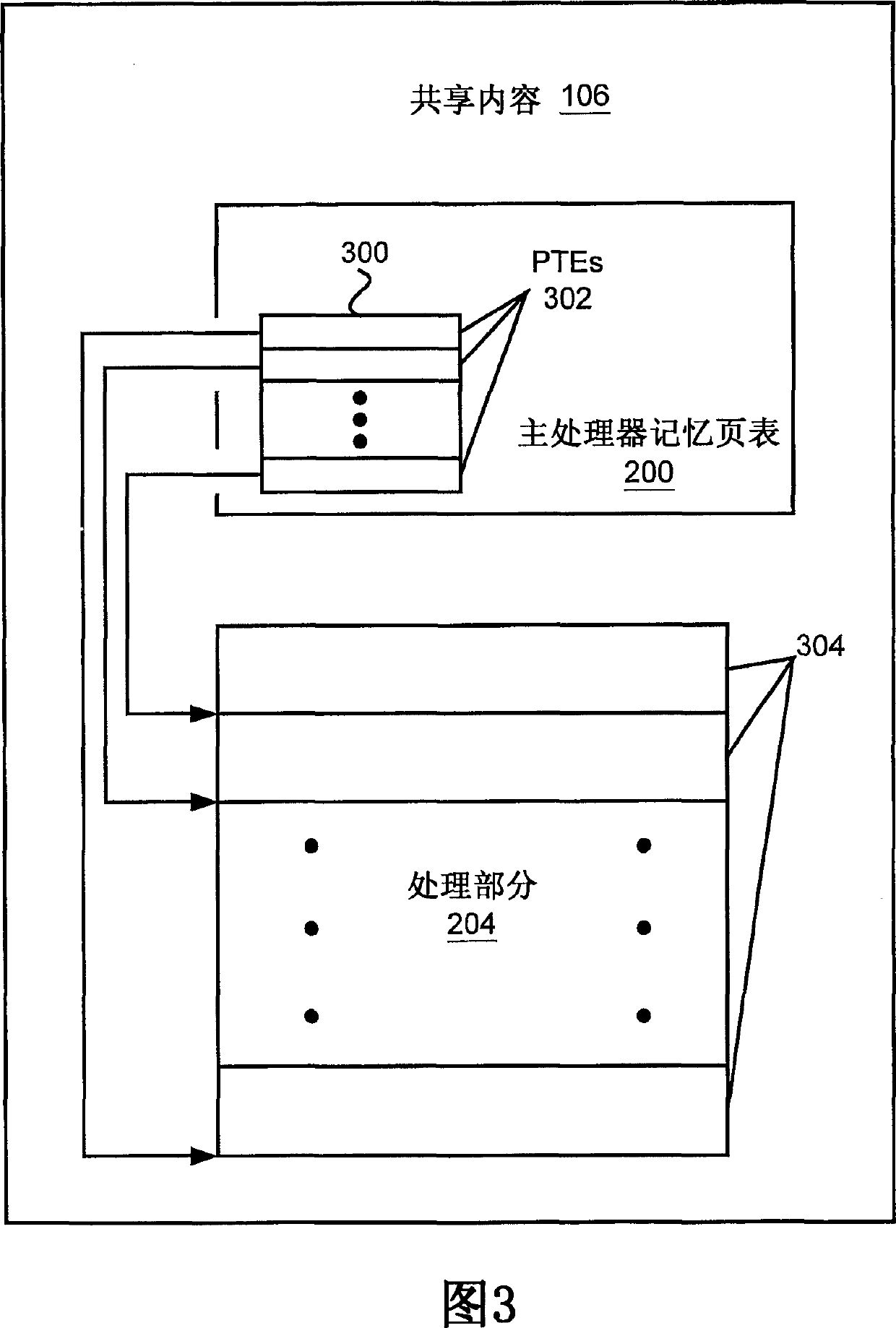

Multiprocessor system implementing virtual memory using a shared memory, and a page replacement method for maintaining paged memory coherence

InactiveCN1524228AMemory architecture accessing/allocationMemory adressing/allocation/relocationVirtual memoryComputer architecture

A computer system (100) including a first processor (102), a second processor (104) in communication with the first processor (102), a memory (106) (i.e., a shared memory) coupled to the first processor (102) and the second processor (104), and a storage device (110 or 112) coupled to the first processor (102). The first processor (102) and the second processor (104) implement virtual memory using the memory (106). The first processor (102) maintains a first and second set of page tables in the memory (106). The first processor (102) uses the first set of page tables to access the memory locations witching the memory (106). The second processor (104) uses the second set of page tables, maintained by the first processor (102), to access the memory locations within the memory. A virtual memory page replacement method is also described for use in the computer system (100).

Owner:GLOBALFOUNDRIES U S INC MALTA

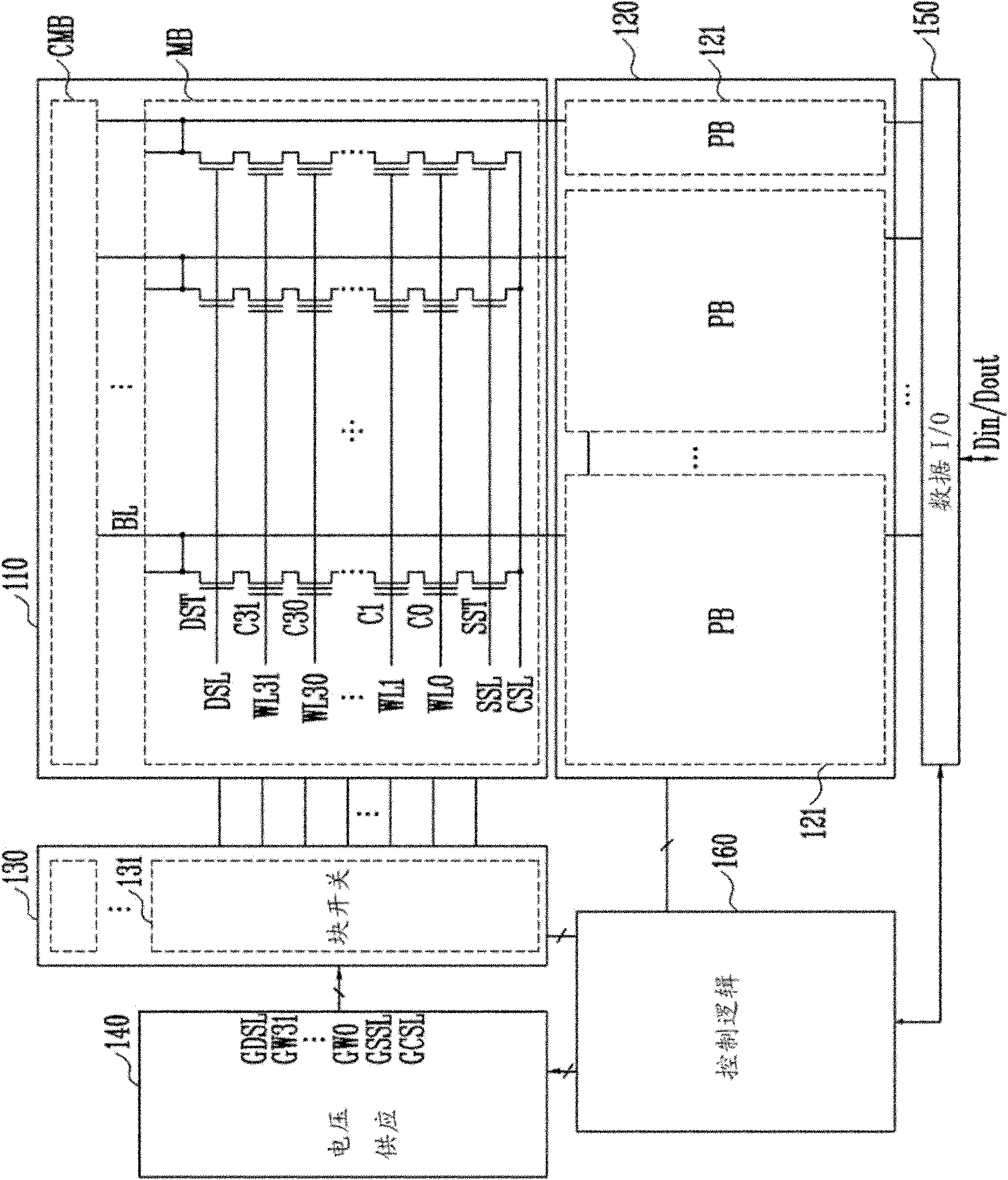

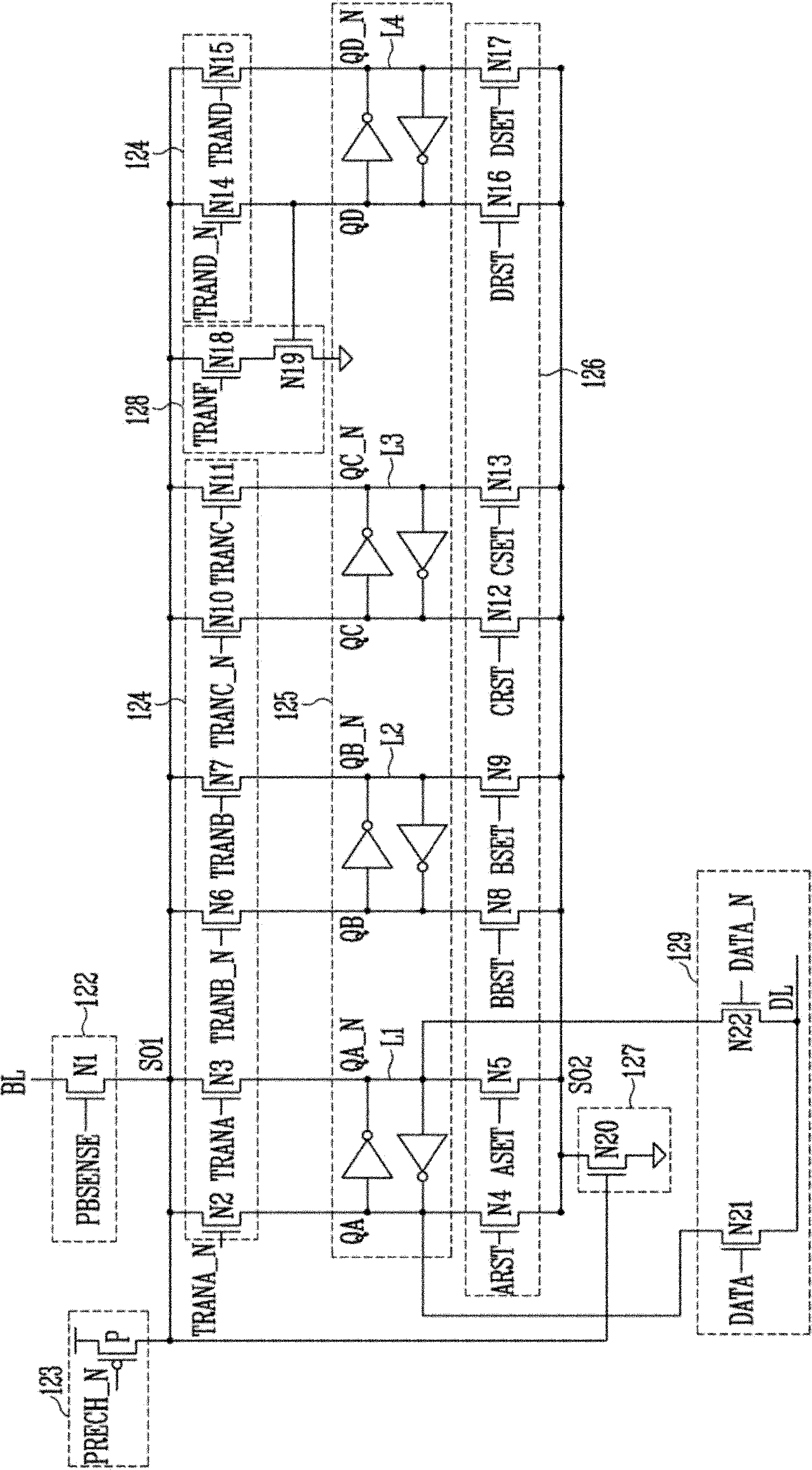

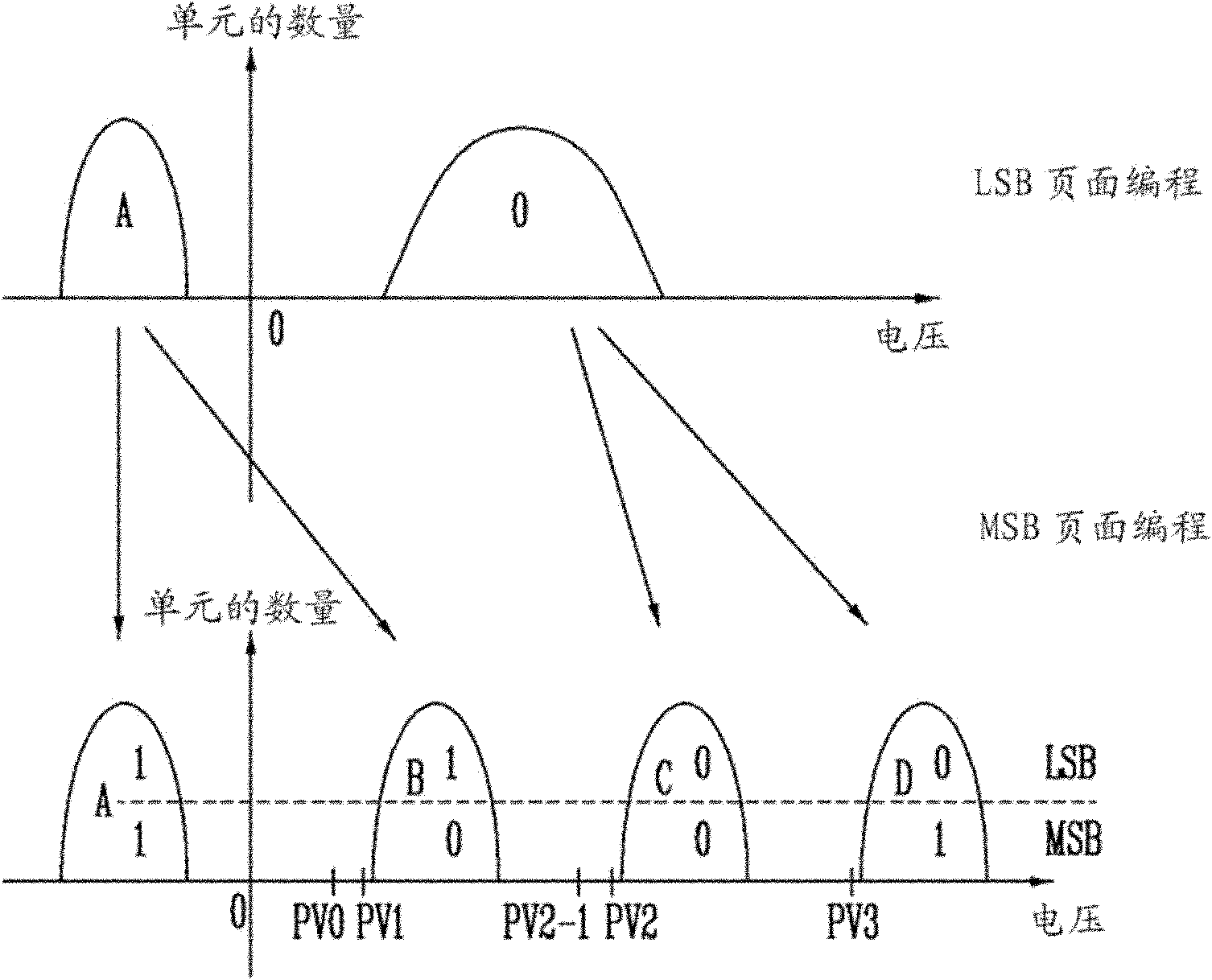

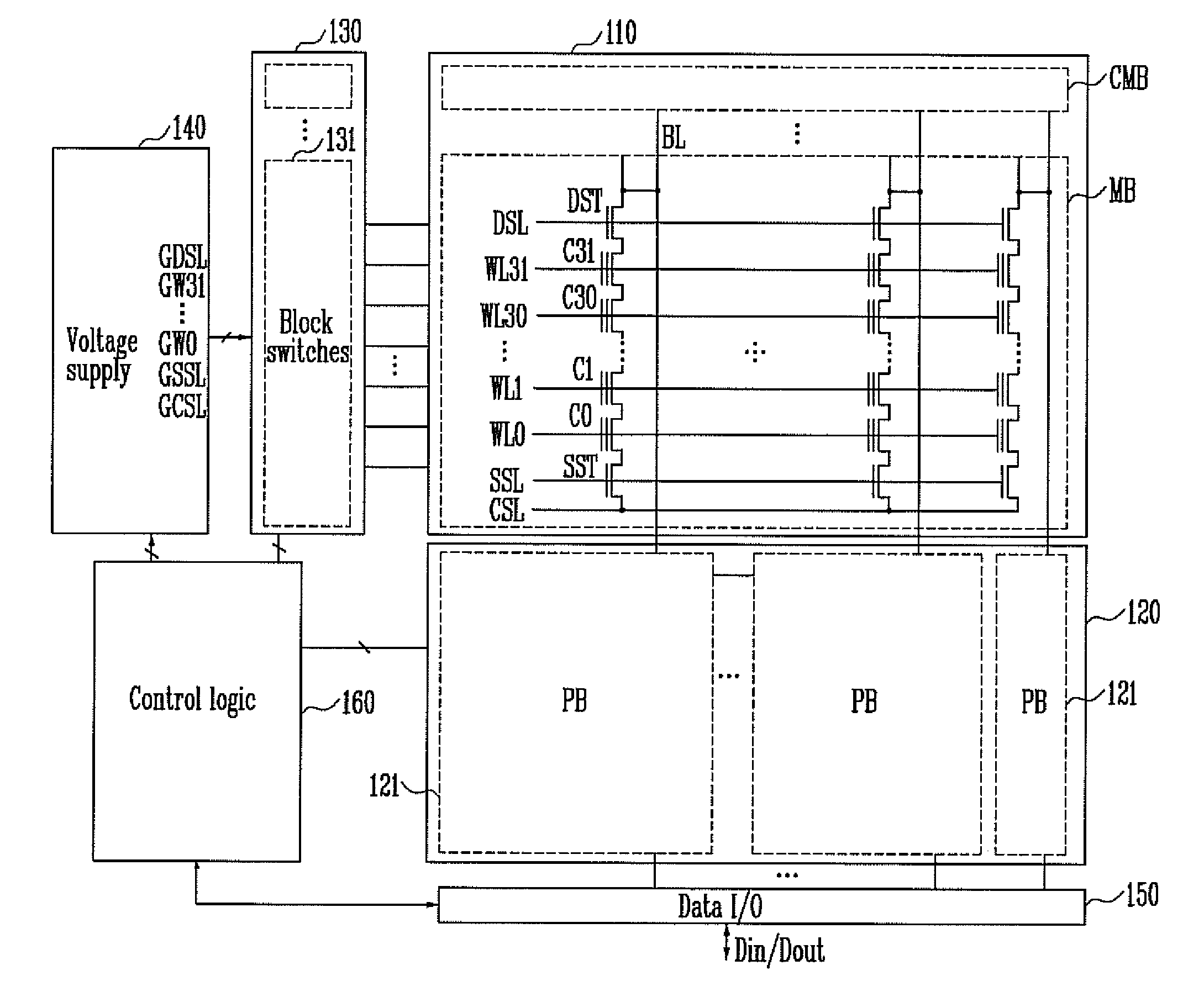

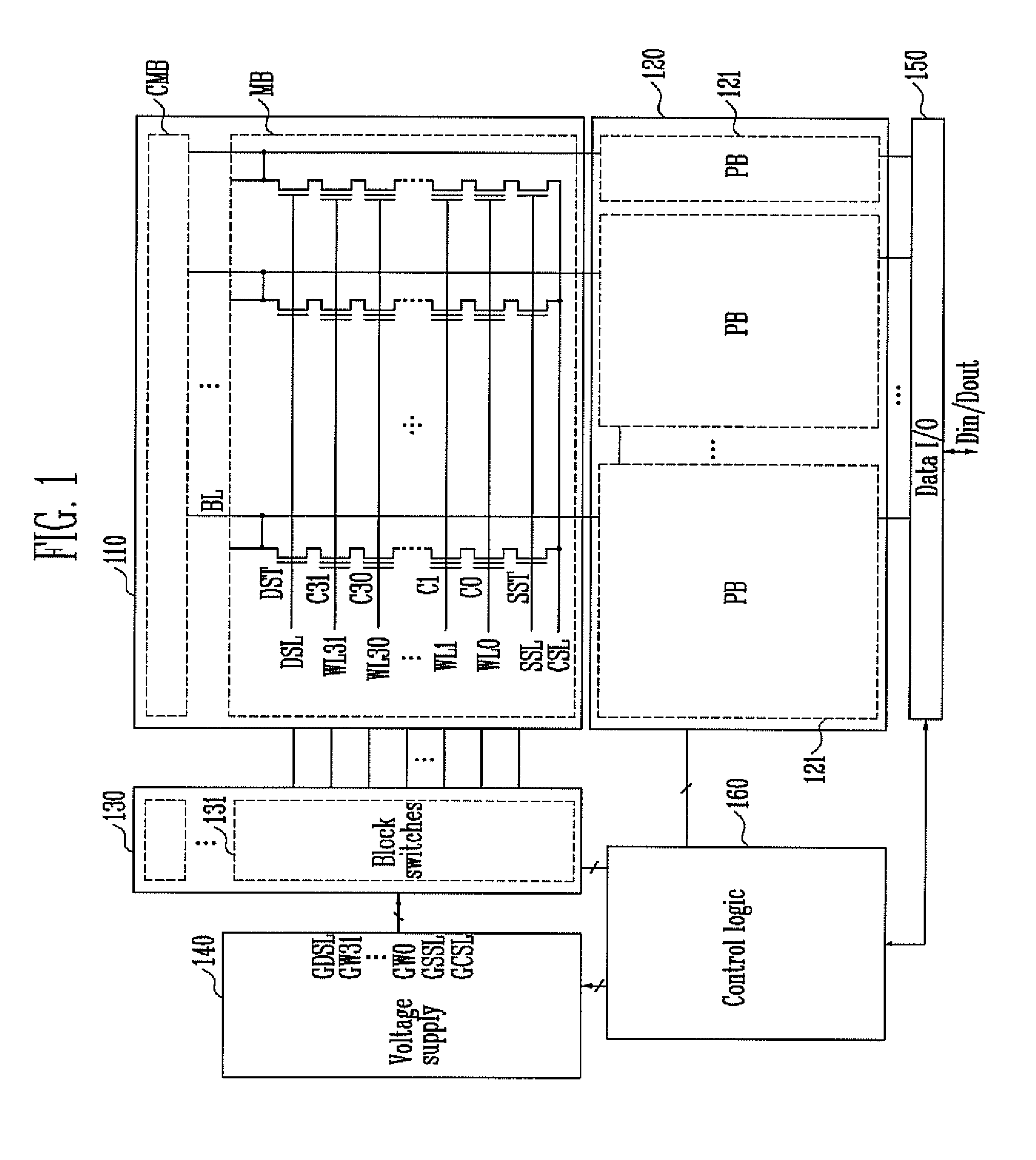

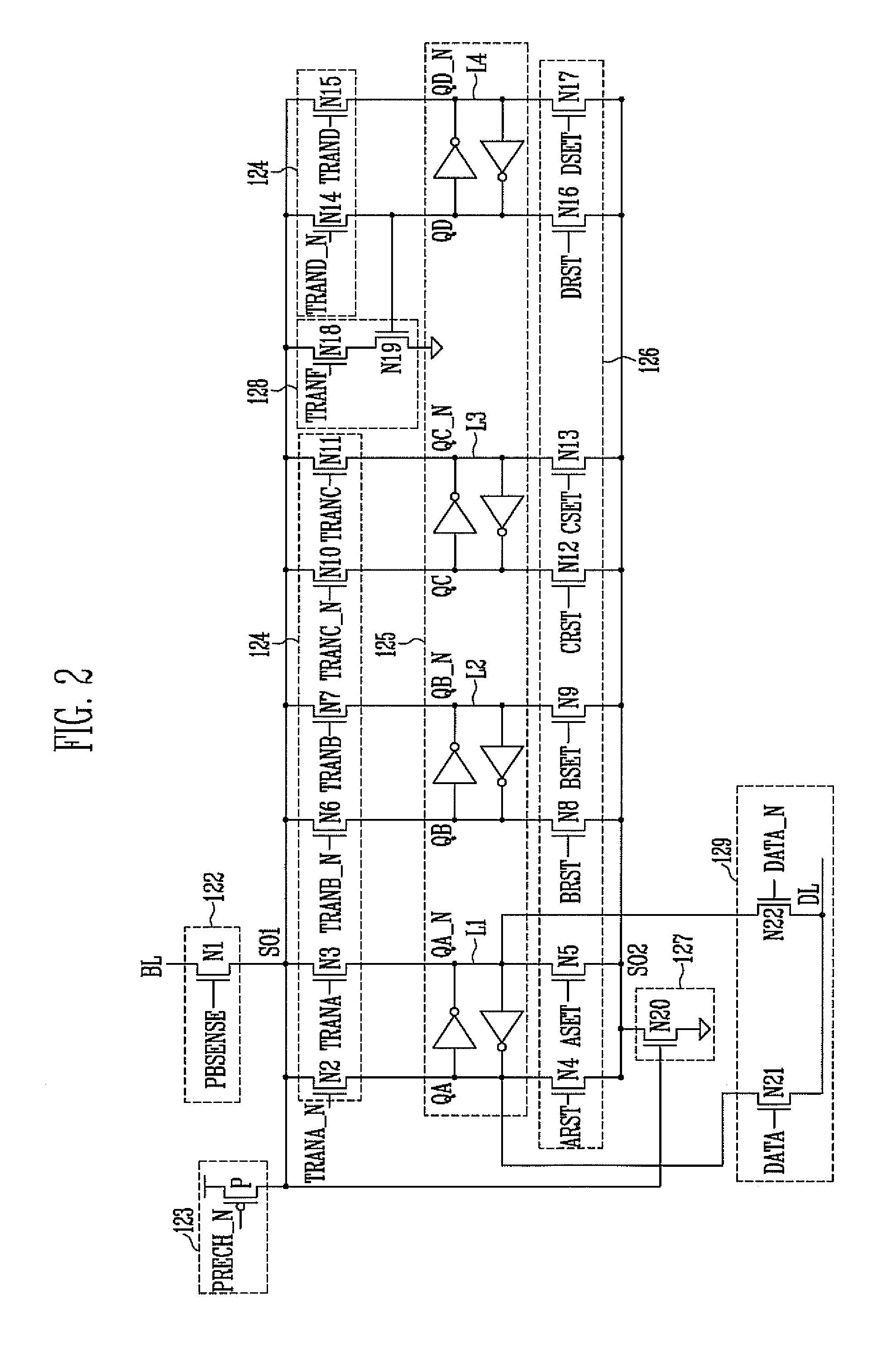

Method for programming semiconductor memory device

ActiveCN102270508AReduce the rate of changeRead-only memoriesDigital storageMemory cellParallel computing

Owner:SK HYNIX INC

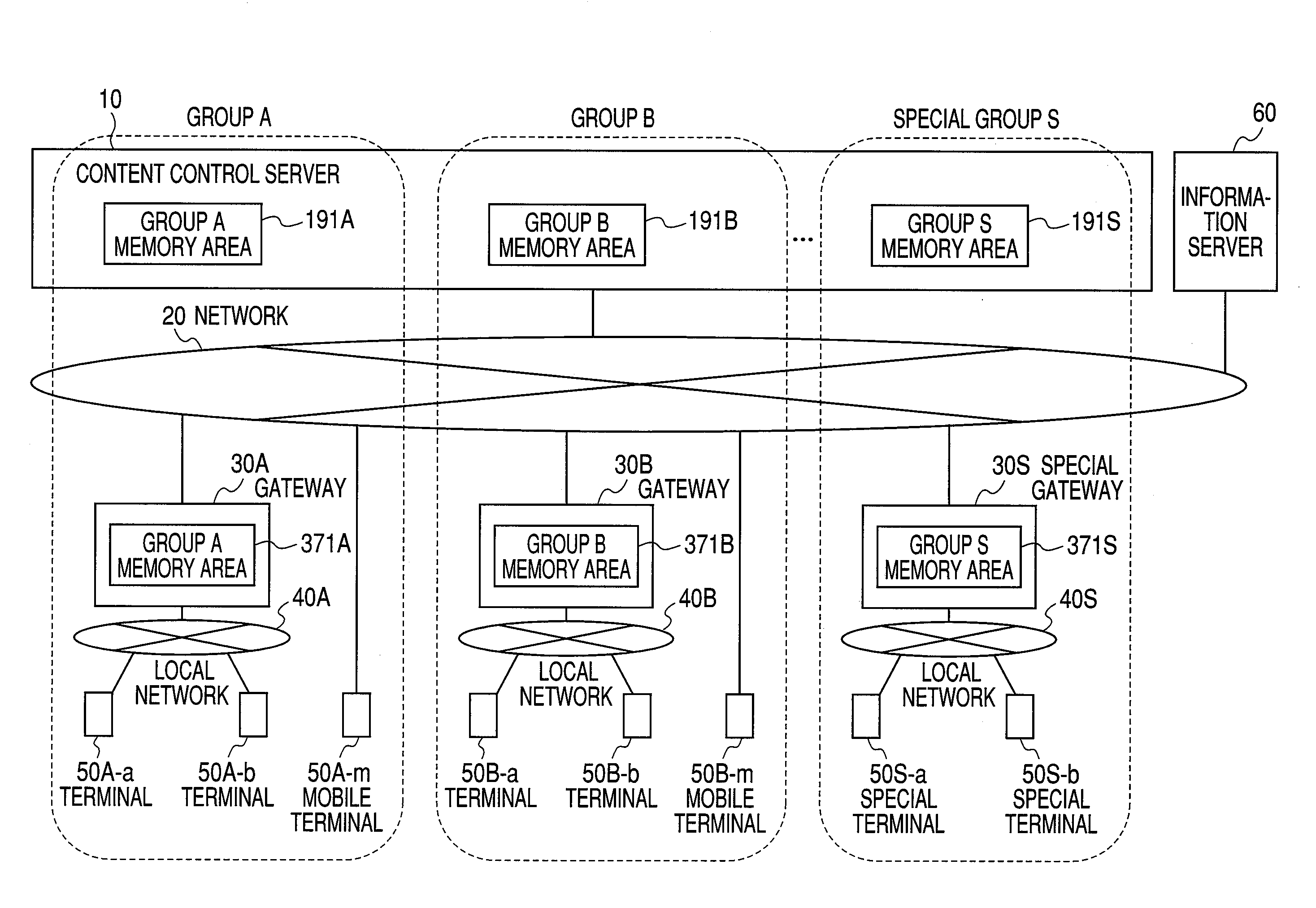

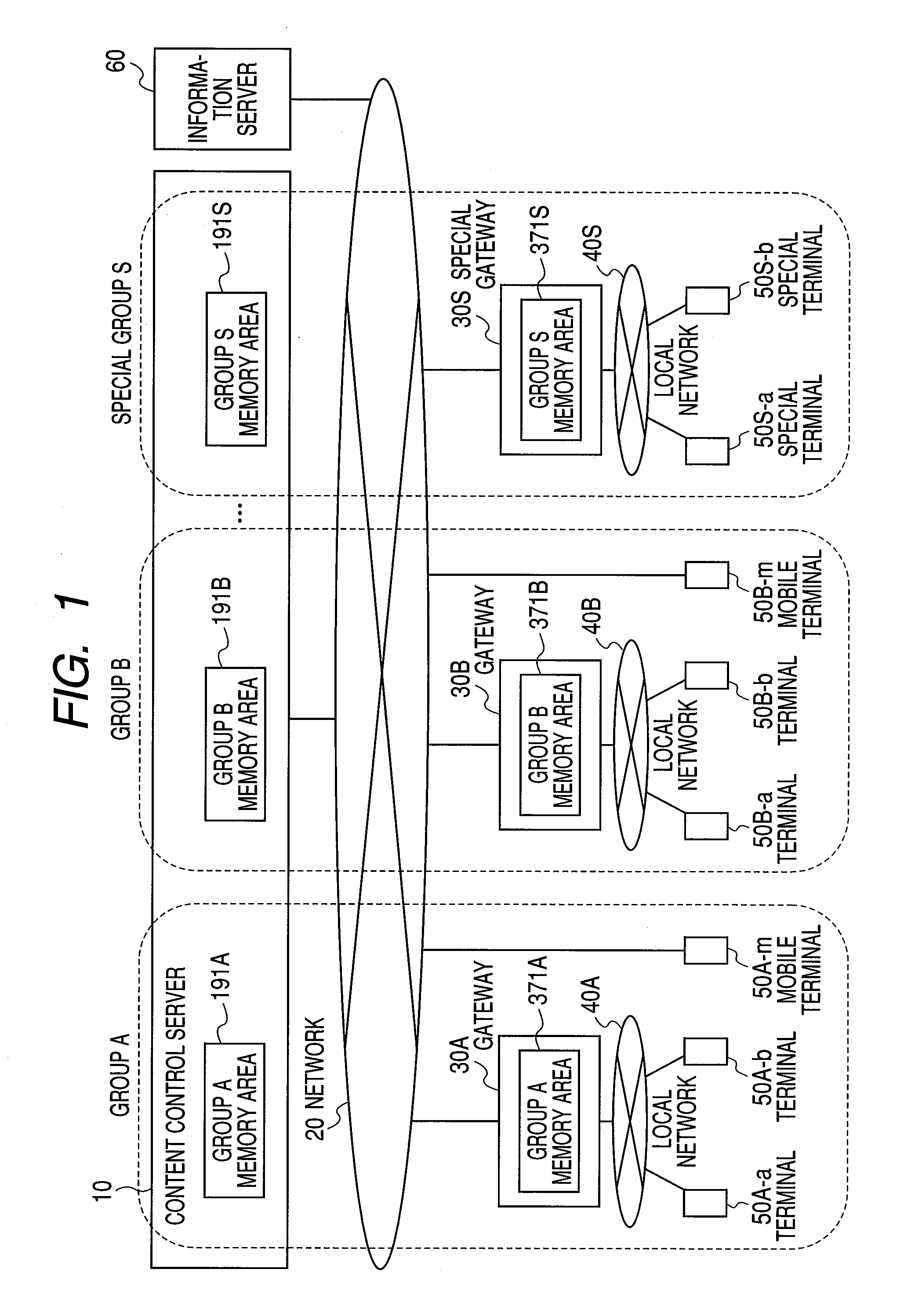

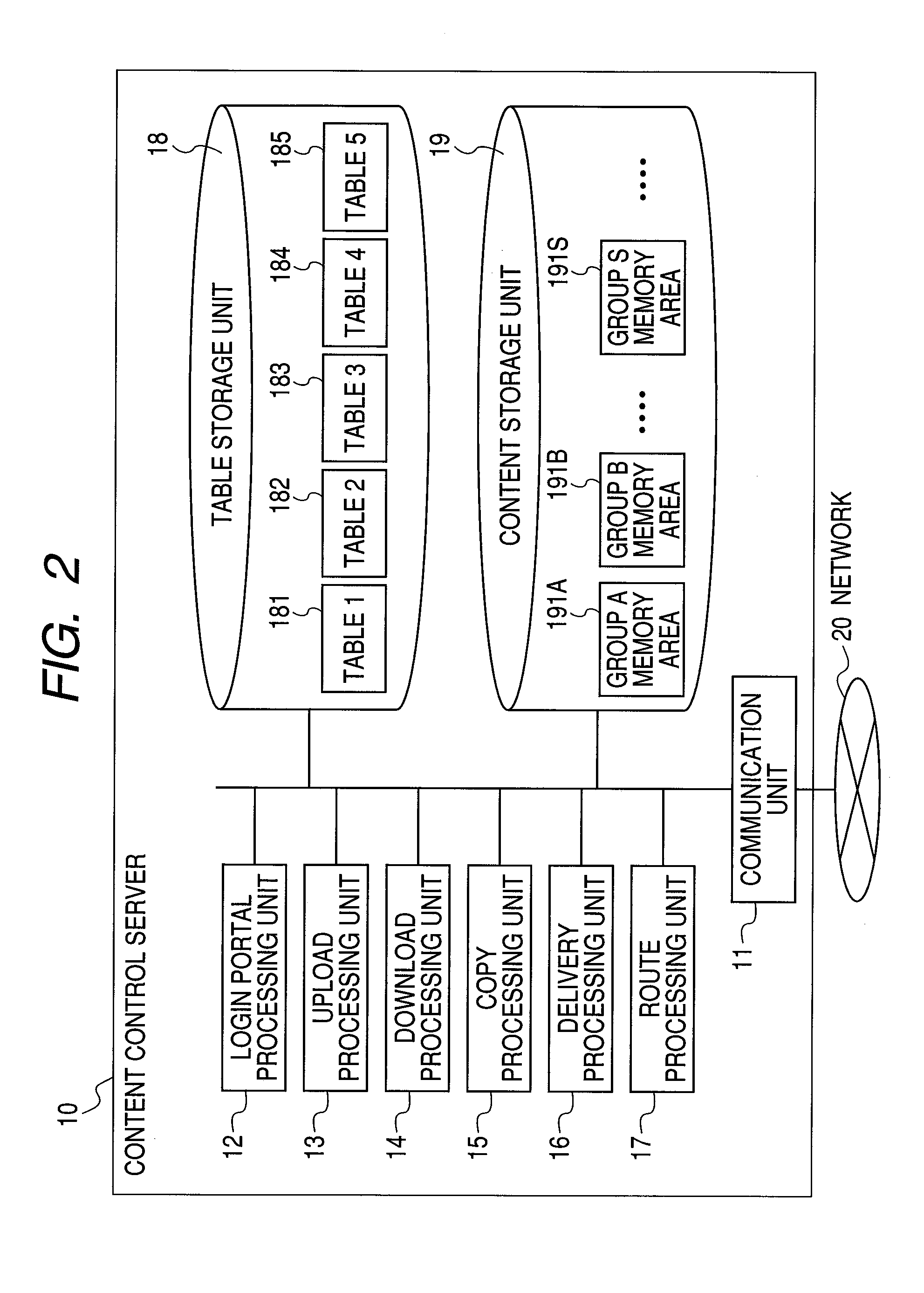

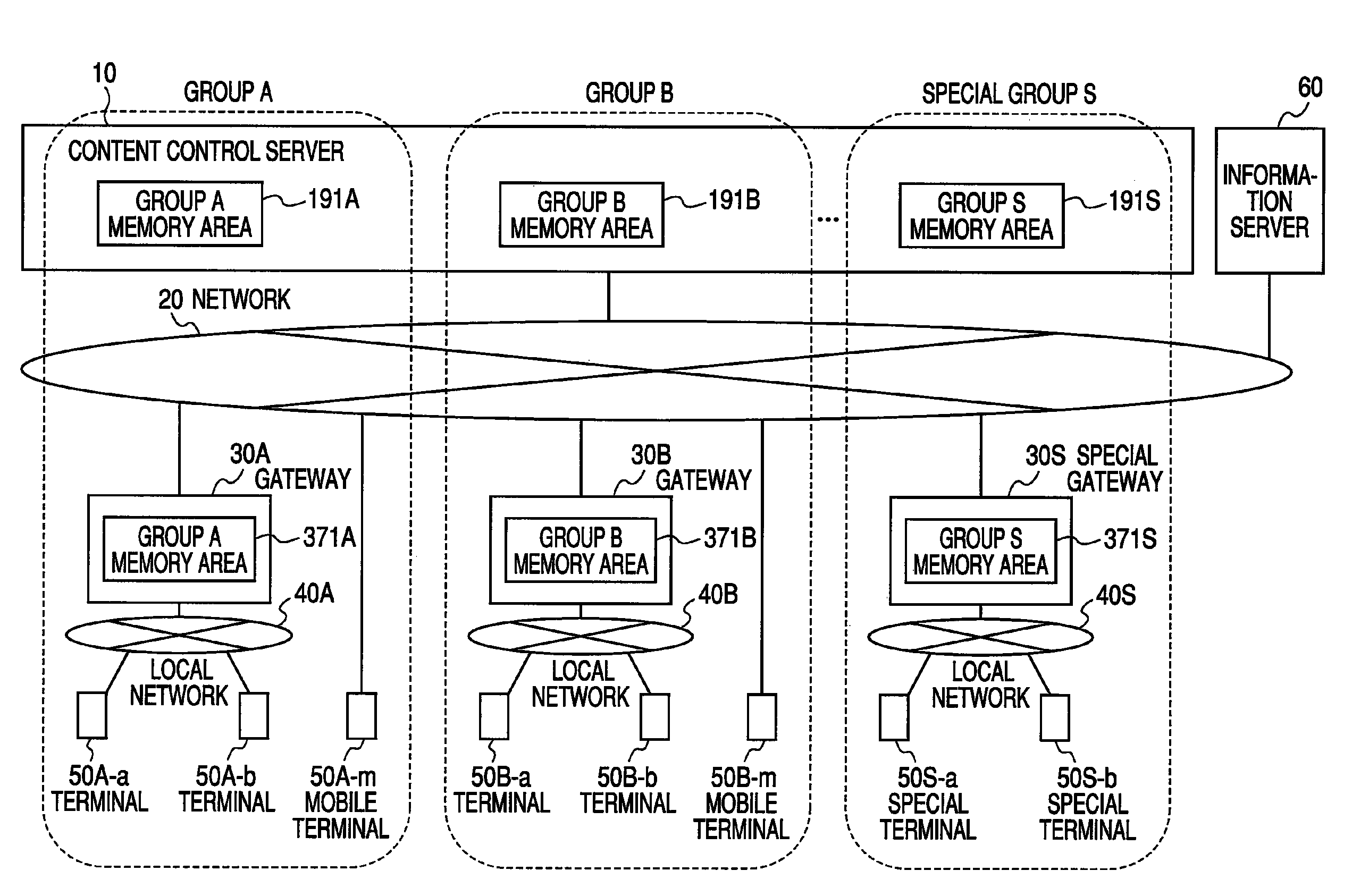

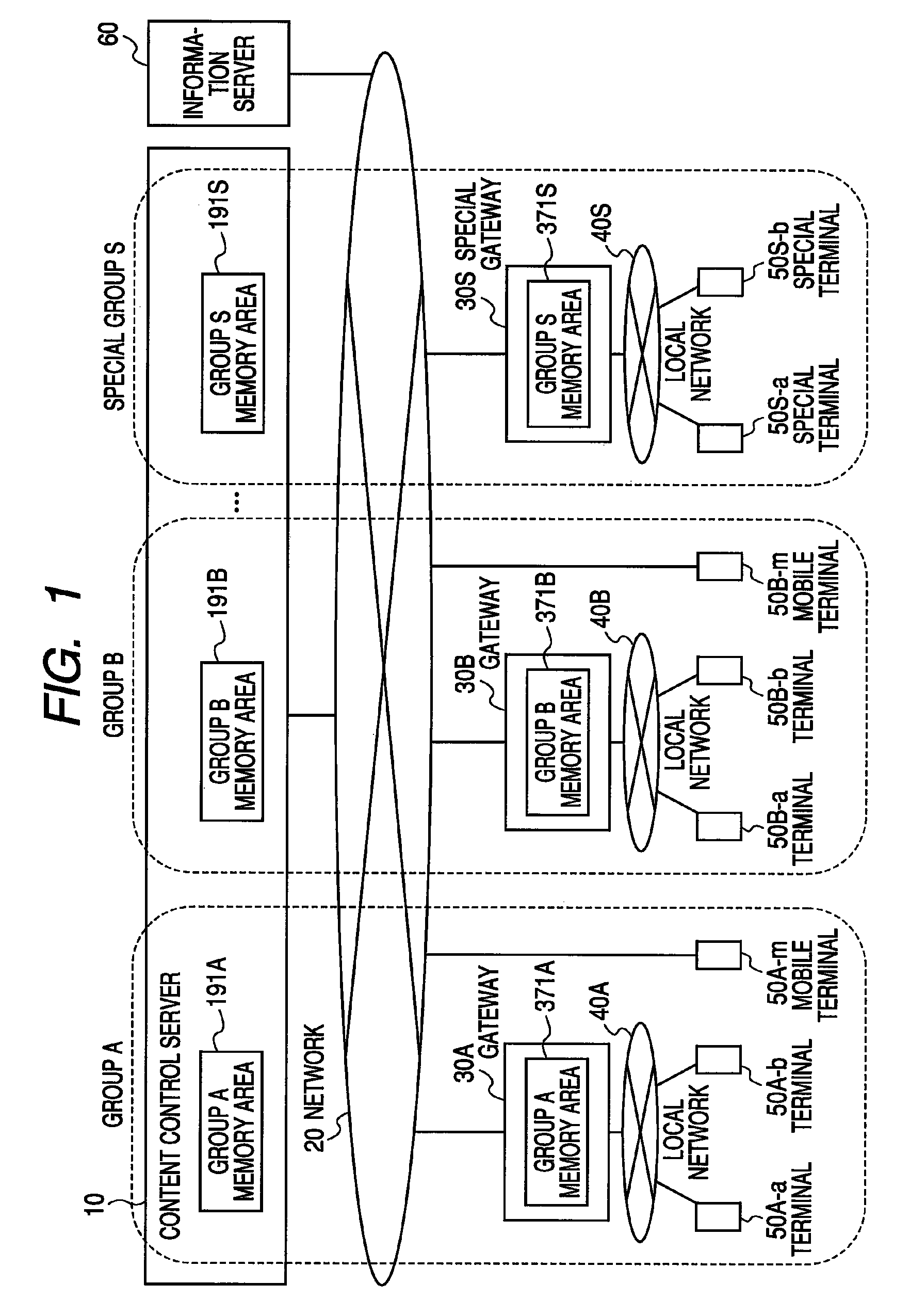

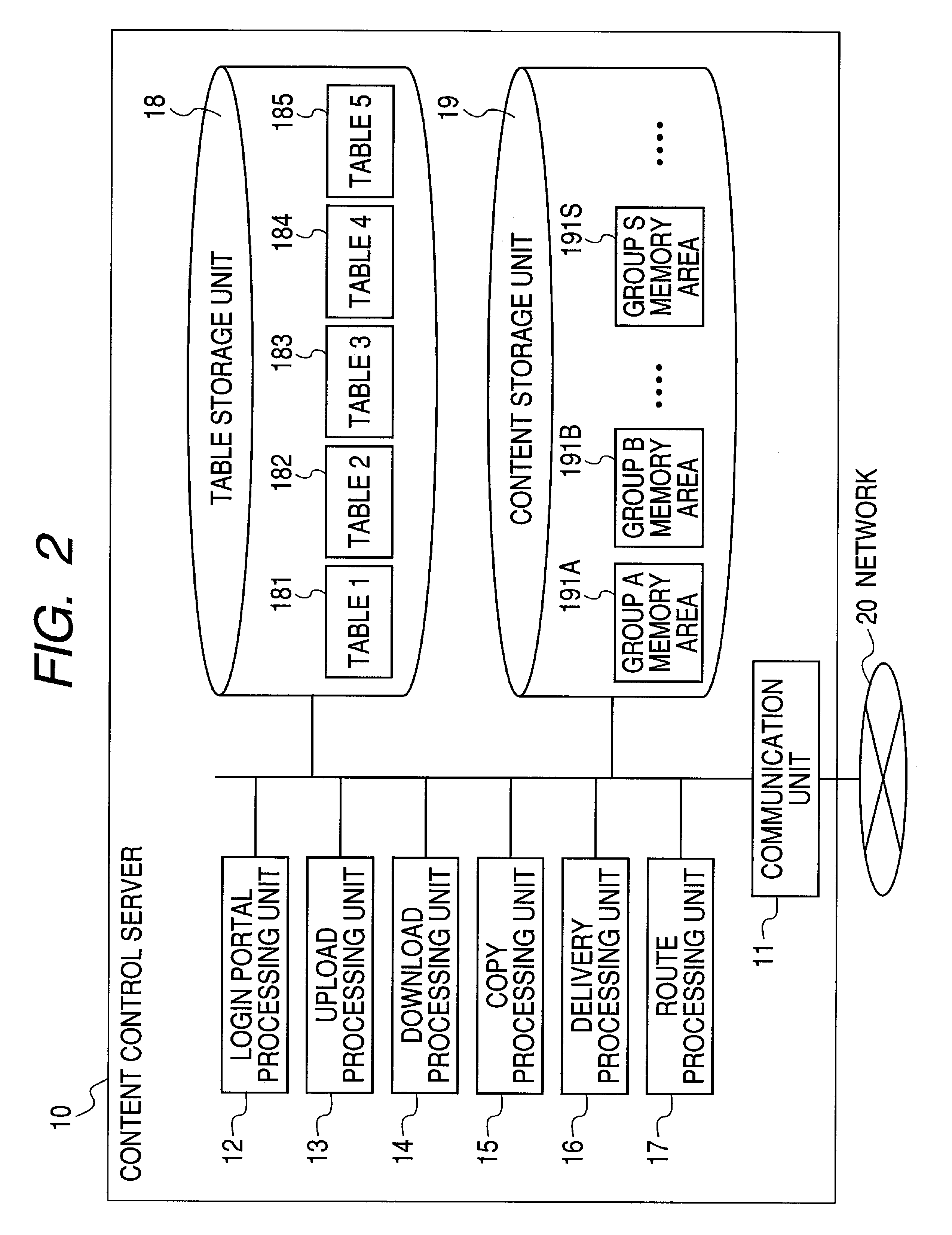

Content control system

InactiveUS20100050274A1Easy to controlReduce convenienceDigital data processing detailsAnalogue secracy/subscription systemsControl systemGroup memory

A content control system capable of controlling delivery destinations of user contents in respective groups, identifying each group through which each content is delivered, and delivering information / advertisements according to the attribution information of the content. In a content control server, group identifying information is set in each user content to be uploaded to or downloaded from a group memory area corresponding to a gateway ID from a terminal through a gateway having a plurality of its subordinate terminals. The information identifies each gateway through which each object content is delivered according to the gateway ID. The control system controls the delivery destination of each content according to the combination of the content delivery route and a table prepared in the content control server.

Owner:HITACHI LTD

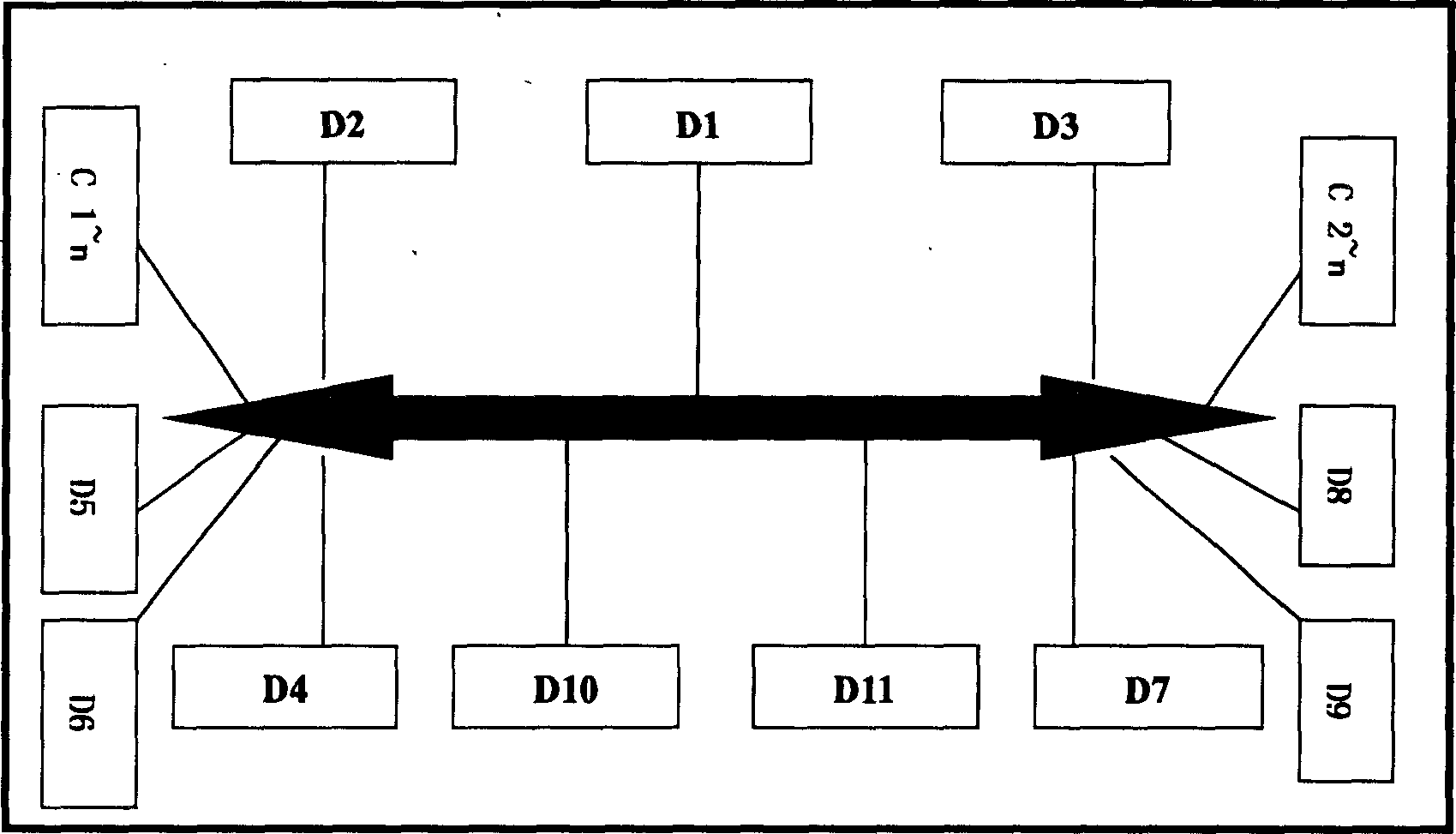

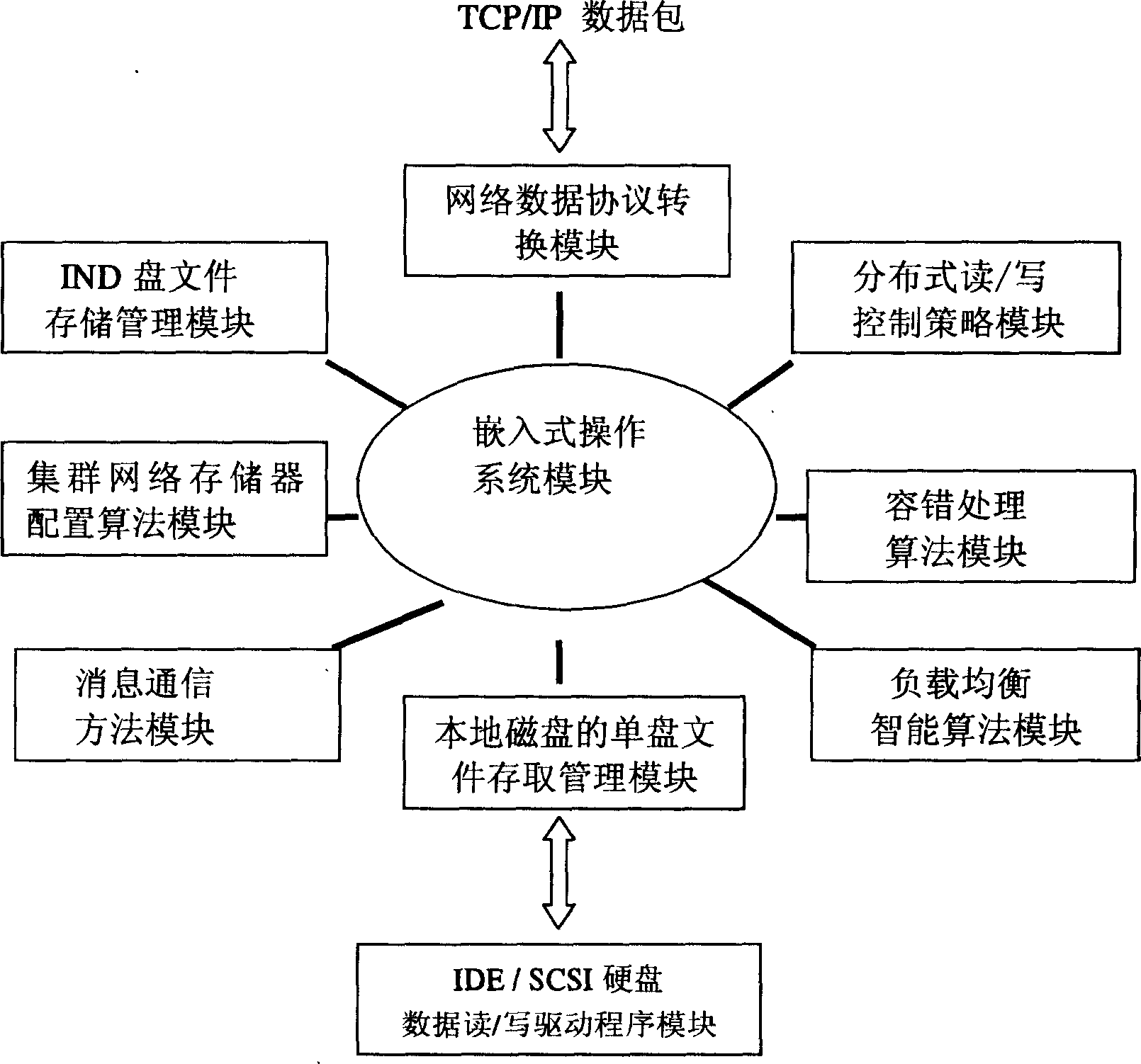

Intelligent network disc storage system and its realizing method

InactiveCN1829230AFast accessShort I/O pathInput/output to record carriersTransmissionVirtualizationIntelligent Network

The present invention provides a network disk memory system and implementation method. Said System is composed of two or more disk subsystems directly connected with network, wherein said network disk memory system set with fixed network address, said disk subsystem having different network sub-address and set with same file routing list. Each disk subsystem is directly connected with network, providing shortest I / O route for user's data file accessing, number of subsystems consisting of one group memory system, providing virtualized mass storage system to user.

Owner:SOUTH CHINA UNIV OF TECH

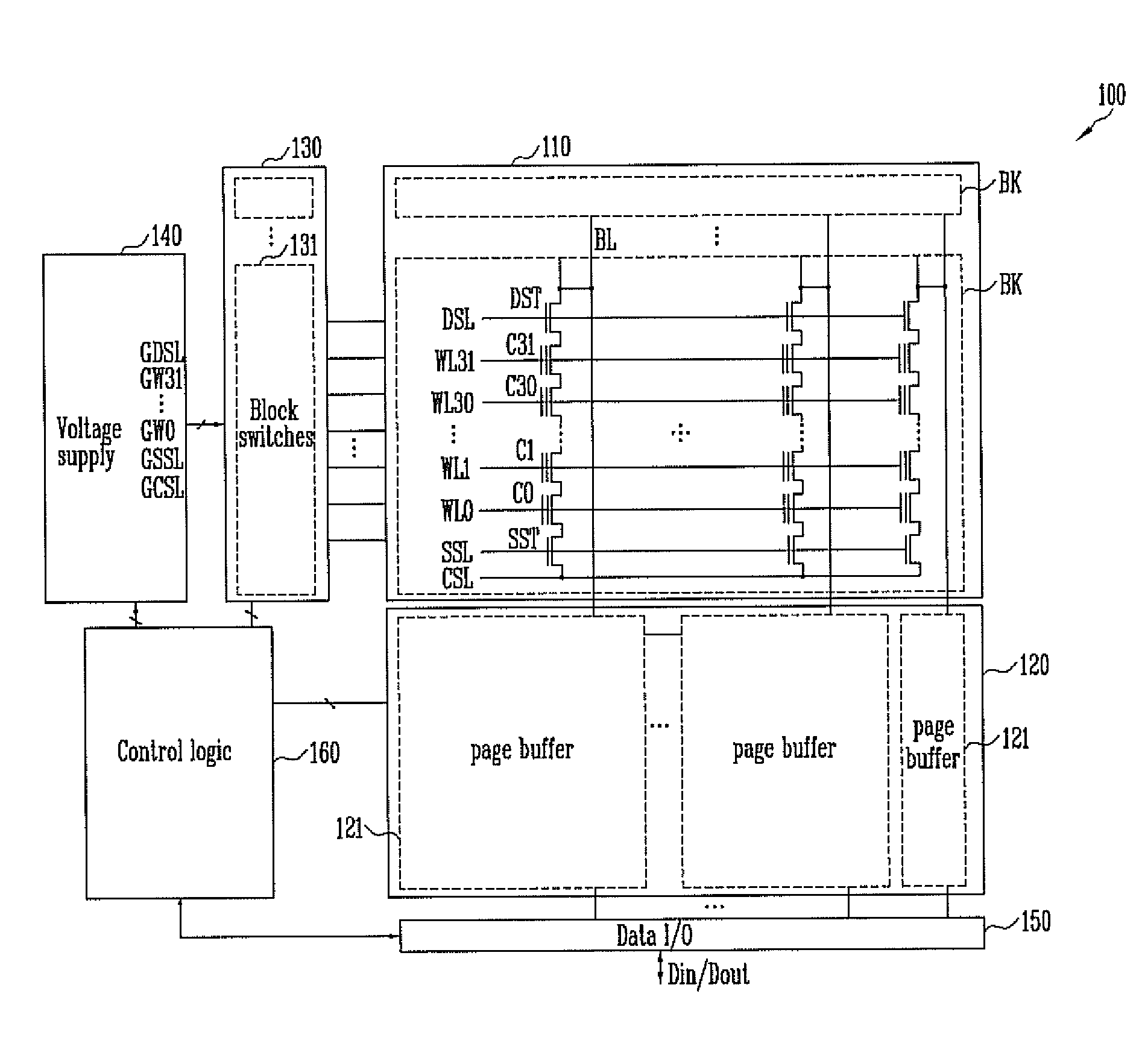

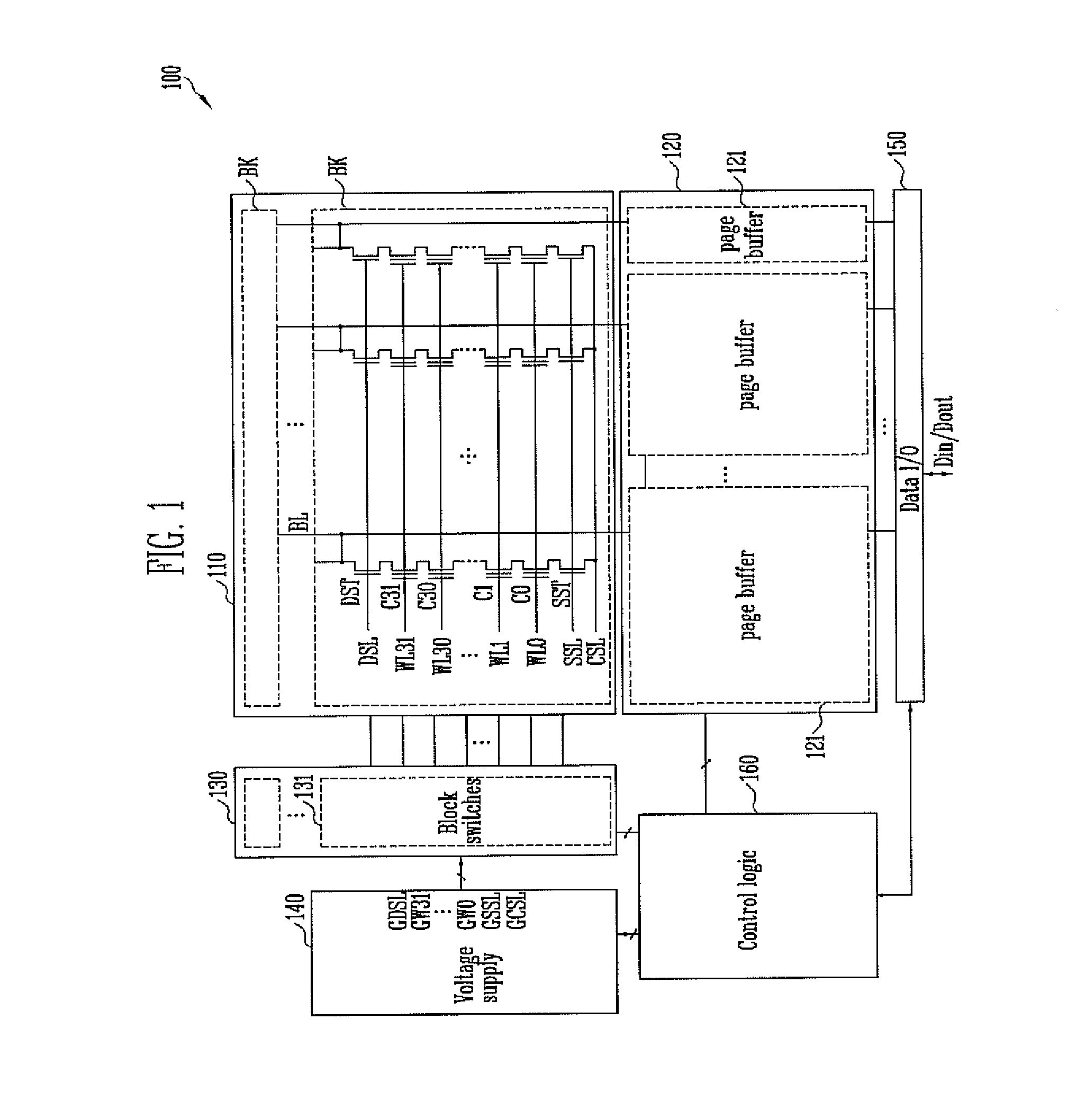

Method of programming a semiconductor memory device

ActiveUS8570801B2Reduce distractionsReduce probabilityRead-only memoriesDigital storageGroup memoryComputer science

A method of programming a semiconductor memory device includes the steps of grouping memory cells in accordance with levels of threshold voltages to be programmed, programming the memory cell groups by sequentially applying program voltages to the memory cell groups, and program-verifying the memory cell groups.

Owner:SK HYNIX INC

Memory control method, memory controller and memory storage device

The invention provides a memory control method, a memory controller and a memory storage device. The method comprises the steps of identifying whether a transmission mode between the memory storage device and a host computer system belongs to a first transmission mode or a second transmission mode, and grouping memory chips of the memory storage device into a plurality of memory chip groups. The method also comprises the steps of erasing data stored in the memory chips by a first erase mode when the transmission mode belongs to the first transmission mode, and erasing the data stored in the memory chips by a second erase mode when the transmission mode belongs to the second transmission mode, wherein at least one part of memory chip groups in the first erase mode can be simultaneously enabled, and any two memory chip groups in the second erase mode are not simultaneously enabled.

Owner:PHISON ELECTRONICS

Method of programming a semiconductor memory device

ActiveUS20110299341A1Reduce distractionsReduce probabilityRead-only memoriesDigital storageGroup memoryComputer science

A method of programming a semiconductor memory device includes the steps of grouping memory cells in accordance with levels of threshold voltages to be programmed, programming the memory cell groups by sequentially applying program voltages to the memory cell groups, and program-verifying the memory cell groups.

Owner:SK HYNIX INC

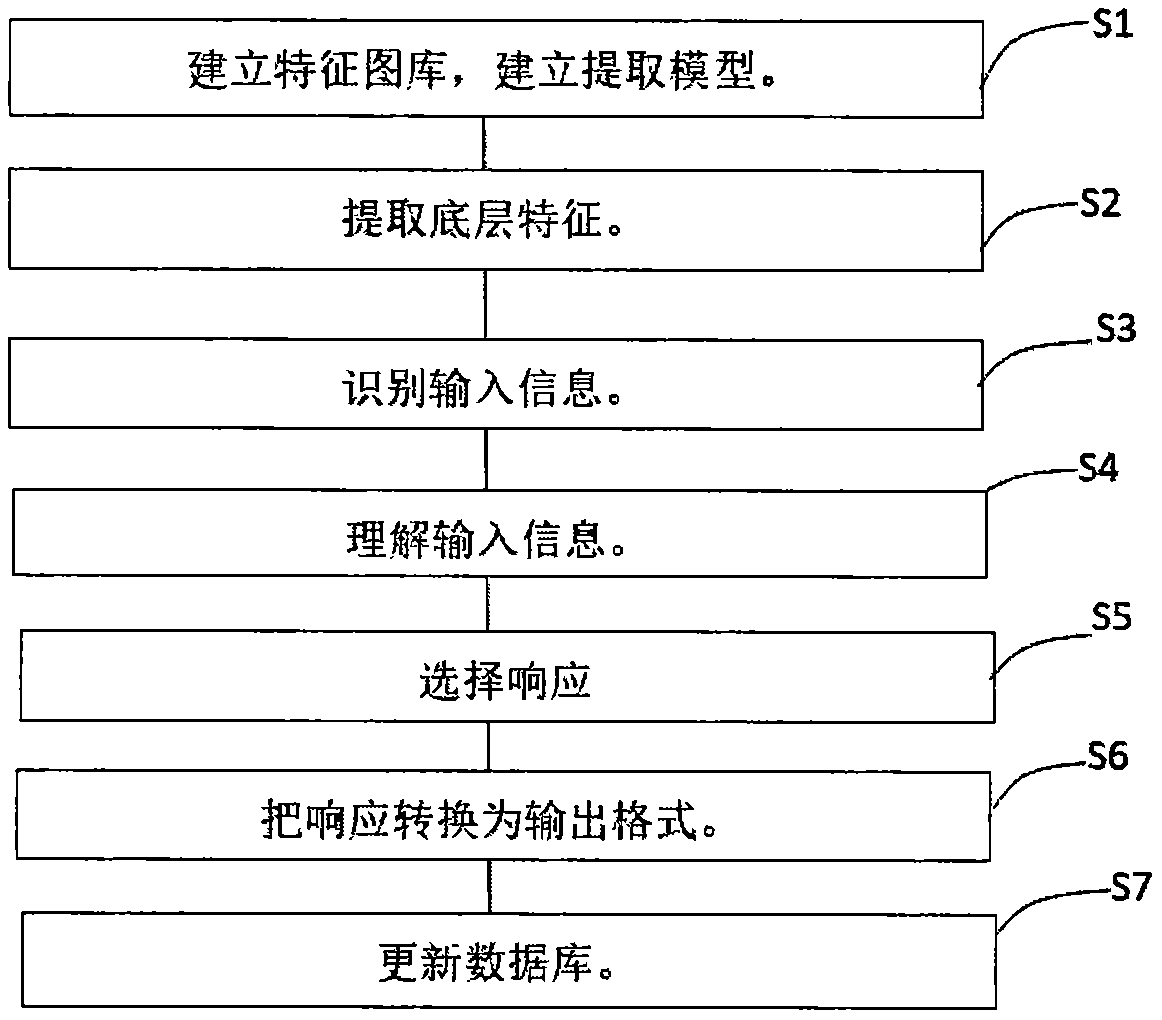

Method for realizing general artificial intelligence

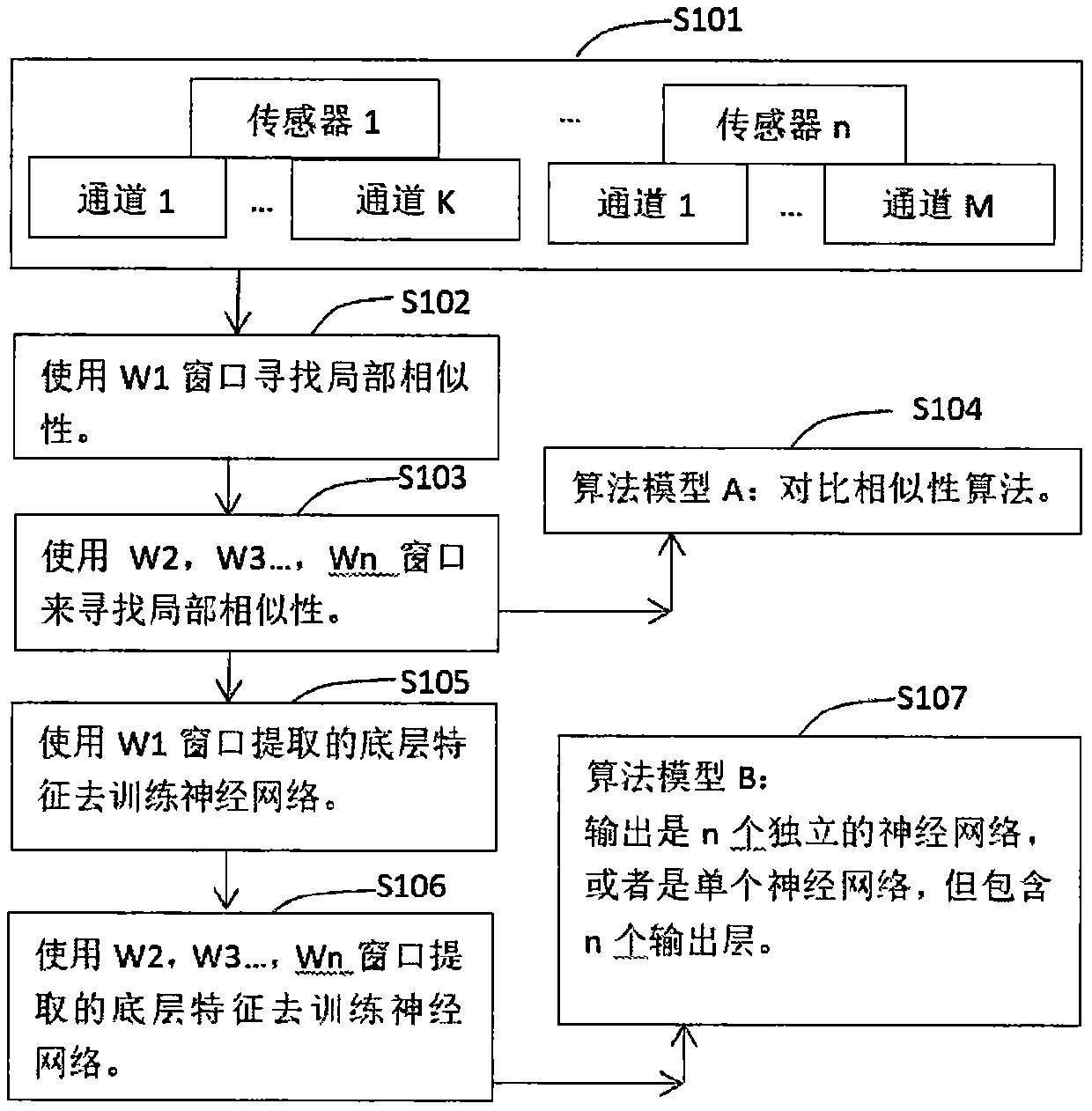

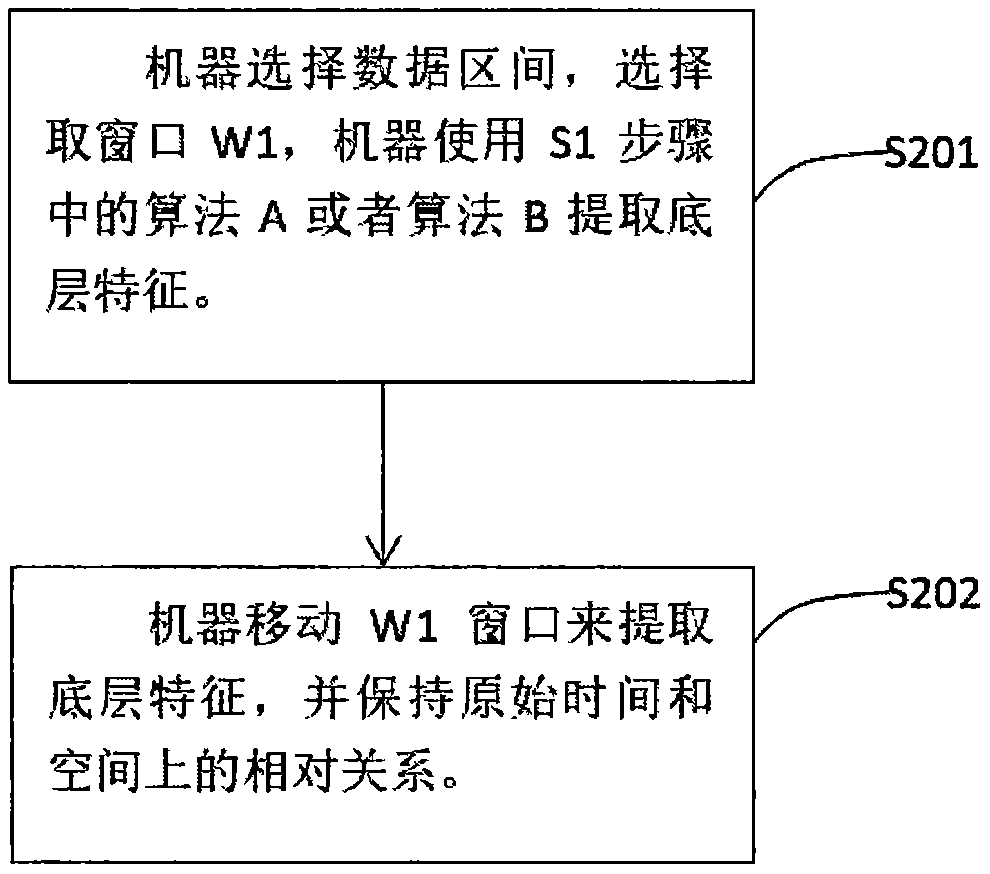

ActiveCN111553467ACharacter and pattern recognitionNeural architecturesAlgorithmArtificial general intelligence

The invention discloses a method for realizing general artificial intelligence. According to the method, only the similarity relation, the time relation and the space relation between the things needto be extracted, and a relation network between the things can be established under the optimization of a memory and forgetting mechanism. Information such as instinctive motivation, income and loss evaluation is also used as input information and is kept in memory. A machine only needs to arrange relations in memory, reorganize the memory by using the relations, select responses by using an income and loss evaluation system, and realize the responses through simulation, so that general artificial intelligence similar to human beings can be established.

Owner:陈永聪

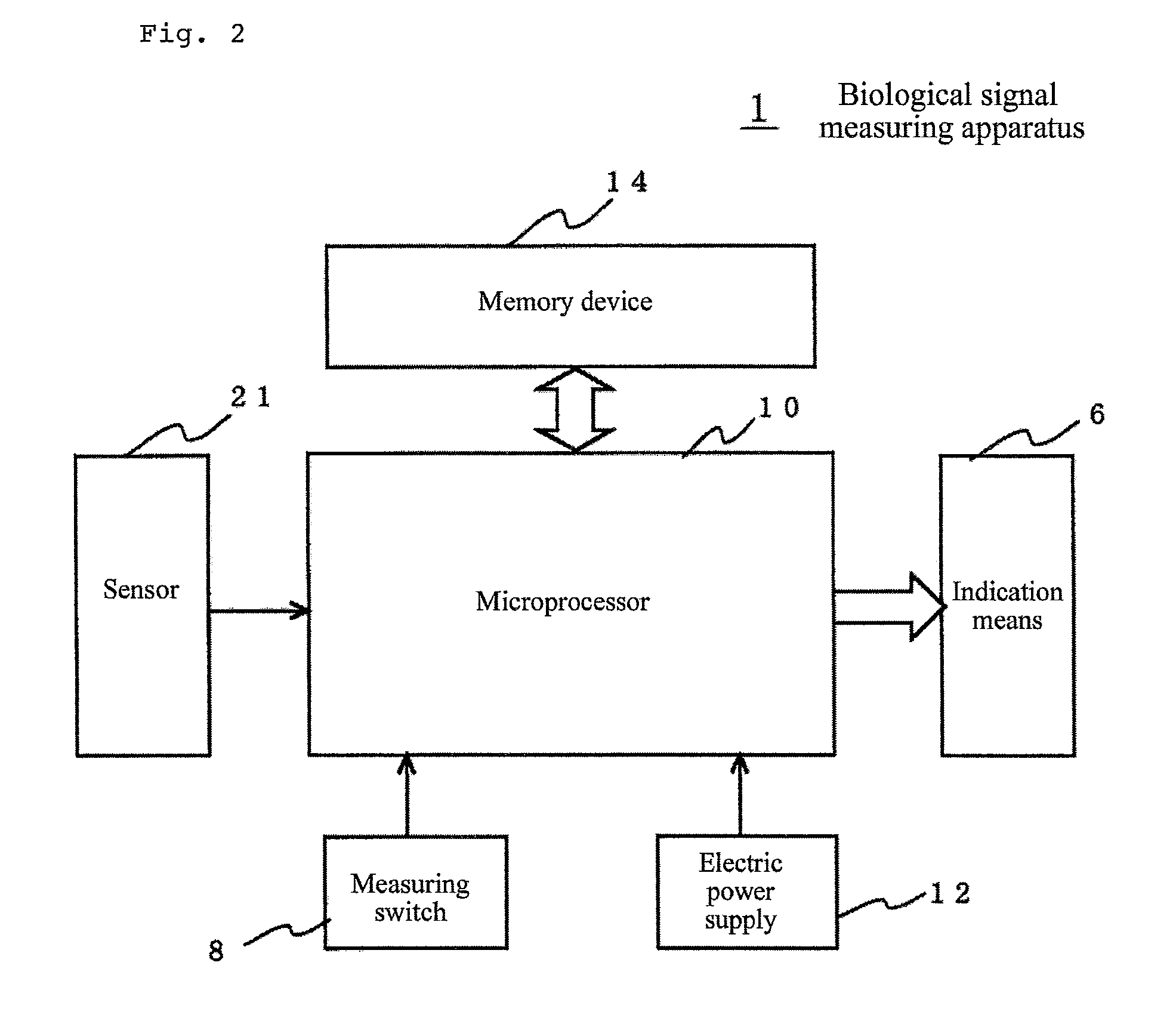

Biological Signal Measuring Apparatus

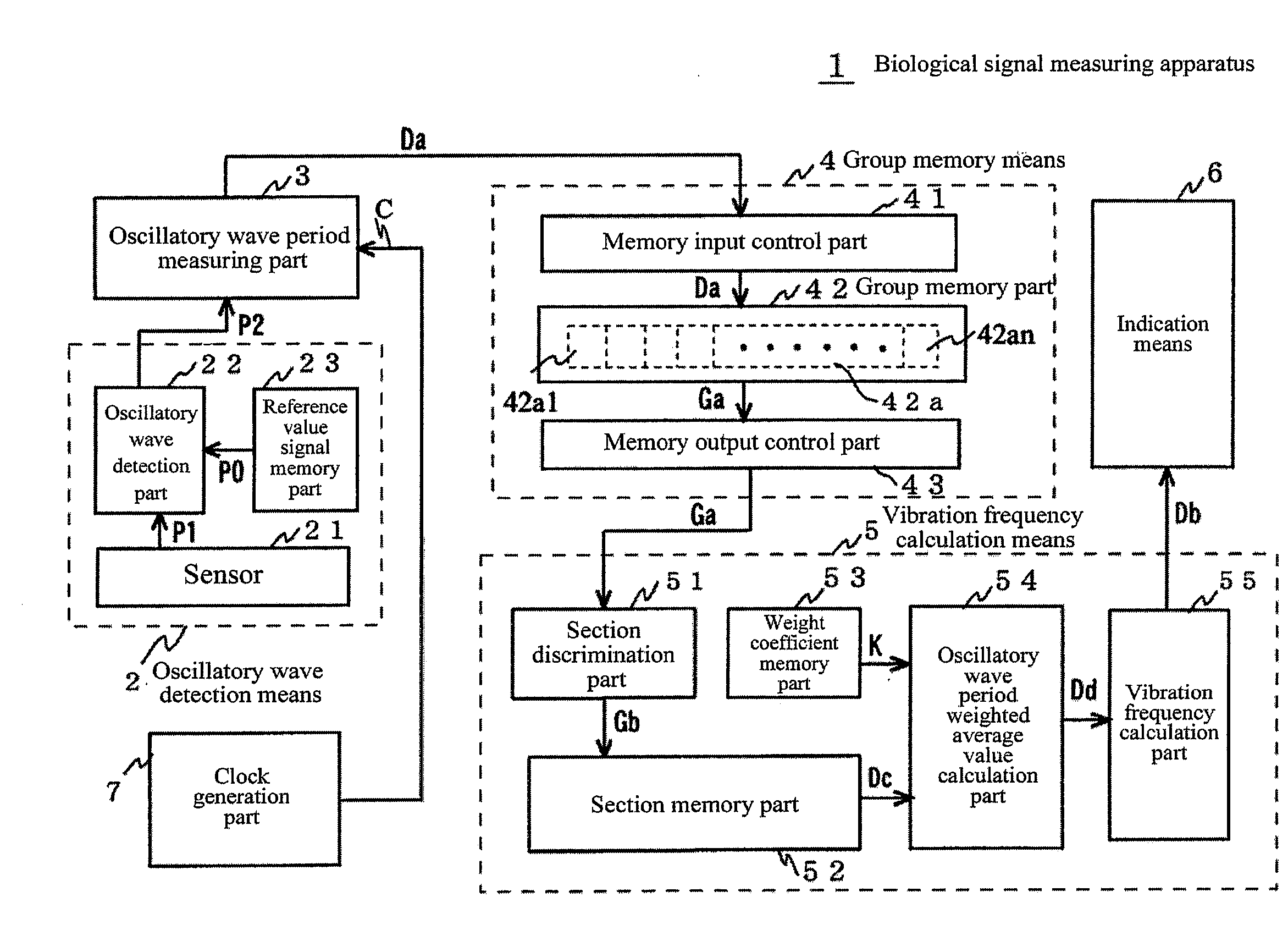

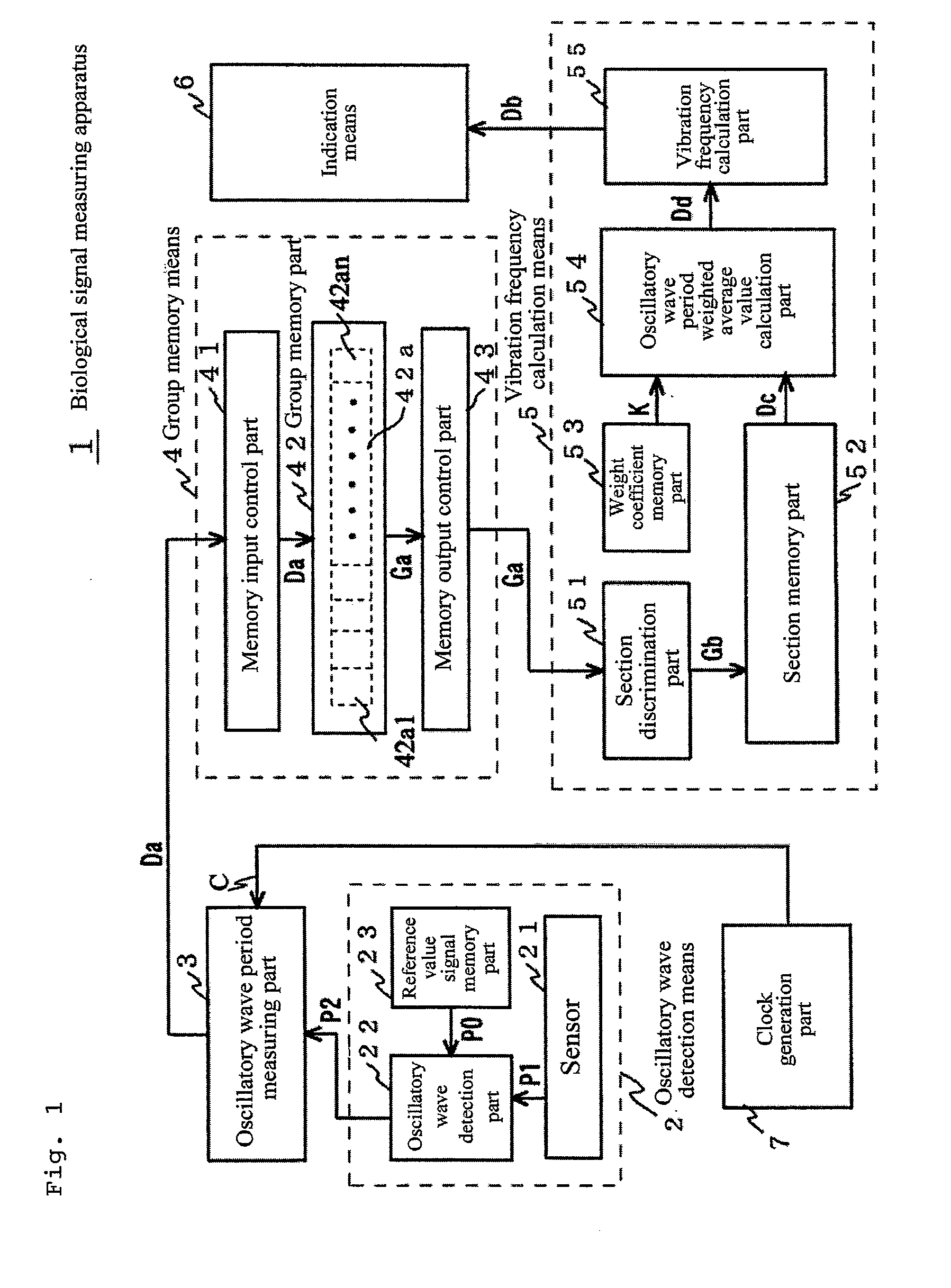

ActiveUS20100249662A1Weight coefficientImprovement factorElectrocardiographyPerson identificationWeight coefficientGroup memory

A biological signal measuring apparatus that is provided with an oscillatory wave detection means, an oscillatory wave period measuring part, a group memory means that is configured to collect the periodic data and to store the periodic data as a group signal, and a vibration frequency calculation means. The vibration frequency calculation means is provided with a section discrimination part configured to compare the group signal with a predetermined value to carry out a section discrimination, a section memory part configured to store to a plurality of sections, a weight coefficient memory part configured to store a weight coefficient, and an oscillatory wave period weighted average value calculation part.

Owner:CITIZEN WATCH CO LTD

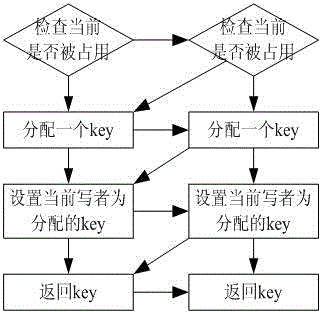

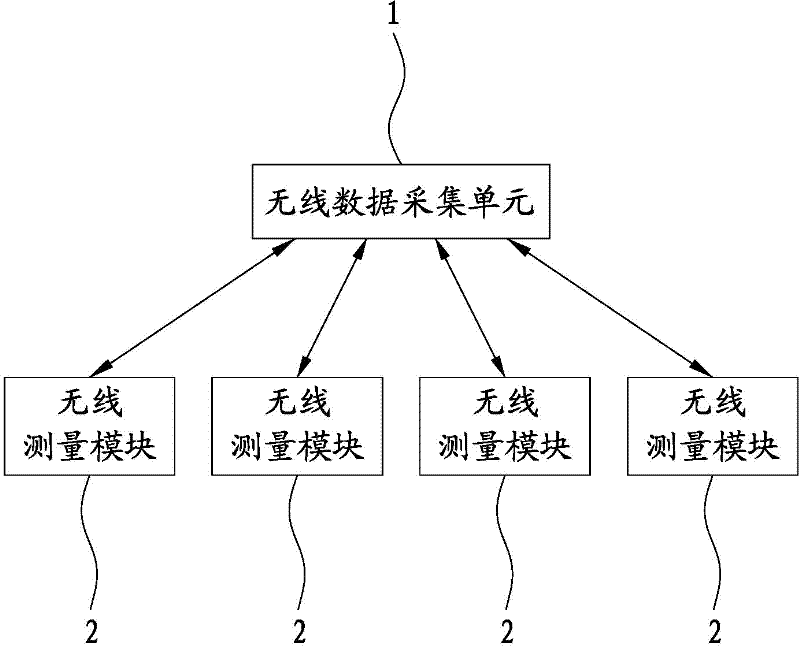

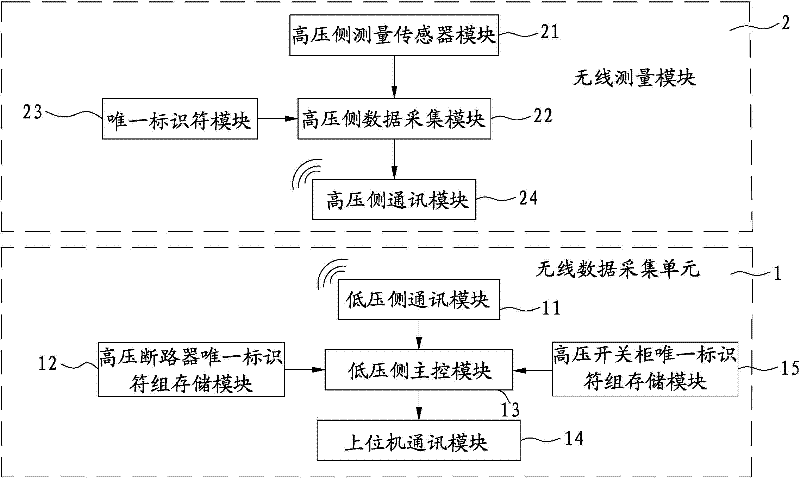

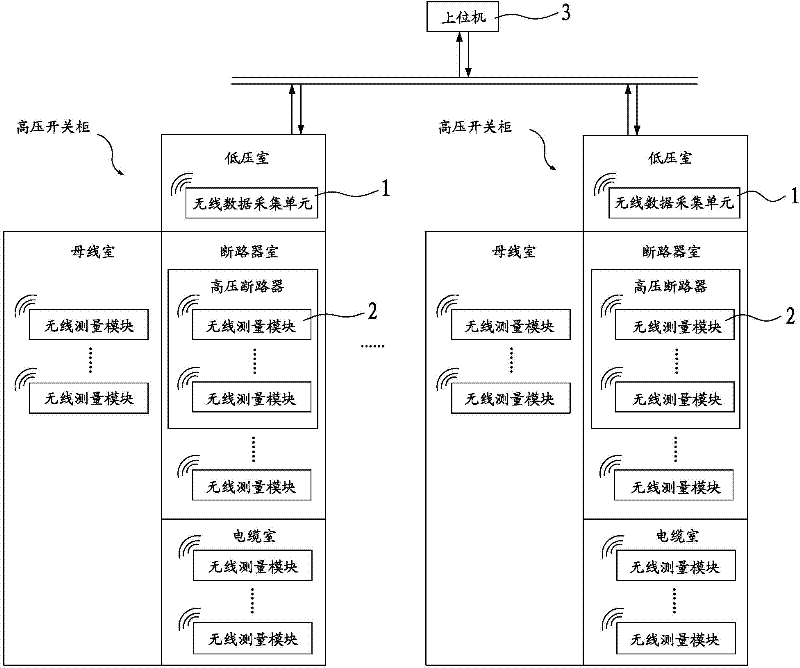

Quick networking device of wireless measuring modules and quick networking method thereof

ActiveCN102377116AFast networkingFully automatedTransmission systemsSwitchgearElectric power systemWireless data

The invention discloses a quick networking device of a plurality of wireless measuring modules and a quick networking method of a plurality of wireless measuring modules, belonging to the technical field of power on-line detection. The quick networking device comprises wireless measuring modules and wireless data acquiring units; each wireless measuring module consists of a high-pressure side measuring sensor module, a high-pressure side data acquiring module, an unique identifier module and a high-pressure side communicating module; and each wireless data acquiring unit consists of a low-pressure side communicating module, a low-pressure side master control module, an unique identifier group memory module and an upper computer communicating module. The unnecessary power outage time and maintenance working capacity can be reduced, the maintenance cost can be reduced, the automation of on-line monitoring treatment can be realized, and the reliability of a power system can be observably improved.

Owner:ABB (SCHWEIZ) AG

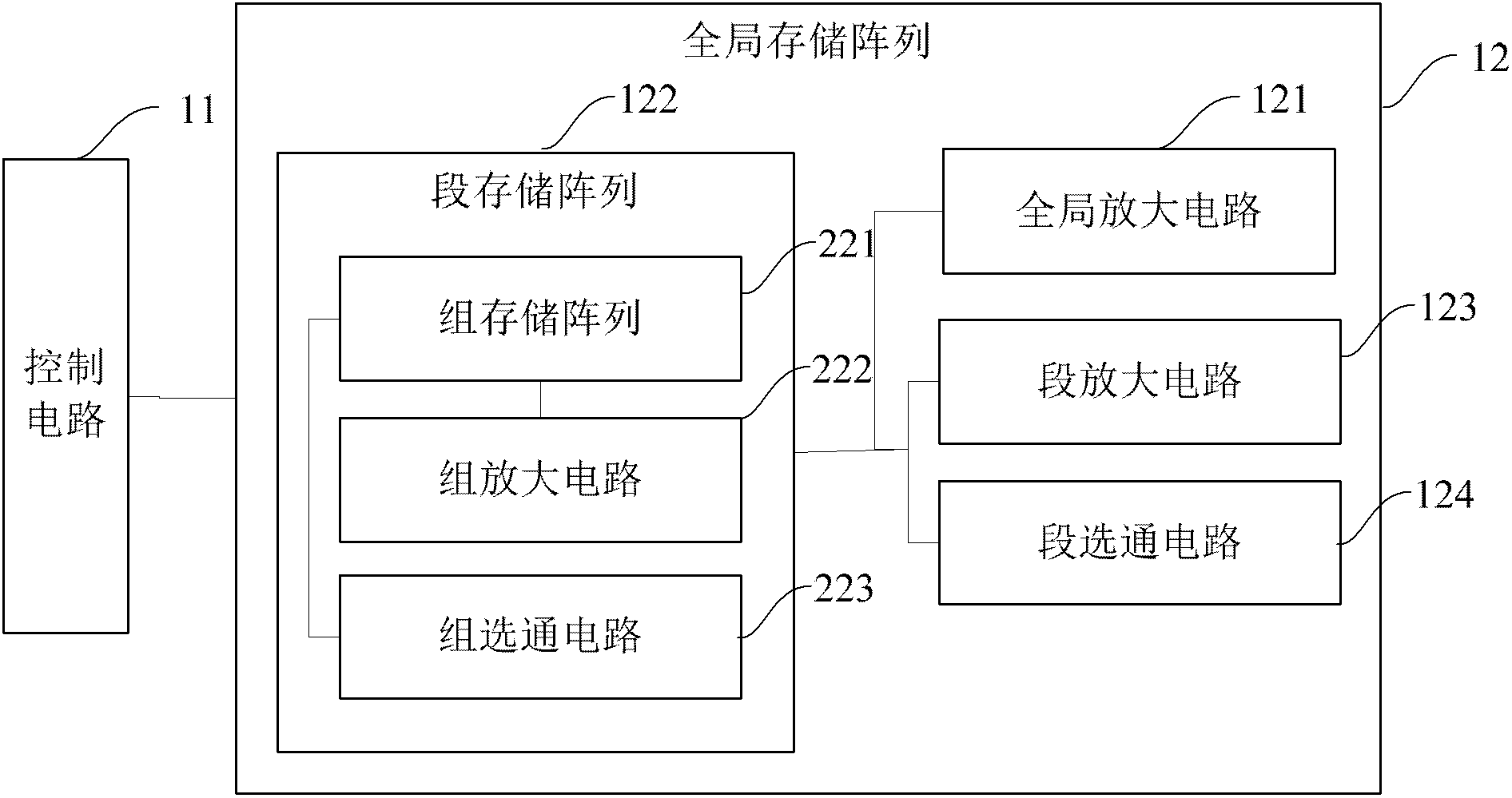

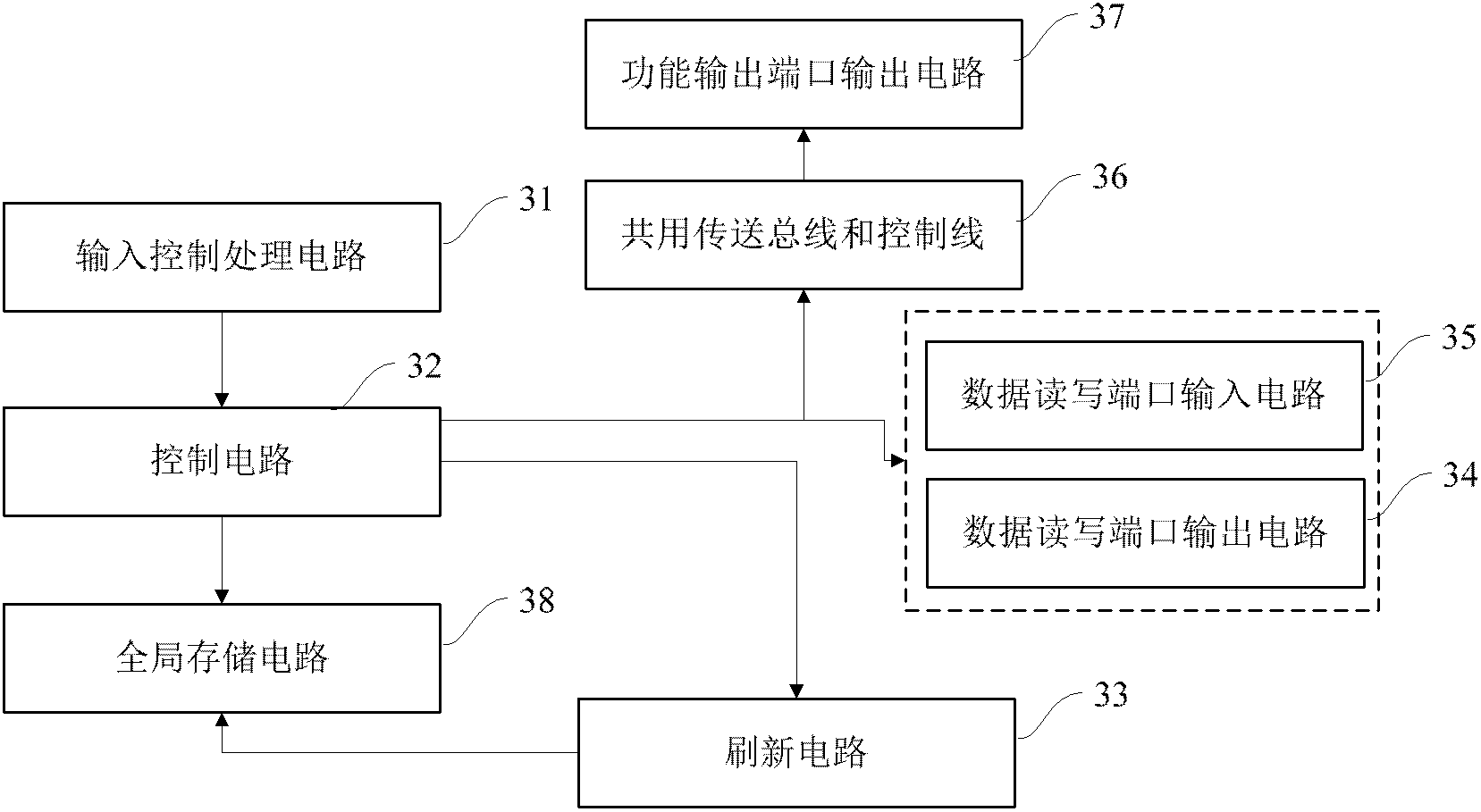

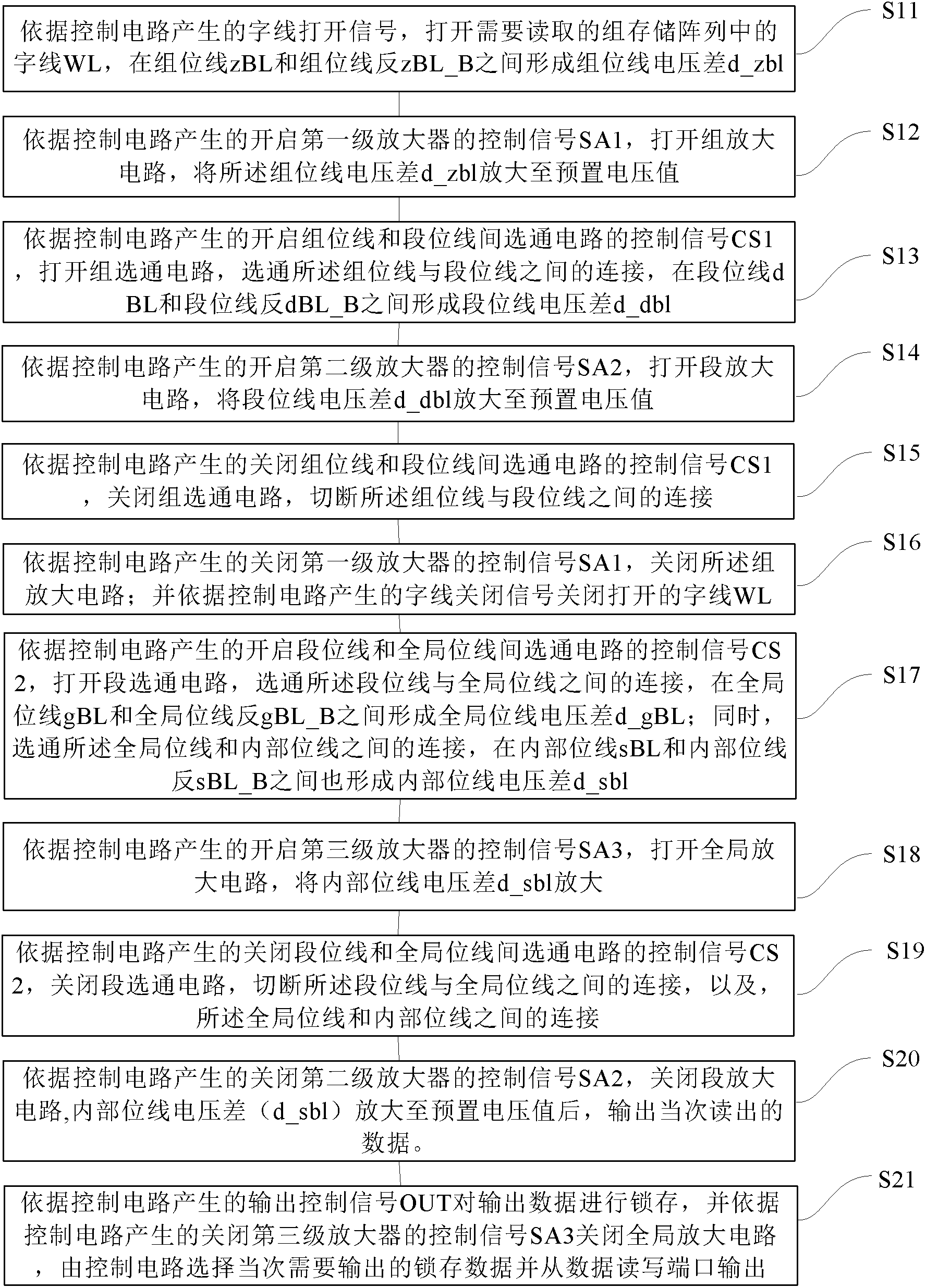

Memory circuit and method for reading data by applying same

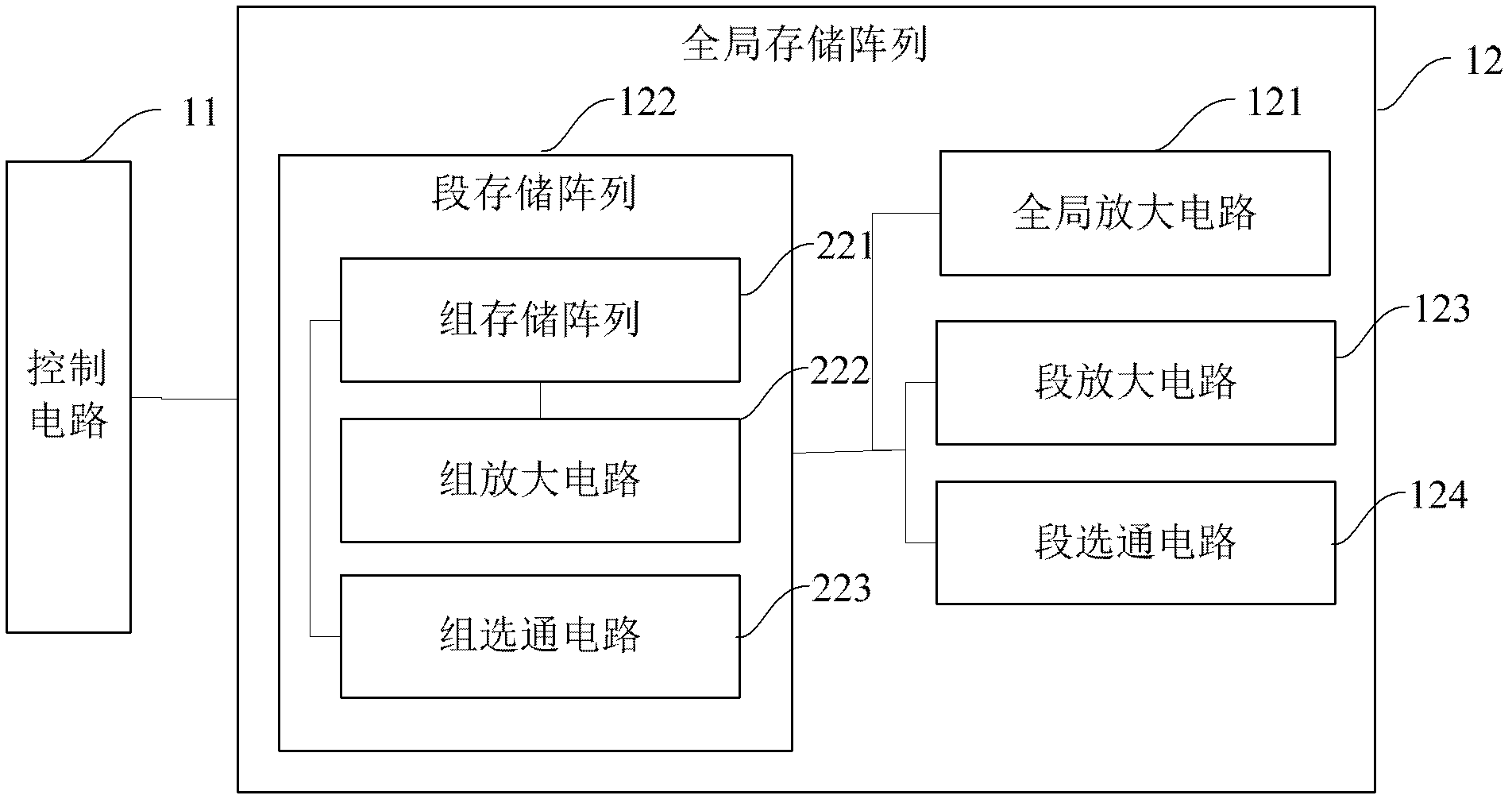

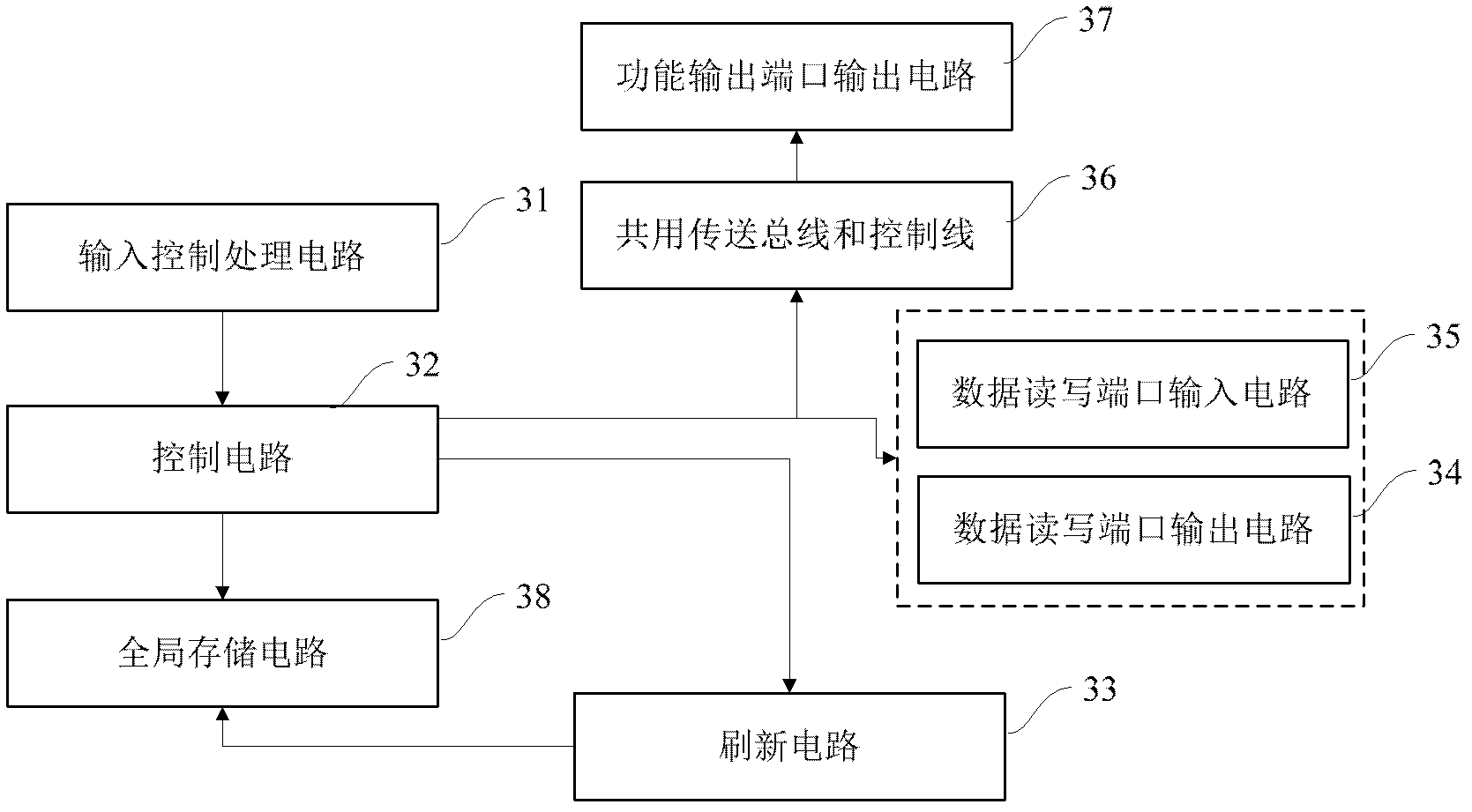

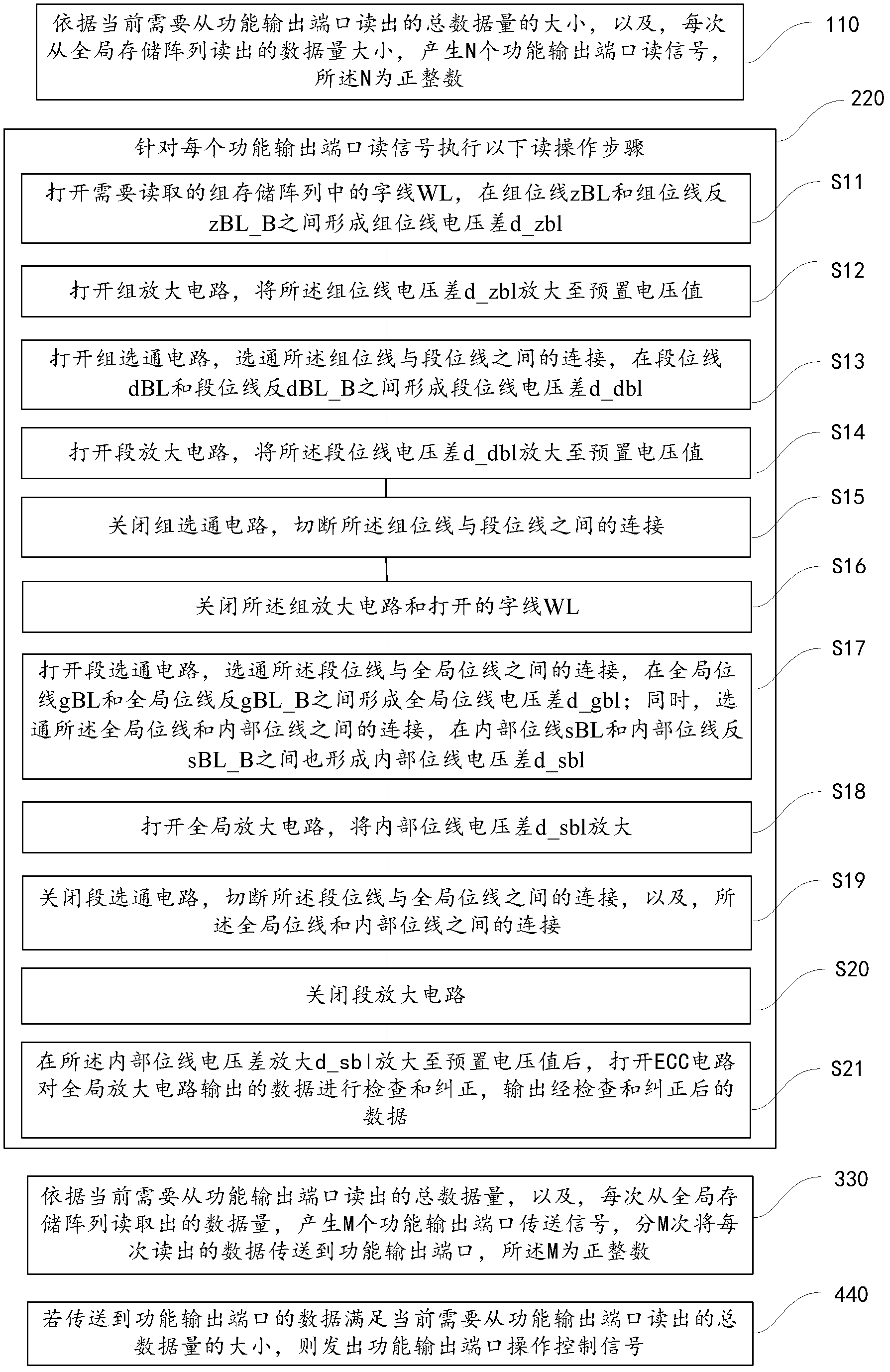

ActiveCN102332288AGuaranteed accuracyImprove yieldDigital storageComputer architectureMemory circuits

The invention provides a memory circuit and a method for reading data by applying the same. The memory circuit comprises a control circuit and a global memory array which are connected with each other, wherein the global memory array comprises a global amplifying circuit, at least a segment memory array, segment amplifying circuits and segment gating circuits, wherein the segment amplifying circuits and the segment gating circuits are connected with the segment memory arrays; each segment memory array comprises at least a group memory array, group amplifying circuits and group gating circuits, wherein the group amplifying circuits and the group gating circuits are connected with the group memory arrays; and the control circuit comprises a read / write control unit and an ECC (error correcting code) circuit. The memory circuit and the method have the following advantage: the area can be reduced as far as possible on the basis of realizing the functions of a static memory circuit.

Owner:GIGADEVICE SEMICON SHANGHAI INC +1

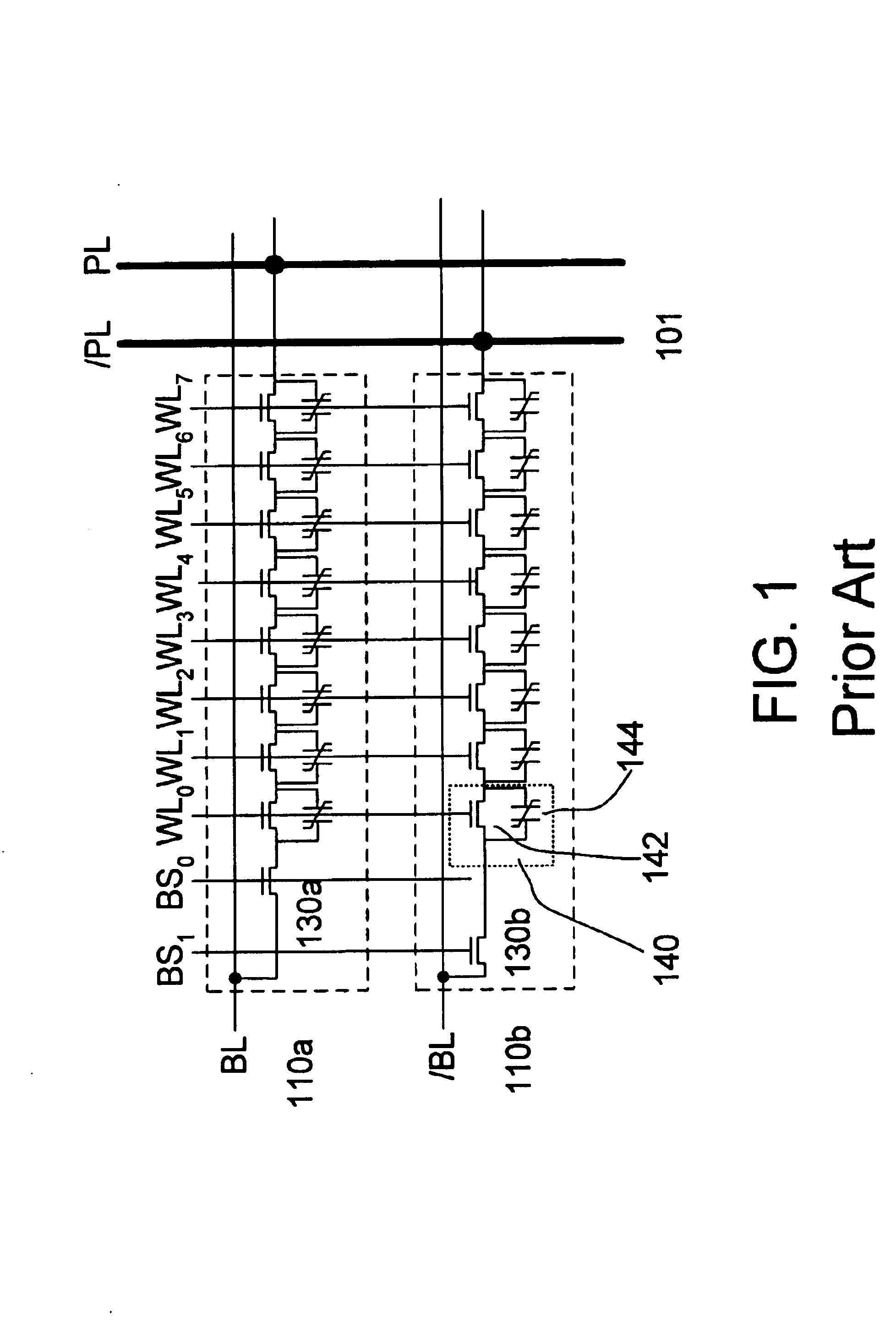

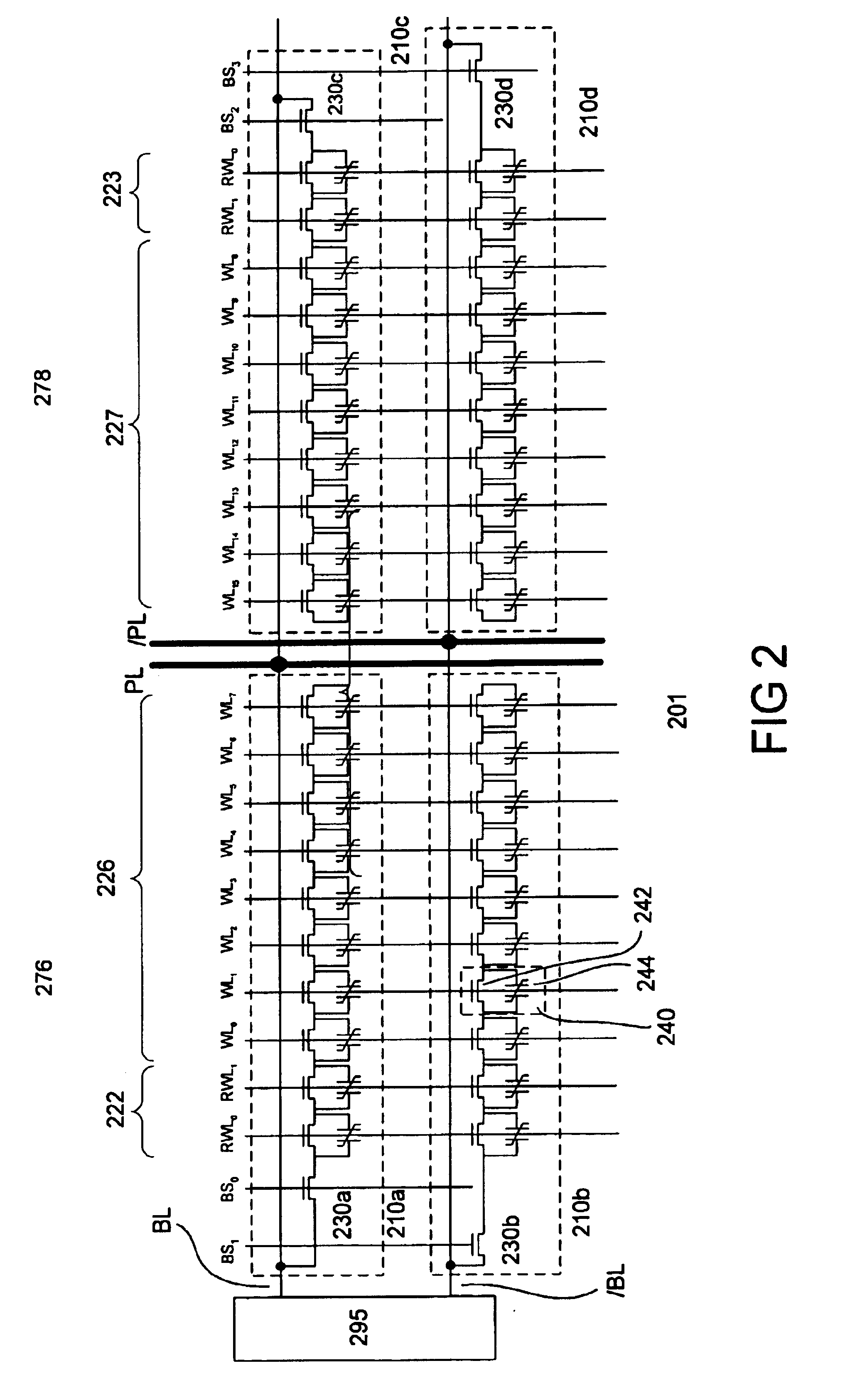

Redundancy in series grouped memory architecture

An improved redundancy scheme for chained memory architecture is disclosed. The redundancy scheme comprises including redundant cells as part of the memory chain. As such, a redundant cell is used to repair a defective cell within the chain. This eliminates the need in conventional chained architecture to replace the whole memory block when there is a defective cell.

Owner:POLARIS INNOVATIONS

Data reading method and data writing method of memory circuit

ActiveCN102332296ASmall footprintImprove read and write speedDigital storageParallel computingMemory circuits

The invention provides a data reading method of a memory circuit and a data writing method of the memory circuit. A global memory array is adopted in the memory circuit; a multi-stage and multi-segment mode is adopted by the global memory array; the global memory array is divided into a group memory array and a segment memory array; the segment memory array comprises the group memory array and a group amplifying gate circuit; the global memory array comprises the segment memory array, a segment amplifying gate circuit and a global amplifying circuit; the global amplifying circuit is connectedwith the segment amplifying gate circuit through a global bit line; the segment amplifying gate circuit is connected with the group amplifying gate circuit through a segment bit line; the group amplifying gate circuit is connected with a memory unit in the group array through a group bit line; and through the multi-stage and multi-segment mode, the occupied area of a memory can be small and the swing amplitude of bit line voltage can also be effectively reduced in the layout, so that the aim of reducing power consumption is fulfilled. During data reading and writing operation, the operation is only required to be performed aiming at the currently selected bit line when the global memory array is adopted, so that the reading and writing speed of a memory can also be effectively increased.

Owner:GIGADEVICE SEMICON (BEIJING) INC

Content control system

InactiveUS8272062B2Easy to controlReduce convenienceDigital data processing detailsAnalogue secracy/subscription systemsControl systemGroup memory

A content control system capable of controlling delivery destinations of user contents in respective groups, identifying each group through which each content is delivered, and delivering information / advertisements according to the attribution information of the content. In a content control server, group identifying information is set in each user content to be uploaded to or downloaded from a group memory area corresponding to a gateway ID from a terminal through a gateway having a plurality of its subordinate terminals. The information identifies each gateway through which each object content is delivered according to the gateway ID. The control system controls the delivery destination of each content according to the combination of the content delivery route and a table prepared in the content control server.

Owner:HITACHI LTD

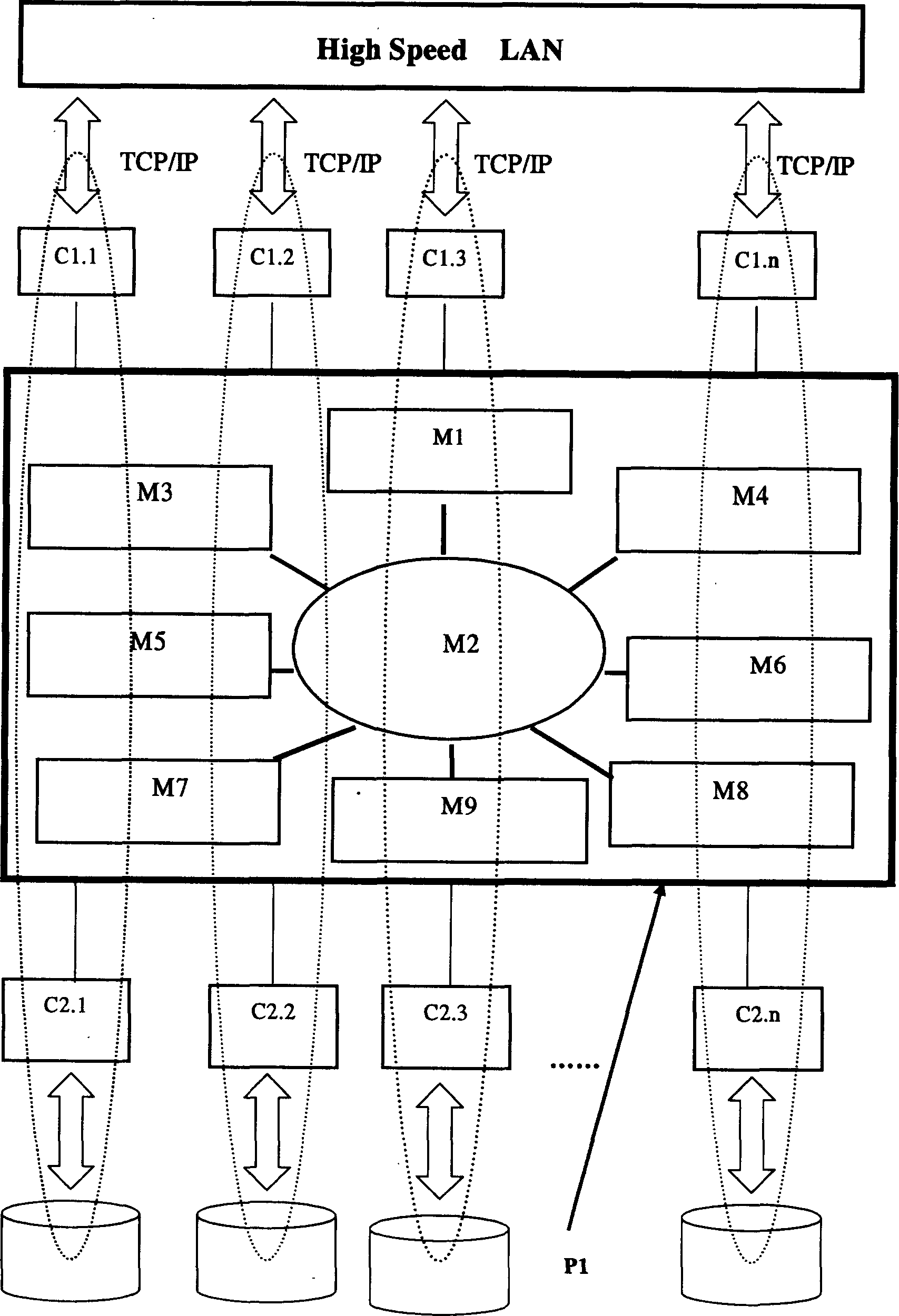

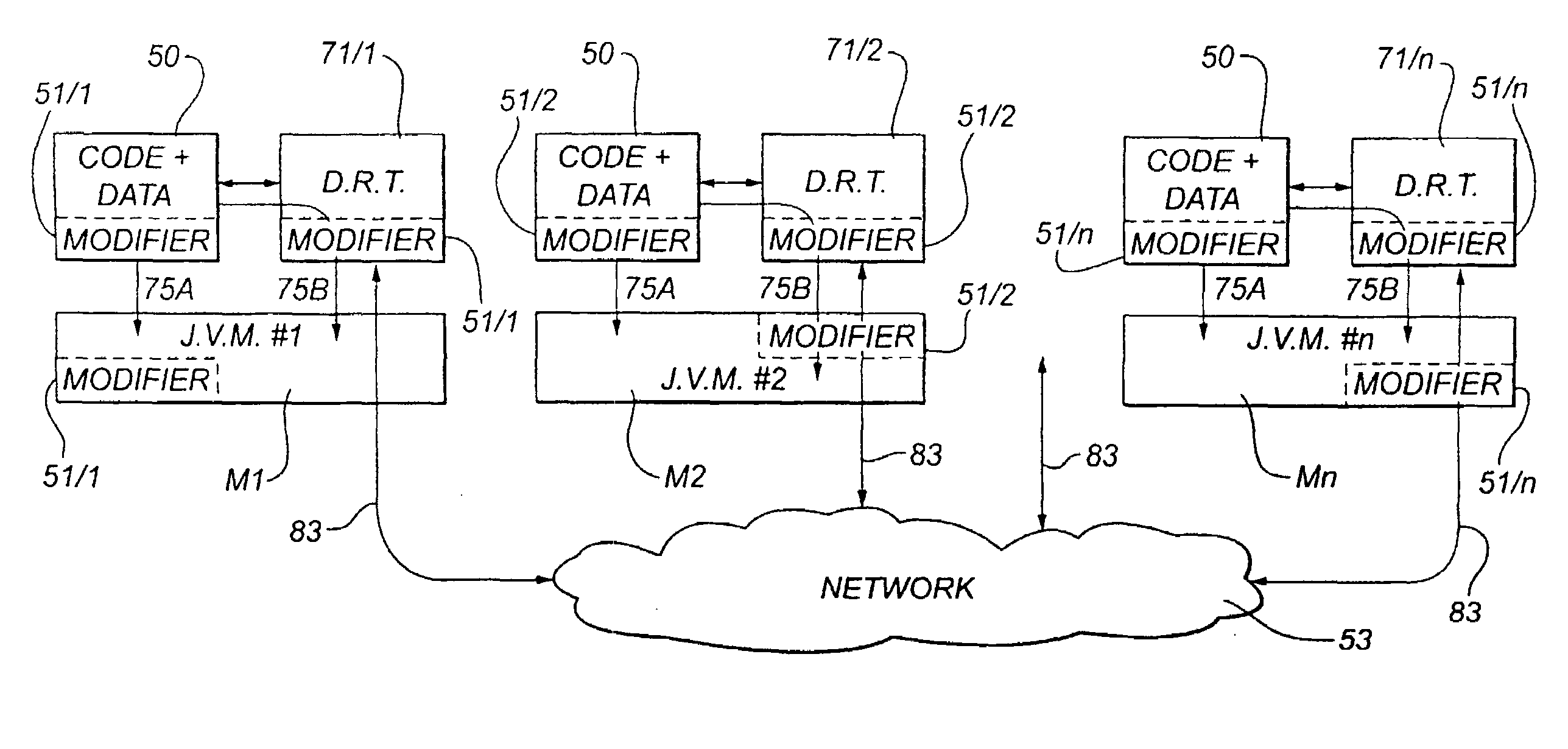

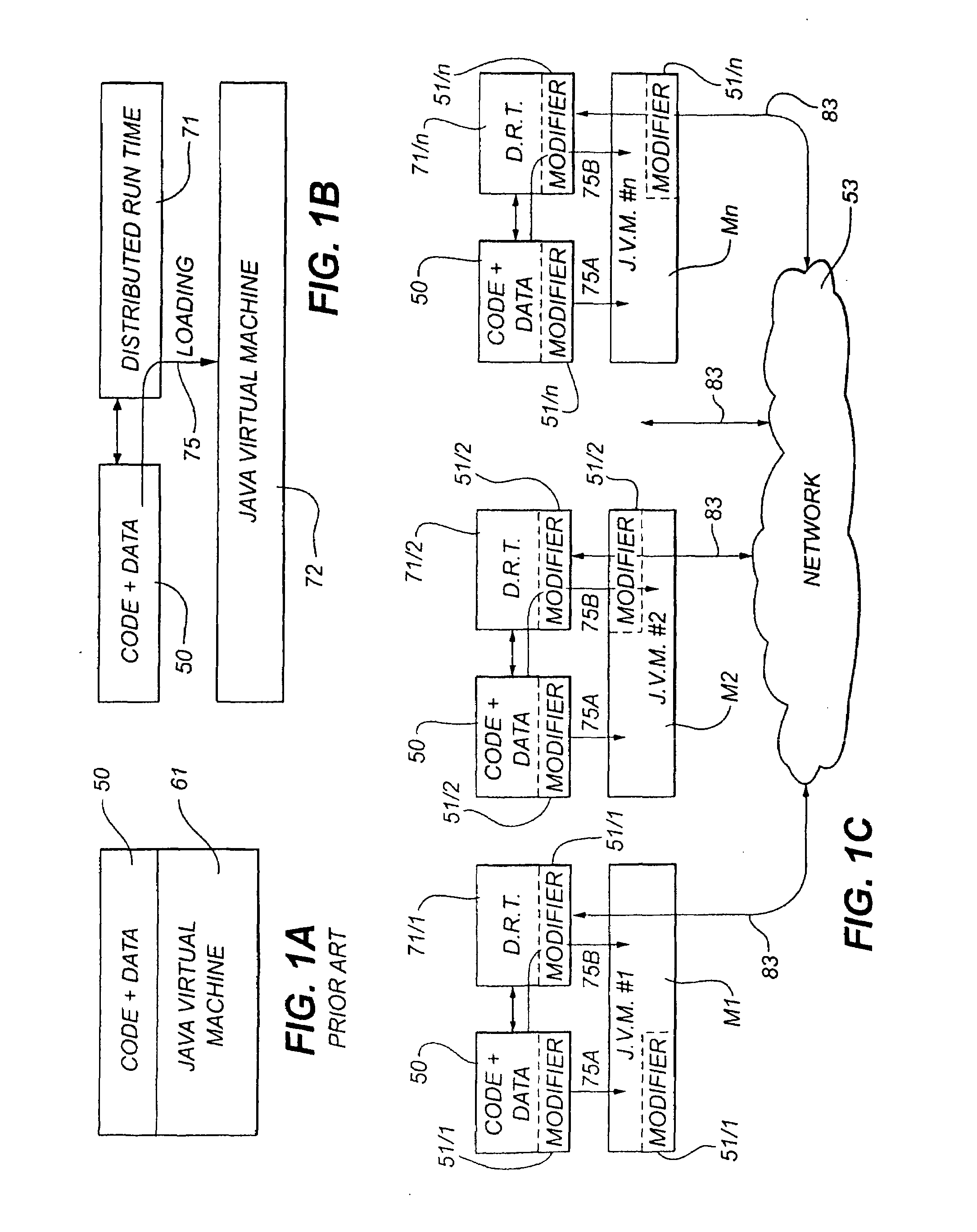

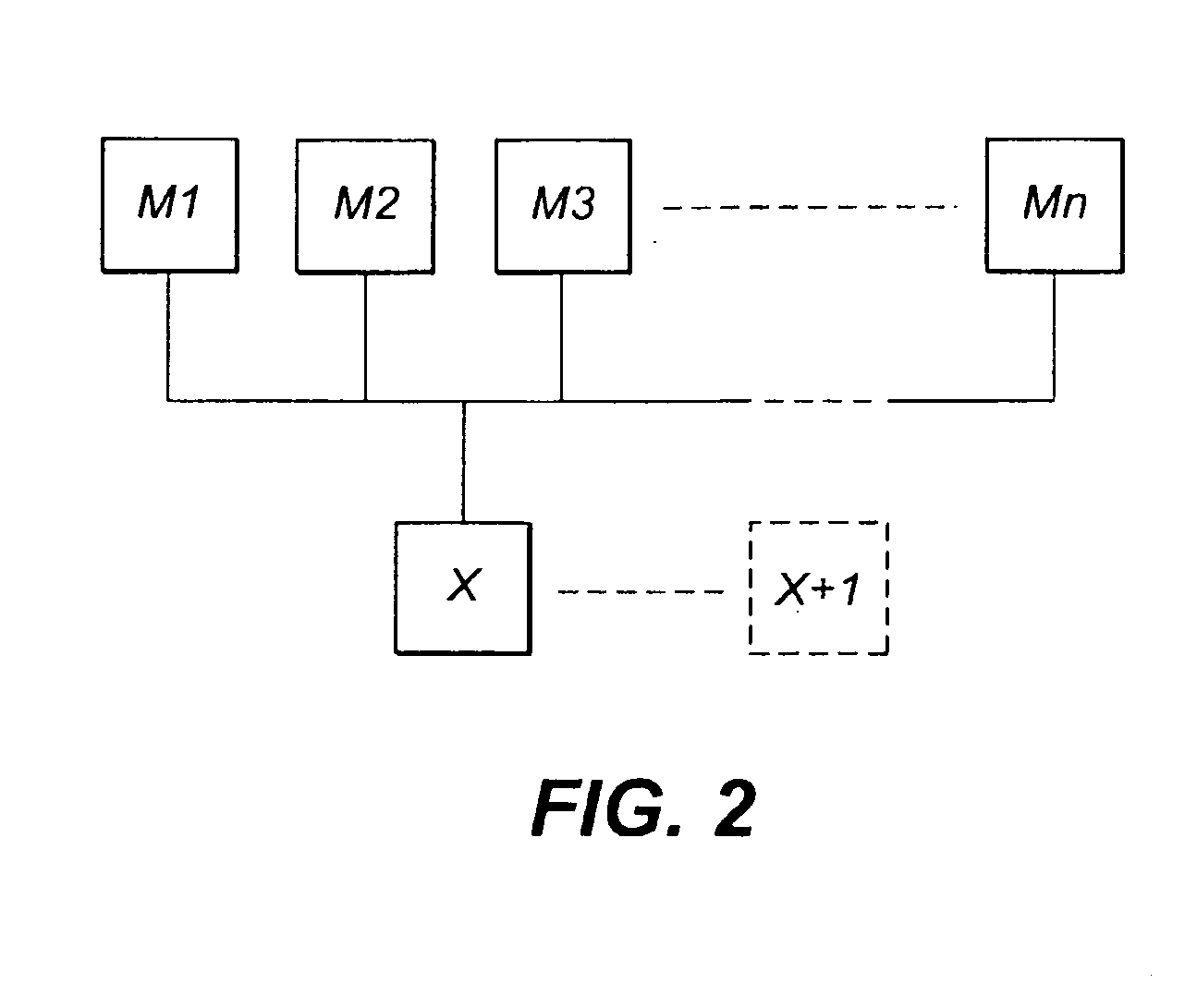

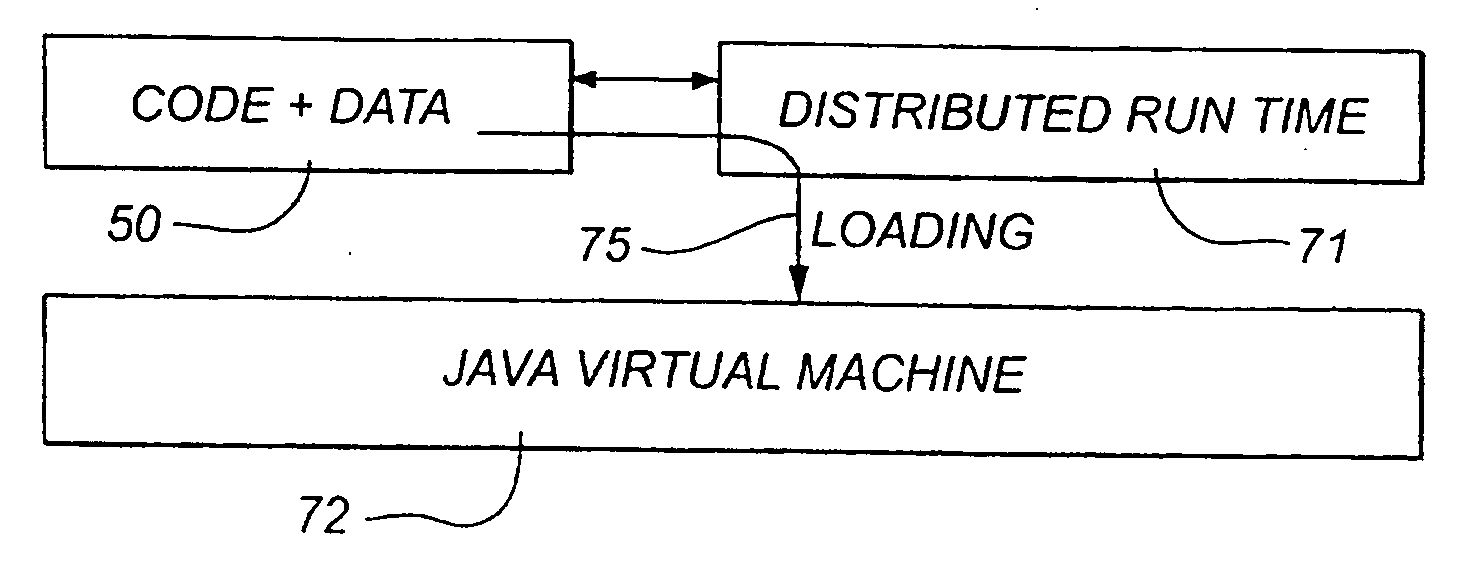

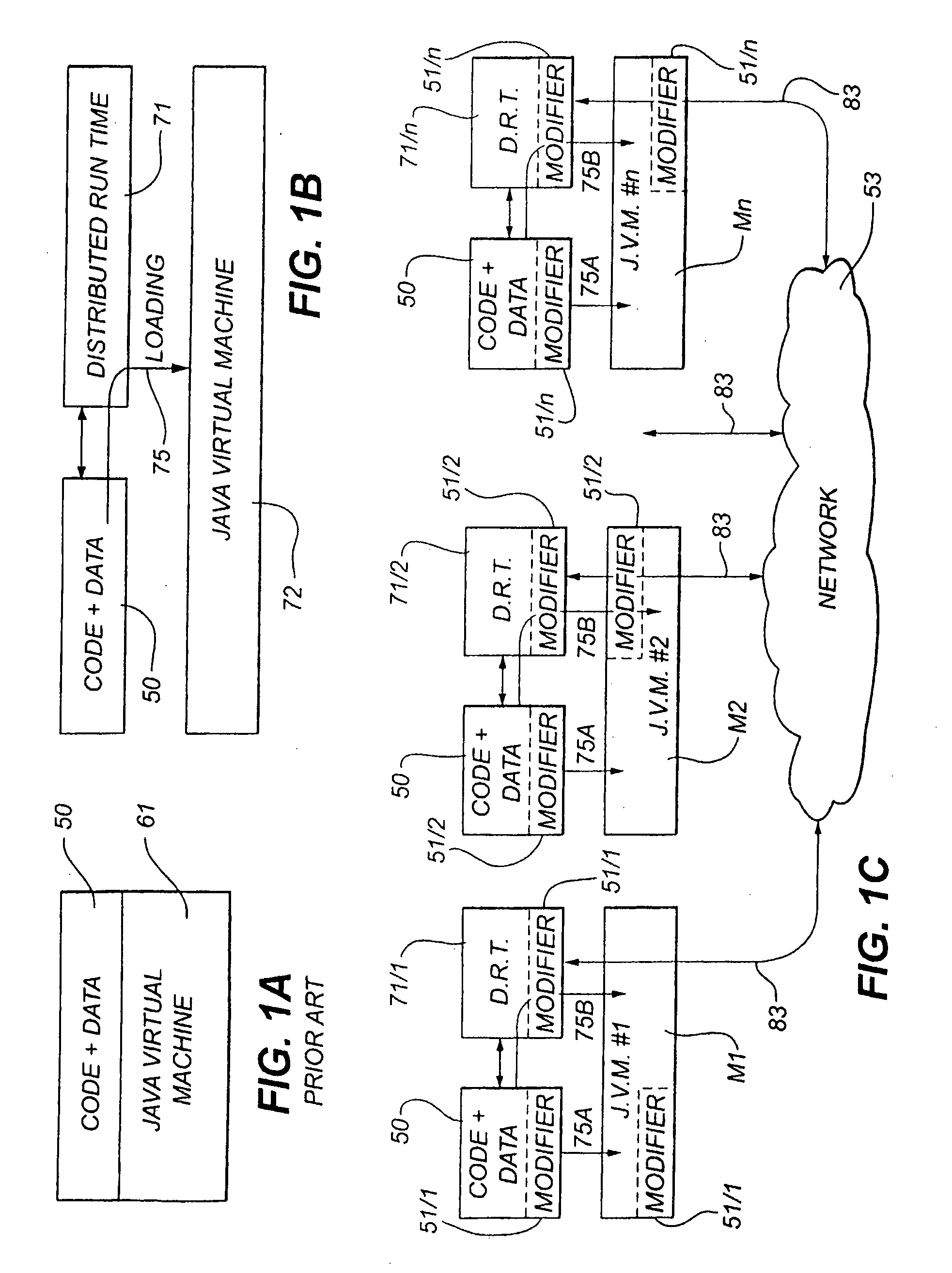

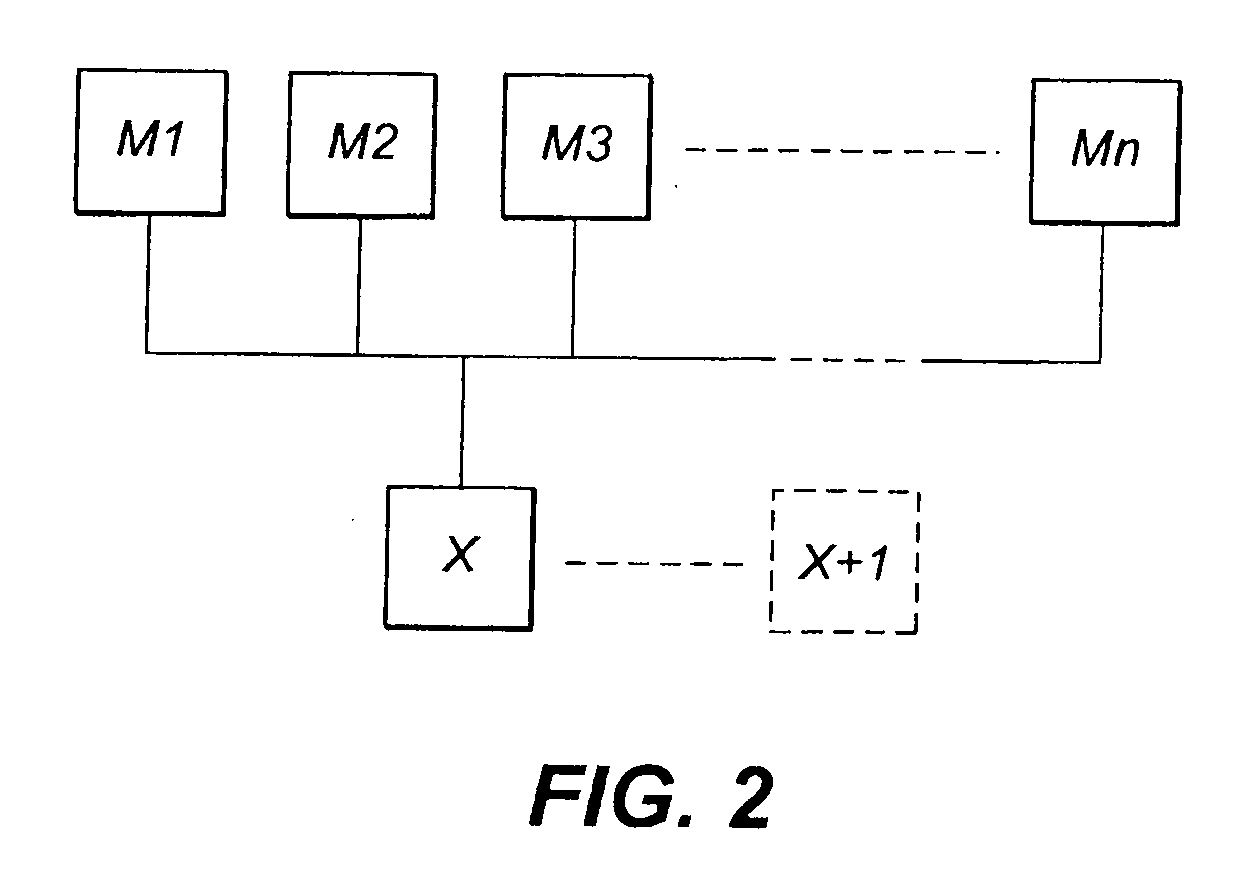

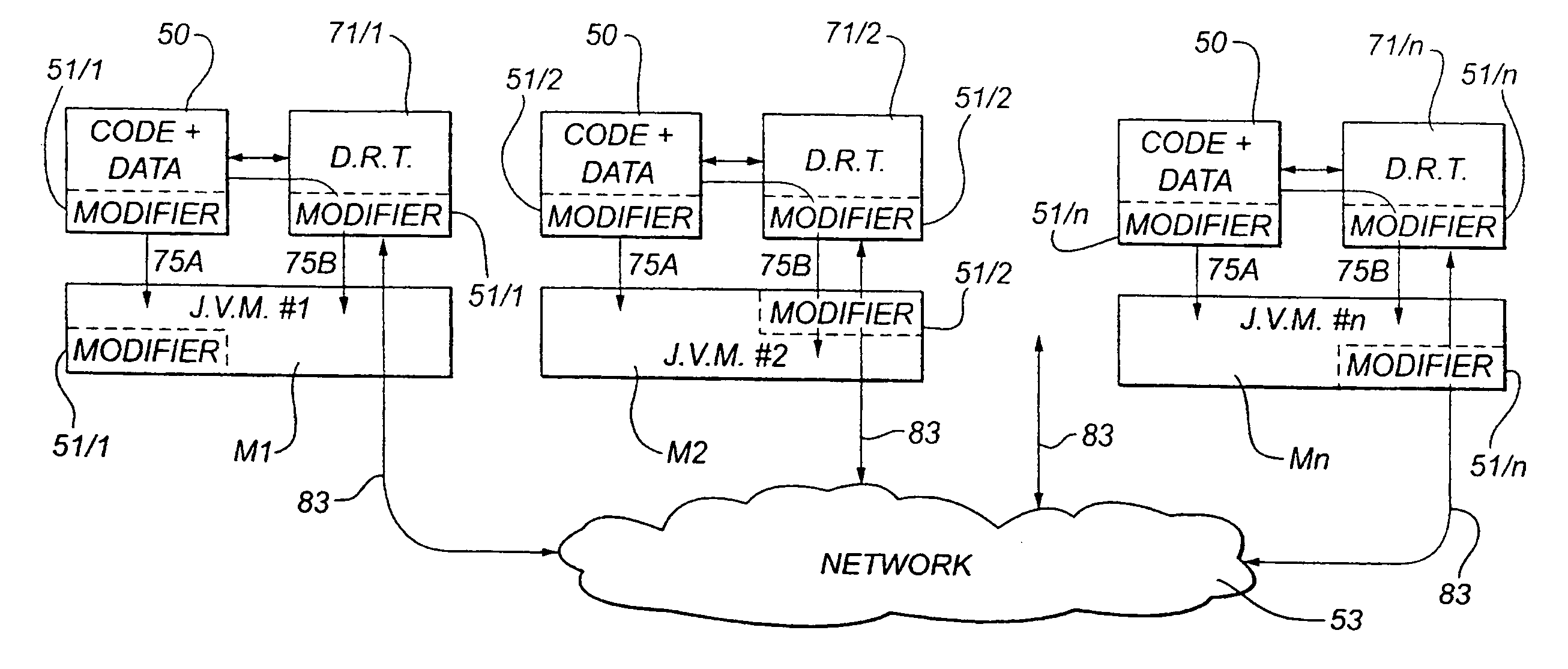

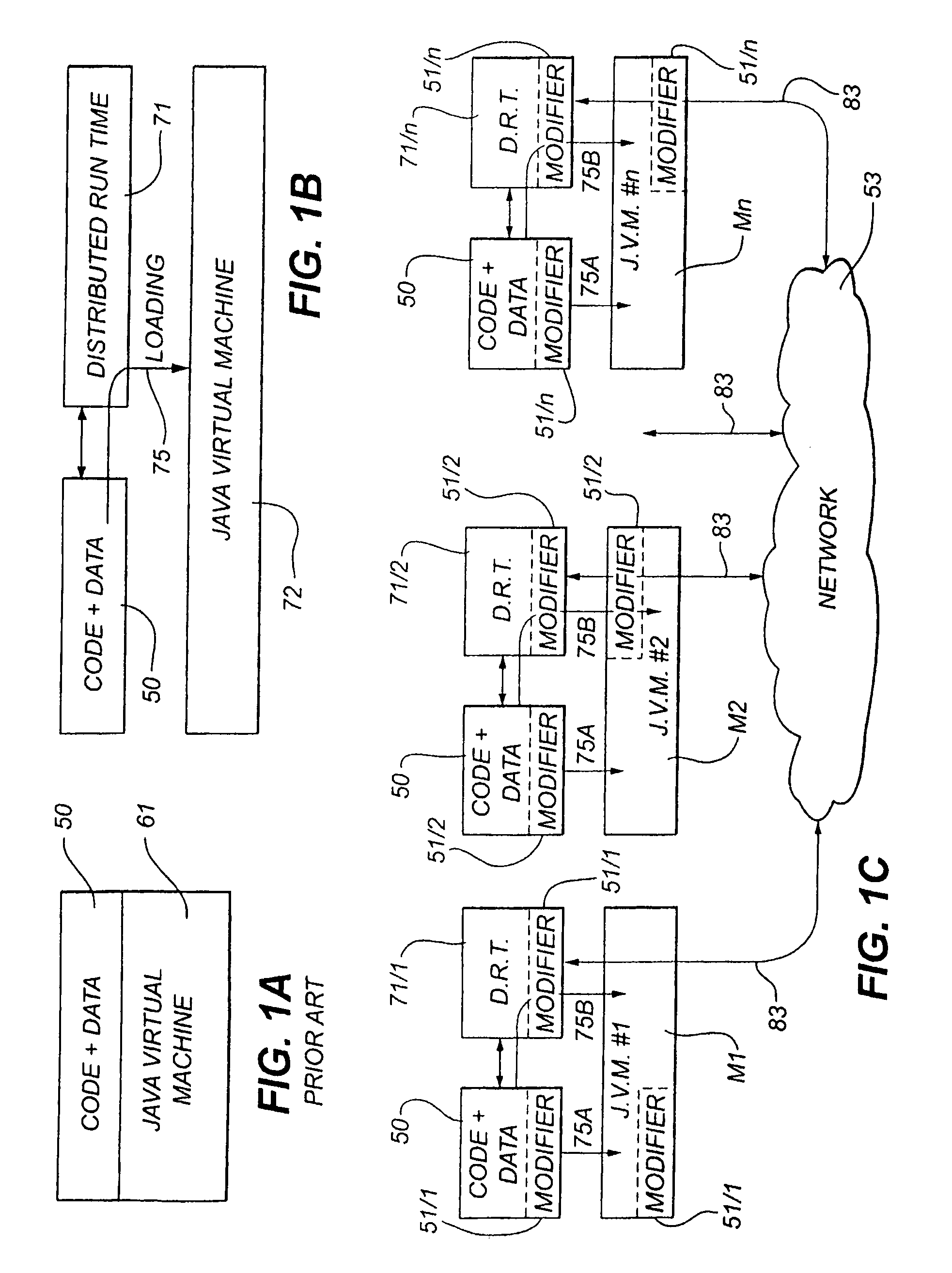

Failure resistant multiple computer system and method

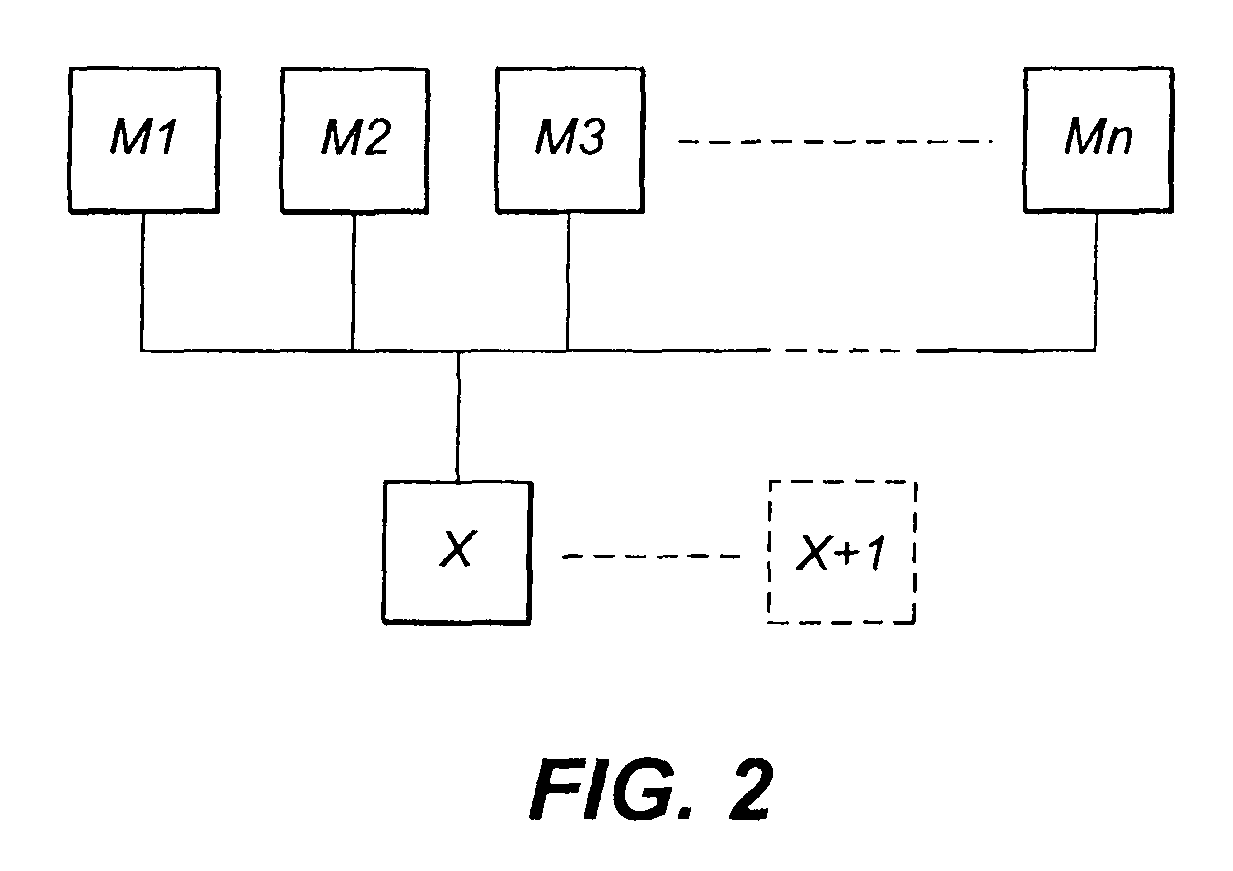

The updating of only some memory locations in a multiple computer environment in which at least one applications program (50) executes simultaneously on a plurality of computers M1, M2 . . . Mn each of which has a local memory, is disclosed. Memory locations (A, B, D, E, X) in said local memory are categorized into two groups. The first group of memory locations (X1, X2, . . . Xn, A1, A2, . . . An) are each present in other computers. The second group of memory locations (B, E) are each present only in the computer having the local memory including the memory location. Changes to the contents of memory locations in the first group only are transmitted to all other computers. A computer failure detection mechanism is disclosed to prevent updating of any first group memory locations of any failed computer.

Owner:HOLT JOHN M

Failure resistant multiple computer system and method

ActiveUS20070174734A1Error detection/correctionMultiple digital computer combinationsComputer failureGroup memory

The updating of only some memory locations in a multiple computer environment in which at least one applications program (50) executes simultaneously on a plurality of computers M1, M2 . . . Mn each of which has a local memory, is disclosed. Memory locations (A, B, D, E, X) in said local memory are categorized into two groups. The first group of memory locations (X1, X2, . . . Xn, A1, A2, . . . An) are each present in other computers. The second group of memory locations (B, E) are each present only in the computer having the local memory including the memory location. Changes to the contents of memory locations in the first group only are transmitted to all other computers. A computer failure detection mechanism is disclosed to prevent updating of any first group memory locations of any failed computer.

Owner:WARATEK LTD

Virtual SIM card multi-number single/double module mobile phone, its implementing method and system

The invention relates to the mobile communication technology. The technical problem to be solved by the invention is to provide a realization method for a virtual SIM card multiple number mobile phone, which makes a user not need to insert other SIM cards besides a home SIM card in the mobile phone and simultaneously have multiple numbers. Correspondingly, the invention also provides a virtual SIM card multiple number single / double mode mobile phone, a number application server and a communication system for realizing the virtual SIM card multiple number mobile phone. The technical proposal adopted by the invention is that: the number application server sends SIM card data corresponding to new numbers to the mobile phone through data channels such as short messages, GPRS / EGPRS, HSDPA / HSUPA, CDMA-nX, WiFi / Wimax or 3G / 4G and so on; the mobile phone receives the SIM card data and stores the SIM card data in a virtual SIM card group memory area. The invention is applied to the applicationspreading range of the prior single / double mode and double-card / double-duration mobile phone; multiple numbers in the mobile phone can follow the user to do free roaming when the mobile phone which is inserted with the prior home SIM card communicates with others.

Owner:HUAWEI TECH CO LTD

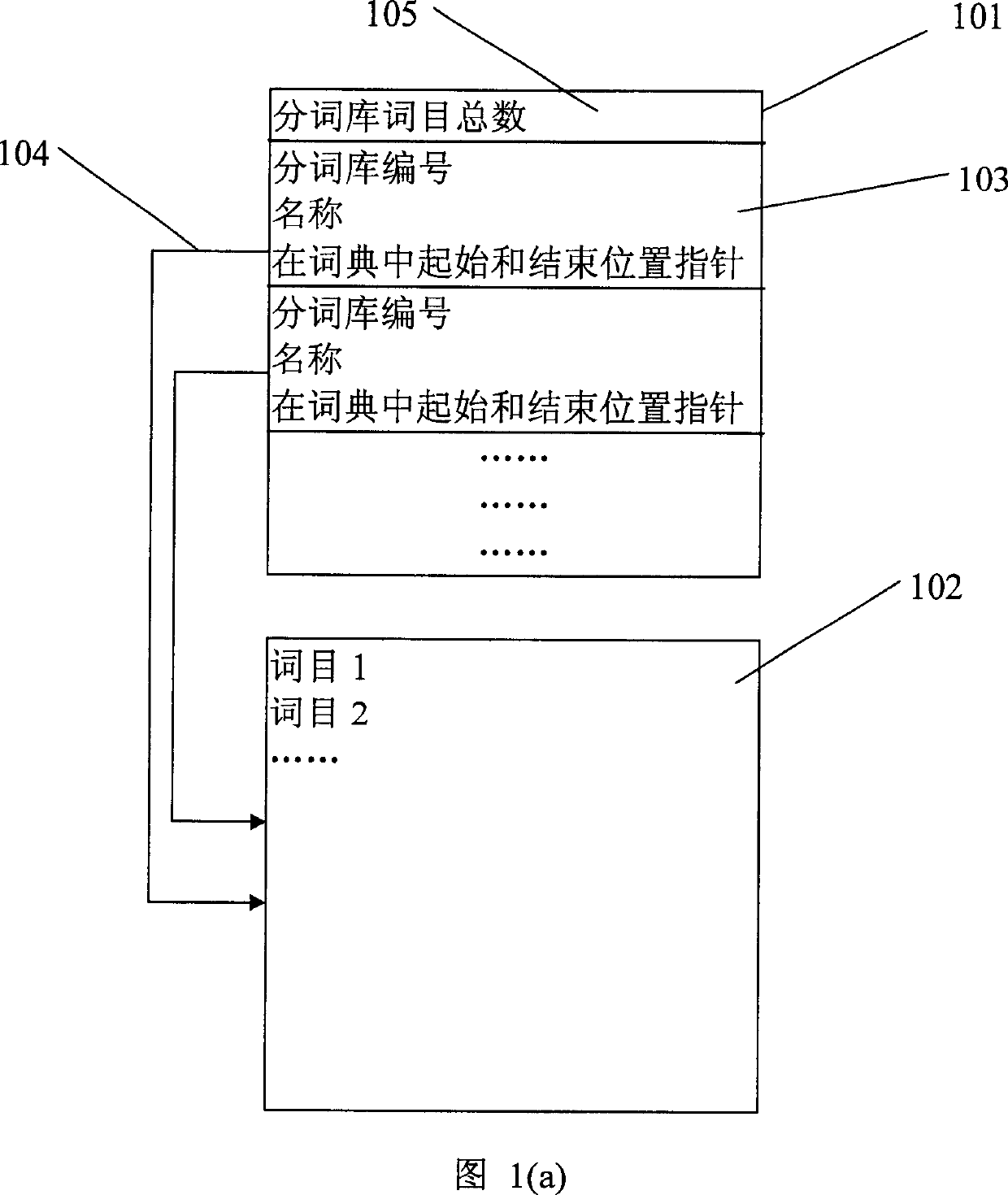

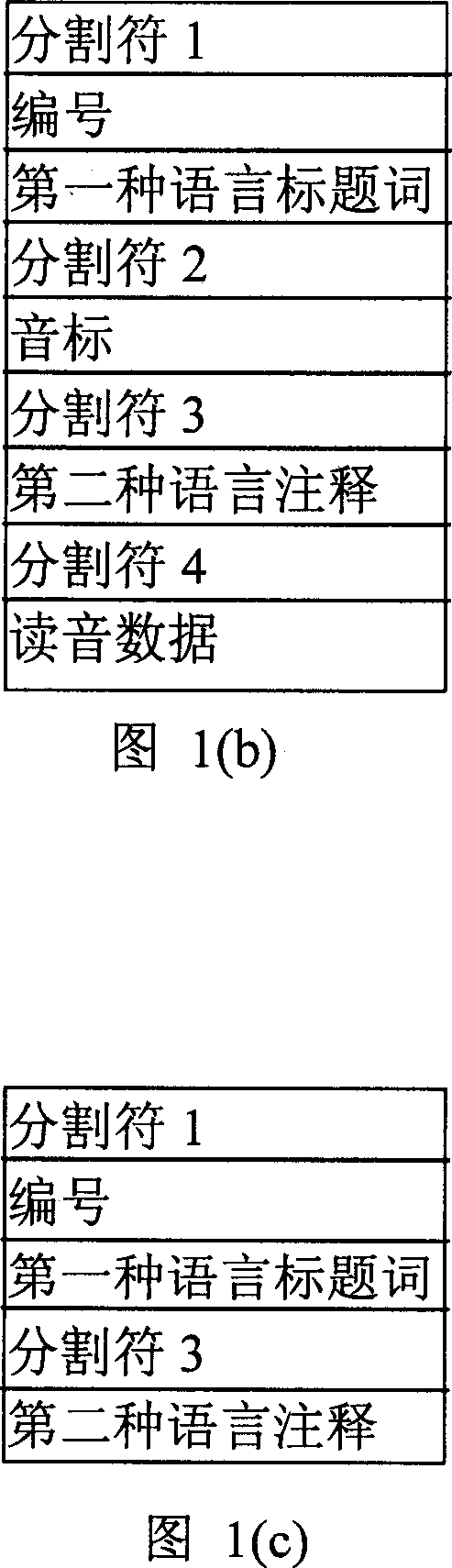

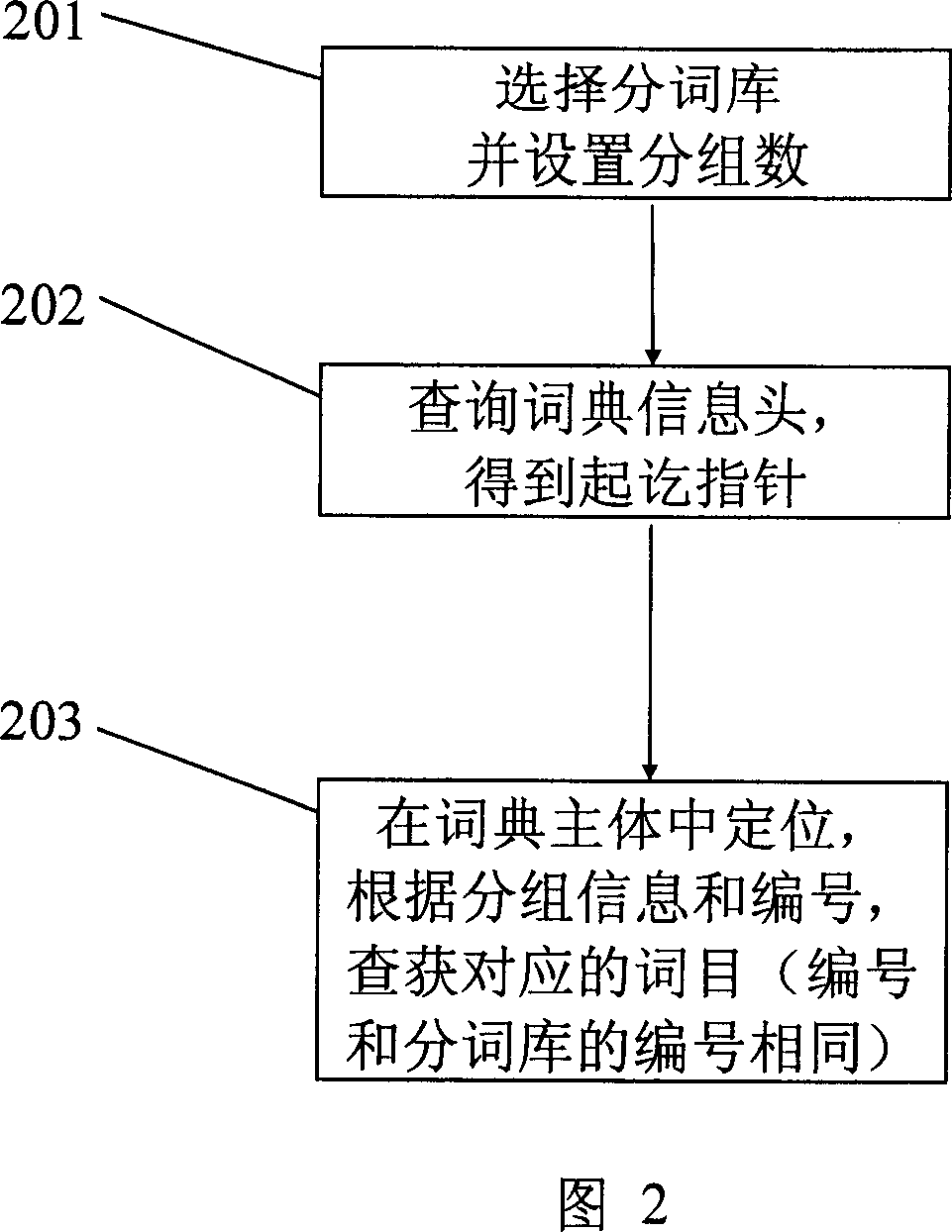

Method for bidirectional translation of terms and group memory of work using single thesaurus

InactiveCN1452101AImplement bidirectional translationSimple methodSpecial data processing applicationsSoftware systemHand held

A method for didirectional word-phrase translation and memorizing words in group with a single word stock is characterized by that a word stock with special structure and relative index table are used. It can be used as a module to embed it in the software system of hand-held electronic device.

Owner:GALAXY INFORMATION TECH CN

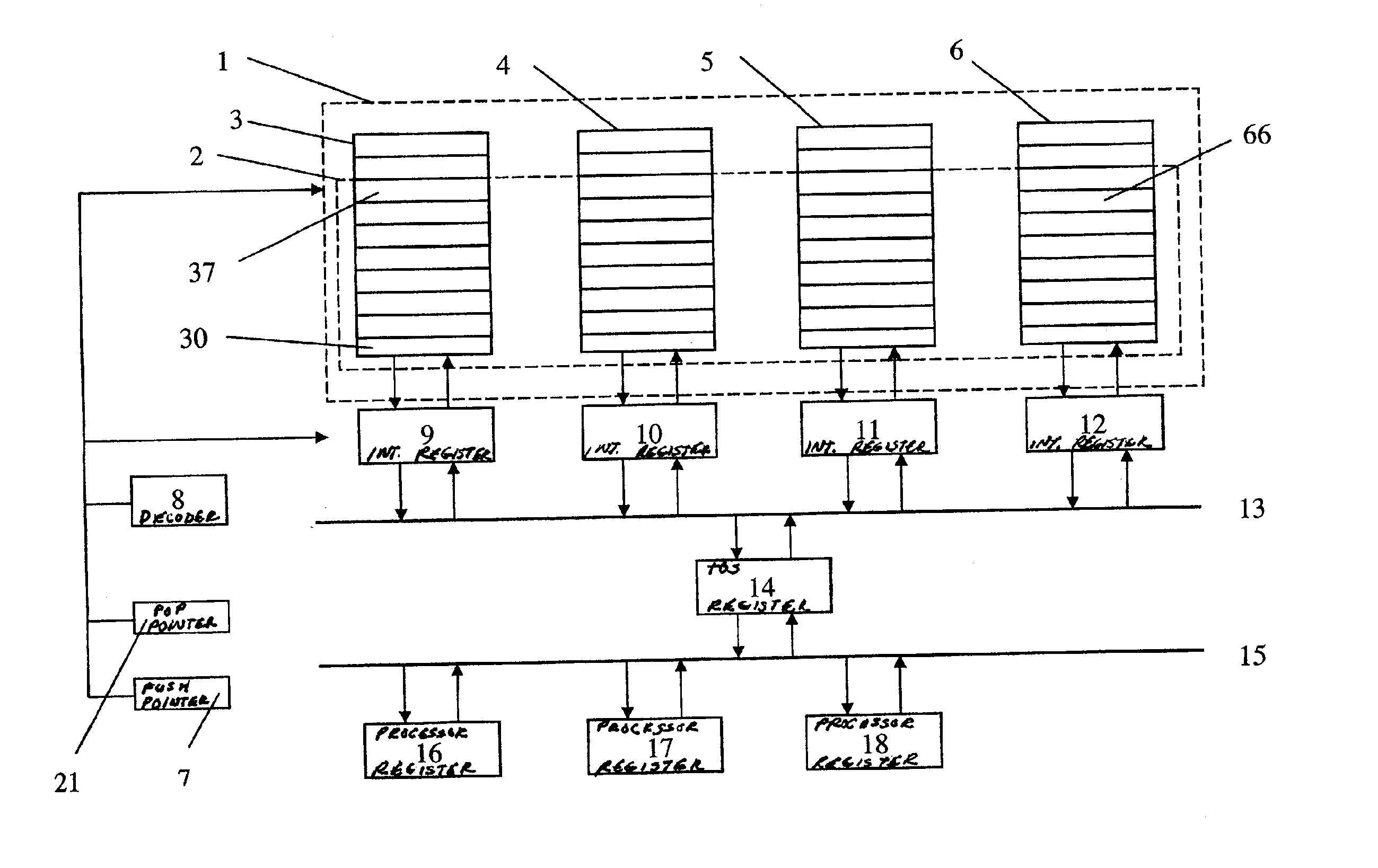

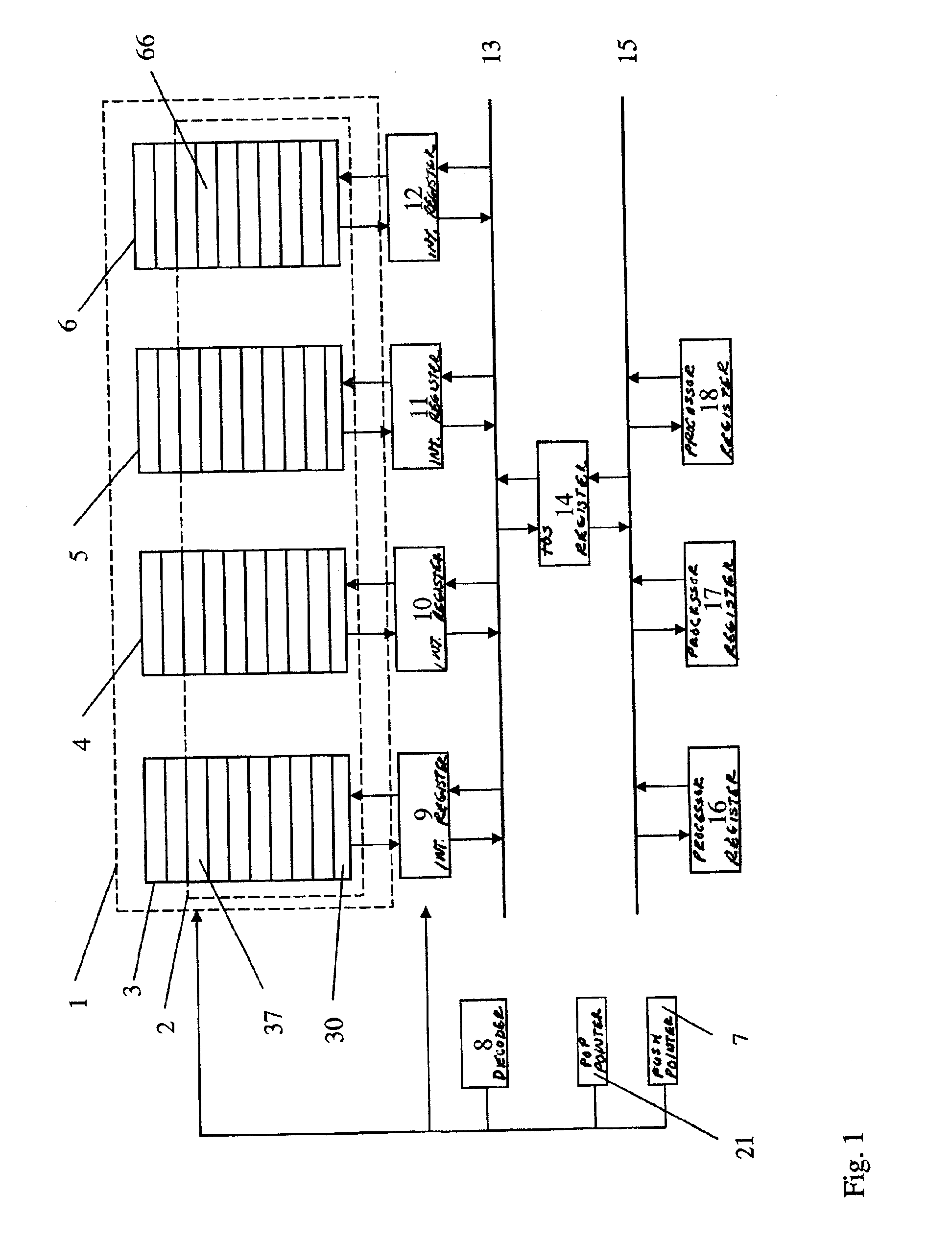

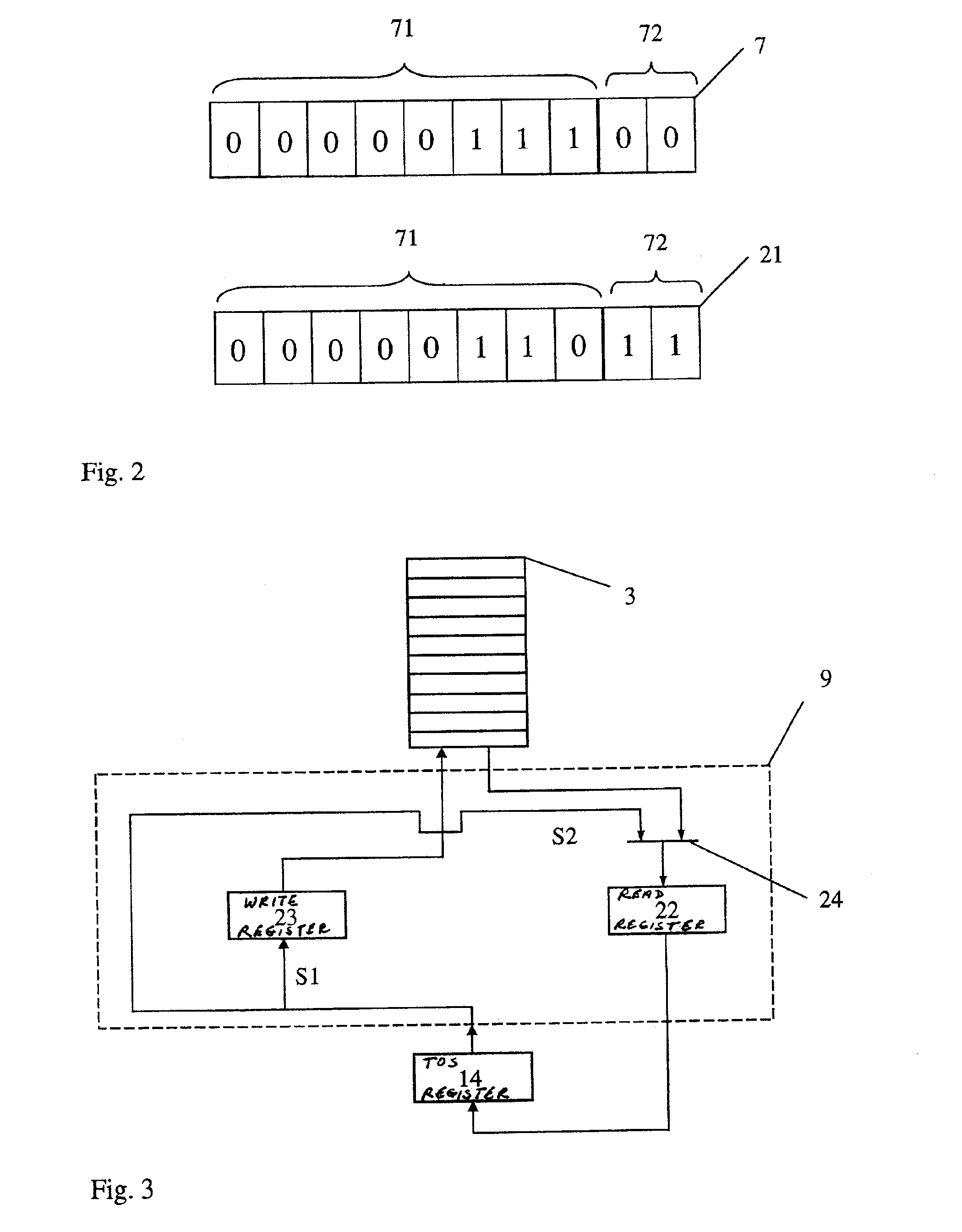

Method and arrangement in a stack having a memory segmented into data groups having a plurality of elements

InactiveUS6871256B2Improve overall utilizationCircuit expenditure of the data memory arrangement accordingHandling data according to predetermined rulesMemory systemsParallel computingData memory

In a data memory arrangement for a microprocessor system, in which the data memory is designed as a group memory composed of element memories in which data are storable in data groups having a plurality of elements under a group address in each instance, in order to make available a stack in which the memory space can be optimally utilized without the occurrence of memory gaps, the use is proposed of at least one memory pointer that has a group address component and an element address component. The stack memory can be operated with data words whose width is smaller than the data group width, without unutilized memory areas occurring in the stack.

Owner:AVAGO TECH INT SALES PTE LTD

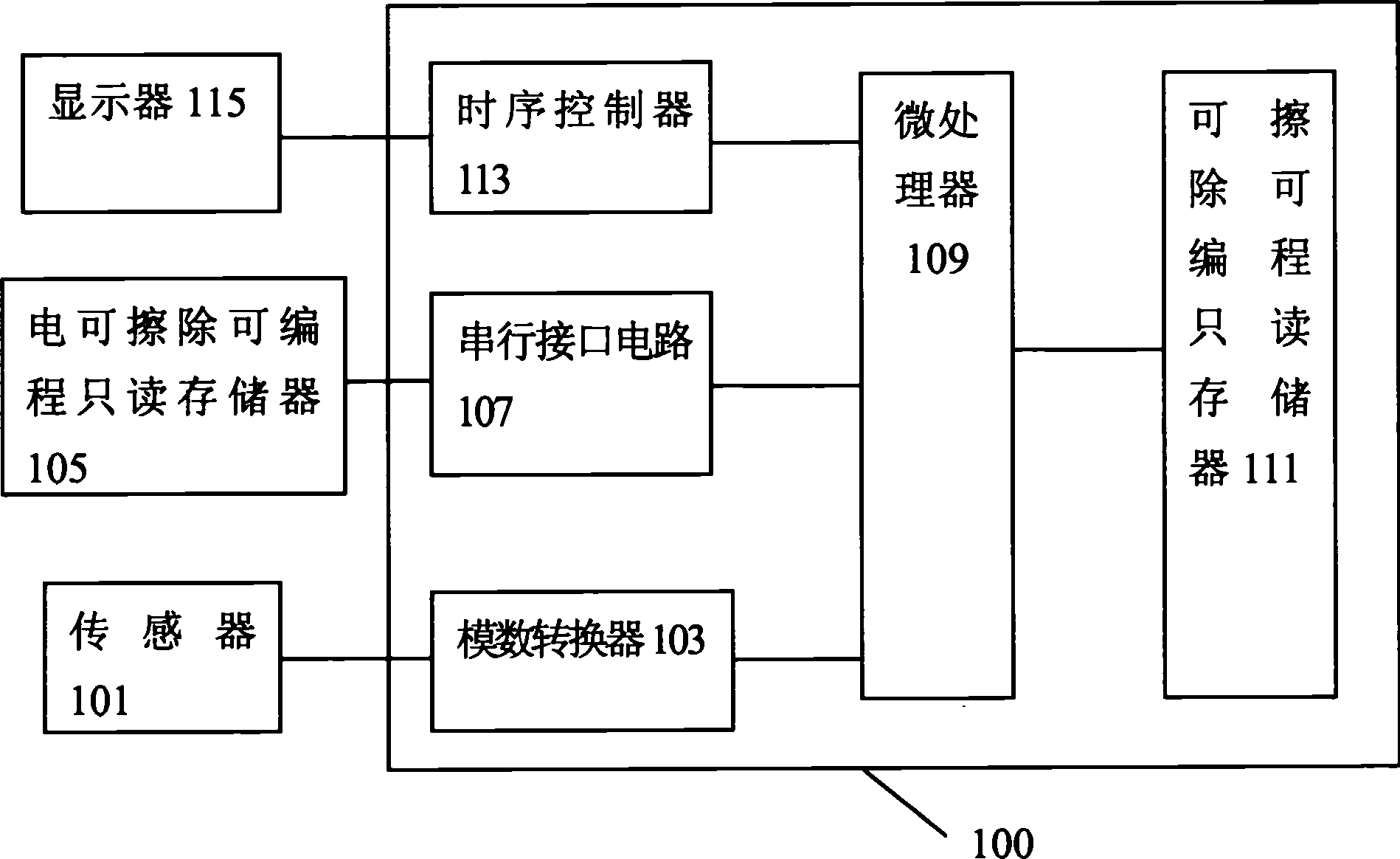

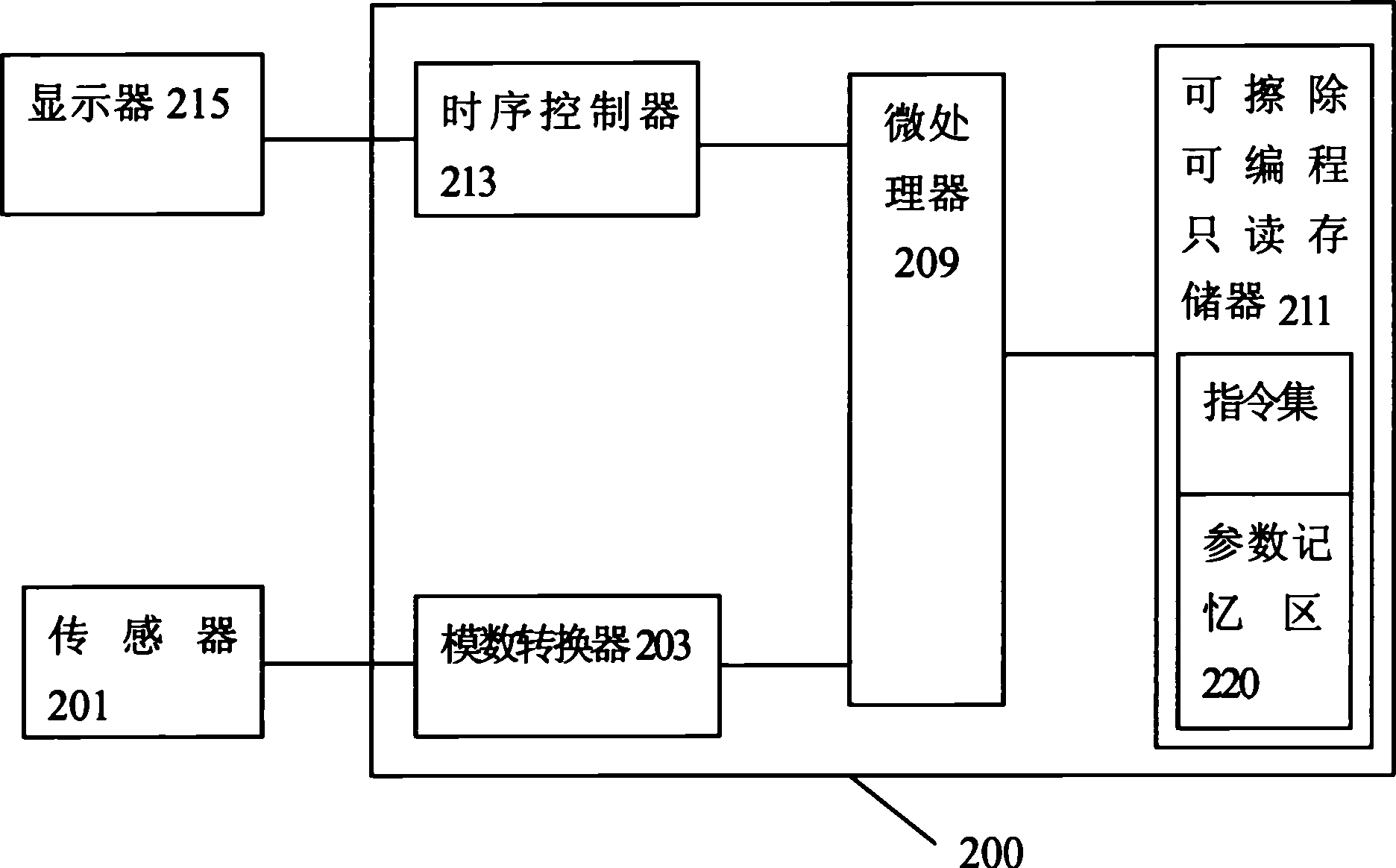

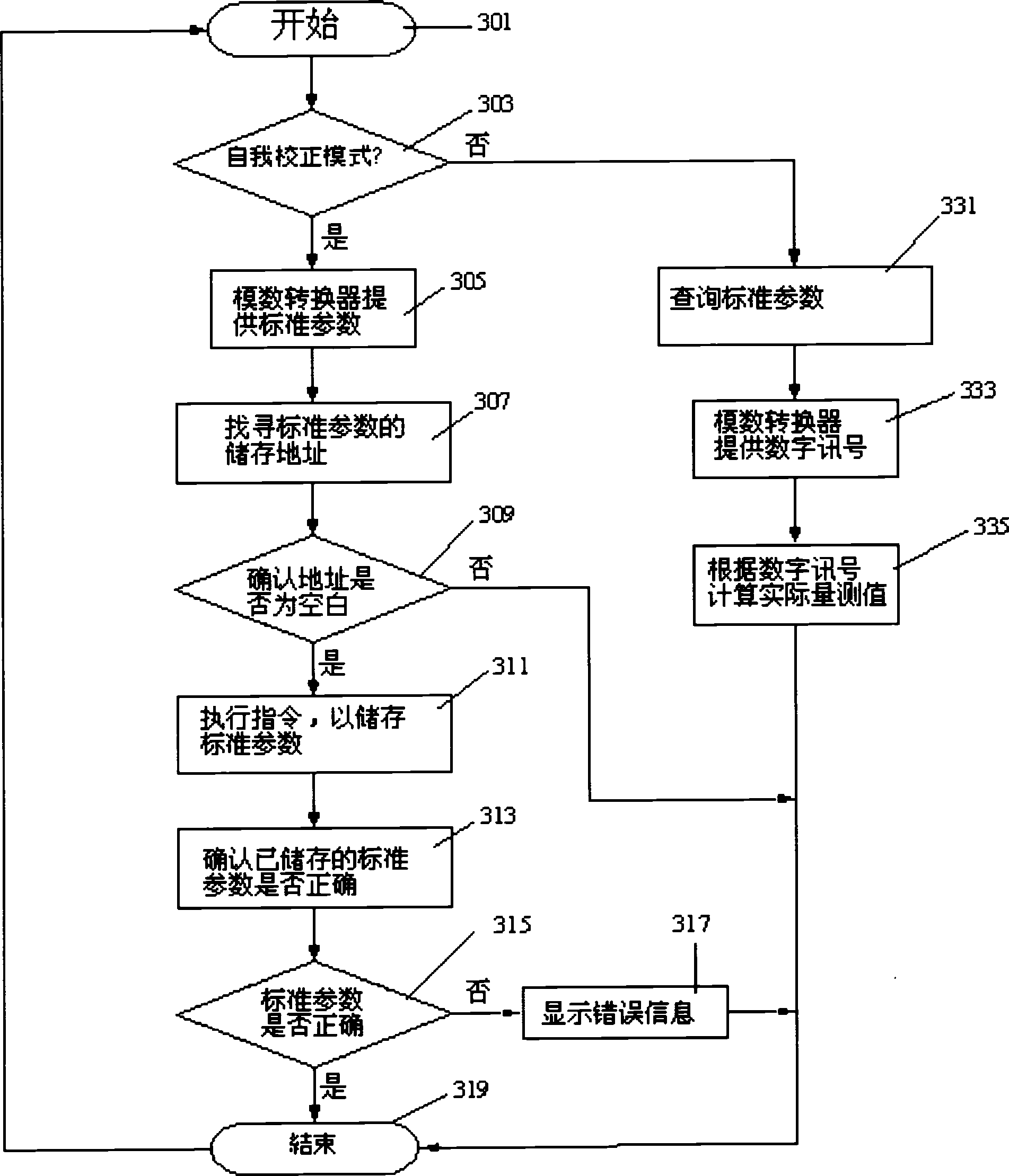

Integrated circuit with self-correcting function, measuring apparatus therefor and parameter self-recording method

InactiveCN1884976ALow costLess componentsConverting sensor outputSpecial purpose recording/indication apparatusMeasurement deviceGroup memory

The invention relates to an integrated circuit, and relative measure device, and a parameter self record method of said integrated circuit, wherein said integrated circuit comprises a micro processor, one-time programmable memory with at least one instruction group memory region, and one parameter memory region for storing correct standard parameter; said micro processor based on the standard parameter of one-time programmable memory calculates out the real measured value relative to the digit signal. The inventive integrated circuit can avoid additional external memory device, to reduce the cost. And the invention has self record correct parameter, to process self-correction after completing the final product, to reduce the cost.

Owner:FUXIANG MICROELECTRONICS SHENZHEN