Data reading method and data writing method of memory circuit

A memory circuit and data reading technology, which is applied in the field of data reading of memory circuits and data writing of memory circuits, can solve problems such as increased power consumption and reduced read and write speed, and achieve reduced power consumption and reduced swing , Improve the effect of reading and writing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0063] In order to make the above objects, features and advantages of the present invention more comprehensible, the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

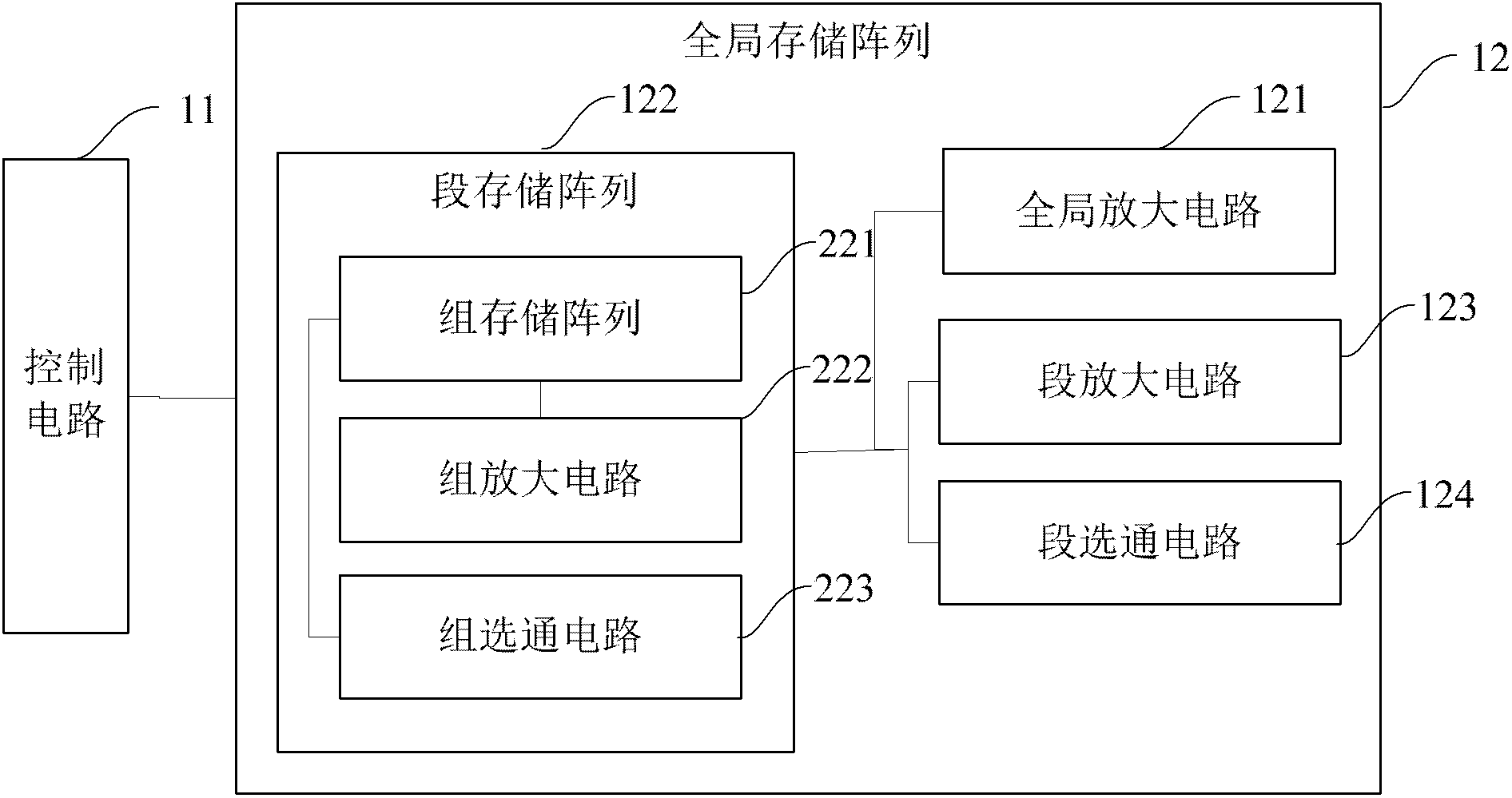

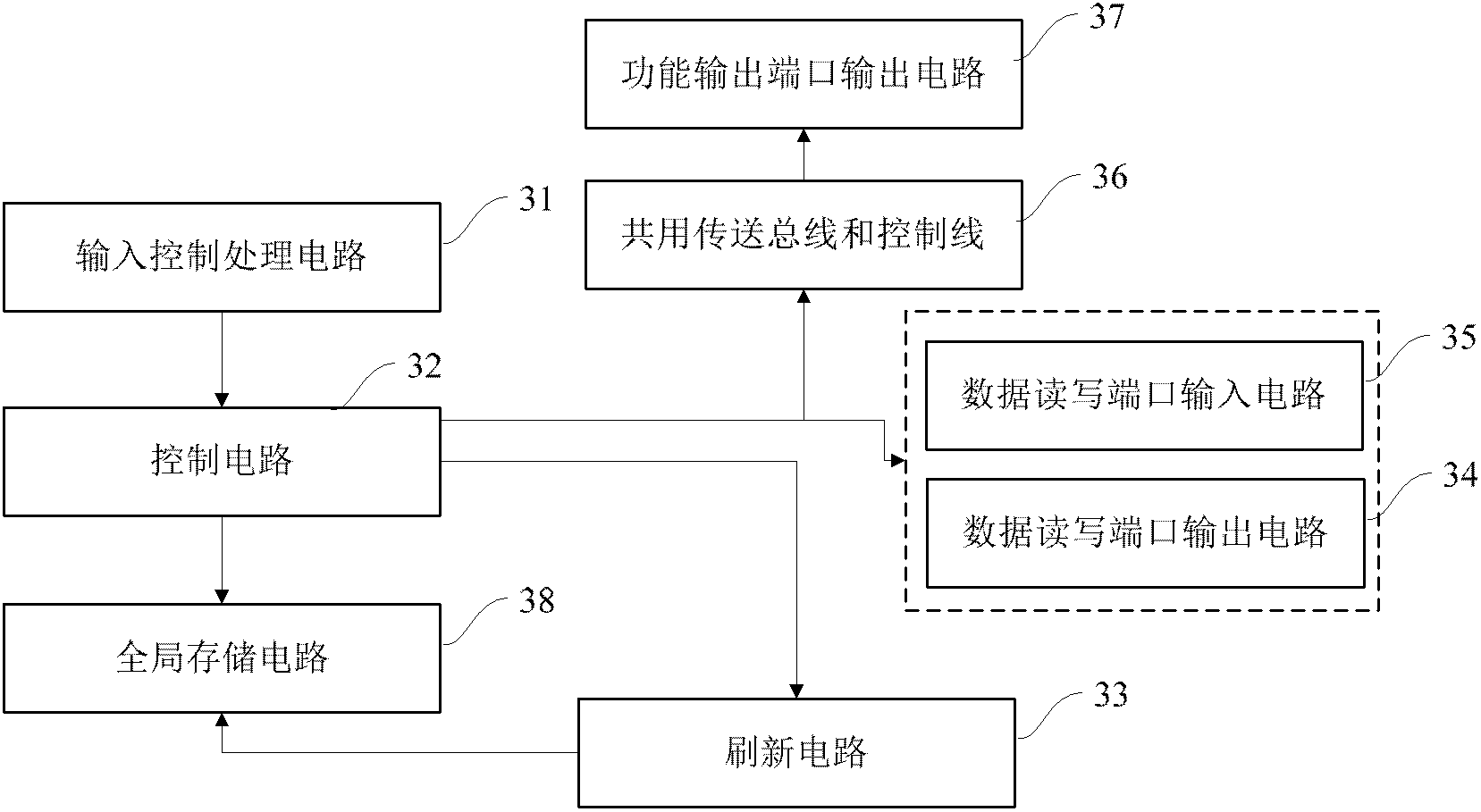

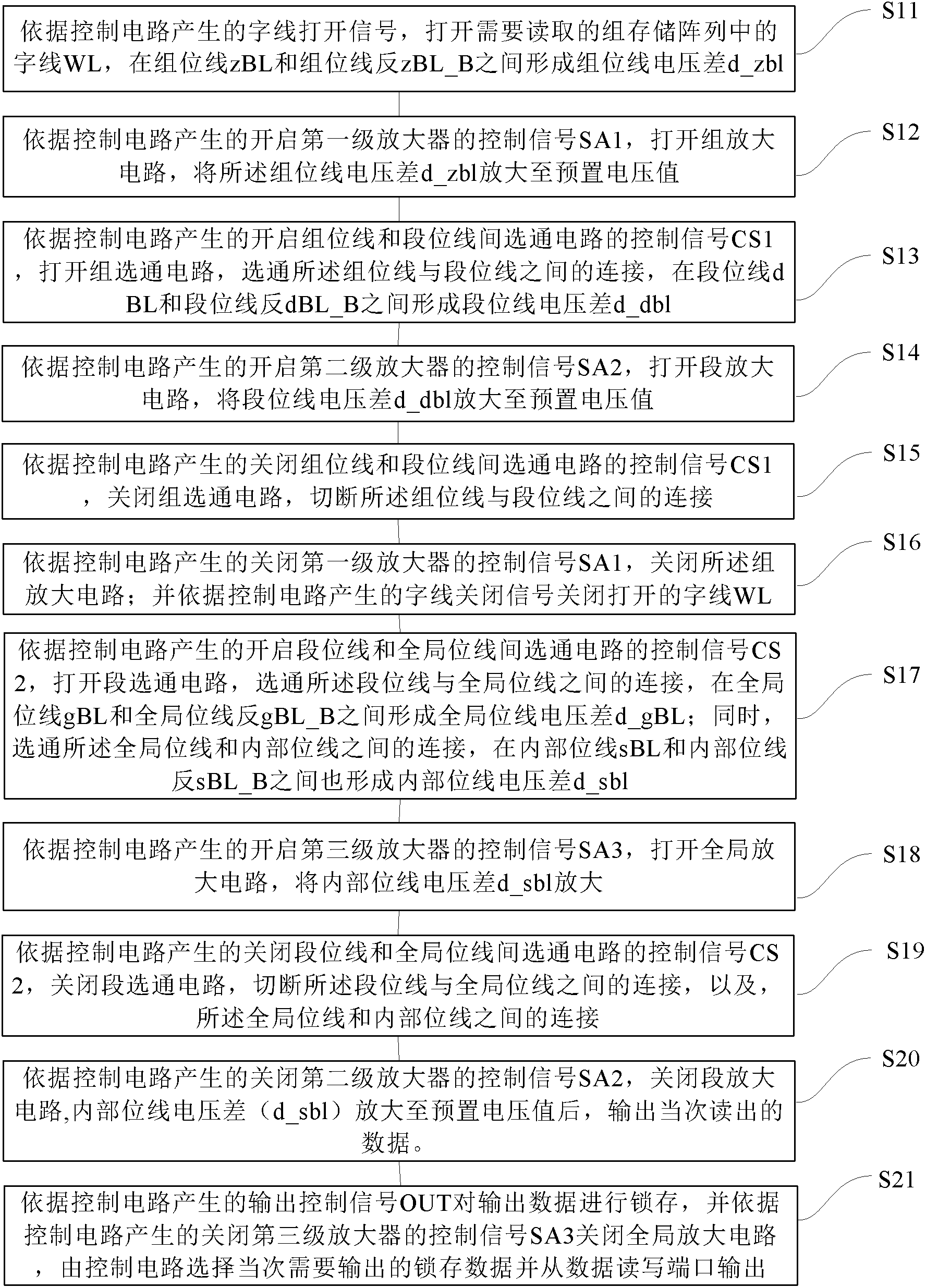

[0064] One of the core concepts of the embodiments of the present invention is to creatively design a global storage array, which is divided into a group storage array and a segment storage array in a multi-level segmented manner, and the segment storage array includes a group storage array Array and group amplification gate circuit; global storage array includes segment memory array, segment amplification gate circuit and global amplification circuit. The global amplifying circuit is connected with the segment amplification gating circuit through the global bit line, the segment amplifying gating circuit is connected with the group amplifying gating circuit through the segment bit line, and the group amplifying gating circuit is c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More