Patents

Literature

586 results about "Logical relationship" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Logical Relationship: A dependency between two project schedule activities, or between a project schedule activity and a schedule milestone. The four possible types of logical relationships are: Finish-to-Start, Finish-to-Finish, Start-to-Start, and Start-to-Finish.

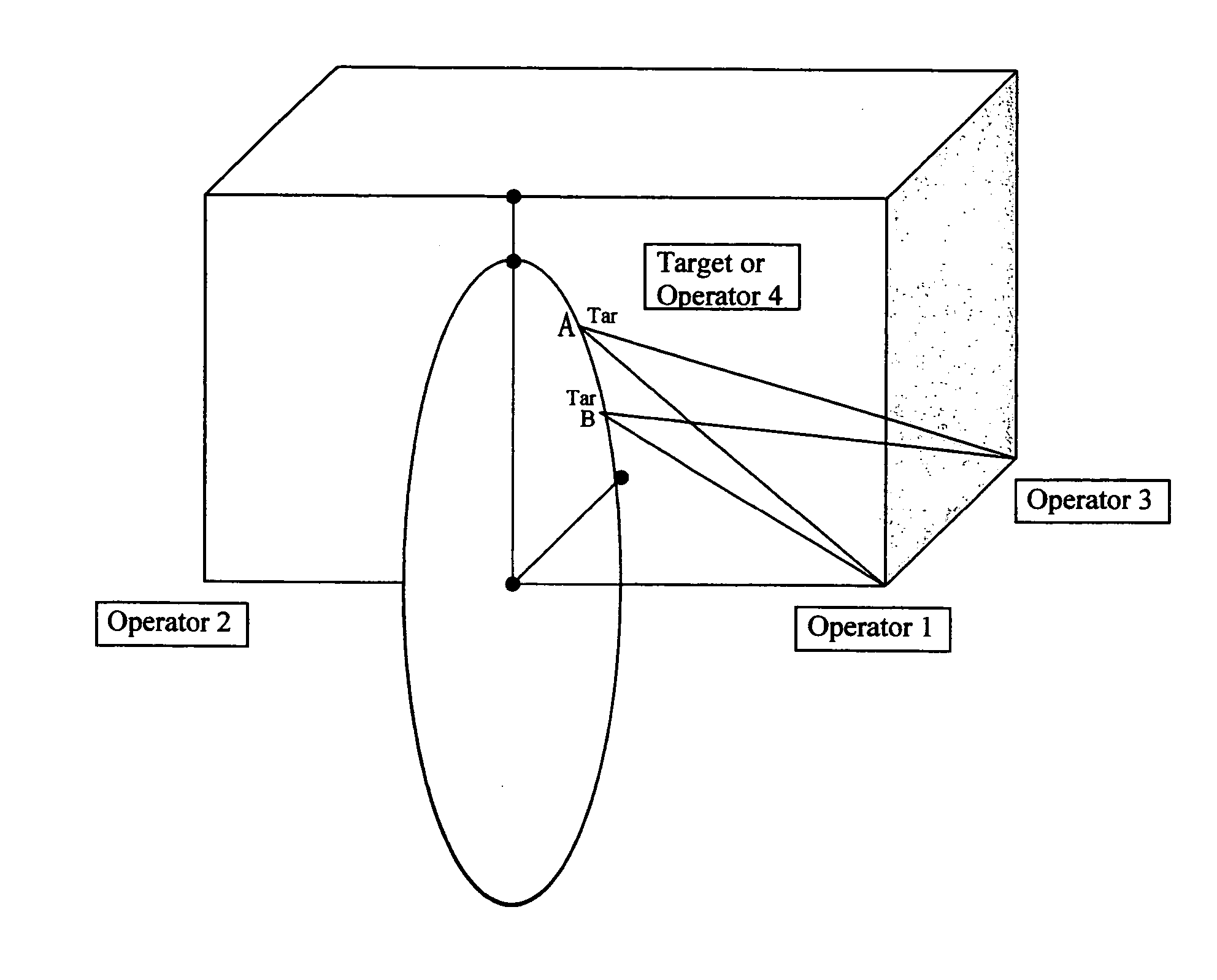

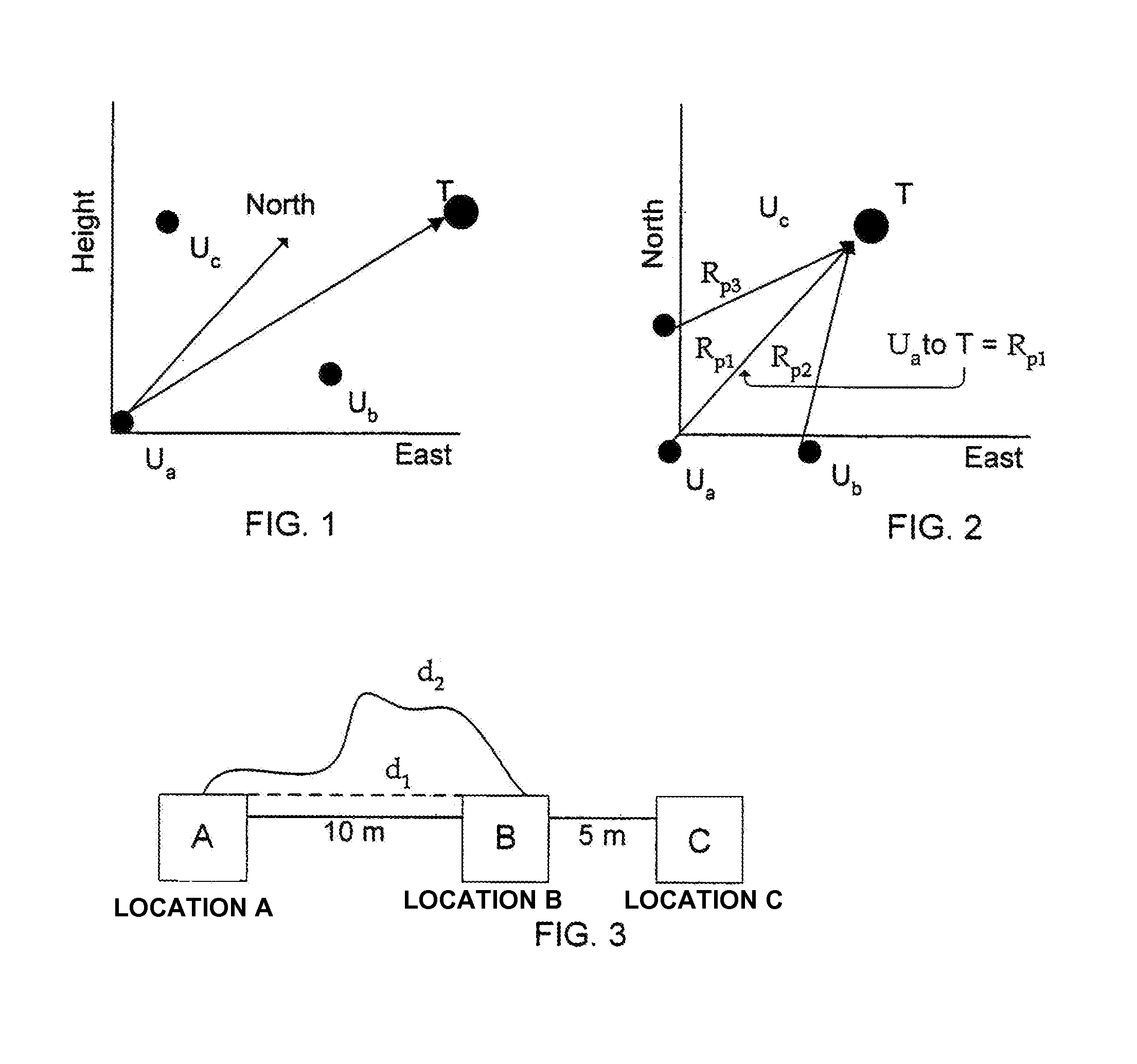

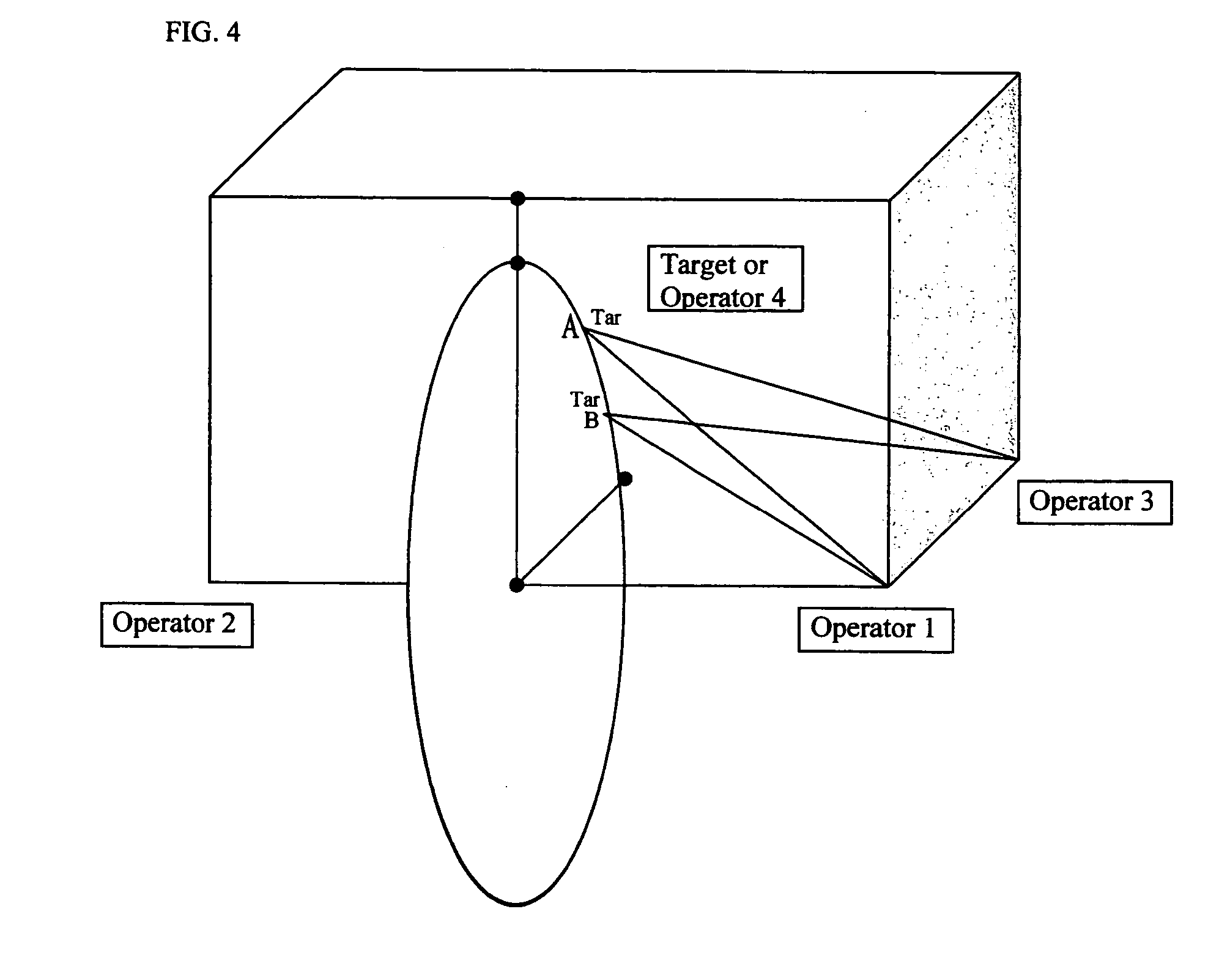

Method and system of three-dimensional positional finding

The present invention is an RF system and methods for finding a target T in three dimensional space configured to have a transponder disposed on the target T, a monitoring unit configured as a transceiver for determining or monitoring the location of the target T and an RF wireless communication system configured with a processor to repeatedly determine position, communication and other values between the transponder and monitoring unit and so as to generate a measured distance between units in three dimensional space by determining the measured distance of the target T by a spherical virtual triangulation relationship when successive values of said position information has a predetermined logical relationship relative to said previous values between said monitoring unit and transponder and / or slave unit disposed on the target T.

Owner:QUALCOMM TECHNOLOGIES INC

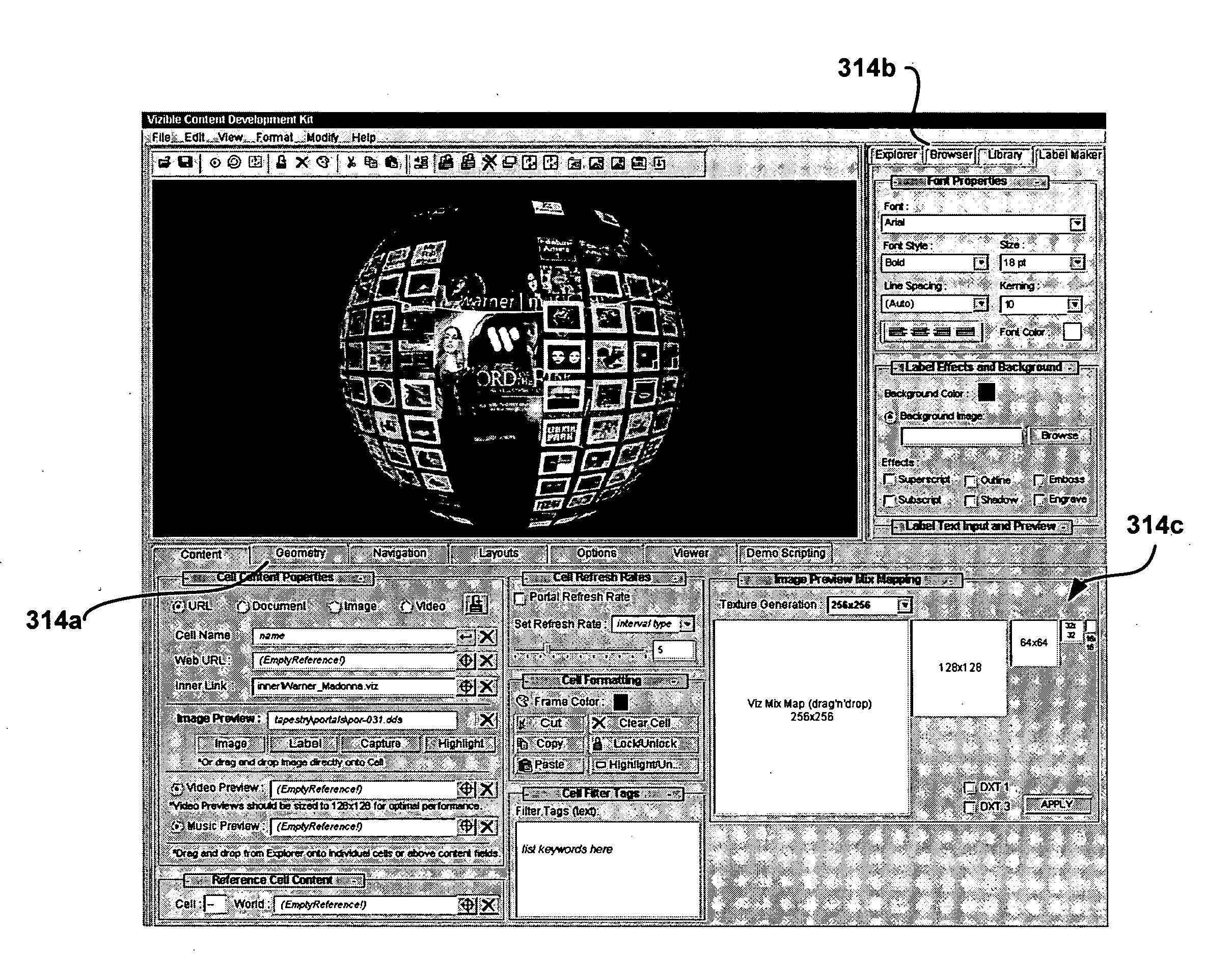

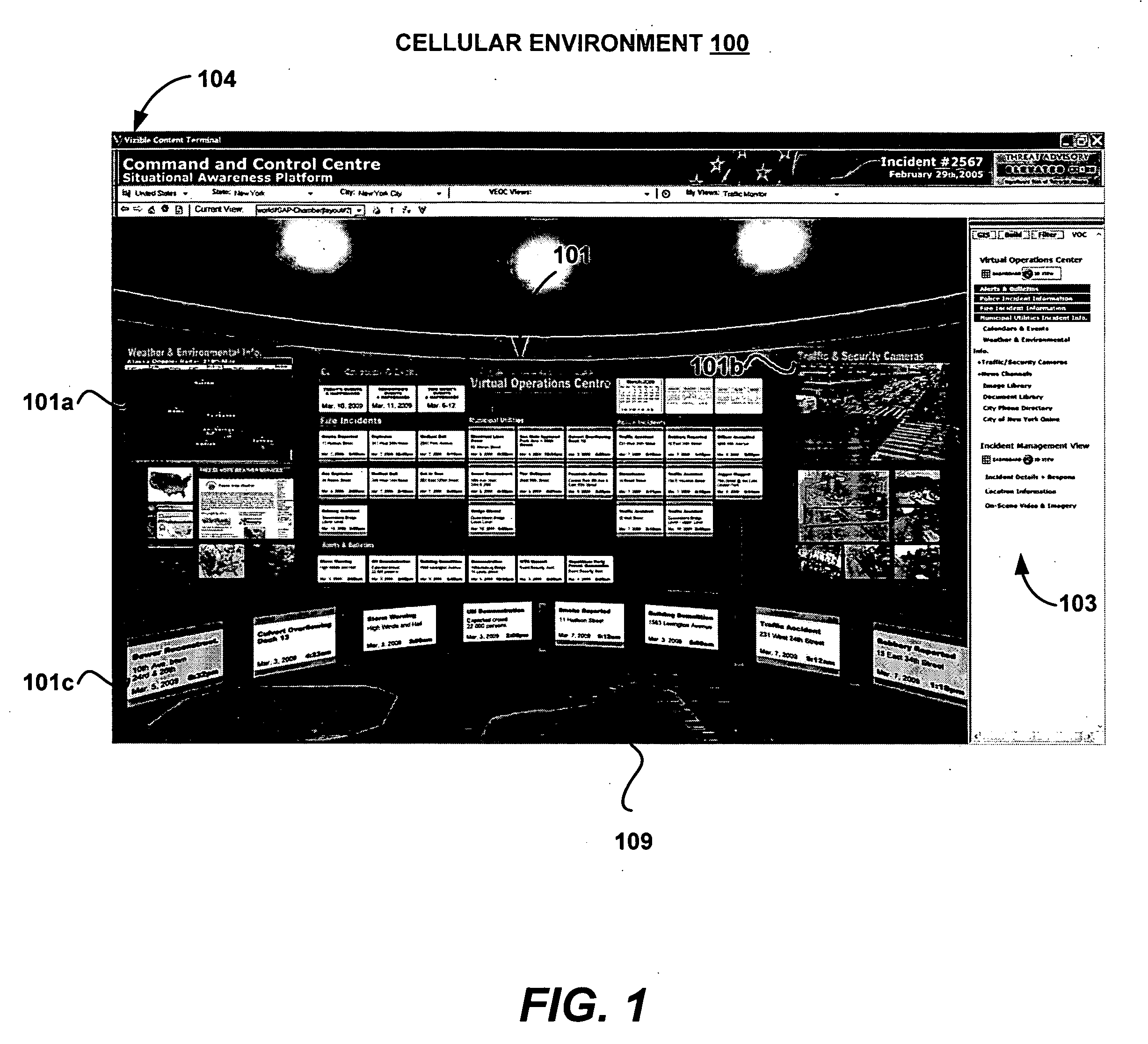

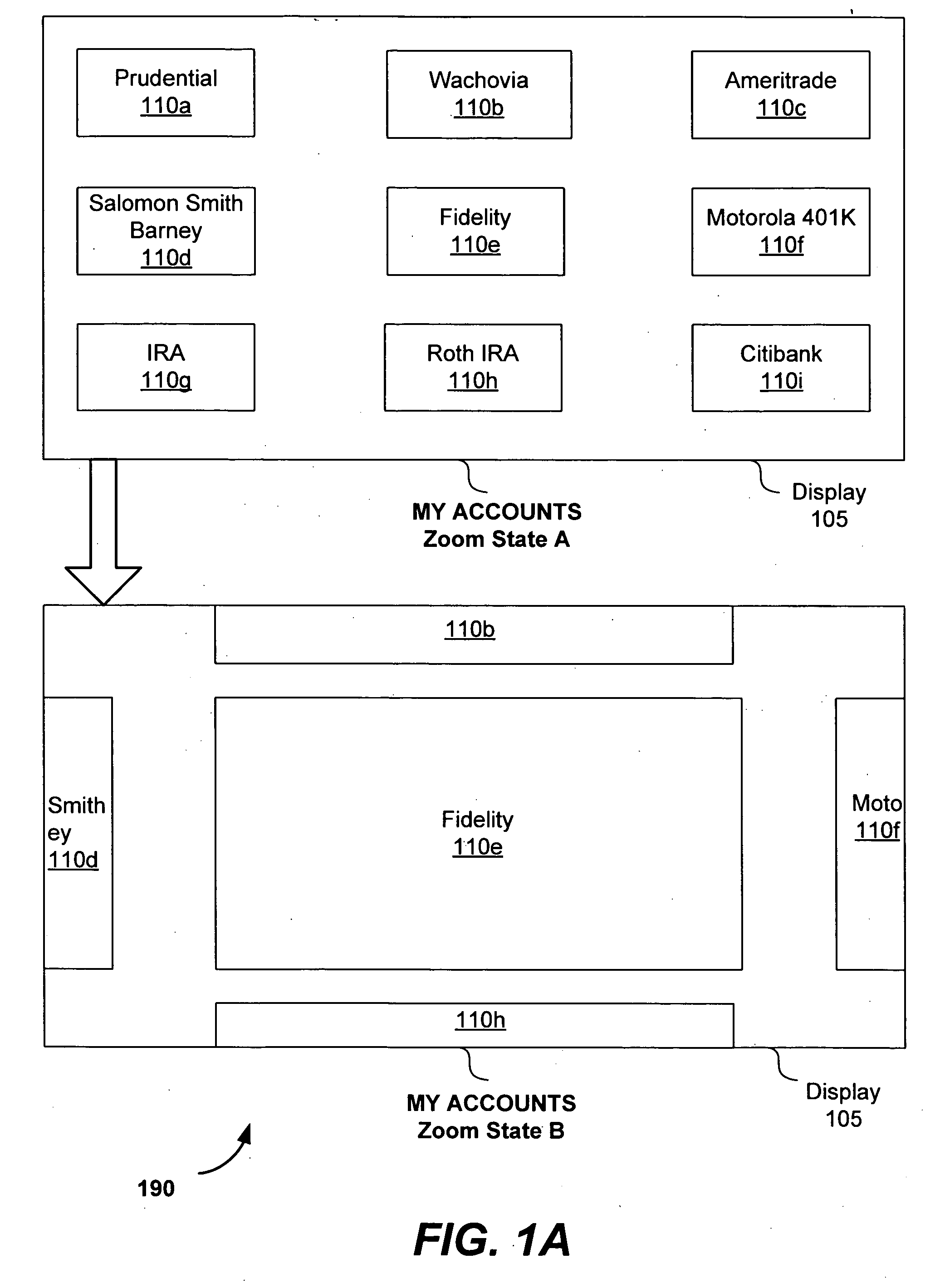

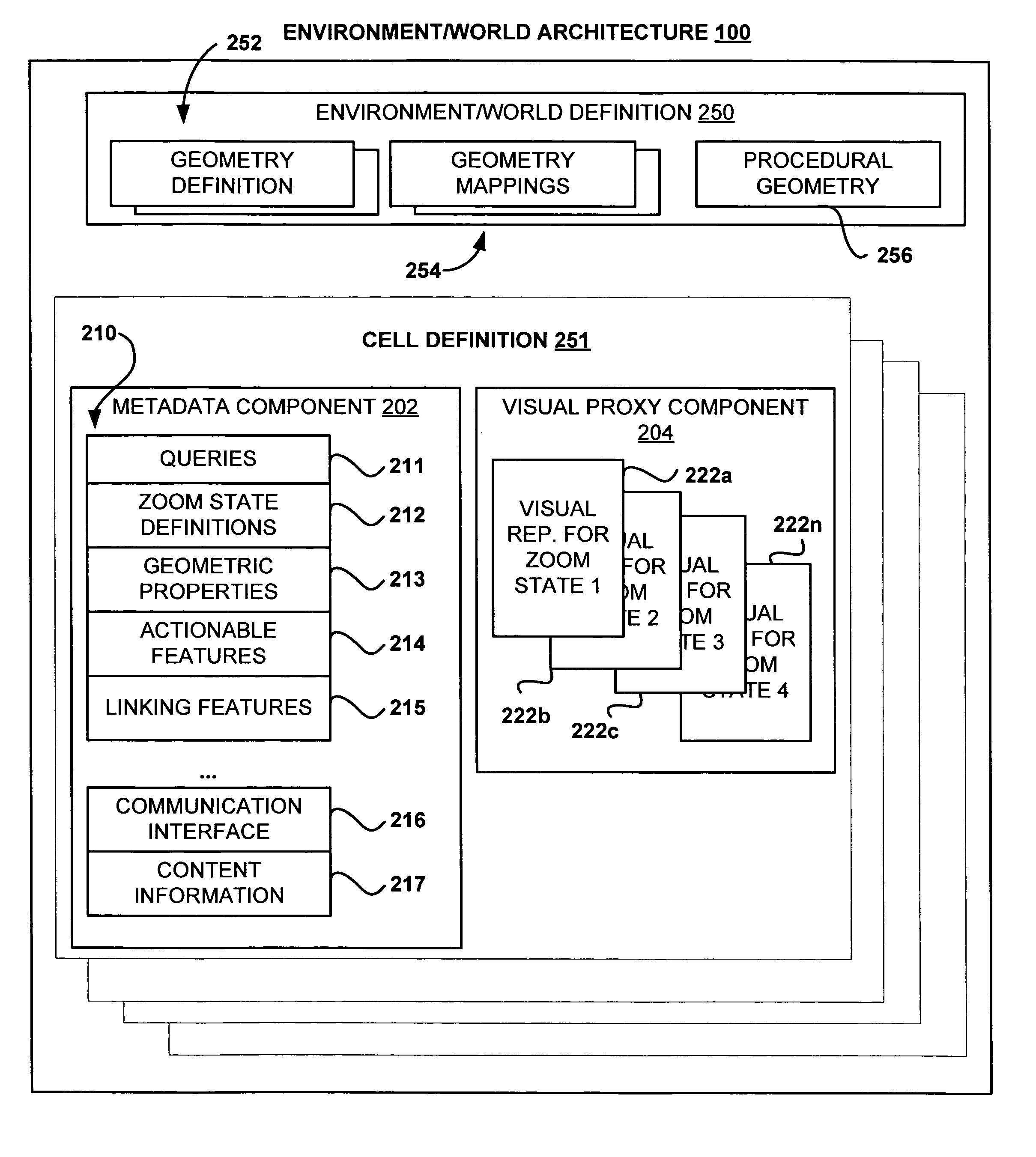

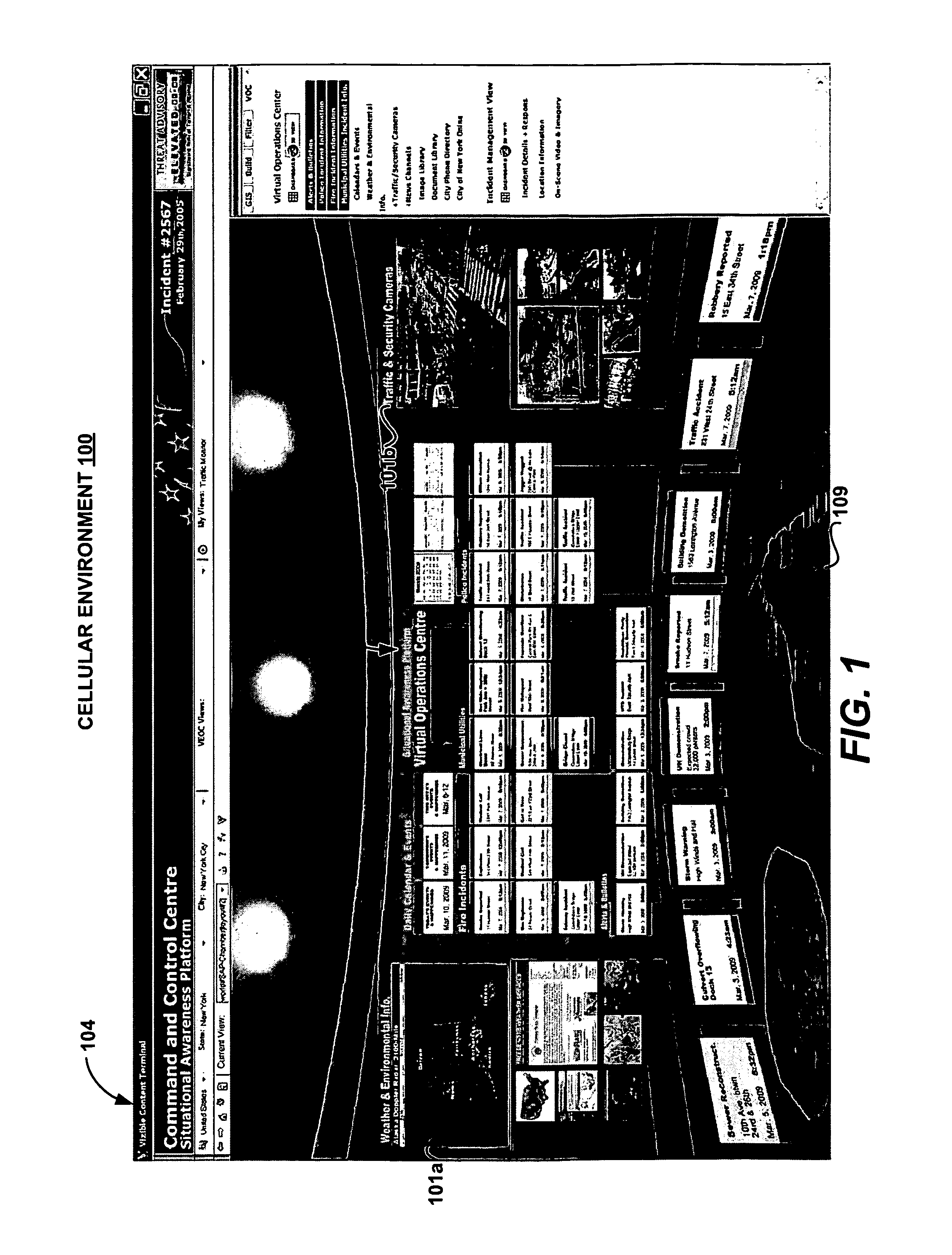

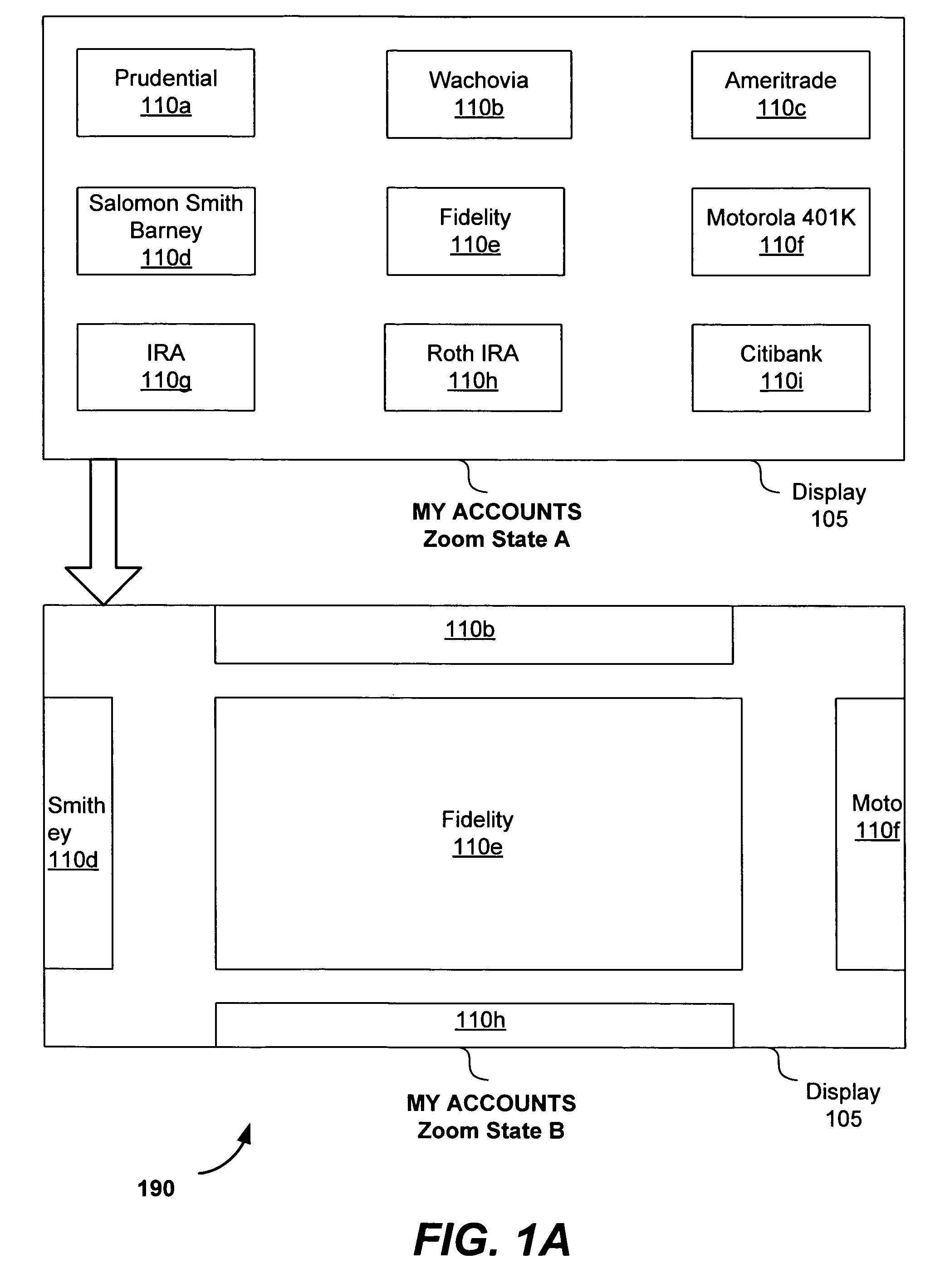

Spatially driven content presentation in a cellular environment

InactiveUS20060156228A1Maintaining senseFacilitate decision-makingDigital data information retrievalText processingMedia typeLogical relationship

Techniques are provided for integrated content presentation via cells arranged geometrically in a cellular environment. Users can navigate various orientations and zoom states of the cellular environment to access information via different applications, different media types, different visual representations and from different underlying content sources. The information can be organized according to various logical relationships. Upon receiving an indication of a zoom state associated with a cell or a group of cells arranged in the cellular environment, a content reference at that zoom state is retrieved. Further, the content reference is resolved to retrieve and output content, including a visual representation associated with the zoom state.

Owner:OPEN TEXT SA ULC

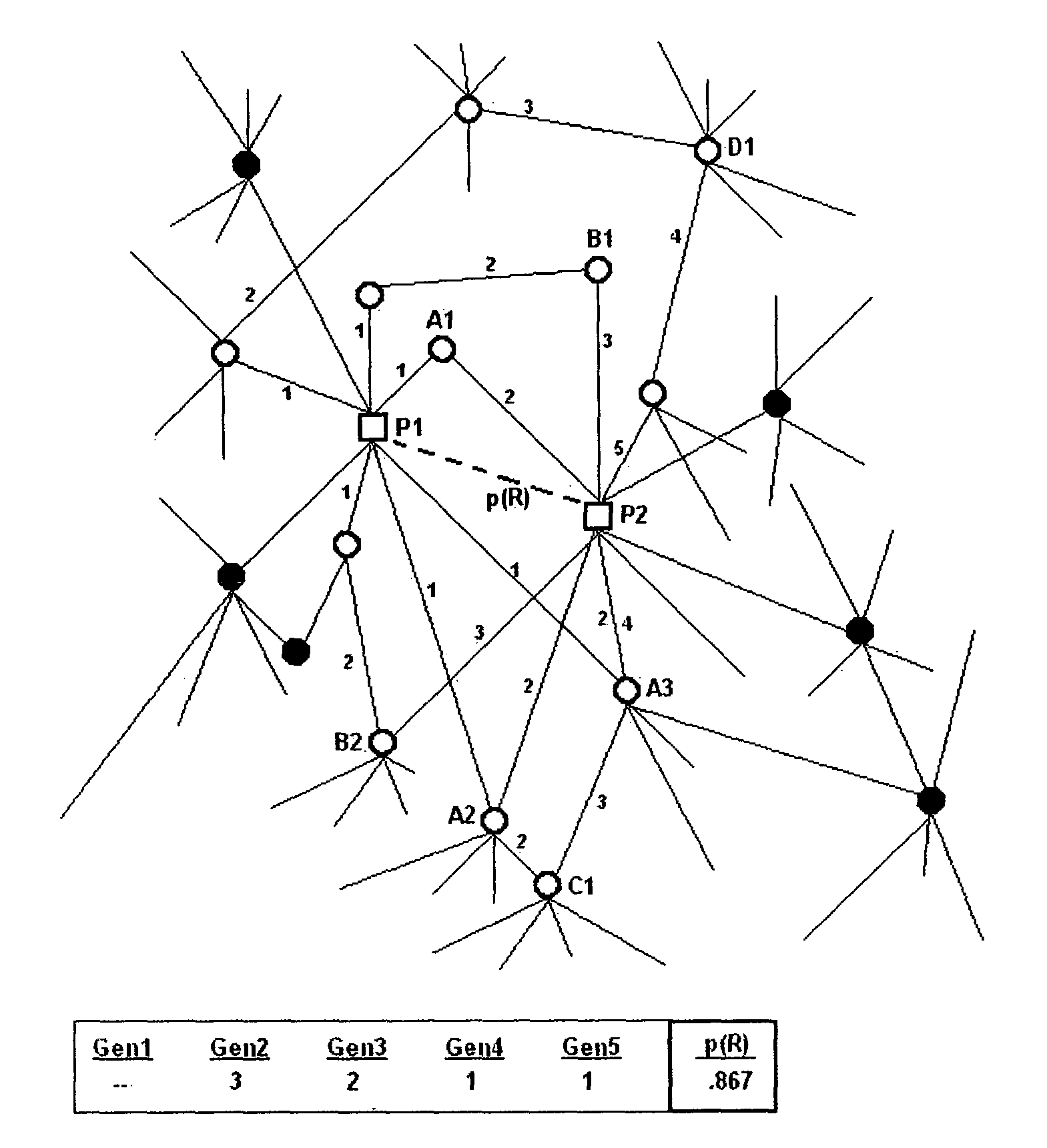

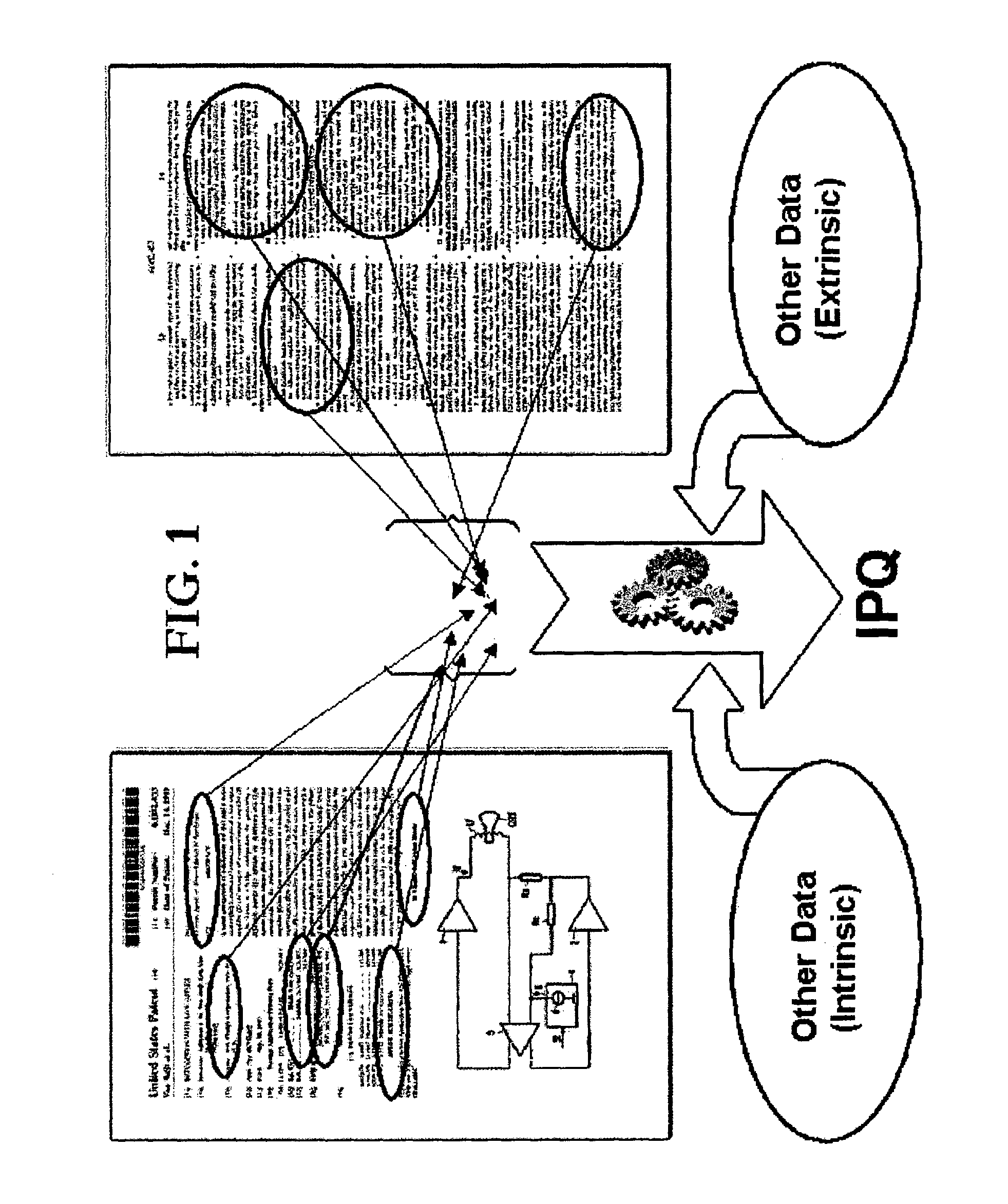

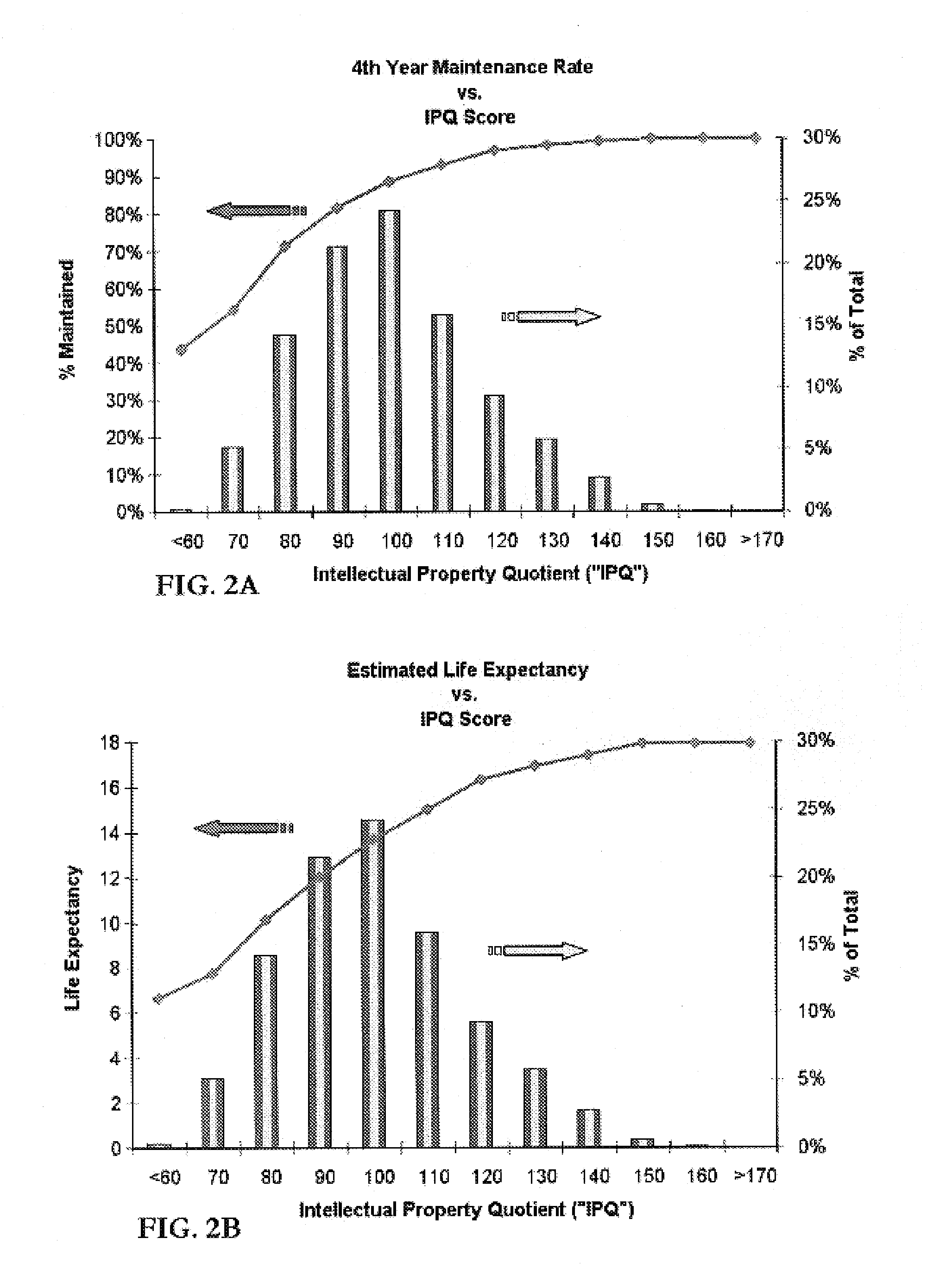

Method and system for probabilistically quantifying and visualizing relevance between two or more citationally or contextually related data objects

InactiveUS7716226B2Easy to understand intuitivelyData processing applicationsWeb data indexingDocumentation procedureDocument preparation

In one embodiment the present invention provides a novel method for probabilistically quantifying a degree of relevance between two or more citationally or contextually related data objects, such as patent documents, non-patent documents, web pages, personal and corporate contacts information, product information, consumer behavior, technical or scientific information, address information, and the like. In another embodiment the present invention provides a novel method for visualizing and displaying relevance between two or more citationally or contextually related data objects. In another embodiment the present invention provides a novel search input / output interface that utilizes an iterative self-organizing mapping (“SOM”) technique to automatically generate a visual map of relevant patents and / or other related documents desired to be explored, searched or analyzed. In another embodiment the present invention provides a novel search input / output interface that displays and / or communicates search input criteria and corresponding search results in a way that facilitates intuitive understanding and visualization of the logical relationships between two or more related concepts being searched.

Owner:PATENTRATINGS

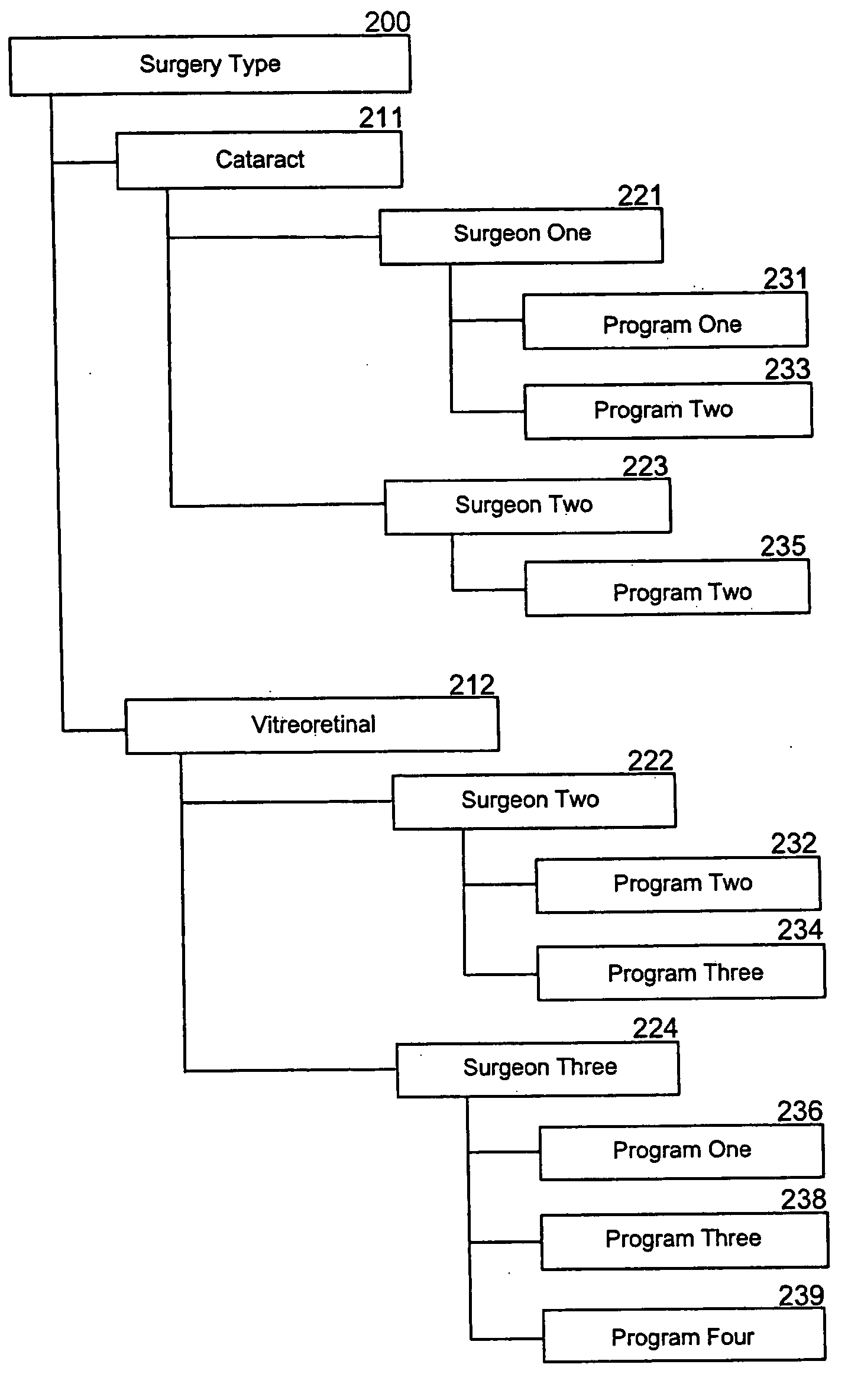

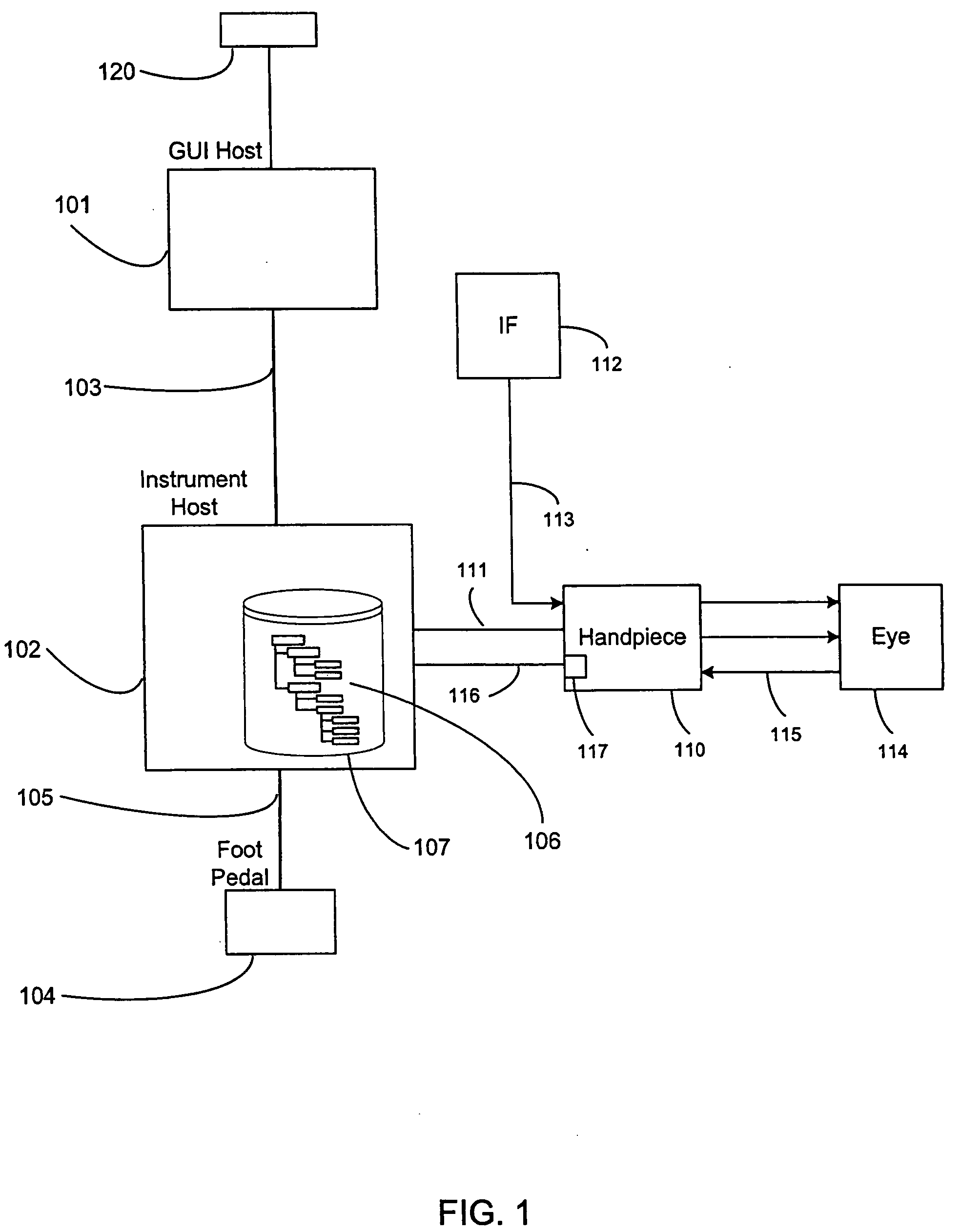

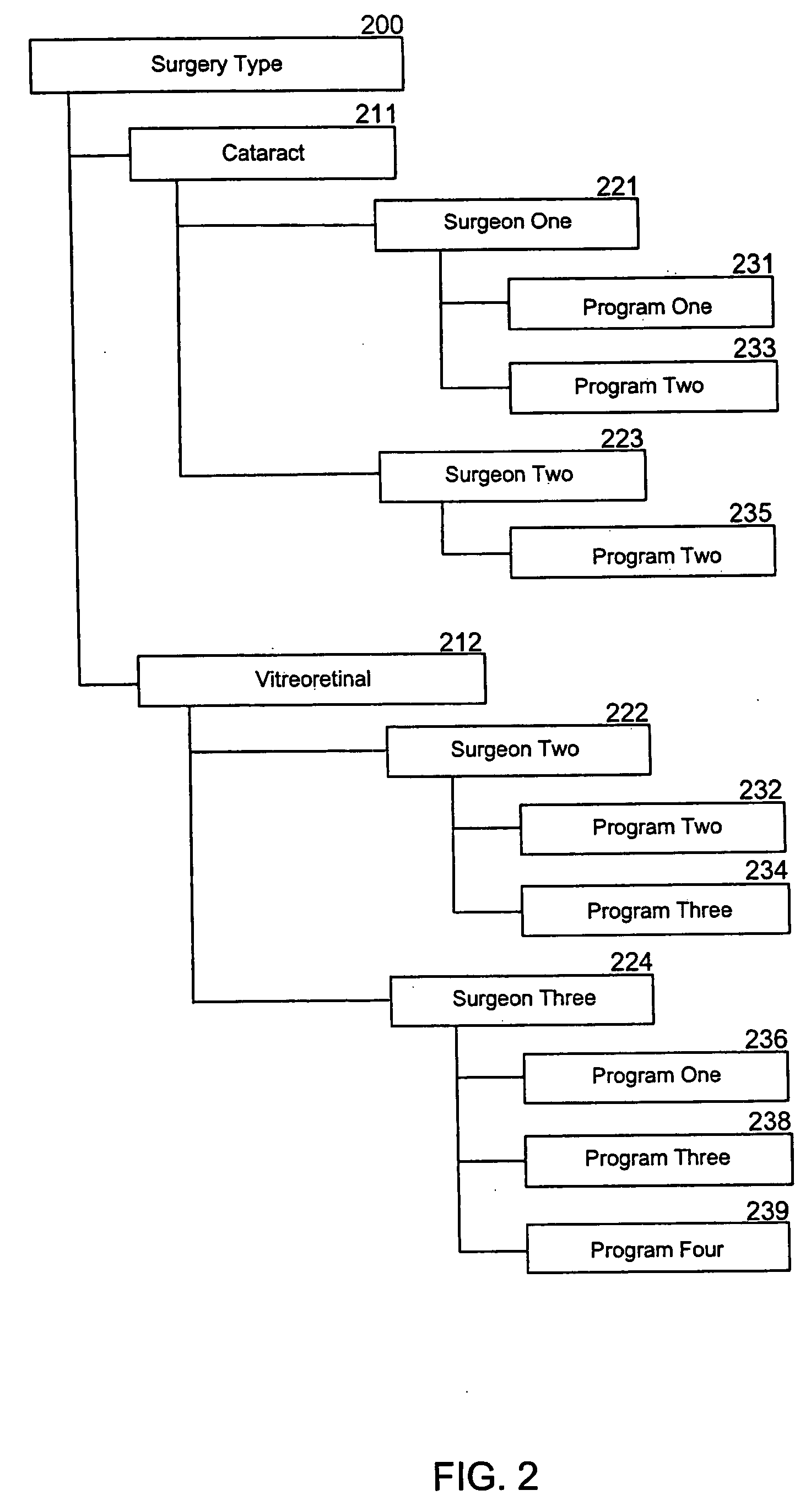

Database design for collection of medical instrument parameters

InactiveUS20080312953A1Data processing applicationsLocal control/monitoringUser interfaceWorld Wide Web

A method and system for maintaining medical items is provided. The system includes a medical database structure, a medical database utility configured to maintain medical database contents by organizing medical information into levels, and a user interface component configured to enable a user to access the medical database utility. The medical database utility provides a user with an ability to access the user's collections of settings in the medical database, the user's collection of settings maintained separately from settings accessible by other users. The method stores medical data items in a database configured with multiple levels of organization, establishes a logical relationship between medical data items at each level of organization, presents a user with available medical system choices at each level of organization, and enables the user to select from among the available medical system choices presented at each level of organization.

Owner:JOHNSON & JOHNSON SURGICAL VISION INC

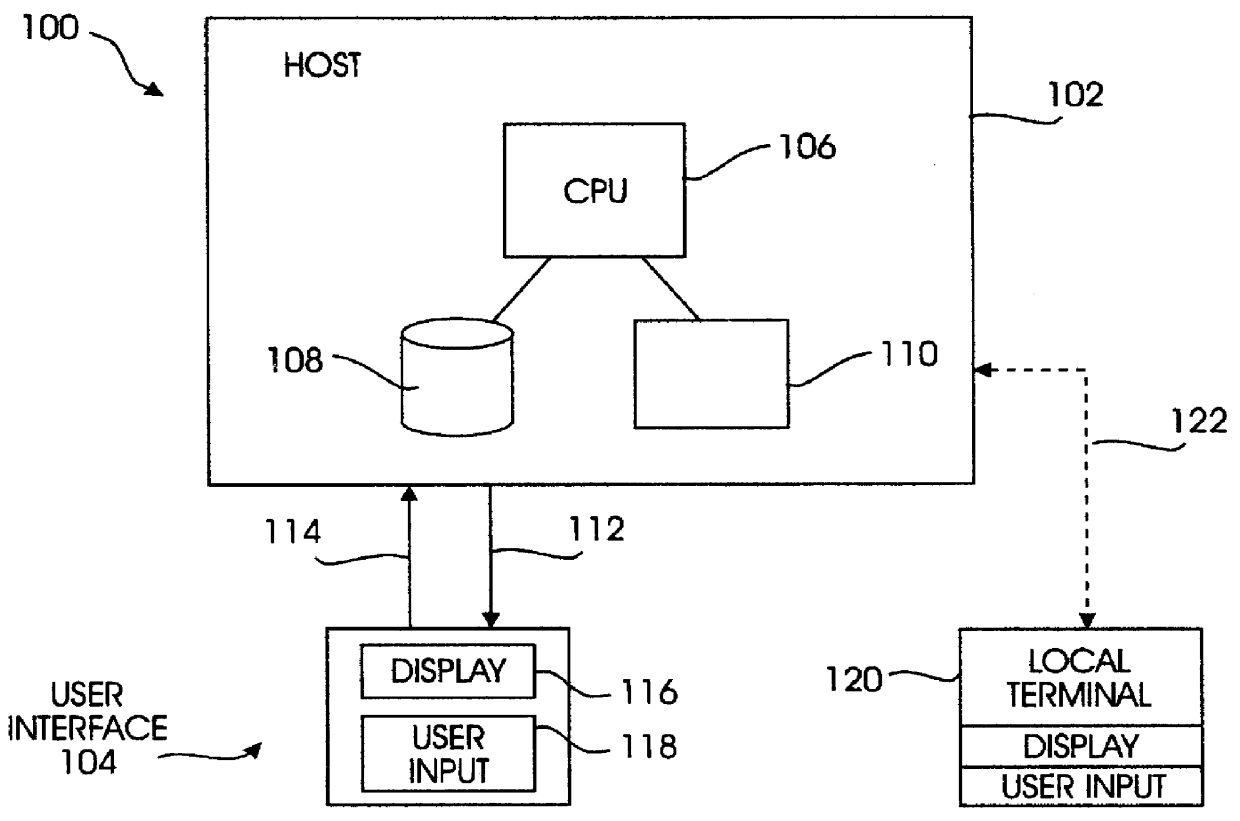

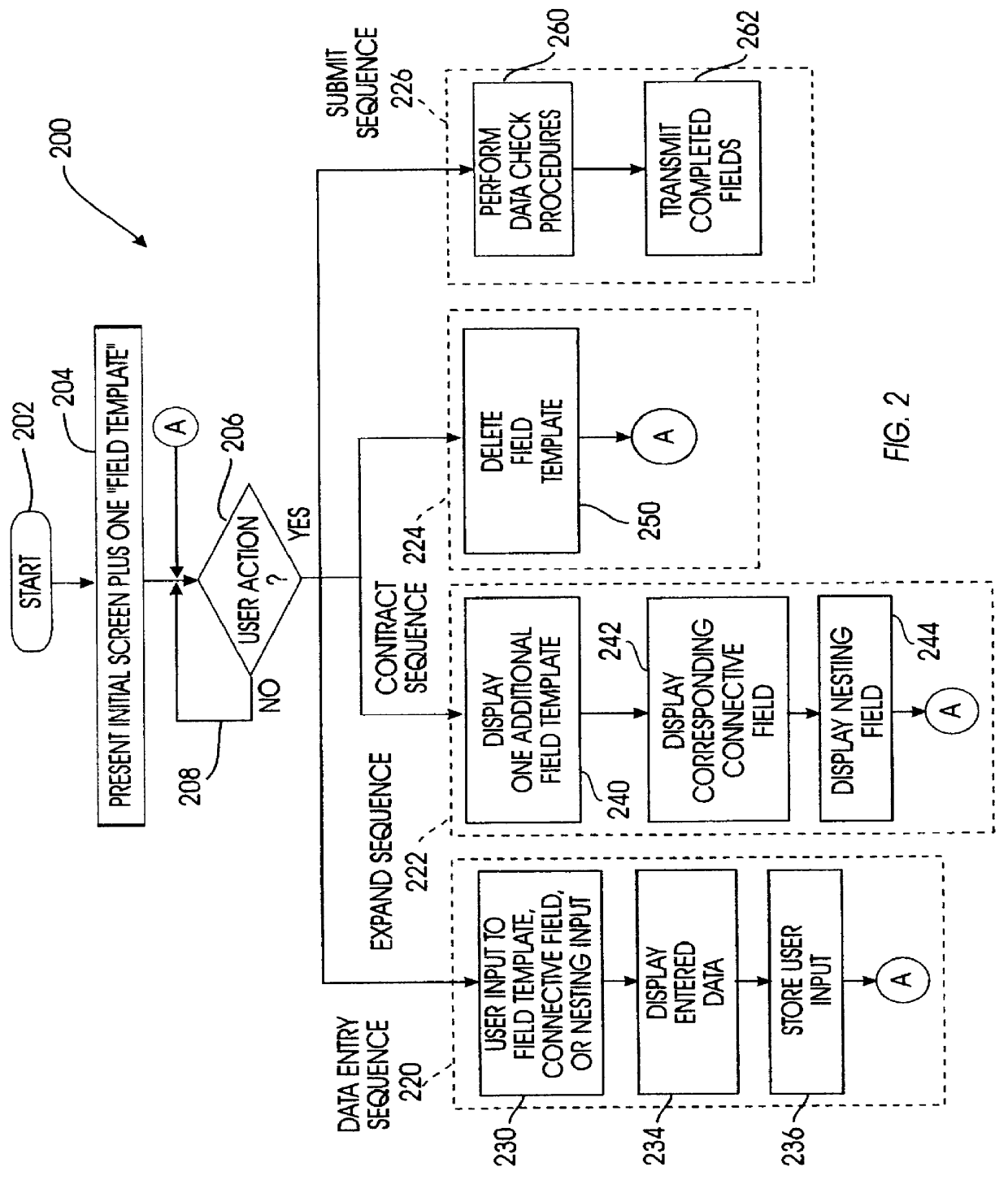

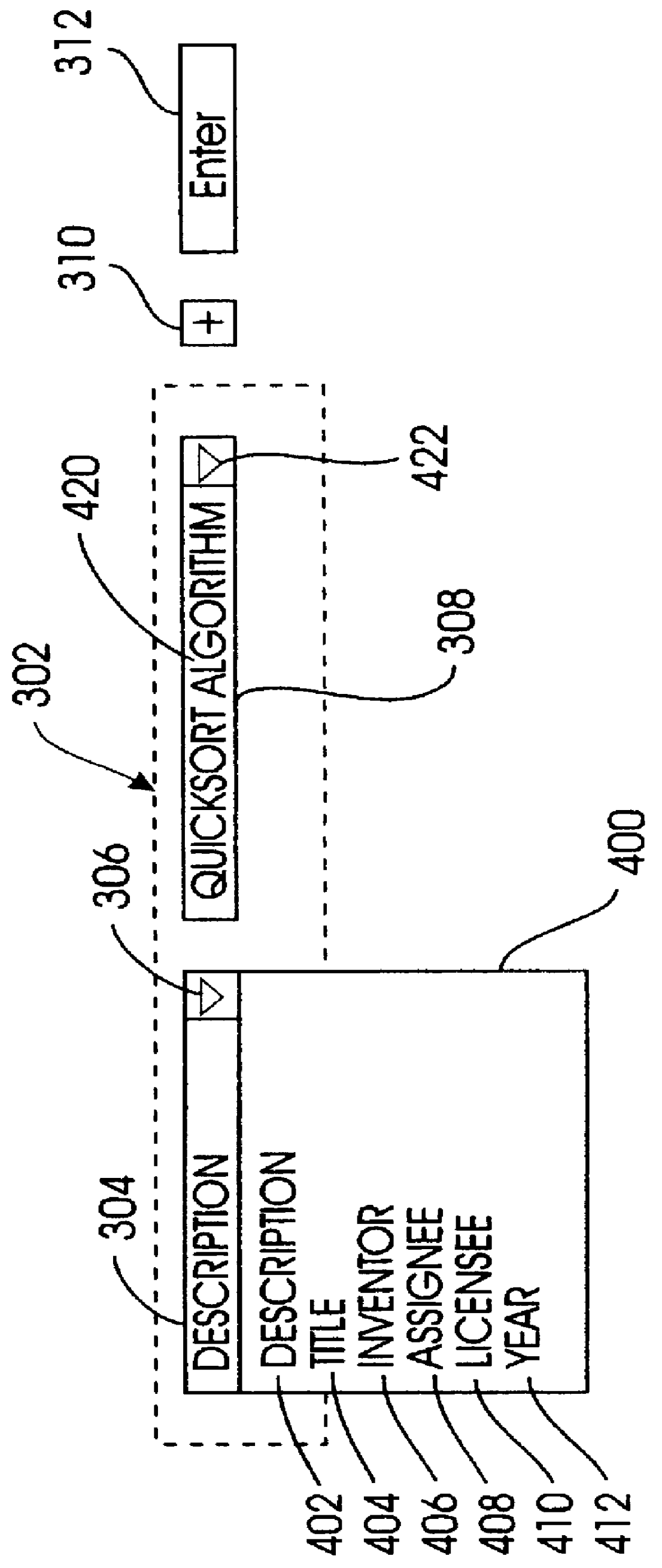

System for creating structured fields on electronic forms

InactiveUS6137488AGreat efficiency and flexibility and powerFacilitates completely custom construction and completionData processing applicationsNatural language data processingGraphical user interfaceLogical relationship

A computer system enables a user to conveniently fill-out, configure, and submit a structure of interrelated data fields, where the order and type of linking between the fields is user selected. A graphical user interface presents a field template having one or more data fields. The user may extend the electronic form by selecting an expand form field; in response to selection of the expand field, the user interface adds a second field template and a connective field to the display. This second template, like the first, includes one or more data fields. Using a connective field, the user identifies a logical relationship between the first field template and the second field template. For instance, the user may select from Boolean or other connective terms to construct a form having a complex format of interrelated fields. As each new field template is added with its corresponding connective field, the user interface also presents a nesting icon, allowing the user to establish a logical hierarchy between the various field templates.

Owner:IBM CORP

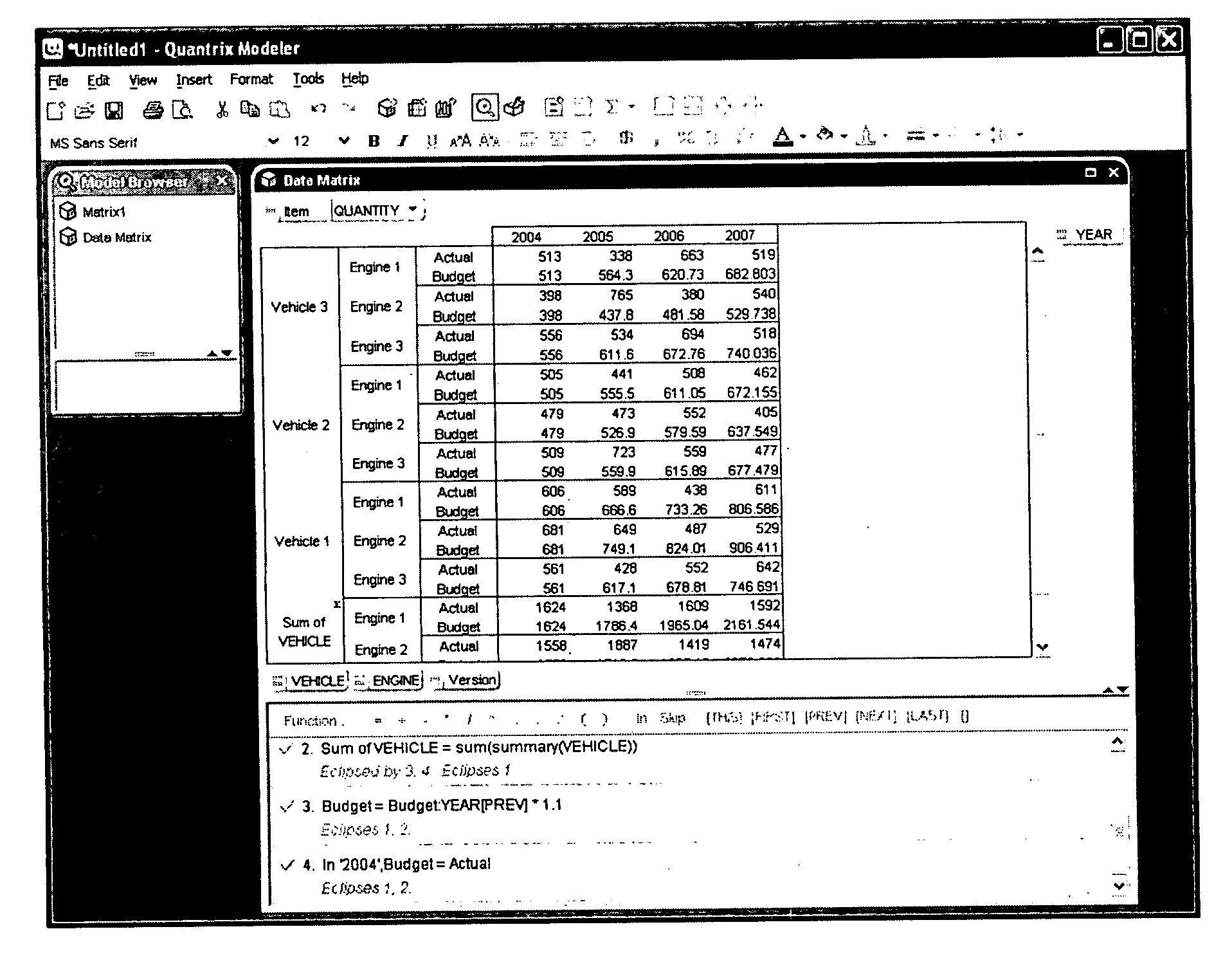

Multidimensional modeling system and related method

InactiveUS20070250295A1Easy to implementHigh transparencyComputation using non-denominational number representationOffice automationTheoretical computer scienceMulti dimensional

A computer-enabled system and related method to perform multi-dimensional modeling. The system includes a model building function, a data link function, a dependency inspector function and a presentation function. The system unlocks the connectivity between model logic, model structure and outcome presentation. Model cells are given understandable names, and the system allows parsing and reorganization of model information without loss of logic, including formulas associated with cell elements. The data link function enables a user to insert into a matrix of the system external information of an array of data types. The dependency inspector function enables a user to quickly and easily identify relationships among cell elements. This capability reduces the time required to detect modeling errors, to audit the model, and / or understand logical relationships embodied in the model.

Owner:SUBX

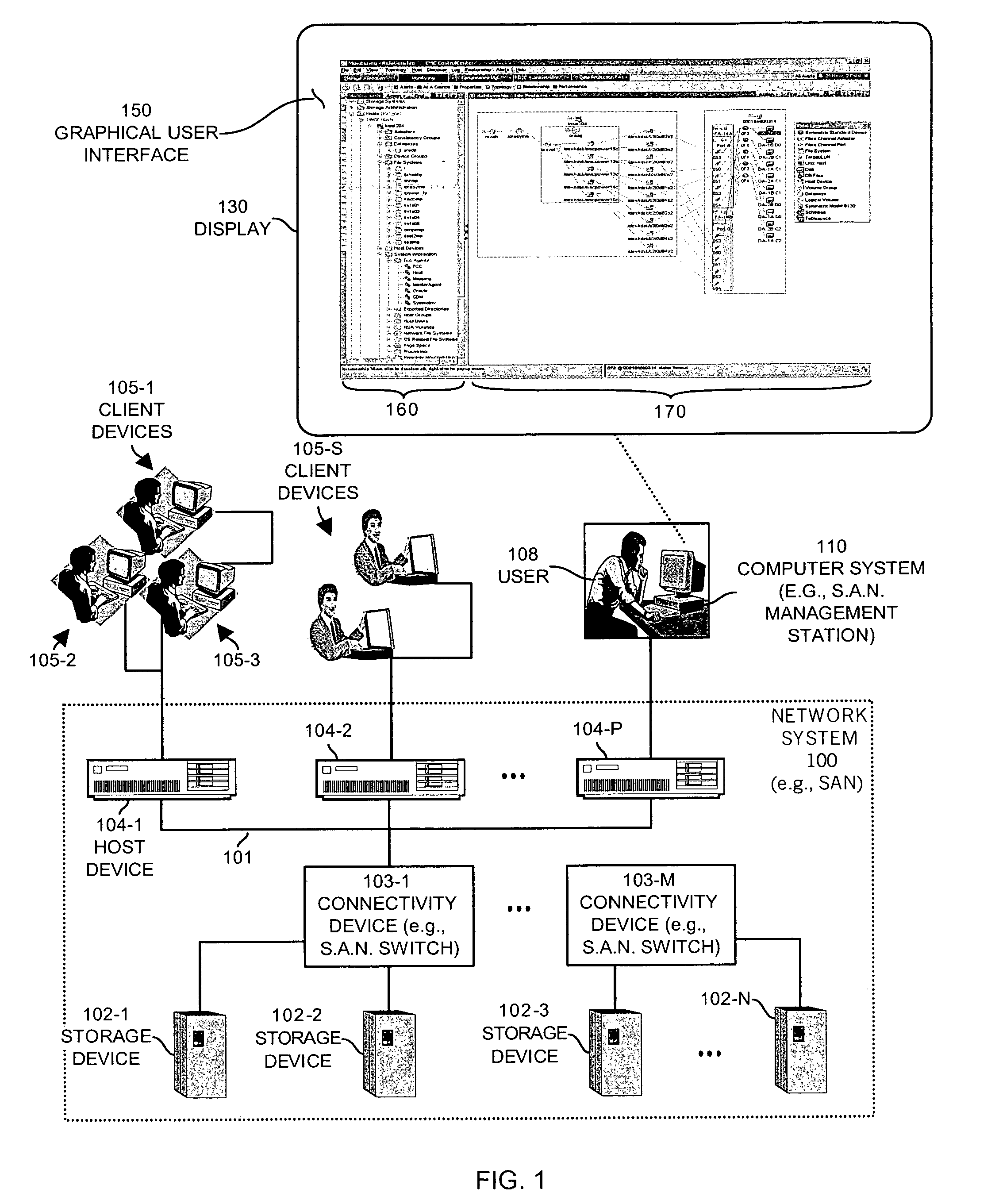

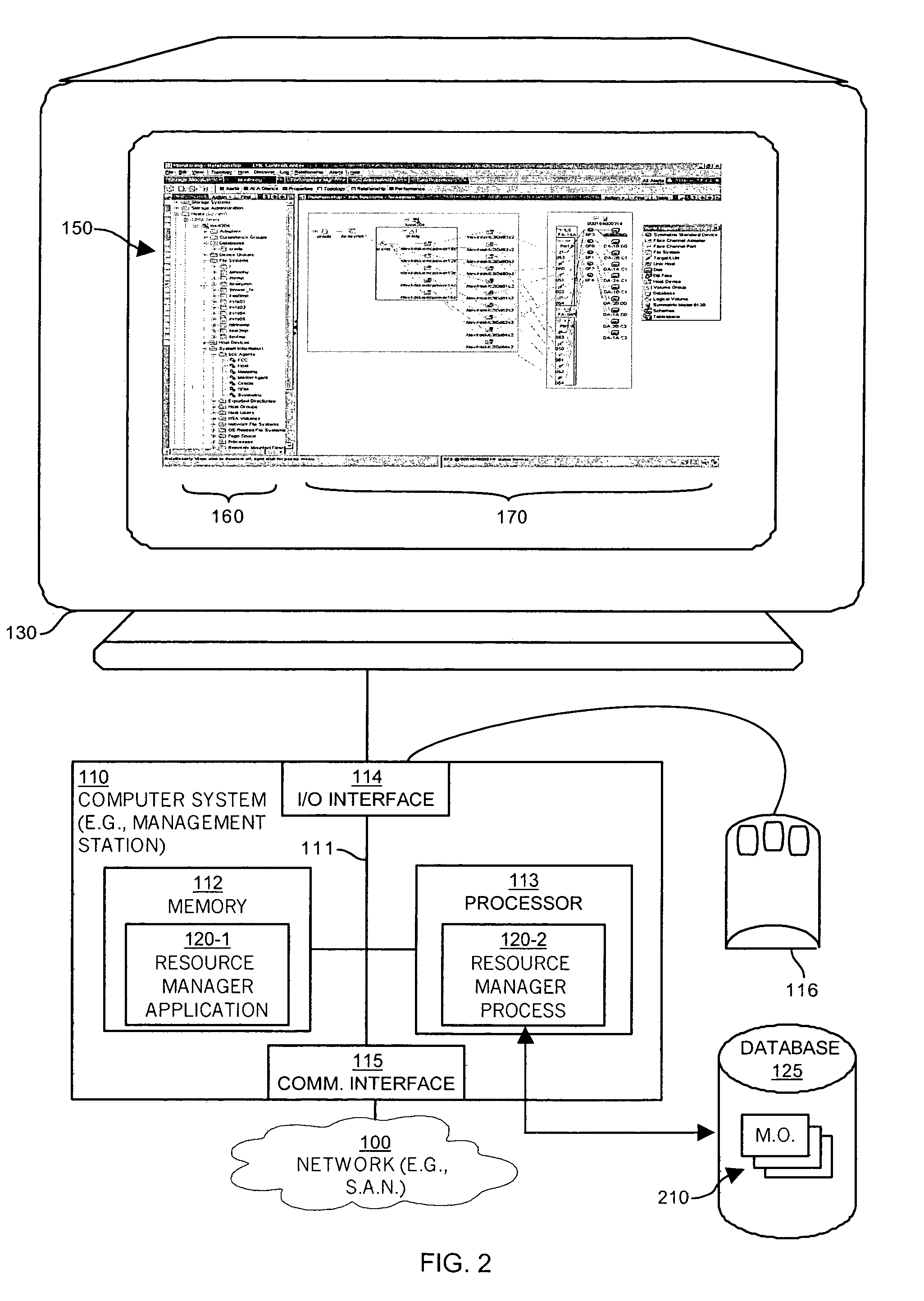

Methods and apparatus for managing network resources via use of a relationship view

ActiveUS7437676B1Quick identificationEasy to identifyDigital computer detailsTransmissionManagement objectStorage area network

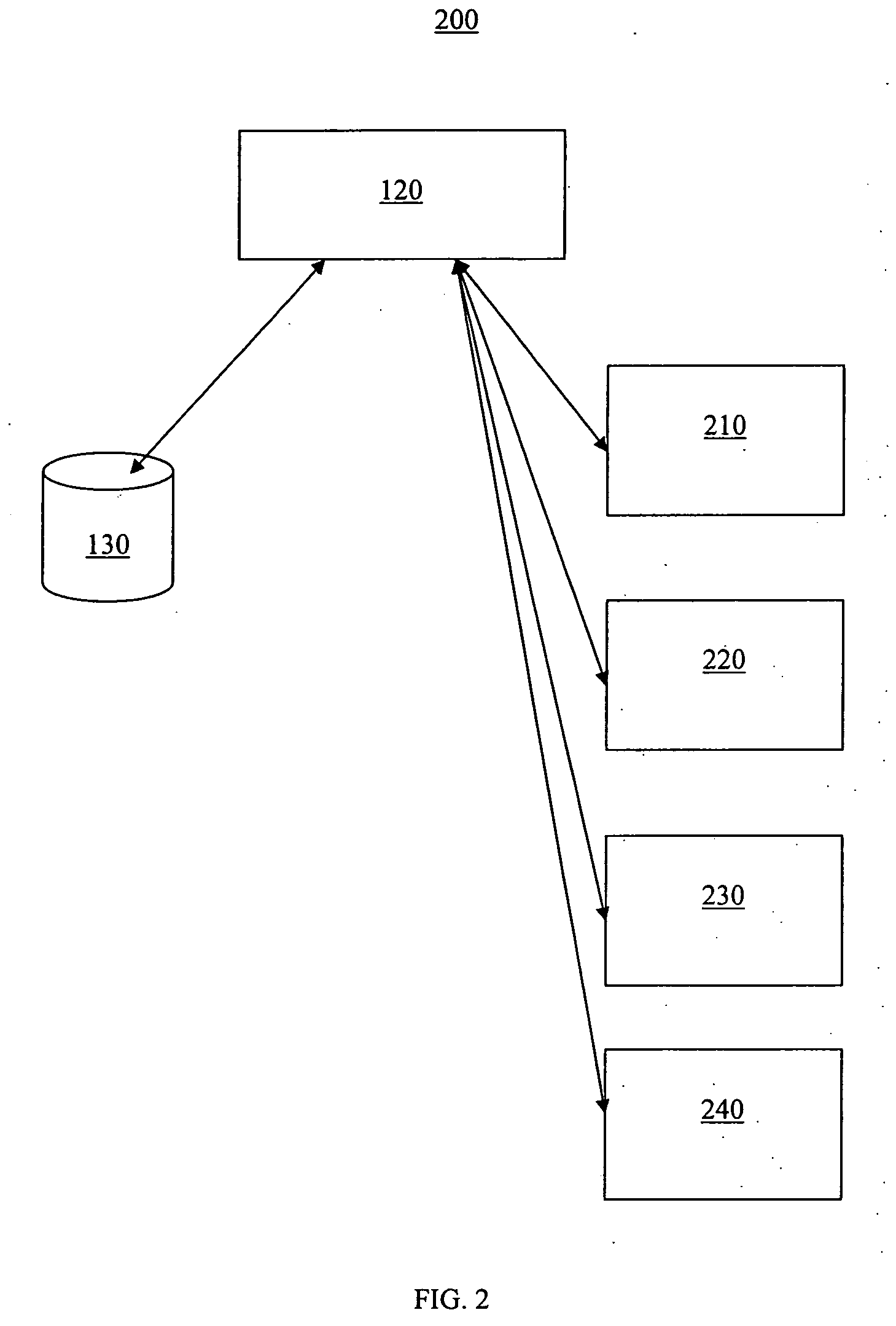

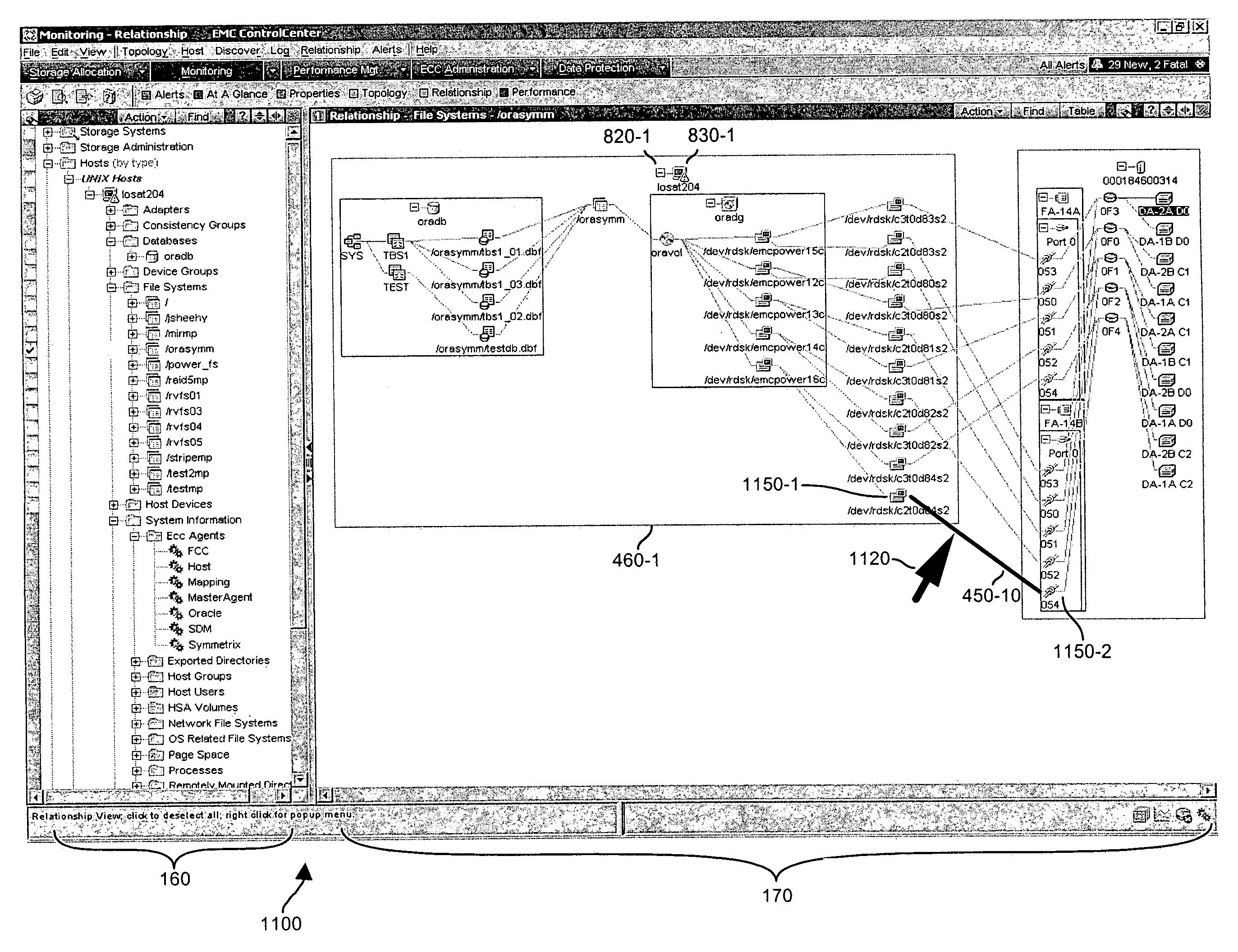

A processing device generates a relationship view of managed entities in a storage area network based on objects stored in a relational database. Each managed entity (e.g., file system, database, volume, storage device, etc.) in the storage area network has a corresponding managed object stored in the relational database. Generally, managed objects of a particular type are categorized into one or more tables. Such tables are related to one another by foreign key attributes, which represent relationships between types of managed objects (and thus a relationship between corresponding managed entities). Relationships among the managed objects in the relational database may be generally classified as either association or containment. Association identifies a logical relationship between managed objects. Containment identifies groups of managed objects that are logically associated with each other. The processing device uses these identified relationships to generate the appropriate relationship view for a selected managed entity.

Owner:EMC IP HLDG CO LLC

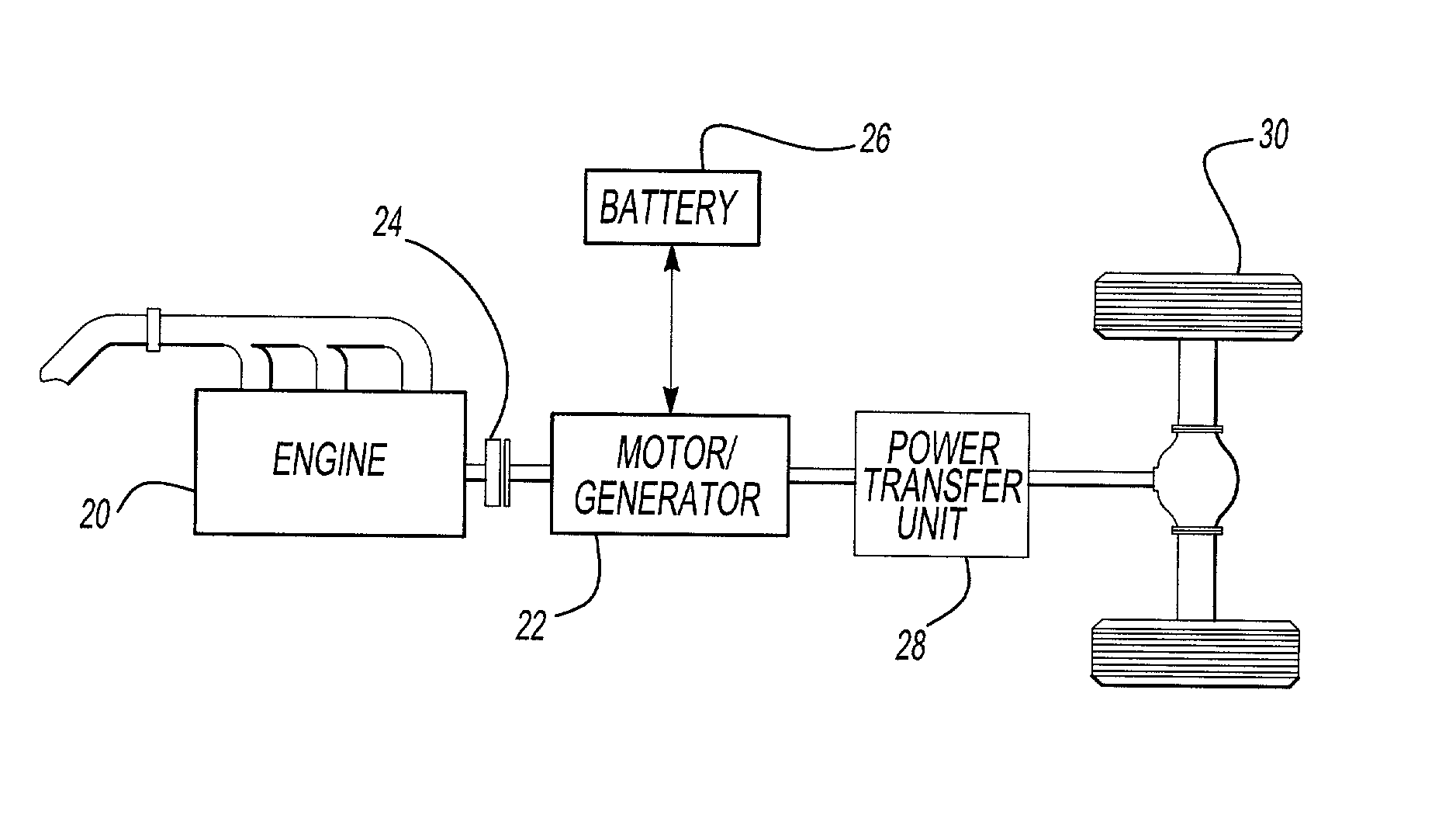

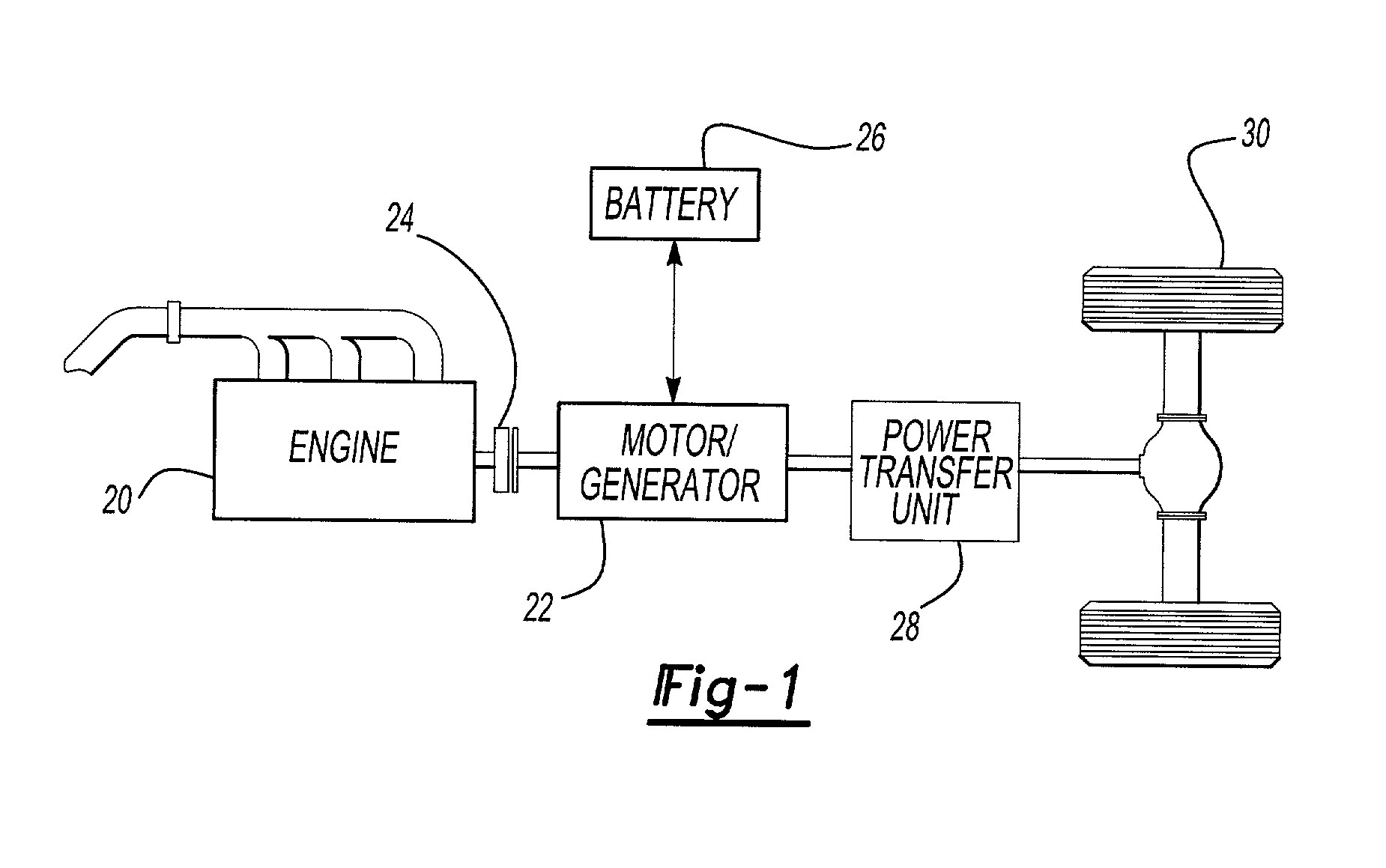

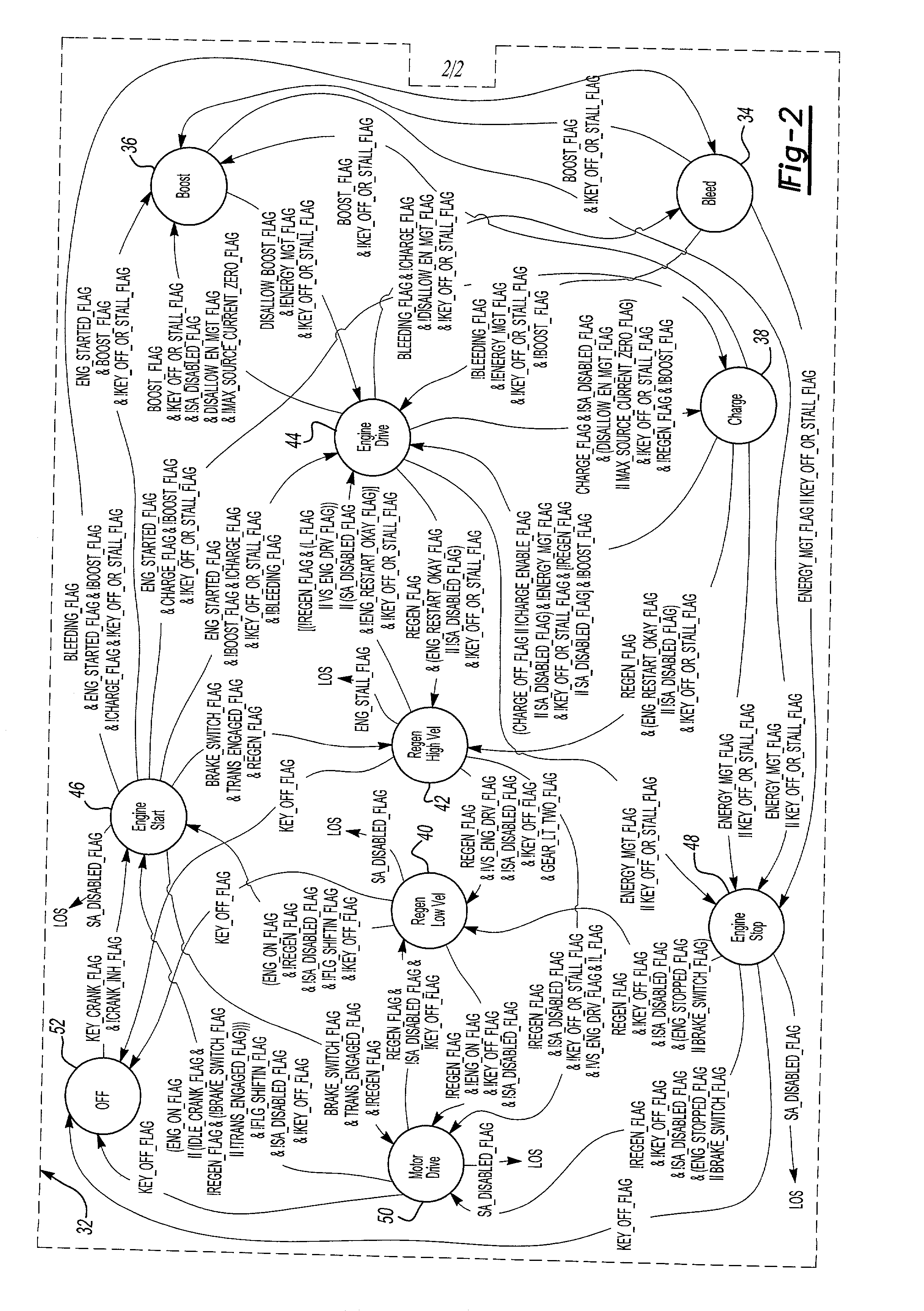

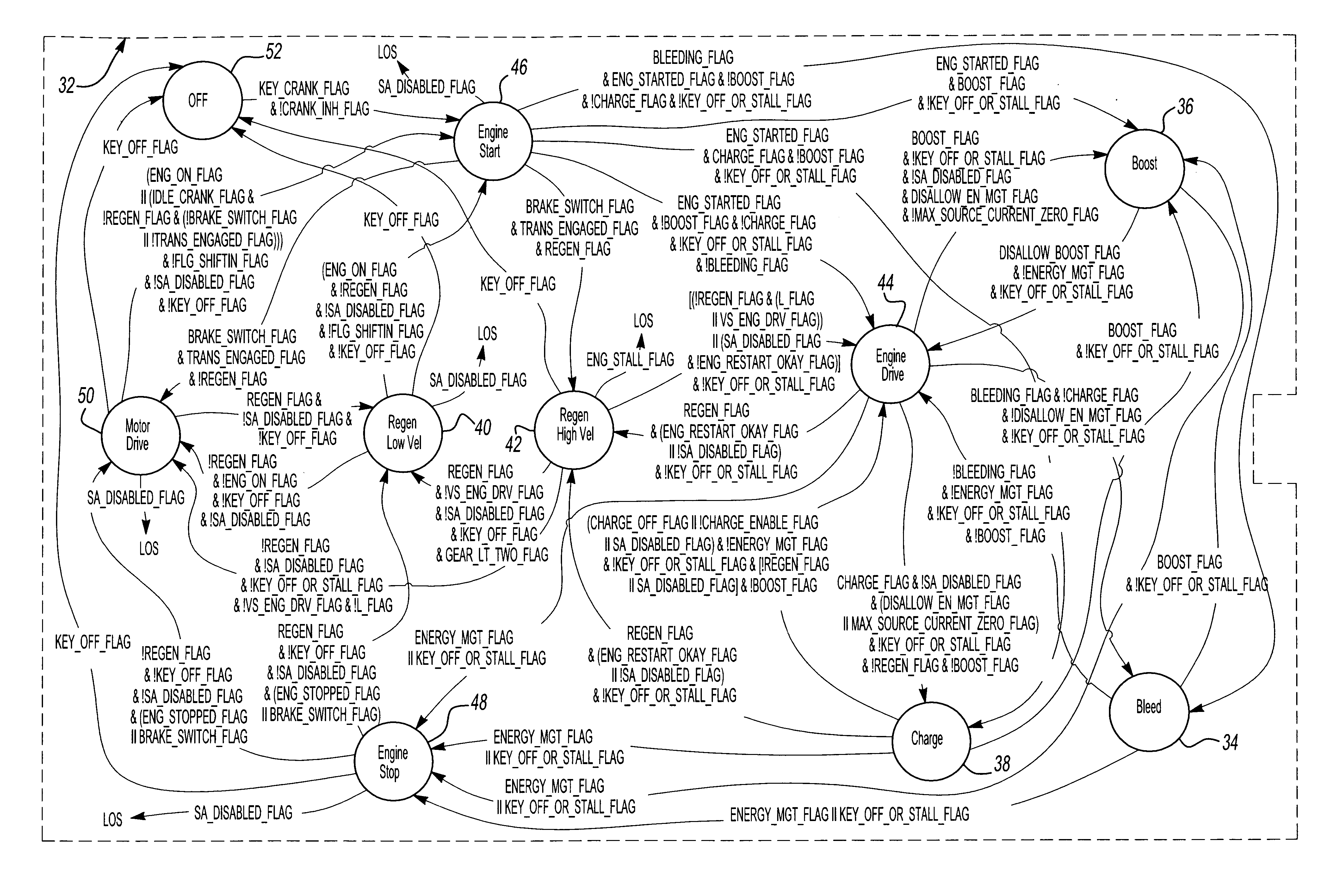

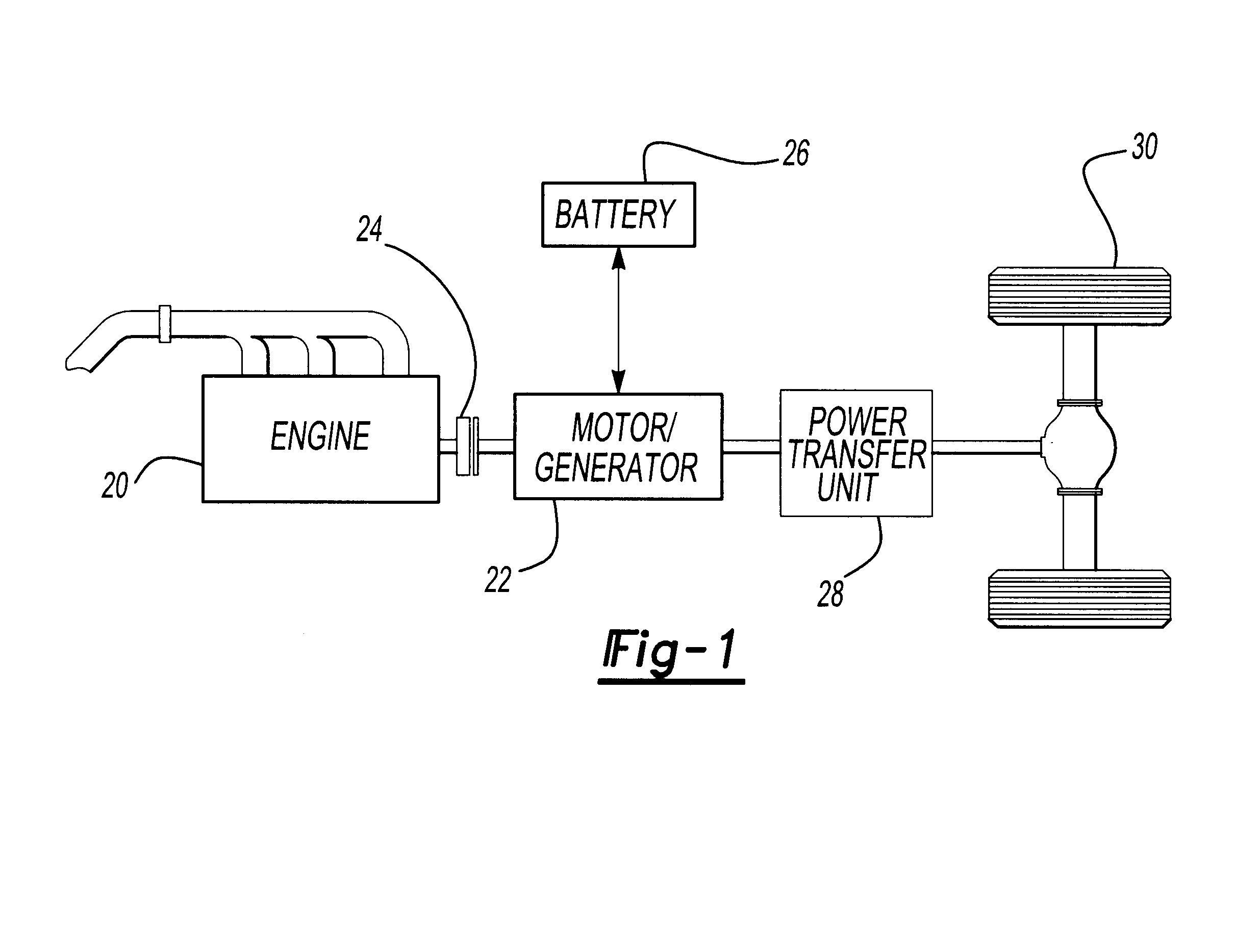

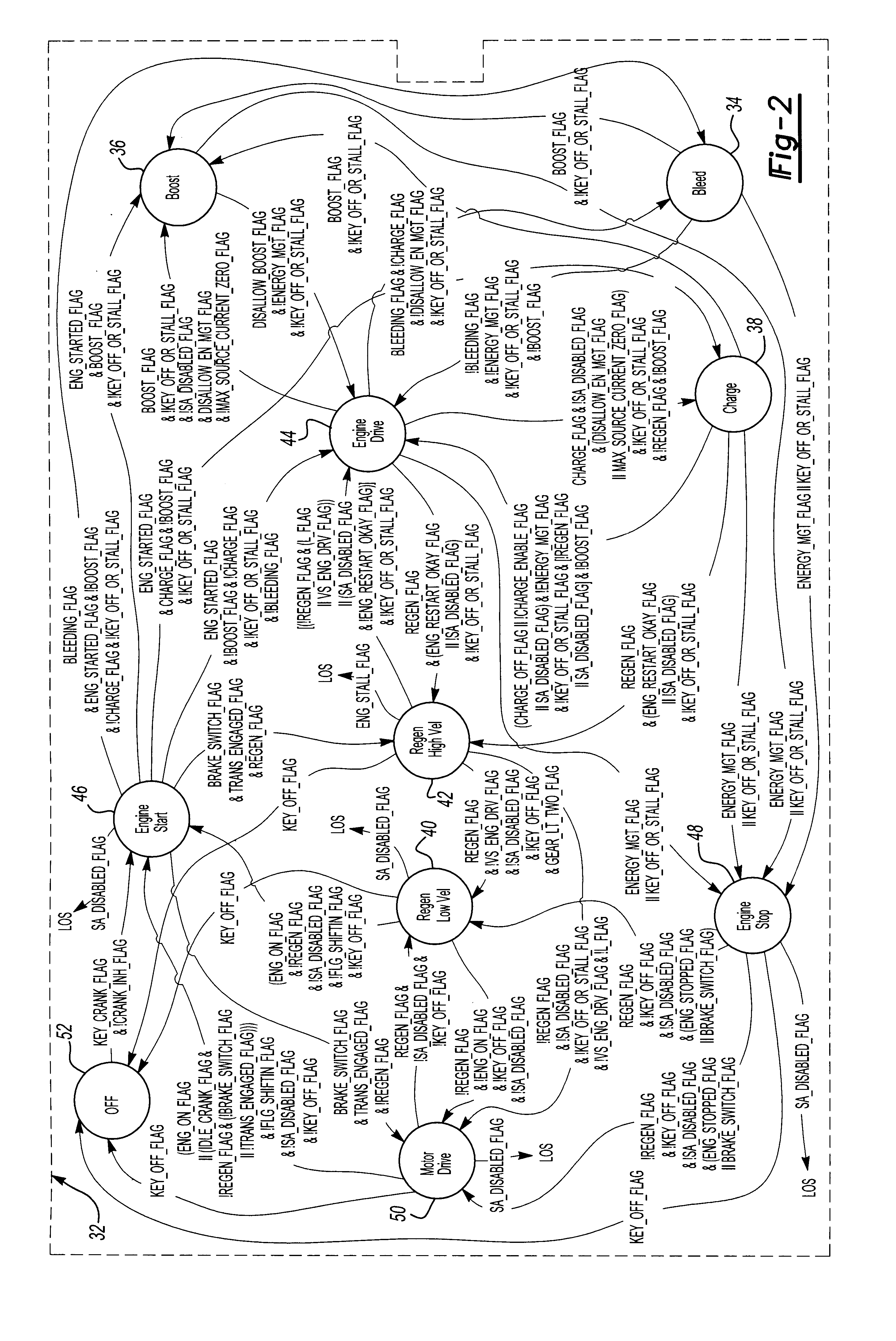

Control system and method for a parallel hybrid electric vehicle

InactiveUS20030098187A1Auxillary drivesElectrical controlControl systemStructure of Management Information

The present invention provides a control strategy for a parallel hybrid electric vehicle (HEV) configuration where power from the engine and the motor can each independently provide torque to the vehicle powertrain. The invention has a logical structure defining main system operating modes (states) and the transition between the different states. In addition to the predefined states, the present invention provides a set of rules defining logical relationships between each of the plurality of predefined states and a set of commands unique to each state. These commands are supplied to subsystem controllers to achieve desired vehicle functionality. The predefined states can be prioritized according to operator demands, energy management requirements, and system fault occurrences. The present invention can also be configured to have at least one of a plurality of transition flags. Each transition flag represents a logical relationship associated with efficient management of energy, operator demand, or system faults.

Owner:FORD GLOBAL TECH LLC

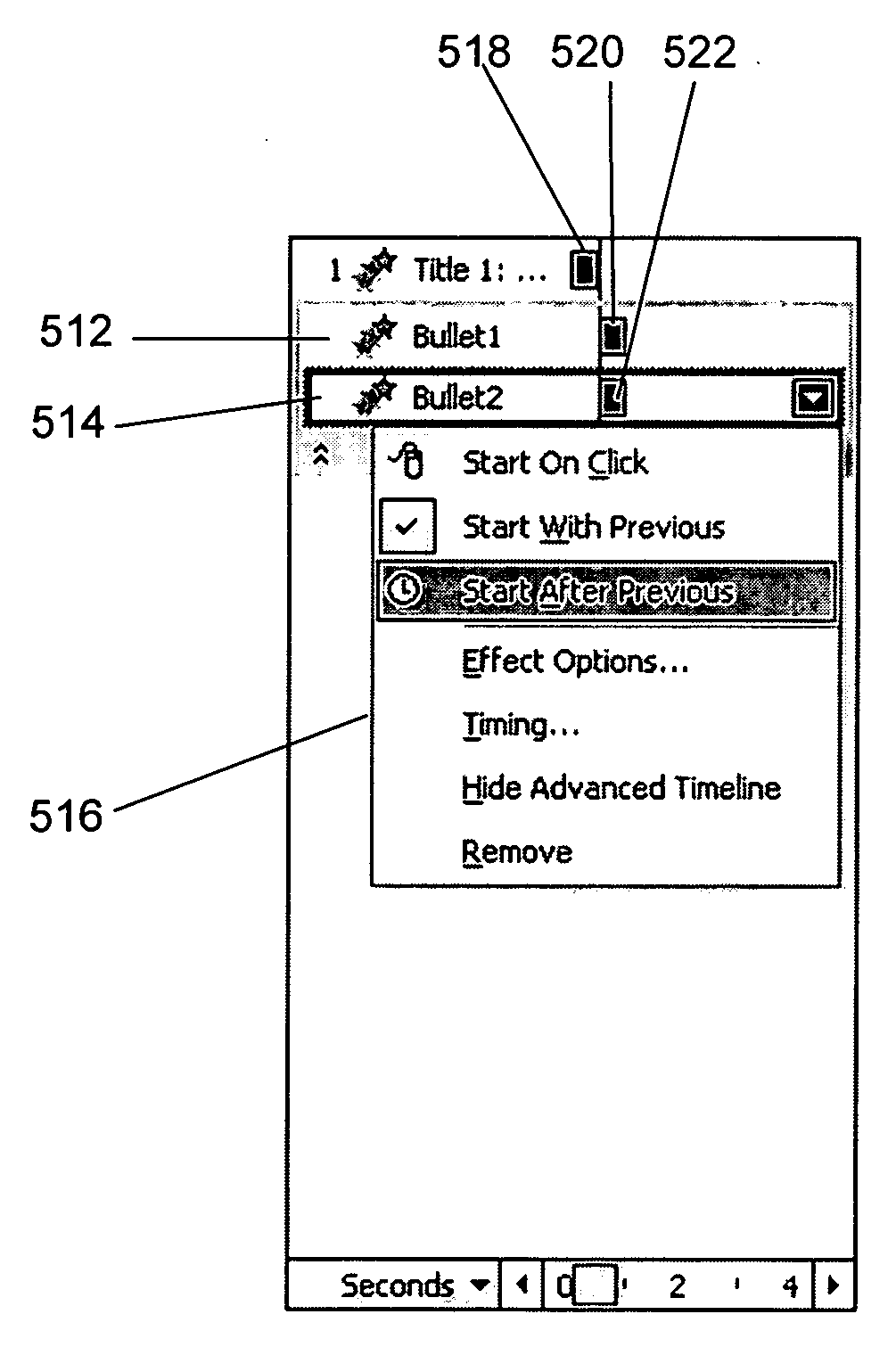

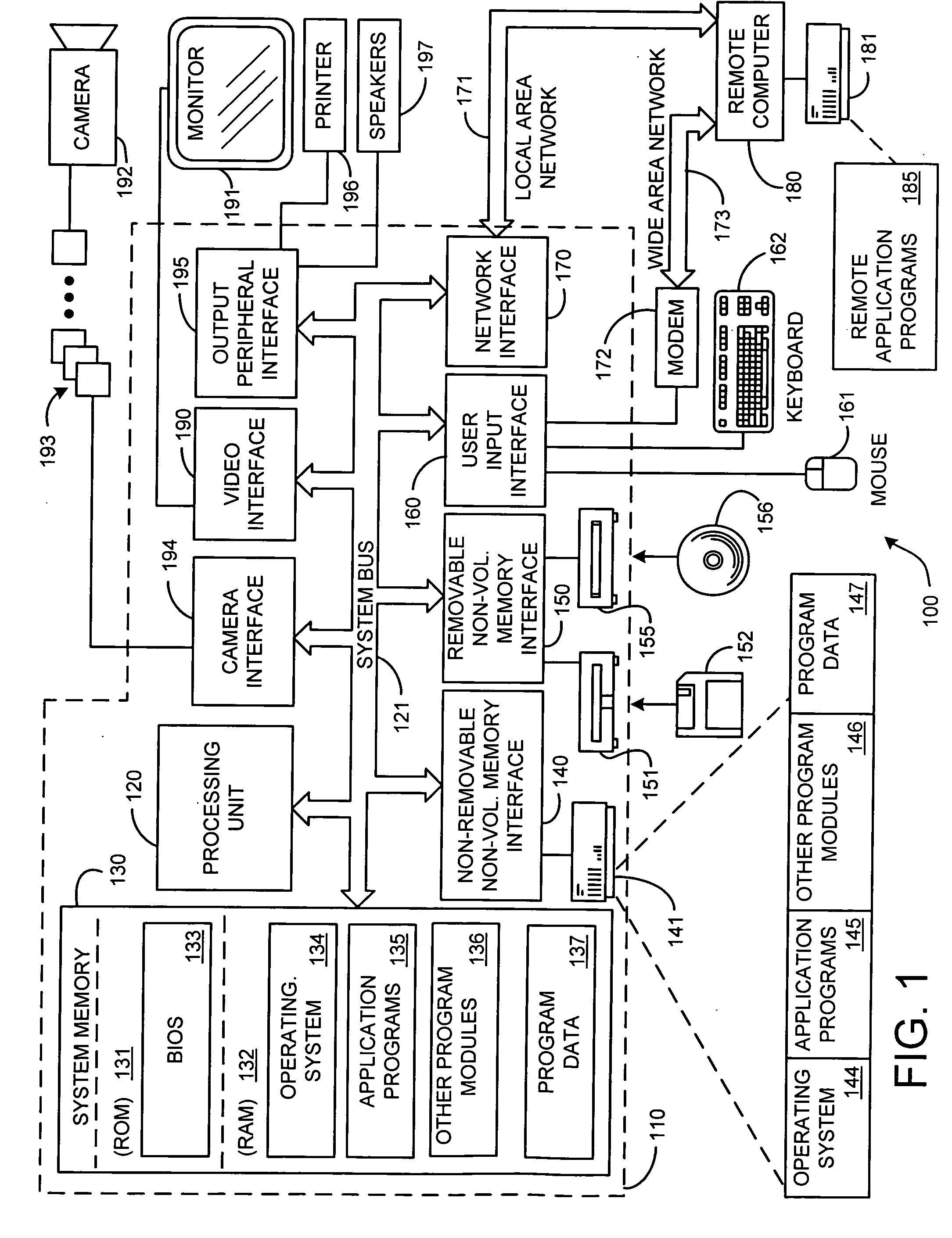

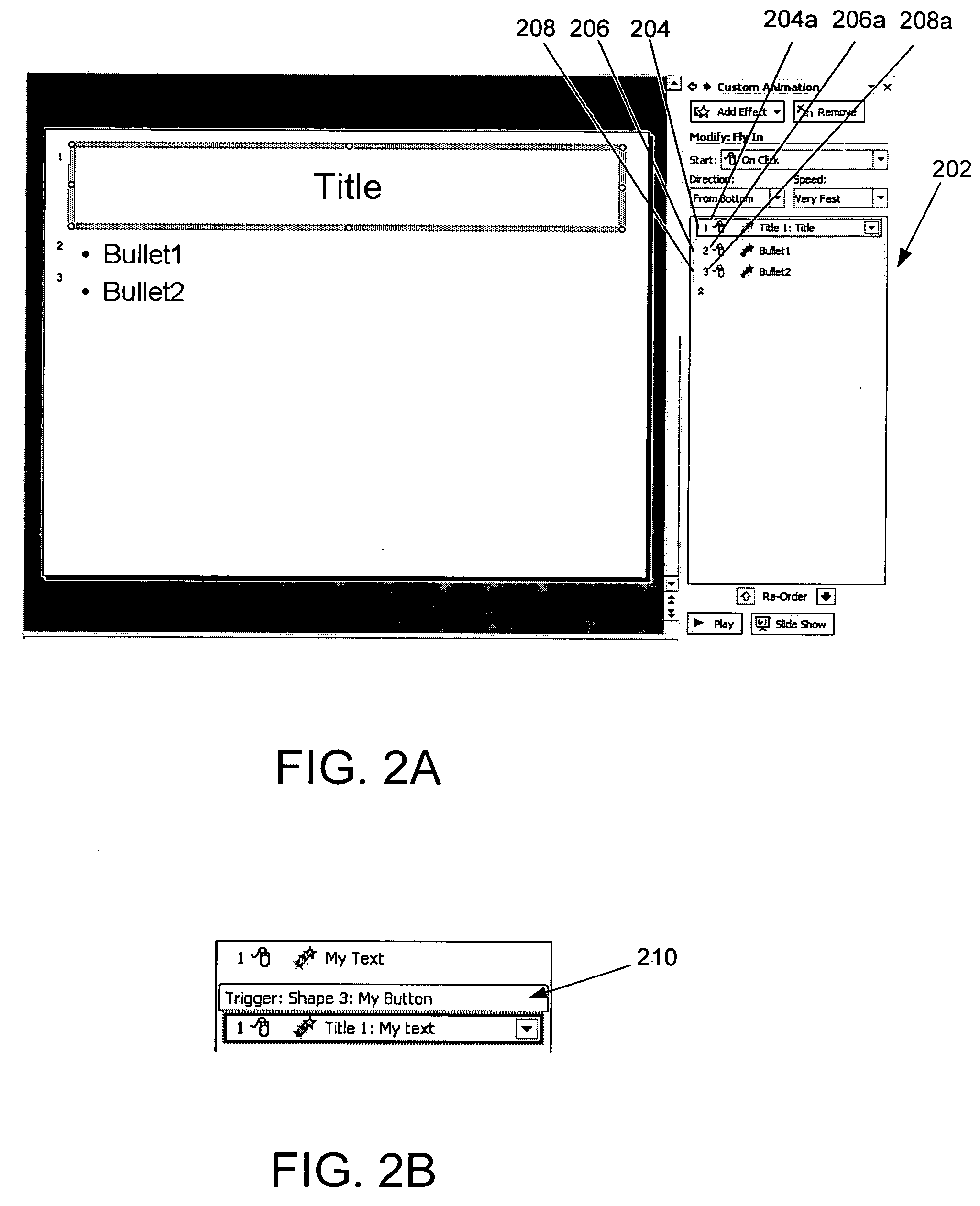

Integrated timeline and logically-related list view

InactiveUS20050097471A1Less screen real estateMore discoverableRecording carrier detailsRecord information storageGraphicsAnimation

A system and method for graphically showing the order and timing of elements in a presentation program or other software. The sequence of events is shown in an event list, a list of events in sequence order, each event being associated with an event timeline bar and correlated with a universal timeline, in the editing window of an electronic presentation or other software that deals with the scheduling of events. In one embodiment, each item in the list represents an individual animation effect. Elements of the event list are logically related to each other and these logical relationships may be used in assisting a user to build a sequence of events (e.g., an animation sequence).

Owner:MICROSOFT TECH LICENSING LLC

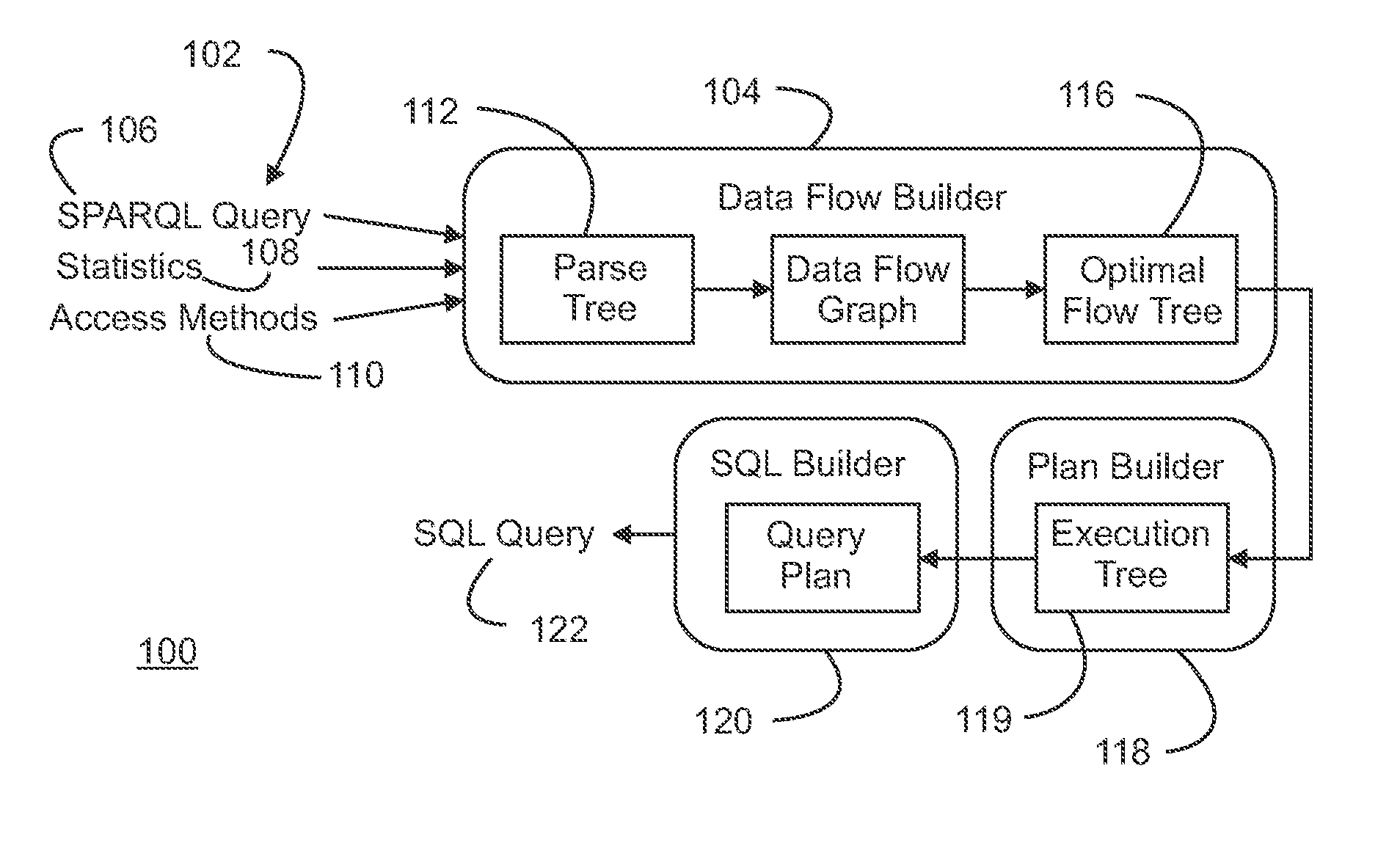

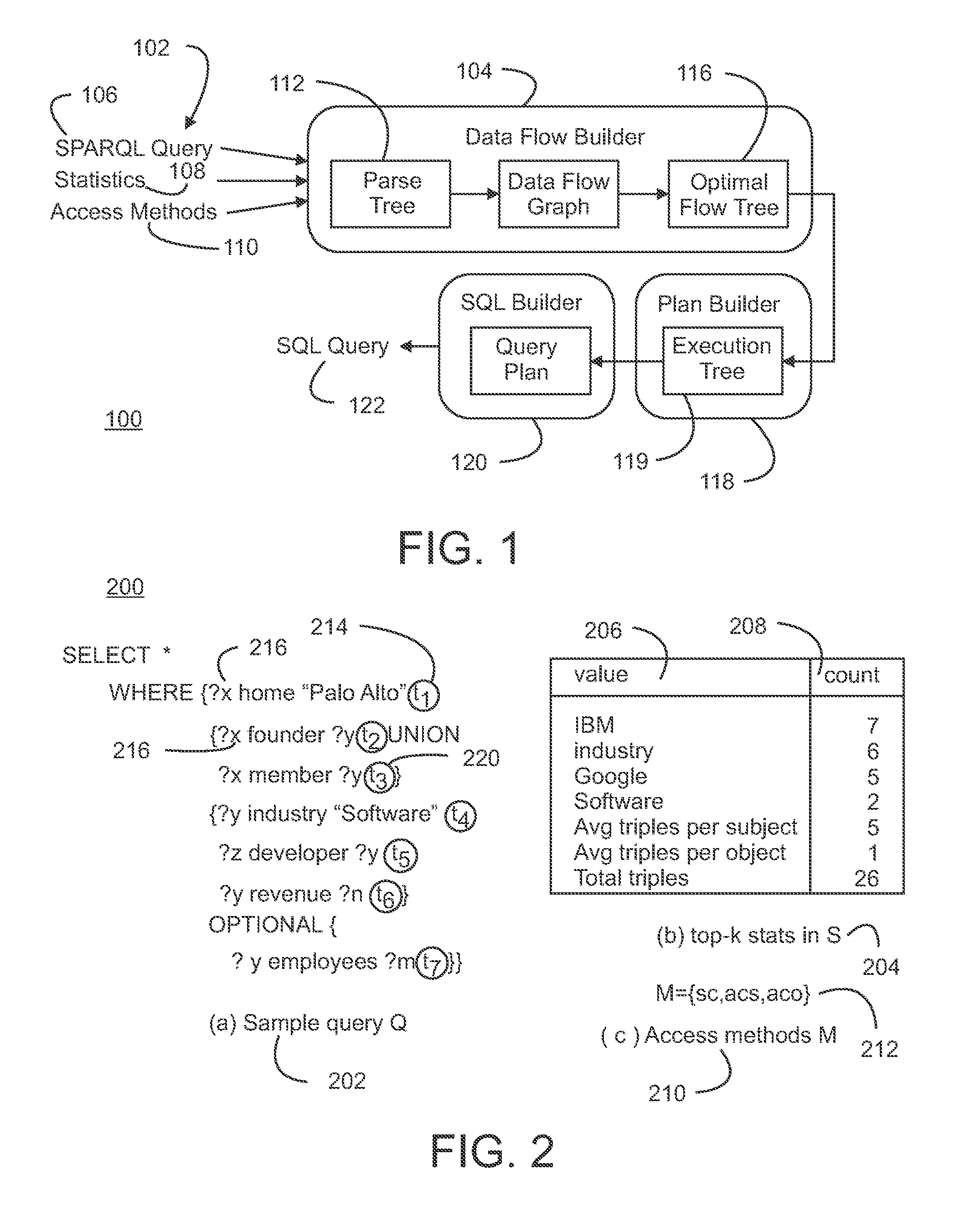

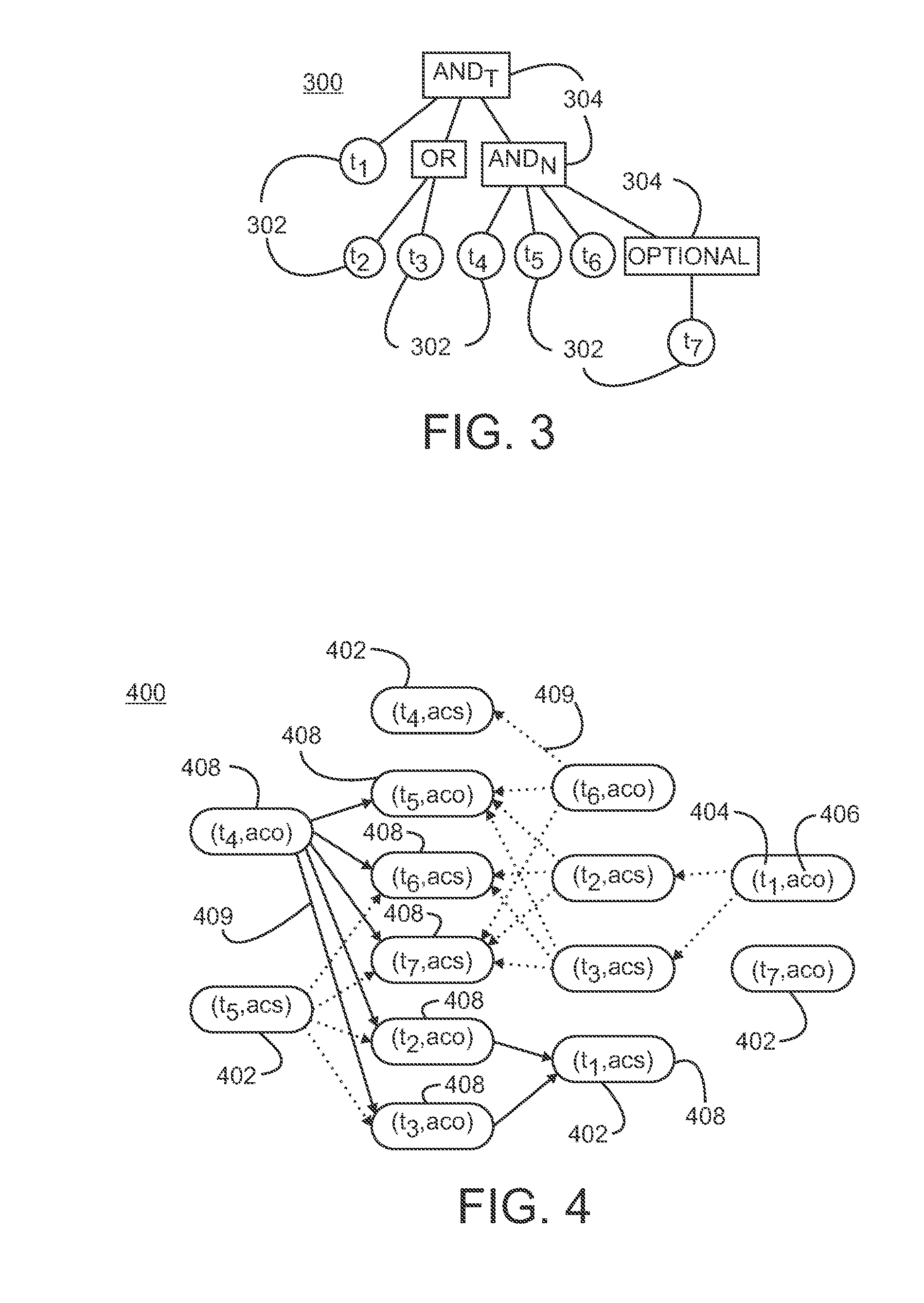

Method and Apparatus for Optimizing the Evaluation of Semantic Web Queries

InactiveUS20140304251A1Effective evaluationAmenable to optimizationDigital data information retrievalDigital data processing detailsQuery planAccess method

A semantic query over an RDF database is received with RDF database statistics and access methods for evaluating triple patterns in the query. The semantic query is expressed as a parse tree containing triple patterns and logical relationships among the triple patterns. The parse tree and access methods create a data flow graph containing a plurality of triple pattern and access method pair nodes connected by a plurality of edges, and an optimal flow tree through the data flow graph is determined such that costs are minimized and all triple patterns in the semantic query are contained in the optimal flow tree. A structure independent execution tree defining a sequence of evaluation through the optimal flow tree is created and is transformed into a database structure dependent query plan. This is used to create an SQL query that is used to evaluate the semantic query over the RDF database.

Owner:IBM CORP

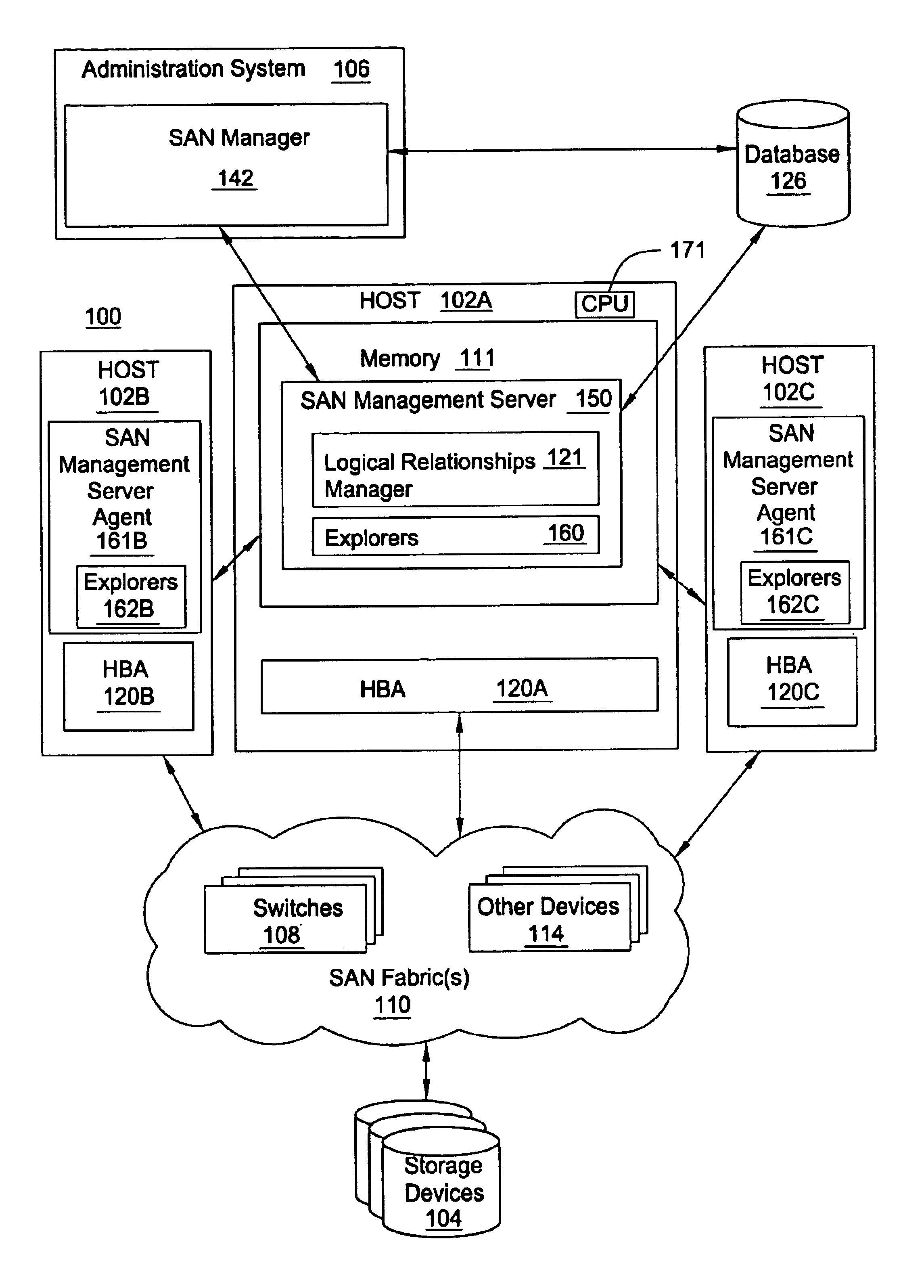

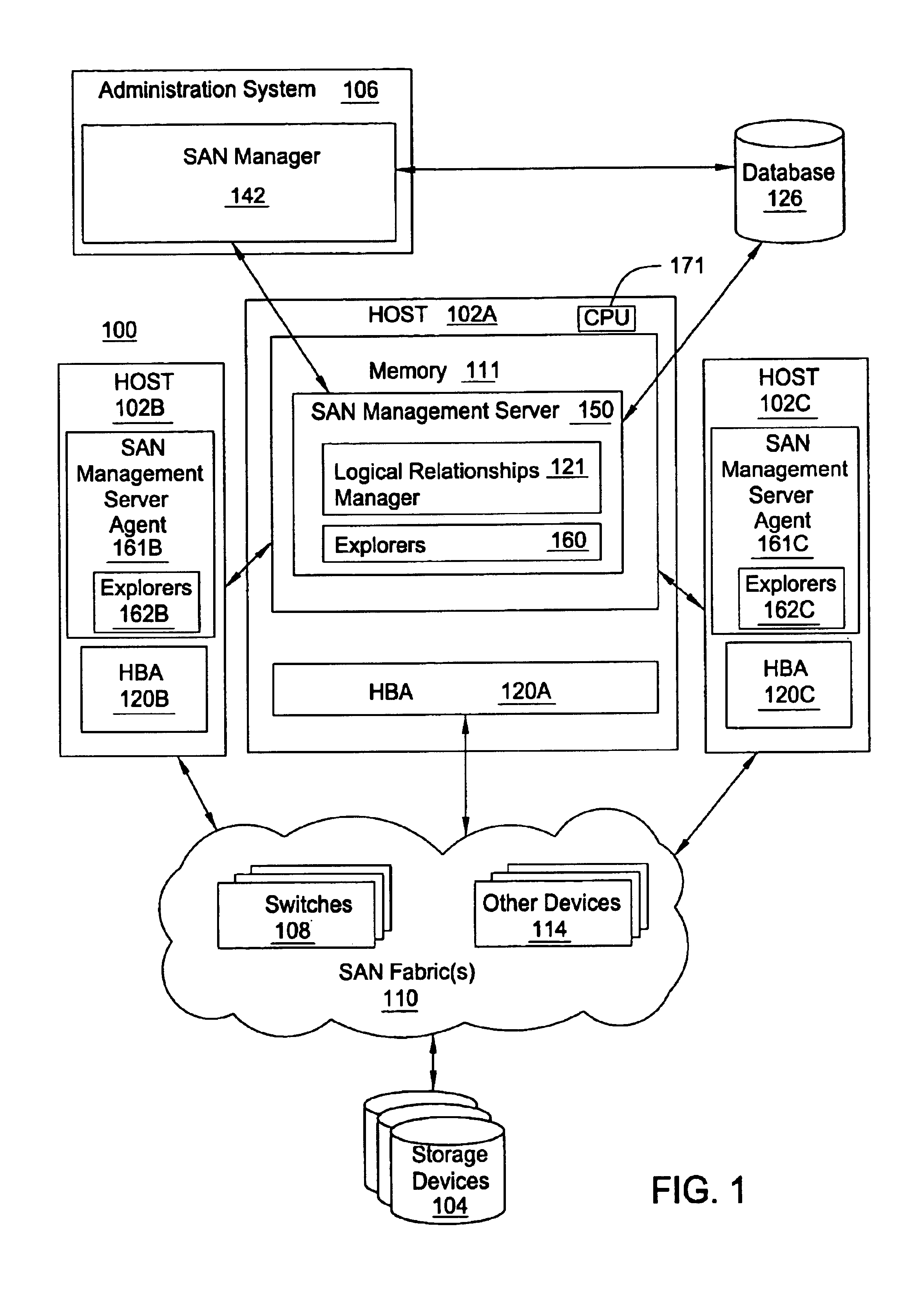

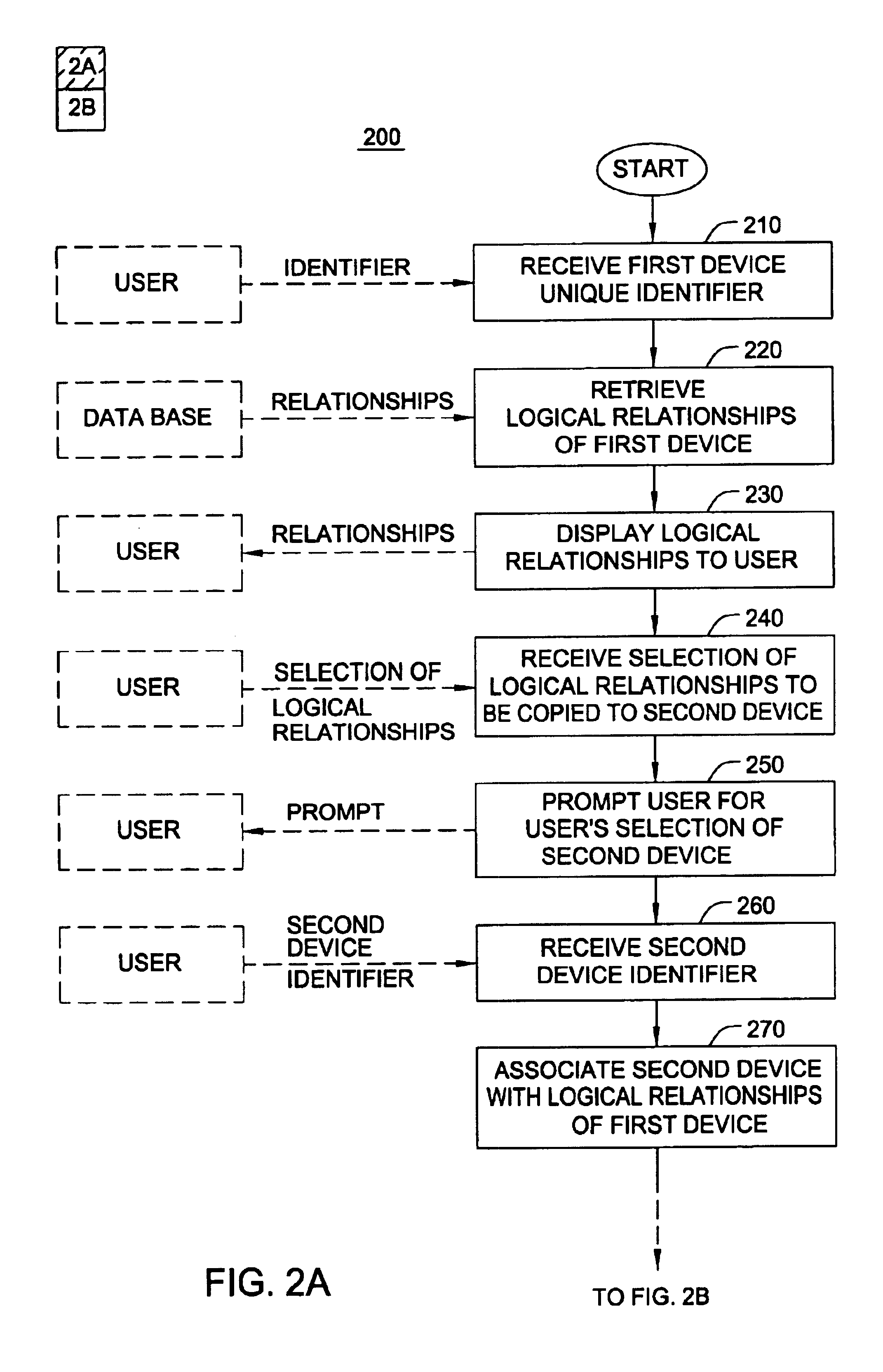

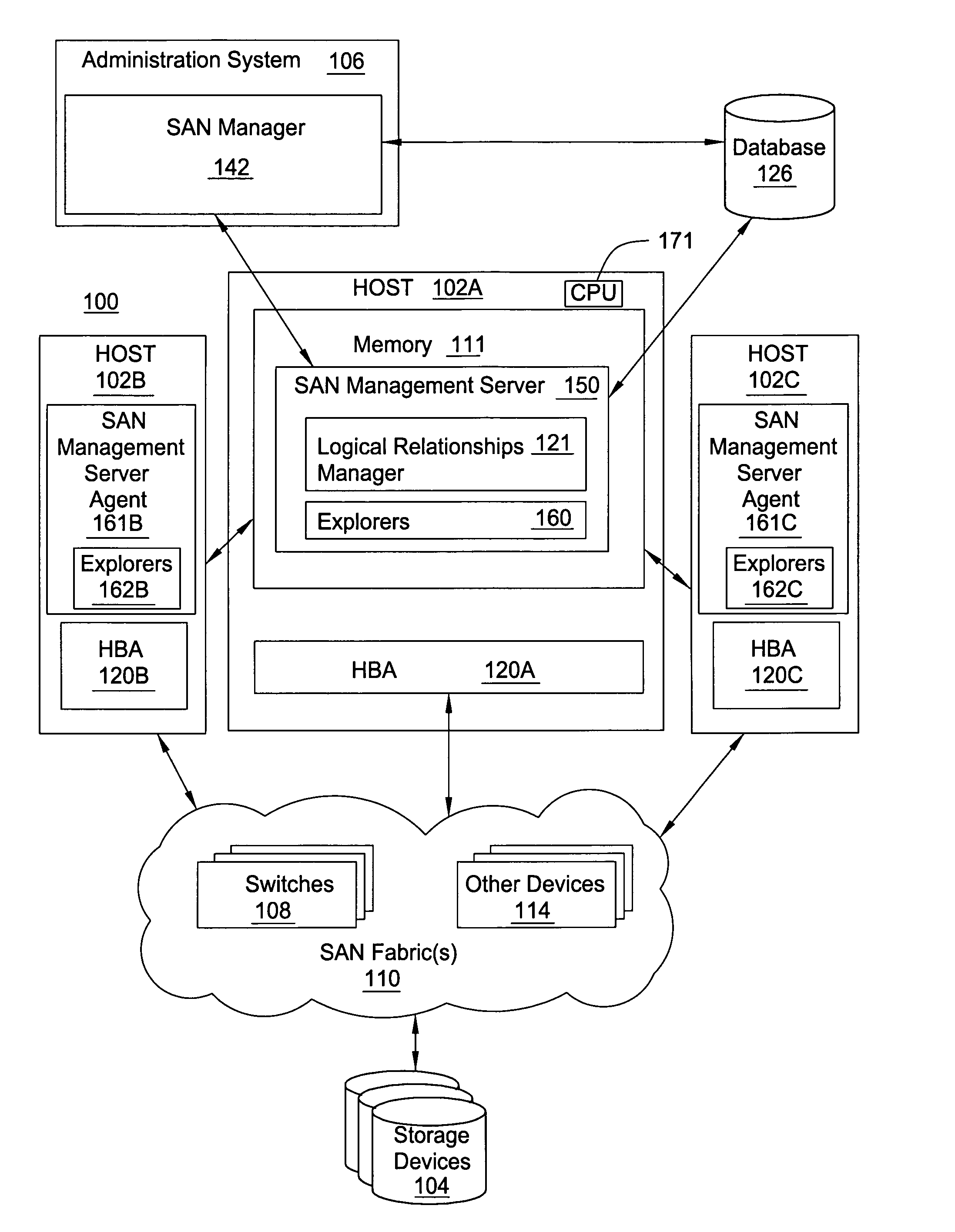

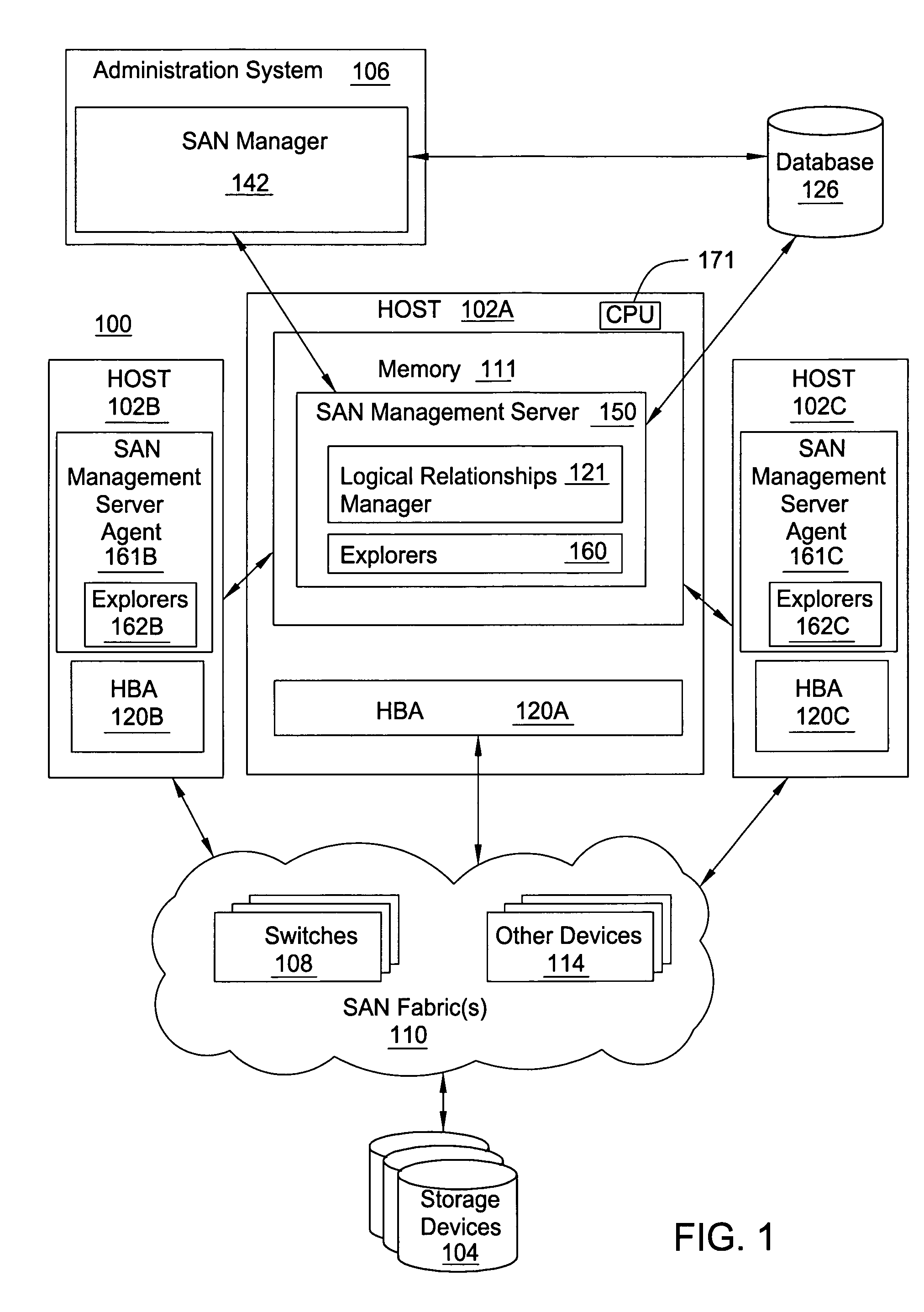

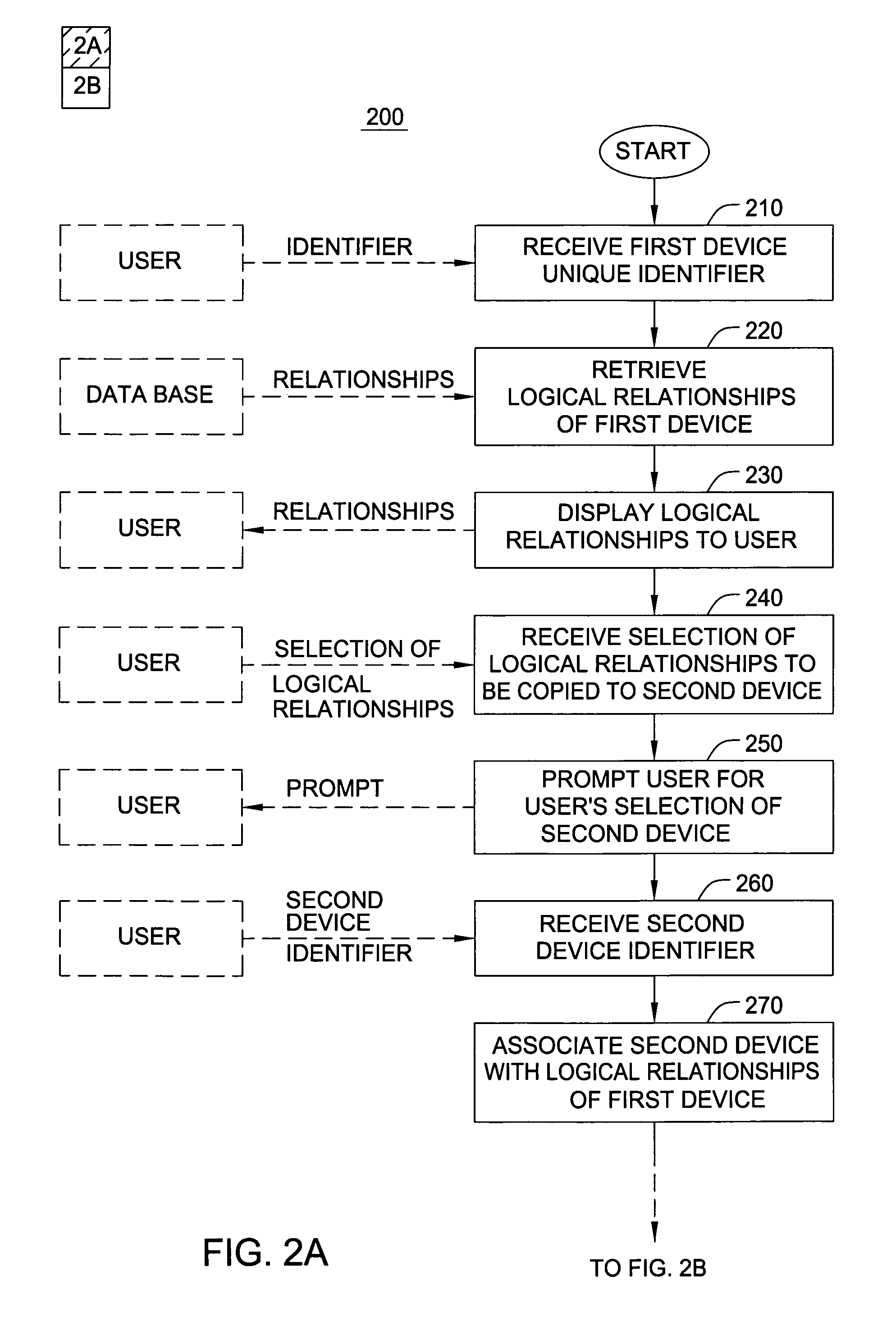

Storage area network (SAN) device logical relationships manager

InactiveUS6839746B1Multiple digital computer combinationsData switching networksStorage area networkOperating system

A method and apparatus for managing one or more logical relationships between a plurality of devices in a storage area network (SAN). The method includes receiving a first identifier associated with a first SAN device, determining the logical relationships associated with the first SAN device, receiving a second identifier associated with a second SAN device, and associating the second identifier to the logical relationships associated with the first SAN device.

Owner:SYMANTEC OPERATING CORP

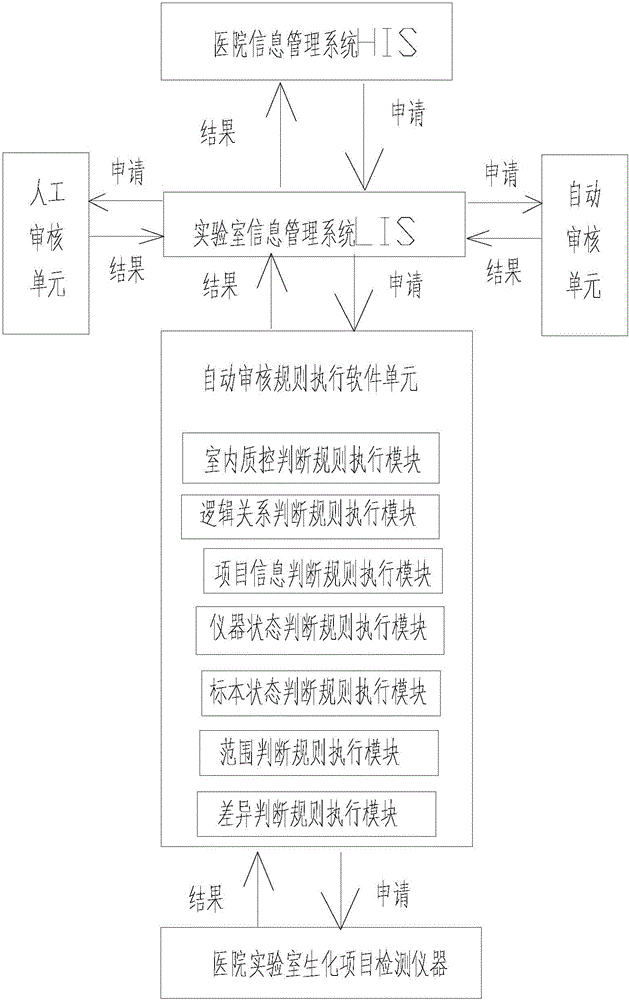

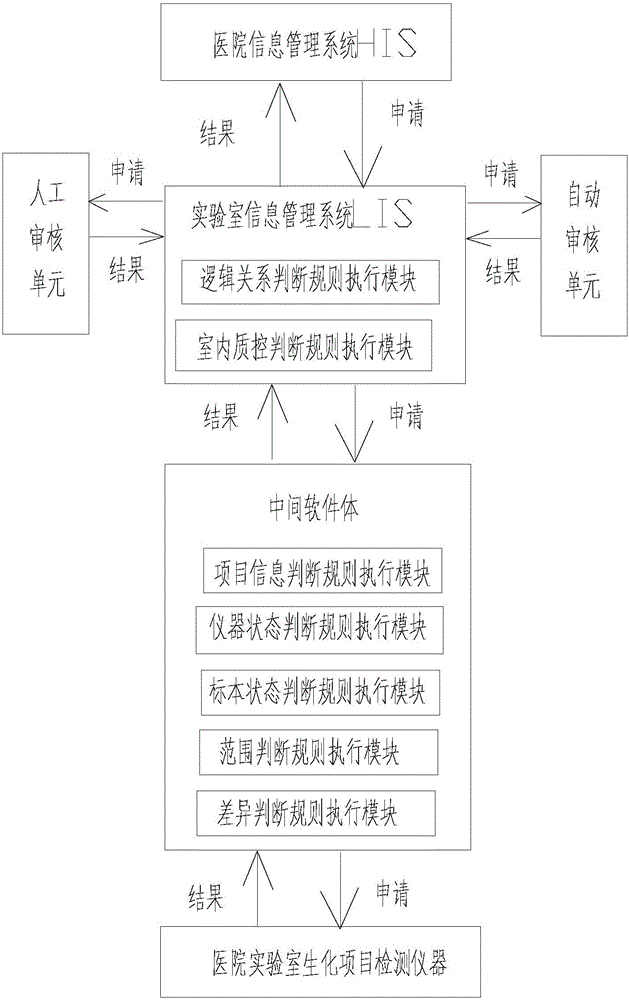

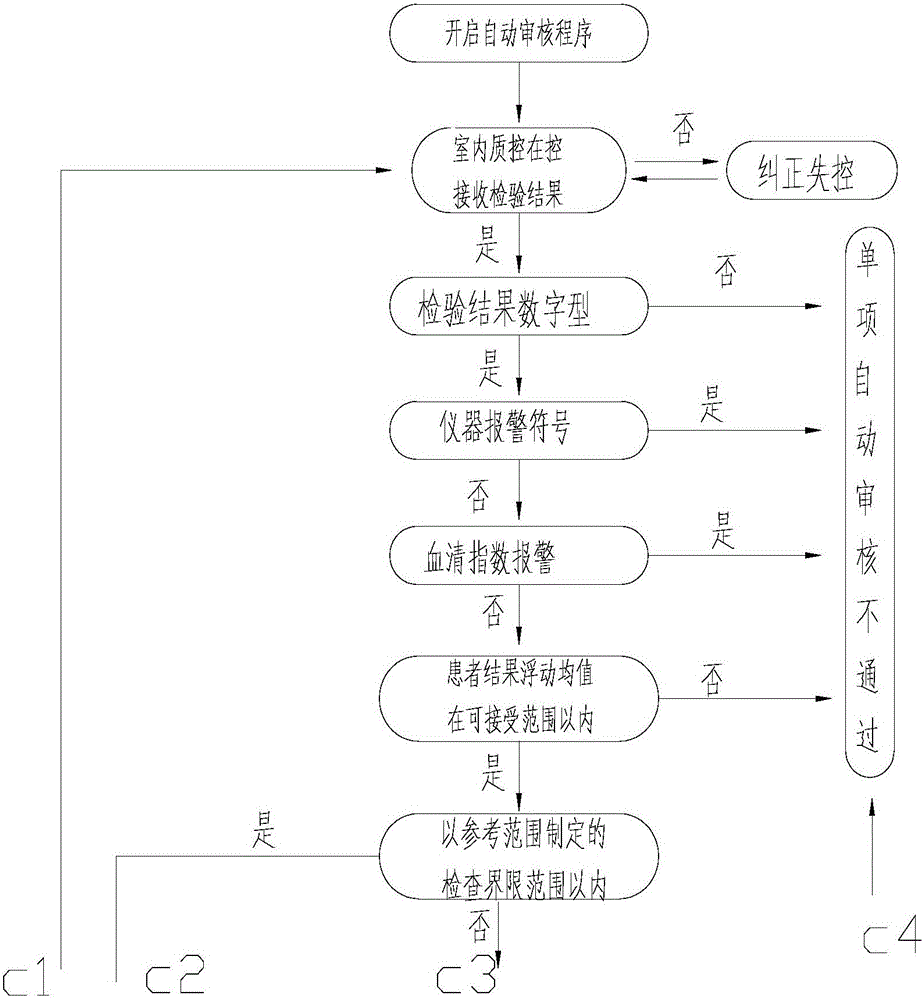

A medical laboratory clinical biochemical detection automatic checking method and system

ActiveCN106126958AImprove pass rateImprove accuracyMedical automated diagnosisMedical equipmentMedical laboratoryProcess quality

The invention provides a medical laboratory clinical biochemical detection automatic checking method and system. The method employs a computer software and hardware system and programs multiple checking rules to form a multiple checking rule execution module to automatically check the detection results of various biochemical immunity detection items. The detection results of the various biochemical immunity detection items cannot be sent to an automatic checking unit for automatic checking until they pass the multiple checking rules; if the detection results of the various biochemical immunity detection items cannot pass the above-mentioned checking rules, the detection results are transferred to a manual checking unit for checking; only after the detection results are checked by the manual checking unit or checked again after automatic treatment of dilution, reexamination, test item adding, unqualified sample return and the like by an assembly line can a detection report be issued; the multiple checking rules mainly include a clinical information judging rule, a sample state judging rule, an indoor quality control judging rule, an instrument state judging rule, a range judging rule, a difference judging rule, and a logical relationship judging rule. The checking rules are reasonable in design and cover the pre-analysis, analysis and post-analysis processes, thereby realizing whole-process quality control on a detection analysis process and guaranteeing the accuracy of detection results.

Owner:温冬梅

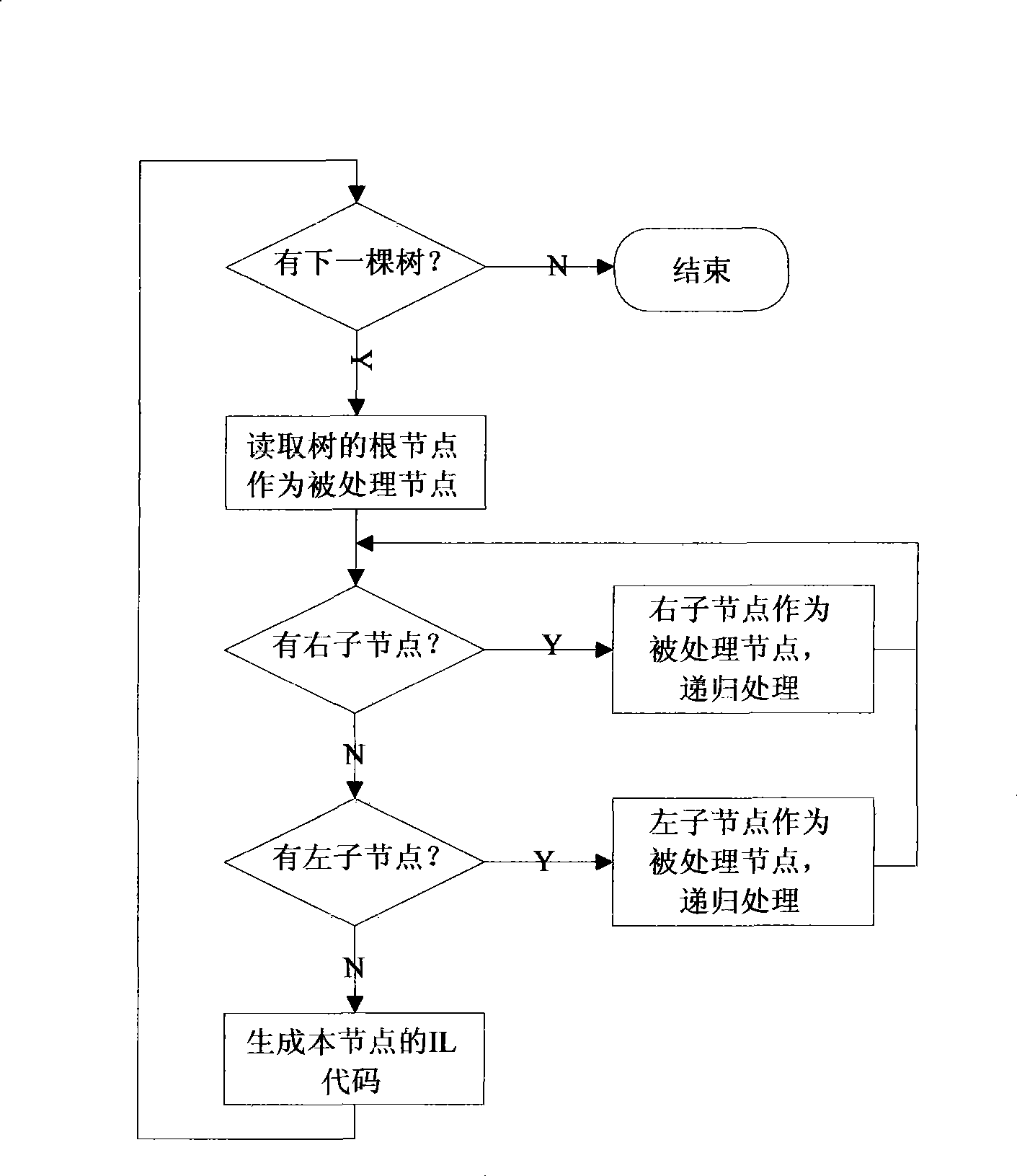

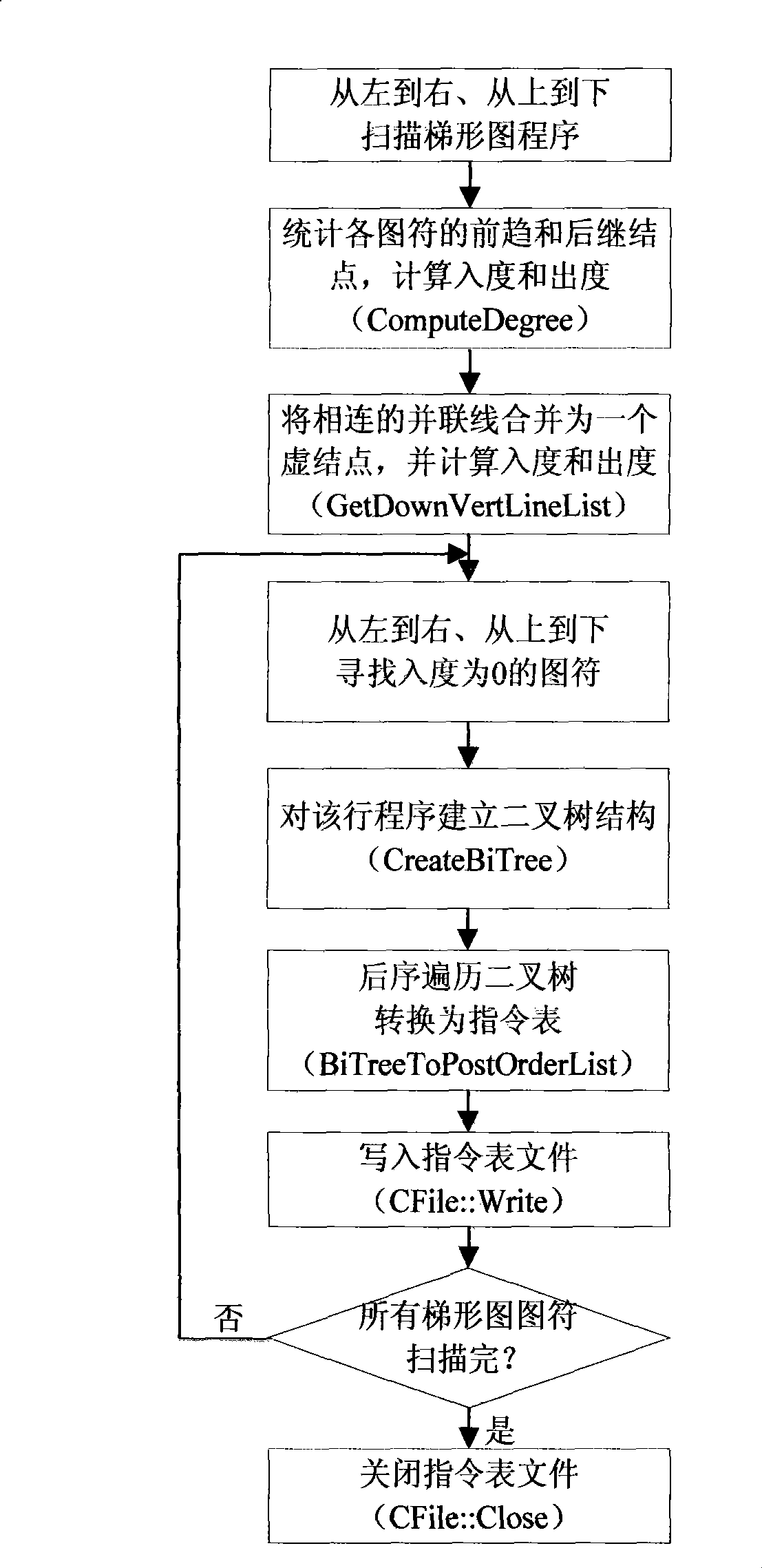

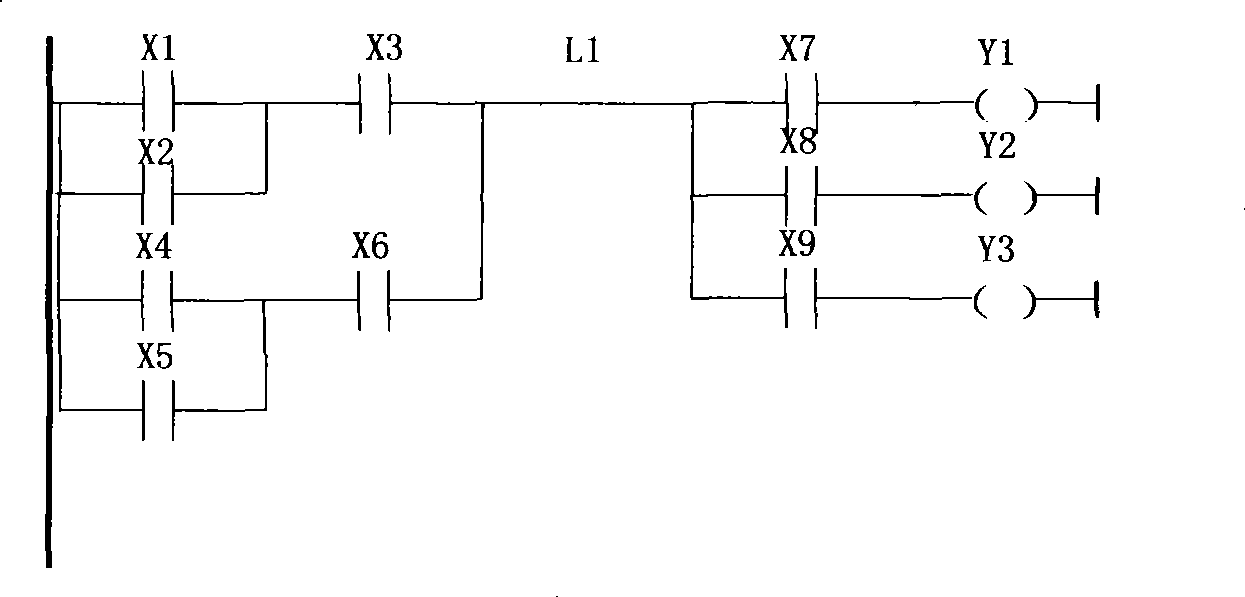

Method and system for conversing trapezoidal pattern to be instruction catalogue program, and interpretation execution method and system

InactiveCN101364098AImprove the efficiency of explain executionAchieve conversionProgramme control in sequence/logic controllersParallel computingMaster controller

The invention discloses a method and a system for converting a ladder diagram into an instruction list and carrying out the interpretive execution of an instruction list. The ladder diagram conversion method comprises the following steps: mapping the ladder diagram to an AOV diagram, establishing a binary tree representative of the logical relationship between the instructions based on the AOV diagram, and converting the ladder diagram to the instruction list by the postorder traversal of the binary tree. The method and the system perform the conversion between various complex ladder diagrams and instruction lists, particularly the conversion of the multi-output ladder diagram to the instruction list. Additionally, the converted instruction list exists in the form of postorder expression, which is conducive to increasing the efficiency of interpretive execution of the PLC master controller.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

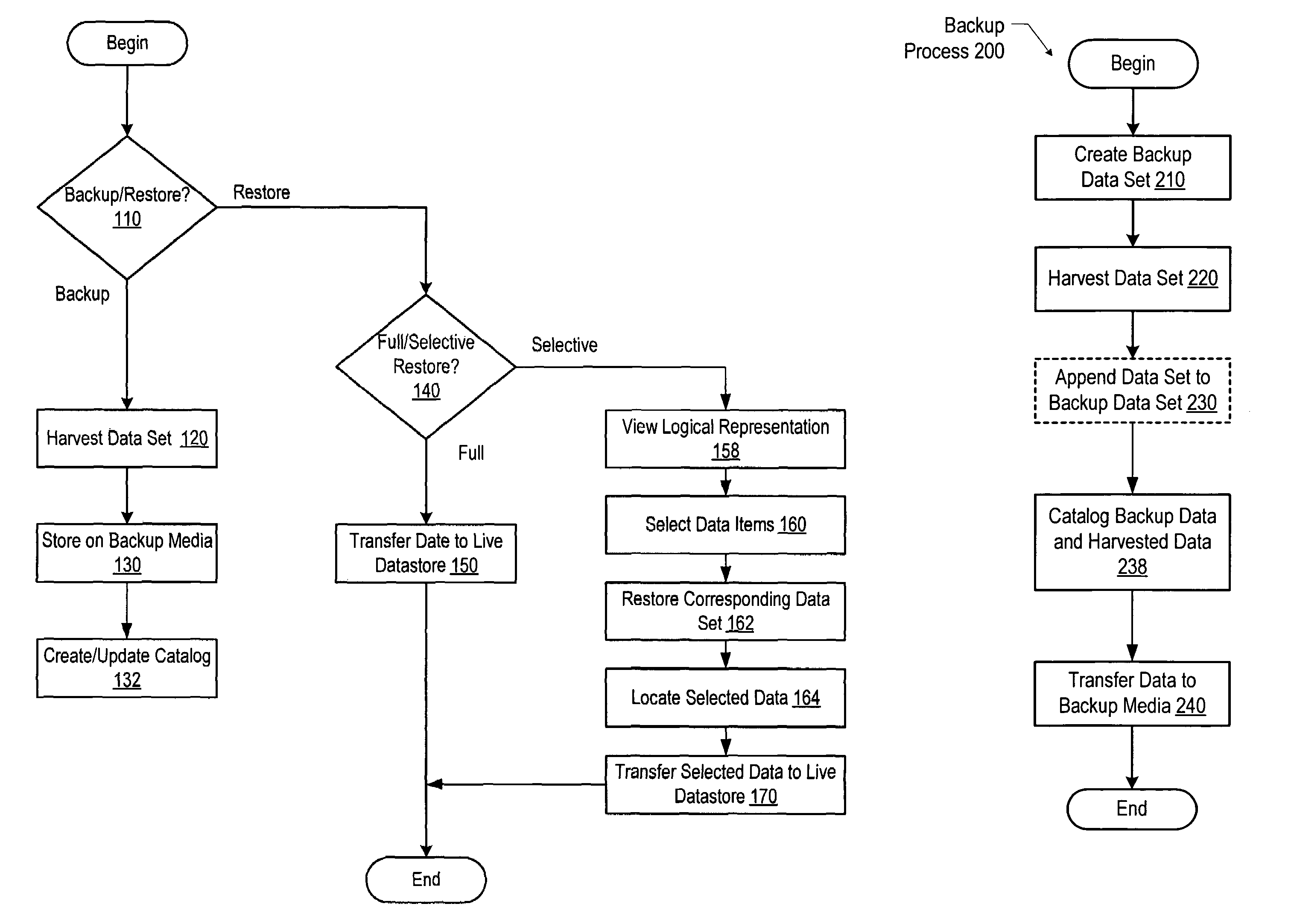

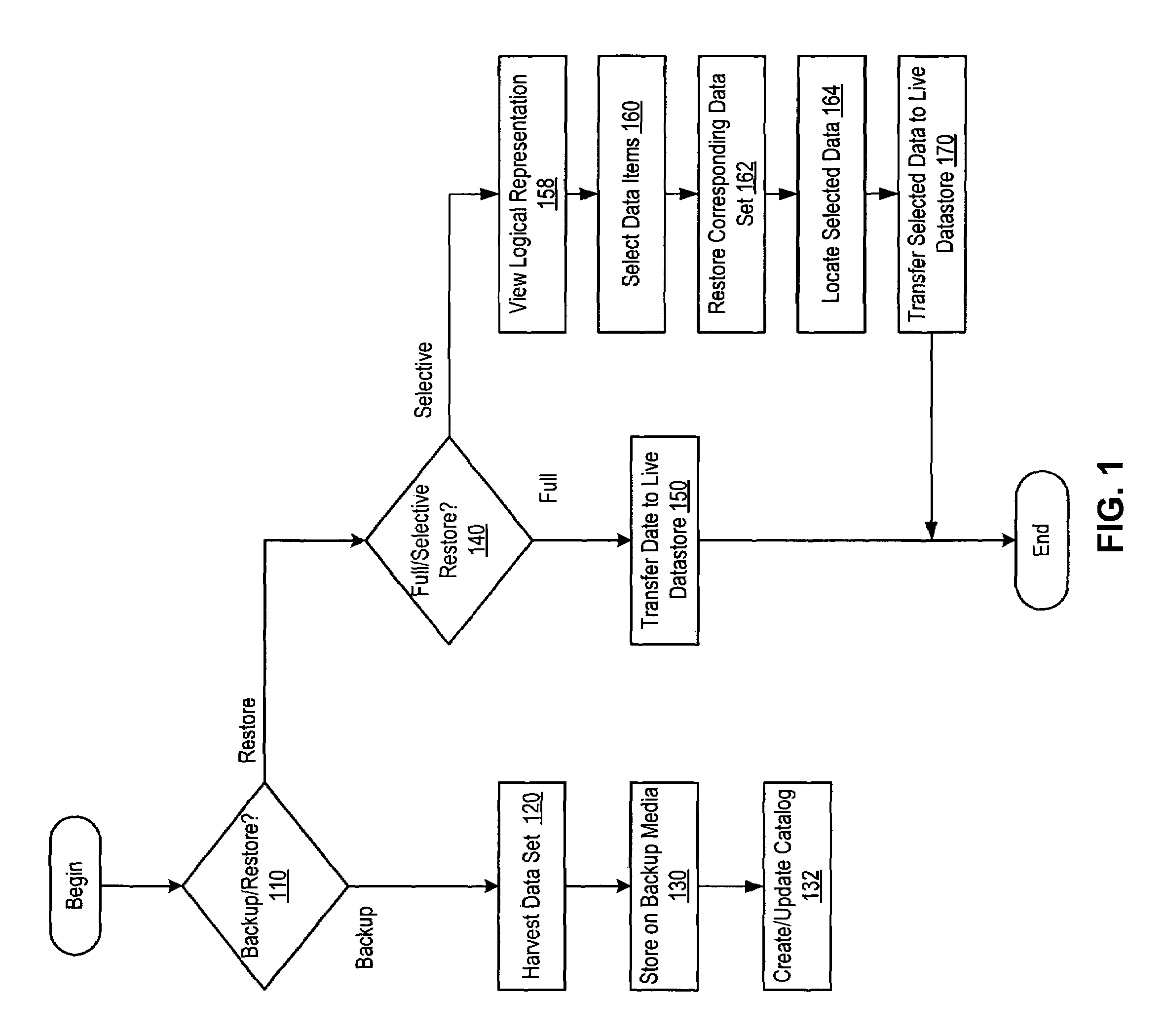

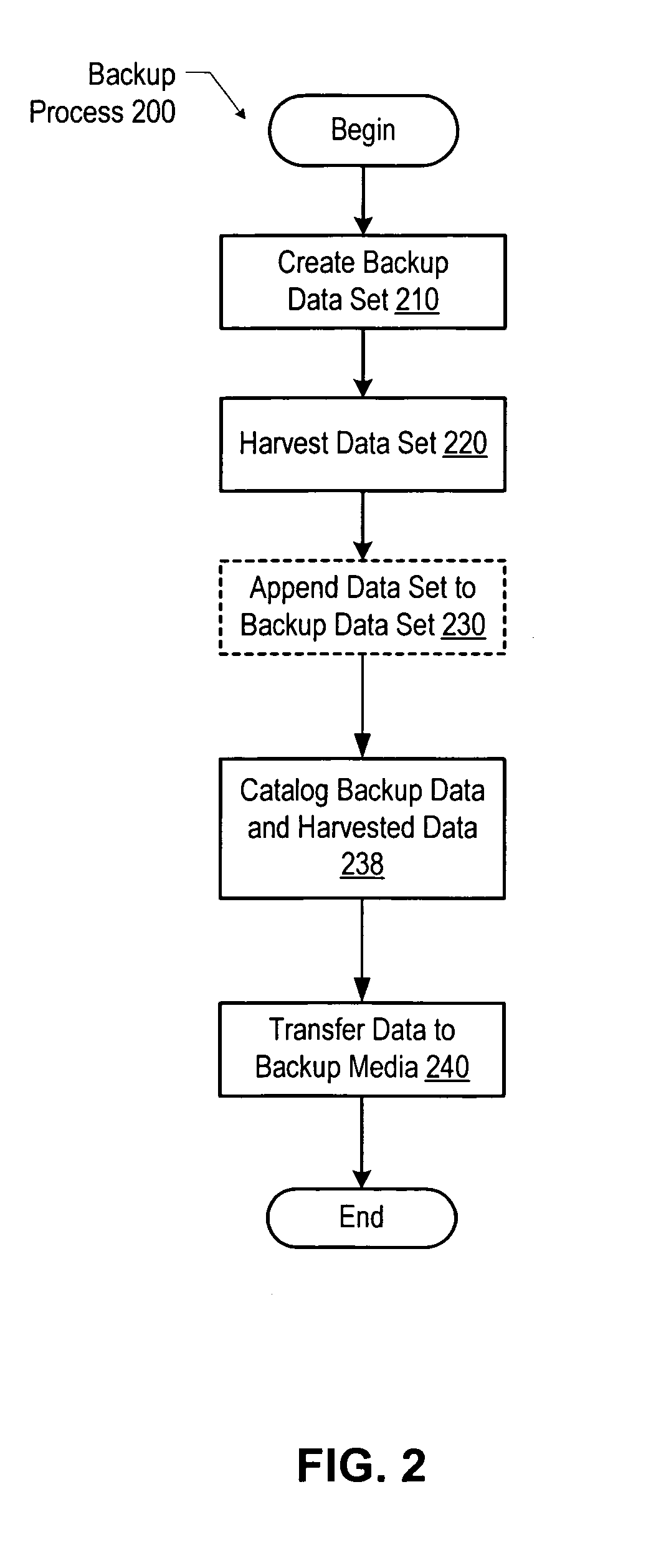

Logical application data restore from a database backup

A system and method for managing data in a computer system. A backup server is configured to harvest data indicative of logical relationships among data entries in a backup data set. The harvested data and backup data set are stored on a backup medium. Catalog entries are created for both the backup data set and the harvested data. The computer system allows a user to browse the backup catalog, including the logical structure of the content of a particular backup data set. The user may select particular items for restoration from the catalog. In response, the server restores the backup data set and harvested data to a temporary location, identifies data in the harvested data which corresponds to the user's selections, searches the backup data set for the selected items, and initiates restoration of the selected items.

Owner:SYMANTEC OPERATING CORP

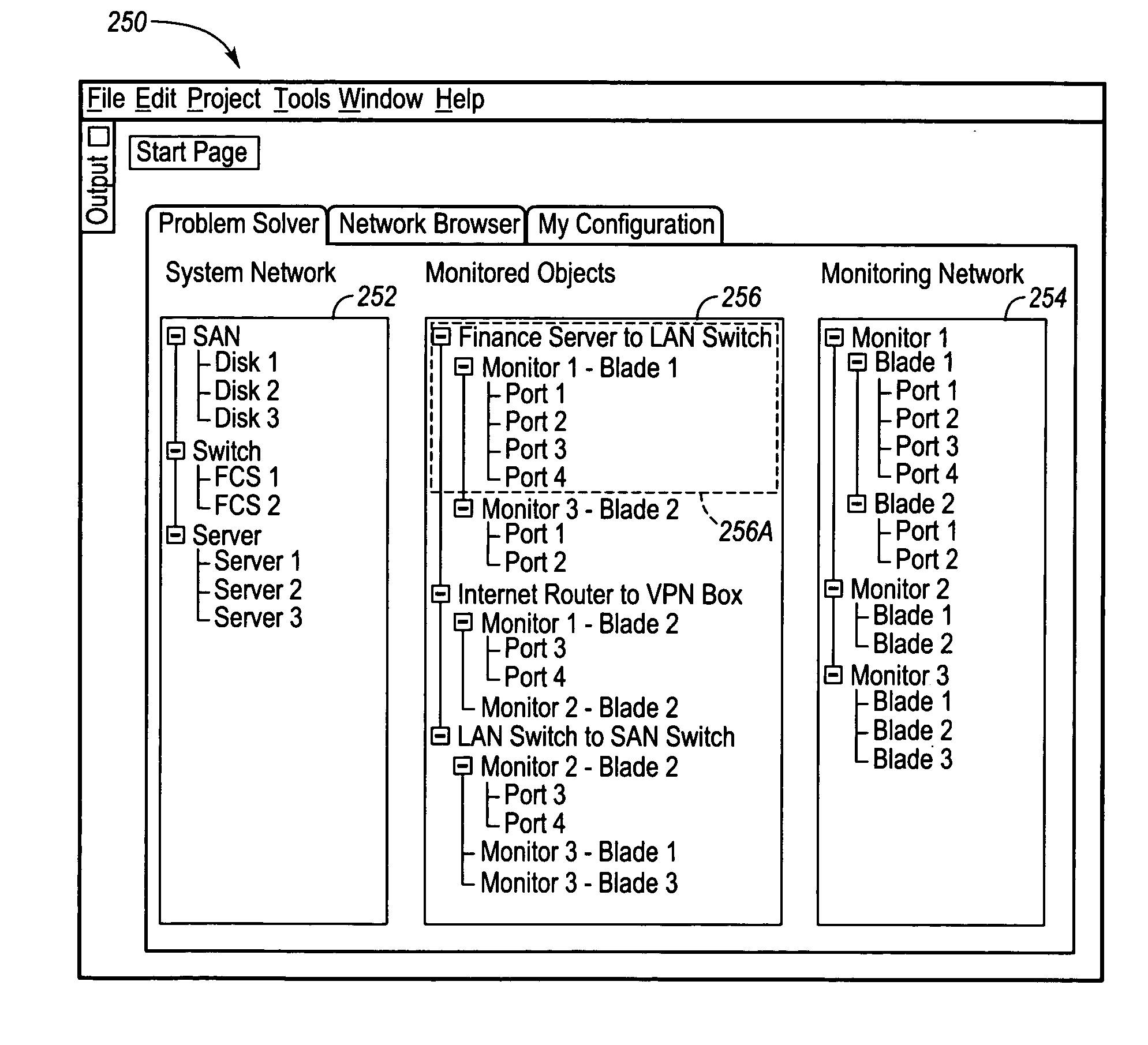

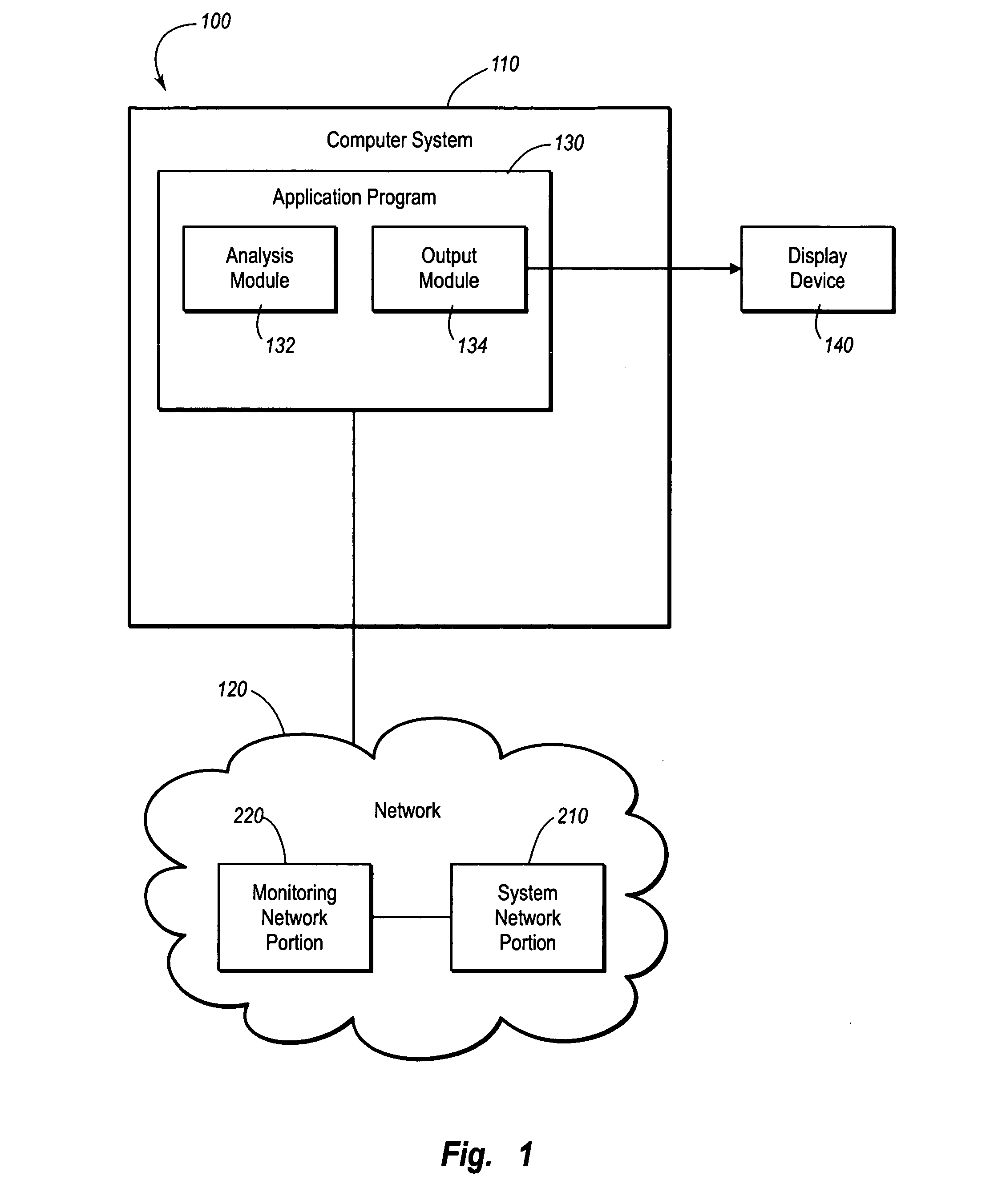

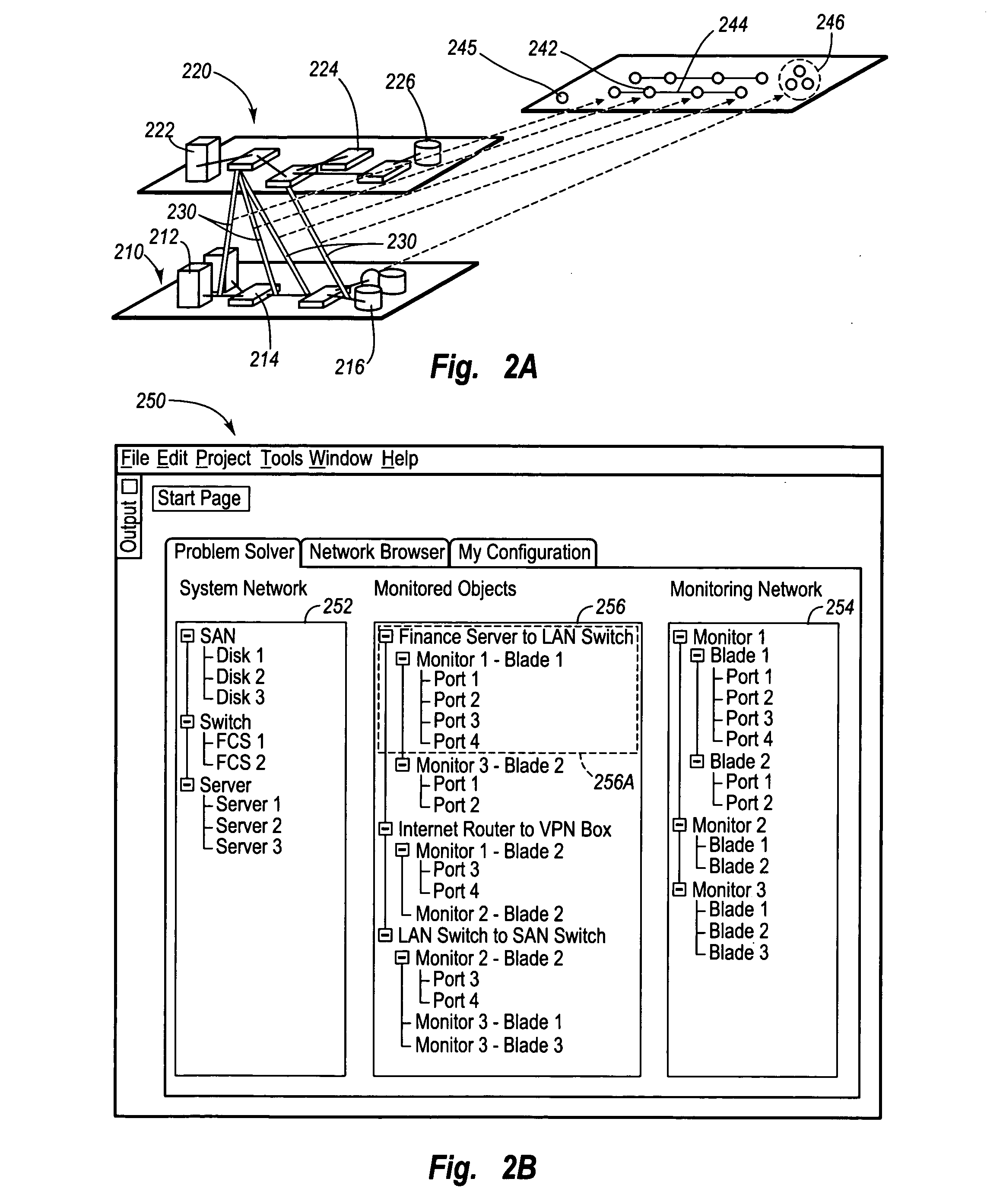

Method of creating a virtual network topology for use in a graphical user interface

InactiveUS20050091361A1Digital computer detailsData switching networksGraphicsGraphical user interface

A method of graphically depicting various network elements of a communications network in a virtual network topology via a graphical user interface (“GUI”) is disclosed. The virtual network topology depicts logical relationships between network components instead of merely depicting physical network component relationships. A system network subset and a monitoring network subset of the communications network are defined according to one layer N of the open system interconnection (“OSI”) layer model. Various logical links are established between the system network and the monitoring network. A virtual topology is defined that depicts the various logical links according to another OSI layer M. The virtual topology is displayed via a GUI that enables modification of the logical links to occur.

Owner:FINISAR

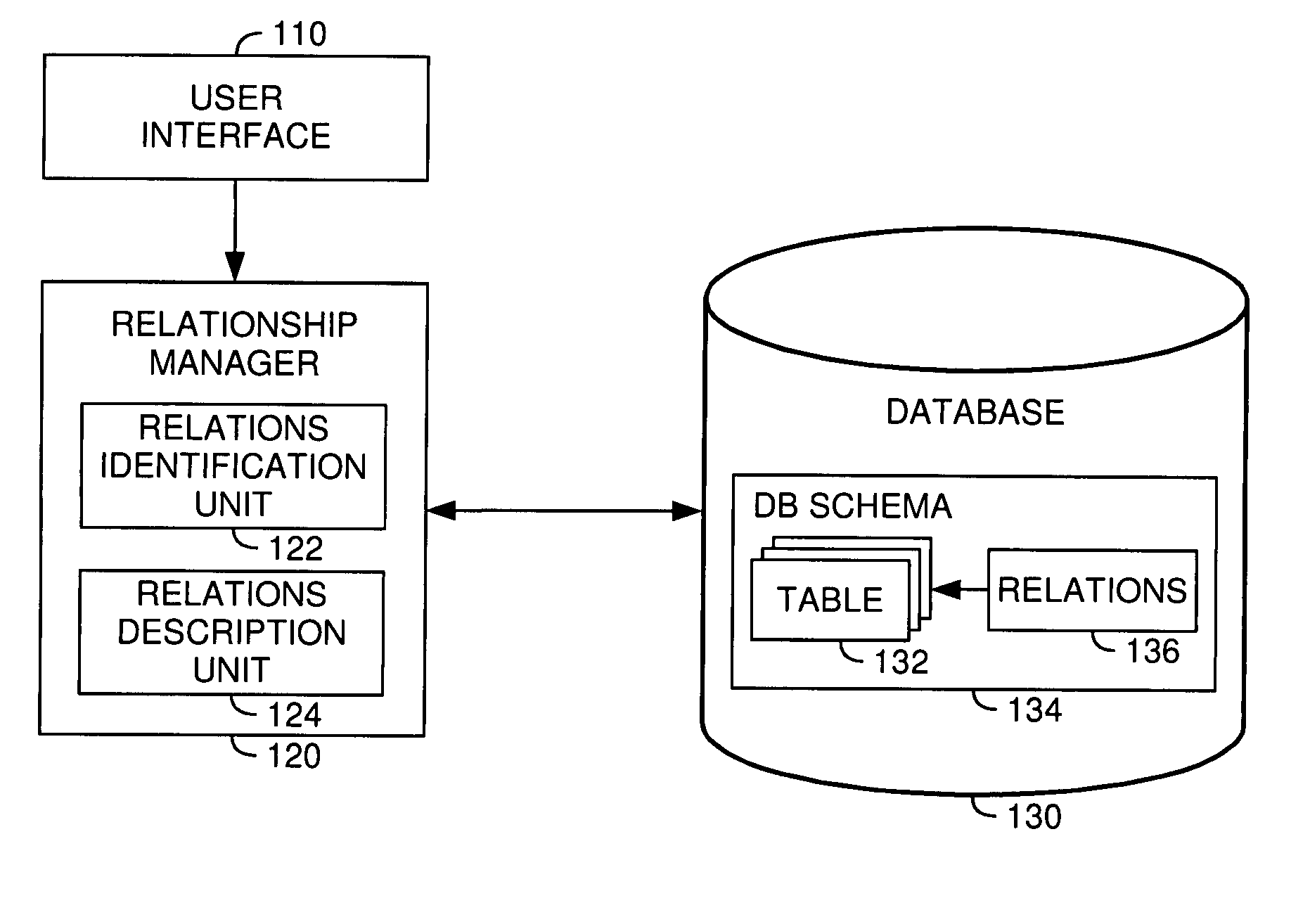

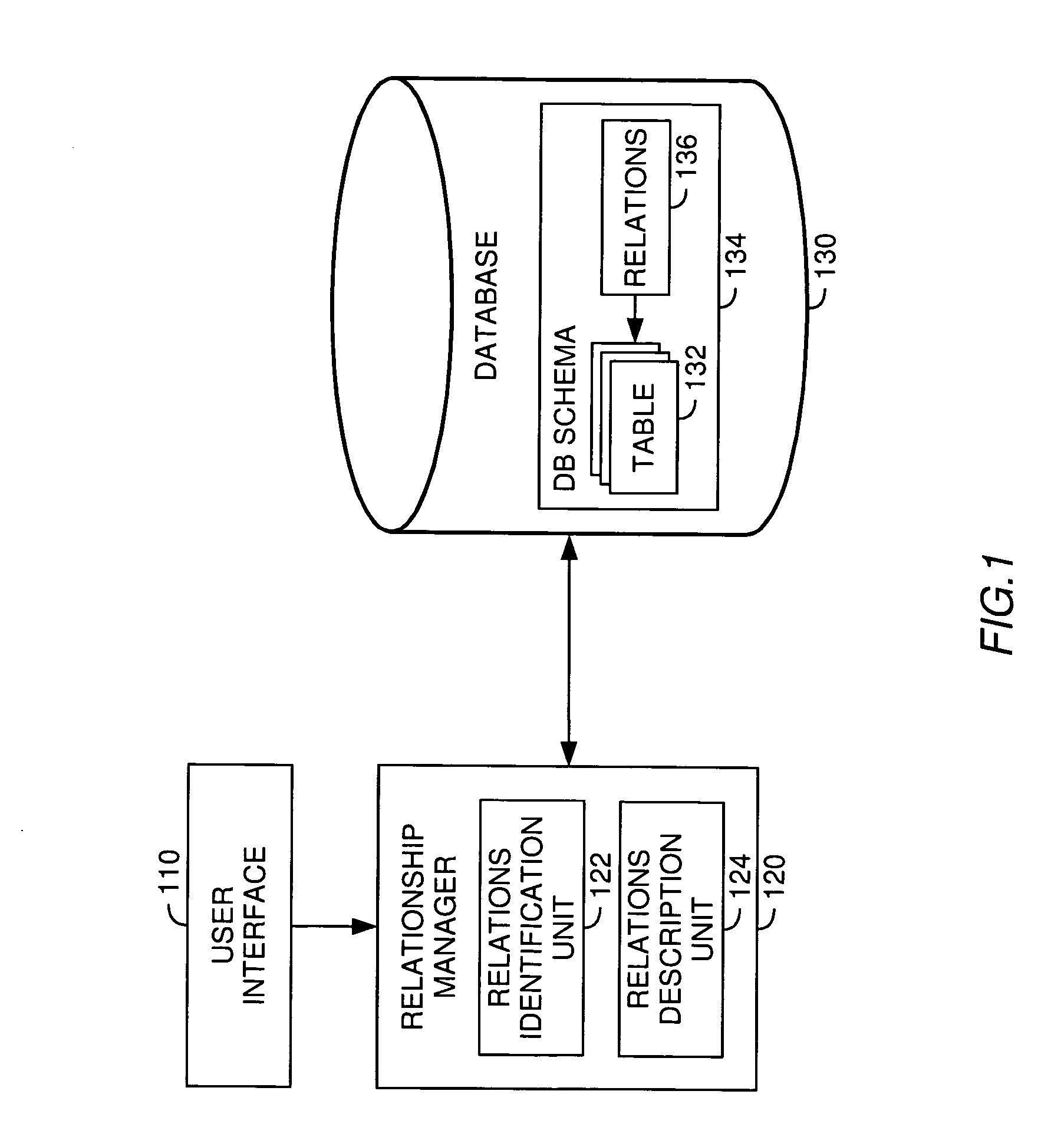

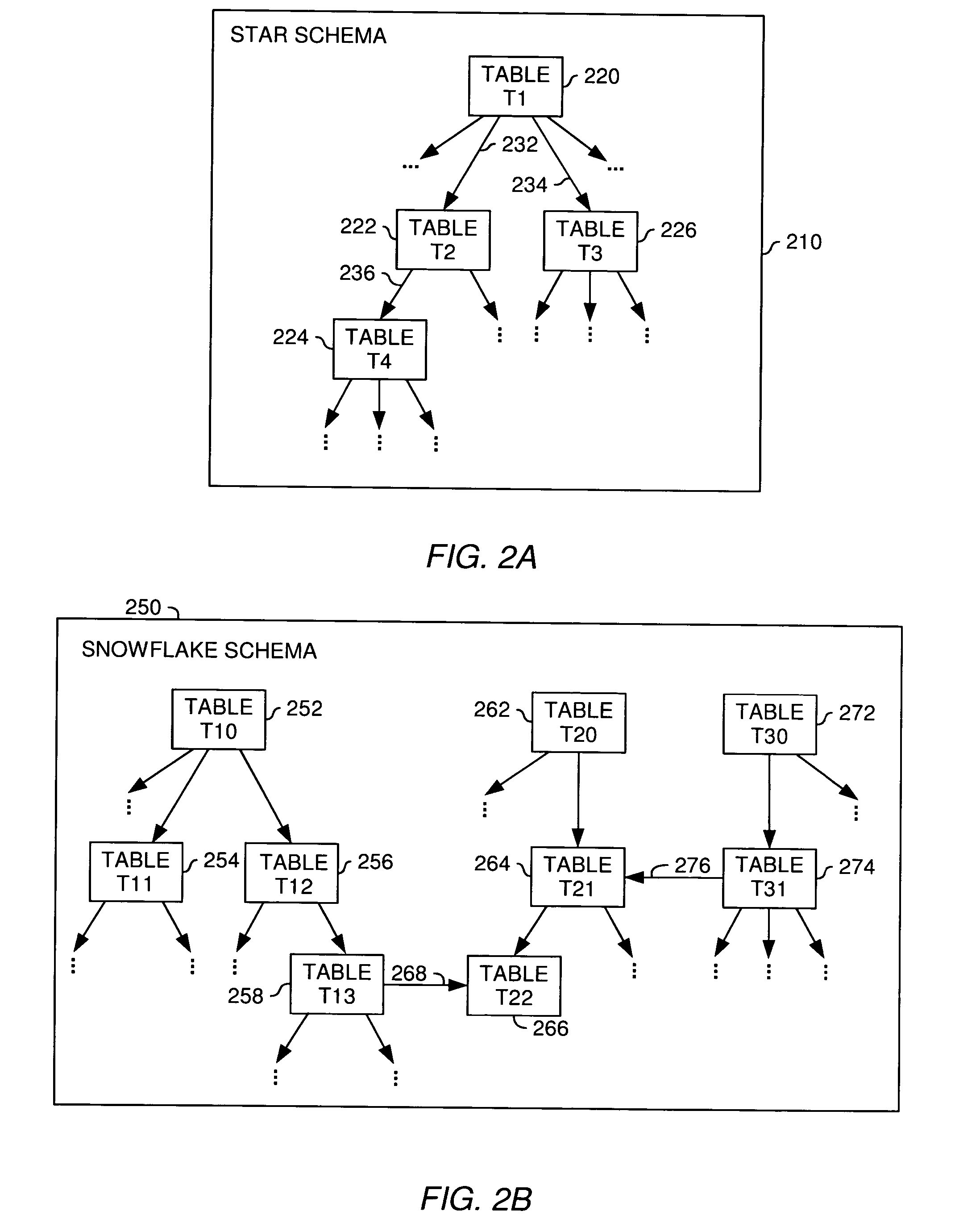

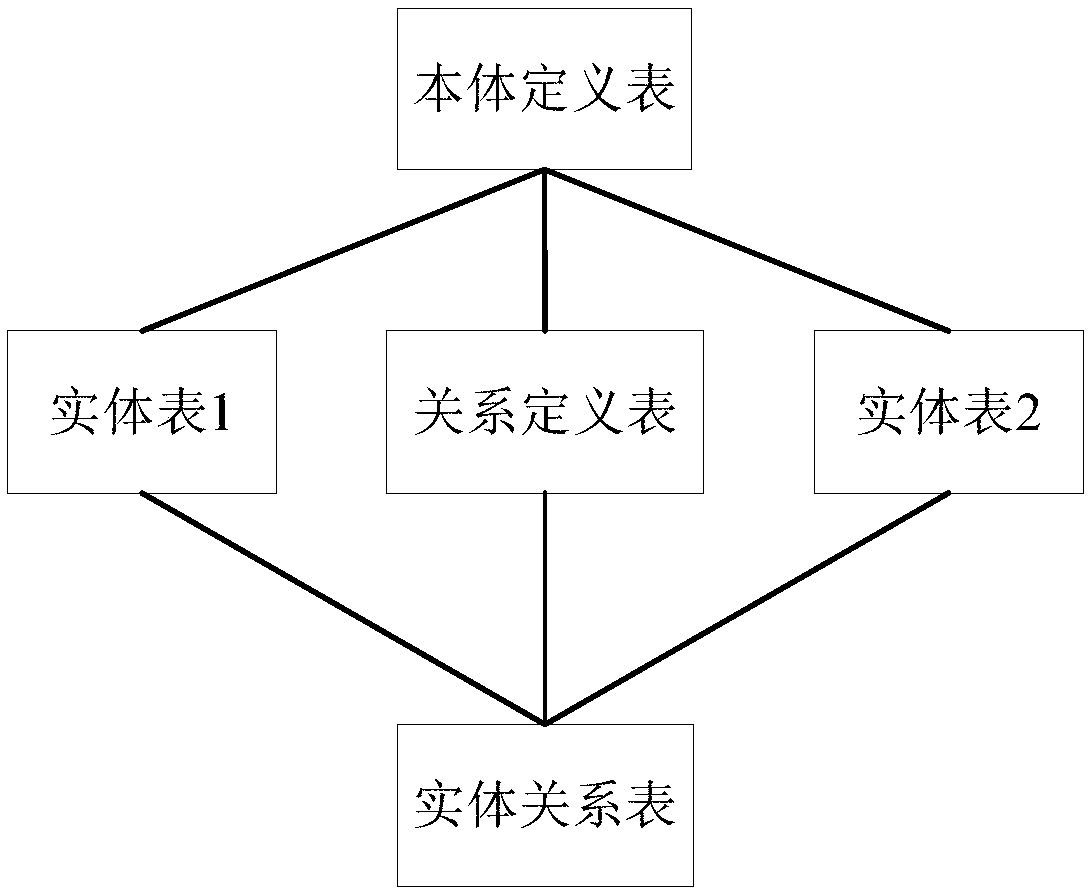

Management of relationships between database tables

A method, system and article of manufacture for managing relationships between database tables and, more particularly, for identifying and accurately describing relationships between tables in a database. One embodiment provides a method for identifying relationships between tables in a database. The method comprises receiving user input selecting a plurality of tables from the database. The plurality of tables is organized into a logical island defining a logical unit related to a particular logical entity. The method further comprises receiving user input identifying, for each of the plurality of tables, a table column containing information that identifies the particular logical entity in the table, whereby the identified table columns of different tables define logical relationships between the different tables in the logical island. On the basis of the identified table columns, relations specifications are created which describe the logical relationships between the different tables in the logical island.

Owner:DOMO

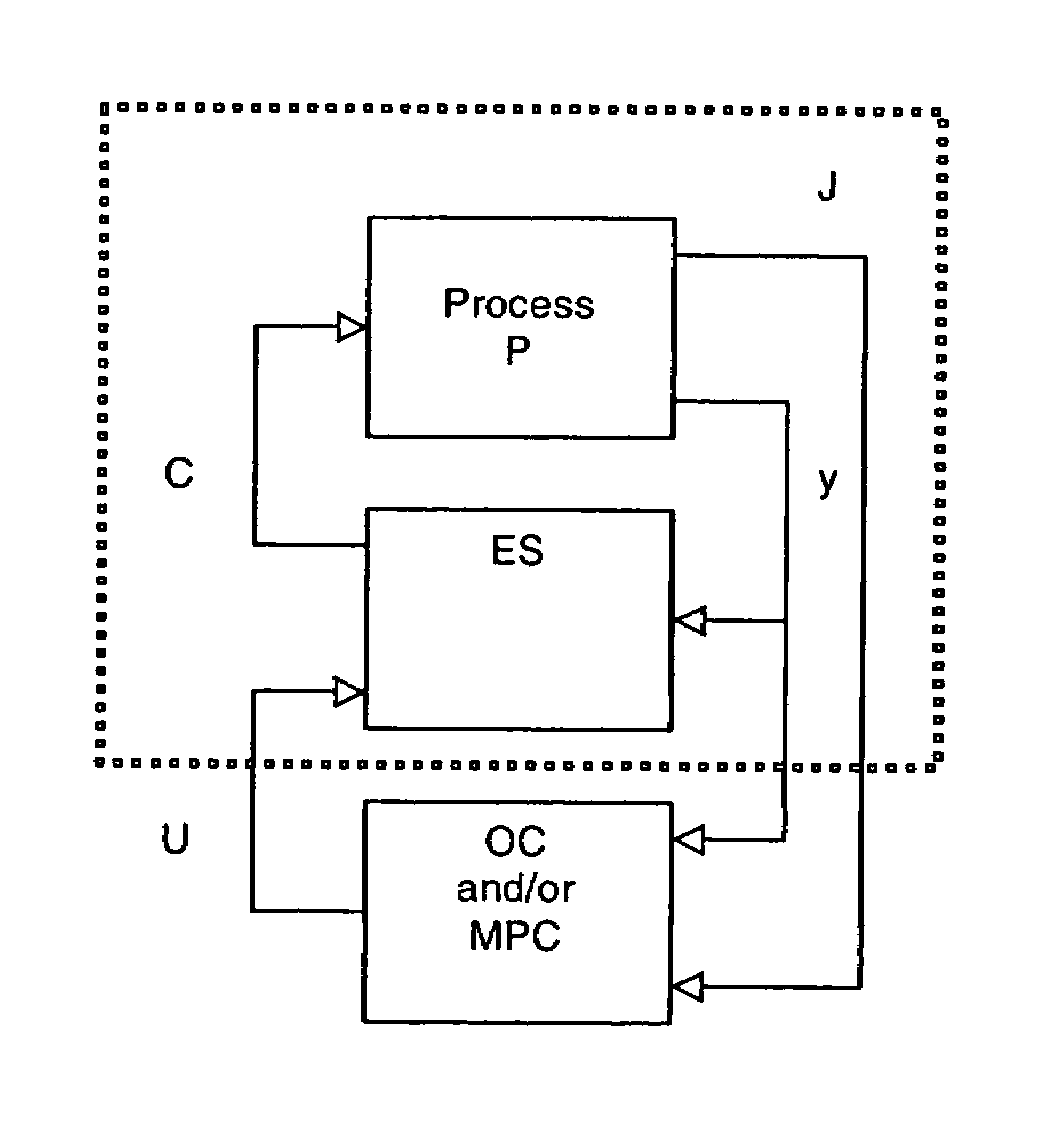

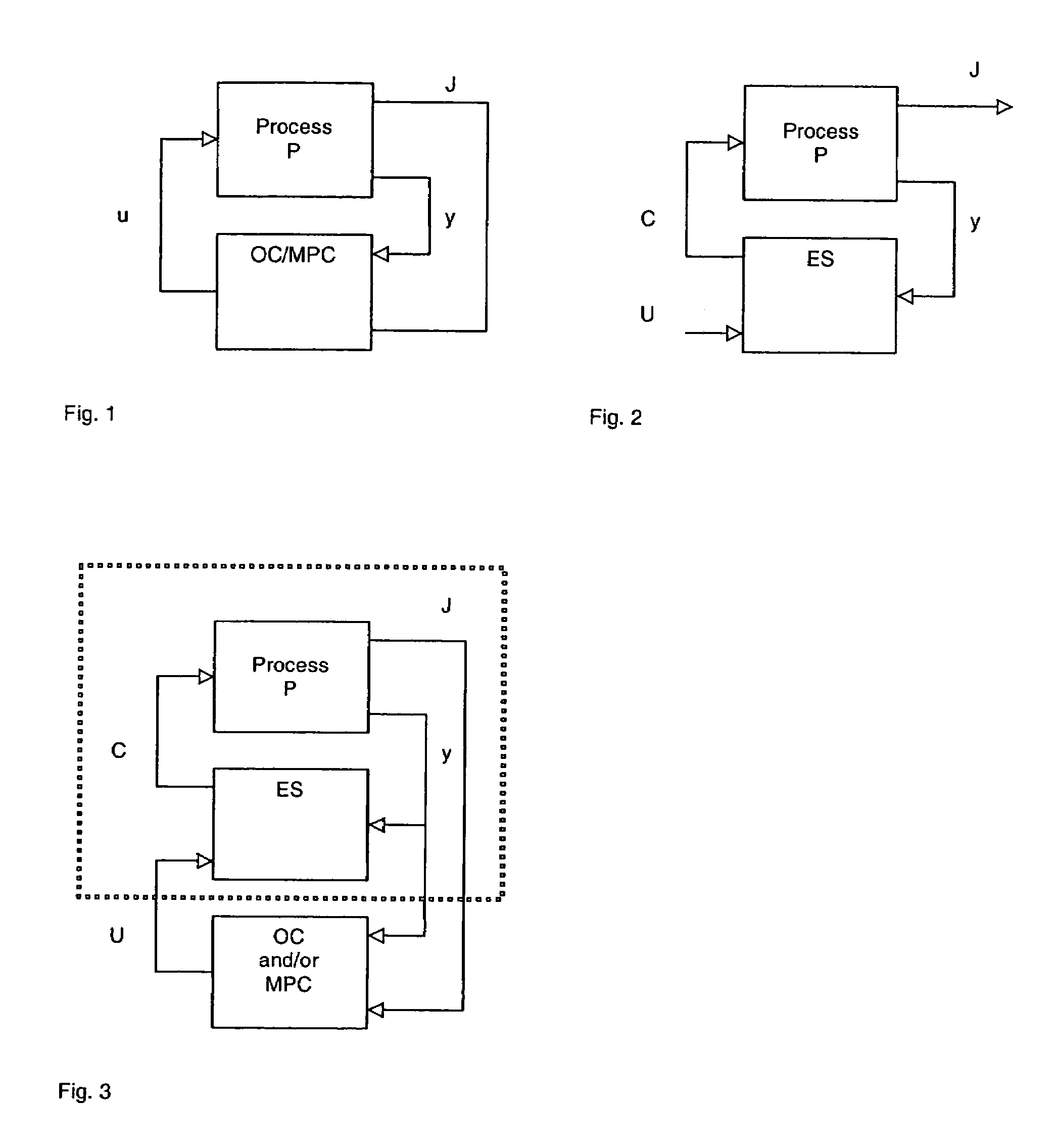

Process control system

The disclosed process control system makes use of Optimal control (OC) and model predictive control (MPC) techniques for selection of the Expert Systems (ES) targets values U. The ES target values U are selected to minimize the performance criterion J. A mathematical model of an extended system given by the process P and the ES is developed. This hybrid mathematical model has both continuous dynamics and logical relationships. Controlled variables of the mathematical model are the ES target values U and inputs are the measurements y and the performance criterion J. The OC and / or MPC techniques are used to compute values U. An optimizer of the OC / MPC selects values of the ES target values U only. This activity has lower sampling rates than selection of controller values, which simplifies the design of the OC / MPC controller.

Owner:ABB (SCHWEIZ) AG

Integrated timeline and logically-related list view

InactiveUS6904561B1Easy to createEasy to editSpecial data processing applicationsInput/output processes for data processingGraphicsAnimation

A system and method for graphically showing the order and timing of elements in a presentation program or other software. The sequence of events is shown in an event list, a list of events in sequence order, each event being associated with an event timeline bar and correlated with a universal timeline, in the editing window of an electronic presentation or other software that deals with the scheduling of events. In one embodiment, each item in the list represents an individual animation effect. Elements of the event list are logically related to each other and these logical relationships may be used in assisting a user to build a sequence of events (e.g., an animation sequence).

Owner:MICROSOFT TECH LICENSING LLC

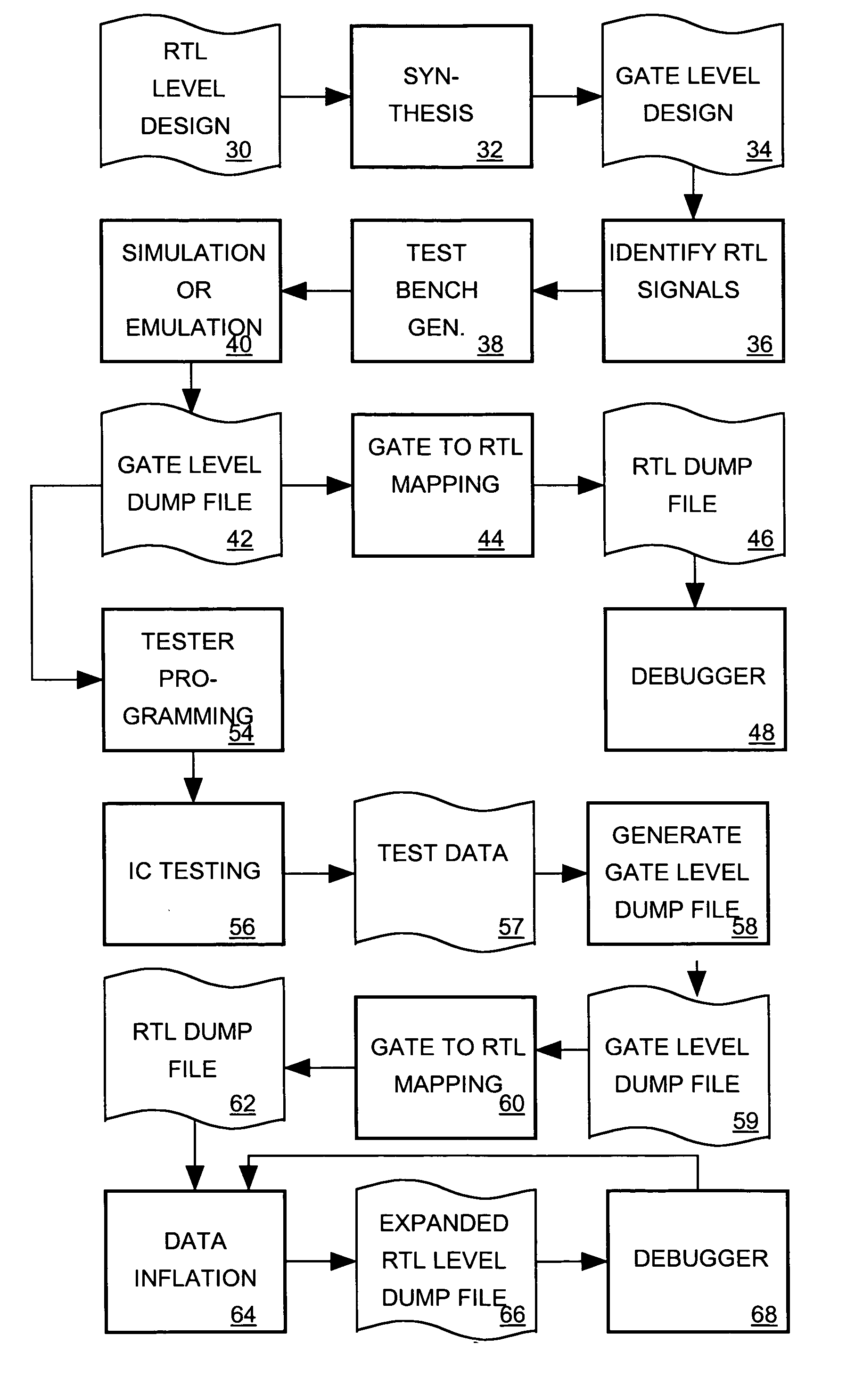

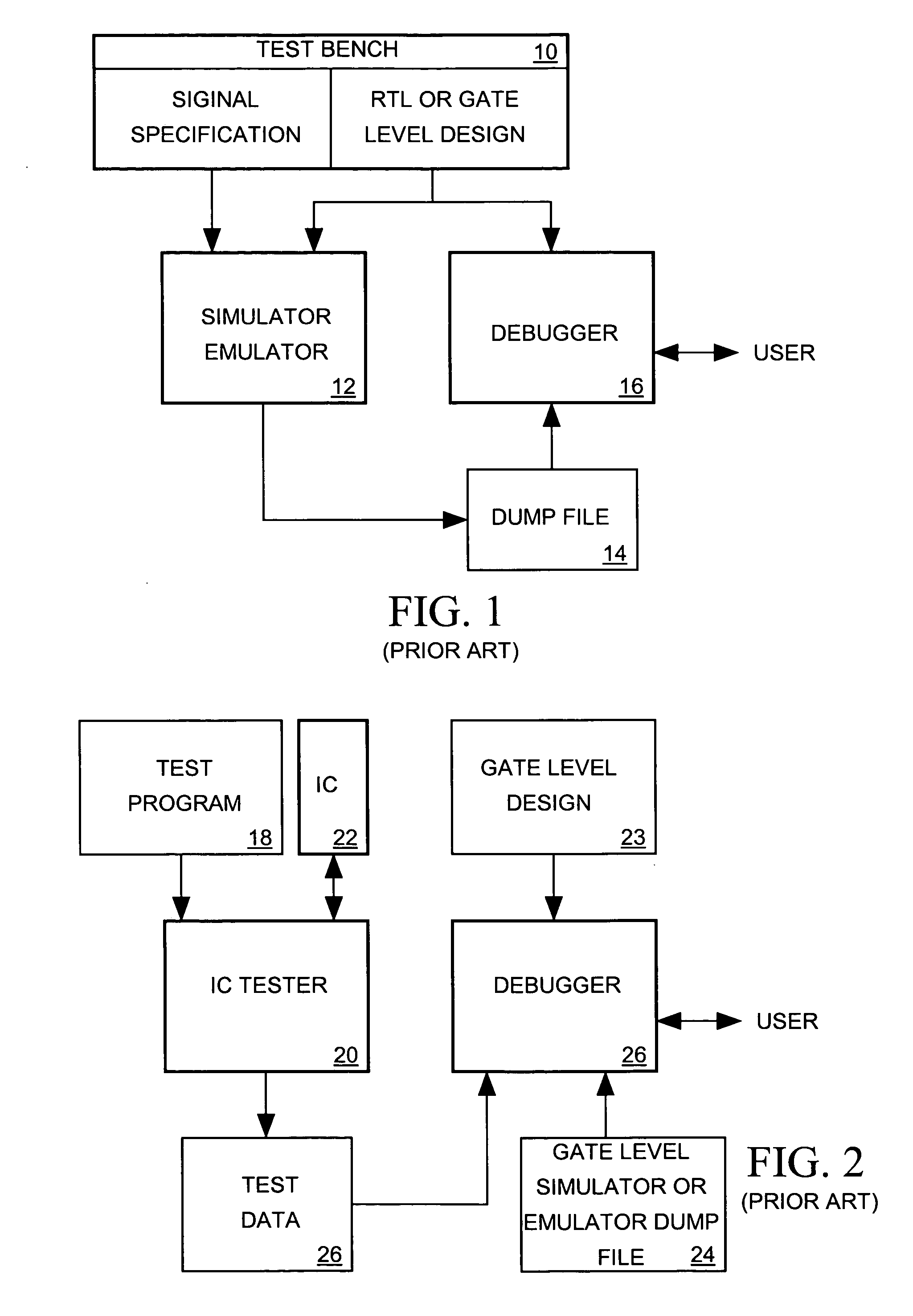

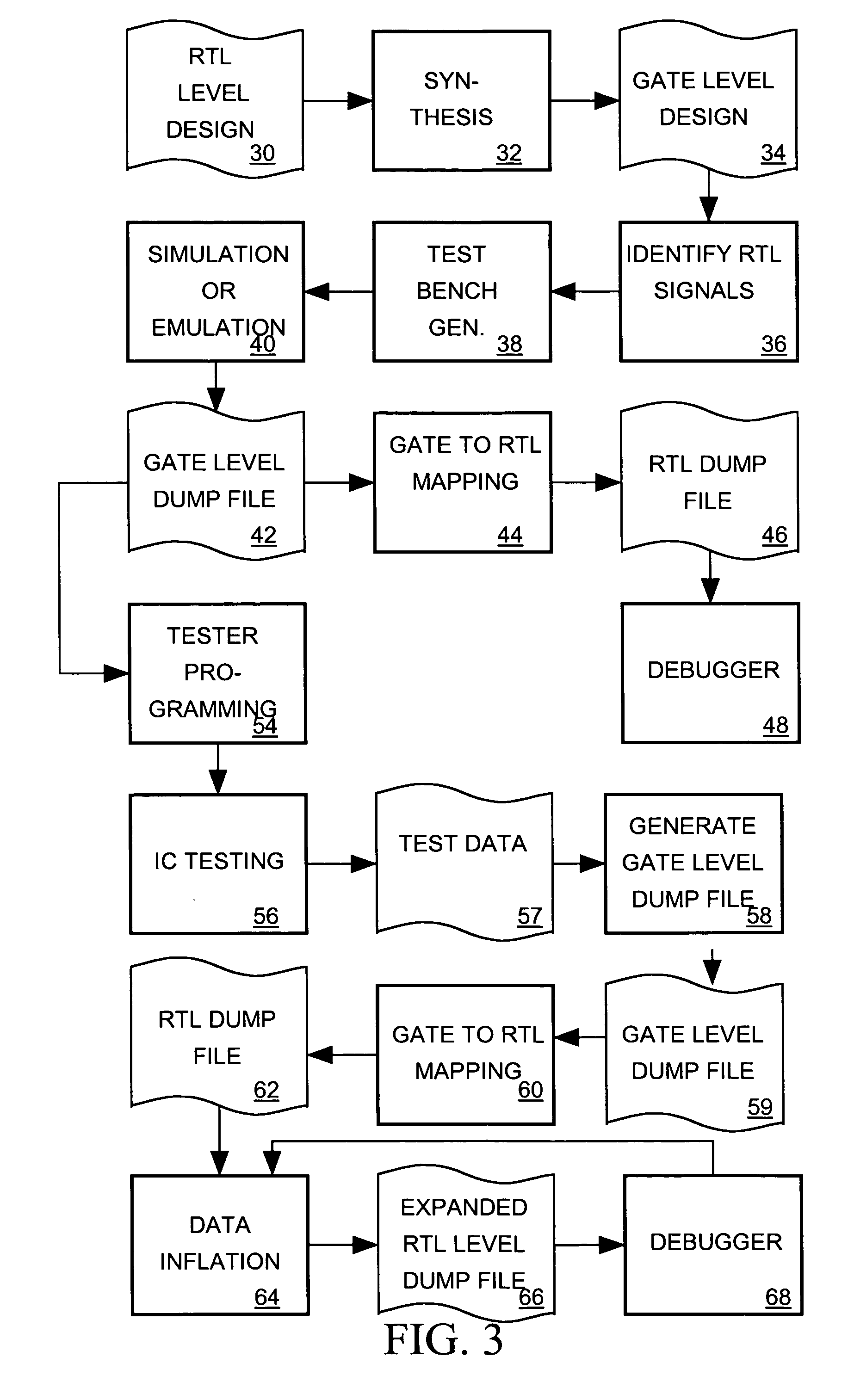

Debugging system for gate level IC designs

ActiveUS20070174805A1Easy to understandSimplify the commissioning processSemiconductor/solid-state device testing/measurementDetecting faulty computer hardwareComputer architectureComputer-aided

A register transfer level (RTL) IC design describing a IC as comprising a plurality of logic blocks communicating via signals and using a high level language to describe the logic blocks according to the logical relationships between signals they receive and signals they generate. A computer-aided synthesizer processes an RTL IC design to produce a gate level design for the IC describing its logic blocks as comprising instances of cells communicating via signals. A synthesizer or emulator processes the gate level design to produce a gate level dump file referencing signals of the gate level design and indicating how those signals behave in response to time-varying signals supplied as inputs to the IC. The gate level dump file is converted into an RTL dump file referencing signals of the RTL design and indicating how those signals behave. A debugger processes the RTL dump file to produce displays depicting the RTL design and behavior of signals indicated by the RTL dump file. Thus while the IC is simulated or emulated at the gate level of the design to produce waveform data for a debugger, the gate level-to-RTL dump file conversion process enables a designer debug the more familiar RTL design based on the gate level simulation or emulation results.

Owner:SYNOPSYS INC

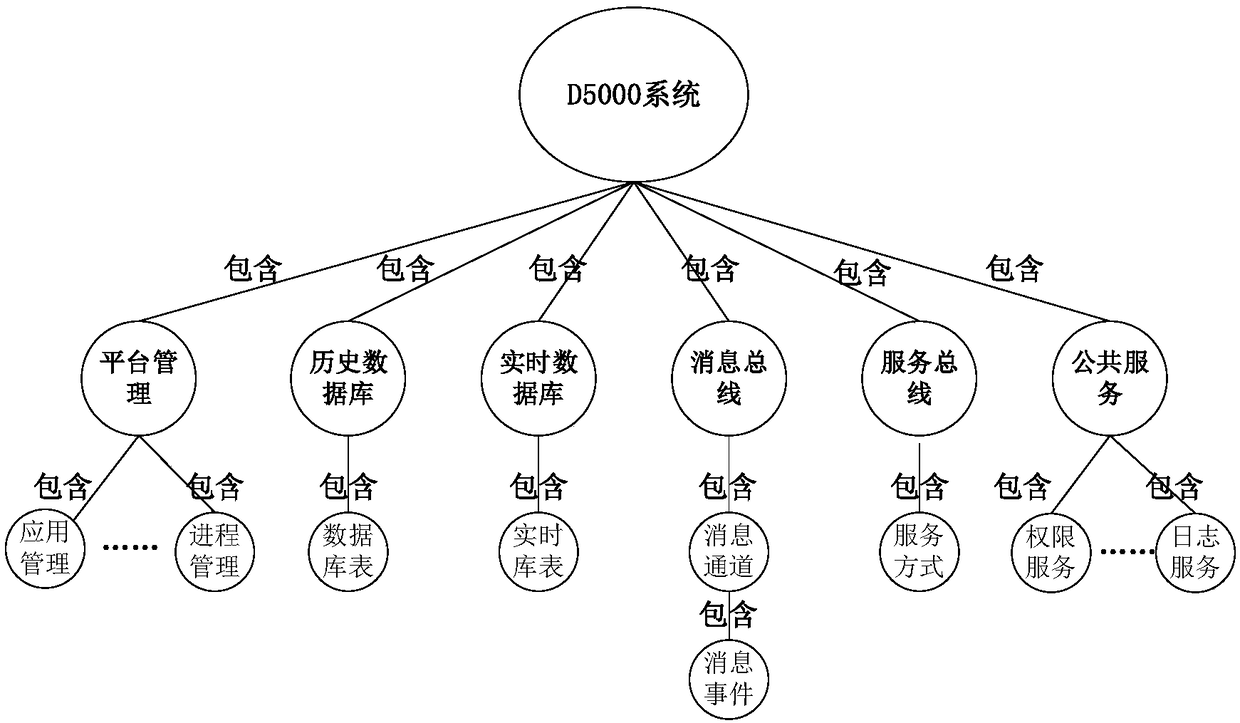

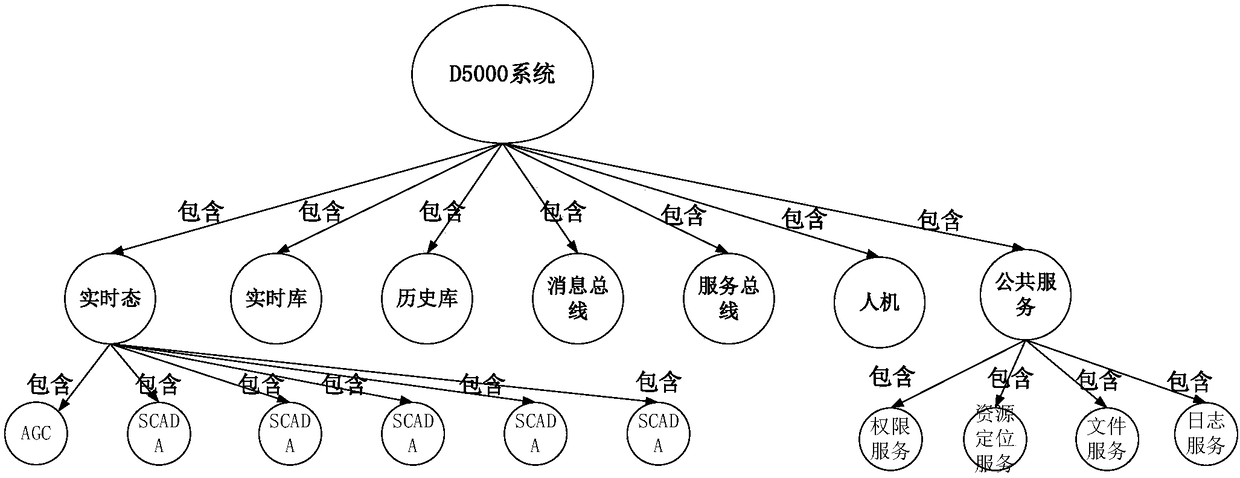

Construction and application method of knowledge map of dispatching automation system

PendingCN108595449AUnderstand intuitiveImprove interactivityData processing applicationsSpecial data processing applicationsControl systemSmart grid

The invention belongs to the field of dispatching automation systems and especially relates to a construction and application method of knowledge map of a dispatching automation system. The method comprises following steps: 1. the construction of knowledge map: the bottom-up and top-down combination method is used to construct the knowledge map of the basic platform and detailed business logic ofan intelligent grid dispatch control system; 2. the storage and maintenance of knowledge; 3. the display and application of the knowledge map: a front page shows the basic platform of the system and the detailed business knowledge map; the knowledge map of the basic platform shows the overall framework knowledge, and the knowledge map of the business logic shows the detailed logical relationship.The knowledge map constructed by the invention presents the abstract dispatching automation system business knowledge in a graphical manner, so that the user has an intuitive understanding of the business knowledge of the entire system. At the same time, users can operate the corresponding entities to selectively view the business knowledge they care about, with strong interactivity and availability.

Owner:BEIJING KEDONG ELECTRIC POWER CONTROL SYST +1

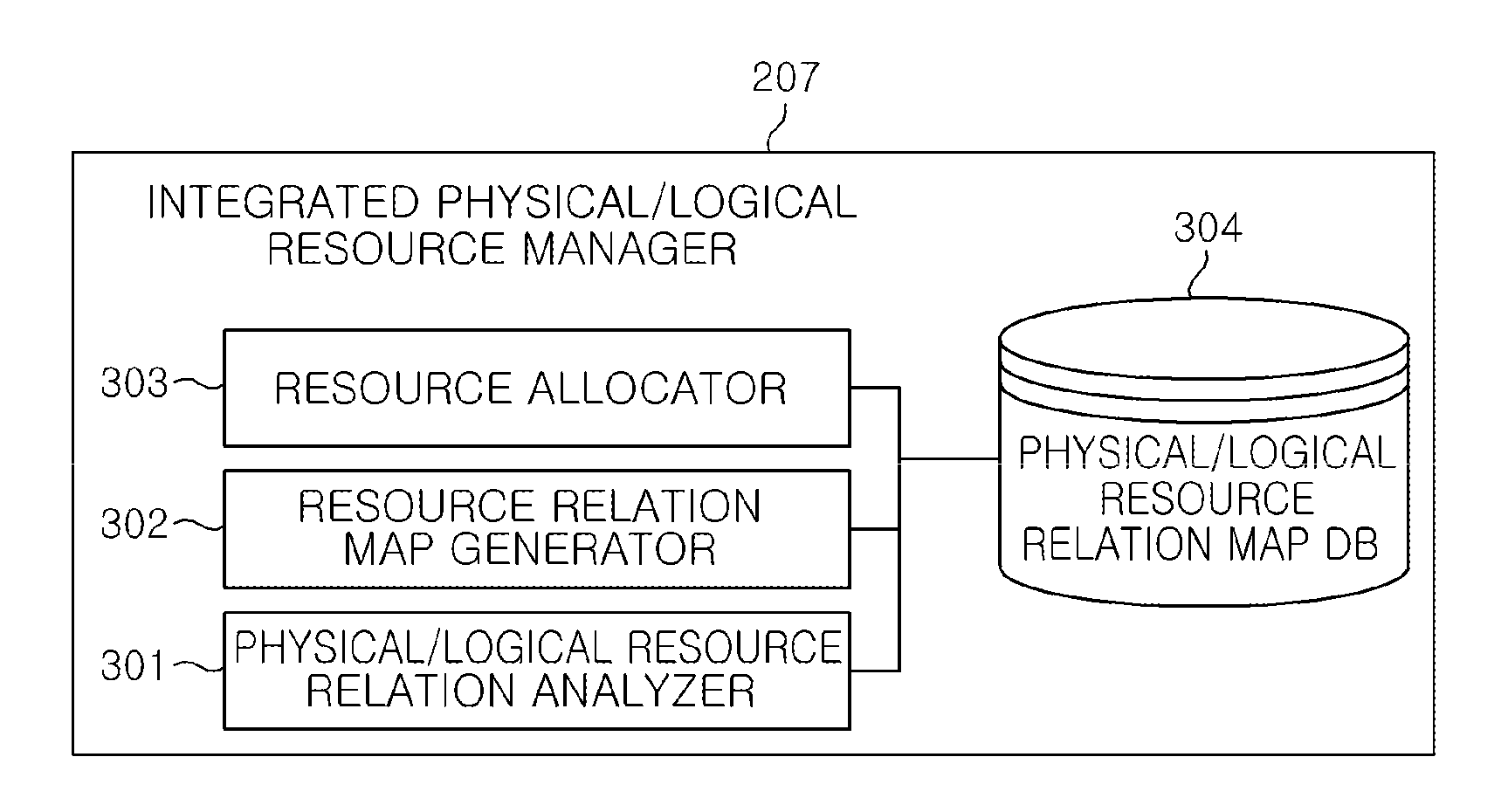

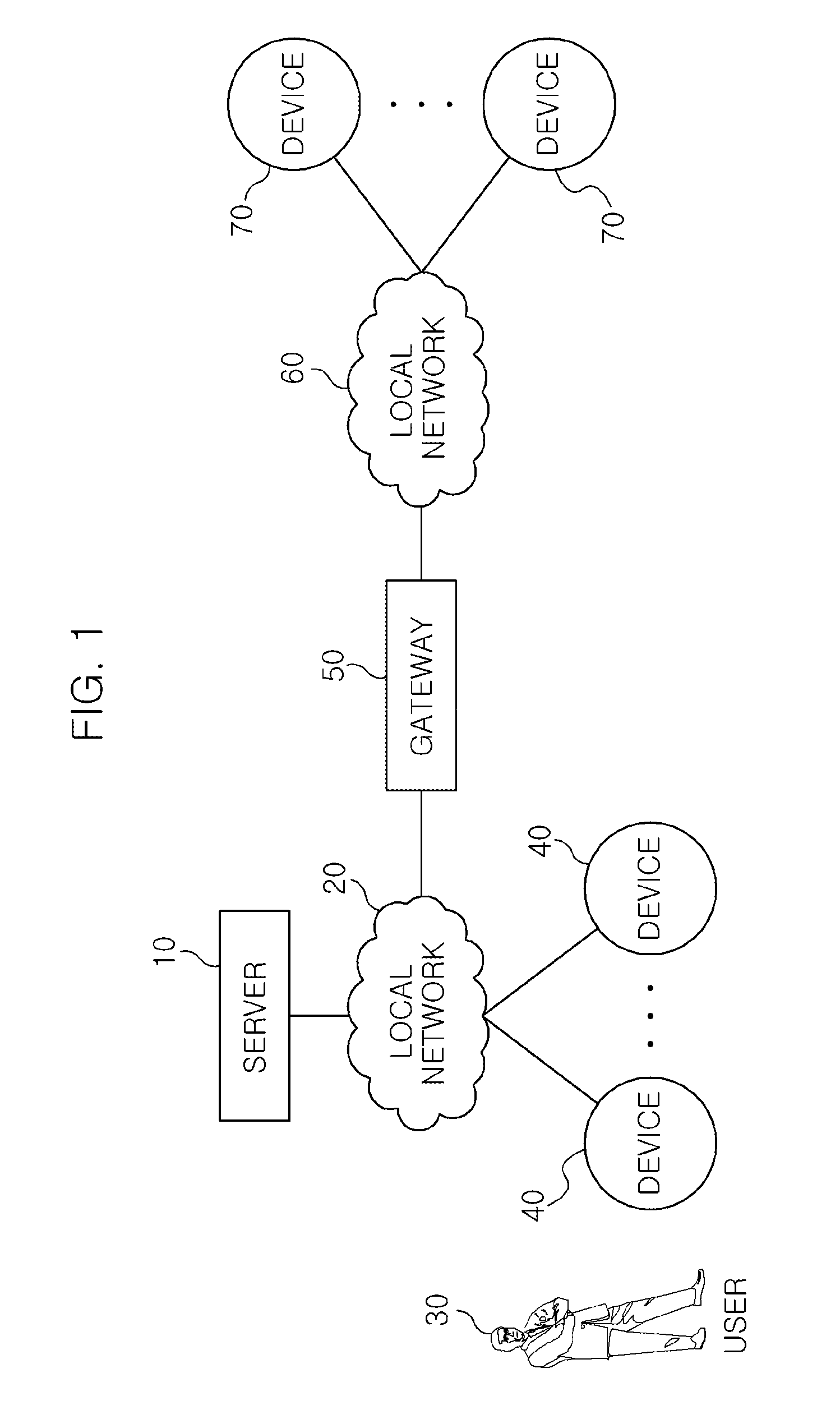

Method and apparatus for physical/logical relationship mapping between resources

ActiveUS20110131252A1Exquisitely manage resourcesResource allocationDigital data processing detailsComputer scienceDatabase

Disclosed is a method for dynamically mapping a physical / logical relationship between resources. The method for physical / logical relationship mapping between resources includes: abstracting heterogeneous environments of physical resources; expressing the physical resources by a resource instance of a predetermined format to generate logical resources which are grouped and managed in accordance with types of the resources; and analyzing the physical / logical relationship between the resources to generate a relation map.

Owner:ELECTRONICS & TELECOMM RES INST

Automatic Test System for Distributed Comprehensive Service and Method Thereof

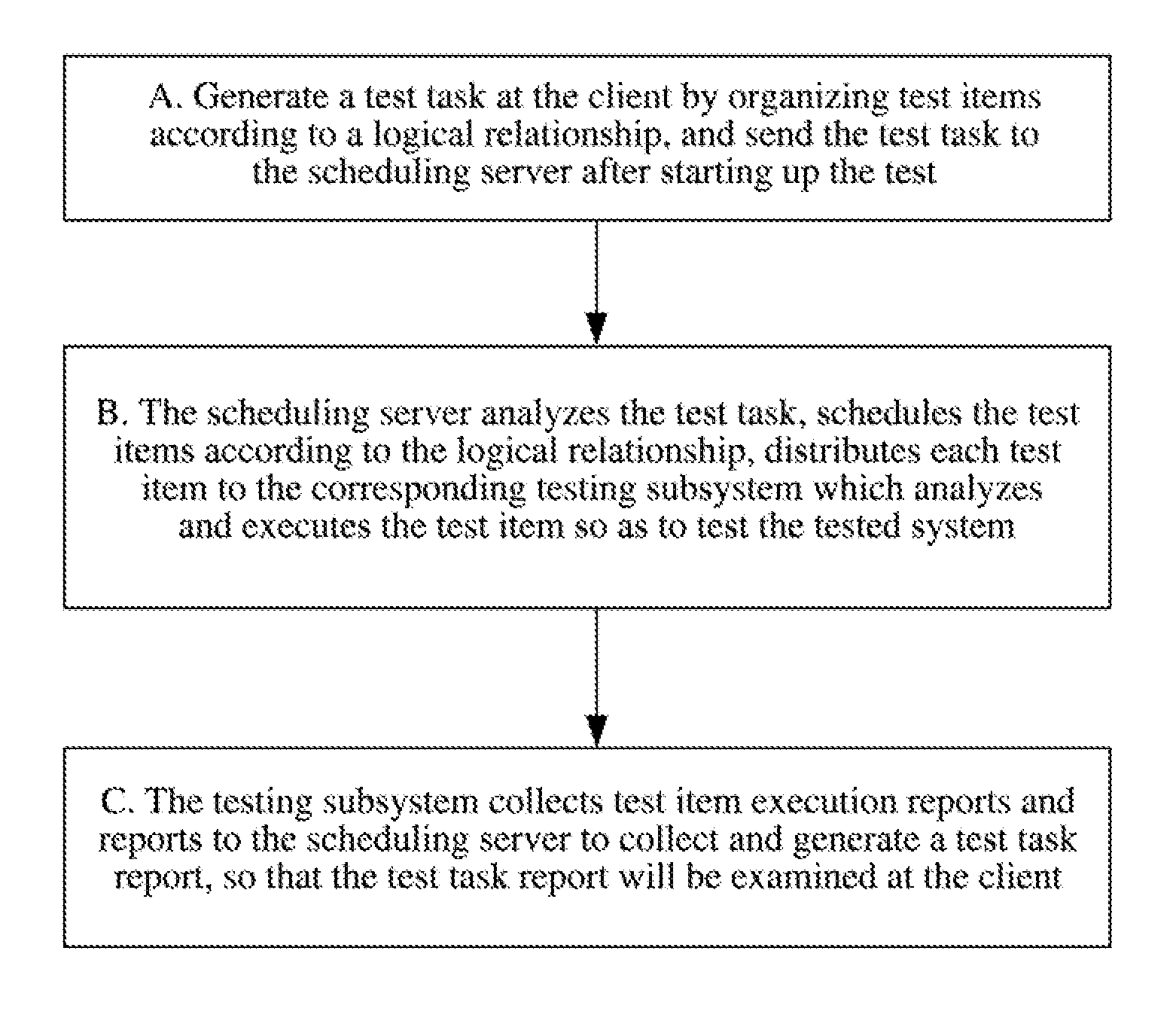

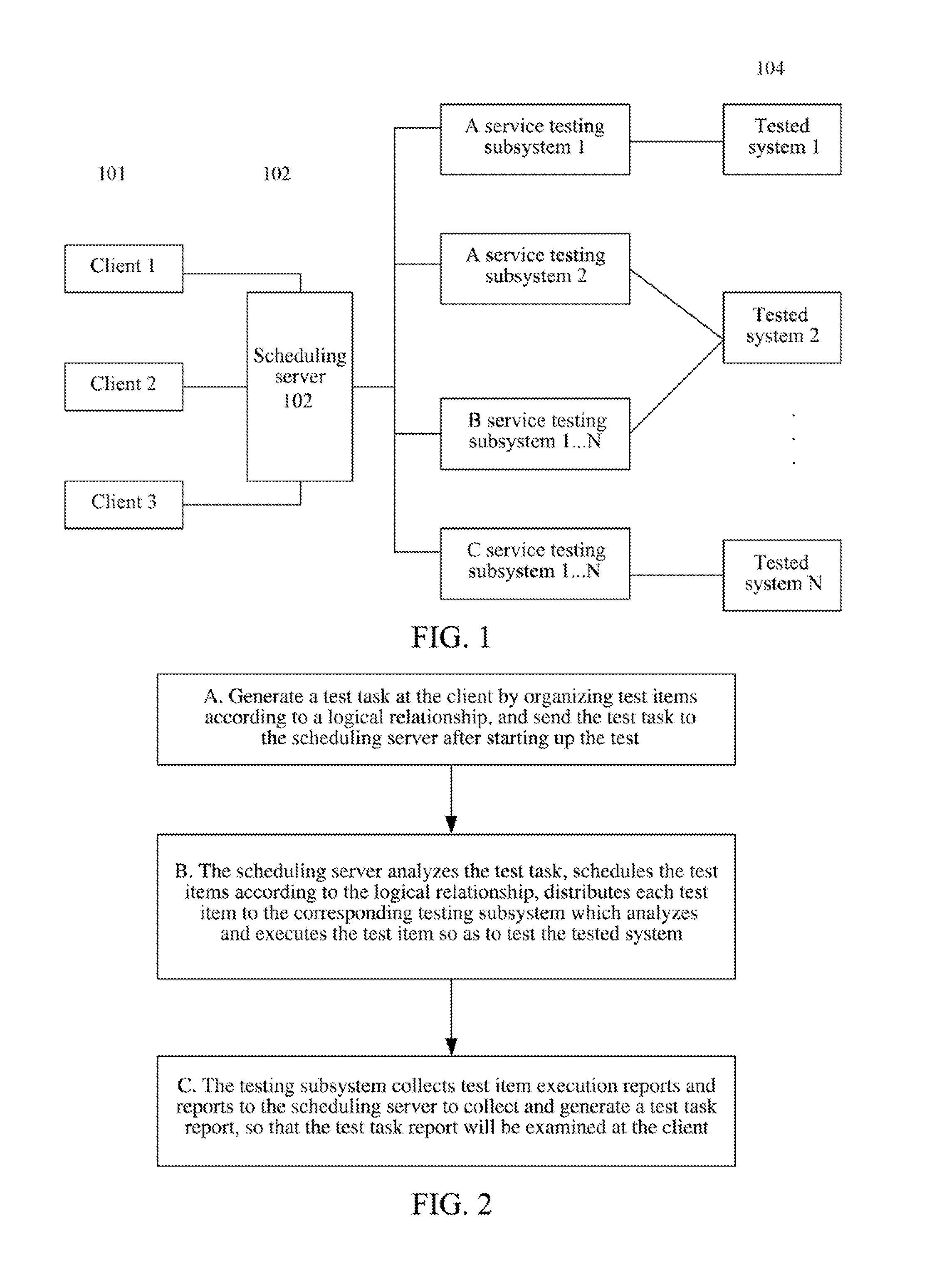

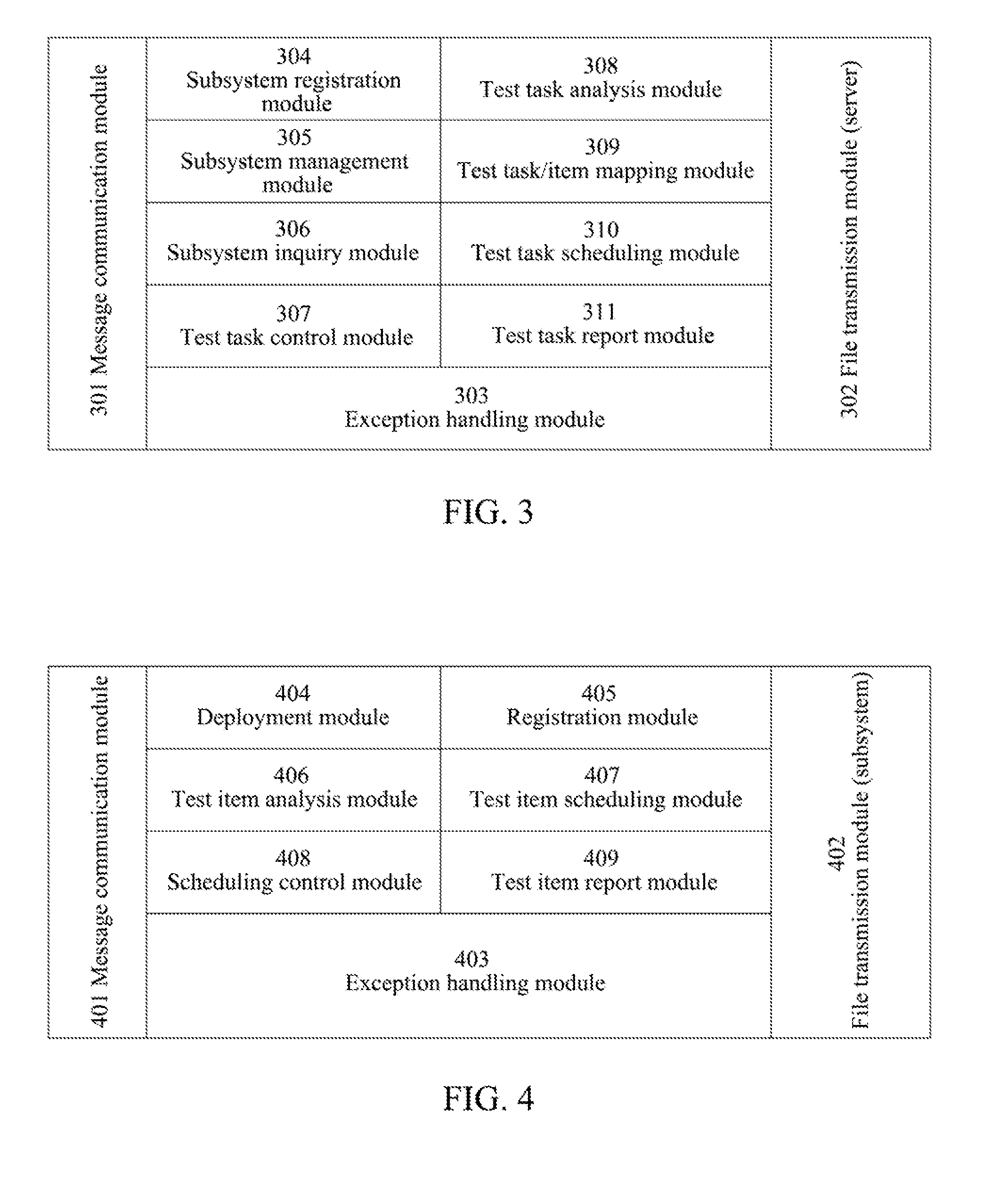

ActiveUS20120221279A1Create flexibleEdition flexibleError detection/correctionElectrical measurementsTest testsTest item

An automatic test system and method for a distributed comprehensive service are disclosed. The system has a client (101), a scheduling server (102) and testing subsystems (103) which are in a distributed deployment and used to test tested systems (104) that are also in a distributed deployment. The scheduling server (102) receives and analyzes test tasks sent from the client (101), schedules test items according to the logical relationship and distributes them to the corresponding testing subsystems (103). The test subsystems (103) analyze and execute the test items to test the tested systems (104), collect test item execution reports and send the execution reports to the scheduling server (102). The scheduling server (102) generates a test task report and sends to the client (101) for examination. The system supports complicated multi-service test scenarios and multi-test task execution.

Owner:ZTE CORP

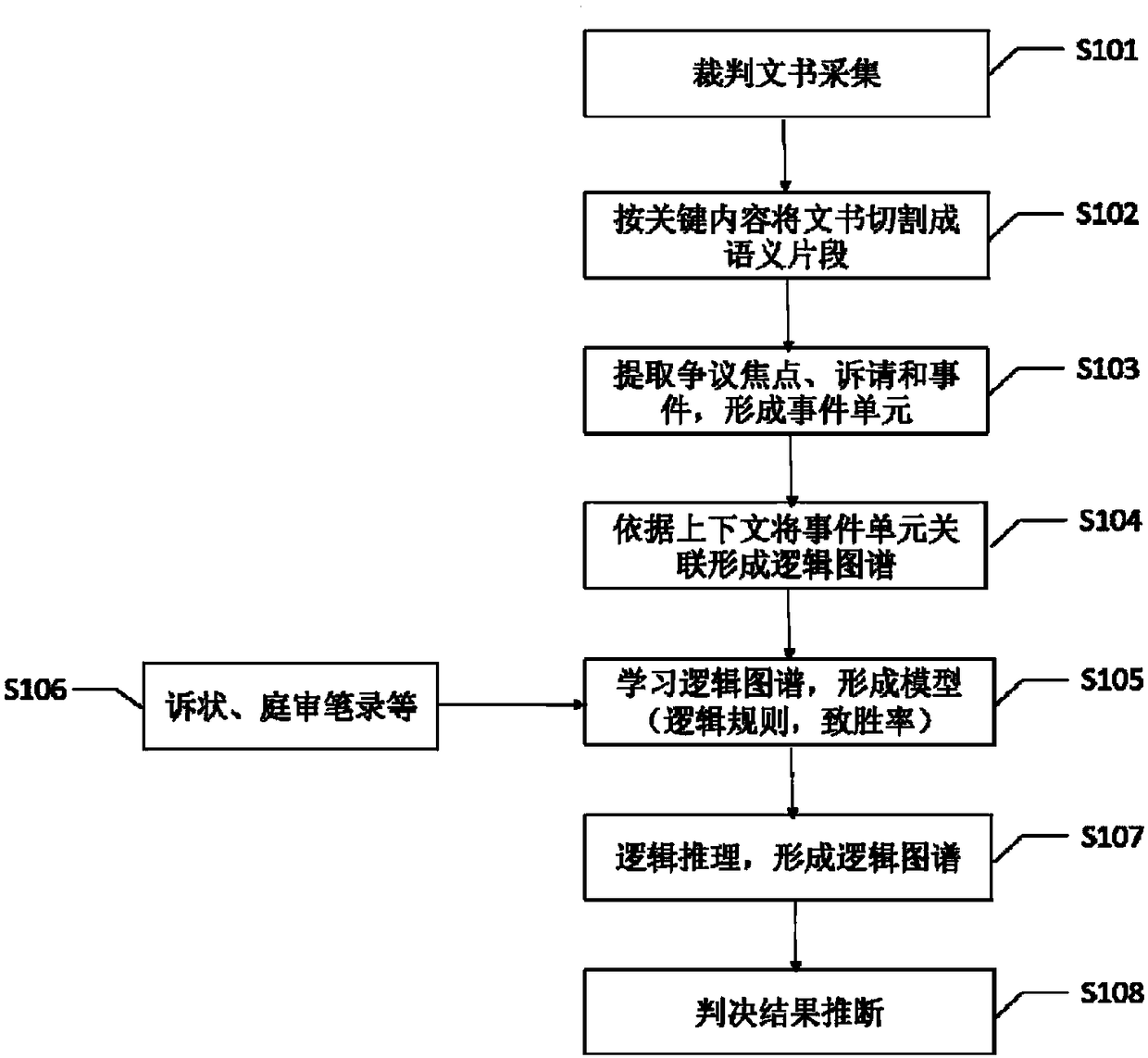

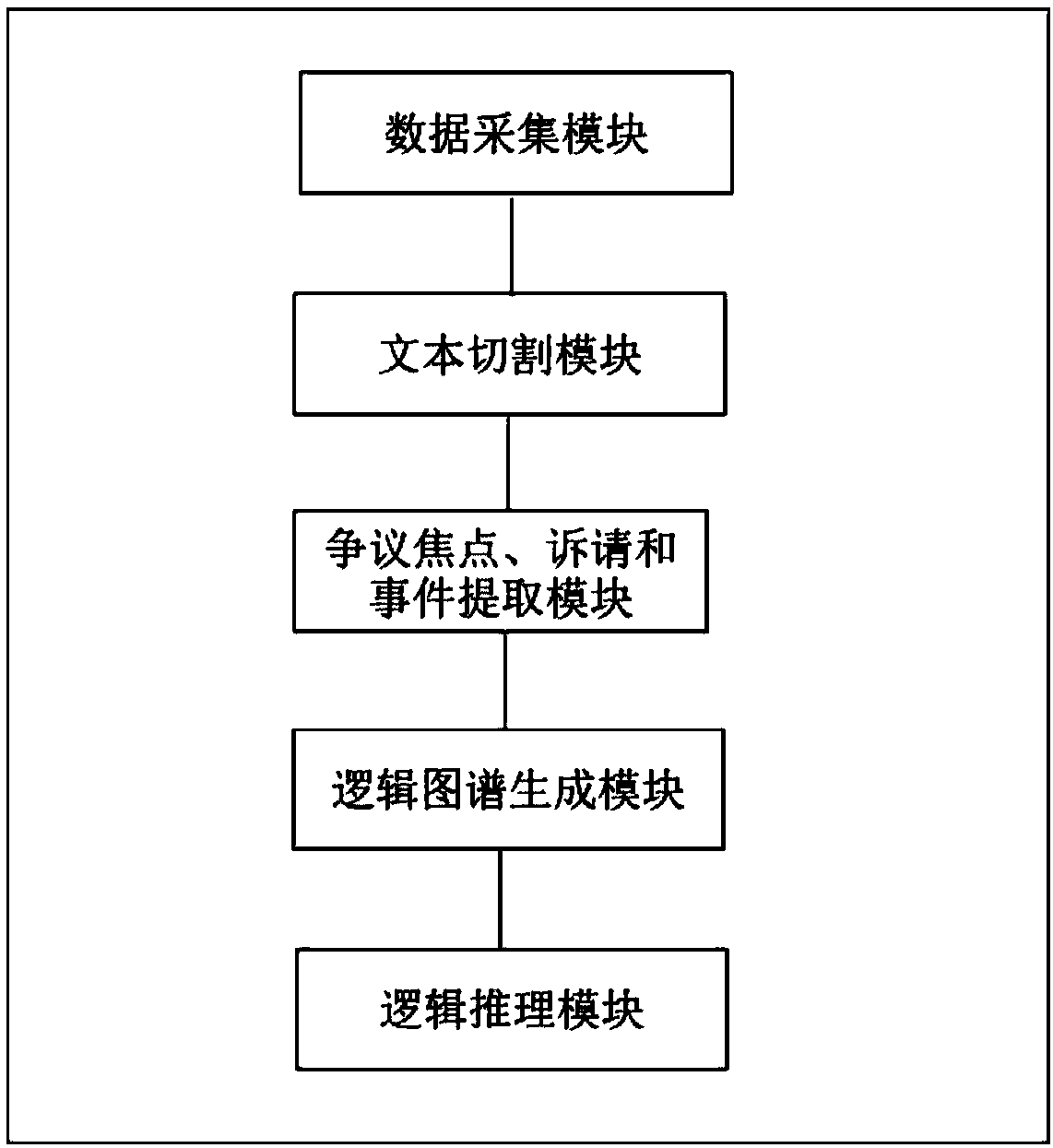

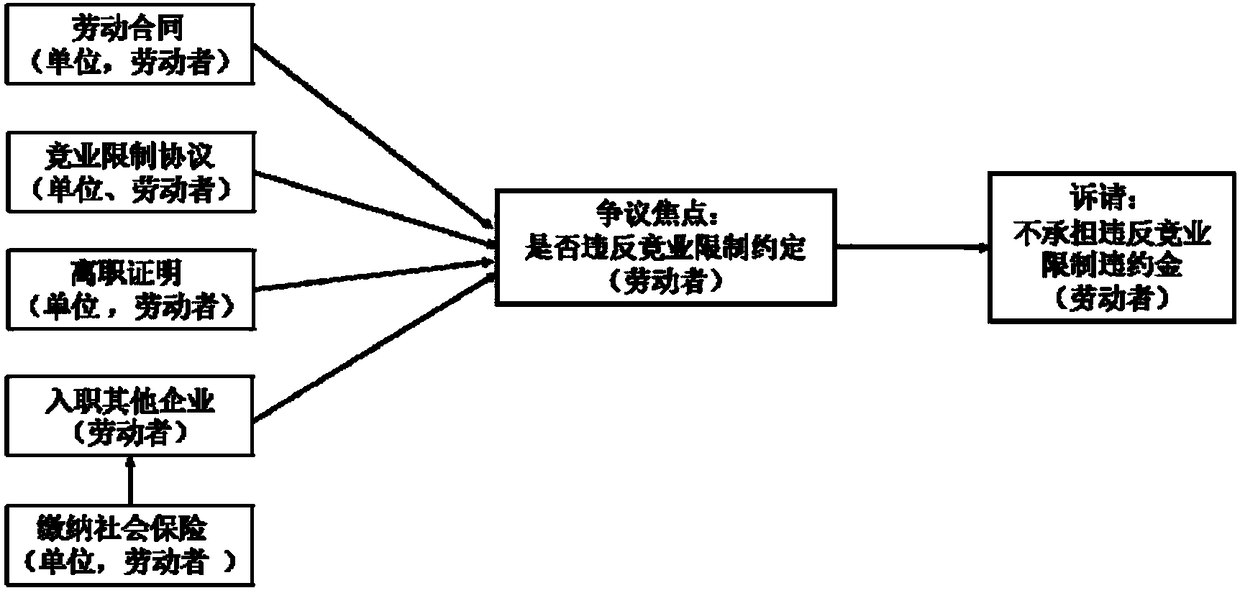

Method and device for inferring decision result of legal document based on logic rules

InactiveCN108304386AEase of evaluationGood choiceData processing applicationsSemantic analysisSemanticsDocument preparation

The invention discloses a method and device for inferring a decision result of a legal document based on logic rules, and relates to the field of judicature. According to the method, key contents areextracted from the decision document and segmented into semantic fragments according to semantics, events are extracted from the semantic fragments and indicated into event units, according to a contextual relationship, each event unit is correlated to form an event logic atlas, and a logic atlas generation model is learned. Weights of each rule are calculated according to the winning frequency ofeach logic rule. Aiming at a new file, the event logic atlas is generated by using the generation model, and the decision result is automatically inferred according to the weights of each logic in the logic atlas. According to the method, key elements and an internal logical relationship of a case are presented in a visualized manner by a generated event logic atlas, the logic thinking manner ofa judge dealing with cases is converted into the logic rules to predetermine a result, and the evaluation of a litigation outcome, the selection of a reconciliation manner and the like of litigants oftwo sides are convenient.

Owner:江西思贤数据科技有限公司

Control system and method for a parallel hybrid electric vehicle

A vehicle system controller for a vehicle having an engine, a motor / generator, and subsystem controllers is provided. The vehicle system controller includes a state machine having a number of predefined states which represent vehicle operating modes. The predefined states include a motor drive state, which represents a vehicle operating mode wherein the motor / generator provides all driveline torques. The vehicle system controller further includes a set of rules which define logical relationships between each of the predefined states. A set of commands, unique to each state, are supplied to the subsystem controllers. The commands are provided to the subsystem controllers to achieve desired vehicle functionality within the states, and to transition between different states.

Owner:FORD GLOBAL TECH LLC

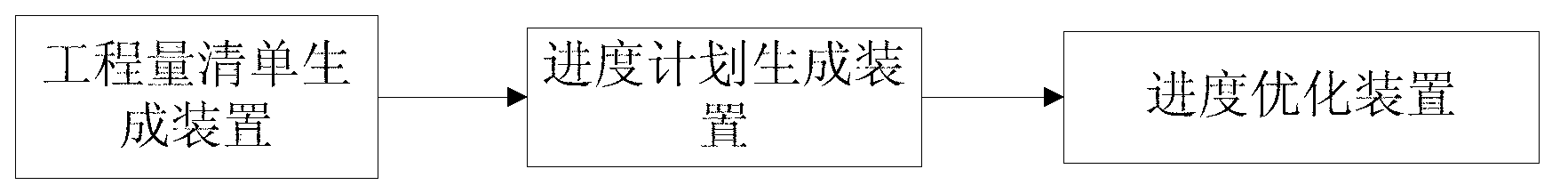

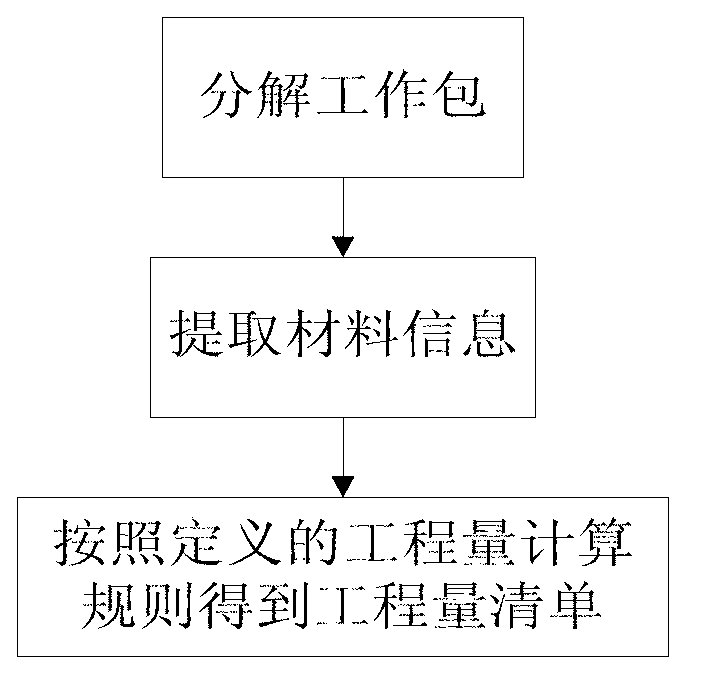

Project management progress arranging method and project management progress arranging system

InactiveCN103295100AAchieve optimal configurationIncrease the speed of orchestrationResourcesProgram planningTime limit

The invention provides a project management progress arranging method and a project management progress arranging system which aim at re-optimizing a progress plan to enable resource allocation of a project to be optimal at any time. The project management progress arranging method includes the following steps: (1), generating a project quantity list, namely decomposing a building information model into work packages, reading material information in the work packages and creating the project quantity list according to defined project quantity calculating rules; (2), generating a progress plan, namely calculating labor time and forming the progress plan on the basis of the project quantity list and according to constraint conditions like a logical relationship between labor quotas and processes and total resources; (3), optimizing the progress plan, namely optimizing the progress plan within a reasonable time limit and based on a PSO (particle swarm optimization) algorithm to obtain an optimal progress schedule meeting requirements of optimization of resource allocation.

Owner:SIPPR ENG GROUP

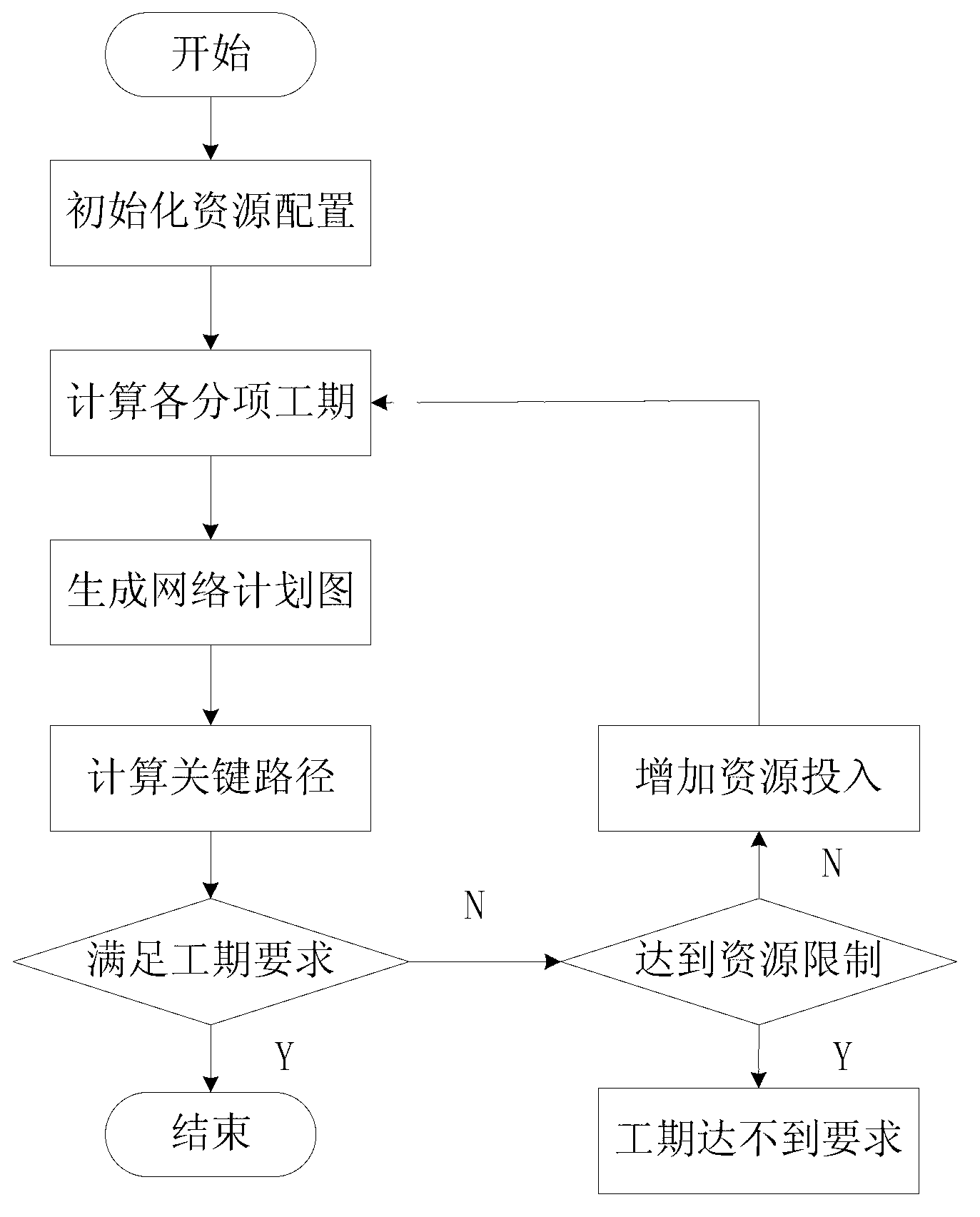

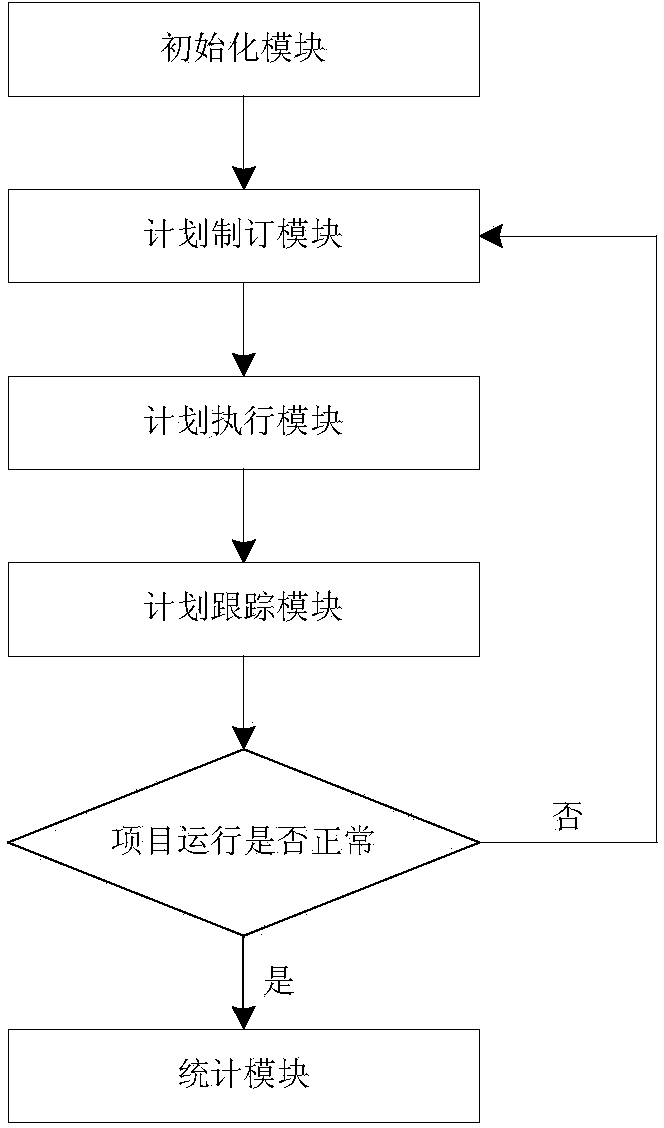

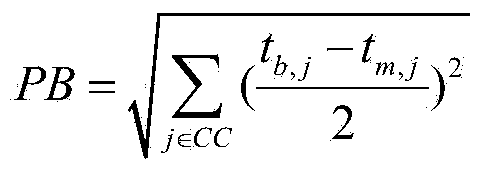

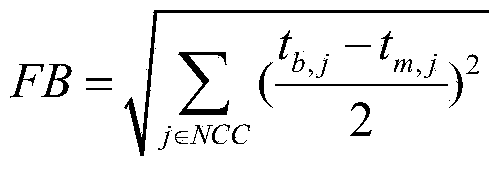

Project progress management method based on critical chain

The invention relates to a project progress management method based on a critical chain. The project progress management method based on the critical chain comprises the following steps that (1) an initialization module is started and a basic framework of project management is generated; (2) a plan making module creates webs, makes a network planning chart and establishes a personnel and resource table; (3) a plan implementation module conducts an estimation on a time limit of a project according to the mean square error method, project buffer time and feeding buffer time are worked out, an MRCPSP module is established, and a final progress planning table constrained by a project logical relationship and resources is determined; (4) a plan tracking module monitors the implementation condition of the project and recognizes a project progress risk; (5) a project statistic module conducts statistics on the project workload and the resource use condition. By the adoption of the project progress management method based on the critical chain, dynamic management of the project implementation progress and the continuous improvement on the whole project management process are achieved on the premise that constraint conditions of the implementation time of jobs and the precedence relationship between the jobs are met and the resource constrain conditions are met.

Owner:BEIJING SIMULATION CENT

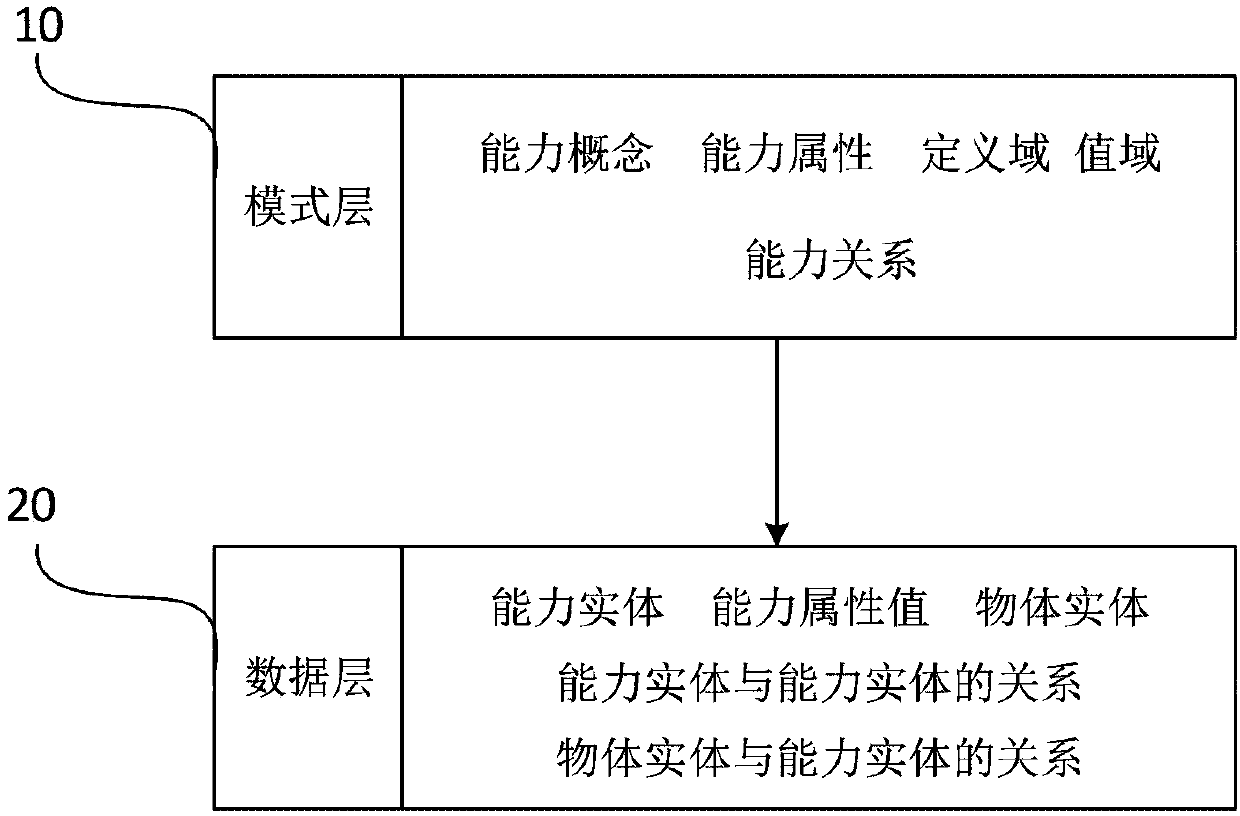

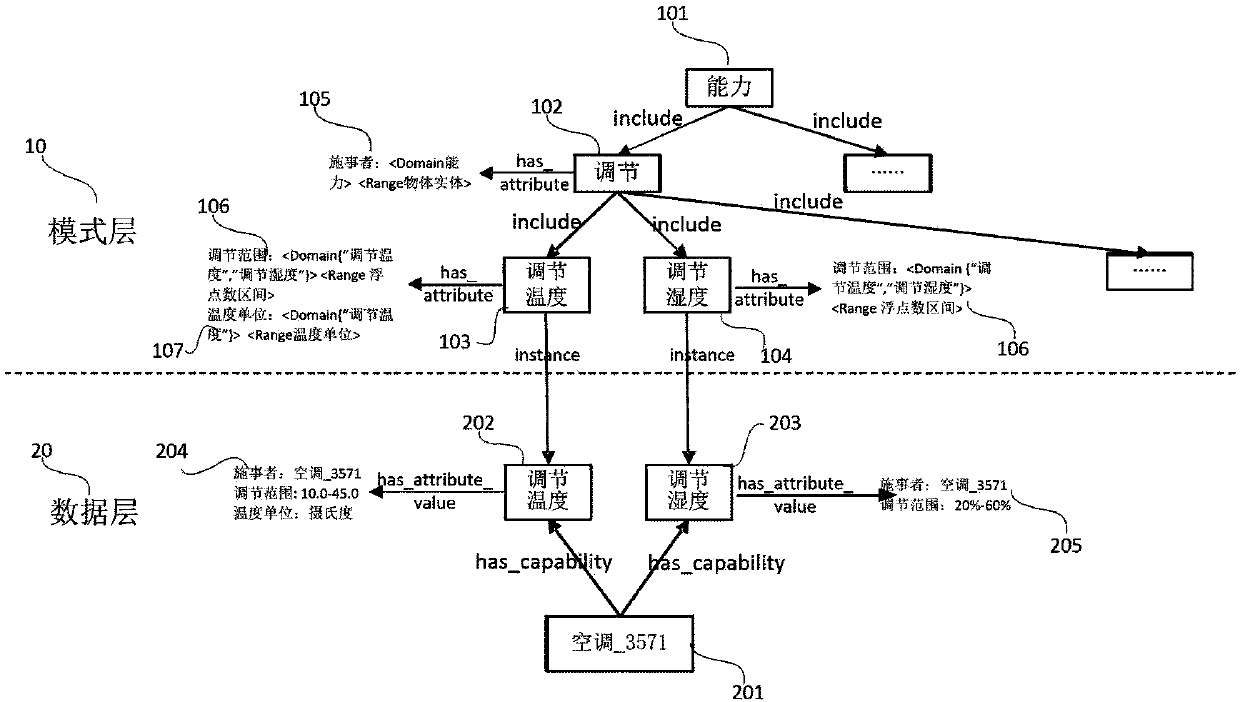

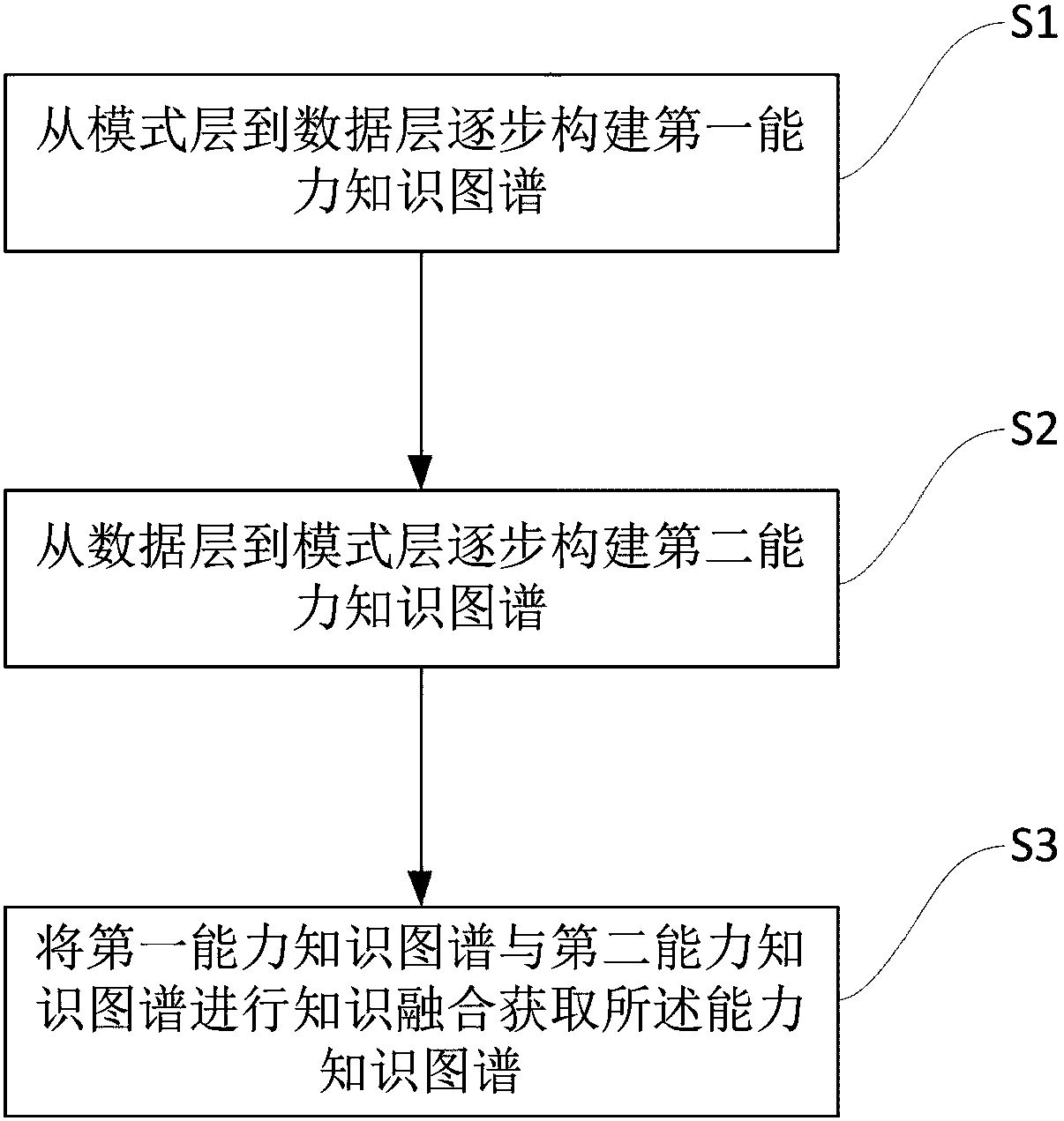

Internet of Things capability and knowledge mapping and construction method thereof

InactiveCN108021718AQuick searchSpecial data processing applicationsService compositionSemantic search

The invention discloses an Internet of Things capability and knowledge mapping and a construction method thereof. The capability and knowledge mapping comprises a model layer and a data layer, whereinthe model layer is used as a capability ontology, comprises specification concept sets and logical relationships of the specification concept sets, and particularly comprises capability concepts, capability relationships, capability attributes, and definition domains and value domains of the capability attributes; the data layer is used as an entity set of the capability and knowledge mapping andinstantiation of the model layer, and particularly comprises capability entities, capability attribute values, relationships between capability entities, object entities, and relationships between the object entities and the capability entities. According to the Internet of Things capability and knowledge mapping and the construction method thereof, capabilities are separated to serve as core nodes of the mapping, meanwhile, the capabilities are distinguished from other attributes of objects, the capabilities can be searched rapidly and relationships between the objects can be established through the capabilities, and supports can be provided for semantic search, service composition and user recommendation in the field of the Internet of Things.

Owner:INFORMATION SCI RES INST OF CETC

Storage area network (SAN) device logical relationships manager

InactiveUS7107328B1Multiple digital computer combinationsData switching networksStorage area networkSystem area network

A method and apparatus for managing one or more logical relationships between a plurality of devices in a storage area network (SAN). The method includes receiving a first identifier associated with a first SAN device, determining the logical relationships associated with the first SAN device, receiving a second identifier associated with a second SAN device, and associating the second identifier to the logical relationships associated with the first SAN device.

Owner:VERITAS TECH

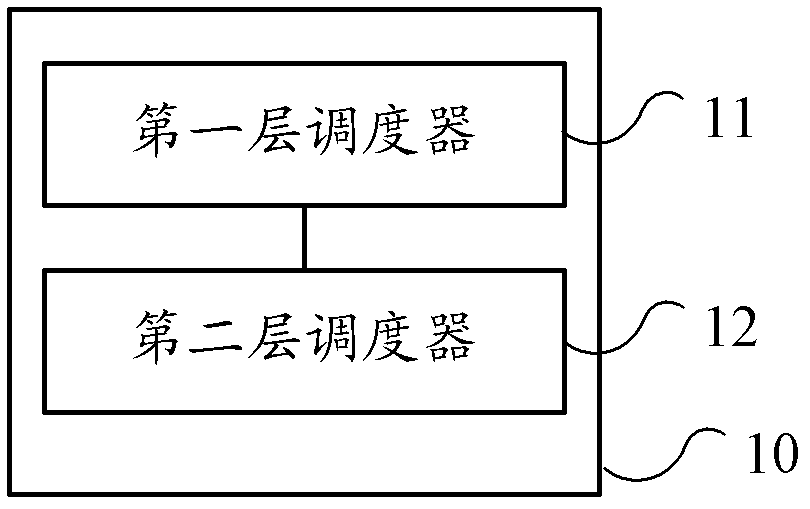

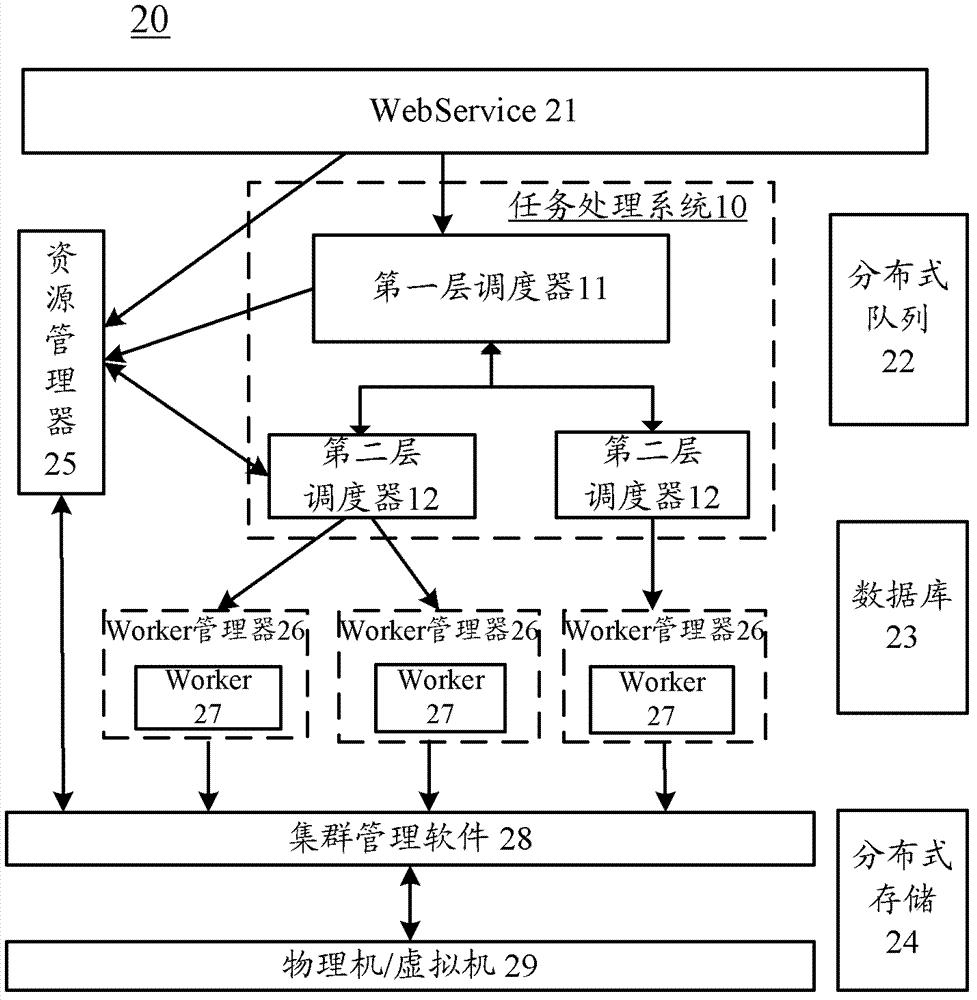

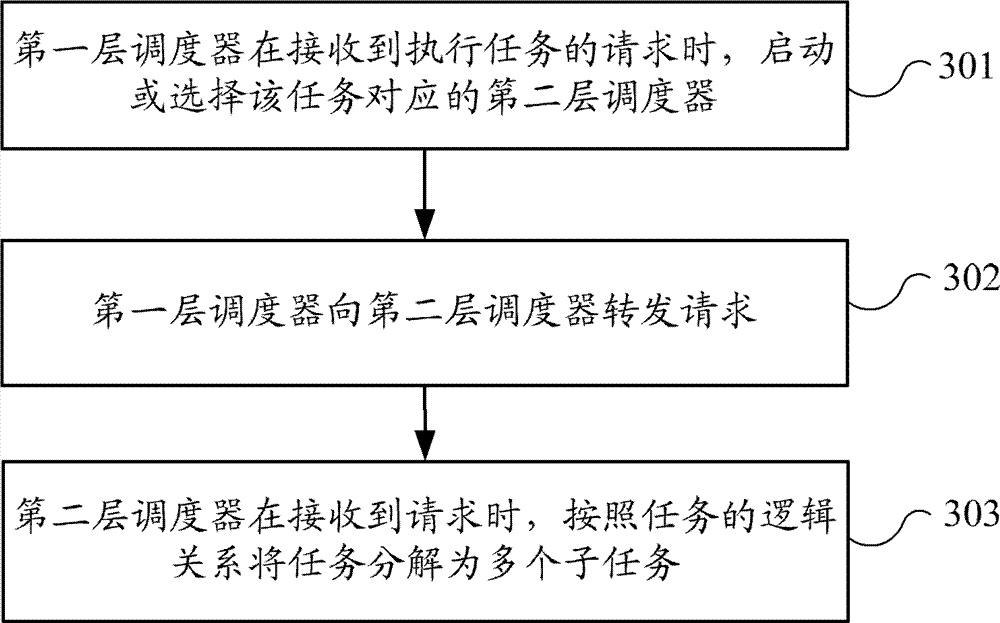

Task processing system for distributed computation and task processing method for distributed computation

InactiveCN102763086AImprove processing efficiencyImprove scheduling flexibilityResource allocationStore-and-forward switching systemsHandling systemDistributed computing

Embodiments of the invention provide a task processing system for distributed computation and a task processing method for the distributed computation. The task processing system comprises a first level scheduler which is used for receiving requests of executing a task, starting or selecting a second level scheduler according to the task, and transmitting the requests to the second level scheduler; and the second level scheduler which is used for decomposing the task into a plurality of subtasks according to a logical relationship of the task when receiving the requests are transmitted by the first level scheduler. The embodiments of the invention employ a two-level scheduling frameworks, with the second level scheduler corresponding to the task and the first level scheduler starting or selecting the second level scheduler corresponding to the task, so that the task processing system and the task processing method can be used in different tasks, and processing efficiency and scheduling flexibility are improved.

Owner:HUAWEI TECH CO LTD

Spatially driven content presentation in a cellular environment

InactiveUS8418075B2Maintaining senseFacilitate decision-makingDigital data information retrievalText processingMedia typeState dependent

Techniques are provided for integrated content presentation via cells arranged geometrically in a cellular environment. Users can navigate various orientations and zoom states of the cellular environment to access information via different applications, different media types, different visual representations and from different underlying content sources. The information can be organized according to various logical relationships. Upon receiving an indication of a zoom state associated with a cell or a group of cells arranged in the cellular environment, a content reference at that zoom state is retrieved. Further, the content reference is resolved to retrieve and output content, including a visual representation associated with the zoom state.

Owner:OPEN TEXT SA ULC