Multi-core SoC architecture design method supporting multi-task parallel execution

An architecture design, multi-task technology, applied in the fields of electronic engineering and computer science, can solve the problems of restricting the development of high integration and miniaturization of UAVs, unable to truly improve data parallel processing, and reduce the real-time performance of data processing. High integration, improve data collection efficiency, and improve real-time effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Combine below Attached picture The present invention is described in further detail.

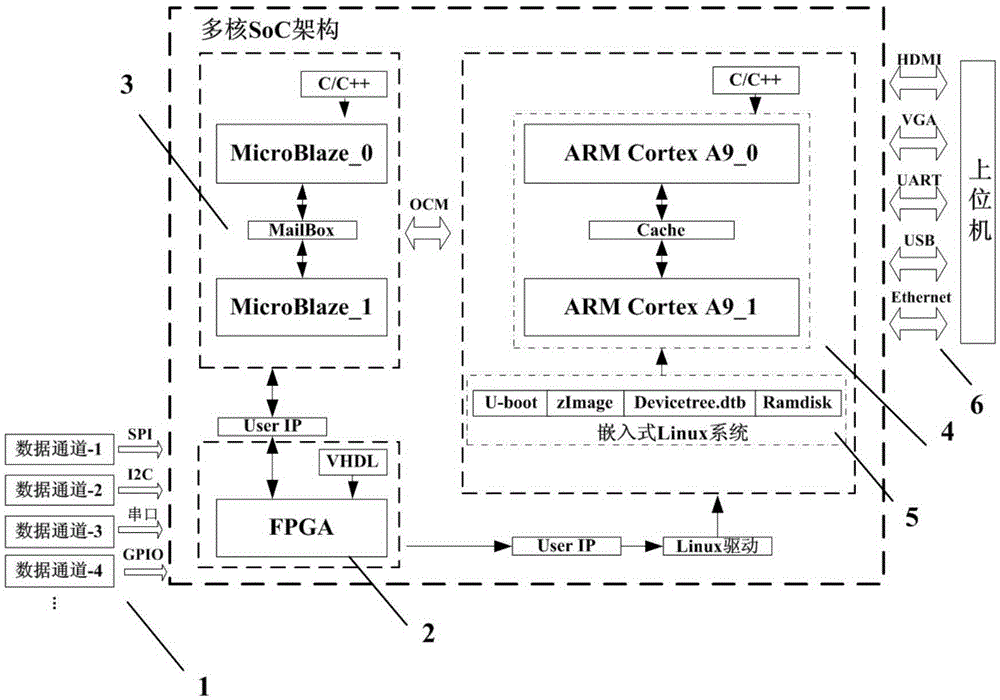

[0029] System Structure Box Figure such as figure 1 As shown, the present invention relates to a multi-core SoC architecture design method that supports multi-task parallelism. By building a multi-core architecture inside the SoC chip, it has multi-task parallel processing capabilities. Compared with the prior art, the present invention can not only significantly improve The real-time nature of data parallel acquisition, processing, output and inter-core interaction can significantly promote the development of UAVs towards high integration and miniaturization. The SoC chip model mentioned is xc7z020clg484-1 of Xilinx Company.

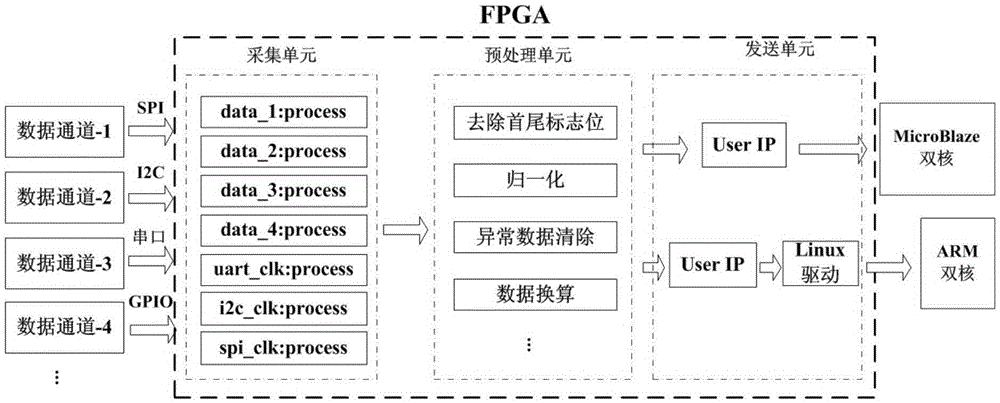

[0030] (1) attached figure 1 Module 1 is the parallel acquisition of multi-channel data. In order to collect data from devices with different interfaces (SPI, I2C, serial port and GPIO interface), module 2 first designed the clocks of these four interf...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More