FPGA-based high-speed adaptive DVB-S2 LDPC decoder and decoding method

A decoder and self-adaptive technology, which is applied in error detection coding, coding, and code conversion using multi-bit parity bits, and can solve the problem that the decoder does not have the adaptive ability of code rate compatibility.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

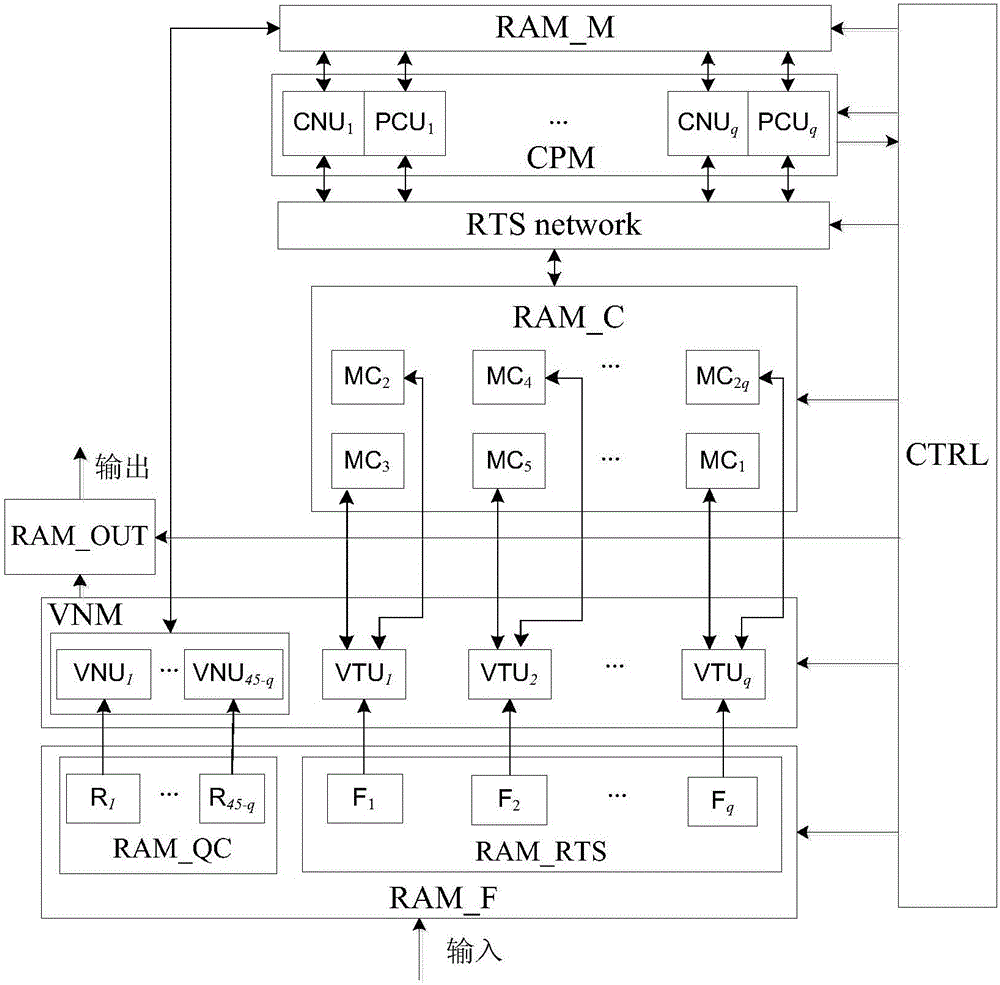

[0036] Adopt the QC-LDPC decoder and the decoding method that improve the node processing parallelism that the present invention proposes, the LDPC code of five code rates that is 16200 with the code length that chooses in the DVB-S2 standard carries out self-adaptive code rate compatible FPGA below High-speed implementation is taken as an example to describe the present invention in detail.

[0037] The H matrix of the LDPC code in the DVB-S2 standard consists of two parts:

[0038] H=[H 1 |H 2 ]

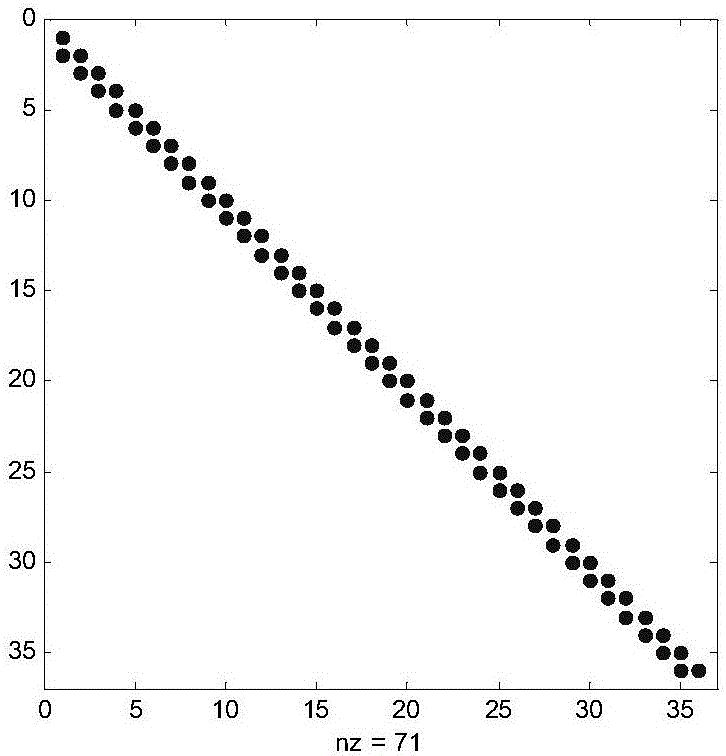

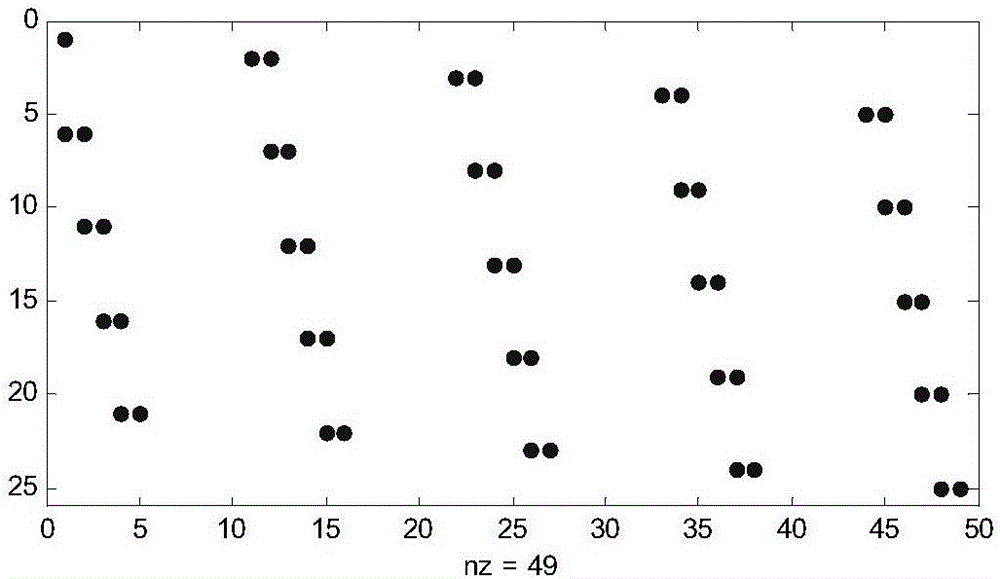

[0039] Among them, H 1 The size is M×K, H 2 is a matrix of lower triangular bidiagonal structure of size M×M, such as figure 1 as shown, figure 2 gives a H for M=36 2 , figure 2 A dot in represents a non-zero element "1". Matrix H 1 The rows are periodic, that is, every q rows (the q values of the five code rates are shown in Table 1) as a whole move one bit to the right to obtain the next q rows, and move 360 times to the right to obtain the parity check matrix h ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More