Method for managing reconfigurable on-chip unified memory aiming at instructions

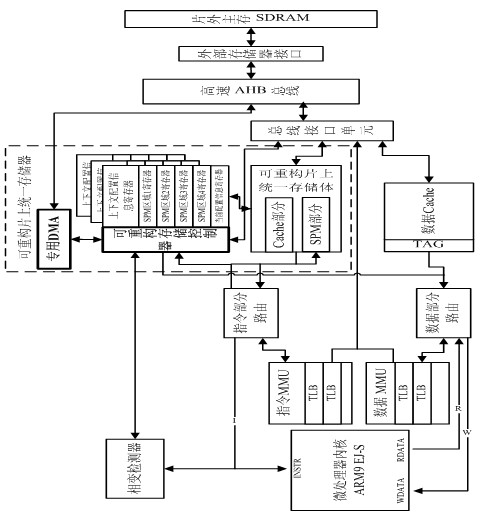

A memory and memory controller technology, used in memory systems, instruments, sustainable buildings, etc., can solve the problems of unpredictable program execution time, inability to improve program performance, and large footprint, reducing the number of accesses and conflicts, The effect of avoiding secondary pollution and reducing system energy consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

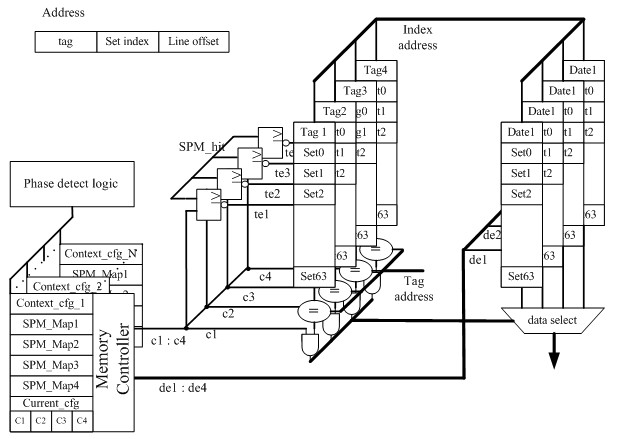

Embodiment Construction

[0029] The inventive method can specifically be realized according to the following steps:

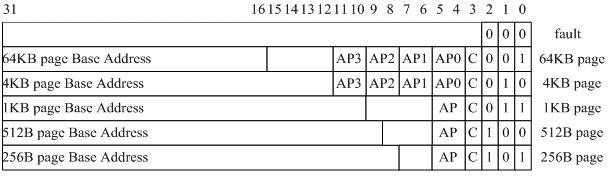

[0030] (1) Establish a virtual memory management mechanism

[0031] The virtual memory management mechanism can form a physically separated and logically continuous address space by modifying the page table entries, so that the addresses of some program pages can be mapped to the SPM part of the reconfigurable memory. Compared with the traditional dynamic SPM optimization technology, the use of virtual memory to complete the change of the address space mapping relationship can realize the complete non-intrusive optimization of the program source code and the binary image generated after compilation. In order to adapt to the method of dynamic management of Cache and SPM and improve the utilization rate of SPM part, the present invention needs to improve the original MMU hardware. By modifying the decoding logic of TLB, support for 512 Bytes / virtual page and 256 Bytes / virtual page is ad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More