high-speed code rate compatible LDPC encoder of a QC-LDPC code based on an FPGA

A code rate compatible, encoder technology, applied in error detection coding using multi-bit parity bits, error correction/detection using block codes, data representation error detection/correction, etc. Variable bit rate compatible design, low encoder throughput, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0077] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

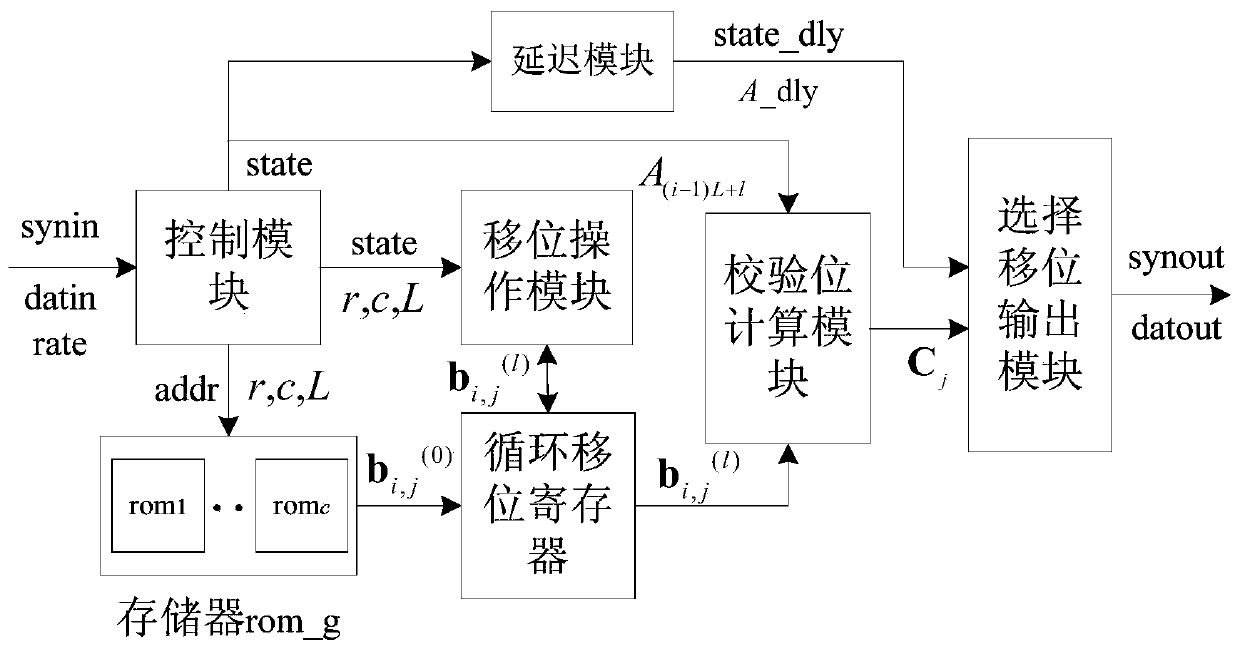

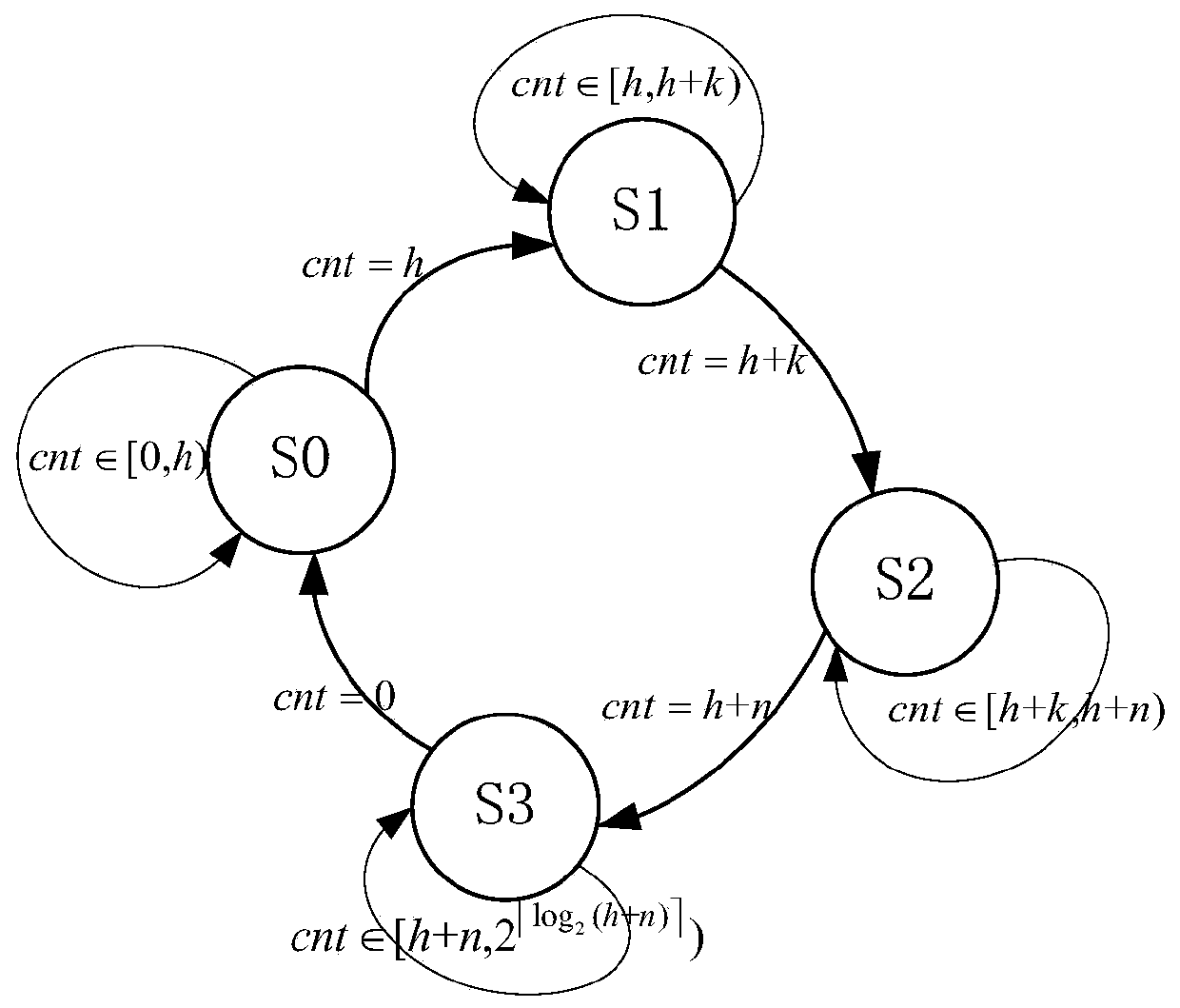

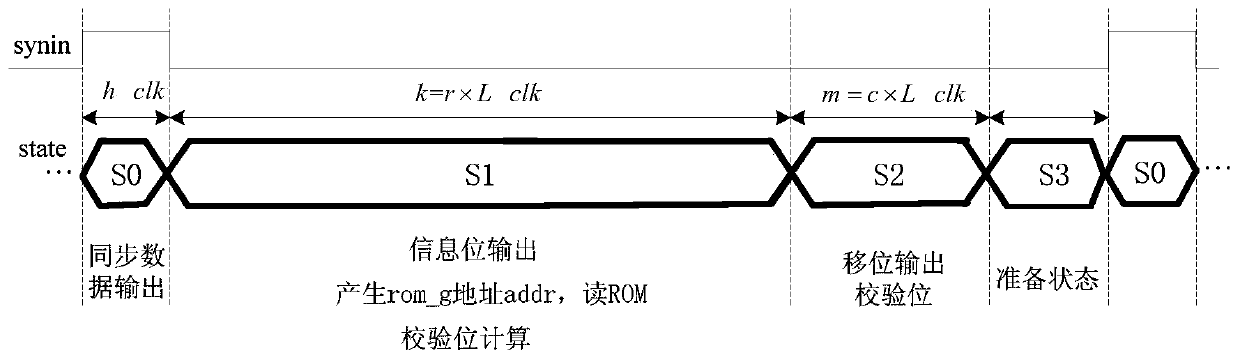

[0078] A high-speed code rate compatible LDPC encoder based on the FPGA-based QC-LDPC code of the present invention sends the column vector of the components of each information sub-block of the input information sequence to the check bit calculation module through the control module; the information sub-block The column vector of the component is time-delayed by the delay module and then sent to the selection shift output module; the shift operation module determines the shift method of the cyclic shift register according to the code rate rate of the encoder, and sends it to the cyclic shift register ;According to the shift method of determining the cyclic shift register, the cyclic sub-matrix B i,j The first row of data b i,j (0) Carry out the shift operation, calculate the check vector according to the result after the shift oper...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More