Patents

Literature

45results about How to "Long latency" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

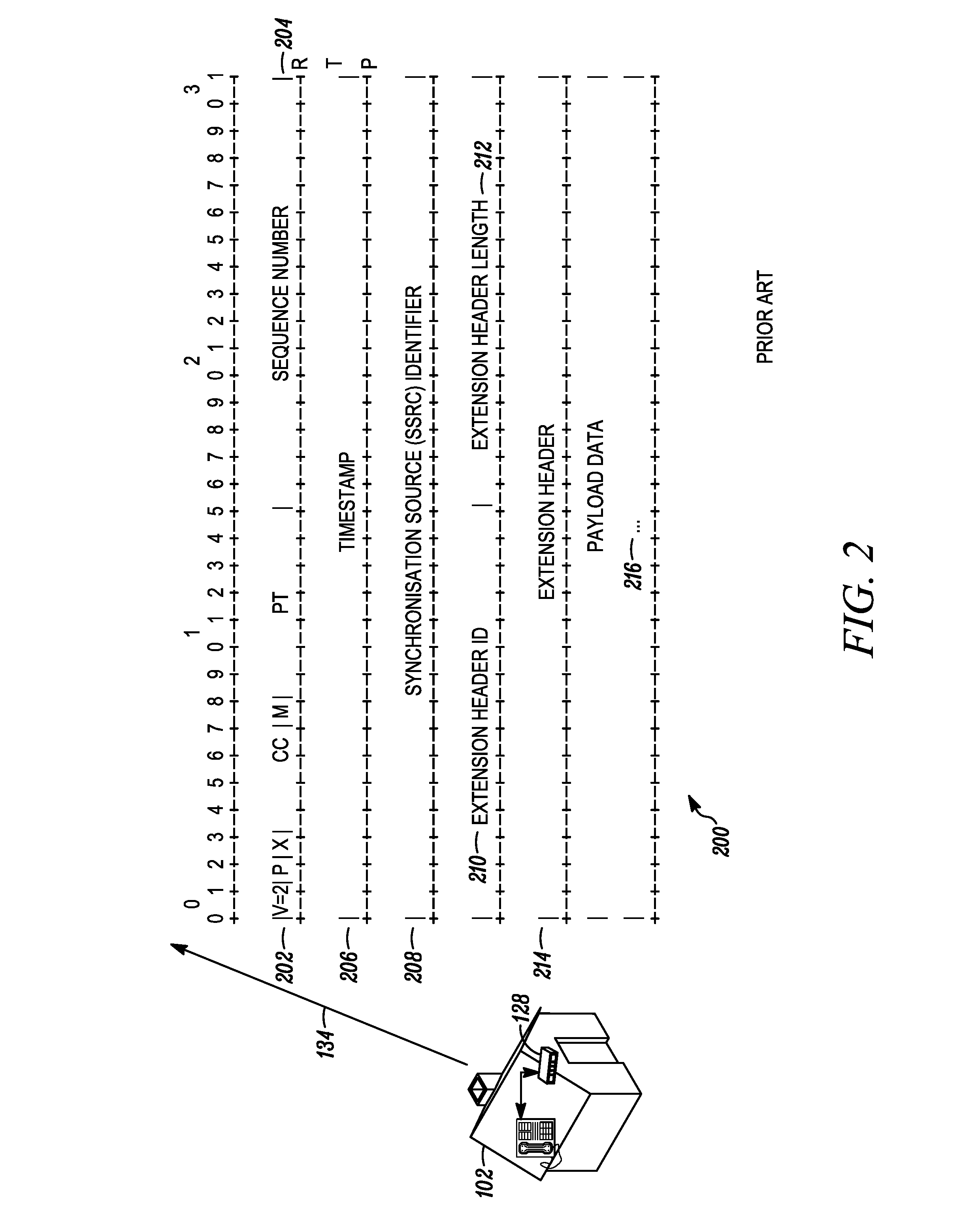

Network testing systems

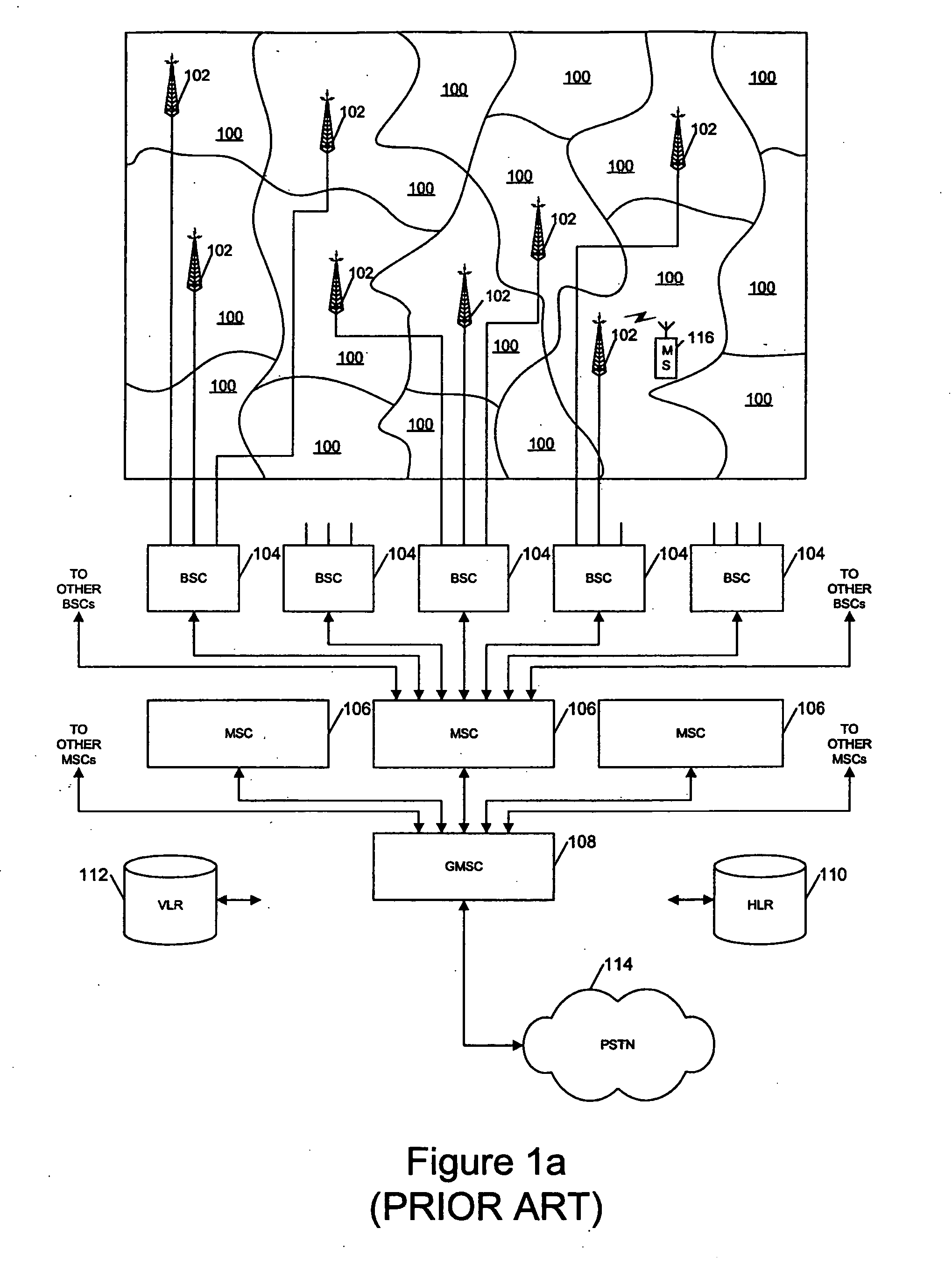

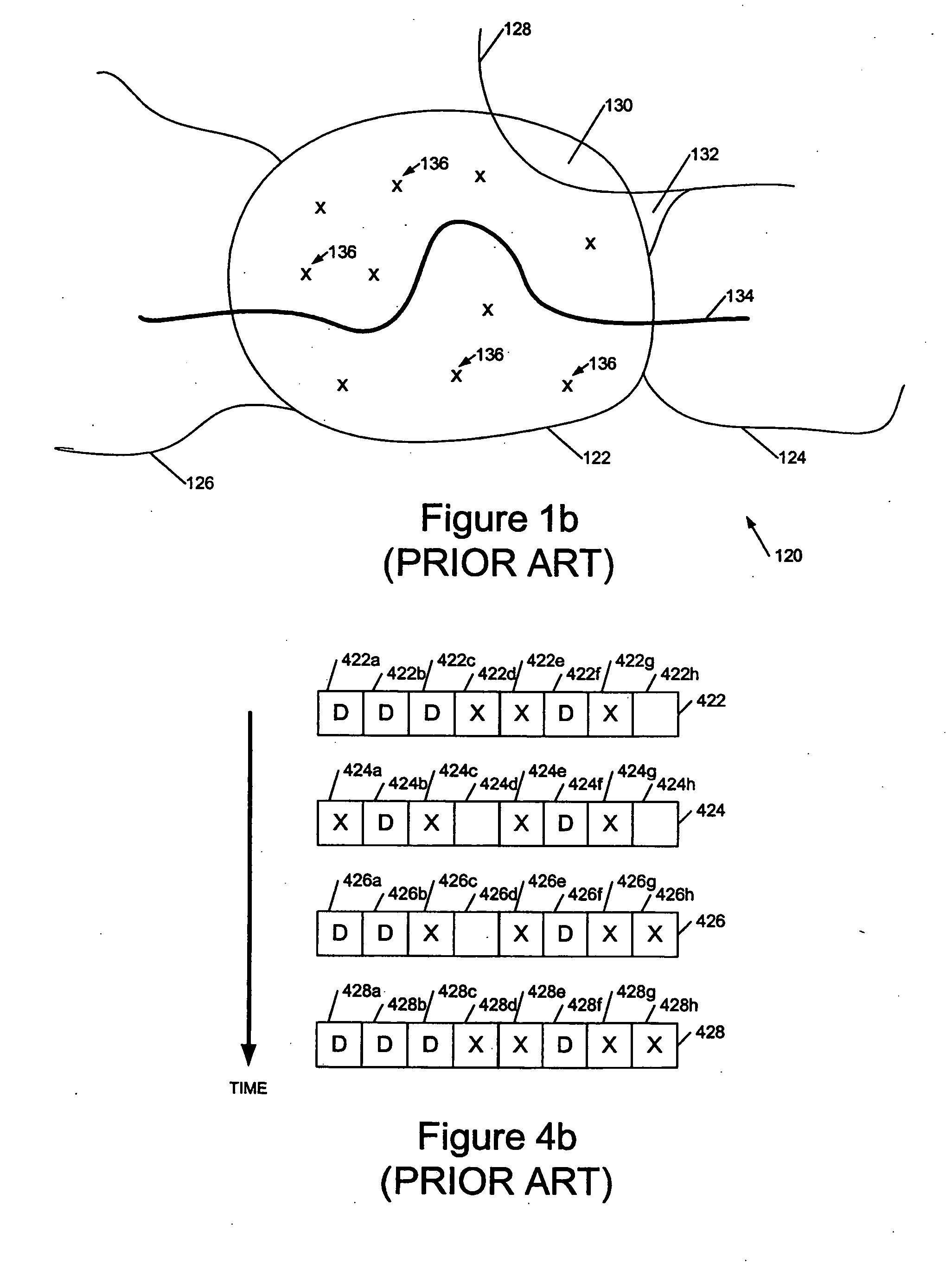

InactiveUS7062264B2Improve noiseReduce in quantitySupervisory/monitoring/testing arrangementsSubstation equipmentTraffic capacityData stream

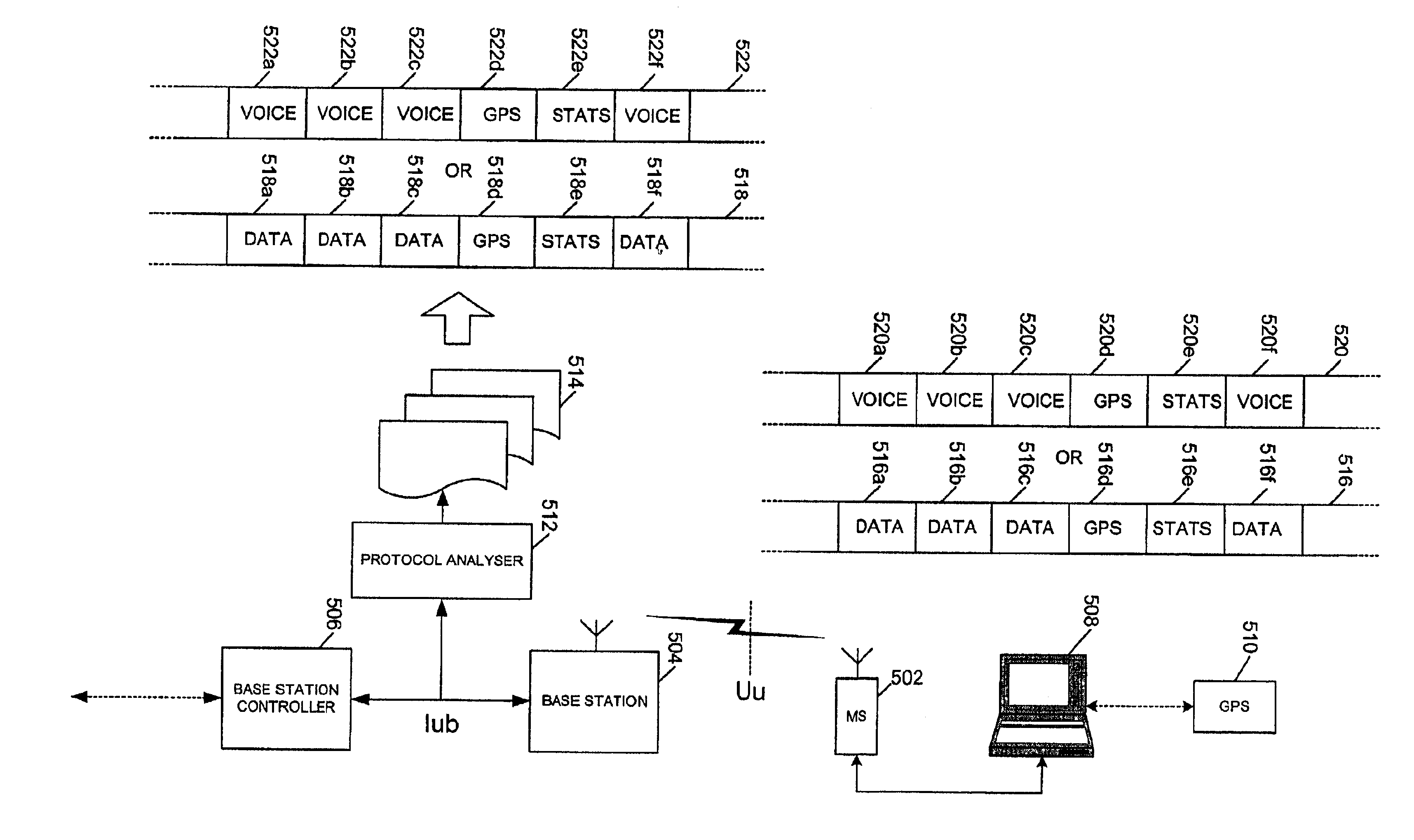

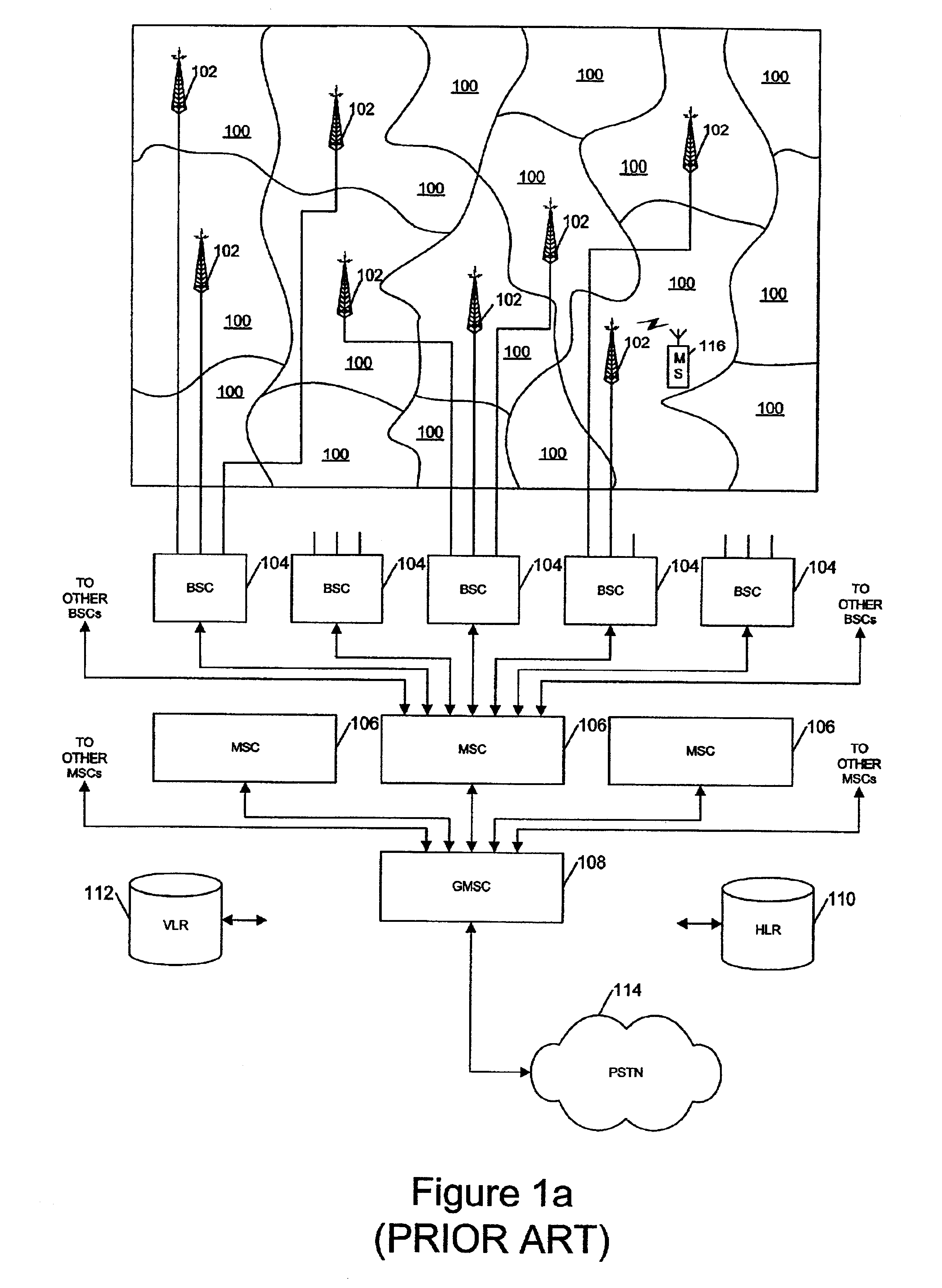

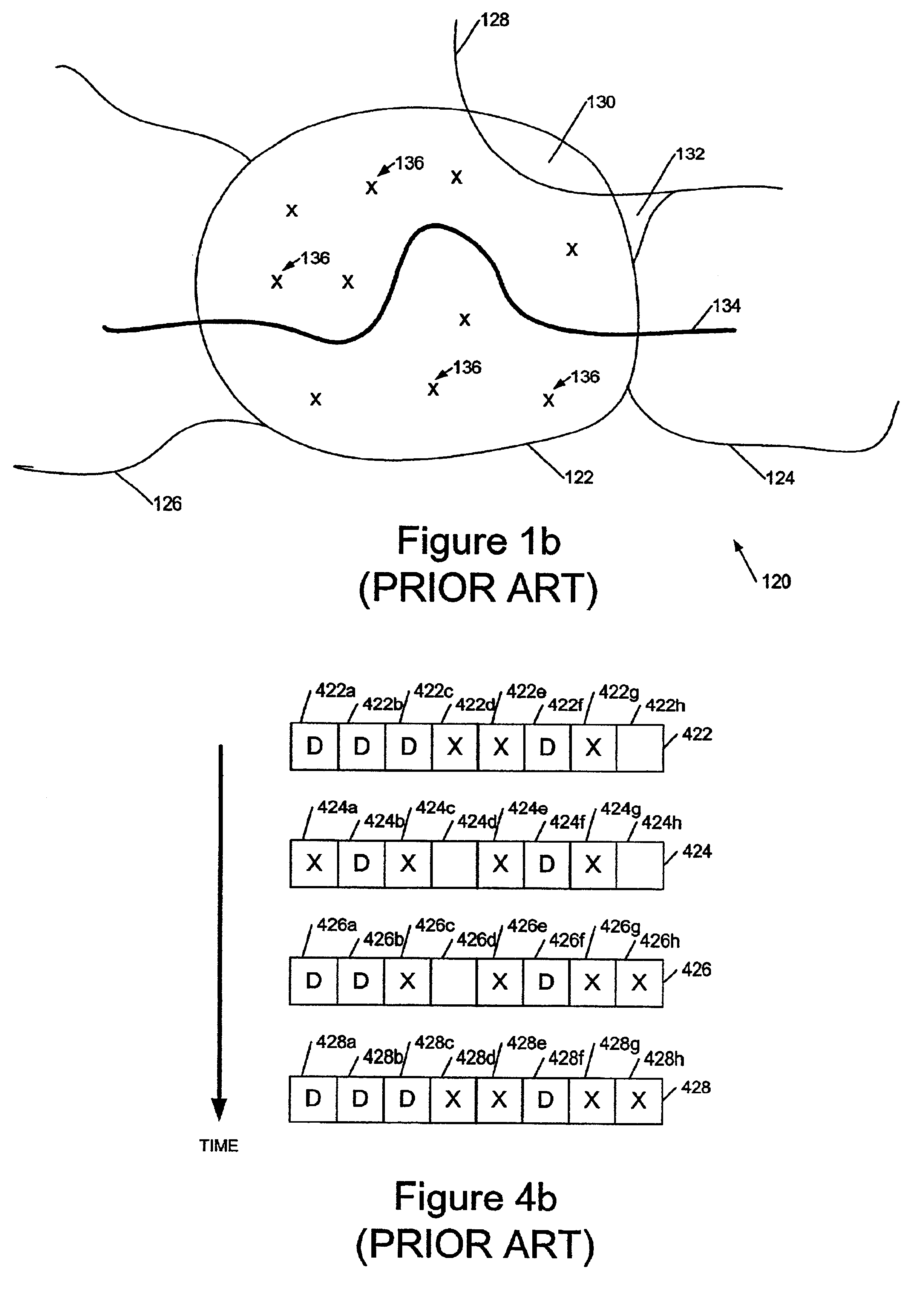

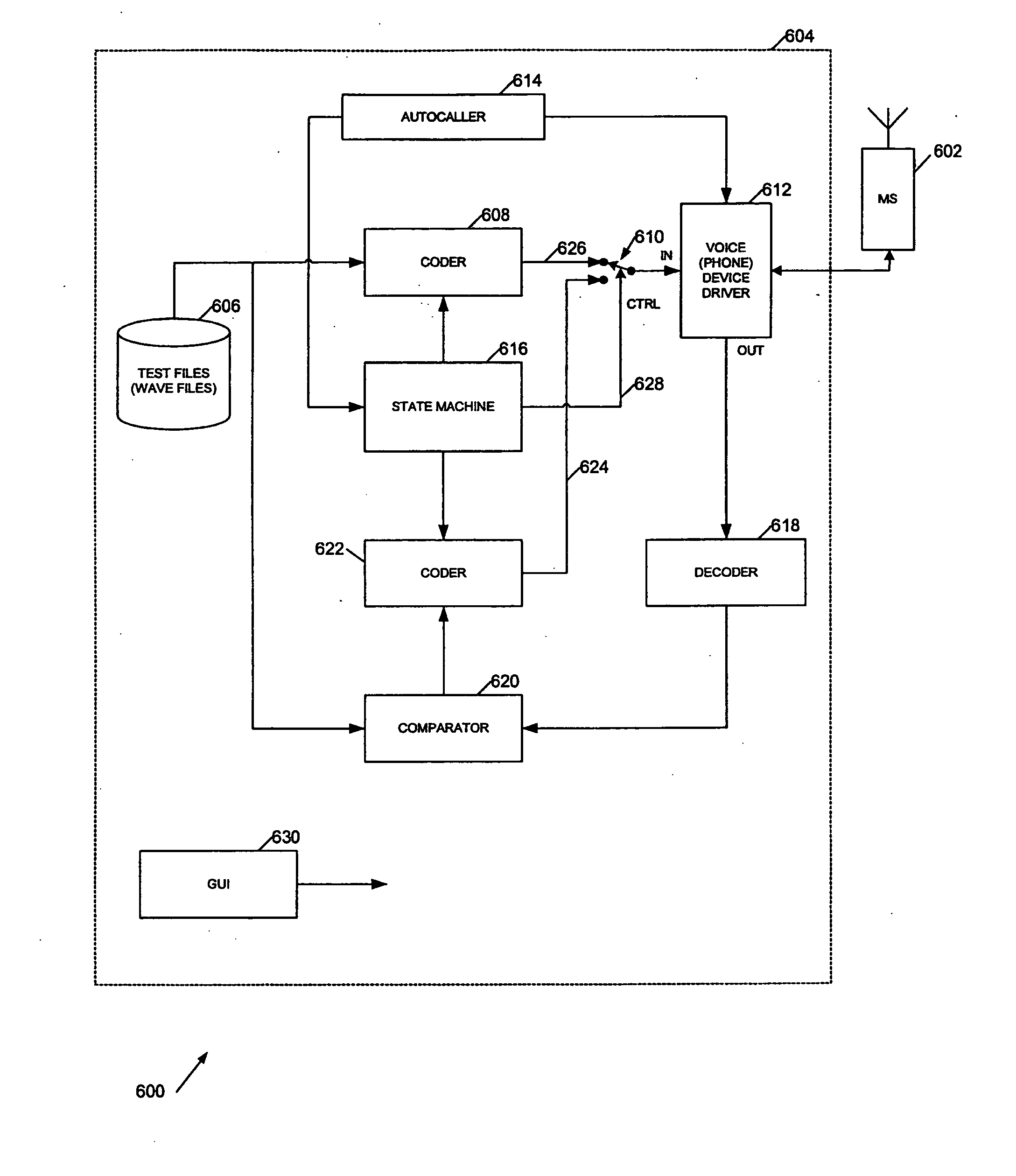

A method of testing a digital mobile phone network such as a GPRS or 3G network comprises creating test traffic using an unmodified test mobile phone coupled to a computer, and using the computer to measure a parameter associated with the network's response to the test traffic. The measurements made by the computer are encoded into the test traffic to create a data stream within the mobile phone network comprising test traffic, measurements relating to the test traffic, and signalling relating to the test traffic, whereby this data stream can be captured at points within the network and analysed to investigate the functioning of the network dynamically as the network is exercised with the test traffic. Software and test equipment for performing the method are also described.

Owner:ACTIX

Network testing systems

InactiveUS20050260982A1Improve noiseReduce in quantityRadio/inductive link selection arrangementsData switching networksData streamThird generation

A method of testing a digital mobile phone network such as a GPRS or 3 G network comprises creating test traffic using an unmodified test mobile phone coupled to a computer, and using the computer to measure a parameter associated with the network's response to the test traffic. The measurements made by the computer are encoded into the test traffic to create a data stream within the mobile phone network comprising test traffic, measurements relating to the test traffic, and signalling relating to the test traffic, whereby this data stream can be captured at points within the network and analysed to investigate the functioning of the network dynamically as the network is exercised with the test traffic. Software and test equipment for performing the method are also described.

Owner:ACTIX

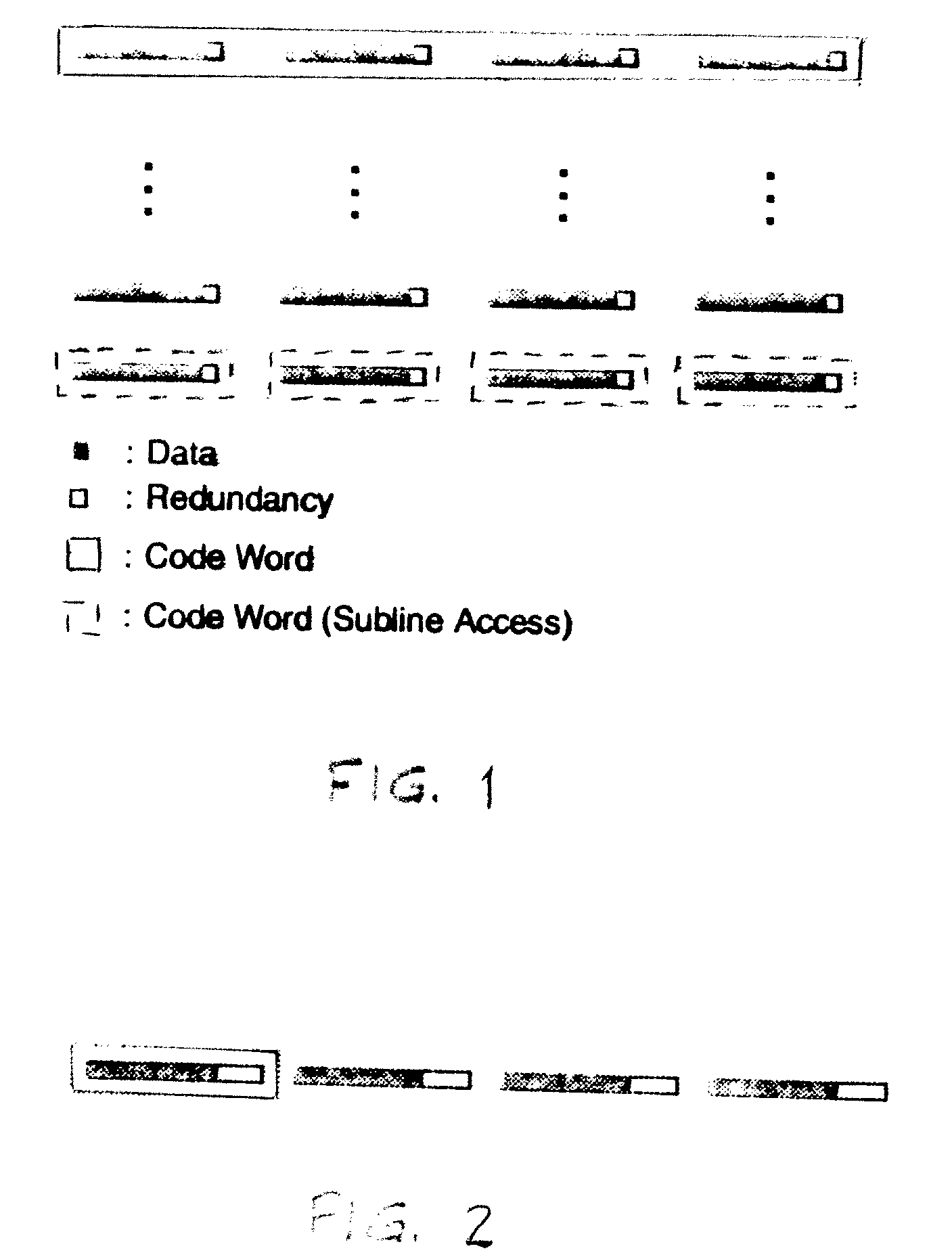

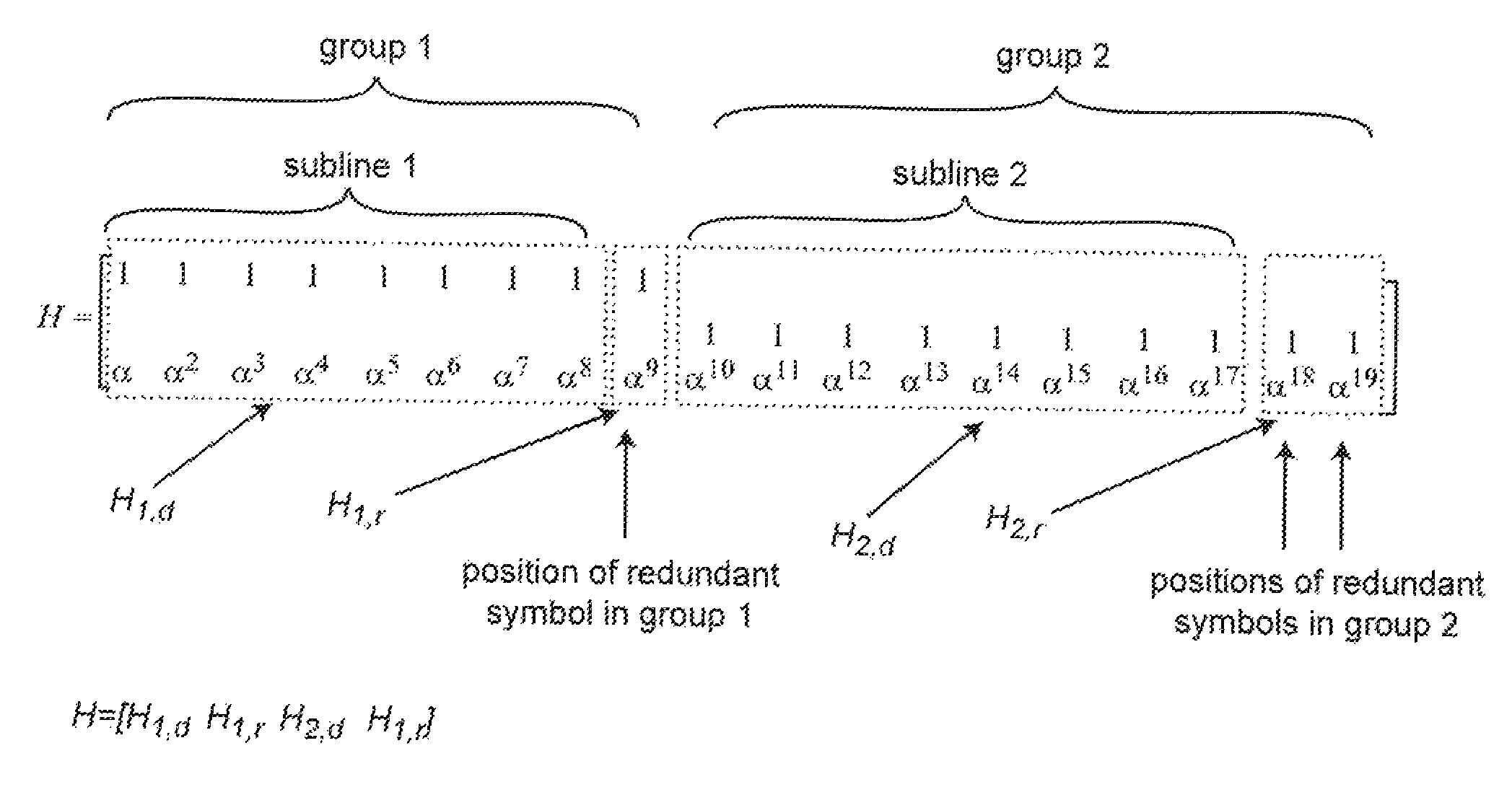

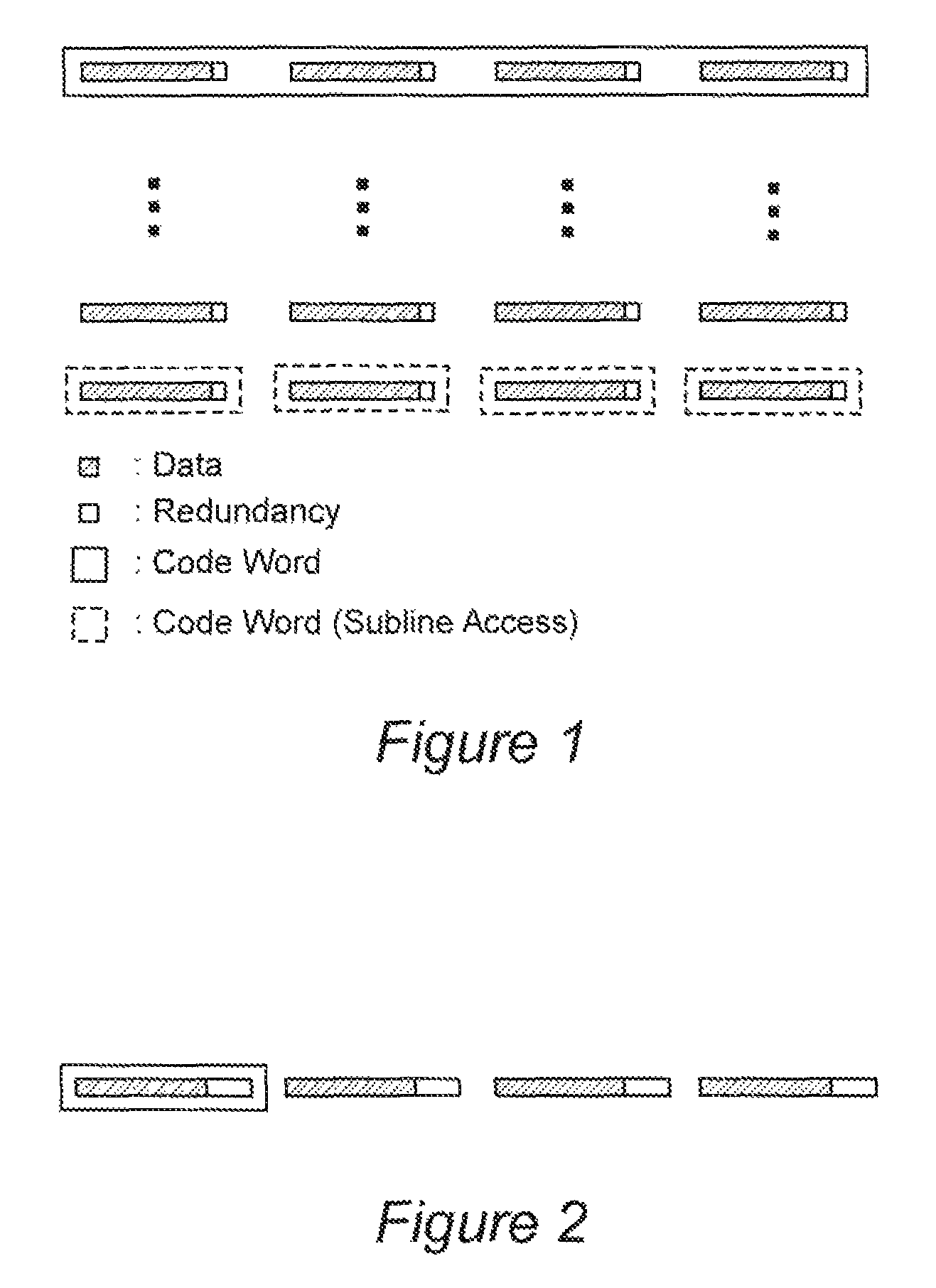

Error control coding methods for memories with subline accesses

InactiveUS20080168329A1Long latencyError detection/correctionCode conversionComputer scienceReal-time computing

A two-level error control protocol detects errors on the subline level and corrects errors using the codeword for the entire line. This enables a system to read small pieces of coded data and check for errors before accepting them, and in case errors are detected, the whole codeword is read for error correction.

Owner:IBM CORP

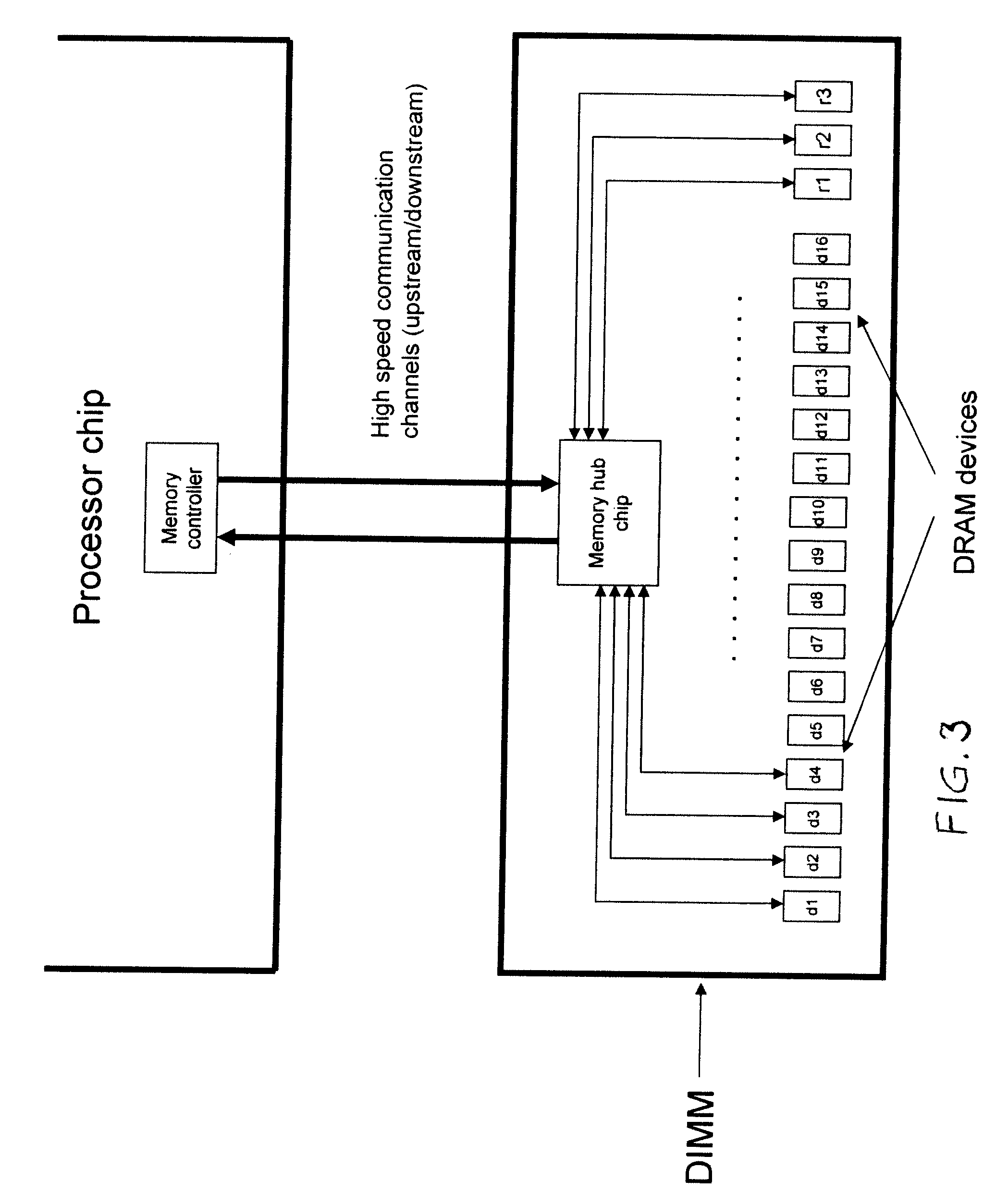

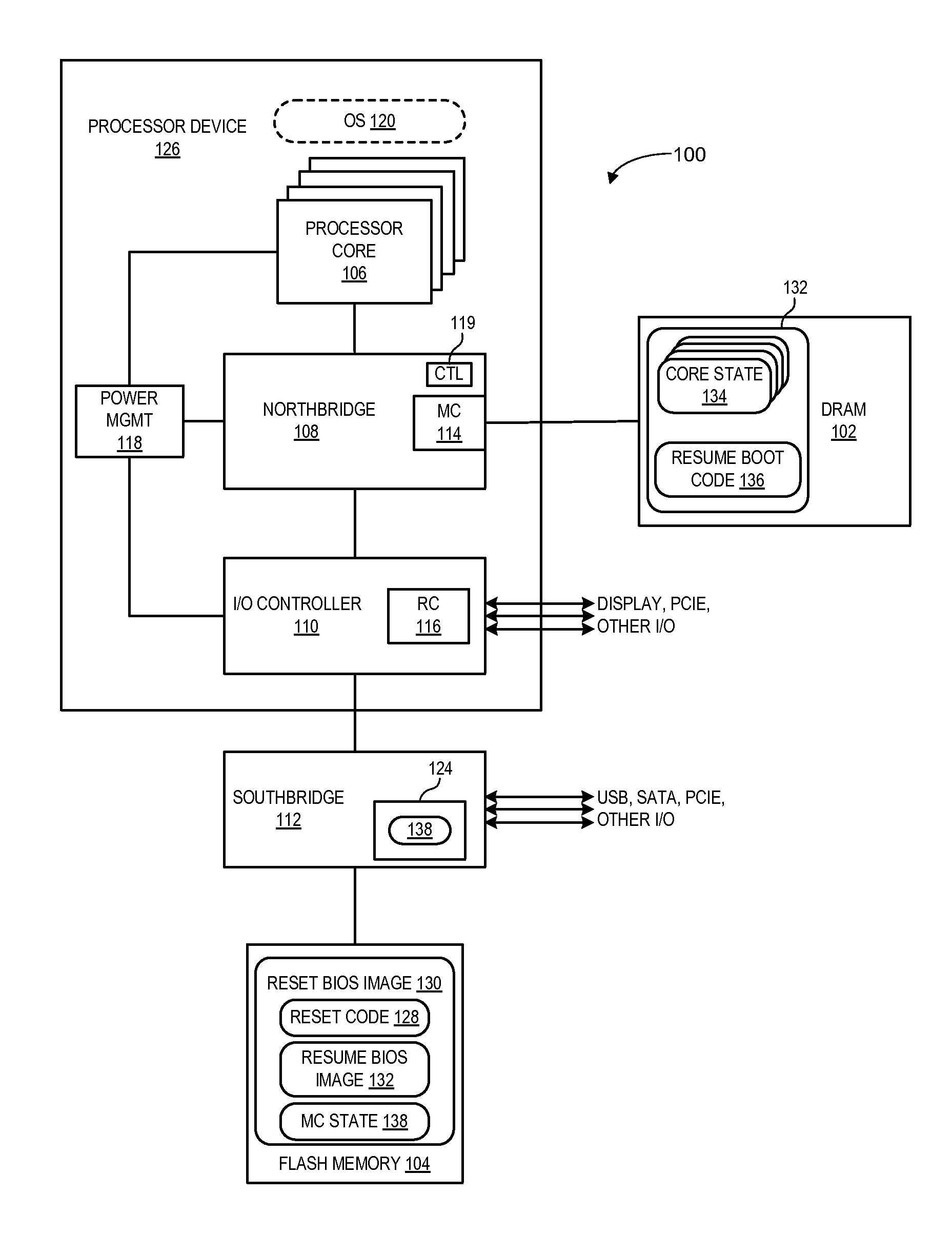

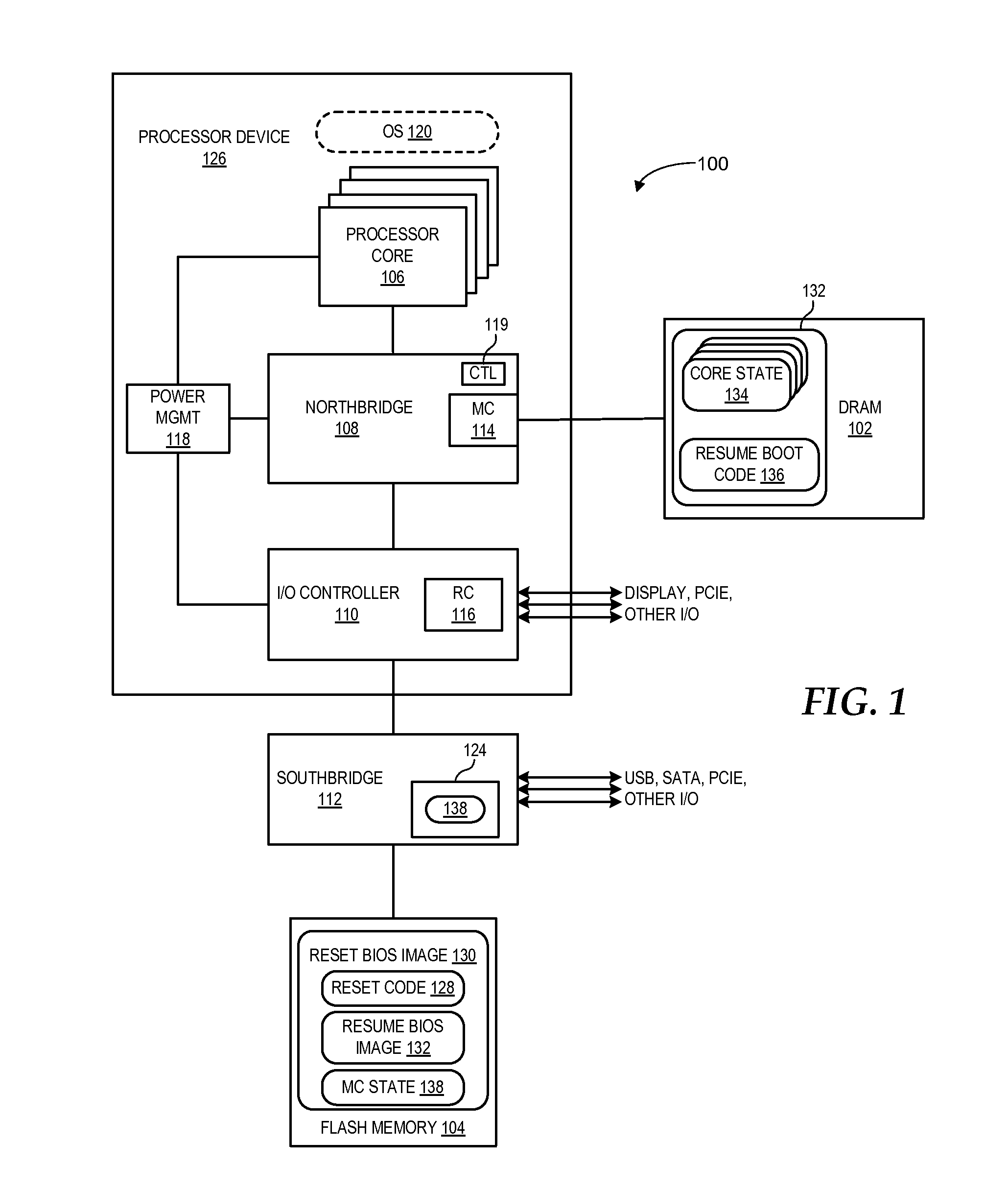

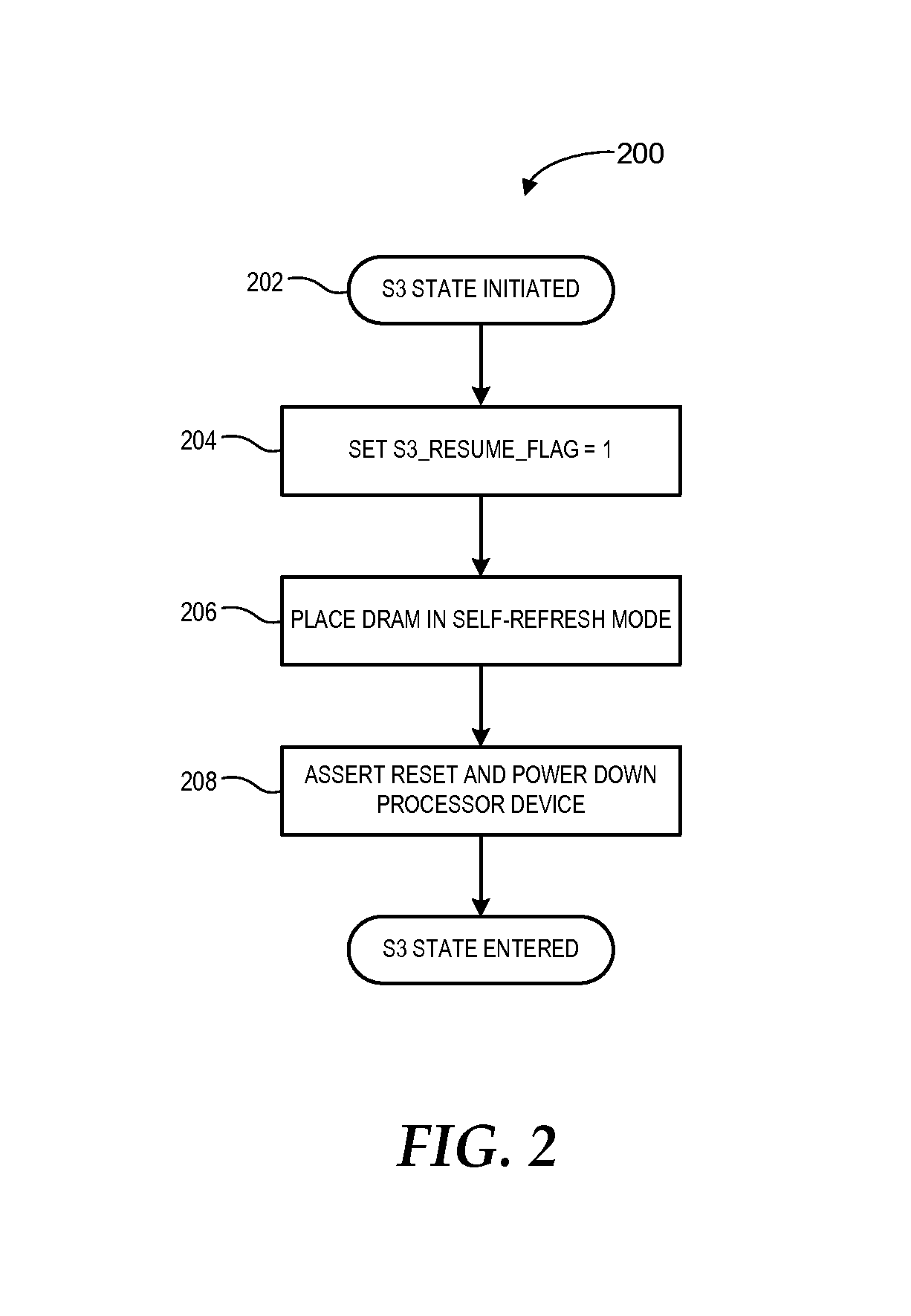

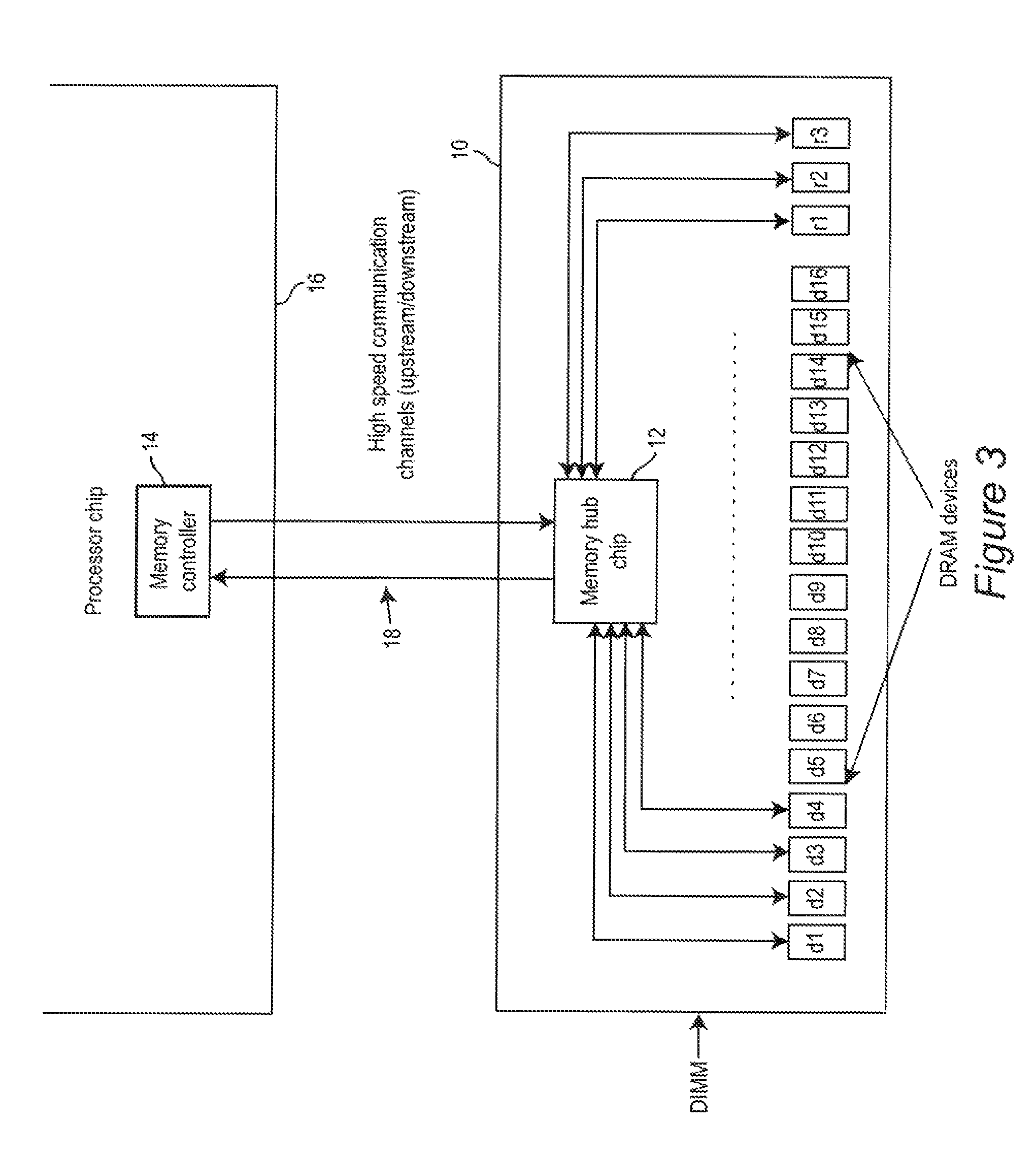

Reintialization of a processing system from volatile memory upon resuming from a low-power state

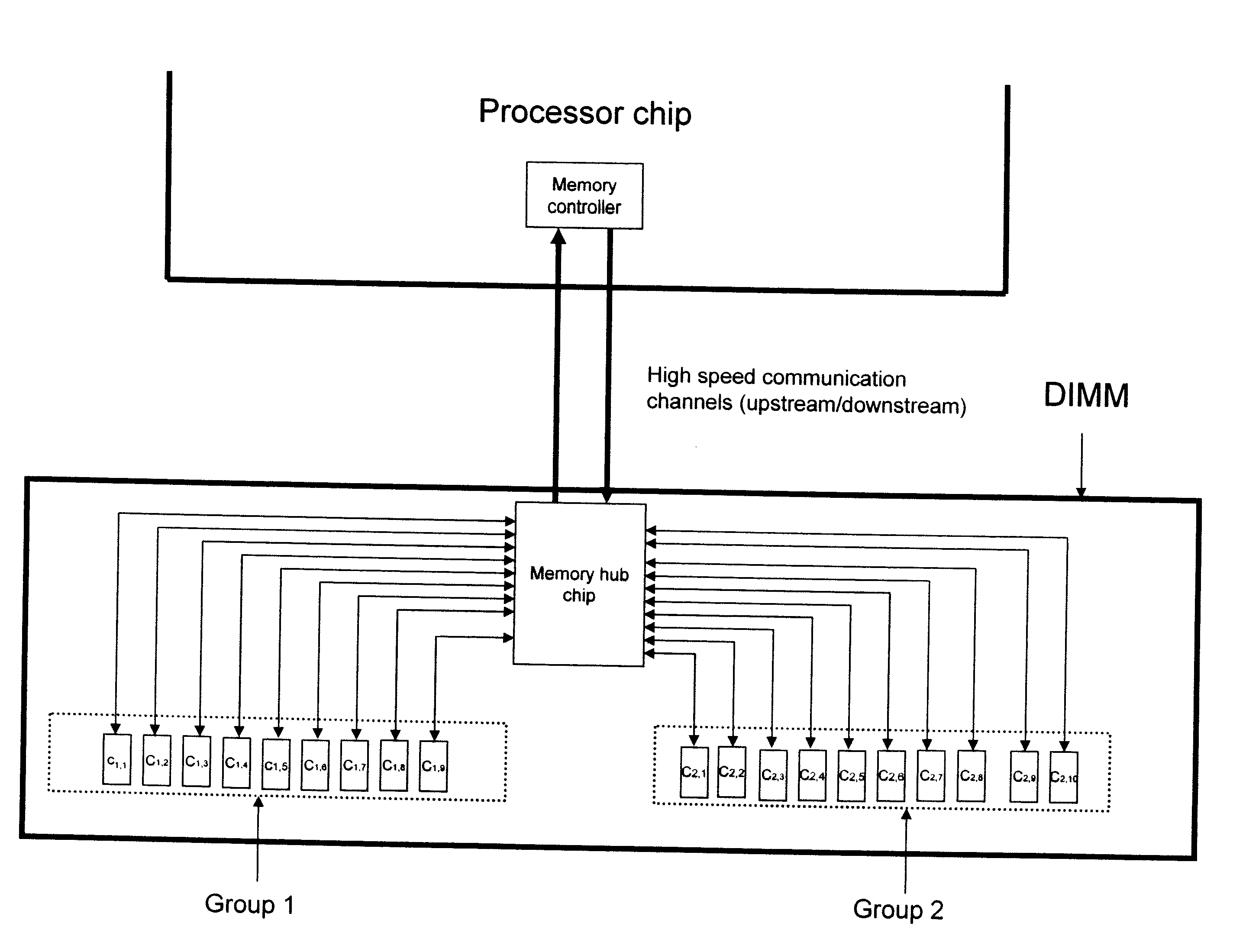

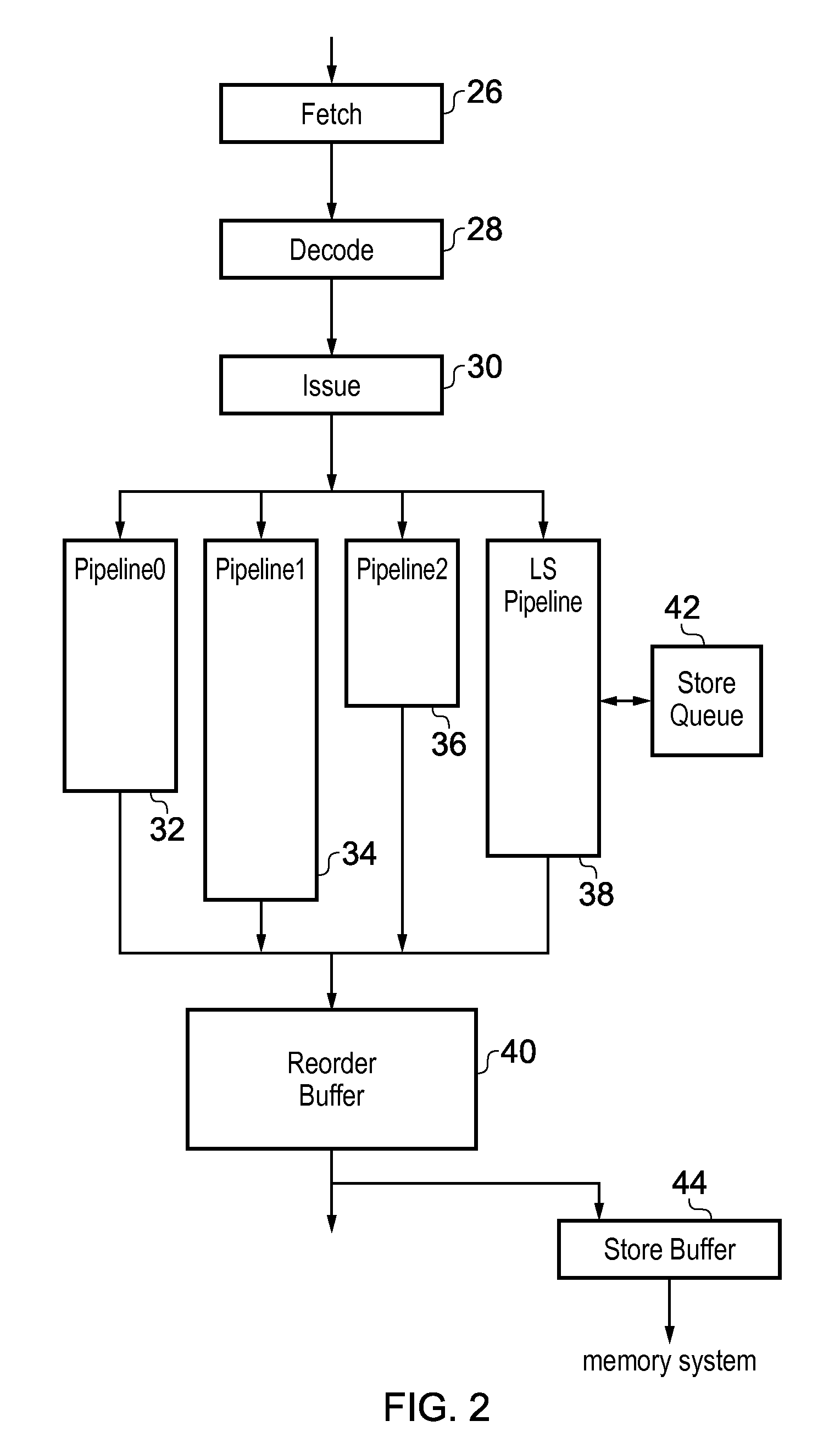

ActiveUS20130326206A1Reduce power consumptionLong latencyDigital computer detailsData resettingMemory controllerHandling system

Boot configuration information is stored to a volatile memory of a processing system during a low-power state. When resuming from the low-power state, a processor device accesses configuration information for a memory controller from a non-volatile memory and restores the memory controller using the configuration information so as to permit access to the volatile memory. The processor device then configures the initial contexts one or more processor cores using the core state information maintained by the volatile memory during the low-power state and accessed via the configured memory controller, and the one or more processor cores completes the boot process by executing resume boot code maintained by the volatile memory during the low-power state and accessed via the configured memory controller, rather than accessing boot code from a non-volatile memory.

Owner:ADVANCED MICRO DEVICES INC

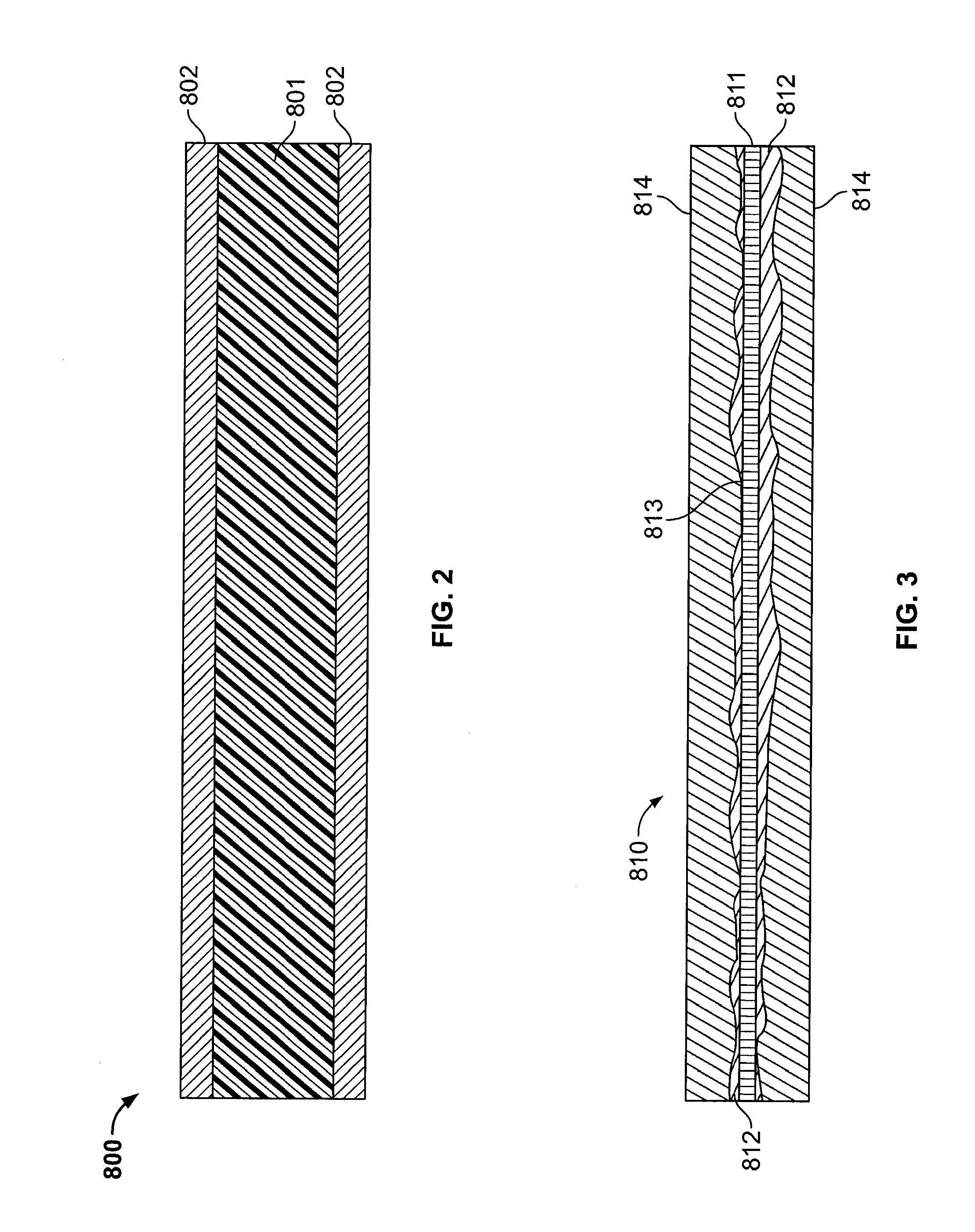

Inkjet ink

InactiveUS20070091156A1Long latencyImprove reliabilityMeasurement apparatus componentsInksEngineeringColoring agents

Owner:EI DU PONT DE NEMOURS & CO

Inkjet ink

The present invention pertains to inkjet ink with long latency and, more particularly, to an aqueous inkjet ink comprising a self-dispersing pigment and certain water soluble vehicle components which, in combination, provide long latency.

Owner:EI DU PONT DE NEMOURS & CO

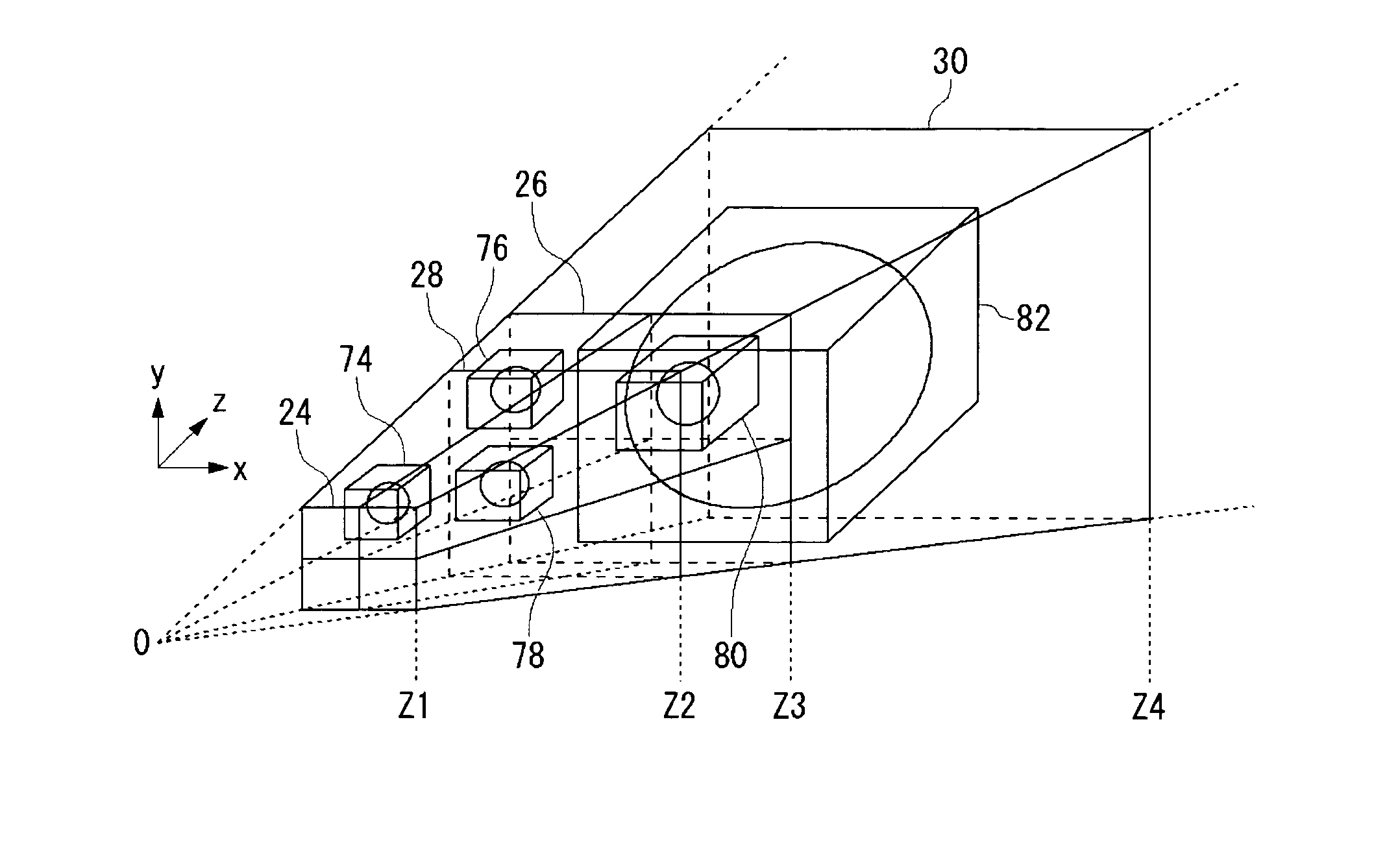

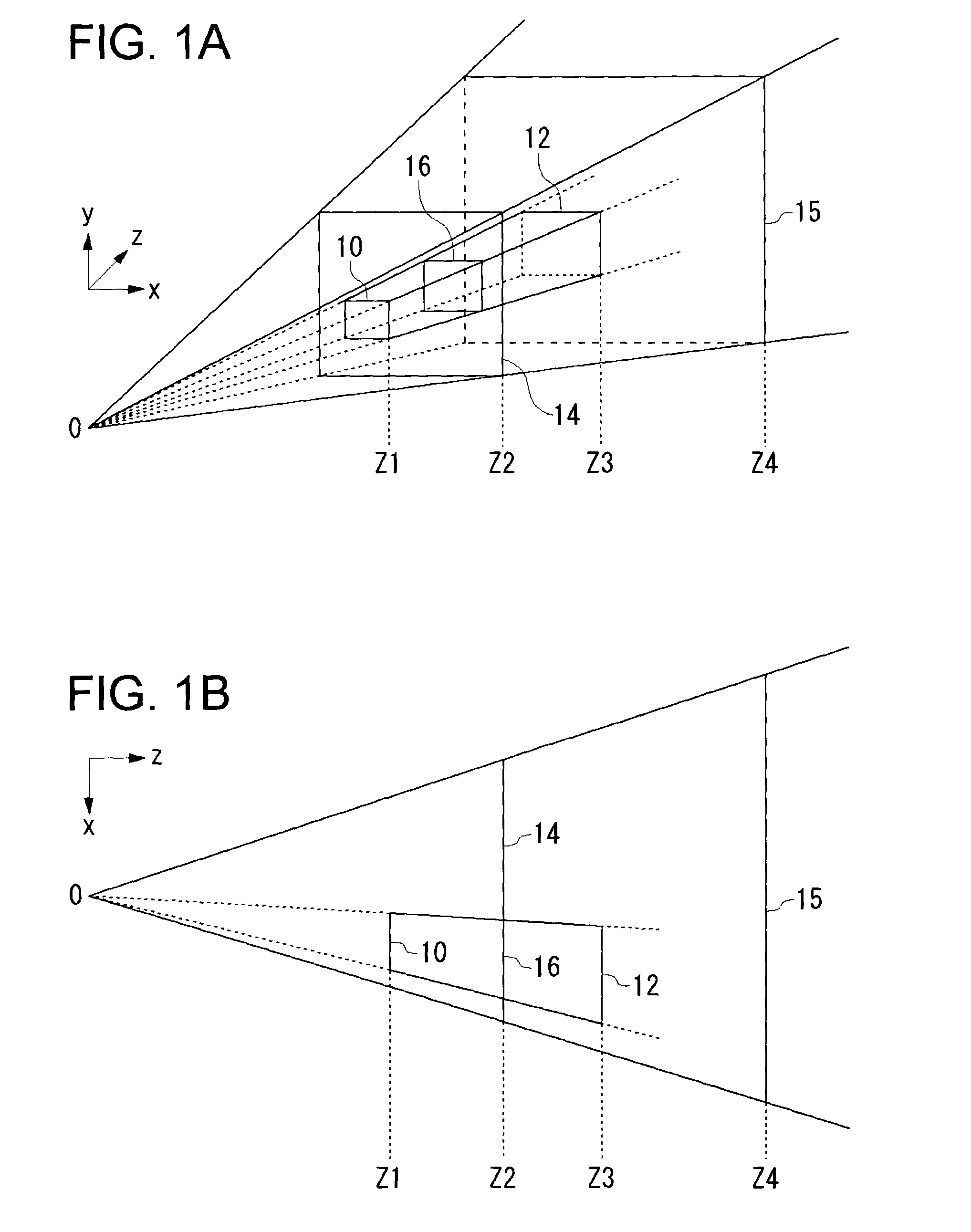

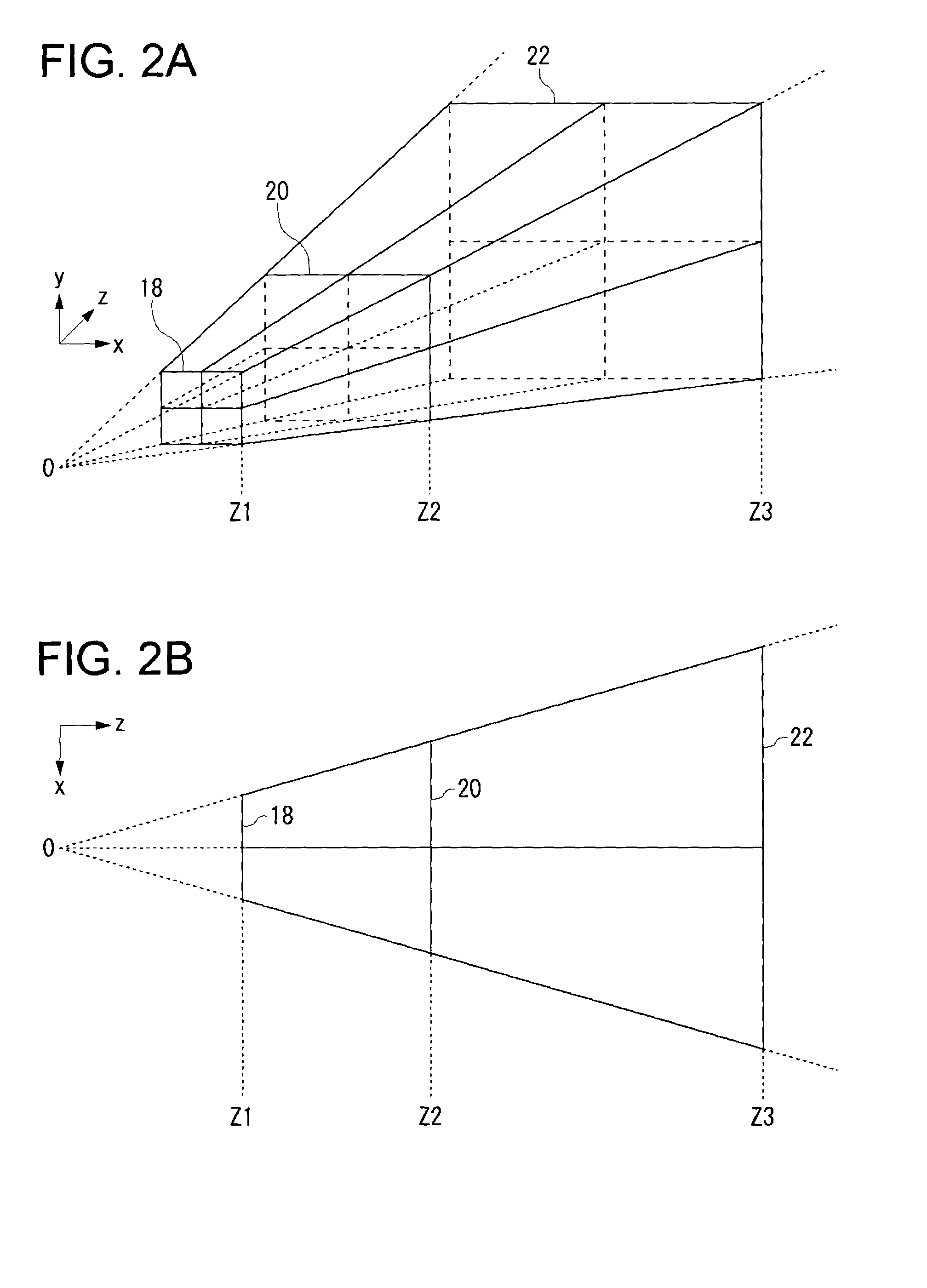

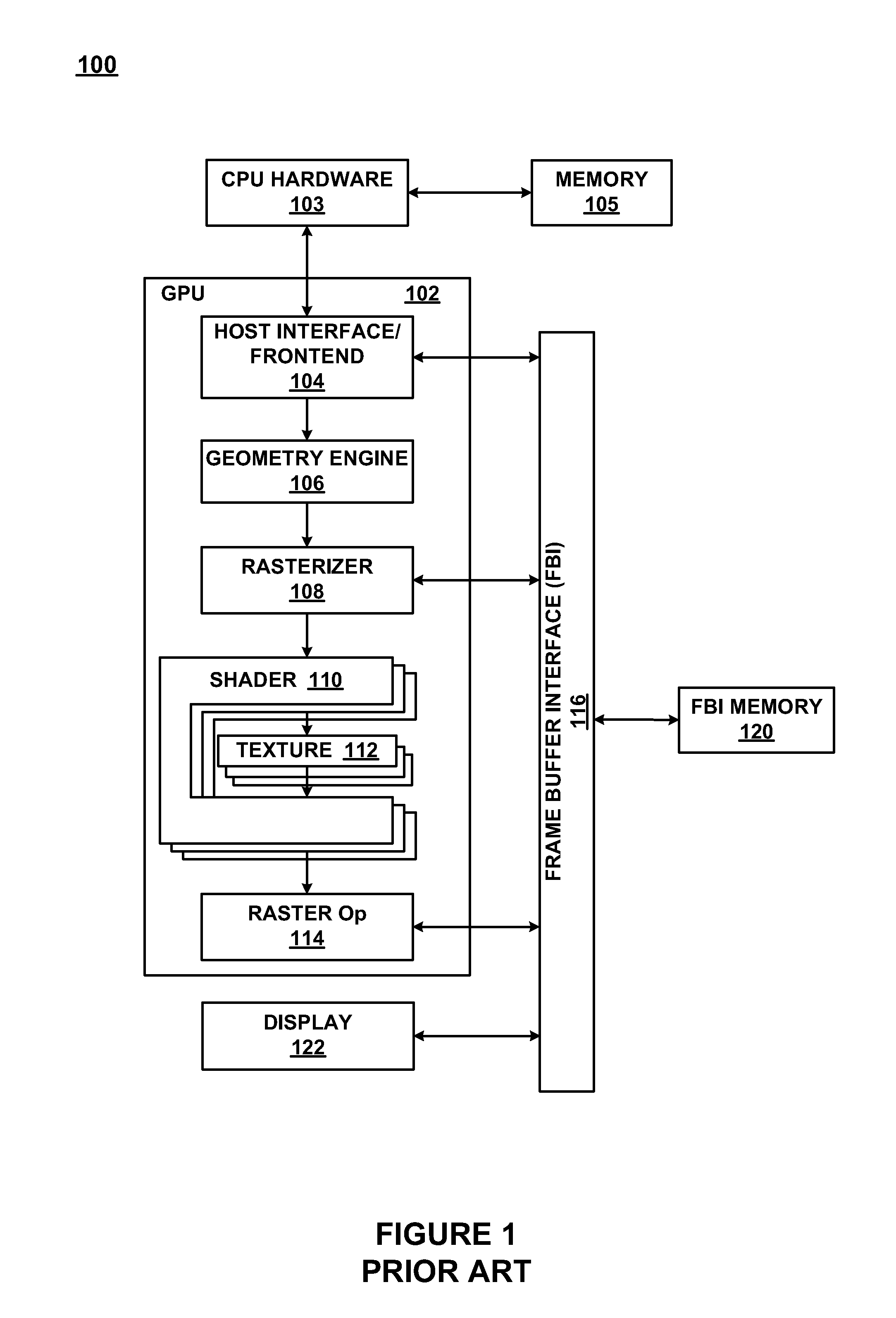

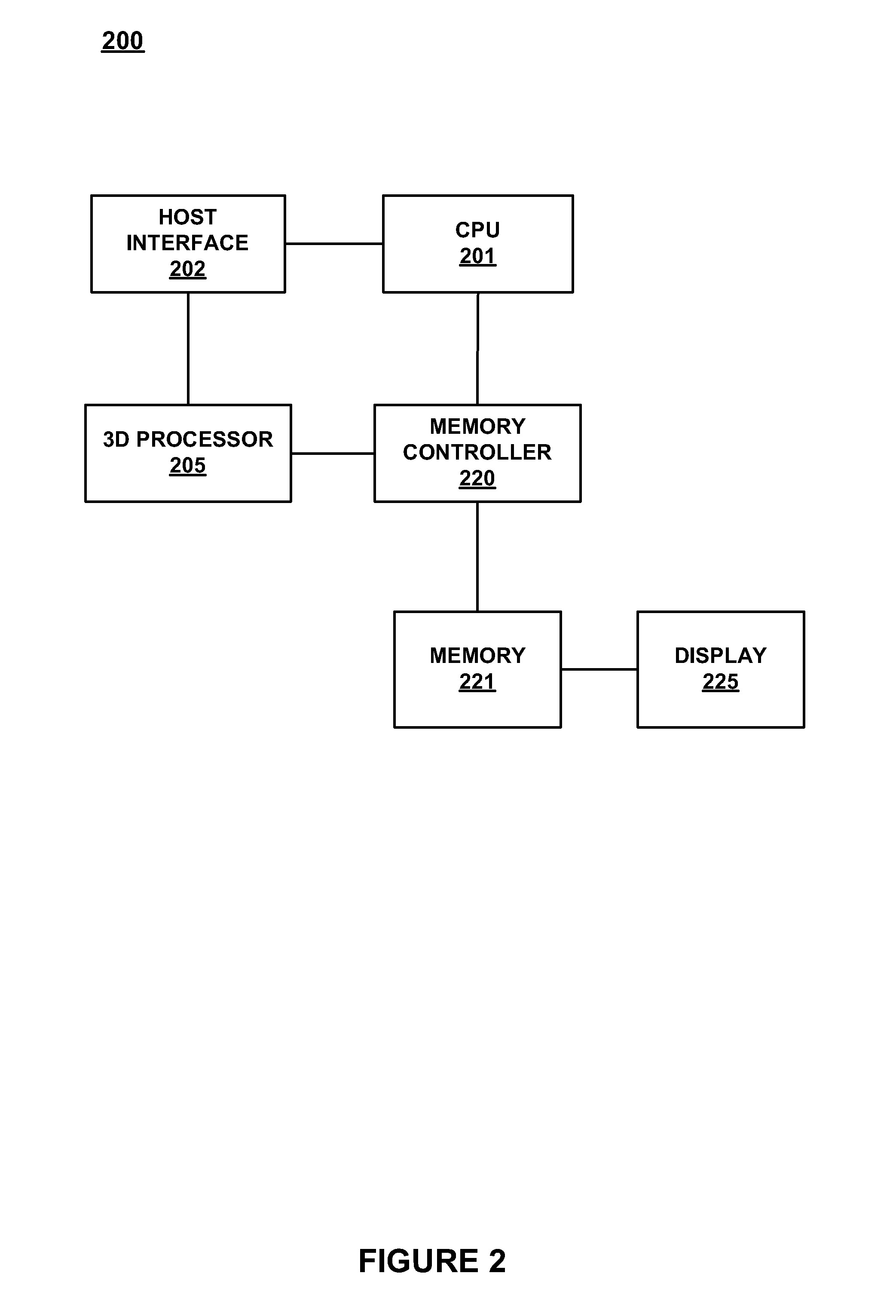

Method and apparatus for rendering three-dimensional object groups

ActiveUS7310098B2Improve efficiencyFlexible handlingCathode-ray tube indicatorsAnimationBrickObject based

An image processing apparatus for performing rendering processing of three-dimensional objects is provided. An object storage unit stores the three-dimensional data of the object and the array data of B-box which encloses the spatial region which the object occupies. A grouping unit reads in the B-box array from the object storage unit, does grouping of multiple B-boxes into groups based on the object characteristics and level of detail information. A rendering processing unit derives a brick in which there are B-boxes belonging to the same group and generates image data by doing rendering processing independently by brick to be stored in an image storage unit. A consolidation unit consolidates the image data per brick stored in the image storage unit and generates the final output image data to be displayed.

Owner:SONY COMPUTER ENTERTAINMENT INC

RF amplification system and method

InactiveUS20060217061A1Reduce chanceLong latencyElectric signal transmission systemsBroadcast-related systemsTelecommunicationsControl signal

Spread-spectrum technology, either direct sequence or frequency hopping, or a combination of the two, is used for transmitting audio signals one way and control signals two ways over an RF channel(s) to reduce interference with / from other RF transmissions and enabling use of multiple such systems in close proximity without requiring pre-selection of transmission frequencies. Alternatively, multiple channels with appended access codes may be used, wherein interference or loss of clear signal results in automatic switching to another channel. The control signals accompany the transmitted audio signal at some time in the transmission interval, or previous to the beginning of the transmission interval, and constitute a coded control message allowing a unique connection. In some cases the encoding keys may only occur at the beginning of the desired message, while in other cases the two-way control signals may continue throughout the interval of the message link.

Owner:RPX CORP

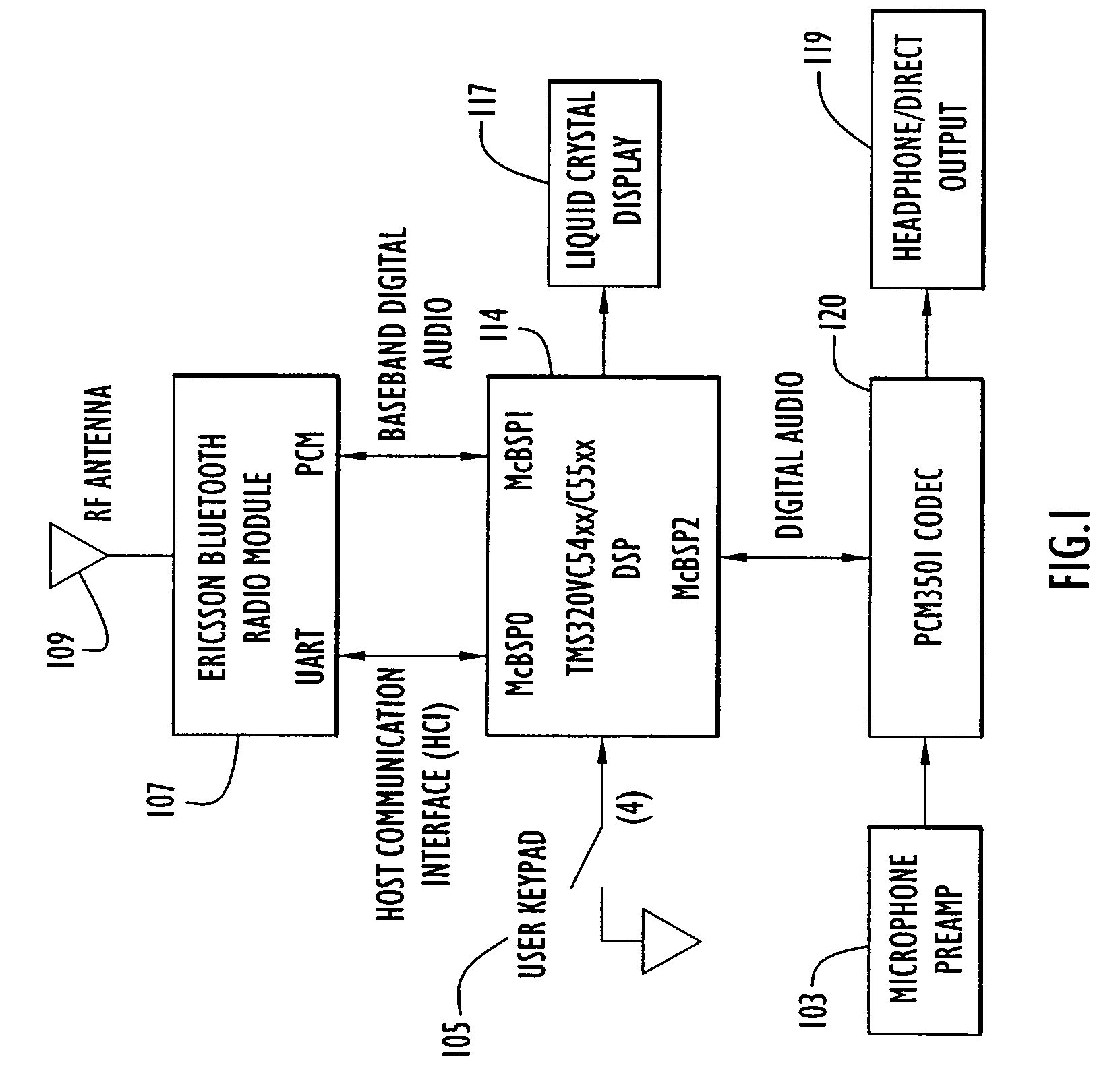

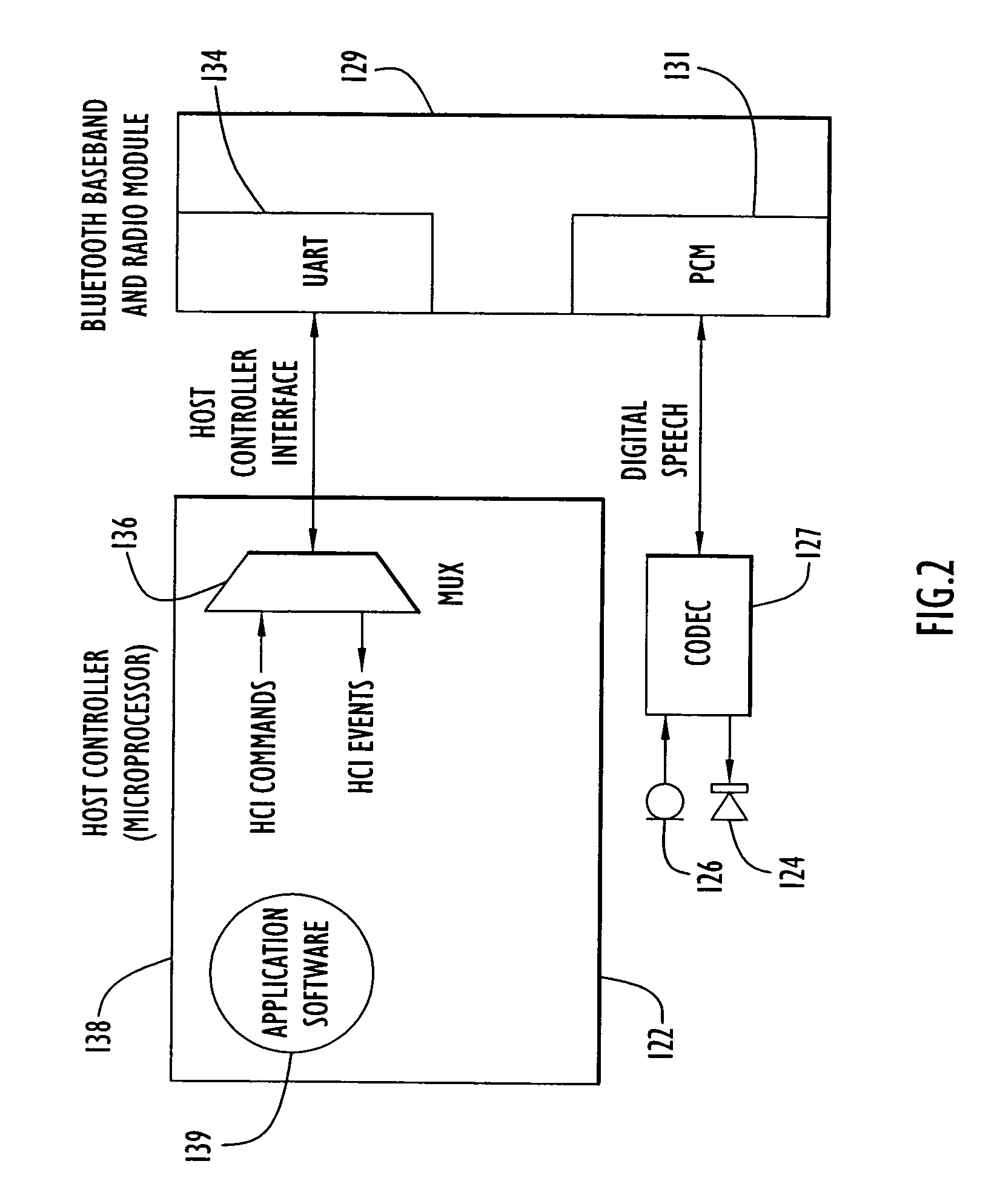

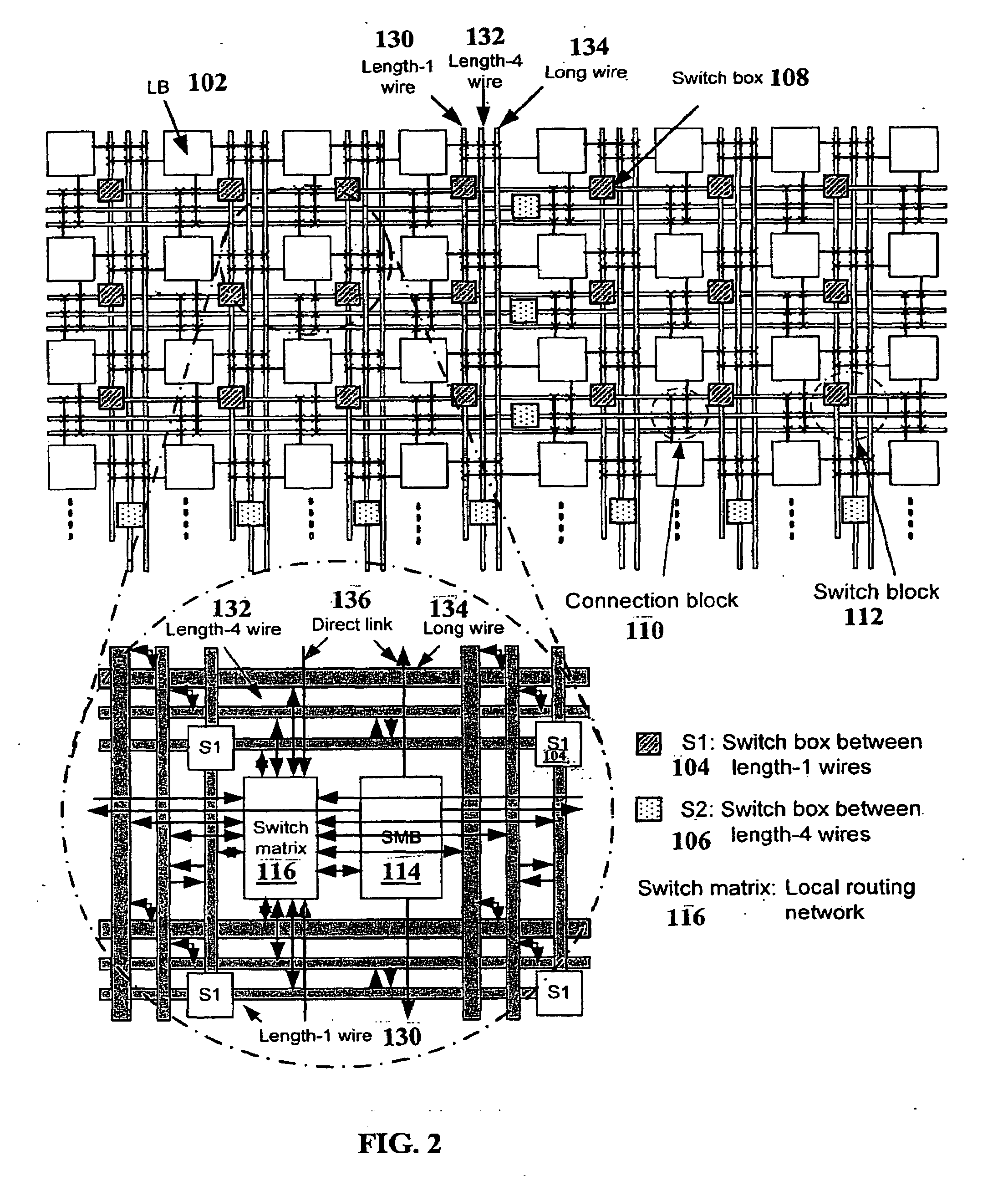

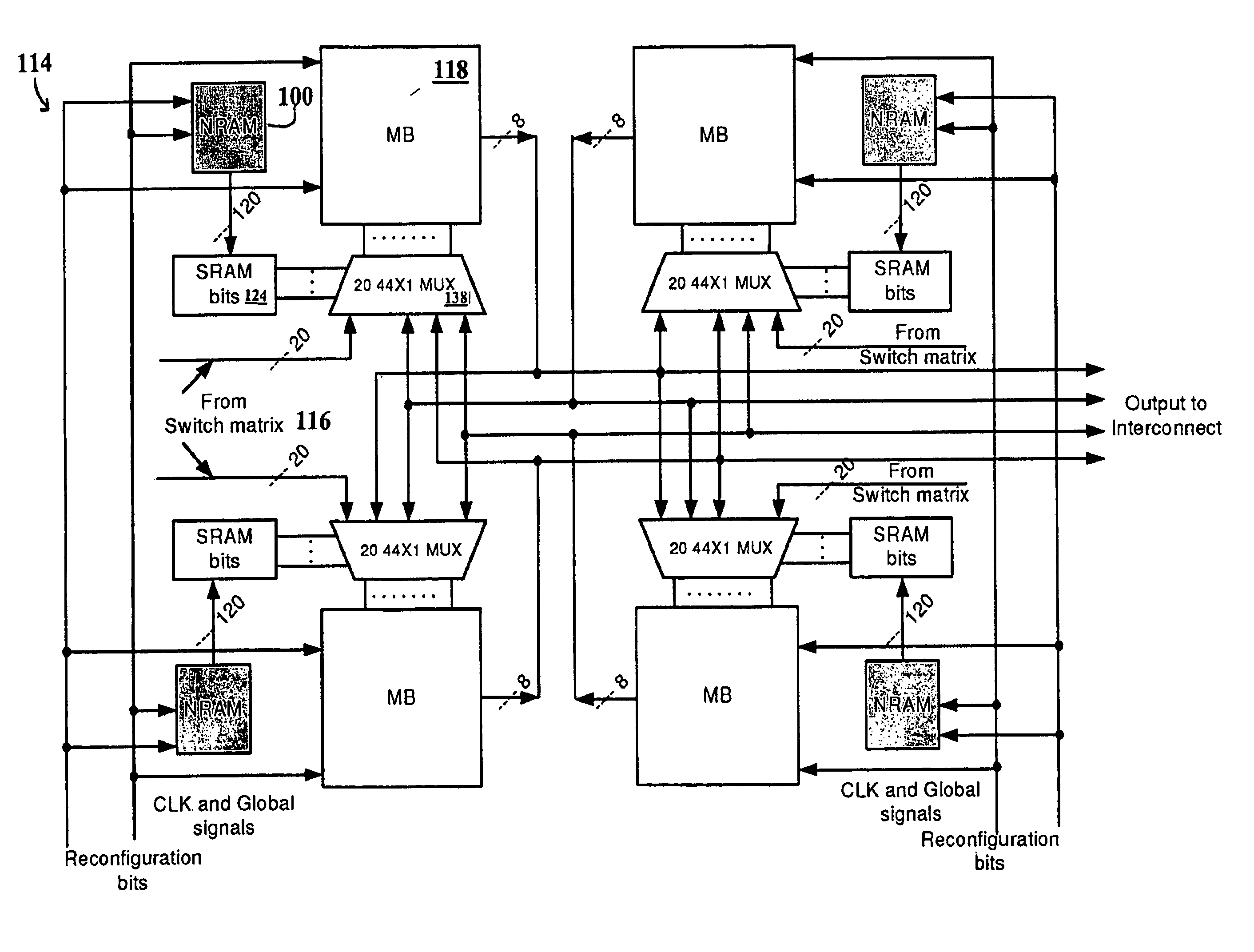

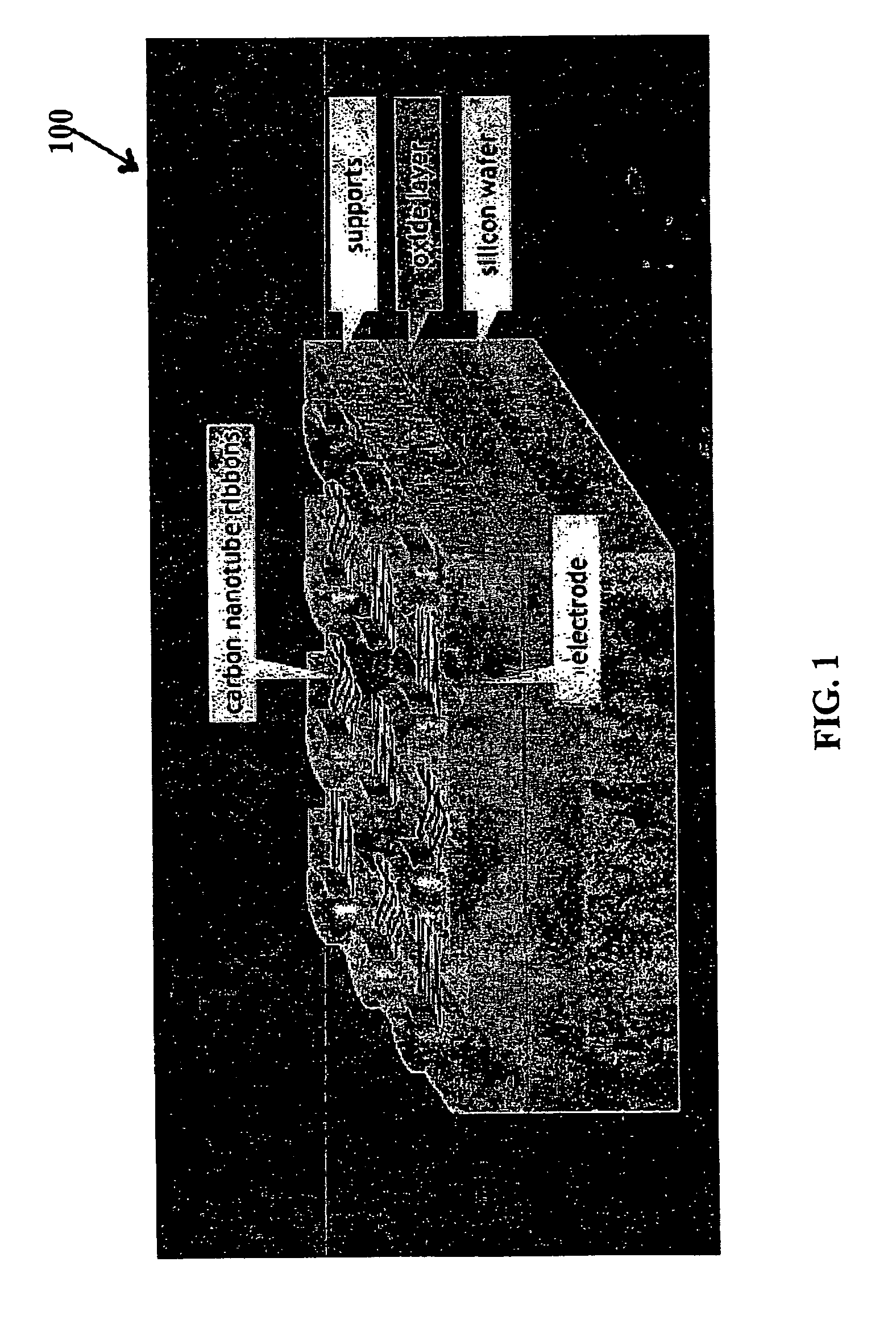

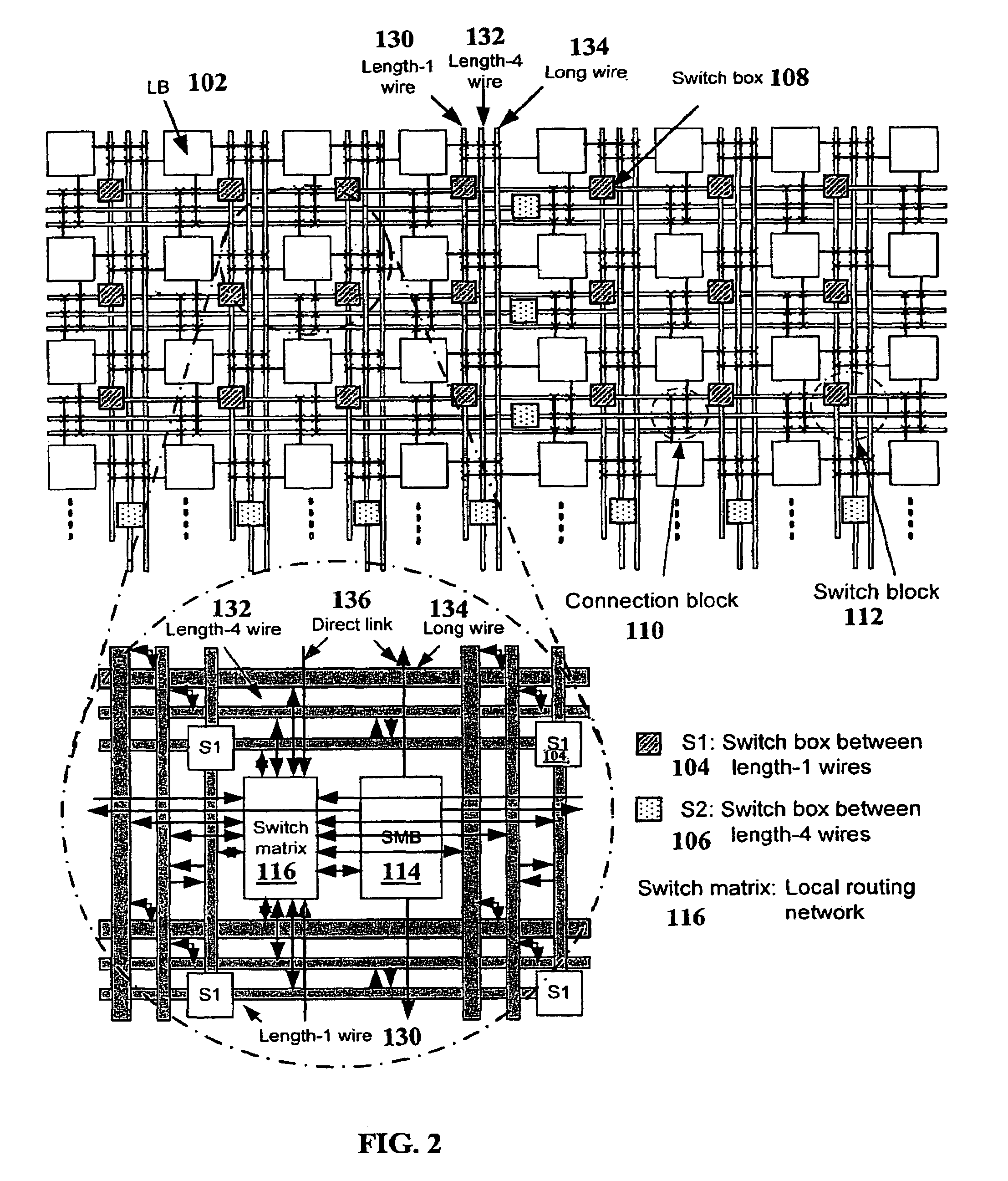

Hybrid nanotube/cmos dynamically reconfigurable architecture and an integrated design optimization method and system therefor

InactiveUS20090219051A1Improve area/execution time featureEfficiencySolid-state devicesDigital storageCMOSLogic element

Owner:QUEENS UNIV OF KINGSTON +1

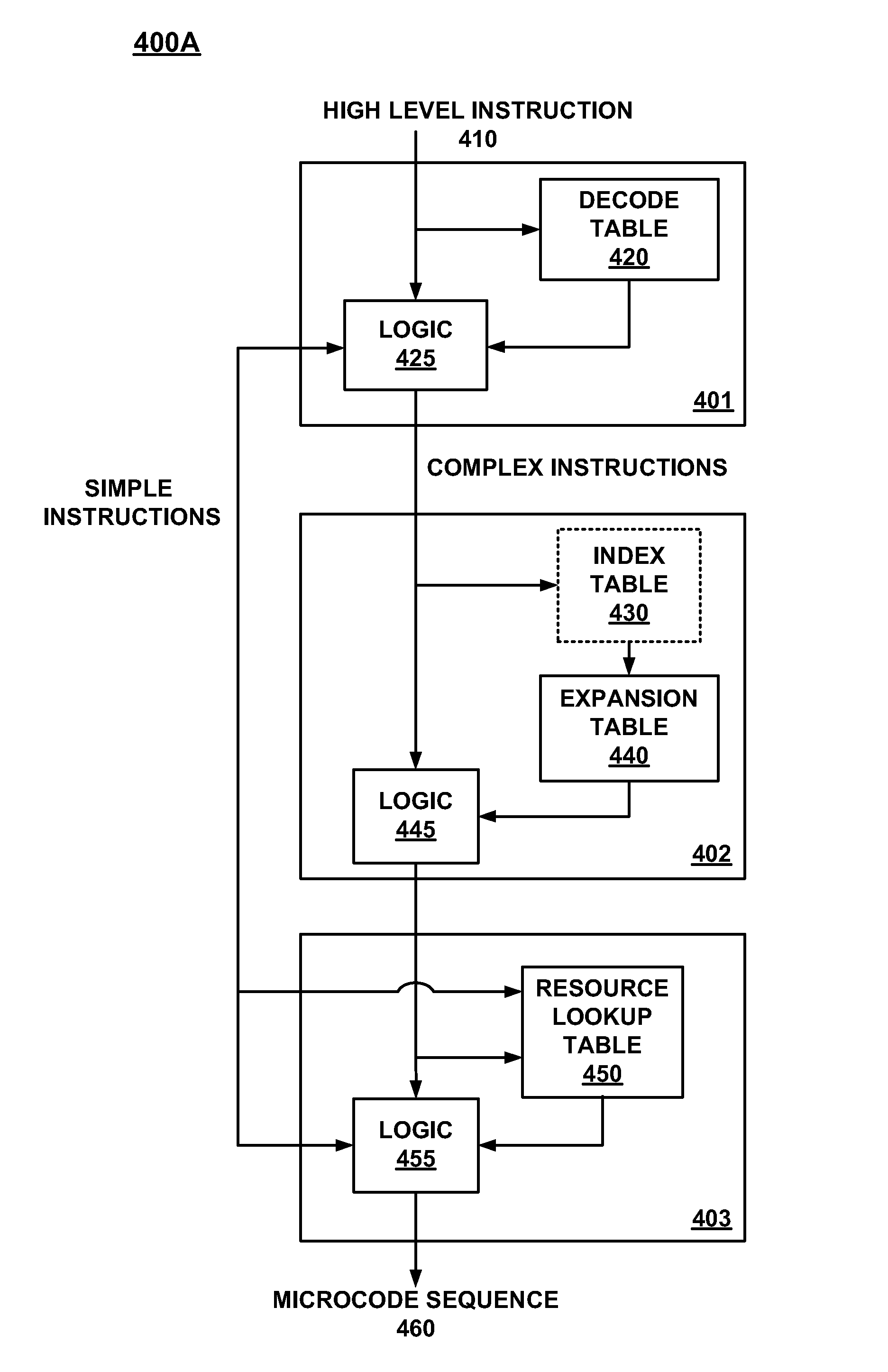

Method and system for patching instructions in a shader for a 3-D graphics pipeline

ActiveUS7852341B1Increase the areaLong latencyMemory adressing/allocation/relocationDigital computer detailsParallel computingMicrocode

A method and system for patching instructions in a 3-D graphics pipeline. Specifically, in one embodiment, instructions to be executed within a scheduling process for a shader pipeline of the 3-D graphics pipeline are patchable. A scheduler includes a decode table, an expansion table, and a resource table that are each patchable. The decode table translates high level instructions to an appropriate microcode sequence. The patchable expansion table expands a high level instruction to a program of microcode if the high level instruction is complex. The resource table assigns the units for executing the microcode. Addresses within each of the tables can be patched to modify existing instructions and create new instructions. That is, contents in each address in the tables that are tagged can be replaced with a patch value of a corresponding register.

Owner:NVIDIA CORP

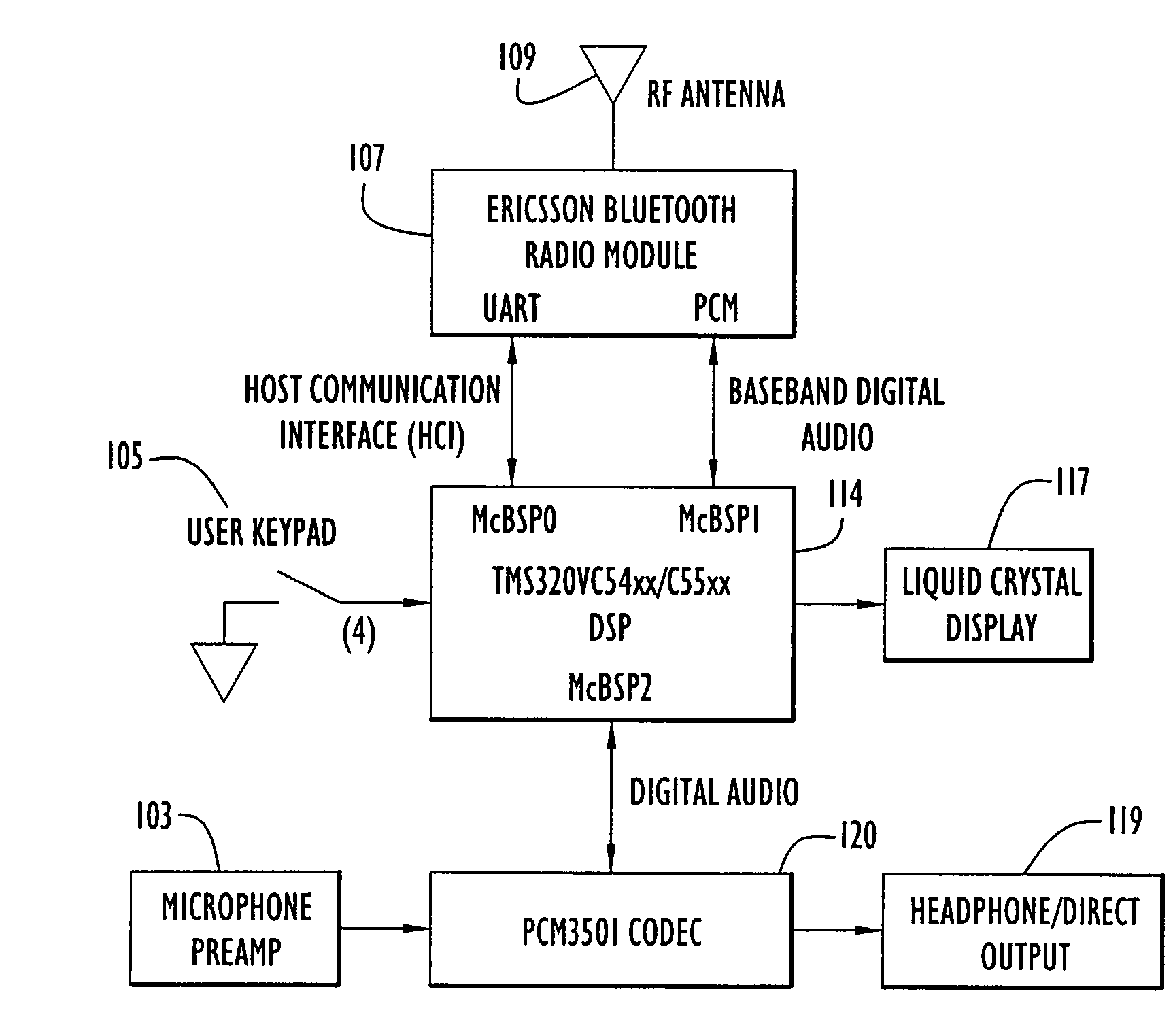

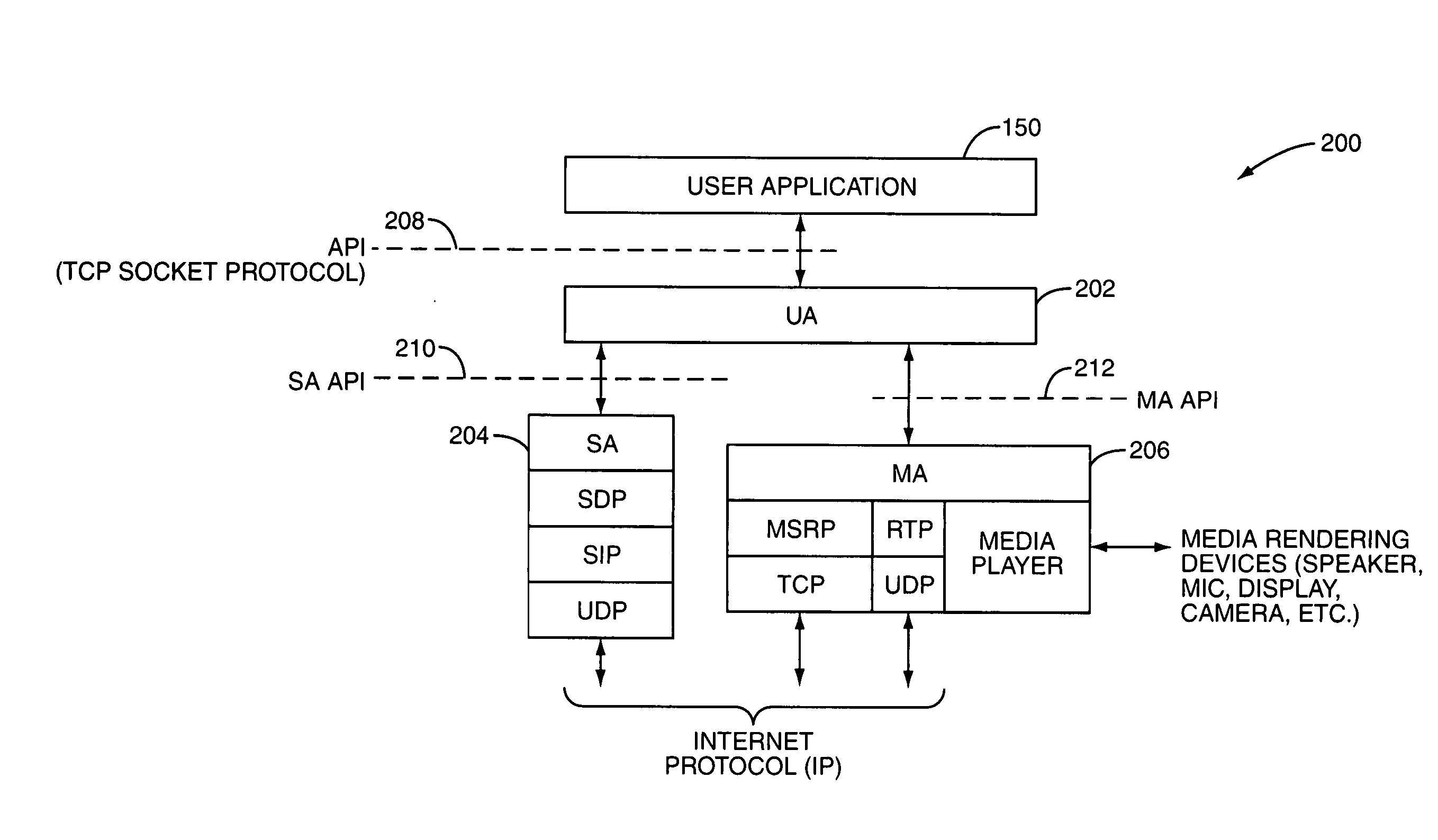

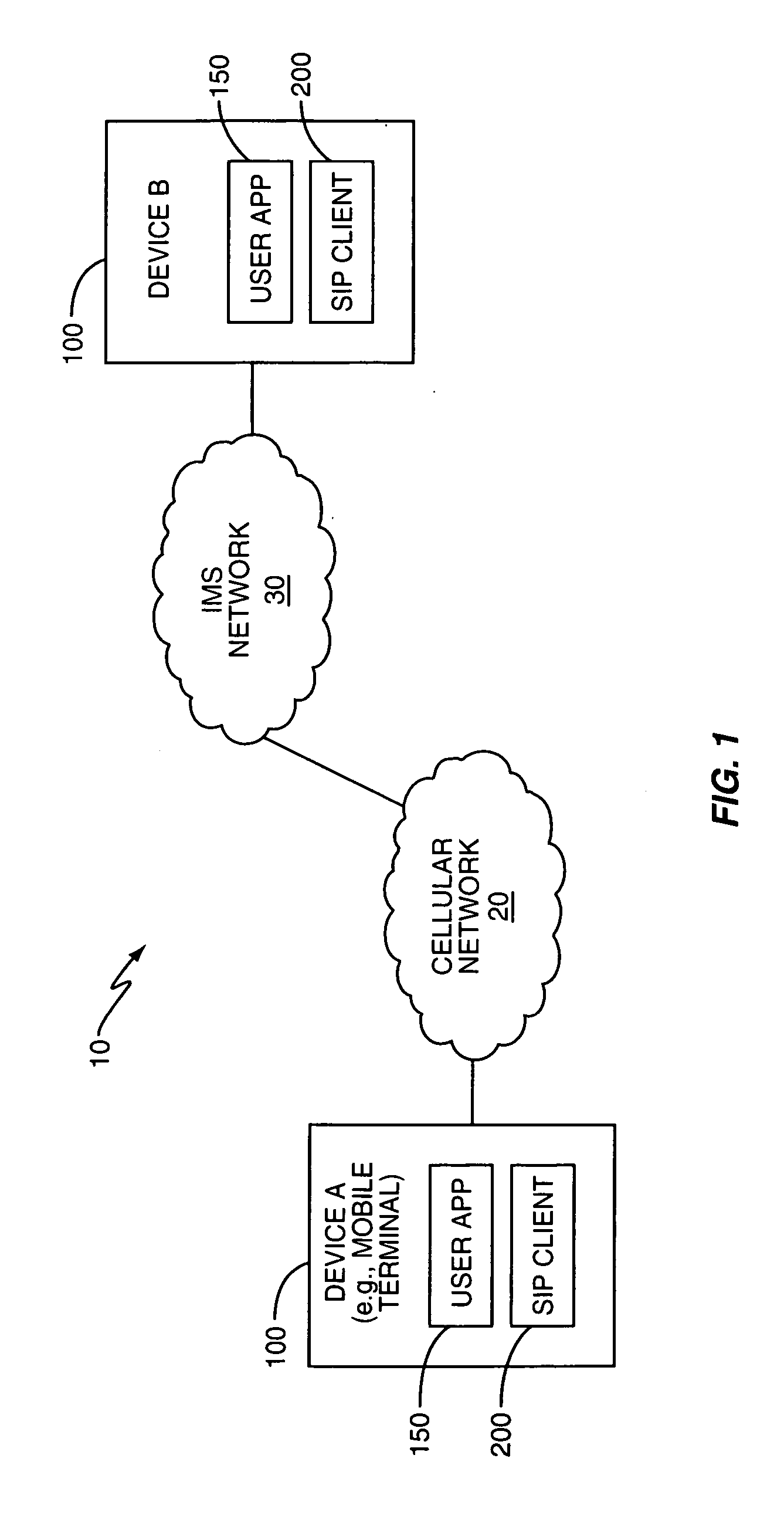

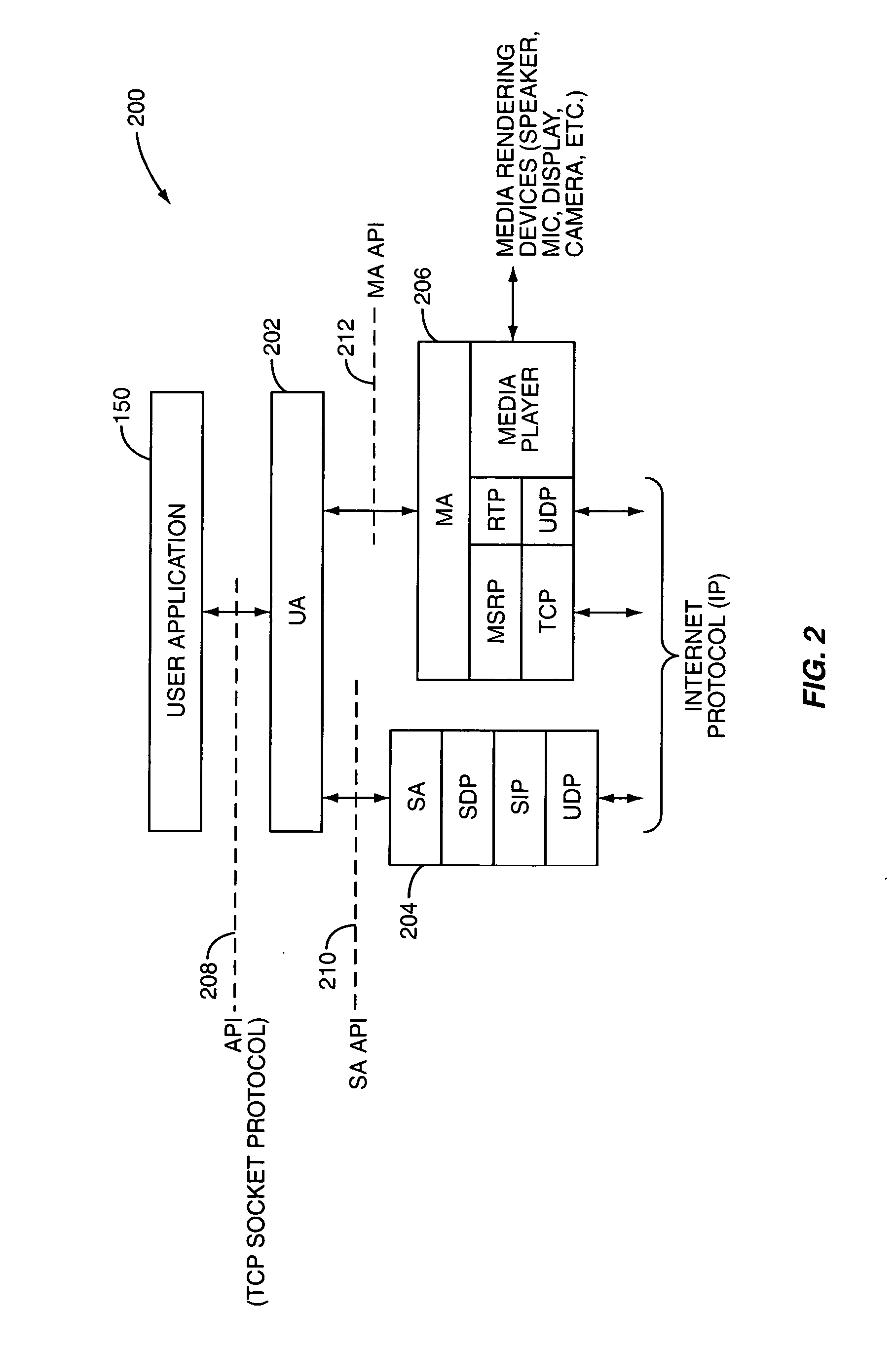

Multi-user media client for communication devices

InactiveUS20060239251A1Reduce signaling overheadLimited bandwidthNetwork connectionsClient-sideComputer science

A SIP client for a communication device includes a user agent to communicate with a user application in the communication device. The user agent provides a high-level application interface to the user application and translates user commands into corresponding signaling and media operations. The same user agent may be shared by a plurality of user applications. A signaling agent controlled by the user agent performs signaling operations necessary to establish and maintain communication sessions. To avoid signaling overhead on a high cost network, the SIP client can be located in a remote network so signaling messages do not need to traverse the high cost network.

Owner:SONY ERICSSON MOBILE COMM AB

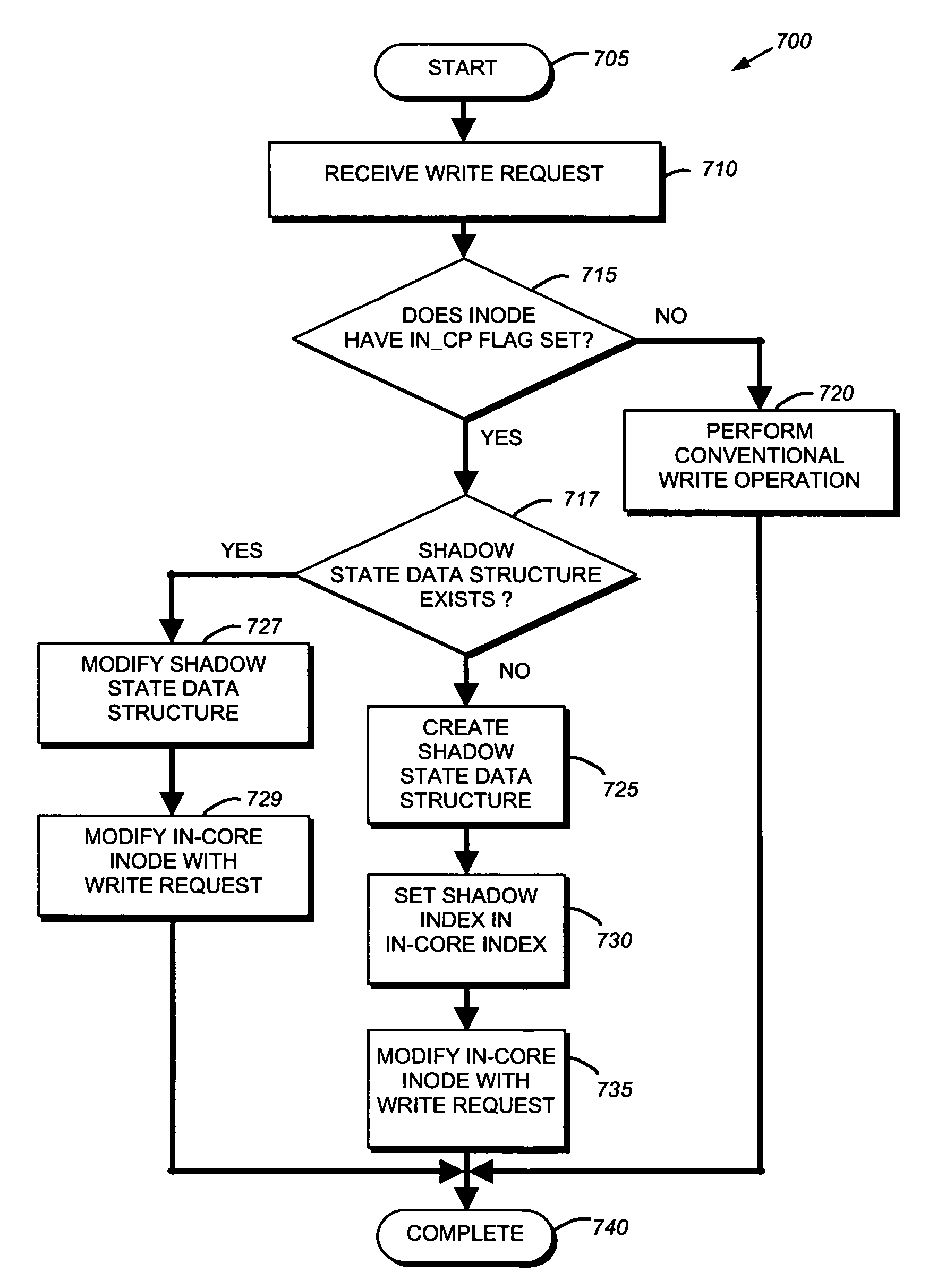

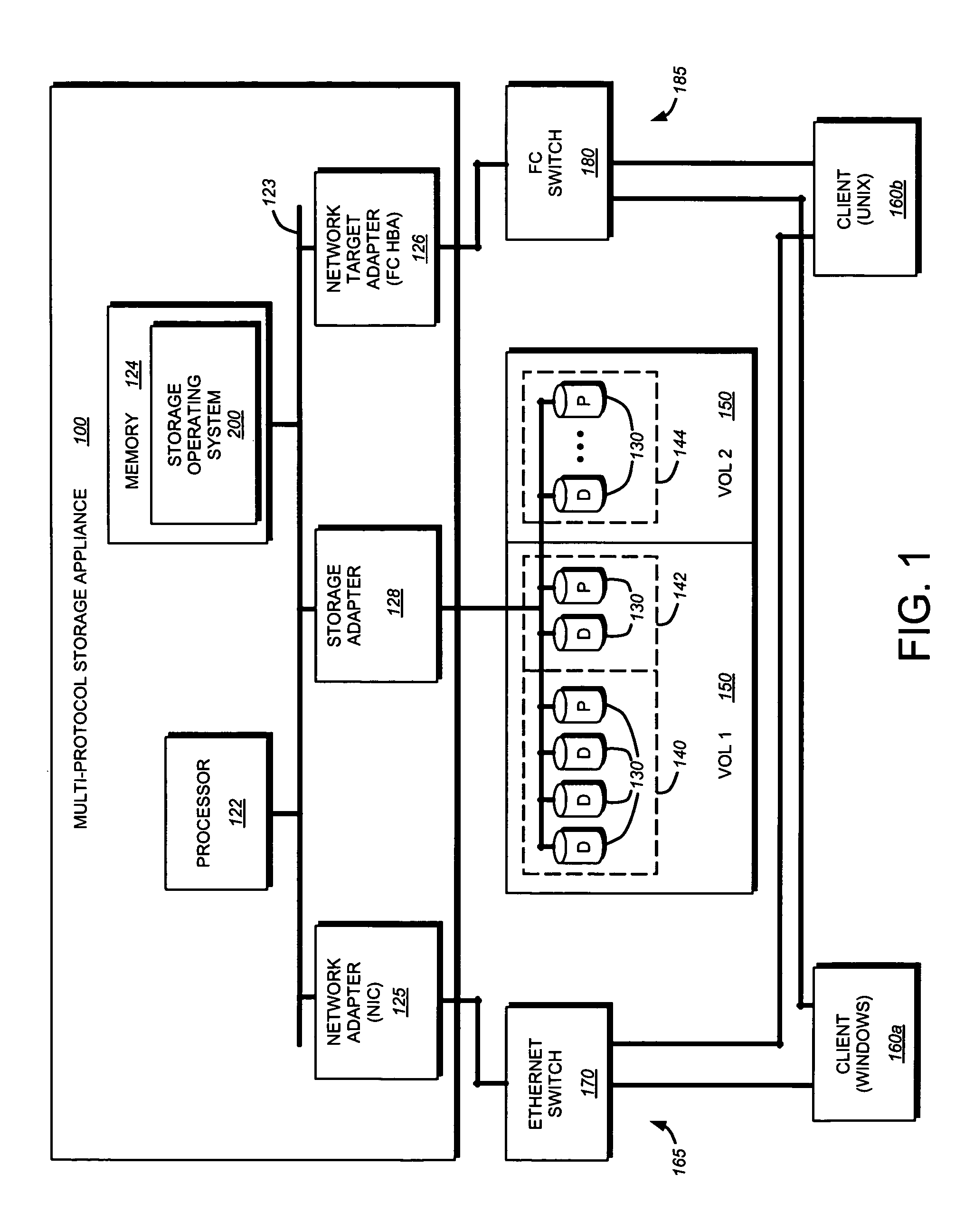

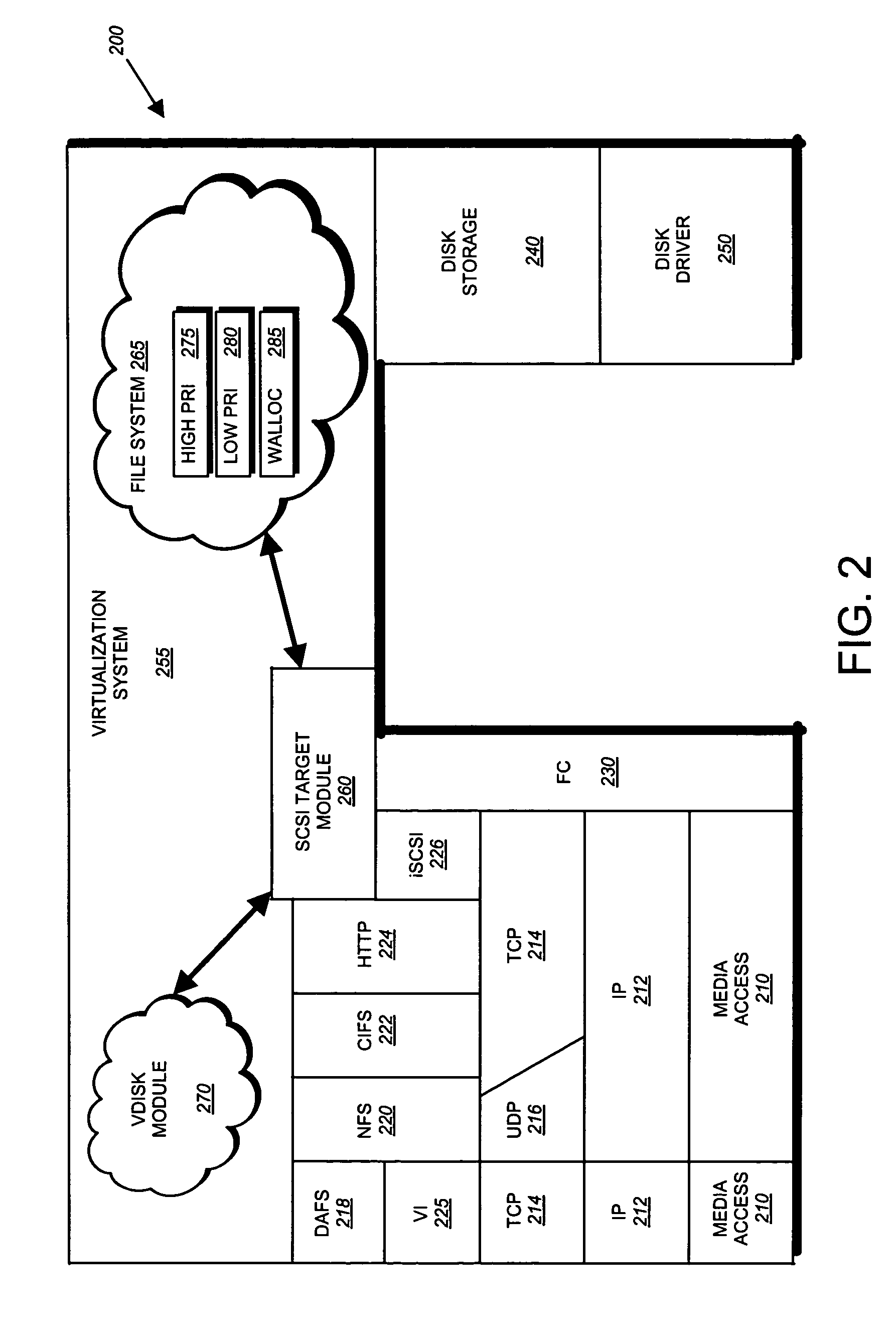

System and method for managing file metadata during consistency points

ActiveUS7783611B1Improve system performanceEliminates long latencyDigital data information retrievalDigital data processing detailsInodeData storing

A system and method for enabling write operations to files undergoing write allocation is provided. The system and method generate a shadow state entry of metadata associated with an inode of the file upon receipt of a write operation. During the write allocation process for the inode, the shadow state information is merged with the data stored in the inode to be written to disk.

Owner:NETWORK APPLIANCE INC

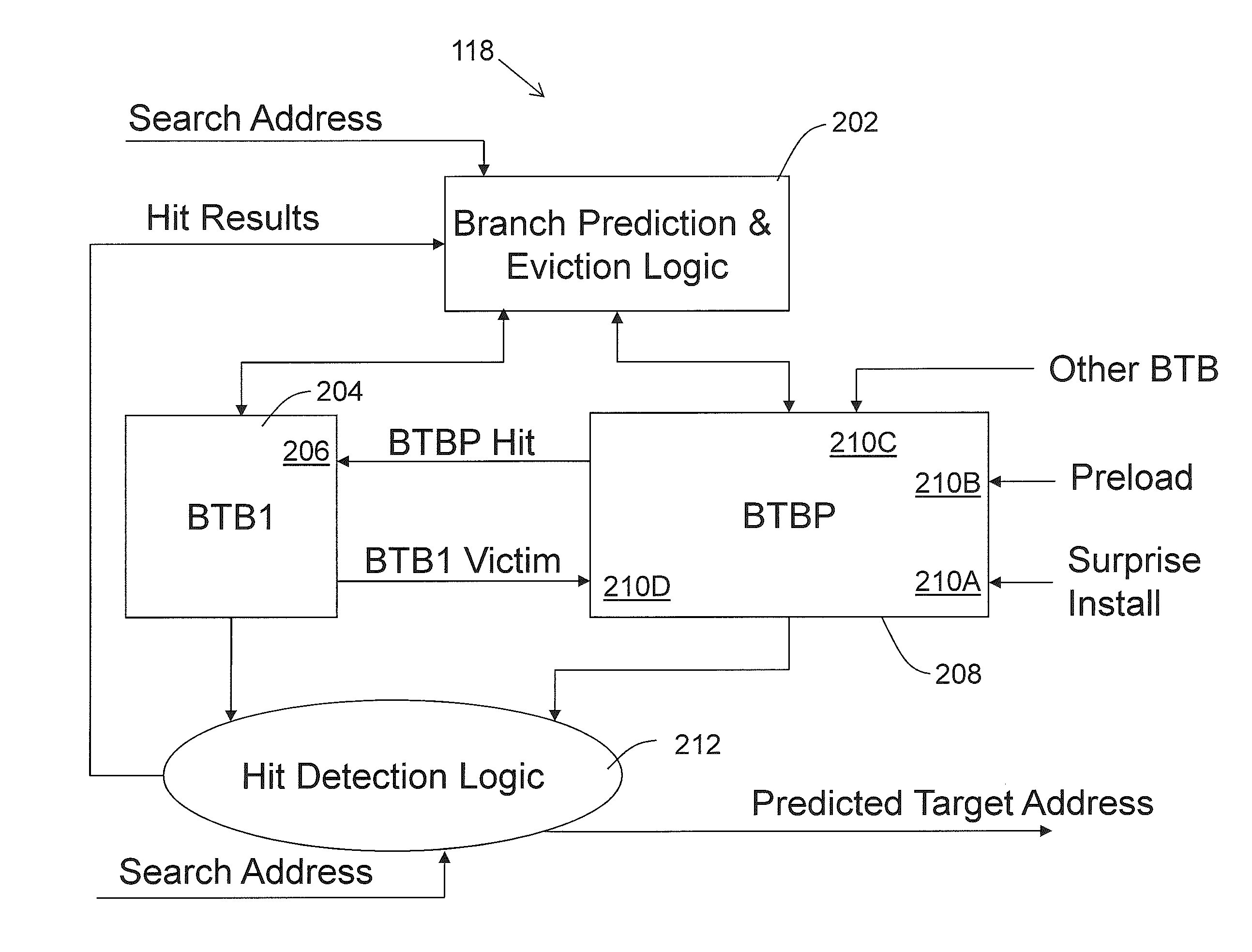

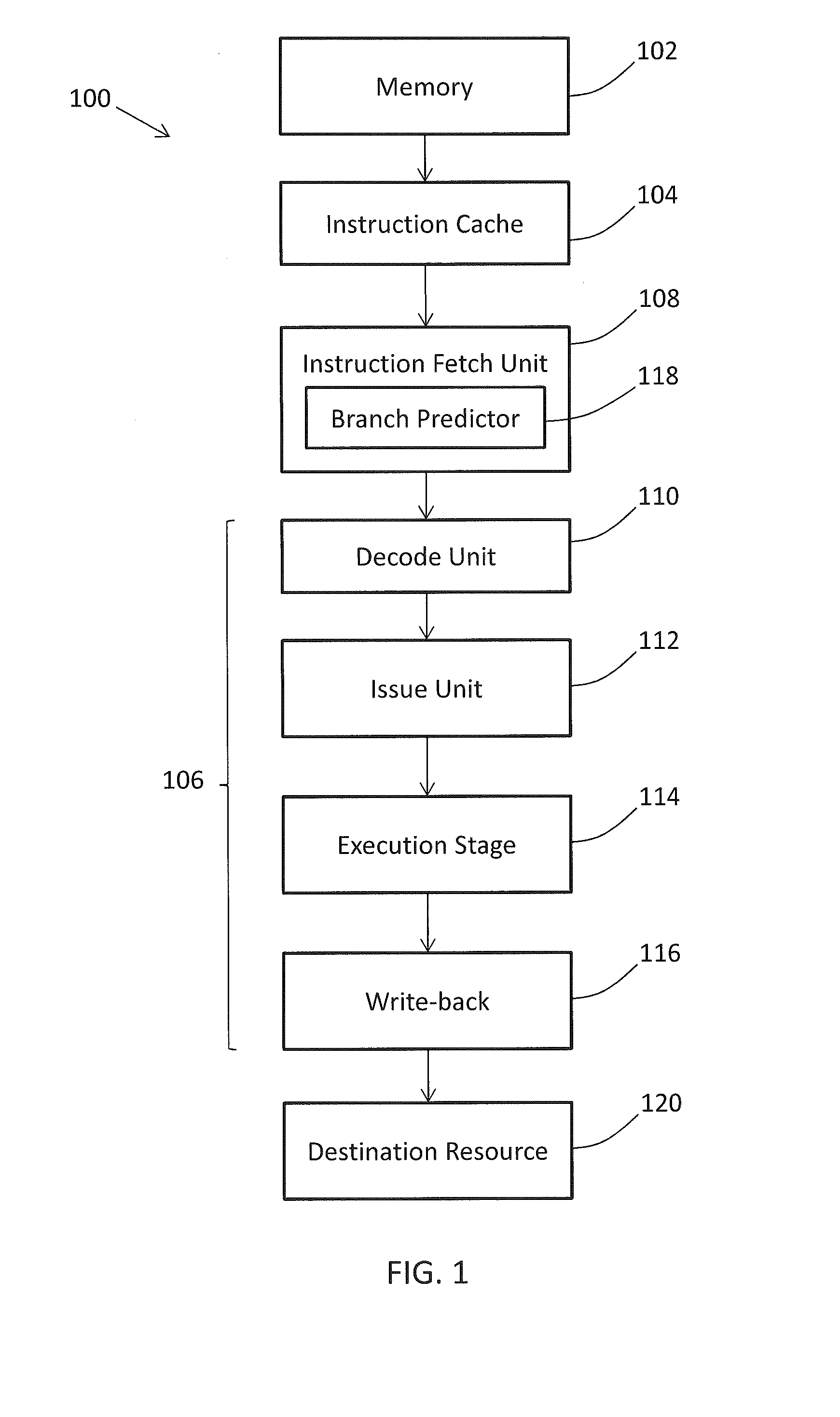

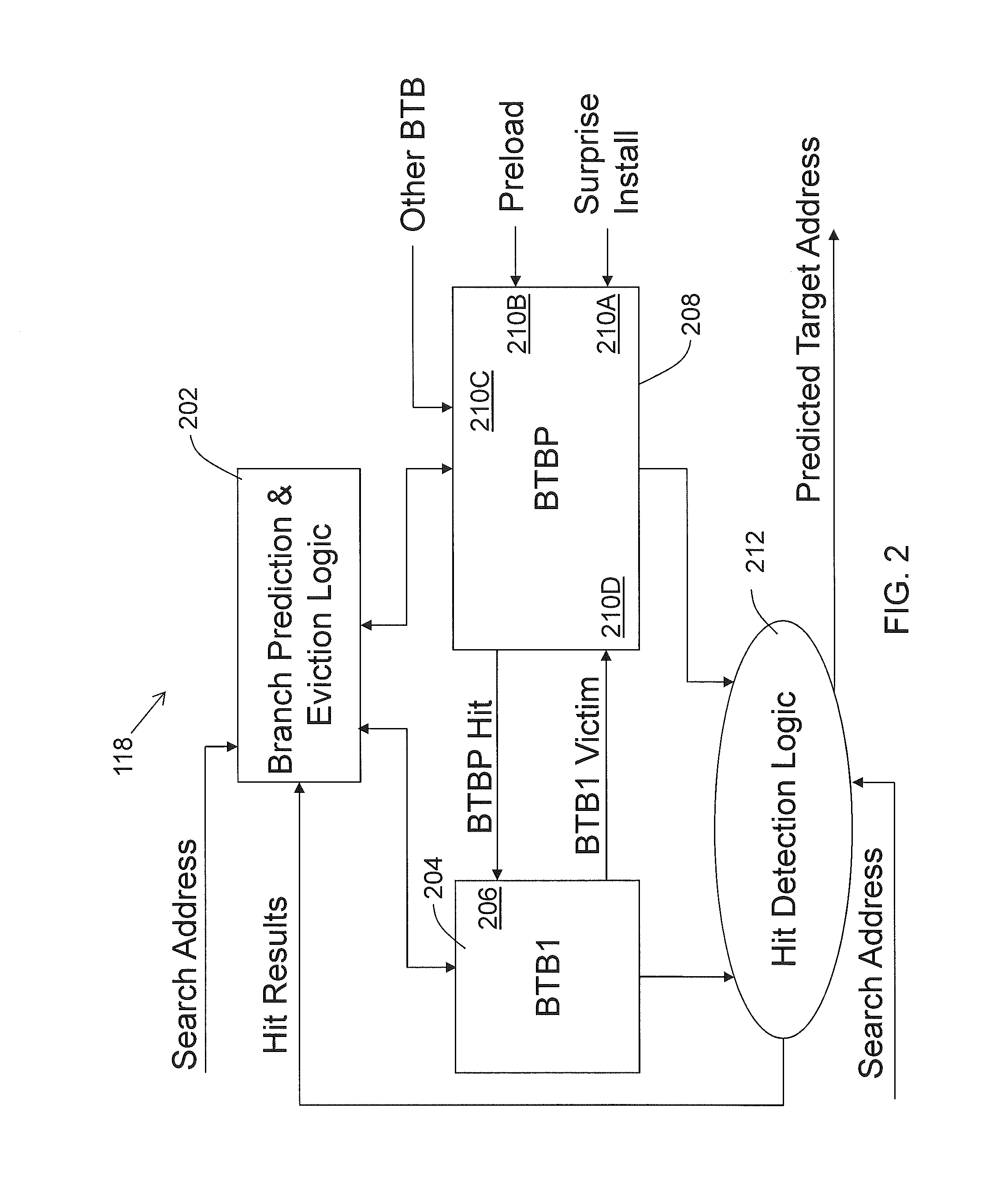

Branch target buffer preload table

InactiveUS20130332716A1Good prediction accuracyLong latencyDigital computer detailsConcurrent instruction executionParallel computing

Embodiments relate to using a branch target buffer preload table. An aspect includes receiving a search request to locate branch prediction information associated with a branch instruction. Searching is performed for an entry corresponding to the search request in a branch target buffer and a branch target buffer preload table in parallel. Based on locating a matching entry in the branch target buffer preload table corresponding to the search request and failing to locate the matching entry in the branch target buffer, a victim entry is selected to overwrite in the branch target buffer. Branch prediction information of the matching entry is received from the branch target buffer preload table at the branch target buffer. The victim entry in the branch target buffer is overwritten with the branch prediction information of the matching entry.

Owner:IBM CORP

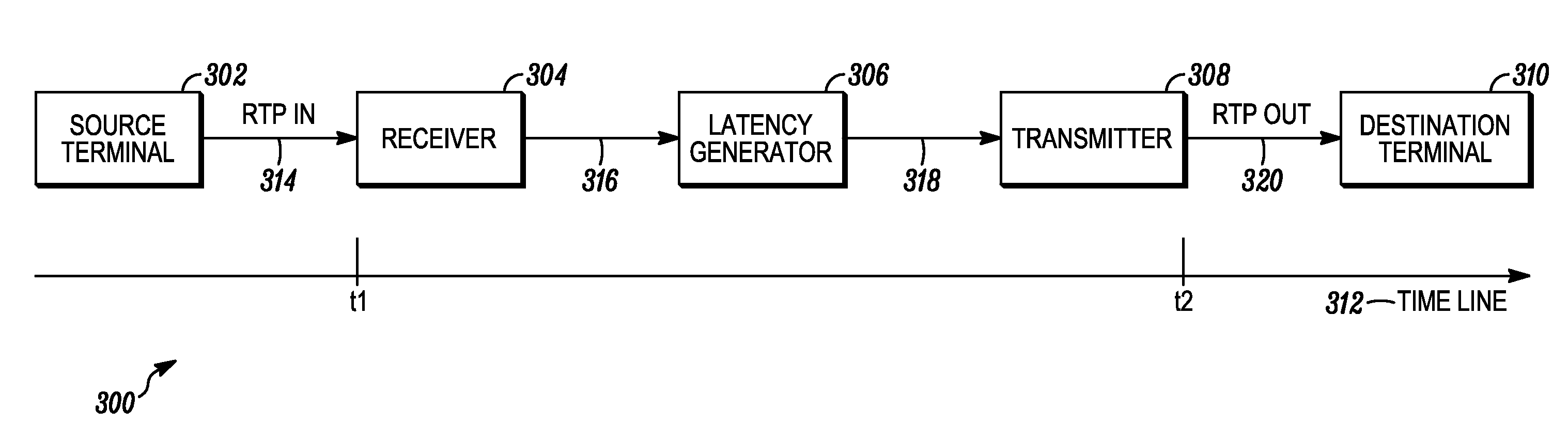

System and method for latency measurement at each network element participating as an rtp relay in a telecommunication network

ActiveUS20130083808A1Long latencyHigh delayTime-division multiplexData switching networksNetwork elementNetsniff-ng

A real-time transport packet creating system and method are provided for use with a source terminal, a destination terminal and a real-time transport packet. The real-time transport packet creating device includes a receiver, a latency generator and a transmitter. The receiver can receive the real-time transport packet from the source terminal at a first time. The latency generator can generate an output real-time transport packet. The transmitter can transmit the output real-time transport packet to the destination terminal at a second time. The output real-time transport packet is based on the received real-time transport packet, the first time and the second time.

Owner:GOOGLE TECH HLDG LLC

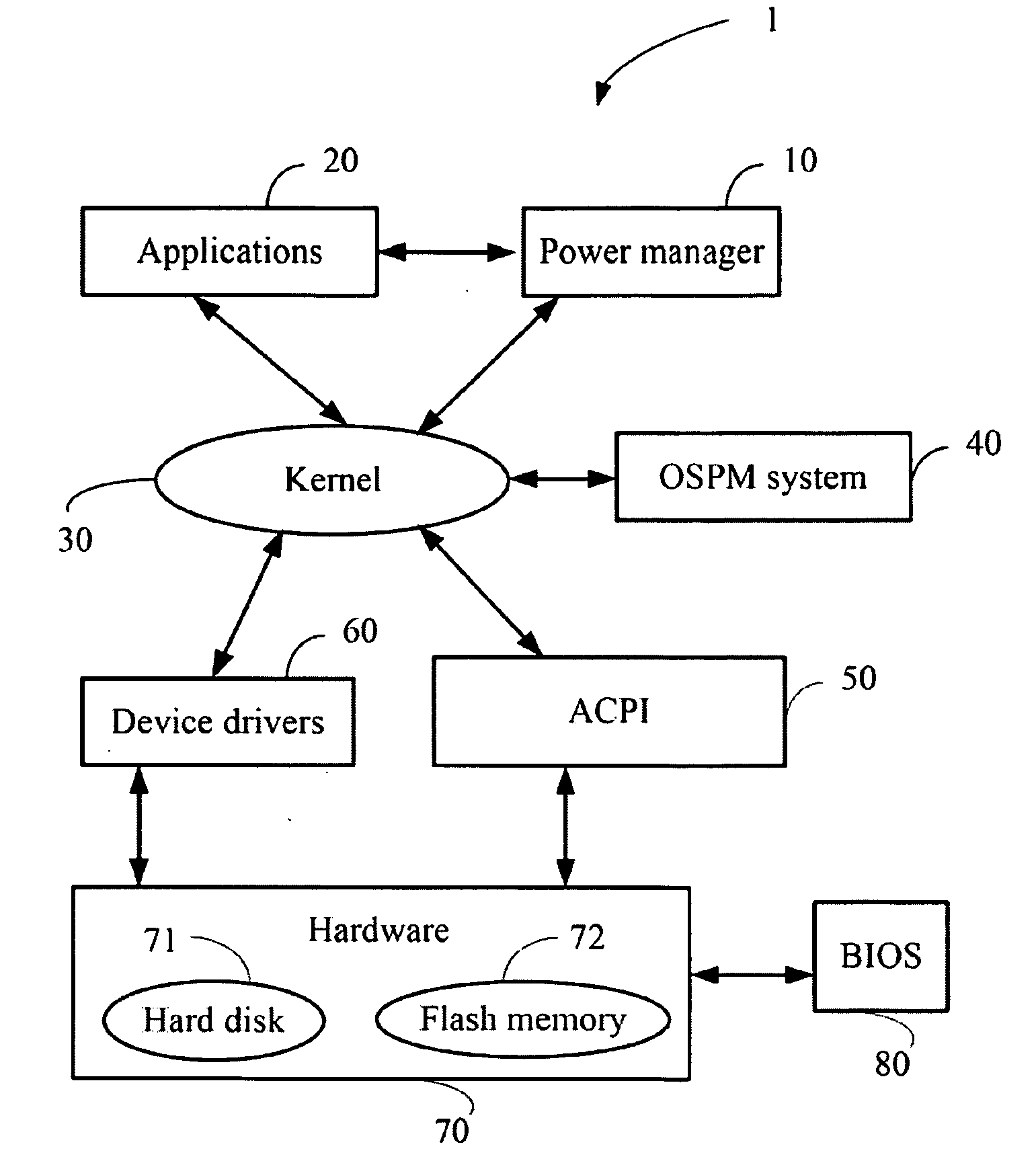

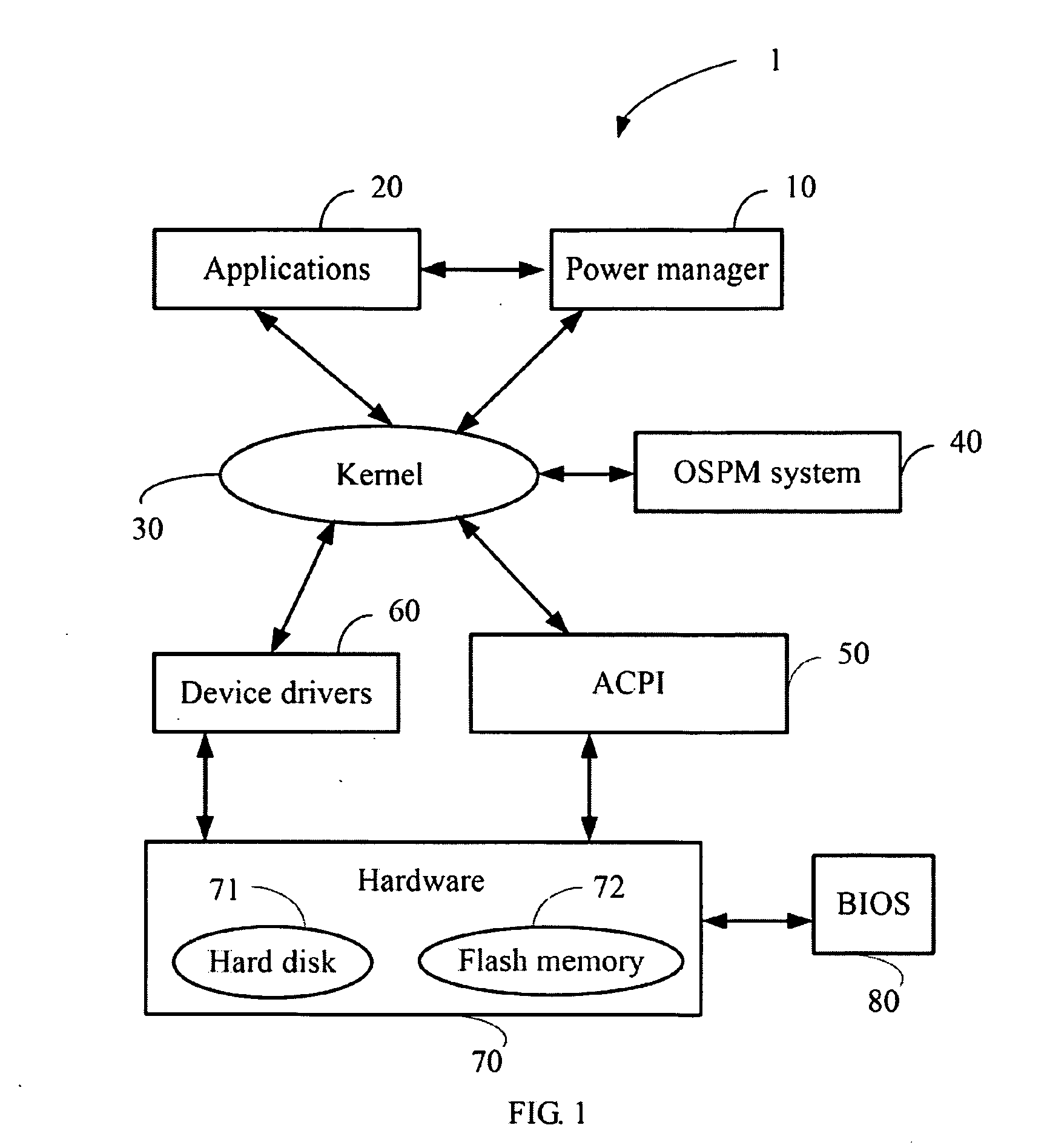

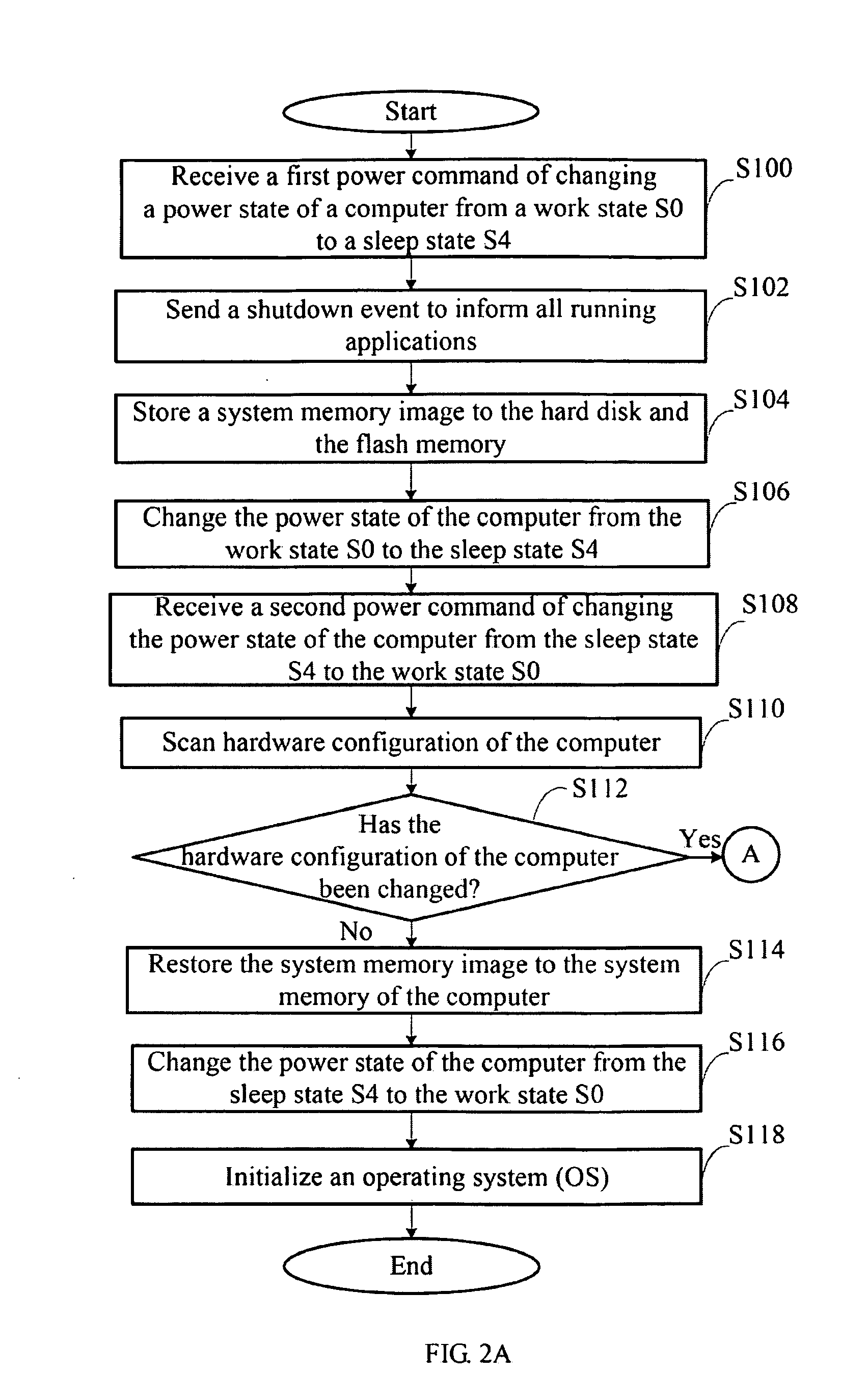

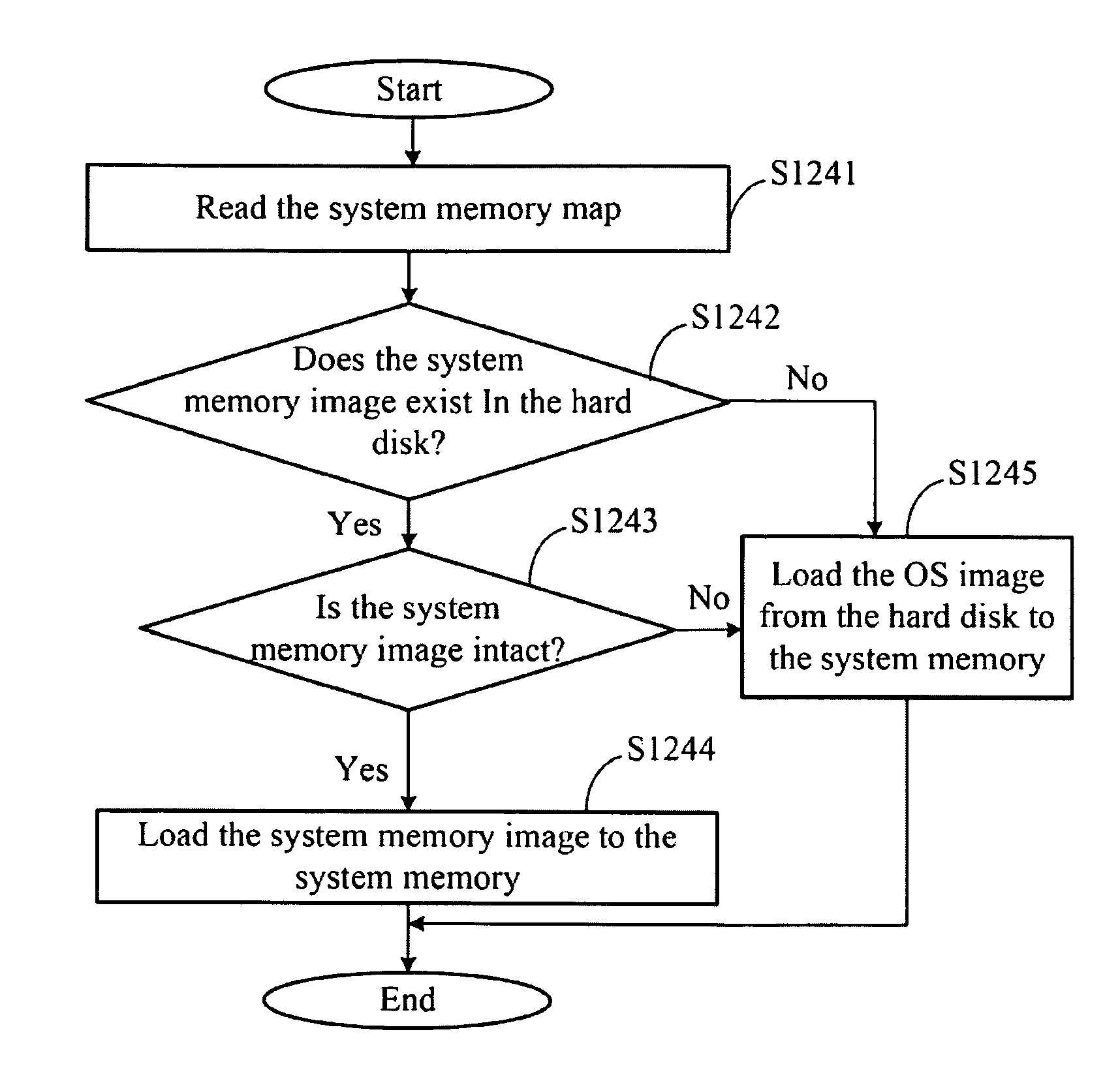

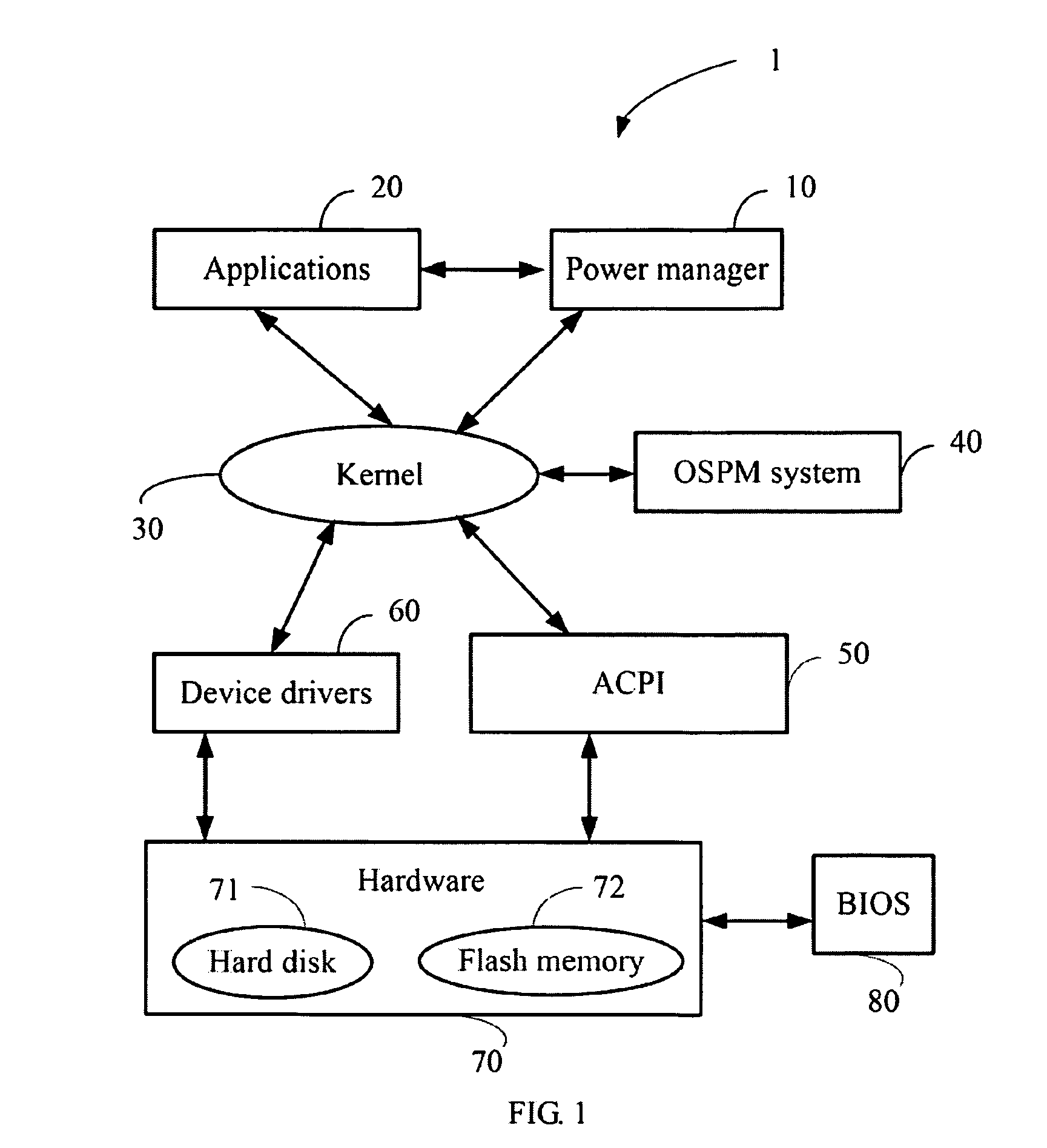

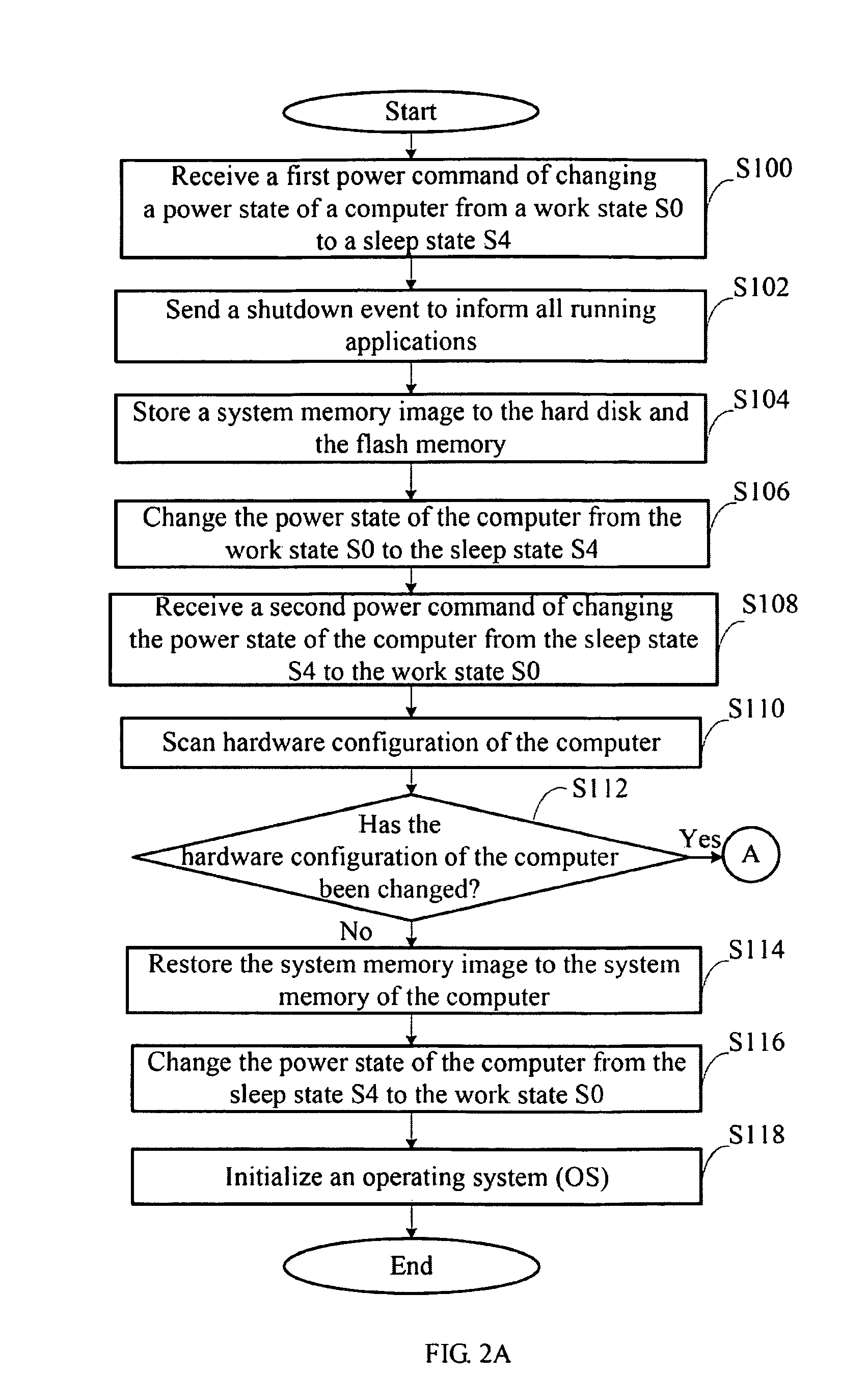

Method for changing power states of a computer

InactiveUS20090217026A1Long latencyVolume/mass flow measurementDigital computer detailsSleep stateReturn work

A method for changing power states of a computer sends a shutdown event to all running applications before the computer goes to sleep to prevent data loss in a sleep state of the computer. Furthermore, the method stores a system memory image into a flash memory before the computer goes to the sleep state. Moreover, the method restores the system memory image from the flash memory to the system memory when the computer exit the sleep state to come back the work state.

Owner:HON HAI PRECISION IND CO LTD

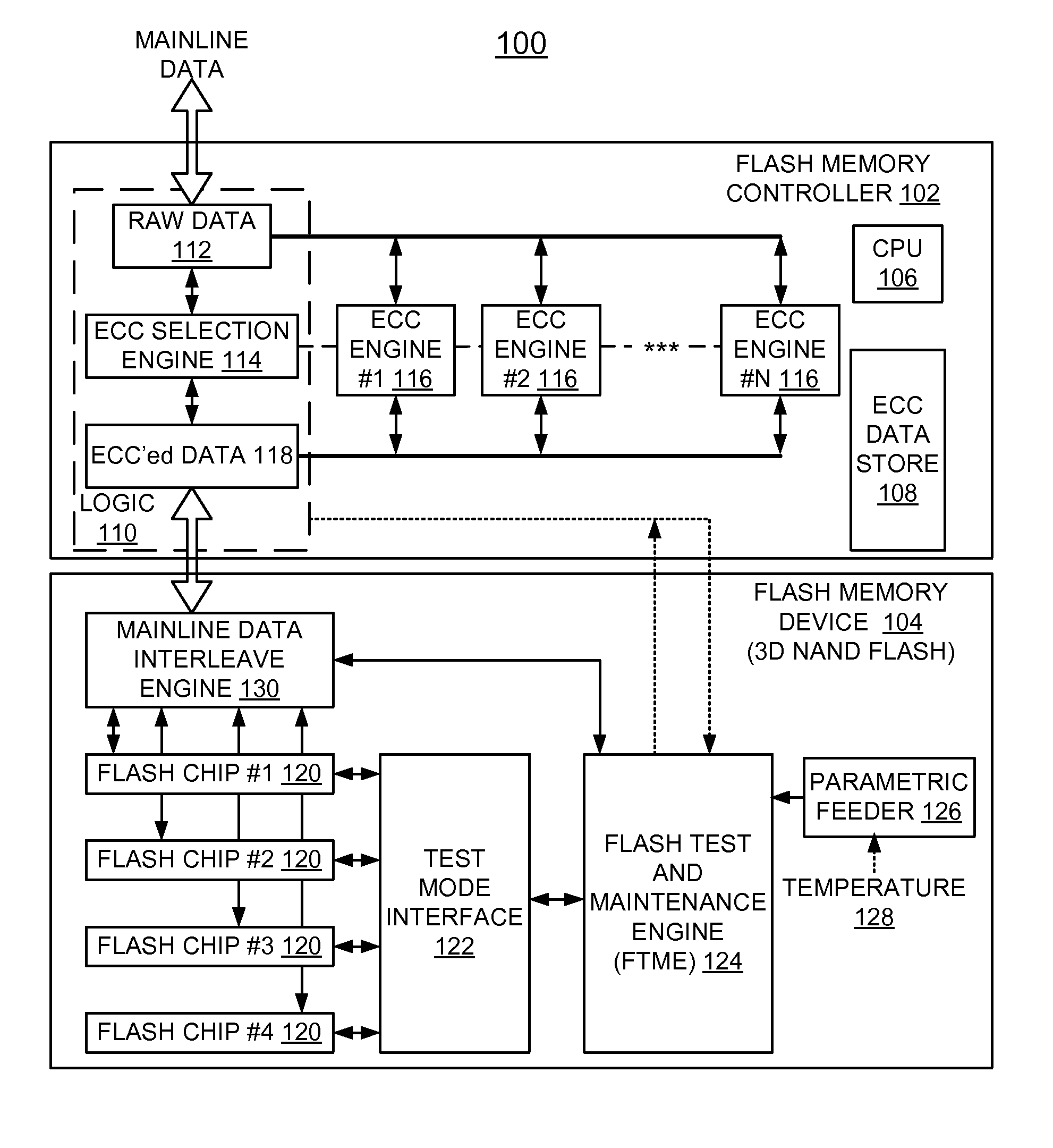

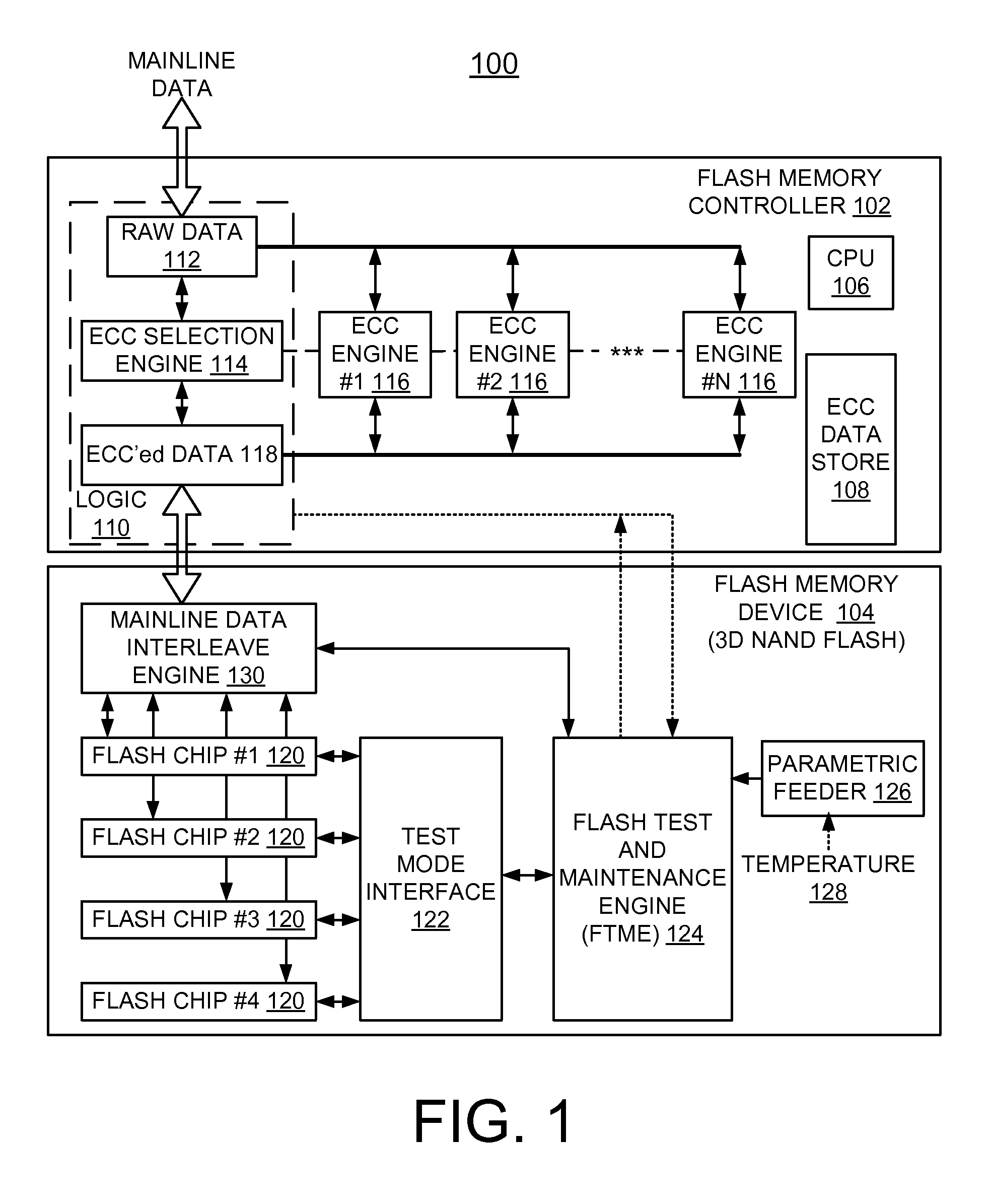

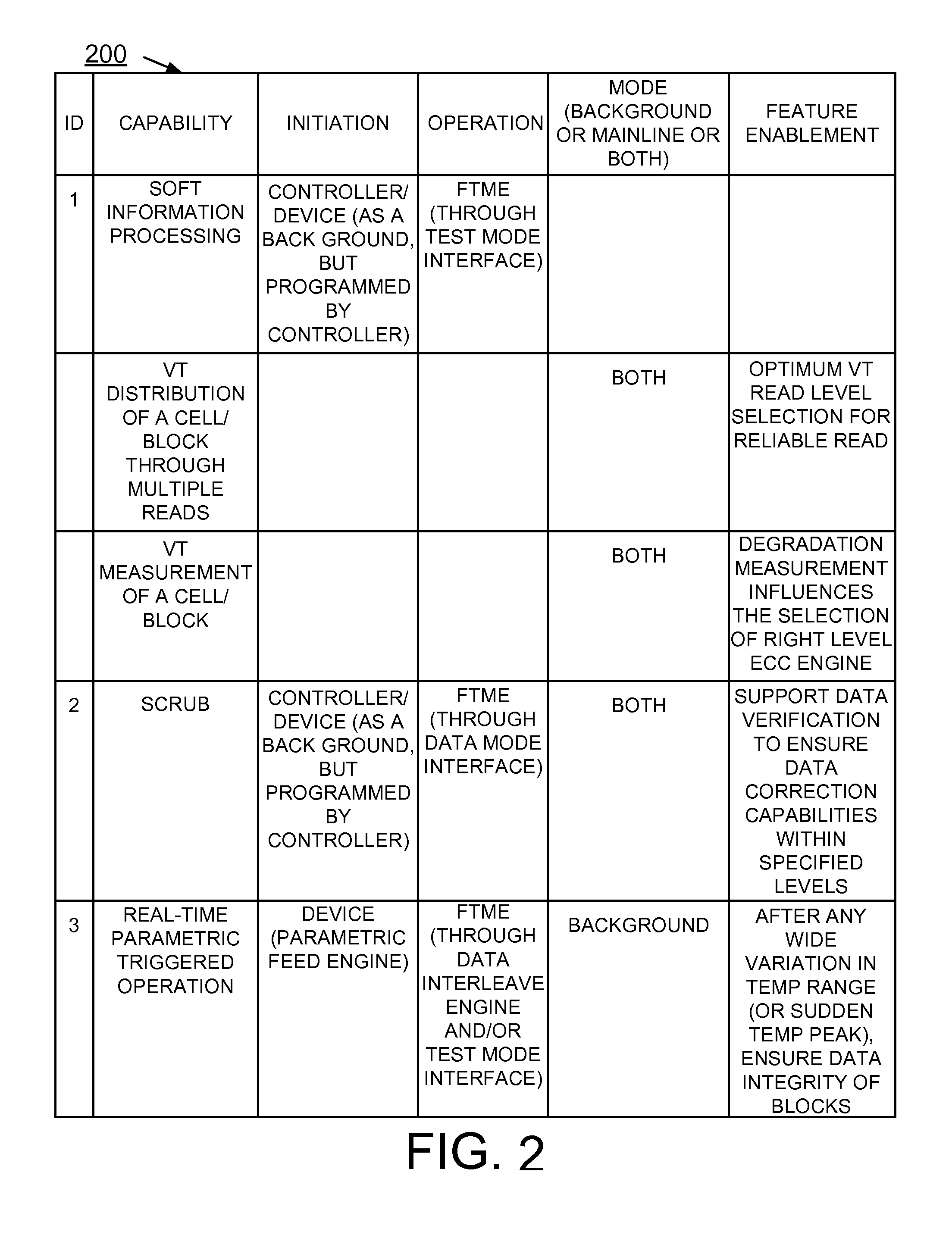

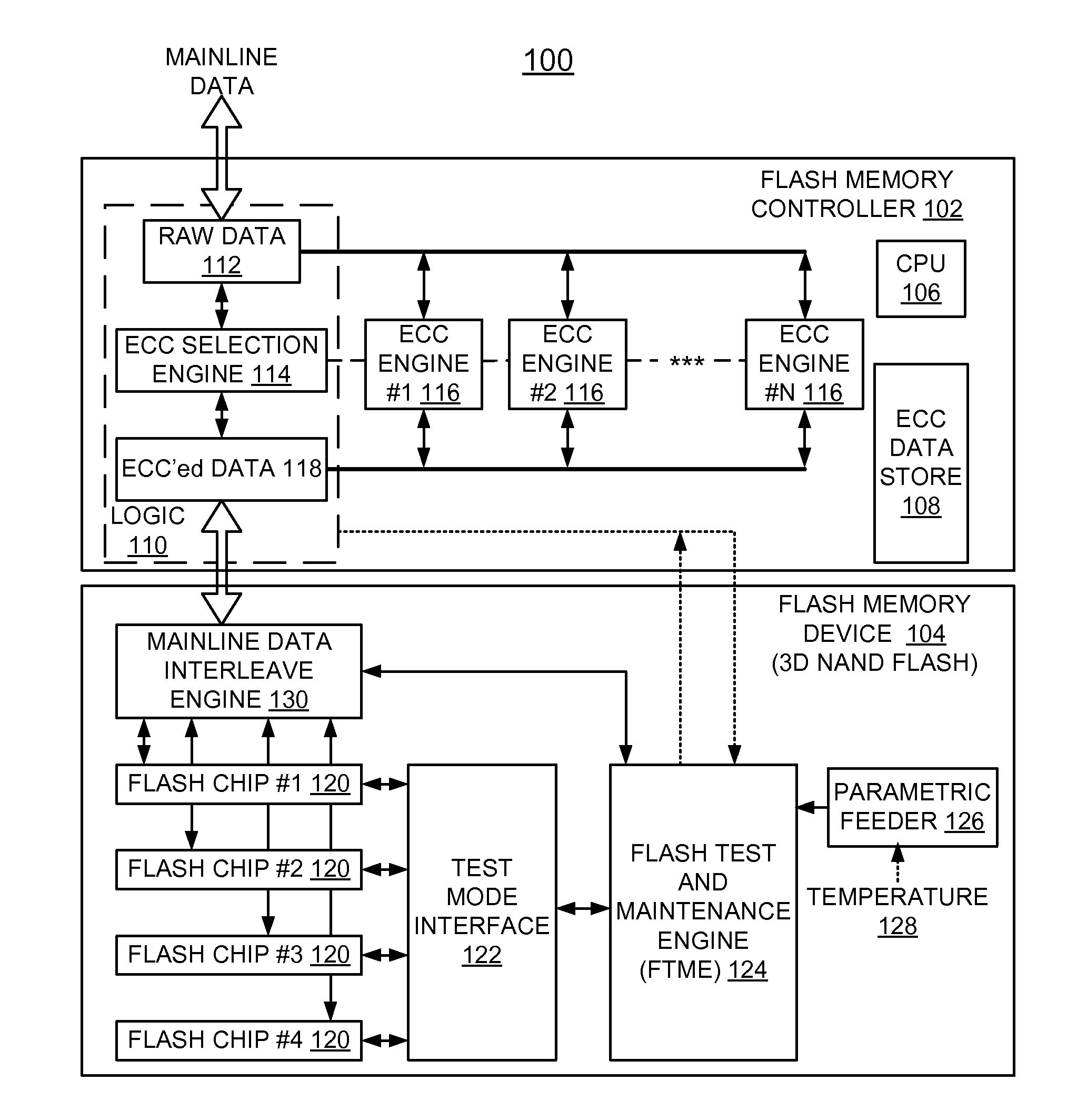

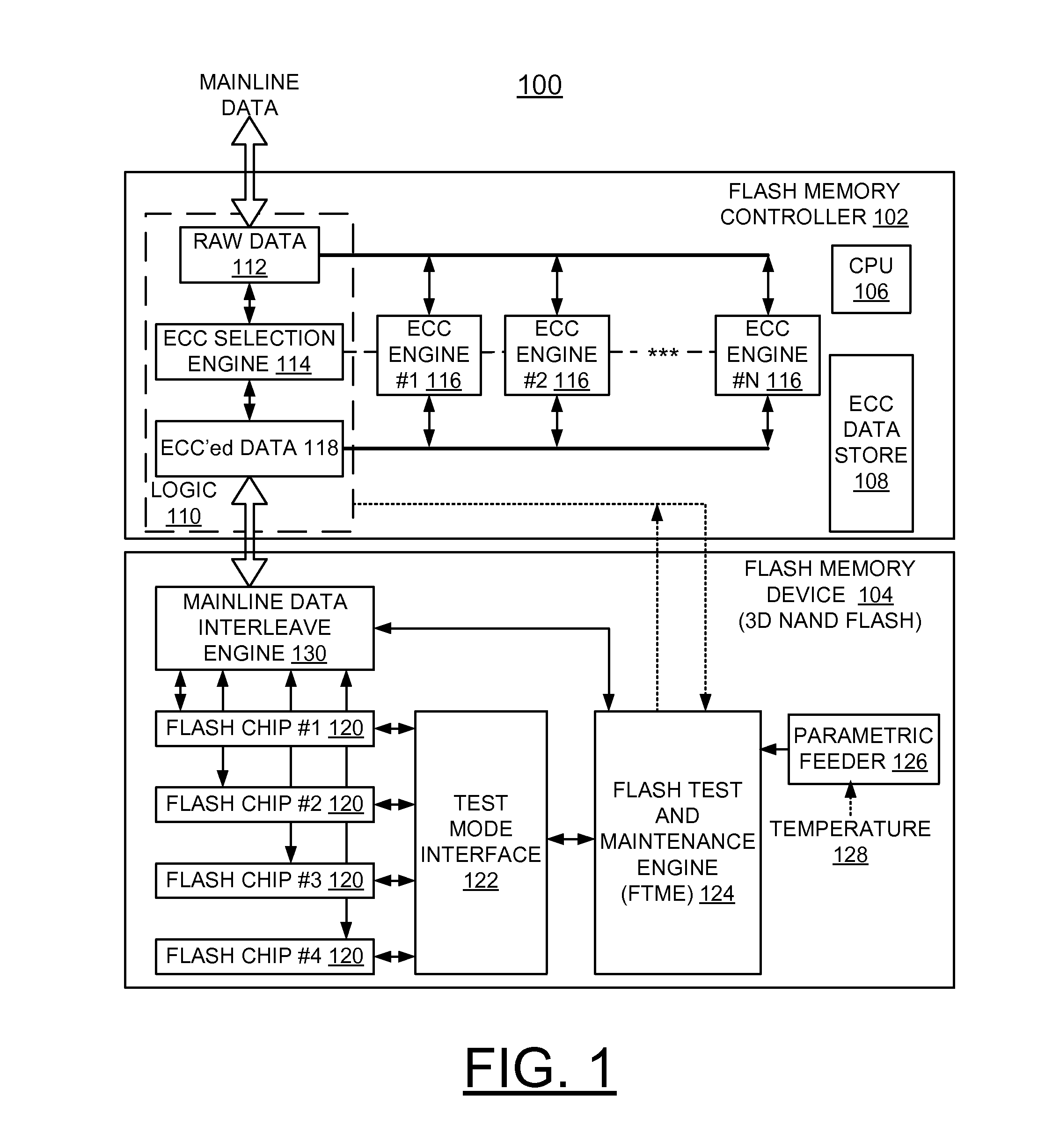

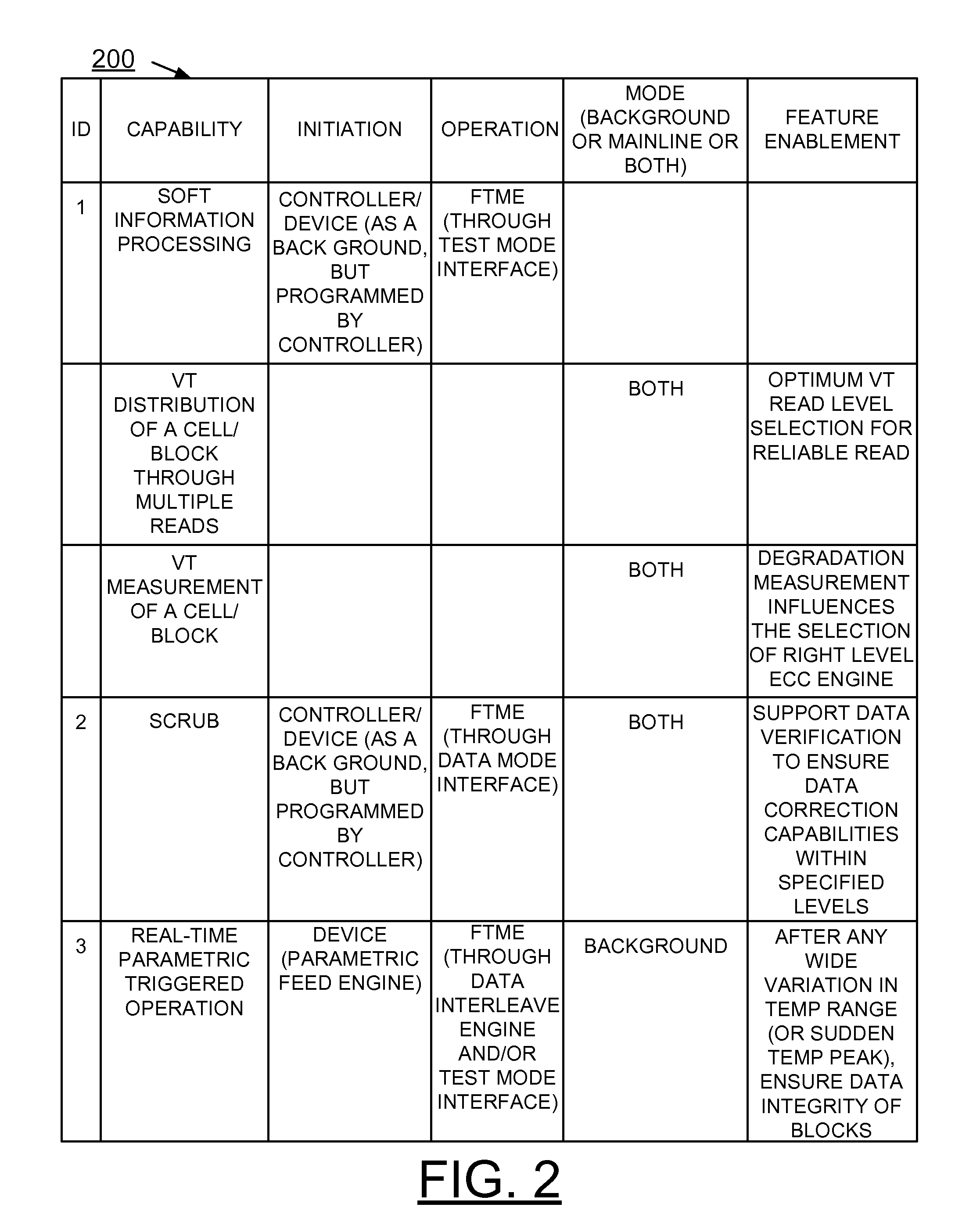

Implementing ECC control for enhanced endurance and data retention of flash memories

InactiveUS9304856B2Enhanced endurance and data retentionWithout negative effectRead-only memoriesCode conversionMemory controllerThreshold voltage

A method, system and memory controller are provided for implementing ECC (Error Correction Codes) control to provide enhanced endurance and data retention of flash memories. The memory controller includes a VT (threshold voltage) monitor to determine VT degradation of cells and blocks; the VT monitor configured to store information about the determined VT degradation; a first ECC engine having a first level of ECC capability; a second ECC engine having a second level of ECC capability, the second level higher than the first level, the second ECC engine having a longer latency than the first ECC engine; a logic to issue a read request to a particular cell / block, and, using the determined VT degradation, use the first ECC engine if the determined VT degradation is less than a threshold and to use the second ECC engine if the determined VT degradation is above the threshold.

Owner:IBM CORP

Error control coding methods for memories with subline accesses

InactiveUS7895502B2Long latencyError detection/correctionCode conversionReal-time computingError control coding

A two-level error control protocol detects errors on the subline level and corrects errors using the codeword for the entire line. This enables a system to read small pieces of coded data and check for errors before accepting them, and in case errors are detected, the whole codeword is read for error correction.

Owner:INT BUSINESS MASCH CORP

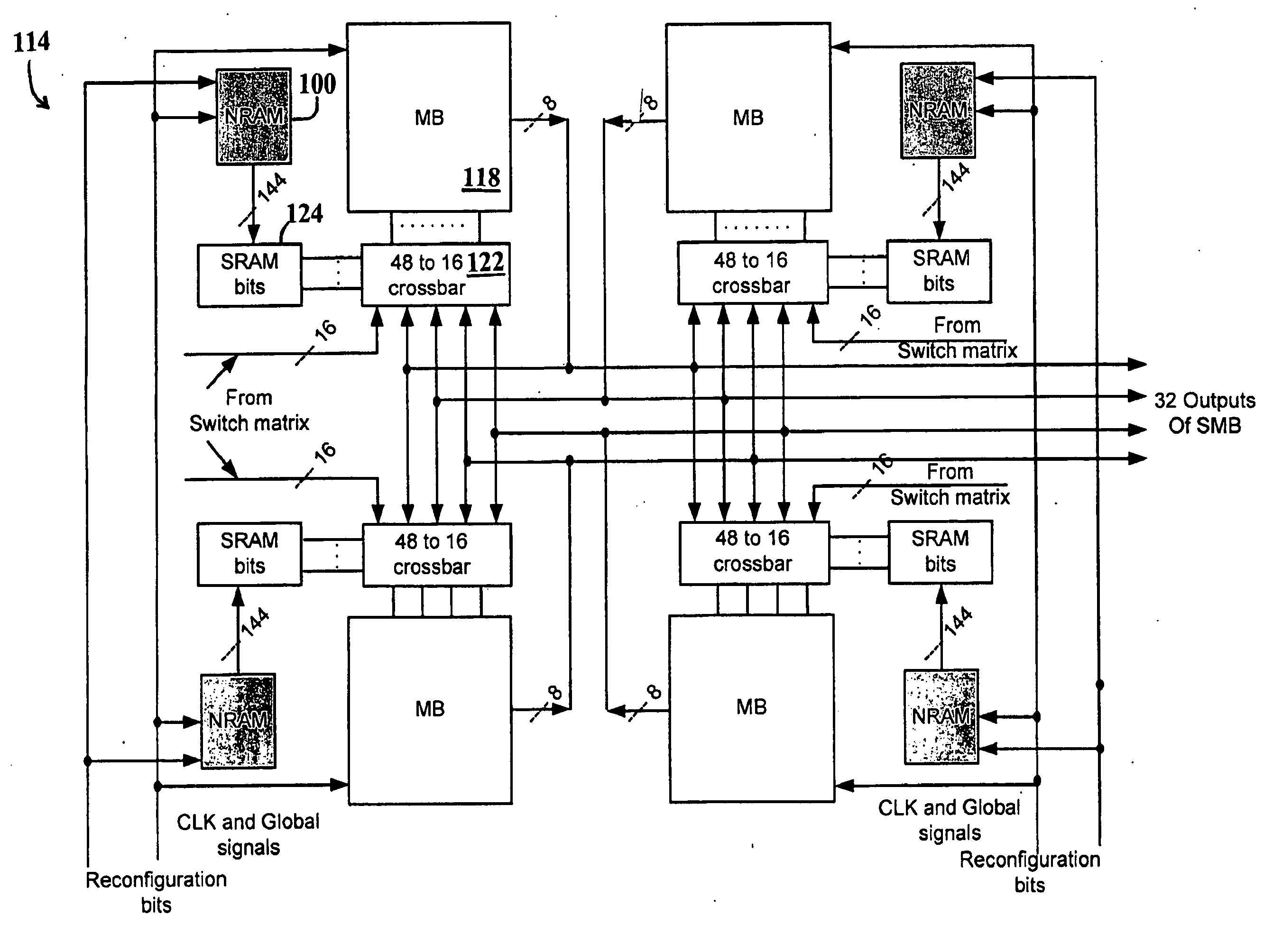

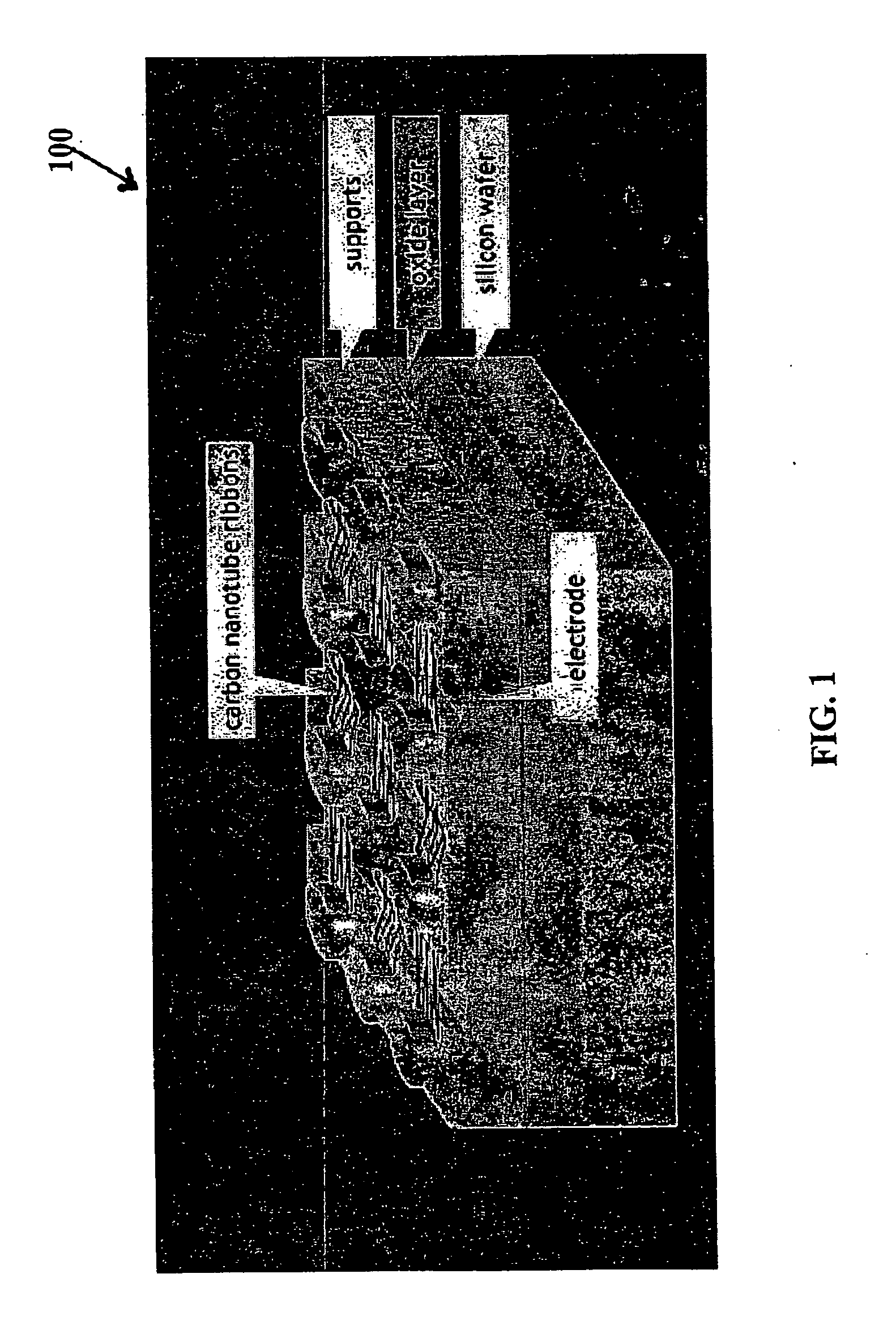

Hybrid nanotube/CMOS dynamically reconfigurable architecture and an integrated design optimization method and system therefor

InactiveUS8117436B2EfficiencyLong latencySolid-state devicesDigital computer detailsLinear temporal logicEngineering

A hybrid nanotube, high-performance, dynamically reconfigurable architecture, NATURE, is provided, and a design optimization flow method and system, NanoMap. A run-time reconfigurable architecture is provided by associating a non-volatile universal memory to each logic element to enable cycle-by-cycle reconfiguration and logic folding, while remaining CMOS compatible. Through logic folding, significant logic density improvement and flexibility in performing area-delay tradeoffs are possible. NanoMap incorporates temporal logic folding during the logic mapping, temporal clustering and placement steps. NanoMap provides for automatic selection of a best folding level, and uses force-direct scheduling to balance resources across folding stages. Mapping can thereby target various optimization objectives and user constraints. A high-density, high-speed carbon nanotube RAM can be implemented as the universal memory, allowing on-chip multi-context configuration storage, enabling fine-grain temporal logic folding, and providing a significant increase in relative logic density.

Owner:QUEENS UNIV OF KINGSTON +1

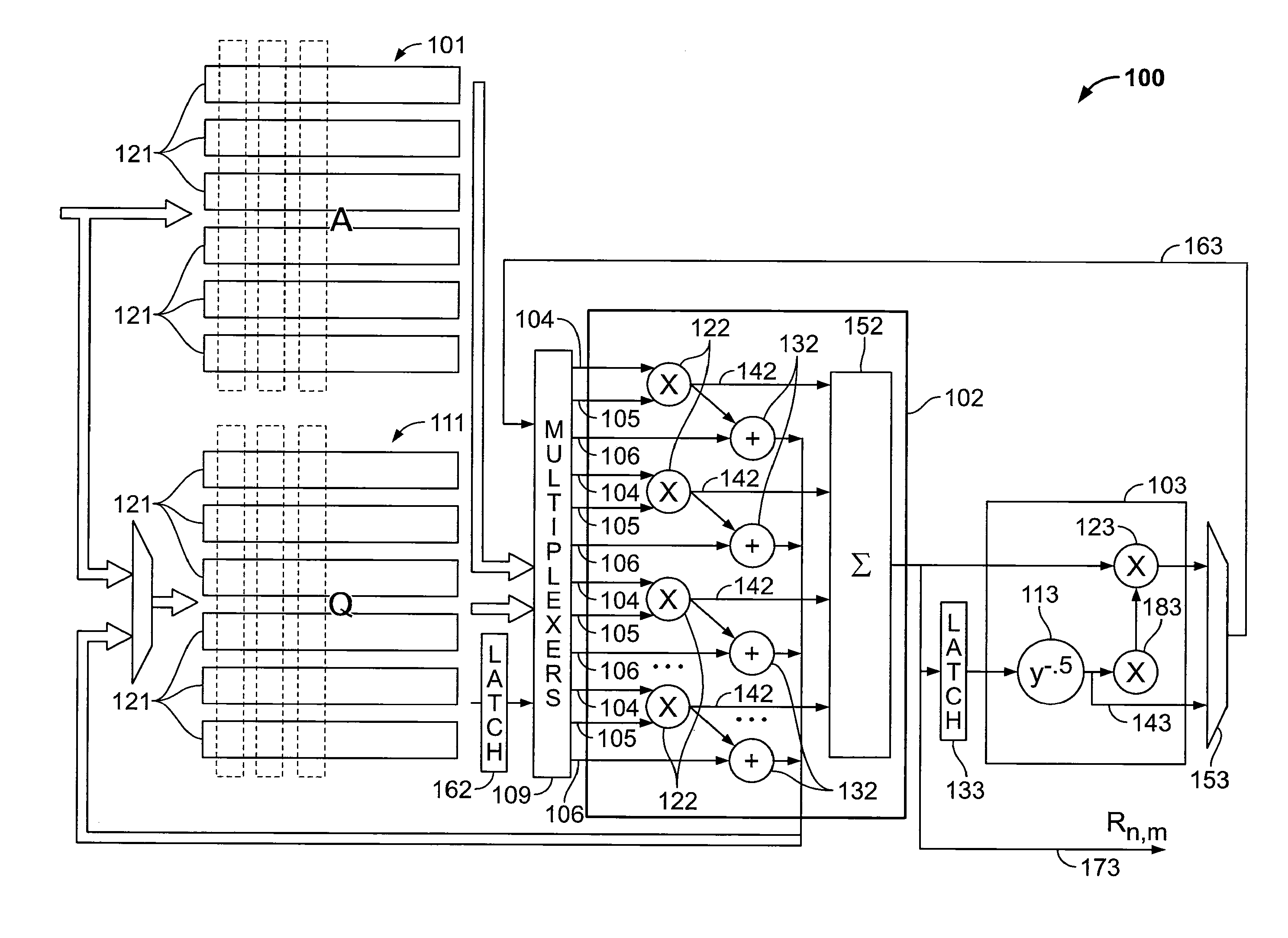

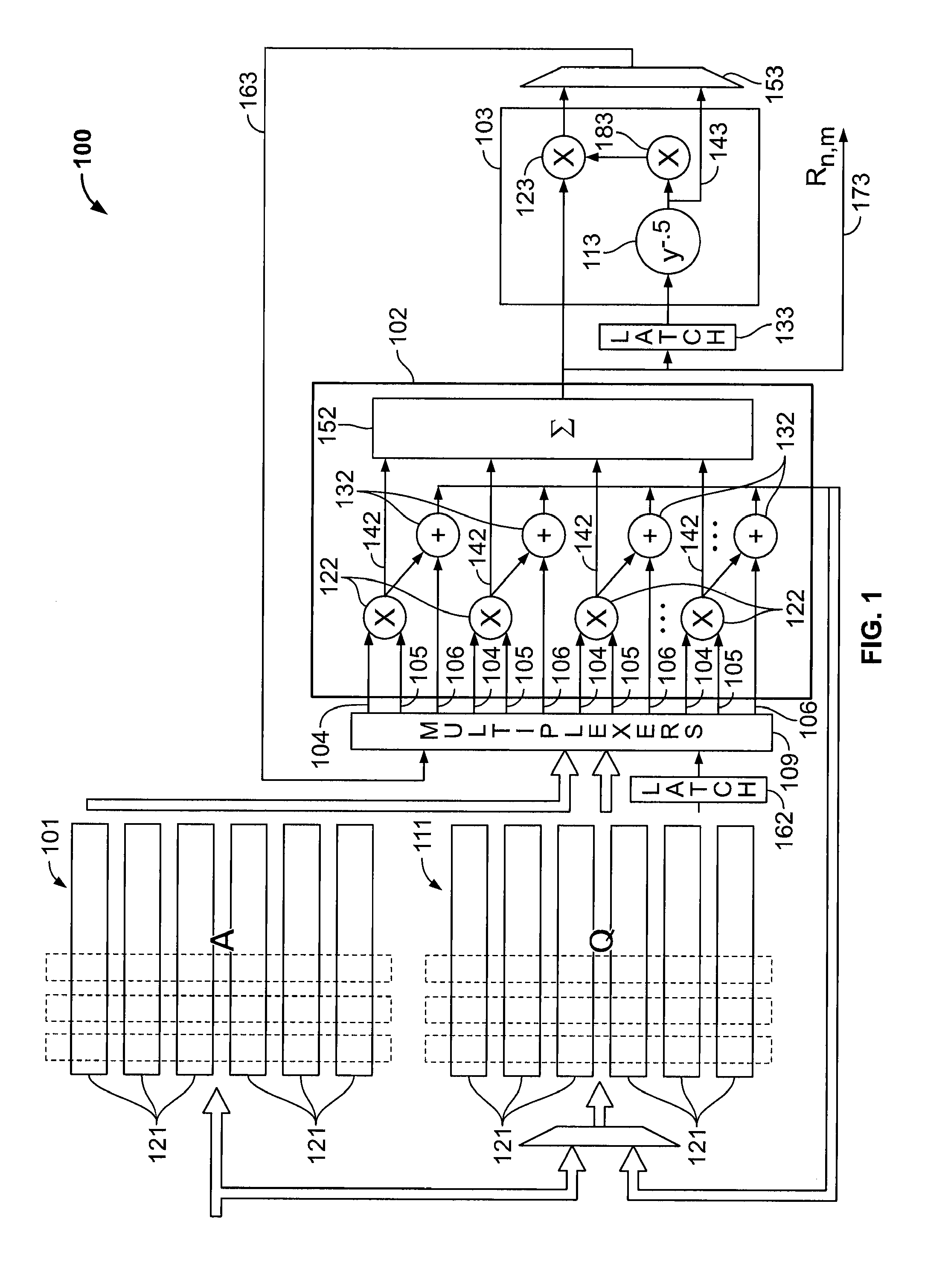

QR decomposition in an integrated circuit device

InactiveUS8539016B1Promote decompositionReduce hardware costsData mergingComplex mathematical operationsQ-matrixQR decomposition

Circuitry speeds up the QR decomposition of a matrix. The circuitry can be provided in a fixed logic device, or can be configured into a programmable integrated circuit device such as a programmable logic device. This implementation performs Gram-Schmidt orthogonalization with no dependencies between iterations. QR decomposition of a matrix can be performed by processing entire columns at once as a vector operation. Data dependencies within and between matrix columns are removed, as later functions dependent on an earlier result may be generated from partial results somewhere in the datapath, rather than from an earlier completed result. Different passes through the matrix are timed so that different computations requiring the same functional units arrive at different time slots. After the Q matrix has been calculated, the R matrix may be calculated from the Q matrix by taking its transpose and multiplying the transpose by the original input matrix.

Owner:ALTERA CORP

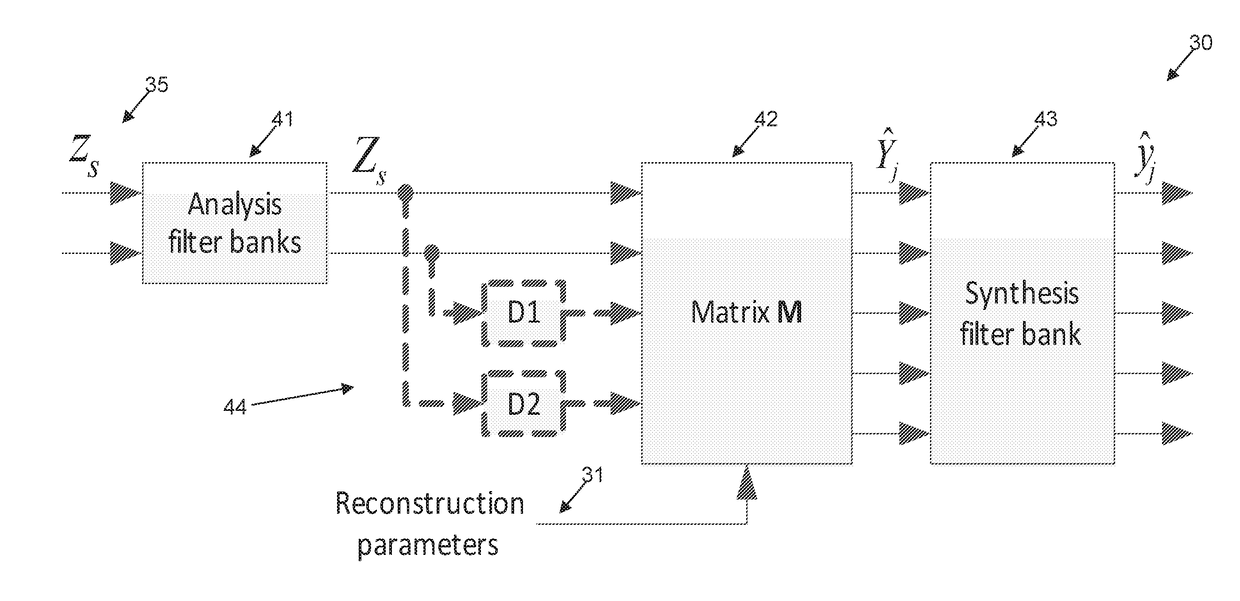

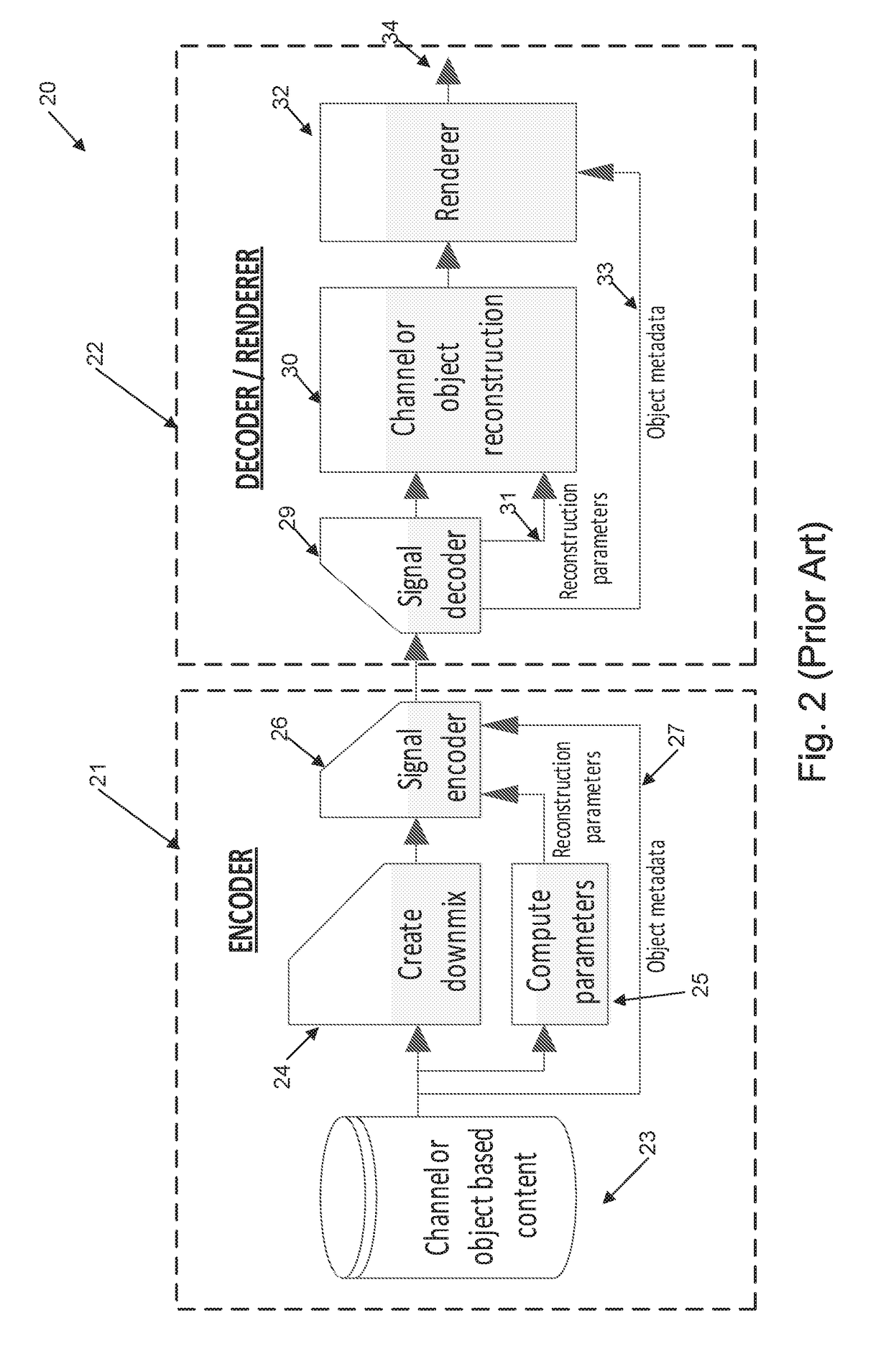

Audio Decoder and Decoding Method

ActiveUS20180233156A1Efficient implementationHigh resolutionHearing device energy consumption reductionSpeech analysisDecoding methodsData stream

A method for representing a second presentation of audio channels or objects as a data stream, the method comprising the steps of: (a) providing a set of base signals, the base signals representing a first presentation of the audio channels or objects; (b) providing a set of transformation parameters, the transformation parameters intended to transform the first presentation into the second presentation; the transformation parameters further being specified for at least two frequency bands and including a set of multi-tap convolution matrix parameters for at least one of the frequency bands.

Owner:DOLBY LAB LICENSING CORP +1

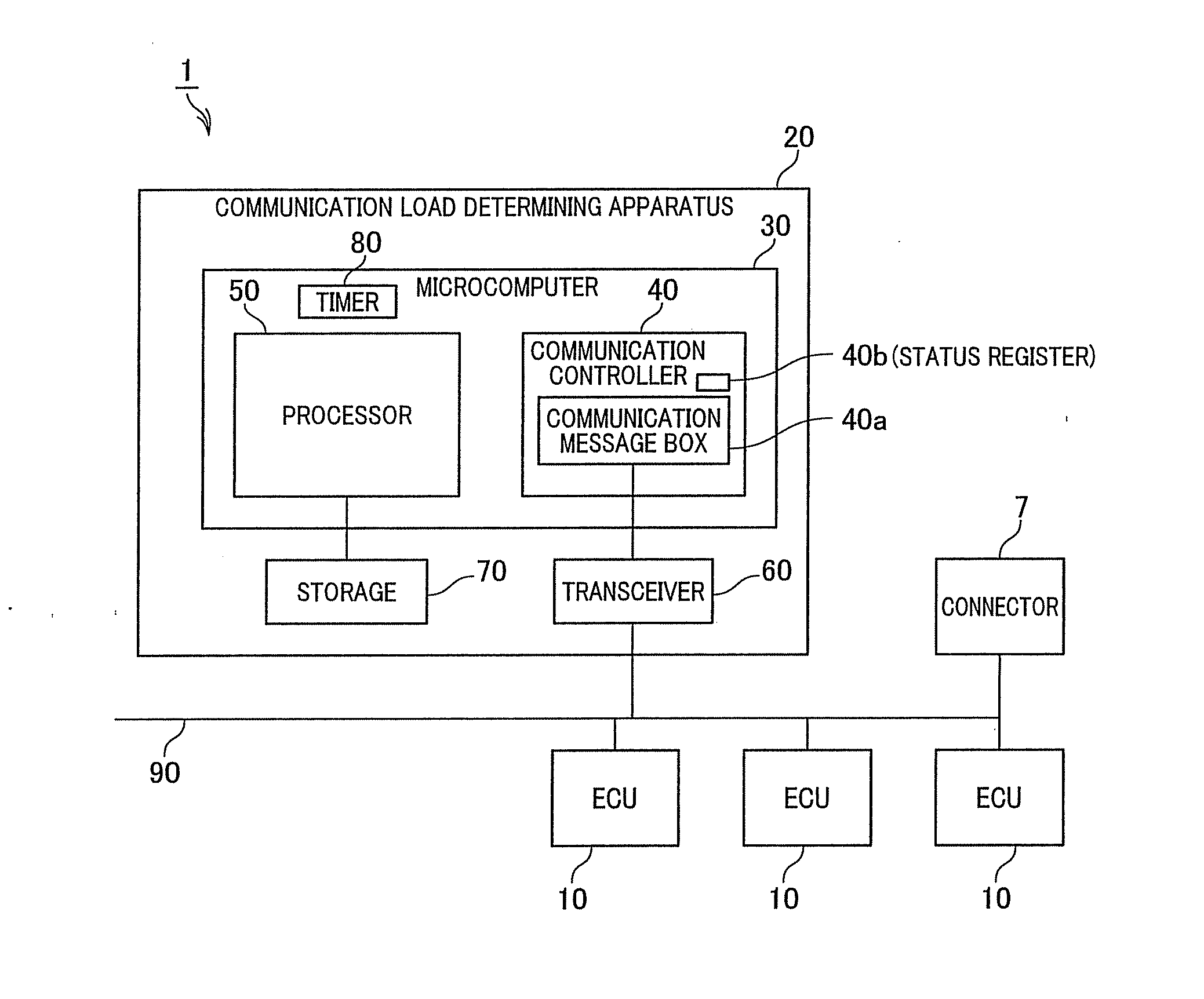

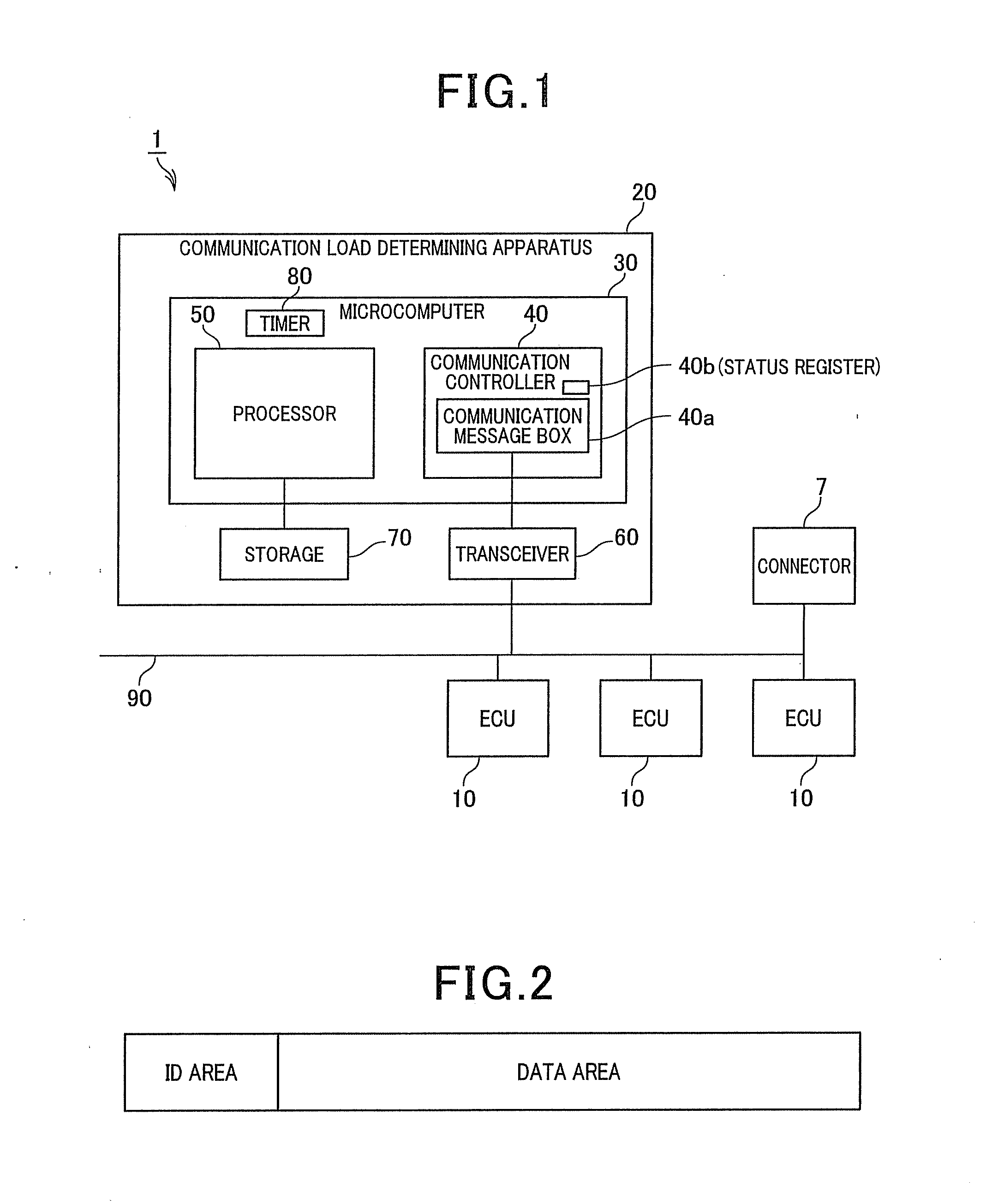

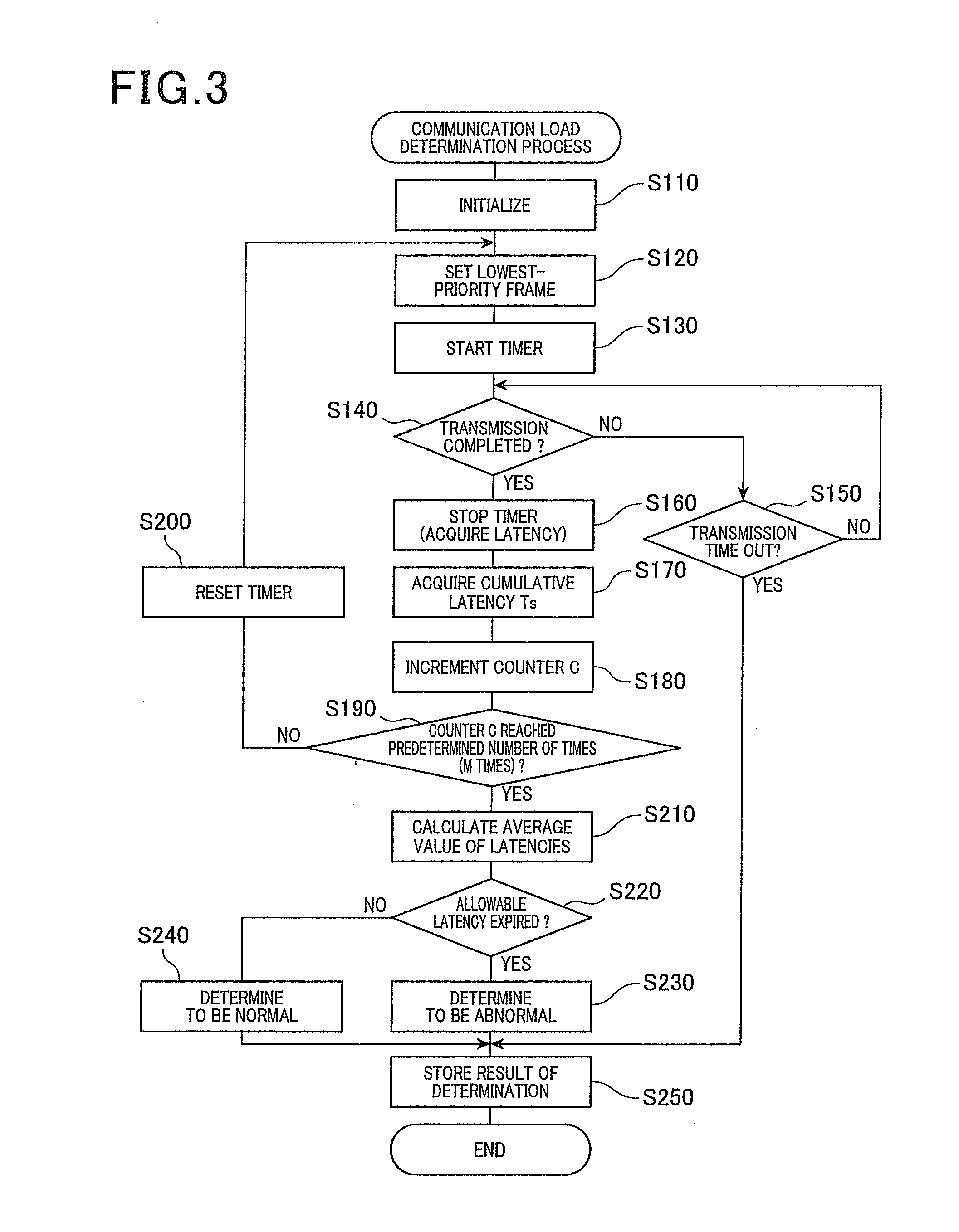

Communication load determining apparatus

ActiveUS20140047146A1Simple configurationIncreasing processing load of CPU and memory capacityError detection/correctionHybrid transportCommunications systemNetwork Communication Protocols

A communication load determining apparatus is used for a communication system which includes a plurality of communication devices performing communication via a common bus. The communication system operates in accordance with a communication protocol that defines which a priority order is set to each of the frames transmitted from the communication devices and which a frame having a lower priority has a longer transmission latency before being transmitted to the bus. In the communication load determining apparatus, a low-priority frame having a lower priority than other frames to the bus is transmitted, and a transmission latency of the low-priority frame is measured. The communication load determining apparatus determines whether or not abnormality has occurred in a communication load in the bus on the basis of the measured transmission latency to produce a determination result. The produced determination result is stored.

Owner:DENSO CORP

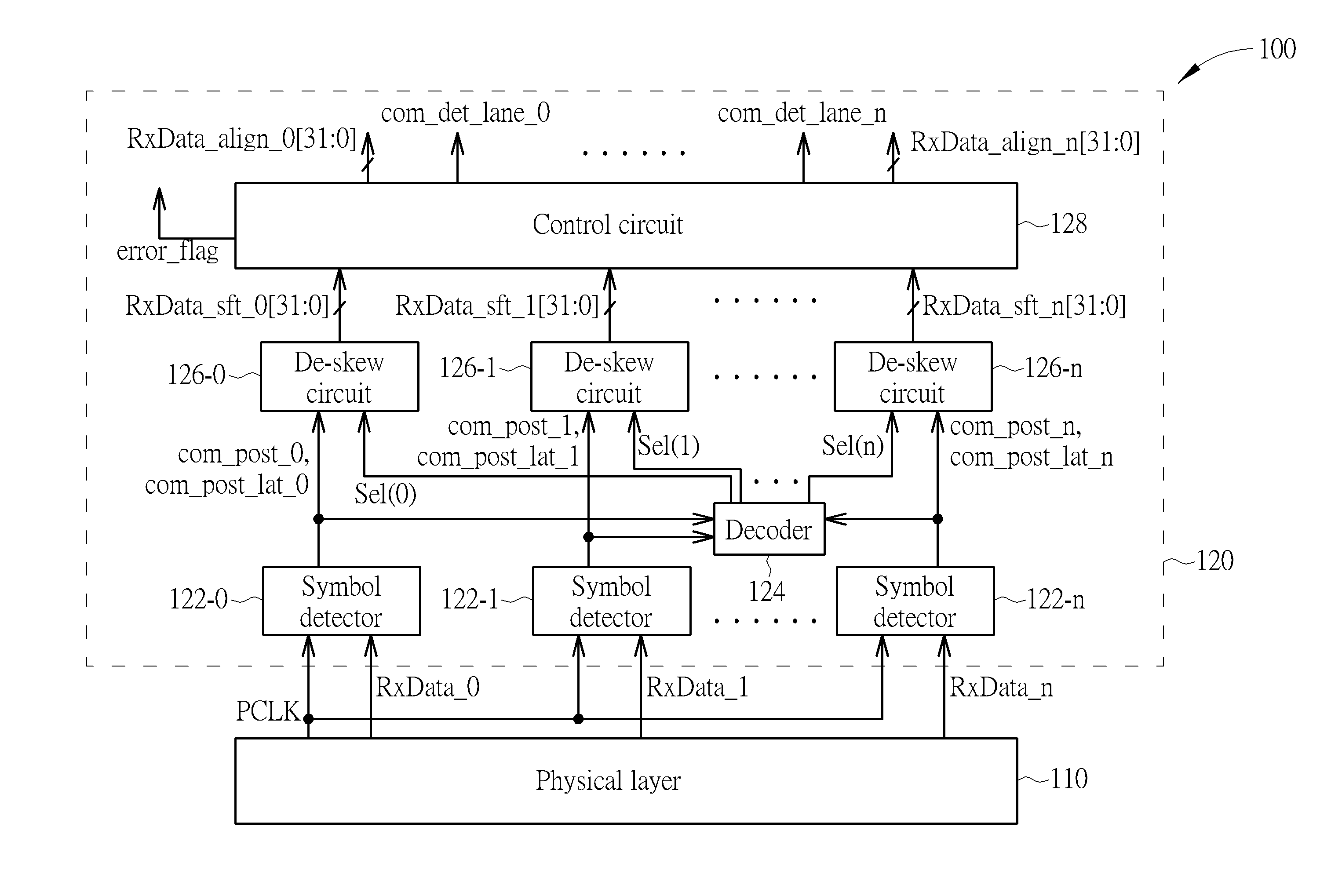

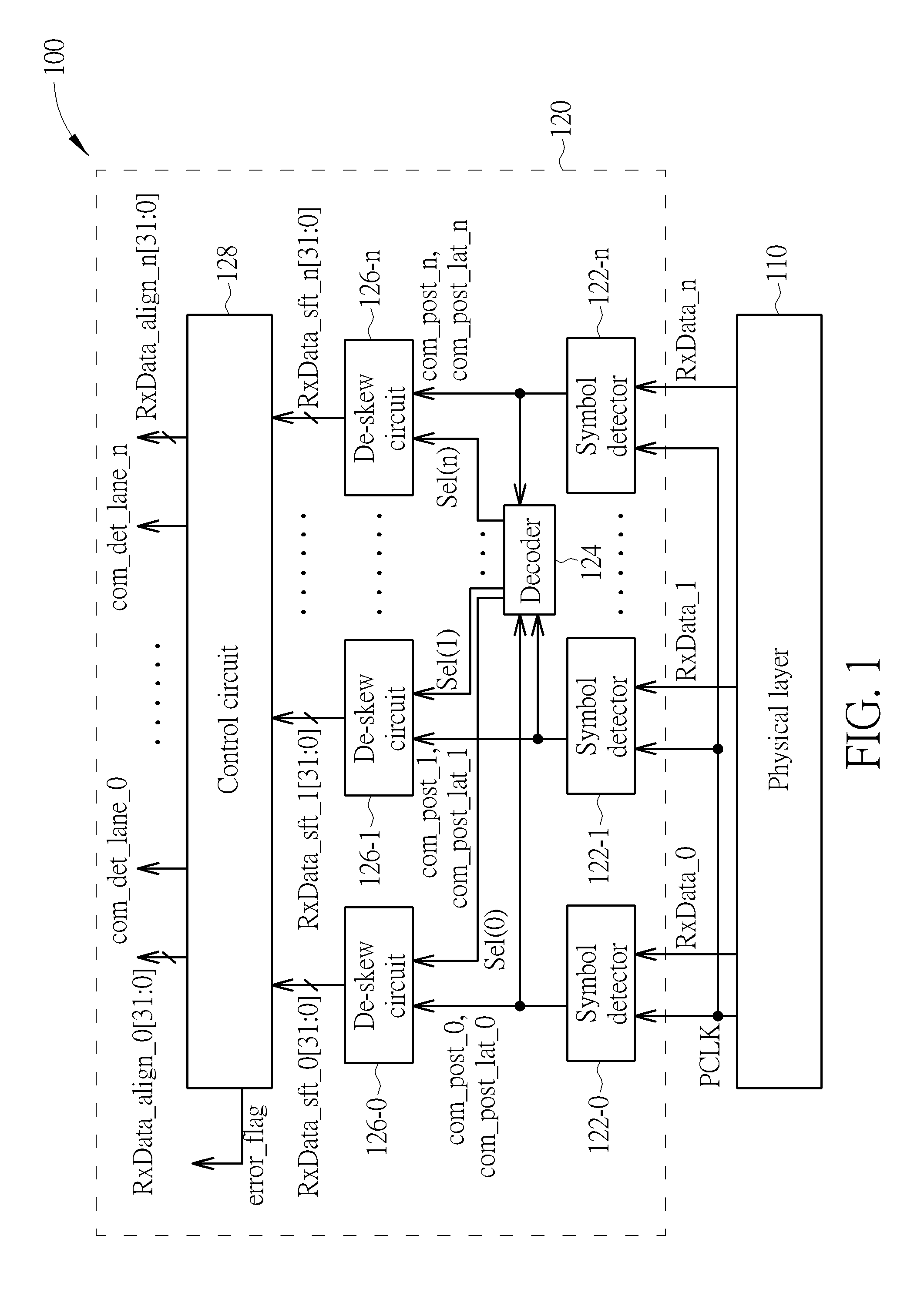

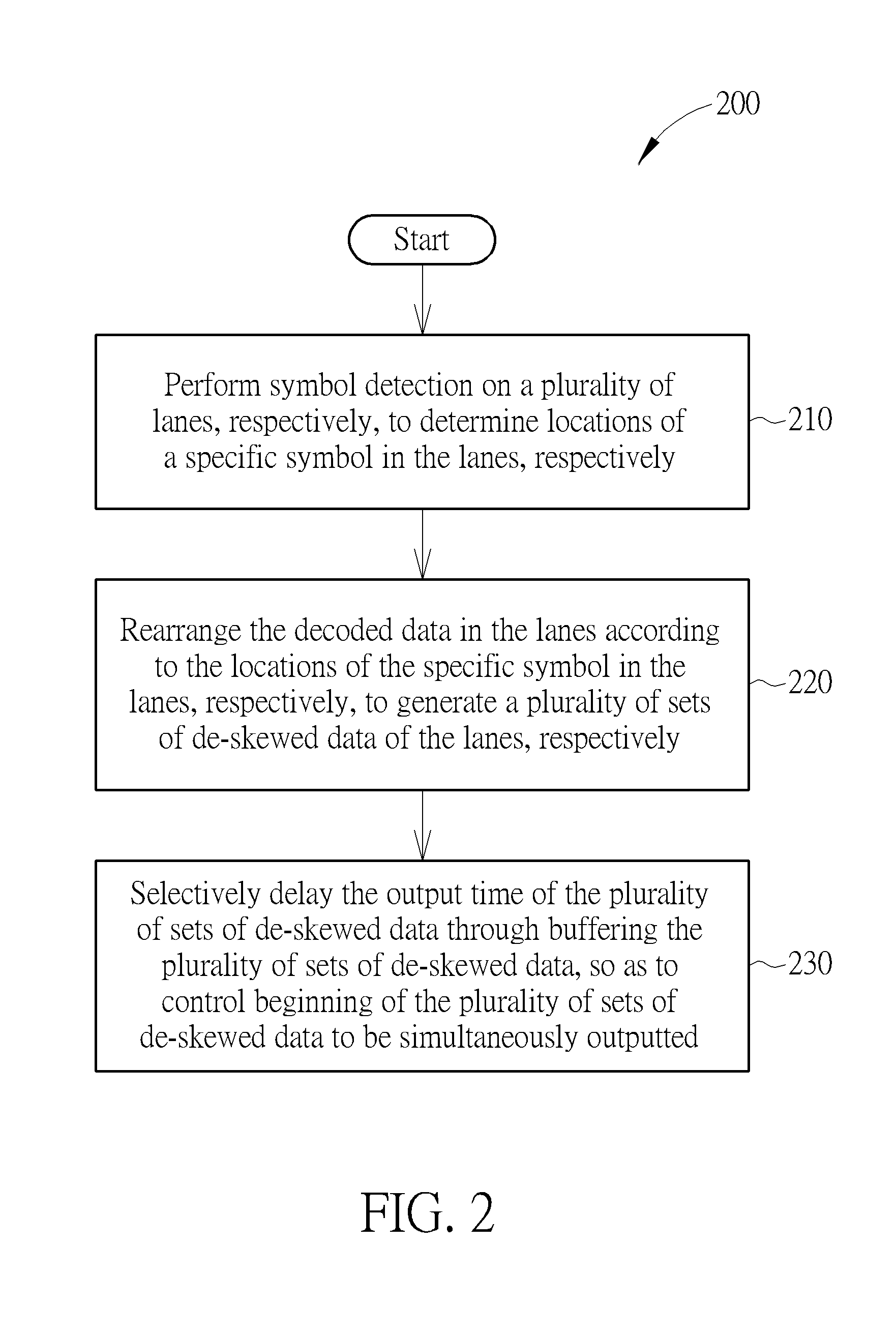

Method and apparatus for performing de-skew control

ActiveUS20150293175A1Improve performanceLong latencyDigital circuit testingRecord information storageSkewed dataElectronic equipment

A method and apparatus for performing de-skew control are provided, where the method is applied to an electronic device. The method includes the steps of: performing a symbol detection at a plurality of lanes of the electronic device, respectively, to determine locations of a specific symbol at the plurality of lanes, respectively; according to the locations of the specific symbol at the plurality of lanes, selectively rearranging decoded data in the plurality of lanes to generate a plurality of sets of de-skewed data respectively corresponding to the plurality of lanes; and by buffering the plurality of sets of de-skewed data, selectively delaying output of the plurality of sets of de-skewed data to control beginning of the plurality of sets of de-skewed data to be simultaneously output.

Owner:FARADAY TECH CORP

Implementing ecc control for enhanced endurance and data retention of flash memories

InactiveUS20150199231A1Improve enduranceImprove data retentionRead-only memoriesCode conversionMemory controllerData retention

A method, system and memory controller are provided for implementing ECC (Error Correction Codes) control to provide enhanced endurance and data retention of flash memories. The memory controller includes a VT (threshold voltage) monitor to determine VT degradation of cells and blocks; the VT monitor configured to store information about the determined VT degradation; a first ECC engine having a first level of ECC capability; a second ECC engine having a second level of ECC capability, the second level higher than the first level, the second ECC engine having a longer latency than the first ECC engine; a logic to issue a read request to a particular cell / block, and, using the determined VT degradation, use the first ECC engine if the determined VT degradation is less than a threshold and to use the second ECC engine if the determined VT degradation is above the threshold.

Owner:IBM CORP

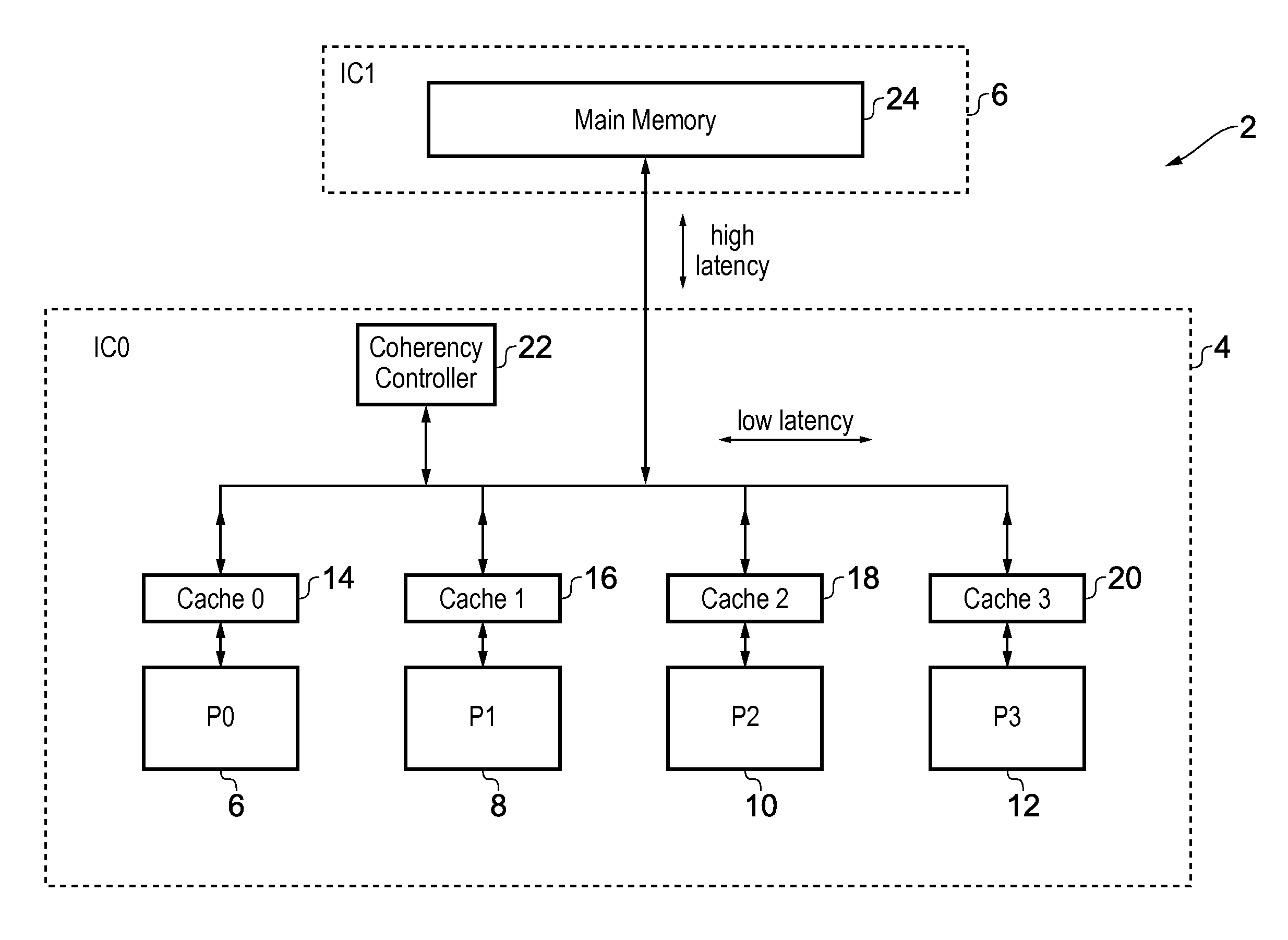

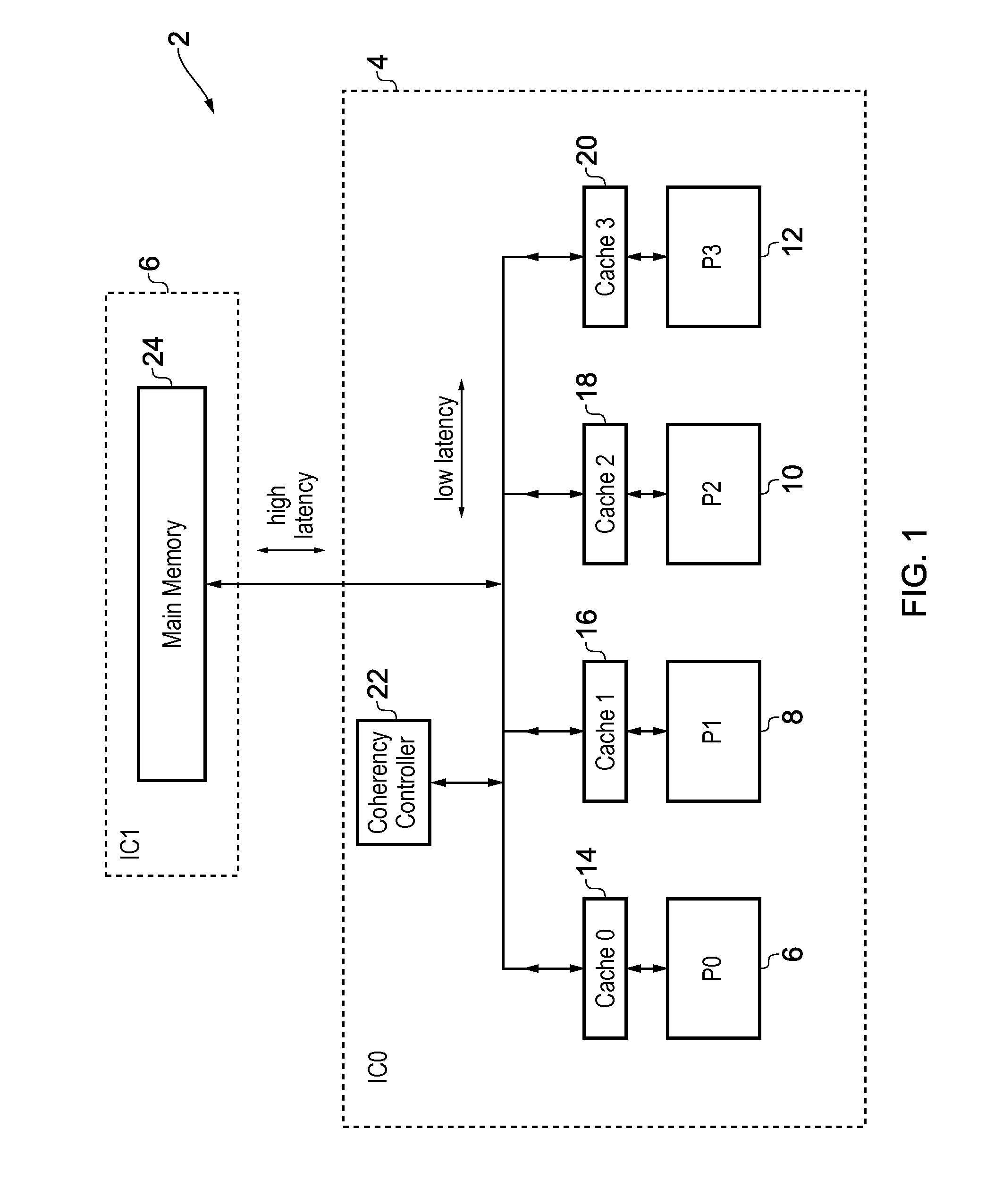

Ordering constraint management within coherent memory systems

ActiveUS20150220440A1Constraint satisfactionLong latencyMemory architecture accessing/allocationMemory adressing/allocation/relocationData valueConsistency control

A data processing system including multiple processors 6, 8, 10, 12 each with a local cache memory 14, 16, 18, 20 share a main memory 24 under control of a coherency controller 22. Store requests from a store requester which are to be serviced by data received from the main memory 24 trigger the coherency controller 22 to return exclusive rights to access the data to the store requester before the corresponding data is returned from the main memory 24. The store requester uses possession of the exclusive rights to access the data to permit further processing with an ordering constraint relative to the store request to proceed even though the store request has yet to be finished. The ordering constraint may be, for example, a fence instruction. The store requester in possession of the exclusive rights to access the data values ensures that the store request is finished and its results observed by any instruction as required by the ordering constraint it has released early.

Owner:THE RGT OF THE UNIV OF MICHIGAN

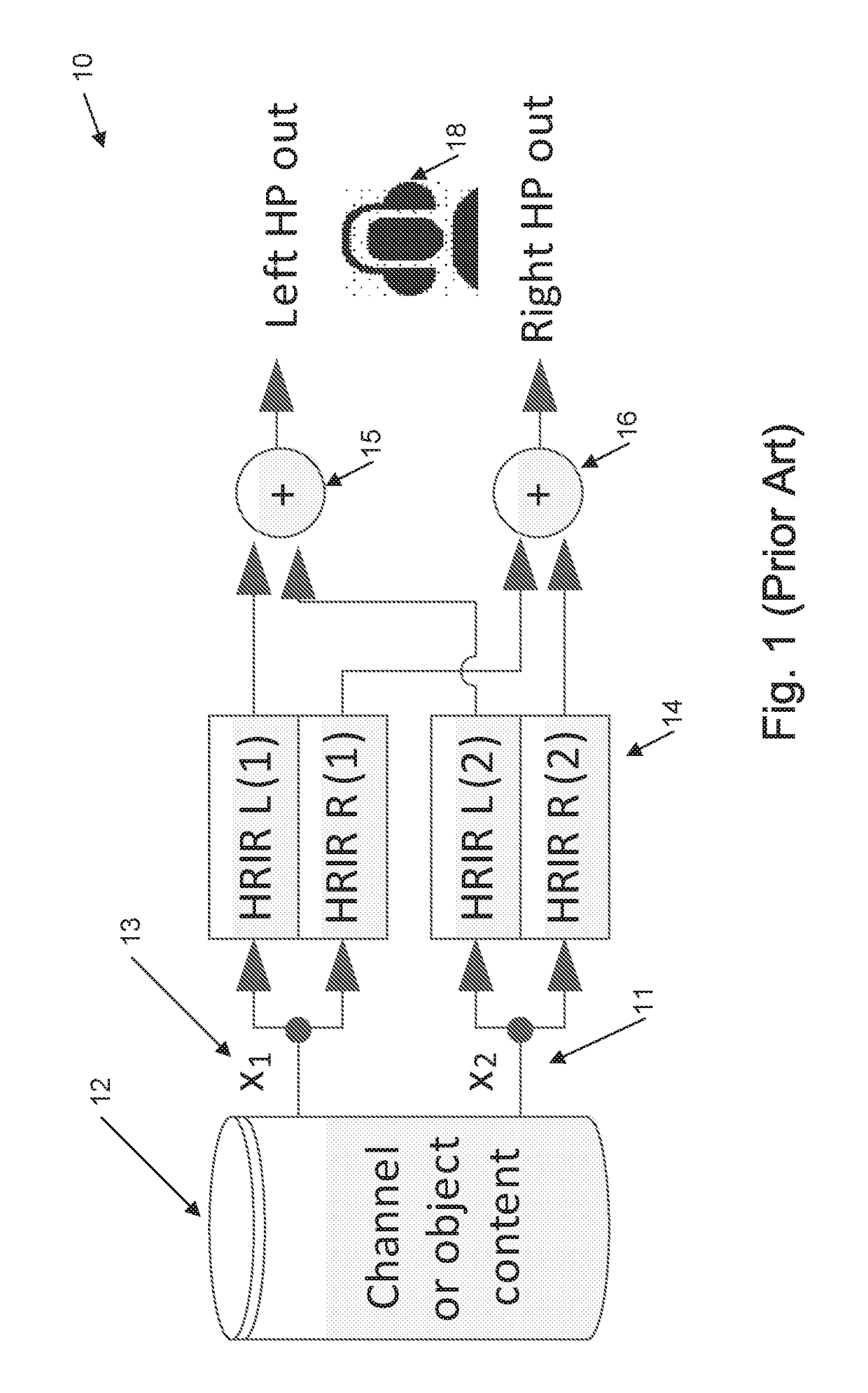

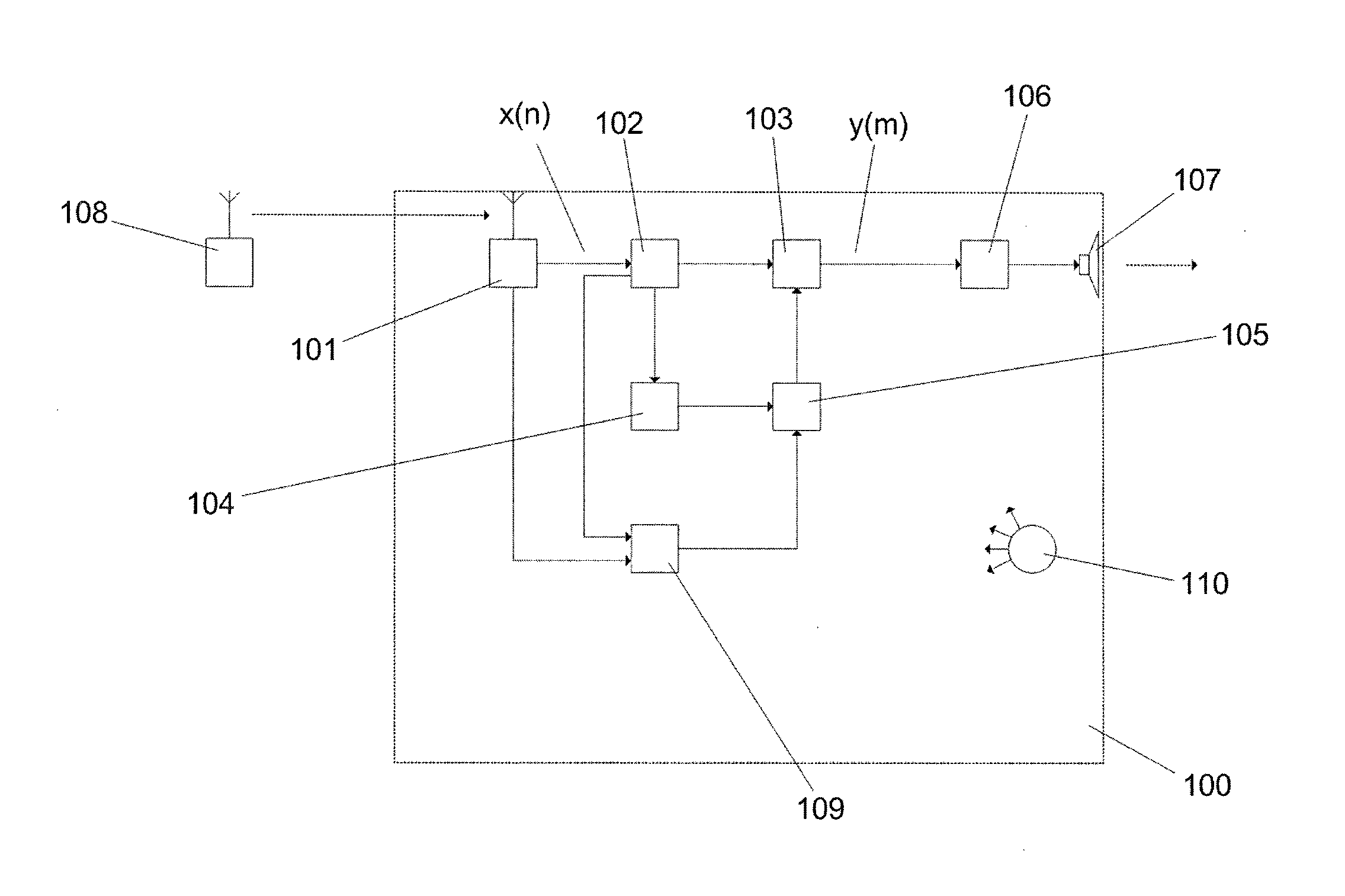

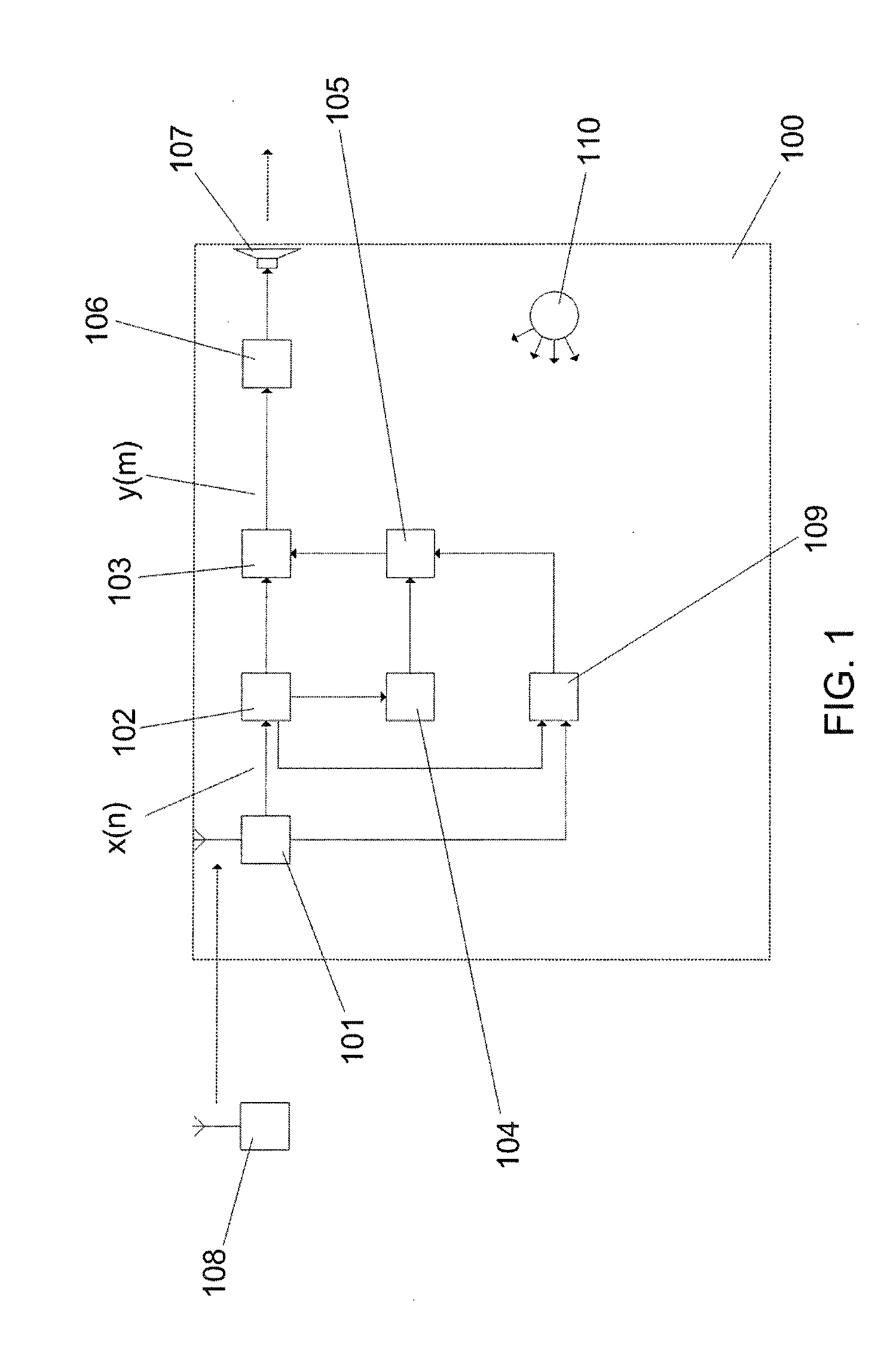

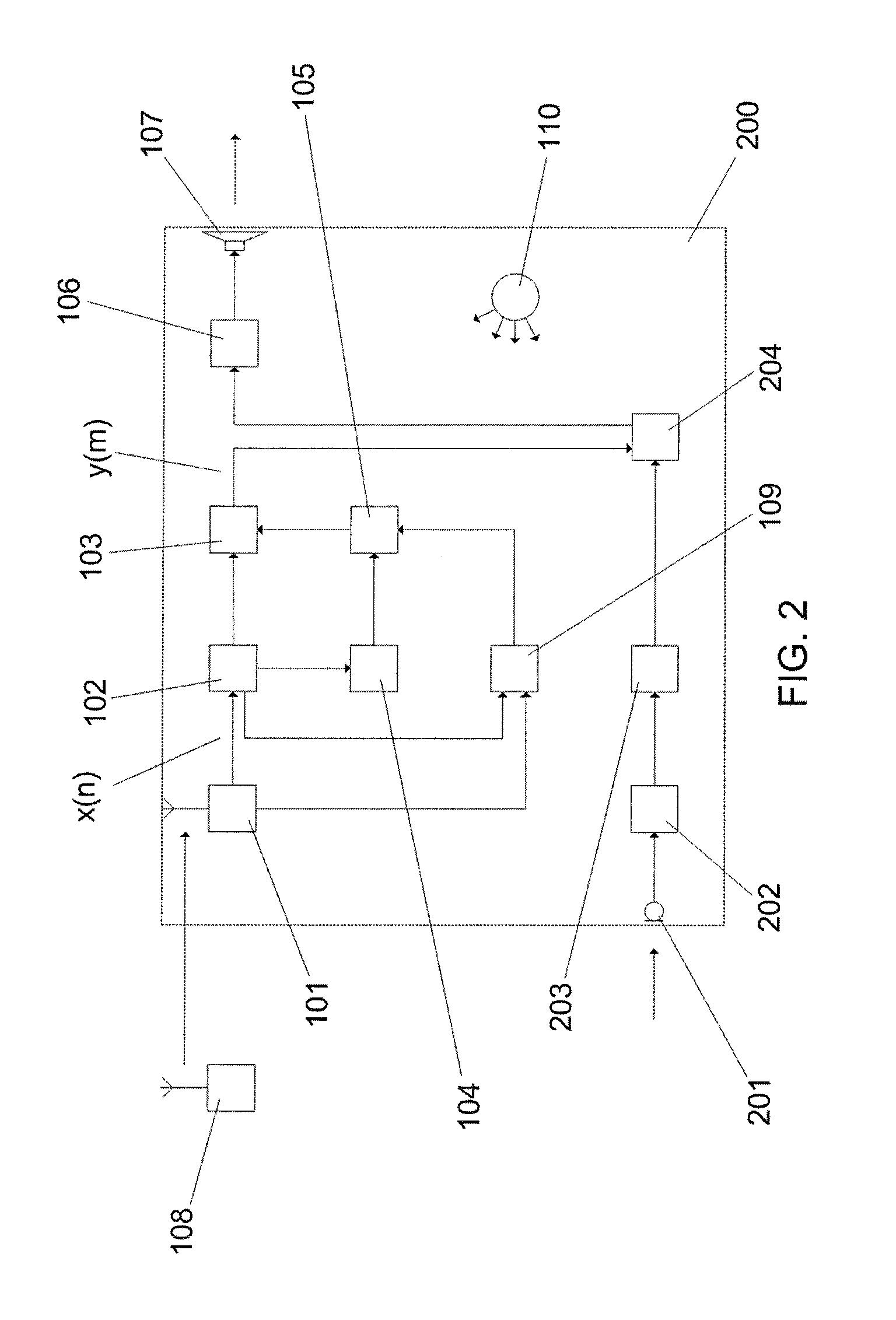

Method for operating a hearing device and hearing device

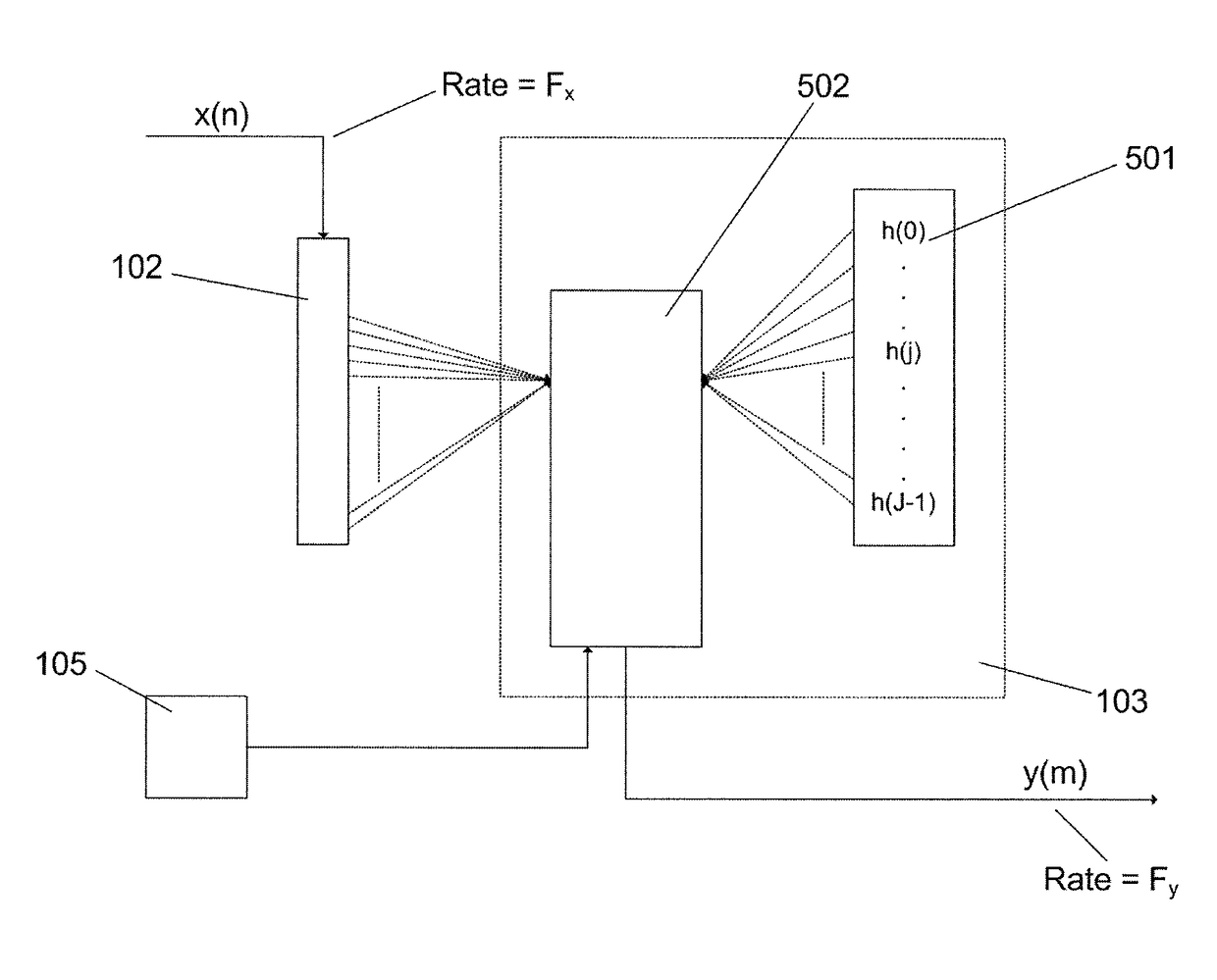

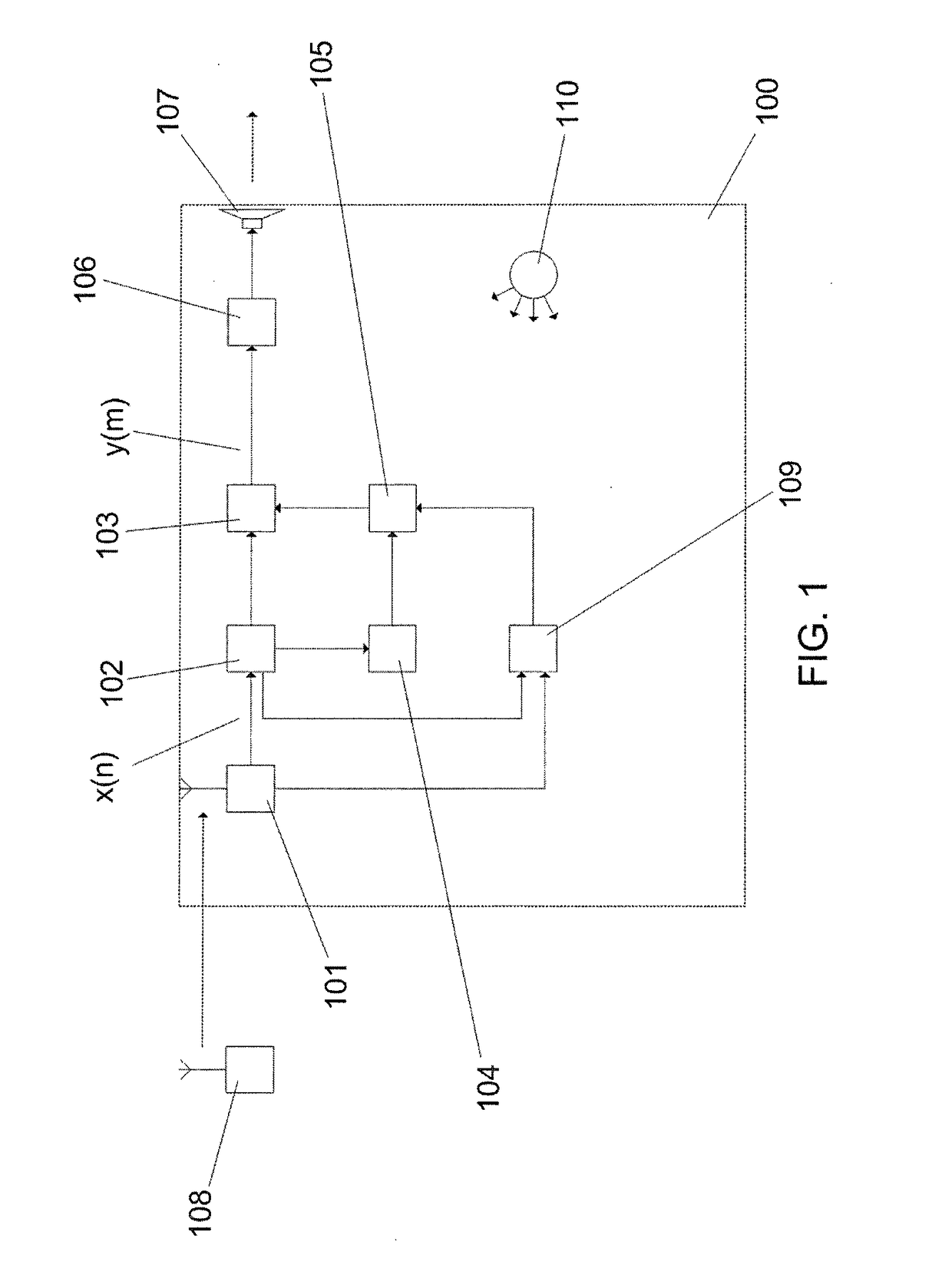

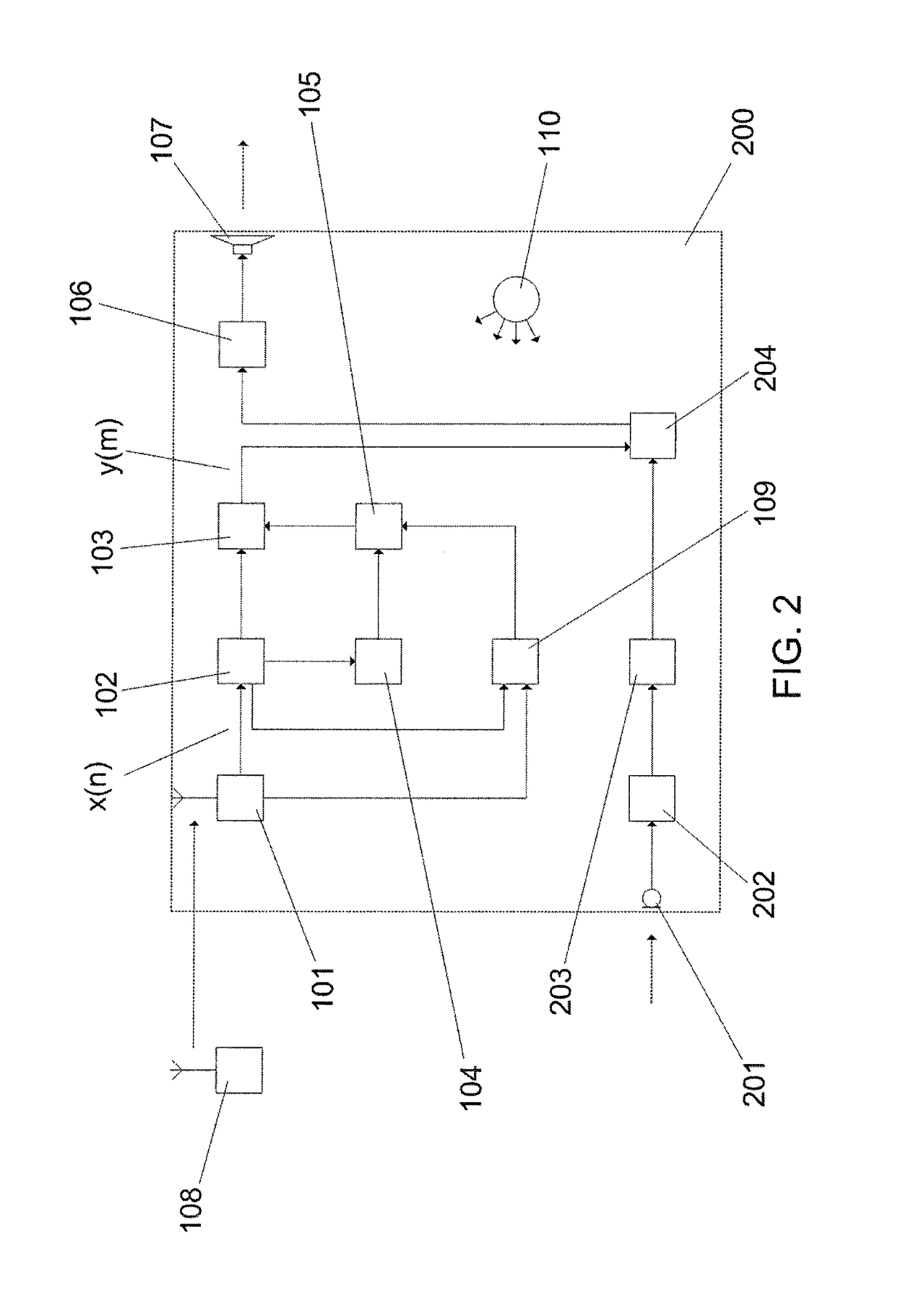

ActiveUS20140226830A1Long latencyIncreased riskHearing aids testing/monitoringSample rate conversionHearing apparatus

A hearing device comprises a receiver, an input buffer and a sample processor, the receiver being adapted to receive samples of a digital audio signal and feed received samples as a digital input signal to the input buffer, the sample processor being adapted to process the buffered samples to provide samples of a digital output signal such that the digital output signal is a sample-rate converted representation of the digital input signal with a predetermined target sample rate. The hearing device further comprises a latency controller adapted to estimate the quality of reception of the digital audio signal and to control the processing of the buffered samples in dependence on the estimated quality of reception.

Owner:SENNHEISER ELECTRONICS GMBH & CO KG +1

Method for operating a hearing device and hearing device

ActiveUS9894445B2Long latencyIncreased riskTime-division multiplexHearing aids testing/monitoringSample rate conversionHearing apparatus

A hearing device comprises a receiver, an input buffer and a sample processor, the receiver being adapted to receive samples of a digital audio signal and feed received samples as a digital input signal to the input buffer, the sample processor being adapted to process the buffered samples to provide samples of a digital output signal such that the digital output signal is a sample-rate converted representation of the digital input signal with a predetermined target sample rate. The hearing device further comprises a latency controller adapted to estimate the quality of reception of the digital audio signal and to control the processing of the buffered samples in dependence on the estimated quality of reception.

Owner:SENNHEISER ELECTRONICS GMBH & CO KG +1

Method for changing power states of a computer

InactiveUS8028177B2Long latencyVolume/mass flow measurementDigital computer detailsSleep stateData loss

Owner:HON HAI PRECISION IND CO LTD

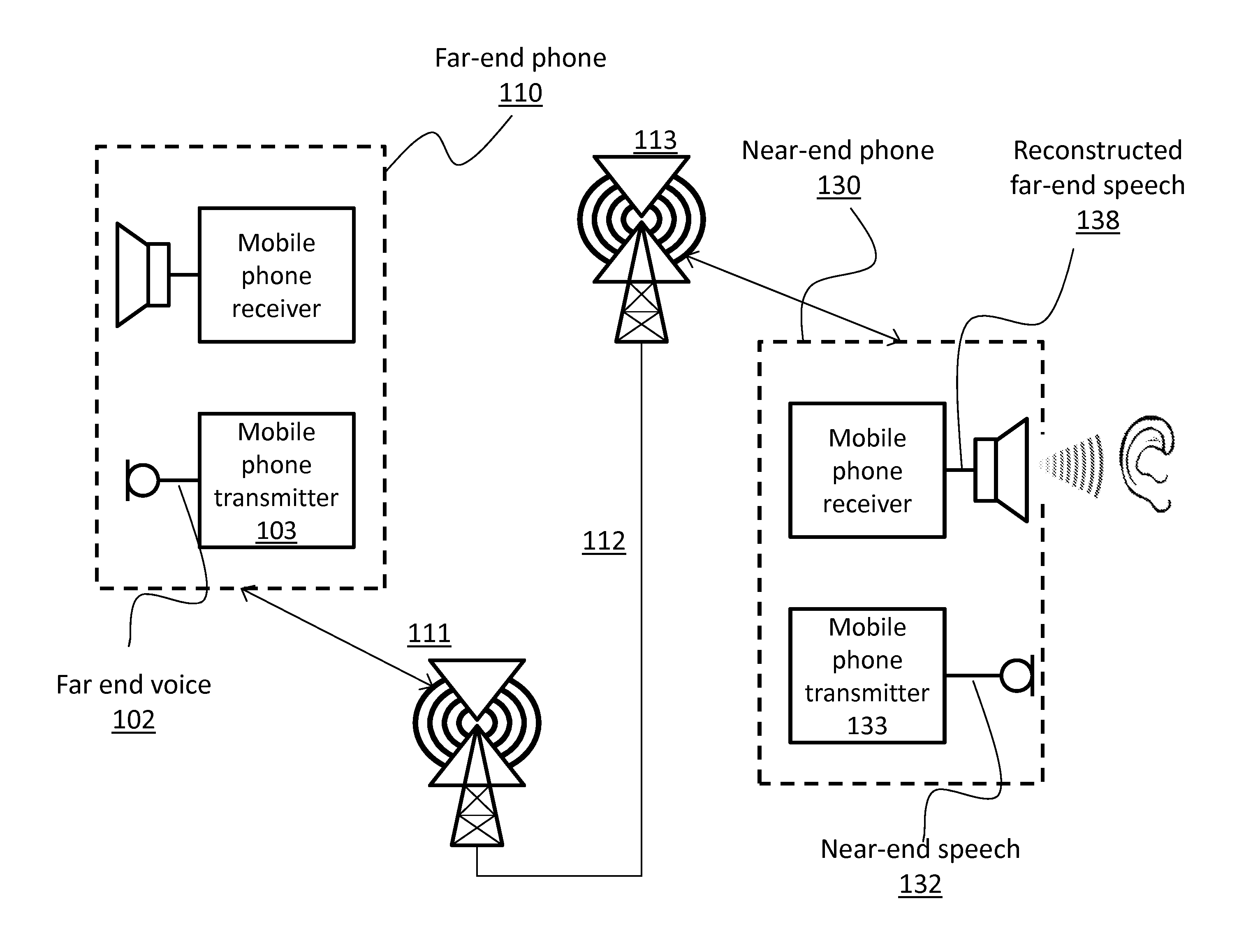

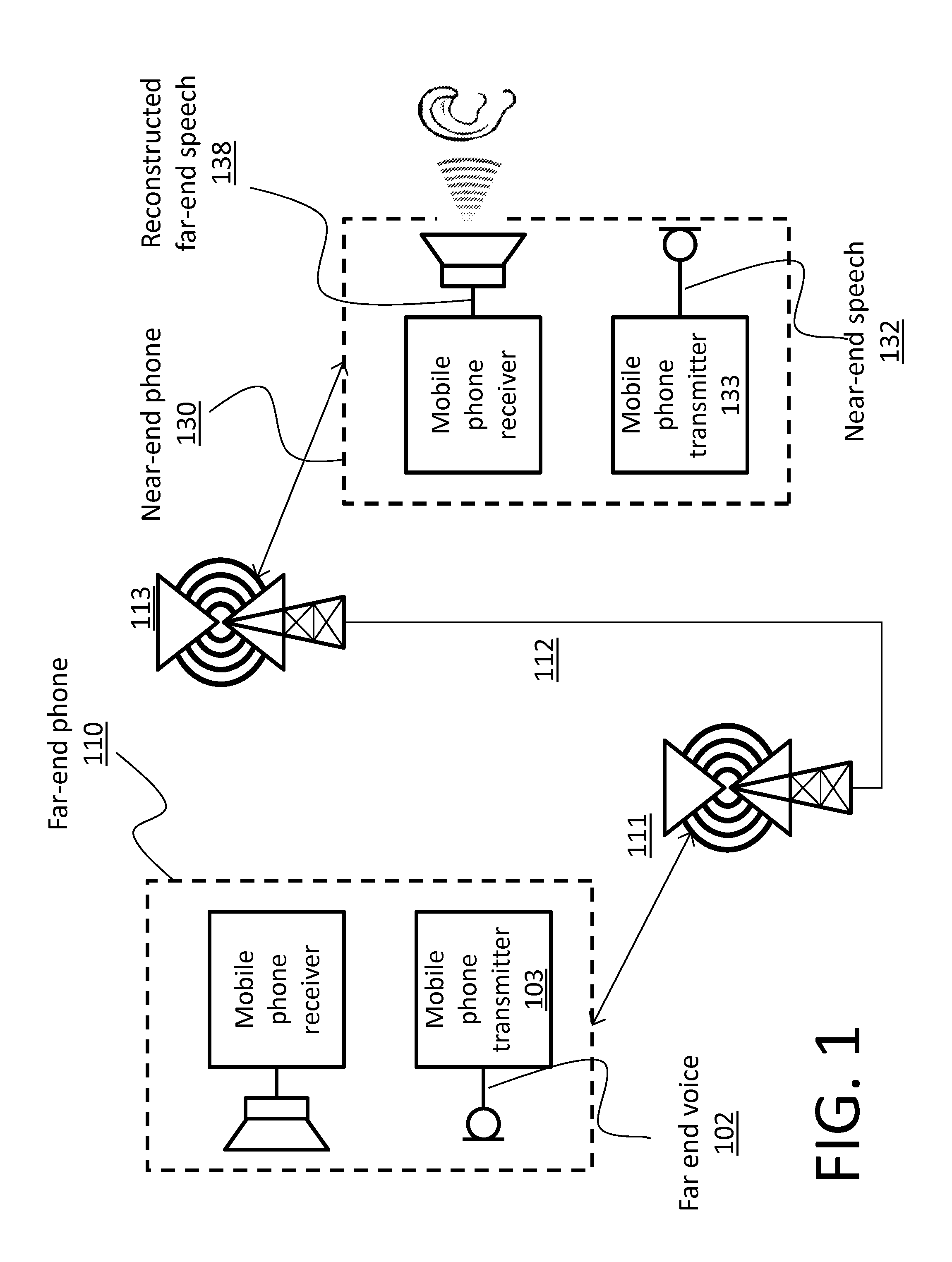

Error concealment for speech decoder

ActiveUS20140257800A1Mitigates degradationIncrease delayReceiver specific arrangementsSpeech analysisError concealmentSpeech sound

Provided is a system, method, and computer program product for improving the quality of speech reproduction in wireless applications where the received speech frames are subject to transmission and packet losses. The speech decoding process is dynamically delayed by at least one frame period in order to perform additional error correction and concealment techniques during times when the wireless link quality if below a predetermined threshold. The wireless link is monitored and if the link quality falls below a predetermined threshold, the decoding process is delayed by at least one frame period so that one or more error correcting techniques can be performed to increase the quality of the reconstructed speech.

Owner:QOSOUND

Method and system for delivering from a loudspeaker into a venue

InactiveUS7672637B2Reduce chanceLong latencyElectric signal transmission systemsBroadcast-related systemsTelecommunicationsControl signal

Spread-spectrum technology, either direct sequence or frequency hopping, or a combination of the two, is used for transmitting audio signals one way and control signals two ways over an RF channel(s) to reduce interference with / from other RF transmissions and enabling use of multiple such systems in close proximity without requiring pre-selection of transmission frequencies. Alternatively, multiple channels with appended access codes may be used, wherein interference or loss of clear signal results in automatic switching to another channel. The control signals accompany the transmitted audio signal at some time in the transmission interval, or previous to the beginning of the transmission interval, and constitute a coded control message allowing a unique connection. In some cases the encoding keys may only occur at the beginning of the desired message, while in other cases the two-way control signals may continue throughout the interval of the message link.

Owner:RPX CORP

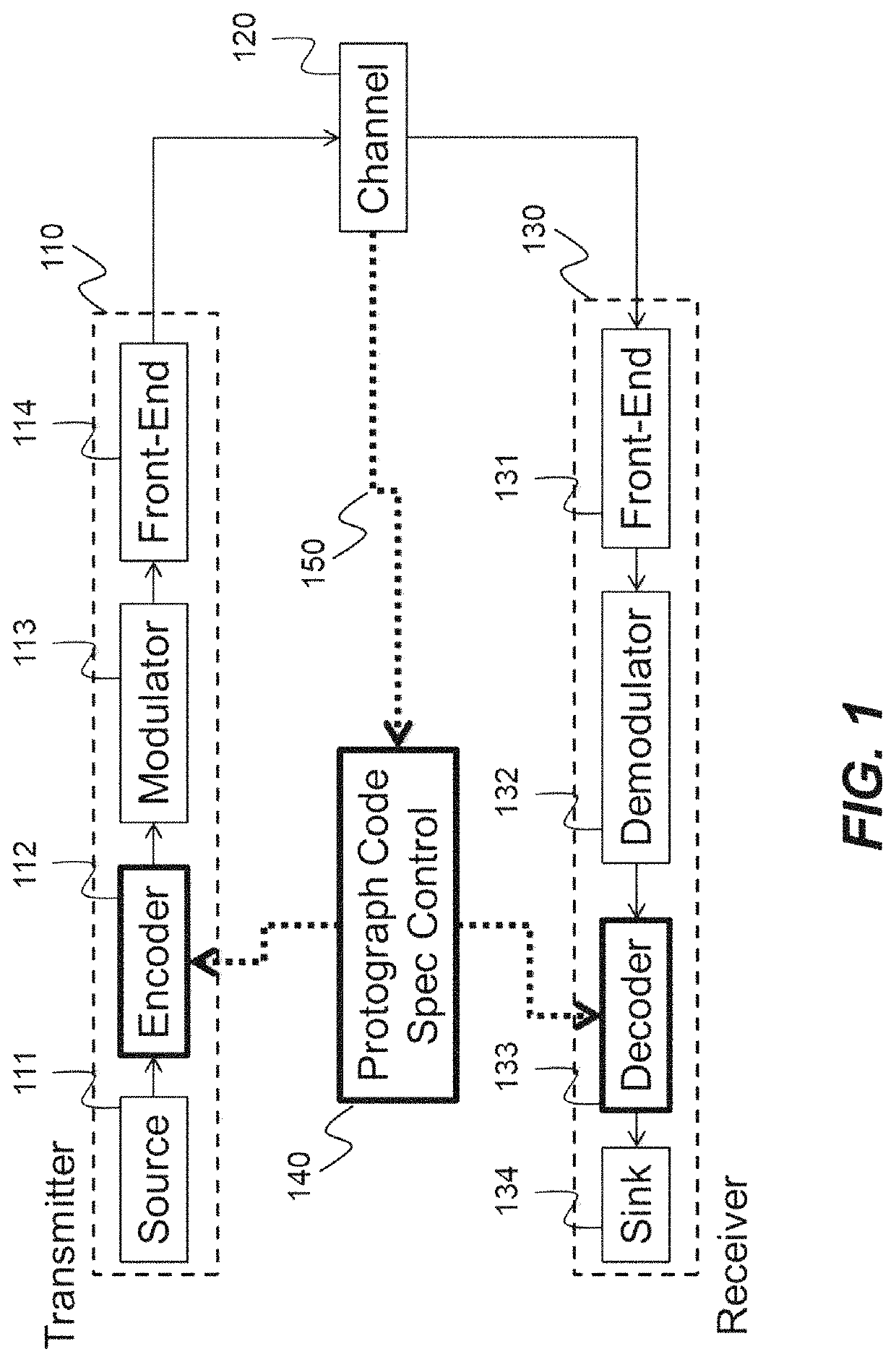

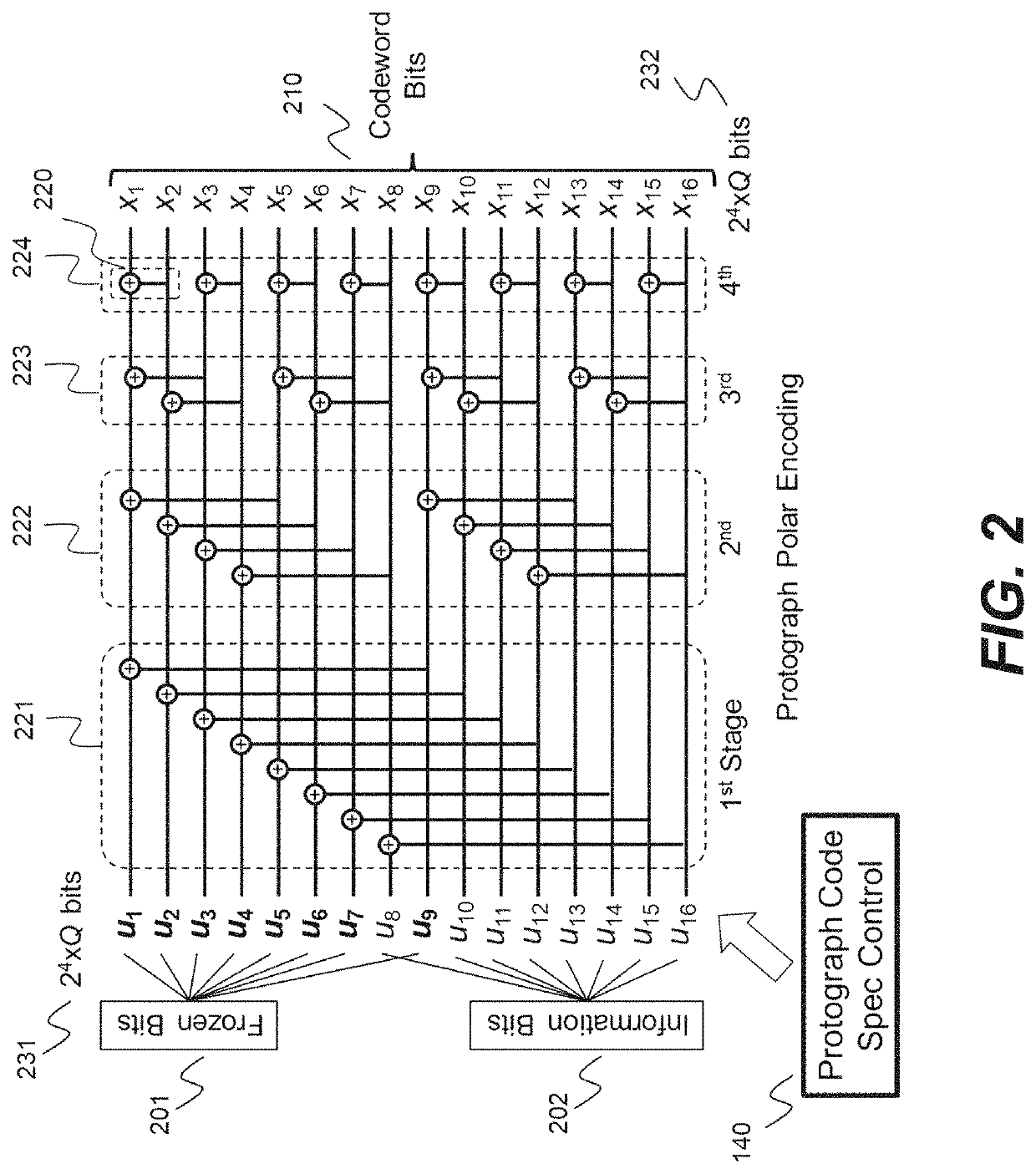

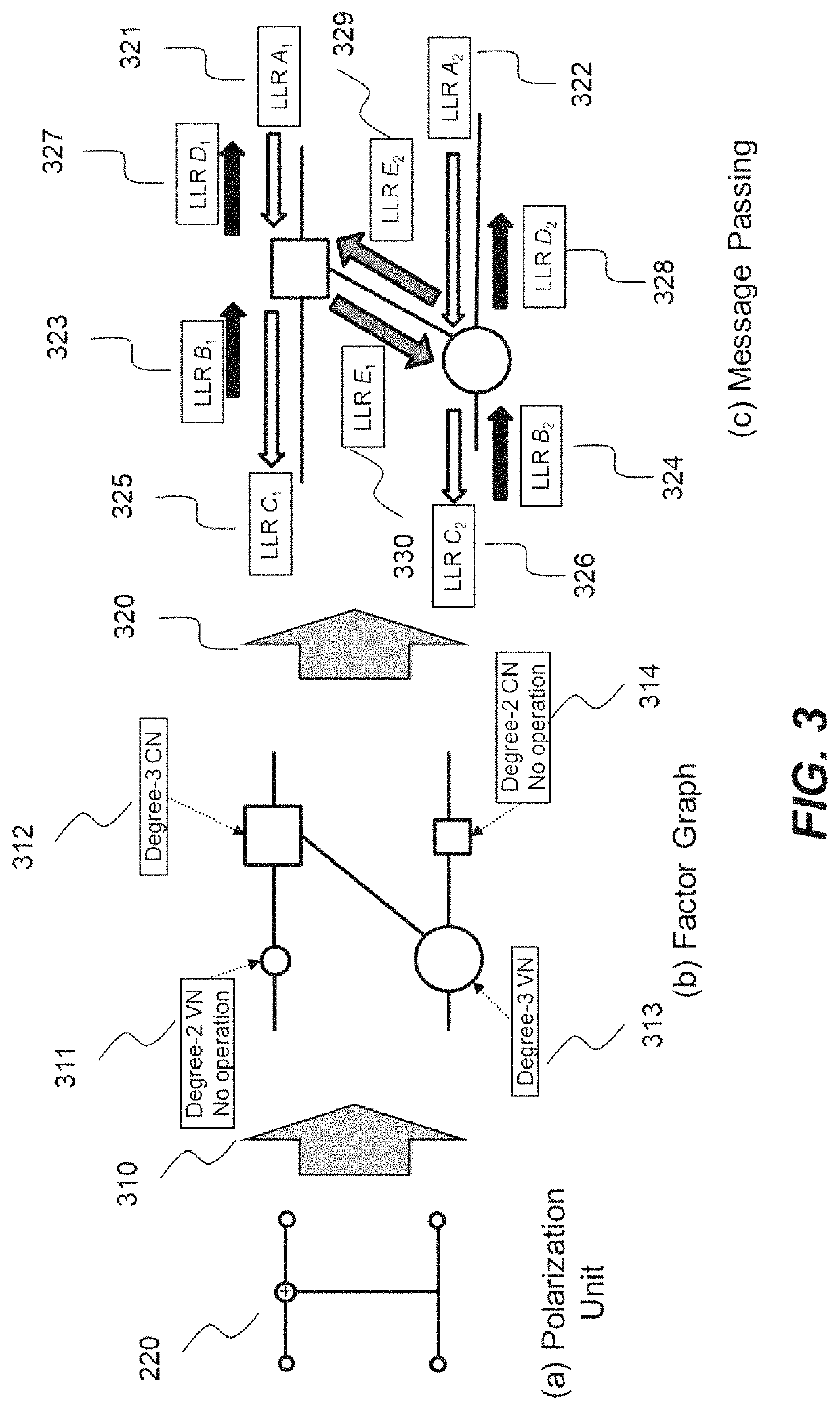

Protograph quasi-cyclic polar codes and related low-density generator matrix family

ActiveUS11463114B2Increased complexityImprove latencyOther decoding techniquesCode conversionComputation complexityMessage delivery

Data communications and storage systems require error control techniques to be transferred successfully without failure. Polar coding has been used as a state-of-the-art forward error correction code for such an error control technique. However, the conventional decoding based on successive cancellation has a drawback in its poor performance and long latency to complete. Because the factor graph of polar codes has a lot of short cycles, a parallelizable belief propagation decoding also does not perform well. The method and system of the present invention provide a way to resolve the issues by introducing a protograph lifting expansion for a polar coding family so that highly parallelizable decoding is realized to achieve a high coding gain and high throughput without increasing the computational complexity and latency. The invention enables an iterative message passing to work properly by eliminating short cycles through a hill-climbing optimization of frozen bits allocation and permutation.

Owner:MITSUBISHI ELECTRIC RES LAB INC