Patents

Literature

107results about How to "Without negative effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and meeting scheduler for automated meeting scheduling using delegates, representatives, quorums and teams

InactiveUS7299193B2Without negative effectOvercome disadvantagesOffice automationResourcesComputer programReal-time computing

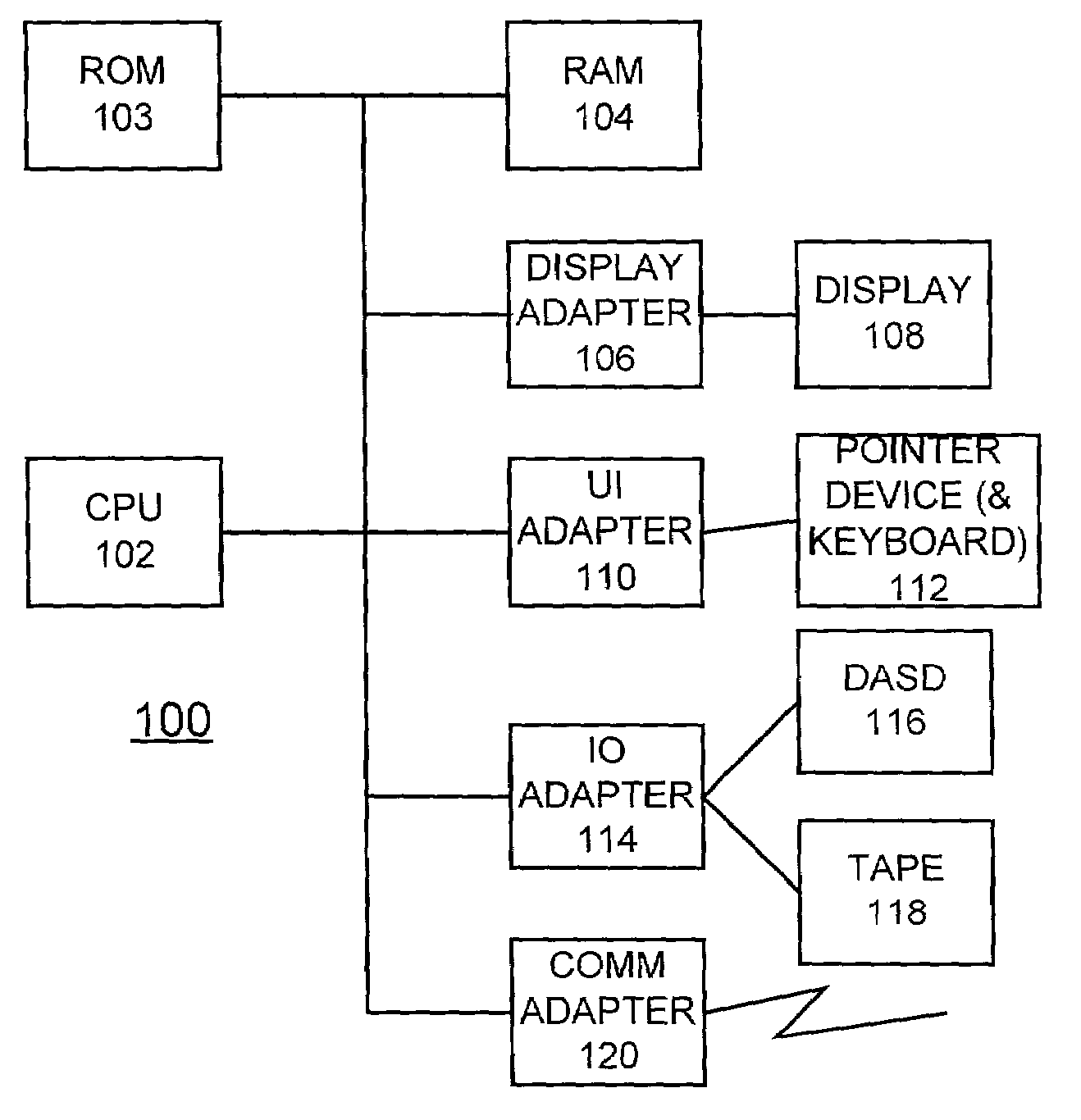

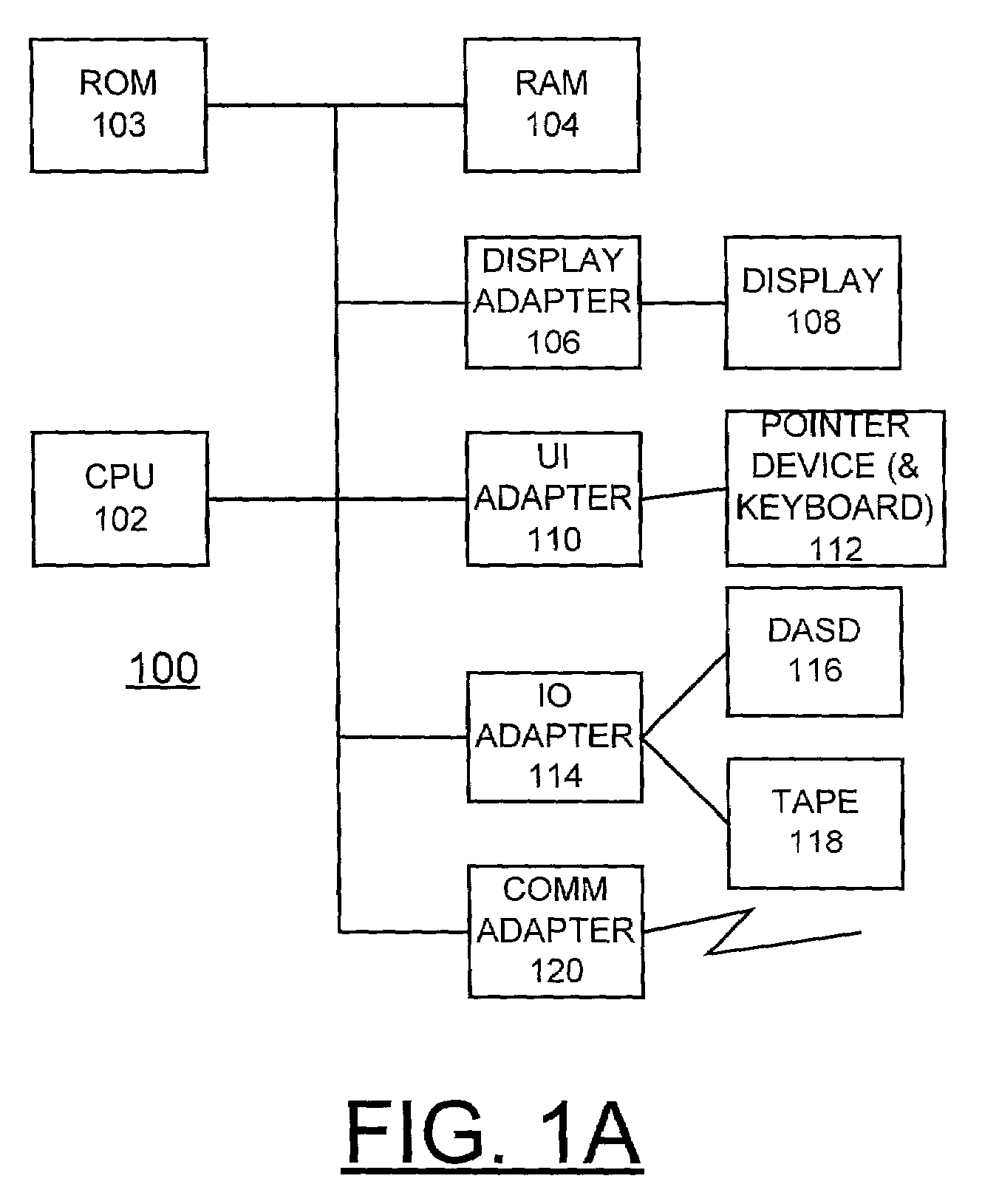

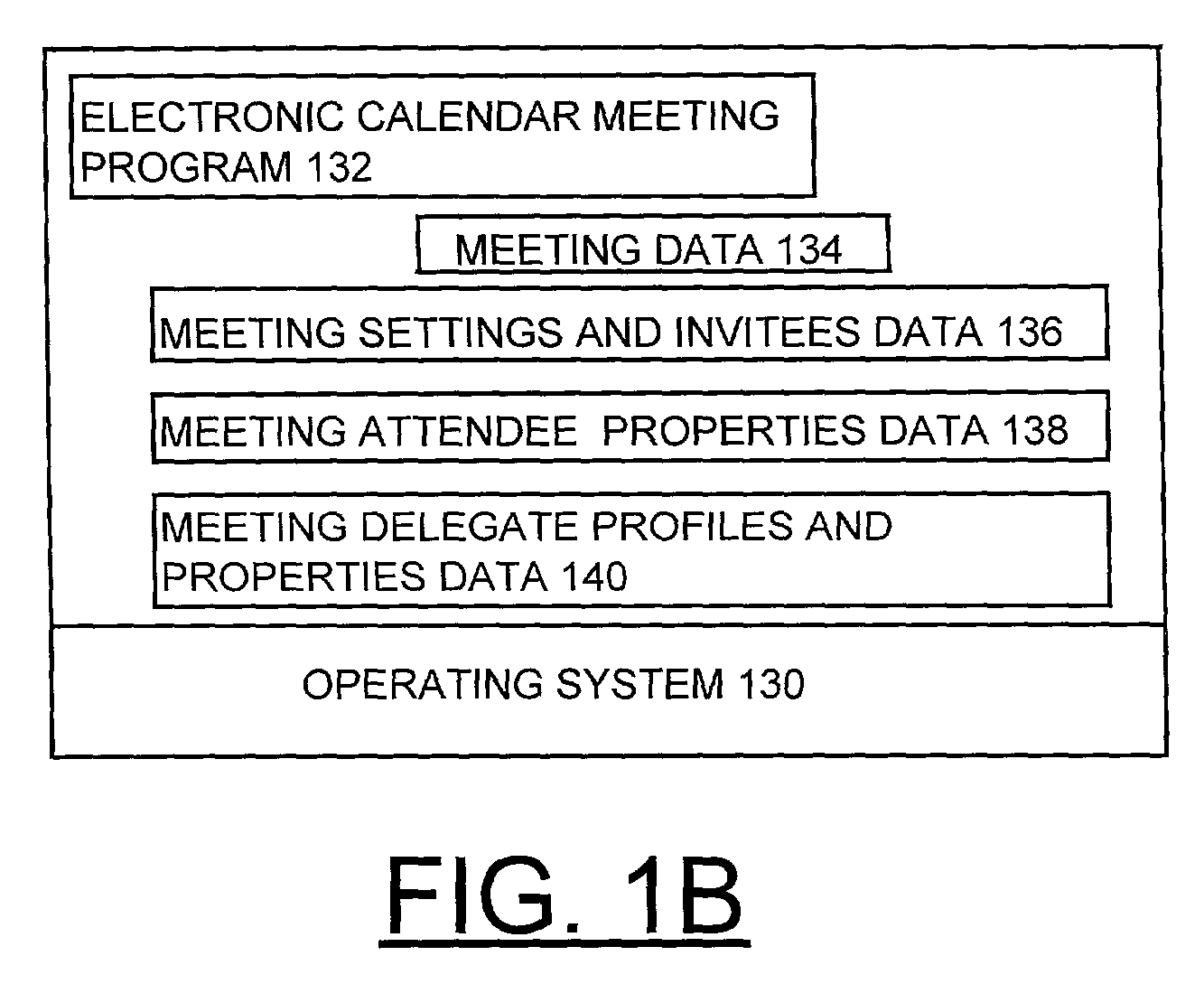

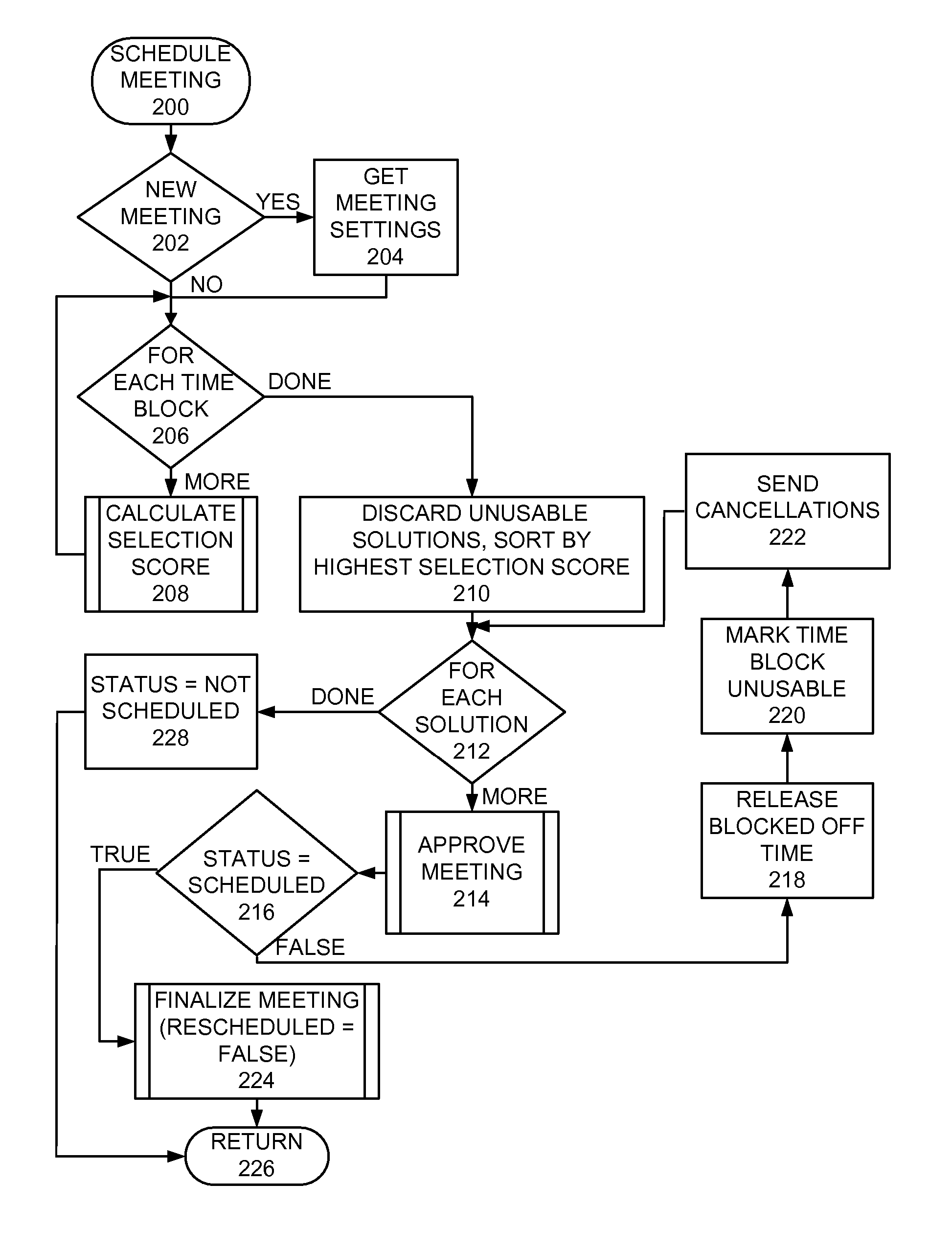

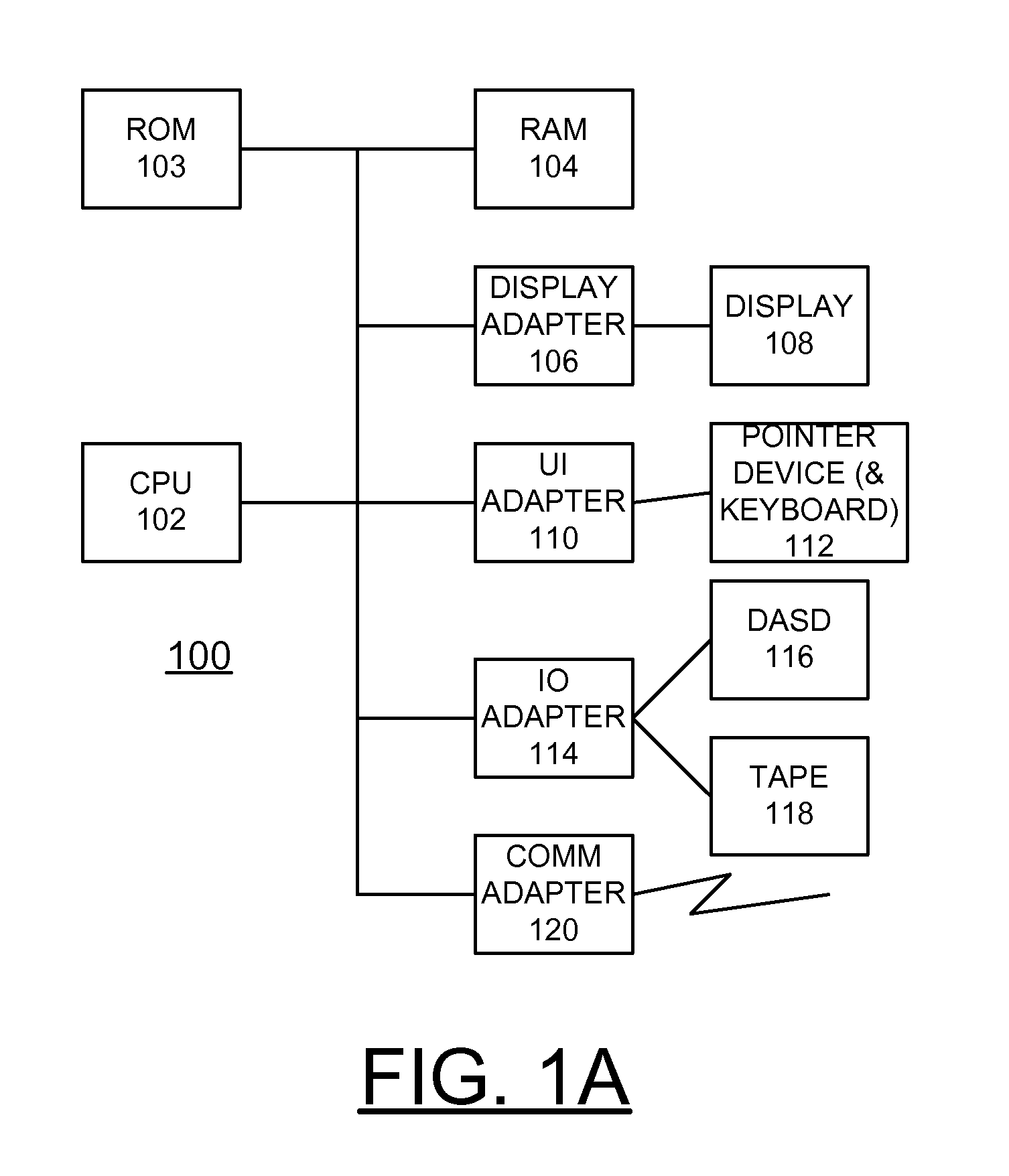

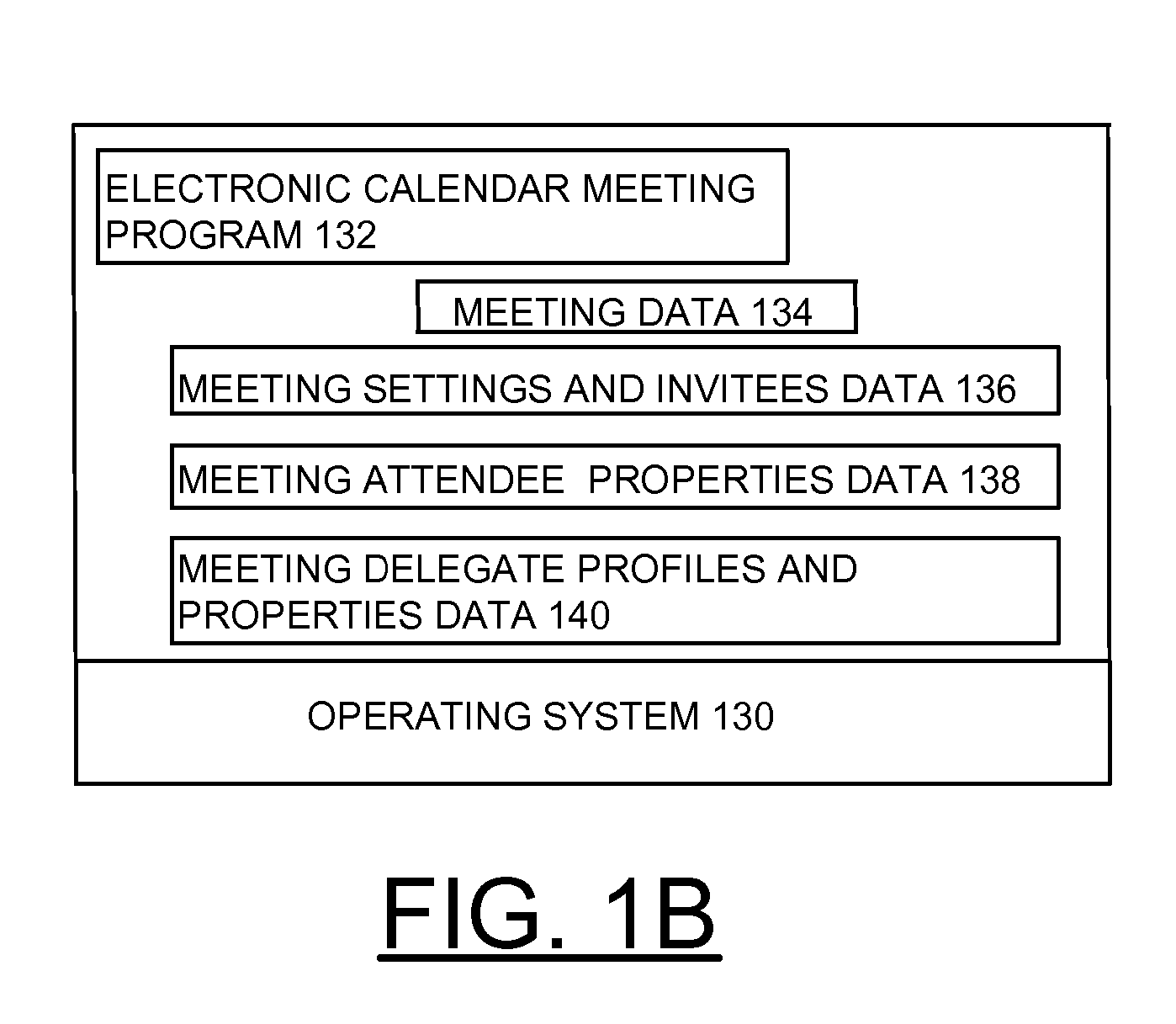

A method, meeting scheduler and computer program product are provided for automated meeting scheduling using delegates, representatives, quorums, and teams. Meeting settings and invitees data are stored for a meeting. The meeting settings and invitees data includes invitee attendance type, delegates, representatives, quorums, and teams data. A solution time block for automated meeting scheduling including at least a subset of a plurality of selected invitees is identified utilizing the invitee attendance type, delegates, representatives, quorums, and teams data. A selection score is calculated for each potential time block for automated meeting scheduling utilizing the stored meeting settings and invitees data including the invitee attendance type, delegates, representatives, quorums, and teams data. The solution time block for automated meeting scheduling including a subset of a plurality of selected invitees is identified utilizing the calculated selection score.

Owner:IBM CORP

Insect control mat

InactiveUS6337080B1Without negative effectInhibition retentionBiocidePhosphorous compound active ingredientsInsect

Owner:SC JOHNSON & SON INC

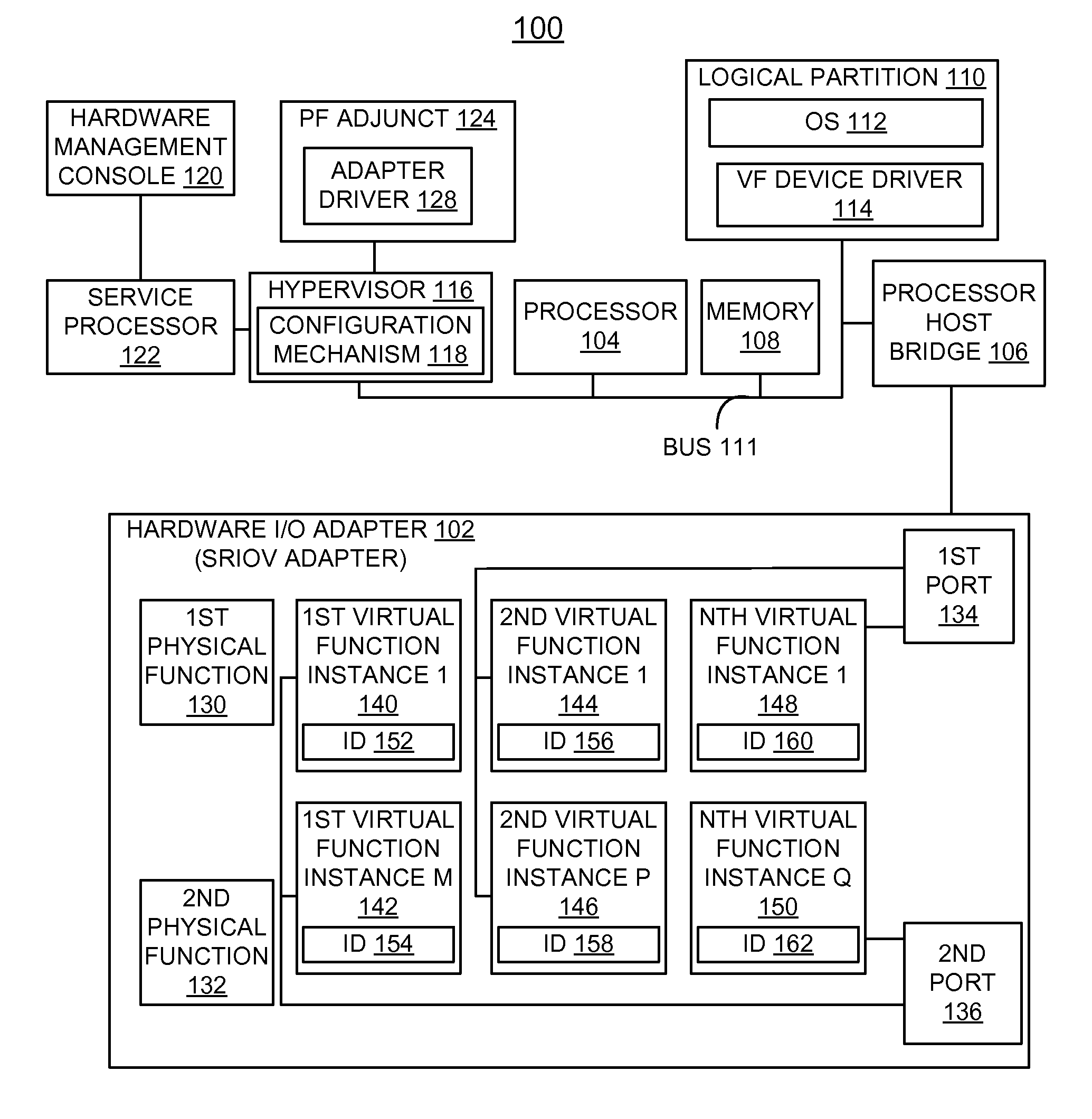

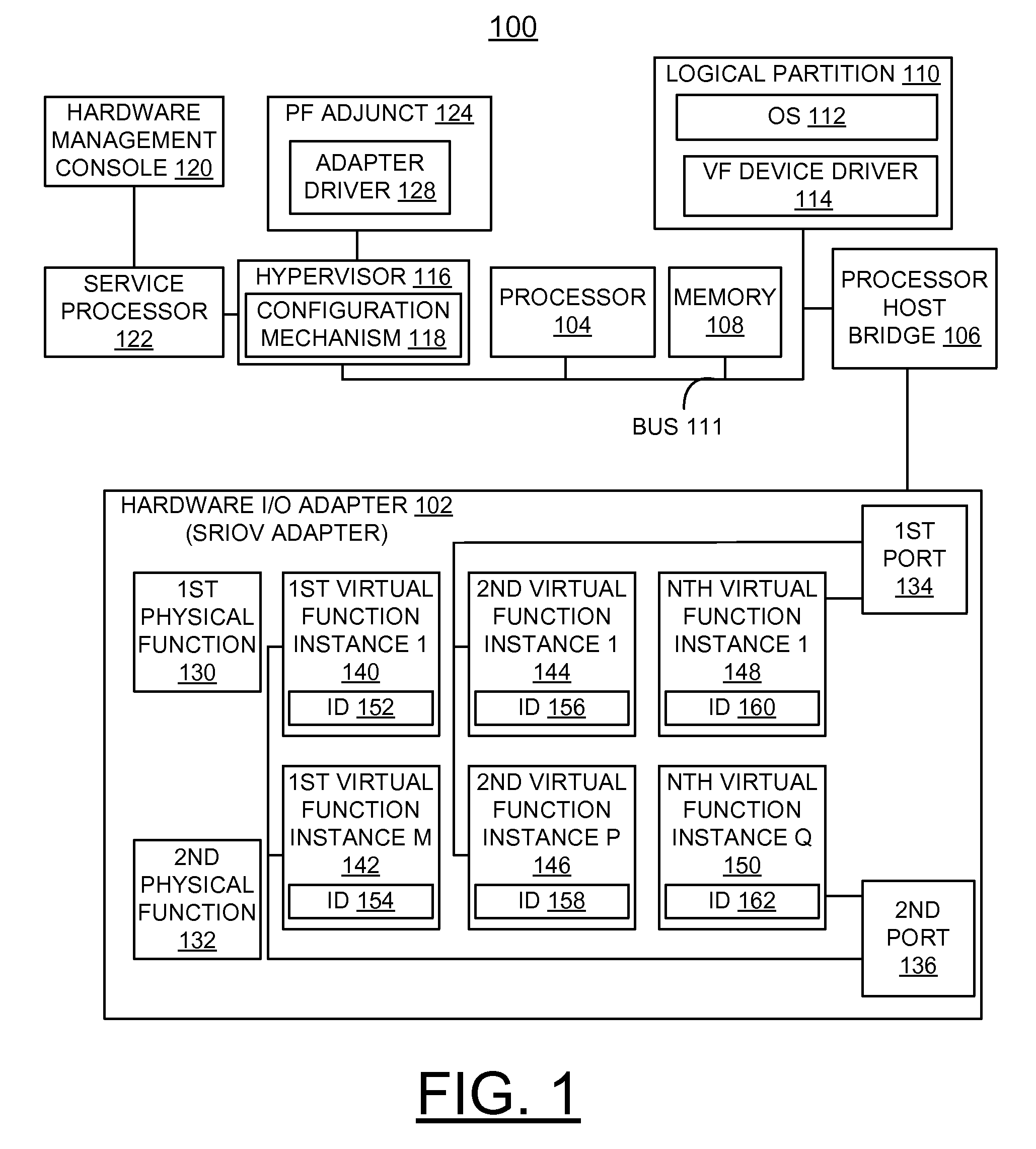

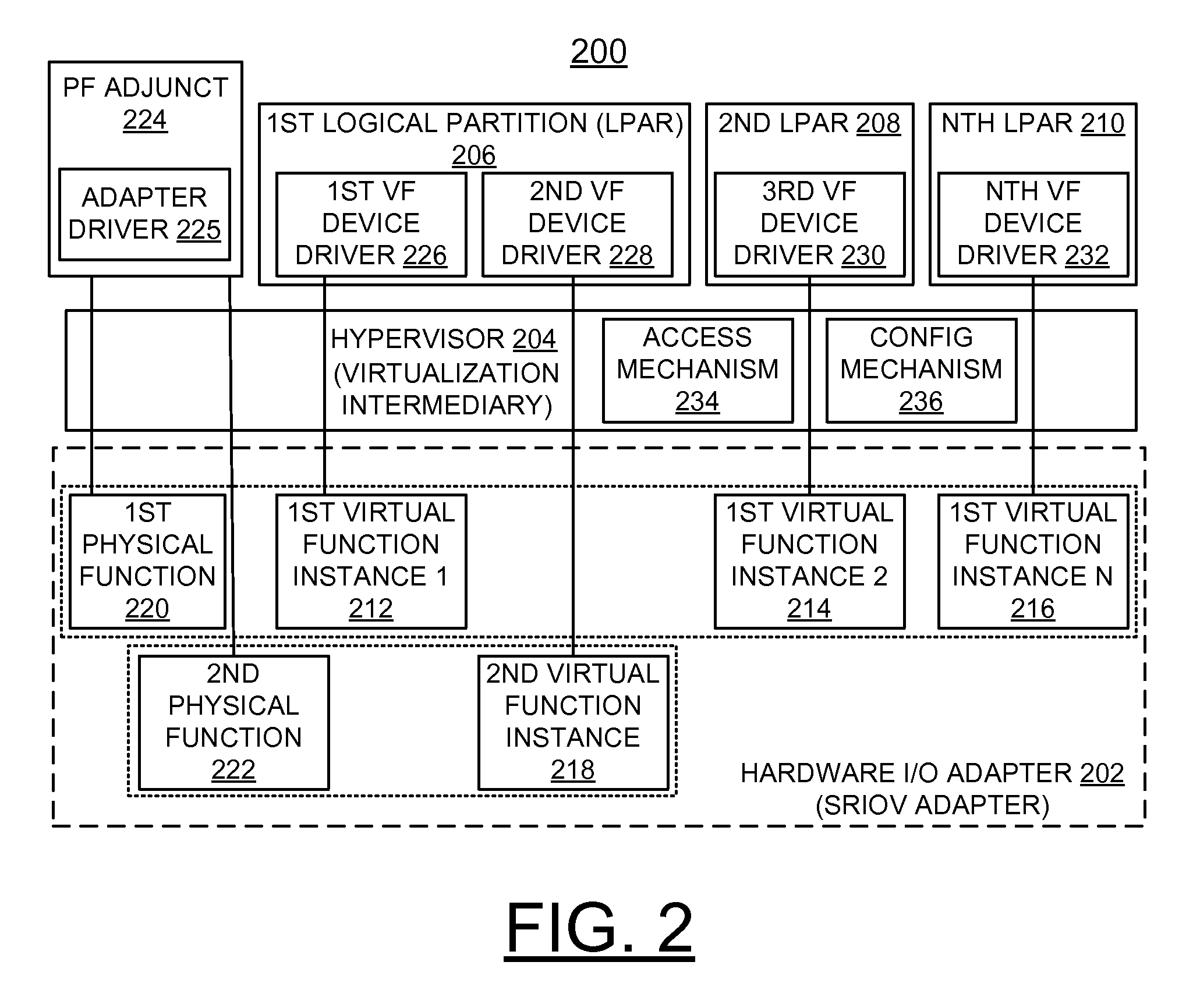

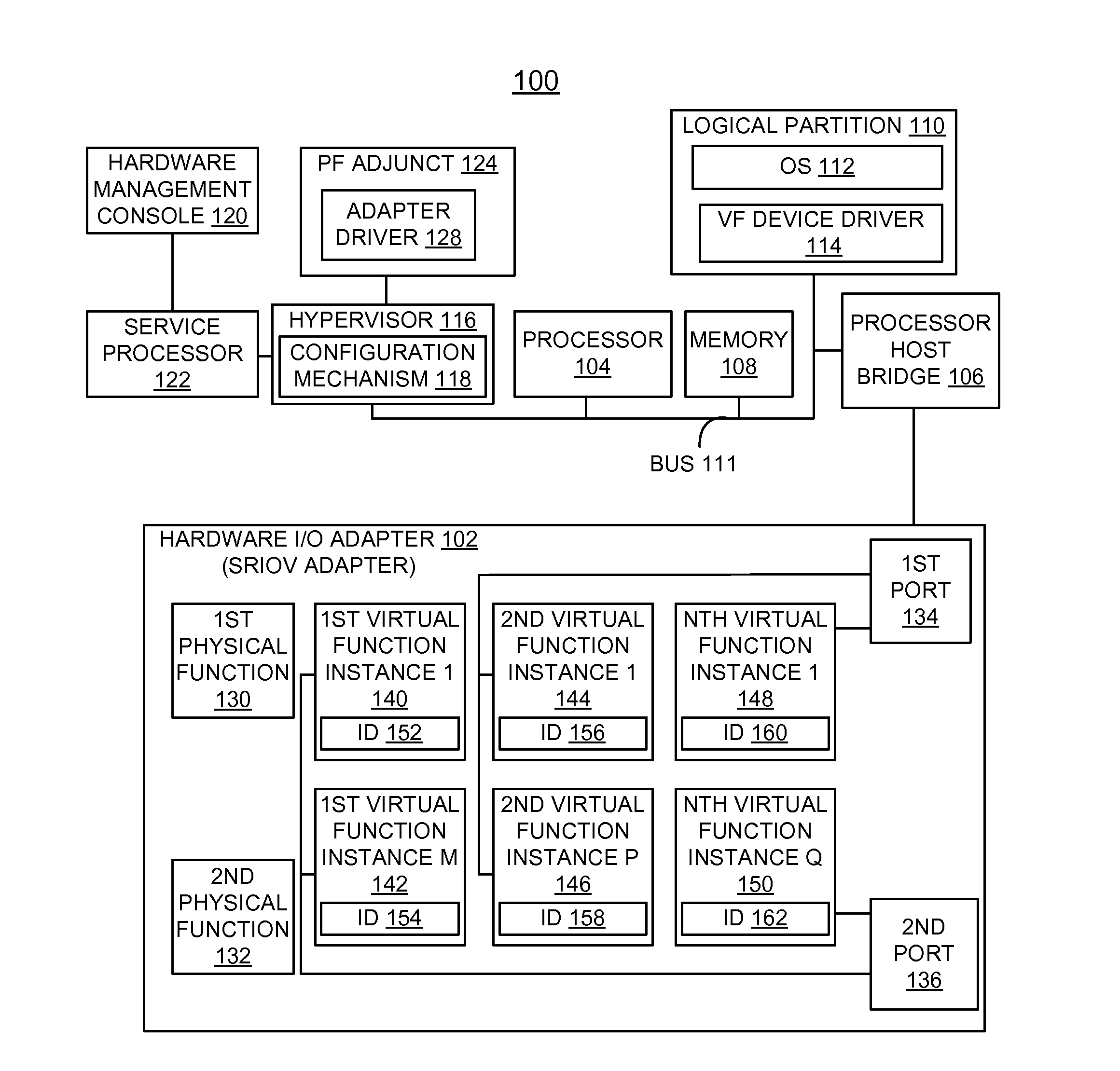

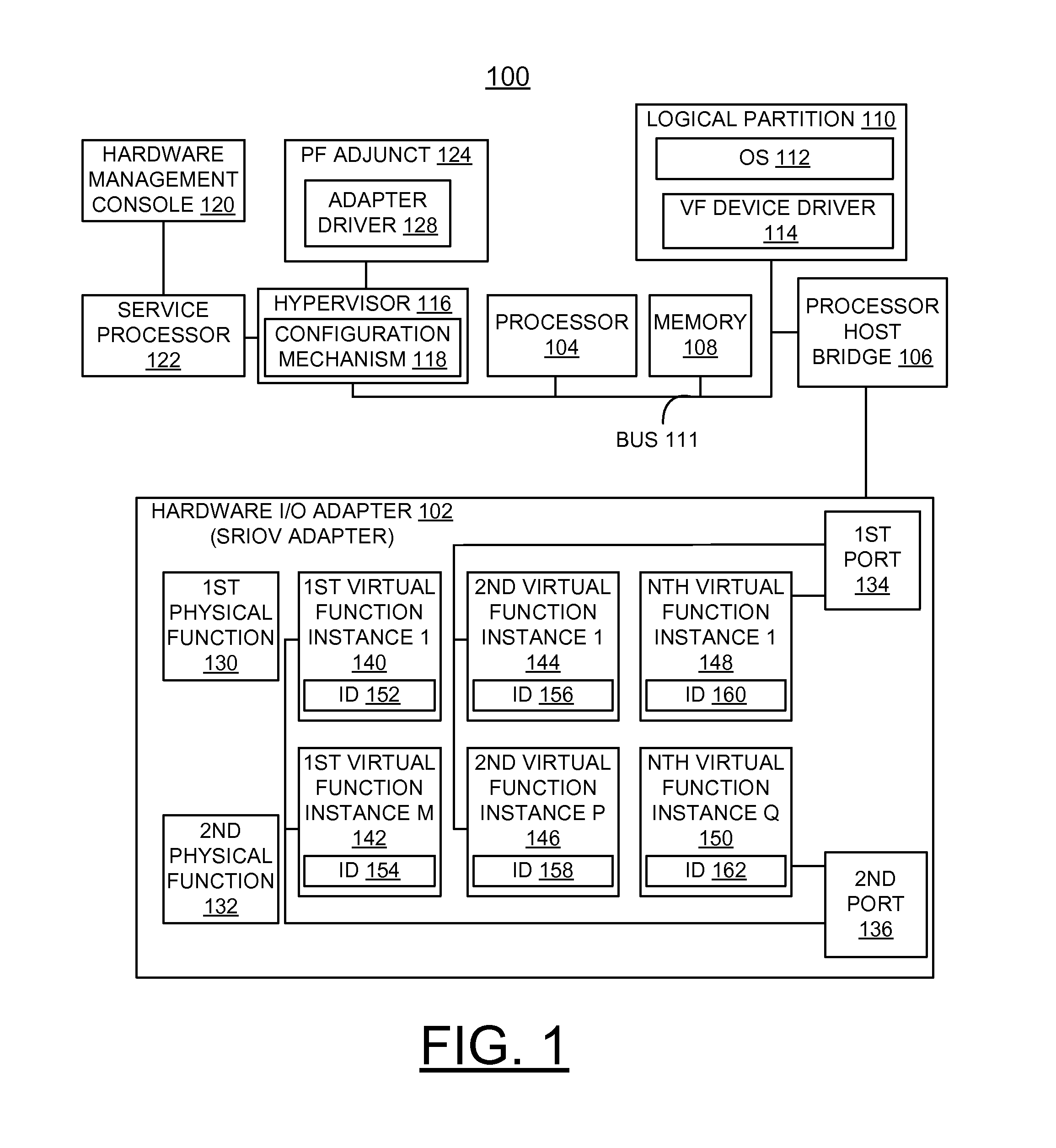

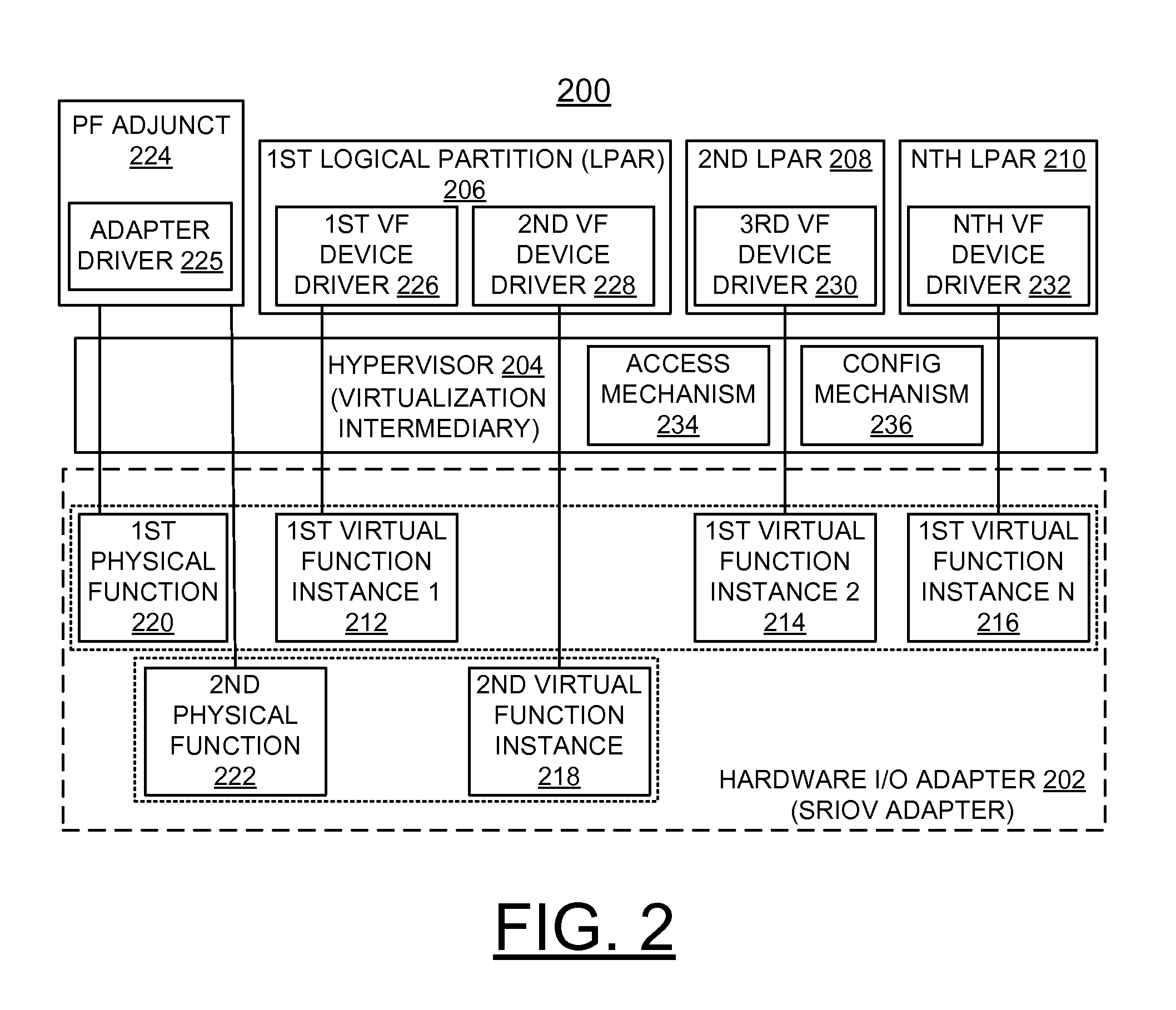

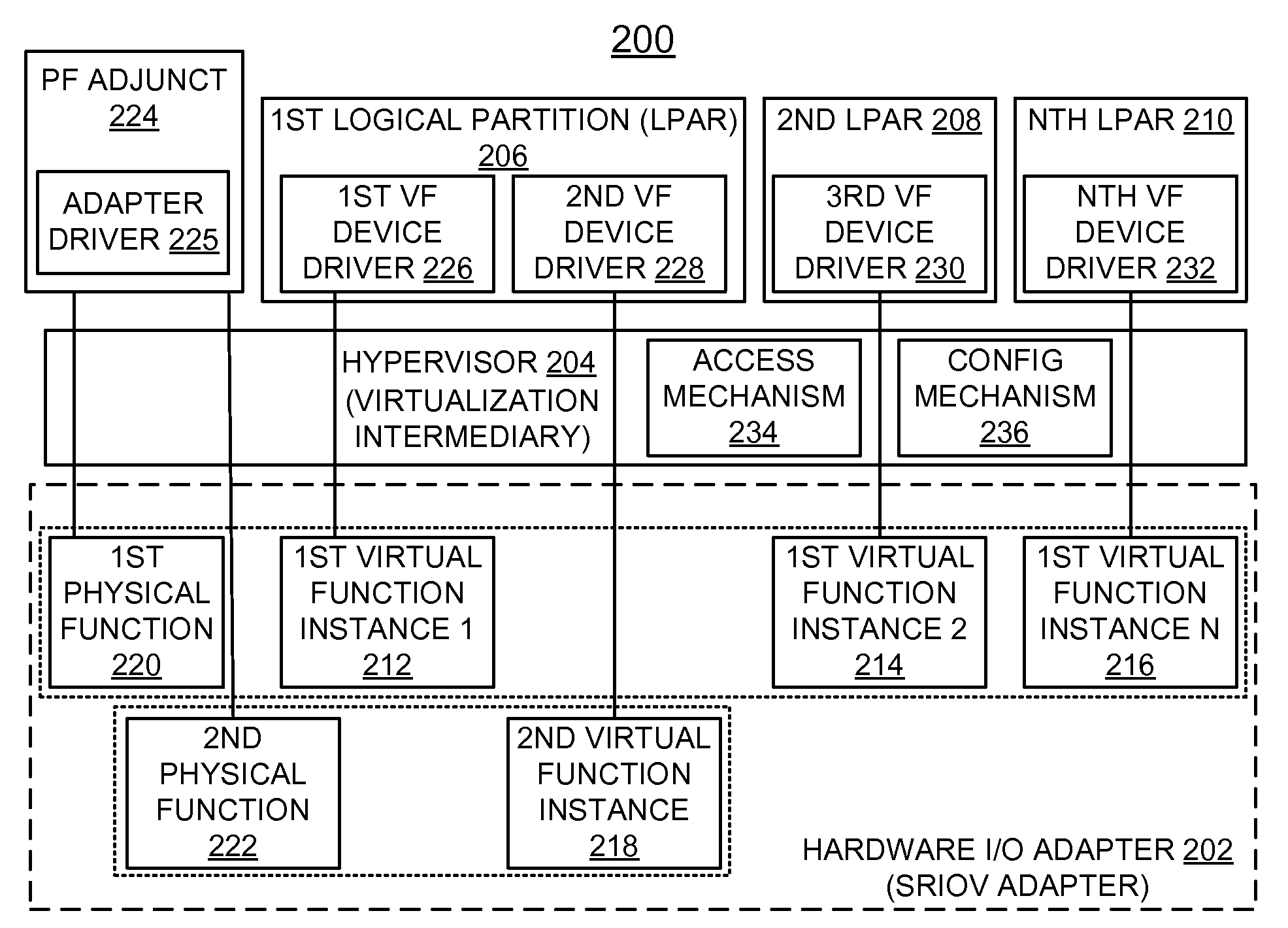

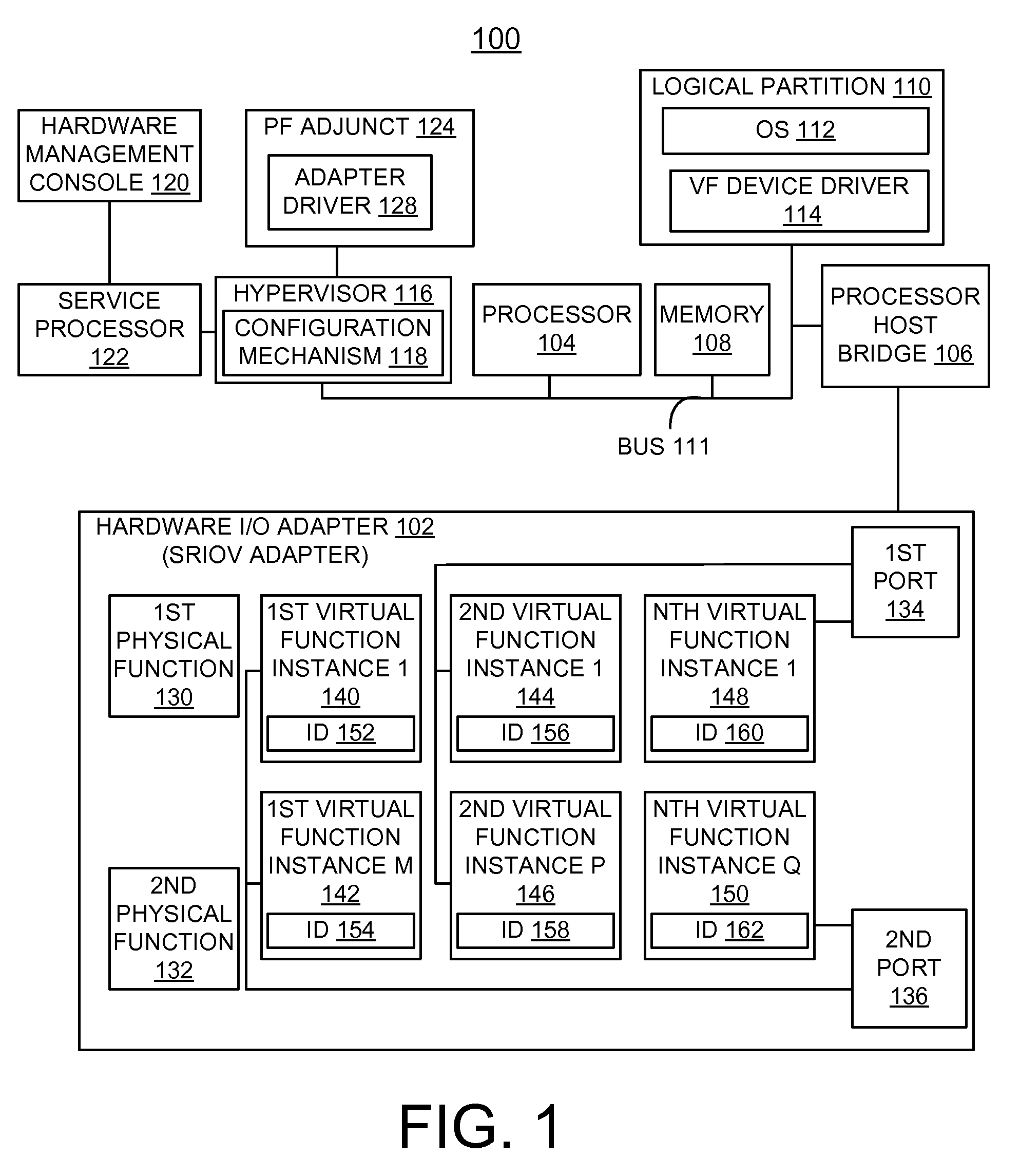

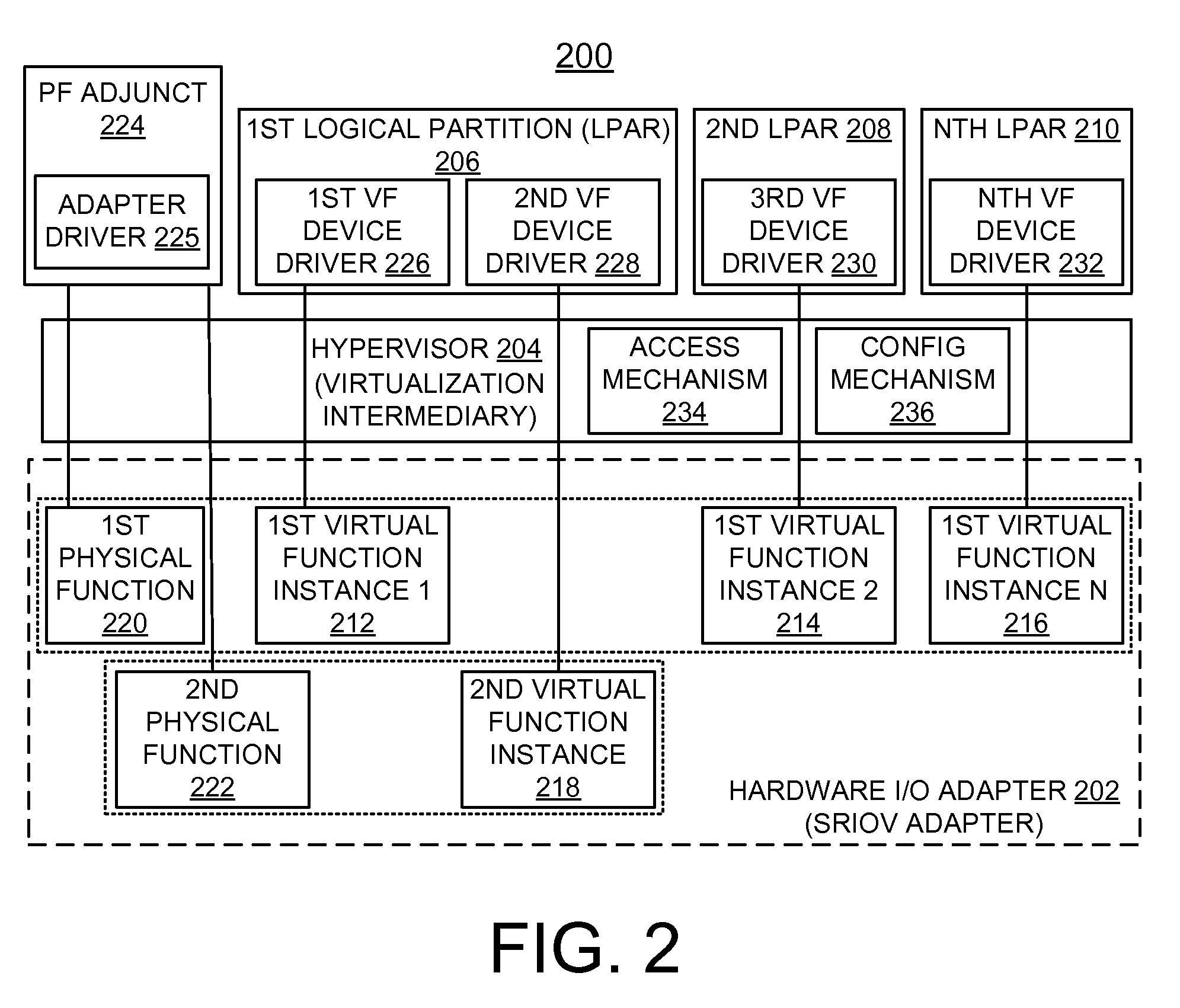

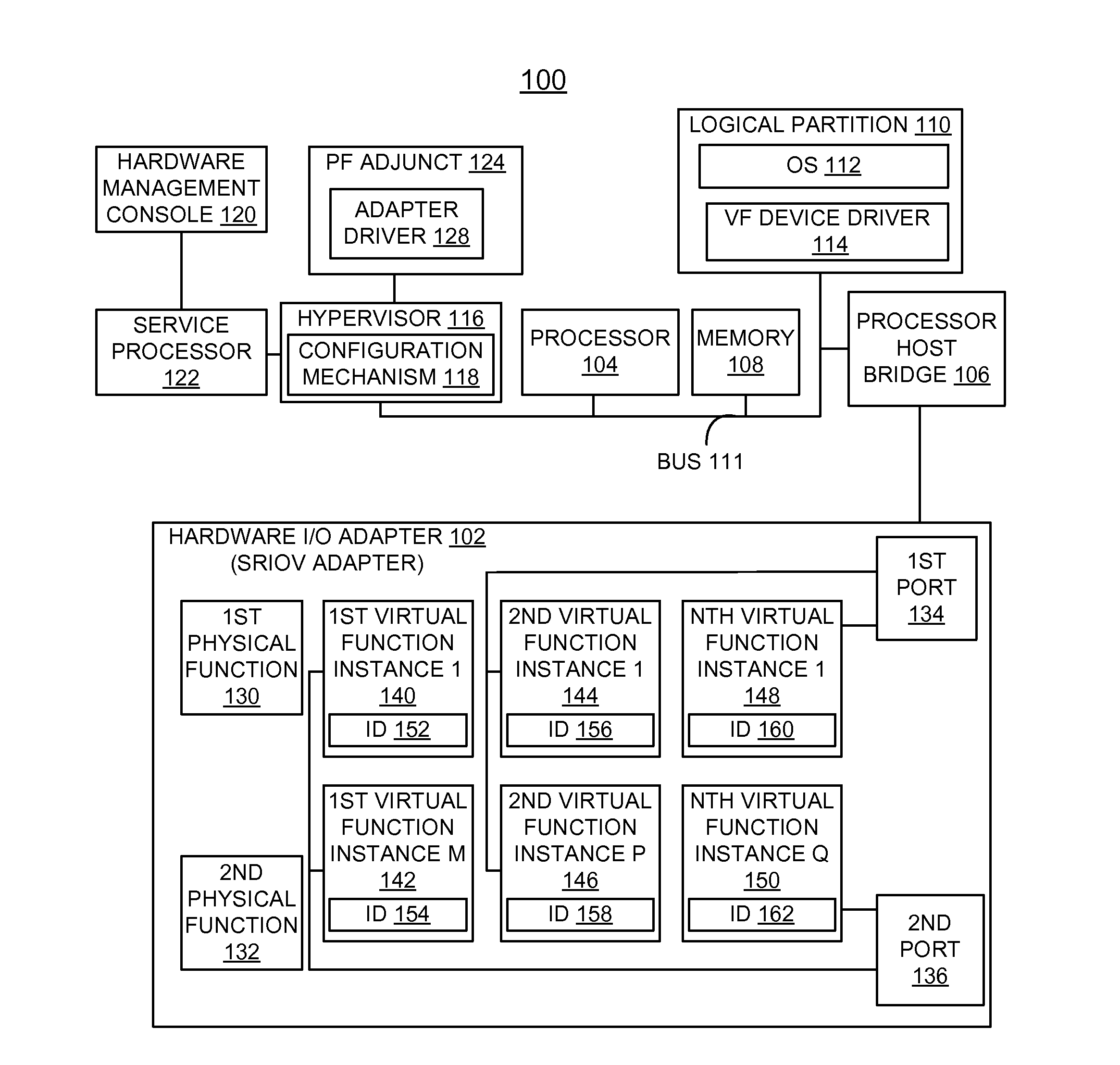

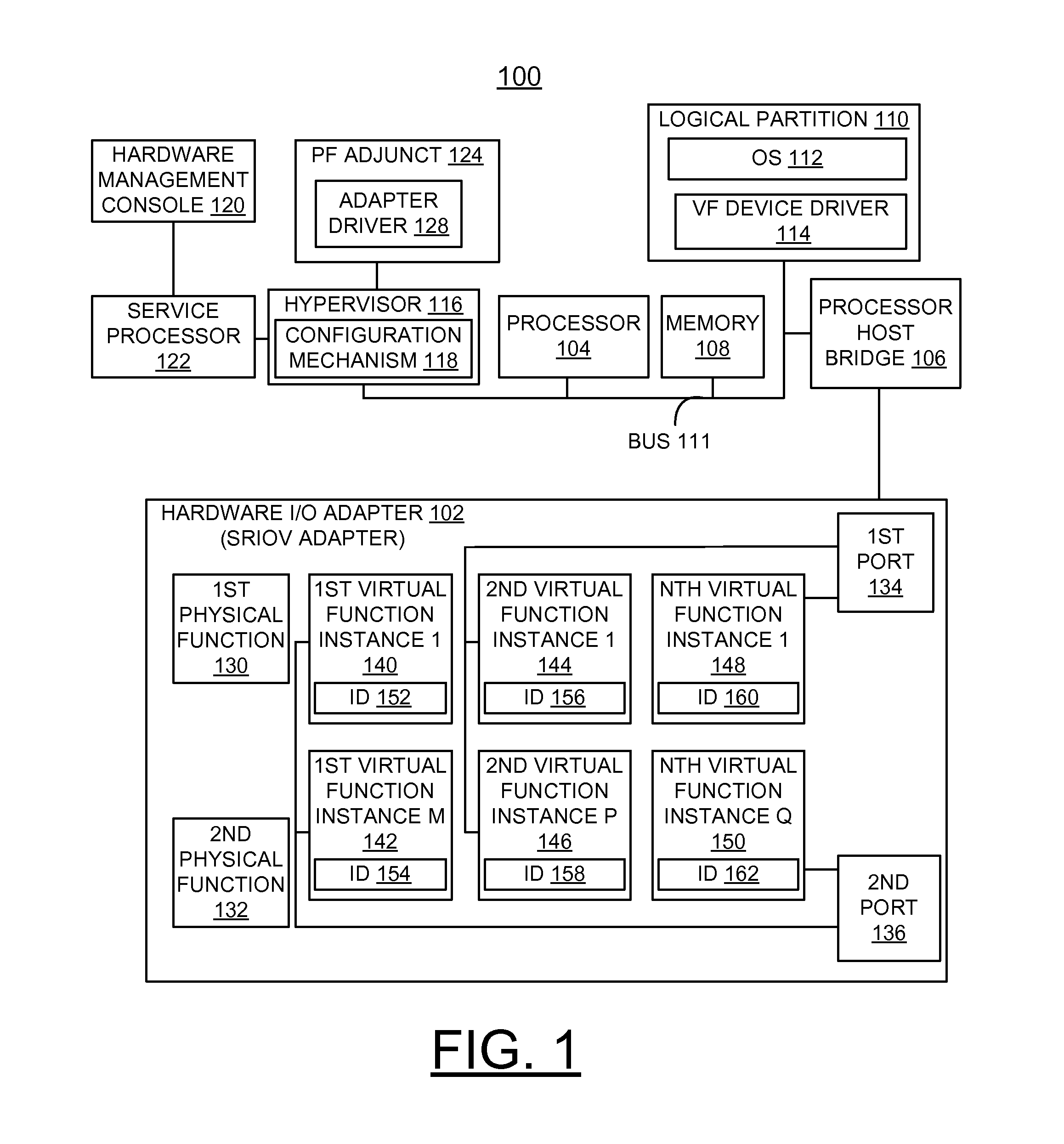

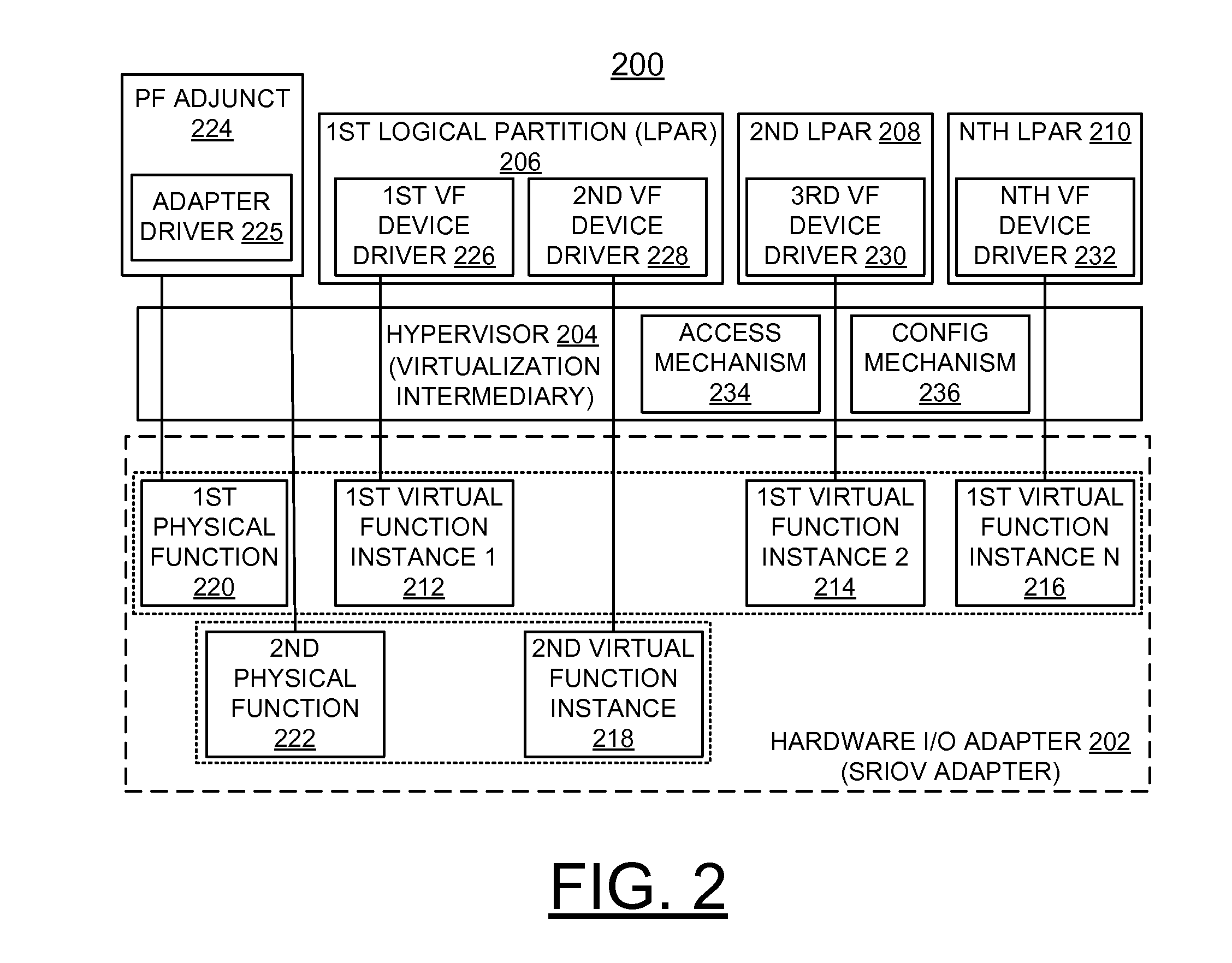

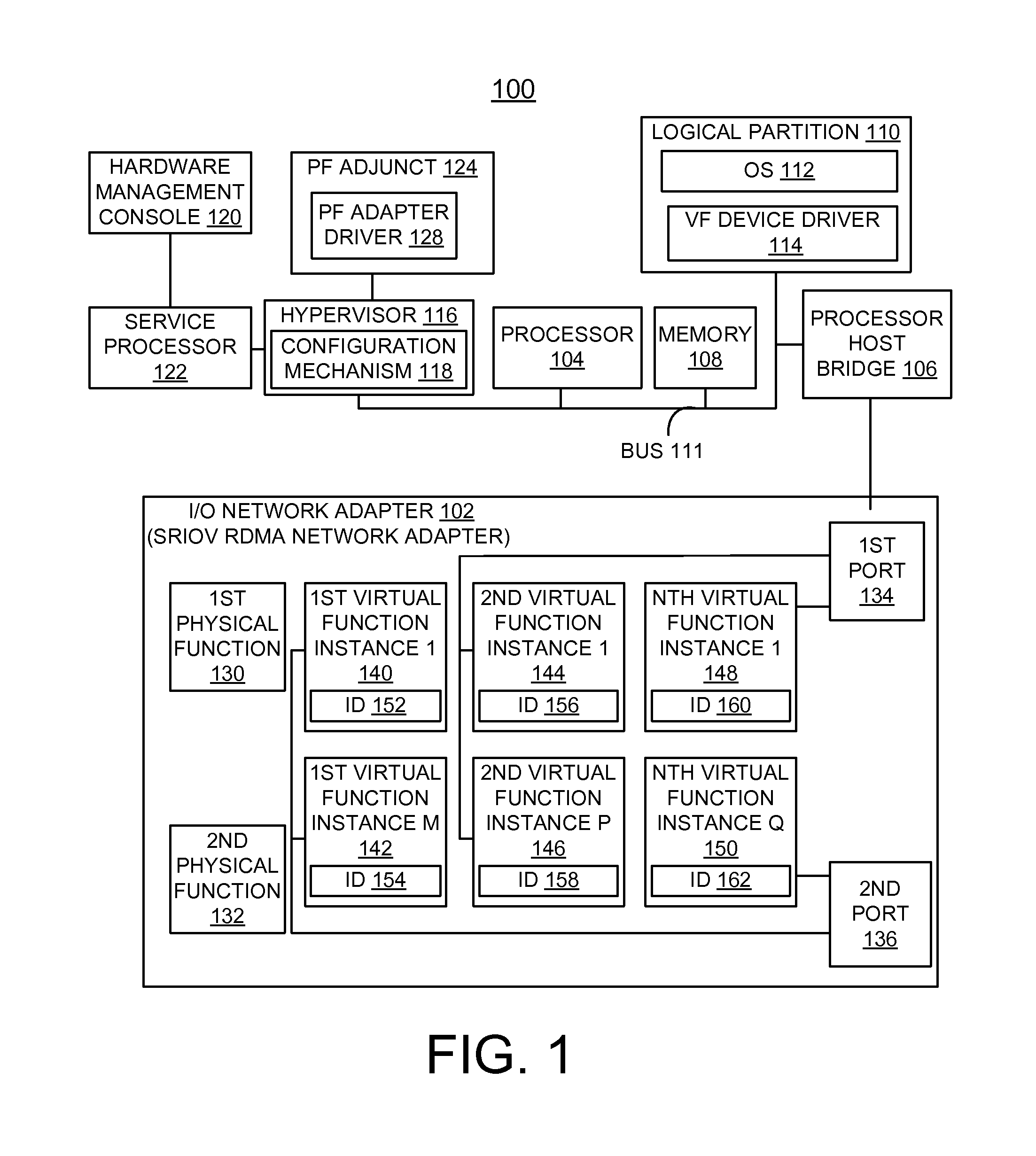

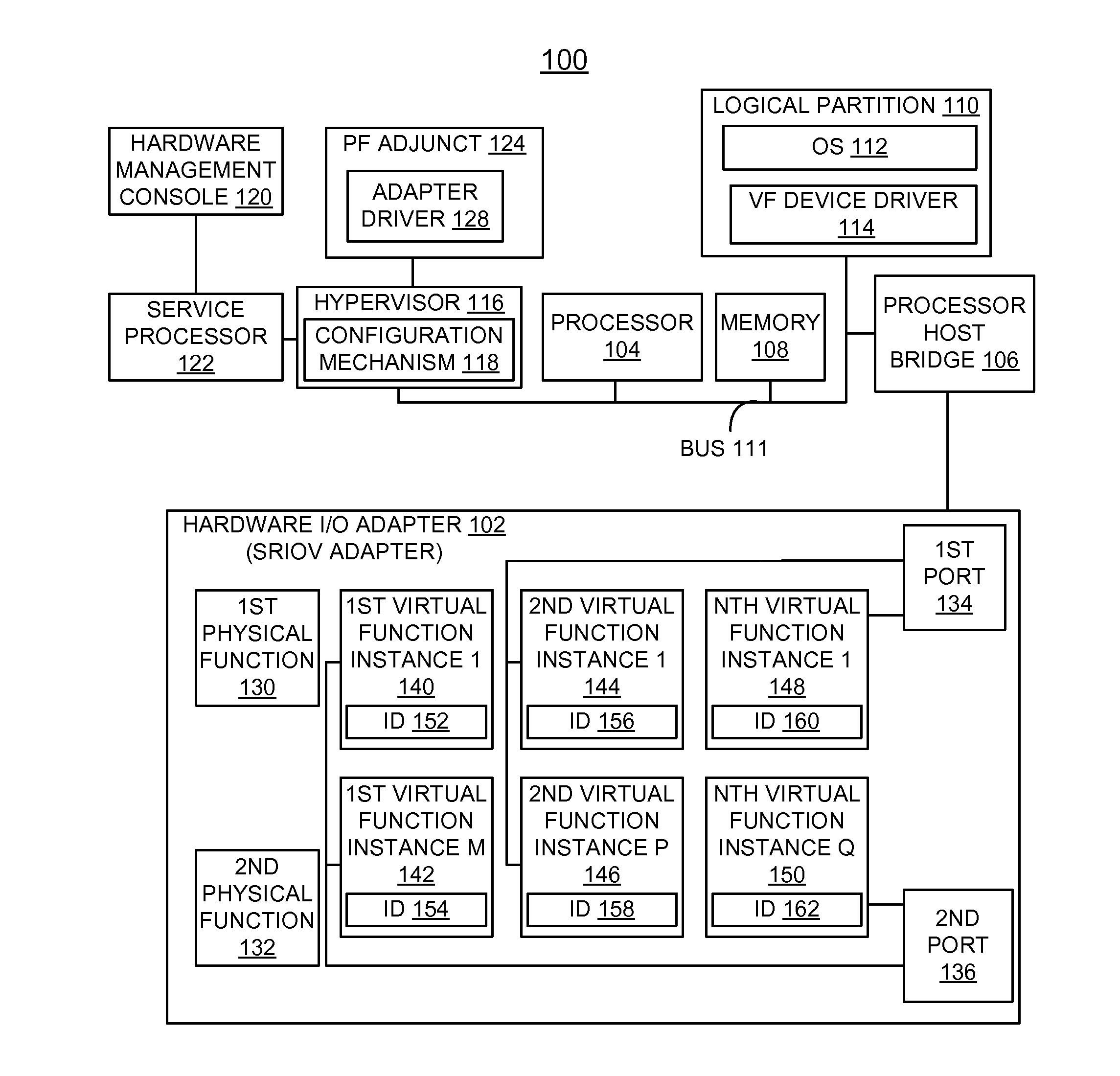

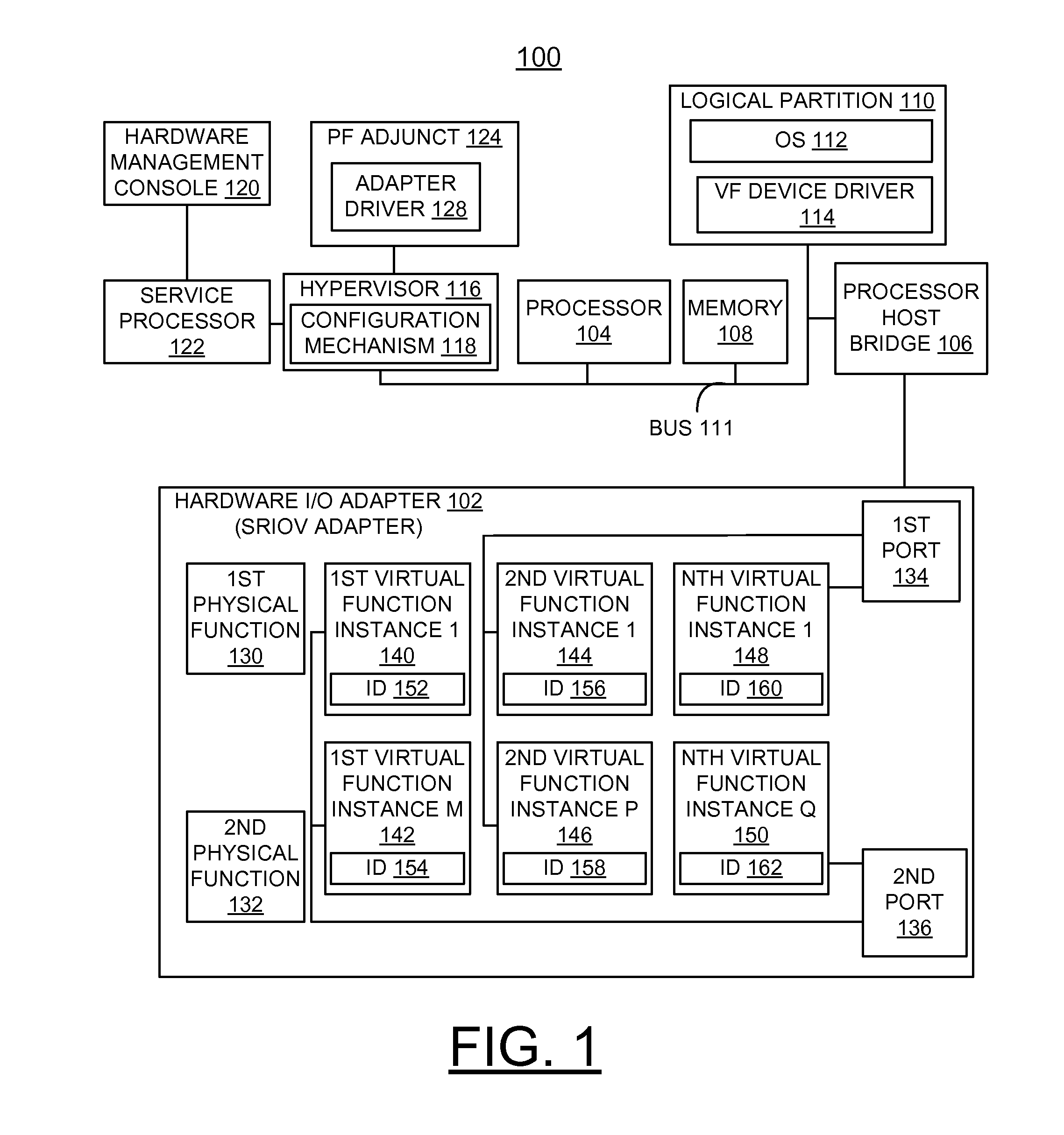

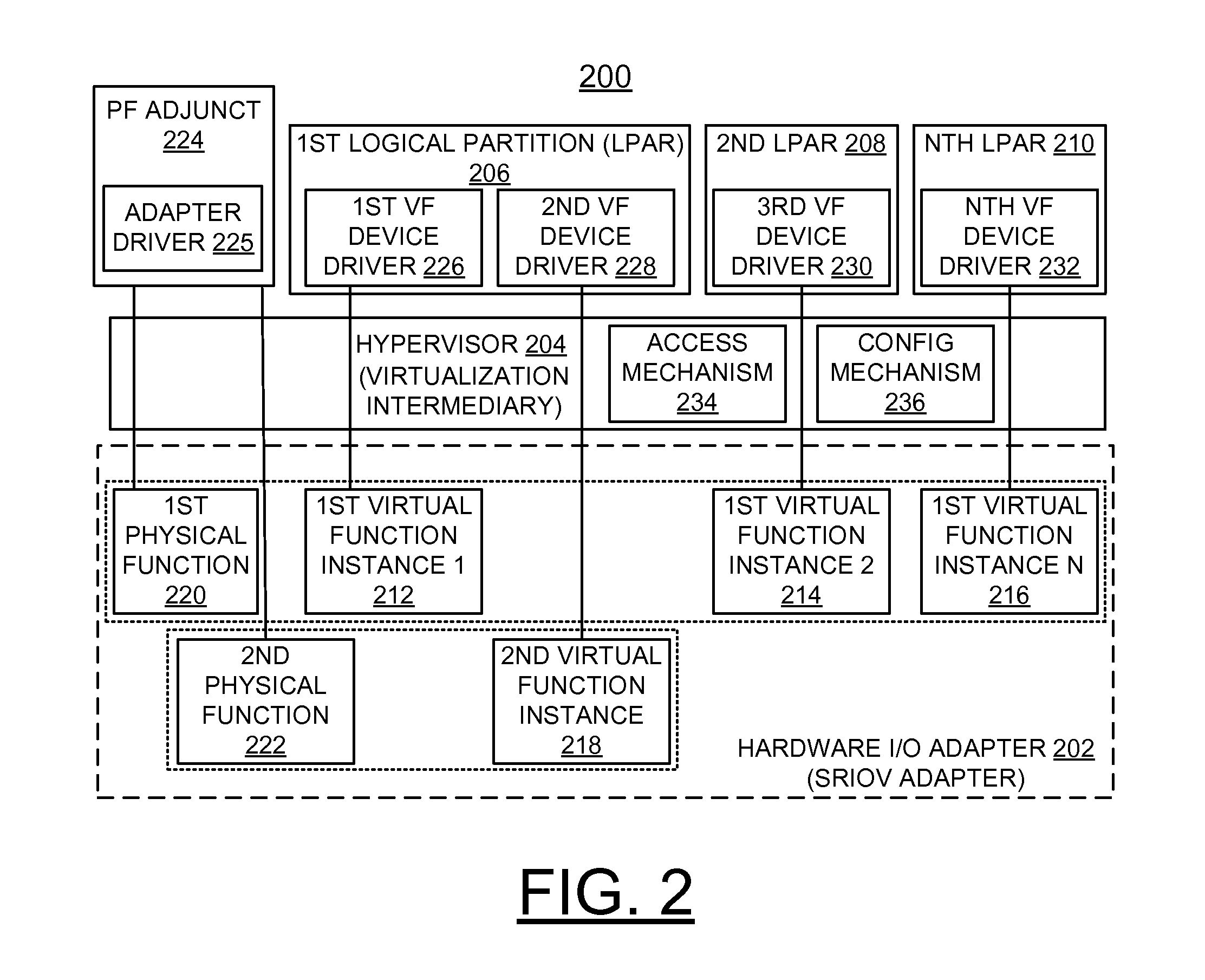

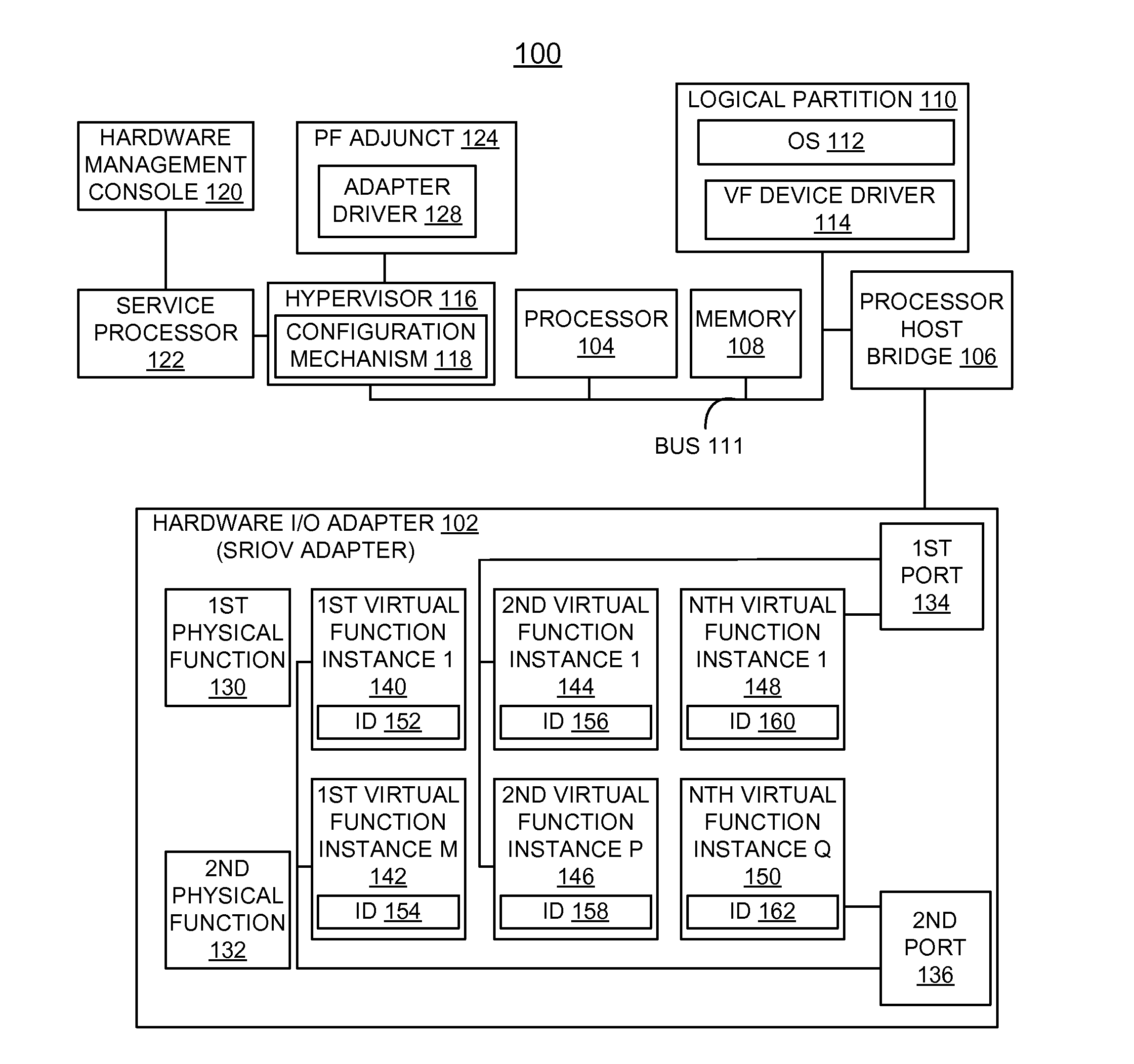

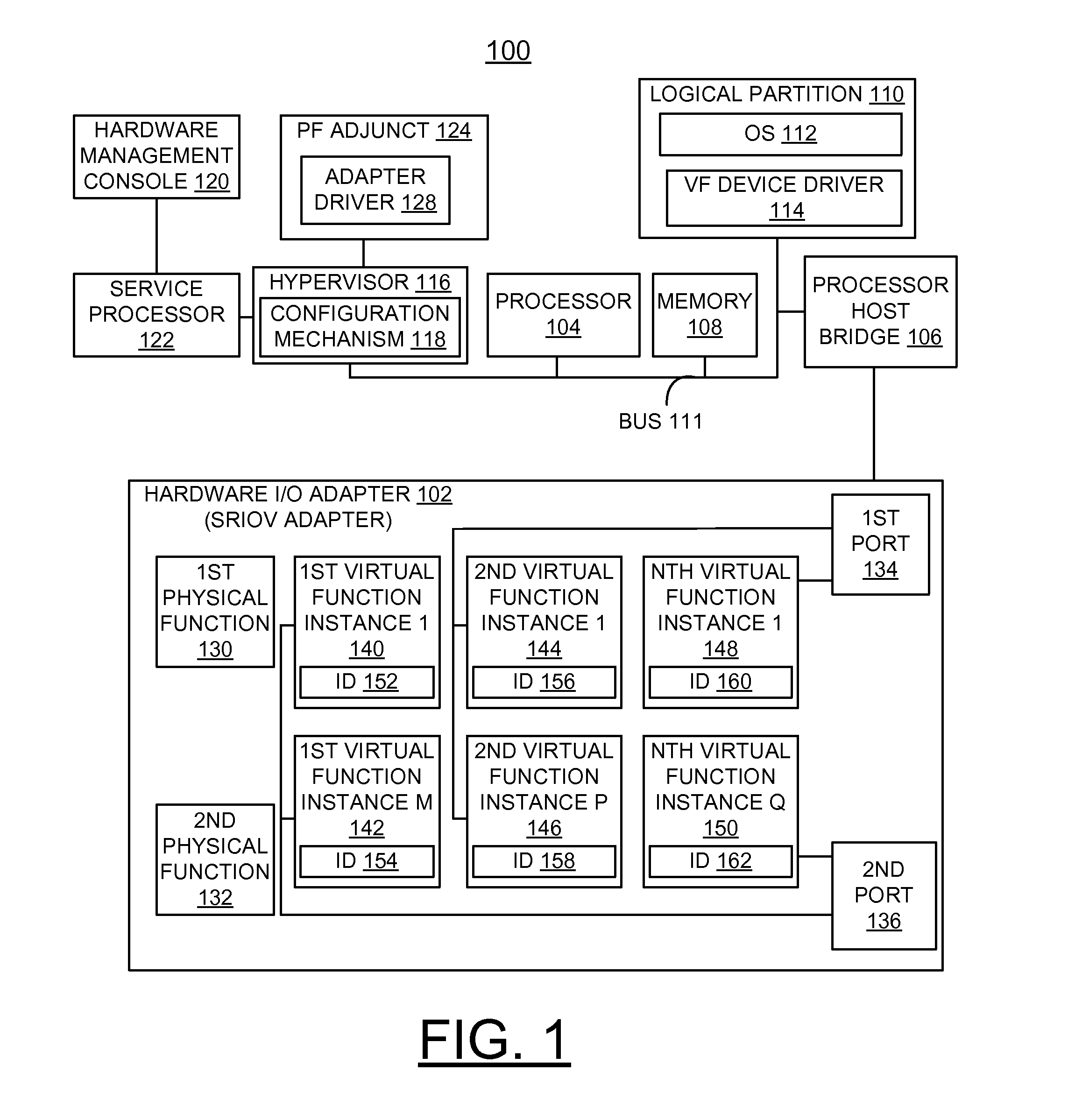

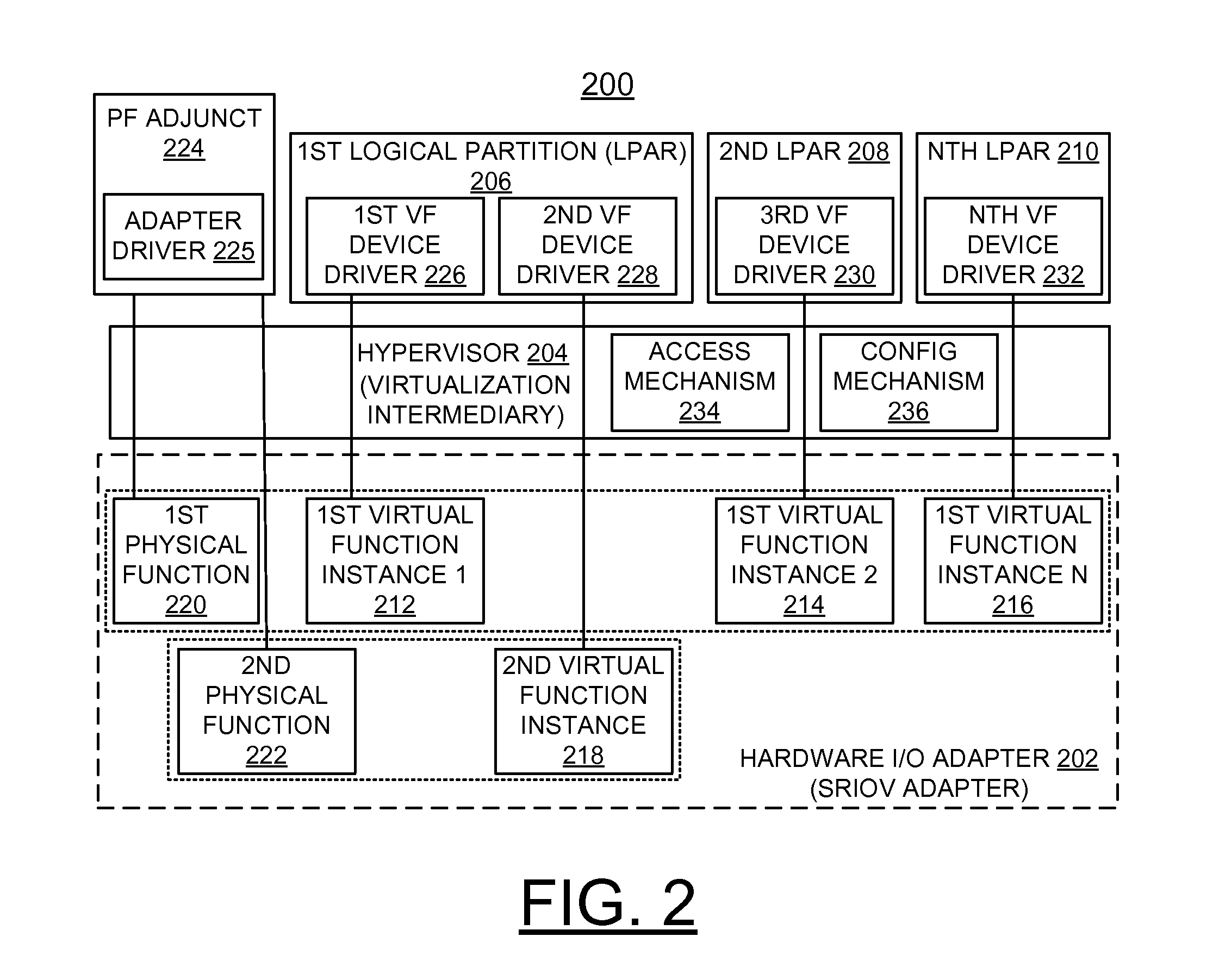

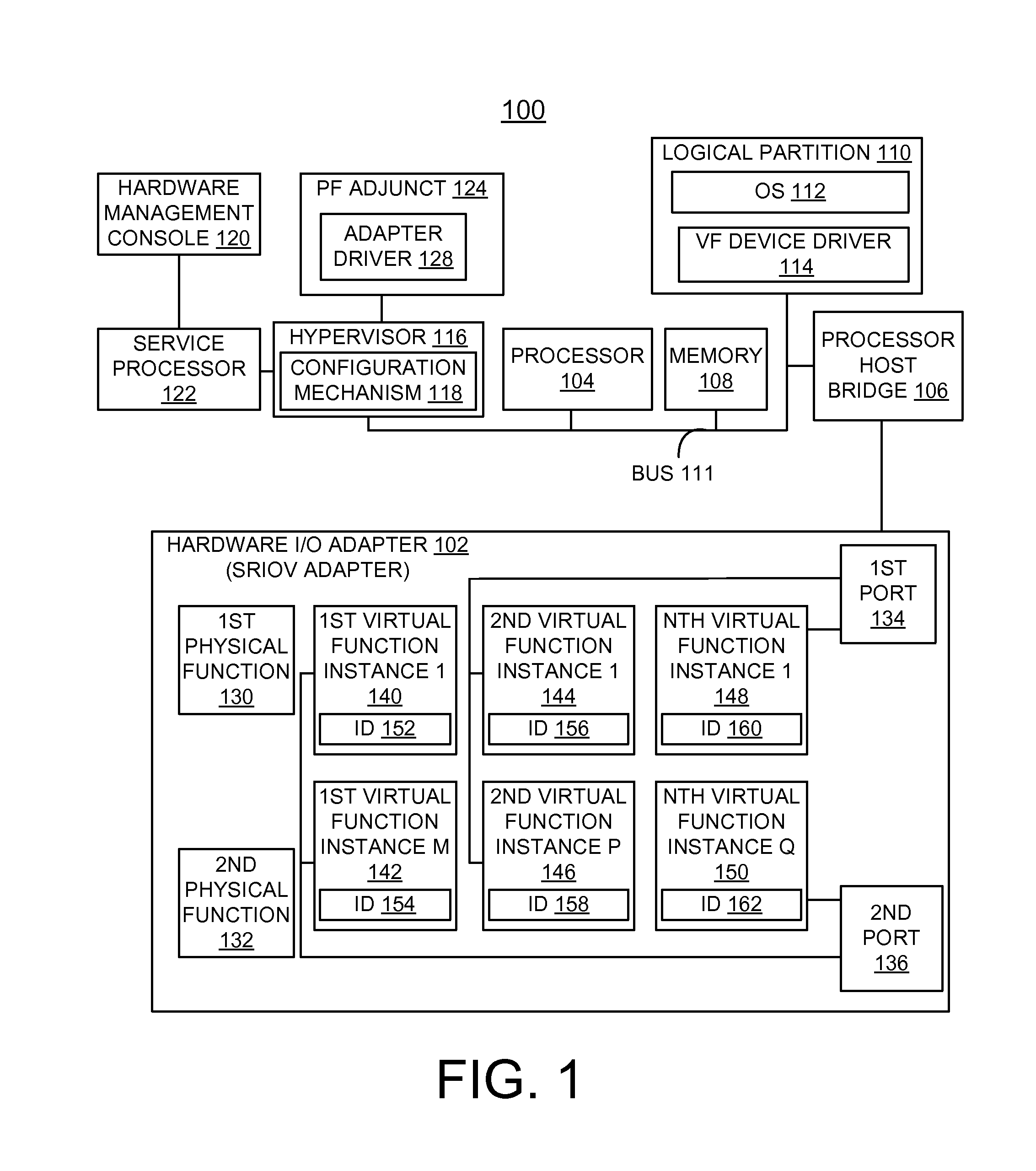

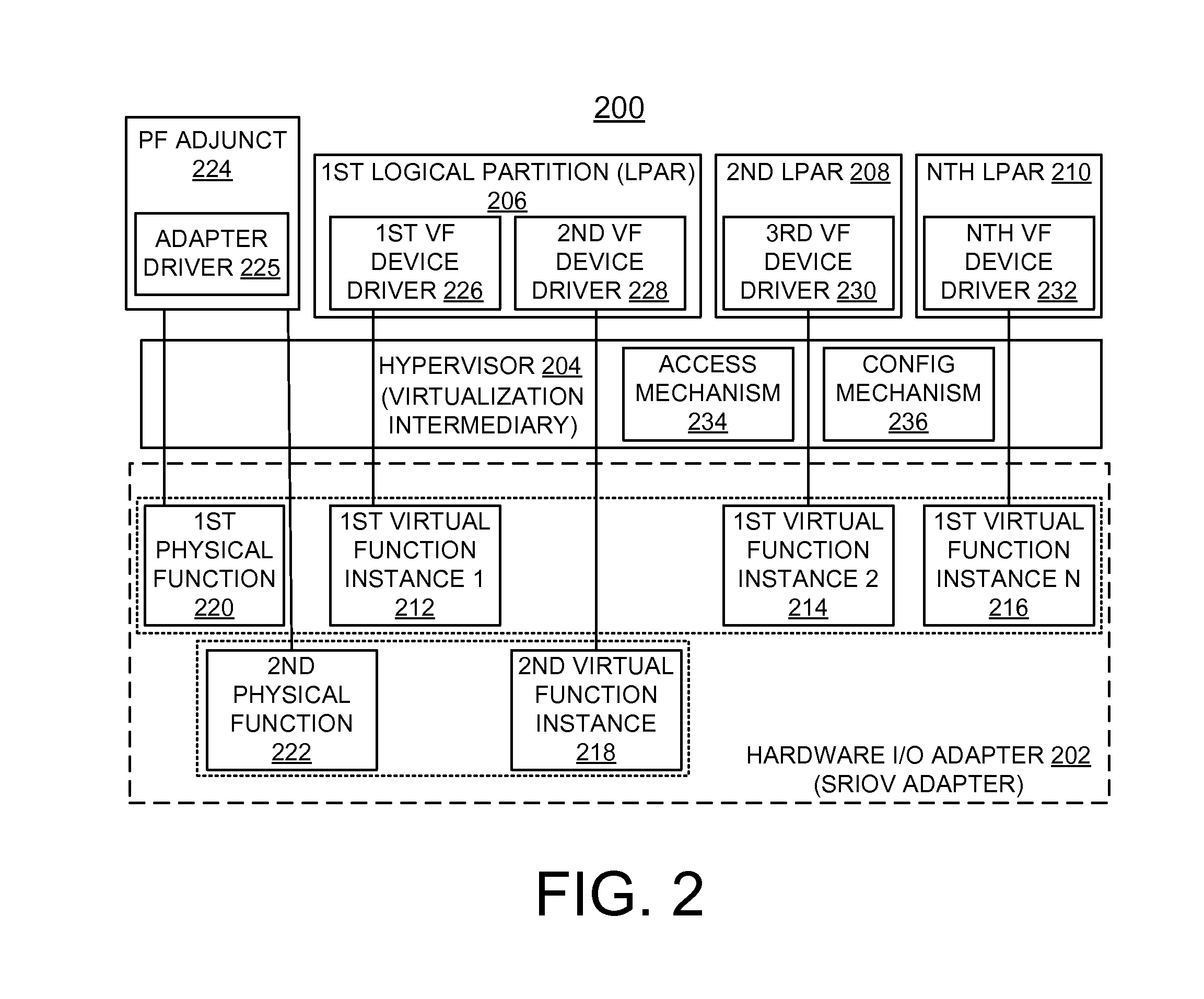

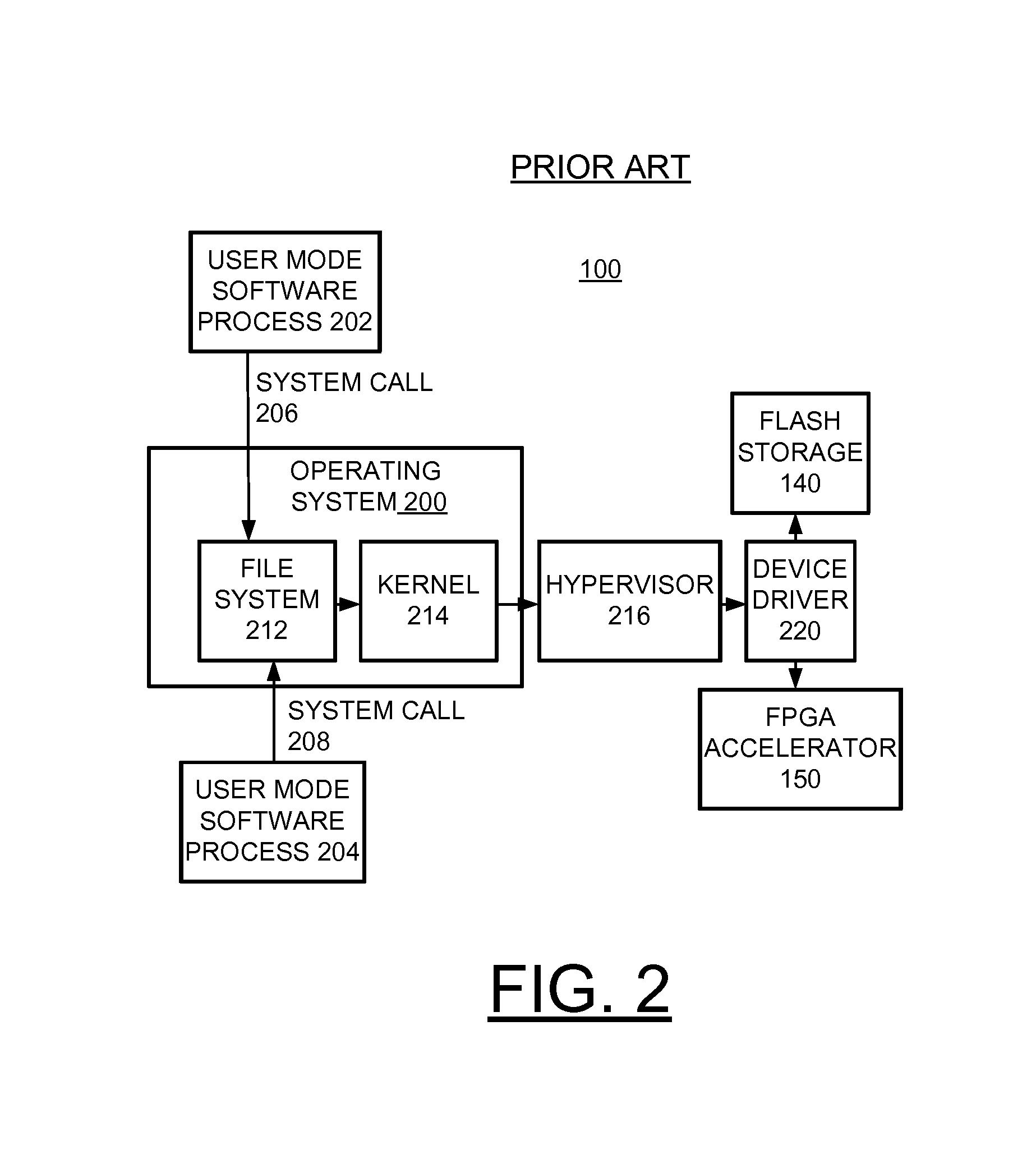

Implementing concurrent device driver maintenance and recovery for an SRIOV adapter in a virtualized system

InactiveUS9317317B2Without negative effectResource allocationSoftware simulation/interpretation/emulationStart up timeComputerized system

A method, system and computer program product are provided for implementing concurrent adapter driver maintenance and recovery for a Single Root Input / Output Virtualization (SRIOV) adapter in a computer system. An adapter driver at start up time performs configuration of the adapter and each of a set of virtual functions (VFs). The adapter driver writes critical adapter and VF configuration data to a scratchpad buffer. When device driver maintenance is needed, such as to load updated adapter driver firmware, all VF drivers are held off temporarily, current adapter driver is detached, and then the adapter driver is reloaded with the updated driver firmware. Then the adapter driver is restarted with the updated adapter driver firmware, and performs a reinitialization process. The adapter driver performs adapter and VF configuration restoring existing configuration using values read from the scratchpad buffer.

Owner:IBM CORP

Method and meeting scheduler for automated meeting scheduling using delegates, representatives, quorums and teams

InactiveUS20080040184A1Without negative effectOvercome disadvantagesMultiprogramming arrangementsOffice automationData storeComputer science

A method, meeting scheduler and computer program product are provided for automated meeting scheduling using delegates, representatives, quorums, and teams. Meeting settings and invitees data are stored for a meeting. The meeting settings and invitees data includes invitee attendance type, delegates, representatives, quorums, and teams data. A solution time block for automated meeting scheduling including at least a subset of a plurality of selected invitees is identified utilizing the invitee attendance type, delegates, representatives, quorums, and teams data. A selection score is calculated for each potential time block for automated meeting scheduling utilizing the stored meeting settings and invitees data including the invitee attendance type, delegates, representatives, quorums, and teams data. The solution time block for automated meeting scheduling including a subset of a plurality of selected invitees is identified utilizing the calculated selection score.

Owner:INT BUSINESS MASCH CORP

Implementing concurrent adapter firmware update for an sriov adapter in a virtualized system

ActiveUS20140372739A1Without negative effectMaintenance freeSoftware engineeringError detection/correctionEngineeringScratchpad memory

A method, system and computer program product are provided for implementing concurrent adapter firmware update of a Single Root Input / Output Virtualization (SRIOV) adapter in a virtualized system. An adapter driver is used to update adapter firmware concurrent with normal I / O operations. When configuration is stored in a scratchpad buffer, the adapter driver detects virtual functions (VFs) configured and operating. An enhanced error handling (EEH) process is initiated, freezing the VFs, and an updated adapter firmware image is loaded to the adapter. The adapter driver completes the EEH recovery, the adapter is restarted using the new updated adapter firmware. The VFs device drivers unfreeze the VFs, and complete the EEH recovery.

Owner:IBM CORP

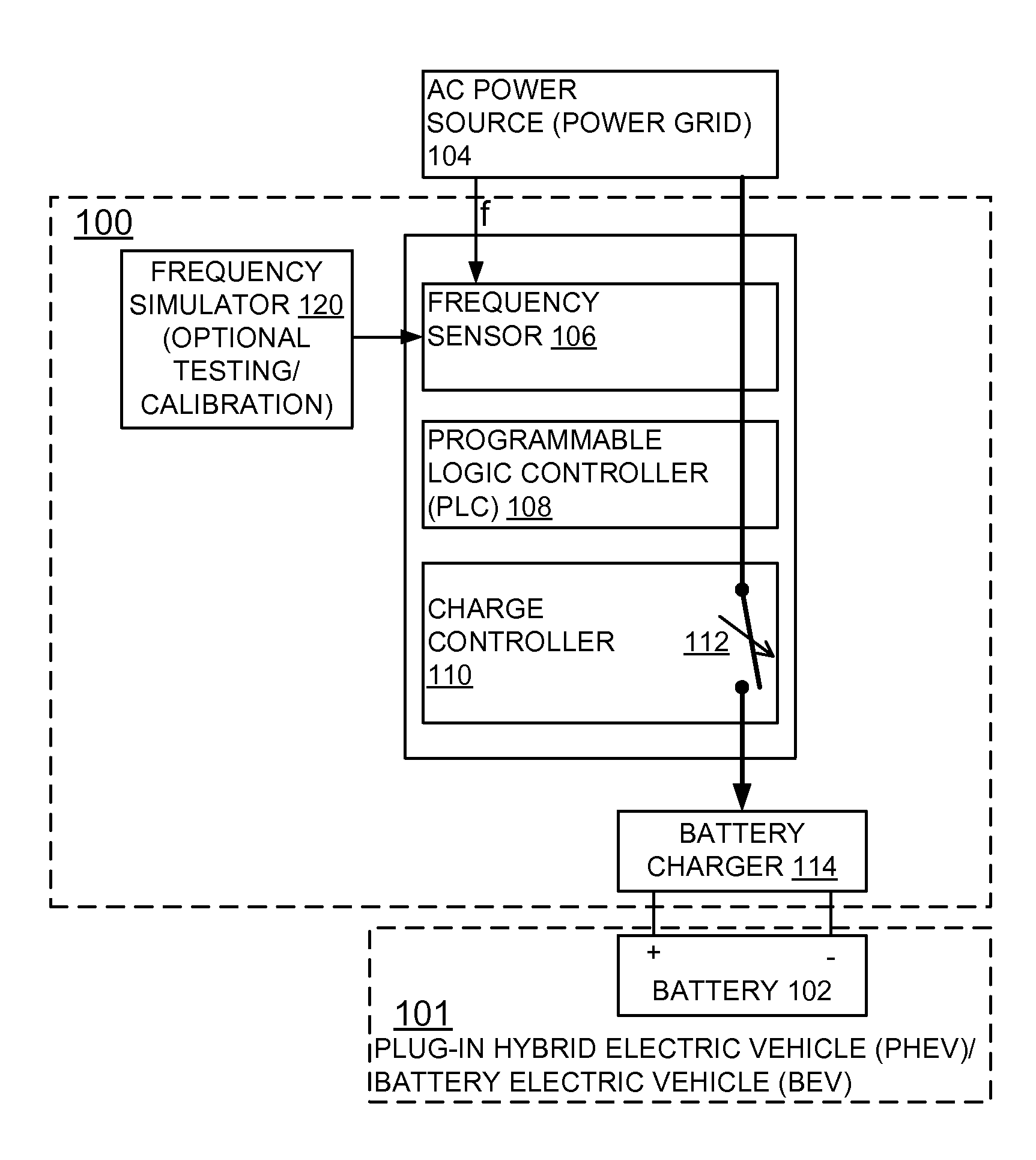

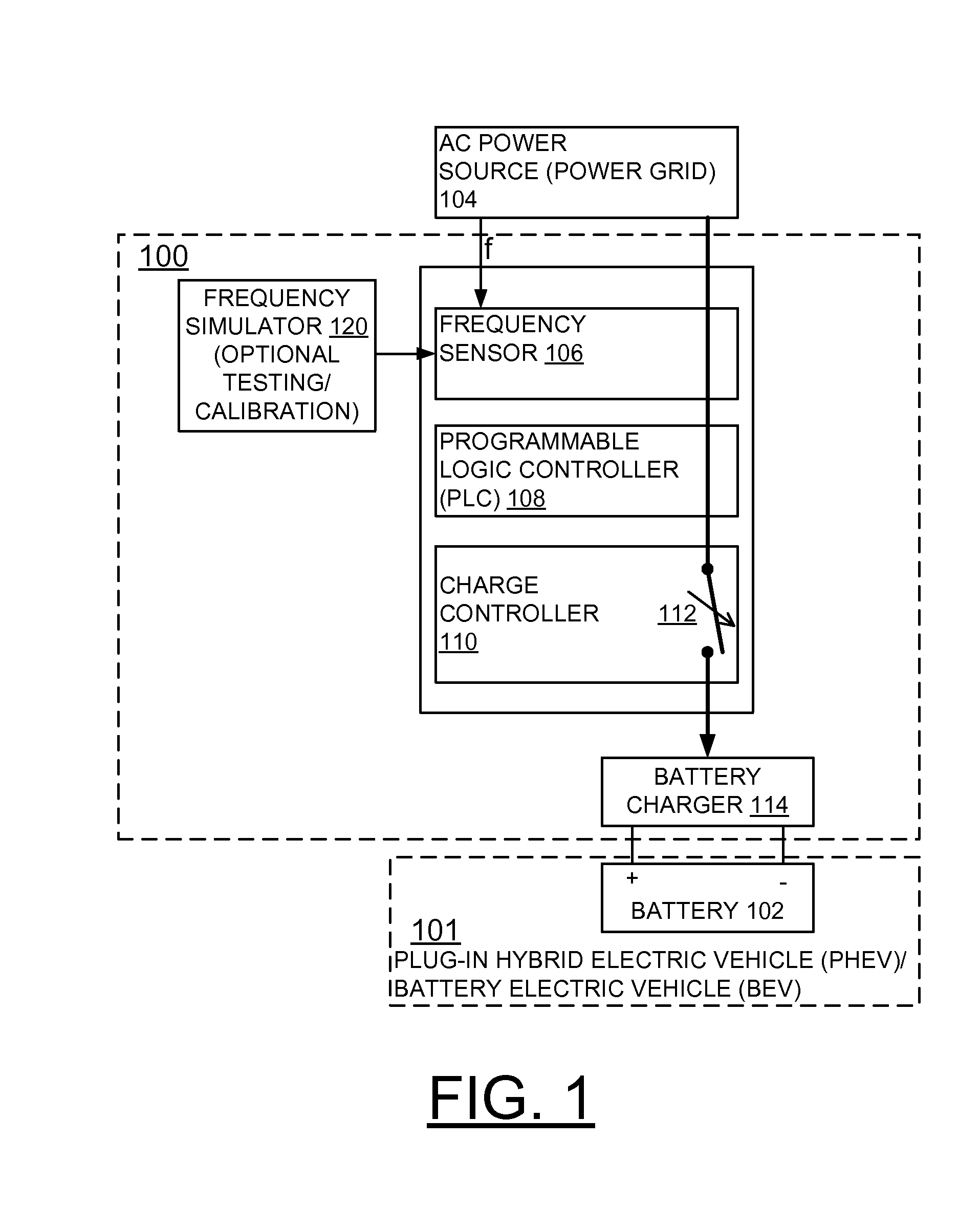

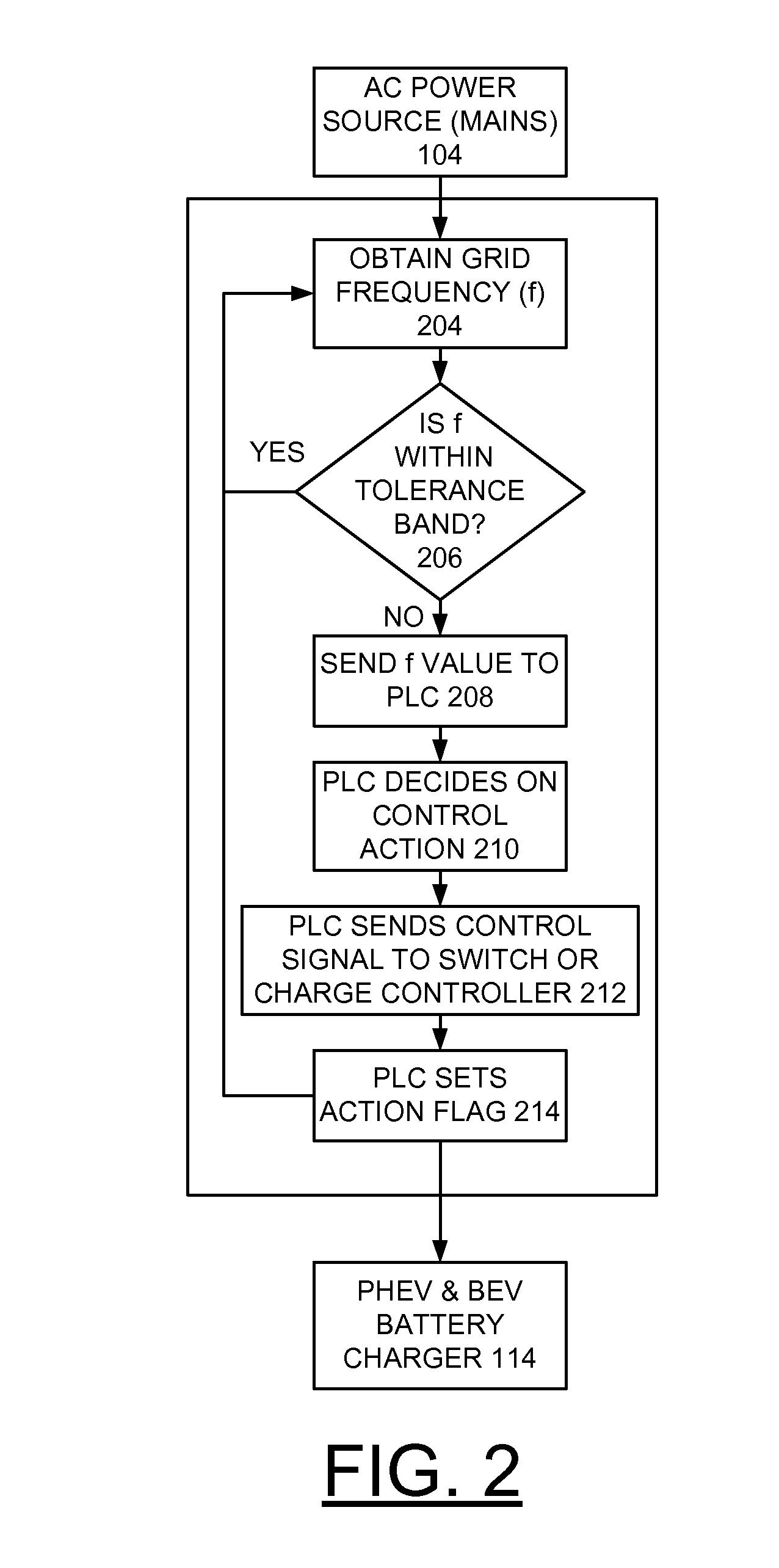

Frequency based electric vehicle charge controller system and method for implementing demand response and regulation services to power grid using frequency detection

ActiveUS20130033234A1Not vulnerableSafer and reliable operationCharging stationsAc network load balancingProgrammable logic controllerPower grid

Frequency responsive charging for plug-in hybrid electric vehicles (PHEV) and battery electric vehicles (BEV), a frequency sensing charging system and a method are provided for implementing demand response and regulation services to power grid using frequency detection for a frequency-based charge controller for plug-in hybrid electric vehicles (PHEV) and battery electric vehicles (BEV). A frequency of the power grid is continuously monitored and compared to a predefined tolerance band by a frequency sensor. Responsive to the frequency being outside the predefined tolerance band, the frequency is applied to a programmable logic controller. The programmable logic controller uses the applied frequency to identify a control action. A charge controller and a switch coupled to a battery charger receive respective identified control actions for controlling the battery charger.

Owner:UCHICAGO ARGONNE LLC

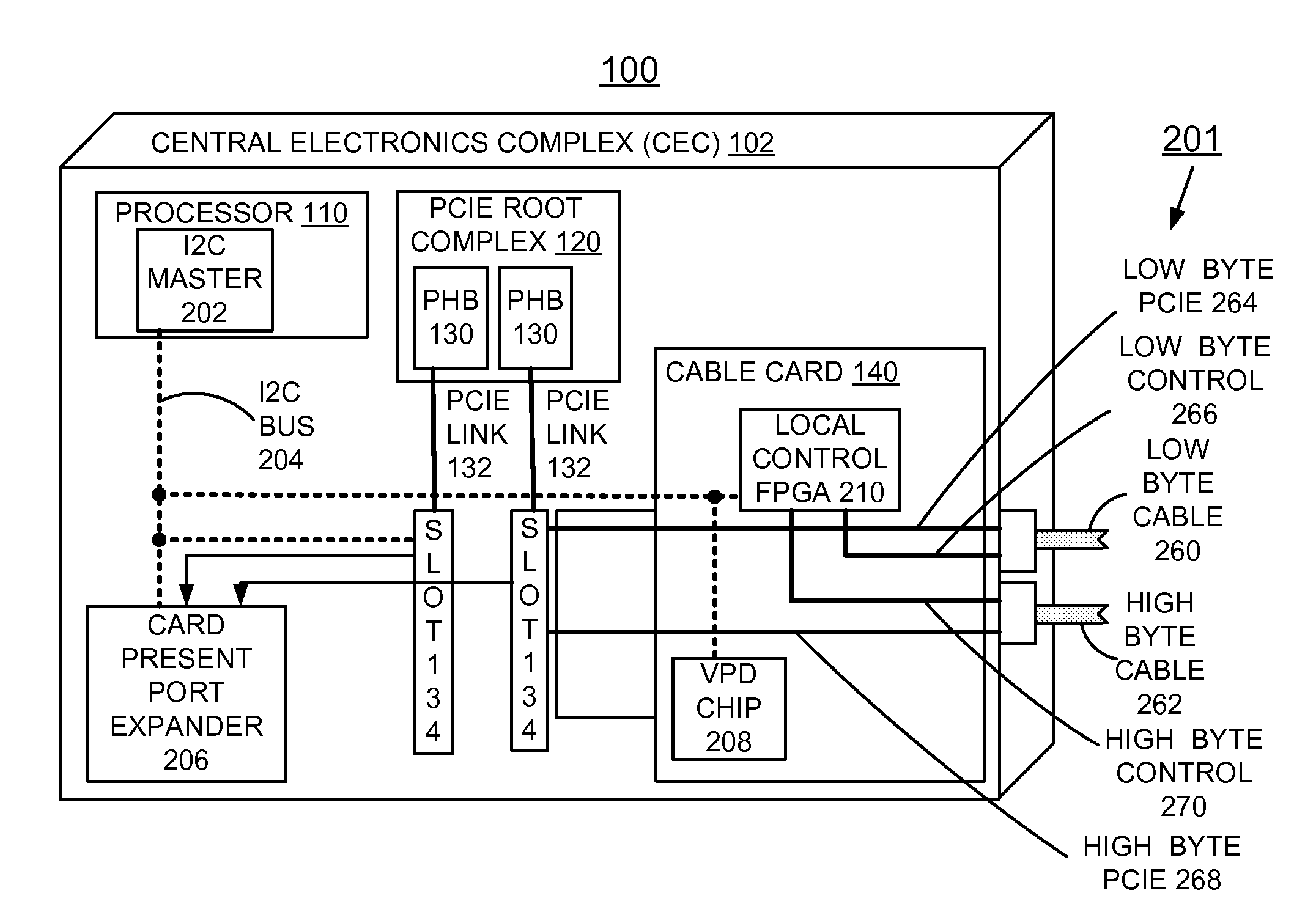

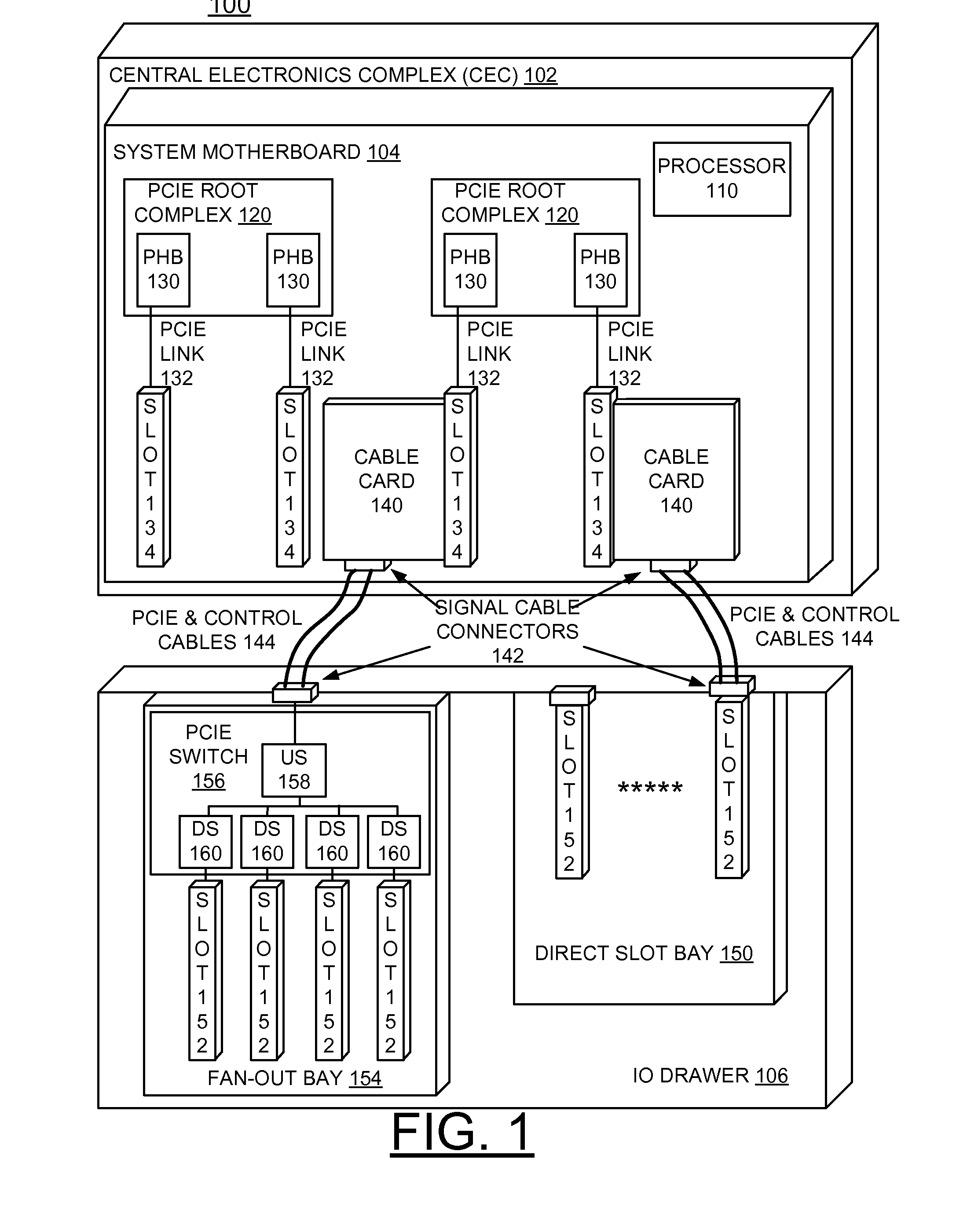

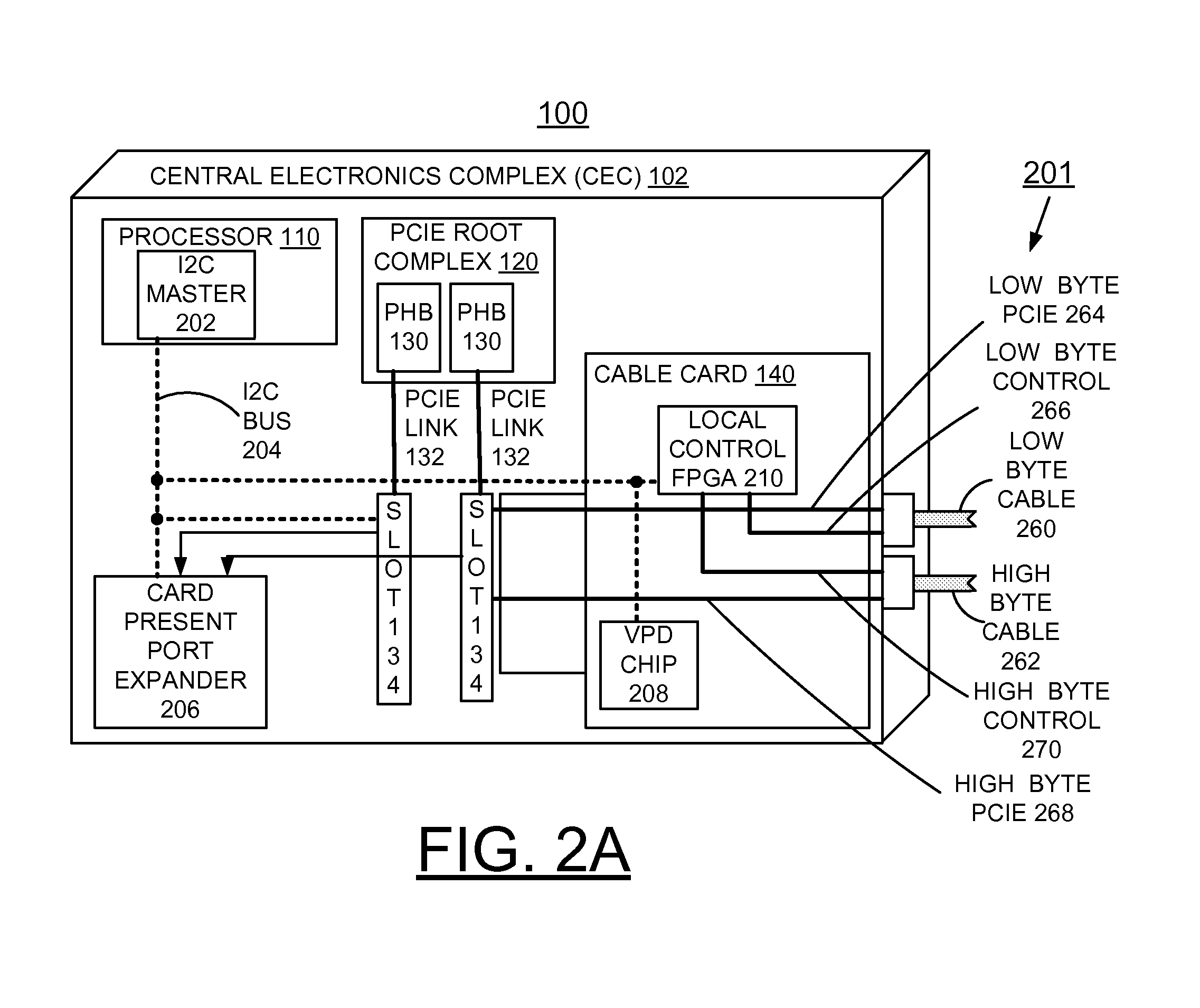

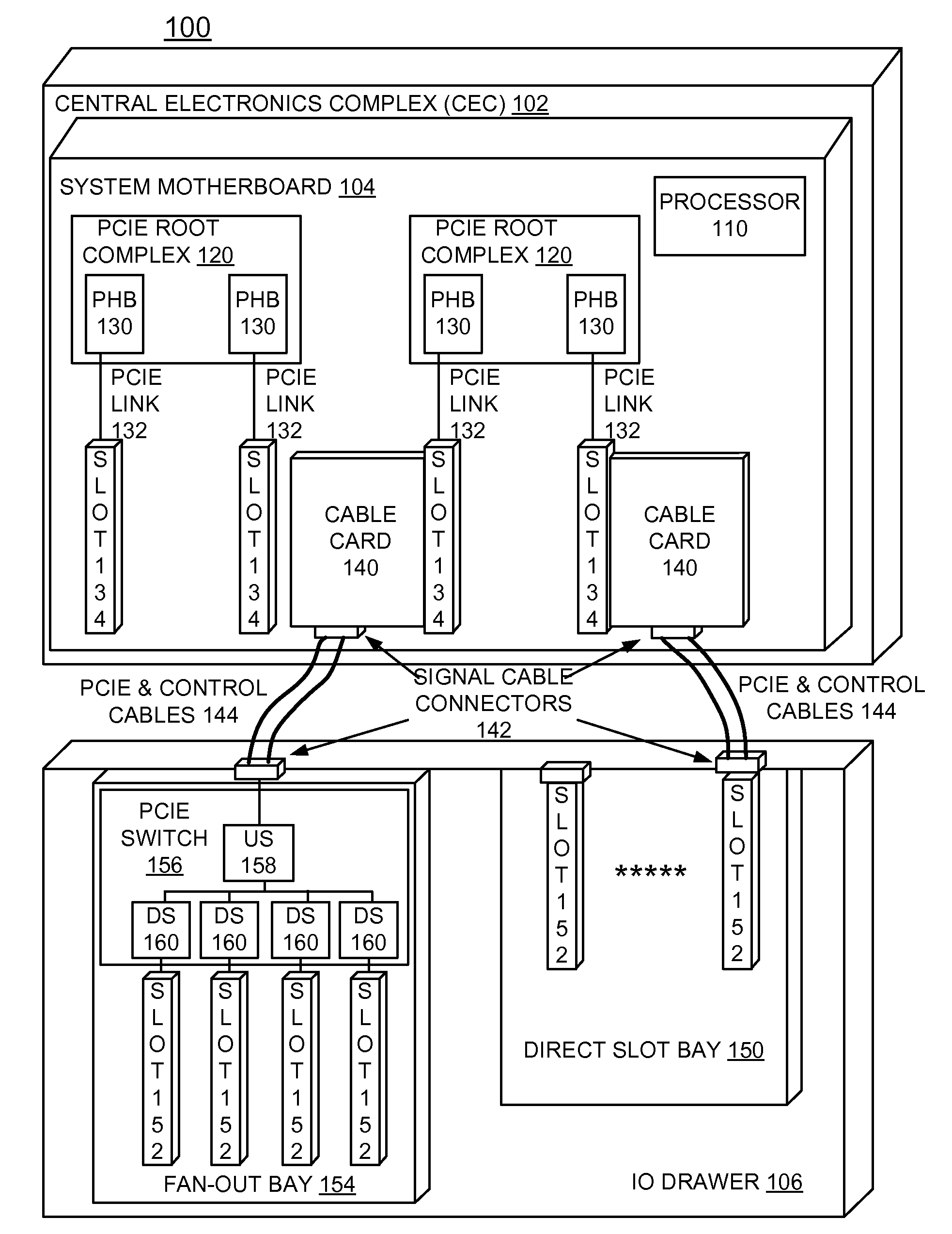

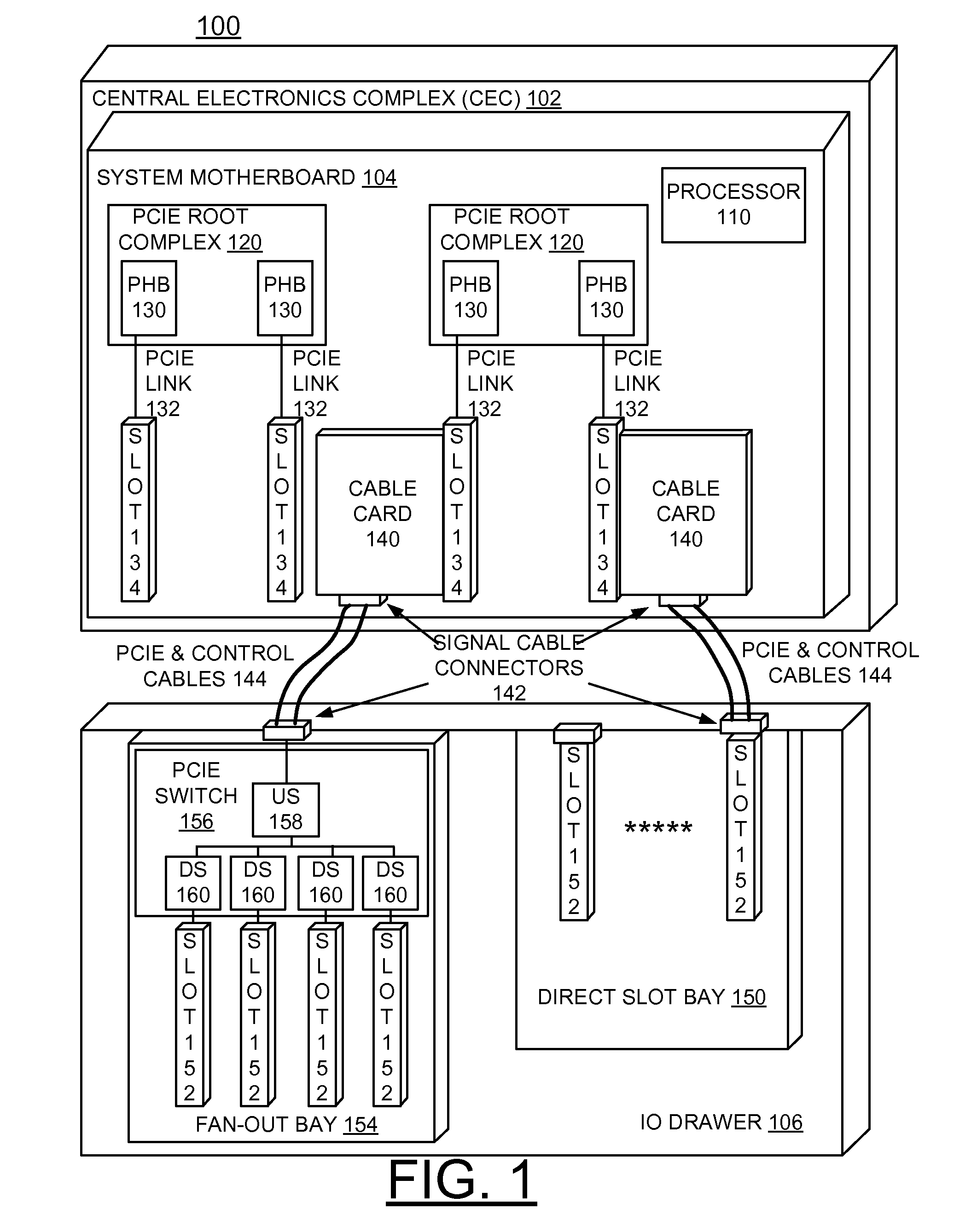

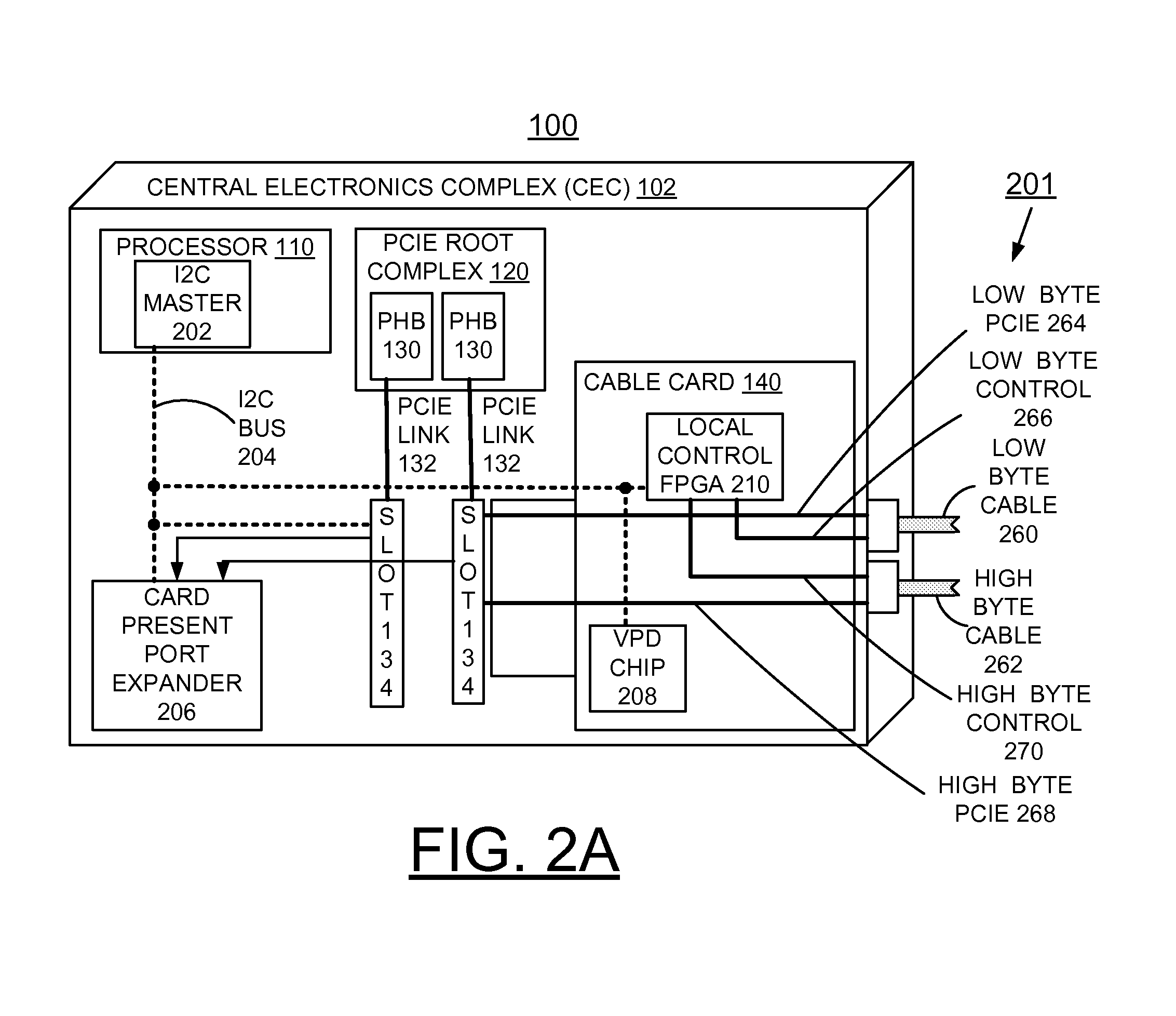

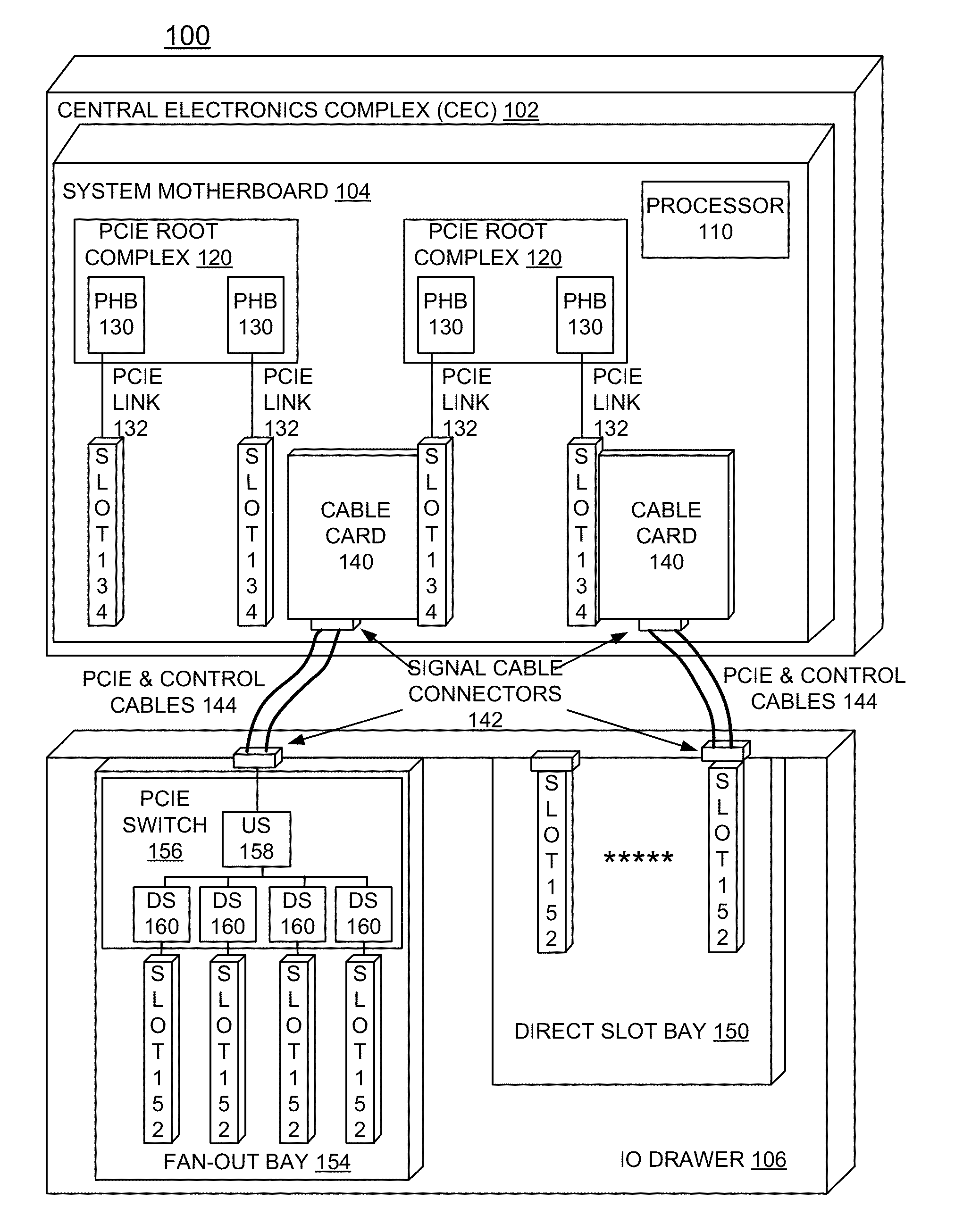

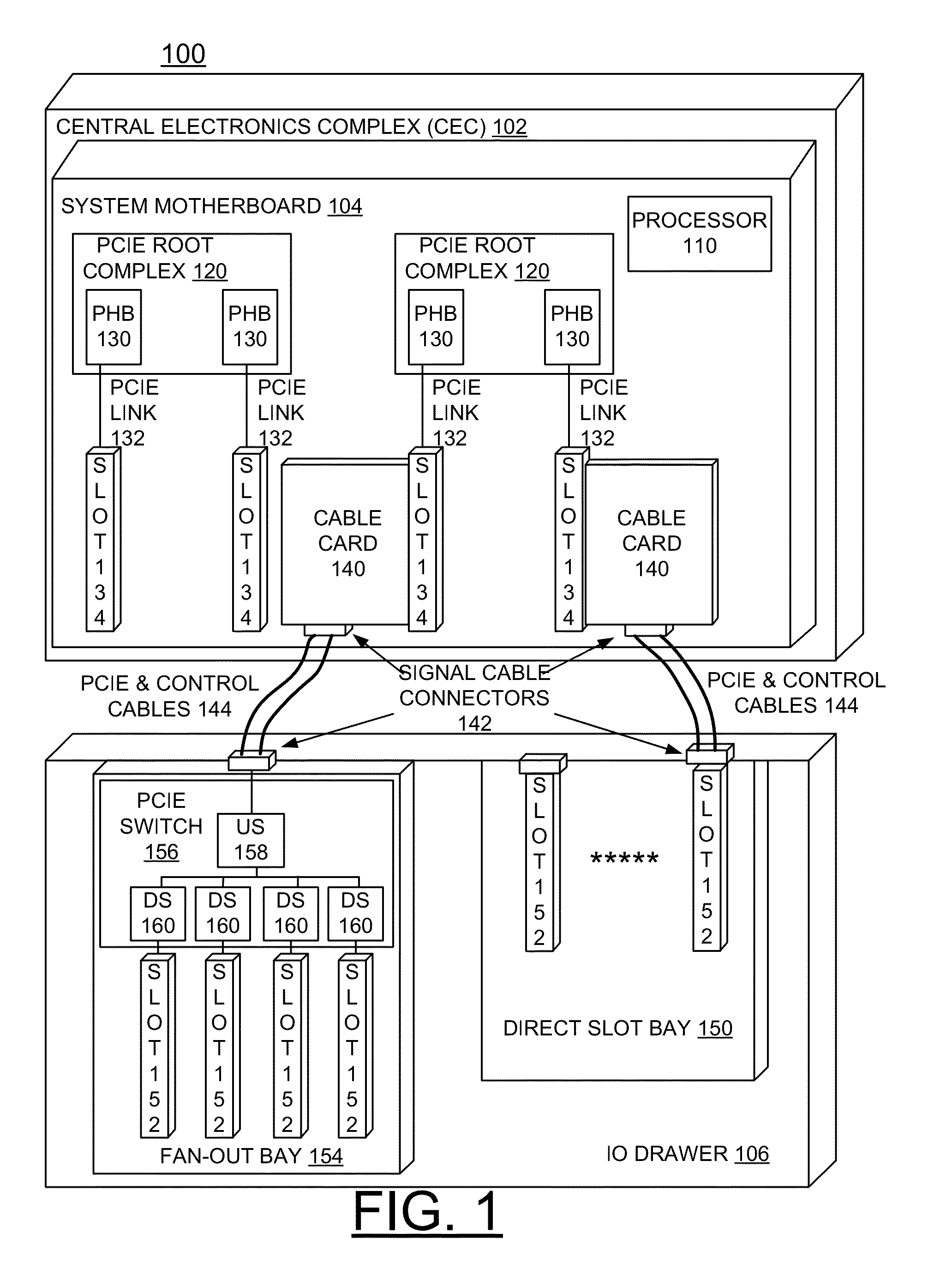

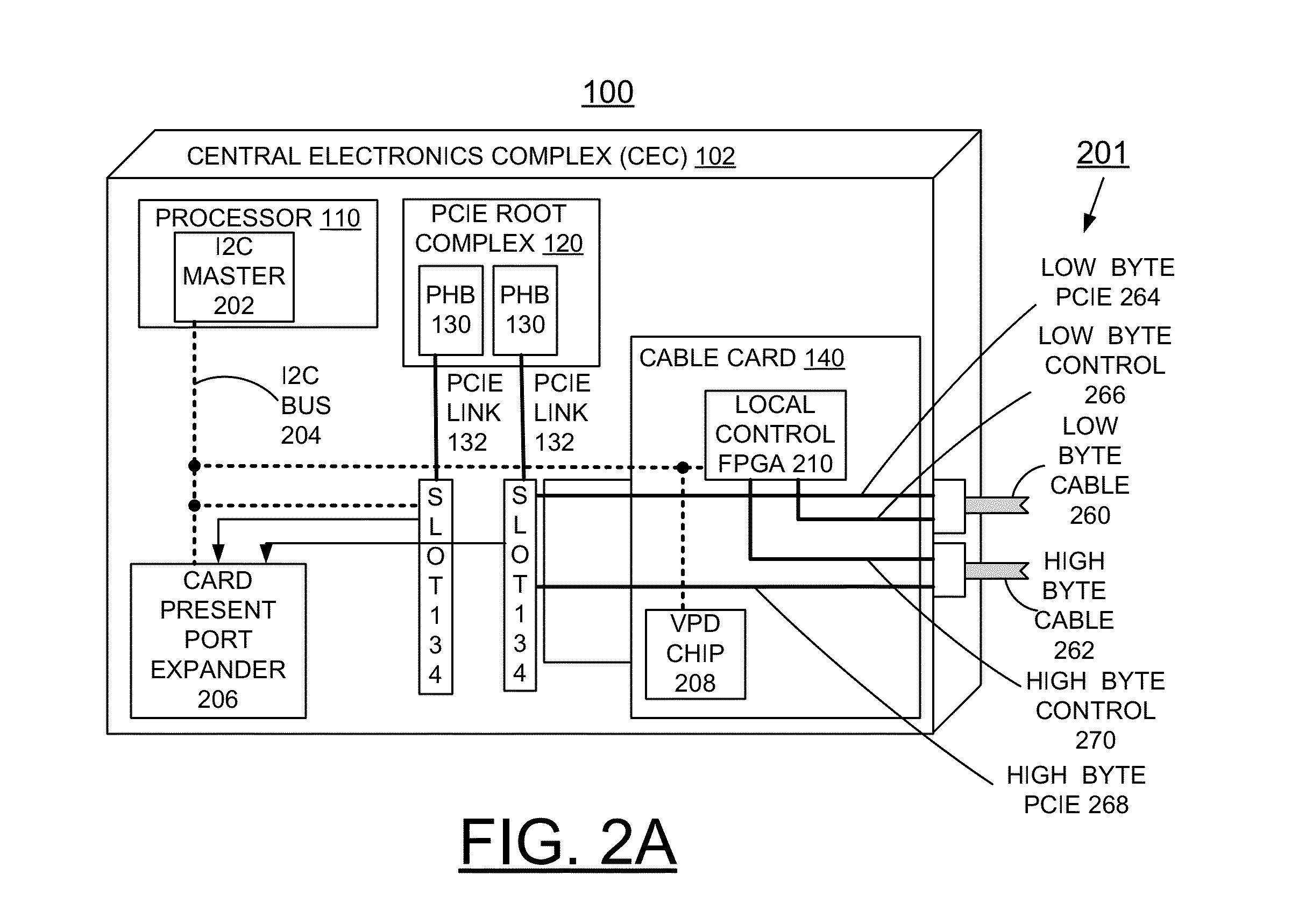

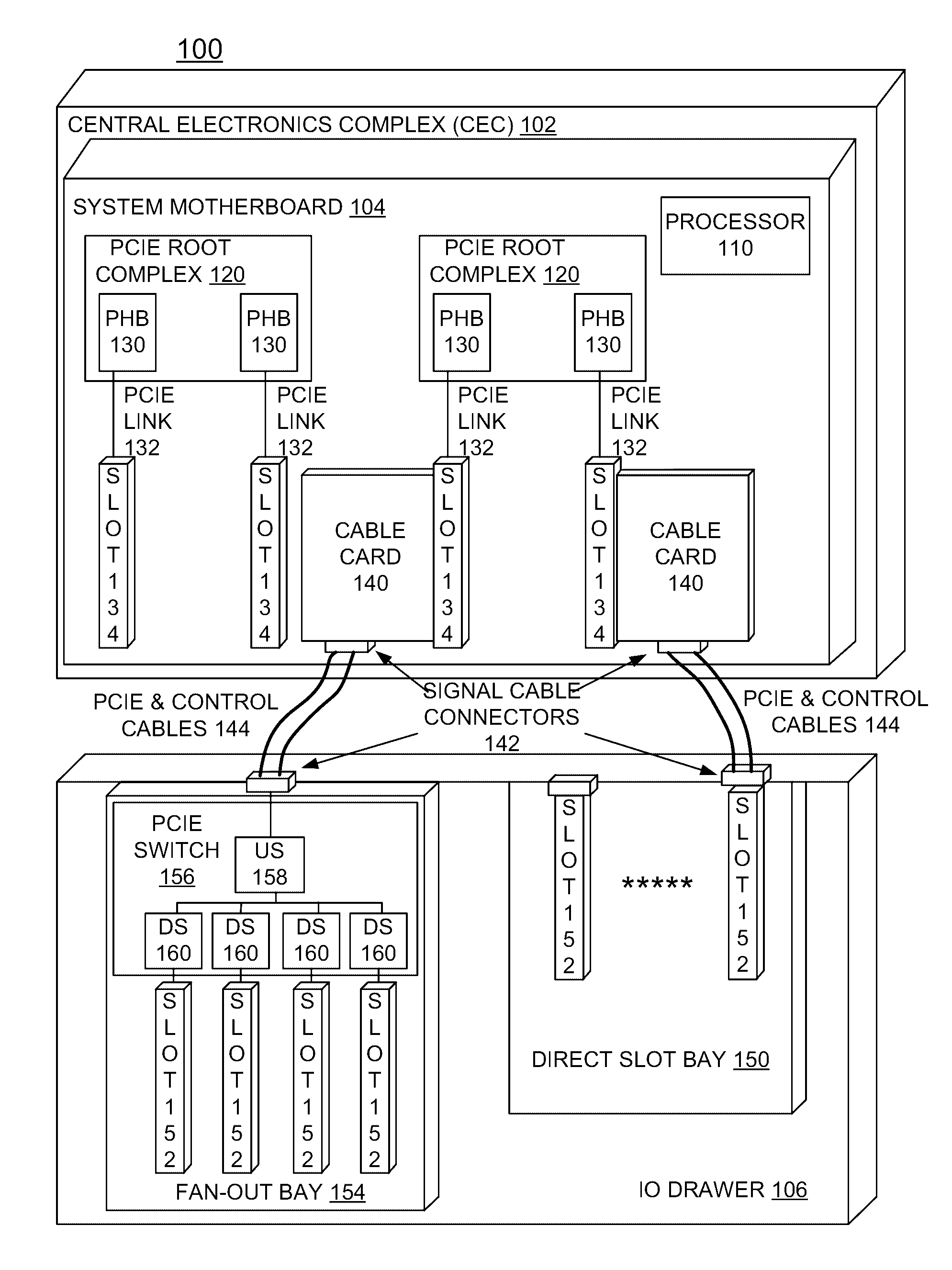

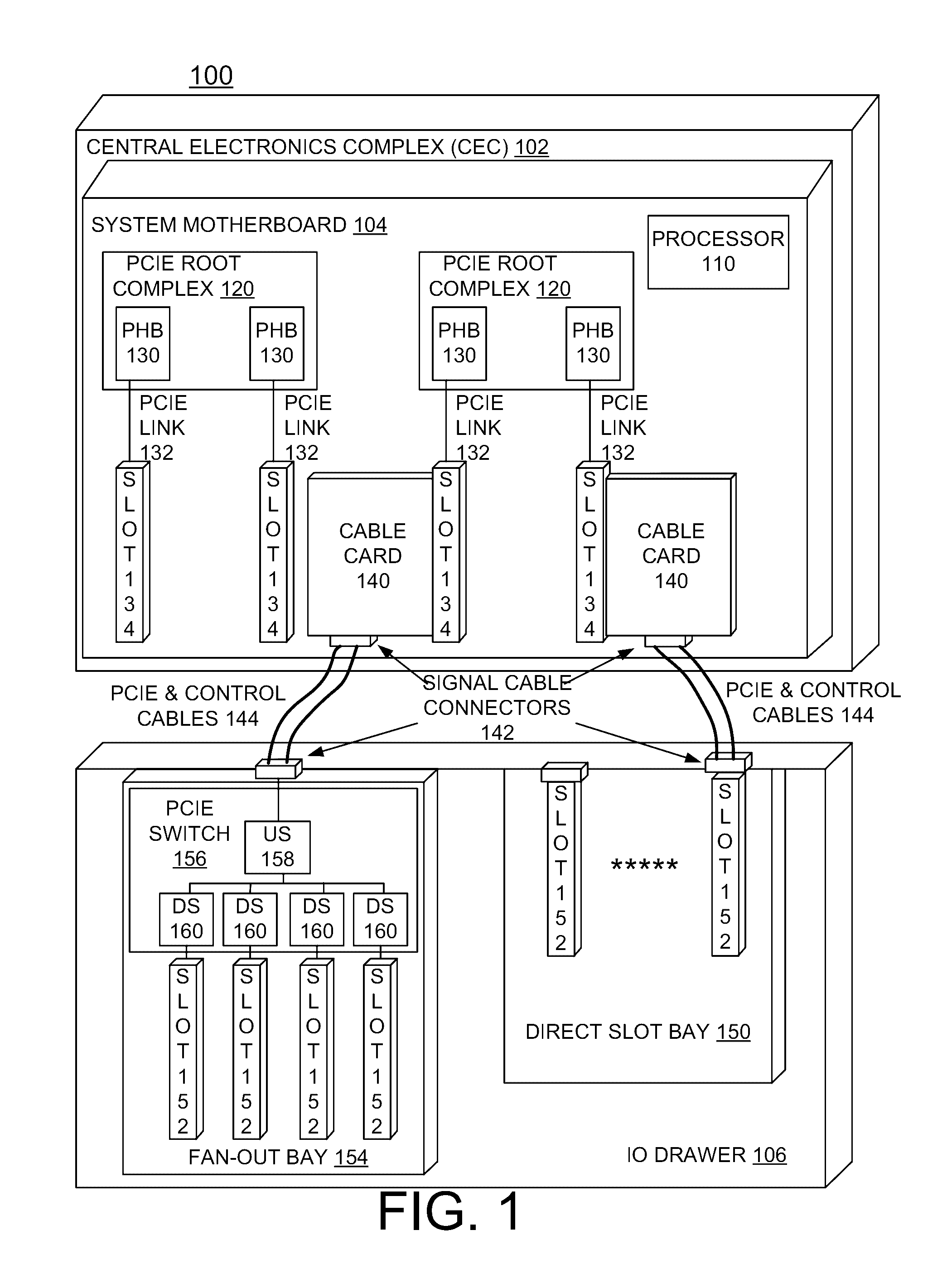

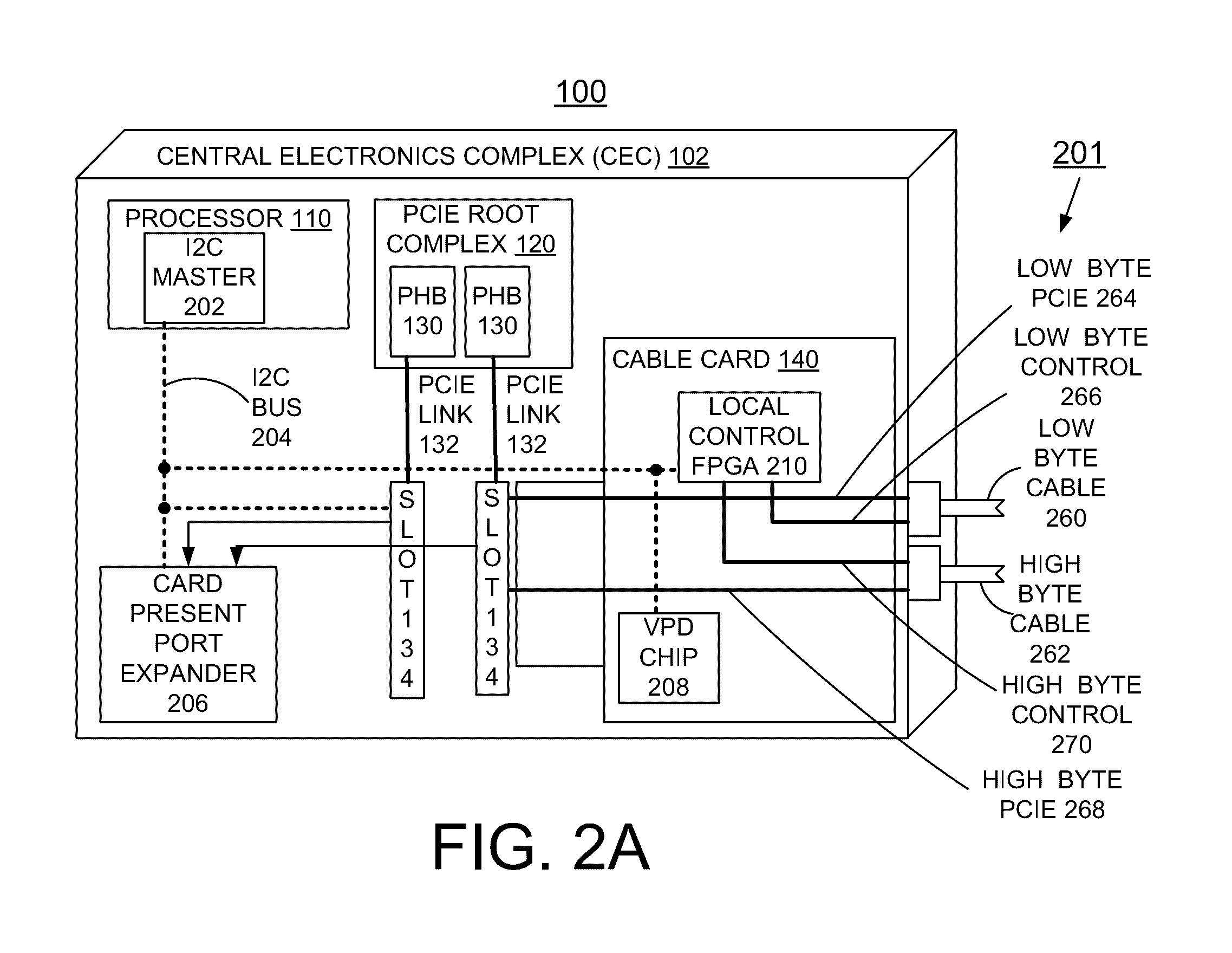

Implementing health check for optical cable attached PCIE enclosure

InactiveUS20160147705A1Without negative effectEasy to cleanNon-redundant fault processingProgram loading/initiatingHealth checkComputerized system

A method, system and computer program product are provided for implementing health check for optical cable attached Peripheral Component Interconnect Express (PCIE) enclosures in a computer system. System firmware is provided for implementing health check functions. One or more optical cables are connected between a host bridge and a PCIE enclosure. A PCIE link to the PCIE enclosure is reset responsive to a predefined event. After a set delay, a PCIE link health check is performed verifying PCIE link width and speed.

Owner:IBM CORP

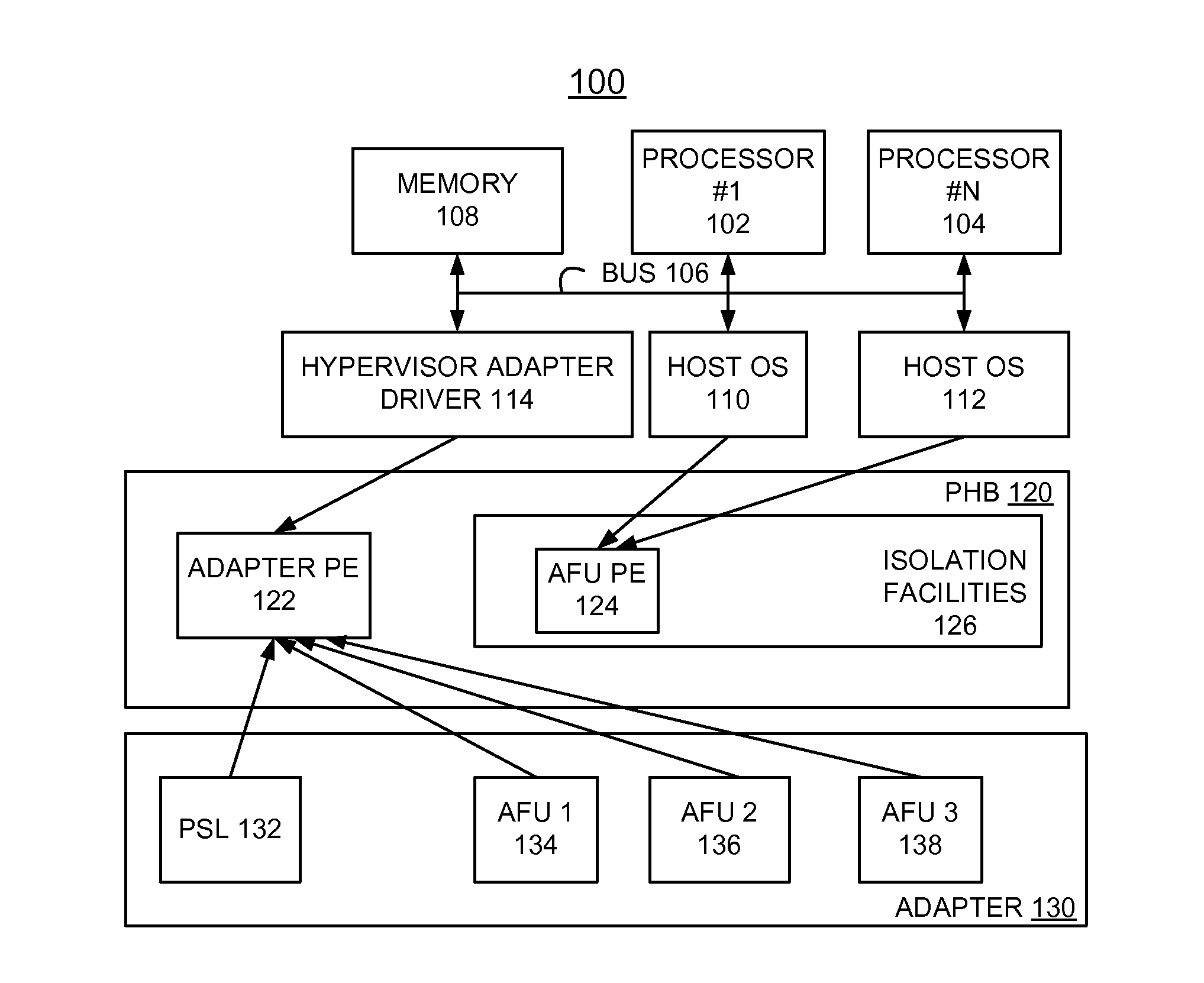

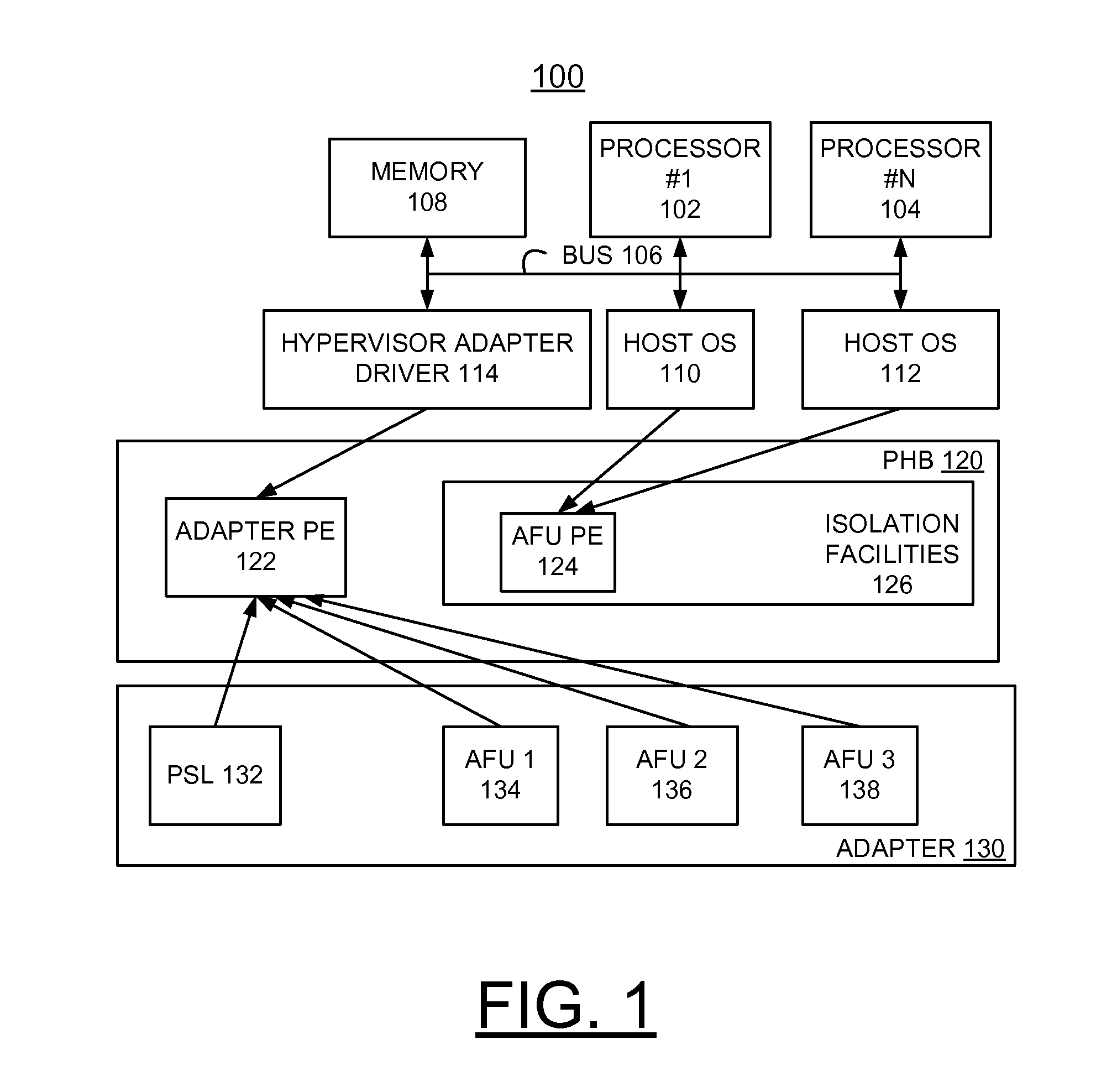

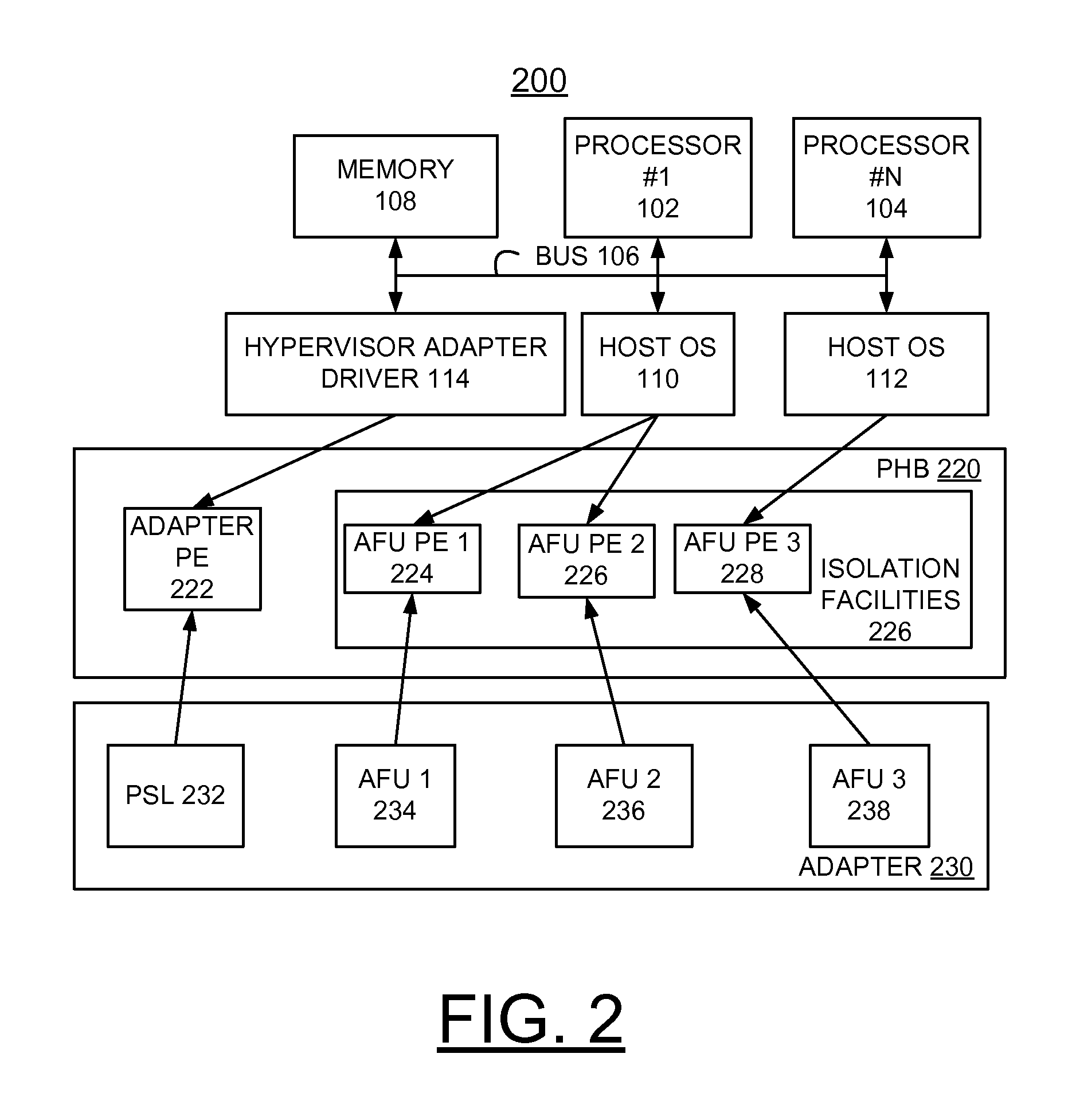

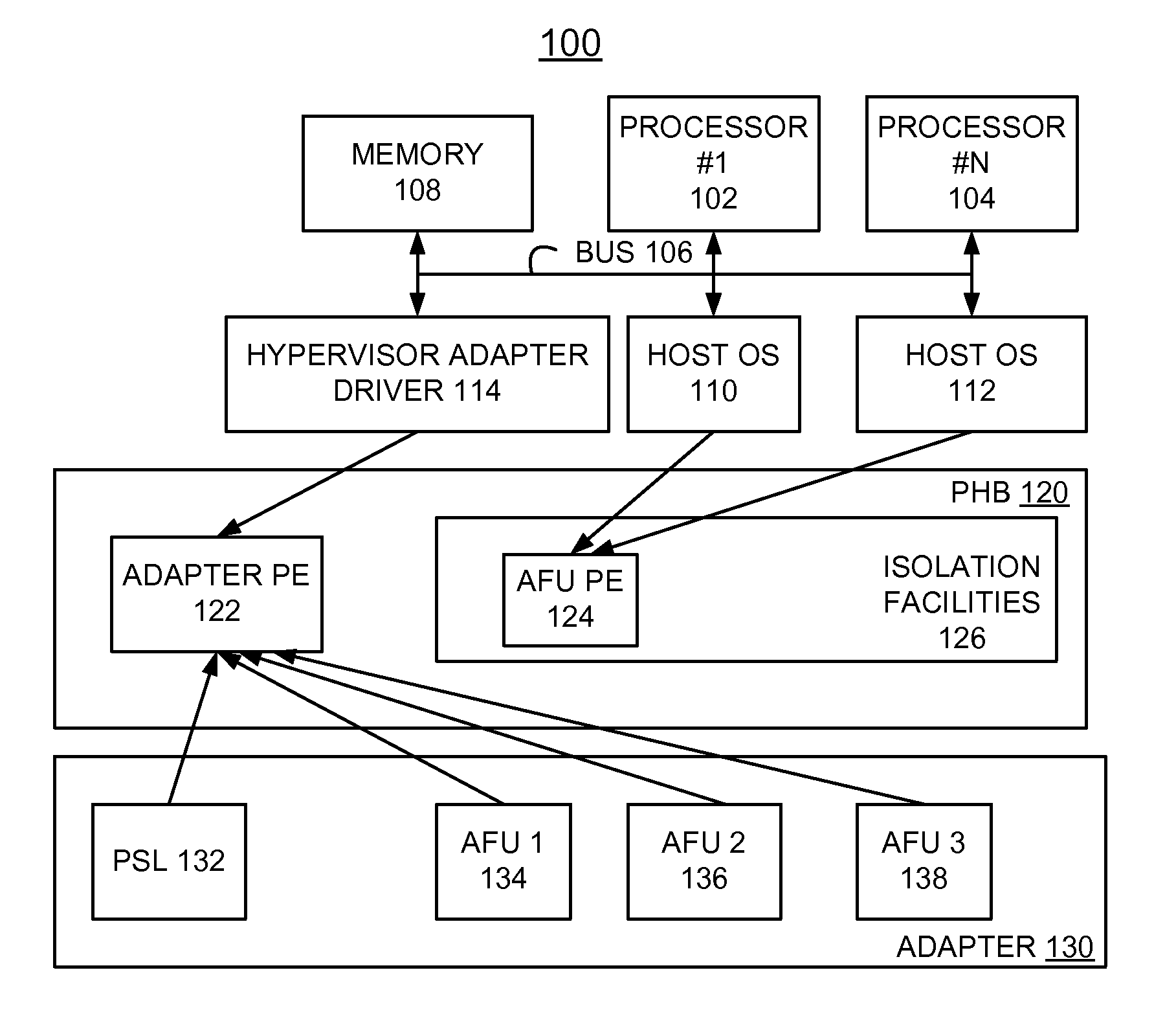

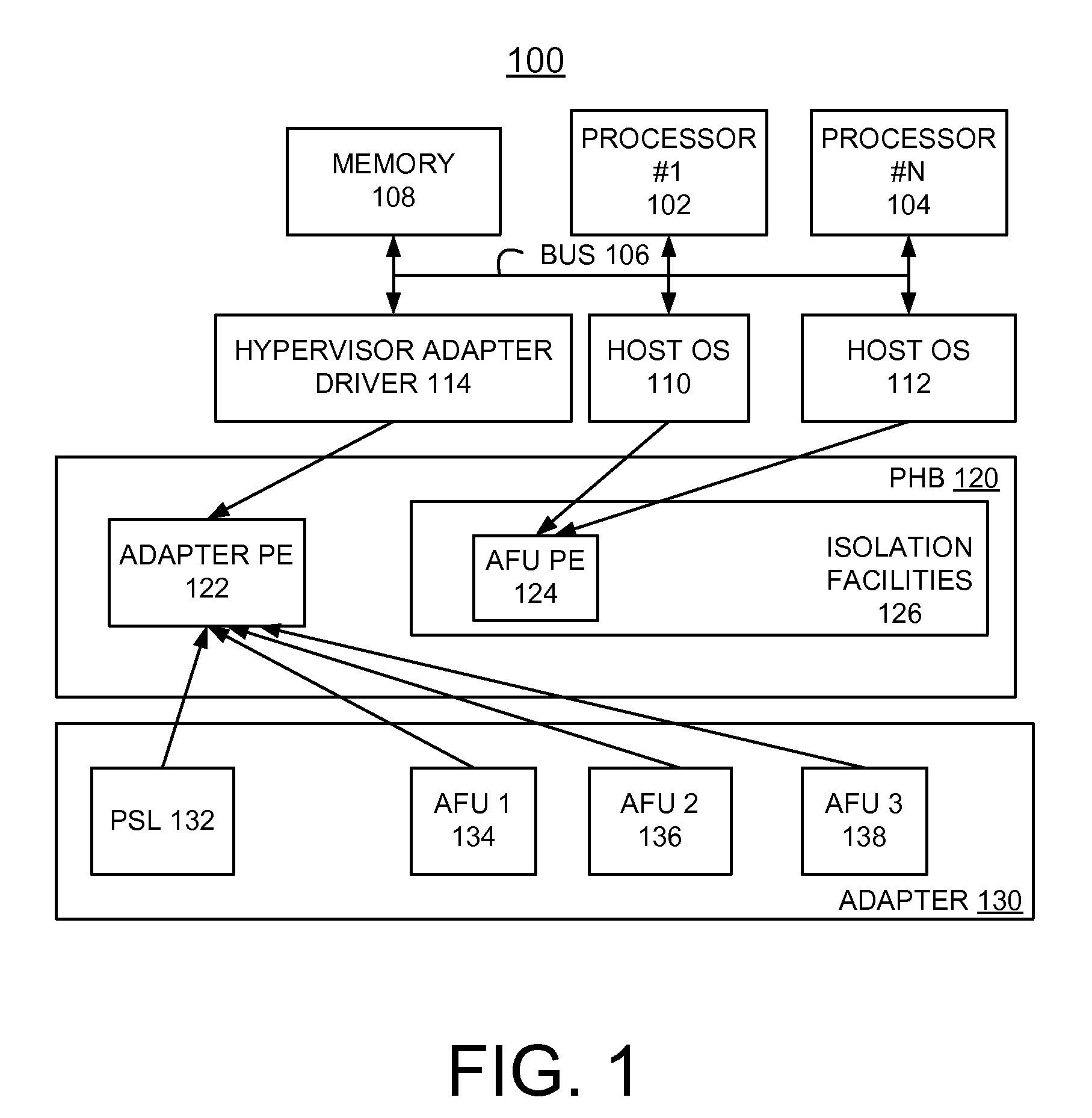

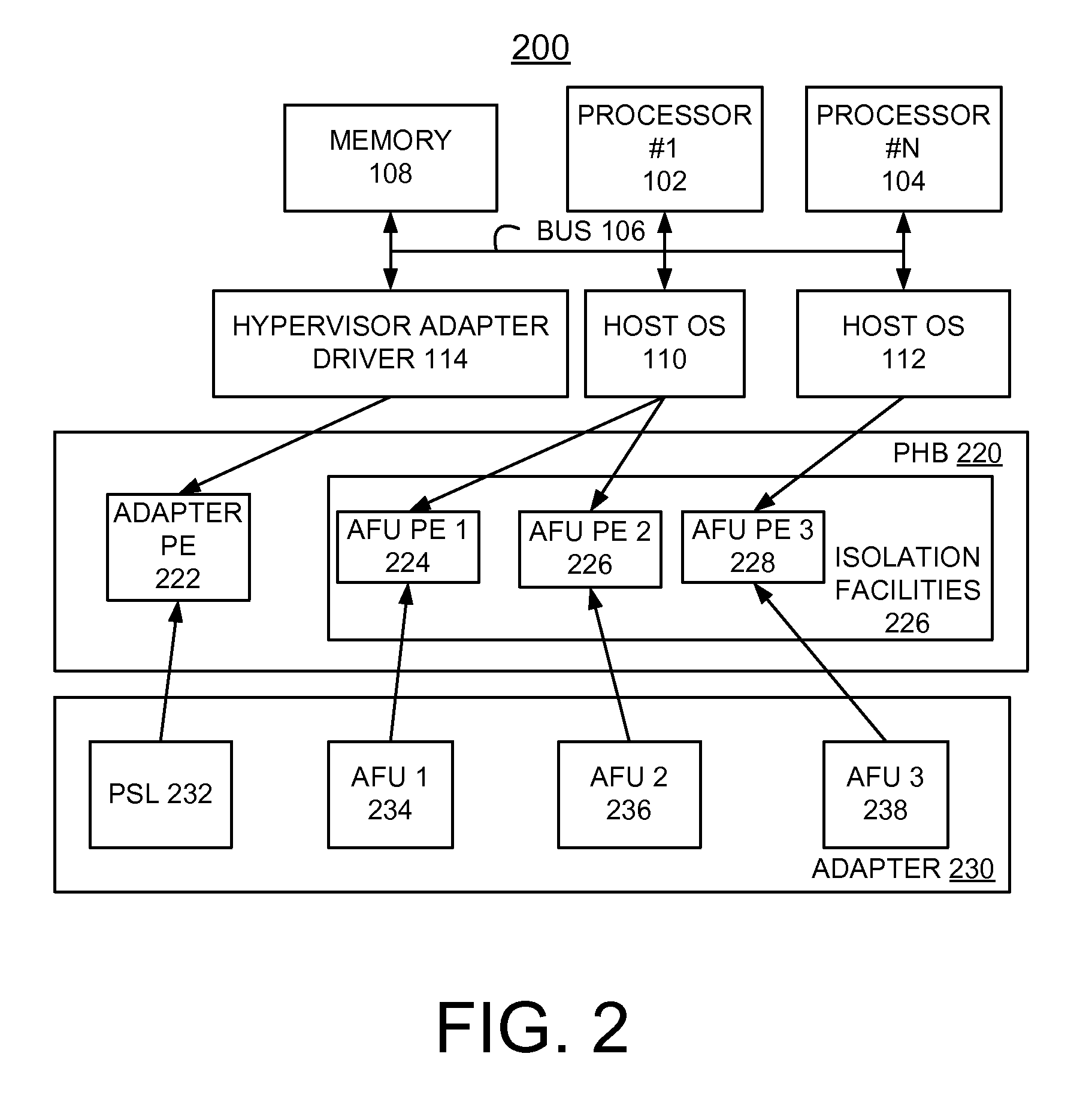

Implementing coherent accelerator function isolation for virtualization

ActiveUS20150317274A1Without negative effectSimple designMemory architecture accessing/allocationMemory adressing/allocation/relocationVirtualizationParallel computing

A method, system and computer program product are provided for implementing coherent accelerator function isolation for virtualization in an input / output (IO) adapter in a computer system. A coherent accelerator provides accelerator function units (AFUs), each AFU is adapted to operate independently of the other AFUs to perform a computing task that can be implemented within application software on a processor. The AFU has access to system memory bound to the application software and is adapted to make copies of that memory within AFU memory-cache in the AFU. As part of this memory coherency domain, each of the AFU memory-cache and processor memory-cache is adapted to be aware of changes to data commonly in either cache as well as data changed in memory of which the respective cache contains a copy.

Owner:IBM CORP

Implementing enhanced error handling of a shared adapter in a virtualized system

ActiveUS9304849B2Improve handlingWithout negative effectNon-redundant fault processingProgram loading/initiatingComputer hardwareError processing

A method, system and computer program product are provided for implementing enhanced error handling for a hardware I / O adapter, such as a Single Root Input / Output Virtualization (SRIOV) adapter, in a virtualized system. The hardware I / O adapter is partitioned into multiple endpoints, with each Partitionable Endpoint (PE) corresponding to a function, and there is an adapter PE associated with the entire adapter. The endpoints are managed both independently for actions limited in scope to a single function, and as a group for actions with the scope of the adapter. An error or failure of the adapter PE freezes the adapter PE and propagates to the VF PEs associated with the adapter, causing the VF PEs to be frozen. An adapter driver and VF device drivers are informed of the error, and start recovery. The hypervisor locks out the VF device drivers at key points enabling adapter recovery to successfully complete.

Owner:INT BUSINESS MASCH CORP

Detecting and sparing of optical pcie cable channel attached io drawer

InactiveUS20160147628A1Without negative effectDetecting faulty computer hardwareHardware monitoringPCI ExpressEngineering

A method, system and computer program product are provided for detecting state and sparing of optical Peripheral Component Interconnect Express (PCI-Express or PCIE) cable channels attached to an IO drawer. System firmware is provided for implementing health check functions and state detection and sparing functions. One or more optical cables are connected between a host bridge and a PCIE enclosure, each optical cable includes one or more spare optical channels. An identified failed optical channel is rerouted to the spare optical channel.

Owner:IBM CORP

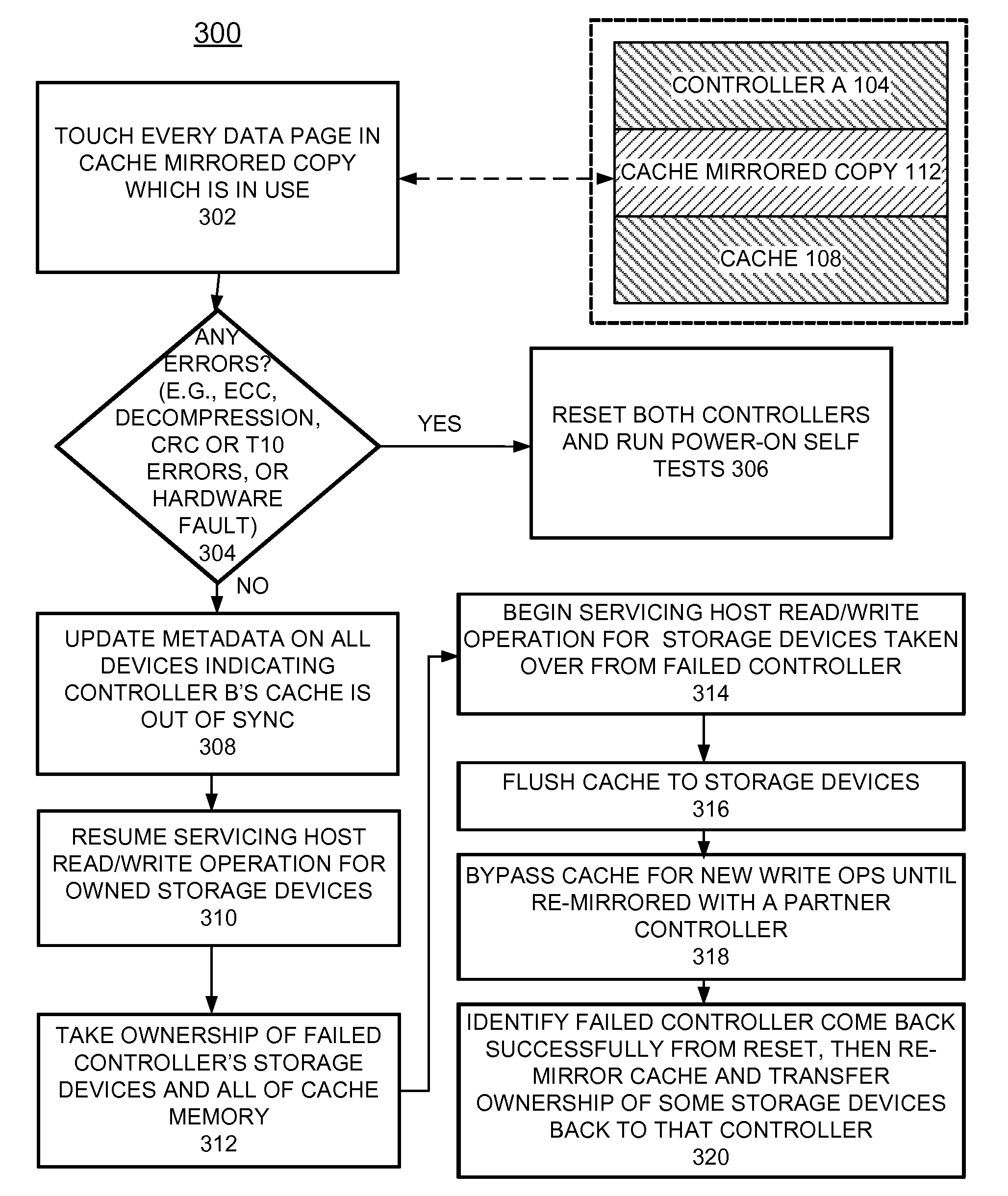

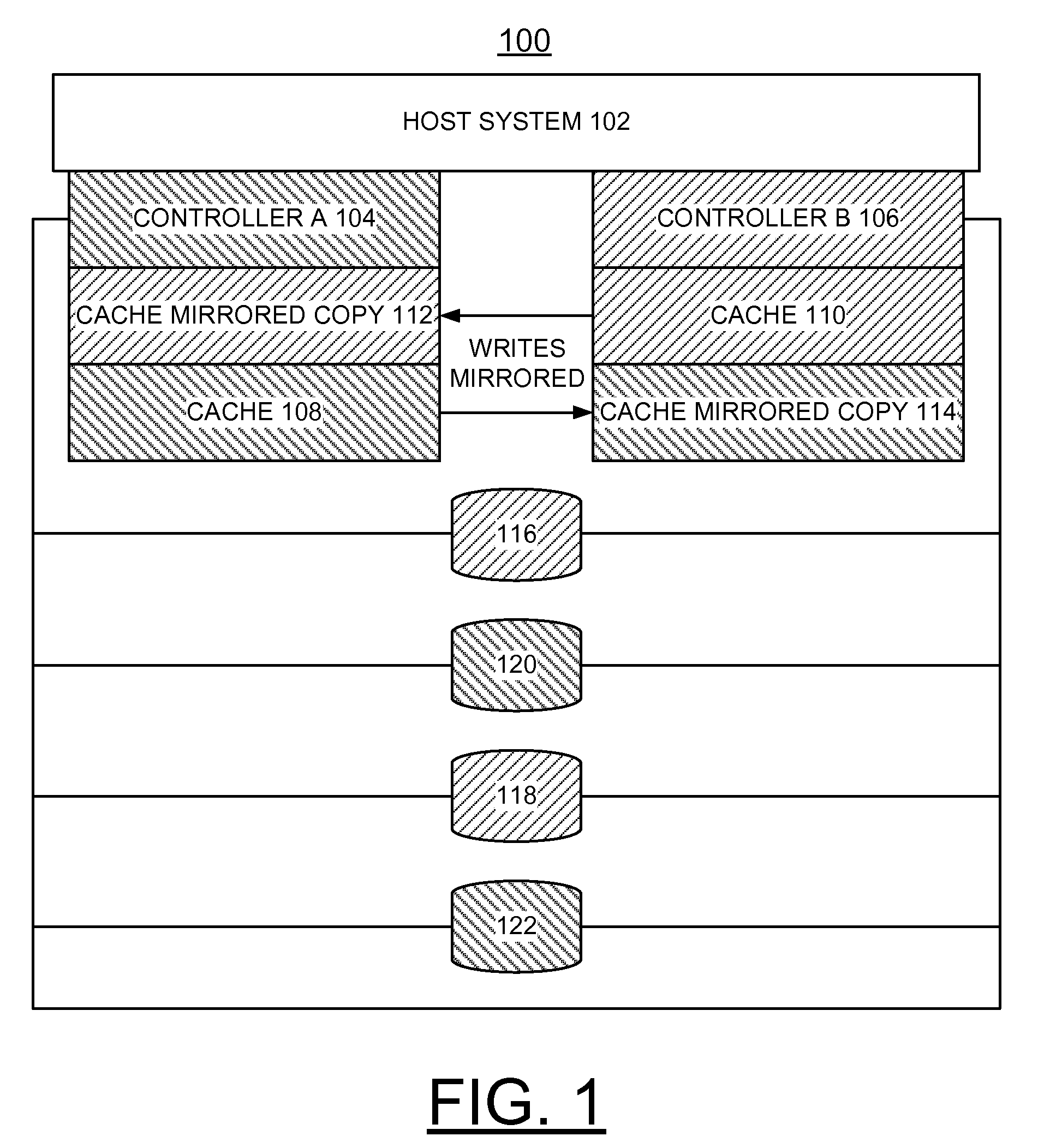

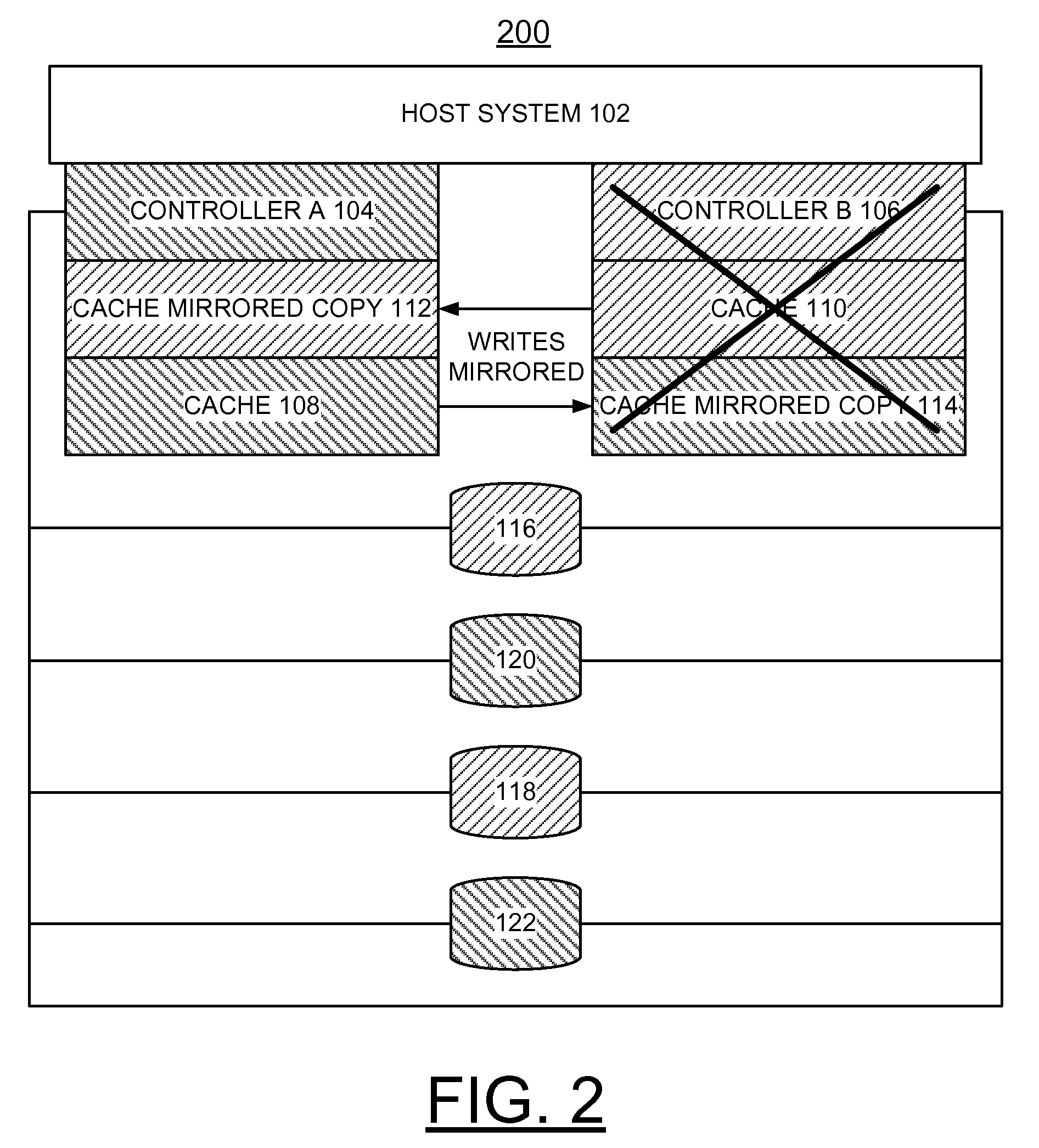

Implementing enhanced data caching and takeover of non-owned storage devices in dual storage device controller configuration with data in write cache

InactiveUS9239797B2Data augmentationWithout negative effectMemory architecture accessing/allocationMemory adressing/allocation/relocationComputerized systemRunning time

A method, system and computer program product are provided for implementing enhanced data caching and takeover of non-owned storage devices in a computer system. Each of a first controller and a second controller has a cache memory. During normal run-time, each storage device controller validates cached write data after it is written to its cache memory by reading the write data from its cache memory. If any error is detected on the read, then unit check failed storage device controller, which results in a reset of the failed storage device controller. When a storage device controller detects its dual partner controller fails, the surviving storage device controller queues host read / write operations for its storage devices already owned, and tests a cache mirrored copy from its cache memory of the failed first storage device controller before takeover of the failed controller's storage devices.

Owner:GLOBALFOUNDRIES INC

Implementing concurrent device driver maintenance and recovery for an sriov adapter in a virtualized system

InactiveUS20140372794A1Negative effectOvercome disadvantageProgram controlRedundant operation error correctionStart up timeVirtual function

A method, system and computer program product are provided for implementing concurrent adapter driver maintenance and recovery for a Single Root Input / Output Virtualization (SRIOV) adapter in a computer system. An adapter driver at start up time performs configuration of the adapter and each of a set of virtual functions (VFs). The adapter driver writes critical adapter and VF configuration data to a scratchpad buffer. When device driver maintenance is needed, such as to load updated adapter driver firmware, all VF drivers are held off temporarily, current adapter driver is detached, and then the adapter driver is reloaded with the updated driver firmware. Then the adapter driver is restarted with the updated adapter driver firmware, and performs a reinitialization process. The adapter driver performs adapter and VF configuration restoring existing configuration using values read from the scratchpad buffer.

Owner:IBM CORP

Direct access storage device (DASD) with a variable spindle rotation speed

InactiveUS6104566AWithout negative effectAC motor controlSingle motor speed/torque controlMotor driveDirect-access storage device

A method and apparatus are provided for variable spindle rotation speed in a direct access storage device (DASD). The direct access storage device (DASD) includes a multi-phase, brushless, direct current (DC) spindle motor. Speed and commutation control signals are applied to a plurality of spindle motor drivers for normally operating the plurality of spindle motor drivers in saturation mode while performing read and write operations. A spindle rotational speed is detected and compared with a predetermined spindle speed range. Responsive to the detected spindle rotational speed being within said predetermined spindle speed range, normal operations of the direct access storage device (DASD) are enabled. One or more write sync fields are provided on each surface of a magnetic disk media. The write sync field is used for timing write operations in the direct access storage device.

Owner:WESTERN DIGITAL TECH INC

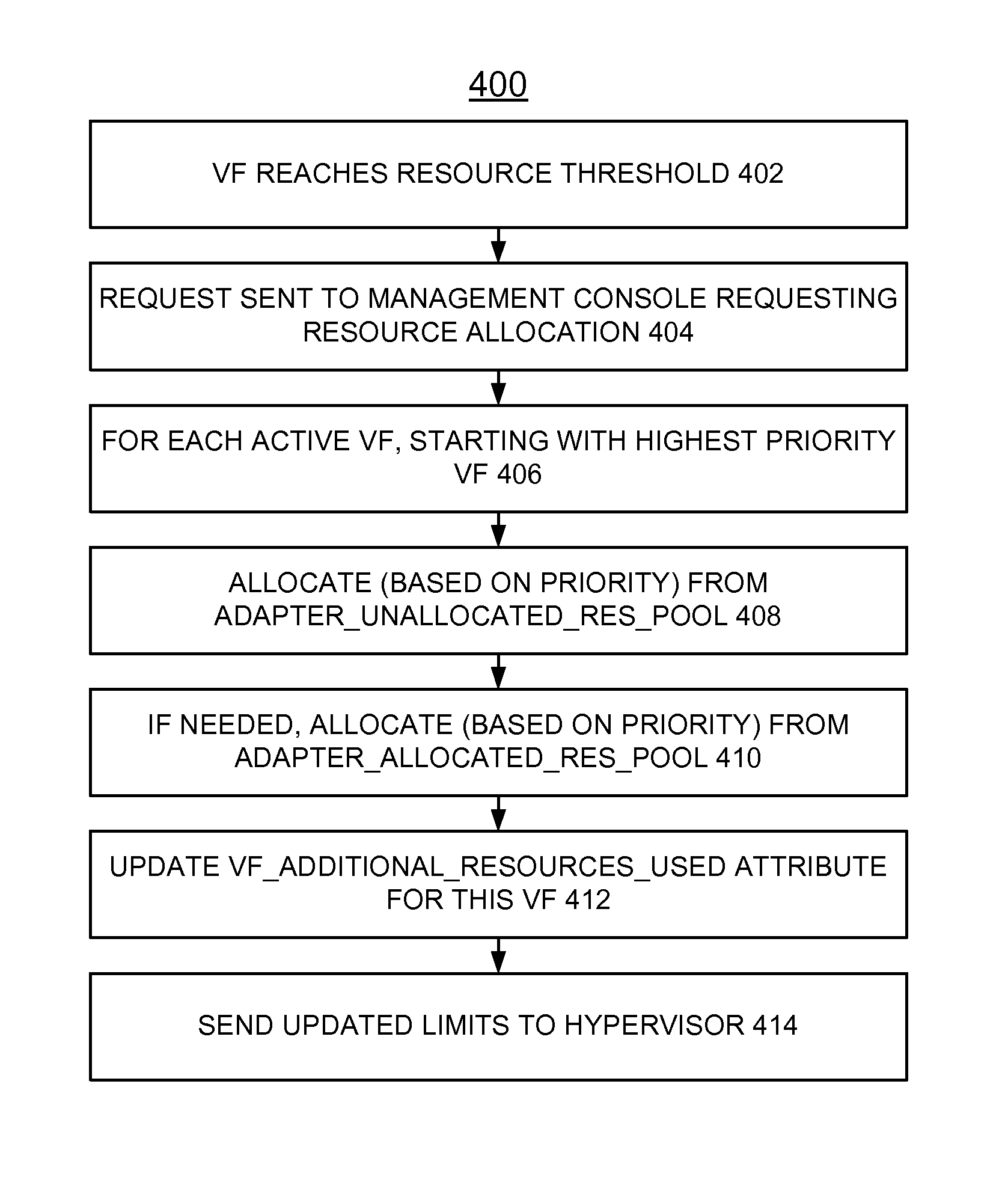

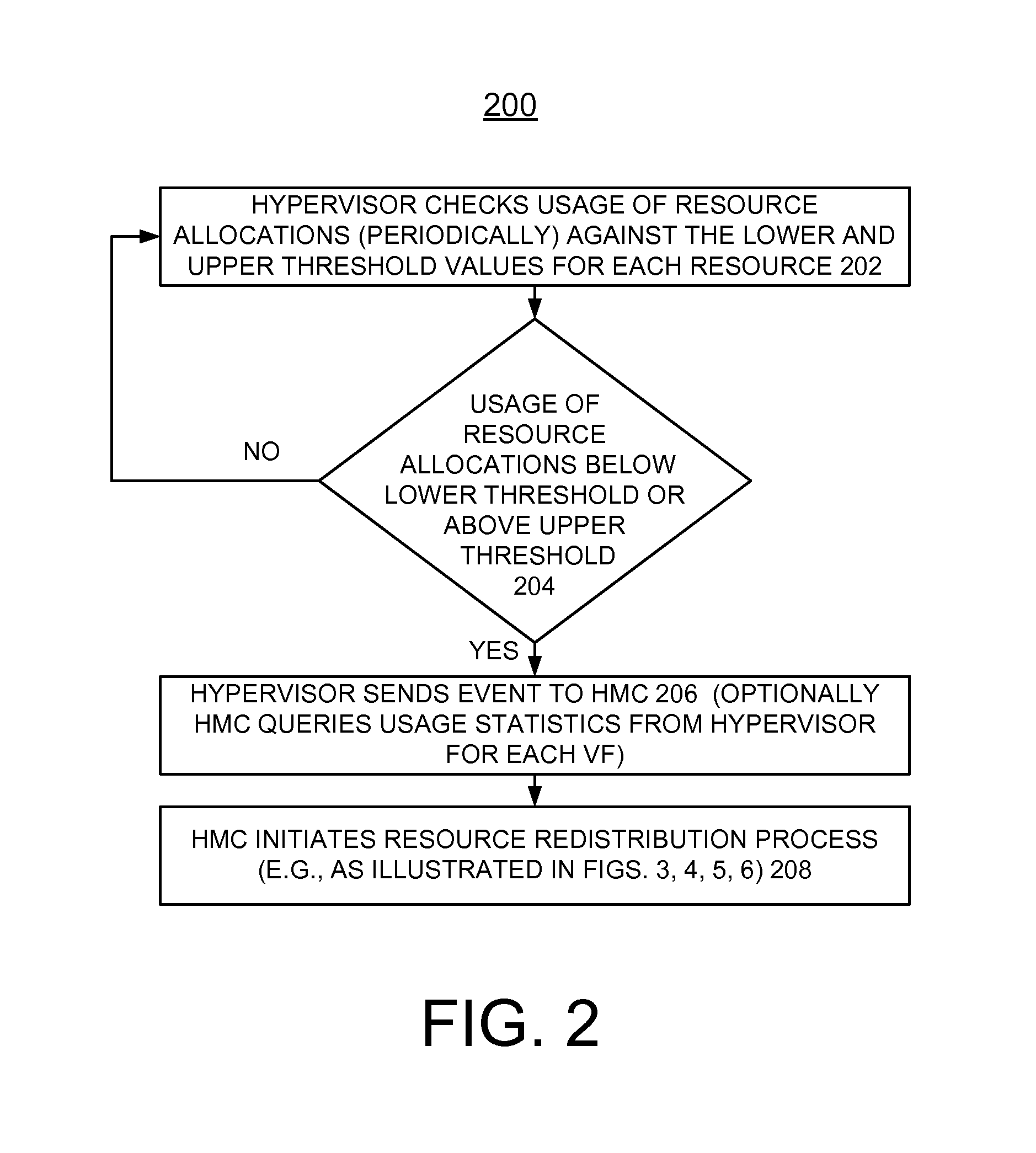

Implementing dynamic adjustment of resources allocated to SRIOV remote direct memory access adapter (RDMA) virtual functions based on usage patterns

InactiveUS9535740B1Negative effectOvercome disadvantageResource allocationSoftware simulation/interpretation/emulationDirect memory accessLower threshold

A method, system and computer program product are provided for implementing dynamic adjustment of resources allocated to Single Root Input / Output Virtualization (SRIOV) Remote Direct Memory Access (RMDA) virtual functions (VFs) in Cloud Software Defined Server environments. A hardware management console (HMC), and a hypervisor are used to implement resource allocation to the SRIOV RDMA VFs based on resource usage. The hypervisor checks resource usage for the resource allocations of the SRIOV RDMA VF relative to lower and upper threshold values. Responsive to identifying the resource usage below the lower threshold or above the upper threshold, the hypervisor sends an event to the HMC, and the HMC starts a resource redistribution process.

Owner:IBM CORP

Implementing coherent accelerator function isolation for virtualization

ActiveUS9501308B2Without negative effectSimple designMemory architecture accessing/allocationMemory adressing/allocation/relocationVirtualizationParallel computing

A method, system and computer program product are provided for implementing coherent accelerator function isolation for virtualization in an input / output (IO) adapter in a computer system. A coherent accelerator provides accelerator function units (AFUs), each AFU is adapted to operate independently of the other AFUs to perform a computing task that can be implemented within application software on a processor. The AFU has access to system memory bound to the application software and is adapted to make copies of that memory within AFU memory-cache in the AFU. As part of this memory coherency domain, each of the AFU memory-cache and processor memory-cache is adapted to be aware of changes to data commonly in either cache as well as data changed in memory of which the respective cache contains a copy.

Owner:IBM CORP

Detecting and sparing of optical pcie cable channel attached io drawer

InactiveUS20160147606A1Without negative effectDetecting faulty computer hardwareHardware monitoringHealth checkComputer program

A method, system and computer program product are provided for detecting state and sparing of optical Peripheral Component Interconnect Express (PCI-Express or PCIE) cable channels attached to an IO drawer. System firmware is provided for implementing health check functions and state detection and sparing functions. One or more optical cables are connected between a host bridge and an PCIE enclosure, each optical cable includes one or more spare optical channels. An identified failed optical channel is rerouted to the spare optical channel.

Owner:IBM CORP

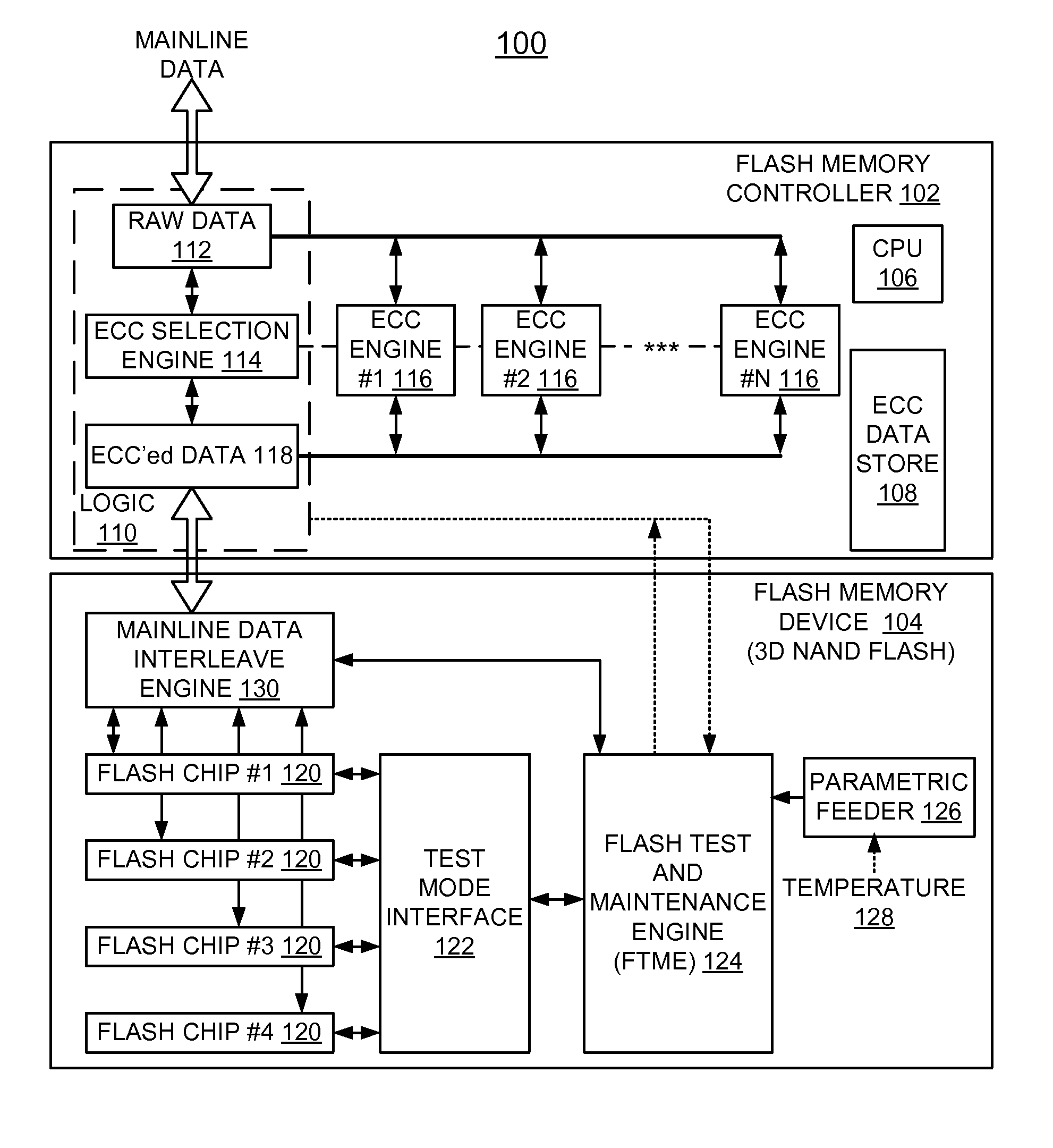

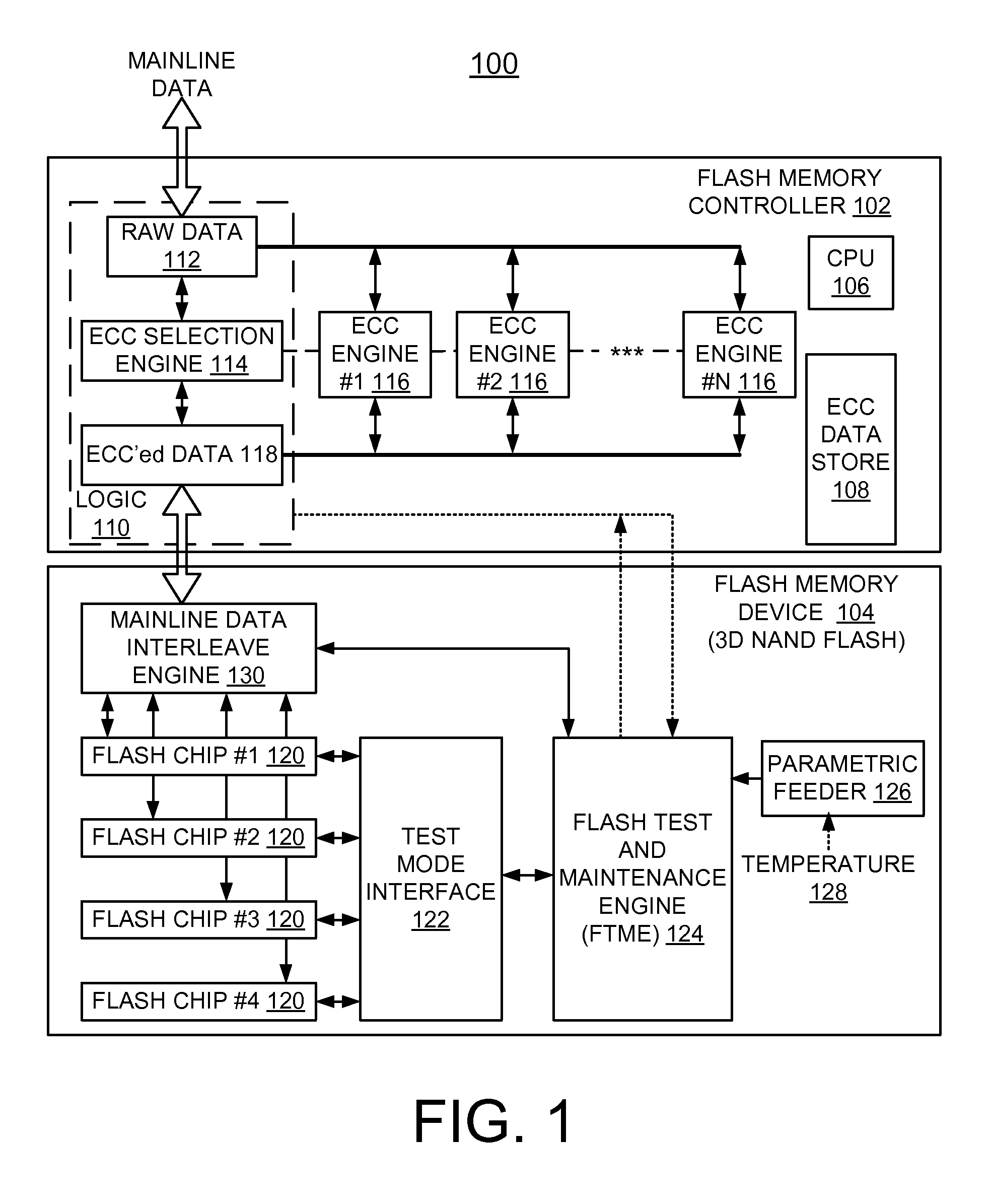

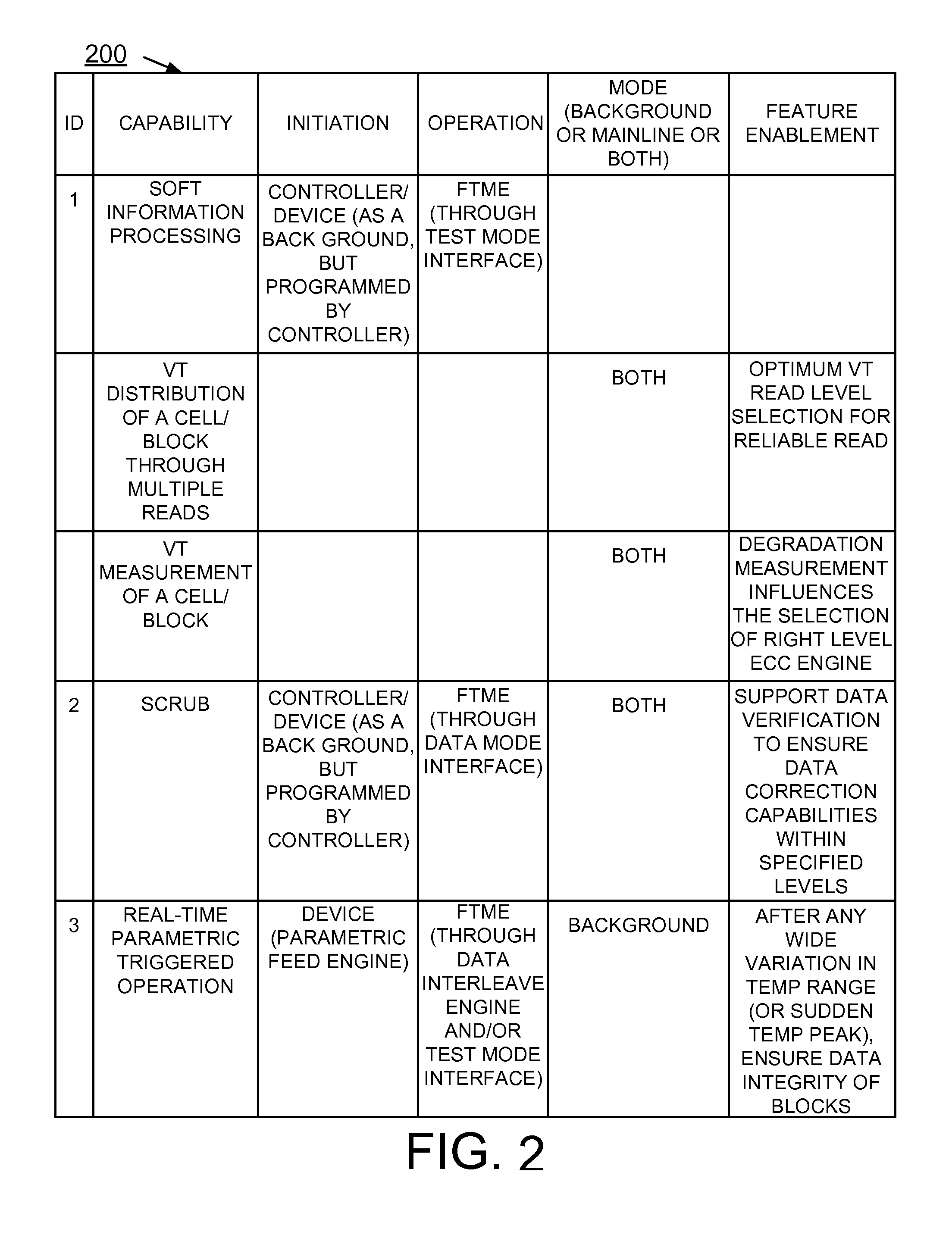

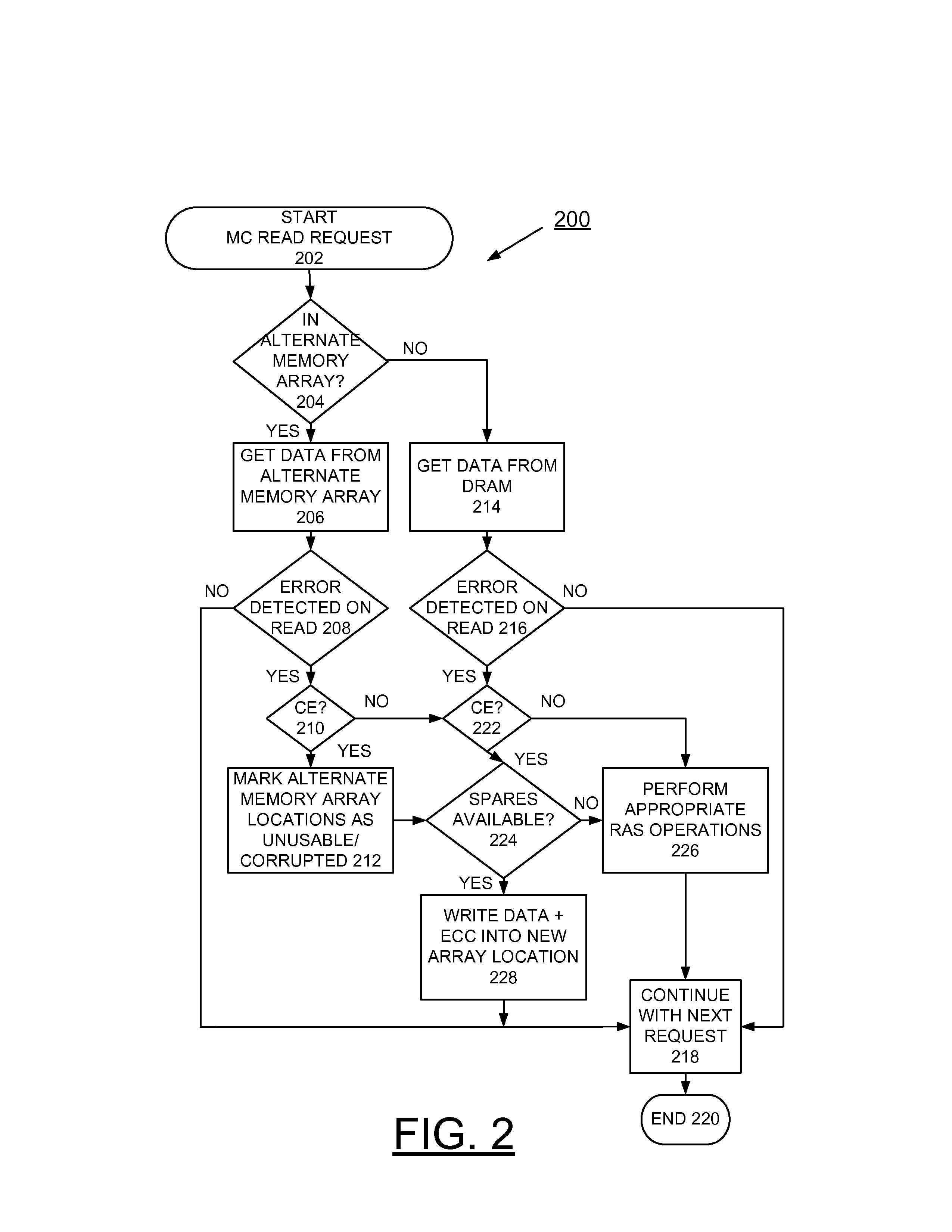

Implementing ECC control for enhanced endurance and data retention of flash memories

InactiveUS9304856B2Enhanced endurance and data retentionWithout negative effectRead-only memoriesCode conversionMemory controllerThreshold voltage

A method, system and memory controller are provided for implementing ECC (Error Correction Codes) control to provide enhanced endurance and data retention of flash memories. The memory controller includes a VT (threshold voltage) monitor to determine VT degradation of cells and blocks; the VT monitor configured to store information about the determined VT degradation; a first ECC engine having a first level of ECC capability; a second ECC engine having a second level of ECC capability, the second level higher than the first level, the second ECC engine having a longer latency than the first ECC engine; a logic to issue a read request to a particular cell / block, and, using the determined VT degradation, use the first ECC engine if the determined VT degradation is less than a threshold and to use the second ECC engine if the determined VT degradation is above the threshold.

Owner:IBM CORP

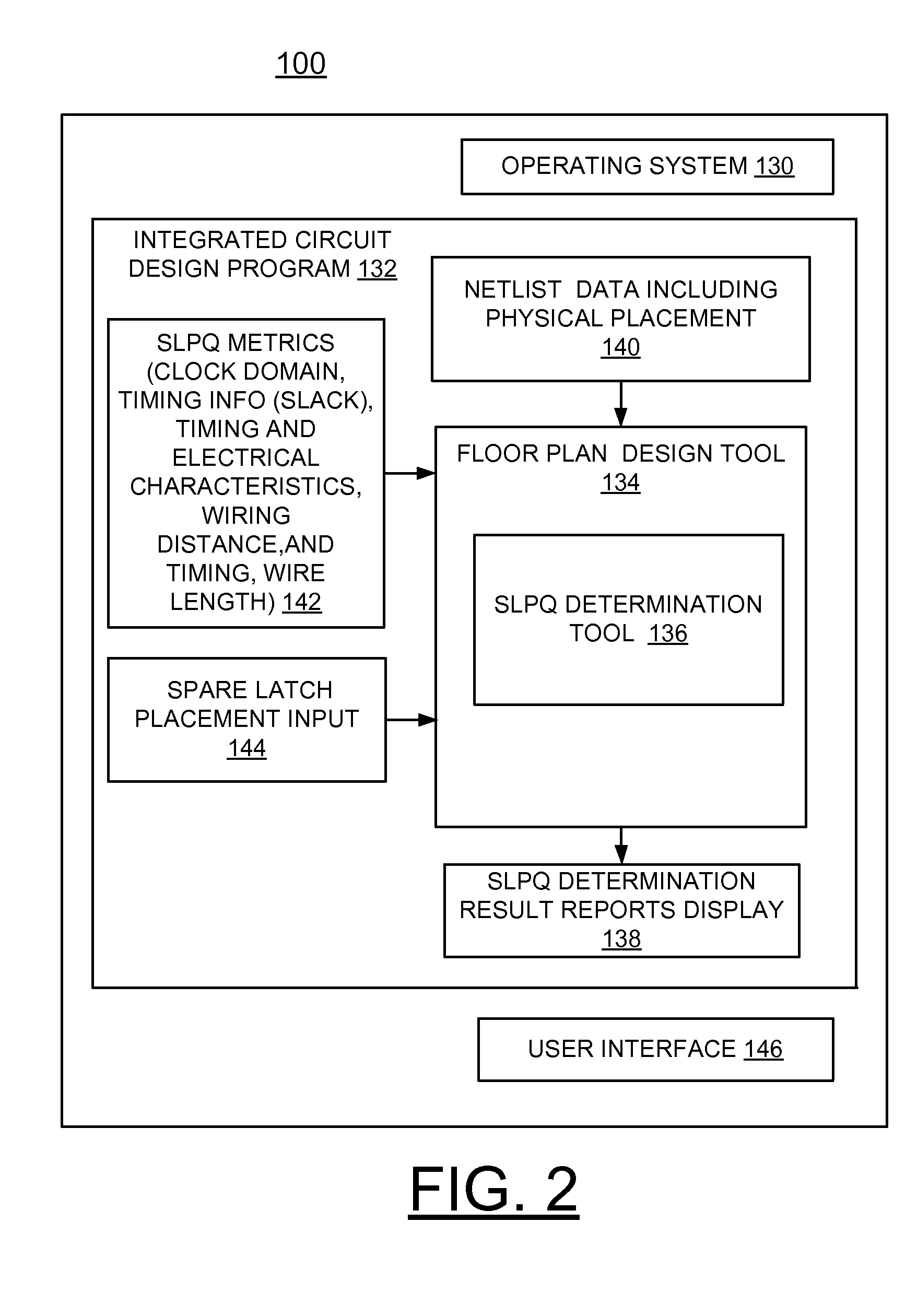

Implementing spare latch placement quality determination

ActiveUS20120124541A1Negative effectOvercome disadvantageCAD circuit designSoftware simulation/interpretation/emulationData functionIntegrated circuit

A method, system and computer program product are provided for implementing spare latch placement quality (SLPQ) determination in a floor plan design of an integrated circuit chip. A spare latch placement quality (SLPQ) metric data function is defined and compared to a spare latch placement input with a series of calculations performed. The spare latch placement quality (SLPQ) determination is made based upon the compared SLPQ metric data function and the spare latch placement input. Then associated reports including textual and visual reports are generated responsive to the SLPQ determination. In addition, a new spare latch placement can be constructed with an algorithm responsive to the SLPQ determination.

Owner:GLOBALFOUNDRIES US INC

Implementing distributed debug data collection and analysis for a shared adapter in a virtualized system

ActiveUS20140372795A1Without negative effectNon-redundant fault processingRedundant operation error correctionComputer hardwareEvent trigger

A method, system and computer program product are provided for implementing distributed debug data collection and analysis for a hardware I / O adapter, such as, a Single Root Input / Output Virtualization (SRIOV) adapter in a virtualized system. A predetermined event triggers a base error collection sequence. Adapter driver data is collected and virtual function (VF) device drivers are locked out responsive to triggering the base error collection sequence. Adapter debug data is collected and the adapter is reinitialized including an indication to VF drivers if VF error data is to be collected. The virtual function (VF) device drivers are unlocked allowing the VF device drivers to commence recovery of a respective virtual function (VF).

Owner:GLOBALFOUNDRIES US INC

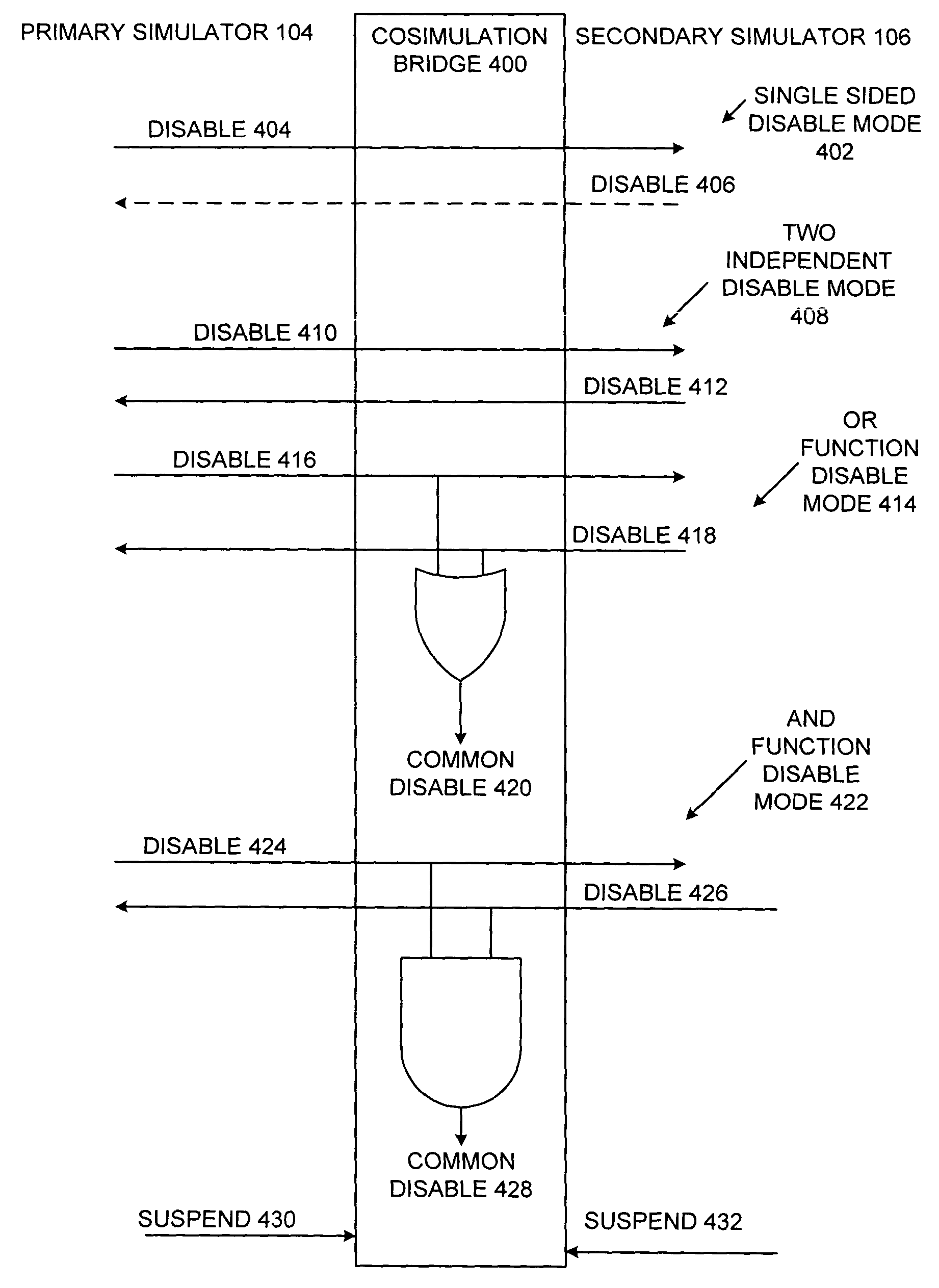

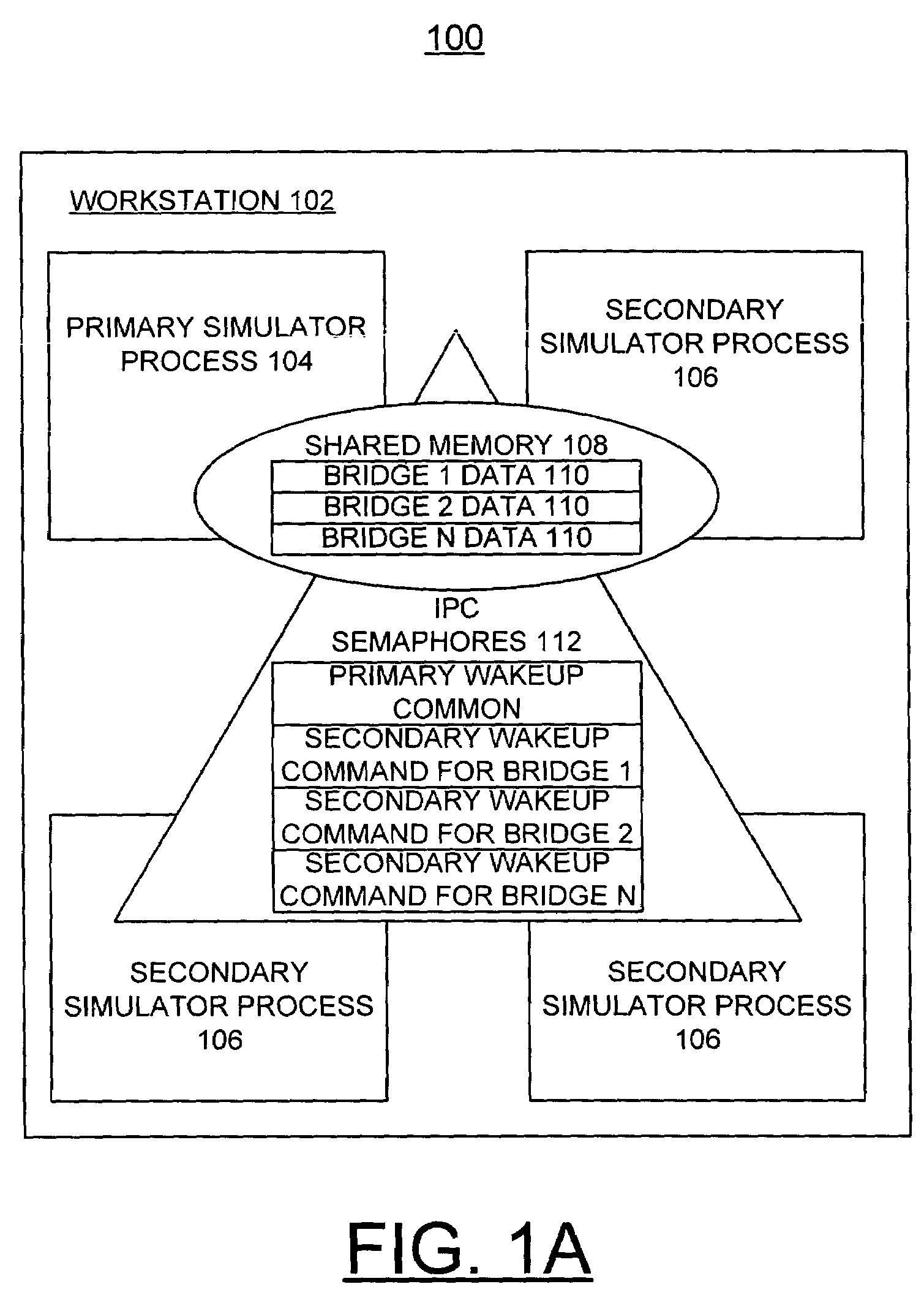

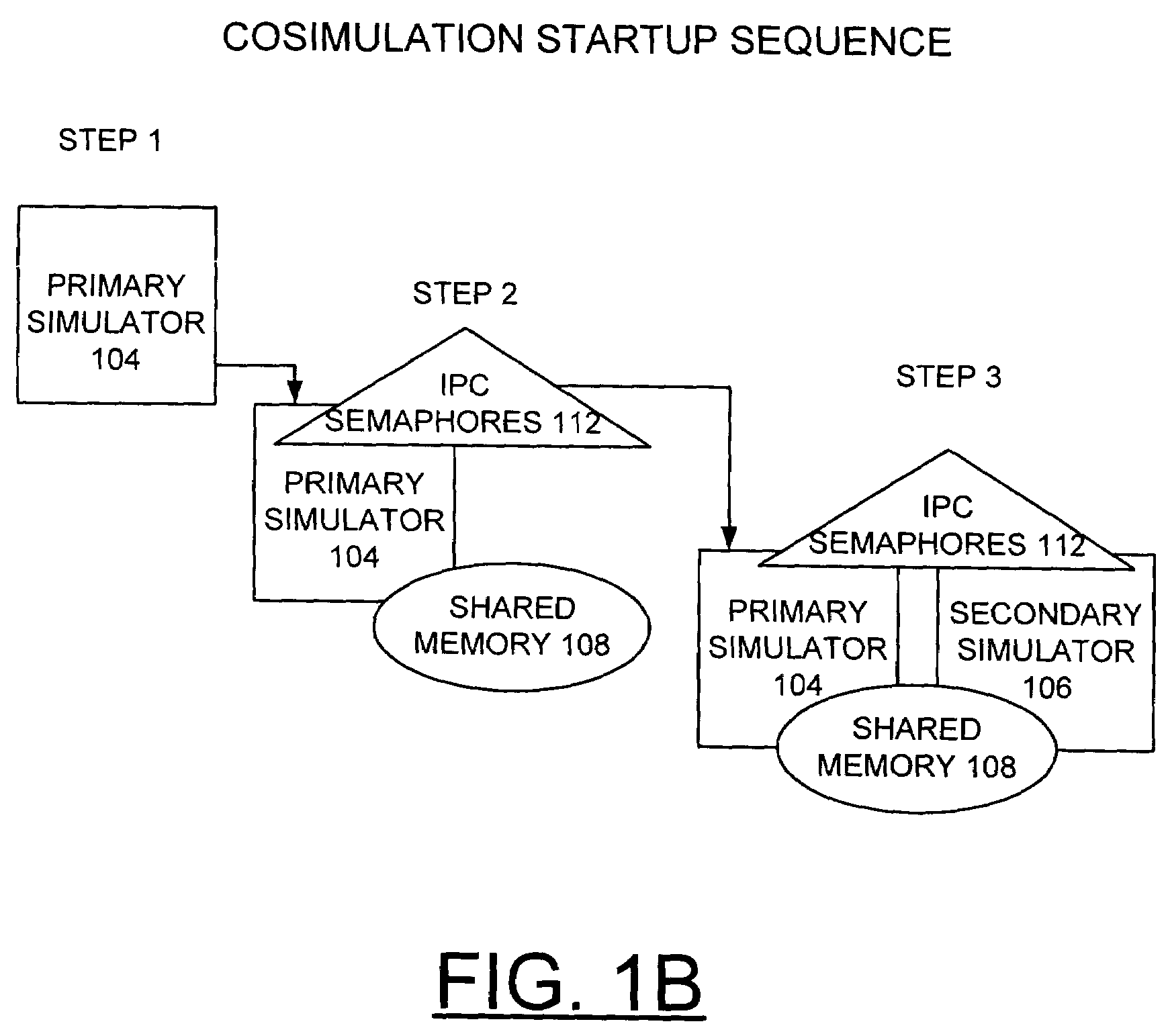

Method, apparatus, and computer program product for implementing dynamic cosimulation

InactiveUS7191111B2Without negative effectDetecting faulty computer hardwareAnalogue computers for electric apparatusControl signalCo-simulation

Dynamic cosimulation is implemented using a cosimulation bridge for data exchange between a primary simulator and a secondary simulator, and a plurality of user selected optimization control signals defined over the cosimulation bridge. At least one user selected optimization control signal is identified for disabling the cosimulation bridge. The primary simulator and secondary simulator are dynamically disengaged for ending data exchange responsive to disabling the cosimulation bridge. Responsive to optimization control signal going inactive, the primary simulator and secondary simulator are dynamically re-engaged for data exchange. The optimization control signals include a single sided disable; a two independent disable; a functional OR disable; a functional AND disable, and suspend signals. The single sided disable and the two independent disable enable disabling one side of the cosimulation bridge and not the other side. Both sides of the cosimulation bridge are disabled together using the functional OR disable and the functional AND disable.

Owner:IBM CORP

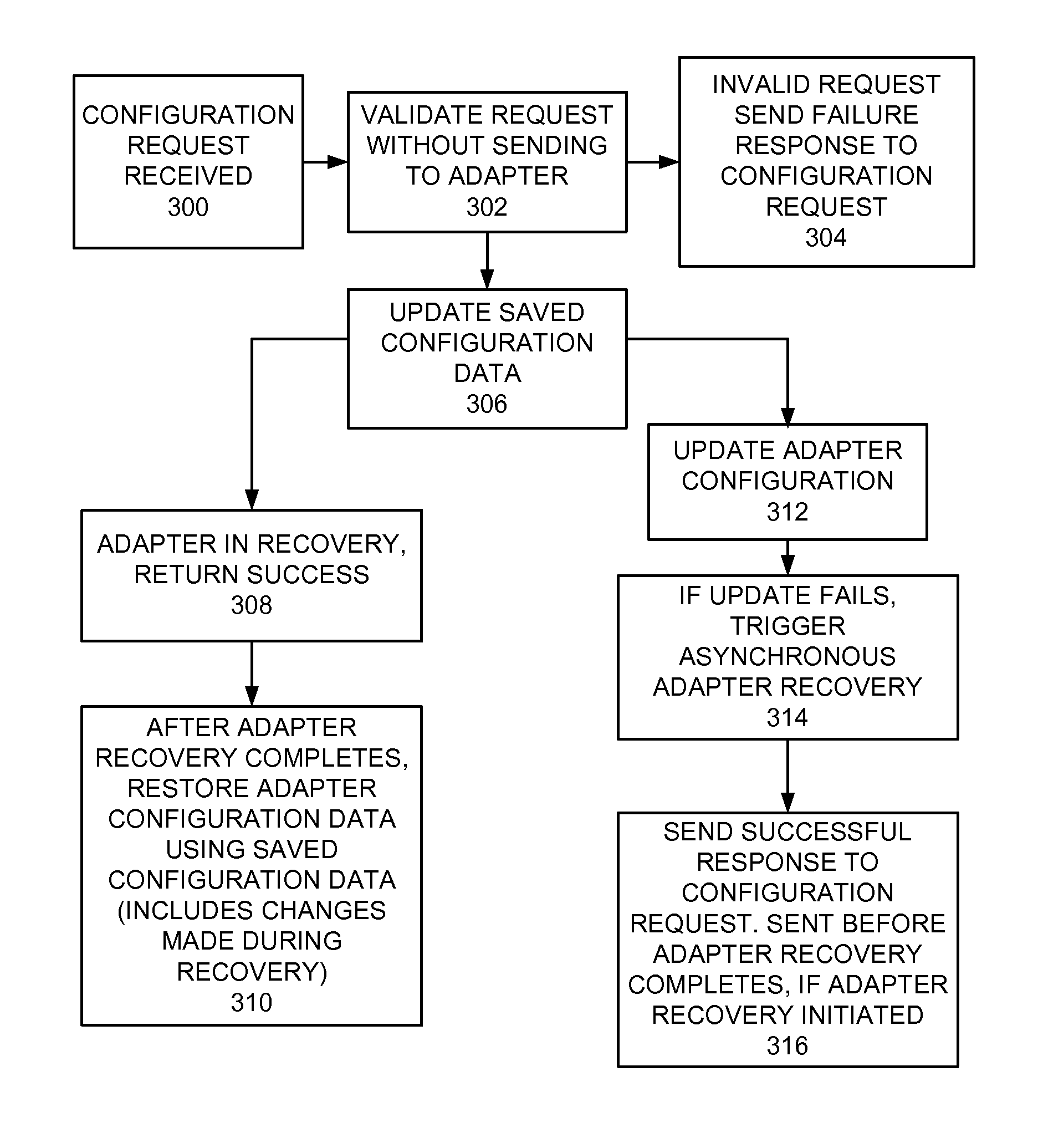

Implementing shared adapter configuration updates concurrent with maintenance actions in a virtualized system

InactiveUS20140372801A1Avoid resource conflictsWithout negative effectDetecting faulty hardware by configuration testNon-redundant fault processingComputer engineeringSingle-root input/output virtualization

A method, system and computer program product are provided for implementing shared adapter configuration updates concurrent with maintenance actions for a Single Root Input / Output Virtualization (SRIOV) adapter in a computer system. A configuration of the adapter is decoupled from the state of the adapter during a recovery period. When a configuration request is received, the configuration request is validated. Responsive to a valid configuration request, the saved configuration state of the adapter is updated. Once the adapter completes recovery, the adapter is restored to the new configuration instead of the configuration prior to failure.

Owner:IBM CORP

Implementing shared adapter configuration updates concurrent with maintenance actions in a virtualized system

InactiveUS9323620B2Without negative effectAvoid resource conflictsDetecting faulty hardware by configuration testNon-redundant fault processingRecovery periodComputer program

A method, system and computer program product are provided for implementing shared adapter configuration updates concurrent with maintenance actions for a Single Root Input / Output Virtualization (SRIOV) adapter in a computer system. A configuration of the adapter is decoupled from the state of the adapter during a recovery period. When a configuration request is received, the configuration request is validated. Responsive to a valid configuration request, the saved configuration state of the adapter is updated. Once the adapter completes recovery, the adapter is restored to the new configuration instead of the configuration prior to failure.

Owner:IBM CORP

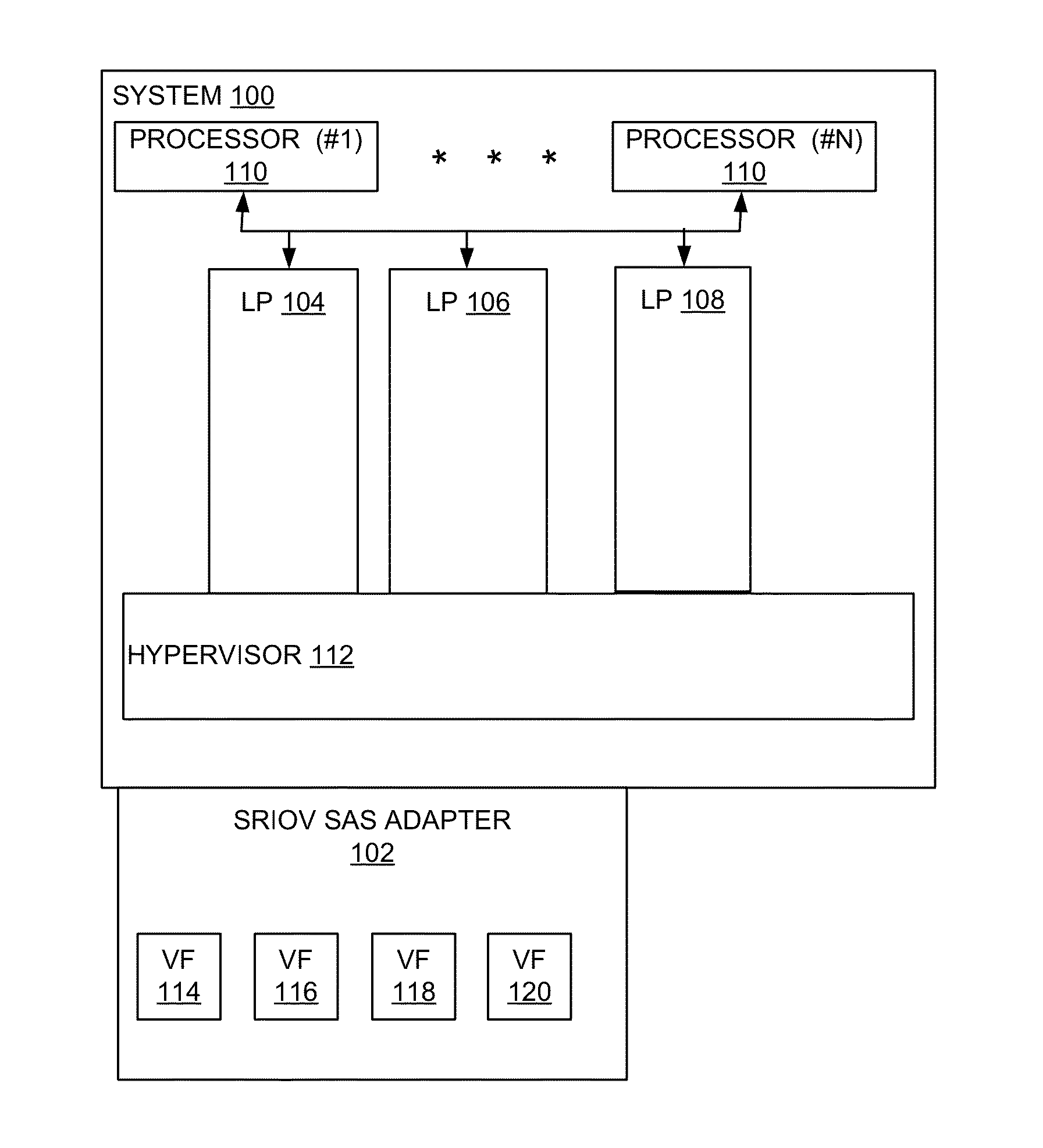

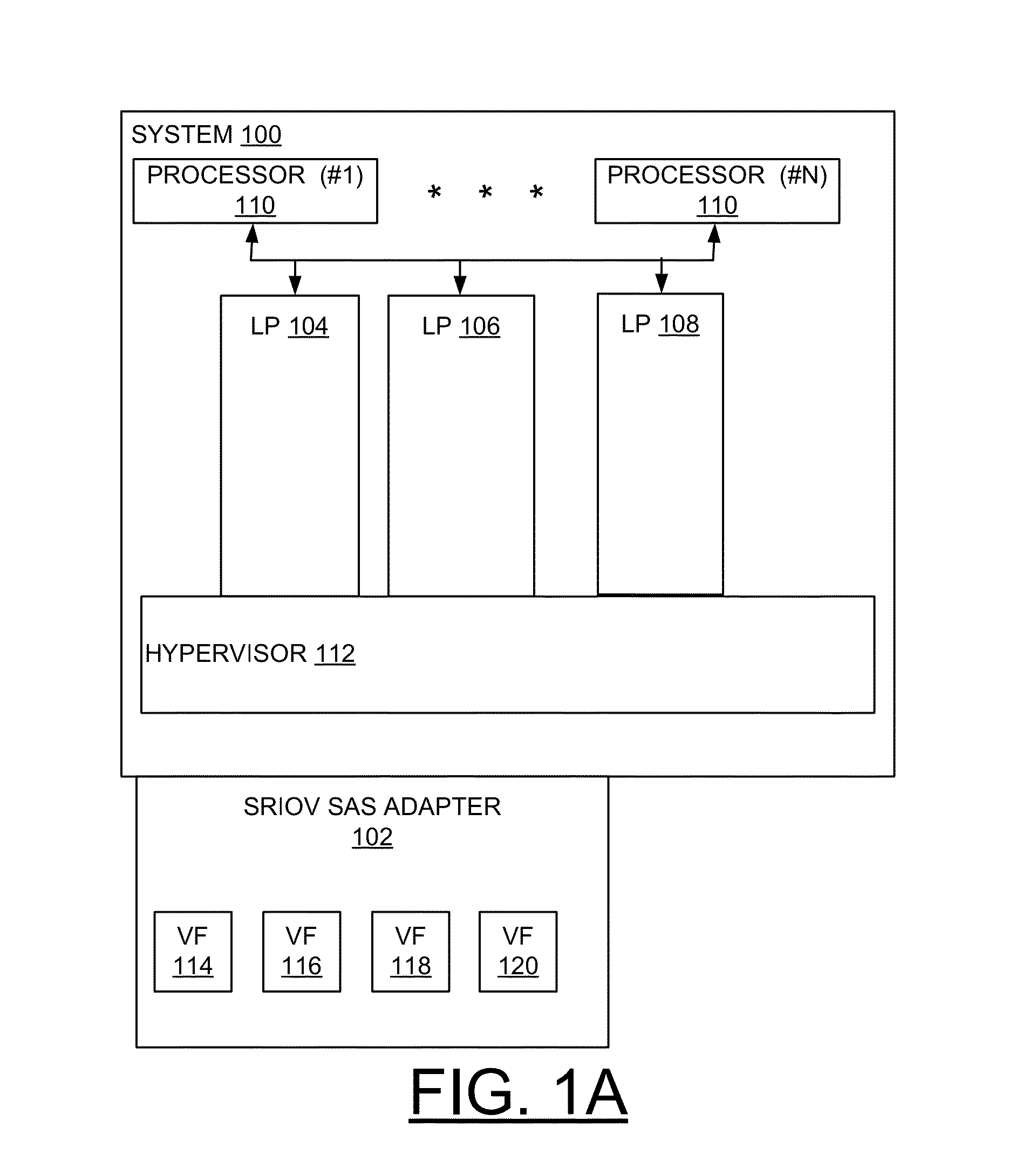

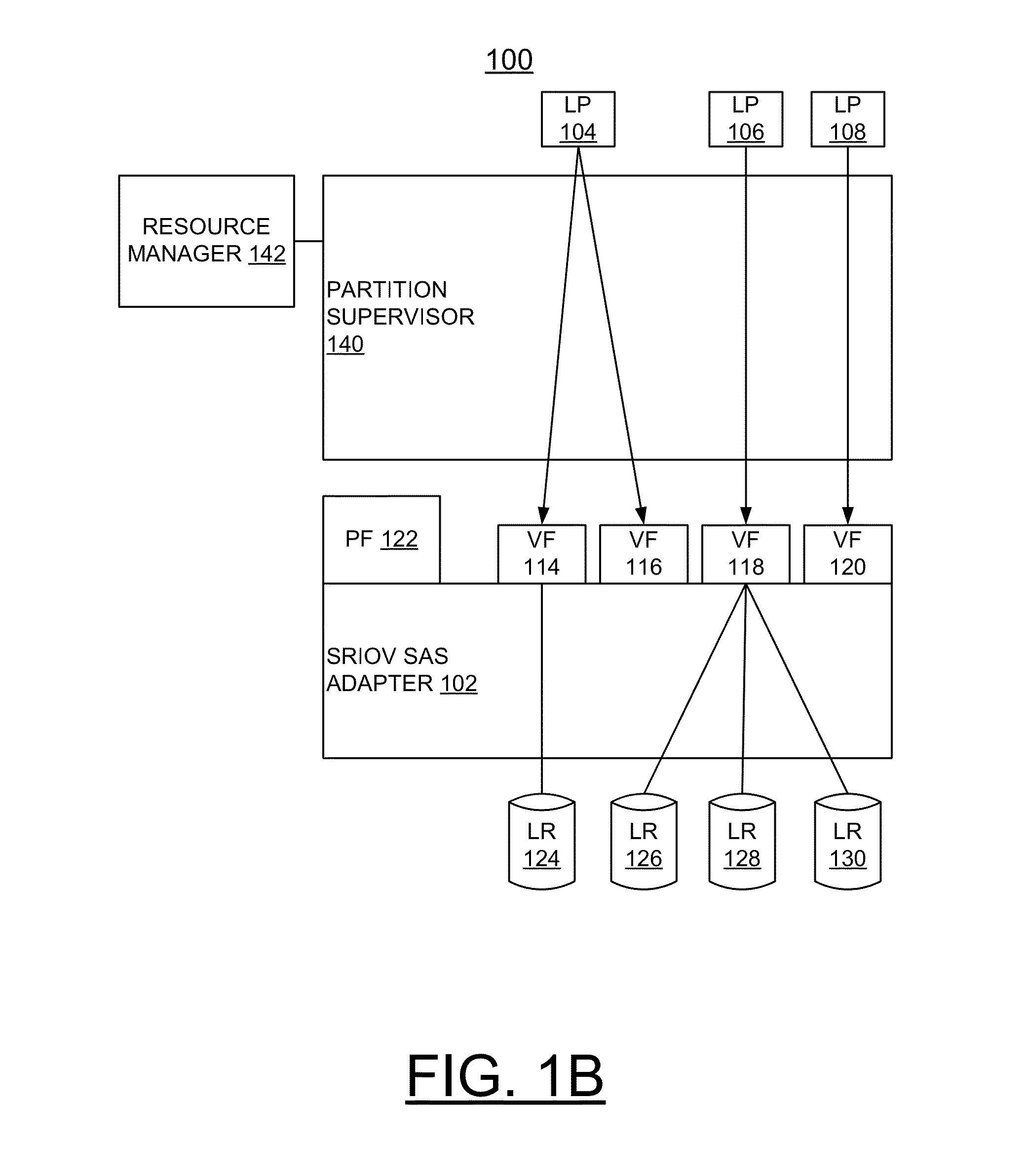

Implementing dynamic virtualization of an sriov capable sas adapter

InactiveUS20150370595A1Without negative effectEnergy efficient computingSoftware simulation/interpretation/emulationData virtualizationSerial Attached SCSI

A method, system and computer program product are provided for implementing dynamic virtualization of a Single Root Input / Output Virtualization (SRIOV) capable Serial Attached SCSI (SAS) adapter. The SRIOV SAS adapter includes a plurality of virtual functions (VFs). Each individual Host Bus Adapter (HBA) resource is enabled to be explicitly assigned to a virtual function (VF); and each VF being enabled to be assigned to a system partition. Multiple VFs are enabled to be assigned to a single system partition.

Owner:INT BUSINESS MASCH CORP

Detecting and sparing of optical PCIE cable channel attached IO drawer

InactiveUS9582366B2Without negative effectDetecting faulty computer hardwareHardware monitoringHealth checkEngineering

Owner:INT BUSINESS MASCH CORP

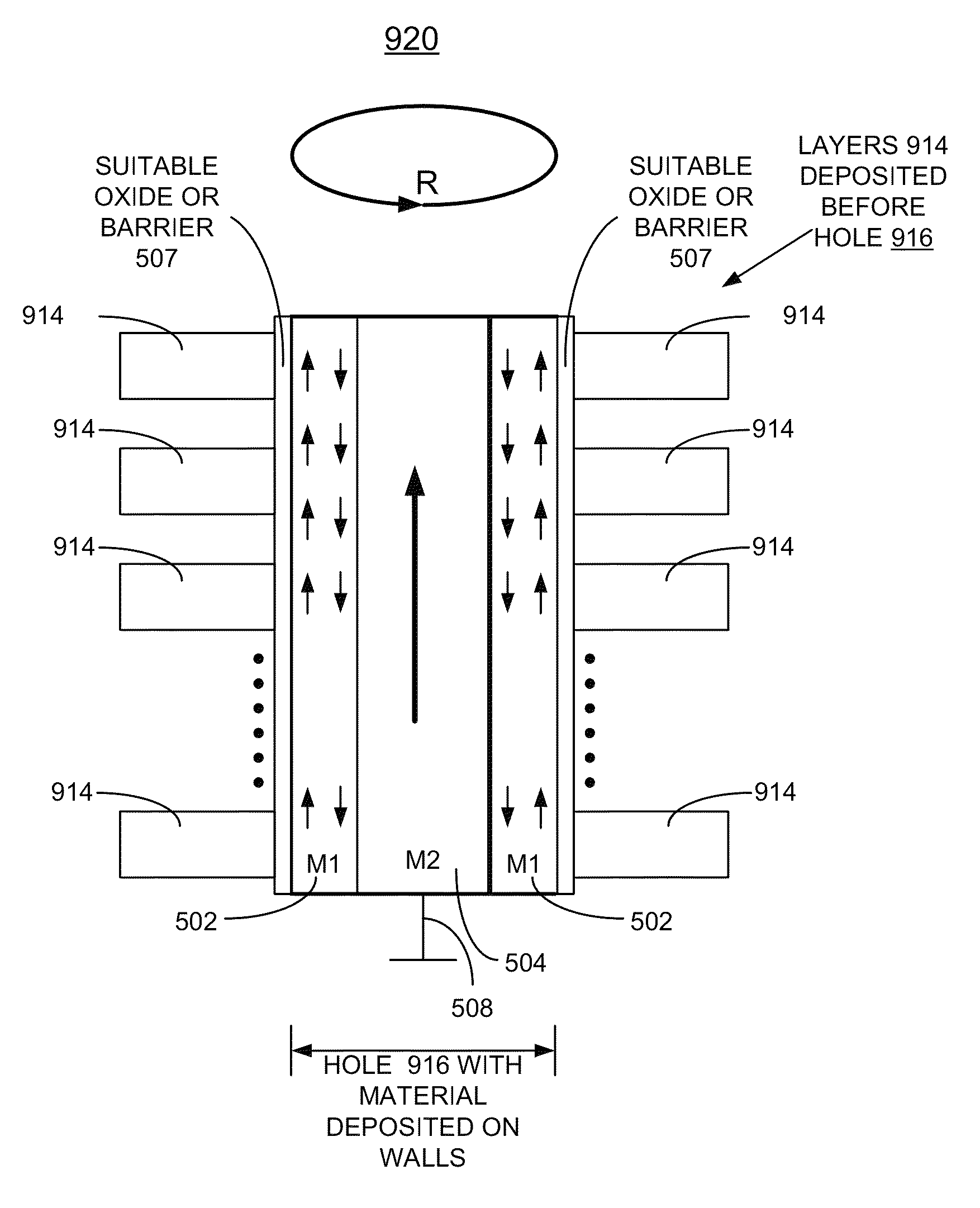

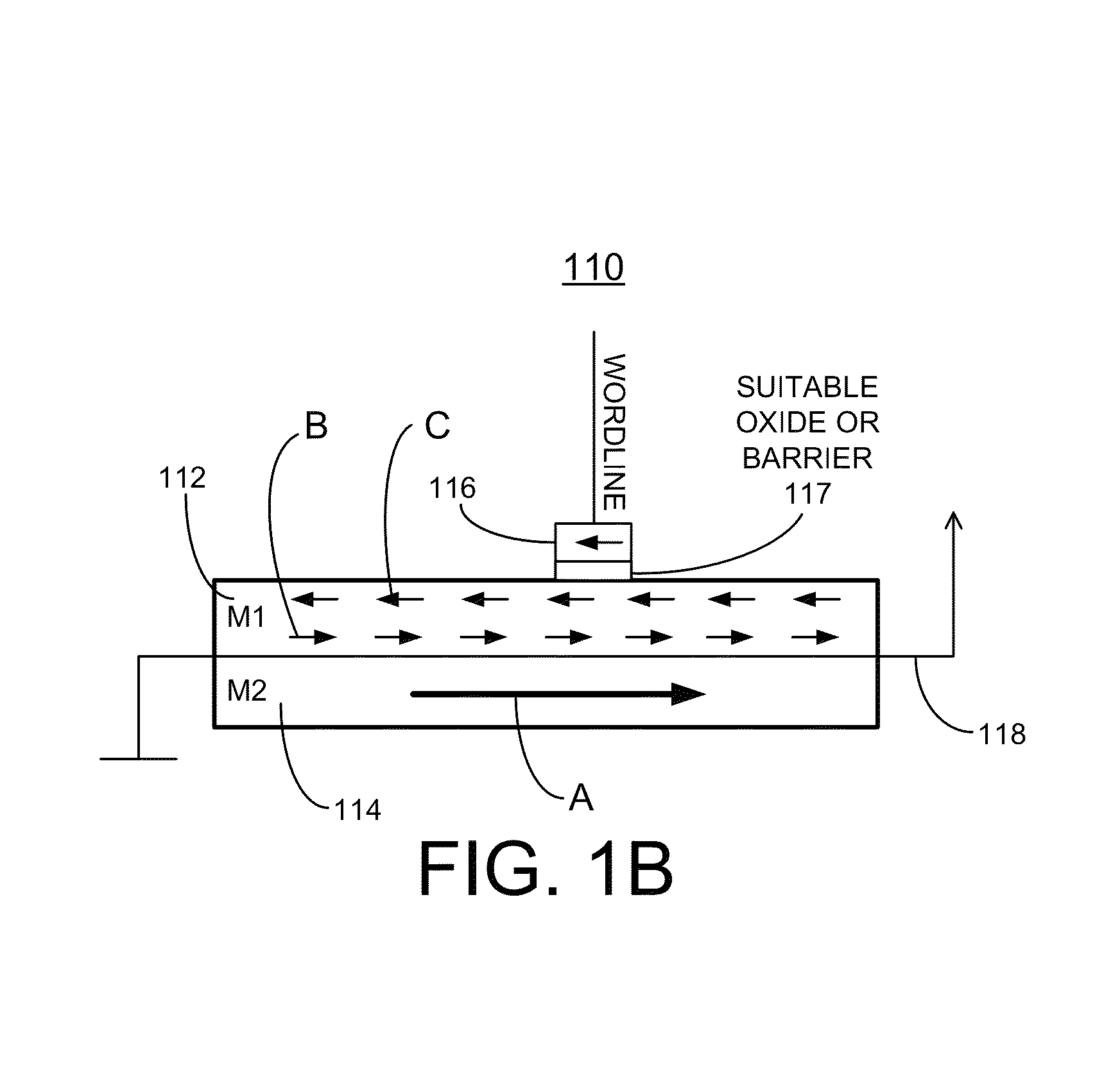

Implementing segregated media based magnetic memory

ActiveUS9444036B1Without negative effectOvercome disadvantageMagnetic-field-controlled resistorsGalvano-magnetic material selectionSolid-stateEngineering

A segregated media based magnetic memory pillar cell and a method for implementing the segregated media based magnetic memory pillar cell for use in Solid-State Drives (SSDs) are provided. The segregated media based magnetic memory pillar cell includes a first conductor M1 and a second conductor M2 with the second conductor M2 surrounded by the first conductor M1. The first conductor M1 is formed of a segregated magnetic media material defining multiple domains.

Owner:WESTERN DIGITAL TECH INC

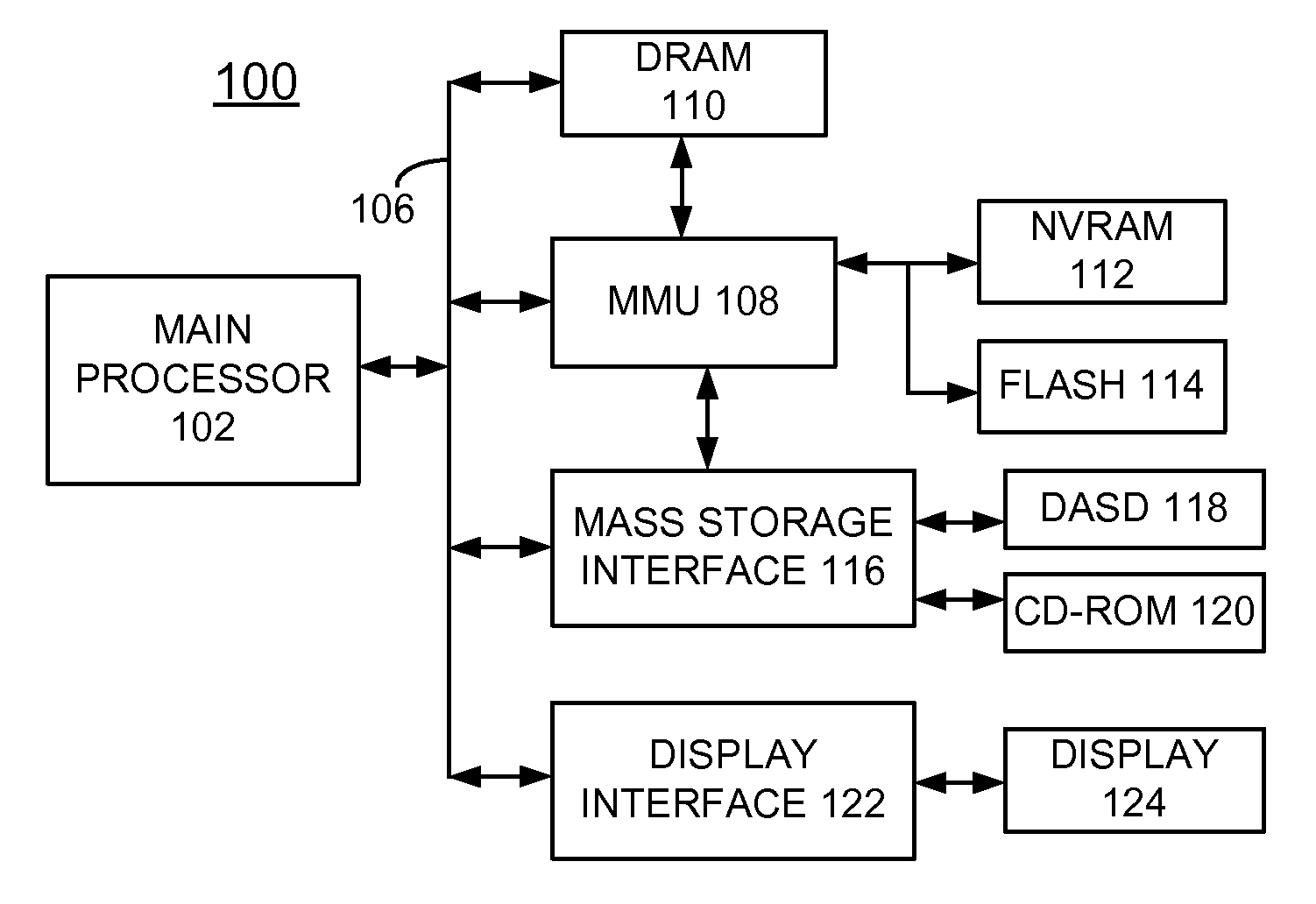

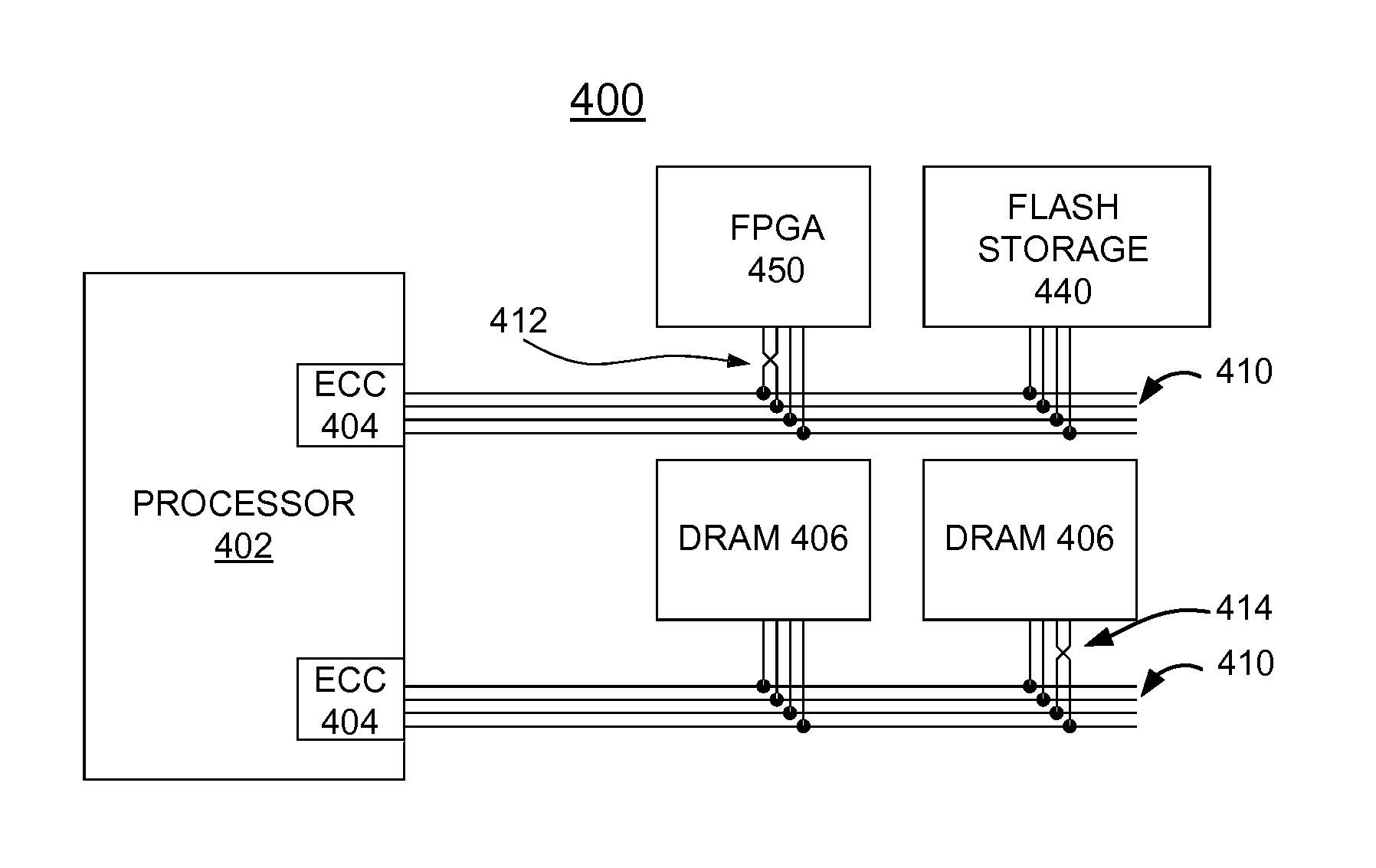

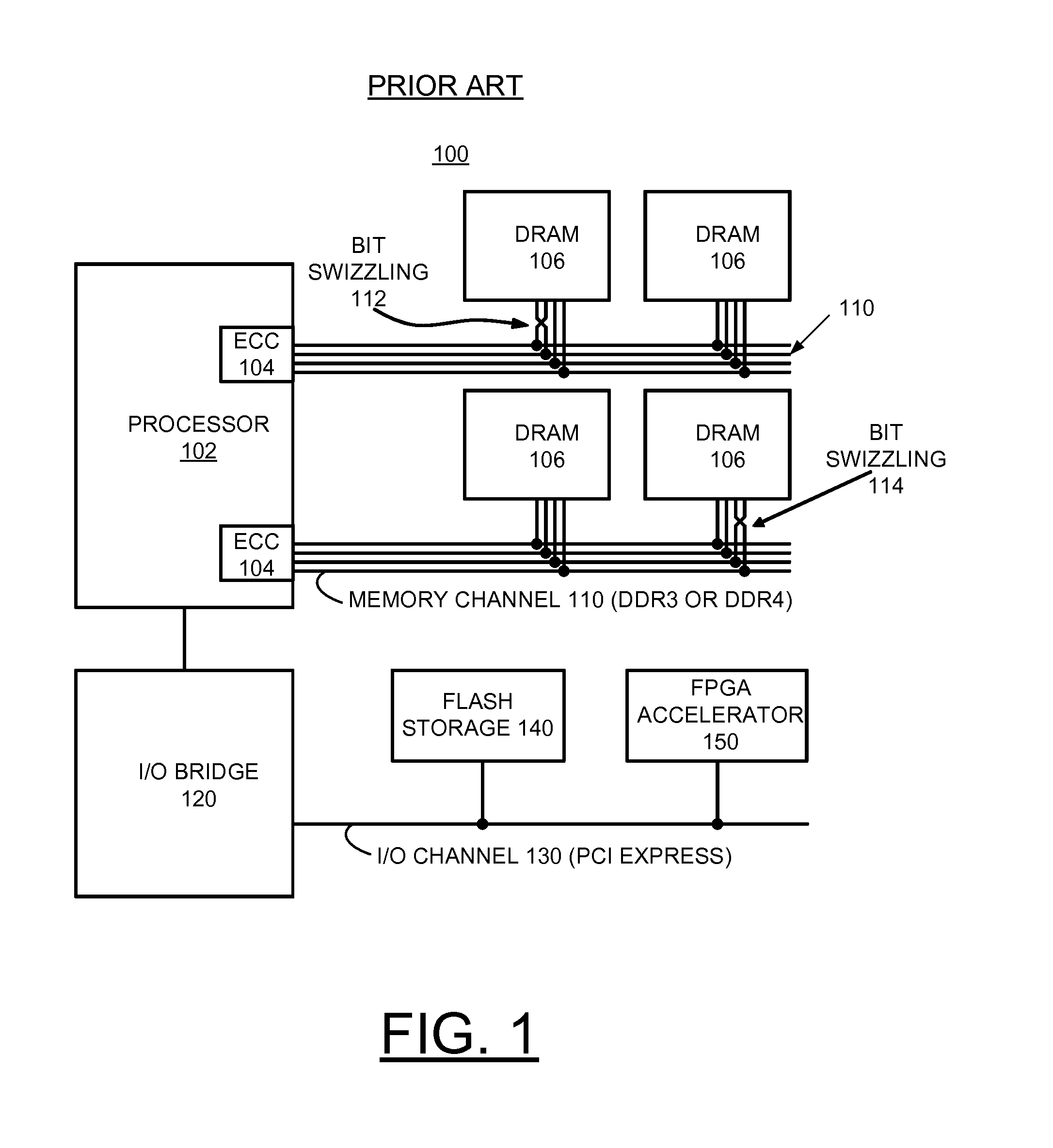

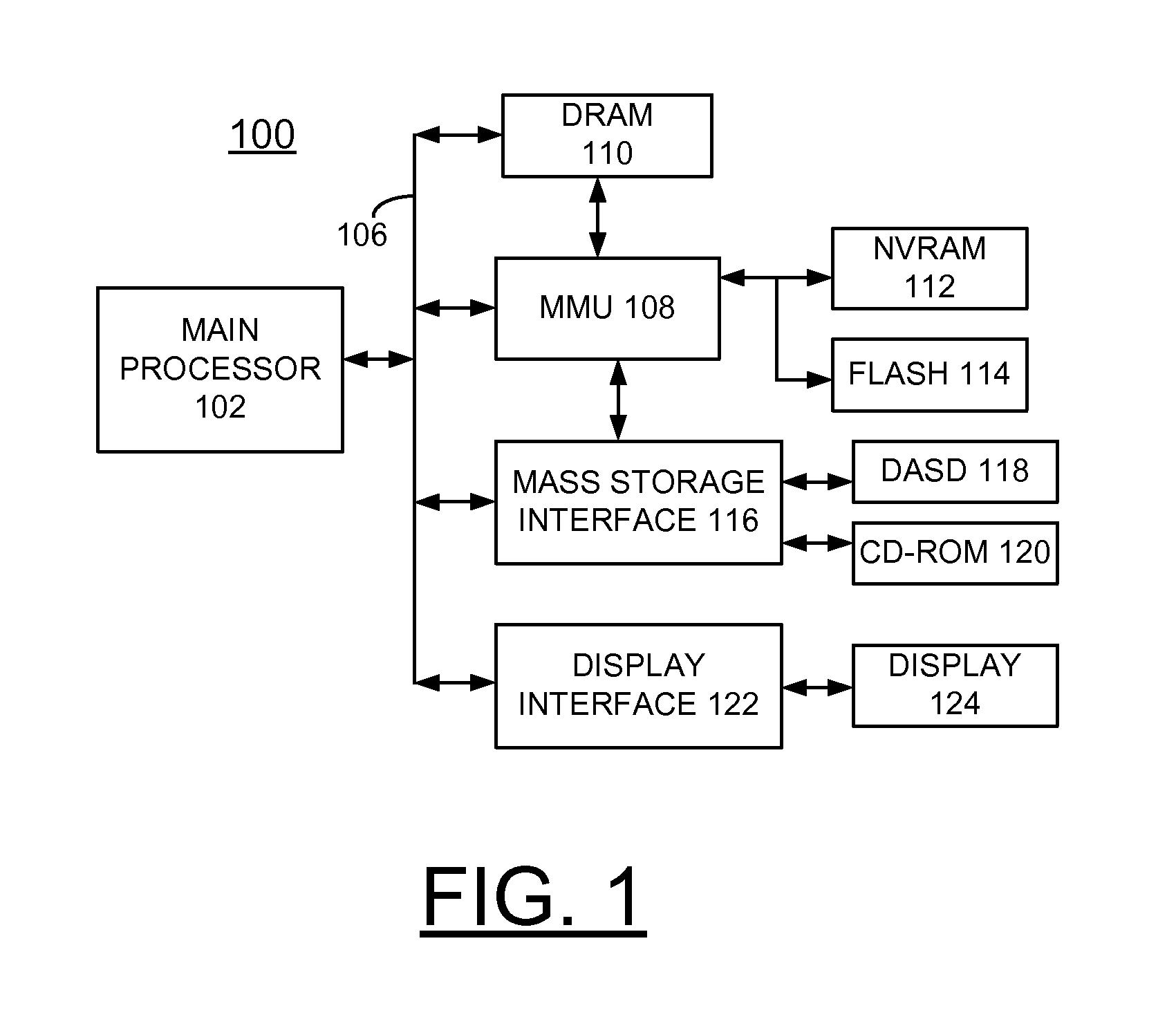

Implementing user mode foreign device attachment to memory channel

InactiveUS20140195765A1Without negative effectEliminate needMemory architecture accessing/allocationError detection/correctionDevice registerSoftware system

A method, system and computer program product are provided for implementing attachment of a user mode foreign device to a memory channel in a computer system. A user mode foreign device is attached to the memory channel using memory mapping of device registers and device buffers to the processor address space. The storage capacity on the device is doubly mapped in the address space creating separate control and data address spaces to allow user mode processes to control the device therefore eliminating the need for software system calls. A processor Memory Management Unit (MMU) coordinates multiple user processes accessing the device registers and buffers providing address space protection of each of interfaces, shifting device protection to the processor MMU from system software.

Owner:IBM CORP

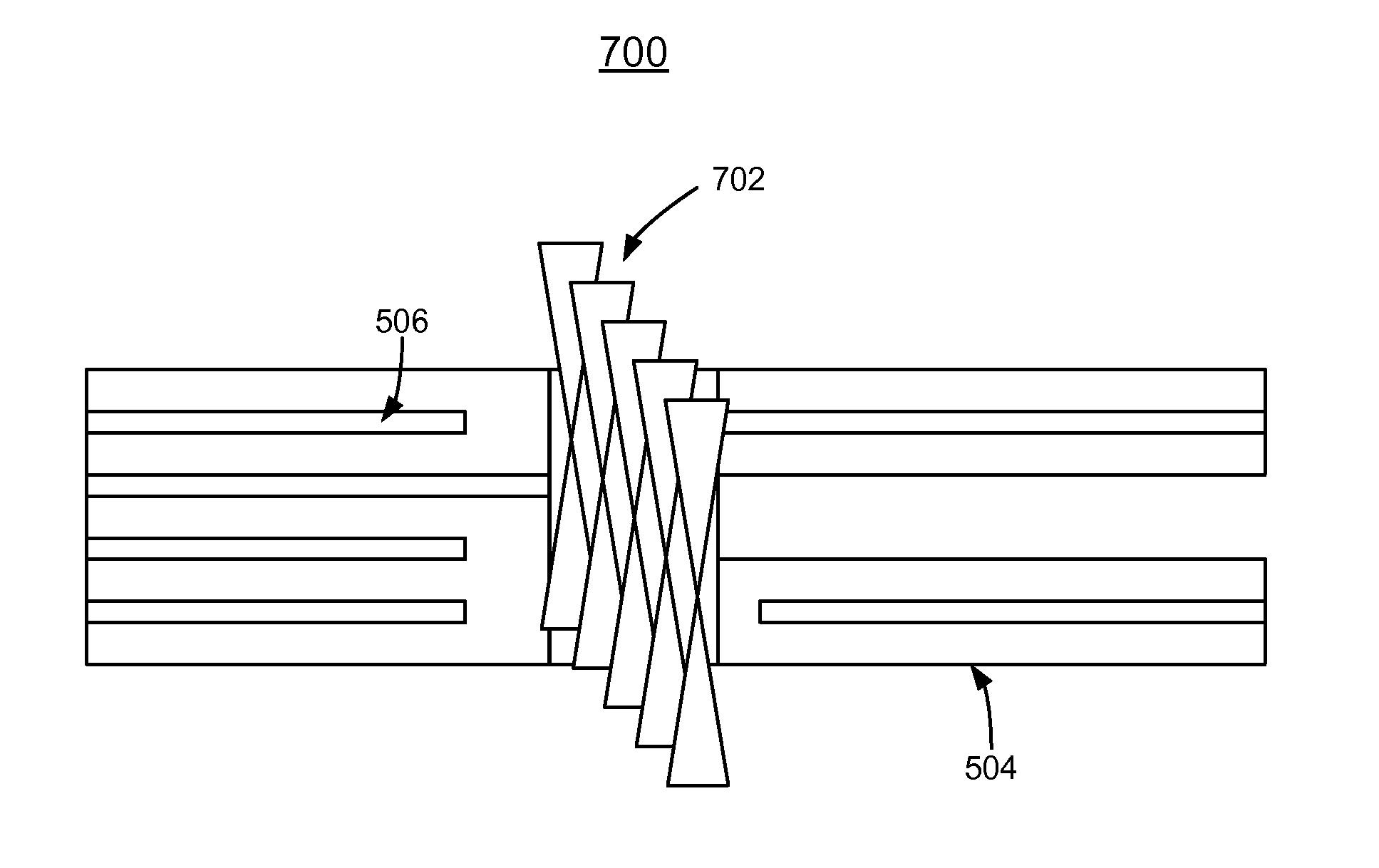

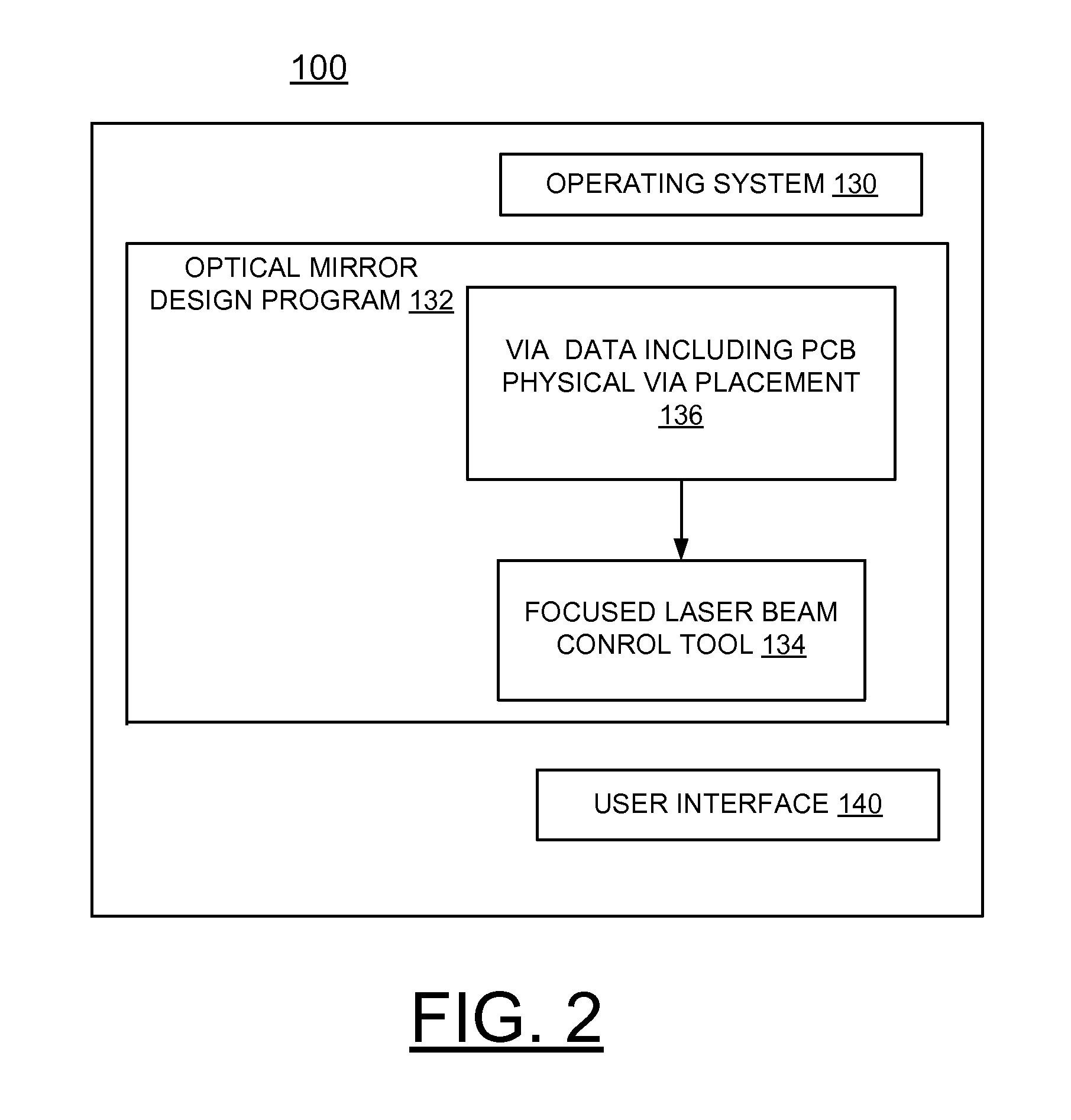

Implementing enhanced optical mirror coupling and alignment utilizing two-photon resist

InactiveUS8968987B2Optimization mechanismWithout negative effectCircuit optical detailsPrinted circuit aspectsResistCoupling

A method, system and computer program product for implementing an enhanced optical mirror coupling and alignment mechanism utilizing two-photon resist. An initial placement is provided for one or more vias on a printed circuit board. A via is filled with a resist. A series of tightly focused light beams suitably exposes the resist at varying depths in the via, the varying depths defining a sloped polymer in the via after removing resist that had not been at the focus of the light beam. The sloped polymer is coated with reflective material to reflect light into or out of the via.

Owner:INT BUSINESS MASCH CORP

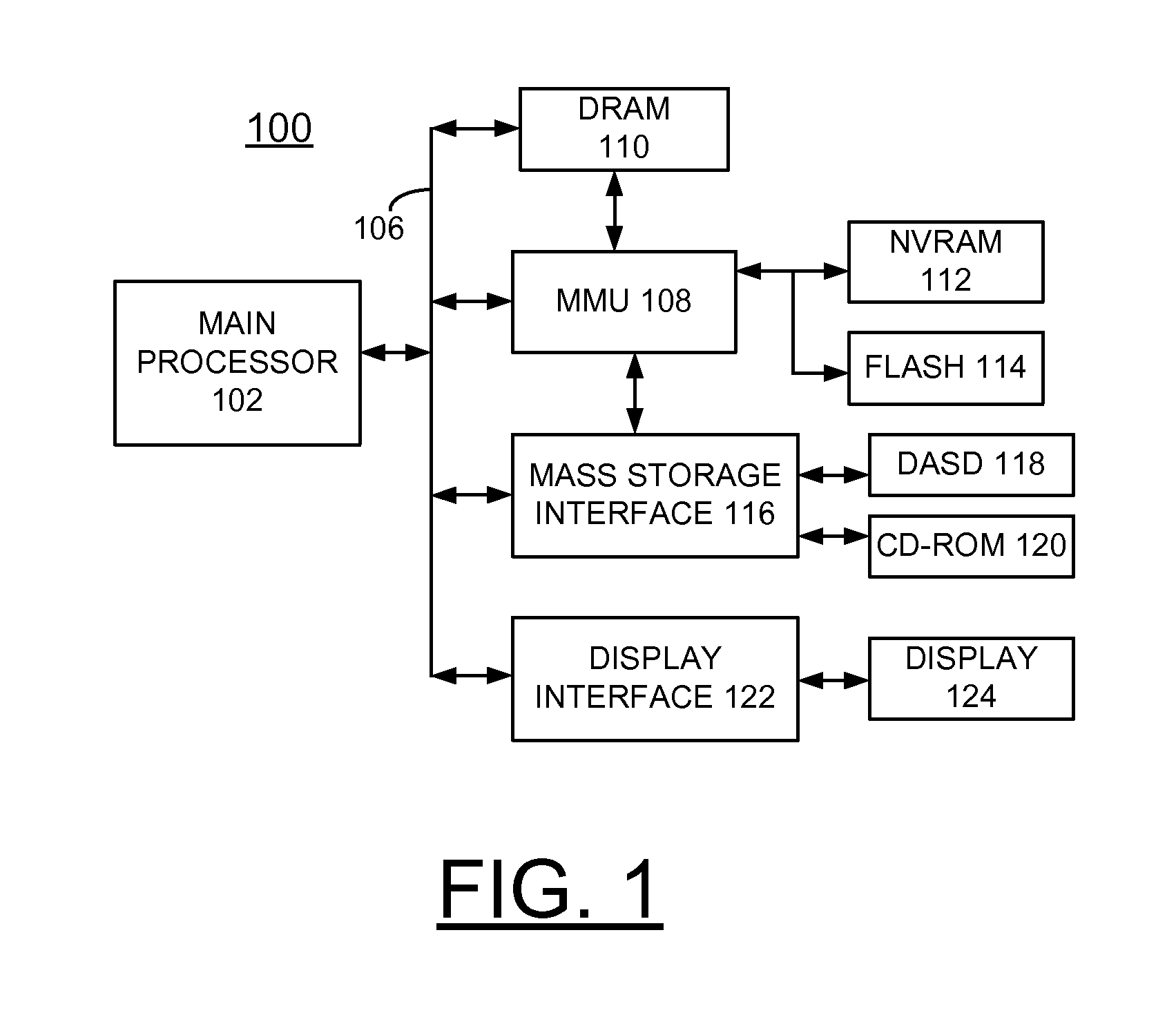

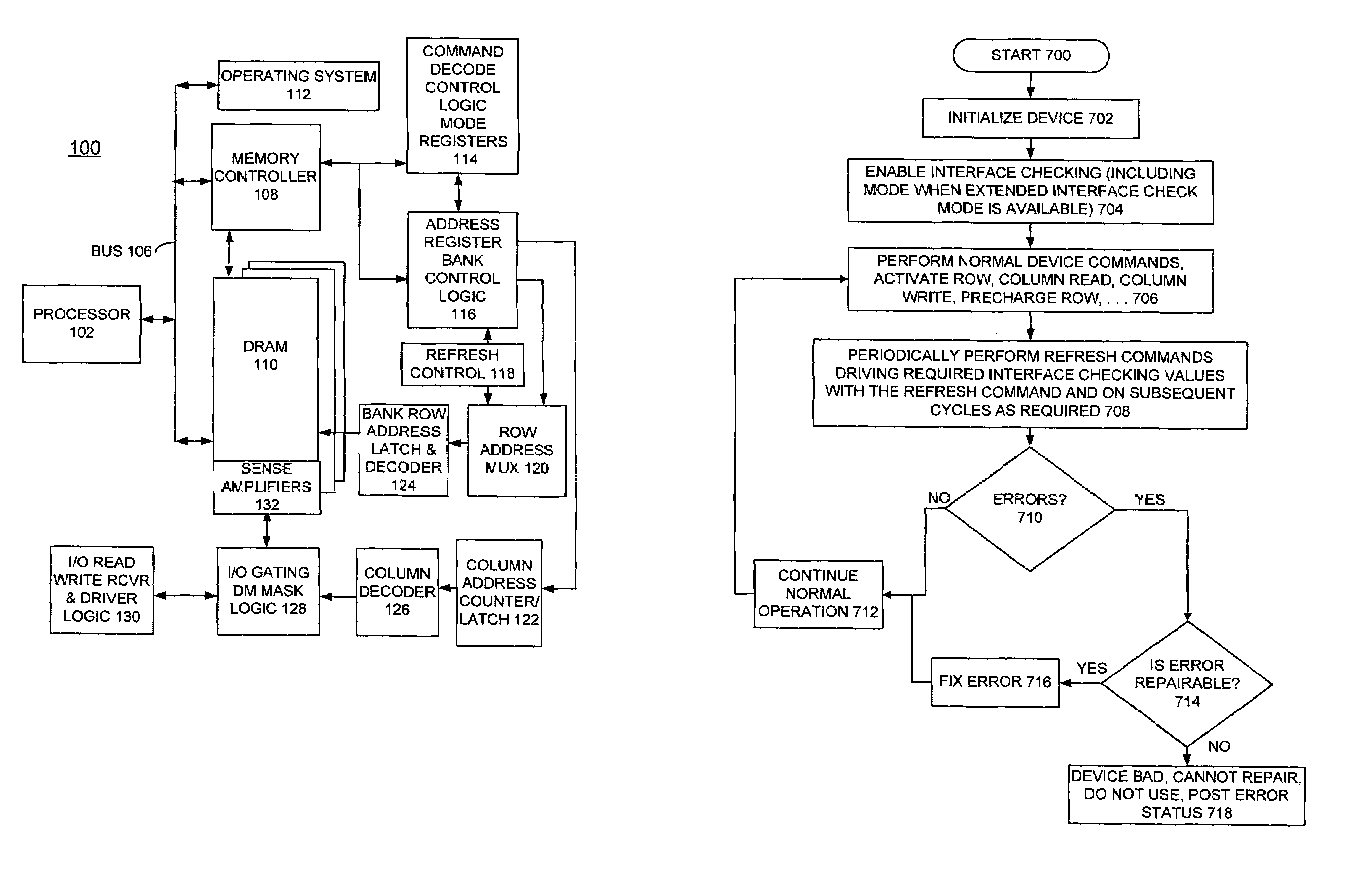

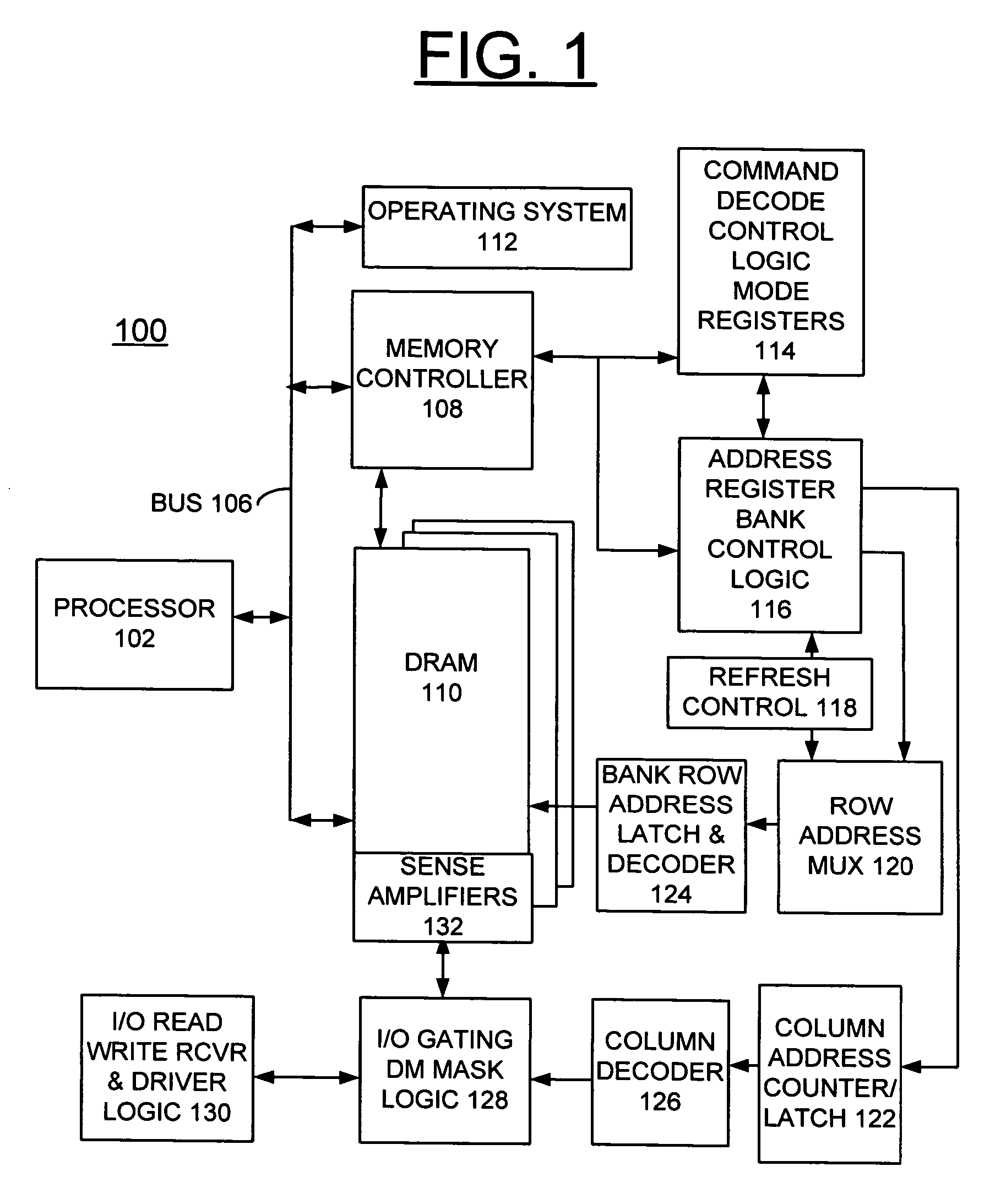

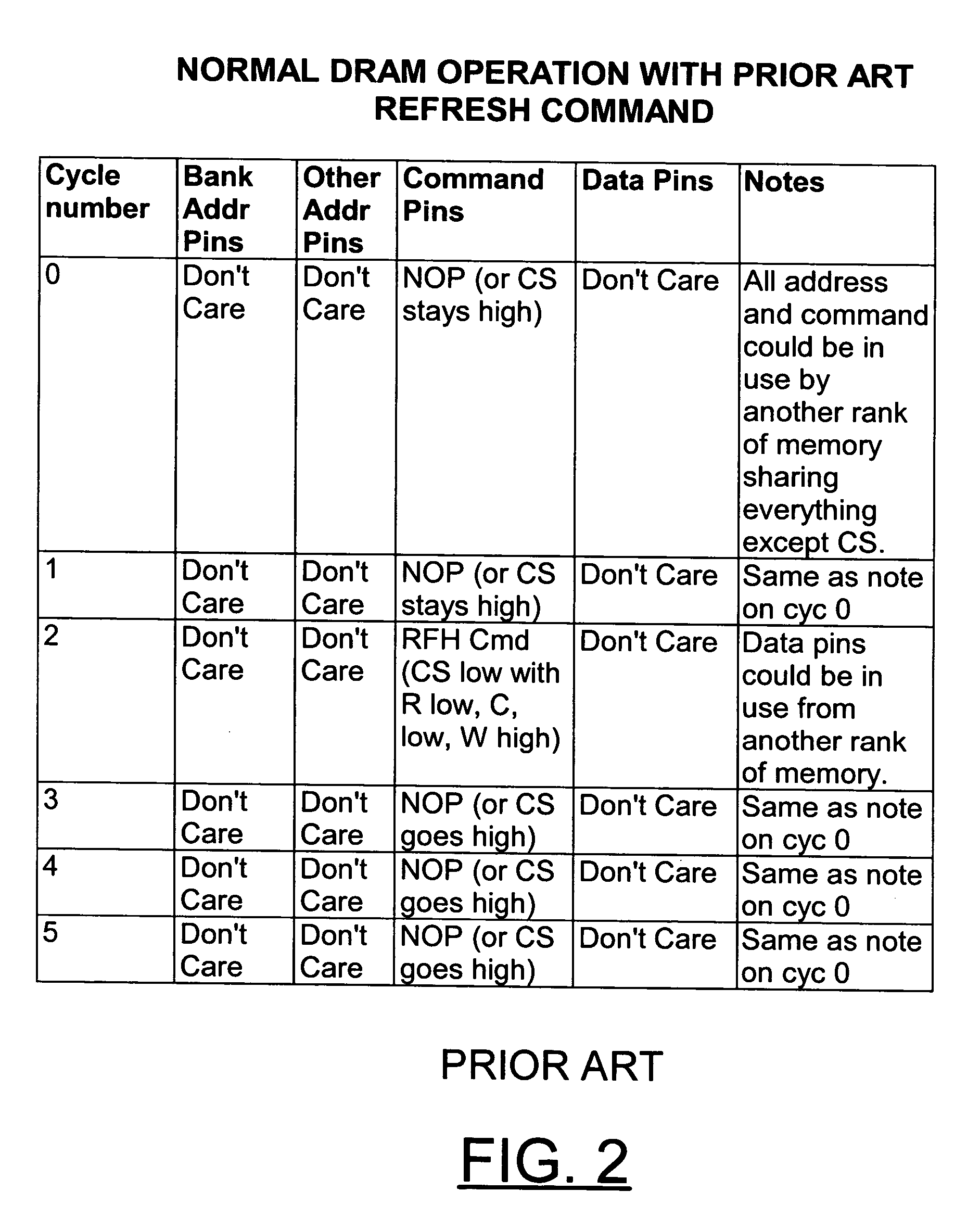

Method, apparatus, and computer program product for implementing enhanced DRAM interface checking

InactiveUS7130231B2Raise checkWithout negative effectDigital storageComputer hardwareComputer program

A method, apparatus, and computer program product are provided for implementing an enhanced DRAM interface checking. An interface check mode enables interface checking using a refresh command for a DRAM. A predefined address pattern is provided for the interface address inputs during a refresh command cycle. Interface address inputs are checked for a proper value being applied and an error is signaled for unexpected results. An extended test mode includes further testing during a cycle after the refresh command cycle. Then command inputs also are checked for a proper value being applied and an error is signaled for unexpected results.

Owner:IBM CORP

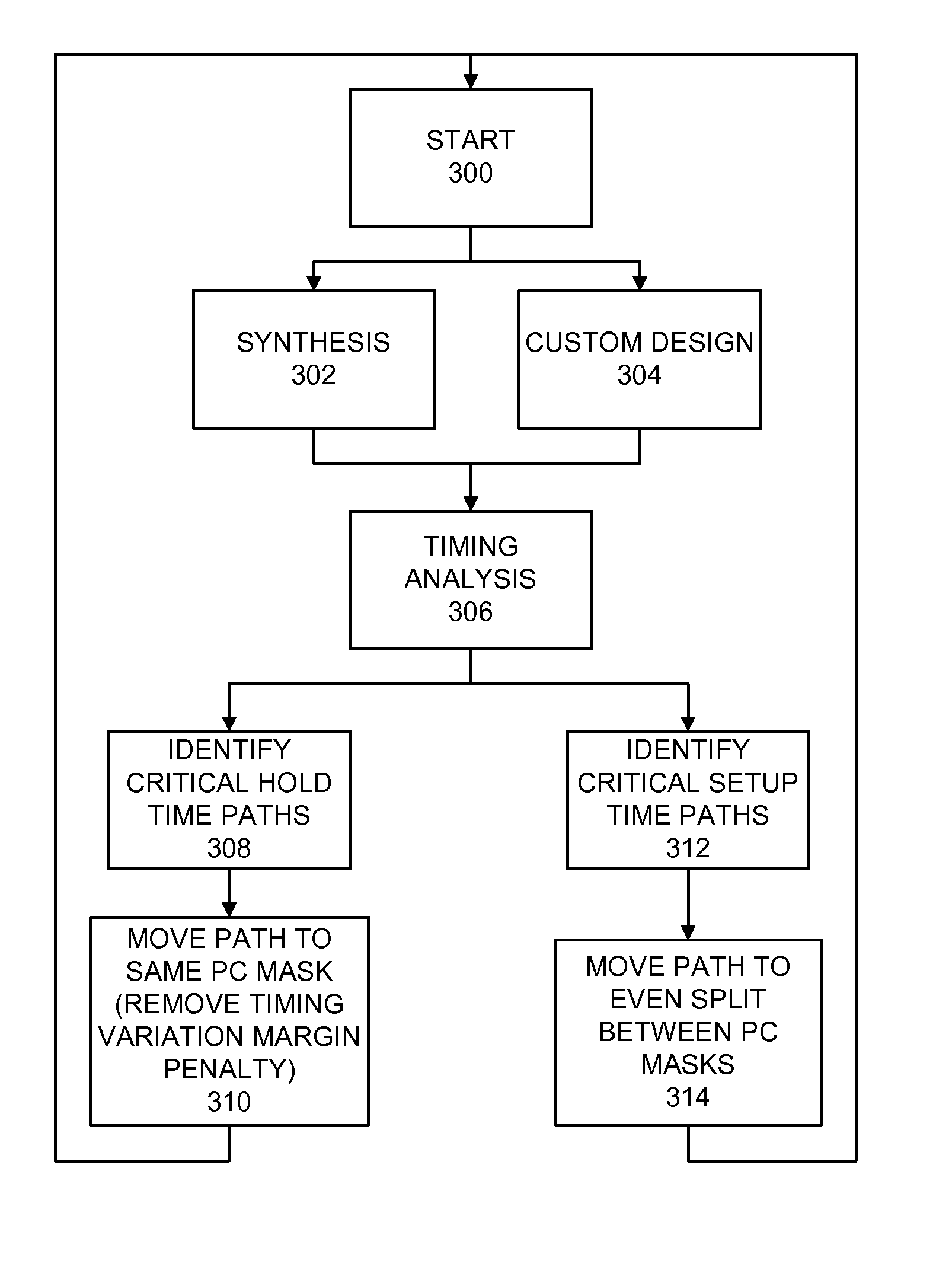

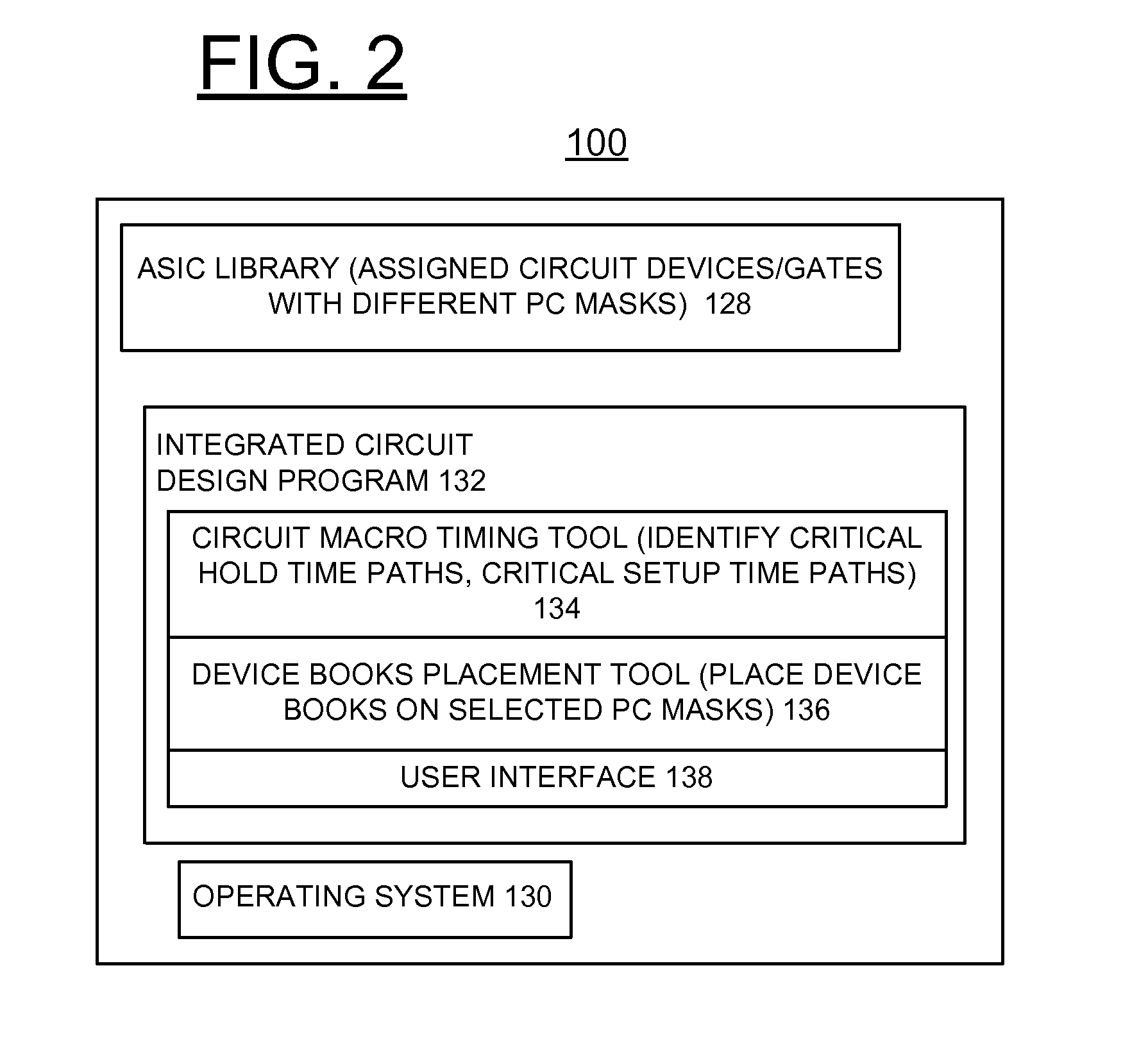

Implementing mulitple mask lithography timing variation mitigation

InactiveUS8578304B1Without negative effectOvercome disadvantagesOriginals for photomechanical treatmentSoftware simulation/interpretation/emulationTime pathApplication-specific integrated circuit

A method, system and computer program product are provided for implementing multiple mask lithography timing variation mitigation for a multiple mask polysilicon (PC) process. An application specific integrated circuit (ASIC) library includes at least one circuit device for a first mask, and at least one circuit device for a second mask. Critical hold time paths and critical setup time paths are identified in a circuit design. For critical hold time paths, circuit devices in the critical hold time paths are placed on a single mask of either the first mask or the second mask. For critical setup time paths, path delays are reduced by providing a mixture of circuit devices on the first mask and the second mask.

Owner:GLOBALFOUNDRIES INC

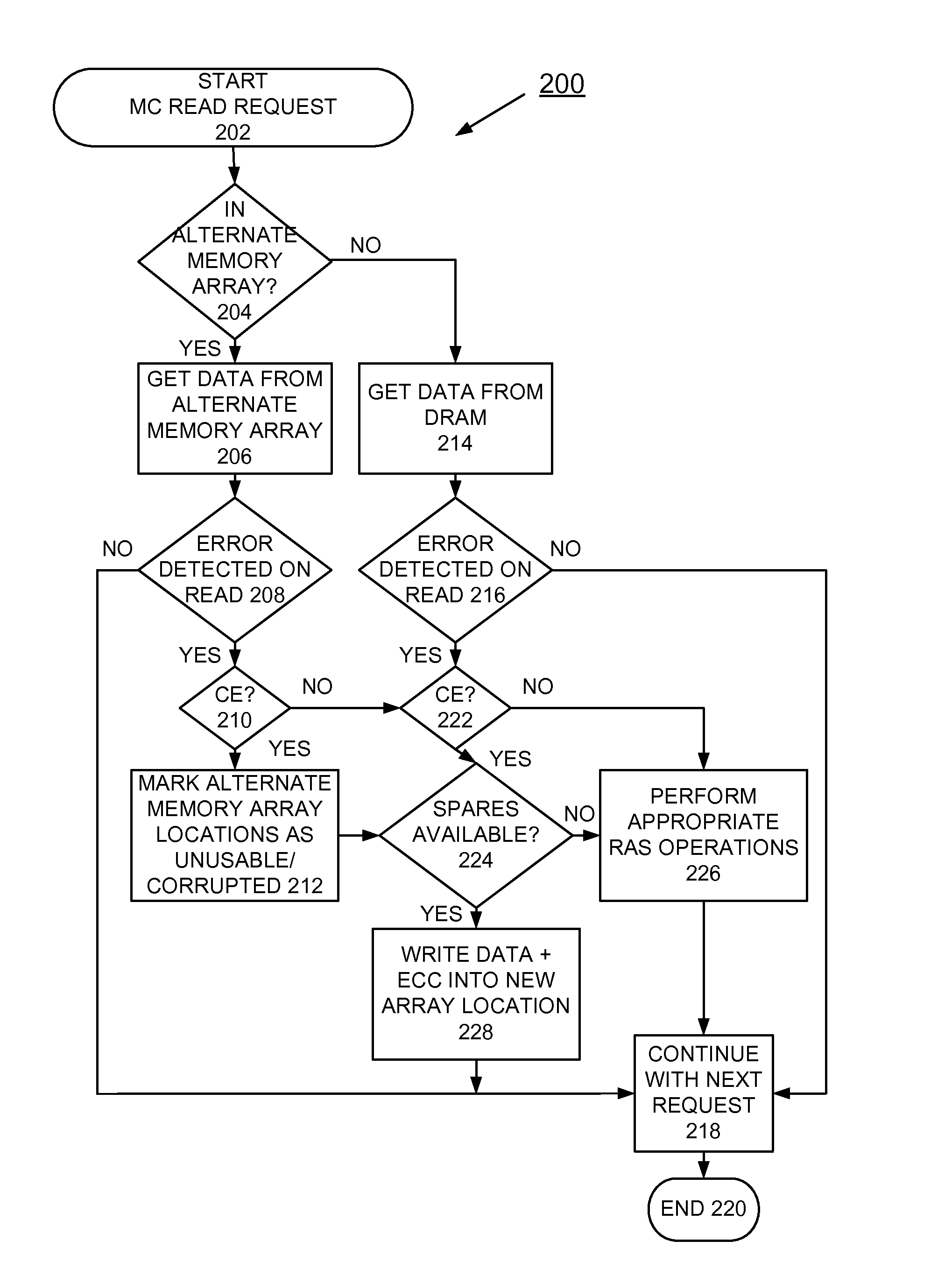

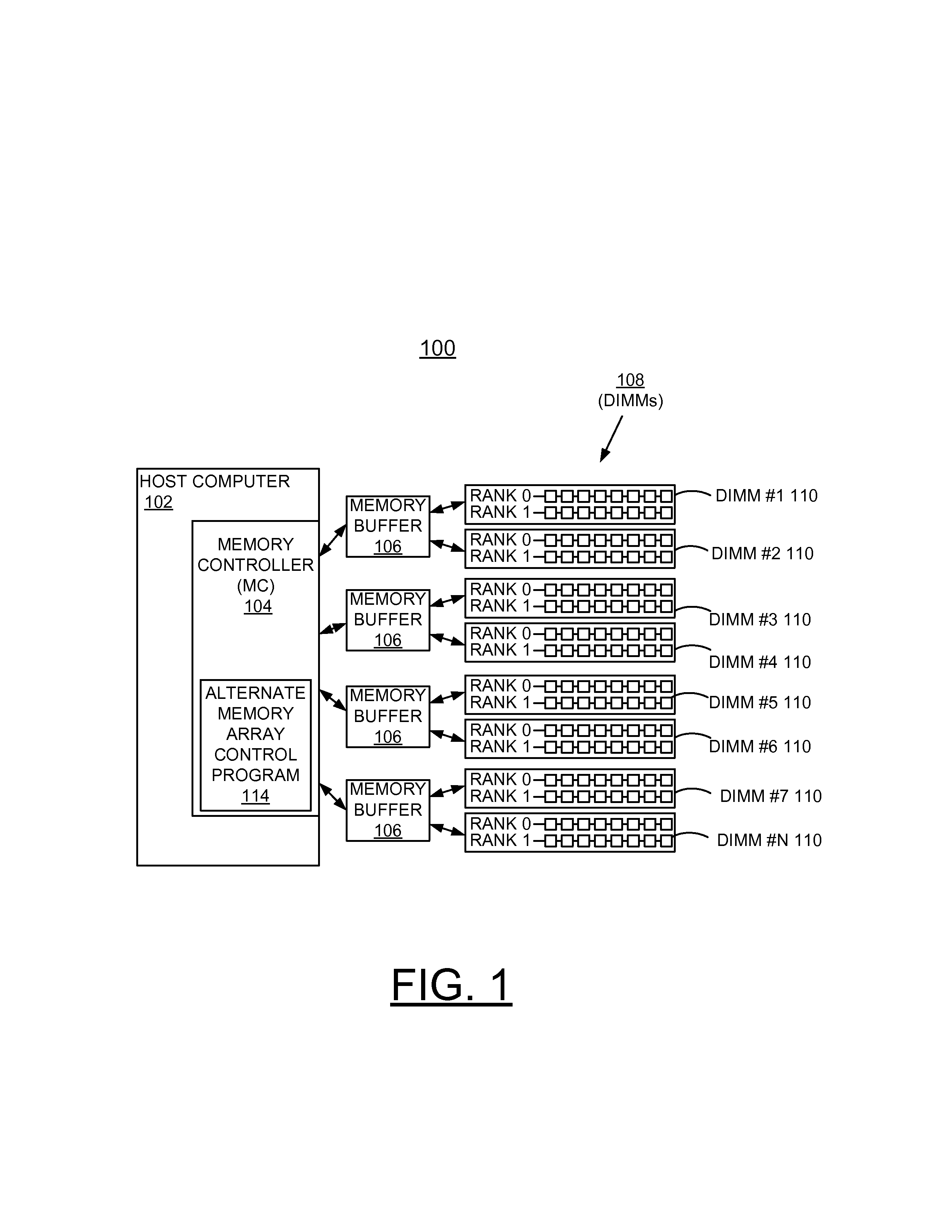

Iimplementing enhanced hardware assisted dram repair

InactiveUS20130179724A1Without negative effectLow costStatic storageRedundant hardware error correctionRegister allocationComputer hardware

A method, system and computer program product are provided for implementing hardware assisted Dynamic Random Access Memory (DRAM) repair in a computer system that supports ECC. A data register providing DRAM repair is selectively provided in one of the Dynamic Random Access Memory (DRAM), a memory controller, or a memory buffer coupled between the DRAM and the memory controller. The data register is configured to map to any address. Responsive to the configured address being detected, the reads to or the writes from the configured address are routed to the data register.

Owner:MARVELL ASIA PTE LTD