Patents

Literature

314 results about "Co-simulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

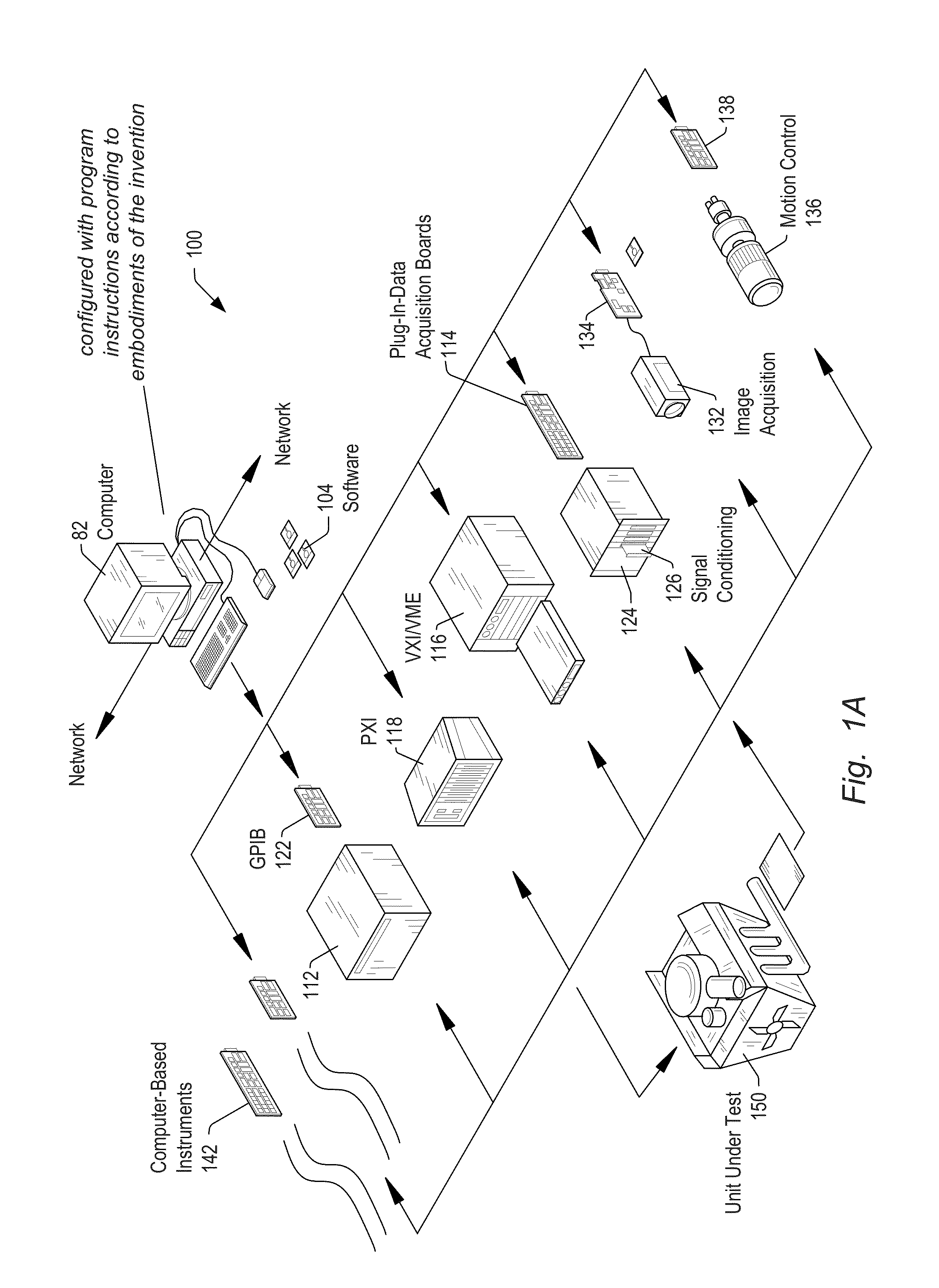

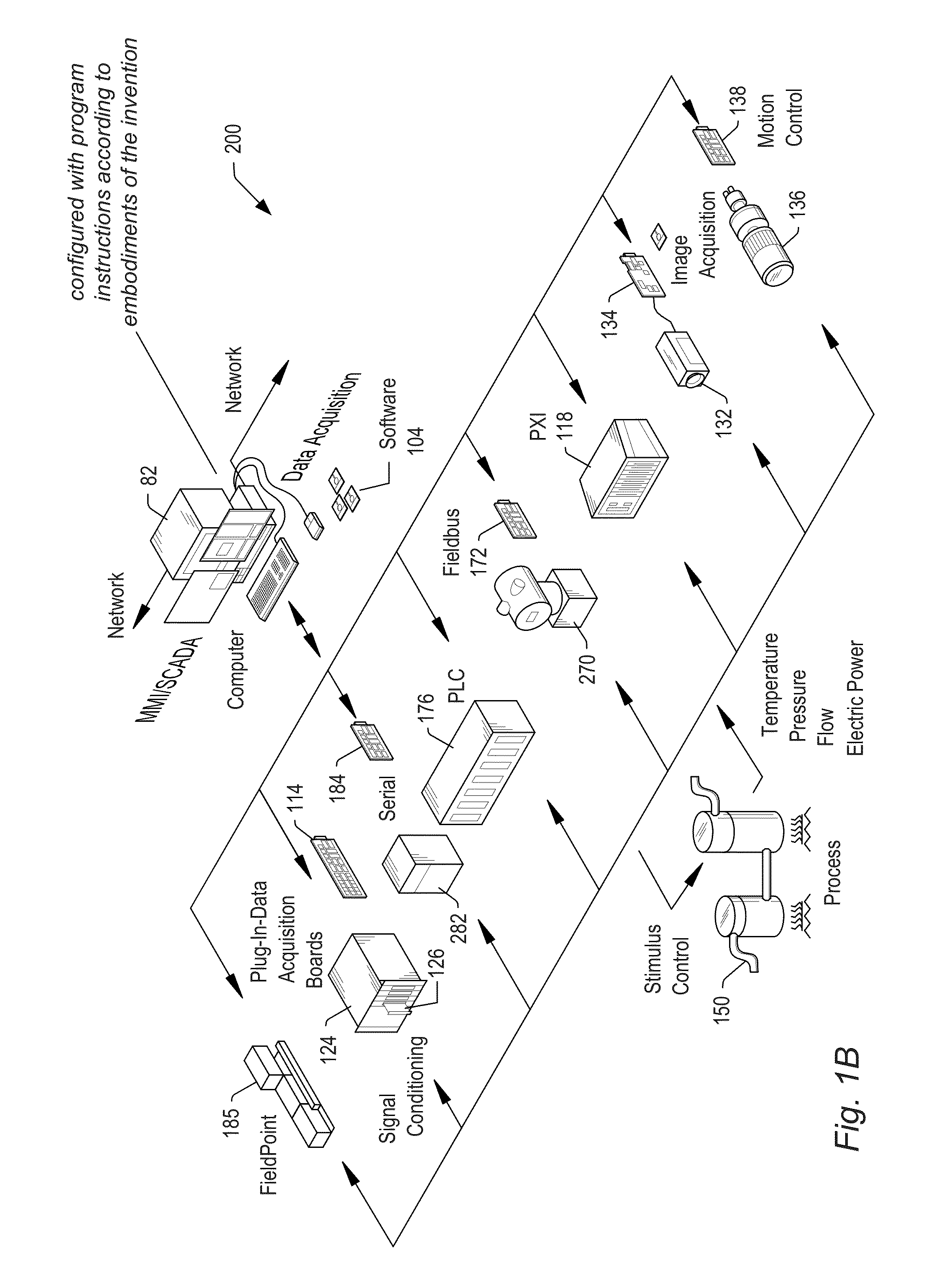

In co-simulation the different subsystems which form a coupled problem are modeled and simulated in a distributed manner. Hence, the modeling is done on the subsystem level without having the coupled problem in mind. Furthermore, the coupled simulation is carried out by running the subsystems in a black-box manner. During the simulation the subsystems will exchange data. Co-simulation can be considered as the joint simulation of the already well-established tools and semantics; when they are simulated with their suitable solvers. Co-simulation proves its advantage in validation of multi-domain and cyber physical system by offering a flexible solution which allows consideration of multiple domains with different time steps, at the same time. As the calculation load is shared among simulators, co-simulation also enables the possibility of large scale system assessment.

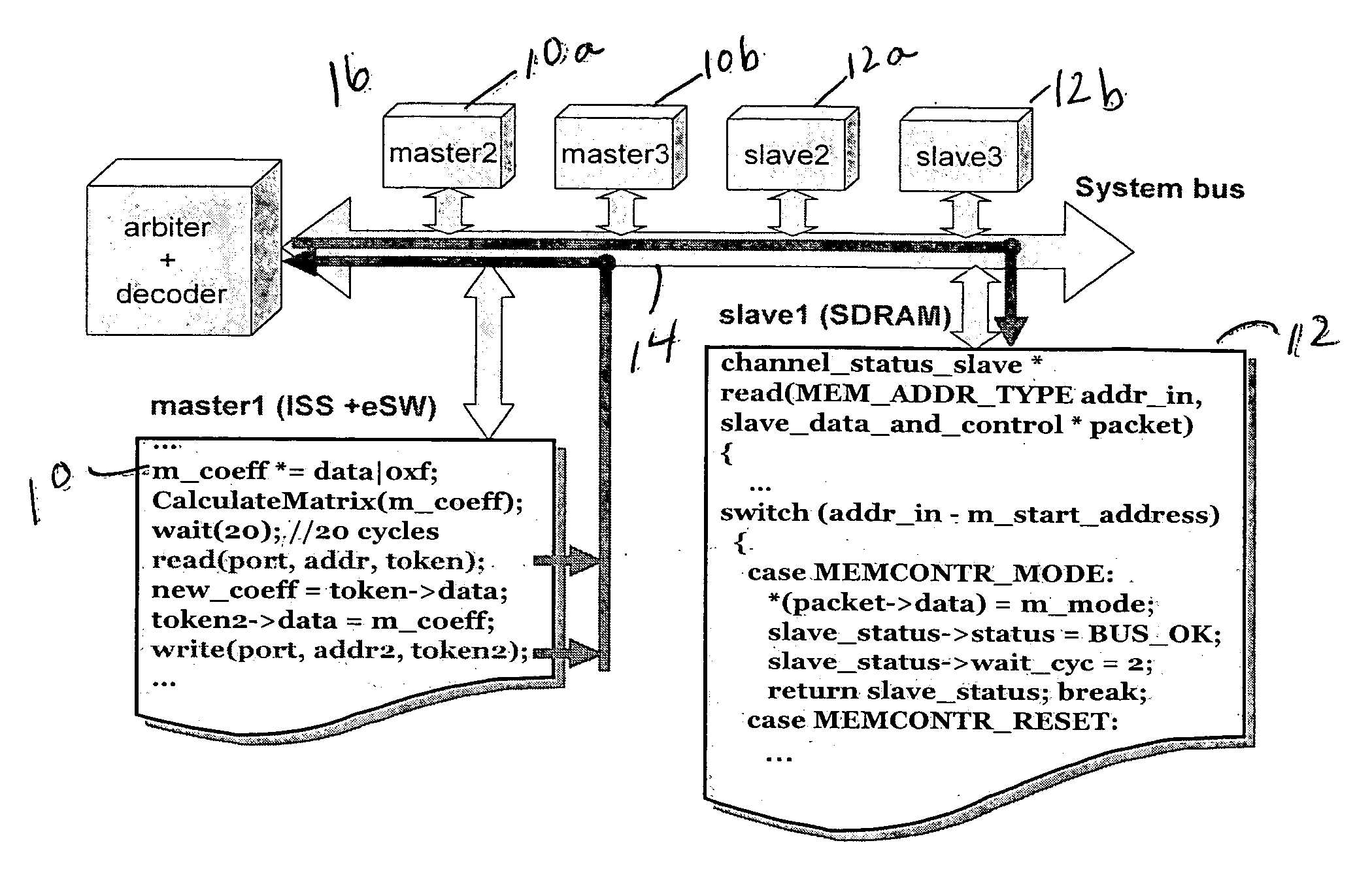

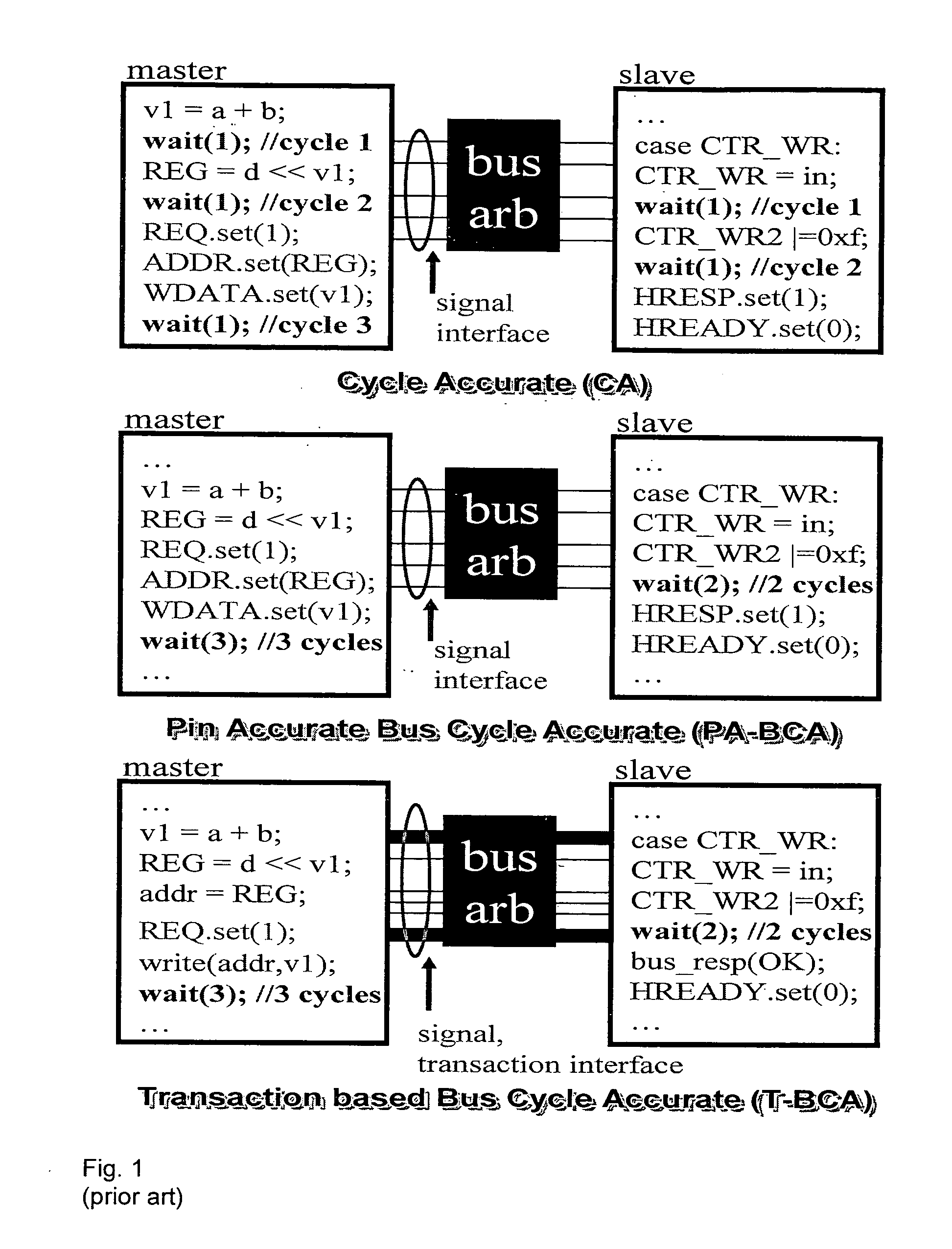

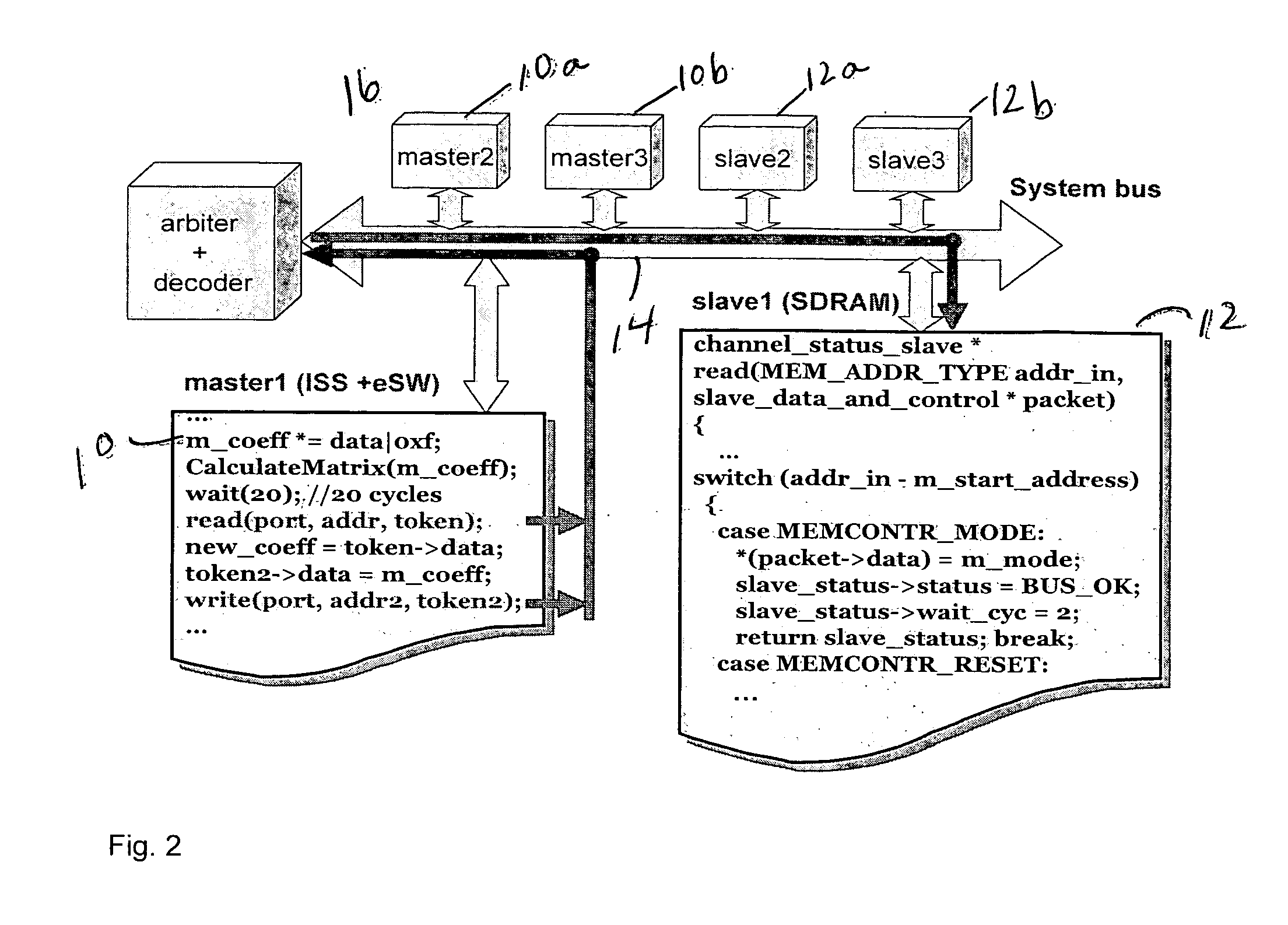

Method for the fast exploration of bus-based communication architectures at the cycle-count-accurate-at-transaction -boundaries (CCATB) abstraction

ActiveUS20060282233A1Speed up system prototypingMaintaining cycle count accuracyAnalogue computers for electric apparatusCAD circuit designComputer hardwareHardware architecture

A computer system simulation method starts with algorithmically implementing a specification model independently of hardware architecture. High level functional blocks representing hardware components are connected together using a bus architecture-independent generic channel. The bus architecture-independent generic channel is annotated with timing and protocol details to define an interface between the bus architecture-independent generic channel and functional blocks representing hardware components. The interface is refined to obtain a CCATB for communication space. The read( ) and write( ) interface calls are decomposed into several method calls which correspond to bus pins to obtain observable cycle accuracy for system debugging and validation and to obtain a cycle accurate model. The method calls are replaced by signals, and the functional blocks representing hardware components are further refined to obtain pin / cycle-accurate models which can be manually or automatically mapped to RTL, or be used to co-simulate with existing RTL components.

Owner:RGT UNIV OF CALIFORNIA

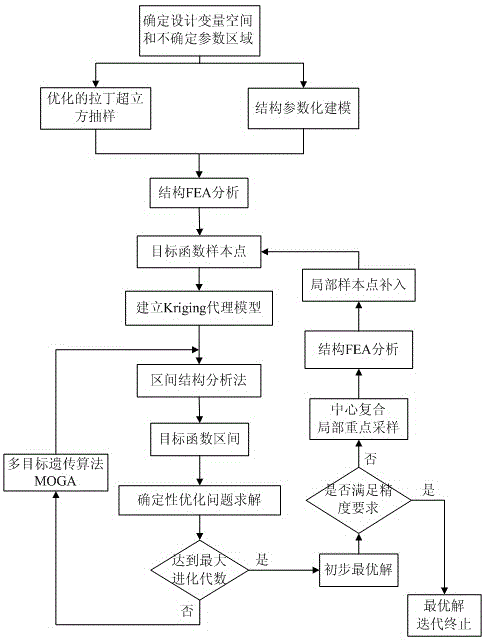

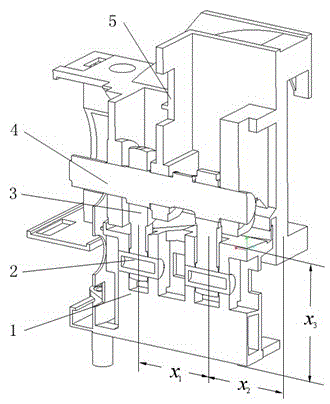

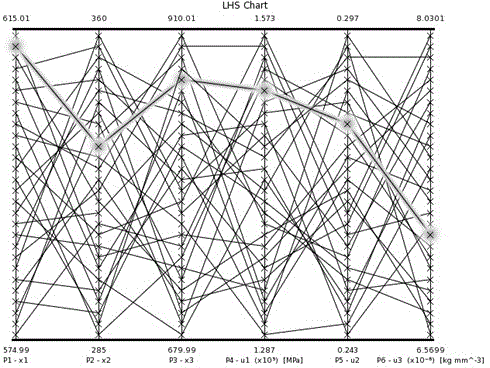

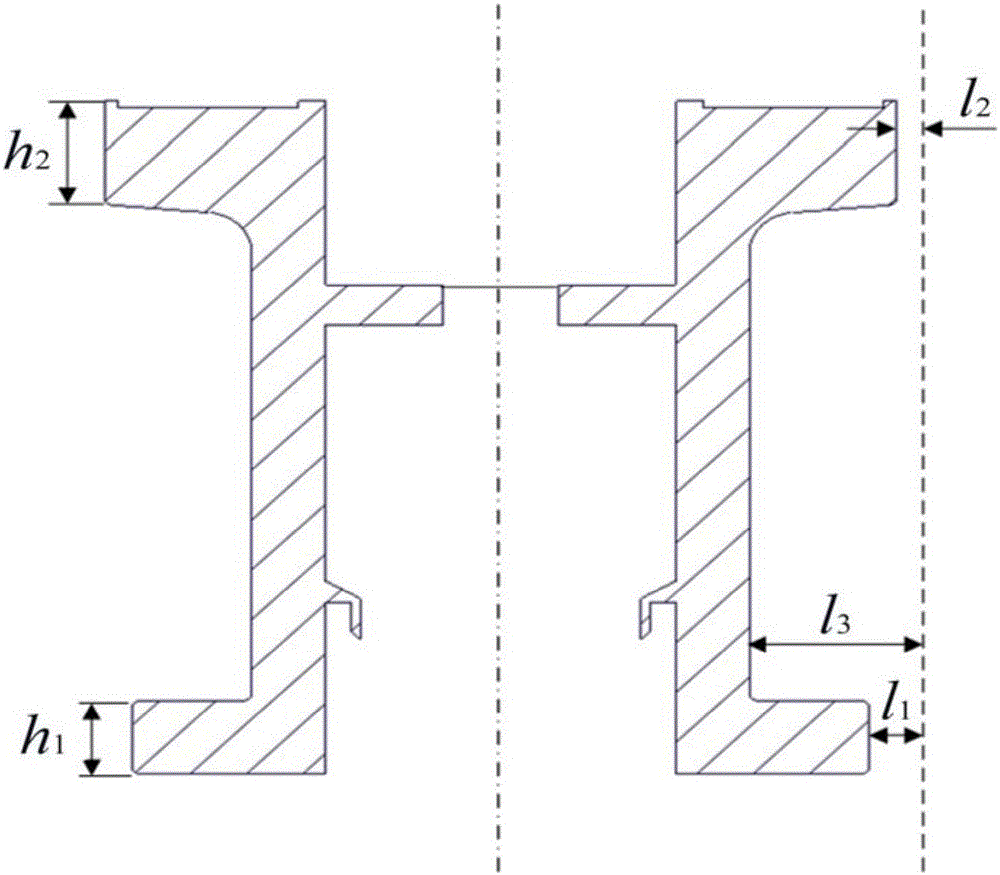

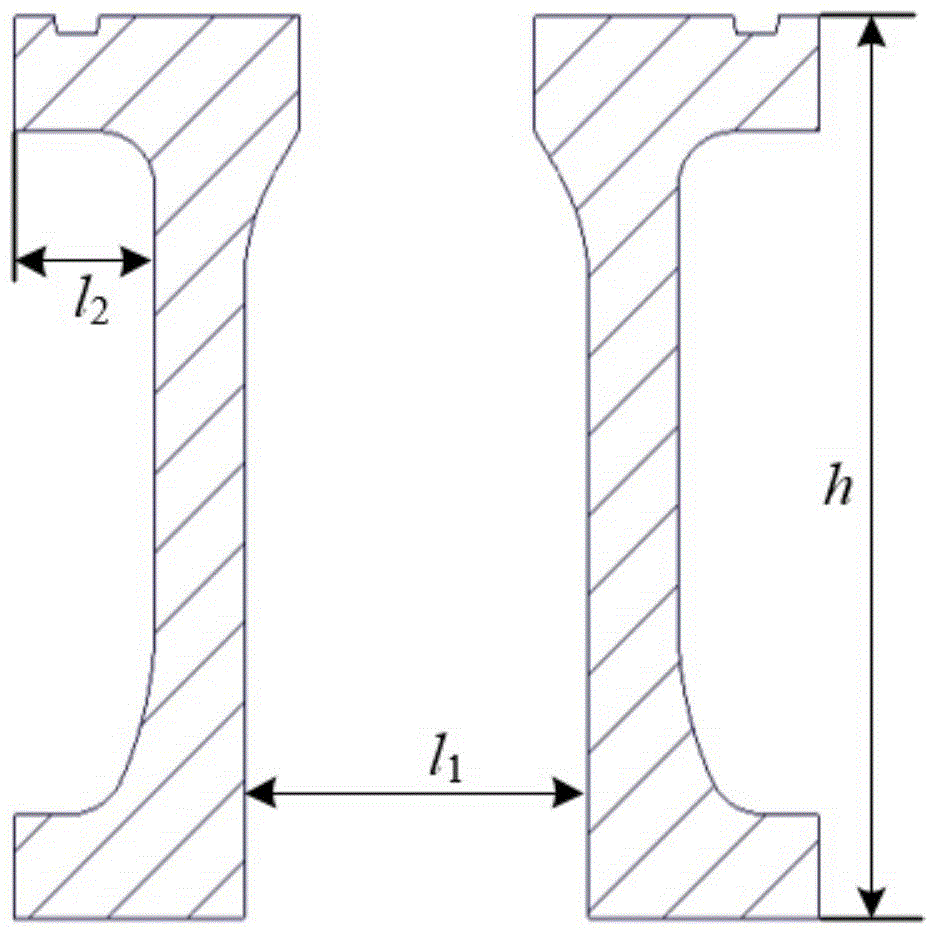

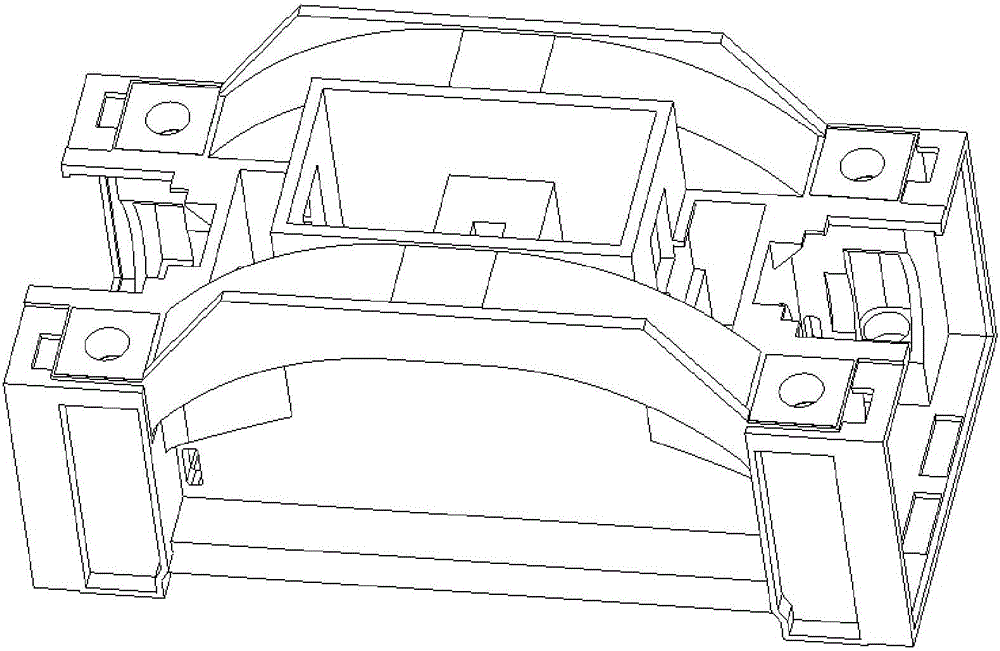

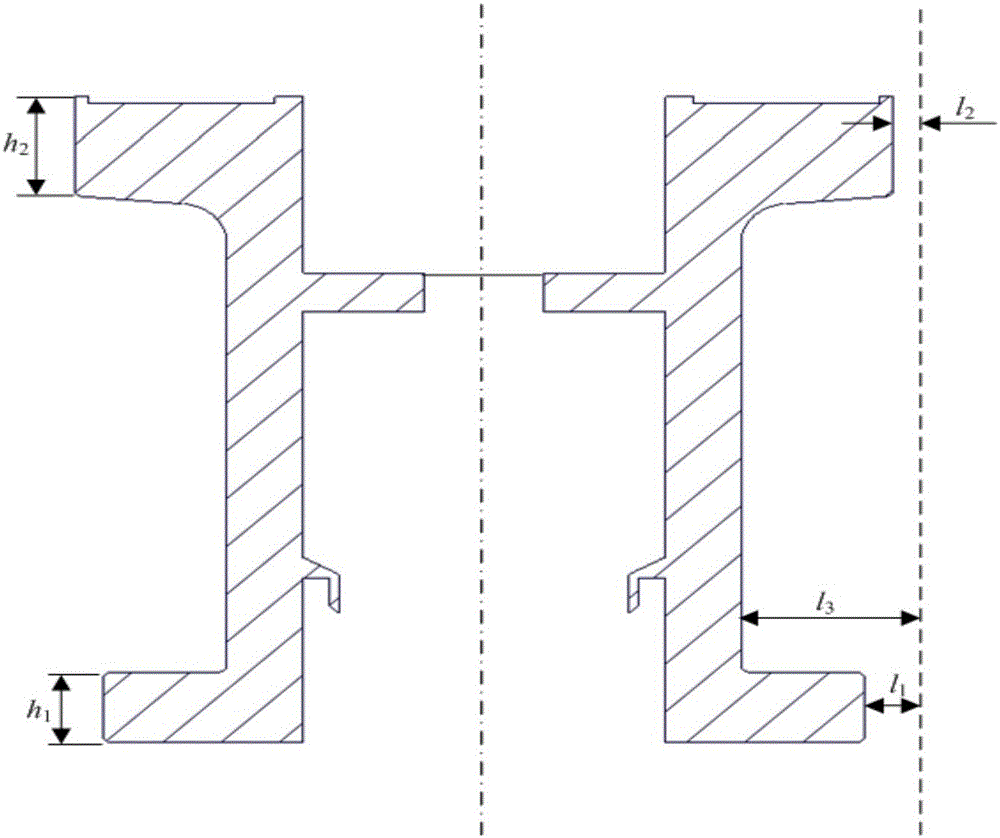

High-rigidity and light-weight design method considering uncertainty of slide block mechanism of press machine

ActiveCN102867083AEasy to set upImplement two-way transmissionSpecial data processing applicationsTest designStructure analysis

The invention discloses a high-rigidity and light-weight design method considering uncertainty of a slide block mechanism of a press machine. The high-rigidity and light-weight design method comprises the steps of: establishing a high-rigidity and light-weight design model considering the uncertainty of the slide block mechanism of the press machine; adopting an optimized Latin hypercube sampling method for a test design, obtaining a target function response value corresponding to each sample point through collaborative simulation and building a Kriging agent model; converting an uncertain target function into a certain target function based on an order relation of interval numbers; and calculating a target function interval by utilizing an internal structure analysis way, finding a Pareto optimal solution collection of a converted certain optimal problem by utilizing a multi-target genetic algorithm, if the precision requirement is not satisfied, performing important sampling at the place where the extreme value of the target function interval locates, and updating the target function sample collection and the agent model to perform iterative optimization. The high-rigidity and light-weight design method considering uncertainty of the slide block mechanism of the press machine, disclosed by the invention, has the advantages of establishing the uncertain optimization model of the slide block mechanism according with the practical project for solving and really realizing the light-weight and high-rigidity design of the slide block mechanism.

Owner:ZHEJIANG UNIV

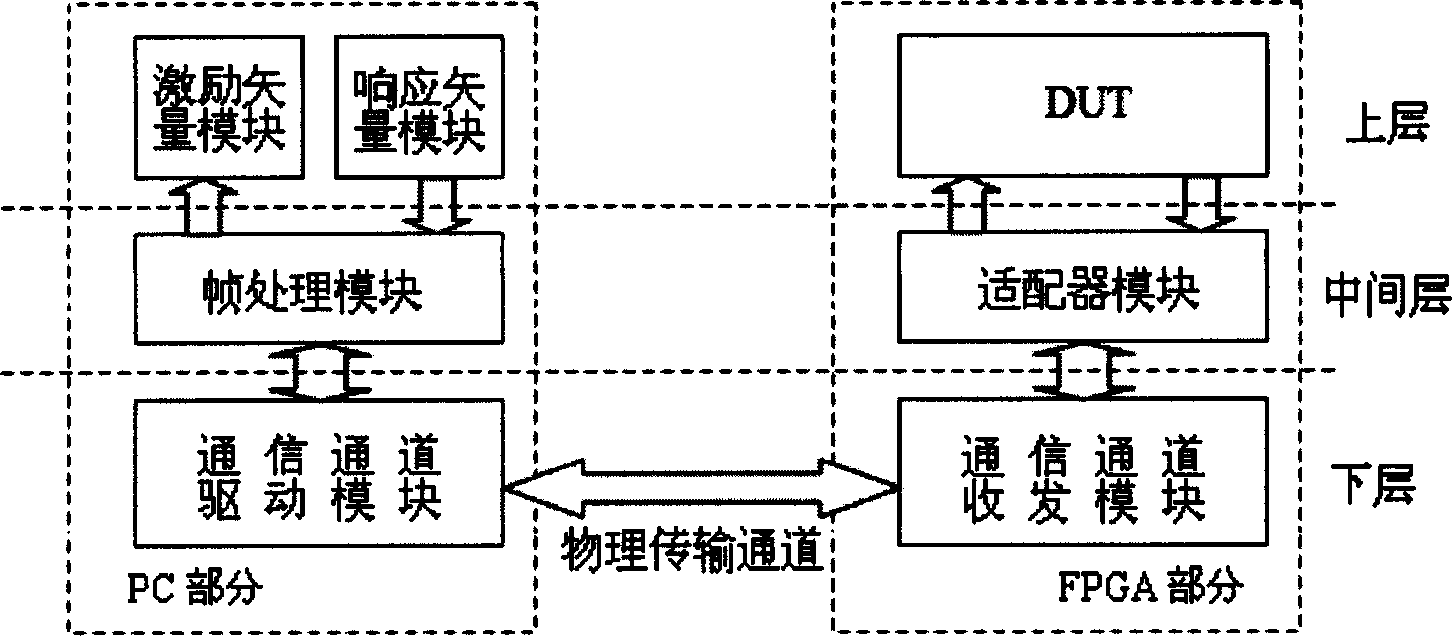

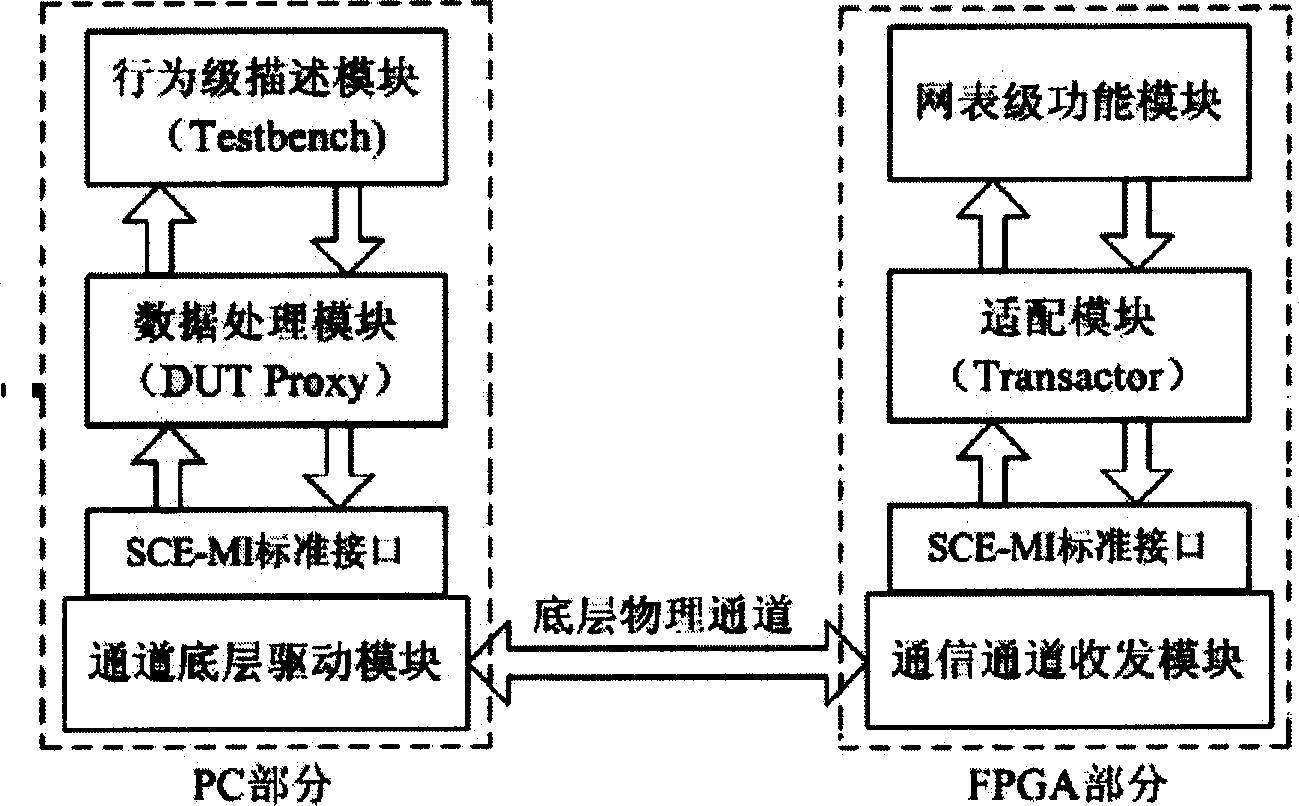

Software and hardware synergistic simulation/ validation system and vector mode simulation/ validation method

ActiveCN1828617AModularHierarchicalSpecial data processing applicationsComputer hardwareValidation methods

The system with a PC software part and FPGA hardware comprises: a bottom layer to transfer information on physical channel, a middle layer to pack and unpack data frame, and a top layer for signal input / output. Wherein, it sends ahead the expected result into the hardware for storage. This invention improves simulation speed greatly with well accuracy.

Owner:成都雷奥风电传感器有限公司

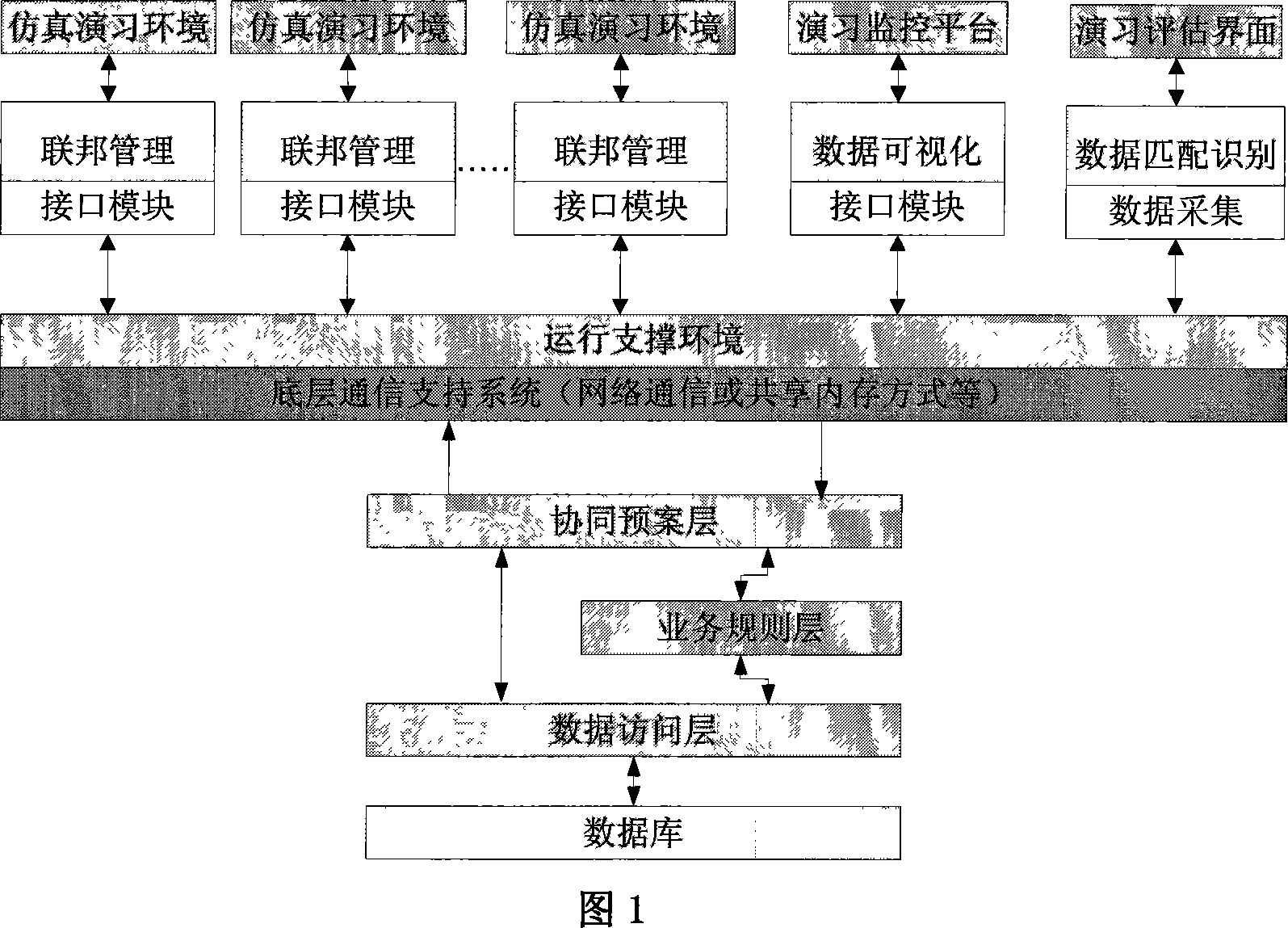

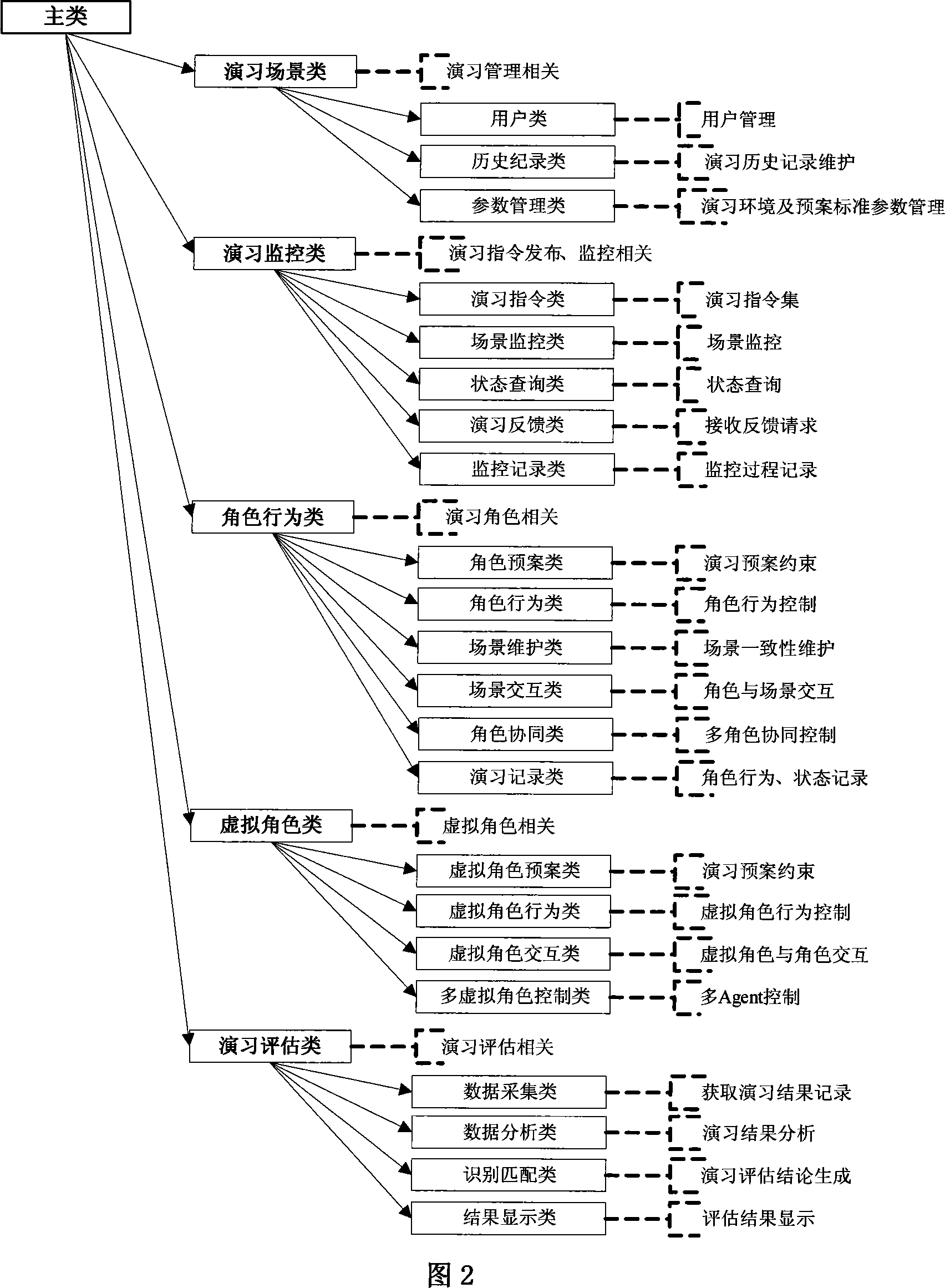

Multi-role distributed cooperating simulation drilling method

InactiveCN101075275AImplement triggerImplement process definitionSpecial data processing applications3D modellingData matchingUnexpected events

A co-simulated manoeuvring method of distributed multi-role mode includes utilizing virtualized reality and distributed simulation technique and using particle system and intelligent substitute to reappear manoeuvre site, using manoeuvre emergency preplan to guide manoruvre process, applying manoeuvre whole course monitor platform in synchronization with 3-D manoeuvre environment to monitor and control maneoeuvre process then applying databank technique and data match-identification technique to evaluate effect of manoeuvre.

Owner:SHANGHAI JIAO TONG UNIV

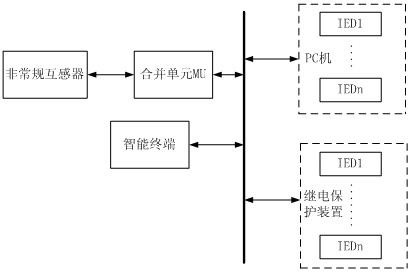

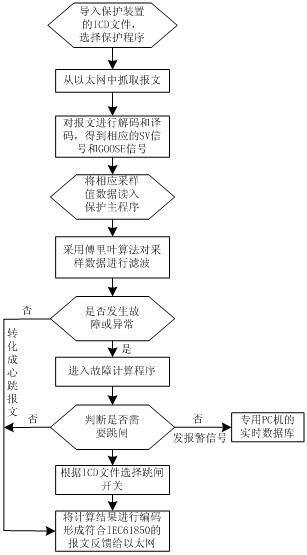

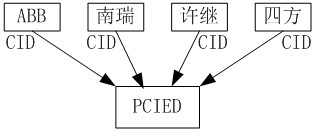

Method for building intelligent substation relay protection cooperation simulation testing system

InactiveCN102565585AReduce the consumption of manpower and material resourcesAvoid mistakesElectrical testingSmart substationOperational system

The invention relates to a method for building an intelligent substation relay protection cooperation simulation testing system. Based on a Windows multithreading operating system of a PC, aiming at related requirements for IEC61850 communication and digitization protection testing, and through reasonably allocating task priority and dispatching and communication among the tasks, a certain type IED function produced by a manufacturer can be realized on the PC through leading-in a CID (configured IED description) document representing external characteristics of different manufacturers, and the mutual coordination, interlocking and shutting relations among the IED provided by different manufacturers in process layers and spacer layers of intelligent substations can be on-line detected without needing a real IED device and under the premise that the main wiring manner of different substations is adopted, so that consumption of manual labor and material resources can be greatly reduced; and the existing IED does not stop operating when the intelligent substation is expanded and rebuilt or the IED is replaced, thereby avoiding careless mistake and error during the disassembly, transportation and reinstallation processes of the IED device.

Owner:SHANGHAI UNIVERSITY OF ELECTRIC POWER +1

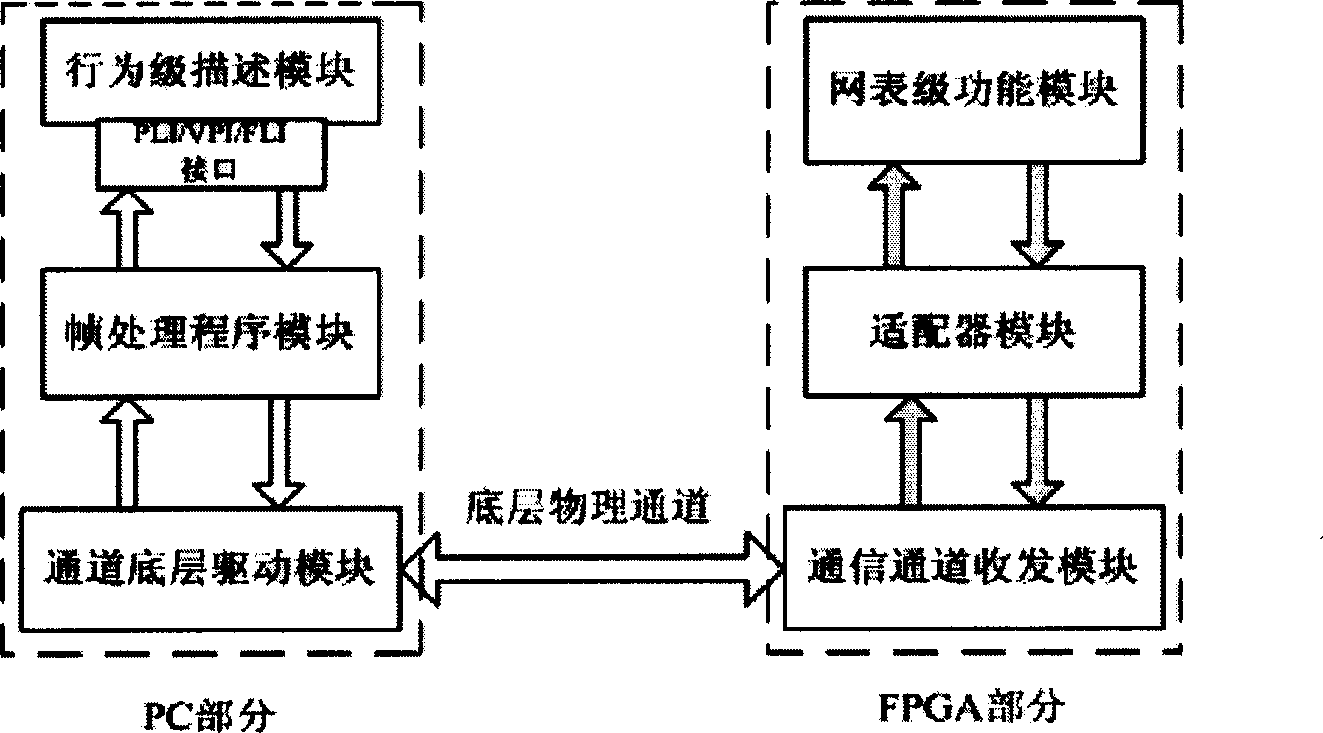

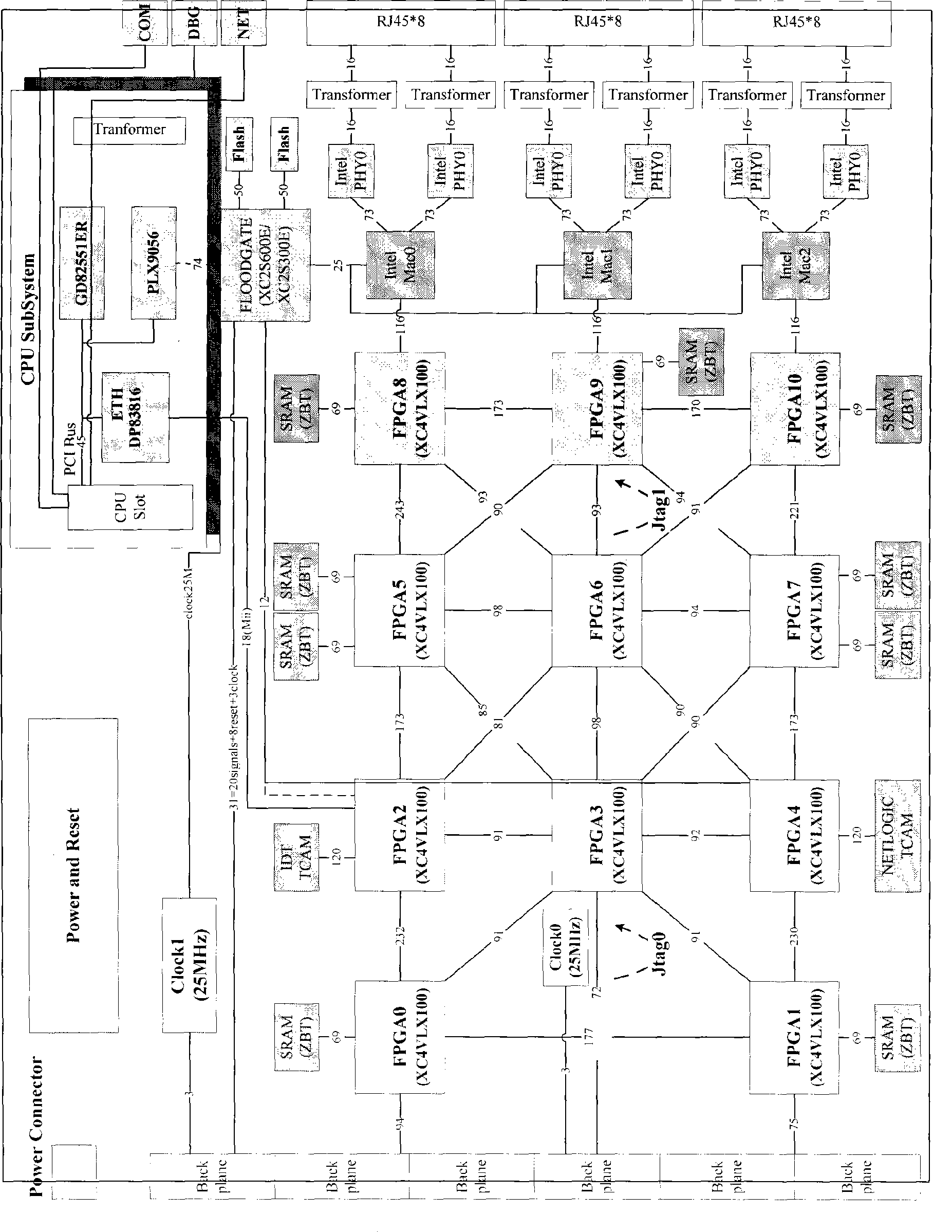

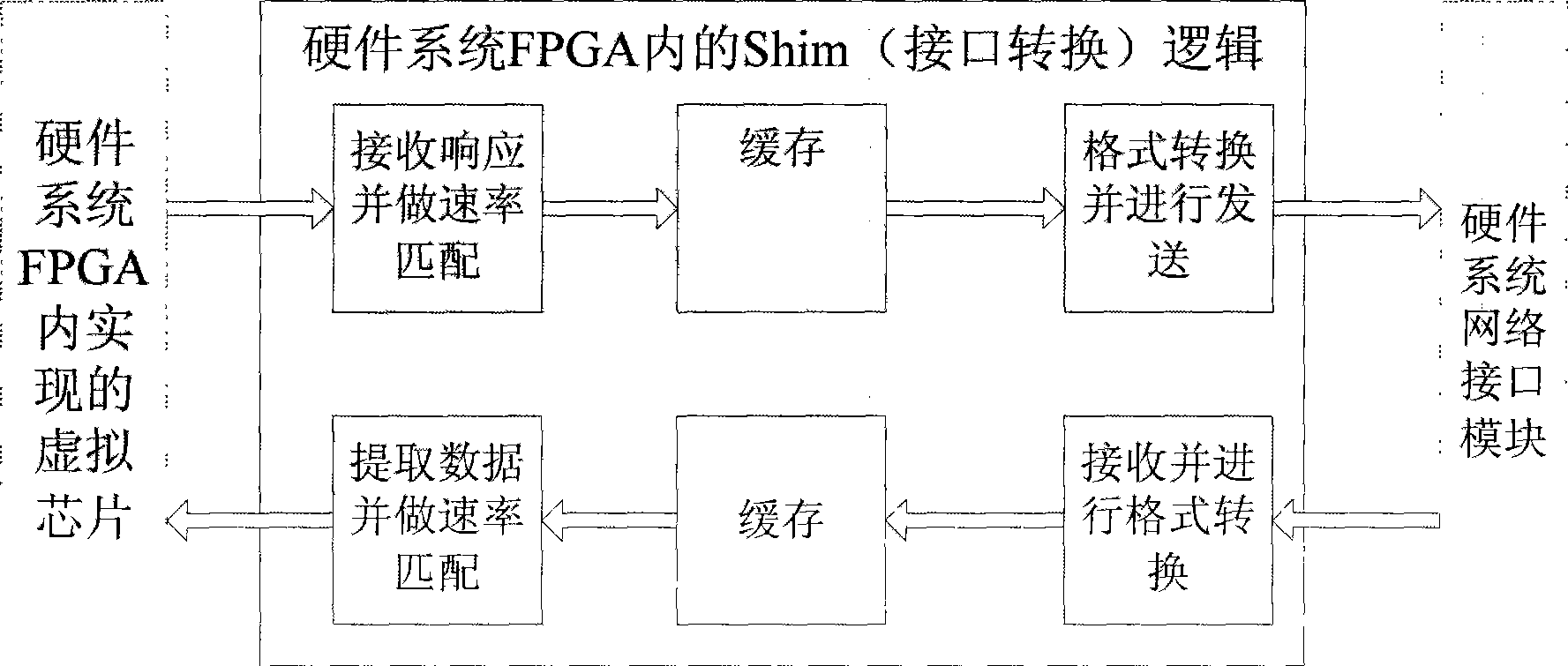

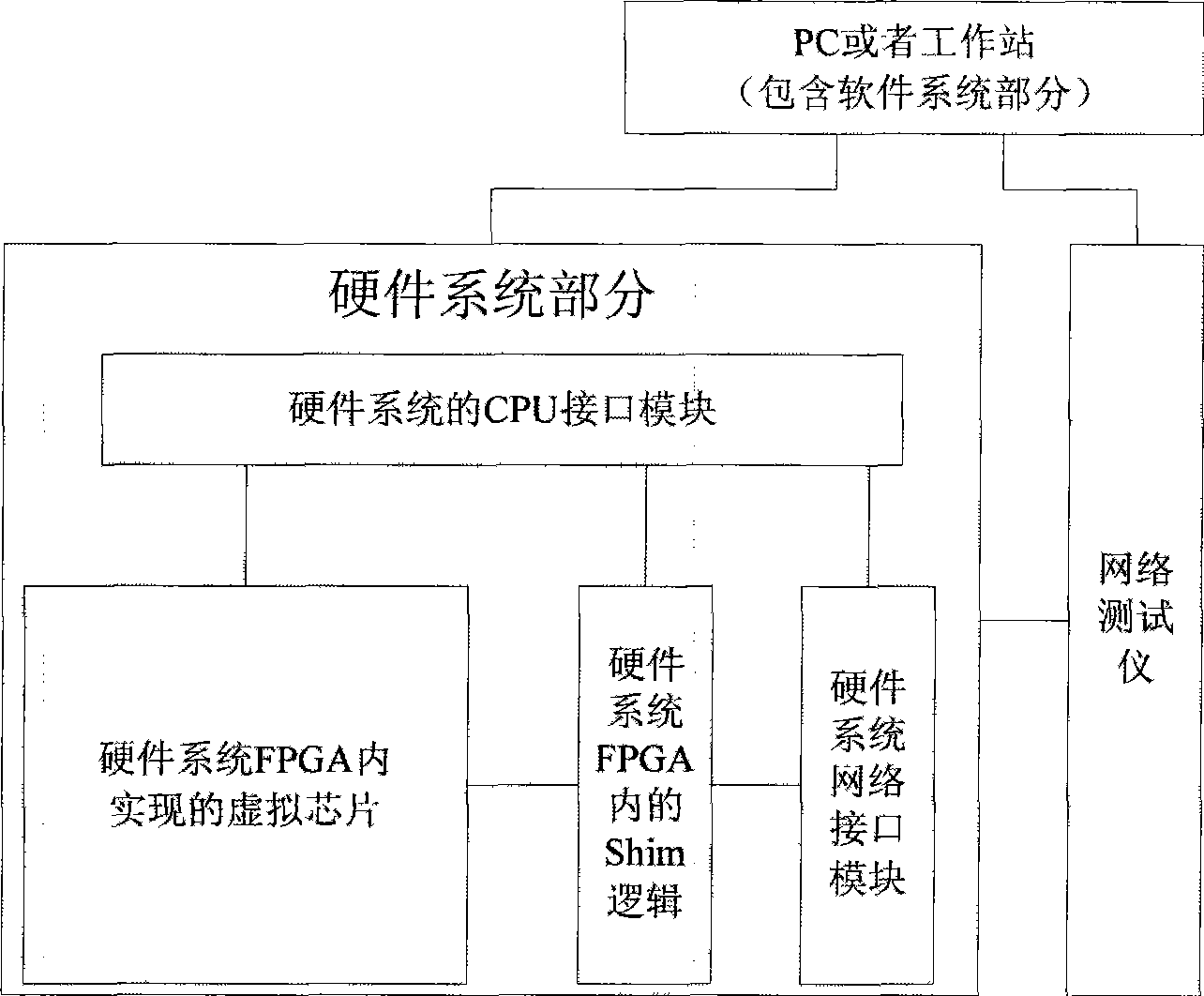

Software and hardware collaborative simulation verification system and method based on FPGA

InactiveCN101499937AReduce verification timeShorten the timeData switching networksSpecial data processing applicationsSoftware systemTester device

The invention relates to a software and hardware co-emulation verification system based on FPGA and a method thereof. The system comprises a network tester, a software system part which is arranged on an user PC terminal and a hardware system part used for simulating an integrated circuit chip; wherein, the software system part comprises a controlling platform of the network tester and an embedded system interface module; the hardware system part comprises a CPU interface module, an interface converter logic module in FPGA, a virtual waiting-for-testing module and a network interface module which can be used for realizing data exchanging between the interface converter logic module and the controlling platform of the network tester. The method is formed on the basis of the systems. The software and hardware co-emulation verification system based on FPGA and the method thereof have the advantages of being capable of carrying out high-speed emulation, greatly saving the time consumption for testing, realizing the whole-chip and whole-function verification and supporting the testing of a plurality of varieties of chips; simultaneously, the invention also has good physical expandability, adopts good debugging tools and further increases the emulation verification efficiency.

Owner:SUZHOU CENTEC COMM CO LTD

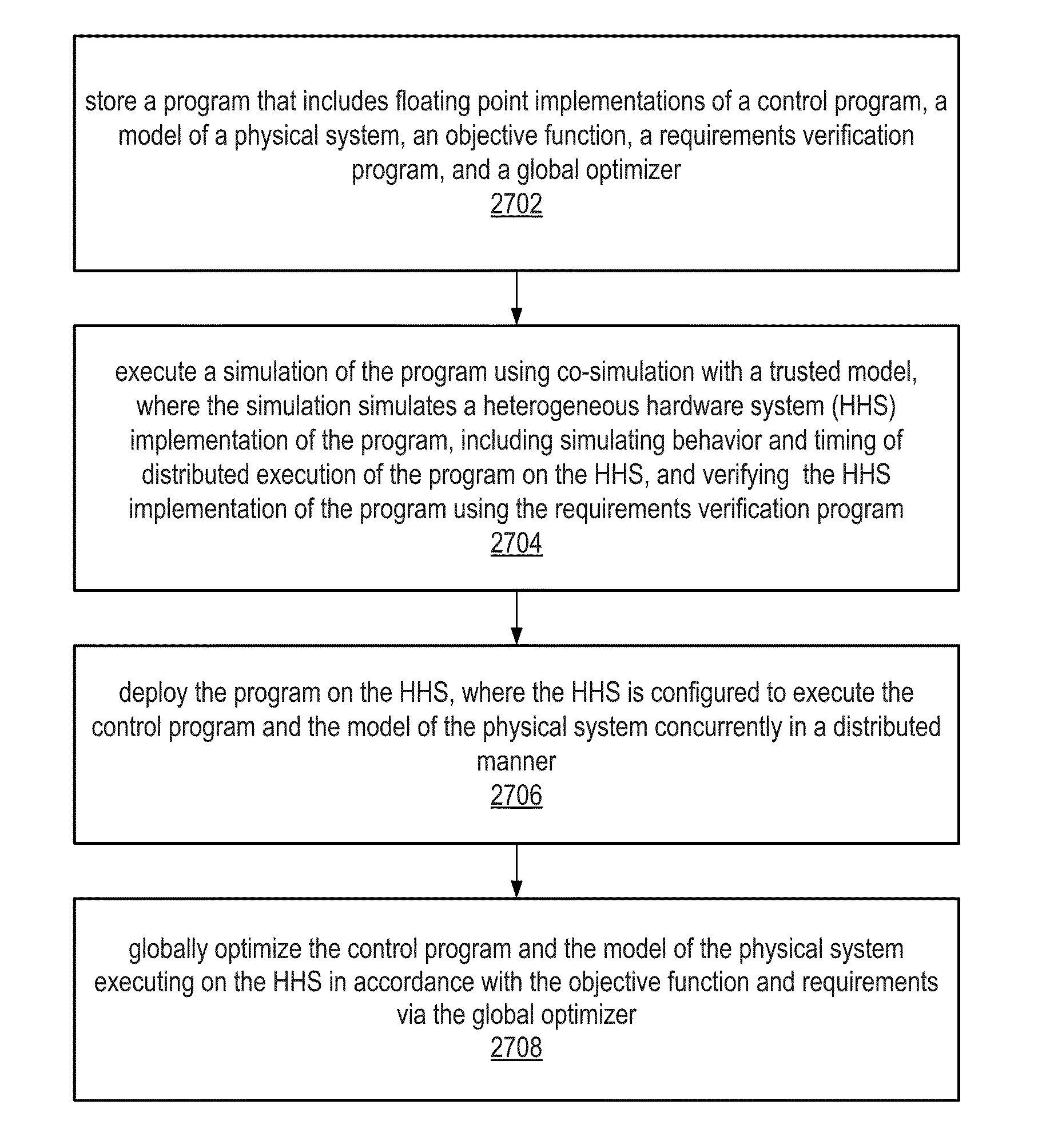

Global Optimization and Verification of Cyber-Physical Systems Using Floating Point Math Functionality on a System with Heterogeneous Hardware Components

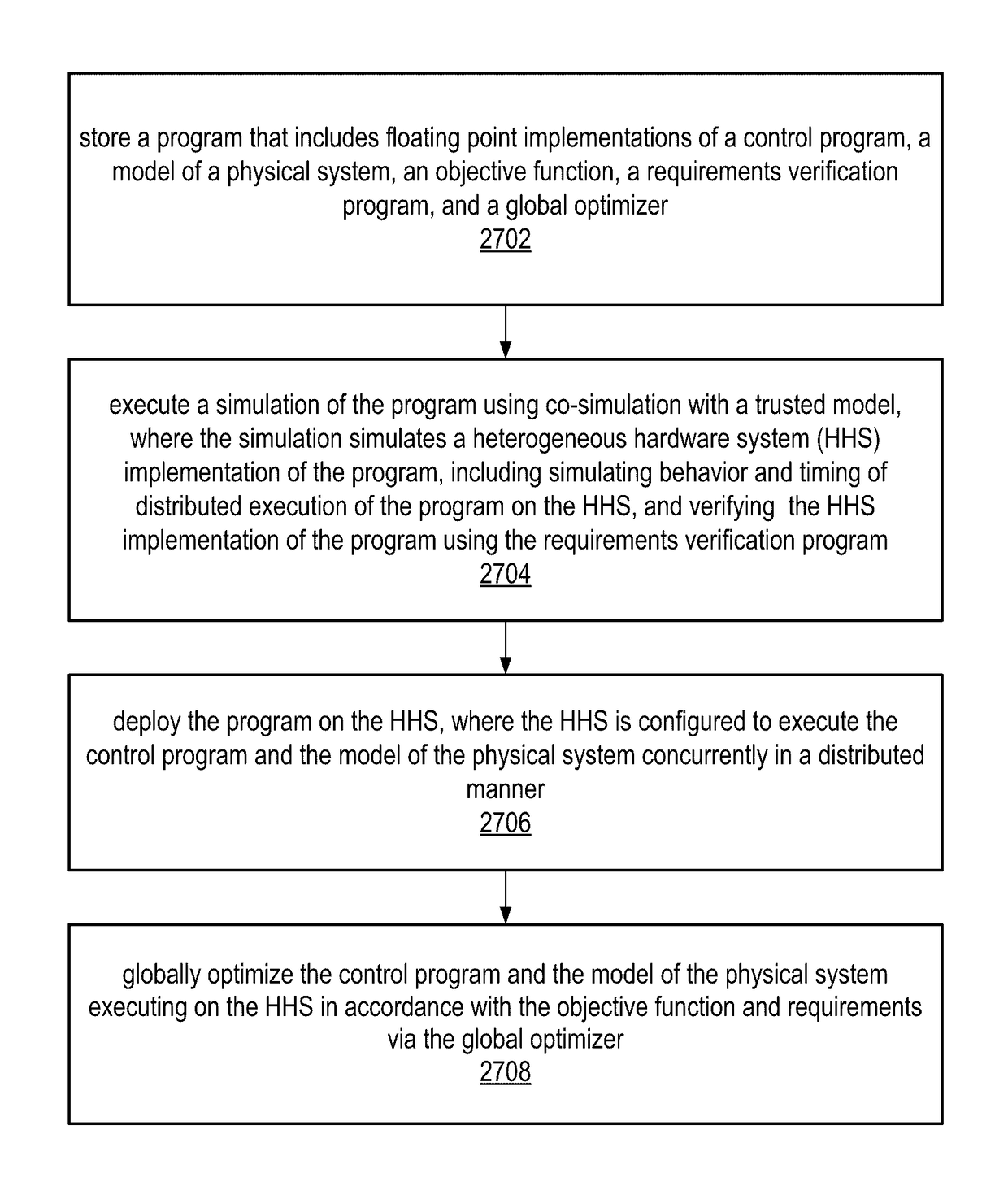

Global optimization and verification of cyber-physical systems using graphical floating point math functionality on a heterogeneous hardware system (HHS). A program includes floating point implementations of a control program (CP), model of a physical system (MPS), objective function, requirements verification program (RVP), and / or global optimizer. A simulation simulates HHS implementation of the program using co-simulation with a trusted model, including simulating behavior and timing of distributed execution of the program on the HHS, and may verify the HHS implementation using the RVP. The HHS is configured to execute the CP and MPS concurrently in a distributed manner. After deploying the program to the HHS, the HHS is configured to globally optimize (improve) the CP and MPS executing concurrently on the HHS via the global optimizer. The optimized MPS may be usable to construct the physical system. The optimized CP may be executable on the HHS to control the physical system.

Owner:NATIONAL INSTRUMENTS

Global optimization and verification of cyber-physical systems using floating point math functionality on a system with heterogeneous hardware components

Owner:NATIONAL INSTRUMENTS

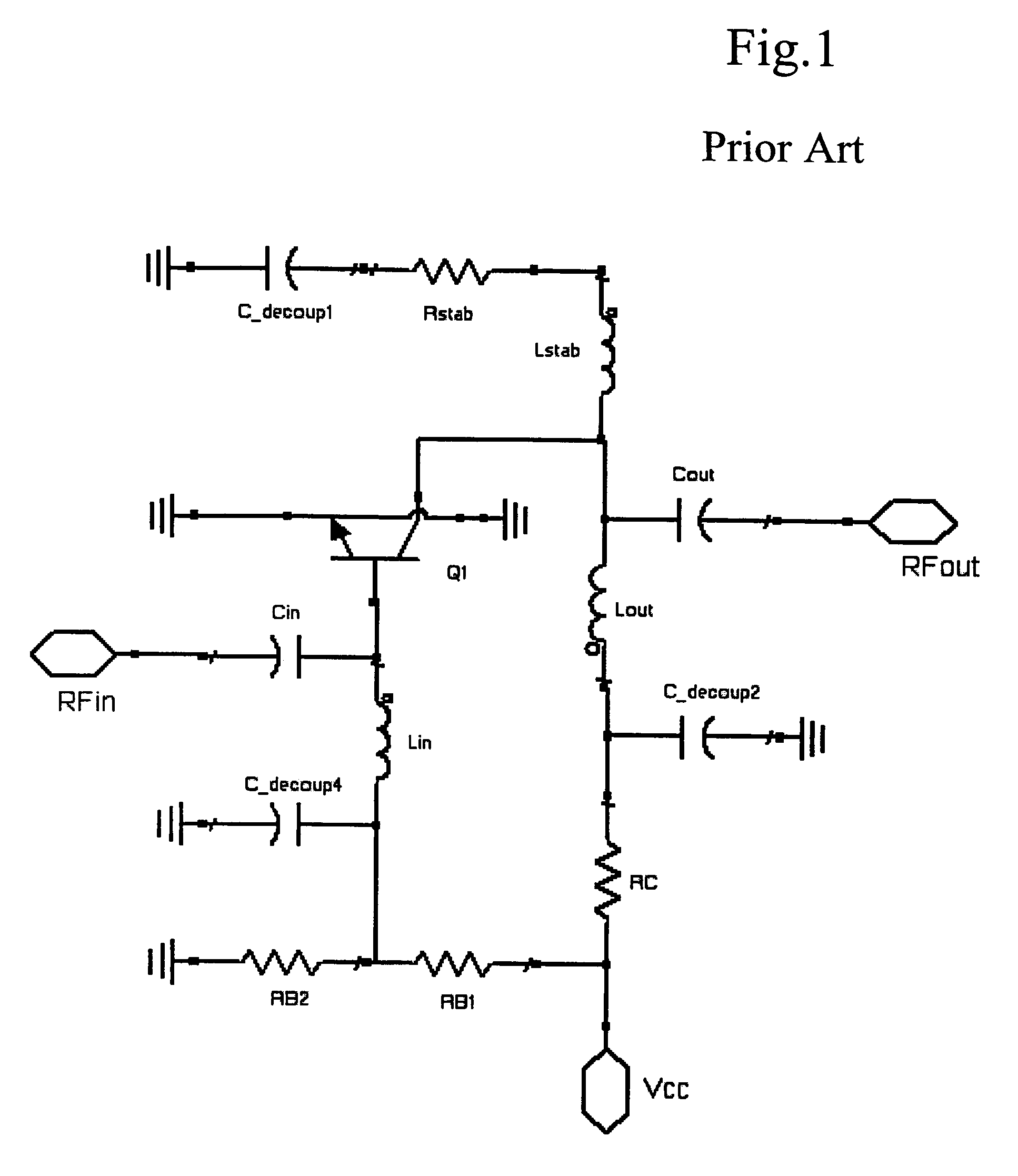

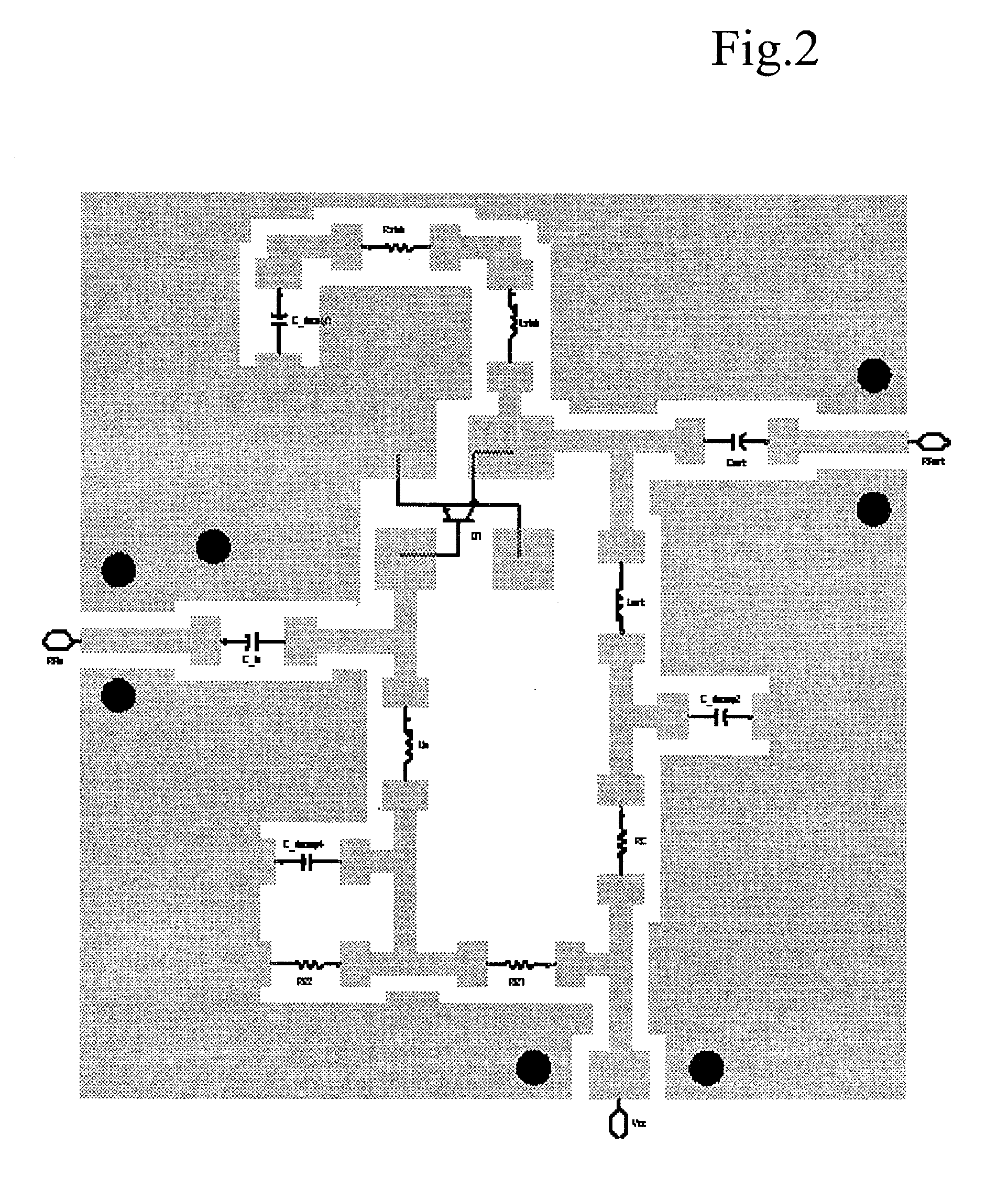

Electromagnetic/circuit co-simulation and co-optimization with parametric layout components

InactiveUS7206731B2Significant to useLimited amountMagnetic/electric field screeningDetecting faulty computer hardwareInterconnectionCo-simulation

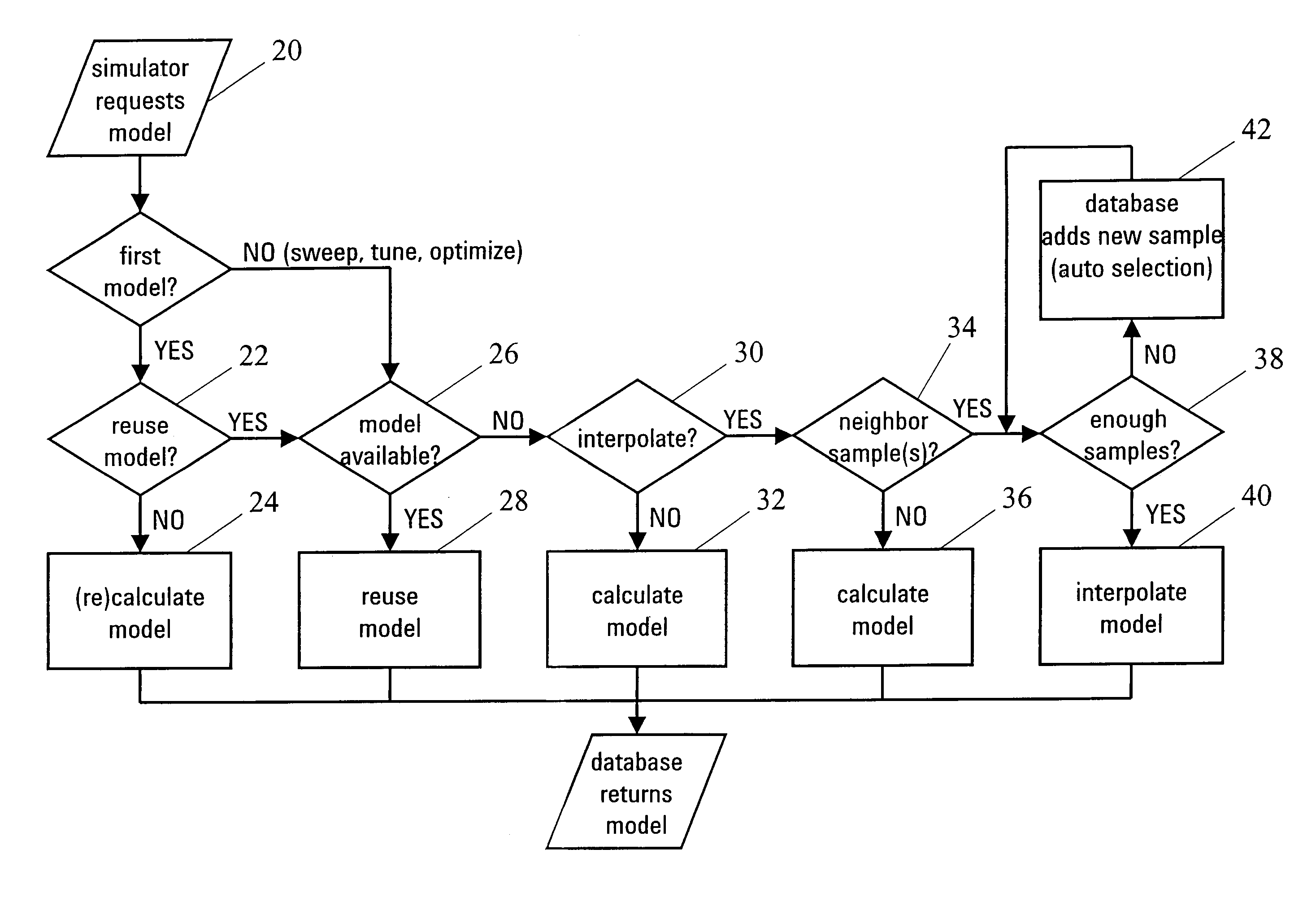

Simulation of electromagnetic characteristics of an electrical circuit uses netlist data defining component instances, including layout component instances, and their topological interconnection in an electrical circuit. A circuit simulation is performed using the netlist data, involving use of a model for each layout component instance. An attempt is made to retrieve an existing simulation model of the layout component instance from a database of such layout component simulation models. If no suitable simulation model can be found in the database, an attempt is made to interpolate a new simulation model from among existing simulation models in the database. If interpolation is determined not to be feasible, then an electromagnetic simulation of the layout component instance is performed to develop a new electromagnetic simulation model. This new model is used in the circuit simulation, and added to the database for future use.

Owner:KEYSIGHT TECH

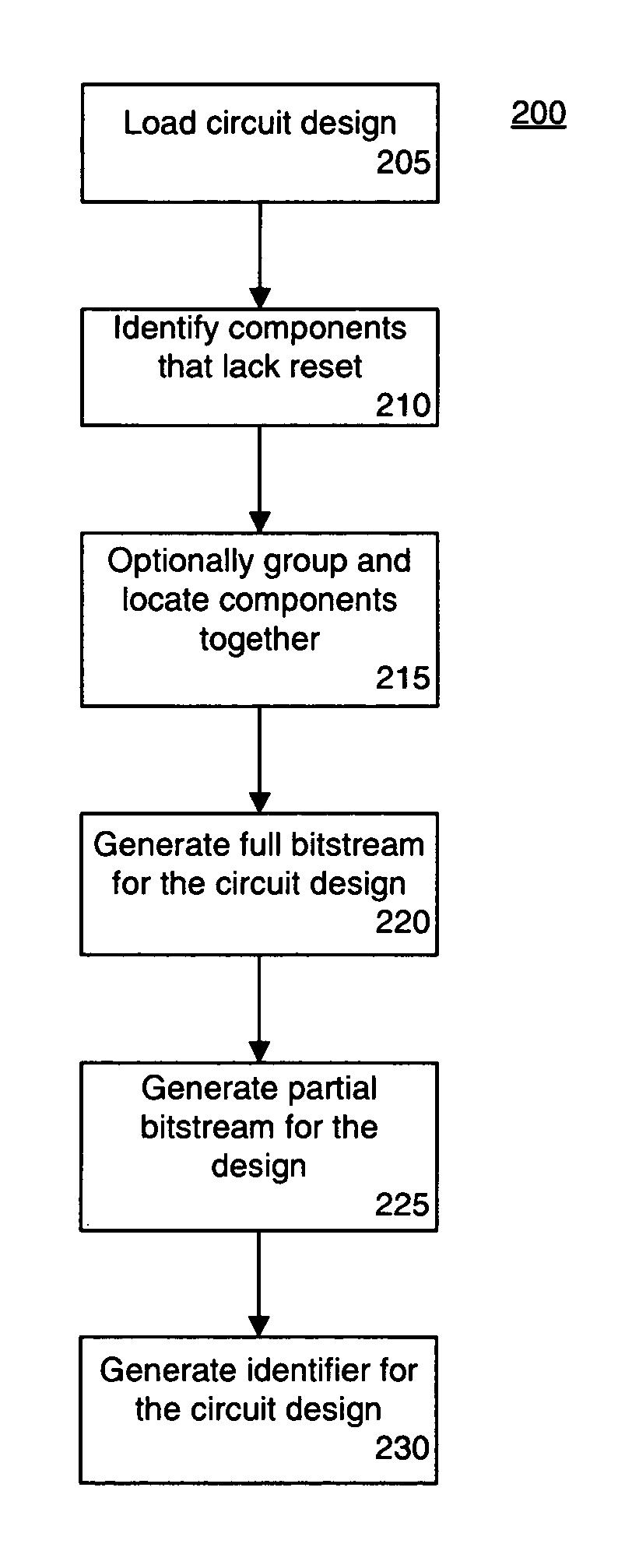

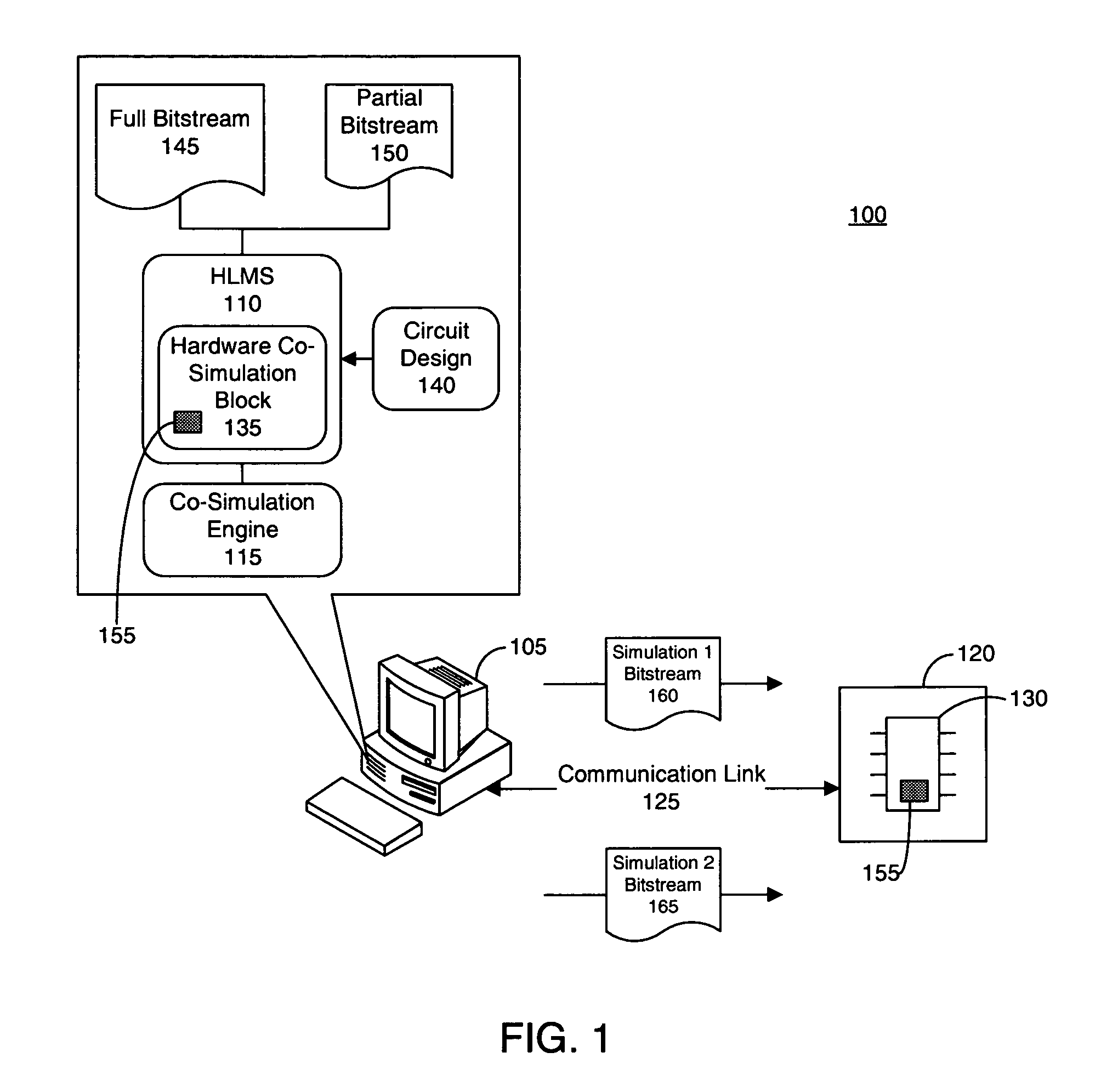

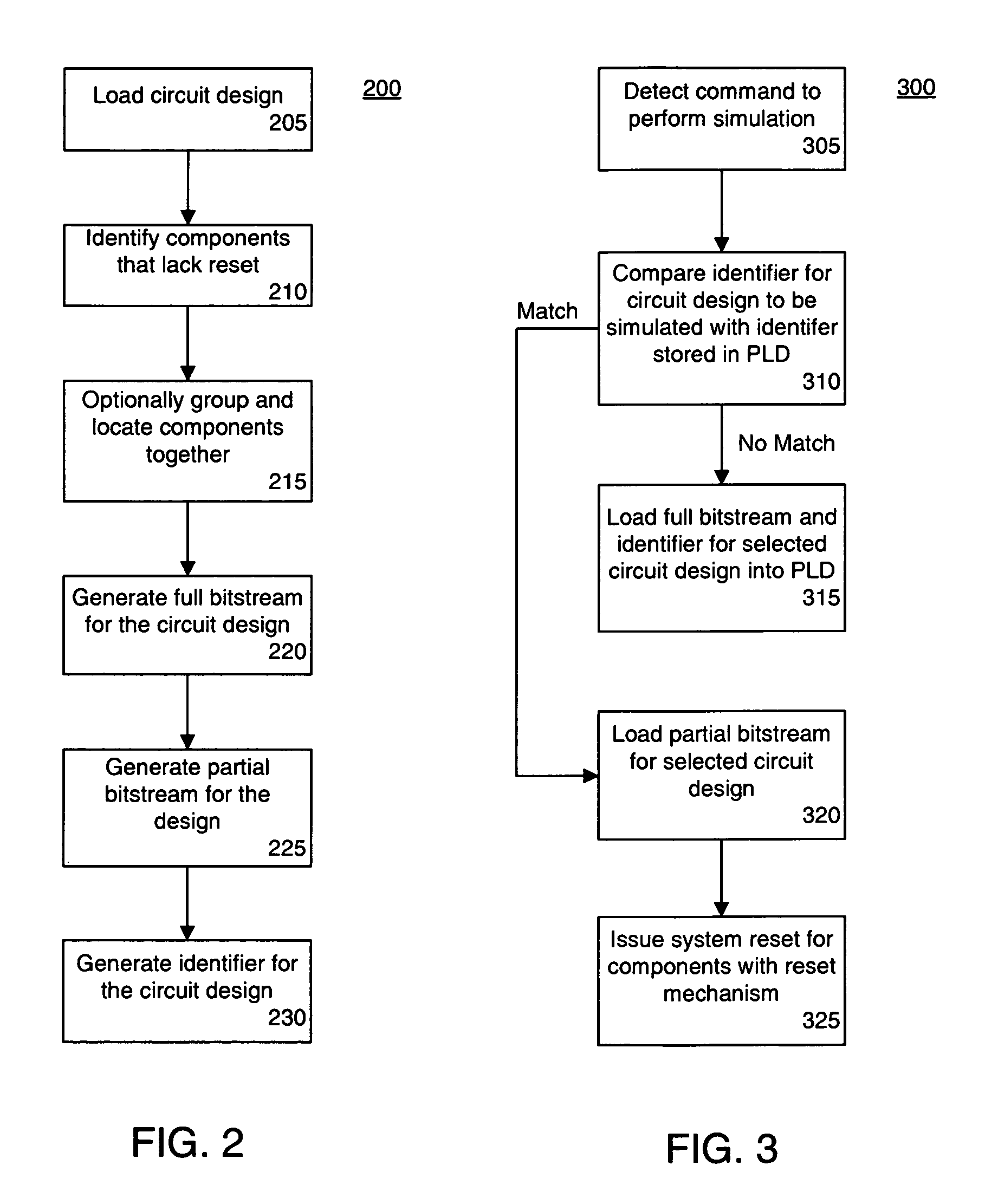

Fast hardware co-simulation reset using partial bitstreams

InactiveUS7739092B1Analogue computers for electric apparatusDigital computer detailsProgrammable logic deviceCo-simulation

A method of resetting a programmable logic device (PLD) for use with hardware co-simulation can include loading a full bitstream into the PLD. The full bitstream can program the PLD with a circuit design to be used with a first simulation. The method further can include loading a partial bitstream into the PLD thereby resetting at least one component of the circuit design that does not have a reset function such that the circuit design is initialized for use in a subsequent simulation.

Owner:XILINX INC

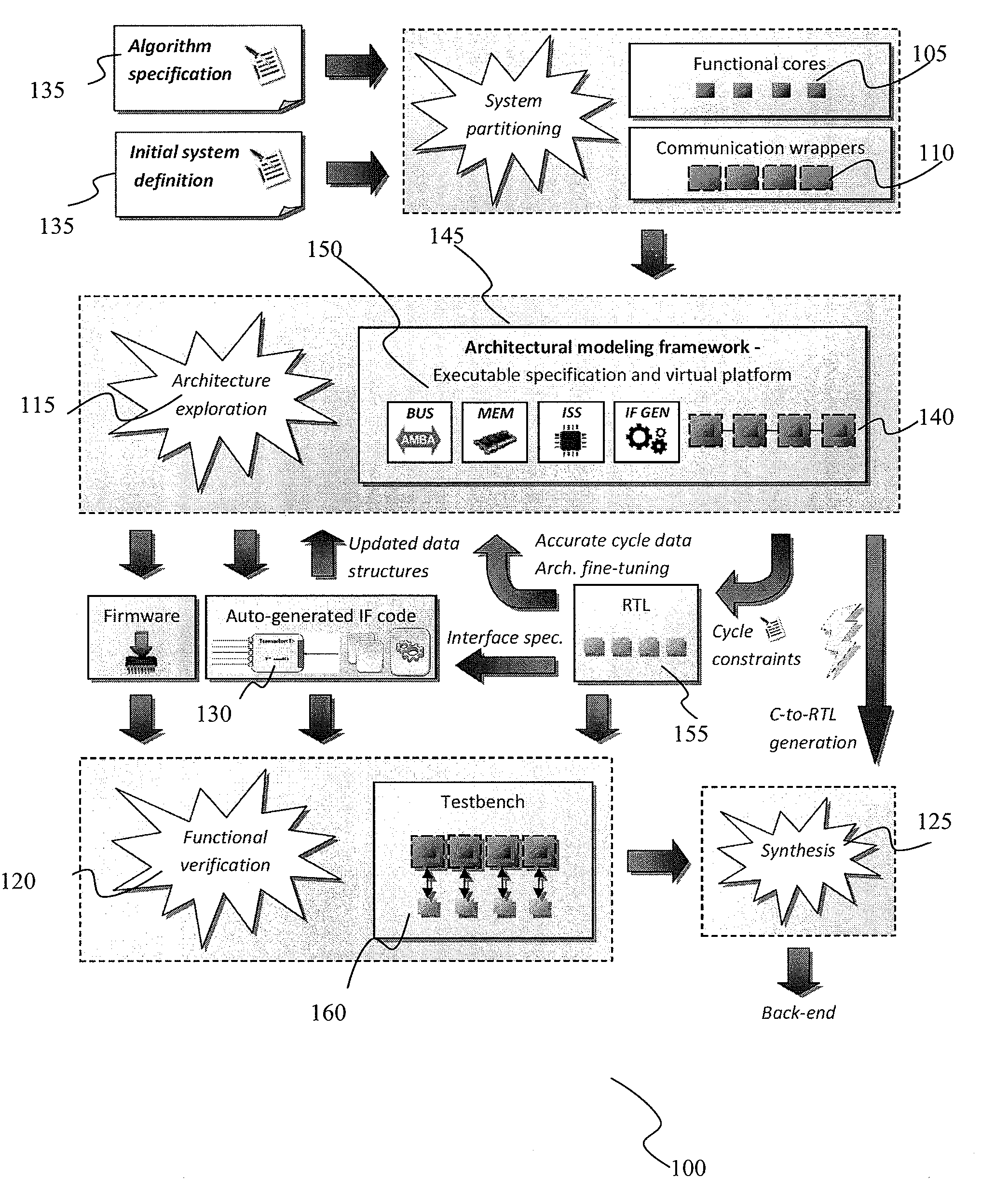

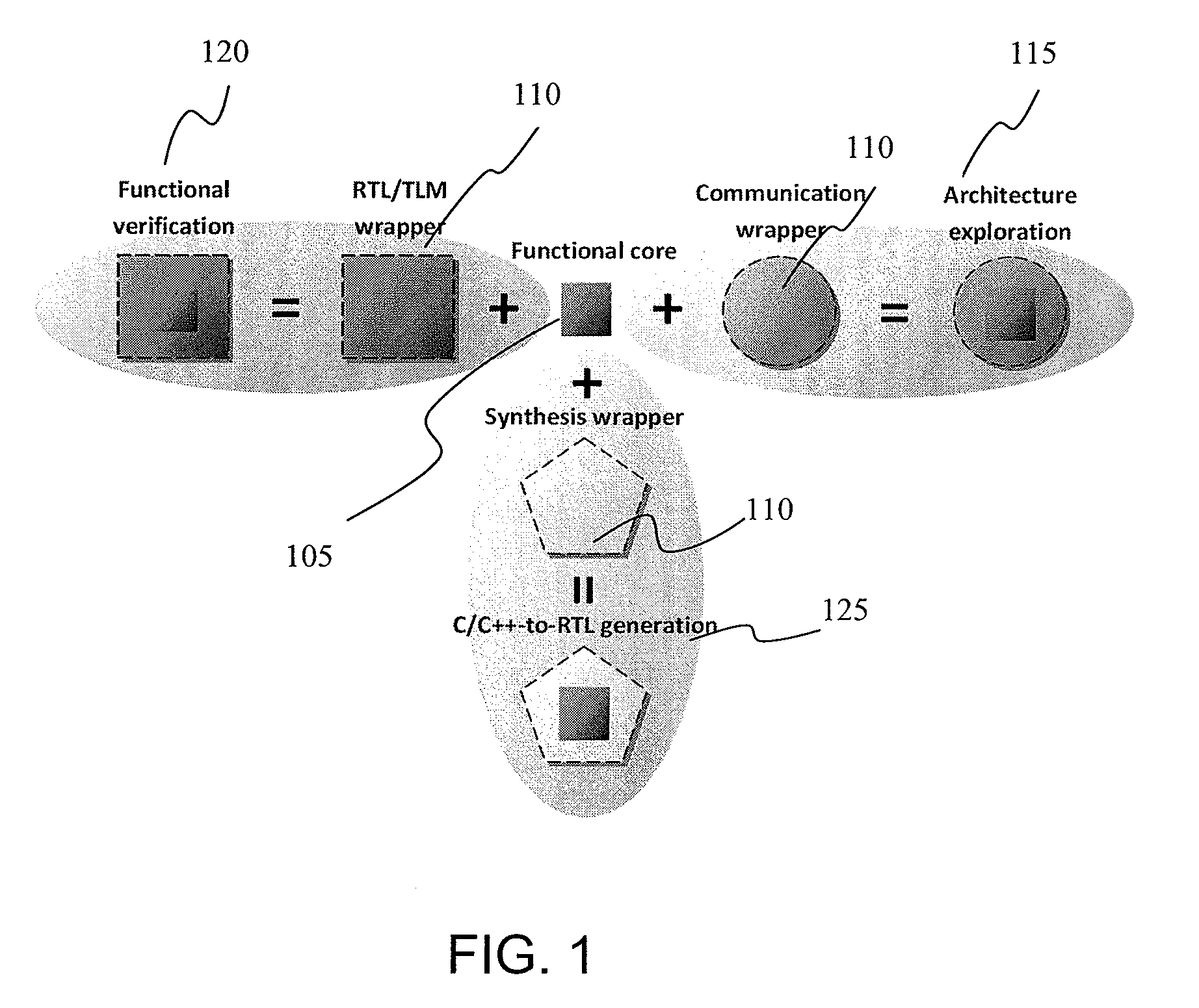

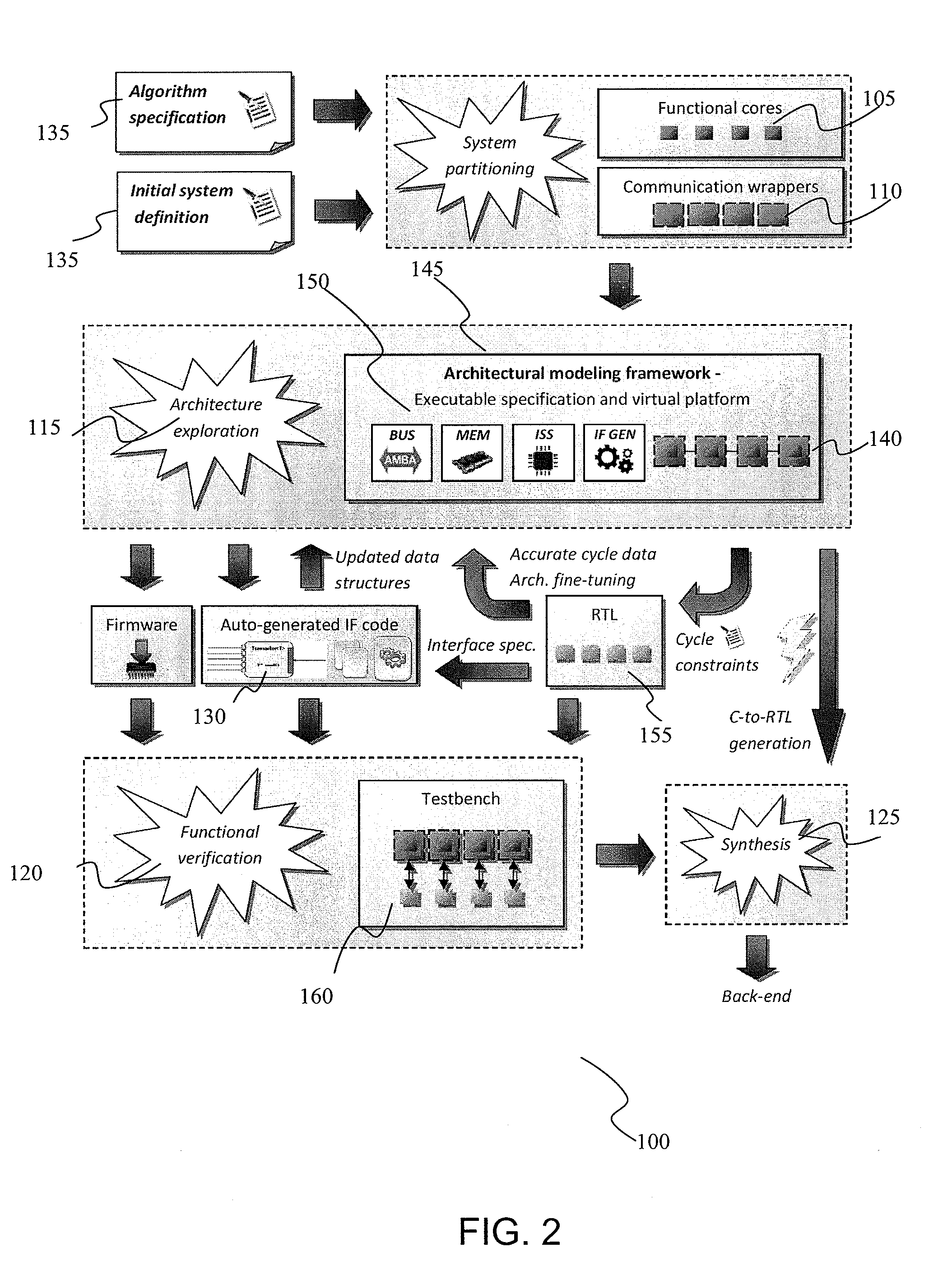

Integrated Circuit Modeling Method and Framework Tool

ActiveUS20110041106A1Easy to planImprove ease of useDetecting faulty computer hardwareCAD circuit designComputer architectureLanguage module

An integrated circuit modeling method 100 implementable on computer, which has an executable software model 145 having modules 140 of reusable functional cores 105 coded in a high level language and a virtual platform of the integrated circuit employable in an architecture exploration step 115. A modeling library of modules coded in high level languages and hardware level languages are provided and instantiated according to user input in a functional verification step 120 having a co-simulation environment, with interface code 170 between modules automatically generated by an interface generator 130 based on a two dimensional data array of hardware specification inputs 205, the interface code 170 further interfacing with wrappers engaged between high and hardware level language modules.

Owner:HONG KONG APPLIED SCI & TECH RES INST CO LTD A LIMITED LIABILITY

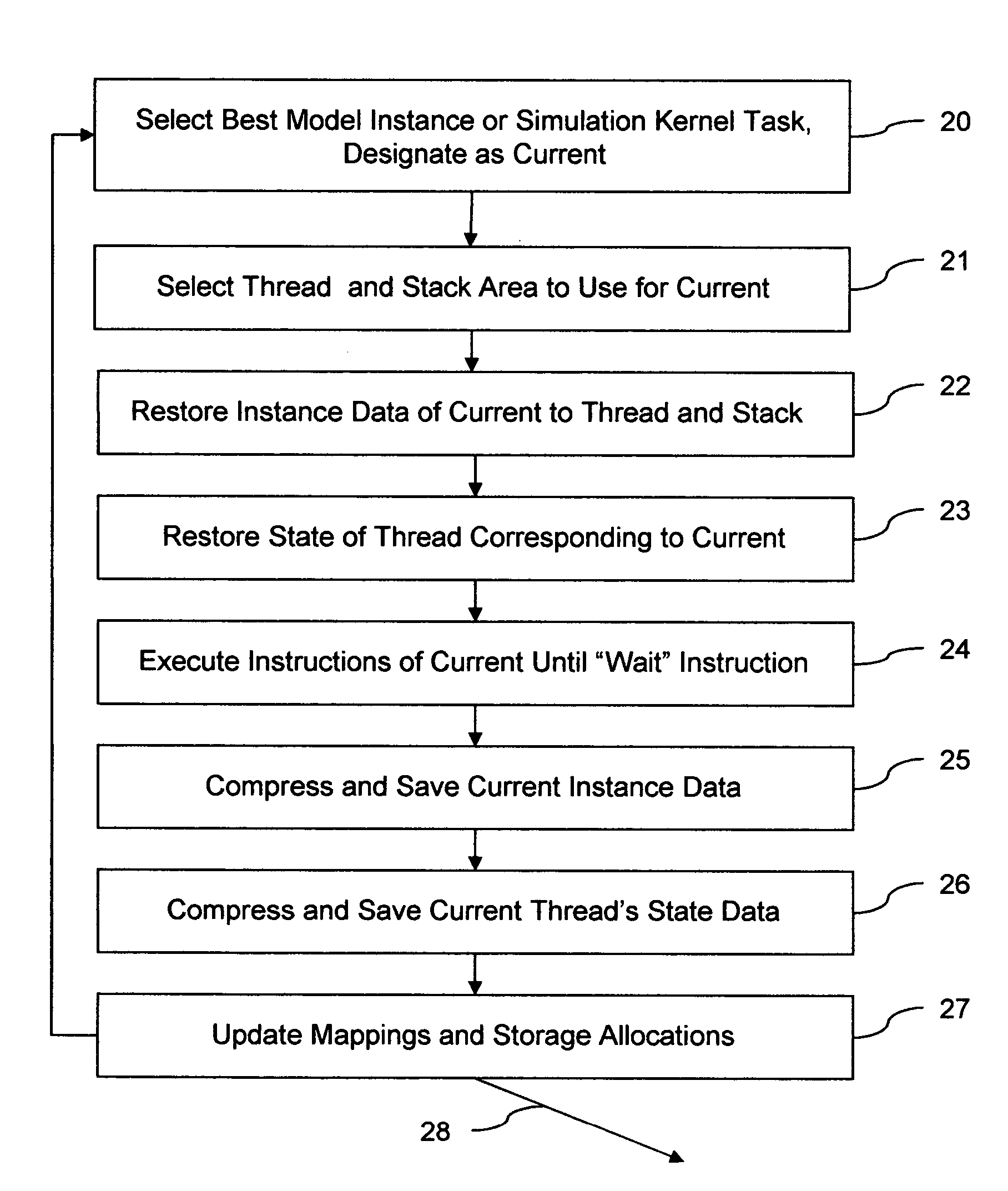

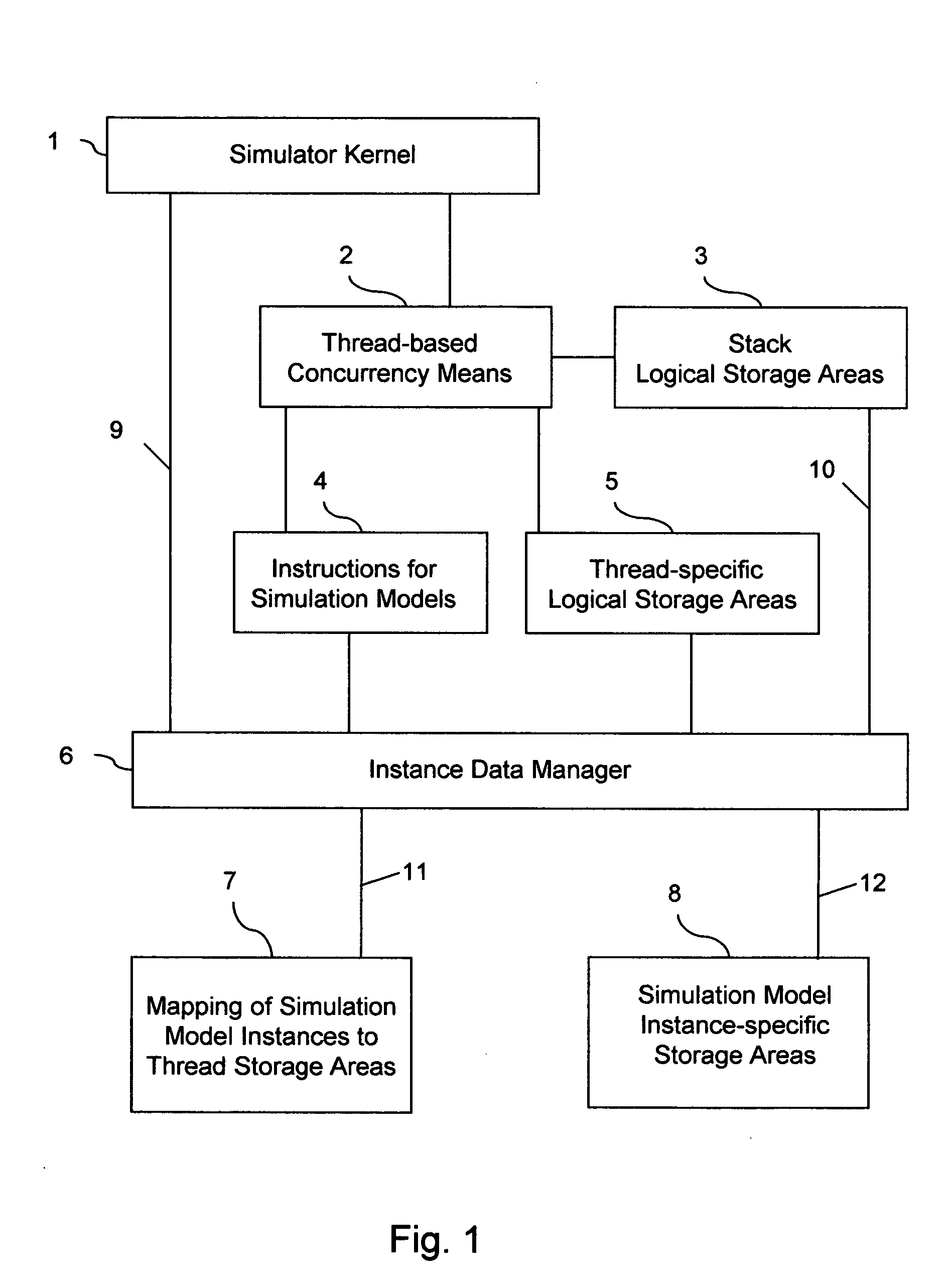

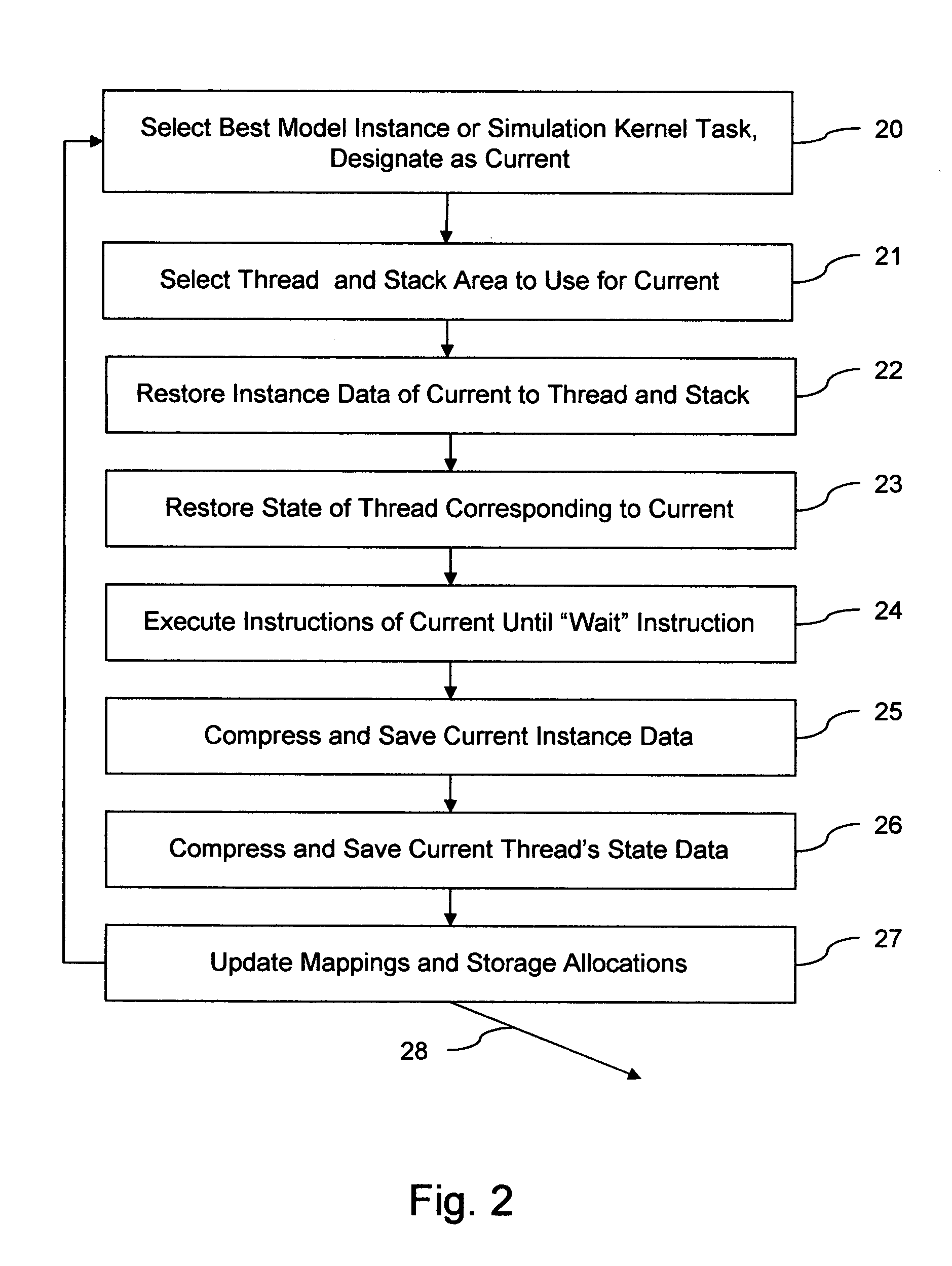

Method and machine for efficient simulation of digital hardware within a software development environment

InactiveUS20050066305A1Reducing CPU branch mis-predictionEasy to useCAD circuit designSpecial data processing applicationsSoftware development processParallel computing

The invention provides run-time support for efficient simulation of digital hardware in a software development enviromnent, facilitating combined hardware / software co-simulation. The run-time support includes threads of execution that minimize stack storage requirements and reduce memory-related run-time processing requirements. The invention implements shared processor stack areas, including the sharing of a stack storage area among multiple threads, storing each thread's stack data in a designated area in compressed form while the thread is suspended. The thread's stack data is uncompressed and copied back onto a processor stack area when the thread is reactivated. A mapping of simulation model instances to stack storage is determined so as to minimize a cost function of memory and CPU run-time, to reduce the risk of stack overflow, and to reduce the impact of blocking system calls on simulation model execution. The invention also employs further memory compaction and a method for reducing CPU branch mis-prediction.

Owner:LISANKE ROBERT JOHN

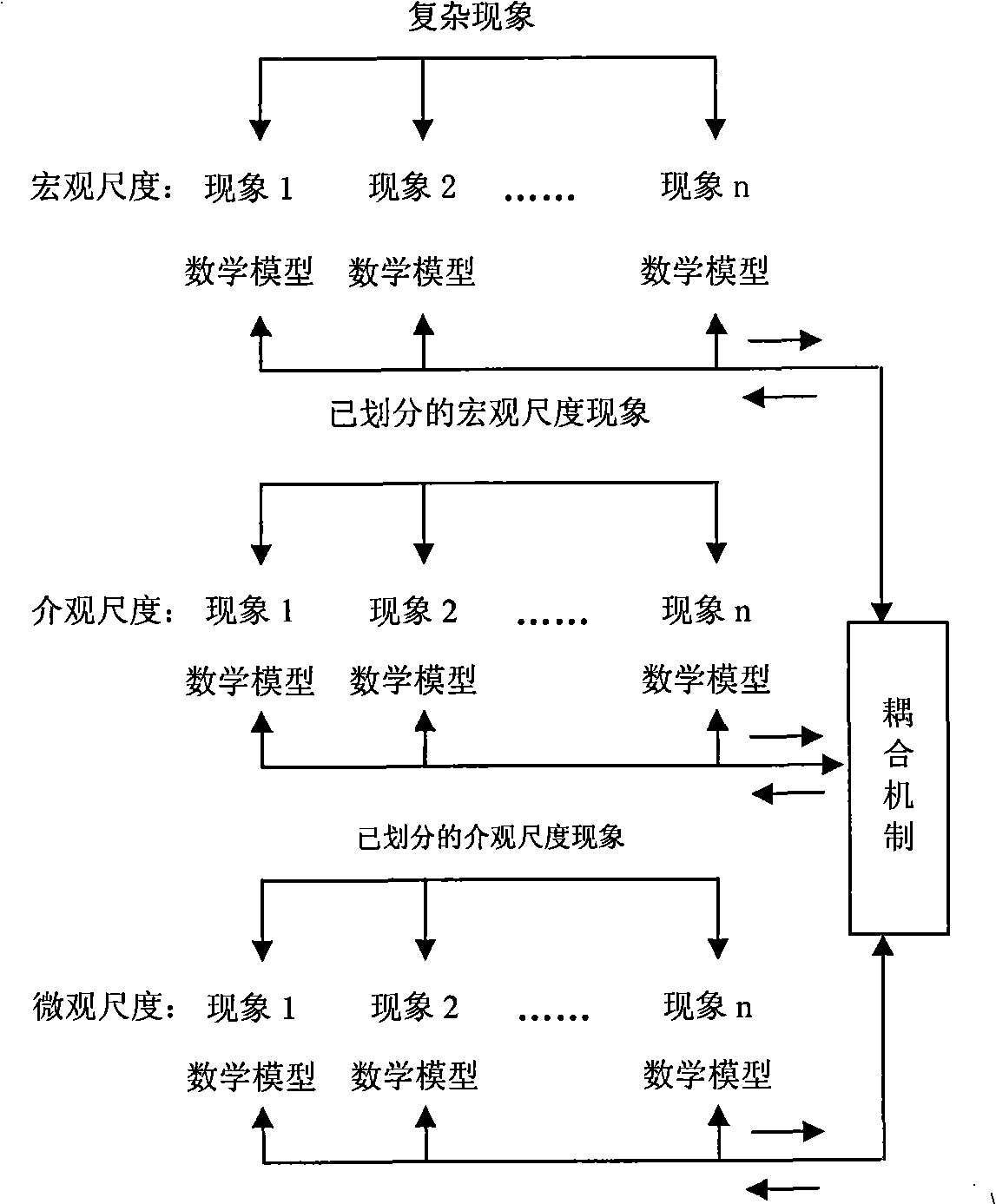

Multi-dimension analogy method of solid-oxide fuel battery

InactiveCN101324908AEnable multiscale simulationsImprove accuracySpecial data processing applicationsElectrochemical responseScale model

The invention relates to a multi-scale simulation method for solid oxide fuel cells, and is characterized in that the method conducts multi-scale simulation from the mesoscopic scale to the macro equipment scale for complex physical and chemical phenomenon, such as coupled heat calorie transmission, electrochemical reaction in the solid oxide fuel cells, etc. The invention further relates to an integration and co-simulation method of a multi-scale model. Because a modeling method provided by the invention adopts the modeling method by mechanism from the macro-scale based on the phenomenon, the model has the advantages of clear physical meaning, high accuracy and strong adaptability. A simulation method is adopted between the mesoscopic scale and the macro equipment scale based on molecules or molecular clusters, thereby compensating for a deficiency of traditional single scale simulation. Layered method and the method of different scales are combined to study the complex system, so as to be conducive to disclosing the nature of complex systems, such the solid oxide fuel cells and provide a novel means for studying complex the systems.

Owner:CHONGQING UNIV

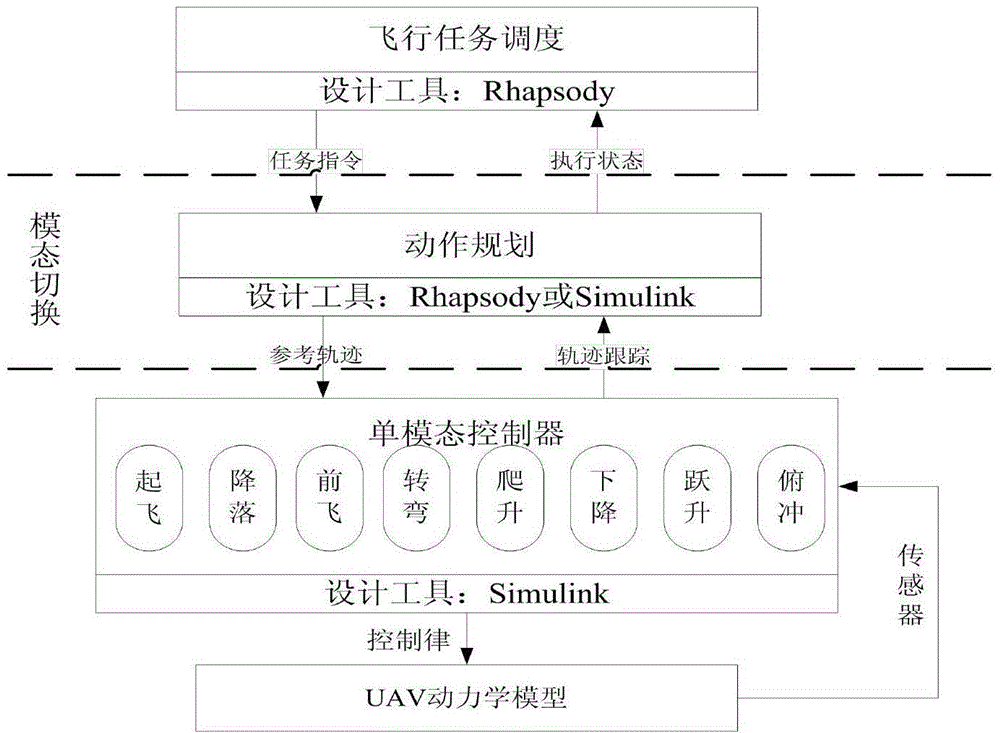

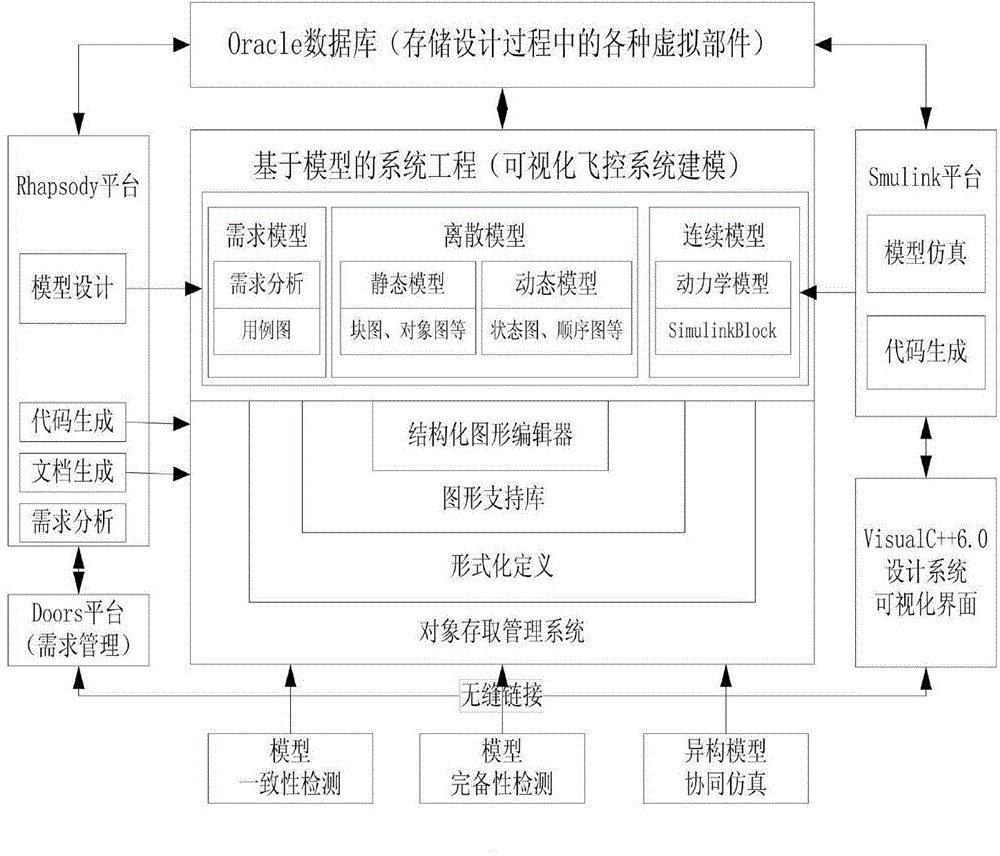

Designing method for multimode control system of aircraft

InactiveCN104573182AShorten the development cycleReduce design costSpecial data processing applicationsSystems designSoftware system

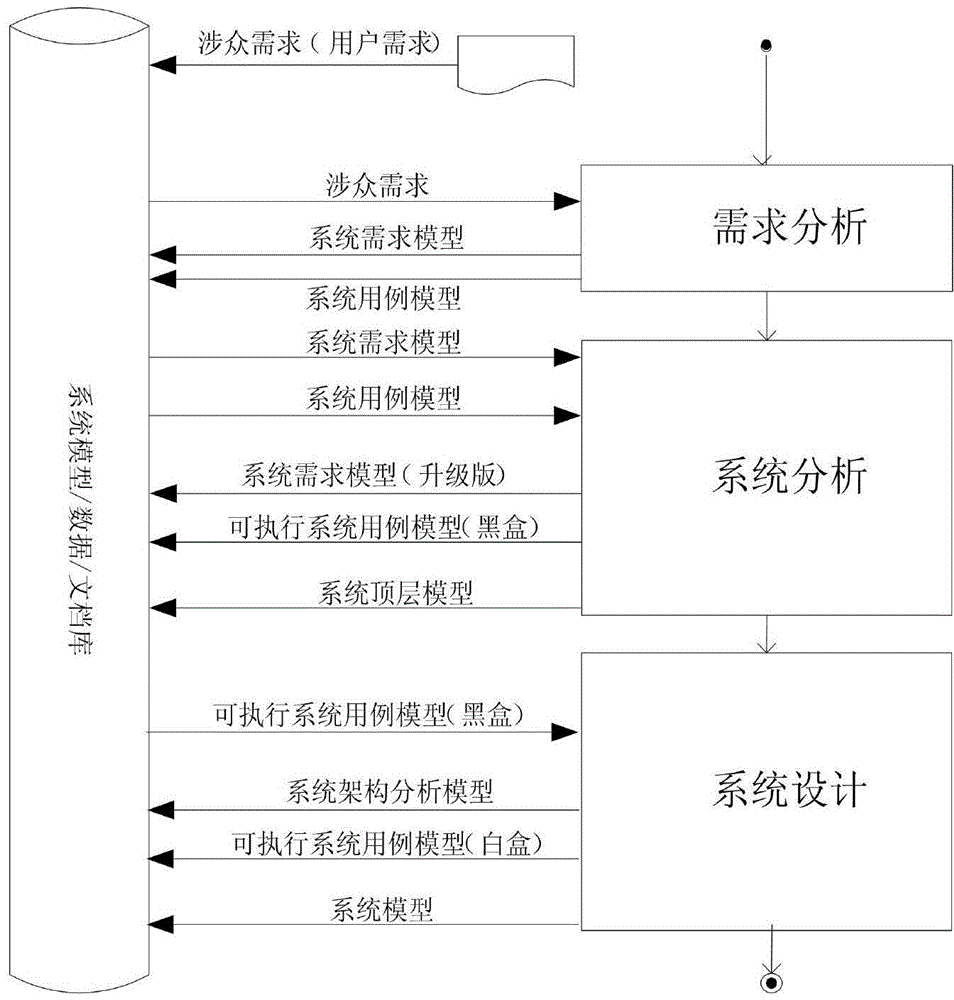

The invention discloses a designing method for a multimode control system of an aircraft. The designing method comprises demand analysis, system analysis and system designing stages, and is characterized in that the demand analysis, and management and confirmation data are from user demand (stakeholder demand) knowledge base; output data is a demand confirmed by an aircraft system and serves as one of system analysis inputs of the aircraft system; the input data of mode switching design at the system design stage is from a control mode conforming with tactics design and tactics type needs; output data are a mode switching controller conforming with the tactics need; co-simulation and verification at the system design stage refers to that co-simulation is performed on isomerism models of an aircraft control system in the fields of machines, hydraulic and the like in a built simulation environment. According to the method, the functional, physical and software system structure of the system can be defined, and demand capturing of the system and system analysis can also be supported.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

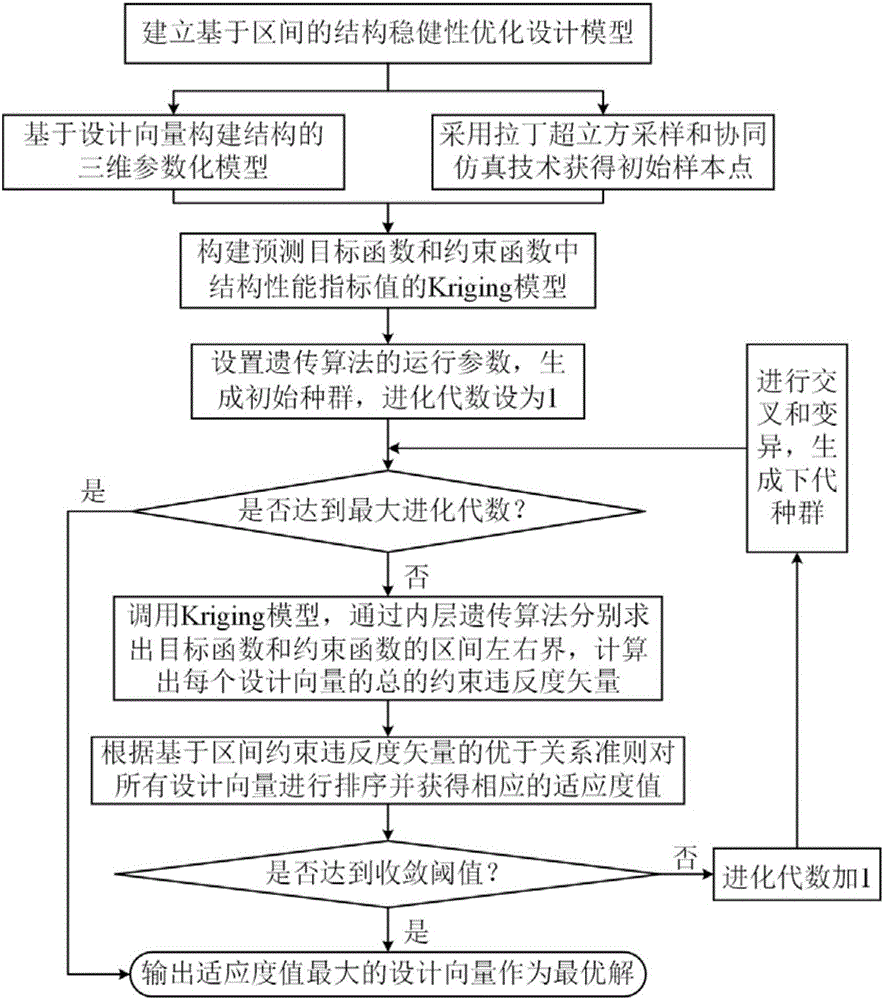

Structure robustness optimization design method containing interval parameter uncertainty

ActiveCN106096127AAvoid lossImprove effectivenessGeometric CADSpecial data processing applicationsEvolution algebraAlgorithm

The invention discloses a structure robustness optimization design method containing interval parameter uncertainty. The method comprises the following steps that a structure robustness optimization design model based on an internal is built; sample points are obtained by adopting a Latin hypercube sampling and co-simulating technique; a Kriging proxy model for predicting a target function and a constraint function is constructed; an interval robustness optimization design model is solved by adopting a double layer-nested genetic algorithm, left boundaries and right boundaries of the target function and the constraint function are calculated in the inner layer of the genetic algorithm, and in the outer layer of the genetic algorithm, total interval constraint violation degree vectors of all design vectors are calculated, and the feasibility of the total interval constraint violation degree vectors is judged; all the design vectors are subjected to advantage and disadvantage sorting according to a superior relationship criterion based on the interval constraint violation degree vectors; when a largest evolution algebra or convergence threshold value is achieved, the optimal solution of the robustness optimization design model is output, and the structure robustness optimization design containing interval parameter uncertainty is achieved.

Owner:ZHEJIANG UNIV

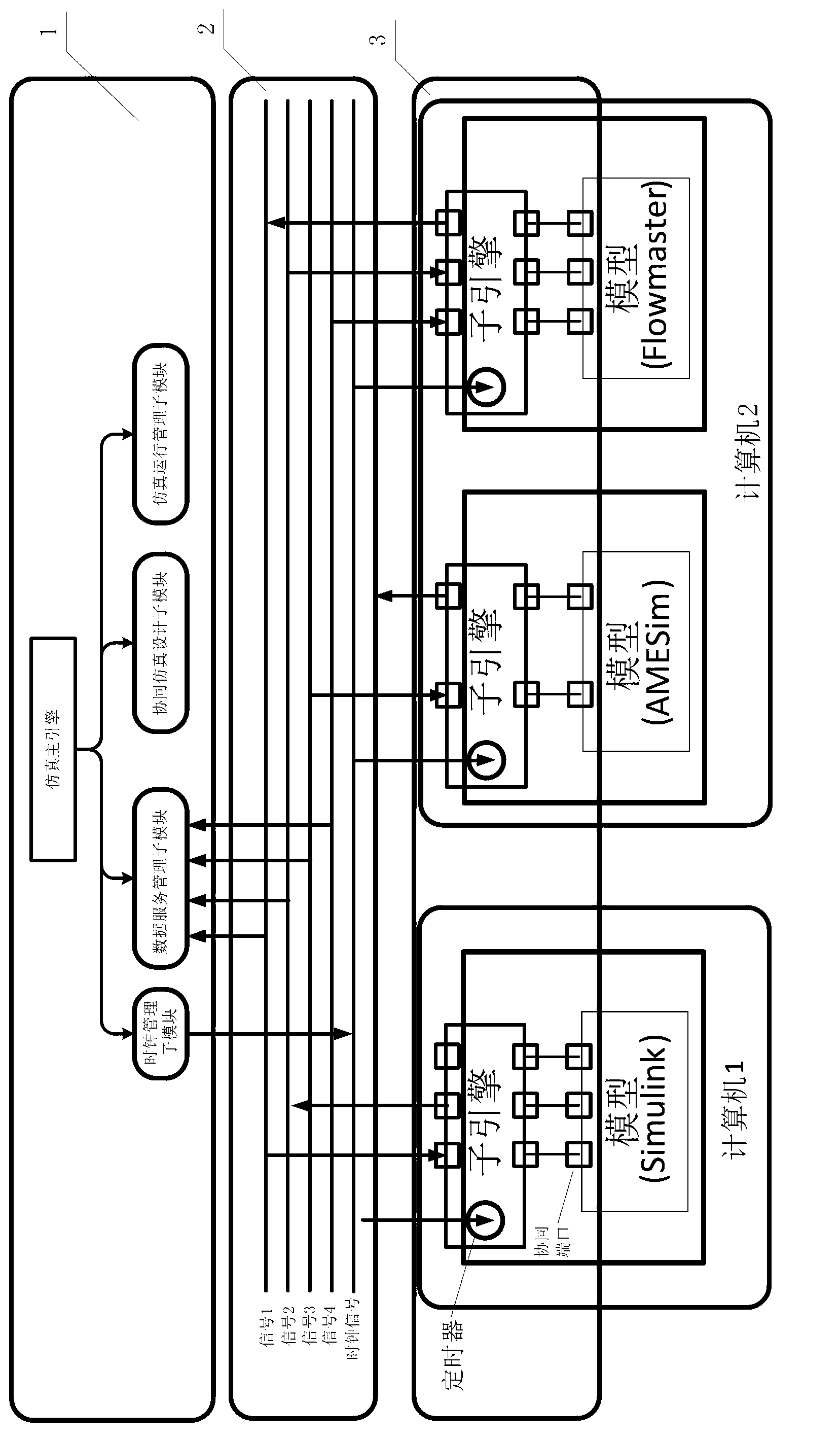

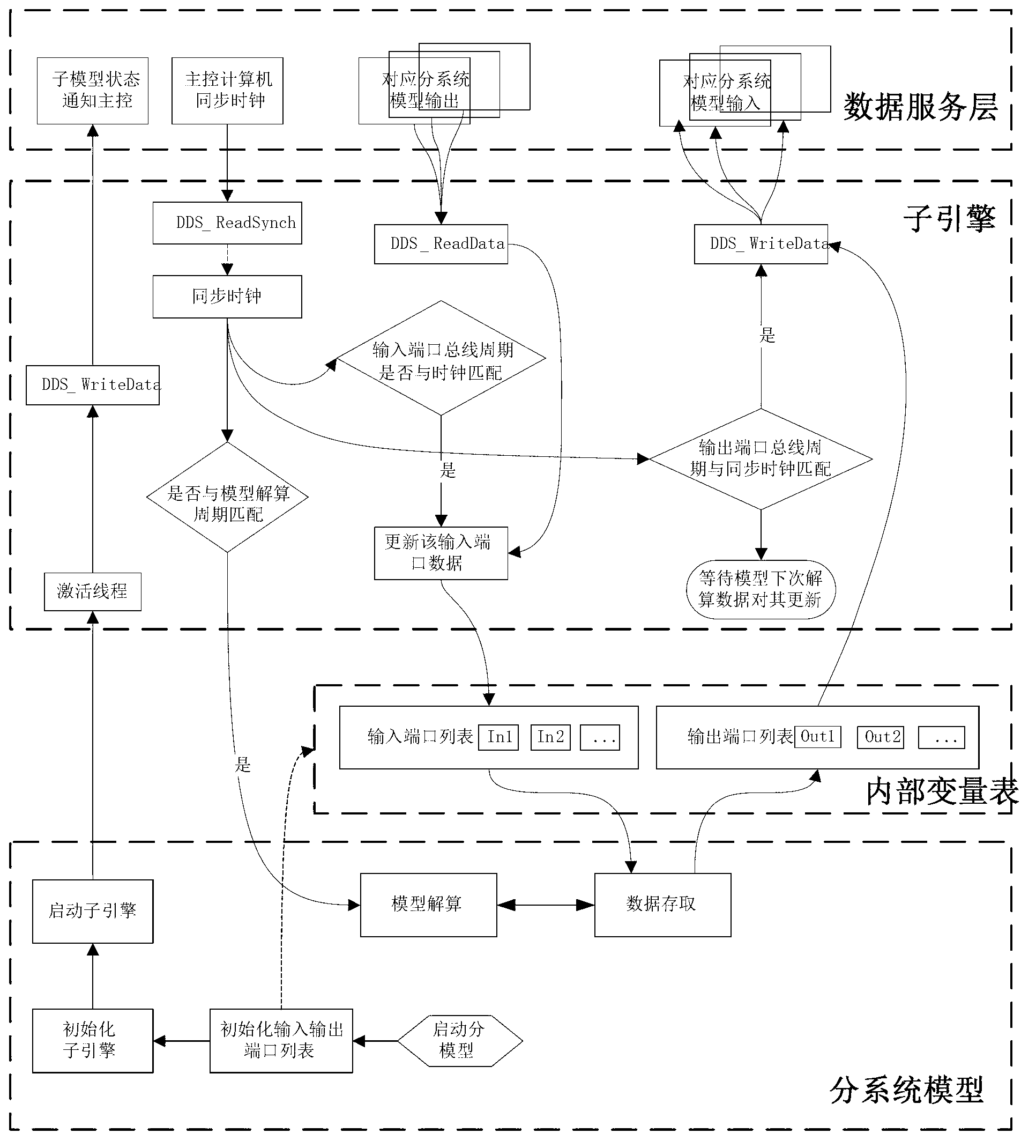

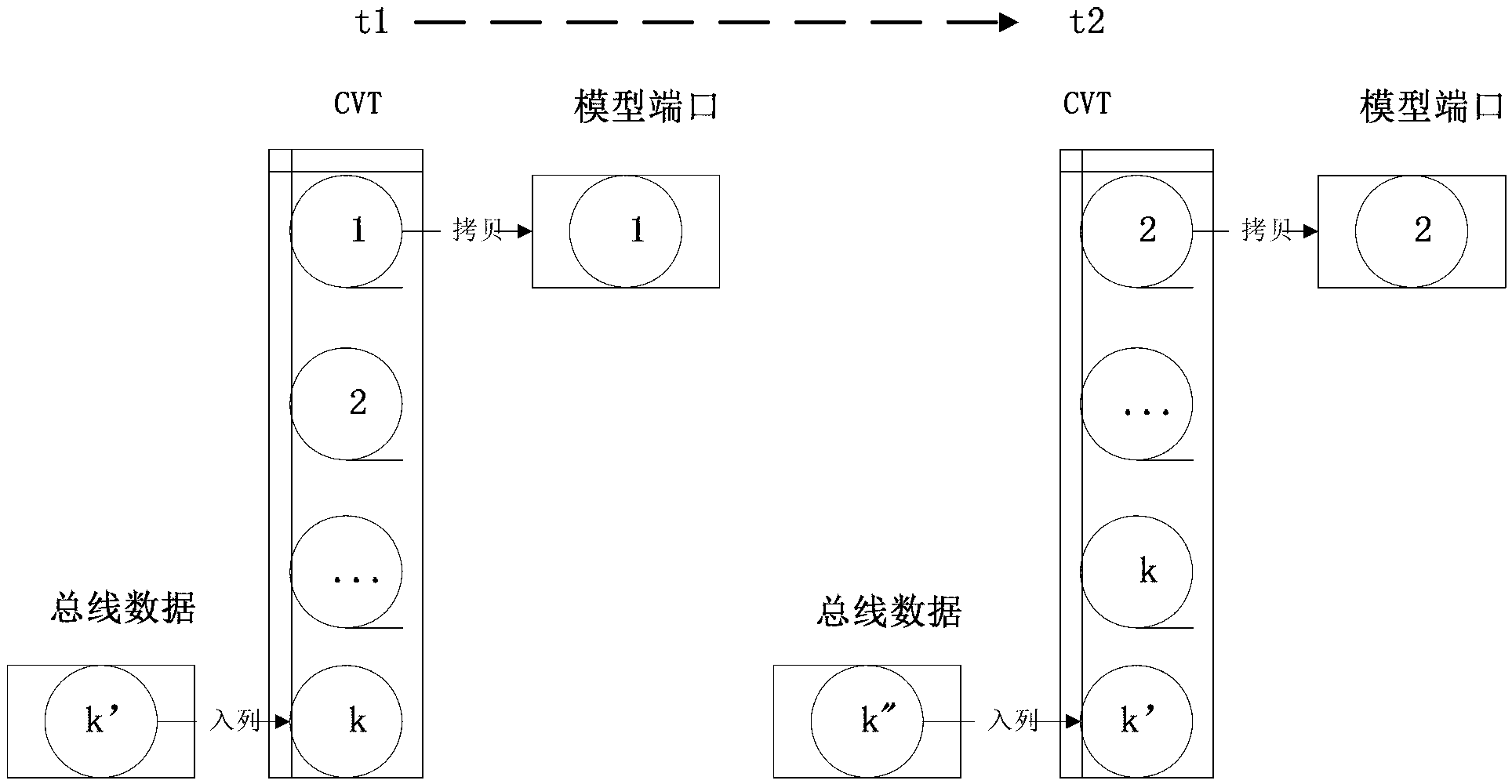

Multi-domain collaborative distribution type simulation system

InactiveCN102982197AEasy to implementEasy to join dynamicallySpecial data processing applicationsFundamental frequencyPaper document

The invention provides a multi-domain collaborative distribution type simulation system comprising a main control module, a data service module and a model interface module. The main control module is used for loading description documents of a preset model to obtain corresponding model information, setting clock fundamental frequency according to the model information, issuing the clock fundamental frequency and simulation control demands, arranging data transmission channels between the models in the data service module according to the model information, and defining data update periods of data channels. The data service module is used for establishing a data link which has an independent data transmission period, and providing the data channels for collaborative distribution type simulation data. The model interface module is used for establishing a connection relationship and schedule management of the main control module and a simulation sub-engine, and sending the clock fundamental frequency and the simulation control demands to the simulation sub-engine to complete calculation of the corresponding models. The multi-domain collaborative distribution type simulation system supports derivation of all simulation soft wares, and has the advantages of being high in calculation precision of collaborative simulation and high in calculation efficiency, and collaborative simulation is not prone to be caused.

Owner:北京华力创通科技股份有限公司

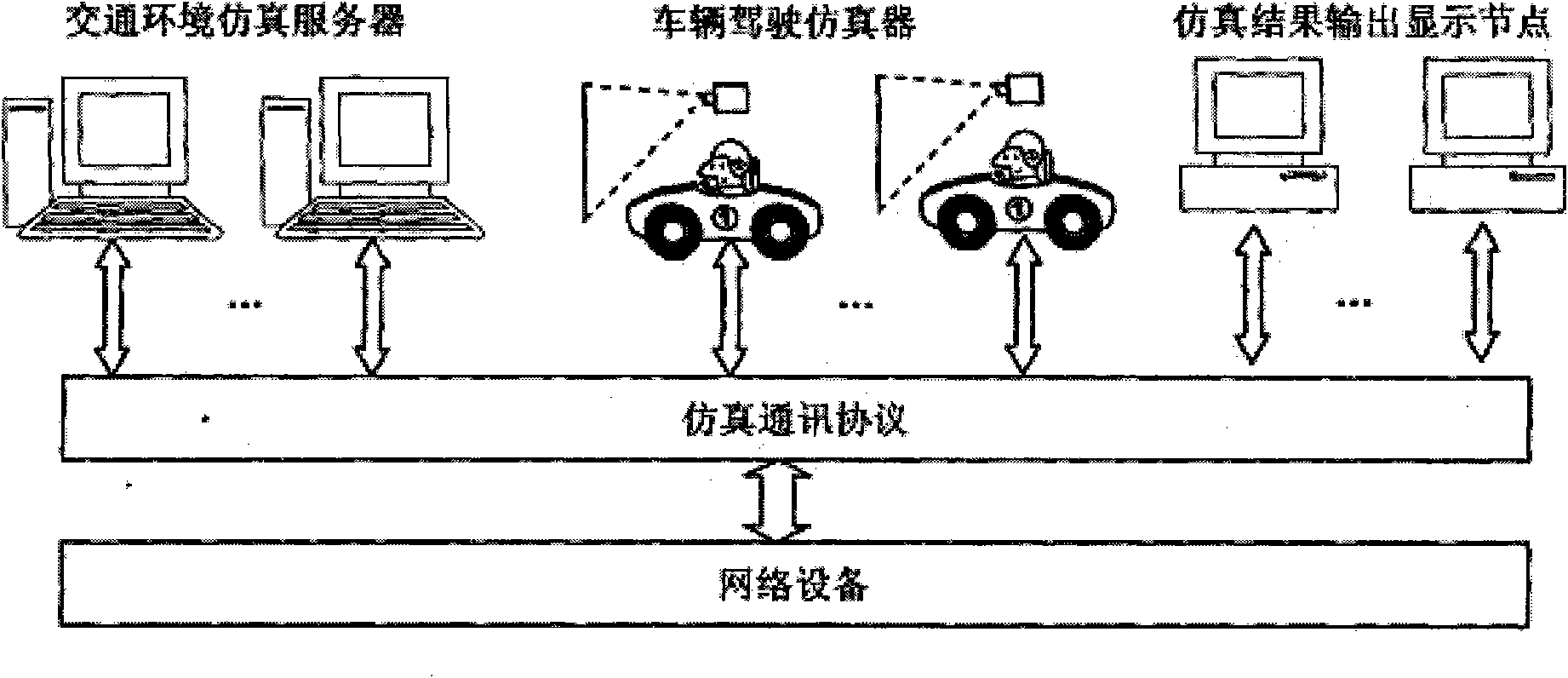

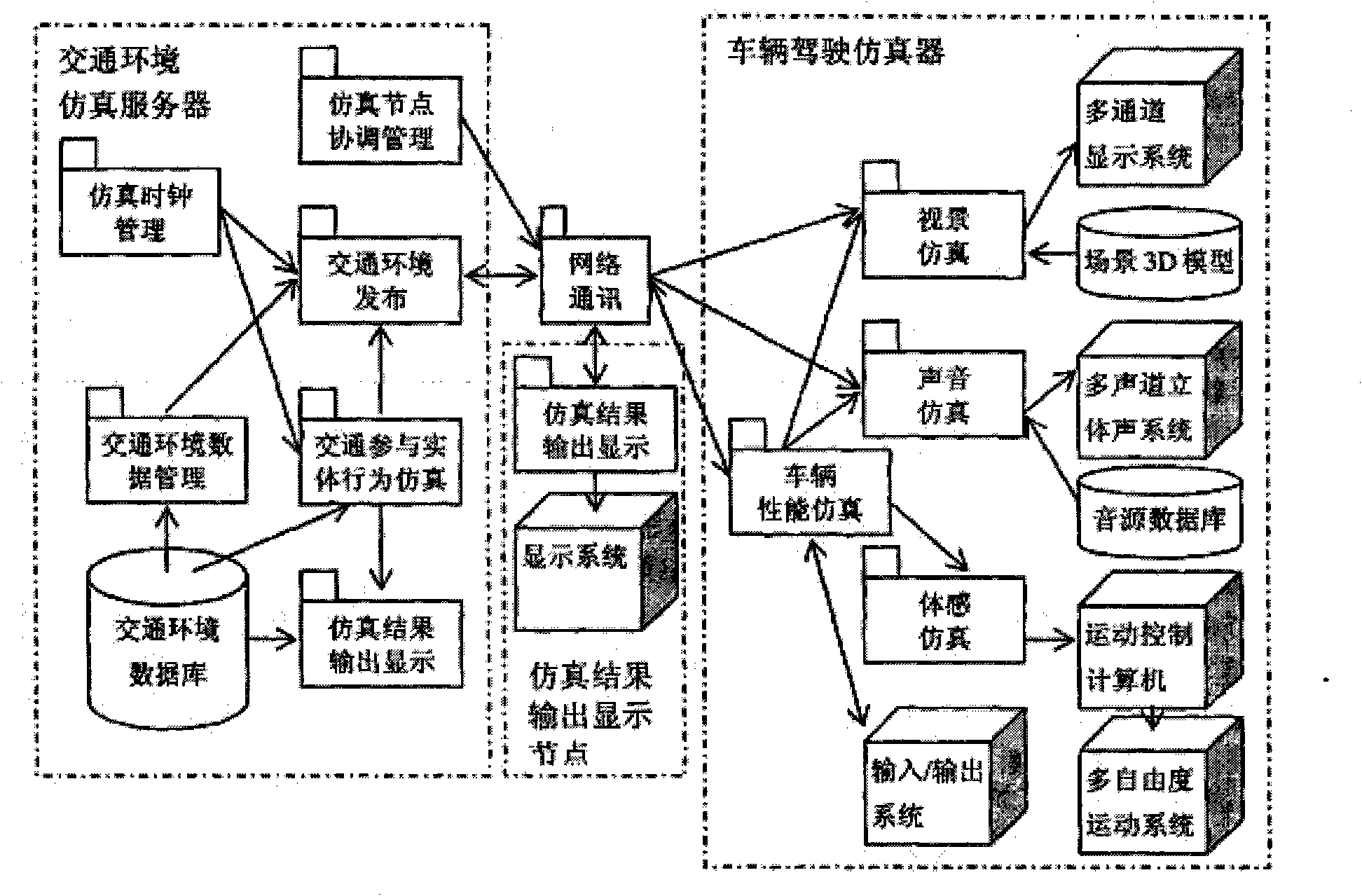

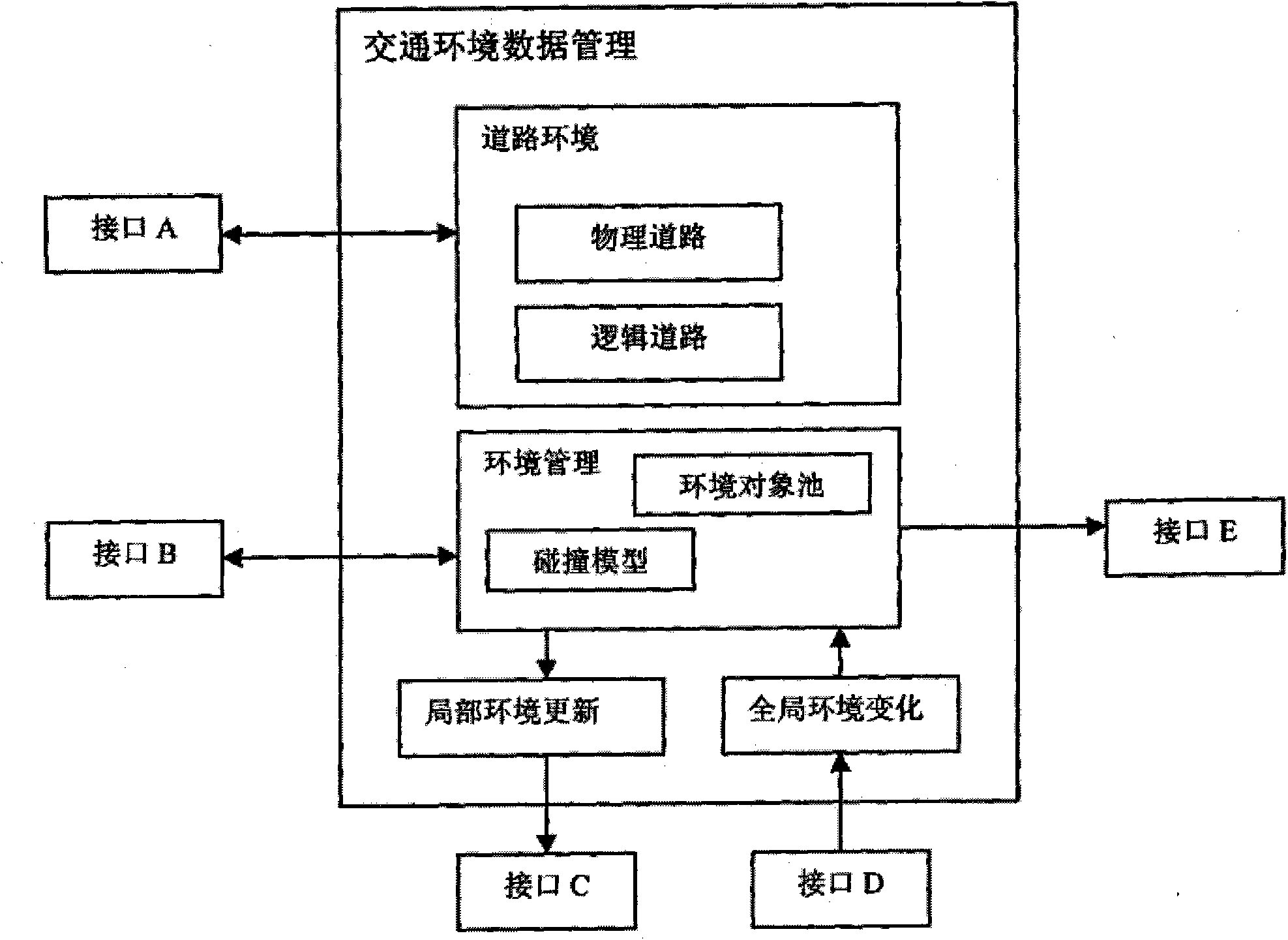

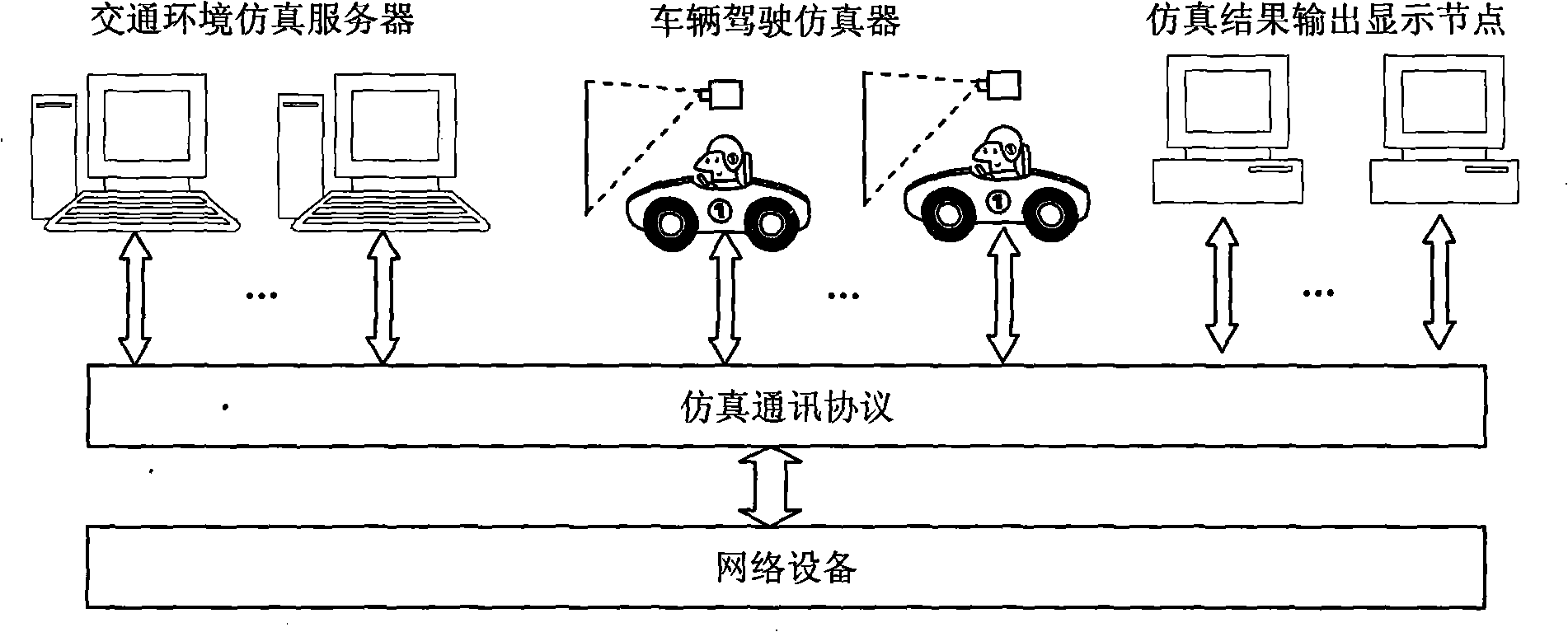

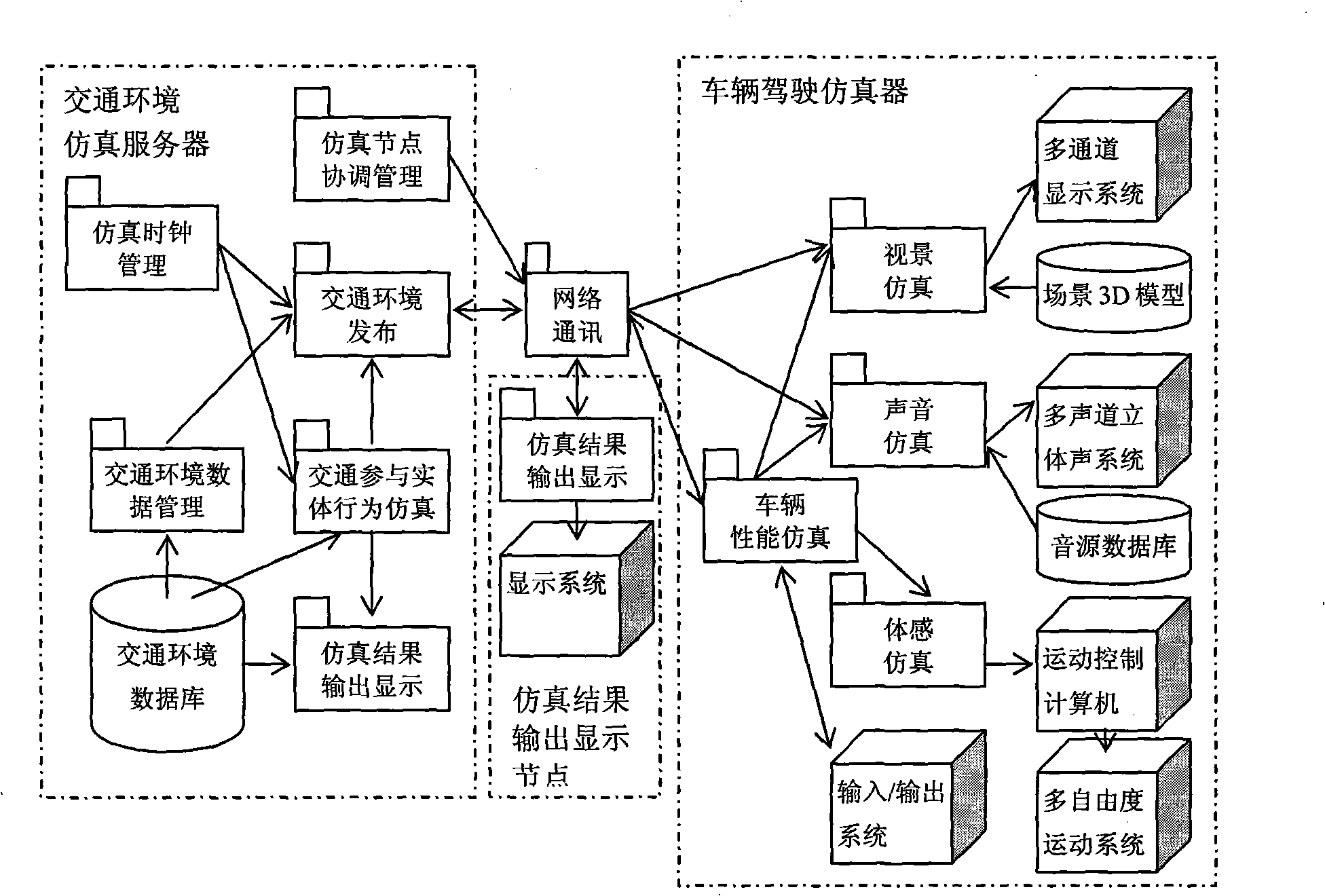

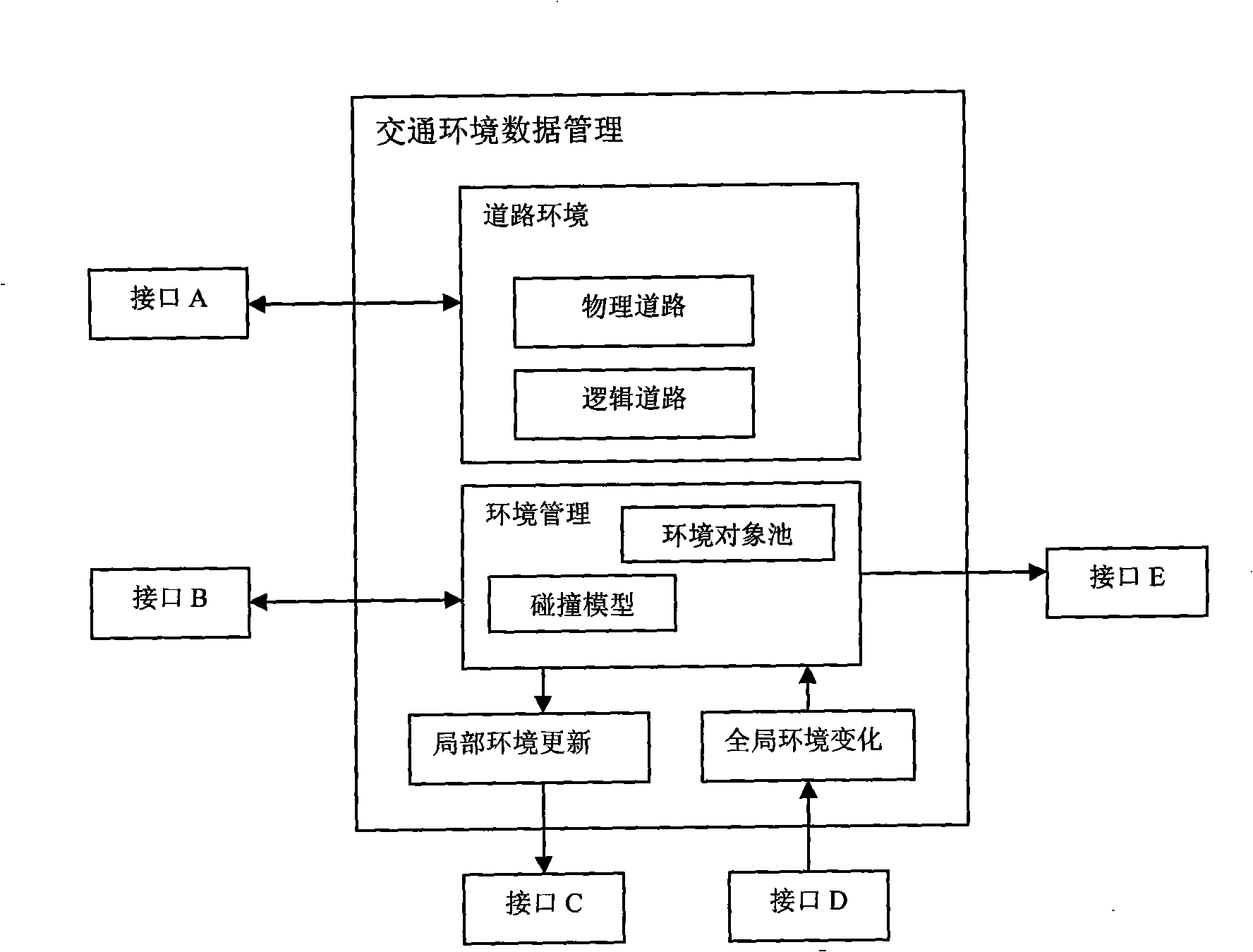

Interactive traffic simulation system

InactiveCN102467589AEnable co-simulationFlexible structureRoad vehicles traffic controlSpecial data processing applicationsCo-simulationTraffic simulation

The invention aims to provide an interactive traffic simulation system with a distributed system structure, which is a novel traffic-driving hybrid simulation system. The core is that: a returning vehicle driving simulator for a person serves as a traffic participation entity and is introduced into the traffic simulation system. The vehicle driving simulator serving as the traffic participation entity controlled by a user driving behavior and a virtual traffic participation entity generated in the traffic simulation system interact and participate traffic simulation calculation together so as to realize cooperative simulation of a plurality of vehicle driving simulators and a plurality of traffic environment simulation servers in the same virtual traffic environment. The invention has the characteristics that: the traffic simulation system has a flexible structure, is convenient to expand, supports man-machine interaction and is high in simulation confidence, and the like; and the system can be used in the fields of traffic simulation and driving simulation and can provide a novel platform for research and application in the fields of driving behaviors, driving psychology, traffic safety, intelligent transportation, road and bridge design and the like.

Owner:上海日浦信息技术有限公司

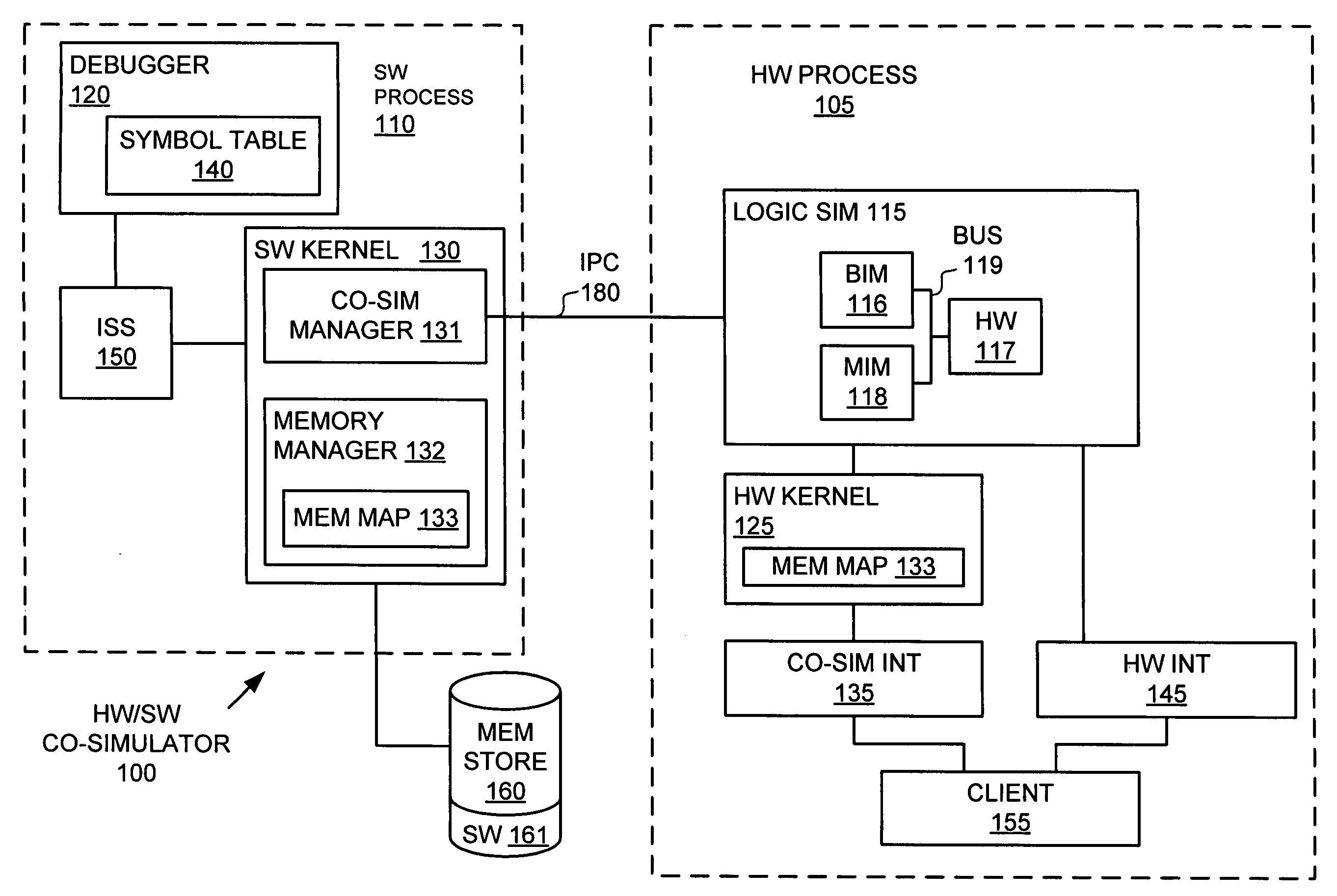

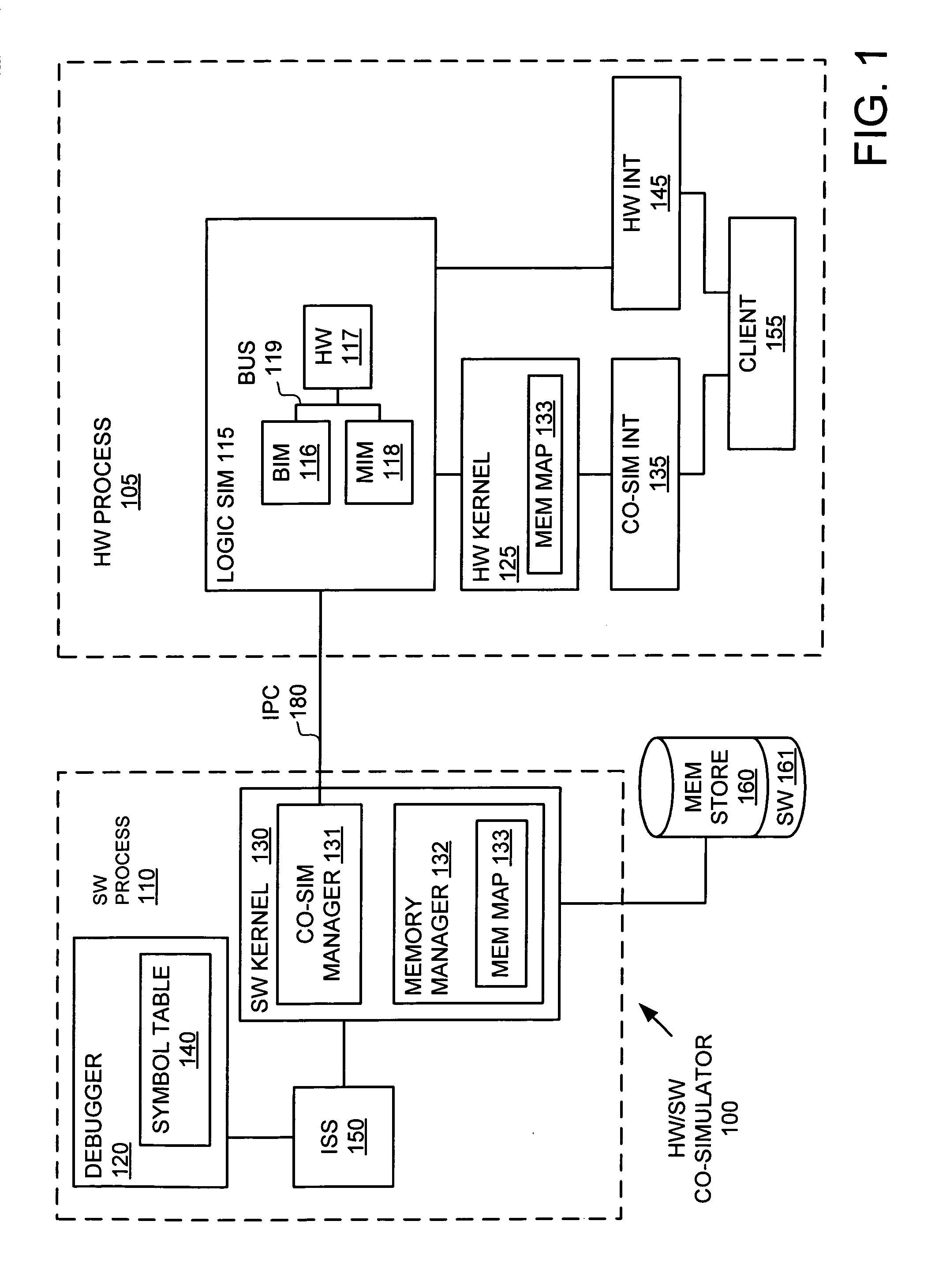

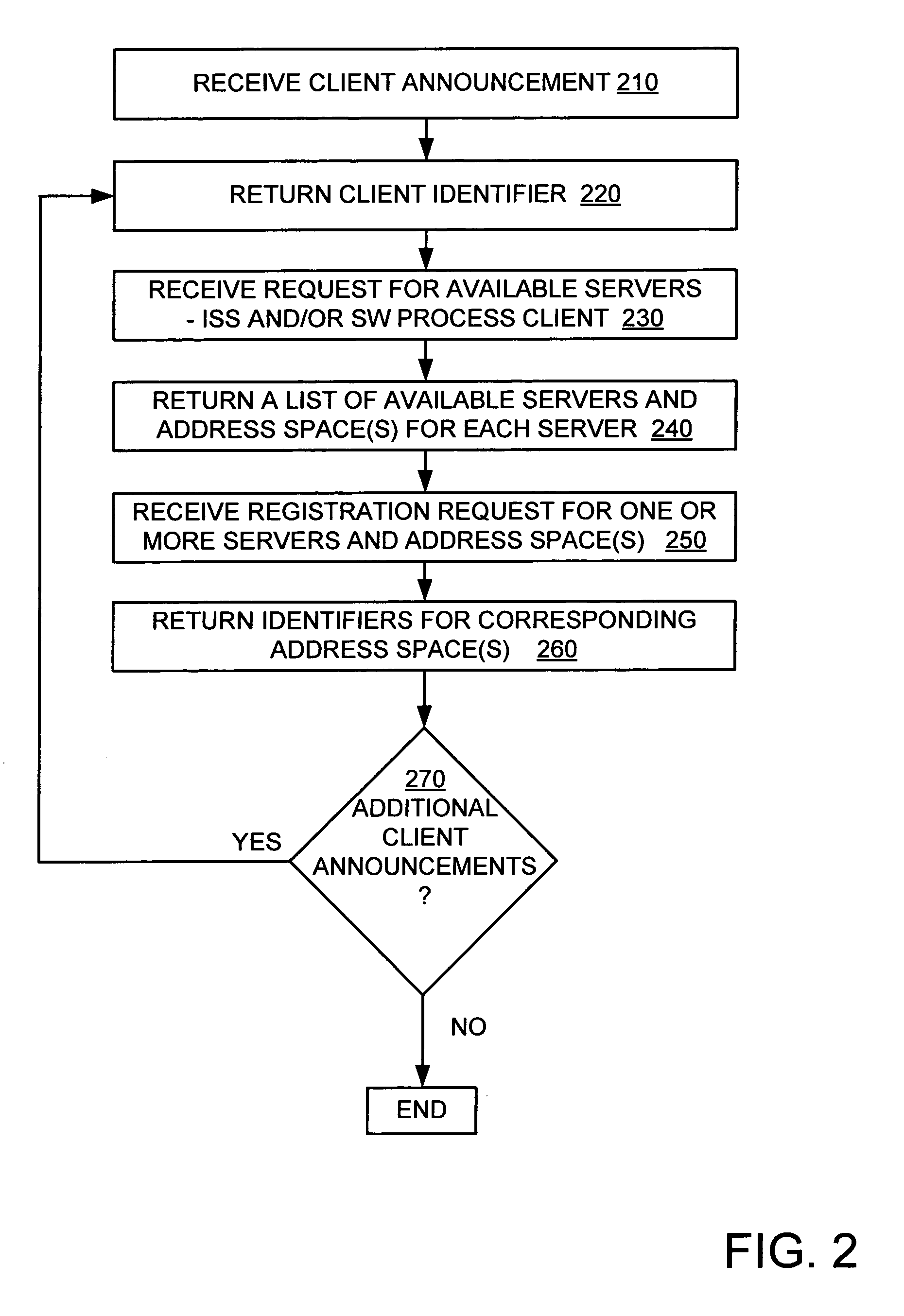

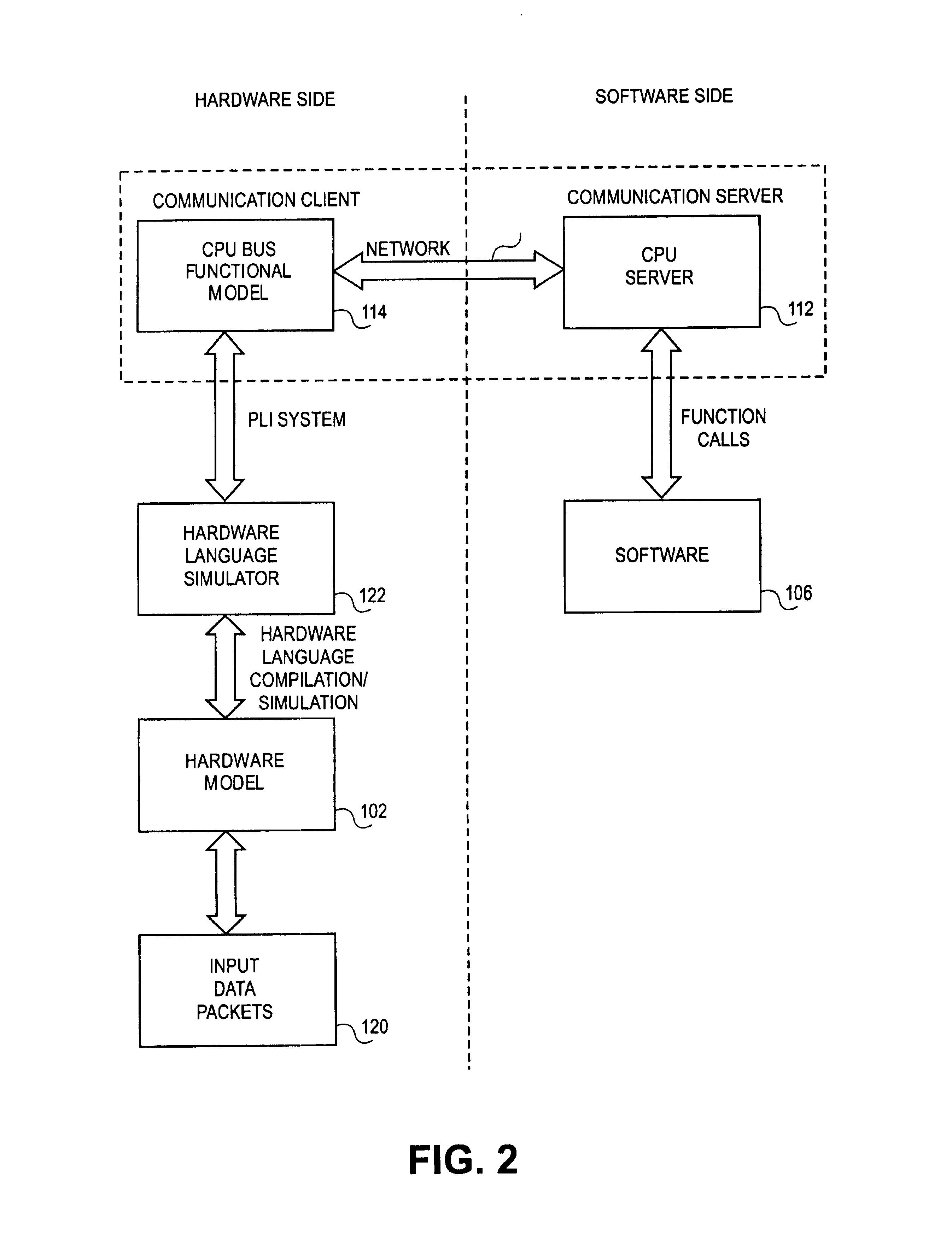

Accessing state information in a hardware/software co-simulation

InactiveUS7072820B1Analogue computers for electric apparatusCAD circuit designCo-simulationClient-side

A hardware / software co-simulation permits access to a server state from any process in the hardware / software co-simulation. In one embodiment, a co-simulation interface receives a request from a client system for configuration data for the server state in of the hardware / software co-simulation. The configuration data defines memory locations in the co-simulation from which the server state can be assembled. The interface inserts the request in the co-simulation. The co-simulation responds with the configuration information. Based on the configuration information, memory operations can be performed on the server state.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

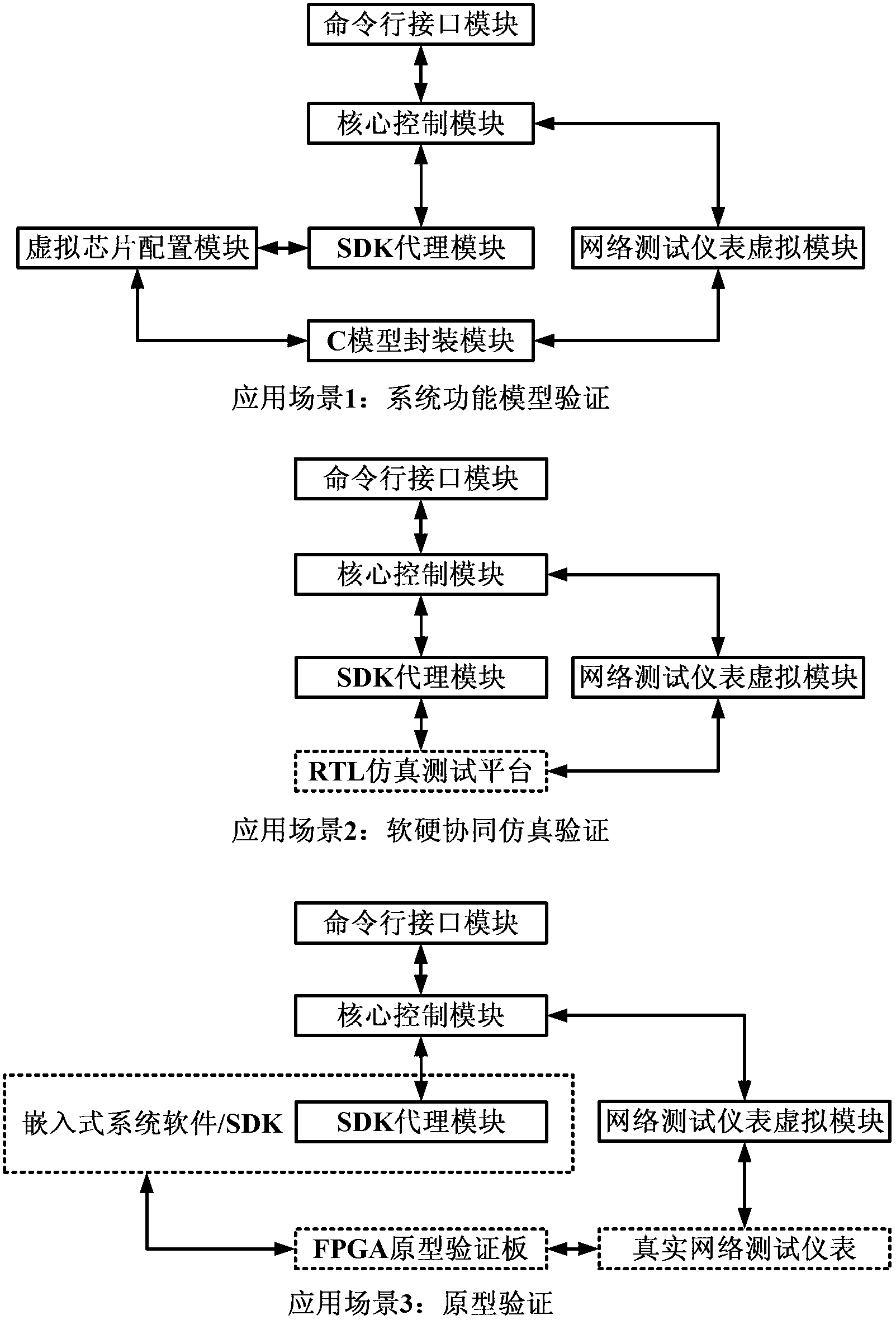

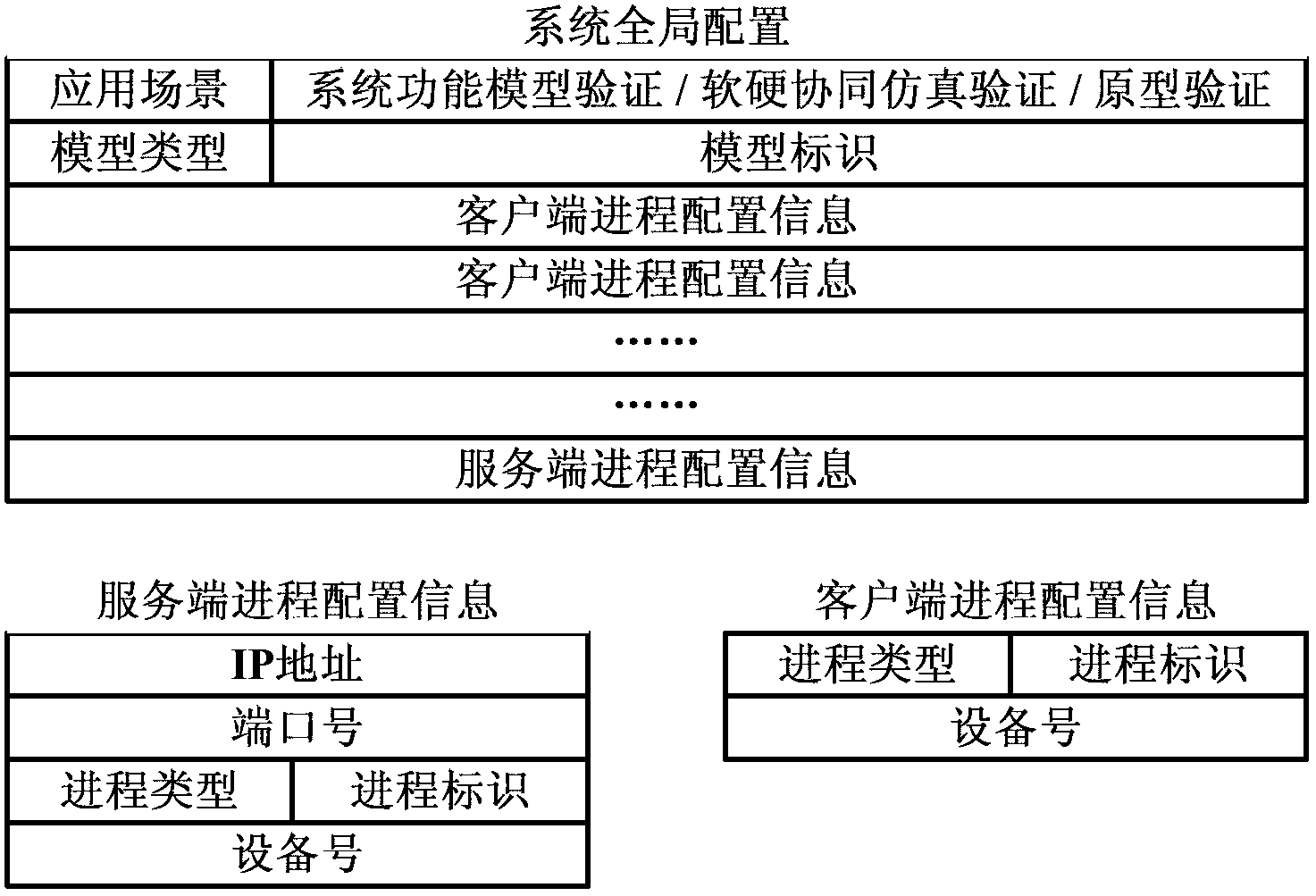

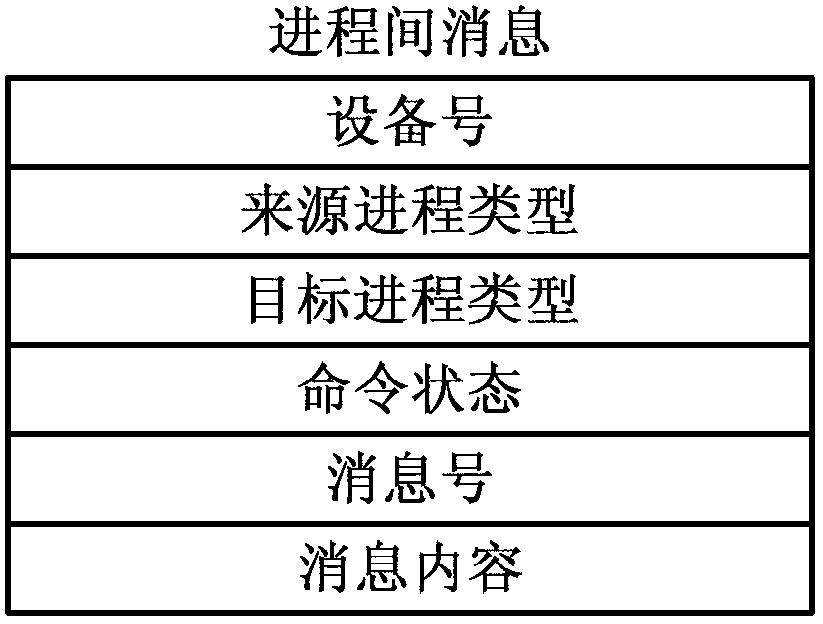

Distributed packet-switching chip model verification system and method

ActiveCN103178996AReduce verification convergence timeGood effectData switching networksCommand-line interfaceValidation methods

The invention discloses distributed packet-switching chip model verification system and method and relates to the field of designing packet processing chips. The system comprises a core control module, a command line interface module, an SDK (software development kit) proxy interface module, a virtual network test meter module, a virtual chip configuration module and a C model package module. The core control module is a server program module. The command line interface module, the SDK proxy interface module, the virtual network test meter instrument, the virtual chip configuration module and the C model package module are client program modules. The system is a C / S / C (client / server / client) structured distributed system supporting three application scenarios, namely, system function model verification, software-hardware cooperated simulation verification and prototype verification. Modules required for different application scenarios are different. Verification closure time of the functions of the system at different levels can be shortened greatly, development efficiency is increased, and debugging cost is lowered.

Owner:武汉二进制半导体有限公司

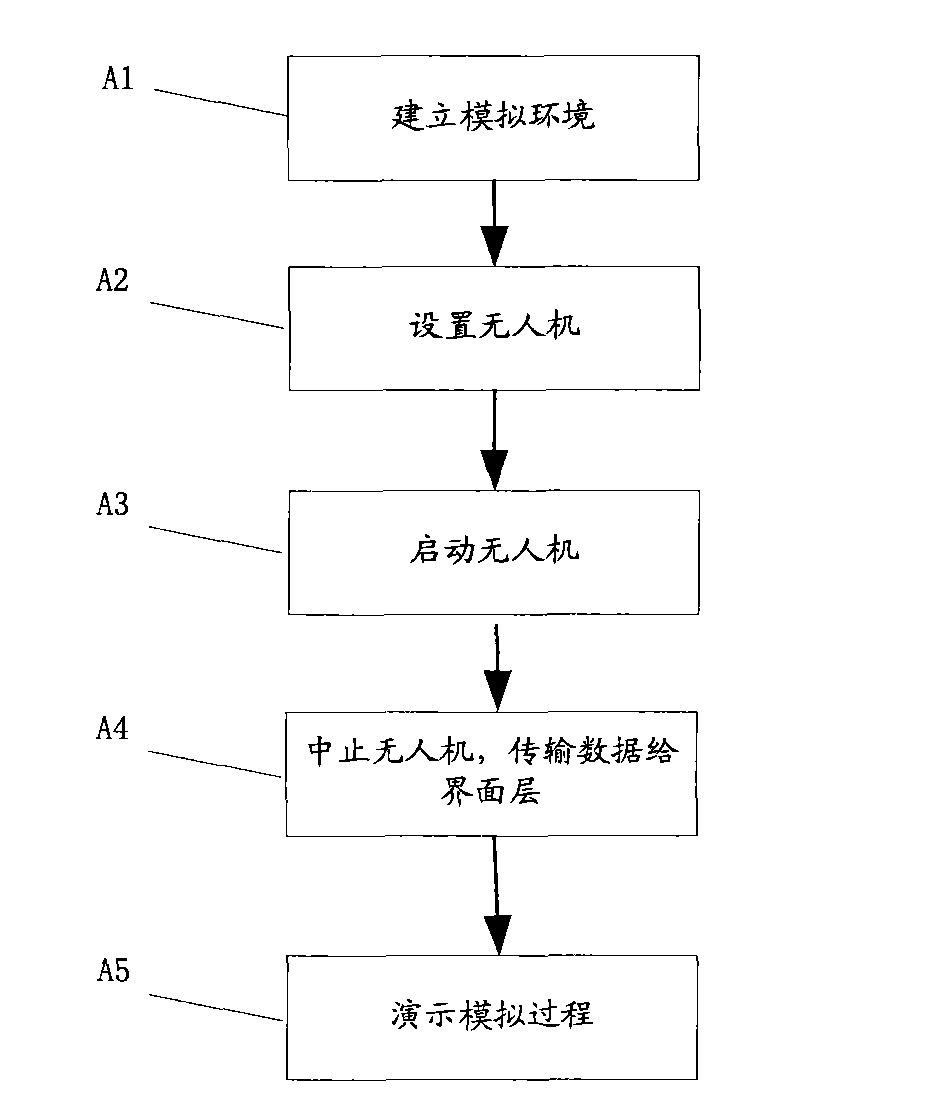

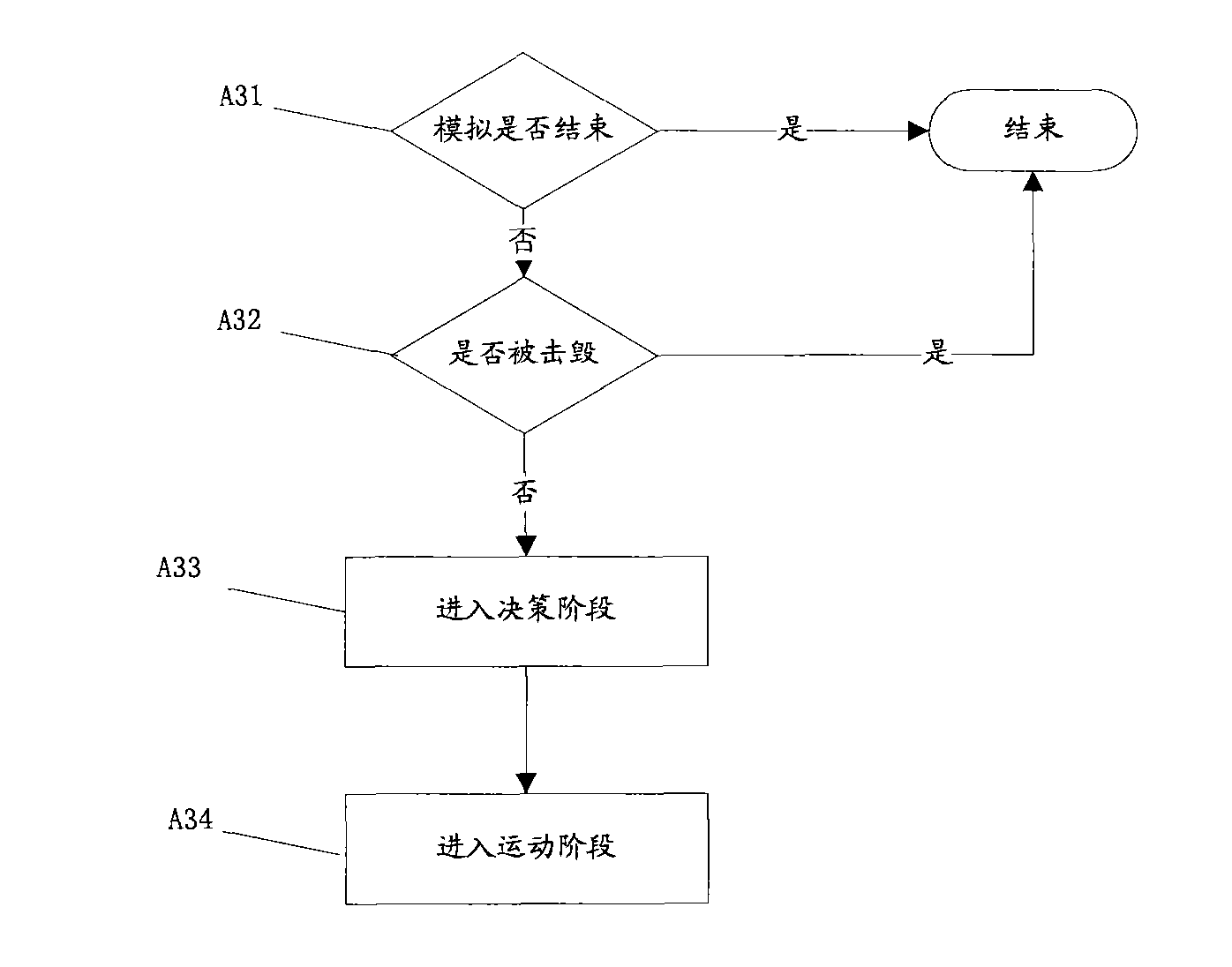

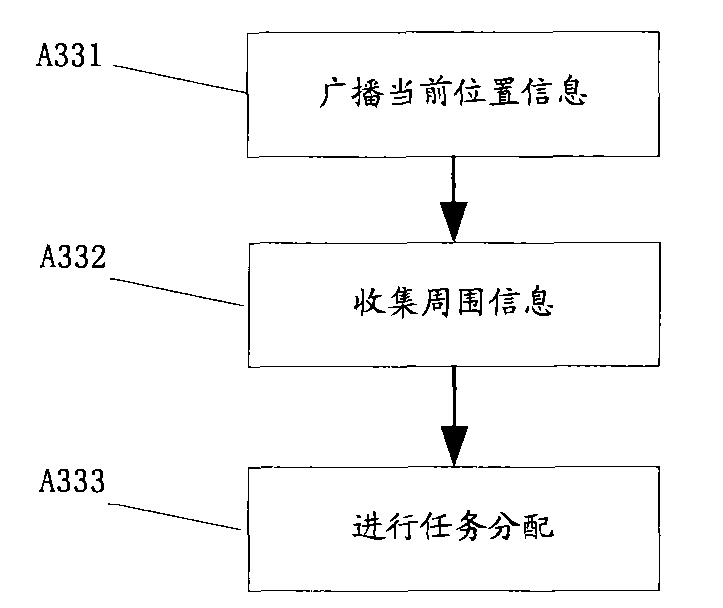

Unmanned co-simulation platform control method and system under no-center environment

The invention provides an unmanned co-simulation platform control method under no-center environment, which comprises the following steps of: A1) establishing a simulation environment according to a simulation configuration file; A2) setting an unmanned machine according to the simulation configuration file; A3) starting the unmanned machine, and periodically acquiring state data of all unmanned machines by using tuple space communication of no-center nodes; A4) stopping the operation of the unmanned machine, and transmitting the acquired state data of all the unmanned machines to an interface layer in a frame form; and A5) demonstrating the whole simulation process through the interface layer. An unmanned co-simulation platform control system comprises an interface layer module, a control platform module, an unmanned machine design module, an algorithm module and a communication module. By using the communication between the unmanned machines in the tuple space, the platform has better expansibility.

Owner:TSINGHUA UNIV

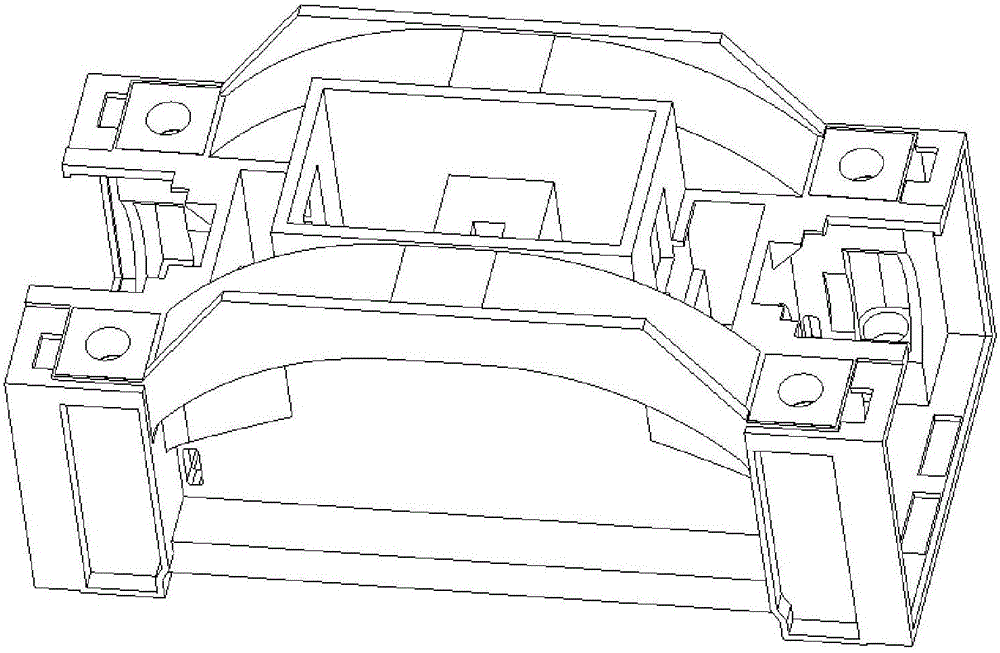

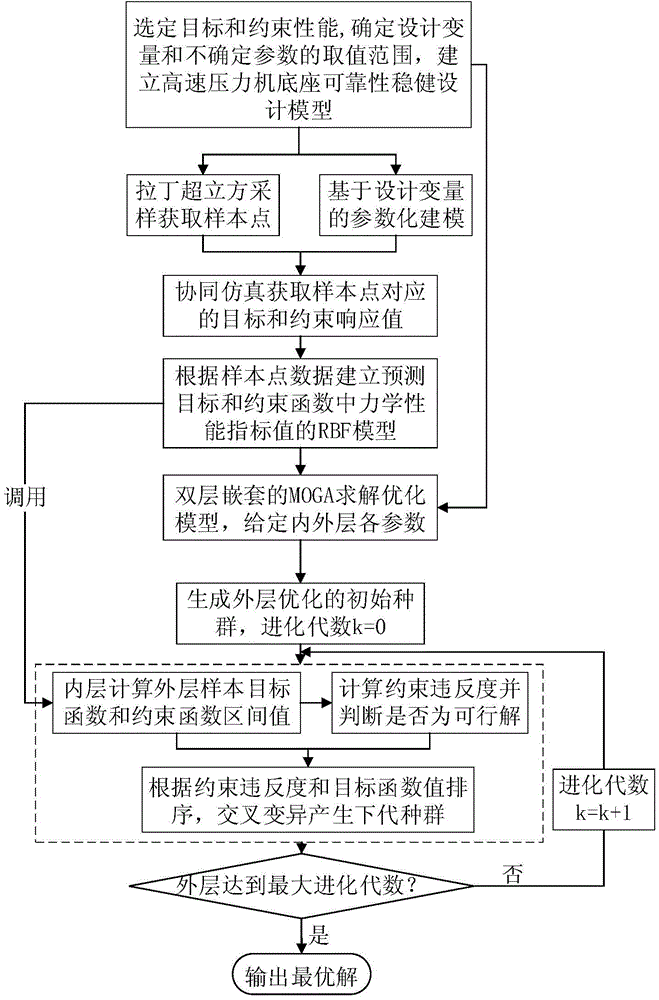

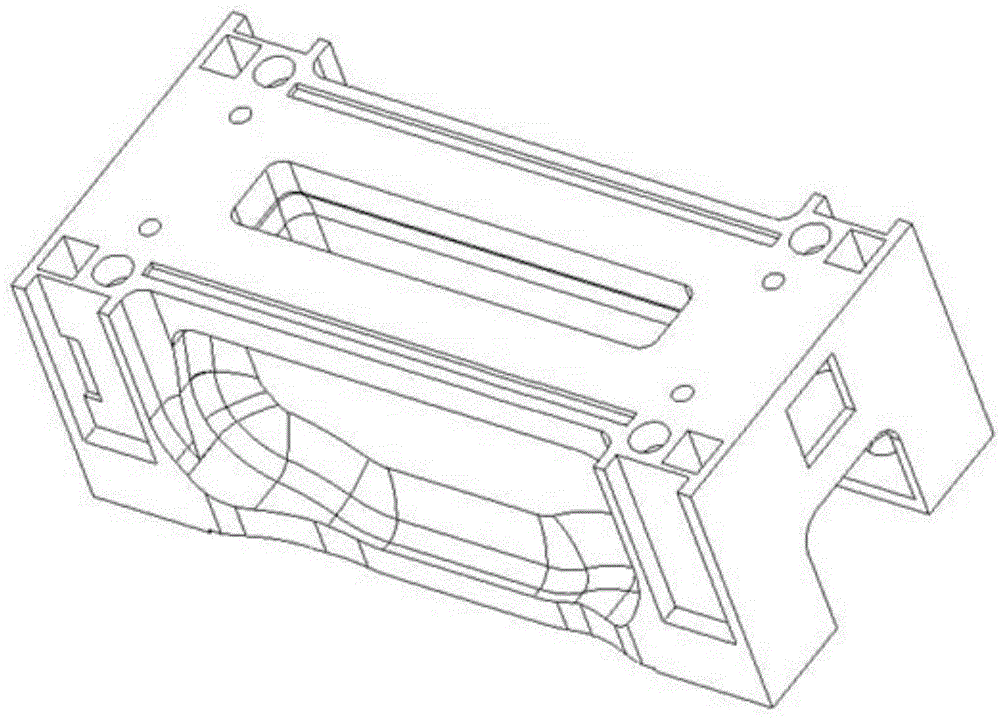

High-speed press base reliability robust design method considering dynamic characteristics

ActiveCN104679956AEasy to set upImplement two-way transmissionGenetic modelsSpecial data processing applicationsGenetic algorithmNetwork model

The invention discloses a high-speed press base reliability robust design method considering dynamic characteristics. The method comprises the following steps of establishing a reliability robust design model for the dynamic characteristics of a high-speed press base; sampling design variables and uncertain parameters by adopting a Latin hypercube sampling method and acquiring a response value of a sample point by a cooperation simulation technology; according to input-output information of the sample point, establishing an RBF (Radial Basis Function) neural network model for forecasting index values of the dynamic characteristics of the base in objective and constraint functions; carrying out iterative refinement by utilizing a double-layer nested genetic algorithm on the basis of interval constraint violation, a uniform interval dominance degree and an interval sequence vector so as to obtain the optimal solution of a base design scheme. The method carries out dynamic characteristic reliability robust design on the high-speed press base on the basis of the RBF neural network model according to the actual design requirements of the high-speed press base and can conveniently and rapidly obtain the design scheme of the high-speed press base which accords with the reliability requirement and has robust.

Owner:ZHEJIANG UNIV

Interactive traffic simulating system

InactiveCN101308616AEnable co-simulationFlexible structureEducational modelsCo-simulationTraffic simulation

The invention aims at providing a distributed interactive traffic simulation system which is a new traffic-driving simulation system. The key point of the traffic simulation system lies in introducing a vehicle driving emulator on the route of the user into the traffic simulation system as a traffic entity. The vehicle driving emulator, as a traffic entity controlled by the driving of the user, interacts with the virtual traffic entity produced by the traffic simulation system, and the traffic entity and the virtual traffic entity together participate in traffic simulation calculation, thus realizing cooperated simulation of a plurality of vehicle driving emulators and a plurality of traffic condition simulation servers under the same virtual traffic condition. The distributed interactive traffic simulation system is flexible in structure, convenient to extend and is high in simulation credibility and supports man-machine interaction. The system not only can be applied to traffic simulation and driving simulation but also provides a new platform for the research and application in the field of driving behavior, driving mentality, traffic safety, intelligent traffic, as well as road and bridge design.

Owner:成都合纵连横数字科技有限公司

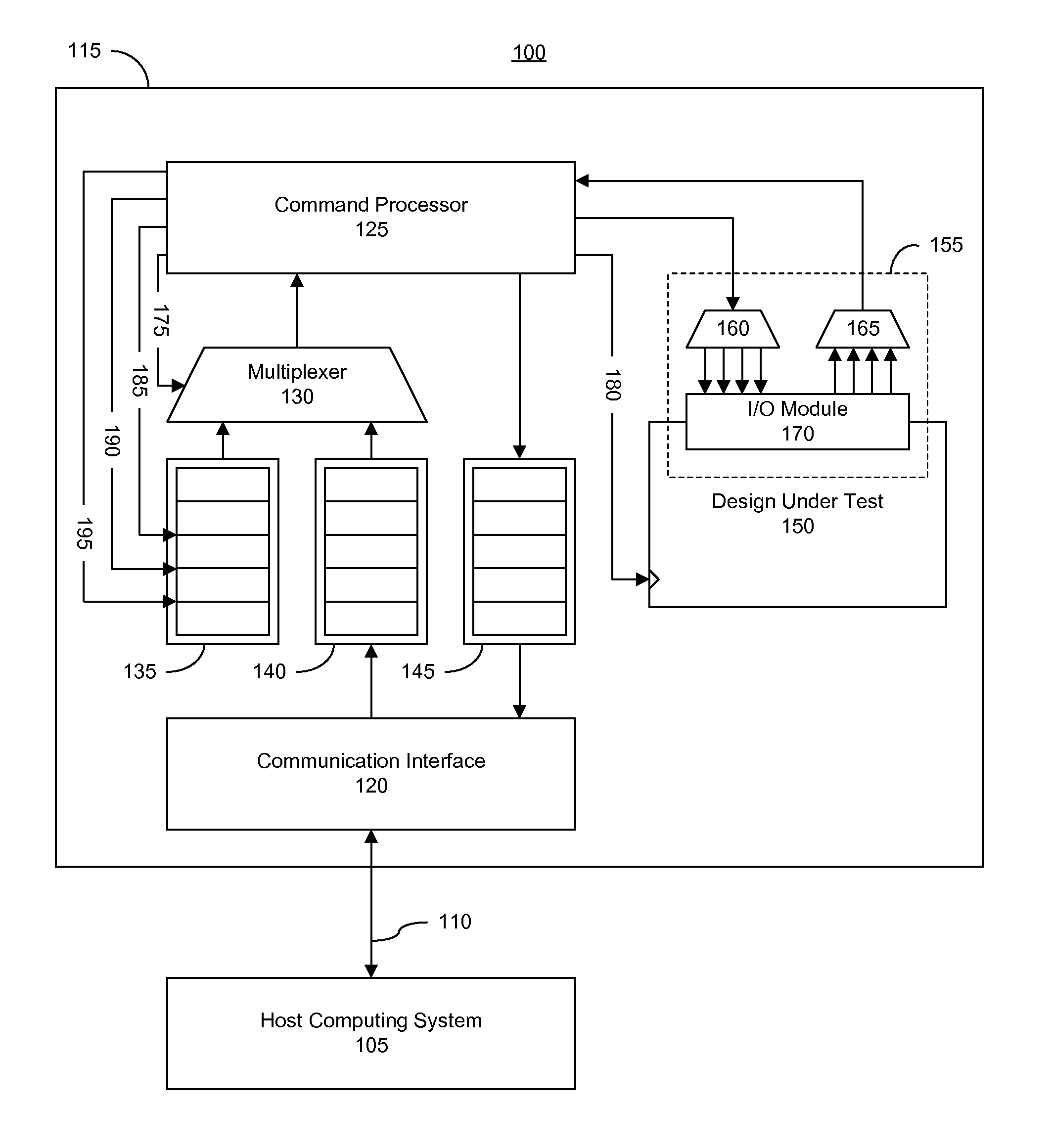

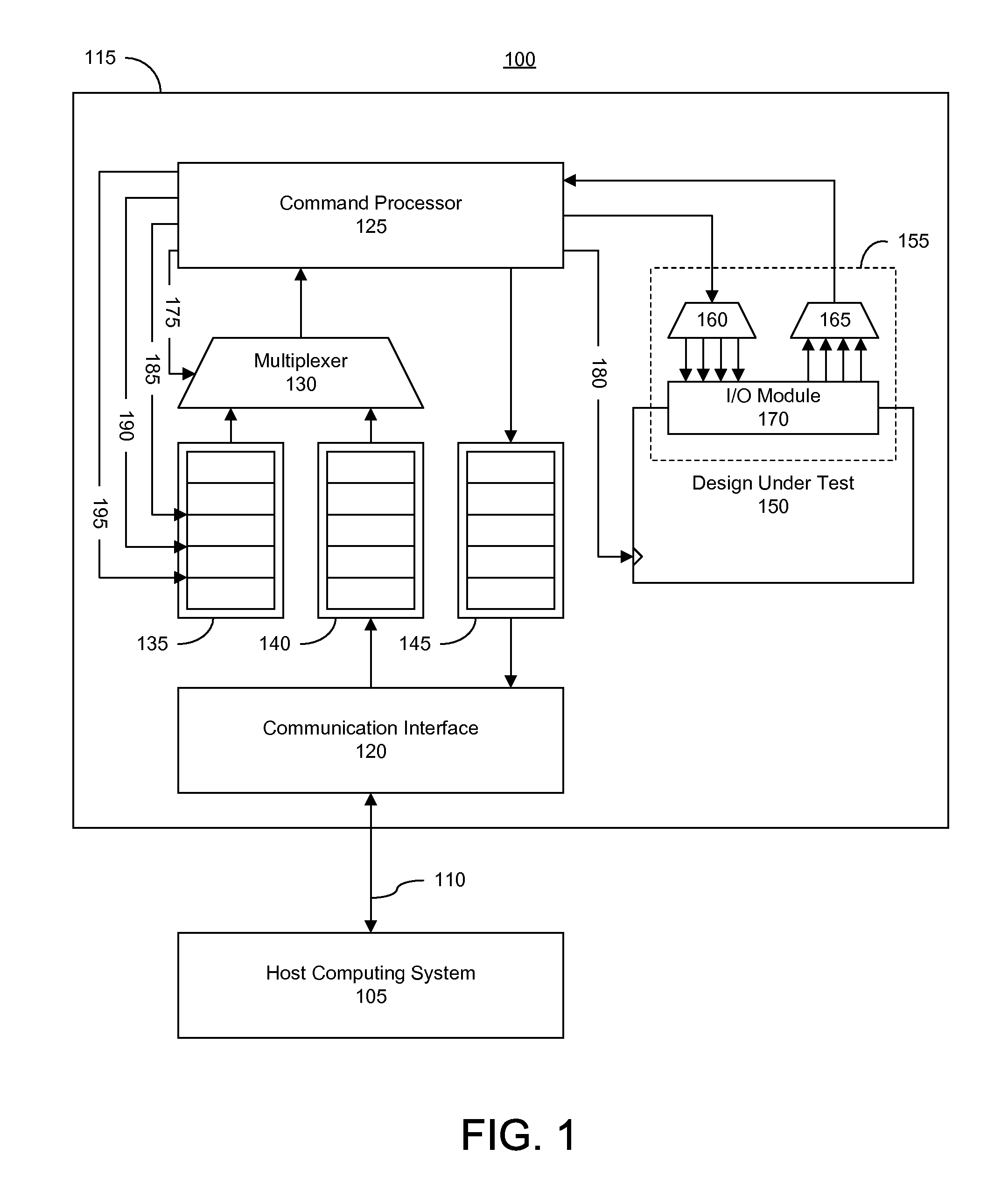

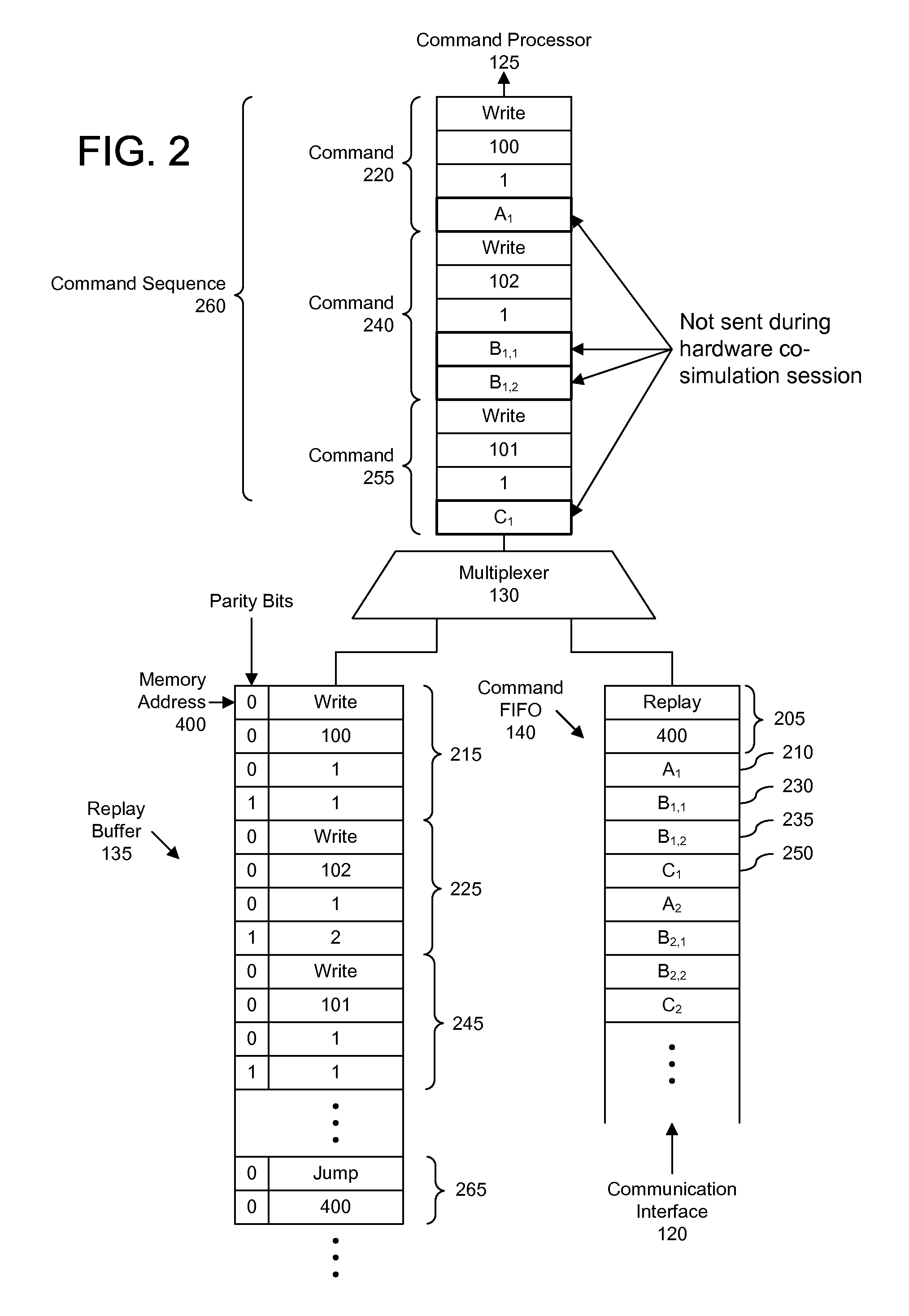

Accelerating hardware co-simulation using dynamic replay on first-in-first-out-driven command processor

An integrated circuit configured for hardware co-simulation can include a command processor, a replay buffer storing a command template, wherein the command template specifies an incomplete command, and a command first-in-first out (FIFO) memory storing complementary data for completion of the command template. The integrated circuit further can include a multiplexer coupled to the command processor, the replay buffer, and the command FIFO. The multiplexer, under control of the command processor, can selectively provide data from the replay buffer or the command FIFO to the command processor. The command processor, responsive to a replay command read during a hardware co-simulation session, can enter a replay mode, obtain the command template from the replay buffer, obtain the complementary data from the FIFO memory according to a symbol read from the command template, and form a complete command by joining the command template with the complementary data.

Owner:XILINX INC

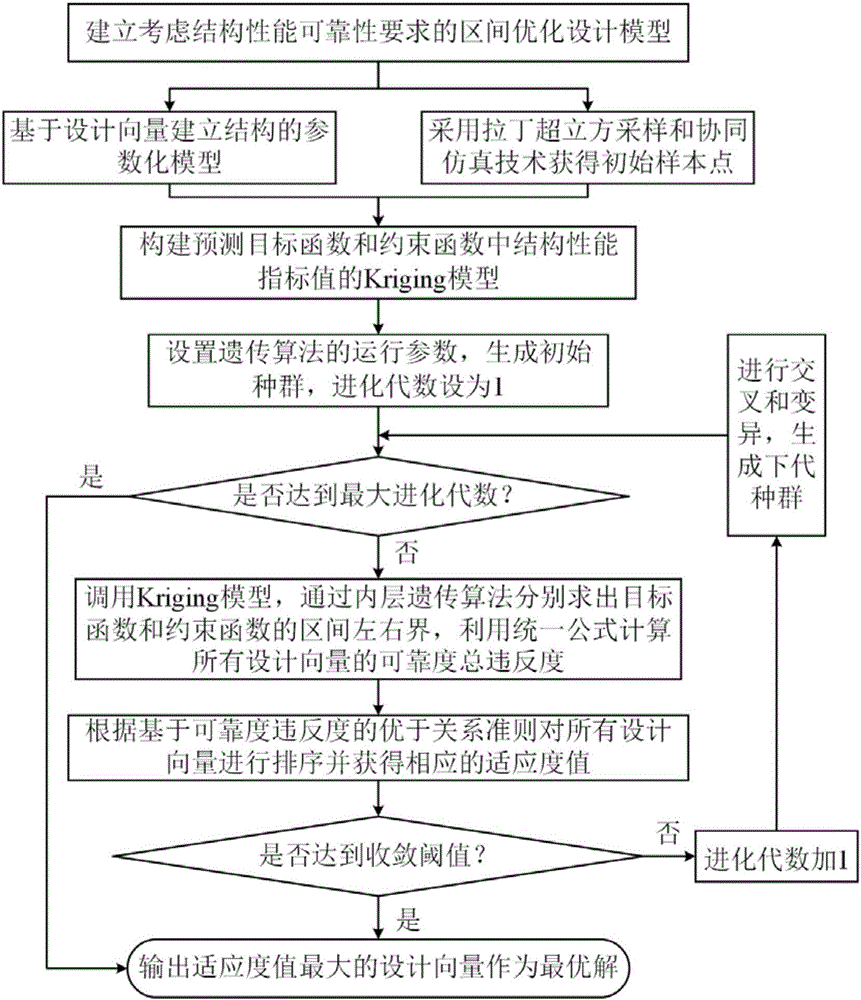

Structural performance optimum design method under non-probability conditions

InactiveCN105930562APracticalAvoid lossGeometric CADDesign optimisation/simulationEvolution algebraStructural reliability

The invention discloses a structural performance optimum design method under non-probability conditions. The method comprises following steps: an interval optimum design model considering structural reliability requirements is established; sample points are obtained by means of Latin hypercube sampling and collaborative simulation; a Kriging surrogate model for predicting objective functions and constraint functions is established; the interval optimum design model is solved by means of a double-layer nested genetic algorithm, wherein in the inner layer of the genetic algorithm, the left and right boundary of the interval values of the objective functions and the constraint functions are calculated, in the outer layer of the genetic algorithm, the interval reliability and reliability violation degree of each constraint function according to an unified formula are calculated to obtain the total reliability violation degree of a design vector, and the feasibility is determined; superiority ordering is performed on all design vectors according to a superior relation criterion based on the total reliability violation degree; the optimal solution of the interval optimum design model is output when maximum evolution algebra or convergence threshold is reached. By means of the method, structural performance optimum design method under non-probability conditions can be realized.

Owner:ZHEJIANG UNIV

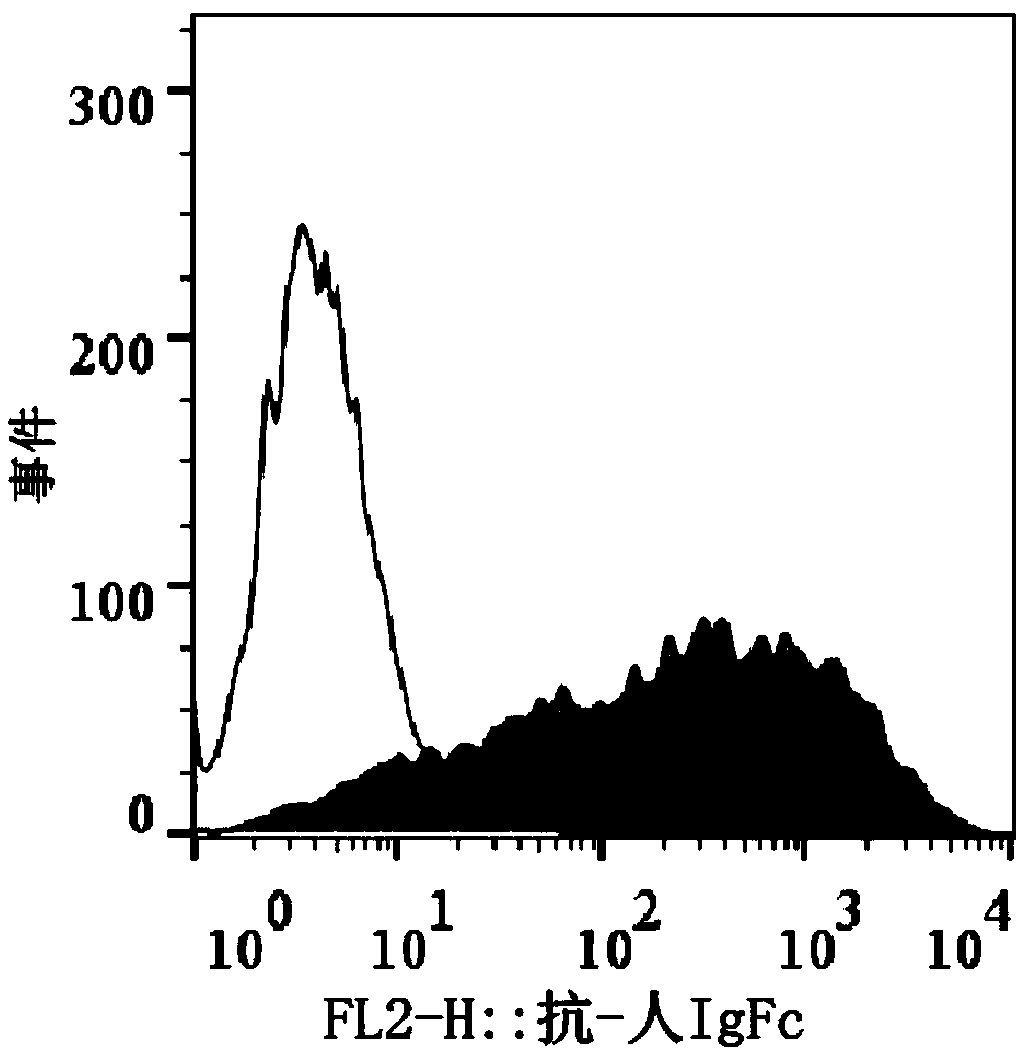

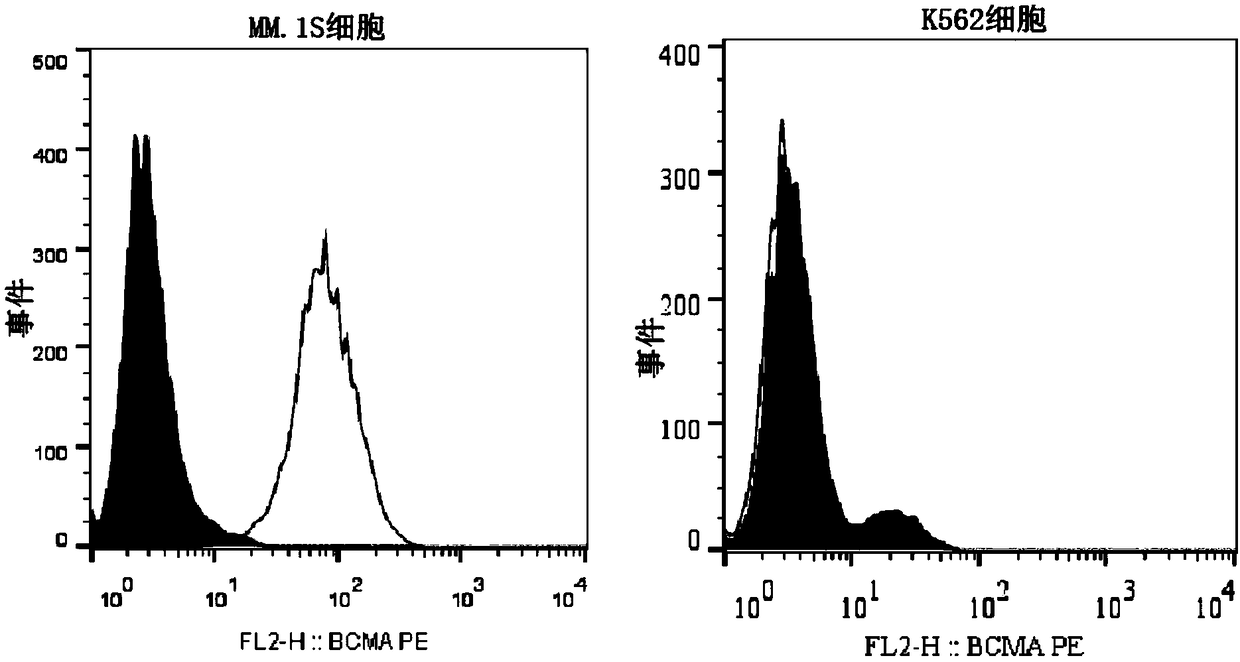

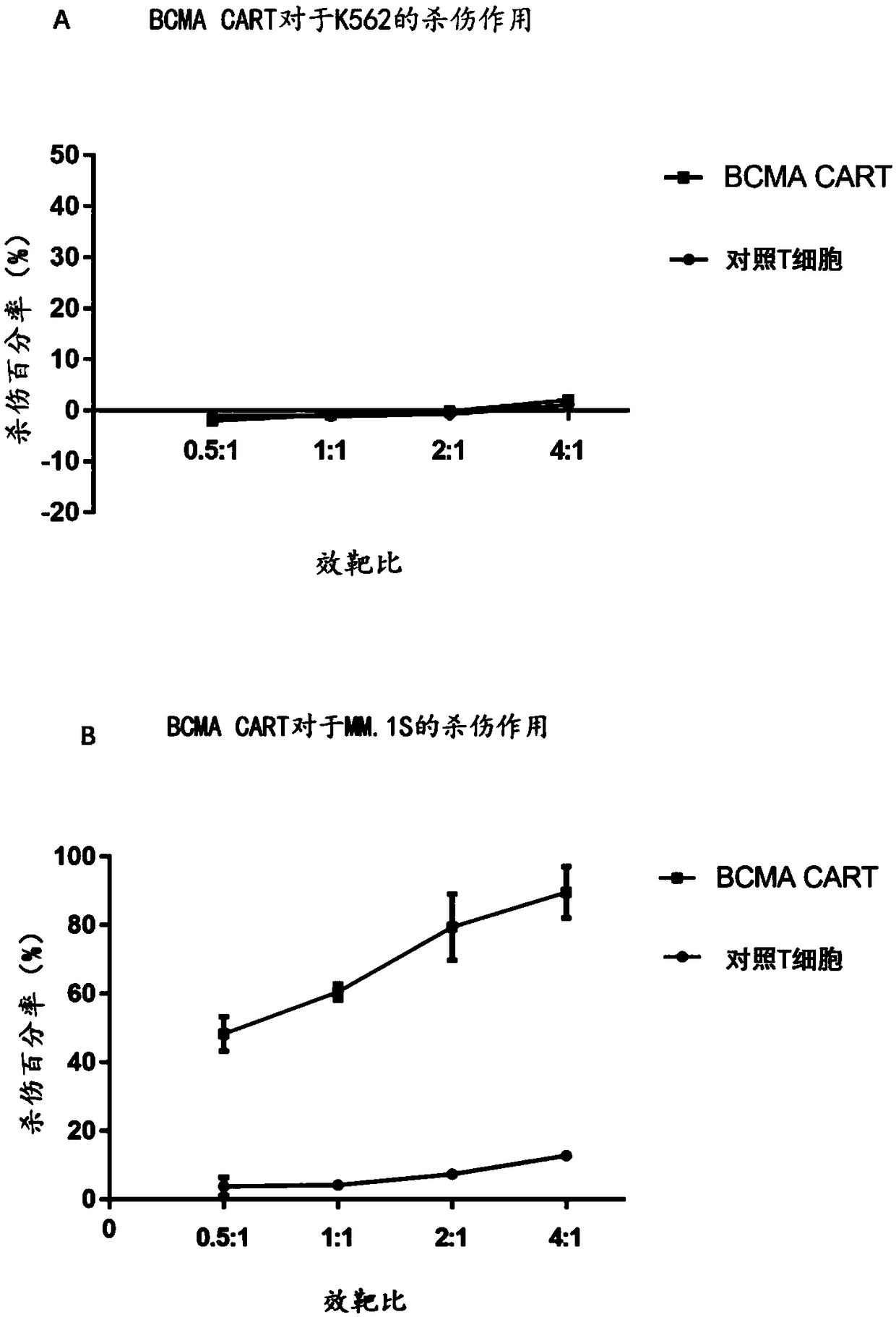

BCMA (B-cell maturation antigen) chimeric antigen receptor on basis of single-domain antibodies and application of BCMA chimeric antigen receptor

ActiveCN109134665AGood treatment effectLethalAntibody mimetics/scaffoldsMammal material medical ingredientsHeavy chainB-Cell Maturation Antigen

The invention relates to a chimeric antigen receptor (CAR) and application thereof. The CAR comprises BCMA (B-cell maturation antigen) binding structural domains, transmembrane structural domains, oneor a plurality of co-simulation structural domains and intracellular signal transduction structural domains. The BCMA binding structural domains comprise heavy chain complementary determining regionsHCDR 1-3, and amino acid sequences of the HCDR 1-3 are sequentially shown as SEQ ID NO:1-3.

Owner:SHANGHAI SIMNOVA BIOTECHNOLOGY CO LTD

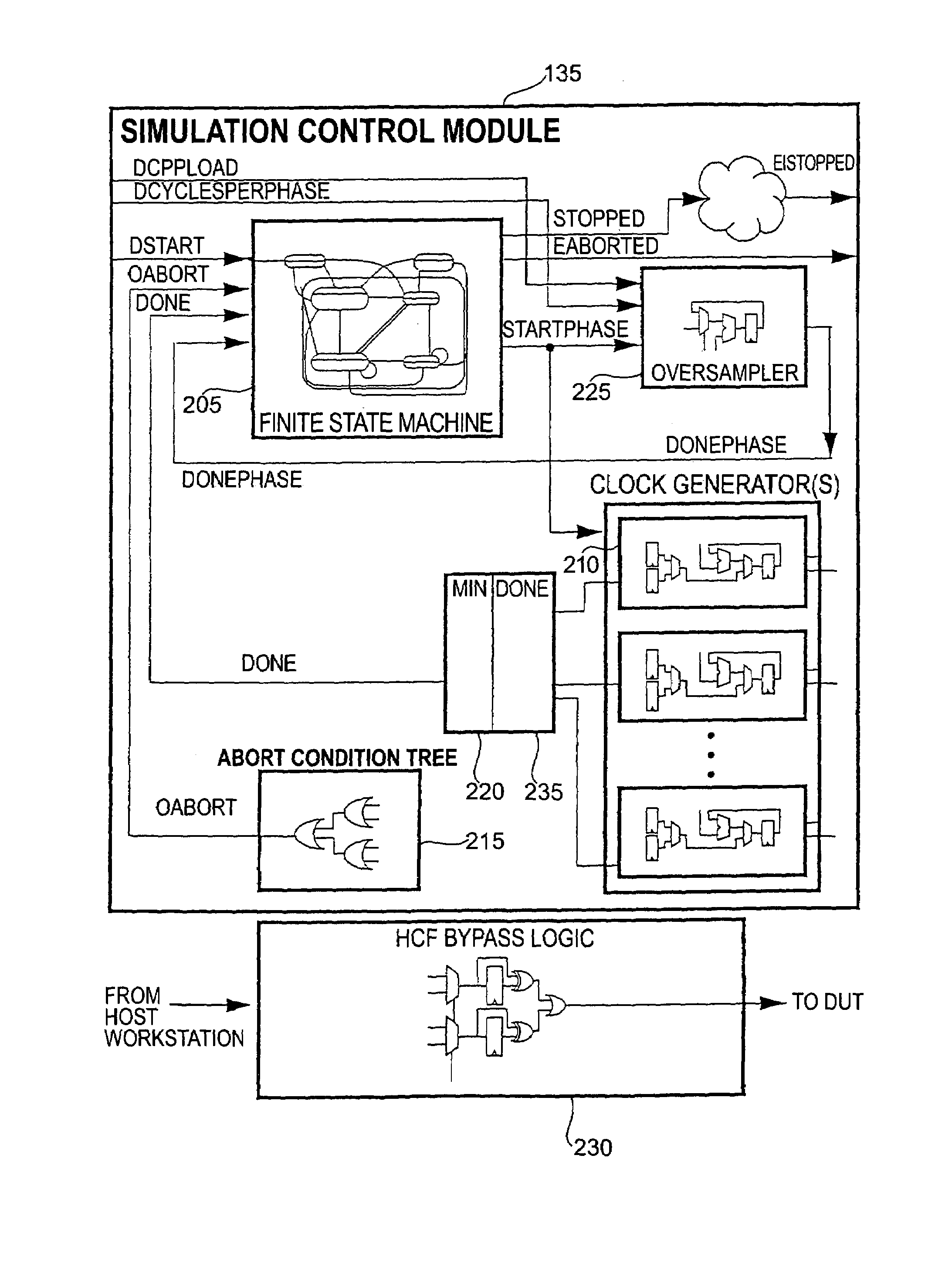

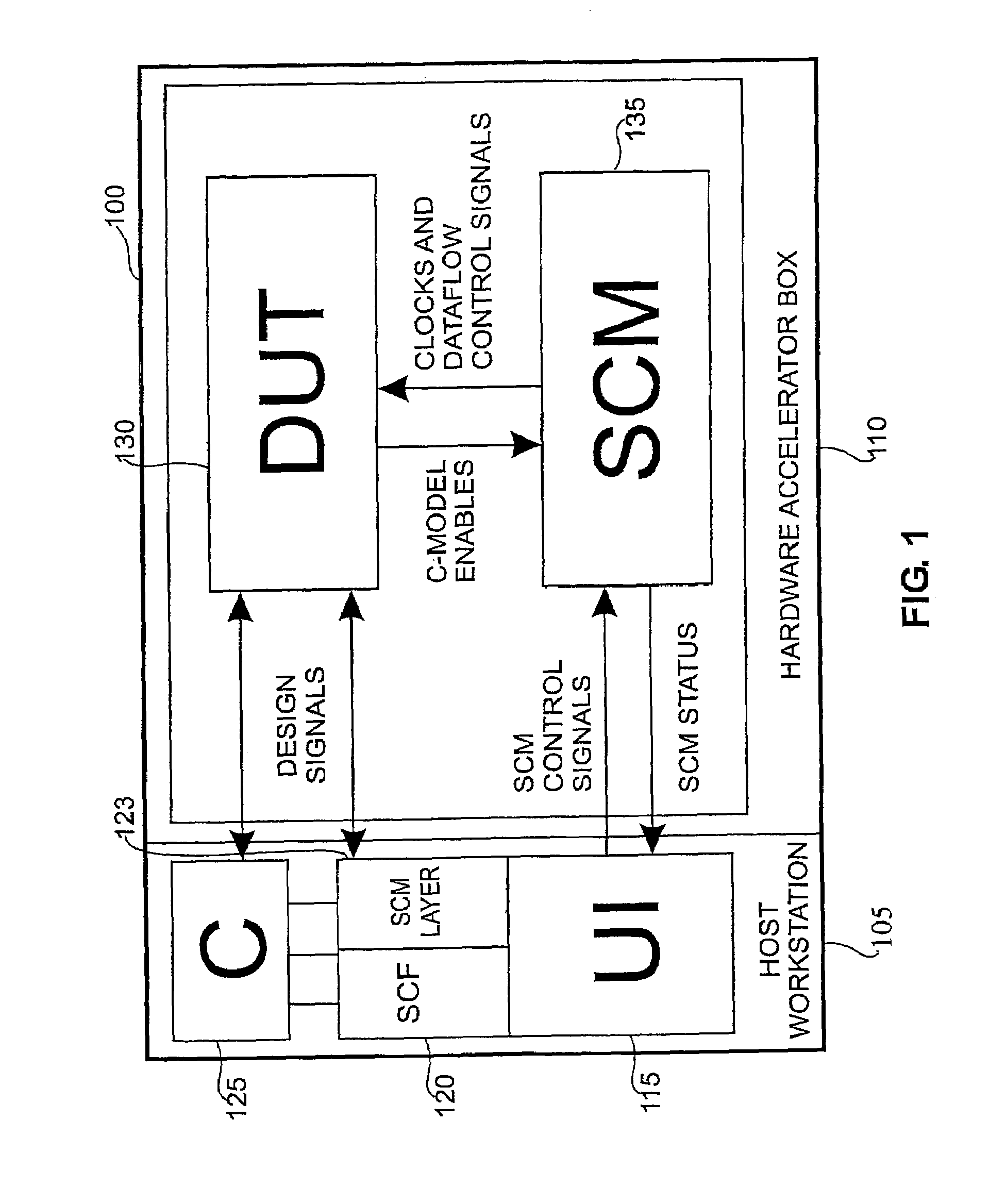

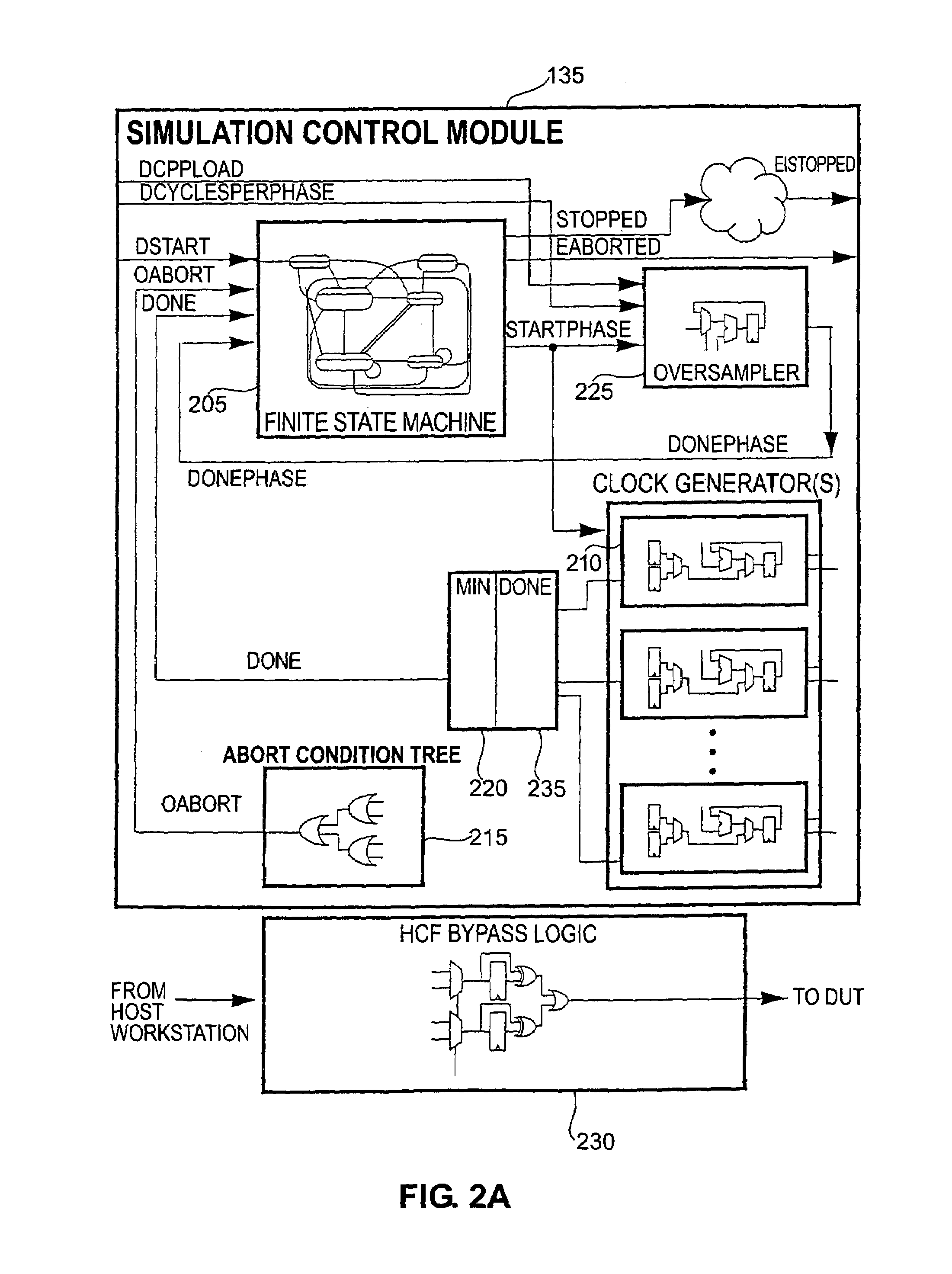

Simulation and timing control for hardware accelerated simulation

InactiveUS7257524B2Analogue computers for electric apparatusCAD circuit designCo-simulationWorkstation

A fully synthesizeable Simulation Control Module (SCM) controls and monitors the simulation of a design under test (DUT). A clock generator within the SCM and a Software clock facility residing on the host workstation are responsible for providing the clocks for the DUT. The SCM and the hardware clock facility are dynamically generated at build time to suit the needs of the DUT. They maximize performance by automatically generating clock waveforms for designs containing multiple asynchronous clocks, thereby decreasing the frequency of accelerator-workstation interaction. The software clock facility has the ability to directly drive the DUT and is responsible for managing the simulation time and clock parameters. The SCM is also responsible for monitoring an abort condition such as a trigger to execute an external software model. The SCM and the clock facilities allow the hardware accelerator to efficiently support multiple asynchronous clock domains, execution of external software models and co-simulation.

Owner:CADENCE DESIGN SYST INC

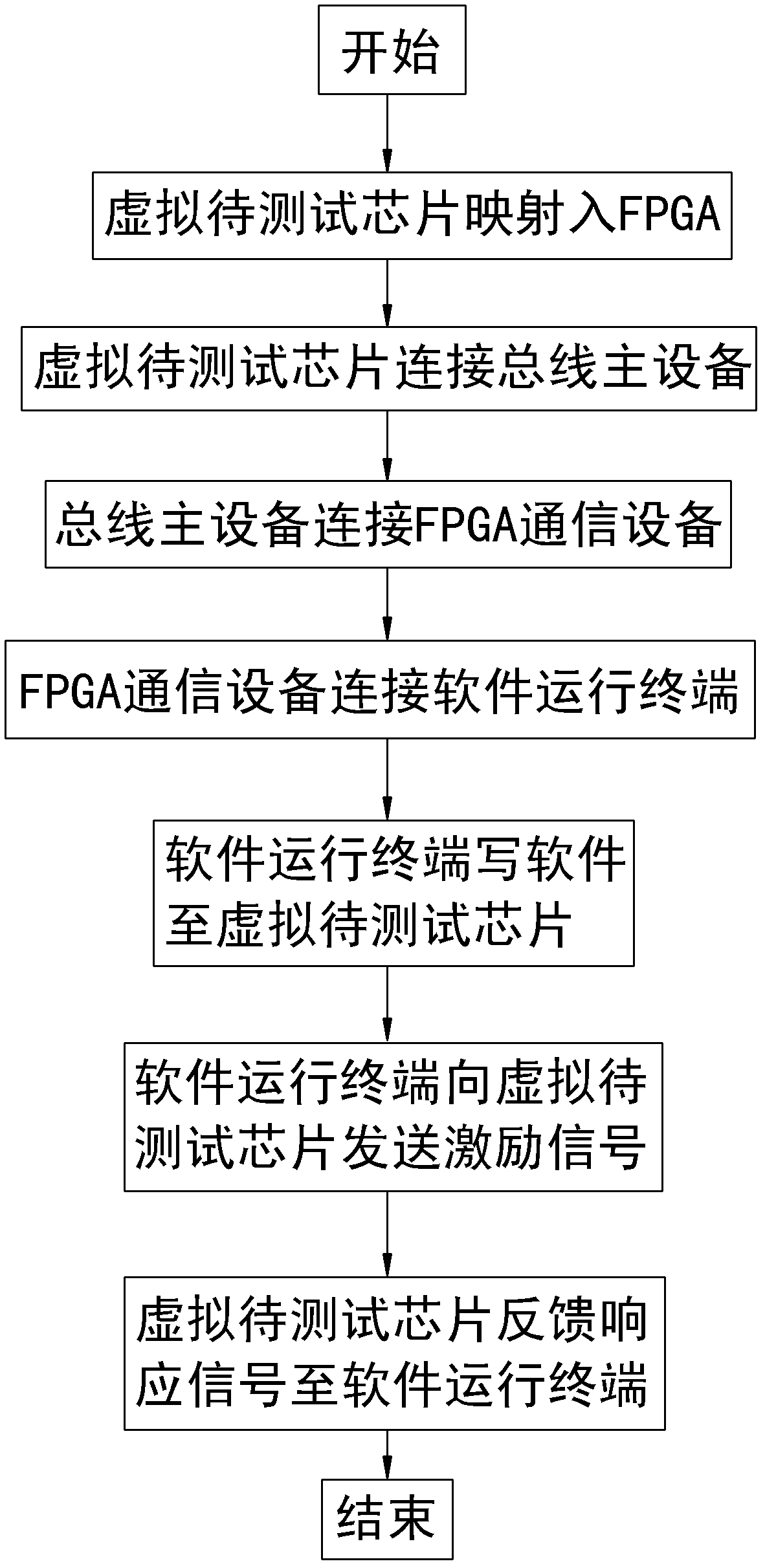

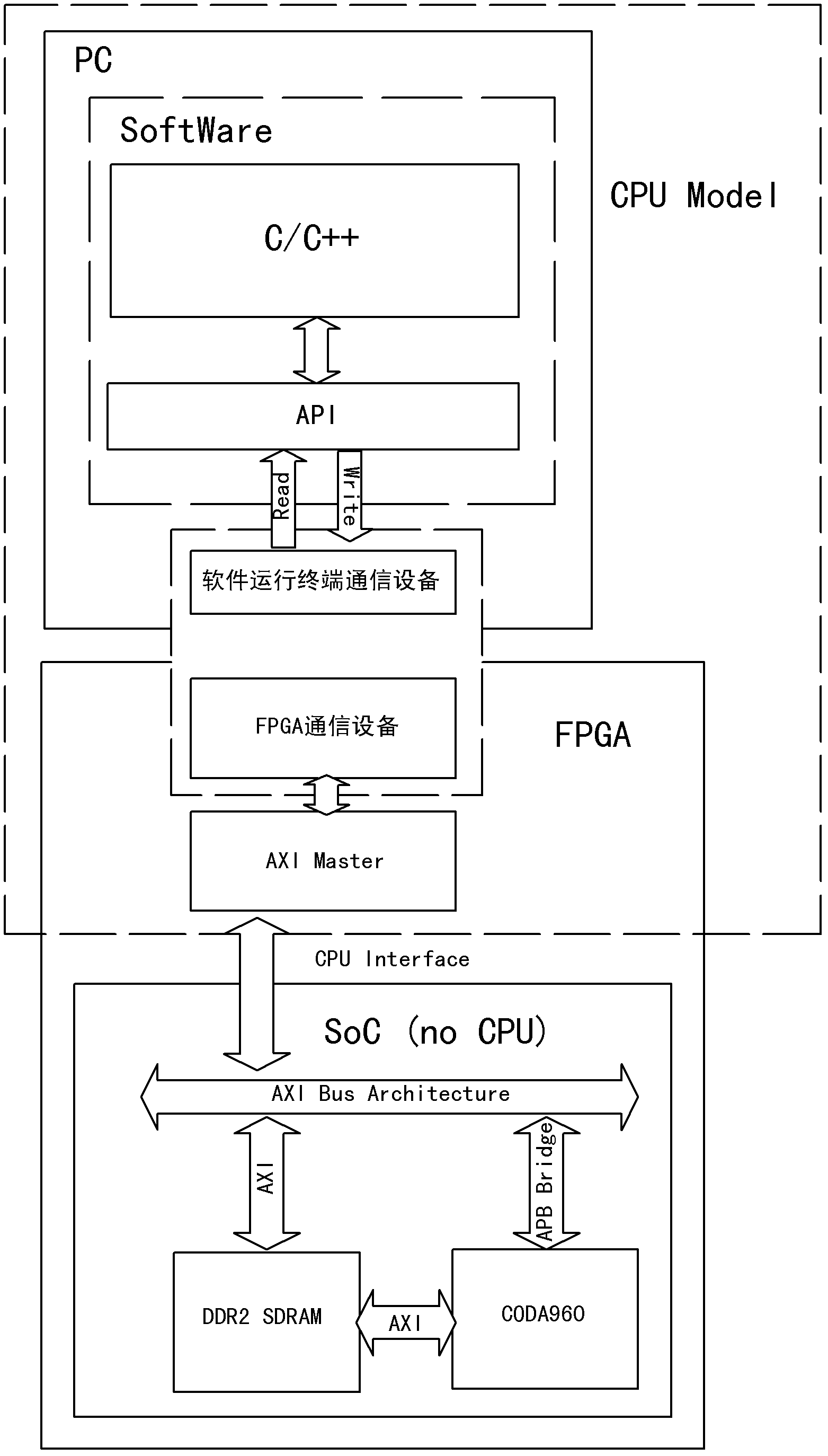

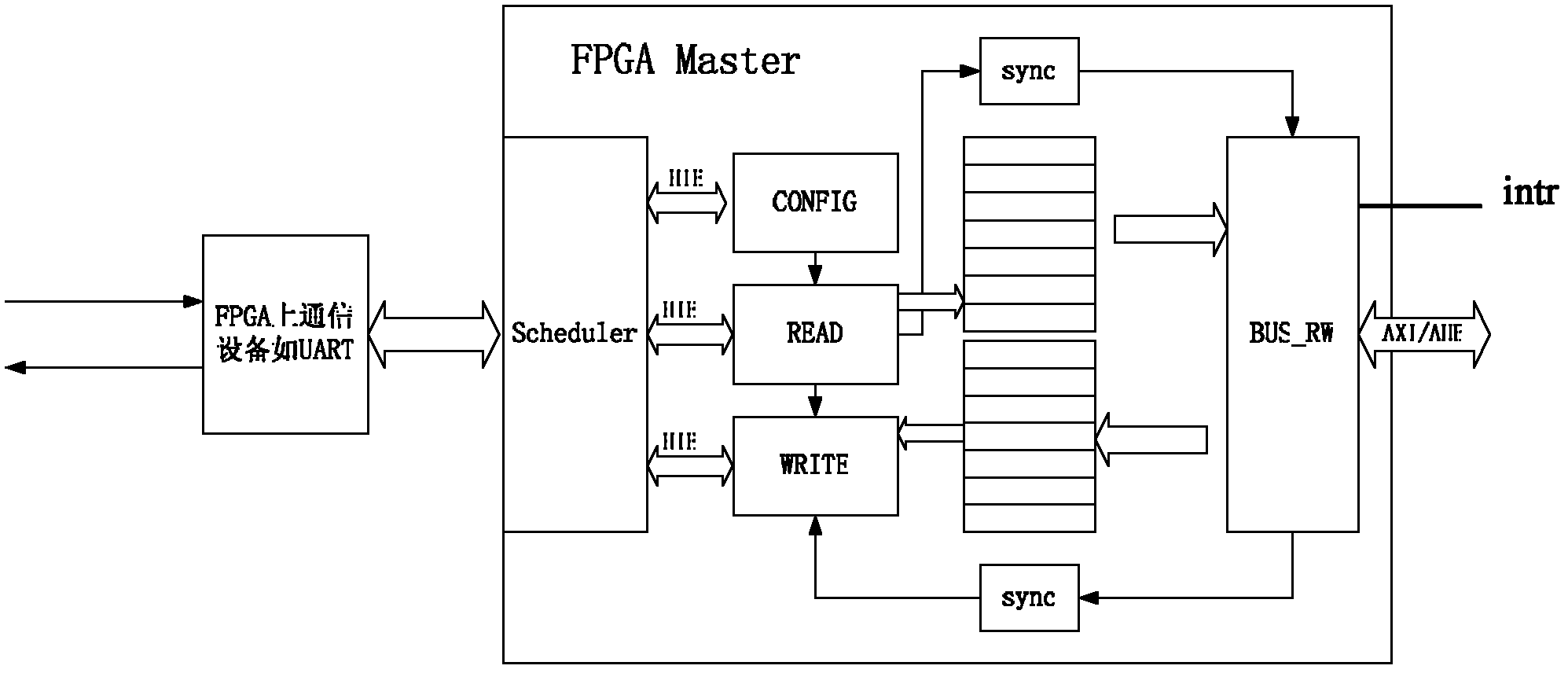

Cooperative simulation/verification method and device for software and hardware

InactiveCN102521444ASpeed up developmentEasy to debugSpecial data processing applicationsValidation methodsCo-simulation

The invention discloses a cooperative simulation / verification method for software and hardware, which uses a software operating terminal to simulate CPU in SoC design to develop / operate the software and develops the software during hardware simulation / verification. The method comprises the steps of mapping the SoC design to a FPGA (Field Programmable Gata Array); connecting the SoC design to the software operating terminal through a bus main device and an FPGA communication device; developing the software required by the SoC design and operating the software at the software operating terminal to send an excitation signal to the SoC design; and responding to the excitation signal by the SoC design, wherein the responding signal is fed back to the software operating terminal. The invention discloses a cooperative simulation / verification device for software and hardware. The device comprises the FPGA mapped to the SoC design without the CPU and the software operating terminal having the software development function and / or operating function. The bus main device converts the read-write operation of the software to read-write operation of the bus.

Owner:HISENSE HIVIEW TECH CO LTD

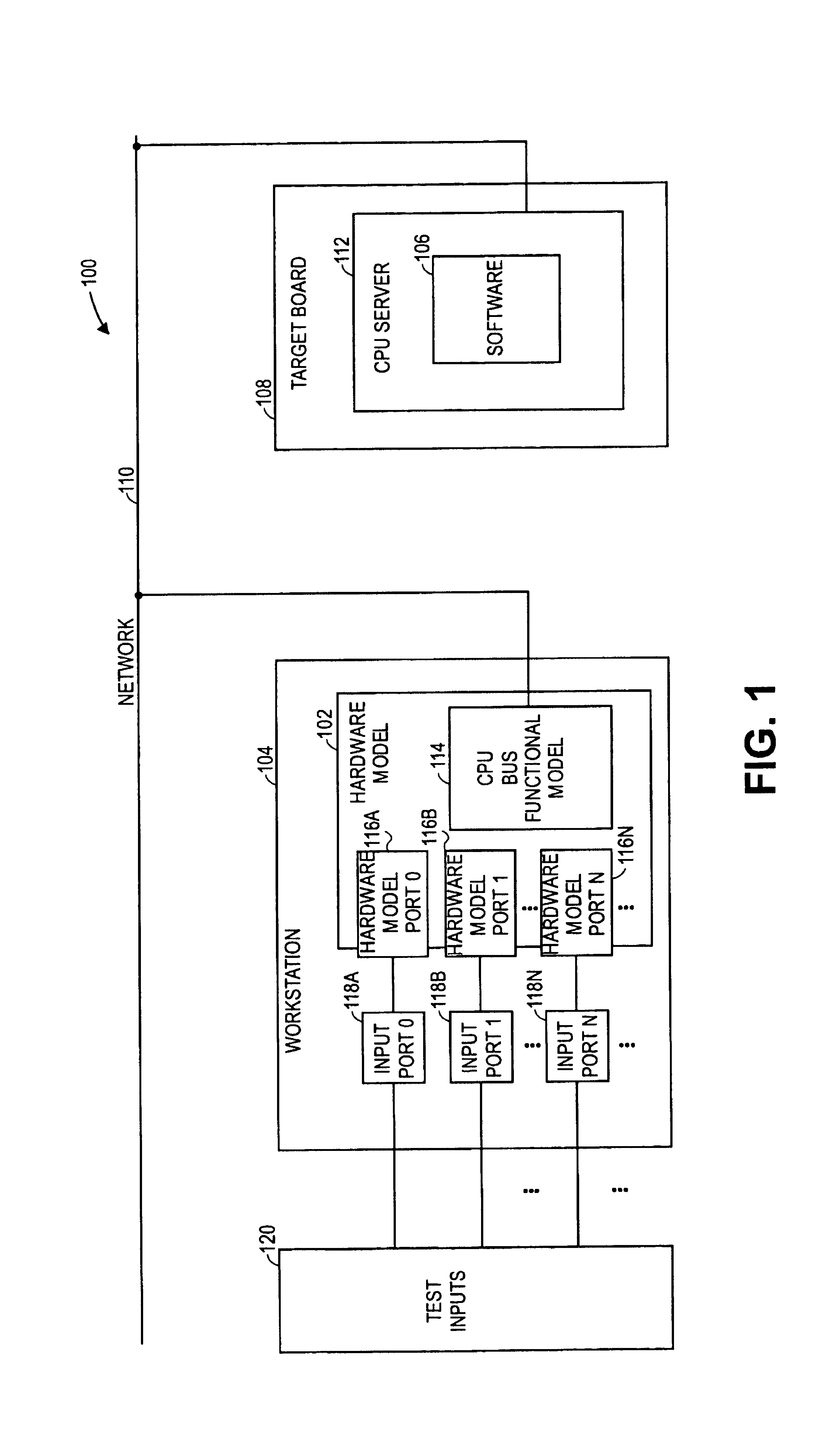

Method and apparatus for hardware and software co-simulation

InactiveUS7107202B1Reduce overall system development cycleShorten the development cycleError preventionFrequency-division multiplex detailsComputer hardwareSoftware development

A method apparatus for hardware and software co-simulation in ASIC development includes developing hardware and software concurrently and co-simulating the hardware and software therebetween via a network while the hardware and software are being developed. The method and apparatus for hardware and software co-simulation allows the software development and testing of hardware and software to start with the design of hardware so as to reduce an overall system development cycle involving ASICs.

Owner:MICRON TECH INC

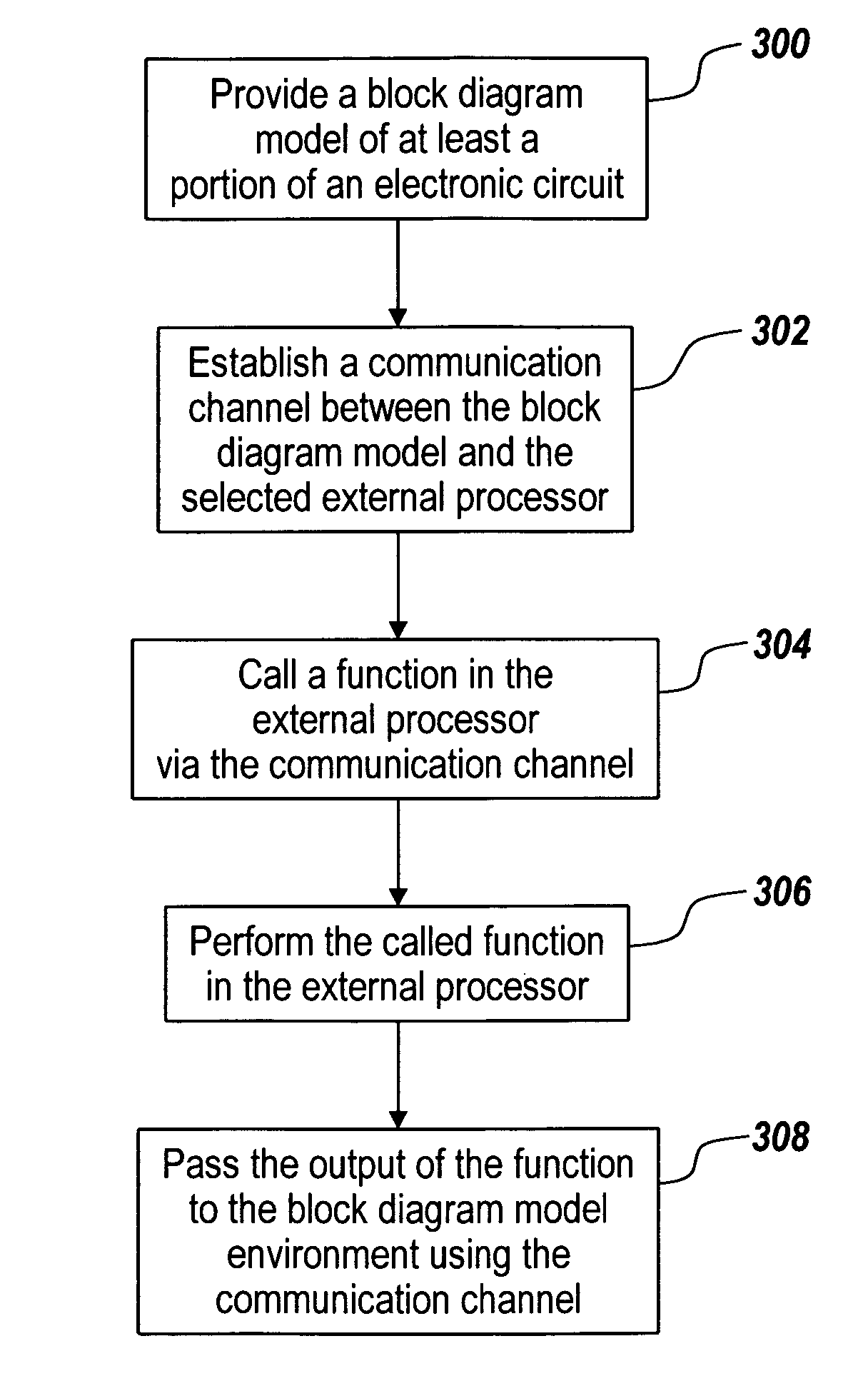

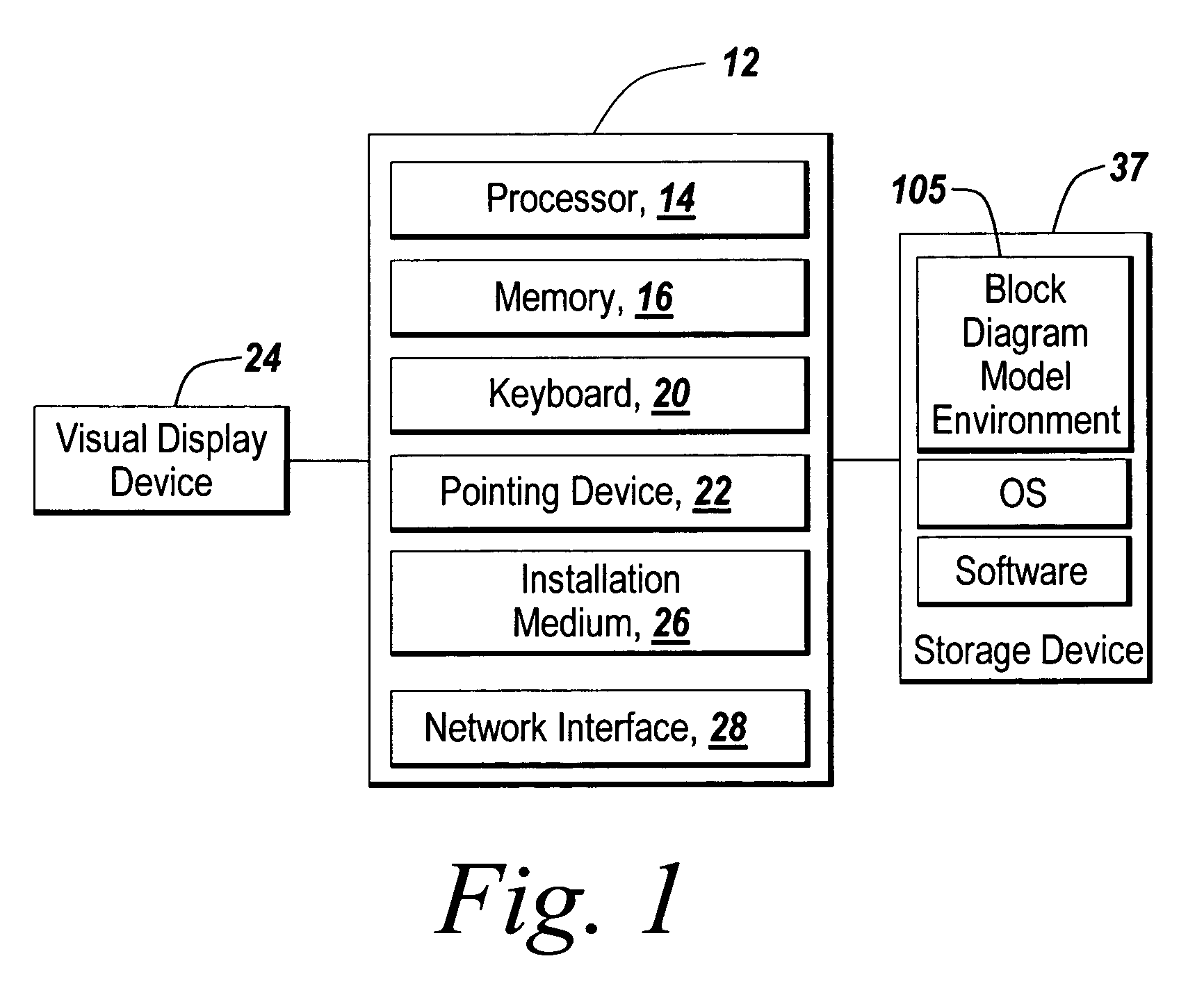

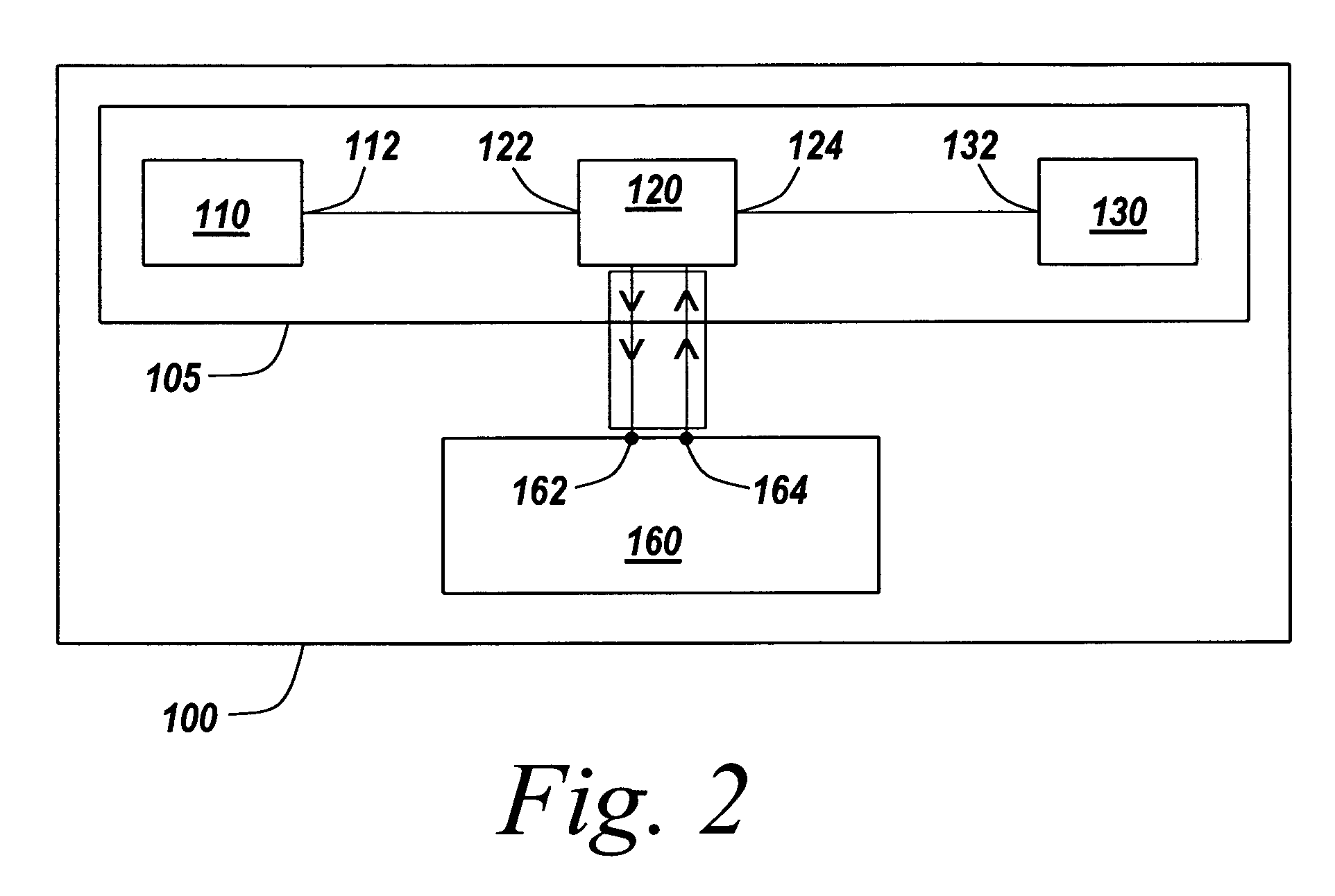

Framework for hardware co-simulation by on-demand invocations from a block model diagram design environment

ActiveUS7490032B1Quick testDesign optimisation/simulationProgram controlParallel computingCo-simulation

The present invention relates to integration of an external processor capable of execution of one or more functions into a block diagram model environment such that the block diagram model environment can make function calls directly into the external processor without the need for traditional wait loops or handshaking means. Furthermore the results of the function that was called in the external processor can be passed to the block diagram model environment from the external processor.

Owner:THE MATHWORKS INC

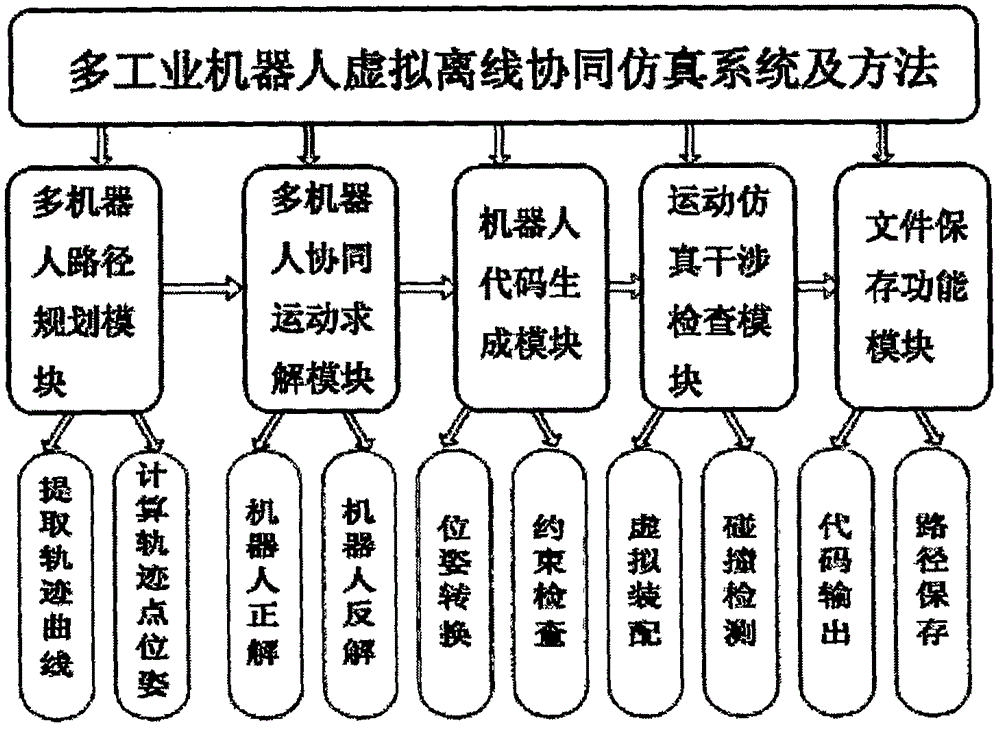

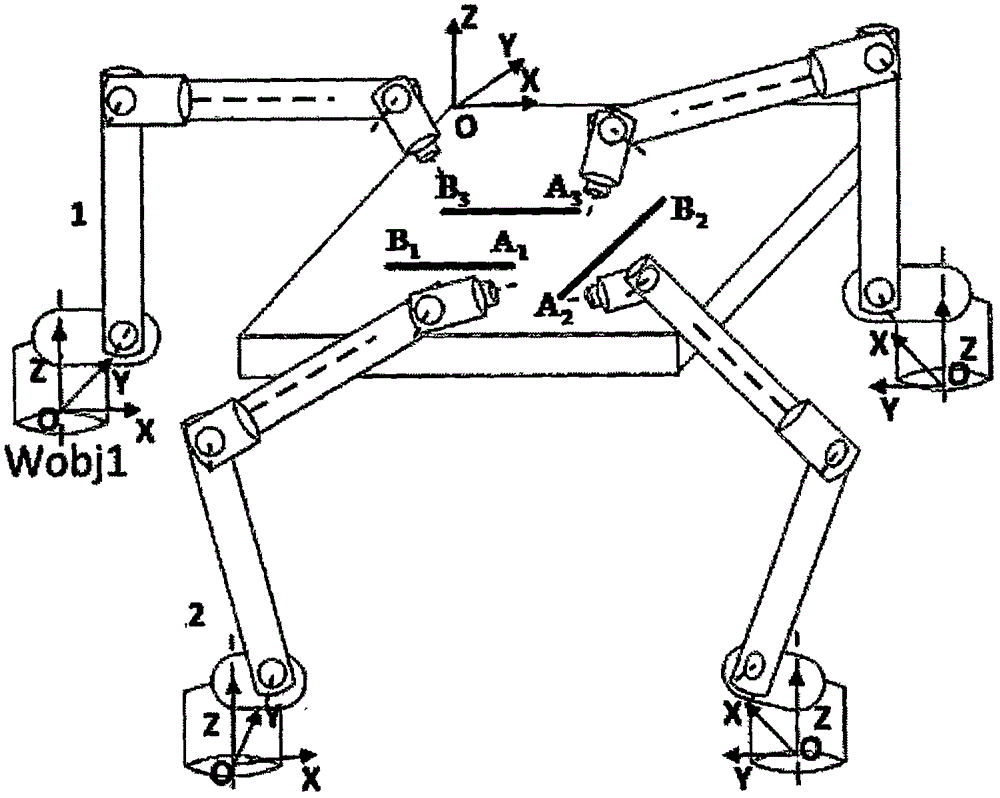

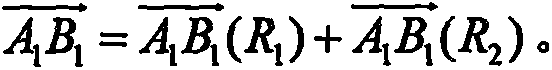

Multi-industrial-robot virtual offline co-simulation system and method

InactiveCN106444739AImprove development efficiencyIncrease productivityPosition/course control in two dimensionsVehiclesKinematicsRobot kinematics

The invention discloses a multi-industrial-robot virtual offline co-simulation system and method. The system comprises a multi-robot path planning module, a multi-robot co-movement solving module, a robot code generating module, a movement simulation interference checking module and a file saving functional module. The method comprises the steps of: 1, constructing a multi-robot virtual workstation; 2, extracting an actual machining path of robots by using workpiece numerical simulation; 3, performing robot kinematics analysis; 4, performing discrete processing on the whole path, and simulating the movement in three-dimensional software by virtual assembly; 5, outputting movement control programs of the robots in the whole movement process according to code formats of different robots; 6, repeating step 4, performing interference checking, and if interference and collision occur, performing safety prompt; and 7, saving necessary information required in the whole co-movement process. The system and the method improve the development efficiency, reduce the technical threshold, and improve the production efficiency of enterprises.

Owner:鹿龙 +1