Distributed packet-switching chip model verification system and method

A model verification and packet switching technology, which is applied in transmission systems, digital transmission systems, data exchange networks, etc., can solve problems such as complex processes, lagging development progress, and unreusable test cases

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0065] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

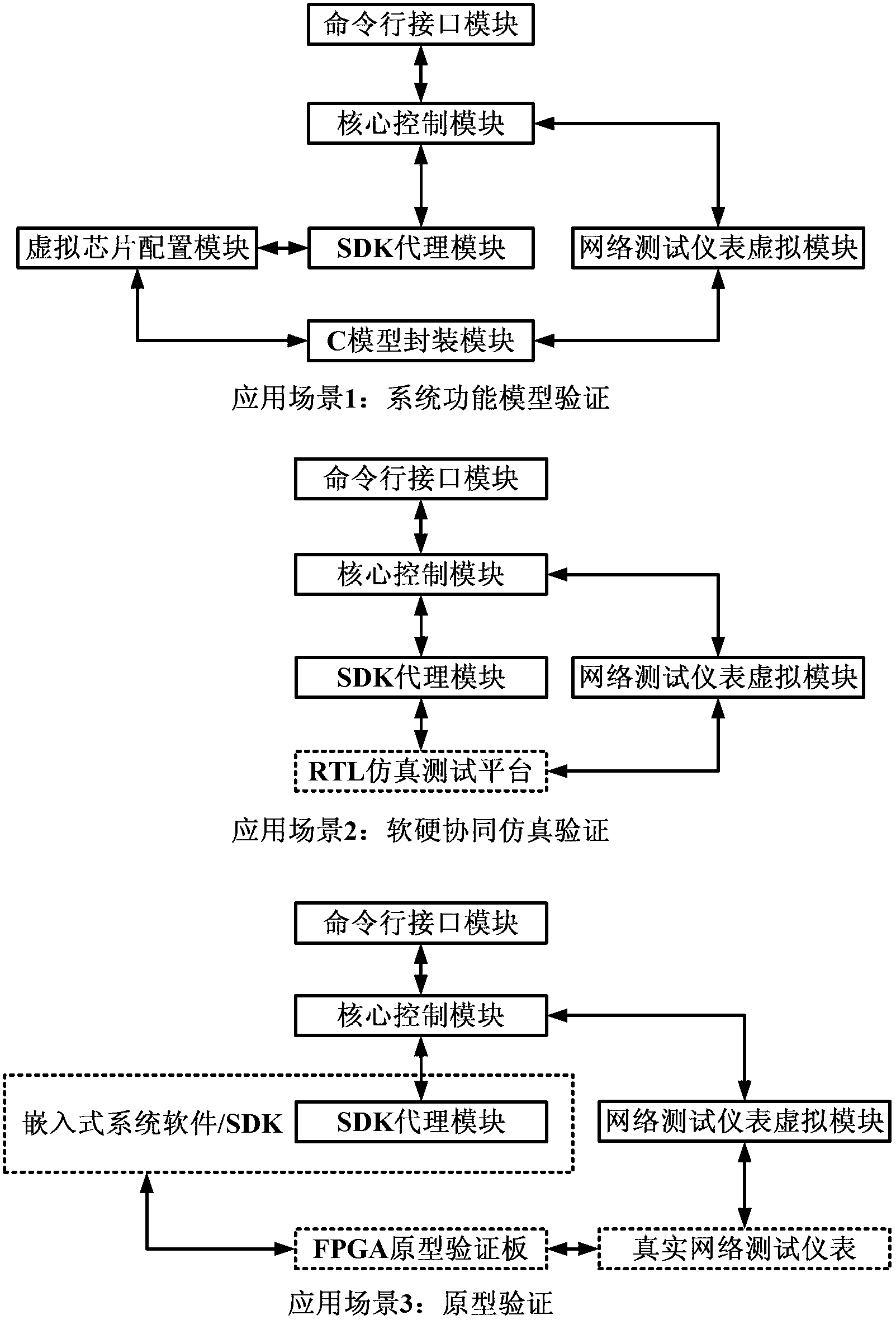

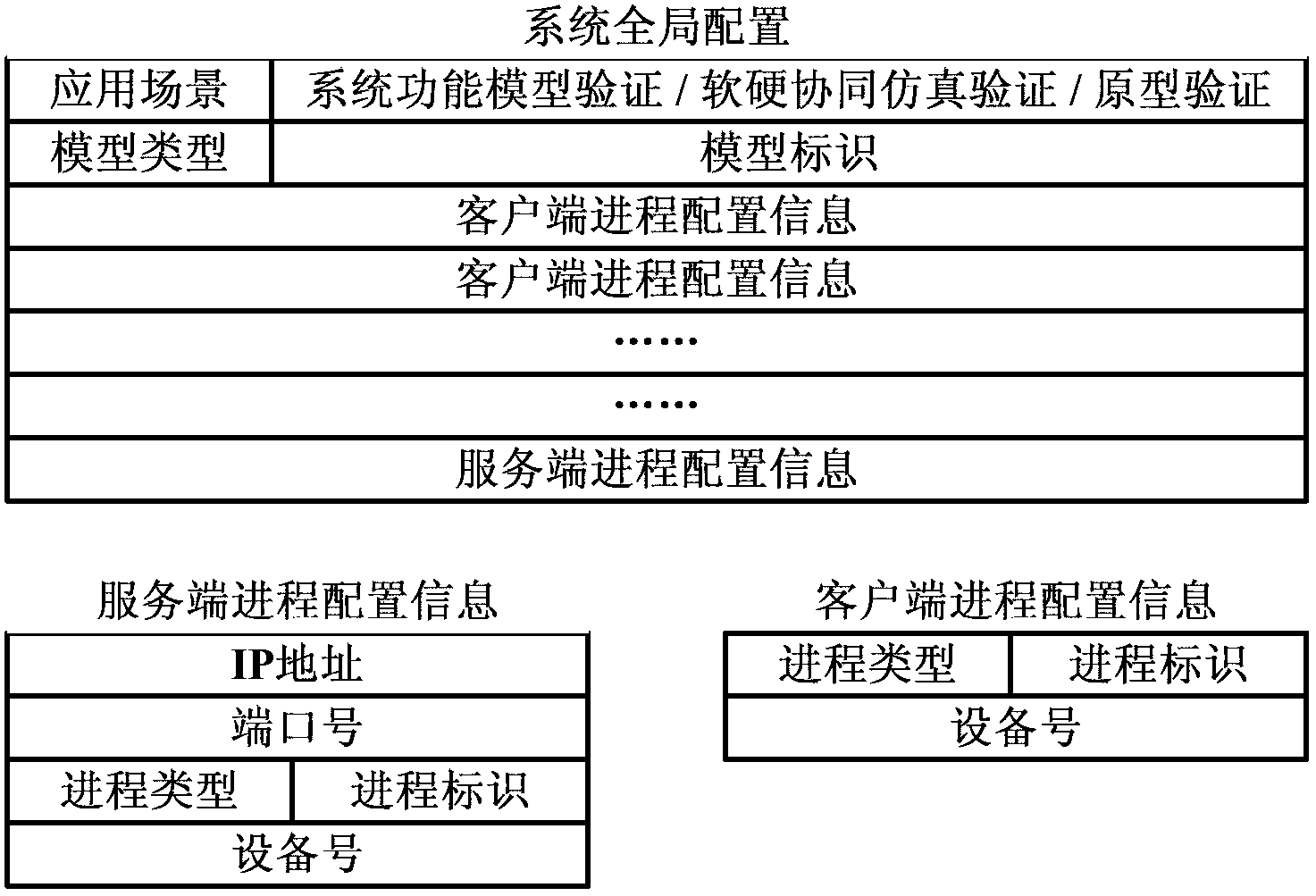

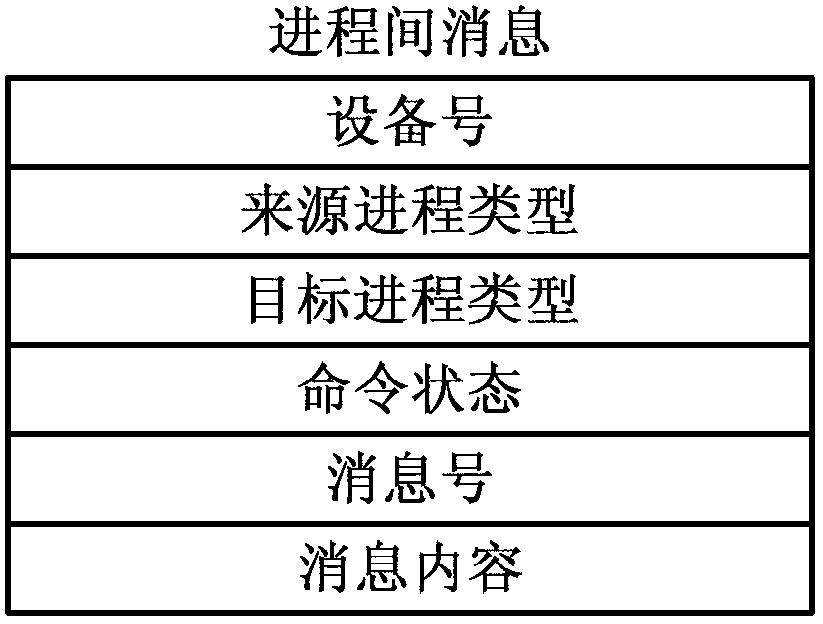

[0066] see figure 1 As shown, the embodiment of the present invention provides a distributed packet switching chip model verification system, including a core control module, a command line interface module, an SDK agent interface module, a virtual network test instrument module, a virtual chip configuration module and a C model packaging module, Among them, the core control module belongs to the server program module, and the command line interface module, SDK proxy interface module, virtual network test instrument module, virtual chip configuration module and C model packaging module belong to the client program module. The verification system belongs to the distributed system of C / S / C (Client-Server-Client client-server-client) structure, and supports three application scenarios at the same time: system function model verification,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More