Software and hardware collaborative simulation verification system and method based on FPGA

A technology of software-hardware collaboration and simulation verification, which is applied in the field of simulation verification systems, can solve problems such as reducing simulation efficiency, and achieve the effects of reducing verification time, good physical scalability, and shortening development time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The technical solutions of the present invention will be further elaborated below in conjunction with the accompanying drawings and specific implementation methods.

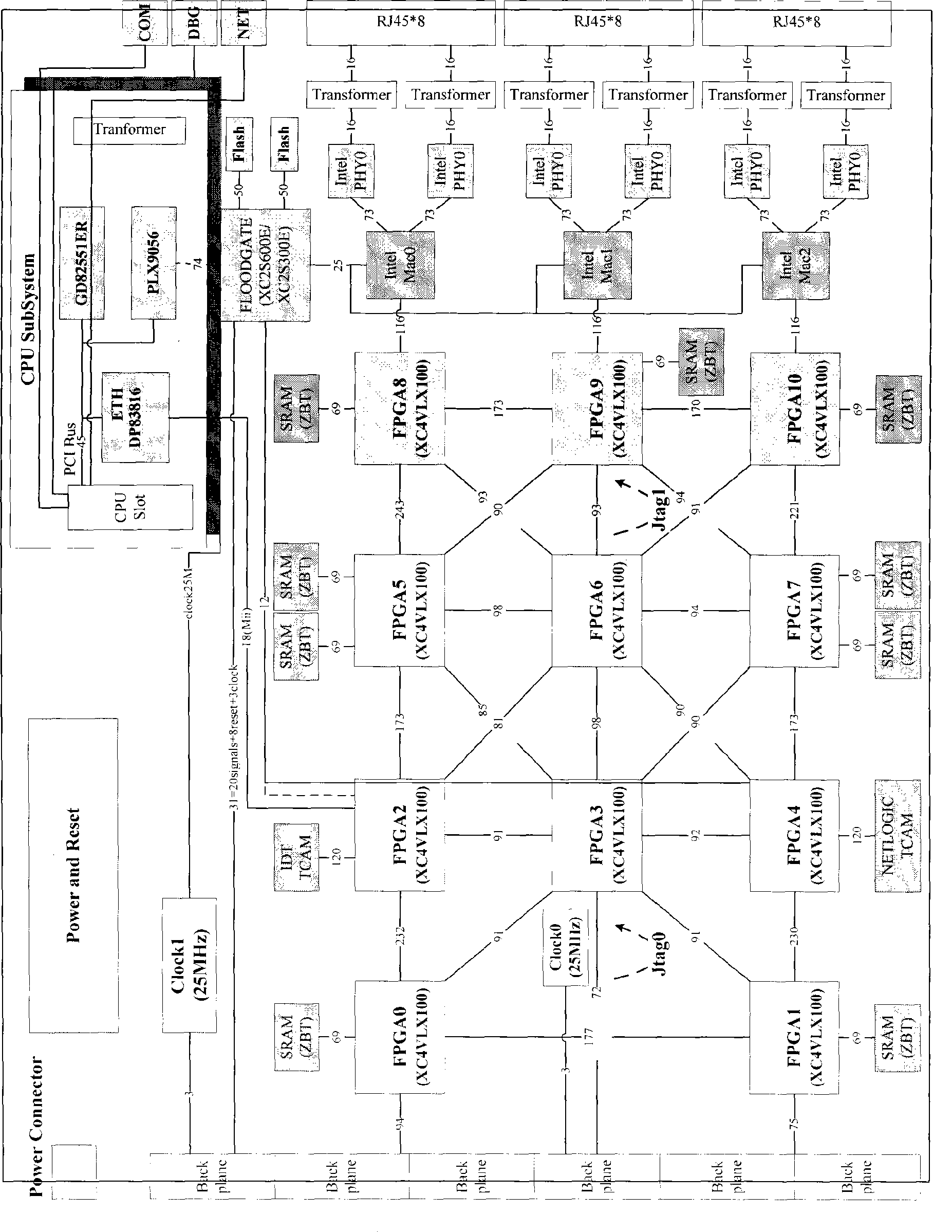

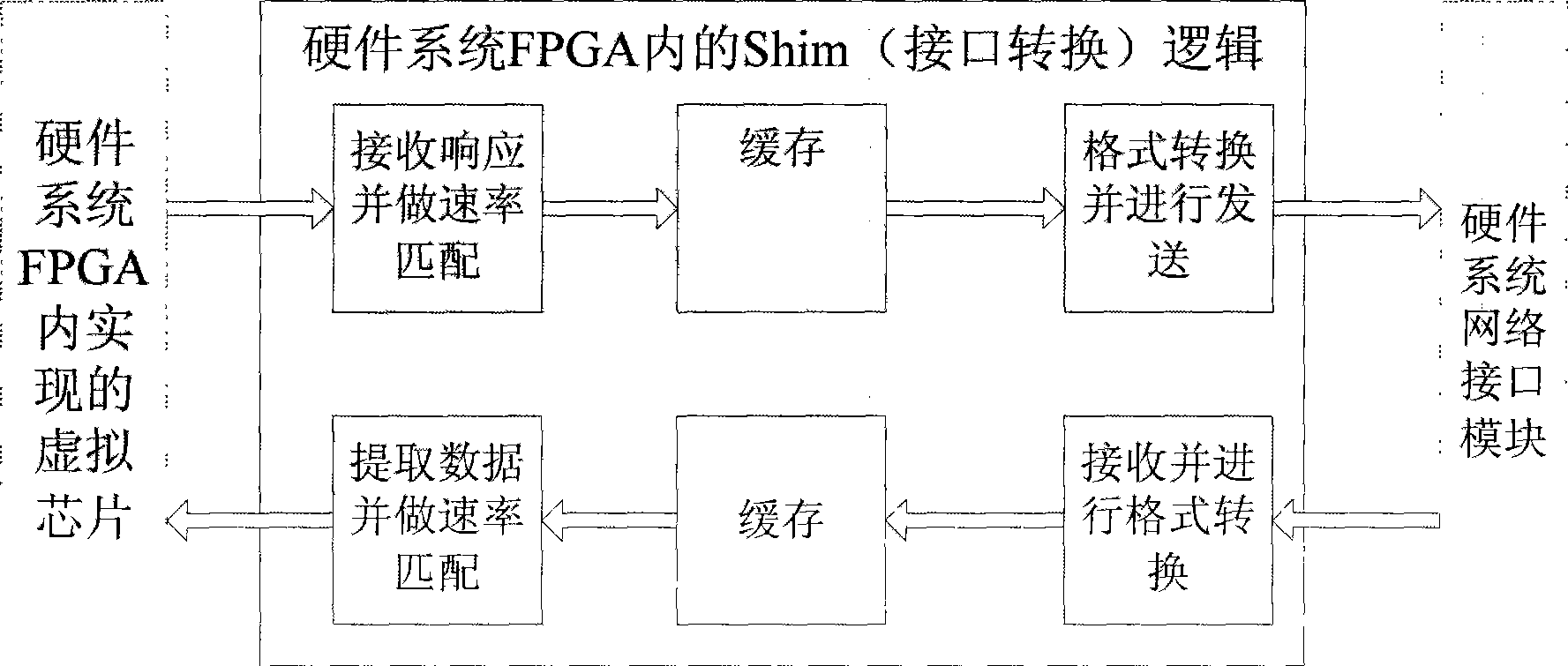

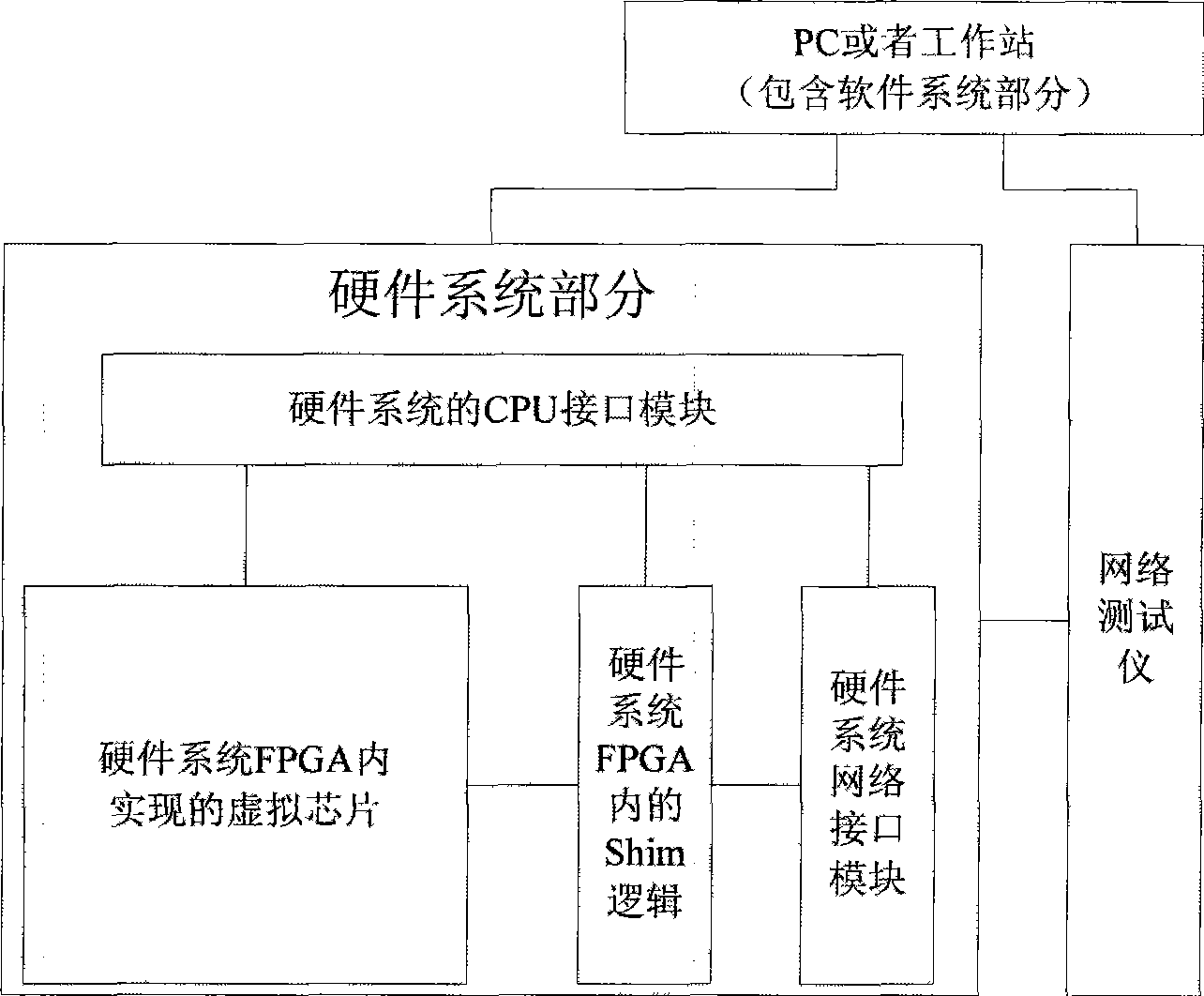

[0042] refer to figure 1 , figure 2 with image 3 , figure 1 It shows the FPGA-based software and hardware co-simulation verification system in the embodiment of the present invention; figure 2 The structure of the hardware system in the FPGA-based software-hardware co-simulation verification system in the embodiment of the present invention is shown; image 3 It shows the logic structure of the interface transformation (Shim) of the hardware system in the FPGA-based software-hardware co-simulation verification system in the embodiment of the present invention.

[0043] Such as figure 1 with figure 2 As shown, the FPGA-based software-hardware co-simulation verification system includes two parts: software system part 1 and hardware system part 2. The software system part mainly refers to the contr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More