Cooperative simulation/verification method and device for software and hardware

A software-hardware collaboration and verification device technology, applied in instrumentation, computing, electrical digital data processing, etc., to reduce costs, accelerate development, and facilitate hardware verification

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

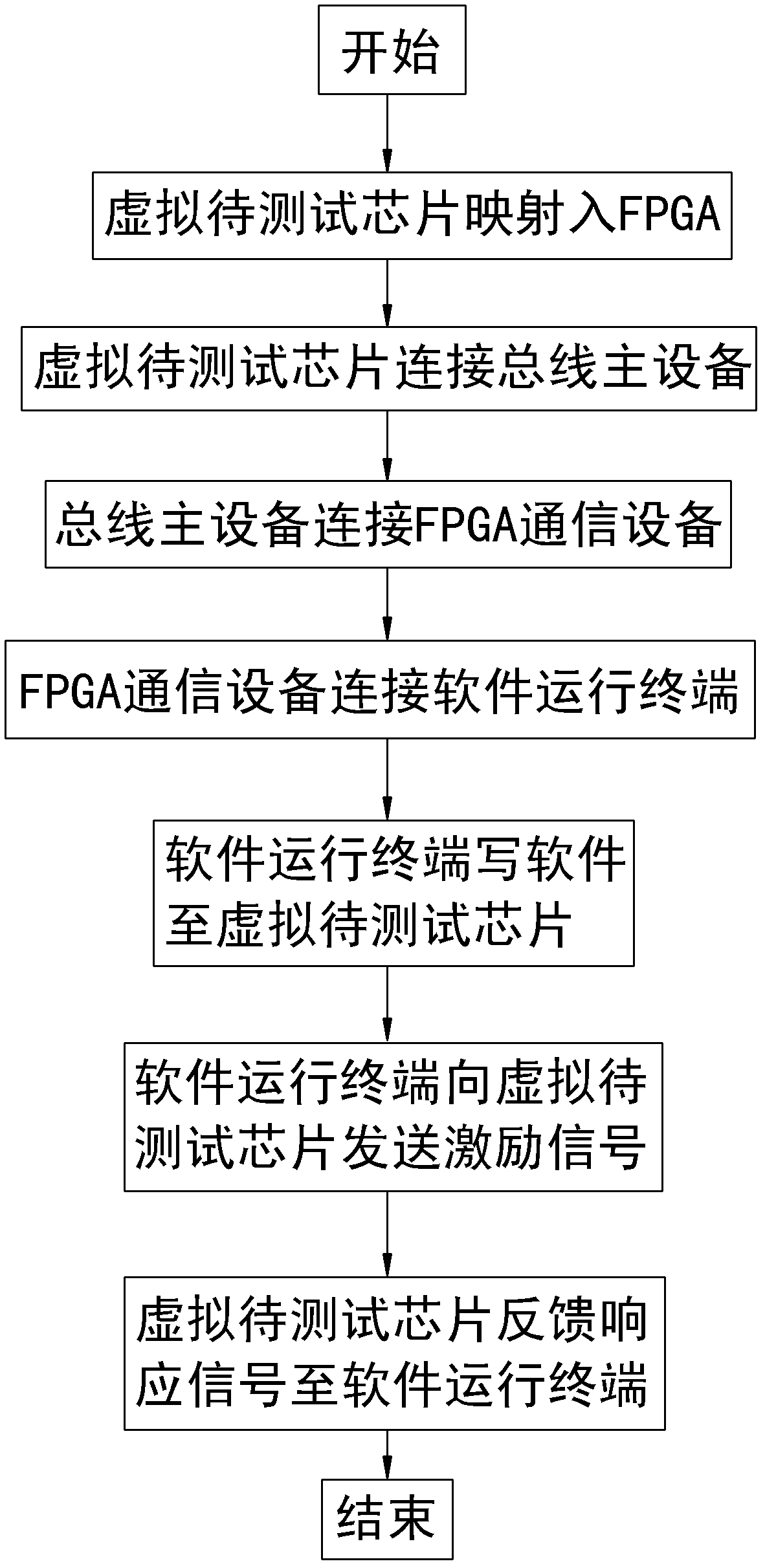

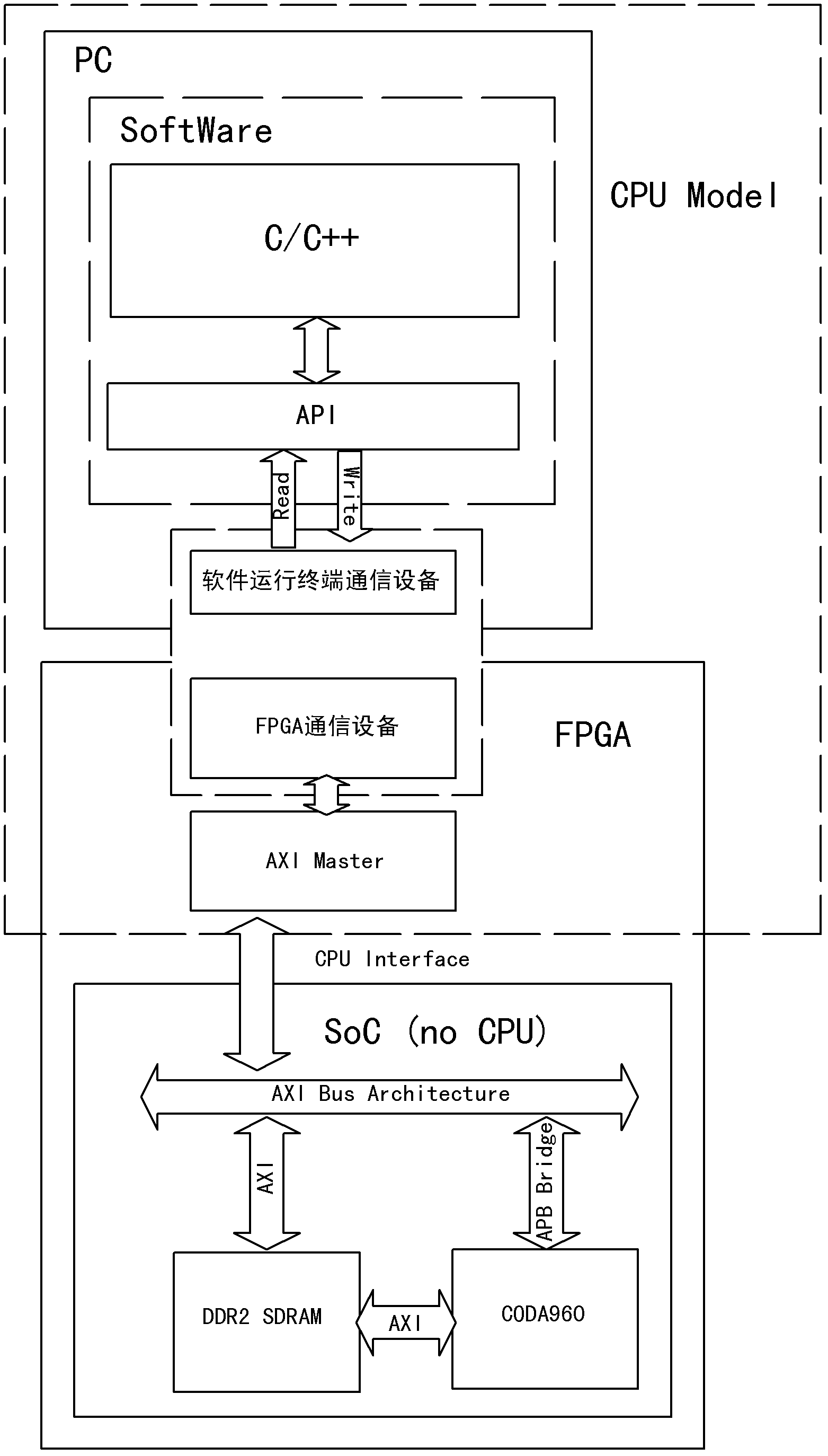

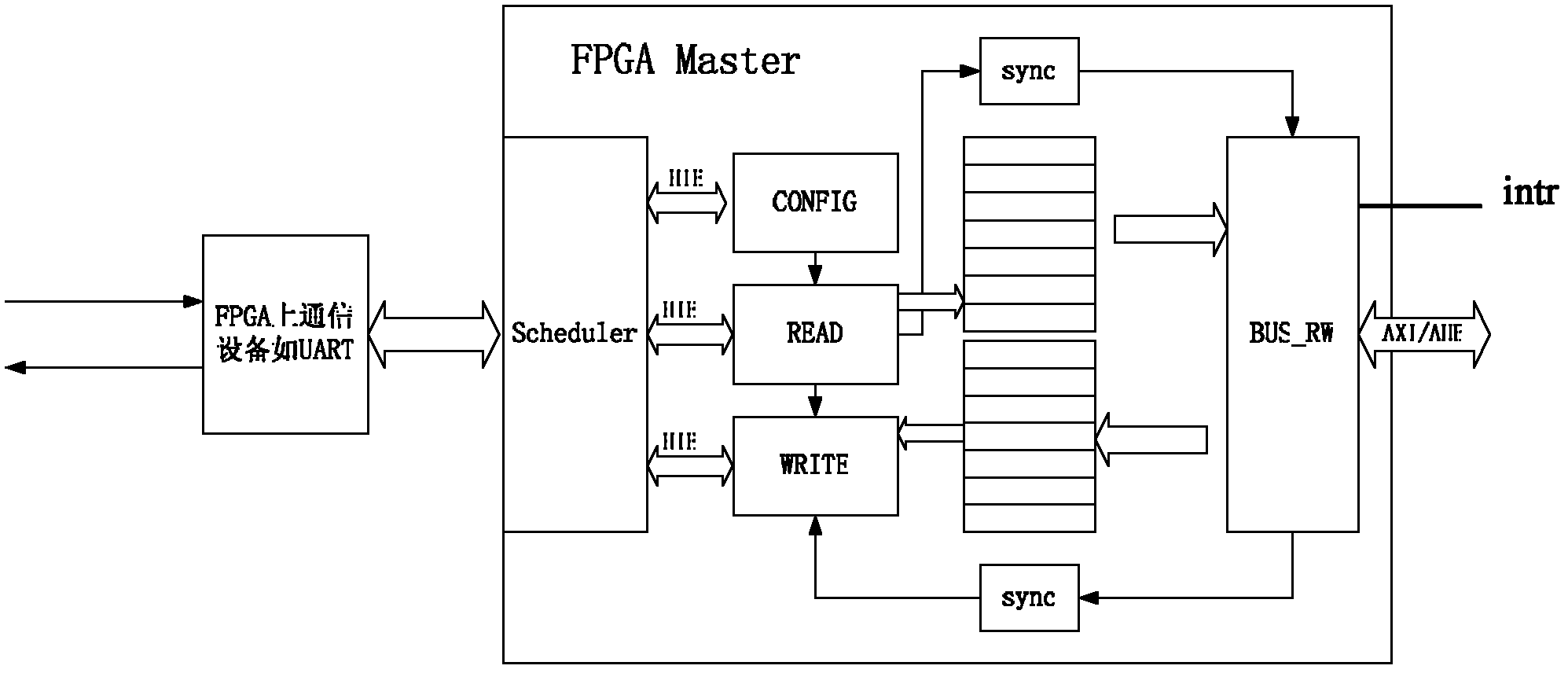

[0055] Preferred Embodiment 1: The SoC design to be verified is mapped in the FPGA by means of burning. The PC is connected to the corresponding USB, serial port or PCI communication device on the FPGA through its USB, serial port, PCI and other communication devices. The FPGA communication device is connected to the bus master, and the bus master is connected to the SoC design. The PC successfully emulates the CPU in the SoC. SoC is designed as the realization of other hardware parts except CPU in FPGA, including on-chip bus (AXI, AHB, etc.), and various IPs with on-chip bus interface.

[0056] Use a C / C++ compiler in the PC environment (such as GNU GCC, etc.) to compile the SoC software into a binary file whose target machine is a PC, develop and run the USB IP driver software required by the SoC design. The PC sends a stimulus signal to the SoC design, and the SoC design responds to the stimulus signal and feeds a response signal back to the PC. Run the SoC software on th...

Embodiment 2

[0059] Preferred Embodiment 2: Take the application of the software-hardware co-simulation / verification device of the present invention in DDRII SDRAM IP (intellectual property core) verification as an example to illustrate the process of hardware verification.

[0060] Compile the SoC without CPU including DDRII SDRAM IP with the compilation tool QuartusII corresponding to FPGA and download it into FPGA, then this FPGA is equivalent to the actual chip of SoC.

[0061] Connect the FPGA to the software running terminal PC. The specific method of connection is: the communication device of FPGA and the communication device of software running terminal are connected to form a communication unit together to realize the information transmission between FPGA and software running terminal.

[0062] Use c / c++ to write driver software on the software running terminal. If you need to access the SoC registers in the FPGA, use the ReadAPI / WriteAPI provided by this device, and wait for the...

Embodiment 3

[0065] Preferred Embodiment Three: The process of hardware verification is illustrated by taking the application of the software-hardware co-simulation / verification device of the present invention in DDRII SDRAM IP (intellectual property core) verification as an example.

[0066] Compile the CPU-less SoC with DDRII SDRAM IP using the compiling tool ISE corresponding to the FPGA and download it into the FPGA, then this FPGA is equivalent to the actual chip of the SoC.

[0067] Connect the FPGA to the software running terminal PC. The specific method of connection is: the communication device of FPGA and the communication device of software running terminal are connected to form a communication unit together to realize the information transmission between FPGA and software running terminal.

[0068] Use c / c++ to write driver software on the software running terminal. If you need to access the SoC memory in the FPGA, use the ReadAPI / WriteAPI provided by this device, and wait for...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More