Patents

Literature

207results about How to "Raise check" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

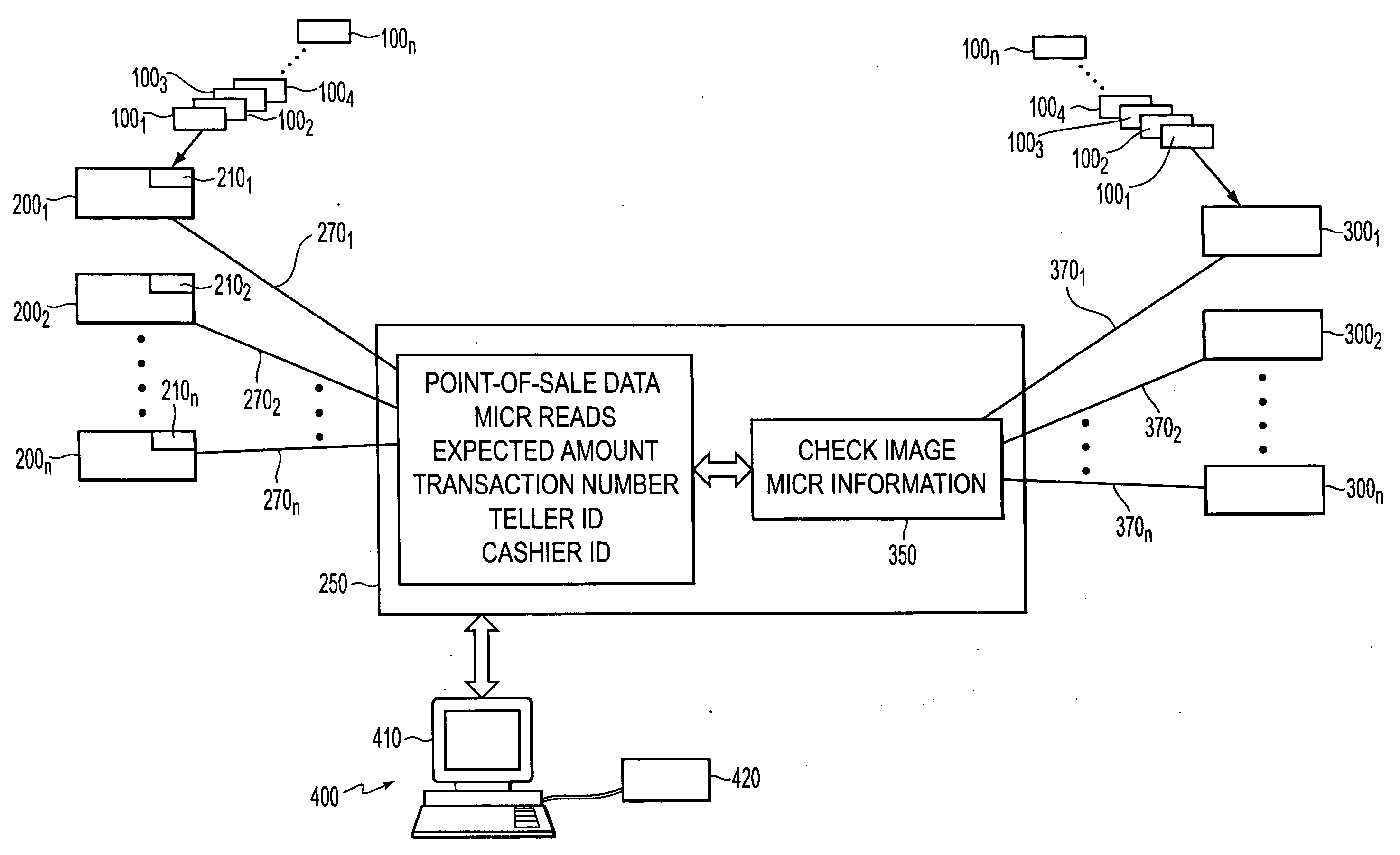

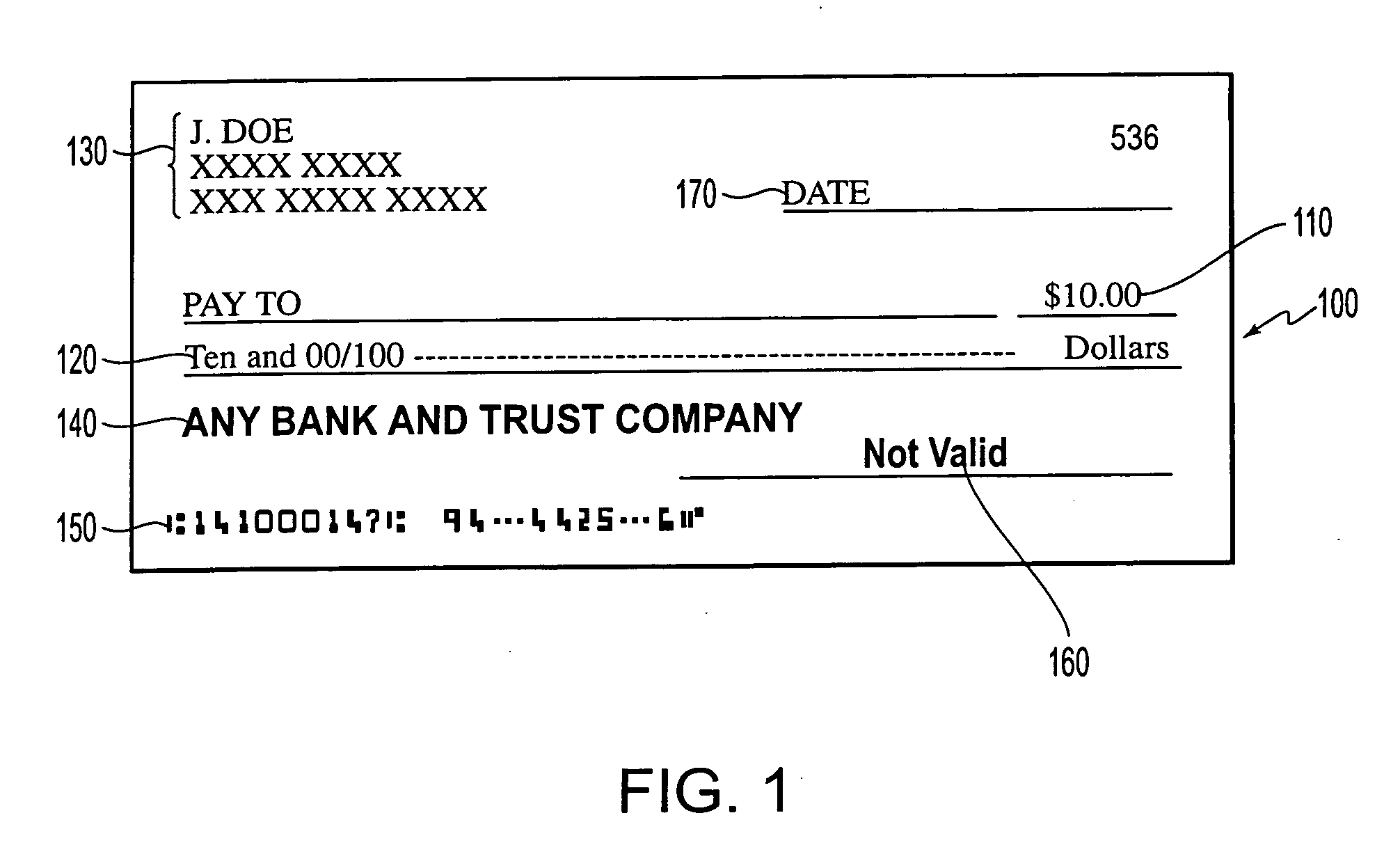

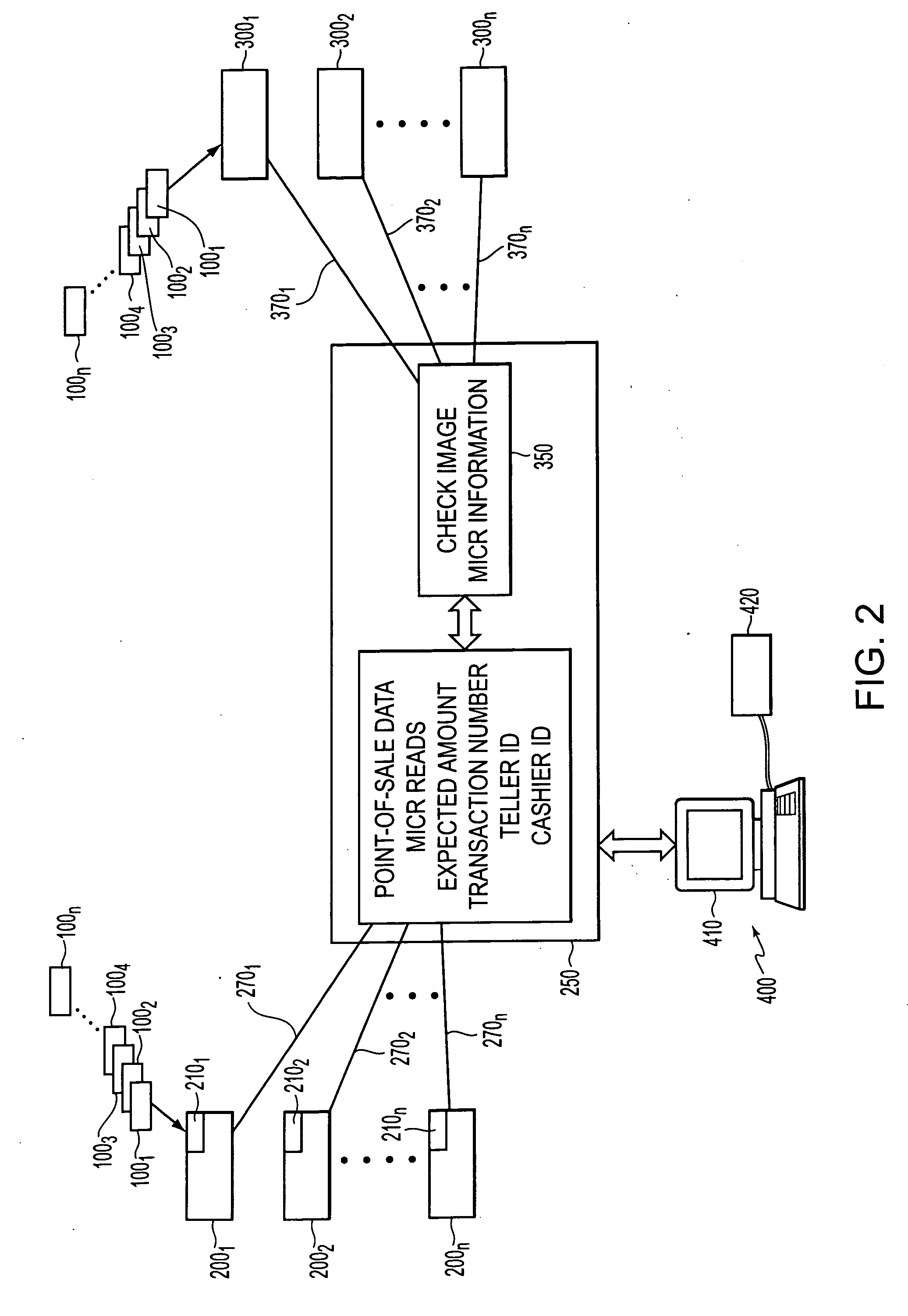

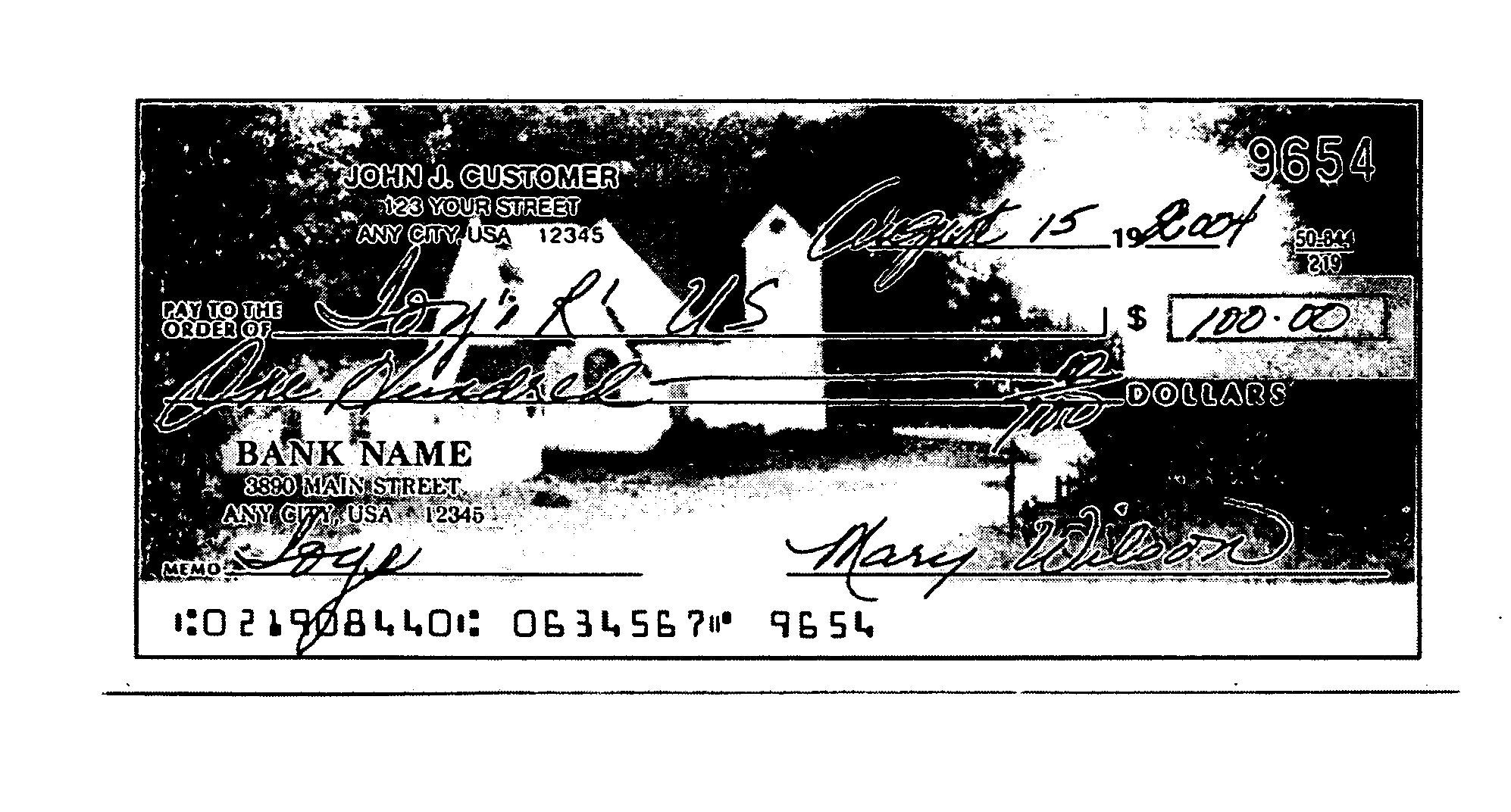

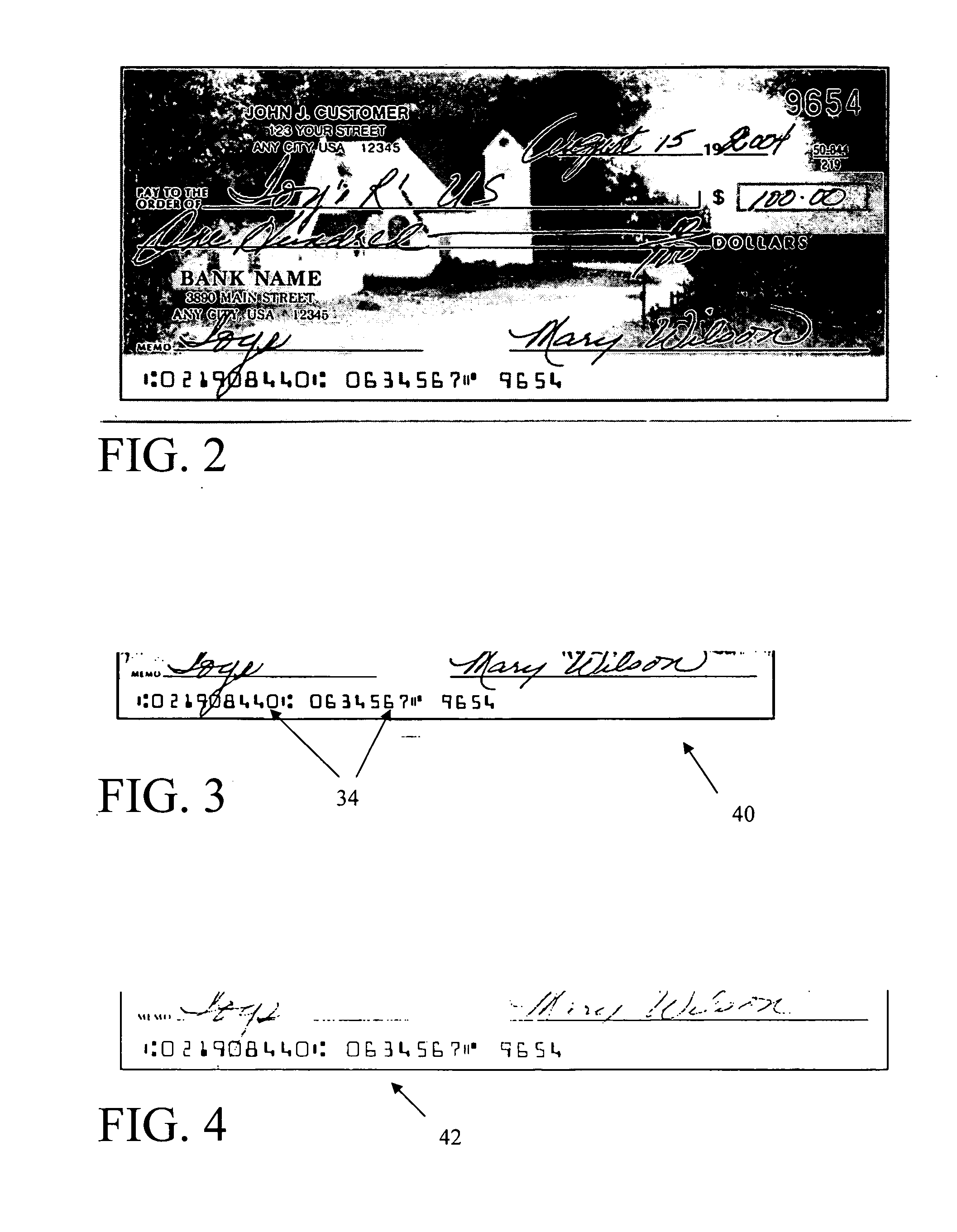

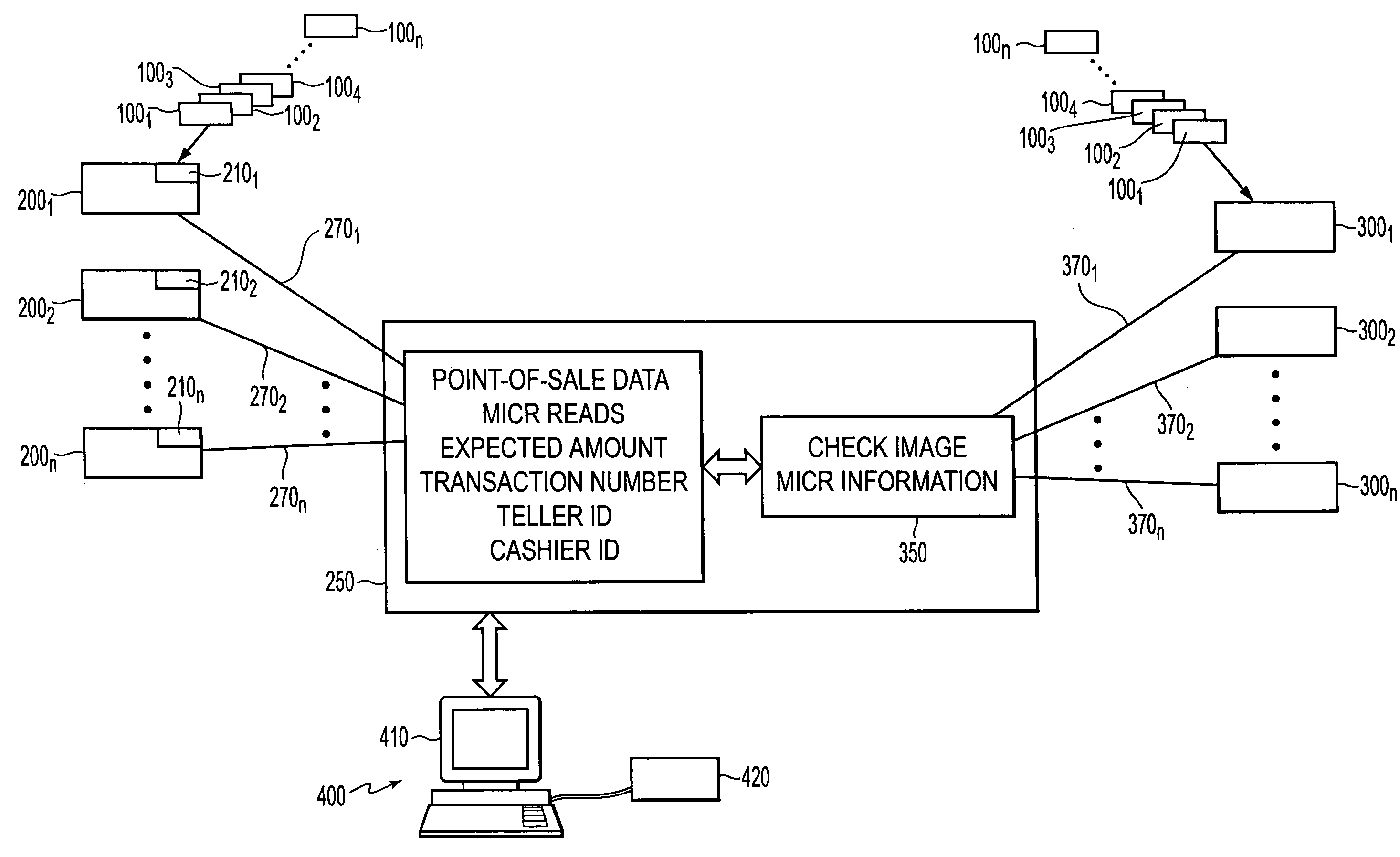

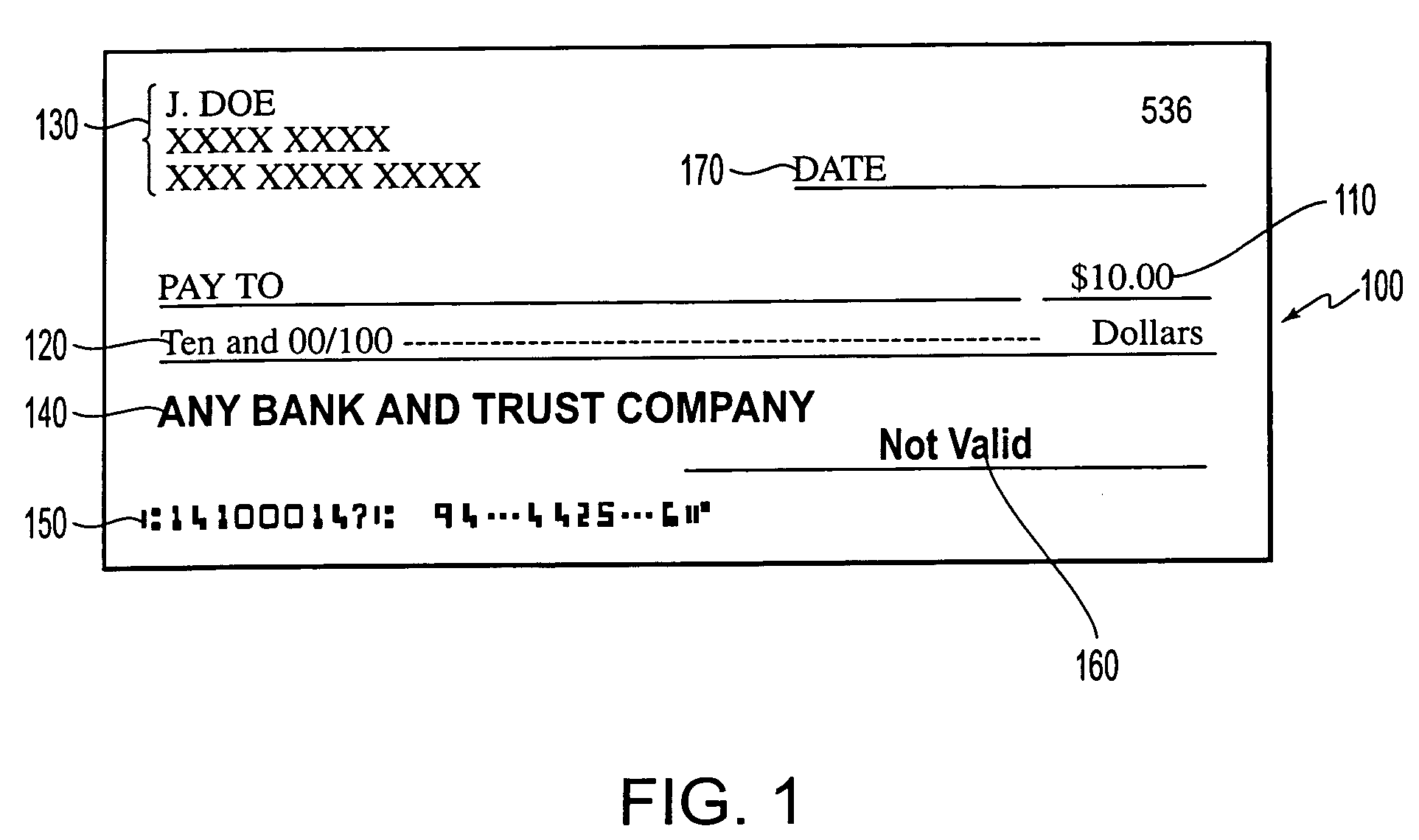

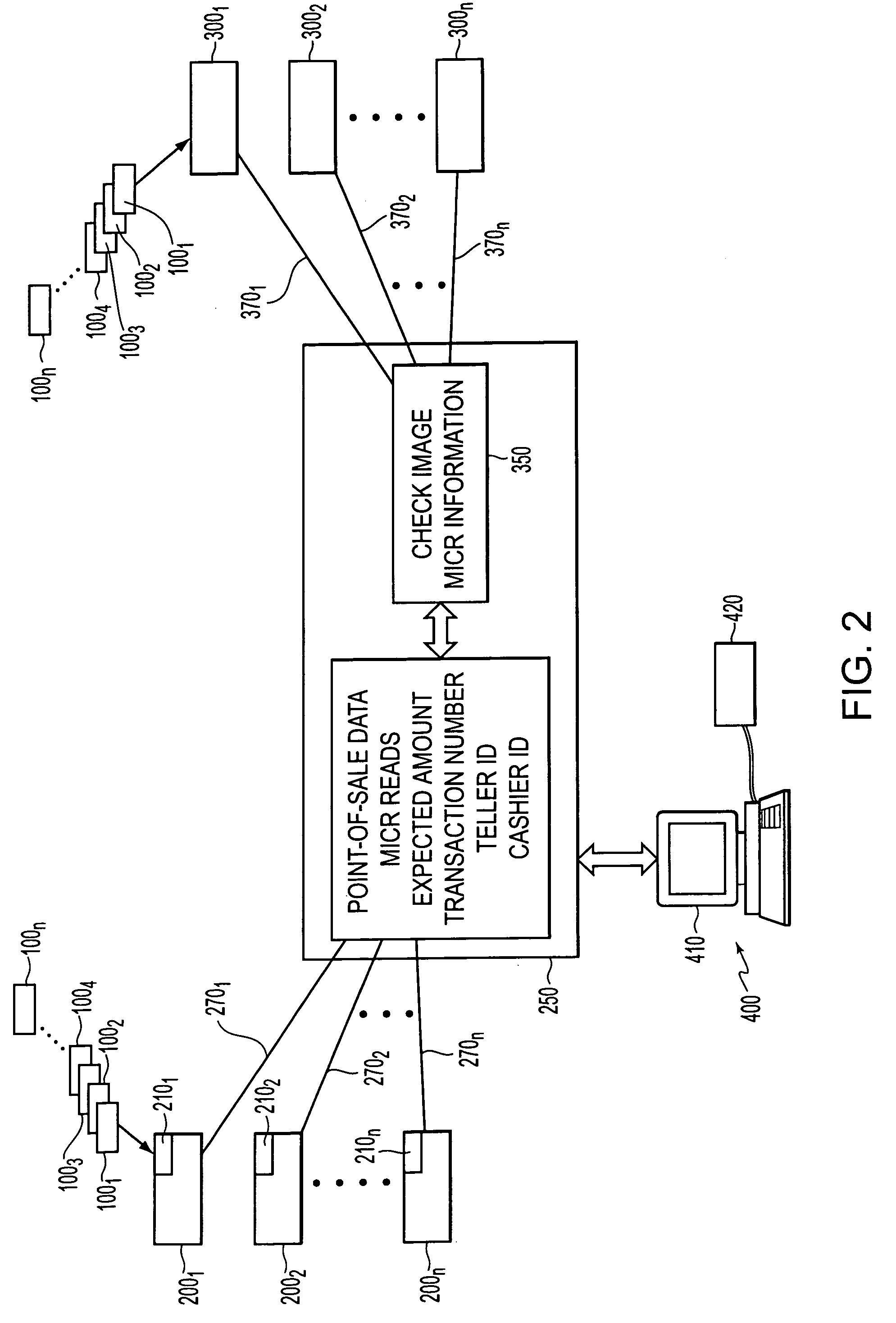

Method and apparatus for processing checks

ActiveUS20050108168A1Reduce physical activityImprove process integrityComplete banking machinesFinanceAlgorithmCheque

A check processing system and method comprising utilizes an image scanner that produces an electronic image of a check upon scanning of the check. The system and method receive the electronic image of the check from the image scanner, receive point-of-sale data generated at a point-of-sale, determine a monetary value of the check from the electronic image of the check, and reconcile the determined monetary value of the check with the point-of-sale data so that the check is correlated with a transaction that occurred at the point-of-sale.

Owner:TALARIS HLDG

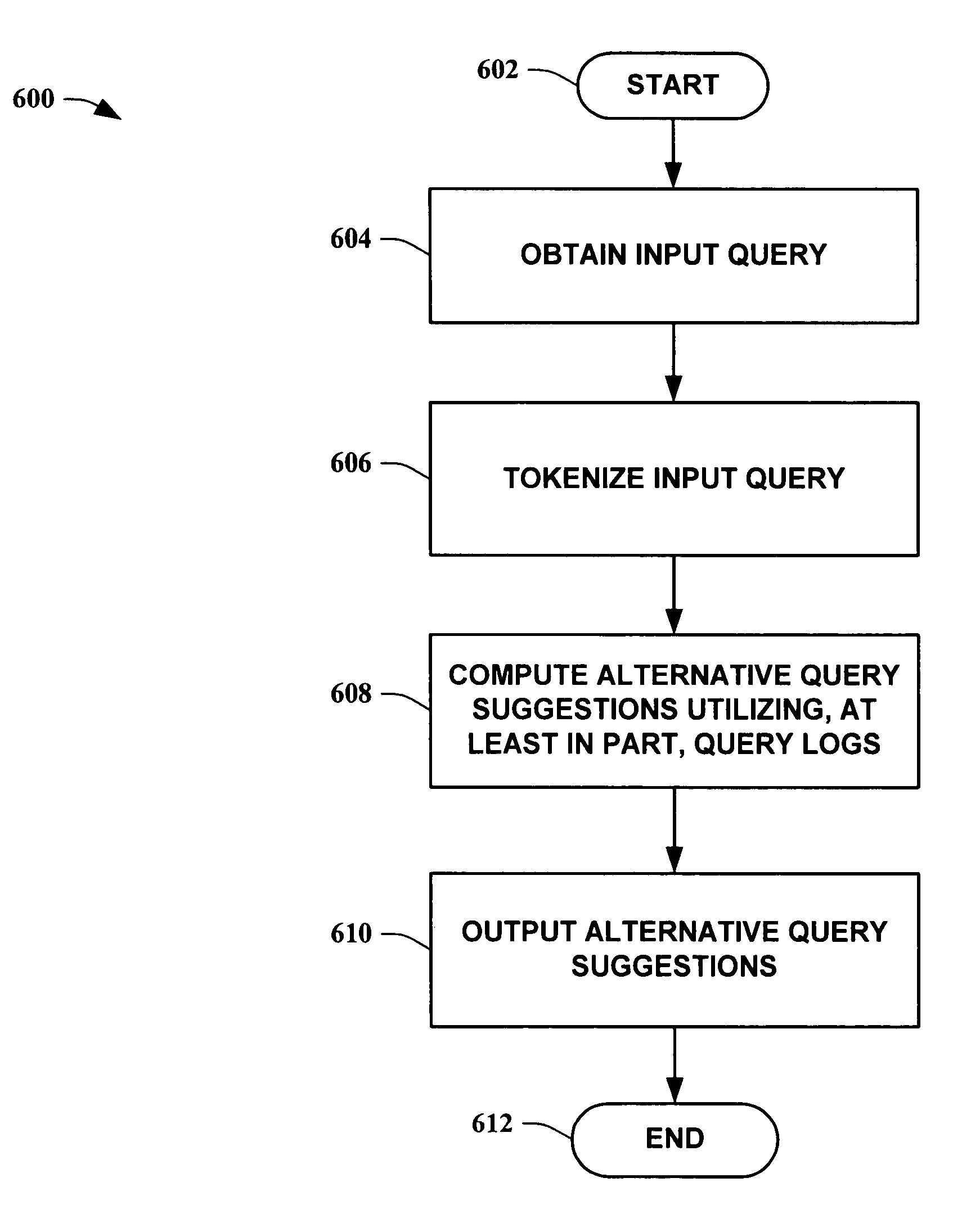

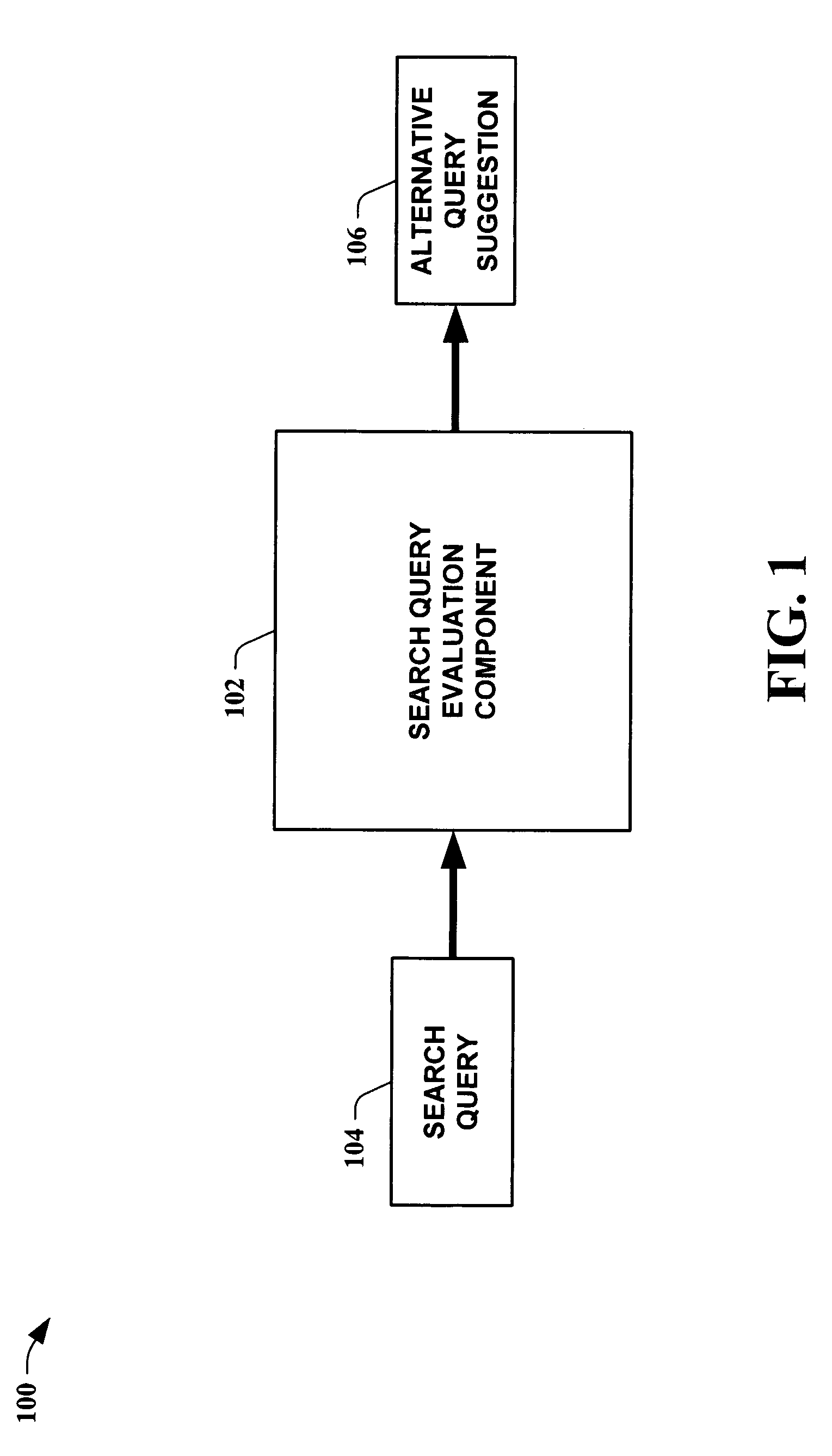

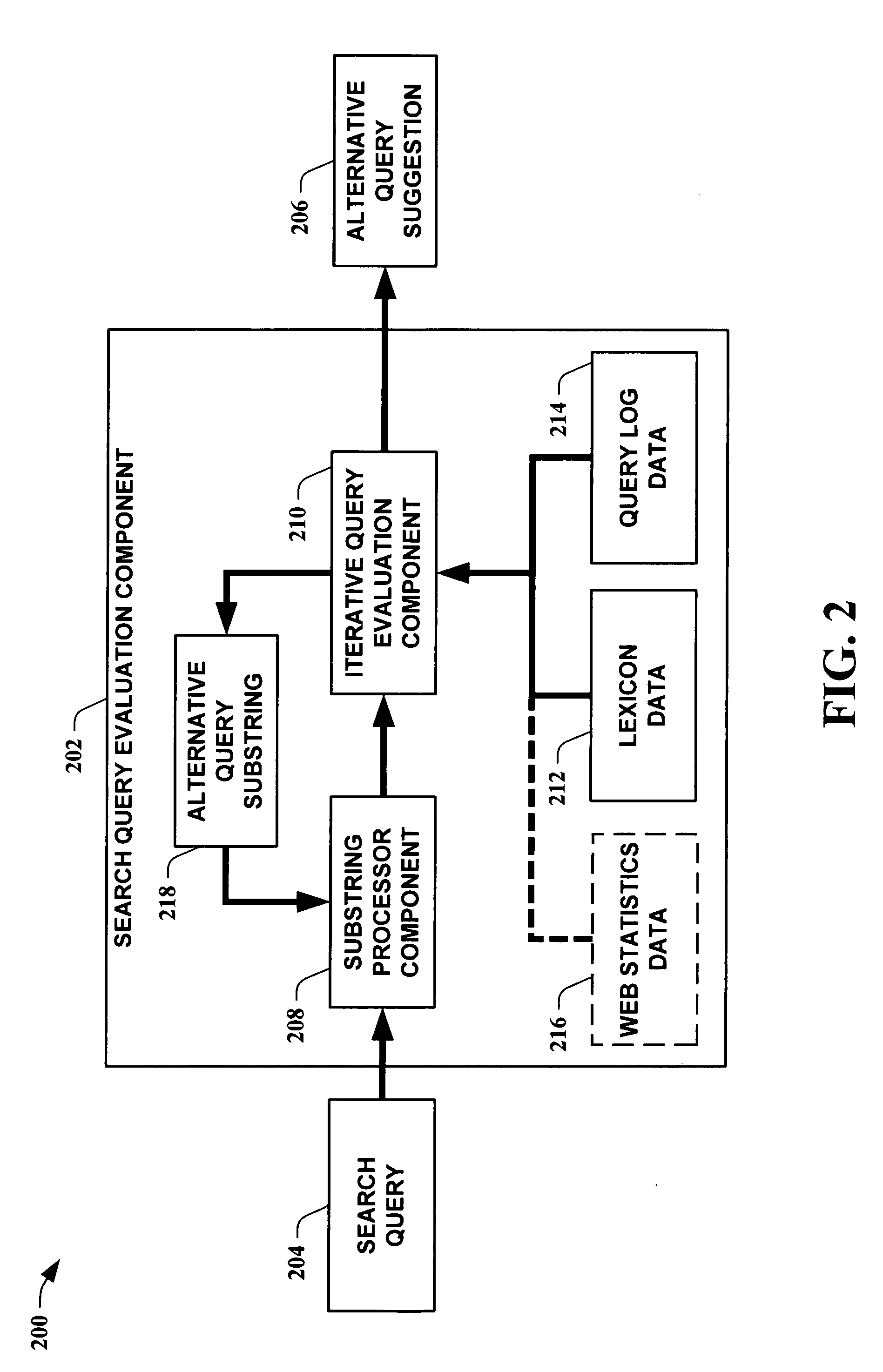

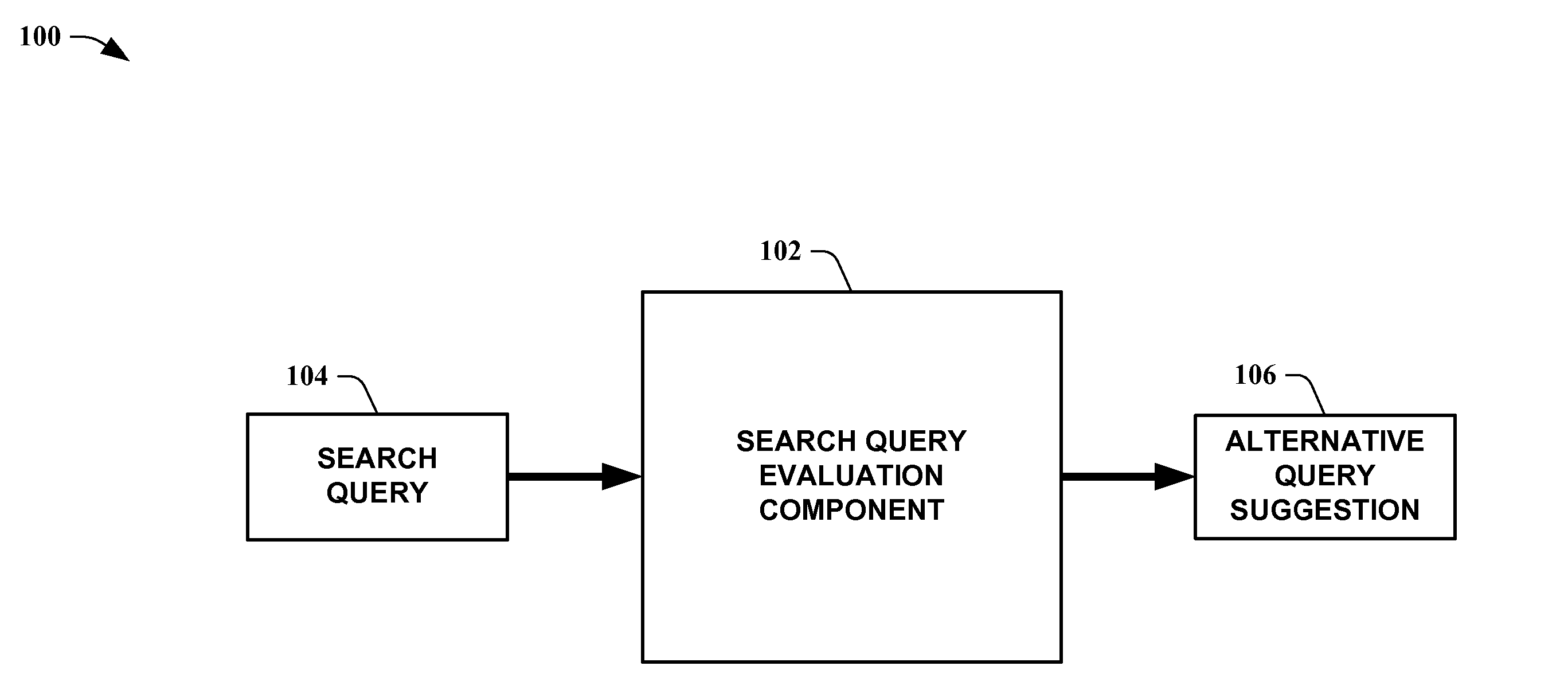

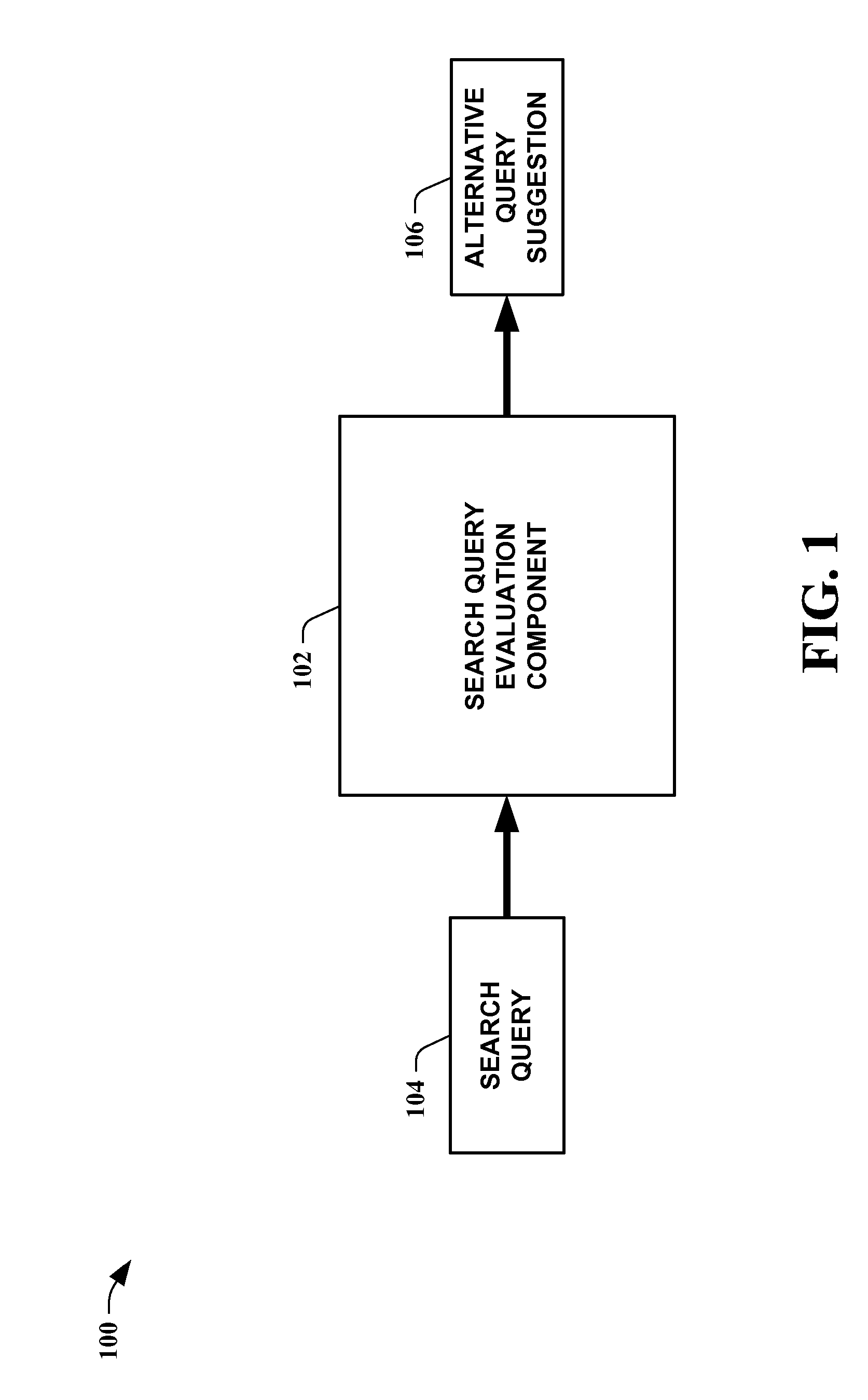

Systems and methods for improved spell checking

InactiveUS20050210383A1Improving spell checkingSpelling alternativeDry-dockingDigital data information retrievalPersonalizationIterative search

The present invention leverages iterative transformations of search query strings along with statistics extracted from search query logs and / or web data to provide possible alternative spellings for the search query strings. This provides a spell checking means that can be influenced to provide individualized suggestions for each user. By utilizing search query logs, the present invention can account for substrings not found in a lexicon but still acceptable as a search query of interest. This allows a means to provide a higher quality proposal for alternative spellings, beyond the content of the lexicon. One instance of the present invention operates at a substring level by utilizing word unigram and / or bigram statistics extracted from query logs combined with an iterative search. This provides substantially better spelling alternatives for a given query than employing only substring matching. Other instances can receive input data from sources other than a search query input.

Owner:MICROSOFT TECH LICENSING LLC

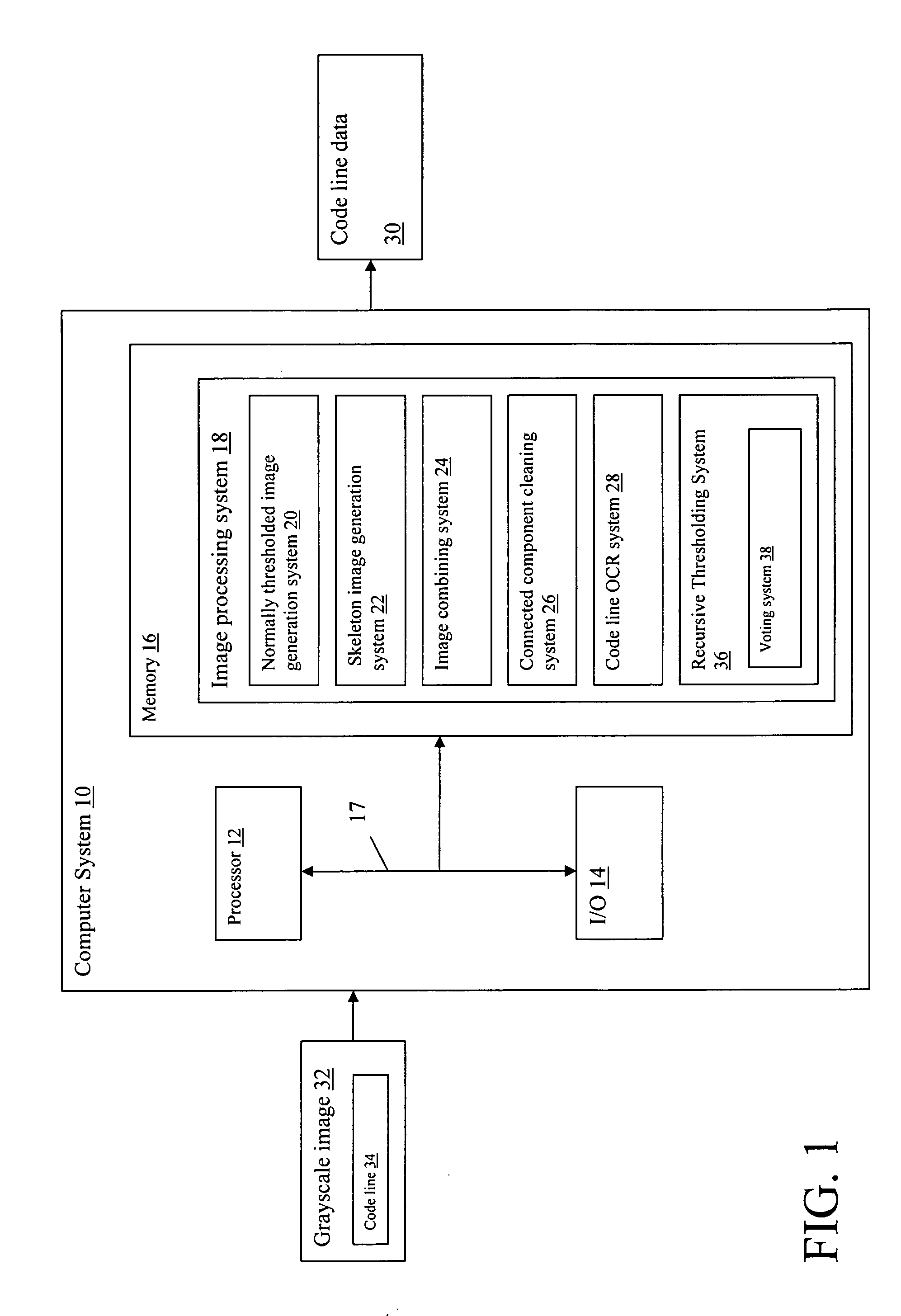

Gray scale image cleaning system and method

ActiveUS20070041629A1Improved check code line OCRRaise the thresholdCharacter recognitionImaging processingComputer science

A gray scale image cleaning algorithm for improved check code line OCR. An image processing system for processing a gray scale image is provided that includes: a system for generating a first thresholded black white image from the gray scale image; a system for generating a second thresholded black white image from the gray scale image, wherein the second thresholded black white image is generated with a higher threshold value than the first thresholded black white image; and a system for logically combining the first and second thresholded black white images to generate a composite image.

Owner:IBM CORP

Systems and methods for improved spell checking

InactiveUS20070106937A1Raise checkQuality improvementDry-dockingDigital data information retrievalPersonalizationQuery string

The present invention leverages iterative transformations of search query strings along with statistics extracted from search query logs and / or web data to provide possible alternative spellings for the search query strings. This provides a spell checking means that can be influenced to provide individualized suggestions for each user. By utilizing search query logs, the present invention can account for substrings not found in a lexicon but still acceptable as a search query of interest. This allows a means to provide a higher quality proposal for alternative spellings, beyond the content of the lexicon. One instance of the present invention operates at a substring level by utilizing word unigram and / or bigram statistics extracted from query logs combined with an iterative search. This provides substantially better spelling alternatives for a given query than employing only substring matching. Other instances can receive input data from sources other than a search query input.

Owner:MICROSOFT TECH LICENSING LLC

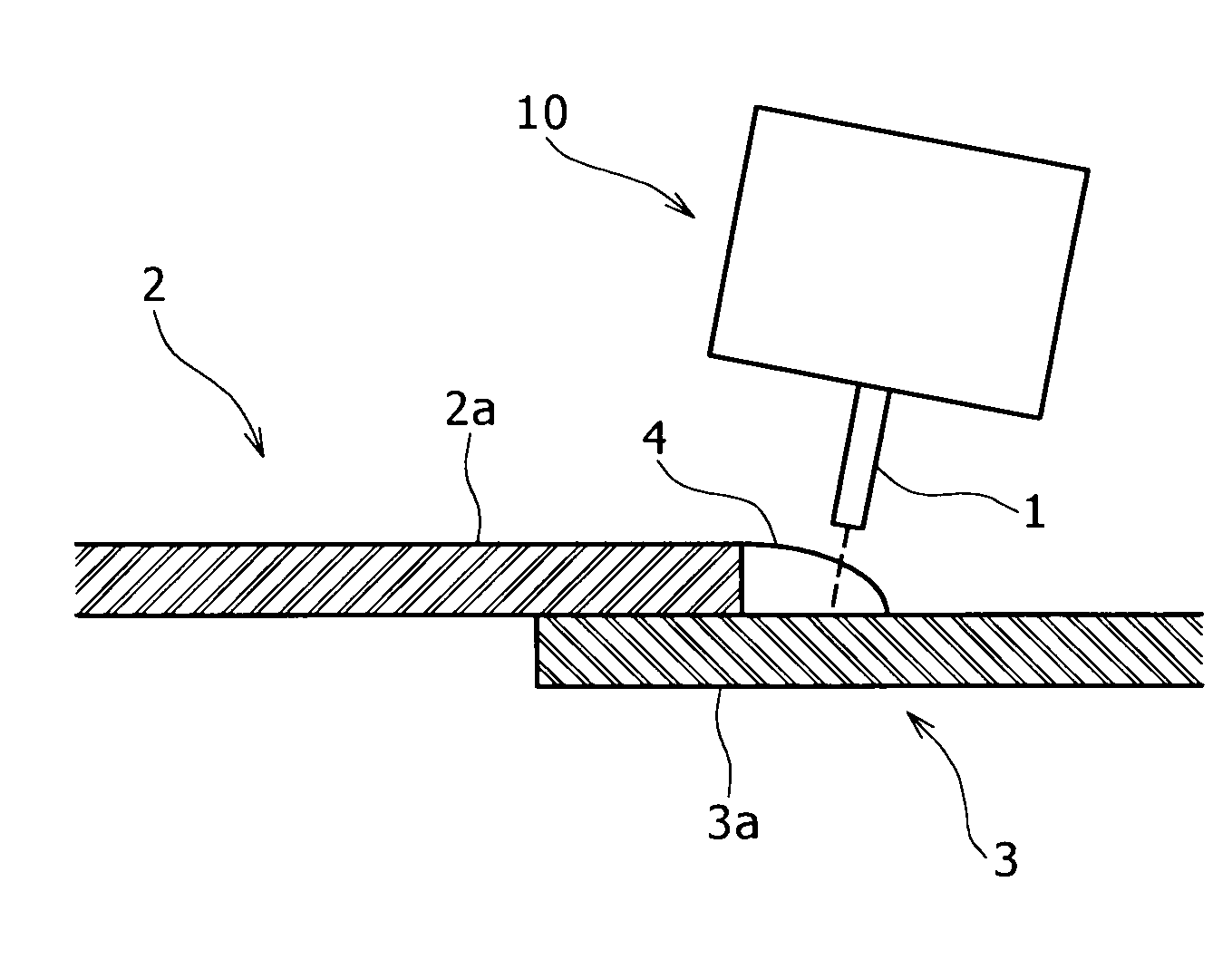

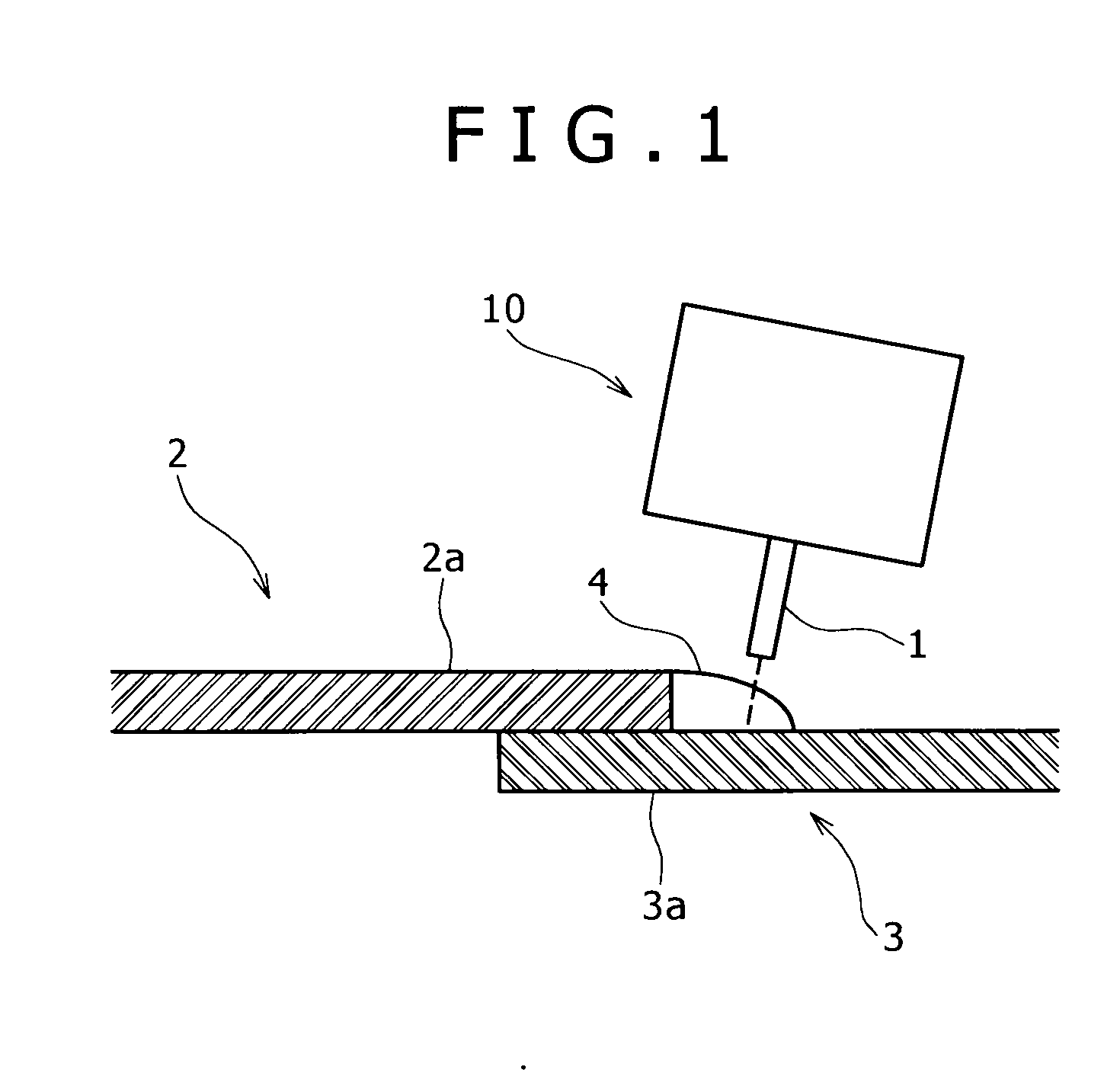

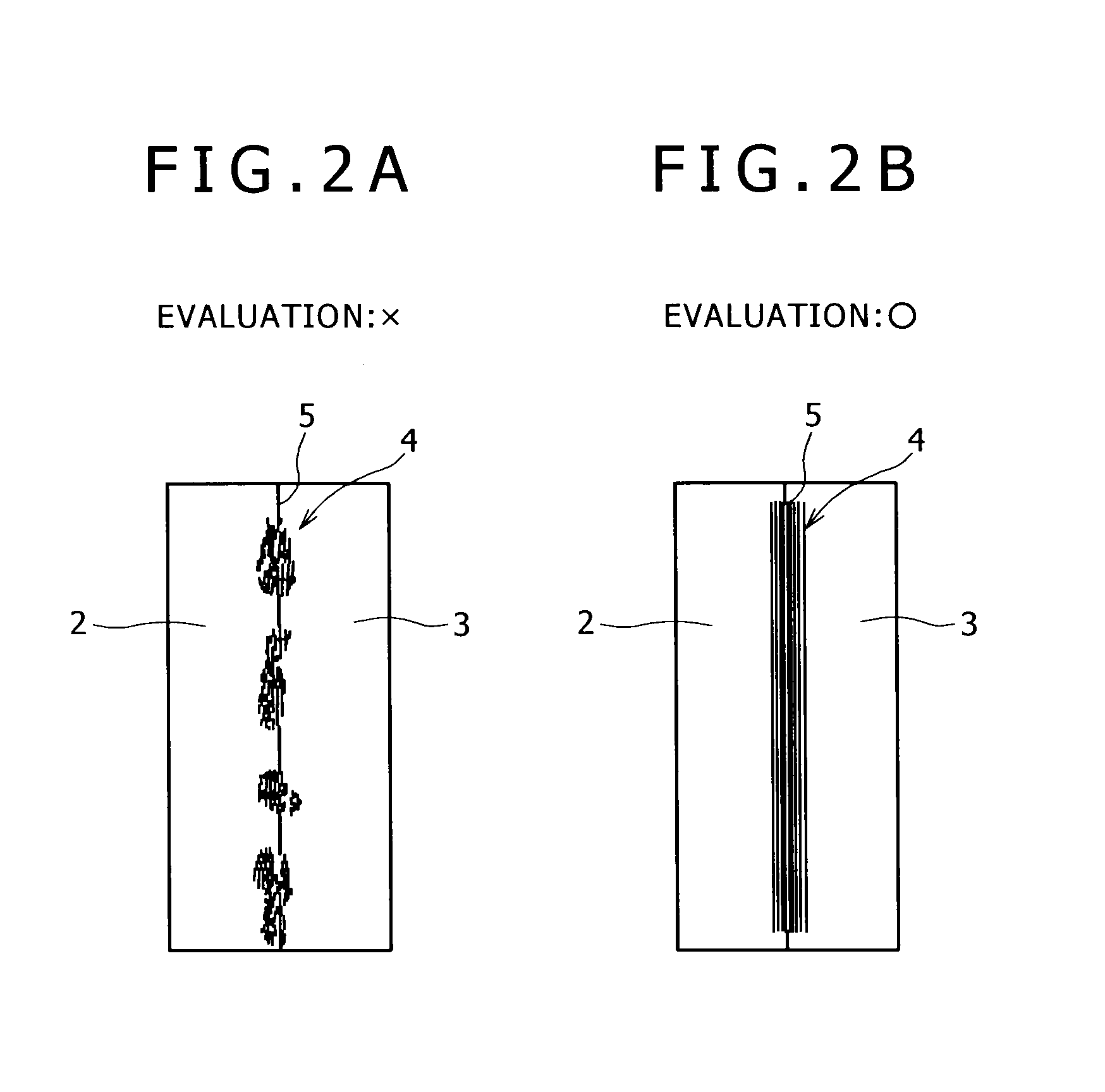

Flux-cored wire for different-material bonding and method of bonding different materials

InactiveUS20090017328A1High bonding strengthRaise checkHot-dipping/immersion processesArc welding apparatusHigh intensityChloride

There are provided a flux cored wire for joining dissimilar materials with each other, capable of enhancing a bonding strength upon joining an aluminum-base material with a steel-base material, and excellent in bonding efficiency, a method for joining the dissimilar materials with each other, and a bonded joint obtained by the method. In particular, there is provided a method for joining dissimilar materials with each other, in the case of melt weld-bonding of high-strength dissimilar materials with each other, that is, the high-strength steel member with the high-strength 6000 series aluminum alloy member and in the case of the steel member being a galvanized steel member. In one mode, use is made of a flux cored wire wherein the interior of an aluminum alloy envelope is filled up with a flux, the flux has fluoride composition containing a given amount of AlF3 without containing chloride, and the aluminum alloy of the envelope contains Si in a range of 1 to 13 mass %. If such a flux cored wire is use, it is possible to obtain a high bonding strength in the case of melt weld-bonding of high-strength dissimilar materials with each other, that is, the high-strength steel member with the high-strength 6000 series aluminum alloy member.

Owner:KOBE STEEL LTD

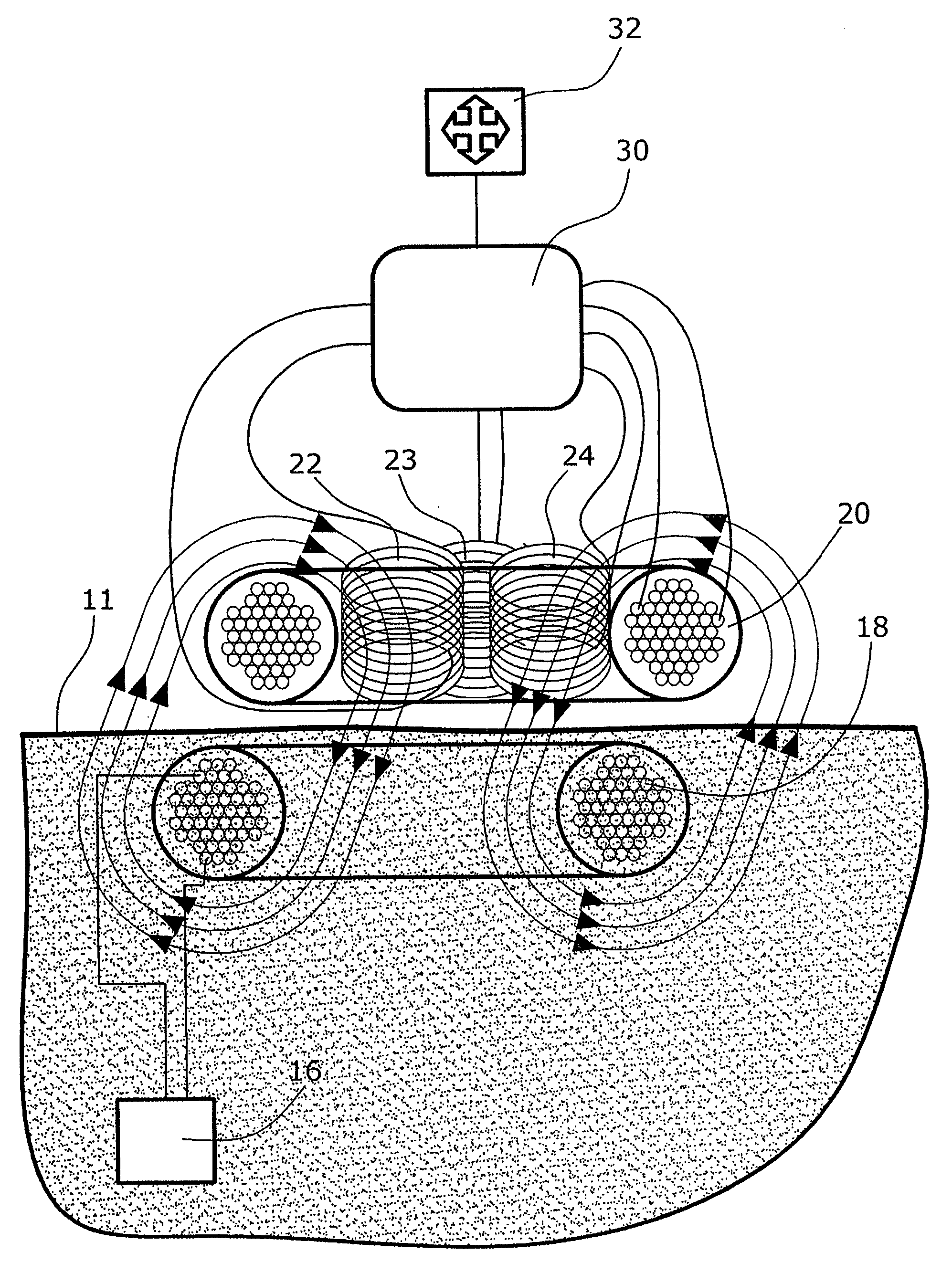

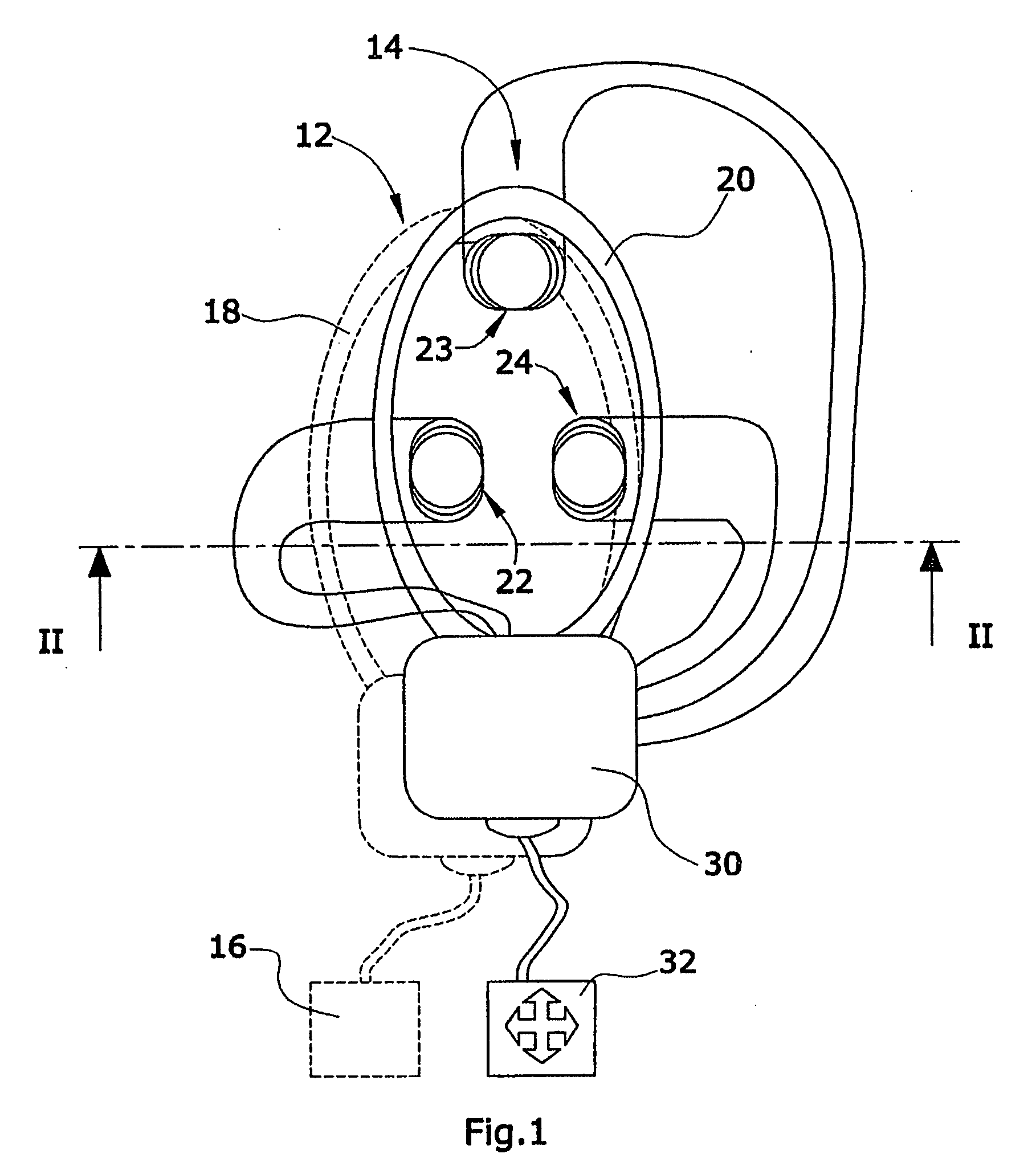

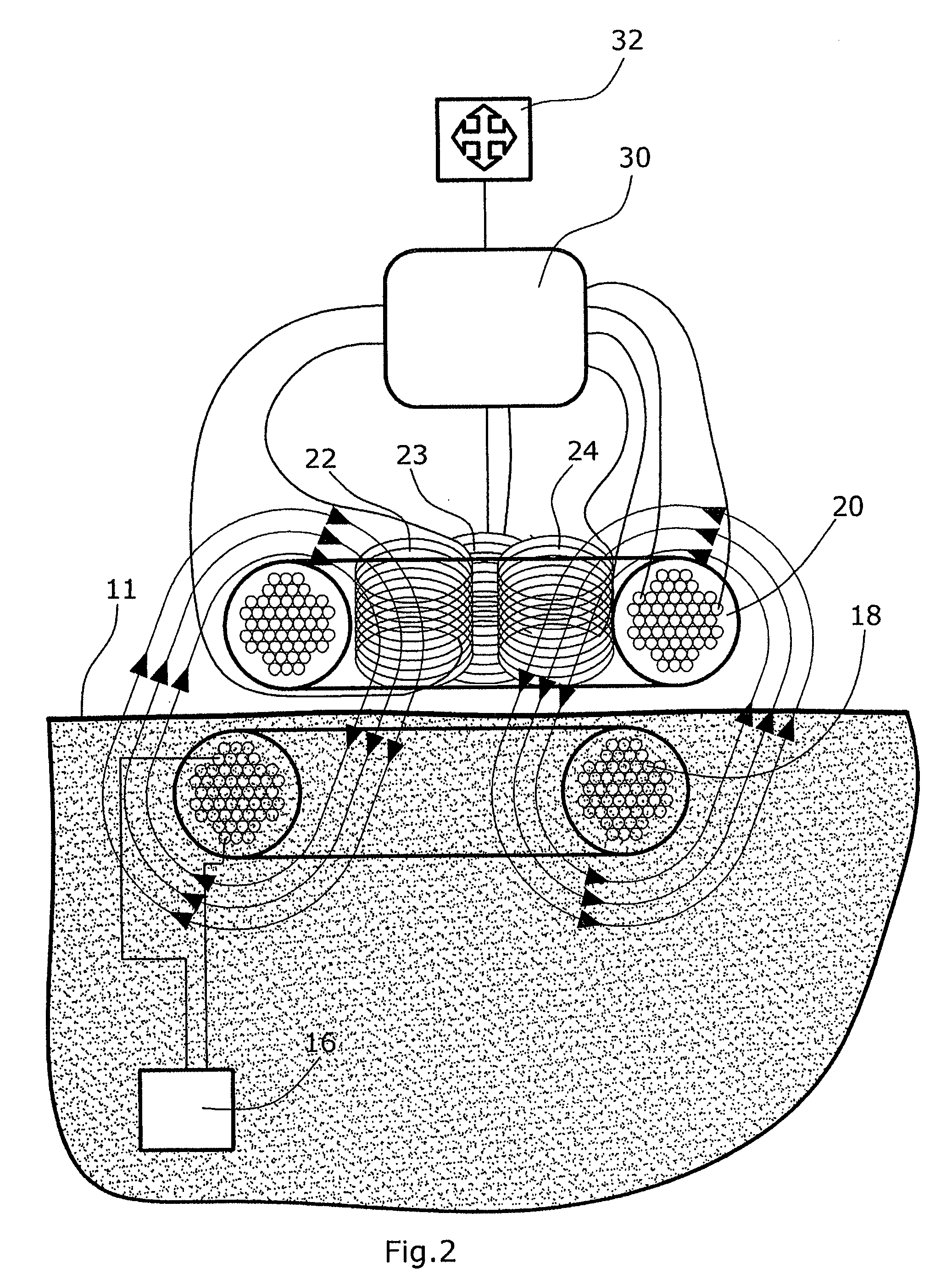

Transfer assembly

ActiveUS20080027293A1Easy transferRaise checkElectrotherapyCircuit arrangementsElectrical and Electronics engineeringEngineering

A transfer assembly comprising an intracorporeal transfer coil of an implant, and an extracorporeal transfer coil of an extracorporeal supply unit. The transfer coil of the implant has permanently associated therewith a transmitting element. The transfer coil of the supply unit has permanently associated therewith at least one receiving element. Further, the supply unit comprises an evaluation module connected with the receiving element and issuing a locating signal depending on an offset and / or a direction of offset of the transmitting element relative to the receiving element.

Owner:DEUTSCHES ZENTRUM FUER LUFT & RAUMFAHRT EV

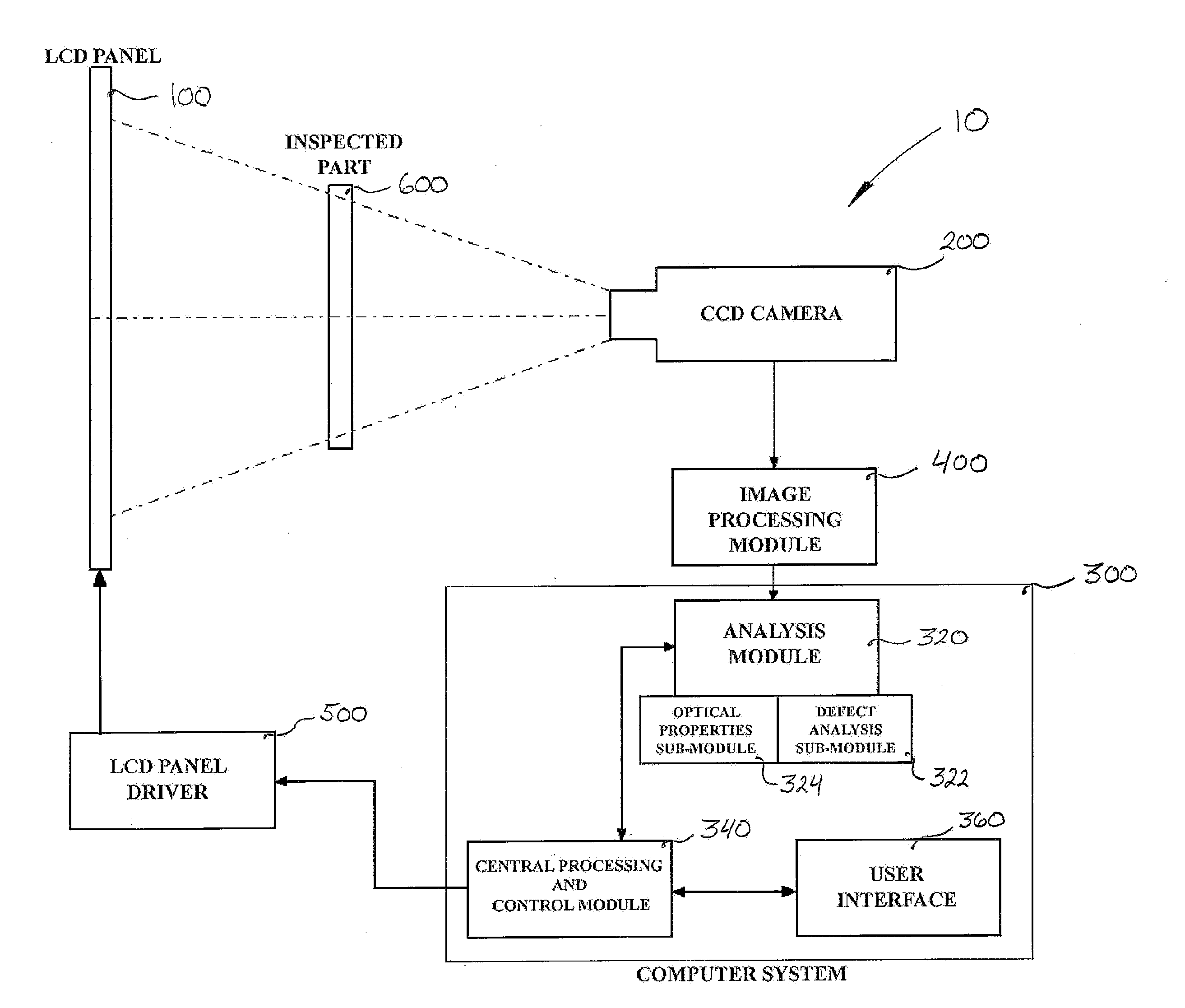

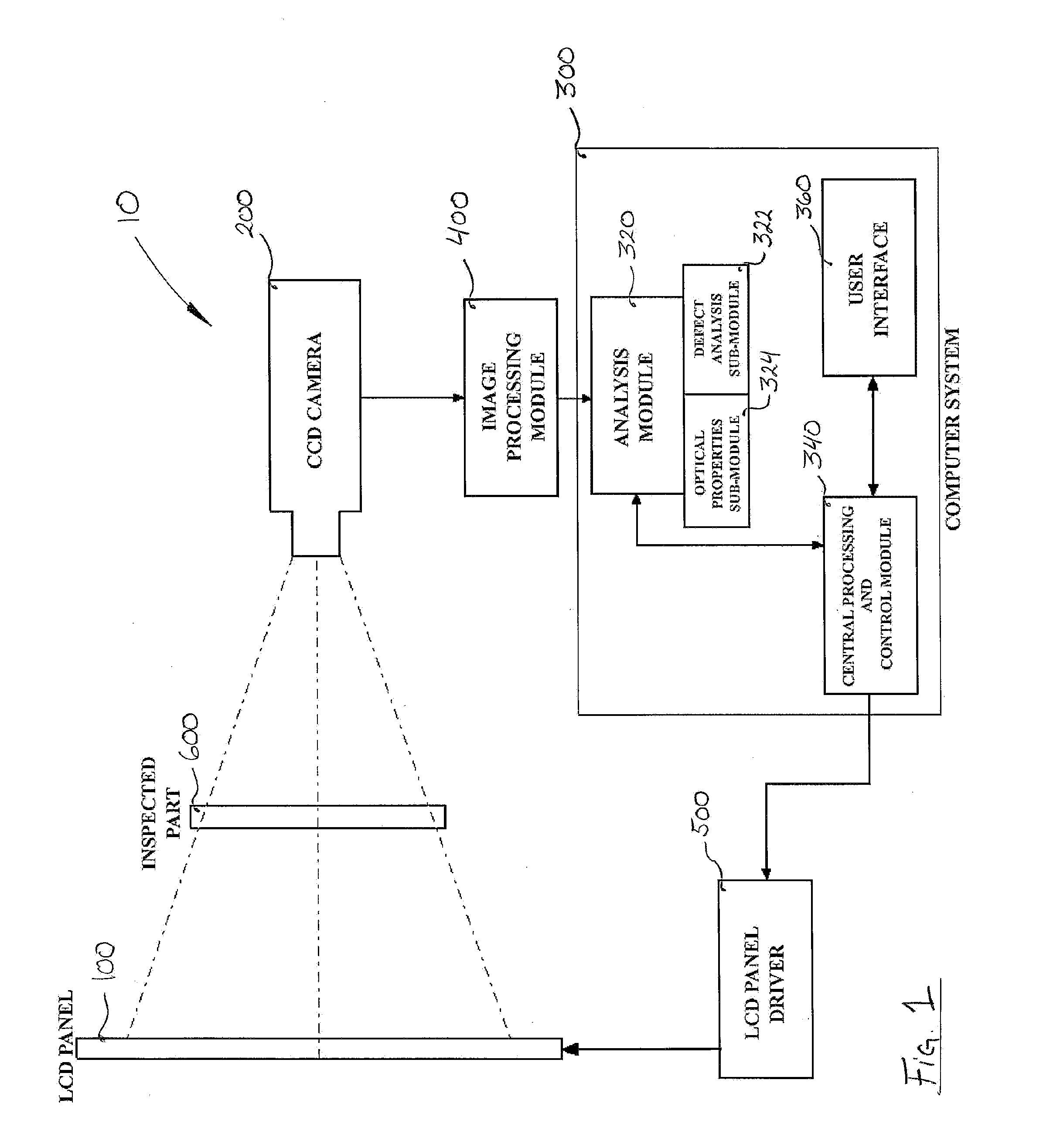

Transparent material inspection system

InactiveUS20080111989A1Detection moreRaise checkMaterial analysis by optical meansUsing optical meansVisorImaging data

A system for the inspection of the optical quality of a part, object or product having a portion comprising transparent material such as ophthalmologic lenses, protective eyewear, visors, eyewear shield and the like is provided. A liquid crystal display (LCD) screen emits variable patterns of light through the transparent part under inspection to a charged coupled device (CCD) camera that captures the image and transmits the image data to an image processing module. The processed image data are then transmitted to an analysis module which then generally measures the dimensions of the part, the transparency, the colour and the optical strength. The analysis module also advantageously detects and measures the presence of dots, stains, scratches, optical distortions, fingerprints, cloudiness and other optical artefacts and / or defects in the transparent material. Accordingly, the patterns emitted by the LCD screen are designed to measure the optical specifications and highlight potential optical defects.

Owner:DUFOUR CHRISTIAN +1

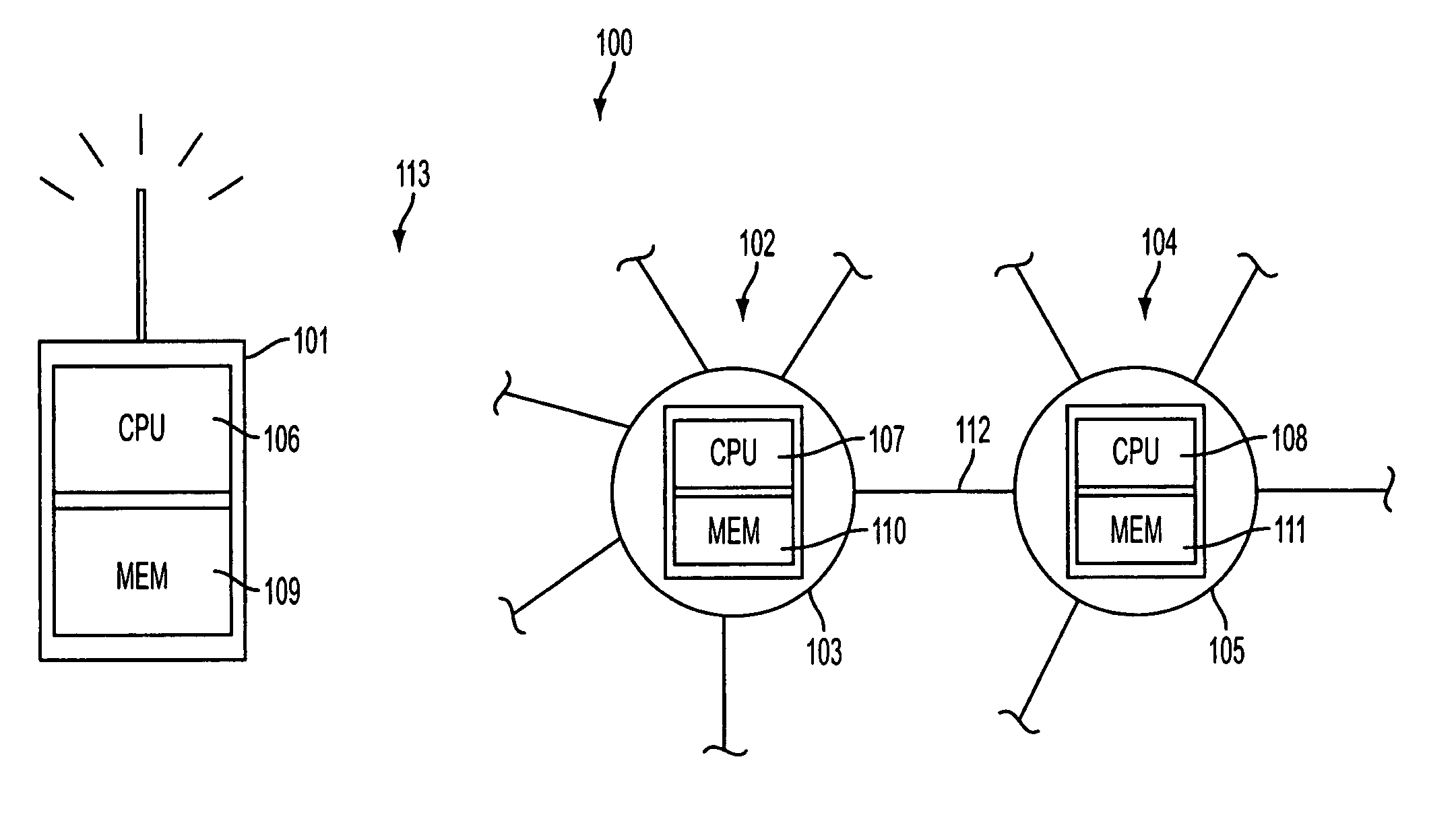

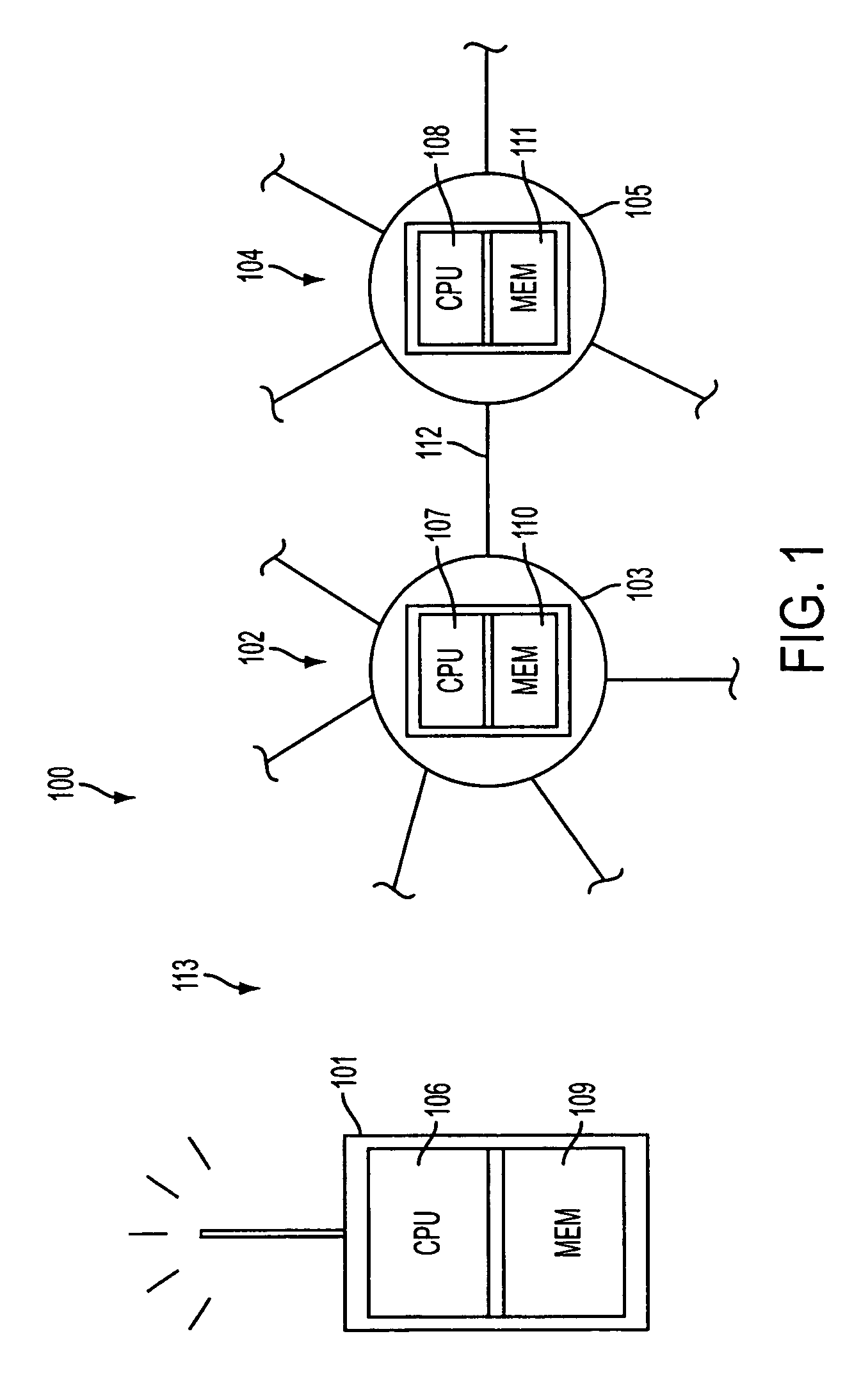

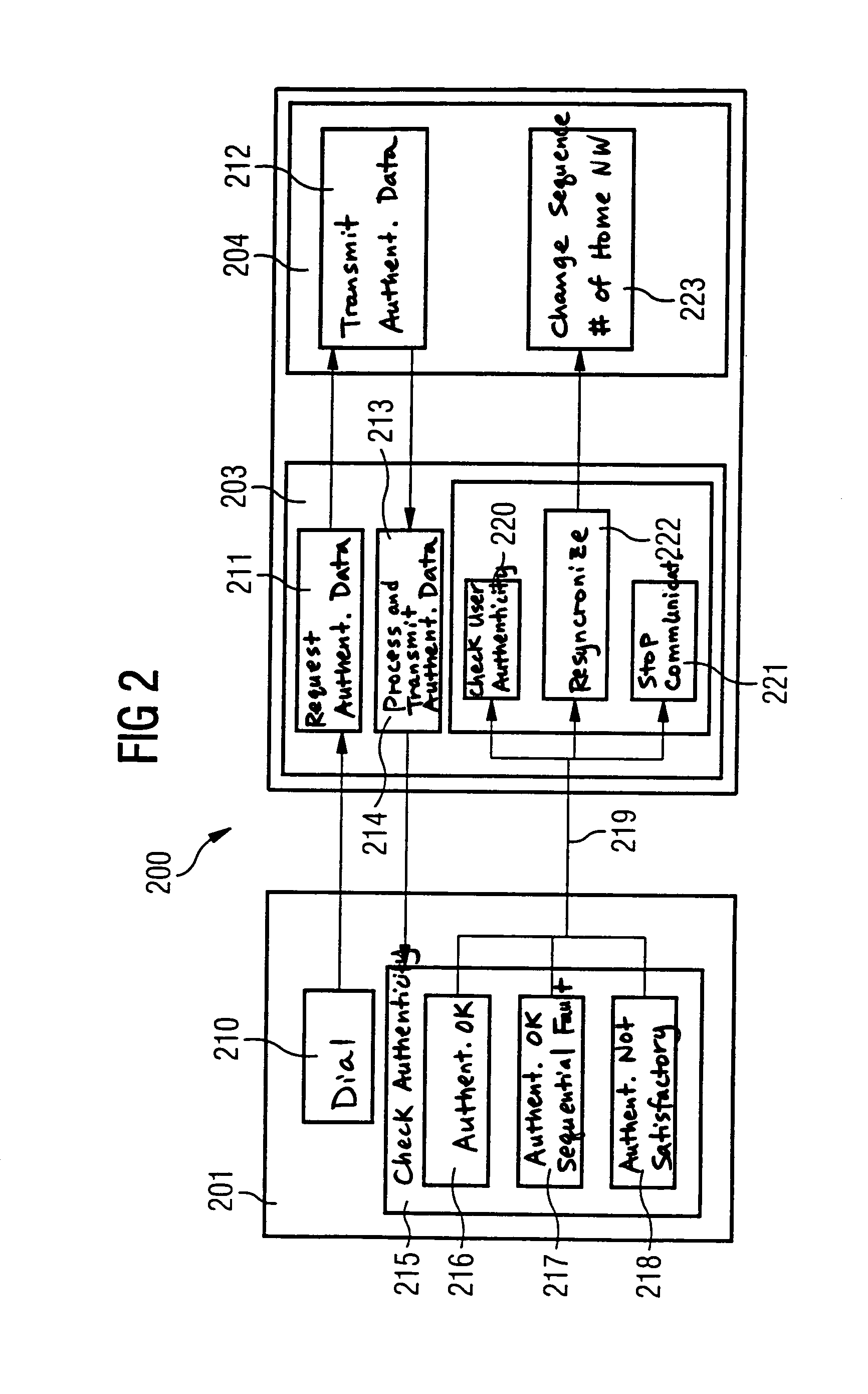

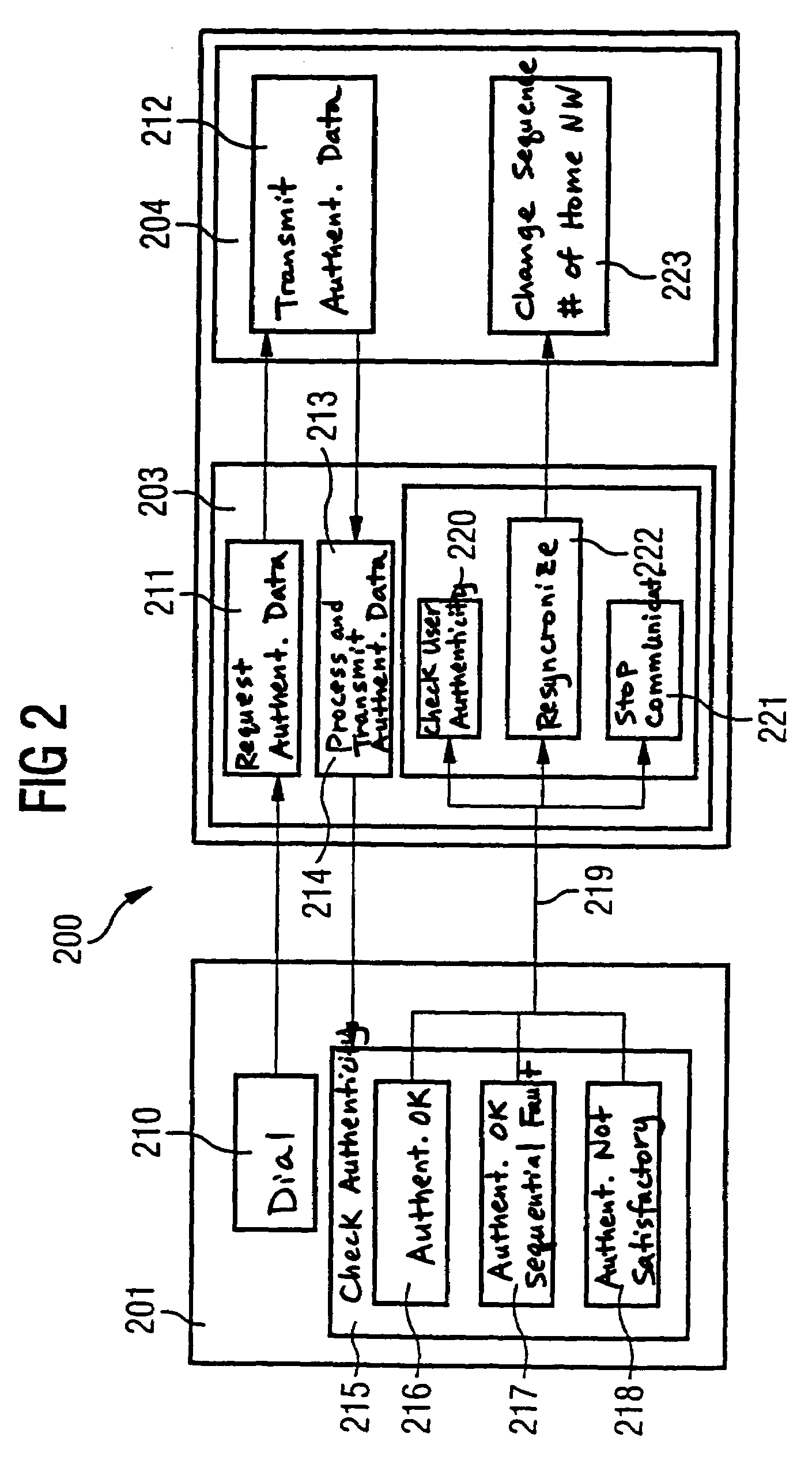

Method and system for verifying the authenticity of a first communication participants in a communications network

InactiveUS6980796B1Improved and simplifiedRaise checkUnauthorised/fraudulent call preventionEavesdropping prevention circuitsBroadcast communication networkNetwork method

Owner:MUNITECH IP S A R L

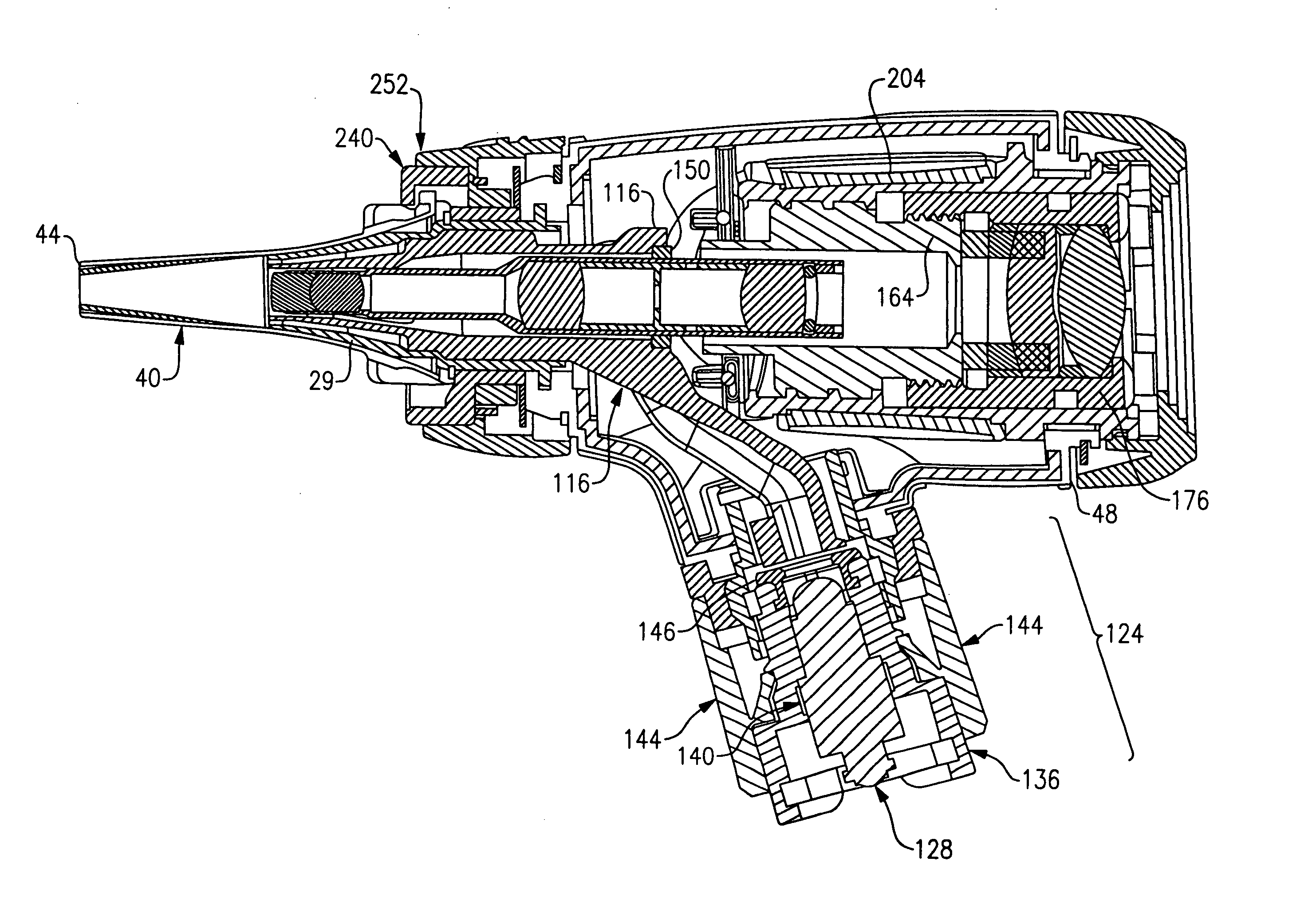

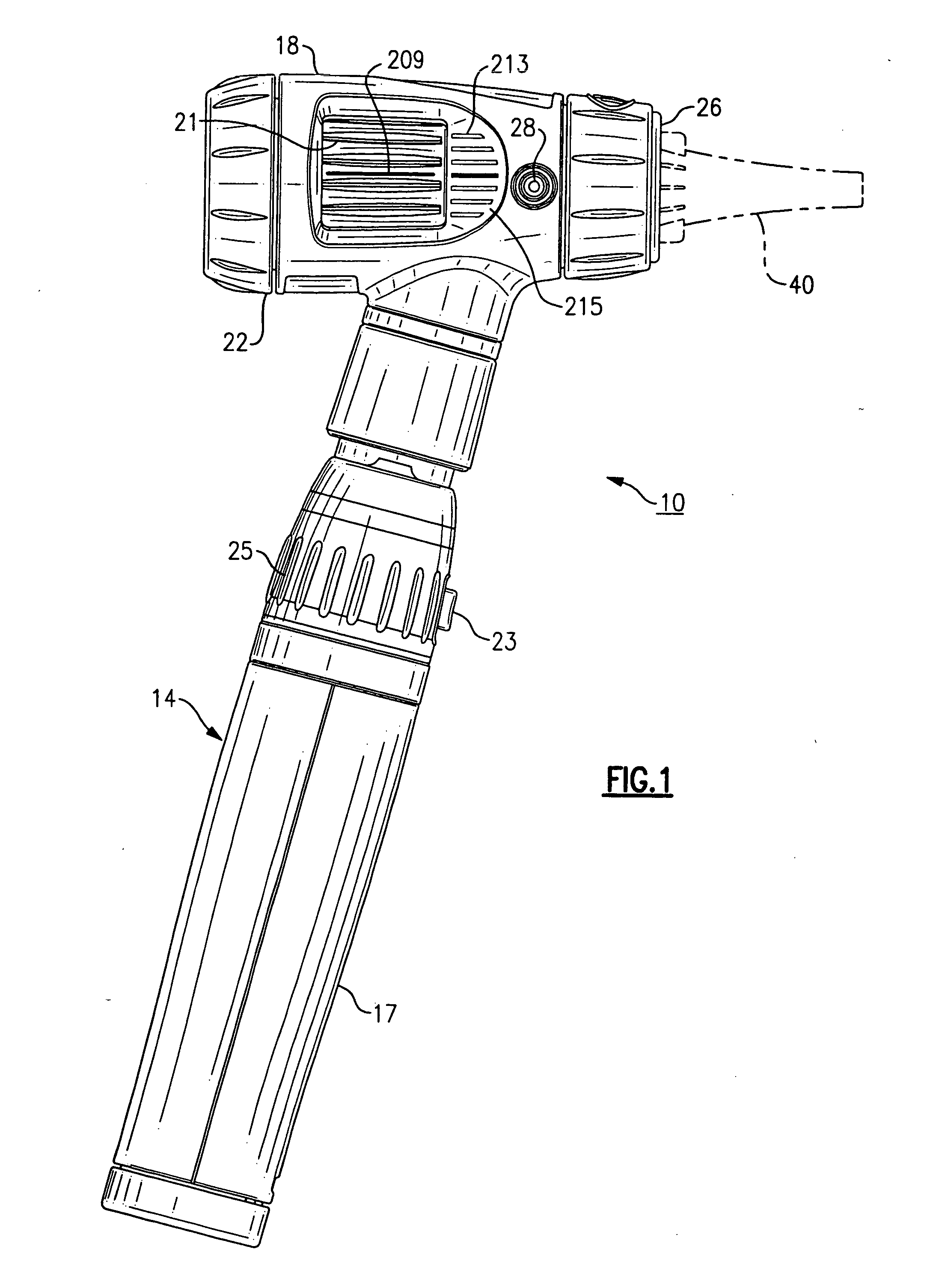

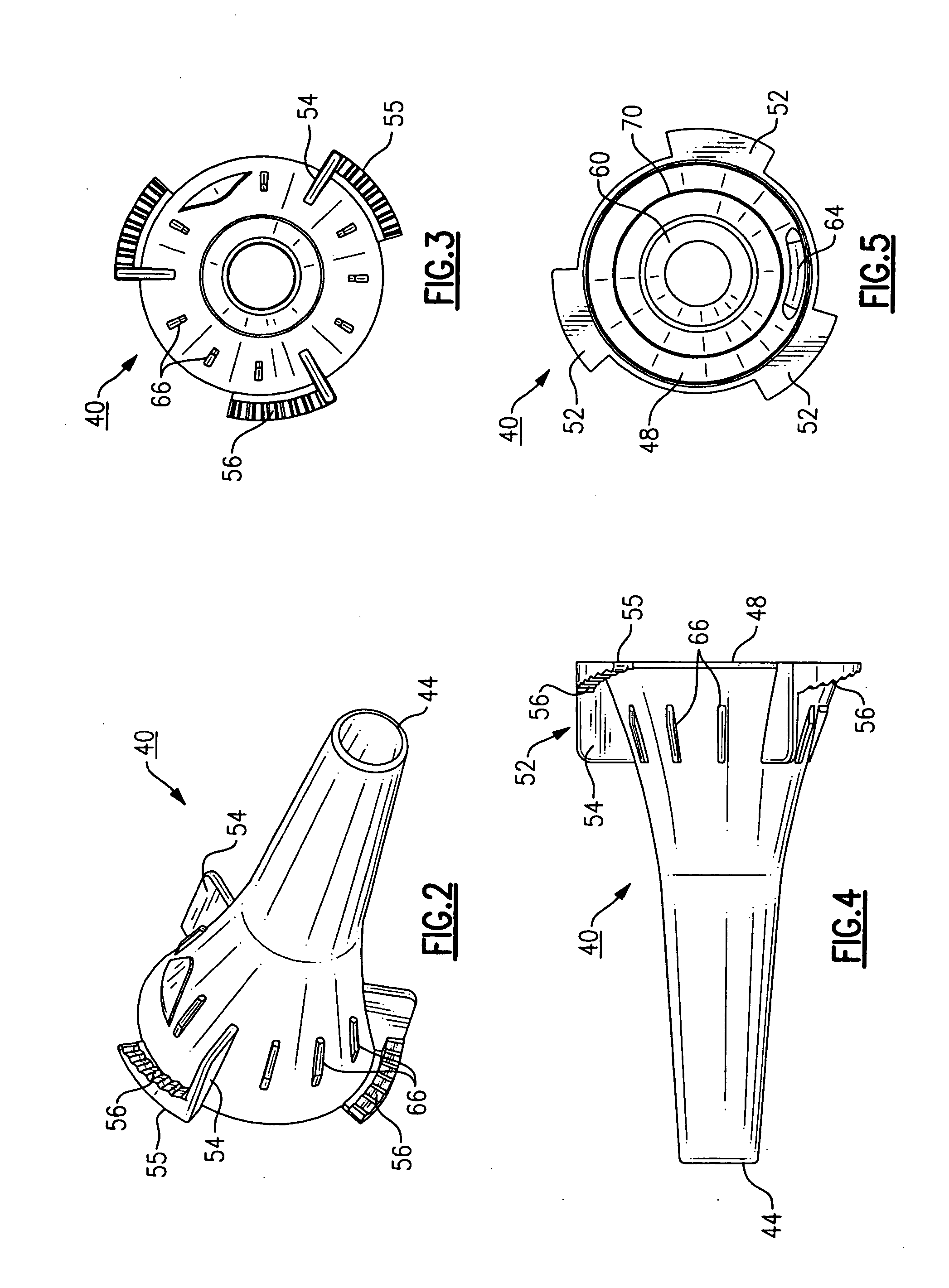

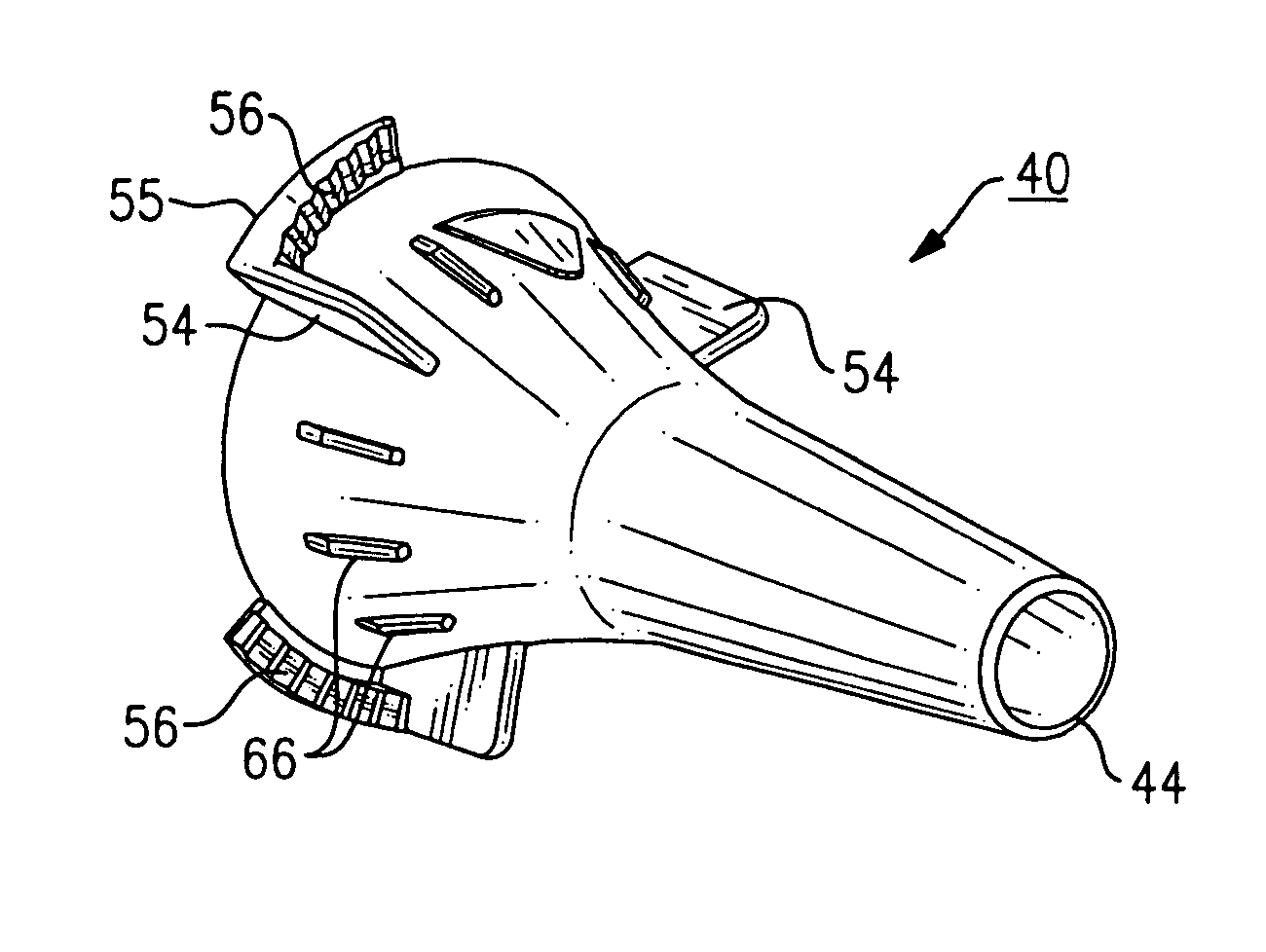

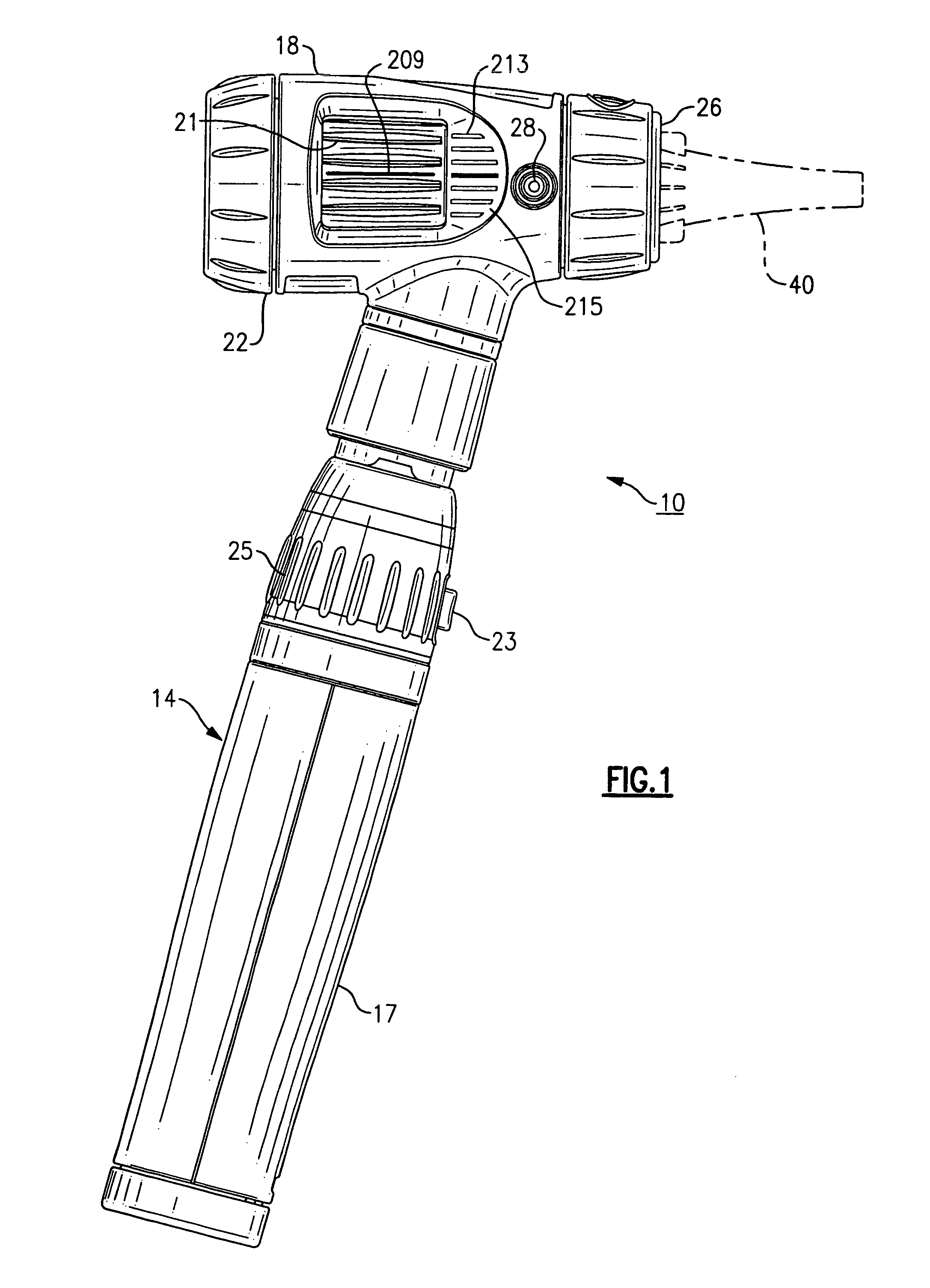

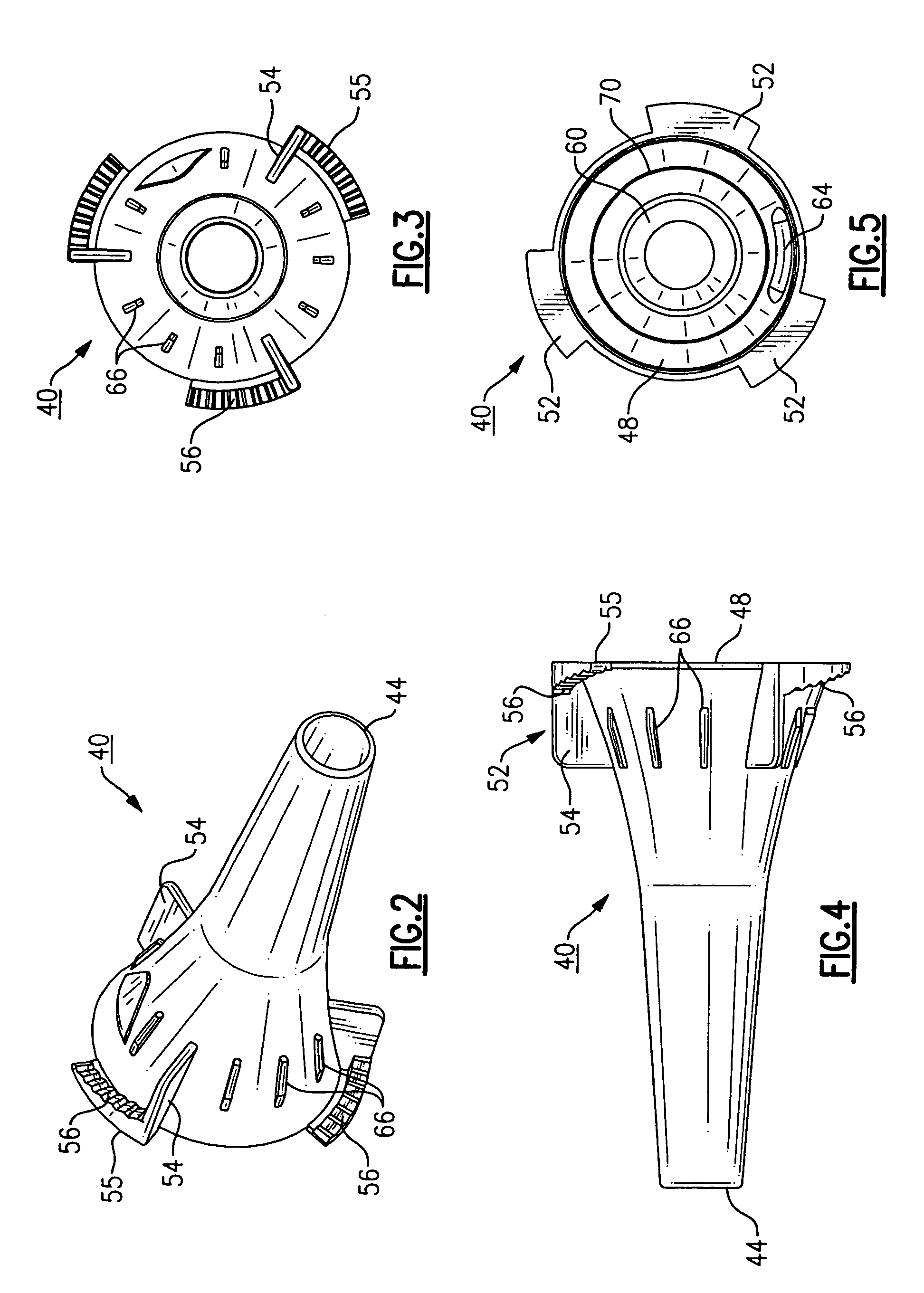

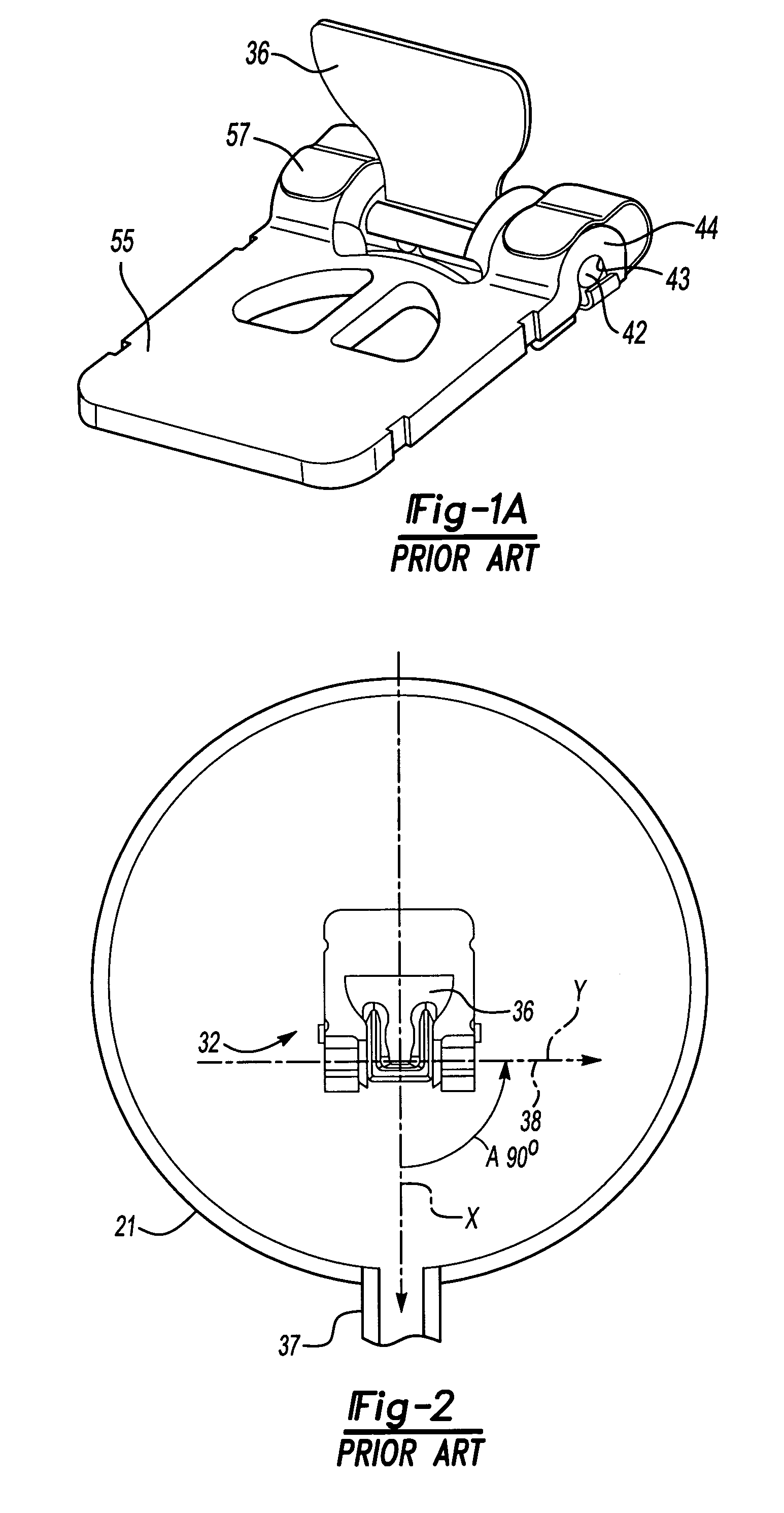

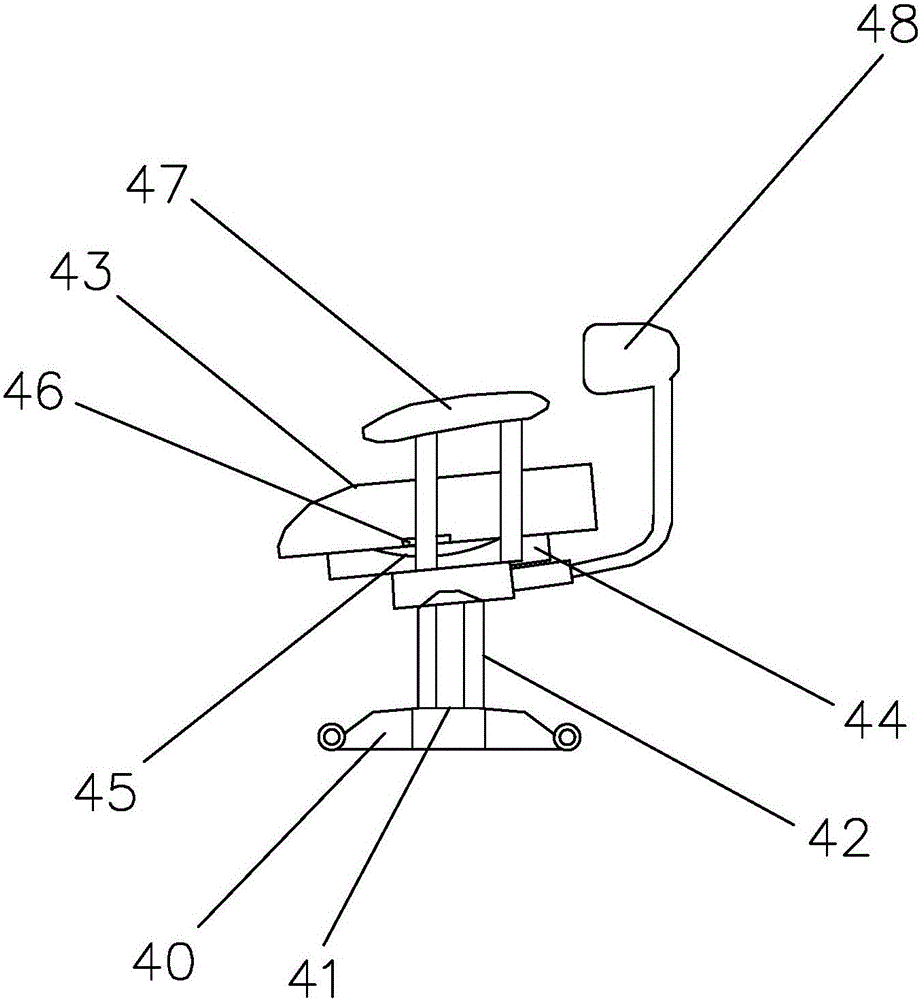

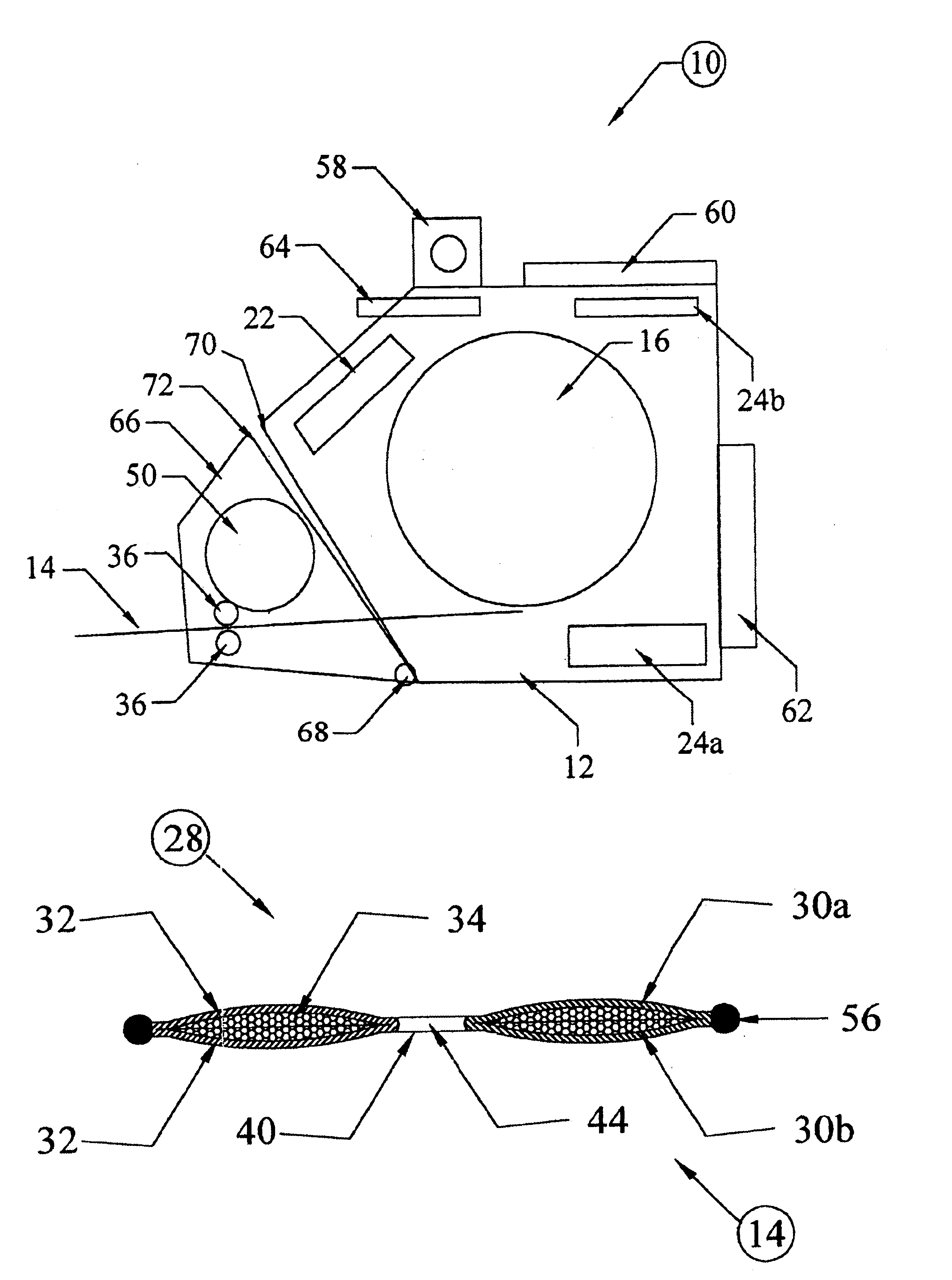

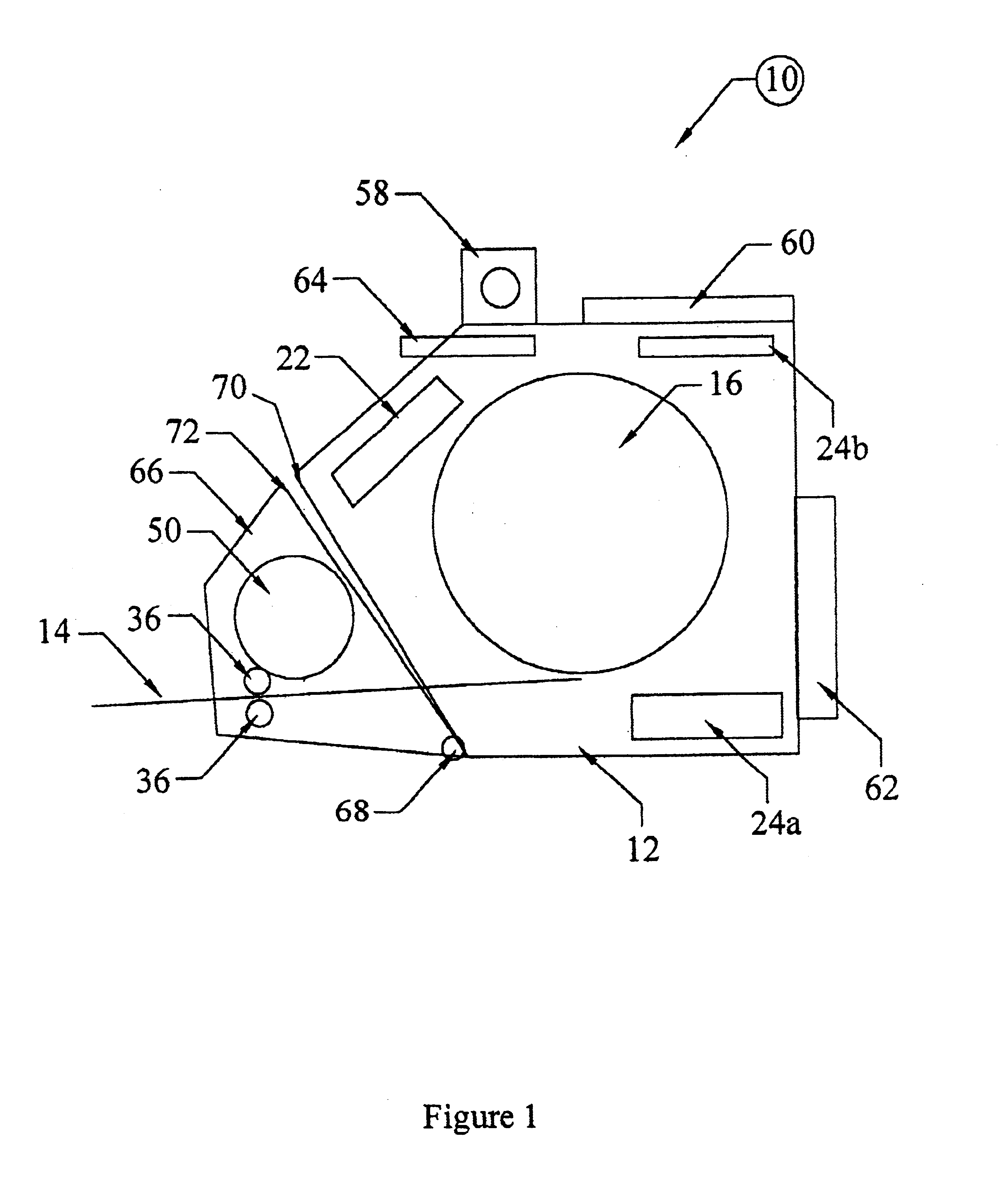

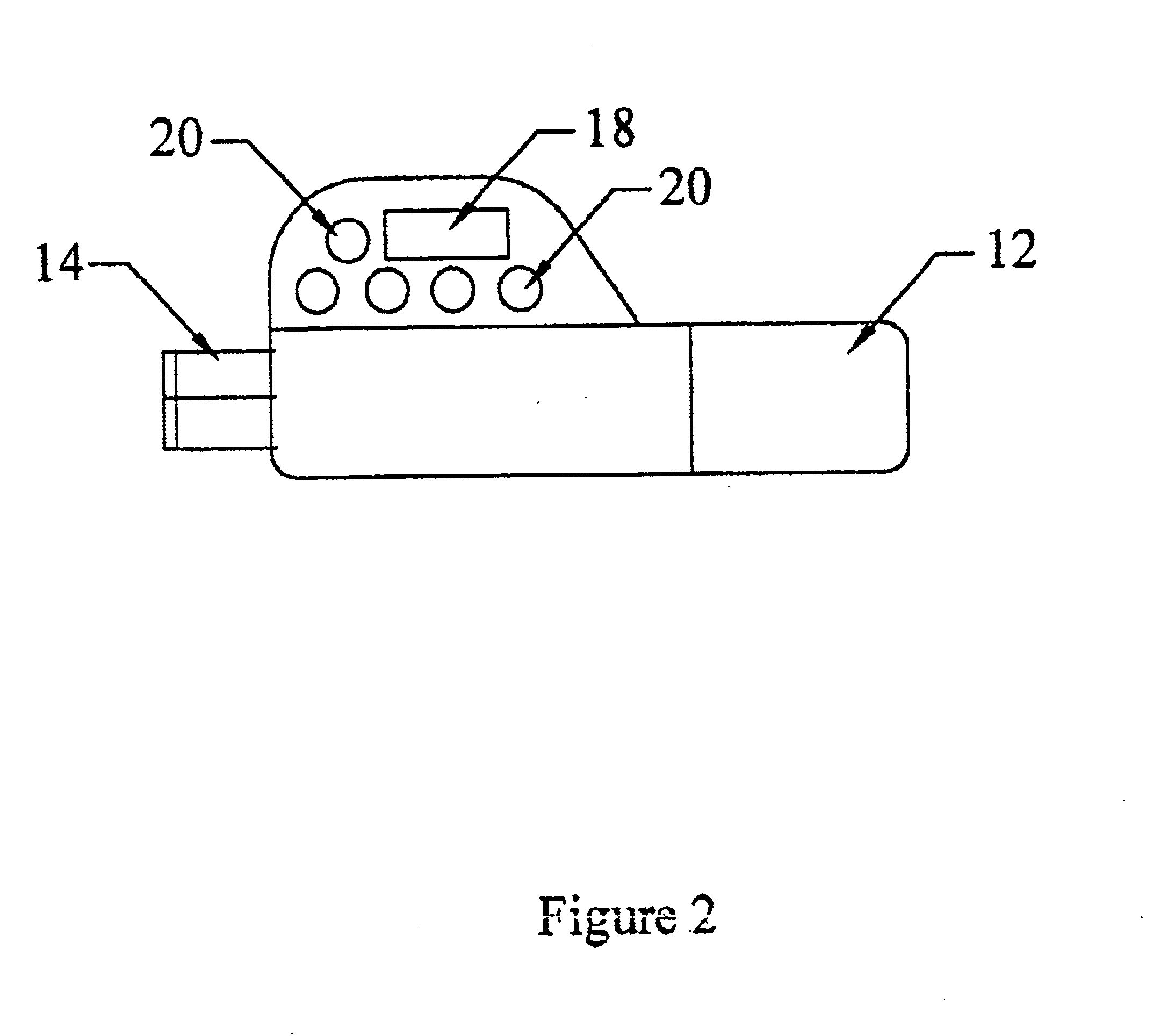

Otoscopic tip element and related method of use

ActiveUS20050027168A1Enhanced otological examinationSimple designBronchoscopesLaryngoscopesOtoscopeEntire tympanic membrane

A tip element for an otoscopic apparatus includes engagement features that permit selective attachment to two different tip attachment mechanisms. The tip element includes both interior and exterior engagement features that provide interchangeability with otoscopes having different tip attachment schemes. The tip element includes an increased distal aperture formed from a decreased slope that enables a larger field of view, permitting the entire tympanic membrane to be viewed at once. External engagement features permit ejection of the tip from the otoscope, as well as stackability of a plurality of tip elements.

Owner:WELCH ALLYN INC

Method and system for verifying the authenticity of a first communication participants in a communications network

InactiveUS7139550B2Raise checkUnauthorised/fraudulent call preventionEavesdropping prevention circuitsReal-time computing

Owner:MUNITECH IP S A R L

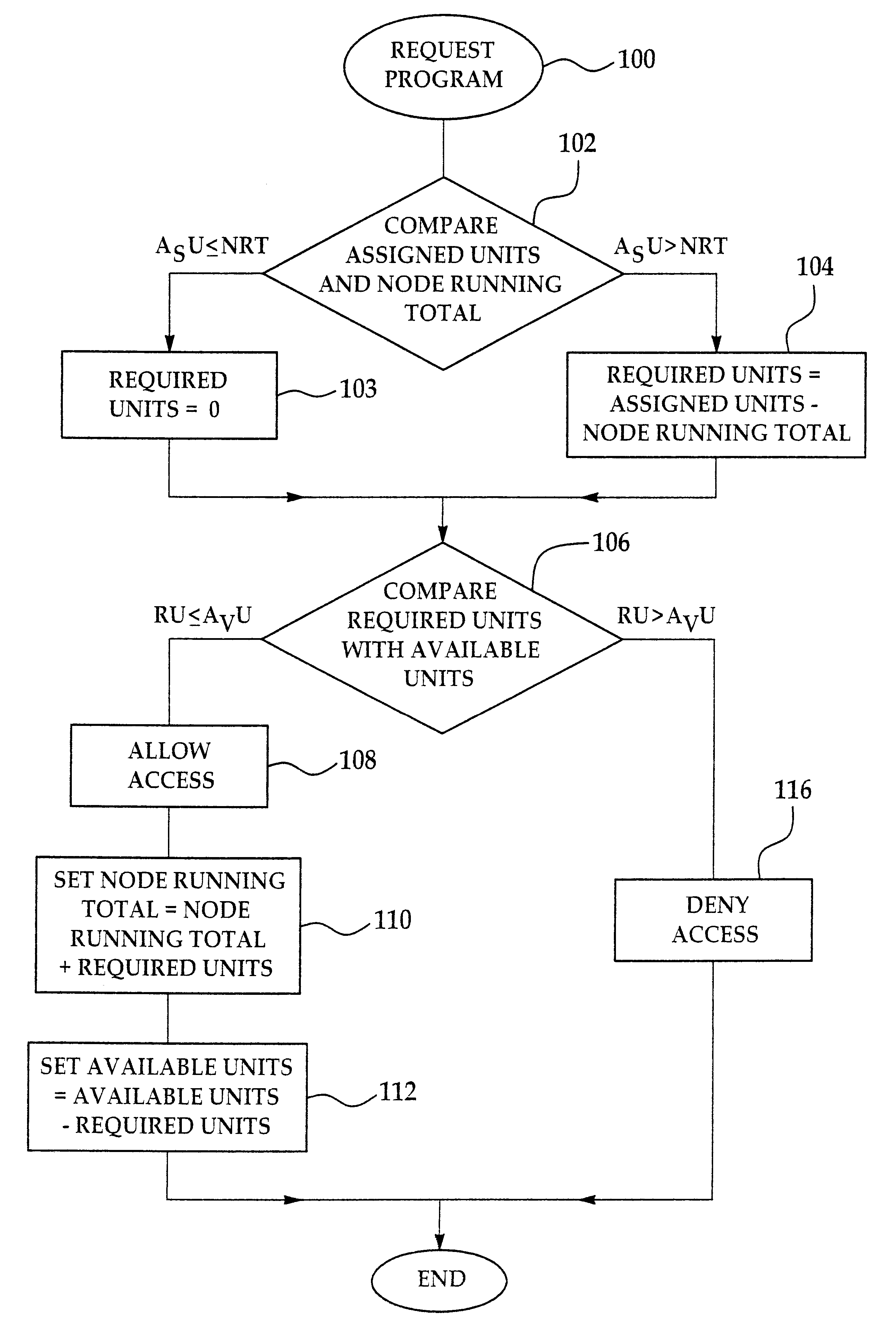

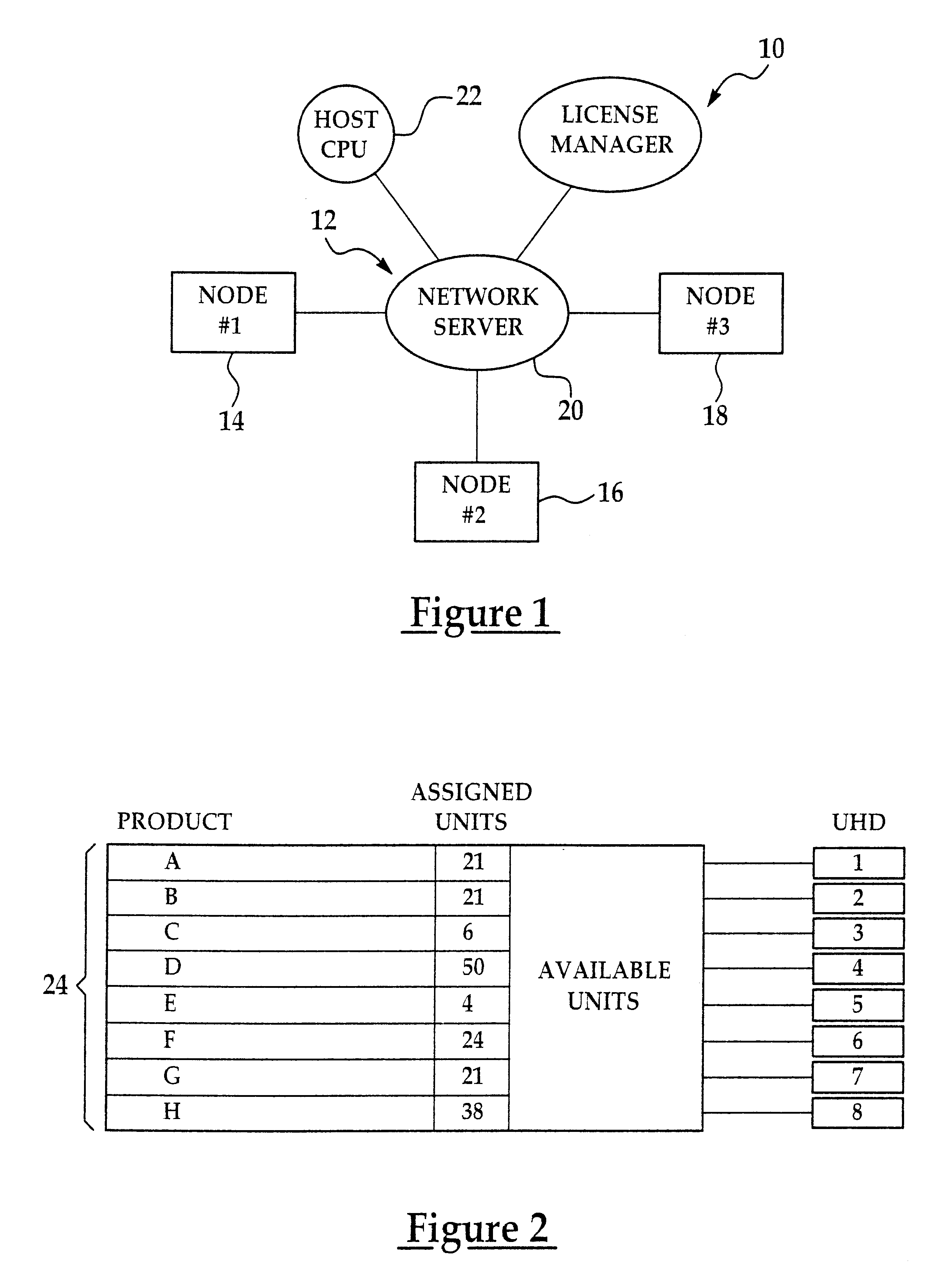

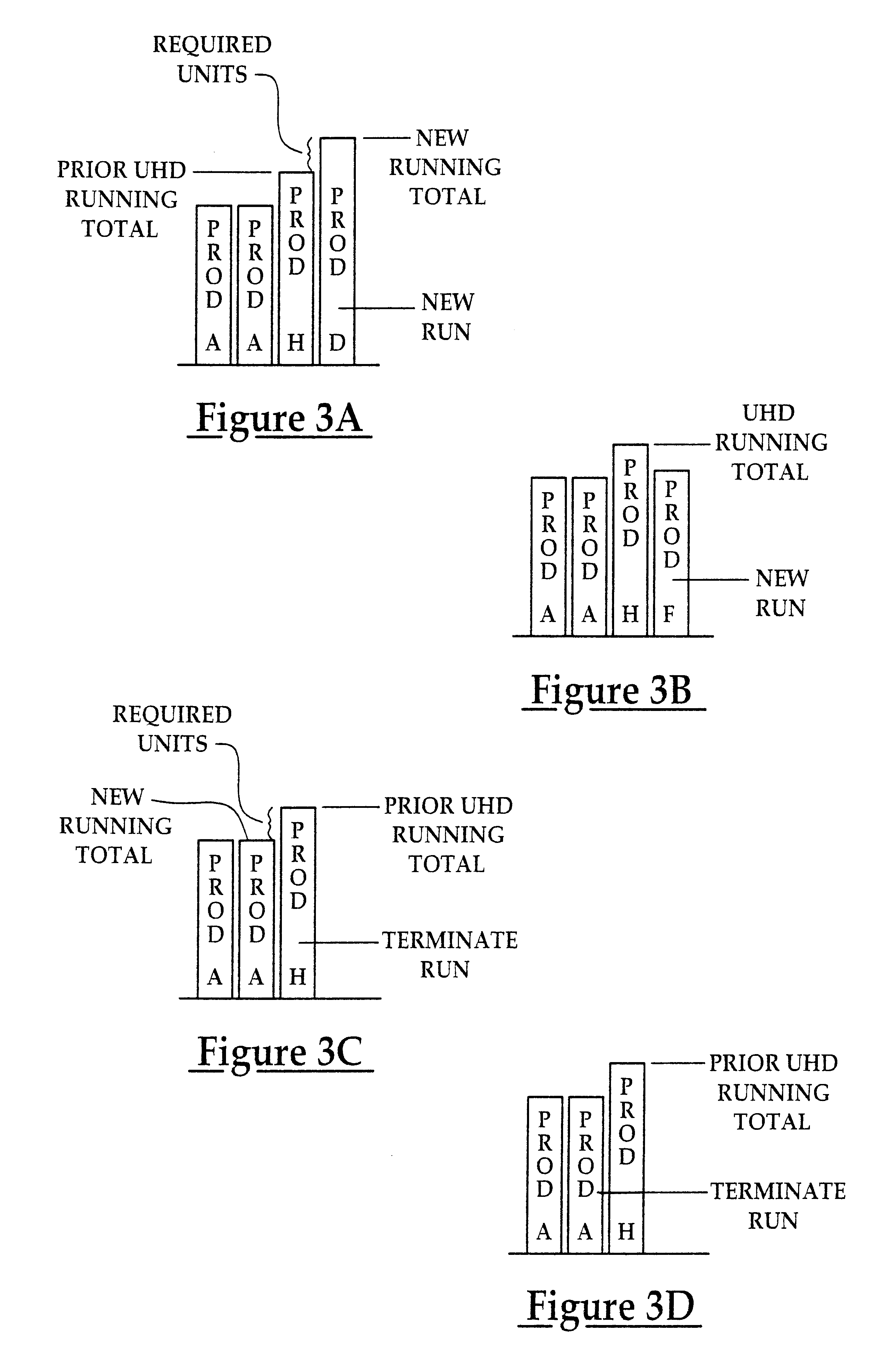

Product suite licensing method

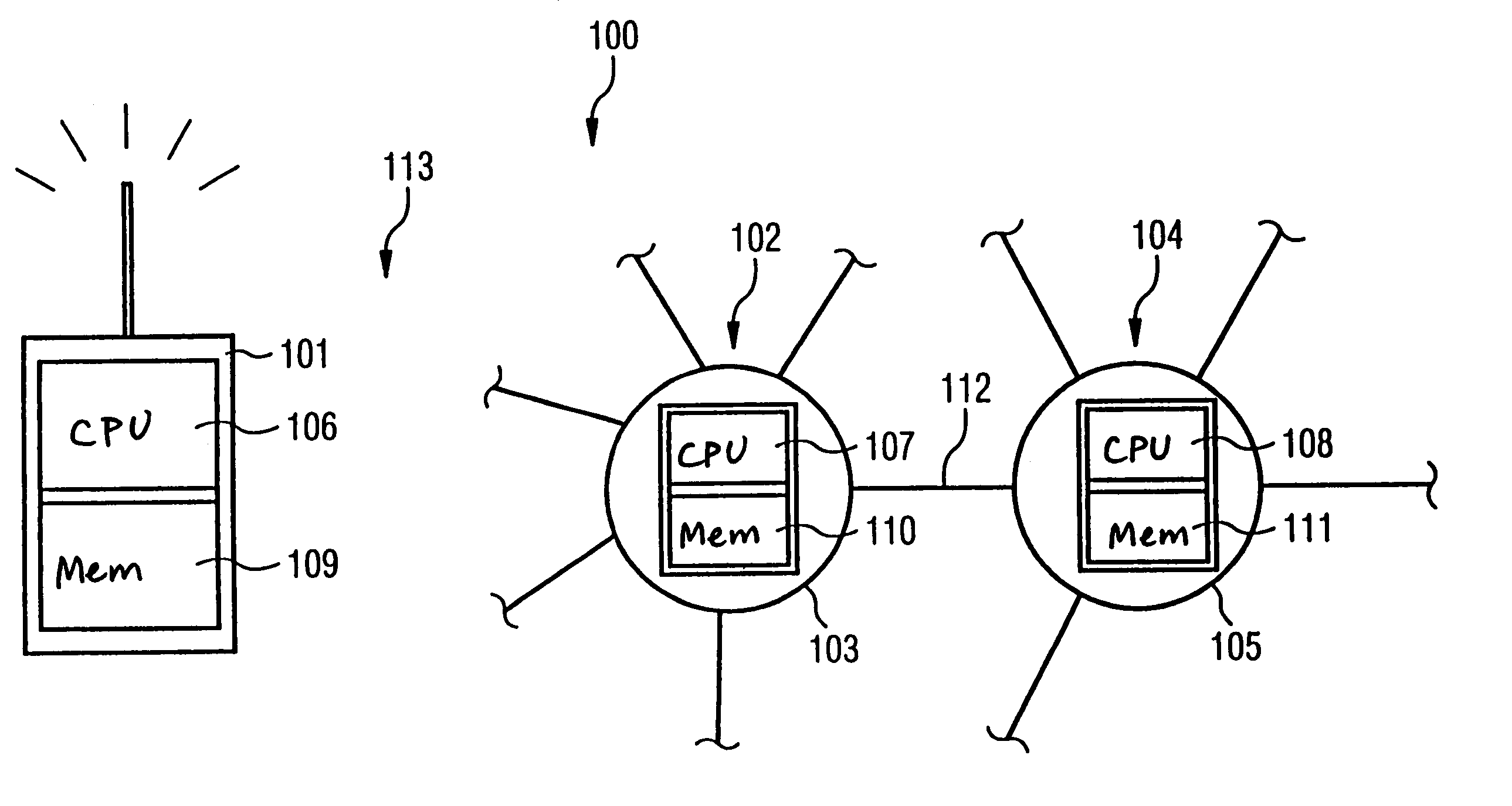

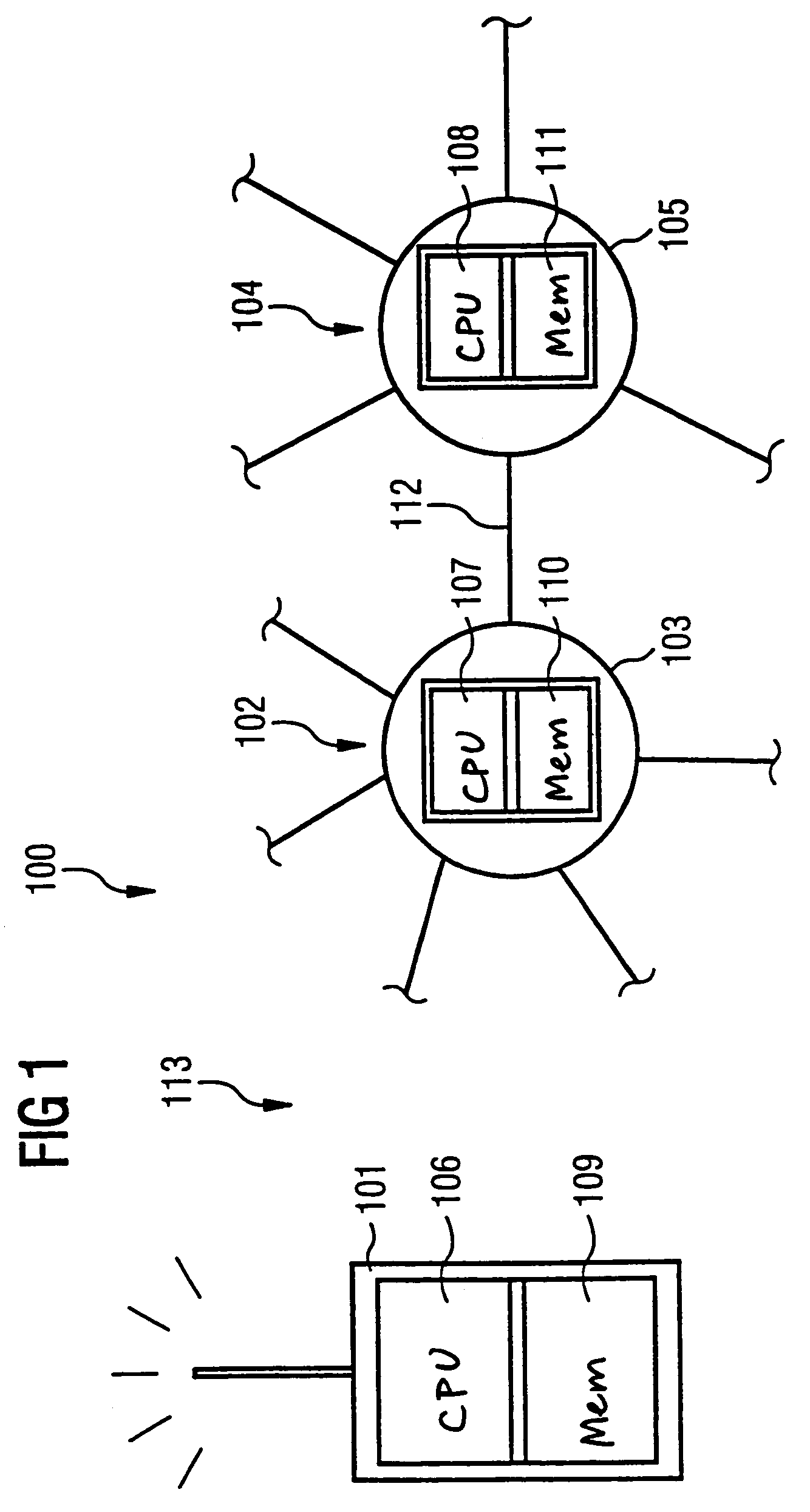

InactiveUS6859792B1Minimize the numberEasy accessDigital data processing detailsMultiple digital computer combinationsParallel computingLicense

A license management method specifies a predetermined number of assigned units for each of a plurality of individually selectable programs in a product suite. A discrete node running total equals the assigned units of the highest assigned units program running on each node. Each node can run additional programs where the assigned units of the additional programs are equal to or less than the node running total without changing the node running total. Termination of the highest assigned units program on a node causes the difference between the assigned units of the terminated program and the next highest assigned units of a program running by the node to be re-added to the available units.

Owner:ALTAIR ENGINEERING

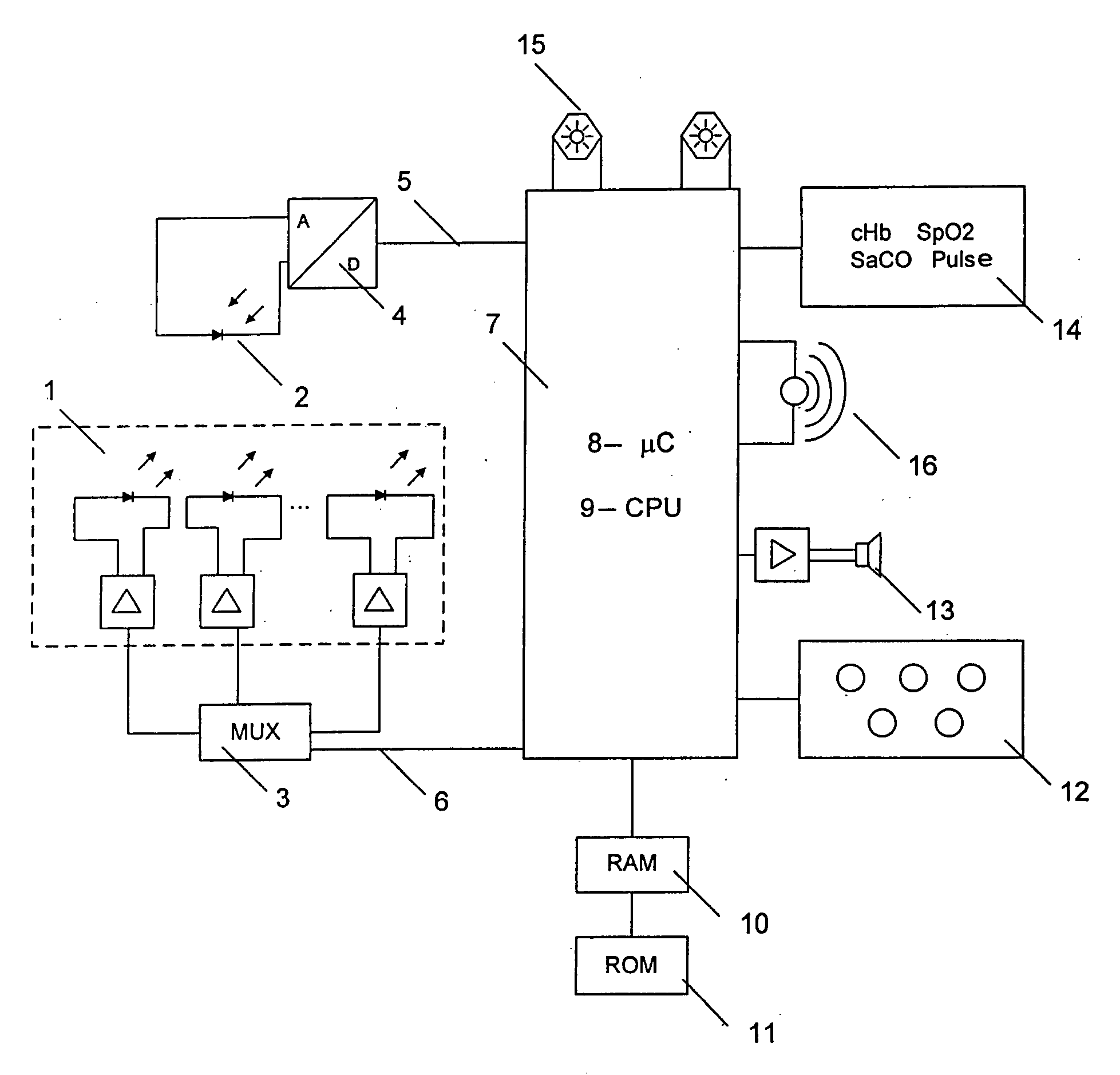

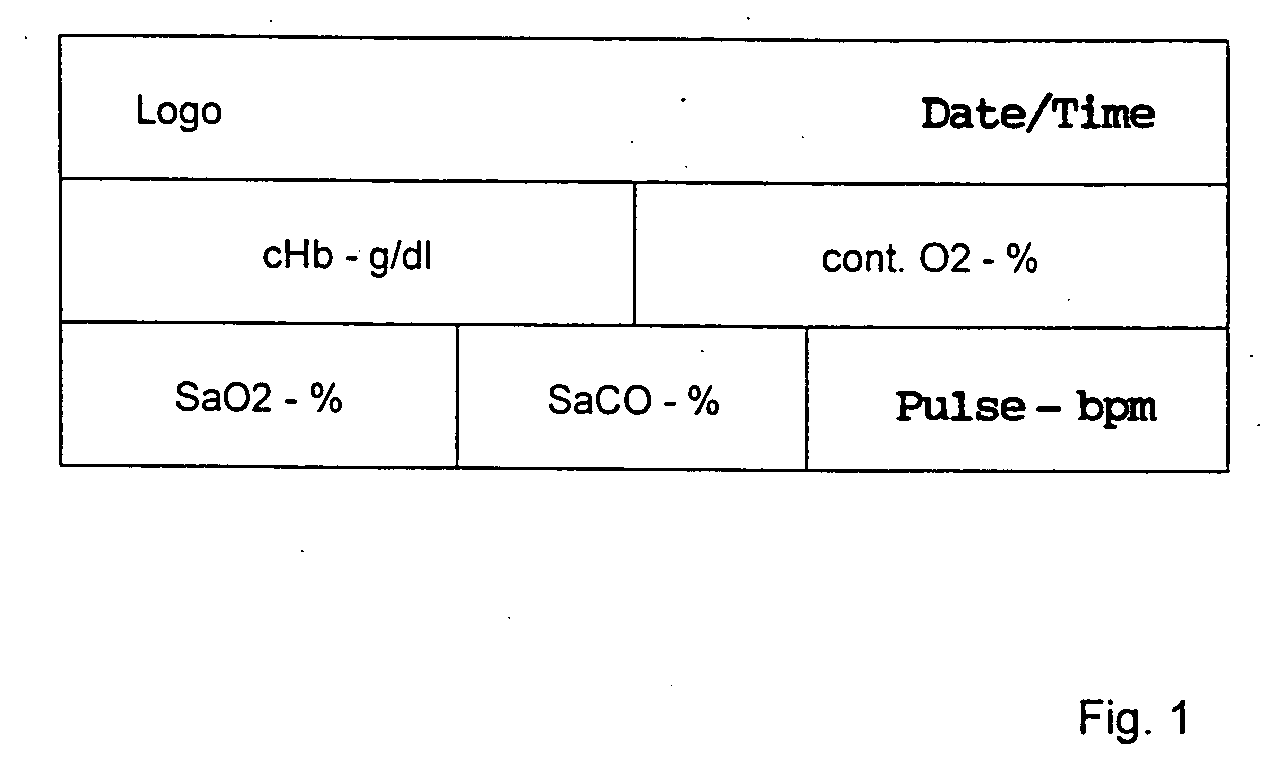

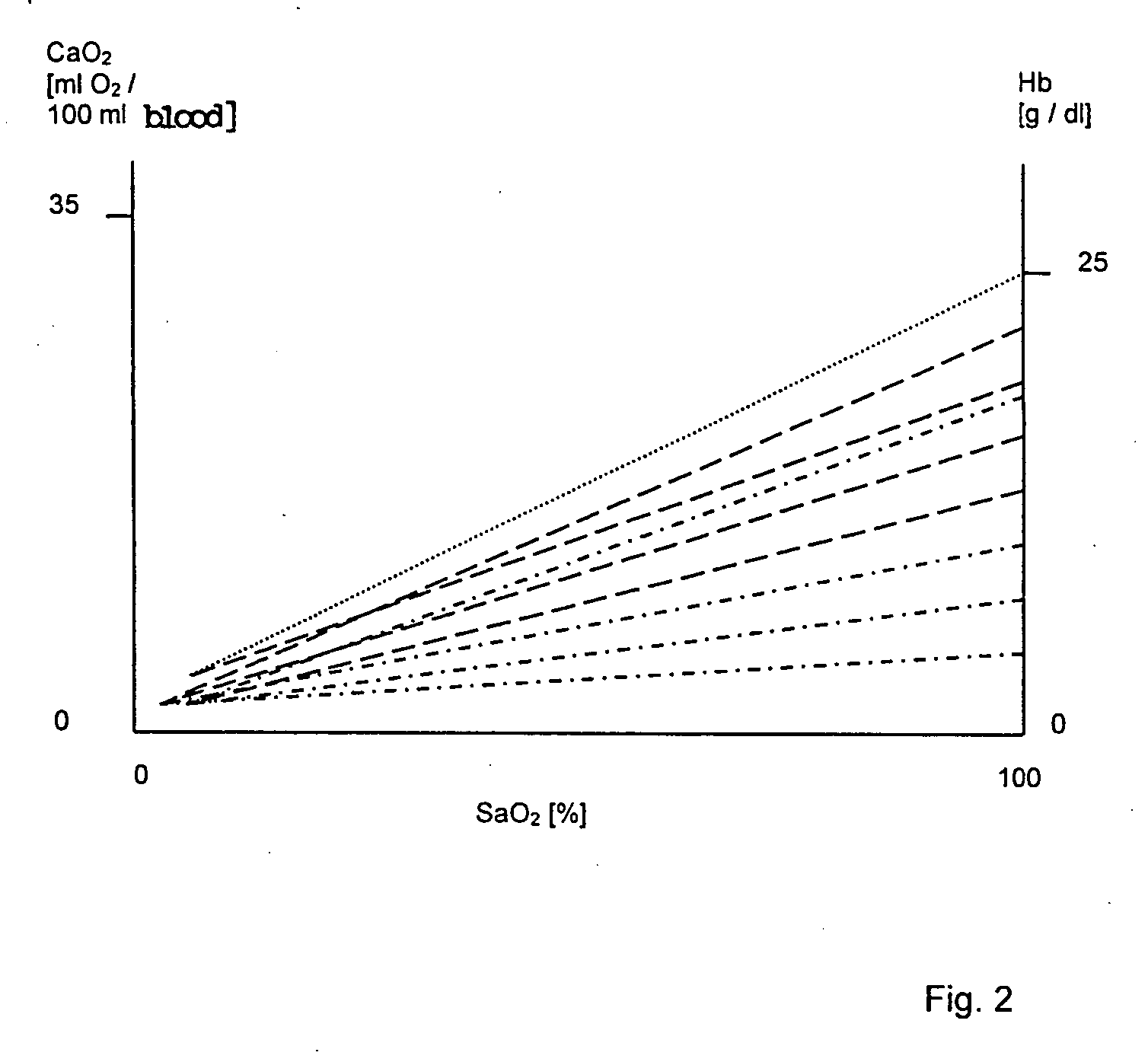

Display means for vital parameters

InactiveUS20070167693A1Raise checkReduce capacityCatheterRespiratory organ evaluationSequence controlDisplay device

A display is connected to at least one sensor for detecting and transmitting physiological measurement values. In addition, one or more displays are used to present the measurement values and / or other associated data visually, acoustically, mechanically, or in some other way perceptible to the senses. A sequence control approach is implemented, according to which the measurement value, before reaching the display, passes through a testing stage, which, on the basis of at least one measured or stored additional value, verifies, checks, or changes the physiological measurement value detected at the sensor or supplements it with additional information. In a process for the noninvasive determination of the oxygen content CaO2 of human and / or animal tissue, the blood oxygen saturation and data on the blood hemoglobin concentration are obtained after the measurements have been acquired by the use of radiation with wavelengths in the range of 400-1,800 nanometers.

Owner:SCHOLLER BERND +5

Otoscopic tip element and related method of use

A tip element for an otoscopic apparatus includes engagement features that permit selective attachment to two different tip attachment mechanisms. The tip element includes both interior and exterior engagement features that provide interchangeability with otoscopes having different tip attachment schemes. The tip element includes an increased distal aperture formed from a decreased slope that enables a larger field of view, permitting the entire tympanic membrane to be viewed at once. External engagement features permit ejection of the tip element from the otoscope, as well as stackability of a plurality of tip elements.

Owner:WELCH ALLYN INC

Method and apparatus for processing checks

ActiveUS7475807B2Minimize human factorOpportunities decreaseComplete banking machinesFinanceAlgorithmCheque

A check processing system and method comprising utilizes an image scanner that produces an electronic image of a check upon scanning of the check. The system and method receive the electronic image of the check from the image scanner, receive point-of-sale data generated at a point-of-sale, determine a monetary value of the check from the electronic image of the check, and reconcile the determined monetary value of the check with the point-of-sale data so that the check is correlated with a transaction that occurred at the point-of-sale.

Owner:TALARIS HLDG

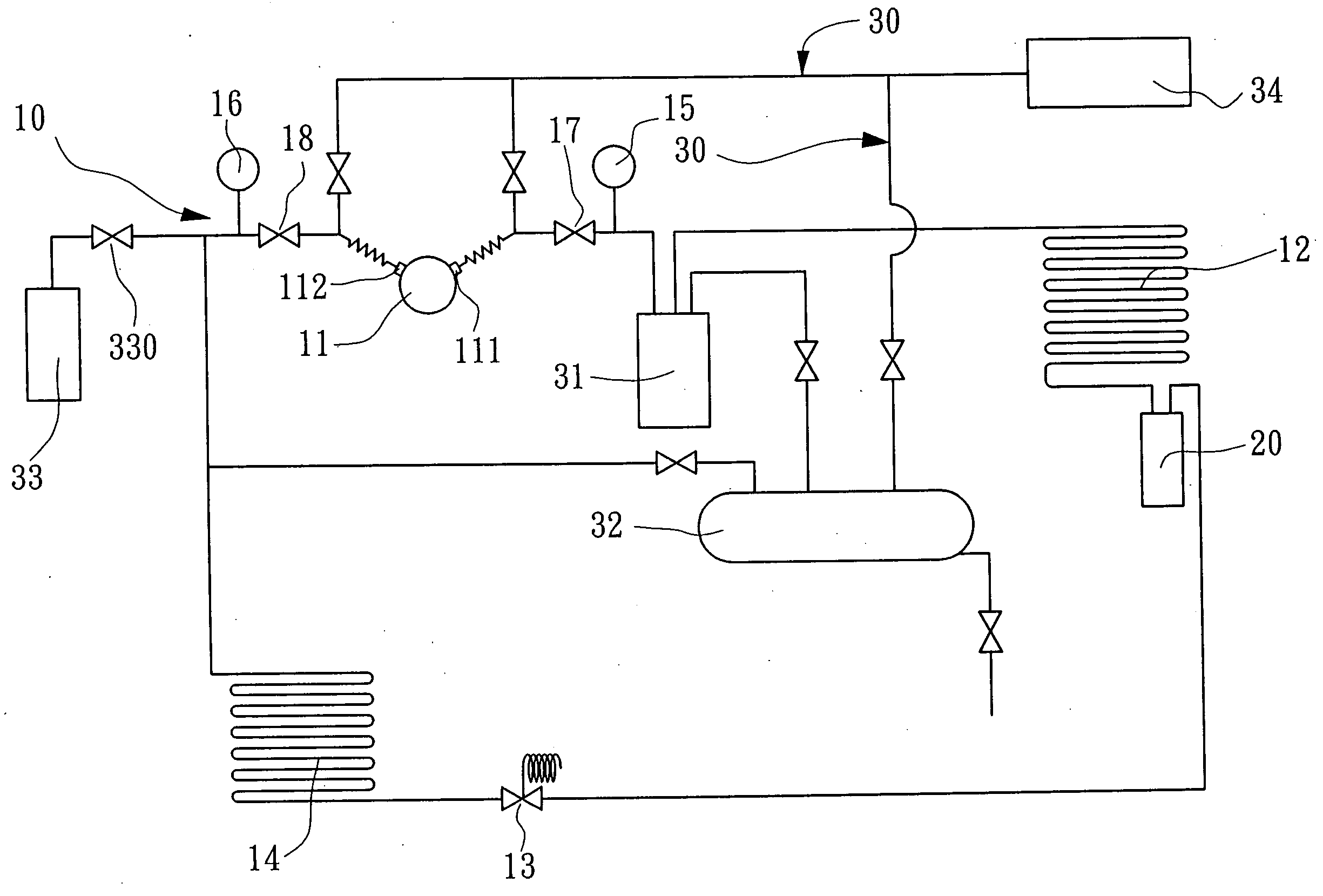

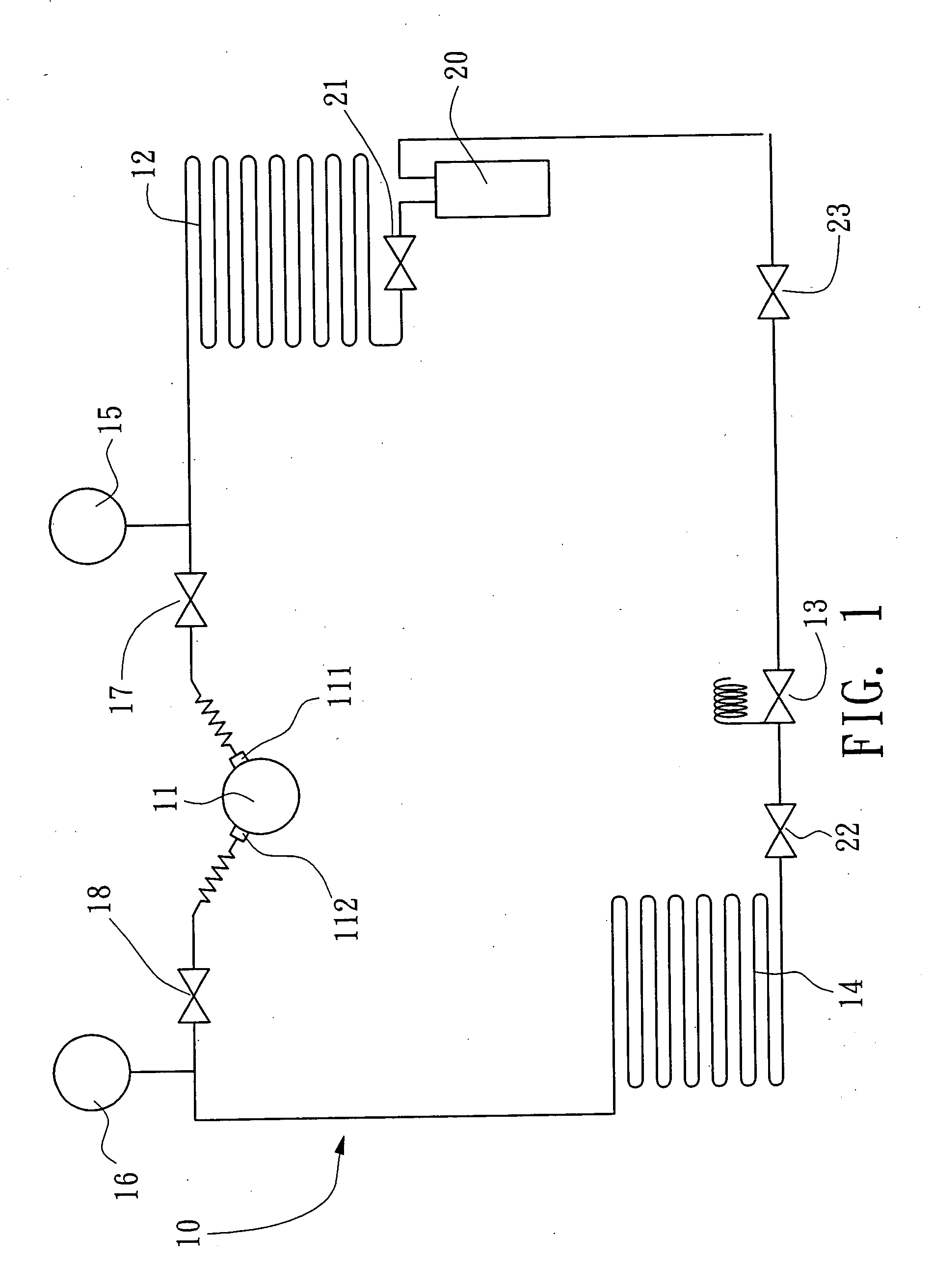

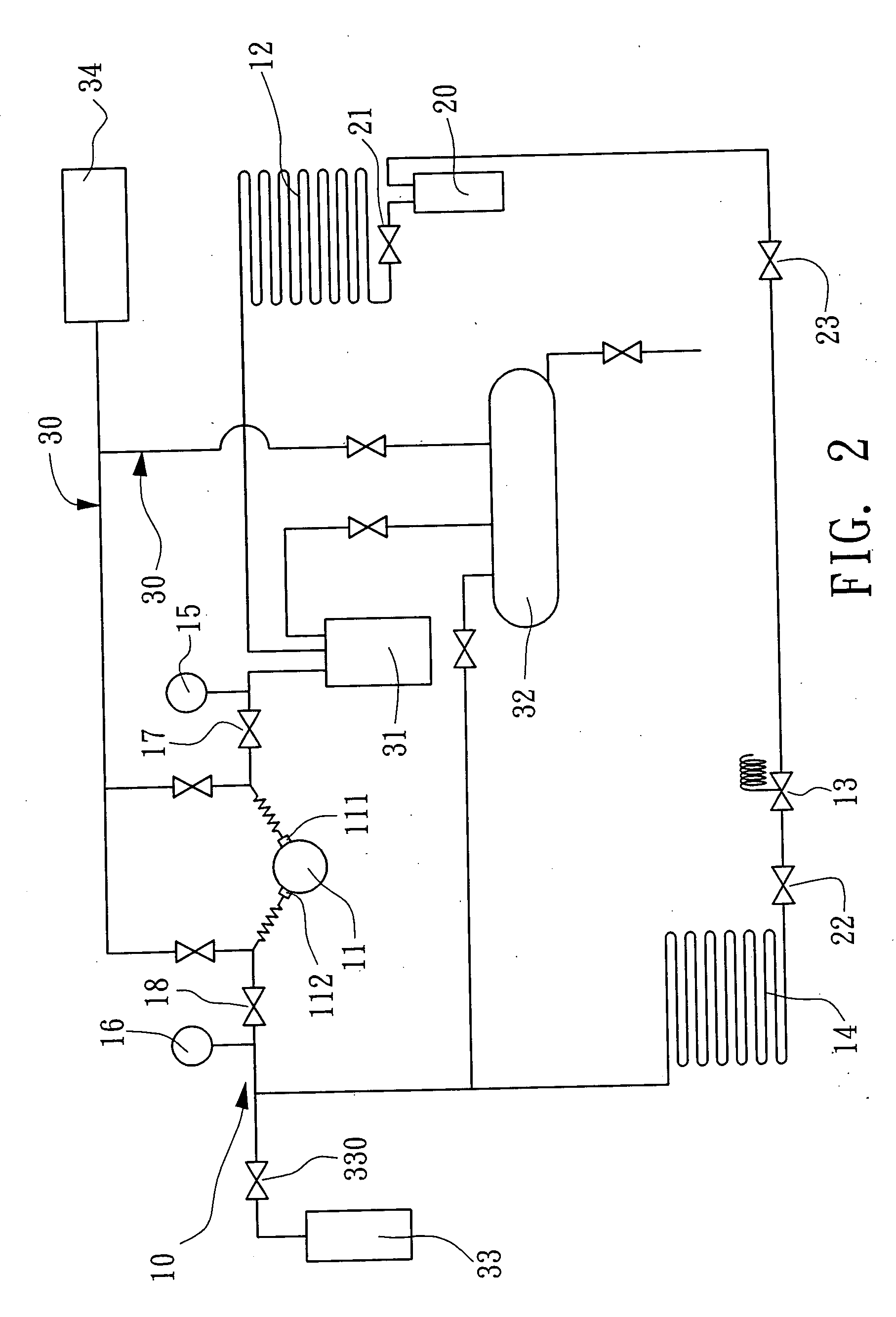

Check device for an air conditioning system of an automobile and an air conditioner compressor

InactiveUS20050039470A1Find quickly and accuratelyRaise checkAir-treating devicesTemperature measurement in air-conditioning systemsCoolant flowHigh pressure

Owner:HENG SHENG PRECISION TECH

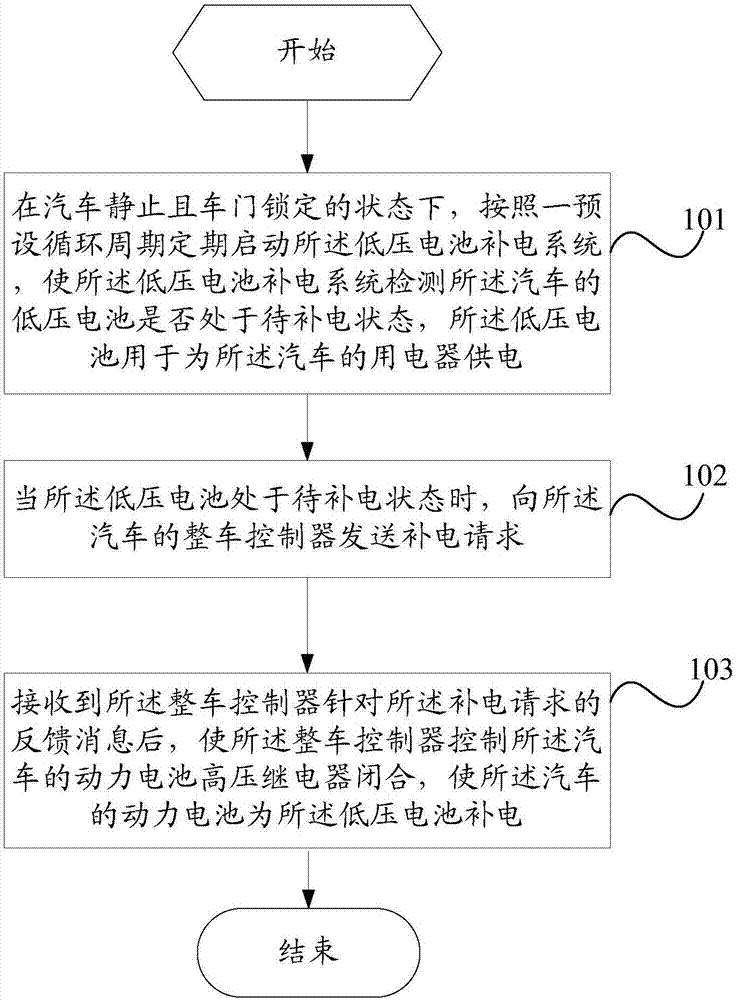

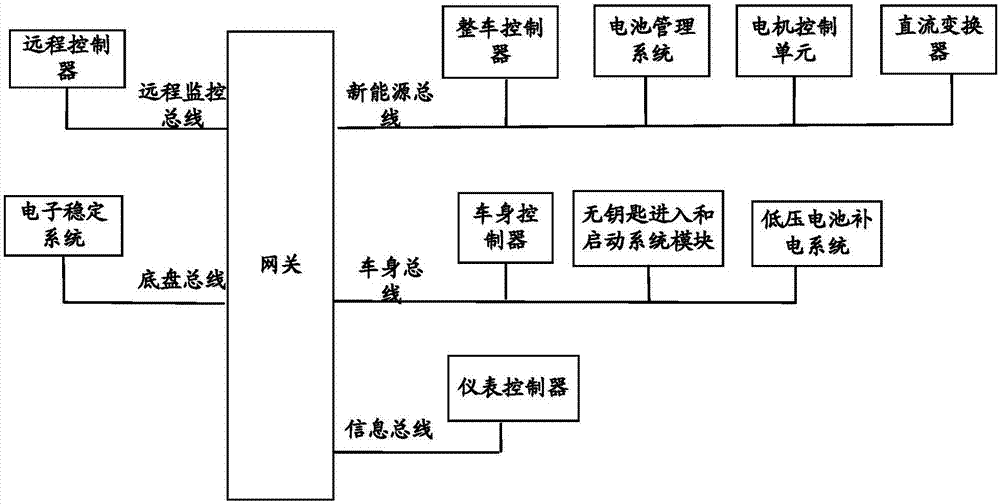

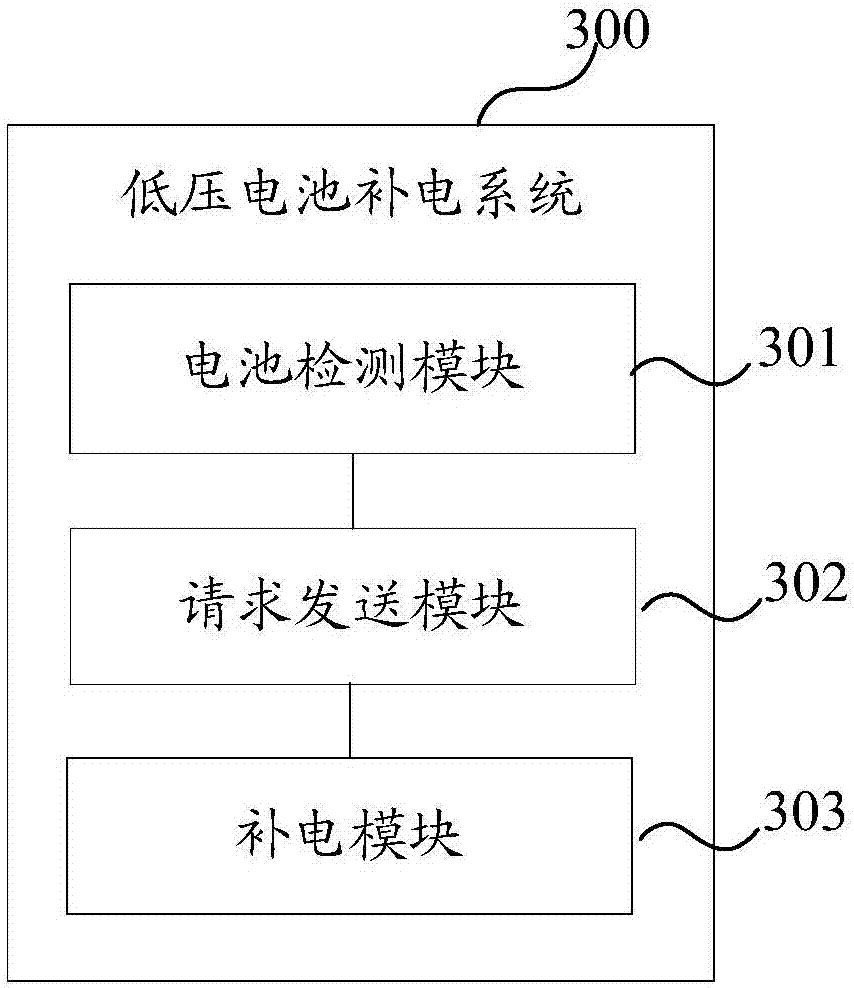

Low-voltage battery recharging method and system, controller and automobile

ActiveCN107458332AIntensified power deficitRaise checkElectric devicesElectric/fluid circuitElectricityPower battery

The invention provides a low-voltage battery recharging method and system, a controller and a vehicle. The method is applied to the low-voltage battery recharging system connected to a gateway of the vehicle through a vehicle body bus. The method comprises the steps that under the condition that the vehicle is stationary and vehicle doors are locked, the low-voltage battery recharging system is periodically started according to a preset cycle, so that the low-voltage battery recharging system detects whether the low-voltage battery of the vehicle is in a to-be-recharged state, and the low-voltage battery is used for supplying power for electrical appliances of the vehicle; when the low-voltage battery is in the to-be-recharged state, a recharging request is sent to a vehicle controller of the vehicle; and after receiving the feedback of the recharging request from the vehicle controller, the vehicle controller controls a power battery high-voltage relay of the vehicle to be closed, so that a power battery of the vehicle performs recharging on the low-voltage battery.

Owner:BEIJING ELECTRIC VEHICLE

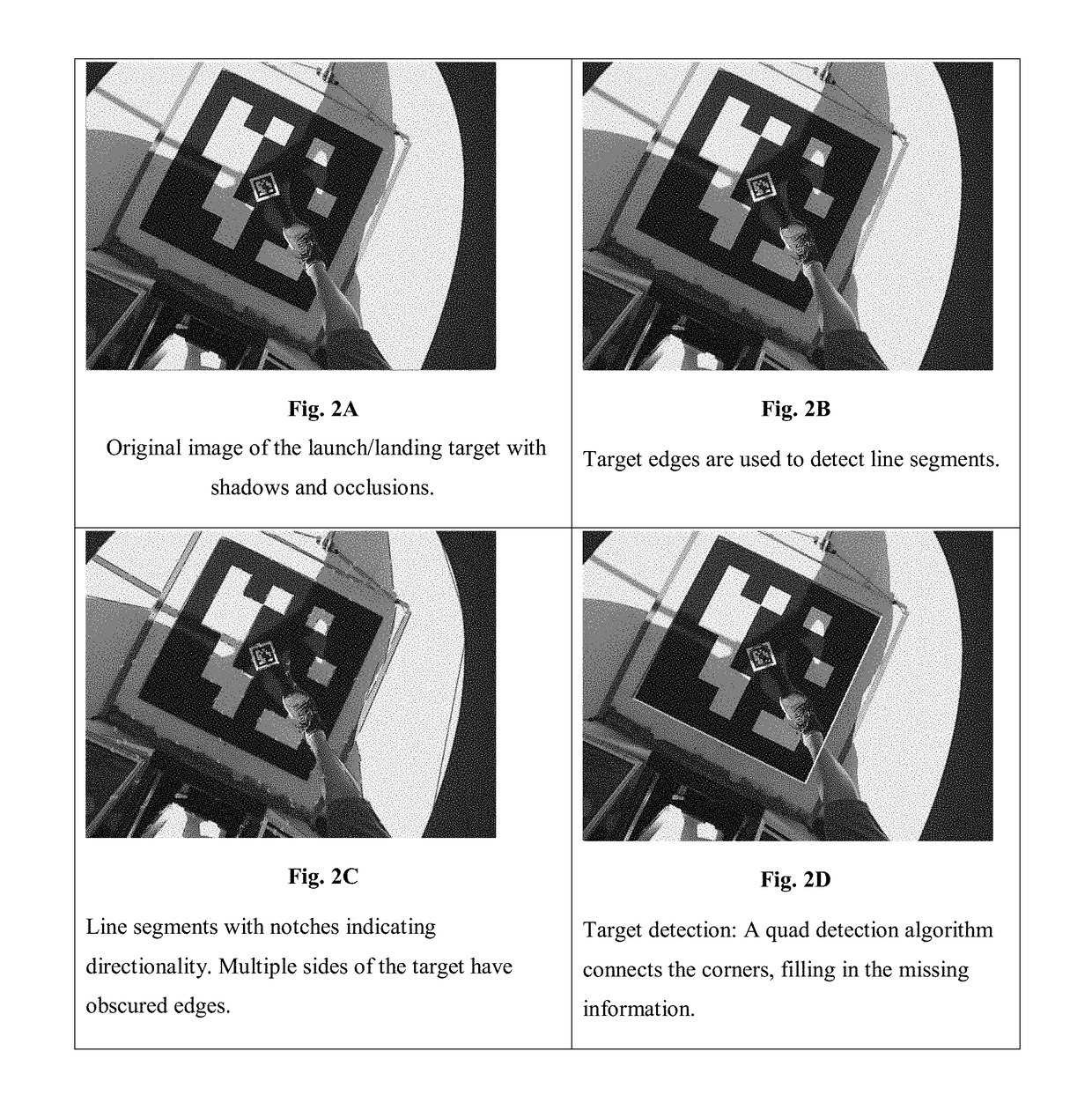

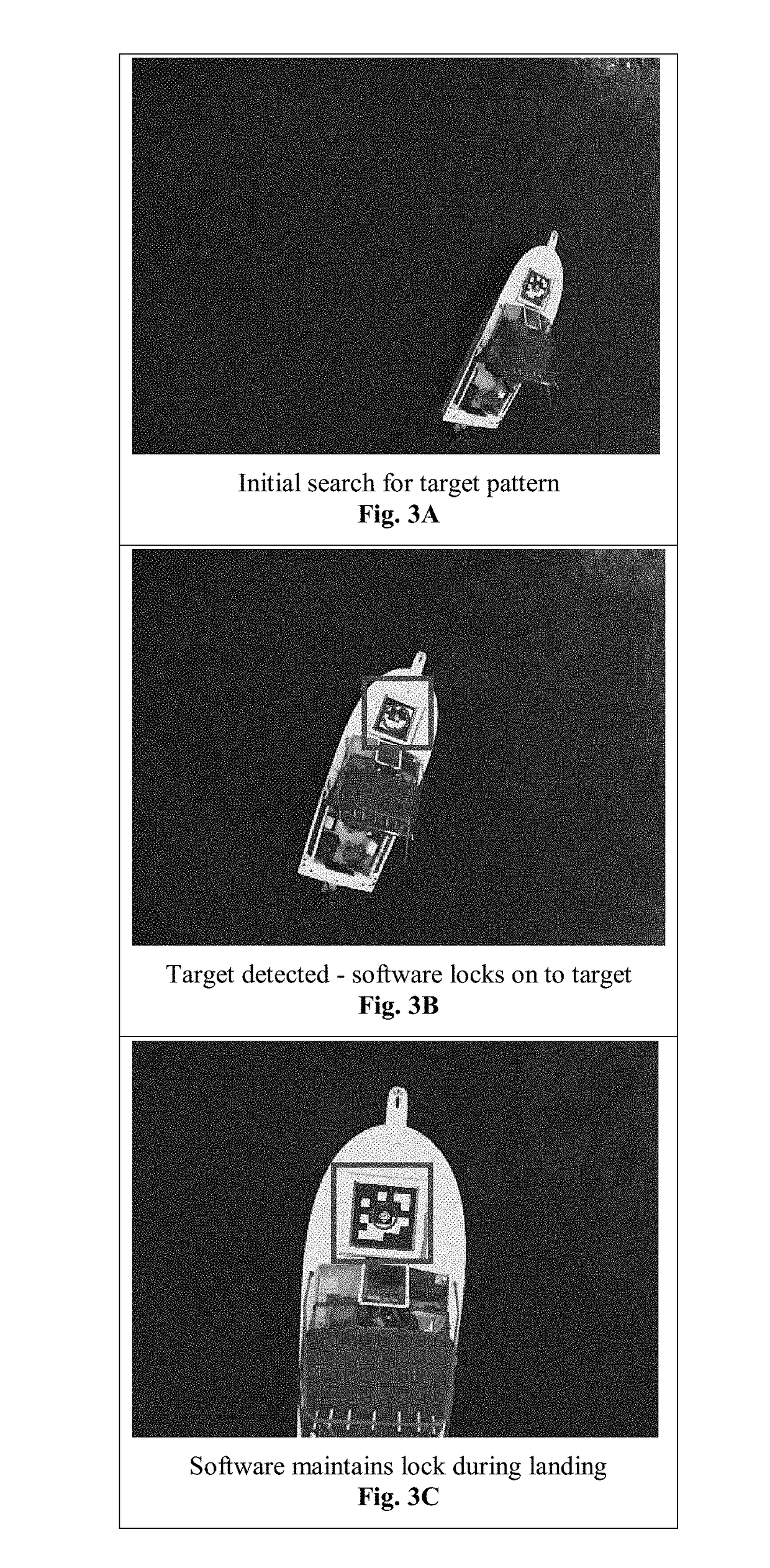

Systems and methods for charging unmanned aerial vehicles on a moving platform

ActiveUS20180364740A1Improve efficiencyReduce riskAutonomous decision making processUnmanned aerial vehiclesComputer moduleComputer science

Disclosed herein are system and method for automatically recharging a unmanned aerial vehicle (UAV) on a moving platform, comprising: a software module identifying the moving platform; a software module estimating a real-time state of the moving platform; a software module controlling automatic landing of the UAV on the moving platform based on the real-time state estimation of the moving platform and data collected from the one or more sensors; a software module controlling automatic connection of the UAV to a charging station of the moving platform with a pre-determined orientation; and a software module controlling automatic taking off of the UAV from the moving platform after charging.

Owner:AEROVIRONMENT INC

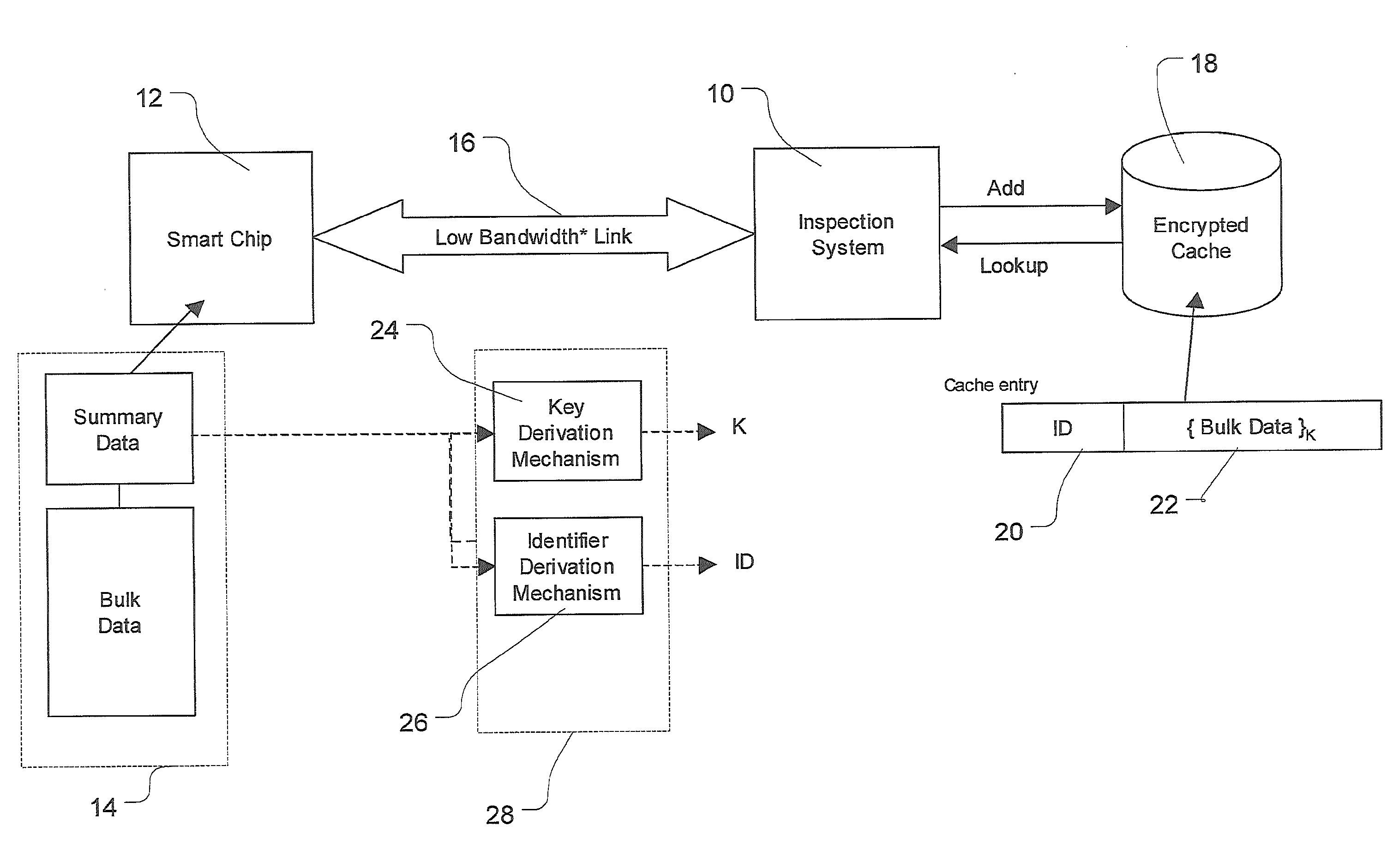

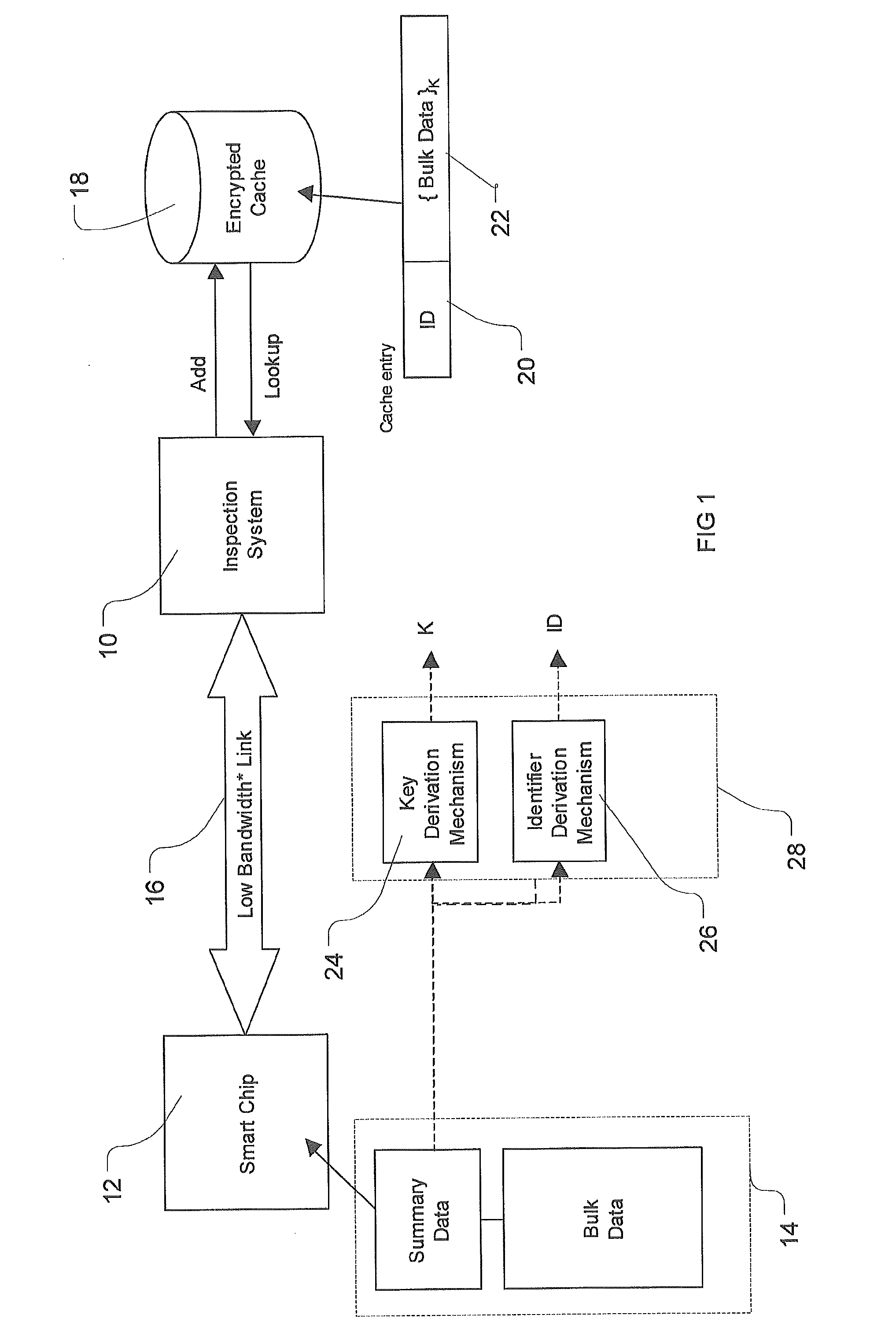

Secure data cache

InactiveUS20110138191A1Raise checkImprove integrityUnauthorized memory use protectionHardware monitoringElectronic documentSmart card

This invention is generally concerned with methods, apparatus and computer program code for securely caching\data, in particular for caching data stored on smart card systems such as those used in ICAO-compliant EU electronic passports. A caching system for providing a secure data cache for data stored in an electronic document, the comprising: an input to receive data to be cached; a processor configured to use all or part of said received data to calculate a unique cryptographic key for said data; encrypt all or part of said data with said unique cryptographic key; and discard said unique cryptographic key after encryption and an output to send said encrypted data to a data cache, with decryption of encrypted data requiring said unique cryptographic key to be recalculated from said electronic document whereby said data cache is secure. Use of such a cache dramatically speeds up the inspection process, by bypassing the need to read data entirely, except for during the first inspection.

Owner:CRYPTOMATHIC LTD

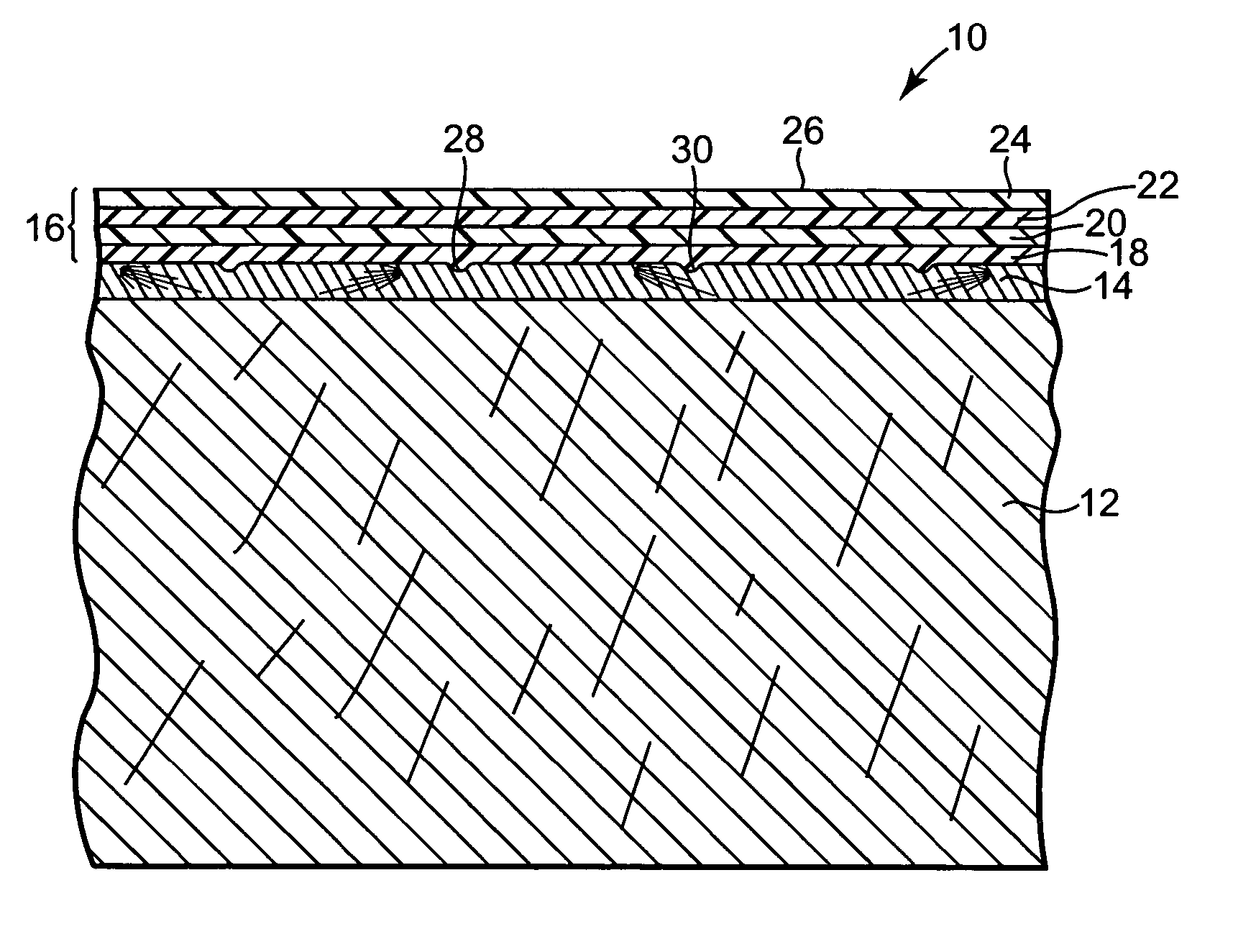

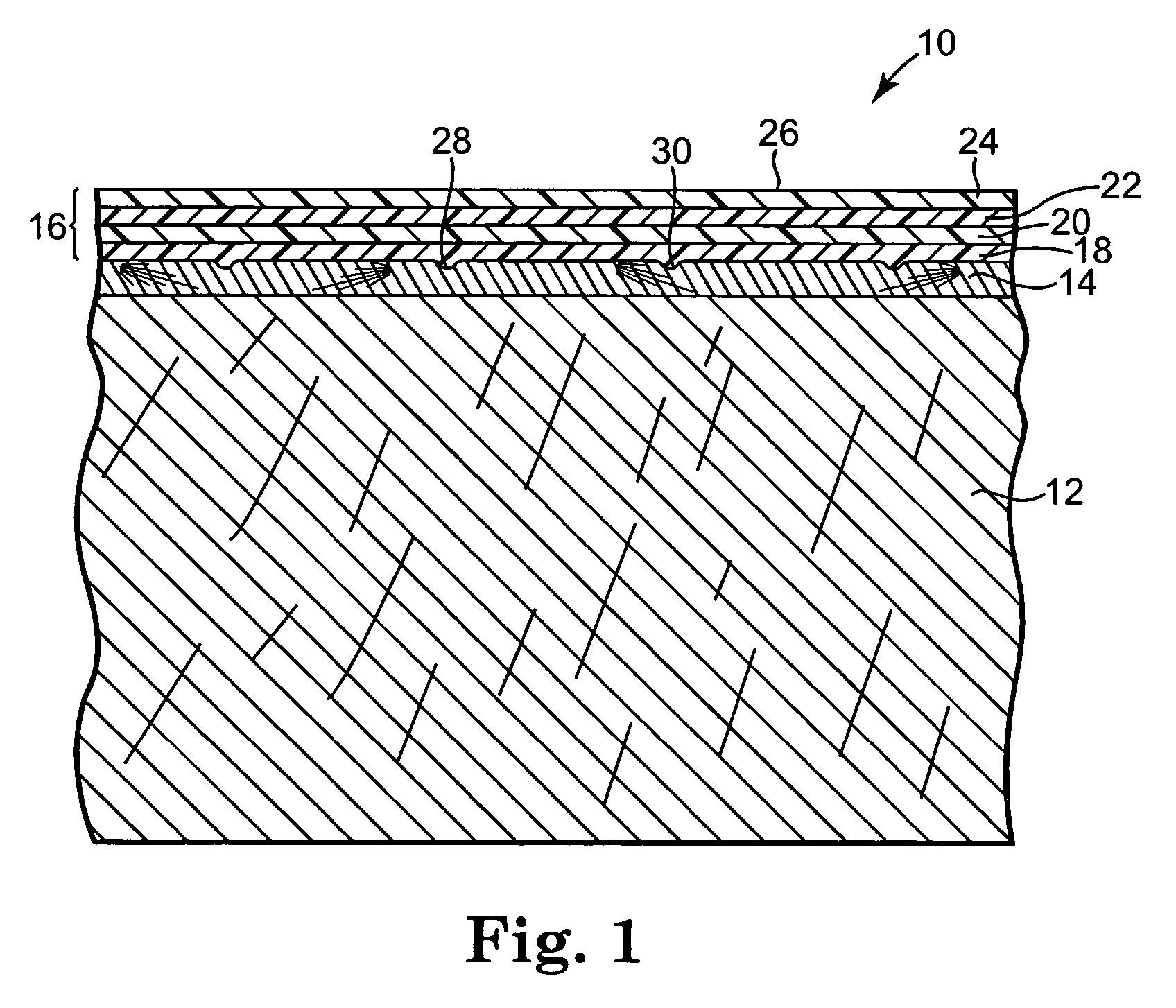

Check-resistant veneer coating system

ActiveUS20060029825A1Less sensitiveMore adhesivePretreated surfacesWood layered productsFiberWood veneer

A veneered wood product is made using a multilayer finishing system wherein at least one of the subsurface layers comprises a UV cured cationically polymerized moiety. Coatings based on UV curable cationically polymerizable moieties appear to be less sensitive to UV overexposure and more adherent to wood fibers than corresponding coatings based on UV curable free radically polymerizable moieties. The multilayer wood veneer finishing system can provide improved intercoat adhesion or improved veneer check resistance, especially under factory conditions.

Owner:AXALTA COATING SYST IP CO LLC

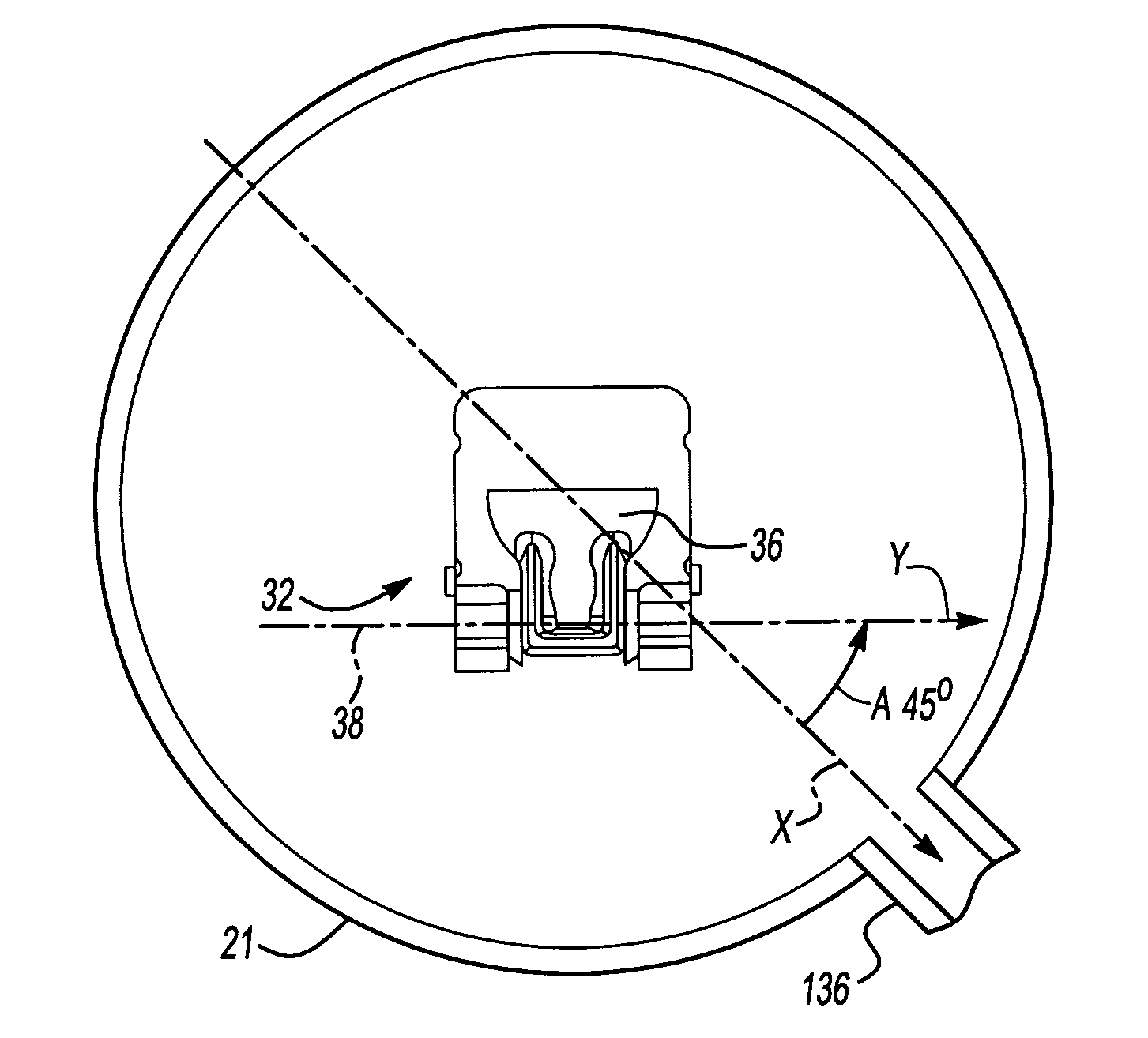

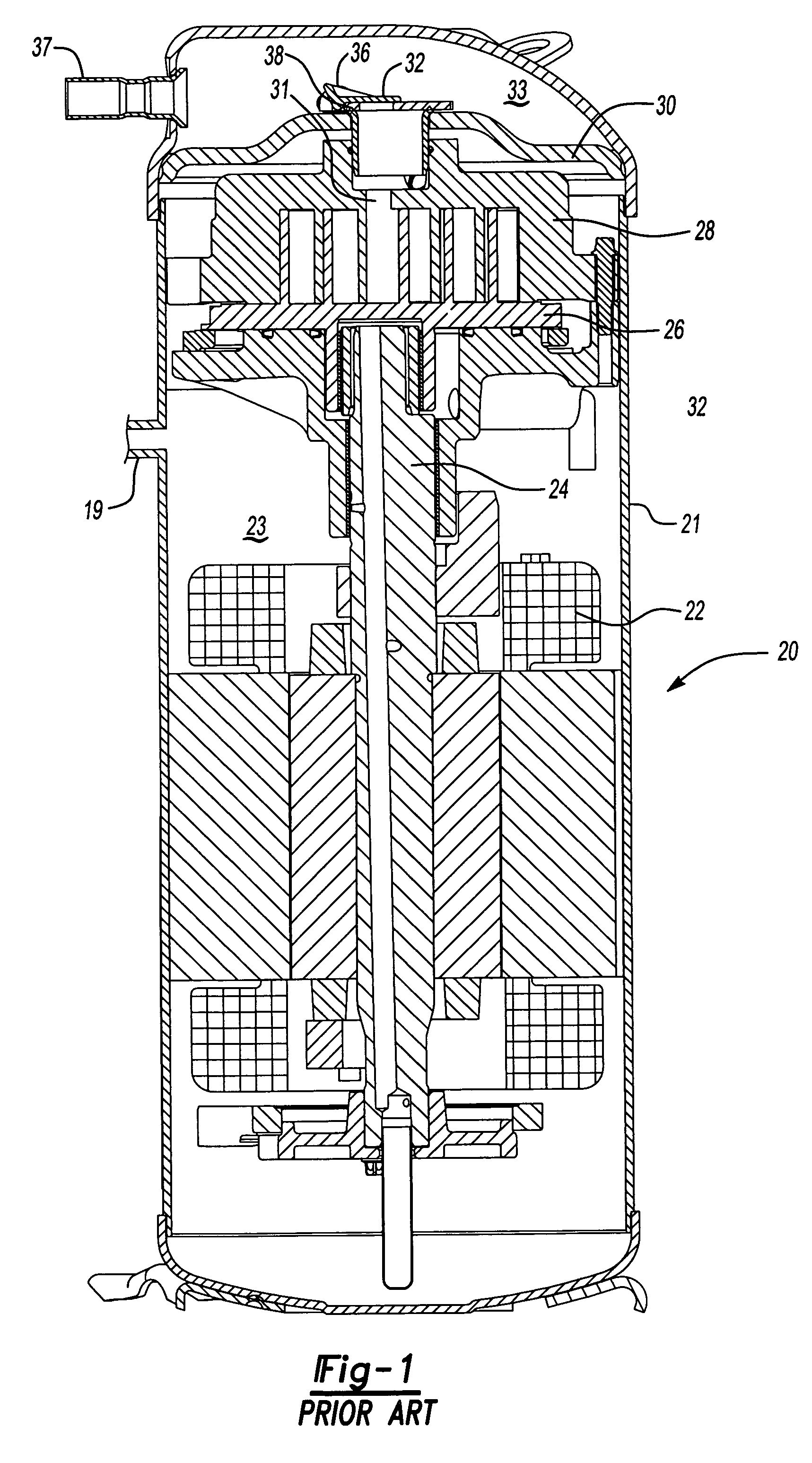

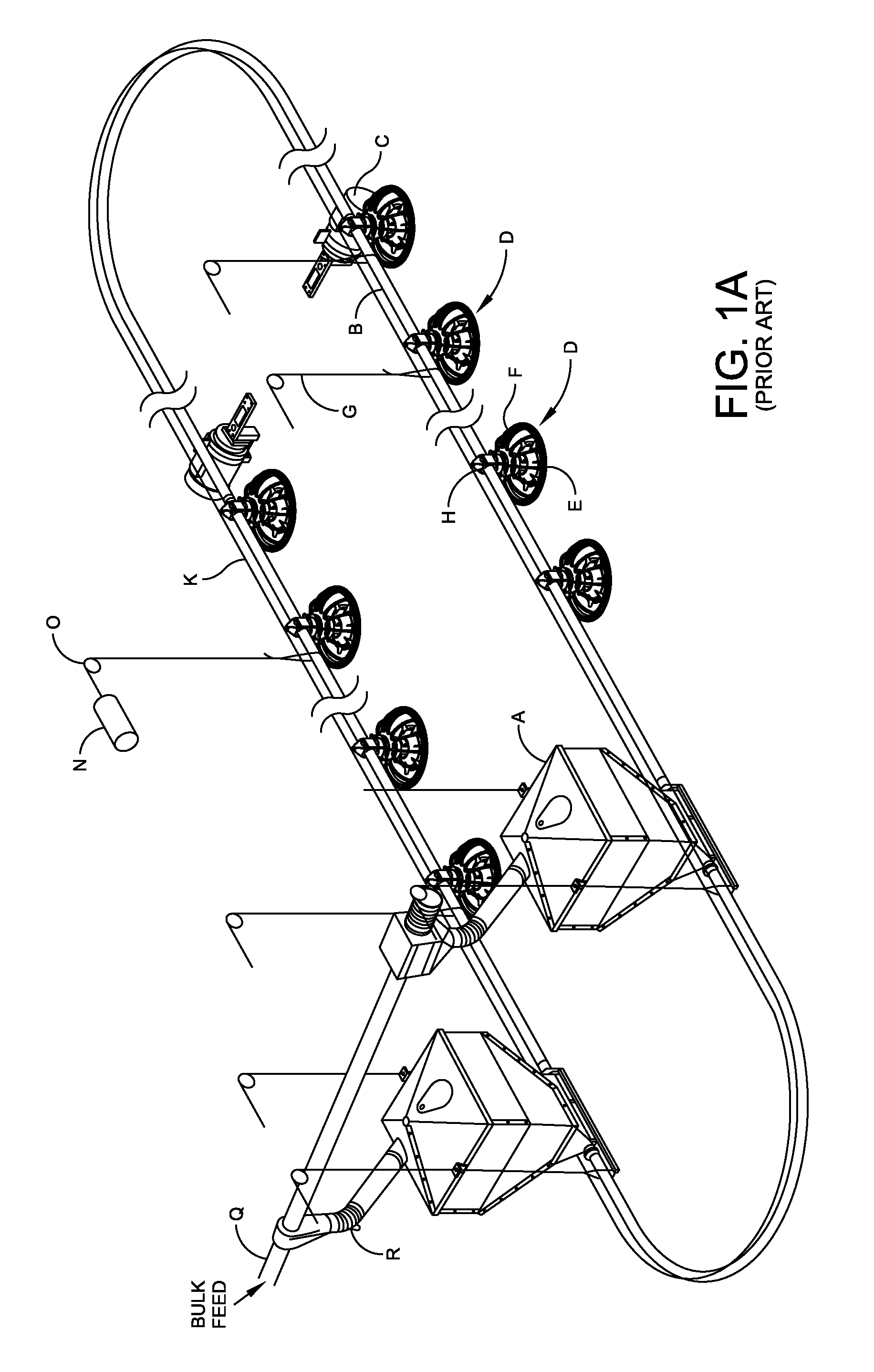

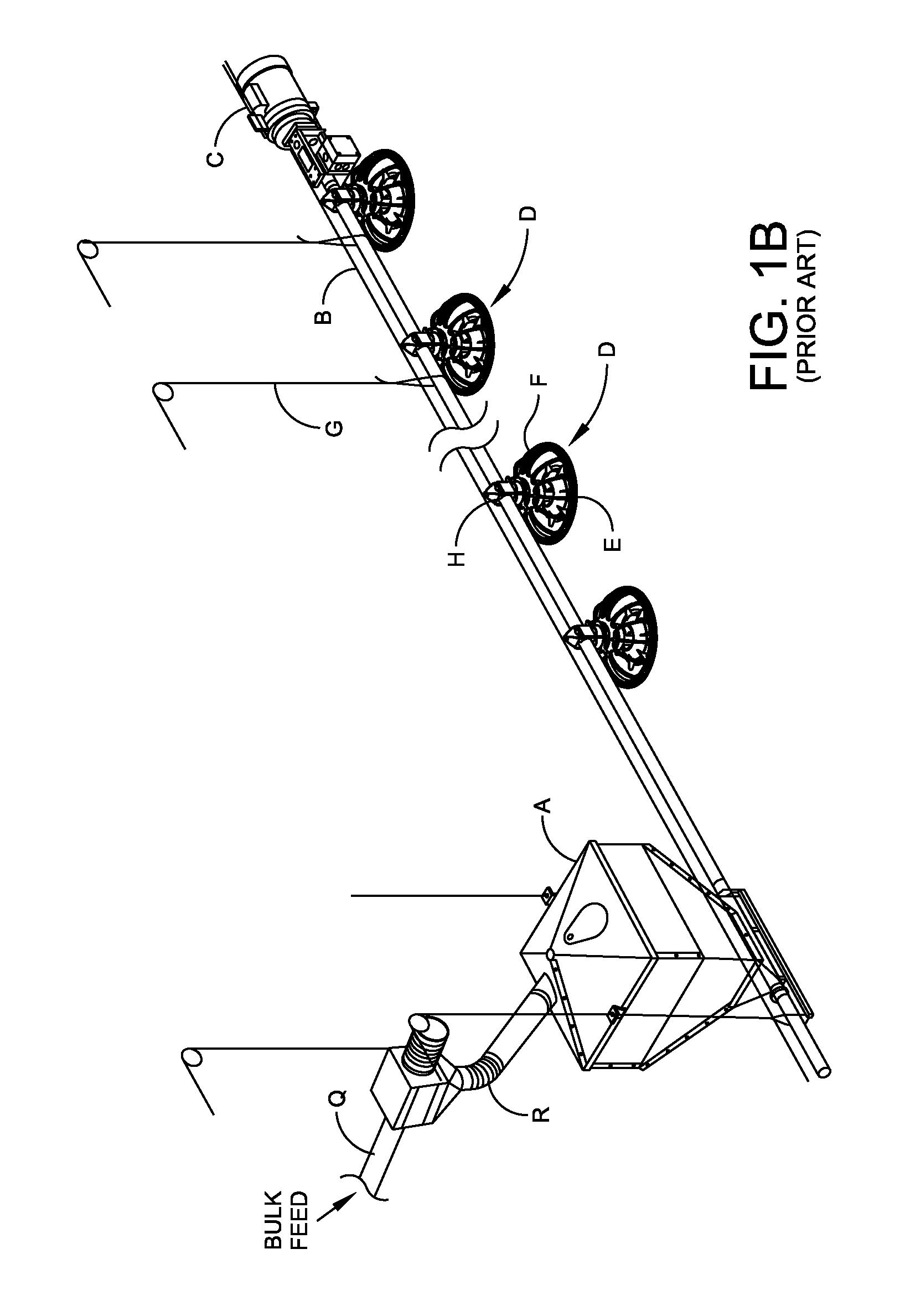

Compressor with check valve orientated at angle relative to discharge tube

InactiveUS7255542B2Reduce fatigue stressRaise checkRotary/oscillating piston combinations for elastic fluidsEngine of arcuate-engagement typeEngineeringCheck valve

A unique positioning of a discharge tube relative to a pivot axis of a check valve in a compressor reduces the wear and fatigue stresses on the pivoting check valve components. The tube is centered on an axis that is non-perpendicular to an axis that is parallel to the pivot axis of the check valve, and in one embodiment was at 45°. With the inventive positioning of the discharge tube relative to the pivot axis, the flow streamlines heading from the discharge port to the discharge tube are no loner normal to the flapper valve surface, and the amount of wear between moving valve components and fatigue stresses are reduced.

Owner:SCROLL TECH

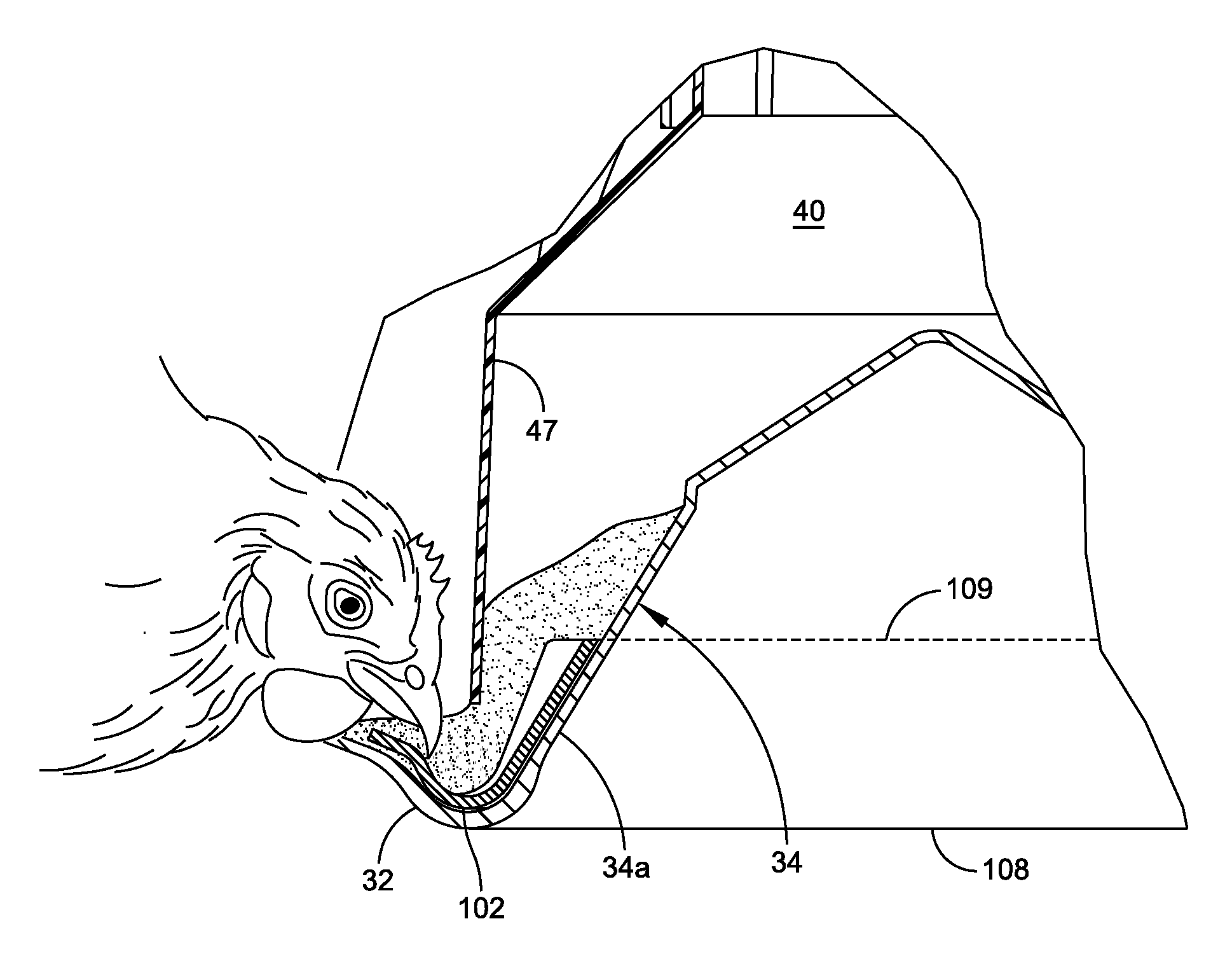

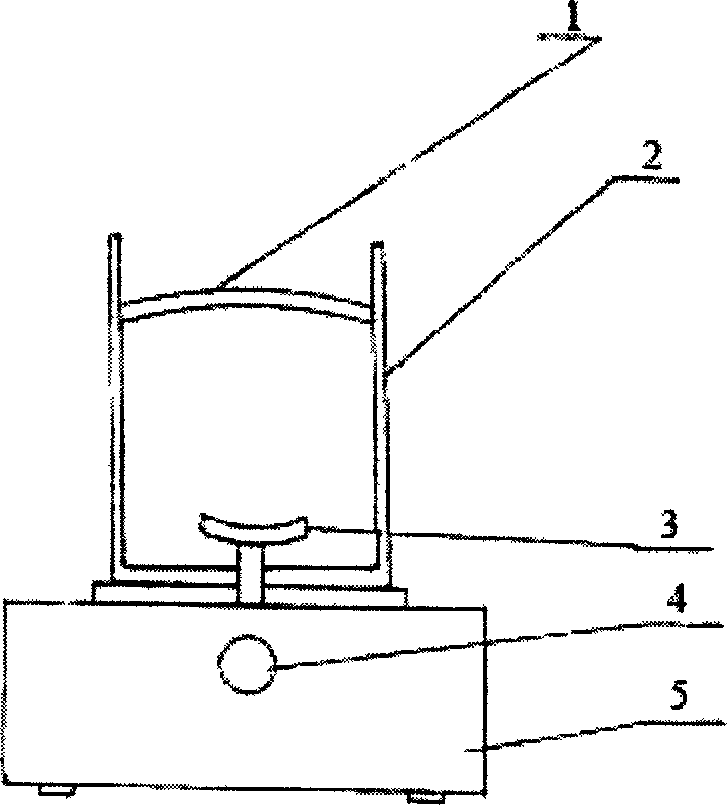

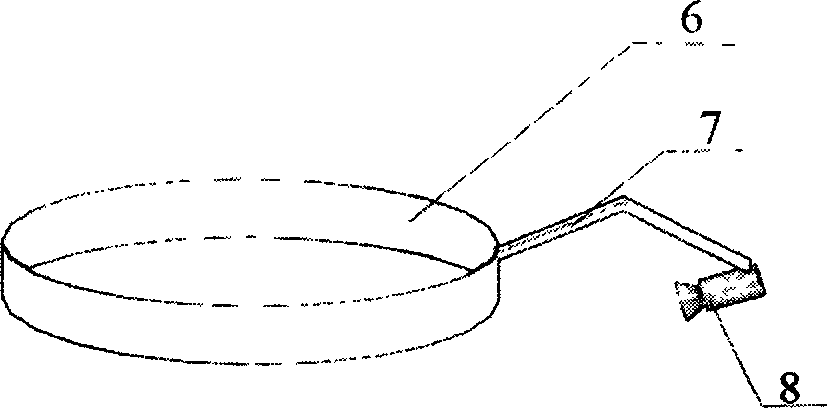

Poultry feeder with beak grooming device

ActiveUS20130139755A1Easily replaceableEasy to replaceAnimal feeding devicesAnimal housingGrowth controlEngineering

A poultry feeder with beak growth control device is provided. In one embodiment, the feeder includes a feeder pan, a feeder tower, and a beak grooming ring. The grooming ring is removably inserted in the feeder and has an annular shape complementary configured to engage a corresponding shape of the feeder pan. Preferably, the grooming ring has a self-supporting structure that retains its complementary shape to the feeder pan independently of the pan when removed therefrom. The grooming ring is insertable and removable from feeder as a separable unit from the feeder and operable to abrade the beak while the birds feed, thereby controlling its growth and length.

Owner:VALCO IND INC

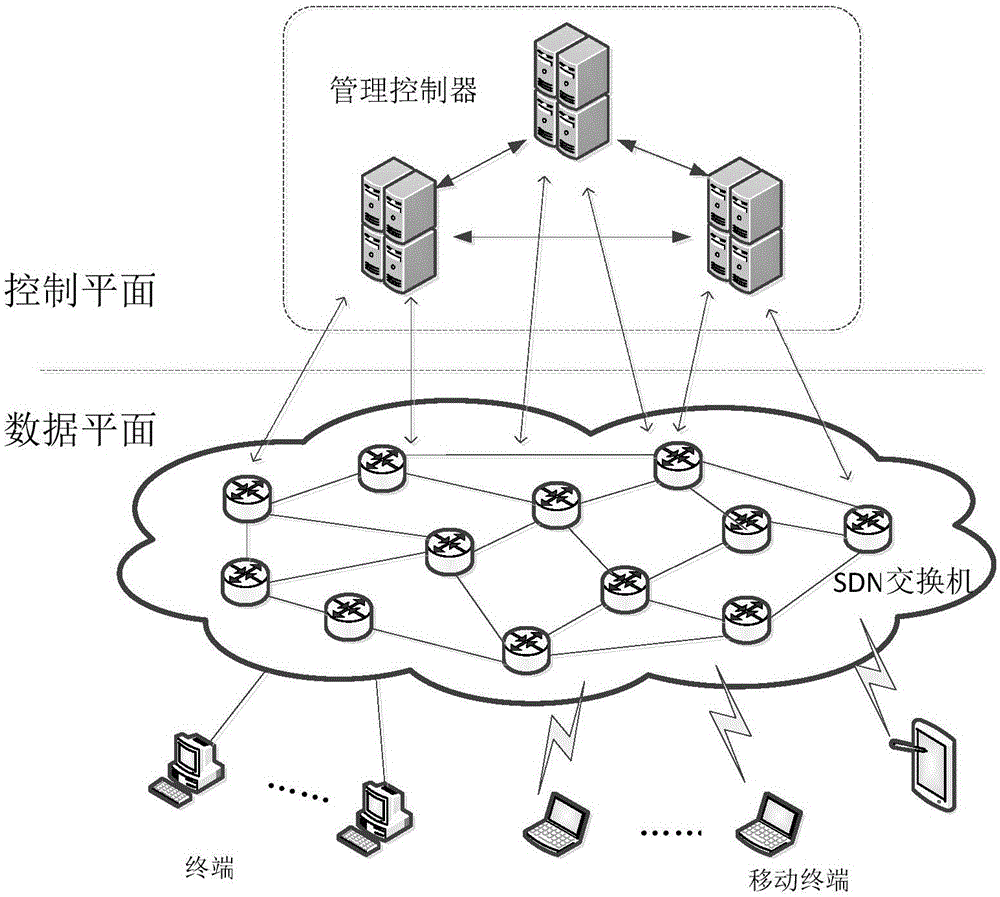

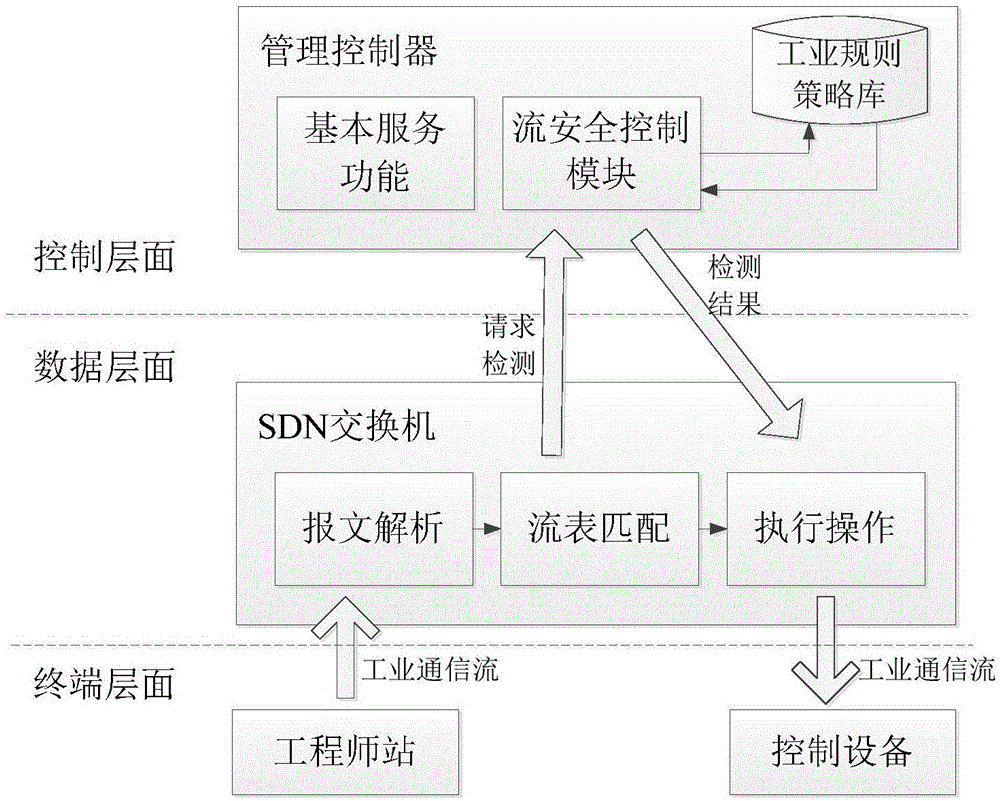

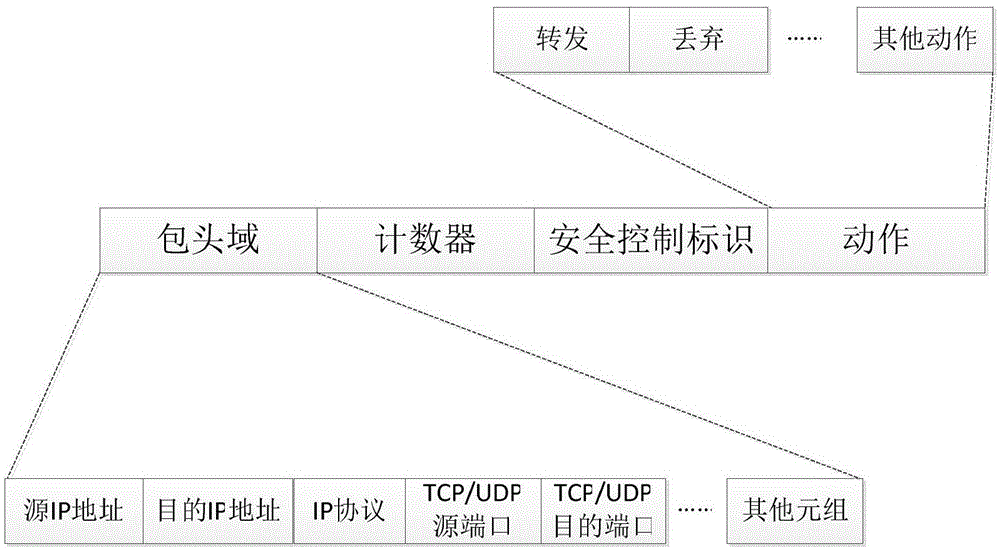

Industrial communication flow transmission safety control method based on SDN architecture

ActiveCN106411820ARaise checkAdd control mechanismSecuring communicationProgramme total factory controlData streamSecure transmission

The invention discloses an industrial communication flow transmission safety control method based on an SDN architecture. According to the method, a flow safety control module is designed in a management controller, deep analysis of industrial communication flow data is conducted, matching is performed with a preset industrial rule strategy, control processing operation in the industrial rule strategy is performed, and transmission control of the industrial communication flow is realized. The management controller comprises an industrial rule strategy database used for storing all industrial rule strategies set by users and an SDN switch maintenance flow table structure, the industrial communication flow is forwarded according to a flow table, and the flow table comprises a safety control identifier used for indicating whether the communication flow needs safety transmission control. According to the method, the legitimacy of the industrial communication data flow can be detected, access control for industrial communication which is not in accordance with the industrial rule strategy is realized, and the security and the reliability of an industrial control system based on the SDN architecture is guaranteed.

Owner:SHENYANG INST OF AUTOMATION - CHINESE ACAD OF SCI

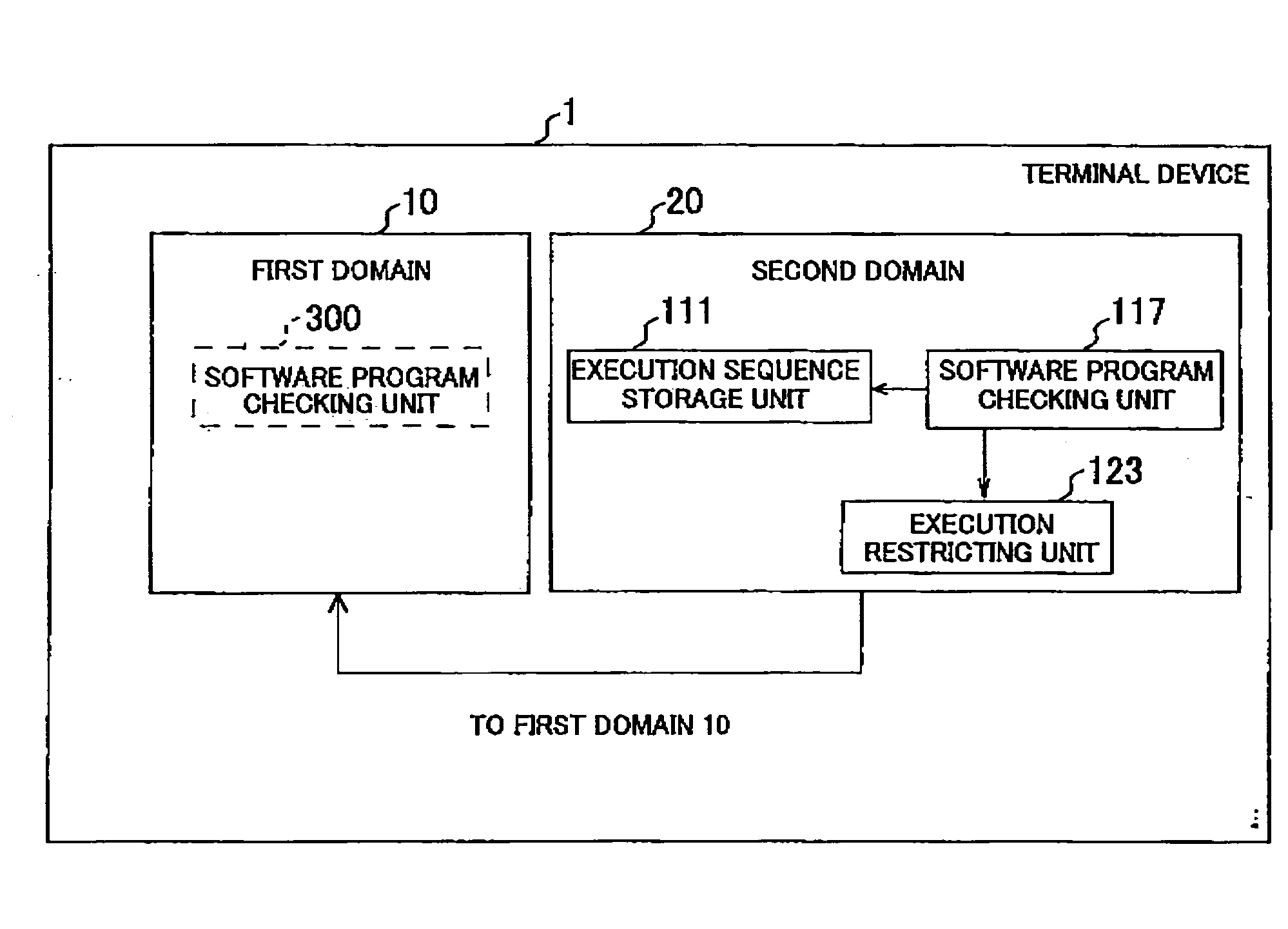

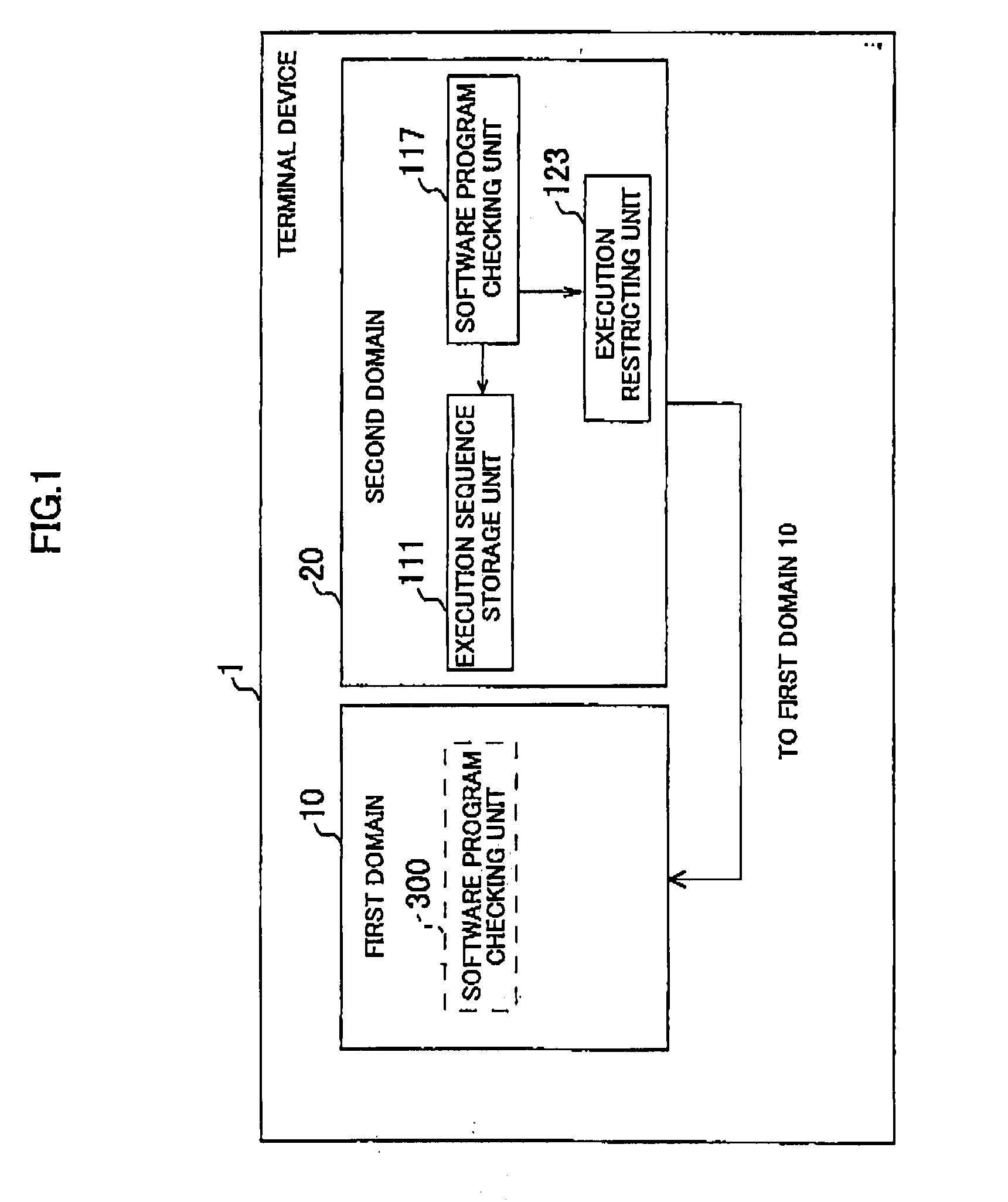

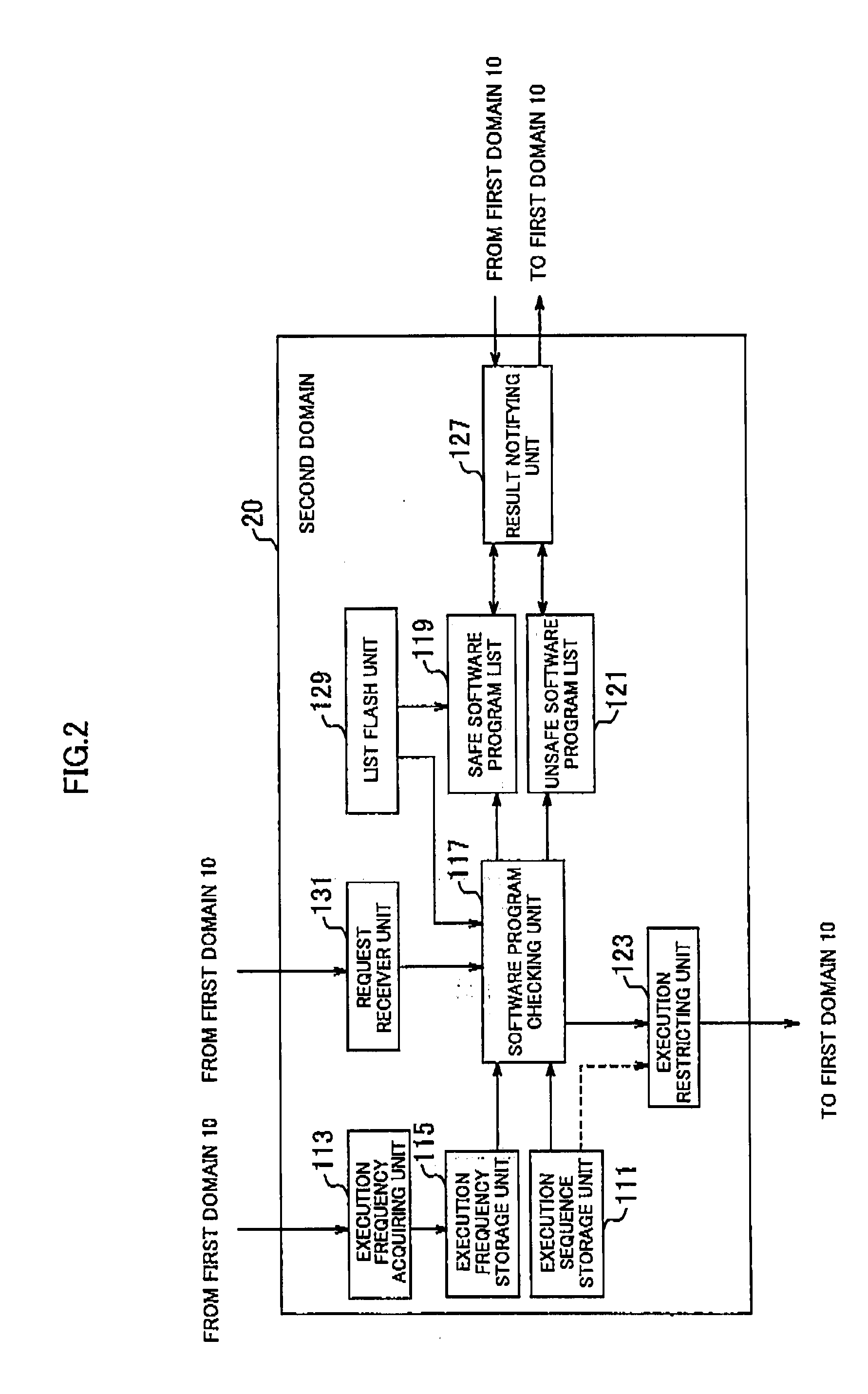

Terminal device and method for checking a software program

ActiveUS20100107246A1Reduce the overall heightSuppressing security degradationMemory loss protectionError detection/correctionSoftware engineeringTerminal equipment

A terminal device according to the present invention includes: a first domain configured to execute multiple software programs; and a second domain configured to operate independently of the first domain and to check whether or not the software programs are safe. The second domain includes: an execution sequence storage unit configured to store execution priority of the multiple software programs to be executed by the first domain; a software program checking unit configured to check whether or not the multiple software programs are safe, according to the execution sequence storage unit; and an execution restricting unit configured to restrict the first domain from executing a software program included in the multiple software programs and having a check result indicating that the software program is unsafe, before checking of all the multiple, software programs is completed.

Owner:NTT DOCOMO INC

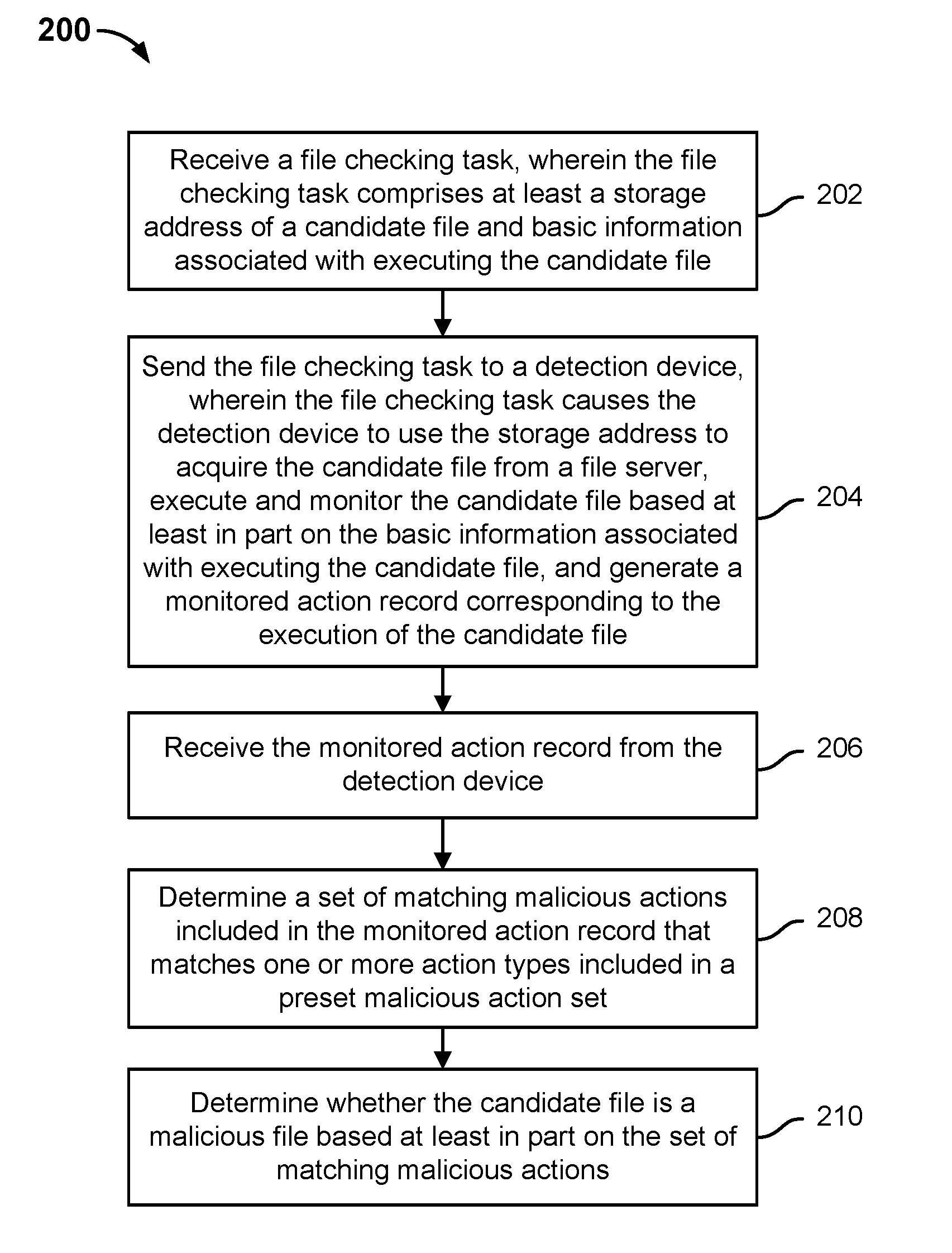

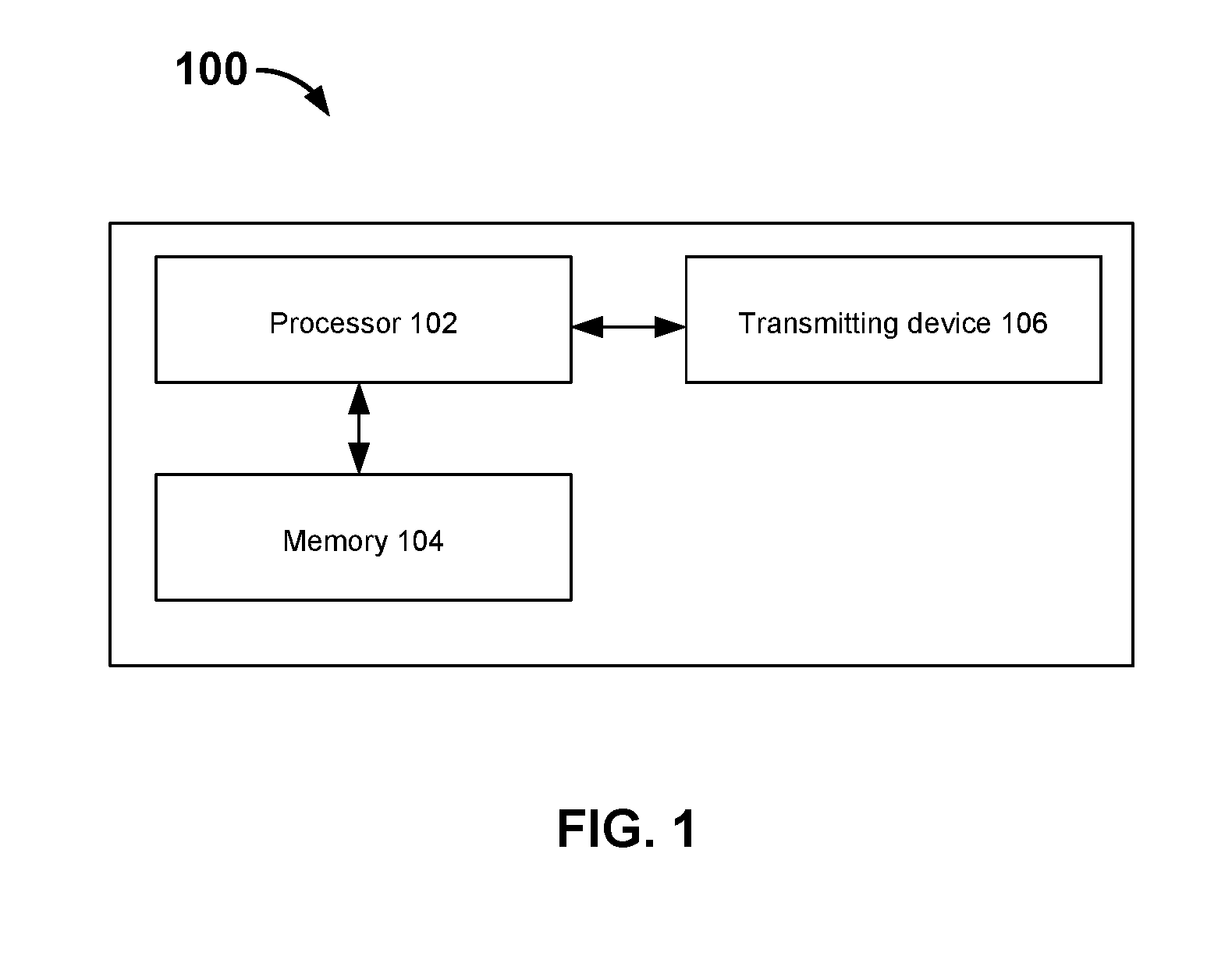

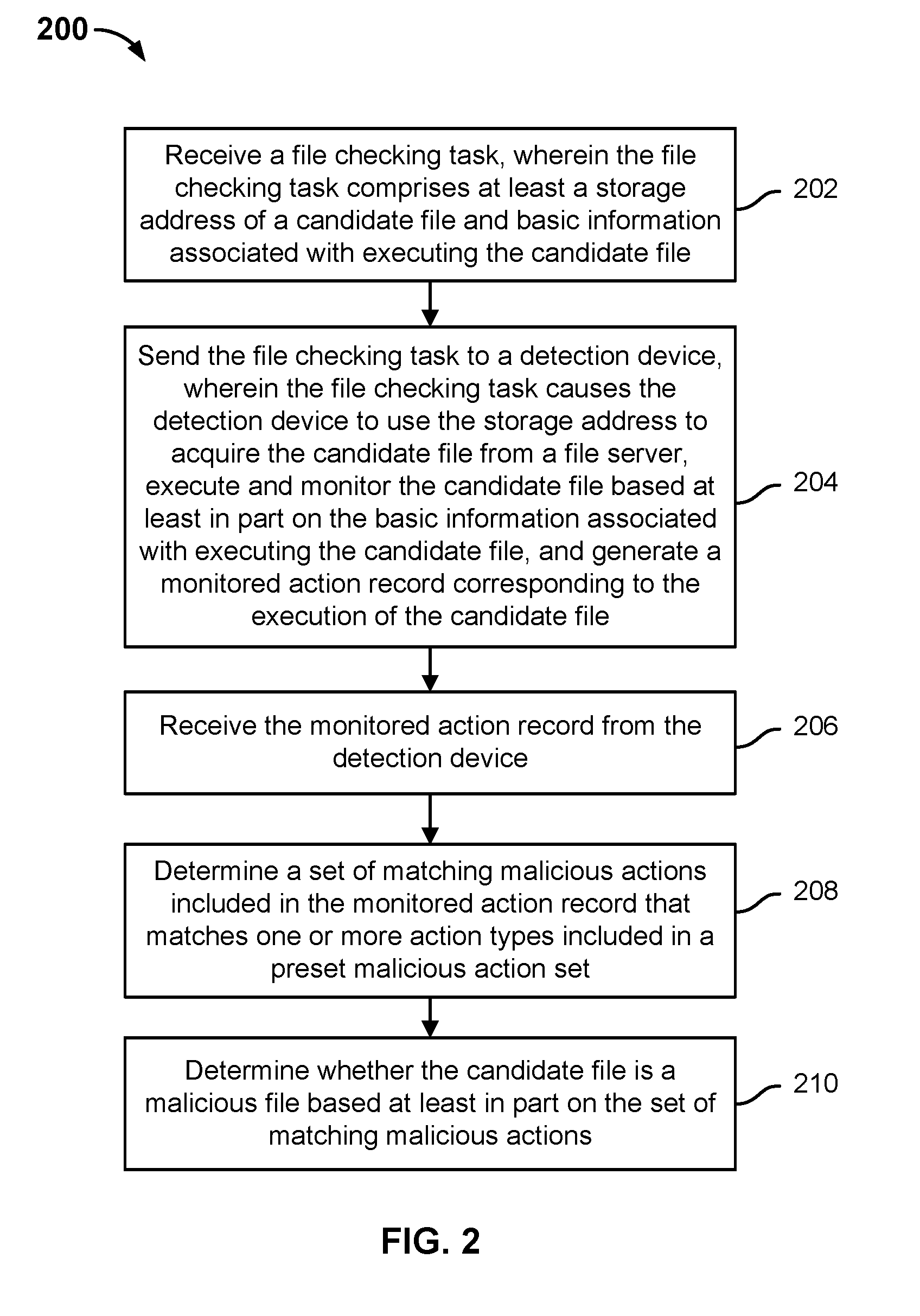

Detecting malicious files

ActiveUS20160342787A1Raise checkPrivacy protectionDigital data protectionPlatform integrity maintainanceFile serverComputer science

Detecting malicious files is disclosed, including: receiving a file checking task, wherein the file checking task comprises a storage address of a candidate file and basic information associated with executing the candidate file; sending the file checking task to a detection device, wherein the file checking task causes the detection device to: use the storage address to acquire the candidate file from a file server; execute the candidate file based at least in part on the basic information associated with the candidate file; monitor the execution of the candidate file; and generate a monitored action record corresponding to the execution of the candidate file; and receiving the monitored action record from the detection device; determining a set of actions included in the monitored action record that matches one or more action types included in a preset malicious action set; and determining whether the candidate file is a malicious file based at least in part on the determined set of actions.

Owner:ALIBABA GRP HLDG LTD

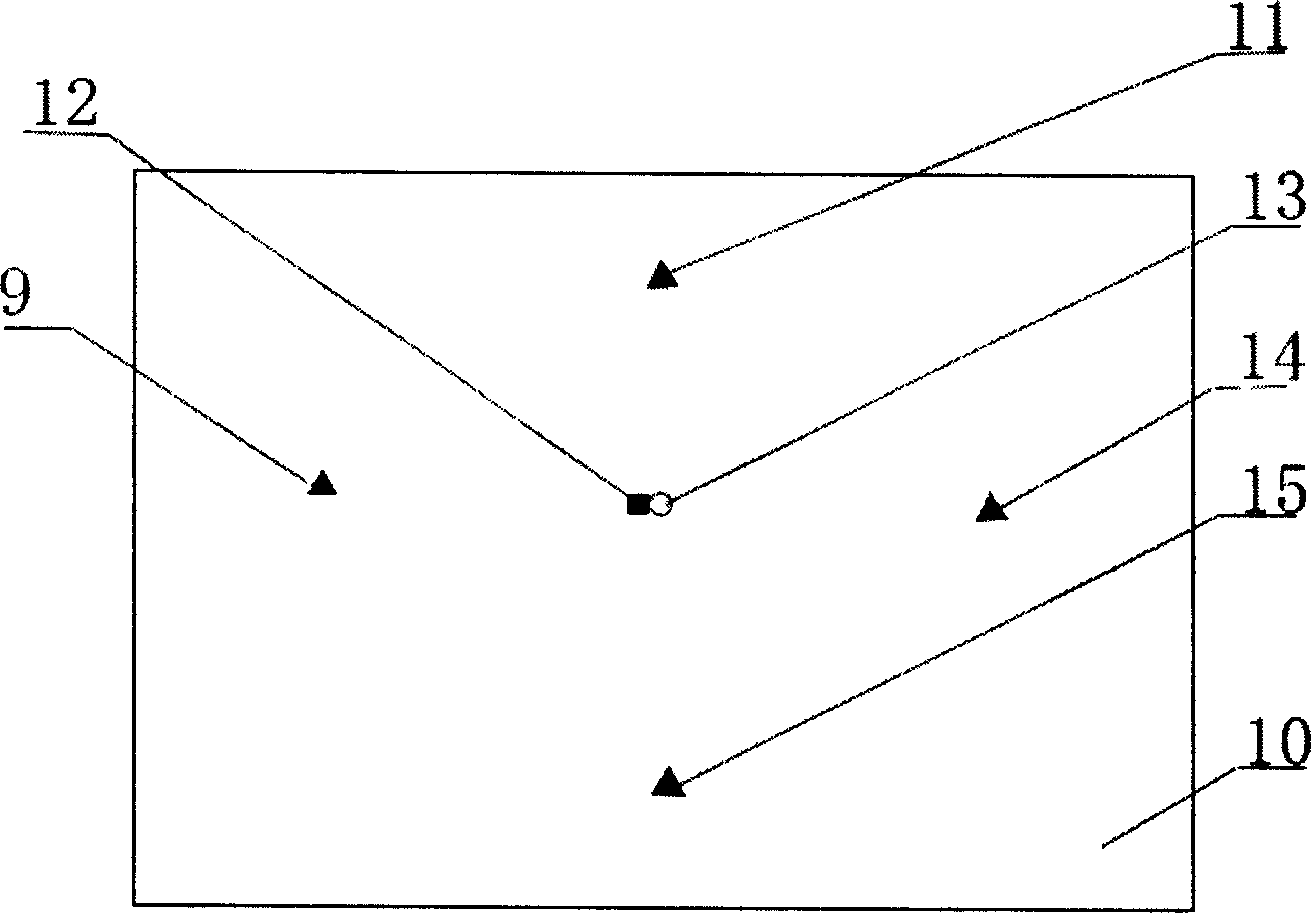

Cockeye degree meter and its measuring instrument

InactiveCN1836625AObjective measurementAccurate measurementEye diagnosticsMeasurement deviceMedical equipment

The present invention belongs to the field of ophthalmic medical equipment and is one strabismus measuring device and method. The strabismus measuring device of the present invention includes a head fixing unit an eye video camera, a system calibrator, a stared target, a light source and a computerized image analysis system. The strabismus measuring instrument designed based on the present invention can measure strabismus fast, precisely and objectively.

Owner:赵阳

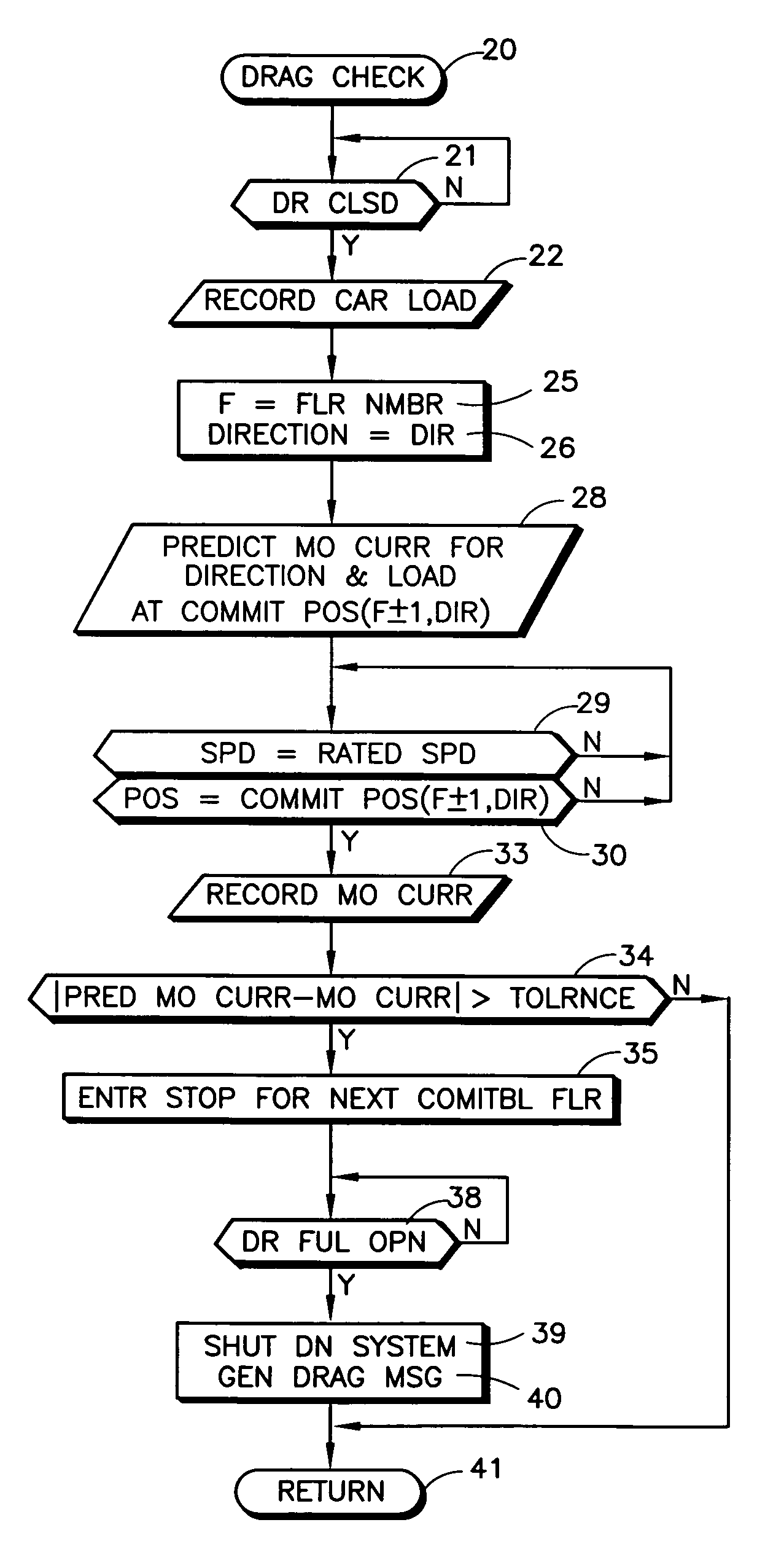

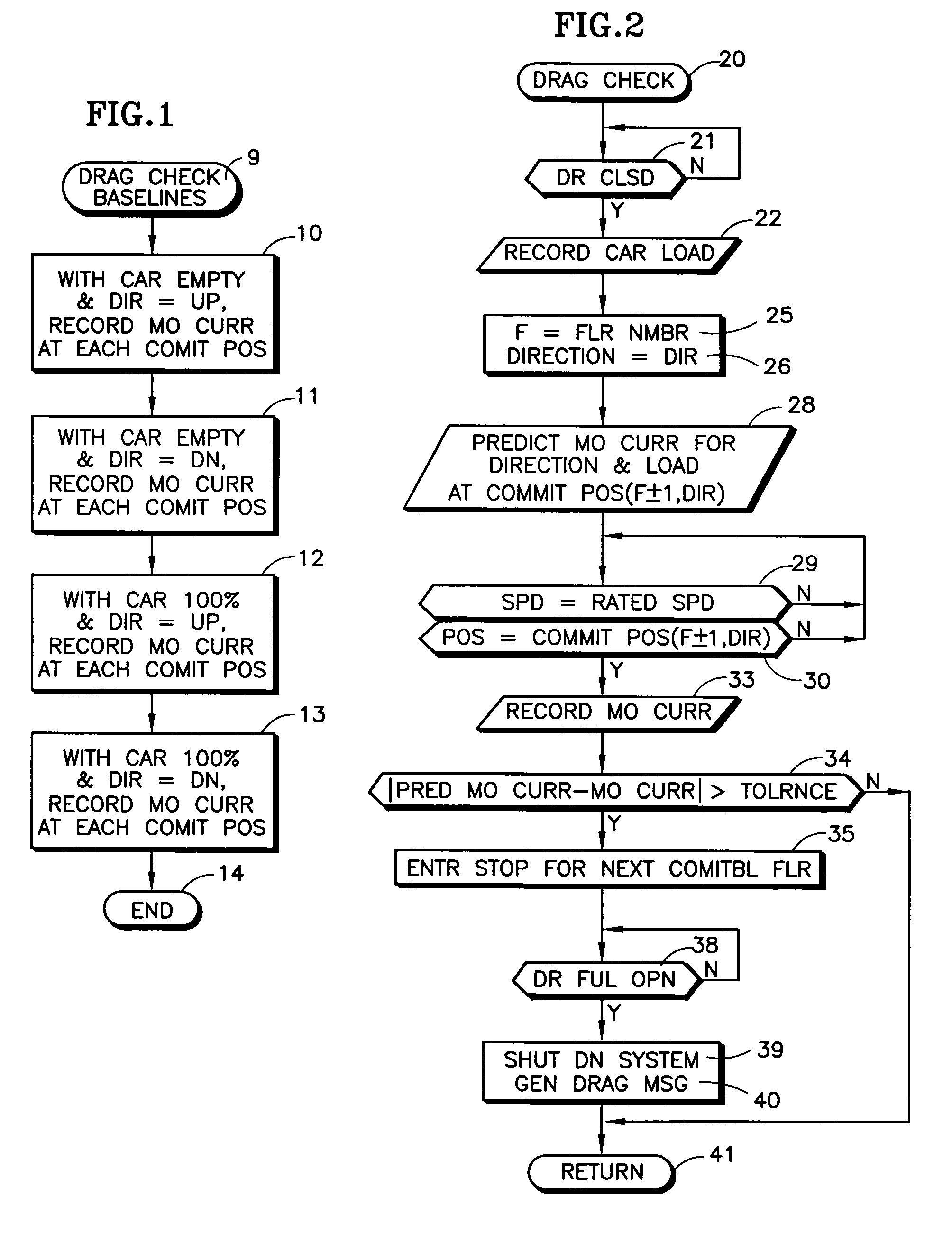

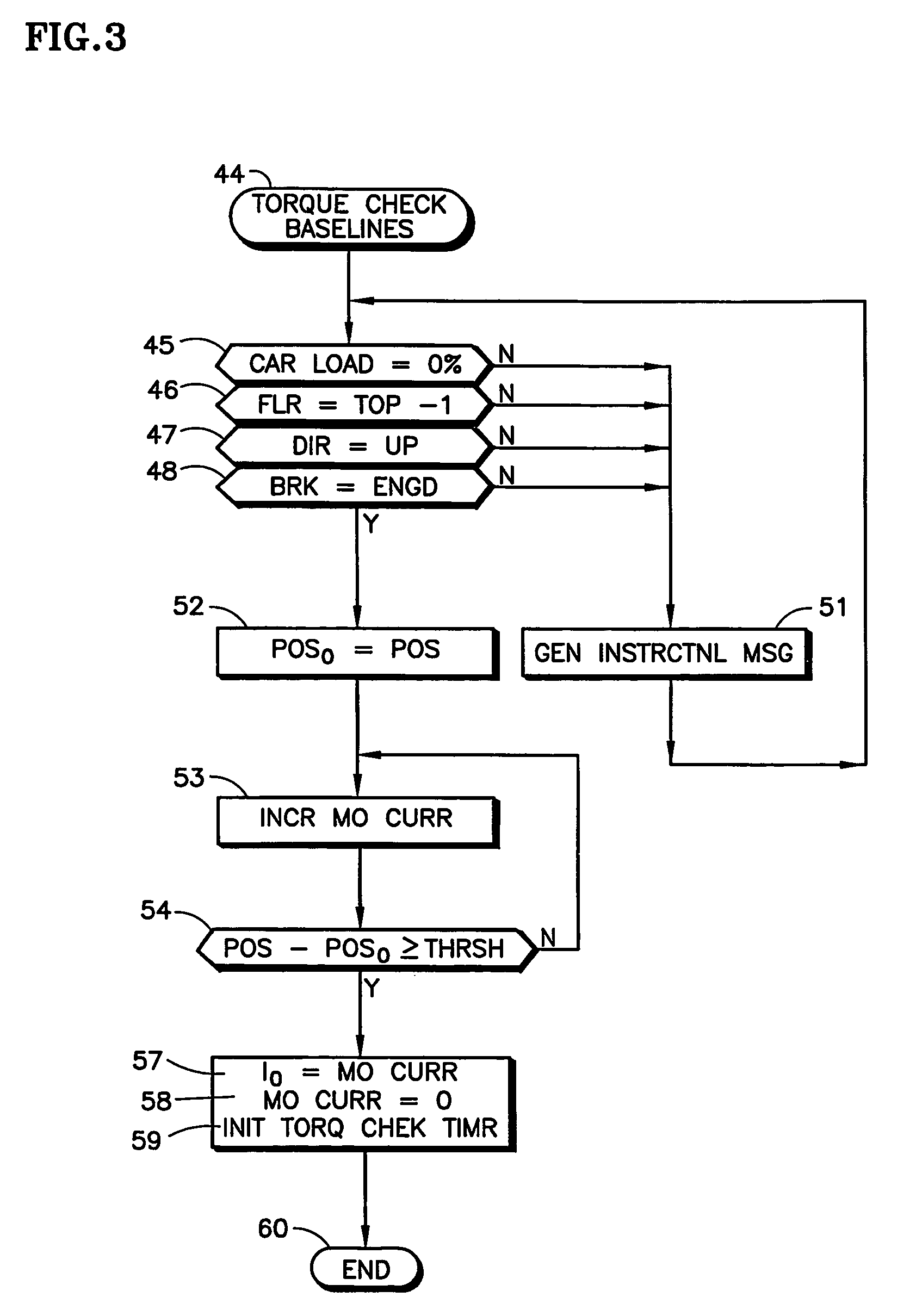

Detecting elevator brake and other dragging by monitoring motor current

Elevator brake or other drag is checked by establishing (10-13) baseline motor currents at plural determined positions as the car is moved up and down both empty and with full load. In a normal run (21), the load is recorded (22) and the motor current required to drive the load at rated speed at the next determined position is both predicted (28) and measured. If the difference between the predicted and actual current exceeds a tolerance (33, 34), the car stops at the next floor (35), the system is shut down (39) and a message generated (40). When the brake is in proper operating condition, baseline motor current required to move a car with the brake engaged is recorded. Thereafter, a high fraction (such as 90%) of baseline motor current is applied to attempt to move the car. If the car moves, the system is shut down (101) and a message generated (102).

Owner:OTIS ELEVATOR CO

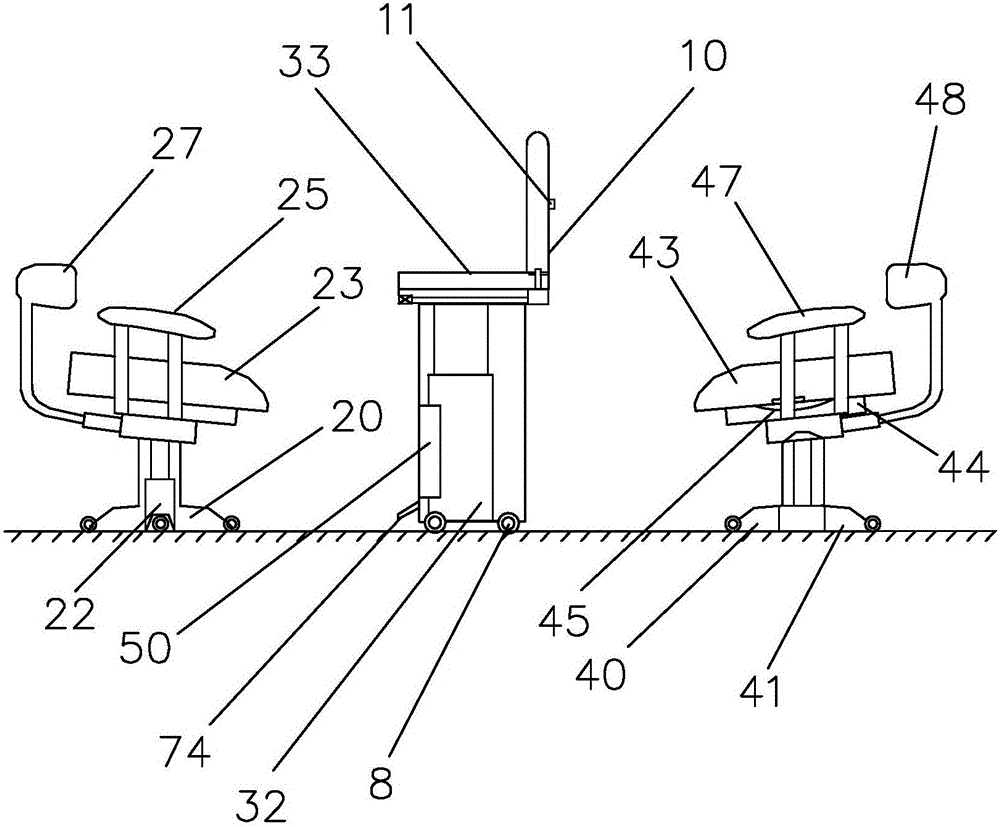

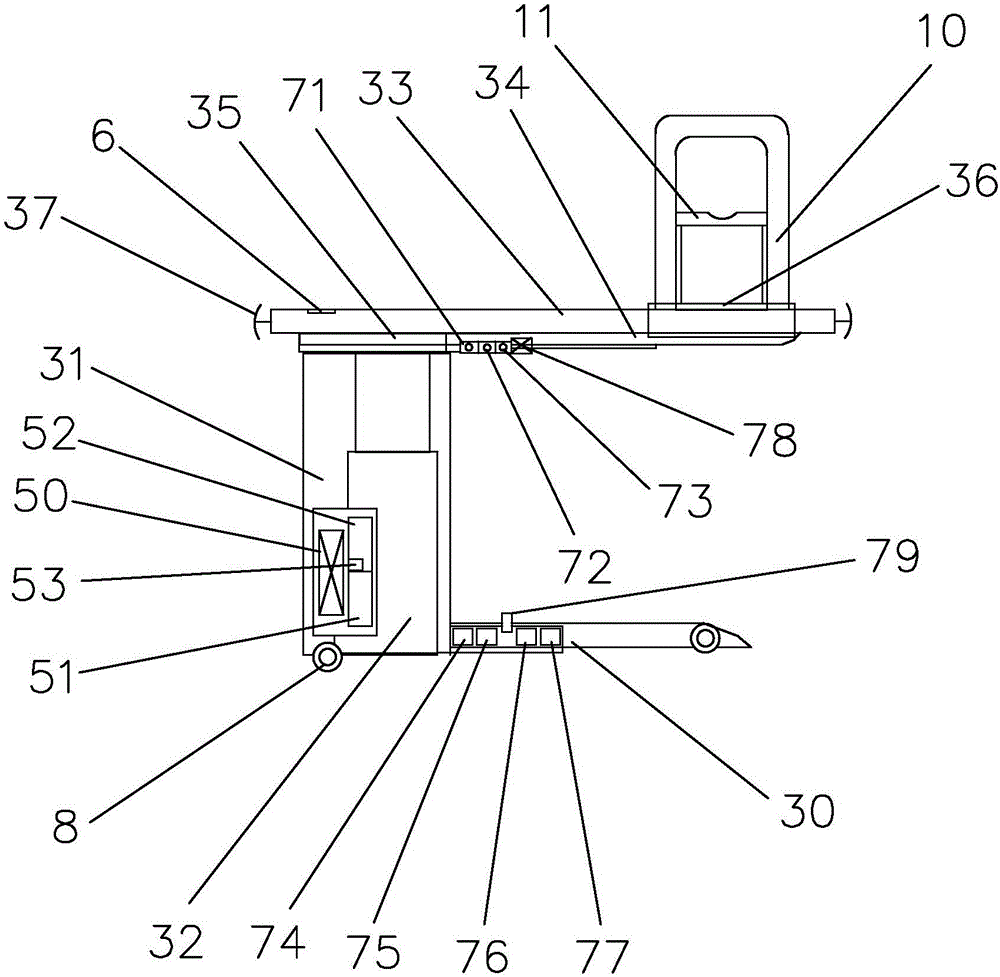

Automatic positioning ophthalmic examining system

ActiveCN105796279AShorten adjustment timeRaise checkOperating chairsDental chairsOperating pointEngineering

An automatic positioning ophthalmic examining system comprises a doctor seat, an examining table, a patient seat and a central controller. A supporting frame capable of being adjusted left and right is arranged on the examining table. A lower jaw support with adjustable height is arranged on the supporting frame. The central controller comprises a control unit, an operating unit and a storage recognition unit. A table top of the examining table is provided with an identification code scanning window used for scanning and identifying identification codes in one-to-one correspondence with the identity of a doctor and the identity of a patient. The identification code scanning window is in signal connection with the storage recognition unit. For the first time, relevant position information is stored in the storage recognition unit immediately after the positions of the doctor seat, the examining table, the patient seat and the lower jaw support are adjusted; when the information needs to be used again, after the identity of the doctor and the identity of the patient are confirmed through the identification code scanning window and the storage recognition unit, the storage recognition unit automatically calls position data, stored in the storage recognition unit, of the doctor and the patient and transmits the position data to the control unit and the operating unit, so that the control unit and the operating unit automatically drive relevant mechanisms to act according to the data and be adjusted in place. Time is saved for the doctor, and examination and treatment efficiency is improved.

Owner:杨勋 +1

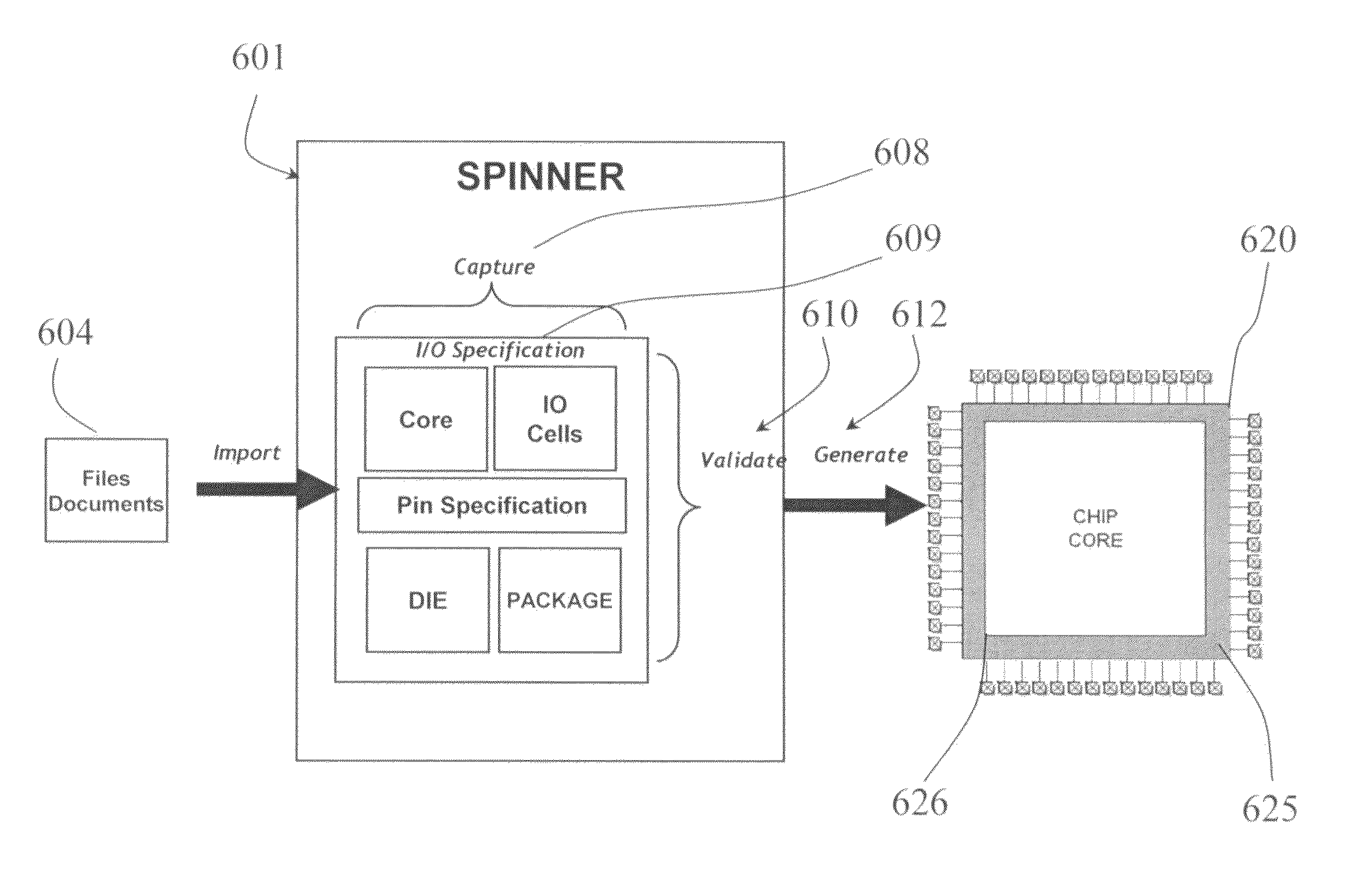

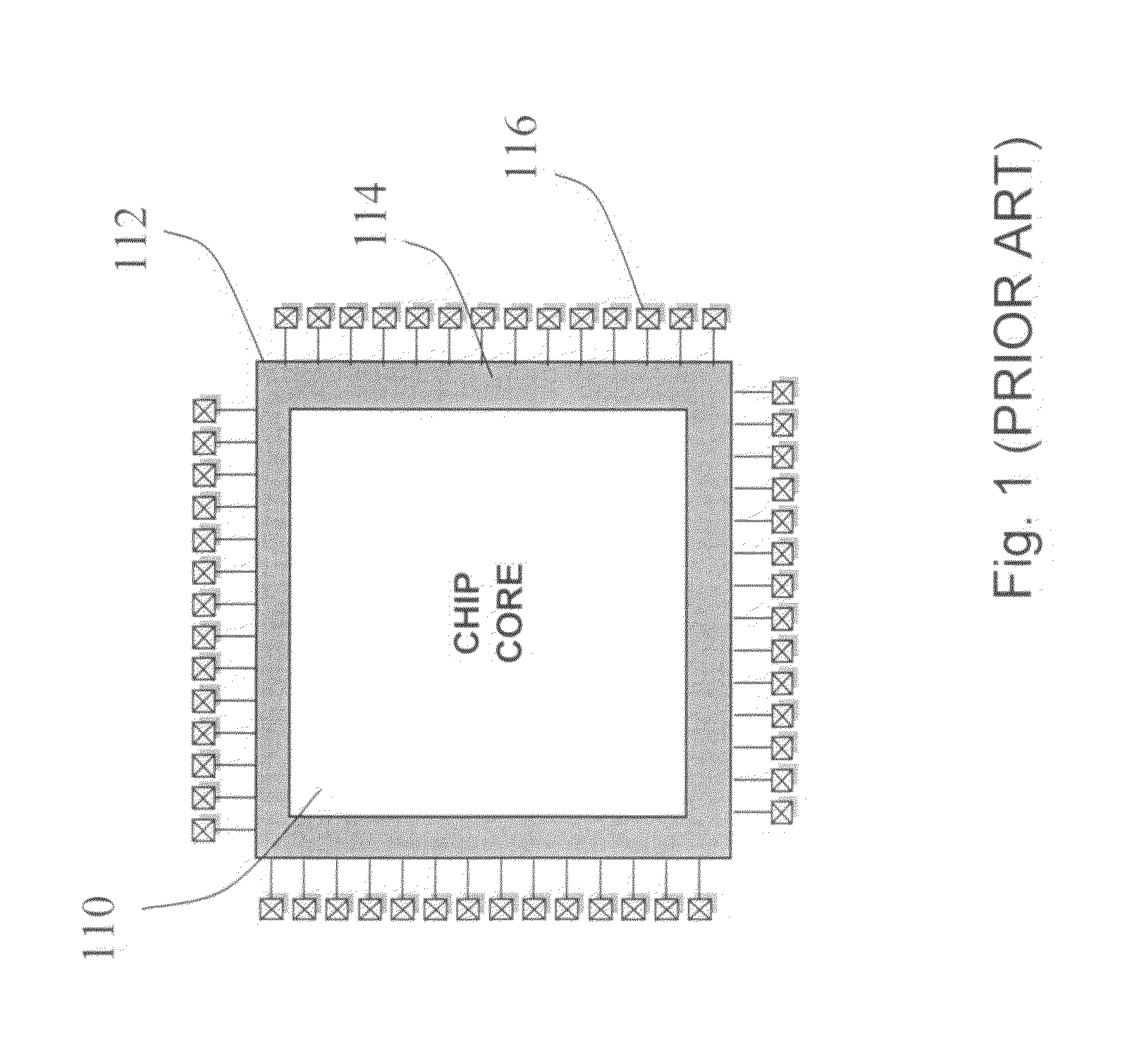

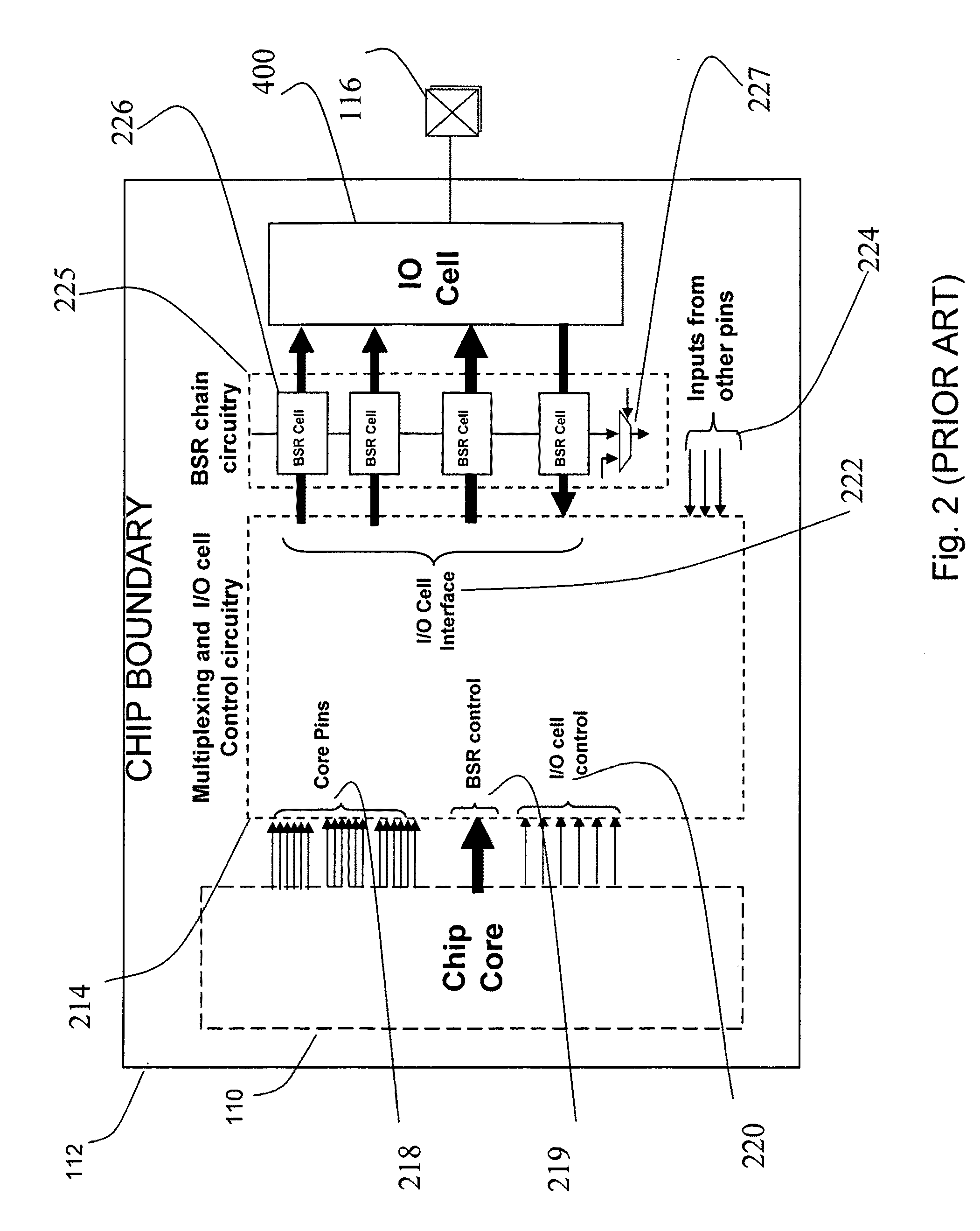

Integrated circuits design

ActiveUS20110119646A1Raise checkFew bugComputer aided designSpecial data processing applicationsMultiplexingComputer architecture

This invention concerns an automated method of generating a design for an I / O fabric of a target integrated circuit having a core and pins. A process tool executes algorithms to generate a synthesizable representation of the I / O fabric ring in hardware description language. It imports integrated circuit design data, and from it captures I / O specification data for a circuit core, library of cells, pin, I / O control, BSR and I / O cell chaining, and die. The tool validates the specification data, and generates the I / O fabric design by configuring and inter-connecting a pin multiplexing and control matrix structures according to constraints for signal control, and timing. The structures includes on both the input and output paths of each pin a functional multiplexer matrix structure, a test multiplexer matrix structure, an override matrix structure, a multiplex select and control matrix structure, and an I / O Cell control logic. A required pin output circuit is configurable by modification of the I / O specification data, and / or, modification of a manner of wiring the algorithms, and / or by modification of the algorithms. The tool wires algorithms according to a wiring framework, and said wiring framework is modifiable.

Owner:ARM IRELAND LTD

Digital display tape measuring device

InactiveUS6898866B2Enhance error checkingReduce probabilityRulers for direct readingMeasuring tapesElectrical resistance and conductanceElectricity

A digital display tape measuring device is disclosed having a display screen exteriorly for displaying the measured distance. A tape having electrical conductivity capabilities and an insulator disposed longitudinally along the tape dividing the tape into two electrical conductors, and having a tip thereof electrically connecting both of the electrical conductors together such that an electrical circuit is formed with resistance that varies as the tape is extracted from device. An ohmmeter electrically coupled across the electrical circuit for measuring the circuit resistance. A microprocessor having inputs thereof coupled to outputs of the ohmmeter and having outputs coupled to said display screen. The microprocessor computes measurements made by as a function of the resistance measured by the ohmmeter.

Owner:WEEKS PEGGY

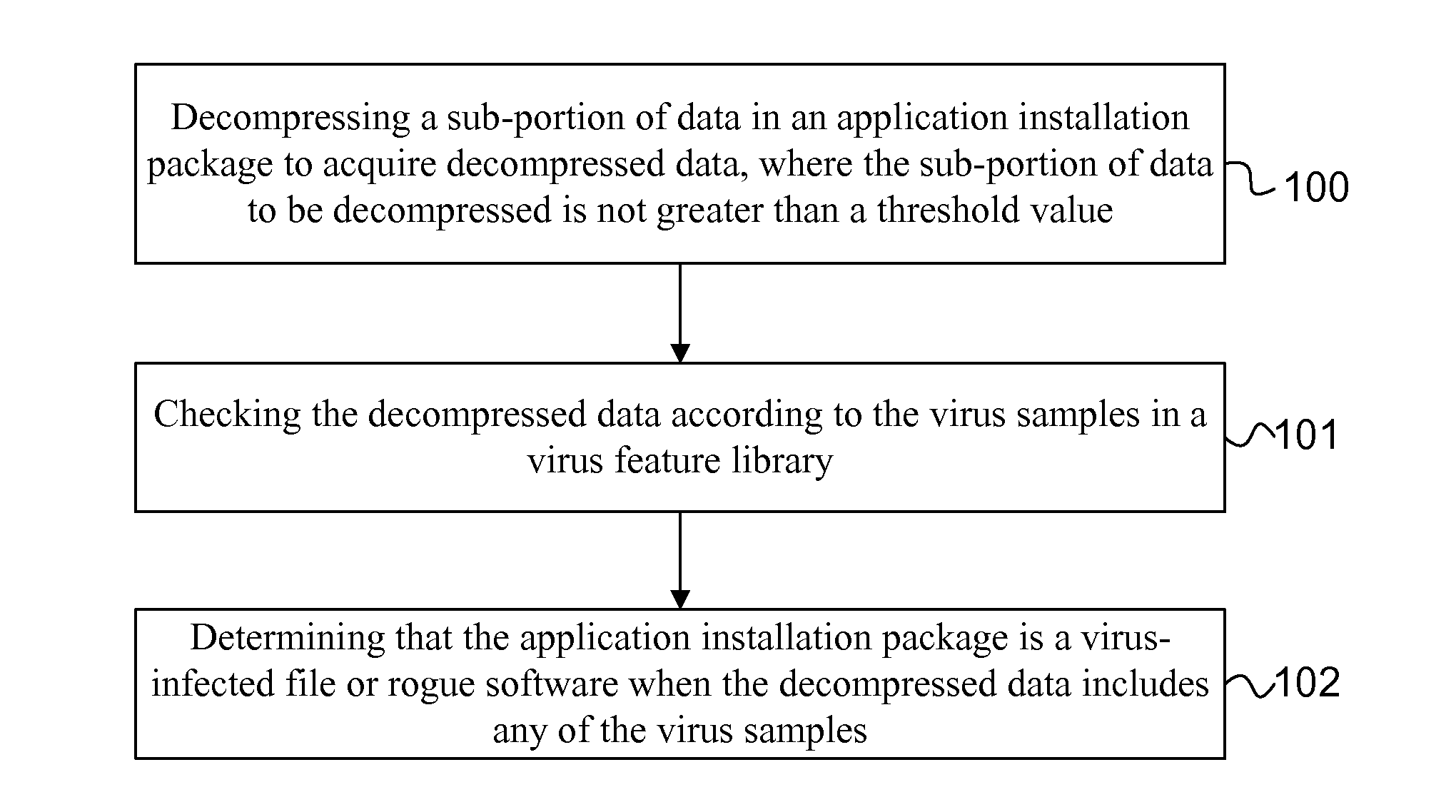

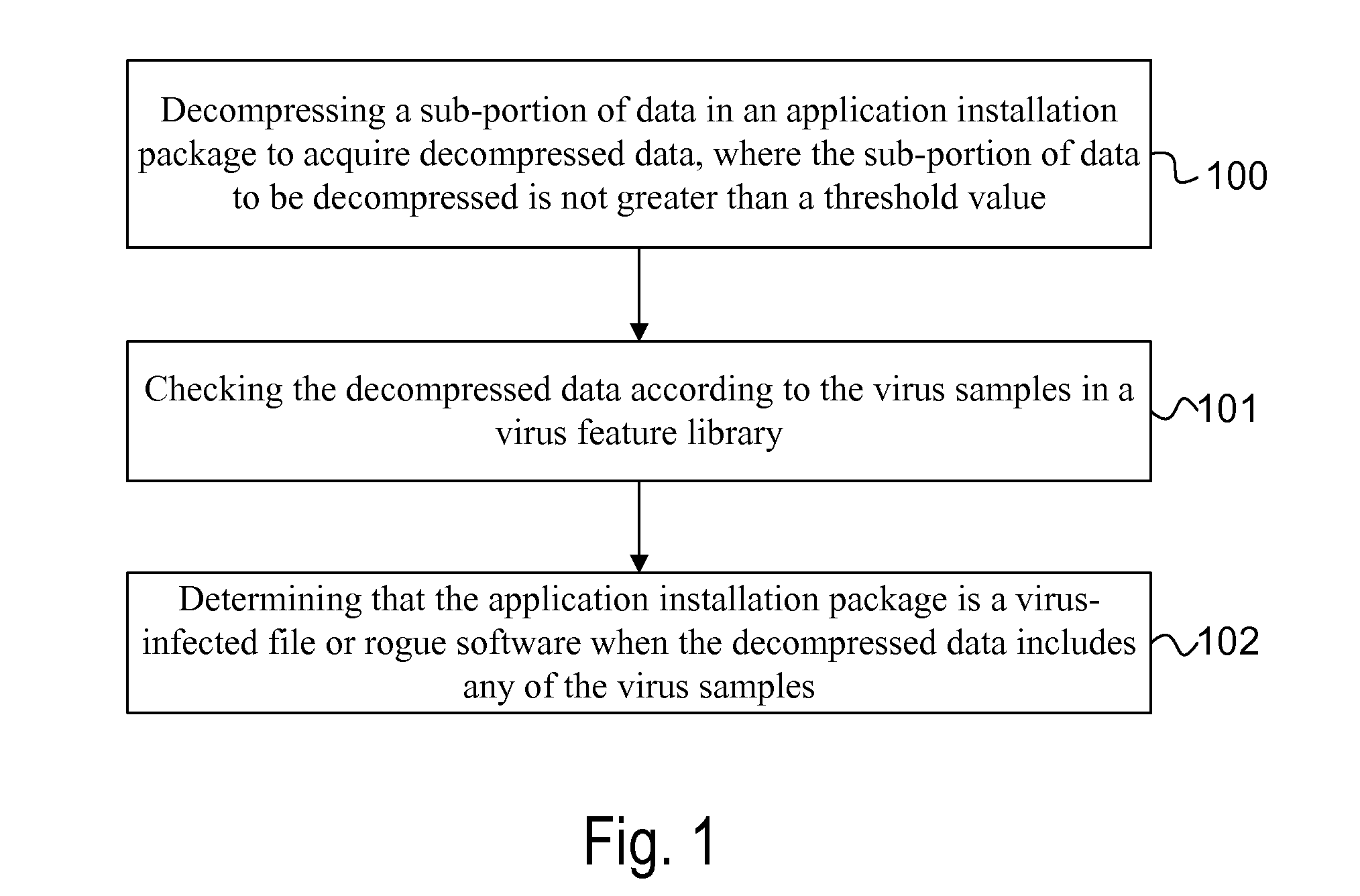

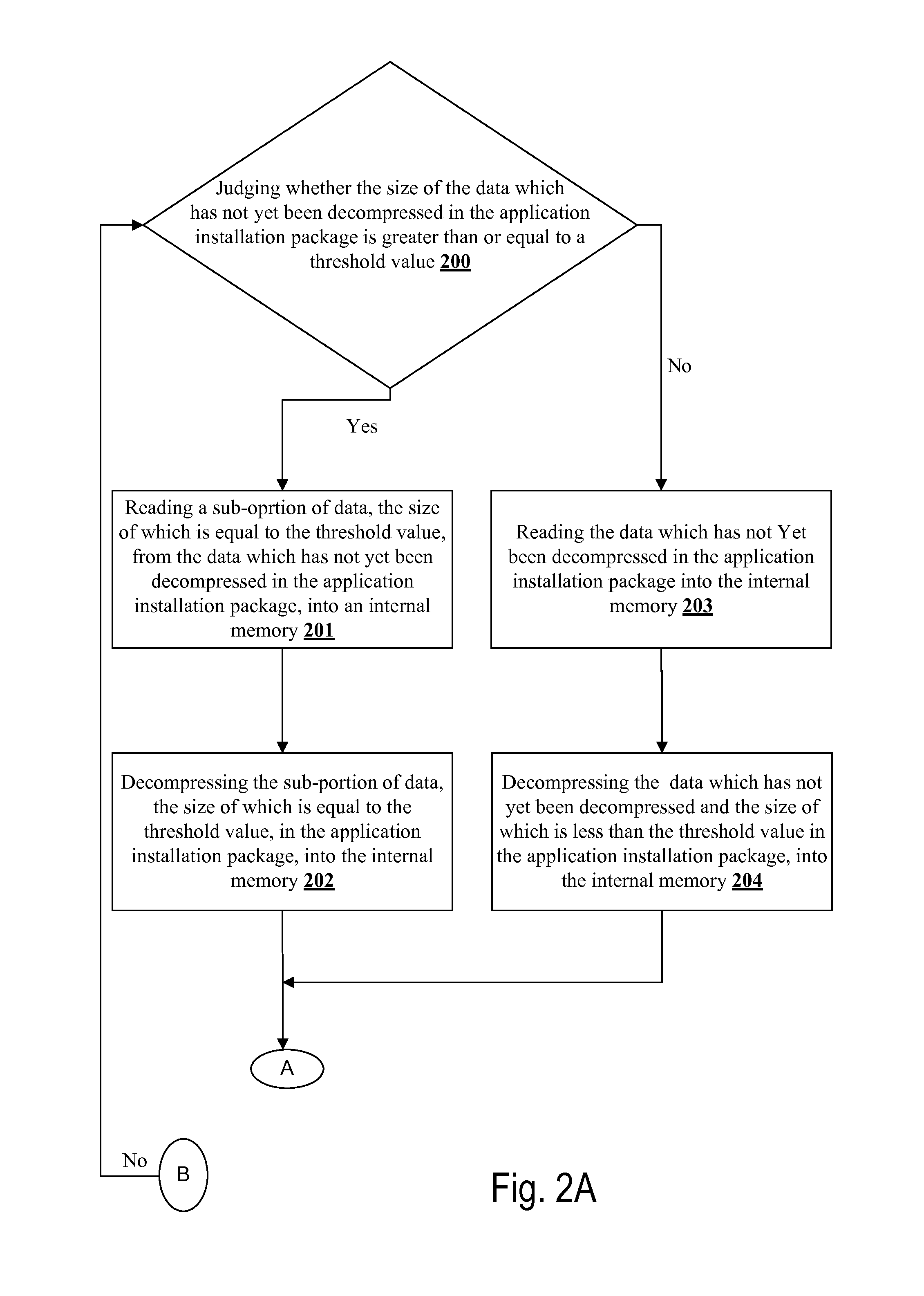

Performing virus scan during decompression of an application installation package

ActiveUS20140041034A1Raise checkShorten inspection timeMemory loss protectionError detection/correctionInternal memorySoftware engineering

Disclosed in the present invention are a method and apparatus for checking a process of decompressing an application installation package. The present invention belongs to the technical field of security. The method comprises: decompressing a sub-portion of data in an application installation package to acquire decompressed data, the sub-portion of data being not greater than a threshold size; checking the decompressed data according to the virus samples in a virus feature library; and determining that the application installation package is a virus-infected file or rogue software when the decompressed data includes any of the virus samples. The technical solution of the present invention can effectively save the internal memory, shorten the checking time, and improve the checking efficiency in determining whether an application installation package is a virus-infected file or rogue software.

Owner:TENCENT TECH (SHENZHEN) CO LTD