Patents

Literature

91 results about "Through-hole technology" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Through-hole technology (also spelled "thru-hole"), refers to the mounting scheme used for electronic components that involves the use of leads on the components that are inserted into holes drilled in printed circuit boards (PCB) and soldered to pads on the opposite side either by manual assembly (hand placement) or by the use of automated insertion mount machines.

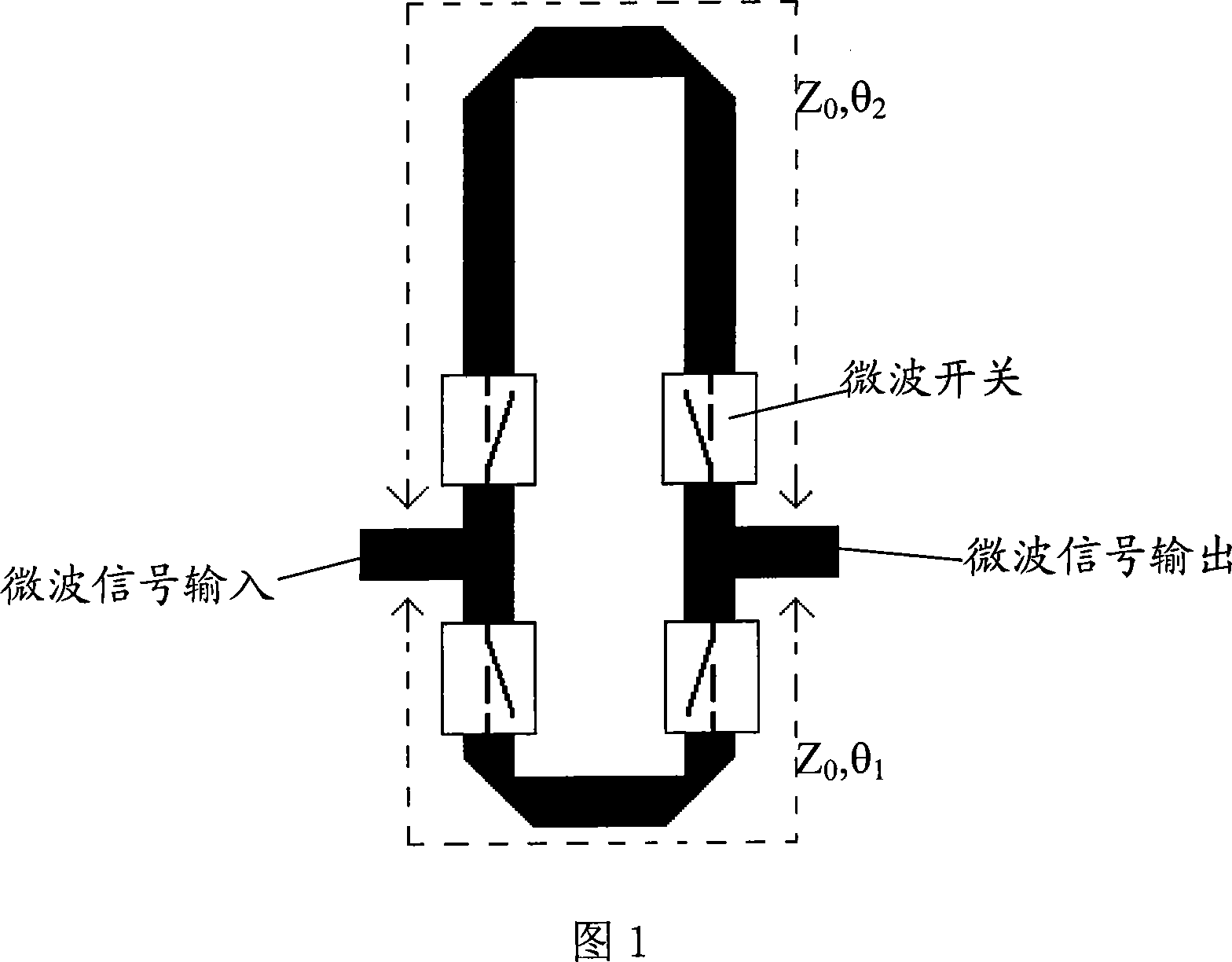

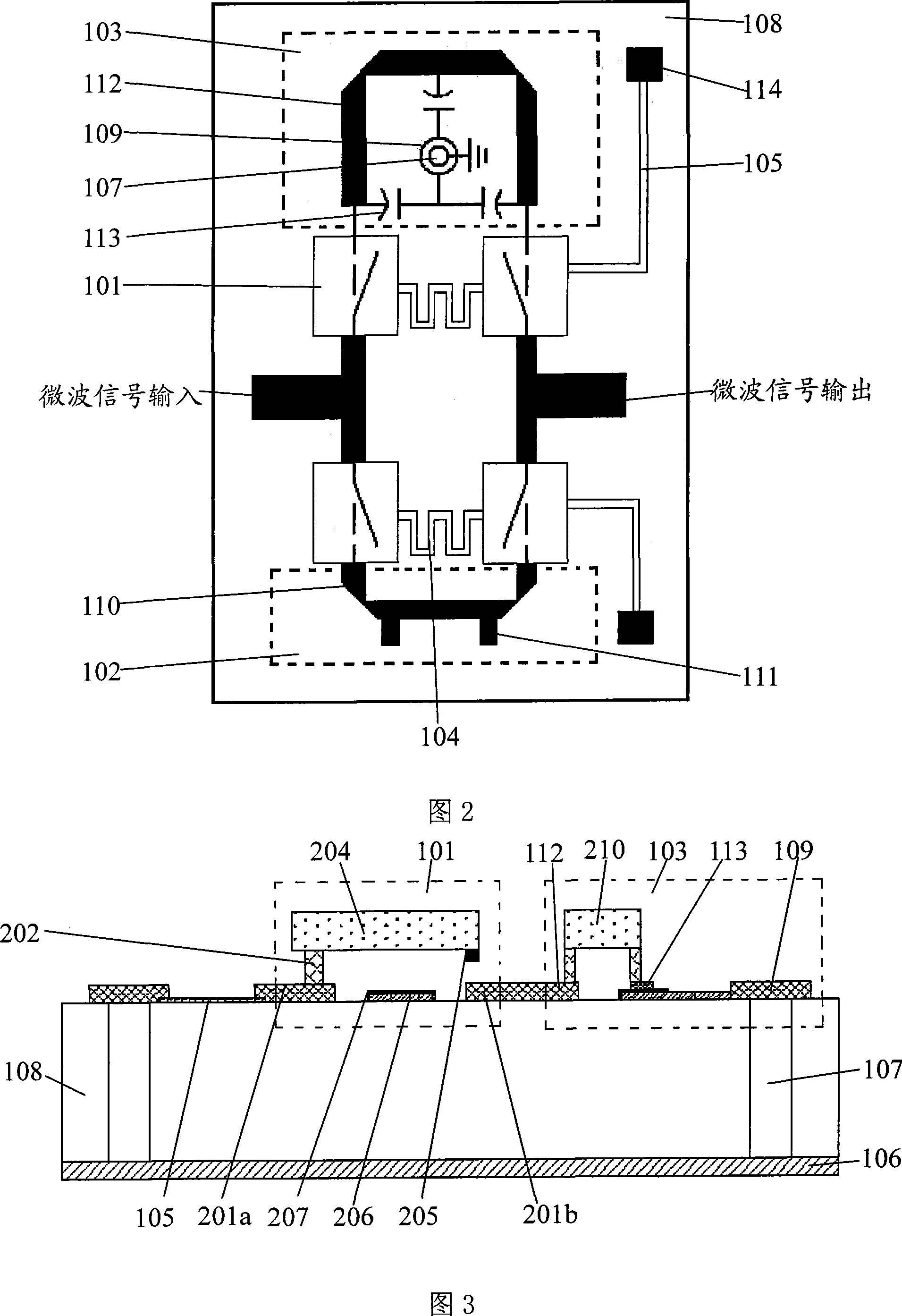

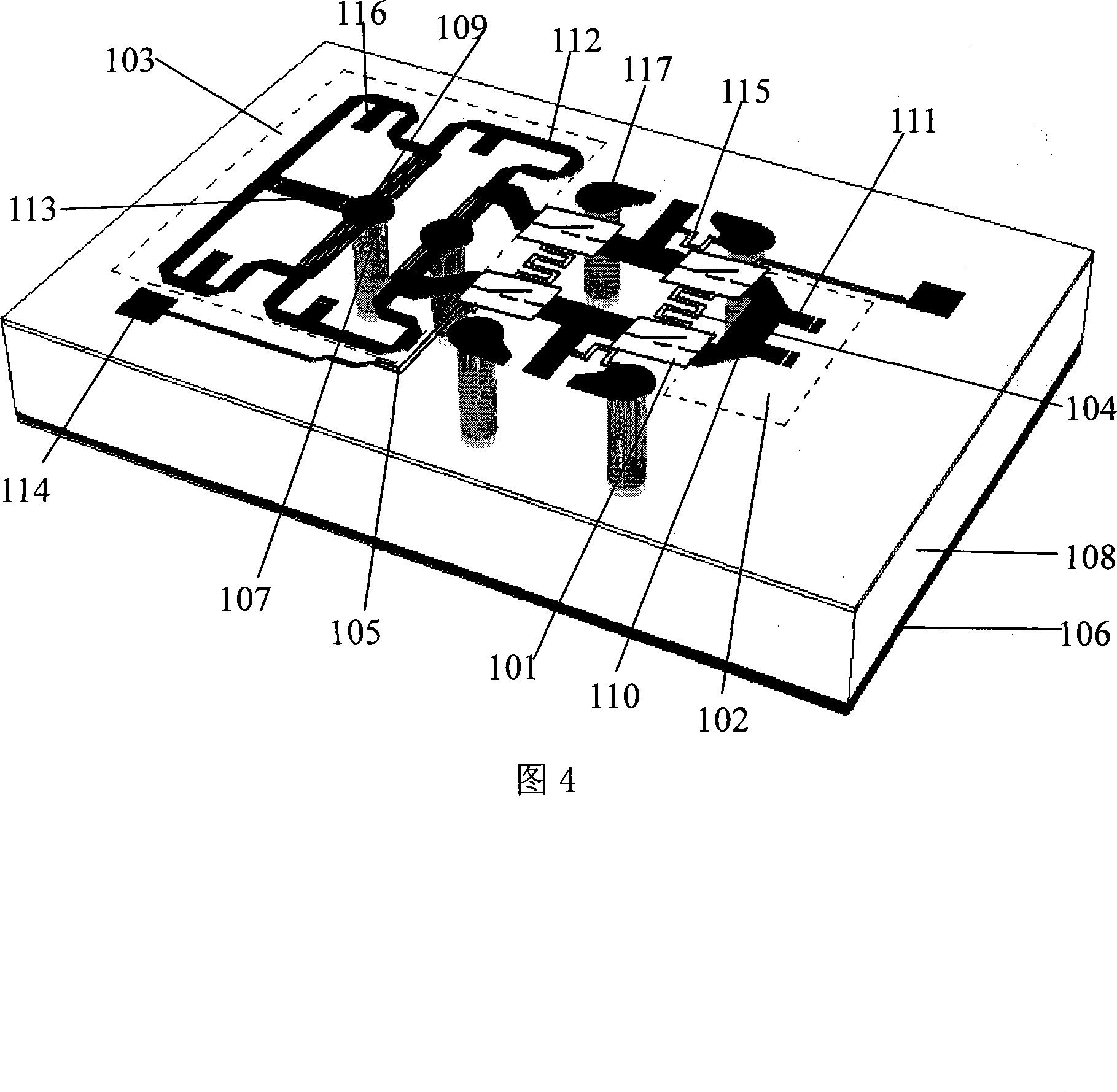

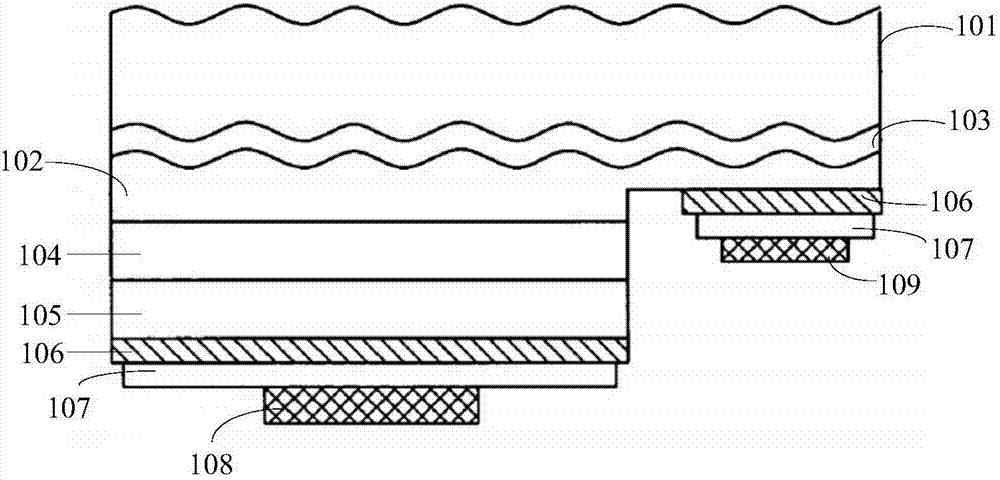

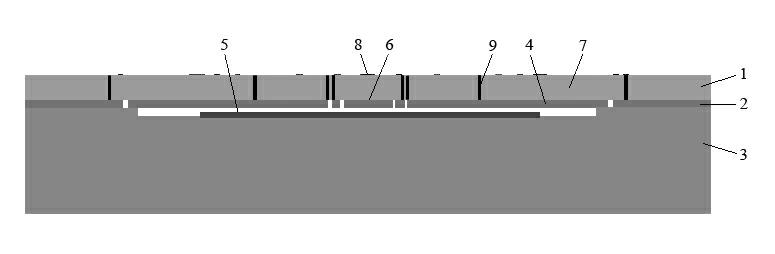

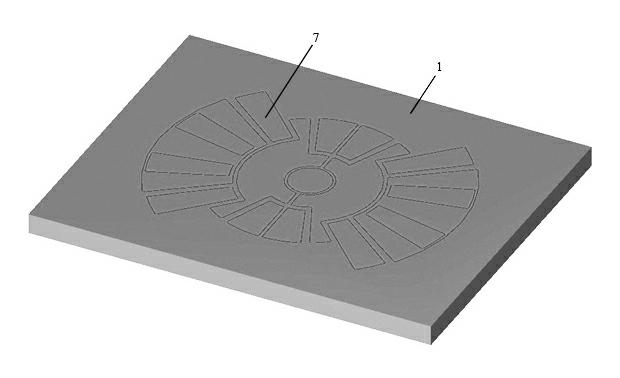

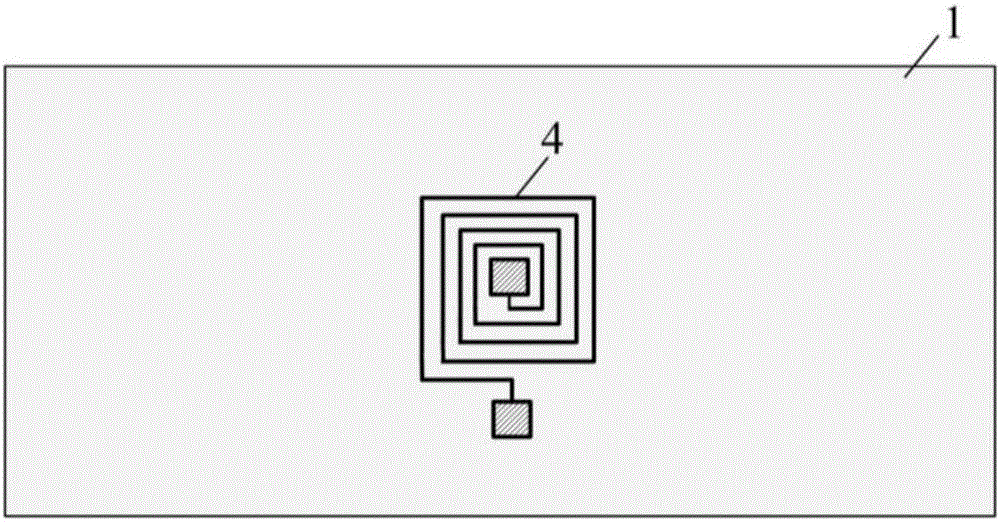

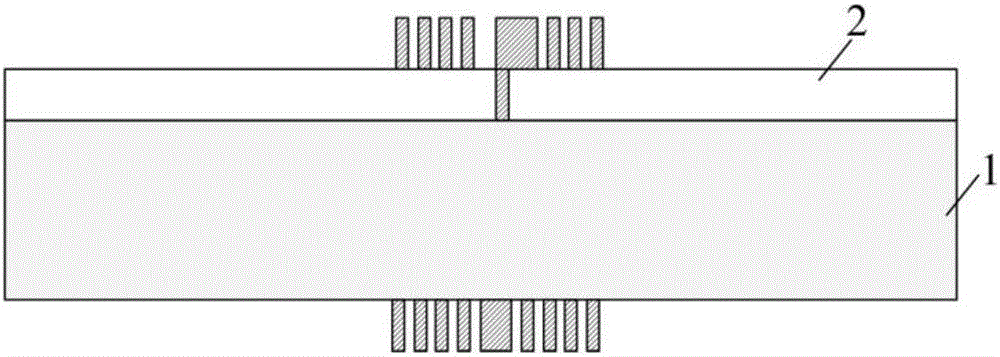

Miniature MEMS switching line phase shifter

ActiveCN101202369ALow insertion loss performanceReduce chip areaWaveguide type devicesAntennasHigh resistanceEngineering

The invention provides a miniaturized MEMS switch-line phase shifter, comprising an MEMS switch, a reference phase shifting transmission line, a phase delay transmission line, a switch offset line, a back surface grounding layer, a medium liner, a microwave grounding terminal, and a micro-mechanical through hole. The invention has the advantages of keeping low insertion loss of a transmission passage and reducing the chip area of a large phase shifting unit bit transmission line of the phase shifter by distribution-typed elements with high resistance and a phase delay transmission network formed by the microwave grounding of a collecting element and the micro-mechanical through hole, reducing the chip area of a small phase shifting unit bit delay line of the phase shifter, reducing the area of the chip, minimizing the chip area occupied by the MEME switch by selecting miniaturized MEMS switches such as a built-in cantilever MEMS switch, keeping the broad band performance of the MEMS switch and the phase shifter and minimizing the chip area occupied by the MEMS switch offset circuit by separating a microwave signal from a switch driving signal, and leading to simple and convenient design of microwave grounding of the chip and reducing the area of the chip to the most extent by the micro-mechanical through hole technology.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

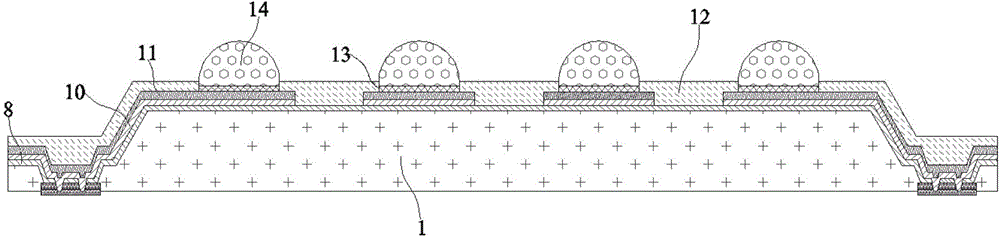

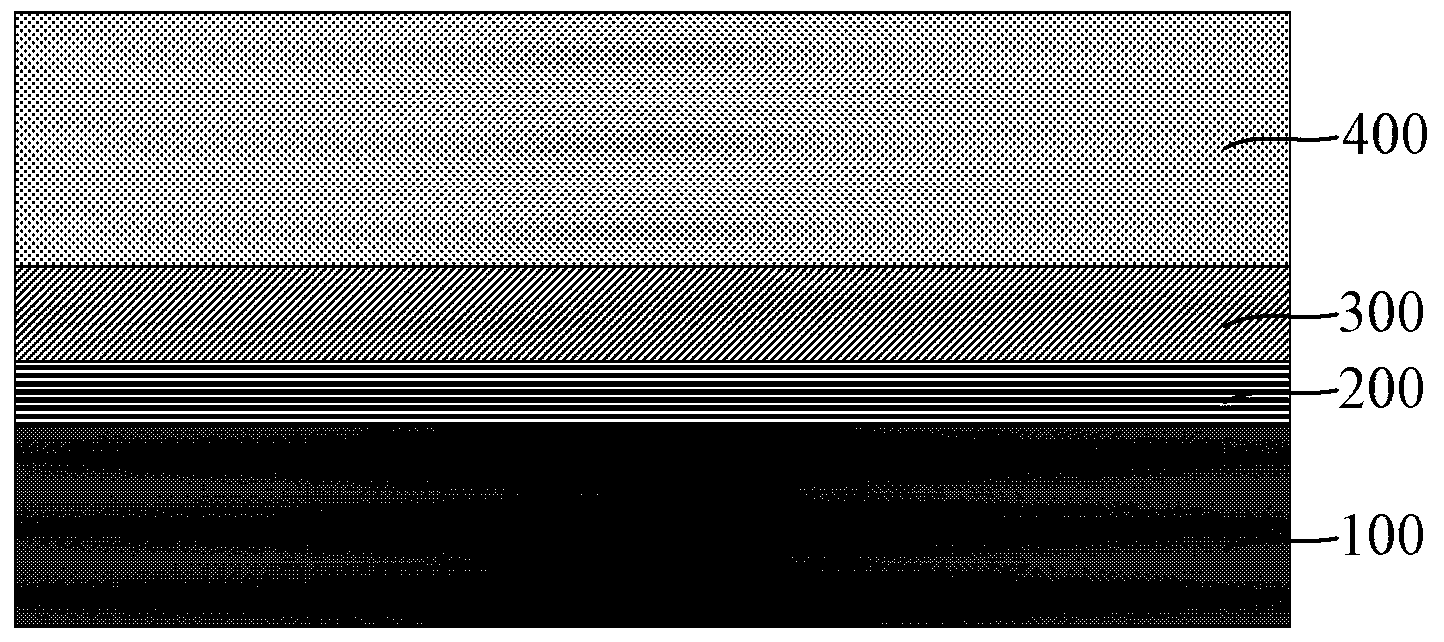

AlGaInP-based light emitting diode and manufacturing method therefor

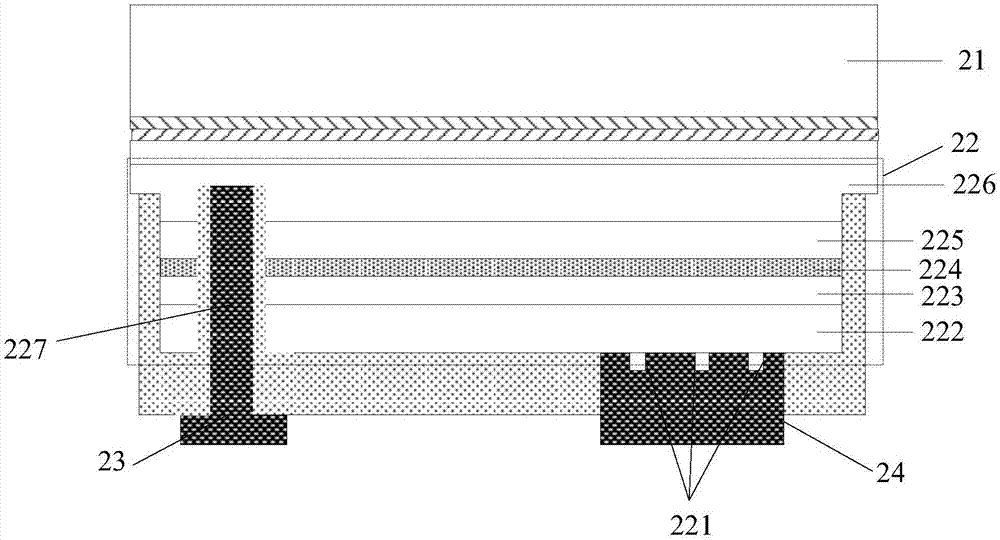

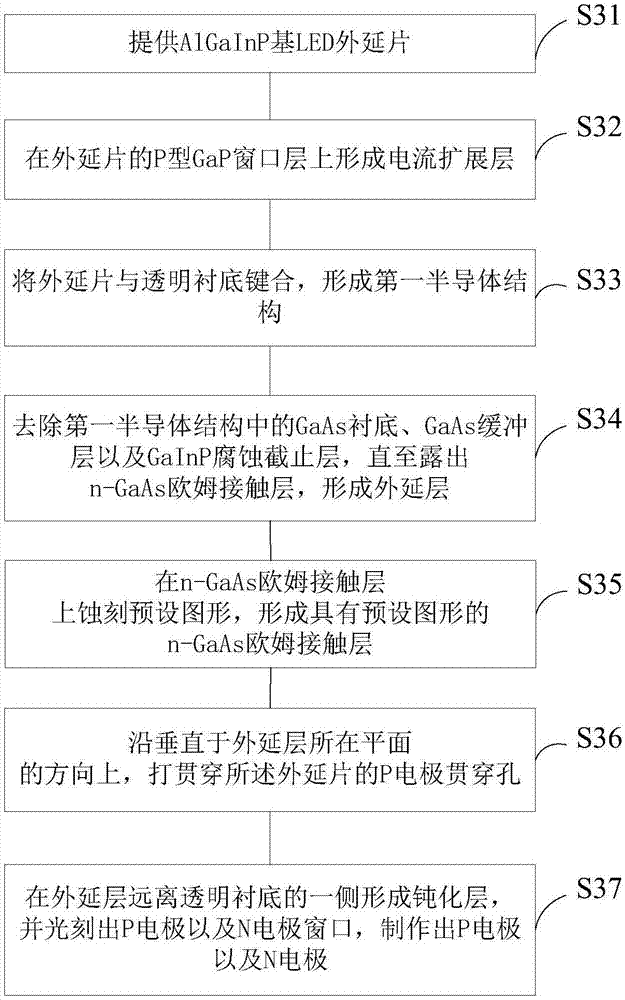

ActiveCN107546303ASolve the leakImprove reflection efficiencySemiconductor devicesDielectricBonding process

The invention provides an AlGaInP-based light emitting diode and a manufacturing method therefor, wherein a P electrode adopts a through hole technology; equivalently, a P electrode through hole for running through an epitaxial layer is formed in a direction perpendicular to the direction of the plane where the epitaxial layer is located, to enable the P electrode main body to be partially locatedin an n type epitaxial layer; and the P electrode and an N electrode are manufactured, and then the P electrode and the N electrode are kept in the same height. The problem of increasing of the packaging difficulty caused by easy side tilting of an LED chip in chip packaging and bonding due to relatively high height difference existing between the P electrode and the N electrode in the existing LED can be solved; in addition, an isolation trench is also formed in the LED on the above basis, so that the problem of easy electric leakage between the P / N electrodes caused by extrusion and deformation of soldering flux in the existing LED packaging and bonding process also can be solved; and in addition, an ODR reflector mirror structure comprises an ODR reflector mirror dielectric film layerand an ODR reflector mirror metal layer, so that high reflection efficiency is realized.

Owner:YANGZHOU CHANGELIGHT

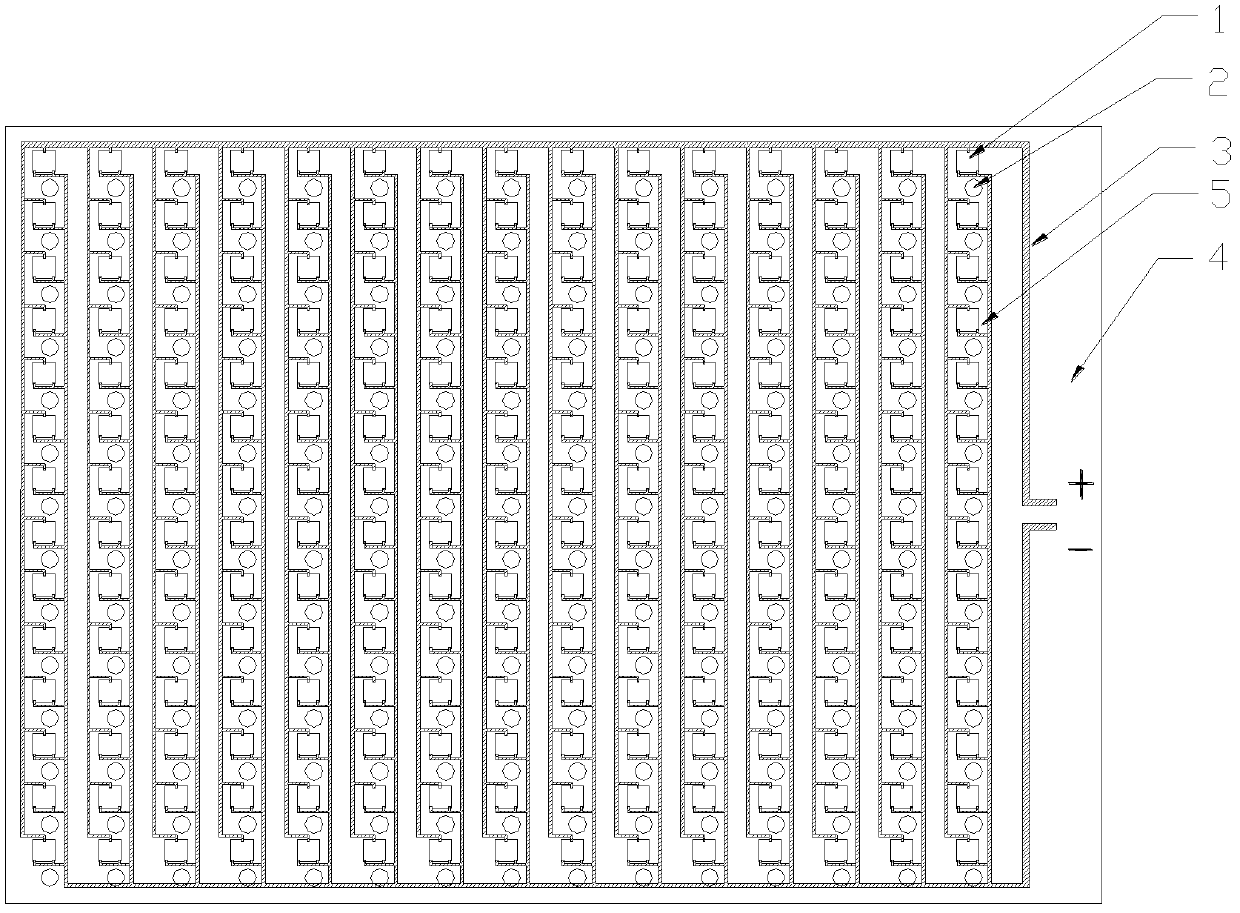

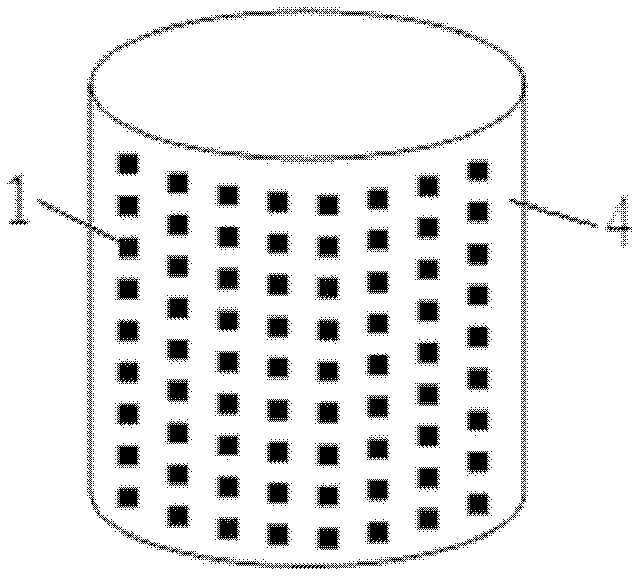

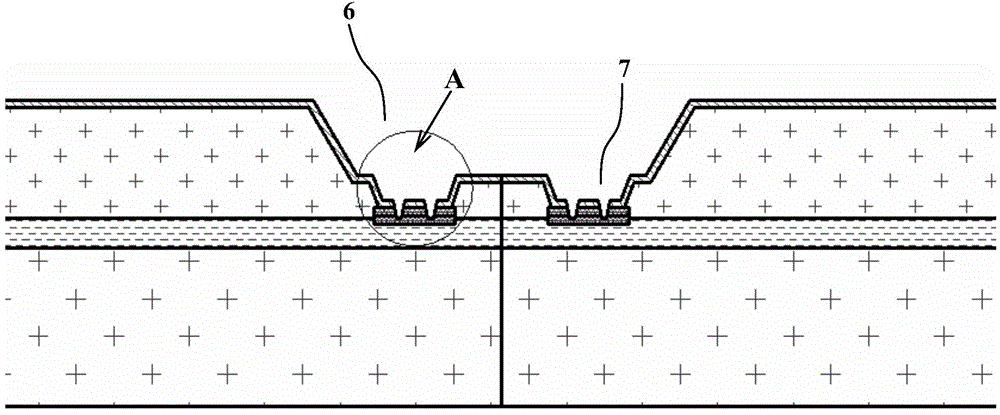

LED (light emitting diode) two-dimensional array light source with flexible circuit substrate

InactiveCN102437148AReduce weightLow costPlanar light sourcesElectric circuit arrangementsSolder maskLed array

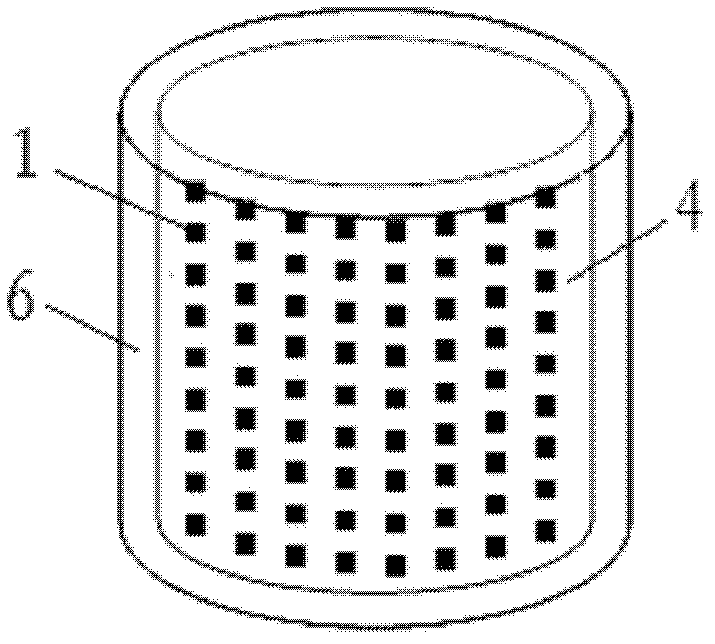

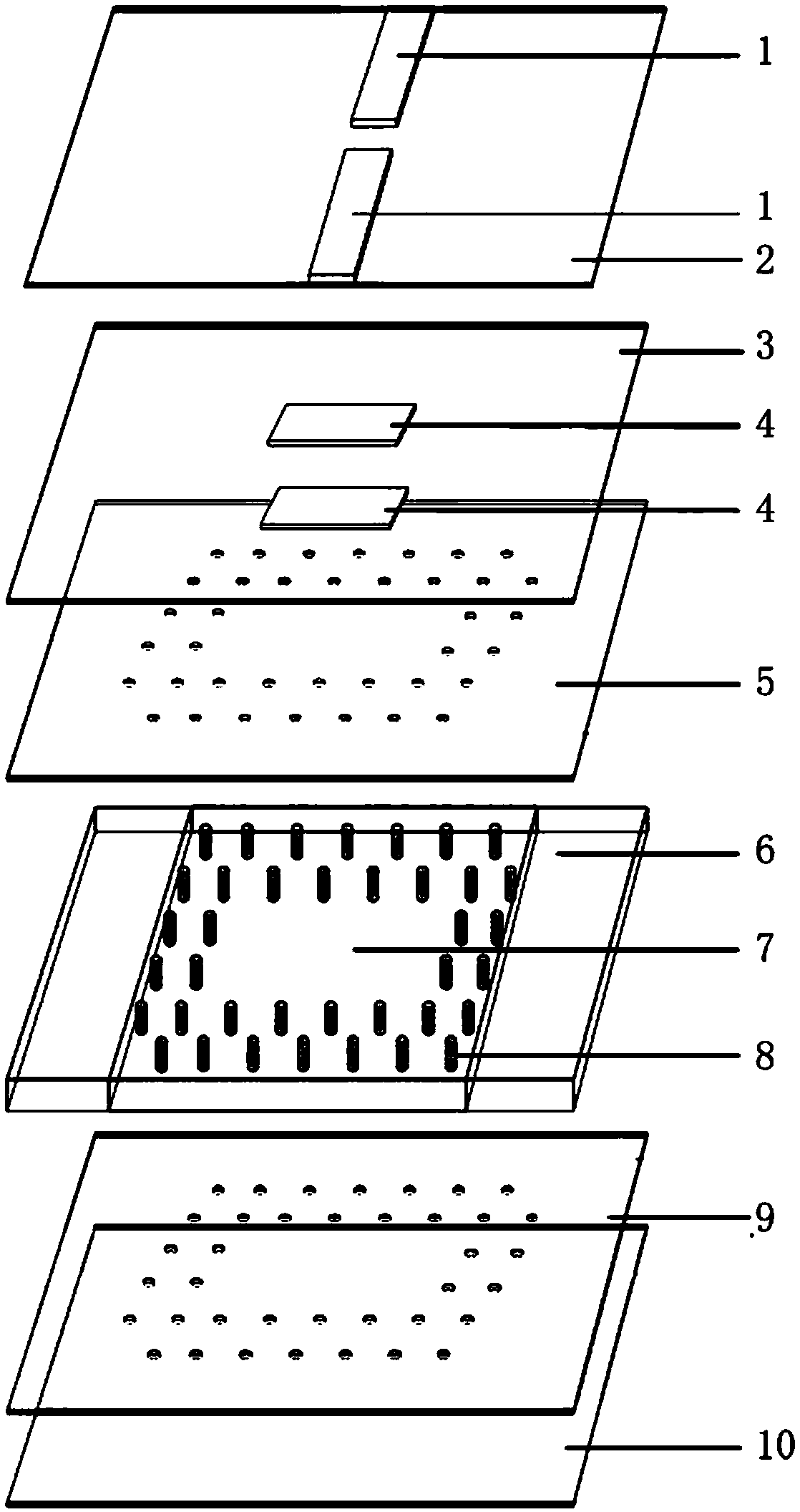

The invention discloses an LED (light emitting diode) two-dimensional array light source with a flexible circuit substrate. The LED two-dimensional array light source comprises a plurality of LED chips or packaged LED light beads. The LED two-dimensional array light source is characterized by also comprising the flexible circuit substrate, wherein the flexible circuit substrate is provided with an electric conducting material with electric conducting patterns; solder mask layers are printed on the flexible circuit substrate to form a plurality of binding regions; the LED chips or the light beads are directly pasted on the binding regions, and are connected and conducted mutually through the electric conducting patterns; and array-type through holes are formed on the flexible circuit substrate. The invention provides the LED two-dimensional array light source with the flexible circuit substrate, a curve surface LED array light source type is solved, at the same time, the LED light source heat radiation effect is improved by the flexible circuit substrate and an array-type through-hole technology, thus the heat radiation capability and light dipping efficiency of a luminous light source are improved greatly, the service life is prolonged, the LED two-dimensional array light source with the flexible circuit substrate is more suitable for automatic production so as to be used by public consumers.

Owner:SUZHOU JINGPIN OPTOELECTRONICS

Vertical-type capacitor structure and manufacturing method thereof

InactiveCN103346148AHighly integratedReduce areaSemiconductor/solid-state device detailsSolid-state devicesCapacitanceEngineering

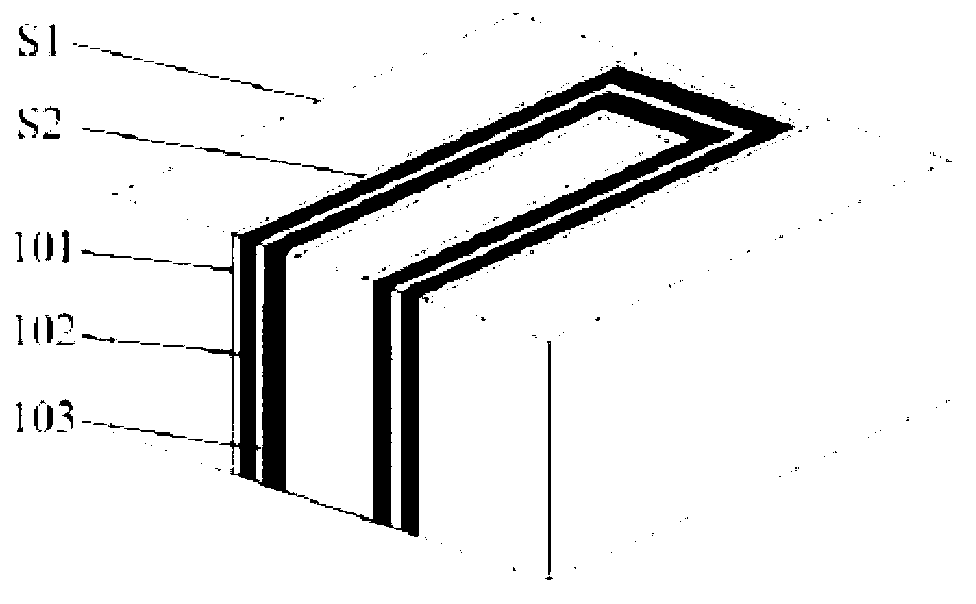

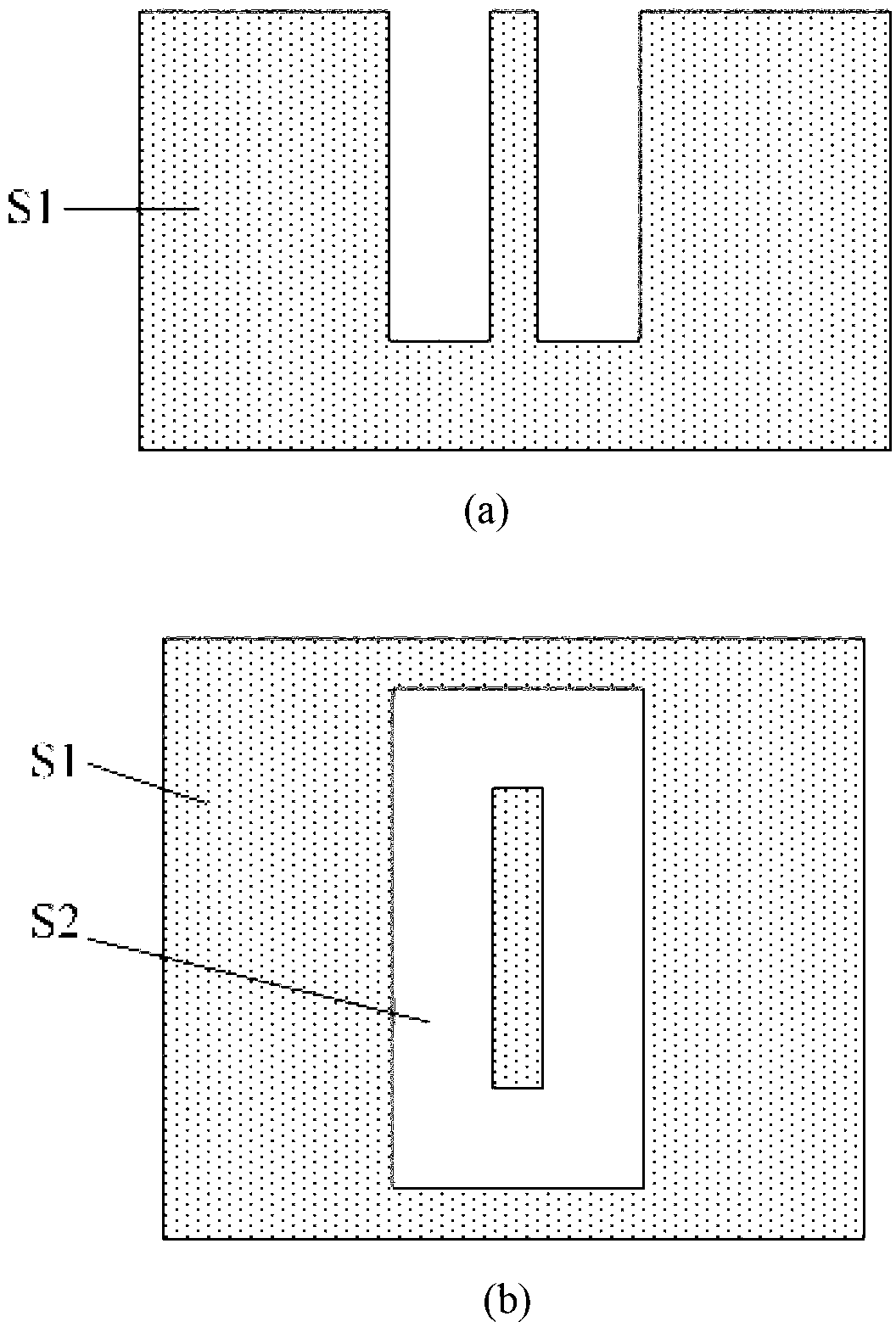

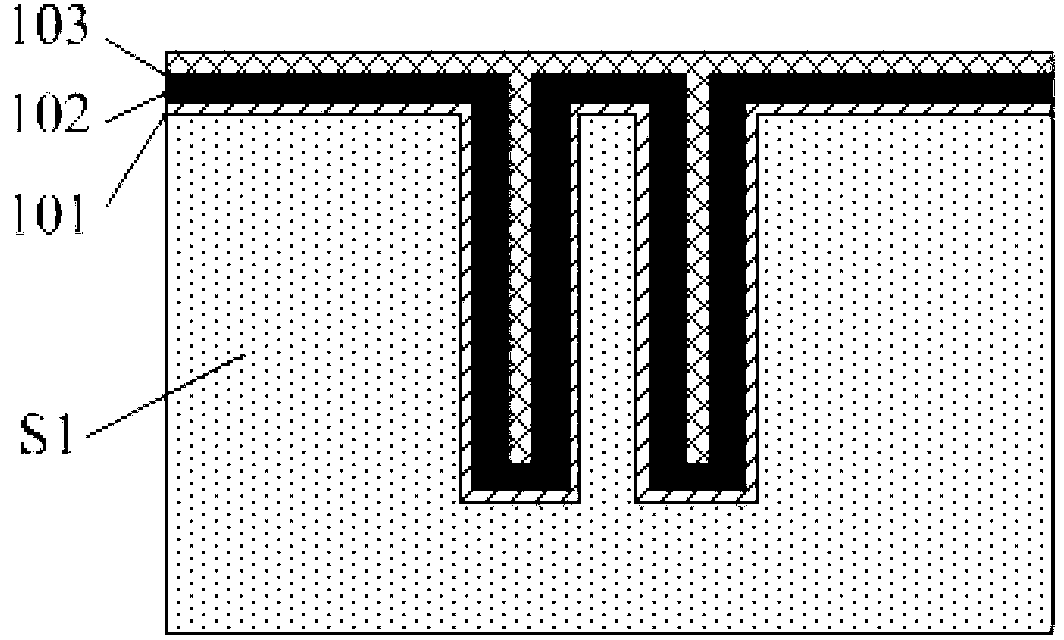

The invention relates to a vertical-type capacitor structure and a manufacturing method of the vertical-type capacitor structure, and belongs to the technical field of micro-electronic passive devices. The vertical-type capacitor structure structurally and specifically comprises a deep-groove structure, insulating layers, conducting layers and a dielectric layer, wherein the deep-groove structure is located inside a wafer substrate, the insulating layers and the conducting layers are sequentially deposited on the inner side wall of a deep groove, and the dielectric layer is filled between the conducting layers. The insulating layers, the conducting layers, the dielectric layer and the deep groove are the same in height. On the basis of the principle that the area of a capacitor is expanded in the direction perpendicular to the substrate, the area of an plate electrode in the perpendicular direction is utilized, the processes such as sputtering and electroplating are adopted to manufacture a metal plate electrode, and the plate electrode is made of low electrical resistivity materials, like metal. With the combination of a silicon through hole technology, the vertical-type capacitor with a large depth-to-width ratio is achieved. With the combination of a substrate back thinning technology, the vertical-type capacitor structure penetrates through the substrate, the vertical-type capacitor structure can be used as a high-frequency channel between multi-layer chips, the area of the plate can be greatly saved, and the integration level of an integrated circuit is improved.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

Packaging technology for novel fingerprint lock device

ActiveCN104681454AEliminate the wiring stepsReduce thicknessSemiconductor/solid-state device manufacturingTotal thicknessThrough-hole technology

The invention discloses a packaging technology for a novel fingerprint lock device. The novel fingerprint lock device comprises a fingerprint recognition chip, a ceramic cover plate, a flexible PCB and a data processing chip. The packaging technology comprises the following steps: filling the surfaces of aluminum welding pads in blind holes of the fingerprint recognition chip with nickel metal layers to extend out of the upper surface and form bulges so as to form bonding pad thickening parts; coating the upper surface, having the bonding pad thickening parts, of the fingerprint recognition chip with a temporary bonding adhesive layer; bonding a glass supporting plate with the surface, having the bonding pad thickening parts, of the fingerprint recognition chip through the temporary bonding adhesive layer; thinning the lower surface opposite to the upper surface of the fingerprint recognition chip so as to reduce the thickness of the fingerprint recognition chip to about 150-300 microns; sequentially forming a first tapered blind hole, a second tapered blind hole and third tapered blind holes in the lower surface of the fingerprint recognition chip by etching gradually. After wafer-level chip packaging technology and a silicon through hole technology are integrated, a set of novel process is formed, so that the thickness is reduced, the total thickness of a product is greatly reduced and the reliability of the product is greatly improved.

Owner:苏州科阳半导体有限公司

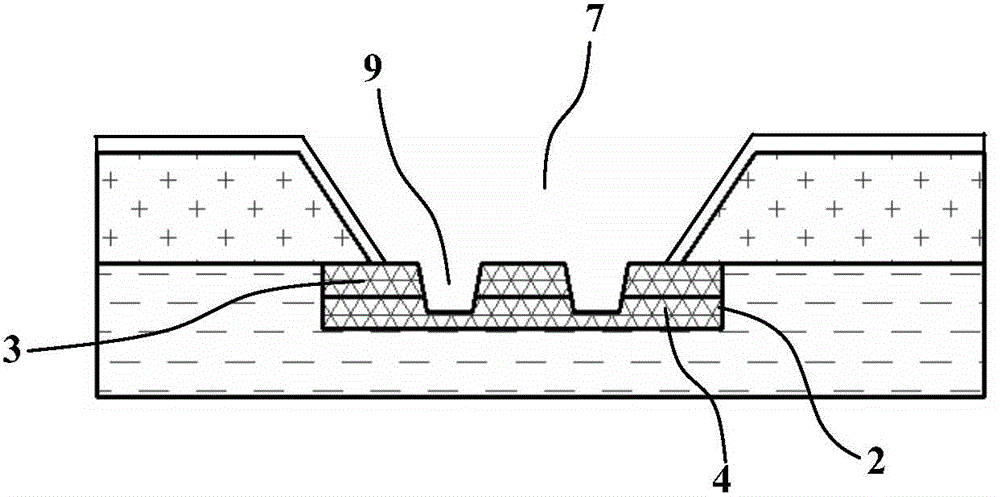

Light emitting diode flip chip packaging method based on through hole technology

ActiveCN103579477AImprove reliabilityImprove light uniformitySemiconductor devicesLaser technologyThrough-hole technology

The invention relates to a light emitting diode flip chip packaging method based on a through hole technology and a manufacturing process thereof. A light emitting diode comprises an LED flip chip, a substrate and a fluorescent glue layer. A light emitting diode flip chip packaging technology and the manufacturing process of the LED flip chip are provided to overcome the heat dissipation defect of an existing high-power LED. By means of an etching technology or a laser technology, the LED flip chip and the silicon substrate are respectively provided with a blind hole electrode and a through hole bonding pad, and the light emitting diode flip chip and the through hole substrate are obtained. By means of the shape design of a soldering-resistant layer, self alignment of the flip chip and the through hole substrate is convenient to achieve. Besides, the method does not need gold bonding, is simple in process and low in cost, improves heat dissipation performance by means of through holes, and improves reliability of LED chip packaging.

Owner:SHANGHAI UNIV

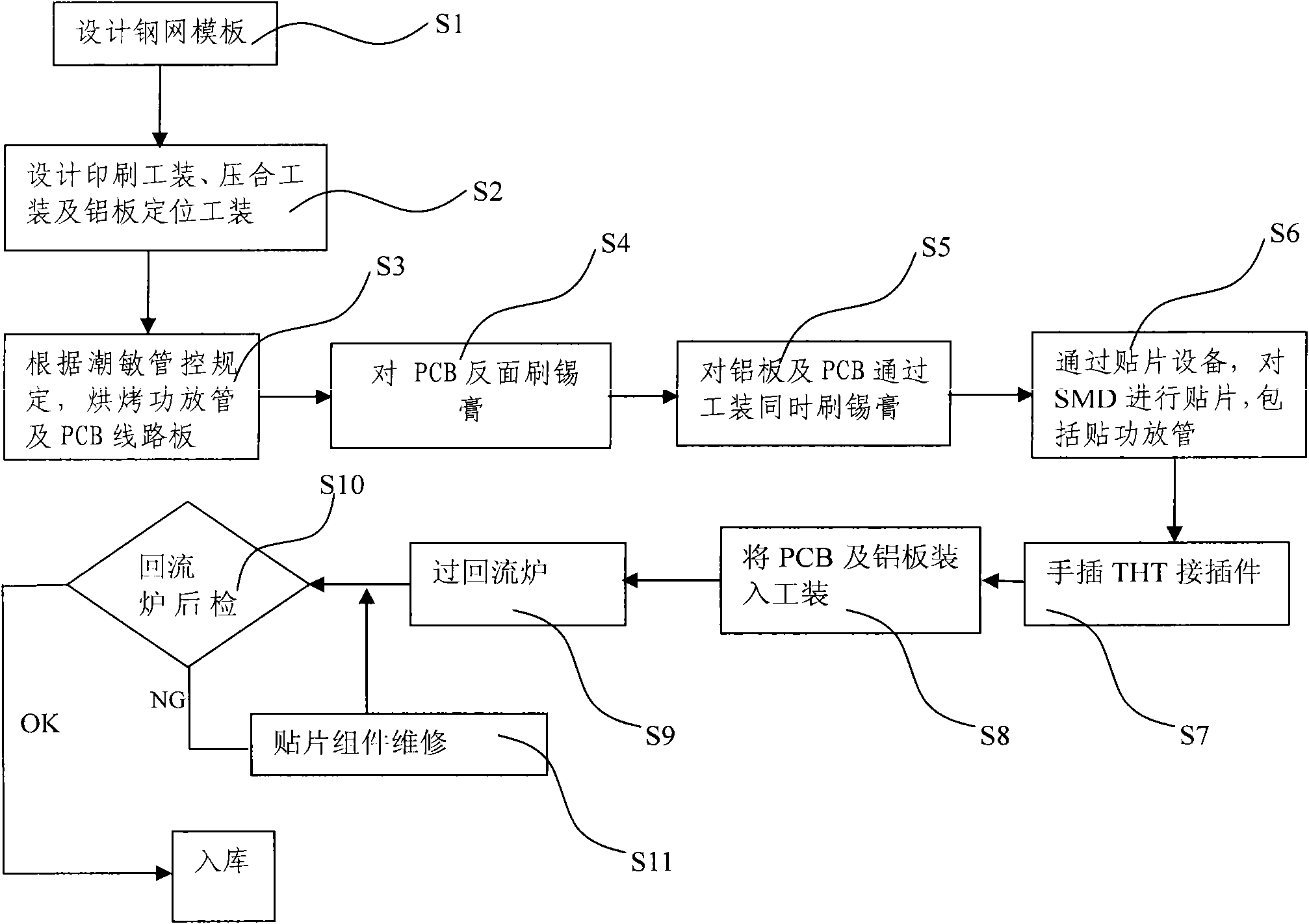

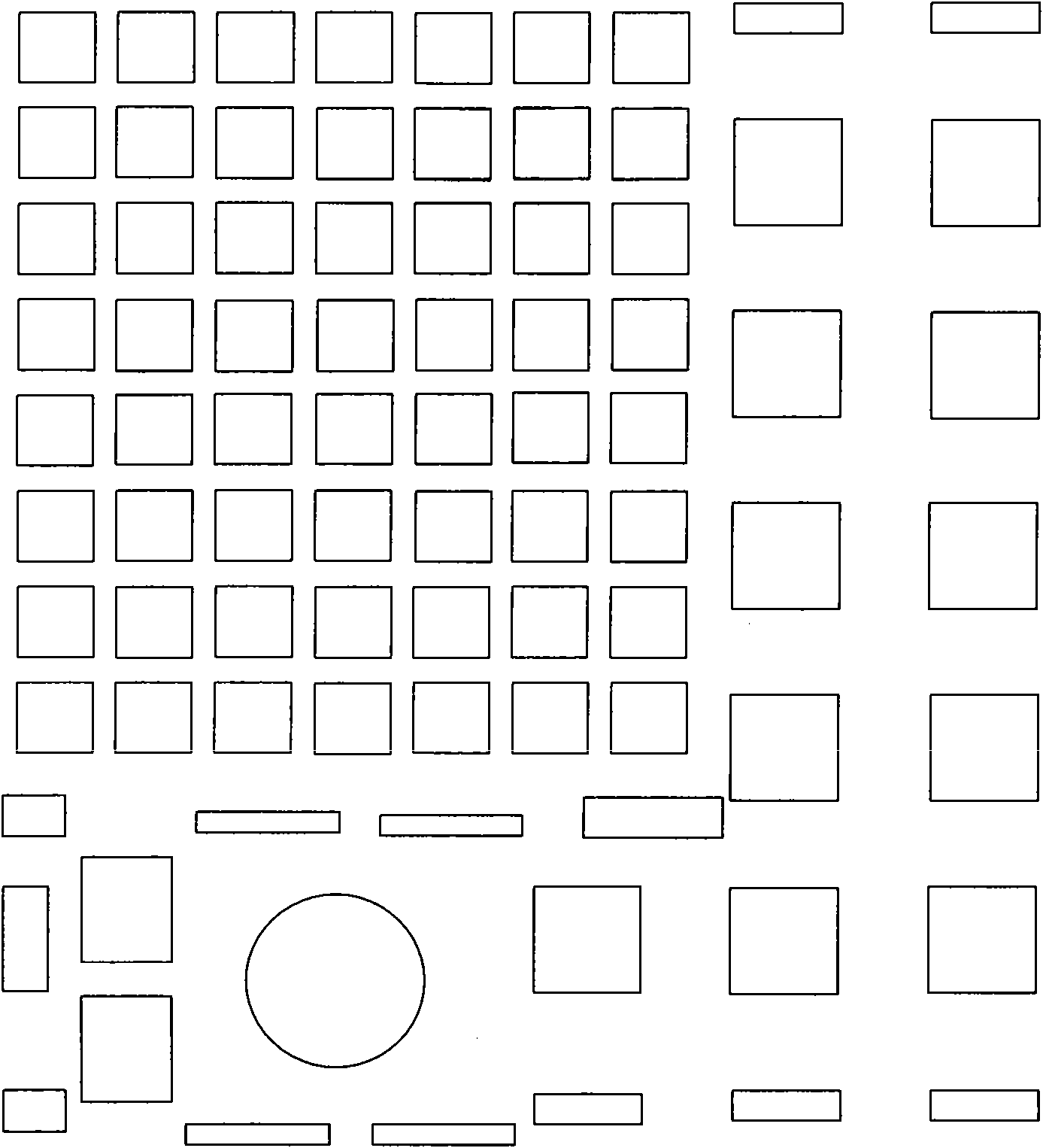

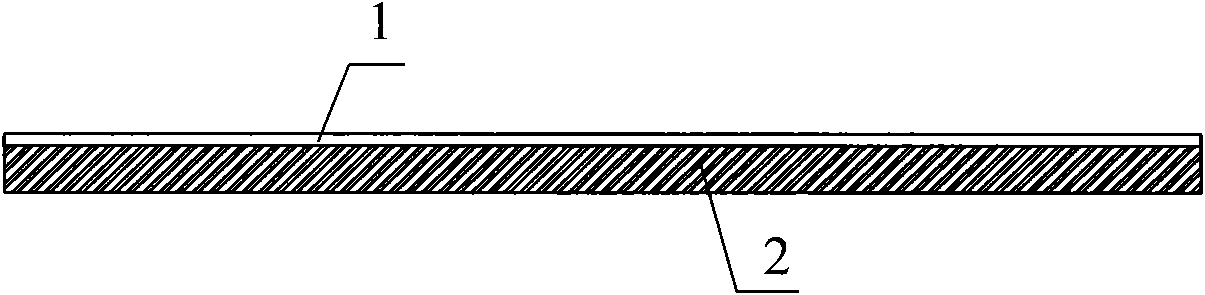

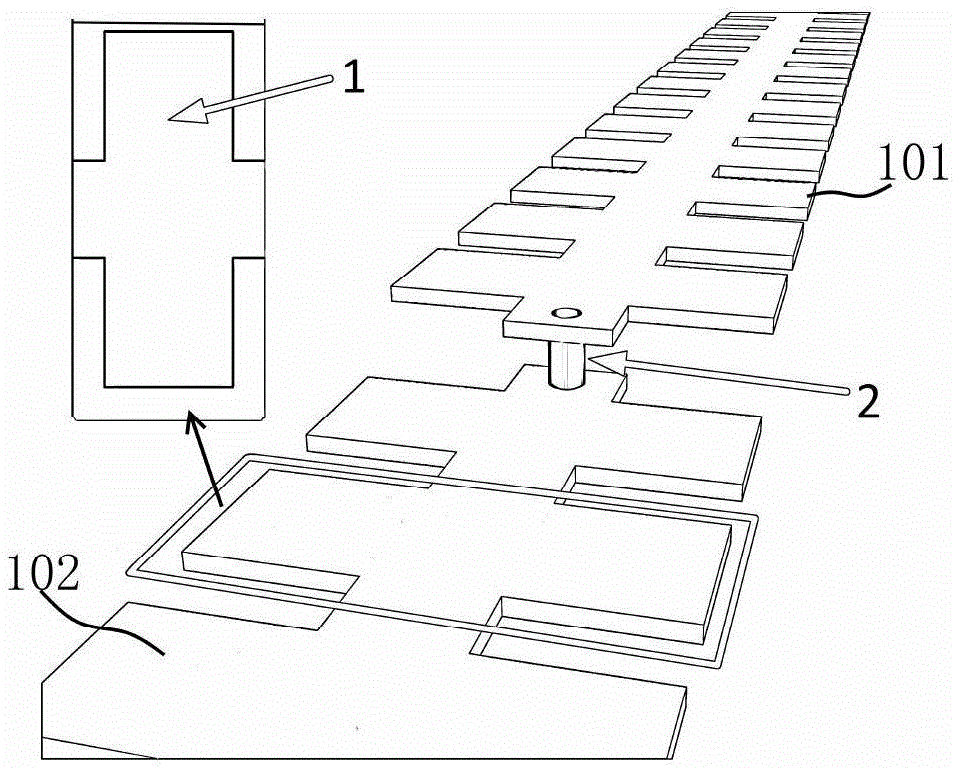

Process for assembling radio frequency power amplifier circuit board

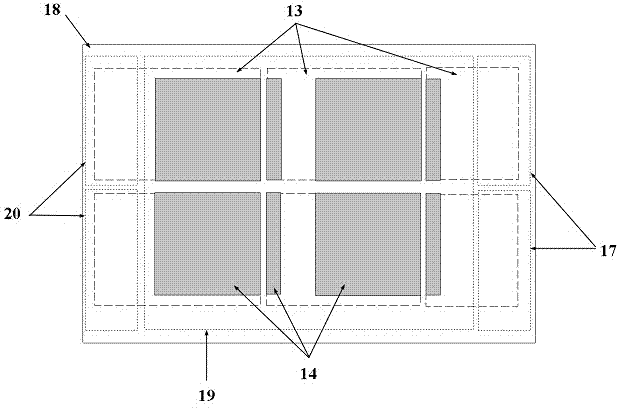

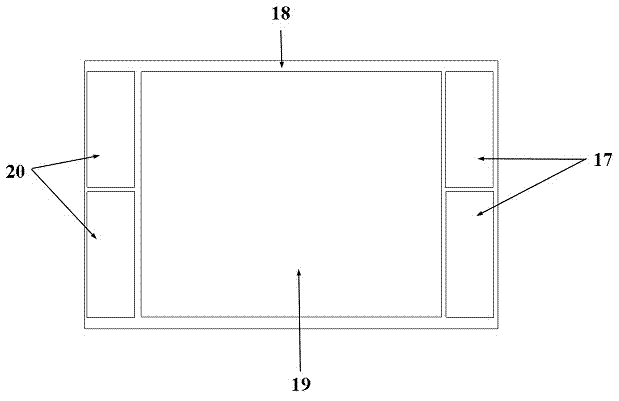

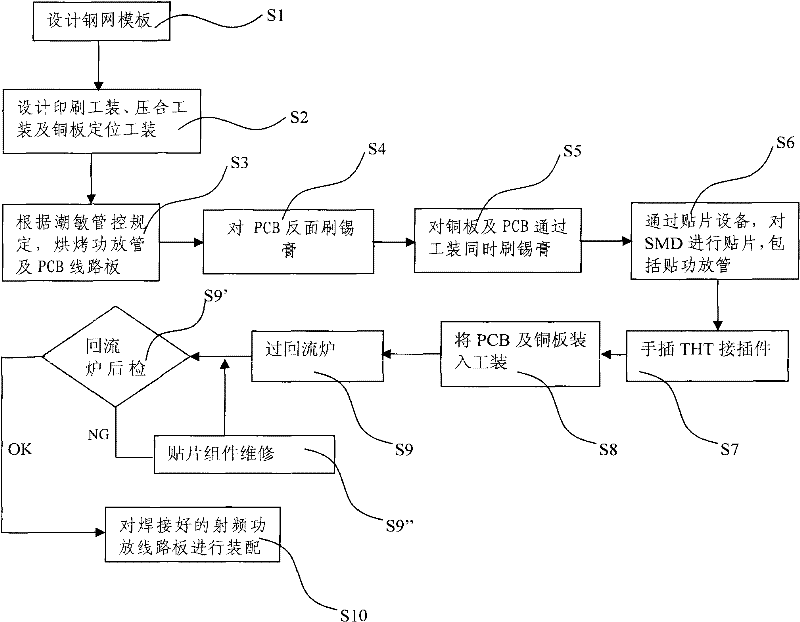

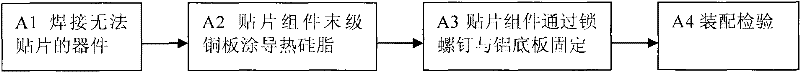

ActiveCN102164455AImprove cooling effectGood grounding effectPrinted circuit assemblingCopperSolder paste

The invention discloses a process for assembling a radio frequency power amplifier circuit board, which comprises the following steps: designing a steel mesh template, a printing assembly, a pressing assembly and a copper plate positioning assembly in order to meet the chip-mounting production; before performing the chip-mounting, roasting the tide sensitive devices such as a power amplifier tube and a PCB (printed circuit board) circuit board according to the tide sensitive control rule; brushing solder paste on the back side of the PCB while brushing solder paste (containing the solder paste used for soldering the power amplifier tube ) on the PCB and copper plate through the assembly; using a chip-mounting machine to mount the chip on the surface chip-mounting devices (including mounting on the power amplifier tube); manually inserting a THT (through hole technology) connector on the PCB circuit board mounted with the device; and lastly loading the PCB and the copper plate into an assembly backflow furnace. By using the process for assembling a radio frequency power amplifier circuit board provided by the invention, the excellent power amplifier radio frequency radiation and grounding properties are ensured, the reliability and the service life of the power amplifier are increased, and the product cost is lowered by adding the copper plate in the last stage.

Owner:WUHAN GEWEI ELECTRONICS TECH

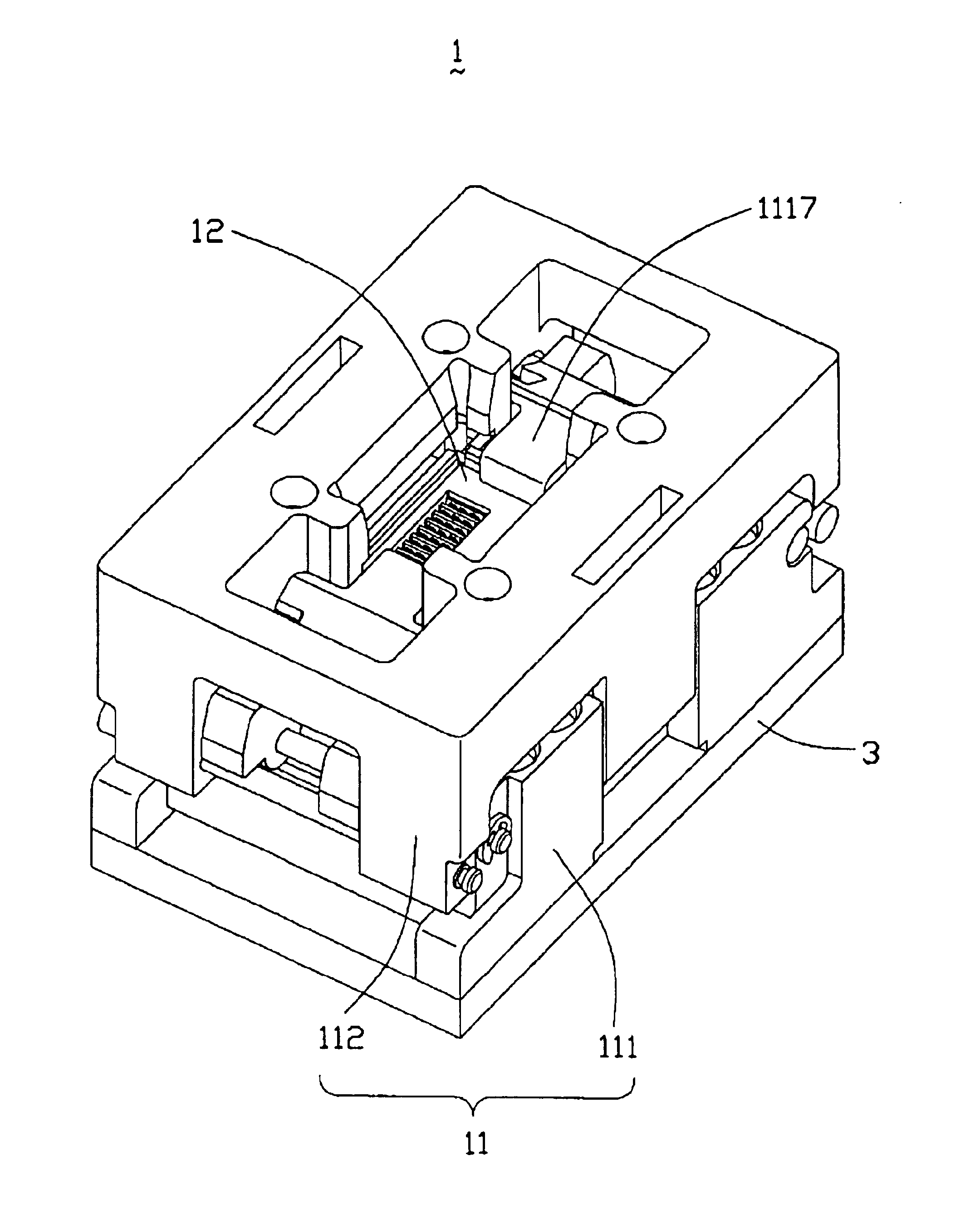

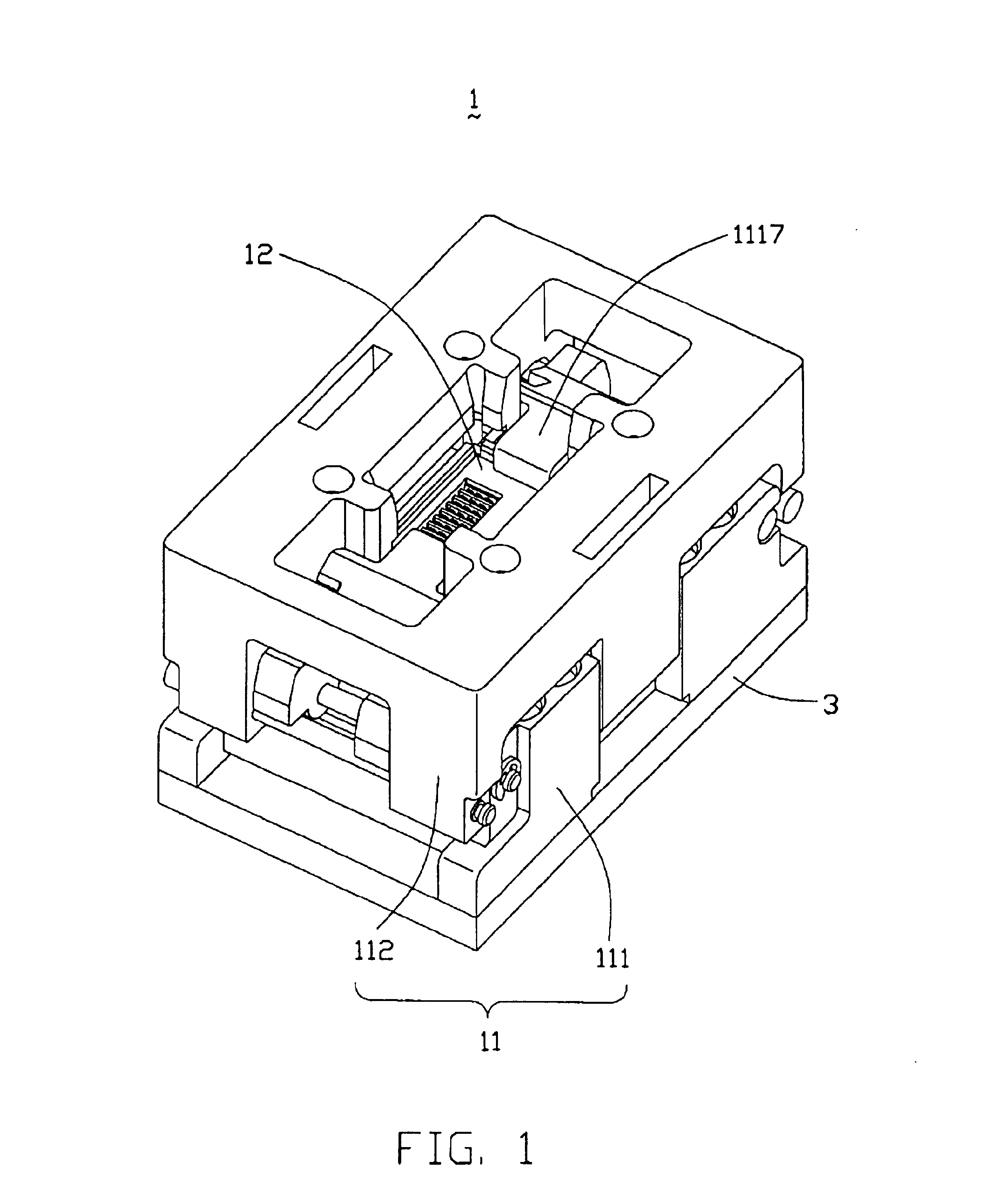

IC socket assembly

InactiveUS6832918B2Reduce manufacturing difficultyLong distanceEngagement/disengagement of coupling partsLine/current collector detailsEngineeringThrough-hole technology

Owner:HON HAI PRECISION IND CO LTD

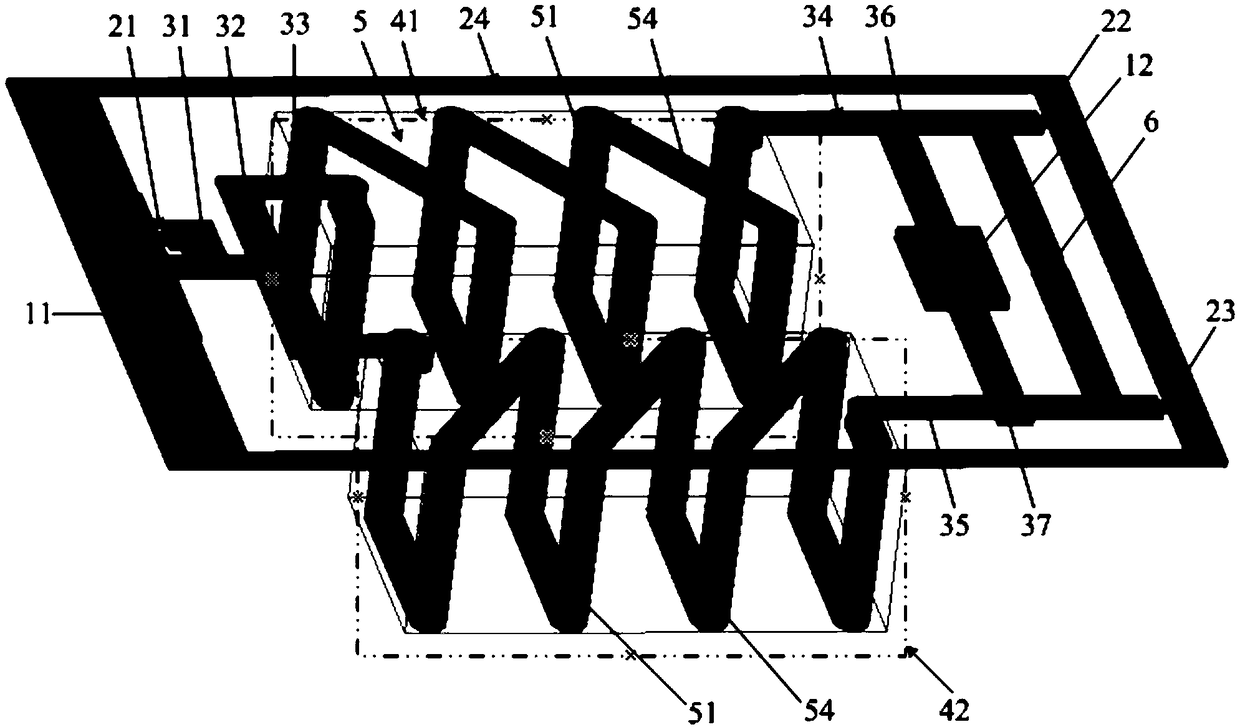

Medium cavity substrate integration waveguide structure based on silicon through hole technology and manufacturing technology thereof

InactiveCN108832245AHigh quality factorReduce power consumptionWaveguidesManufacturing technologyElectrical conductor

The invention discloses a medium cavity substrate integration waveguide structure based on a silicon through hole technology and a manufacturing technology thereof. A TSV three-dimensional packaging technology is used to integrate the substrate integration waveguide (SIW) structure into a three-dimensional chip system with a small volume. In the structure, a silicon substrate around TSV metal conductor columns is etched and a medium between the TSV metal conductor columns is changed into a high-molecular polymer benzocyclobutene (BCB) insulation material with a low dielectric constant from a low-resistance silicon substrate so that the eddy current effect of the silicon substrate in a high frequency circuit is eliminated, the corresponding high frequency losses of the silicon substrate donot exist, the power consumption of the substrate integration waveguide (SIW) structure of the invention is further reduced and a quality factor is increased. The resonant extraction of the substrateintegration waveguide (SIW) structure of the invention is greatly improved by the introduction of low-consumption high-molecular polymer benzocyclobutene (BCB) (filled in a BCB medium cavity).

Owner:XIDIAN UNIV

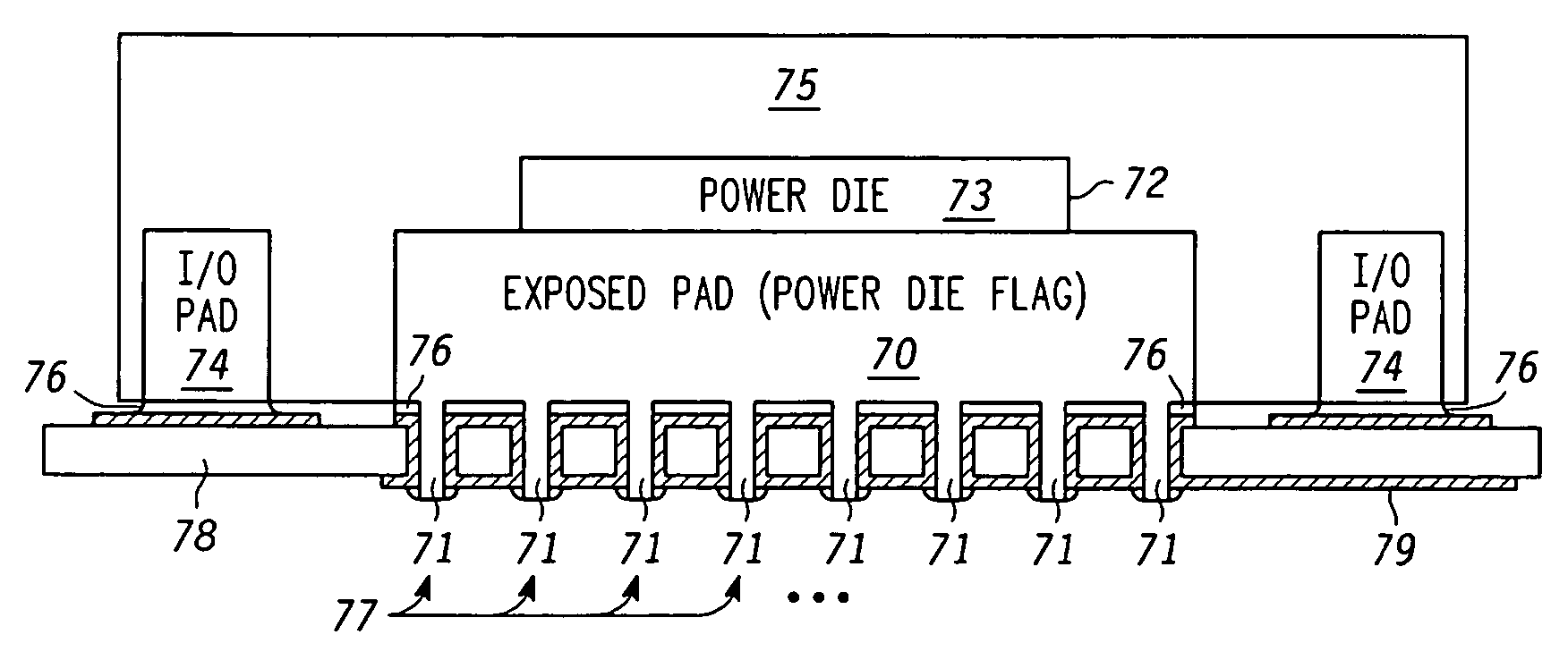

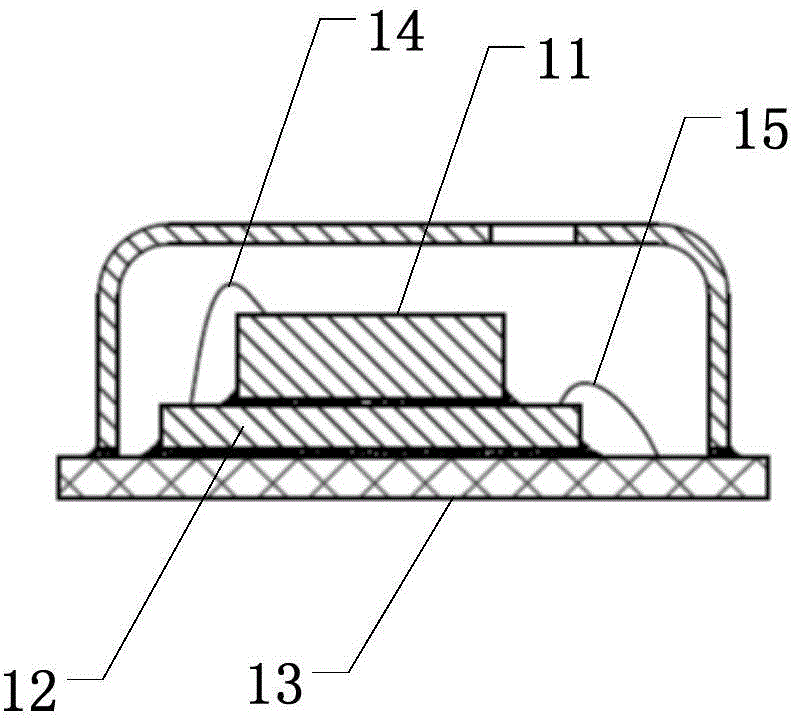

Lead frame based, over-molded semiconductor package with integrated through hole technology (THT) heat spreader pin(s) and associated method of manufacturing

ActiveUS7772036B2Reduce thermal resistanceControl performanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSemiconductor packageEngineering

A method and apparatus are provided for manufacturing a lead frame based, over-molded semiconductor package (7) with an exposed pad or power die flag (70) having multiple integrated THT heat spreader pins (71) configured for insertion into one or more vias (77) formed in a printed circuit board (78). The through hole heat spreader pins (71) may be formed as an integral part of the exposed pad (52) or may be solidly connected with the exposed pad (62).

Owner:NXP USA INC

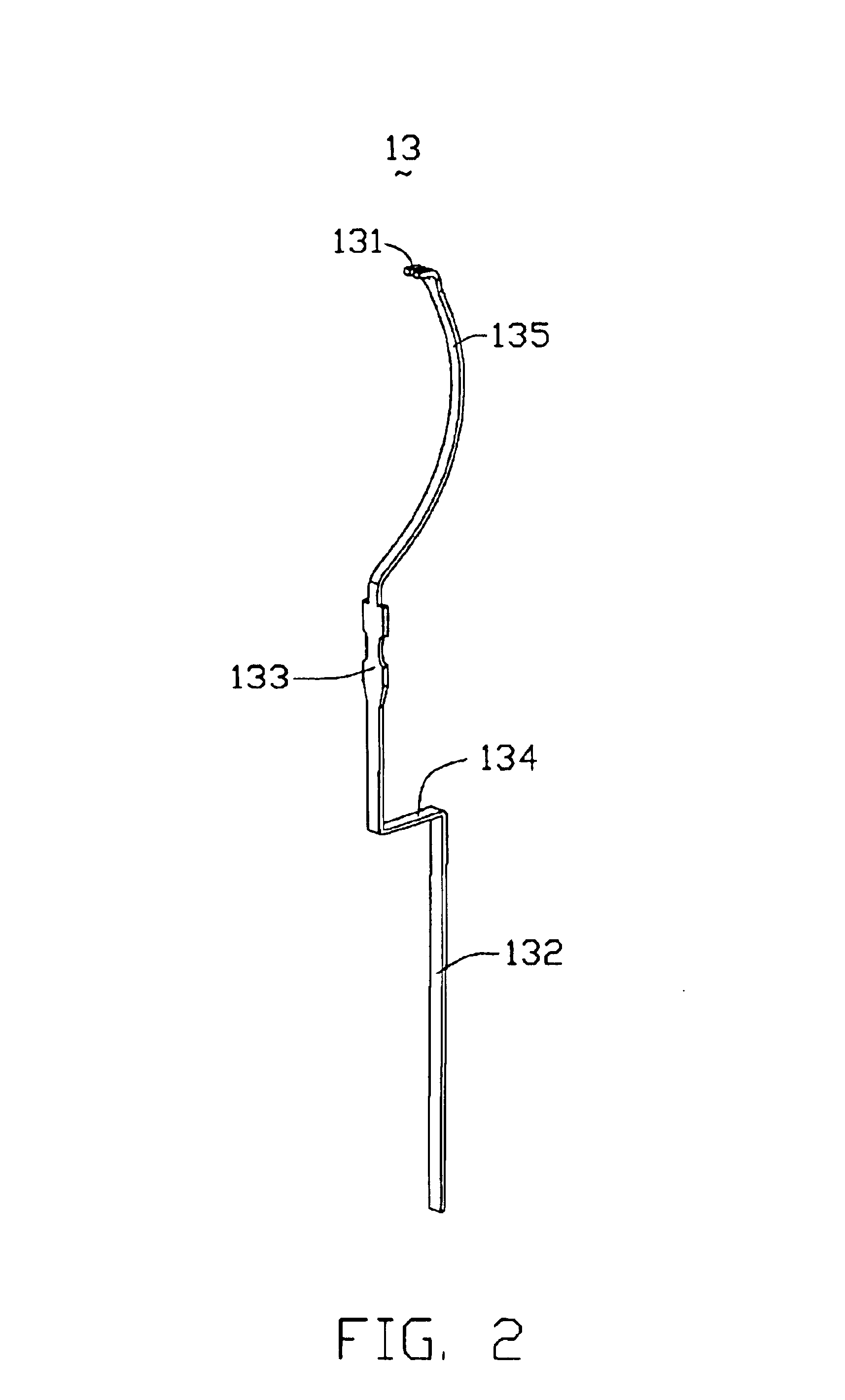

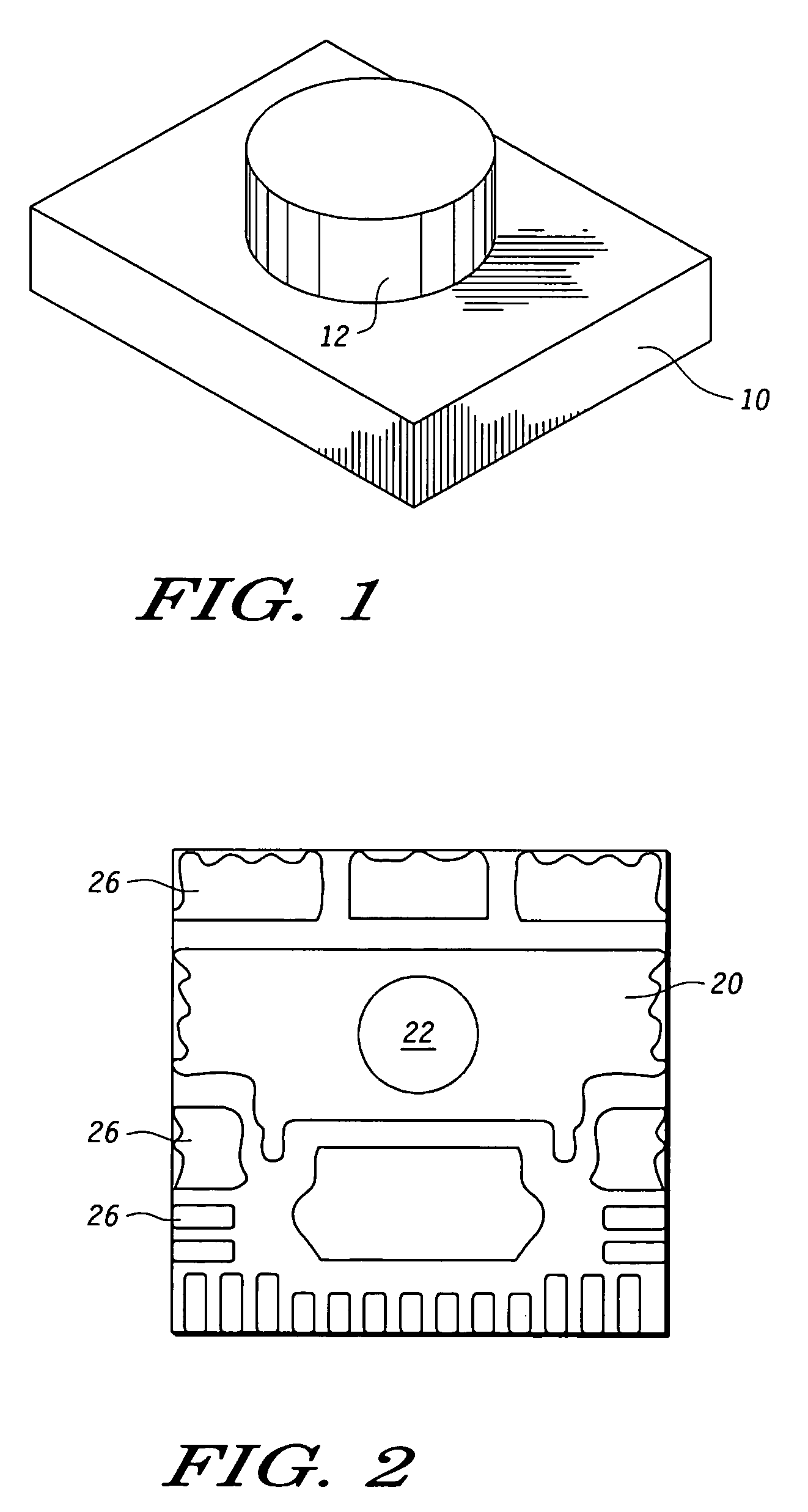

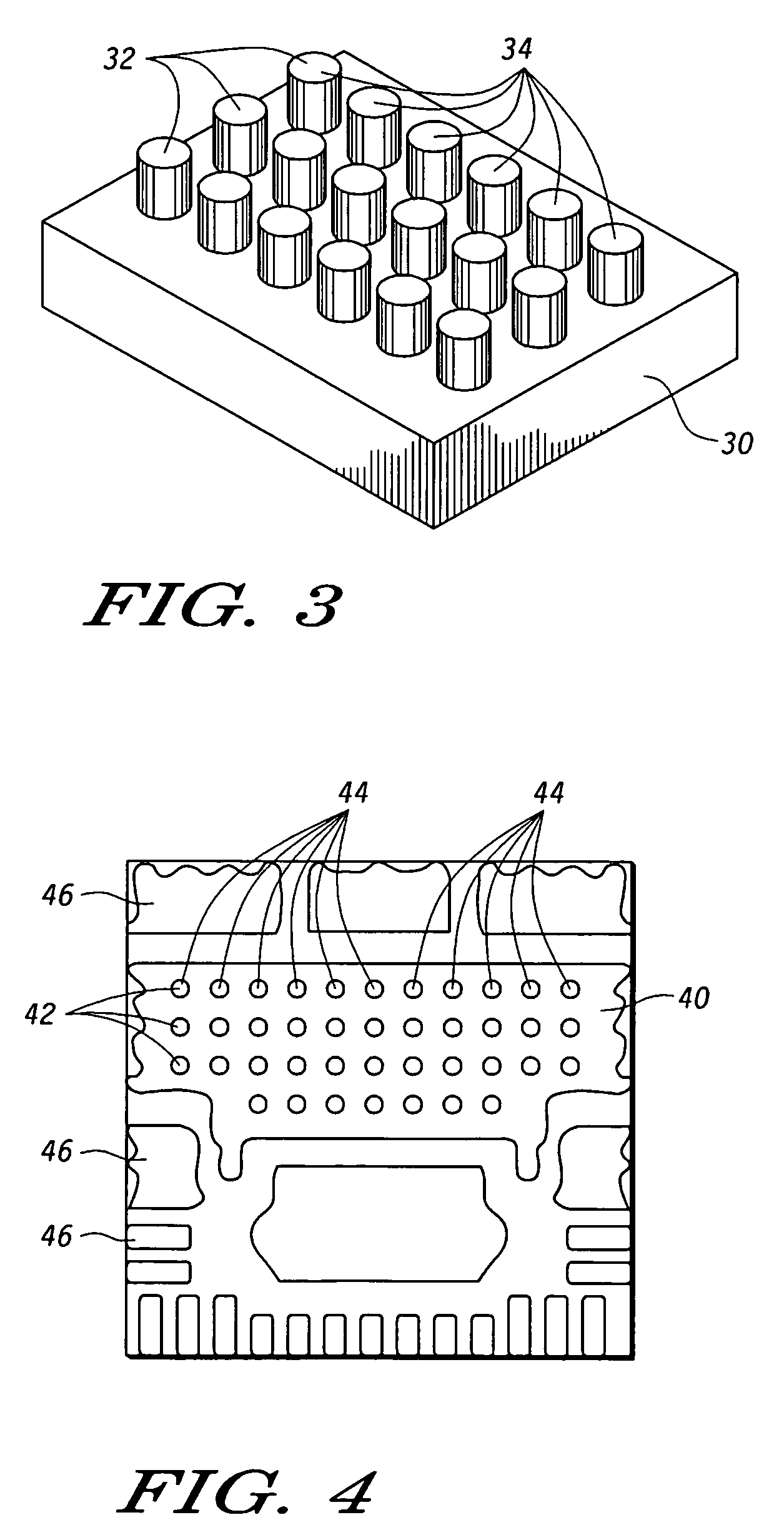

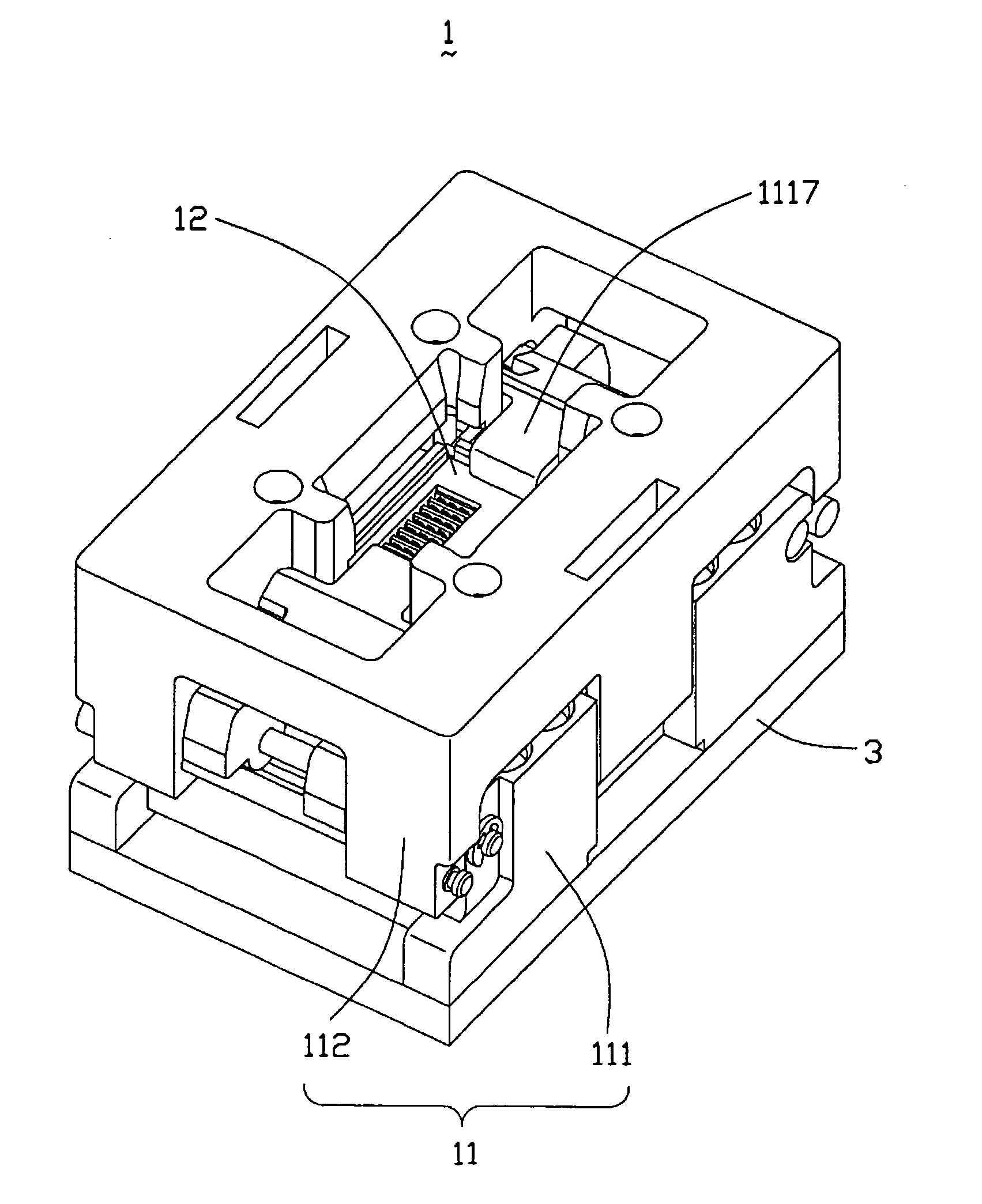

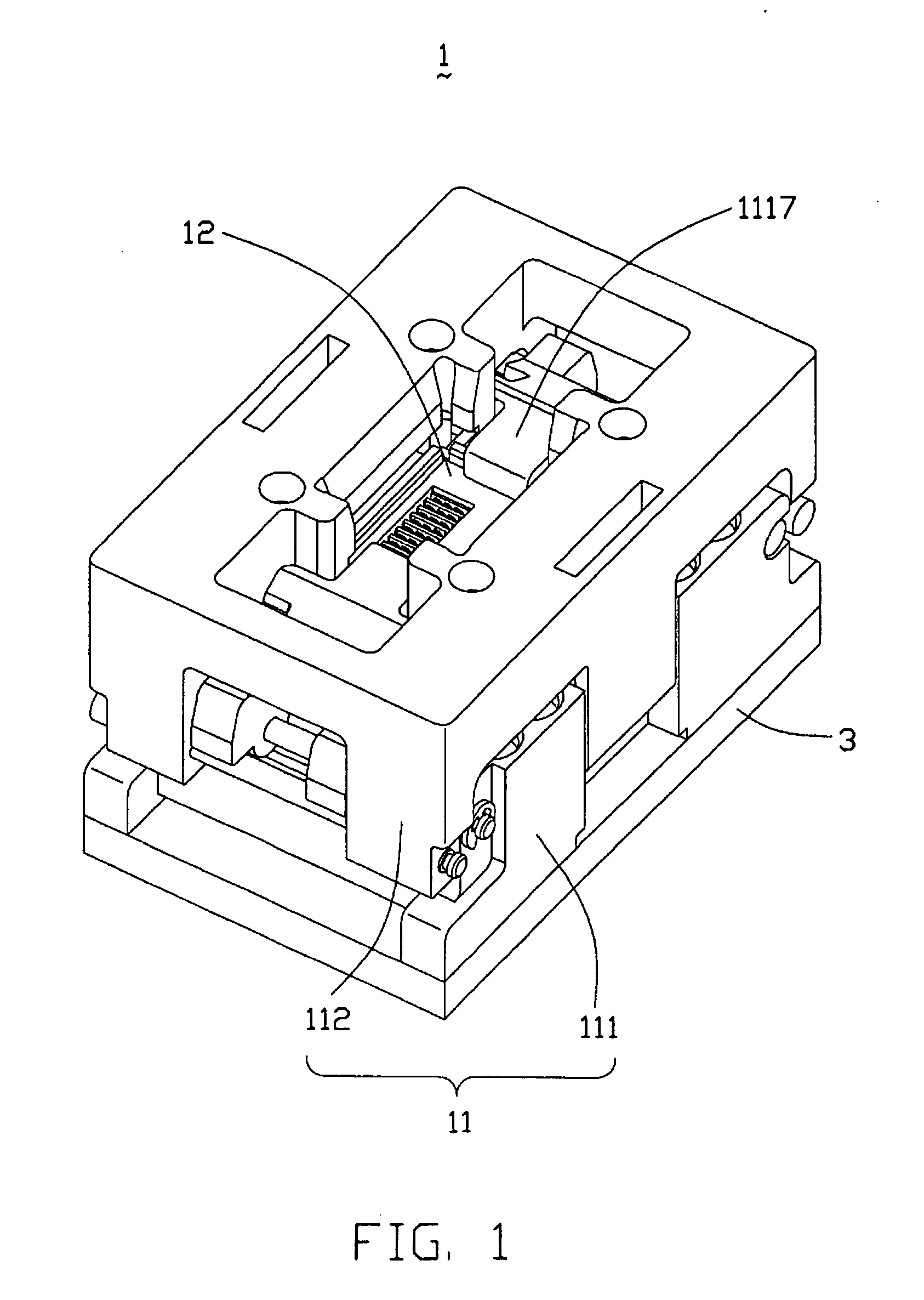

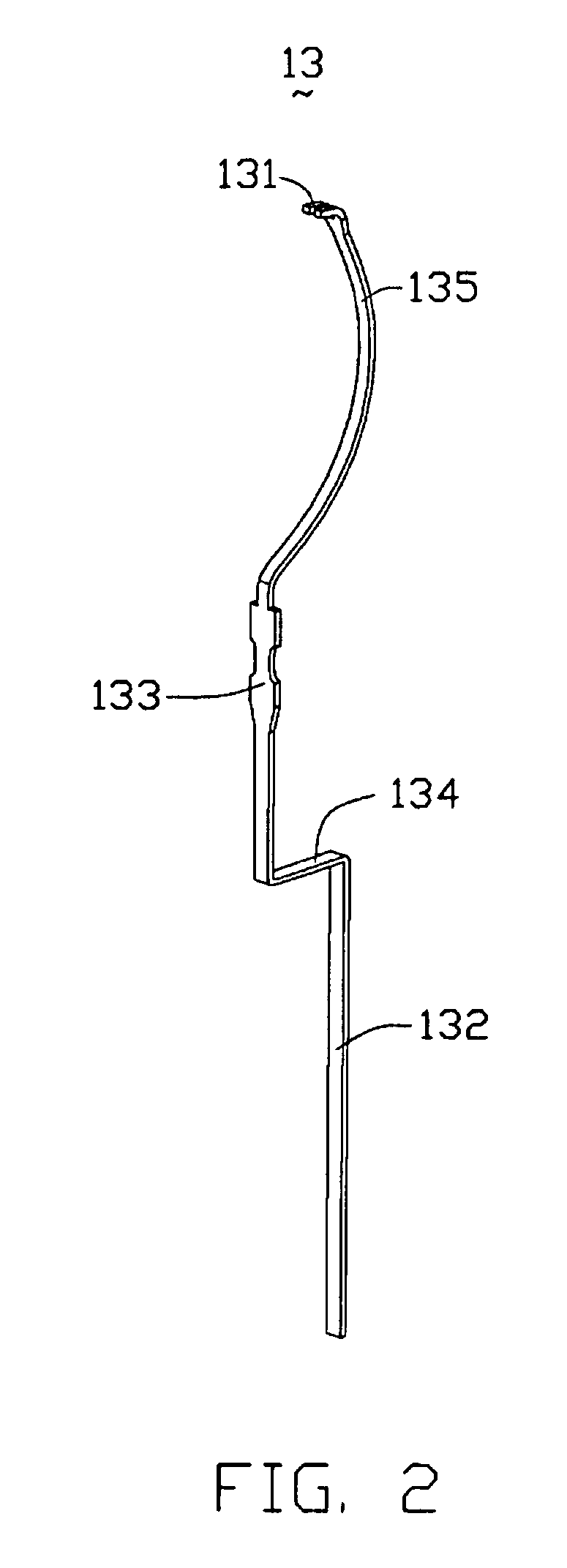

IC socket assembly

InactiveUS20040219816A1Engagement/disengagement of coupling partsLine/current collector detailsEngineeringThrough-hole technology

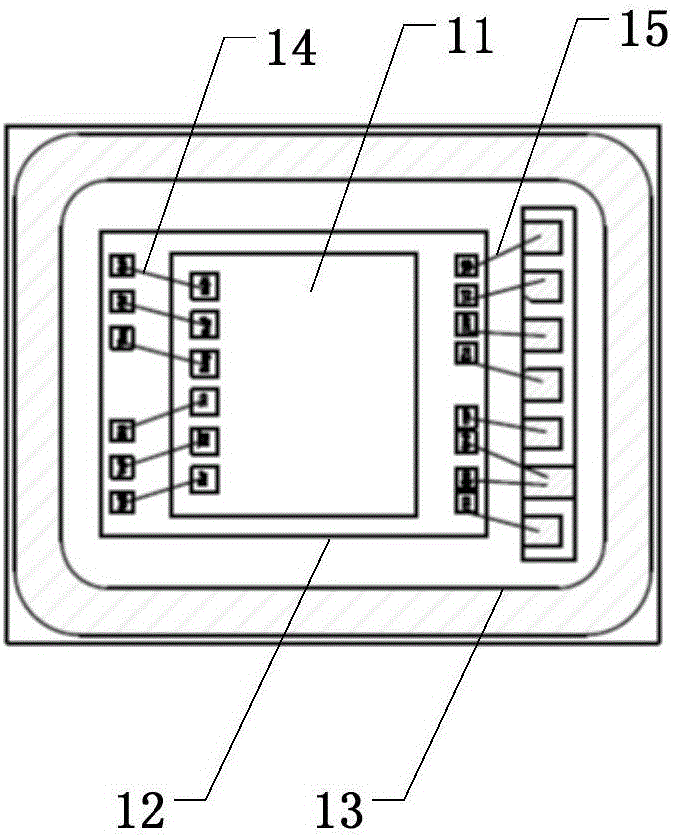

An integrated circuit (IC) socket assembly (1) includes an insulative housing (11), a holding component (12) and a multiplicity of electrical terminals (13). Each of the terminals includes a head portion (135) forming a first contact portion (131) at a free end thereof for electrically contacting an IC (2), a holding portion (133) engaging the terminal in the holding component, and a second contact portion (132) for electrically contacting a burn-in board (3) by Through Hole technology. Some of the terminals further include connecting portions (134) each bending from ends of the holding portions to ends of the second contact portions. Each of the connecting portions has a desired length in a horizontal direction, to decreases the difficulty of making the holes in the burn-in board and assembling the second contact portions into the burn-in board by Through Hole technology.

Owner:HON HAI PRECISION IND CO LTD

Flip LED packaging structure and manufacturing method

ActiveCN104979447AThe overall thickness is thinHigh light transmittanceSemiconductor devicesEngineeringUltimate tensile strength

The invention discloses a flip LED packaging structure and a manufacturing method. The electrode surface of the LED flip chip in the packaging structure is coated or not coated with an upper surrounding layer, and the electrode of the LED flip chip is connected with a solder convex block; the light-emitting surface and each side surface of the LED flip chip are embedded in a lower surrounding layer in a multilayer or two-layer or a single-layer structure and a peripheral surrounding layer; the peripheral surrounding layer is used for adjusting function applications of the chip or enhancing the mechanical strength of the chip, the lower surrounding layer is used for adjusting the color of the emitted light and enhancing the mechanical strength of the chip, and the electrode is connected with an external device via the solder convex block. Structures such as a silicon substrate or a silicon through hole are saved, technological advantages that the structure is simple, the thickness is thin, the mechanical strength is good, the packaging size is small and the like are provided, the light emitting surface and the light emitting color can be changed, the light emitting rate is improved, and function applications of the chip are multiple. According to the manufacturing method, the flip technology and the wafer level packaging technology are adopted, the silicon through hole technology is avoided during the manufacturing process, the process is simple, and the packaging cost is lower.

Owner:HUATIAN TECH KUNSHAN ELECTRONICS

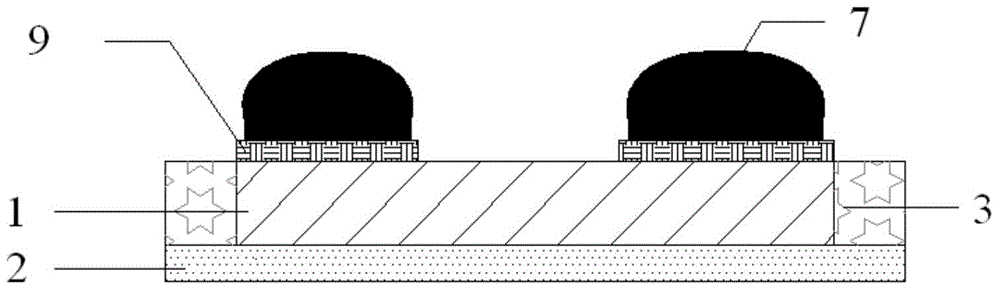

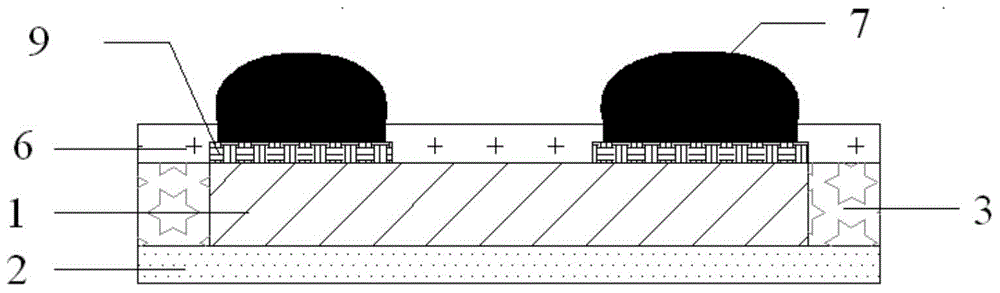

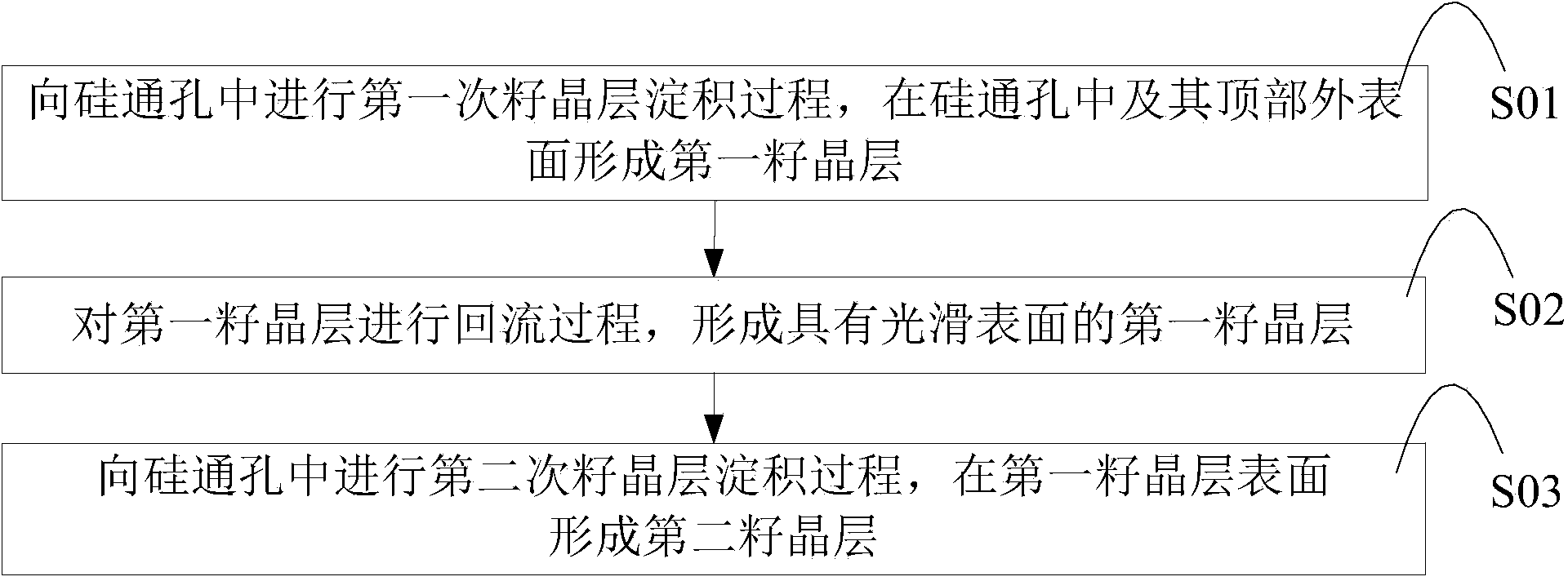

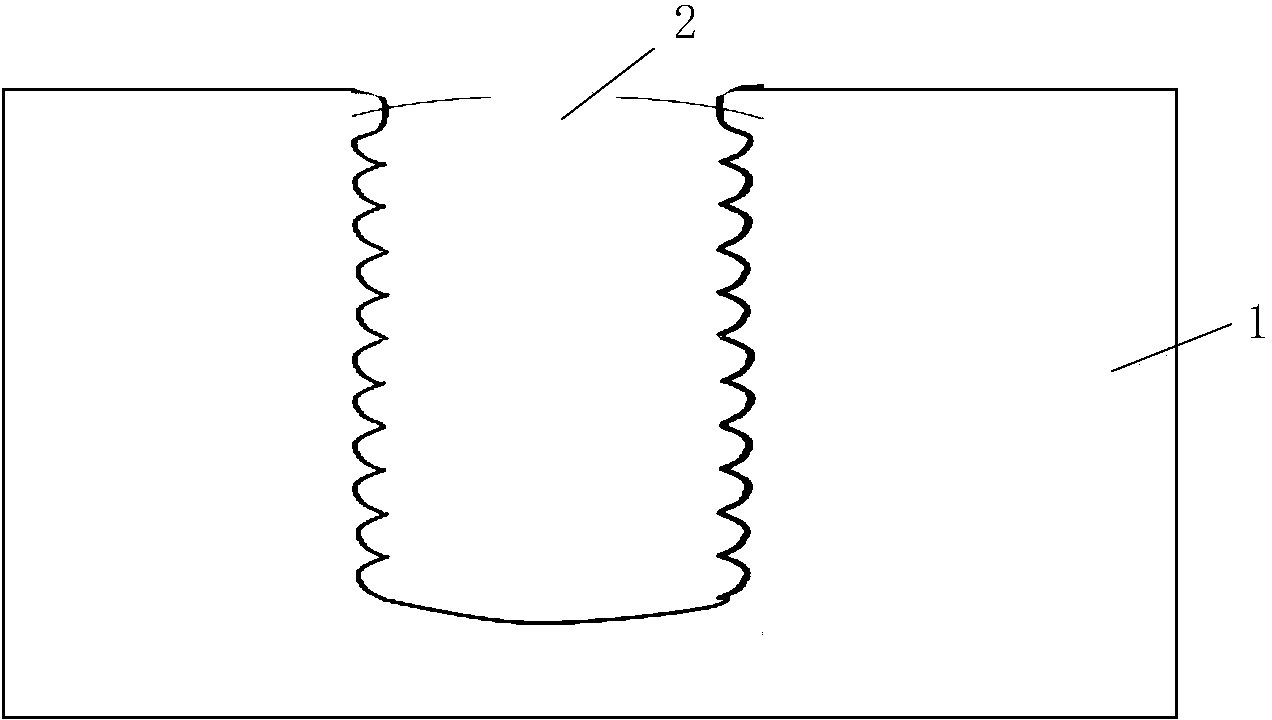

Method for forming seed crystal layers in silicon through hole technology

ActiveCN104183546AImprove reliabilityAvoid Void DefectsSemiconductor/solid-state device manufacturingDeposition processCopper

The invention provides a method for forming seed crystal layers in a silicon through hole technology. The method comprises the steps that a first-time seed crystal layer deposition process is conducted in a silicon through hole, and first seed crystal layers are formed in the silicon through hole and on the outer surface of the top of the silicon through hole; a backflow process is conducted on the first seed crystal layers, and the first seed crystal layers with the smooth surfaces are formed; a second-time seed crystal layer deposition process is conducted in the silicon through hole, and second seed crystal layers are formed on the surfaces of the first seed crystal layers. Due to the fact that the prepared seed crystal layers are provided with the smooth surfaces, advantageous conditions are provided for the subsequent copper electroplating, the detect that holes are generated inside the padded copper is effectively overcome, the technological quality of copper electroplating is improved, and the reliability of the silicon through hole is ensured.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT

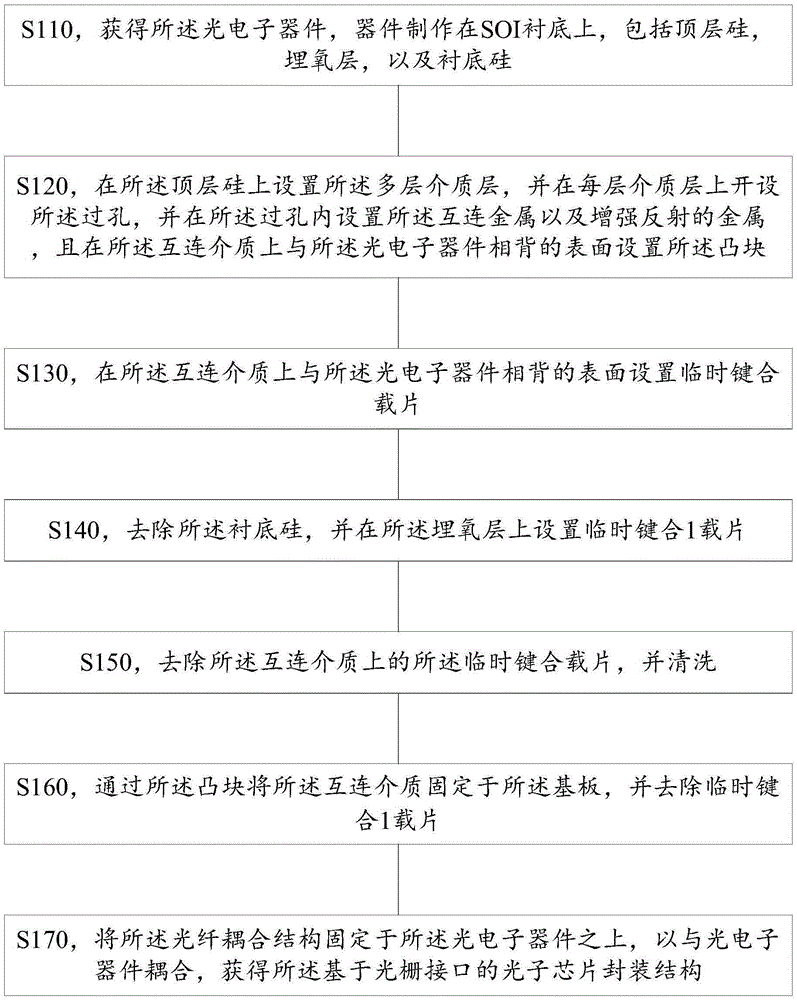

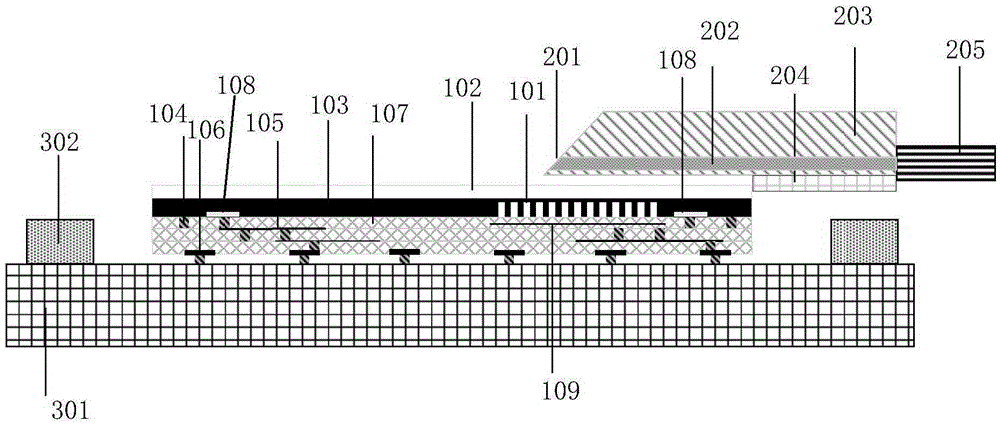

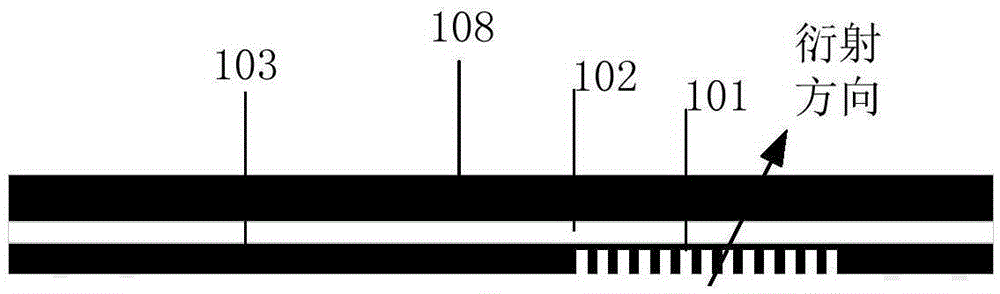

Photon chip packaging structure based on grating interface, and manufacturing method for photon chip packaging structure

ActiveCN105336795AGuaranteed performanceImprove performanceFinal product manufactureSemiconductor devicesGratingPhotonic Chip

The invention discloses a photon chip packaging structure based on a grating interface, and a manufacturing method for the photon chip packaging structure. The structure is characterized in that the structure comprises a photoelectron chip; an interconnection medium, wherein the surface, opposite to the photoelectron chip, of the interconnection medium is provided with a convex block; and an optical fiber coupling structure which is fixed on the photoelectron chip and is used for coupling with a back reflection grating on the photoelectron chip. The structure is provided with a multi-layer medium, the multi-layer medium is provided with a via hole, and the interior of the via hole is provided with an interconnection metal. The structure employs the mature rewiring technology, is simple in technology, achieves the leading-out of input / output interfaces, and can flexibly distribute the input / output interfaces according to the subsequent integration needs, thereby achieving the interlayer connection, avoiding the employing of the silicon through hole technology, and protecting the performance of the photoelectron chip. In addition, the photoelectron chip is disposed at the same side of the interconnection medium and a substrate, thereby enabling the photoelectron chip to be connected in an inverted buckling manner, improving the transmission speed, and improving the heat-dissipation effect.

Owner:NAT CENT FOR ADVANCED PACKAGING

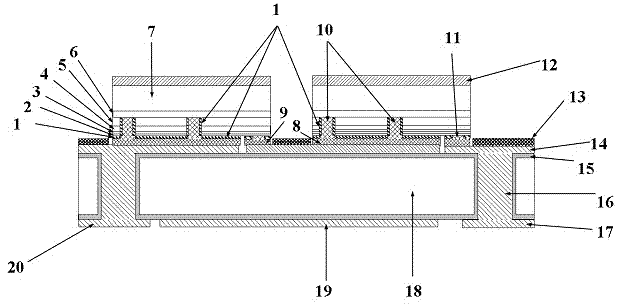

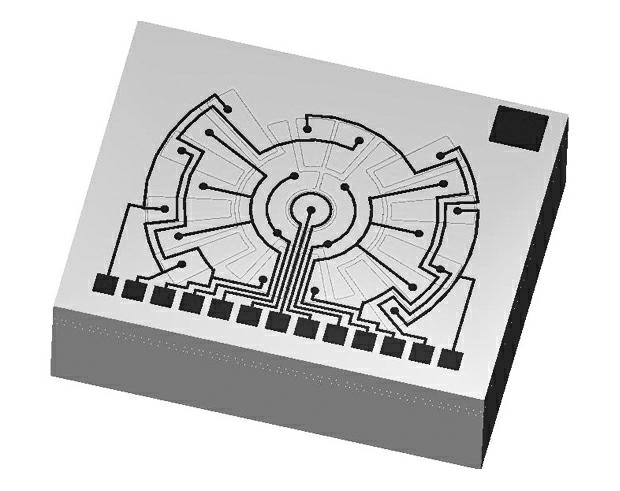

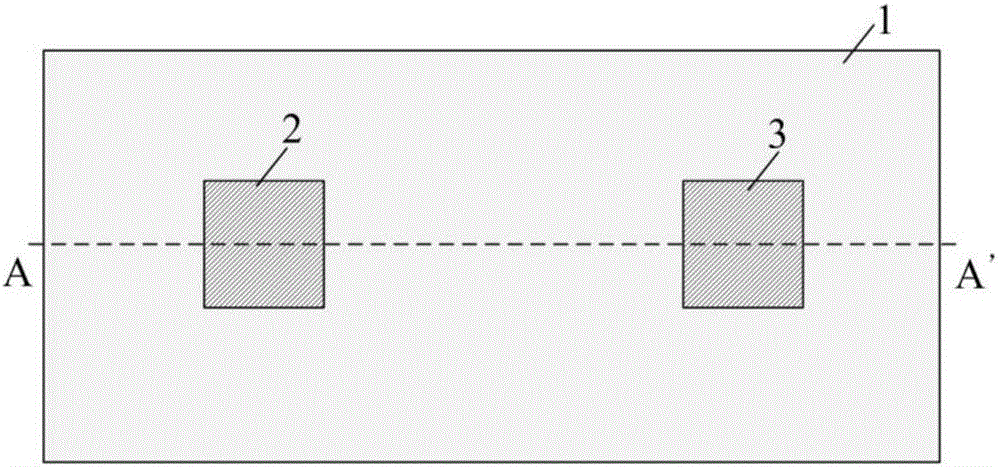

Integrated micro pressure flow sensor based on silicon through-hole technology

InactiveCN102680158AReduce package sizeReduce packaging costsVolume/mass flow measurementFluid pressure measurement by electric/magnetic elementsMems pressure sensorSignal conditioning

The invention provides an integrated micro pressure flow sensor based on silicon through-hole technology. The flow sensor consists of an MEMS (Micro-electromechanical System) pressure sensor, an MEMS flow sensor, an ASIC (Application Specific Integrated Circuit) sensor signal modulation chip, interconnected through holes and salient points, wherein the MEMS pressure sensor, the MEMS flow sensor and the ASIC sensor signal modulation chip are vertically stacked sequentially and are in electrical connection through the interconnected through holes and the salient points; and the ASIC sensor signal modulation chip carries out signal modulation on the MEMS pressure sensor and the MEMS flow sensor. The flow sensor has the advantages that with the adoption of the silicon through-hole technical process, the packaging size of the sensor is reduced greatly, the packaging cost is reduced, and the application range of the pressure sensor and the flow sensor is enlarged.

Owner:刘胜

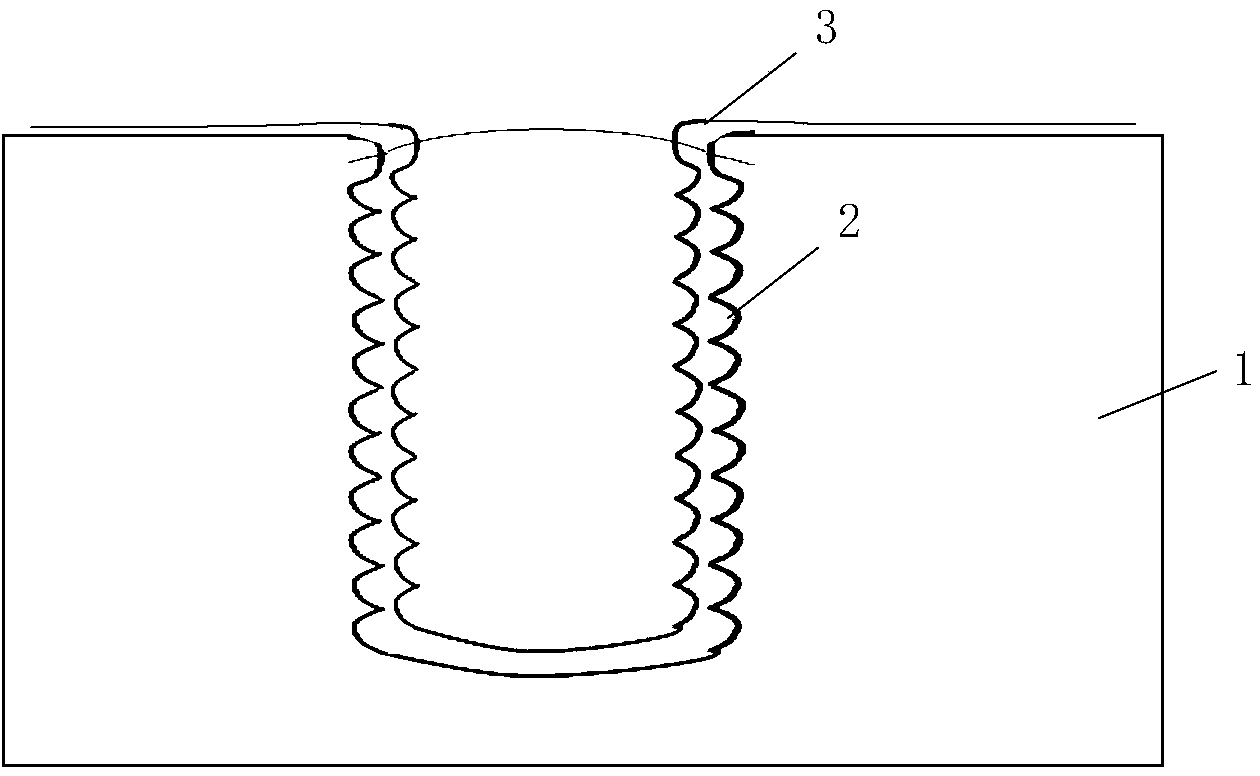

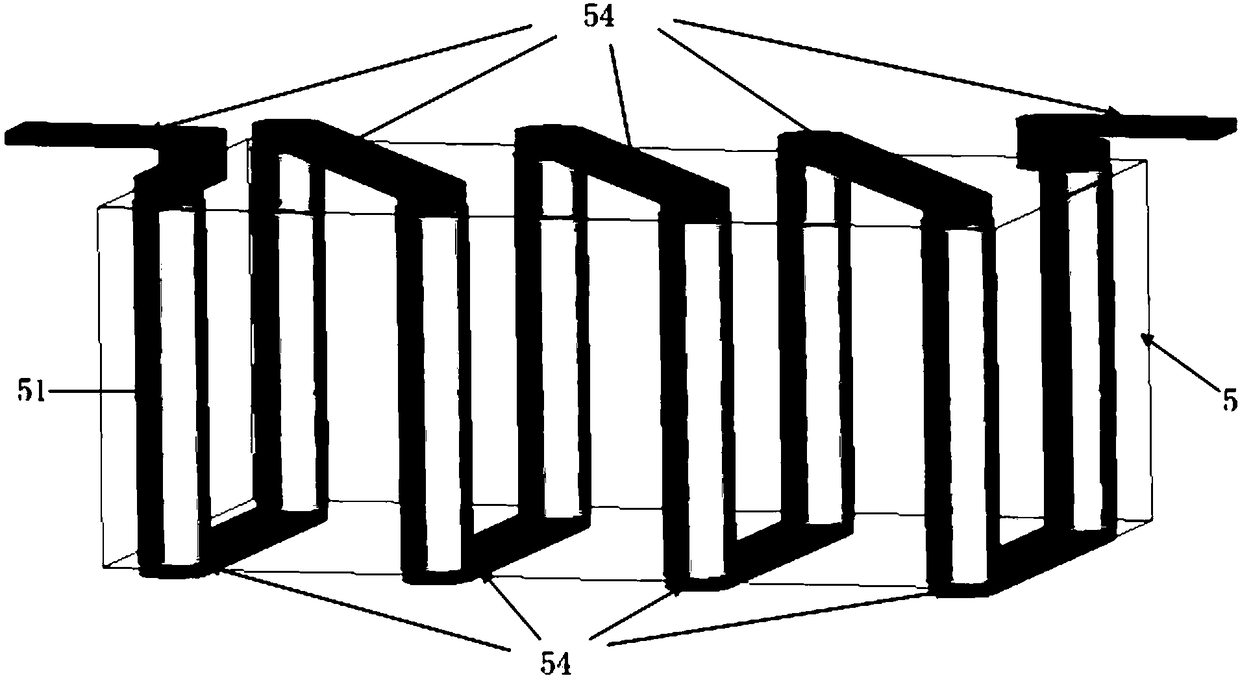

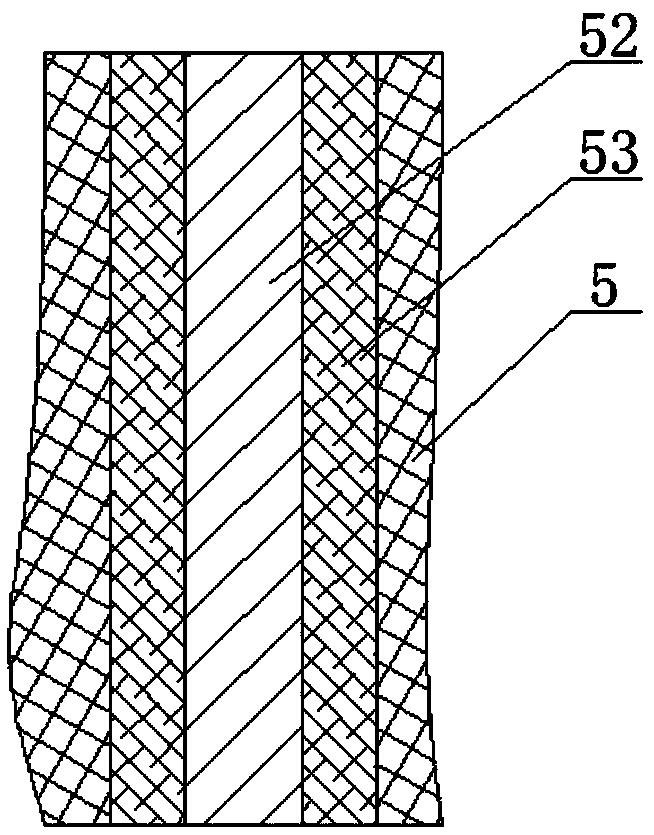

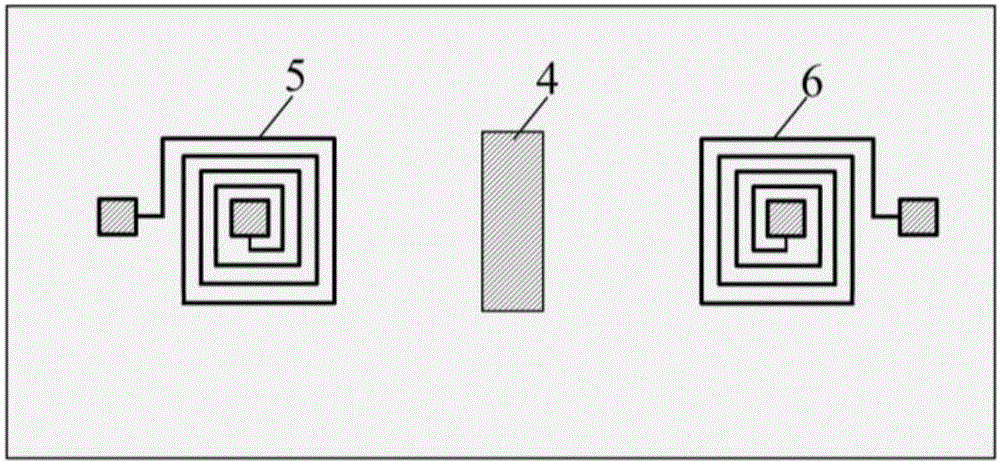

Solenoid type difference inductor based on silicon through hole

InactiveCN103824840AEnhanced Magnetic Field CouplingReduce Inductor SizeSemiconductor/solid-state device detailsSolid-state devicesElectrical connectionInterconnection

The invention discloses a solenoid type difference inductor based on a silicon through hole. The solenoid type difference inductor is composed of a horizontal metal line which is disposed in the top metal layer and the bottom metal layer of a silicon substrate, and the silicon through hole which vertically penetrates the silicon substrate. By use of a via-first silicon through hole technology, first of all, a metal through hole is etched in a silicon adaptor plate, then a horizontal interconnection line is constructed at the top and the back portion of the silicon adaptor plate, and electrical connection with the silicon through hole is carried out so that a coil is formed. A plurality of intersected lines exist in the metal line in the horizontal direction, and by use of the metal through hole and the two metal layers, a completely symmetrical structure is realized. By using the inductor provided by the invention, the dimension is reduced, and the overall inductance value can be improved at the same time.

Owner:NANJING UNIV OF SCI & TECH

Surface mount technology of ratio frequency power amplification mainboard

ActiveCN102065646AImprove cooling effectGood grounding effectPrinted circuit assemblingSurface mountingSurface-mount technology

The invention discloses a surface mount technology of a ratio frequency power amplification mainboard. The technology comprises the following steps of: designing a steel mesh template; designing a printing tool, a pressing tool and an aluminum sheet positioning tool so as to meet the requirement for surface mounted device production; roasting a power amplification tube and a PCB (Printed Circuit Board) according to a moist sensitivity control rule; printing solder paste on the back of the PCB; simultaneously printing the solder paste including solder paste required by welding the power amplification tube on the PCB and the aluminum sheet through a tool; carrying out surface mount on a surface mounted device through surface mount equipment, including the operation of mounting the amplification tube; inserting a THT (Through Hole Technology) connector assembly by hands on the PCB mounted with the device; loading the PCB and the aluminum sheet into the tool; and treating the PCB and the aluminum sheet in a backflow furnace. The surface mount technology of the ratio frequency power amplification mainboard guarantees good power amplification ratio frequency heat dissipation and grounding property and greatly improves the reliability and the service life of the power amplification; meanwhile, because aluminum sheet welding is adopted and a nickel plating process is used for treating the surface of the aluminum sheet, the product cost is reduced.

Owner:WUHAN GEWEI ELECTRONICS TECH

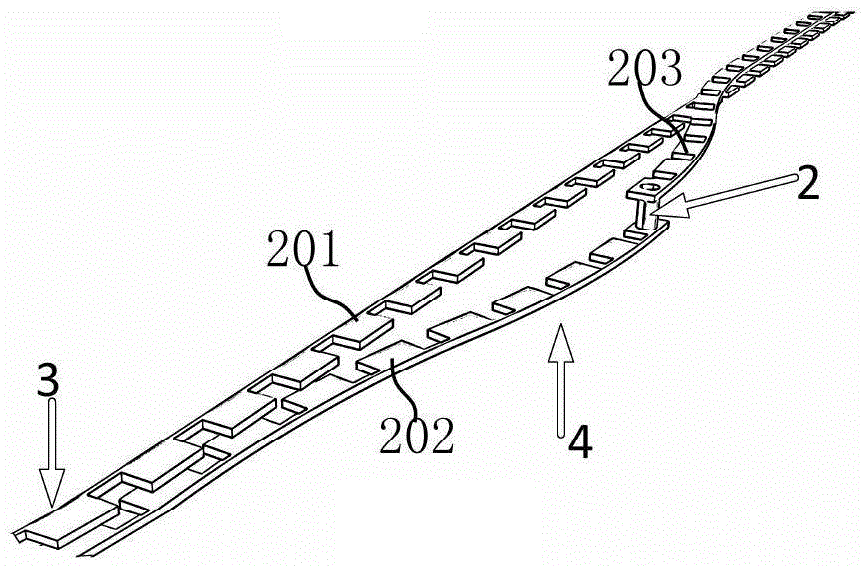

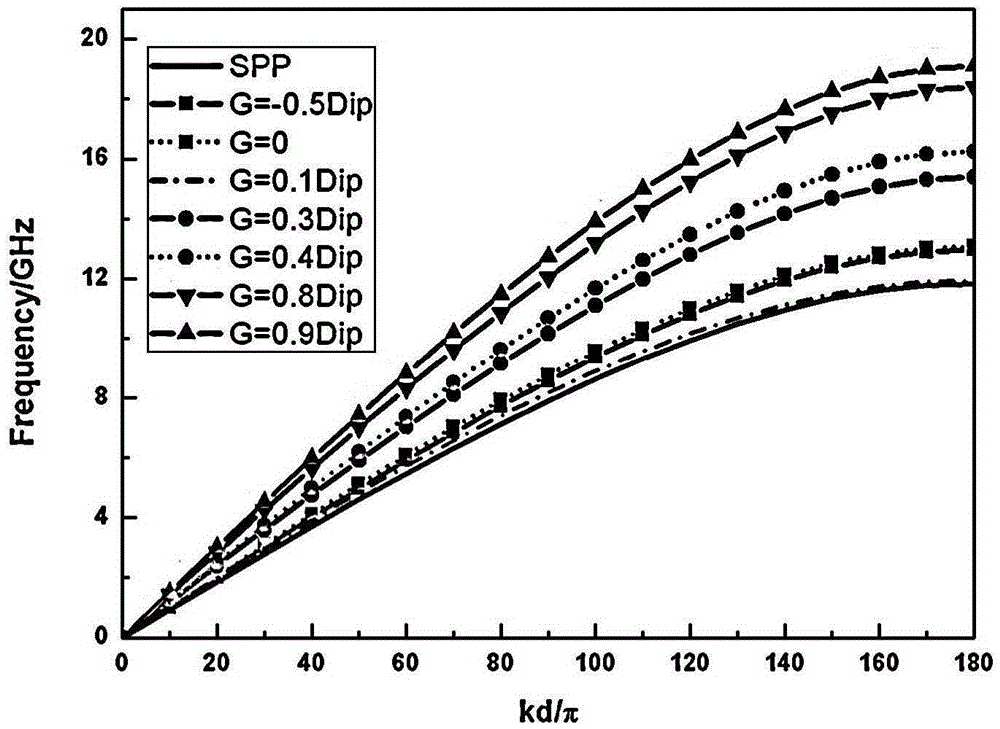

Jump layer transmission line based on artificial surface plasma polaritons

ActiveCN105633522AGuaranteed normal transmissionEasy to makeWaveguidesDielectric substrateEngineering

The invention discloses a jump layer transmission line based on artificial surface plasma polaritons. The jump layer transmission line comprises a dielectric substrate, a first metal strip and a second metal strip which are arranged at the two sides of the dielectric substrate, and a metalized through hole which penetrates through the dielectric substrate and is connected with the tail ends of the first metal strip and the second metal strip so as to connect the metal strips from one side of the dielectric substrate to the other side. The first metal strip and the second metal strip are formed by periodic slot units. Interlayer high-efficiency transmission of multiple layers in broadband bandwidth can be realized through a metal through hole technology, and the jump layer transmission line also has the characteristics of being easy to manufacture and convenient to process, and low in crosstalk and high in efficiency. The single-layer transmission line structure can be applied to a limitless thin dielectric substrate so that the characteristics of ultrathin ultralow loss transmission can be realized. Meanwhile, the two transmission lines are not sensitive to deformation of the dielectric substrate and can be attached to a spherical surface, a conical surface and other uneven dielectric substrate surfaces so as to form a conformal device and a circuit system.

Owner:SOUTHEAST UNIV

Silicon wafer directly-bonded micro-mechanical gyroscope based on silicon through hole technology

ActiveCN102607543ASmall sizeImprove air tightnessTurn-sensitive devicesSilicon electrodeMicromachinery

The invention relates to a silicon wafer directly-bonded micro-mechanical gyroscope based on a silicon through hole technology, comprising three silicon wafer layers in a silicon-silicon direct bonding mode, namely, a fixing electrode silicon wafer layer, a mass block silicon wafer layer and a sealing cover silicon wafer layer; the fixing electrode silicon wafer layer is a through hole silicon wafer layer and is provided with a plurality of through hole silicon electrodes vertical to the through hole silicon wafer layer, and through hole silicon insulating layers vertical to the through hole silicon wafer layers are arranged between the adjacent through hole silicon wafer layers; the mass block silicon wafer layer comprises a pair of eudipleural fan-shaped mass blocks, the fan-shaped mass blocks form mass block electrodes, and the mass block silicon wafer layer is symmetrically suspended below the fixing electrode silicon wafer layer through a single anchor point in the silicon-silicon direct bonding mode; and the mass block electrodes and the through hole silicon electrodes form two electrodes of a variable capacitor. According to the invention, through hole silicon is used as an electrode material of a variable capacitor sensor structure and the silicon-silicon direct bonding mode is utilized for reducing the thermal stress to be minimum and the sensor performance is improved.

Owner:NORTH ELECTRON RES INST ANHUI CO LTD

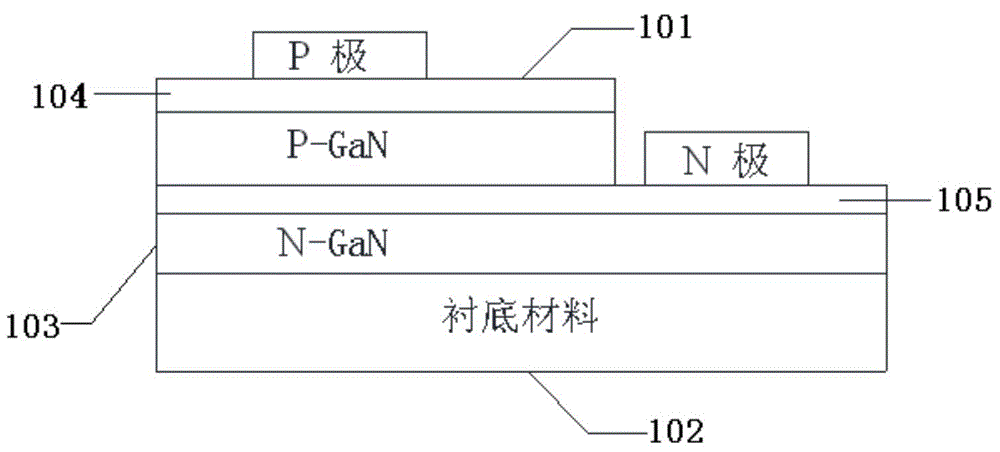

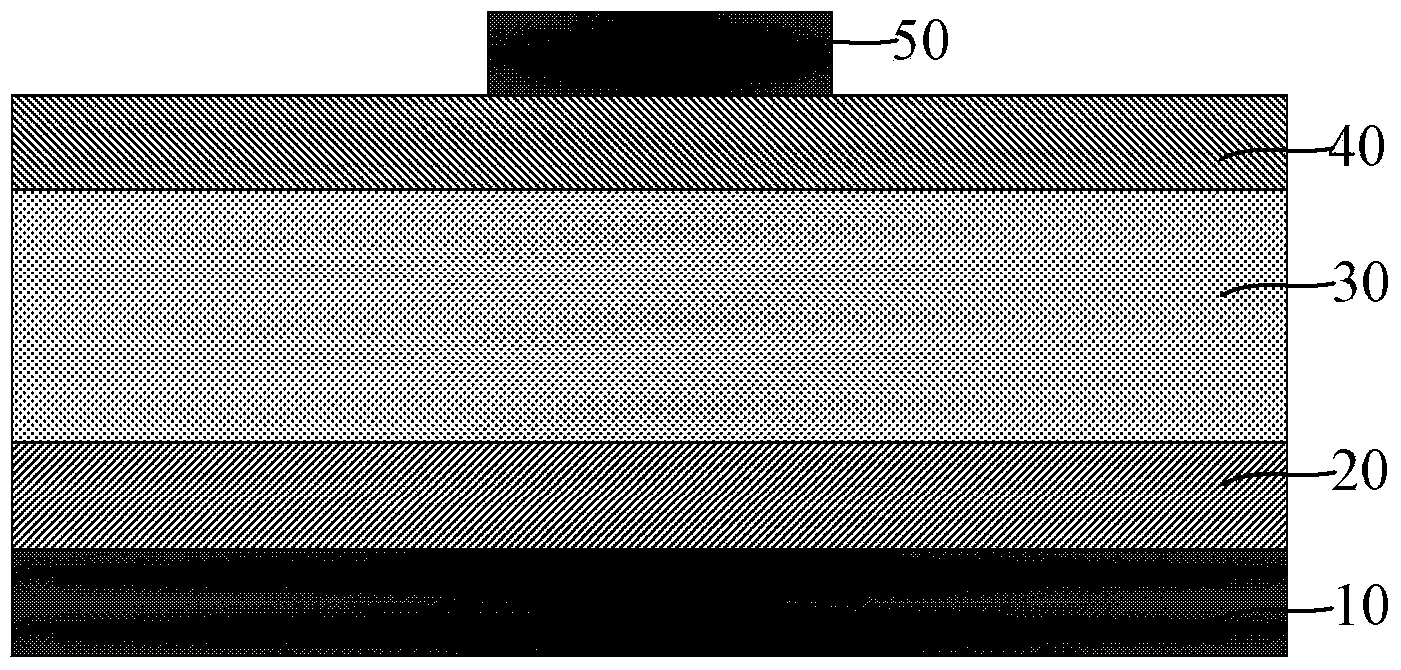

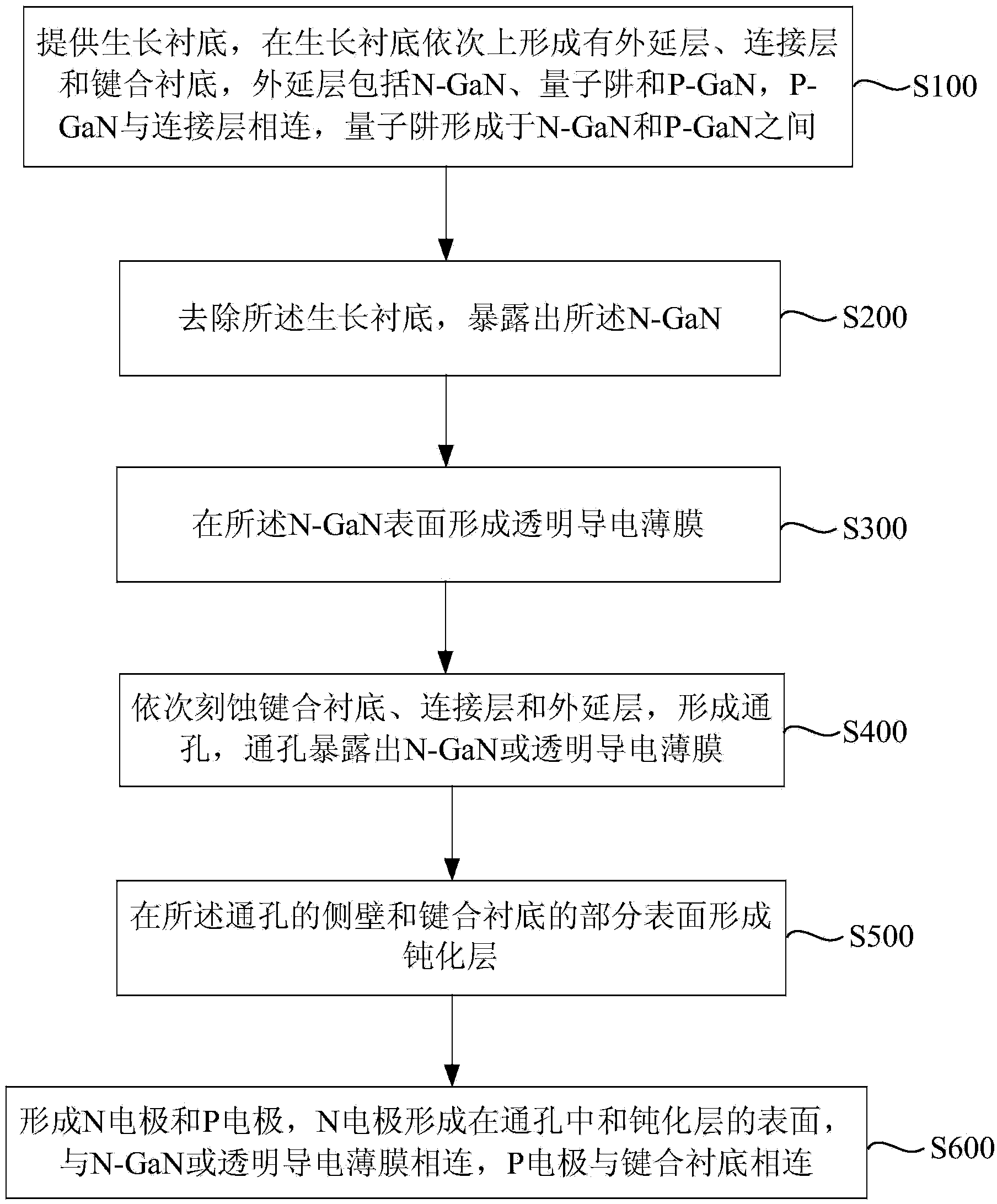

Method for manufacturing LED with vertical type through holes

The invention provides a method for manufacturing an LED with vertical type through holes. Before the N electrode and the P electrode are formed, the through hole technology is adopted, the through holes are formed in a bonding substrate, a connecting layer and an epitaxial layer, N-GaN or transparent conducting thin film is exposed out through the through holes, then passivation layers are formed on the lateral walls of the through holes and the partial surface of the bonding substrate, the N electrode is formed in the through holes and the surfaces of the passivation layers, the P electrode is formed on the bonding substrate, the N electrode is connected with the N-GaN or the transparent conducting thin film, the N electrode is accordingly led out from the bonding substrate through the through holes, blocking of the N electrode on emitted light of the light emitting face is reduced, and the external quantum efficiency is improved; meanwhile, the N electrode is formed on the surface of the bonding substrate, then the reflow soldering packaging mode is adopted, and packaging with the routing process is not needed, so that damage of routing to the epitaxial layer is avoided, and the cost of gold wires for the packaging process is reduced.

Owner:ENRAYTEK OPTOELECTRONICS

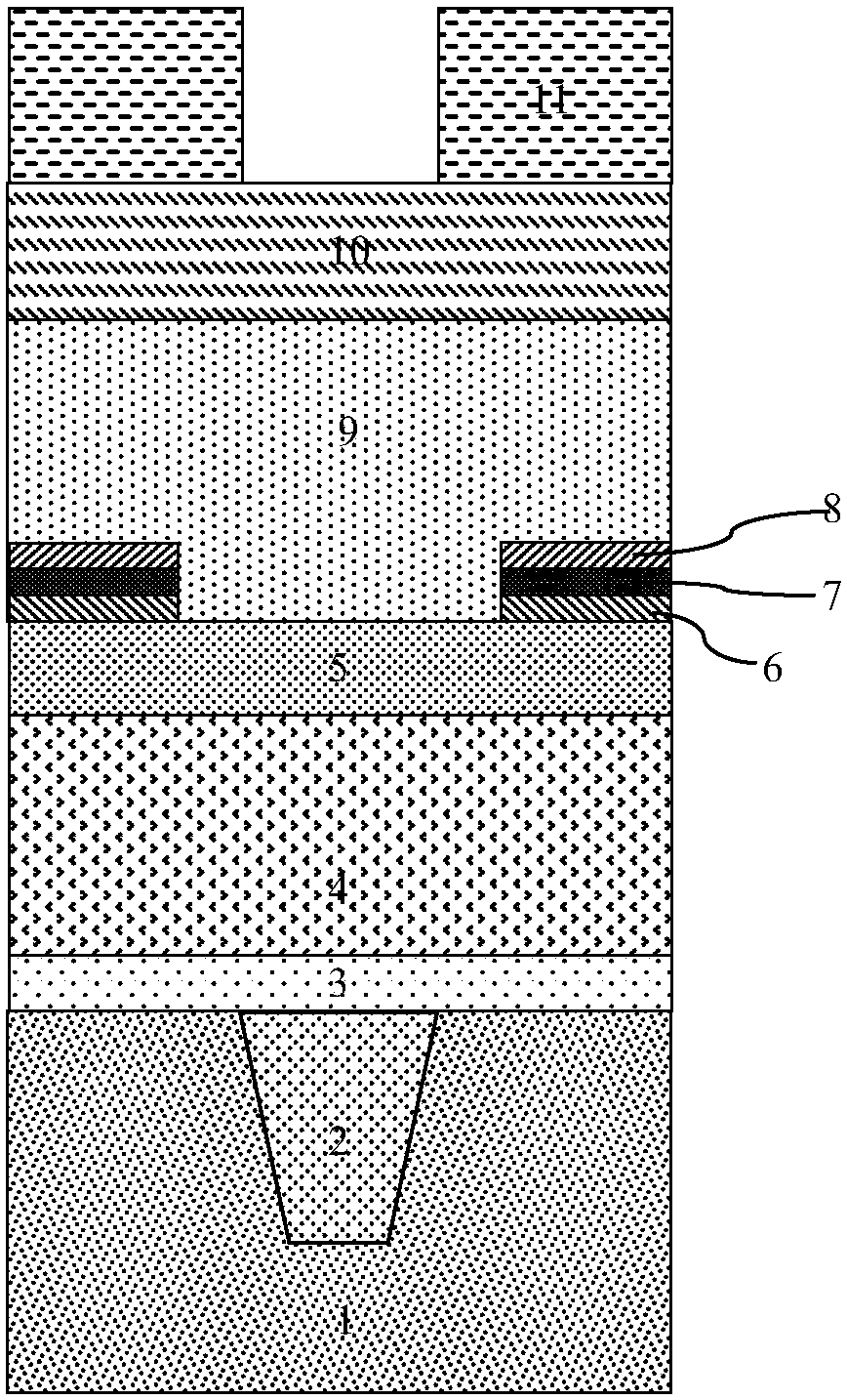

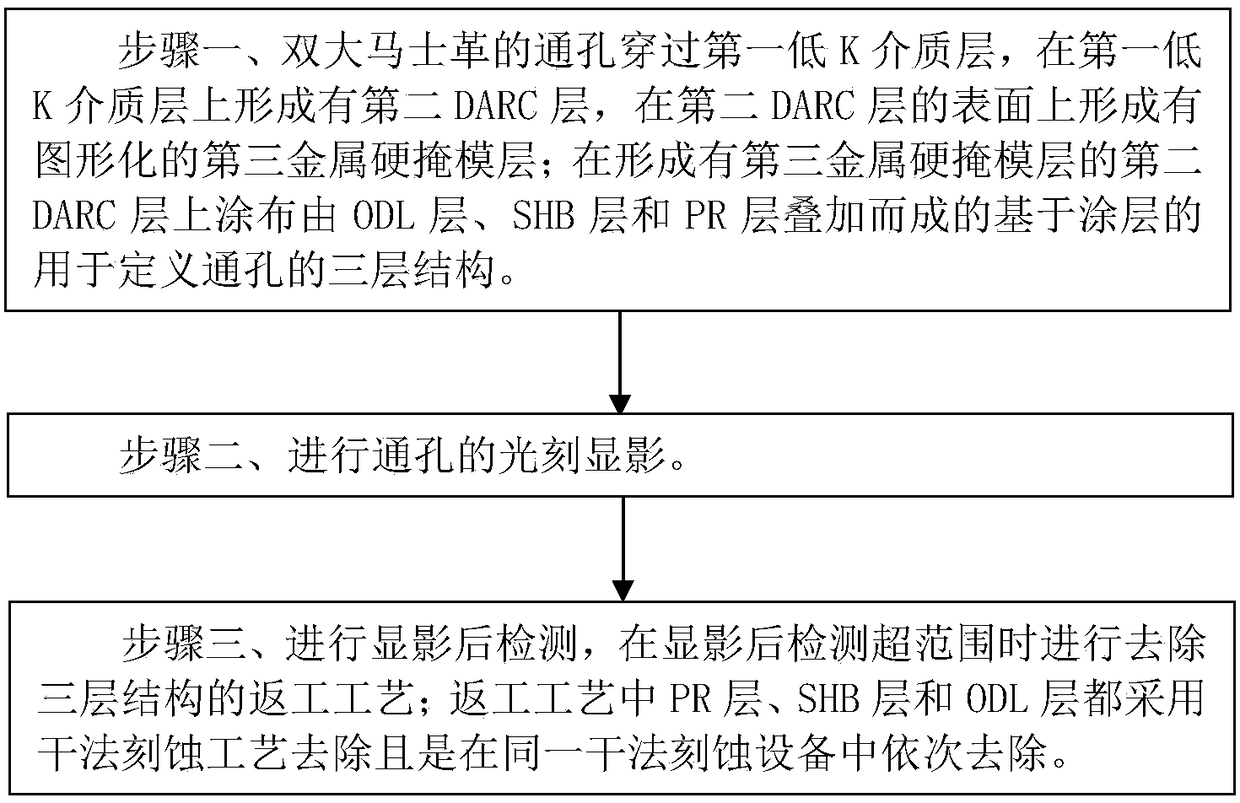

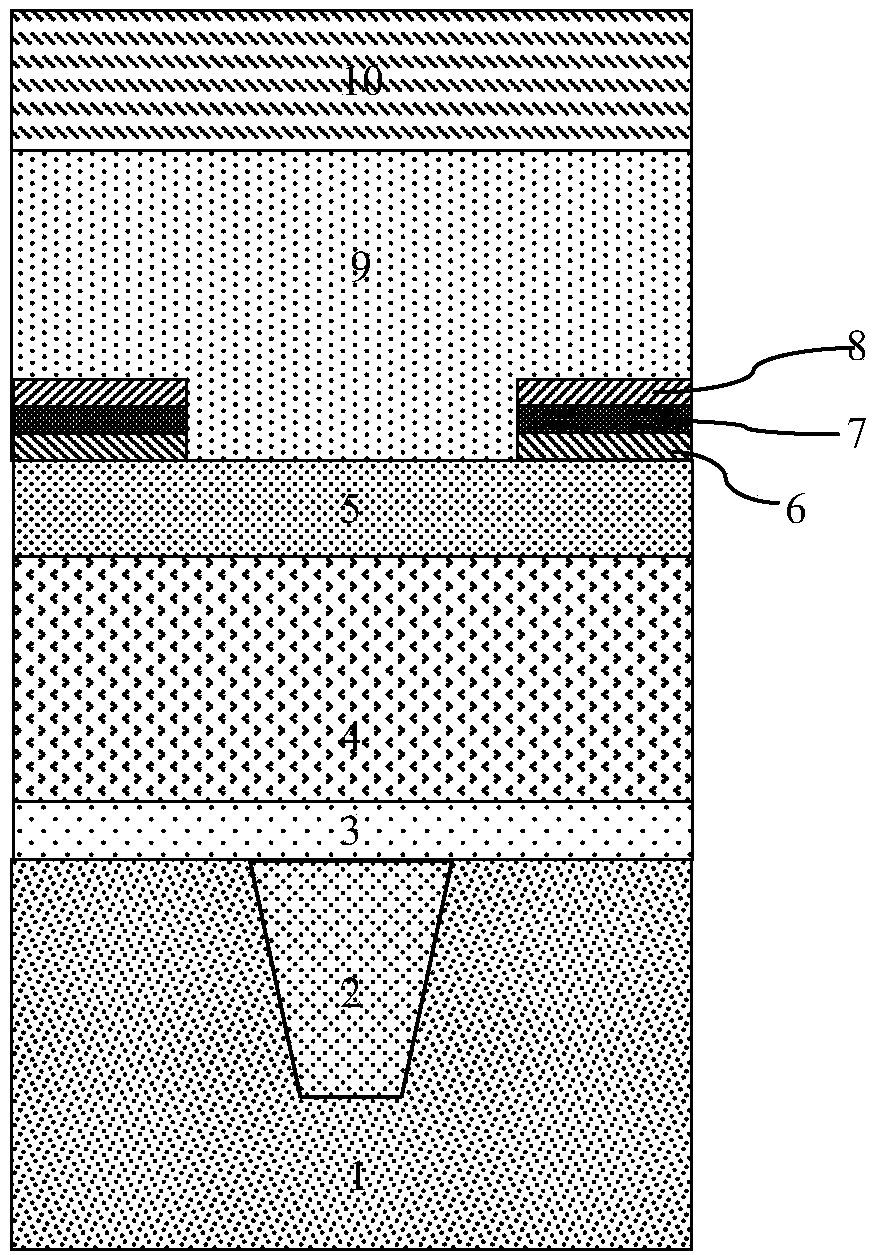

Rework method for dual damascene through-hole technology

ActiveCN108565216AEasy to monitorReduce rework processSemiconductor/solid-state device manufacturingLithographic artistDry etching

The invention discloses a rework method for a dual damascene through-hole technology. The method comprises the following steps that 1, a through hole of the damascene runs through a first low K dielectric layer, a second DARC layer is formed on the first low K dielectric layer, and a graphical third metal hard mask layer is formed on the surface of the second DARC layer; the second DARC layer withthe third metal hard mask layer is coated with a coating-based three-layer structure which is formed by overlaying an ODL layer, an SHB layer and a PR layer and used for defining the through hole; 2,lithography development of the through hole is performed; 3, detection is preformed after development is performed, after development is performed, when detection is out of the range, the rework technology of removing the three-layer structure is performed; in the rework technology, the PR layer, the SHB layer and the ODL layer are removed by adopting a dry etching technology and sequentially removed in the same dry etching equipment. Accordingly, the steps of the rework technology can be reduced, and the rework efficiency and quality are improved.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

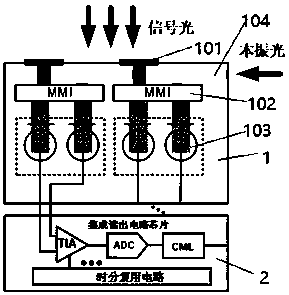

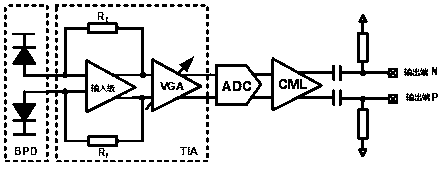

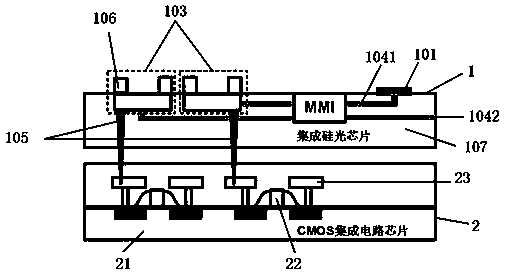

Receiving device based on waveguide balance detector and integration method thereof

ActiveCN111508949AHighly integratedHigh detection sensitivityWave based measurement systemsSolid-state devicesCMOSHemt circuits

The embodiment of the invention provides a receiving device based on a waveguide balance detector and an integration method thereof, and the device comprises: an integrated silicon optical chip whichis used for receiving space signal light and local oscillation light, and obtaining a group of differential optical current signals through photoelectric conversion; a reading circuit chip which is used for converting the differential optical current signal into a digital voltage signal; and an integrated silicon optical chip which comprises a passive silicon optical device and an active waveguidebalance detector, wherein the integrated silicon optical chip and the readout circuit chip are interconnected and integrated in a three-dimensional stacking mode through silicon through holes. The receiving device based on the waveguide balance detector has the advantages of being high in integration degree, high in detection sensitivity, high in signal-to-noise ratio, capable of being expanded to a large view field and the like, three-dimensional integration of the integrated silicon optical chip and the CMOS integrated reading circuit chip is achieved through the silicon through hole technology, the size is small, the structure is simple, optical loss is small, and adjustment difficulty is low.

Owner:INFORMATION SCI RES INST OF CETC

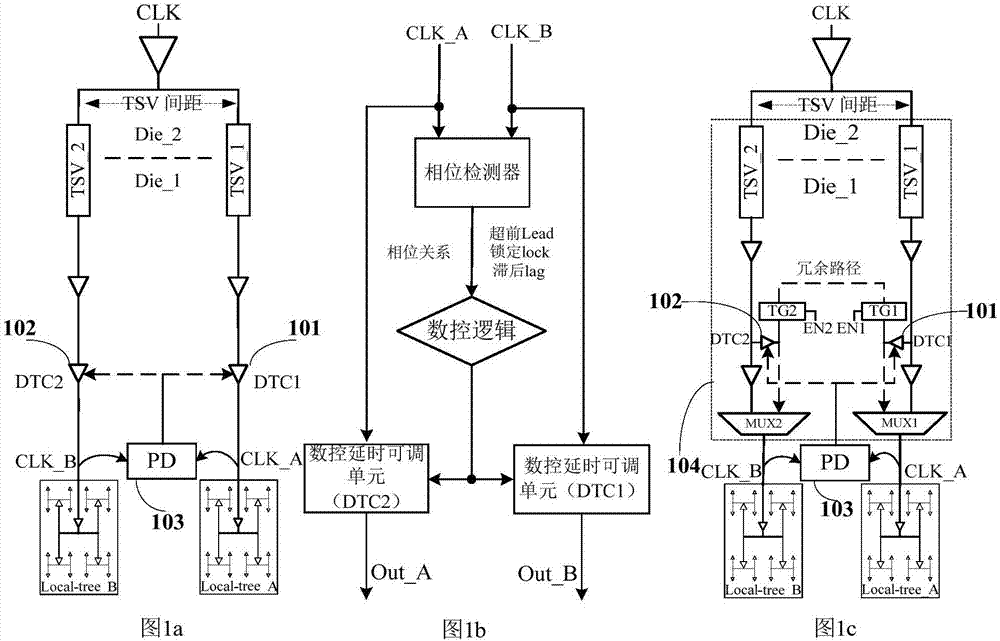

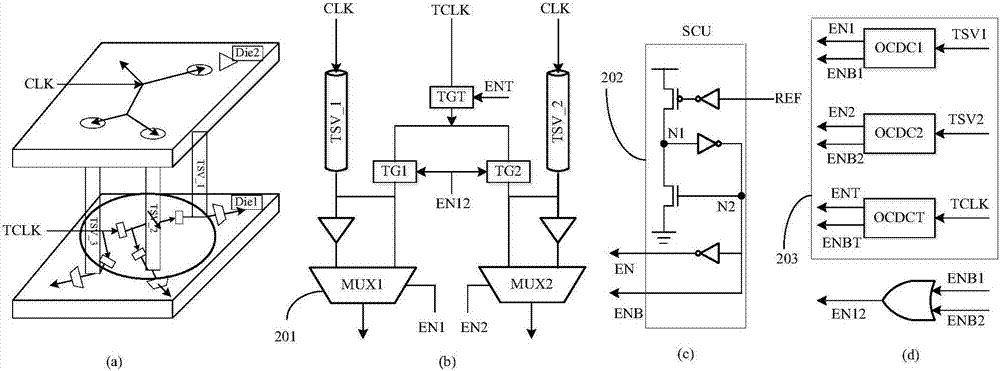

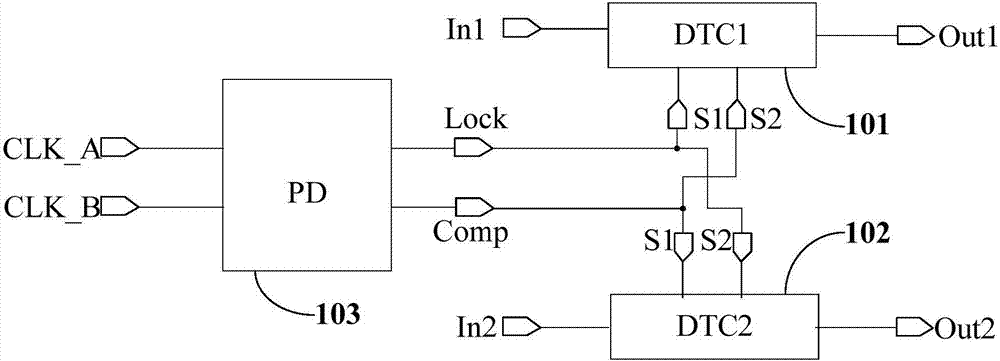

Three-dimensional clock deviation compensation method based on silicon through hole technology and apparatus thereof

InactiveCN106888008ASpacing free expansionSolve the problem of clock skew caused by delay mismatchContinuous to patterned pulse manipulationNumerical controlFault tolerance

The invention provides a three-dimensional clock deviation compensation method which can be used to rapidly optimize and carry out high precision fine tuning on clock path delay and an apparatus thereof. The apparatus mainly comprises a phase detector and a numerical control time-delay adjustable unit. The method is used to mainly carry out clock deviation compensation on two three-dimensional clock paths whose delay is not matched in a three-dimensional integrated circuit chip. In the invention, a three-dimensional clock path deviation problem without considering clock TSV fault tolerance can be solved and a clock deviation problem generated because three-dimensional clock path delay is not matched after the clock TSV fault tolerance is considered can be solved too. The method and the apparatus are used to solve the clock deviation problem generated because the clock path delay is not matched in a three-dimensional integrated circuit clock network, which is good for ensuring high reliability of a three-dimensional clock network and increasing a yield of the three-dimensional integrated circuit chip.

Owner:NAT UNIV OF DEFENSE TECH

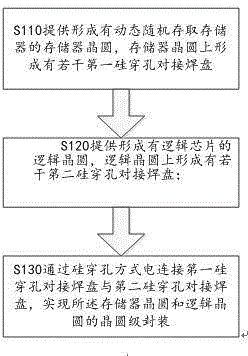

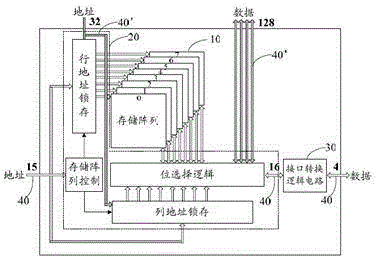

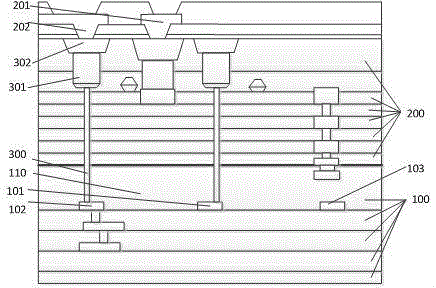

Semiconductor package method, semiconductor package piece, and method for manufacturing dynamic random access memory

InactiveCN105826274AImprove read and write speedSmall sizeSemiconductor/solid-state device detailsSolid-state devicesElectricityStatic random-access memory

The present invention provides a semiconductor package method which comprises a step of providing a memory wafer with the formation of a dynamic random access memory and a plurality of first silicon through hole connection pads, a step of providing a logic wafer with the formation of a logic chip and a plurality of second silicon through hole connection pads, and a step of electrically connecting the first silicon through hole connection pads and the second silicon through hole connection pads through a silicon through hole mode, and realizing the wafer level package of the memory wafer and the logic wafer. A super wide bus is directly connected to the silicon through hole connection pads on the metal layer of a surface, the electrical connection with an external logic wafer is realized through the silicon through hole technology, and the reading and writing bit width and reading and writing speed of the dynamic random access memory are extended.

Owner:GALAXYCORE SHANGHAI

Wilkinson power divider based on glass through hole technology

The invention discloses a Wilkinson power divider based on a glass through hole technology. The Wilkinson power divider comprises a parallel plate condenser unit, a rewiring layer, three-dimensional solenoid inductor units and an isolating resistor; the power divider is composed of a reactance network consisting of lumped parameter elements, the three-dimensional solenoid inductor units and the parallel plate condenser unit which are compact in structure and low in loss are adopted, solenoid inductors passing through a glass substrate are taken as the lumped parameter elements of the power divider, the solenoid inductors take full advantage of the characteristics of glass through hole vertical arrangement and low electric loss, the power divider is small in area, large in inductance valueand low in loss, and the dimensions of the power divider are greatly decreased; the volume of the power divider is greatly reduced, and the performance of the power divider is guaranteed while the integration level of the circuit is improved. According to the power divider disclosed by the invention, input signal power can be halved into two output ports, the power divider has the advantages of low power loss, high port isolation, small phase difference, compact dimensions and the like, and the power divider is particularly applicable for micro three-dimensional heterogeneous integration packaging.

Owner:NINGBO UNIV

Packaging structure of MEMS (Micro Electro Mechanical Systems) chip integration

InactiveCN106335868AAvoid oversized requirementsSmall sizeSolid-state devicesFluid speed measurementLead bondingParasitic capacitance

The invention discloses a packaging structure of MEMS (Micro Electro Mechanical Systems) chip integration. On an ASIC (Application Specific Integrated Circuit) chip, a silicon through hole is manufactured to lead signal output on the front side of the ASIC chip to the back surface of the ASIC chip, and the electrical interconnection of the ASIC chip and a base plate is realized through a metal re-wiring layer and solder bumps on the back surface. According to the way, a signal transmission path is reduced, meanwhile, a phenomenon that a lead bonding connection way requires an overlarge base plate area is avoided, and the size of the packaging structure is reduced. The front side of the MEMS chip and the front side of the ASIC chip are electrically connected directly through a metal lead to guarantee the minimum path of signal transmission and avoid introducing stray capacitance. Or a silicon through hole technology is used for leading the signal output on the front side of the MEMS chip to the back surface of the MEMS chip, then the electric interconnection of the MEMS chip and the ASIC chip is realized through the metal re-wiring layer and the solder bumps, furthermore, the signal transmission path is reduced, and the connection way of lead bonding is completely avoided so as to further reduce the size of the packaging structure of the chip.

Owner:GOERTEK INC

Silicon through hole technology

InactiveCN102376642AImprove reliabilityGood removal effectSemiconductor/solid-state device manufacturingInsulation layerCopper

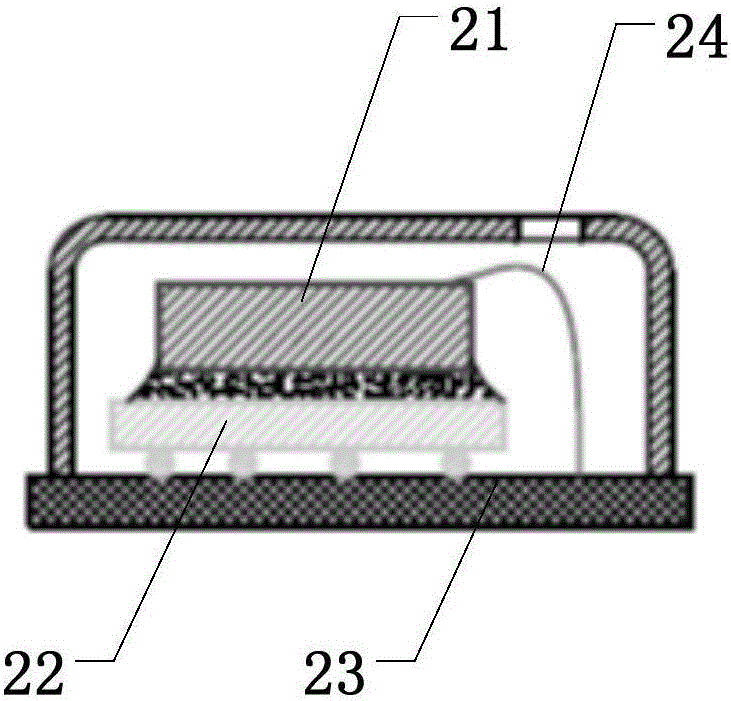

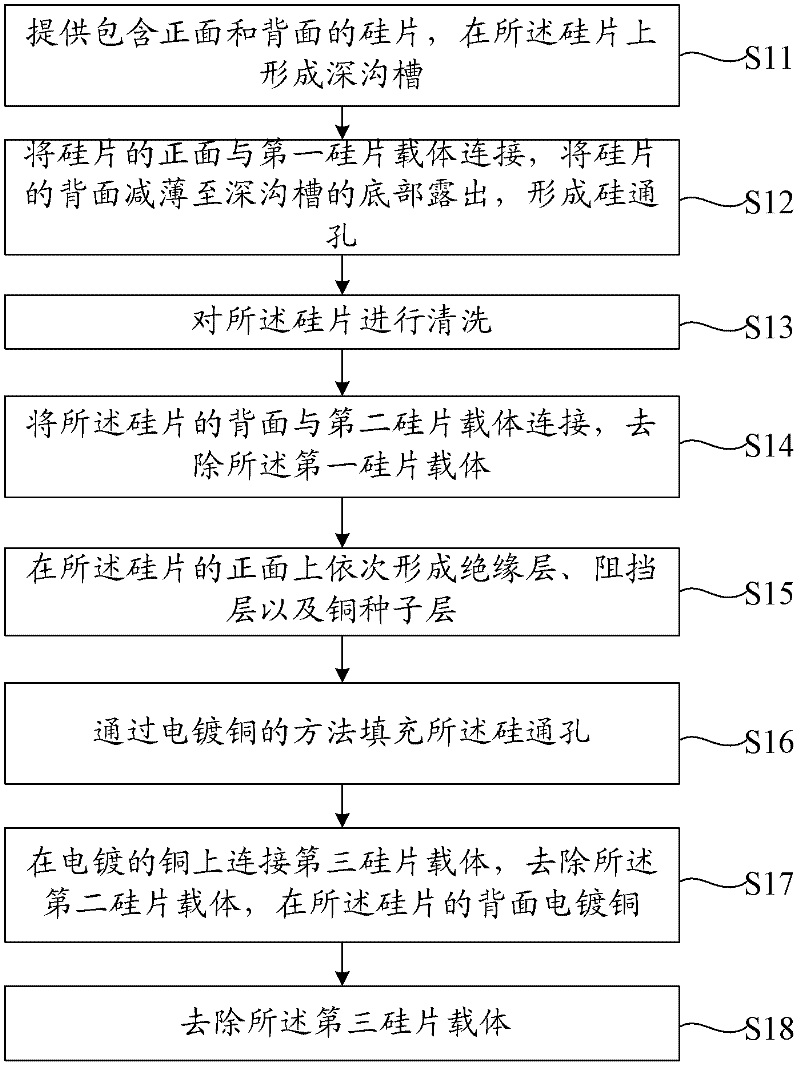

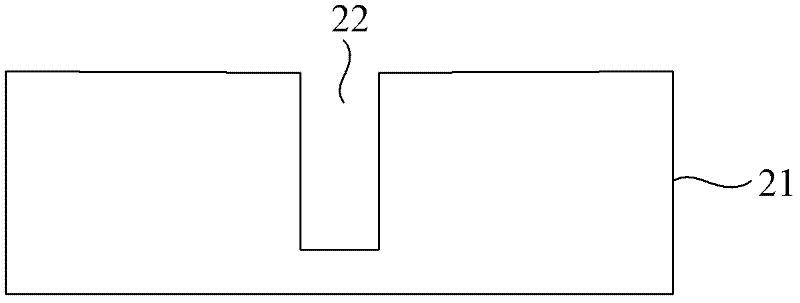

The invention provides a silicon through hole technology comprising the steps of: providing a silicon slice with a front surface and a back surface, wherein a deep slot is formed on the silicon slice; connecting the front surface of the silicon slice with a first silicon slice carrier, thinning the back surface of the silicon slice until the bottom of the deep slot is exposed so as to form a silicon through hole; cleaning the silicon slice; connecting the back surface of the silicon slice with a second silicon slice carrier, and removing the first silicon slice carrier; sequentially forming an insulation layer, a barrier layer and a copper seed layer on the front surface of the silicon slice; filling the silicon through hole by electroplating copper; connecting a third silicon carrier on the electroplated copper, removing the second silicon carrier, and electroplating copper on the back surface of the silicon slice; and removing the third silicon slice carrier. According to the silicon through hole technology provided by the invention, the back surface of the silicon slice is thinned until the bottom of the deep slot is exposed so as to form the silicon through hole, and the silicon slice is cleaned so as to remove polymer and particles in the through hole much better, therefore, the reliability of the silicon through hole is enhanced, and finally the product yield is increased.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

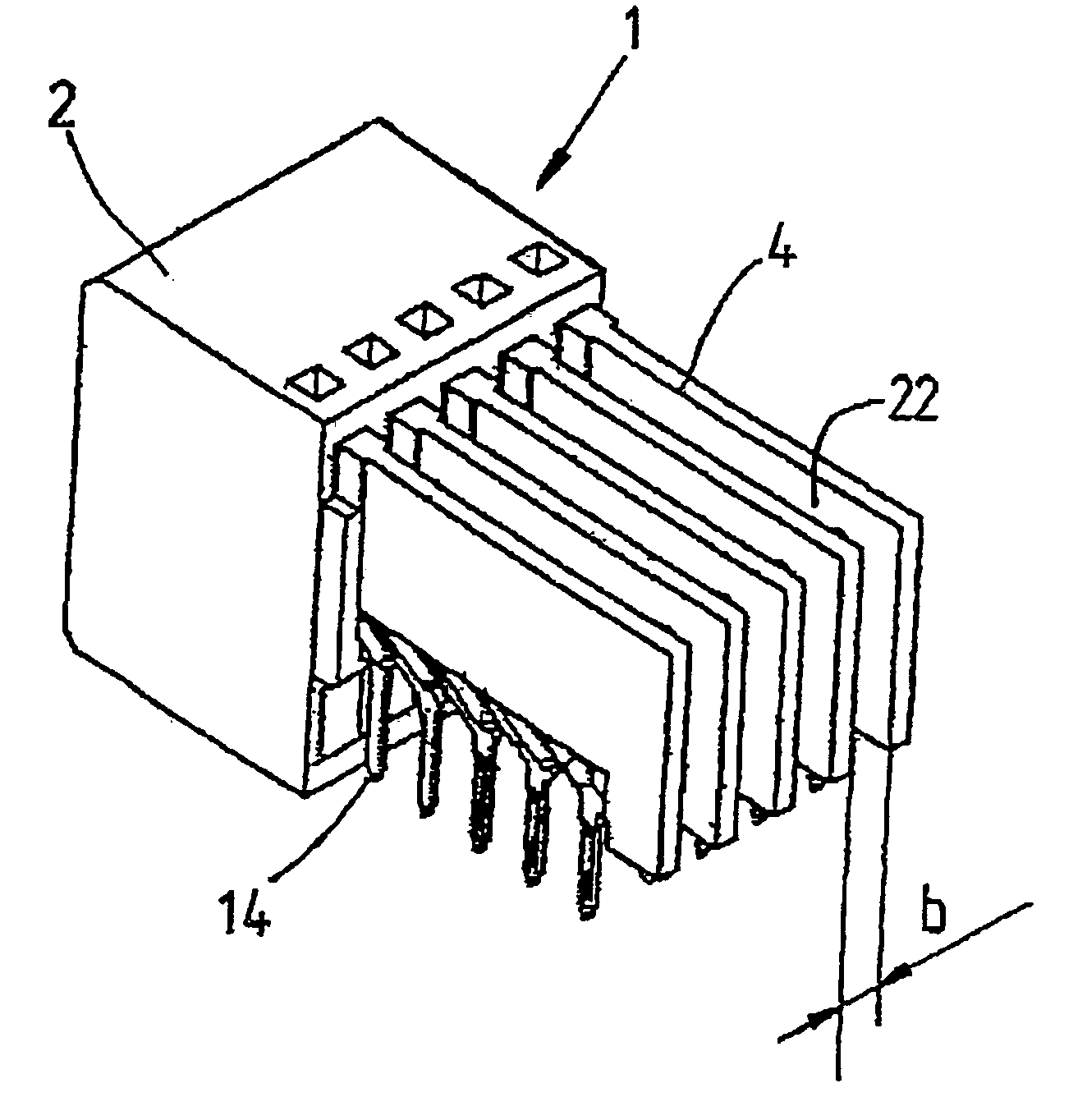

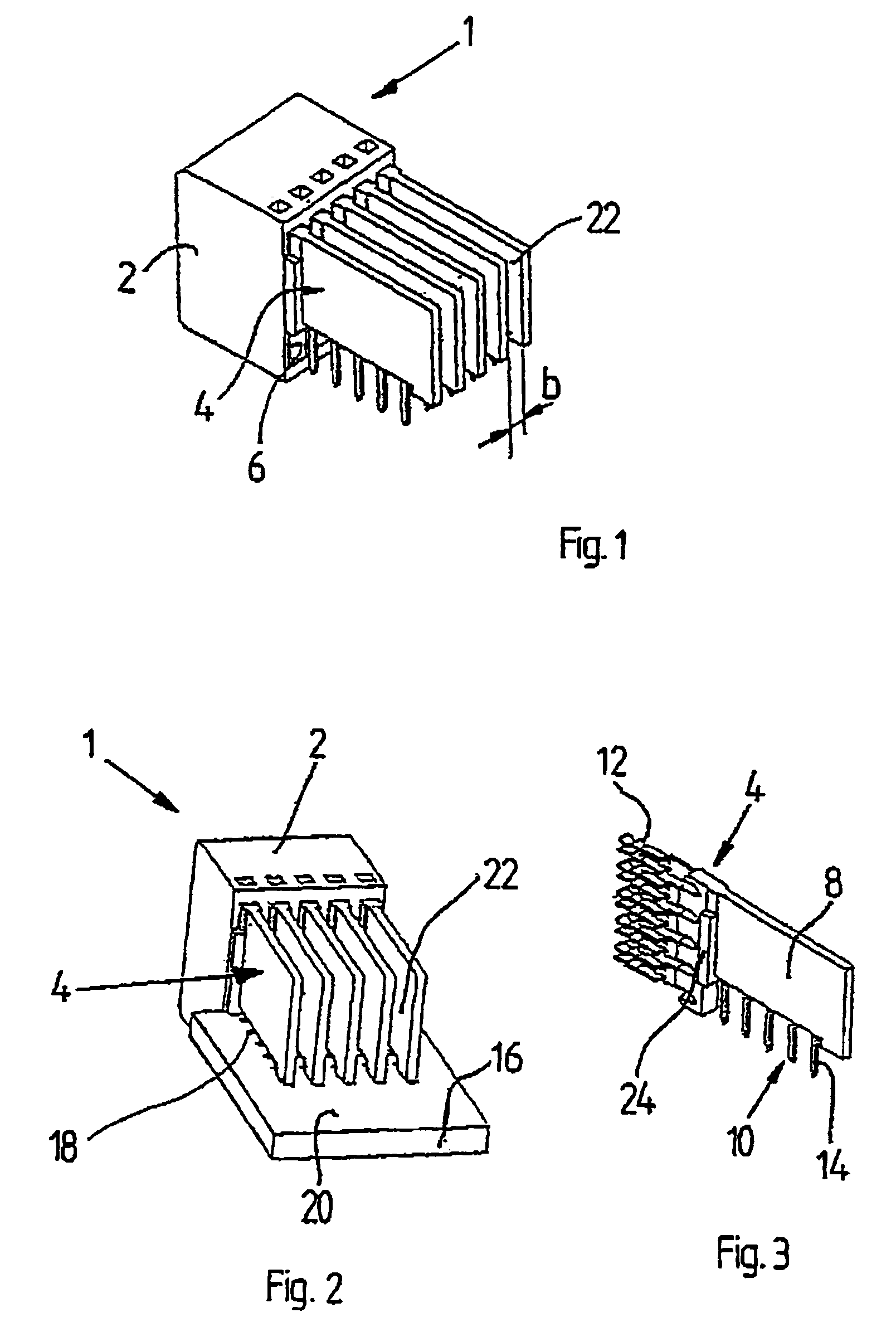

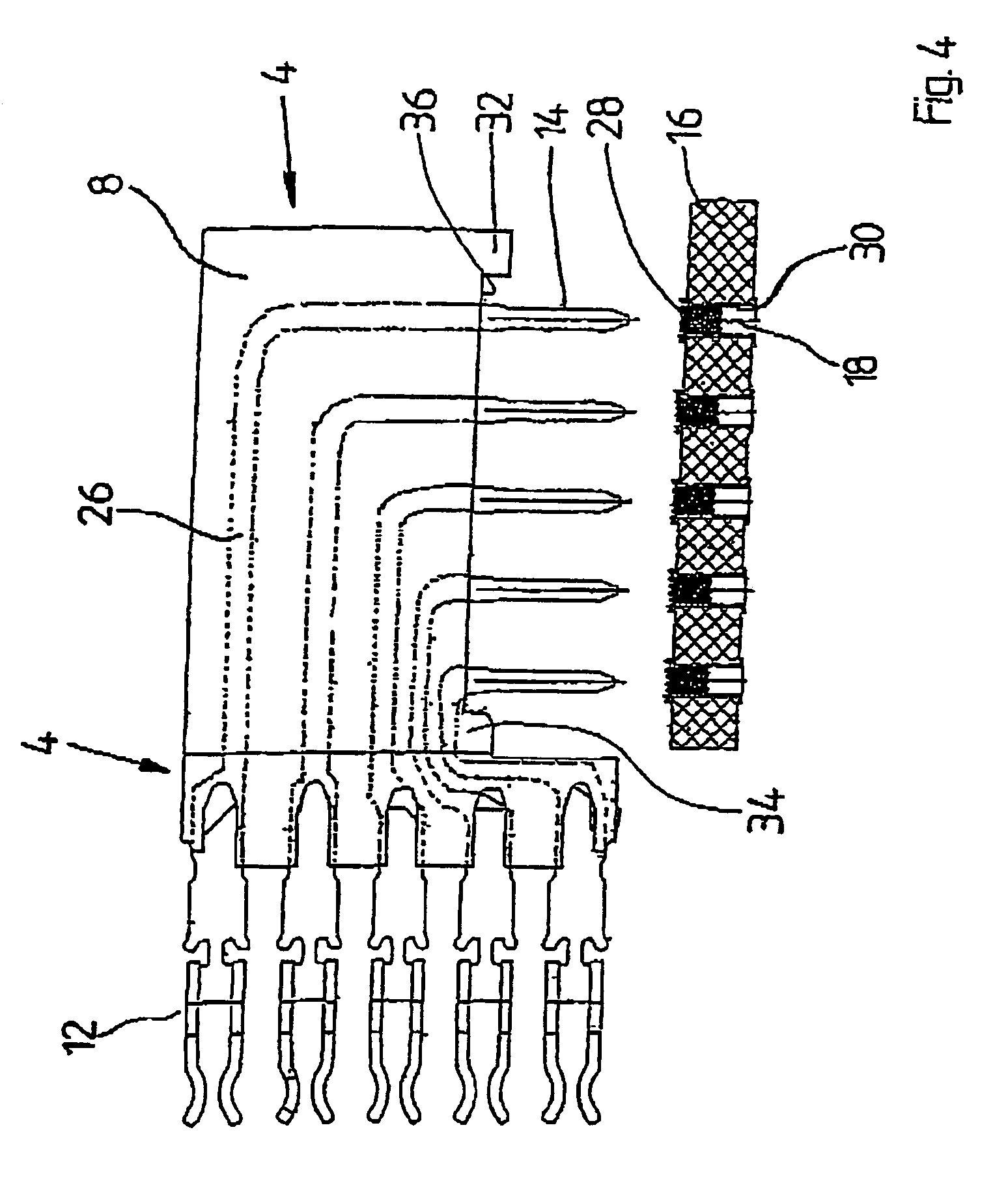

Connector

InactiveUS7018243B2Fast heat conductionIncrease the heat exchange areaPrinted circuit assemblingCoupling device detailsTransport mediumEngineering

What is disclosed is a plug-in connector in through-hole technology that is suited for the surface soldering technique. The plug-in connector includes an insulating carrier part wherein a multiplicity of wafers each having soldering tags and contact terminals are inserted. In accordance with the invention, the wafers are placed at a distance from each other, whereby flow channels for supplying the heat transport medium, e.g. air, are created. In an advantageous alternative or additional development of the invention, there is formed in the range of the feedthrough a flow space permitting a flow of the heat transport medium perpendicularly to the plane of the platelets. This passage may be formed by a recess of the insulating material or by suitable spacer elements.

Owner:EPT

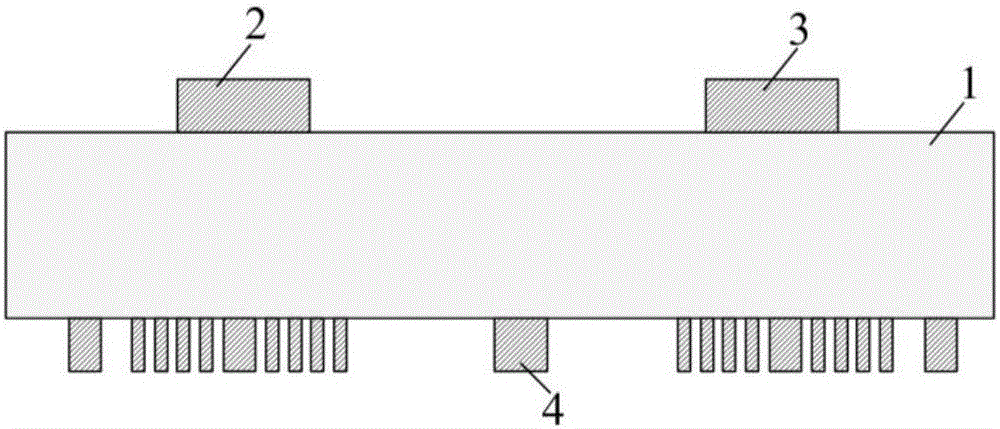

Temperature difference type wind speed sensor, preparation method thereof and wind speed detecting method

ActiveCN106814212ALarge temperature differenceHigh sensitivityFluid speed measurement using thermal variablesCeramic substrateWire bonding

The invention provides a temperature difference type wind speed sensor which comprises the components of a ceramic substrate, a heating element which is configured on the ceramic substrate, at least two sets of temperature sensing elements which are configured on the front surface of the ceramic substrate and are arranged around the heating element in a central symmetry manner, and at least two sets of temperature measuring elements which are configured on the back surface of the ceramic substrate and correspond with the positions of the temperature sensing elements. Furthermore the heating element is configured on the back surface of the ceramic substrate and performs heating through application of DC power. The temperature sensing elements are metal blocks, and the temperature measuring elements are inductance coils. The invention further discloses a preparation method of the temperature difference type wind speed sensor, and a wind speed detecting method based on the temperature difference type wind speed sensor. The temperature difference type wind speed sensor with the structure has advantages of realizing wind speed detection for positive-direction wind, improving sensitivity of the wind speed sensor, reducing power consumption, preventing wire bonding technology and substrate through hole technology, and realizing low cost and easy industrial production.

Owner:SOUTHEAST UNIV

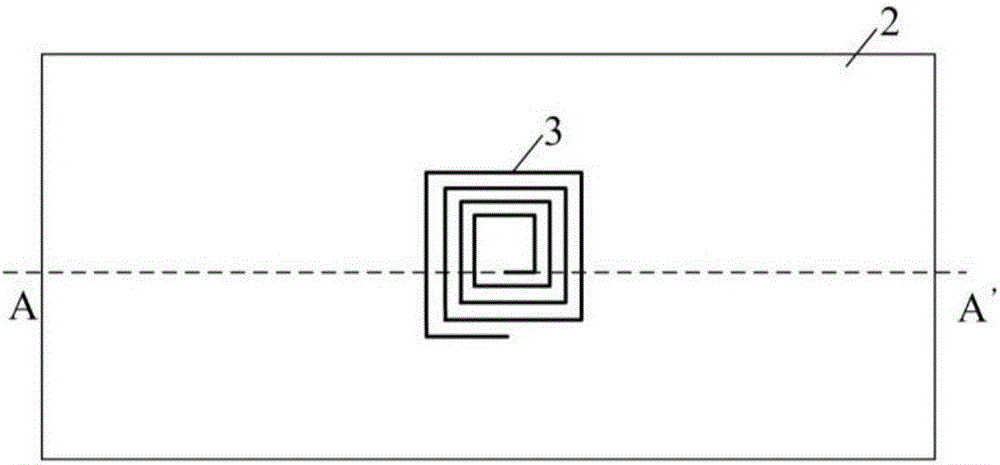

Thermal loss type air velocity sensor and preparation method and detection method thereof

ActiveCN106771339AHigh sensitivityReduce power consumptionFluid speed measurement using thermal variablesThin layerClosed loop

The invention discloses a thermal loss type air velocity sensor which comprises an insulating substrate, a heating inductive coil and a radiation inductive coil, wherein the heating inductive coil is arranged on the back side of the insulating substrate, and the radiation inductive coil is arranged on the front side of the insulating substrate and is right opposite to the position of the heating inductive coil; a silicon dioxide layer is arranged on the front side of the insulating substrate, and two end terminals of the heating inductive coil are connected in the silicon dioxide thin layer so as to form a closed loop circuit. At the same time, the invention further discloses a preparation method of the thermal loss type air velocity sensor and an air velocity detection method based on the thermal loss type air velocity sensor. Front side air sensing is realized, the sensitivity of the air velocity sensor is improved, and power consumption of the air velocity sensor is reduced; the lead problem is solved by the interreaction of the inductive coils on the front side and the back side, front side wireless heating and wireless temperature measuring are realized, and the bonding wire technology and the substrate through-hole technology are avoided.

Owner:SOUTHEAST UNIV