Packaging structure of MEMS (Micro Electro Mechanical Systems) chip integration

A packaging structure, ASIC chip technology, applied in the field of chip packaging, can solve the problems of large package size and signal input path product performance degradation, and achieve the effect of reducing size, reducing signal transmission path, and avoiding excessive substrate area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

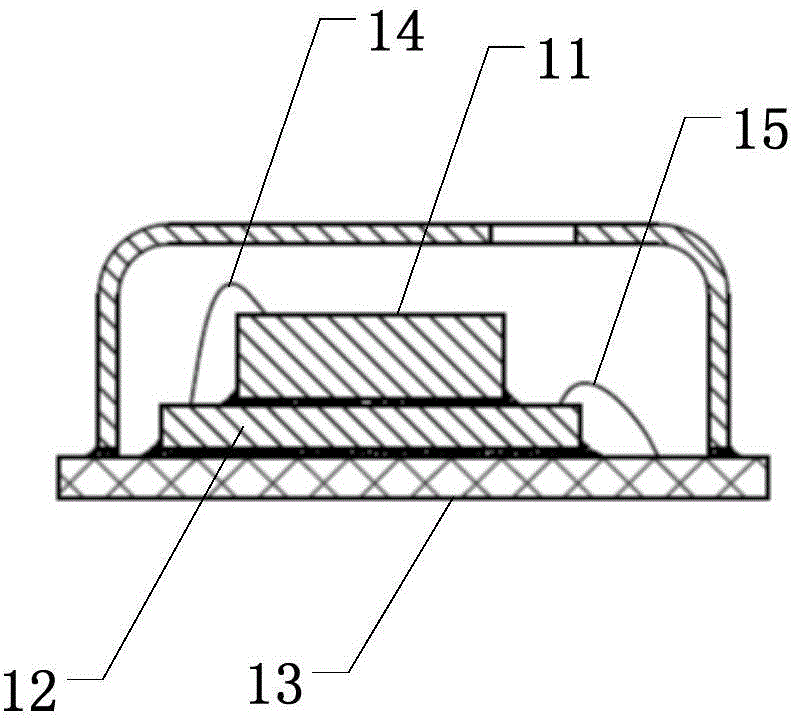

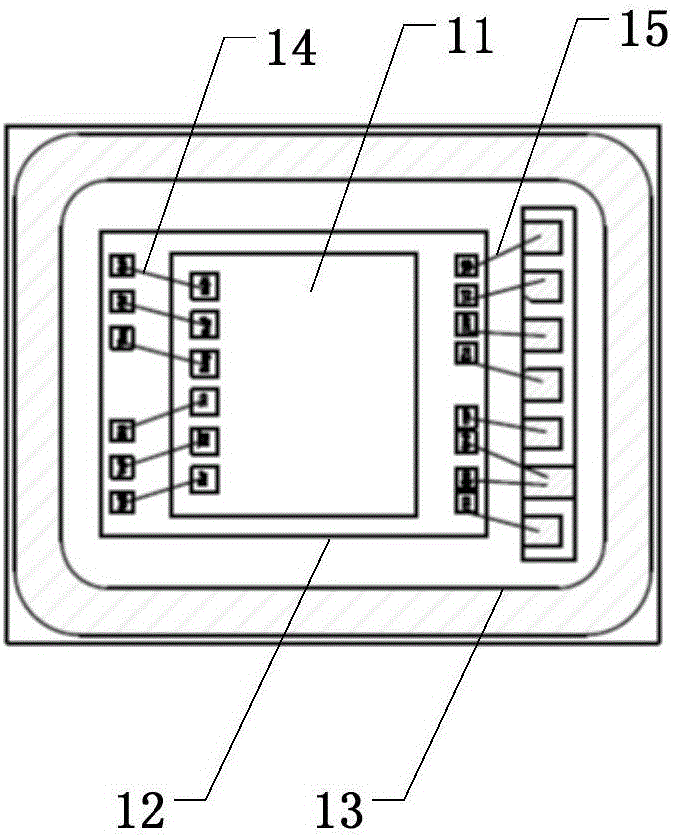

[0032] Embodiments of the present invention provide a MEMS chip integrated packaging structure, such as Figure 5 and Figure 6 As shown, the packaging structure includes: a substrate 33, a MEMS chip 31 and an ASIC chip 32, the MEMS chip 31 is arranged on the ASIC chip 32 in a stacked manner, the back of the ASIC chip 32 faces the substrate 33, and the back of the MEMS chip 31 faces The front side of the ASIC chip 32 .

[0033] The back side of the MEMS chip 31 and the front side of the ASIC chip 32 are mechanically connected by a patch adhesive layer. Both the front side of the MEMS chip 31 and the front side of the ASIC chip 32 have soldering pads 35, and the soldering pads 35 of the MEMS chip 31 and the soldering pads 35 of the ASIC chip 32 are A metal wire 34 is arranged between them to realize the electrical interconnection between the signal input of the ASIC chip 32 and the signal output of the MEMS chip 31, so that the signal of the MEMS chip 31 is output to the ASIC ...

Embodiment 2

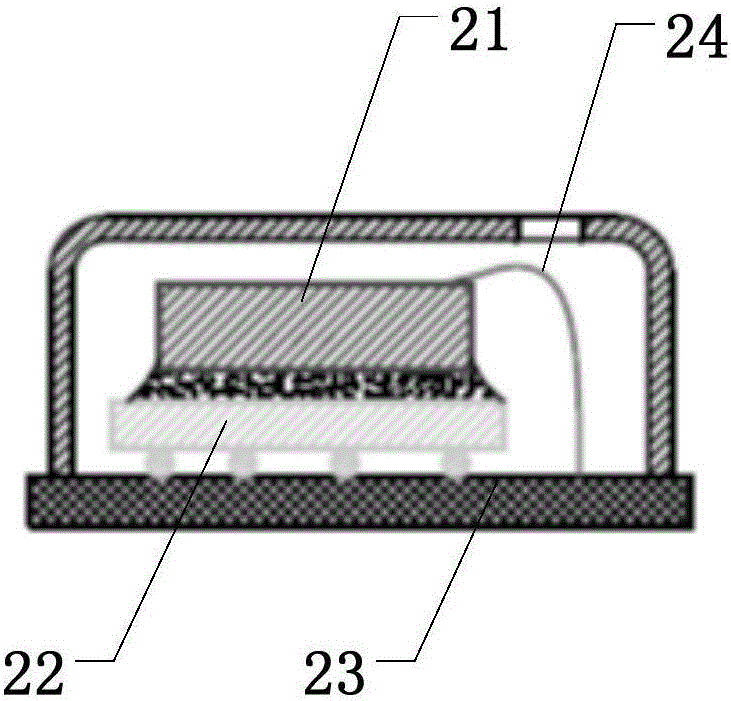

[0039] Such as Figure 7As shown, in the embodiment of the present invention, a number of TSVs 44 are formed on the MEMS chip 41, and the signal output on the front side of the MEMS chip 41 is guided to the back side through the TSVs 44; the back side of the MEMS chip 41 has a metal rewiring layer (not shown in the figure) and solder bumps 45 , the electrical interconnection between the MEMS chip 41 and the ASIC chip 42 is realized through the metal rewiring layer and the solder bumps 45 .

[0040] The packaging structure of the embodiment of the present invention further includes a plastic sealing layer 48, and the material of the plastic sealing layer 48 is a polymer or a film. The plastic encapsulation layer 48 covers the ASIC chip 42 and the MEMS chip 41 , fills the gap between the MEMS chip 41 and the ASIC chip 42 , and connects the ASIC chip 42 and the MEMS chip 41 together. During plastic sealing, care should be taken to protect the sensitive part of the chip from bein...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More