A/D converter circuit and solid-state imaging device

A technology for converting circuits and circuits, applied in the direction of analog/digital conversion, code conversion, analog-to-digital converter, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 approach

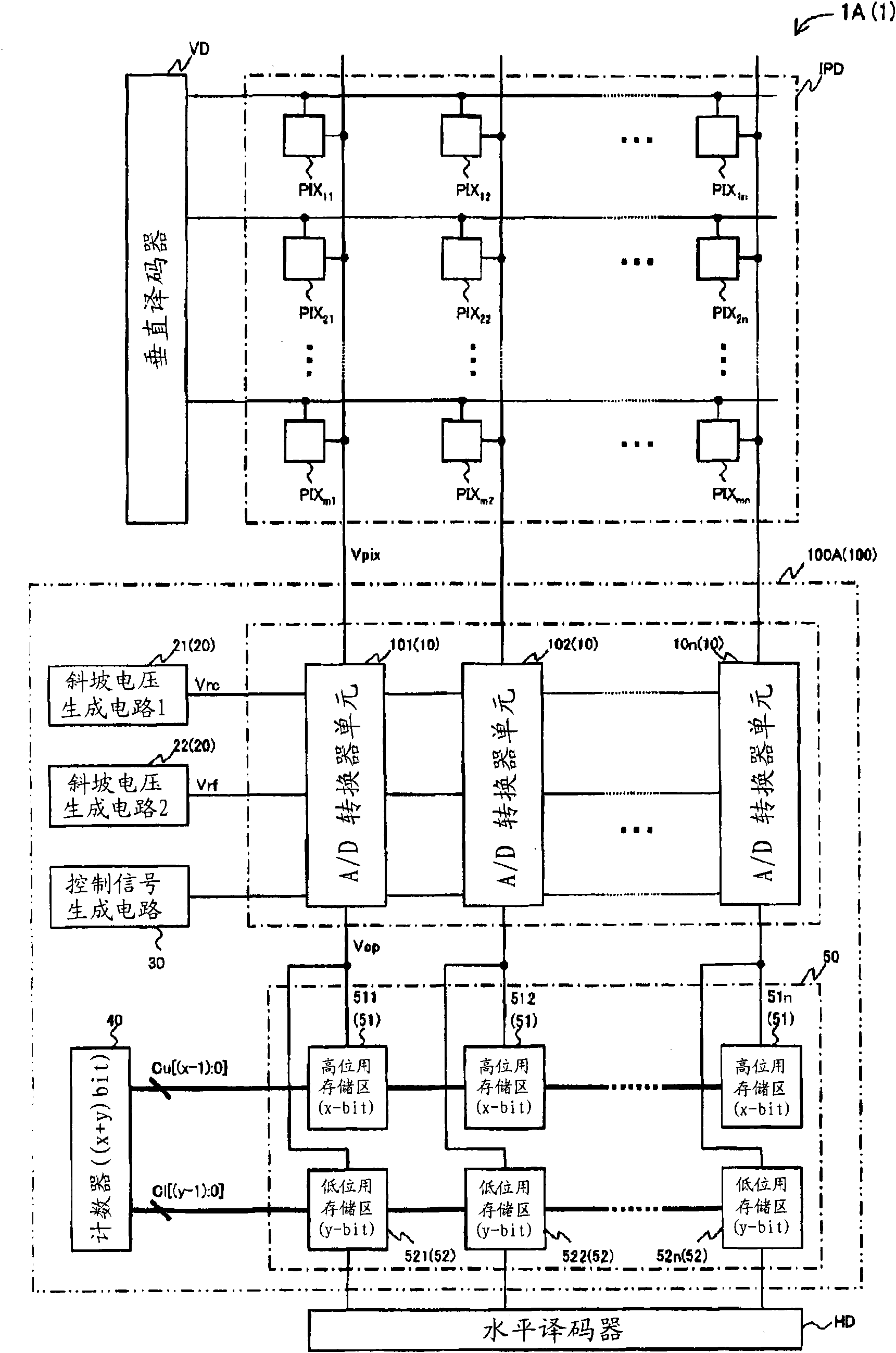

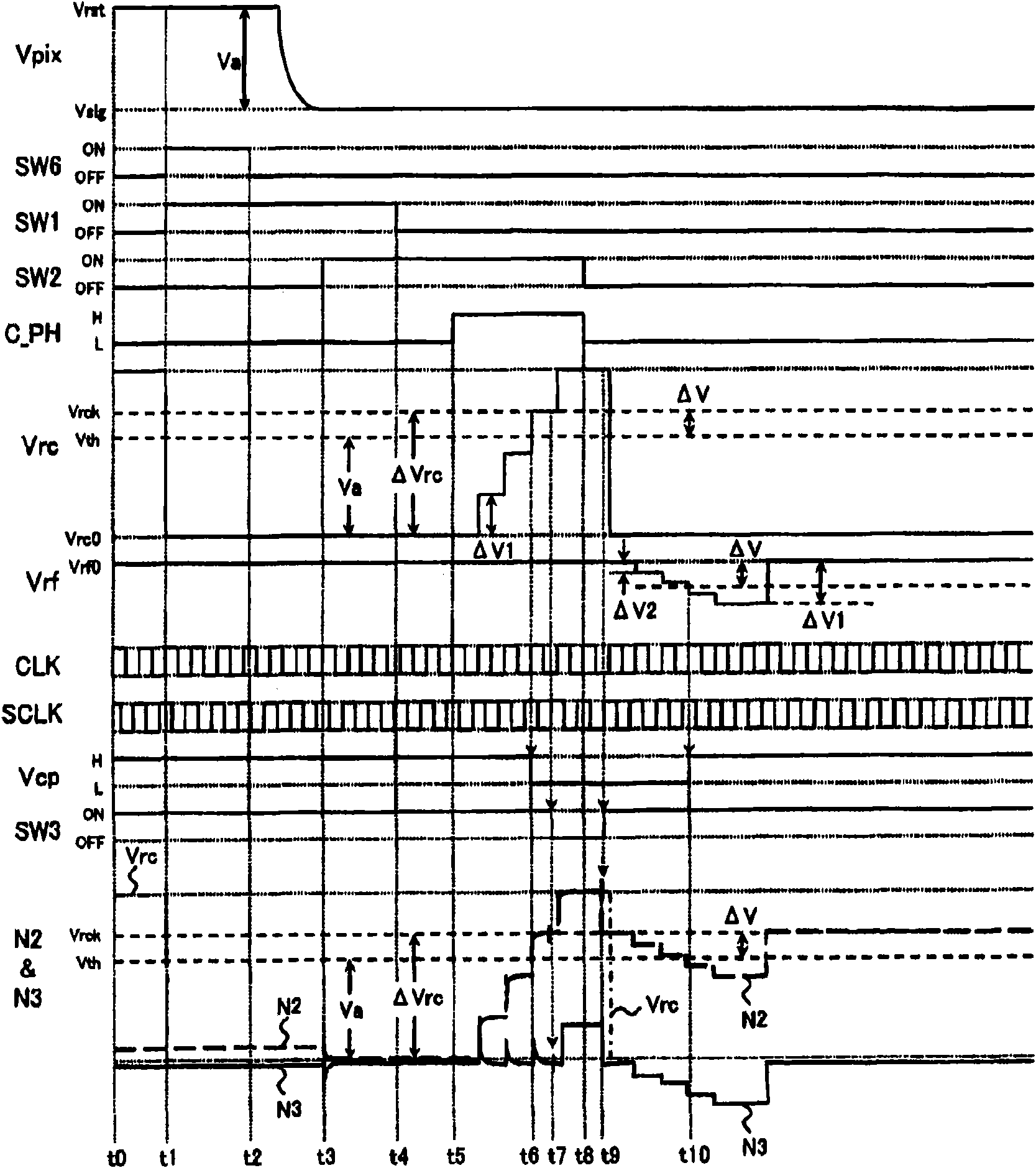

[0133] based on Figure 1 ~ Figure 3 A first embodiment of the circuit of the present invention and the device of the present invention will be described.

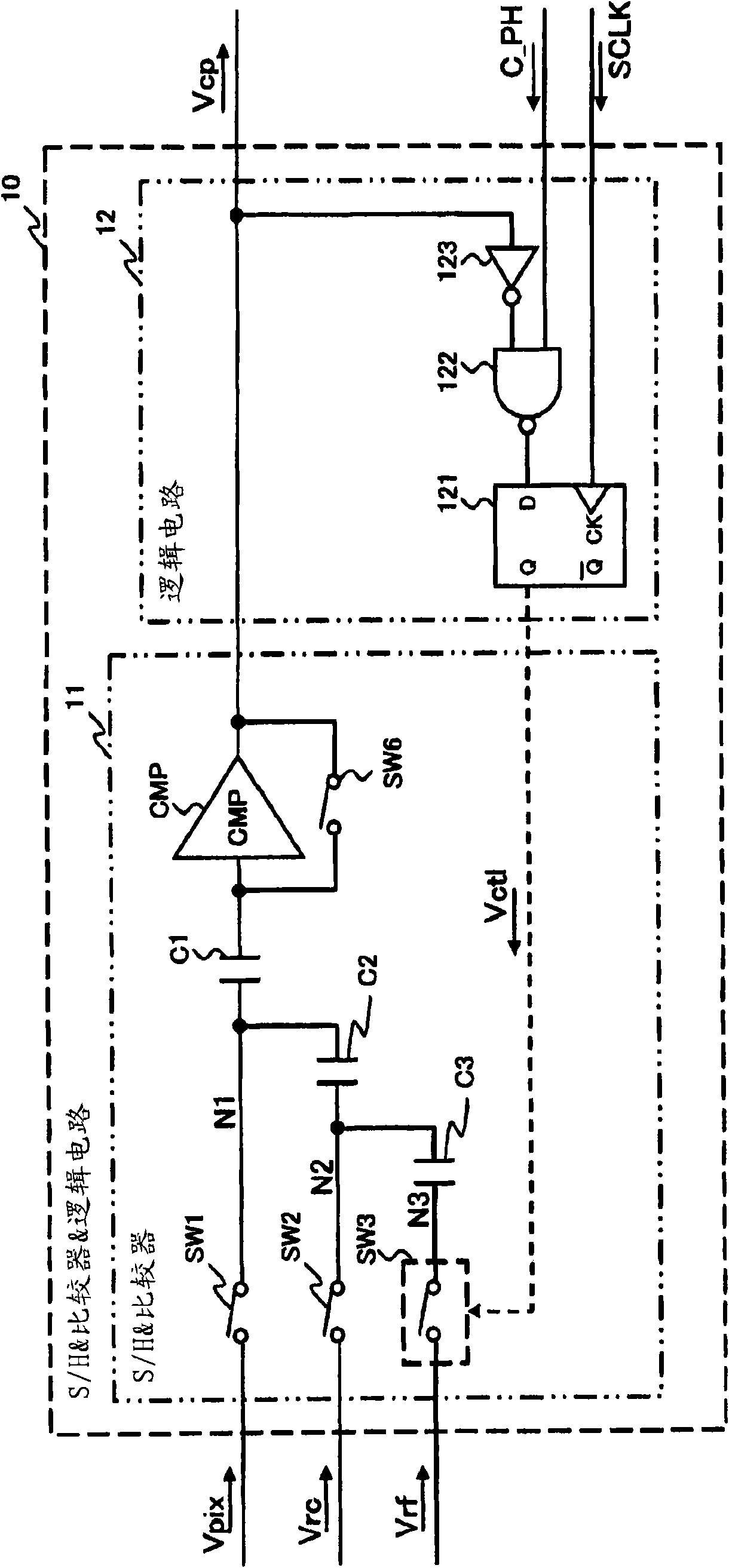

[0134] First, based on figure 1 and figure 2 The structure of the circuit of the present invention and the device of the present invention will be described. here, figure 1 A schematic configuration example of a device 1A of the present invention equipped with a circuit 100A of the present invention is shown, figure 2 A schematic configuration example of the circuit 100A of the present invention according to the present embodiment is shown.

[0135] In addition, the circuit 100A of the present invention is a partitioned A / D conversion circuit that performs a two-stage conversion process of the first conversion process and the second conversion process. The value of a part of consecutive bits including the highest bit in the data; the above-mentioned second conversion process obtains the value of the unconverted bi...

no. 2 approach

[0196] based on Figure 4 ~ Figure 6 A second embodiment of the circuit of the present invention and the device of the present invention will be described. In addition, in this embodiment, the case where the configurations of the A / D conversion unit and the first ramp voltage generating circuit are different from those of the first embodiment described above will be described.

[0197] First, based on Figure 4 and Figure 5 The structure of the circuit of the present invention and the device of the present invention will be described. here, Figure 4 A schematic configuration example of an inventive device 1B equipped with an inventive circuit 100B according to the present embodiment is shown, Figure 5 A schematic configuration example of the circuit 100B of the present invention according to this embodiment is shown.

[0198] like Figure 4 As shown, similarly to the first embodiment, the device 1B of the present invention is configured to include, on the same chip, a...

no. 3 approach

[0237] based on Figure 7 (b) A third embodiment of the circuit of the present invention and the device of the present invention will be described. In addition, in this embodiment, the case where the structure of the 2nd ramp voltage Vrf differs from the said 1st Embodiment and 2nd Embodiment is demonstrated. here, Figure 7 (b) shows the structure of the second ramp voltage Vrf in this embodiment; Figure 7 (a) The second ramp voltage Vrf of the first and second embodiments described above is shown as a comparison object of the second ramp voltage Vrf of the present embodiment.

[0238] First, the structures of the circuit 100A of the present invention and the device 1 of the present invention will be briefly described based on the drawings. like figure 1 As shown, similarly to the first embodiment, the device 1 of the present invention is configured to include, on the same chip, a solid-state imaging device group IPD, and a plurality of A / D conversion units individually...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More