Patents

Literature

158results about How to "High delay accuracy" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

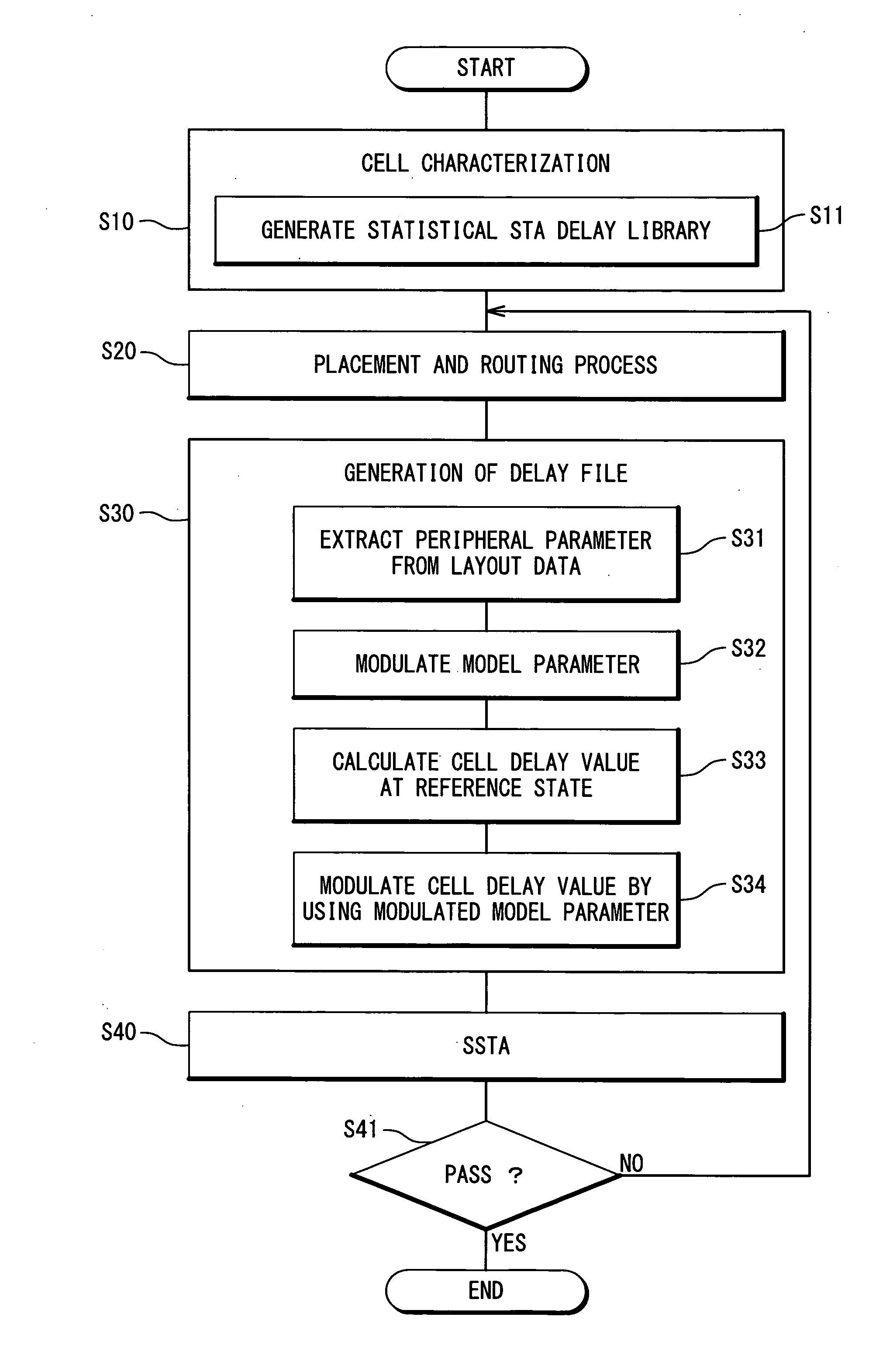

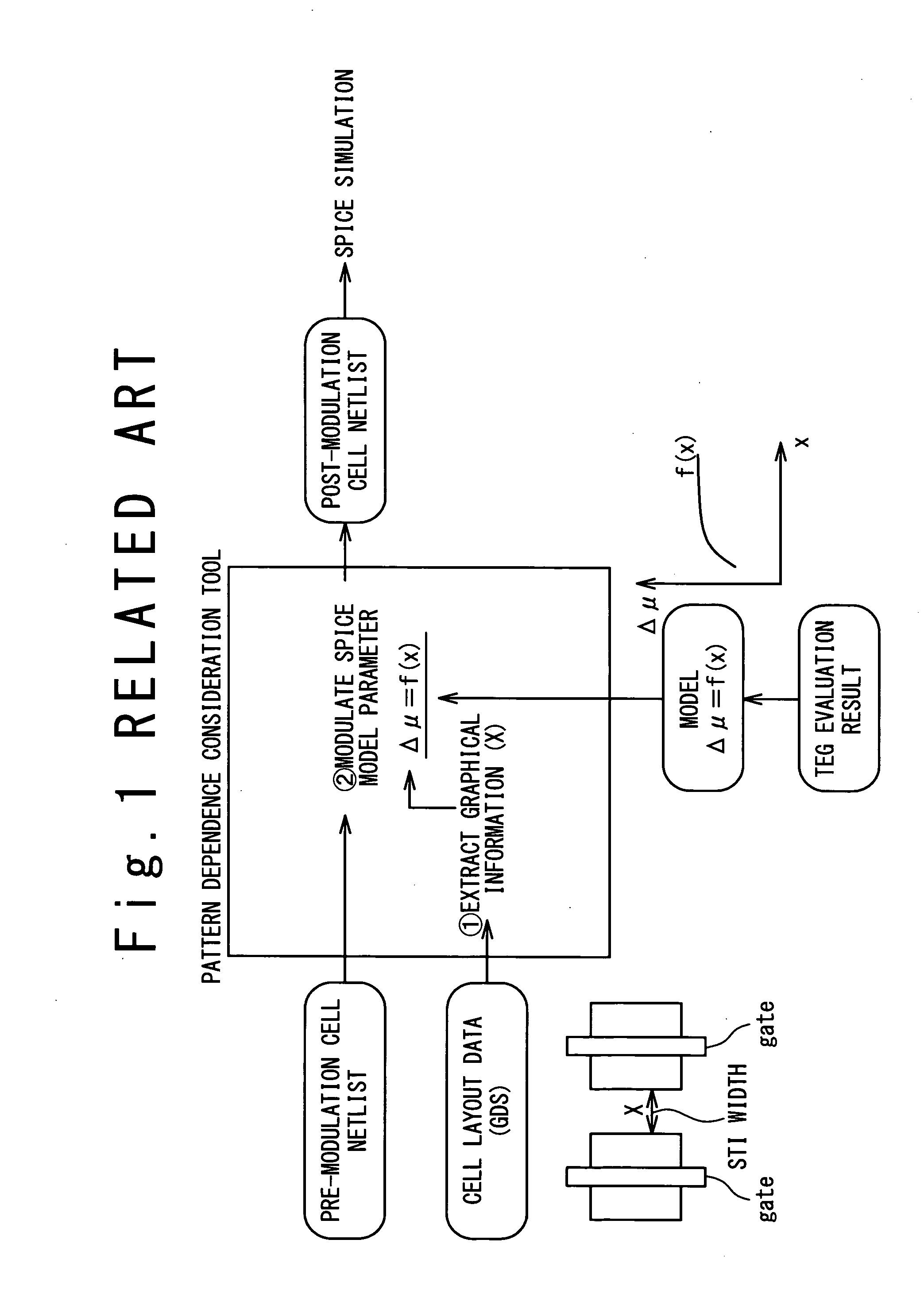

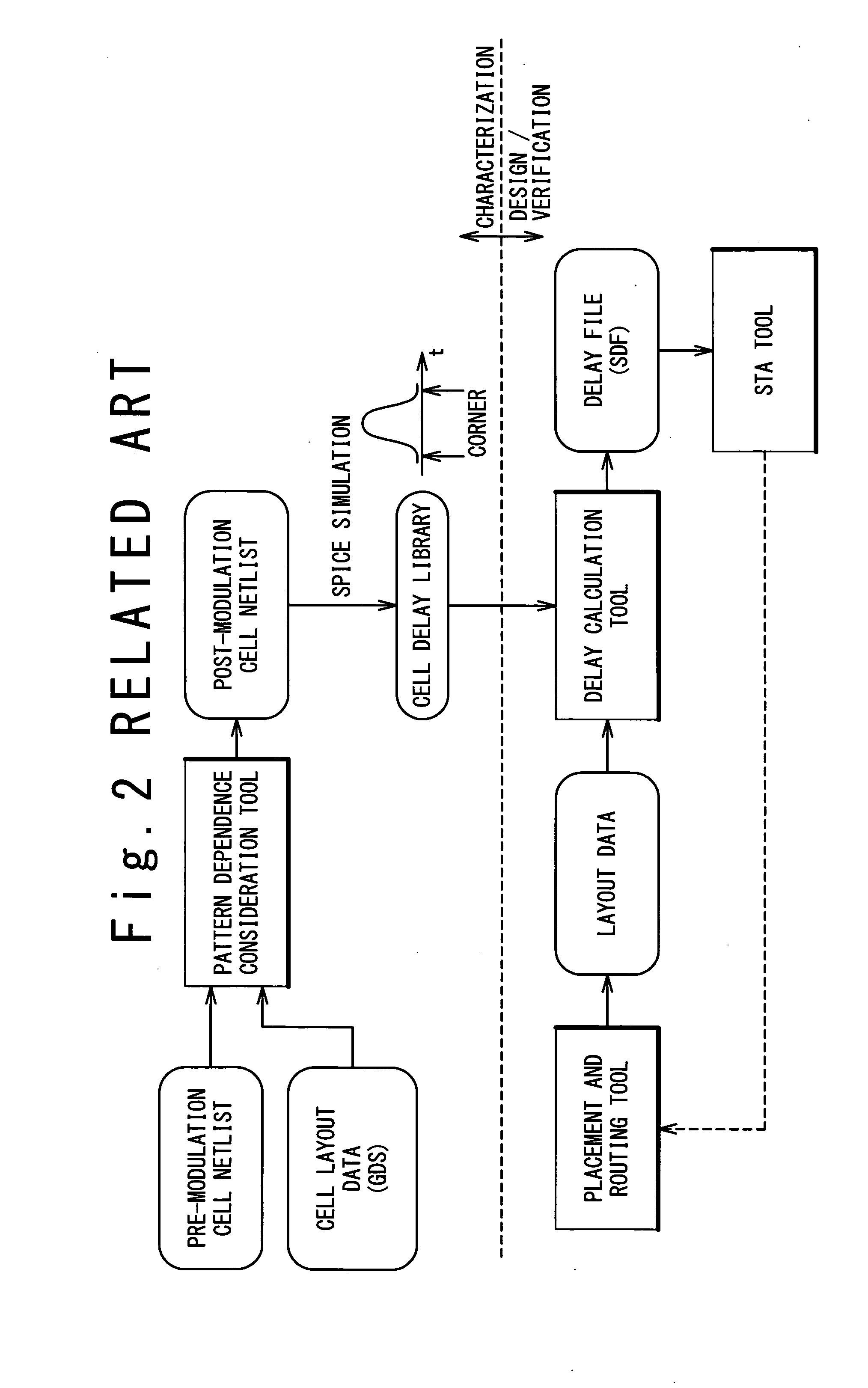

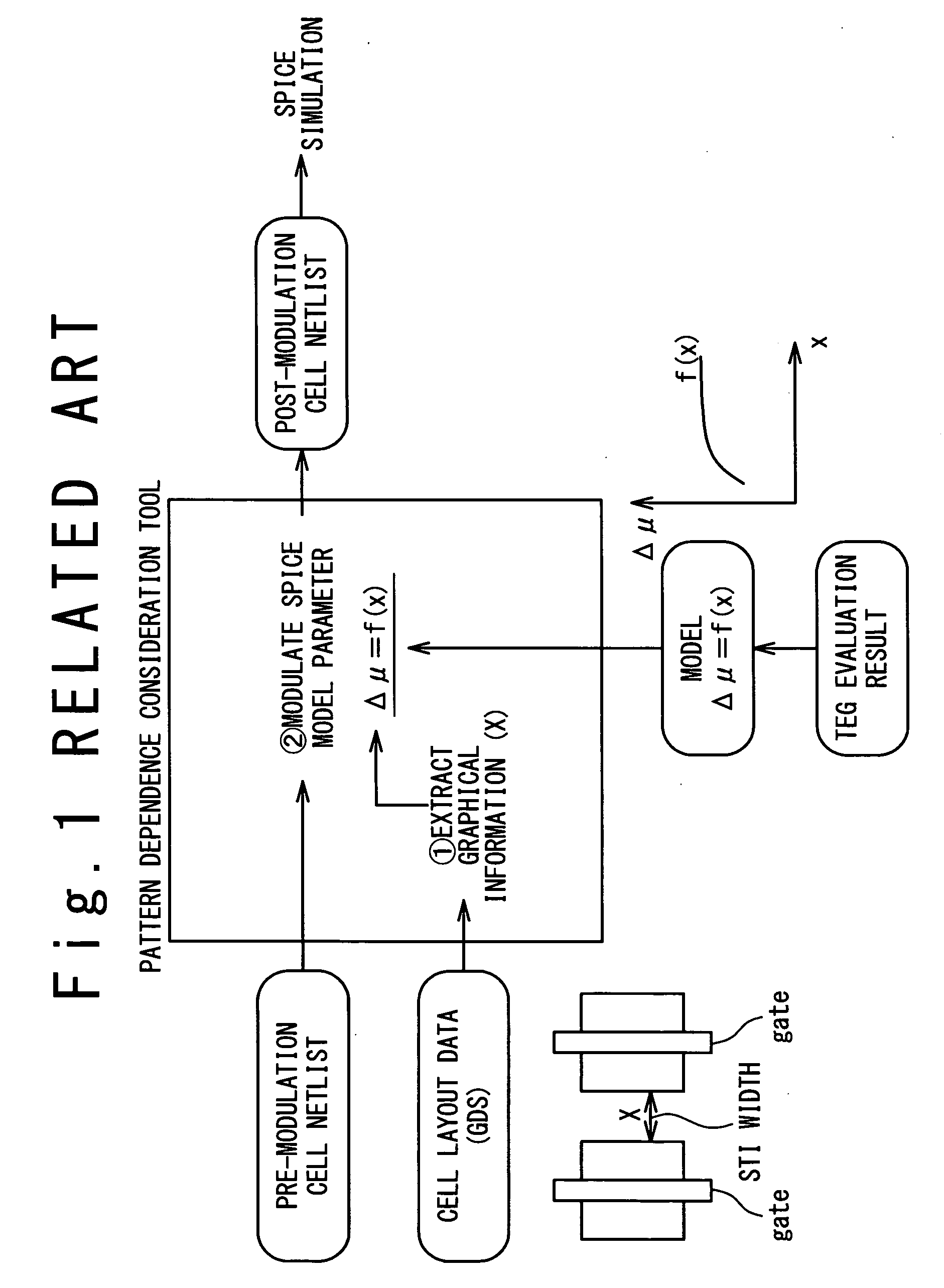

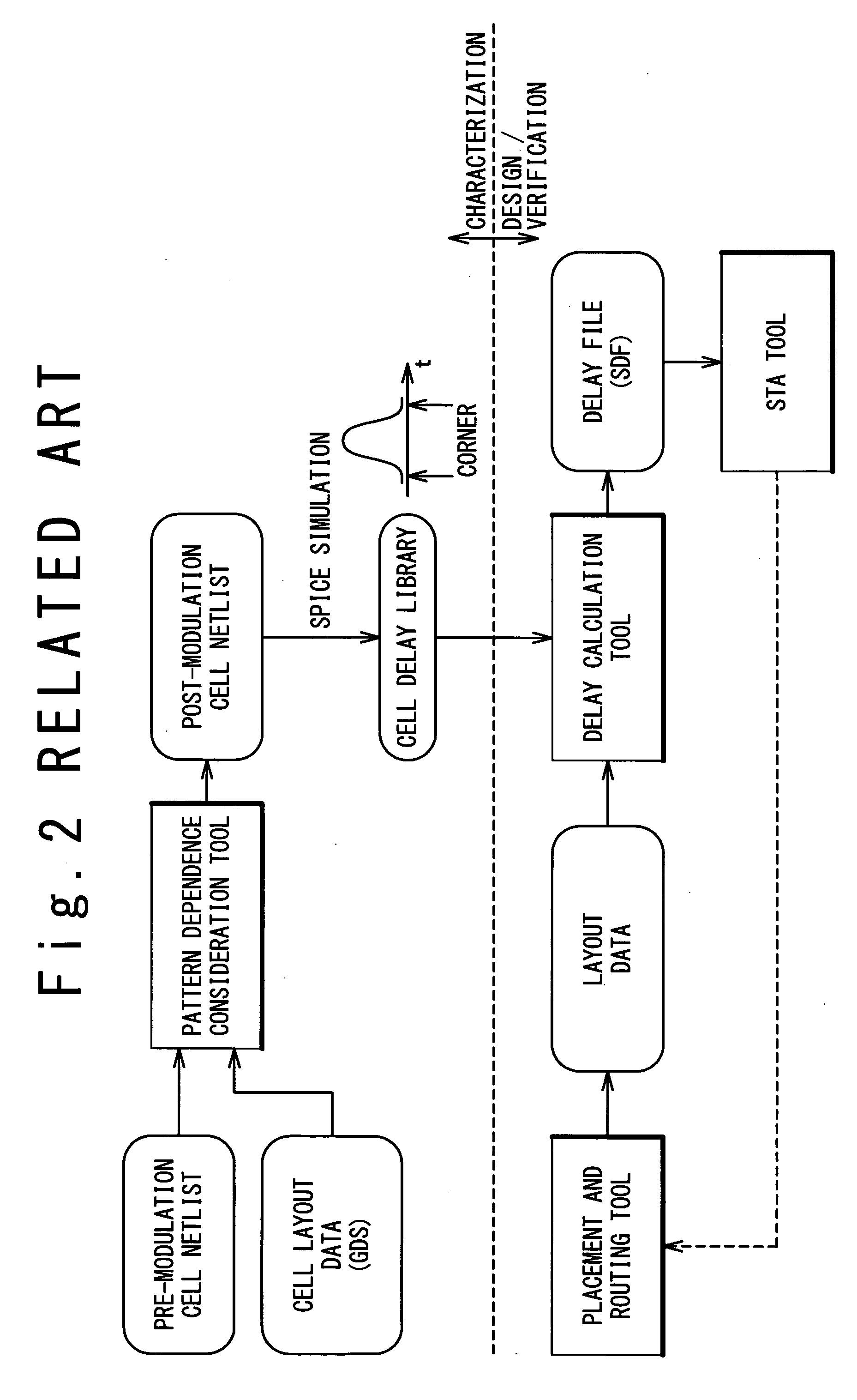

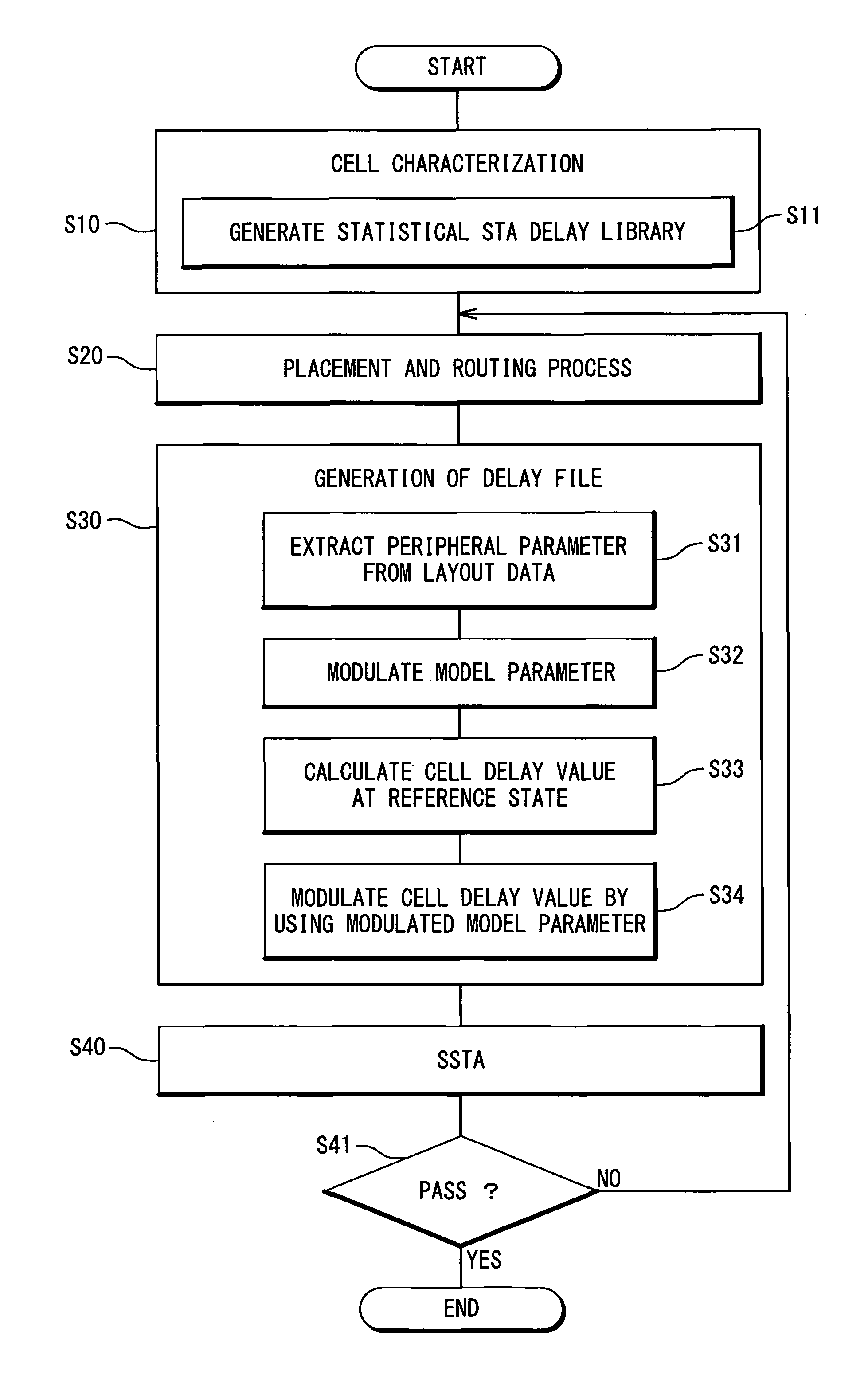

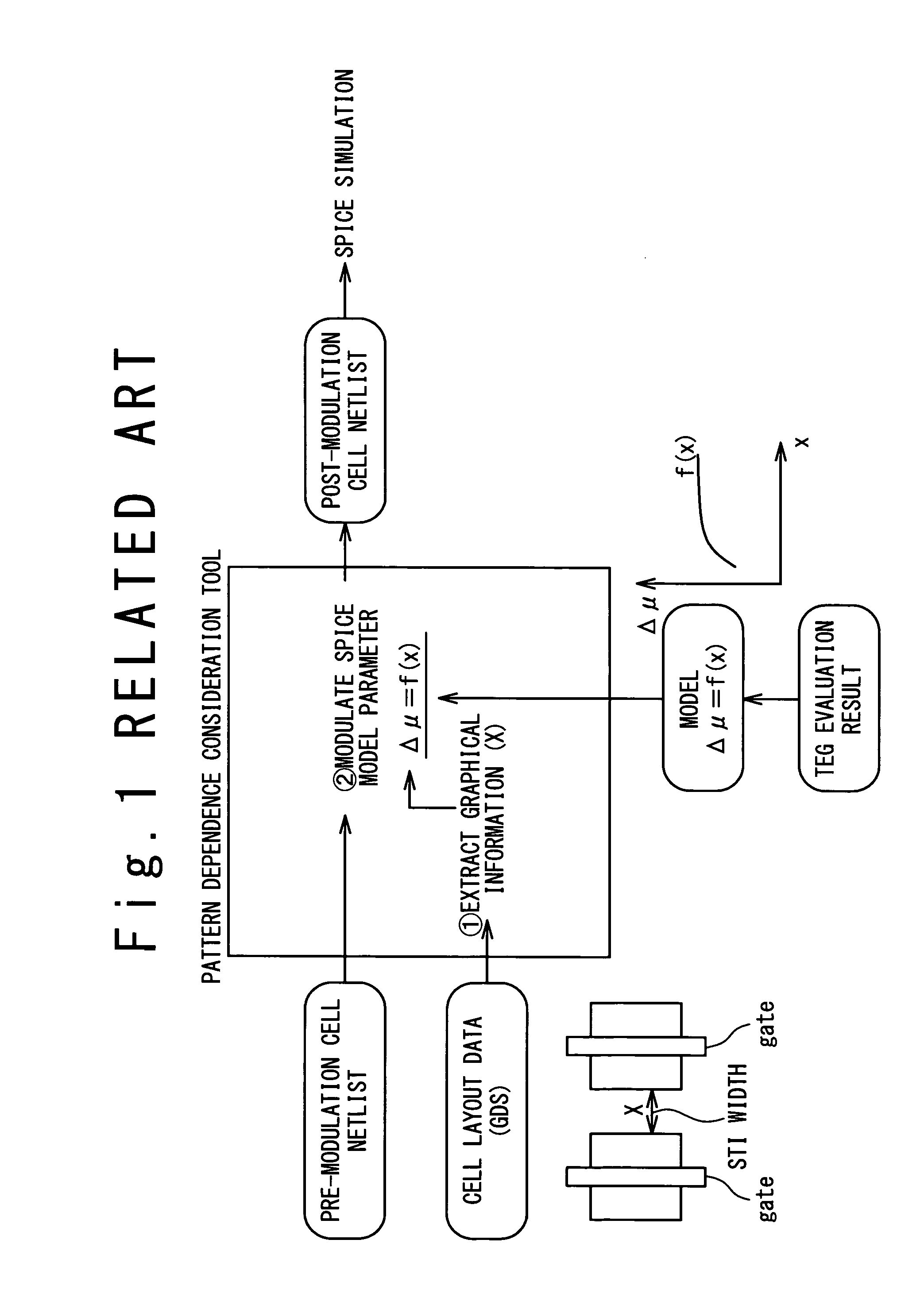

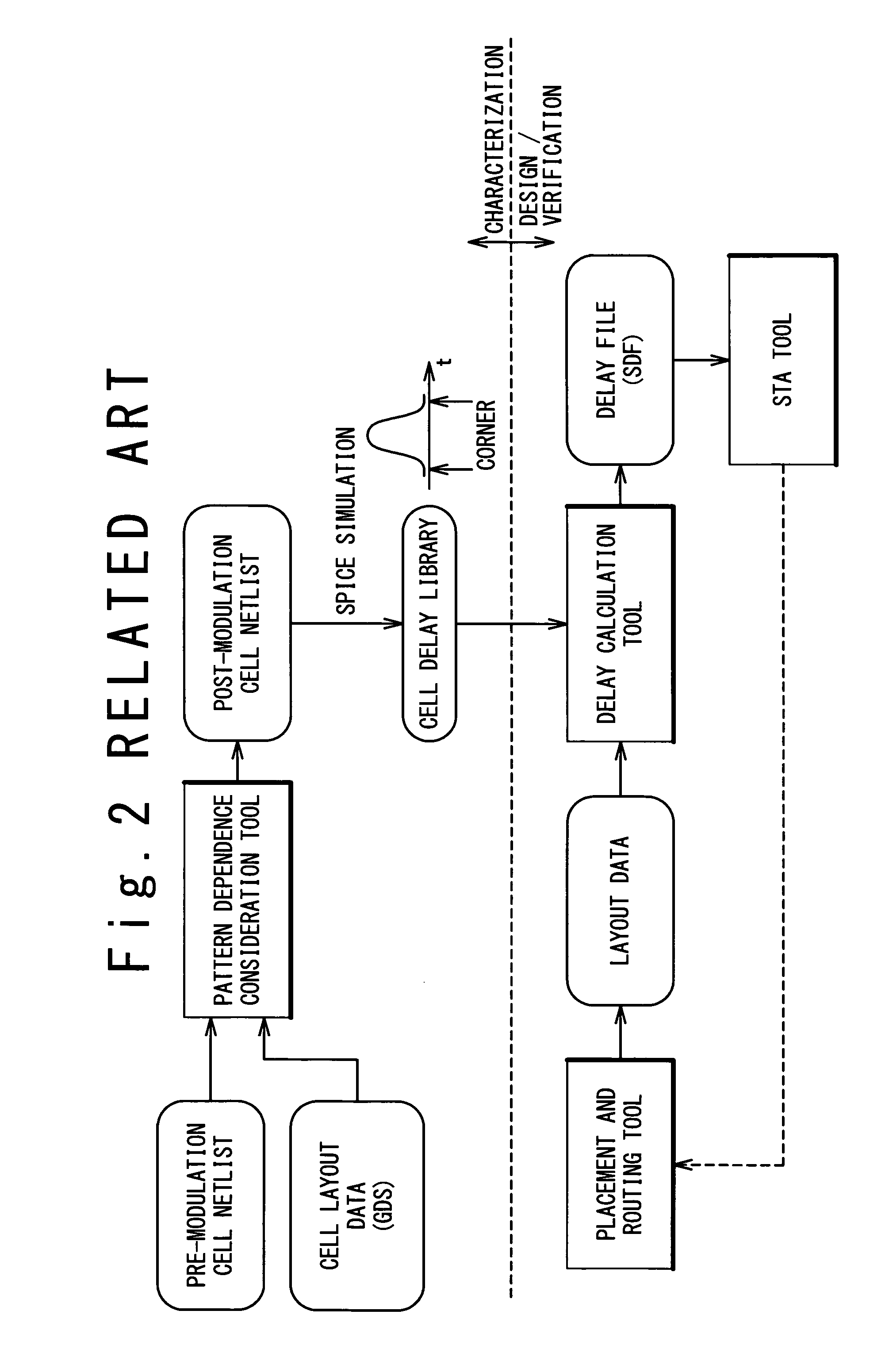

Method and program for designing semiconductor integrated circuit

InactiveUS20090024974A1Increase in design/verification TAT can be preventedHigh delay accuracyCAD circuit designSoftware simulation/interpretation/emulationModel parametersCell based

A design method for an LSI includes: generating a delay library for use in a statistical STA, wherein the delay library provides a delay function that expresses a cell delay value as a function of model parameters of a transistor; generating a layout data; and calculating a delay value of a target cell based on the delay library and the layout data. The calculating includes: referring to the layout data to extract a parameter specifying a layout pattern around a target transistor; modulating model parameters of the target transistor such that the characteristics corresponding to the extracted parameter is obtained in a circuit simulation; calculating, by using the delay function, a reference delay value of the target cell; and calculating, by using the delay function and the modulation amount of the model parameter, a delay variation from the reference delay value depending on the modulation amount.

Owner:RENESAS ELECTRONICS CORP

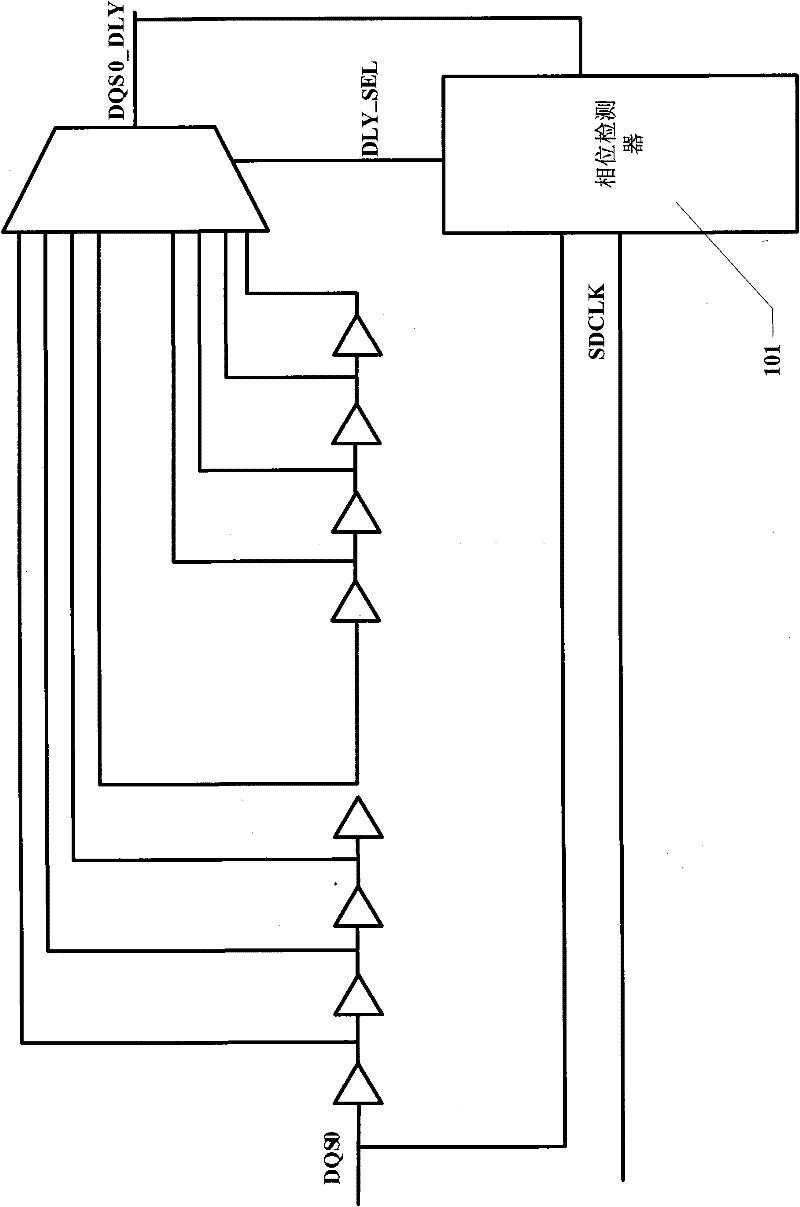

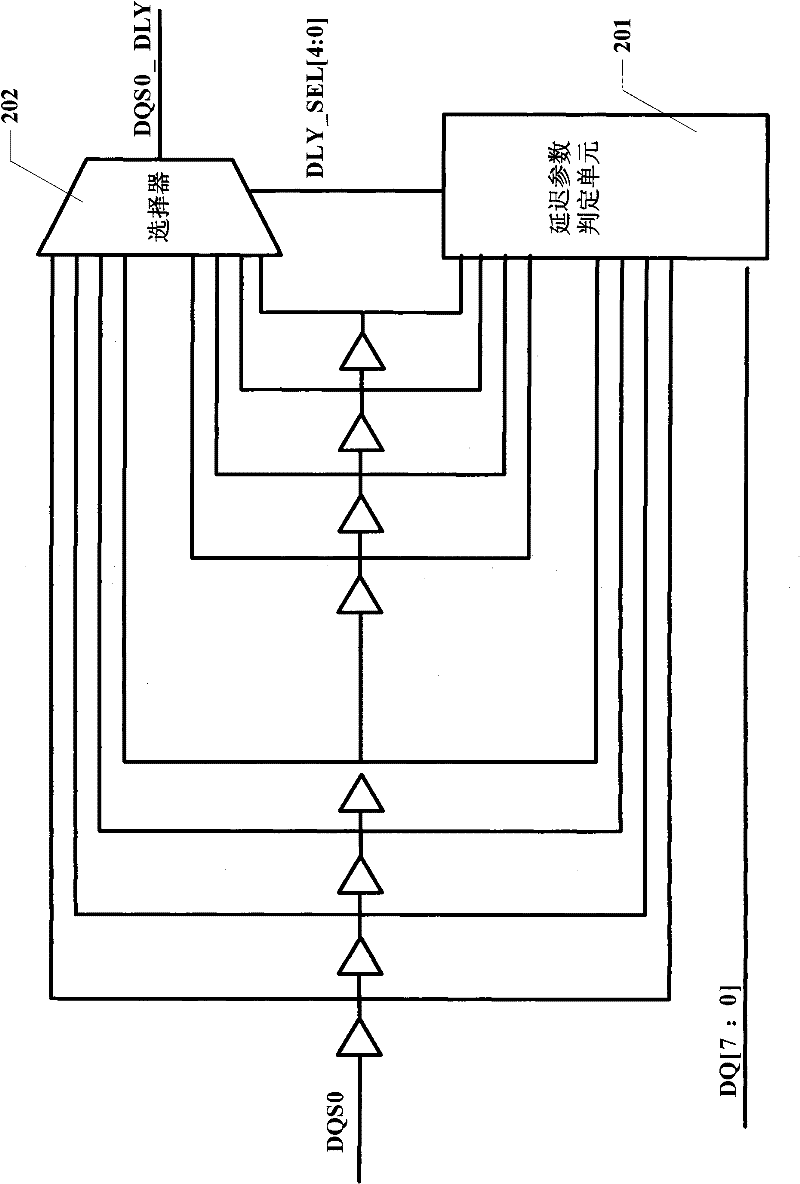

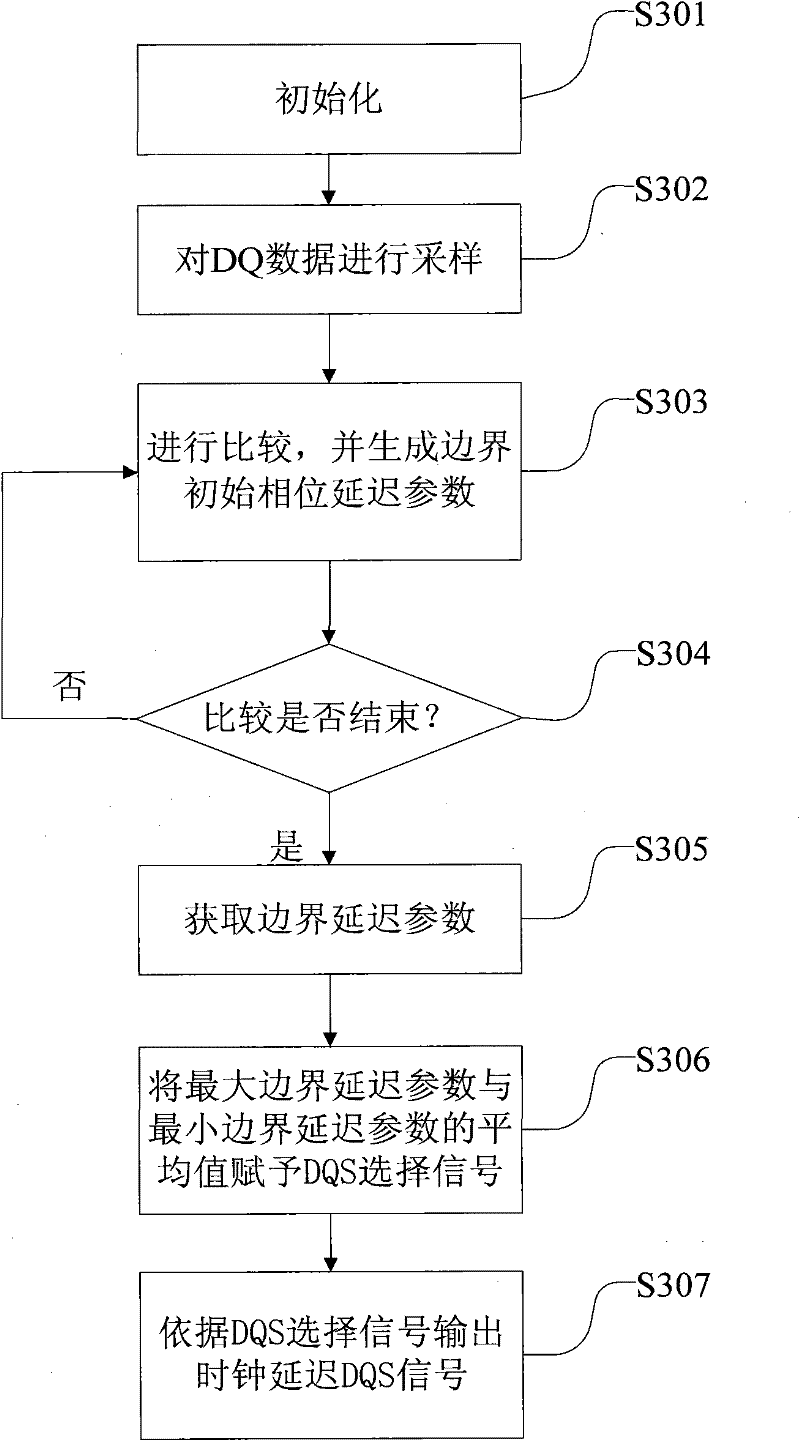

Method for calibrating phase of DQS (bidirectional data strobe) delay for DDR (double data rate) controller and apparatus thereof

ActiveCN102347081AImprove stabilityImprove anti-interference abilityStatic storageDouble data rateScreening method

The invention discloses a phase calibration method of the DQS delay for a DDR controller and an apparatus thereof. The method comprises the following steps: 1, sampling DDR data DQ according to trigger signals after different grade delays of a DQS signal; 2, comparing the data DQ acquired by sampling with a preset self-check datum in byte, and acquiring a minimum boundary delay parameter and a maximum boundary delay parameter through delaying for two beats; 3, endowing a mean value of the minimum boundary delay parameter and the maximum boundary delay parameter to a DQS selection signal; and 4, delaying the DQS signal according to the output clock of the DQS selection signal to obtain a DQS signal at the center of an effective datum window. According to the invention, the phase calibration of the DQS delay is realized through adopting a delay parameter determination unit and hardware in a delay parameter output circuit, and the delayed DQS can accurately fall on the center of the effective datum window through a datum screening method with the delay parameter determination unit, thereby the stability, the accuracy and the interference immunity of datum sampling are enhanced.

Owner:LEADCORE TECH

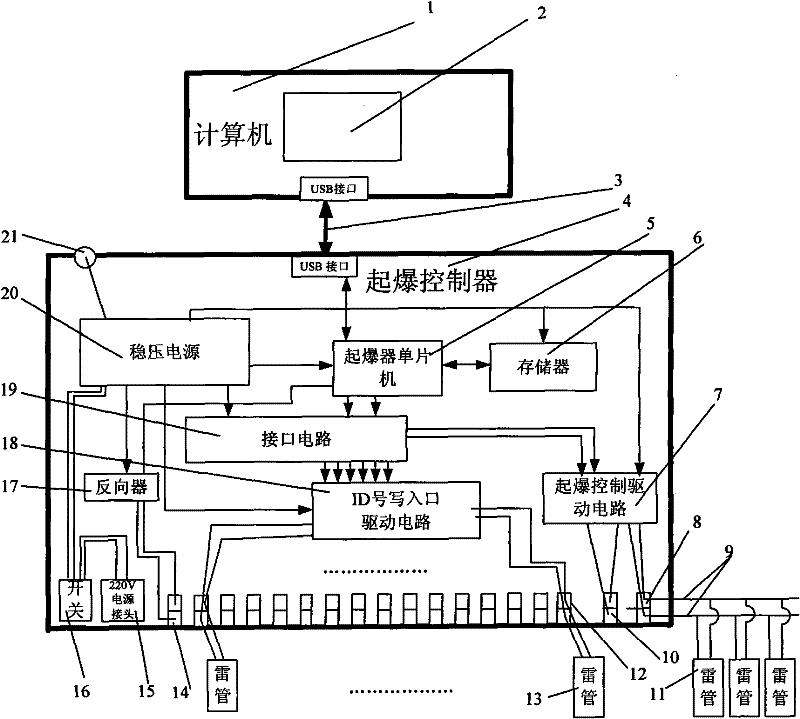

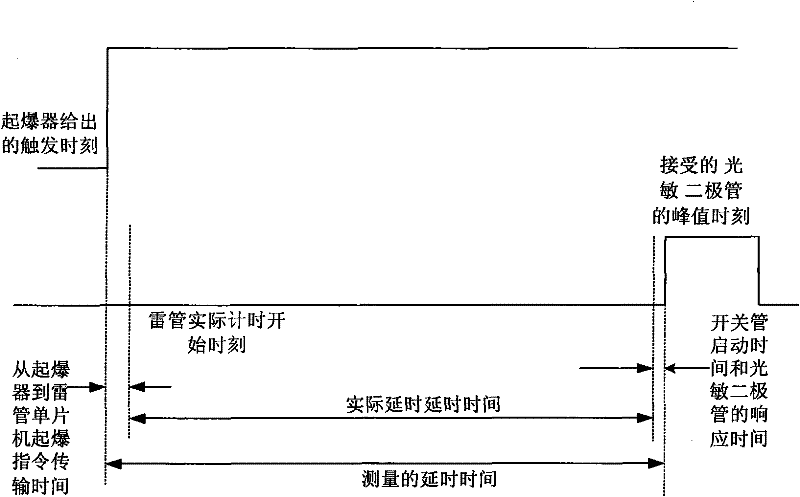

Intelligent detonation control system and method thereof

InactiveCN102278924AImprove securityConvenient circulation managementBlastingMicrocontrollerDetonator

The invention discloses an intelligent detonation control system, which comprises a detonation controller and electronic detonators, wherein the detonation controller is connected with a computer through a USB interface line; control instruments for writing ID numbers of the detonators and writing the delay time, roll call of addressing identification, charge and discharge of the detonator and detonation are transmitted into the detonation controller by a computer through the USB interface line; the detonation controller comprises a detonator singlechip microcomputer, an interface circuit, anID number writing-in port driving circuit, a detonation control drive circuit, a reverse controller, a voltage-stabilized power supply, an ID writing-in interface and a detonation port; and the detonation singlechip microcomputer is respectively connected with the ID number writing-in port drive circuit and the detonation control drive circuit through the interface circuit. According to the invention, because ID numbering is adopted, each detonator has a fixed serial number, which facilitates the safety management and circulation management of the detonators; because the detonators the ID numbers of which are known cannot be detonated, and misuse and fault detonation of the detonators are avoided and controlled.

Owner:NANJING UNIV OF SCI & TECH

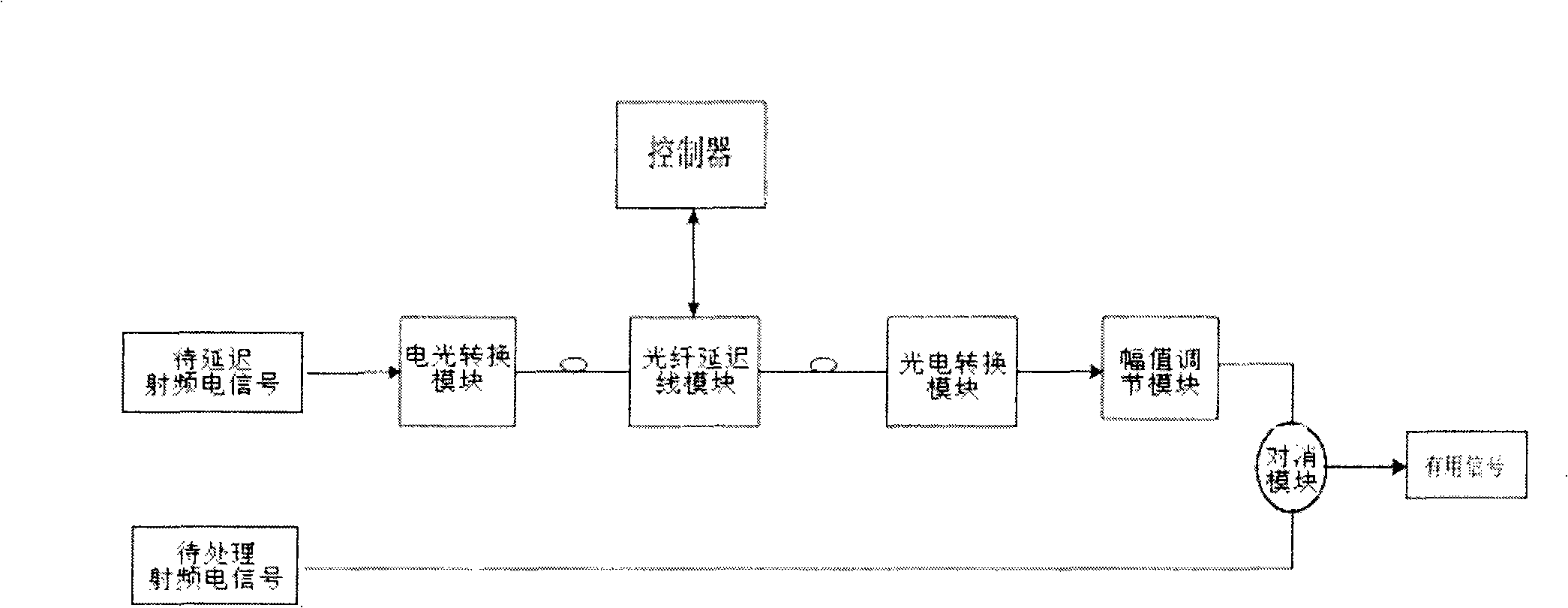

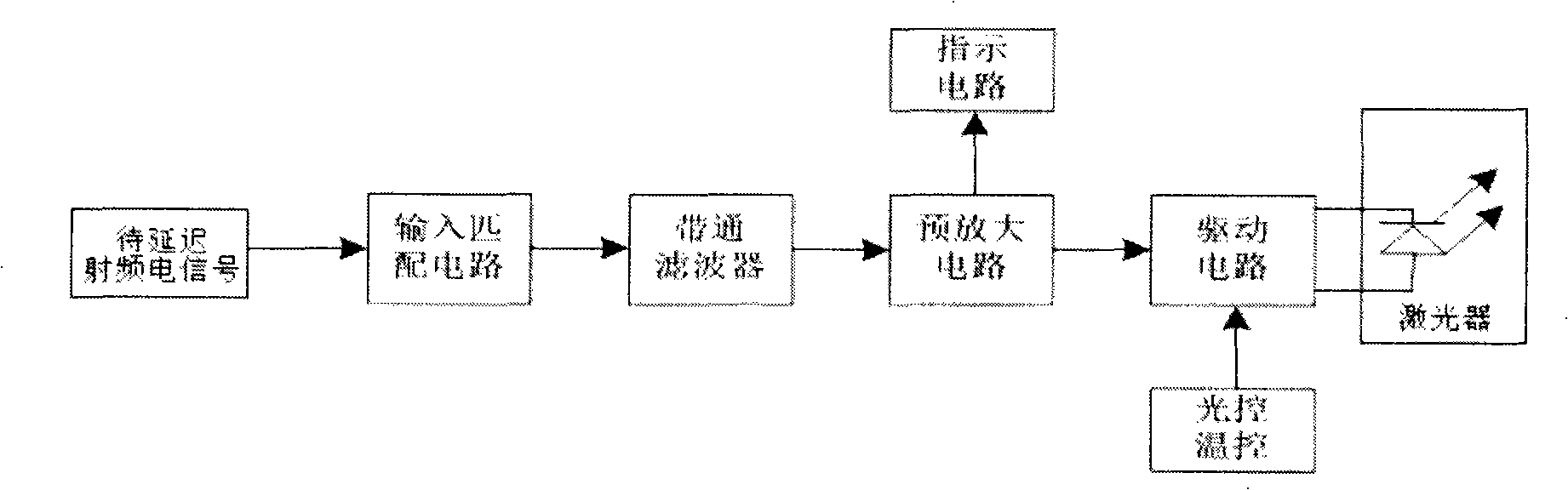

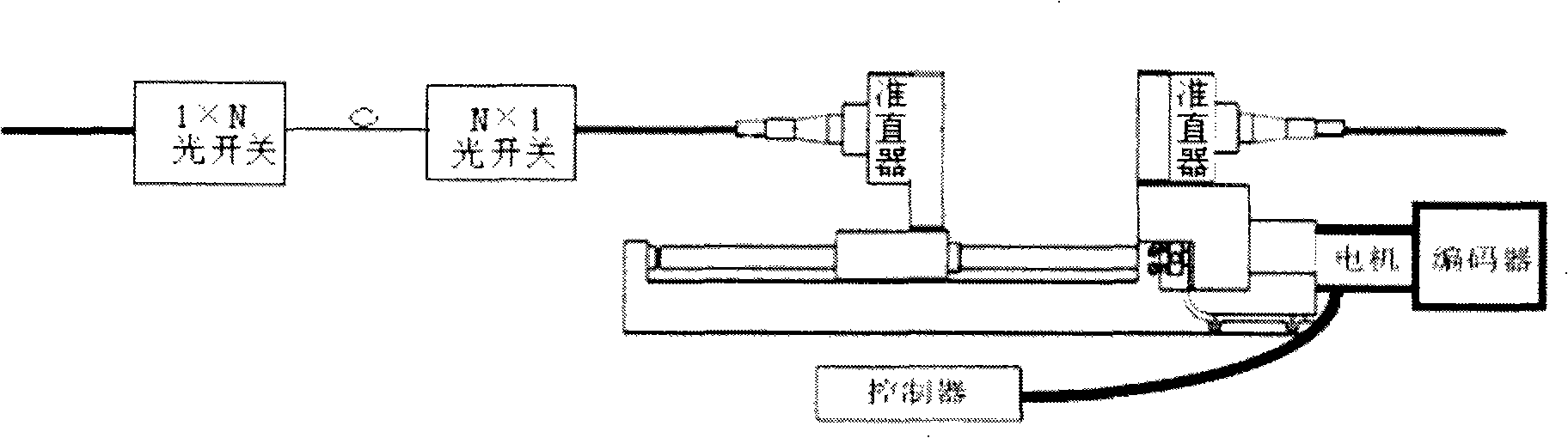

Signal interference canceller and signal interference canceling method

InactiveCN101404509AThe output amplitude is continuously adjustableStrong resistance to electromagnetic interferenceElectromagnetic transmissionTransmission noise suppressionOptical pathlengthElectromagnetic interference

The invention discloses a signal interference canceller and a signal interference cancelling method. The signal interference canceller converts an electric interference signal into an optical modulation signal and then transmits the signal to an optical delay line for changing the corresponding optical length passed by the optical signal, so as to realize the delaying of the optical signal and finally converts the optical signal to an electric signal, thereby realizing to transfer the phase of a RF electric signal by (2n+1)180 degrees; wherein, n is equal to 0, 1, 2, 3, and the like; finally the interference signal which affects useful signals is filtered by cancelling. The invention can effectively remove useless signals received by a receiving terminal during the process of multi-carrier transmission; moreover, the invention is characterized by high delaying precision and high electromagnetic interference resistance.

Owner:桂林航天光比特科技股份公司

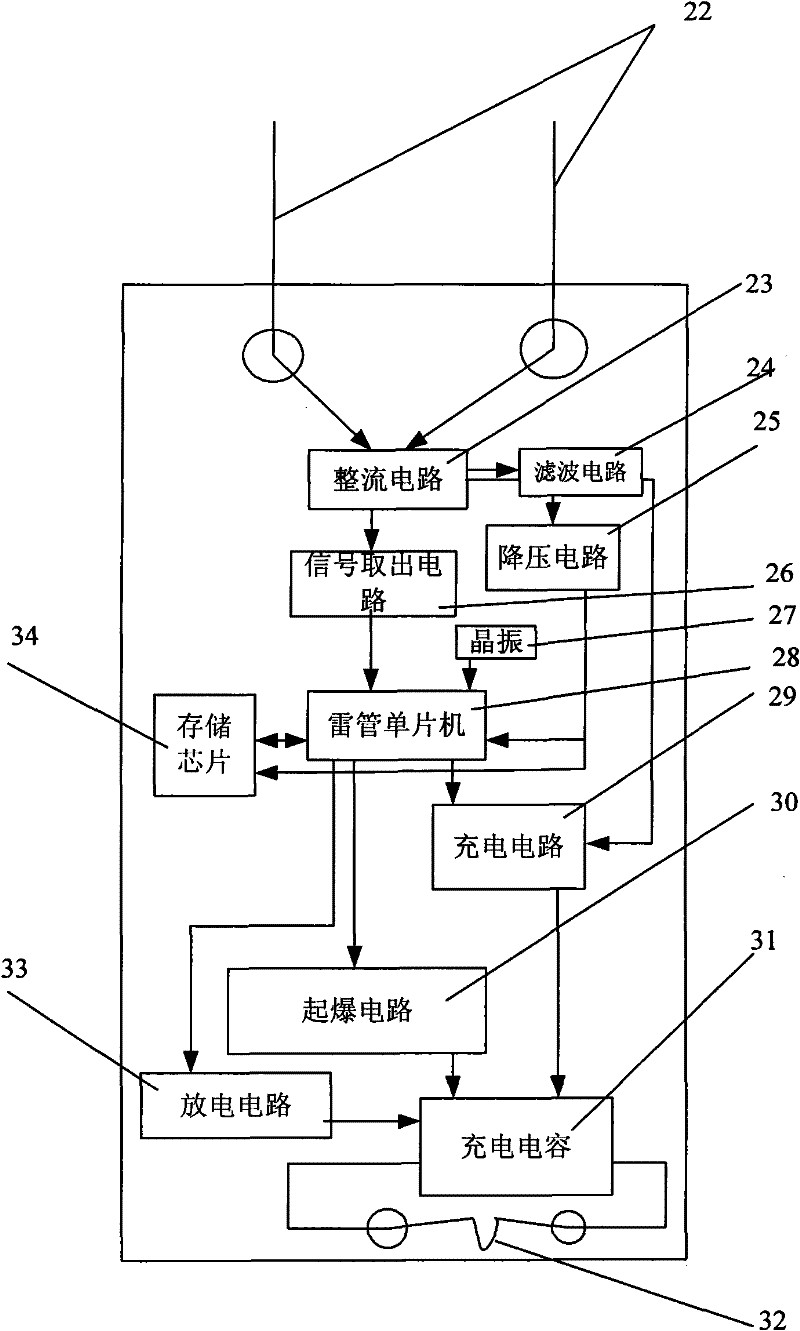

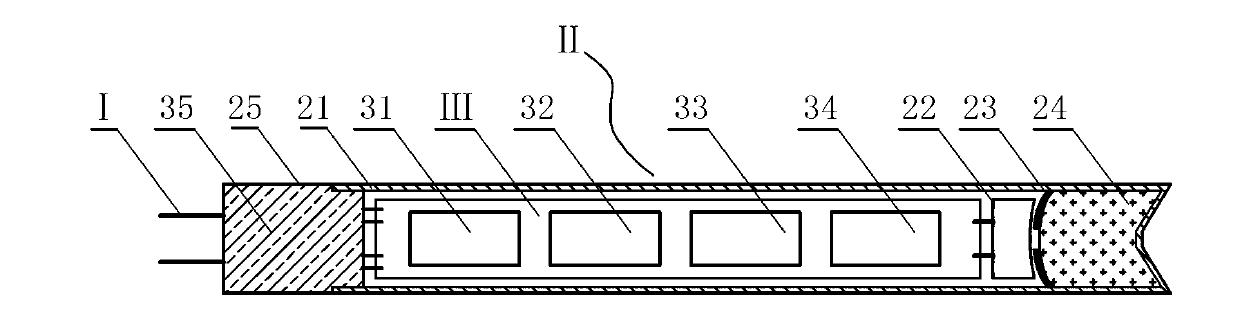

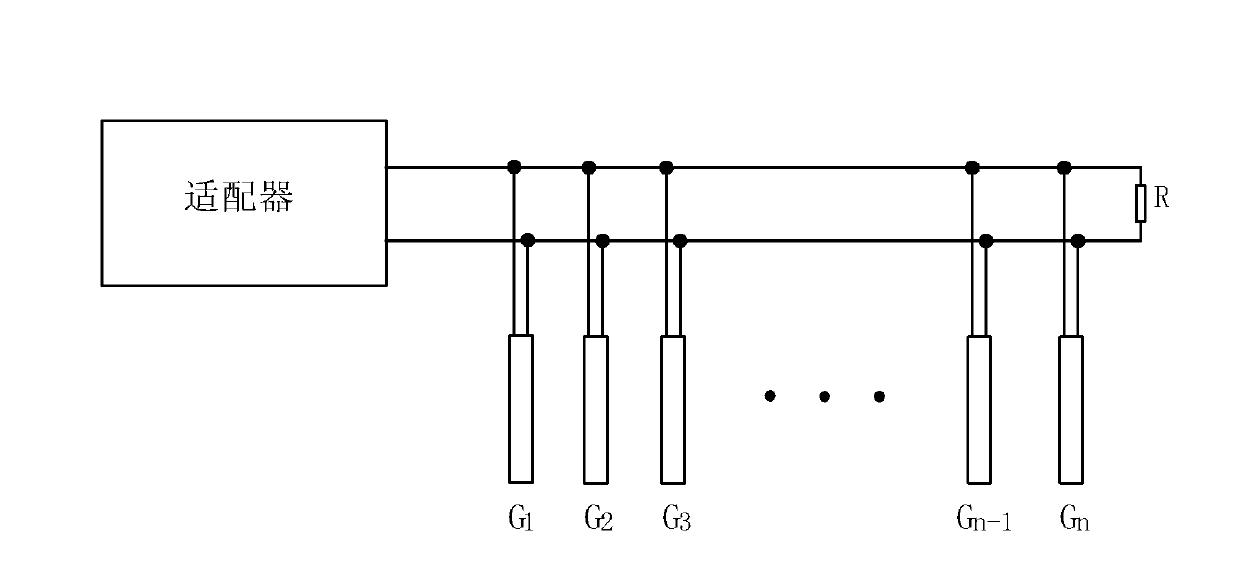

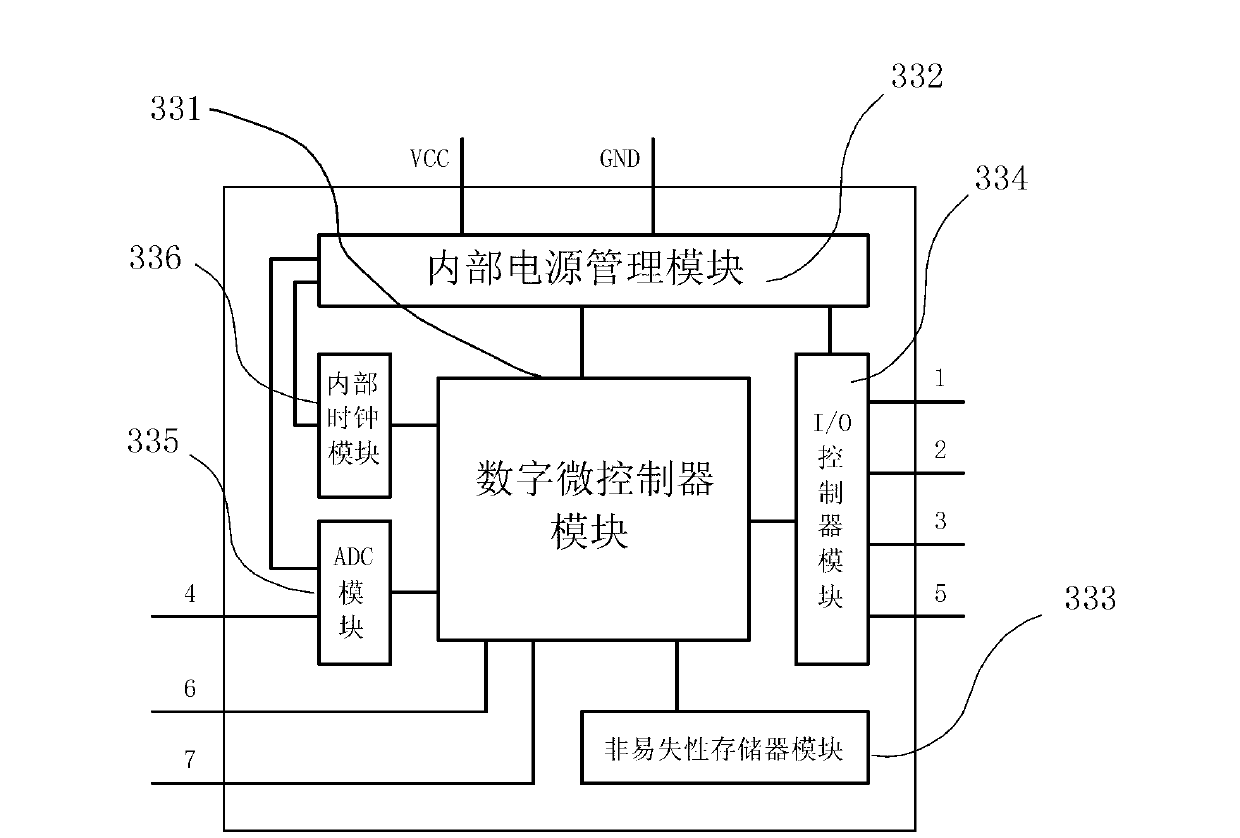

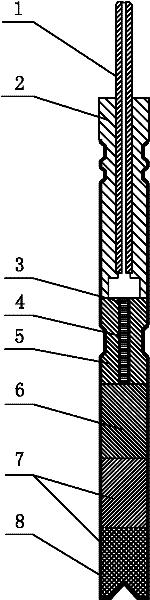

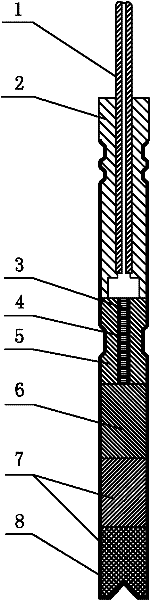

Nonpolar double-wire communication digital electronic detonator capable of self-delaying and detonation method thereof

ActiveCN103217079AHigh authority securityImprove controllabilityBlasting cartridgesElectric fuzesDetonatorDetonation

A nonpolar double-wire communication digital electronic detonator capable of self-delaying, comprises a leg wire and a pipe body, wherein the pipe body comprises a pipe casing, and an ignition device, a detonator charging and tail plugging device, a control circuit and an ignition energy storage device, which are installed in the pipe casing. The control circuit comprises a power supply module, a communication module, a core control module and an ignition loop module, which are orderly electrically connected; input terminals A and B of the power supply module are connected to the leg wire, the ignition loop module is electrically connected with the ignition device and the ignition energy storage device; and a detonation method comprises: (1) detonator configuration, (2) networking, and (3) detonation operation. The nonpolar double-wire communication digital electronic detonator has a UID code and detonation authorization code verifying function, has advantages of controllable itself, high authority security, convenient self-delay, on-site laying, accuracy detonation control, good explosion effect, no need to distinguish polarities of the leg wire, convenient usage and low human error rate, and can obtain higher delay precision by using an internal clock module or an external clock module.

Owner:LIUZHOU CHANGHONG MACHINE MFG +1

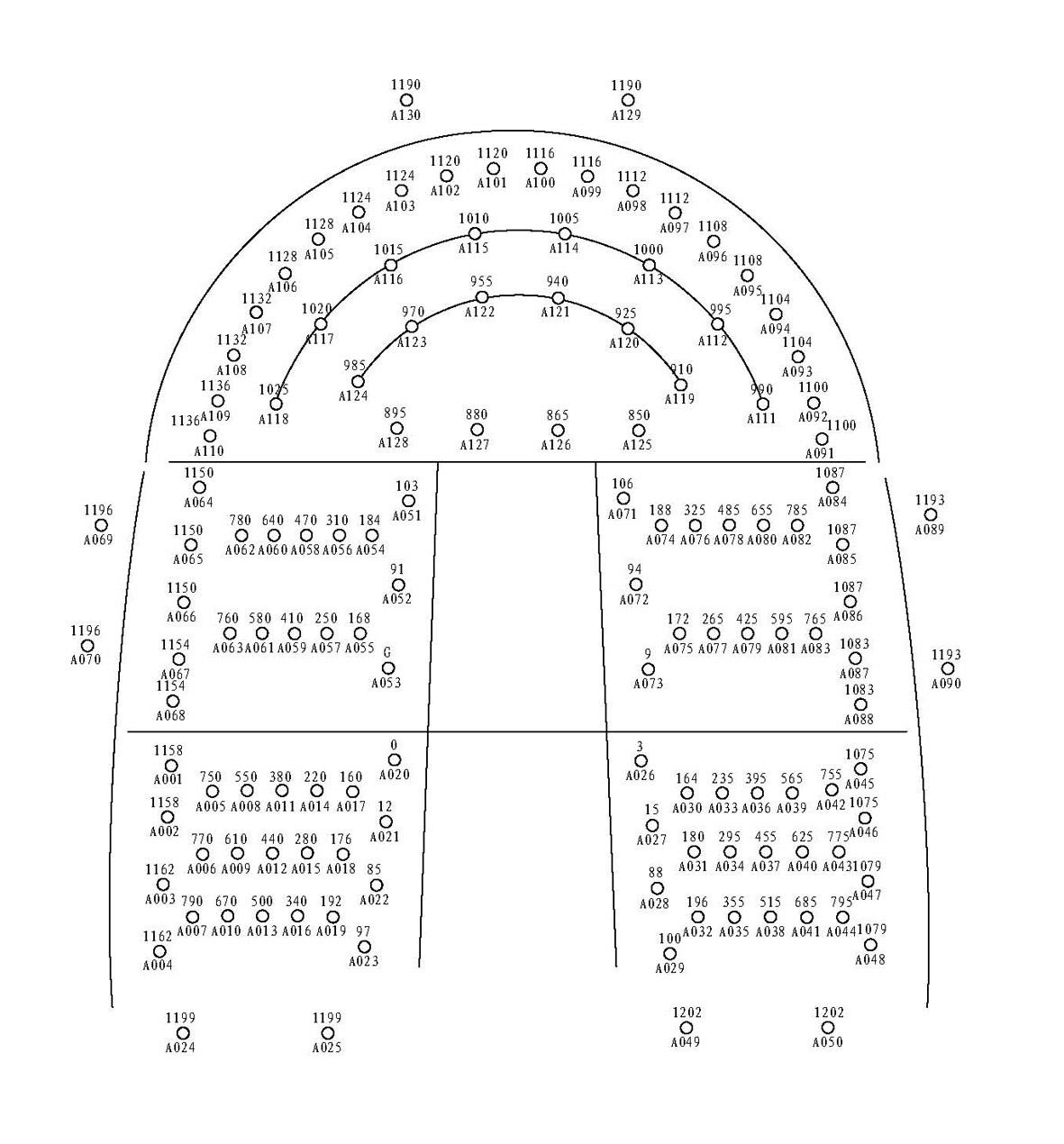

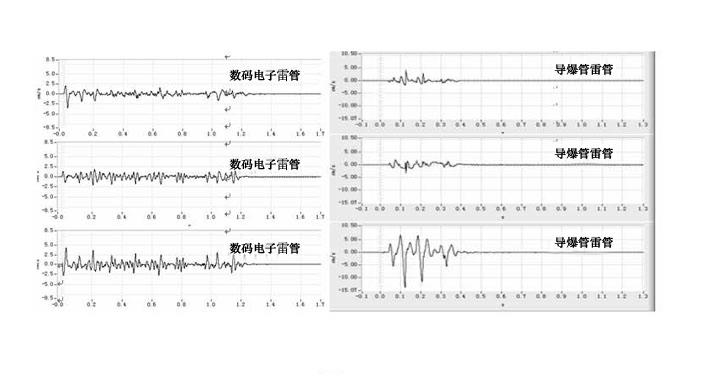

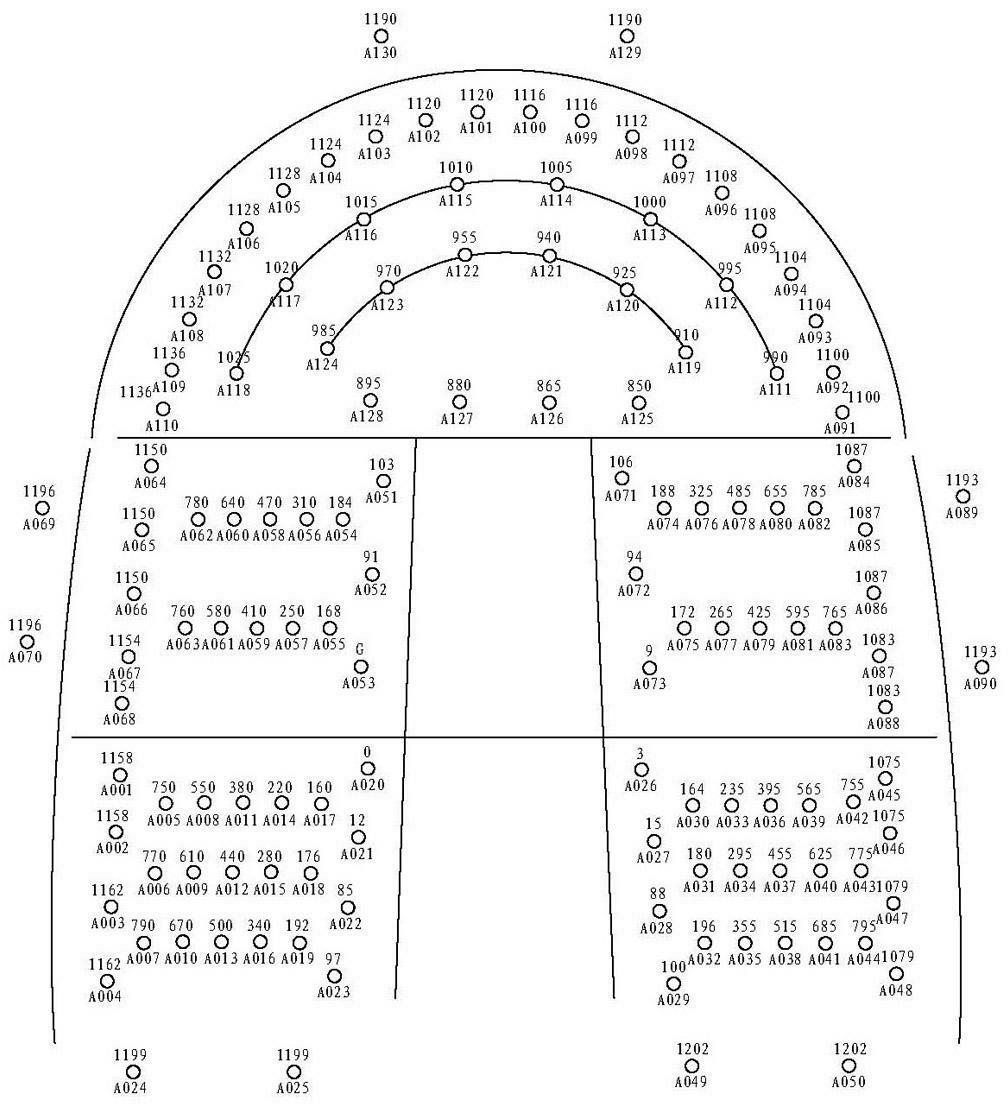

Tunneling electron detonator blasting construction method

InactiveCN102095338AHigh delay accuracyMeet the design requirements of vibration reductionBlastingDetonatorEngineering

The invention discloses a novel blasting construction method. In the method, an electron detonator is used for blasting. The method also comprises the following steps of: designing a detonator arrangement diagram; detonating at least one detonator; analyzing a generated blasting vibration waveform; detonating a special detonator; and eliminating the blasting vibration to the maximum extent by a phase-stagger vibration damping technology. By the technology of the method, the blasting vibration is obviously reduced, full cross section blasting can be performed, circulating drilling footage is increased, blasting residues are well crushed and an obvious polished surface effect is achieved.

Owner:CHINA CONSTR EIGHT ENG DIV CORP LTD +1

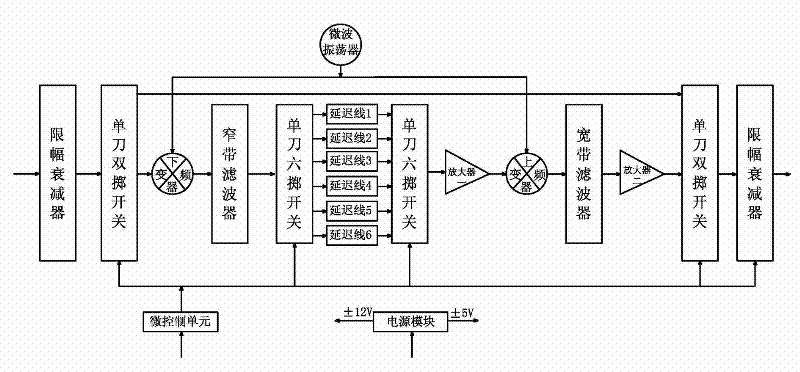

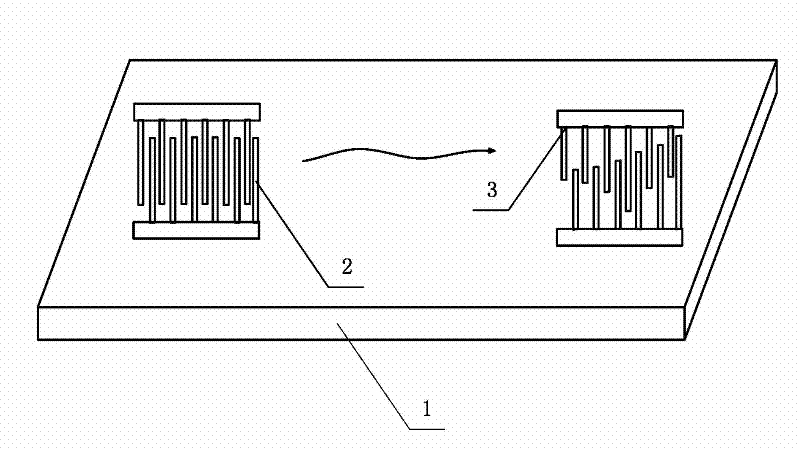

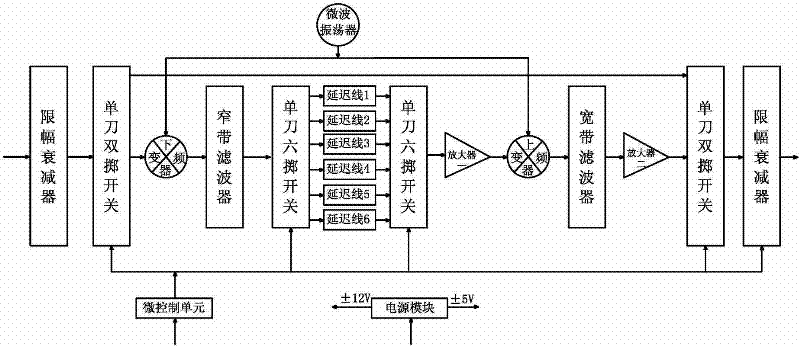

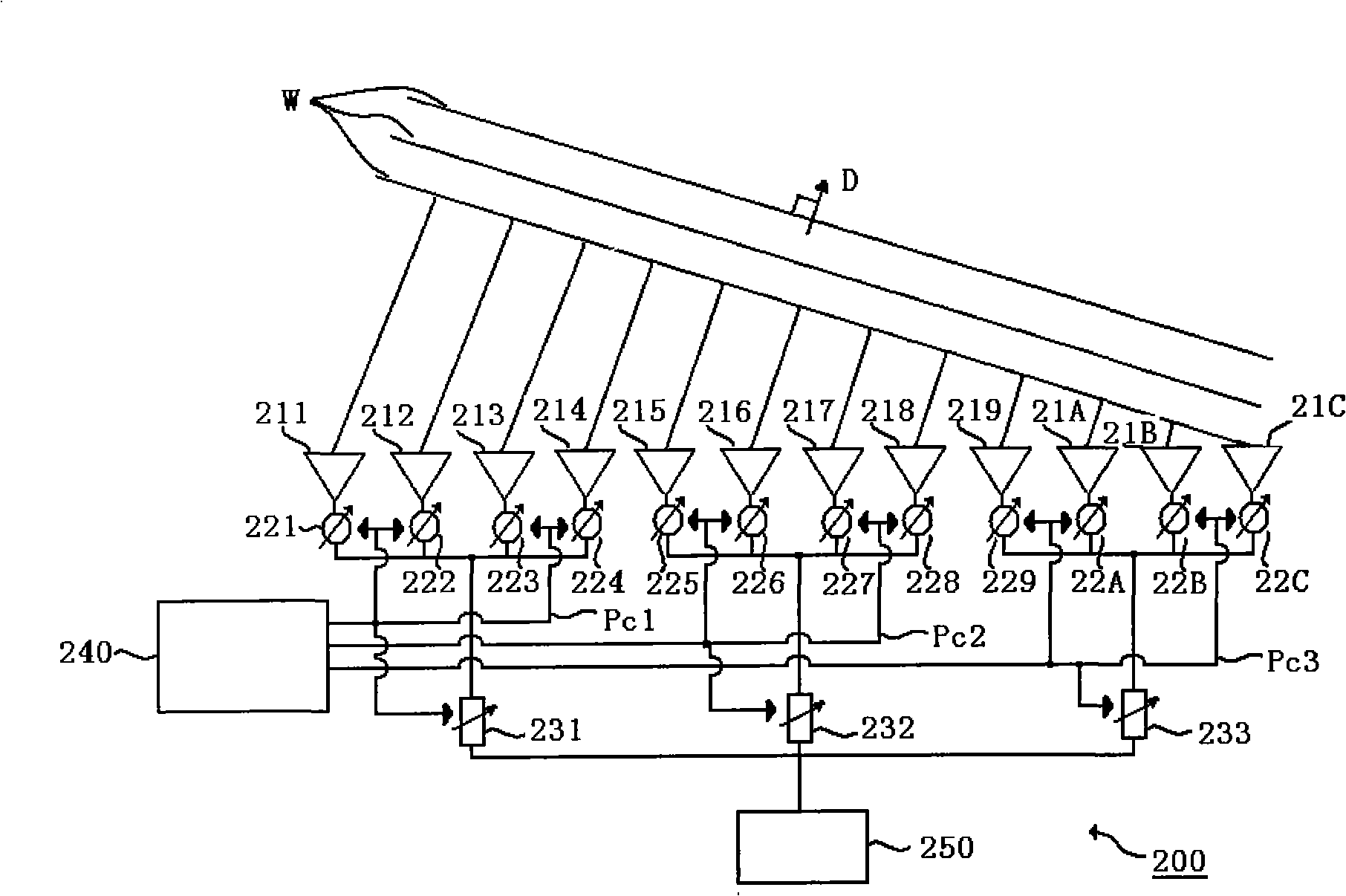

Radio altitude signal simulator assembly based on surface acoustic wave delay lines

InactiveCN102565768AHigh precisionImprove refinementWave based measurement systemsRadio wave reradiation/reflectionNumerical controlAutomatic control

The invention discloses a radio altitude signal simulator assembly based on surface acoustic wave delay lines, relating to an avionic device detection instrument, in particular to a signal simulator assembly of a radio altimeter detector. According to the invention, a plurality of delay lines are arranged and a numerical-control electrically controlled attenuator is additionally arranged; the radio altitude signal simulator assembly also comprises a single-pole multi-throw switch and a single-pole double-throw switch, wherein the single-pole multi-throw switch is used for selecting to switch a radio frequency signal to pass different delay lines; the single-pole double-throw switch is used for selecting to switch a radio frequency signal to pass a delay line path or pass a straight channel path which bypasses a frequency-conversion filtering element and component path; and the single-pole multi-throw switch, the single-pole double-throw switch and the numerical-control electrically controlled attenuator are respectively electrically connected with a micro control unit. According to the radio altitude signal simulator assembly disclosed by the invention, due to adoption of modularized design, the plurality of delay lines which are capable of carrying out different time delays are arranged on one set of assembly, the single-pole multi-throw switch is controlled by the MCU micro control unit to realize selection and switching. Compared with the prior art, the radio altitude signal simulator assembly has the advantages of improving the detection efficiency and realizing the automation because programmed automatic control and switchover can be carried out.

Owner:唐金元

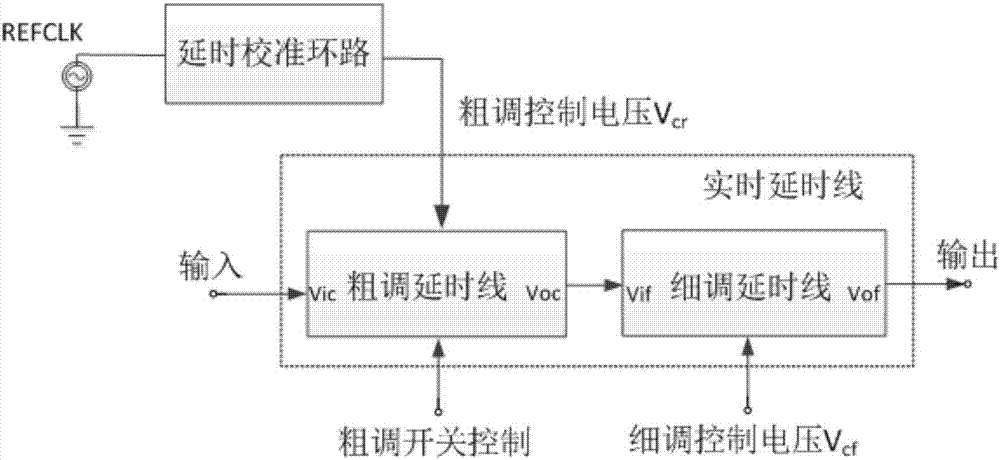

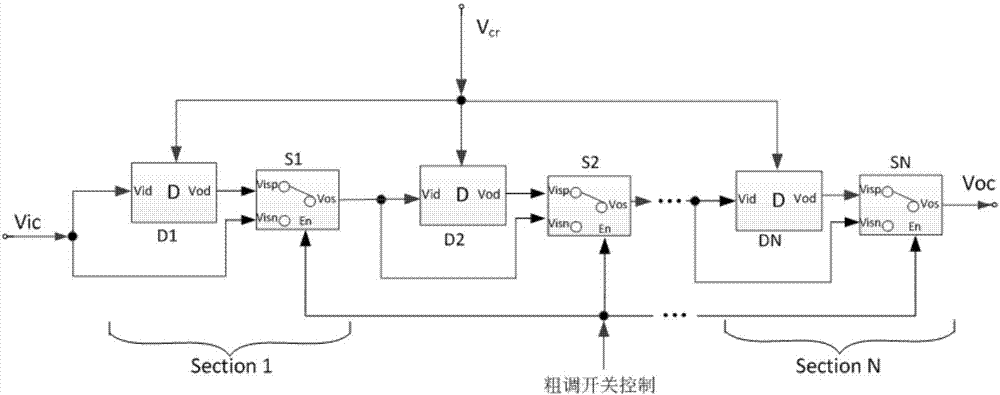

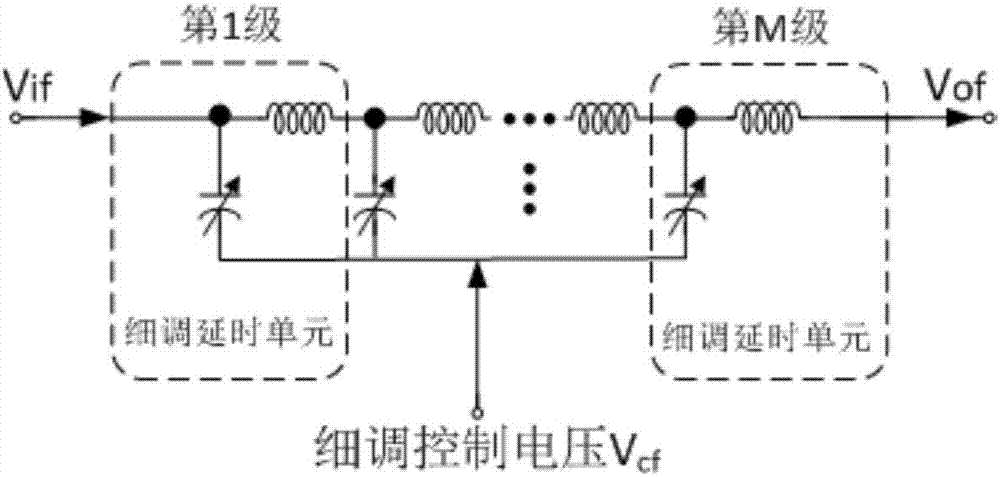

High-accuracy broadband continuous adjustable real-time time delay line circuit

InactiveCN107395164ALarge variable rangeImprove stabilityPulse automatic controlPulse manipulationCapacitanceAudio power amplifier

The invention discloses a high-accuracy broadband continuous adjustable real-time time delay line circuit, adopts a method of combining an active coarse adjustment time delay line with a passive fine adjustment time delay line and improves a bandwidth and a time delay range of the time delay line circuit. The active coarse adjustment time delay line comprises an active voltage control time delay unit and a path selection amplifier. The passive fine adjustment time delay line is formed by cascading a plurality of inductor and variable capacitor pairs, by changing a voltage control variable capacitance value, delay time of the fine adjustment time delay line is changed, and the delay time can make up resolution of coarse adjustment time delay, thereby implementing the delay time continuous change of a real-time time delay line. The real-time time delay line carries out time delay accurate control on active time delay units by a time delay calibration loop, so that time delay is not influenced by changes of the outside environment. The circuit has the advantages of high time delay resolution, wide time delay range, high anti-interference capacity, broadband, high integration, low cost and easiness for integration.

Owner:SOUTHEAST UNIV

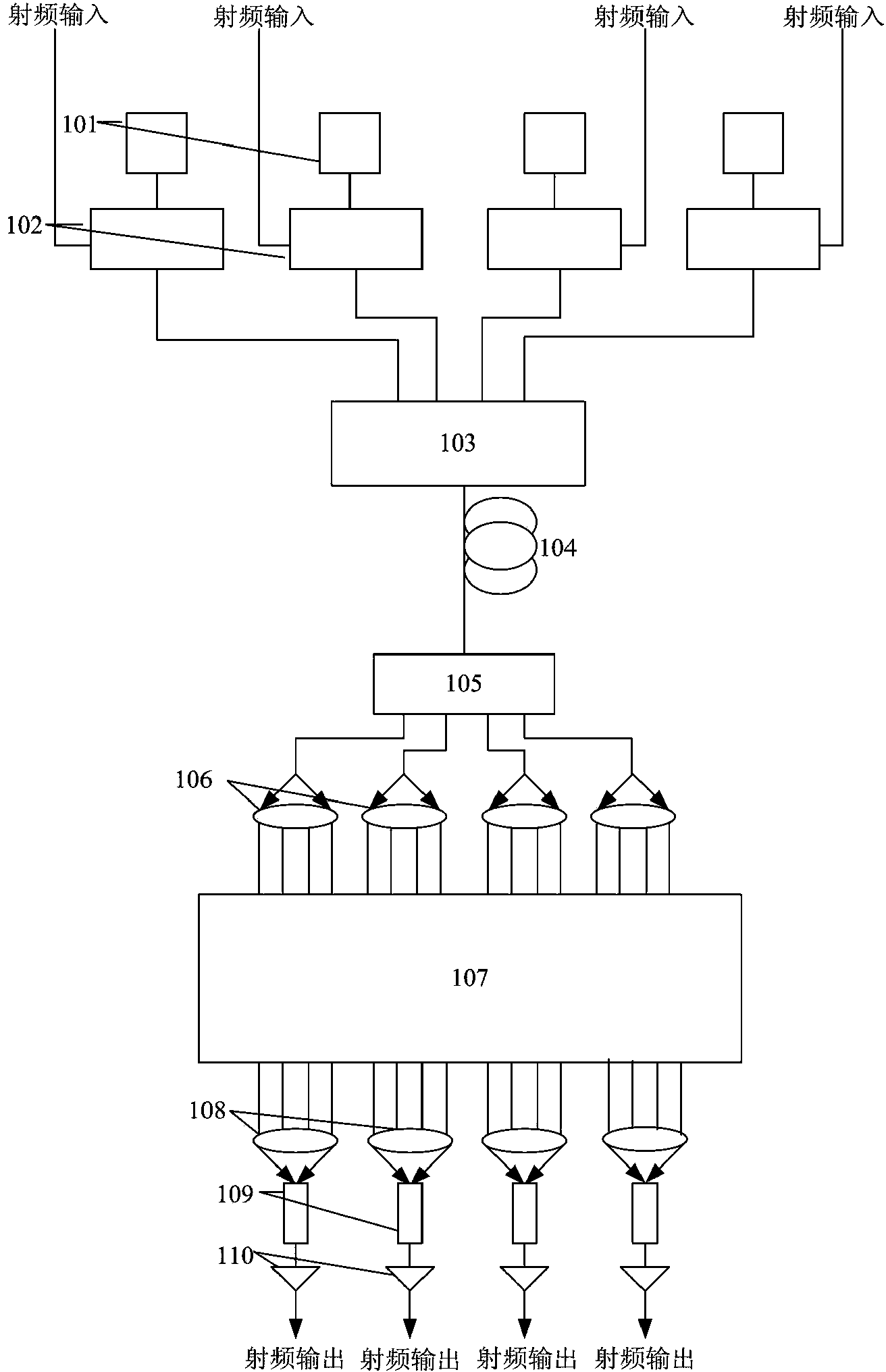

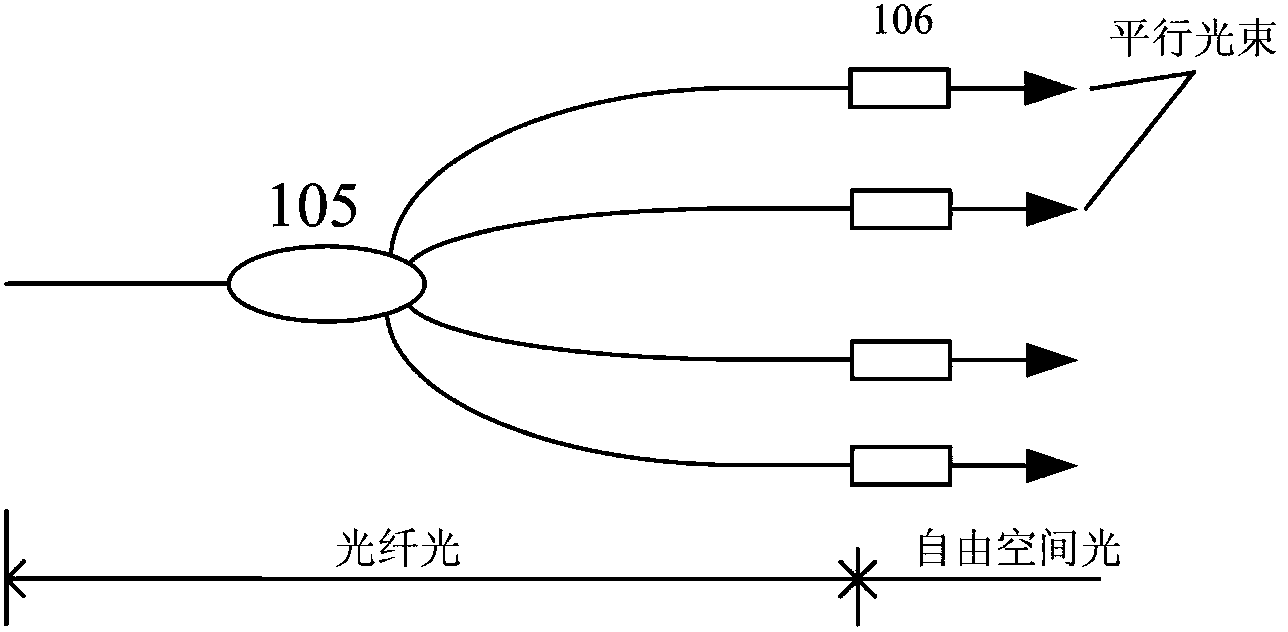

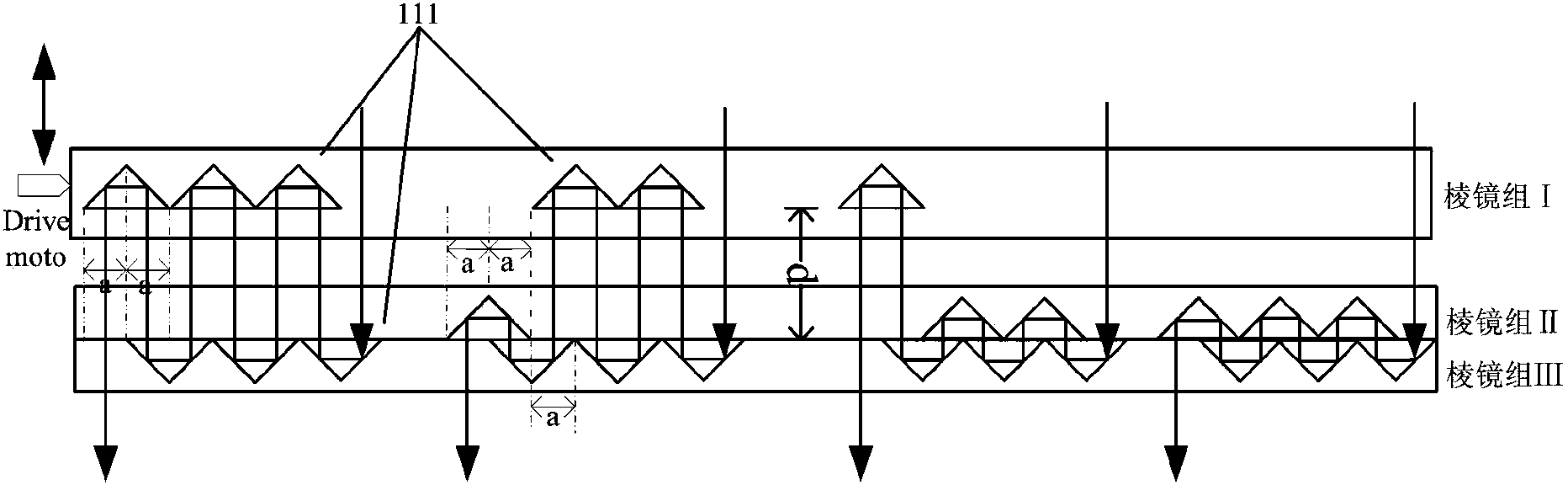

Optically-controlled microwave beam forming networks

ActiveCN103414519AReduced stabilityUniform gainAntenna arraysWavelength-division multiplex systemsFiberLow noise

Optically controlled microwave beam forming networks comprise 2N single frequency DFB lasers of different wavelengths, , 2N electro-optic intensity modulators, 2N *1 passive wavelength division multiplexers, an optical fiber, 1*2N optical beam splitter, 2N fiber collimator, a time delay network module, 2N coupled lenses, 2N photoelectric detectors and 2N low noise amplifiers, wherein N is an integer larger than 2. The optically controlled microwave beam forming networks have the advantages of the high signal to noise ratio, good dynamic performance, high time delay precision, continuous adjustability, and good stability, and are easy to be extended in the system array size.

Owner:SHANGHAI INST OF OPTICS & FINE MECHANICS CHINESE ACAD OF SCI

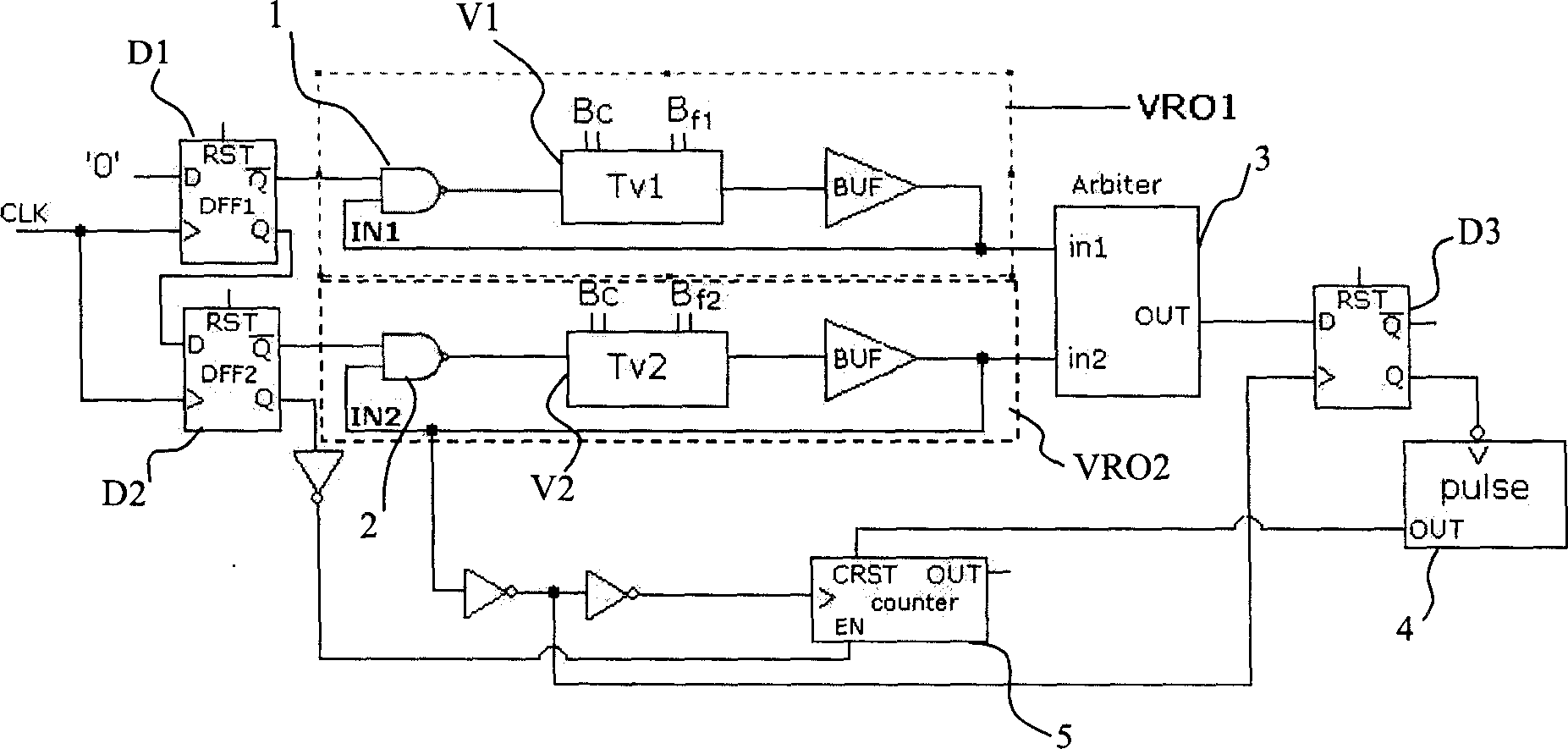

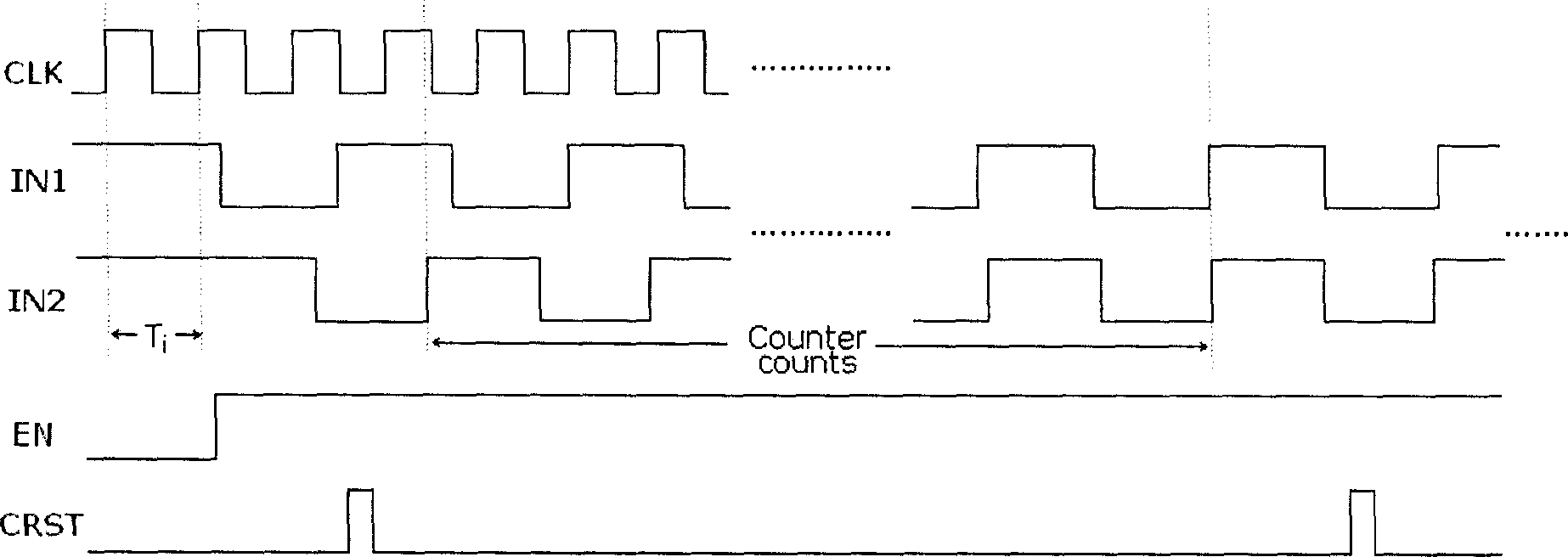

High-frequency clock jitter measuring circuit and calibration method thereof

InactiveCN1837835AAvoid errorsSmall footprintPulse train pattern monitoringElectrical testingPhysicsJitter

This invention relates to a high-frequency clock jitter measuring circuit and calibration method thereof, which comprises a first / second oscillation signal unit to generate the first / second oscillation signal with TV1 / TV2 period (TV1 G01R 29 / 02 G01R 23 / 02 G01R 31 / 00 H03K 5 / 19 6 13 4 2006 / 4 / 18 1837835 2006 / 9 / 27 100501423 2009 / 6 / 17 2009 / 6 / 17 2009 / 6 / 17 Peking University Shenzhen Graduate School 518057 Zhang Jingkai Li Chongren Yu Fei Tian Chao guo yan 44223

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

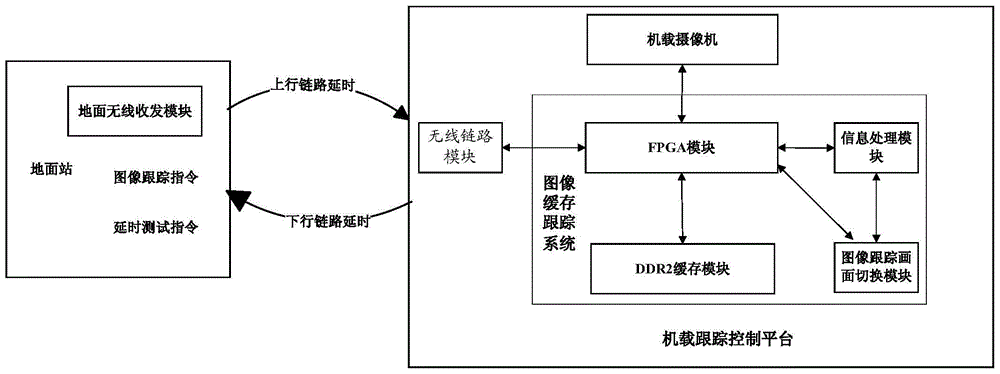

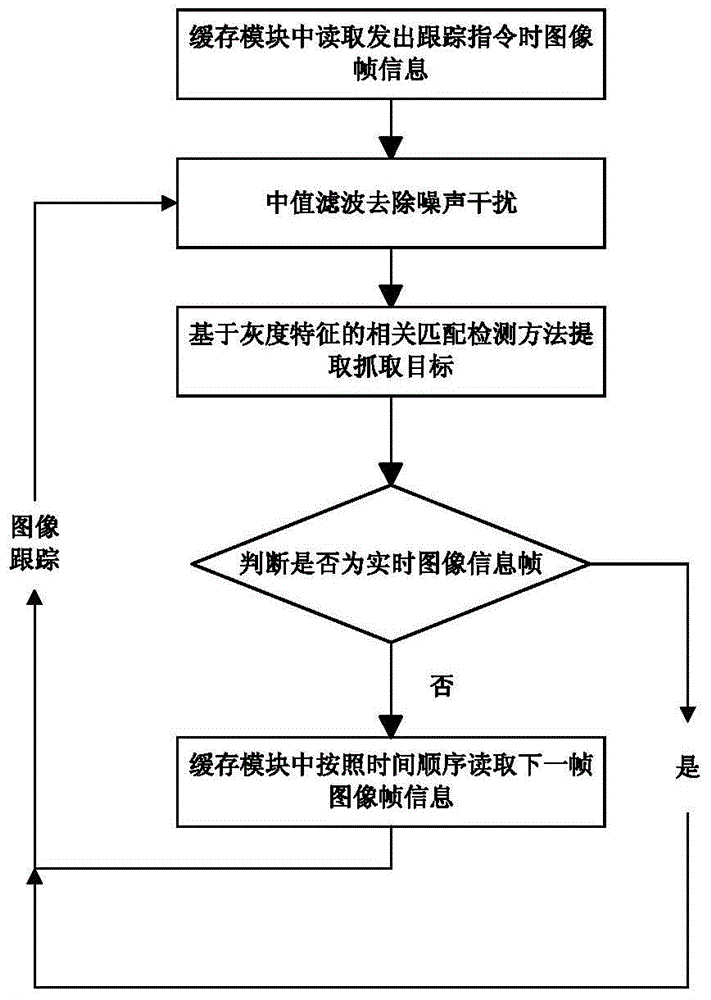

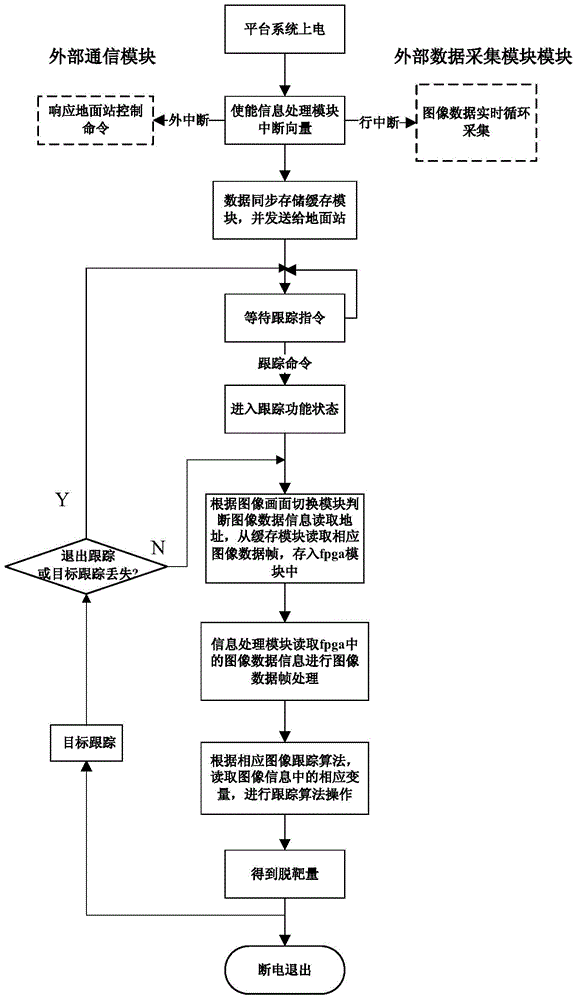

Image caching and tracking method capable of overcoming wireless link delay characteristic

ActiveCN104574383ASolve the problem of inconsistent crawl tracking targetsIncrease success rateImage analysisClosed circuit television systemsInformation processingElectromagnetic interference

The invention provides an image caching and tracking method capable of overcoming a wireless link delay characteristic. The method is implemented by an image caching and tracking system which comprises an information processing module, an FPGA (field programmable gate array) module, a caching module and an image tracking picture switching module. According to the method, the image caching module is used for caching image data in real time, and the cached data are extracted and processed according to wireless link delay values obtained through calculation during tracking, so that the problem that grabbing of tracking targets by a ground station is not consistent with grabbing of tracking targets by an airborne reconnaissance platform due to wireless link delay can be effectively solved, the target grabbing success rate and the tracking speed are increased, the fact that the remote wireless tracking target grabbing success rate is affected by the wireless link delay problem caused by factors such as image compression, the ground environment, peripheral electromagnetic interference and the like is effectively avoided, the target grabbing success rate is high, the grabbing difficulty is low, and the working efficiency of image tracking operators is substantially improved.

Owner:BEIJING INST OF AEROSPACE CONTROL DEVICES

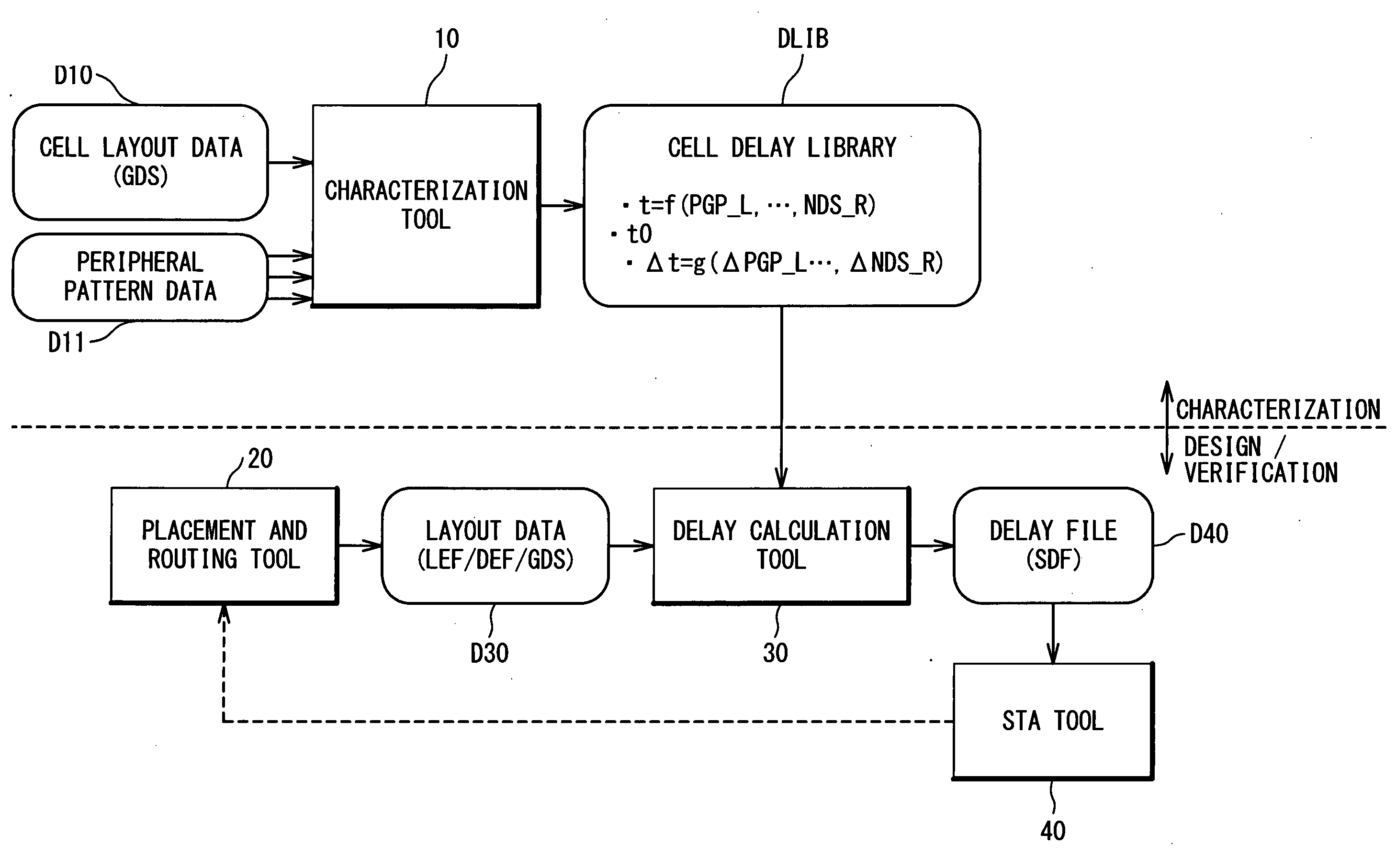

Method and program for designing semiconductor integrated circuit

InactiveUS20090024973A1Prevent increase in design/verification TATHigh delay accuracyCAD circuit designSoftware simulation/interpretation/emulationExecution unitCell based

A method of designing a semiconductor integrated circuit includes: performing a circuit simulation of a cell with changing a parameter that specifies a layout pattern around the cell; and generating a delay function expressing a delay value of the cell as a function of the parameter, based on a result of the circuit simulation. The method further includes: generating a layout data indicating a layout of the semiconductor integrated circuit, based on a cell-based design technique. The method further includes: referring to the generated layout data to extract the parameter associated with a target cell included in the semiconductor integrated circuit; and calculating a delay value of the target cell by using the extracted parameter and the delay function.

Owner:RENESAS ELECTRONICS CORP

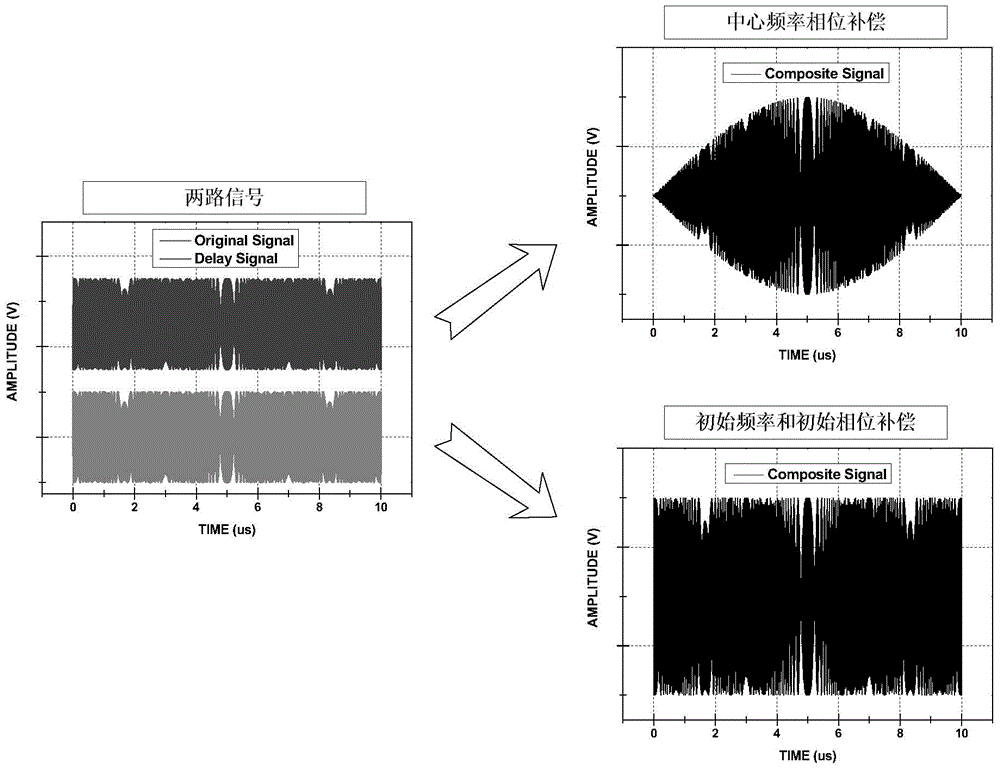

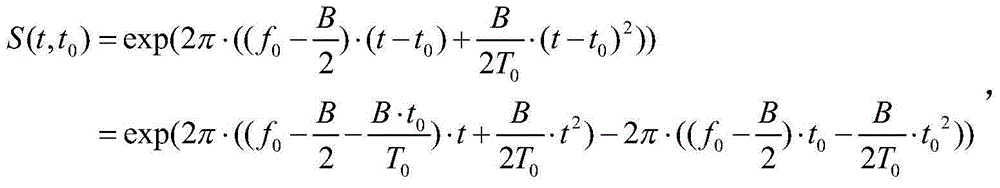

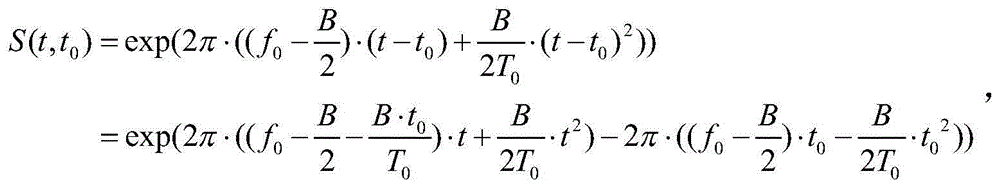

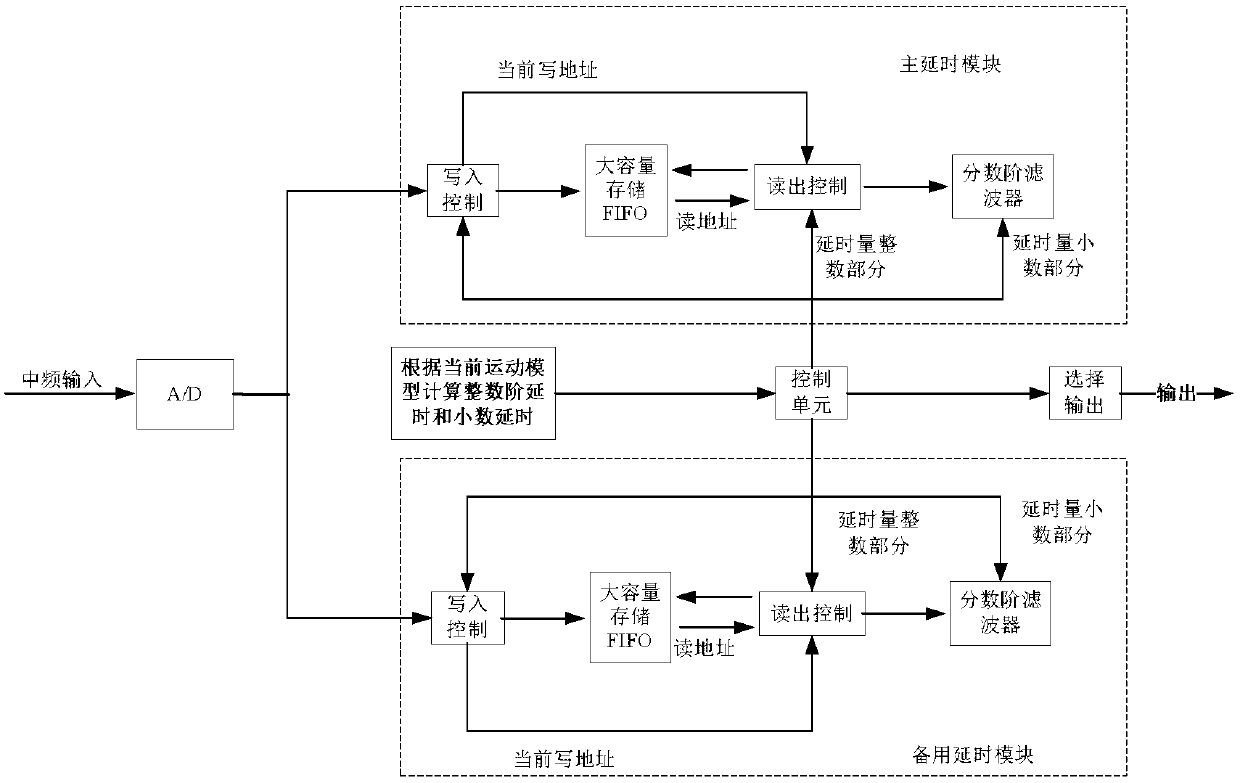

Digital delaying compensation device and method and achieving device and method

InactiveCN104391298AHigh delay accuracyEasy to implementSpecial data processing applicationsRadio wave reradiation/reflectionTime delaysDigital array

The invention discloses a digital delaying compensation device and method and an achieving device and method. The digital delaying compensation device is used for compensating time delay between frequency modulation signals aiming at the broadband digital array radar aperture transition time. The device comprises a receiving module and a compensation module. The receiving module is used for receiving frequency modulation signals. The expression of the frequency modulation signals is provided as follows, wherein t stands for time, t0 stands for delay, S (t, t0) stands the modulation signals delayed for t0 from t, f0 stands for center frequency, B stands for signal bandwidth, and T0 stands for pulse width. The compensation module is used for compensating the frequency modulation signals. The expression of the frequency modulation signals is provided as follows, wherein the fi is the initial frequency, and the delay of the frequency modulation signals is compensated.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

Method and program for designing semiconductor integrated circuit

InactiveUS7913214B2Increase in design/verification TAT can be preventedHigh delay accuracyCAD circuit designSoftware simulation/interpretation/emulationModel parametersCell based

Owner:RENESAS ELECTRONICS CORP

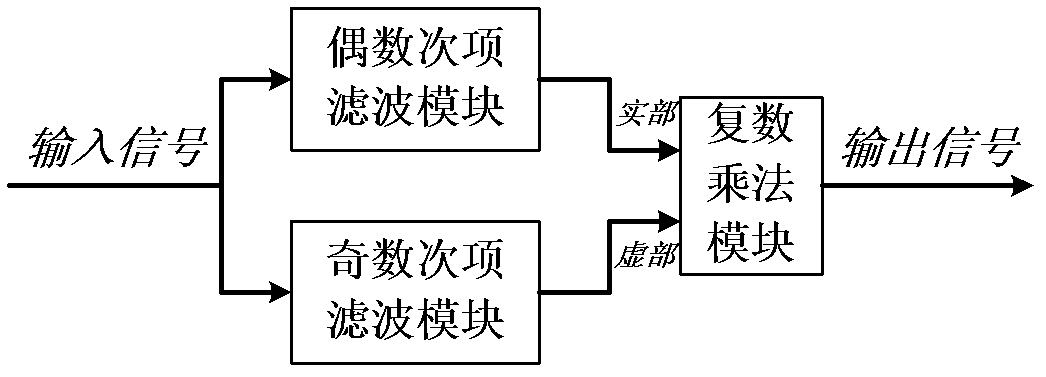

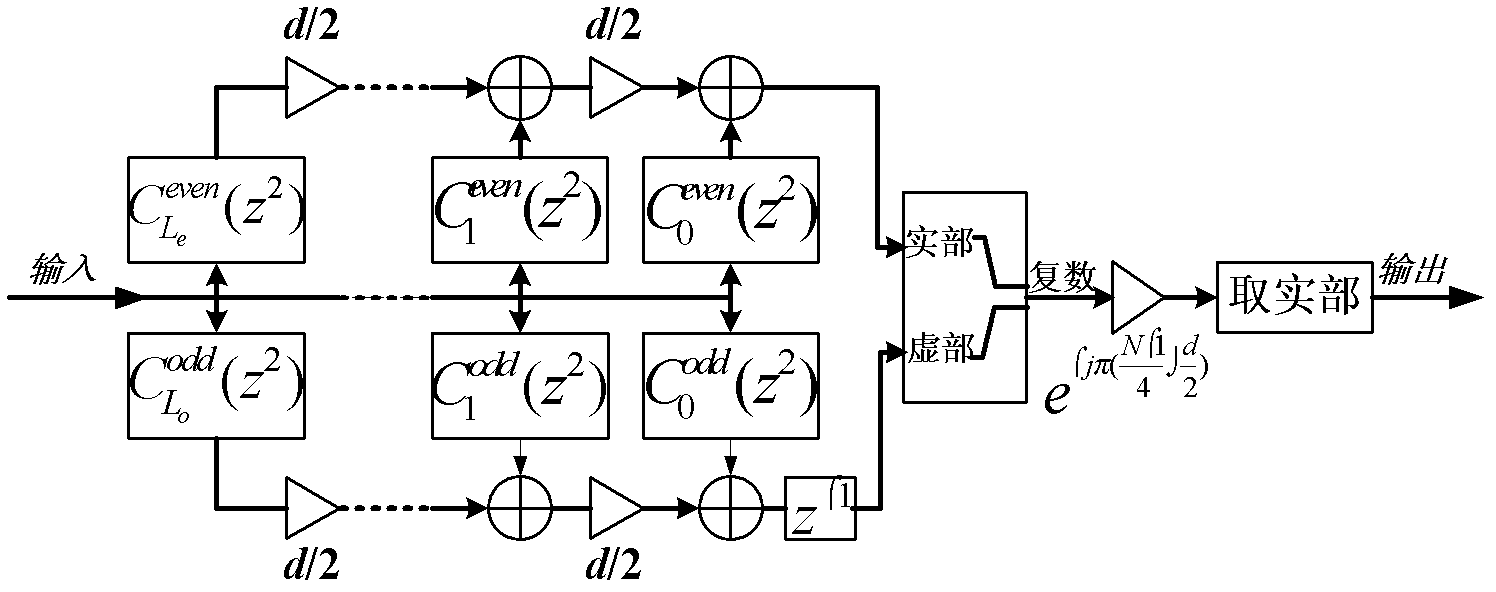

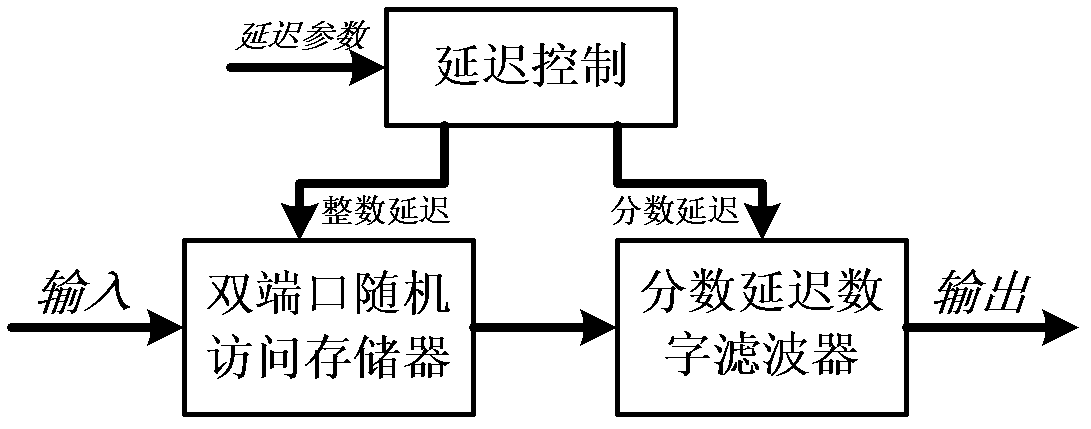

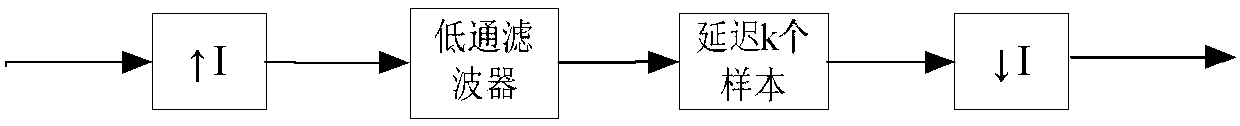

Implementation structure of fractional delay digital filter

InactiveCN102624357ASmall range of variationReduce the order of fitDigital technique networkCurve fittingDigital filter

The invention provides an implementation structure of a fractional delay digital filter. By factorizing odd term and even term of independent variable z in the frequency response function of the fractional delay digital filter, a high-level fractional delay digital filter operation can be factorized into two low-level fractional delay digital filter operations and one complex multiplication operation, thus the variation range of the target fitting curve which takes the delay parameter as the independent variable can be narrowed, the curve fitting orders can be lowered, the number of taps of the filter can be decreased, and hardware resources required for realizing the fractional delay digital filter can be reduced on the premise of not reducing the delay precision.

Owner:SHANGHAI JIAO TONG UNIV

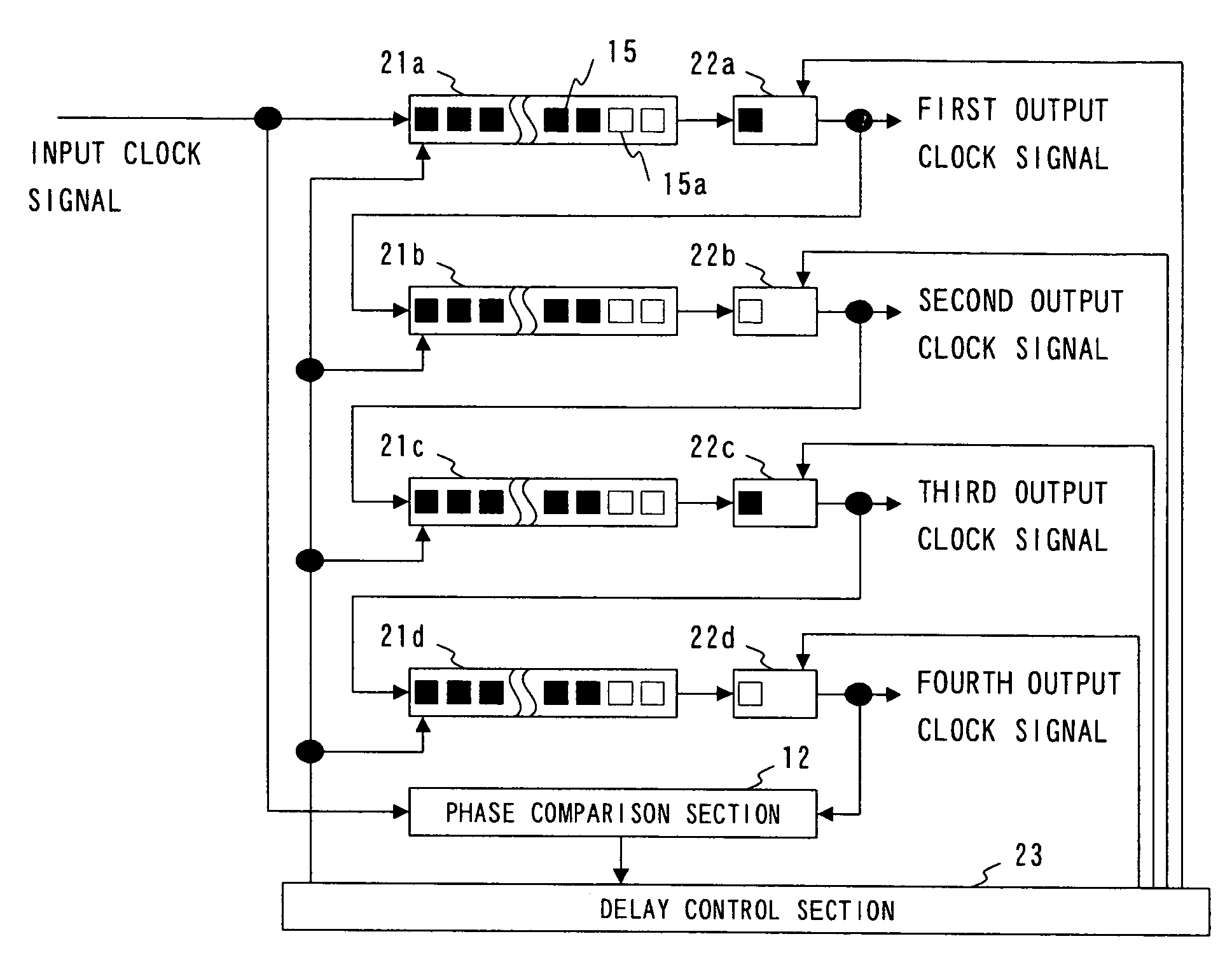

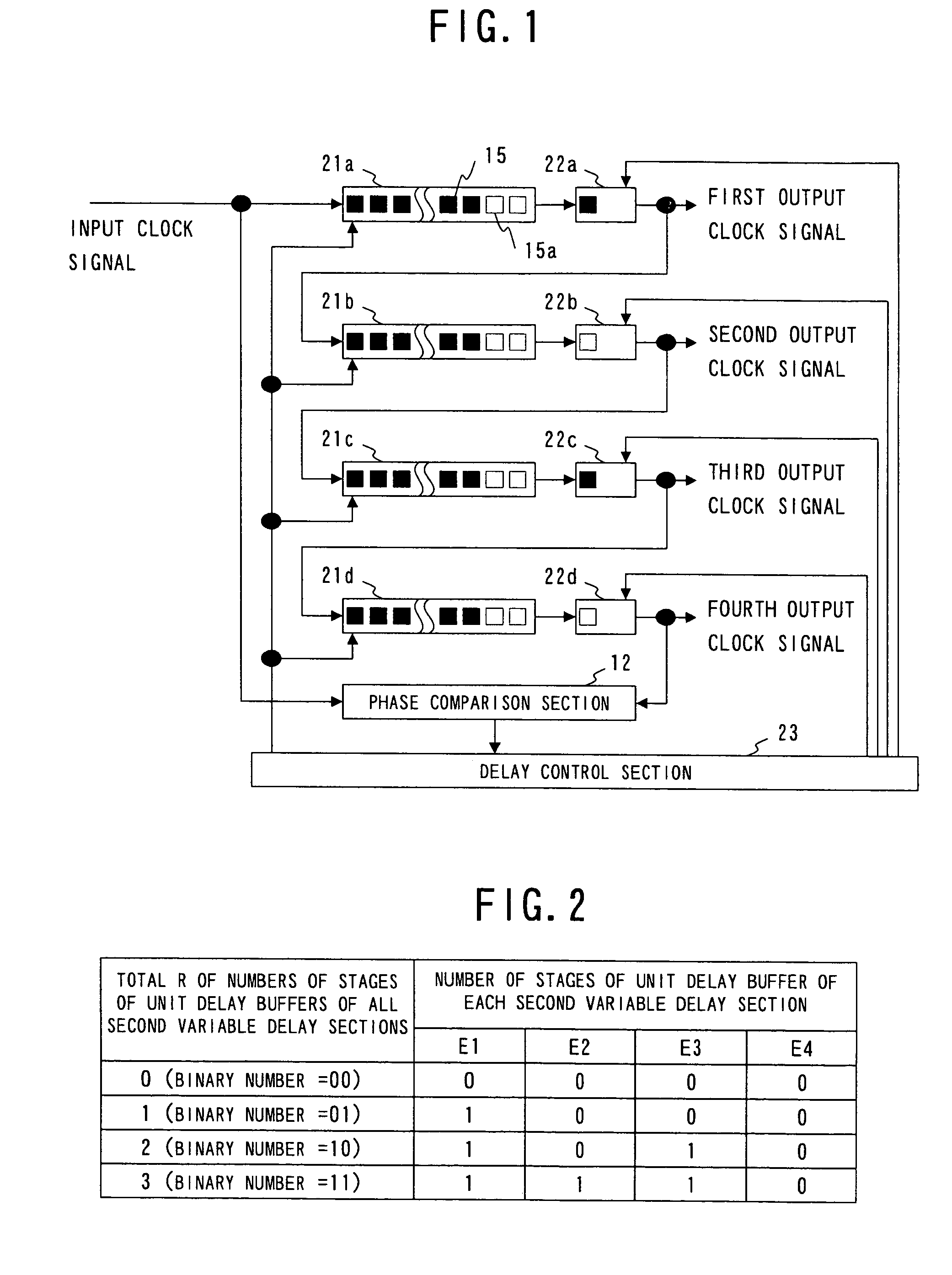

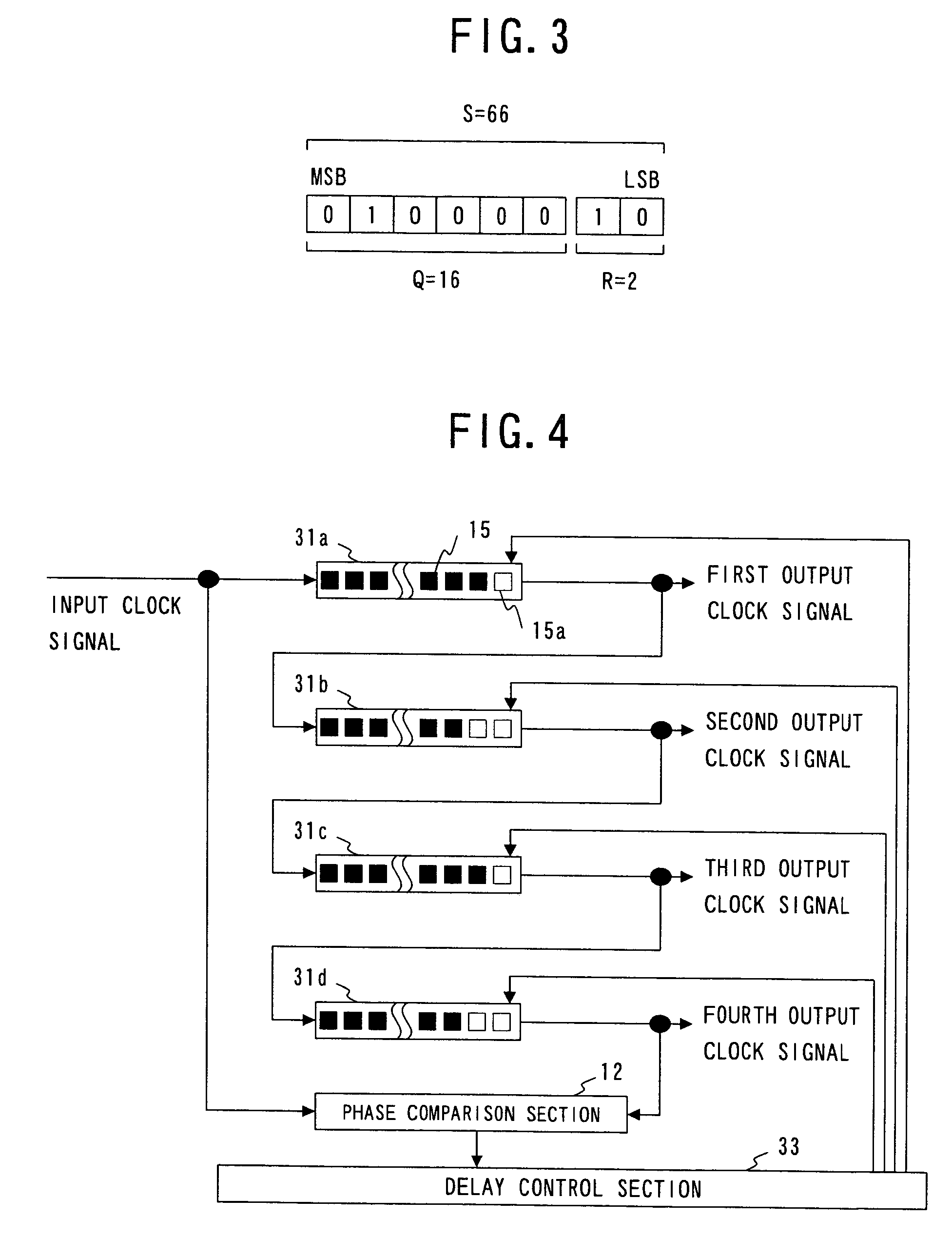

Digital DLL device, digital DLL control method, and digital DLL control program

InactiveUS7116146B2Reduce errorsHigh delay accuracyPulse automatic controlDigital storageOutput compareComputer science

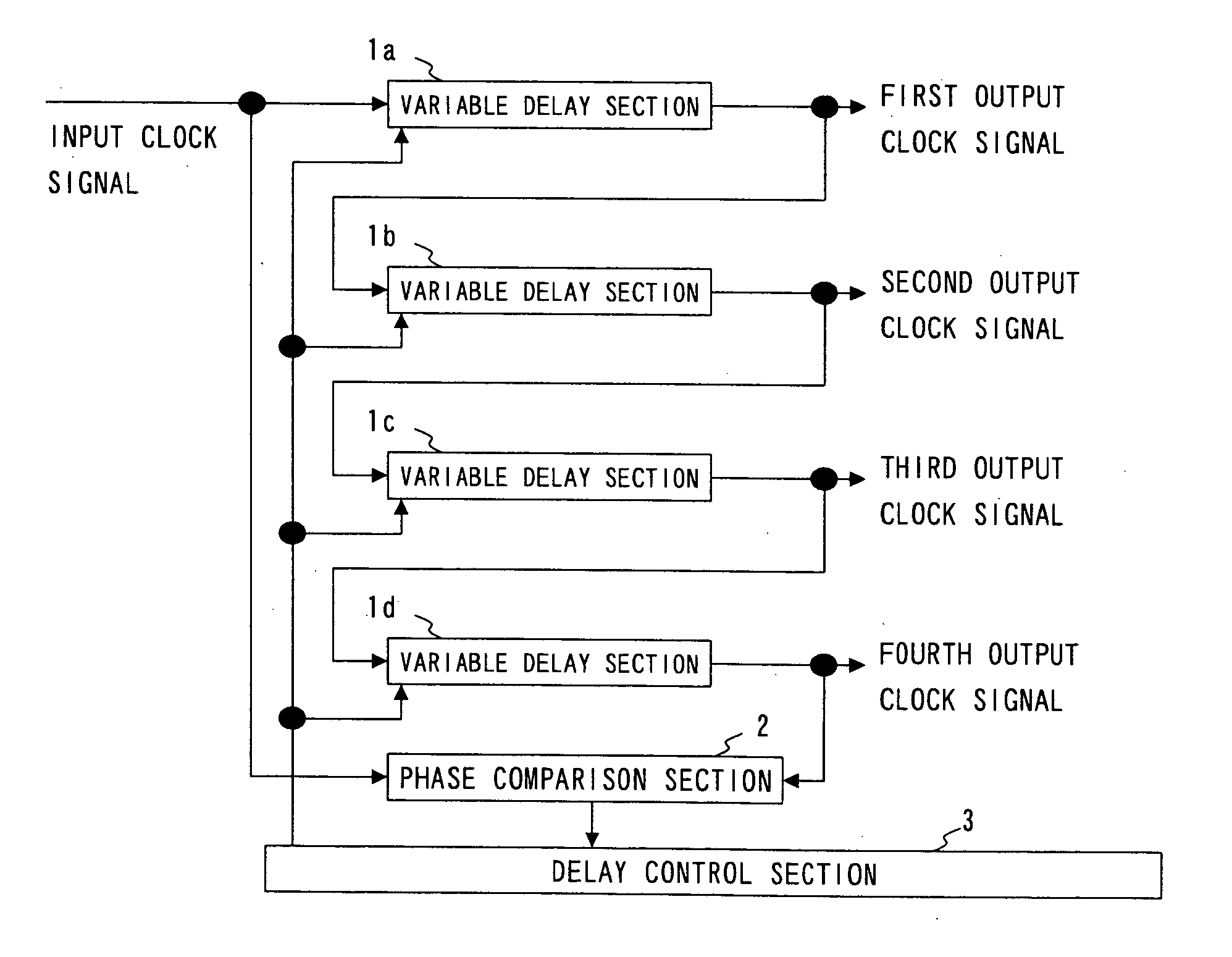

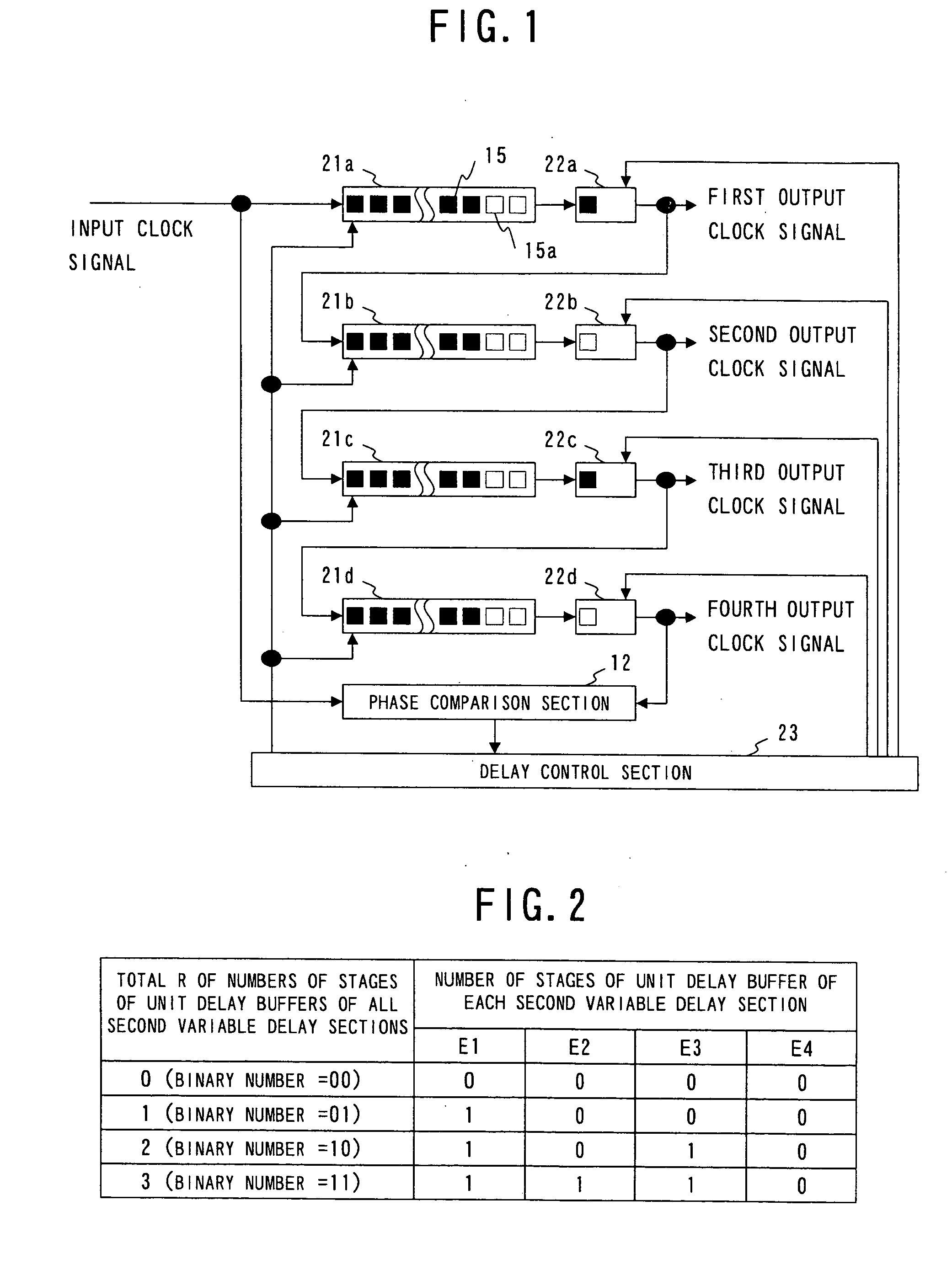

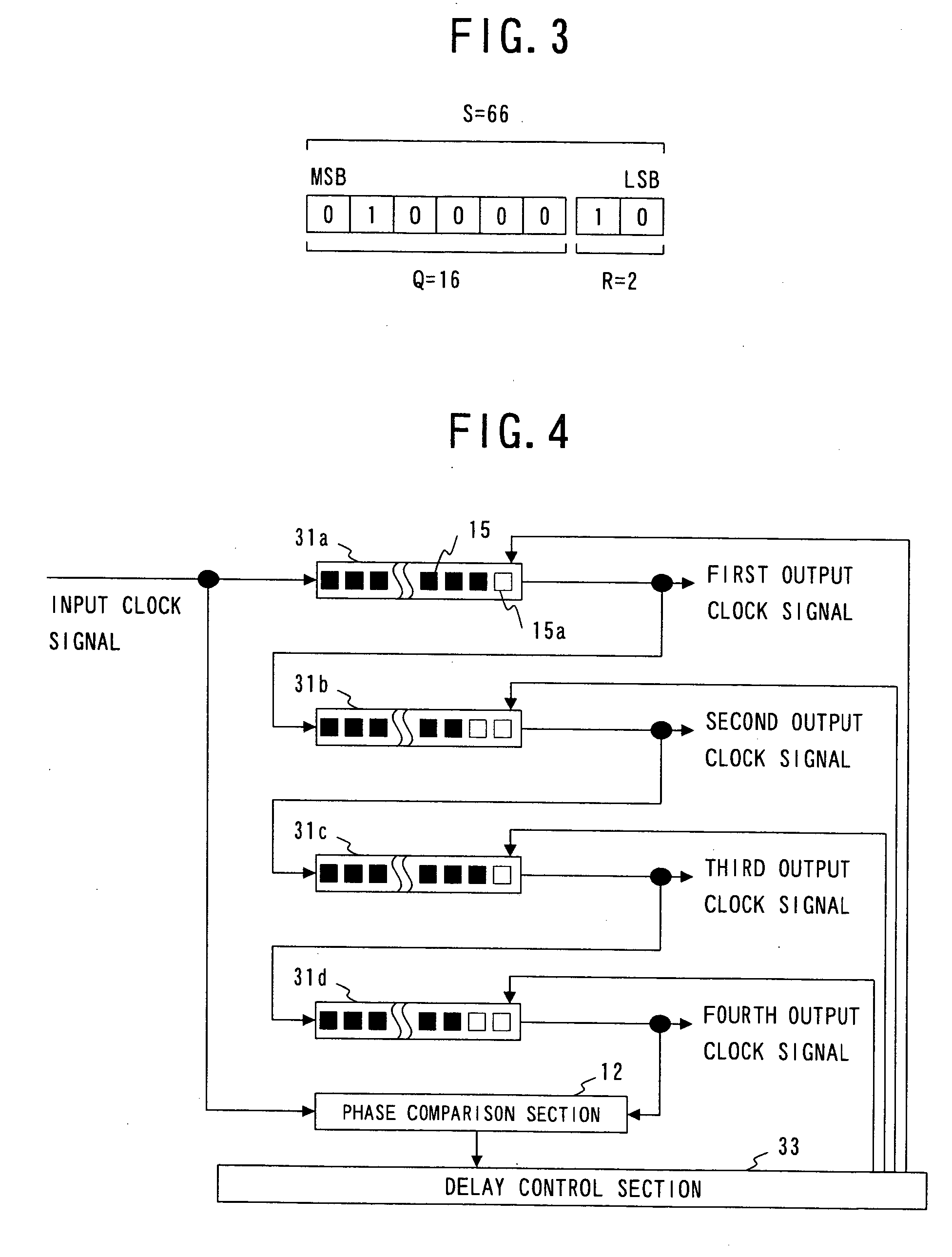

A digital DLL device is provided which can reduce an error with respect to a target delay amount. The device provides a delay to an input clock signal so as to equally divide a clock cycle T thereof into N parts, and includes first variable delay sections and second variable delay sections, each of which is formed of an arbitrary number of unit delay buffers connected in series with one another. A phase comparison section makes a compare between the phase of the input clock signal and the phase of an output signal which is the input signal having been delayed while passing through all the first and second variable delay sections, and outputs a result of the comparison. A delay control section calculates a total number of unit delay buffers S required based on the phase comparison result, sets a quotient Q of S divided by N to be the number of unit delay buffers for each of the first variable delay sections, and allocates a remainder R of S divided by N to the second variable delay sections, respectively.

Owner:FUJITSU LTD

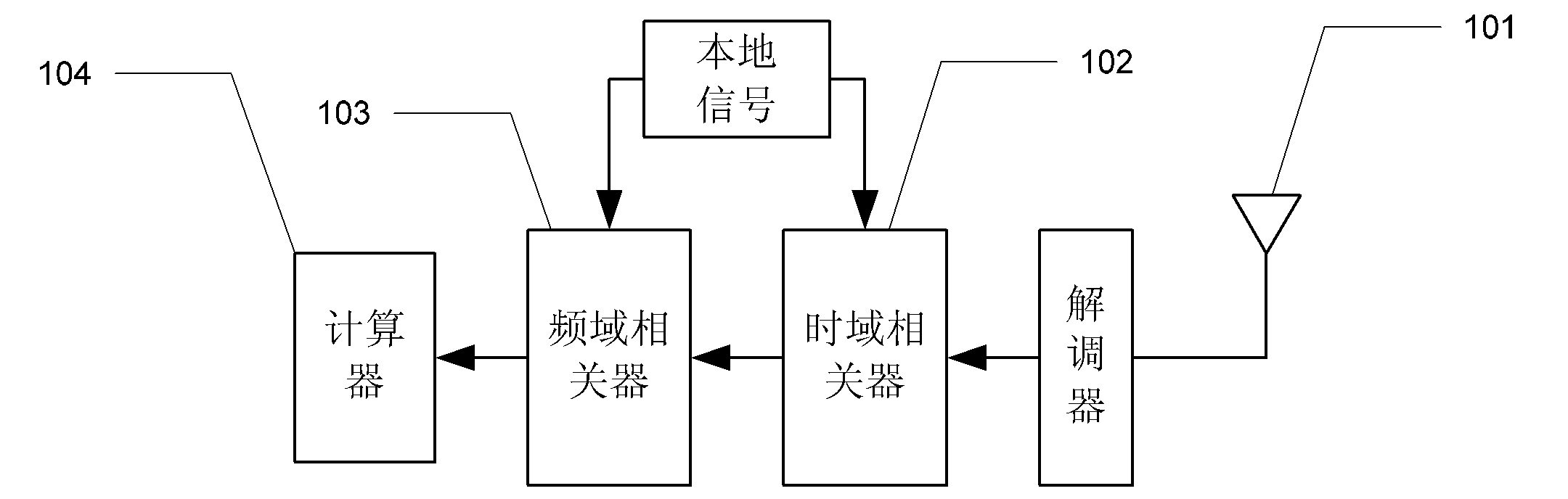

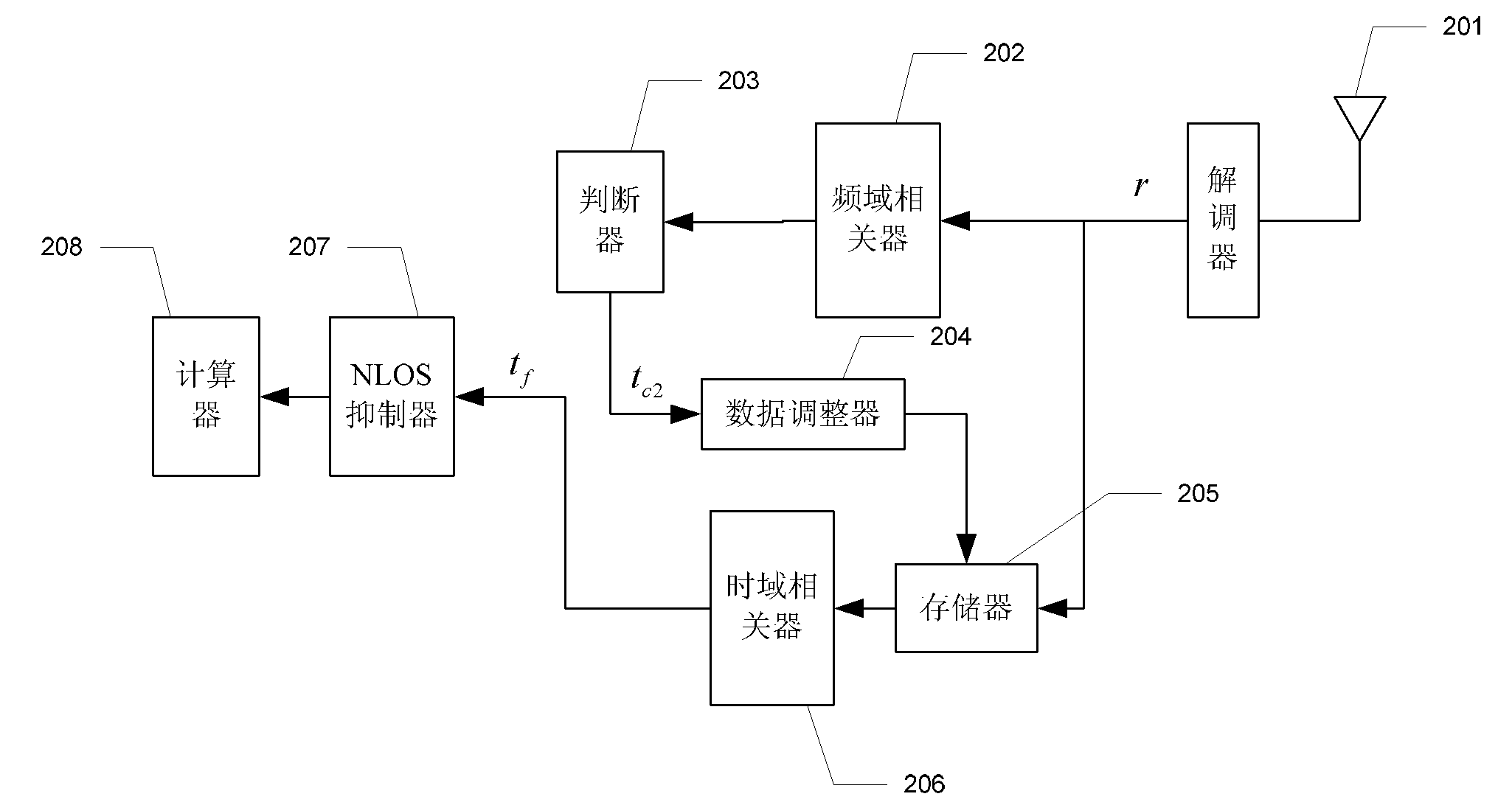

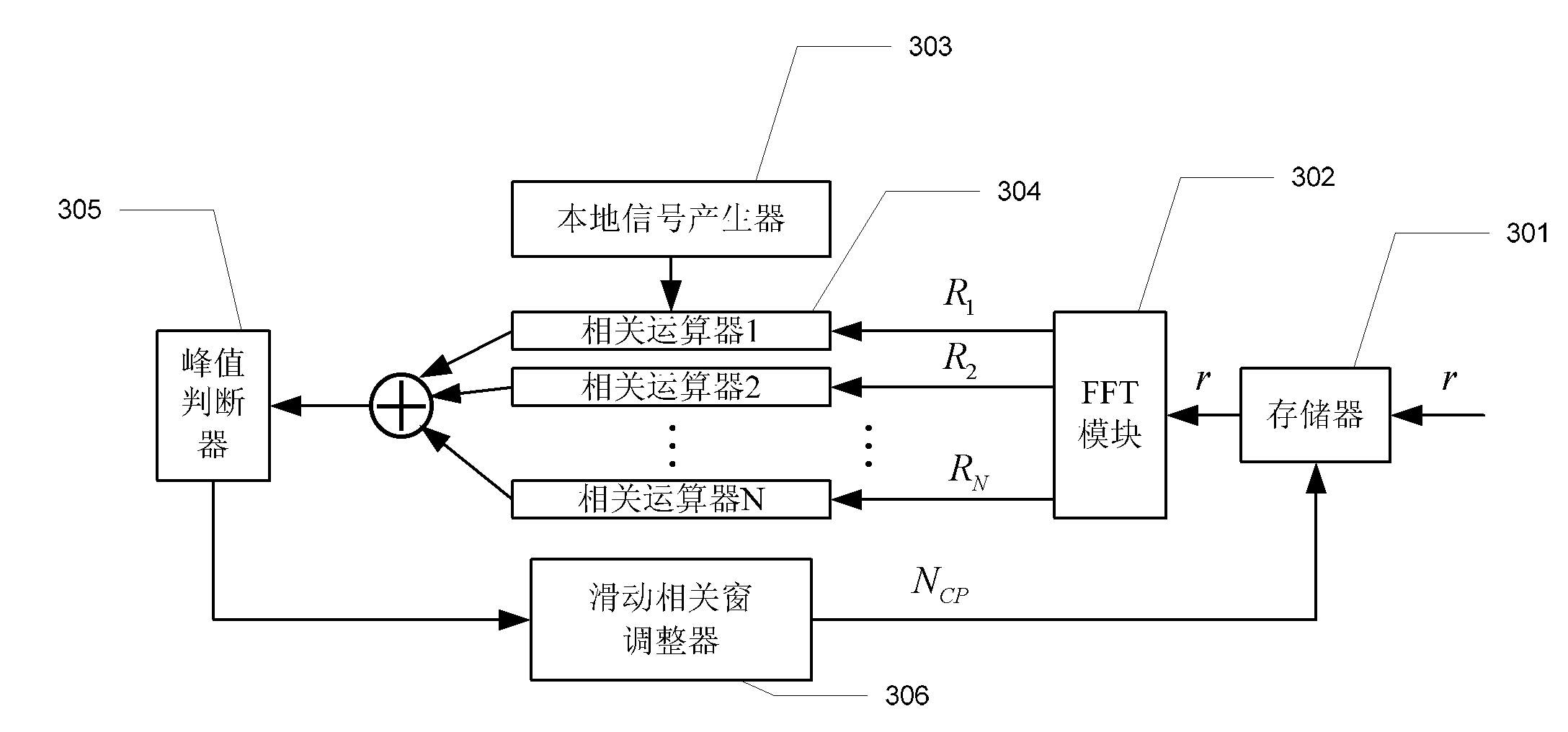

LTE (long term evolution) terminal wireless positioning system based on quick time-delay parameter search

InactiveCN102131289AGood for delay accuracyHigh engineering significance and commercial valueMulti-frequency code systemsWireless communicationVIT signalsSlide window

The invention discloses an LTE (long term evolution) terminal wireless positioning system based on quick time-delay parameter search. In the invention, the positional parameter solution process comprises the following steps: performing frequency domain correlation operation between a received signal and a local signal in a frequency domain correlator (202); judging related peak values in a judging device (203), and sending feedback information to a data adjuster (204); obtaining the maximum peak value through judgment after sliding window transformation, and recording the position in which the peak value is located; reading data in a memory (205), sending the data to a time domain correlator (206) for time domain correlation operation so as to obtain the maximum related peak value, and recording a time delay position; suppressing NLOS influence of the signal by an NLOS (non-line-of-sight) suppressor (207); and finally calculating a target position in a calculator (208). The LTE terminal wireless positioning system is applicable to an LTE communication system, and has good application value in different noise interference environments; and relative to the traditional engineering system, the system has the advantages of fast positioning speed and high positioning precision, thus having wide engineering realization significance.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

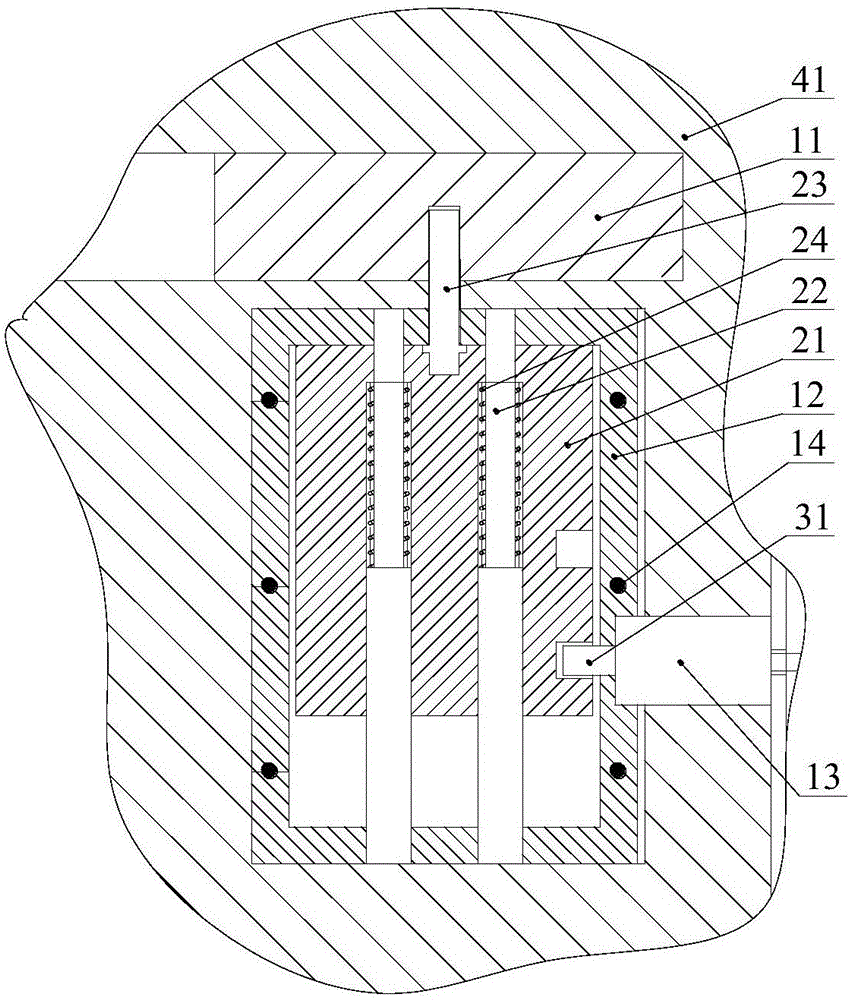

Time delay releasing structure for inertia safety mechanism

ActiveCN106314812ASimple structural designHigh delay accuracyAircraft indicatorsFixed frameDelayed time

The invention provides a time delay releasing structure for an inertia safety mechanism. The time delay releasing structure for the inertia safety mechanism comprises an isolation slider, a fixing frame, an electromagnetic pin puller, an inertial slider, a guide shaft, a slider end pin, and a compression spring; the isolation slider is transversely arranged on the base, and the bottom of the isolation slider is provided with a blind hole; the fixing frame is fixed on the base and at the lower position of the isolation slider, a slidable inertial slider is arranged within the fixing frame, the guide shaft is fixed within the inertial slider, and the compression spring is arranged on the guide shaft in a sleeved mode; the slider end pin is fixed on the middle of the top of the inertial slider, and the upper end of the slider end pin is arranged in the inside of the middle section of the isolation slider in a inserted mode; the side of the fixing frame is provided with the electromagnetic pin puller arranged on the base. According to the time delay releasing structure for inertia safety mechanism, the structure design of inertia safety mechanism is simplified, the delay time of the inertia safety mechanism can be decided at will, the delay precision of the inertia safety mechanism is improved, the anti vibration ability and reliability of the inertia safety mechanism are improved, the adaptive capacity to environment of the inertia safety mechanism is increased, and the time delay releasing structure is beneficial for the miniaturization development of the inertia safety mechanism.

Owner:GUIZHOU AEROSPACE ELECTRONICS TECH CO LTD

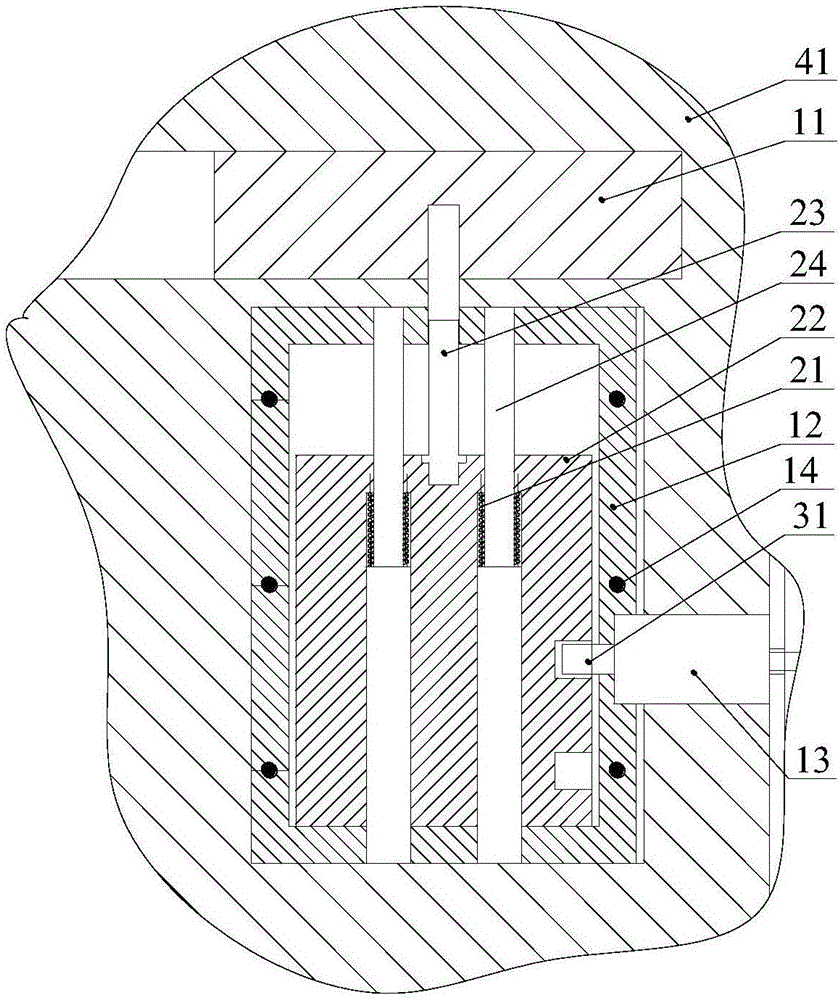

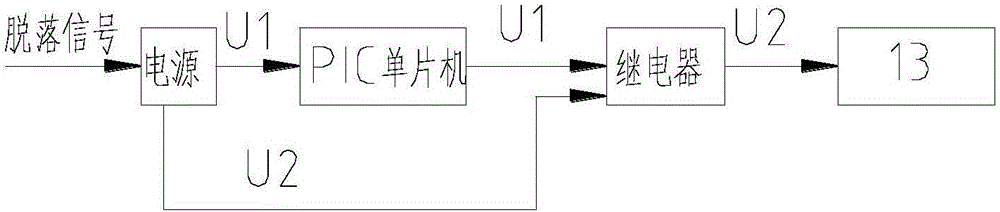

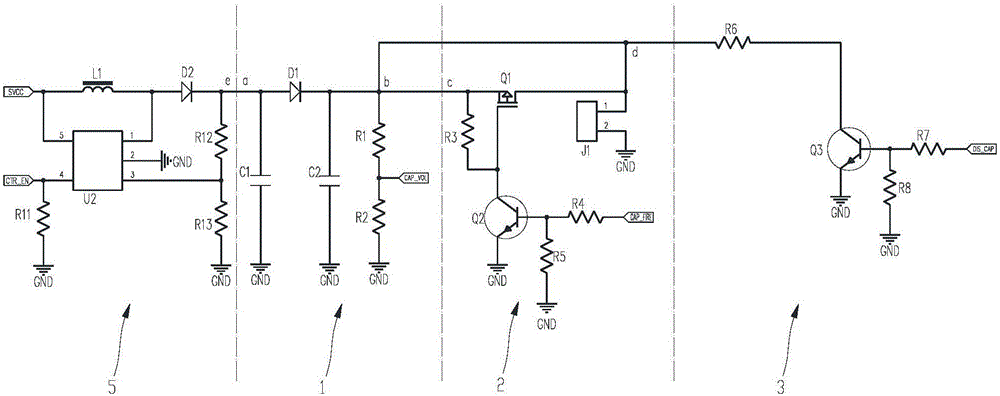

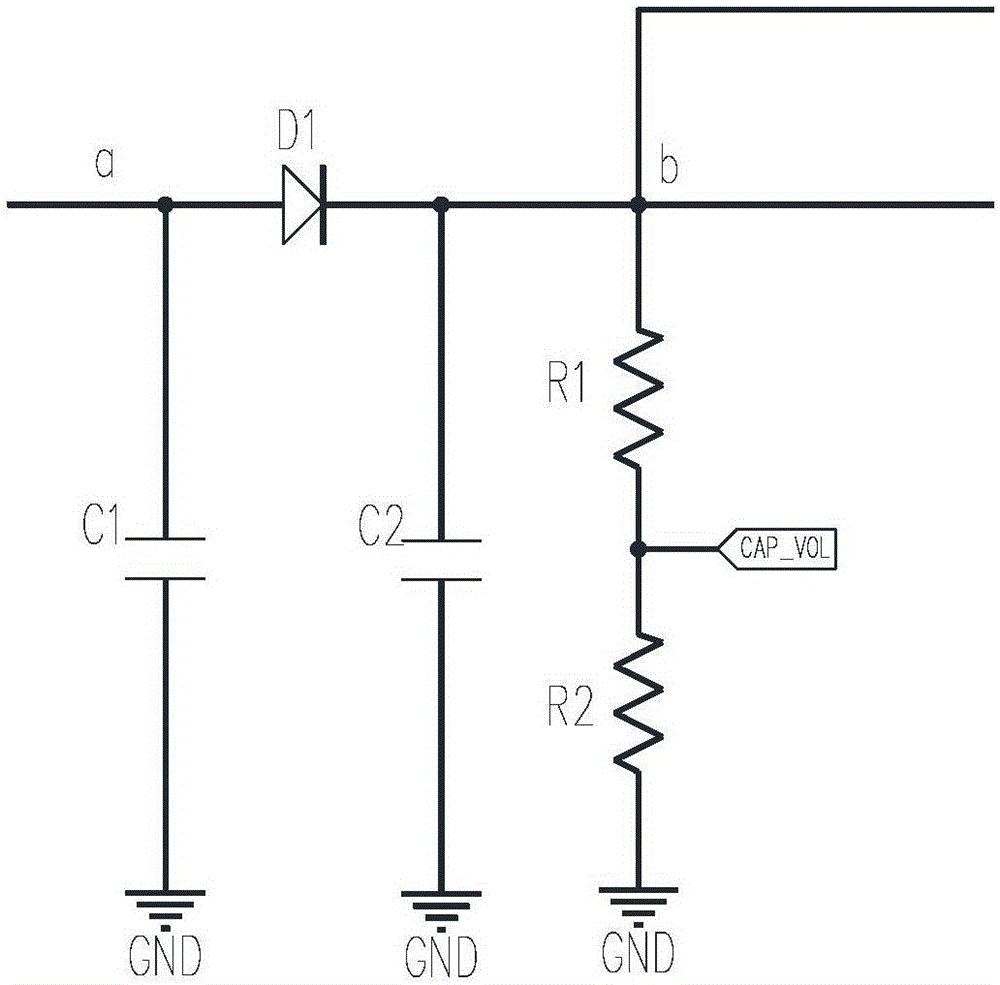

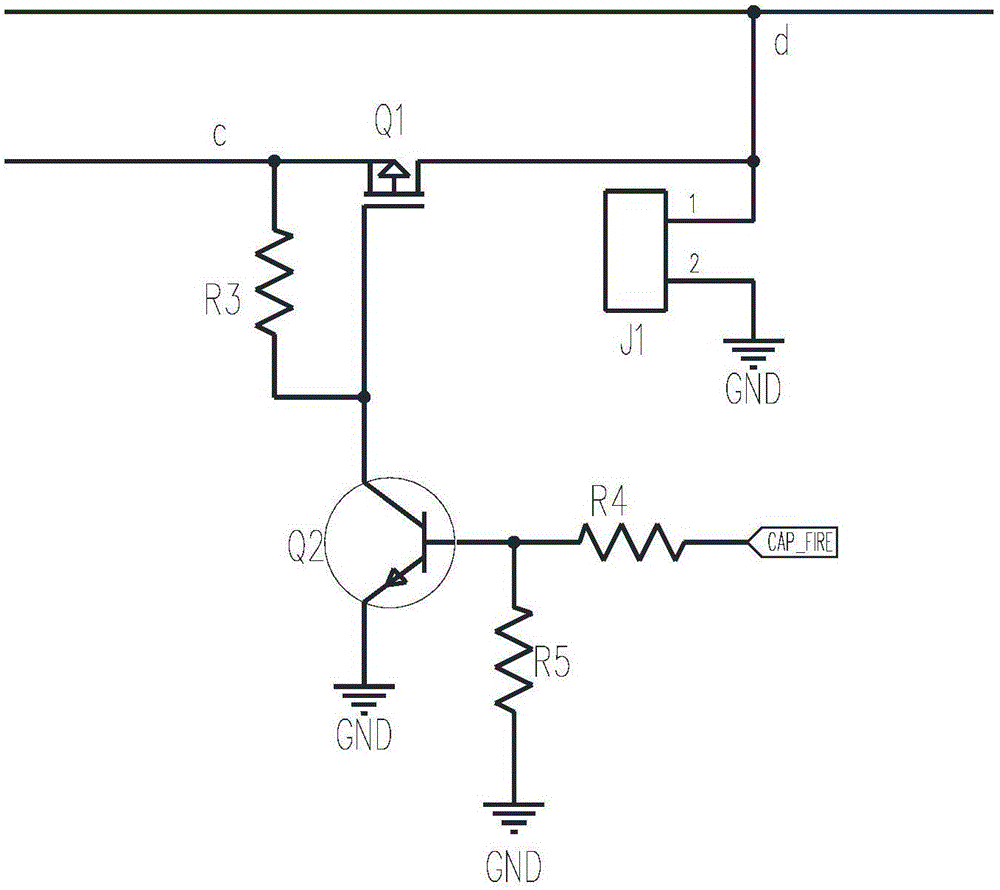

Delay detonation control circuit

ActiveCN105043173ANo false triggerFlexible setting of delayed turn-on timeElectric fuzesElectricityDetonator

The invention discloses a delay detonation control circuit. The delay detonation control circuit comprises a charging circuit, a discharging circuit, a protection circuit and a function circuit. The charging circuit comprises an energy storage element used for carrying out energy storage after current signals are received. The discharging circuit comprises a first switch circuit used for being connected with an electric detonator, and when the first switch circuit is conducted, energy stored in the energy storage element is released to the electric detonator through the first switch circuit, and the remote detonation control over a short electric detonator is achieved. The function circuit comprises a programmable device through which the delay conduction time of the first switch circuit can be flexibly set, and the delay precision is high. In addition, the protection circuit further comprises a second switch circuit. When the first switch circuit is in a stop state, the second switch circuit is conducted, the energy stored in the energy storage element is released through the second switch circuit, and the electric detonator is effectively prevented from being mistakenly triggered when the first switch circuit is in the stop state.

Owner:成都天博威科技有限公司

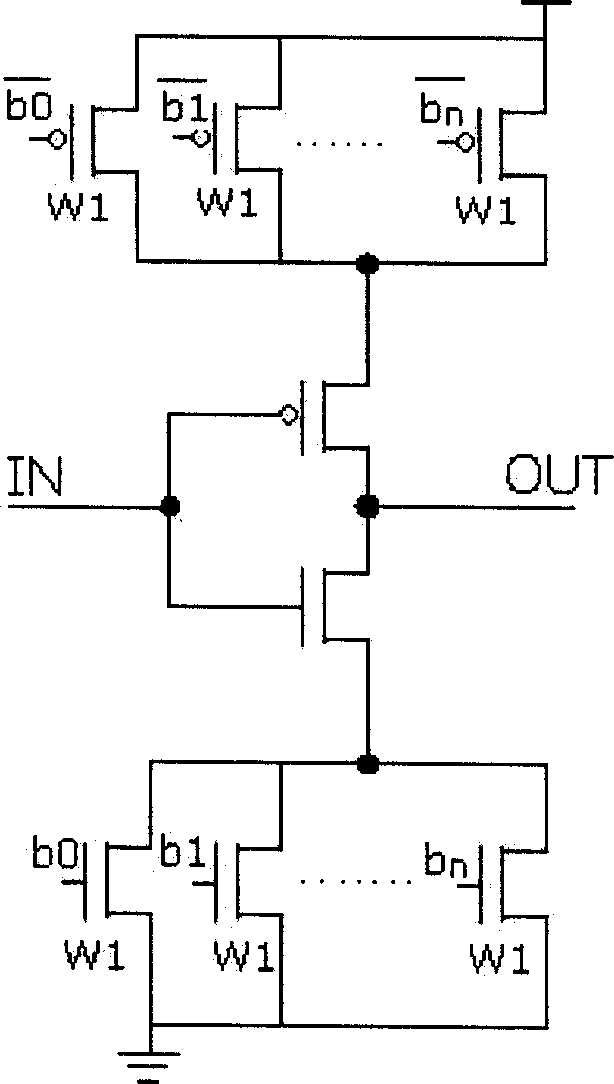

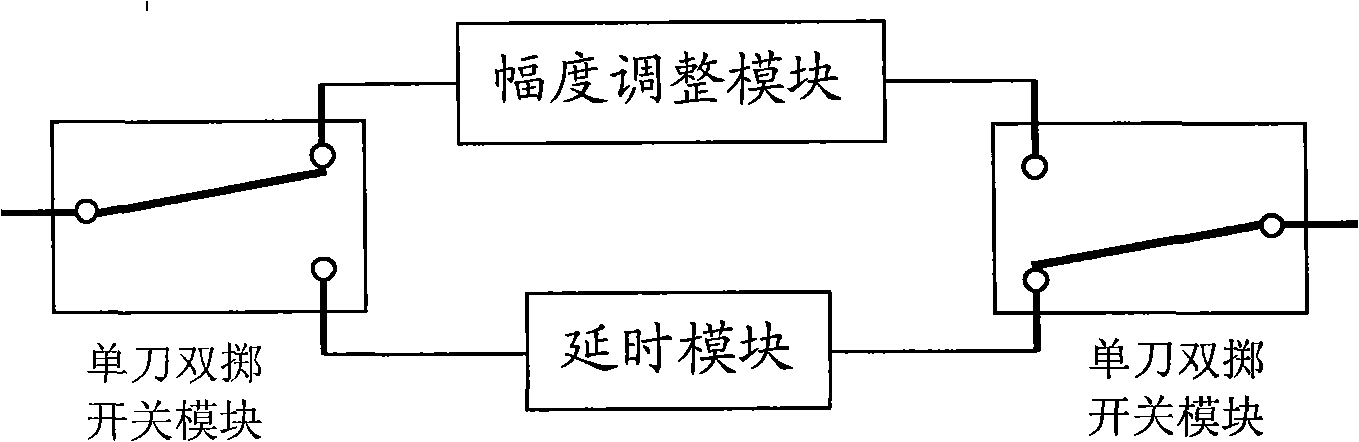

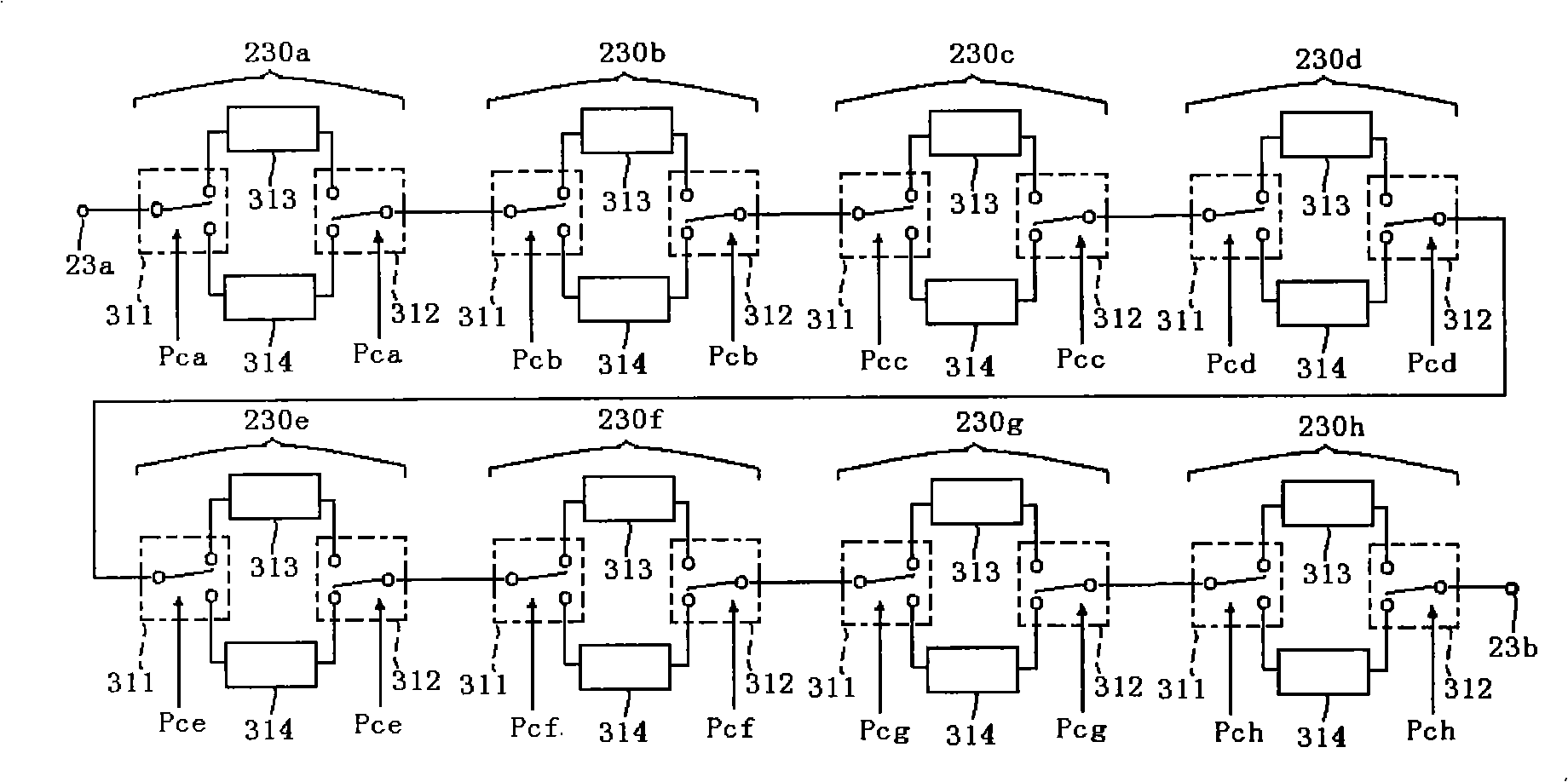

Gallium arsenide monolithic integrated numerical-control real time delay circuit

ActiveCN101527550AHigh delay accuracyGood electrical performance consistencyMultiple-port networksDelay linesTime delaysIntegrated circuit

The invention discloses a gallium arsenide monolithic integrated numerical-control real time delay circuit which consists of different basic delay potentials and is characterized in that more than two different basic delay potentials are integrated on the same chip by adopting the integrated circuit technology and the basic delay potentials are connected in series, wherein, each basic delay potential comprises single-pole double-throw switch modules, a delay module and an amplitude adjustment module; the common terminal of one single-pole double-throw switch module is connected with the input signals, and the other two terminals thereof are connected with the input terminals of the delay module and the amplitude adjustment module respectively; and the common terminal of the other single-pole double-throw switch module is the signal output terminal, and the output terminals of the delay module and the amplitude adjustment module are connected with the other two ends thereof. The invention can improve the delay precision, so that better consistency of electrical properties is ensured and the invention is least controlled and affected by the technology; meanwhile, the invention increases the signal amplitude adjustment circuit, compensates for the amplitude fluctuation of the delay branch, fulfils the functions of a plurality of circuits in the transceiver system and reduces the complexity of the system.

Owner:河北新华北集成电路有限公司

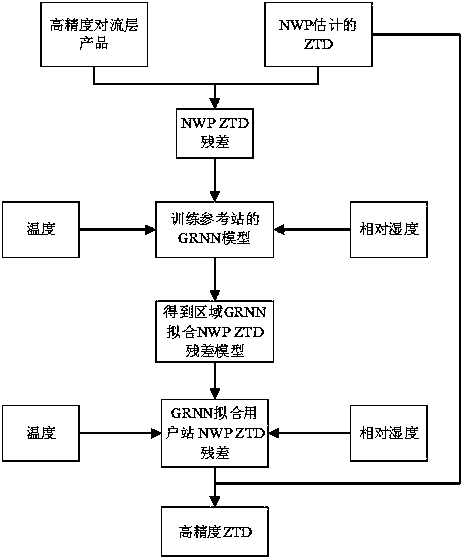

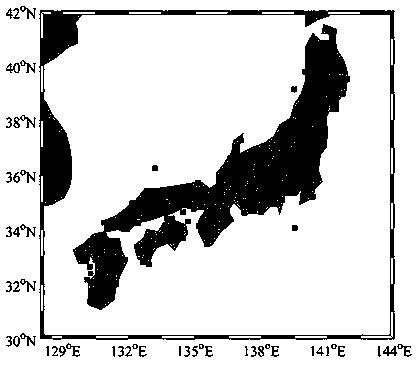

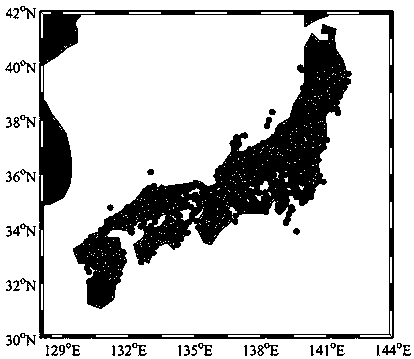

Regional NWP tropospheric delay correction method based on GRNN model

ActiveCN110031877AHigh delay accuracyLatency Accurate EstimationIndication of weather conditions using multiple variablesSatellite radio beaconingNumerical weather predictionComputer science

The invention discloses a regional NWP (Numerical Weather Prediction) tropospheric delay correction method based on a GRNN (General Regression Neural Network) model. According to the method, firstly,ZTD (Zenith Tropospheric Delay) in one continuous year of all selected continuous operational reference stations in an operation region and reanalysis data provided by NWP in the region in the continuous year are acquired, and an integral method is utilized to invert the ZTD of the continuous operational reference stations in the region; secondly, parts of the stations are selected to serve as training stations, the remaining stations serve as test stations, a GRNN is utilized to fit residual errors of the ZTD inverted according to NWP data of the training stations, and a GRNN residual error fitting model is obtained; and thirdly, error compensation is performed on the ZTD inverted according to the NWP data of the test stations through the GRNN residual error fitting model, and then precise NWP_ZTD of the test stations is obtained. Through the method, error compensation is performed on the NWP_ZTD by fitting the residual errors of the NWP_ZTD through the GRNN model according to the change law of the residual errors of the NWP_ZTD along with multiple meteorological factors for the first time, and NWP inverted tropospheric delay precision is improved.

Owner:SHANDONG UNIV OF SCI & TECH

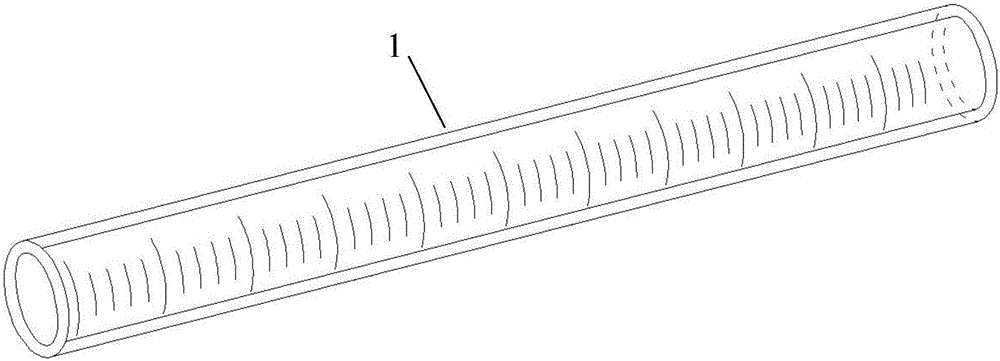

Manufacturing method of micro lead delay detonating detonator

The invention relates to a manufacturing method of a micro lead delay detonating detonator, belonging to the field of production of civil blasting devices. The manufacturing method of the micro lead delay detonating detonator comprises the following steps of: (1) charging delay powder into an aluminum metal pipe; (2) drawing the aluminum metal pipe charged with the delay powder into a slim metal pipe with the diameter of 1.4-2.6 mm; (3) carrying out plastic coating on the slim metal pipe to form a delay body, wherein plastic coating thickness is 1.5-2.5 mm; (4) cutting the delay body into delay elements with the lengths of 8-200 mm; and (5) assembling to manufacture the micro lead delay detonating detonator. According to the invention, the heavy metal lead is prevented from polluting the environment, the delay accuracy of the micro lead delay detonating detonator is enhanced and the cost of the micro lead delay detonating detonator is reduced; in addition, the micro lead delay detonating detonator can be produced by adopting an integral type structure and also adopting a split type outer delay structure, and delay time is not influenced by the body length of a fire detonator, therefore the requirements on special users can be met by greatly prolonging the delay time.

Owner:山东圣世达化工有限责任公司

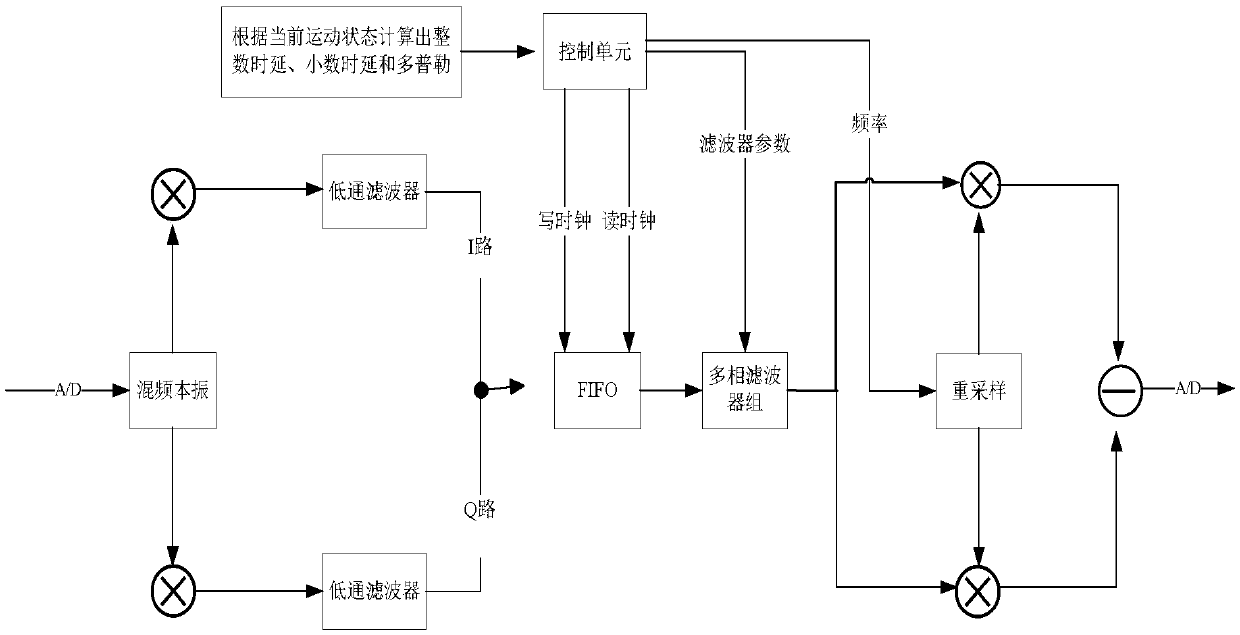

Method for simulating dynamic characteristics of target with non-coherent demodulation

ActiveCN108111450AReduce occupancyReduce consumptionCarrier regulationTransmission monitoringControl signalPhase filter

The invention discloses a method for simulating dynamic characteristics of a target with non-coherent demodulation, aiming at providing a method with the characteristics that the time delay precisionis high, the signal demodulation is not required, and signal motion characteristics can be simulated dynamically with high precision. The invention is realized through the following technical scheme:mixing is carried out with a mixer with a fixed local oscillator after A / D sampling to obtain two low frequency signals of I and Q; a control unit reads the two low frequency signals of I and Q from afirst in first out queue FIFO, calculates orbital data such as the integer time delay, the fractional delay, the carrier Doppler frequency and so on according to the distance and velocity informationof the motion state of the current target, sends the obtained filtering parameters into a poly-phase filter and a re-sampling module, so as to obtain the two baseband data of I and Q after delay adjustment; and an intermediate frequency digital signal is recovered through re-sampling of the re-sampling module and carrier Doppler adjustment; wherein the intermediate frequency digital signal afterthe control unit delay adjustment and the sampling carrier frequency adjustment satisfies the dynamic characteristics of the downlink intermediate frequency measurement and control signal.

Owner:10TH RES INST OF CETC

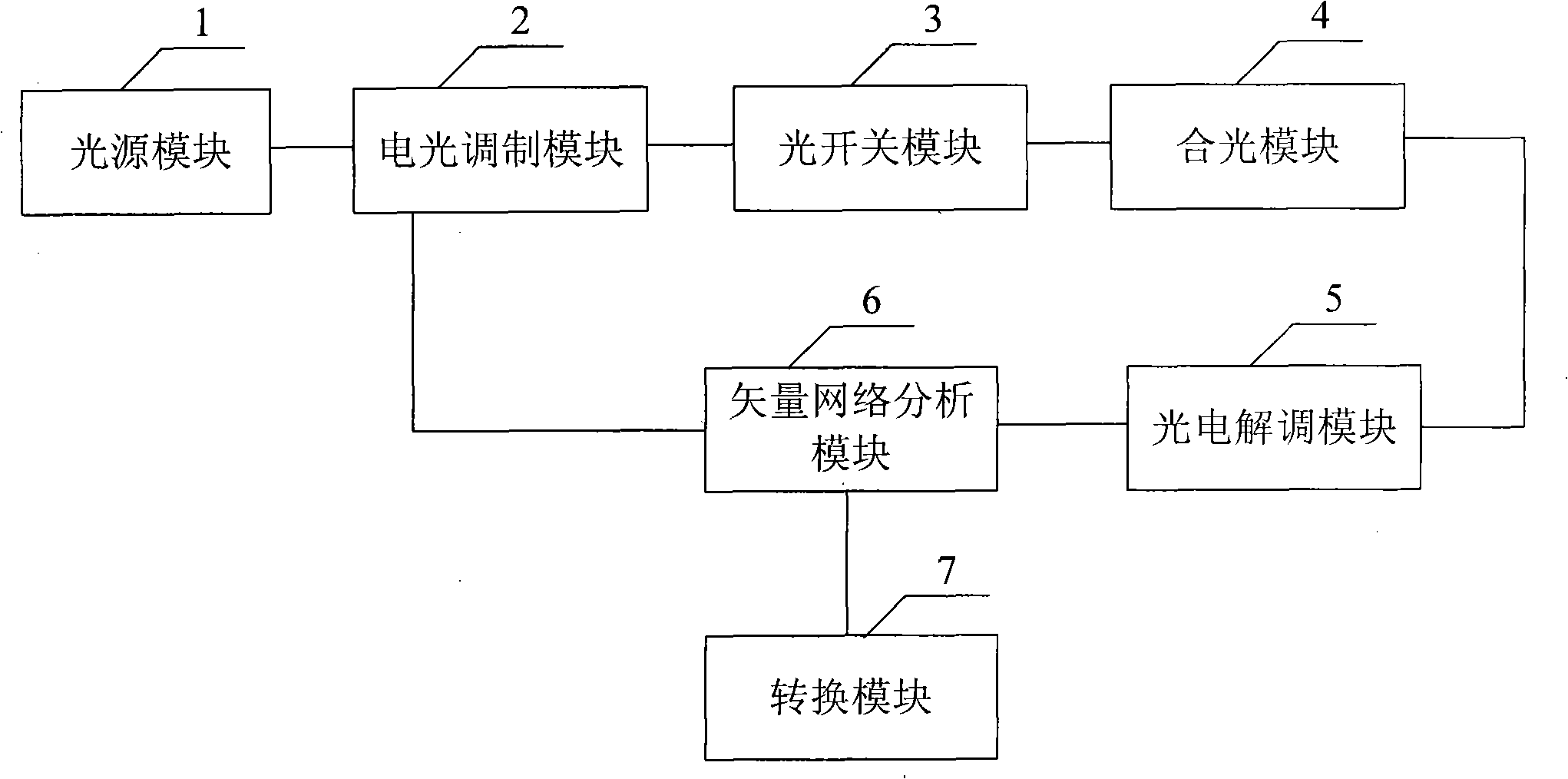

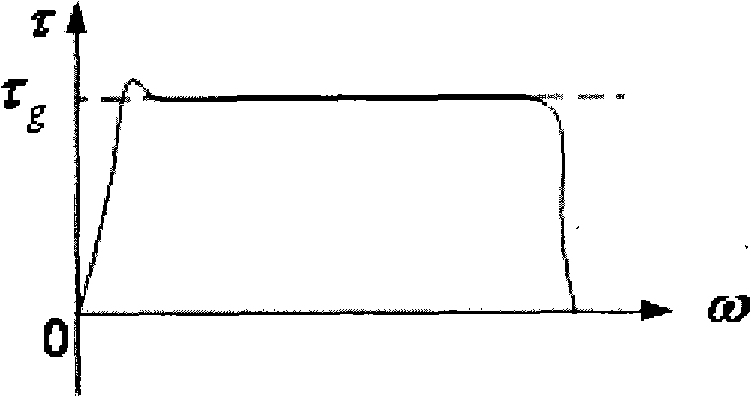

Method for obtaining optical path difference of optical switch and device

InactiveCN101539474ASimple and fast operationHigh precisionTesting optical propertiesElectric lightEngineering

The invention relates to a method for obtaining optical path difference of an optical switch and a device. The proposal thereof is as follows: firstly an input electric signal provided by a vector network analysis module is modulated on an optical carrier by electric light to obtain an optical signal; then the optical signal is switched to an access by the optical switch, and a path of optical fiber transmission signal is obtained by combined light; the optical fiber transmission signal are demodulated by photoelectricity and then the group delay of the two accesses in the optical switch is obtained by vector network analysis; and finally the group delay of the two accesses is switched to obtain the optical path difference of the two accesses in the optical switch. The invention realizes the measurement of little optical path difference in the optical switch, thus improving the delay precision of an implementation system of the optical switch of the OTTD technology.

Owner:BEIHANG UNIV

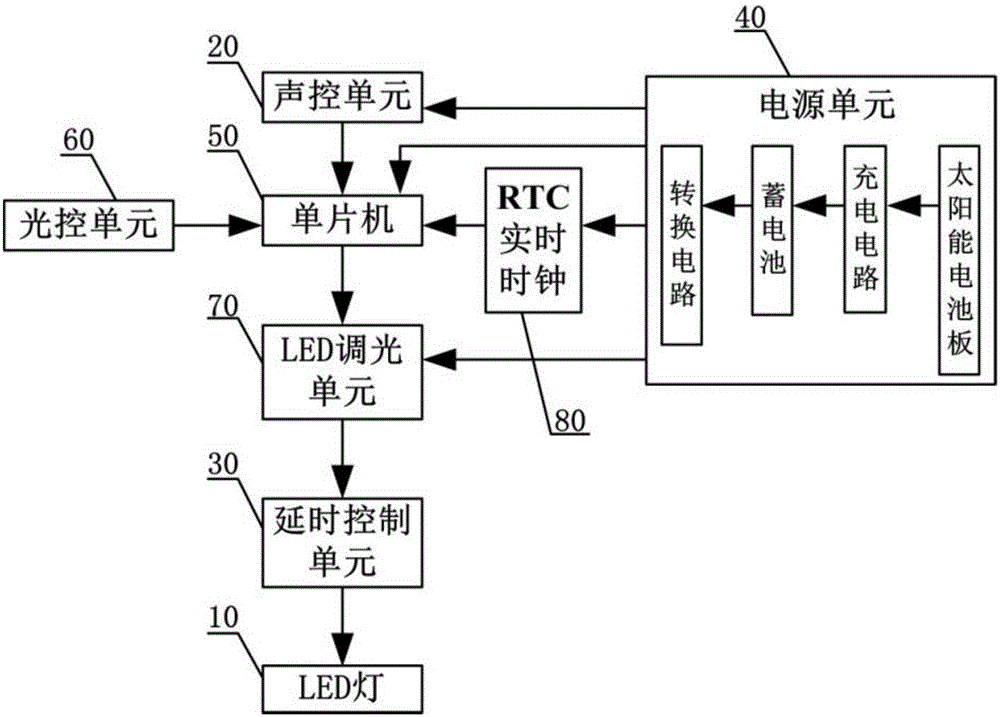

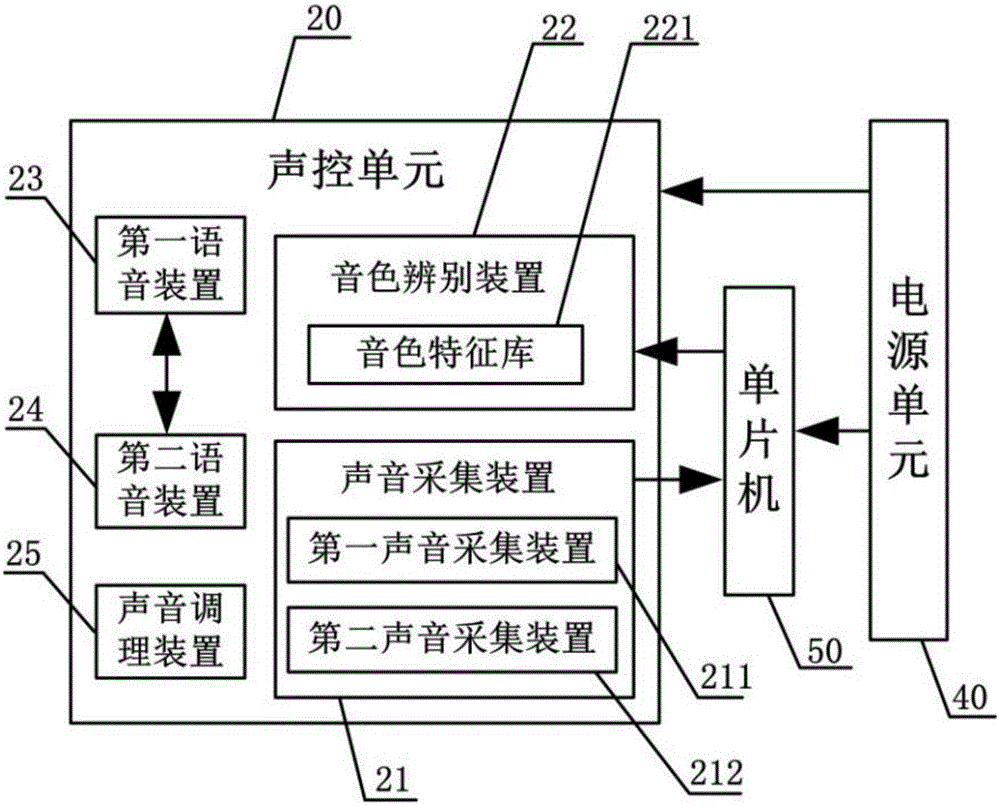

Solar light-emitting diode (LED) voice-controlled corridor lighting system

InactiveCN105050282AImprove securityMake full use of energyElectric light circuit arrangementEnergy saving control techniquesLighting systemElectricity

The invention discloses a solar light-emitting diode (LED) voice-controlled corridor lighting system which comprises an LED lamp, a voice-controlled unit, a delay control unit, a singlechip and a power supply unit, wherein the LED lamp is used for lighting in a corridor; the voice-controlled unit is used for turning on the LED lamp and comprises a voice acquisition device and a tone discrimination device; the delay control unit is used for delaying after the LED lamp is turned on by the voice-controlled unit; the singlechip is electrically connected with the voice-controlled unit and the delay control unit respectively; the power supply unit is used for supplying power to the LED lamp, the voice-controlled unit, the delay control unit and the singlechip and comprises a solar cell panel, a charging circuit, a storage battery and a conversion circuit which are sequentially connected; the tone discrimination device is provided with a tone feature library of pre-extracted voices of corridor users; the voice acquisition device is used for sending the acquired voice to the singlechip for tone feature extraction; and the singlechip is used for comparing the extracted tone feature with the tone feature of the tone feature library and sending discrimination information to the LED lamp through the delay control unit. The solar LED voice-controlled corridor lighting system has the advantages of safety for the corridor users, energy saving and environmental friendliness.

Owner:SUZHOU JINGLEI PHOTOELECTRIC LIGHTING TECH

Electric firing explosive head ignition pressure test method

The invention provides an electric firing explosive head ignition pressure test method. Under a vacuum condition, a flying sheet in contact with an electric firing explosive head is designed; a moving track of the flying sheet in a test tube in an electric firing explosive head ignition process is shot by a high-speed camera, and is simplified into a physical model; a mathematical measure is used for processing relevant data in the flying sheet moving model for solving stress of the flying sheet, i.e., the ignition pressure of the tested electric firing explosive head. The method has the advantages that the ignition pressure of the electric firing explosive head and the dynamic change of the electric firing explosive head can be precisely measured; the problem of difficulty in dynamic measurement of the electric firing explosive head ignition pressure is solved; reliable theoretical basis is provided; the operation is convenient; a measurement result is precise.

Owner:ANHUI UNIV OF SCI & TECH

Method of simulating real-time calibration of large time-delay analog source with high precision

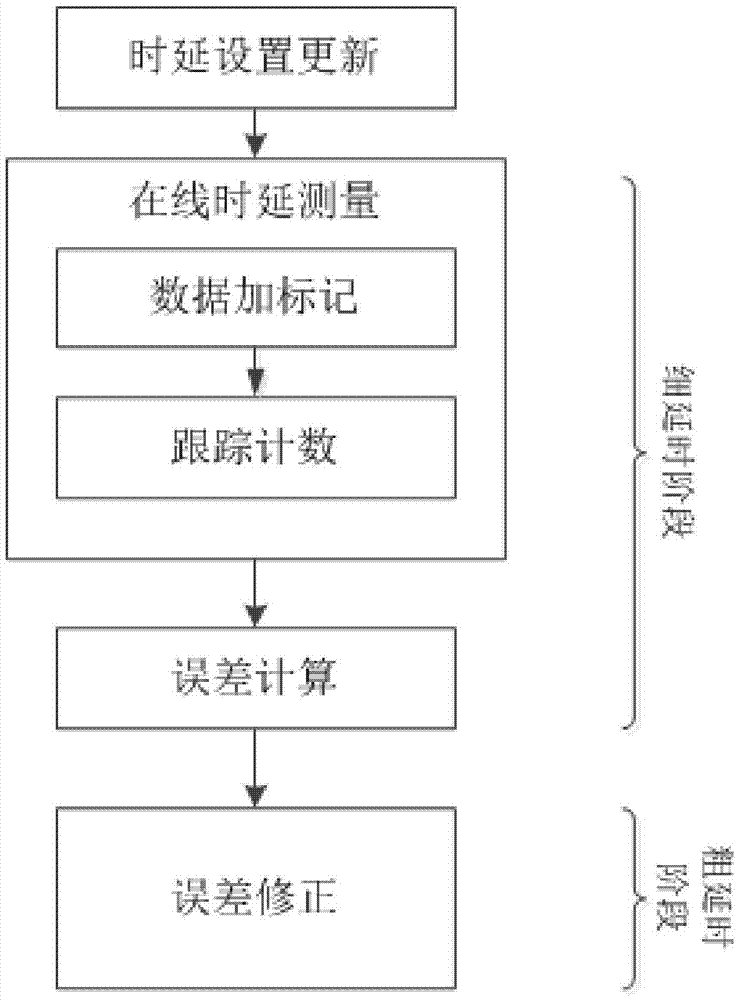

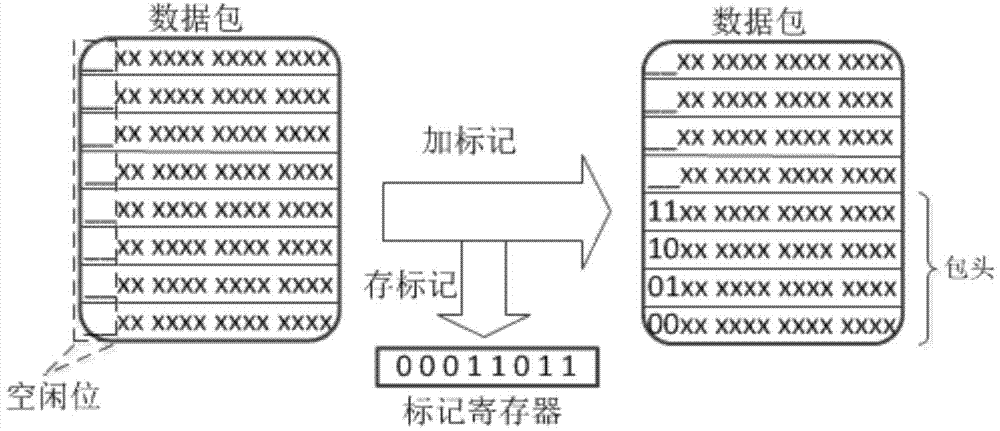

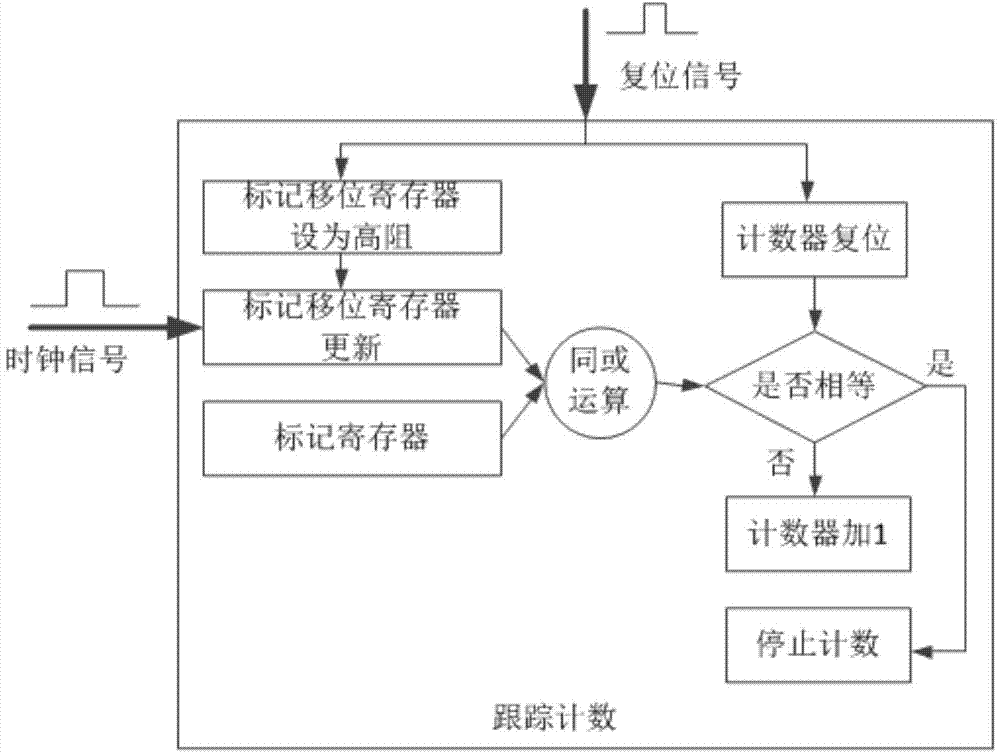

ActiveCN104749561AHigh precisionBreak through the delay accuracy bottleneckWave based measurement systemsMemory addressProcessor register

The invention provides a method of simulating the real-time calibration of a large time-delay analog source with high precision which is low in consumption and low in cost, and is incapable of influencing the normal operation of the large time-delay analogue source, so as to improve a method of improving the time delay precision as an objective. The method comprises the steps of adding data marks to idle bits in several bytes at the head part or the tail part of a database, and installing a special mark register to memorize a packet header mark, and marking delayed data; meanwhile, installing a counter which is synchronous with the frequency of a write block stored at the state; generating a reset pulse to the counter when the time delay set is updated, updating and marking a value of a shifting register and judging whether the value is equal to a value of a mark register, adding 1 to the value of the counter if the value of the shifting register is not equal to the mark register, and completing the time delay online measurement if the value of the counter is equal to the mark register; compensating a time delay error generated by fine time delay by virtue of changing a thick time delay memory terminating address at the coarse time delay state, and completing the real-time delay verification by changing the termination memory address.

Owner:10TH RES INST OF CETC

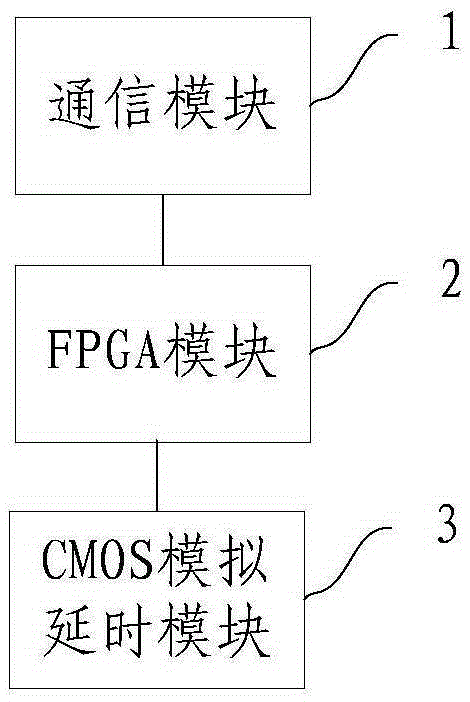

Synchronous multiplex pulse generating system and method

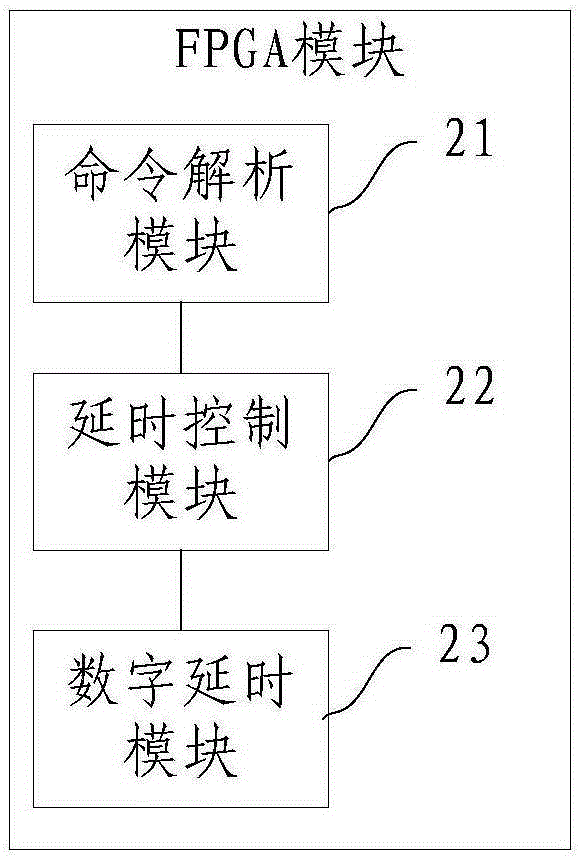

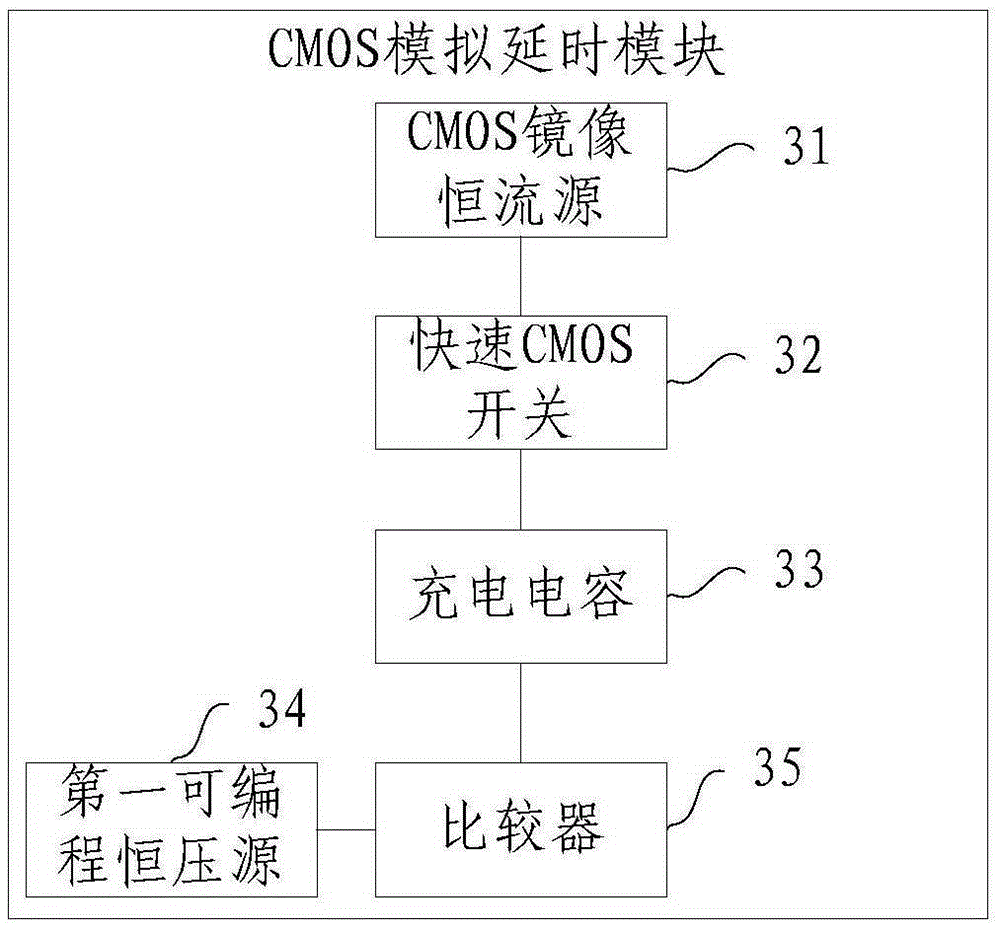

The invention relates to a synchronous multiplex pulse generating system and a method. The system comprises a communication module used for receiving a command frame and sending the command frame to an FPGA module, an FPGA module used for generating synchronous pulse signals with long time-delay time according to the command frame, and a CMOS analog time-delay module used for generating synchronous pulse signals with short time-delay time according to the command frame. According to the synchronous multiplex pulse generating system and the method, nanosecond time-delay adjustment is performed via the FPGA module, and picosecond time-delay adjustment is performed via the CMOS analog time-delay module so that synchronous pulse with high time-delay precision and wide time-delay time range is generated, the size and the cost of the pulse generating system are reduced, the universality of the pulse generating system is greatly improved, and the system and the method are advantaged by simple operation, low cost, and easy promotion.

Owner:BEIJING RES CENT OF INTELLIGENT EQUIP FOR AGRI

Multipath searching method and multipath searcher

ActiveUS20130188668A1High delay accuracyImprove performanceBaseband system detailsPeak valueCircumflex

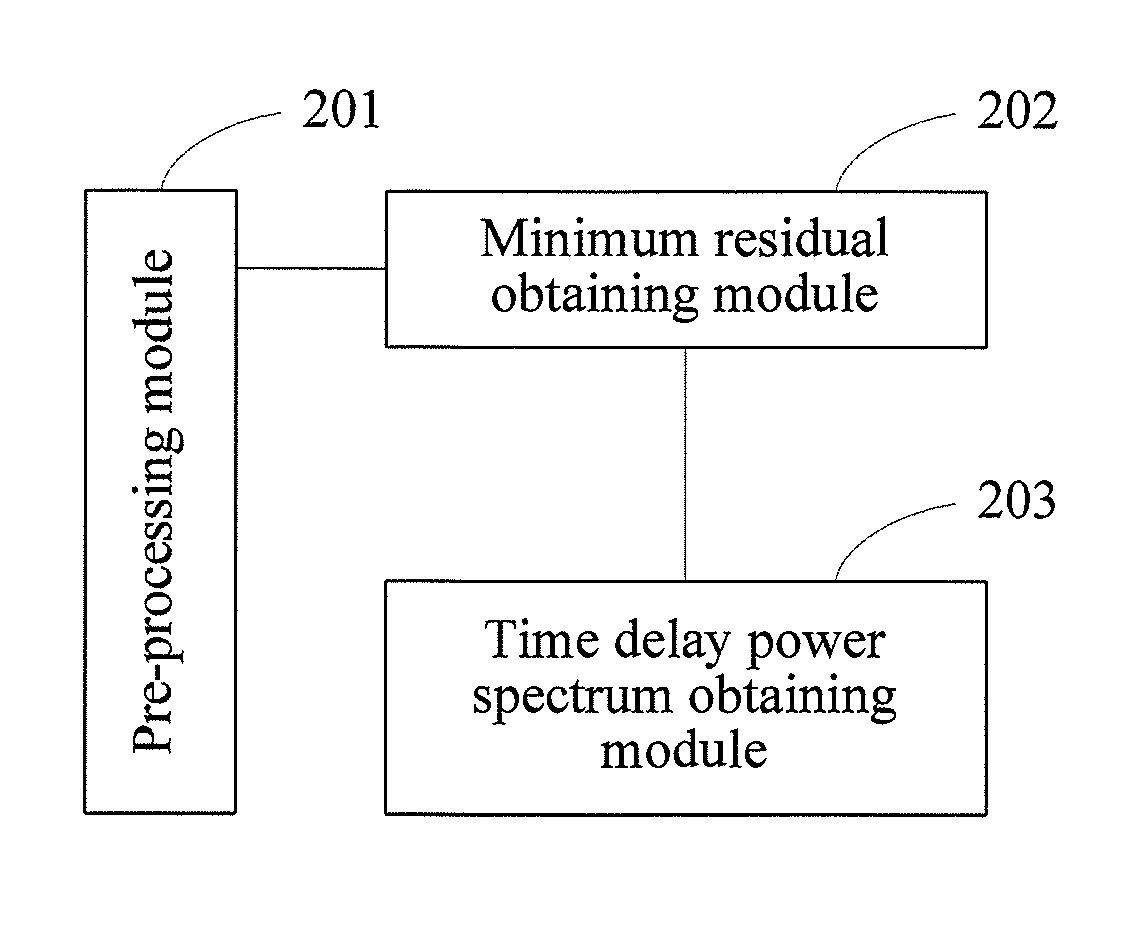

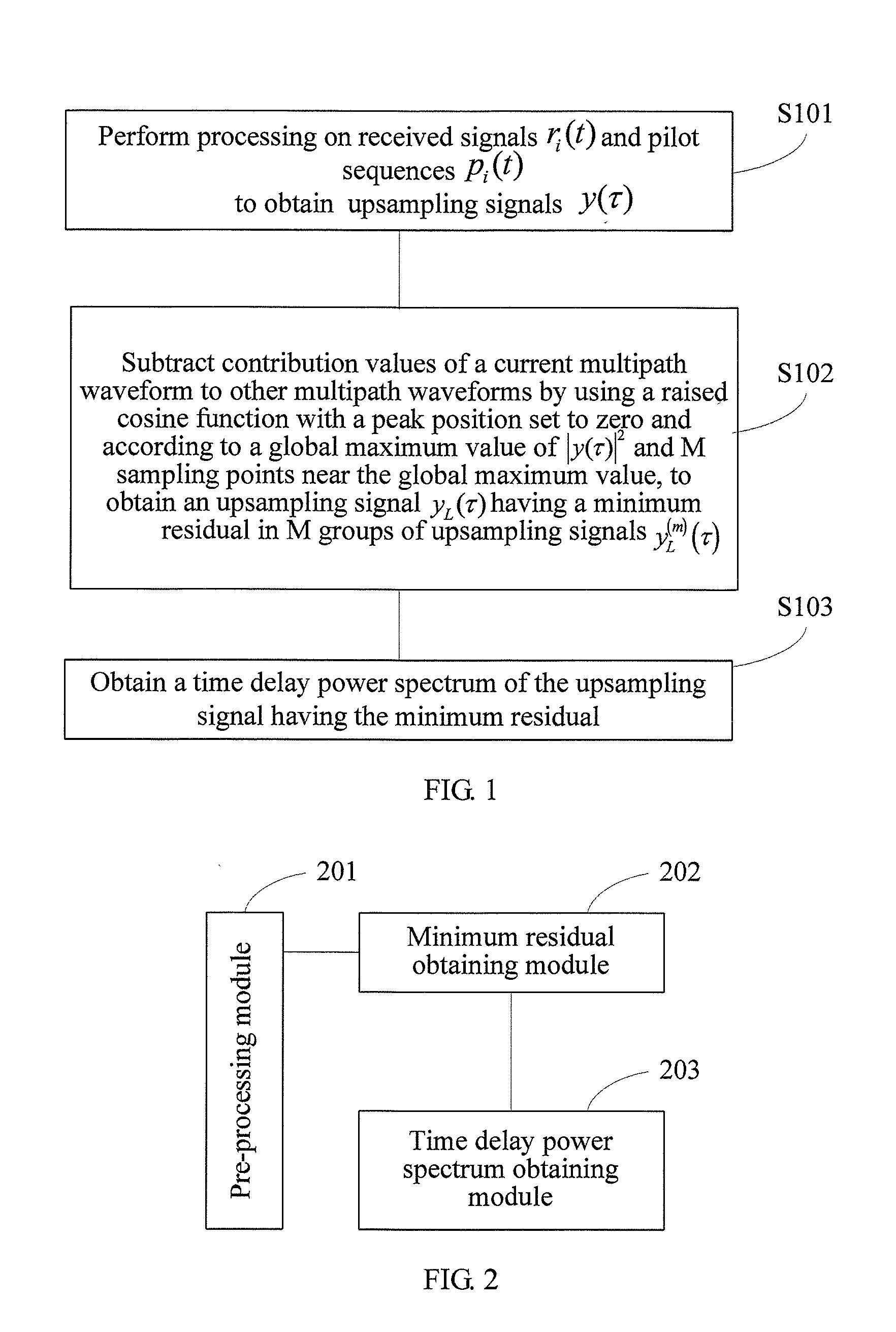

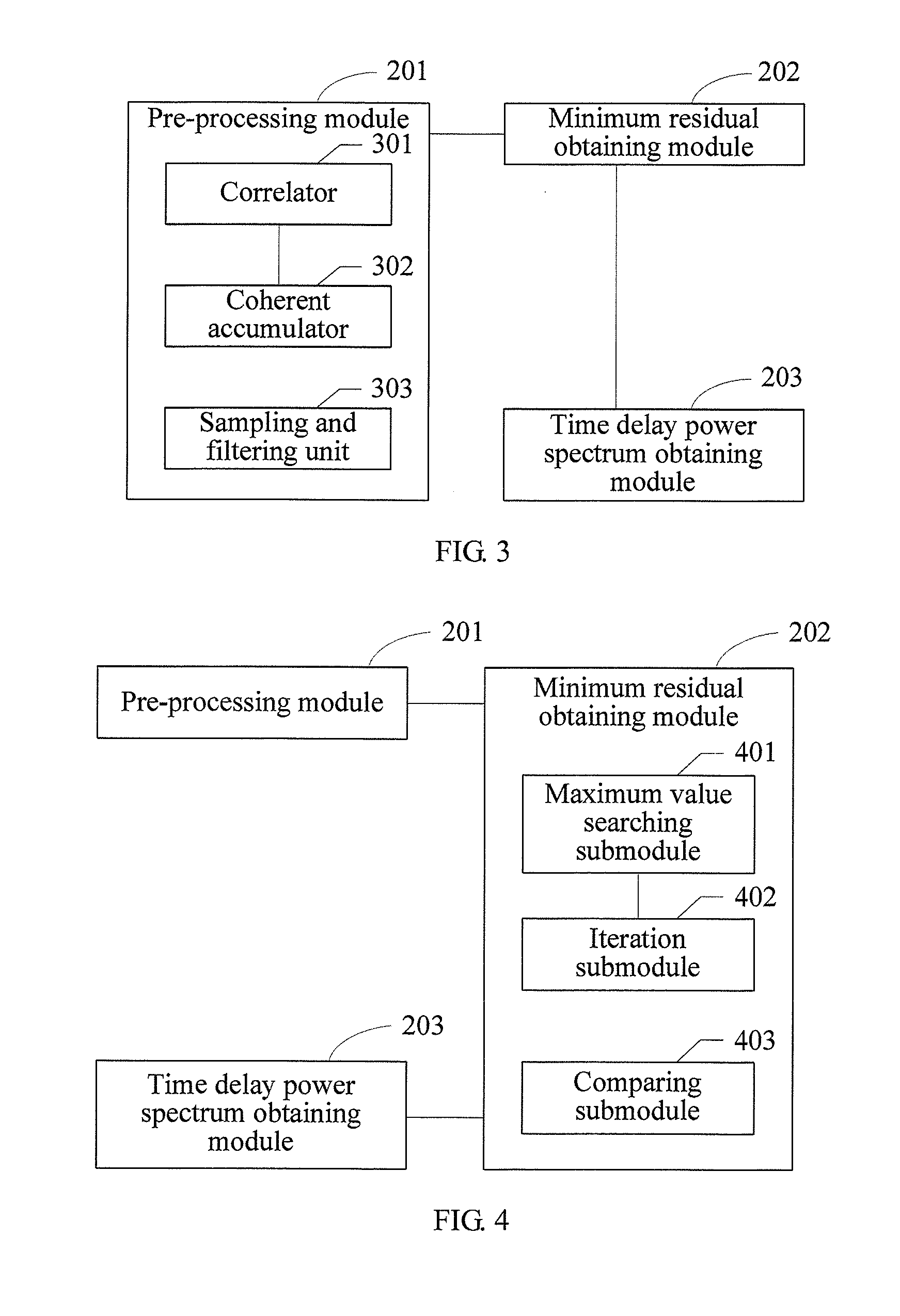

Embodiments of the present invention provide a multipath searching method and a multipath searcher, to improve accuracy of delay estimation, thereby improving performance of a receiver. The method includes: performing processing on received signals ri(t) and pilot sequences pi(t) to obtain upsampling signals y(τ); subtracting contribution values of a current multipath waveform to other multipath waveforms by using a raised cosine function with a peak position set to zero and according to a global maximum value of |y(τ)|2 and a total of M sampling points {circumflex over (τ)}l(m) near the global maximum value, to obtain an upsampling signal yL(τ) having a minimum residual in M groups of upsampling signals yL(m)(τ); and obtaining a time delay power spectrum of the upsampling signal yL(τ) having the minimum residual.

Owner:HONOR DEVICE CO LTD

Digital DLL device, digital DLL control method, and digital DLL control program

InactiveUS20050212574A1Reduce errorsHigh delay accuracyPulse automatic controlDigital storageOutput compareComputer science

A digital DLL device is provided which can reduce an error with respect to a target delay amount. The device provides a delay to an input clock signal so as to equally divide a clock cycle T thereof into N parts, and includes first variable delay sections and second variable delay sections, each of which is formed of an arbitrary number of unit delay buffers connected in series with one another. A phase comparison section makes a compare between the phase of the input clock signal and the phase of an output signal which is the input signal having been delayed while passing through all the first and second variable delay sections, and outputs a result of the comparison. A delay control section calculates a total number of unit delay buffers S required based on the phase comparison result, sets a quotient Q of S divided by N to be the number of unit delay buffers for each of the first variable delay sections, and allocates a remainder R of S divided by N to the second variable delay sections, respectively.

Owner:FUJITSU LTD