Gallium arsenide monolithic integrated numerical-control real time delay circuit

A monolithic integration, integrated circuit technology, applied in delay lines, circuits, electrical components, etc., can solve the problem that fiber optic delay devices or microwave hybrid circuits cannot meet the requirements of batch engineering, increase circuit complexity, delay accuracy, problems such as the influence of electrical performance, to achieve the effect of good electrical performance consistency, simplifying complexity, and reducing volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The present invention is described in further detail below in conjunction with accompanying drawing:

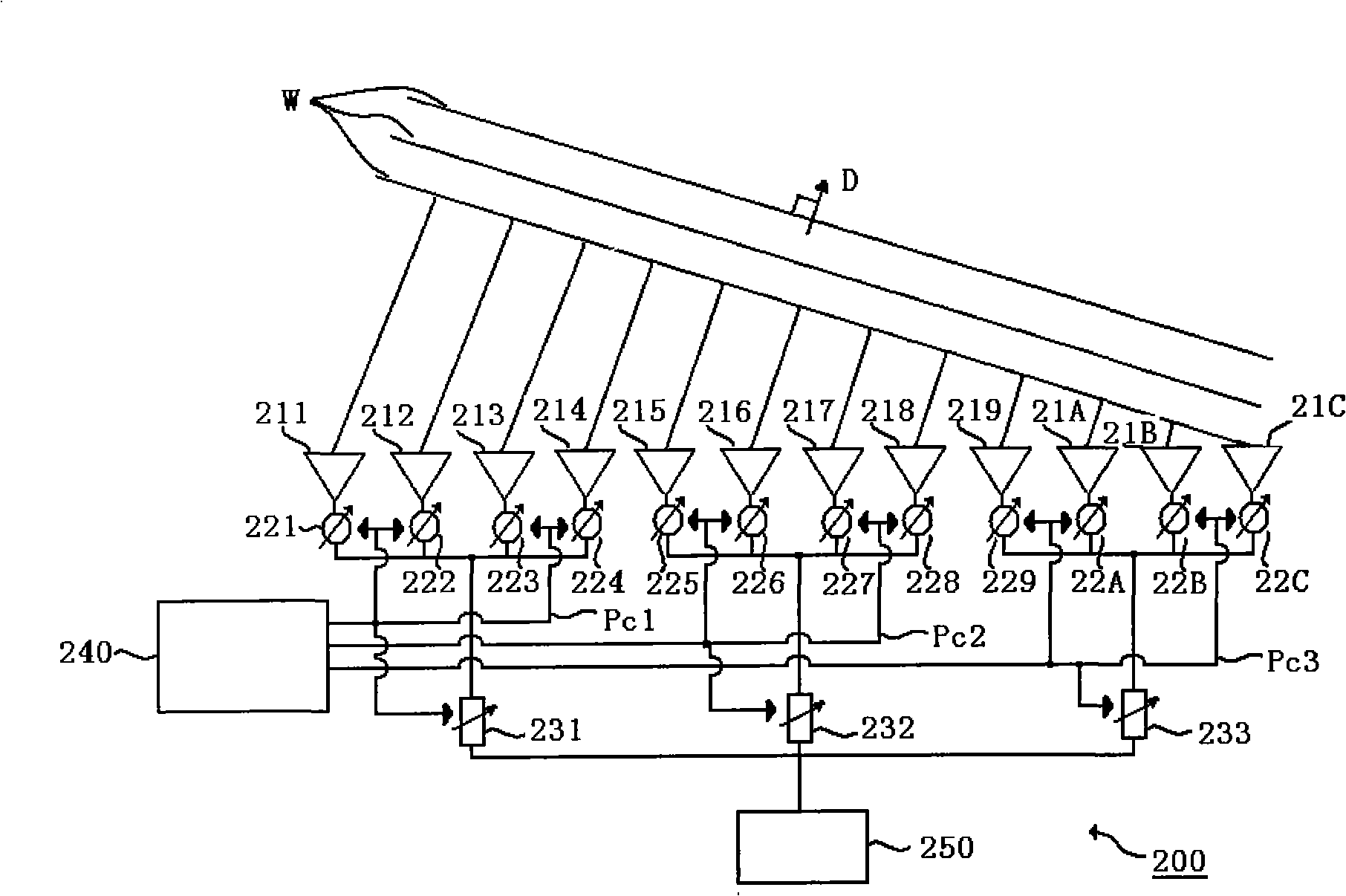

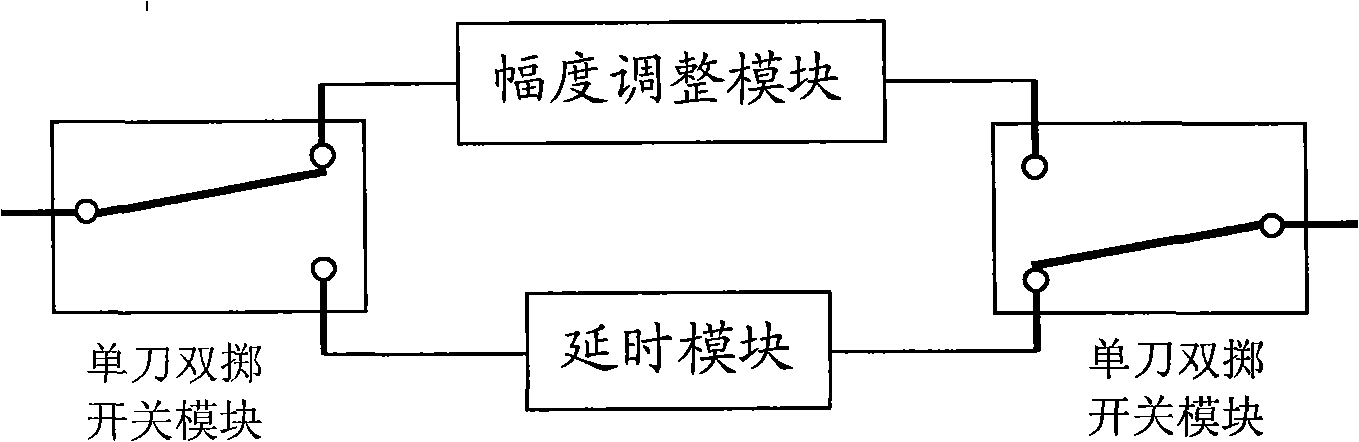

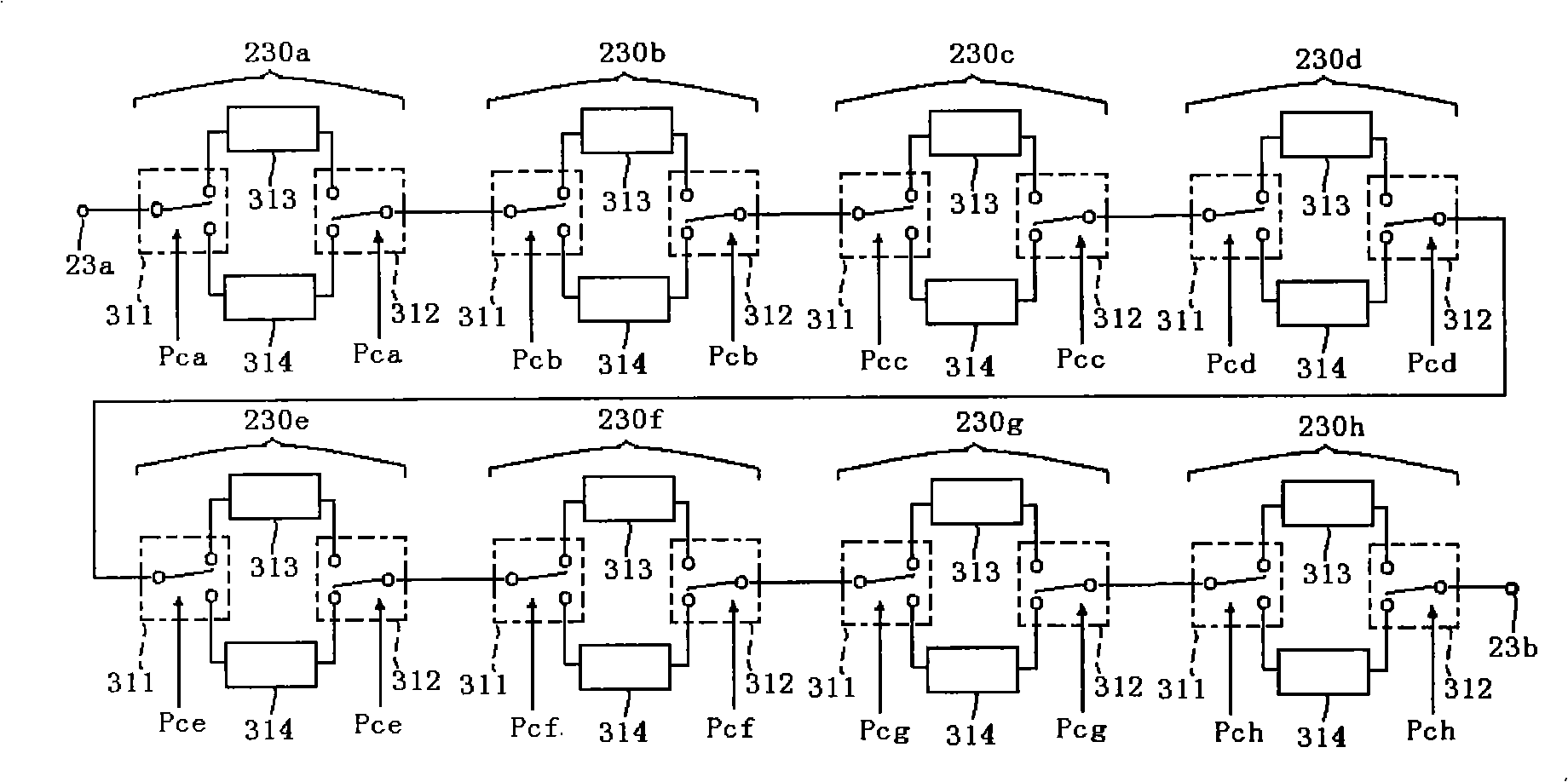

[0018] The present invention adopts the integrated circuit manufacturing process, and the basic delay bit circuit elements are manufactured on the substrate (substrate) by thin film technology, and a plurality of basic delay bit circuits with different delay times are integrated in the same chip, and all the basic delay bit circuits are integrated in the same chip. The bit circuits are connected in series, and each basic delay bit circuit includes a single-pole double-throw switch module, a delay module, and an amplitude adjustment module, and its structural block diagram is as follows figure 2 As shown, the common terminal of the SPDT switch module is connected to the input signal, the other two ports are respectively connected to the input terminals of the delay module and the amplitude adjustment module, and the output terminals of the delay module and the amplitude...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More