Method for calibrating phase of DQS (bidirectional data strobe) delay for DDR (double data rate) controller and apparatus thereof

A phase calibration and controller technology, applied in the phase calibration field of DQS delay, can solve the problems of accuracy dependence, insufficient stability and accuracy, affecting DDR data reading, etc., and achieve high delay accuracy, enhanced stability and anti-interference. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] For reference and clarity, descriptions, abbreviations or abbreviations of technical terms used in the following text are summarized as follows:

[0048] DDR: Double Data Rate, double rate synchronous dynamic random access memory;

[0049] DQS: Bidirectional data strobe, bidirectional data filtering signal;

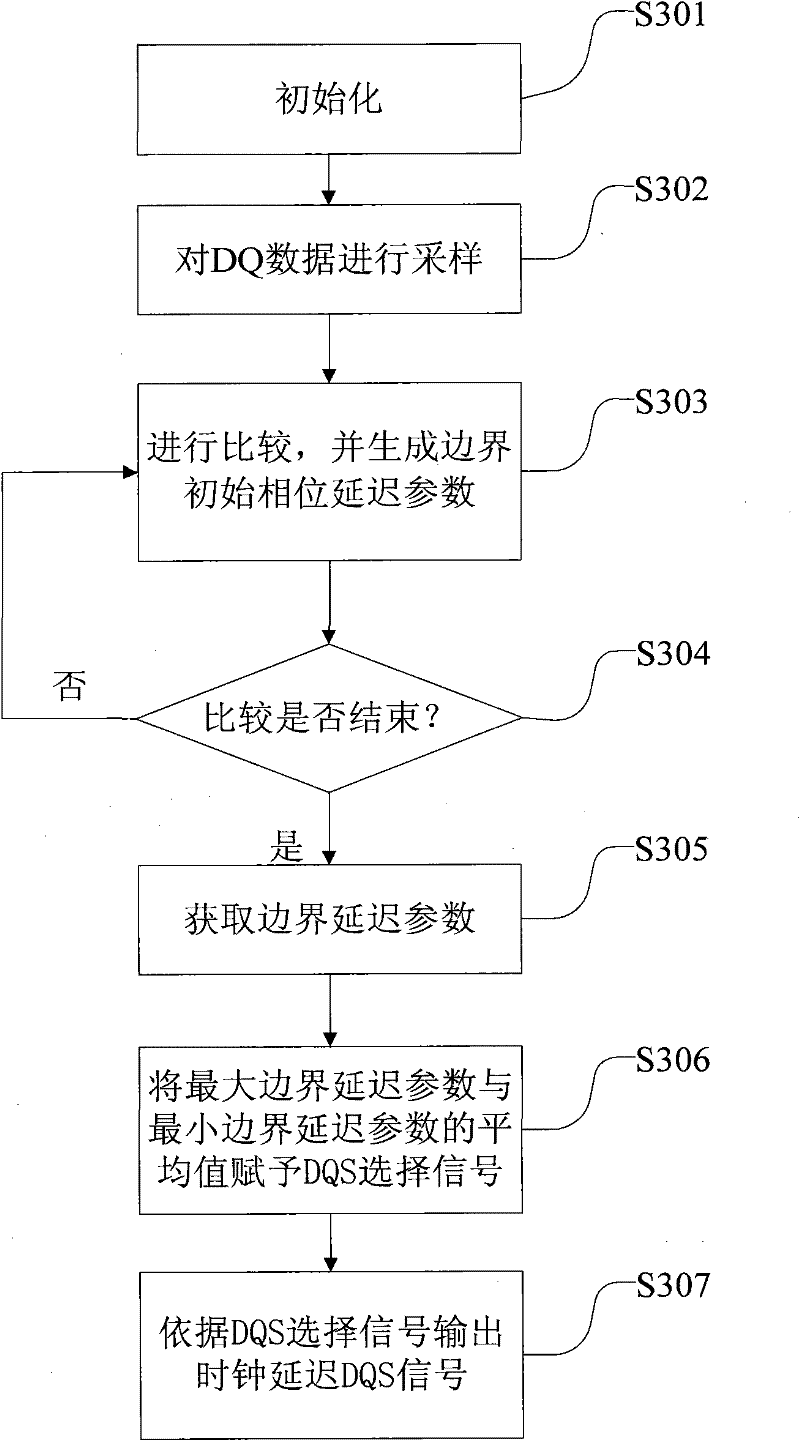

[0050] DLY_Before: the minimum boundary delay parameter;

[0051] DLY_Last: the maximum boundary delay parameter;

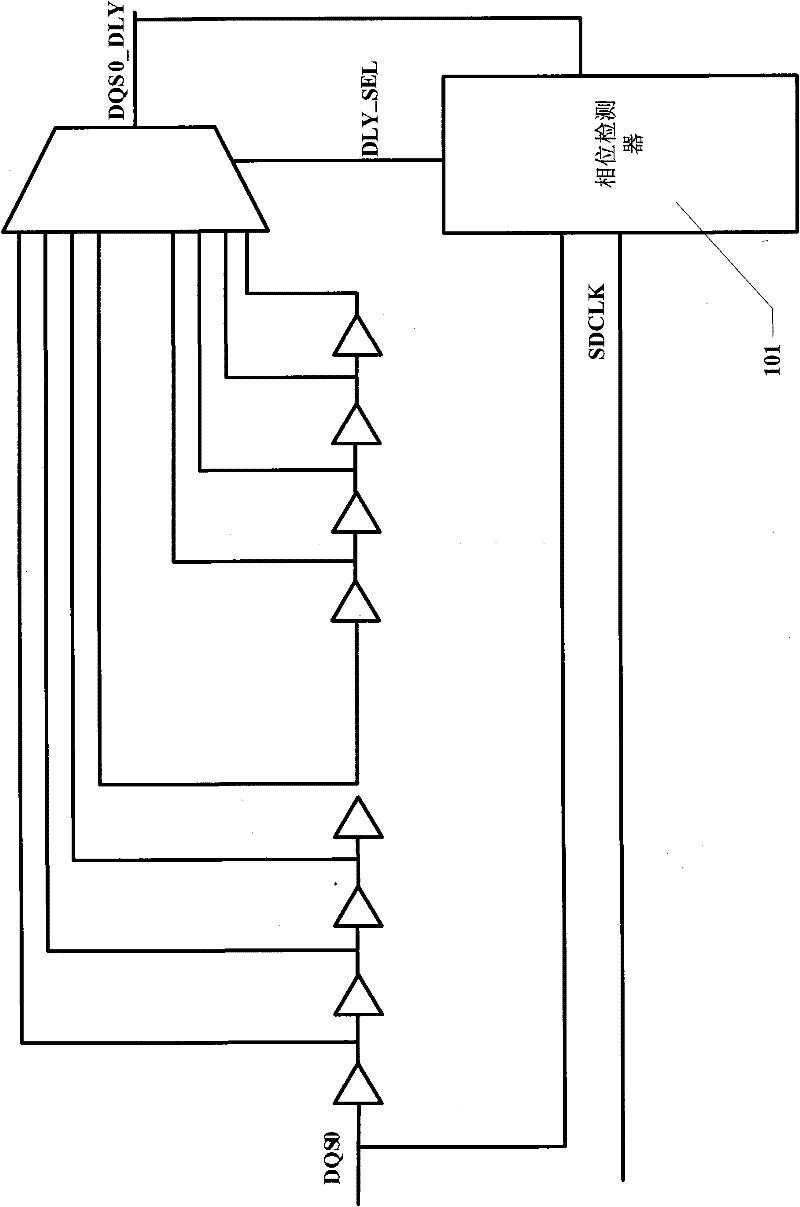

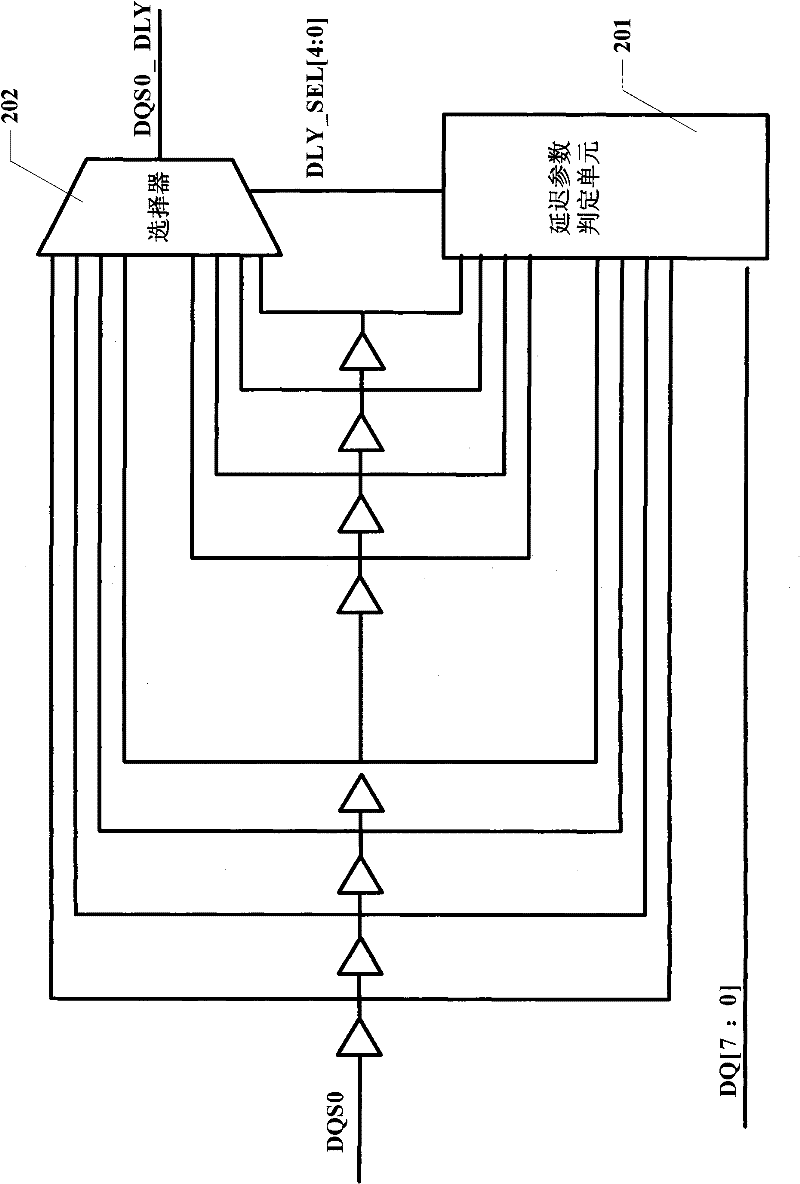

[0052] DQS_DLY: delay the DQS signal for the clock;

[0053] DQS_SEL: select signal for DQS;

[0054] MEMORY chip: memory storage chip;

[0055] In the text, the symbol ">>" means to move one bit to the right.

[0056] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com