Memory fault injection method and simulator thereof for software built-in test (BIT)

A fault injection and software testing technology, applied in the field of memory, can solve problems such as inability to execute, components cannot be injected, and the design of abnormal use cases is not comprehensive enough to ensure reliability and accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described in detail with reference to the accompanying drawings and embodiments.

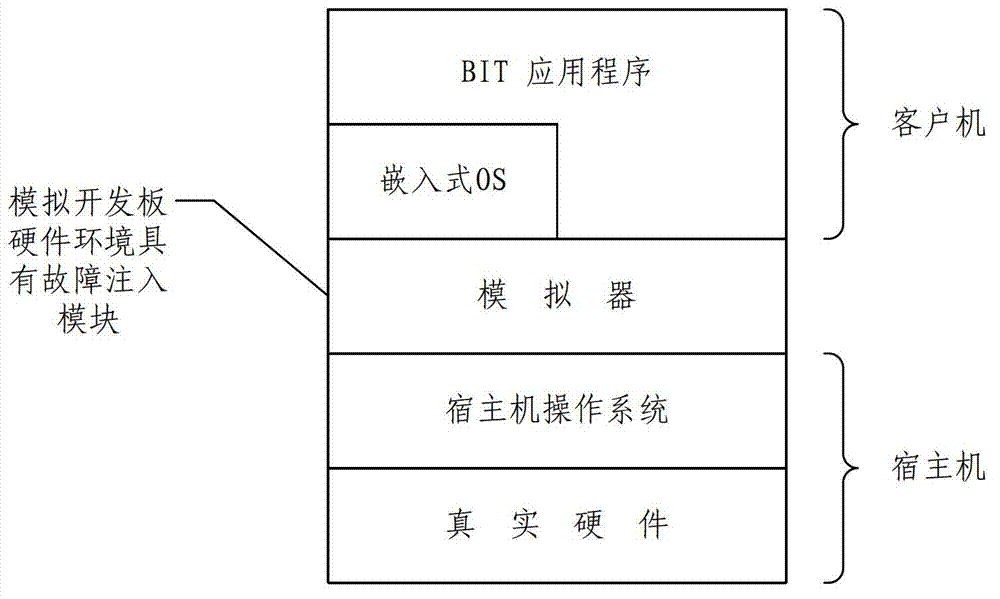

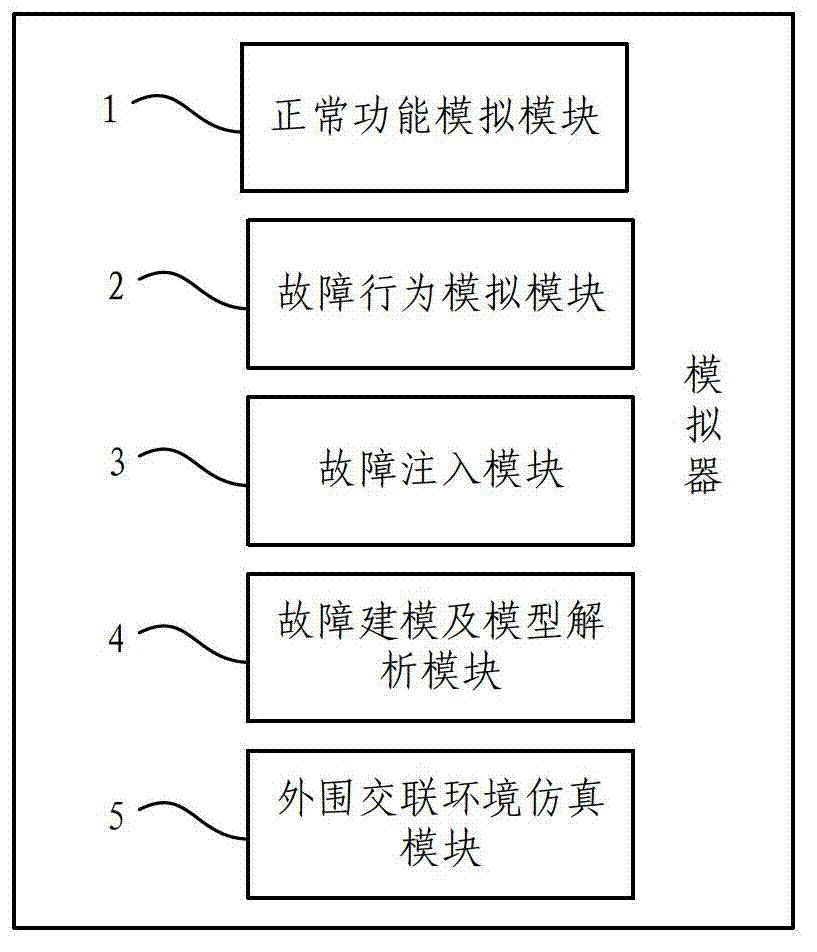

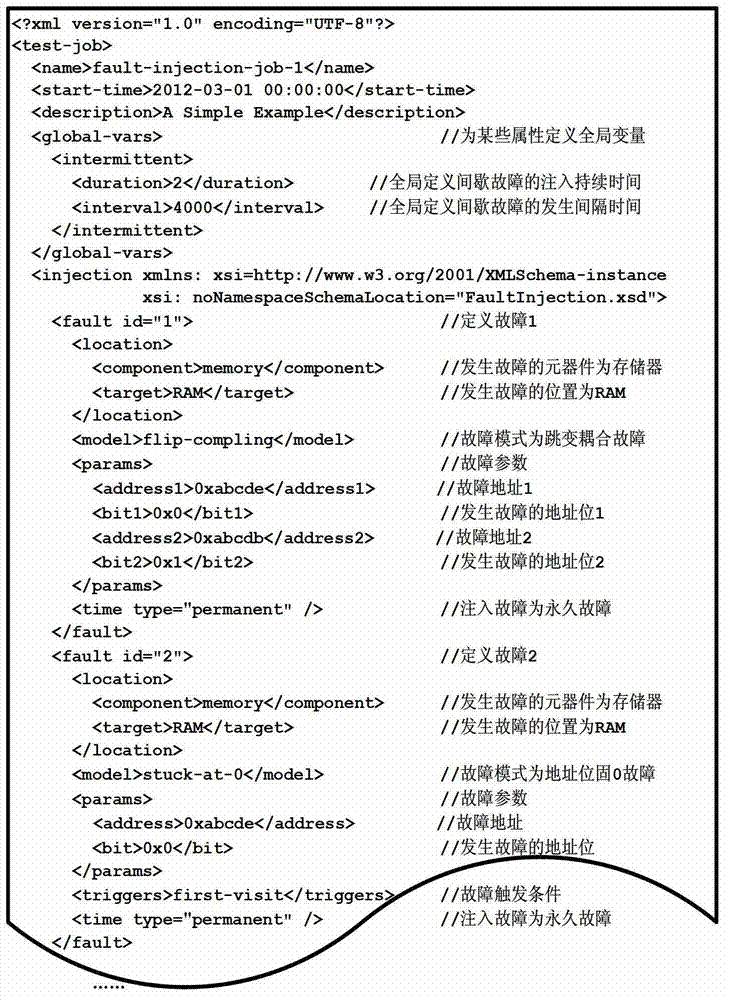

[0042] Due to the closedness and non-invasiveness of the aviation board, it is not possible to directly inject faults into the hardware to test the board-level BIT software. Since the emulator is implemented in software according to the real hardware functions, it can be modified arbitrarily without intrusion and damage to the hardware and the applications running on it. Therefore, it is a feasible solution to apply the simulator and fault injection technology to BIT software testing. The basic technical thought of the present invention is: take the hardware circuit board of running BIT software as simulation object, adopt the method for simulator simulation to solve the bottleneck problem of BIT software test, give full play to the advantage of simulator, such as detailed function analysis to simulation object, The simulation method can inject the m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More