Method and system for RAM fault testing

A technology for fault testing and memory, applied in static memory, error detection/correction, instruments, etc., can solve the problems of unreliable results of the internal unit of the address bus memory, cannot rule out the existence of internal chip faults of memory address bus faults, etc., to achieve improvement reliability effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

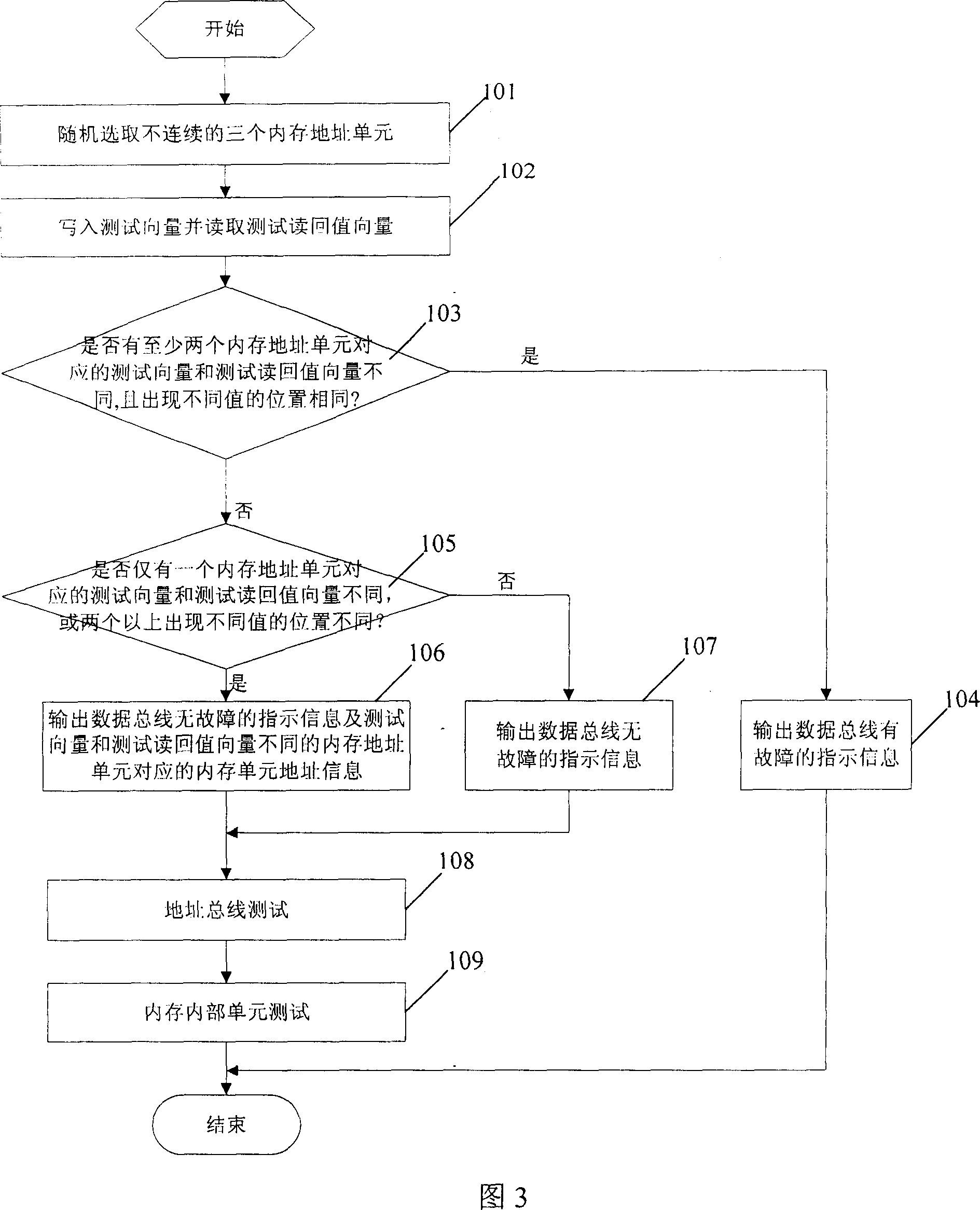

[0046] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0047] The memory fault testing method of the present invention is aimed at the fact that the prior art cannot solve the problem of ensuring the accuracy and reliability of the memory data bus fault test results when testing memory faults, and proposes a method for eliminating possible faults when testing memory faults. The existing address bus failure and memory internal unit failure interfere with the data bus failure test results, thus ensuring the reliability and accuracy of the memory data bus failure test results and providing reliability guarantee for other tests of the memory test.

[0048] Referring to Fig. 3, it is a schematic flow chart of the method for memory fault testing of the present invention. In this embodiment, the specific implementation process of the method is as follows:

[0049] In step 101, randomly select at least th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More