Patents

Literature

494 results about "Failure detector" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In a distributed computing system, a failure detector is a computer application or a subsystem that is responsible for the detection of node failures or crashes. Failure detectors were first introduced in 1996 by Chandra and Toueg in their book Unreliable Failure Detectors for Reliable Distributed Systems. The book depicts the failure detector as a tool to improve consensus (the achievement of reliability) and atomic broadcast (the same sequence of messages) in the distributed system. In other word, failure detectors seek for errors in the process, and the system will maintain a level of reliability. In practice, after failure detectors spot crashes, the system will ban the processes that are making mistakes to prevent any further serious crashes or errors.

Fault tolerant shared system resource with communications passthrough providing high availability communications

InactiveUS6865157B1Improve usabilityError preventionTransmission systemsRouting tableHigh availability

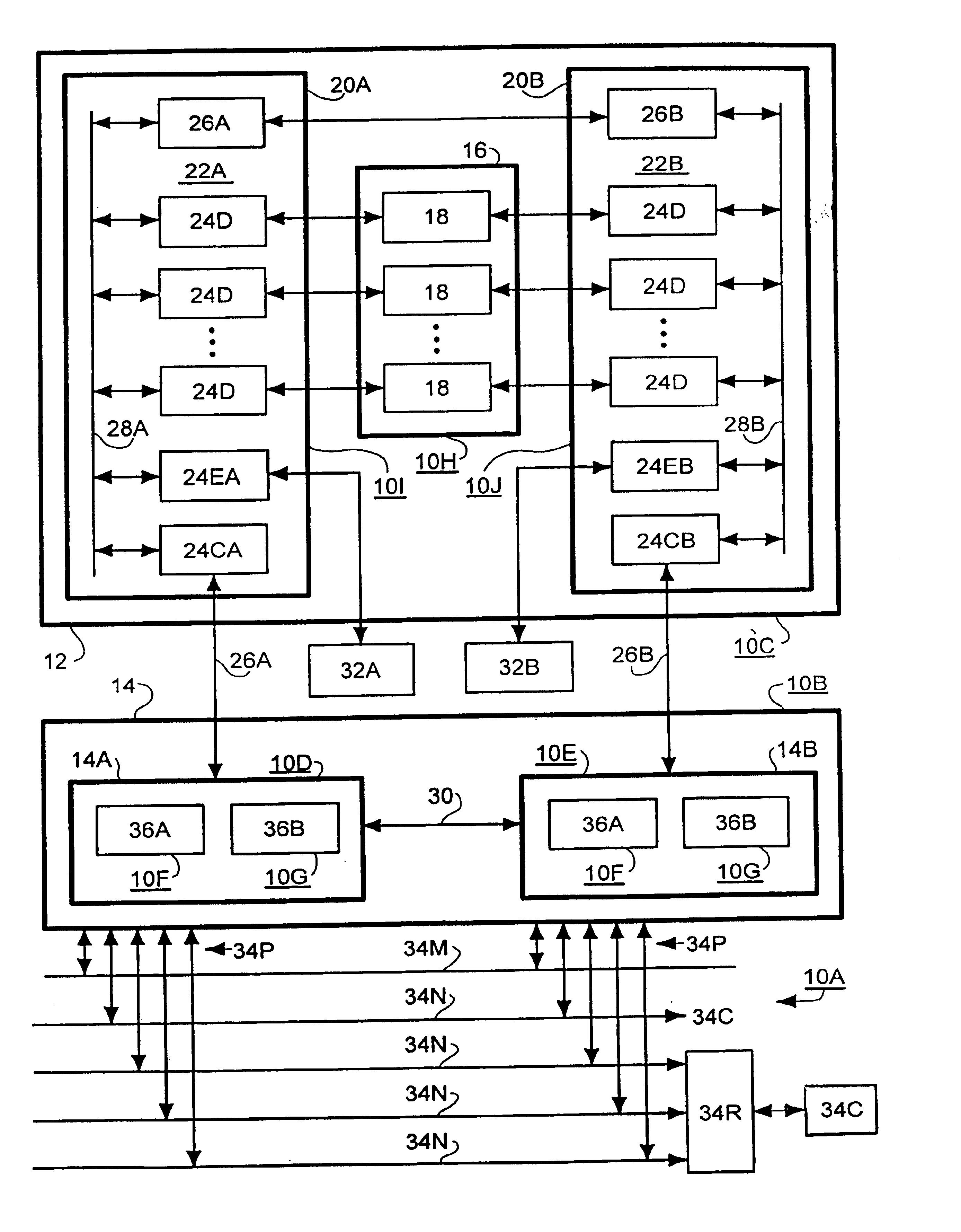

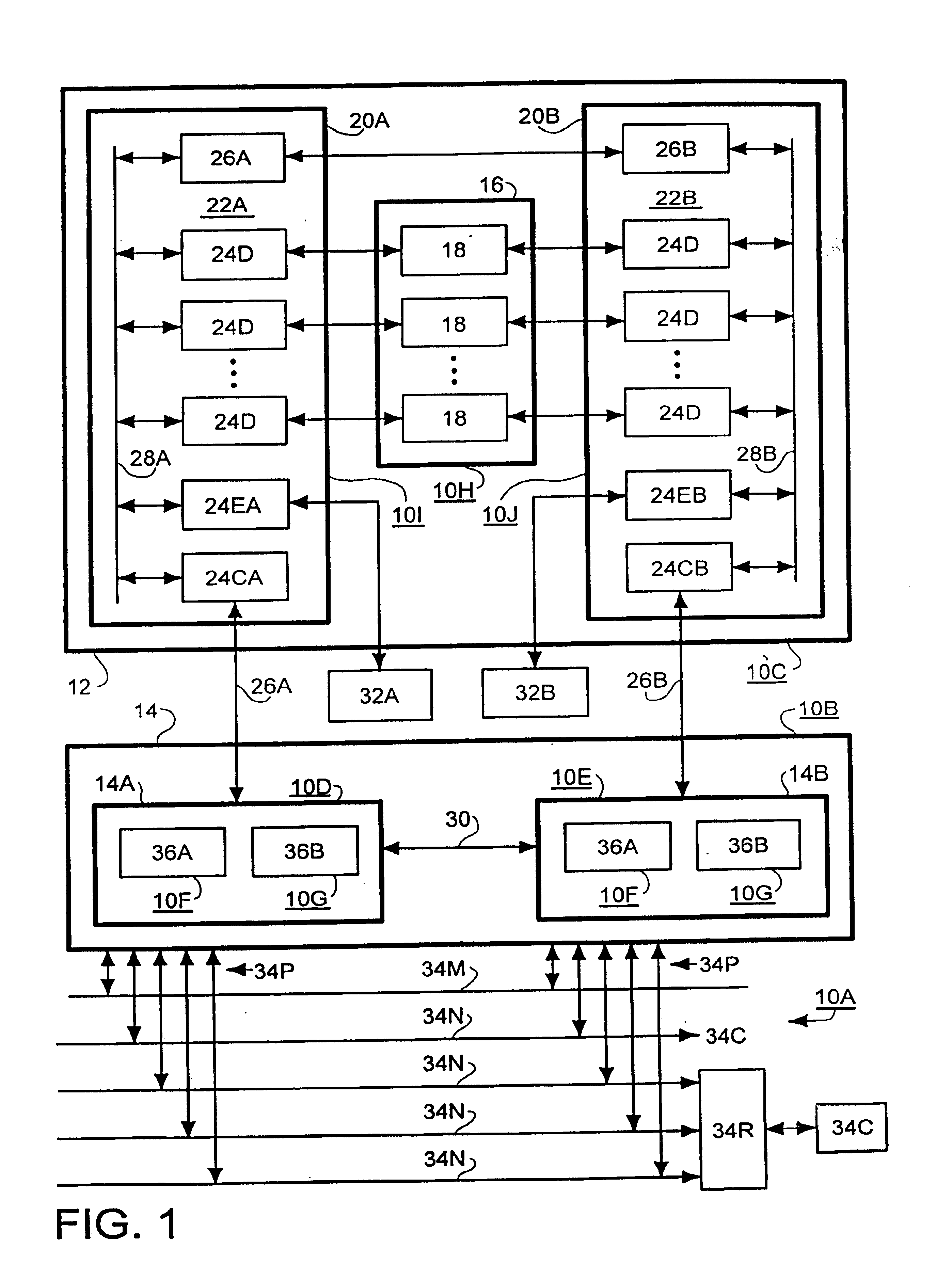

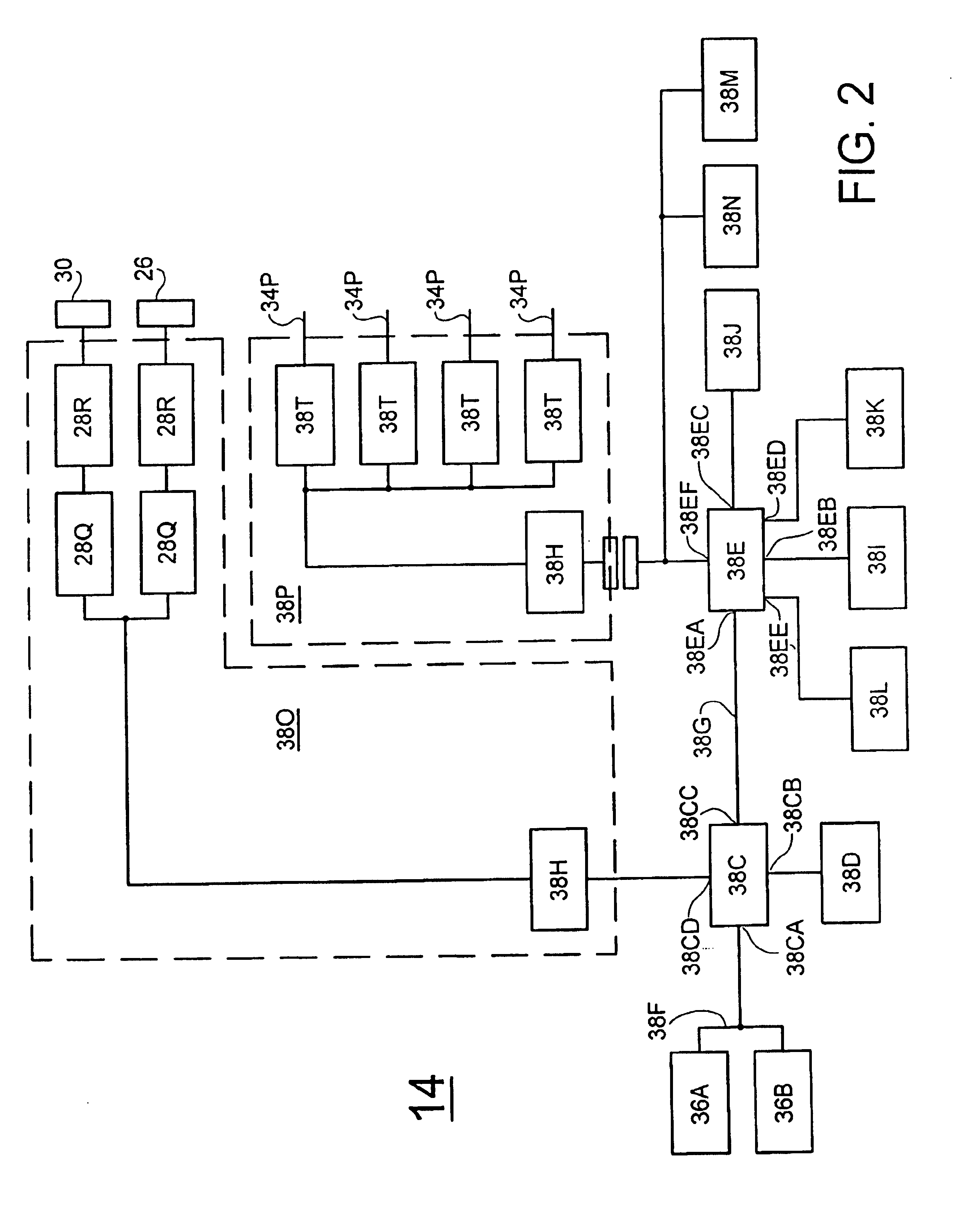

A communications passthrough mechanism for high availability network communications between a shared system resource and clients of the system resource. The system resource includes a control / processing sub-system including multiple peer blade processors. A port of each blade processor is connected to each client / server network path and each client is connected to a corresponding port of each blade processor. Each blade processor includes a network fault detector exchanging beacon transmissions with other blade processors through corresponding blade processor ports and network paths. Each blade processor includes response generator responsive to a failure to receive a beacon transmission from a failed port of an other blade processor for redirecting the client communications to the failed port on the other blade processor to the corresponding port of the blade processor. A path manager in the blade processor is responsive to operation of the response generator for modifying the communications routing table to correspond with the redirection message to route the client communications to the failed port of the other blade processor to the other blade processor through the inter-processor communications link. Each blade processor may also include an inter-blade communications monitor for detecting a failure in the inter-processor communications link between the blade processor and another blade processor, reading the communications routing table to select a functional network communications path to a port of the other blade processor, and modifying the communications routing table to redirect inter-processor communications to the selected functional network communications path.

Owner:EMC CORP

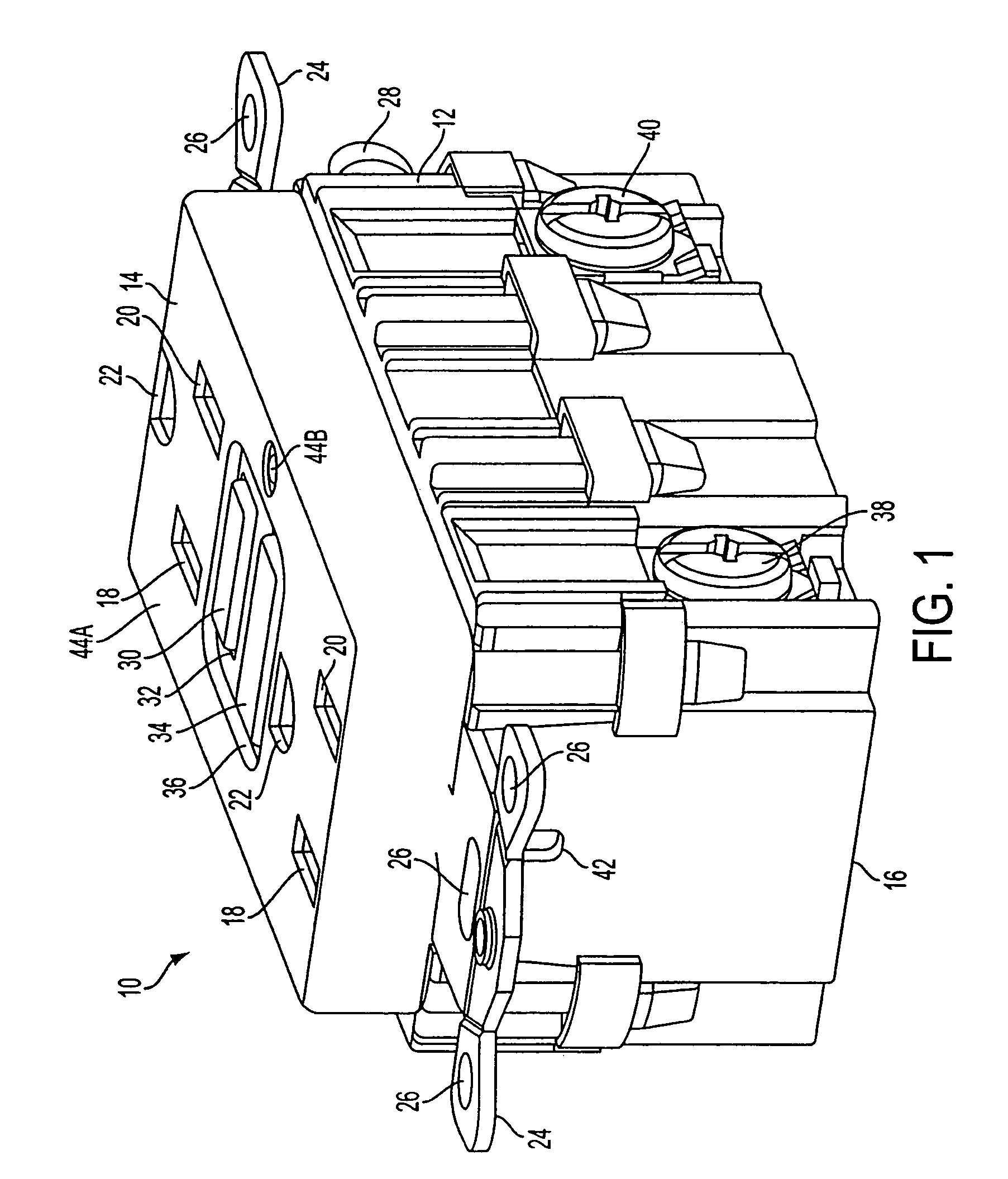

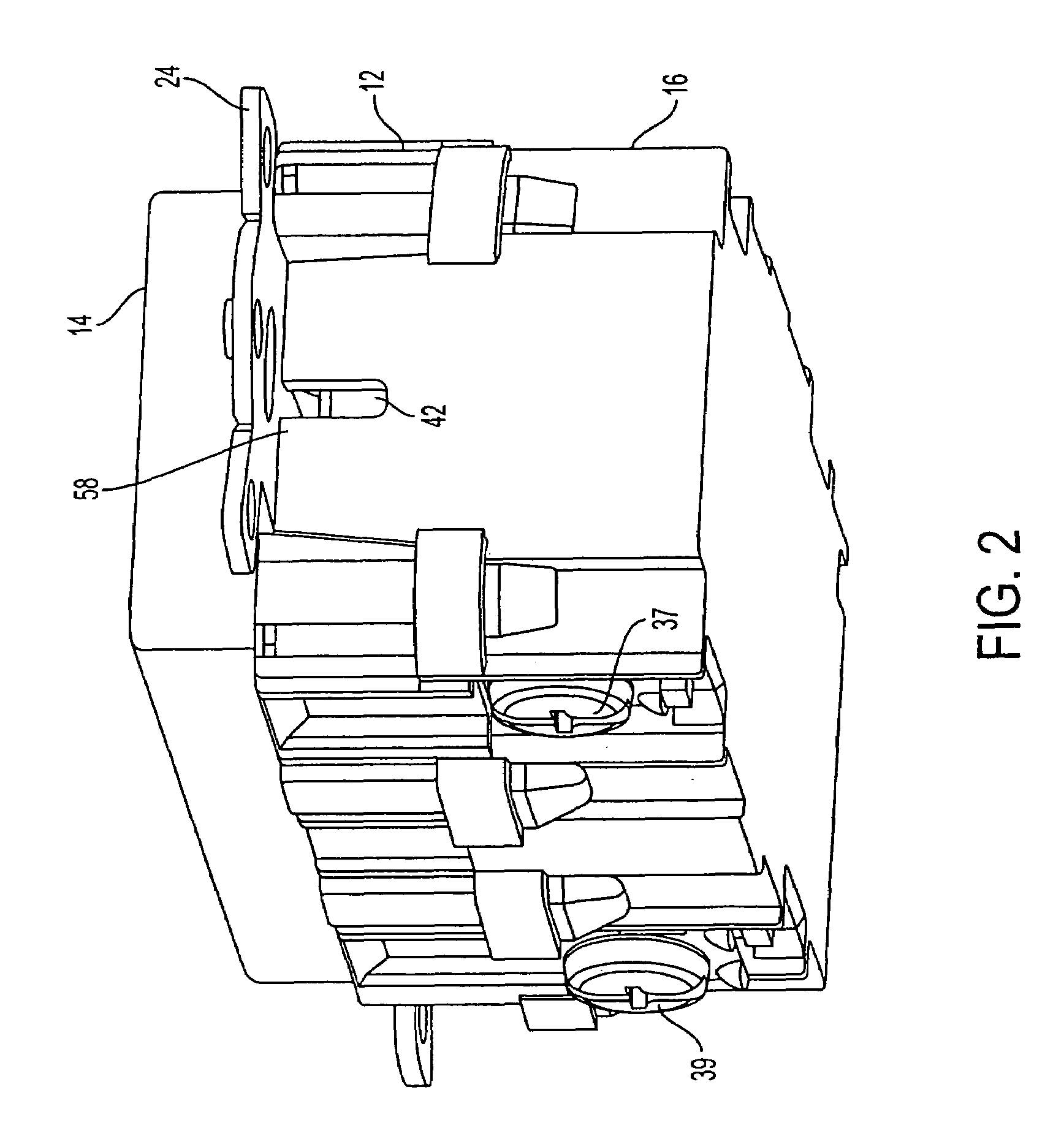

Direct current arc fault circuit interrupter, direct current arc fault detector, noise blanking circuit for a direct current arc fault circuit interrupter, and method of detecting arc faults

ActiveUS20110141644A1Emergency protective arrangement detailsArrangements responsive to excess currentCurrent sensorPeak current

A direct current arc fault circuit interrupter includes separable contacts and a trip circuit to trip open the contacts. The trip circuit includes a number of alternating current sensors structured to sense a current flowing through the separable contacts, a number of filter circuits cooperating with the AC current sensors to output a number of AC signals, a number of peak detectors cooperating with the filter circuits to output a number of peak current signals, and a processor cooperating with at least the peak detectors. The processor inputs the number of peak current signals as a plurality of peak current signals or inputs the number of peak current signals and determines the plurality of peak current signals. The processor also determines if the peak current signals exceed corresponding predetermined thresholds for a predetermined time, and responsively causes the contacts to trip open.

Owner:EATON INTELLIGENT POWER LTD

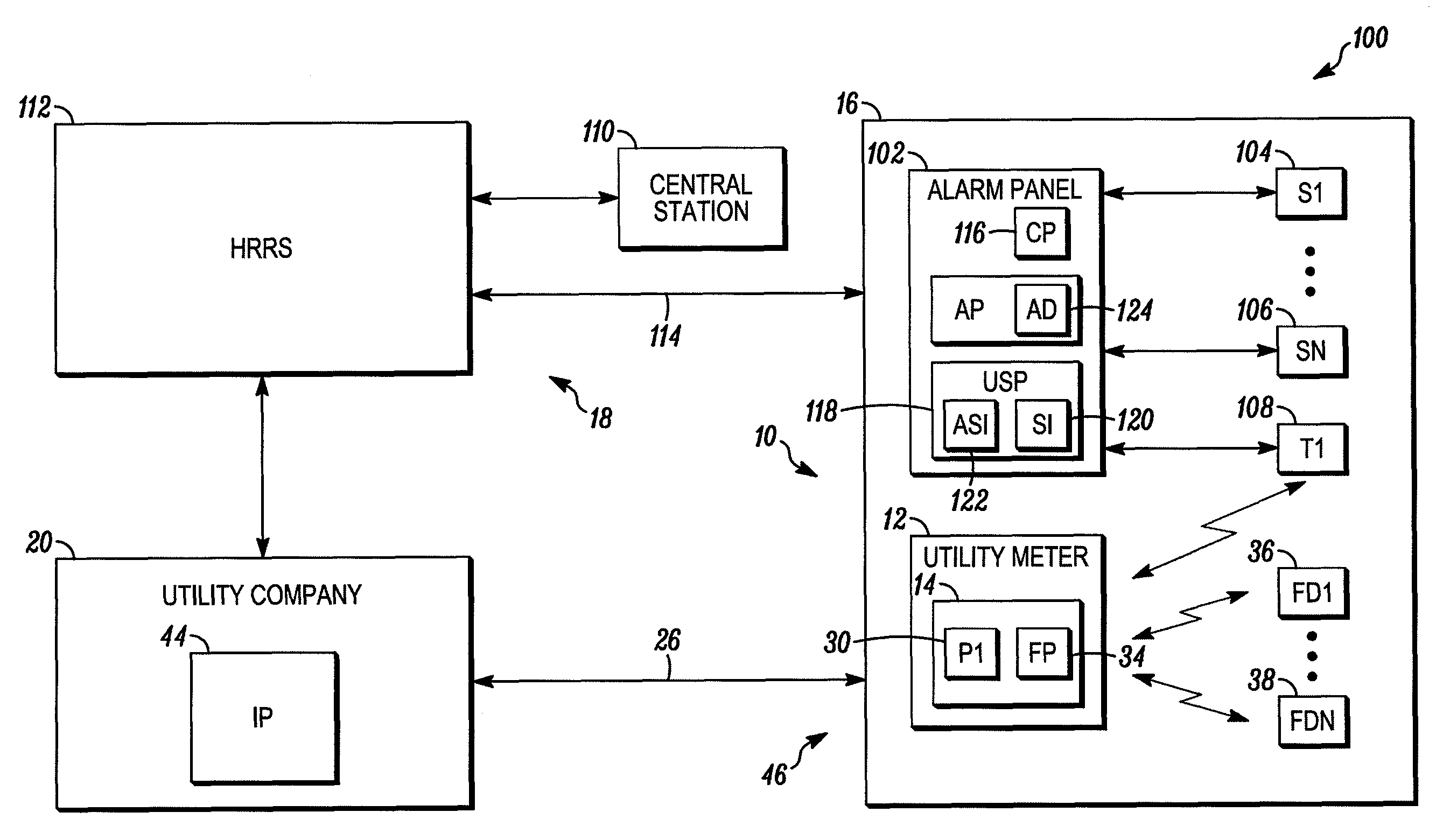

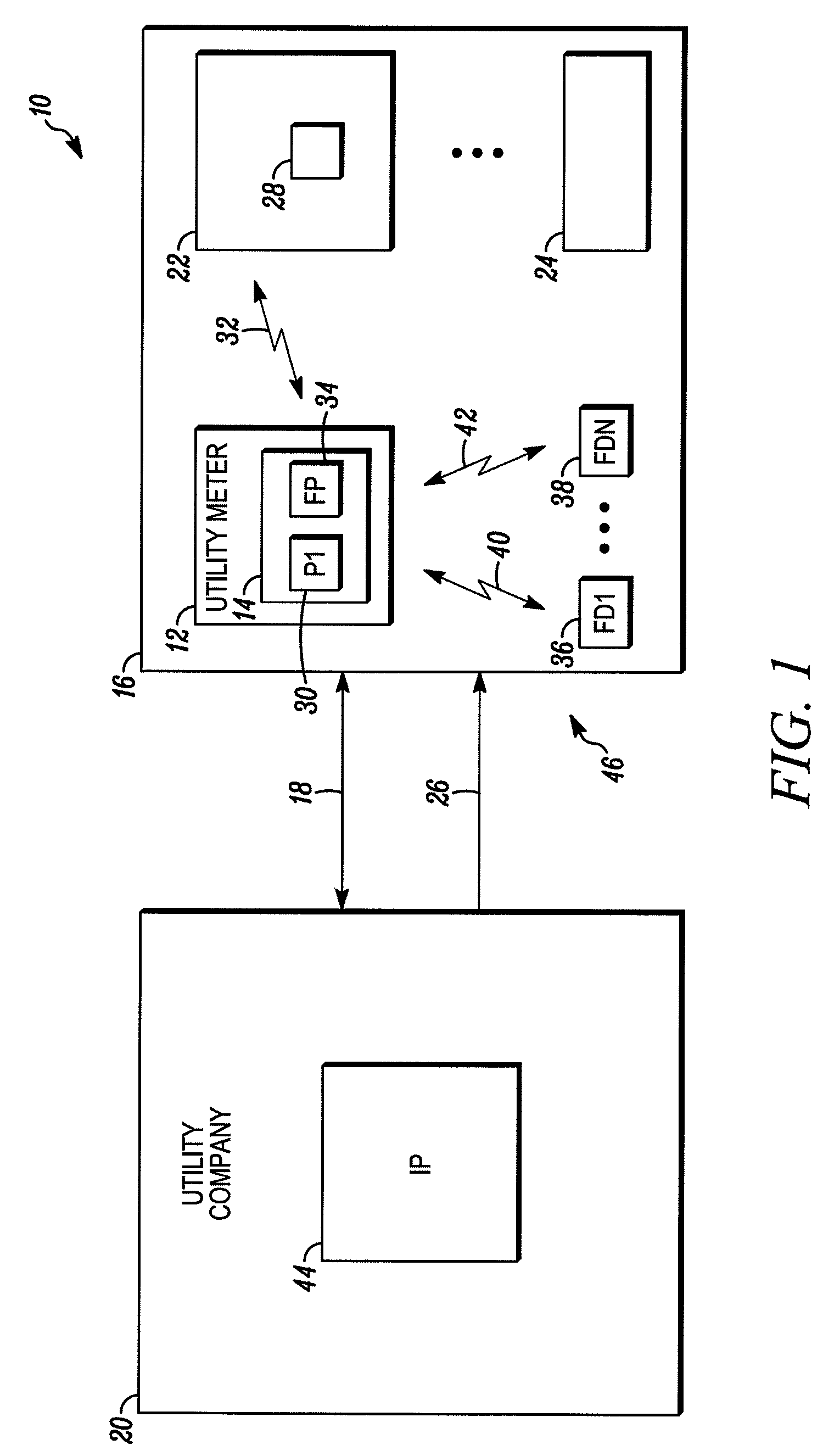

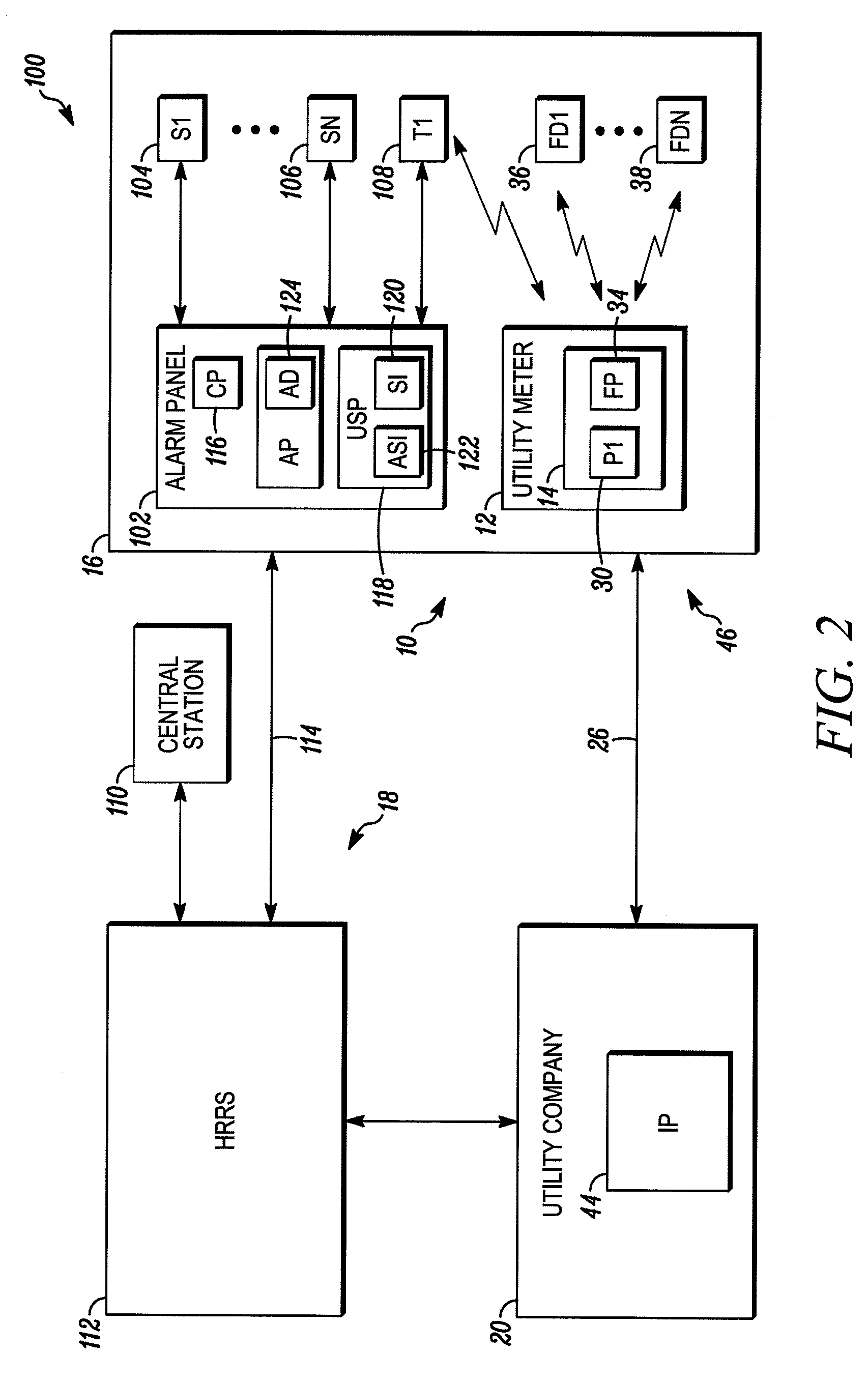

Alarm reporting through utility meter reading infrastructure

ActiveUS8054199B2Electric signal transmission systemsTariff metering apparatusUtility companyComputer science

A system is provided that includes a utility meter of a utility company that measures consumption of a utility within a space occupied by a user, a wireless fault detector associated with the utility located within the space and a wireless transmitter of the utility meter that receives a fault message from the fault detector, confirms consumption of the utility within the space and transmits a fault message that identifies the space to the utility company.

Owner:ADEMCO INC

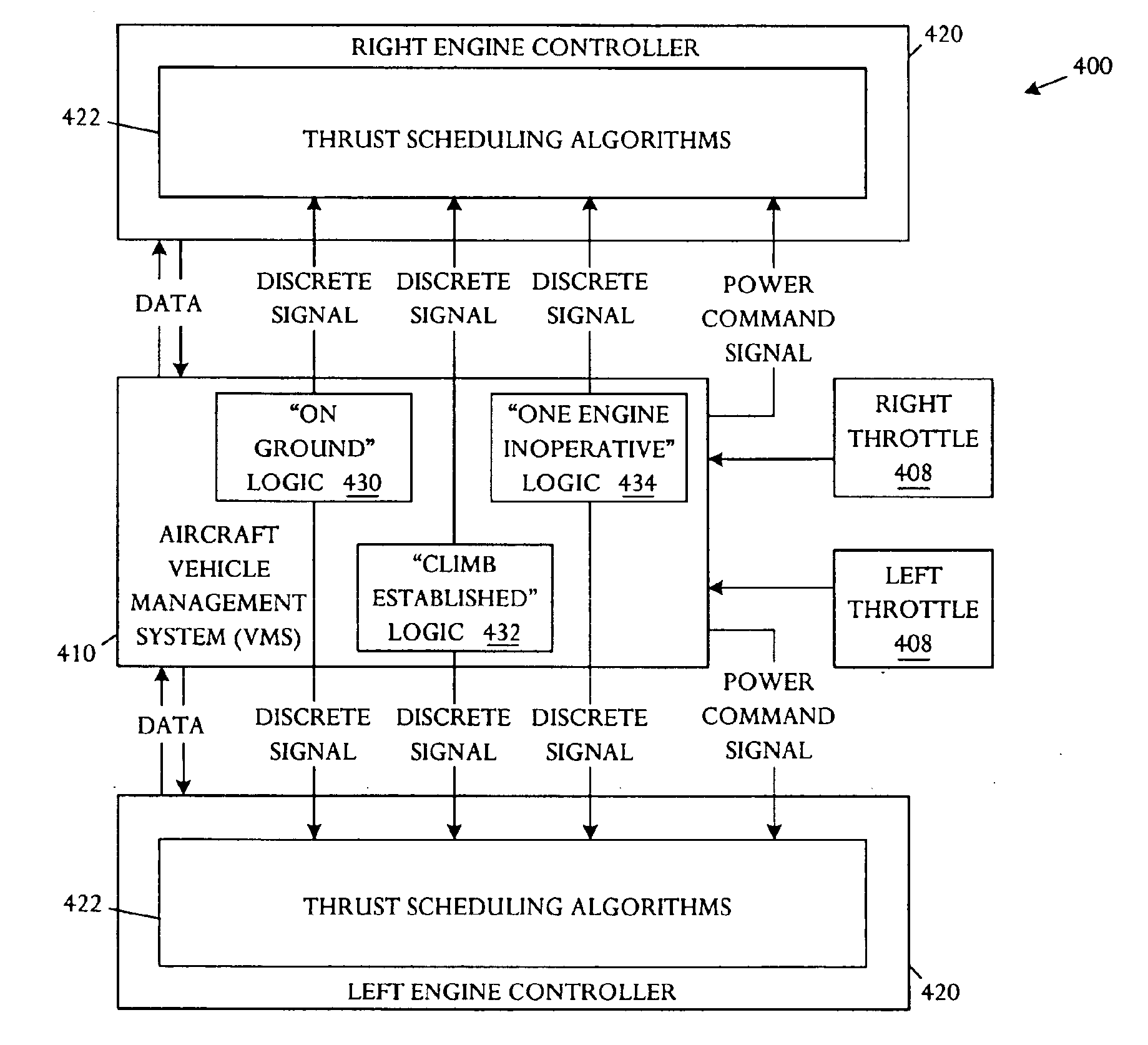

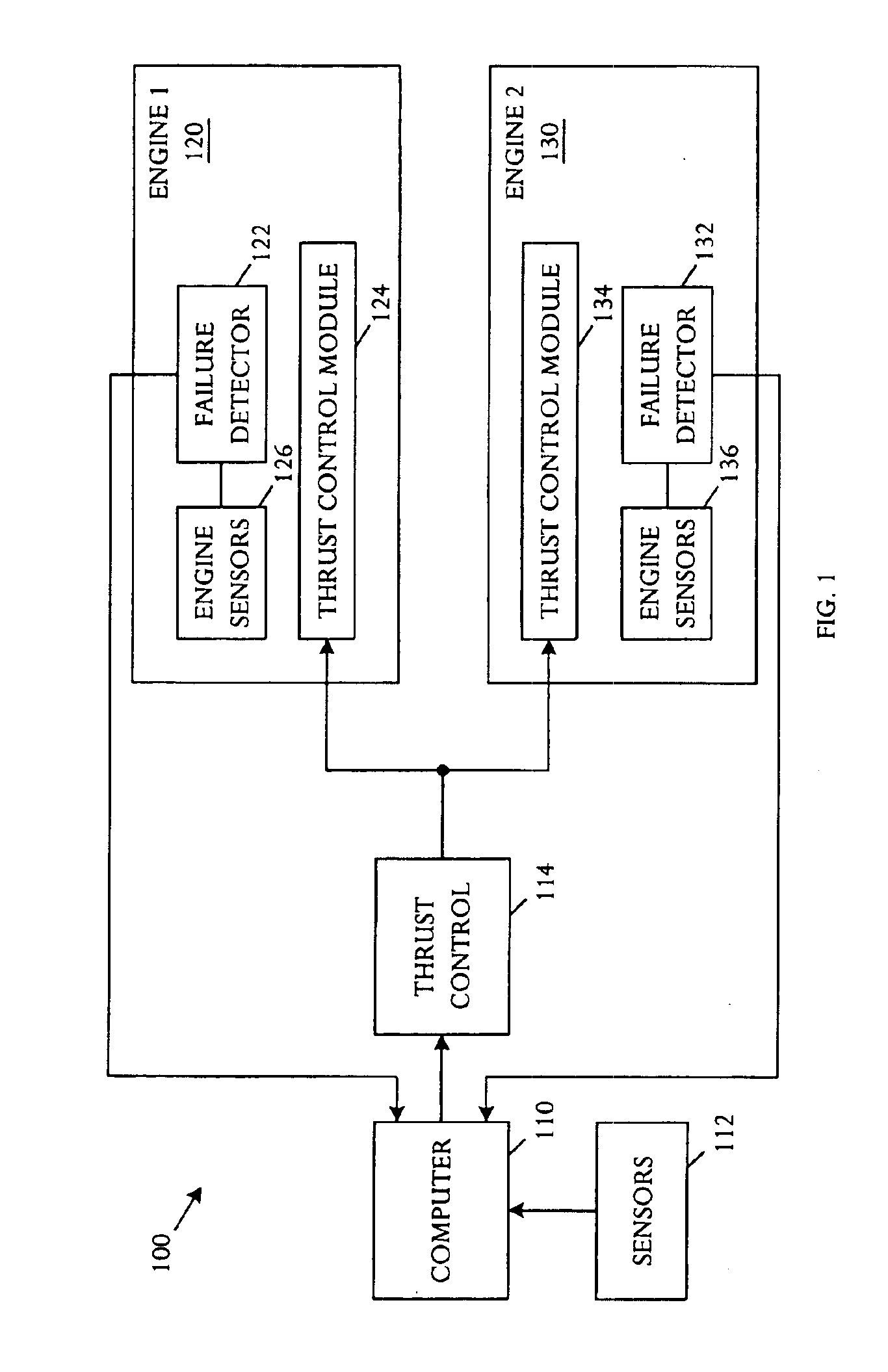

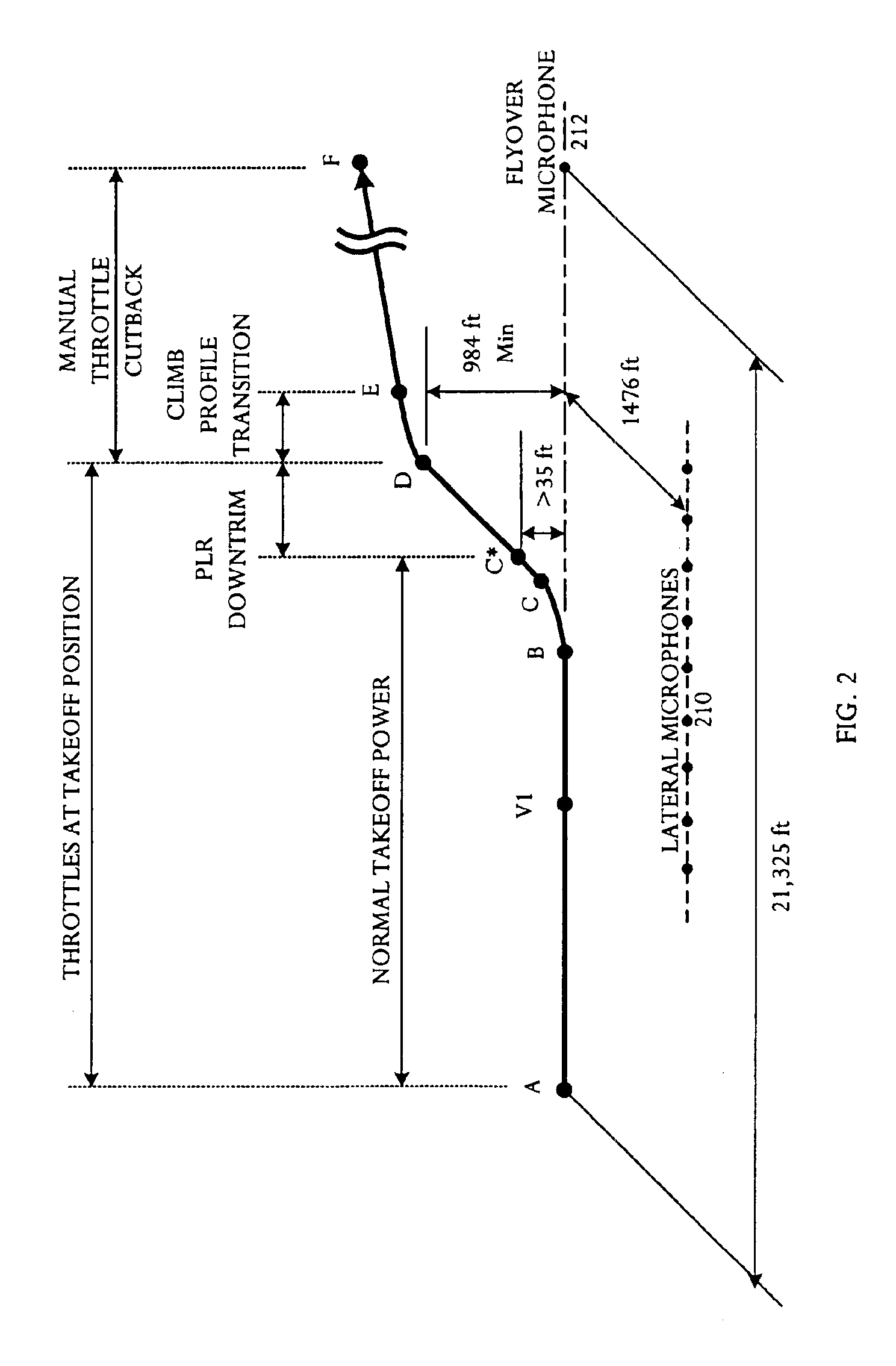

Automatic takeoff thrust management system

InactiveUS6880784B1Reduce and minimize takeoff noiseReduce thrustAircraft power plantsAircraft stabilisationFlight vehicleManagement system

An automatic takeoff thrust management system can be used in an aircraft with at least two engines. The management system comprises an aircraft status sensor or set of sensors capable of detecting establishment of takeoff climb conditions, and engine failure detectors respectively coupled to the at least two engines and capable of detecting engine failure. The management system further comprises thrust control modules respectively coupled to the at least two engines and capable of controlling the thrust of the engines, and a controller coupled to the aircraft status sensors, the engine failure detectors, and the thrust control modules. The controller reduces thrust by a selected amount upon detecting establishment of takeoff climb conditions and, if engine failure is detected, restoring thrust to an initial or a higher schedule.

Owner:SUPERSONIC AEROSPACE INT

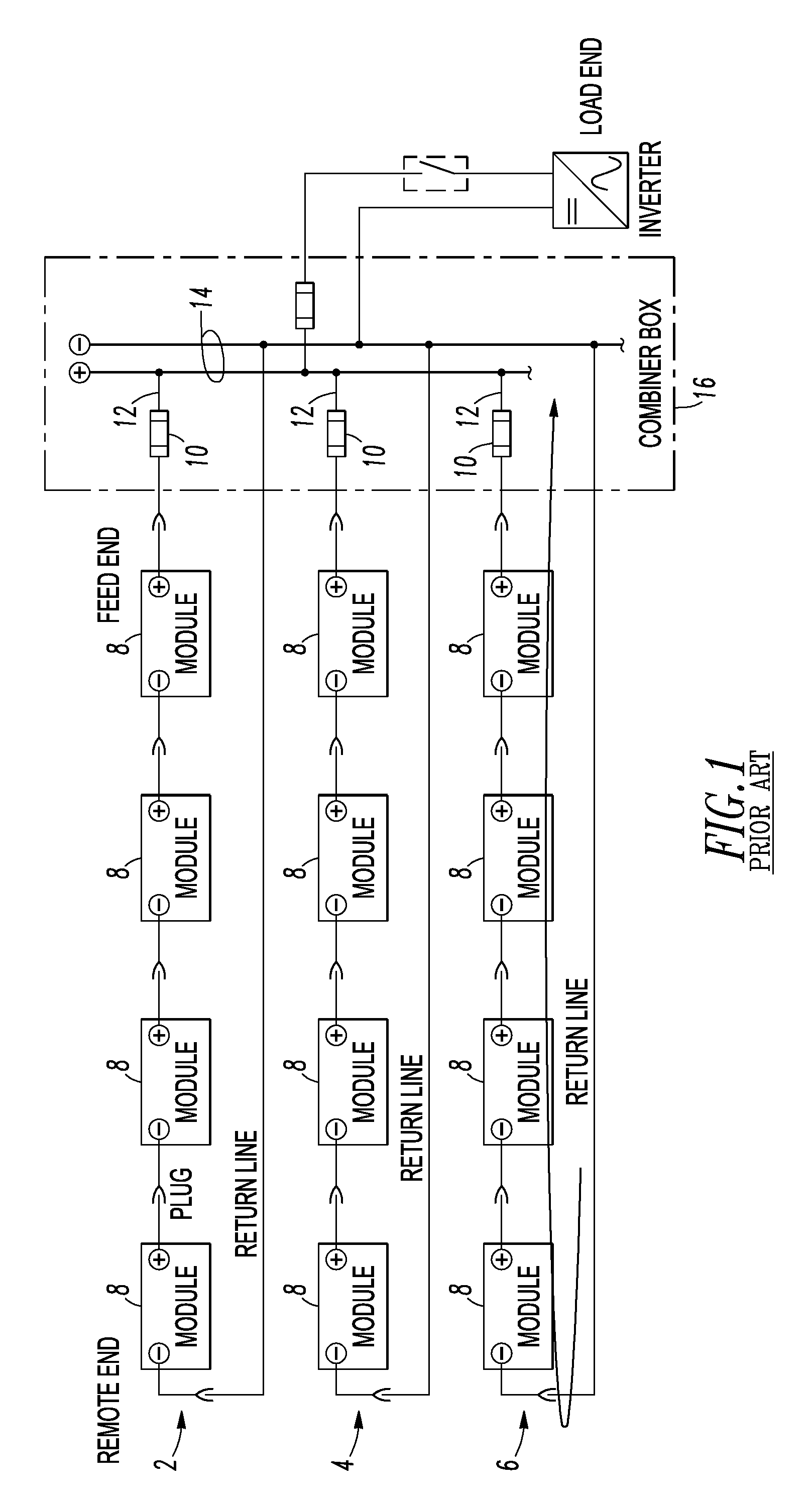

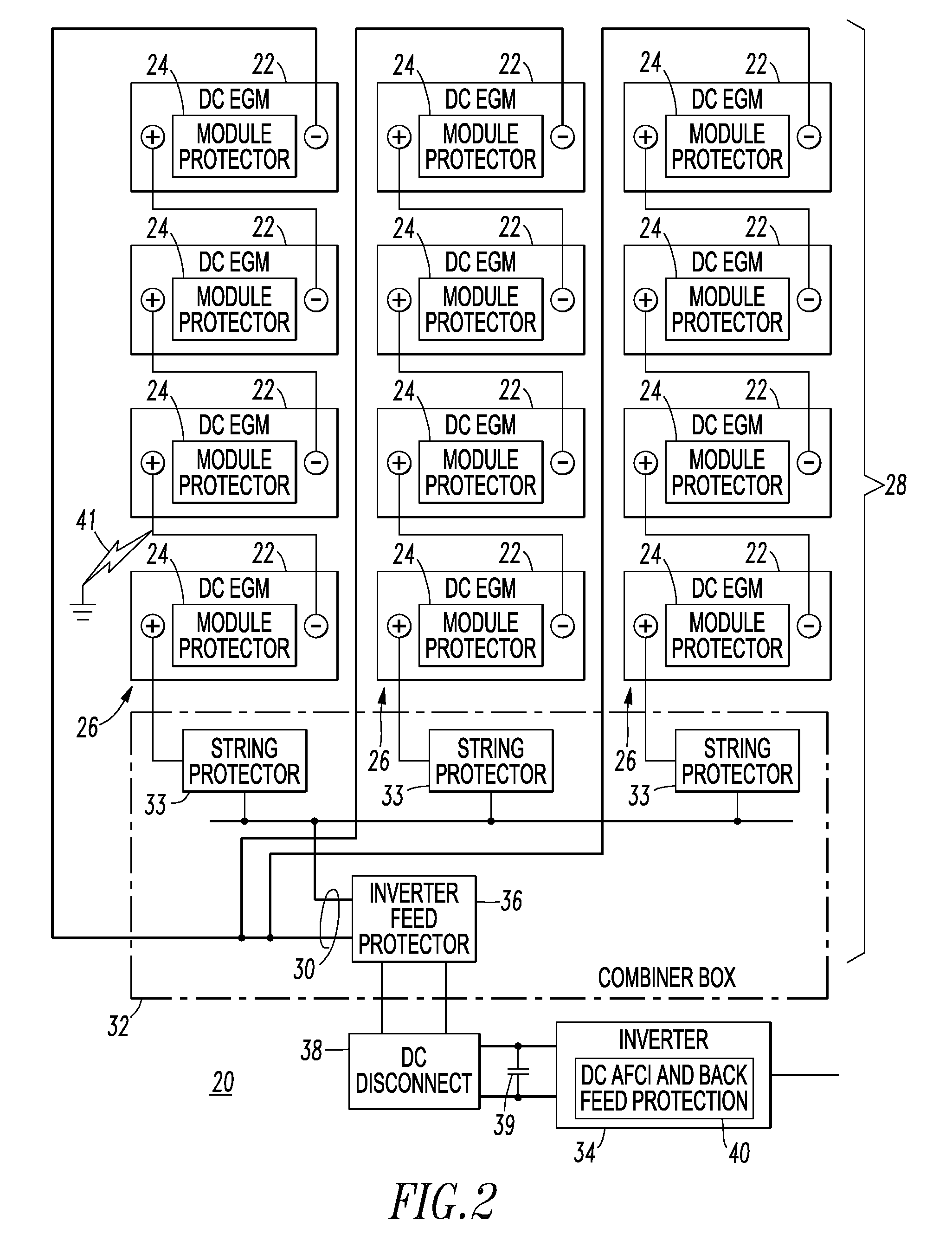

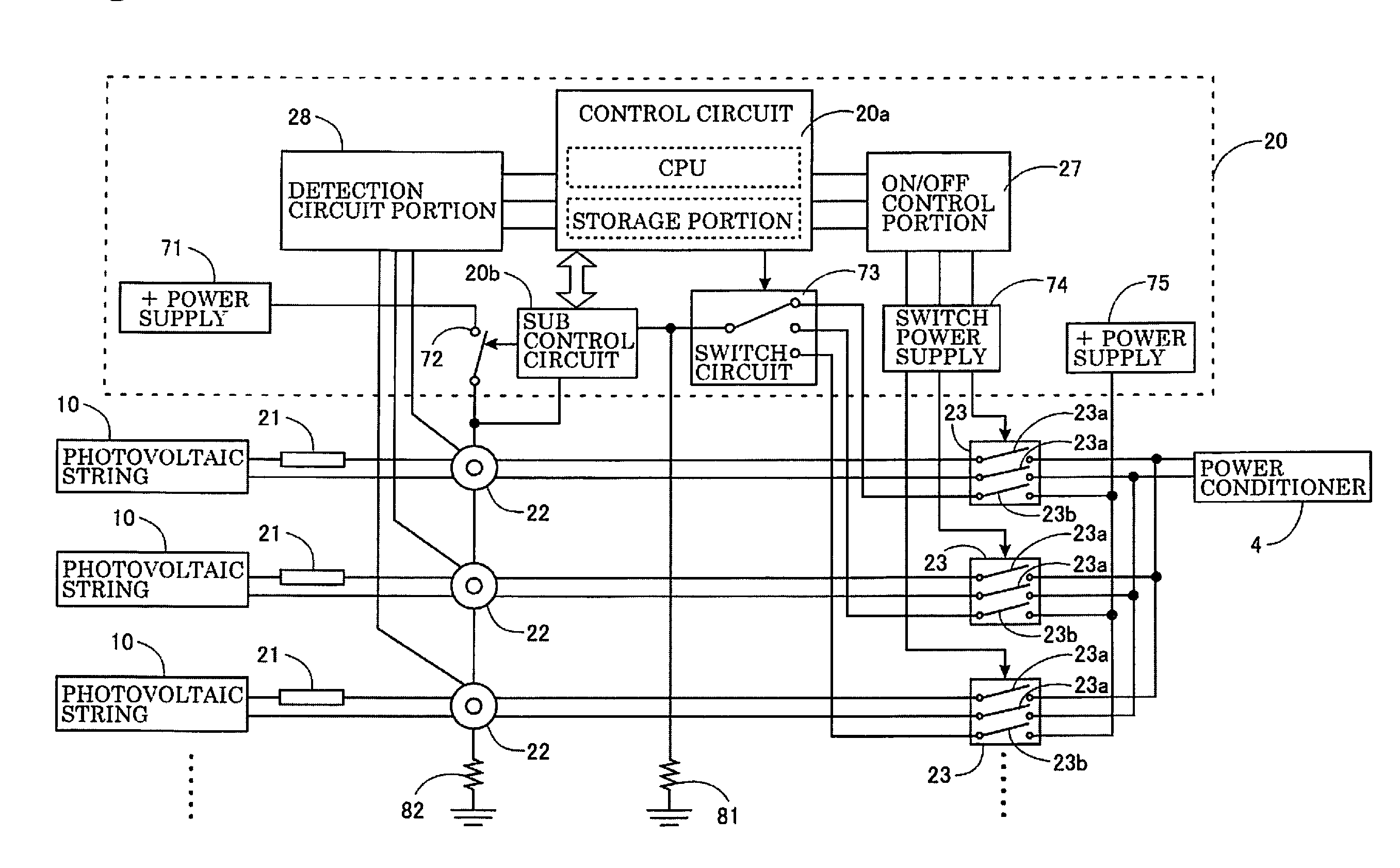

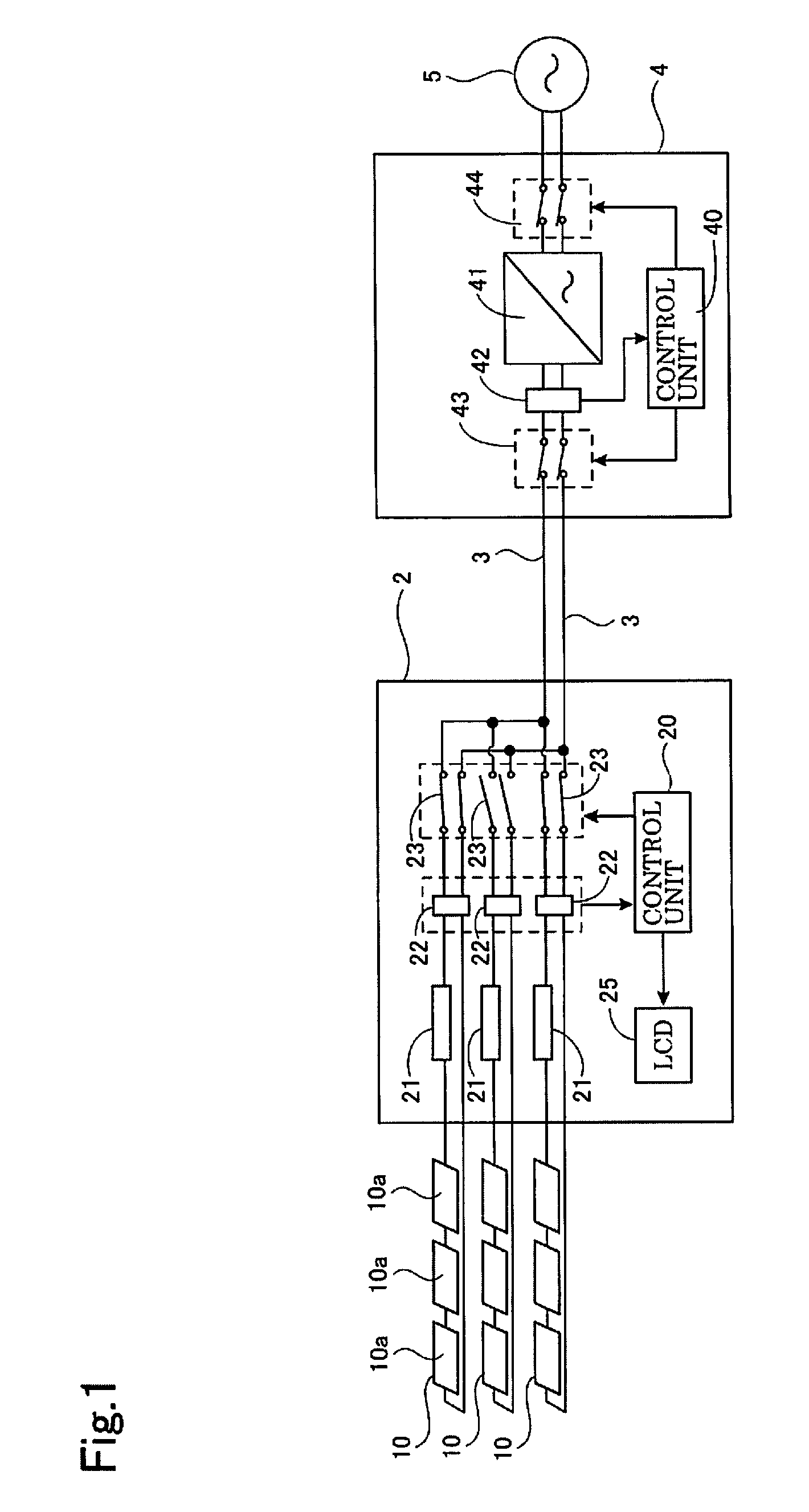

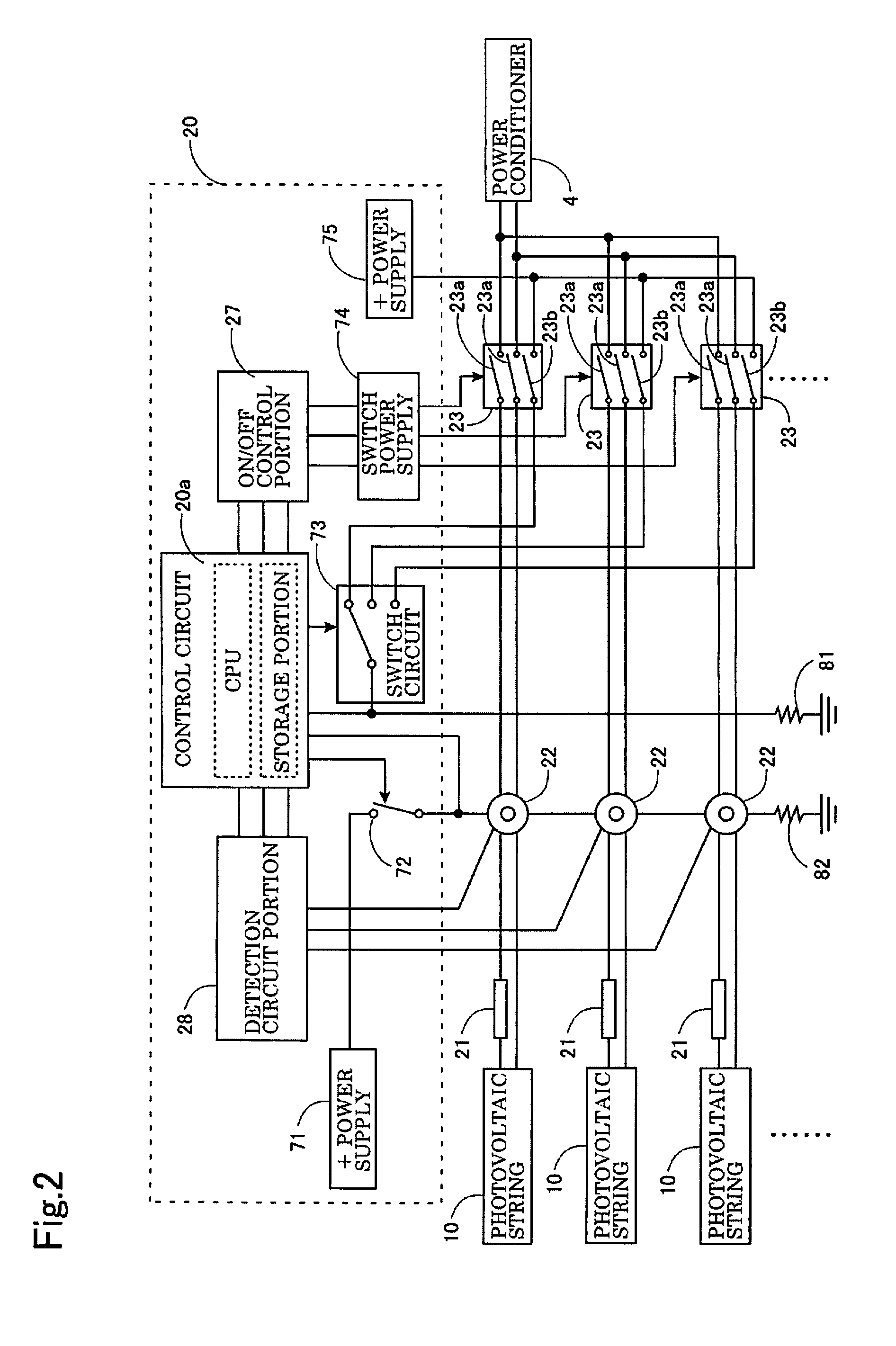

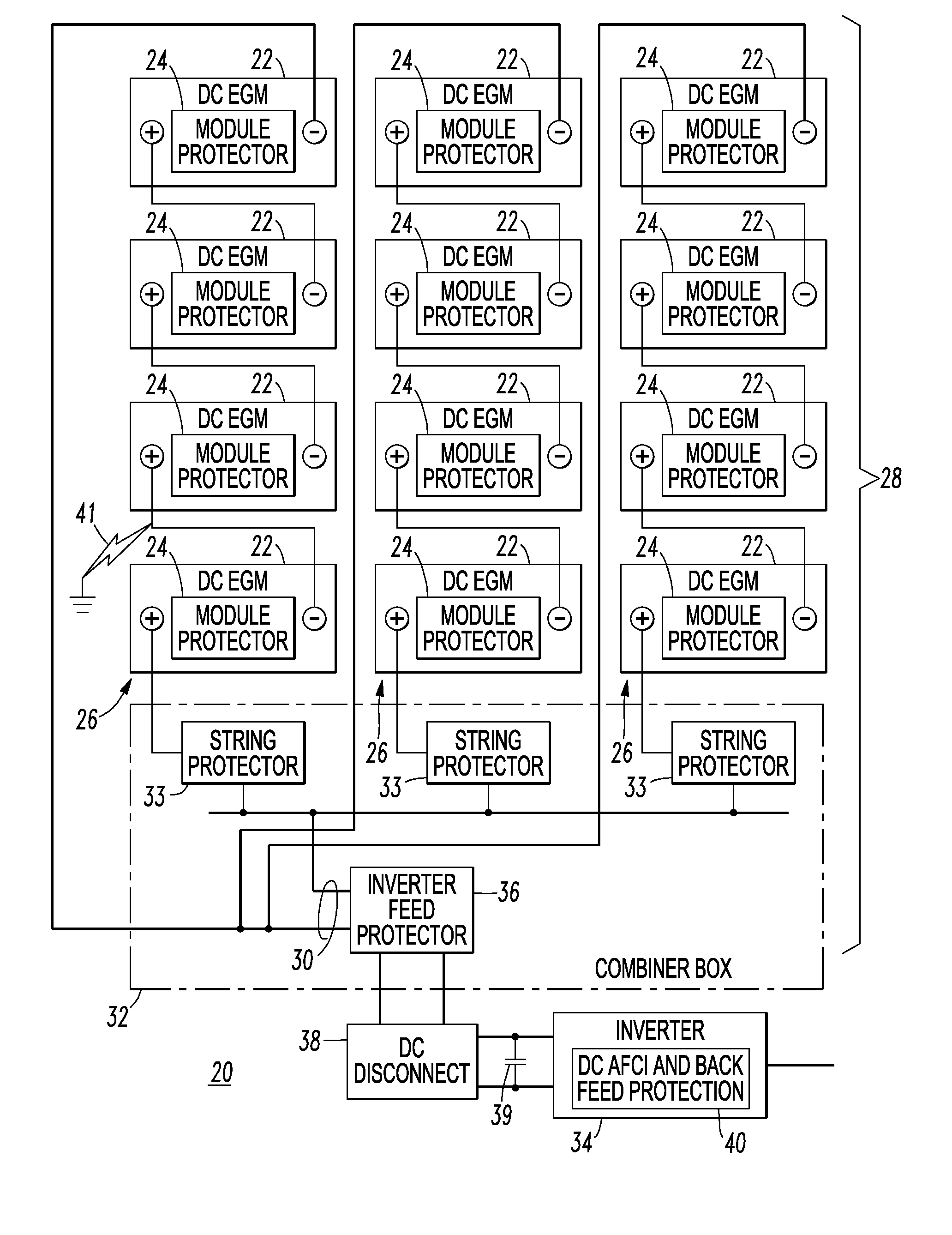

Current collecting box for photovoltaic power generation

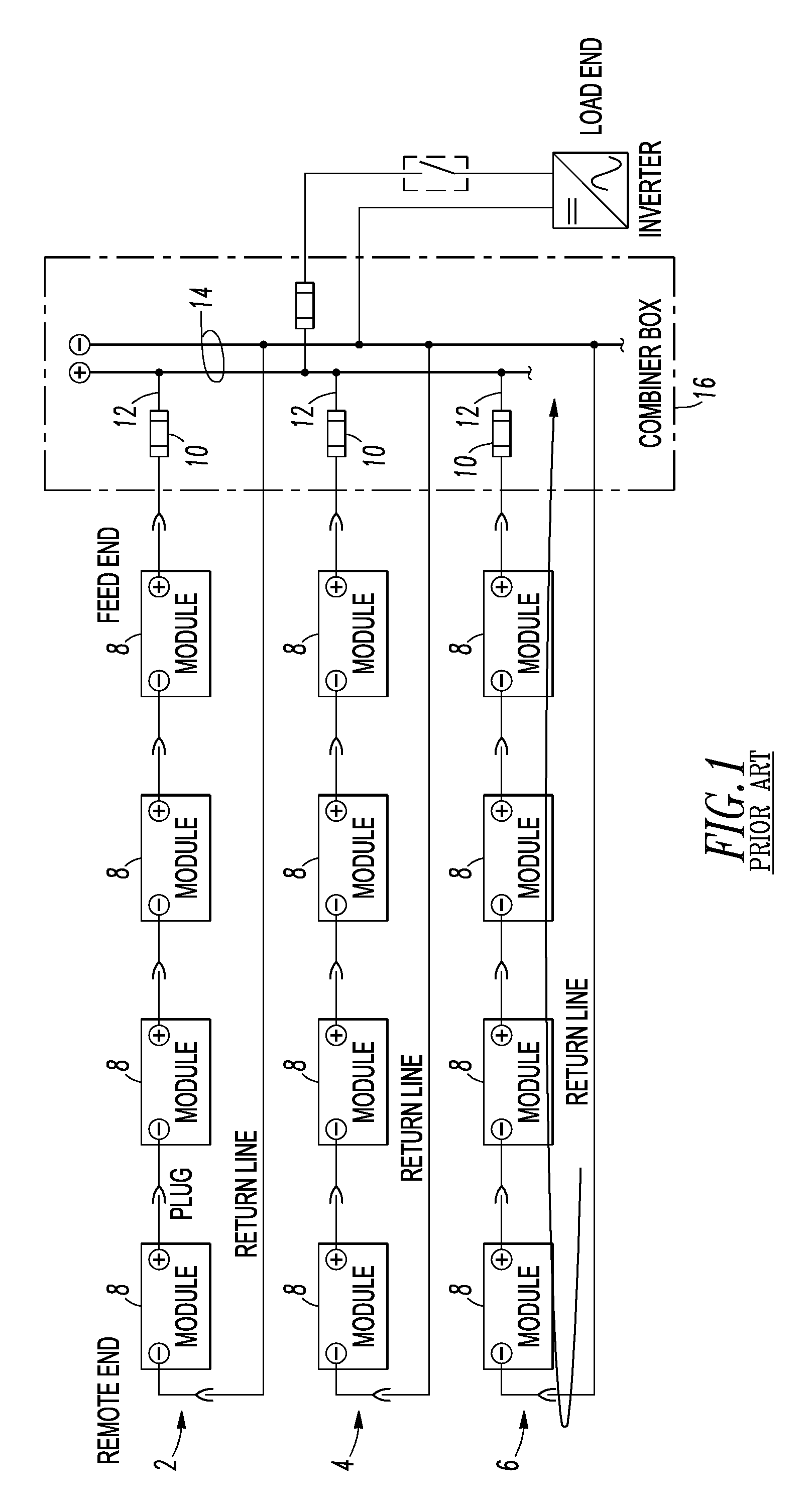

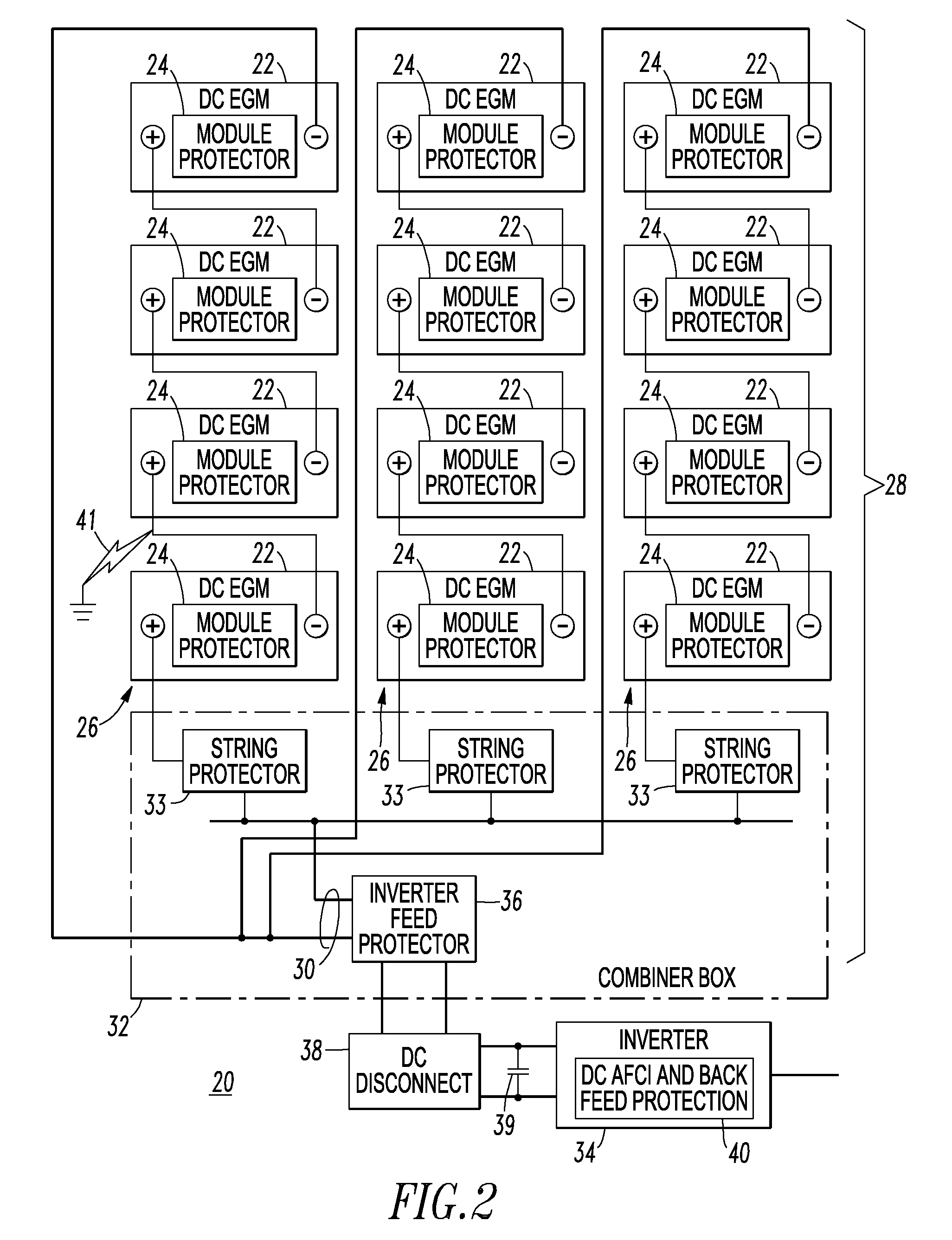

InactiveUS20120049627A1Easy to checkDc source parallel operationShort-circuit testingControl circuitPhotovoltaic power generation

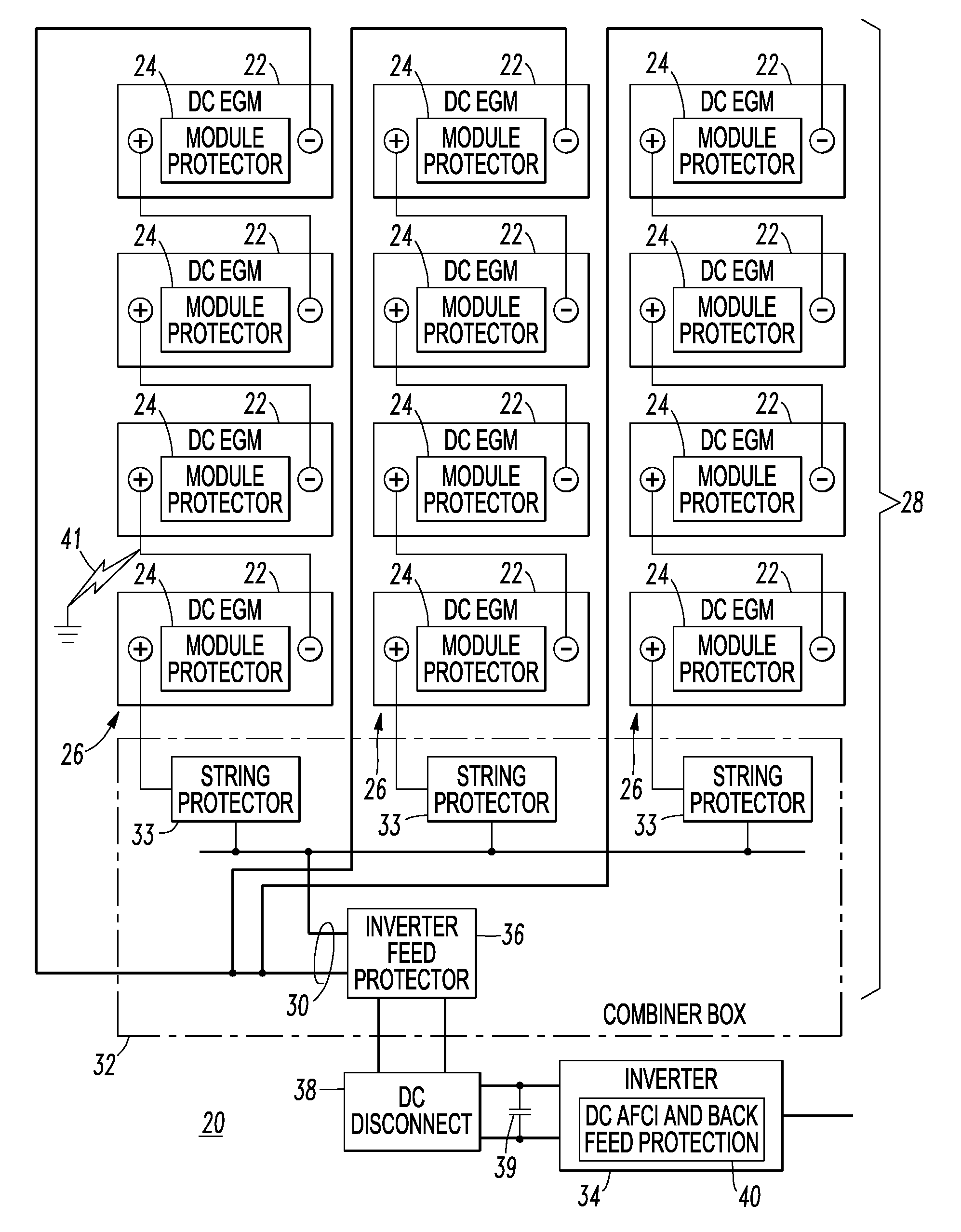

A current collecting box for photovoltaic power generation comprising a ground fault detector detecting a ground fault in photovoltaic strings; a switch disposed for each of the photovoltaic strings and interposed between the photovoltaic string and a connecting cable; a control circuit determining the presence of a ground fault and providing an on / off control of the switch; and a power supply supplying the current to the grand fault detector, and the power supply is supplied from a power supply so that the operation check for the ground fault detector is performed based on an output from the ground fault detector. The current supply is supplied and the operation check for an auxiliary switch operating according to an on / off operation of a main switch is performed so that the operation check for a switch is performed.

Owner:SANYO ELECTRIC CO LTD

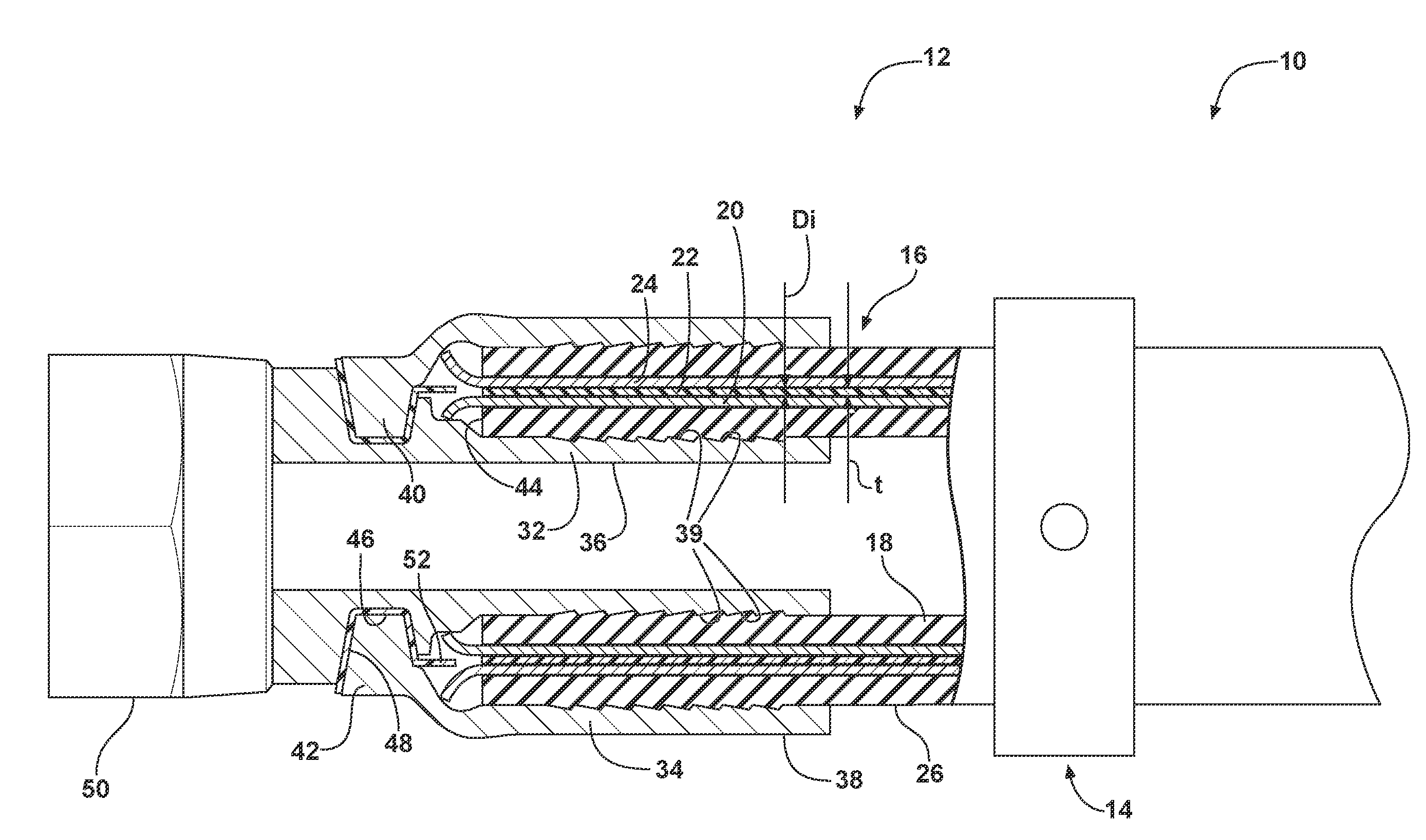

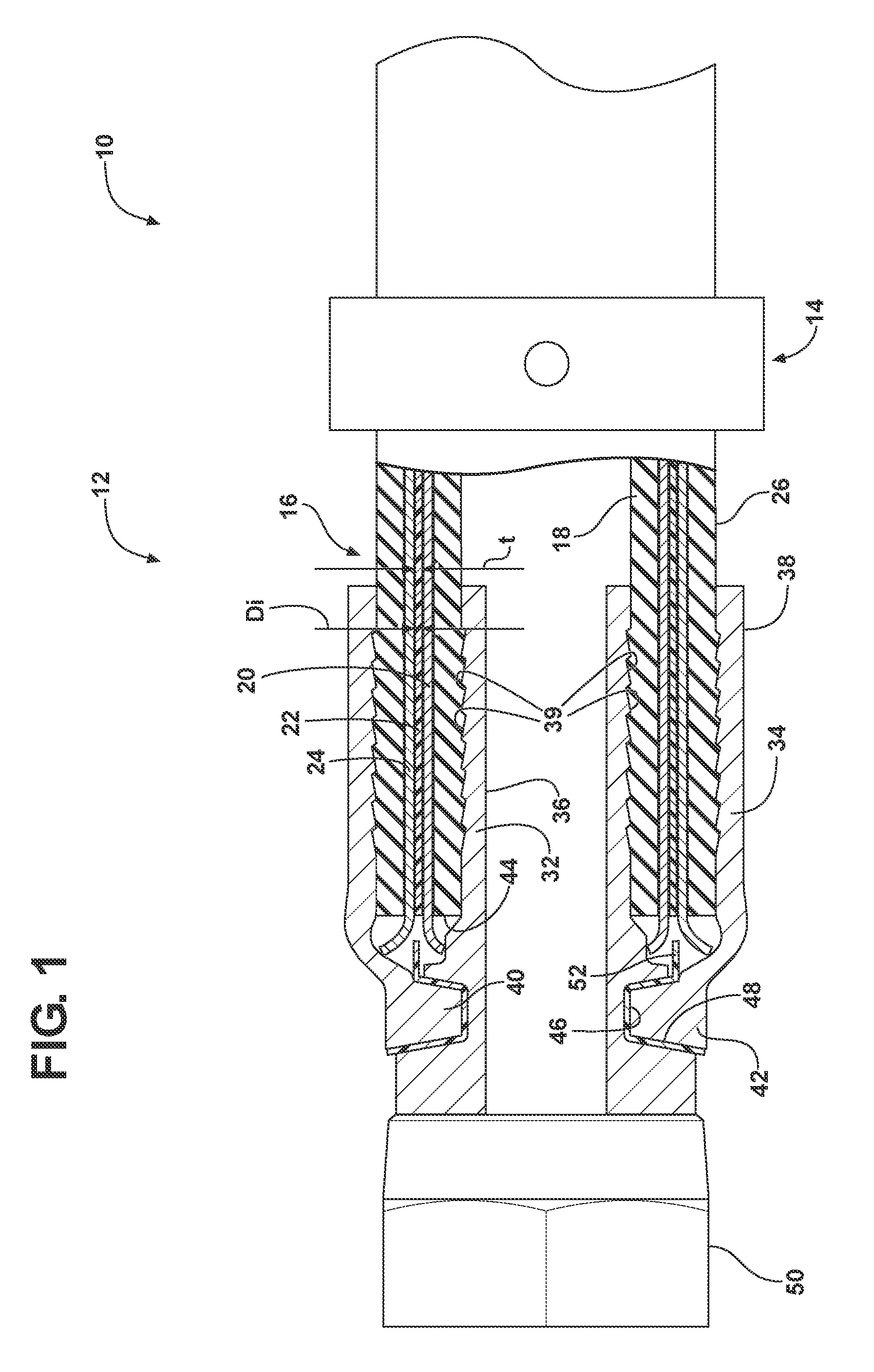

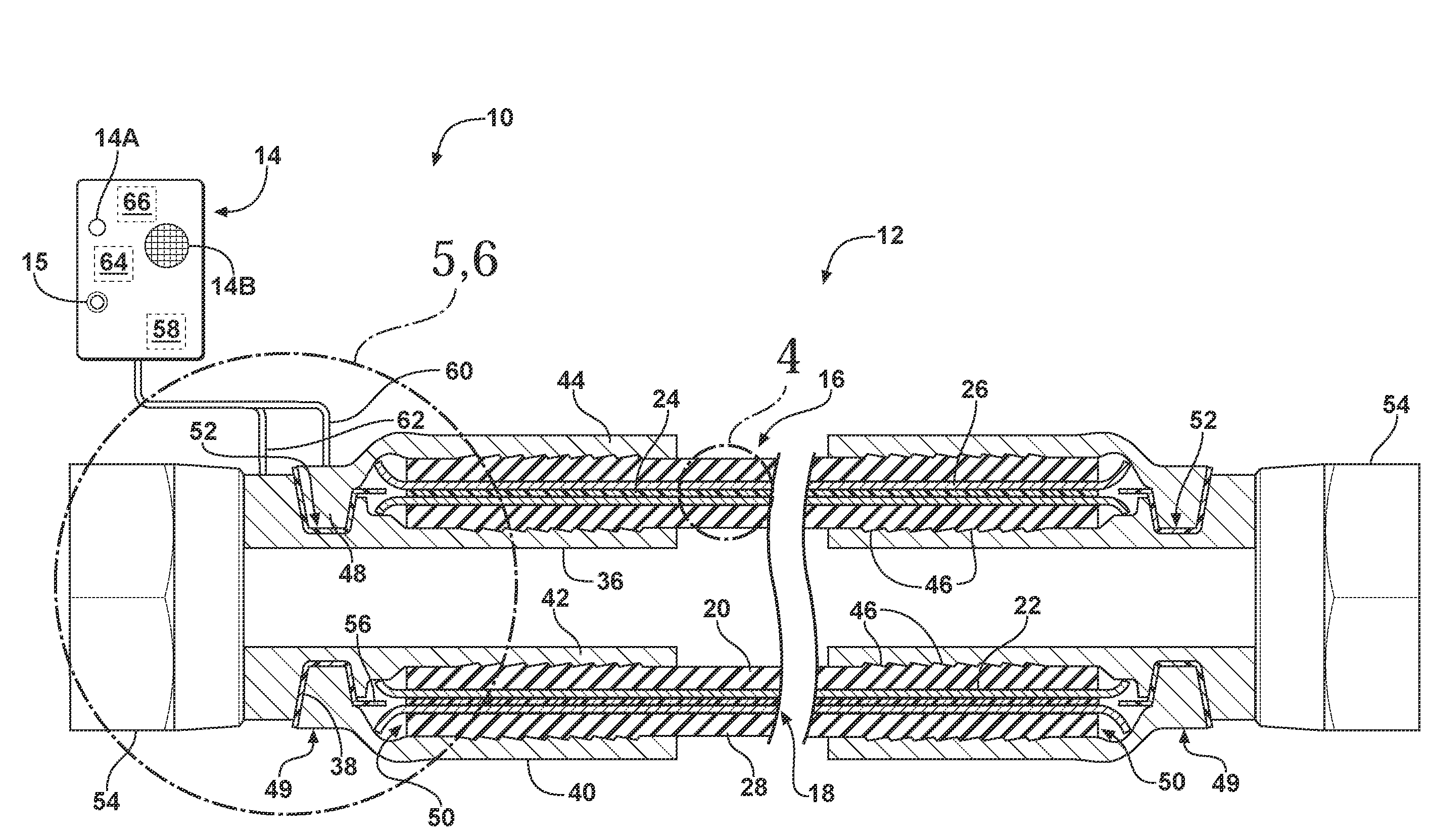

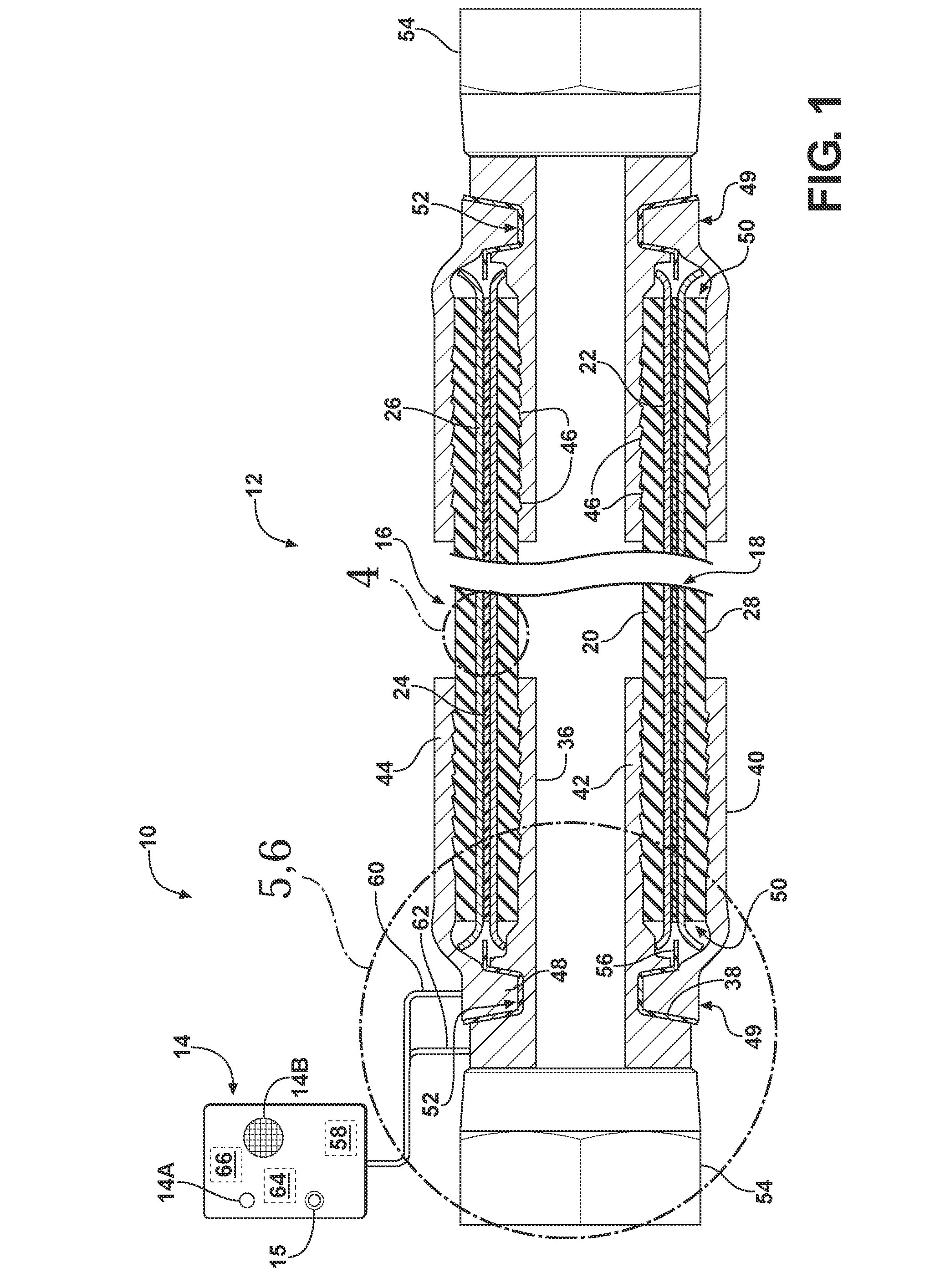

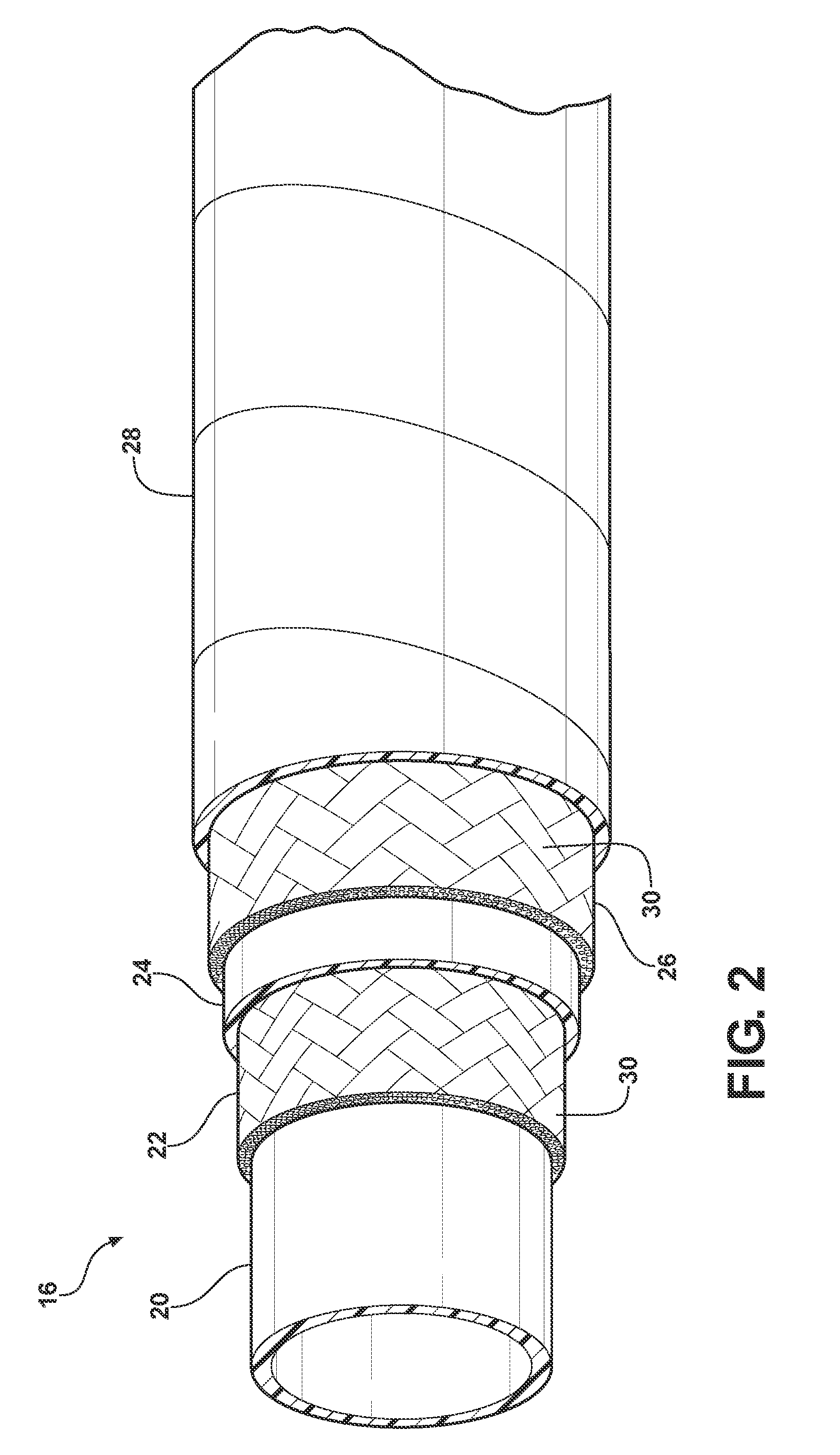

Degradation detection system for a hose assembly

A hose fault detection system includes a hose assembly including a hose having first and second conductive layers. The hose assembly has an electrical characteristic. A fault detector is in electrical communication with the first and second conductive layers. The fault detector includes an indicator operatively connected to the hose assembly. A method for monitoring the structural integrity of a hose assembly includes providing a fault detection system having a hose assembly including a hose having a first conductive layer and a second conductive layer. The hose assembly has an electrical characteristic. The electrical characteristic of the hose assembly is compared to a threshold value. A visual indicator in operative communication with the hose assembly is illuminated when the electrical characteristic goes beyond the threshold value.

Owner:DANFOSS POWER SOLUTIONS II TECH AS

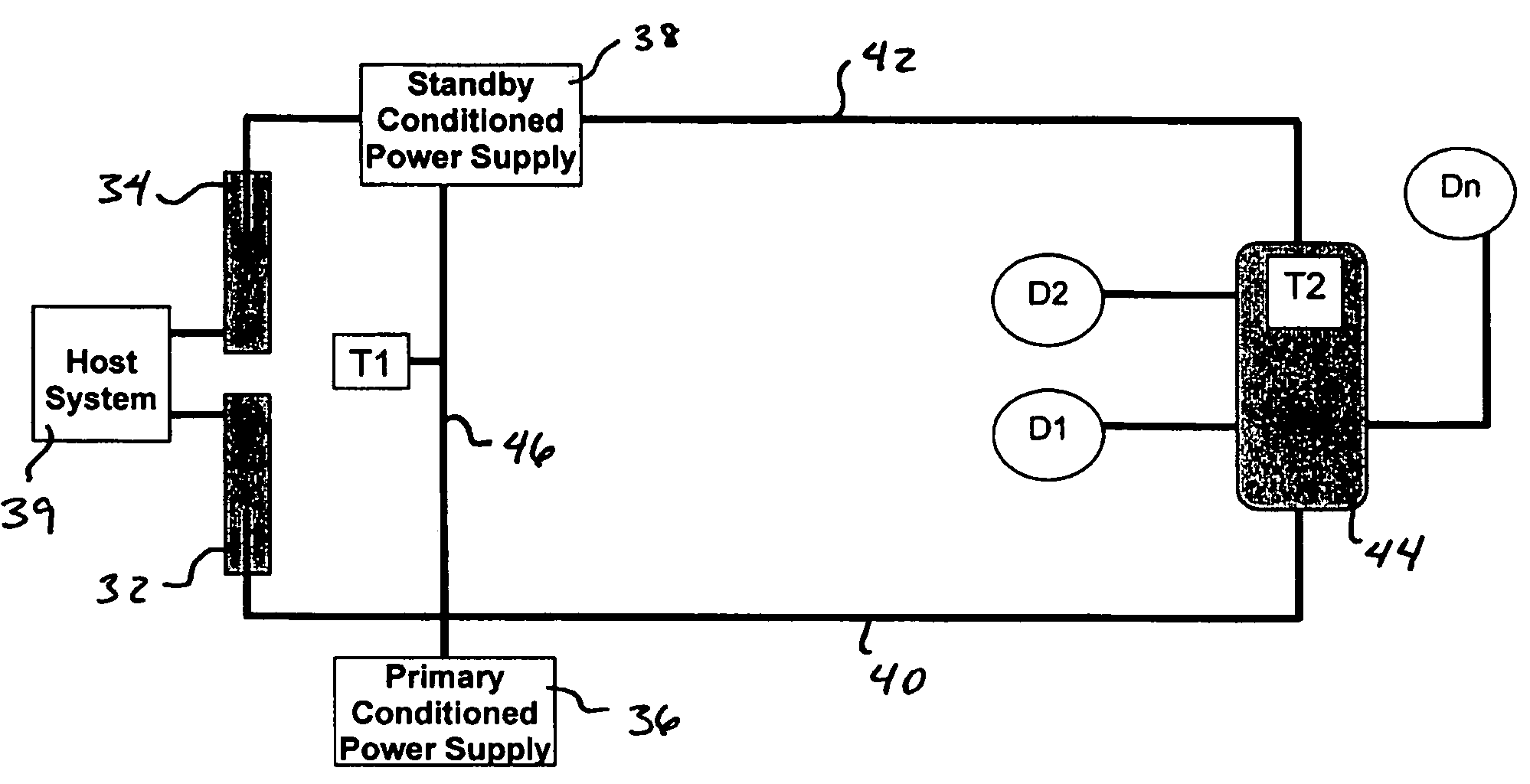

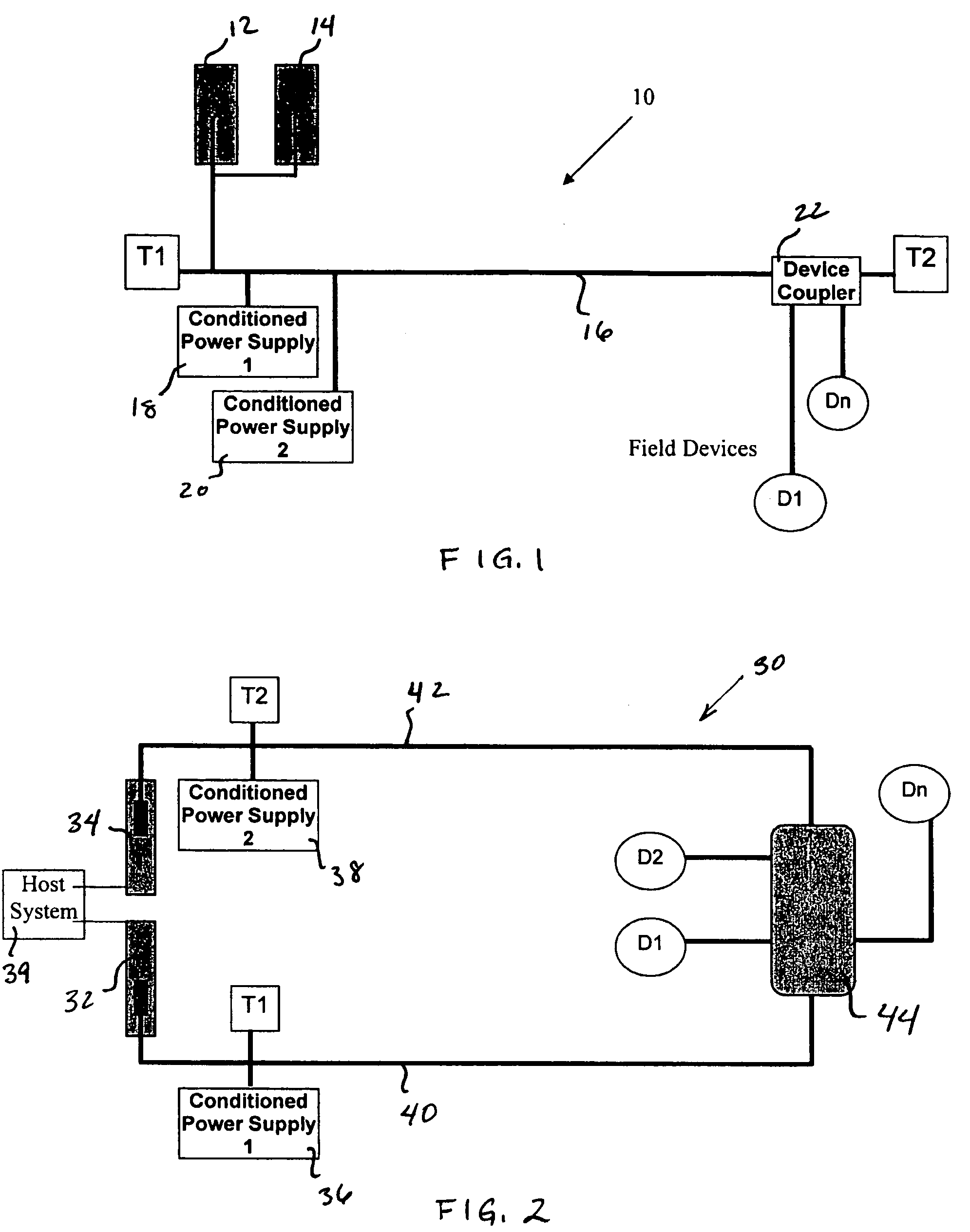

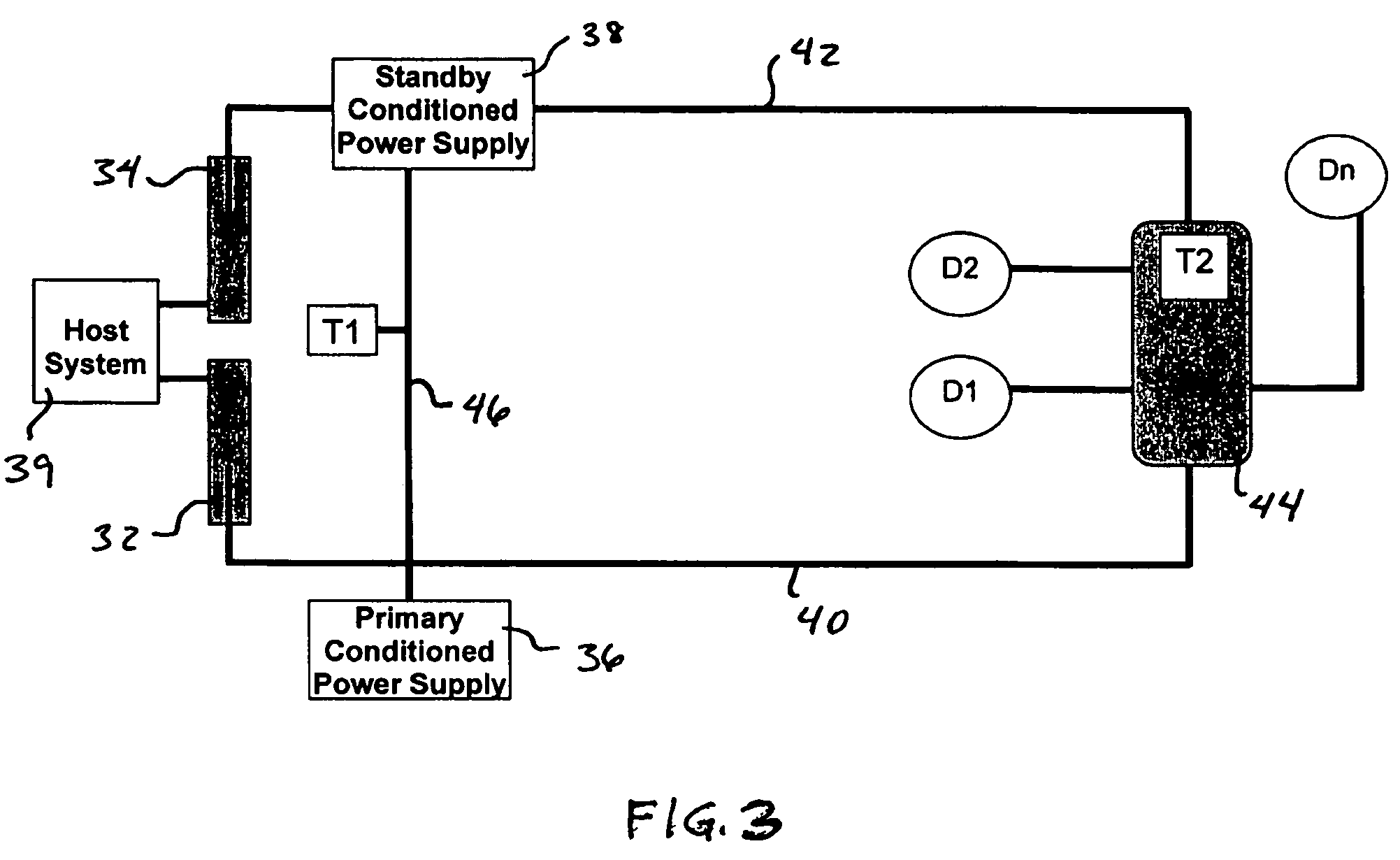

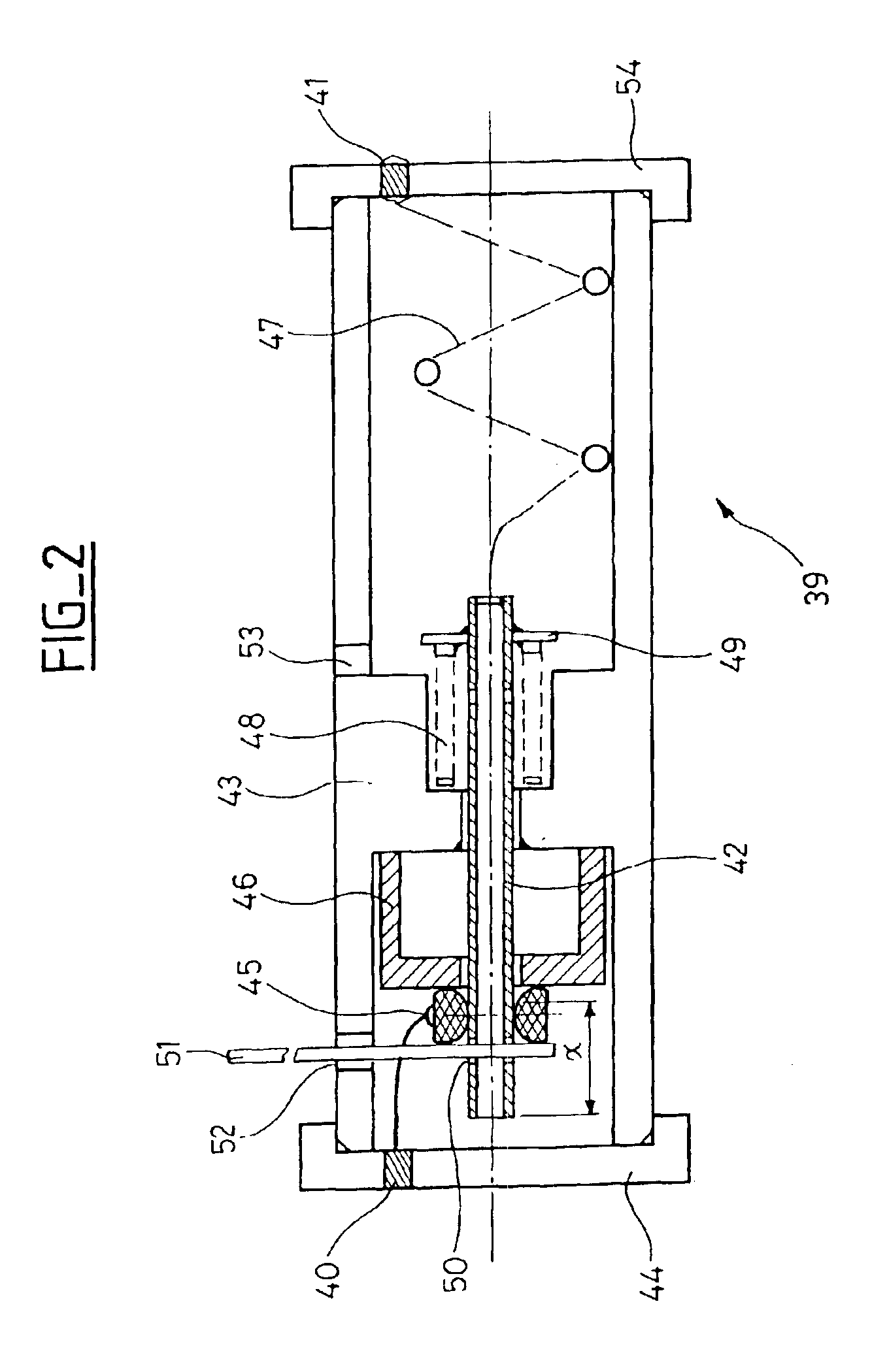

Redundant fieldbus system

A redundant fieldbus system provides power and communications in a parallel physical configuration between the host system and attached field devices irrespective of any single point failure in the network. In case of a fault, the redundant fieldbus system automatically eliminates the faulty section of the network, switches power and communications to the healthy portion of the network and terminates the network for signal integrity. A device coupler for the system may include a fault detector coupled to an auto-termination circuit that terminates a fieldbus cable when a fault is detected. The device coupler may include fault detection and isolation coupled to each set of spur terminals used to connect field devices to the device coupler. A field device for the system may include circuitry for deselecting a faulty cable while maintaining connection to a healthy cable.

Owner:MOORE IND INT

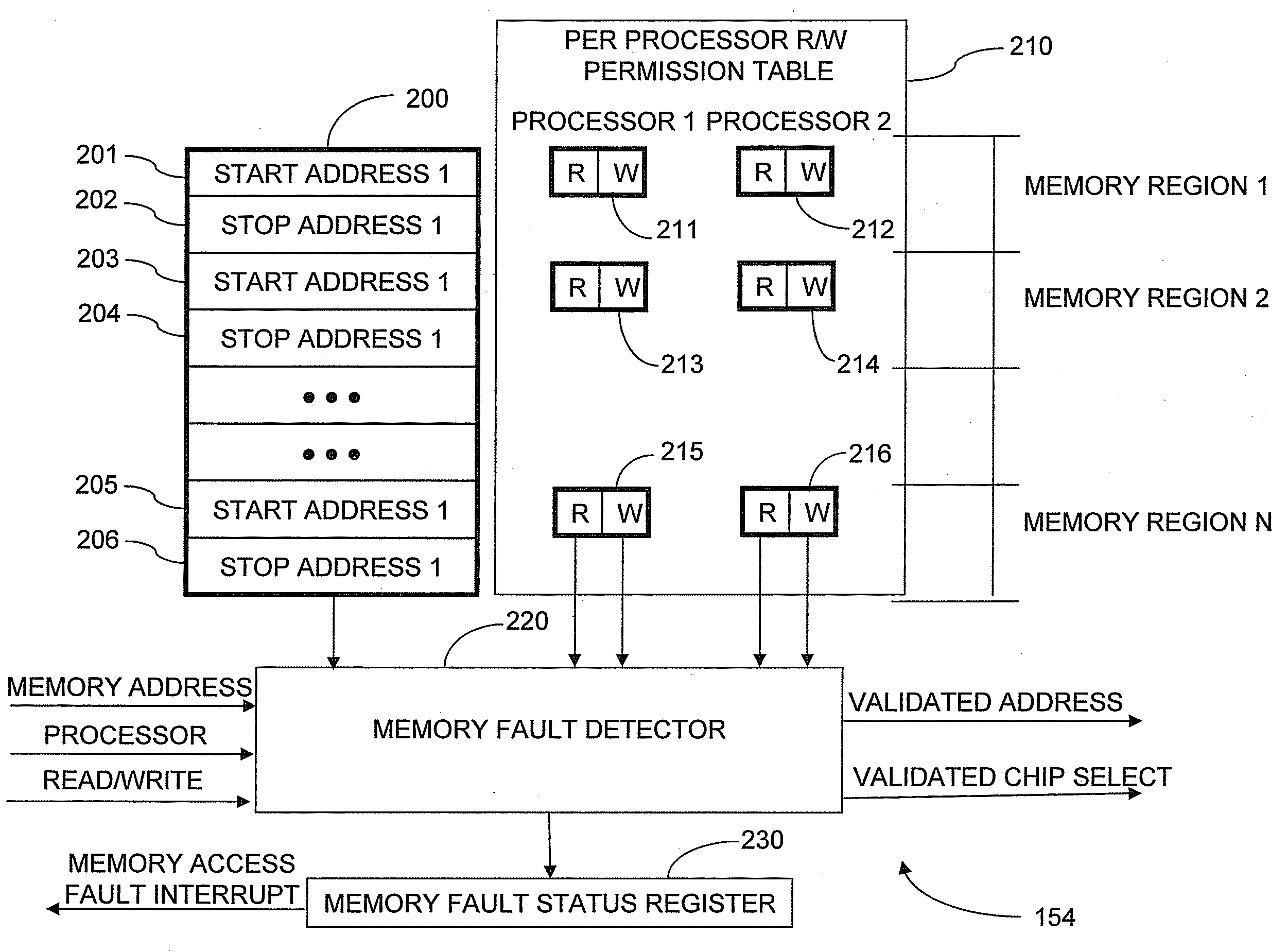

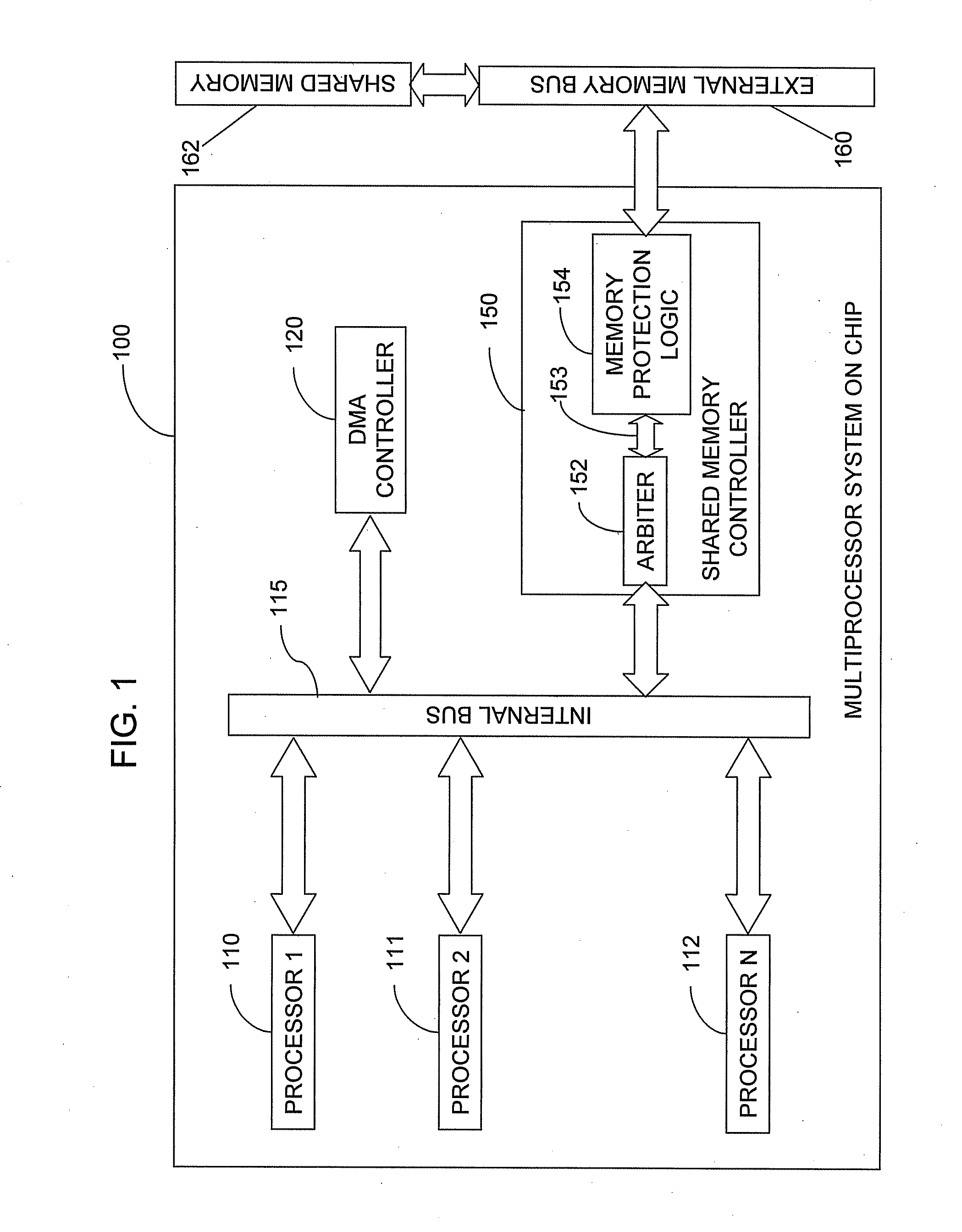

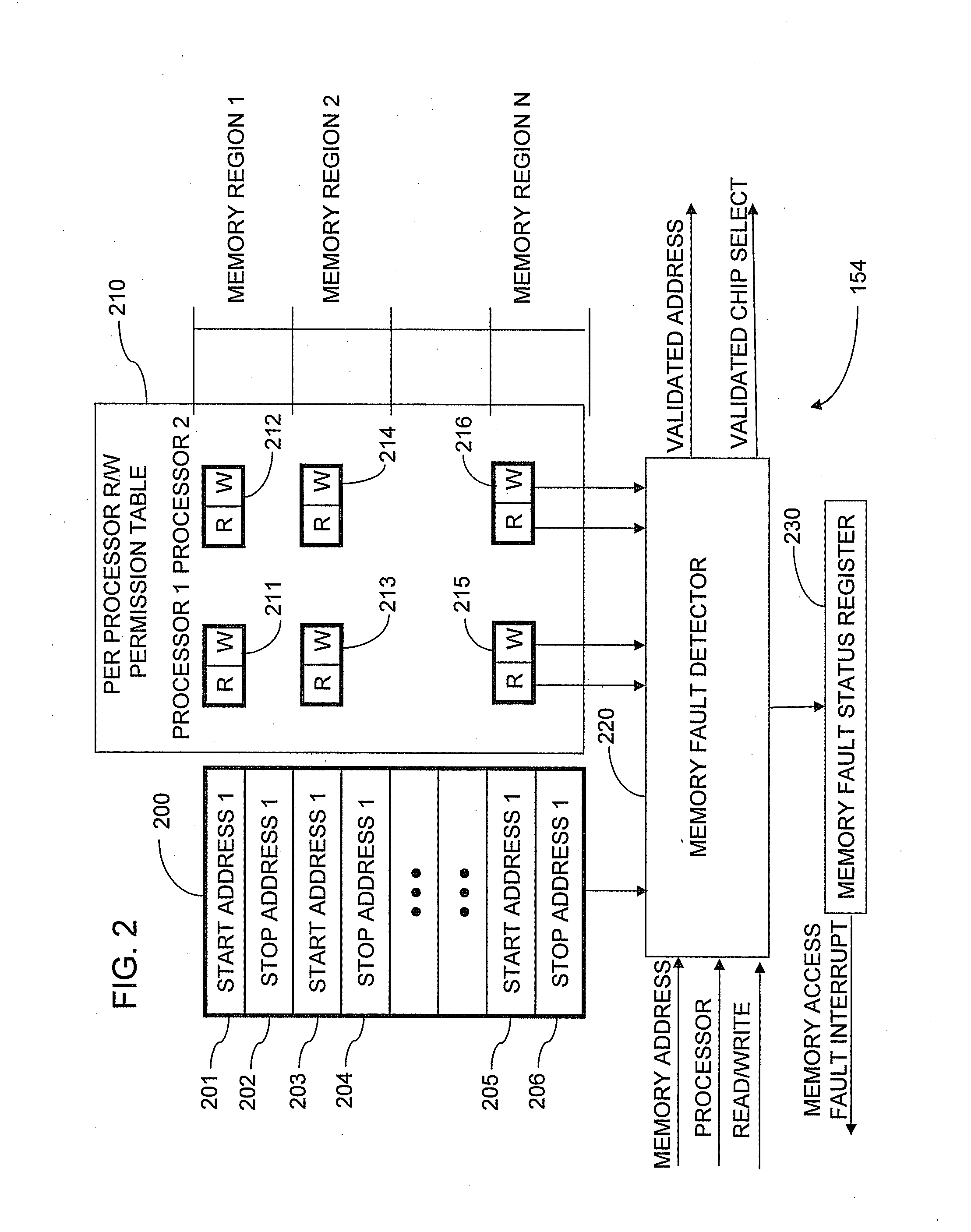

Memory protection system and method

A shared memory controller is provided for controlling access to a shared memory by a plurality of processors. At least one device includes a storage area for storing a respective address range for each of a plurality of memory regions. The at least one device further includes a permission table containing, for each of the plurality of memory regions, read and write permission data for each of the plurality of processors. A memory fault detector is coupled to the at least one device and has an input for receiving a memory access request including a memory address, a processor identification and a read / write indicator. The memory fault detector includes logic for determining whether a memory access according to the memory access request would conflict with the read and write permission data in the permission table.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

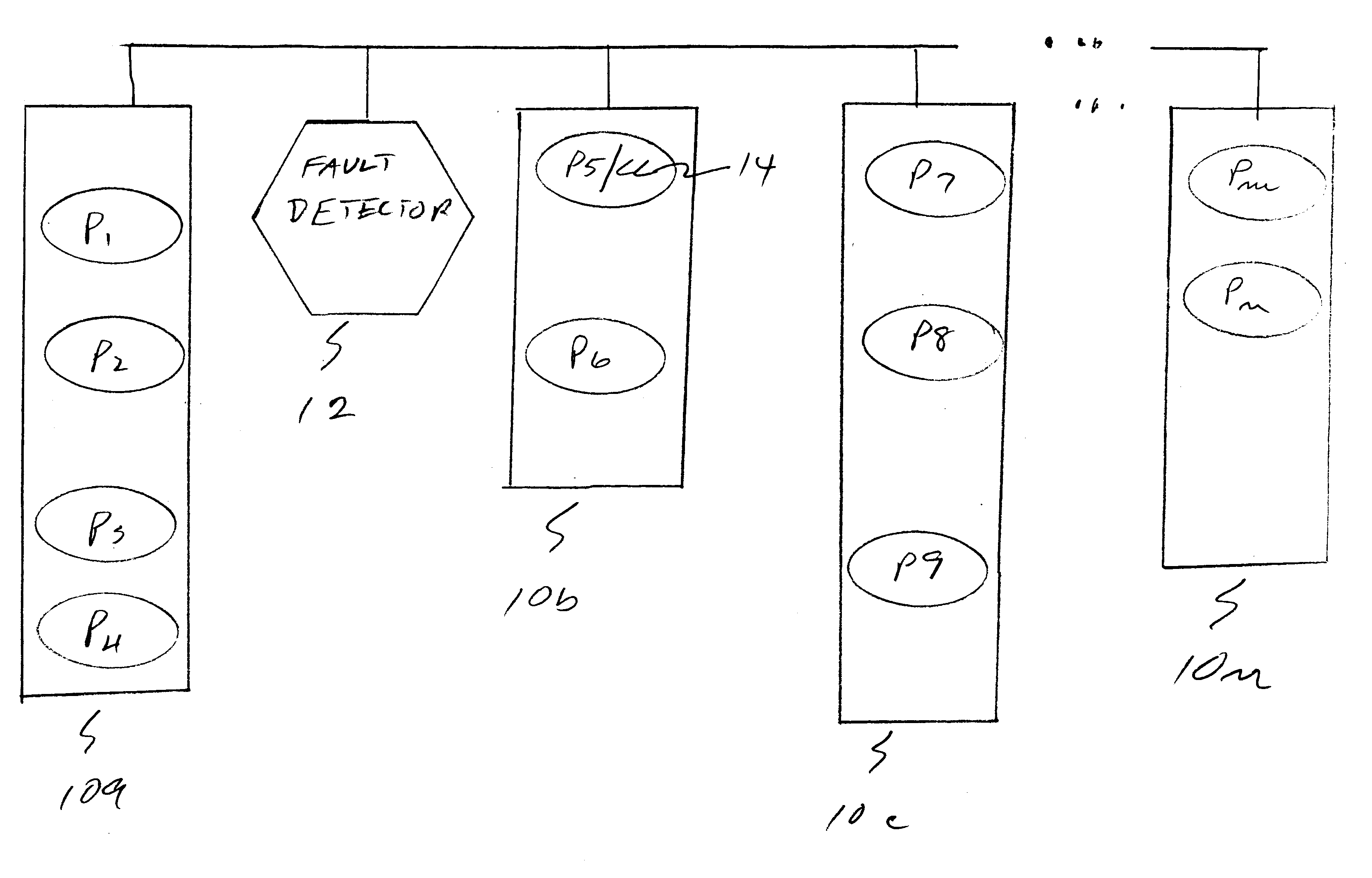

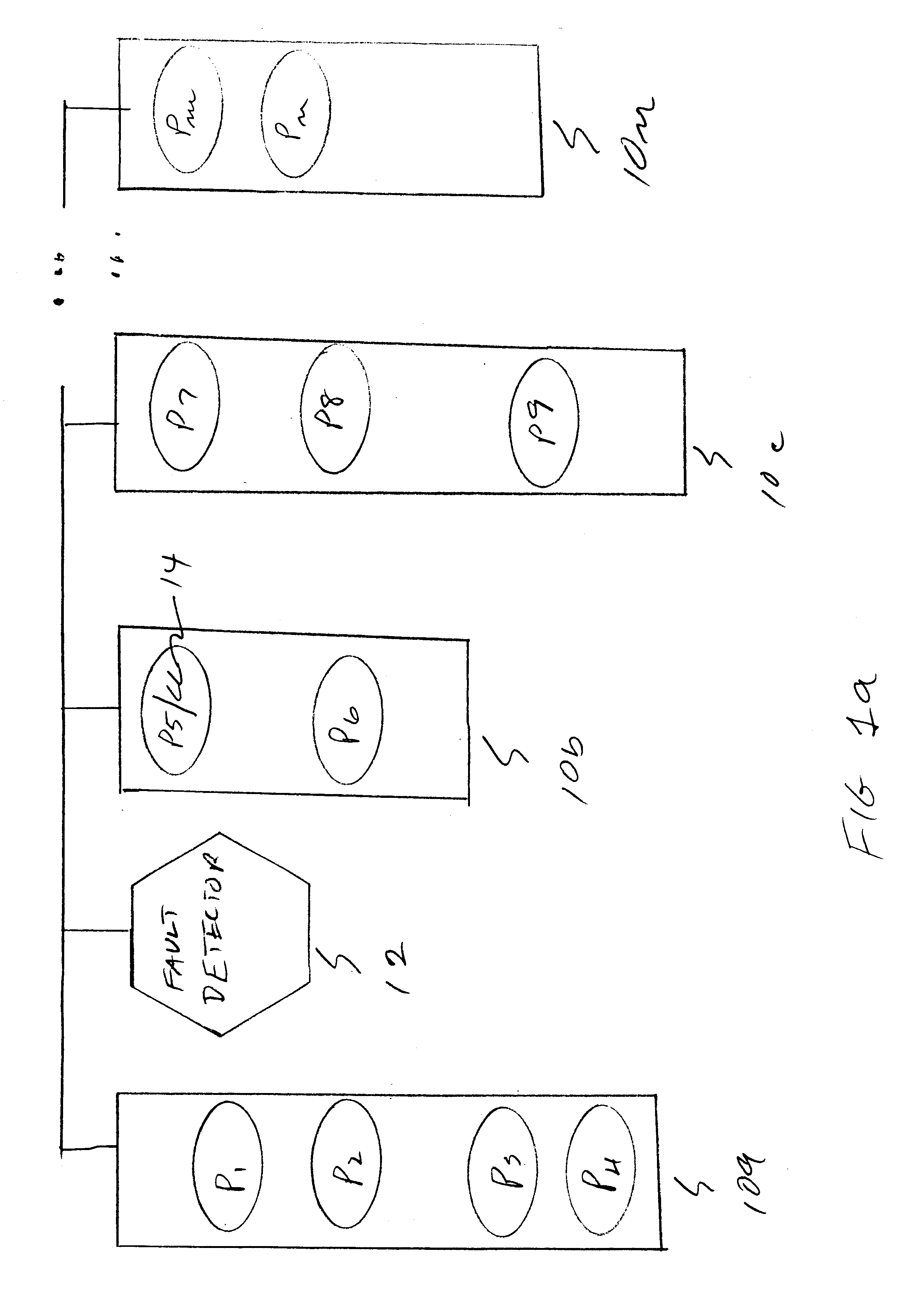

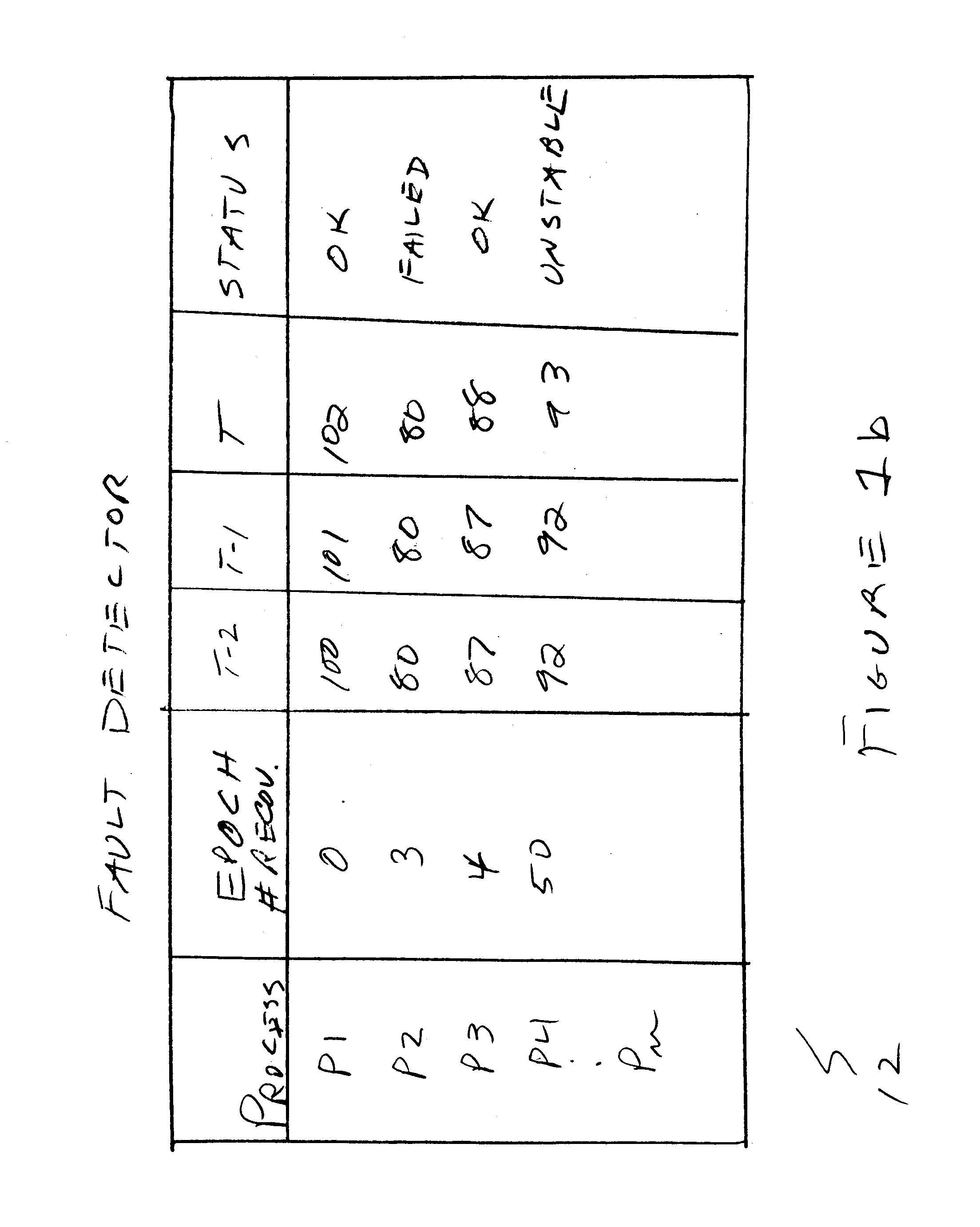

Failure detector with consensus protocol

InactiveUS6687847B1Emergency protective arrangements for automatic disconnectionNon-redundant fault processingStable storageComputing systems

New failure detector mechanisms particularly suitable for use in asynchronous distributed computing systems in which processes may crash and recover, and two crash-recovery consensus mechanisms, one requiring stable storage and the other not requiring it. Both consensus mechanisms tolerate link failures and are particularly efficient in the common runs with no failures or failure detector mistakes. Consensus is achieved in such runs within 3□ time and with 4n messages, where □ is the maximum message delay and n is the number of processes in the system.

Owner:CORNELL RES FOUNDATION INC

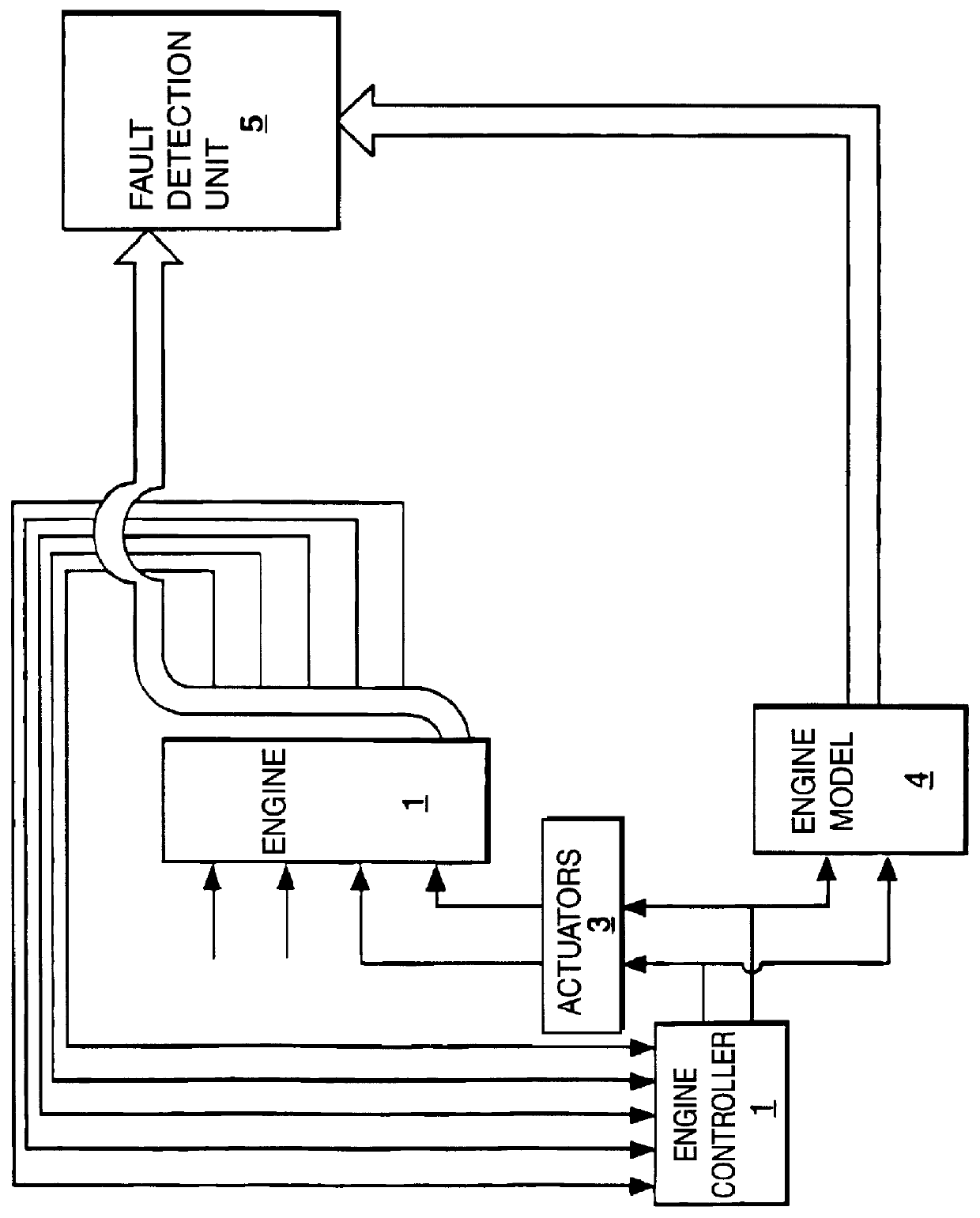

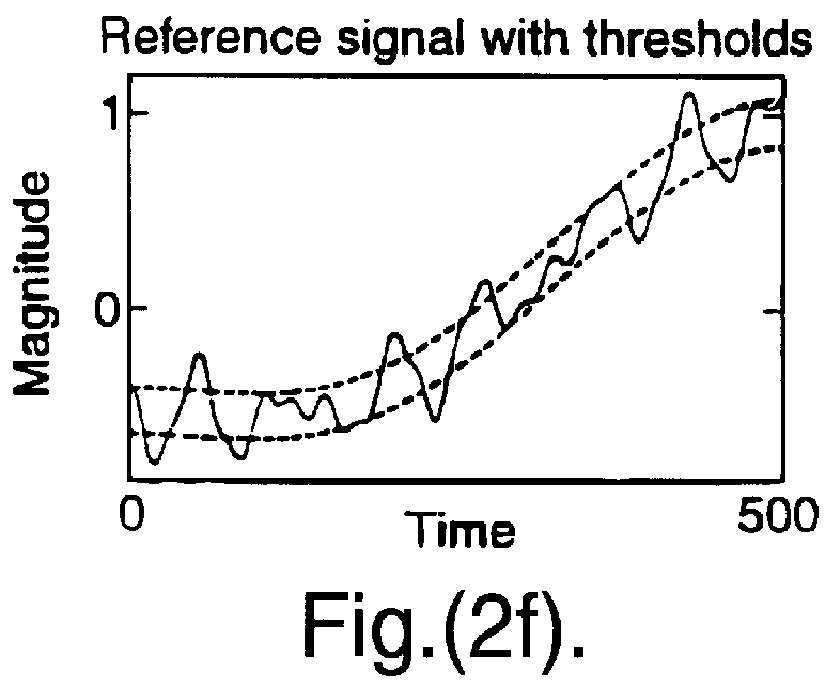

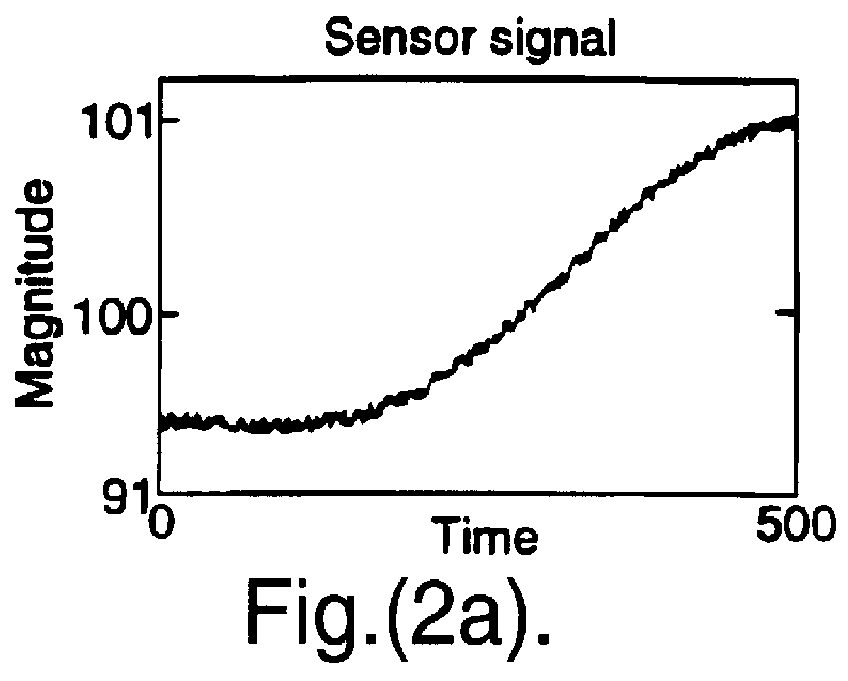

Sensor fault detection system

InactiveUS6016465ASafety arrangmentsElectric devicesFinite timeElectrical and Electronics engineering

The sensor fault detector is one in which each sensor signal is compared with a reference signal provided by e.g. a model of the system being monitored. Prior art sensor fault detectors subtract the output of the sensor and the corresponding reference signal from each other, and a fault is declared when the residual difference exceeds a prescribed threshold. However, modelling errors (such as scaling discrepancies), d.c bias and noise mean that faults are often wrongly declared, or alternatively that only large faults can be detected. These problems are overcome according to the invention by comparing the "shape" of the sensor signal with that of the corresponding reference signal (i.e. comparing the signal outlines) over a finite time window, using e.g. correlation techniques. A fault is declared when the shapes differ by a prescribed amount.

Owner:QINETIQ LTD

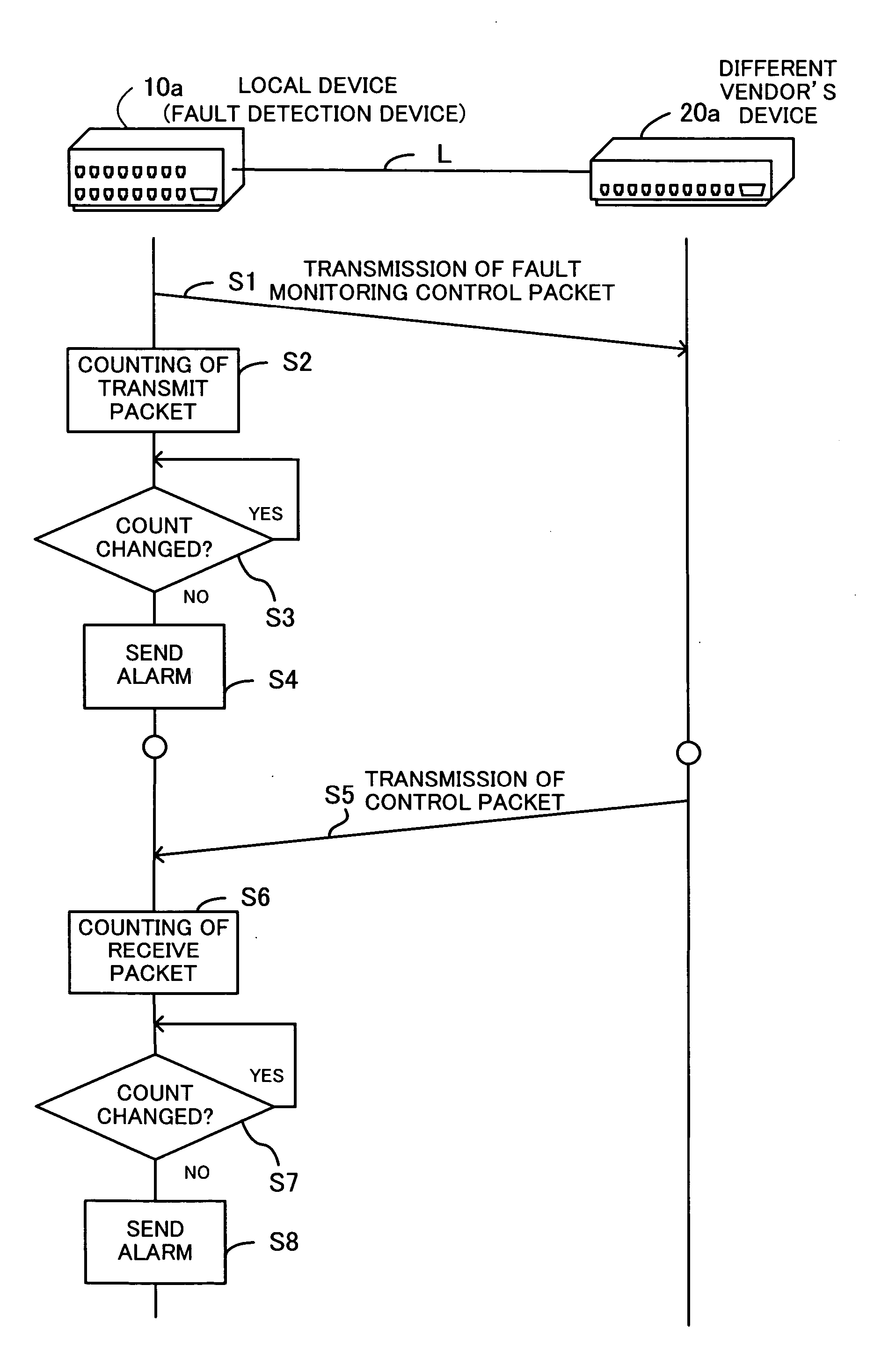

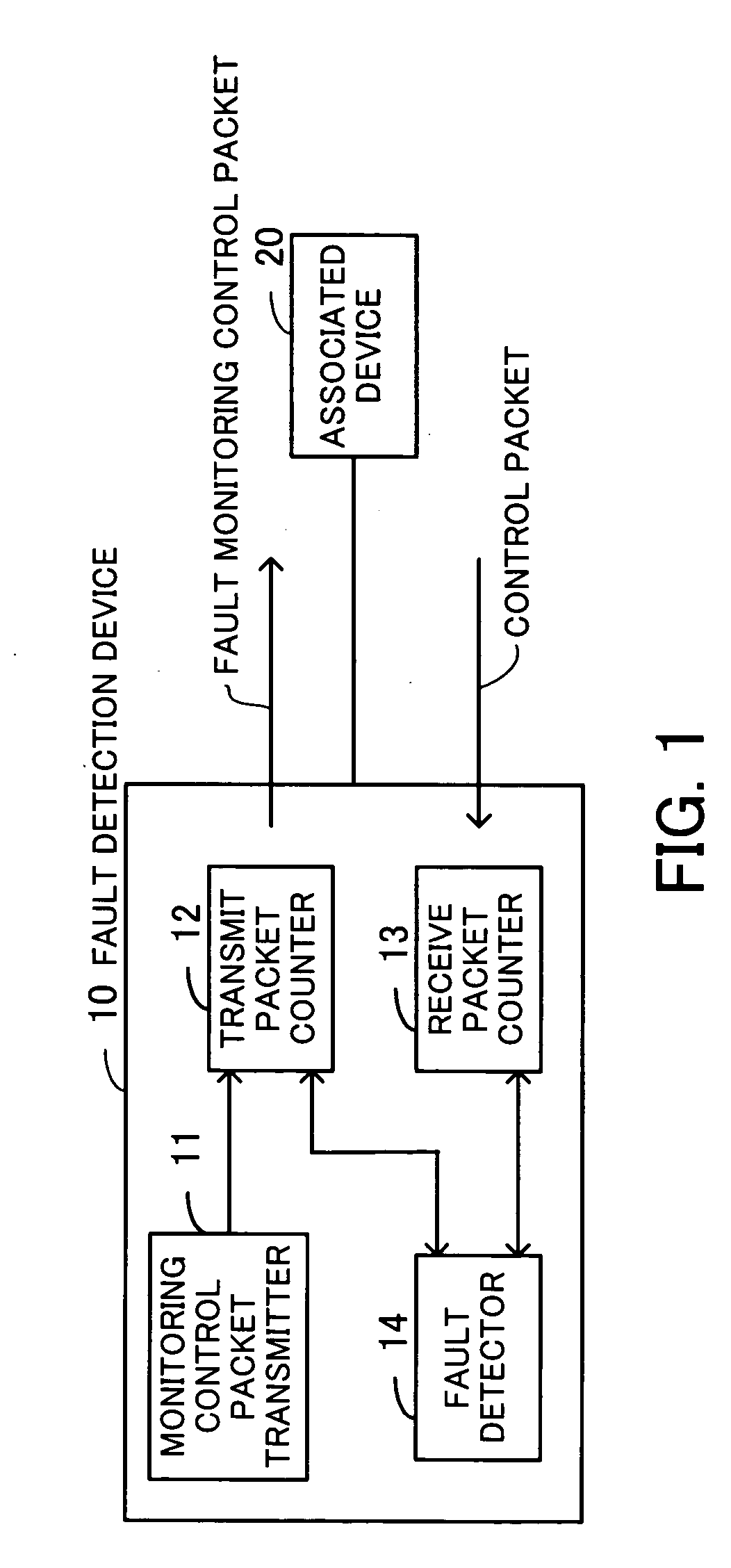

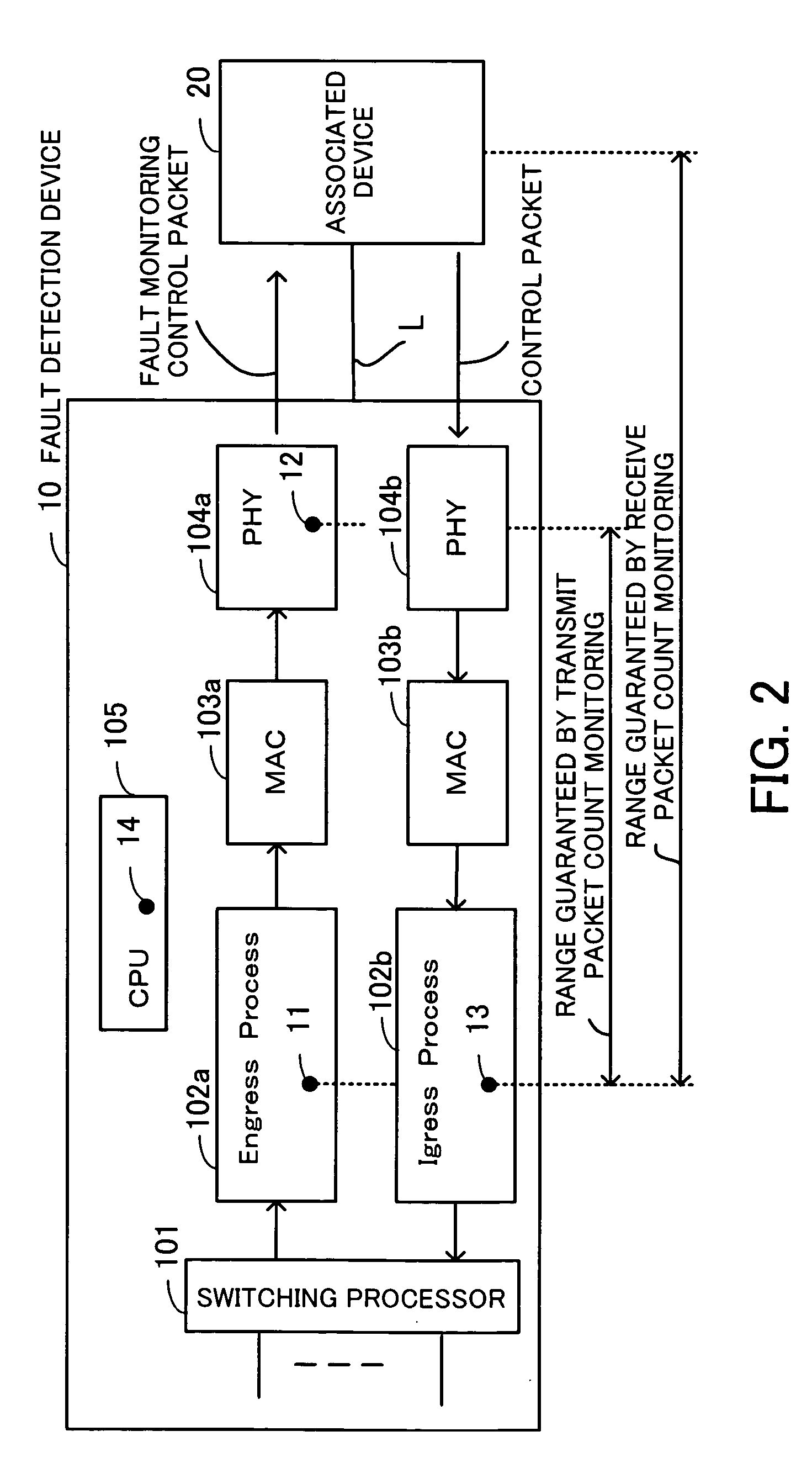

Fault detection device

InactiveUS20060182036A1High-precision detectionCorrect operation testingTransmission systemsTime segmentTransmitter

A fault detection device capable of detecting network faults by itself with high accuracy in multi-vendor environments, without the need to interoperate with an associated device according to an identical protocol. A monitoring control packet transmitter generates a fault monitoring control packet and transmits the generated packet to the associated device with which the fault detection device need not interoperate to detect faults according to the same protocol. A transmit packet counter keeps count of the transmitted fault monitoring control packet. A receive packet counter receives a control packet transmitted from the associated device, and keeps count of the received control packet. A fault detector monitors the count of transmitted packets and the count of received packets and, if at least one of the counts remains unchanged for a fixed period of time, judges that a fault has occurred and sends a fault notification to outside.

Owner:FUJITSU LTD

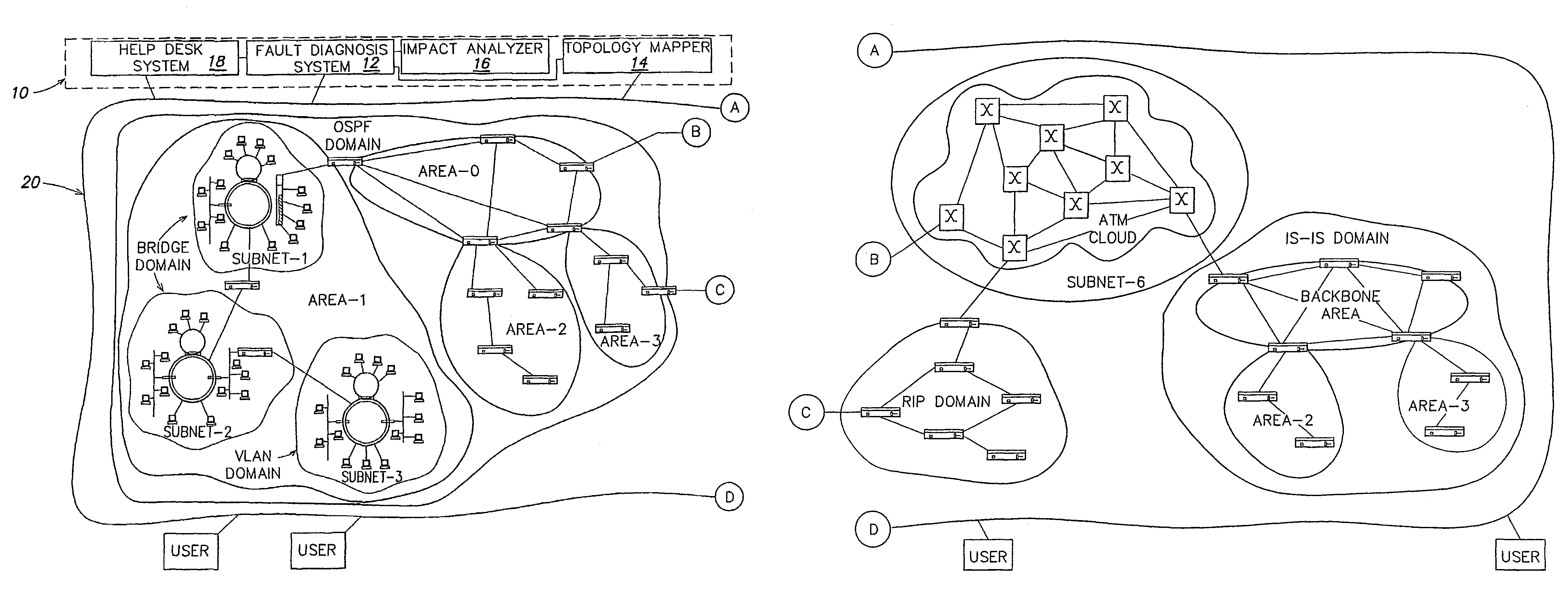

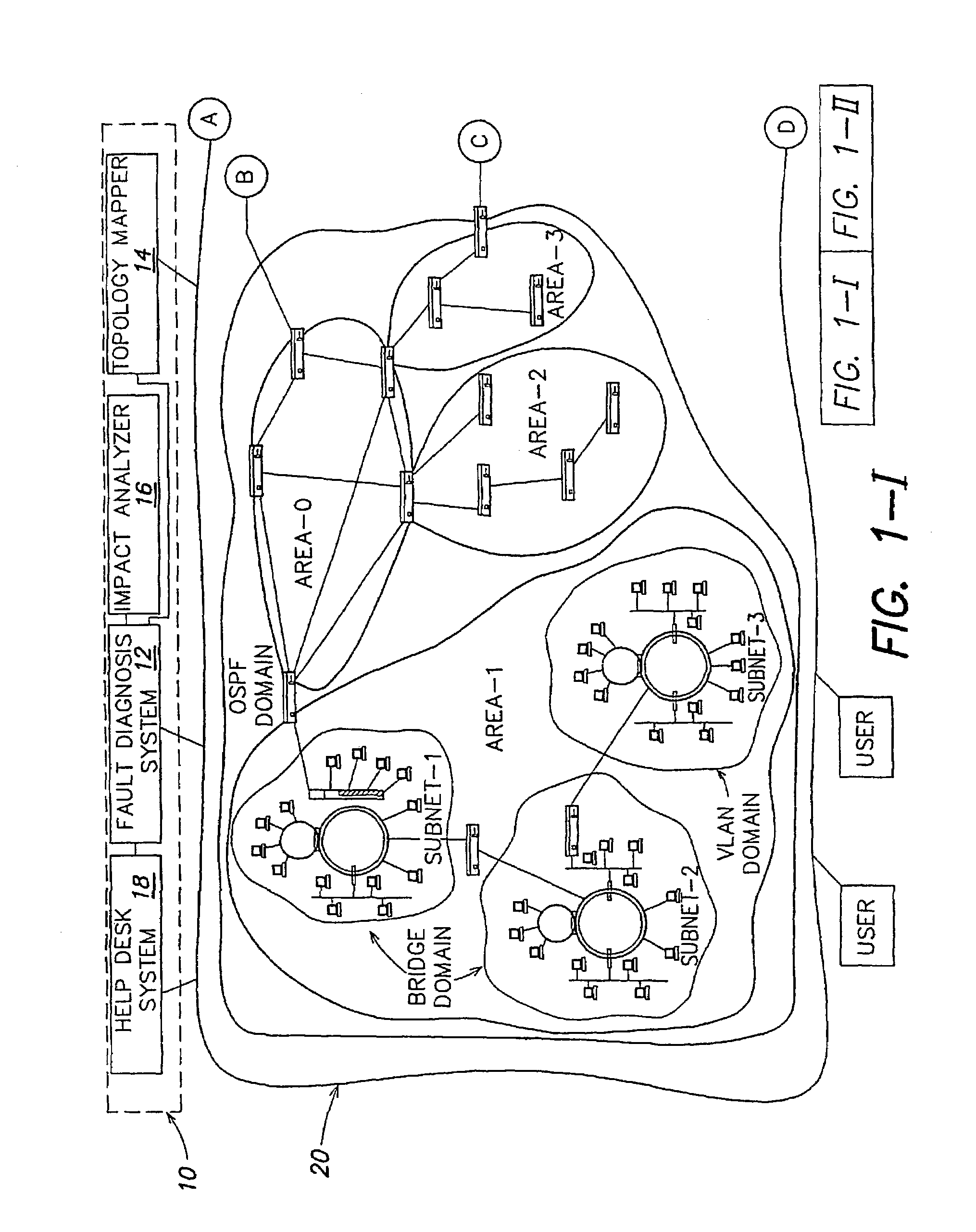

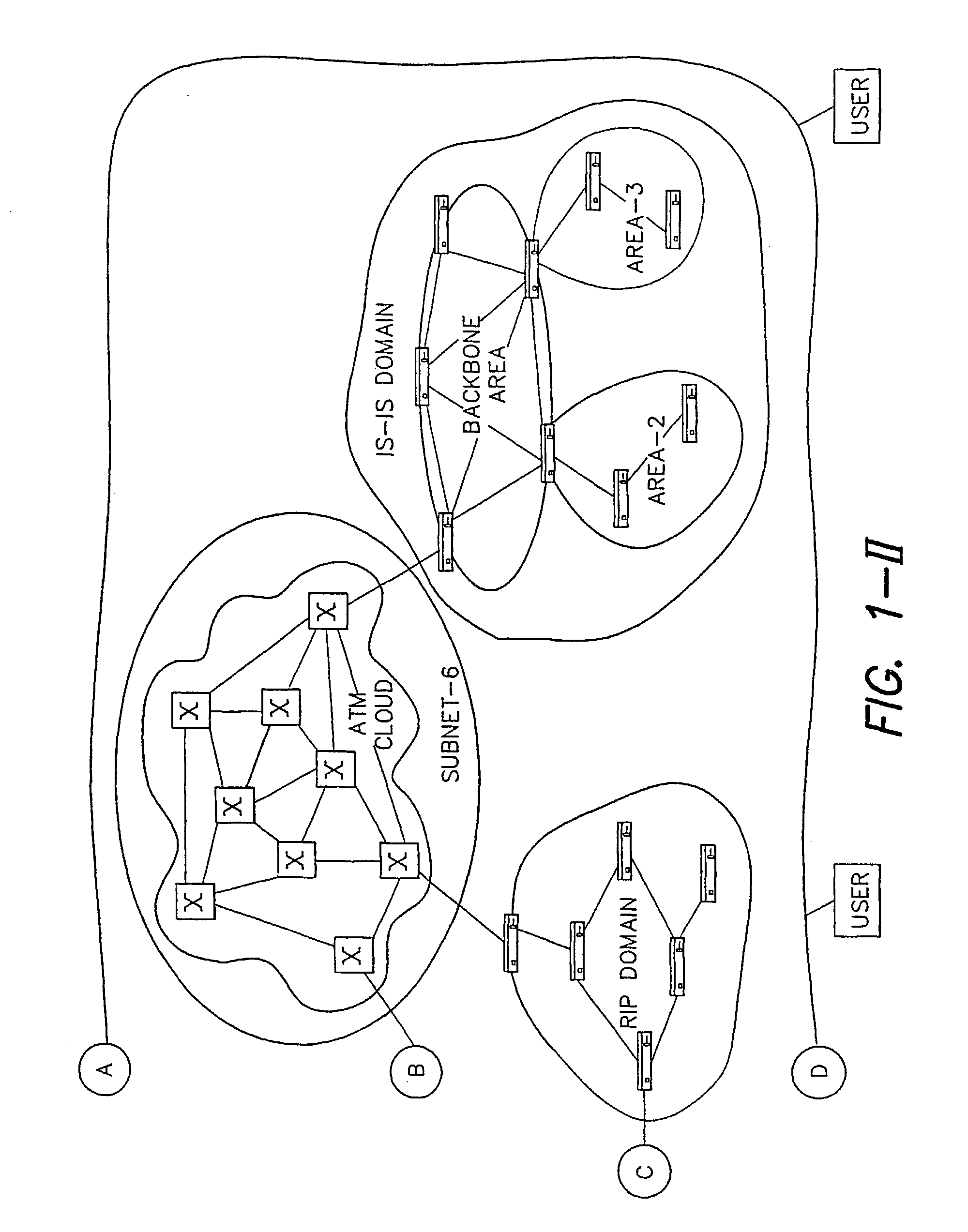

Systems and methods for managing and analyzing faults in computer networks

InactiveUS7500143B2Facilitates root cause isolationAccelerated settlementError detection/correctionNetwork connectionsRoot cause analysisFailure detector

A system (100) for analyzing a fault includes a fault object factory (110) constructed and arranged to receive fault data and create a fault object (112), and a fault diagnosis engine (101) constructed and arranged to perform root cause analysis of the fault object. The system may further include a fault detector (130) constructed and arranged to detect the fault data in a monitored entity, a fault repository (140) constructed and arranged to store and access the fault object; and a fault handler (150) constructed and arranged to be triggered by the fault diagnosis engine to analyze the fault object.

Owner:COMP ASSOC THINK INC

Hose with fault detection capability

A hose fault detection system includes a hose assembly and a fault detector. The hose assembly includes a first conductive layer, second conductive layer, and an intermediate layer that is disposed between the first and second conductive layers. Each of the first and second conductive layers has an electrical characteristic. The fault detector is configured for detecting an electrical change based on the electrical characteristic to signify a potential impending failure of at least one of the first and second conductive layers of the hose. The fault detector includes a sensing device, a recording device and a digital processor. The sensing device is in electrical communication with the first and second conductive layers to measure the electrical characteristic. The recording device is configured for storing the measured electrical characteristic.

Owner:DANFOSS POWER SOLUTIONS II TECH AS

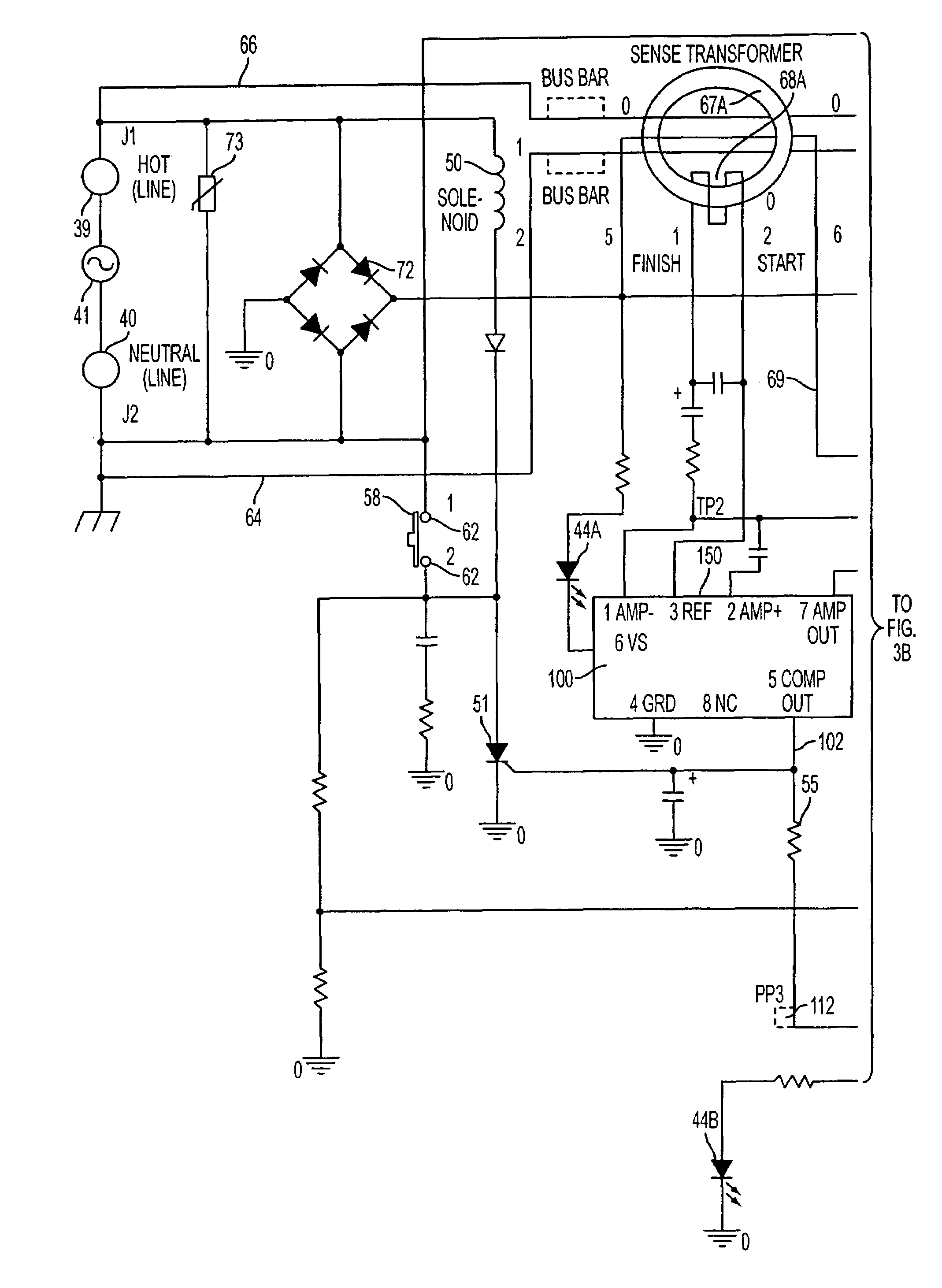

Self testing ground fault circuit interrupter (GFCI)

ActiveUS7443309B2Determines the operability of the switching deviceProtective switch detailsElectronic circuit testingStatus testGround failure

A self testing fault detector having a line side and a load side and a conductive path there between, said apparatus is provided. The self testing fault detector includes a controller, adapted to perform periodic status tests on a protection circuit of the self testing fault detector without interrupting power to the load.

Owner:HUBBELL INC

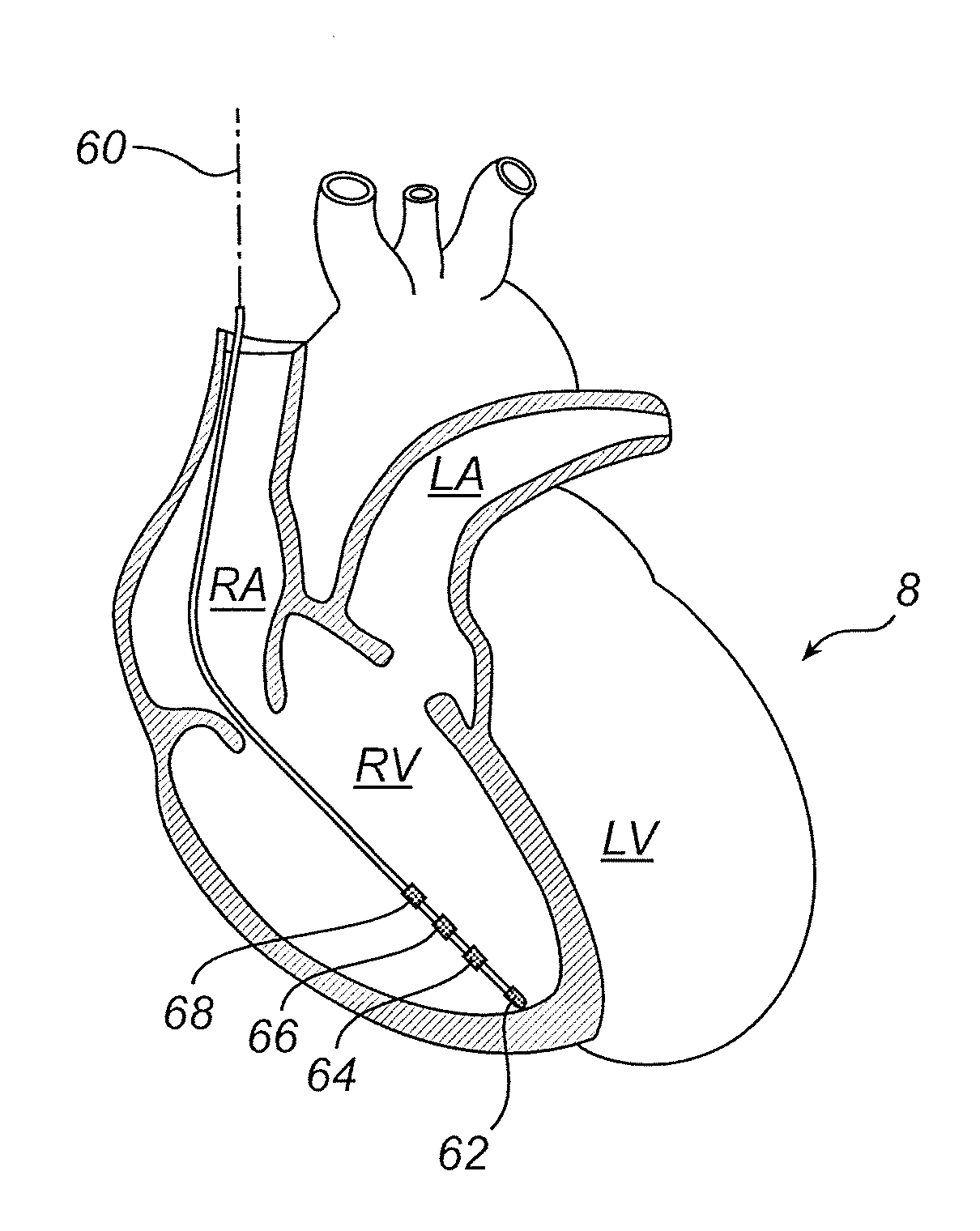

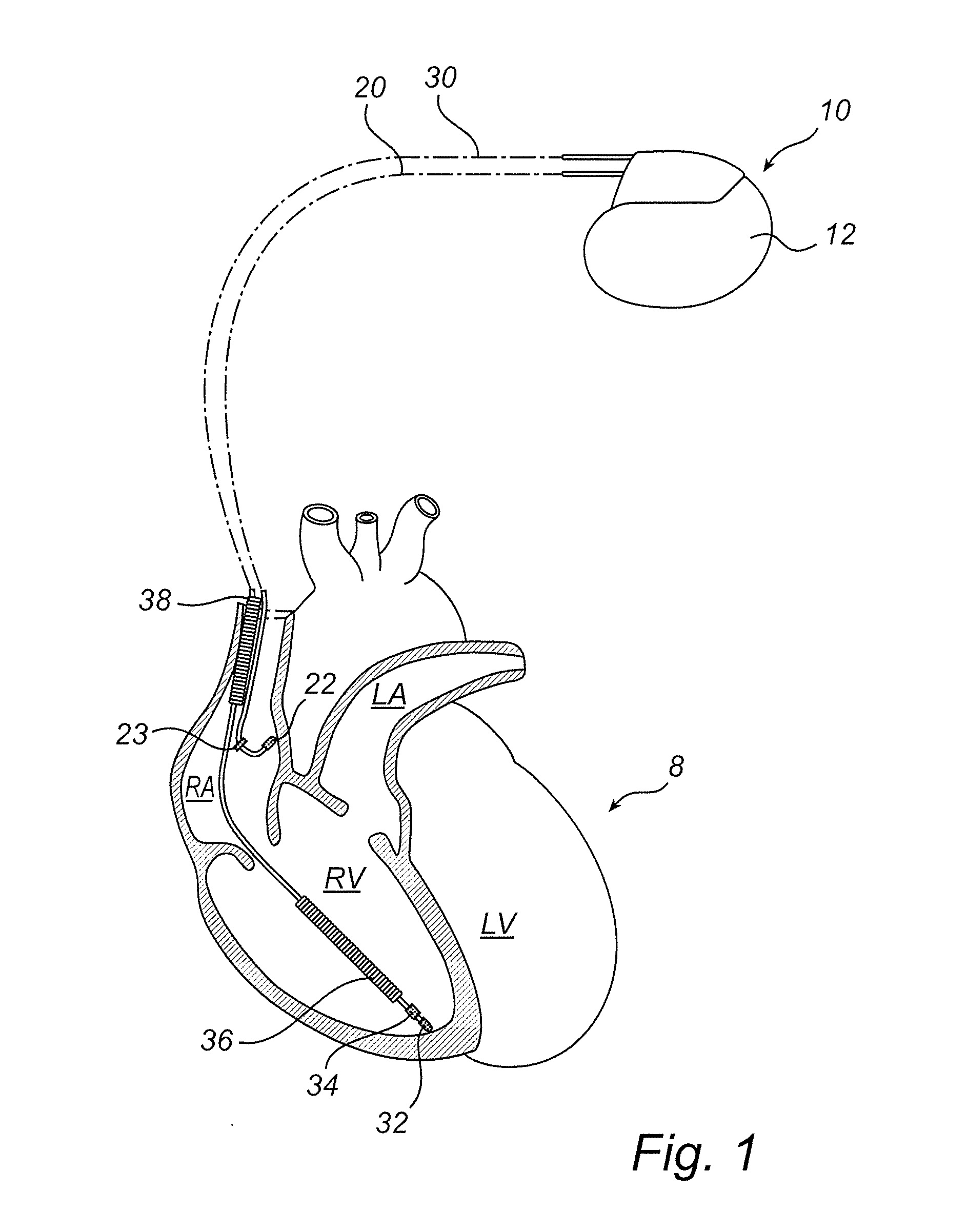

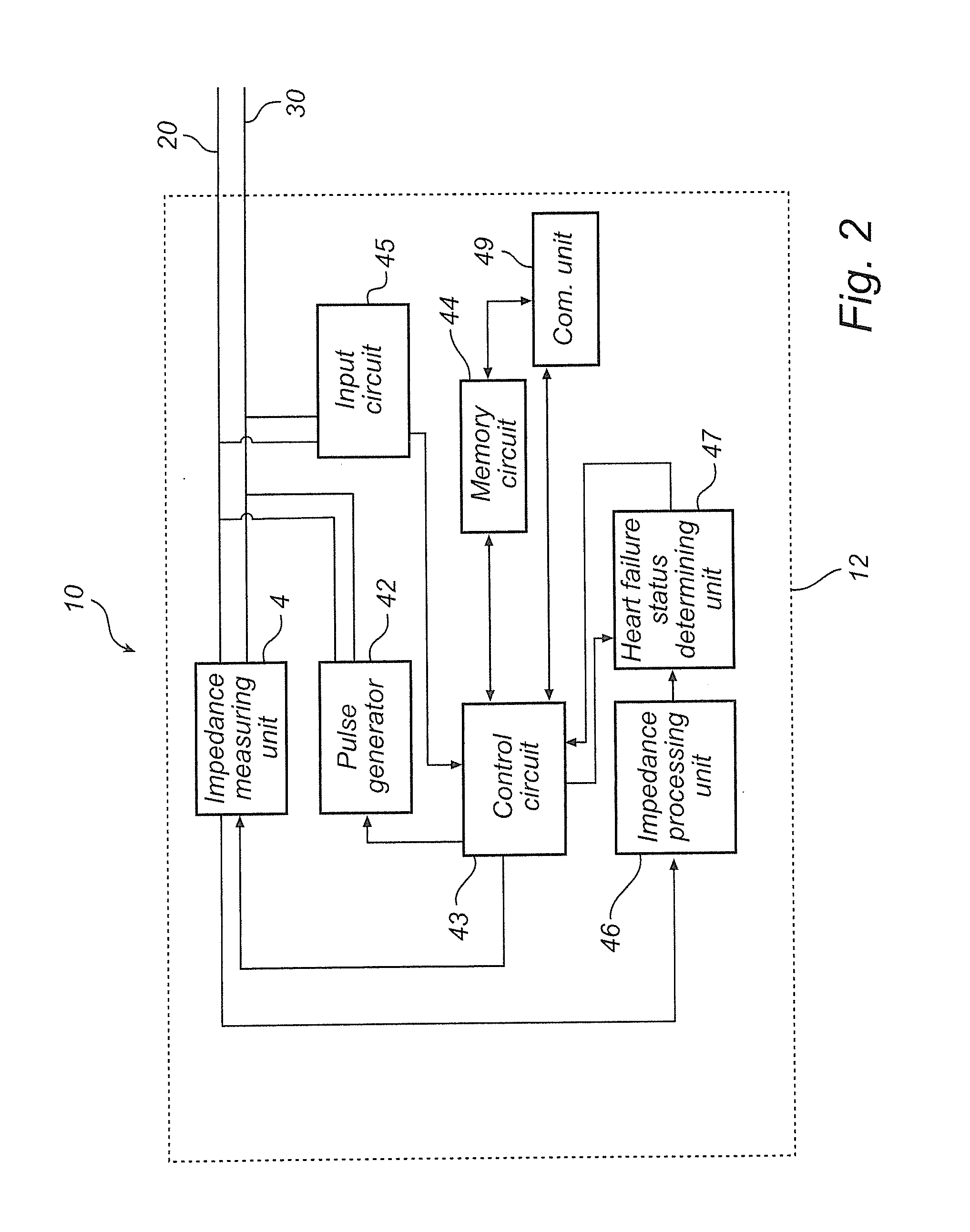

Heart failure detector

InactiveUS20110184301A1Reduce frequencyEasy to fillElectrotherapyElectrocardiographyRight atriumRight ventricles

In an apparatus and method for detecting incipient heart failure of a patient. Impedance signals reflecting volume changes of the right ventricle and / or the right atrium of a heart of the patient are obtained. The impedance signals are processed to determine a first impedance parameter substantially reflecting a volume of the right ventricle, and a heart failure status is determined based on the first impedance parameter, wherein a decreasing first impedance parameter is determined to be an indication of a deterioration of the heart failure status.

Owner:ST JUDE MEDICAL

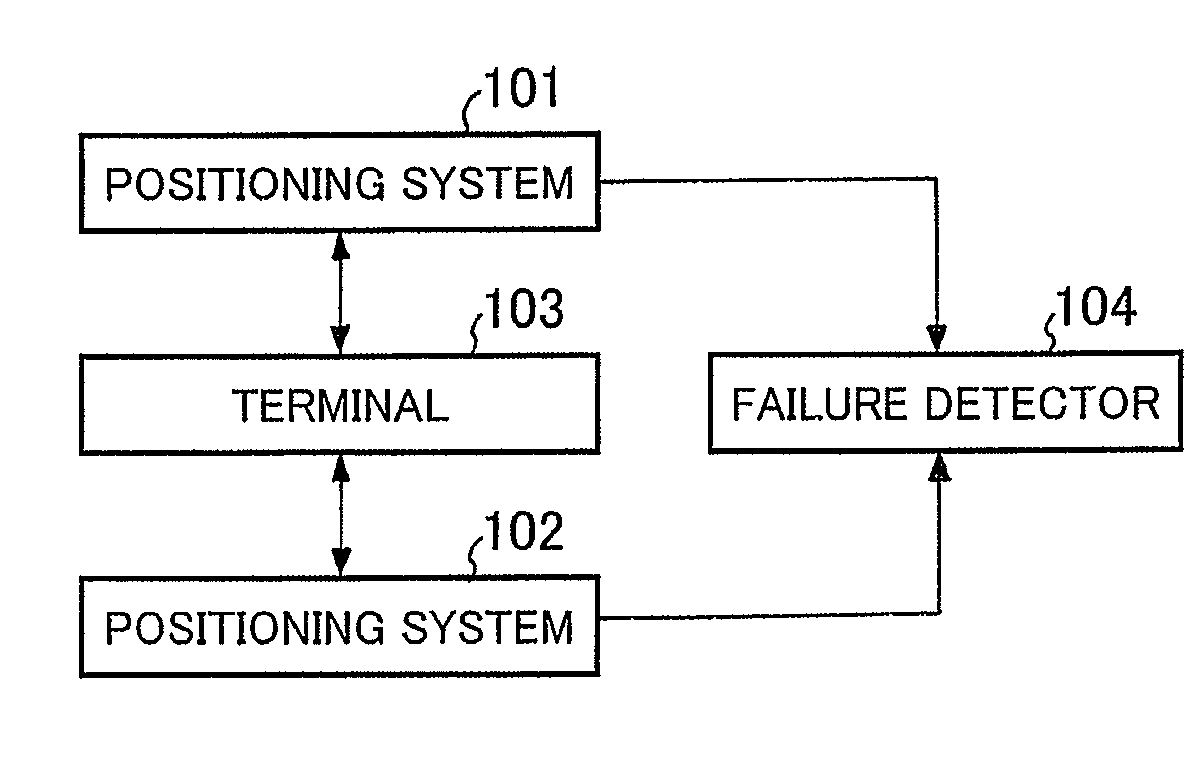

Terminal positioning method, terminal positioning system, positioning server, and program

InactiveUS20090042585A1Easy to failPosition fixationLocation information based serviceEngineeringPositioning system

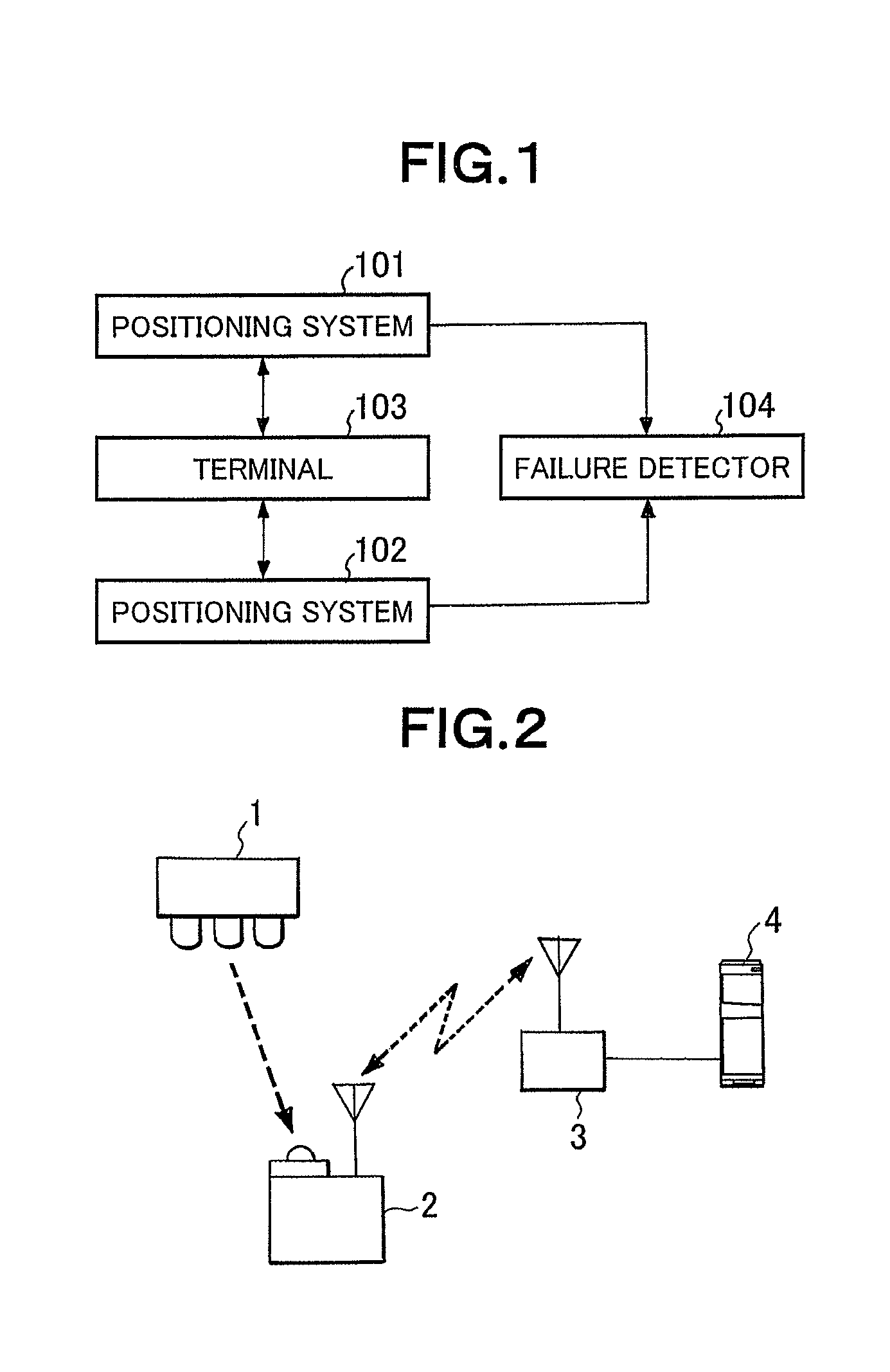

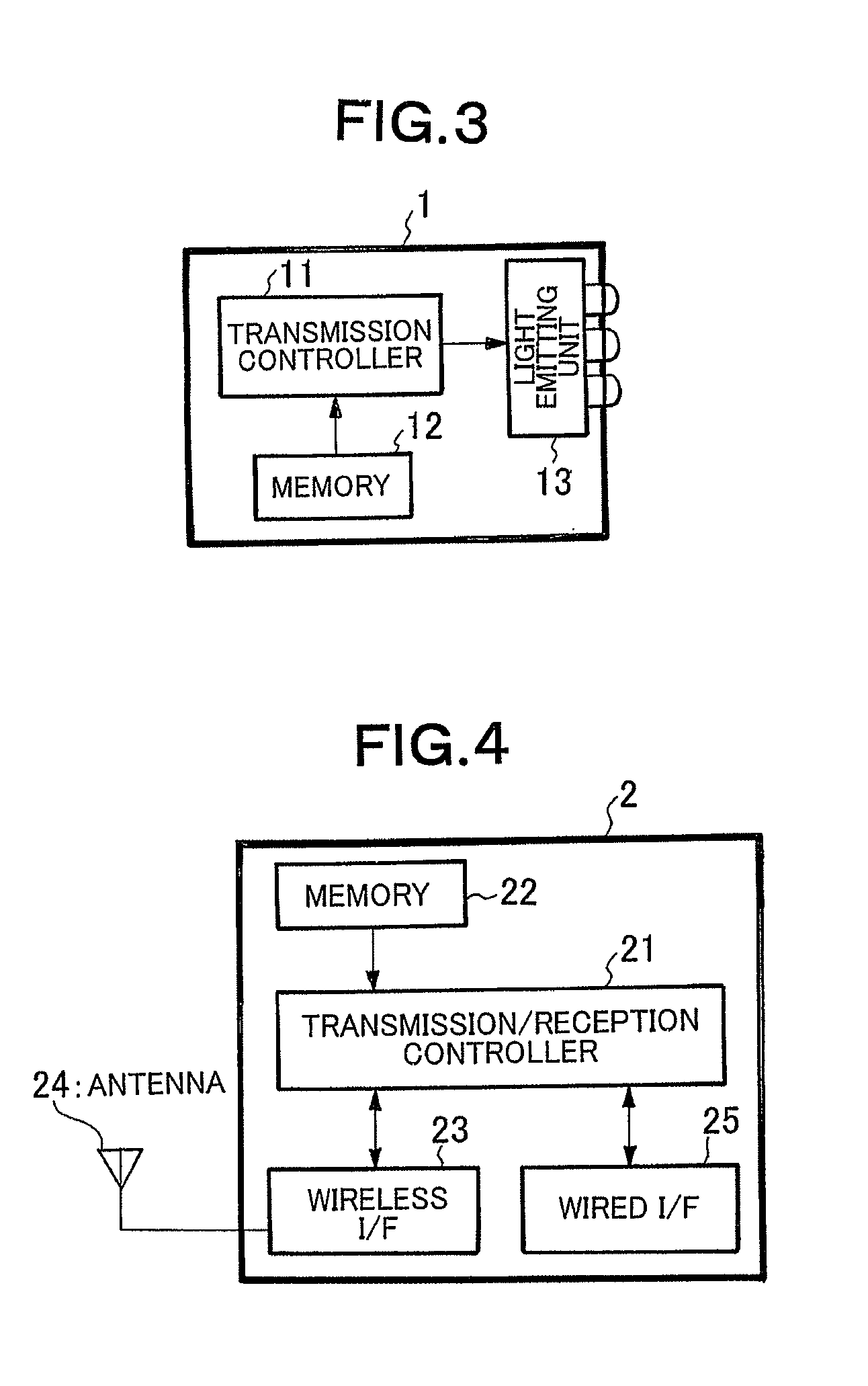

[Subject] The present invention is directed to realize failure detection without directly detecting a failed positioning system.[Solving Means] A terminal positioning system includes positioning systems 101 and 102 and a failure detector 104. When a failure occurs in one of the positioning systems 101 and 102, by monitoring a use state of the other positioning system, the failure in one of the positioning systems is detected. Priorities of positioning process on the positioning systems 101 and 102 may be determined so that the priority of positioning process on one of the positioning systems is higher than that on the other positioning system. The one of the positioning systems can perform positioning at higher precision than the other positioning system.

Owner:NEC CORP

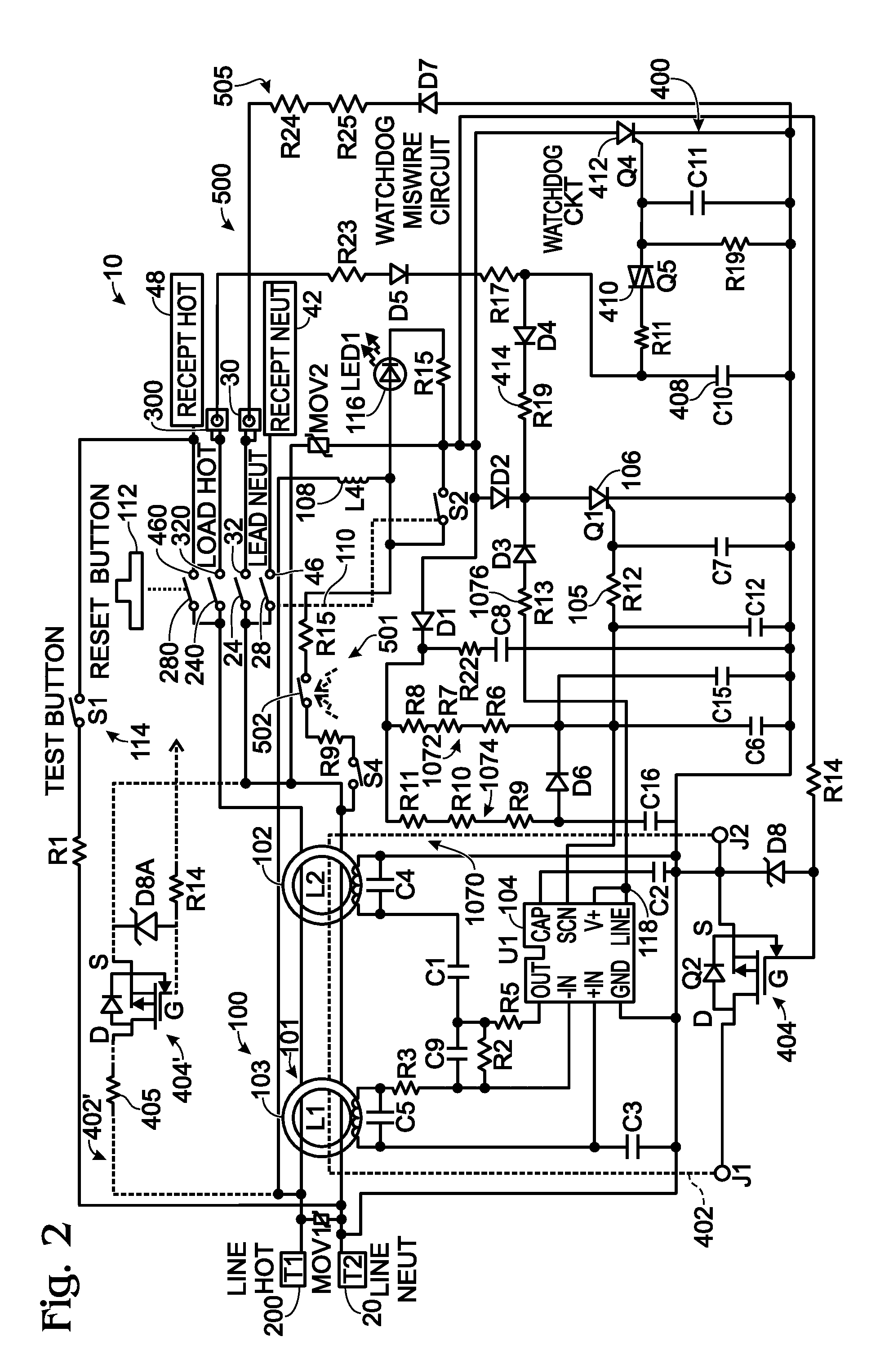

Electrical wiring device with protective features

InactiveUS20120154972A1Inexpensively detectsElectrical testingContact testing/inspectionElectricityIntegrity assessment

The present invention is directed to an electrical wiring device for use in an electrical distribution system. The device includes a plurality of line terminals configured to terminate the plurality of line conductors and a plurality of load terminals configured to terminate the plurality of load conductors. The protective circuit assembly includes at least one fault detector configured to generate a fault detection signal based on electrical perturbations propagating on at least one of the plurality of line terminals or at least one of the plurality of load terminals. A device integrity evaluation circuit includes a timing circuit coupled to the source of AC power by way of the plurality of load terminals and configured to generate a time measurement. The device integrity evaluation circuit is configured to reset the time measurement if the protective circuit assembly generates the fault detection signal during a predetermined test interval in the properly wired condition. The device integrity evaluation circuit is configured to generate a device integrity fault signal when the time measurement exceeds a predetermined threshold. A circuit interrupter assembly includes movable contacts configured to be latched into a reset state in response to a reset stimulus. The movable contacts are configured to be driven into a tripped state in response to the fault detection signal or the device integrity fault signal.

Owner:PASS SEYMOUR

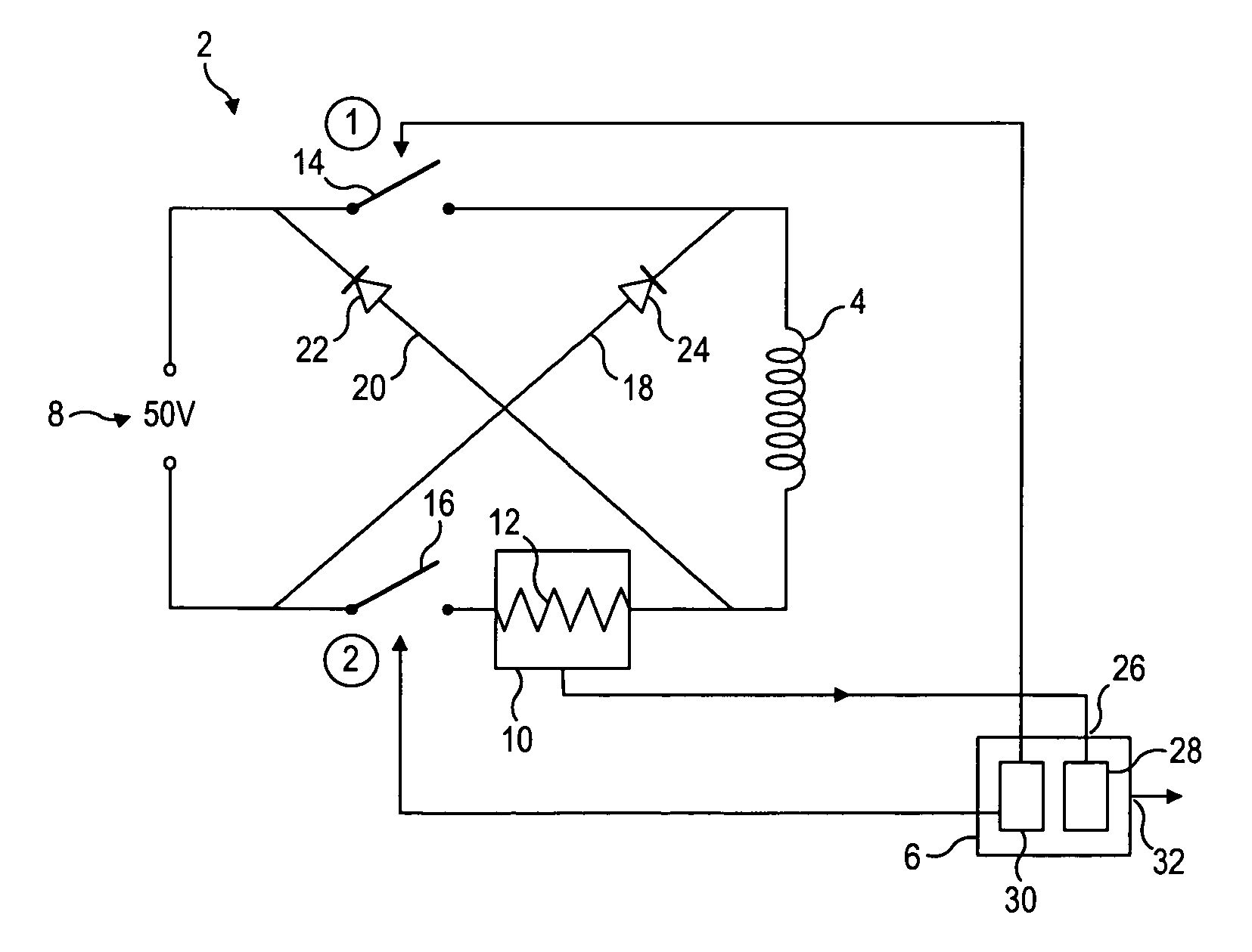

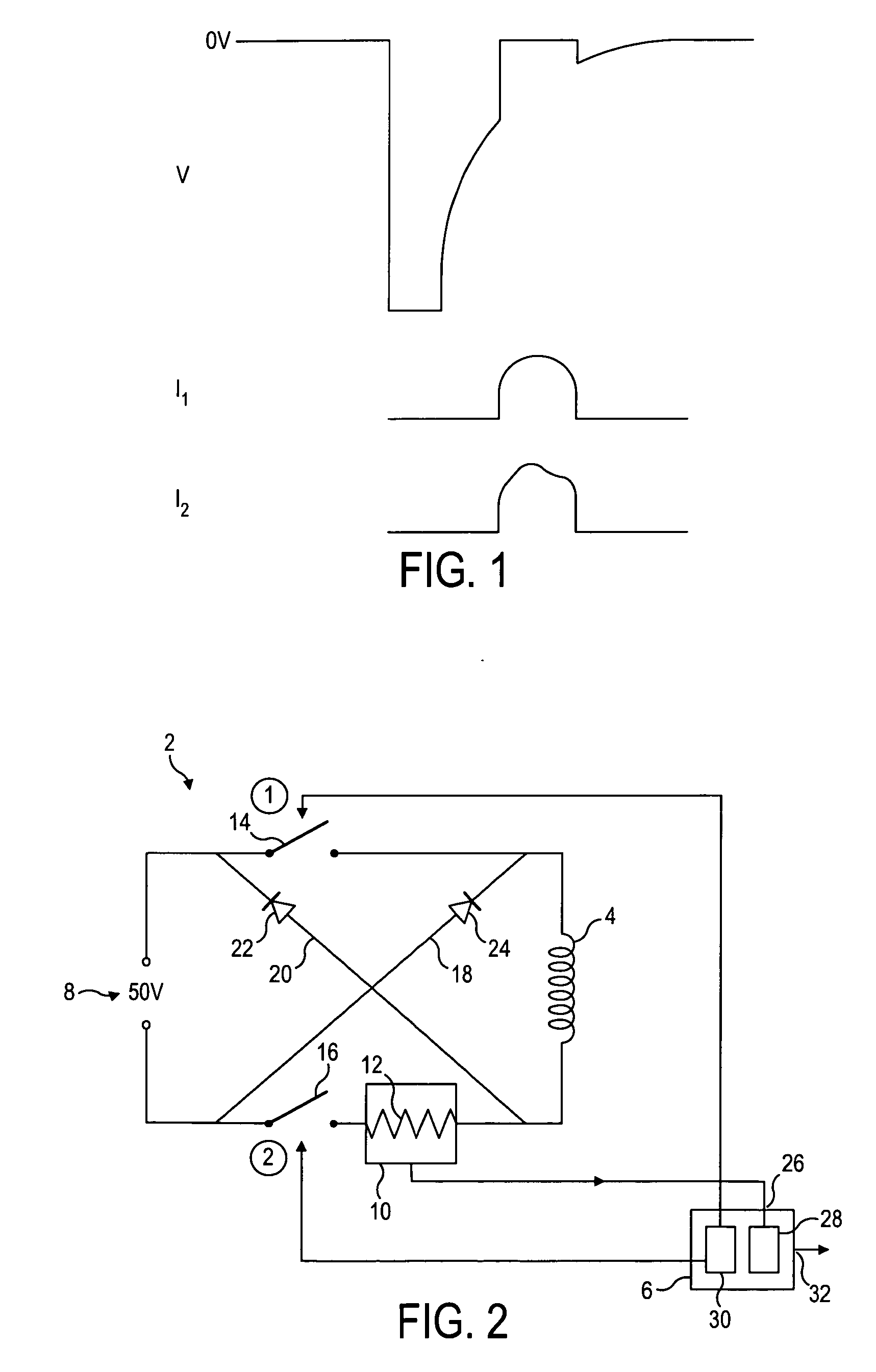

Fault detector and method of detecting faults

ActiveUS20090132180A1Minimize data handlingMinimize manipulation requirementElectrical controlNuclear monitoringControl theoryElectrical current

A fault detector for detecting valve movement of a valve in a fuel injector of an engine system, the valve comprising an electromagnetic actuator arranged to move the valve between first and second valve positions during a valve cycle, the engine system comprising a sensor for sensing a current through the actuator. The detector comprises a controller arranged to control the sensor; inputs for receiving from the sensor data related to the current through the actuator; a processor arranged to analyze the received data for current discontinuities; and outputs for outputting a valve movement signal in dependence upon the current discontinuities determined by the processor. The controller is arranged to enable the sensing means during a finite sampling window and to: (i) move the sampling window from a first window position for a first injection event to a progressively later window position for one or more subsequent injection events; (ii) to determine a new sampling window position on the basis of a valve movement signal output for at least two of the preceding window positions; and (iii) to feedback the new sampling window position for a subsequent injection event.

Owner:DELPHI TECH IP LTD

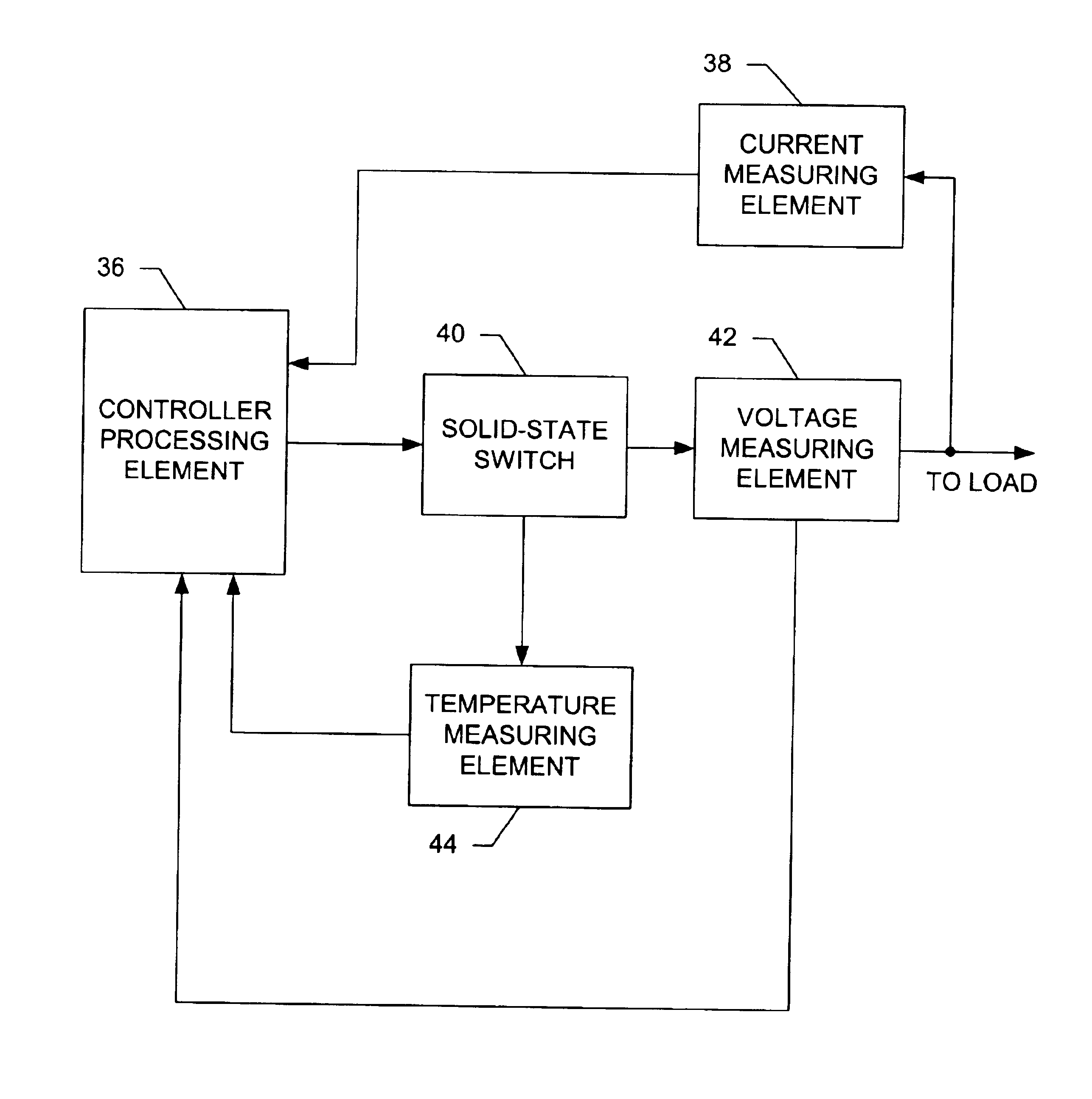

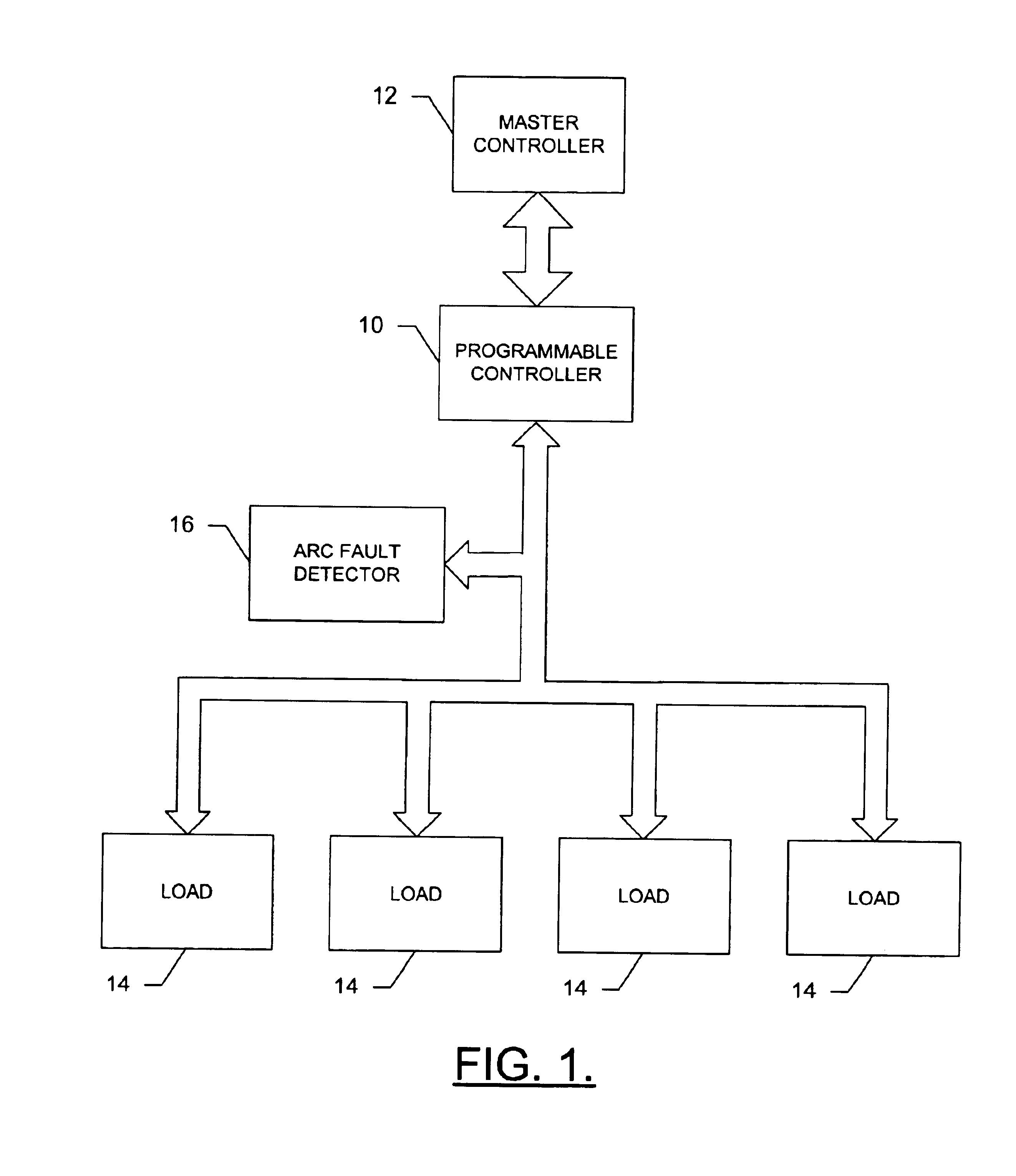

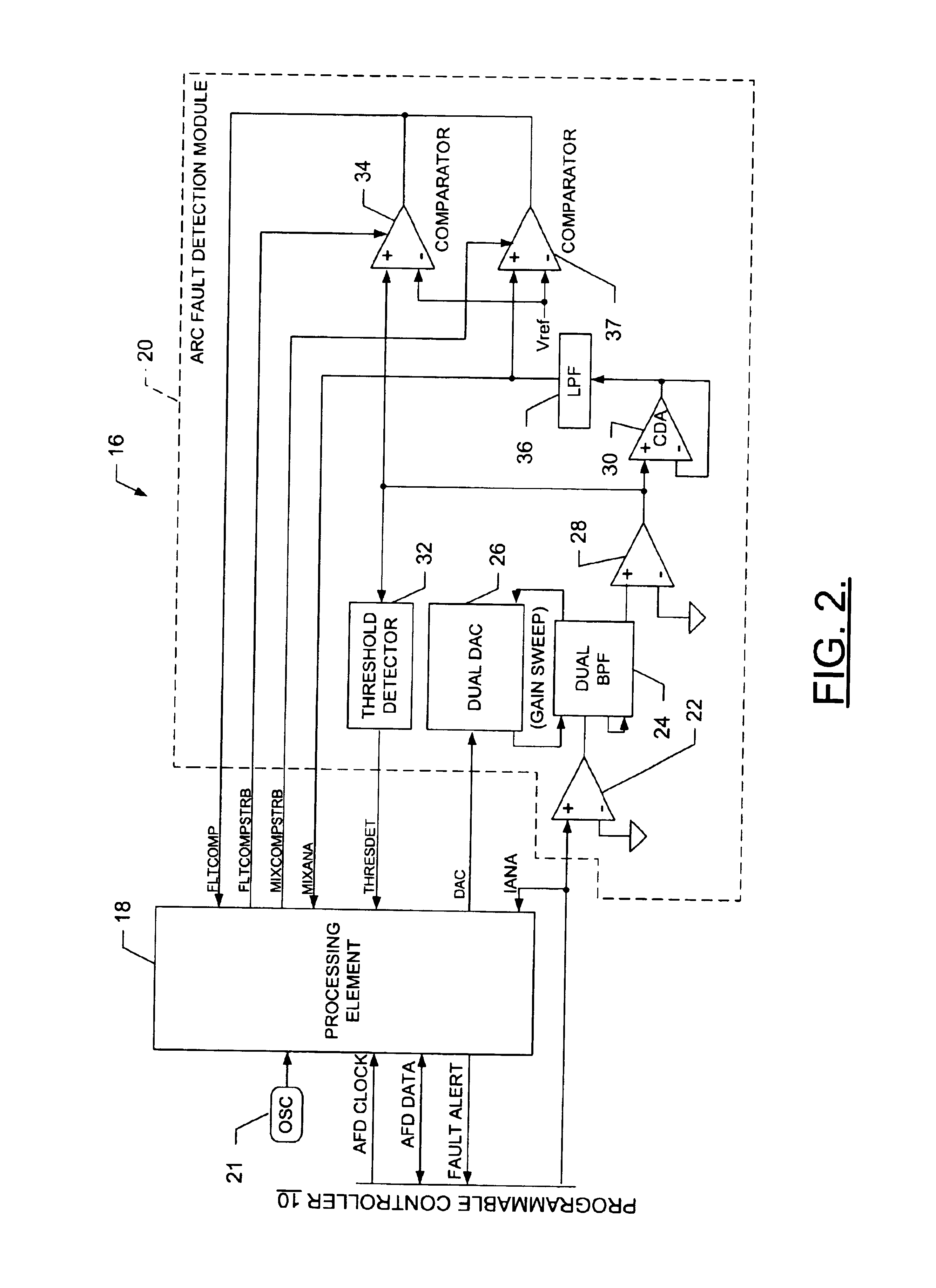

System and method for remotely detecting electric arc events in a power system

InactiveUS6943558B2Reduce the possibilityTesting dielectric strengthEmergency protective arrangement detailsElectricityElectrical conductor

A system is provided for remotely detecting and locating damaged conductors. The system includes at least one slave controller disposed proximate at least one load and electrically connected to the loads via at least one conductor. The slave controller includes at least one solid-state switch capable of controllably altering the input current to the loads, and at least one measuring element for measuring at least one parameter associated with the loads and the solid-state switches. In this regard, the solid-state switches controllably alter the input current to the loads according to the parameters. The system also includes at least one arc fault detector electrically connected to the conductors between the slave controller and the loads, where the fault detector is capable of detecting an electric arc event.

Owner:THE BOEING CO

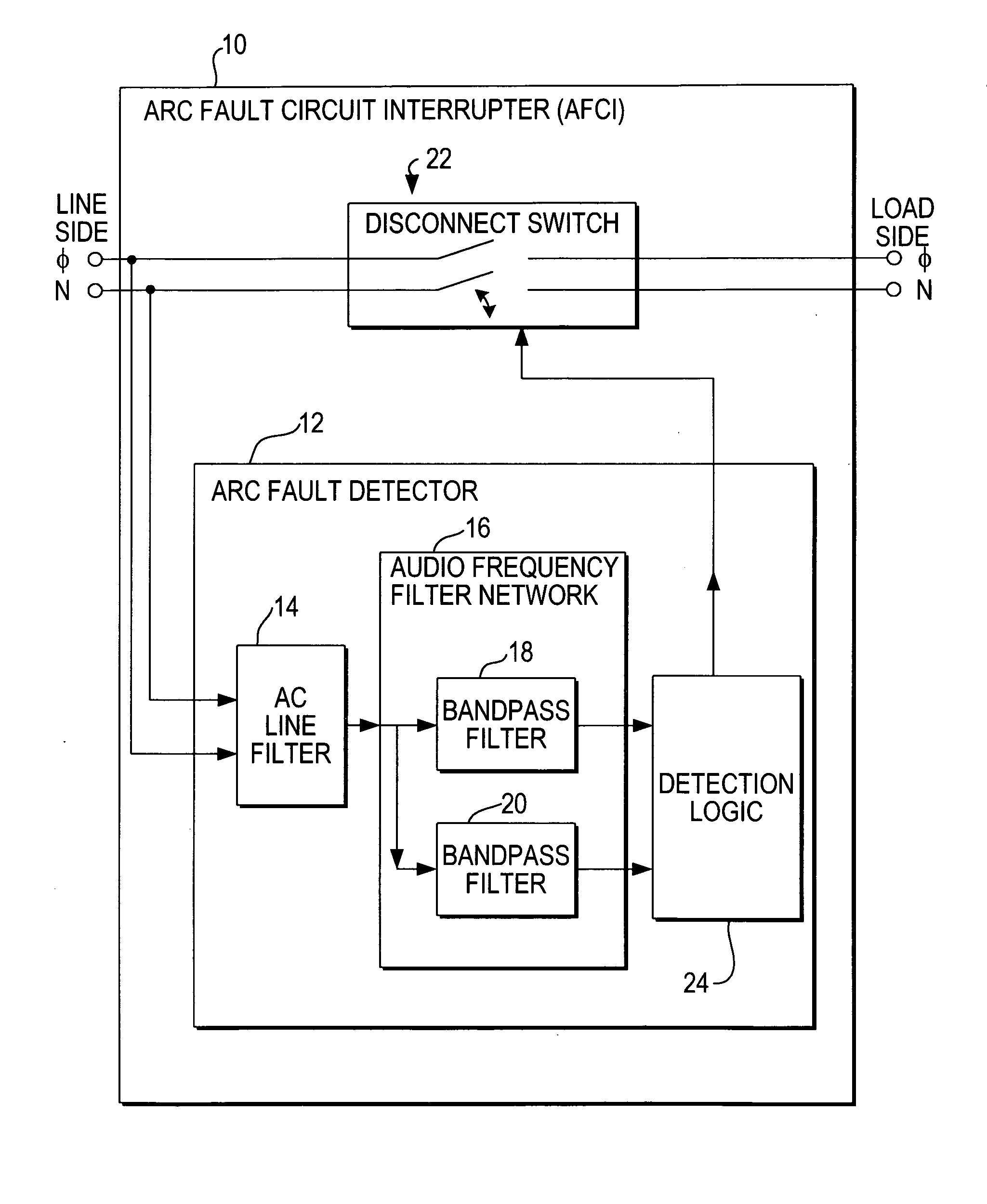

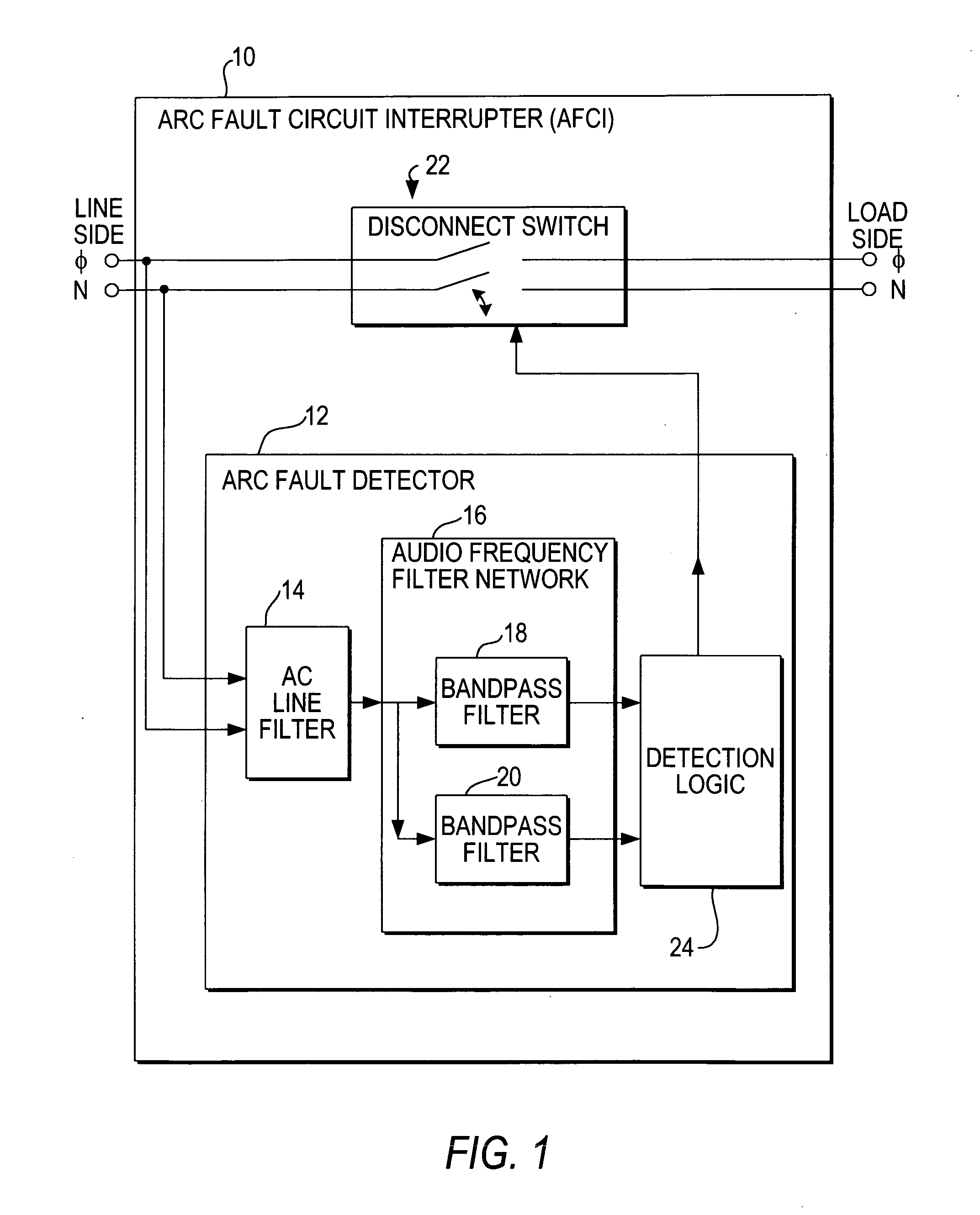

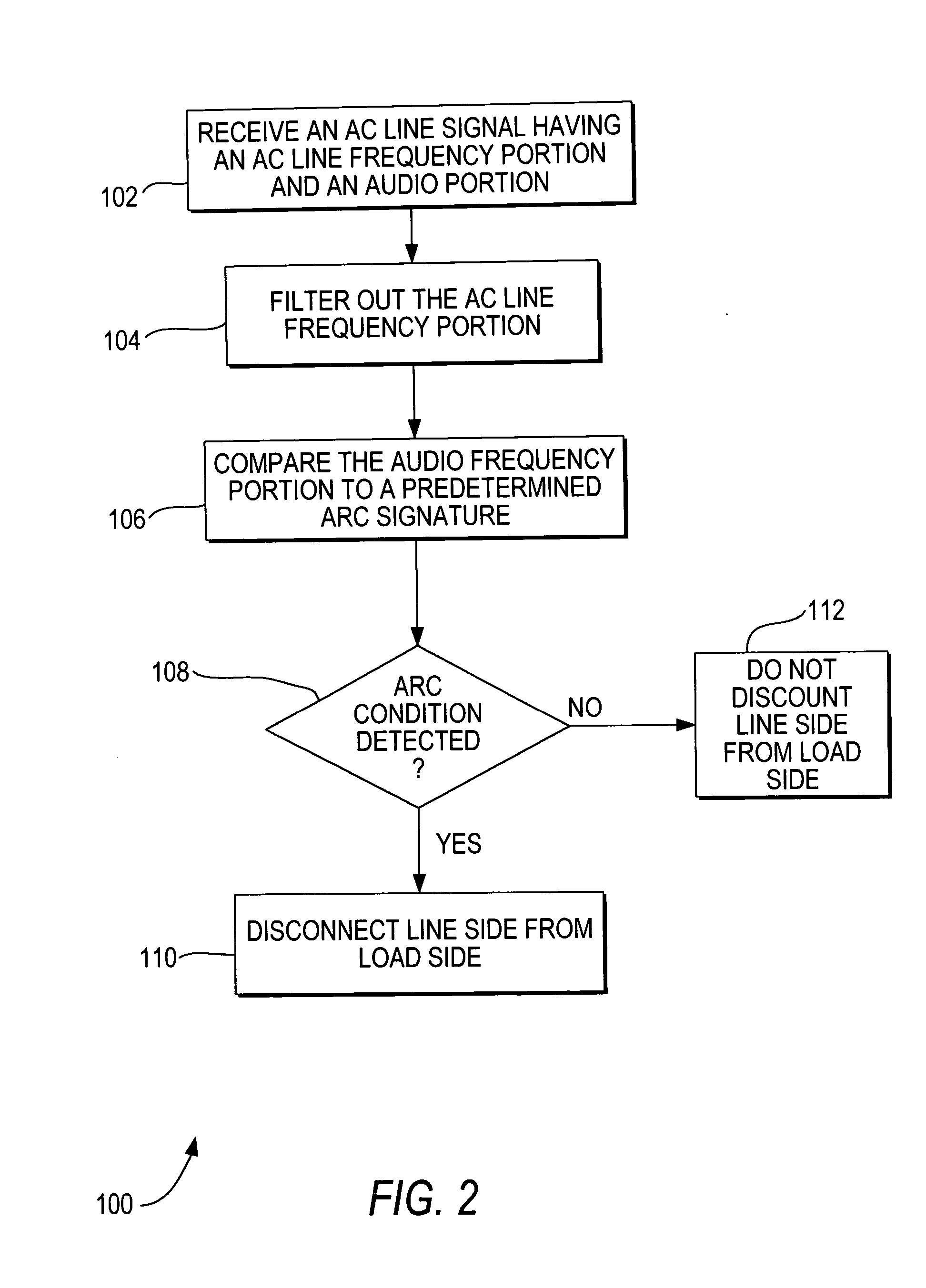

Arc fault detection

InactiveUS20060171085A1Emergency protective arrangement detailsEmergency protective arrangements for automatic disconnectionFrequency spectrumElectromagnetic spectrum

An arc fault detector configured to process audio frequencies associated with an arc fault condition to detect the occurrence of an arc fault condition. In one embodiment, the arc fault detector includes an alternating current (AC) line filter for receiving an AC line signal having a line frequency portion and an audio frequency portion in the electromagnetic spectrum associated with at least one arc condition. The AC line filter removes the line frequency portion and passes the audio frequency portion to an audio frequency filter which processes the audio frequency portion for an arc fault signature to detect for the occurrence of an arc fault condition.

Owner:LEVITON MFG

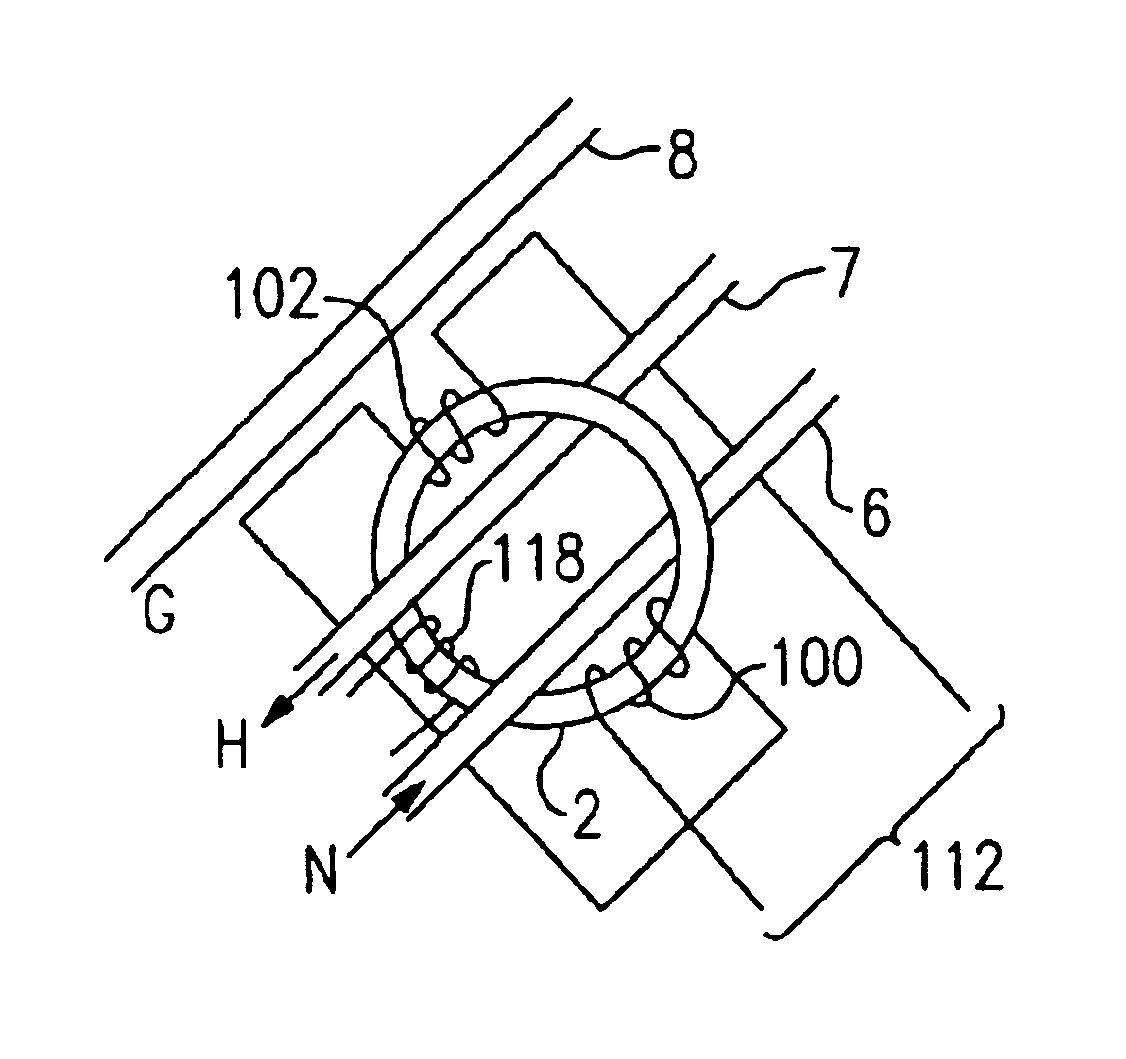

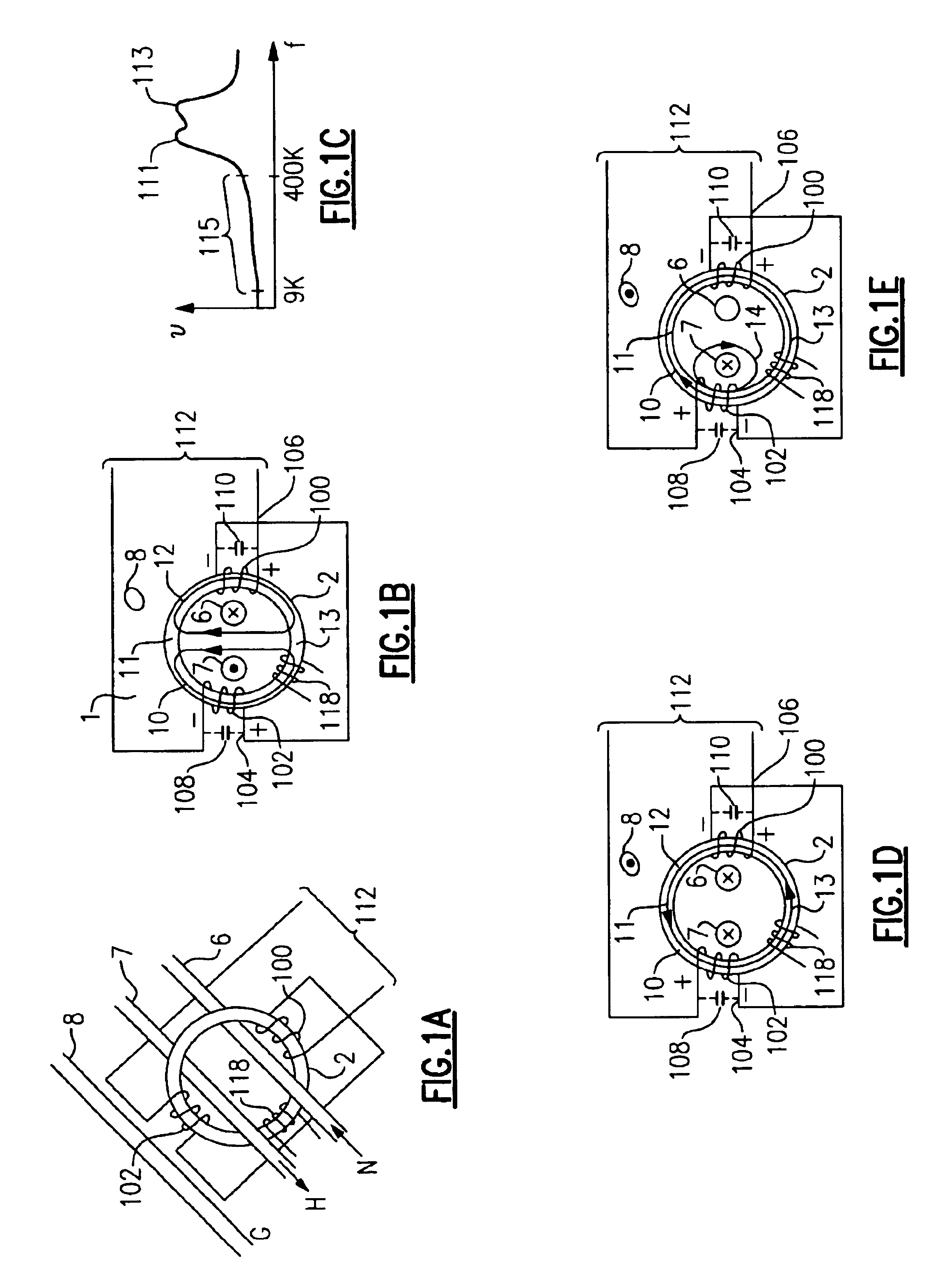

Two winding resonating arc fault sensor which boosts arc fault signals while rejecting arc mimicking noise

InactiveUS6876528B2Reinforces arc fault noiseReduce signalingEmergency protective arrangement detailsVoltage/current isolationSimulation noiseCarrier signal

A fault detector sensor includes a current transformer, with two multi-turn windings each formed around a portion of the core, with one winding adjacent to each of the hot and neutral wires of the power line being protected. Both windings are connected in series in a way which reinforces arc fault noise generated by arc faults involving the line and neutral, but which causes signal reduction for noise signals from the line and neutral, or either, to ground. The windings and core are selected to self resonate at a frequency that excludes power line carrier frequencies but which includes arc fault frequencies. The core optionally has a third winding, forming a grounded neutral transformer, or ground fault detector. Instead of a third winding, one of the arc fault sensing windings can act as a dual function sensor.

Owner:PASS SEYMOUR

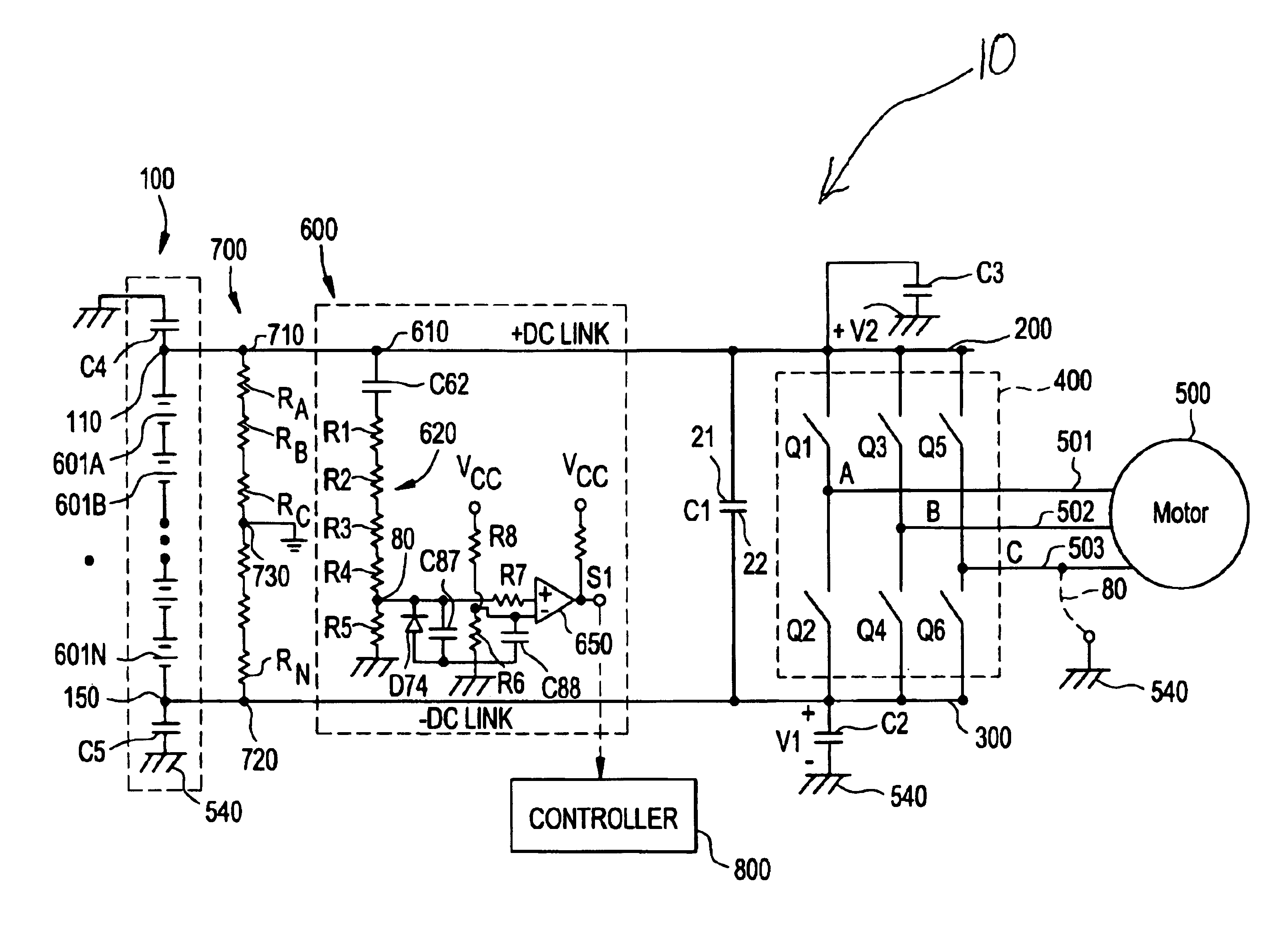

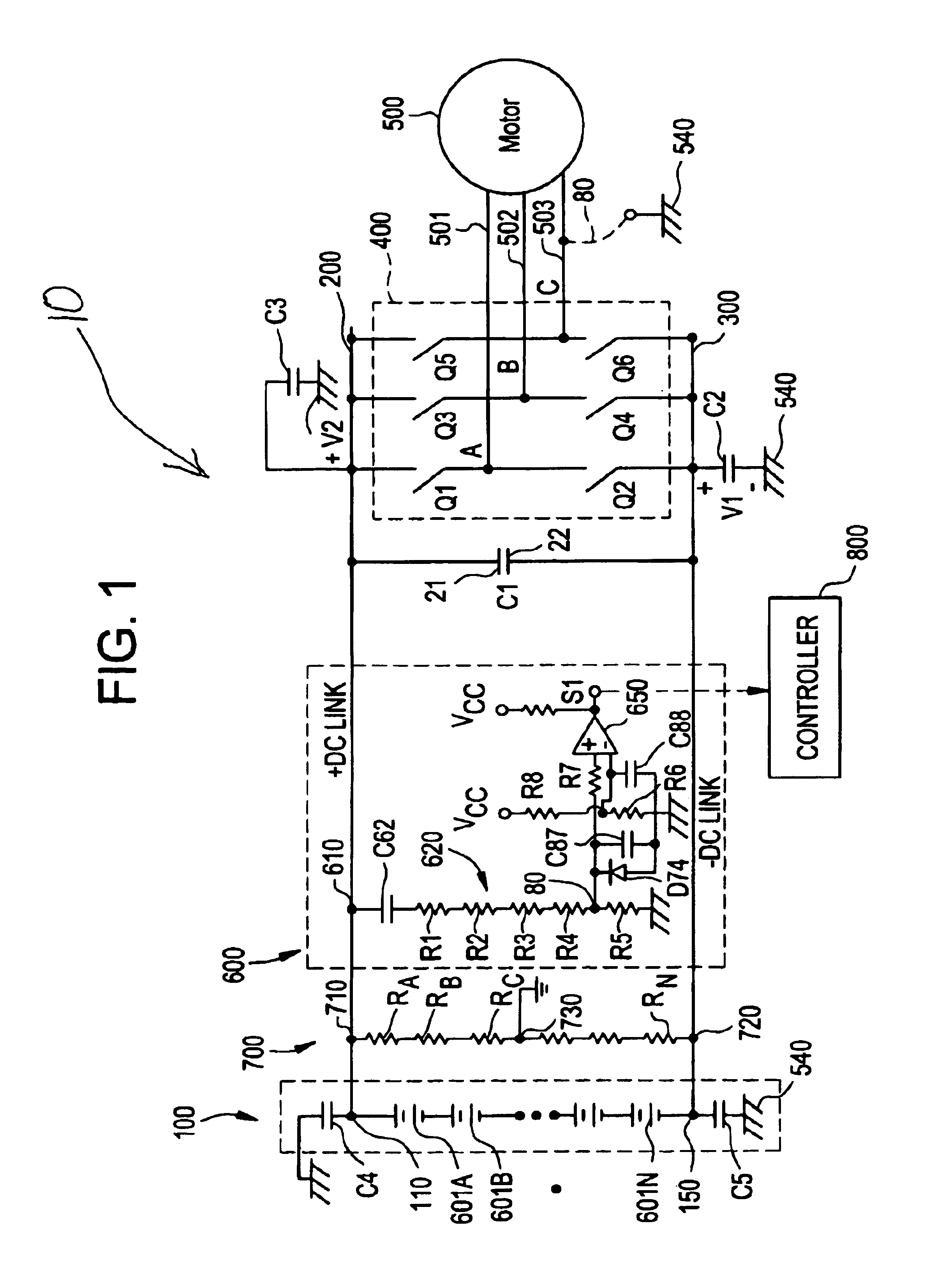

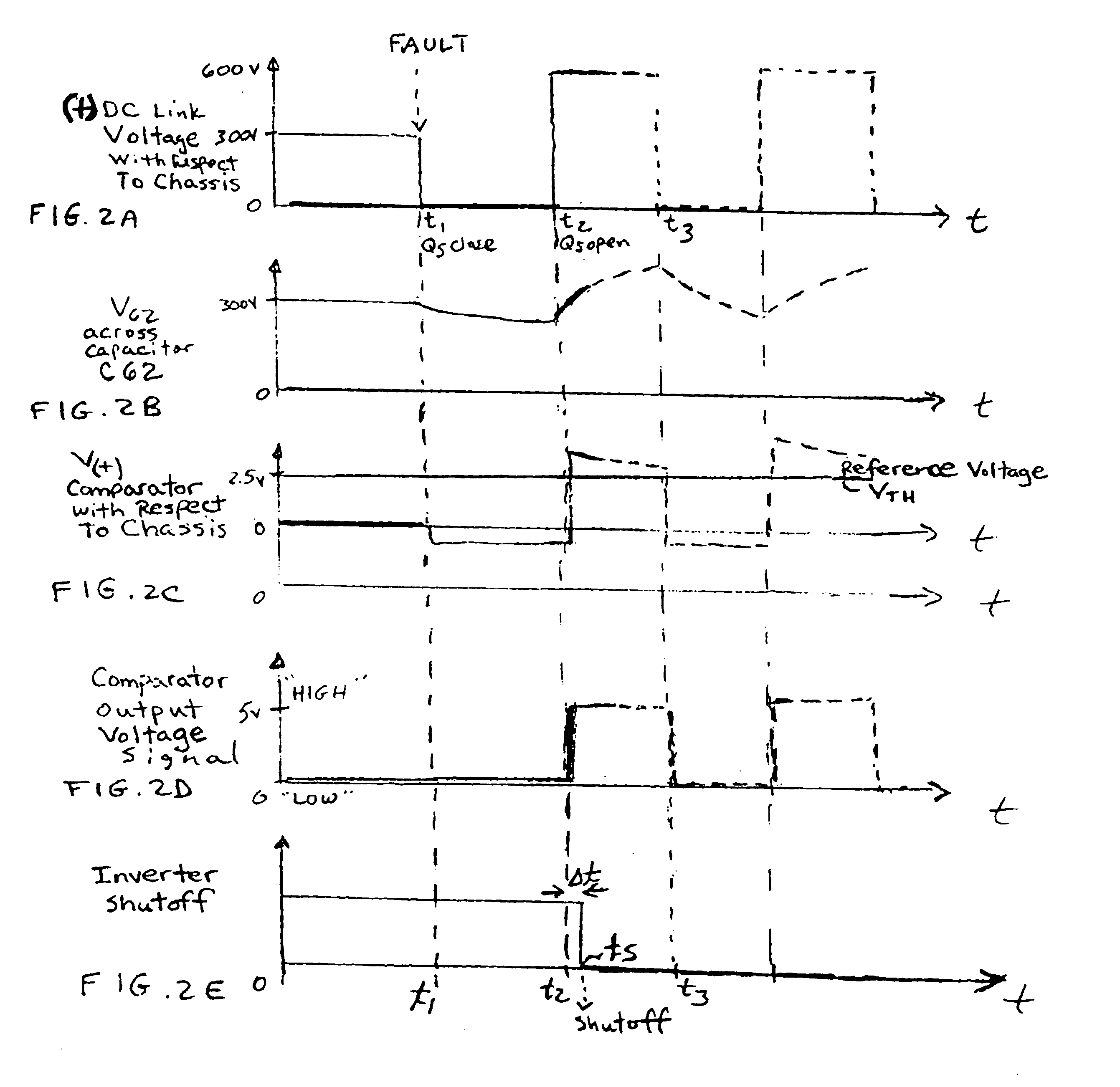

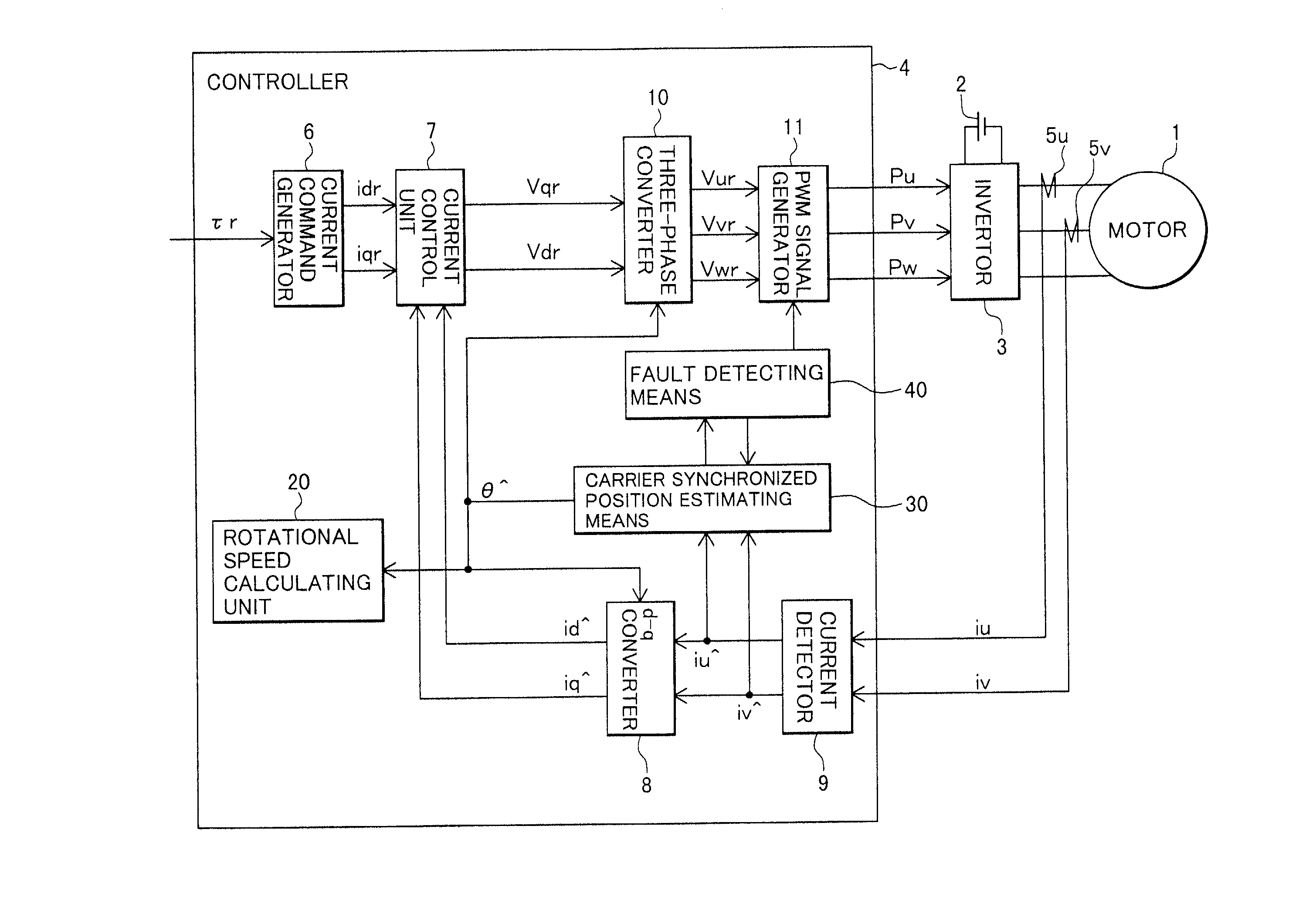

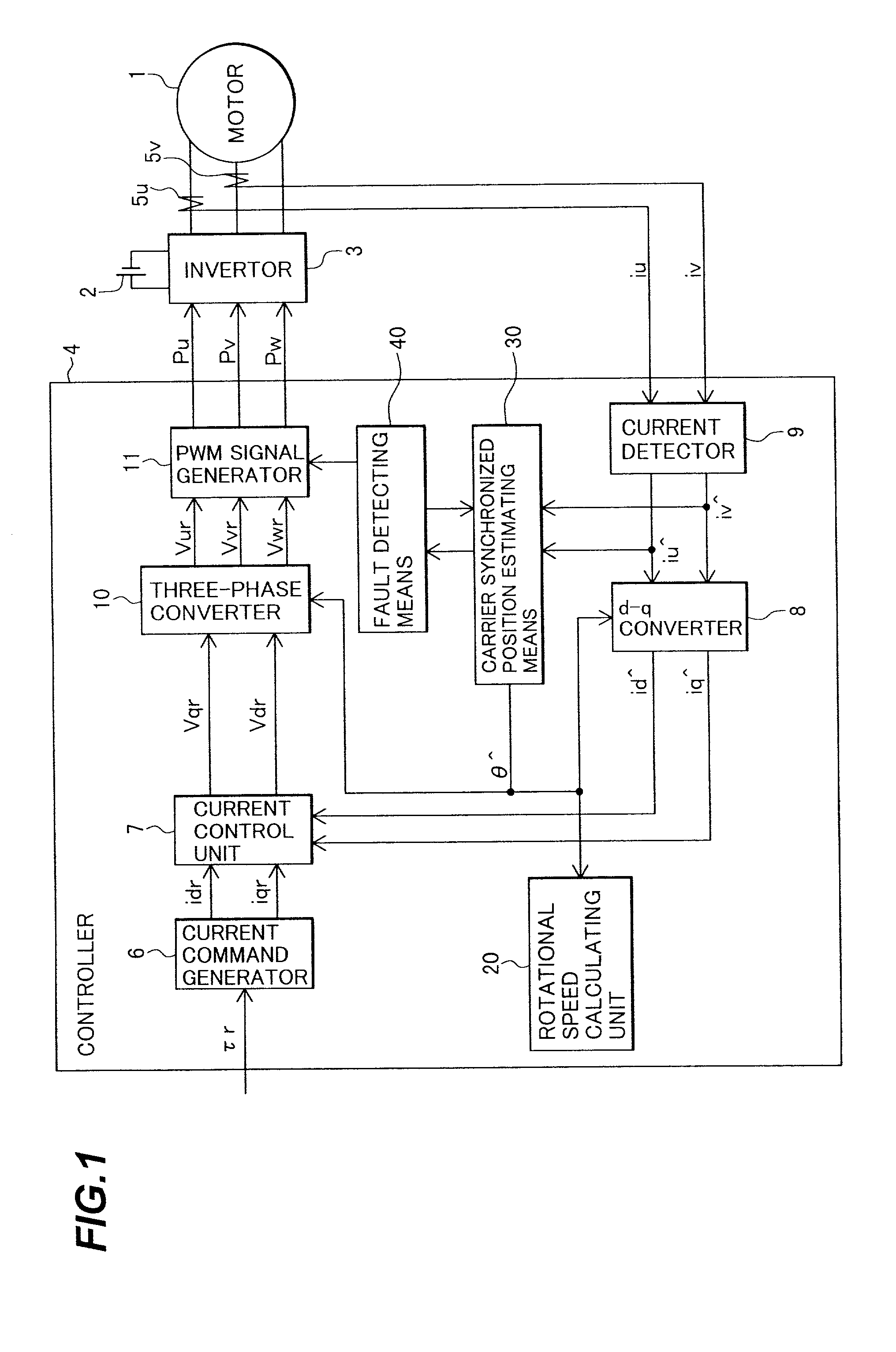

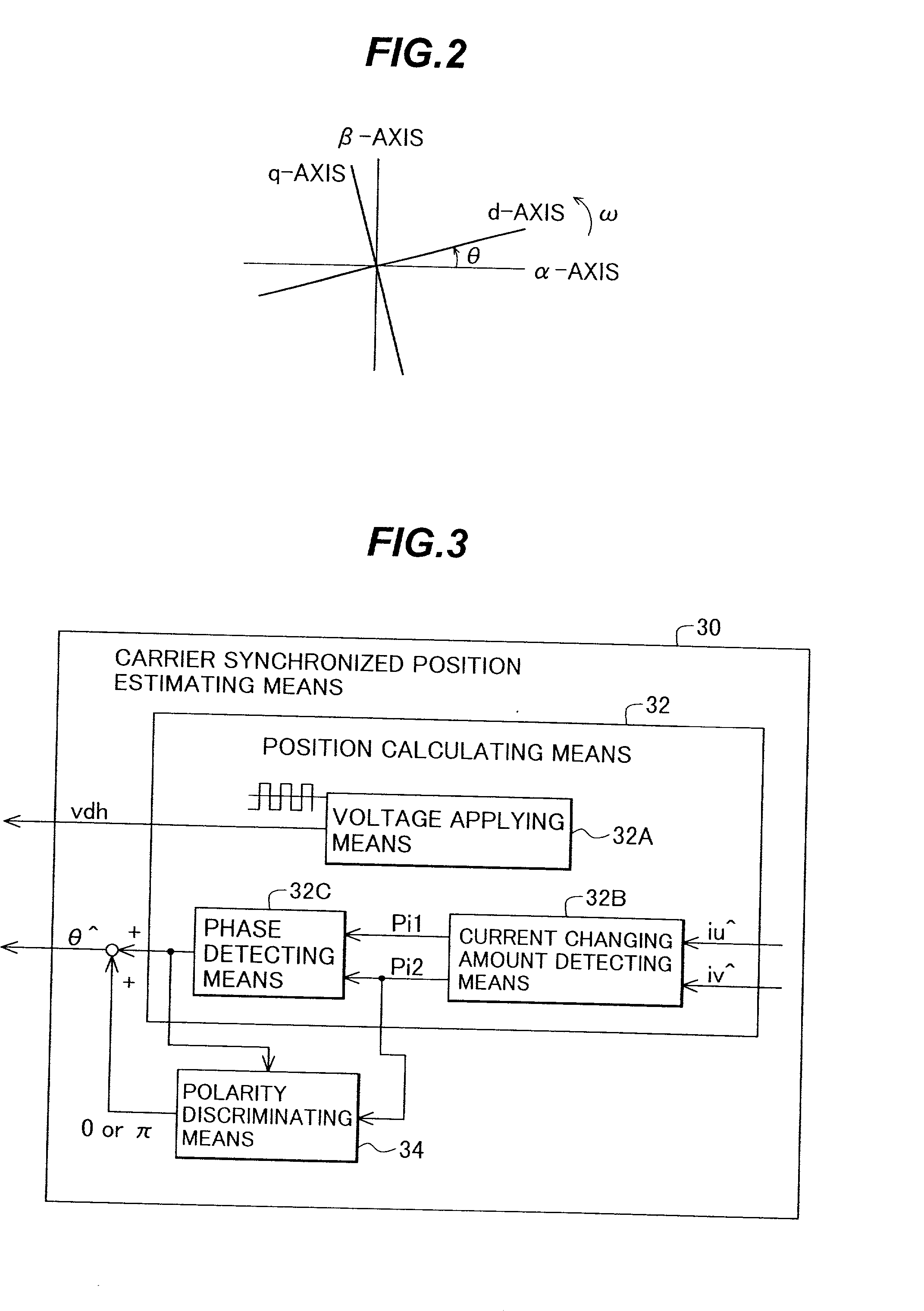

Motor control apparatus and electric vehicle using same

InactiveUS20020117990A1Single-phase induction motor startersDC motor speed/torque controlSynchronous motorMagnetic poles

A synchronous motor controlling apparatus which can be applied to the carrier synchronized position estimating method as well and have protection-related functions such as detection of inverted magnetic pole position of a motor in a simple method, and an electric motor using the synchronous motor control apparatus. A controller controls a voltage applied to an AC motor with a PWM signal. A magnetic pole position detector of the controller detects a current of the AC motor to estimate a pole position of the AC motor. A fault detector detects a fault in the estimated magnetic position of the AC motor.

Owner:HITACHI LTD

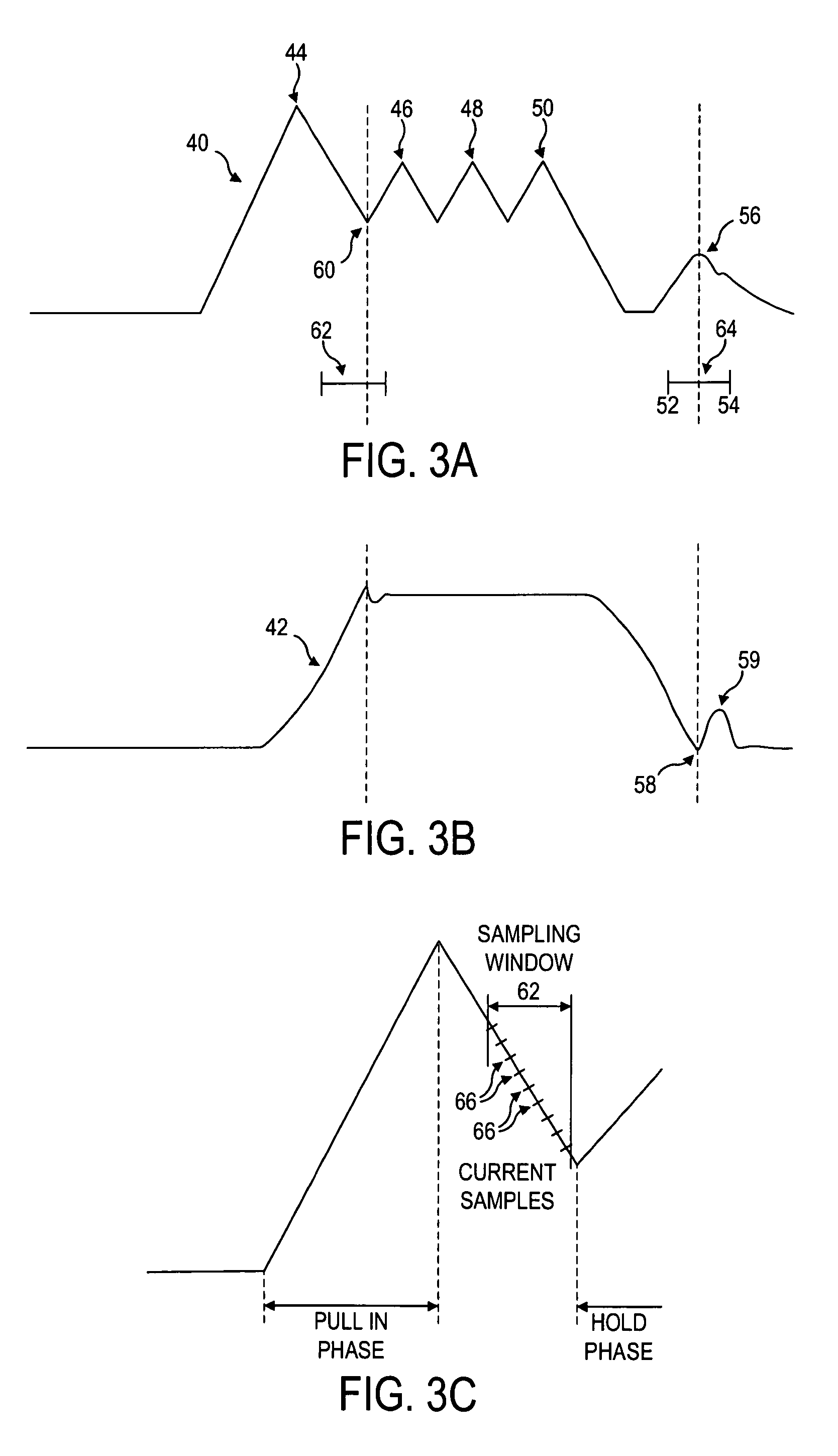

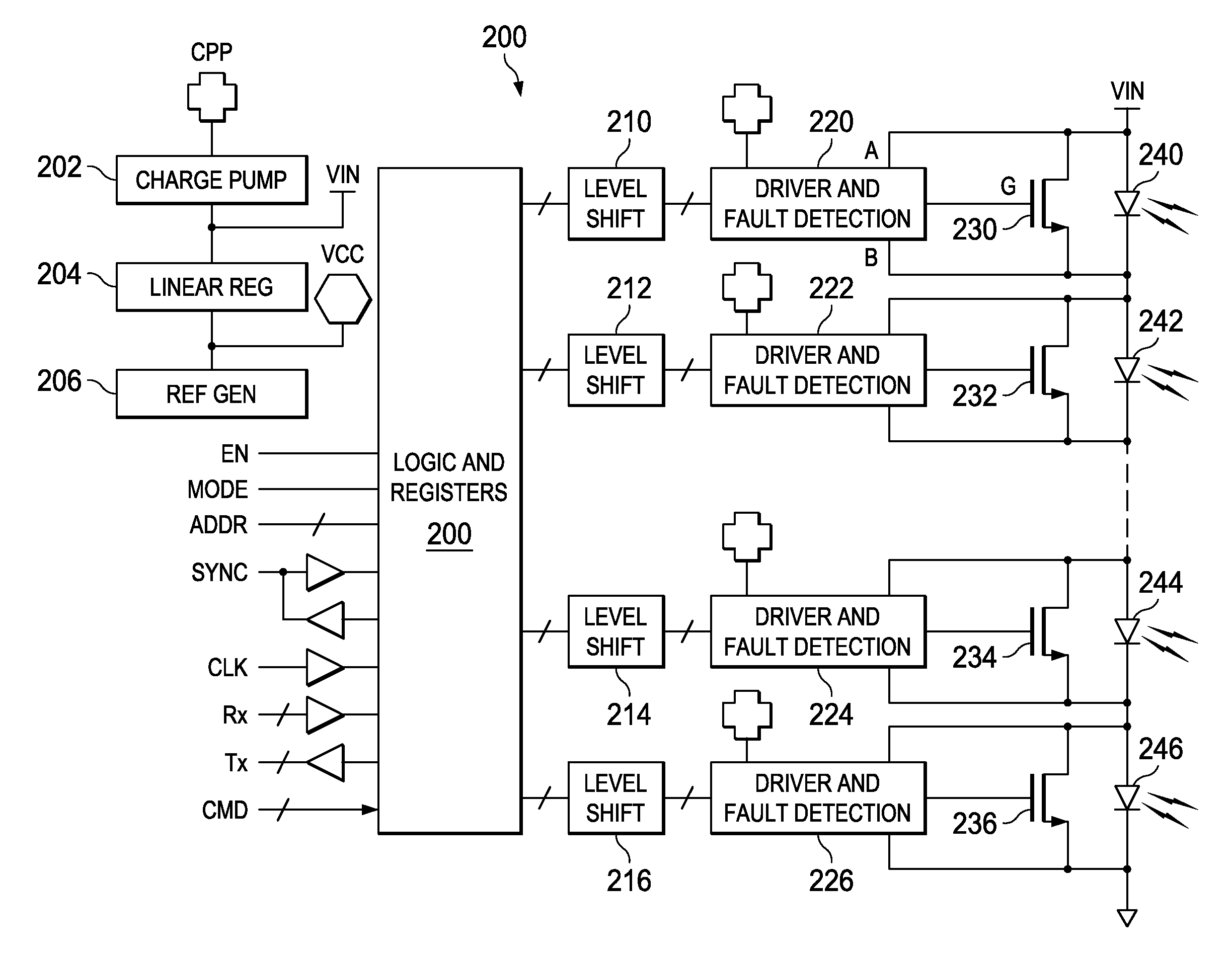

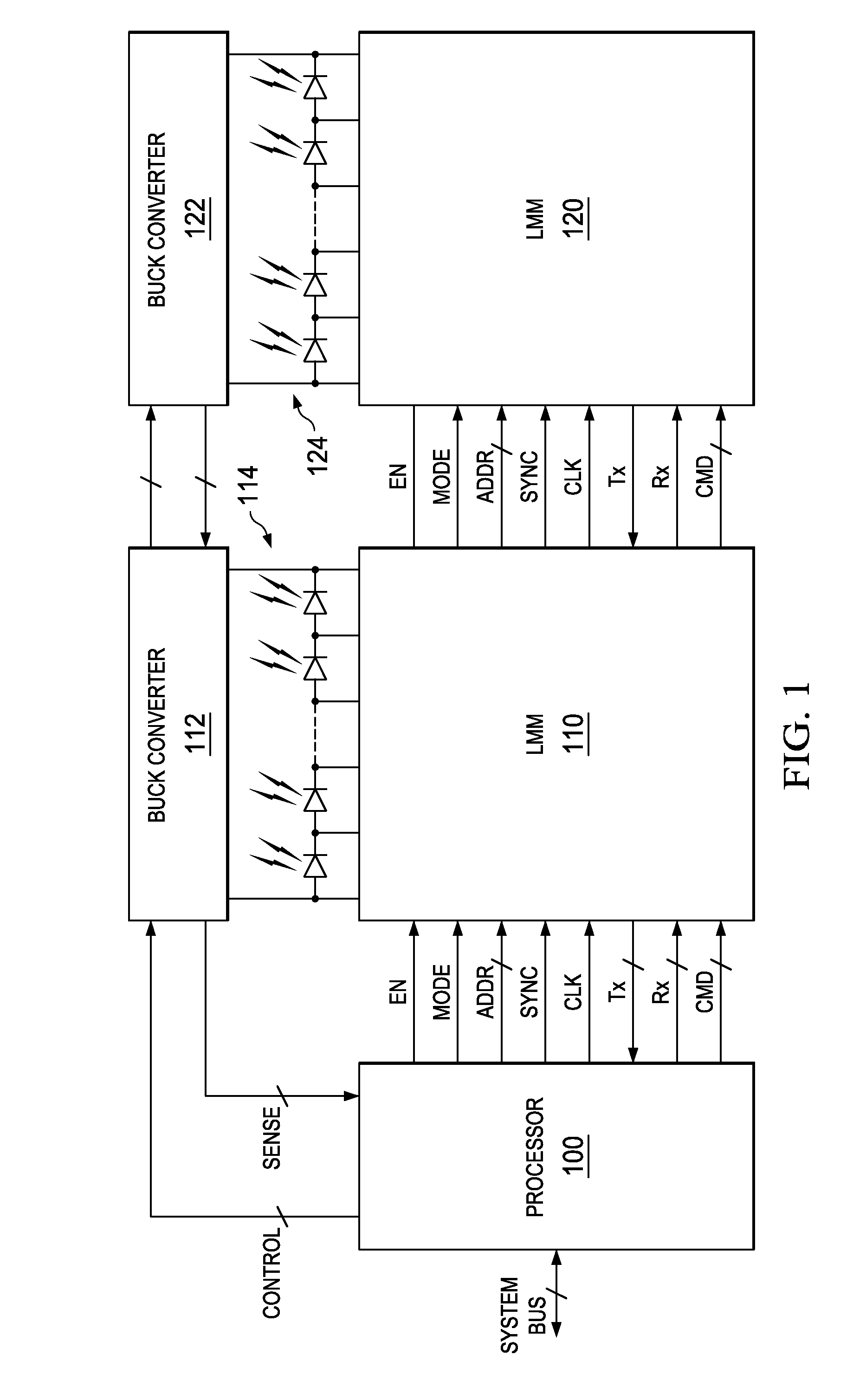

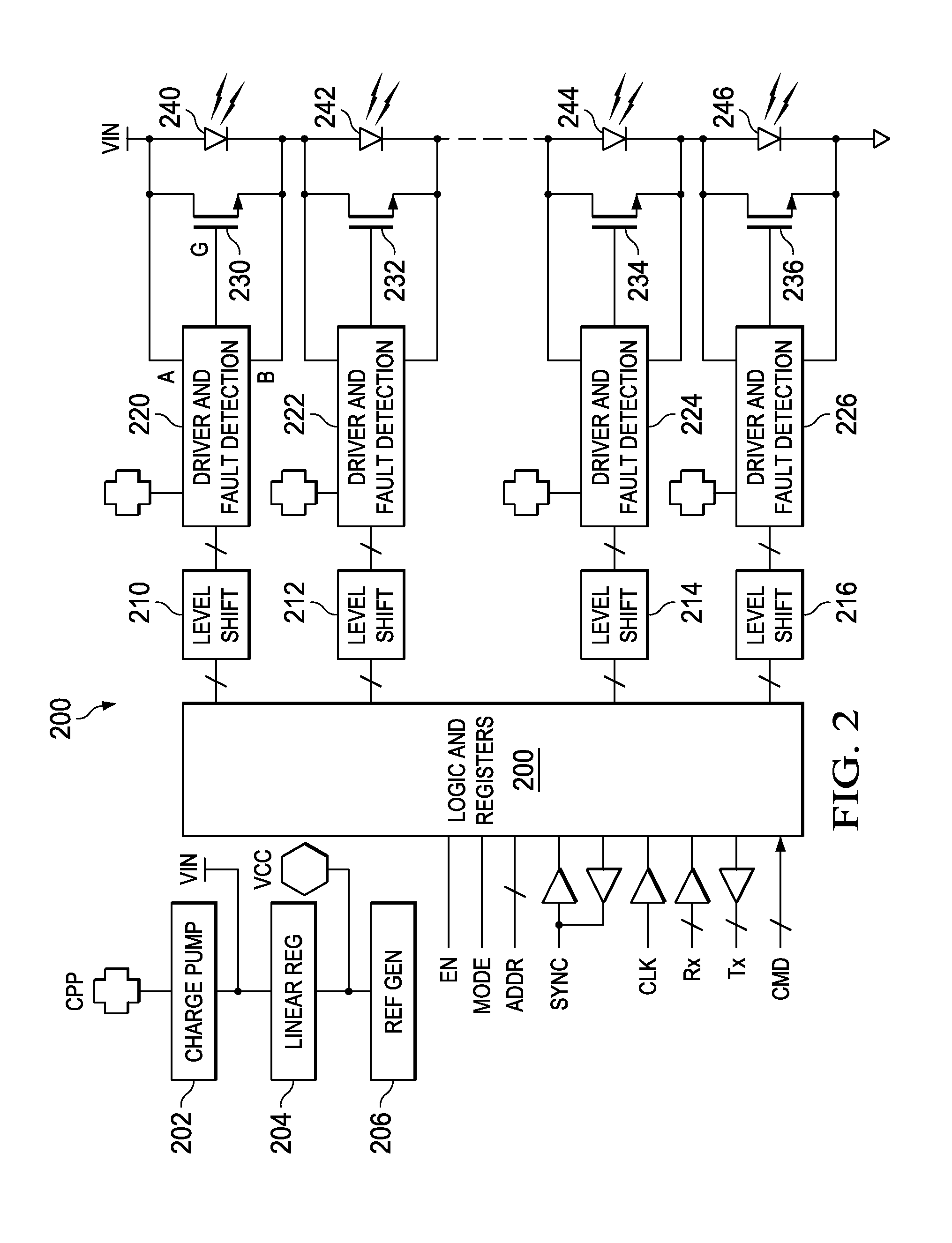

LED bypass and control circuit for fault tolerant LED systems

ActiveUS20130313973A1Boards/switchyards circuit arrangementsElectroluminescent light sourcesDetector circuitsControl signal

A light system (FIG. 2) is disclosed. The light system includes a plurality of series connected light emitting diodes (240-246). Each of a plurality of switching devices (230-236) has a control terminal and each has a current path coupled in parallel with a respective LED. A plurality of fault detector circuits (220-226) are each coupled in parallel with a respective light emitting diode. Each fault detector circuit has a first comparator (FIG. 7,704) arranged to compare a voltage across the respective light emitting diode to a respective first reference voltage (708). When a fault is defected, a control signal is applied to the control terminal to turn on a respective switching device of the plurality of switching devices.

Owner:TEXAS INSTR INC

Direct current arc fault circuit interrupter, direct current arc fault detector, noise blanking circuit for a direct current arc fault circuit interrupter, and method of detecting arc faults

ActiveUS8218274B2Emergency protective arrangement detailsArrangements responsive to excess currentCurrent sensorPeak current

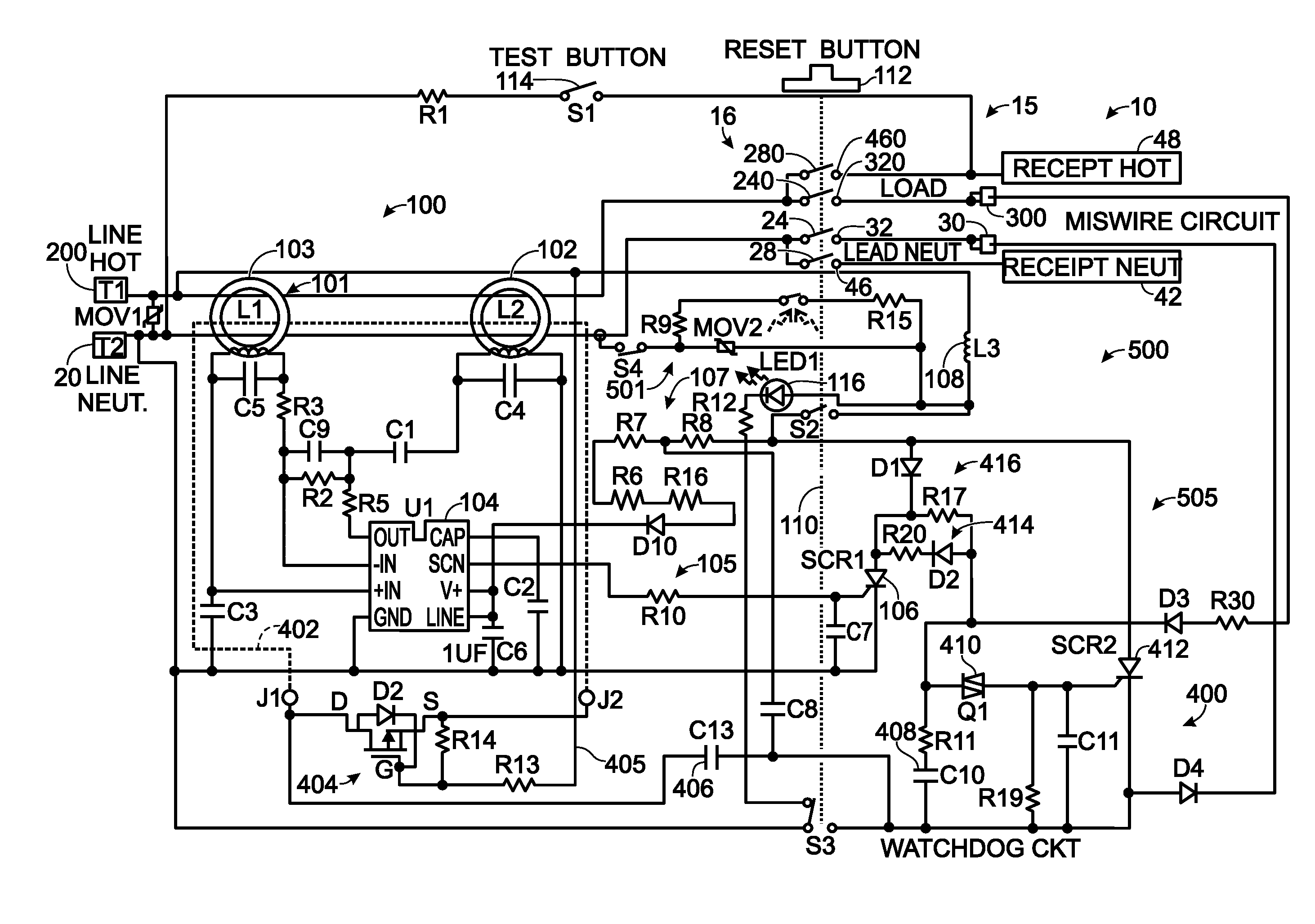

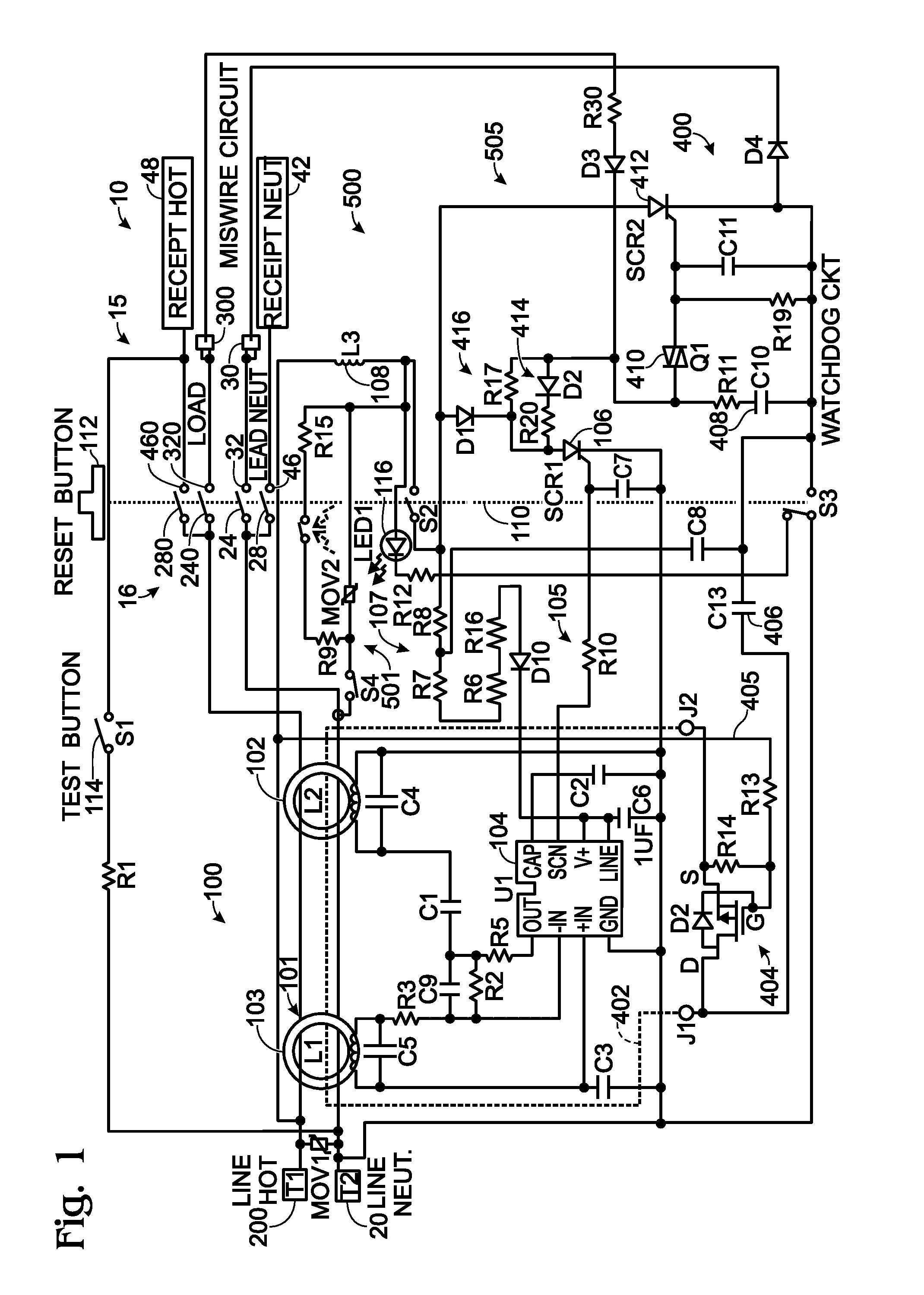

A direct current arc fault circuit interrupter includes separable contacts and a trip circuit to trip open the contacts. The trip circuit includes a number of alternating current sensors structured to sense a current flowing through the separable contacts, a number of filter circuits cooperating with the AC current sensors to output a number of AC signals, a number of peak detectors cooperating with the filter circuits to output a number of peak current signals, and a processor cooperating with at least the peak detectors. The processor inputs the number of peak current signals as a plurality of peak current signals or inputs the number of peak current signals and determines the plurality of peak current signals. The processor also determines if the peak current signals exceed corresponding predetermined thresholds for a predetermined time, and responsively causes the contacts to trip open.

Owner:EATON INTELLIGENT POWER LTD

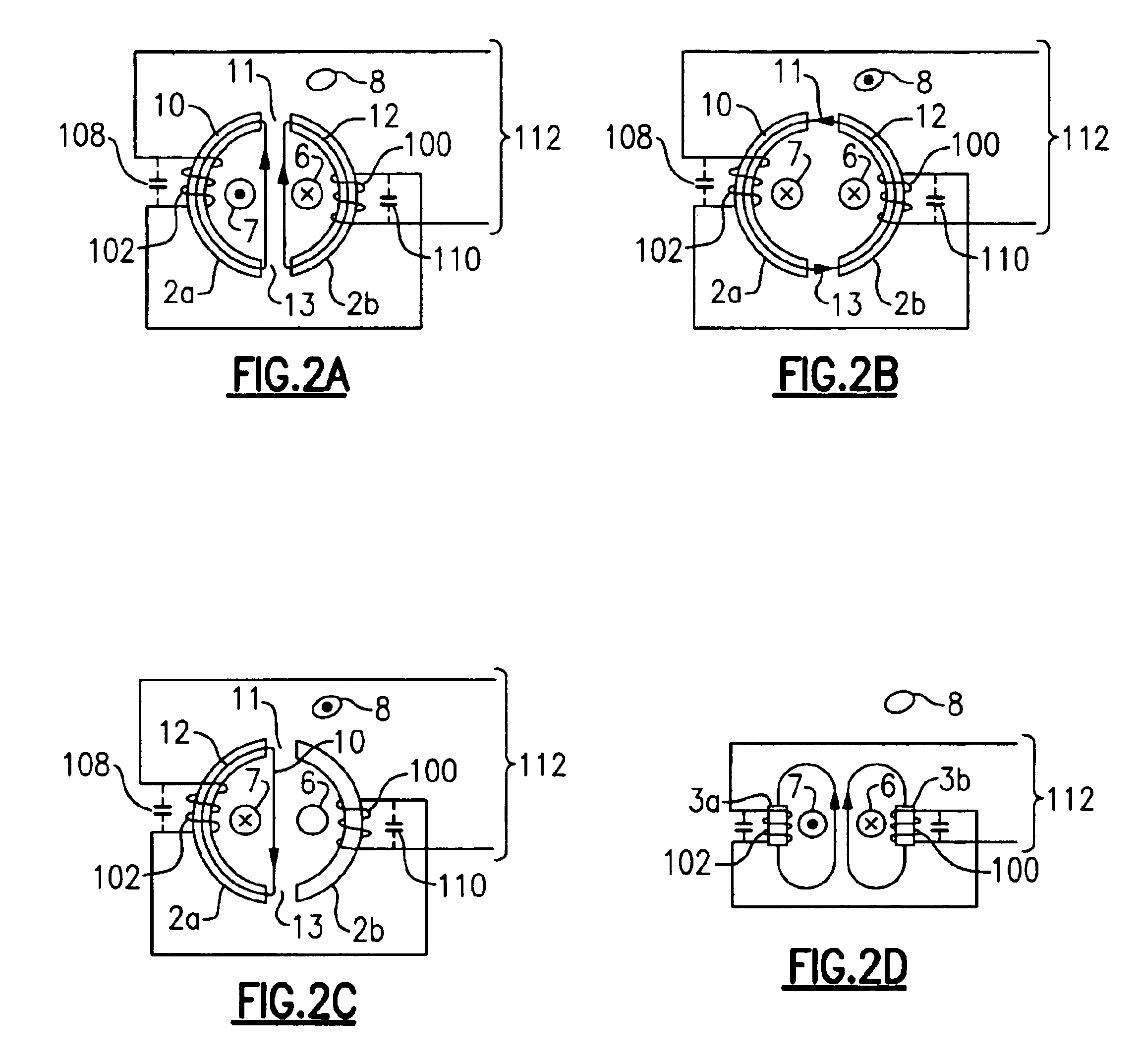

Protection system for protecting a poly-phase distribution transformer insulated in a liquid dielectric, the system including at least one phase disconnector switch

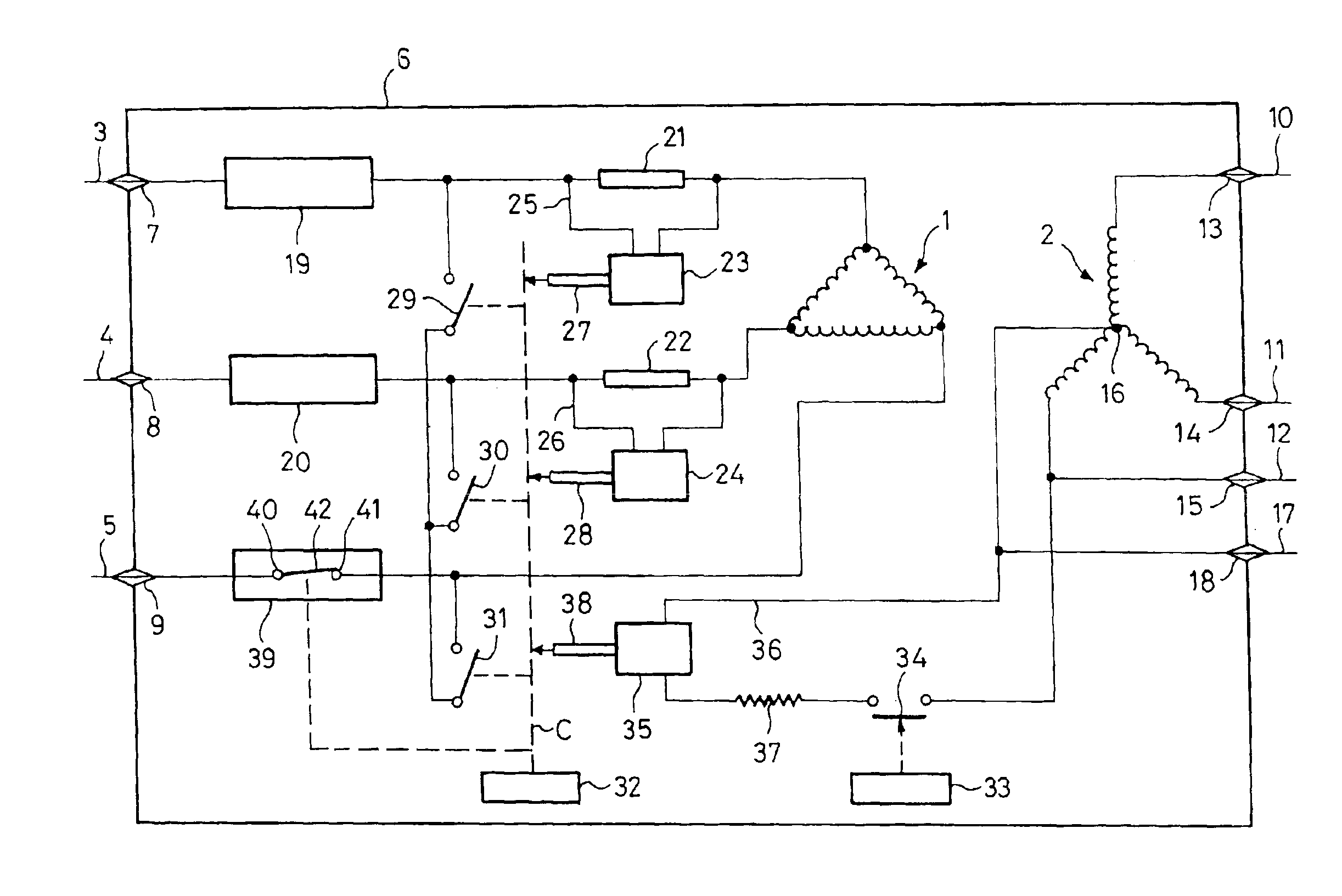

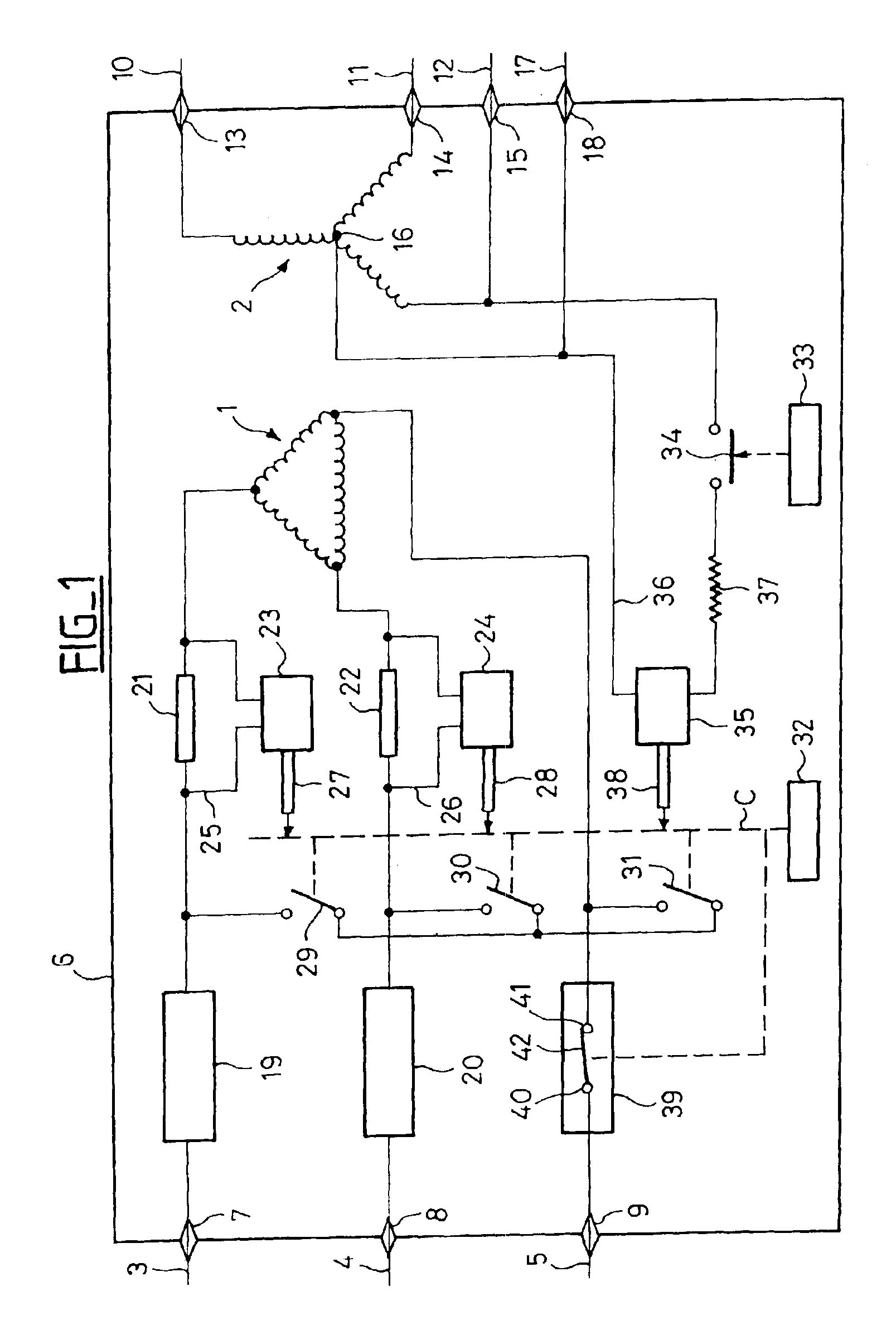

InactiveUS6839207B2Prevent pressureEmergency protective circuit arrangementsProtective switchesElectricityCurrent limiting

The distribution transformer is installed in a station having N phases, at least N-1 phases being equipped on the high-voltage side of the transformer with respective current-limiting fuses capable of blowing in the event of a dead short circuit between the phases. The protection system includes: at least one fault detector for detecting faults on the basis of at least one of the following indicators: pressure in the tank, level of the dielectric, or temperature of the transformer; a short-circuiter acting on all the phases situated upstream from the high-voltage windings, said short-circuiter being capable of being triggered by said fault detector to establish a dead short circuit between the phases; and on at least N-1 phases, a detector for detecting an abnormal current upstream from the transformer, said detector being associated with a controller for controlling said short-circuiter. In the system, at least the phase that is not equipped with a limiting fuse is equipped with a disconnector switch which is normally closed in the absence of any fault, said disconnector switch being disposed on the high-voltage side of the transformer upstream from the short-circuiter, and opening thereof being triggered by the short-circuiter in the event of a fault, but with a certain delay.

Owner:AREVA T&D

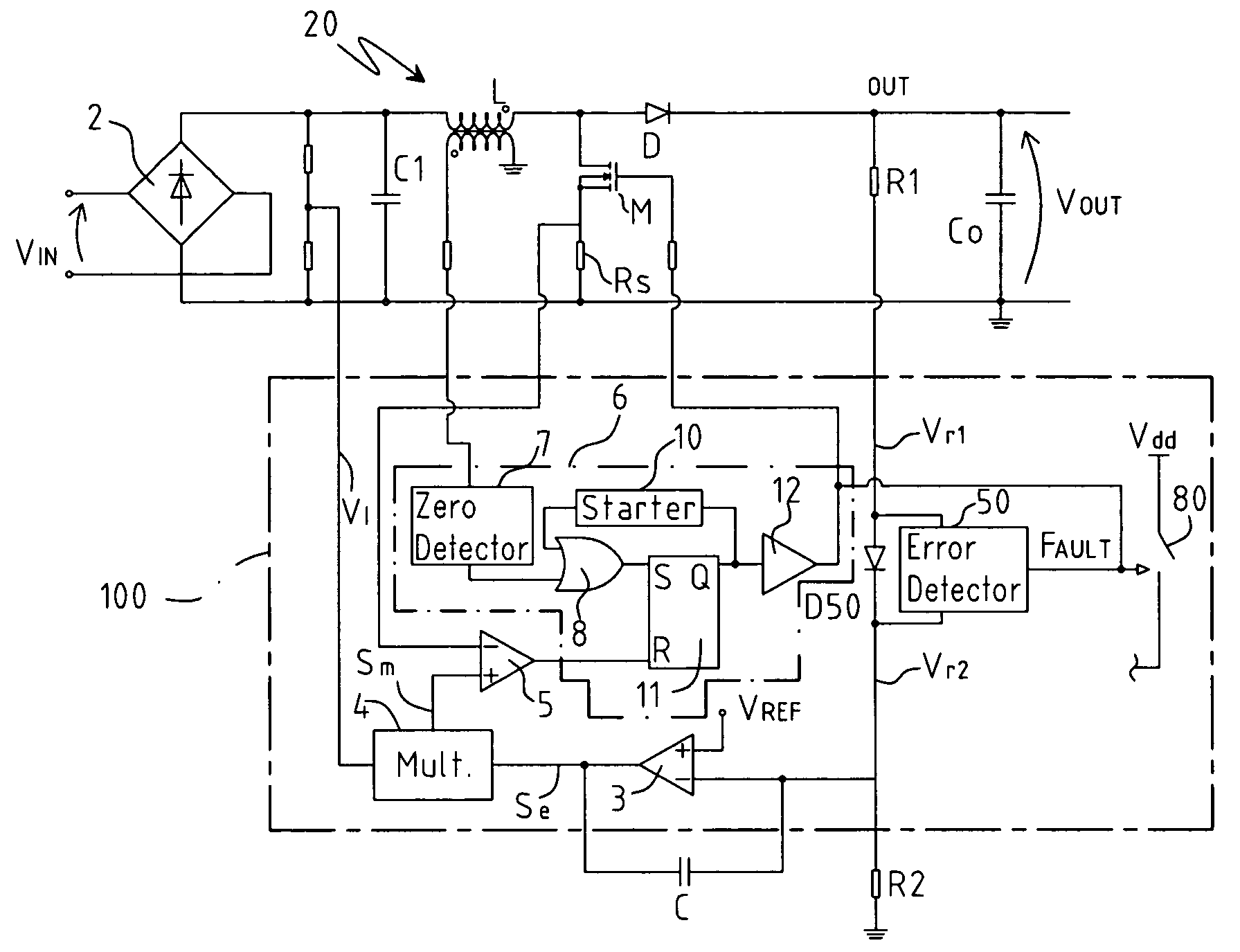

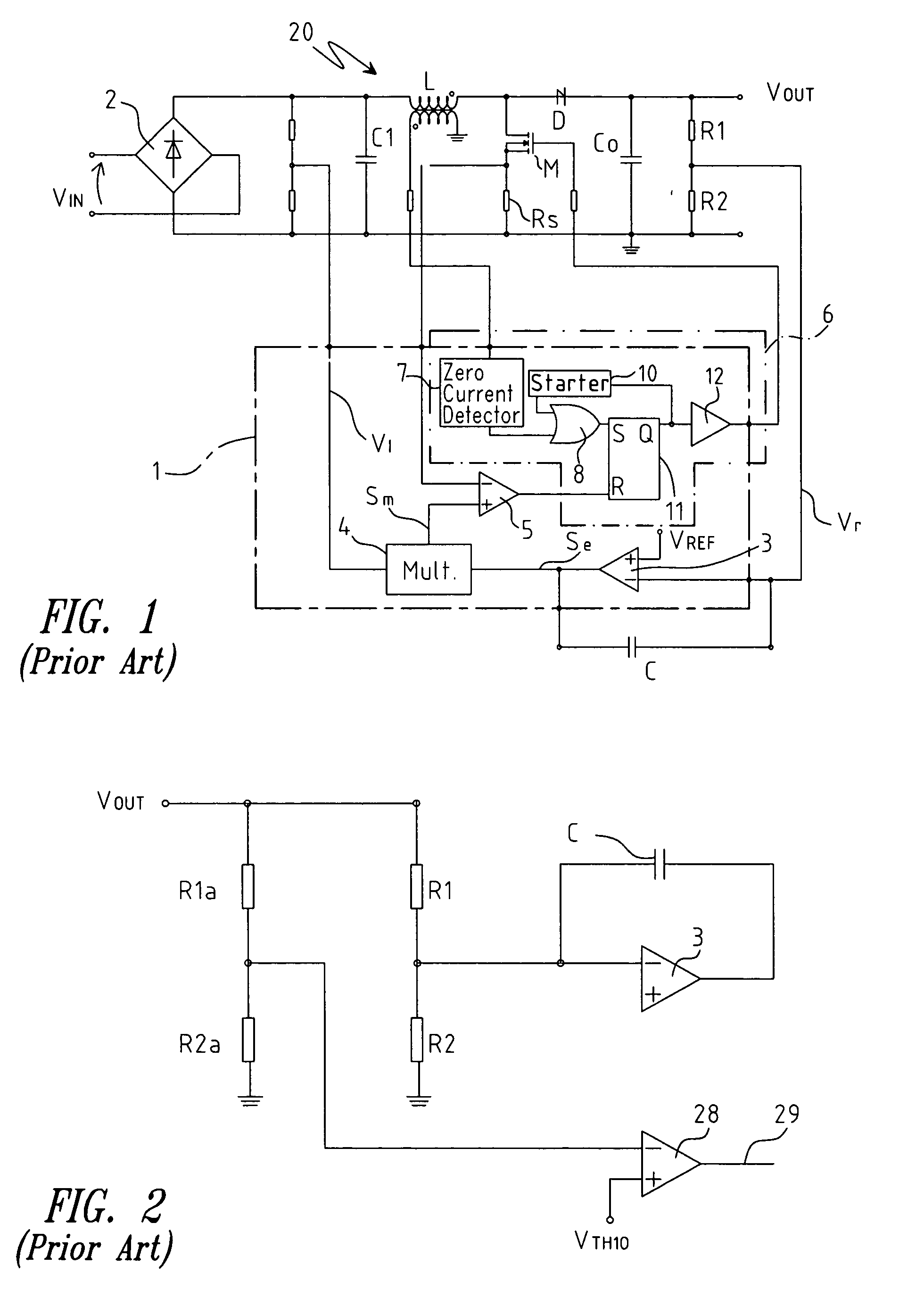

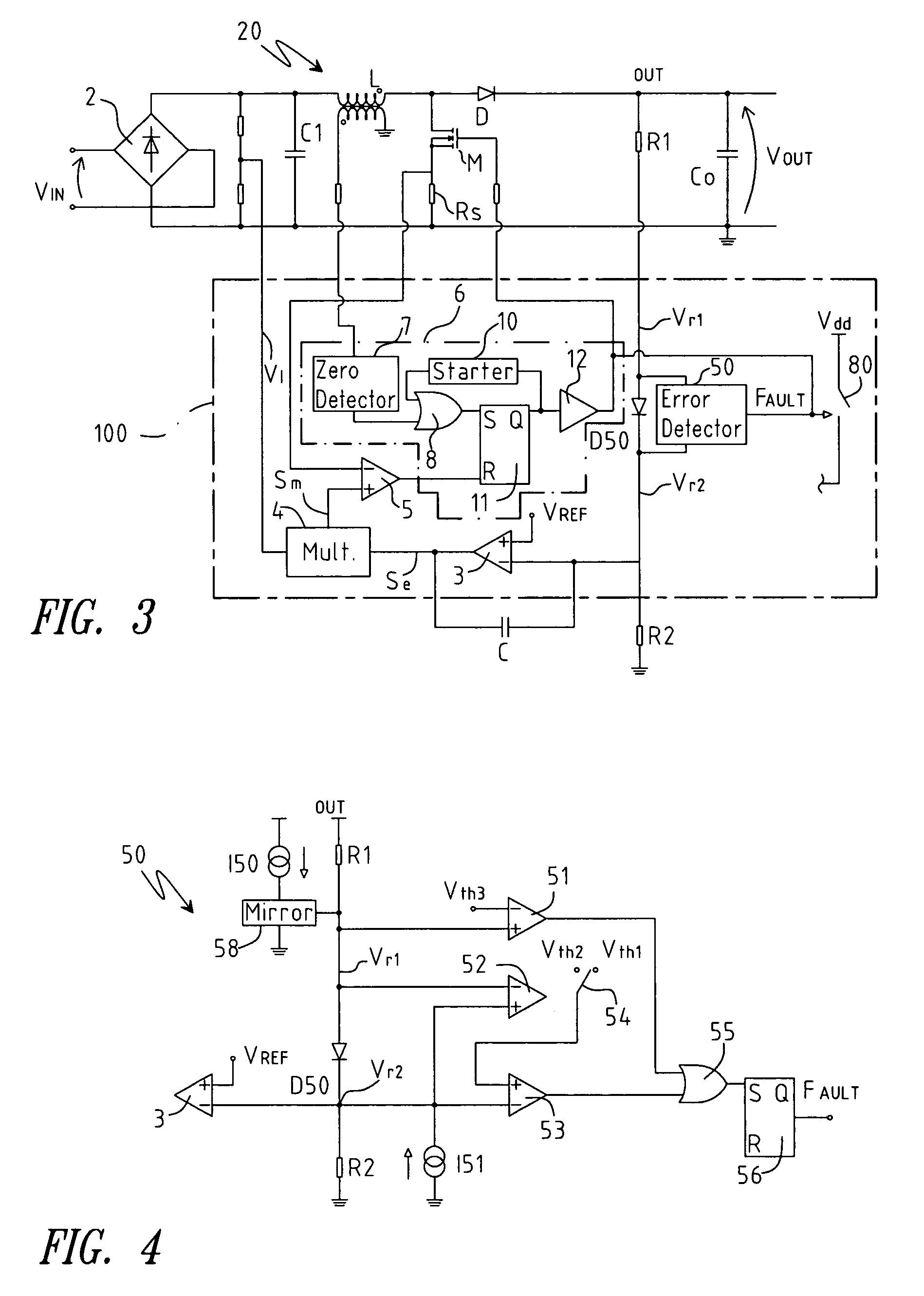

Fault detection for loss of feeback in forced switching power supplies with power factor correction

ActiveUS7440297B2Efficient power electronics conversionDc-dc conversionElectrical resistance and conductanceElectricity

A device corrects the power factor in forced switching power supplies and includes a converter and a control device to obtain a regulated voltage on an output terminal. The control device comprises an error amplifier having an inverting terminal (Vout) and a non-inverting terminal receiving a reference voltage. The device includes first and second resistances coupled in series with a conduction element positioned between the first resistance and the inverting terminal of the error amplifier and a fault detector suitable for detecting the electrical connection of the conduction element with the output terminal and suitable for detecting an output signal of the second resistance. The fault detector is suitable for supplying a malfunction signal upon detecting an electric disconnection of the conduction element from the output terminal or when the output signal of the second resistance tends to zero.

Owner:STMICROELECTRONICS SRL

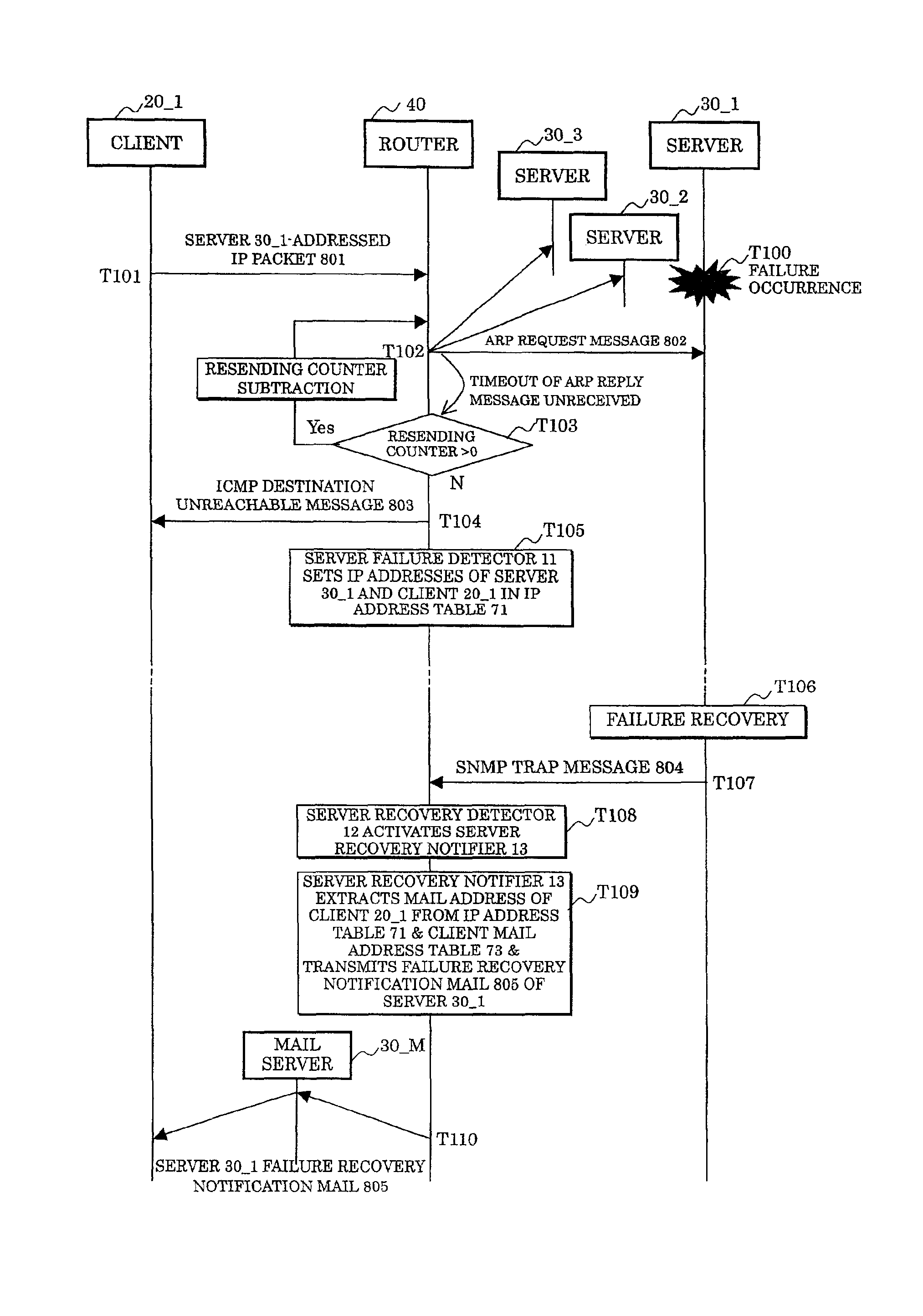

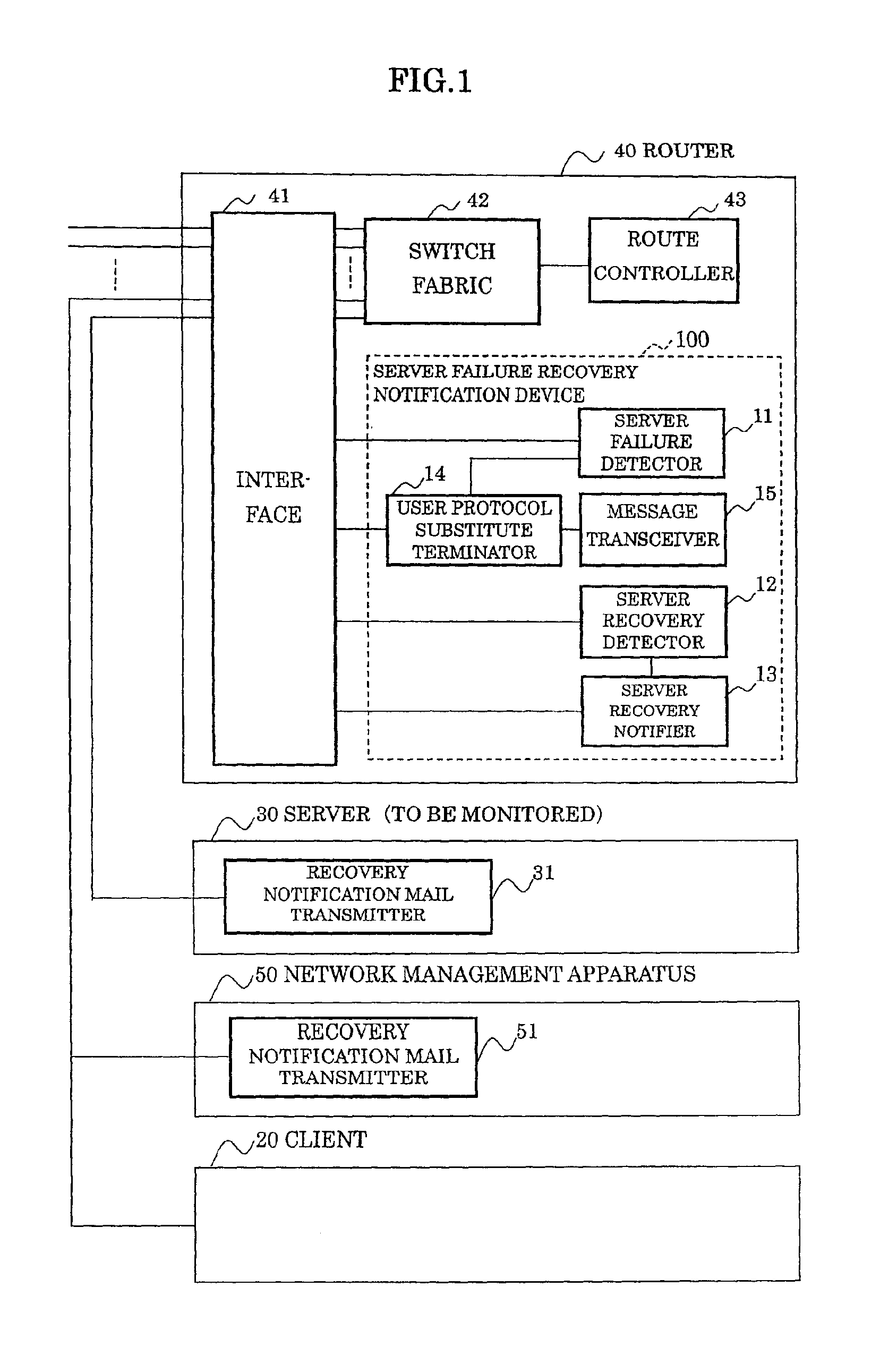

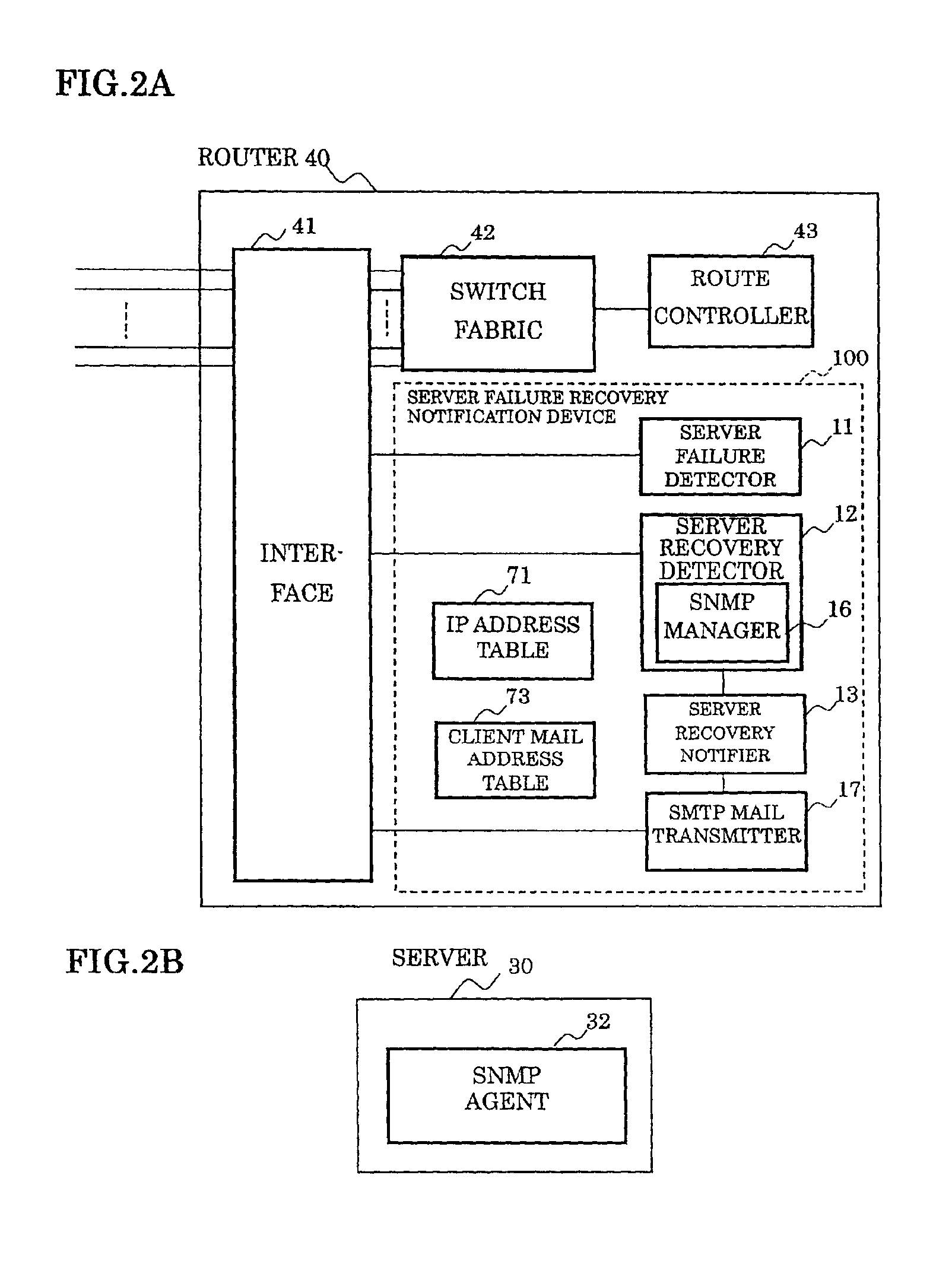

Method and device for notifying server failure recovery

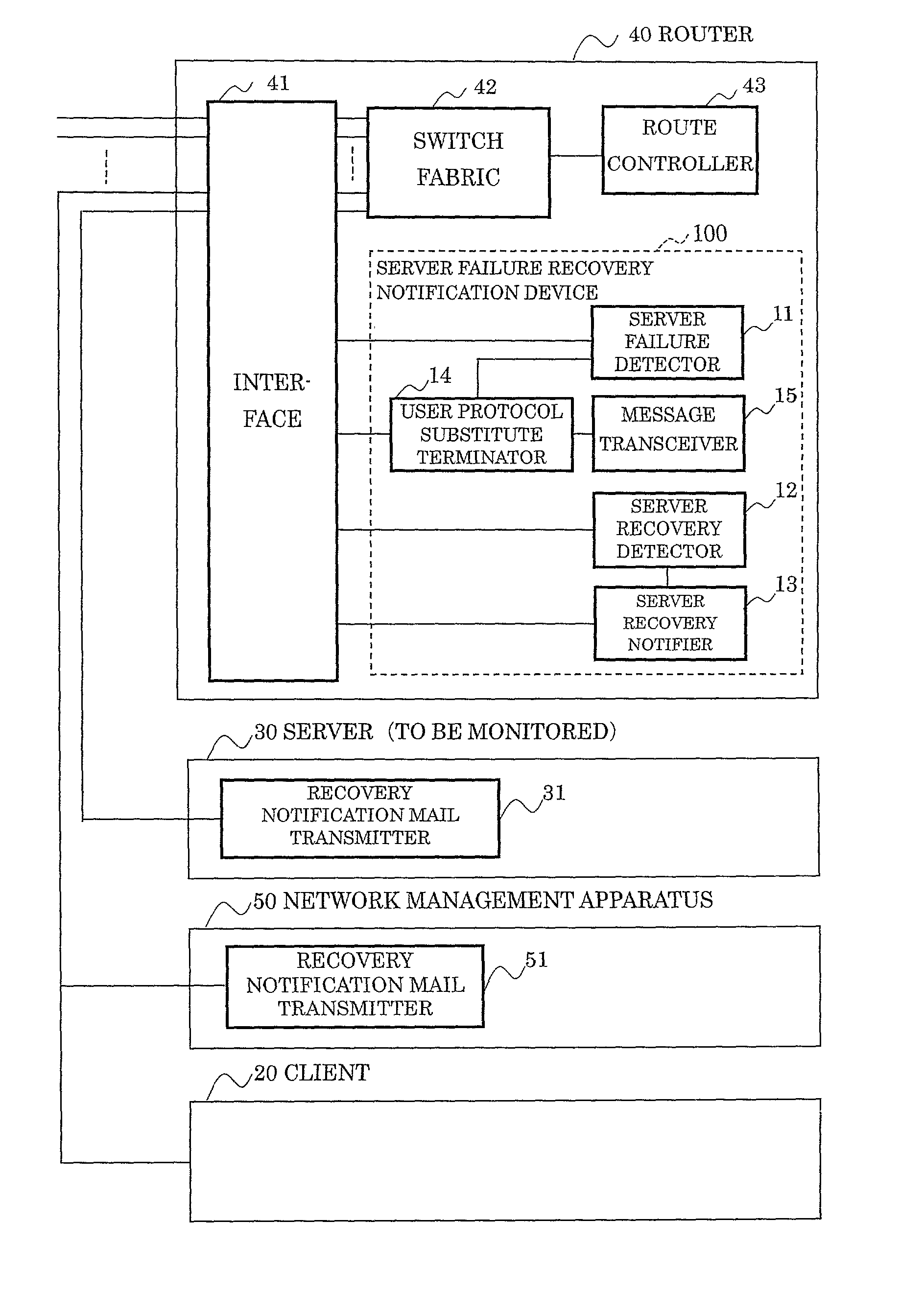

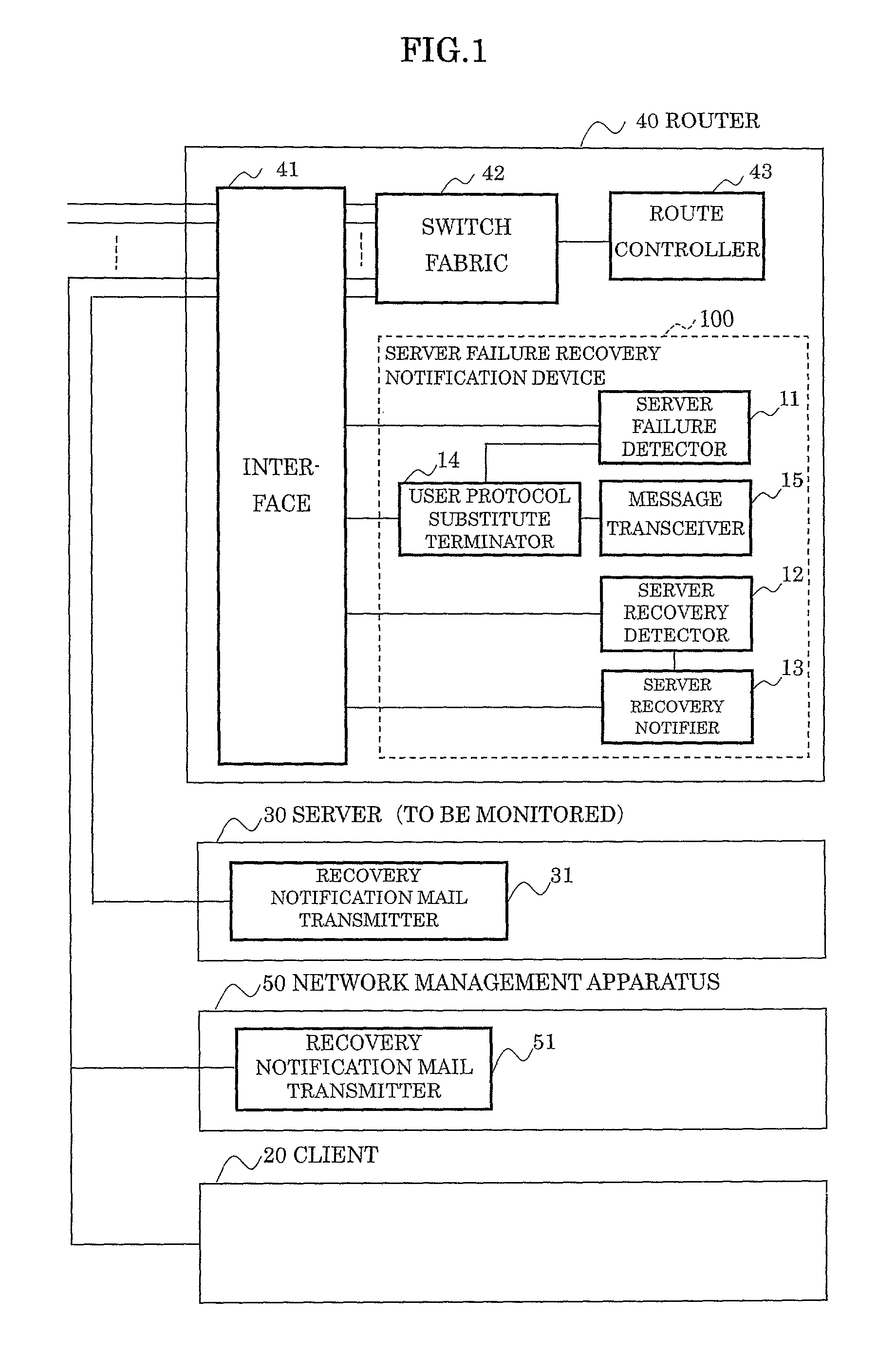

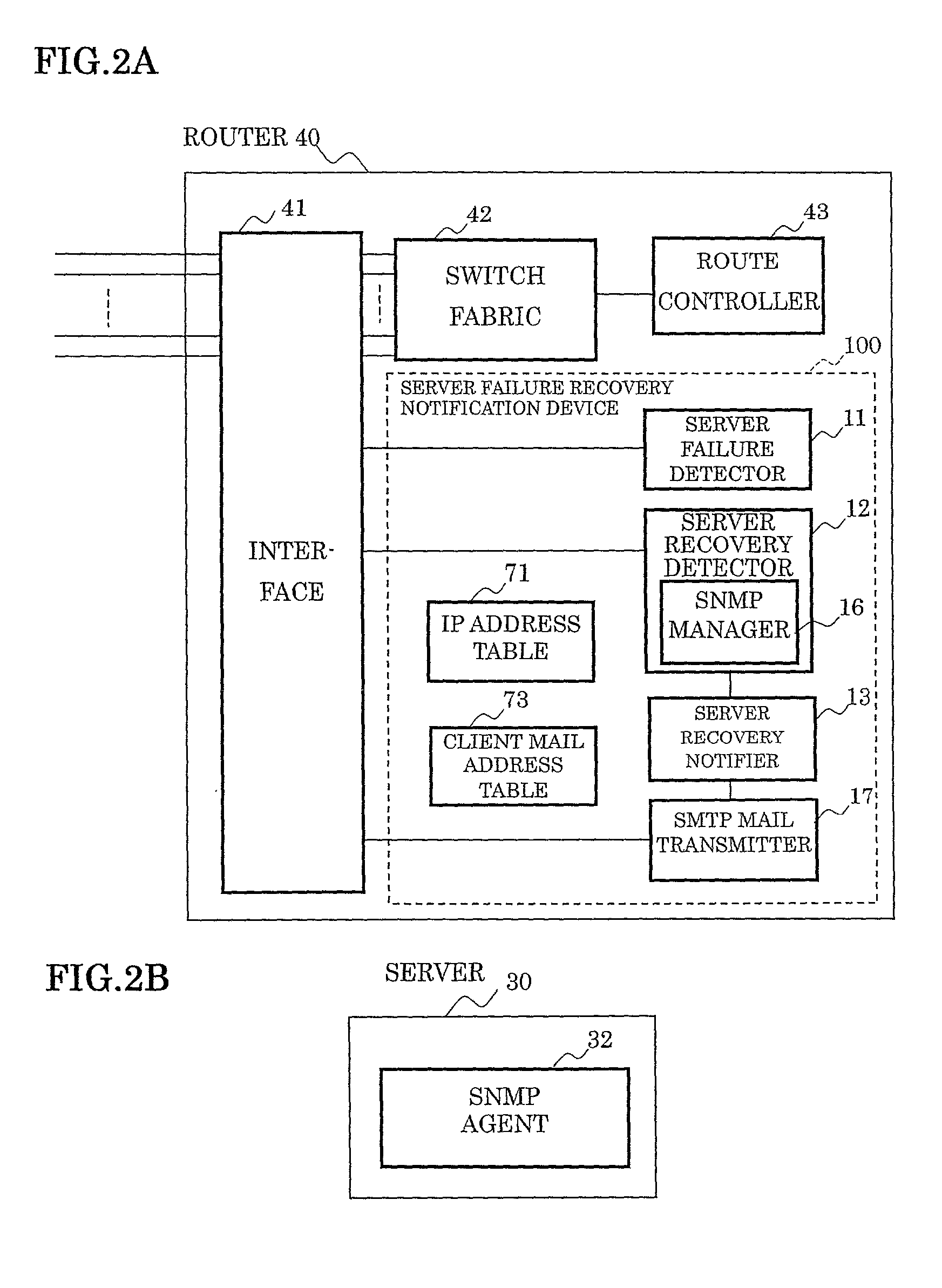

InactiveUS20030028817A1Easy accessEliminate troubleError preventionDigital computer detailsNetwork packetClient-side

In a method and a device for notifying a server failure recovery which notify a failure recovery of a server or the like to a client, a server failure detector detects a client having tried but failed to access a server due to a failure, a server recovery detector detects a failure recovery, and a server recovery notifier gives a failure recovery notification to the client having failed to access. Also, the server failure recovery notification device is mounted on a router. The server failure detector detects the client having failed to access based on a destination unreachable message of an ICMP of the router 40, or detects the client having failed to access by determining the failure is being occurred in the server, in the absence of a reply IP packet to the IP packet addressed to the server from the client.

Owner:FUJITSU LTD

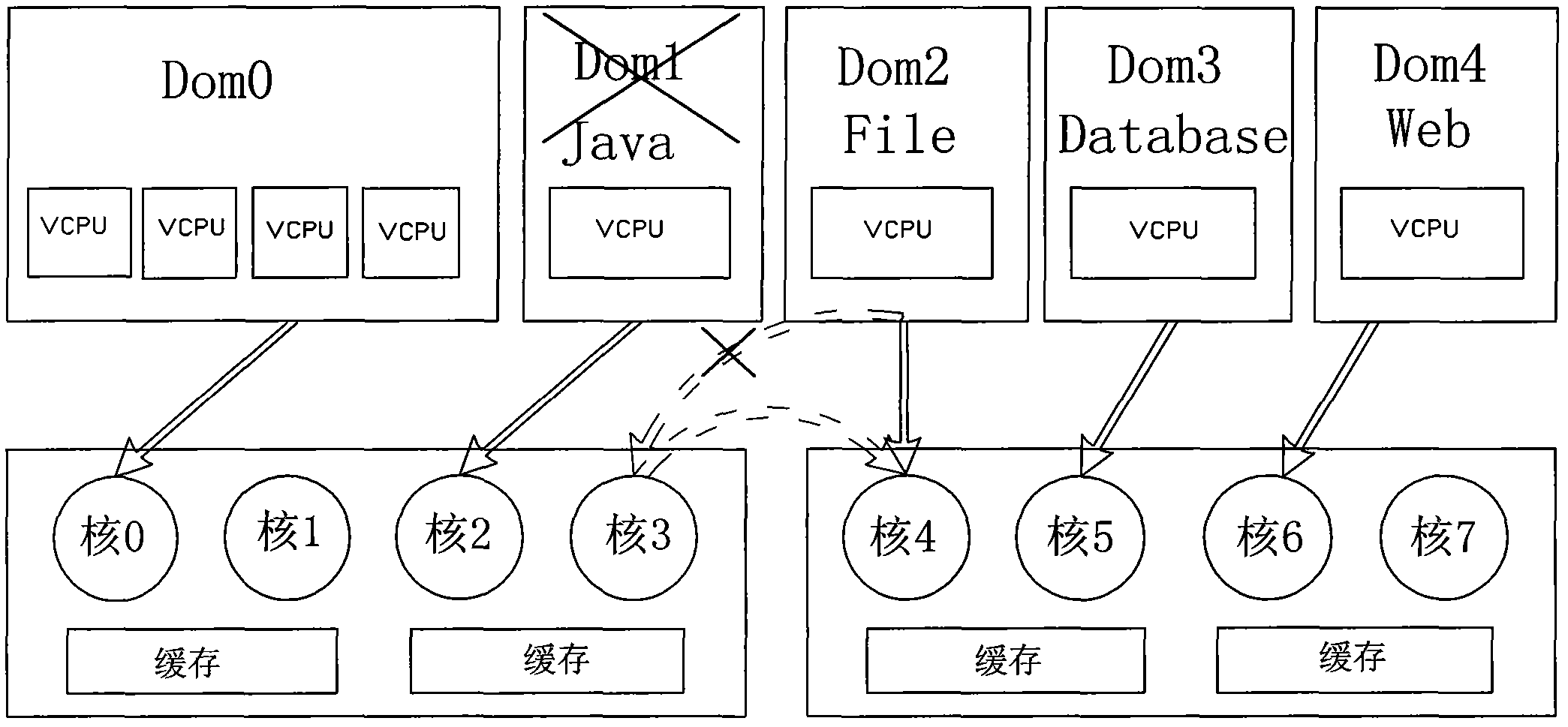

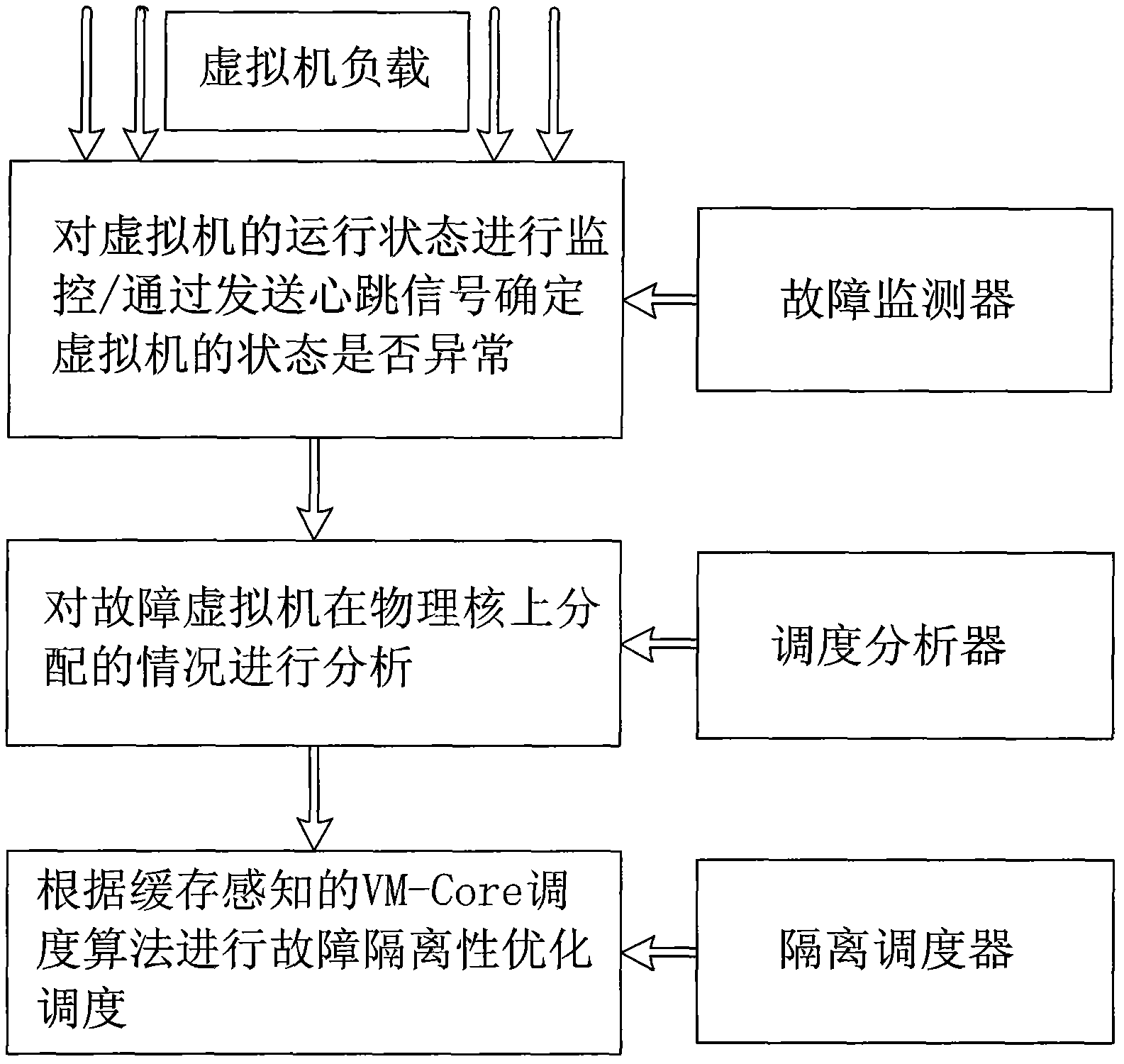

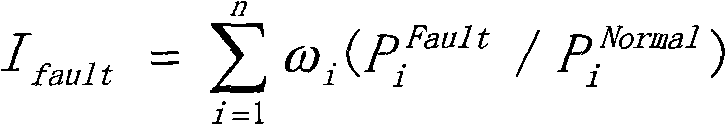

Method for ensuring fault isolation of virtual machines of cache-aware multi-core processor

ActiveCN102053873AAvoid pollutionGood technical effectError detection/correctionComputer architectureMulti processor

The invention relates to the system-level virtual technology and the virtual machine scheduling technology on a multi-core processor in the field of computer system structures and discloses a method for ensuring fault isolation of virtual machines of a cache-aware multi-core processor. The method comprises the steps of: carrying out state abnormity monitoring and heartbeat information detection on all the running virtual machines by a fault detector; when detecting an abnormal virtual machine, firstly recording the distribution condition of the fault virtual machine on a core of the processorby an isolation scheduler; and when finding that the loads of the other virtual machines share one L2 cache with the fault virtual machine, transferring the fault virtual machine to a core corresponding to an independent cache by the isolation scheduler and carrying out VM-core scheduling on the other normal virtual machines according to cache sensitivity characteristics. The invention discloses a method for the dynamic isolation scheduling of the virtual machines on the multi-core processor, thereby preventing the other normal virtual machines from being polluted by the cache, reducing the running influence of the fault virtual machine on the normal virtual machines and enhancing the whole isolation of the system.

Owner:ZHEJIANG UNIV

Method and device for notifying server failure recovery

InactiveUS6874106B2Access can be uselessDigital computer detailsHardware monitoringNetwork packetClient-side

Owner:FUJITSU LTD