Patents

Literature

130 results about "Interprocessor communication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Interprocessor communication is associated with a mechanism for sending messages among z/Architecture® configurations in a loosely coupled complex, where the content of the message does not necessarily imply that a lock is called. There is also communication between programs running in different systems...

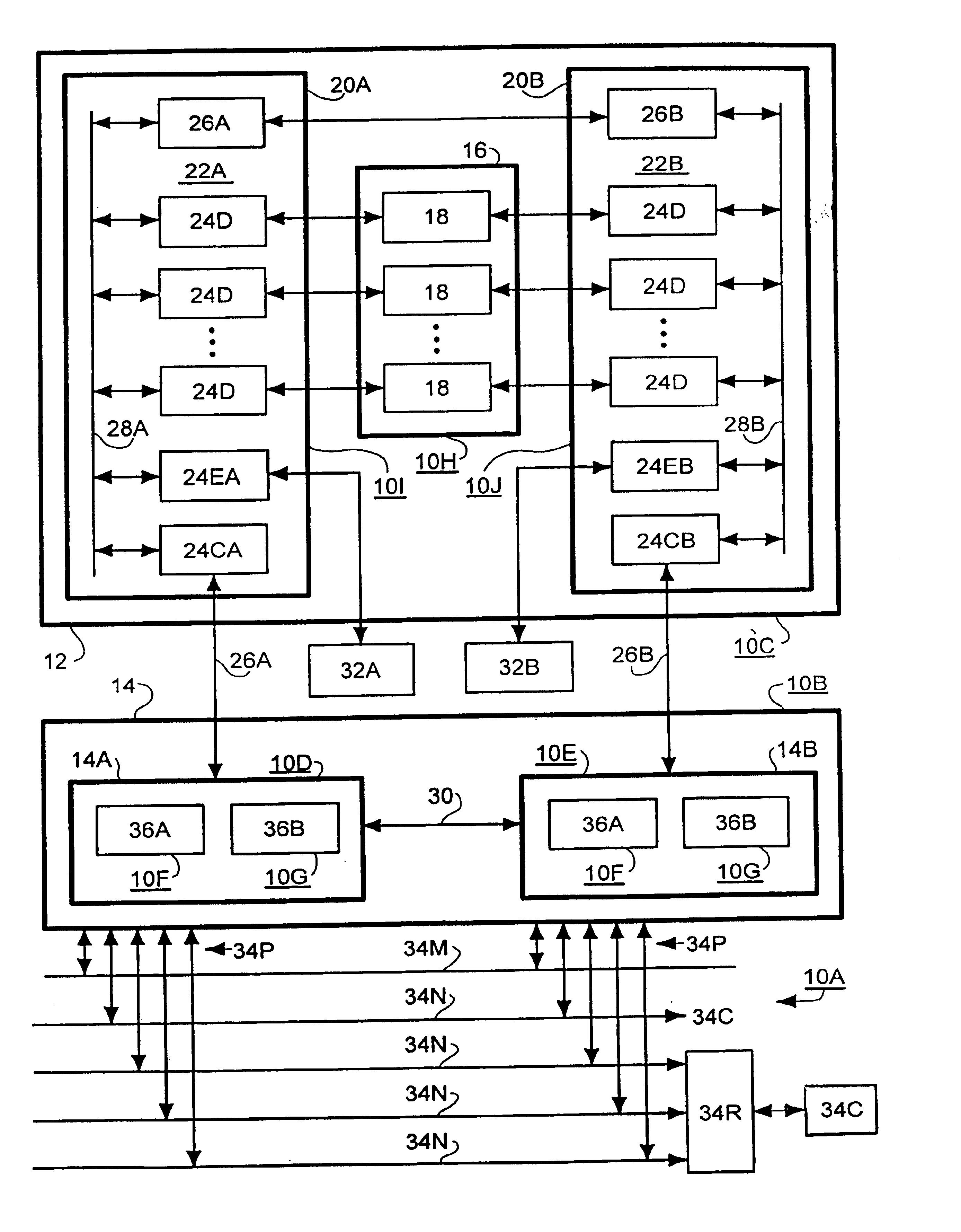

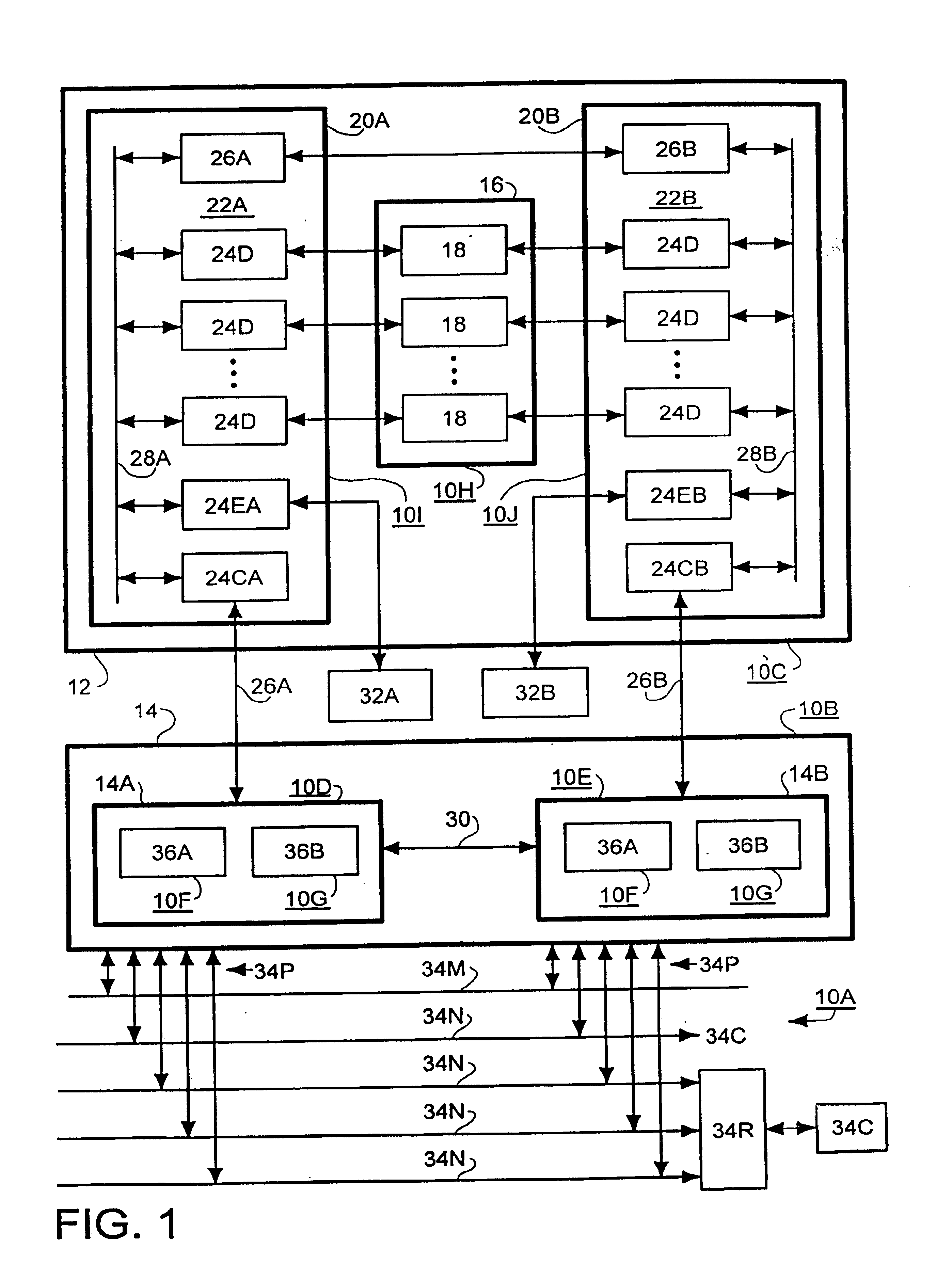

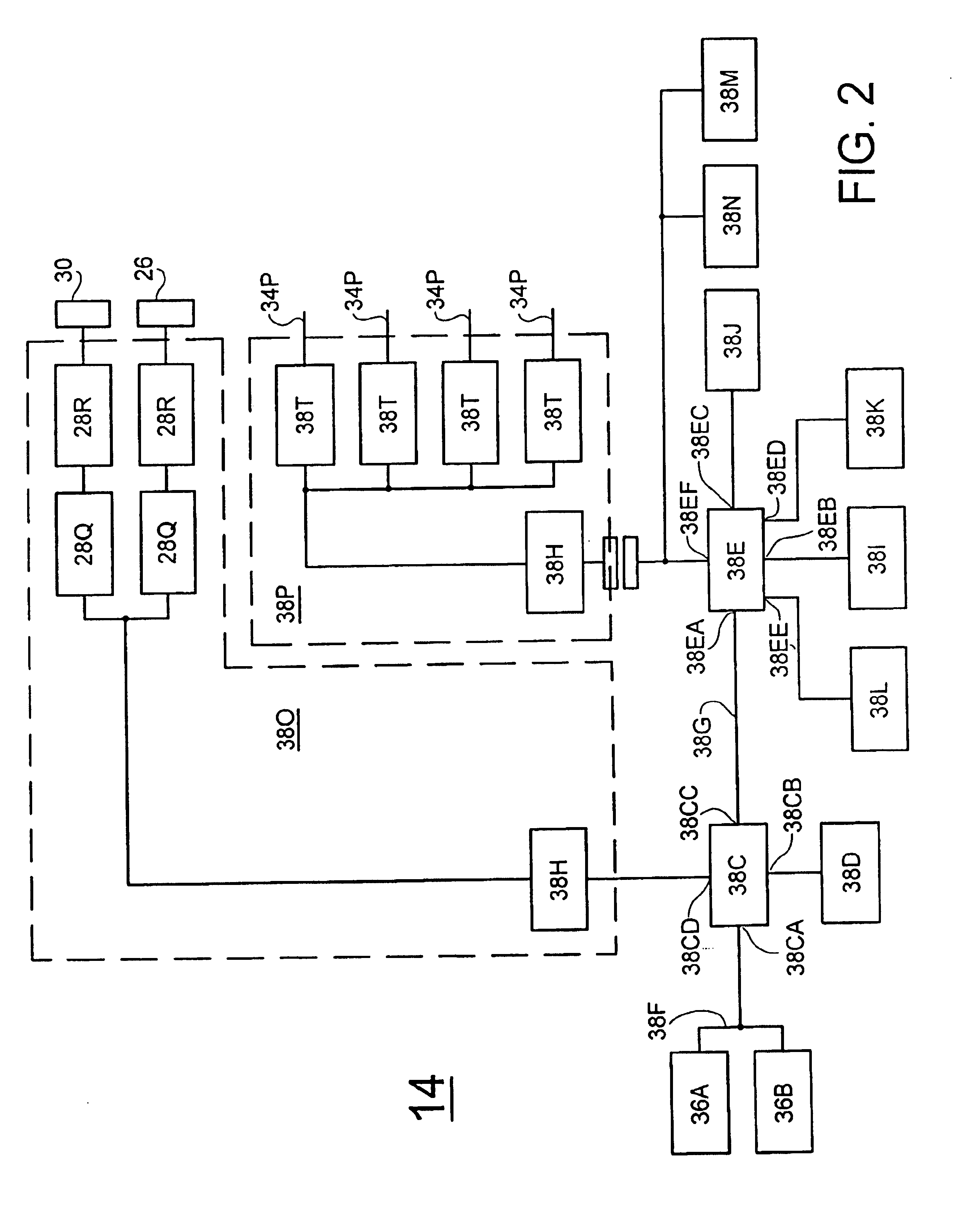

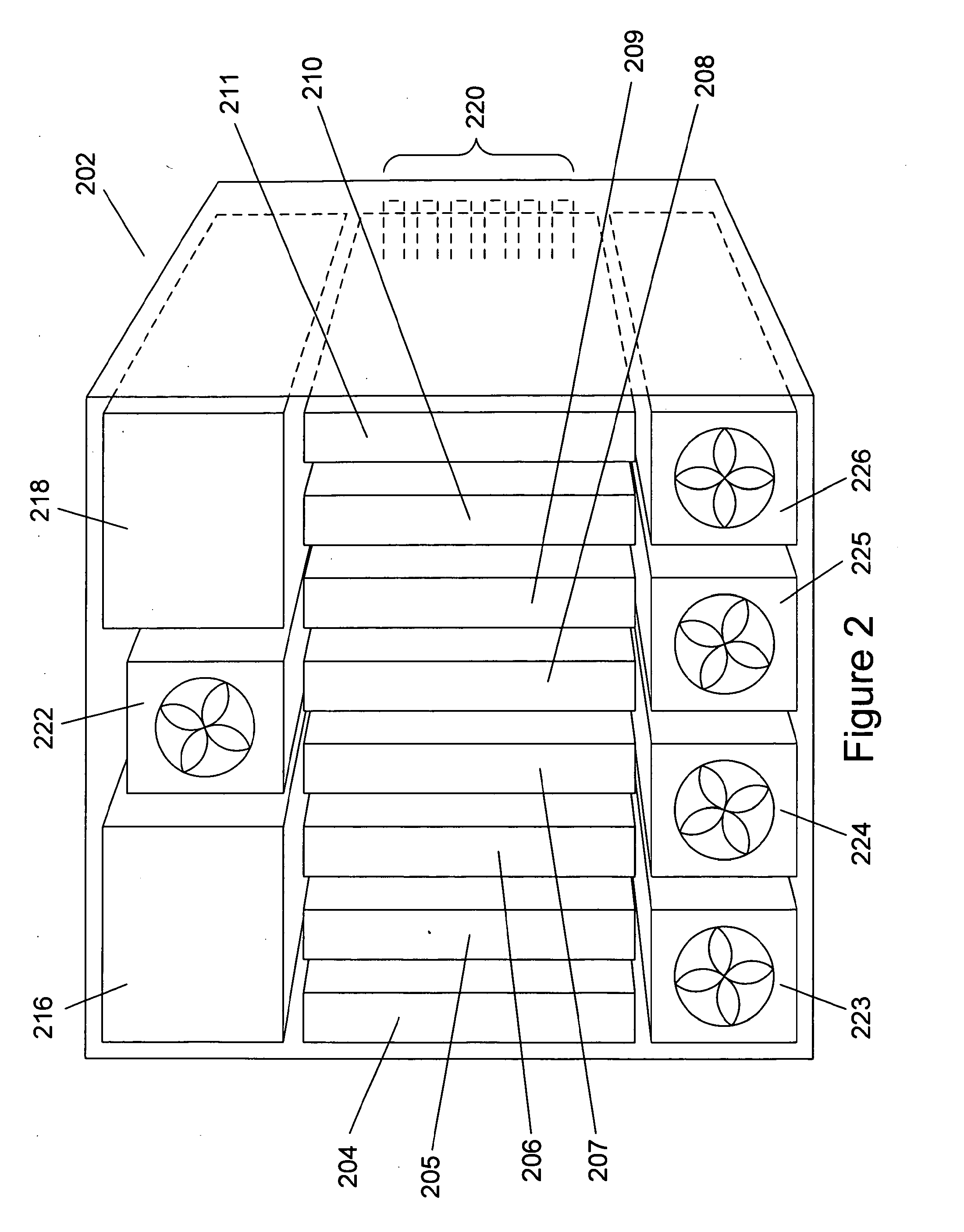

Fault tolerant shared system resource with communications passthrough providing high availability communications

InactiveUS6865157B1Improve usabilityError preventionTransmission systemsRouting tableHigh availability

A communications passthrough mechanism for high availability network communications between a shared system resource and clients of the system resource. The system resource includes a control / processing sub-system including multiple peer blade processors. A port of each blade processor is connected to each client / server network path and each client is connected to a corresponding port of each blade processor. Each blade processor includes a network fault detector exchanging beacon transmissions with other blade processors through corresponding blade processor ports and network paths. Each blade processor includes response generator responsive to a failure to receive a beacon transmission from a failed port of an other blade processor for redirecting the client communications to the failed port on the other blade processor to the corresponding port of the blade processor. A path manager in the blade processor is responsive to operation of the response generator for modifying the communications routing table to correspond with the redirection message to route the client communications to the failed port of the other blade processor to the other blade processor through the inter-processor communications link. Each blade processor may also include an inter-blade communications monitor for detecting a failure in the inter-processor communications link between the blade processor and another blade processor, reading the communications routing table to select a functional network communications path to a port of the other blade processor, and modifying the communications routing table to redirect inter-processor communications to the selected functional network communications path.

Owner:EMC CORP

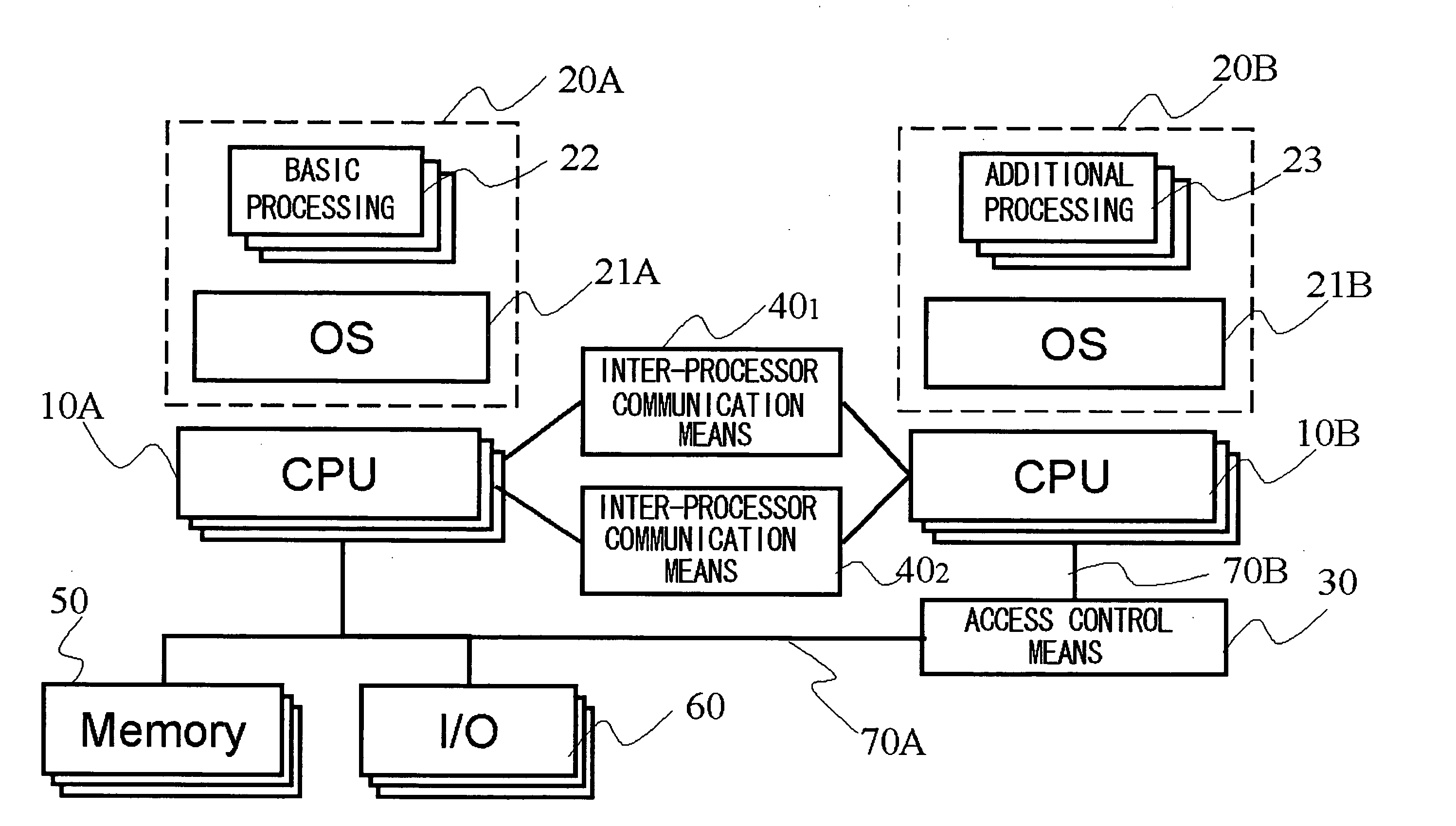

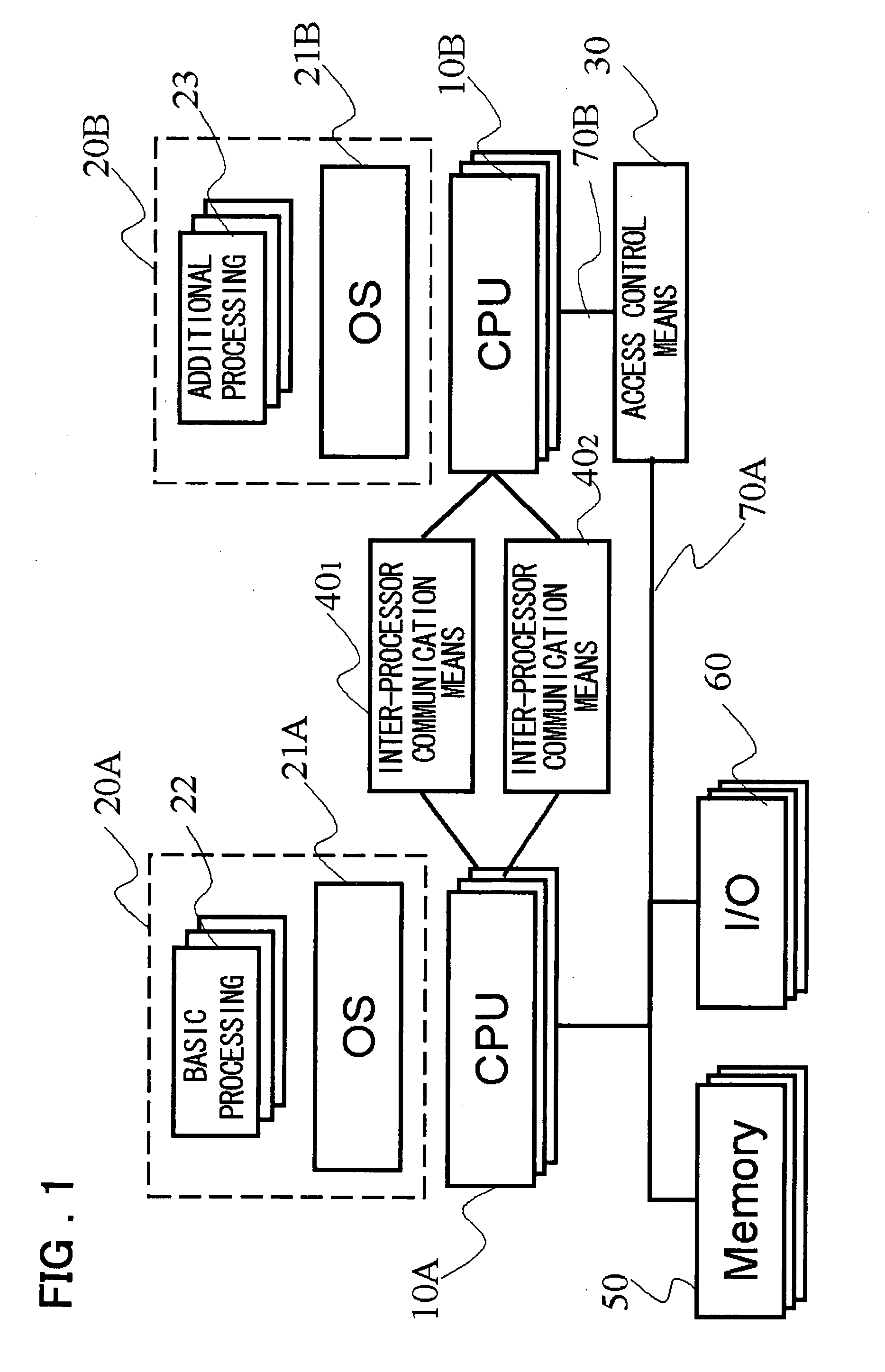

Information Communication Device and Program Execution Environment Control Method

ActiveUS20080005794A1Ensure safetyHigh speed machiningResource allocationMemory loss protectionInterprocessor communicationCommunication device

A device and a method are provided for increasing processing speed and for ensuring system security when an application or a driver is added. The device includes a first CPU group 10A that executes software 20A composed of basic processing 22 and an OS 21A; a second CPU group 10B that executes software 20B composed of additional processing 23 and OS 21B corresponding to the additional processing, inter-processor communication means 40, and 402 used for communication between the first CPU 10A and the second CPU 10B, and access control means 30 that controls access made by the second CPU 10B to a memory 50 and / or an input / output device 60.

Owner:NEC CORP

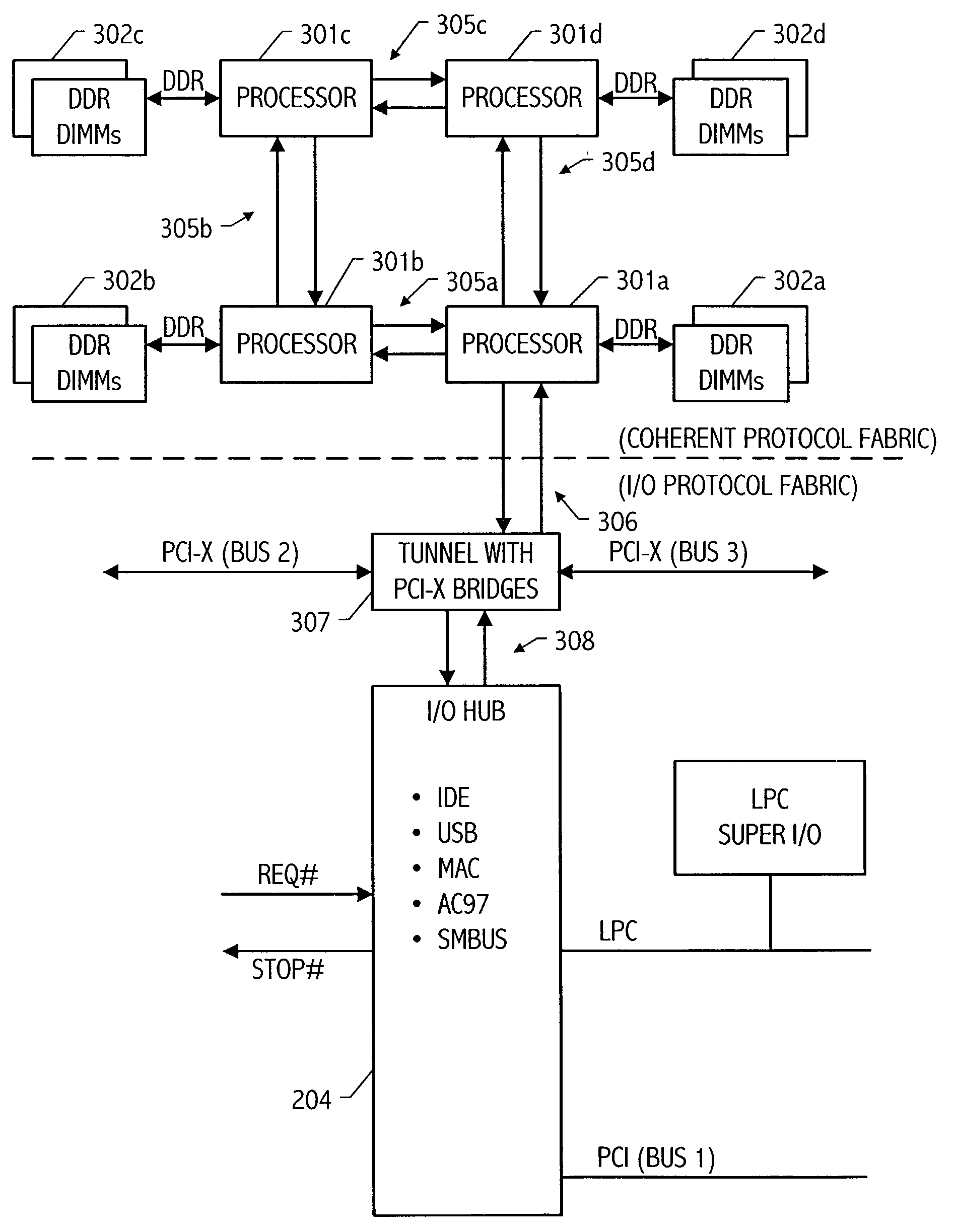

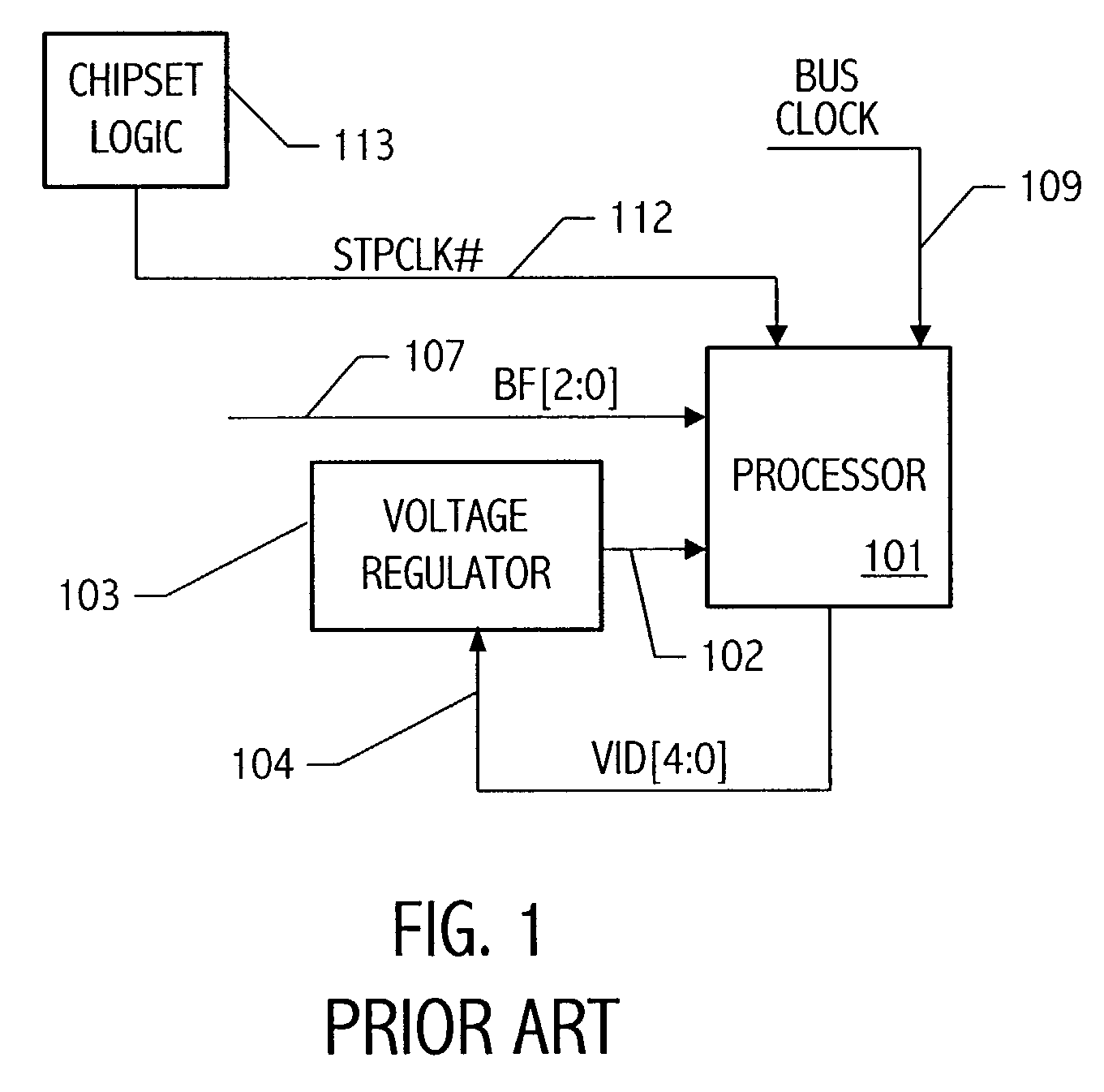

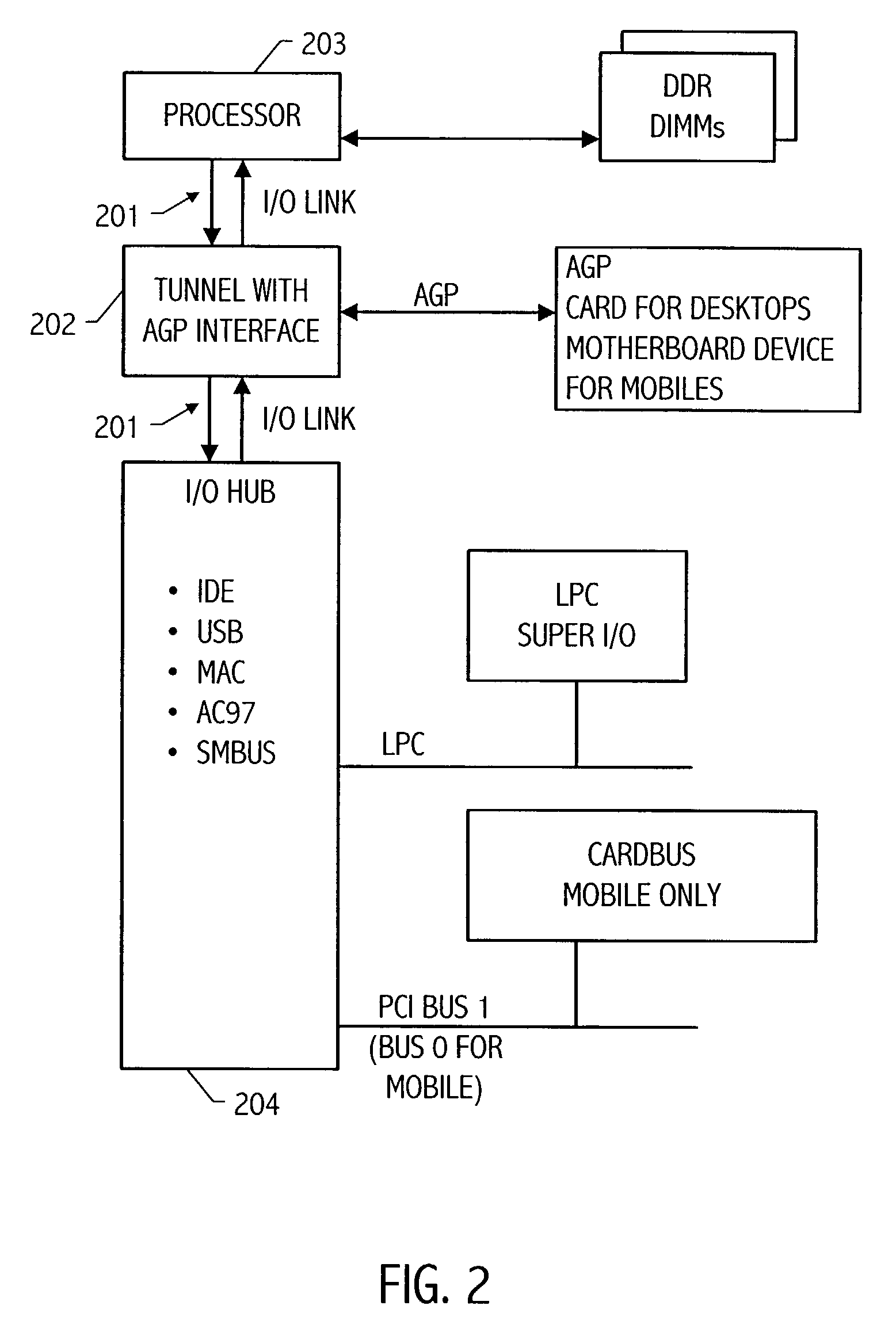

Message based power management in a multi-processor system

ActiveUS7174467B1Energy efficient ICTVolume/mass flow measurementTelecommunications linkMulti processor

A message based power management approach is utilized to provide power management for a multi-processor system. A power management message is received at one processor of the multi-processor system over an input / output communication link that provides input / output access for the processors of the multi-processor system. The power management message includes a power management field encoding a power management state for processors of the multi-processor system. The processor that received the power management message over the input / output communication link sends a power management message to other processors in the multi-processor system over one or more inter-processor communication links encoding the power management state.

Owner:ADVANCED MICRO DEVICES INC

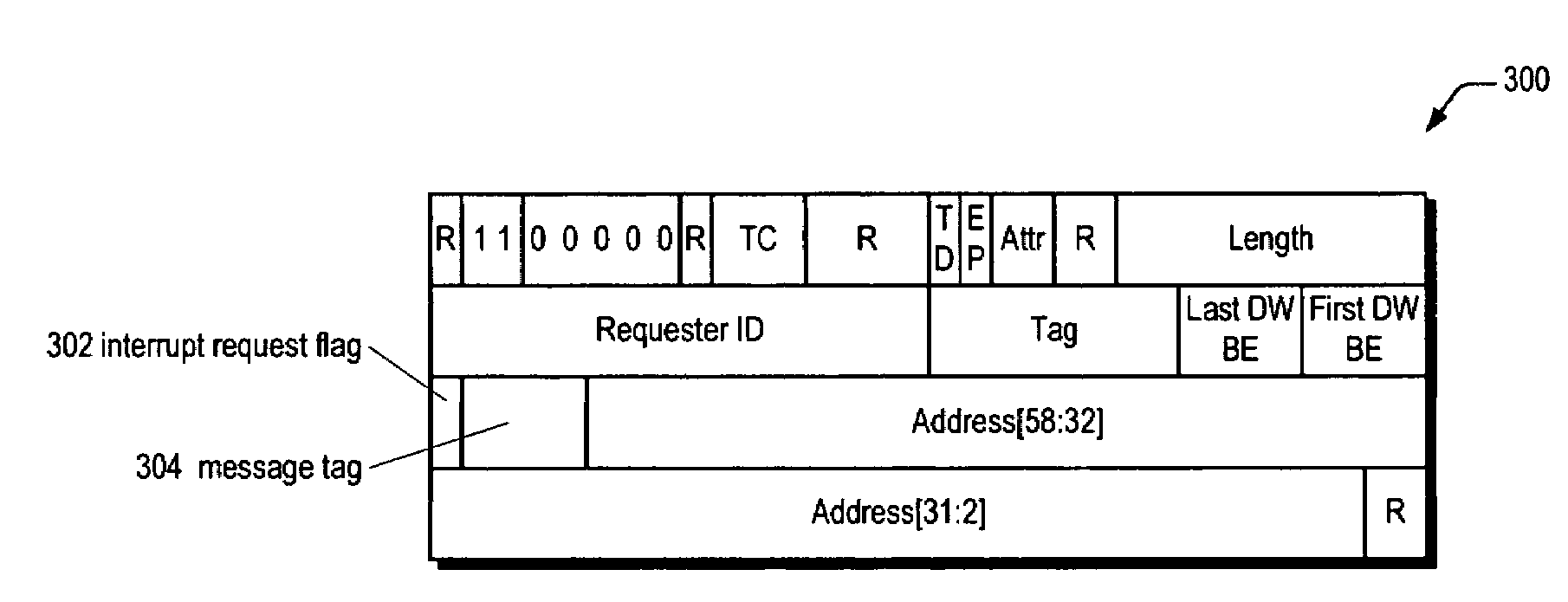

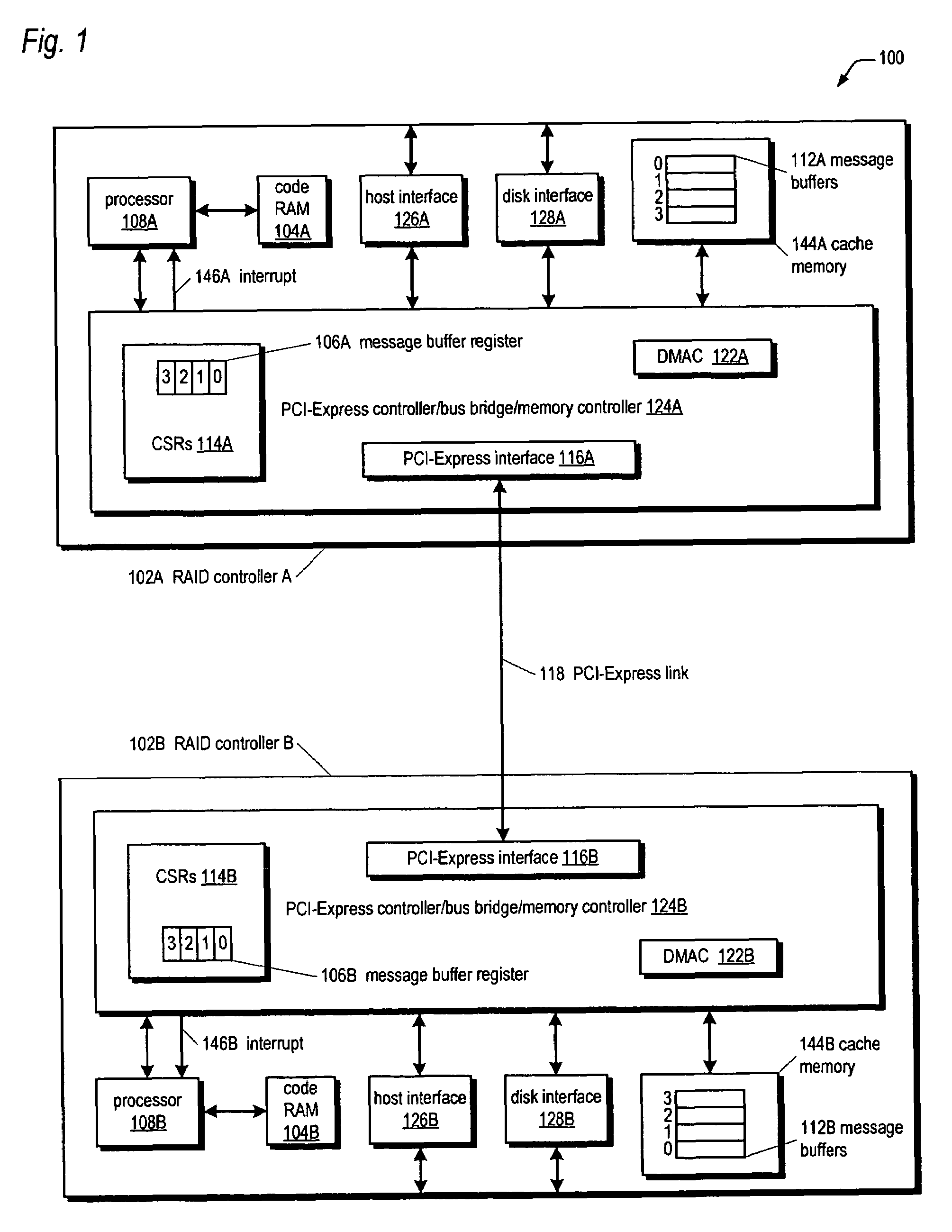

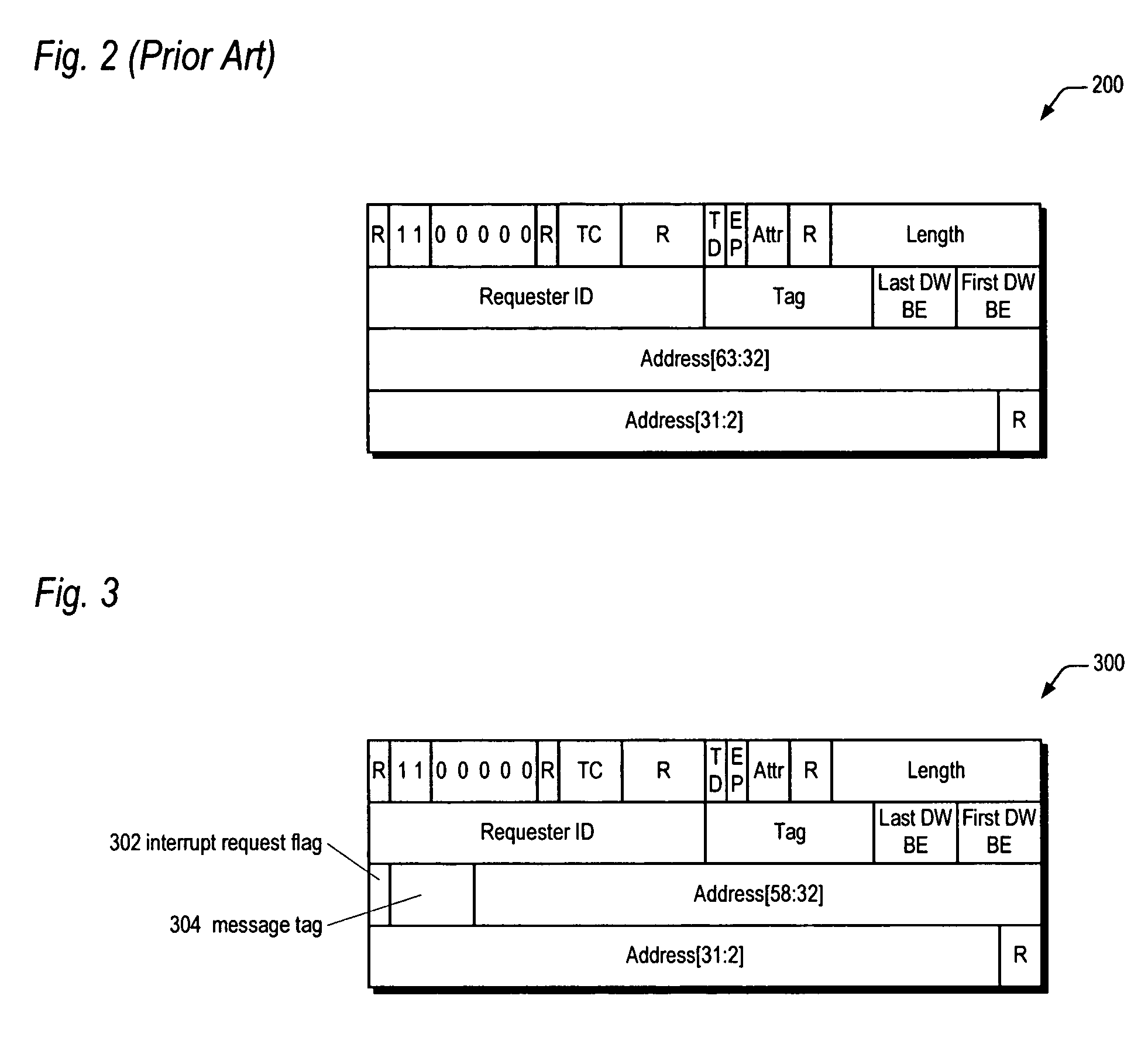

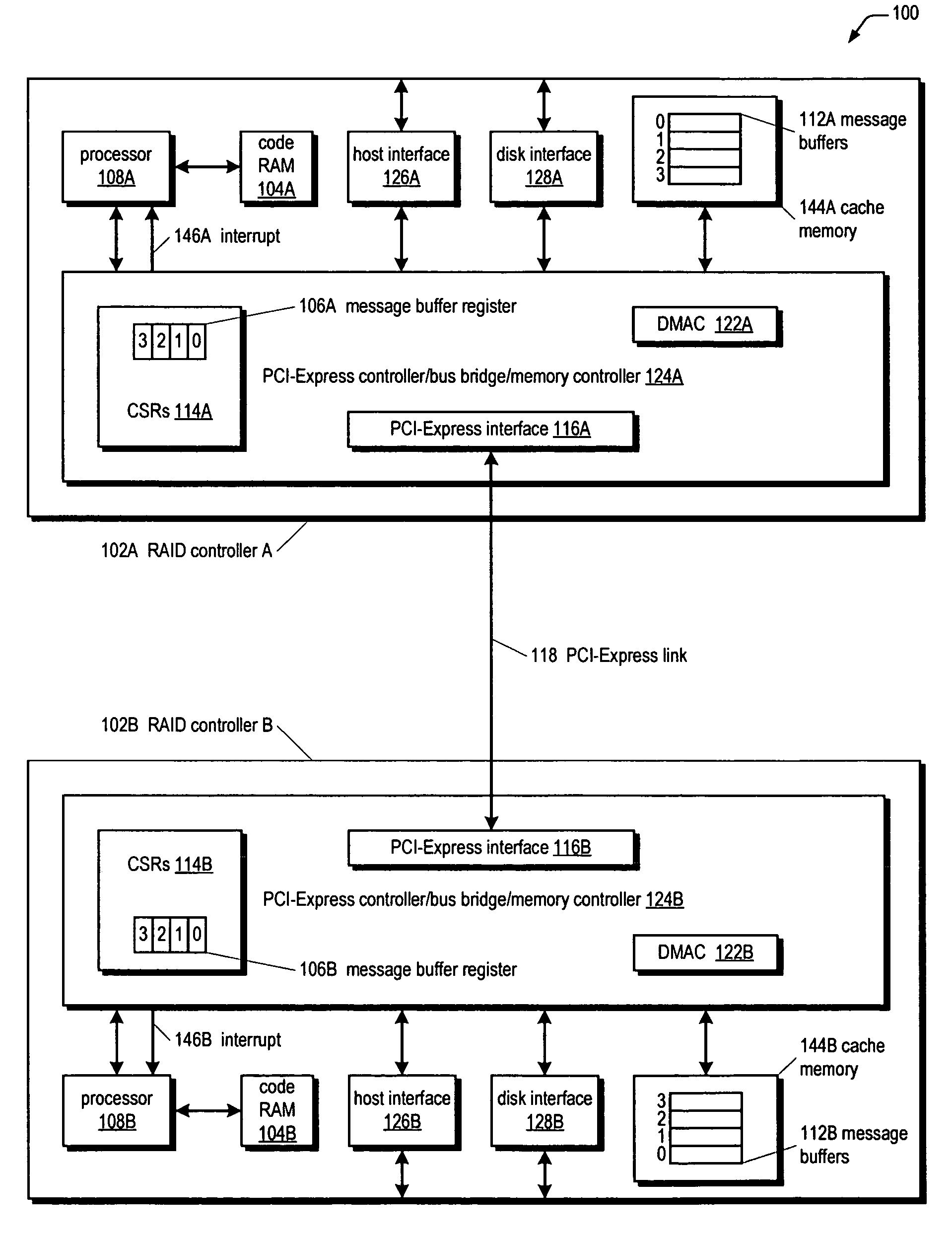

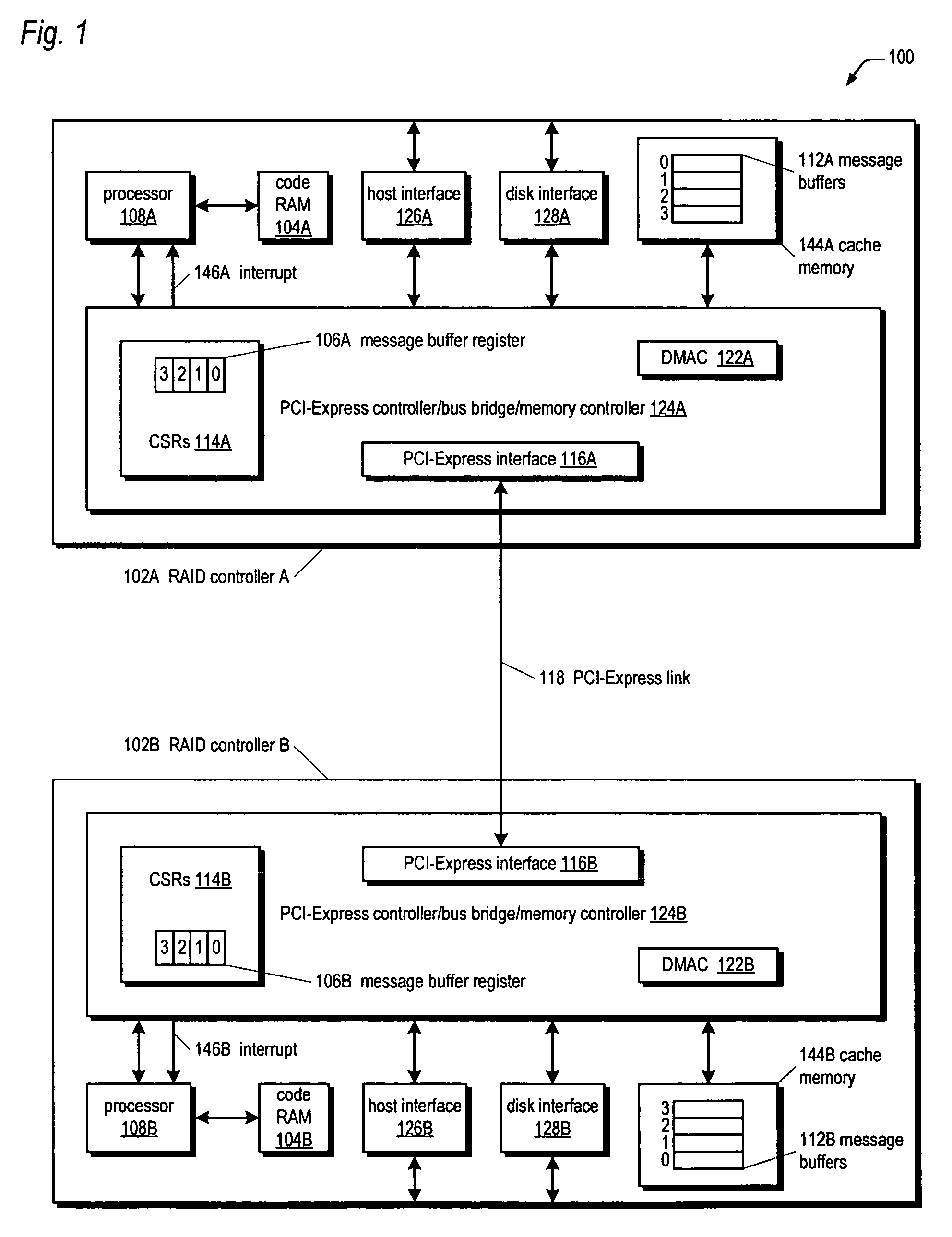

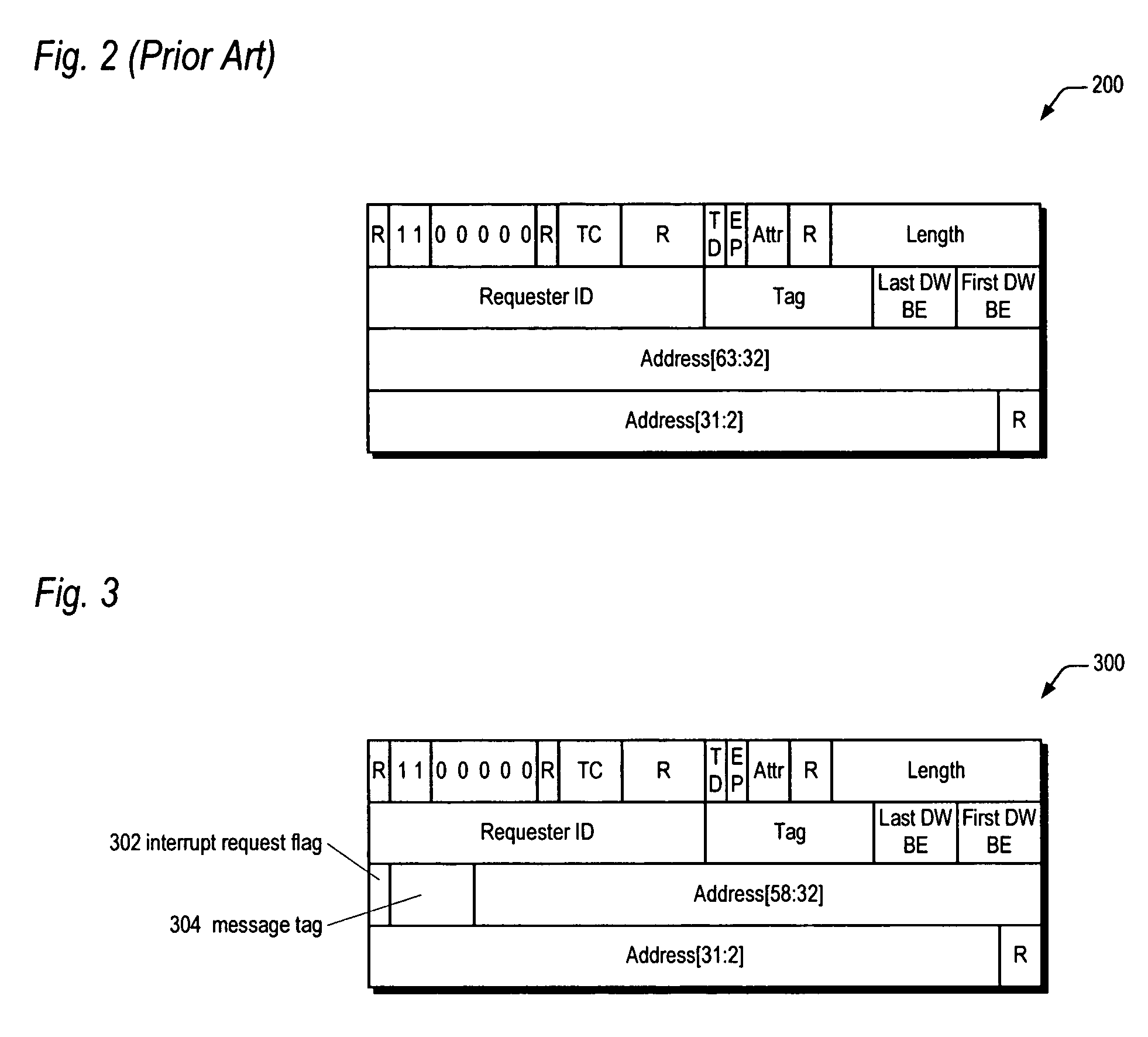

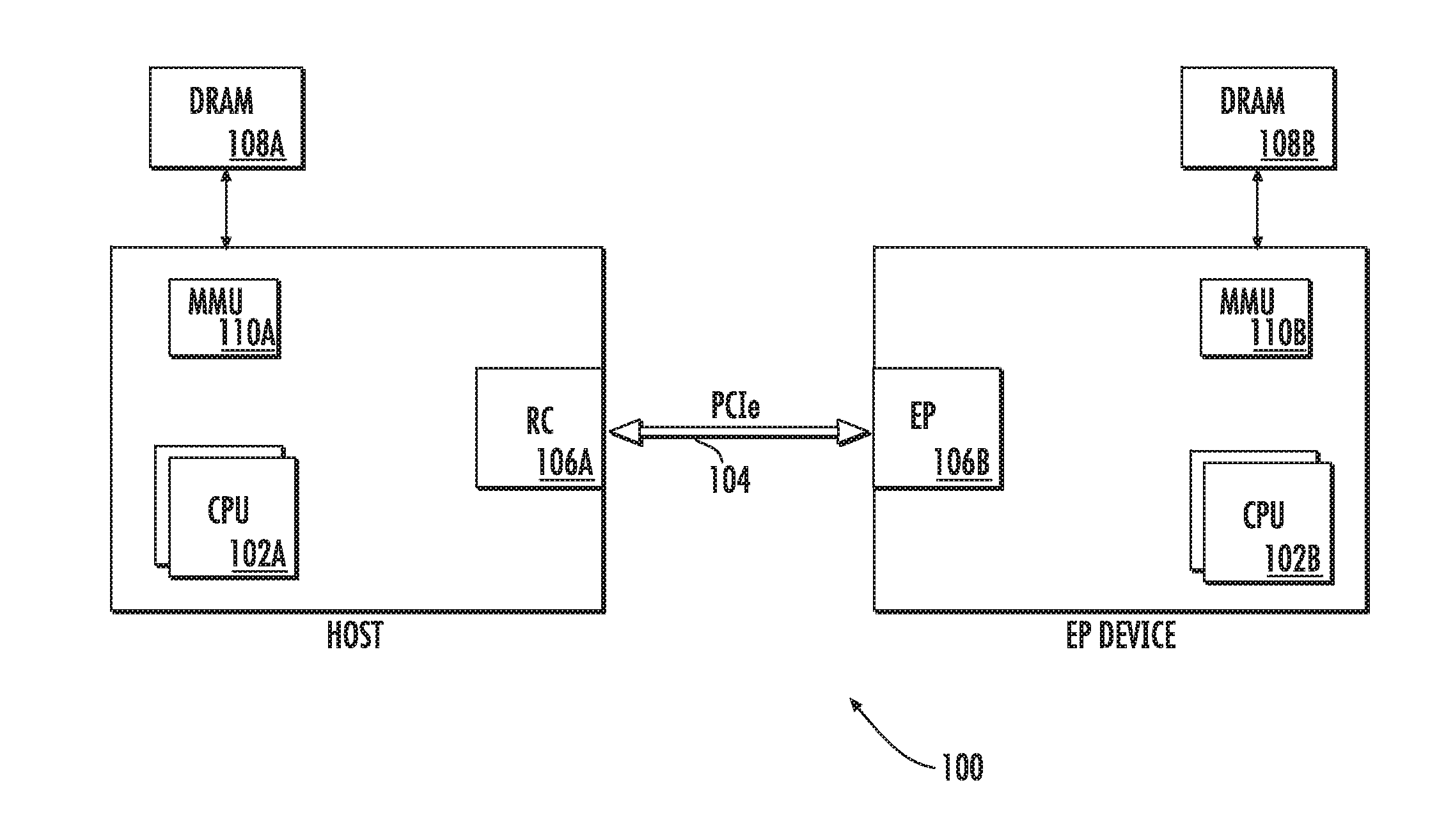

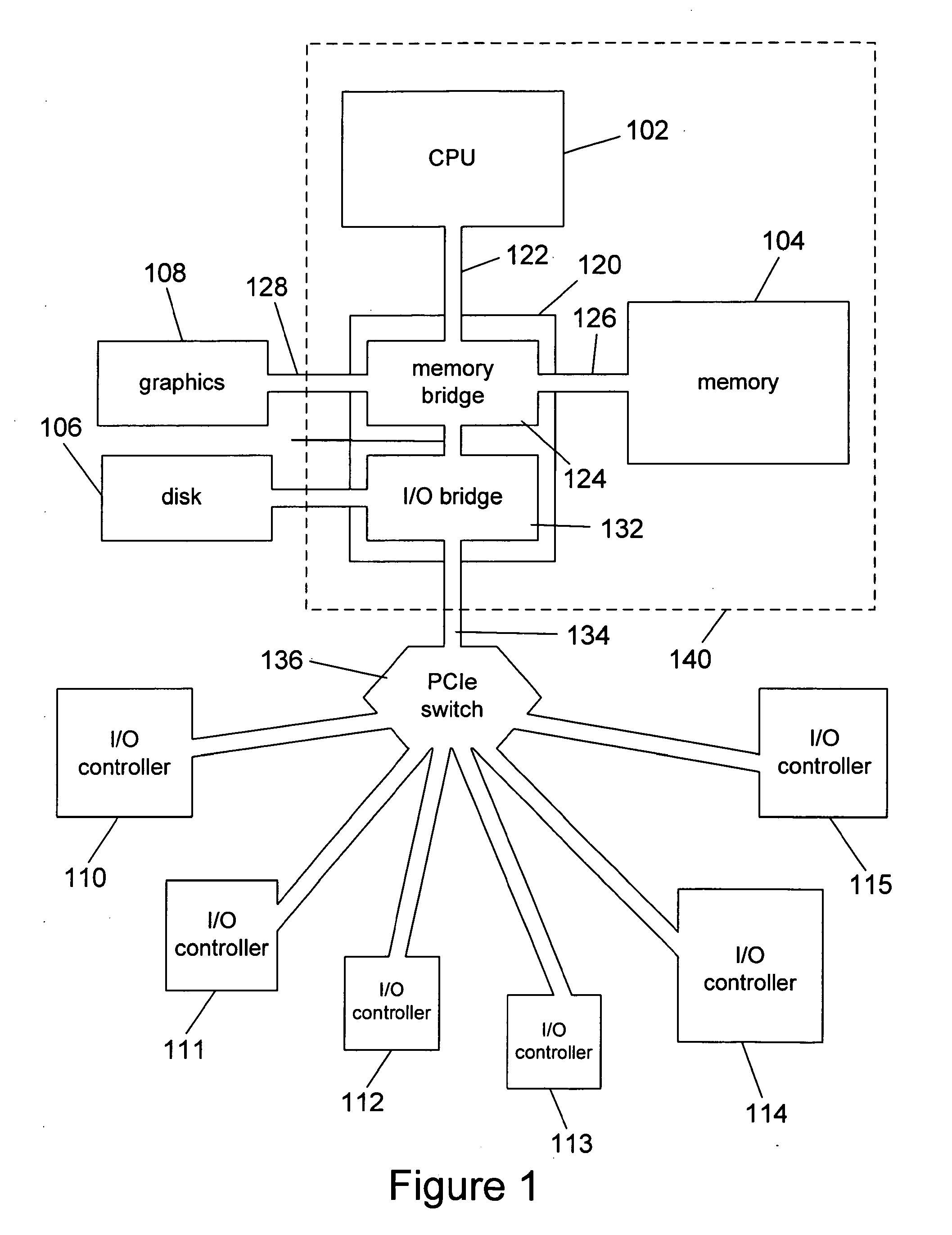

Method for efficient inter-processor communication in an active-active RAID system using PCI-express links

ActiveUS7315911B2Efficiently determinedError detection/correctionMemory systemsRAIDProcessor register

A fault-tolerant RAID system is disclosed. The system includes redundant RAID controllers coupled by a PCI-Express link. When a PCI-Express controller of one of the RAID controllers receives a PCI-Express memory write request transaction layer packet (TLP), it interprets a predetermined bit in the header as an interrupt request flag, rather than as its standard function specified by the PCI-Express specification. If the flag is set, the PCI-Express controller interrupts the processor after storing the message in the payload at the specified memory location. In one embodiment, an unused upper address bit in the header is used as the interrupt request flag. Additionally, unused predetermined bits in the TLP header are used as a message tag to indicate one of a plurality of message buffers on the receiving RAID controller into which the message has been written. The PCI-Express controller sets a corresponding bit in a register to indicate which message buffer was written.

Owner:DOT HILL SYST

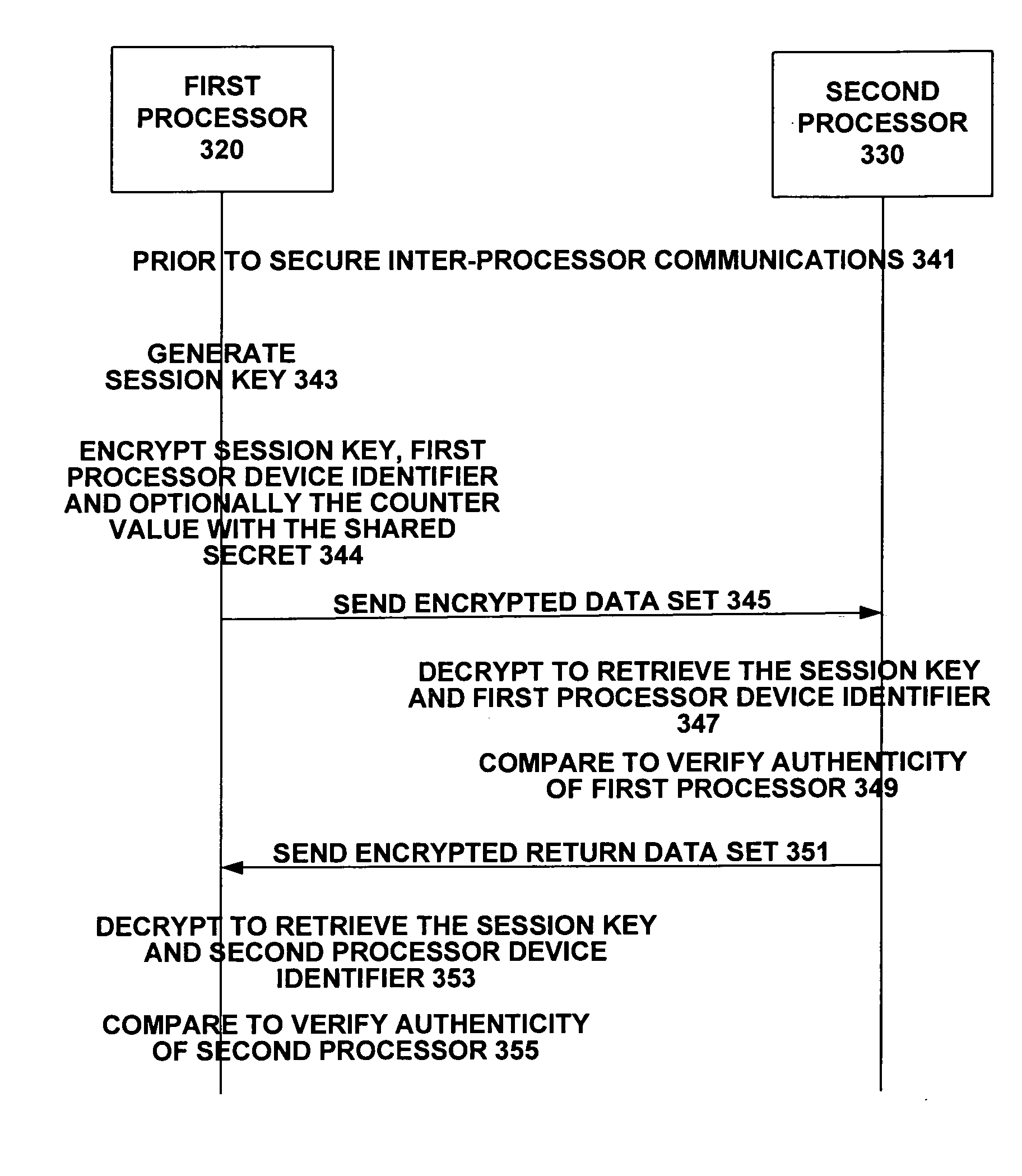

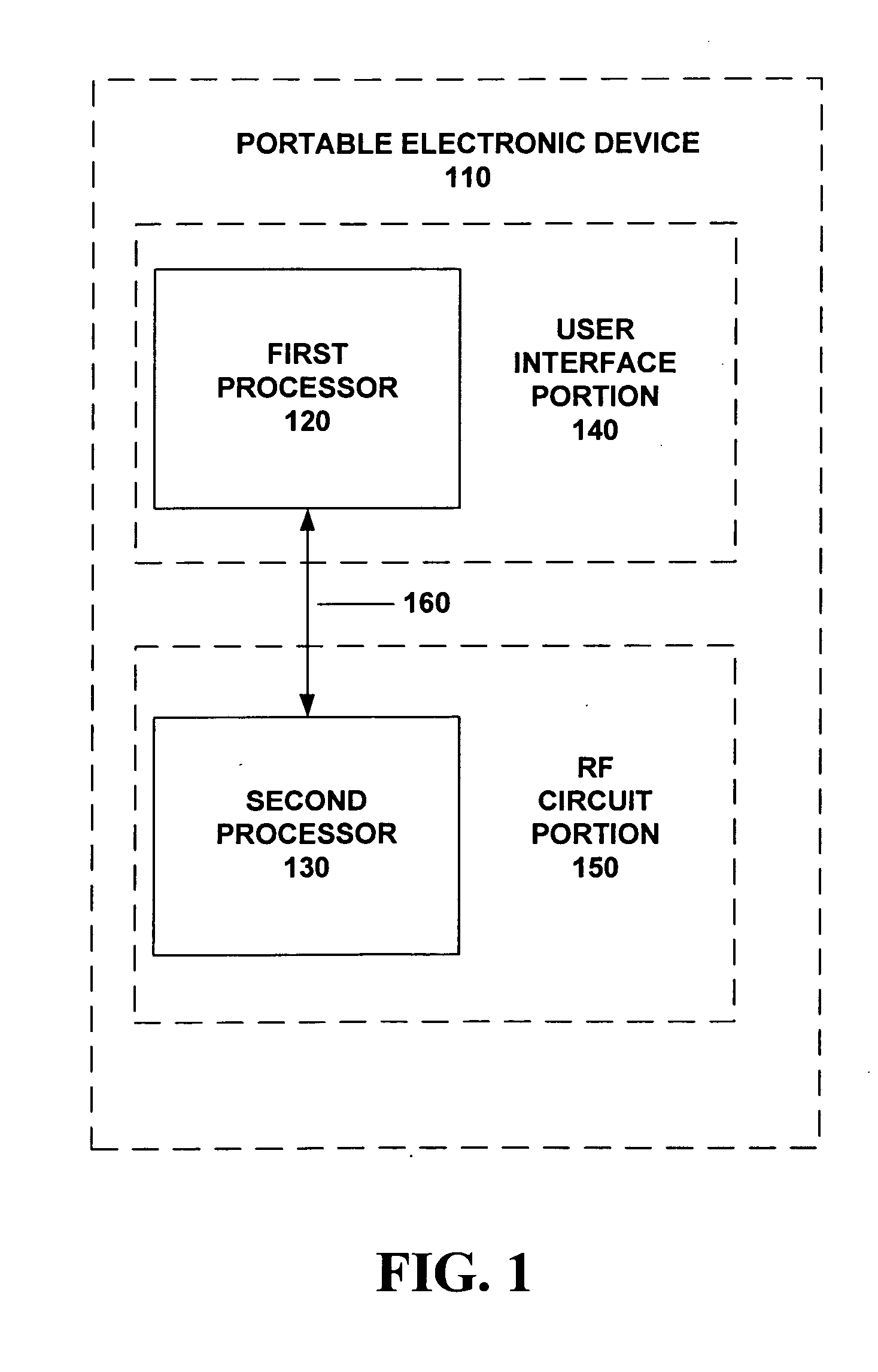

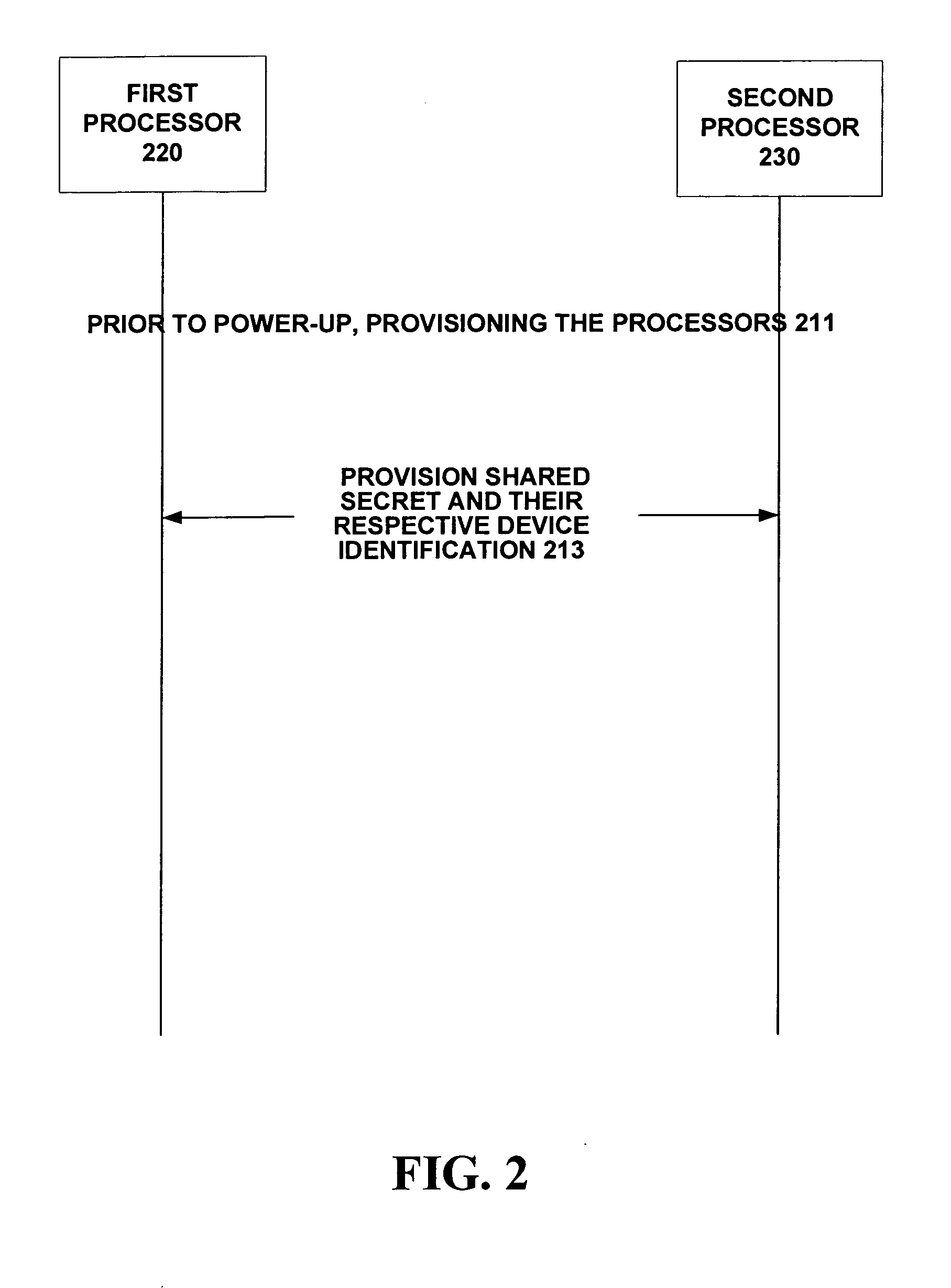

Method and apparatus for secure inter-processor communications

InactiveUS20060288209A1Considerable overheadMinimize overheadUser identity/authority verificationComputer hardwareInterprocessor communication

A portable electronic device (110) is capable of secure inter-processor communications (160) between processors (120, 130). The processors have unique and unalterable device identifiers used to encrypt session key data using shared secrets. A first processor device identifier is encrypted by a first processor (120) and decrypted by a second processor (130) and compared against a known device identifier to verify authenticity. Then the second processor (130) likewise encrypts and the first processor (120) likewise decrypts and likewise compares device identity to verify authenticity.

Owner:MOTOROLA INC

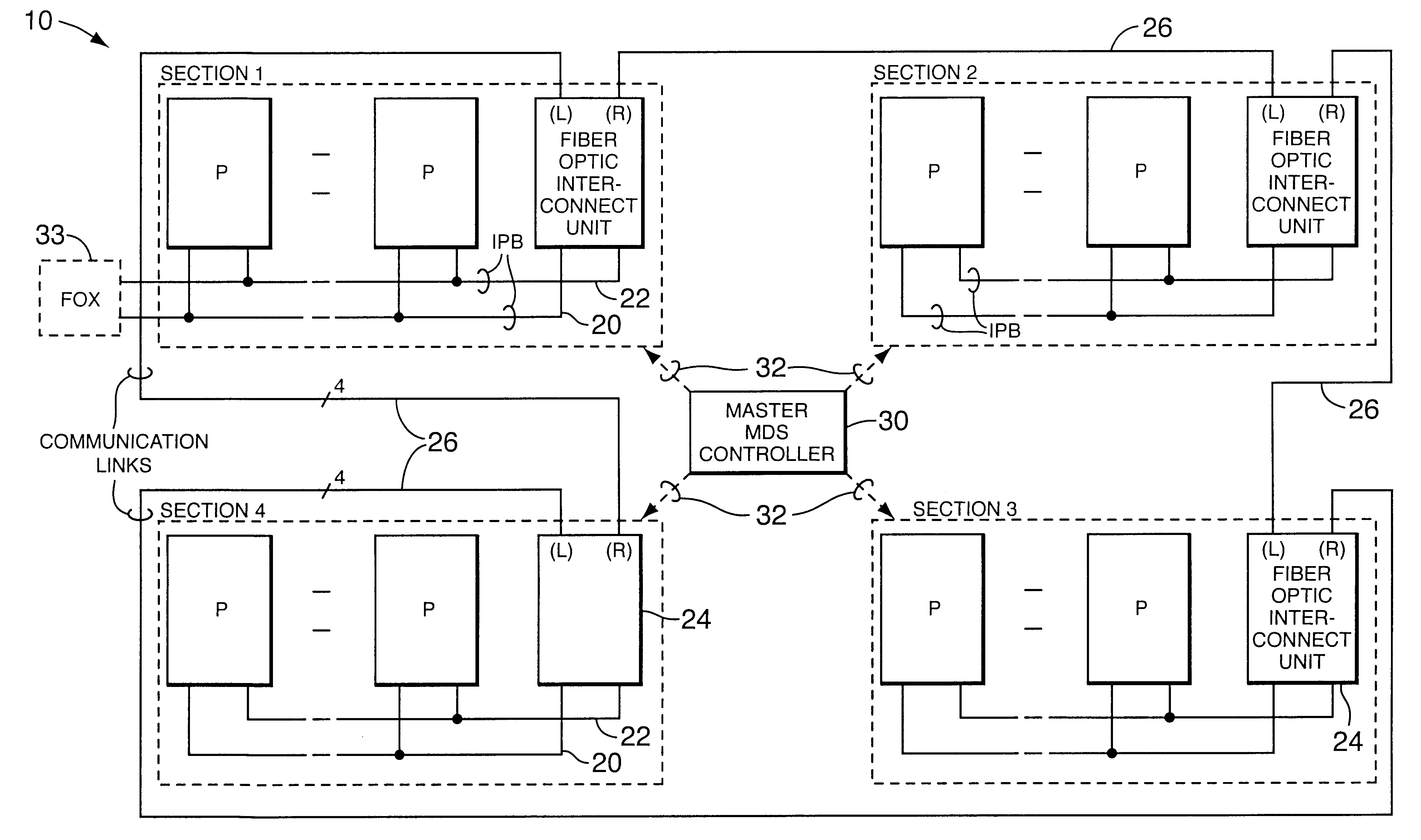

Multiprocessor system with fiber optic bus interconnect for interprocessor communications

InactiveUS6453406B1Avoid less flexibilityGeneral purpose stored program computerData switching networksData processing systemFiber

In a data processing system of the type having multiple processor units coupled to one another by a bus means for interprocessor communications there is provided a fiber optic interconnection system to interconnect the bus means of multiple processor sections to one another, thereby allowing groups of the processor units to be physically spaced from one another. The fiber optic interconnect system includes, for each multiprocessor unit section functions to receive messages communicated on the interprocessor bus of that section for receipt by a destination processor of the other section, format the message for fiber optic transmission, and transmit the message; and circuitry for receiving messages on the fiber optic link, scheduling the message for transmission to the destination processor, and maintaining that scheduling in the face of receipt of another message for the same processor unit. The fiber optic interconnect system includes means for configuring the system to identify which processor units are in which section and, when more than two sections are interconnected by the fiber optic link, provide information as to the shortest route to the destination processor from a section.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

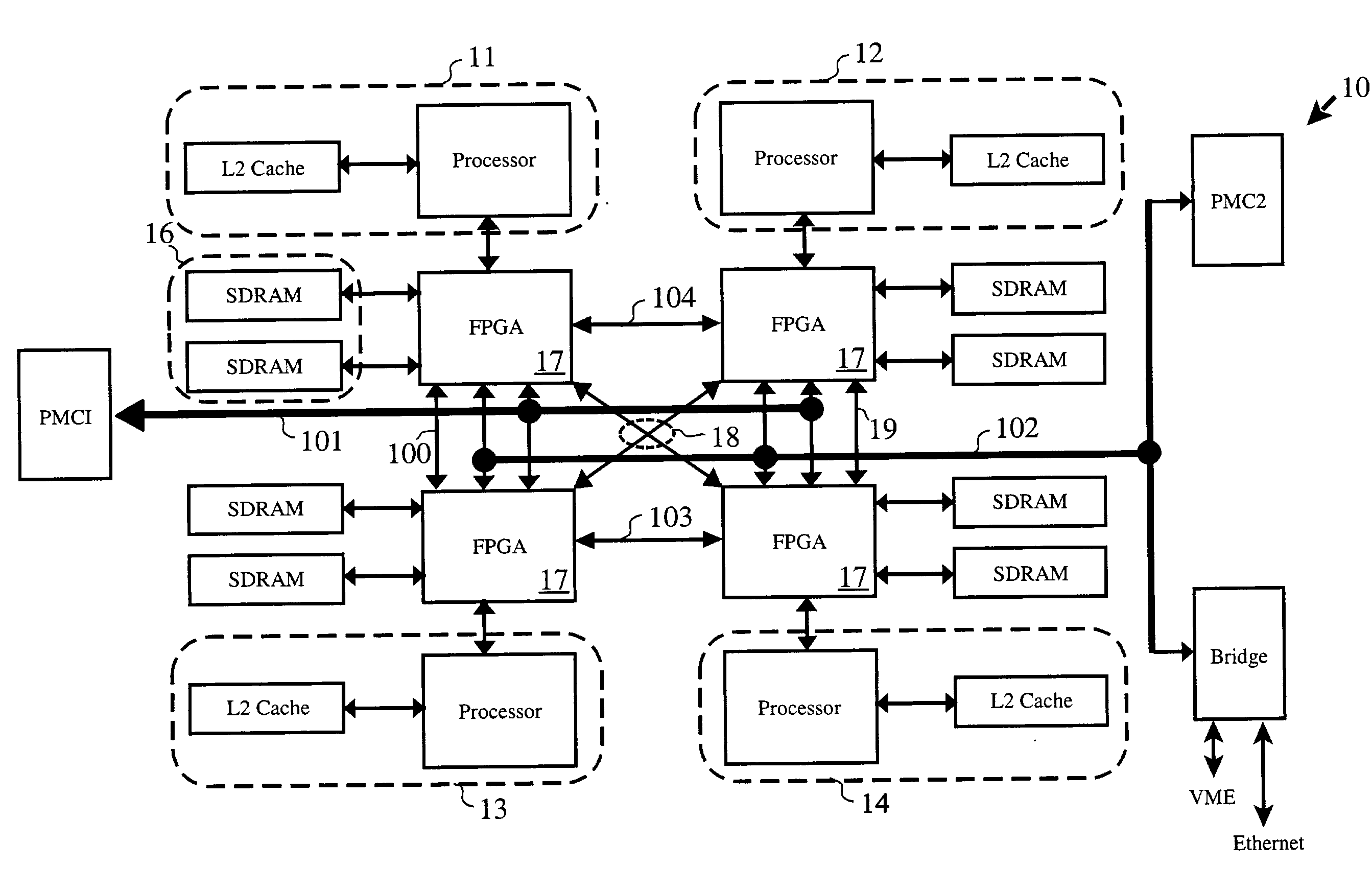

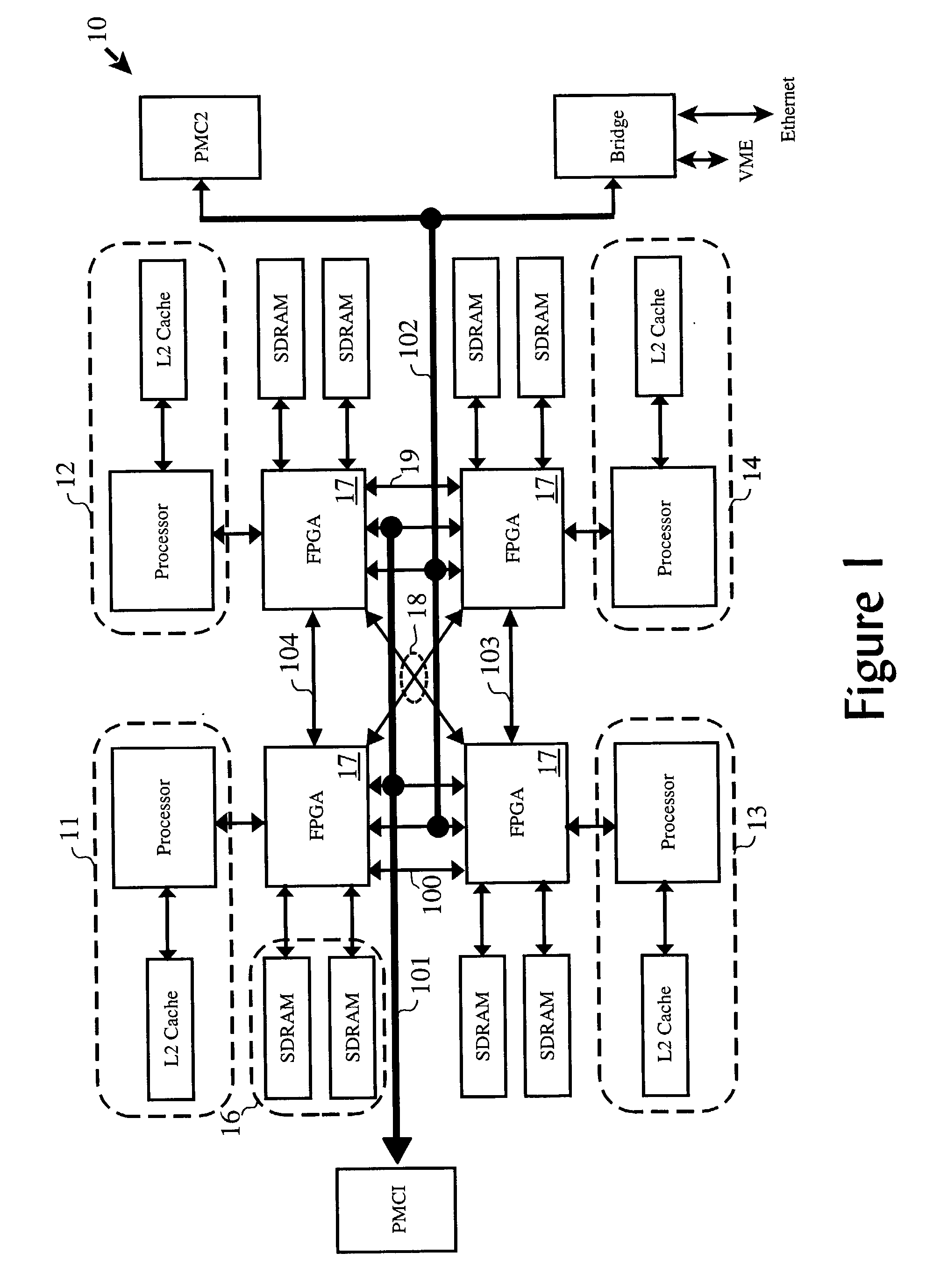

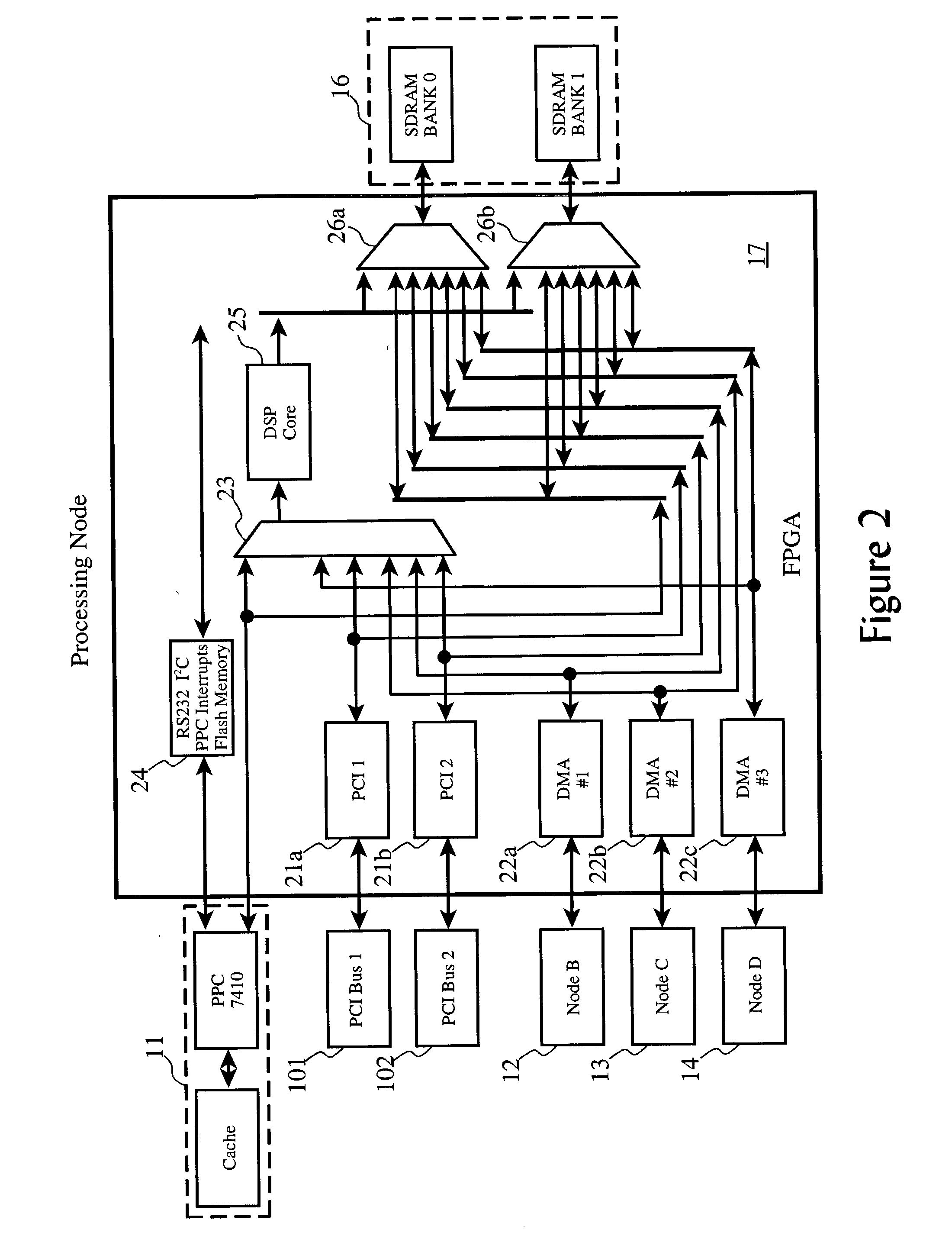

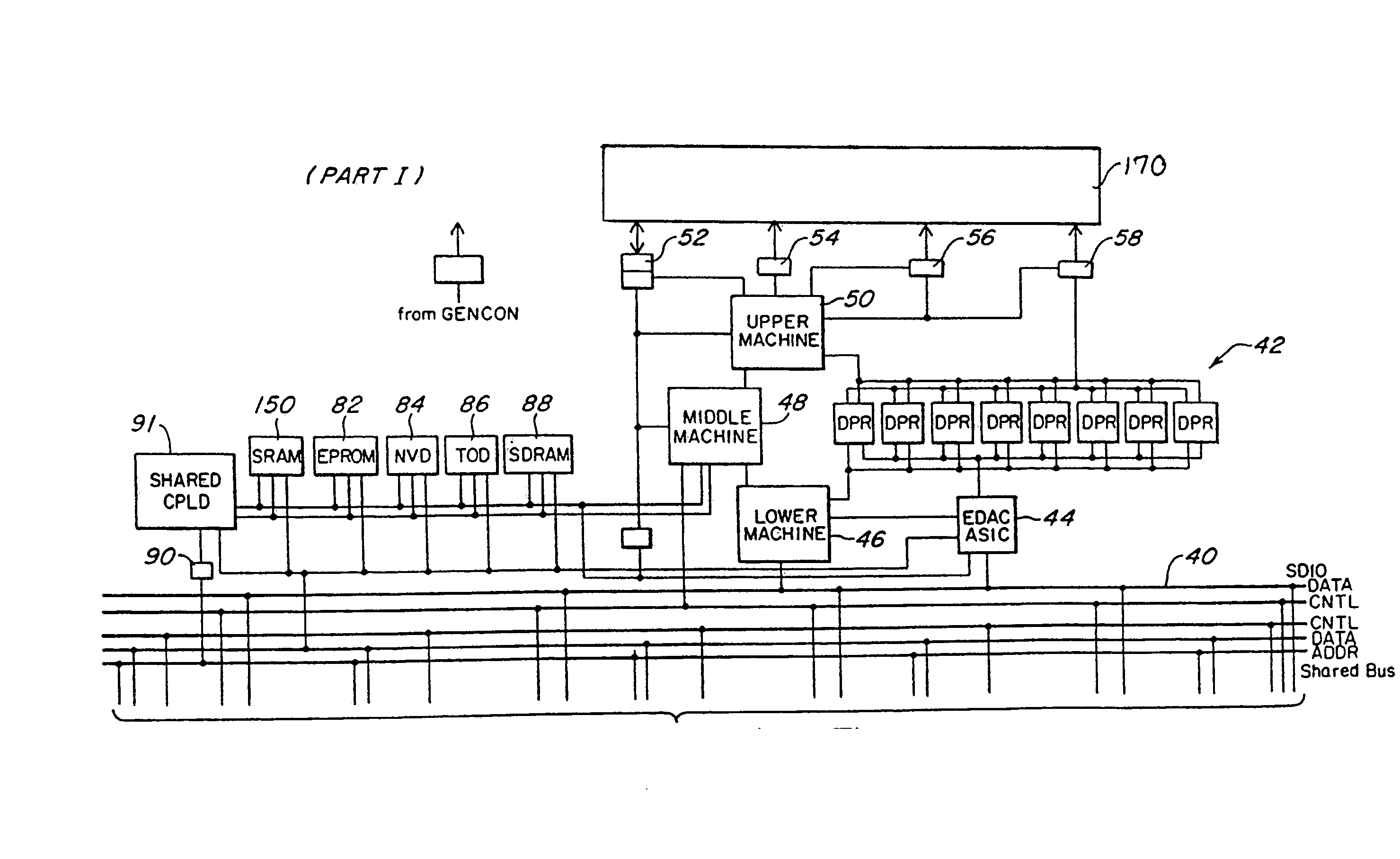

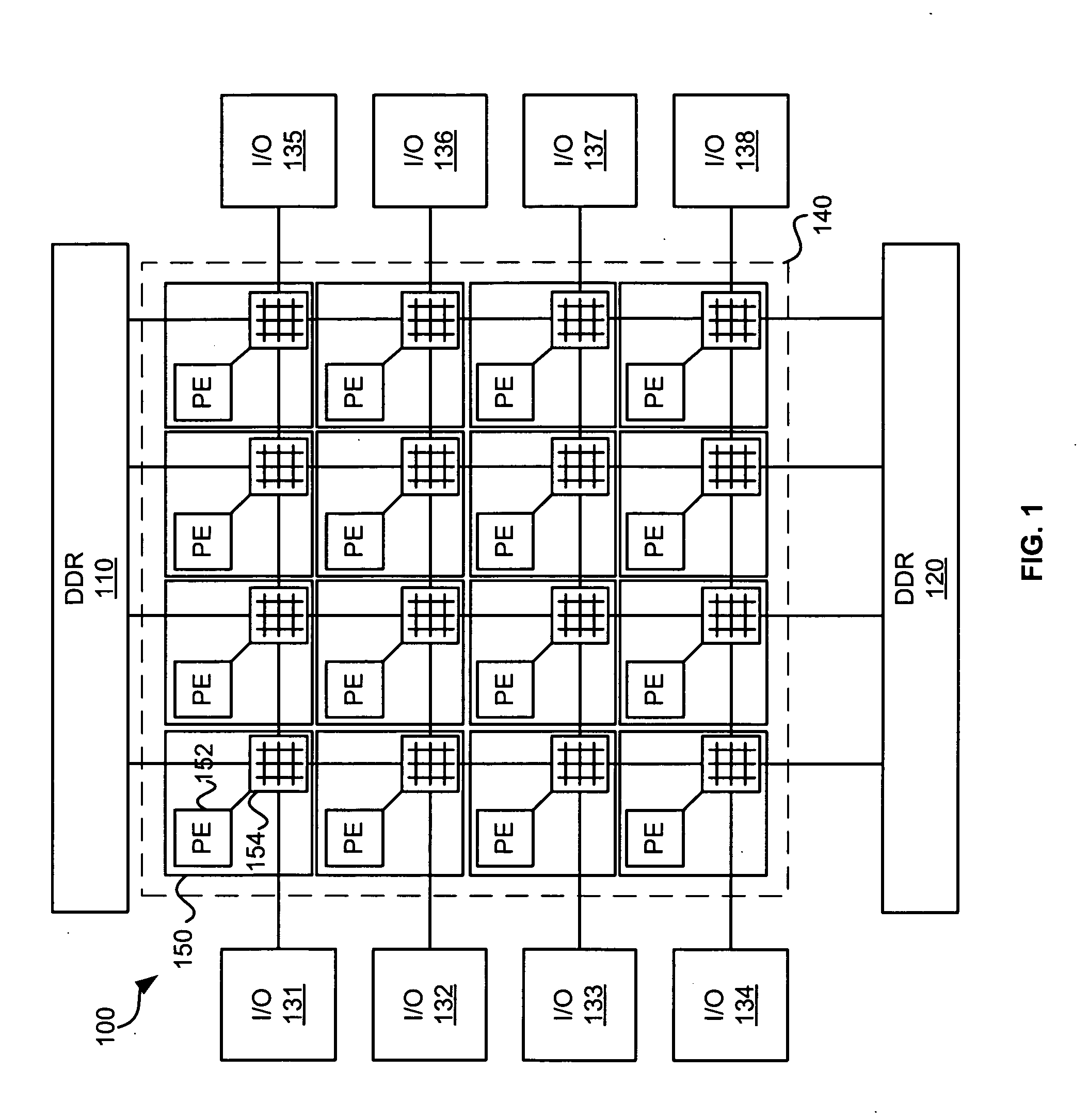

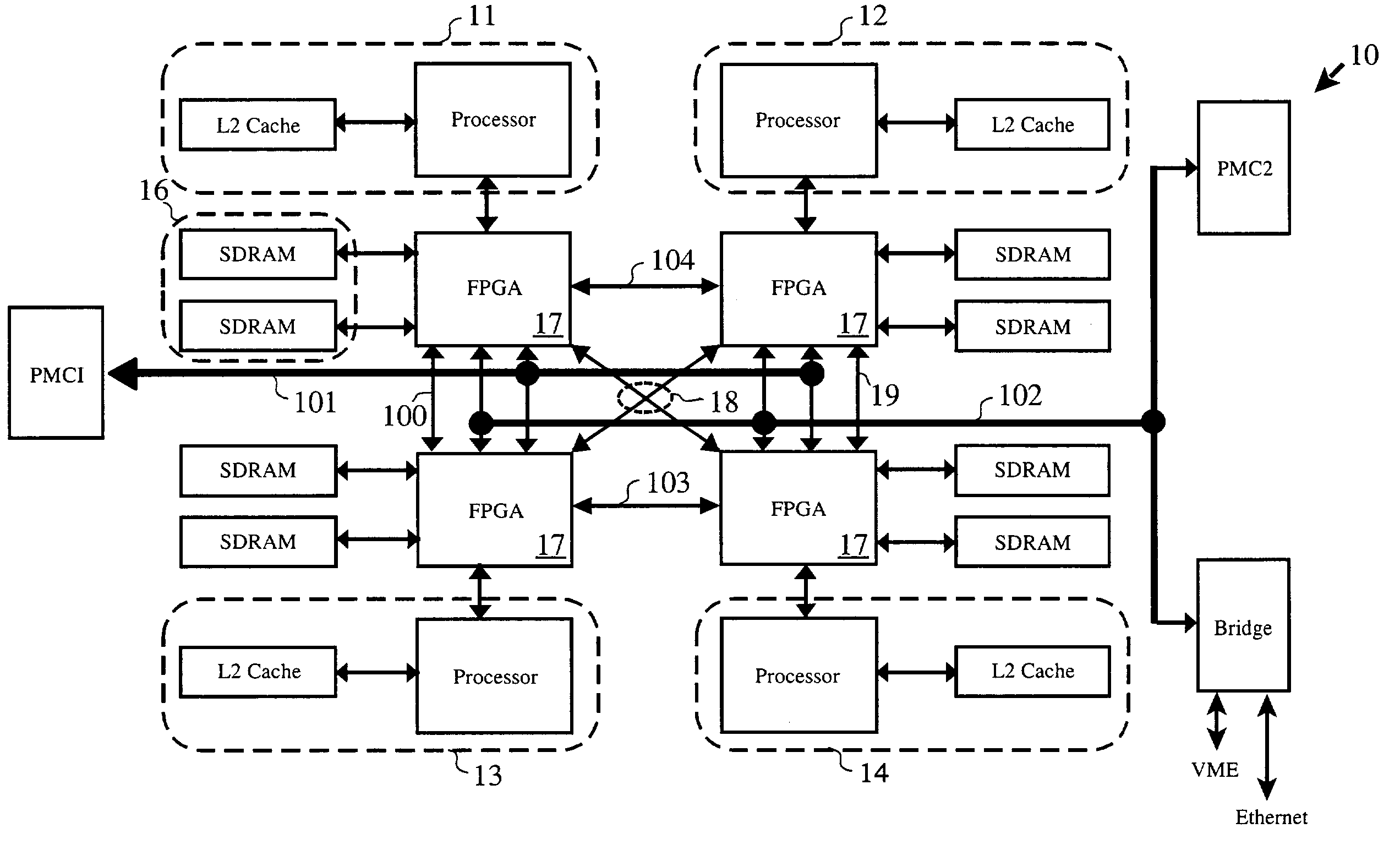

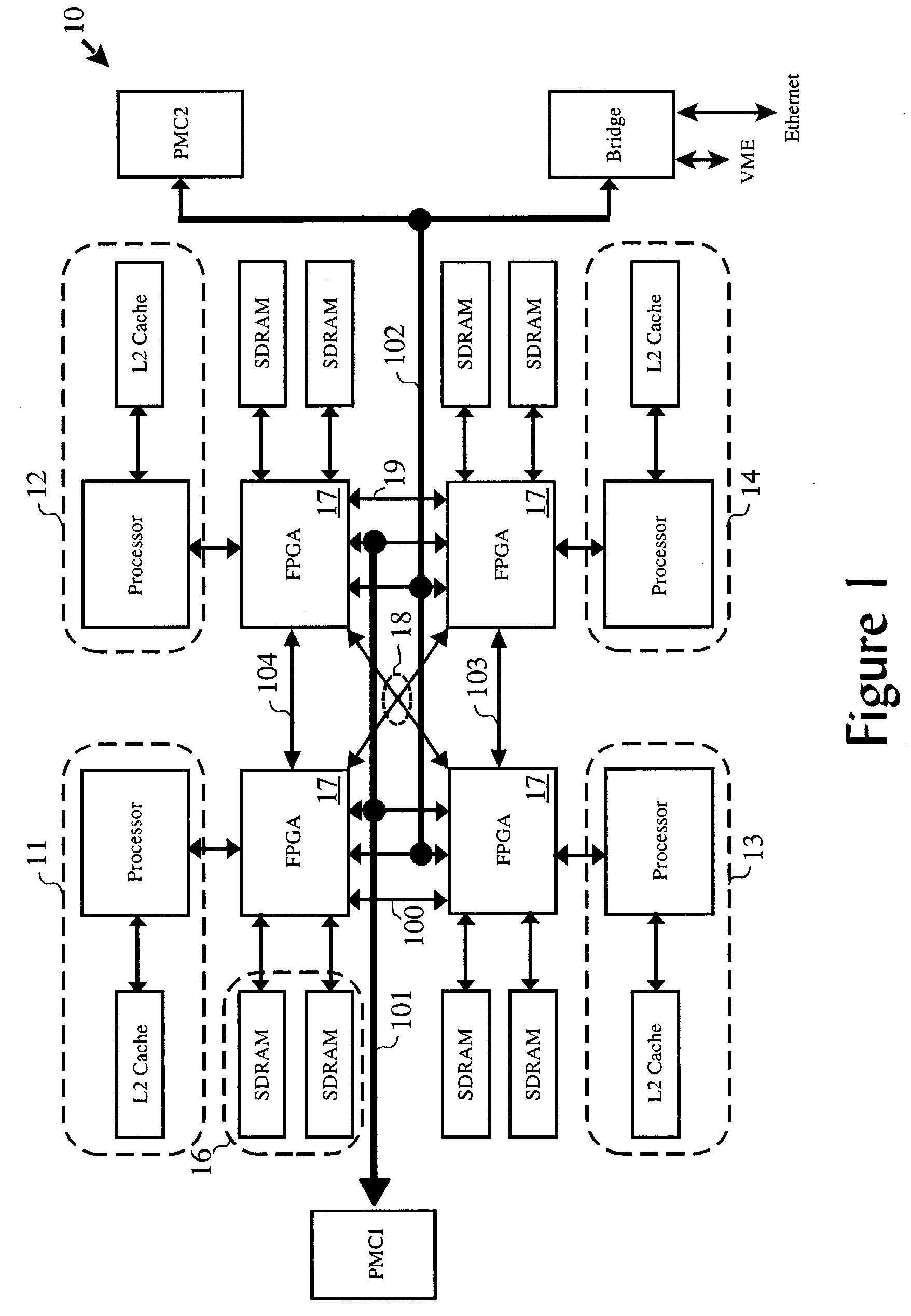

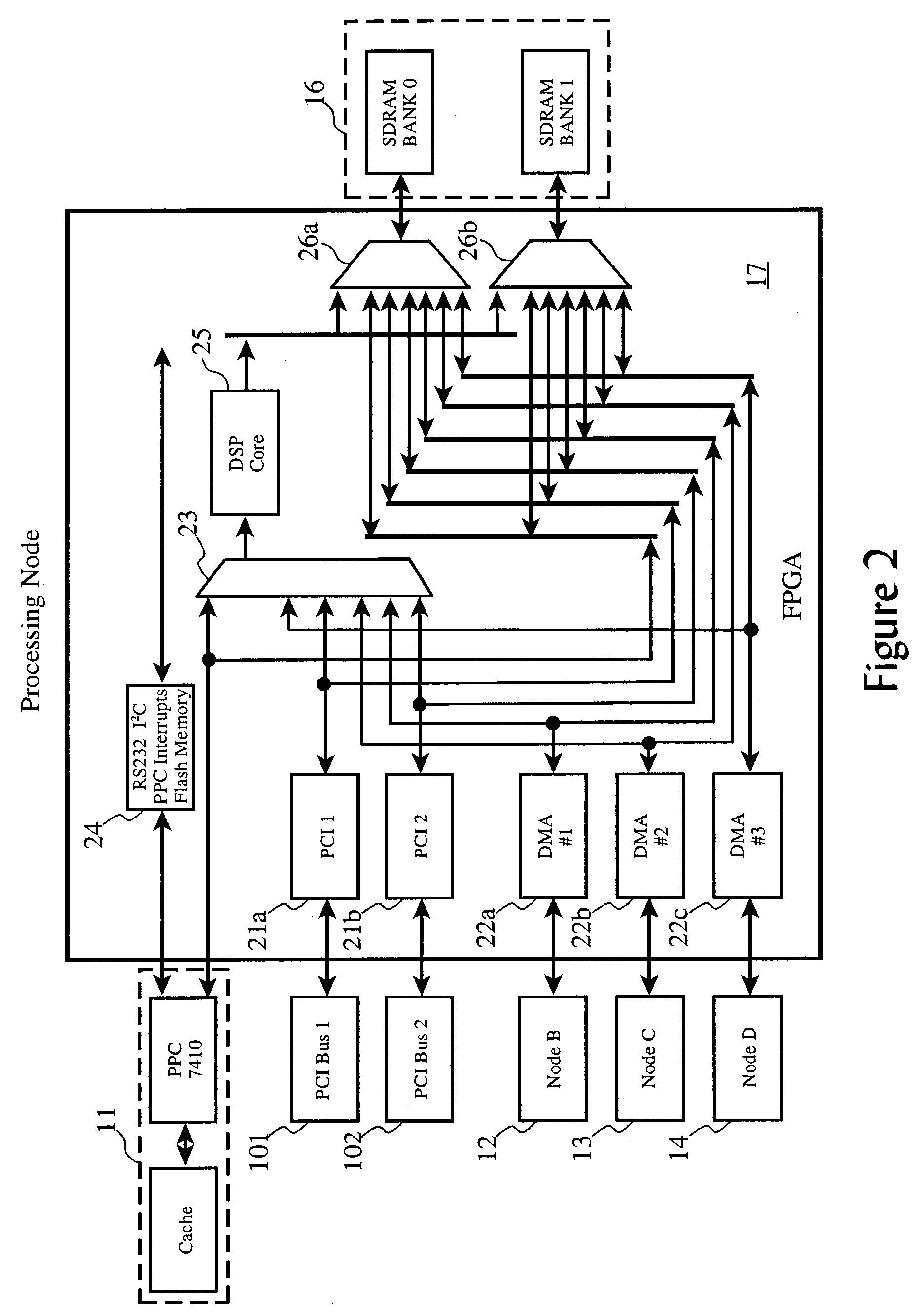

Signal processing resource for selective series processing of data in transit on communications paths in multi-processor arrangements

InactiveUS20040015633A1General purpose stored program computerElectric digital data processingMulti processorInterprocessor communication

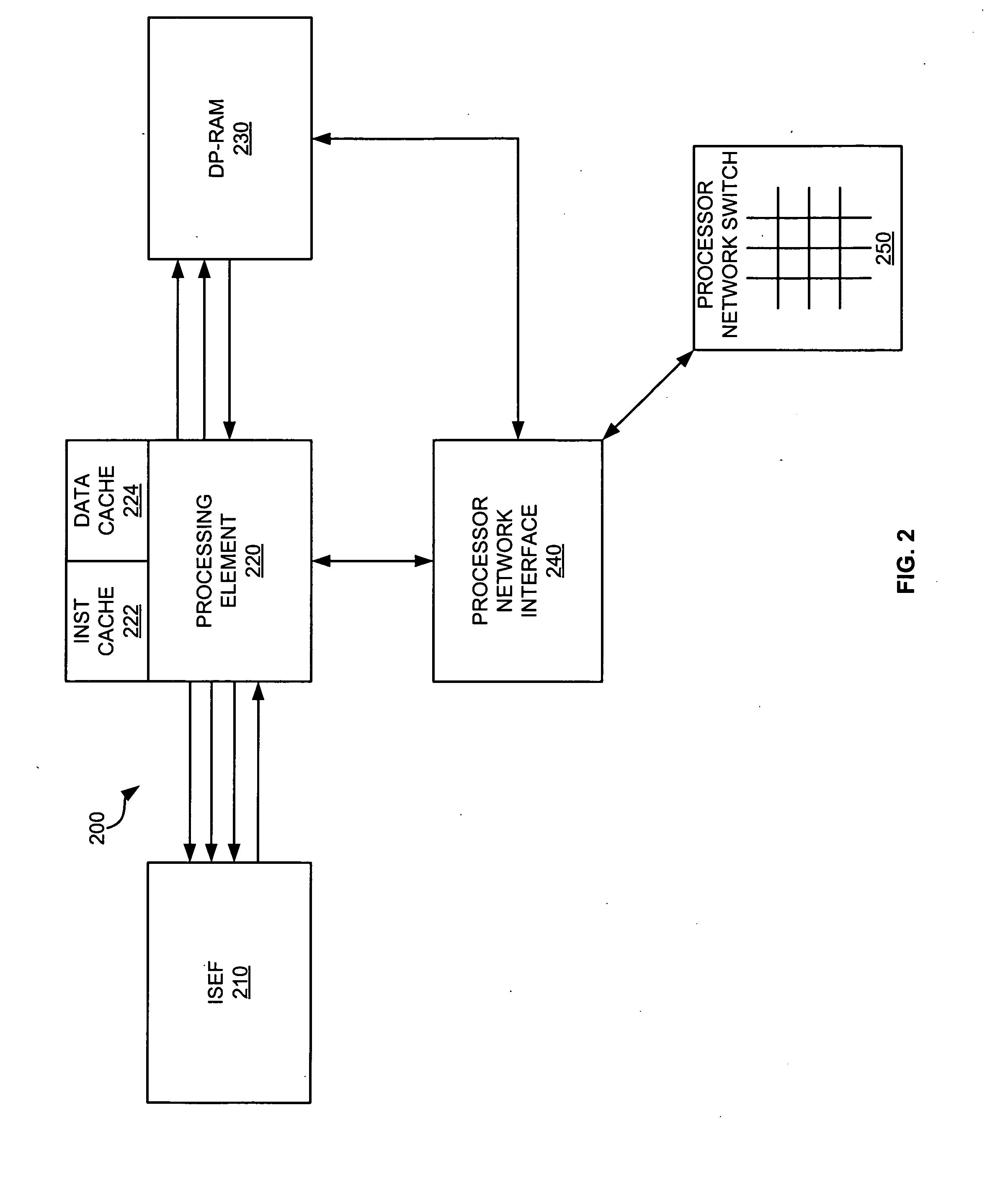

A multi-processor arrangement having an interprocessor communication path between each of every possible pair of processors, in addition to I / O paths to and from the arrangement, having signal processing functions configurably embedded in series with the communication paths and / or the I / O paths. Each processor is provided with a local memory which can be accessed by the local processor as well as by the other processors via the communications paths. This allows for efficient data movement from one processor's local memory to another processor's local memory, such as commonly done during signal processing corner turning operations. The configurable signal processing logic may be configured to host one or more signal processing functions to allow data to be processed prior to its deposit into local memory.

Owner:GE FANUC EMBEDDED SYST

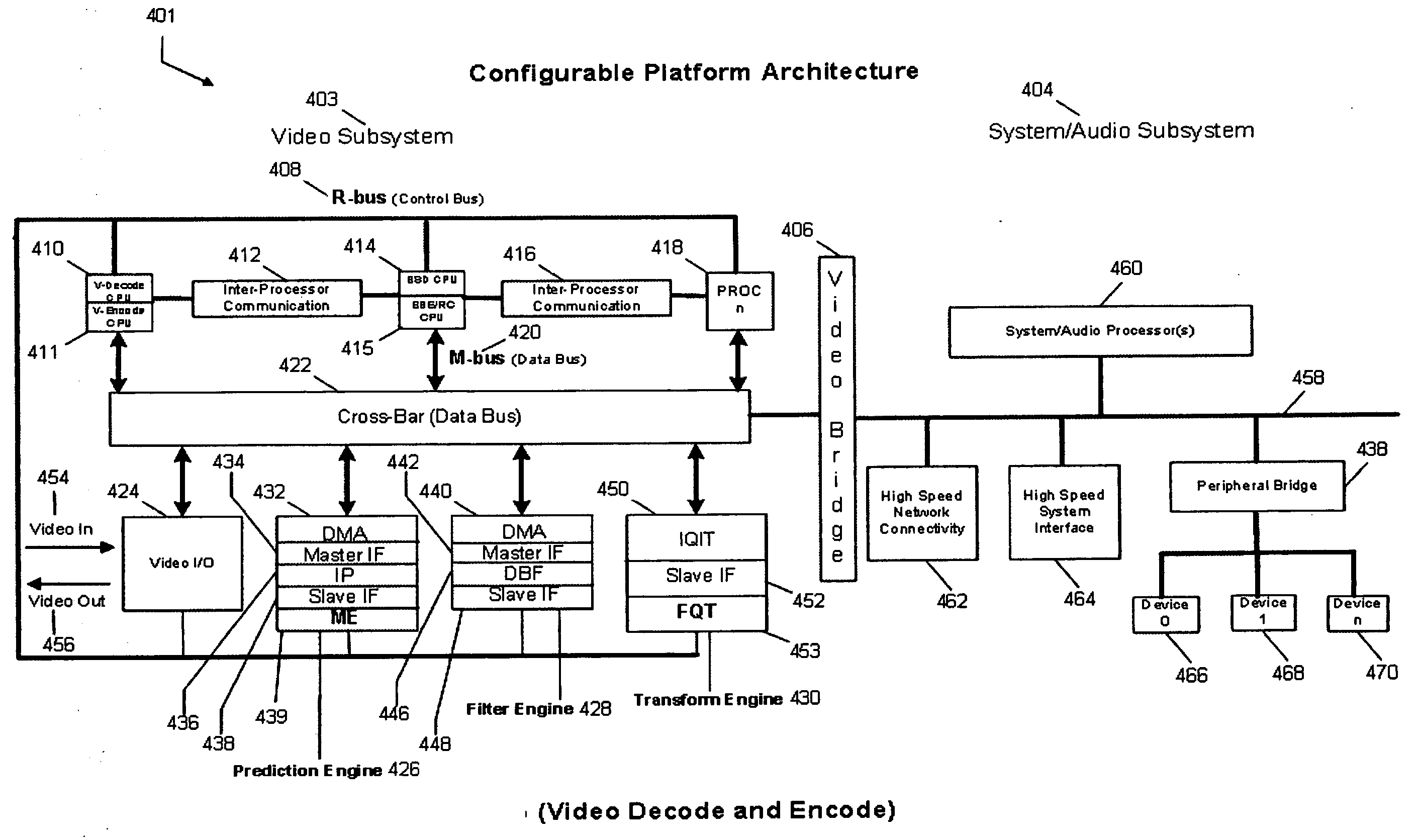

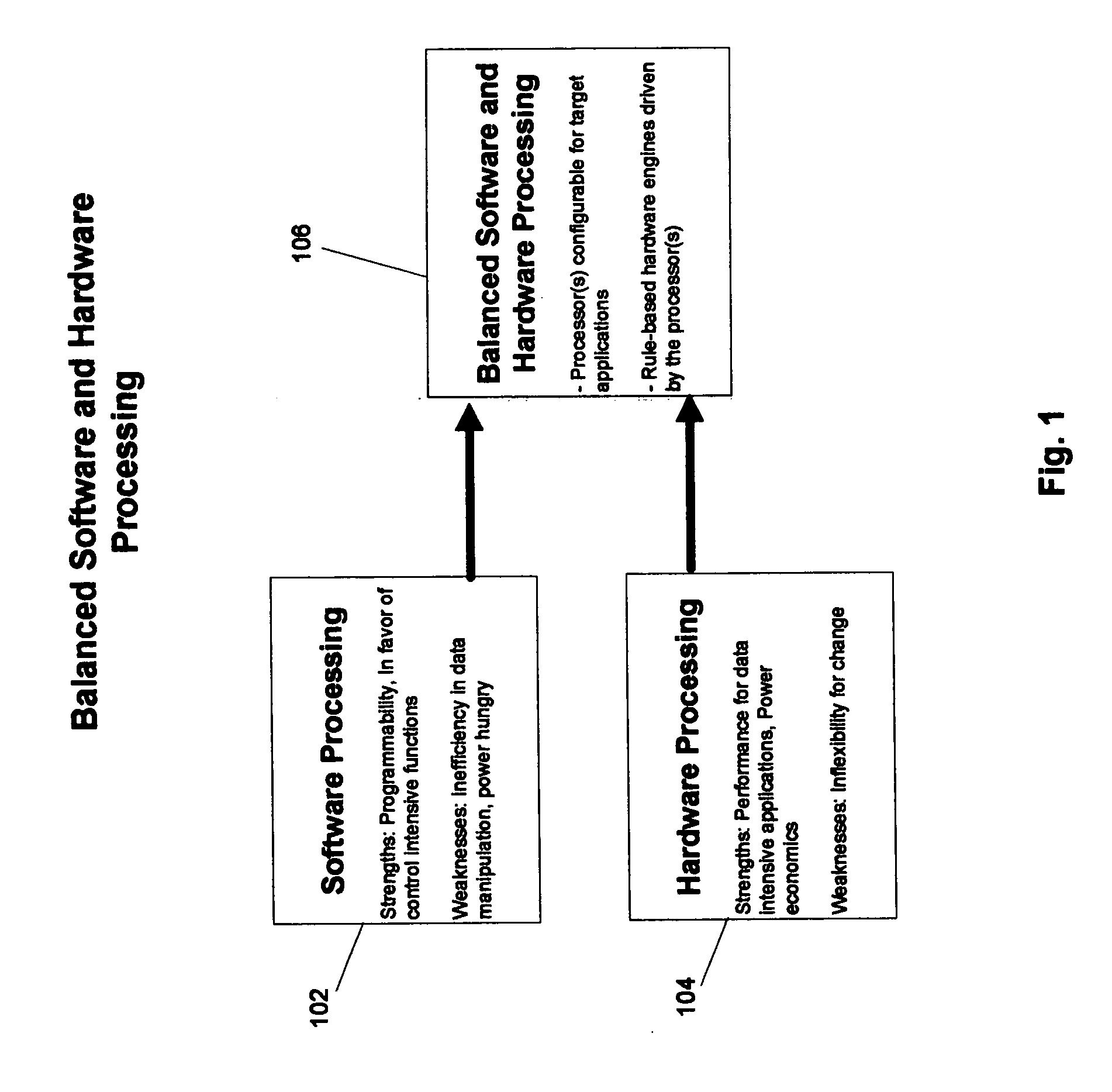

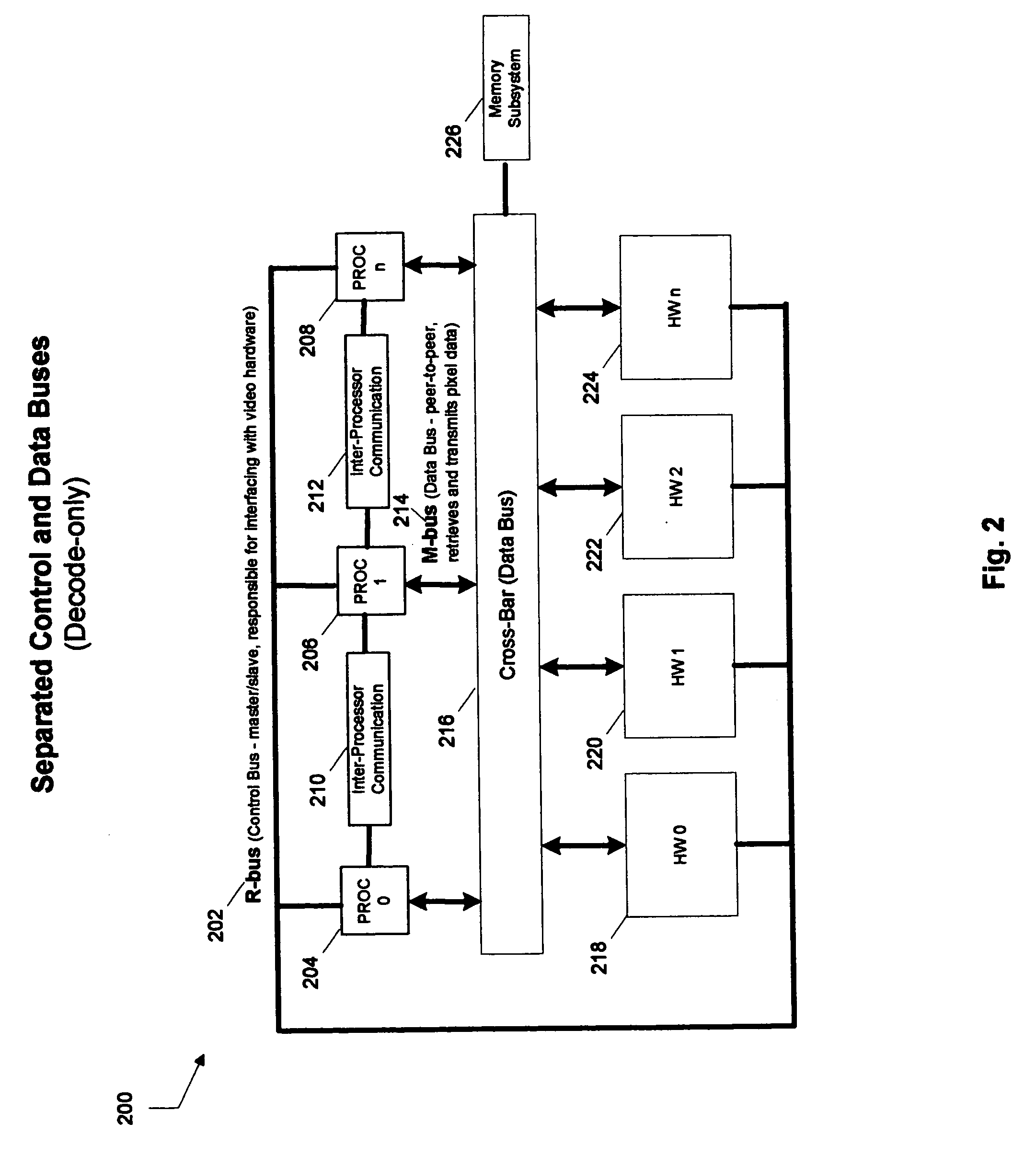

Software and hardware partitioning for multi-standard video compression and decompression

InactiveUS20050094729A1Maximizes flexibility and adaptabilityWithout significant hardware overheadColor television with pulse code modulationColor television with bandwidth reductionControl flowData stream processing

A system, method, and computer readable medium adapted to provide software and hardware partitioning for multi-standard video compression and decompression comprises a master-slave bus, a peer-to-peer bus, and an inter-processor communications bus, a prediction engine, a filter engine, and a transform engine, and a video encode control processor, and a video decode control processor adapted to utilize the master-slave bus to interact with the video hardware engines for control flow processing, the peer-to-peer bus for data flow processing, and the inter-processor communications bus for inter-processor communications, and a system data bus adapted to permit data exchange between system resources, the busses, the engines, and the processors.

Owner:VISIONFLOW

Method for efficient inter-processor communication in an active-active RAID system using PCI-express links

ActiveUS20060161707A1Efficiently determinedError detection/correctionUnauthorized memory use protectionRAIDProcessor register

A fault-tolerant RAID system is disclosed. The system includes redundant RAID controllers coupled by a PCI-Express link. When a PCI-Express controller of one of the RAID controllers receives a PCI-Express memory write request transaction layer packet (TLP), it interprets a predetermined bit in the header as an interrupt request flag, rather than as its standard function specified by the PCI-Express specification. If the flag is set, the PCI-Express controller interrupts the processor after storing the message in the payload at the specified memory location. In one embodiment, an unused upper address bit in the header is used as the interrupt request flag. Additionally, unused predetermined bits in the TLP header are used as a message tag to indicate one of a plurality of message buffers on the receiving RAID controller into which the message has been written. The PCI-Express controller sets a corresponding bit in a register to indicate which message buffer was written.

Owner:DOT HILL SYST

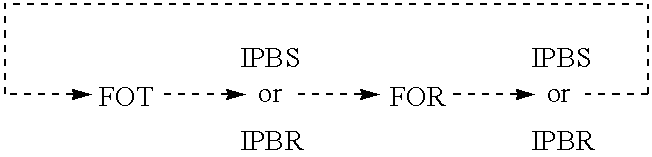

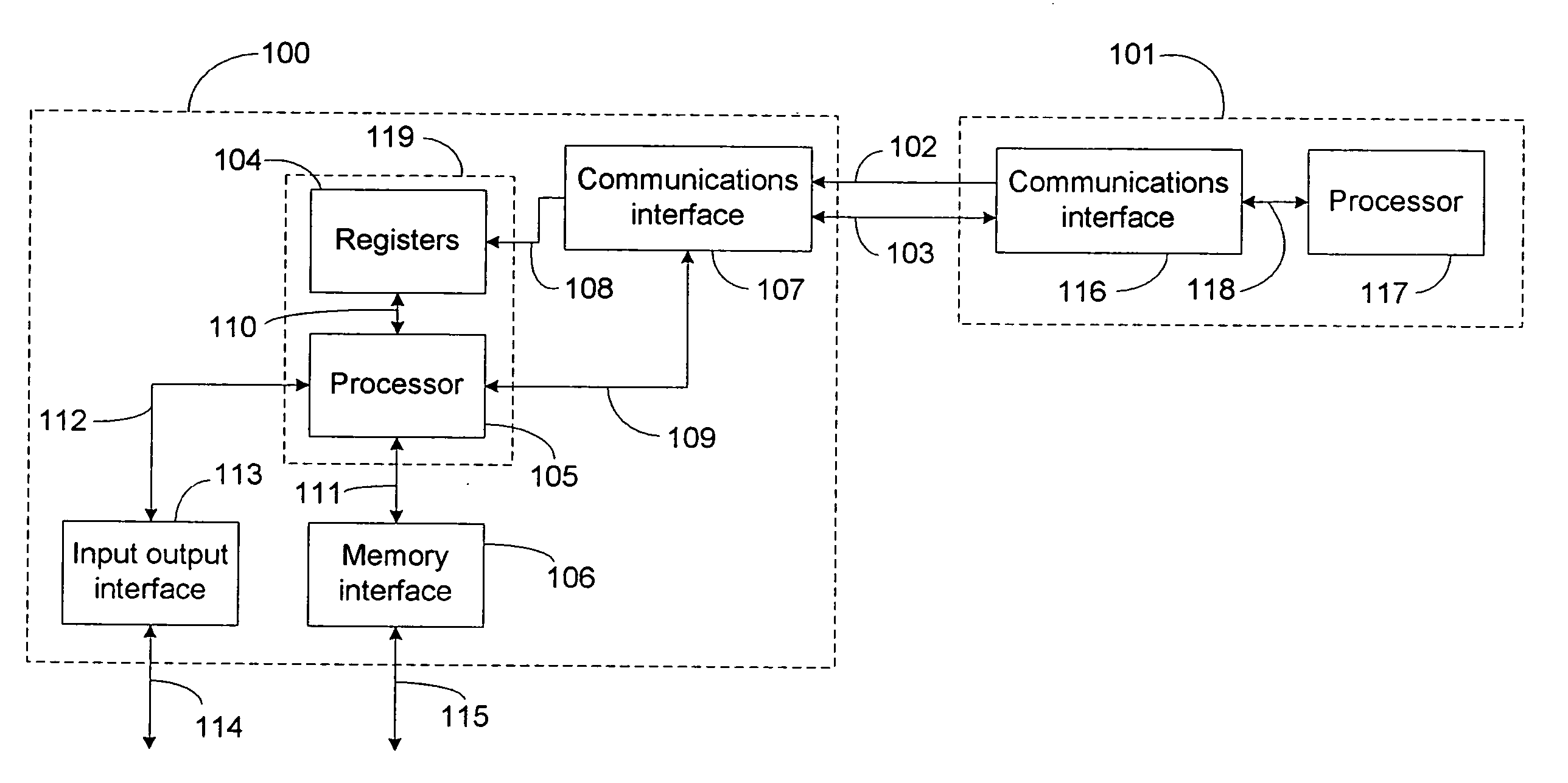

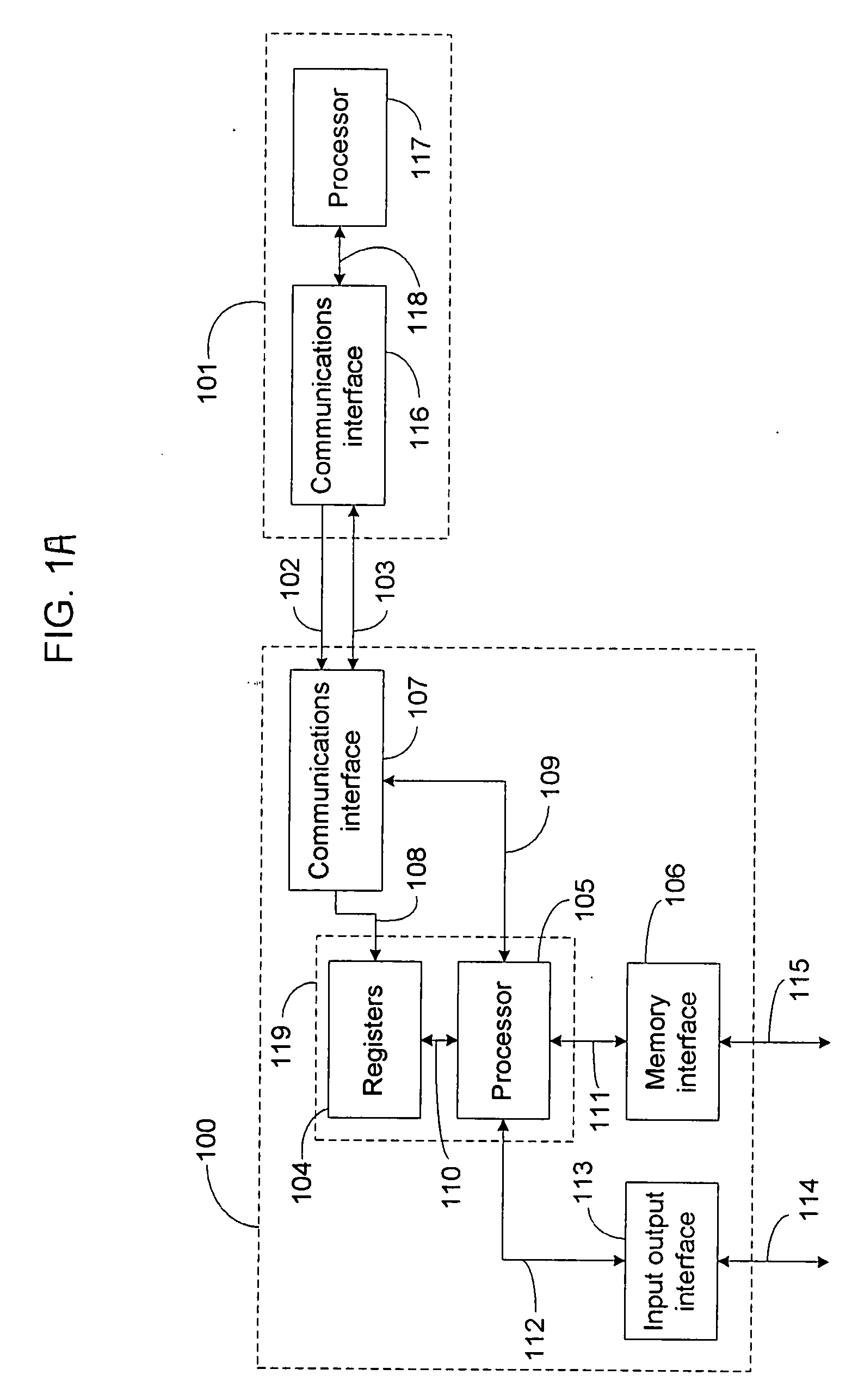

Methods and apparatus for managing power with an inter-processor communication link between independently operable processors

ActiveUS20160103480A1Reduce power consumptionElectric power consumptionError detection/correctionPower supply for data processingError processingMemory interface

Methods and apparatus for an inter-processor communication (IPC) link between two (or more) independently operable processors. In one aspect, the IPC protocol is based on a “shared” memory interface for run-time processing (i.e., the independently operable processors each share (either virtually or physically) a common memory interface). In another aspect, the IPC communication link is configured to support a host driven boot protocol used during a boot sequence to establish a basic communication path between the peripheral and the host processors. Various other embodiments described herein include sleep procedures (as defined separately for the host and peripheral processors), and error handling.

Owner:APPLE INC

Methods and apparatus for recovering errors with an inter-processor communication link between independently operable processors

Methods and apparatus for an inter-processor communication (IPC) link between two (or more) independently operable processors. In one aspect, the IPC protocol is based on a “shared” memory interface for run-time processing (i.e., the independently operable processors each share (either virtually or physically) a common memory interface). In another aspect, the IPC communication link is configured to support a host driven boot protocol used during a boot sequence to establish a basic communication path between the peripheral and the host processors. Various other embodiments described herein include sleep procedures (as defined separately for the host and peripheral processors), and error handling.

Owner:APPLE INC

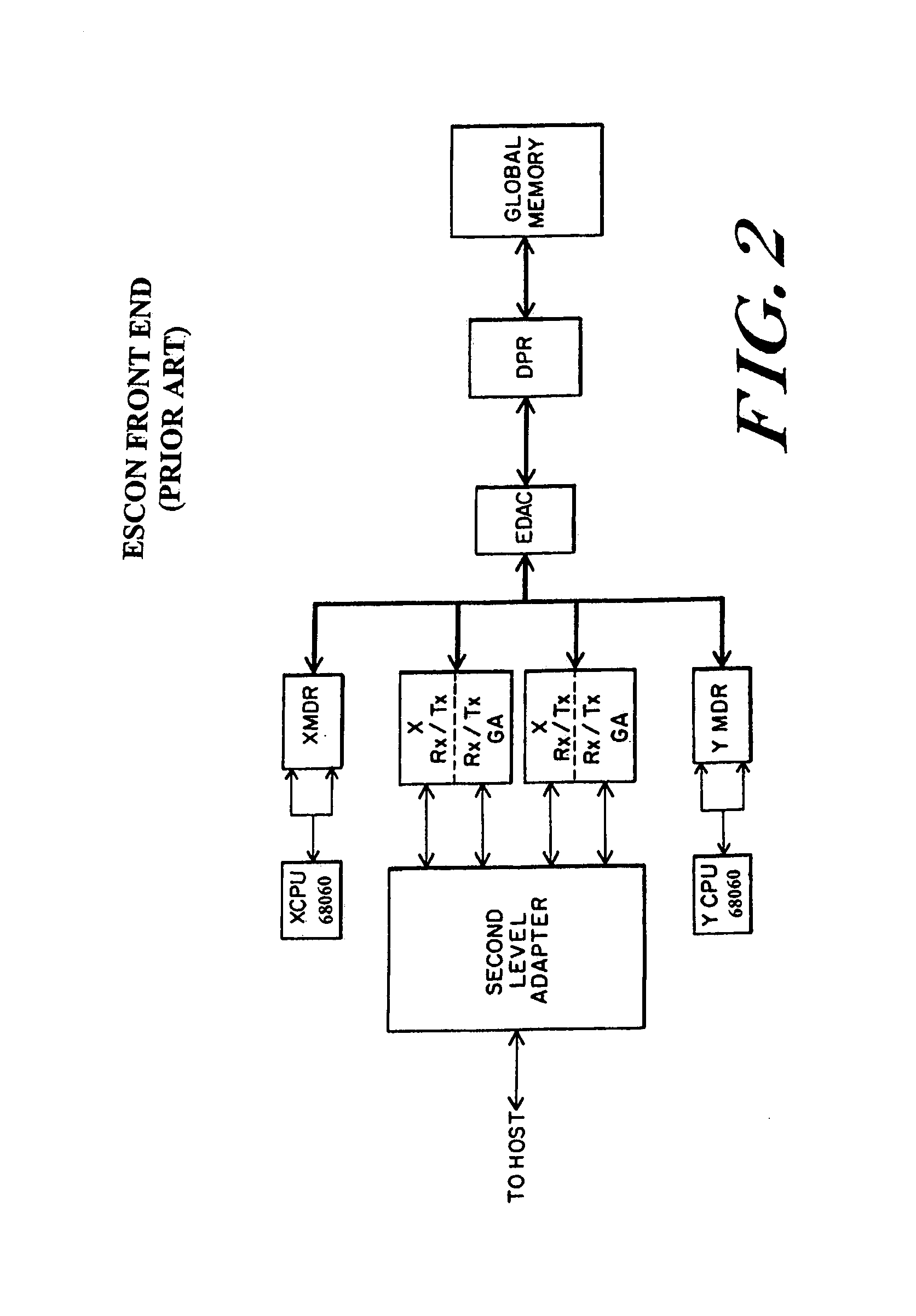

Messaging mechanism for inter processor communication

InactiveUS20070271572A1Easy to operateMinimizing affectionMultiprogramming arrangementsMultiple digital computer combinationsComputer hardwareESCON

An apparatus and method are provided for connecting a host Enterprise System Connection Architecture (ESCON) Input / Output (I / O) interface to a cache of a data storage system. The apparatus includes (a) a set of at least 4 pipelines, each pipeline being coupled on a first end to the host ESCON I / O interface and being coupled on a second end to the cache, (b) a plurality of line processors, each line processor controlling one or more of the pipelines of the set of pipelines, and (c) in each pipeline, a protocol engine, the protocol engine configured to distinguish user data from frame header data and separate the user data from the frame header data for transport over the pipeline.

Owner:EMC IP HLDG CO LLC

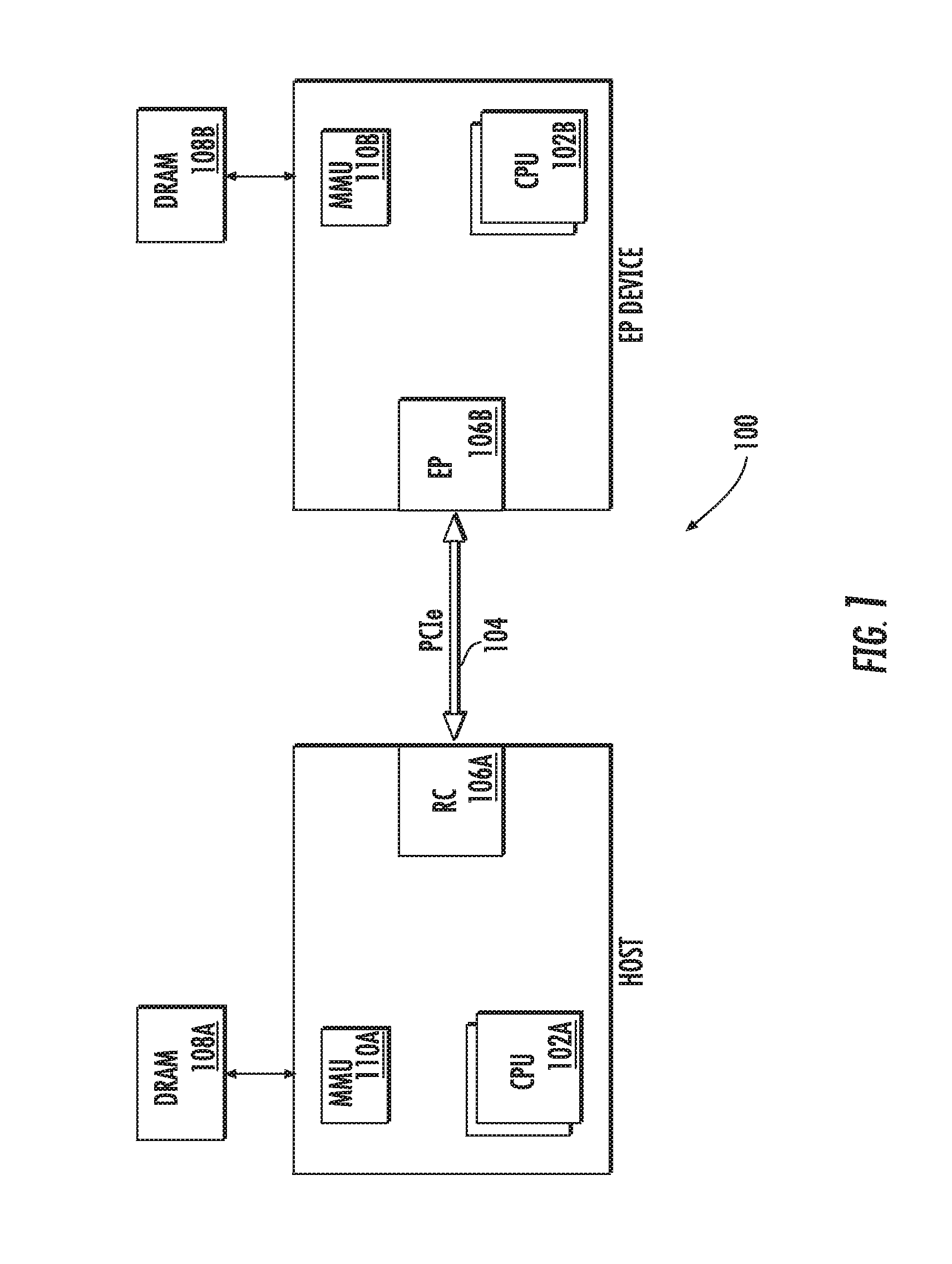

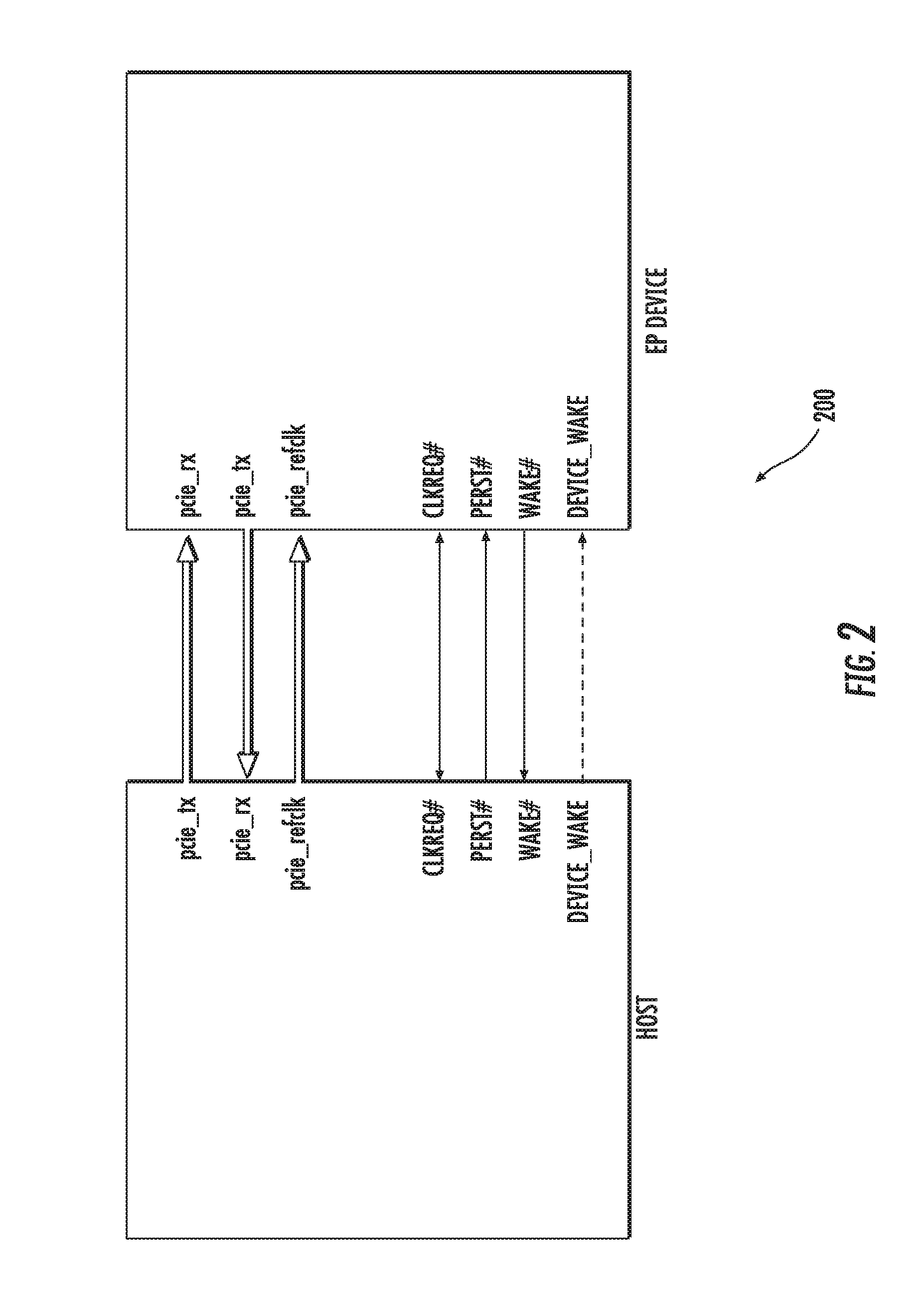

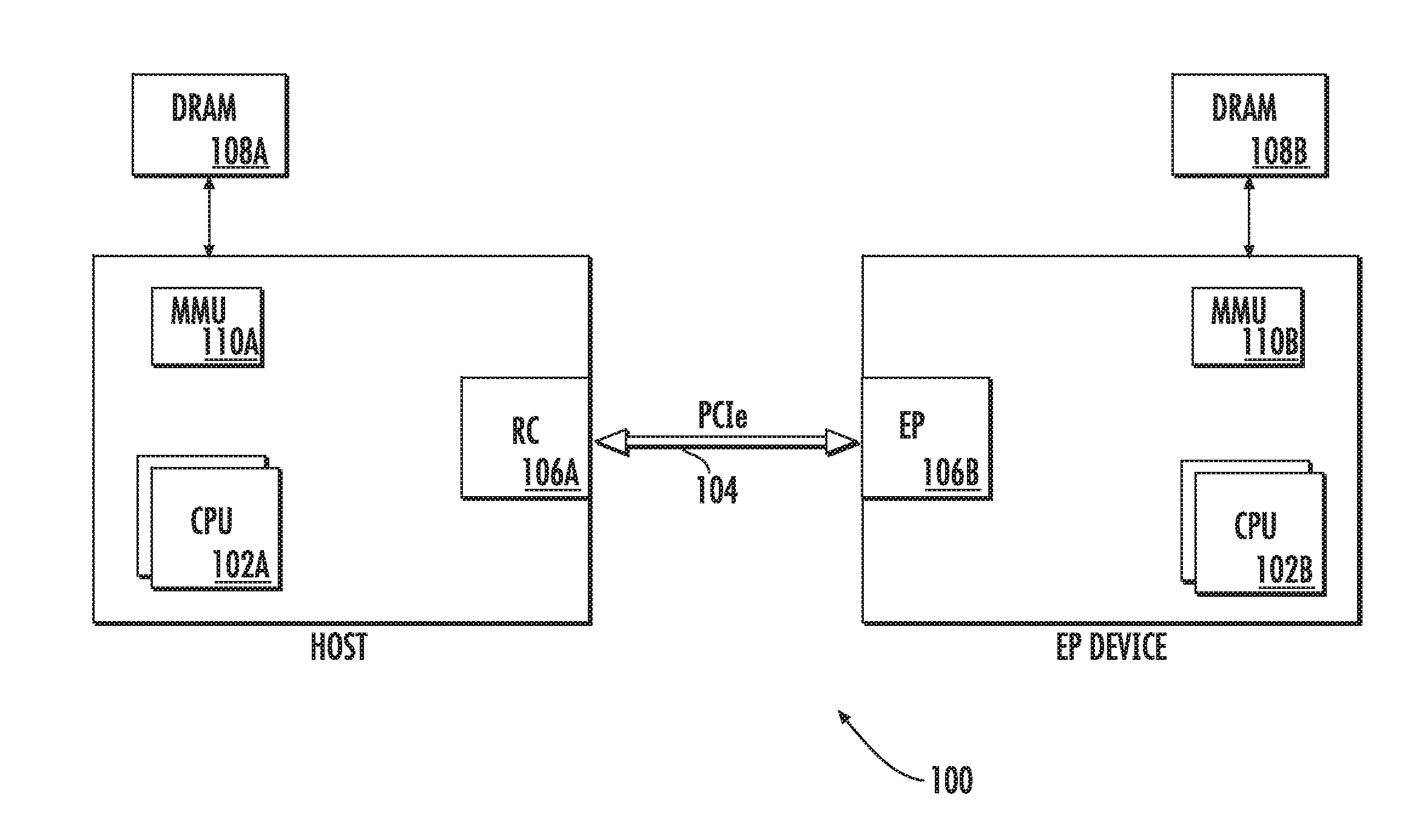

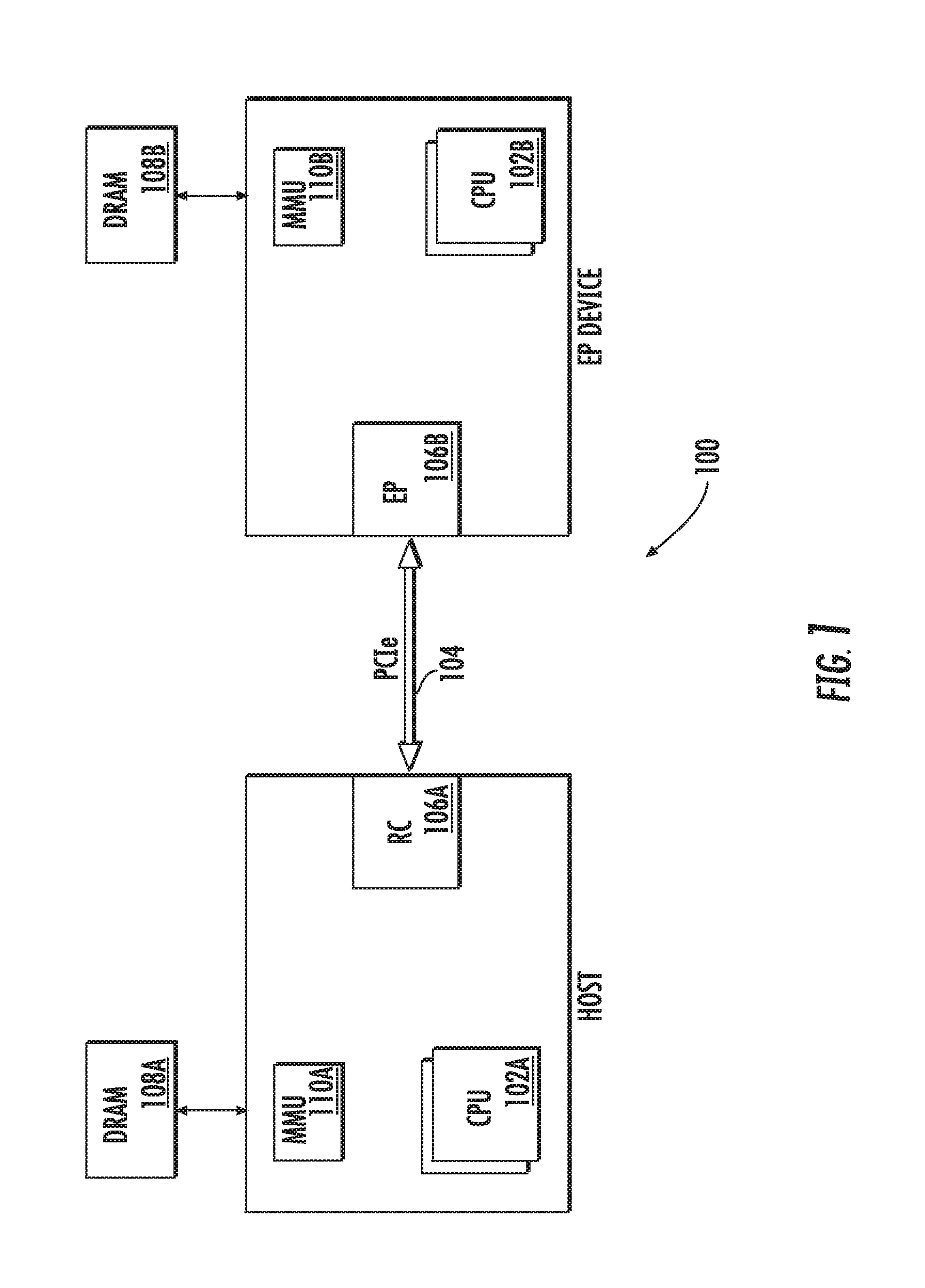

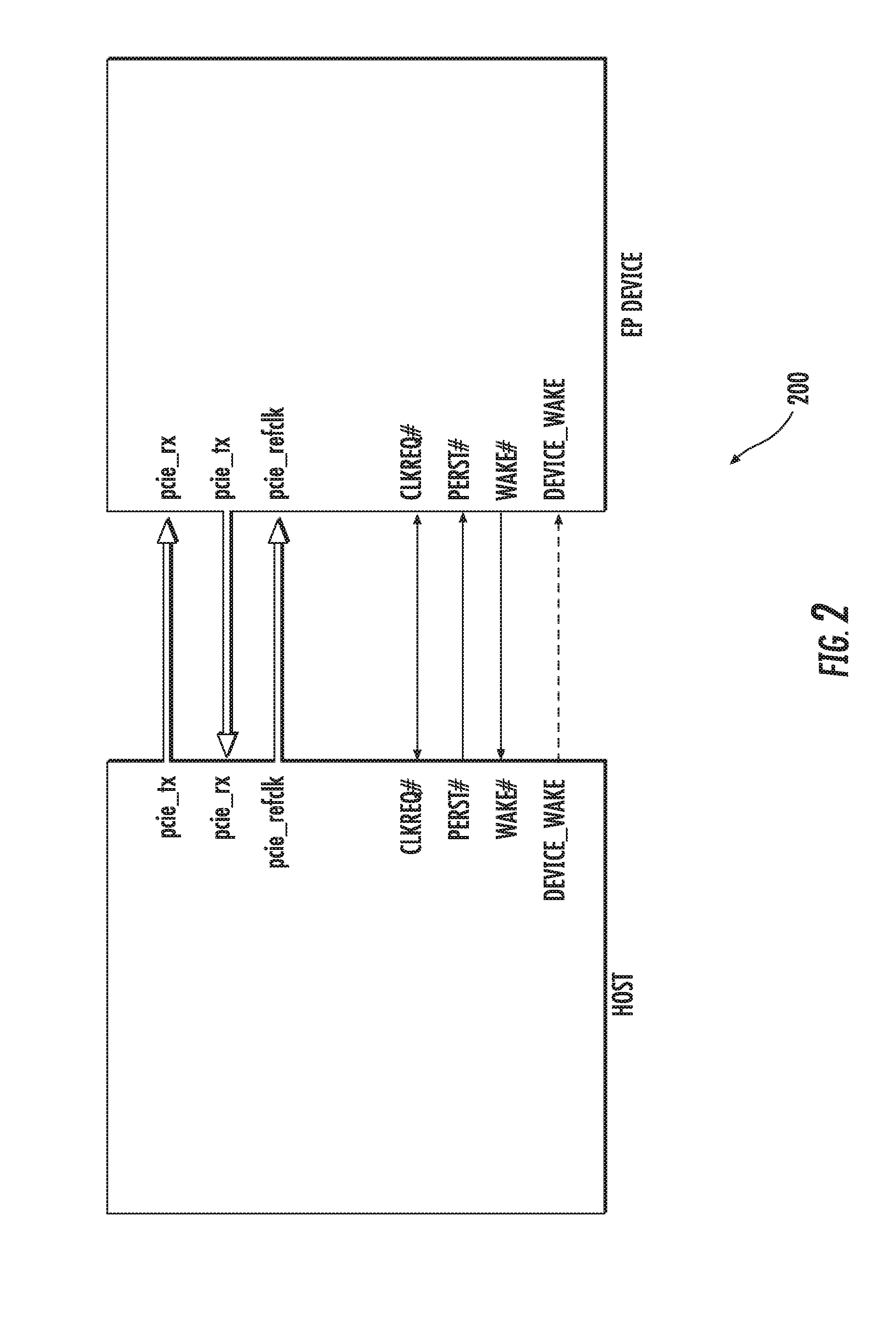

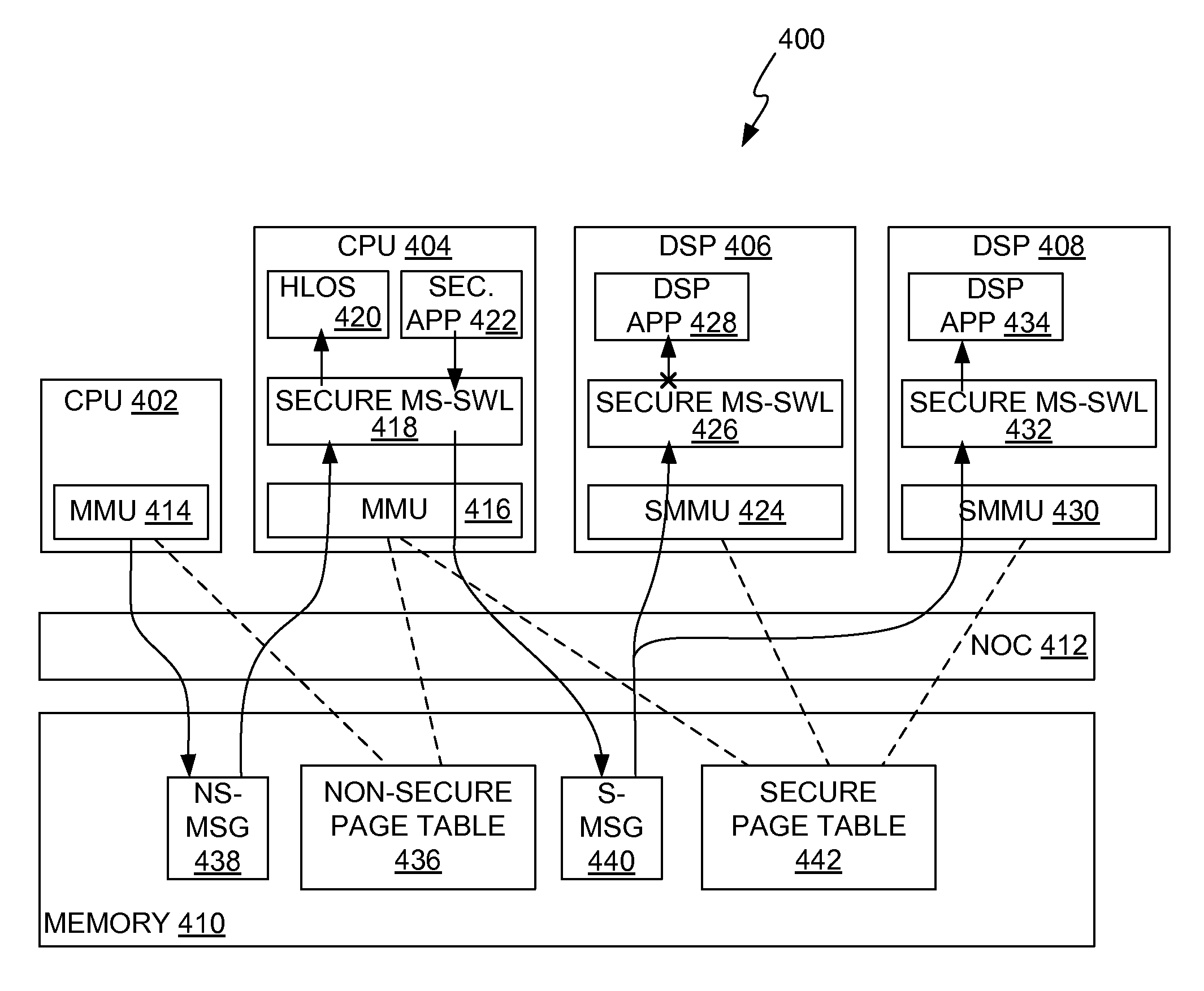

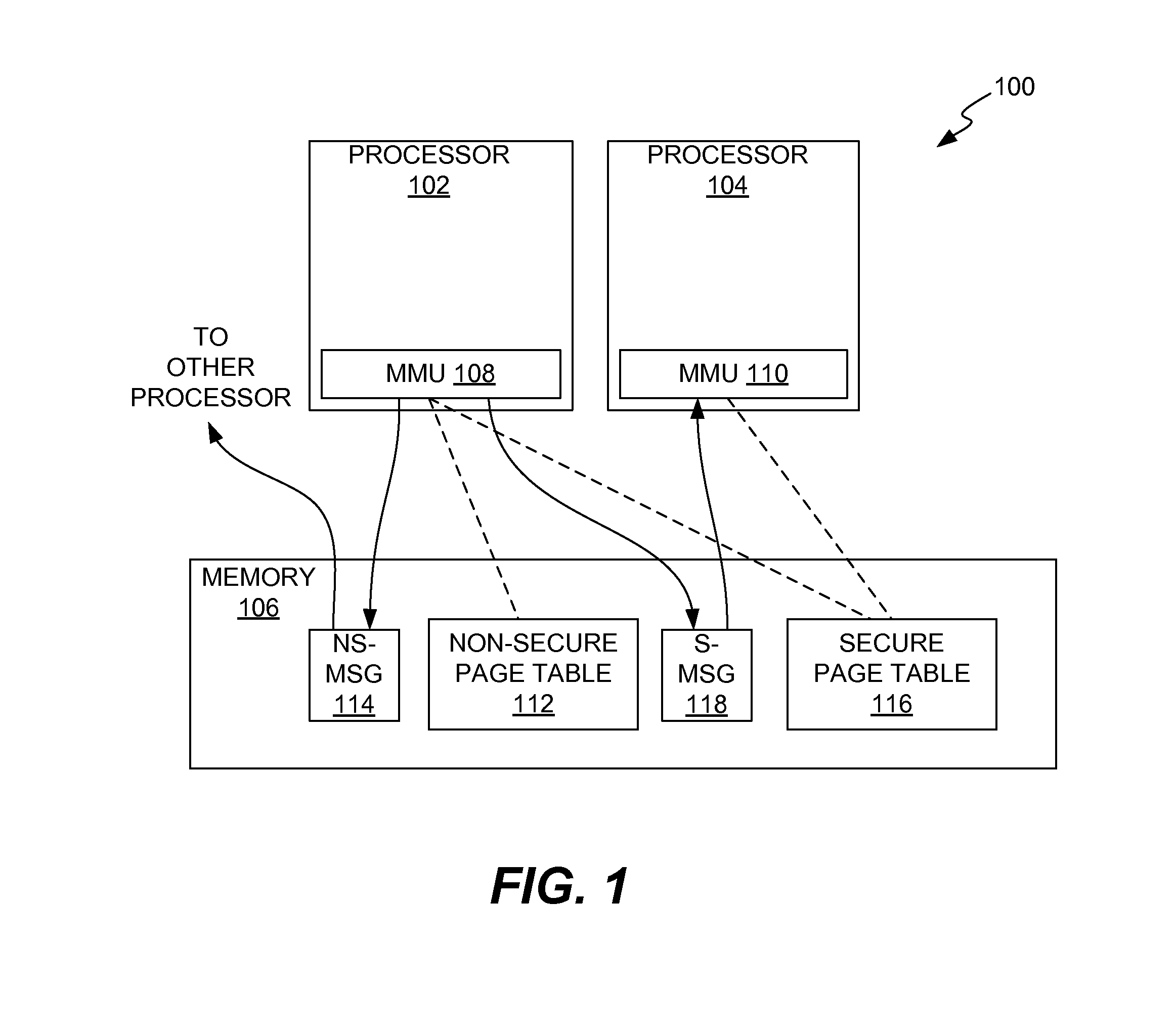

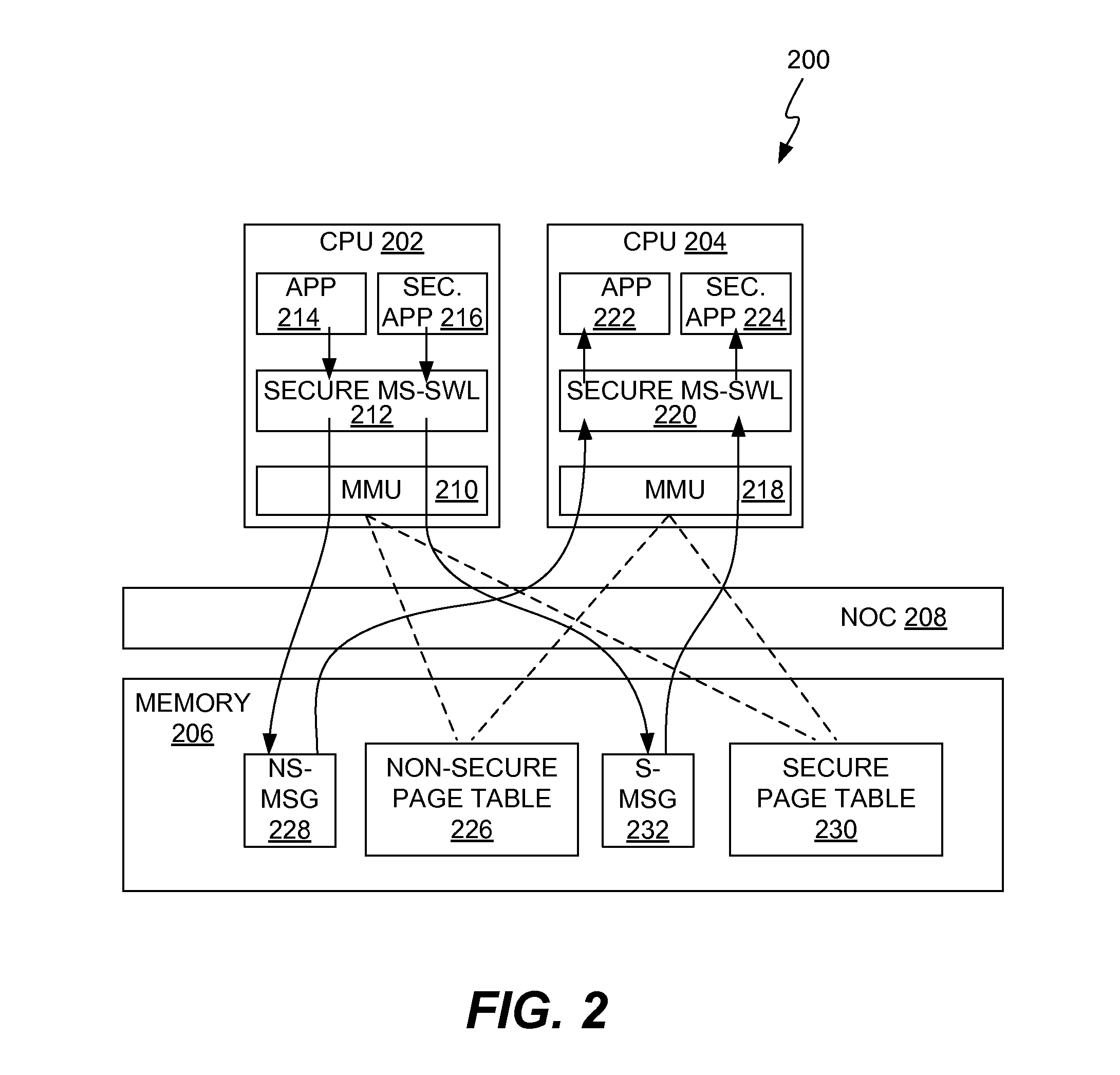

Distributed dynamic memory management unit (MMU)-based secure inter-processor communication

InactiveUS9170957B2Memory architecture accessing/allocationMemory adressing/allocation/relocationPage tableInterprocessor communication

A first processor and a second processor are configured to communicate secure inter-processor communications (IPCs) with each other. The first processor effects secure IPCs and non-secure IPCs using a first memory management unit (MMU) to route the secure and non-secure IPCs via a memory system. The first MMU accesses a first page table stored in the memory system to route the secure IPCs and accesses a second page table stored in the memory system to route the non-secure IPCs. The second processor effects at least secure IPCs using a second MMU to route the secure IPCs via the memory system. The second MMU accesses the second page table to route the secure IPCs.

Owner:QUALCOMM INC

Systems and methods for selecting input/output configuration in an integrated circuit

ActiveUS20050114565A1Single instruction multiple data multiprocessorsInput/output processes for data processingComputer hardwareInterprocessor communication

An integrated circuit with selectable input / output includes a first processor configured to execute instructions, an input / output interface configured to receive and transmit standard input / output communications, an inter-processor interface configured to process interprocessor communications with a second processor, and selection circuitry coupled to both the input / output interface and the inter-processor interface and configured to select between the input / output interface and the inter-processor interface.

Owner:XILINX INC

Multiprocessor communication system and method

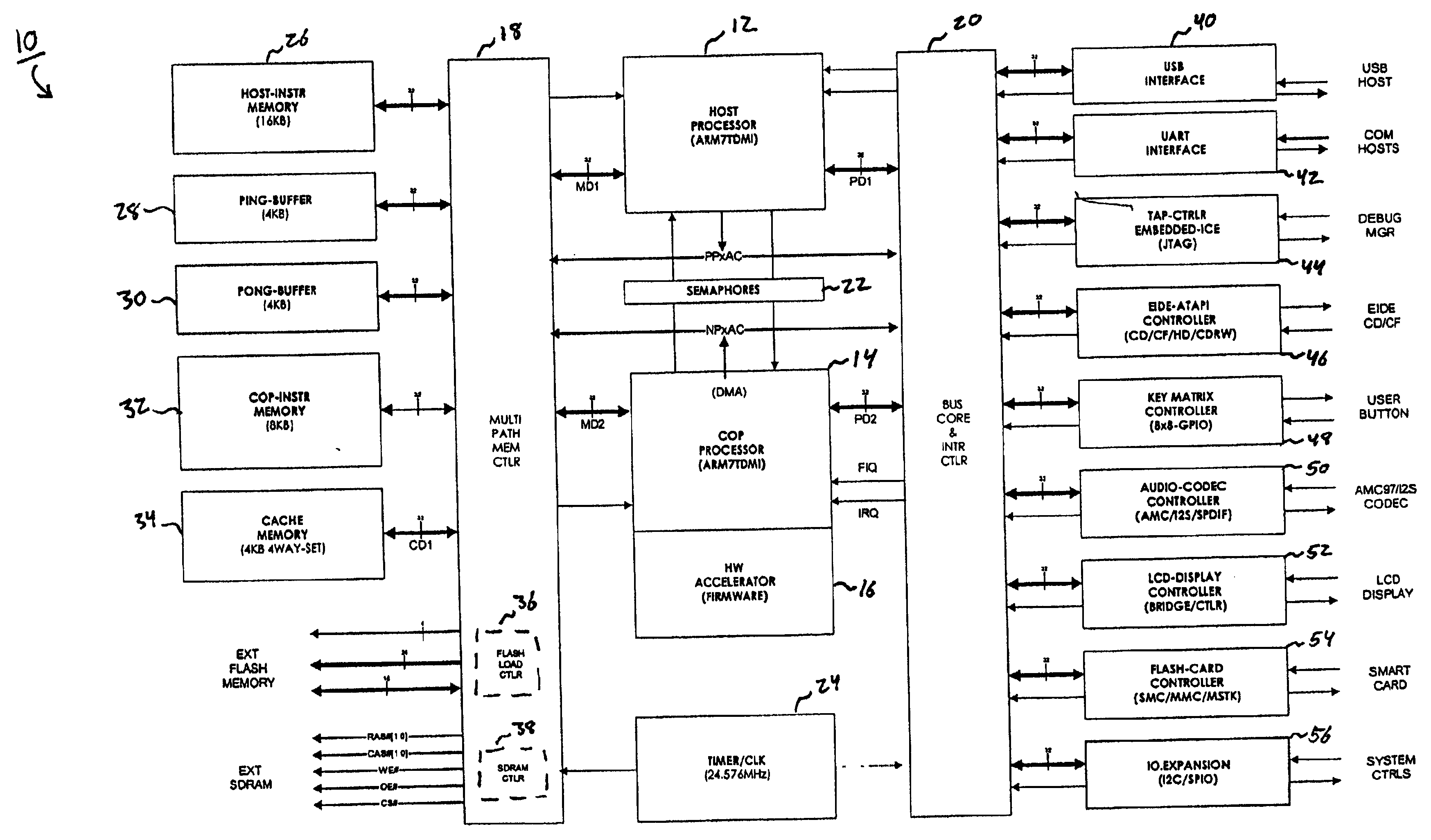

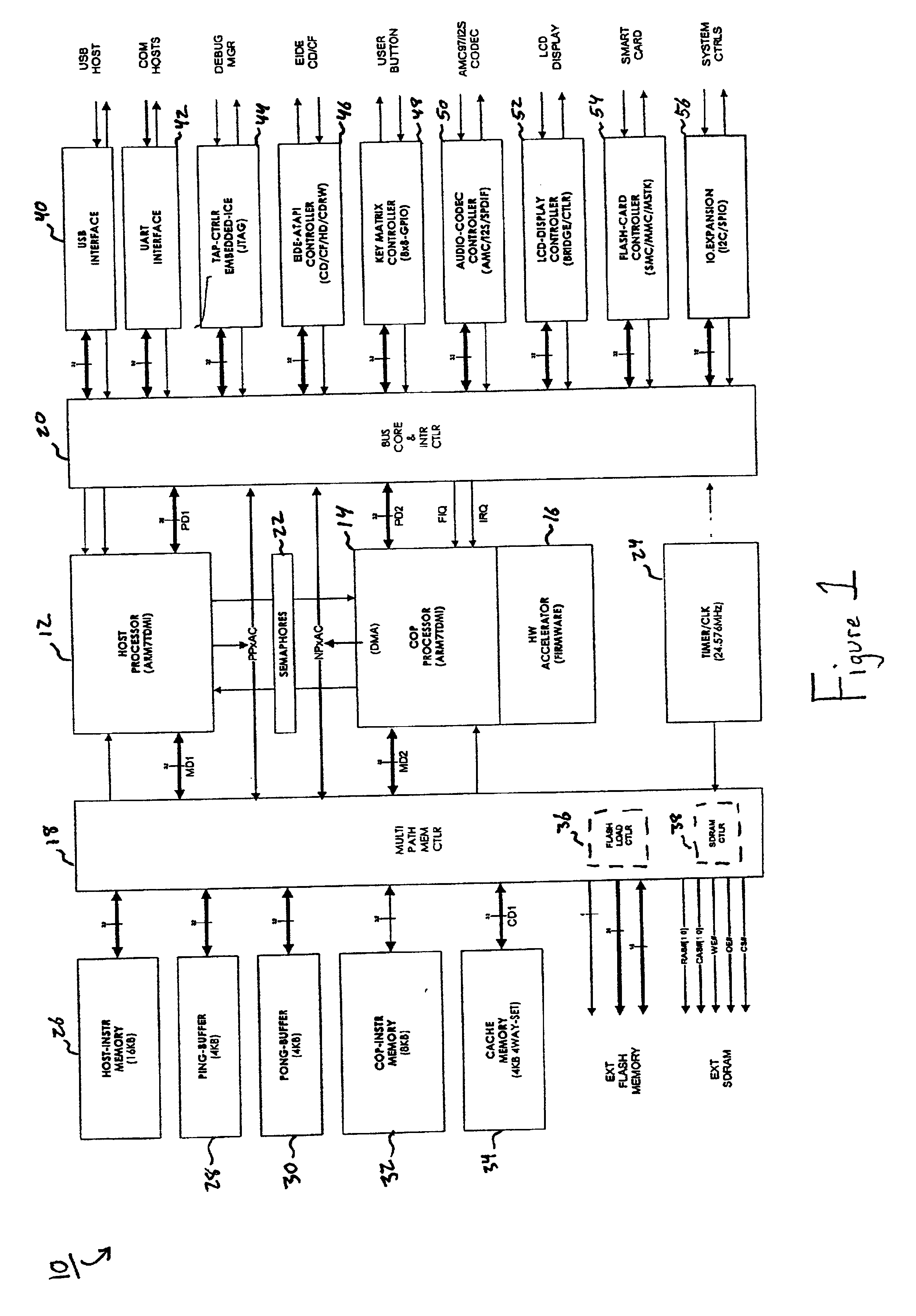

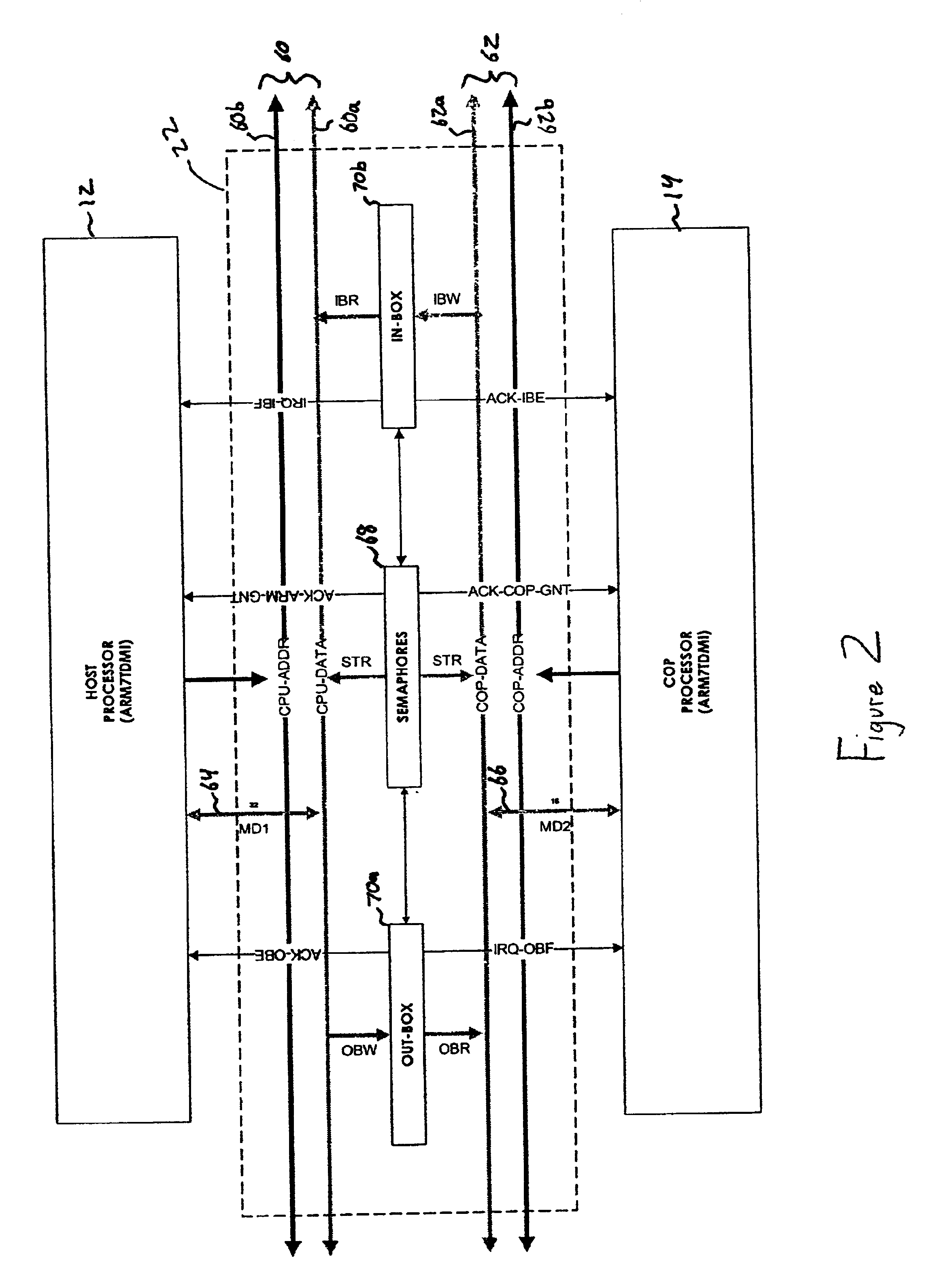

ActiveUS6938253B2Facilitate inter-processor communicationFacilitating inter-processor communicationProgram synchronisationInterprogram communicationCommunications systemNonpreemptive multitasking

To facilitate inter-processor communication between multiple processors in a computer system and to enable the accessing of a dual port memory, or other system resources, without requiring the memory or the data / address bus to be locked, the present invention provides a semaphore unit that preferably incorporates a shared mailbox architecture that, in combination with a set of hardware semaphore registers, enables inter-process communication among the multi-processors. Cooperative multitasking may be accomplished through the use of shared mailbox communication protocols while a preemptive multitasking may be accomplished through the use of hardware semaphore registers.

Owner:NVIDIA CORP

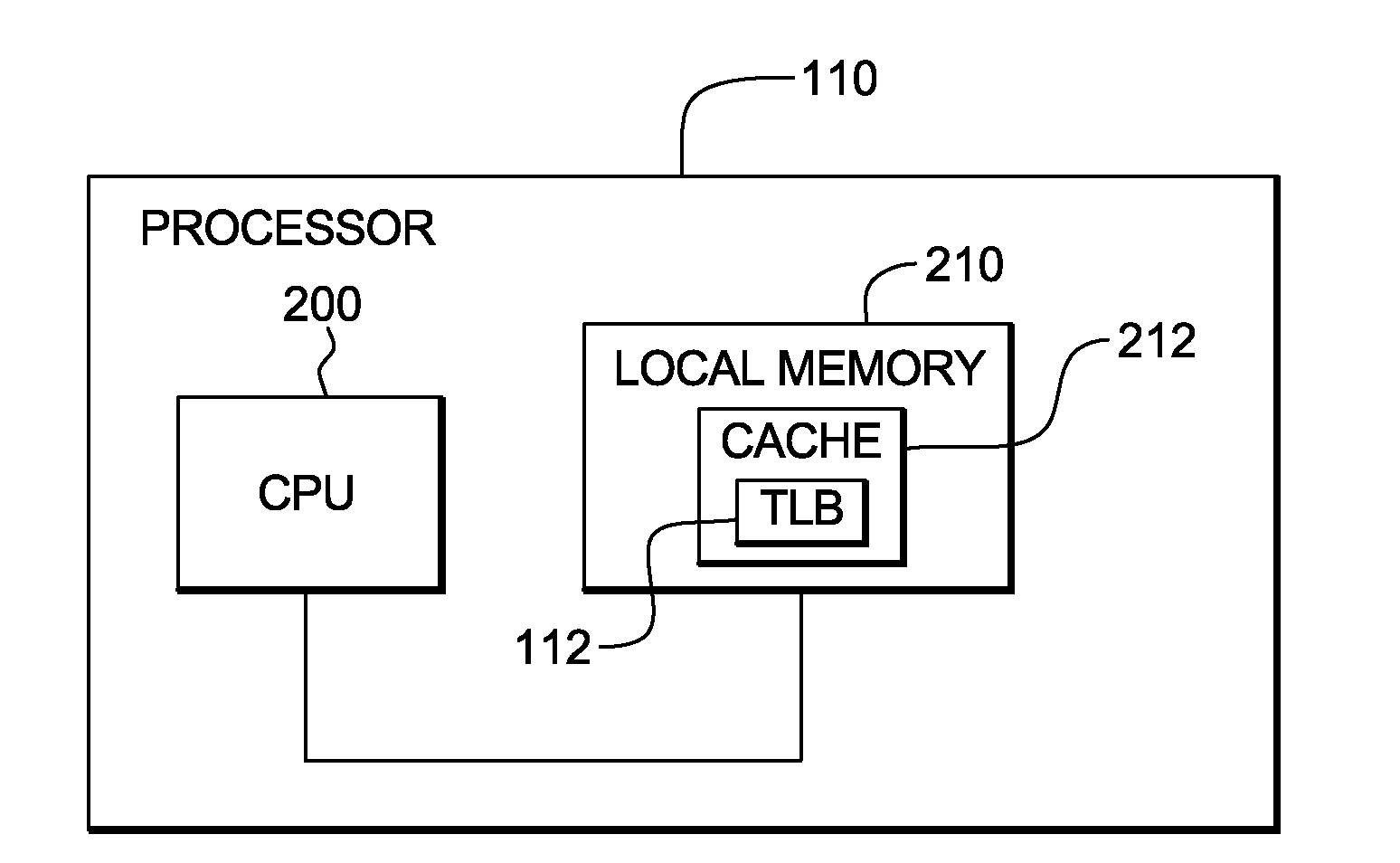

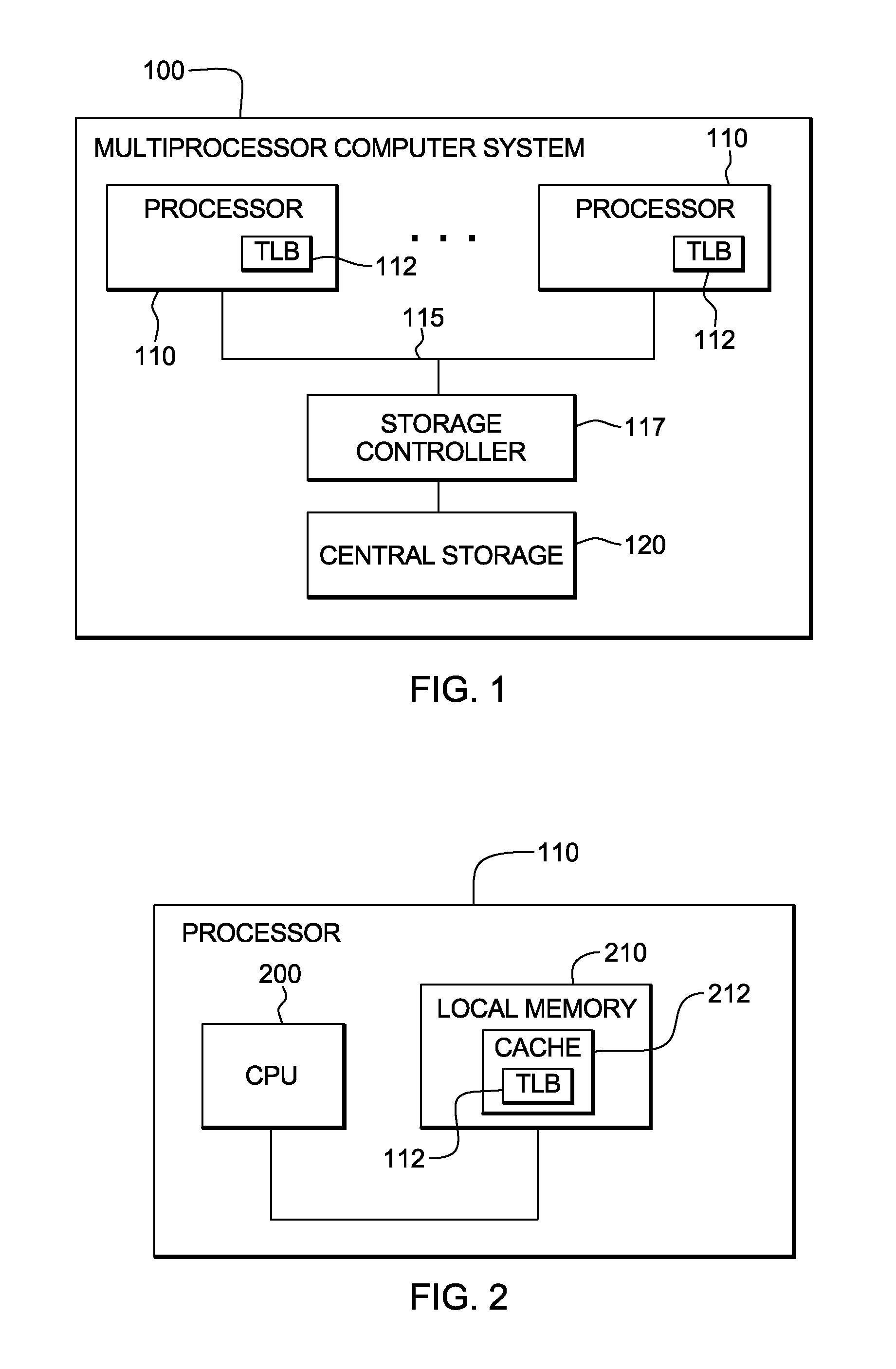

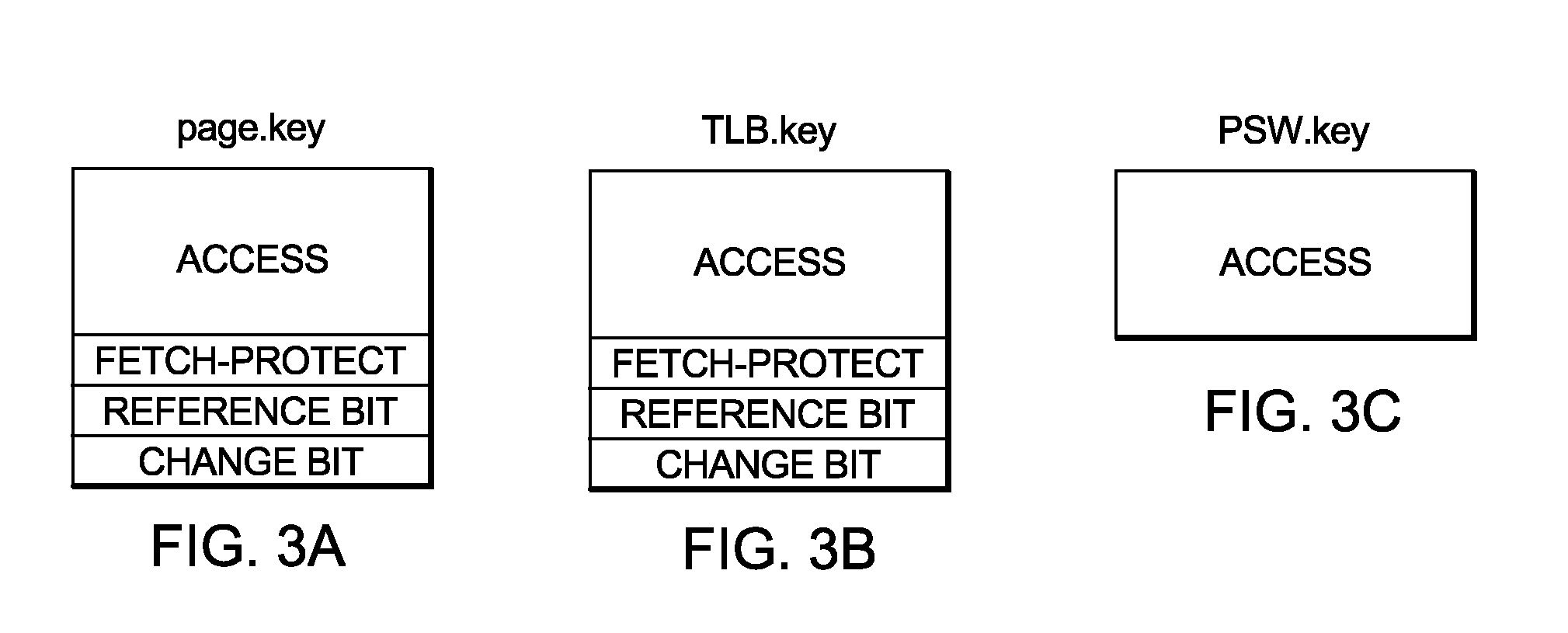

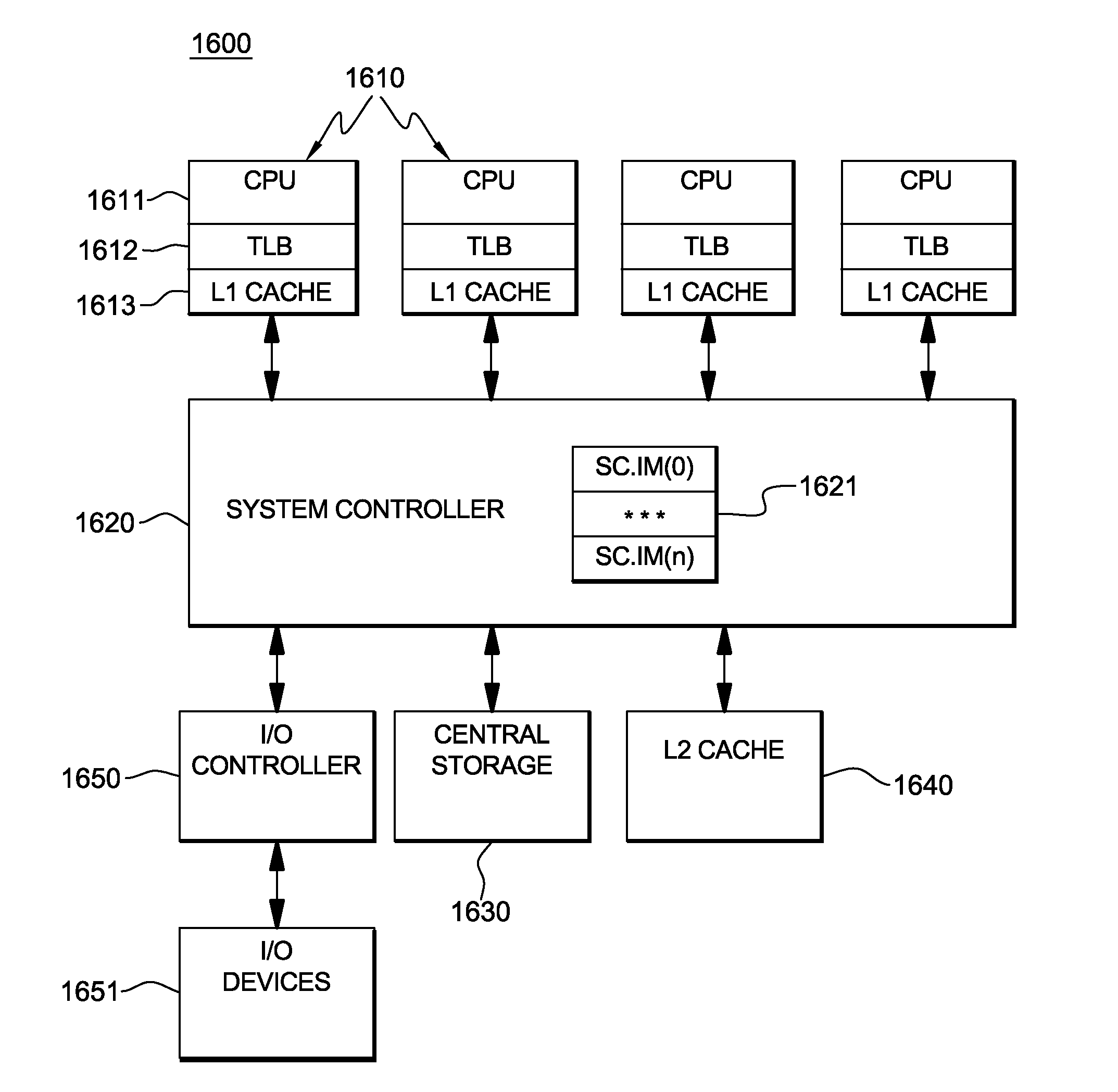

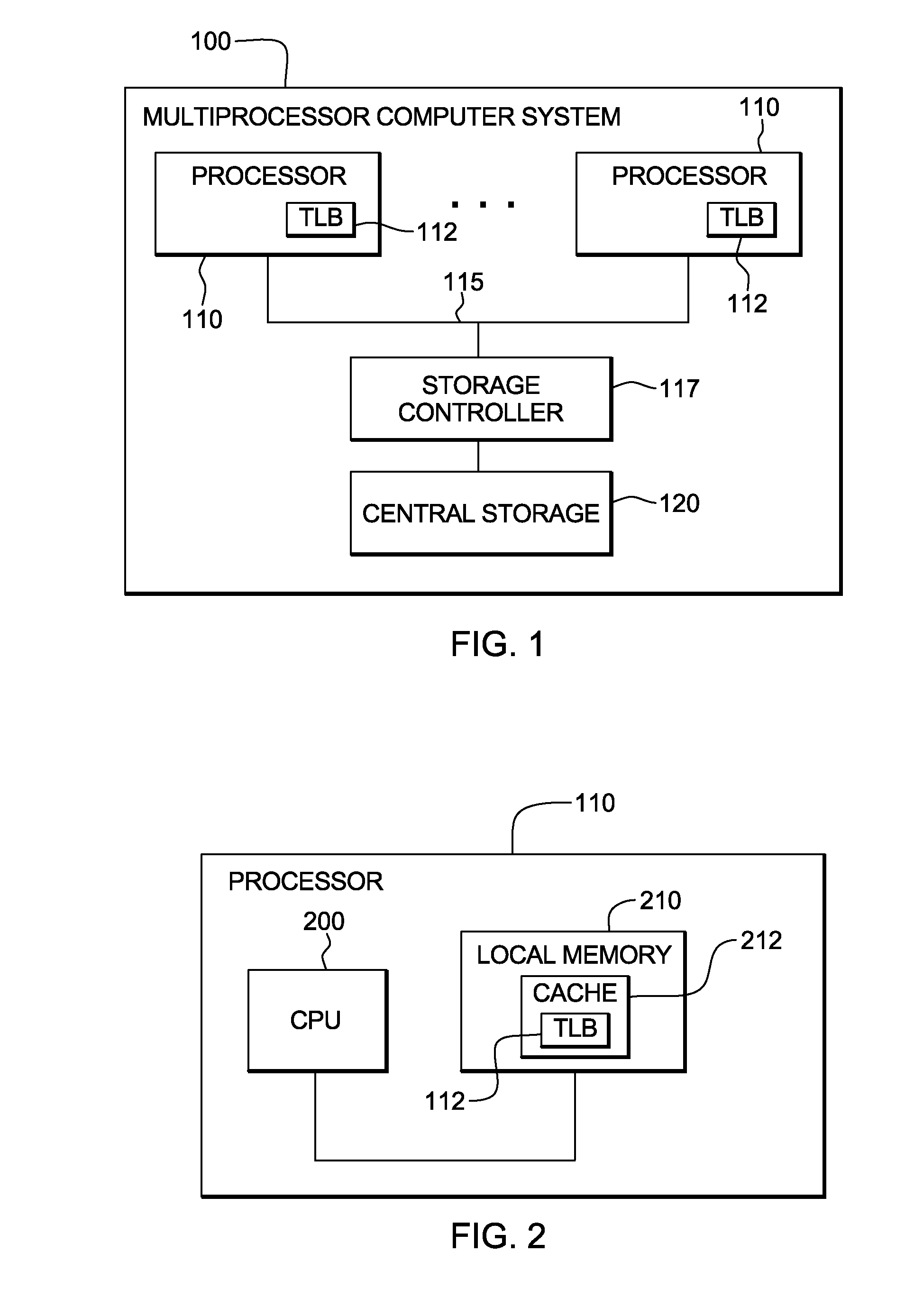

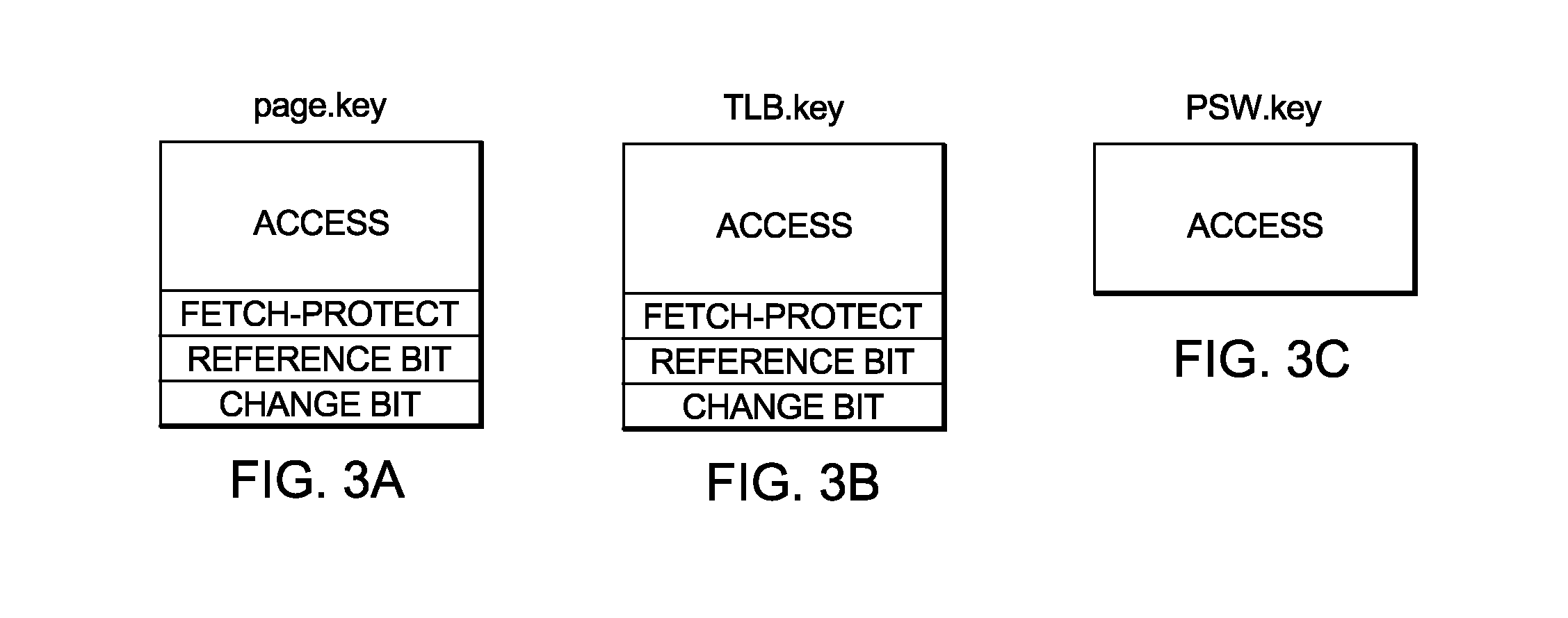

Page invalidation processing with setting of storage key to predefined value

InactiveUS20110145511A1Easy to processMinimizing interprocessor communicationMemory architecture accessing/allocationMemory systemsInterprocessor communicationPage table

Processing within a multiprocessor computer system is facilitated by: setting, in association with invalidate page table entry processing, a storage key at a matching location in central storage of a multiprocessor computer system to a predefined value; and subsequently executing a request to update the storage key to a new storage key, the subsequently executing including determining whether the predefined value is an allowed stale value, and if so, replacing in central storage the storage key of predefined value with the new storage key without requiring purging or updating of the storage key in any local processor cache of the multiprocessor computer system, thus minimizing interprocessor communication pursuant to processing of the request to update the storage key to the new storage key.

Owner:IBM CORP

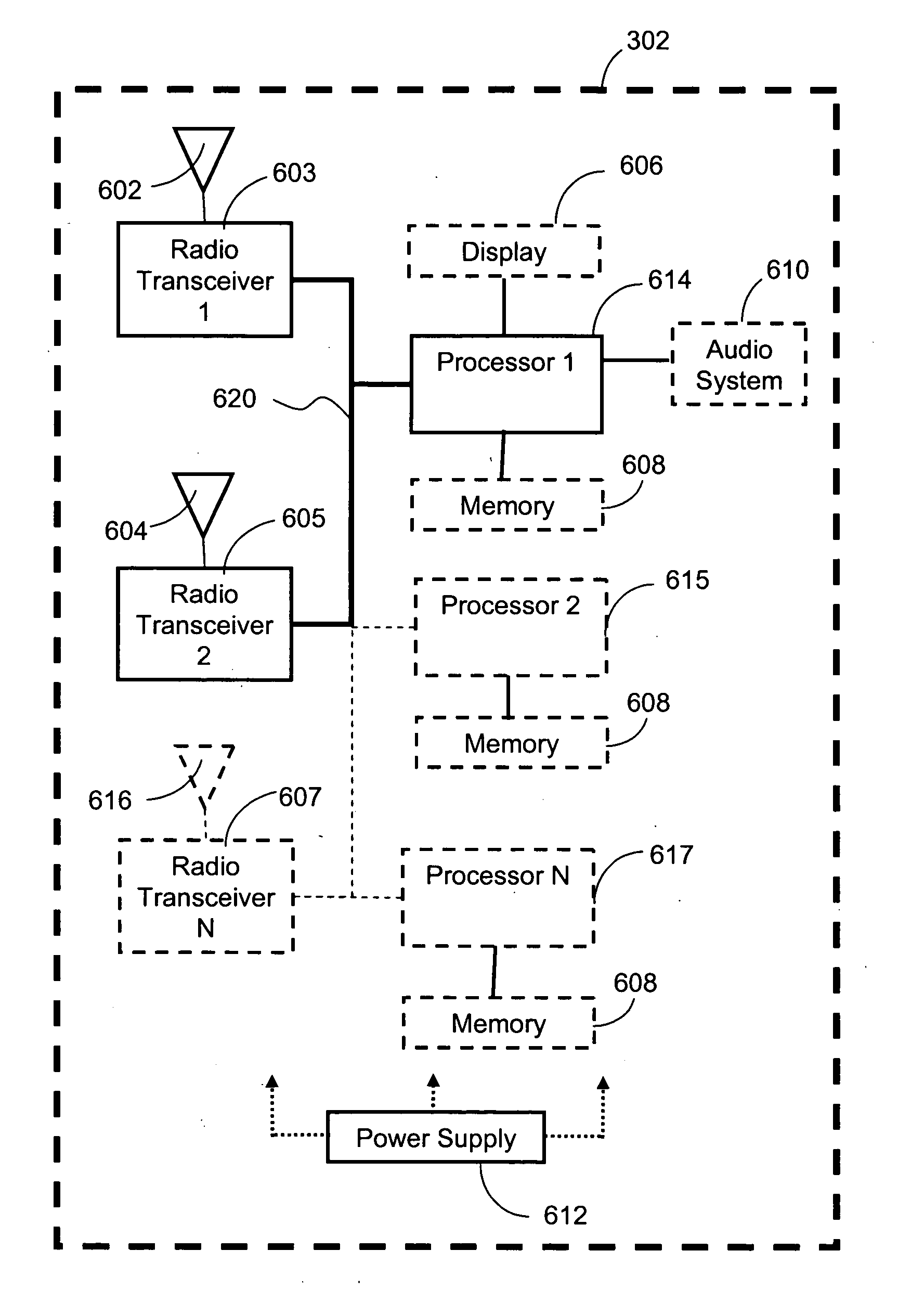

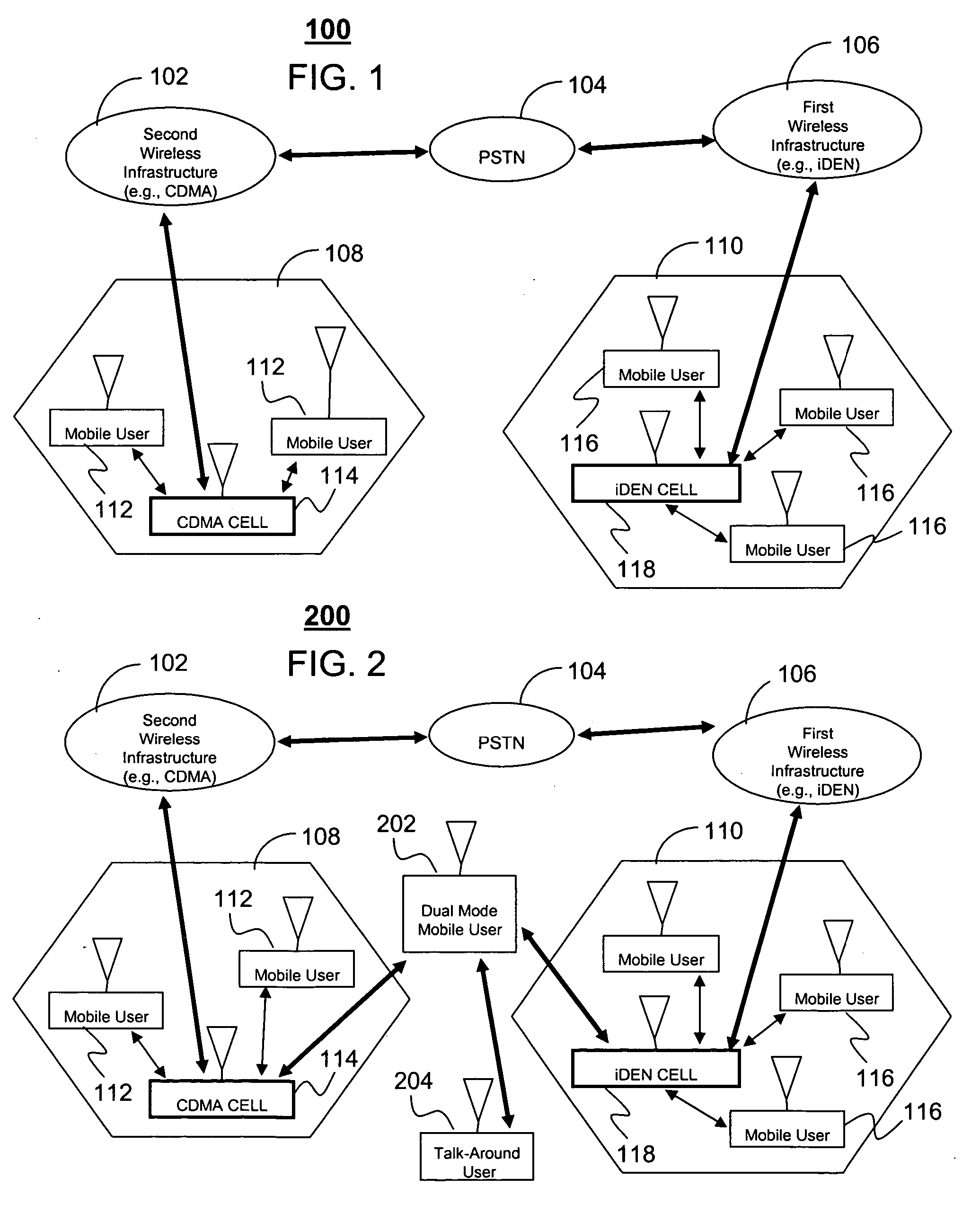

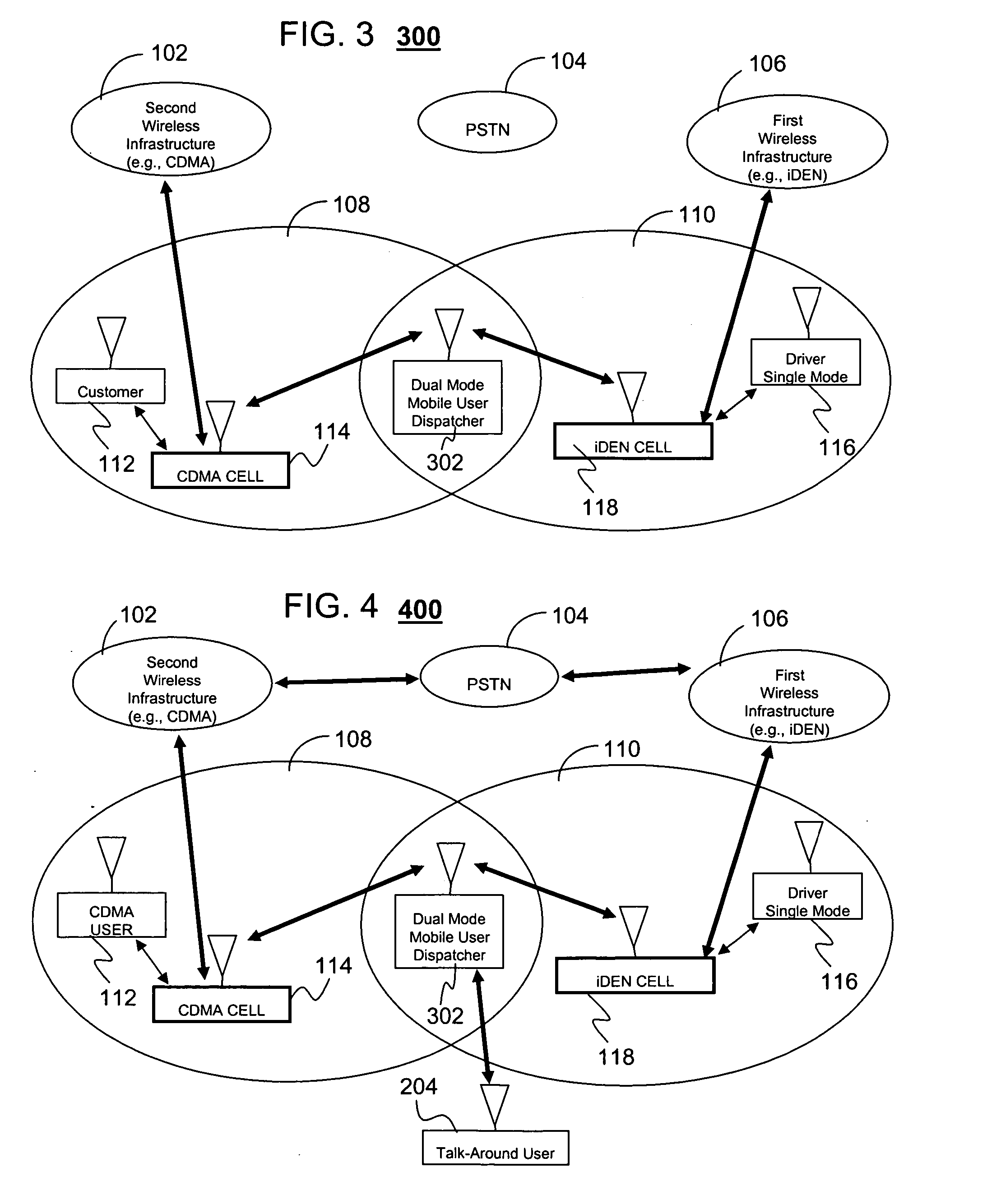

Method and system for communication across different wireless technologies using a multimode mobile device

InactiveUS20070140255A1Connection managementData switching by path configurationWireless communication protocolTelecommunications link

A mobile wireless device (302) can include a first processor (614) for establishing a first communication link using a first wireless communication protocol, a second processor (615) for establishing a second communication link using a second wireless communication protocol different from the first wireless communication protocol, and an interprocessor communication link (620) between the first processor and the second processor enabling communication between the first communication link and the second communication link. The mobile wireless device can serve as a dispatcher coupling a first mobile radio 112 using the first wireless communication protocol with a second mobile radio 116 using the second wireless communication protocol. The first wireless communication protocol can be a cellular communication protocol and the second wireless communication protocol can be a dispatch radio communication protocol. The first wireless communication protocol and the second wireless communication protocol can also utilize a wireline communication link (104).

Owner:MOTOROLA INC

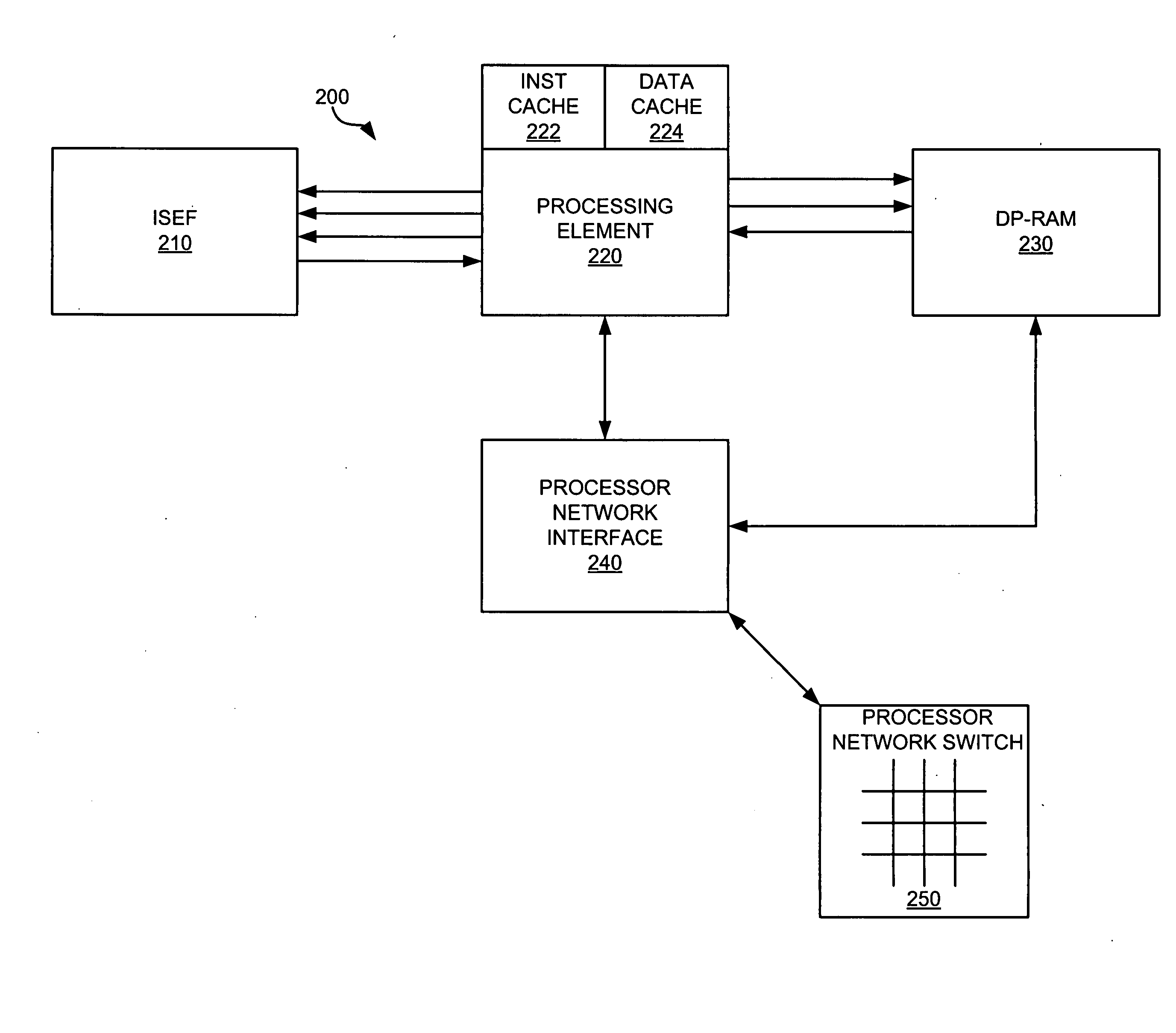

Autonomous signal processing resource for selective series processing of data in transit on communications paths in multi-processor arrangements

InactiveUS20040117519A1General purpose stored program computerElectric digital data processingMulti processorInterprocessor communication

A multi-processor arrangement having an interprocessor communication path between each of every possible pair of processors, in addition to I / O paths to and from the arrangement, having signal processing functions configurably embedded in series with the communication paths and / or the I / O paths. Each processor is provided with a local memory which can be accessed by the local processor as well as by the other processors via the communications paths. This allows for efficient data movement from one processor's local memory to another processor's local memory, such as commonly done during signal processing corner turning operations. Configurable signal processing logic may be configured to host one or more signal processing functions which allow data to be autonomously accessed from the processor local memories, processed, and re-deposited in a local memory.

Owner:GE FANUC EMBEDDED SYST

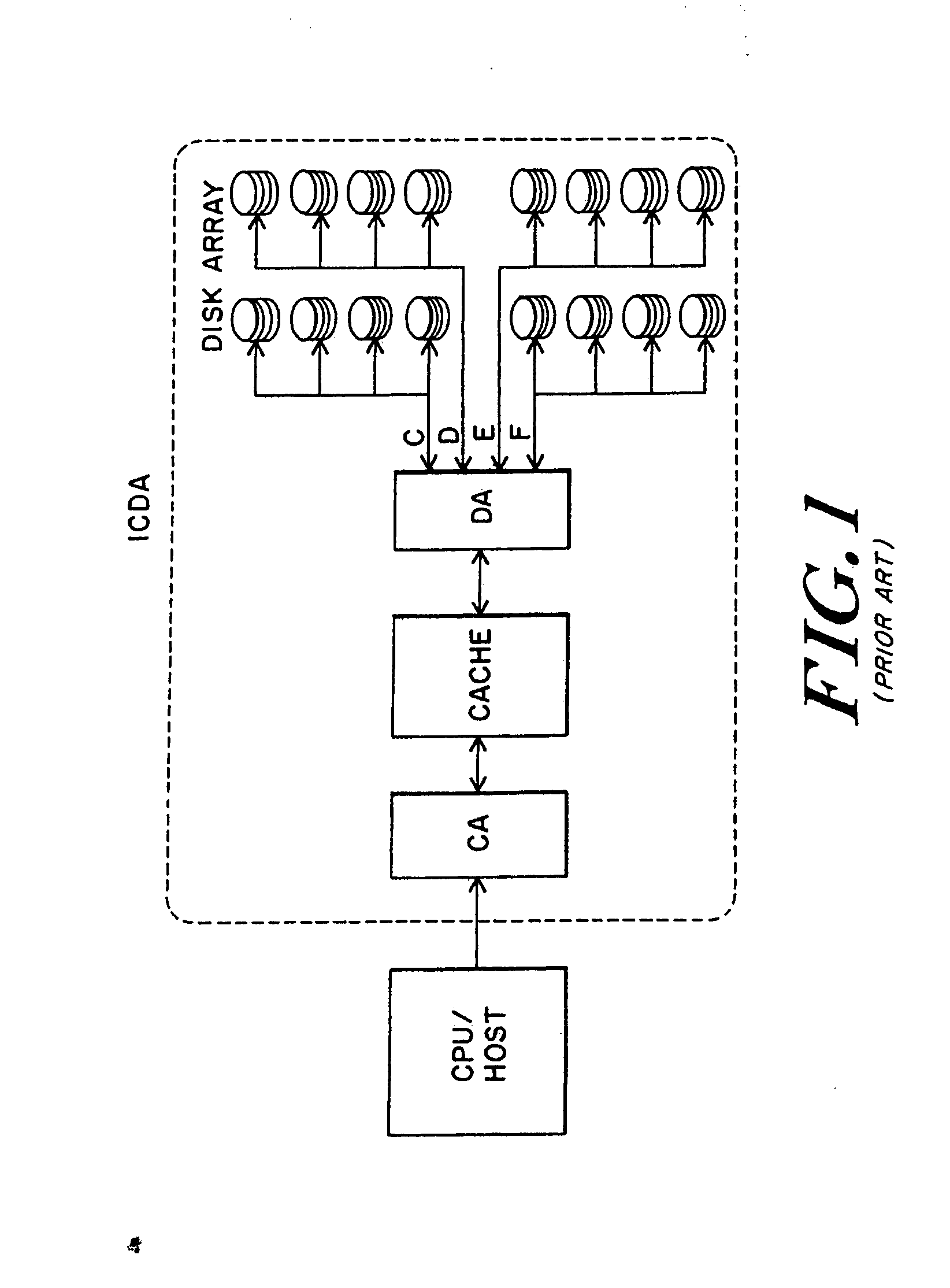

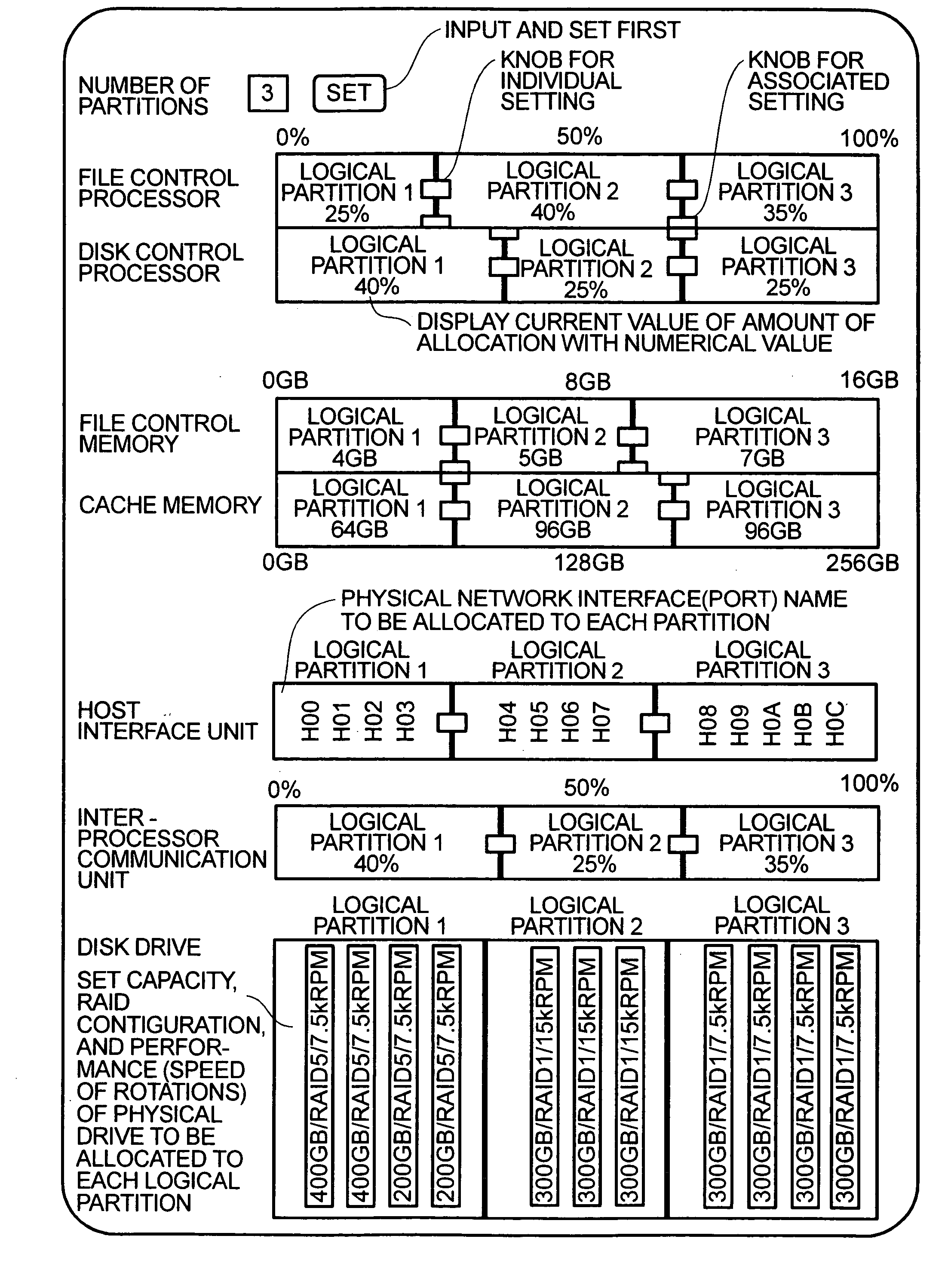

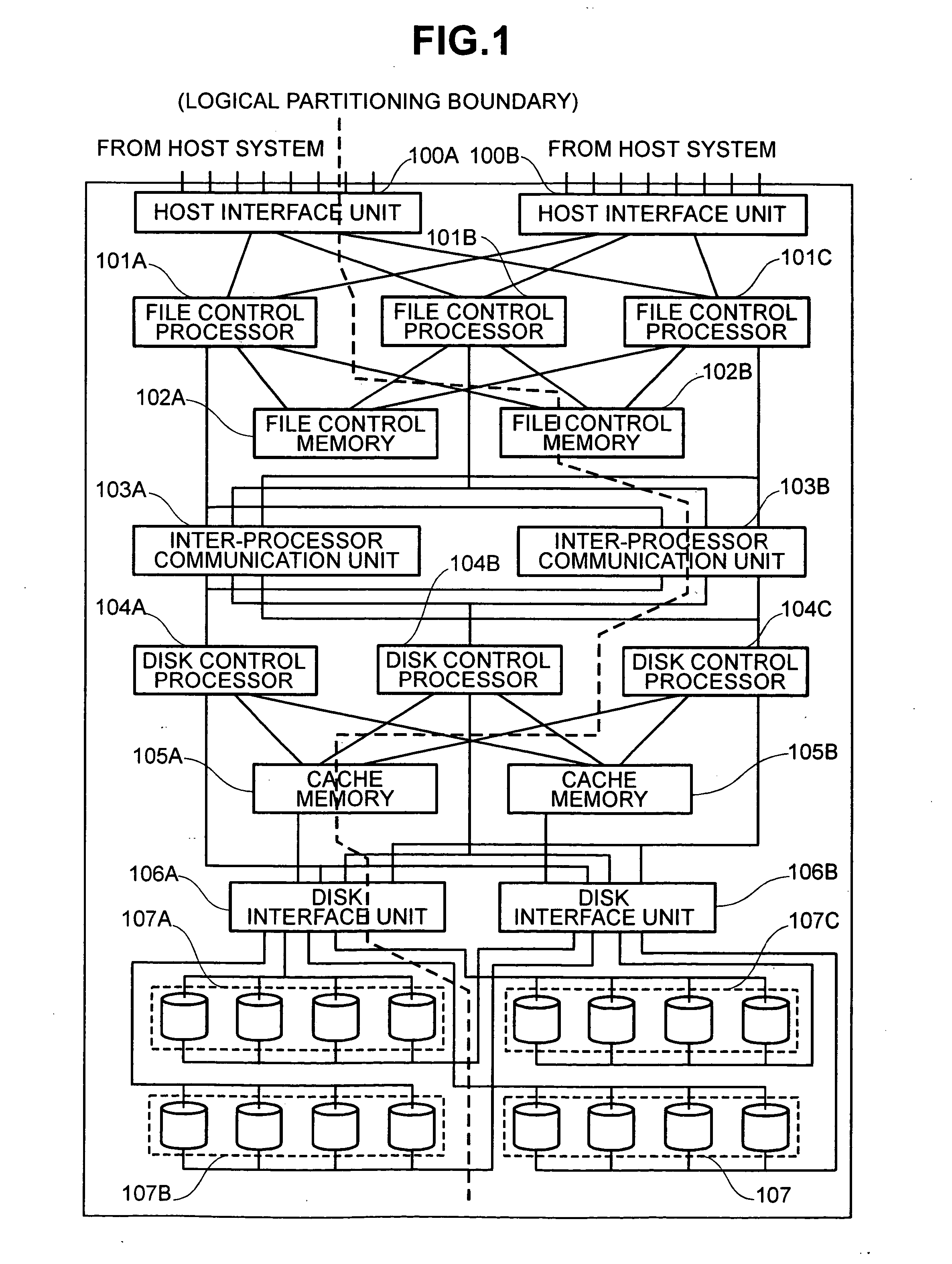

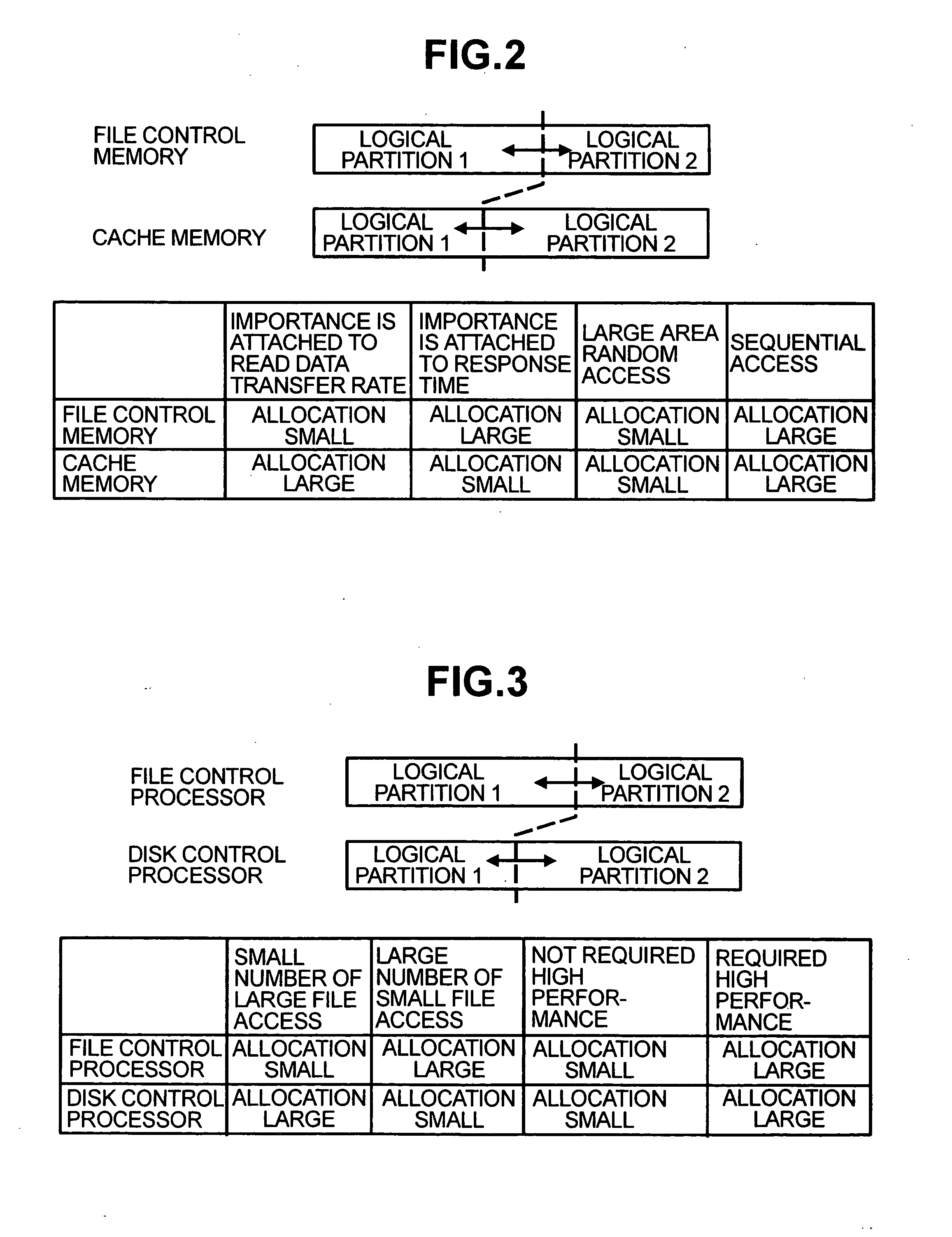

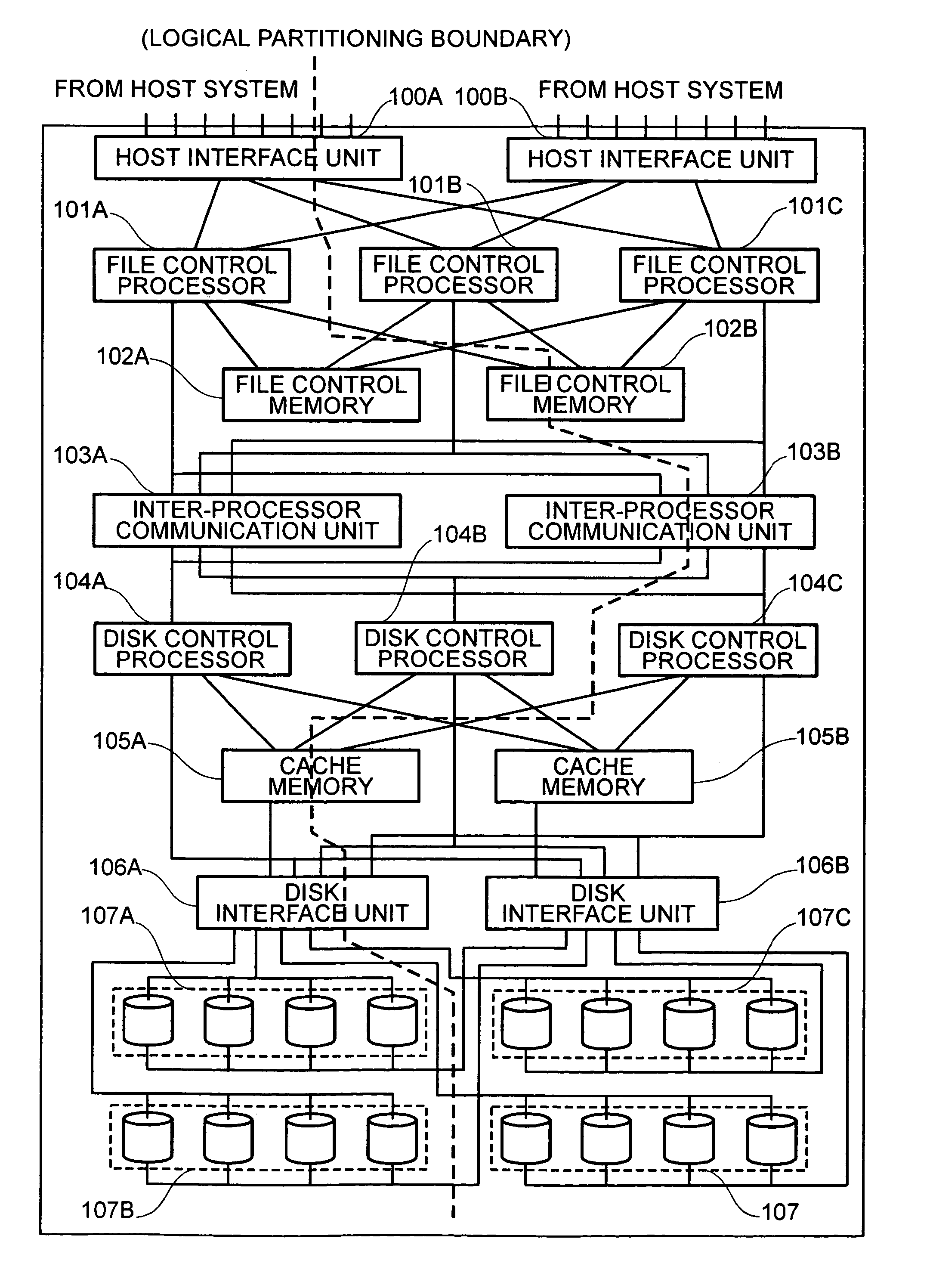

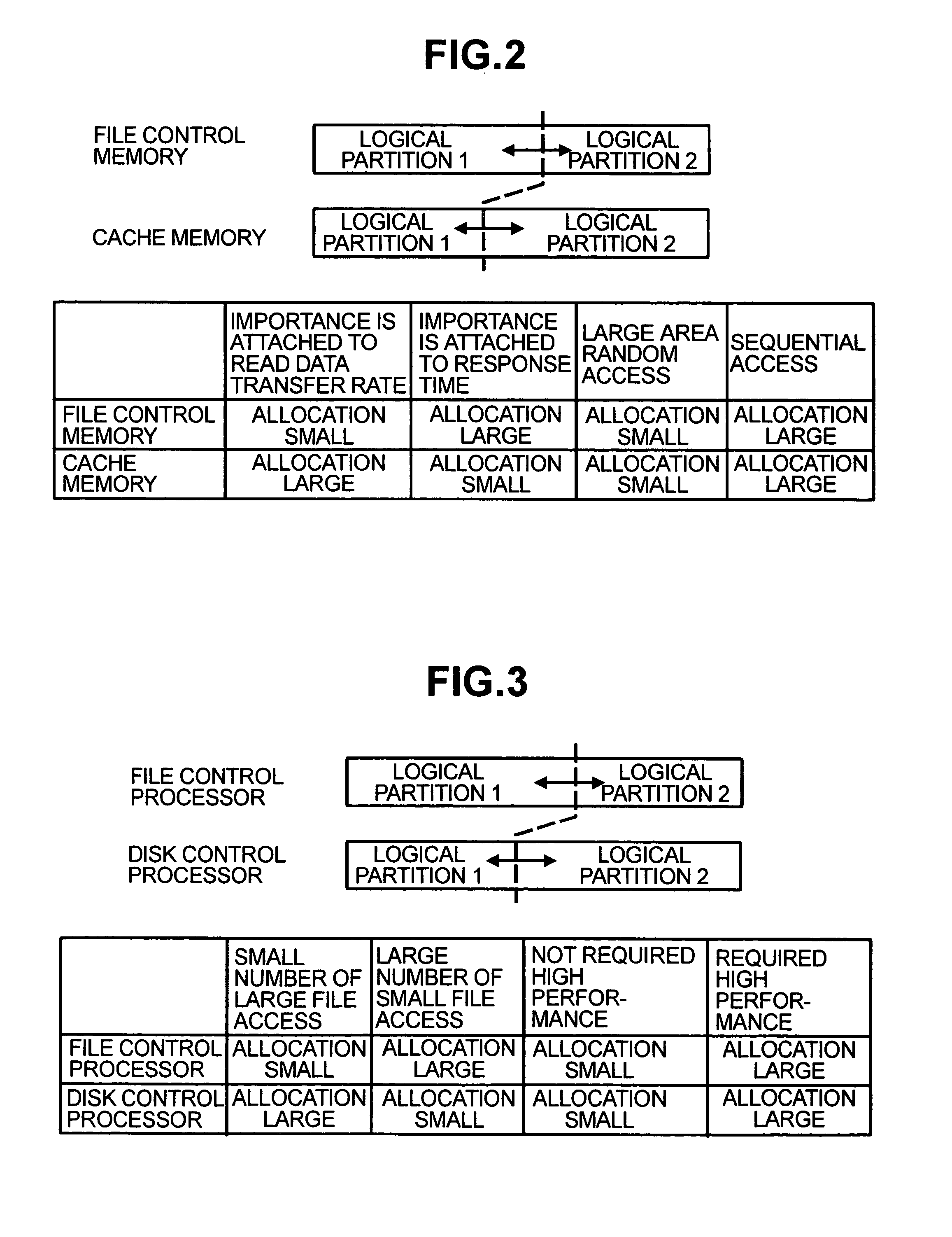

Storage having logical partitioning capability and systems which include the storage

InactiveUS20050091454A1Reduce controlEliminate mutual interferenceInput/output to record carriersMemory systemsCommunication unitInterprocessor communication

A storage includes: host interface units; file control processors which receives a file input / output request and translates the file input / output request into a data input / output request; file control memories which store translation control data; groups of disk drives; disk control processors; disk interface units which connect the groups of disk drives and the disk control processors; cache memories; and inter-processor communication units. The storage logically partitions these devices to cause the partitioned devices to operate as two or more virtual NASs.

Owner:HITACHI LTD

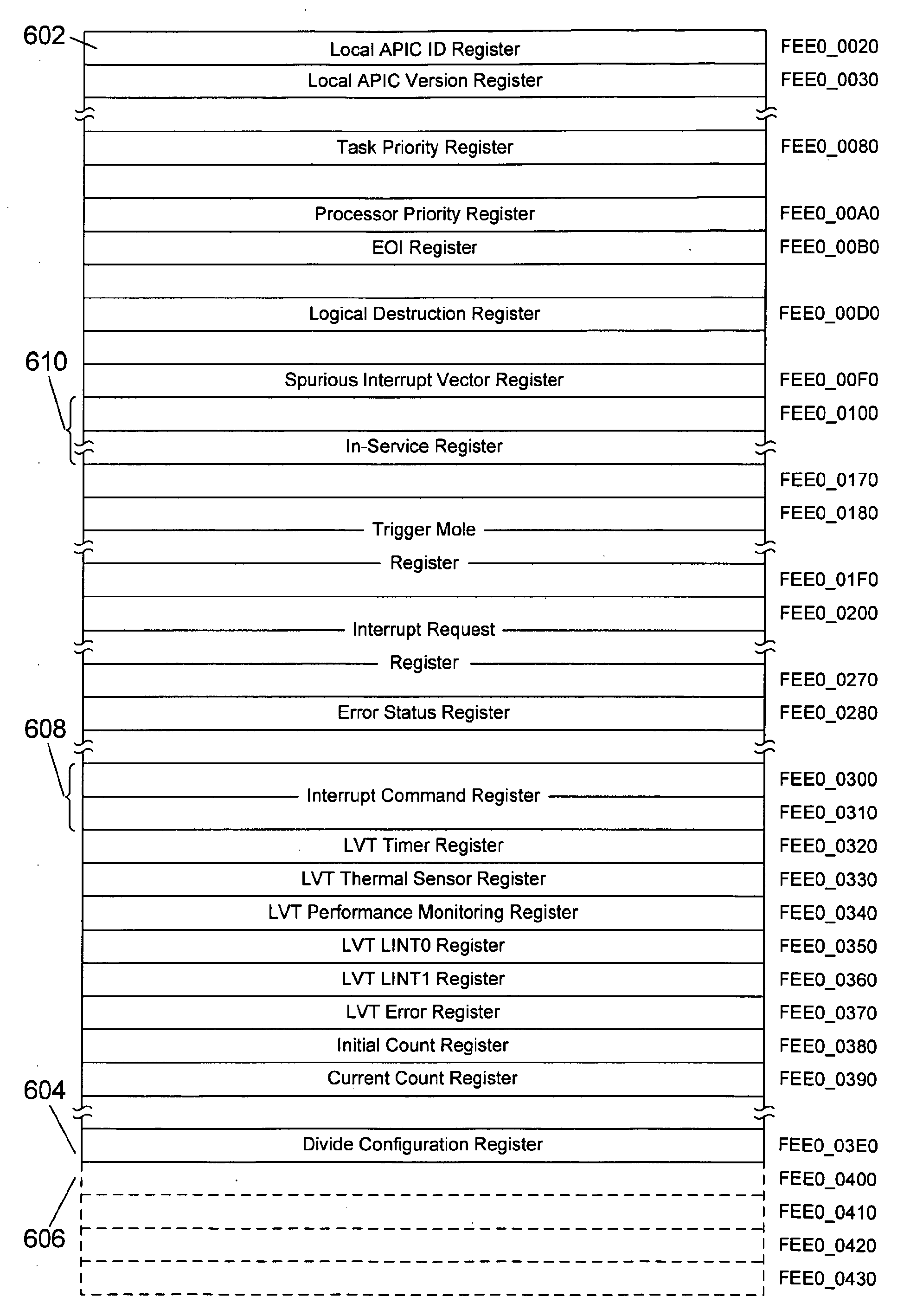

Method and System for Generating and Delivering Inter-Processor Interrupts in a Multi-Core Processor and in Ceterain Shared Memory Multi-Processor Systems

ActiveUS20110047310A1Facilitate shared-memory-based communicationEfficient use ofProgram controlMulti processorInter-processor interrupt

Certain embodiments of the present invention arc directed to providing efficient and easily-applied mechanisms for inter-core and inter-processor communications and inter-core and inter-processor signaling within multi-core microprocessors and certain multi-processor systems. In one embodiment of the present invention, local advanced programmable interrupt controllers within, or associated with, cores of a multi-core microprocessor and / or processors of a multi-processor system are enhanced so that the local advanced programmable interrupt controllers can be configured to automatically generate inter-core and inter-processor interrupts when WRITE operations are directed to particular regions of shared memory.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

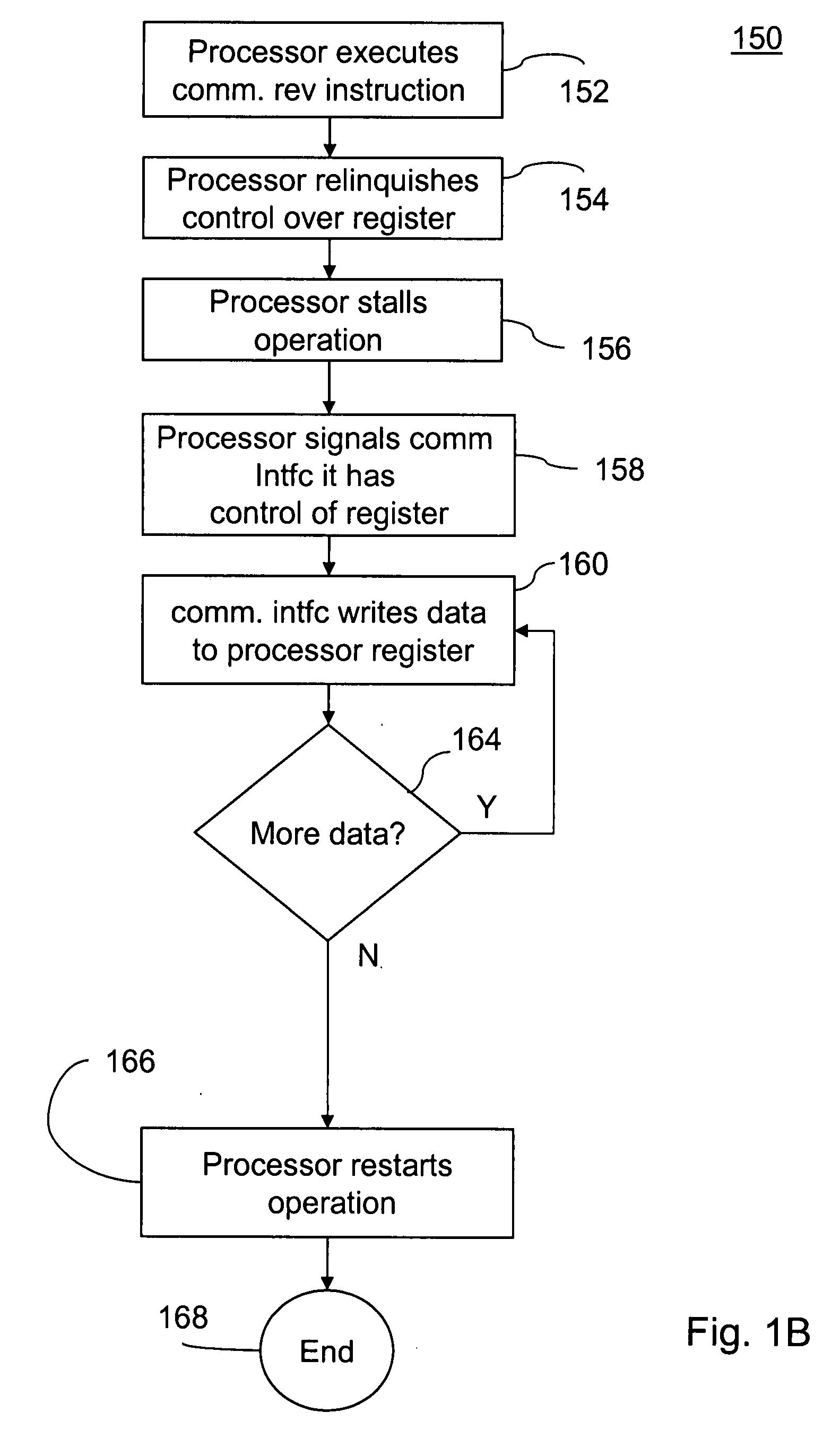

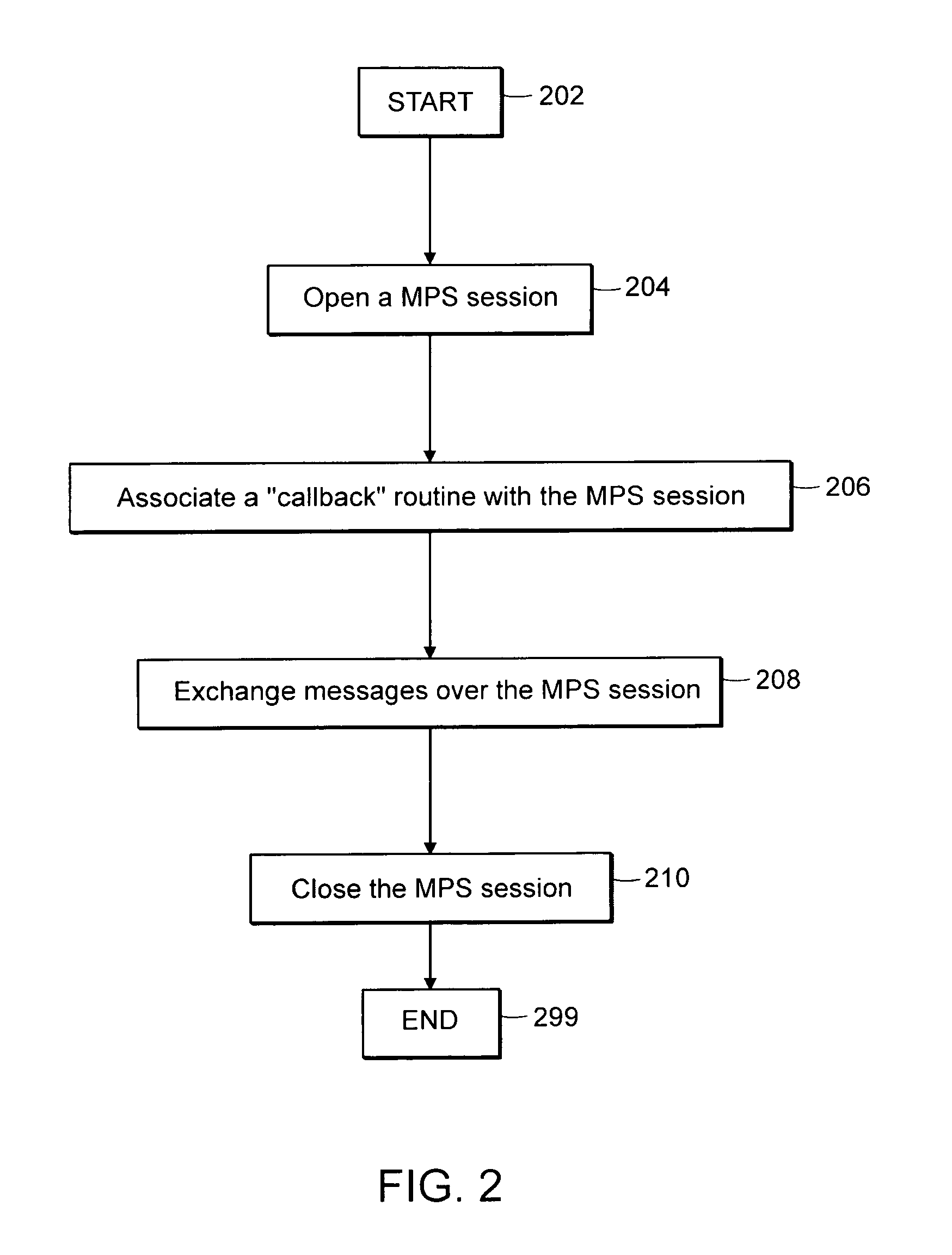

Inter-processor communication method

ActiveUS20080086626A1Reduce power consumptionImprove performanceSingle instruction multiple data multiprocessorsInstruction analysisCommunication interfaceCommunications system

Inter-processor communication systems and methods that define within the instruction set of the microprocessor a command for directing the microprocessor to relinquish control over at least one of the microprocessor's internal registers. The microprocessor may then signal a communication interface that collects data from external sources. The communication interface takes control over the internal register released by the microprocessor and inputs the collected external data directly into the internal register of the microprocessor. Once data is place into the internal register, control of that register may be returned to the microprocessor.

Owner:SYNOPSYS INC

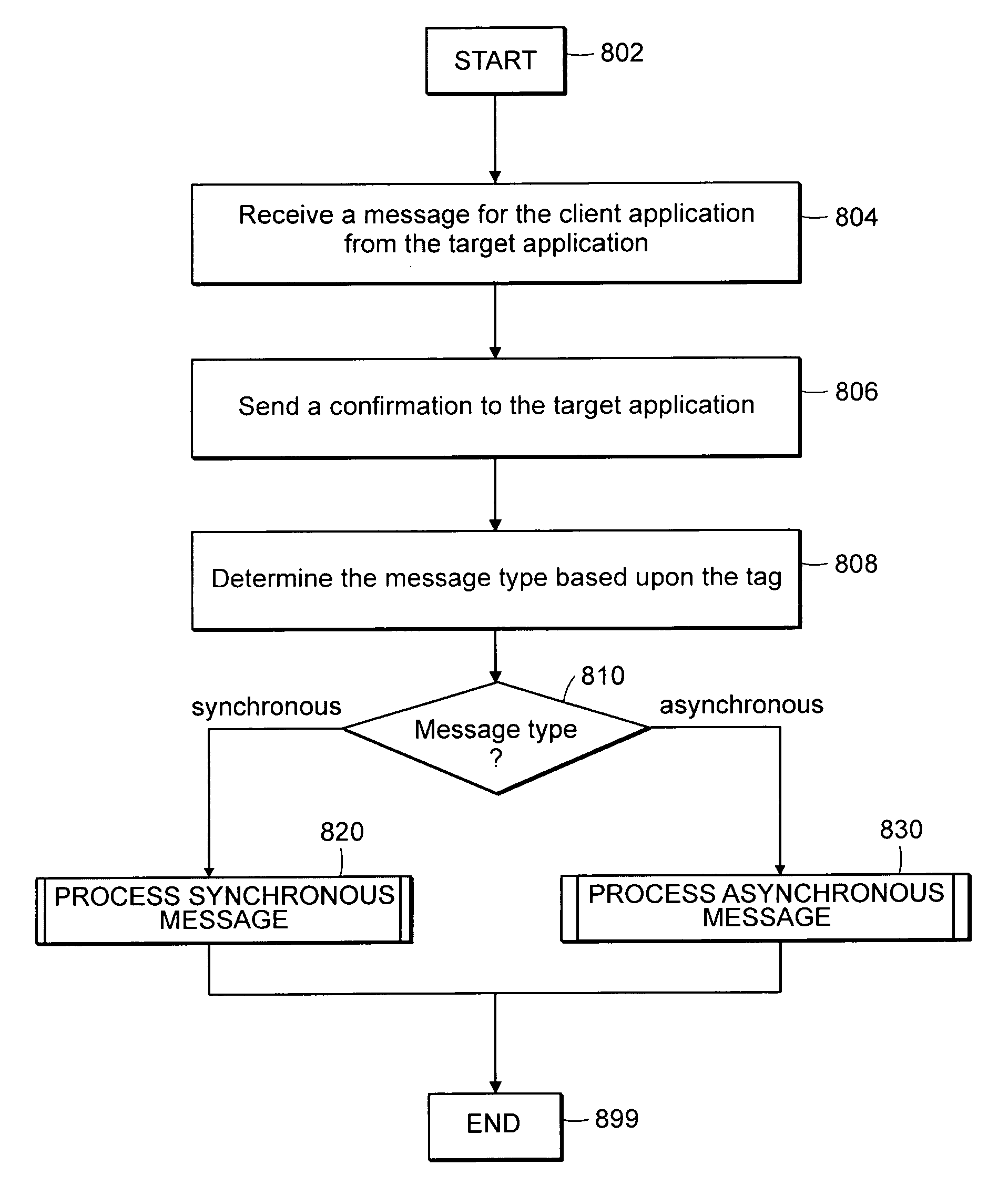

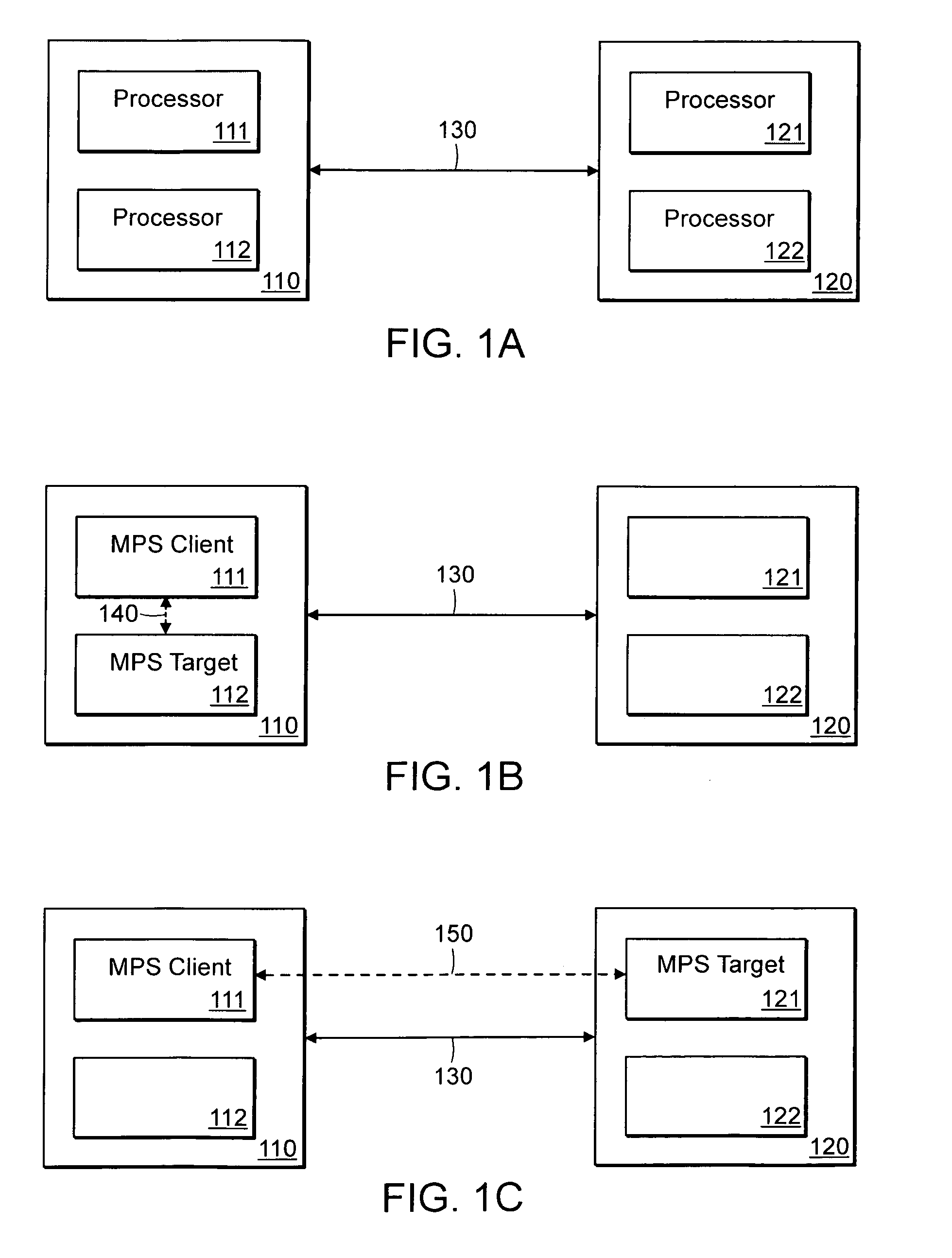

System, device and method for interprocessor communication in a computer system

InactiveUS7013465B1Program controlInput/output processes for data processingAsynchronous communicationTelecommunications link

A system, device, and method for interprocessor communication in a computer system utilizes a special Message Passing Service (MPS) to provide interprocessor communications. The MPS enables a client application running on one processor in a computer to communicate with a target application running a different processor in the same or a different computer. In order for the client application to communicate with the target application, the client application establishes a session to the target application over an existing communication link using the MPS. The MPS provides for both synchronous and asynchronous communication services. When the client application establishes the session to the target application, the client application specifies, among other things, a “callback” routine. The MPS invokes the “callback” routine to report certain asynchronous events to the client application. The MPS blocks the client application during certain synchronous operations so that the client application does not proceed until the synchronous operation is completed.

Owner:EMC IP HLDG CO LLC +1

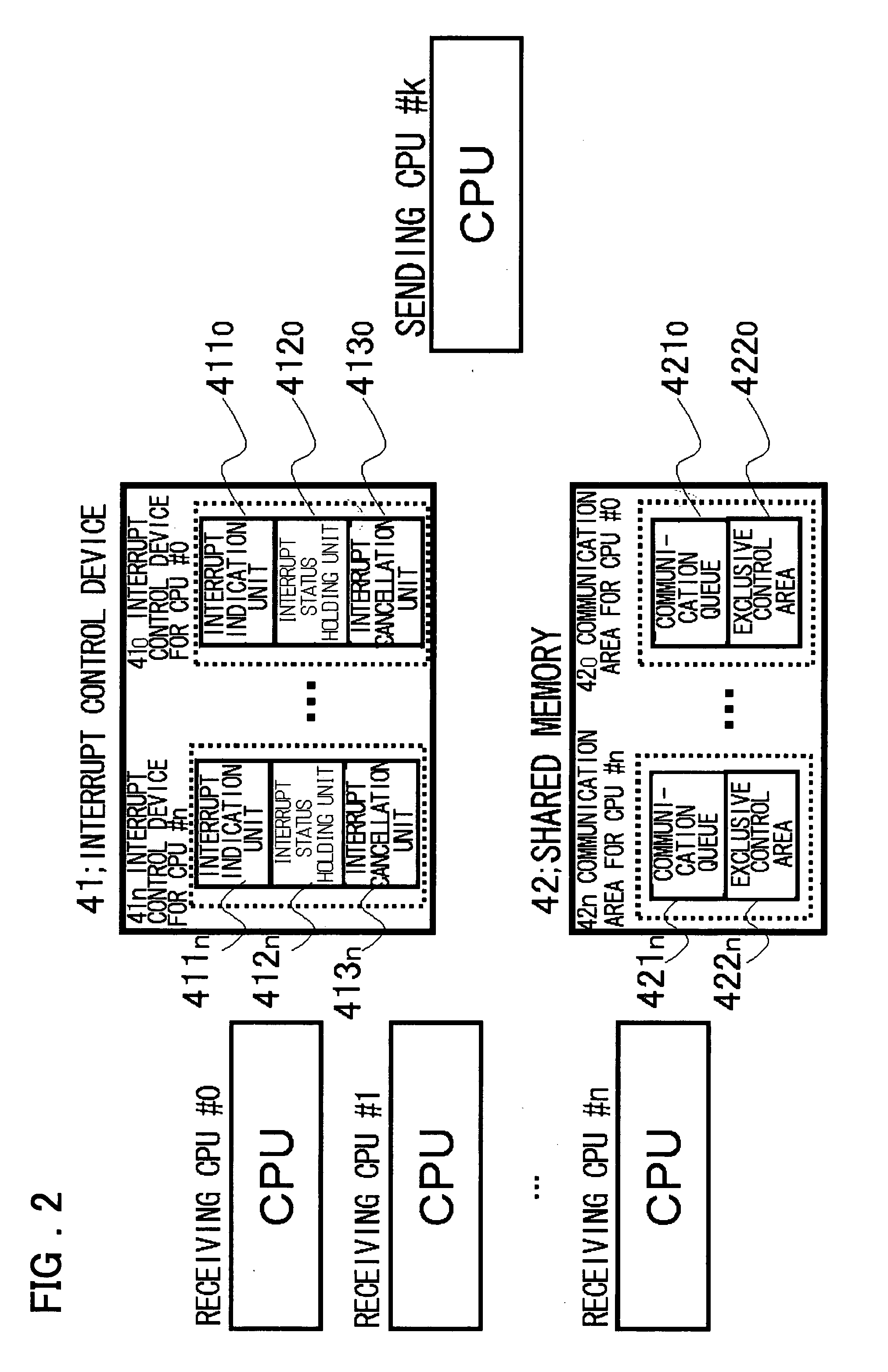

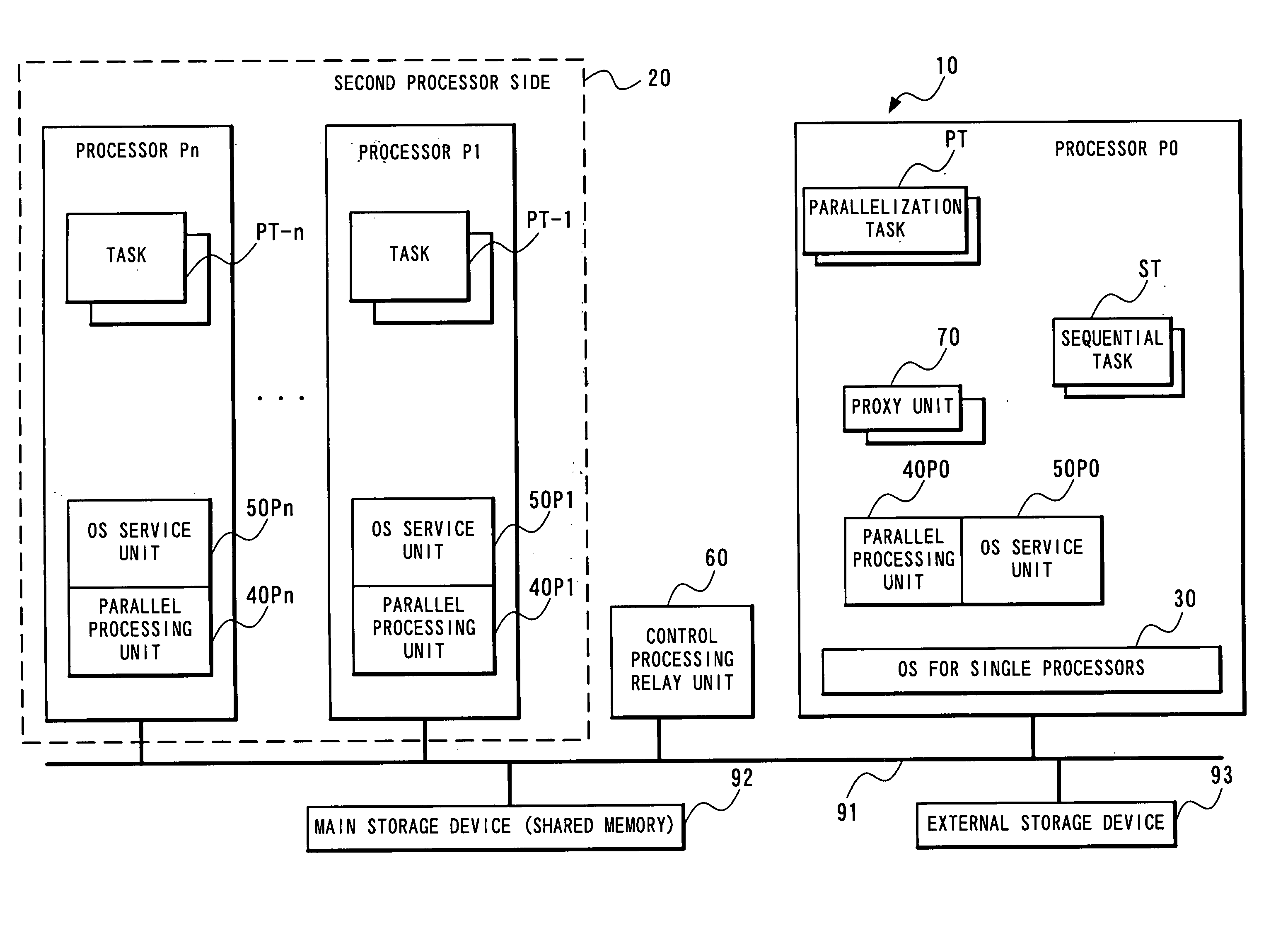

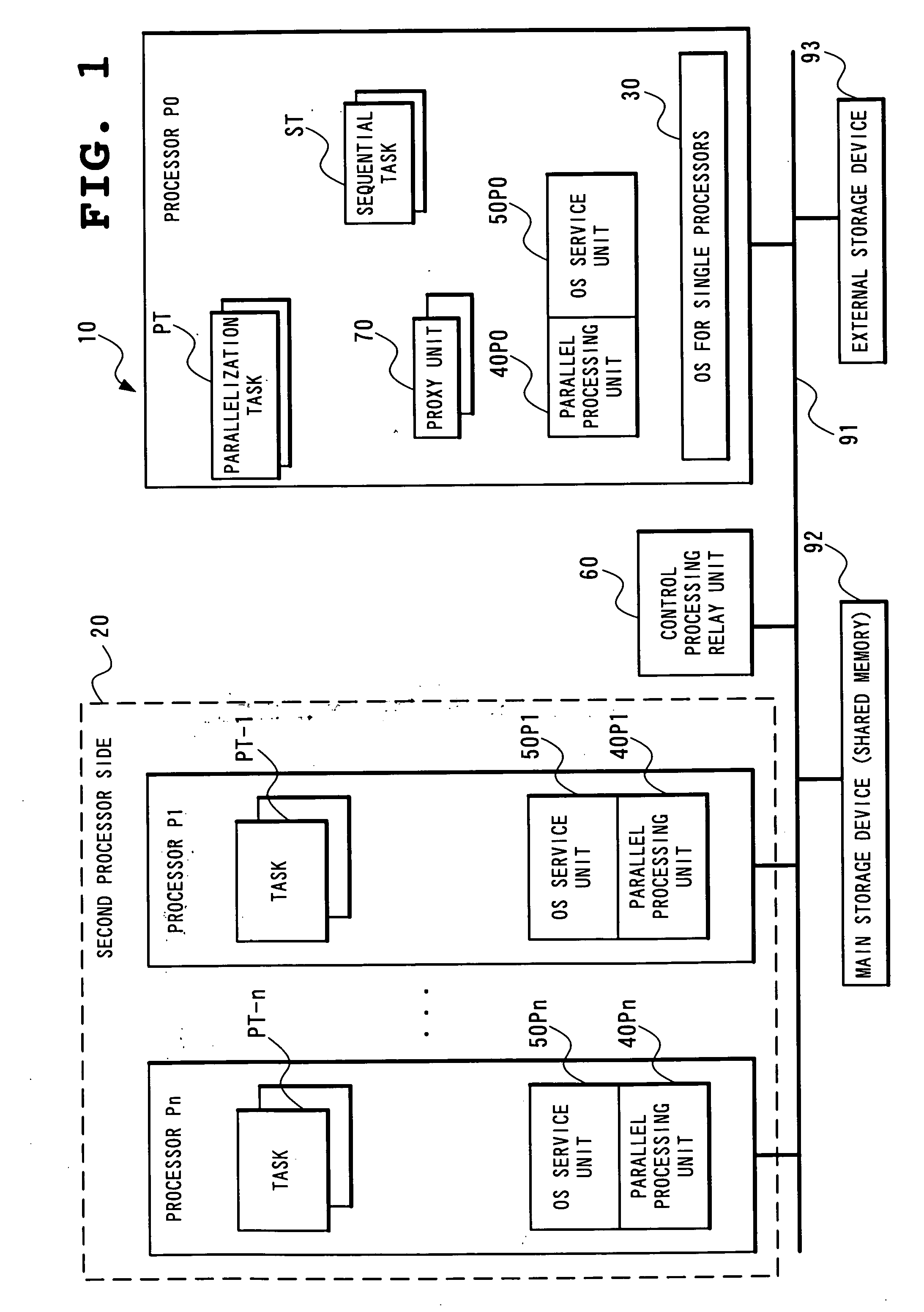

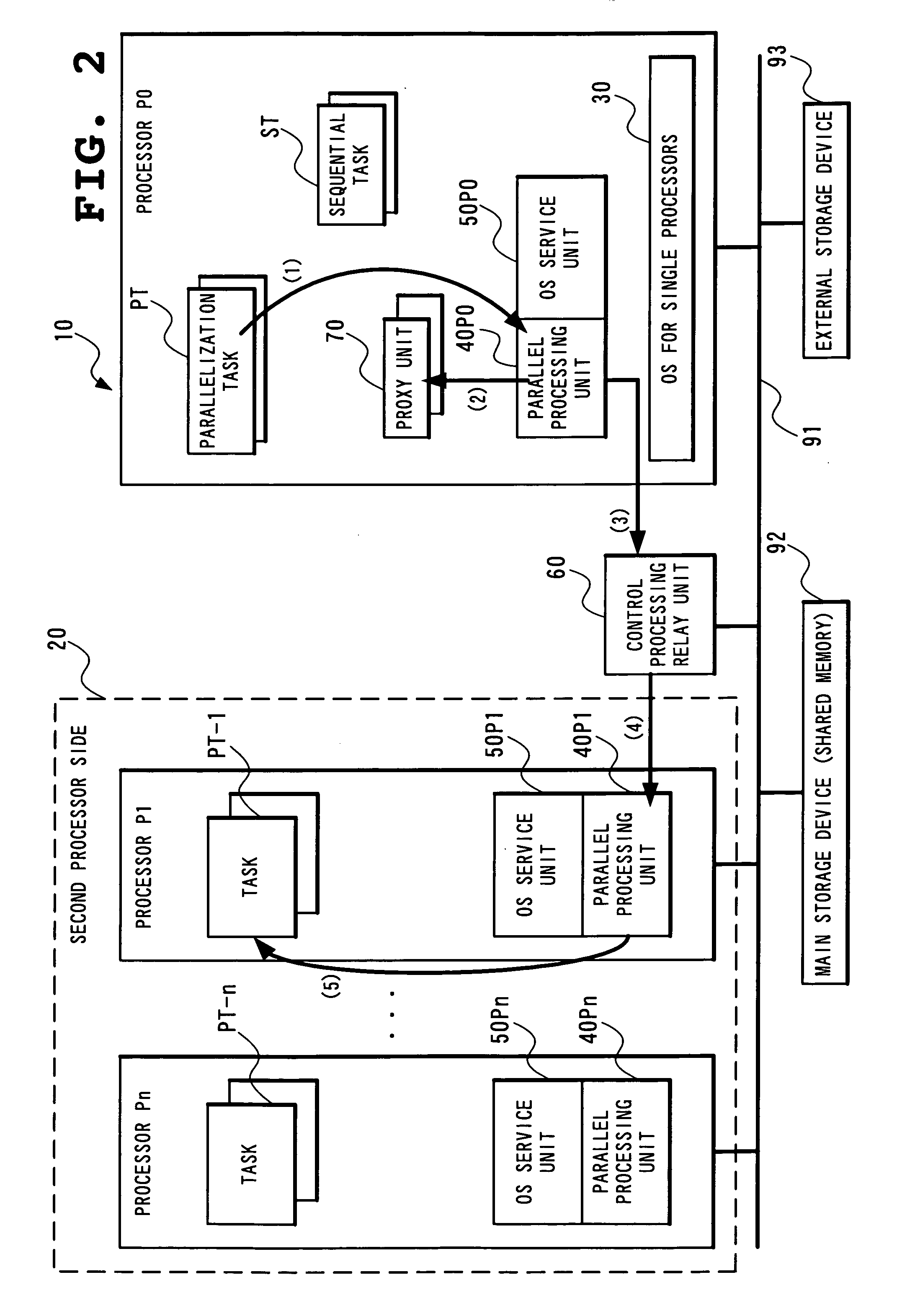

Inter-processor communication system in parallel processing system by OS for single processors and program thereof

ActiveUS20050229184A1Digital computer detailsMultiprogramming arrangementsCommunications systemOperational system

On a parallel processing system by an OS for single processors which operates, on a multiprocessor, an OS for single processors and an existing application to realize parallel processing by the multiprocessor with respect to the application, each processor includes a communication proxy unit which transfers data between tasks spreading over the processors by proxy and the communication proxy unit on a processor in which a task on a transmission side operates holds information about an address, on a processor, of a task on a reception side to receive data transferred from the task on the transmission side as proxy for the task on the reception side.

Owner:NEC CORP

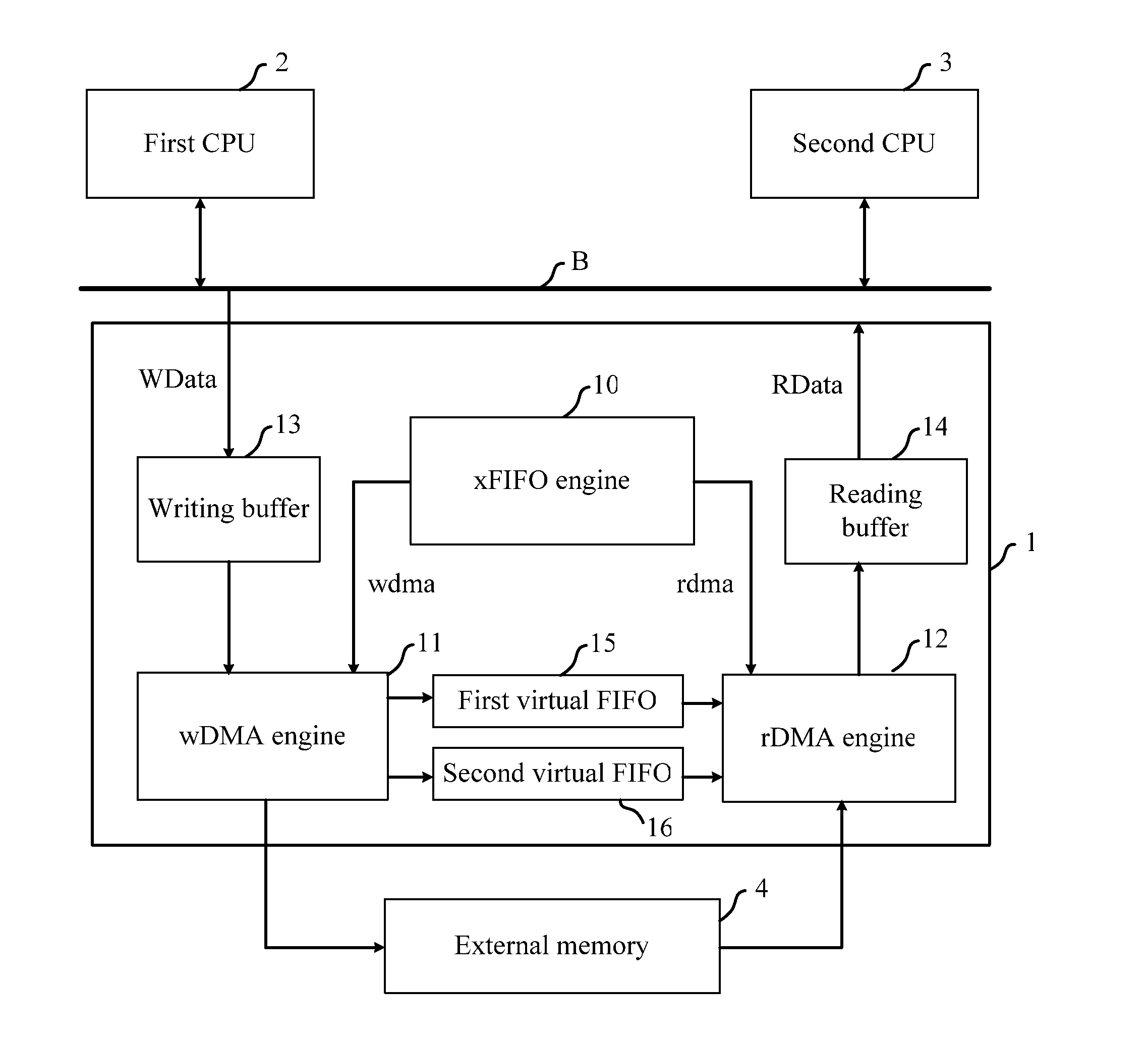

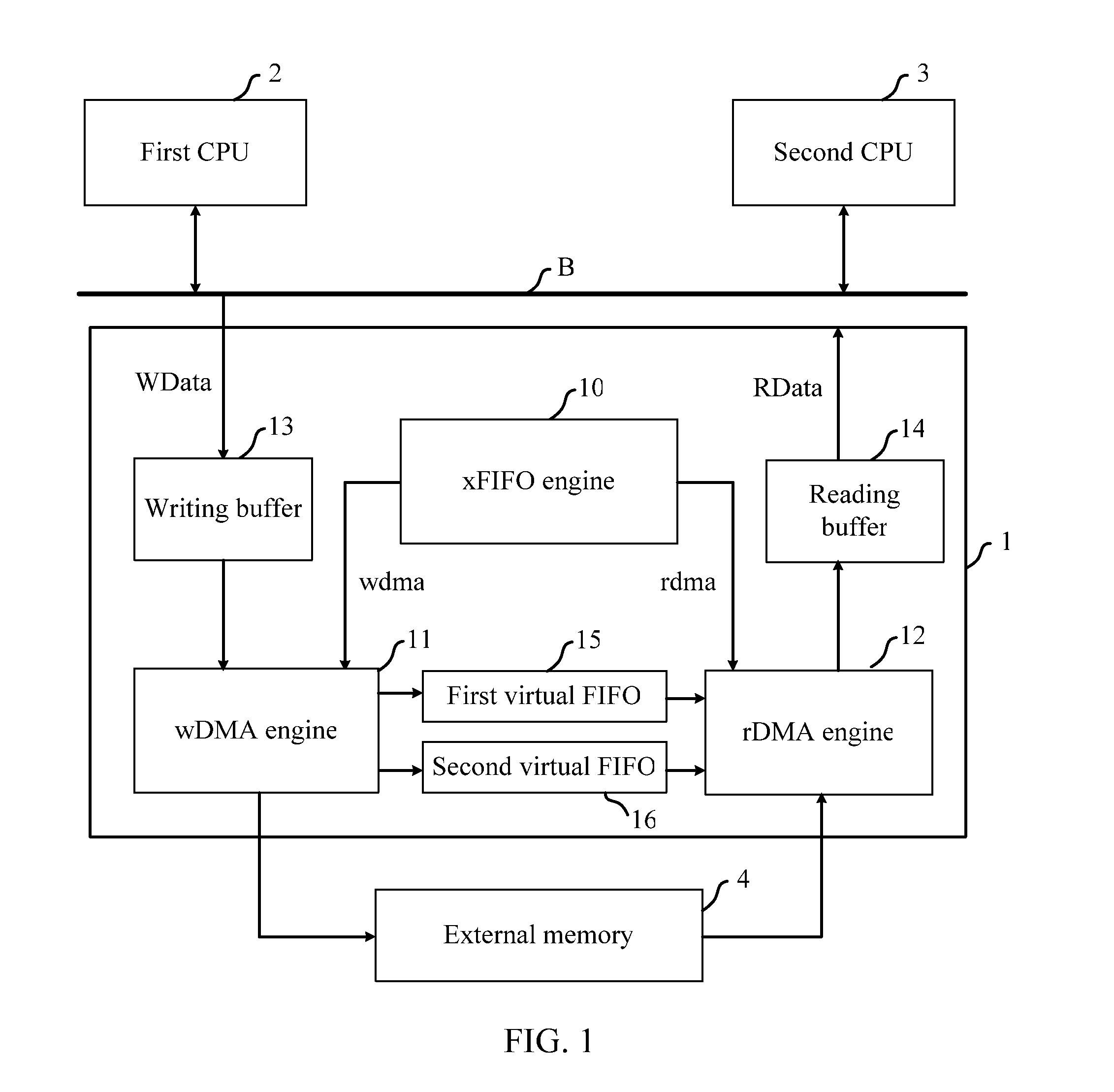

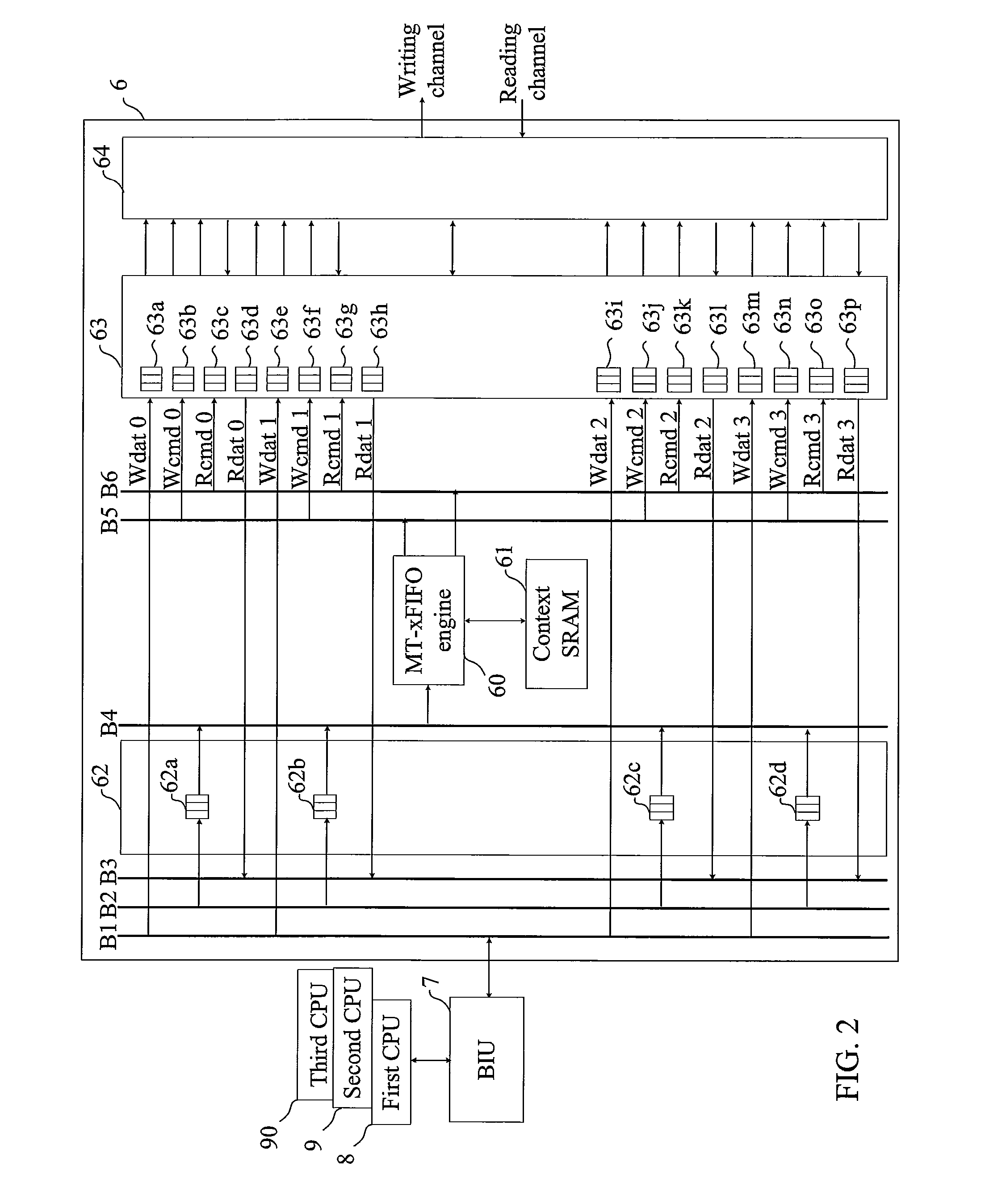

Hardware assisted inter-processor communication

InactiveUS20100325334A1Reduce access latencyCheap off-chip memoryMultiple digital computer combinationsElectric digital data processingProcessor registerInterprocessor communication

An external memory based FIFO (xFIFO) apparatus coupled to an external memory and a register bus is disclosed. The xFIFO apparatus includes an xFIFO engine, a wDMA engine, an rDMA engine, a first virtual FIFO, and a second virtual FIFO. The xFIFO engine receives a FIFO command from the register bus and generates a writing DMA command and a reading DMA command. The wDMA engine receives the writing DMA command from the xFIFO engine and forwards an incoming data to the external memory. The rDMA engine receives the reading DMA command from the xFIFO engine and pre-fetches a FIFO data from the external memory. The wDMA engine and the rDMA engine synchronize with each other via the first virtual FIFO and the second virtual FIFO.

Owner:ABLAZE WIRELESS

Reducing interprocessor communications pursuant to updating of a storage key

InactiveUS20110145510A1Memory adressing/allocation/relocationMulti processorInterprocessor communication

Processing within a multiprocessor computer system is facilitated by: deciding by a processor, pursuant to processing of a request to update a previous storage key to a new storage key, whether to purge the previous storage key from, or update the previous storage key in, local processor cache of the multiprocessor computer system. The deciding includes comparing a bit value(s) of one or more required components of the previous storage key to respective predefined allowed stale value(s) for the required component(s), and leaving the previous storage key in local processor cache if the bit value(s) of the required component(s) in the previous storage key equals the respective predefined allowed stale value(s) for the required component(s). By selectively leaving the previous storage key in local processor cache, interprocessor communication pursuant to processing of the request to update the previous storage key to the new storage key is minimized.

Owner:IBM CORP

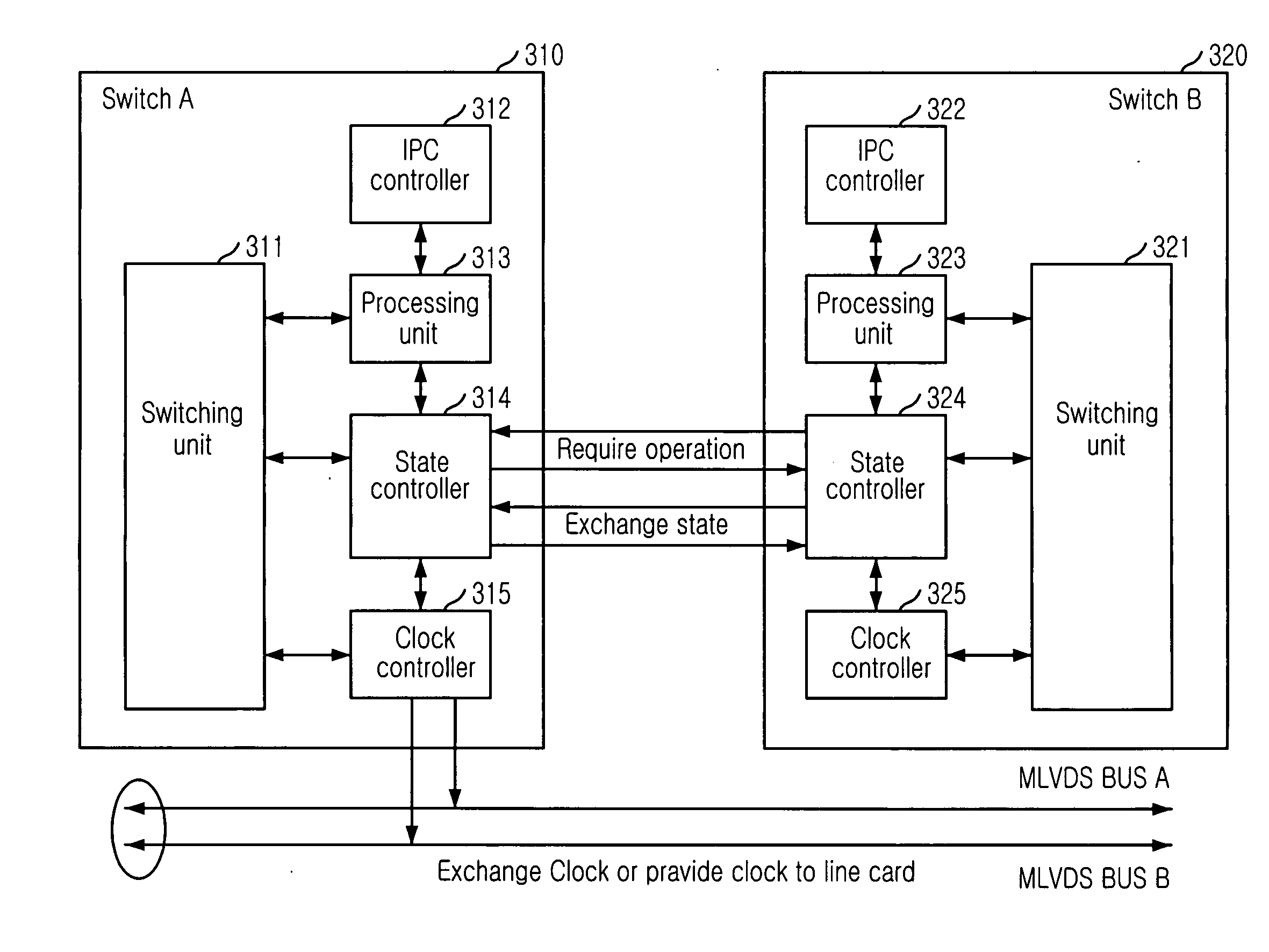

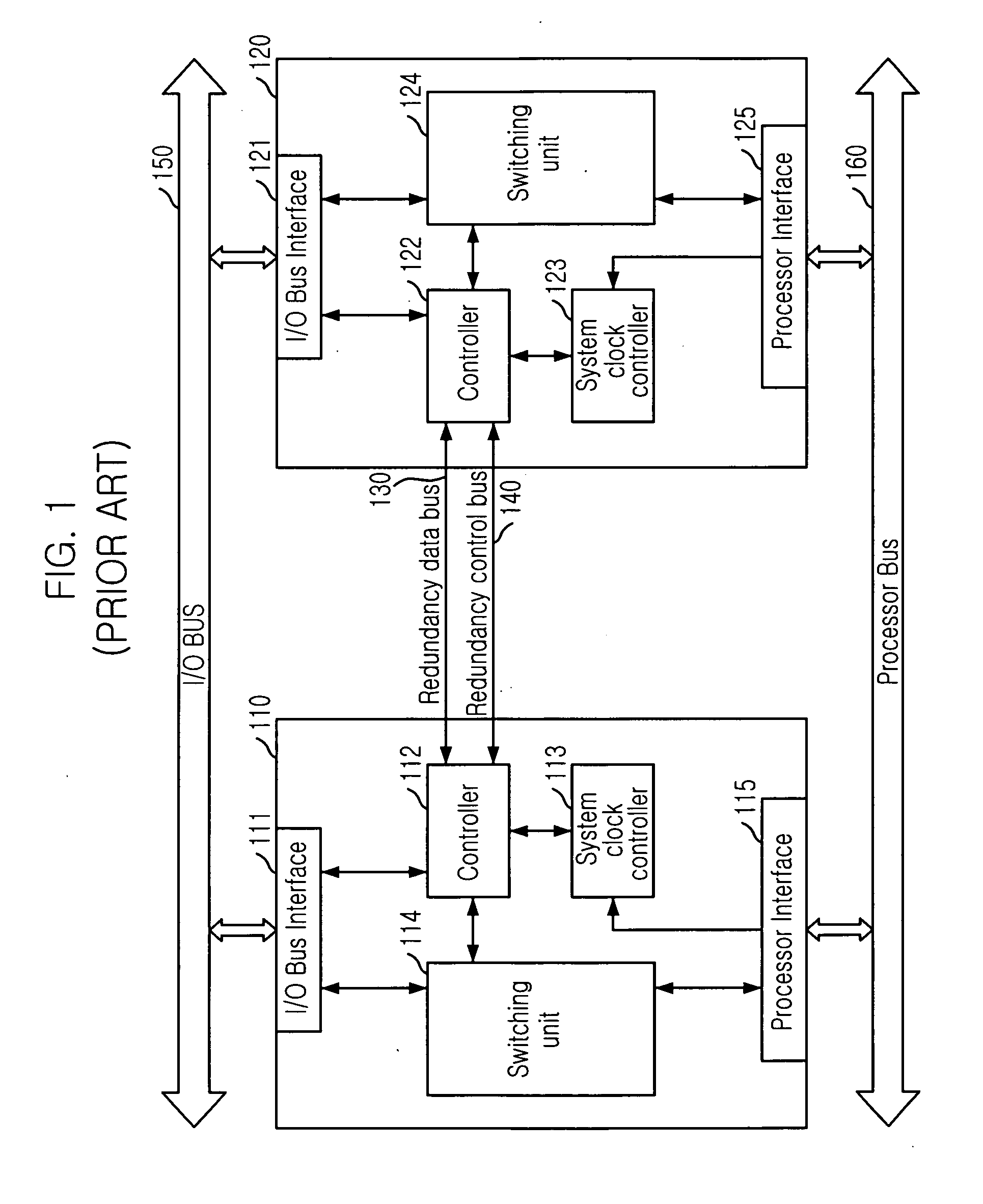

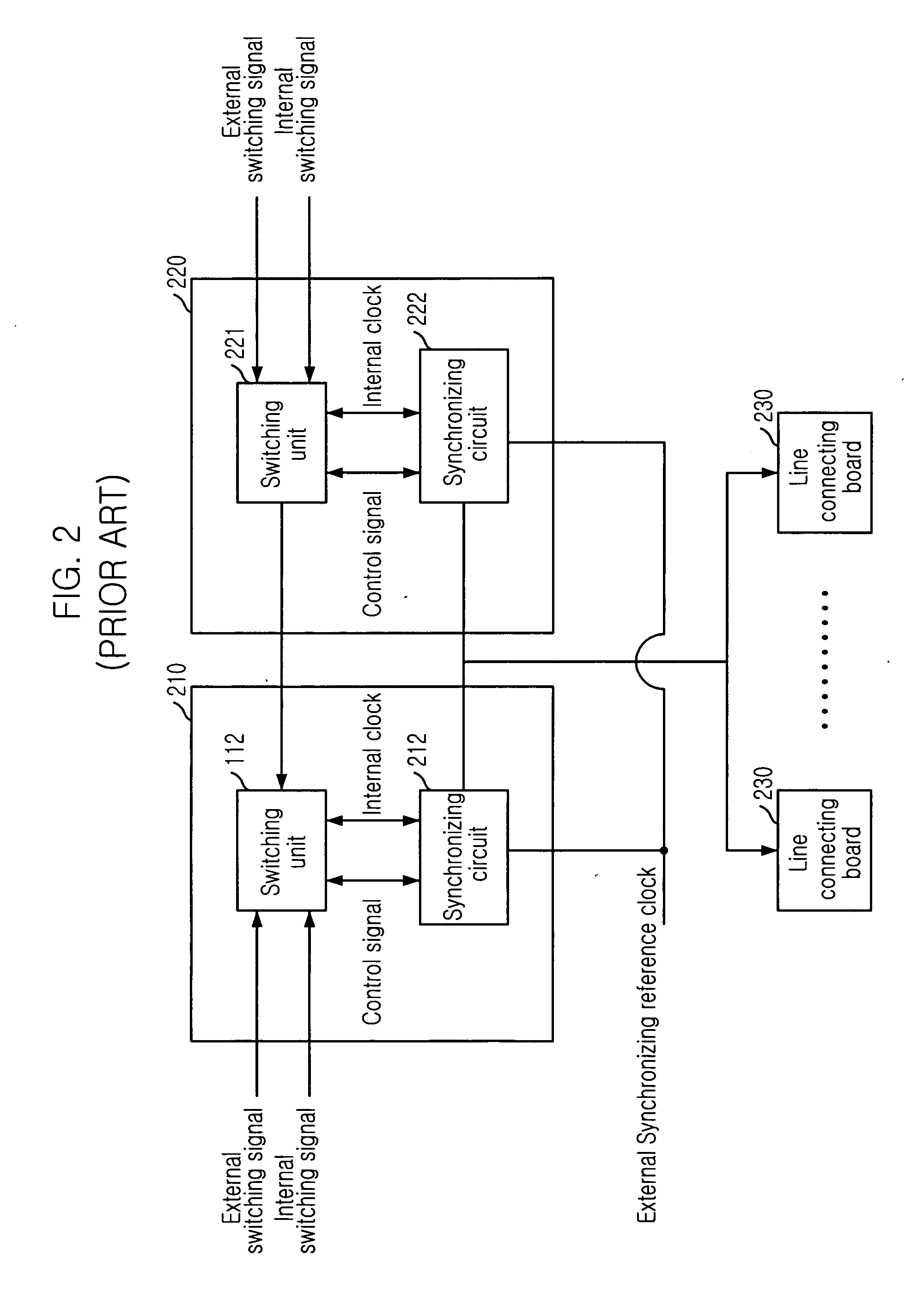

Apparatus and method for redundancy control of duplex switch board

InactiveUS20060109782A1Synchronisation information channelsError preventionControl communicationsLine card

An apparatus and method for a redundancy control in duplex switch boards in a high speed network system are provided. The apparatus includes: a switching unit for switching data inputted one of the duplex switch boards to a destination line card; a state controlling unit for controlling a clock state of an opponent switch board between the duplex switch boards; an IPC controlling unit for controlling an inter processor communication (IPC) of a platform of the communication network system; a processing unit for controlling the IPC controlling unit and the state controlling unit of the duplex switch boards; and a clock controlling unit for synchronizing a clock between the duplex switch boards.

Owner:ELECTRONICS & TELECOMM RES INST

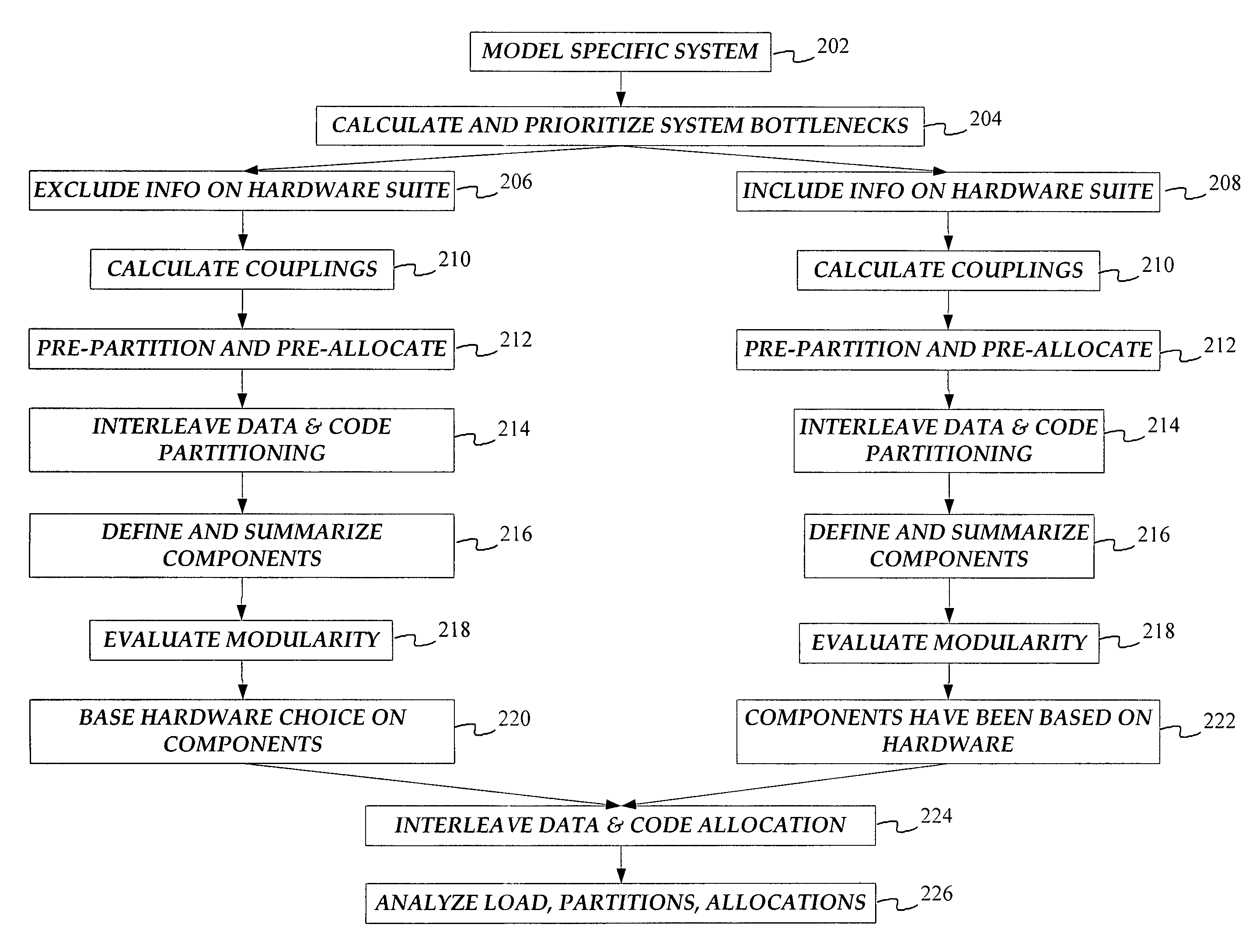

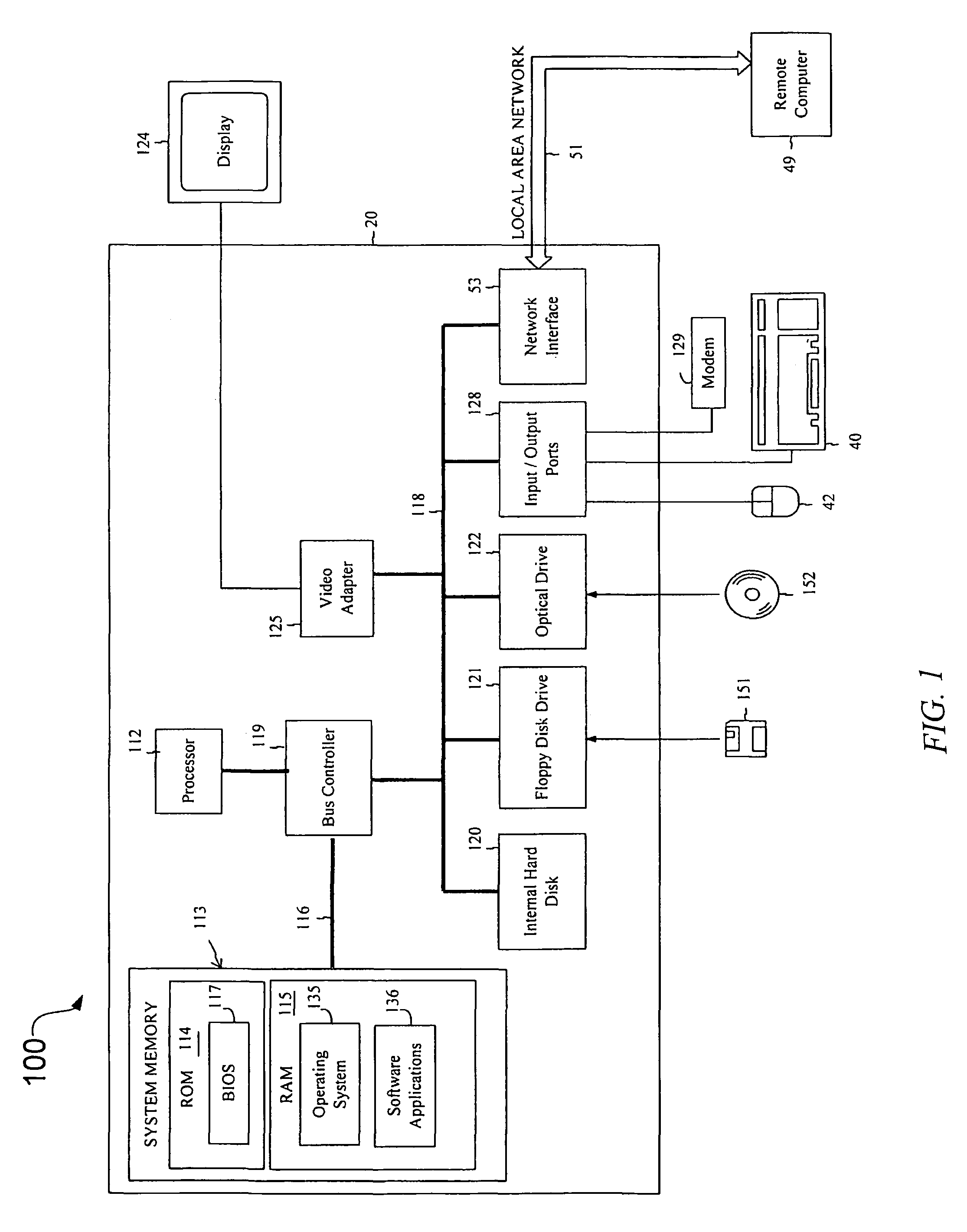

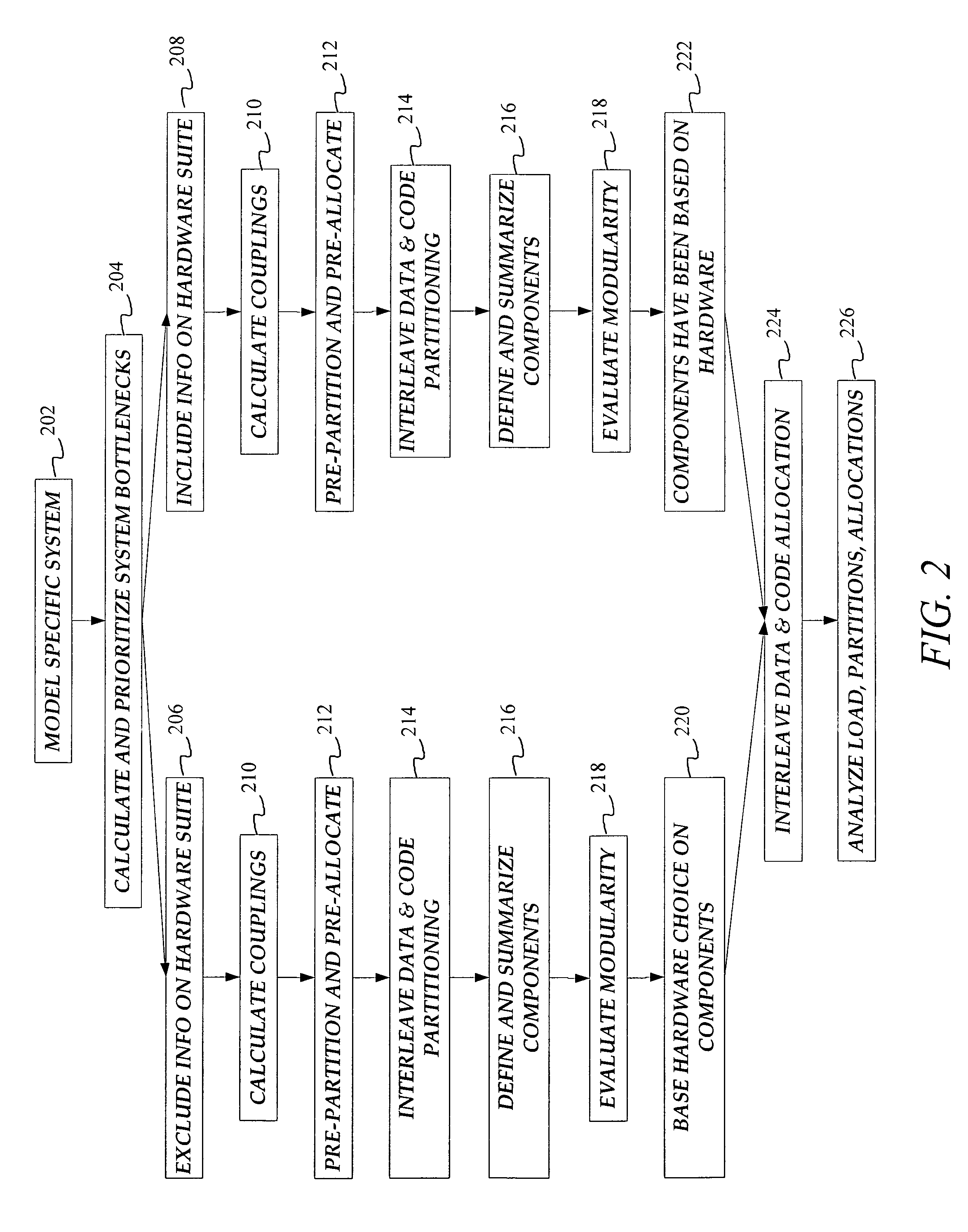

Using constraint-based heuristics to satisfice static software partitioning and allocation of heterogeneous distributed systems

InactiveUS7747422B1Avoid bottlenecksFine granularityAnalogue computers for electric apparatusMultiprogramming arrangementsSoftware distributionCoupling

Systems and methods automatically design a system's architecture by modeling the architectural complexity of large-scale distributed systems to drive a partitioning and allocation algorithm. The result is a configuration based on the structure of the software tasks and data access, and the capacities of the hardware. Coupling and cohesion are relative, dependent on the ratio of load to capacity, and not independent software characteristics. The partitioning and allocation algorithm includes tradeoffs between processor utilization, memory utilization, inter-processor communication, and peripheral contention. The systems and methods take into account both precedence constraints and the directional flow of data. Further aspects include interleaving the decisions of database segmentation and software distribution. This approach is demonstrated with a simplified example of a real distributed system.

Owner:SISLEY ELIZABETH

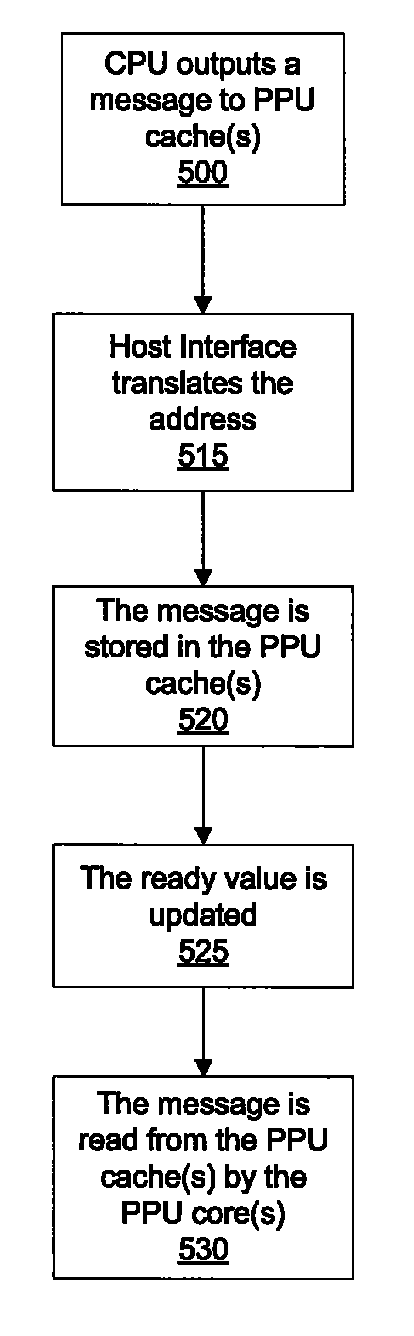

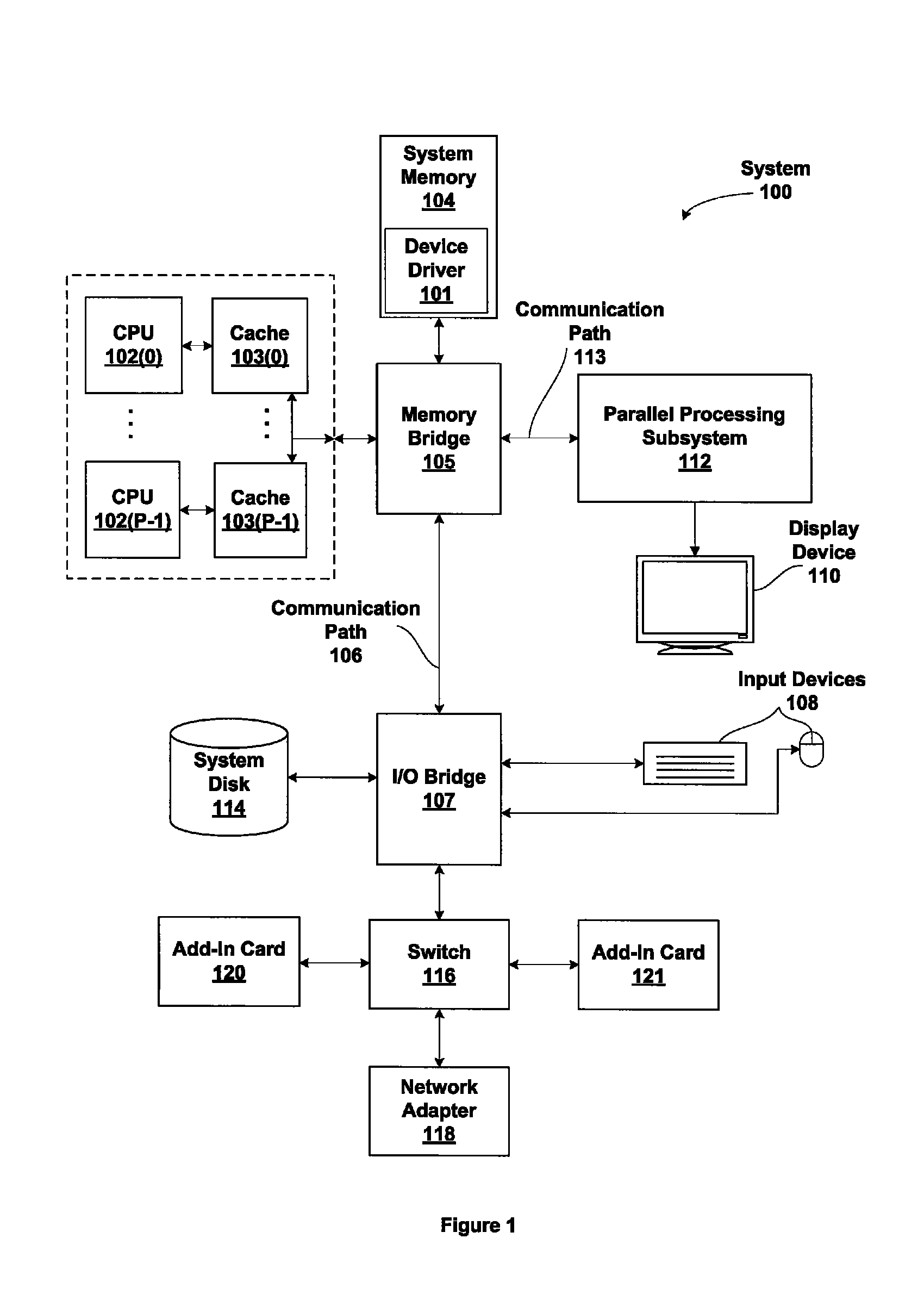

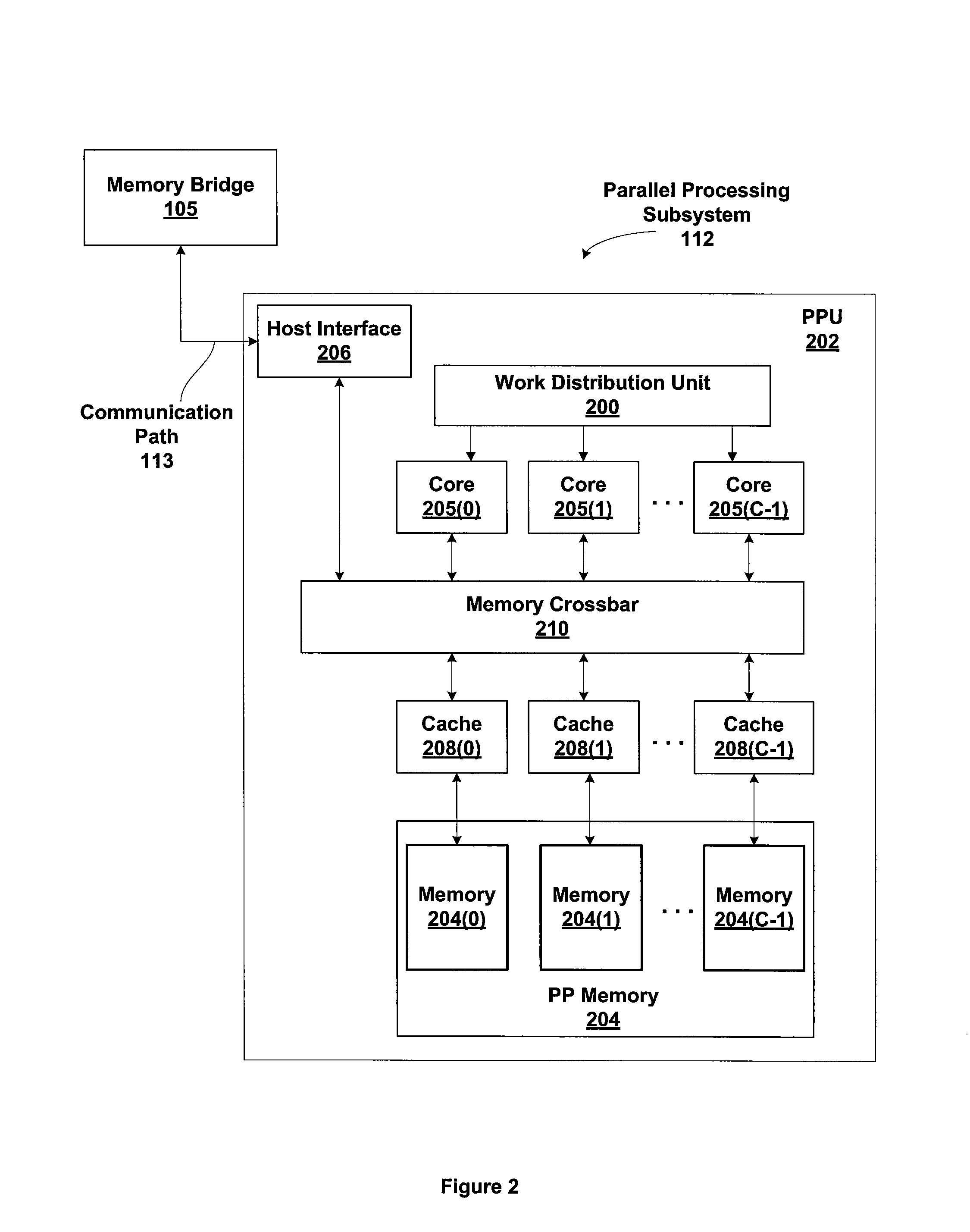

Interprocessor direct cache writes

ActiveUS8327071B1Reduce complexityLower latencyCathode-ray tube indicatorsMemory systemsCrossbar switchInterprocessor communication

In a multiprocessor system level 2 caches are positioned on the memory side of a routing crossbar rather than on the processor side of the routing crossbar. This configuration permits the processors to store messages directly into each other's caches rather than into system memory or their own coherent caches. Therefore, inter-processor communication latency is reduced.

Owner:NVIDIA CORP

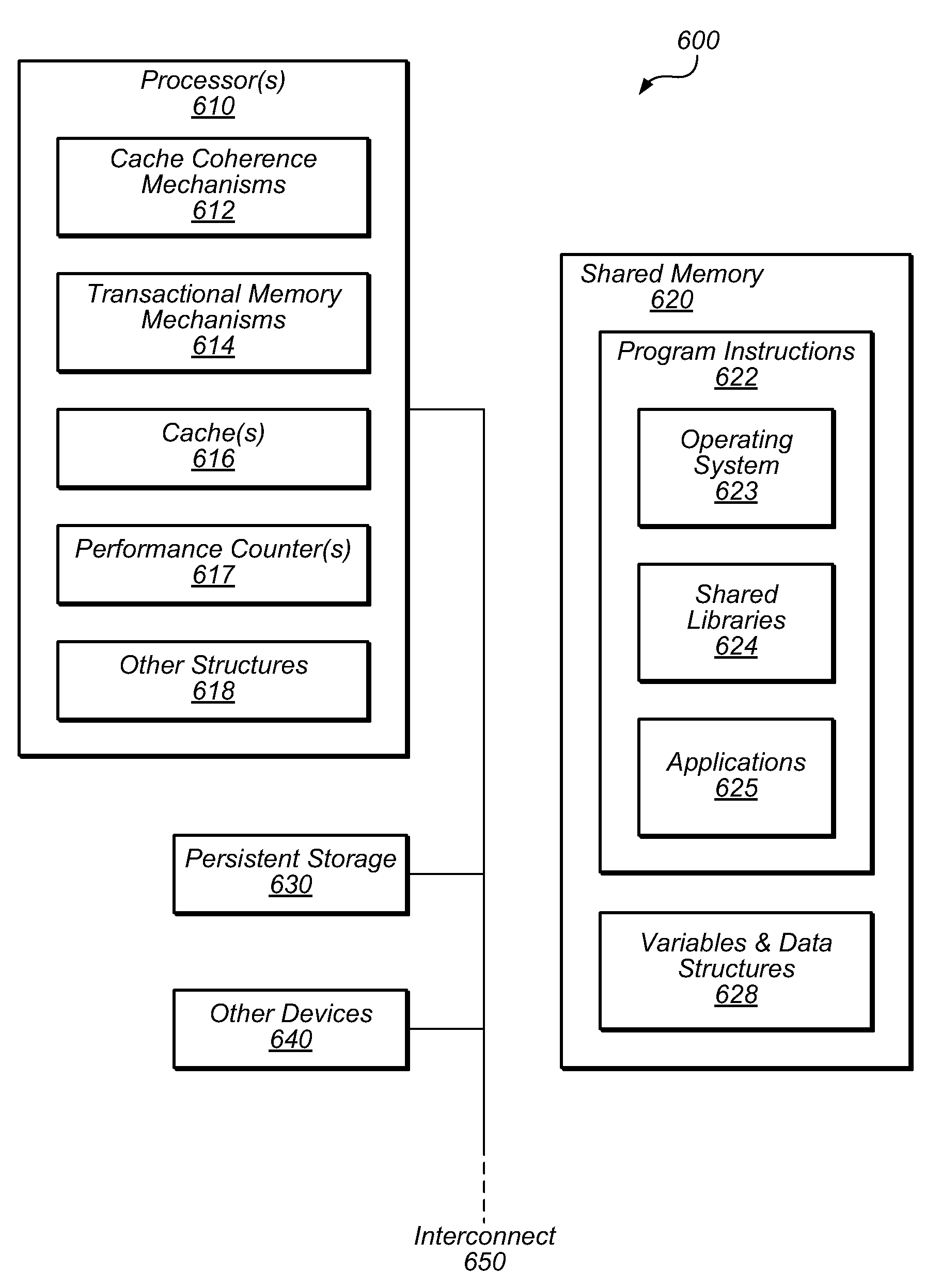

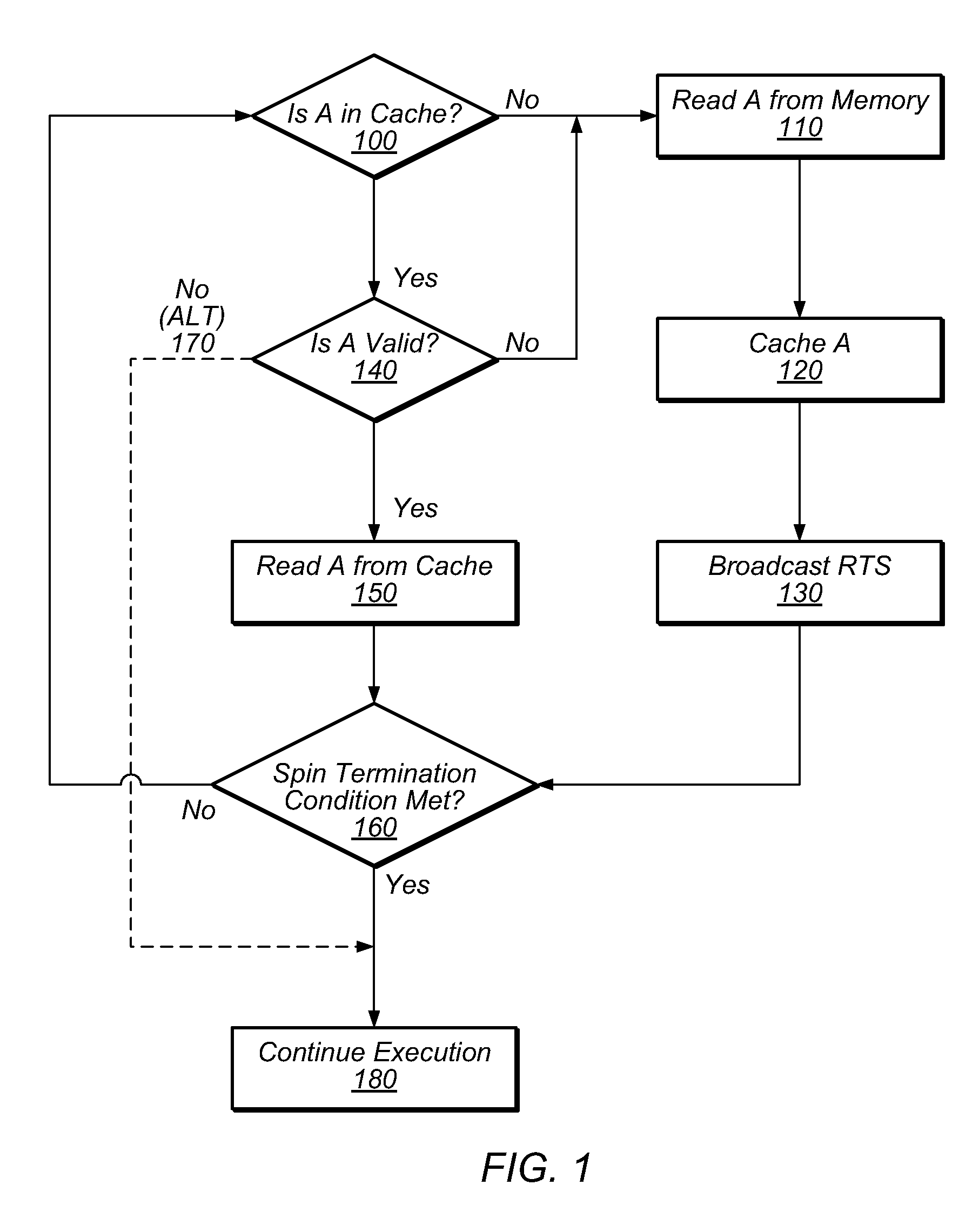

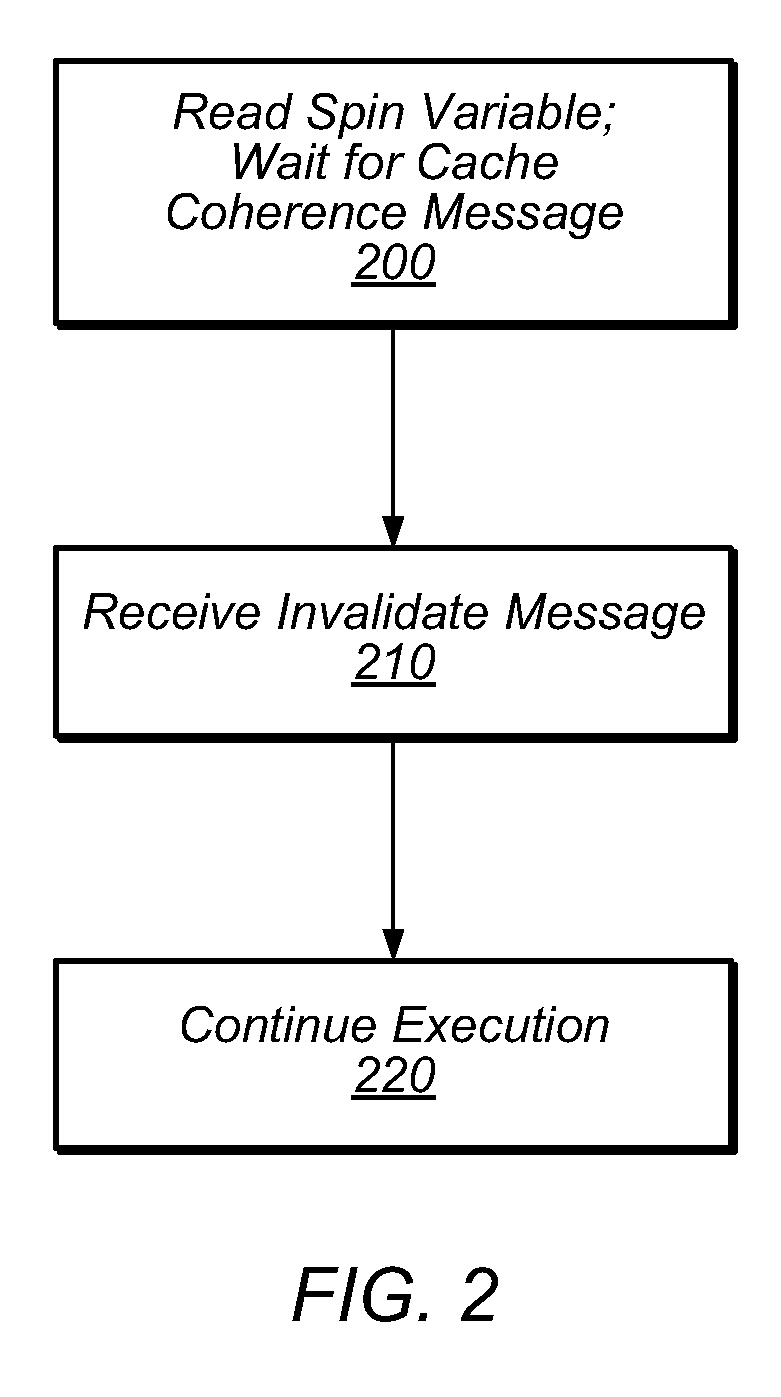

Method and System for Inter-Thread Communication Using Processor Messaging

In shared-memory computer systems, threads may communicate with one another using shared memory. A receiving thread may poll a message target location repeatedly to detect the delivery of a message. Such polling may cause excessive cache coherency traffic and / or congestion on various system buses and / or other interconnects. A method for inter-processor communication may reduce such bus traffic by reducing the number of reads performed and / or the number of cache coherency messages necessary to pass messages. The method may include a thread reading the value of a message target location once, and determining that this value has been modified by detecting inter-processor messages, such as cache coherence messages, indicative of such modification. In systems that support transactional memory, a thread may use transactional memory primitives to detect the cache coherence messages. This may be done by starting a transaction, reading the target memory location, and spinning until the transaction is aborted.

Owner:SUN MICROSYSTEMS INC

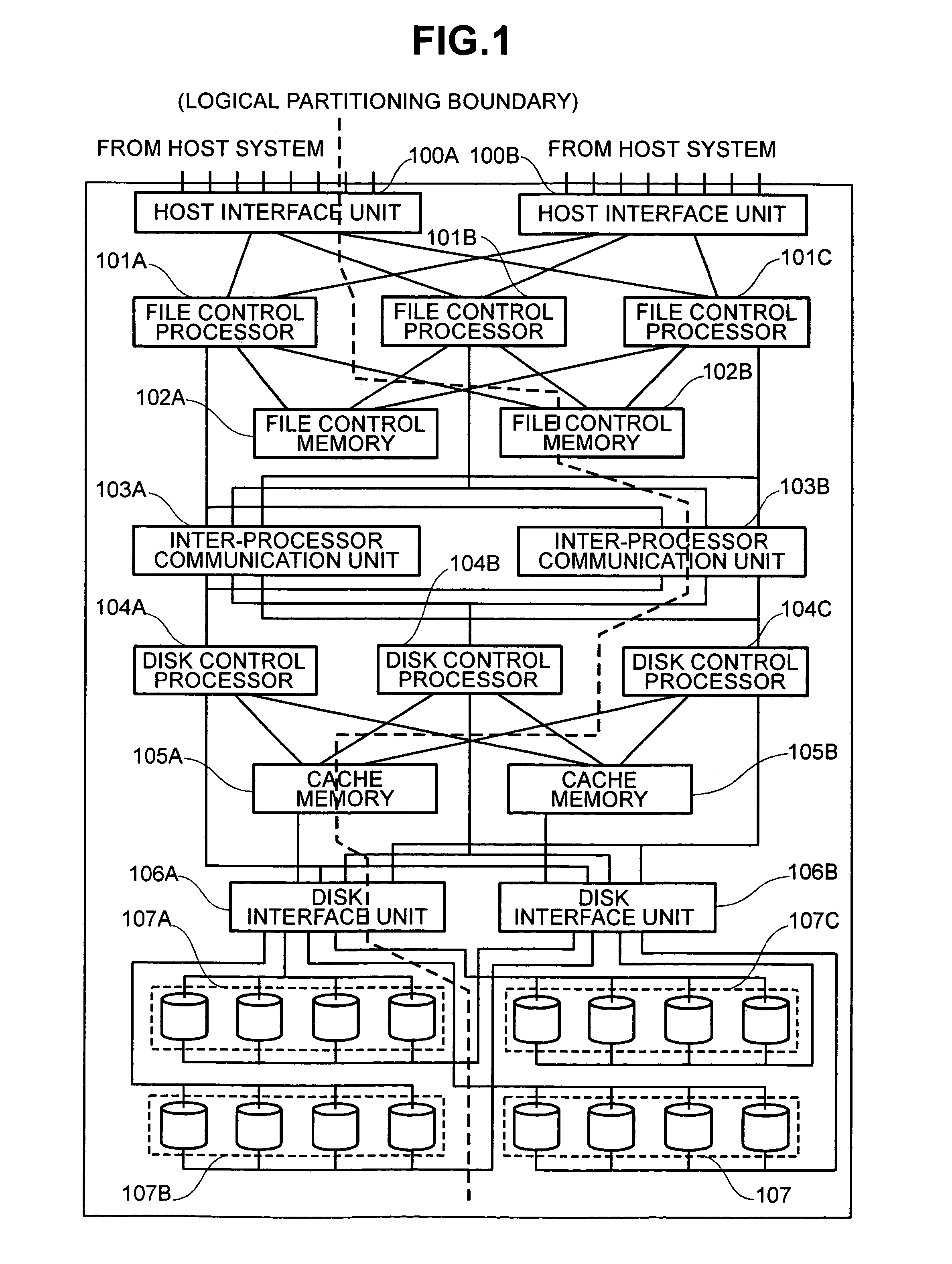

Storage having logical partitioning capability and systems which include the storage

InactiveUS7127585B2Reduce controlEliminate mutual interferenceInput/output to record carriersMemory systemsCommunication unitInterprocessor communication

A storage includes: host interface units; file control processors which receives a file input / output request and translates the file input / output request into a data input / output request; file control memories which store translation control data; groups of disk drives; disk control processors; disk interface units which connect the groups of disk drives and the disk control processors; cache memories; and inter-processor communication units. The storage logically partitions these devices to cause the partitioned devices to operate as two or more virtual NASs.

Owner:HITACHI LTD