Patents

Literature

30 results about "Inter-processor interrupt" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

An inter-processor interrupt (IPI) is a special type of interrupt by which one processor may interrupt another processor in a multiprocessor system if the interrupting processor requires action from the other processor.

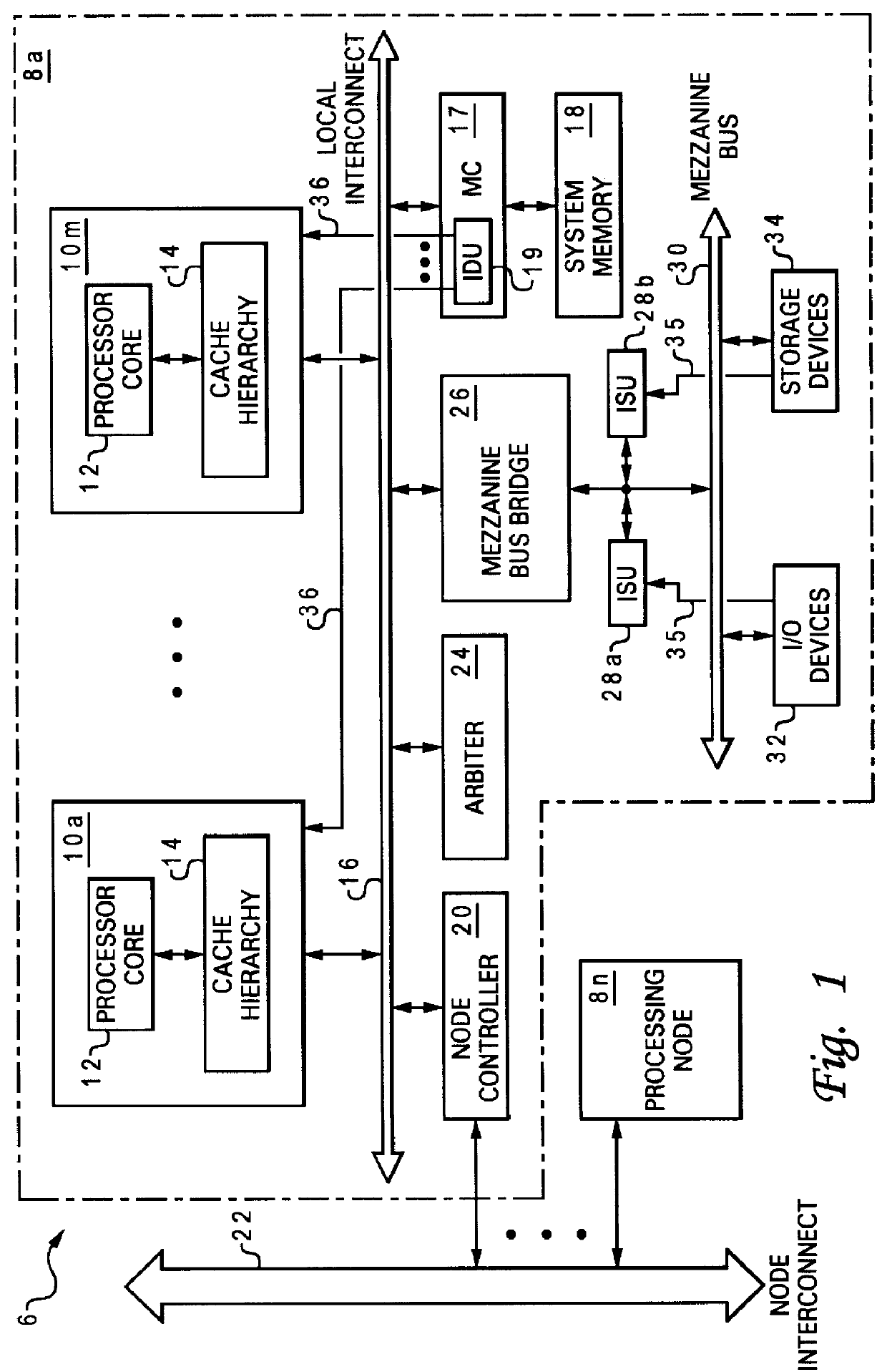

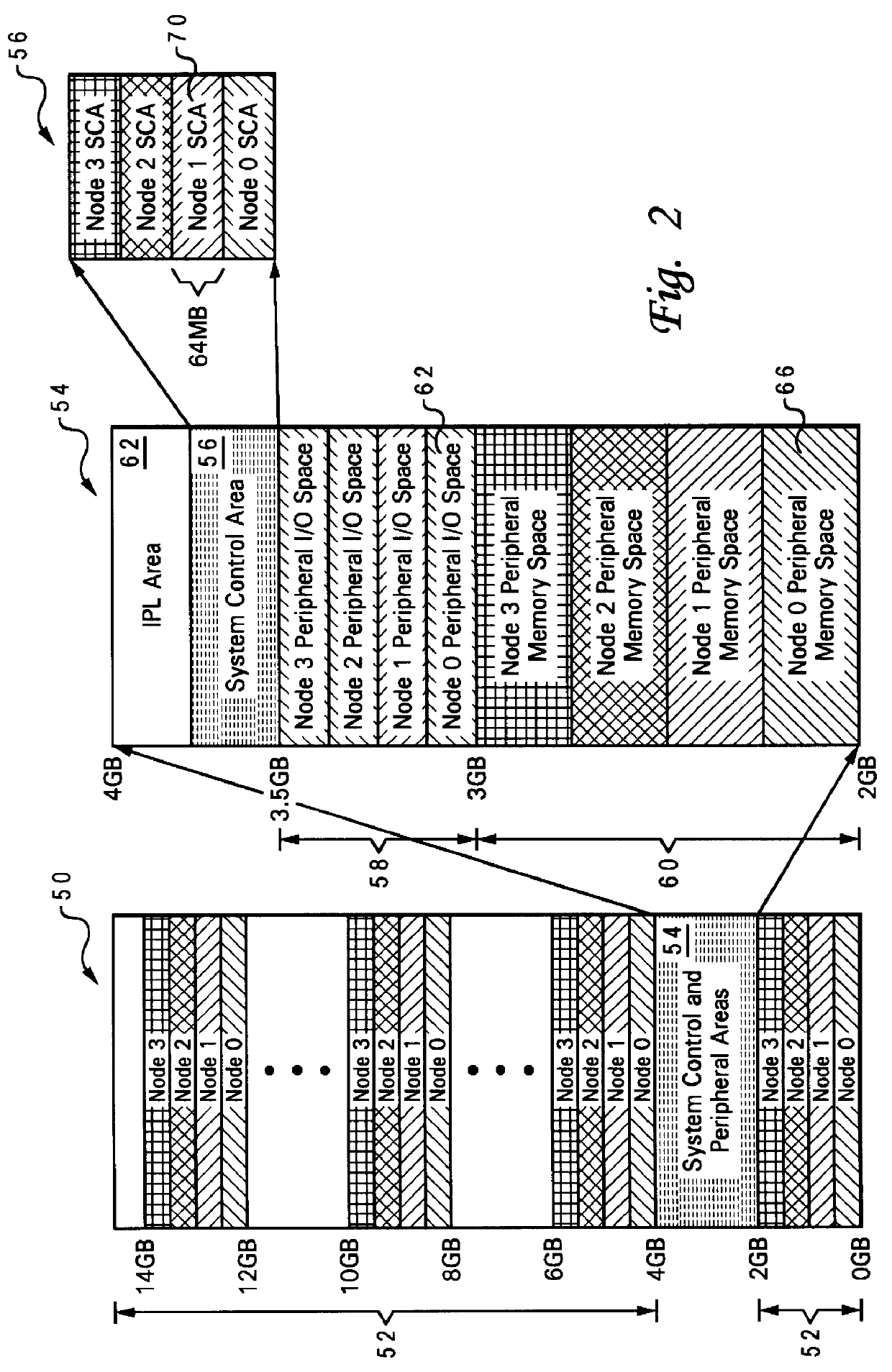

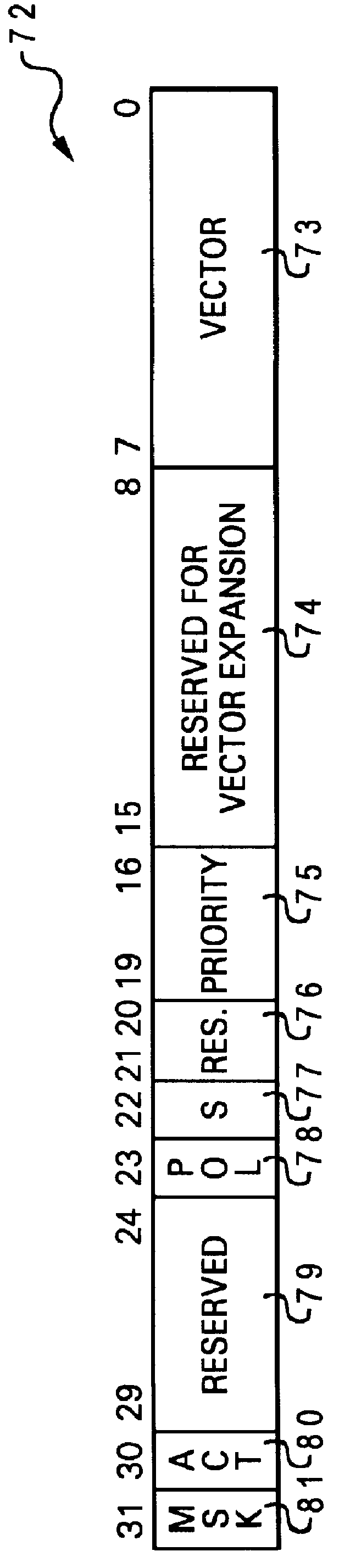

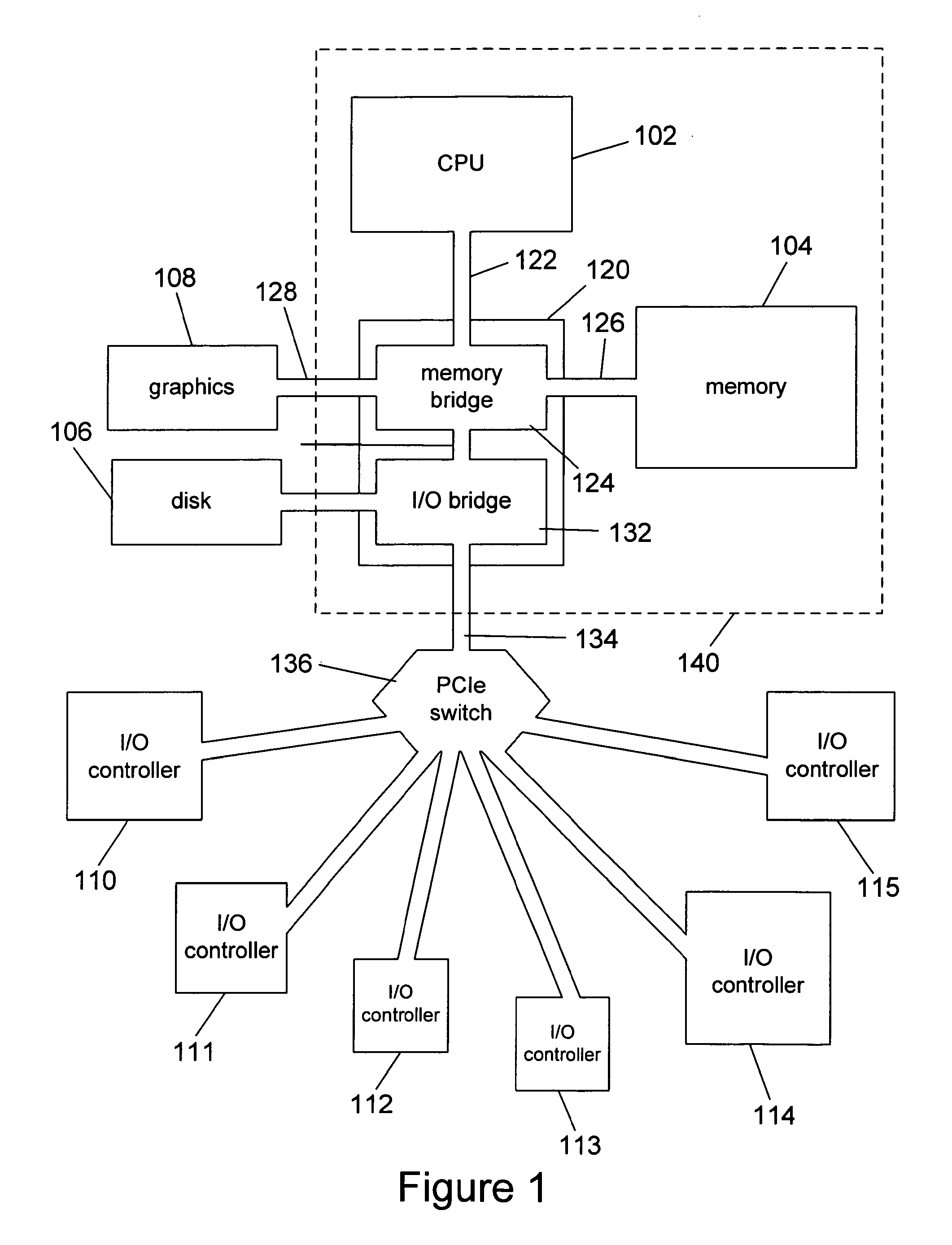

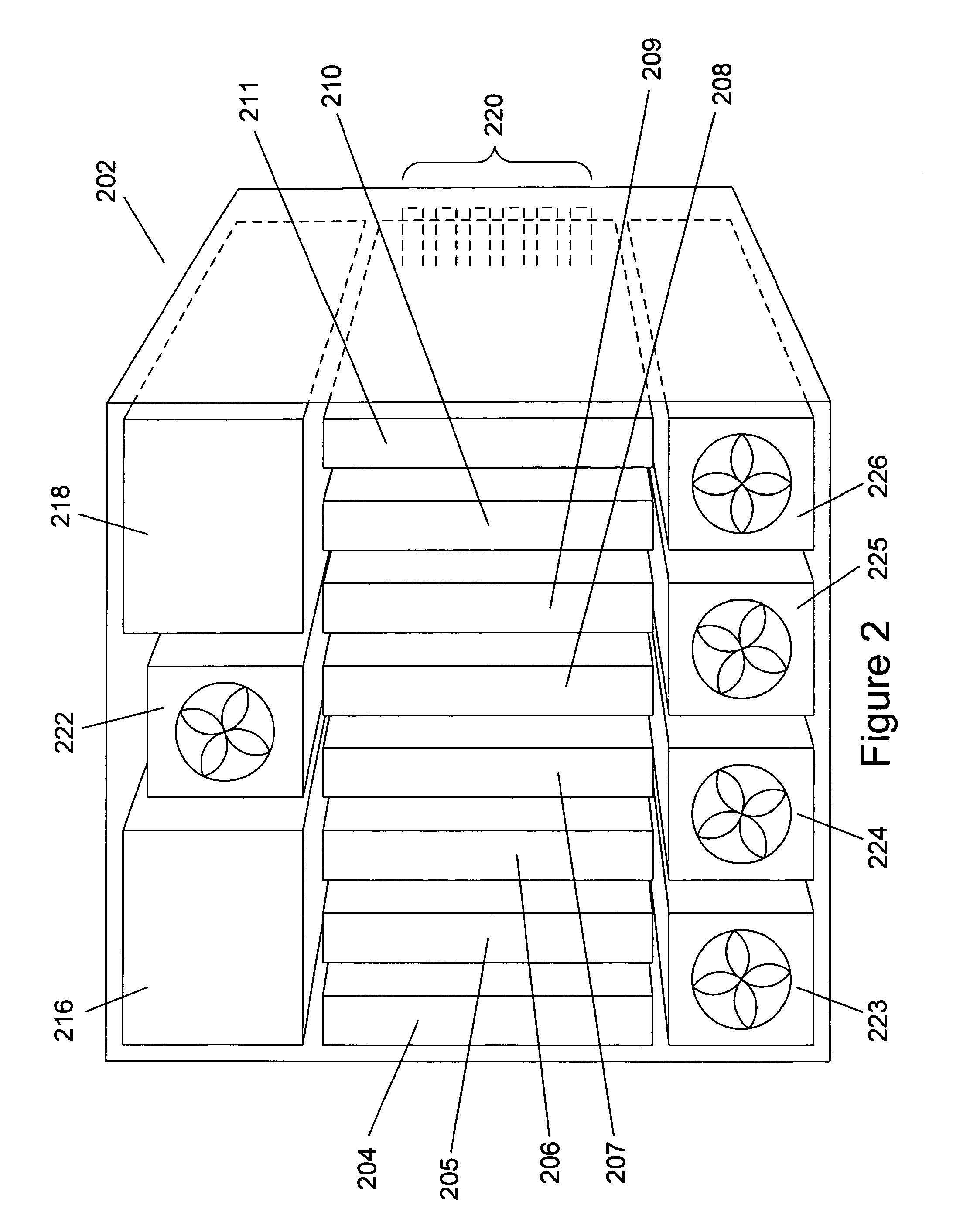

Interrupt architecture for a non-uniform memory access (NUMA) data processing system

InactiveUS6148361ASmall sizePromote disseminationProgram initiation/switchingGeneral purpose stored program computerExtensibilityData processing system

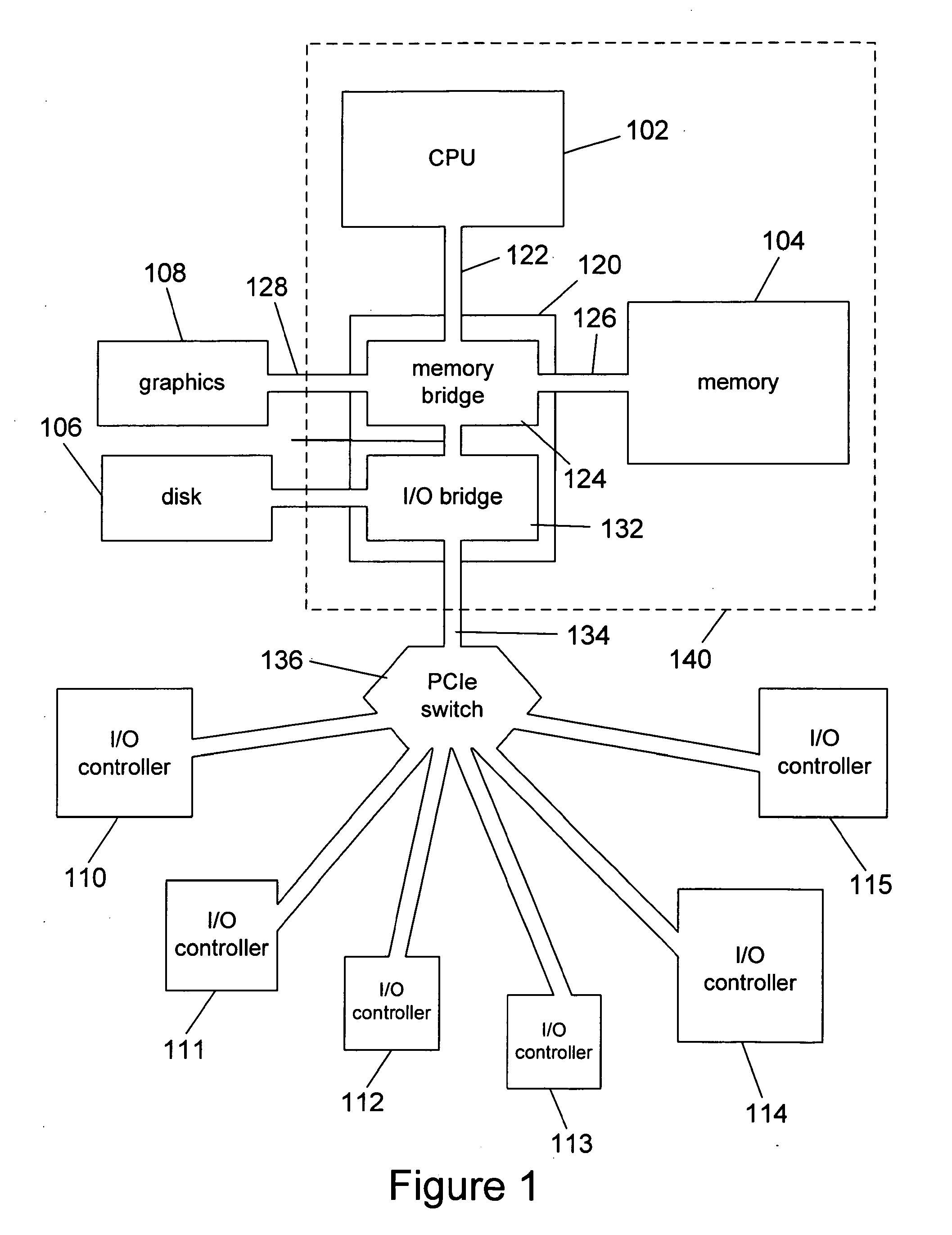

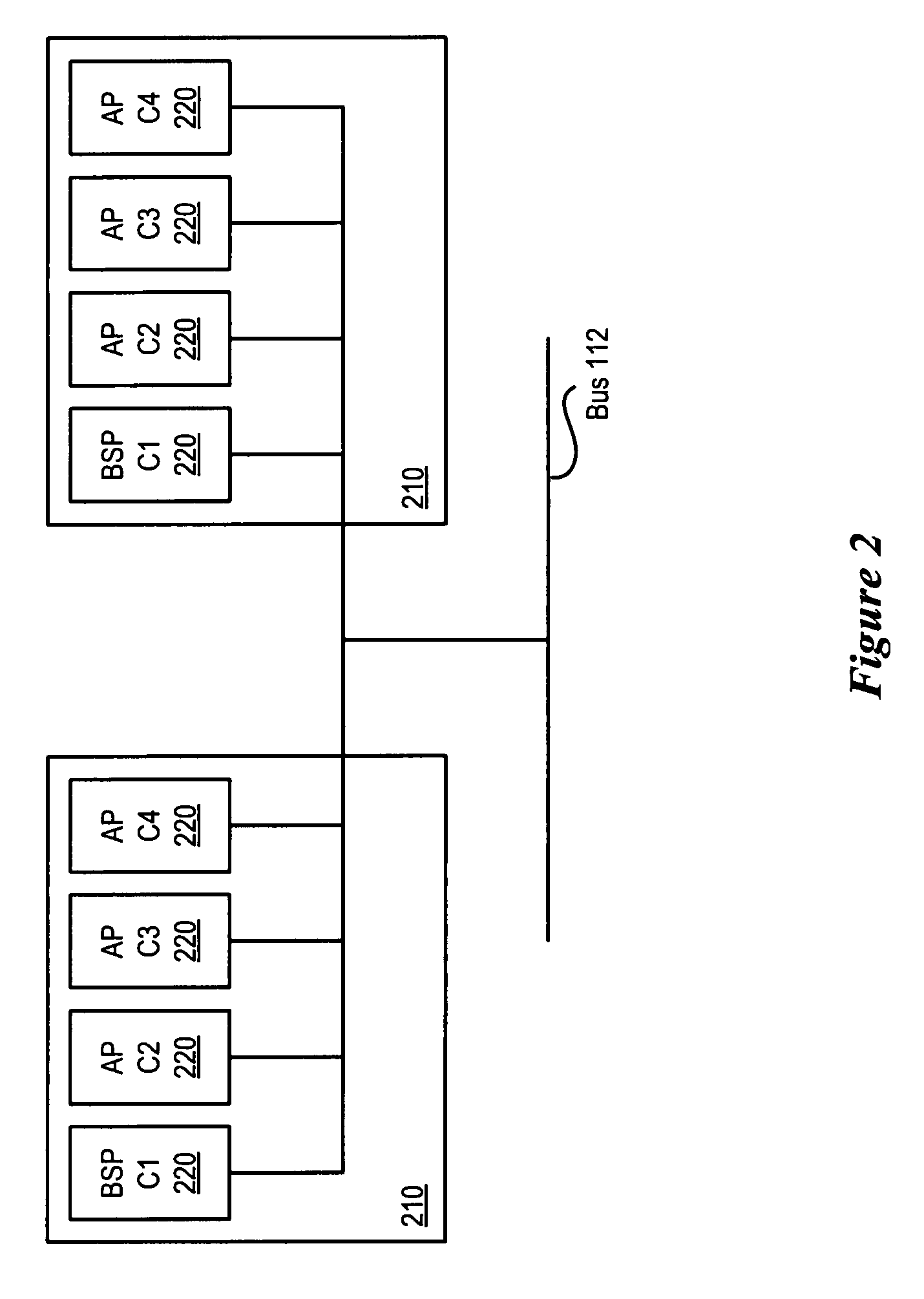

A non-uniform memory access (NUMA) computer system includes at least two nodes coupled by a node interconnect, where at least one of the nodes includes a processor for servicing interrupts. The nodes are partitioned into external interrupt domains so that an external interrupt is always presented to a processor within the external interrupt domain in which the interrupt occurs. Although each external interrupt domain typically includes only a single node, interrupt channeling or interrupt funneling may be implemented to route external interrupts across node boundaries for presentation to a processor. Once presented to a processor, interrupt handling software may then execute on any processor to service the external interrupt. Servicing external interrupts is expedited by reducing the size of the interrupt handler polling chain as compared to prior art methods. In addition to external interrupts, the interrupt architecture of the present invention supports inter-processor interrupts (IPIs) by which any processor may interrupt itself or one or more other processors in the NUMA computer system. IPIs are triggered by writing to memory mapped registers in global system memory, which facilitates the transmission of IPIs across node boundaries and permits multicast IPIs to be triggered simply by transmitting one write transaction to each node containing a processor to be interrupted. The interrupt hardware within each node is also distributed for scalability, with the hardware components communicating via interrupt transactions conveyed across shared communication paths.

Owner:IBM CORP

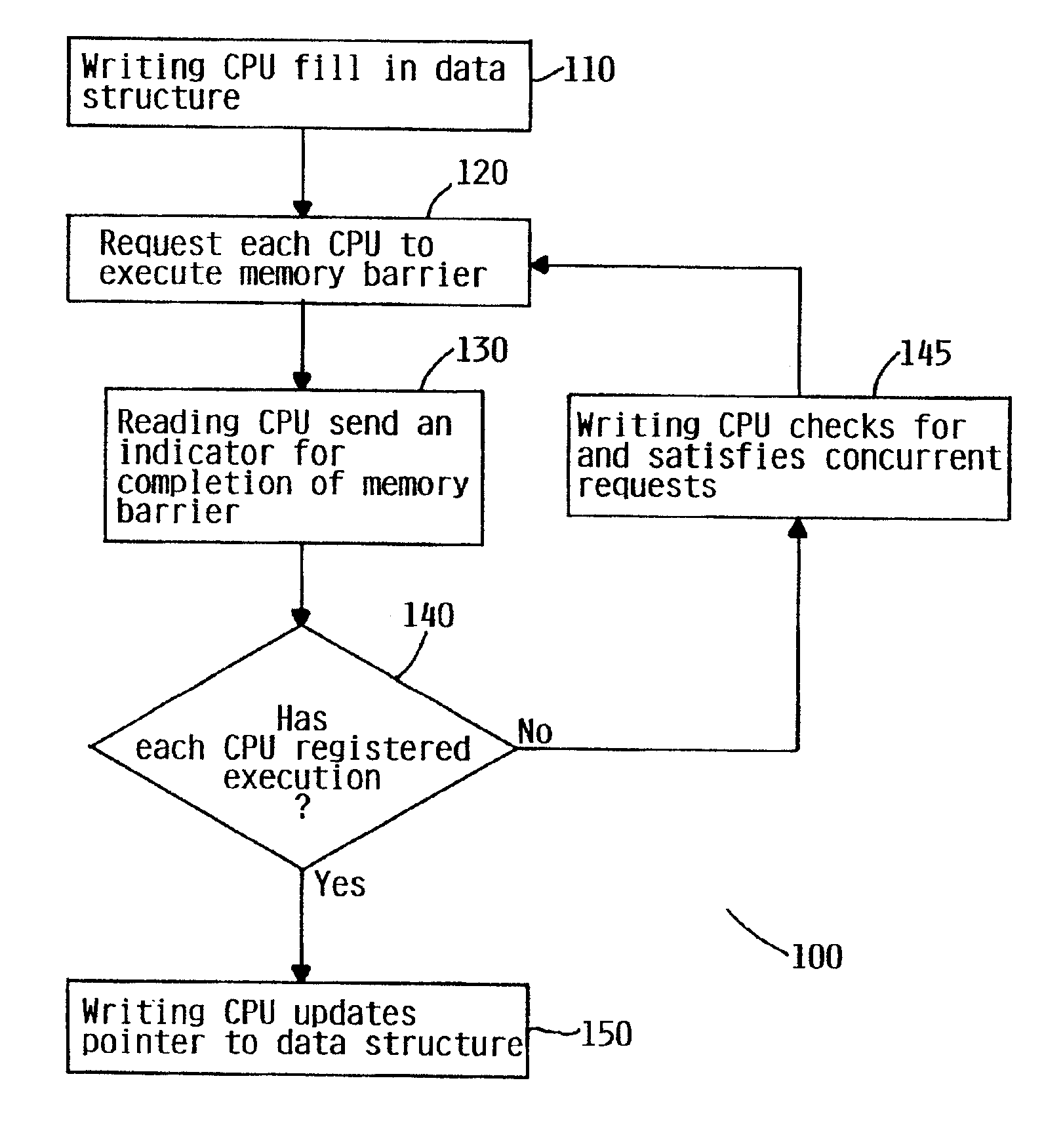

Software implementation of synchronous memory barriers

InactiveUS6996812B2Program synchronisationDigital computer detailsProcessor registerInter-processor interrupt

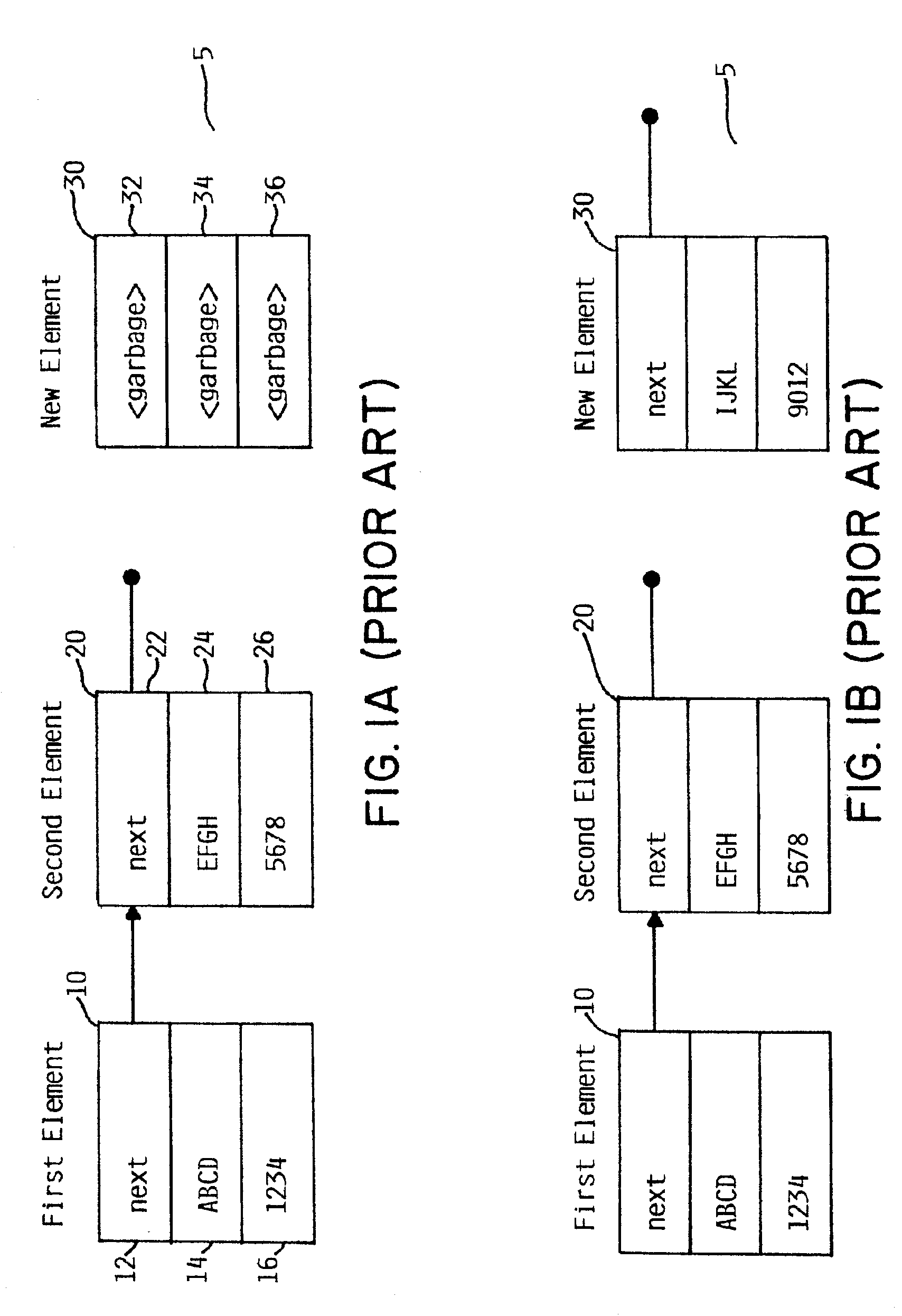

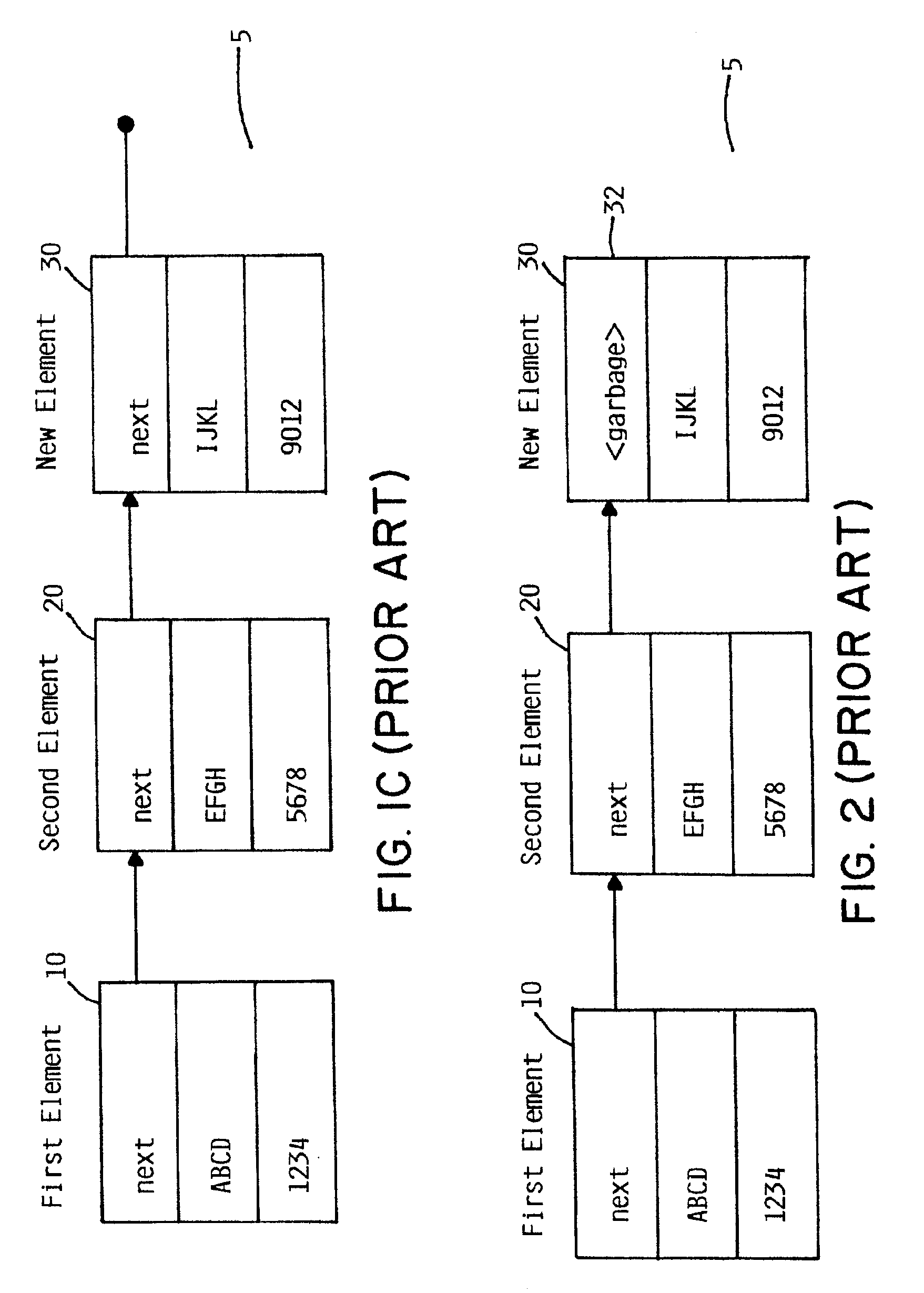

Selectively emulating sequential consistency in software improves efficiency in a multiprocessing computing environment. A writing CPU uses a high priority inter-processor interrupt to force each CPU in the system to execute a memory barrier. This step invalidates old data in the system. Each CPU that has executed a memory barrier instruction registers completion and sends an indicator to a memory location to indicate completion of the memory barrier instruction. Prior to updating the data, the writing CPU must check the register to ensure completion of the memory barrier execution by each CPU. The register may be in the form of an array, a bitmask, or a combining tree, or a comparable structure. This step ensures that all invalidates are removed from the system and that deadlock between two competing CPUs is avoided. Following validation that each CPU has executed the memory barrier instruction, the writing CPU may update the pointer to the data structure.

Owner:IBM CORP

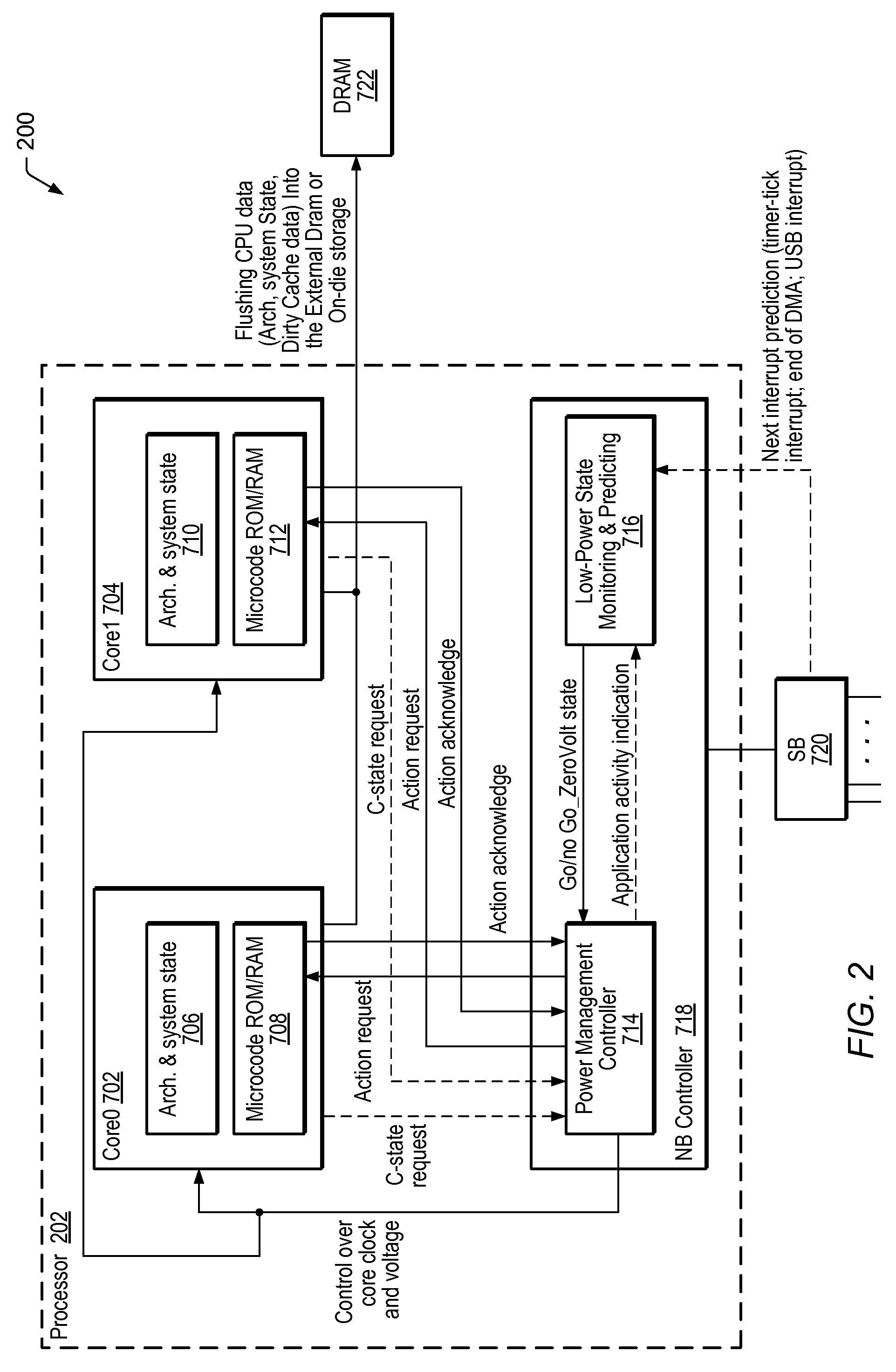

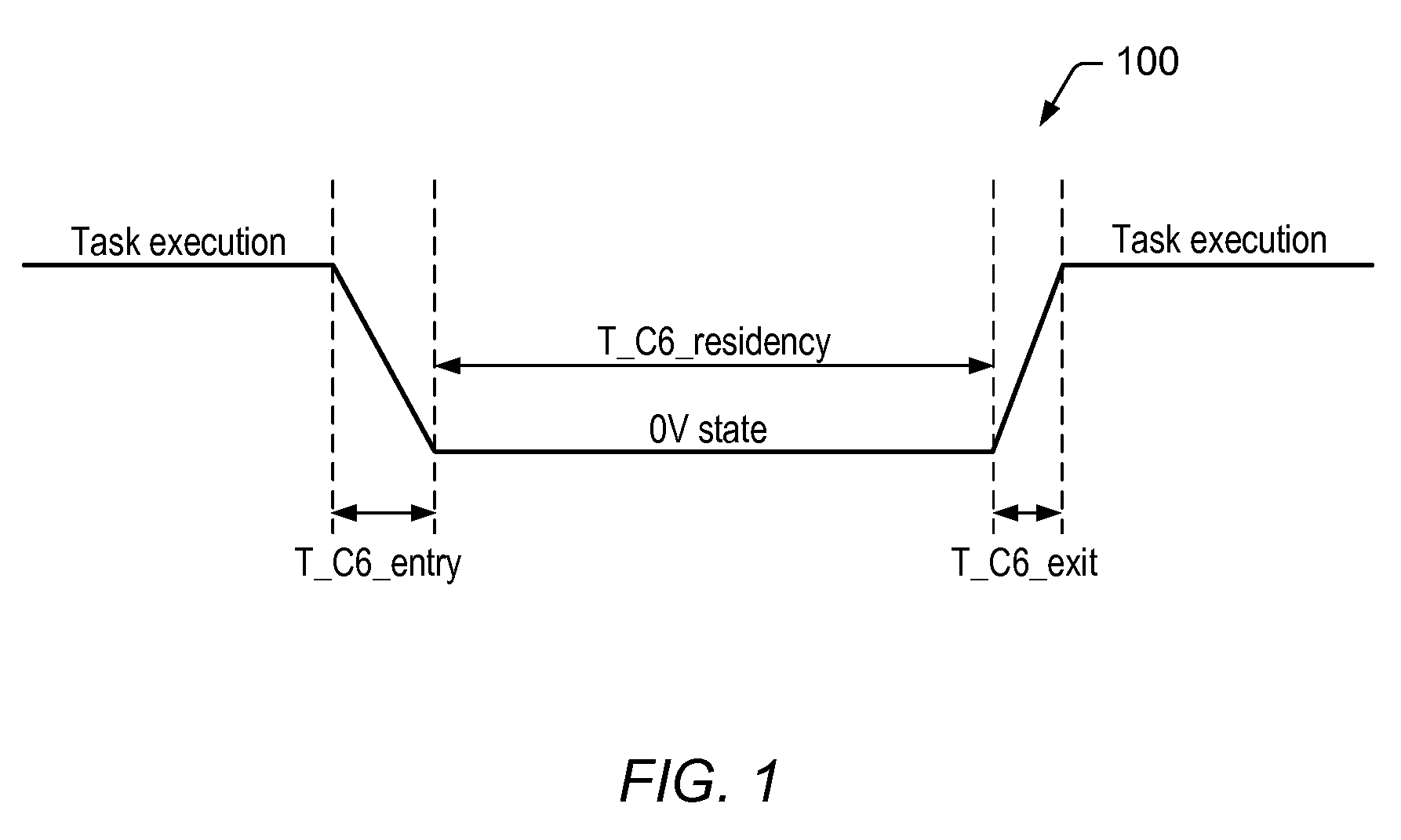

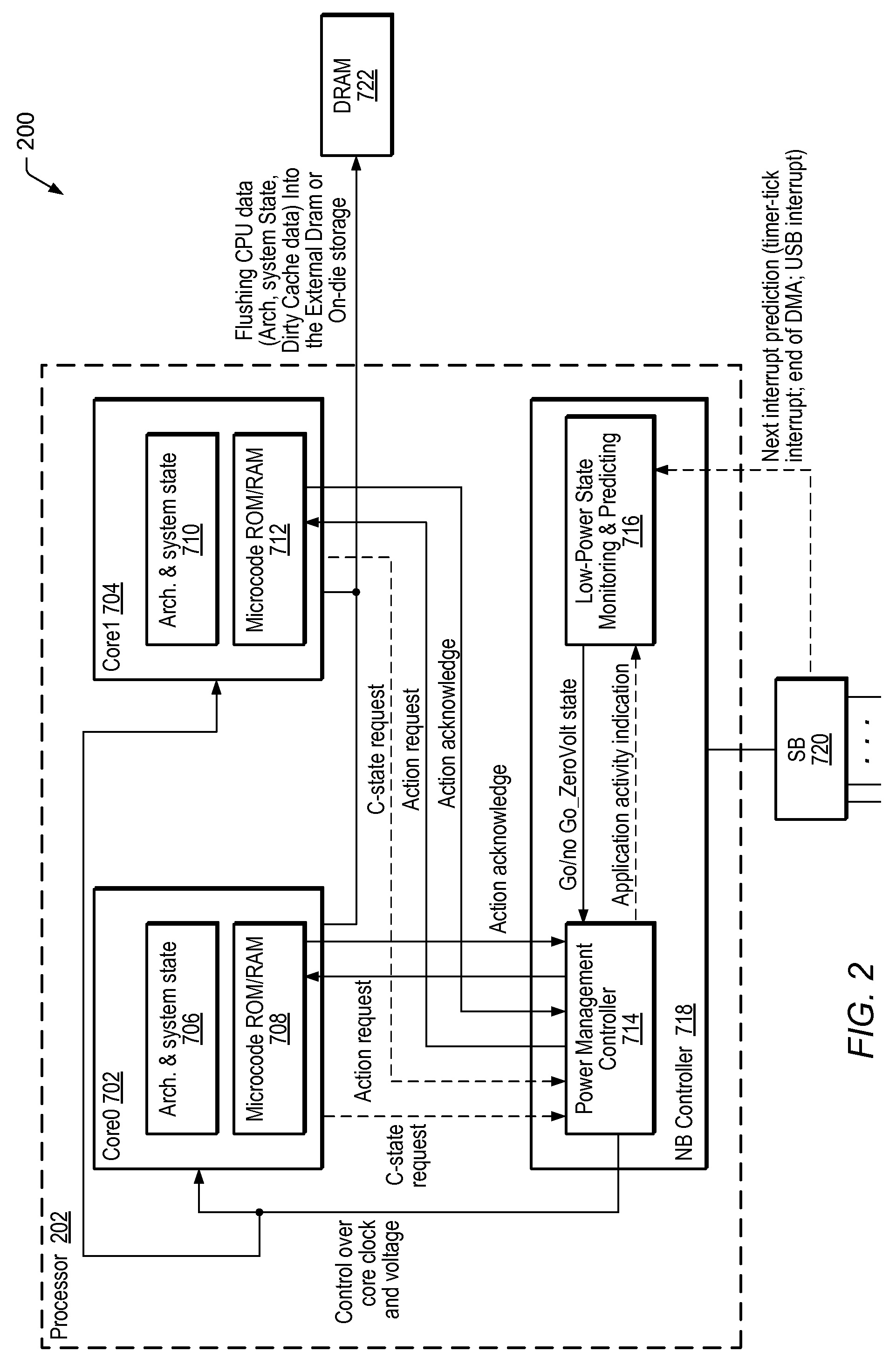

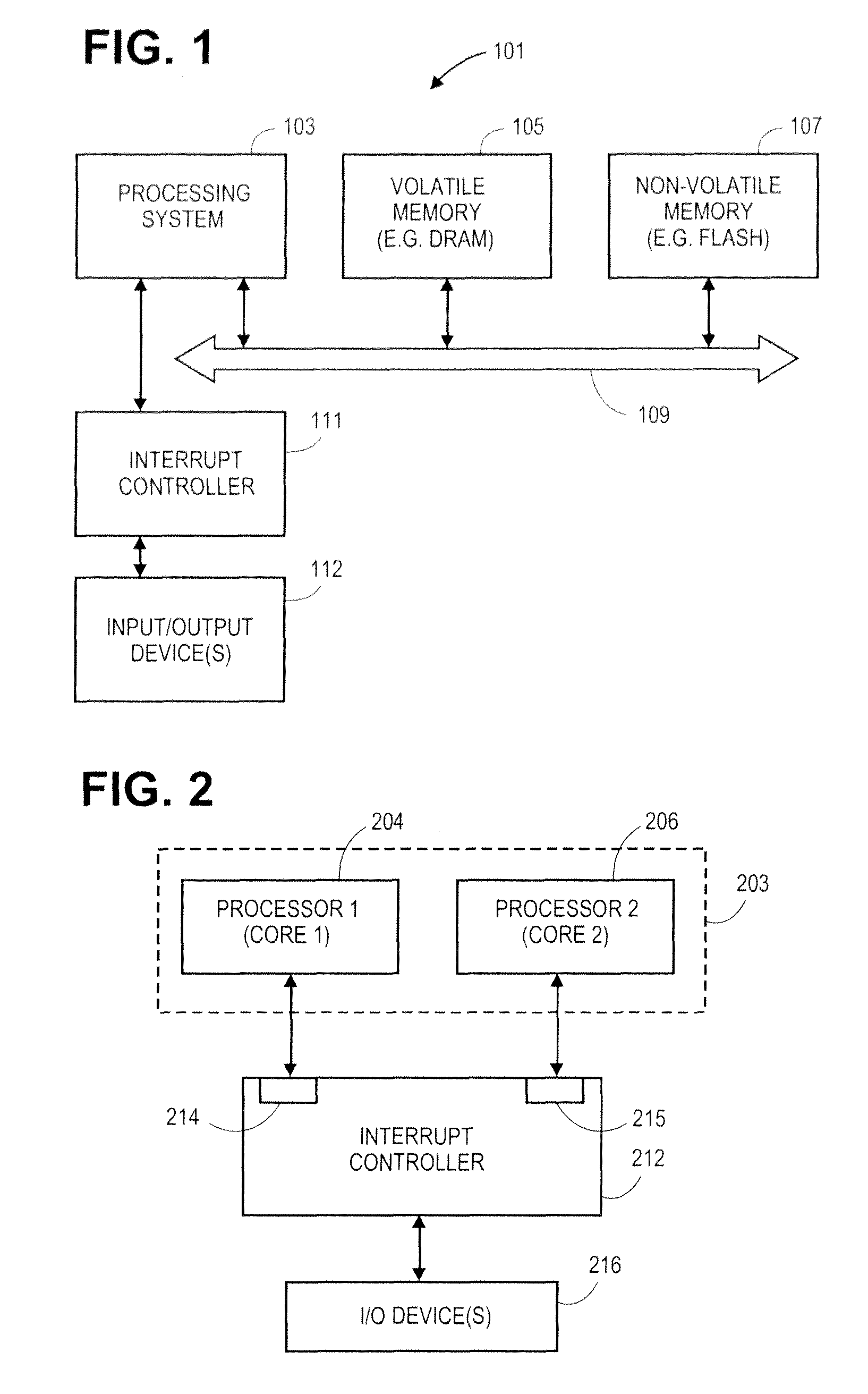

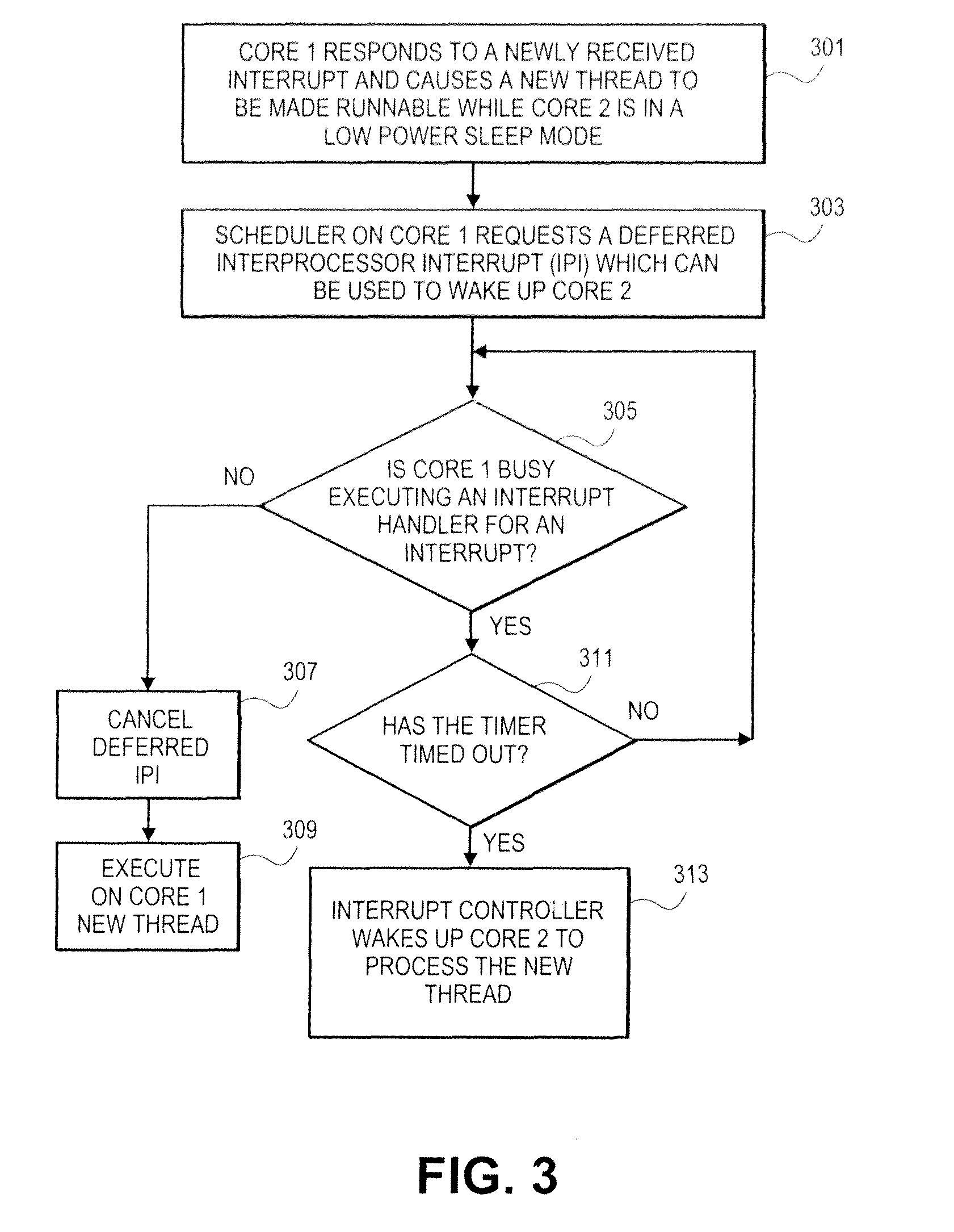

Enhanced Control of CPU Parking and Thread Rescheduling for Maximizing the Benefits of Low-Power State

ActiveUS20090235260A1Energy efficient ICTVolume/mass flow measurementParallel computingInter-processor interrupt

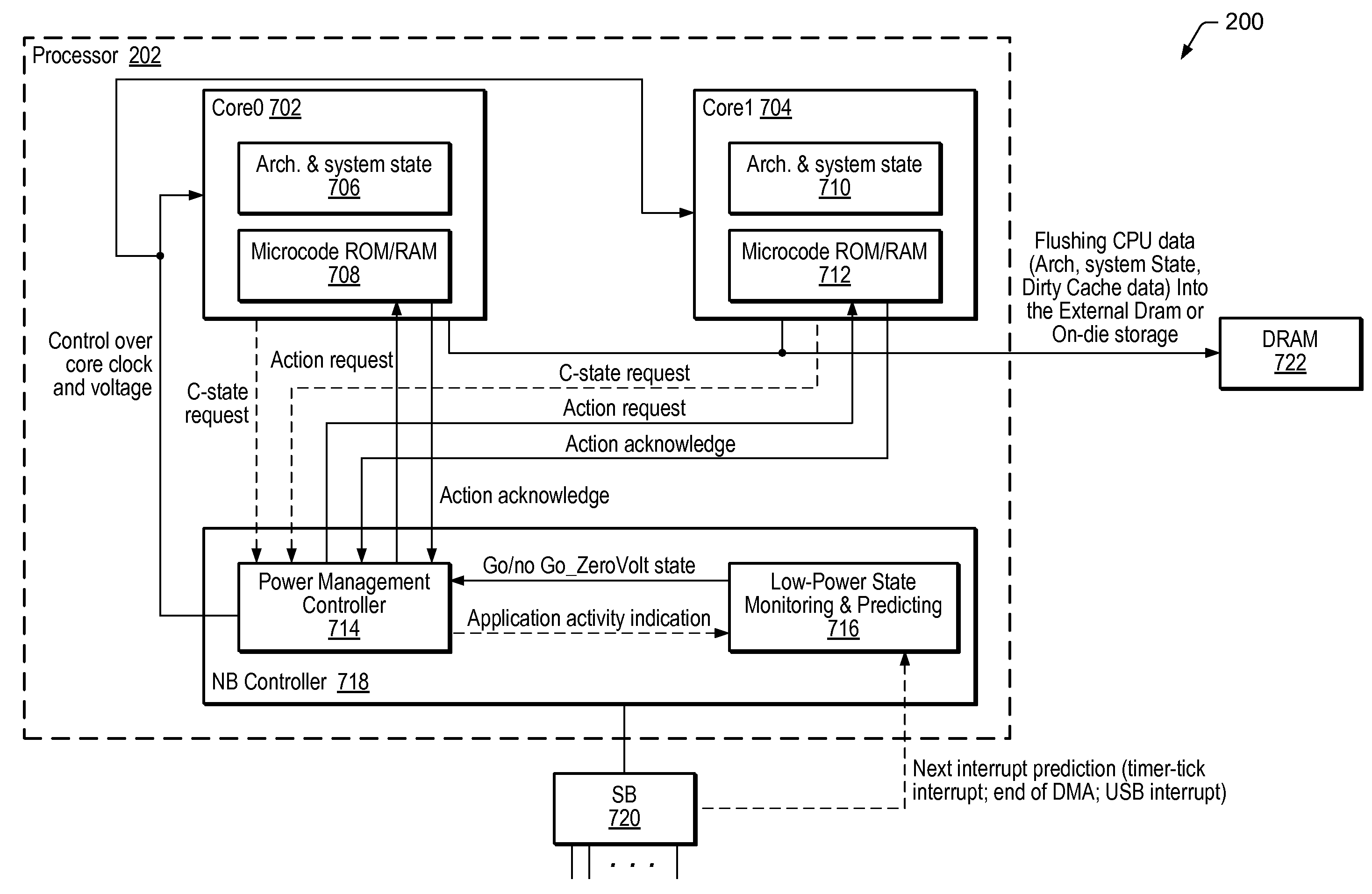

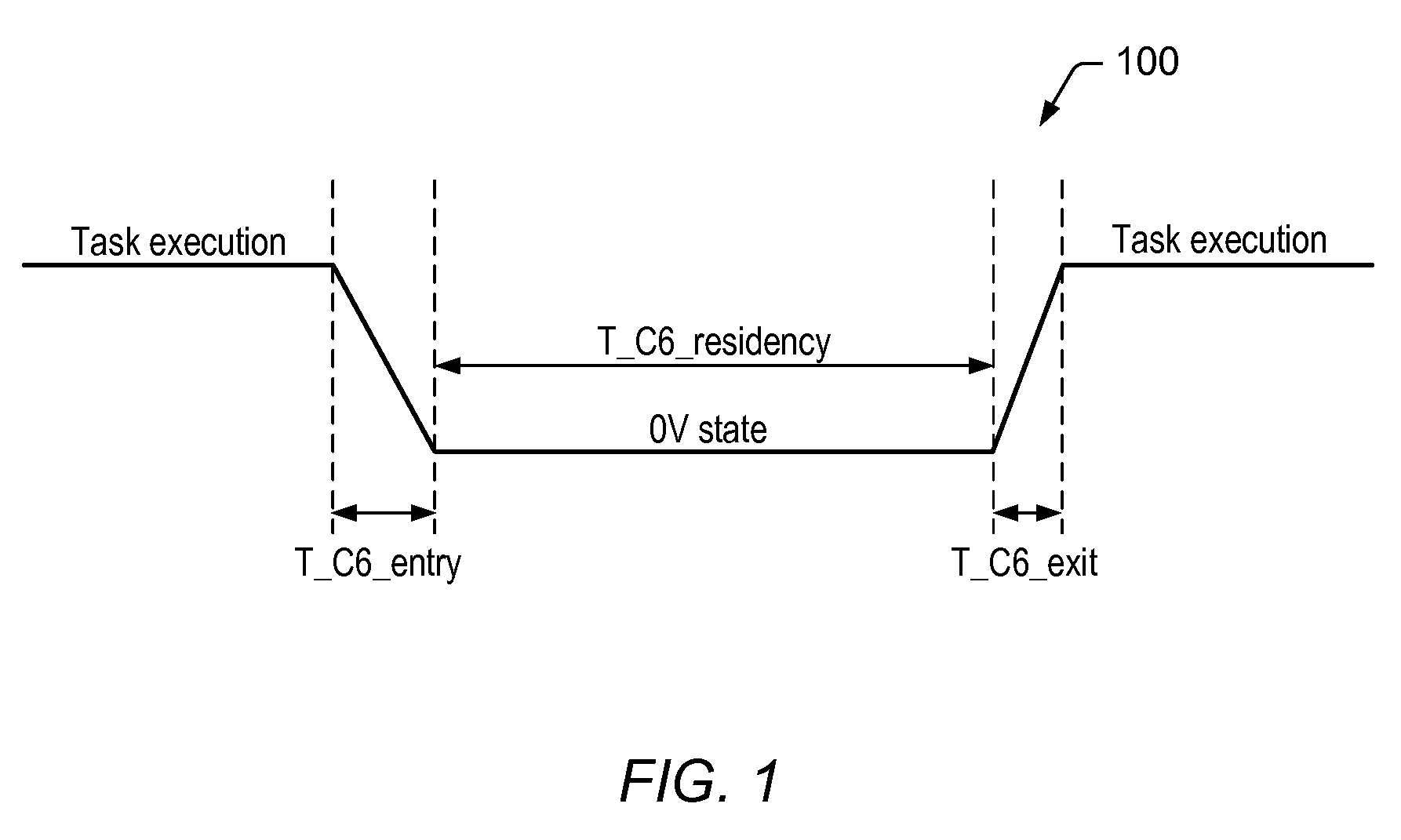

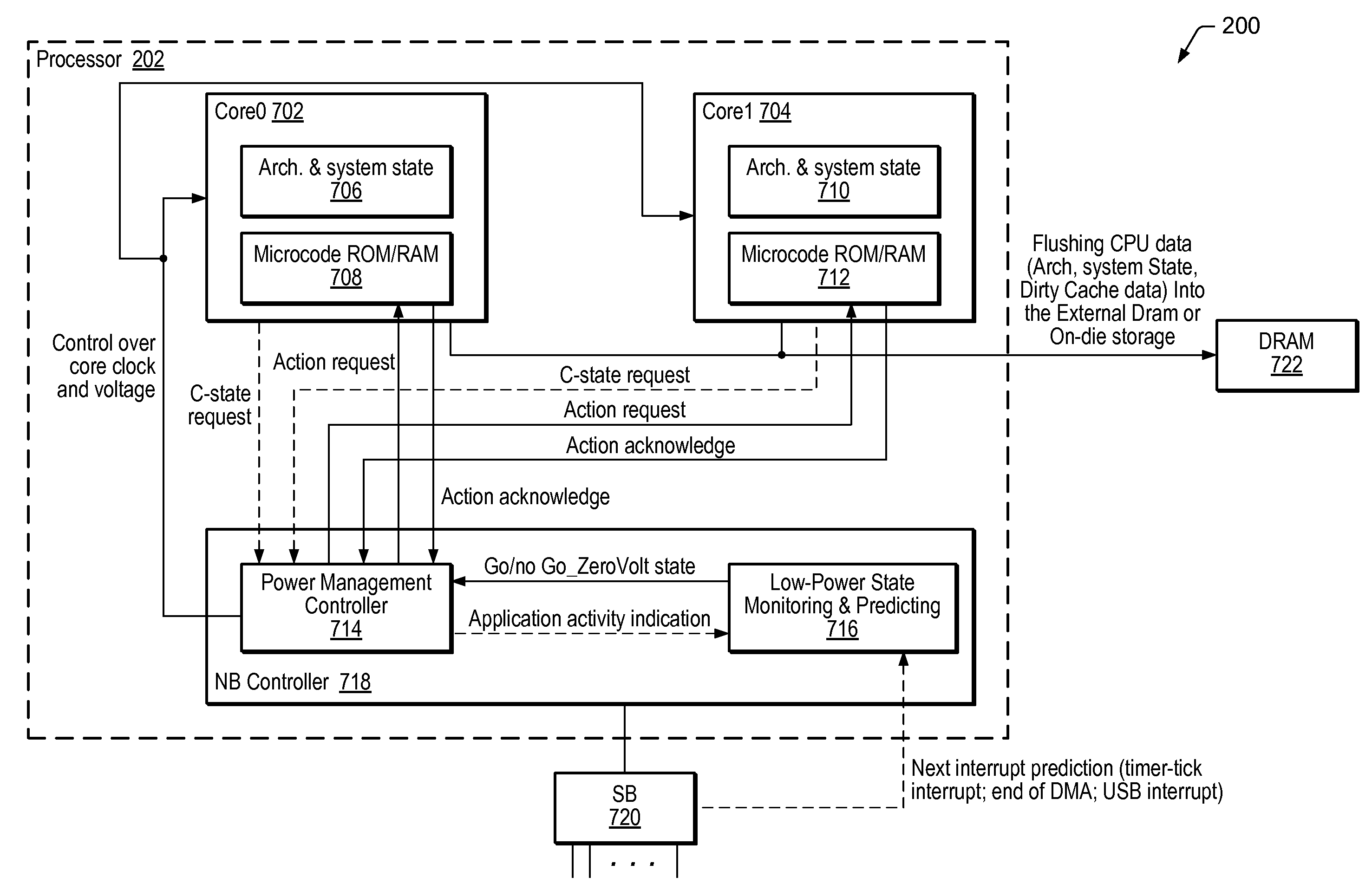

A system may comprise a plurality of processing units and a scheduler configured to maintain a record for each respective processing unit. Each respective record may comprise entries which may indicate 1) how long the respective processing unit has been residing in an idle state, 2) a present power-state in which the respective processing unit resides, and 3) whether the respective processing unit is a designated default (bootstrap) processing unit. The scheduler may select one or more of the plurality of processing units according to their respective records, and assign impending instructions to be executed on the selected one or more processing units. Where additional processing units are required, the scheduler may also insert an instruction to trigger an inter-processor interrupt to transition one or more processing units out of idle-state. The scheduler may then assign some impending instructions to these one or more processing units.

Owner:MEDIATEK INC

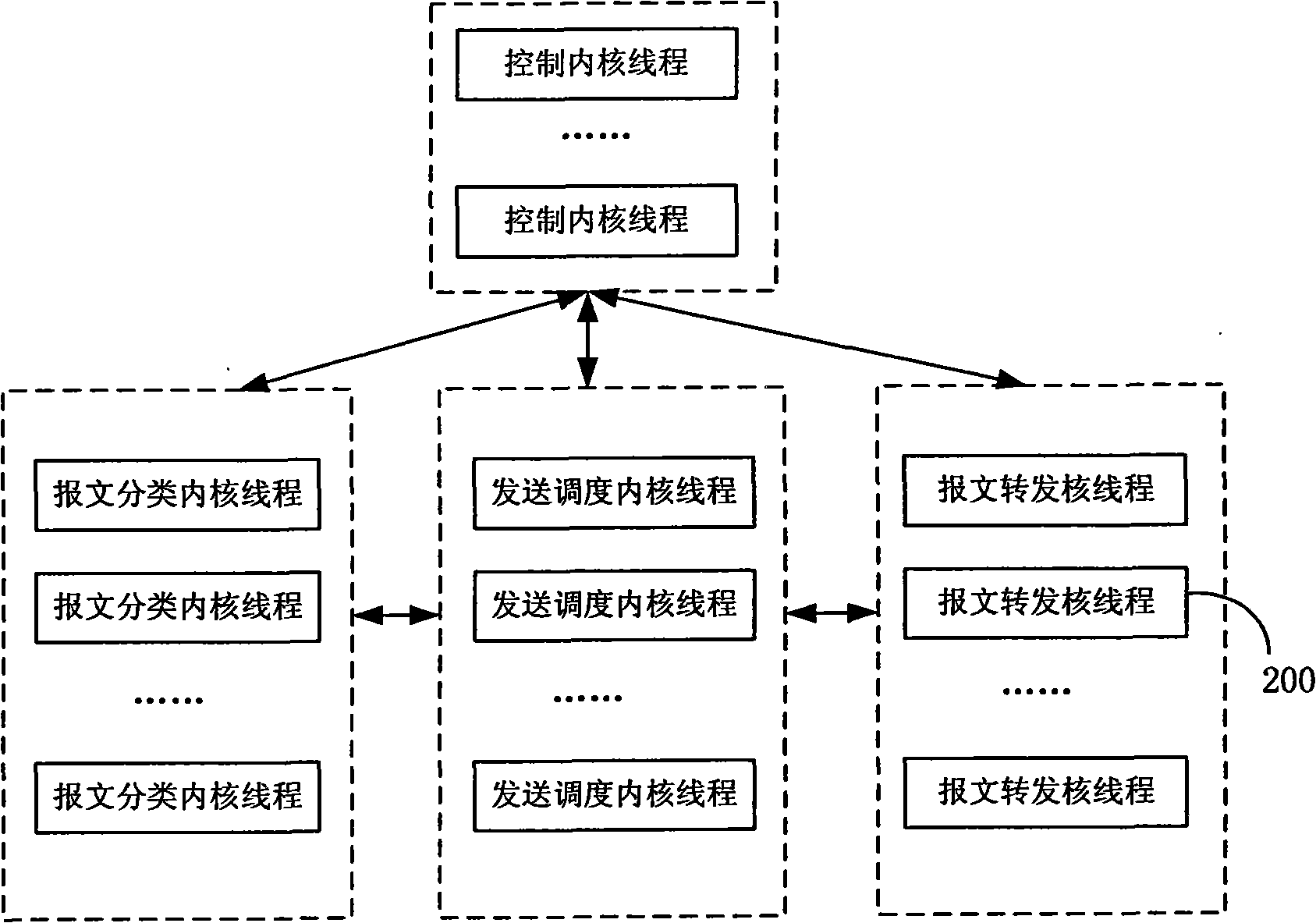

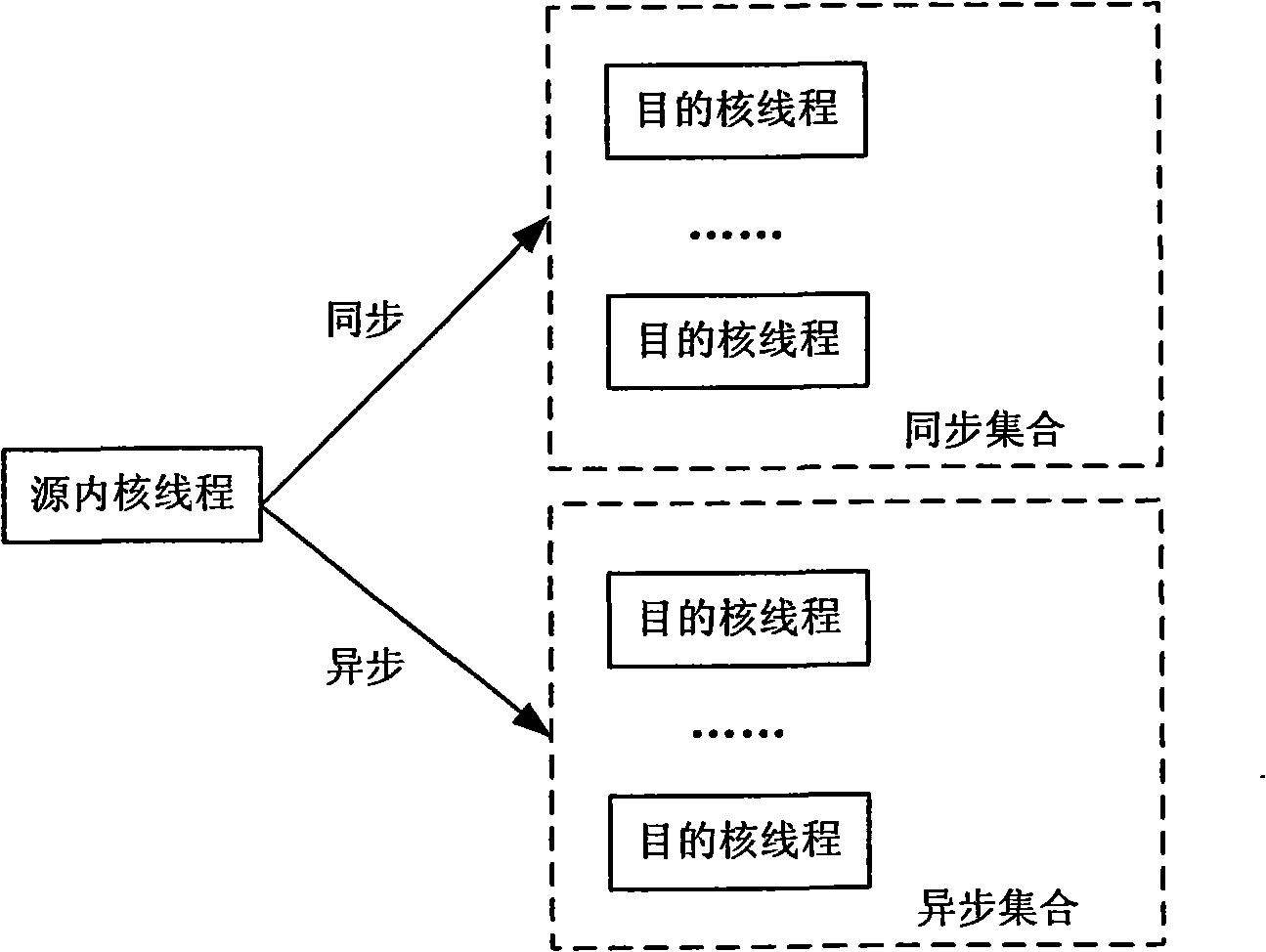

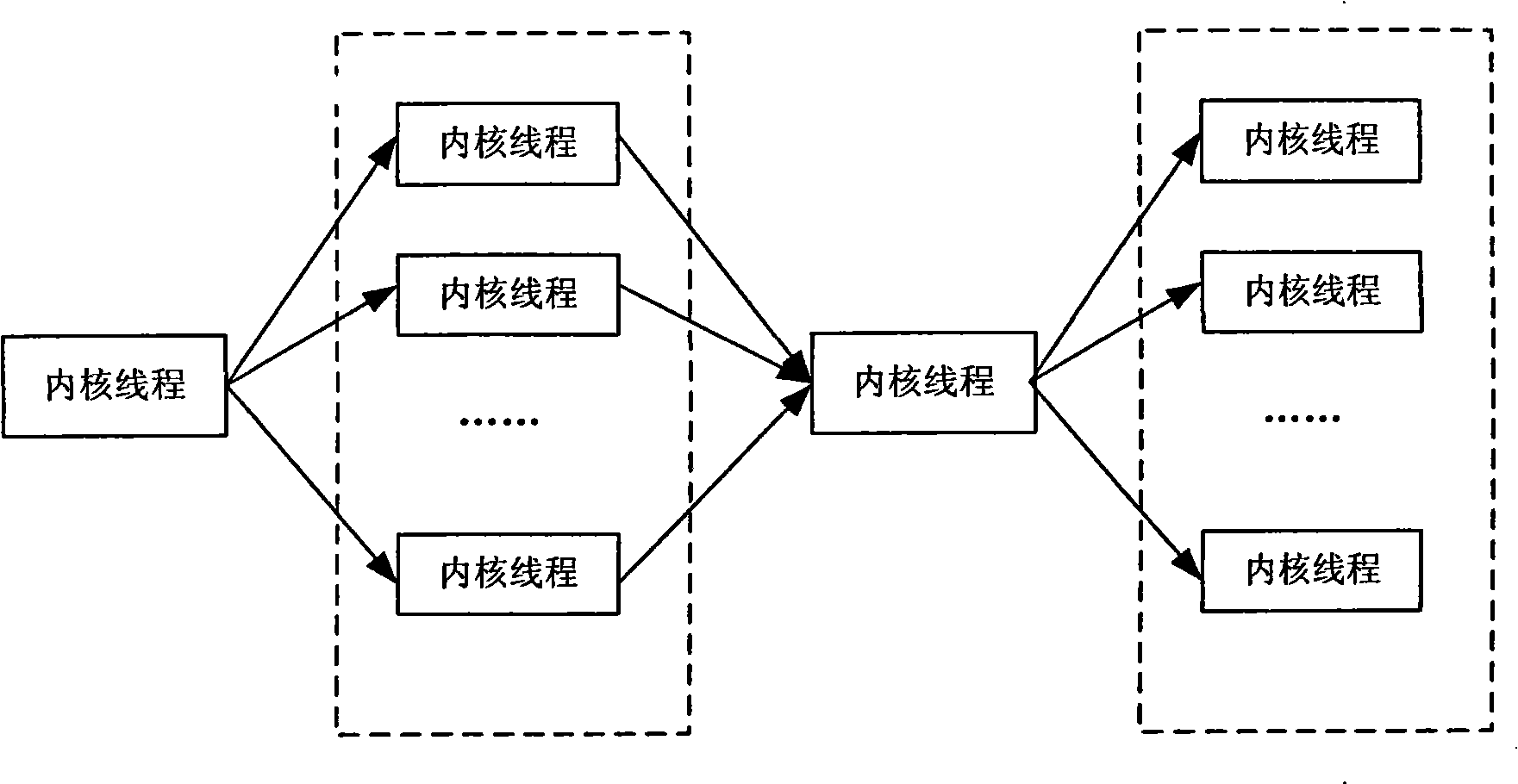

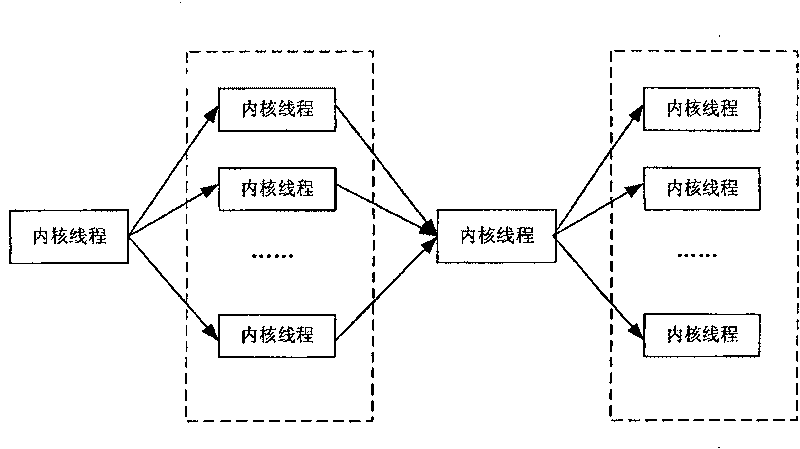

Inter-core message communication method for multi-core multithread processor

ActiveCN101266561AMeet development needsImprove reliabilityInterprogram communicationMessage typeInter-processor interrupt

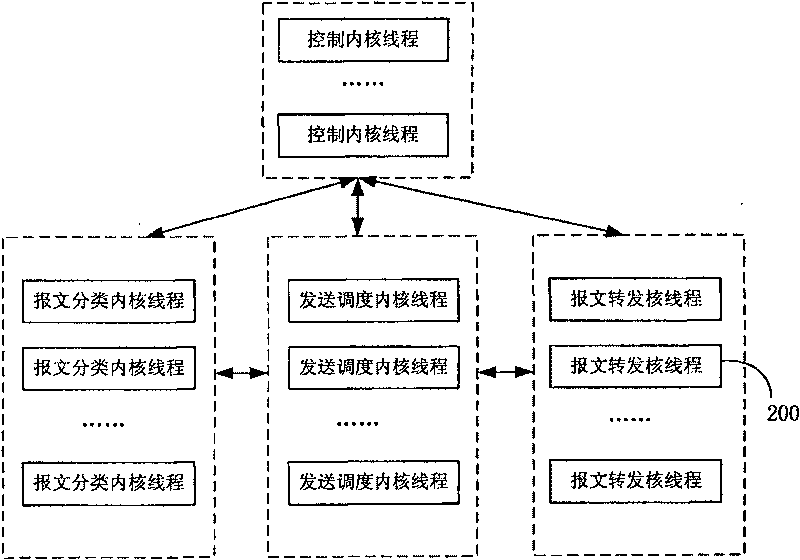

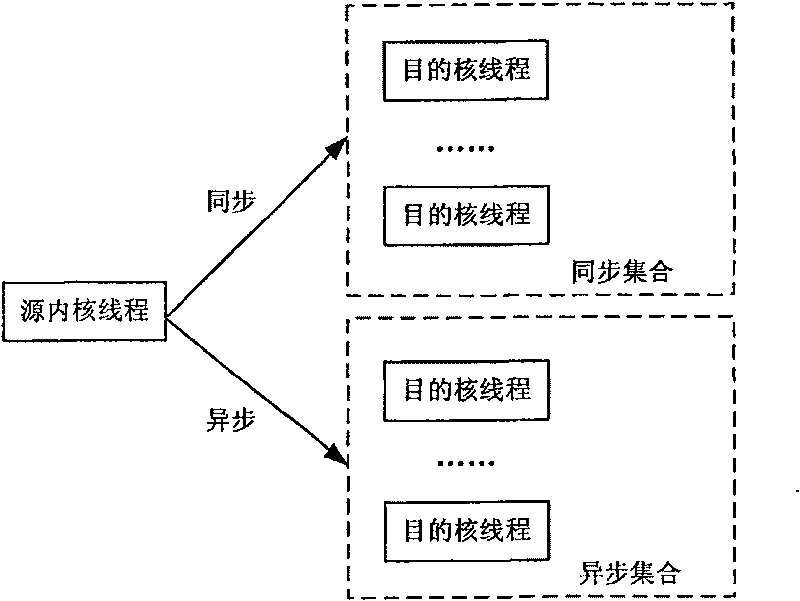

The invention discloses an internuclear news communication method in a between the multi-core multi-thread processor, which includes the following steps: establishing synchronization or the asynchronous relations of each kernel thread under the triggering of various message types, establishing the asynchronous news queue and the synchronized news buffer memory between various kernel threads; reading the synchronization set or the asynchronous set of the kernel thread corresponding to current news by a source kernel thread, putting a news body sealed into the asynchronous news queue and the synchronized news buffer memory; after a goal kernel thread receiving interrupts between the processors, analyzing the news contend from the asynchronous news queue and the synchronized news buffer memory and carrying out finish operations. Because the synchronized / asynchronous news communication pattern sealed between the multi-core multi-thread processors processor to interrupt the seal is used, various kernel threads can be guaranteed to operate the execution of correct relative relations in different application scene, which meets the development needs of certain key application platform, and enormously enhances the operation reliability and the flexibility of the multi-core multi-thread system.

Owner:ZTE CORP

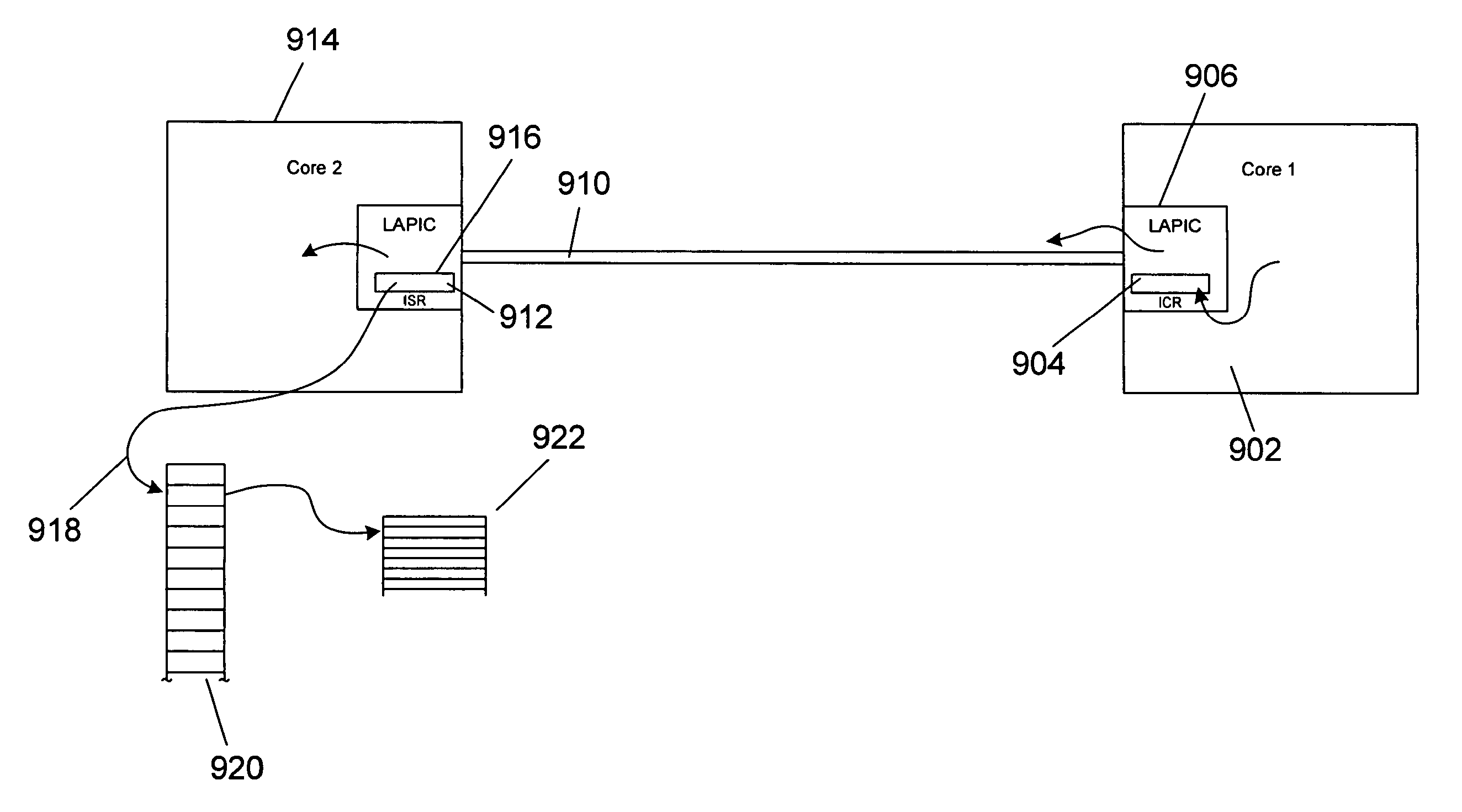

Method and System for Generating and Delivering Inter-Processor Interrupts in a Multi-Core Processor and in Ceterain Shared Memory Multi-Processor Systems

ActiveUS20110047310A1Facilitate shared-memory-based communicationEfficient use ofProgram controlMulti processorInter-processor interrupt

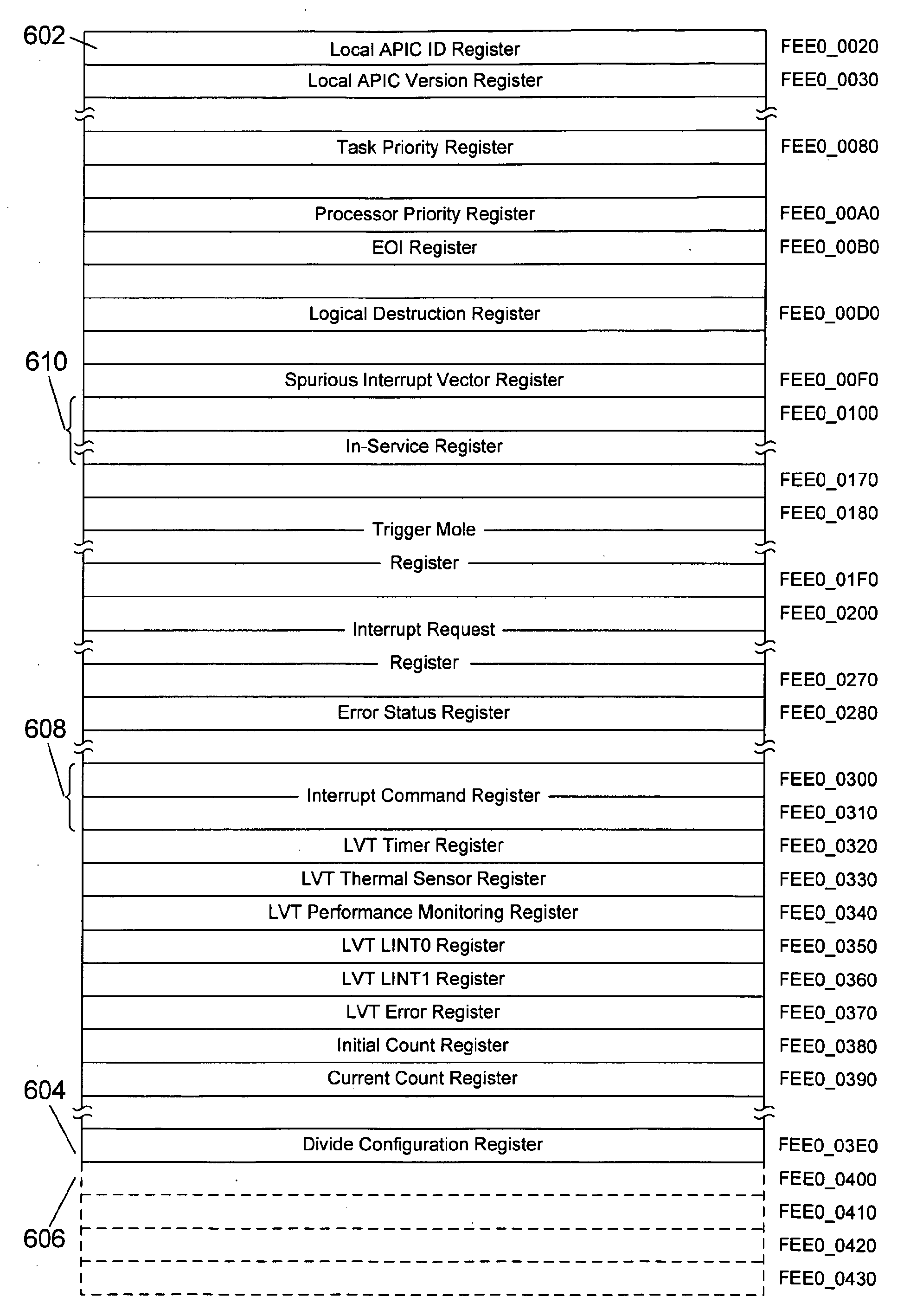

Certain embodiments of the present invention arc directed to providing efficient and easily-applied mechanisms for inter-core and inter-processor communications and inter-core and inter-processor signaling within multi-core microprocessors and certain multi-processor systems. In one embodiment of the present invention, local advanced programmable interrupt controllers within, or associated with, cores of a multi-core microprocessor and / or processors of a multi-processor system are enhanced so that the local advanced programmable interrupt controllers can be configured to automatically generate inter-core and inter-processor interrupts when WRITE operations are directed to particular regions of shared memory.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Enhanced control of CPU parking and thread rescheduling for maximizing the benefits of low-power state

ActiveUS8112648B2Energy efficient ICTVolume/mass flow measurementParallel computingInter-processor interrupt

A system may comprise a plurality of processing units and a scheduler configured to maintain a record for each respective processing unit. Each respective record may comprise entries which may indicate 1) how long the respective processing unit has been residing in an idle state, 2) a present power-state in which the respective processing unit resides, and 3) whether the respective processing unit is a designated default (bootstrap) processing unit. The scheduler may select one or more of the plurality of processing units according to their respective records, and assign impending instructions to be executed on the selected one or more processing units. Where additional processing units are required, the scheduler may also insert an instruction to trigger an inter-processor interrupt to transition one or more processing units out of idle-state. The scheduler may then assign some impending instructions to these one or more processing units.

Owner:MEDIATEK INC

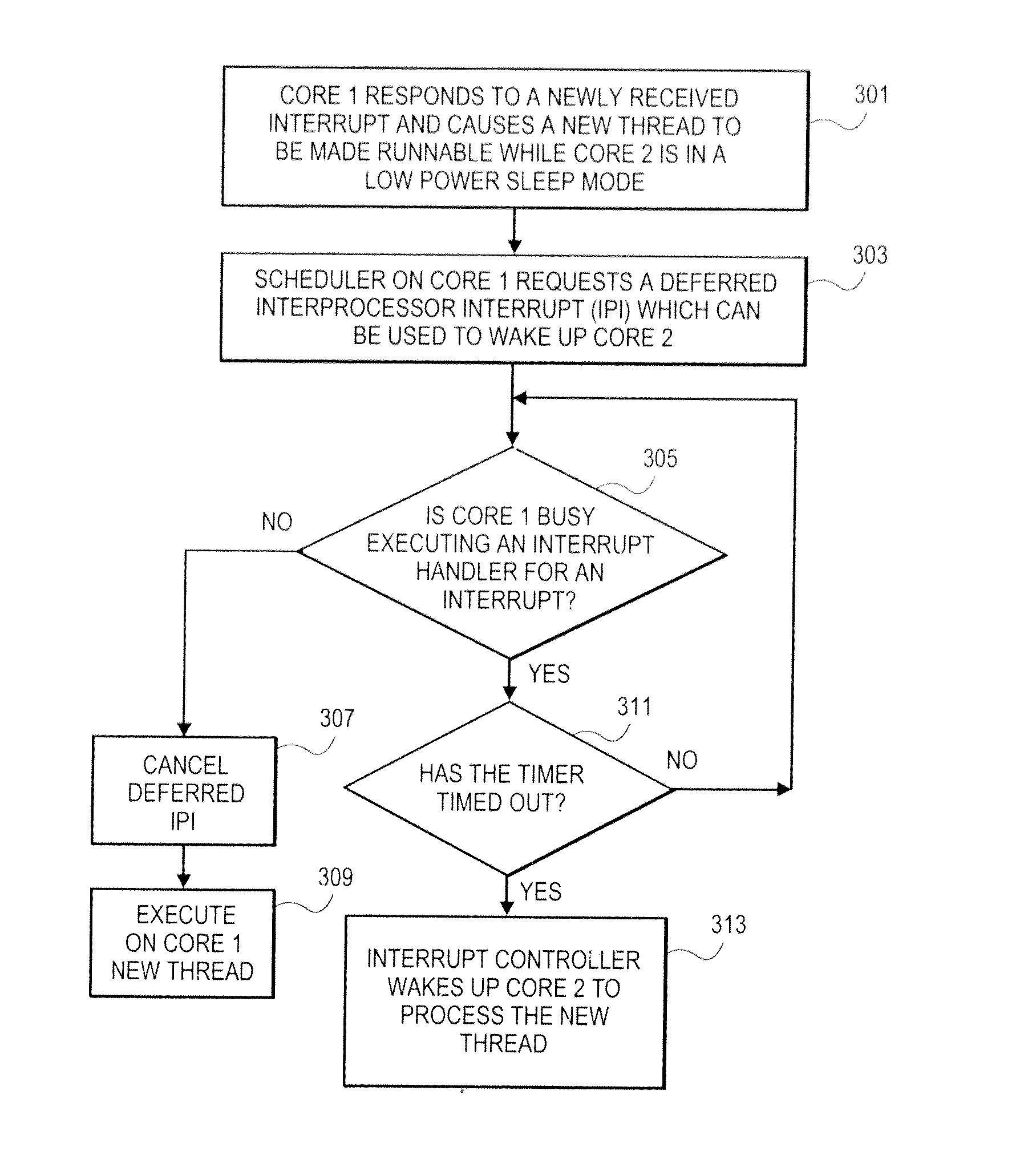

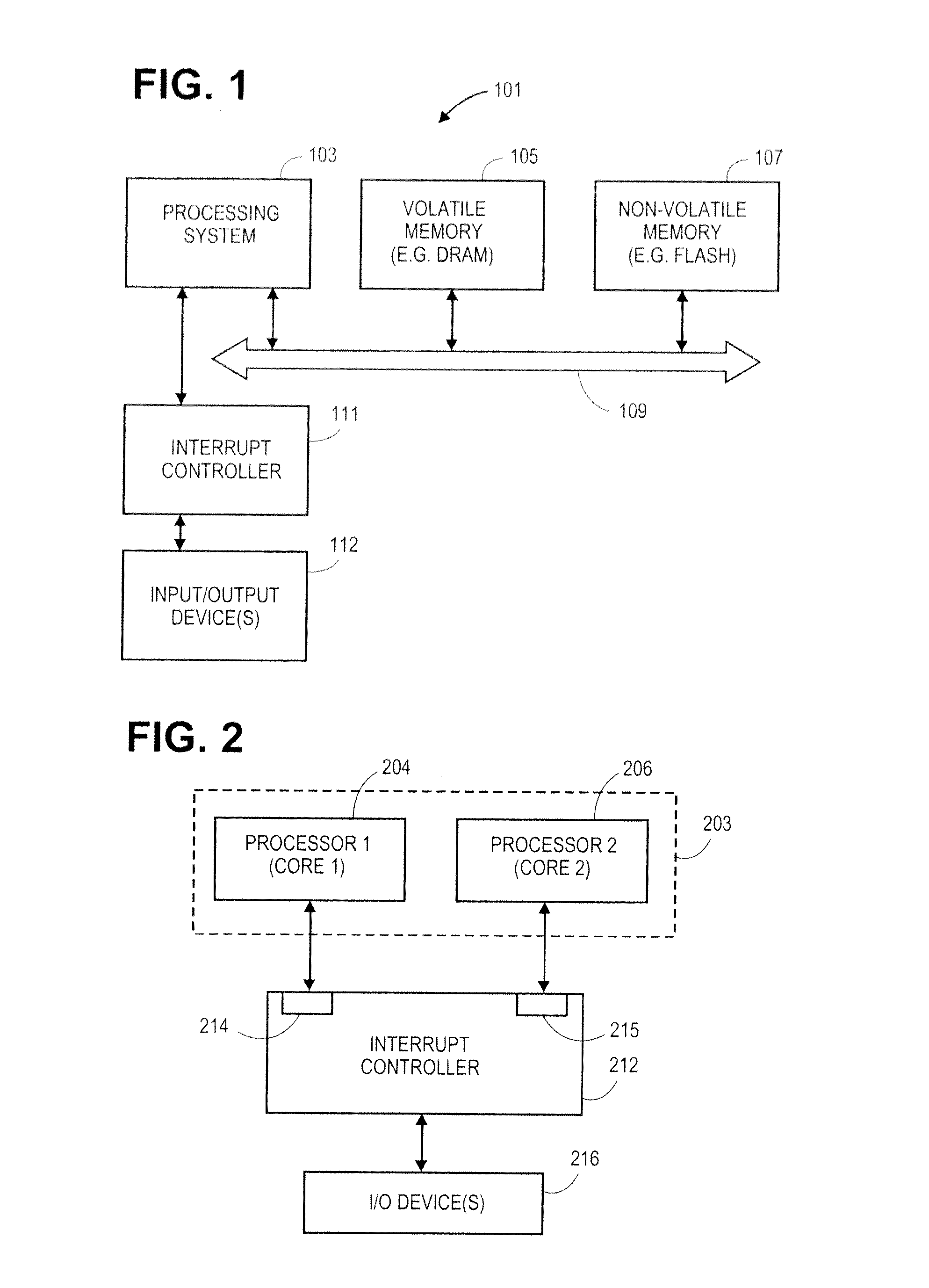

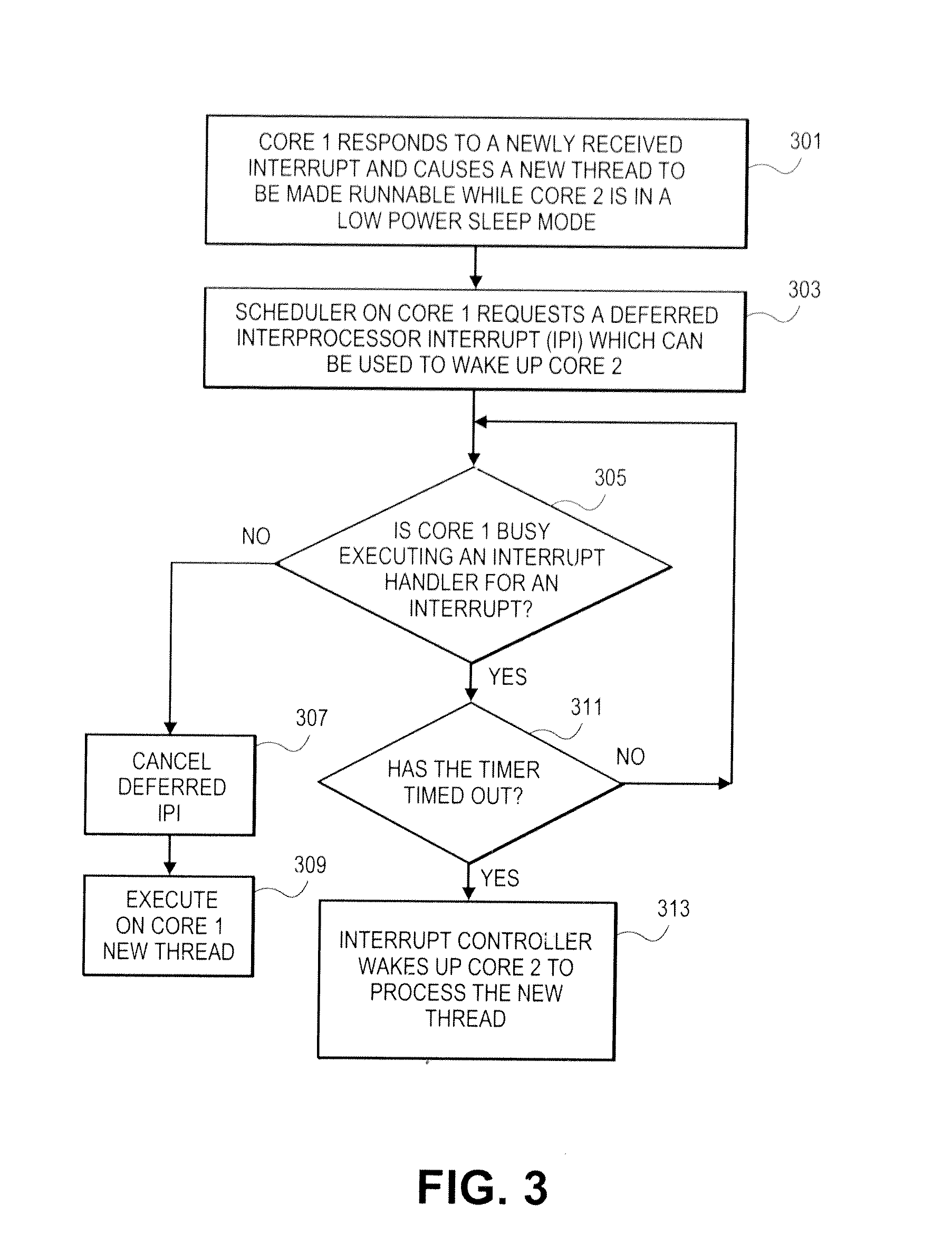

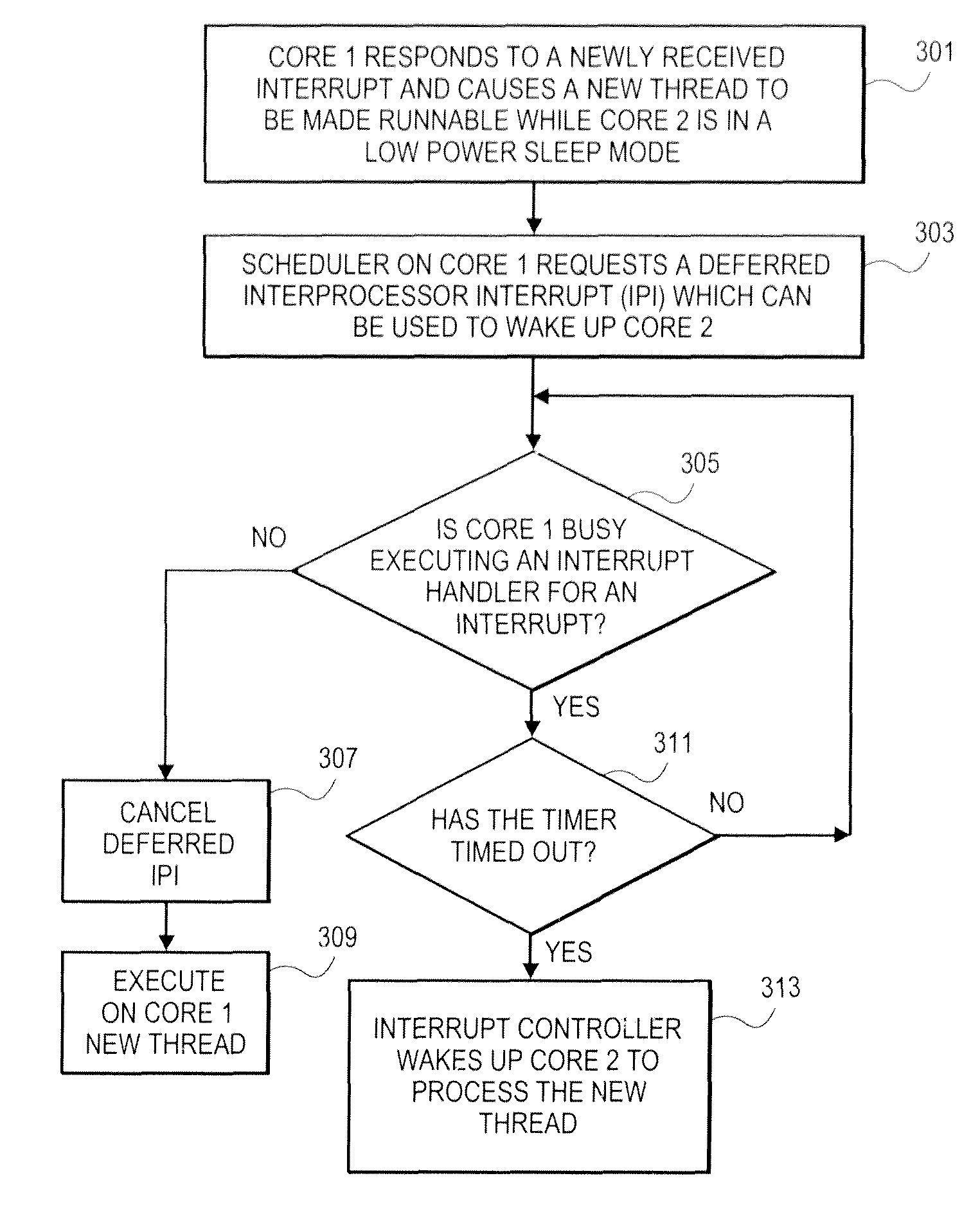

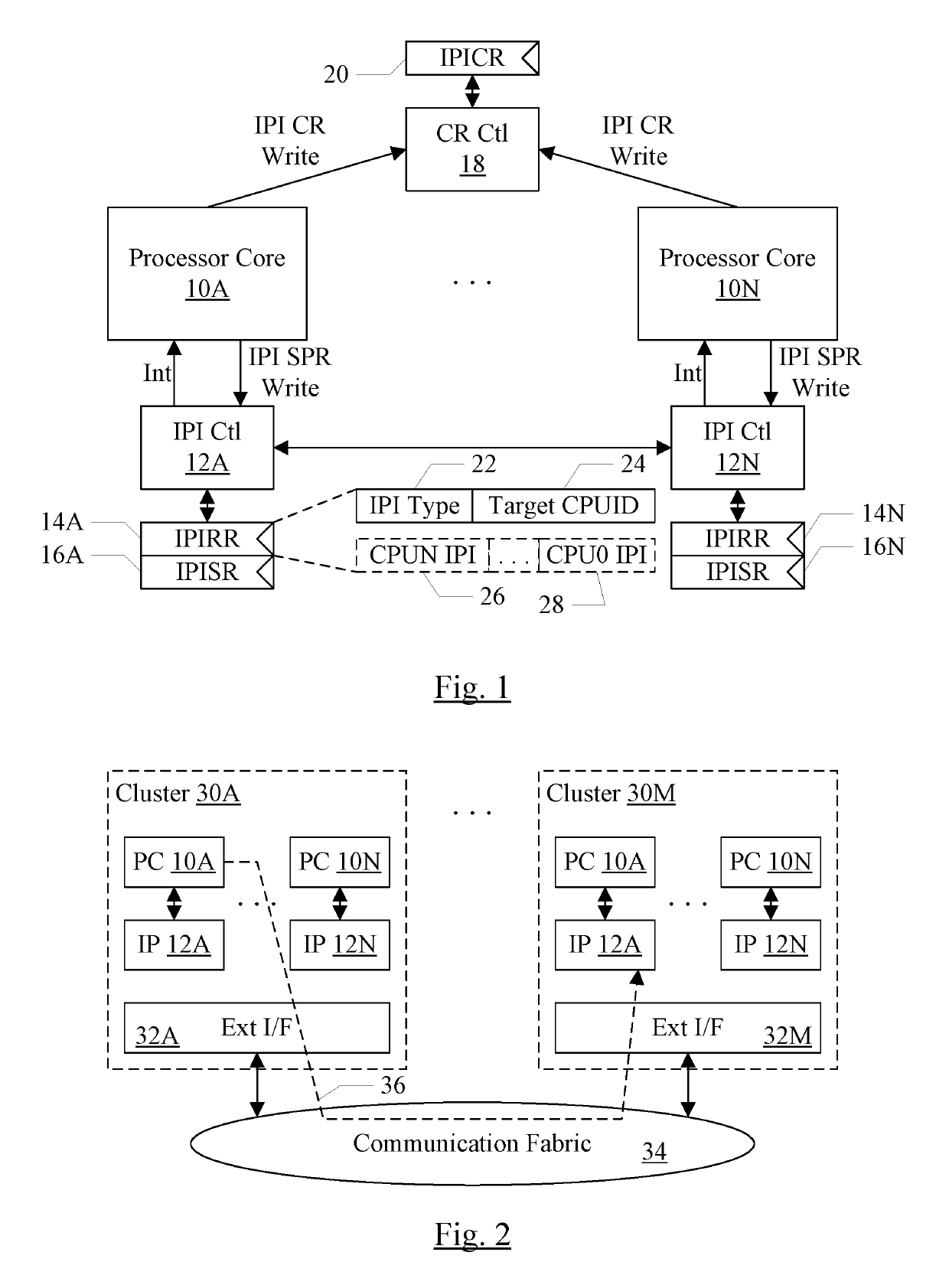

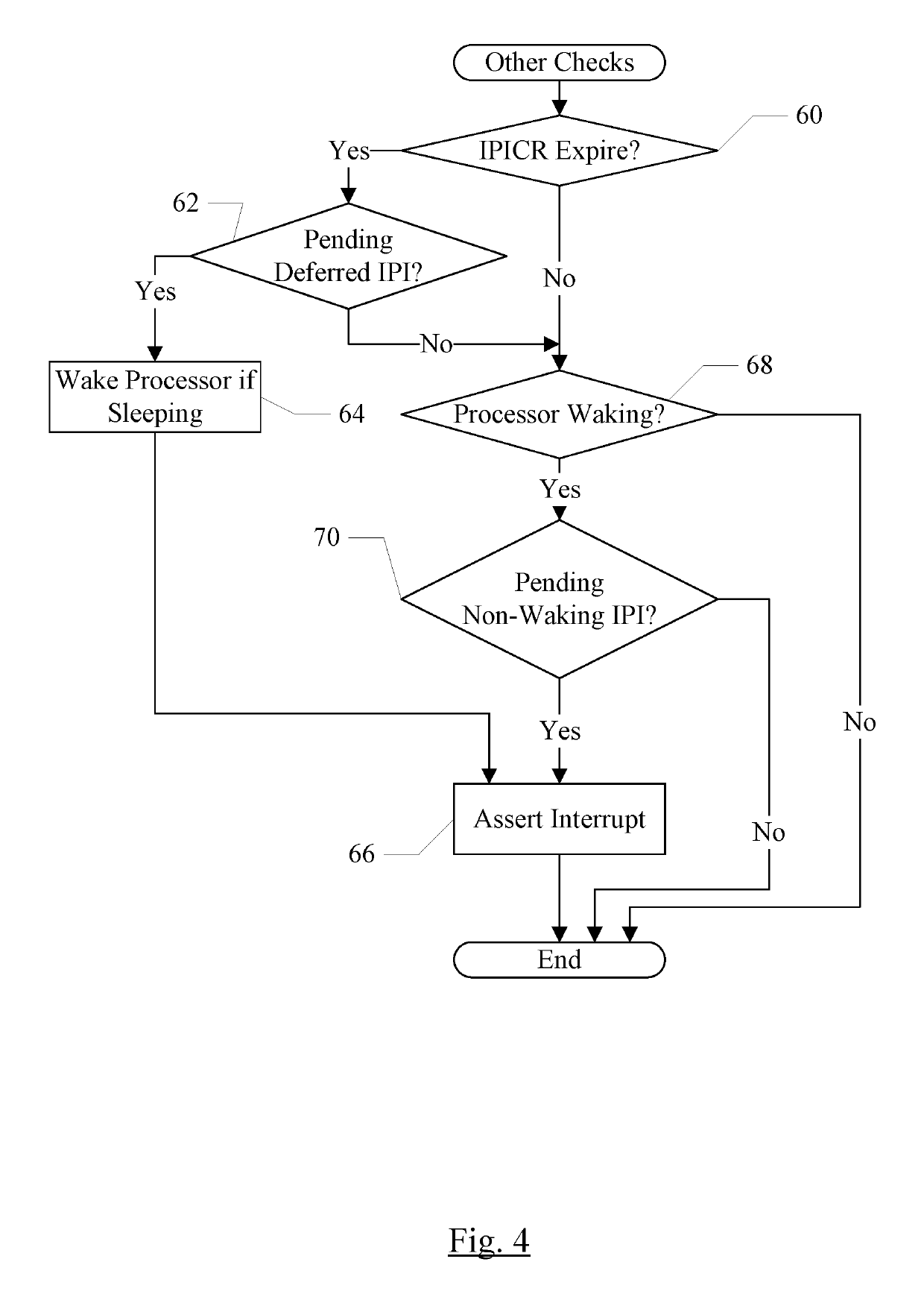

Deferred inter-processor interrupts

ActiveUS20140201411A1Digital data processing detailsProgram controlData processing systemSleep state

A data processing system includes, in one embodiment, at least a first processor and a second processor and an interrupt controller, and the system provides a deferred inter-processor interrupt (IPI) that can be used to wake up the second processor from a low power sleep state. The deferred IPI is, in one embodiment, delayed by a timer in the interrupt controller, and the deferred IPI can be cancelled by the first processor if the first processor becomes available to execute a thread that was made runnable by an interrupt which triggered the deferred IPI.

Owner:APPLE INC

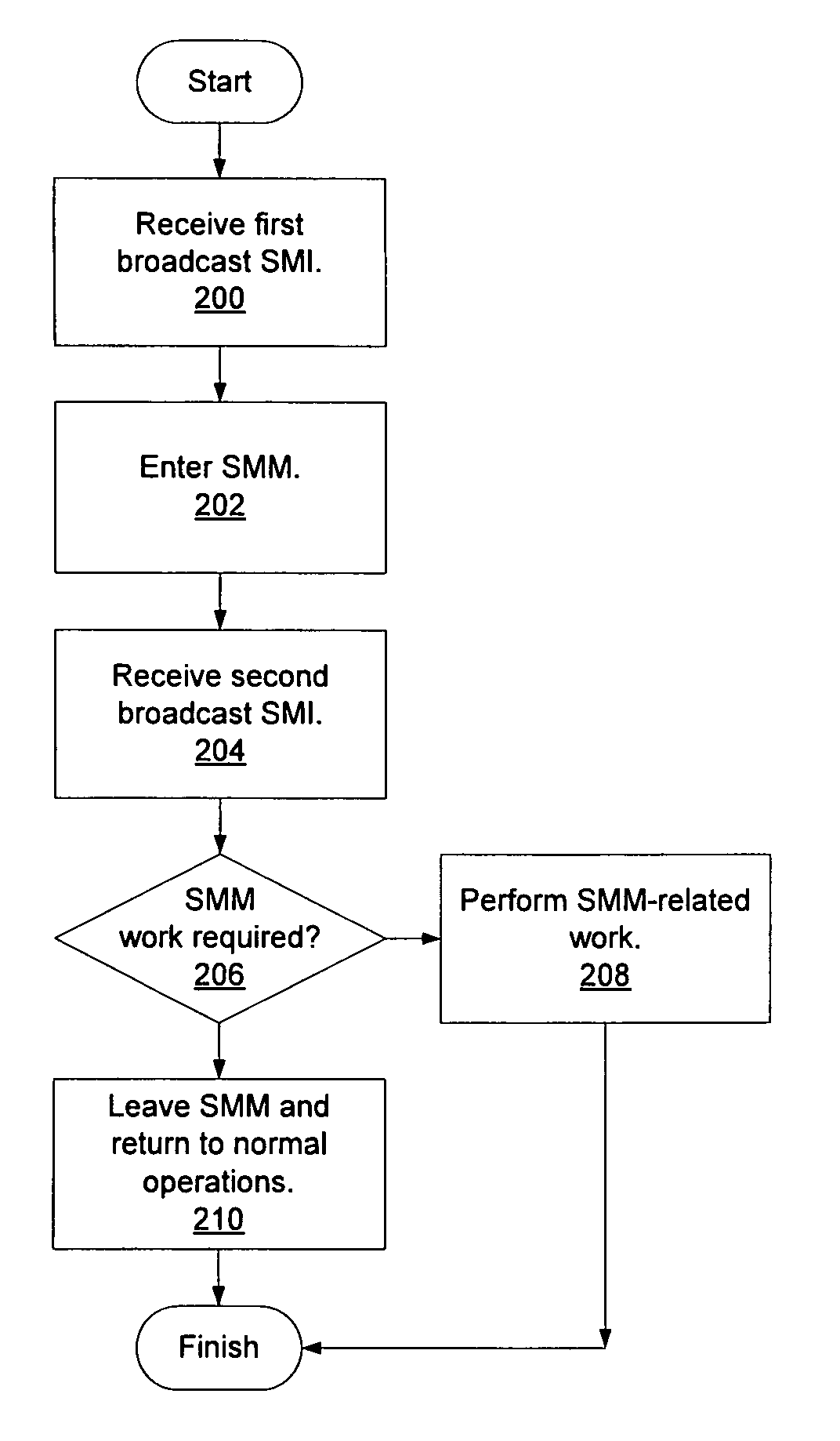

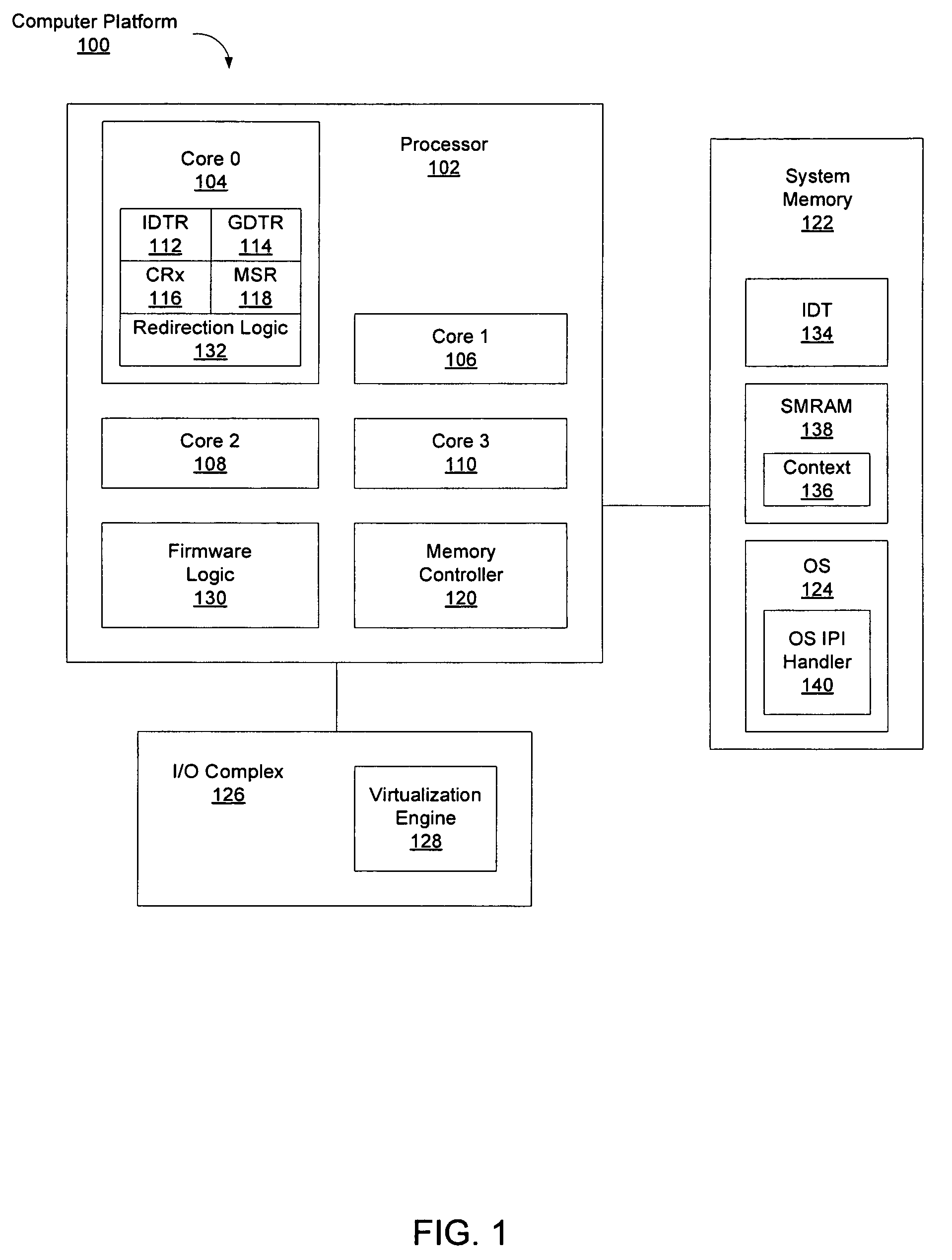

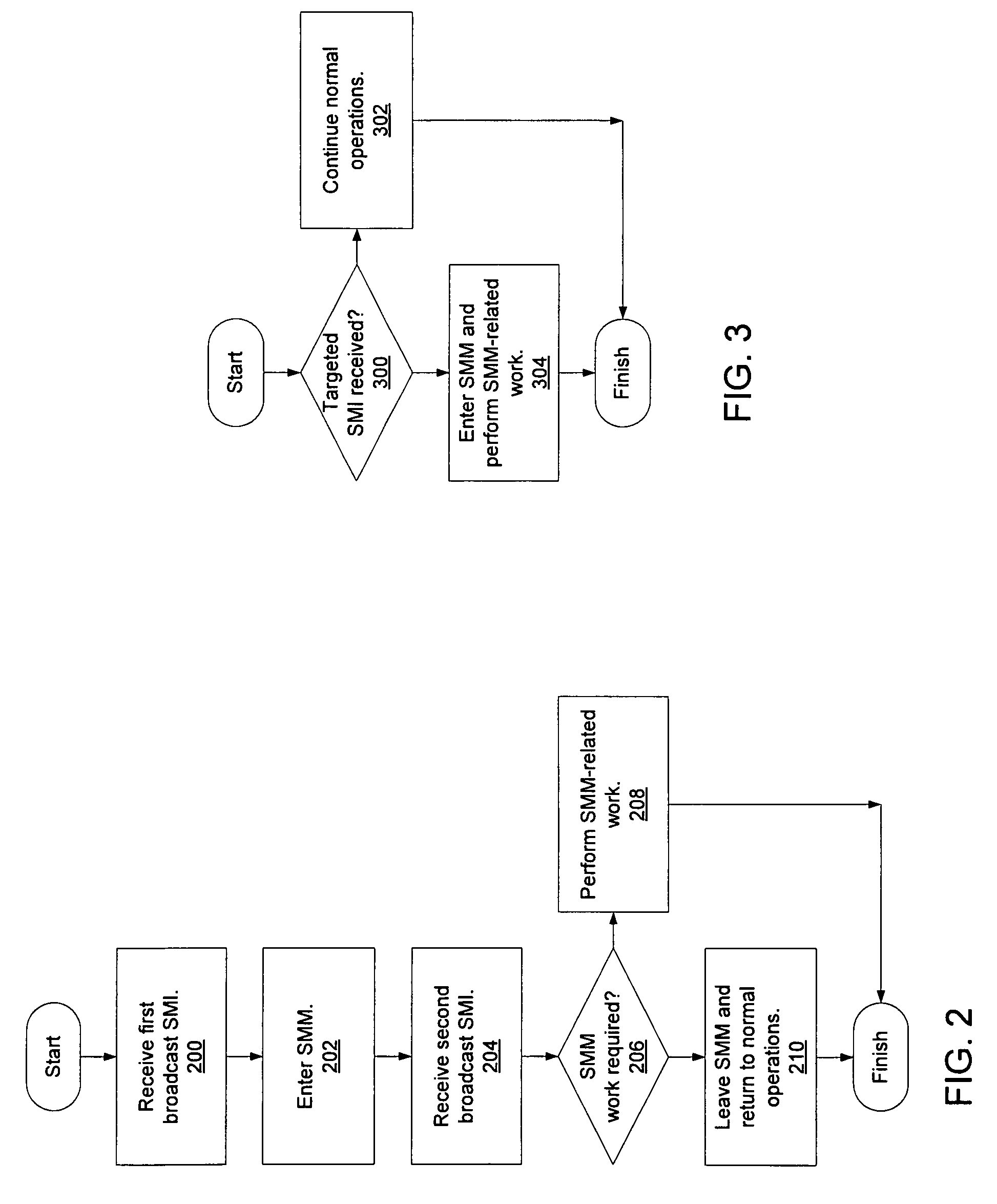

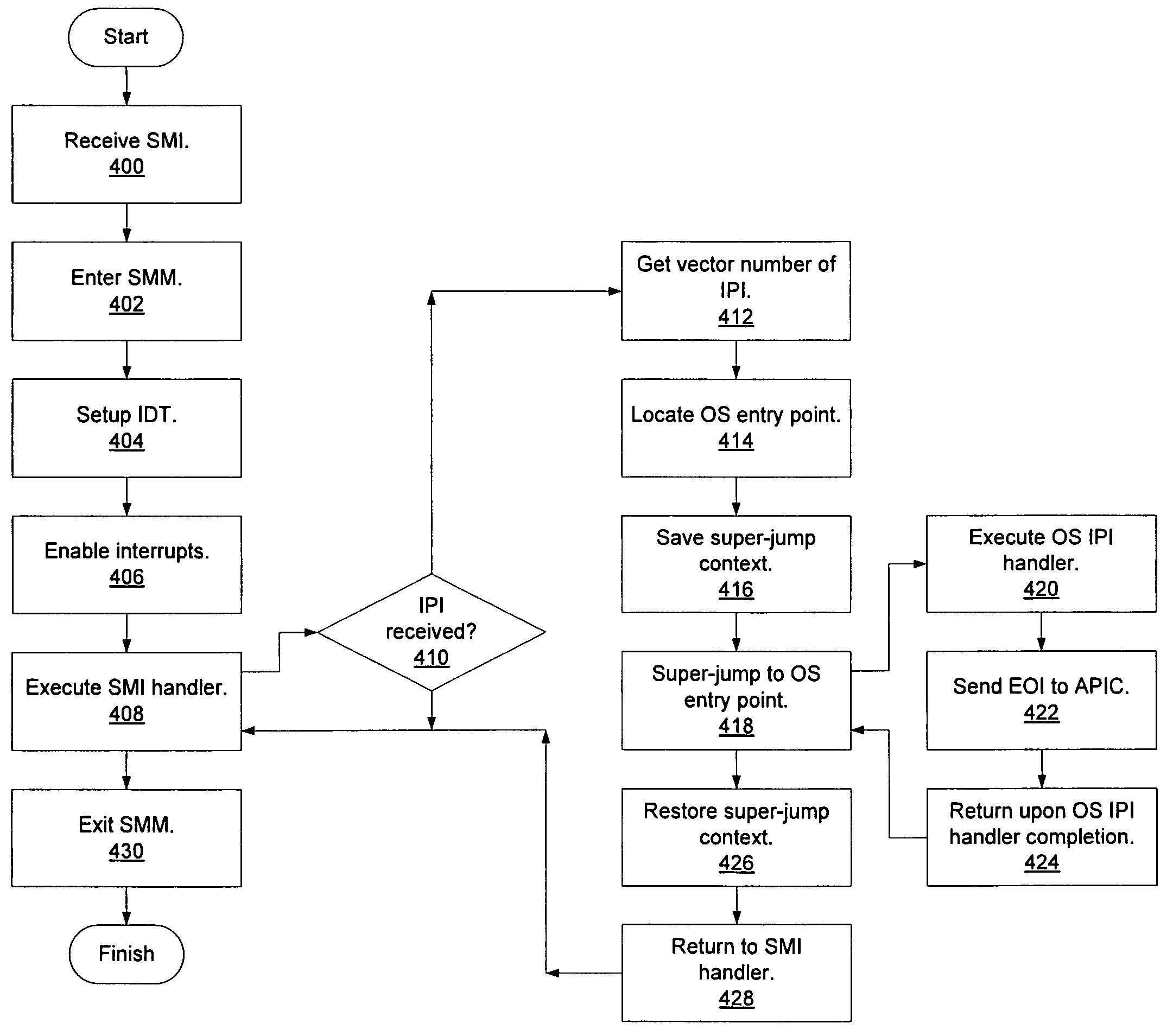

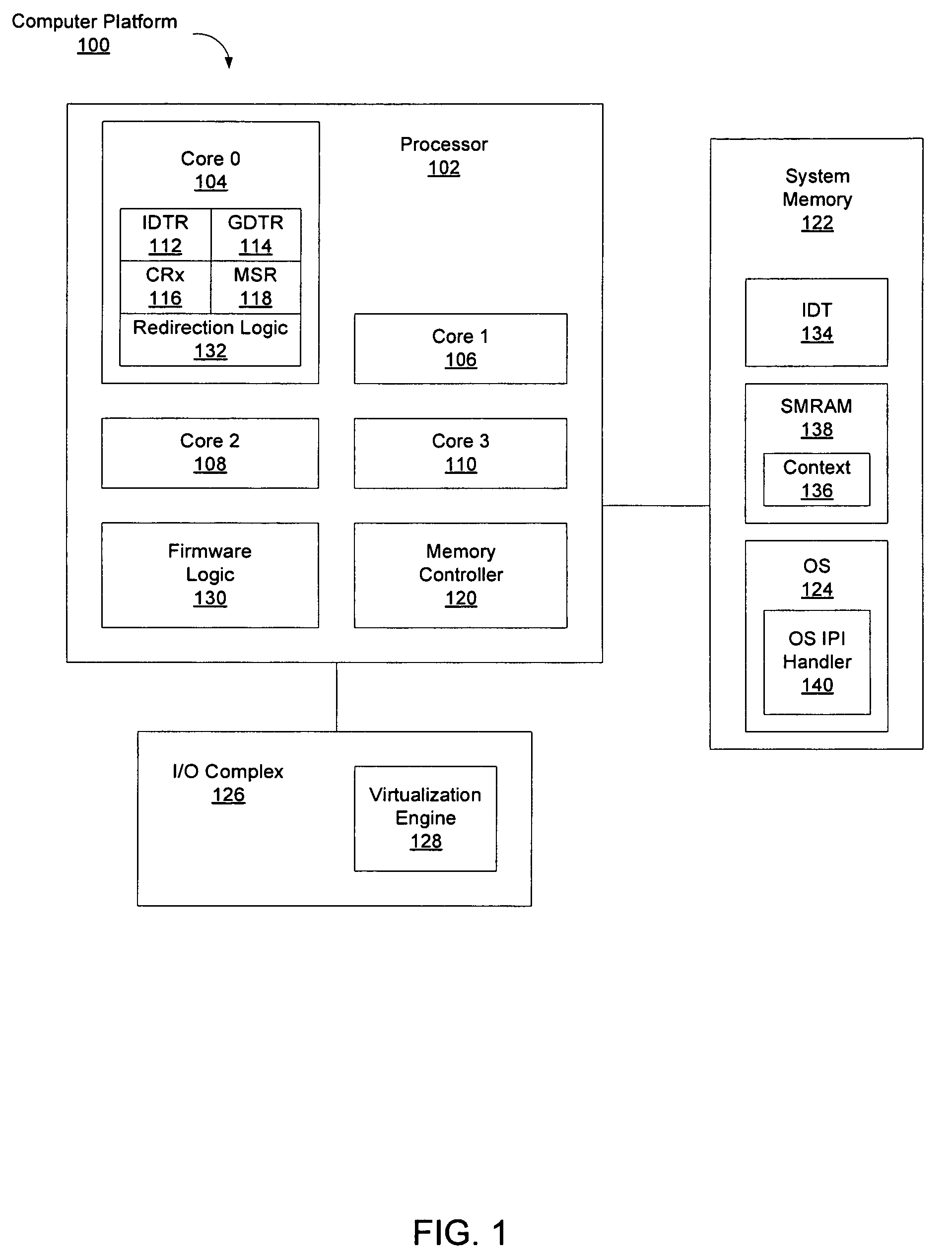

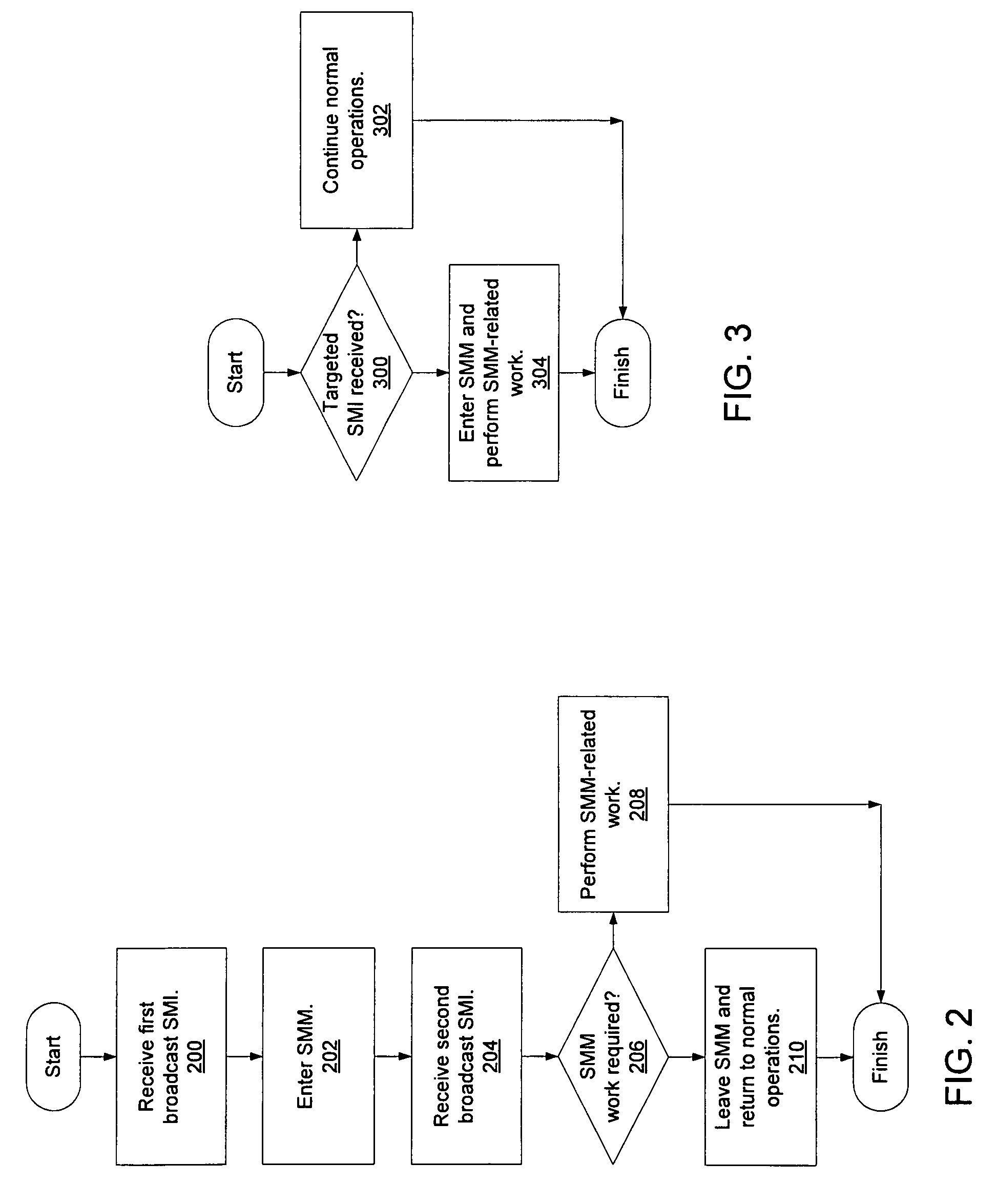

System management mode inter-processor interrupt redirection

A method, processor, and system are disclosed. In one embodiment method includes a first processor core among several processor cores entering into a system management mode. At least one of the other additional processor cores apart from the first processor core remain operational and do not enter the system management mode. Then, once in the system management mode, the first processor core responds to an inter-processor interrupt.

Owner:INTEL CORP

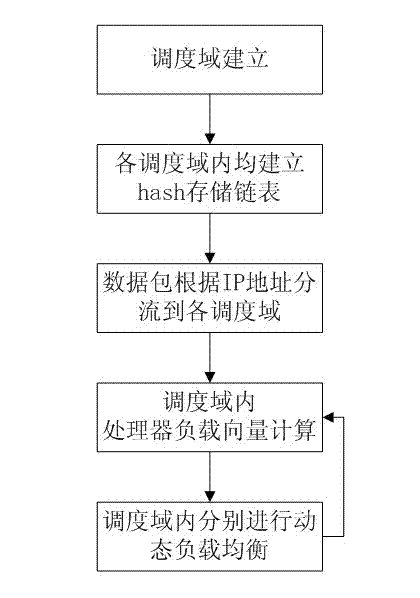

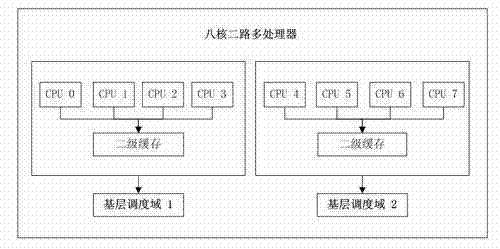

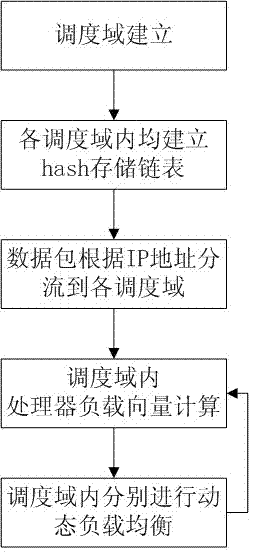

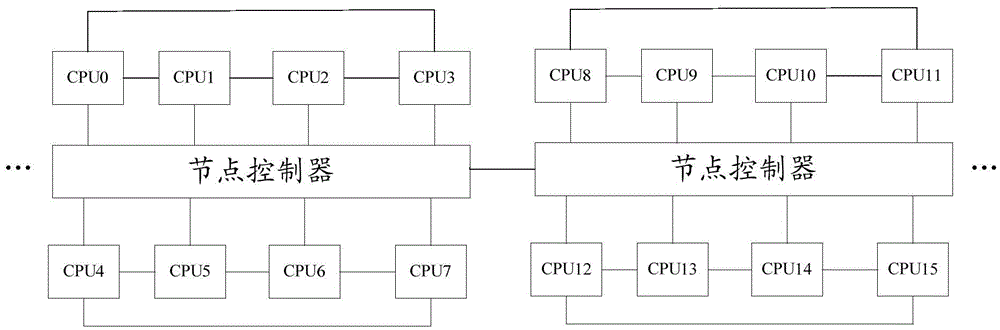

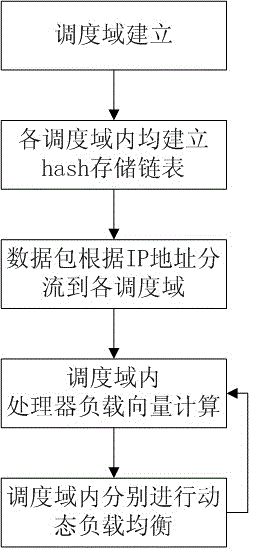

Method for realizing interrupted load balance among multi-core processors

ActiveCN102521047AImprove parallelismLoad balancingResource allocationOperational systemNetwork packet

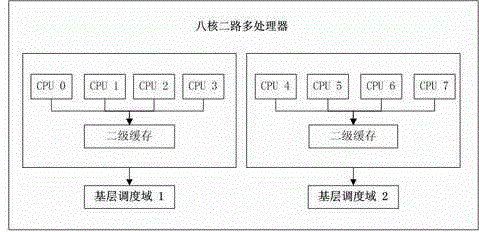

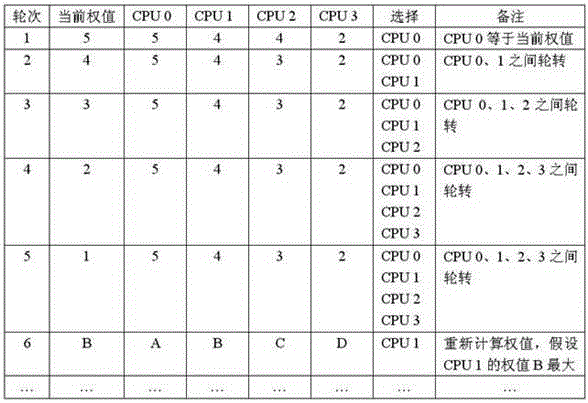

The invention relates to a method for realizing interrupted load balance among multi-core processors, belonging to the computer network technology. The technical scheme adopted by the balancing method of the invention is as follows: dividing processors sharing a second level cache to the same scheduling region, distributing all data packets to each scheduling region according to source IP addresses, establishing a hash table, and carrying out analytical statistics on the data packets, wherein each scheduling region can have a critical access to respective hash table; and adopting a weighted cycle scheduling algorithm to realize the load balance in each scheduling region, allocating the interruption sent by a network card to each processor, and setting a server priority according to weight values, wherein the server with a higher weight value preferentially receives and processes the interruption, and the processors with the same weight values process the interruption in a cycle scheduling manner. Since an operating system can balance the interrupted load, the interruption sent by the network card can be subjected to balanced distribution on the multiple processor cores, thus the processing efficiency of the system can be improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

System management mode inter-processor interrupt redirection

A method, processor, and system are disclosed. In one embodiment method includes a first processor core among several processor cores entering into a system management mode. At least one of the other additional processor cores apart from the first processor core remain operational and do not enter the system management mode. Then, once in the system management mode, the first processor core responds to an inter-processor interrupt.

Owner:INTEL CORP

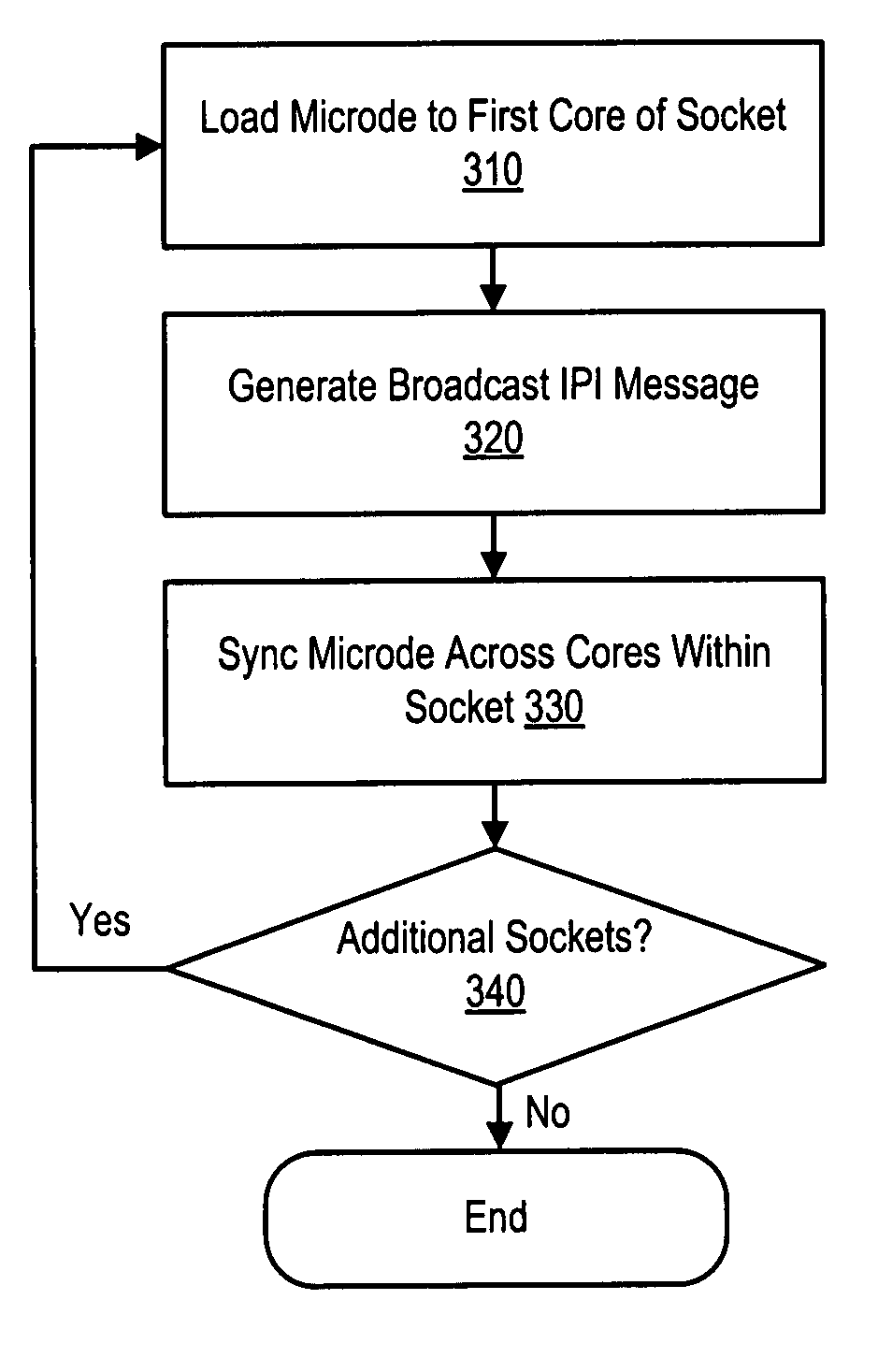

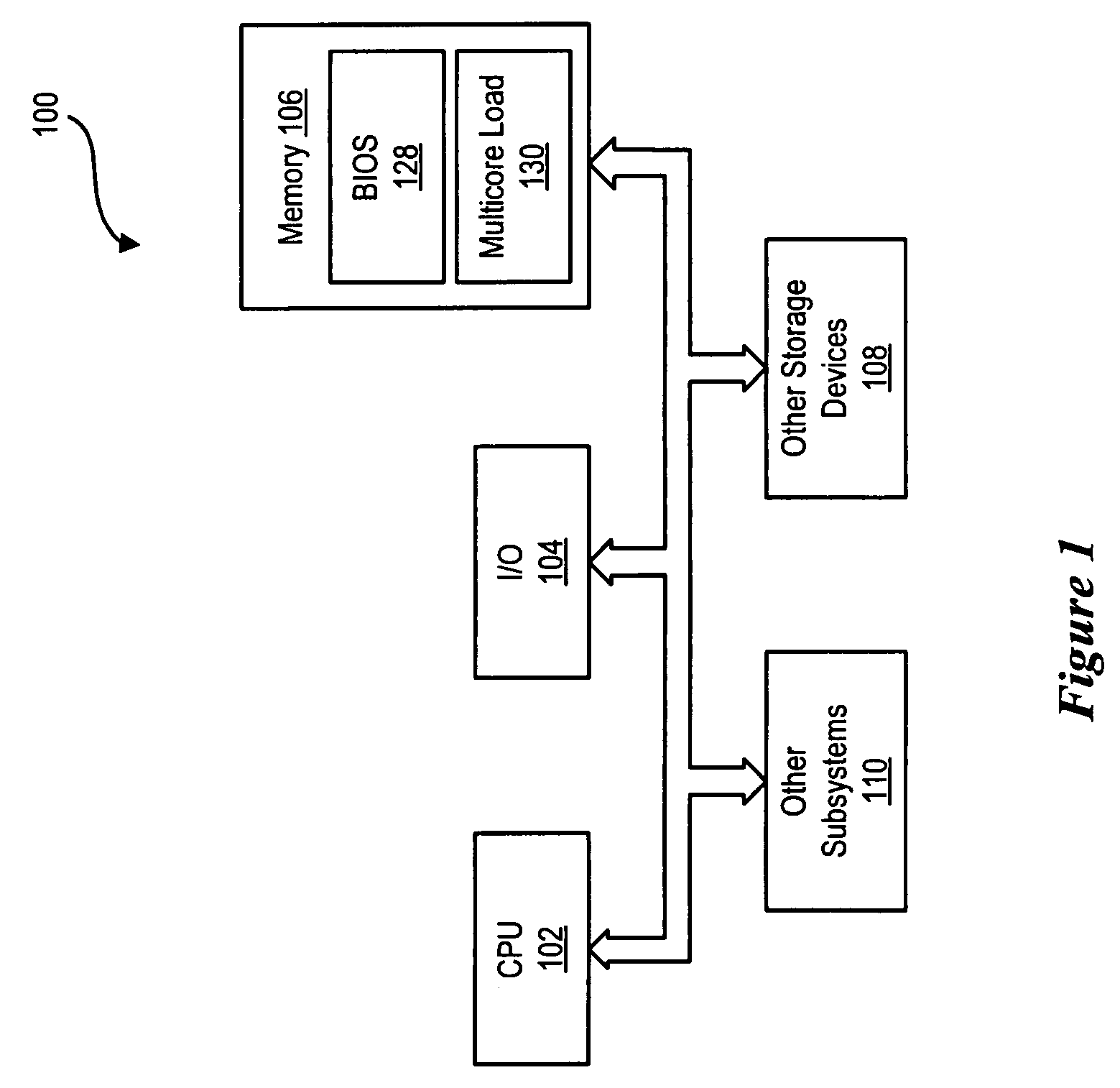

Architectural enhancements to CPU microcode load mechanism using inter processor interrupt messages

ActiveUS7882333B2General purpose stored program computerBootstrappingInter-processor interruptMicrocode

A method for loading microcode to a plurality of cores within a processor. The method includes loading the microcode to a first core of the plurality of cores within the processor system and generating a broadcast inter process interrupt (IPI) message via the first core. The IPI message causes other cores within the processor system to synchronize respective microcode with the microcode that is loaded into the first core. The synchronizing loads microcode to the plurality of cores without requiring independent loads of microcode to each core.

Owner:DELL PROD LP

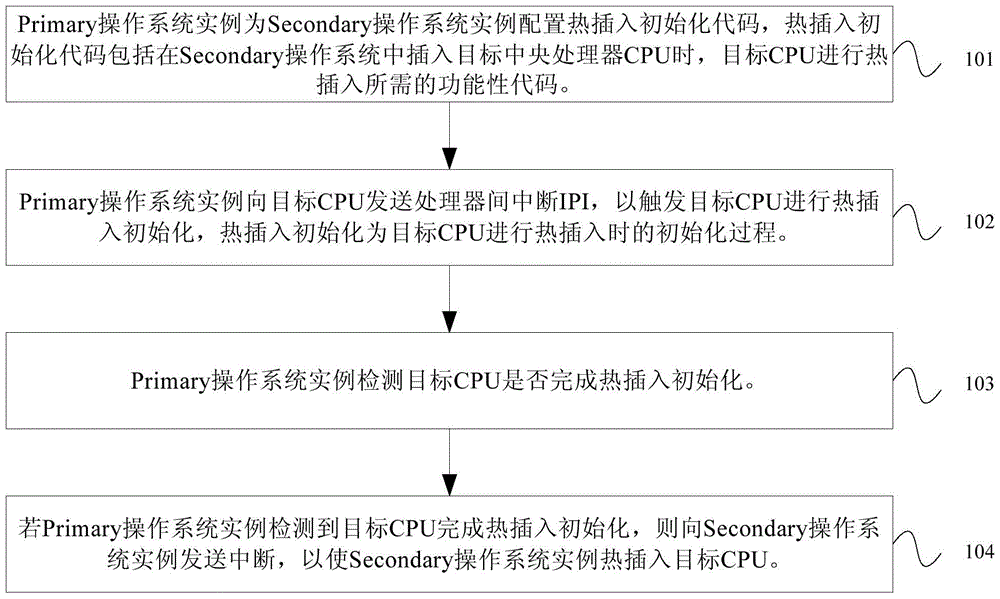

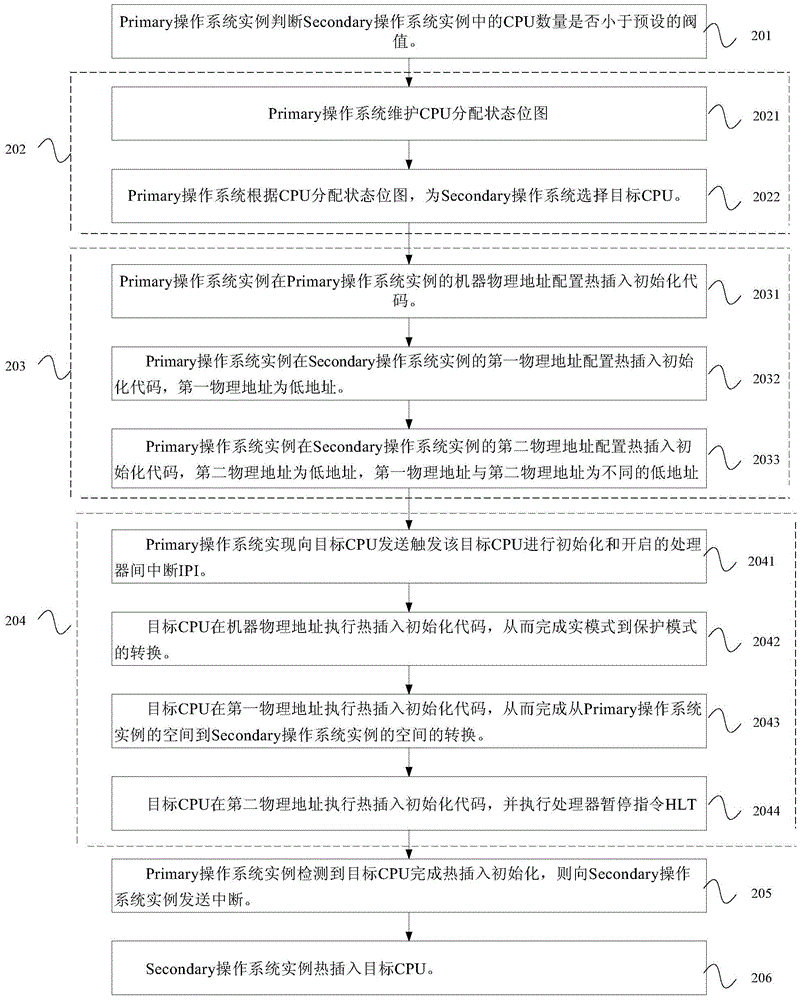

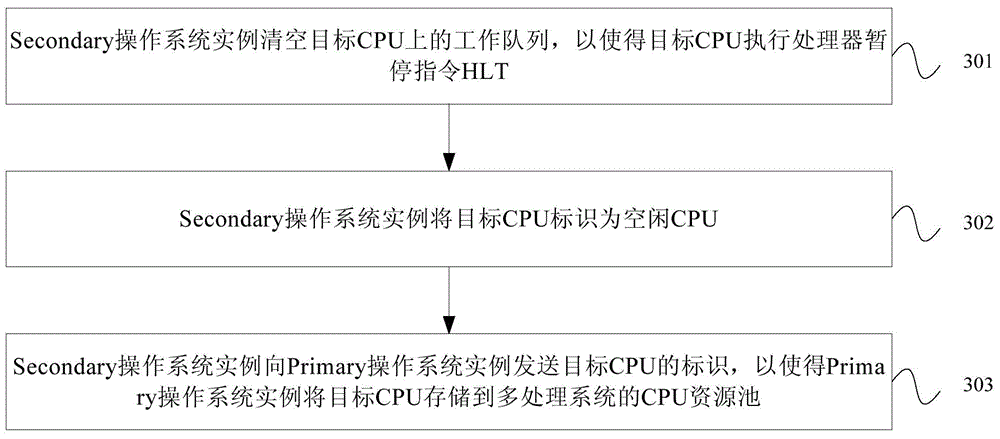

CPU (central processing unit) hot plug implementing method and device

ActiveCN103699444AResource allocationProgram loading/initiatingOperational systemInter-processor interrupt

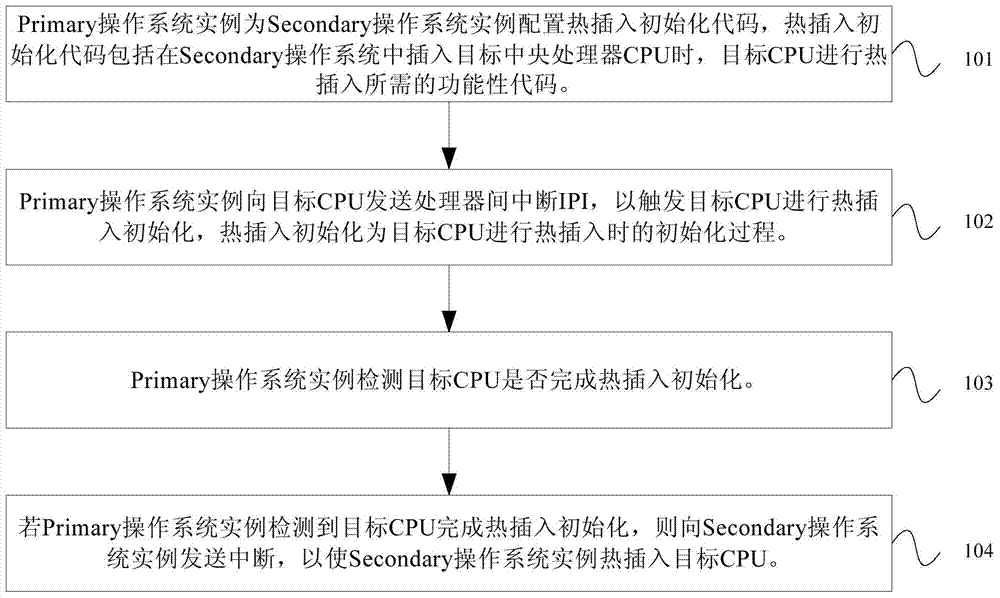

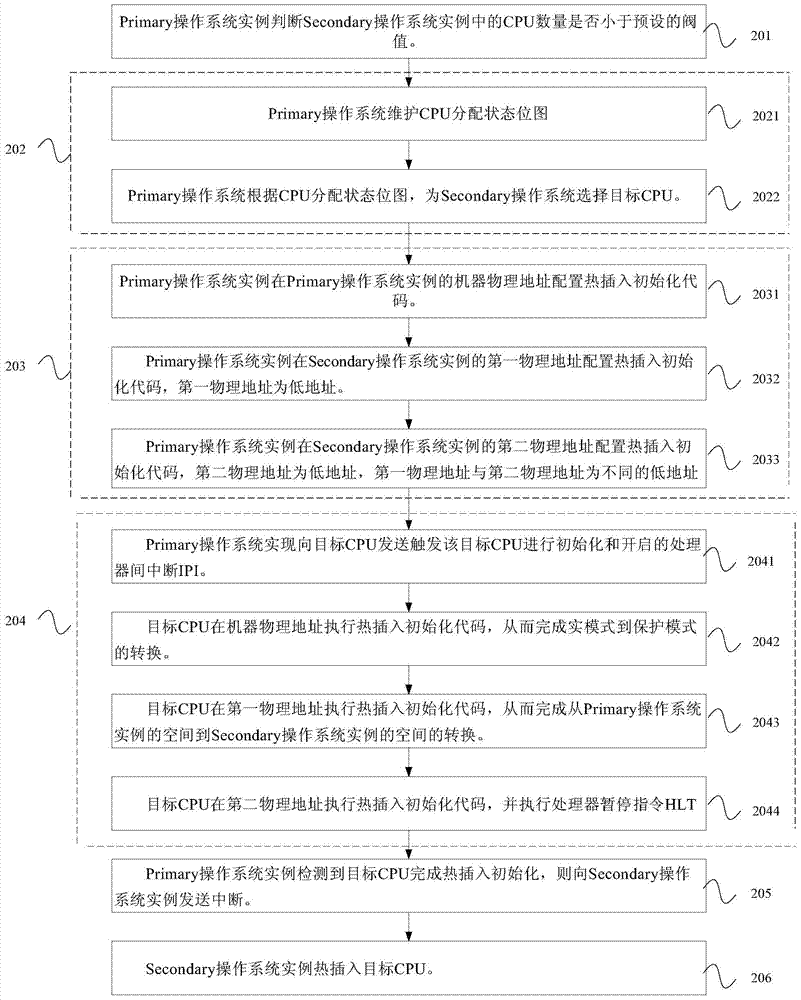

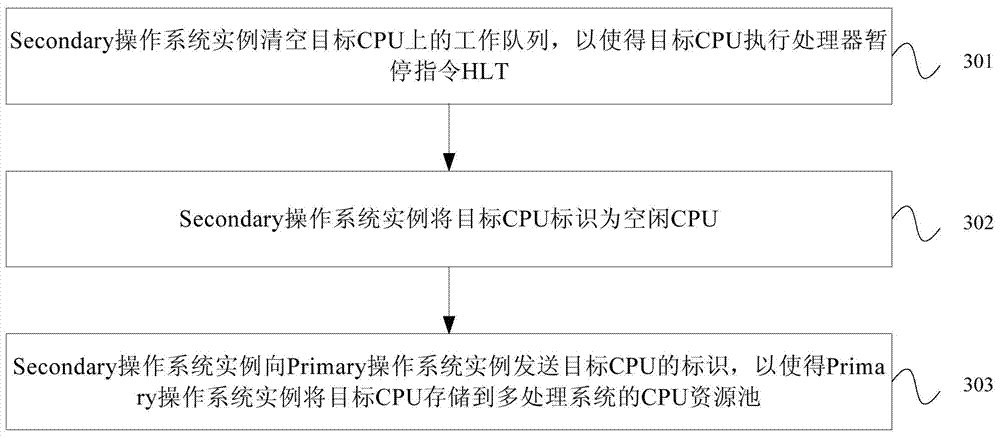

The embodiment of the invention provides a CPU hot plug implementing method and device. The method comprises that a Primary operating system example configures hot plug initialization codes for a Secondary operating system example; the Primary operating system example sends IPI (inter-processor interrupt) to a target CPU to trigger the target CPU to perform hot plug initialization, wherein the hot plug initialization is an initialization process during which the target CPU is hot-plugged; the Primary operating system example detects whether the target CPU completes the hot plug initialization; if so, the Primary operating system example sends IPI to the Secondary operating system to enable the Secondary operating system example to perform hot plugging of the target CPU, and accordingly, to achieve CPU Hot Plug in the Secondary operating system.

Owner:HUAWEI TECH CO LTD +1

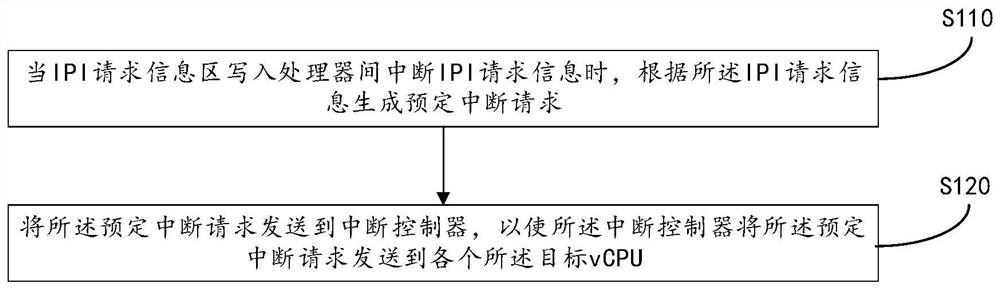

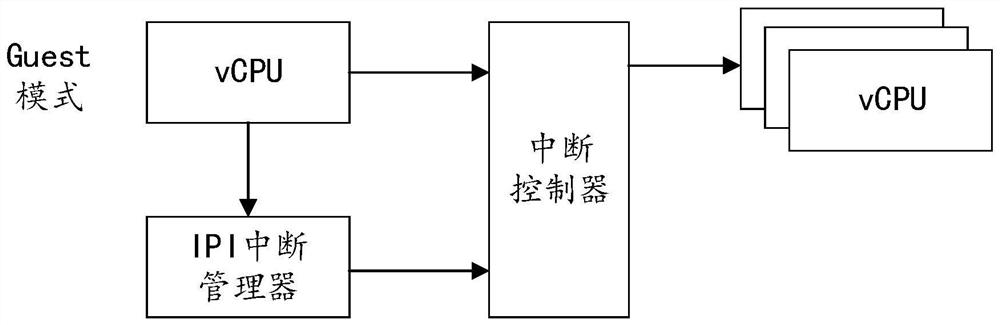

Interrupt processing method, interrupt manager, electronic equipment and computer readable medium

PendingCN112783600AImprove operational efficiencyReduce performance lossSoftware simulation/interpretation/emulationSoftware engineeringPhysical address

The invention provides an interrupt processing method. The method comprises the steps: when IPI request information is written into an IPI request information area among processors, generating a predetermined interrupt request according to the IPI request information, wherein the IPI request information carries an identifier of at least one target virtual central processing unit vCPU, the storage space of a current IPI interrupt manager comprises at least one IPI request information area, the IPI request information area corresponds to a virtual machine, and the physical address of the IPI request information area is mapped to the corresponding virtual machine through memory mapping input and output (MMIO); and sending the predetermined interrupt request to an interrupt controller, and enabling the interrupt controller to send the predetermined interrupt request to each target vCPU. The invention further provides the interrupt processing method, the IPI interrupt manager, electronic equipment and a computer readable medium.

Owner:ZTE CORP

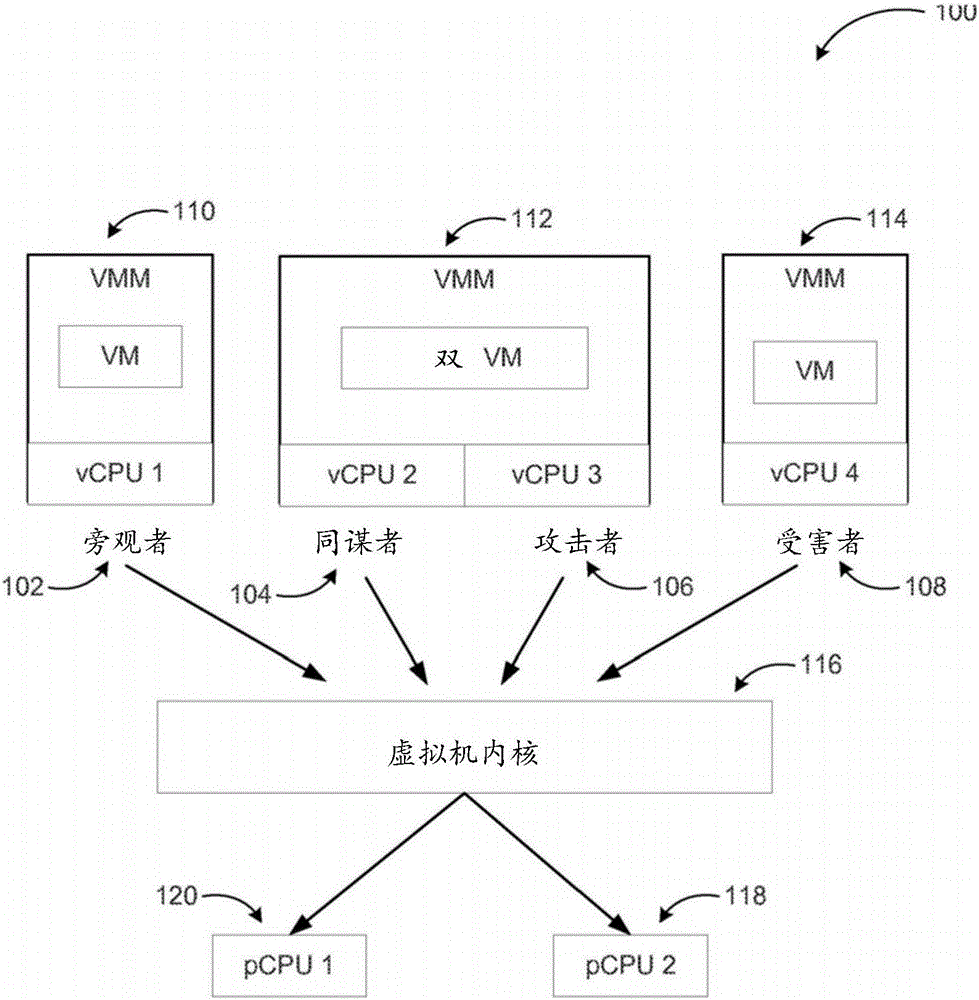

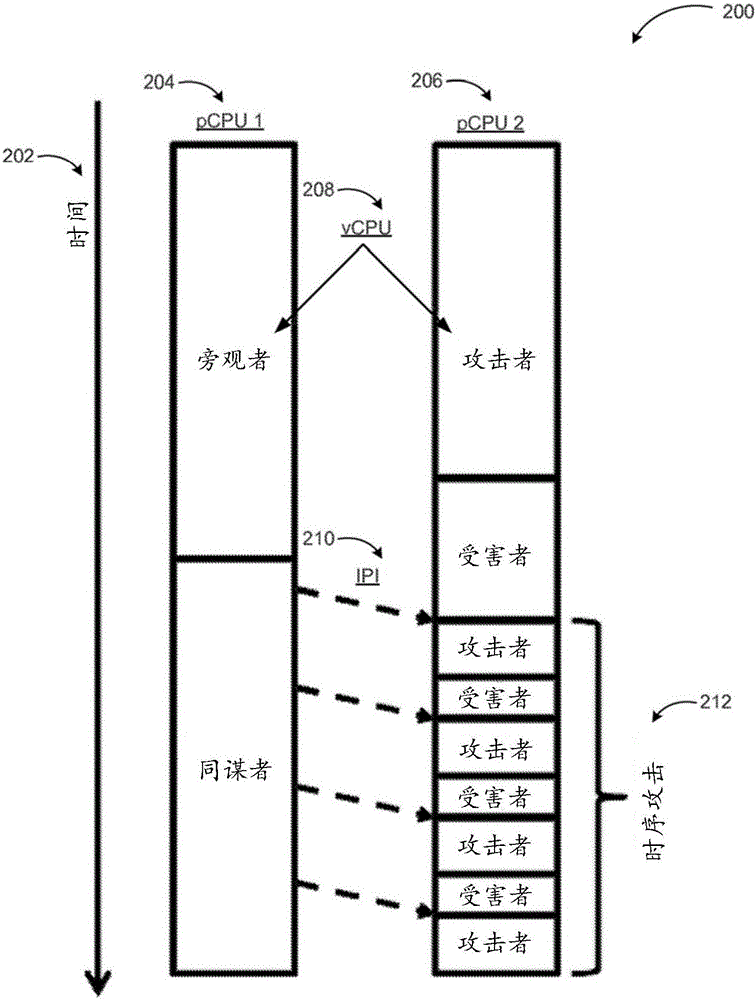

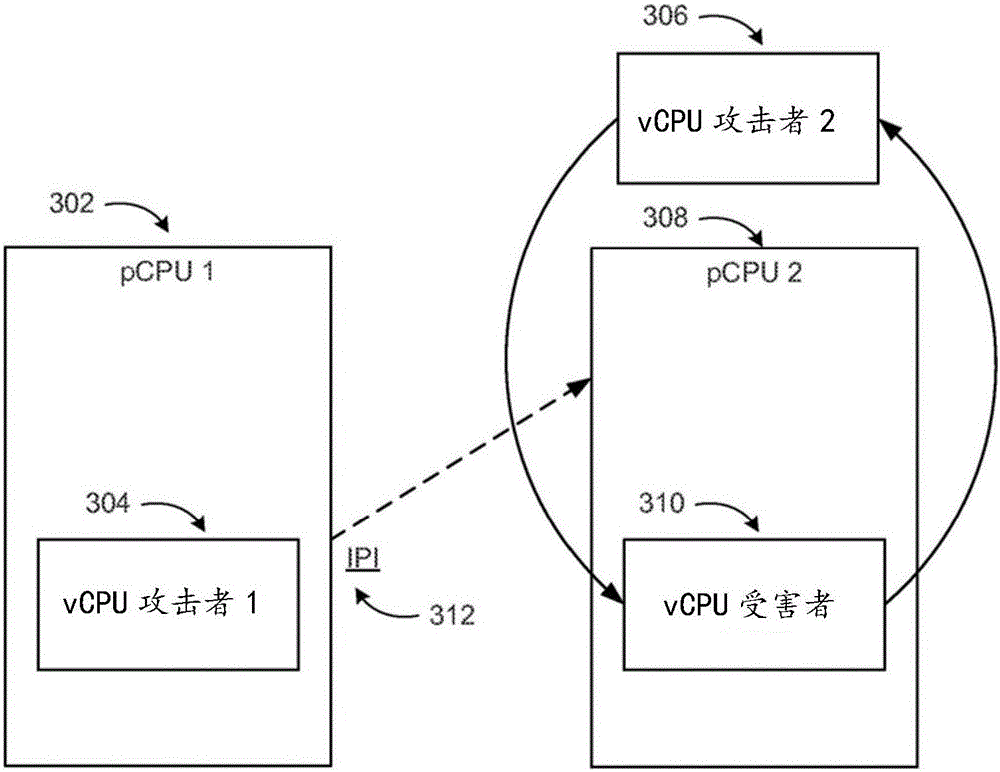

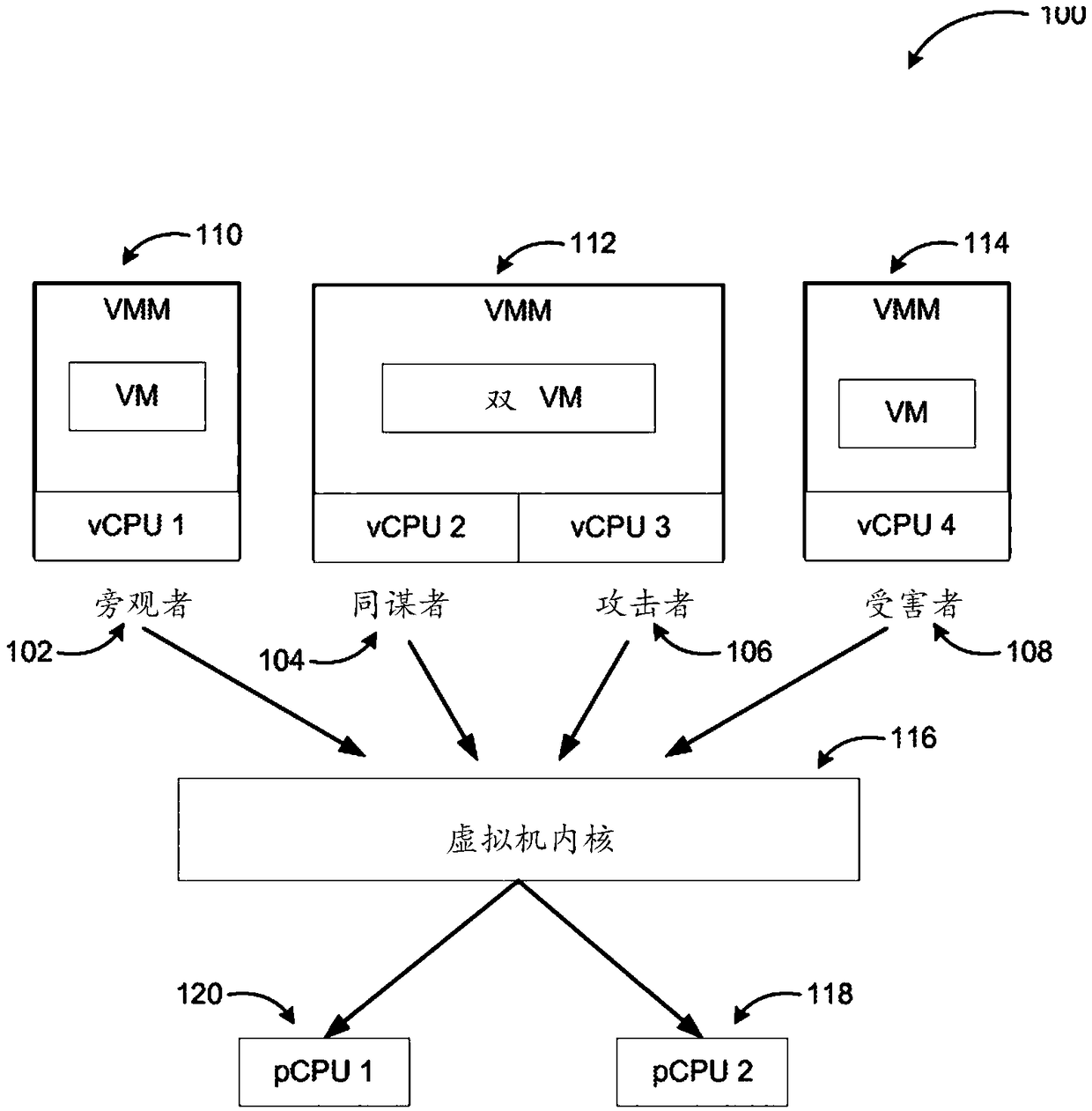

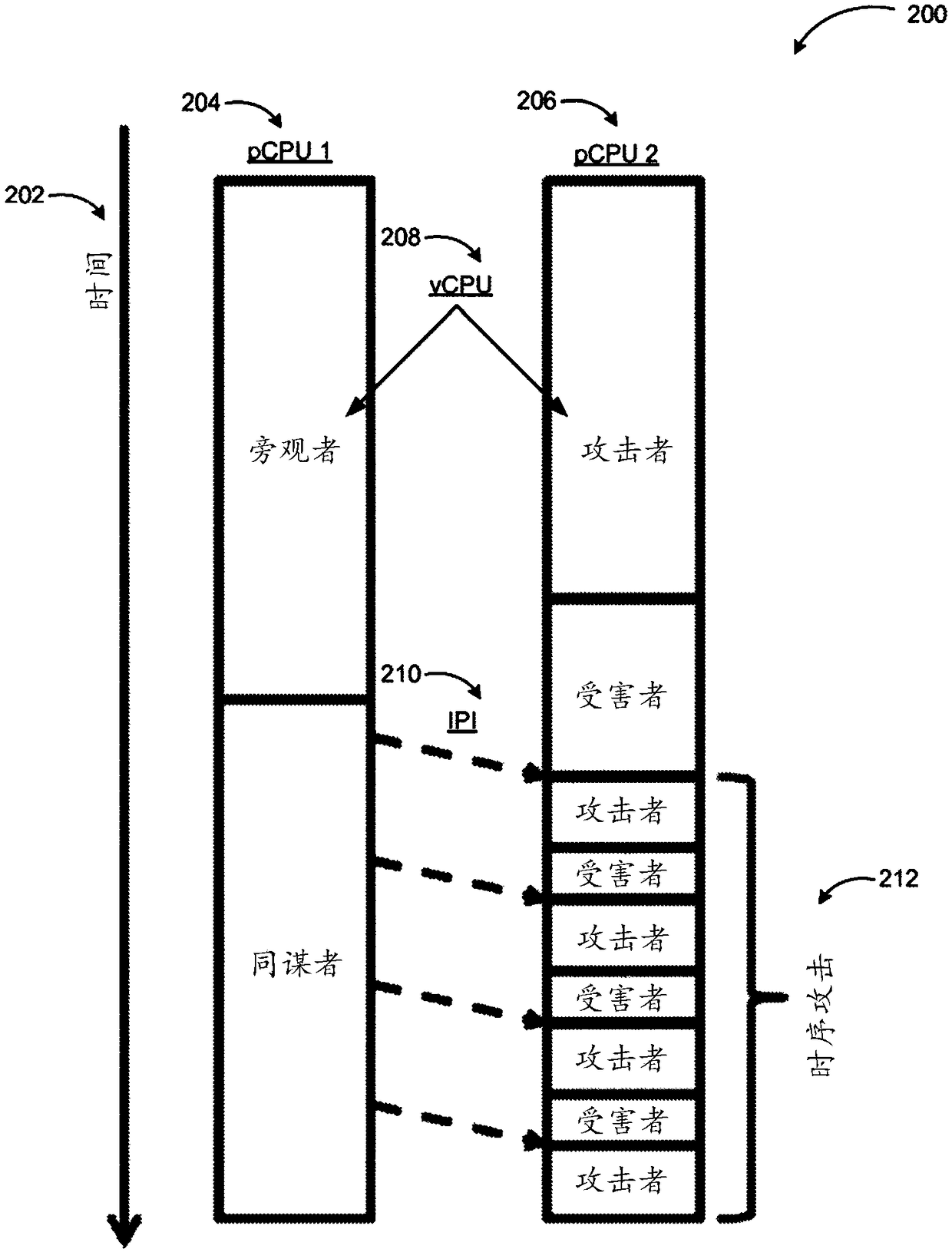

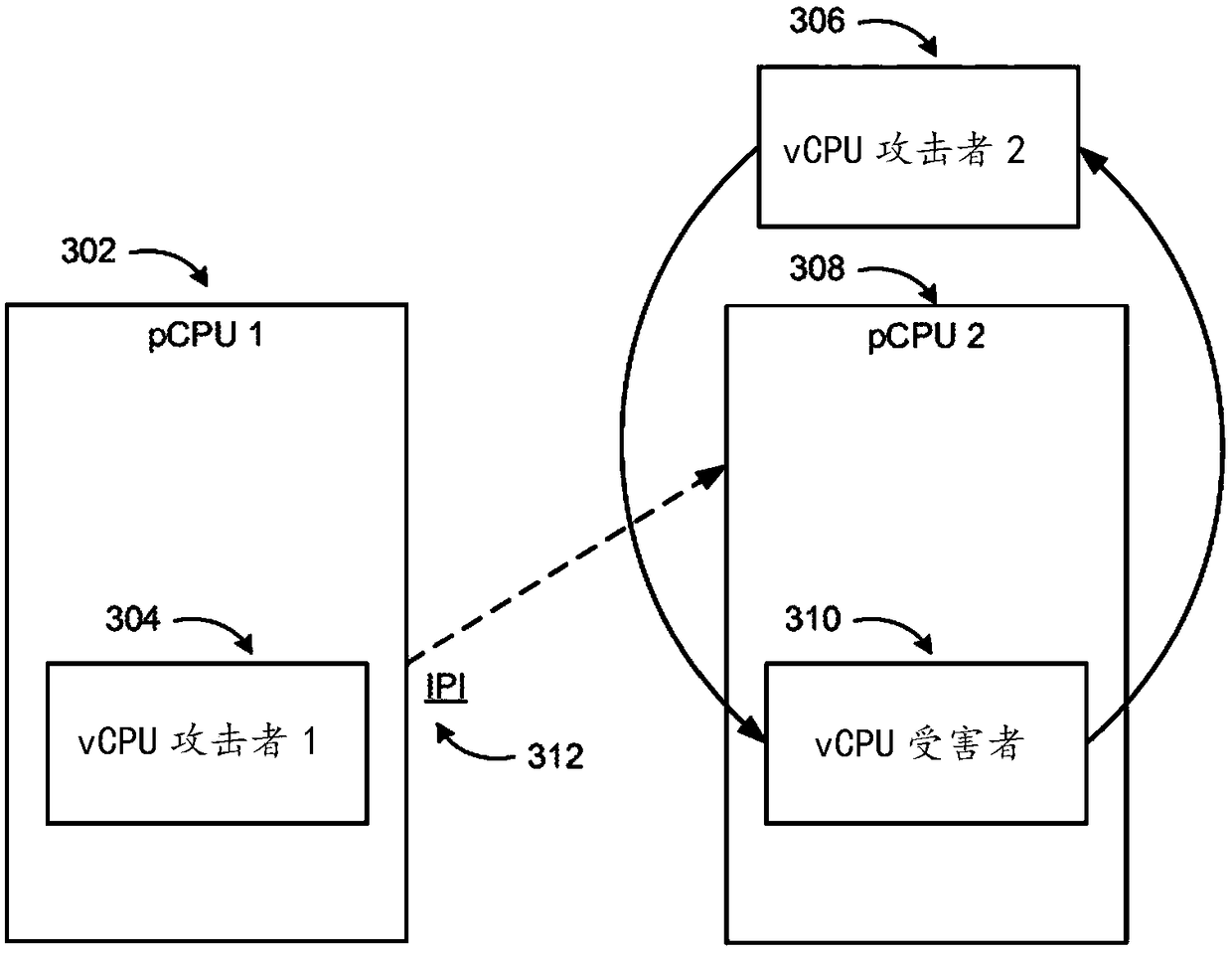

Detection of side channel attacks between virtual machines

InactiveCN105917345APlatform integrity maintainanceProgram controlInter-processor interruptComputer science

Technologies are directed to a detector to identify a side channel attack between virtual machines. According to some examples, an inter-processor interrupt (IPI) rate of a first virtual machine (VM), a time stamp counter (TSC) rate of a second VM, and a cache miss ratio (CMR) of a third VM may be monitored. A side channel attack may then be detected based on the IPI rate, the TSC rate, and the CMR.

Owner:EMPIRE TECH DEV LLC

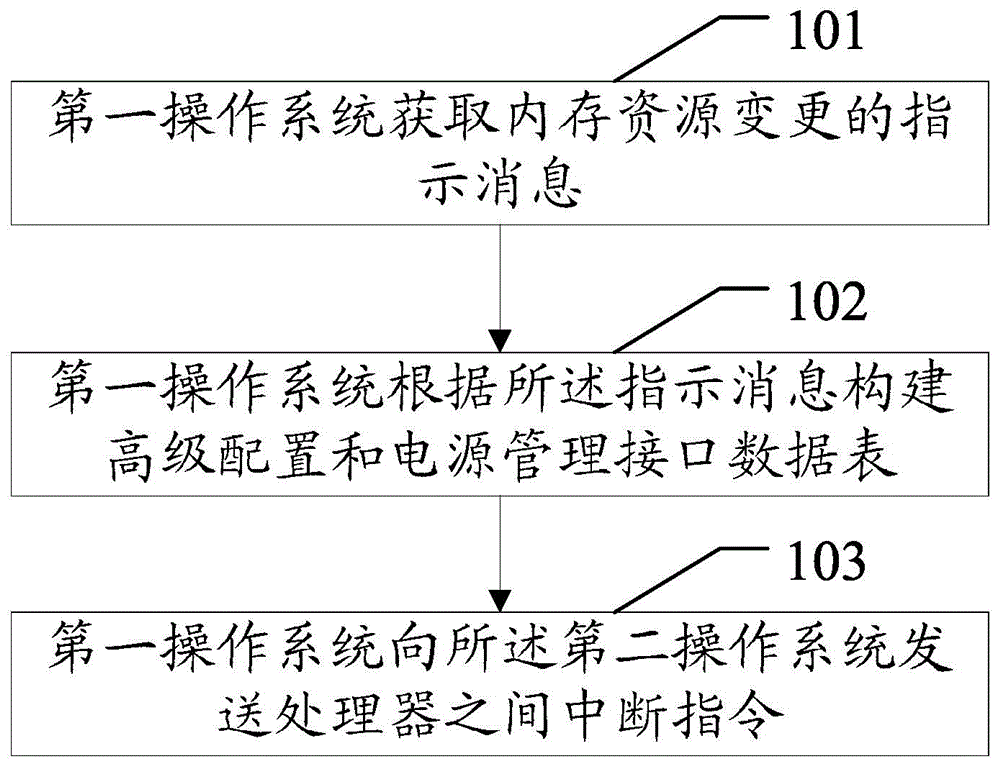

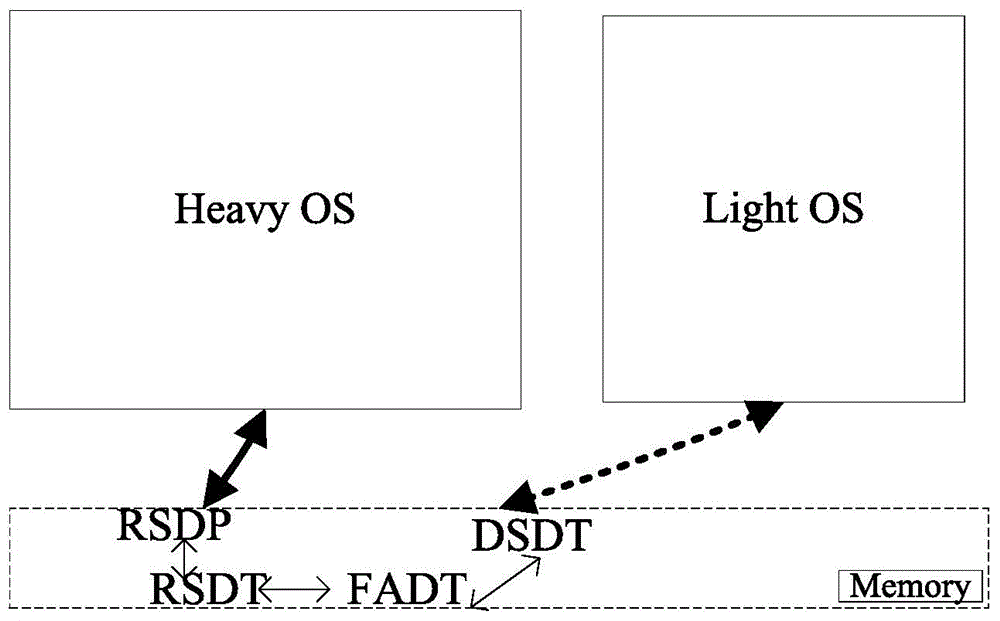

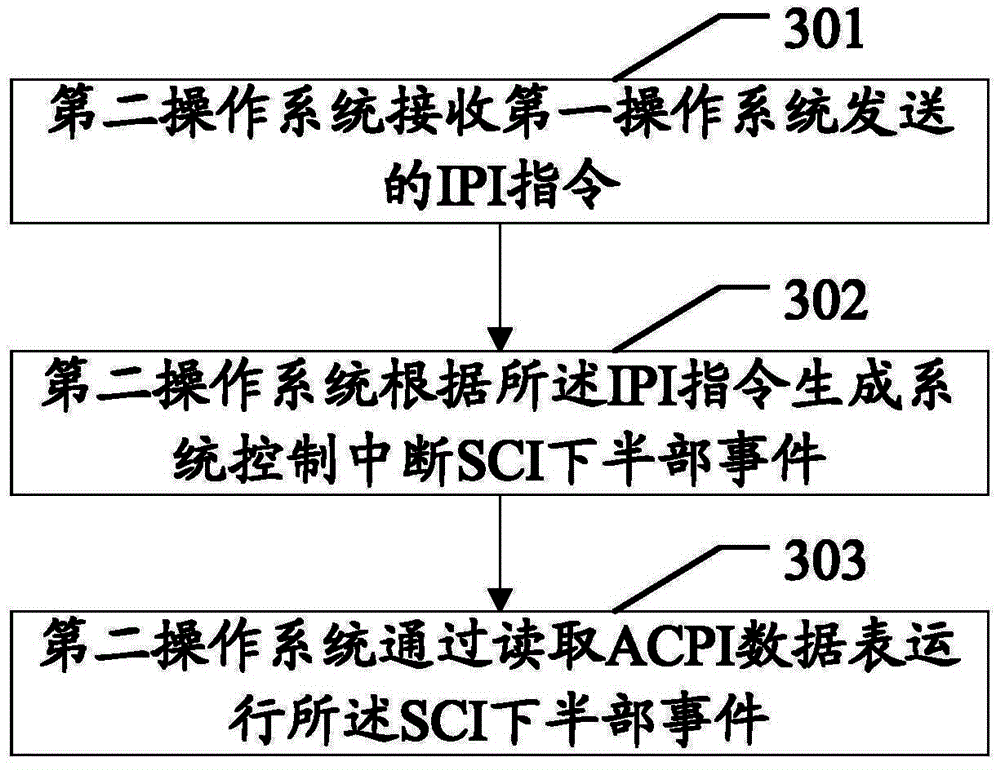

Memory change processing method and operating systems

ActiveCN105335228AResource allocationAdvanced Configuration and Power InterfaceInter-processor interrupt

The embodiment of the invention discloses a memory change processing method and operating systems. The memory change processing method is used for performing memory change processing on a plurality of multi-core operating systems. The method provided by the embodiment of the invention comprises the following steps that a first operating system obtains a memory resource change indication message, wherein the indication message is used for indicating that the memory resource of a second operating system changes; the first operating system builds an ACPI (Advanced Configuration and Power Interface) data table according to the indication message; and the first operating system sends an IPI (Inter-Processor Interrupt) instruction to the second operating system so that the second operating system generates an SCI (System Control Interrupt) lower half part event through an IPI event in a simulated way according to the IPI instruction, and the second operating system runs the SCI lower half part event through reading the ACPI data table.

Owner:HUAWEI TECH CO LTD +1

Method and system for generating and delivering inter-processor interrupts in a multi-core processor and in certain shared memory multi-processor systems

ActiveUS9032128B2Facilitate shared-memory-based communicationEfficient use ofProgram initiation/switchingMulti processorInter-processor interrupt

Certain embodiments of the present invention are directed to providing efficient and easily-applied mechanisms for inter-core and inter-processor communications and inter-core and inter-processor signaling within multi-core microprocessors and certain multi-processor systems. In one embodiment of the present invention, local advanced programmable interrupt controllers within, or associated with, cores of a multi-core microprocessor and / or processors of a multi-processor system are enhanced so that the local advanced programmable interrupt controllers can be configured to automatically generate inter-core and inter-processor interrupts when WRITE operations are directed to particular regions of shared memory.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

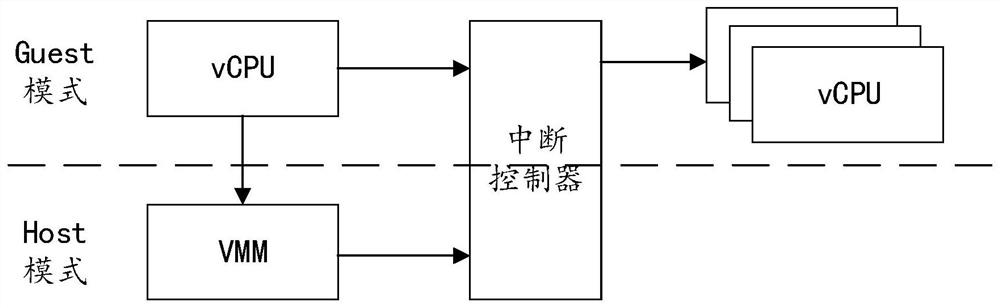

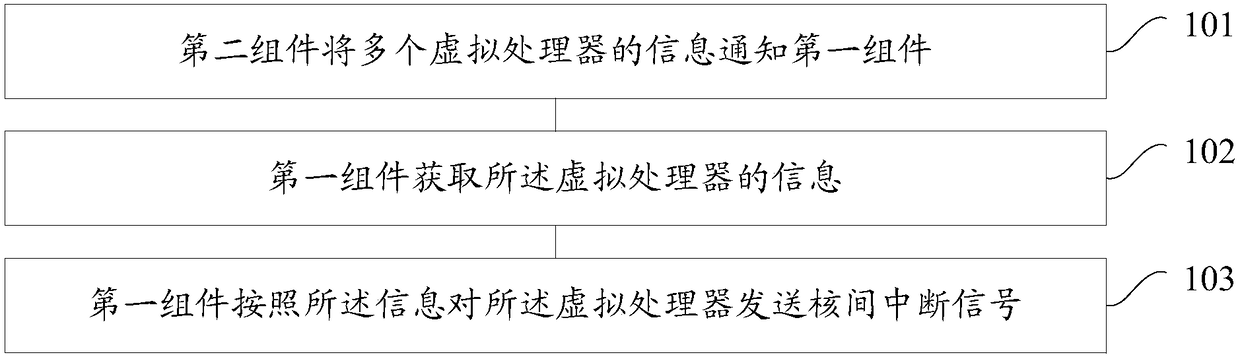

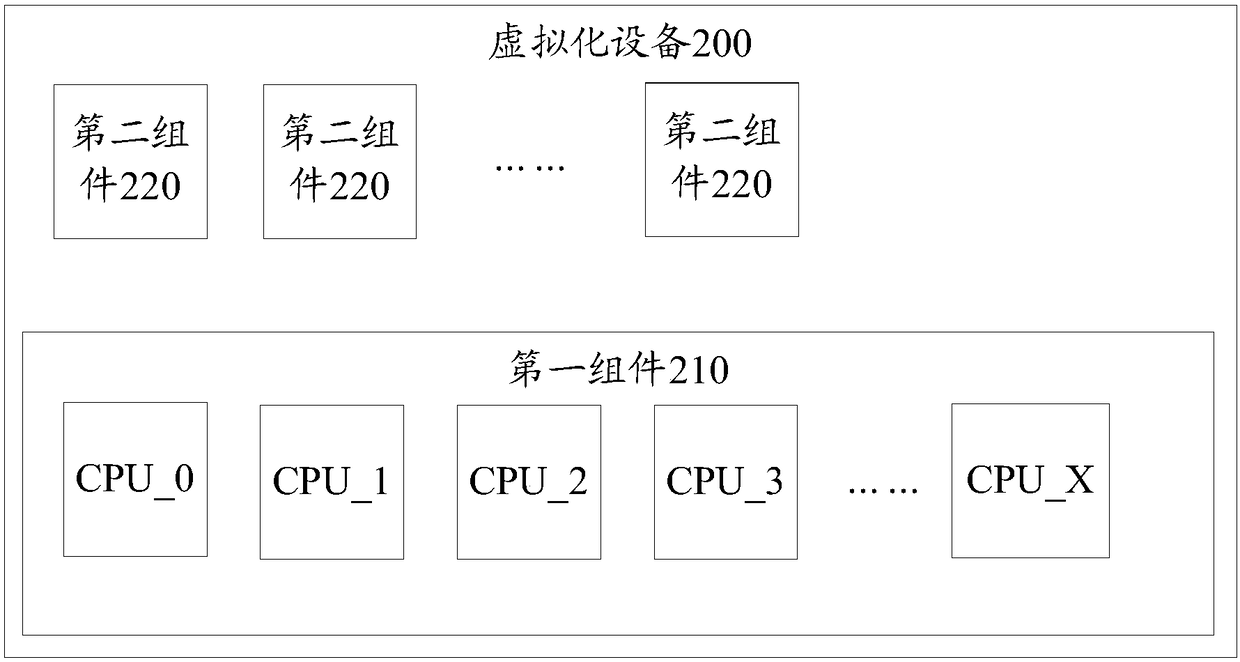

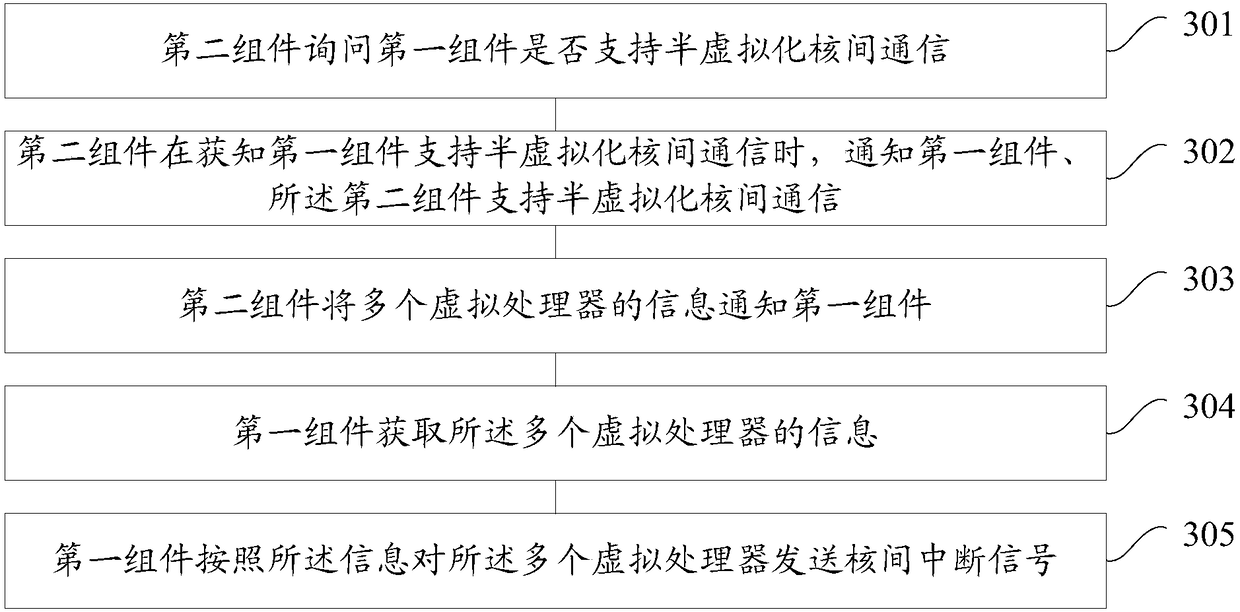

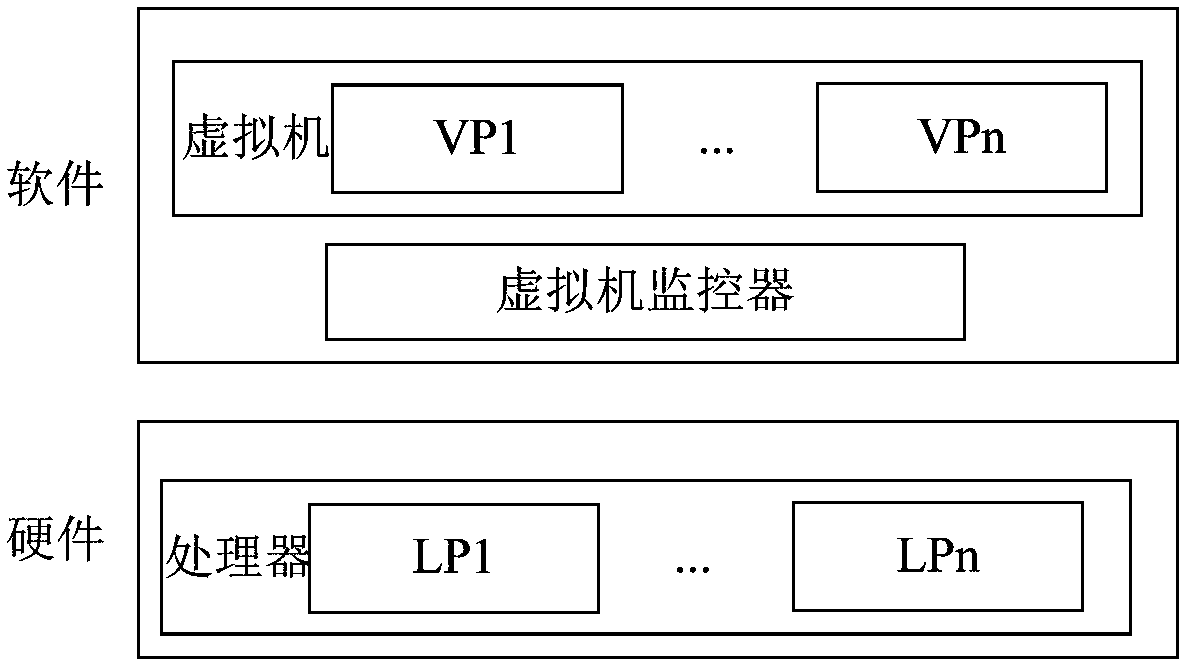

Inter-processor communication method and device, and virtualization equipment

ActiveCN108196945AReduce the number of exitsReduce the number of communicationsProgram initiation/switchingSoftware simulation/interpretation/emulationVirtualizationInter-processor interrupt

The embodiment of the invention provides an inter-processor communication method and device, and virtualization equipment. The method is applied to the virtualization equipment. A first component is operated in the virtualization equipment, and a second component is constructed through virtualization on the first component. The method comprises the following steps that: the second component notifies the first component of the information of a plurality of virtual processors; the first component obtains the information of the plurality of virtual processors; and the first component sends an inter-processor interrupt signal to the plurality of virtual processors according to the information. The first component is notified of the information of the virtual processors in one time, so that communication frequencies between the first component and the second component are greatly reduced so as to greatly reduce the exiting frequency of the second component due to communication between the second component and the first component, the second component only exits for one time in a one-time multicast process, the time consumption of inter-processor communication is reduced, and the performance of the second component and the performance of the first component are improved.

Owner:ALIBABA CLOUD COMPUTING LTD

Deferred inter-processor interrupts

A data processing system includes, in one embodiment, at least a first processor and a second processor and an interrupt controller, and the system provides a deferred inter-processor interrupt (IPI) that can be used to wake up the second processor from a low power sleep state. The deferred IPI is, in one embodiment, delayed by a timer in the interrupt controller, and the deferred IPI can be cancelled by the first processor if the first processor becomes available to execute a thread that was made runnable by an interrupt which triggered the deferred IPI.

Owner:APPLE INC

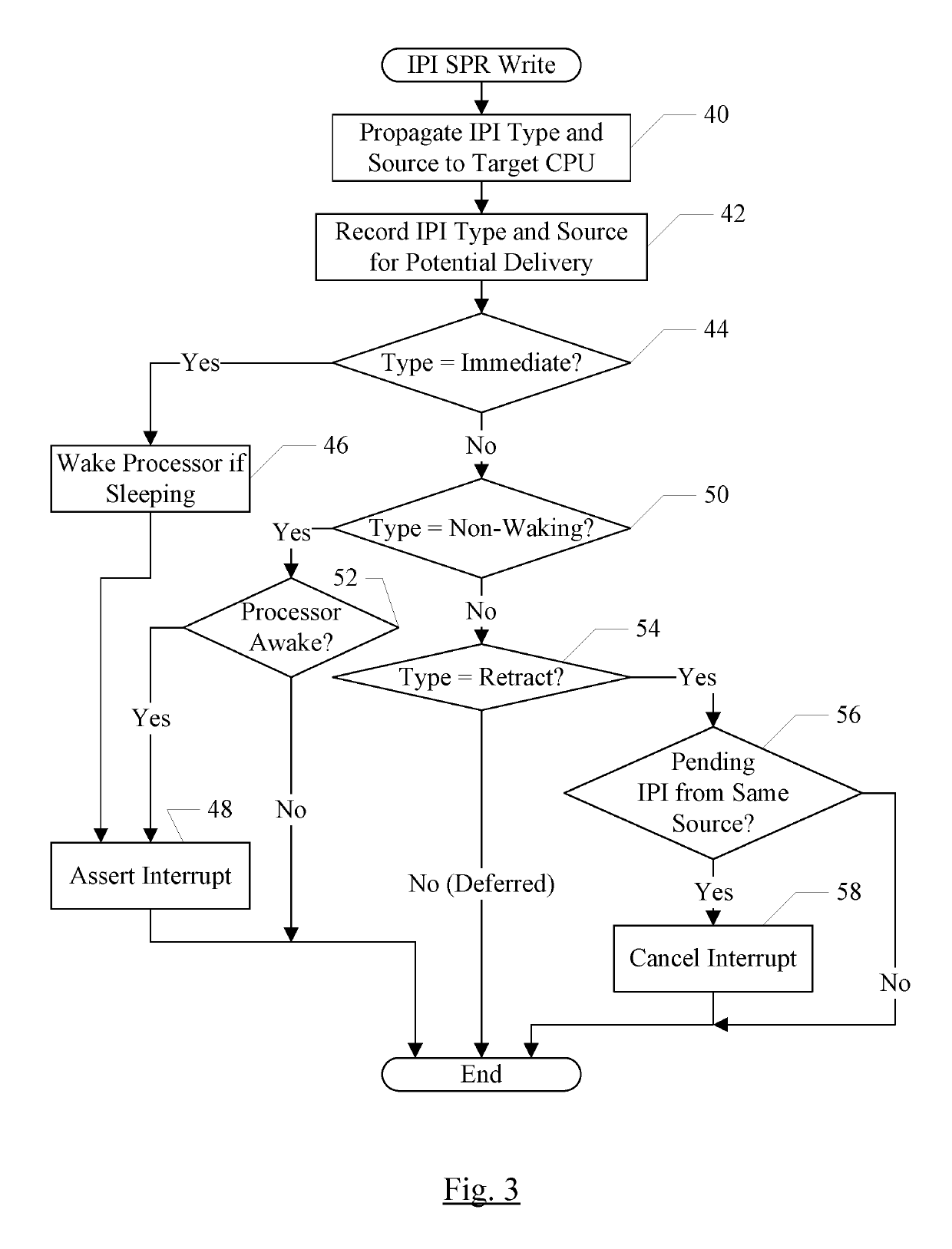

Intracluster and intercluster interprocessor interrupts including a retract interrupt that causes a previous interrupt to be canceled

ActiveUS10496572B1Lower latencyReduce transmissionDigital data processing detailsProgram controlTime limitInter-processor interrupt

In an embodiment, processors may have associated special purpose registers (SPRs) such as model specific registers (MSRs), used to communicate IPIs between the processors. In an embodiment, several types of IPIs may be defined, such as one or more of an immediate type, a deferred type, a retract type, and / or a non-waking type. The immediate IPI may be delivered and may cause the target processor to interrupt in response to receipt of the IPI. The deferred IPI may be delivered within a defined time limit, and not necessarily on receipt by the target processor. The retract IPI may cause a previously transmitted IPI to be cancelled (if it has not already caused the target processor to interrupt). A non-waking IPI may not cause the target processor to wake if it is asleep, but may be delivered when the target processor is awakened for another reason.

Owner:APPLE INC

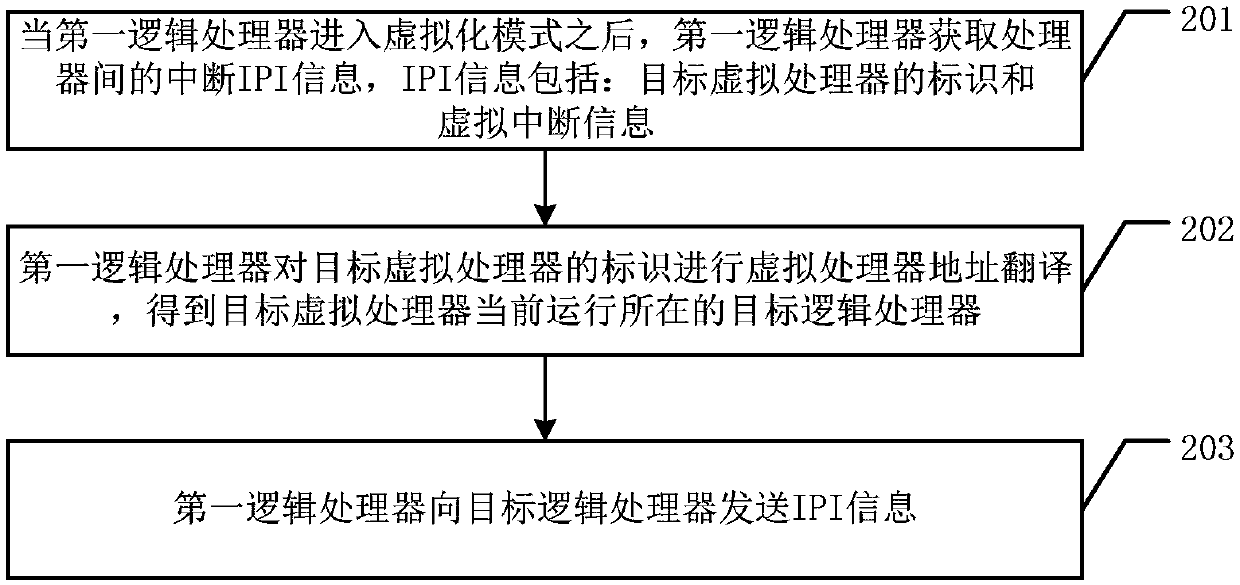

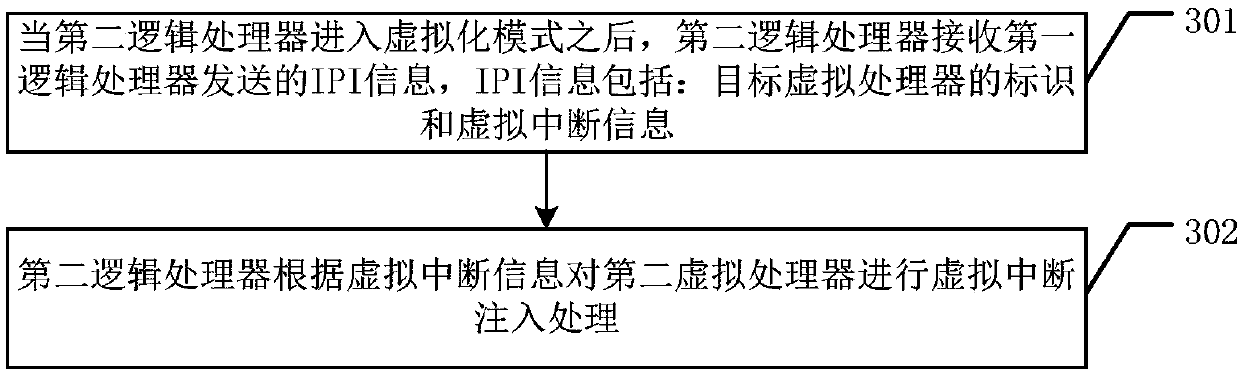

A communication method and logic processor

PendingCN110162377AReduce final transport delayReduce resource usageProgram initiation/switchingSoftware simulation/interpretation/emulationVirtualizationInter-processor interrupt

The embodiment of the invention discloses a communication method and a logic processor, which are used for reducing processor resource occupation of a sender and final transmission delay of an IPI. The communication method provided by the embodiment of the invention comprises the steps that after a first logic processor enters a virtualization mode, the first logic processor obtains inter-processor interrupt IPI information, and the IPI information comprises an identifier of a target virtual processor and virtual interrupt information; the first logic processor performs virtual processor address translation on the identifier of the target virtual processor to obtain a target logic processor where the target virtual processor currently runs; and the first logic processor sends the IPI information to the target logic processor.

Owner:HUAWEI TECH CO LTD

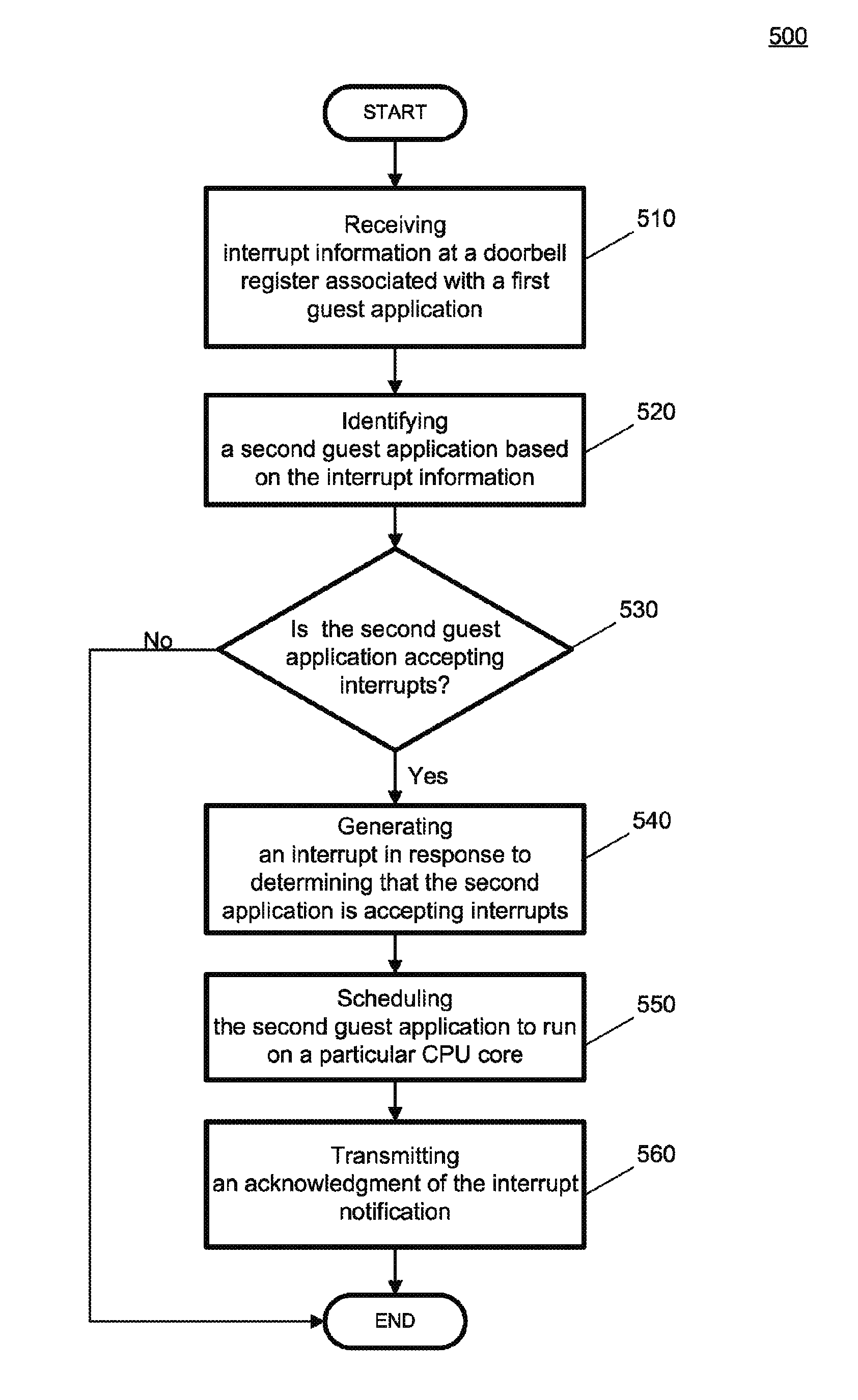

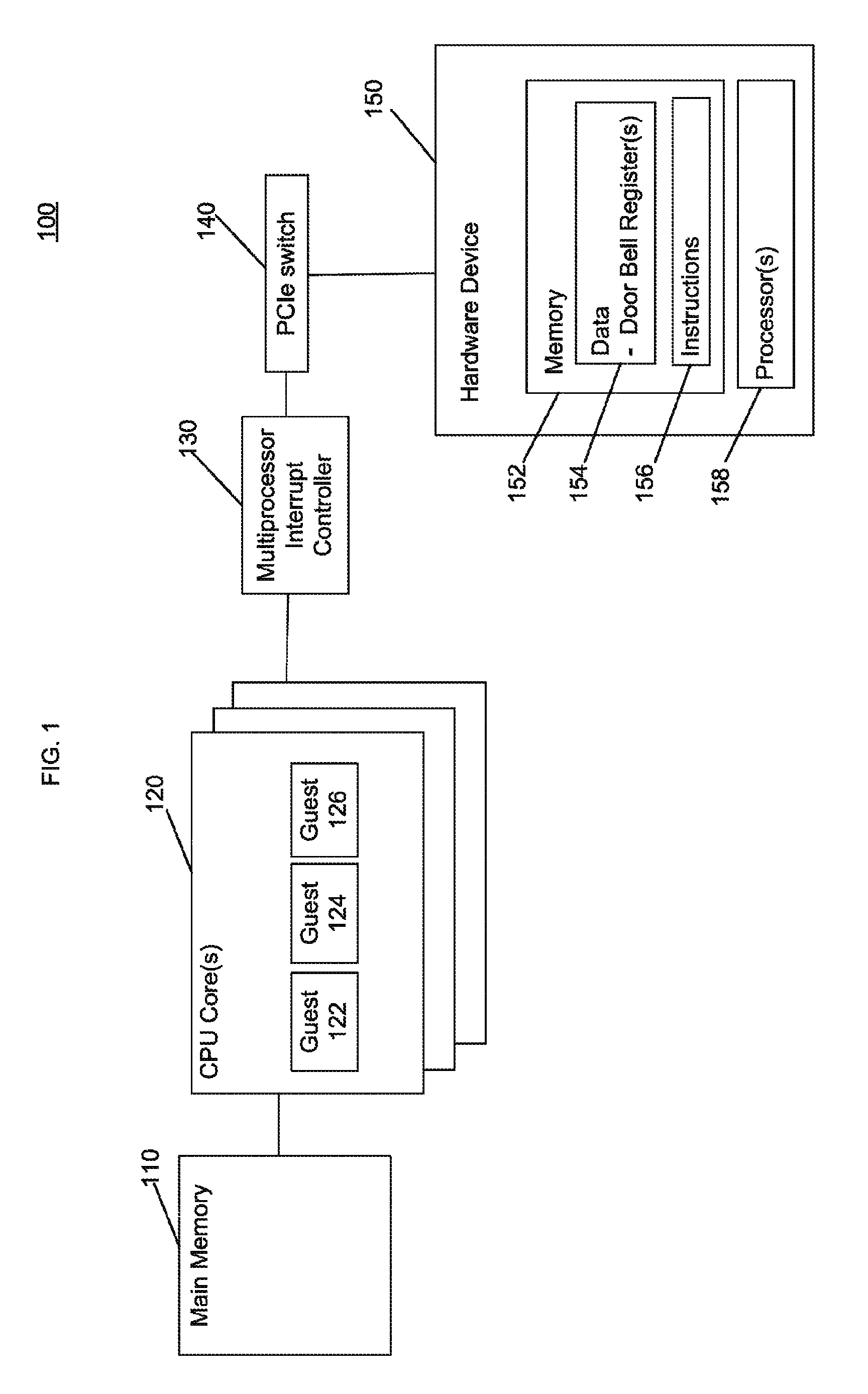

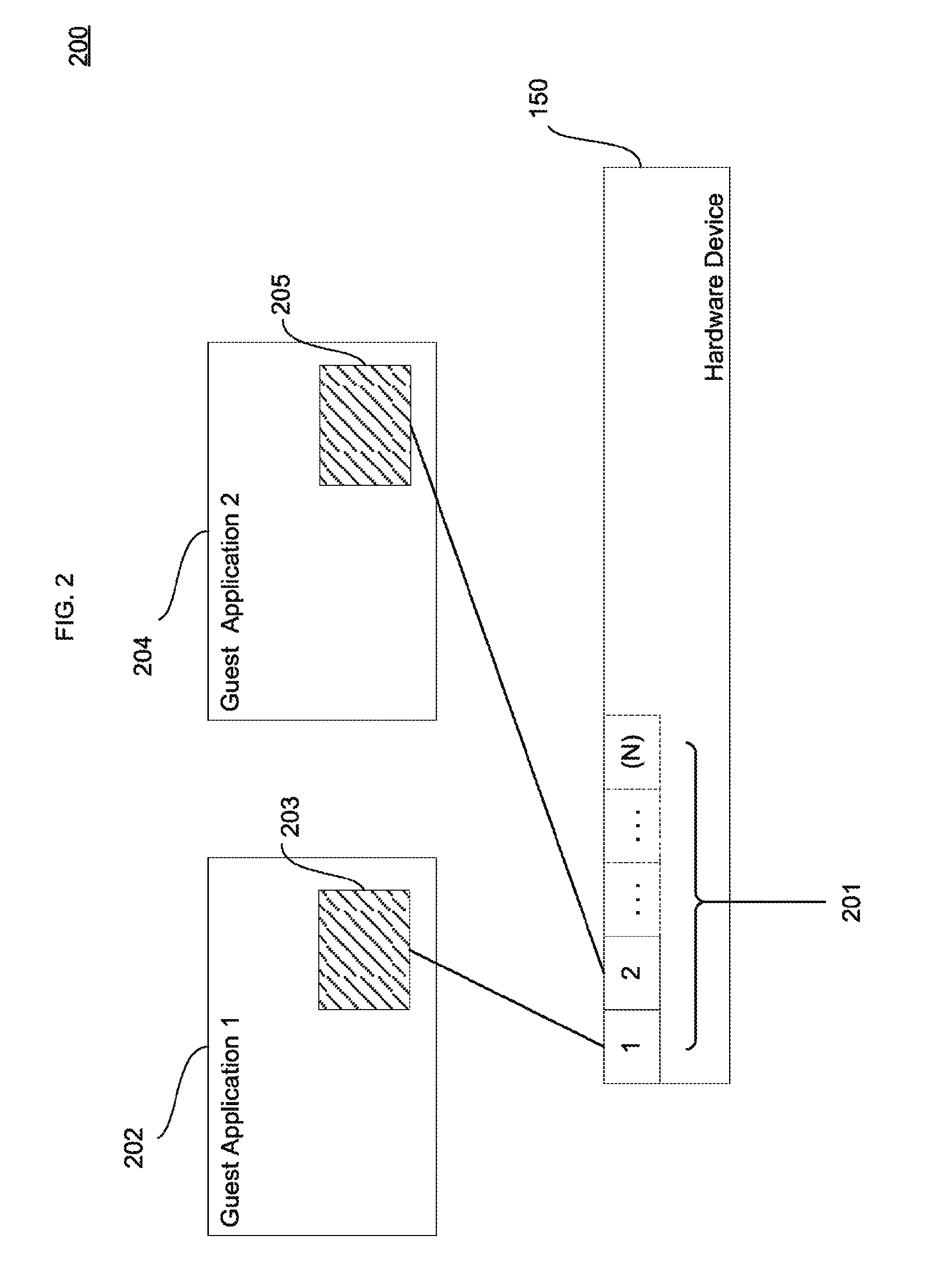

OS bypass inter-processor interrupt delivery mechanism

The present disclosure provides methods and systems to allow user space applications running on different cores to efficiently communicate interrupts between each other without have to enter an OS kernel. In one aspect, a hardware device for delivering inter-processor interrupts is provided. The hardware device includes a memory having a memory space that corresponds to a virtual memory space of a first guest process and a controller coupled to the memory. The controller may be configured to detect when interrupt information is recorded in the memory space. In that regard, the interrupt information is directed to a second guest process associated with a particular CPU core. In response to detecting interrupt information recorded in the memory space, the controller is configured to cause the second guest process to run on a different CPU core without making an operating system call.

Owner:GOOGLE LLC

Realization method and device of central processing unit hot swap

ActiveCN103699444BResource allocationProgram loading/initiatingOperational systemInter-processor interrupt

The embodiment of the invention provides a CPU hot plug implementing method and device. The method comprises that a Primary operating system example configures hot plug initialization codes for a Secondary operating system example; the Primary operating system example sends IPI (inter-processor interrupt) to a target CPU to trigger the target CPU to perform hot plug initialization, wherein the hot plug initialization is an initialization process during which the target CPU is hot-plugged; the Primary operating system example detects whether the target CPU completes the hot plug initialization; if so, the Primary operating system example sends IPI to the Secondary operating system to enable the Secondary operating system example to perform hot plugging of the target CPU, and accordingly, to achieve CPU Hot Plug in the Secondary operating system.

Owner:HUAWEI TECH CO LTD +1

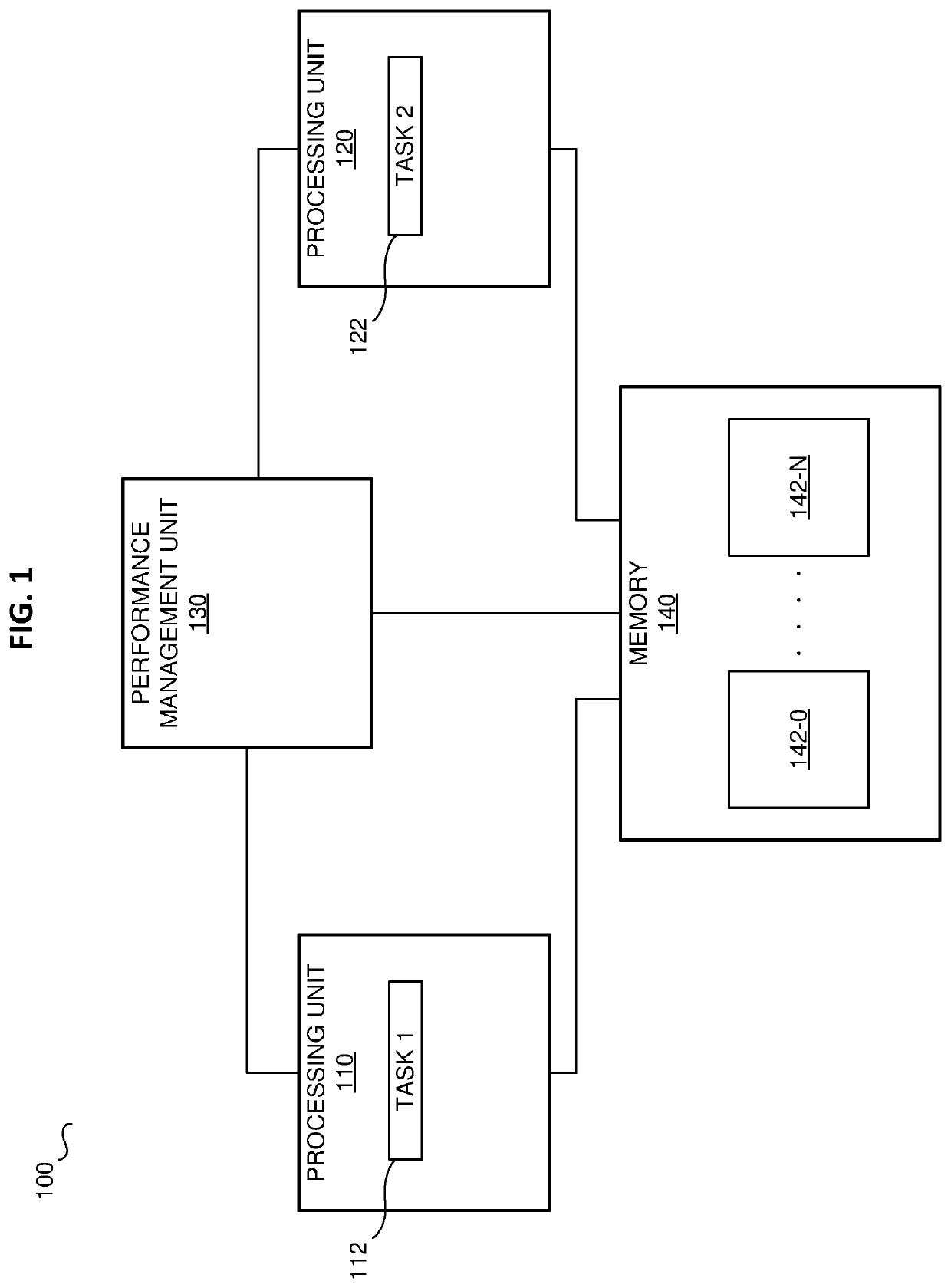

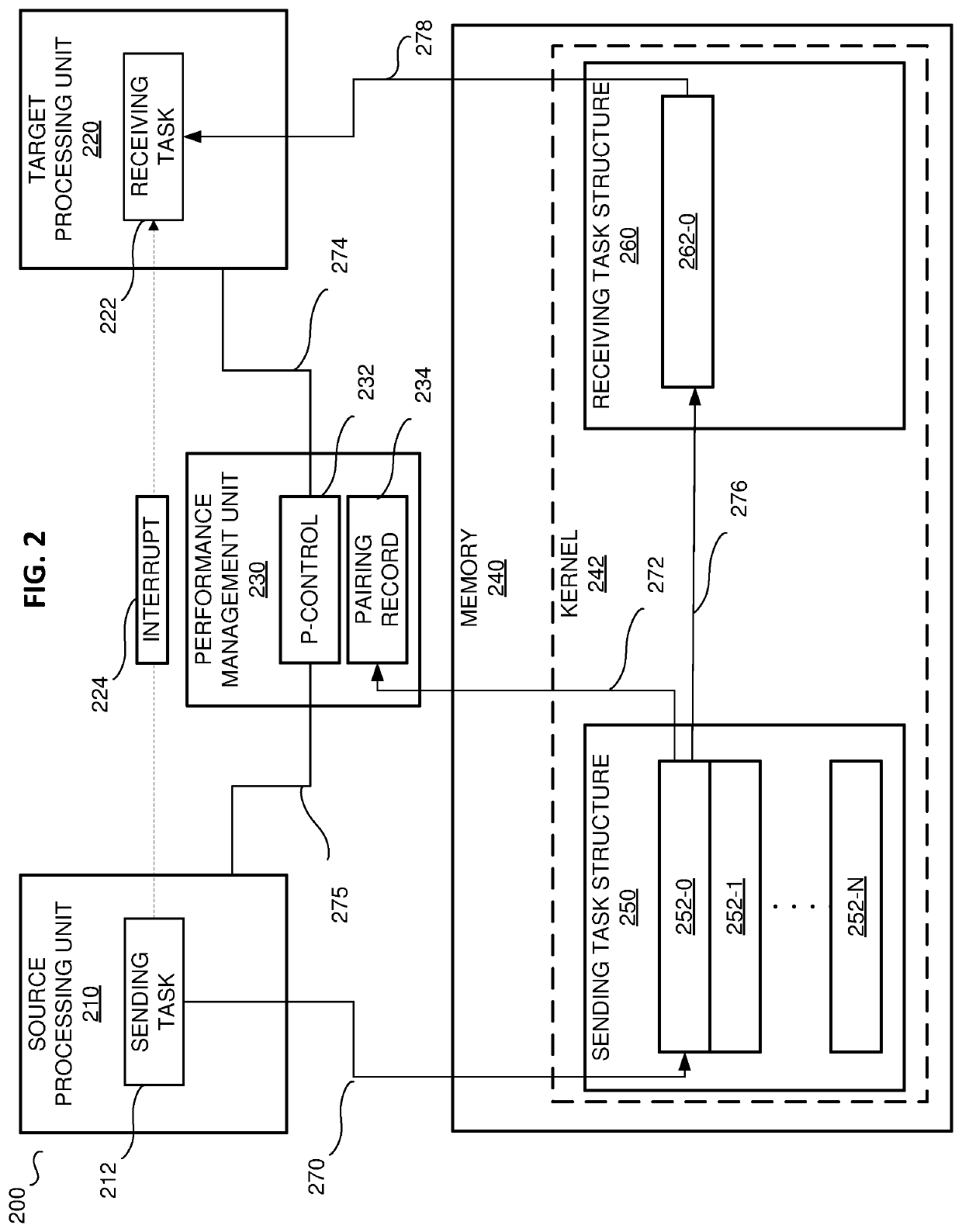

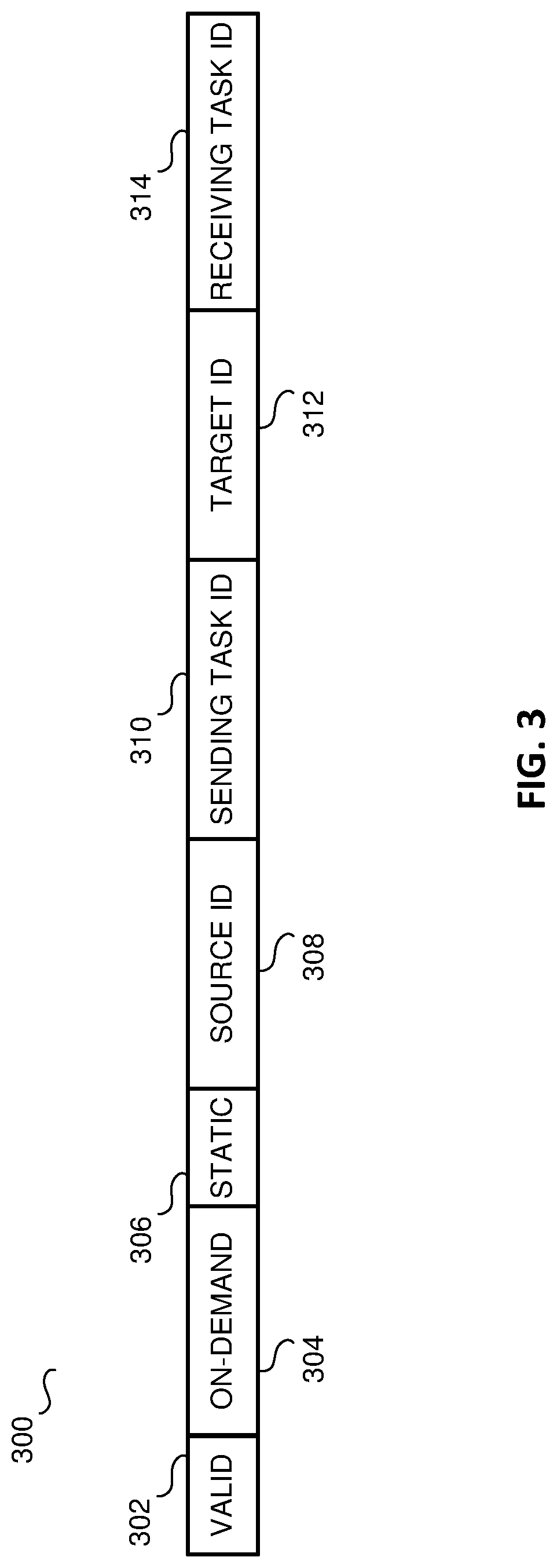

Apparatus and method for performance state matching between source and target processors based on interprocessor interrputs

ActiveUS20210191753A1Program initiation/switchingDigital data processing detailsComputer architectureEngineering

Apparatus, method, and machine-readable medium to provide performance state matching between source and target processors based on inter-processor interrupts. An exemplary apparatus includes a target processor to execute a receiving task at a first performance level and a source processor to execute a sending task at a second performance level higher than the first performance level. The sending task is to store interrupt routing data indicating a pairing between the sending task and the receiving task into a memory location and that the sending task is to dispatch work to be processed by the receiving task. The apparatus further includes a performance management unit to detect the pairing between the sending task and the receiving task based on the interrupt routing data and responsively adjust the performance level of the target processor from the first performance level to the second performance level based, at least in part, on the pairing.

Owner:INTEL CORP

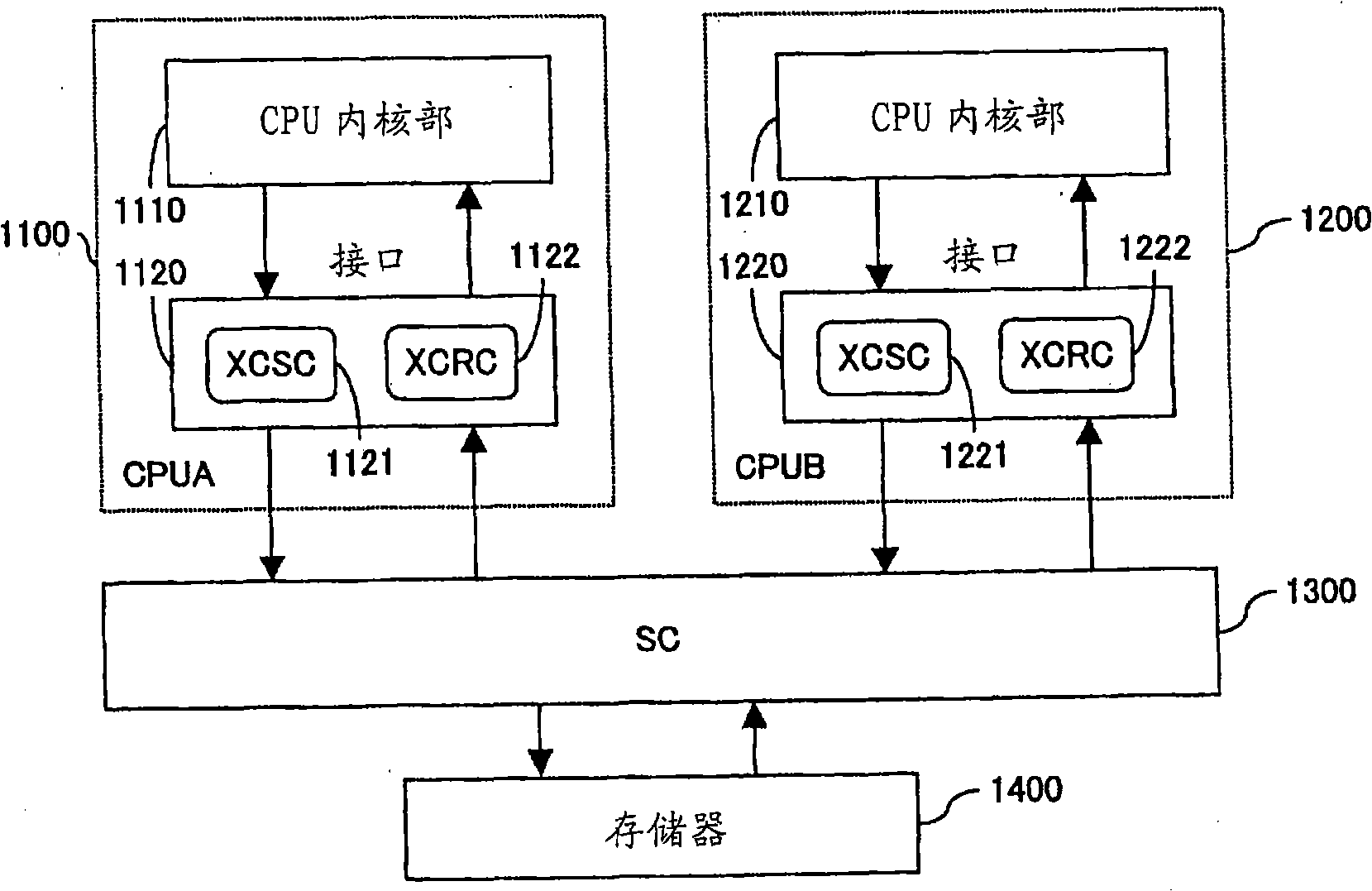

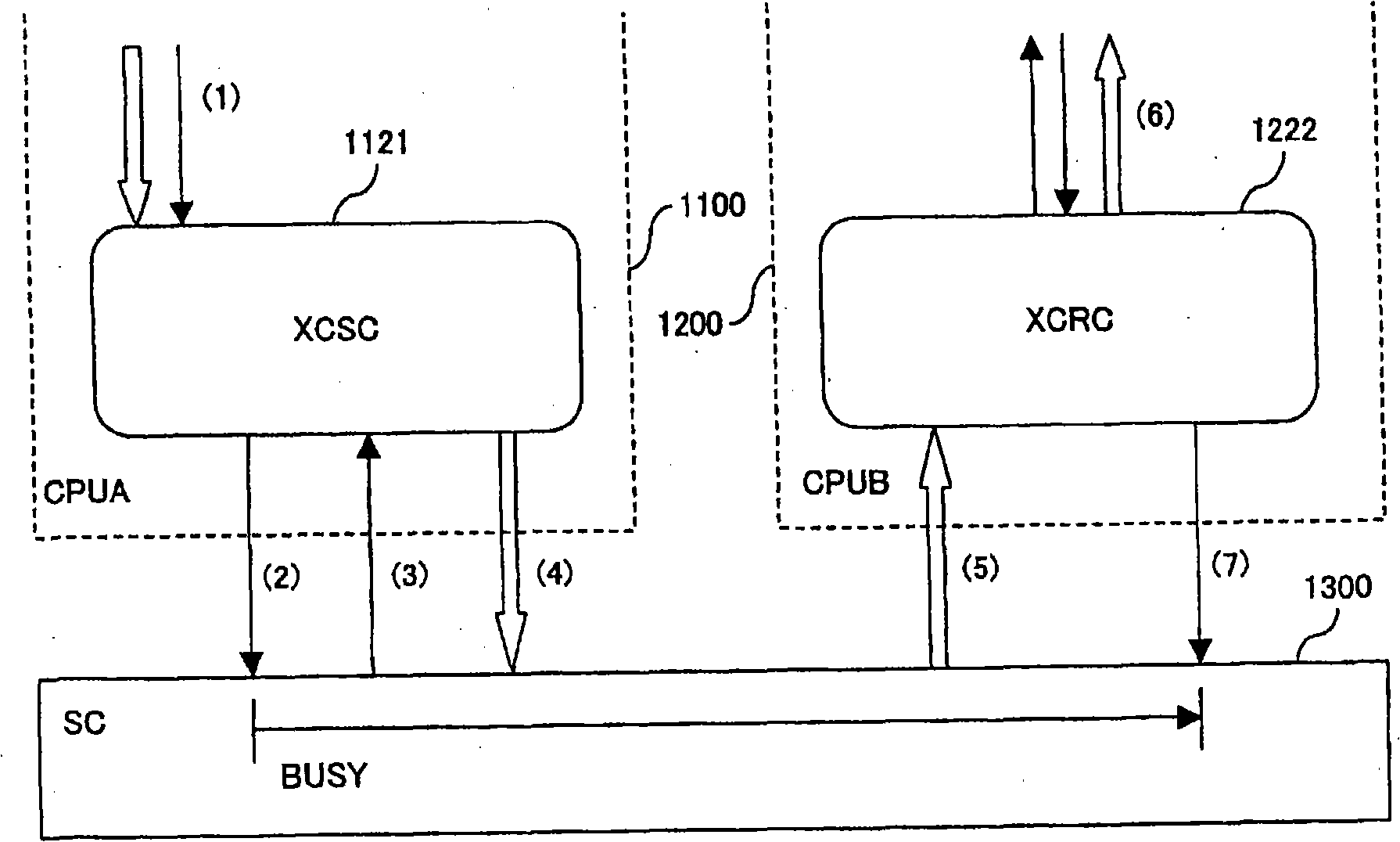

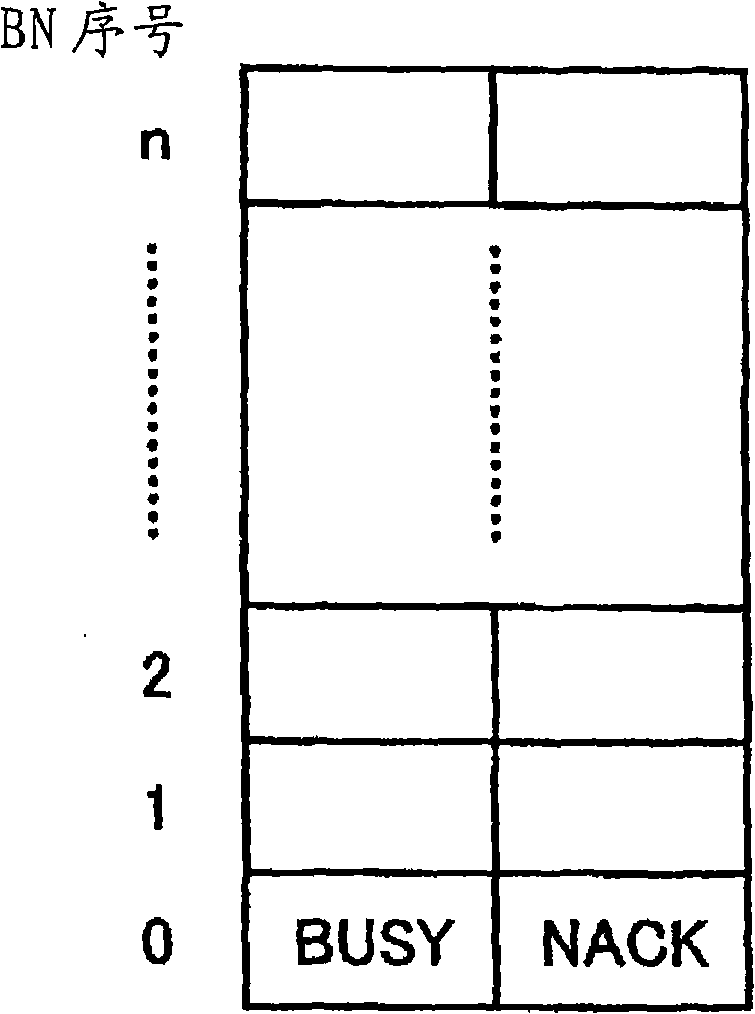

Operation processing device

InactiveCN101278277ASuppress multikernelizationIncrease resourcesResource allocationMultiple digital computer combinationsProcessor registerComputerized system

The present invention is intended to control the increase in the resources required for controlling internal processor interrupt (cross call) for communication between CPUs of a computer system. A cross call send control unit (XCSC 40) of an external interface unit of each CPU controls cross call transmission issued by a CPU core unit 20 to another CPU. The XCSC 40 has a register 41 for keeping the processing state of the processing relating to the cross call directly associated with an issue history of the cross call for each entry.

Owner:FUJITSU LTD

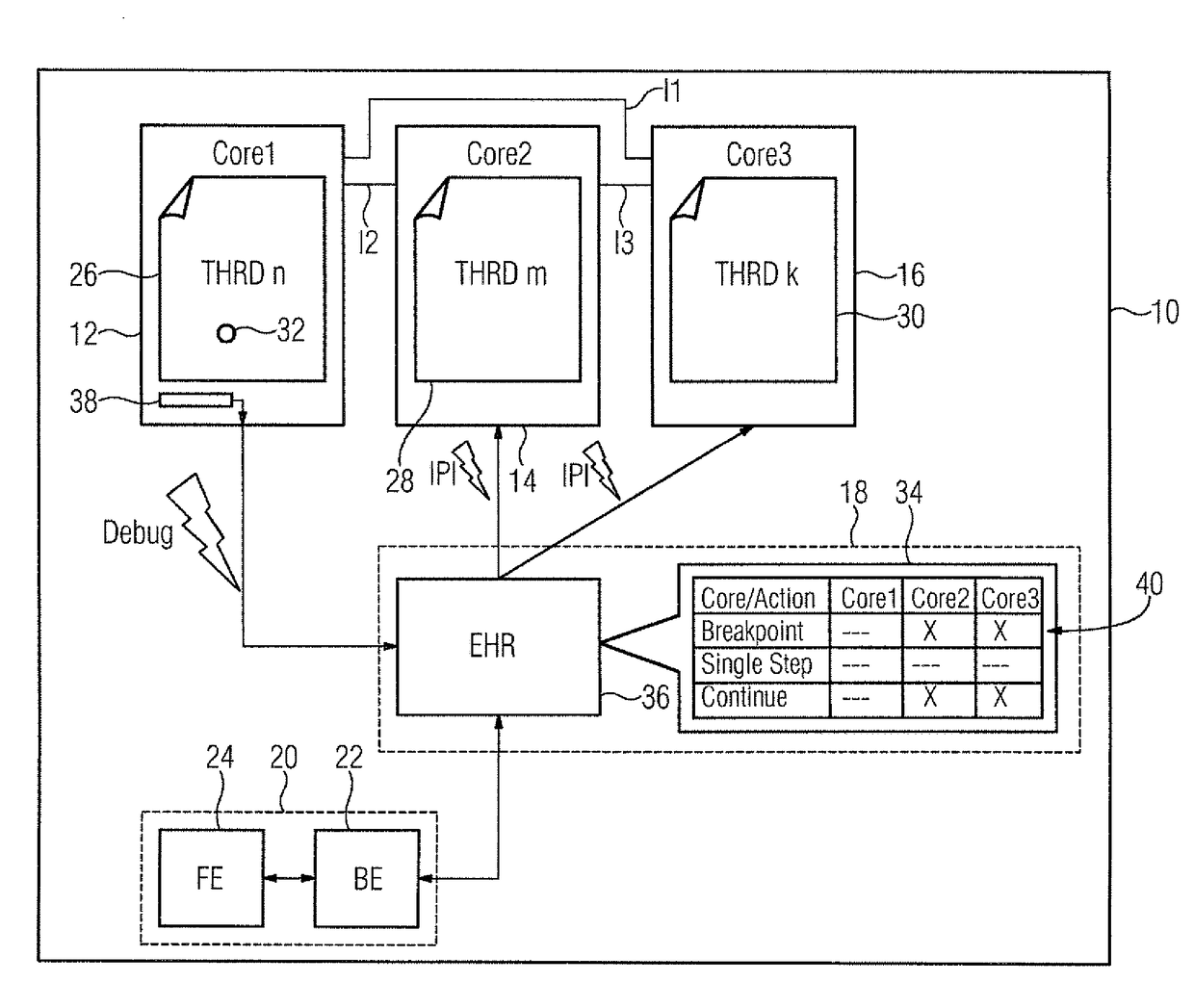

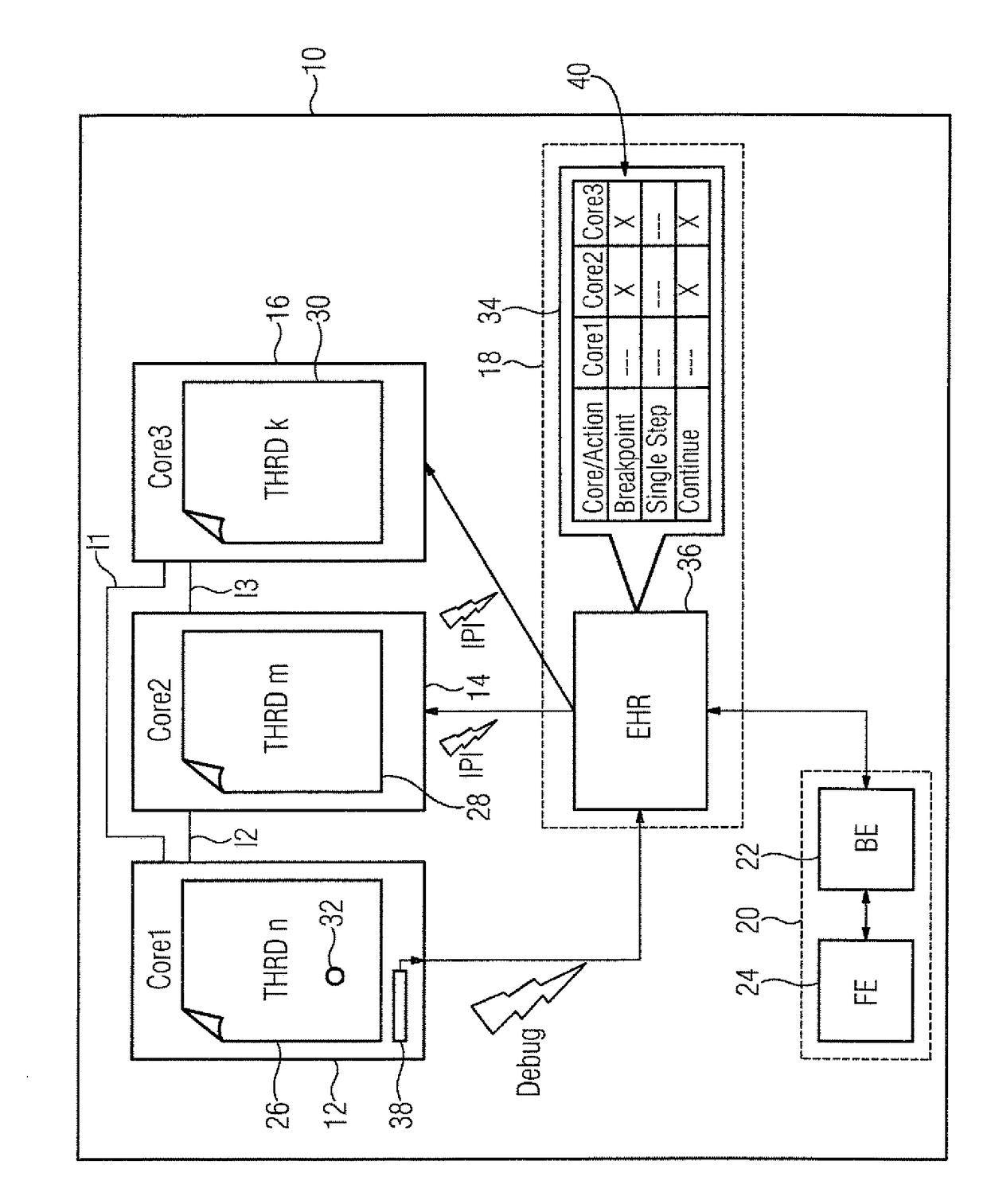

Multicore processor system having an error analysis function

ActiveUS9952954B2Inaccurate analysisEnsure data consistencyDetecting faulty computer hardwareSoftware testing/debuggingInter-processor interruptMulti-core processor

A method for operating a multi-core processor system, wherein different of a program are each executed simultaneously by a different respective processor core of the multi-core processor system includes inserting a breakpoint in a first of the threads for interrupting the first processor core and instead executing an exception handling routine. At least one processor core to be additionally interrupted is determined with the exception handling routine on the basis of an association matrix, and an inter-processor interrupt (IPI) is sent to the at least one processor core by the exception handling routine in order to interrupt the at least one processor core.

Owner:SIEMENS AG

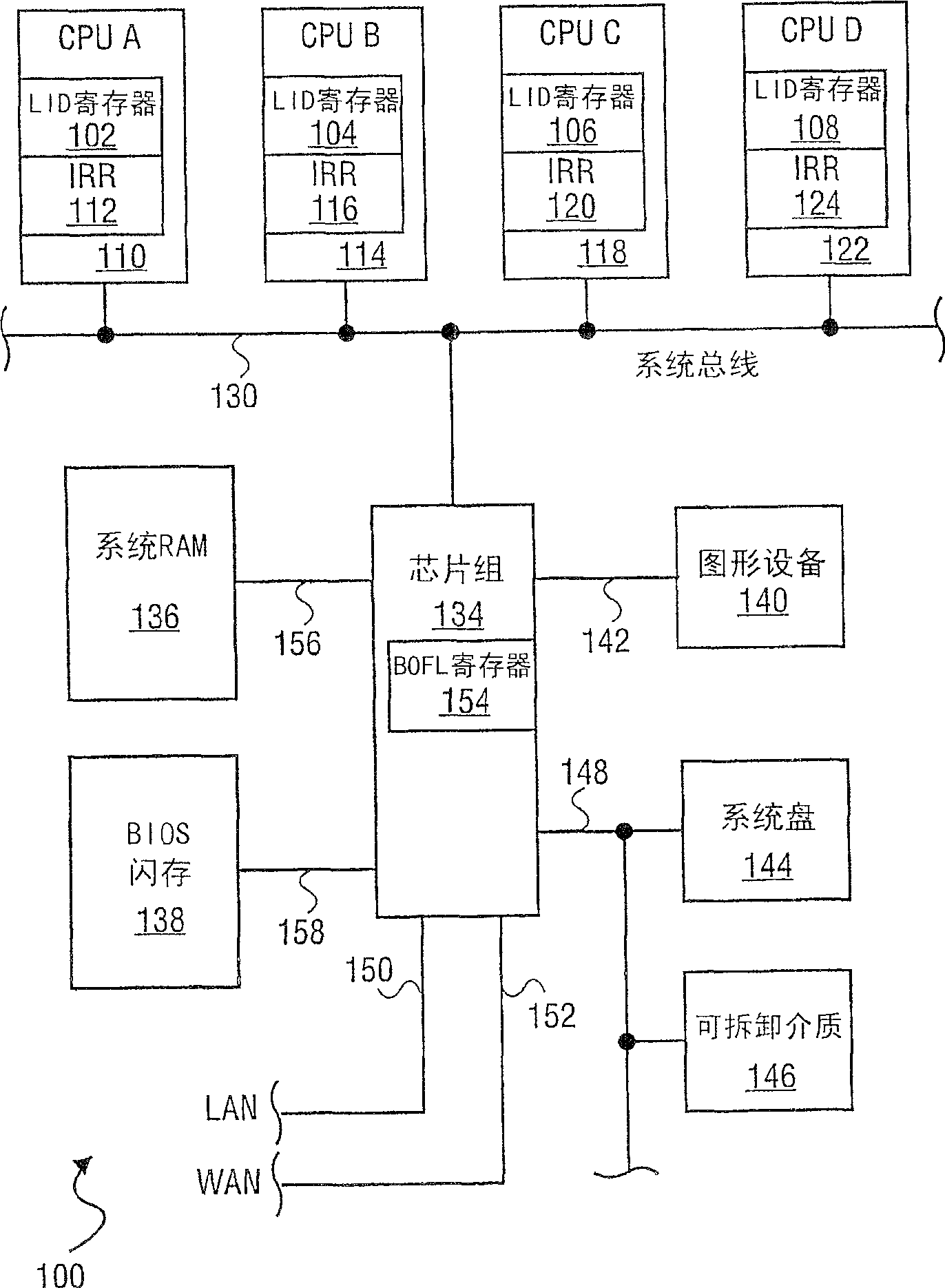

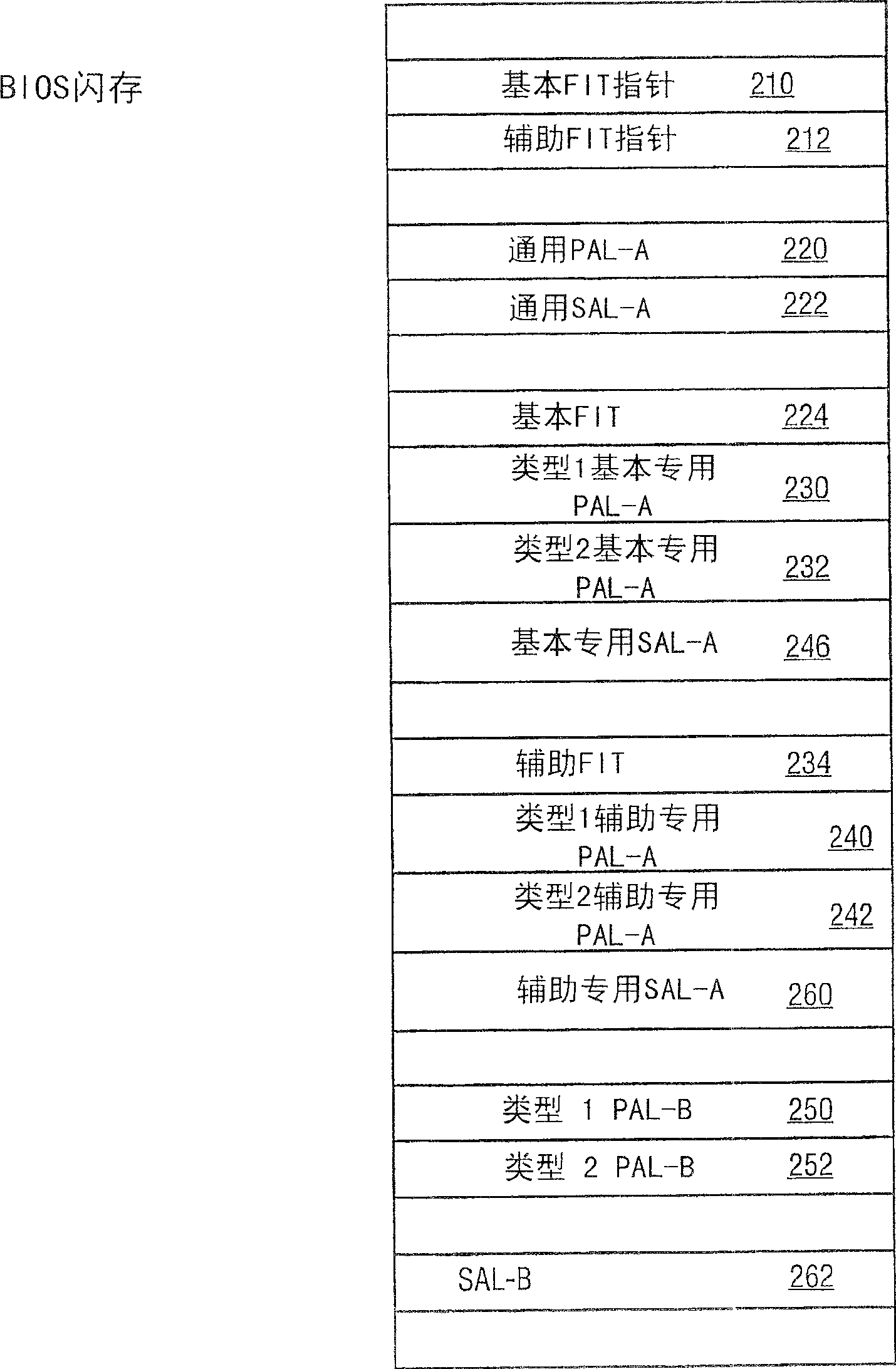

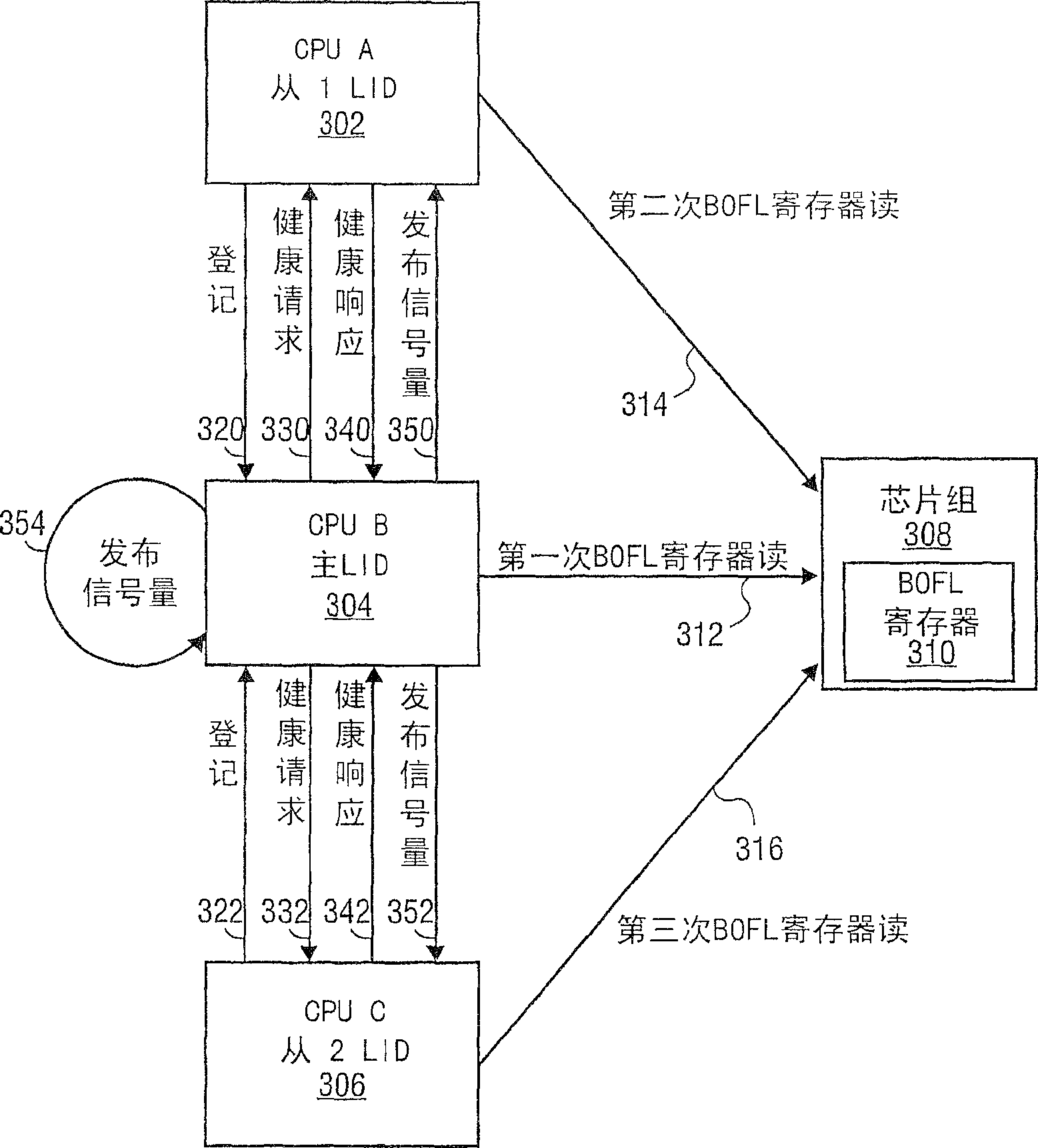

System and method to determine a set of healty processor and guiding associated firmware of system

InactiveCN100498728CLink editingDetecting faulty computer hardwareState of healthInter-processor interrupt

The present invention discloses a system and method for determining a healthy set of processors and associated firmware to boot the system after a reset event. Validation of redundant copies of processor-specific firmware is checked. Processors determine their own health status, and a processor determines a set of processors with the best available health status. The communication mechanism provided by interprocessor interrupt messages allows an algorithm to determine the set of processors to continue booting the system.

Owner:INTEL CORP

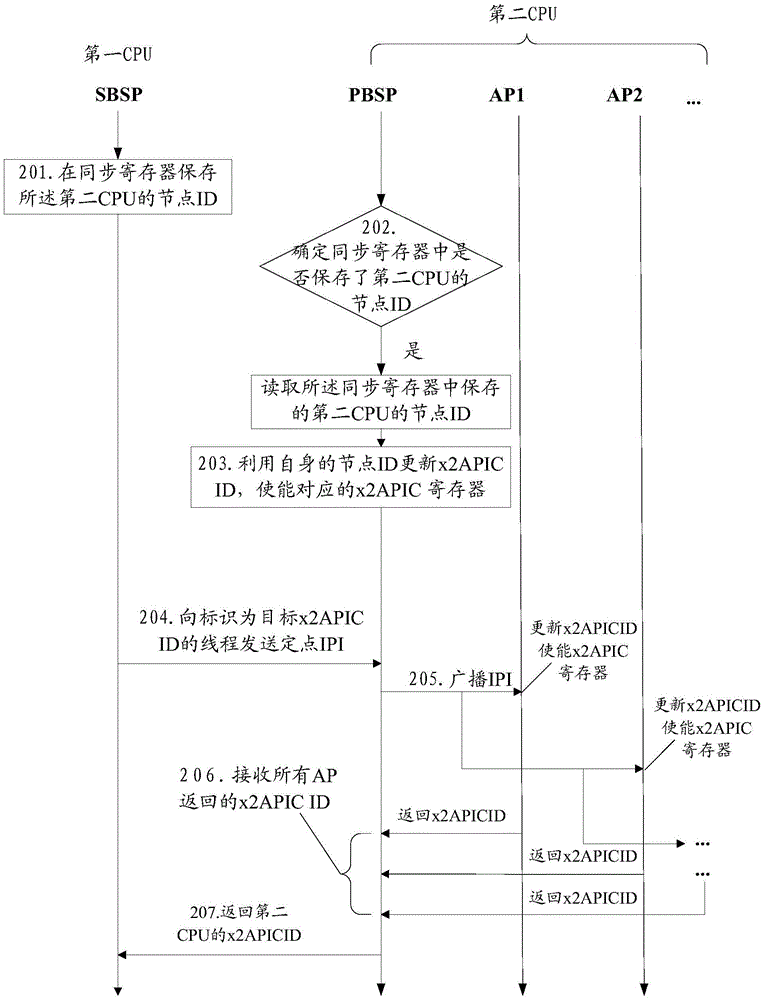

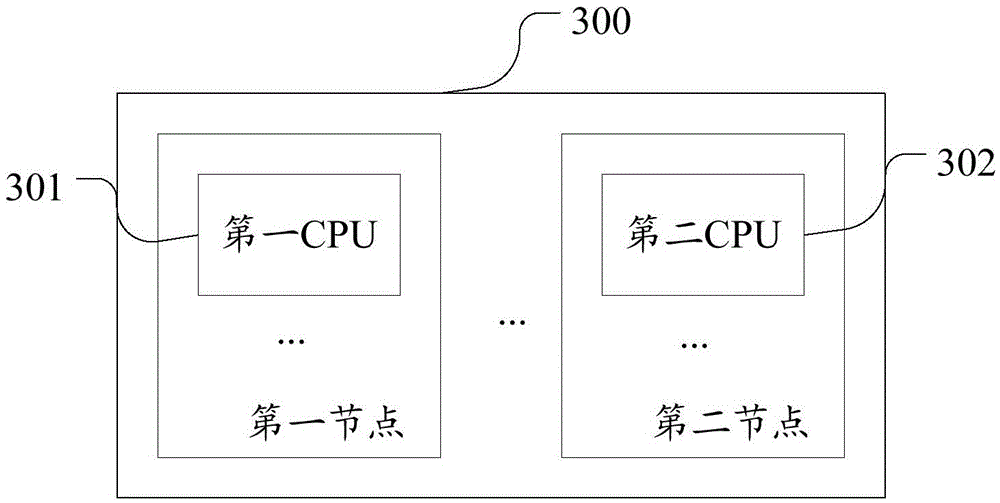

Method for enabling x2APIC by hot-add CPU, and server system

ActiveCN106844258AEasy to implementElectric digital data processingProcessor registerInter-processor interrupt

The invention discloses a method for enabling an x2APIC (Advanced Programmable Interrupt Controller) by a hot-add CPU (Central Processing Unit), CPUs and a server system. The method comprises the steps that an SBSP (System Boot Strap Processor) of a first CPU stores a node ID of a second CPU in a synchronous register; a PBSP (Processor Boot Strap Processor) of the second CPU determines that the node ID of the second CPU is stored in the synchronous register; an x2APIC ID of the PBSP of the second CPU is obtained by utilizing the node ID and a default APIC ID of a PBSP of the hot-add CPU; a register corresponding to the PBSP enabling the second CPU is configured; the SBSP sends a fixed-point IPI (Inter-Processor Interrupt) to the PBSP of the second CPU through the x2APIC ID of the second CPU; and the SBSP collects x2APIC IDs of the PBSP of the second CPU and all APs (Application Processors). According to the method, the CPUs and the server system, the operation of enabling the x2APIC by the hot-add CPU is effectively realized when the hot-add CPU and the CPU where the SBSP is located are located at different nodes, and a realization mode is simple.

Owner:XFUSION DIGITAL TECH CO LTD

Detection of side-channel attacks between virtual machines

InactiveCN105917345BPlatform integrity maintainanceProgram controlInter-processor interruptTime Stamp Counter

Technology involves a detector that identifies side-channel attacks between virtual machines. According to some examples, an interprocessor interrupt (IPI) rate of a first virtual machine (VM), a time stamp count (TSC) rate of a second virtual machine, and a cache miss ratio (CMR) of a third virtual machine may be monitored. Side-channel attacks can then be detected based on interprocessor interrupt rates, timestamp count rates, and cache miss ratios.

Owner:EMPIRE TECH DEV LLC

Method for realizing interrupted load balance among multi-core processors

ActiveCN102521047BImprove parallelismLoad balancingResource allocationOperational systemNetwork packet

The invention relates to a method for realizing interrupted load balance among multi-core processors, belonging to the computer network technology. The technical scheme adopted by the balancing method of the invention is as follows: dividing processors sharing a second level cache to the same scheduling region, distributing all data packets to each scheduling region according to source IP addresses, establishing a hash table, and carrying out analytical statistics on the data packets, wherein each scheduling region can have a critical access to respective hash table; and adopting a weighted cycle scheduling algorithm to realize the load balance in each scheduling region, allocating the interruption sent by a network card to each processor, and setting a server priority according to weight values, wherein the server with a higher weight value preferentially receives and processes the interruption, and the processors with the same weight values process the interruption in a cycle scheduling manner. Since an operating system can balance the interrupted load, the interruption sent by the network card can be subjected to balanced distribution on the multiple processor cores, thus the processing efficiency of the system can be improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM