Patents

Literature

329 results about "Interrupt handler" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computer systems programming, an interrupt handler, also known as an interrupt service routine or ISR, is a special block of code associated with a specific interrupt condition. Interrupt handlers are initiated by hardware interrupts, software interrupt instructions, or software exceptions, and are used for implementing device drivers or transitions between protected modes of operation, such as system calls.

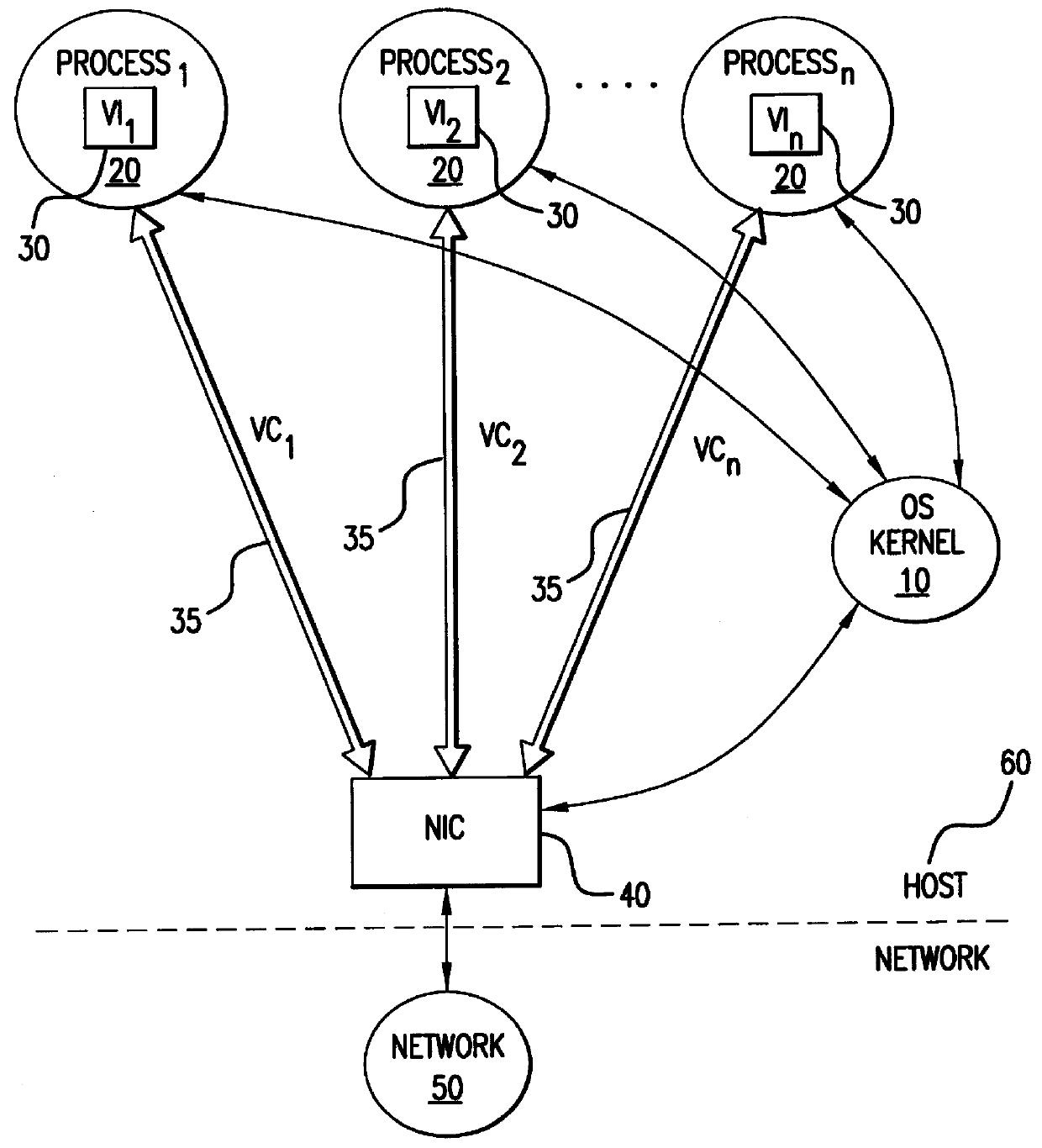

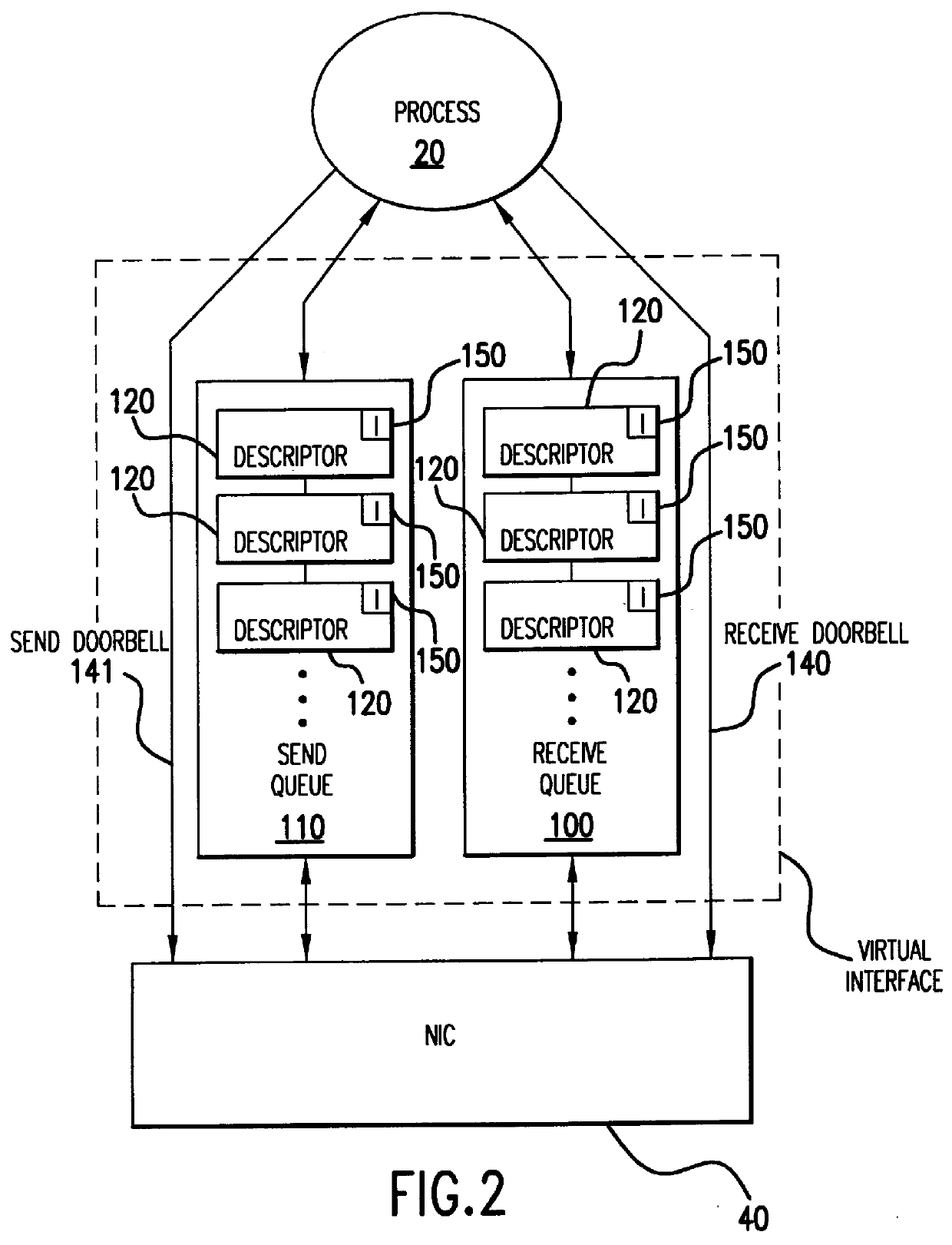

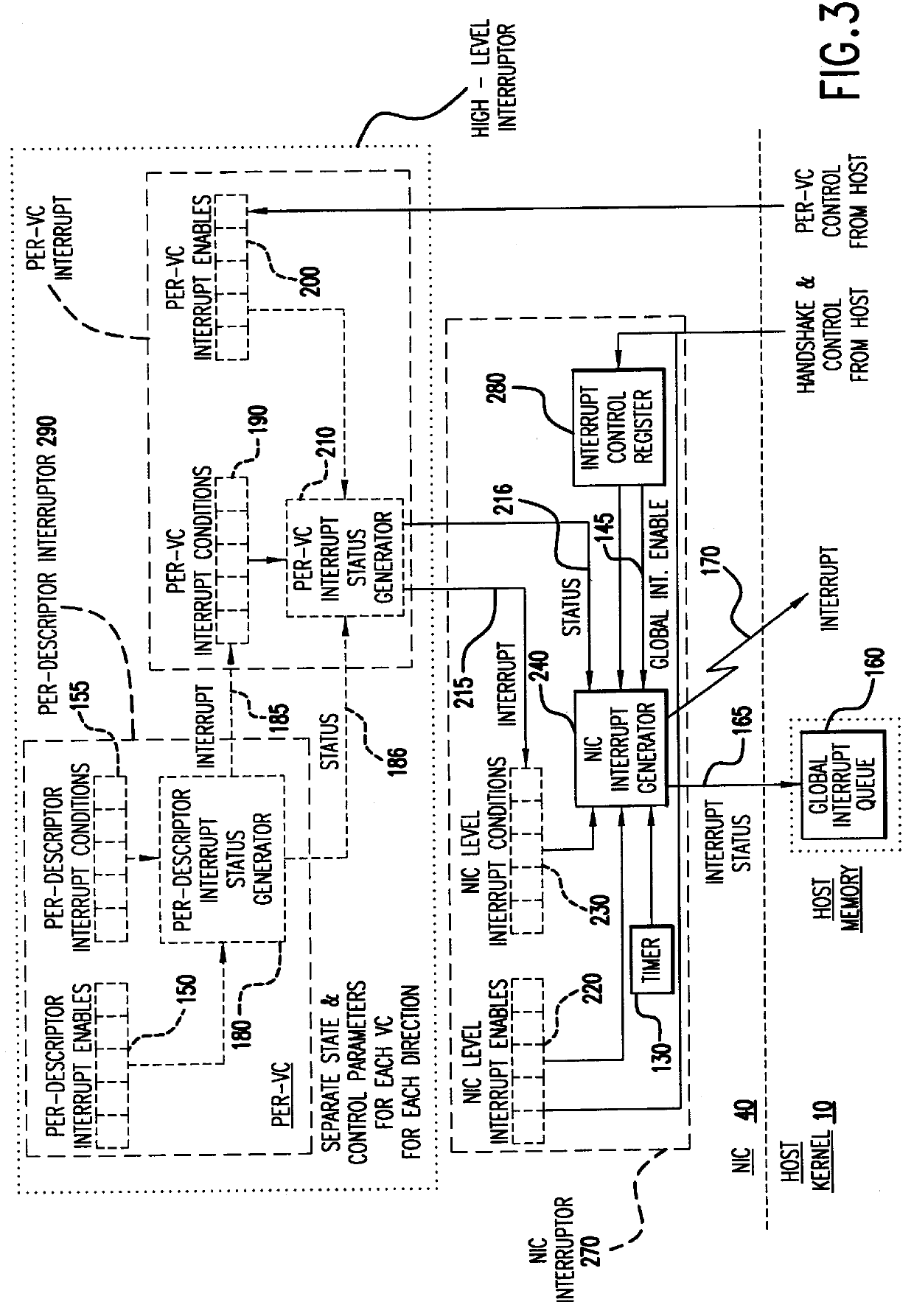

Hierarchical interrupt structure for event notification on multi-virtual circuit network interface controller

Methods and apparatus process a plurality of interrupt status words from a network interface controller (NIC) to a plurality of processes. A first per-virtual circuit interrupt status word and a second per-virtual circuit interrupt status word can be sent by a per-virtual circuit interrupter having a per-virtual circuit interrupt output. A NIC interrupter can be in communication with the per-virtual circuit interrupt output and have a NIC interrupt output to send a first NIC interrupt status word and a second NIC interrupt status word to a global interrupt queue of a host system. The NIC interrupter can generate an interrupt signal to the host system, and a proxy interrupt handler of the host system can be in communication with the NIC interrupter. The proxy interrupt handler can awaken at least in part in response to the interrupt signal, and read the first NIC interrupt status word and the second NIC interrupt status word from the global interrupt queue, wake the first process and the second process, and send the first NIC interrupt status word to the first process and the second NIC interrupt status word to the second process.

Owner:INTEL CORP

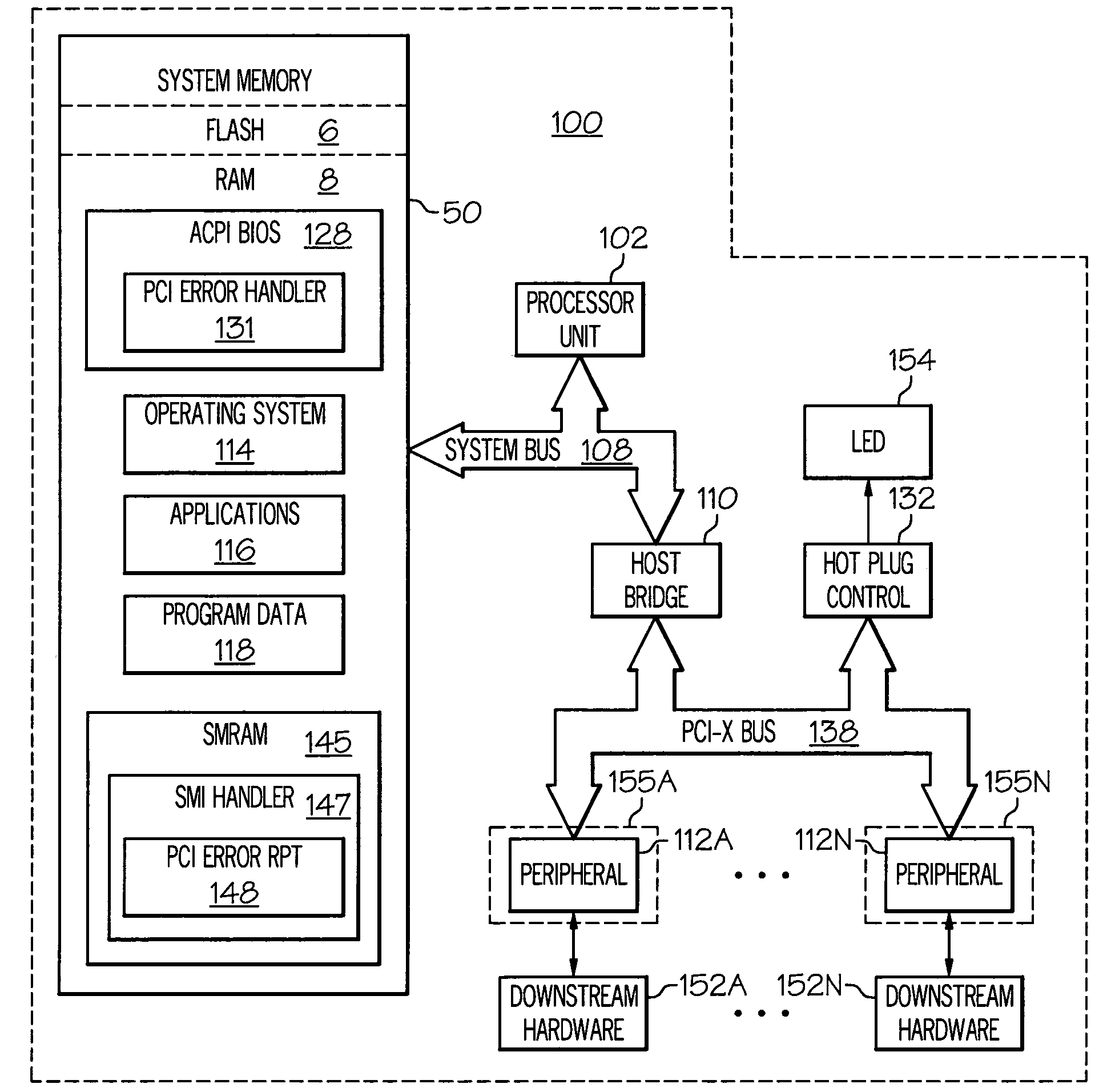

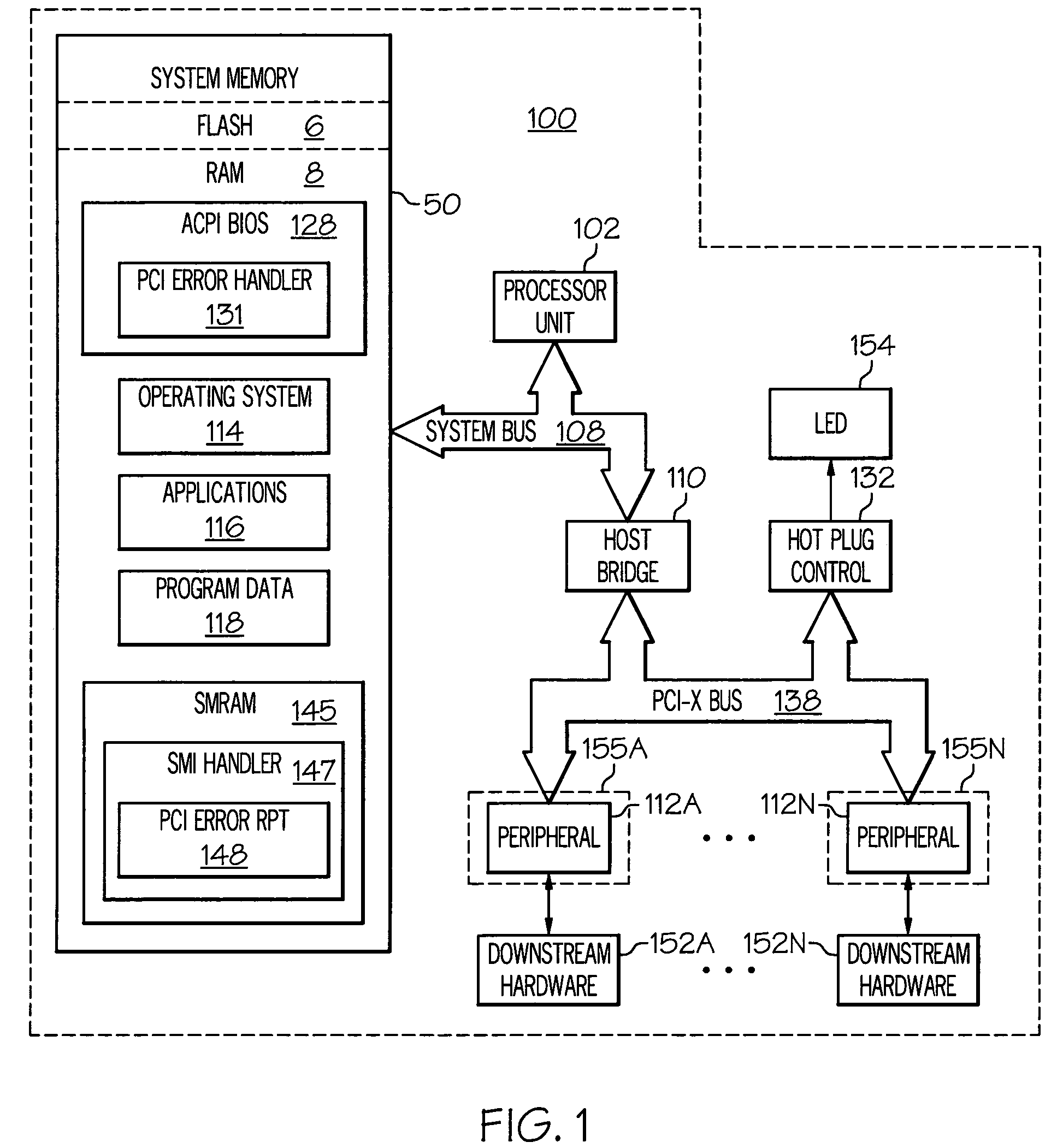

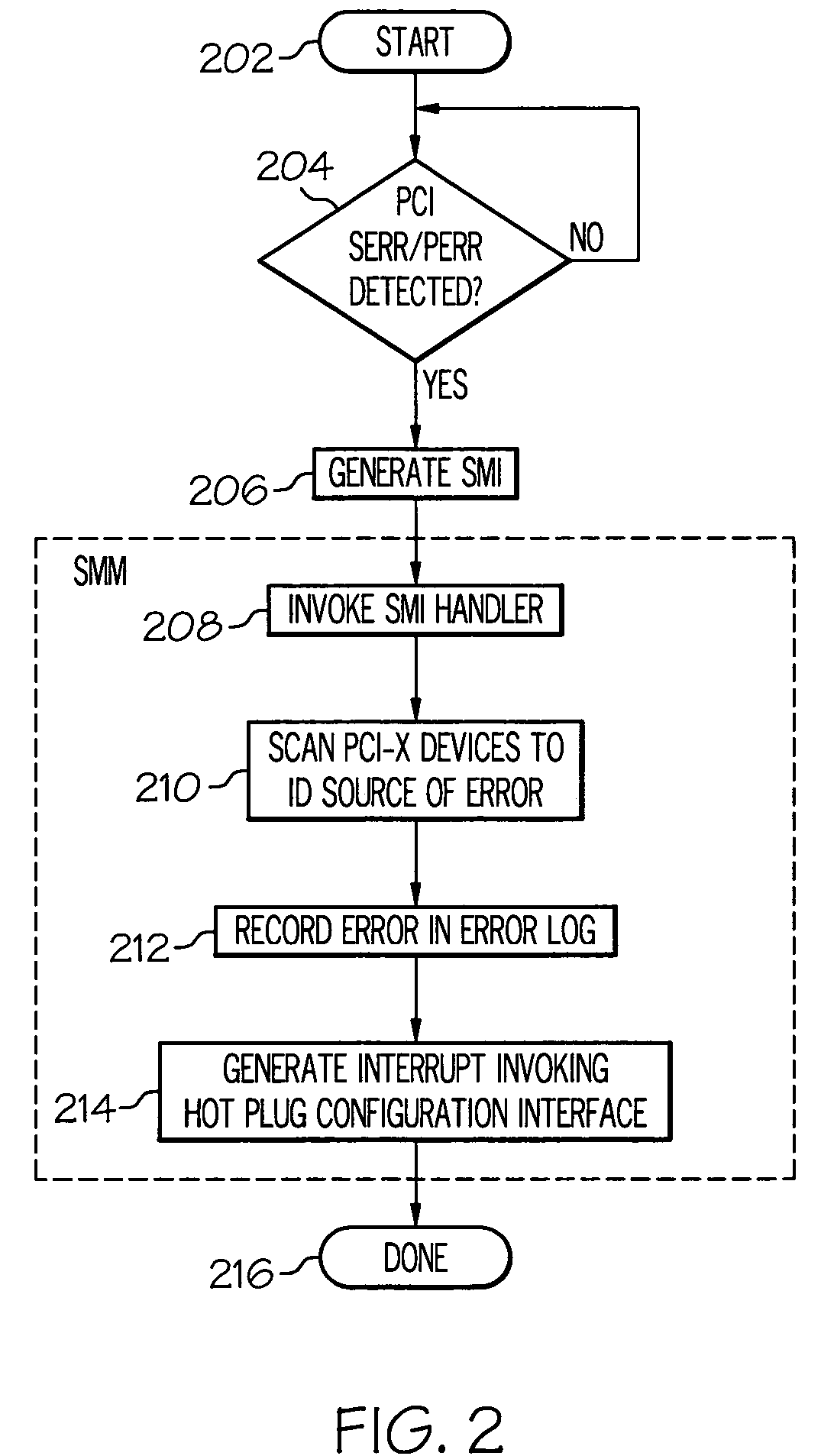

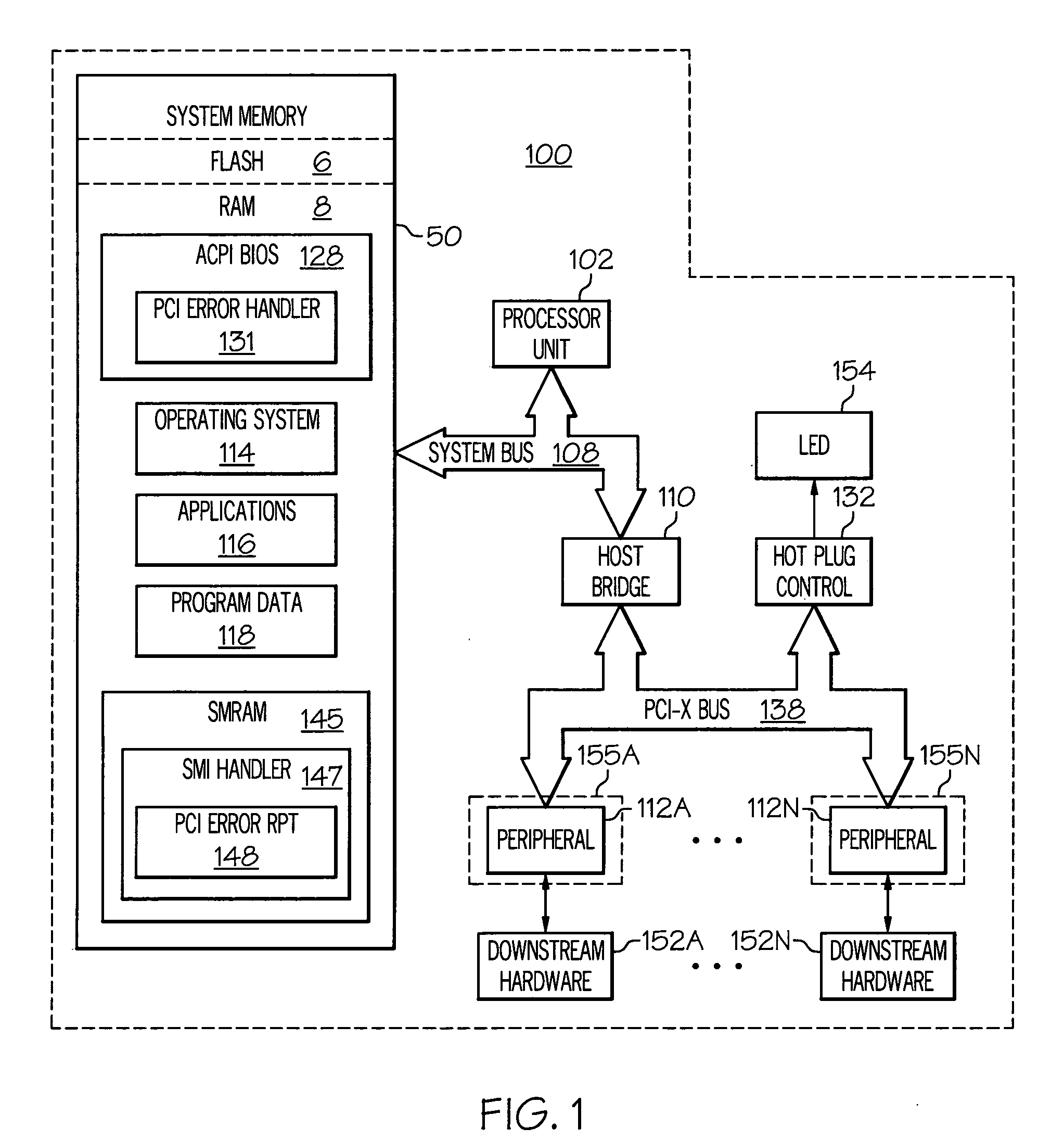

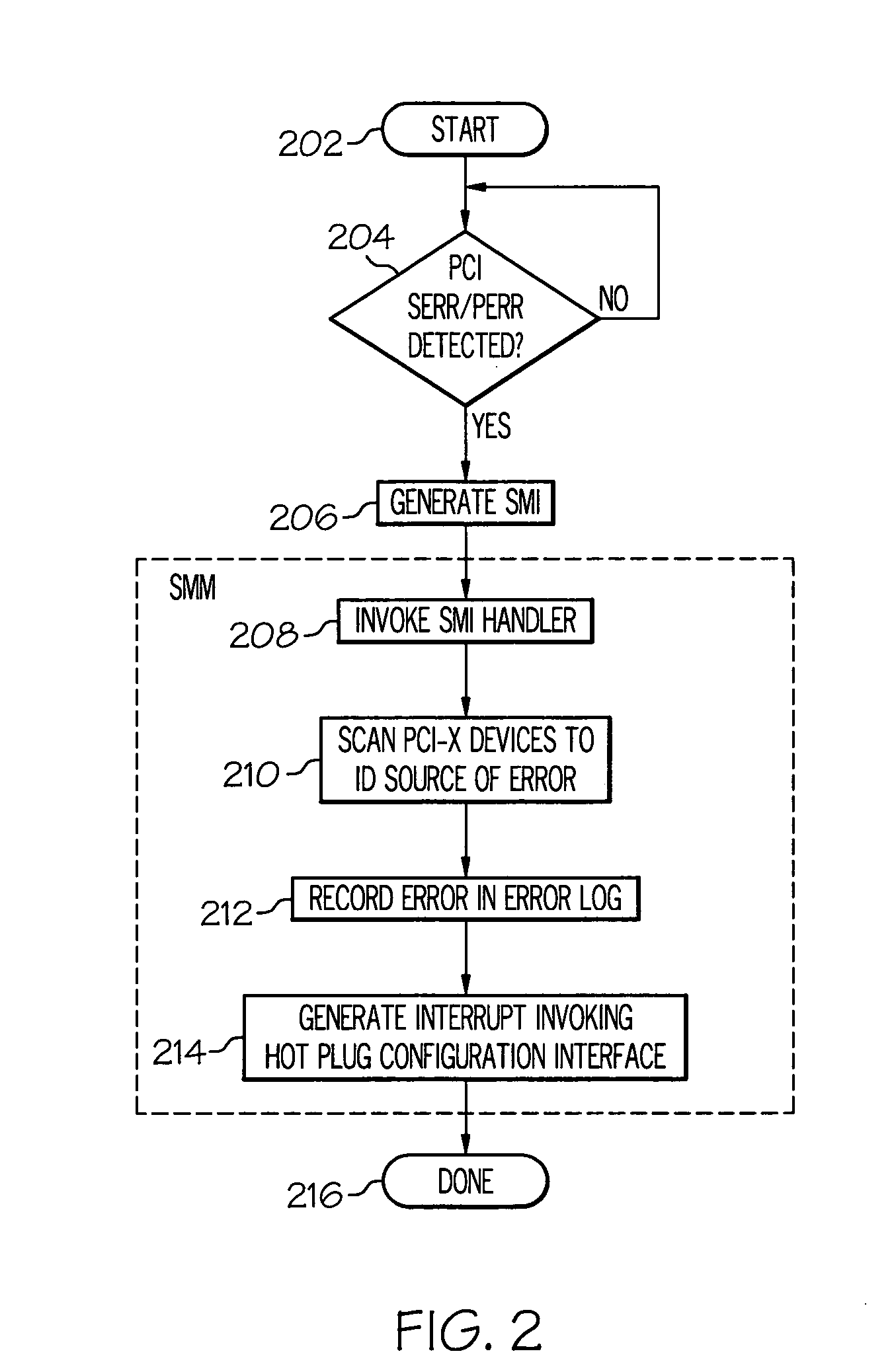

System and method for using hot plug configuration for PCI error recovery

InactiveUS7447934B2Non-redundant fault processingAdvanced Configuration and Power InterfaceOperational system

Owner:LENOVO GLOBAL TECH INT LTD

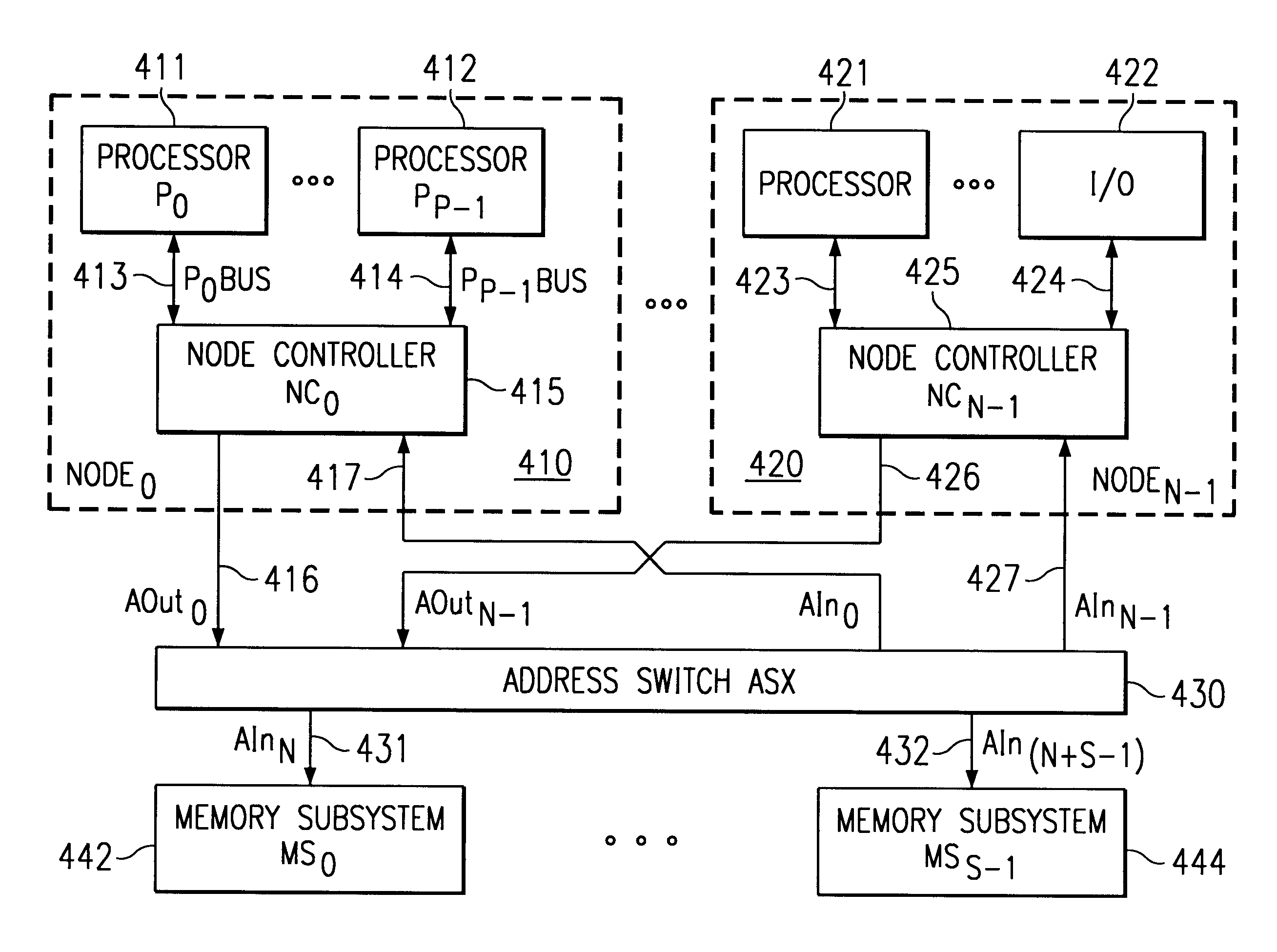

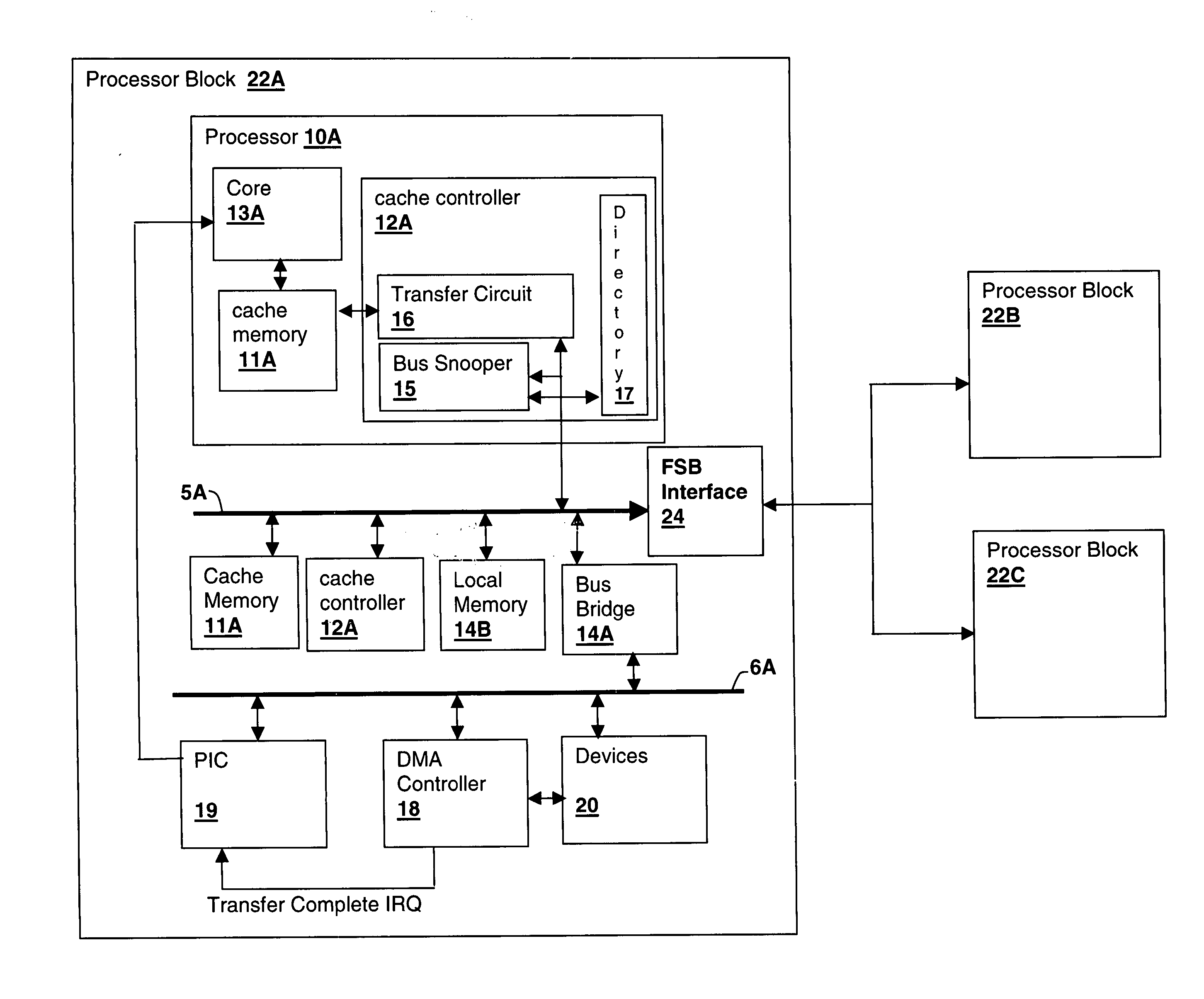

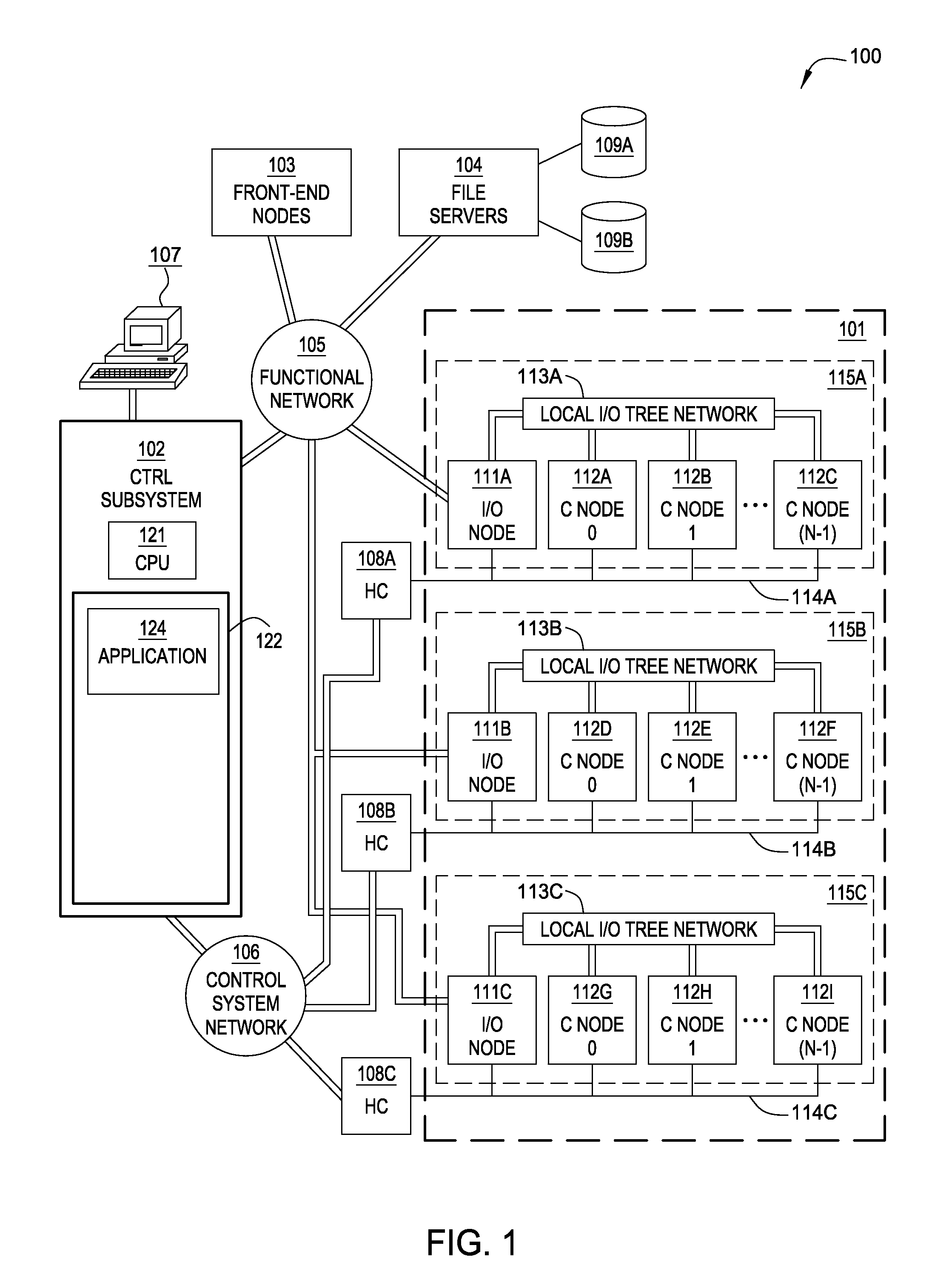

Method and apparatus to distribute interrupts to multiple interrupt handlers in a distributed symmetric multiprocessor system

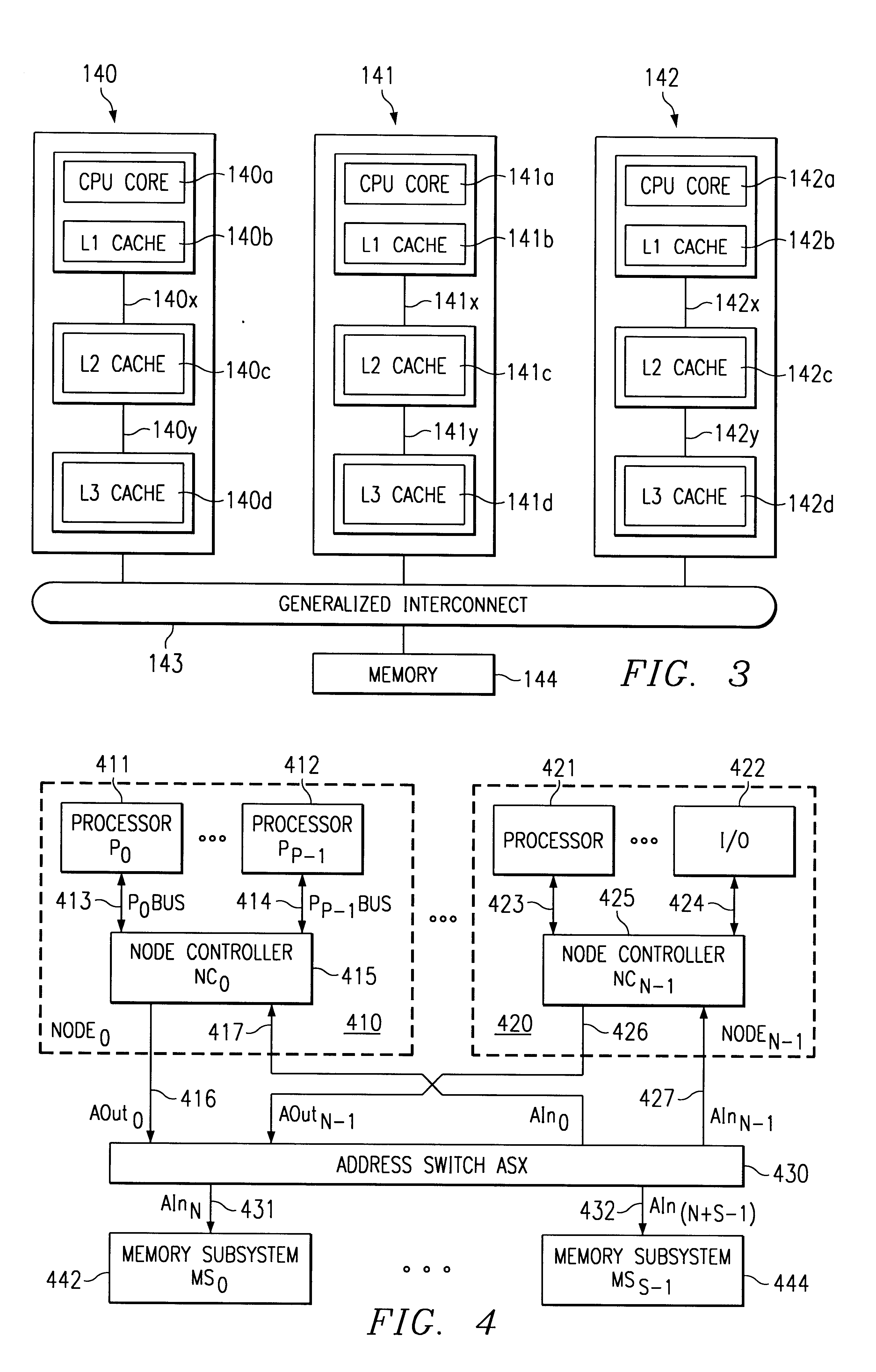

A distributed system structure for a large-way, symmetric multiprocessor system using a bus-based cache-coherence protocol is provided. The distributed system structure contains an address switch, multiple memory subsystems, and multiple master devices, either processors, I / O agents, or coherent memory adapters, organized into a set of nodes supported by a node controller. The node controller receives transactions from a master device, communicates with a master device as another master device or as a slave device, and queues transactions received from a master device. Since the achievement of coherency is distributed in time and space, the node controller helps to maintain cache coherency. The node controller also implements an interrupt arbitration scheme designed to choose among multiple eligible interrupt distribution units without using dedicated sideband signals on the bus.

Owner:GOOGLE LLC

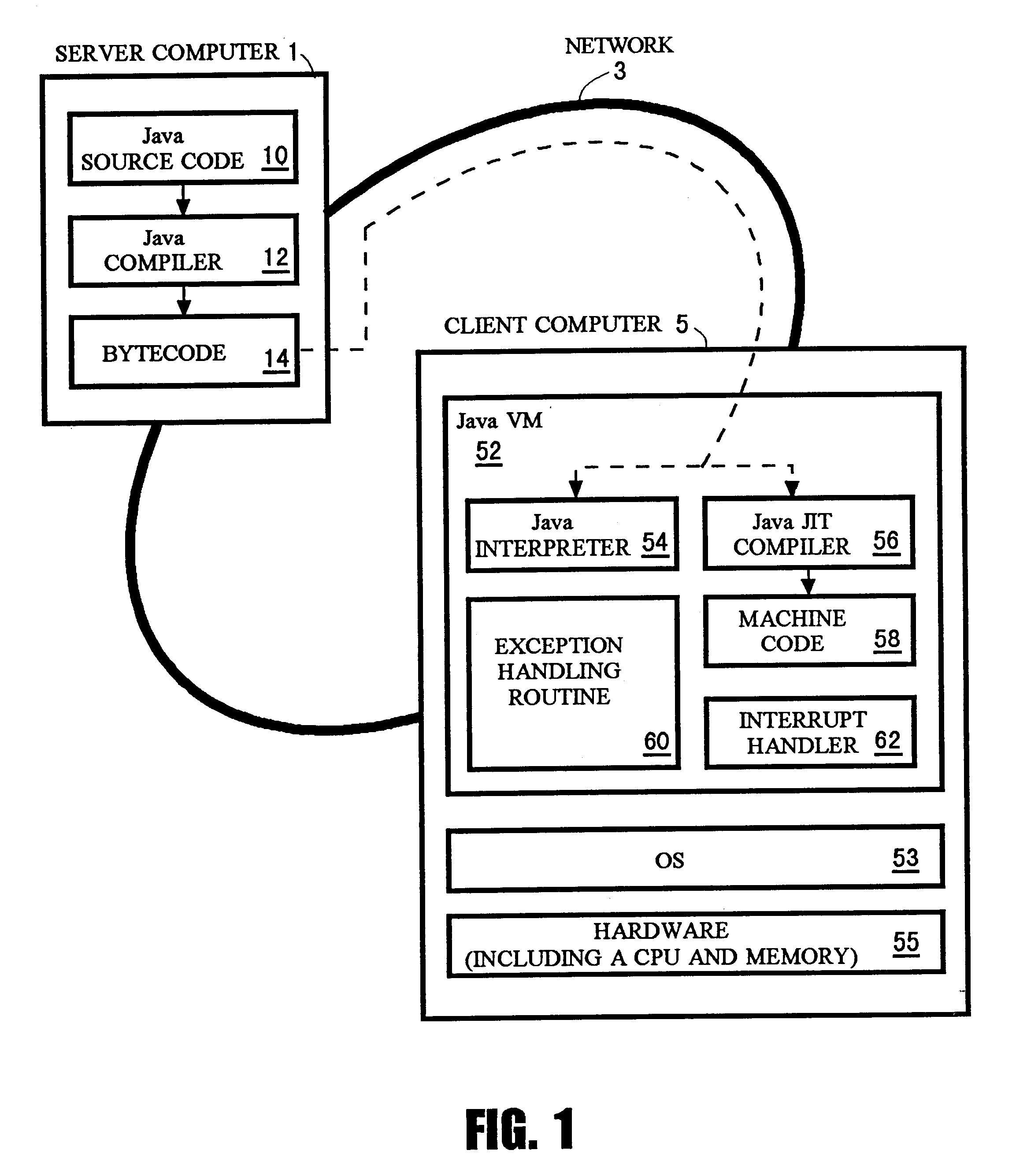

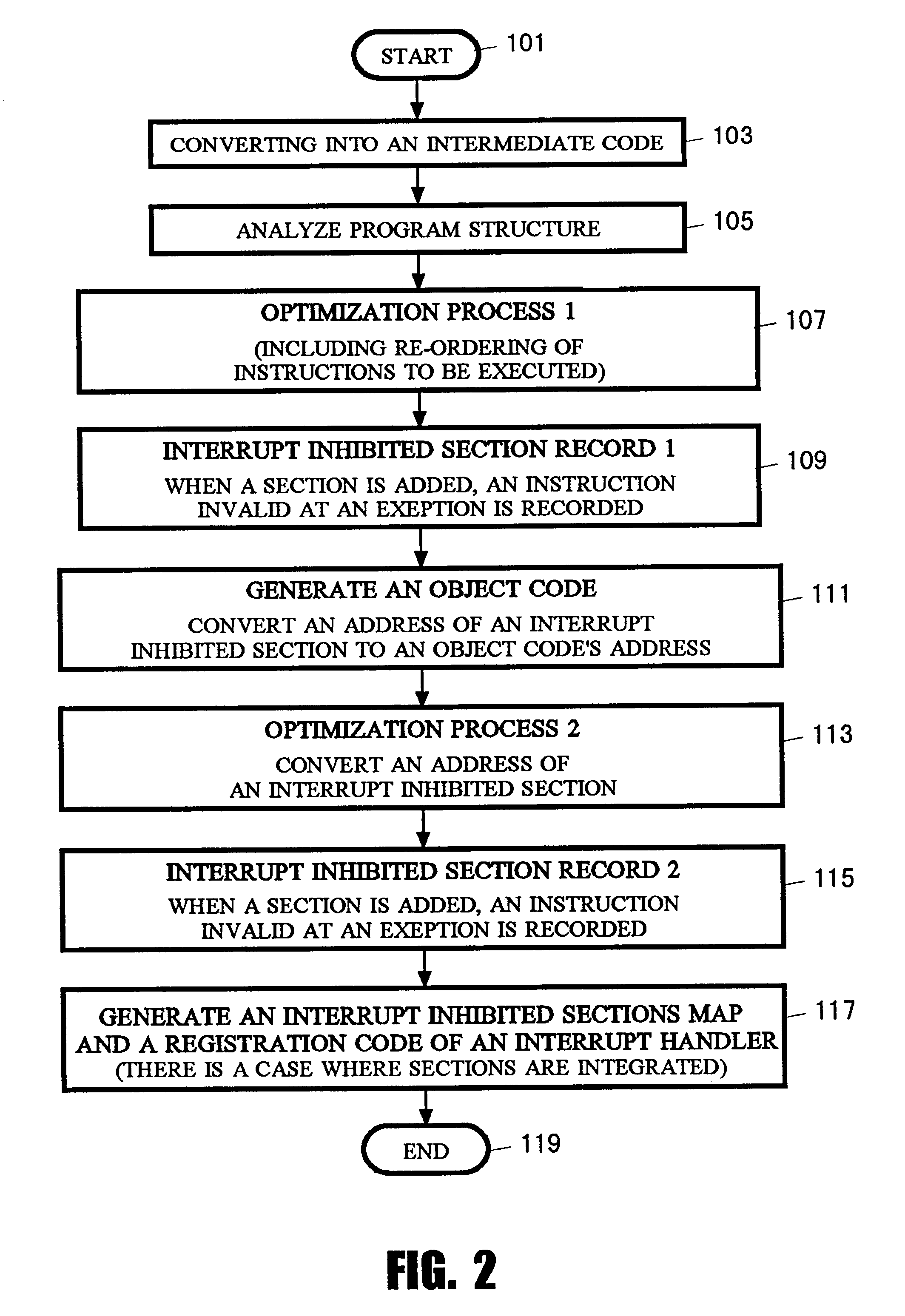

Compile method, exception handling method and computer

InactiveUS6634023B1Easy to getDecreasing can be registeredProgram initiation/switchingSoftware engineeringPDAT enzymeInterrupt handler

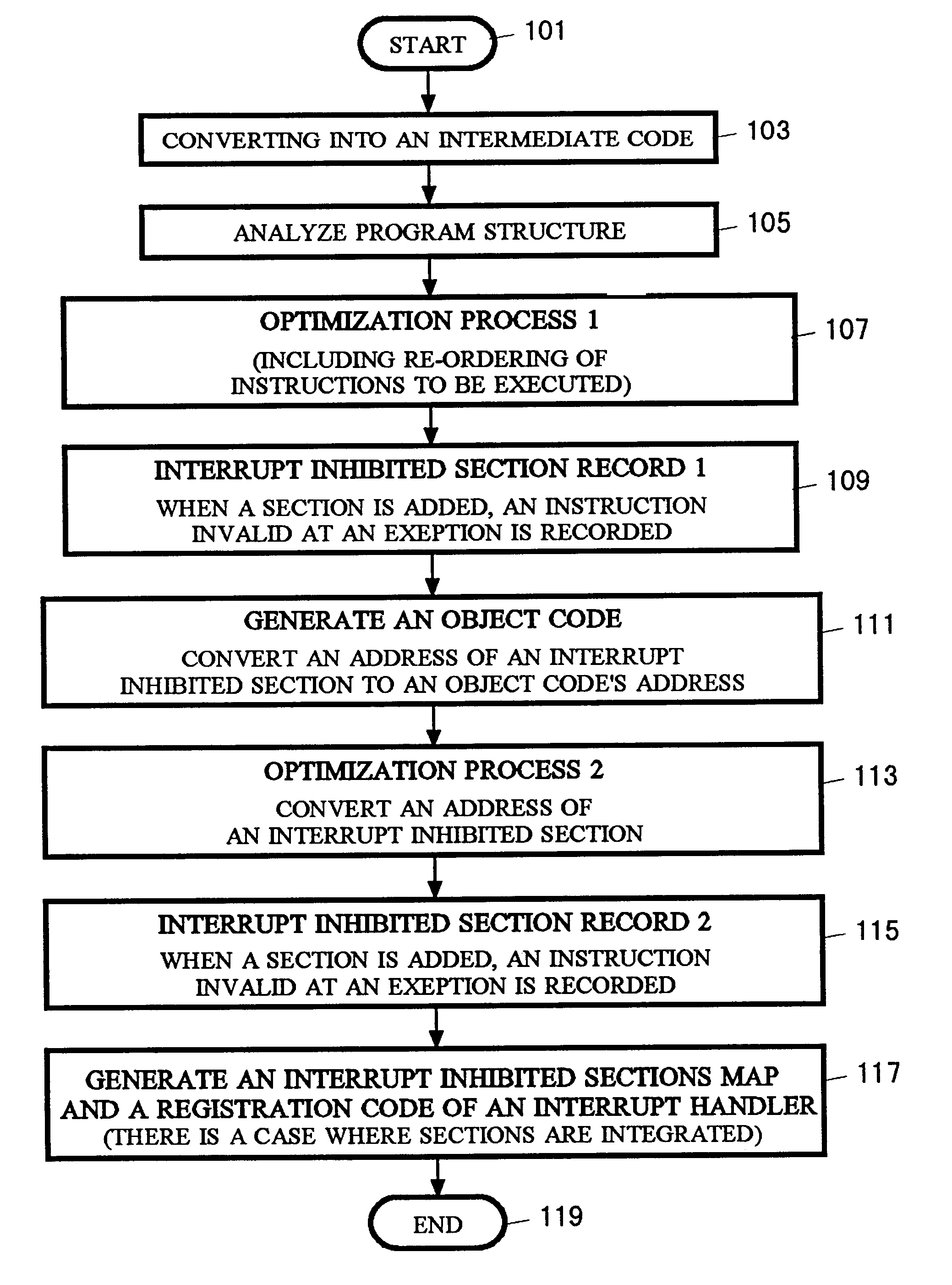

The present invention enables re-ordering of instructions to be executed while assuring a precise exception. In Java language, an optimization process of re-ordering instructions to be executed is performed by Just-In-Time compiler. For instance, the instructions lining in order from instruction E<HIL><PDAT>1 < / BOLD><PDAT>which was moved forward to instruction S<HIL><PDAT>2< / BOLD><PDAT>which had been located before E<HIL><PDAT>1 < / BOLD><PDAT>is registered as interrupt inhibited section R<HIL><PDAT>1< / BOLD><PDAT>, and from instruction S<HIL><PDAT>4 < / BOLD><PDAT>which was moved forward to instruction S<HIL><PDAT>3 < / BOLD><PDAT>which had been located before S<HIL><PDAT>4 < / BOLD><PDAT>is registered as interrupt inhibited section R<HIL><PDAT>2 < / BOLD><PDAT>(S is an instruction which has an affect observable from the outside at the execution, and E is an instruction which may cause an exception). Also, in FIG. <HIL><PDAT>7< / BOLD><PDAT>, S<HIL><PDAT>4 < / BOLD><PDAT>which was an instruction behind E<HIL><PDAT>1 < / BOLD><PDAT>in the original order is registered as R<HIL><PDAT>1< / BOLD><PDAT>'s instruction invalid at an exception. If E<HIL><PDAT>1 < / BOLD><PDAT>causes an exception, an interrupt handler is activated and the instructions of interrupt inhibited section R<HIL><PDAT>1 < / BOLD><PDAT>are copied to another area. S<HIL><PDAT>4 < / BOLD><PDAT>is not copied in that case. In addition, a branch code to an exception handling routine is attached to the end of the copy. If execution is restarted from S<HIL><PDAT>1< / BOLD><PDAT>, the instructions required to be executed for assuring the precise exception are executed, and it may move on to an exception handling routine thereafter.< / PTEXT>

Owner:GOOGLE LLC

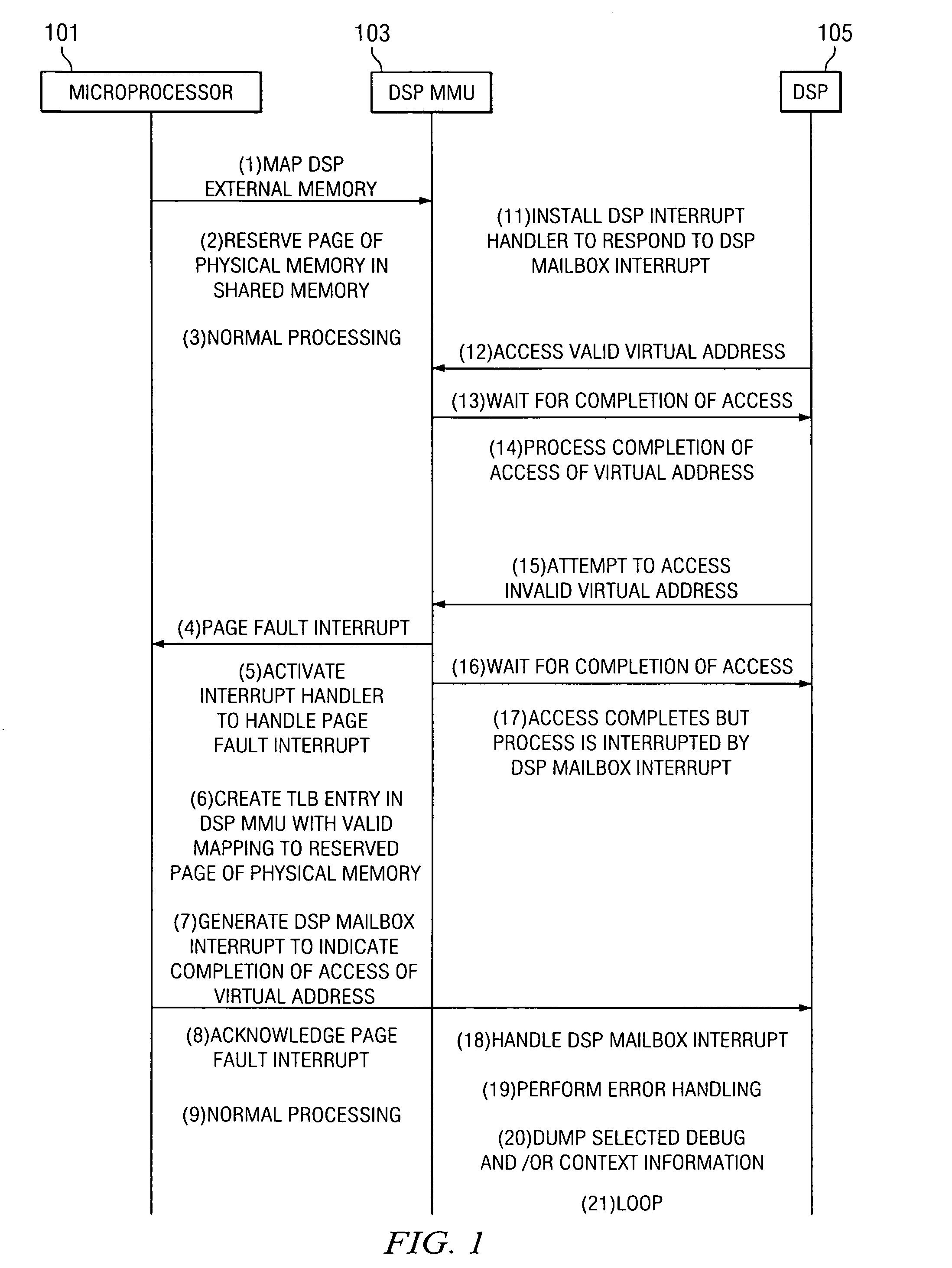

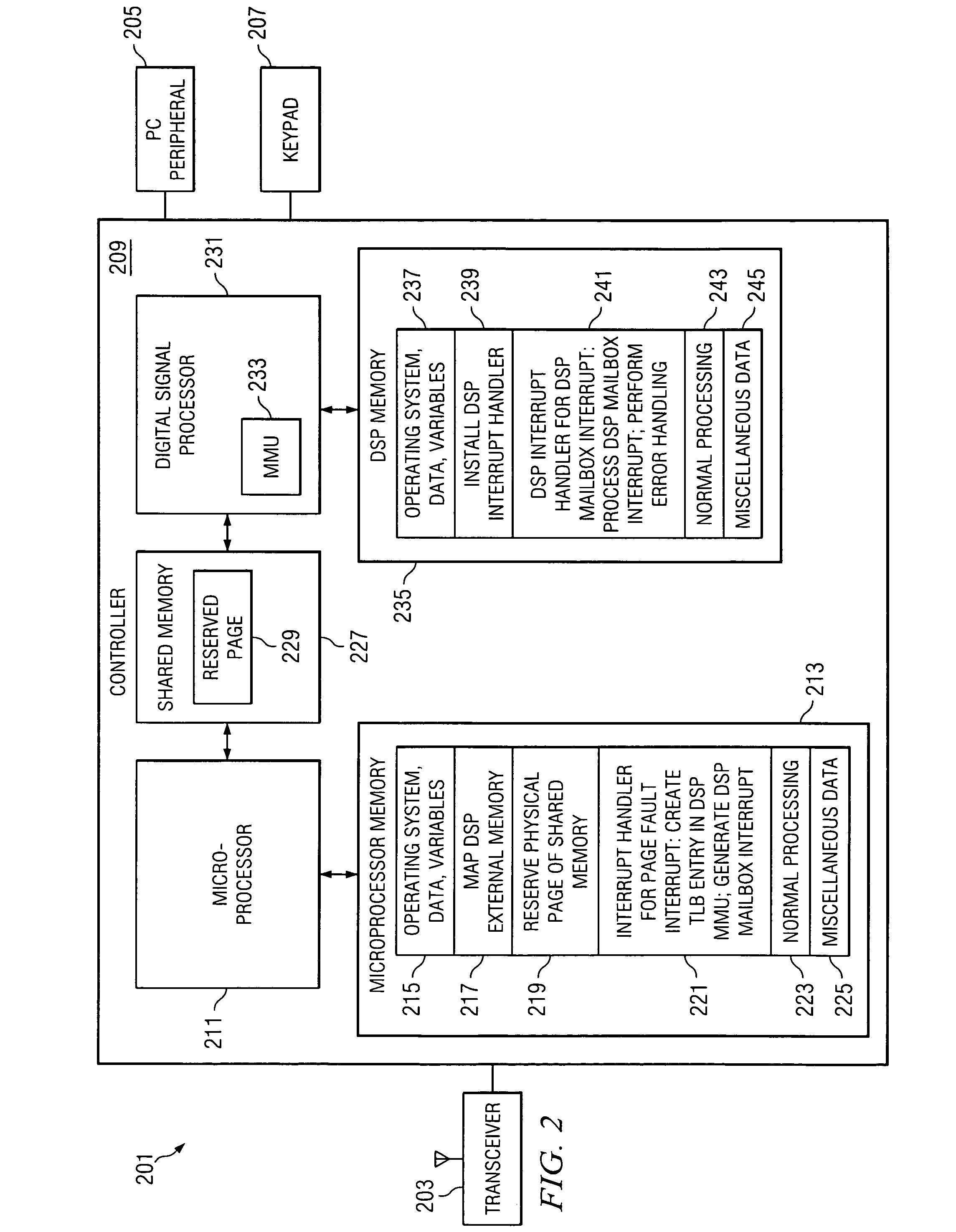

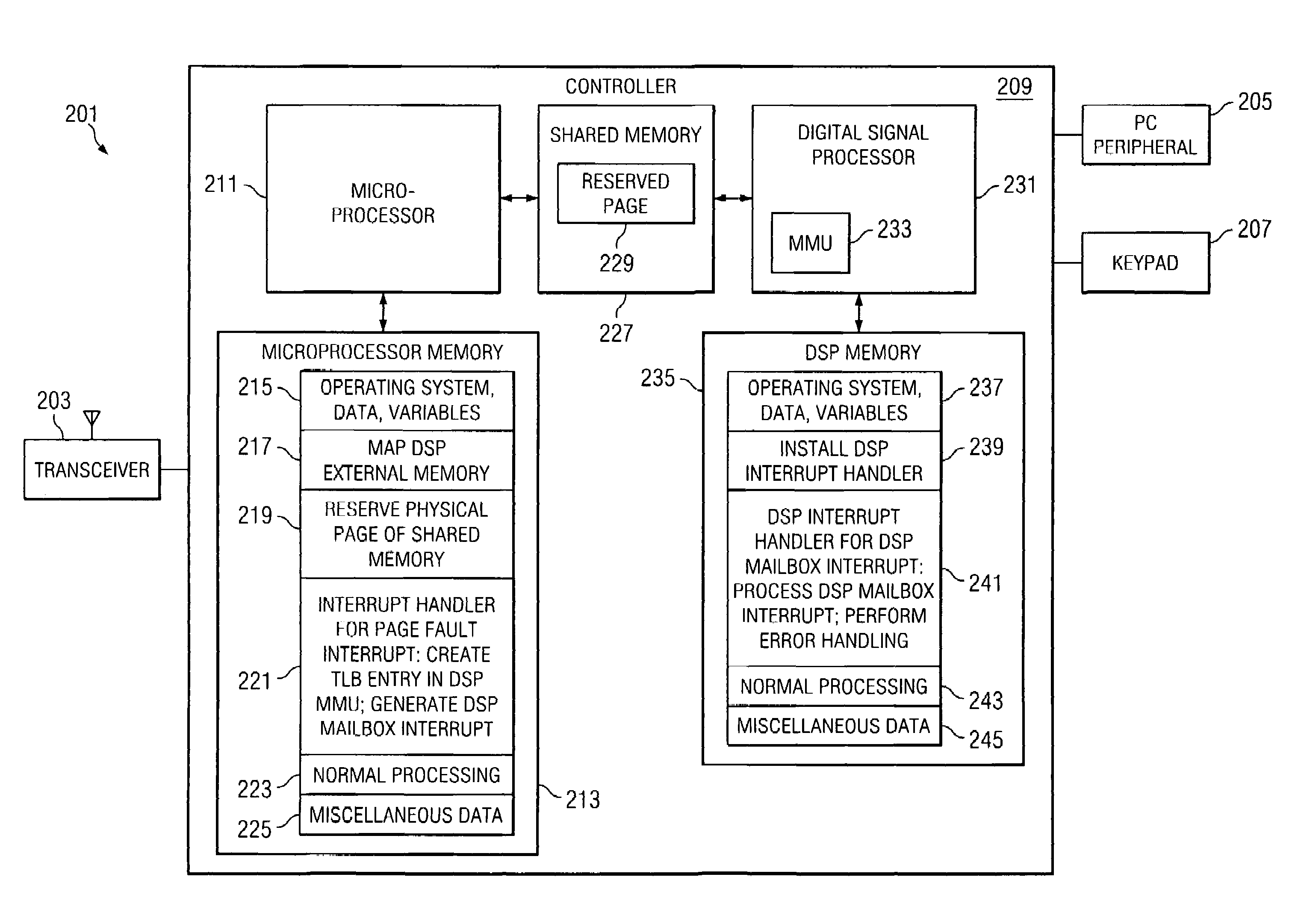

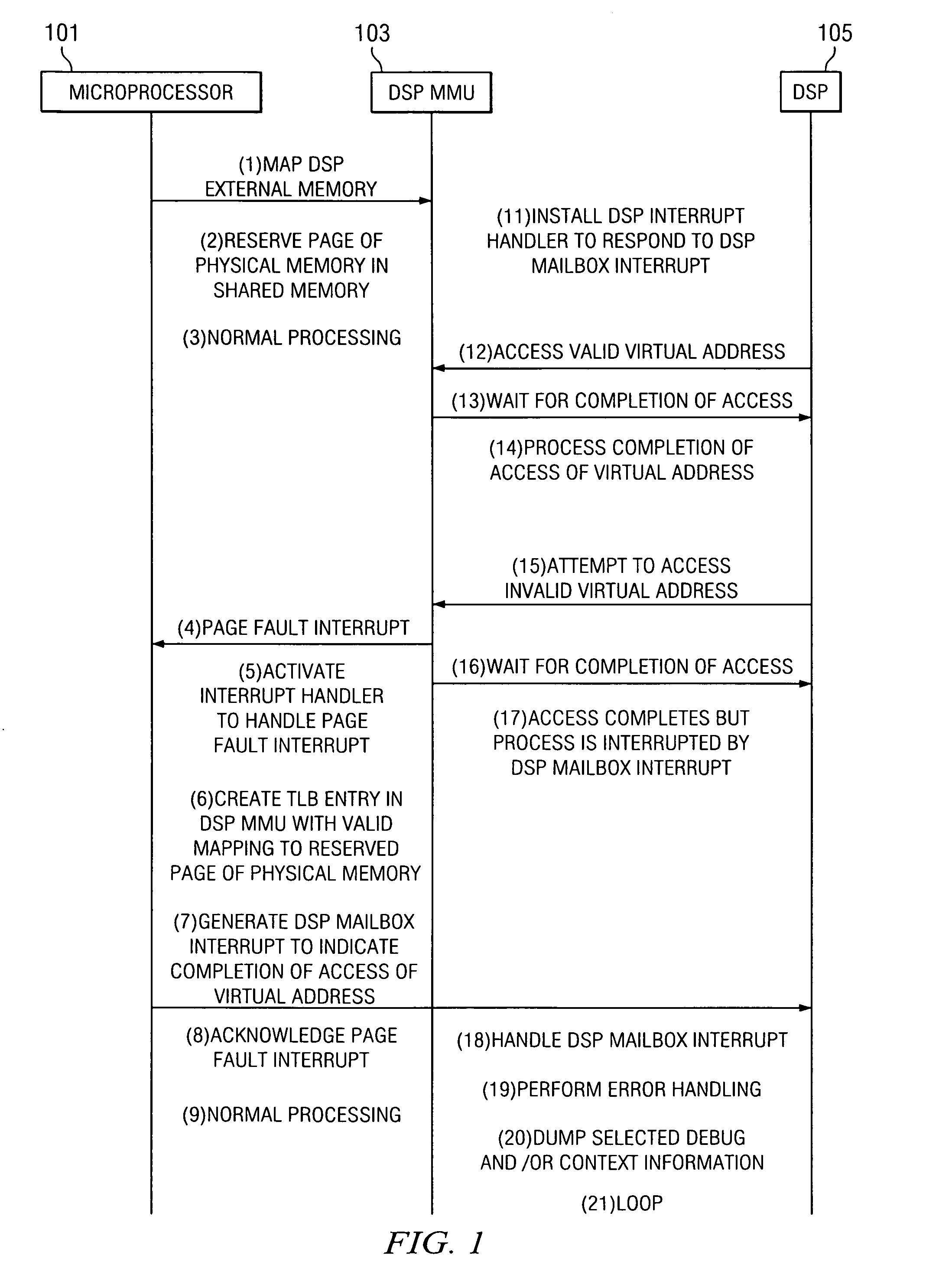

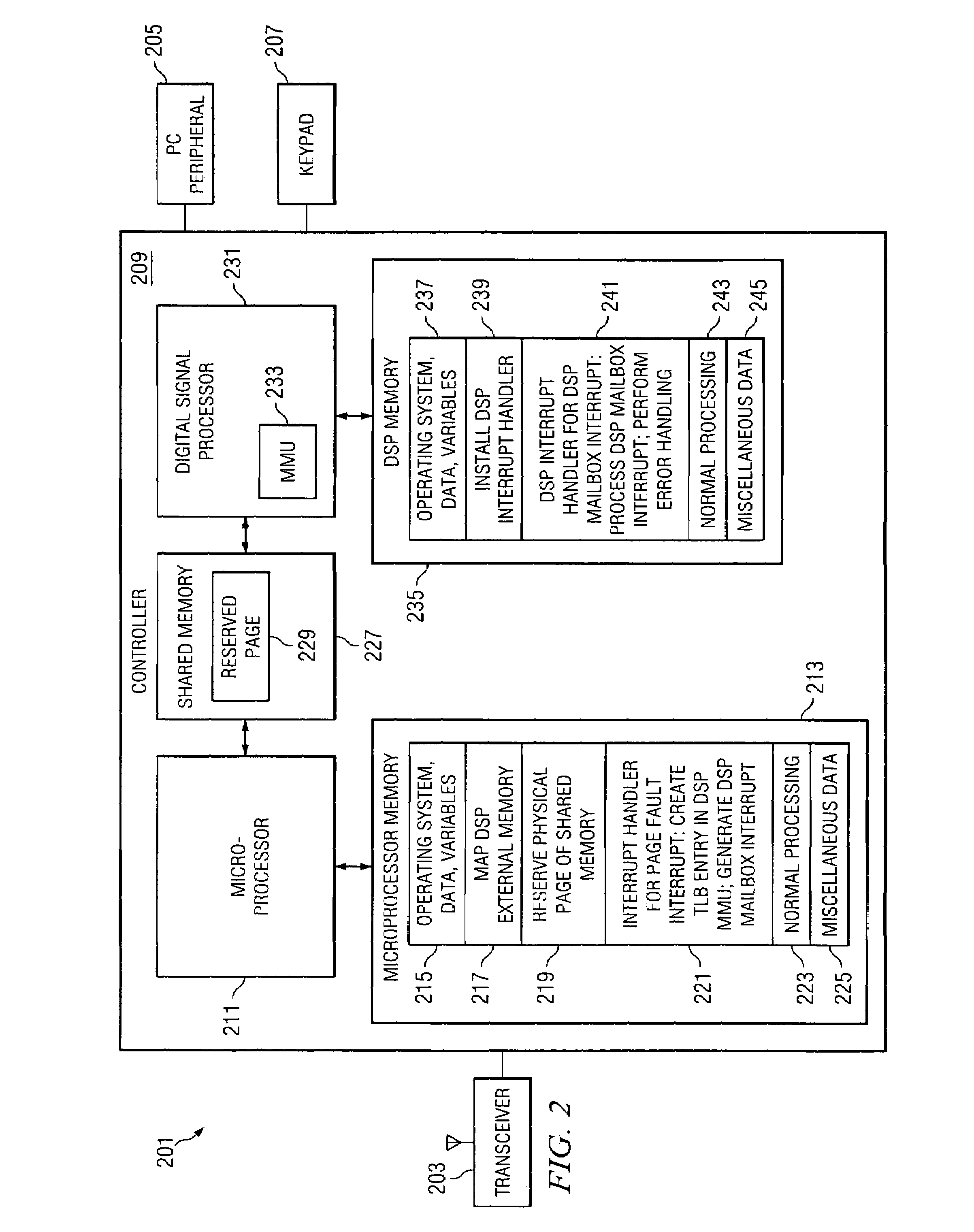

Method, system and device for handling a memory management fault in a multiple processor device

ActiveUS20080183931A1Memory architecture accessing/allocationFault responseComputer architectureMulti processor

A method or device handles memory management faults in a device having a digital signal processor (“DSP”) and a microprocessor. The DSP includes a memory management unit (“DSP MMU”) to manage memory access by the DSP, and the DSP and the microprocessor access shared physical memory. Upon the DSP executing an instruction attempting to access a virtual address wherein the virtual address is invalid, a page fault interrupt is generated by the DSP MMU. A microprocessor interrupt handler in the microprocessor is activated in direct response to the page fault interrupt. Thereafter in the microprocessor, a translation lookaside buffer (“TLB”) entry is created in the DSP MMU, which includes a valid mapping between the virtual address and a page of physical memory. After creating the TLB entry, the microprocessor indicates to the DSP that the access by the DSP of the virtual address is completed.

Owner:TEXAS INSTR INC

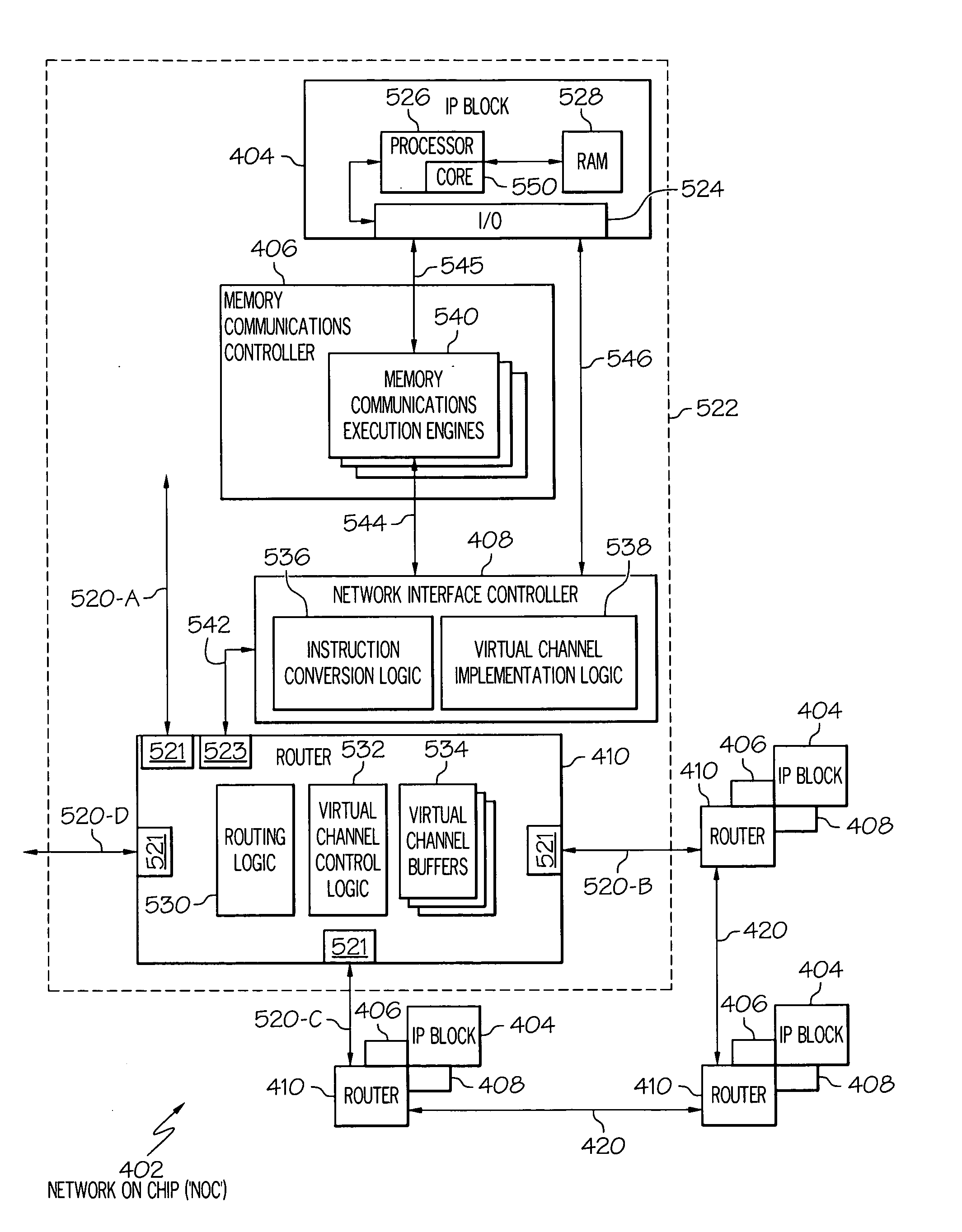

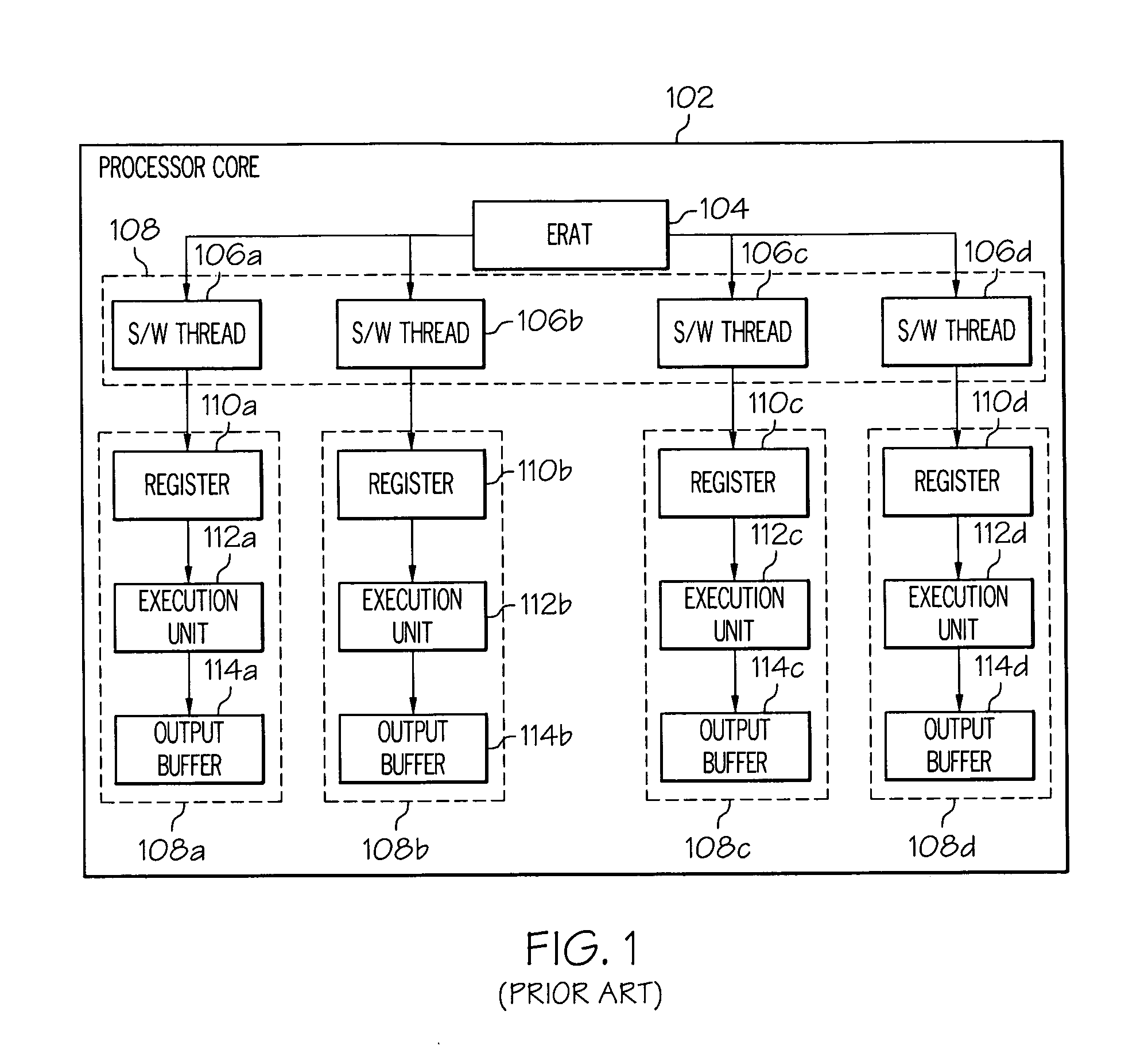

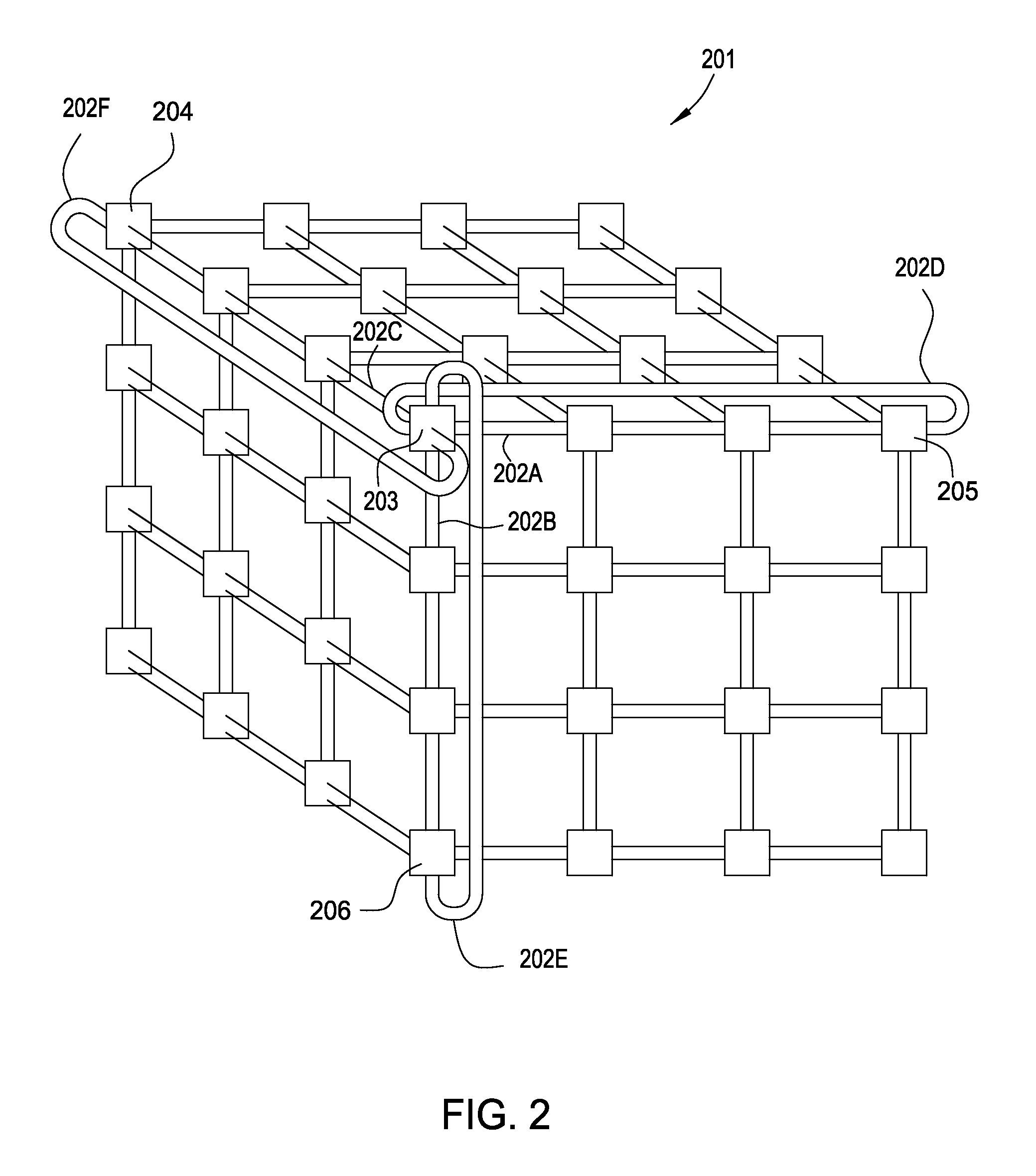

Software table walk during test verification of a simulated densely threaded network on a chip

ActiveUS20100223505A1Error detection/correctionAnalogue computers for electric apparatusParallel computingNetwork on

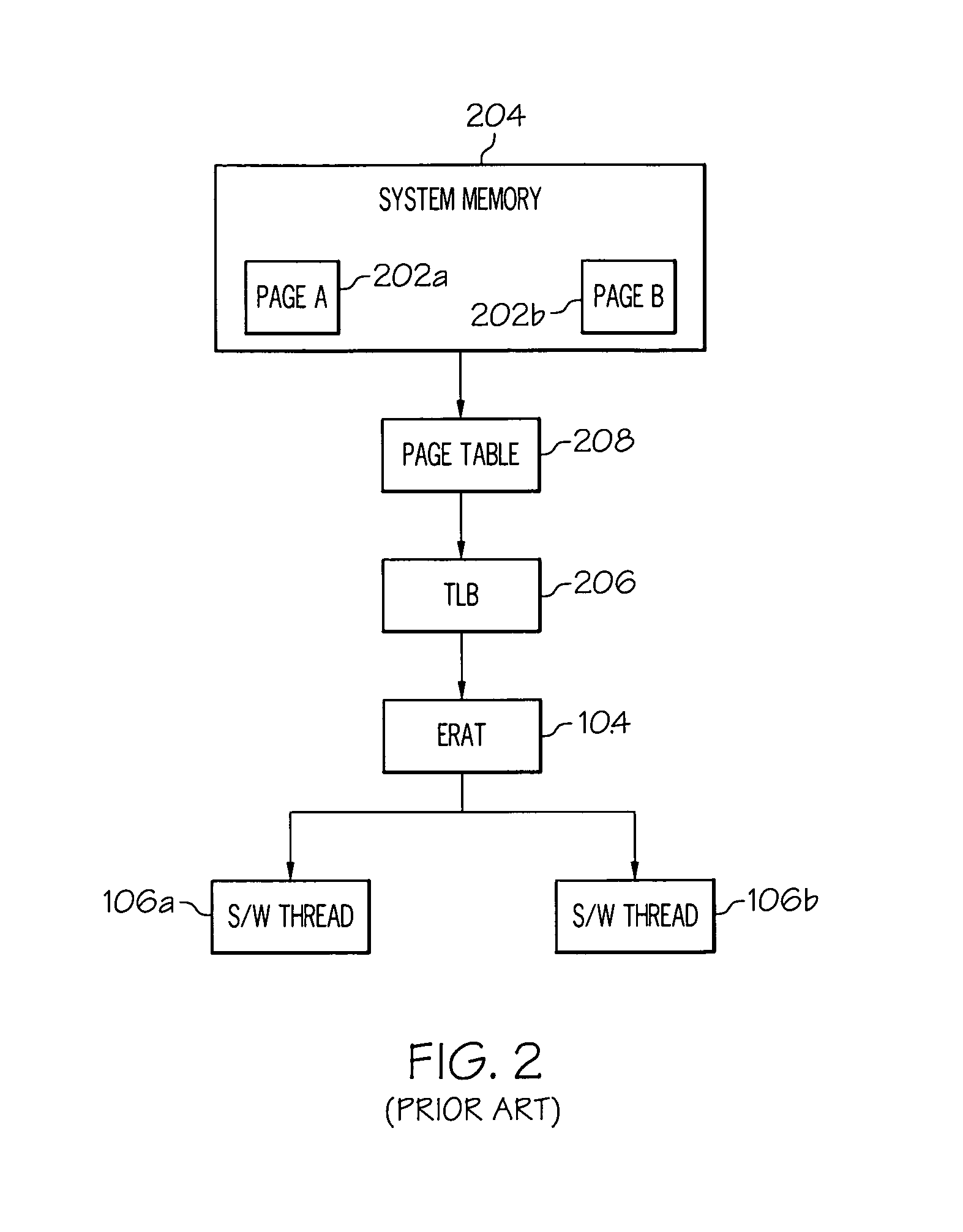

A computer-implemented method, system and computer program product are presented for managing an Effective-to-Real Address Table (ERAT) and a Translation Lookaside Buffer (TLB) during test verification in a simulated densely threaded Network On a Chip (NOC). The ERAT and TLB are stripped out of the computer simulation before executing a test program. When the test program experiences an inevitable ERAT-miss and / or TLB-miss, an interrupt handler walks a page table until the requisite page for re-populating the ERAT and TLB is located.

Owner:GLOBALFOUNDRIES US INC

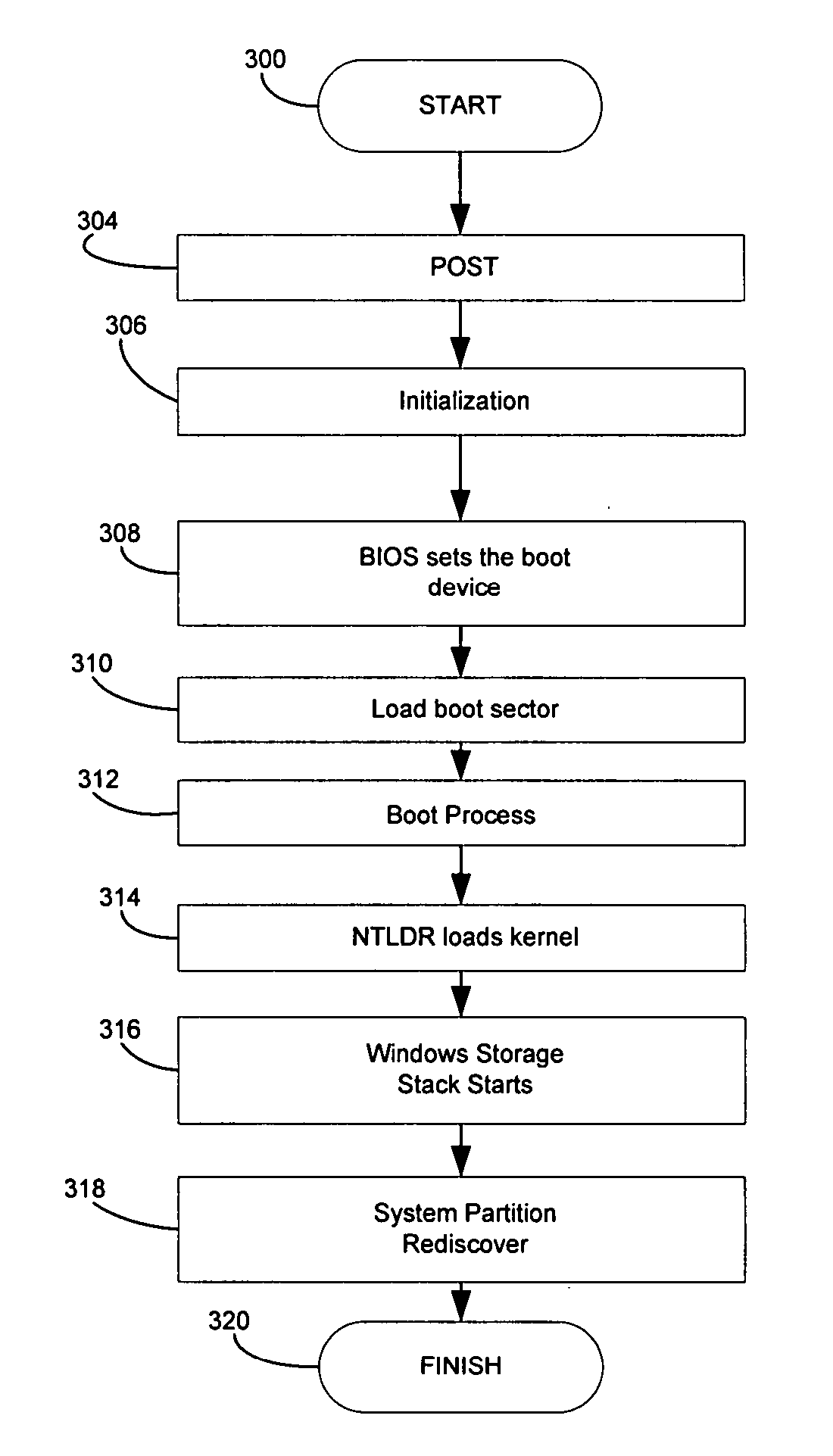

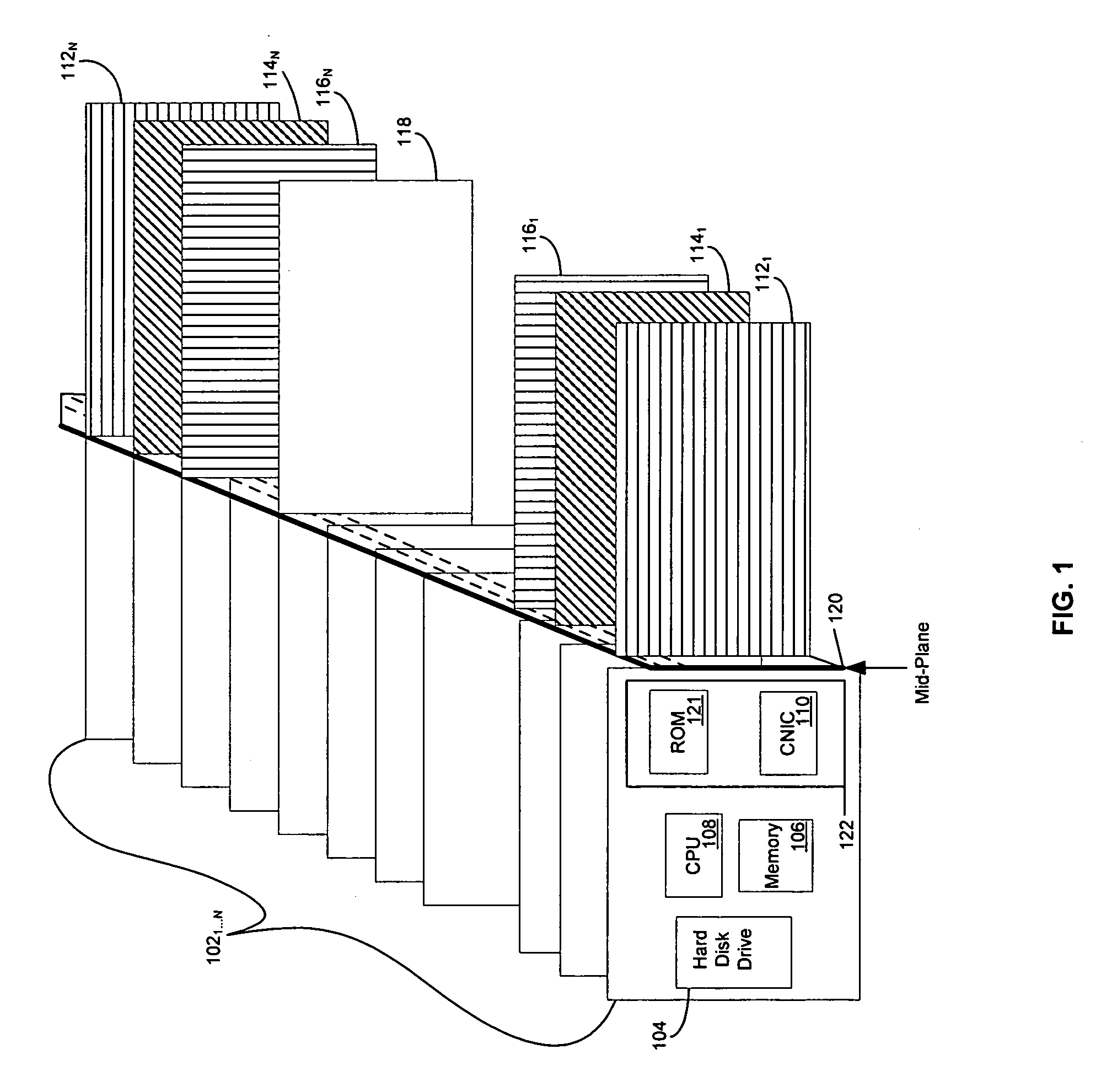

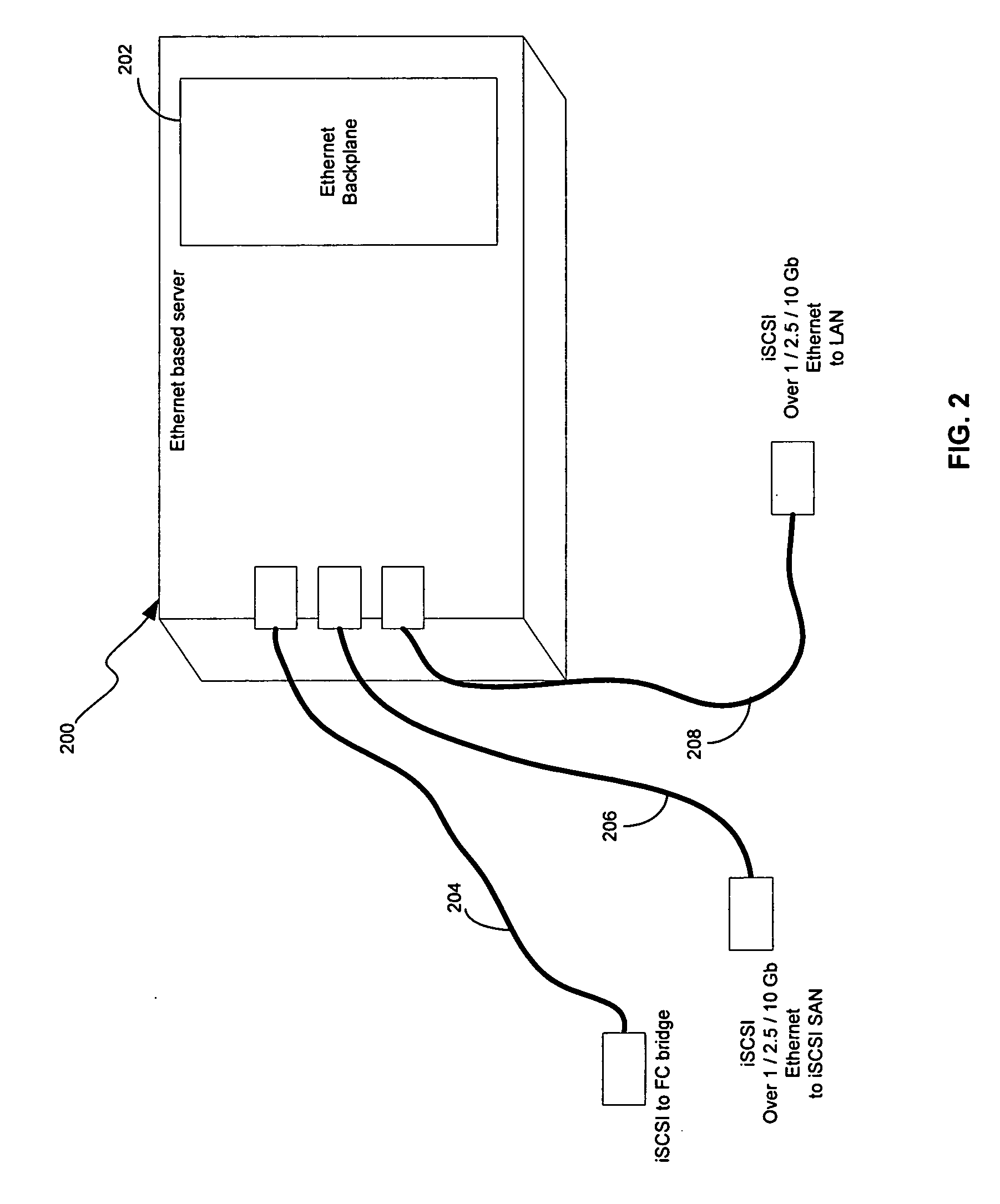

Method and system for iSCSl boot

Certain aspects of a method for iSCSI boot may include loading boot BIOS code from a host bus adapter or a network interface controller (NIC) by an iSCSI client device. A connection may be established to an iSCSI target by the iSCSI client device after loading the boot BIOS code. The boot BIOS code may be chained to at least one interrupt handler over iSCSI protocol. An operating system may be remotely booted from the iSCSI target by the iSCSI client device based on chaining the interrupt handler. An Internet protocol (IP) address and / or location of the iSCSI target may be received. At least one iSCSI connection may be initiated to the iSCSI target based on chaining at least one interrupt handler. The iSCSI target may be booted in real mode if at least one master boot record is located in the memory.

Owner:AVAGO TECH INT SALES PTE LTD

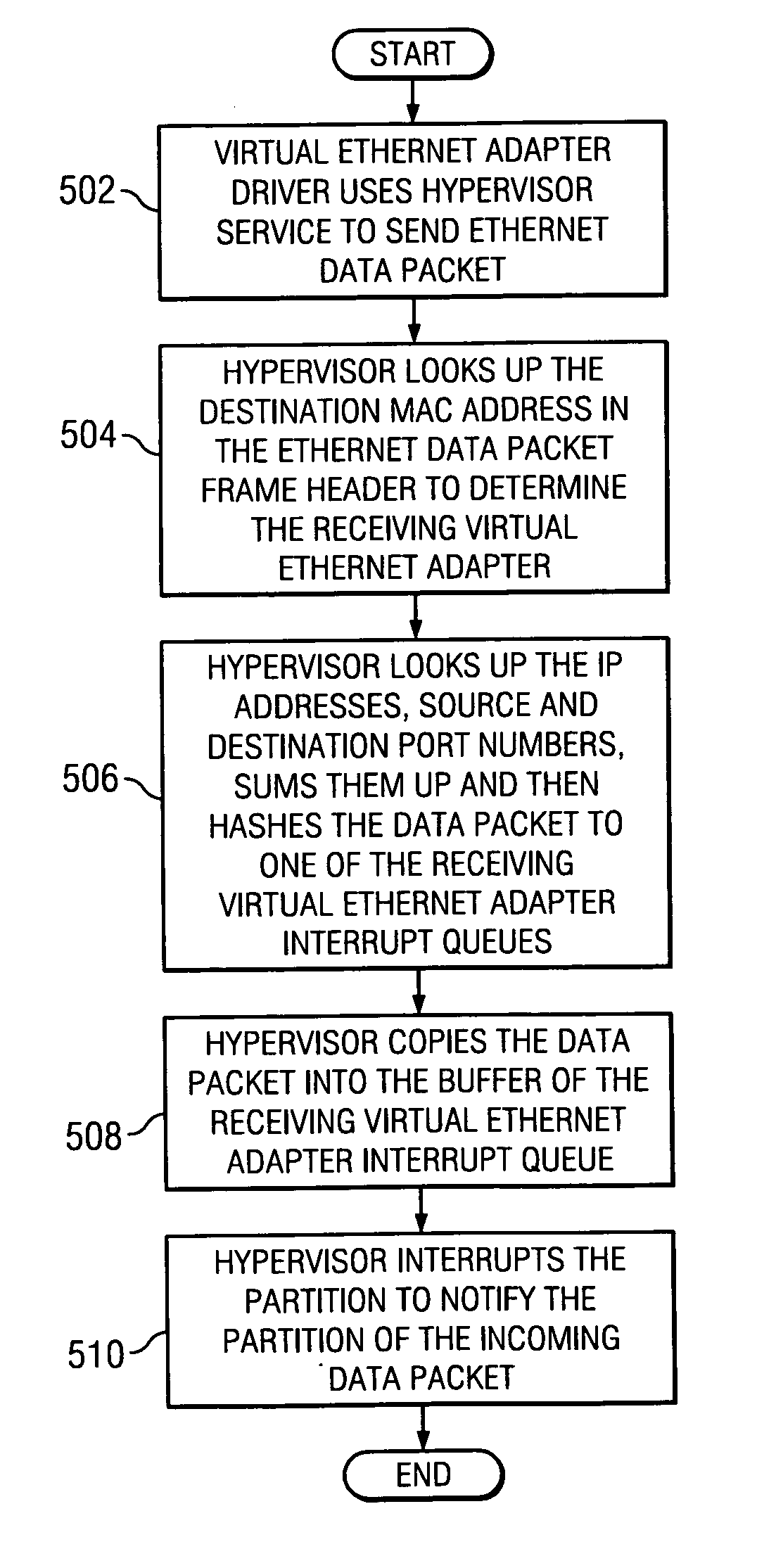

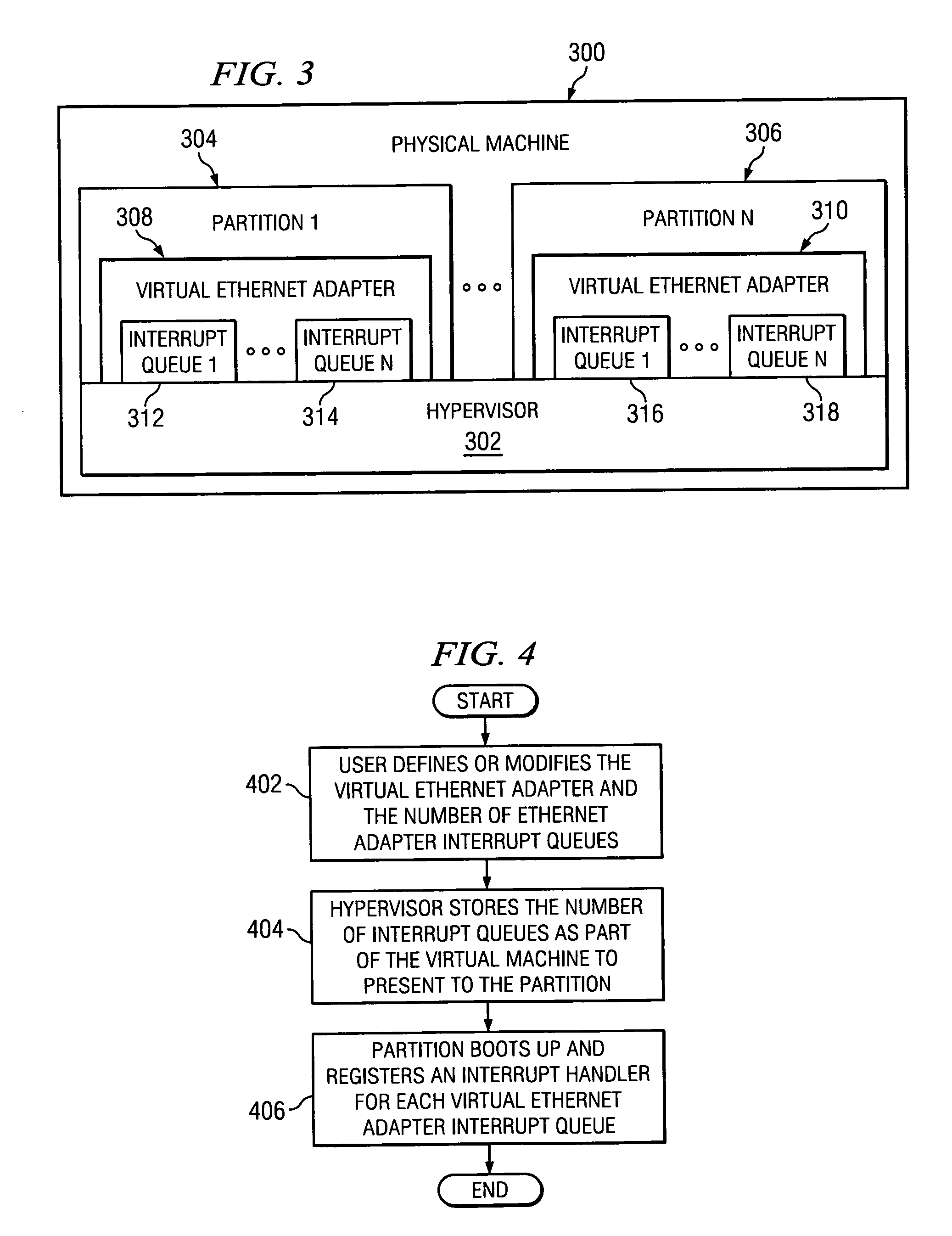

Method for improved virtual adapter performance using multiple virtual interrupts

InactiveUS20070168525A1Multiple digital computer combinationsProgram controlData packInterrupt handler

The present invention provides a computer implemented method, apparatus, and computer usable program code for processing multiple interrupts for multiple packets concurrently. First, data packets are assigned one of a set of interrupt queues for a virtual adapter in response to detecting the data packets. Each of the interrupt queues is processed by one of a set of interrupt threads for executing an interrupt handler. Next, an interrupt is dispatched for each of the interrupt queues receiving the data packets. The data packets in the interrupt queues are concurrently processed by one of the set of interrupt threads.

Owner:MACHINES CORP INT BUSINESS

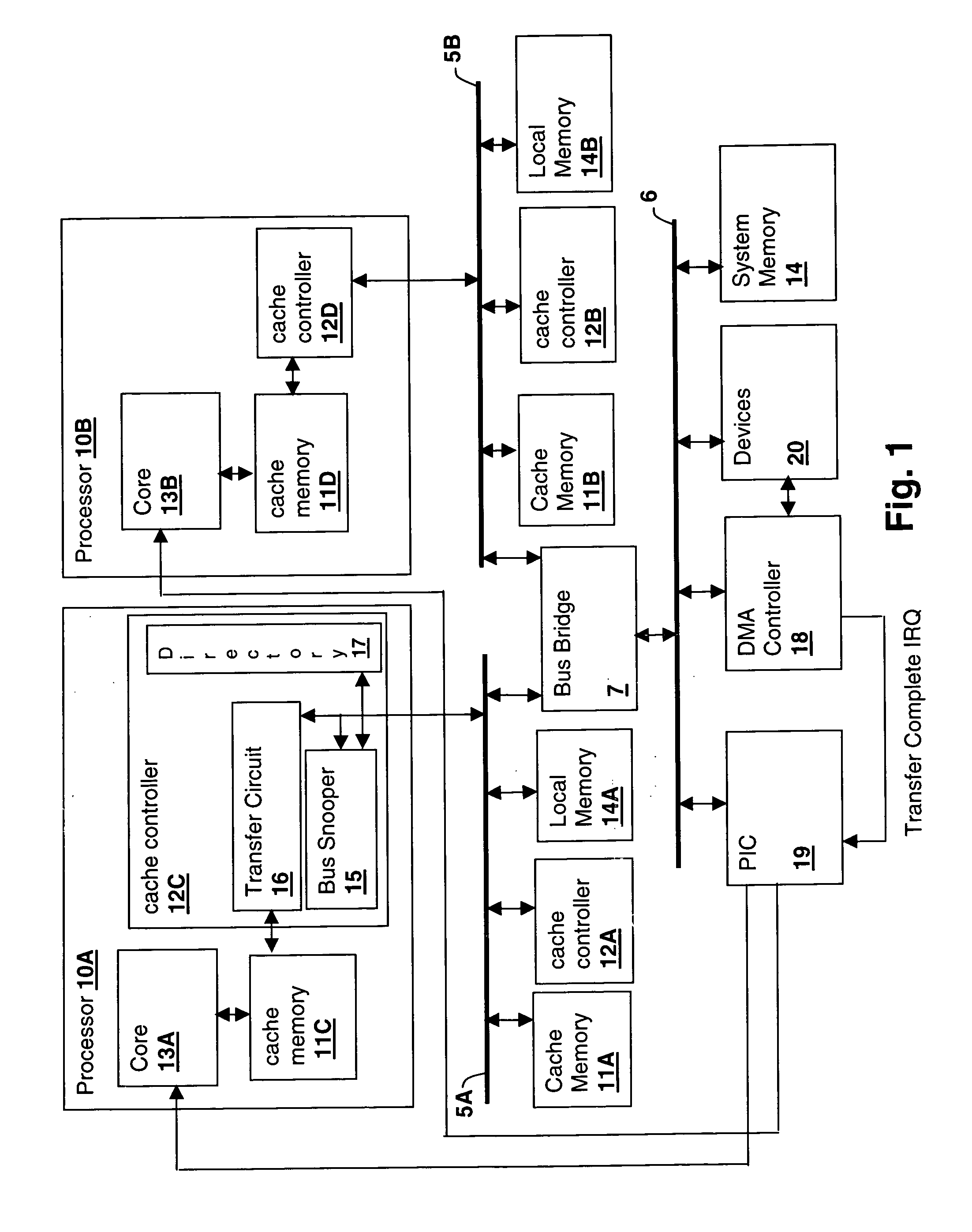

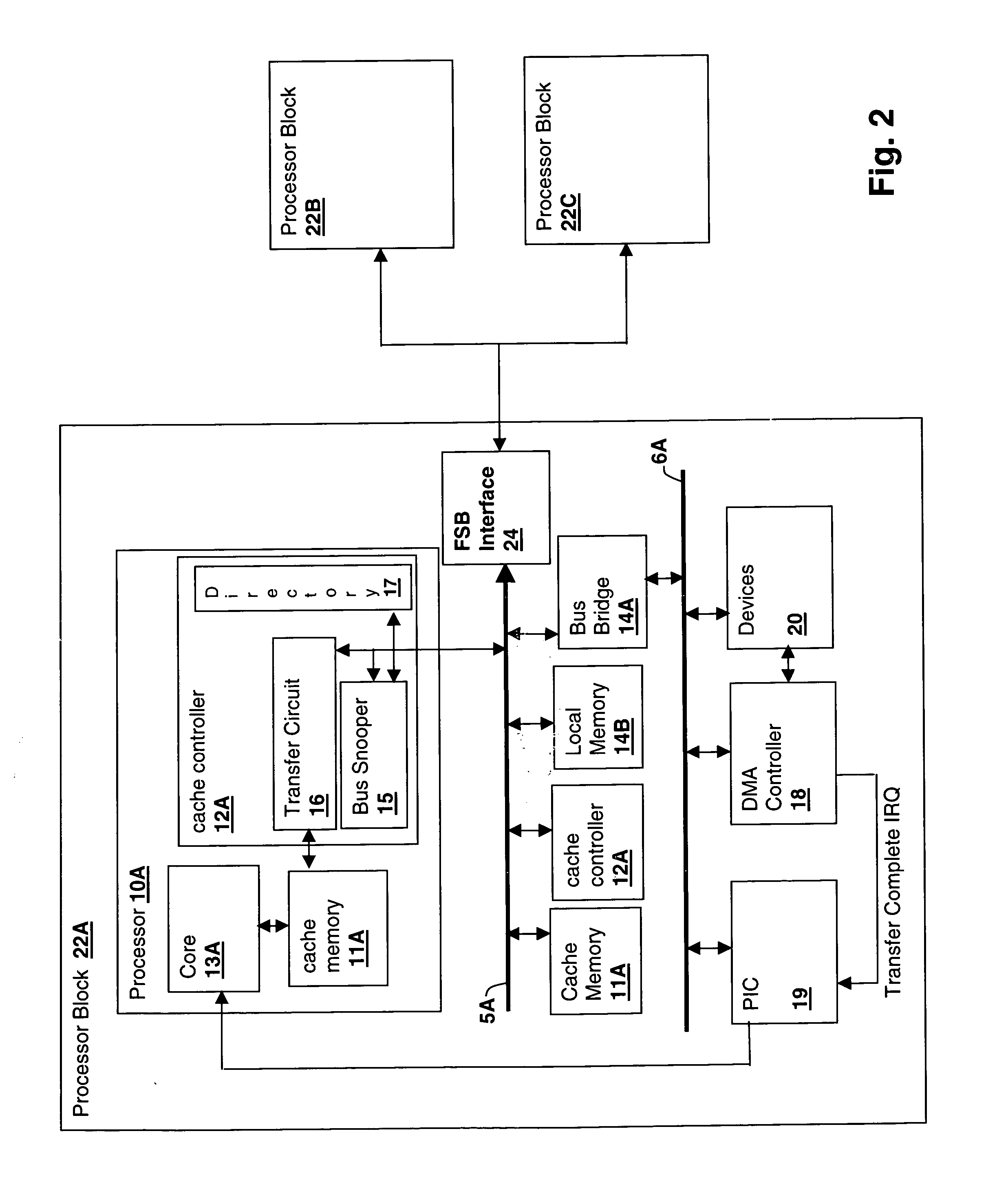

Method and system for managing cache injection in a multiprocessor system

A method and apparatus for managing cache injection in a multiprocessor system reduces processing time associated with direct memory access transfers in a symmetrical multiprocessor (SMP) or a non-uniform memory access (NUMA) multiprocessor environment. The method and apparatus either detect the target processor for DMA completion or direct processing of DMA completion to a particular processor, thereby enabling cache injection to a cache that is coupled with processor that executes the DMA completion routine processing the data injected into the cache. The target processor may be identified by determining the processor handling the interrupt that occurs on completion of the DMA transfer. Alternatively or in conjunction with target processor identification, an interrupt handler may queue a deferred procedure call to the target processor to process the transferred data. In NUMA multiprocessor systems, the completing processor / target memory is chosen for accessibility of the target memory to the processor and associated cache.

Owner:IBM CORP

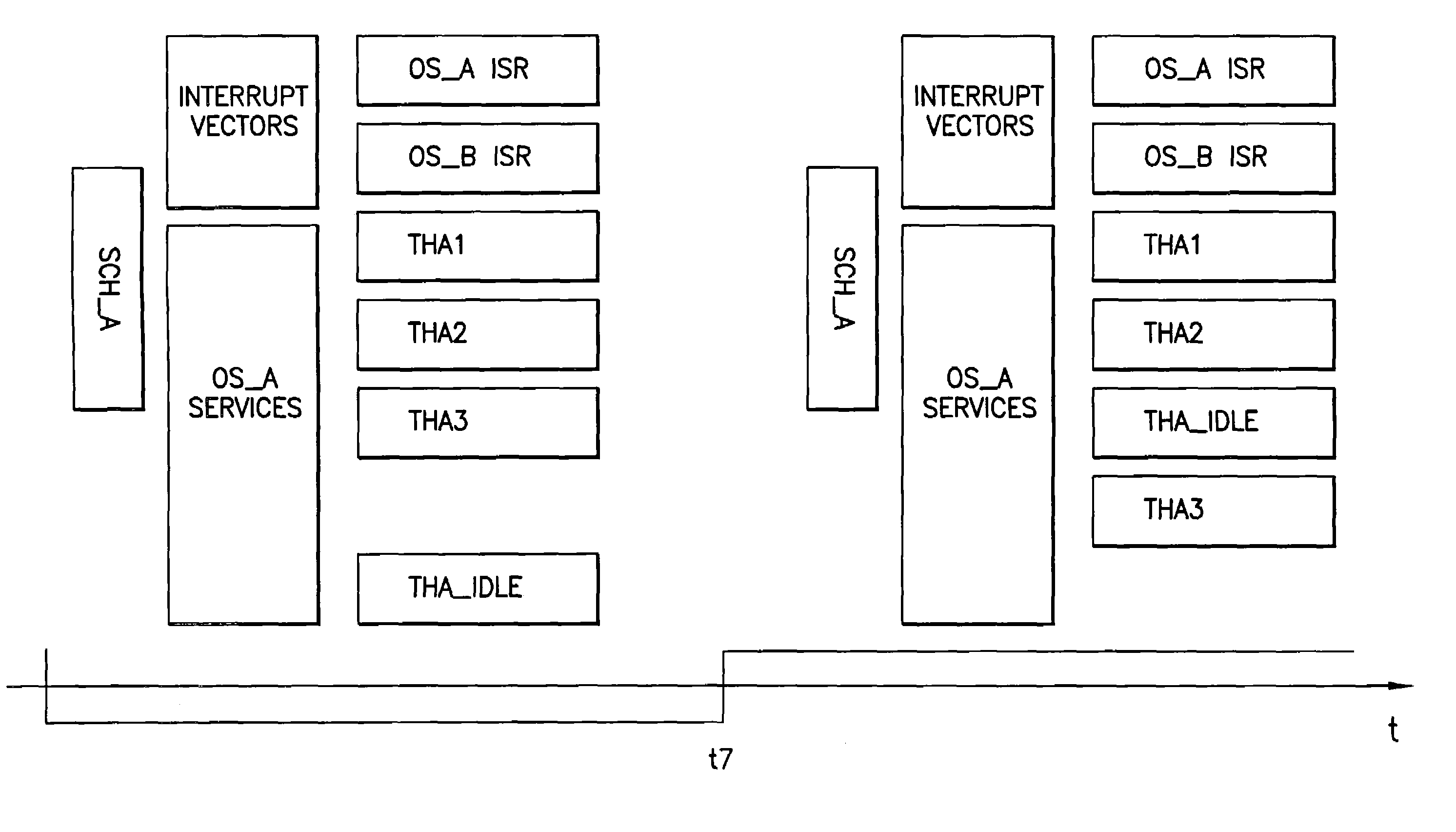

Embedded system with interrupt handler for multiple operating systems

InactiveUS7062766B2Reduces need for spaceReduce workloadProgram initiation/switchingBootstrappingOperational systemMobile station

A communication device includes one processor to run at least two operating systems simultaneously. The at least two operating systems include a first operating system for mobile station functions having a first group of threads, the mobile station functions including operations for communicating with another device, and a second operating system for data processing functions having a second group of threads, the data processing functions including operations for processing data internally in the communication device, where the operating systems communicate with each other. The communication device further includes at least one user interface, provides for generating an interrupt, provides for selecting a thread to execute as a result of the interrupt including a common interrupt handler for the at least two operating systems, and provides for transmitting interrupt data to the operating system from which the thread was selected, including the thread to execute.

Owner:WSOU INVESTMENTS LLC

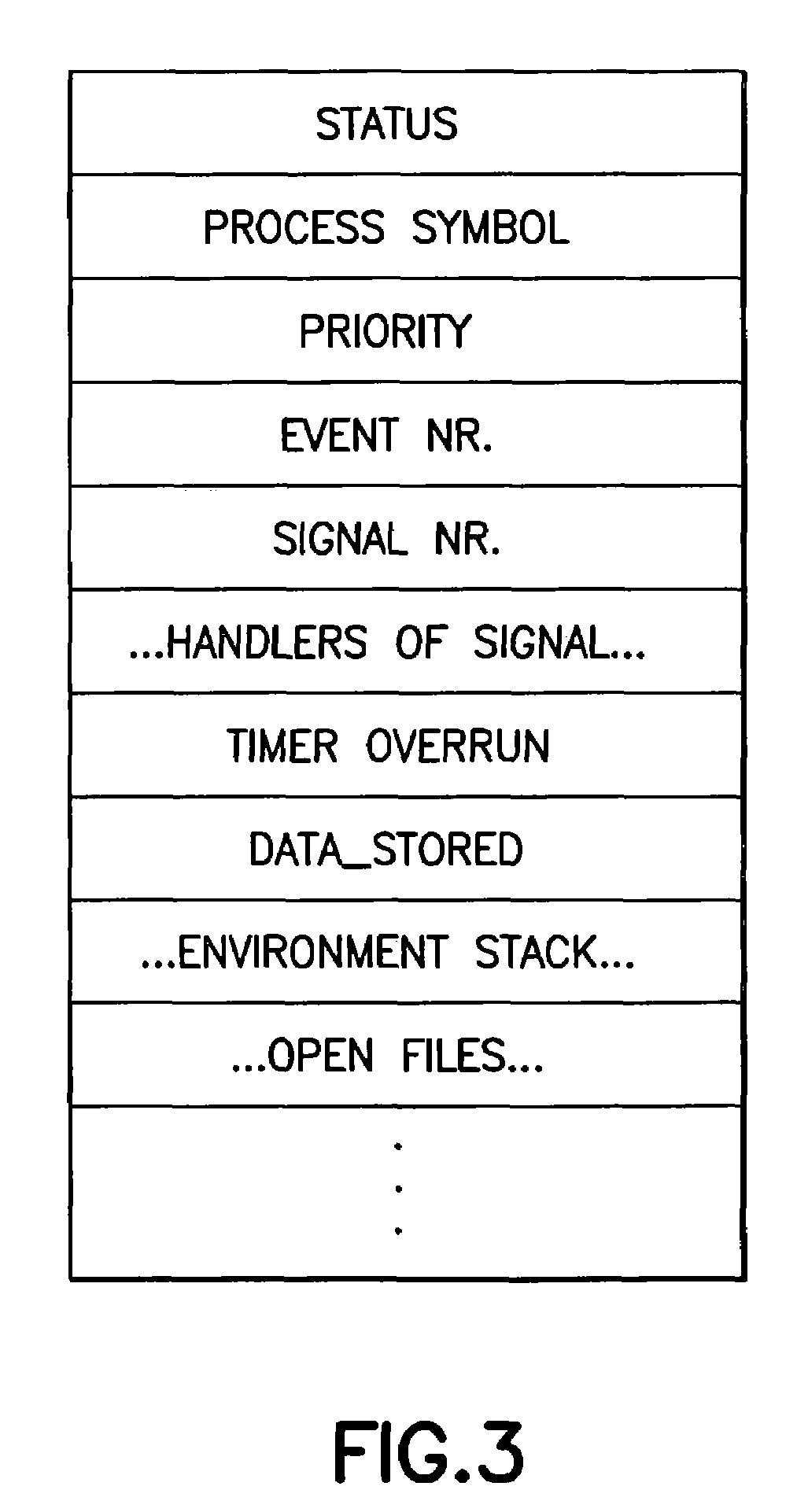

Method, system and device for handling a memory management fault in a multiple processor device

ActiveUS7681012B2Memory architecture accessing/allocationError detection/correctionManagement unitMulti processor

A method or device handles memory management faults in a device having a digital signal processor (“DSP”) and a microprocessor. The DSP includes a memory management unit (“DSP MMU”) to manage memory access by the DSP, and the DSP and the microprocessor access shared physical memory. Upon the DSP executing an instruction attempting to access a virtual address wherein the virtual address is invalid, a page fault interrupt is generated by the DSP MMU. A microprocessor interrupt handler in the microprocessor is activated in direct response to the page fault interrupt. Thereafter in the microprocessor, a translation lookaside buffer (“TLB”) entry is created in the DSP MMU, which includes a valid mapping between the virtual address and a page of physical memory. After creating the TLB entry, the microprocessor indicates to the DSP that the access by the DSP of the virtual address is completed.

Owner:TEXAS INSTR INC

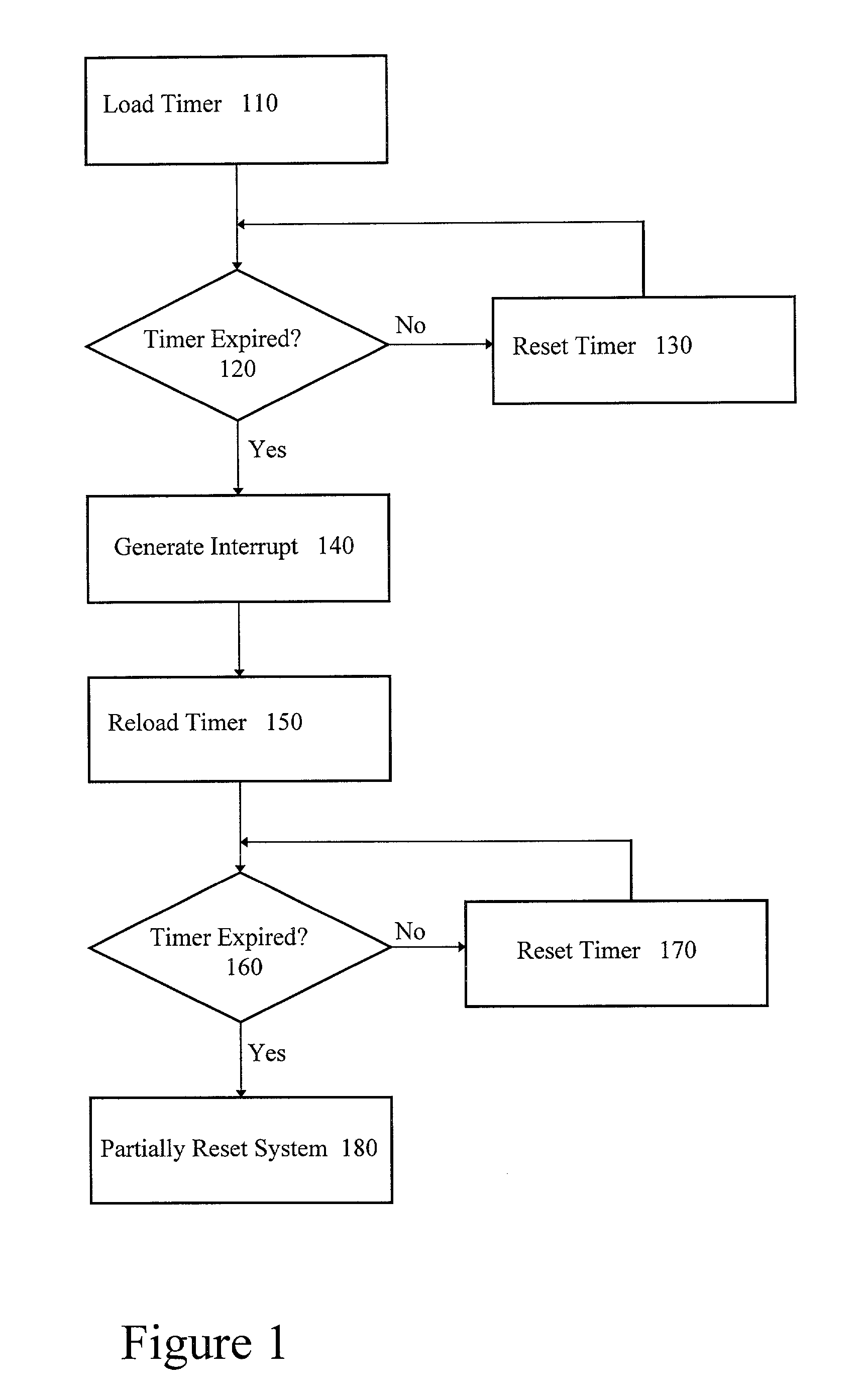

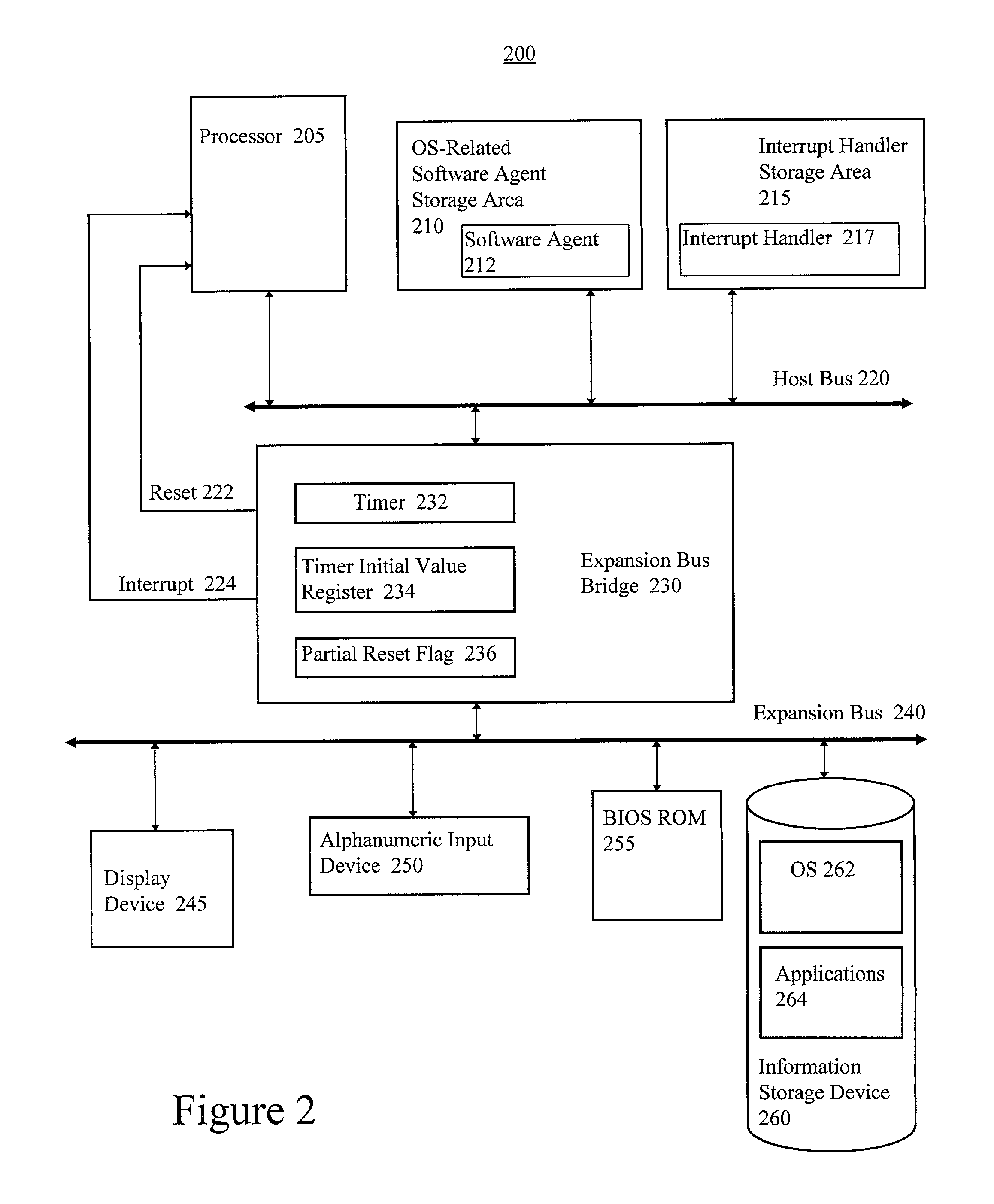

Method for recovering from computer system lockup condition

InactiveUS6438709B2Error detection/correctionDigital computer detailsOperational systemComputerized system

Owner:INTEL CORP

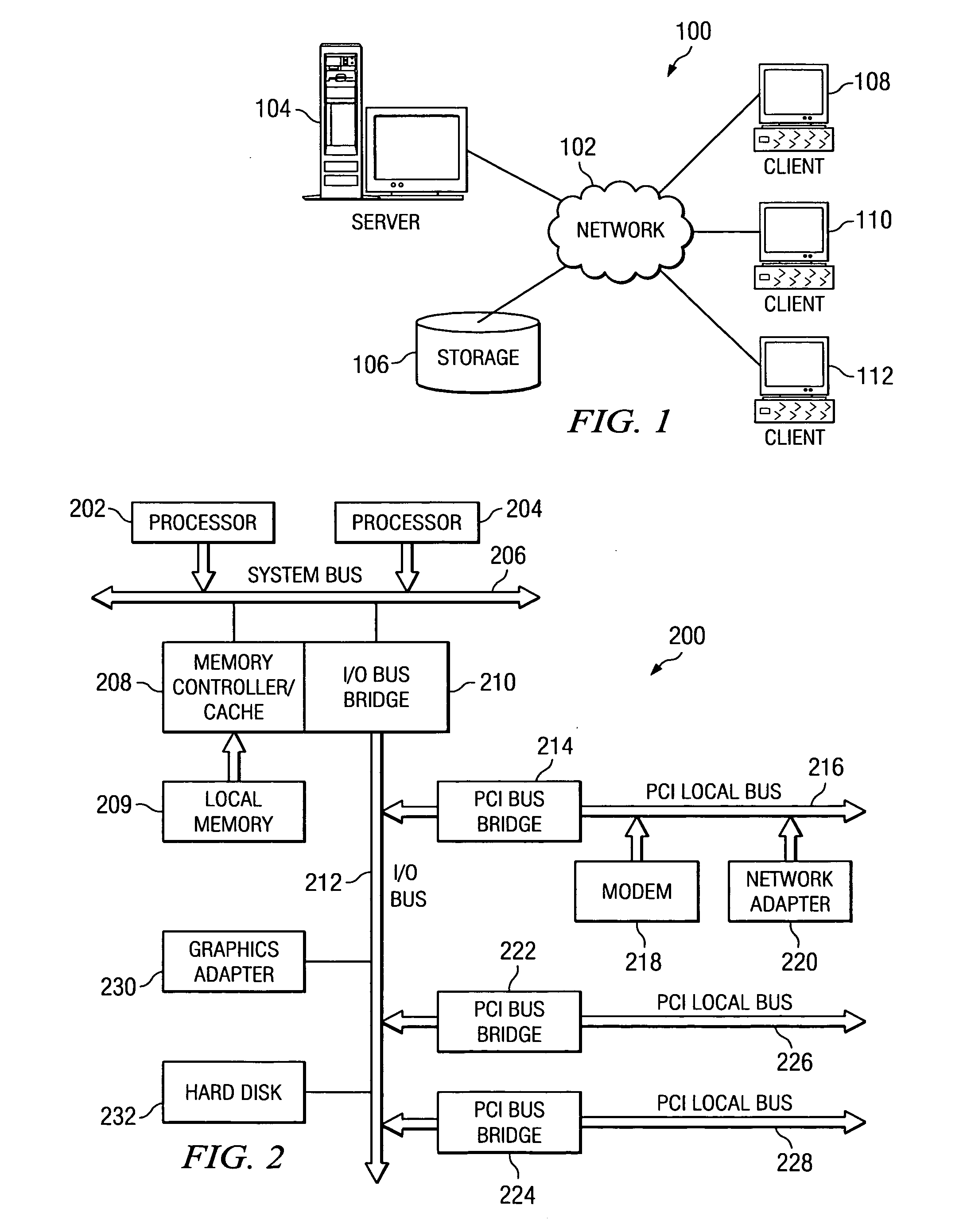

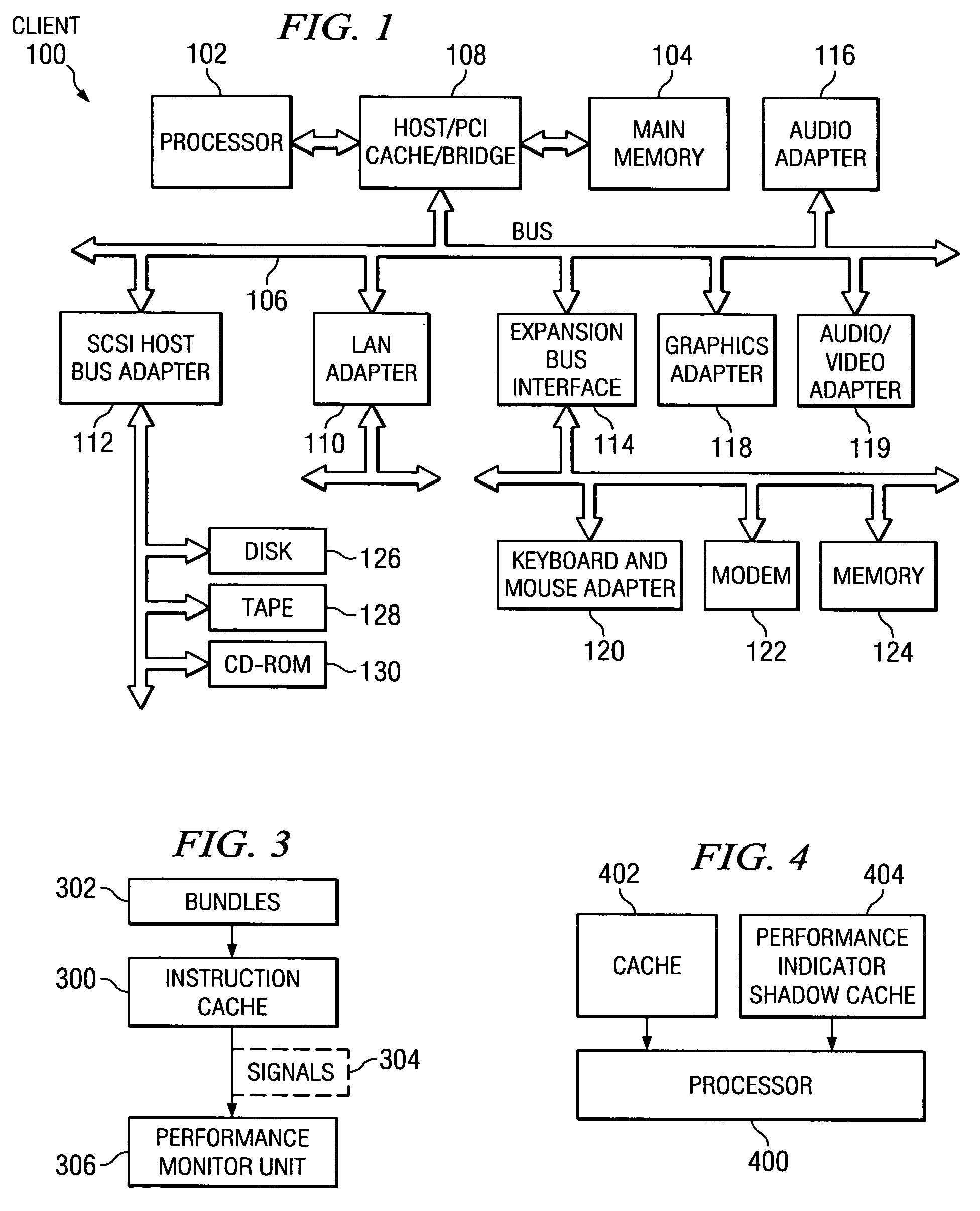

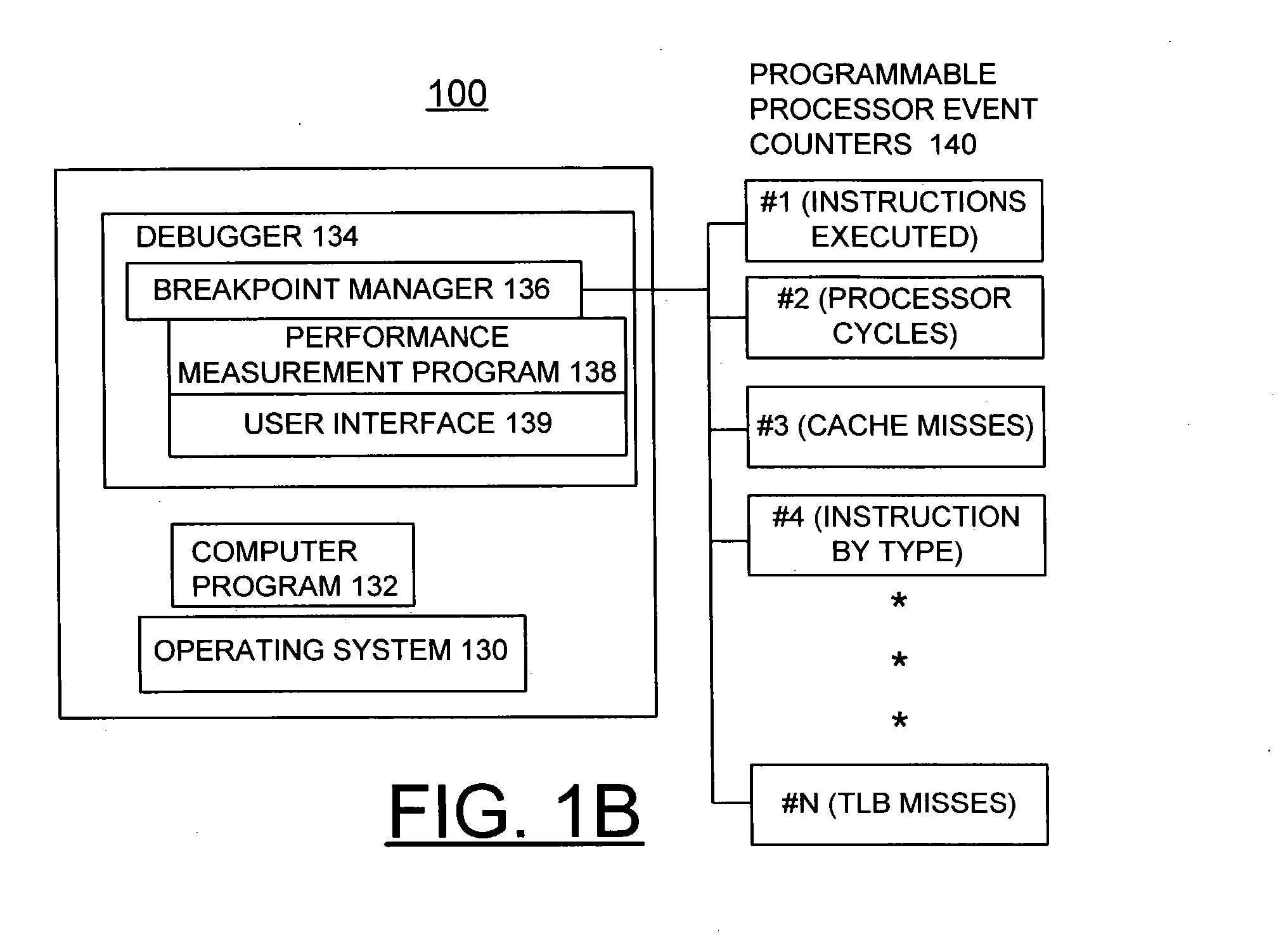

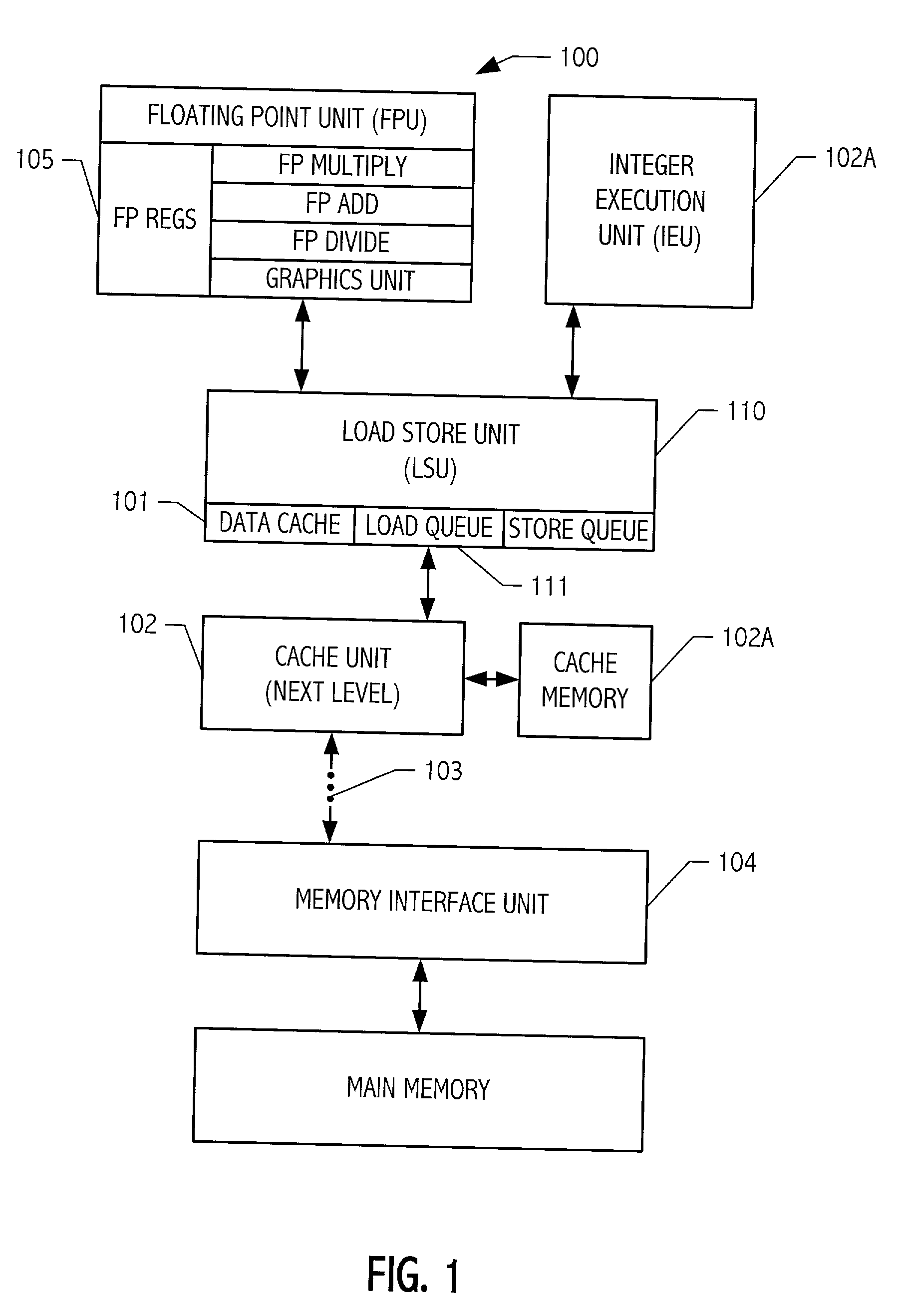

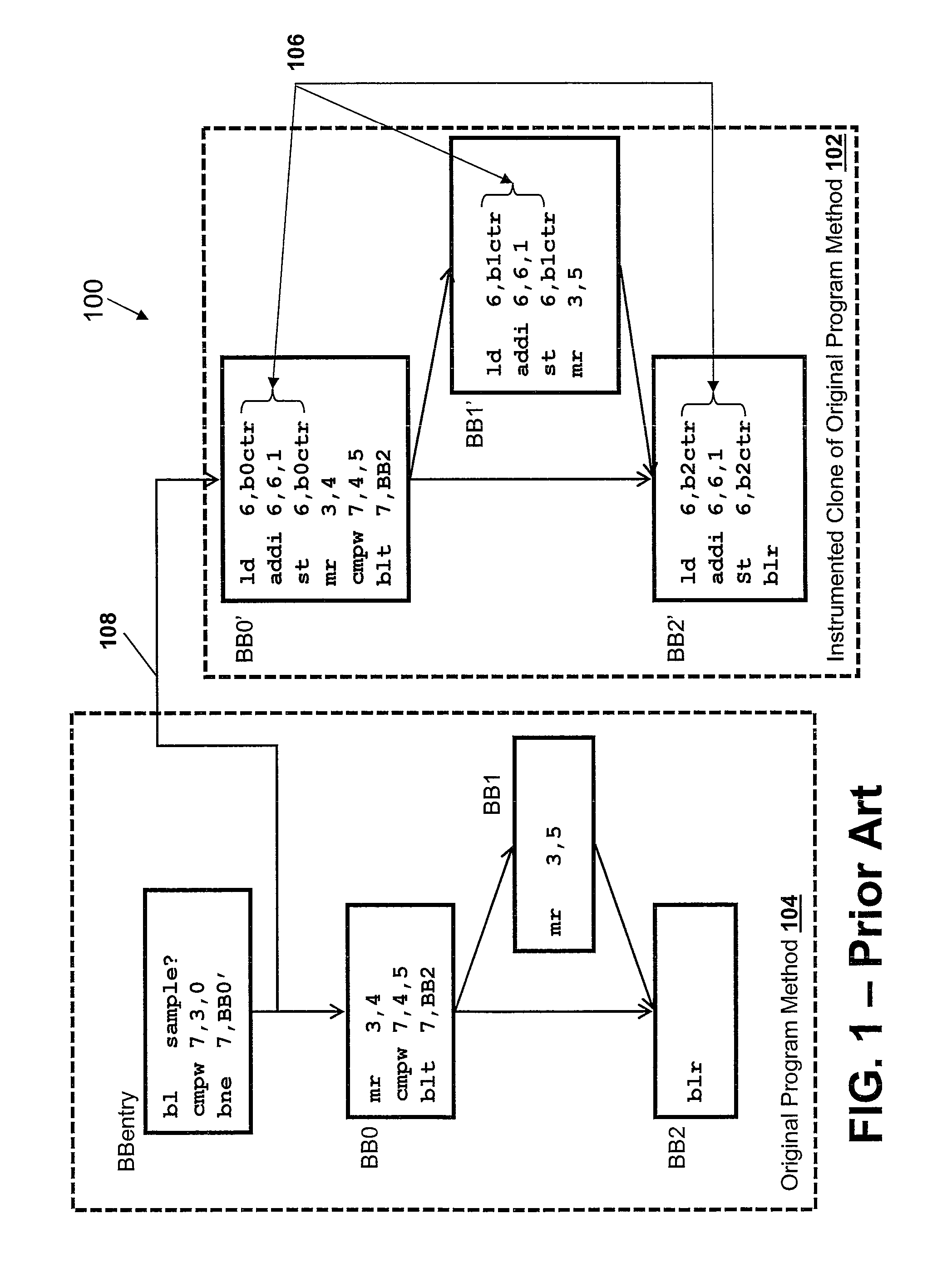

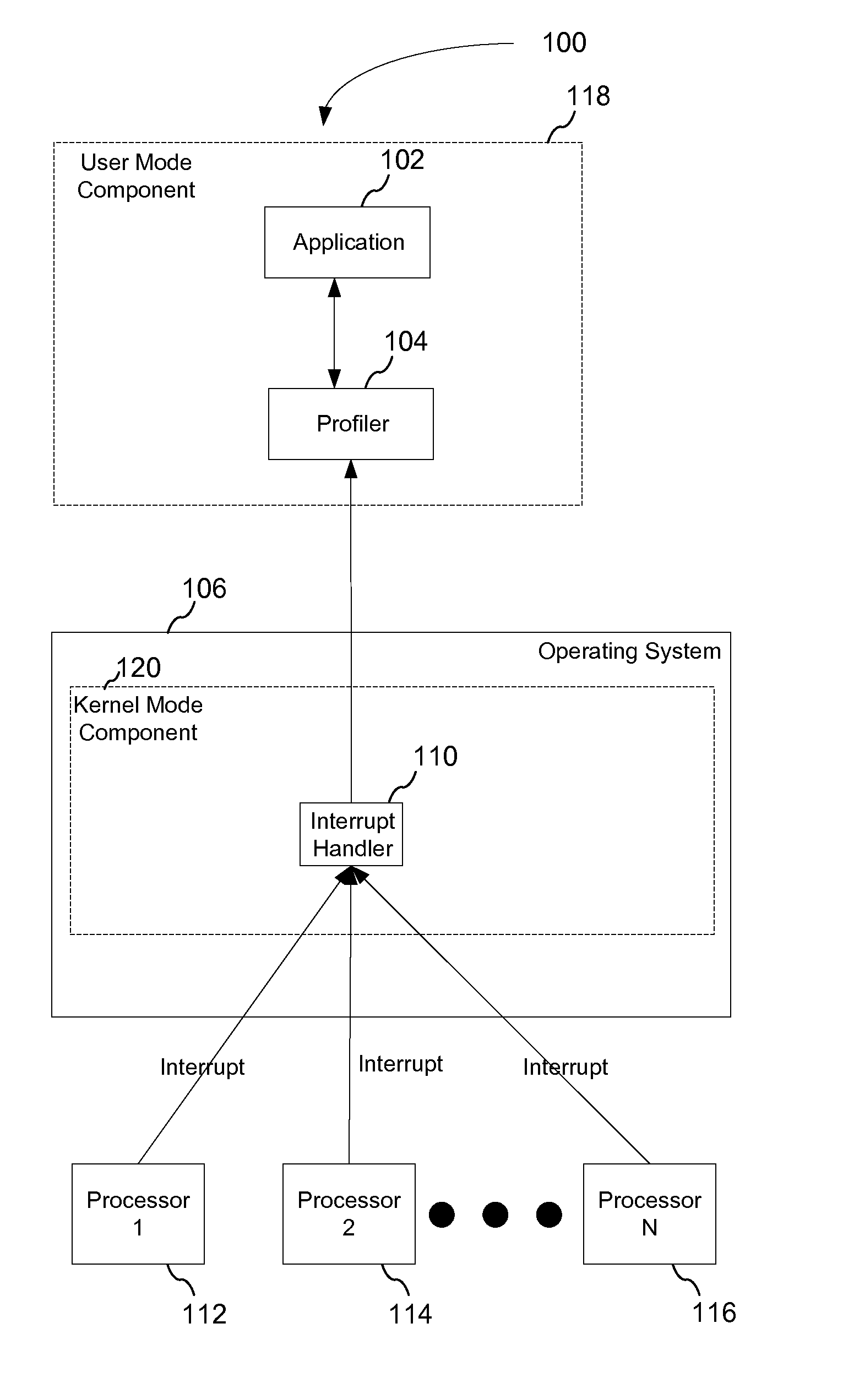

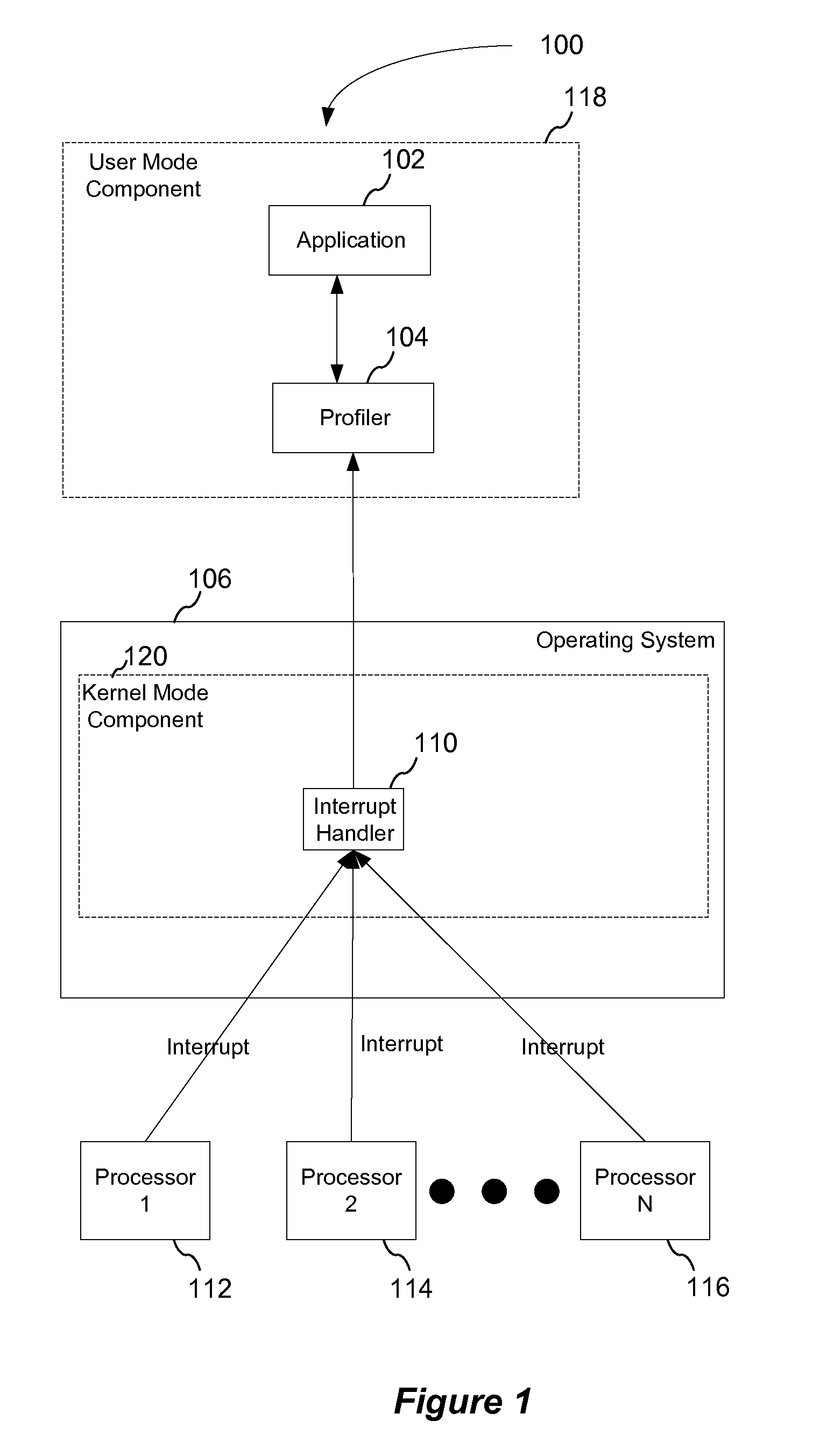

Instruction profiling using multiple metrics

InactiveUS20060230390A1Error detection/correctionSpecific program execution arrangementsInterrupt handlerComputer program

A system and method for collecting a plurality of metrics during a single run of a computer program. The mechanism of the present invention initializes a plurality of counters to count events associated with metrics of interest. The mechanism of the present invention then counts the occurrence of events associated with metrics of interest during a single execution of a computer program. Responsive to a determination that a counter in a plurality of counters has generated an interrupt, the interrupt is rerouted to an interrupt handler, wherein the interrupt handler generates trace records comprising trace information corresponding to the interrupt. The mechanism of the present invention then generates profiles for the trace records, wherein the profiles differentiate the trace records based on the metric type associated with each trace record.

Owner:IBM CORP

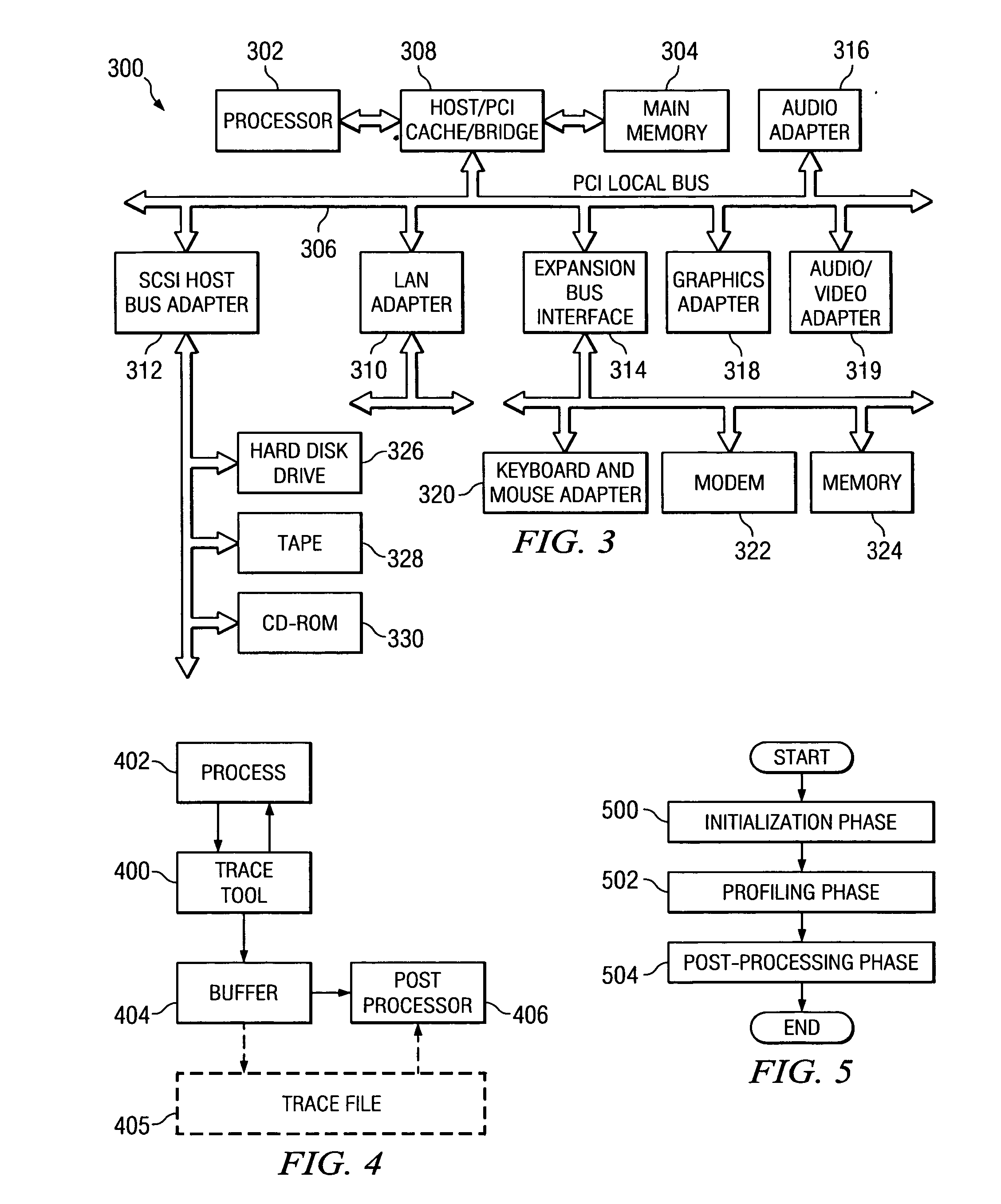

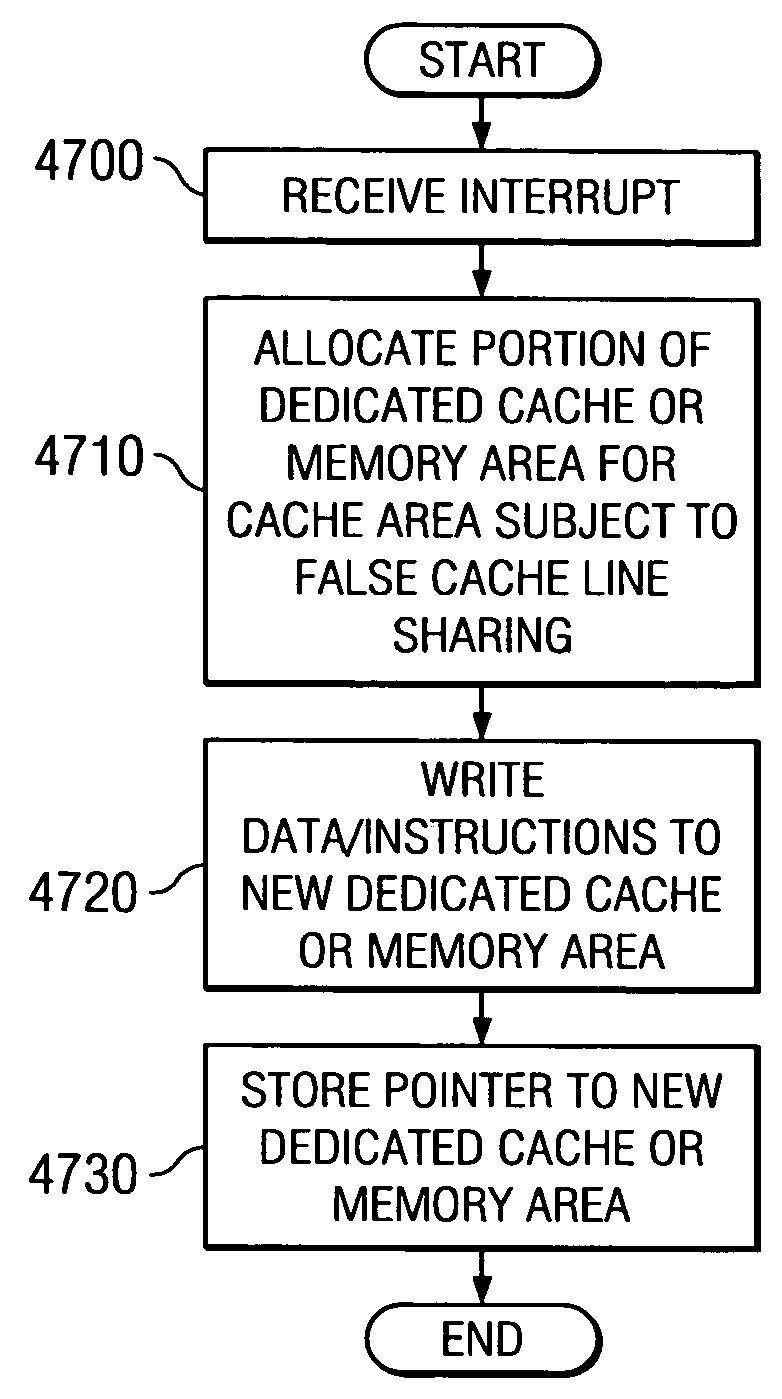

Method and apparatus for autonomically moving cache entries to dedicated storage when false cache line sharing is detected

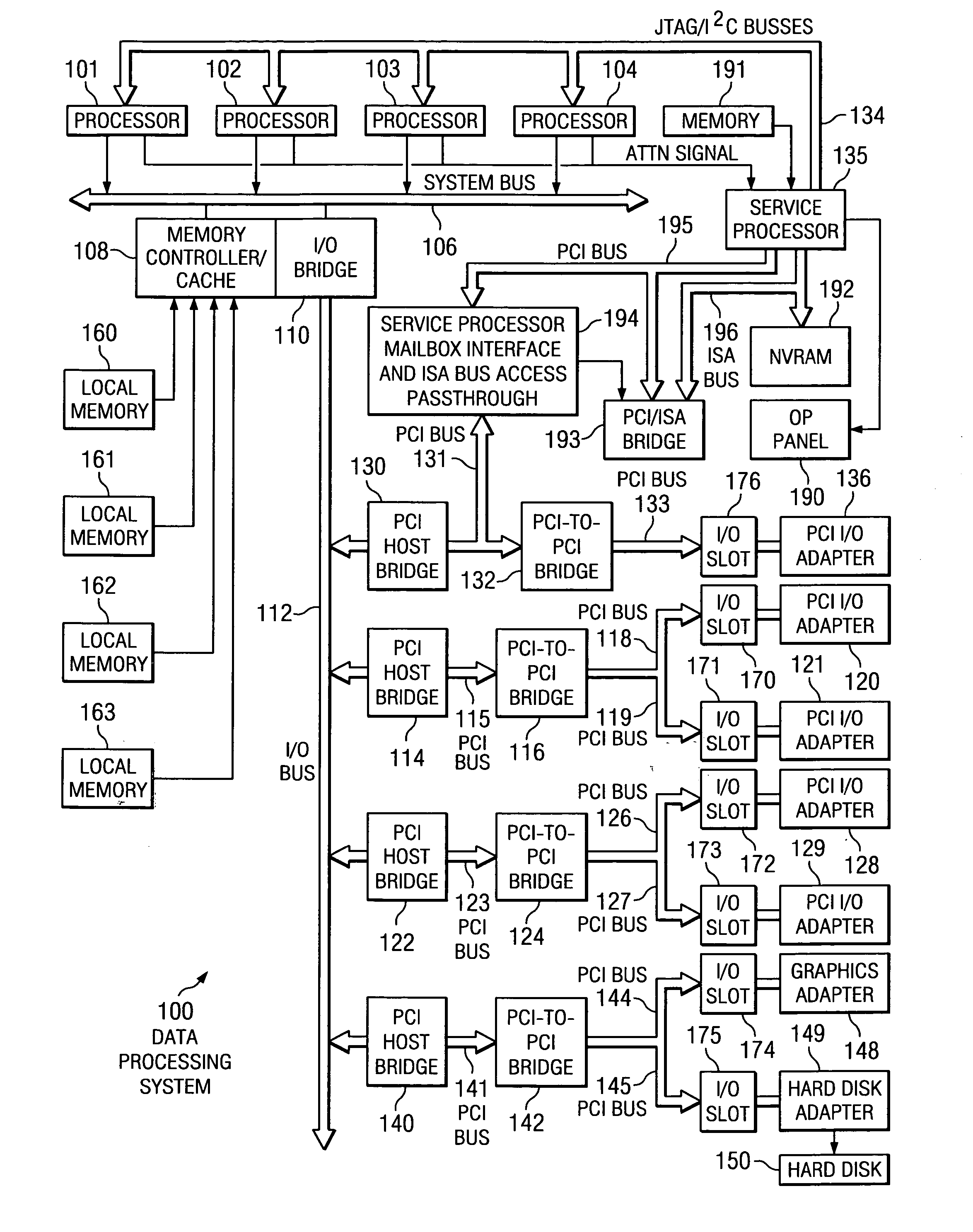

InactiveUS7114036B2Improve performanceMemory adressing/allocation/relocationDigital computer detailsData processing systemProcessing Instruction

A method, apparatus, and computer instructions in a data processing system for processing instructions are provided. Instructions are received at a processor in the data processing system. If a selected indicator is associated with the instruction, counting of each event associated with the execution of the instruction is enabled. In some embodiments, when it is determined that a cache line is being falsely shared using the performance indicators and counters, an interrupt may be generated and sent to a performance monitoring application. An interrupt handler of the performance monitoring application will recognize this interrupt as indicating false sharing of a cache line. Rather than reloading the cache line in a normal fashion, the data or instructions being accessed may be written to a separate area of cache or memory area dedicated to false cache line sharing data. The code may then be modified by inserting a pointer to this new area of cache or memory. Thus, when the code again attempts to access this area of the cache, the access is redirected to the new cache or memory area rather than to the previous area of the cache that was subject to false sharing. In this way, reloads of the cache line may be avoided.

Owner:IBM CORP

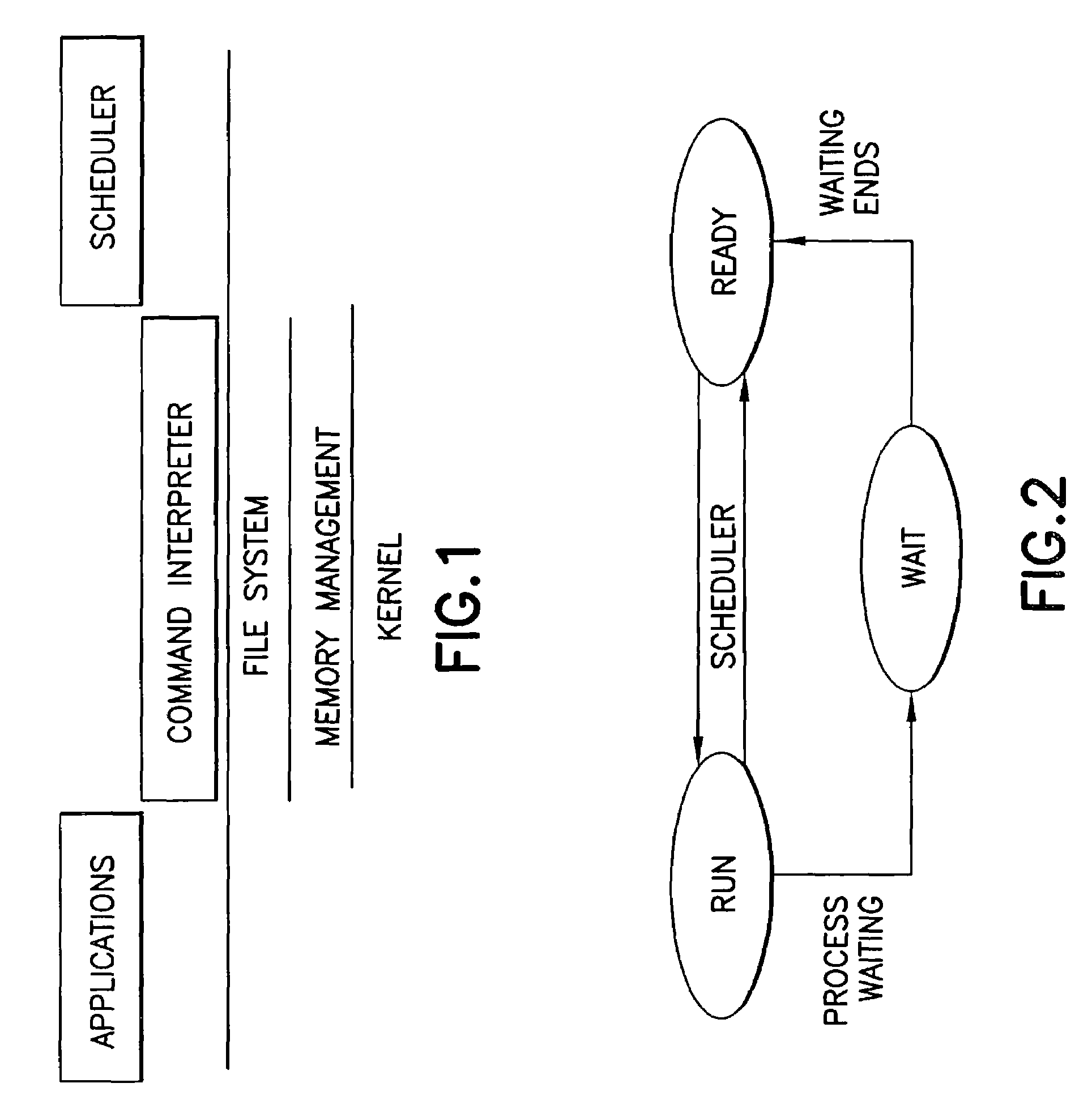

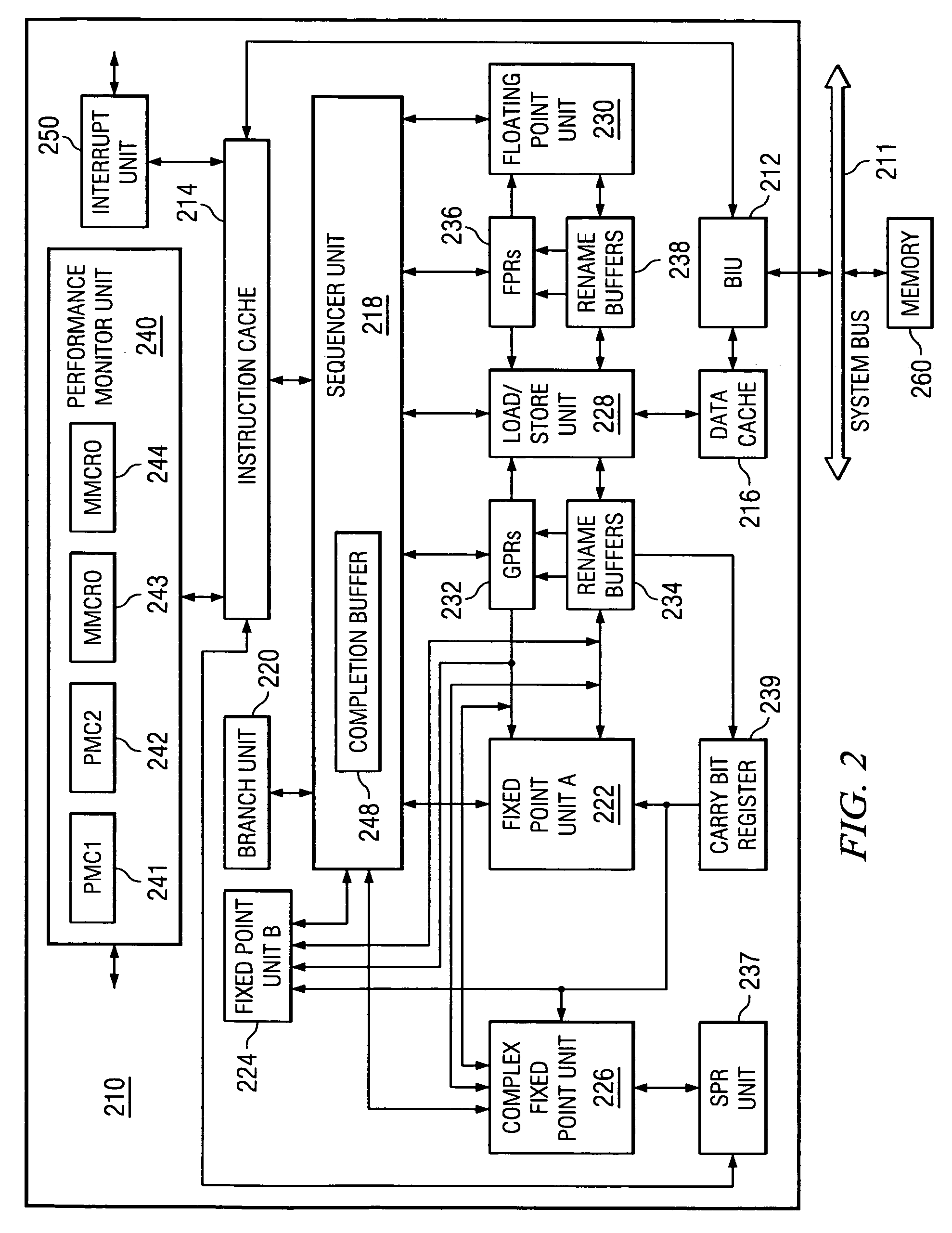

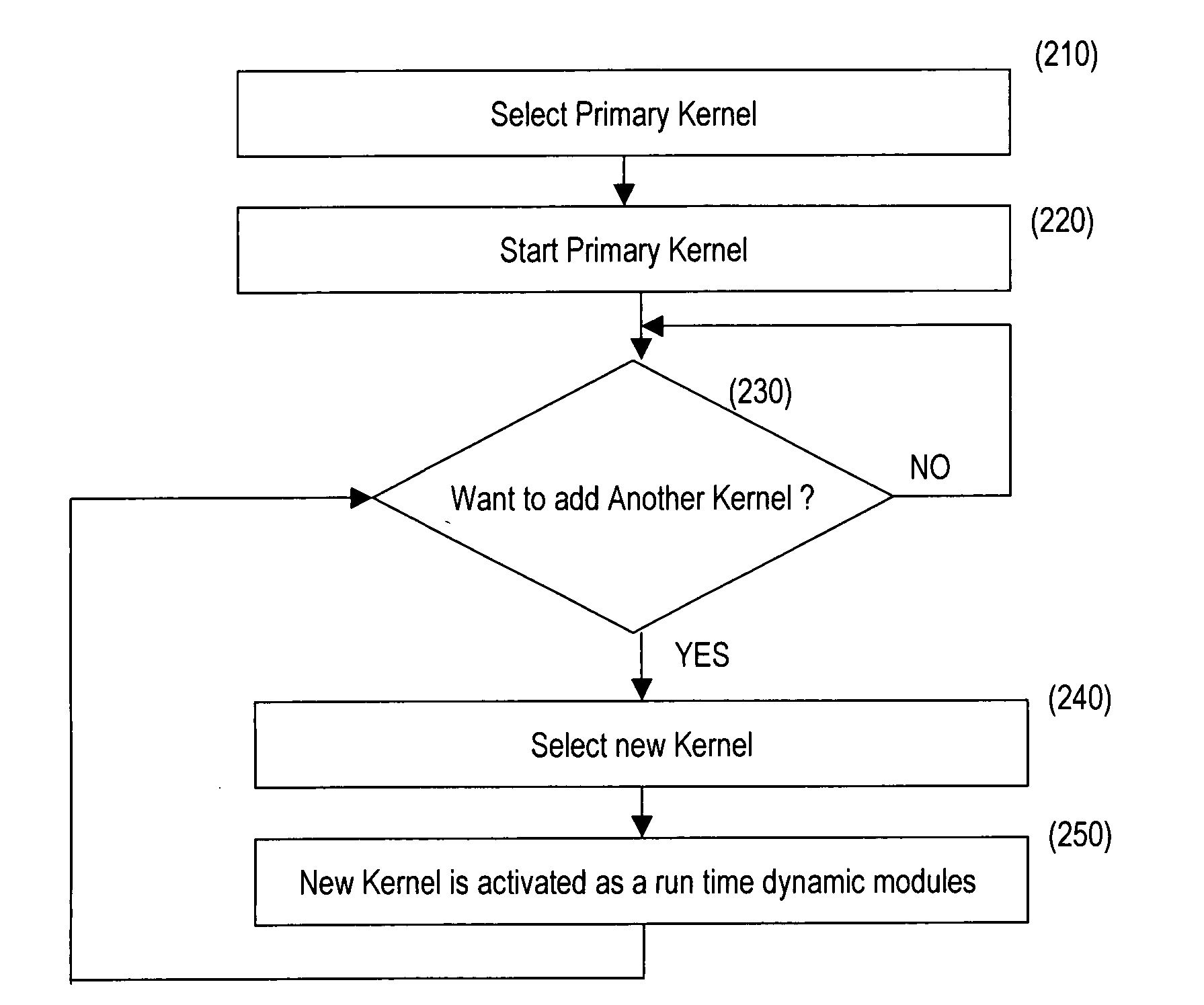

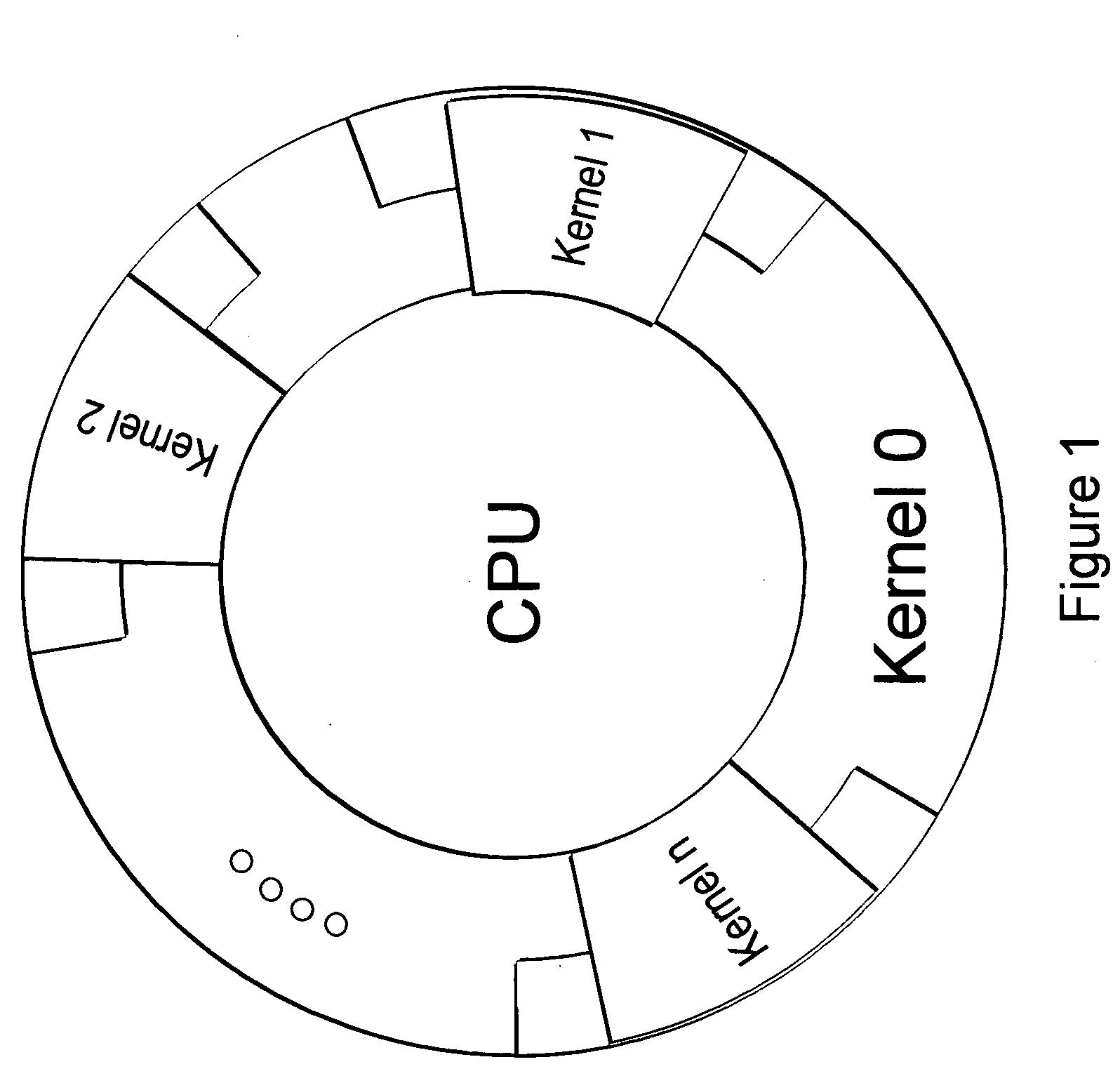

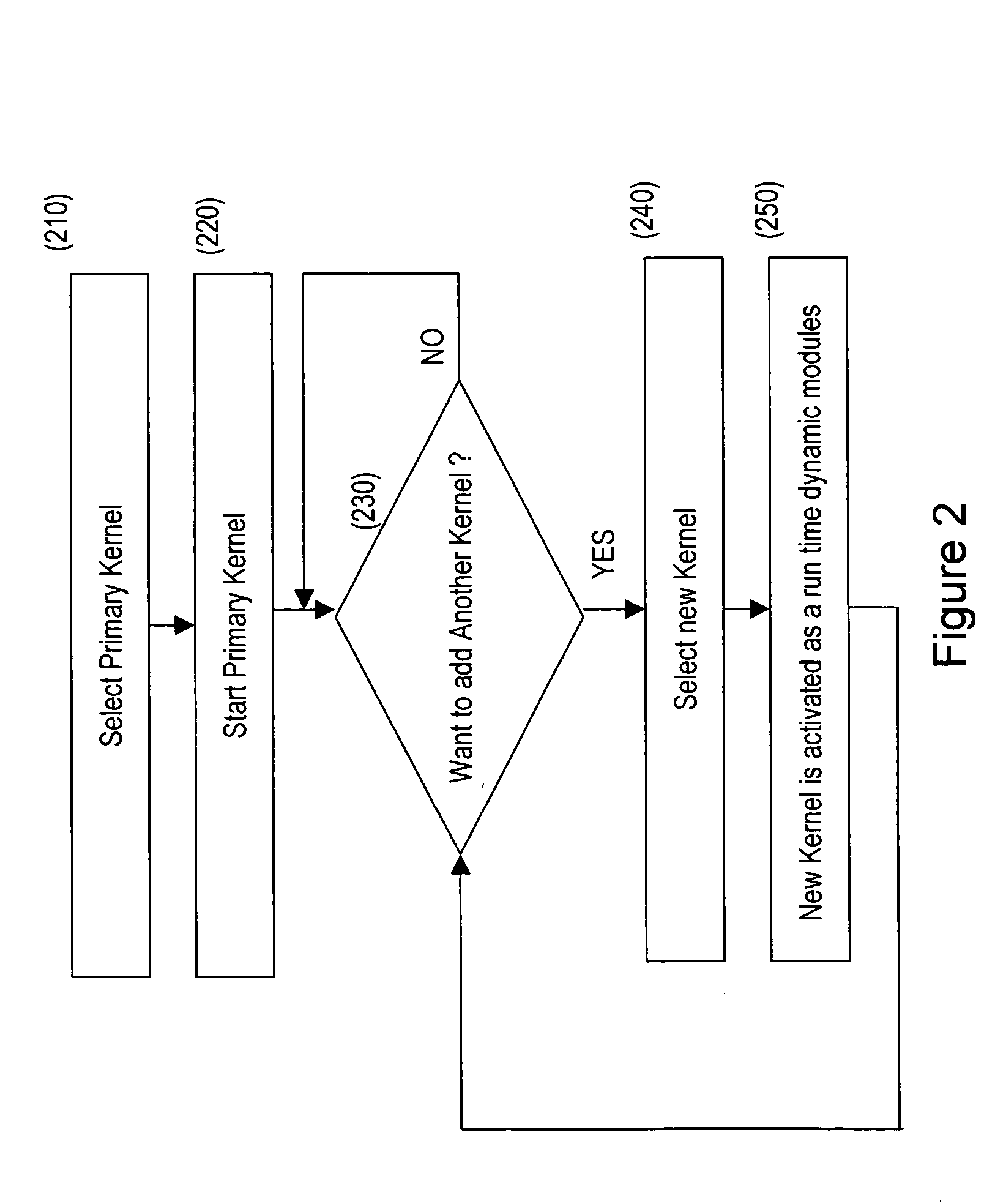

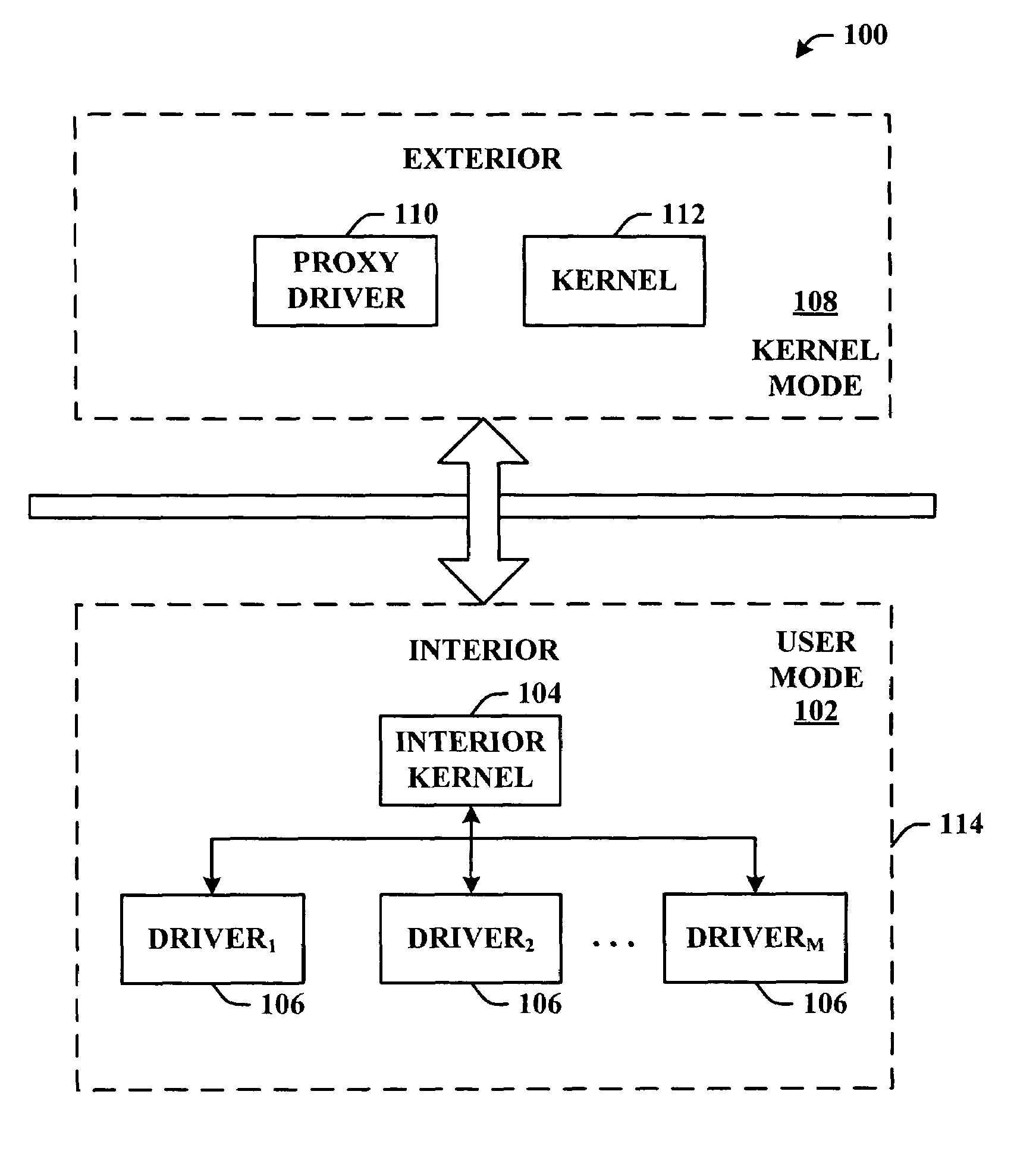

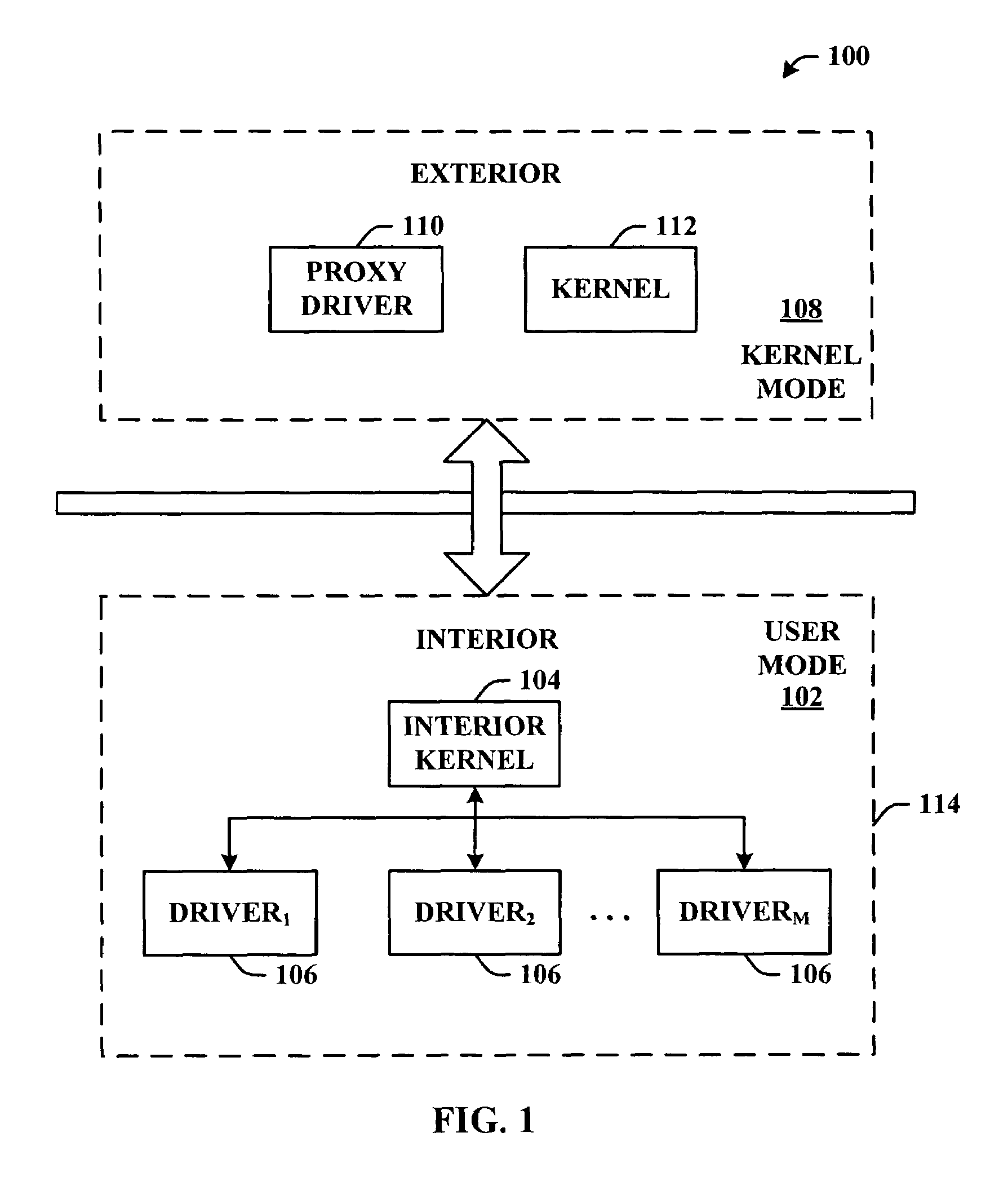

Method and system for concurrent execution of multiple kernels

An approach for concurrently running multiple kernels using a common interrupt handler and an optional common scheduler is provided. Techniques are also provided to switch execution among the kernels. Execution and interrupt preemption among kernels in shown using interrupt mask levels. Techniques are also provided for the sharing of resources between tasks running on different kernels.

Owner:EMBEDIO INC

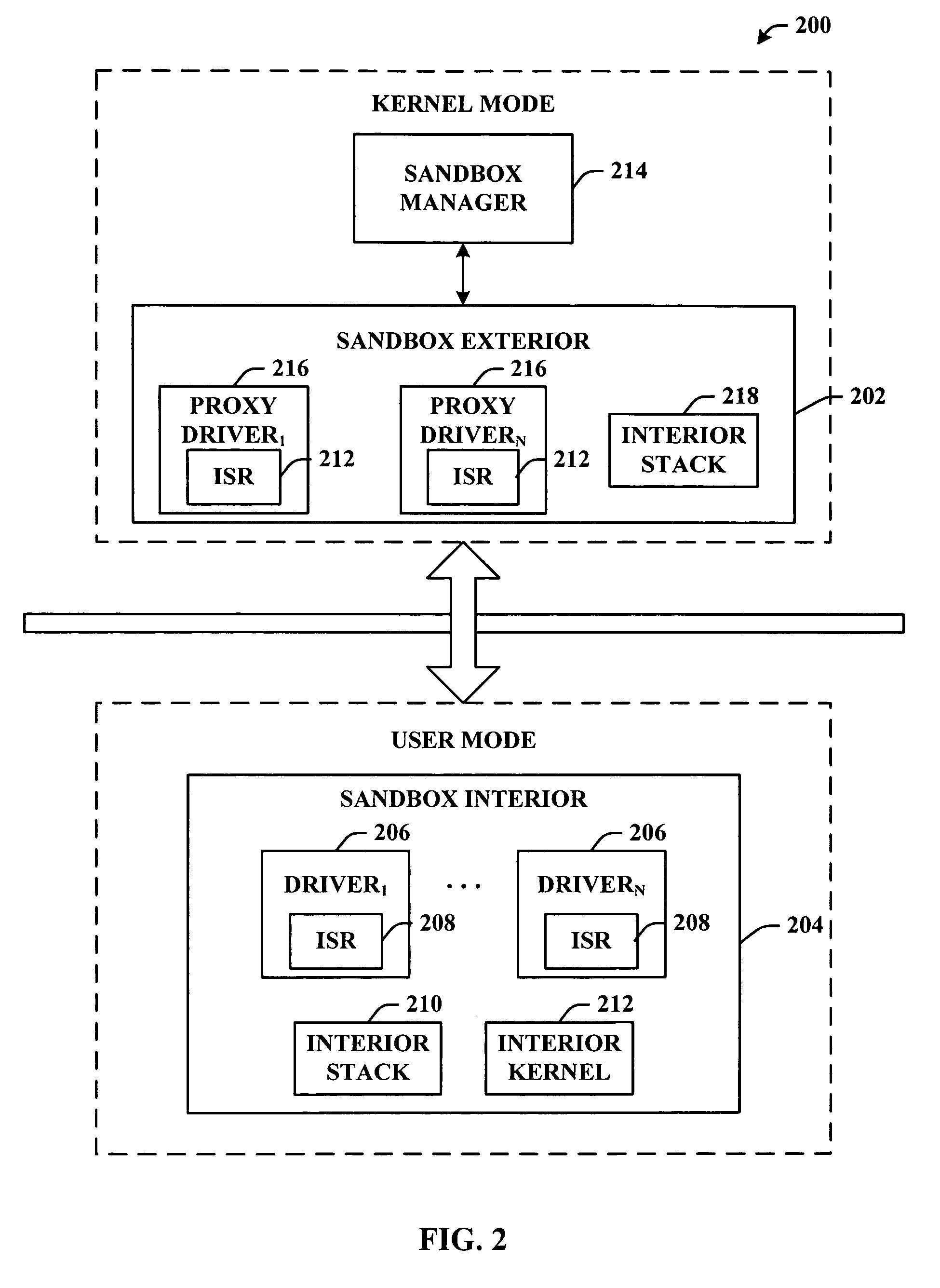

System and method for interrupt handling

A system, methodology and / or computer architecture that facilitates processing device interrupts (including level-triggered interrupts) in a user-mode process is provided. The kernel interrupt handler can cause a dedicated thread in the process to wake and invoke the driver interrupt service routine. This thread can then return control to the kernel interrupt handler. In addition to processing interrupts in an isolated mode, the context switching technique could be used in any isolated environment to process interrupts via dedicated execution context methods.

Owner:MICROSOFT TECH LICENSING LLC

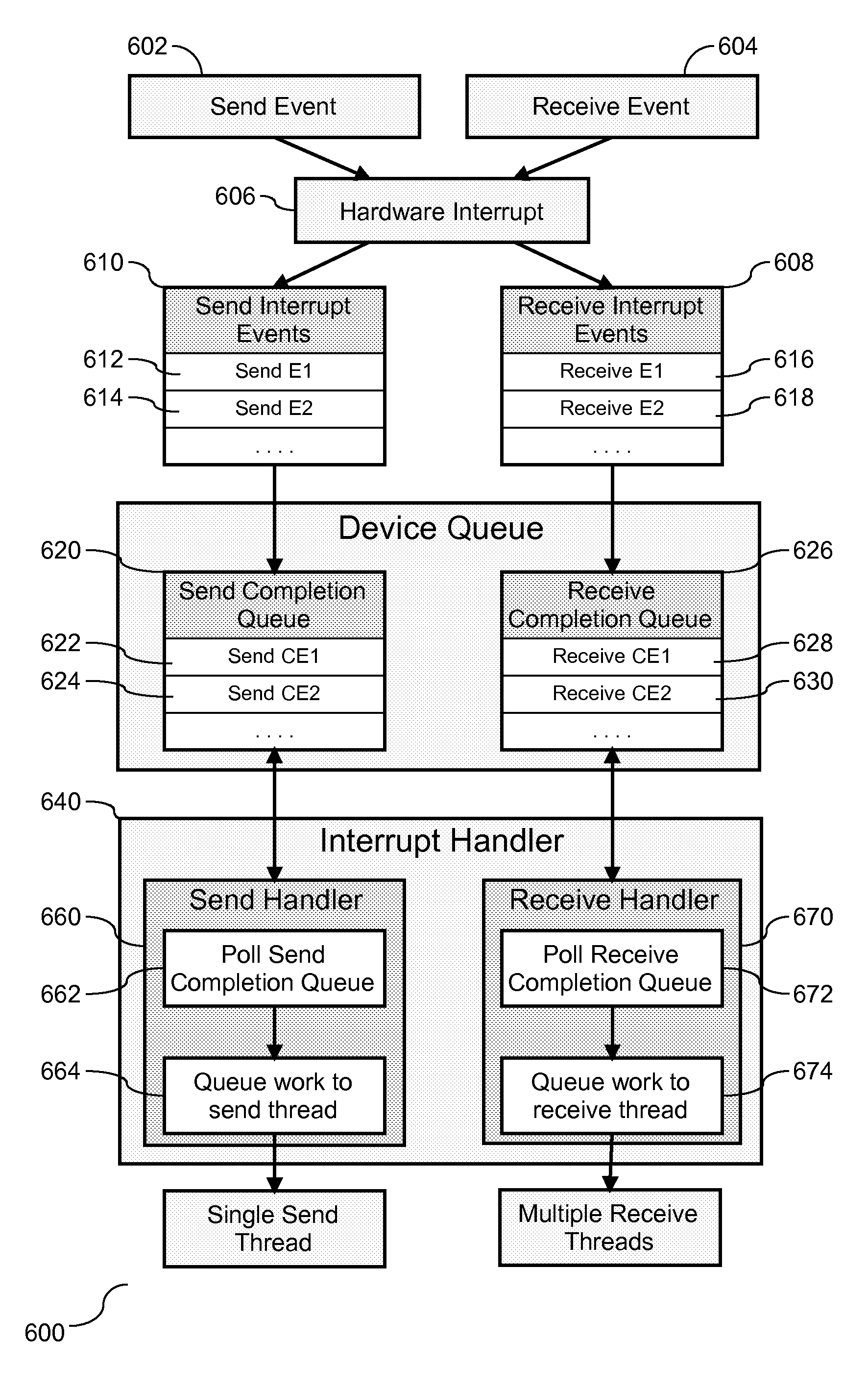

Splitting One Hardware Interrupt To Multiple Handlers

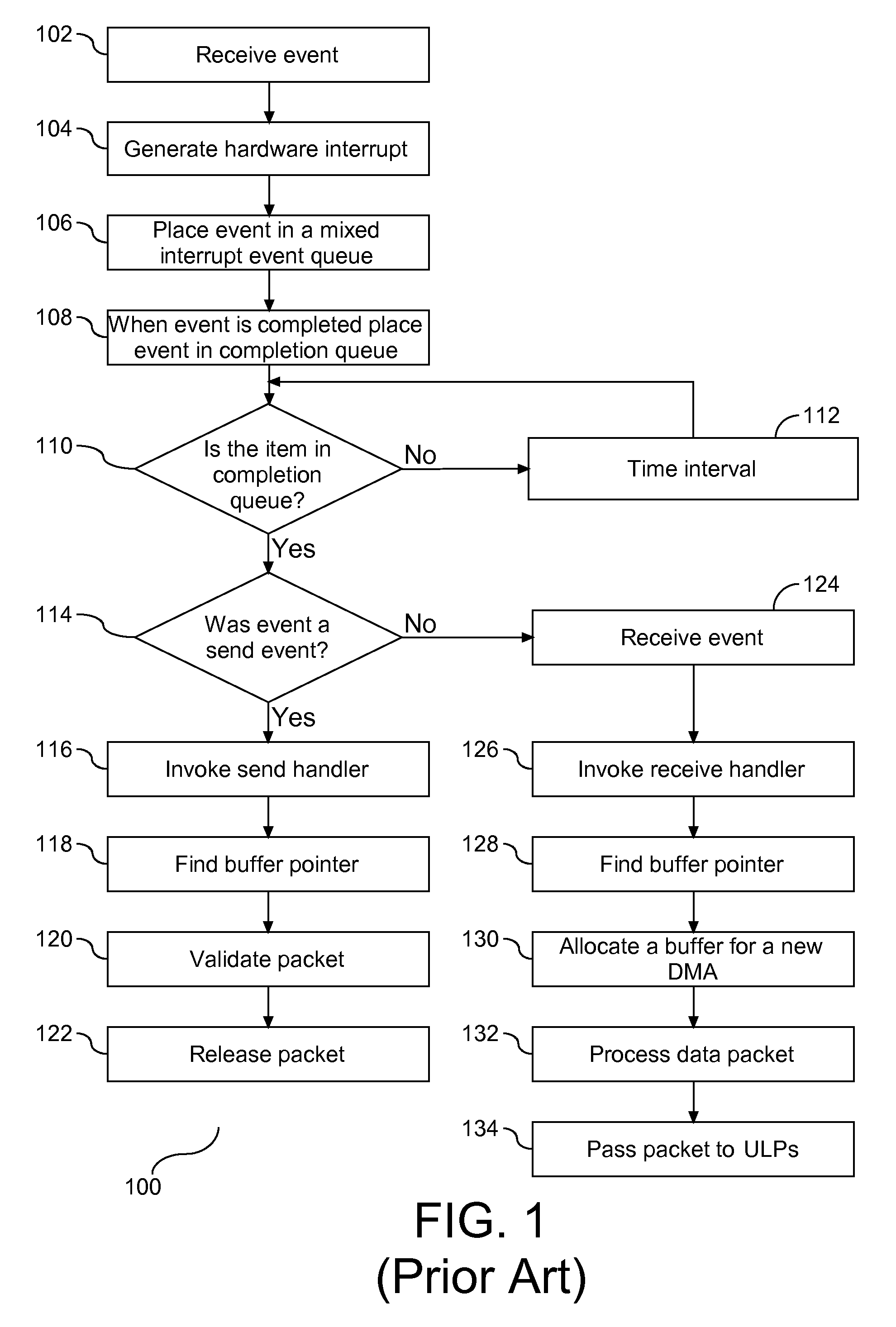

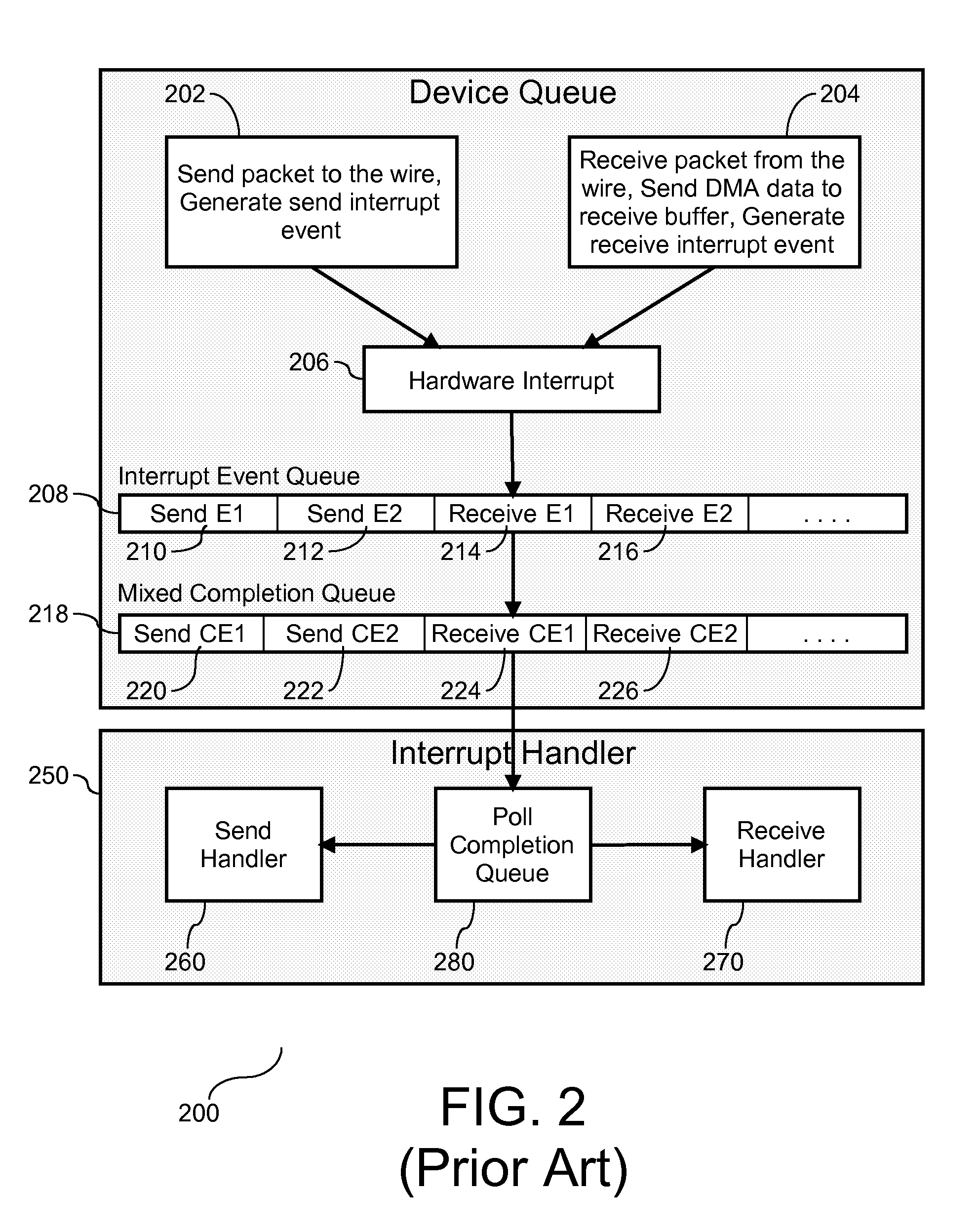

A method and apparatus are provided for reducing latency associated with processing events of a hardware interrupt. Send and receive events share the same hardware interrupt. A receive handler and a separate send handler are provided to simultaneously process completion of a send event and a receive event. In addition, separate queues are provided to communicate receipt of an event to the respective interrupt handler.

Owner:IBM CORP

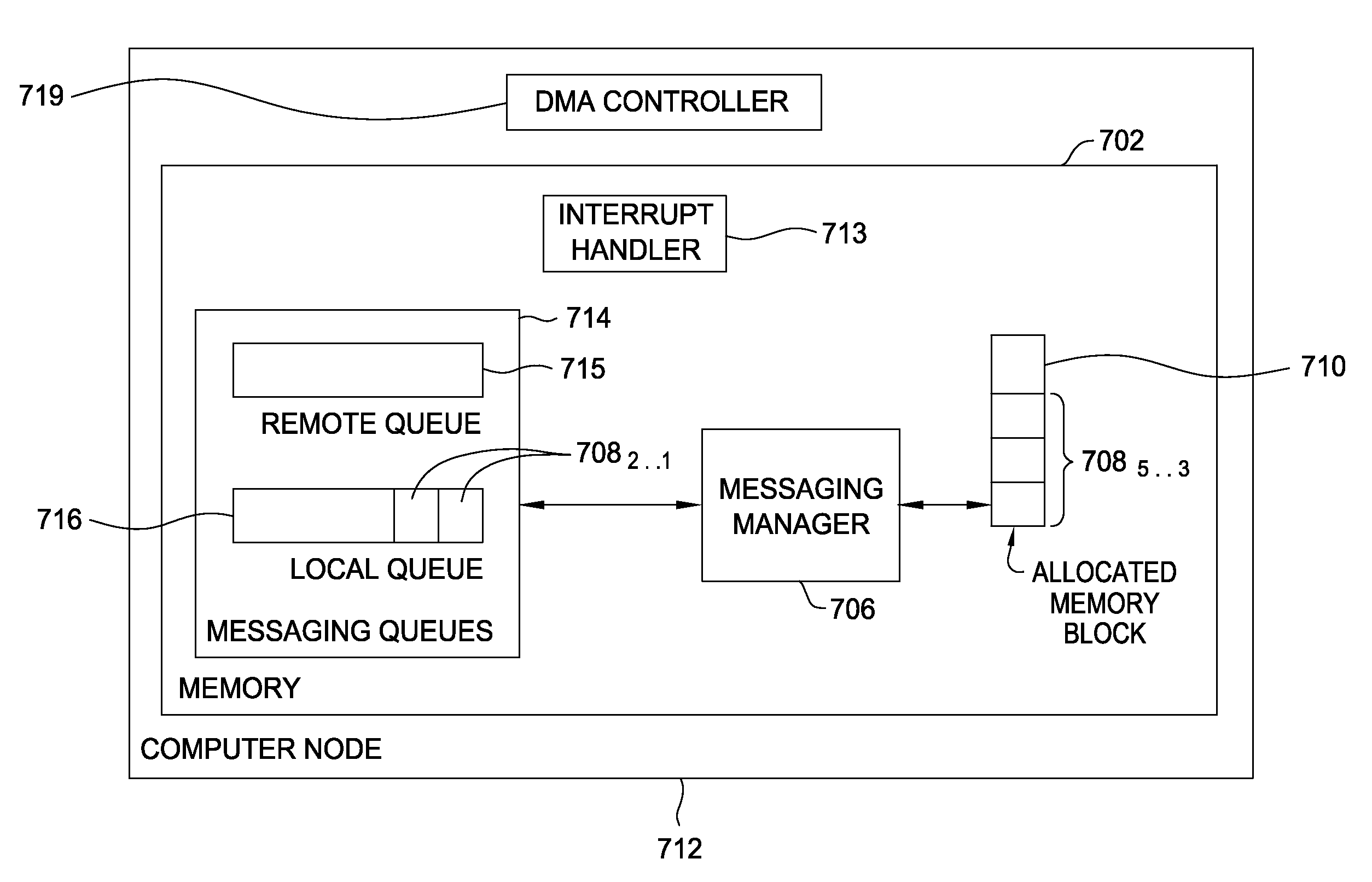

Increasing available FIFO space to prevent messaging queue deadlocks in a DMA environment

InactiveUS20100082848A1Digital computer detailsElectric digital data processingMessage queueDirect memory access

Owner:IBM CORP

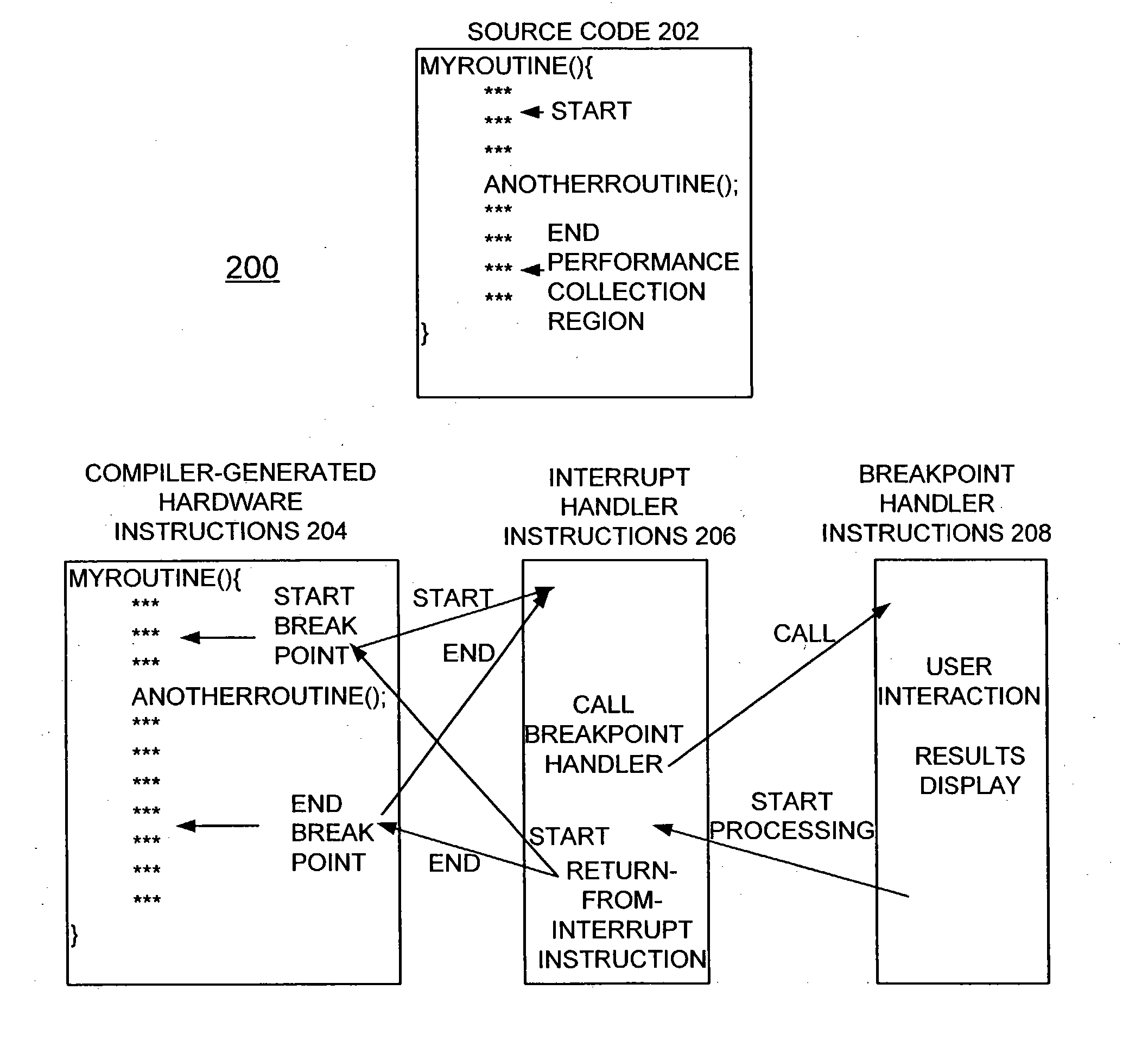

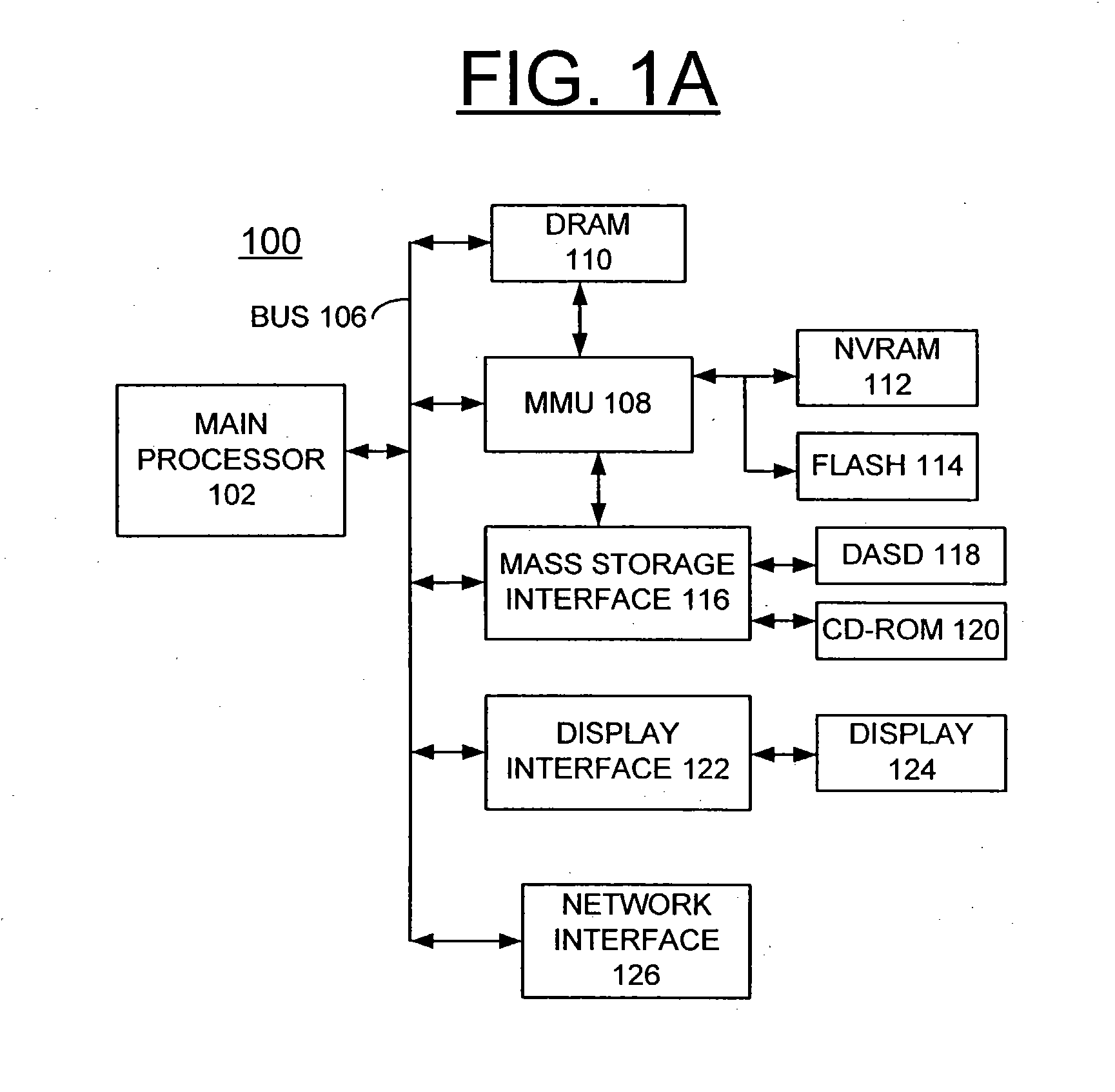

Method, apparatus and computer program product for implementing breakpoint based performance measurement

InactiveUS20050010908A1Negative effectError detection/correctionGeneral purpose stored program computerParallel computingInterrupt handler

A method, apparatus and computer program product are provided for implementing breakpoint based performance measurement. A set of hardware counters is defined for counting user specified hardware events. The hardware counters are programmable for counting predefined processor events and the predefined processor events include processor cycles. A start breakpoint instruction and a stop breakpoint instruction are inserted in hardware instructions. The hardware instructions are executed and processing of the hardware instructions is suspended responsive to executing the start breakpoint instruction. Responsive to executing the start breakpoint instruction, interrupt handler instructions are entered and breakpoint instructions are called. The breakpoint instructions generating a return from interrupt instruction to start the defined set of hardware counters and to return processing from the interrupt handler instructions to the hardware instructions. Then executing the hardware instructions is suspended responsive to executing the end breakpoint instruction to stop the defined set of hardware counters.

Owner:IBM CORP

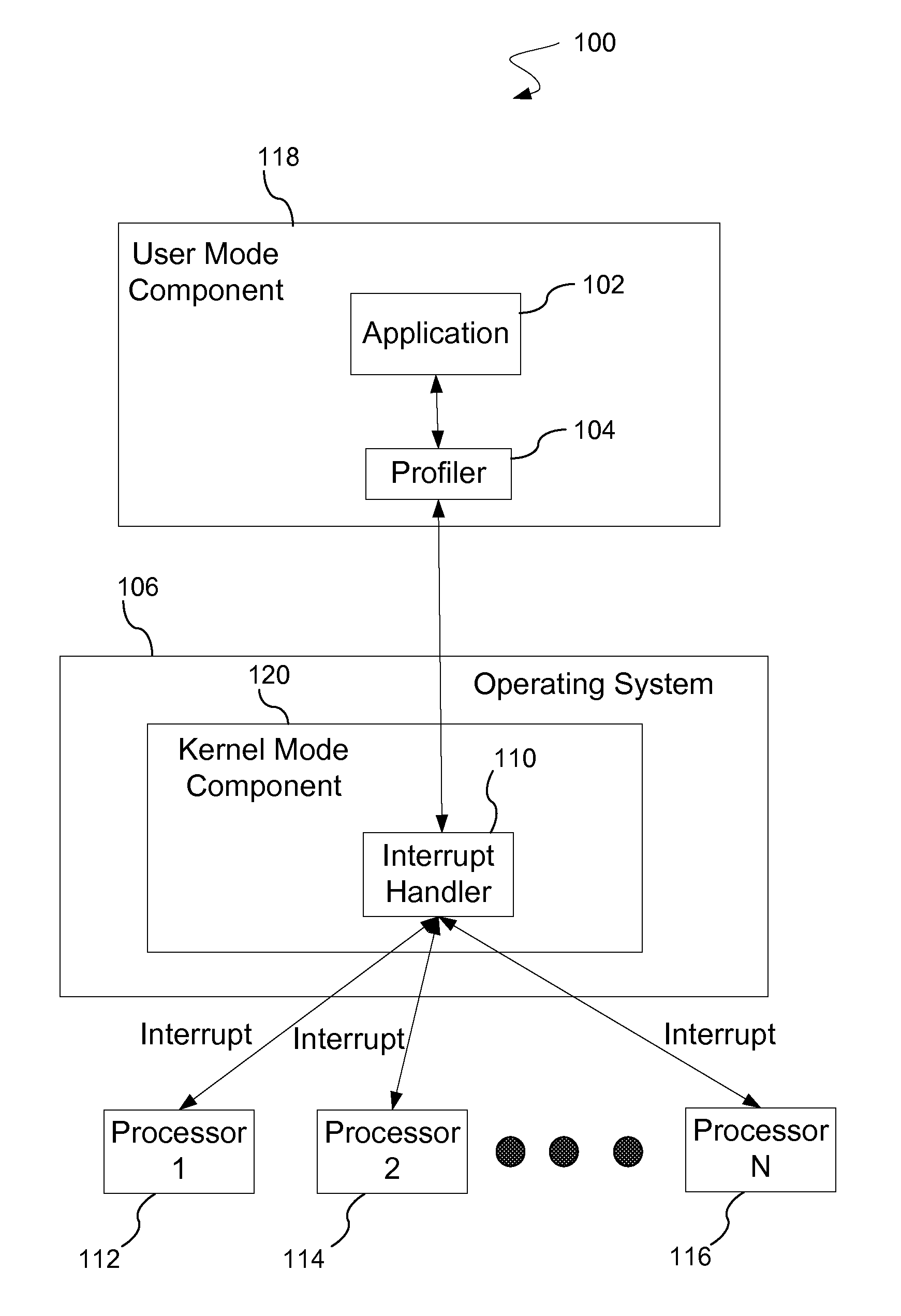

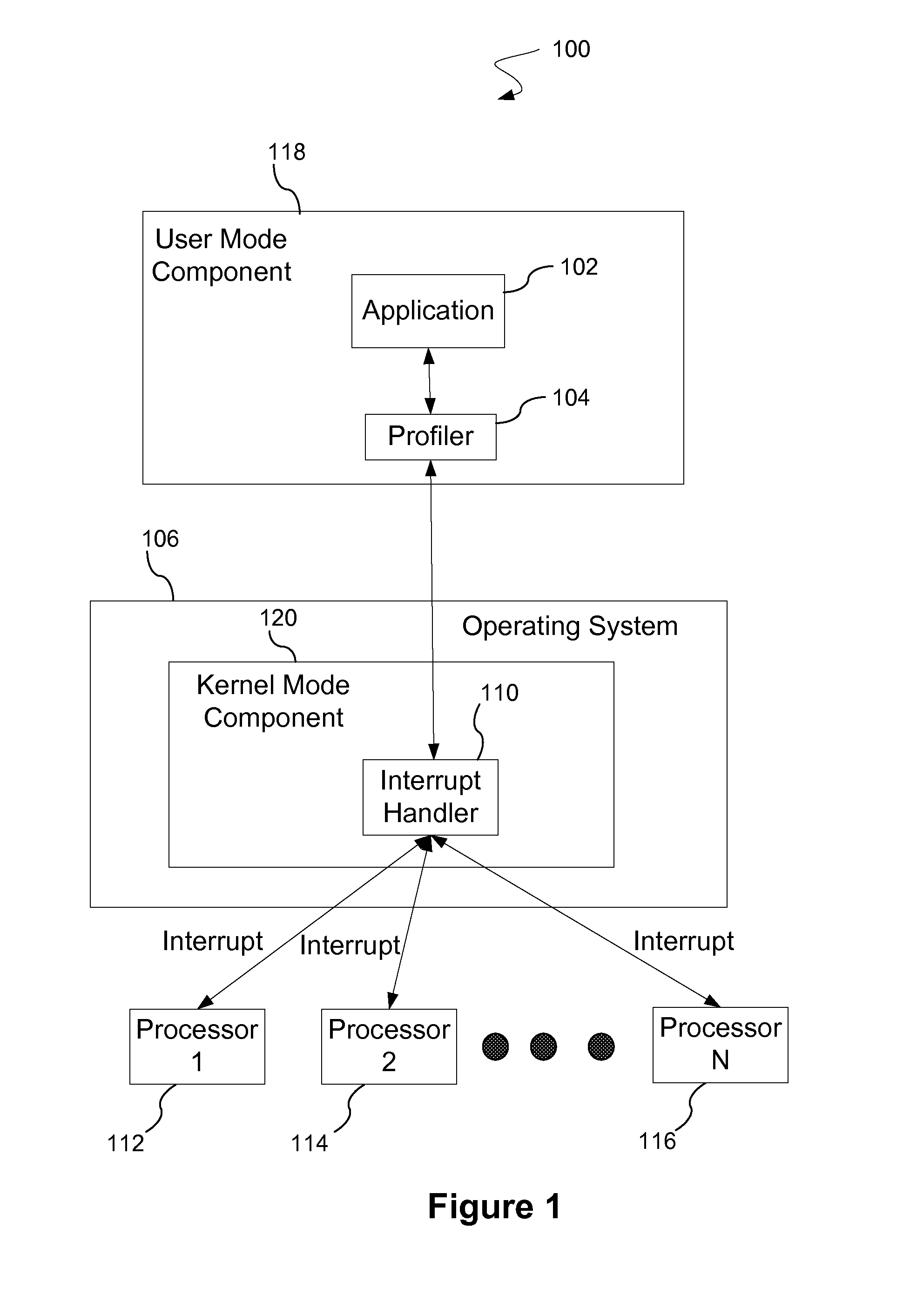

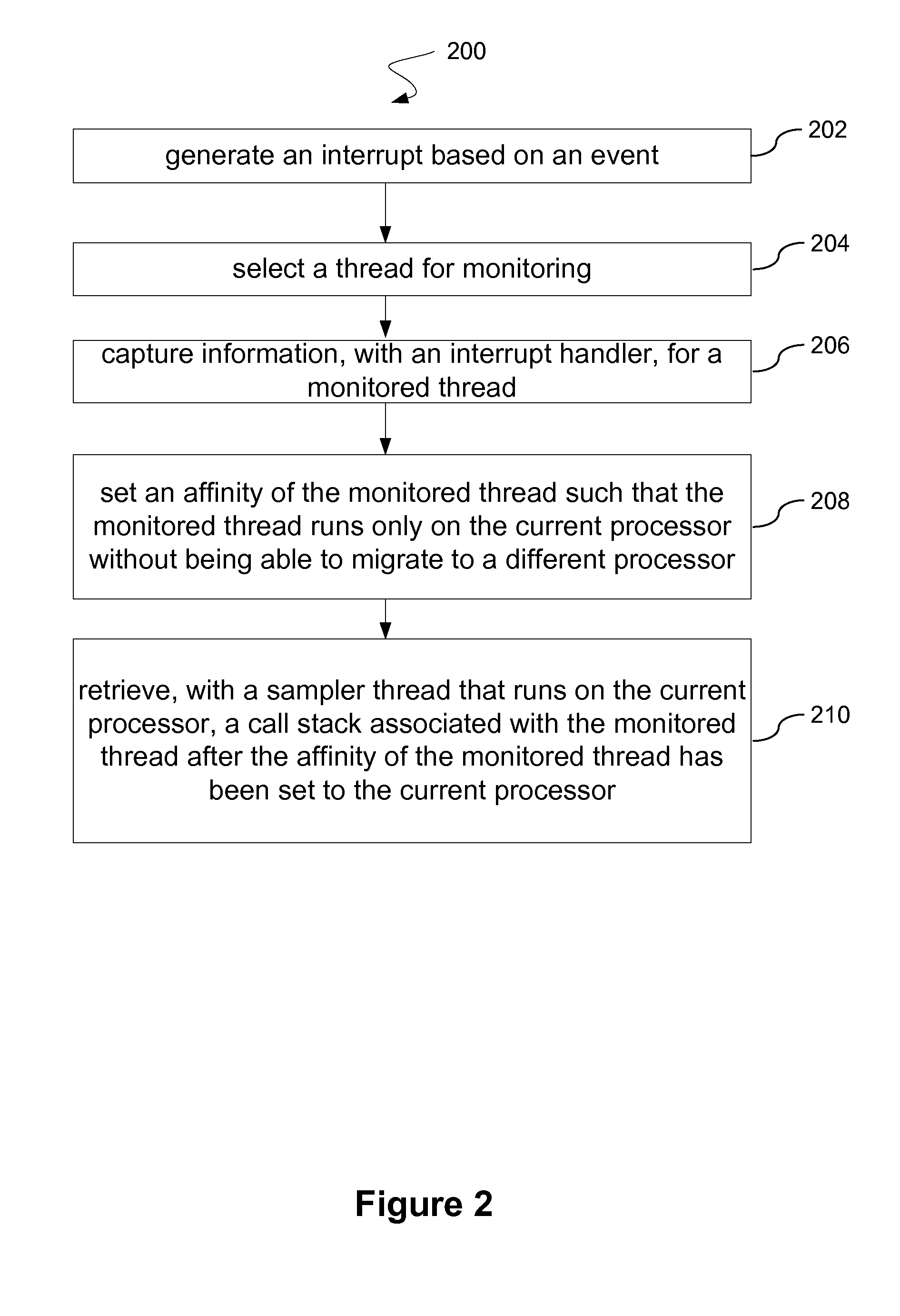

Scalable call stack sampling

An interrupt is generated based on an event. Further, a thread is selected for monitoring. In addition, an interrupt handler captures information for the monitored thread. An affinity of the monitored thread is set such that the monitored thread runs only on a current processor without being able to migrate to a different processor. A sampler thread that runs on the current processor retrieves a call stack associated with a monitored thread after the affinity of the monitored thread has been set to the current processor.

Owner:IBM CORP

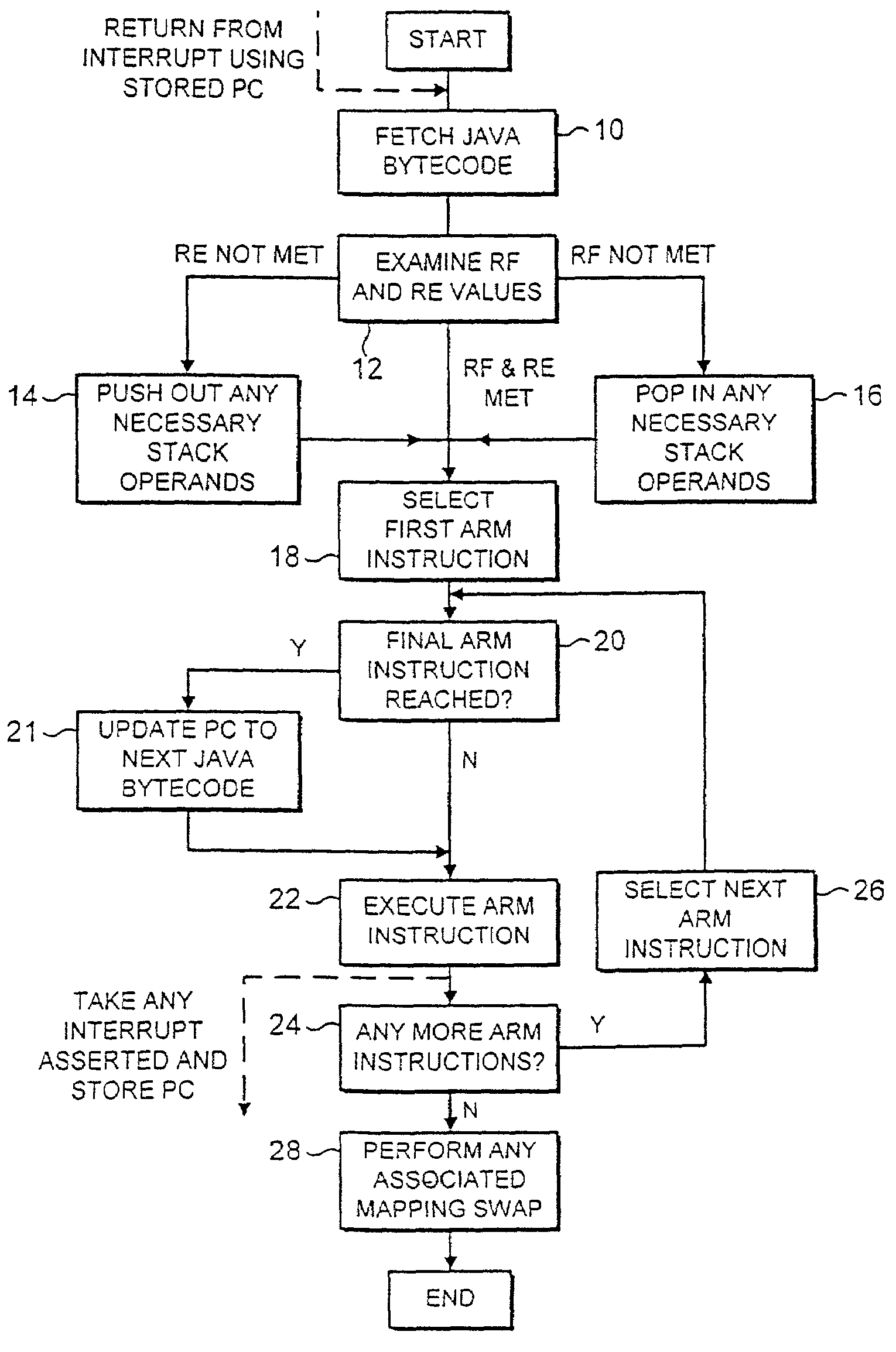

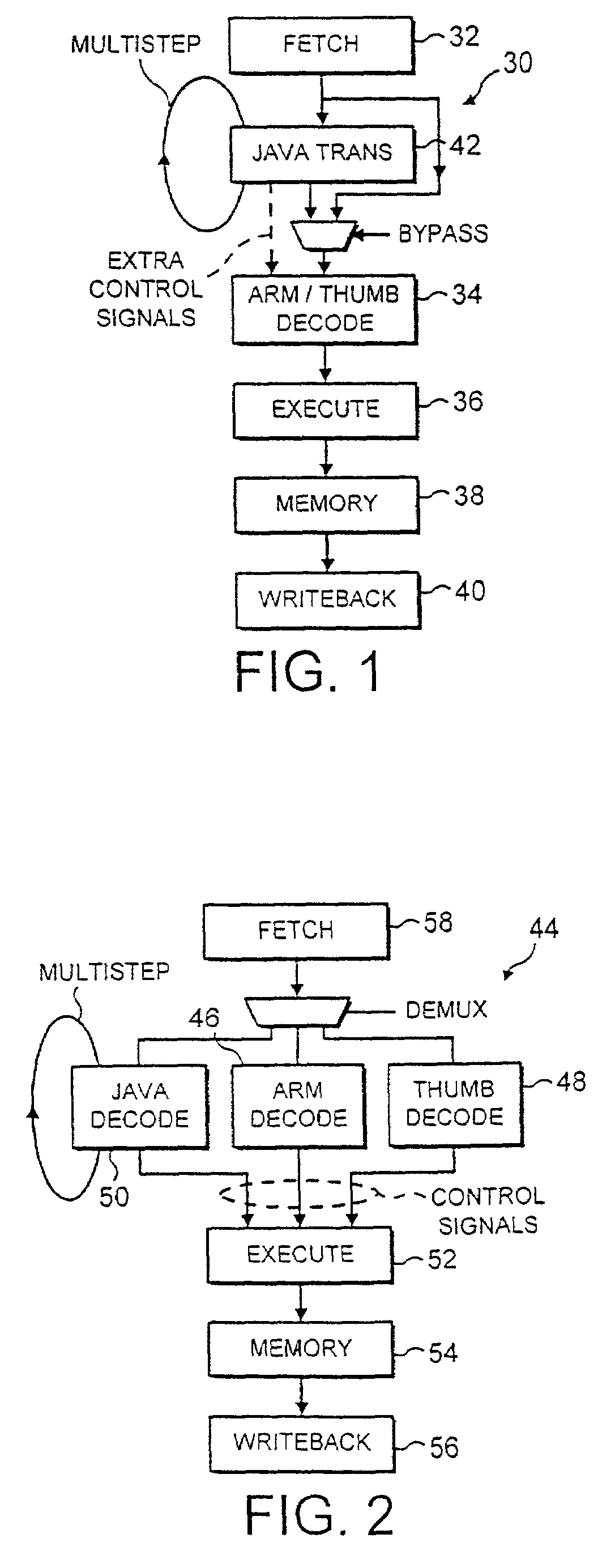

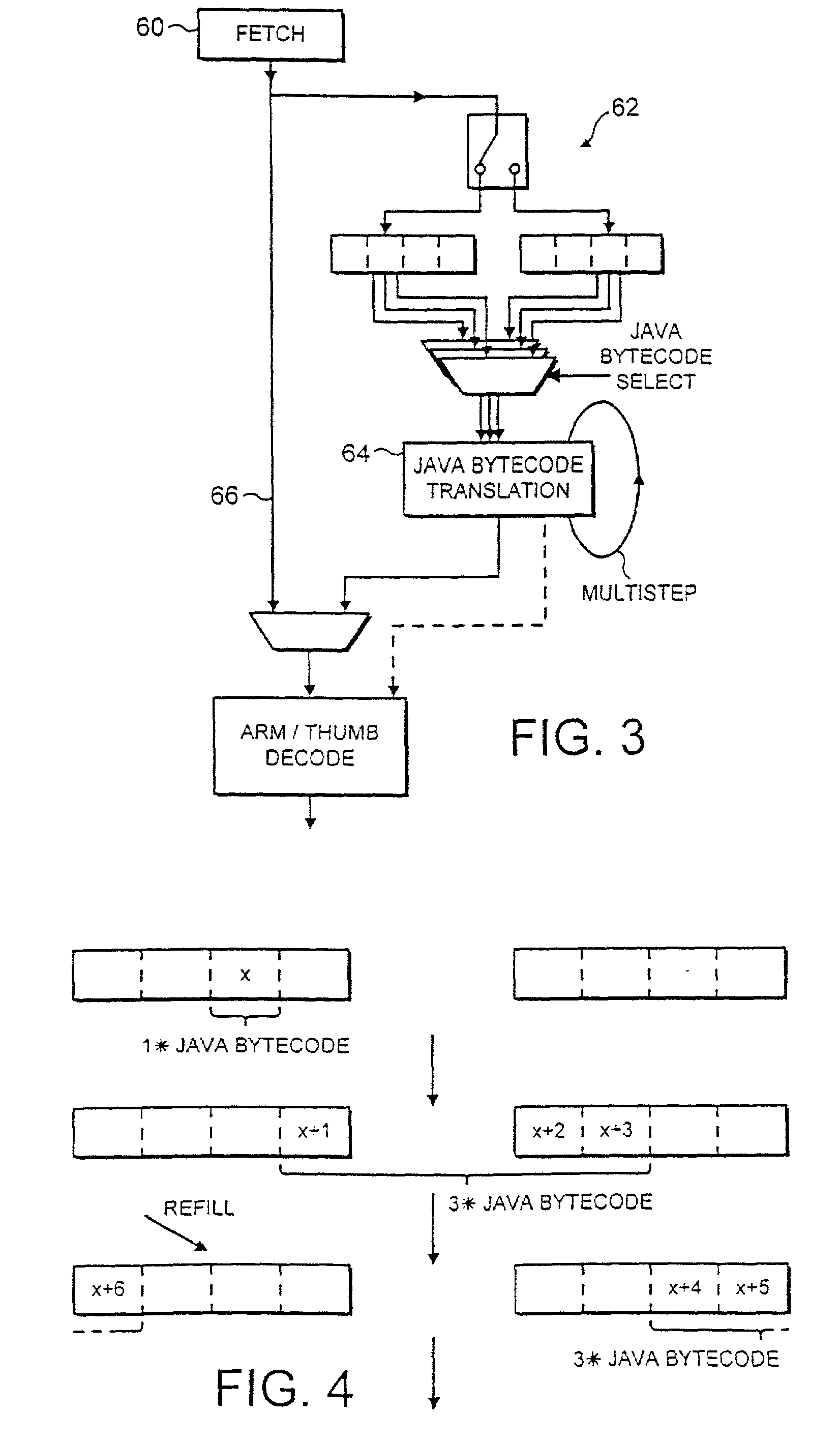

Restarting translated instructions

InactiveUS7003652B2Interrupt latencyImpact on processing speedProgram initiation/switchingInstruction analysisInterrupt handlerInstruction set

A processing system has a processor core executing instructions of a first instruction set and an instruction translator for generating translator output signals corresponding to one or more instructions of the first instruction set so as to emulate instructions of a second instruction set. The instruction translator provides translator output signals specifying operations that are arranged so that the input variables to an instruction of the second instruction set are not changed until the final operation emulating that instruction is executed. An interrupt handler services an interrupt after execution of an operation of the instructions of the first instruction set. Arranging the translated sequences of instructions such that the input state is not altered until the final instruction is executed has the result that processing may be restarted after the interrupt either by rerunning the complete emulation if the final operation had not started when the interrupt occurred, or by running the next instruction from the second instruction set if the final operation had started when the interrupt occurred.

Owner:ARM LTD

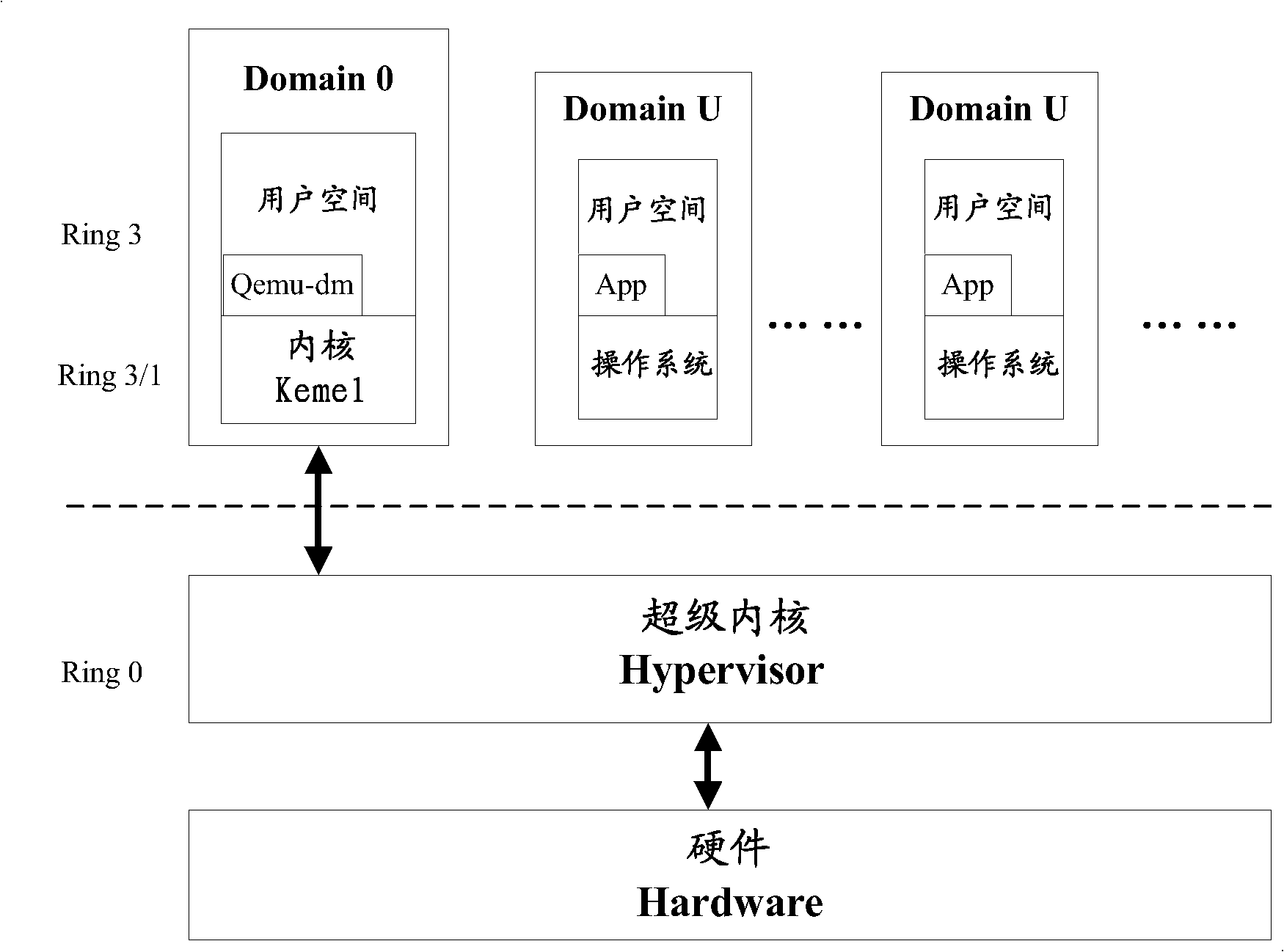

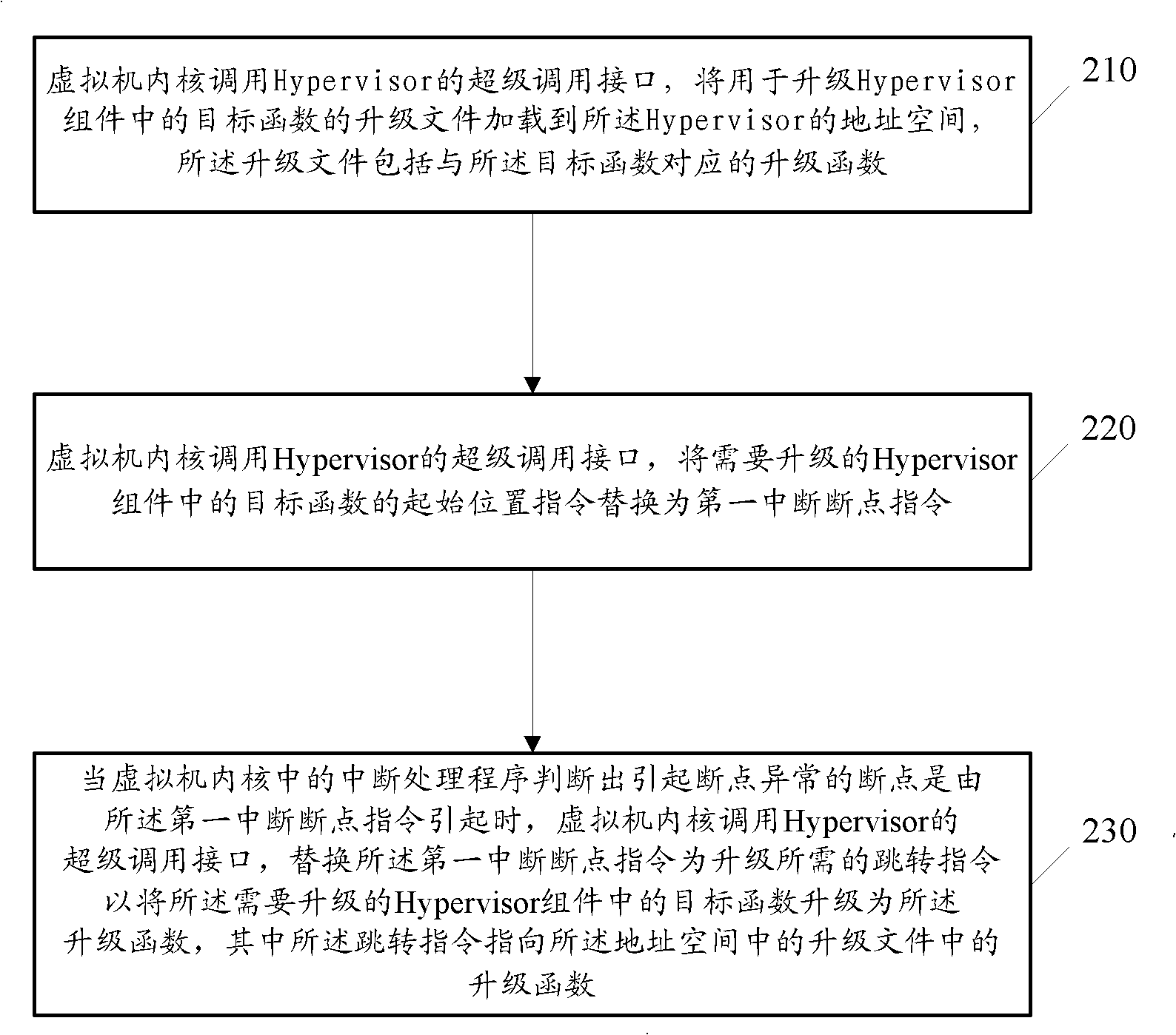

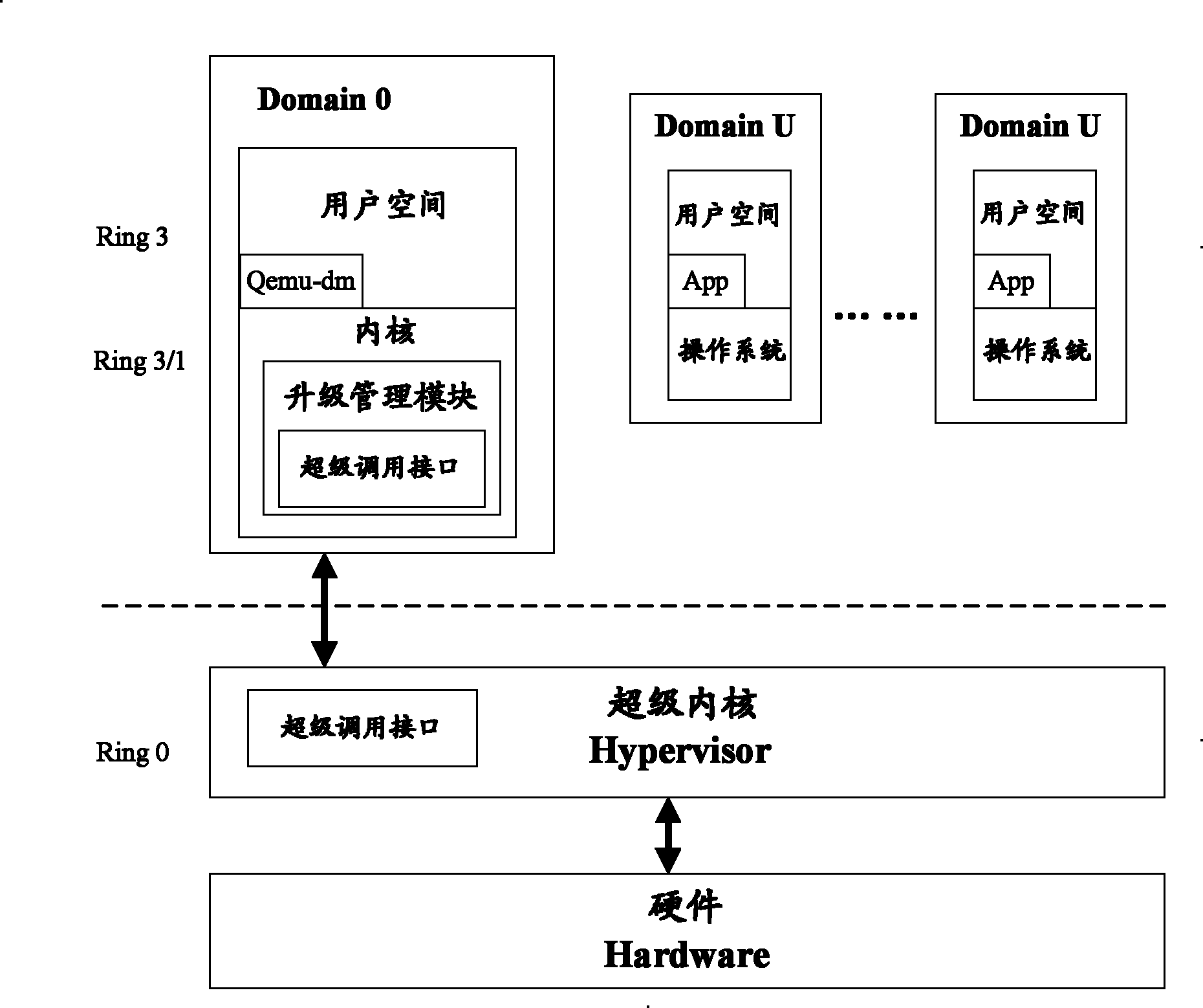

Method and computer system for upgrading super kernel component

ActiveCN102073529AReduce occupancyReduce the impactSoftware engineeringProgram loading/initiatingComputerized systemInterrupt handler

The embodiment of the invention discloses a method and computer system for upgrading a super kernel component. The method for upgrading the super kernel component comprises the following steps: the kernel of a virtual machine calls a super call interface of a super kernel to load a upgrading file of a target function used for upgrading in the super kernel component to the address space of the super kernel; the kernel of the virtual machine calls the super call interface of the super kernel to replace an initial position instruction of the target function to be upgraded with an interruption breakpoint instruction; and the kernel of the virtual machine calls the super call interface of the super kernel to replace a first interruption breakpoint instruction with a jump instruction required by the upgrading when an interruption processing program in the kernel of the virtual machine determines that a breakpoint result in breakpoint exception is caused by the interruption breakpoint instruction, so as to upgrade the target function in the super kernel component to be upgraded into an upgrade function. By applying the technical scheme of the embodiment of the invention, facilities resources required by the super kernel component upgrading process can be reduced, and the influence of the upgrading on services can be reduced.

Owner:HUAWEI TECH CO LTD

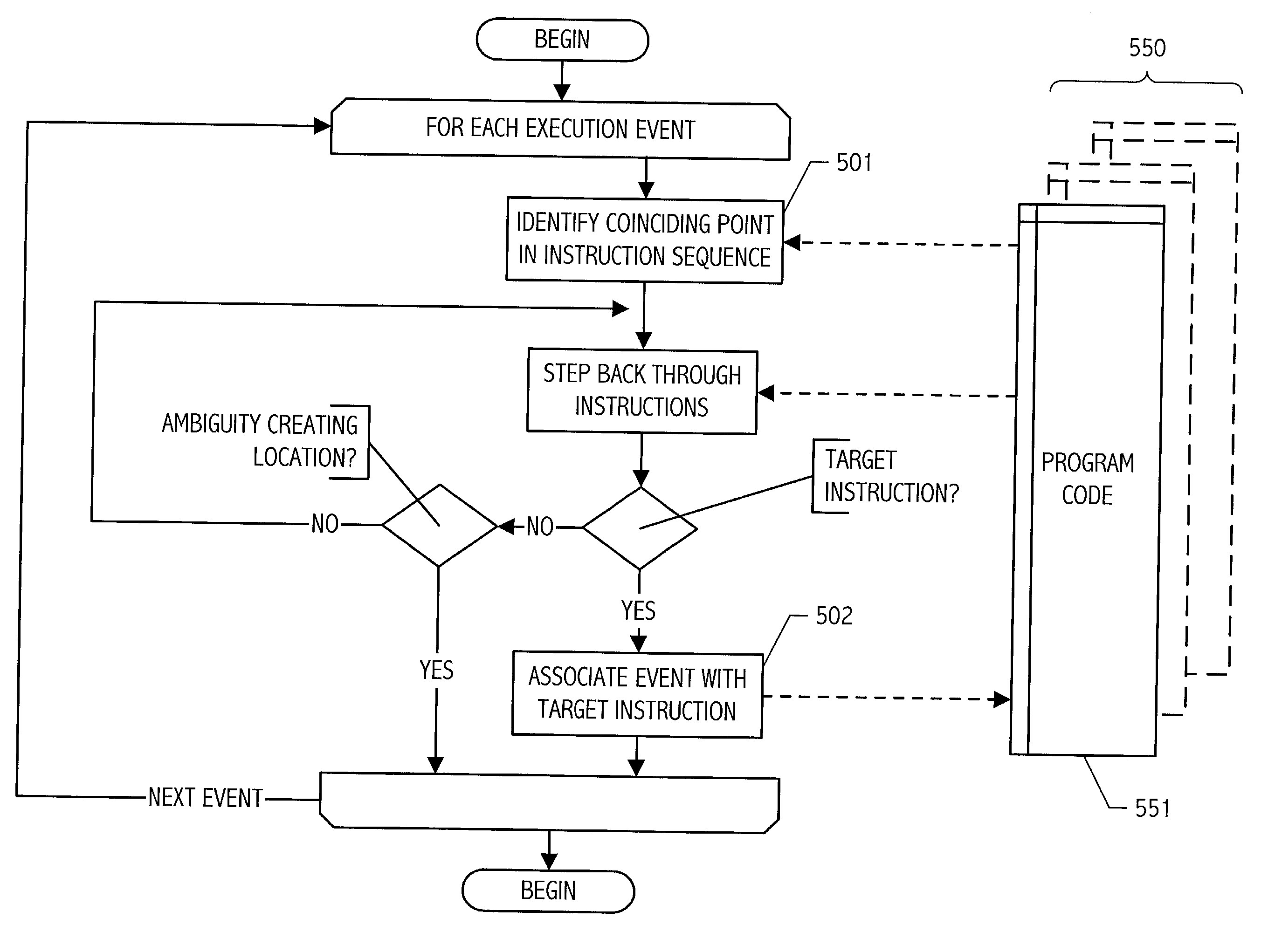

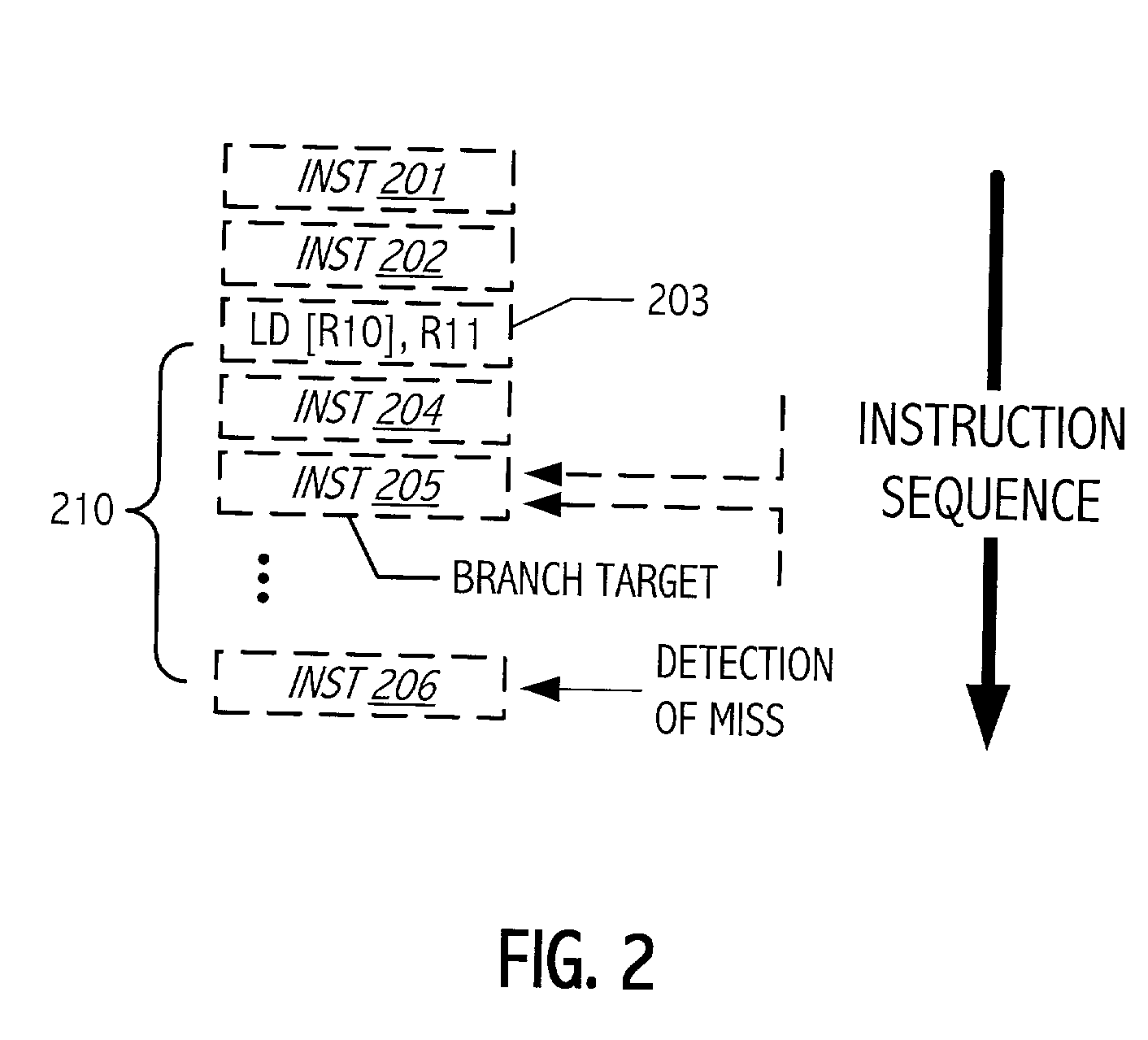

Technique for associating instructions with execution events

InactiveUS20030101336A1Digital computer detailsSoftware testing/debuggingEntry pointParallel computing

Program code executed in an environment in which latency exists between an execution event and detection of the execution event may be profiled using a technique that includes backtracking from a point in a representation of the program code, which coincides with the detection toward a preceding operation associated with the execution event. Backtracking identifies the preceding operation at a displacement from the detection point unless an ambiguity creating location is disposed between the detection point and the preceding operation. In general, the relevant set of ambiguity creating locations is processor implementation dependent and program code specific; however, branch targets locations, entry points, and trap or interrupt handler locations are common examples. In some realizations, the techniques may be used to associate cache miss (or hit) information with execution of particular memory access instructions. However, more generally, such techniques may be employed to associate observed execution characteristics with particular instructions of program code or associated operations based on event detections that may, in general, lag execution of the triggering instruction or operation by an interval that allows intervening program flow ambiguity.

Owner:SUN MICROSYSTEMS INC

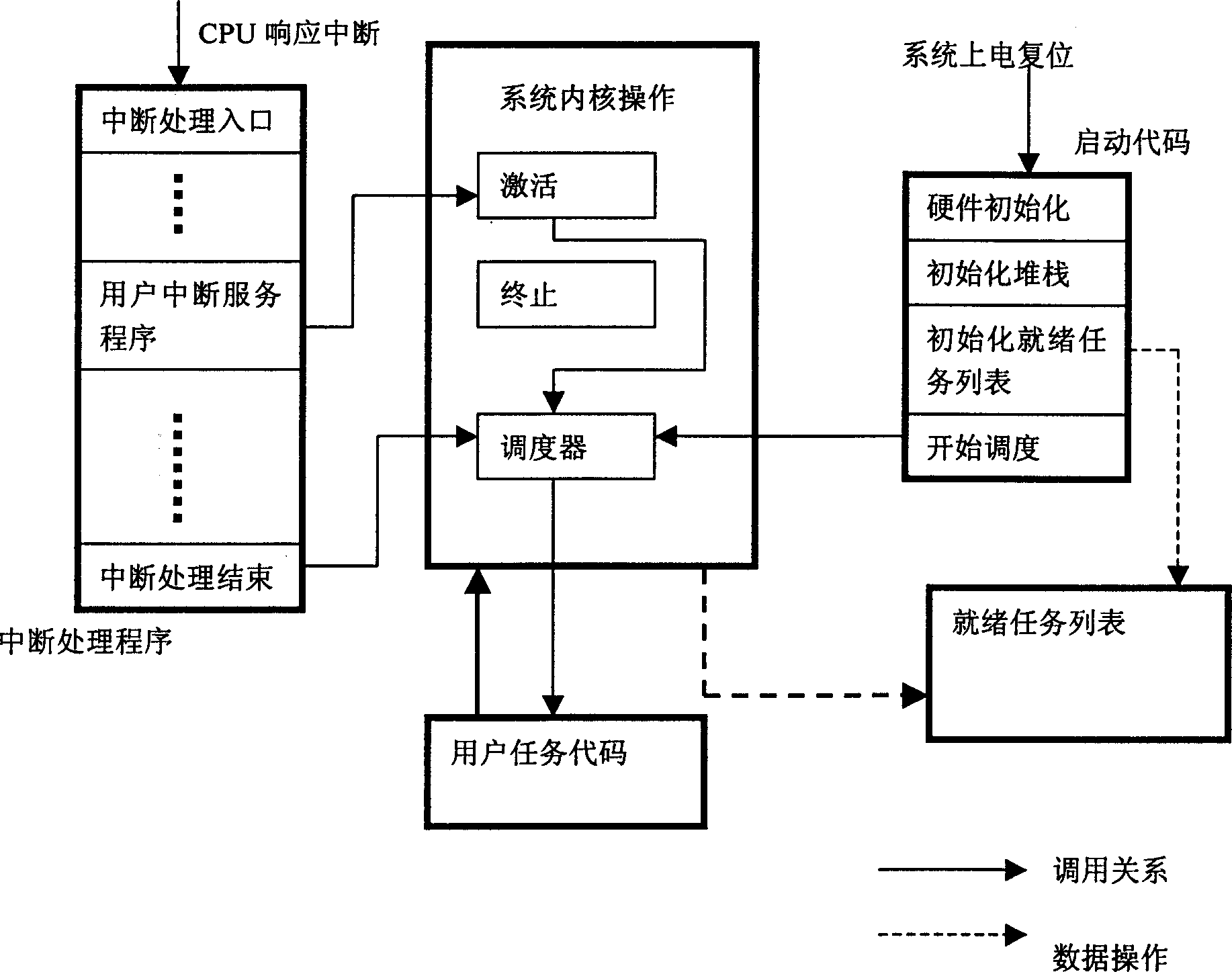

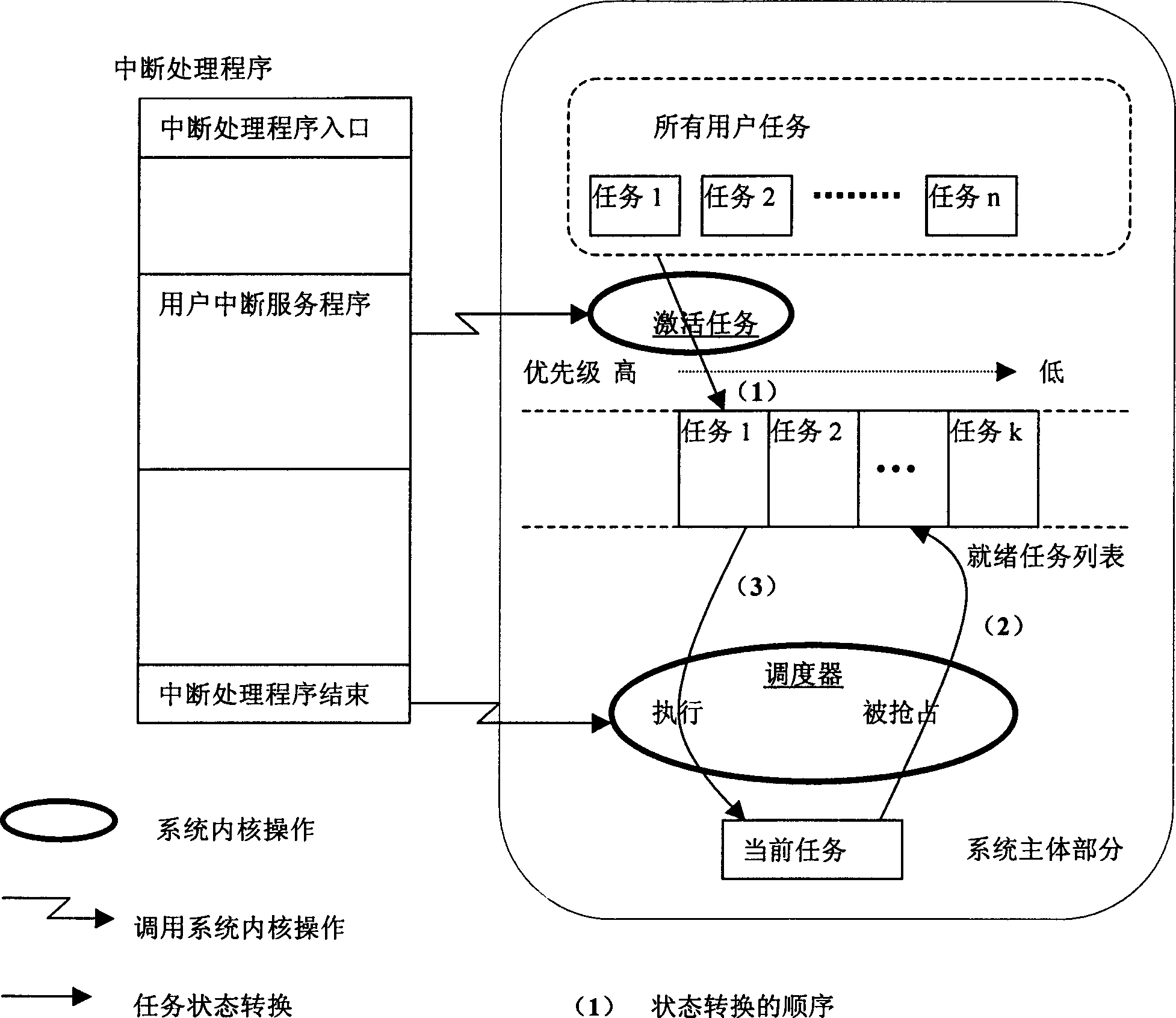

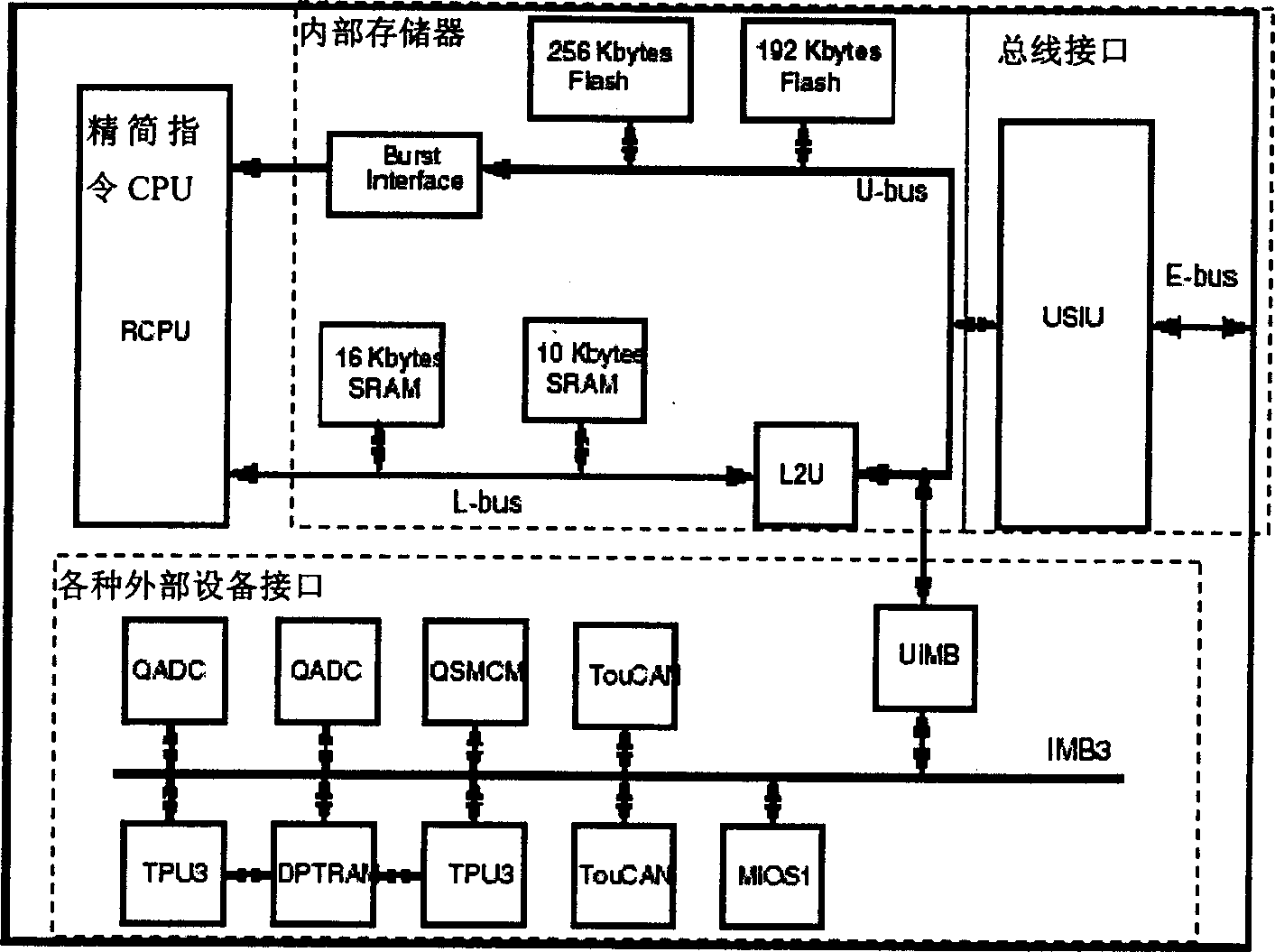

Graded task switching method based on PowerPC processor structure

InactiveCN1490722AShorten the timeImprove the efficiency of task switchingProgram initiation/switchingOperational systemPowerPC

The method has the following characteristics: the task contex of the user can be divided into three parts of basic, expansion and selectable according to speciality of Power PC processor structure. In interruption process, only three stack entering modes of basic, basicand expansion as well as all context part are applied according to condition of system disposal and task dispatching. The basic part stack entering is executed first. After interruption process is finished the nature of task dispatching is judged for selecting to execute the next stage of stack entering operation, to call dispatcher or to return to the user task in order to reduce unnecessary stacking operation.

Owner:TSINGHUA UNIV

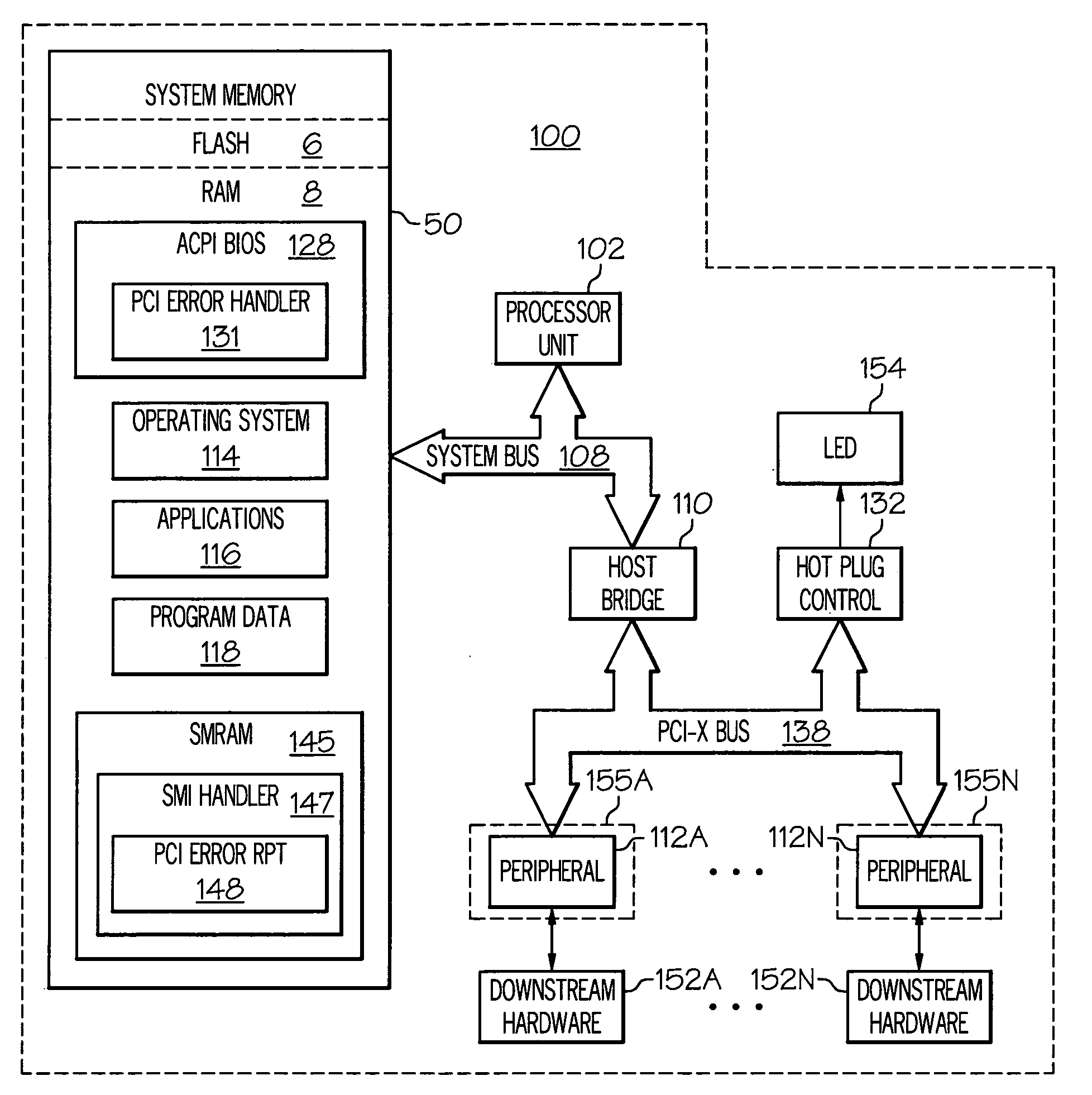

System and method for using hot plug configuration for PCI error recovery

InactiveUS20070011500A1Non-redundant fault processingAdvanced Configuration and Power InterfaceOperational system

A method, system, and program product for recovering from a bus error in a computer system having a hot plug interface. In accordance with the method of the present invention, an operating system transparent interrupt, such as a system management interrupt, is generated in response to a bus error. Responsive to the operating system transparent interrupt, the hot pluggable bus is scanned and a device associated with the error is identified by an interrupt handler invoked by the interrupt. Finally, a hot plug configuration manager, such as an advanced configuration and power interface is utilized to remove the identified device from system operations without having to restart the system.

Owner:LENOVO GLOBAL TECH INT LTD

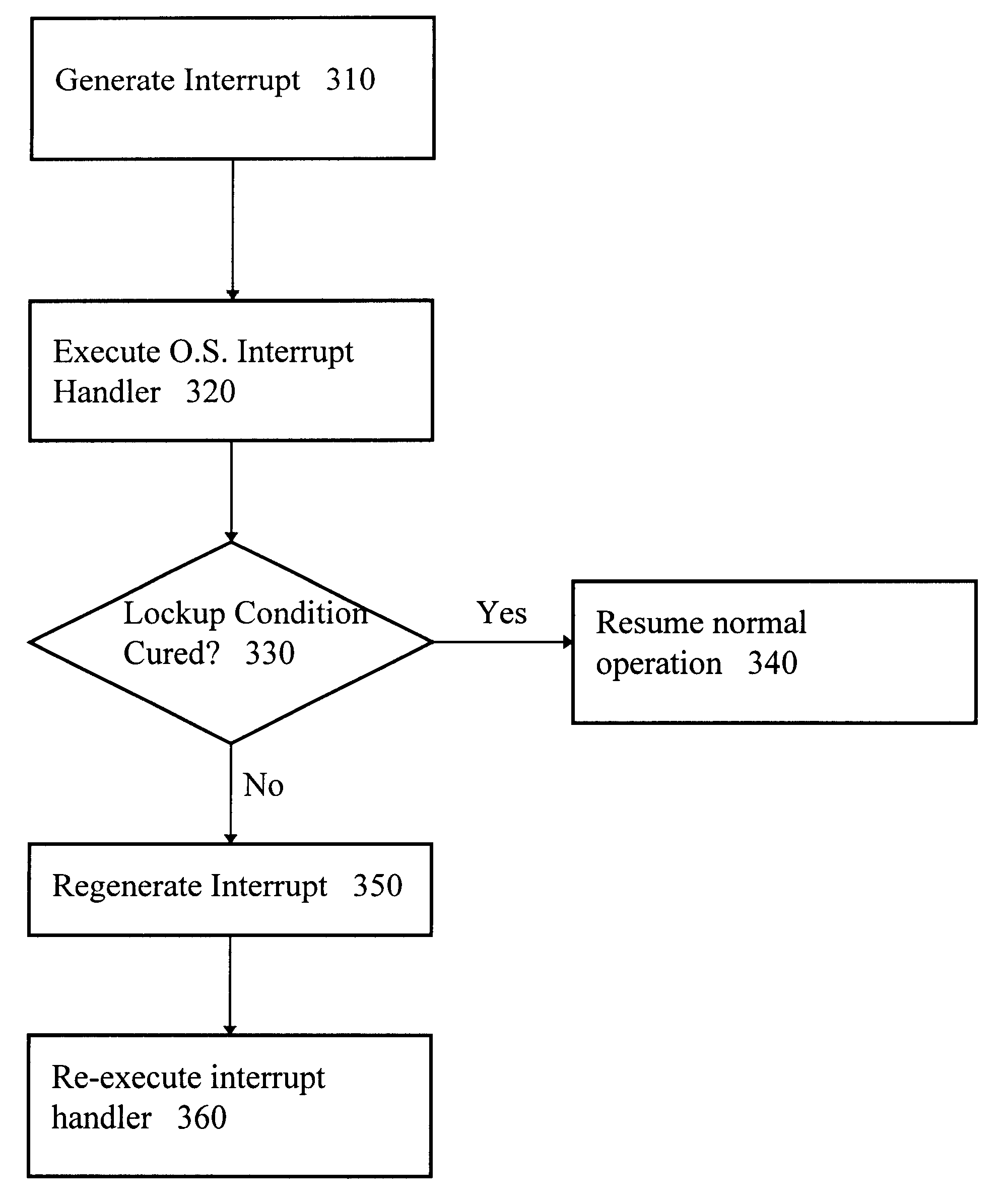

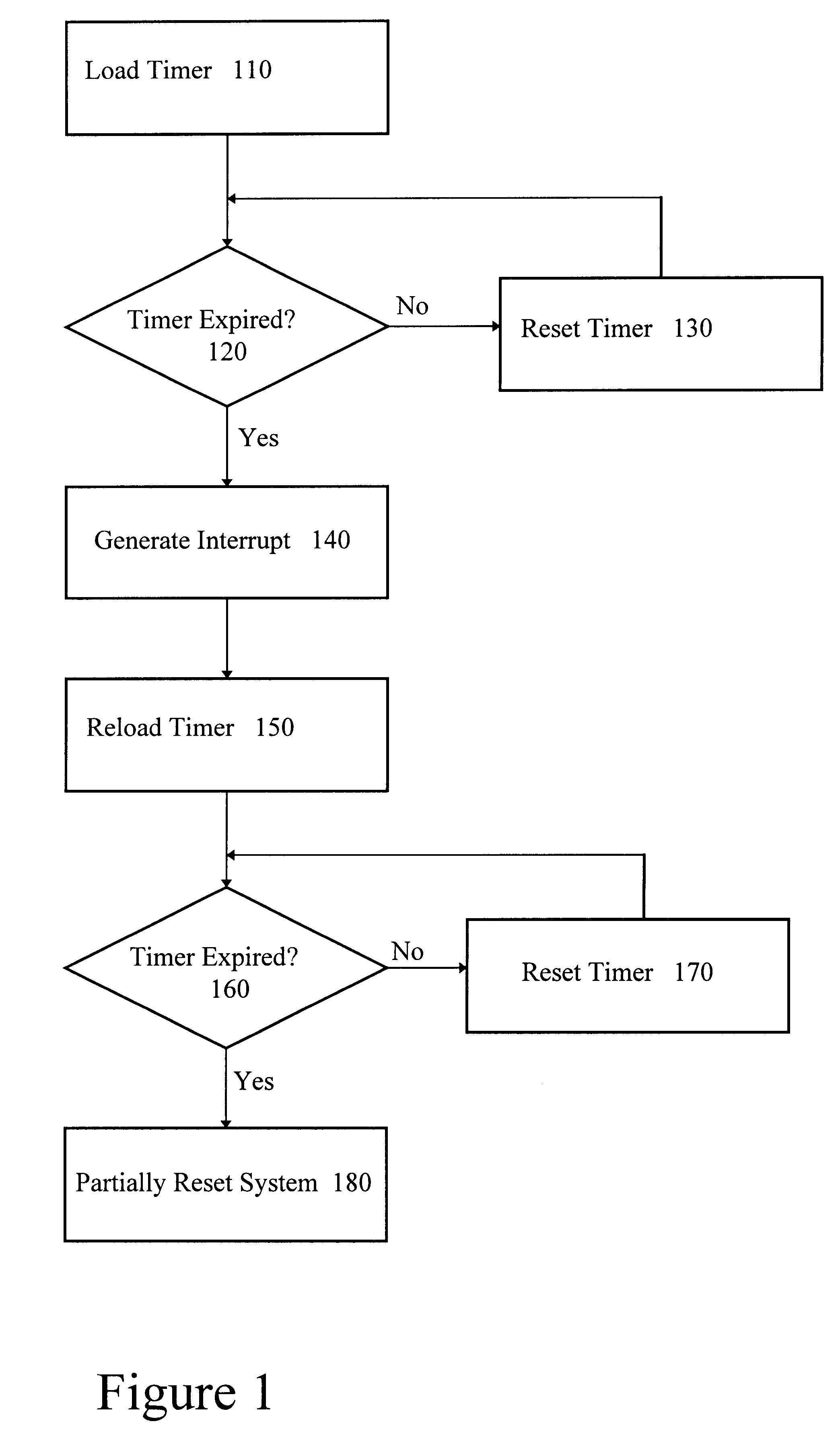

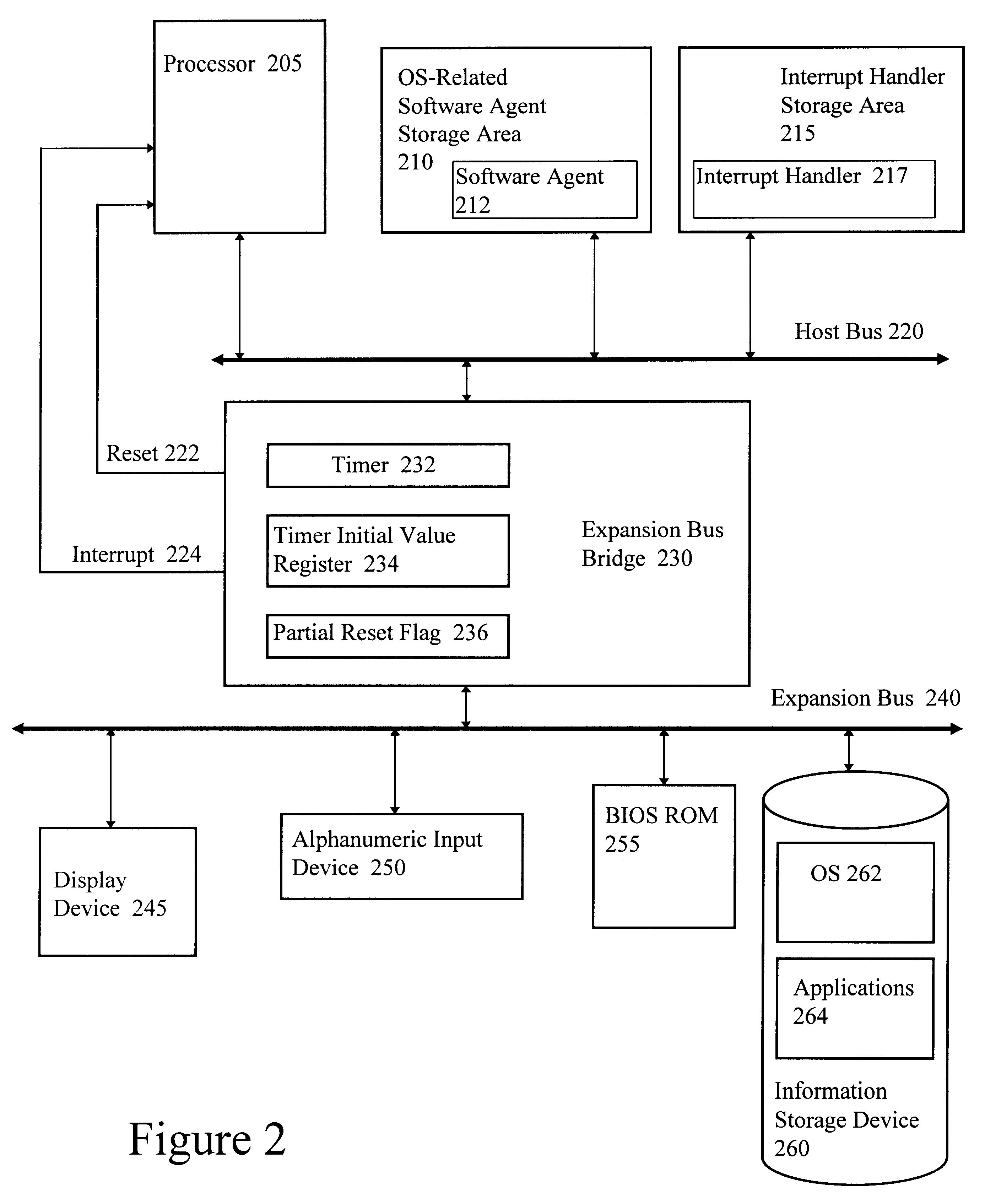

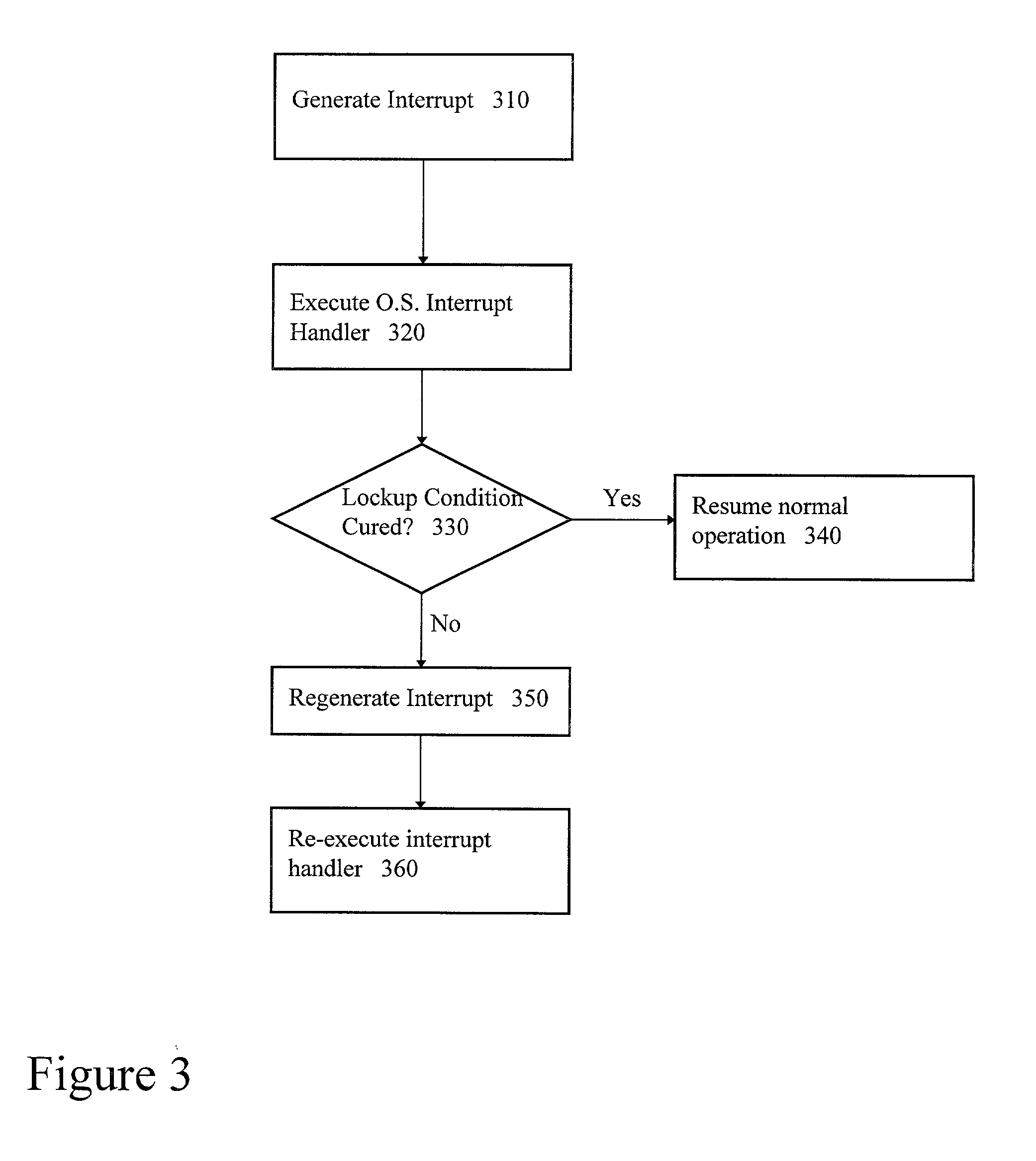

Method for recovering from computer system lockup condition

In one embodiment of a method for recovering from a computer system lockup condition, an interrupt is generated to the computer system's operating system notifying the operating system of the lockup condition. An operating system interrupt handler is then executed. The interrupt handler performs at least one step to attempt to cure the lockup condition. If the interrupt handler fails to cure the lockup condition, the interrupt is regenerated to the operating system notifying the operating system of the lockup condition. The interrupt handler is then re-executed in response to the regeneration of the interrupt, with the interrupt handler performing a further step in attempting to cure the lockup condition.

Owner:INTEL CORP

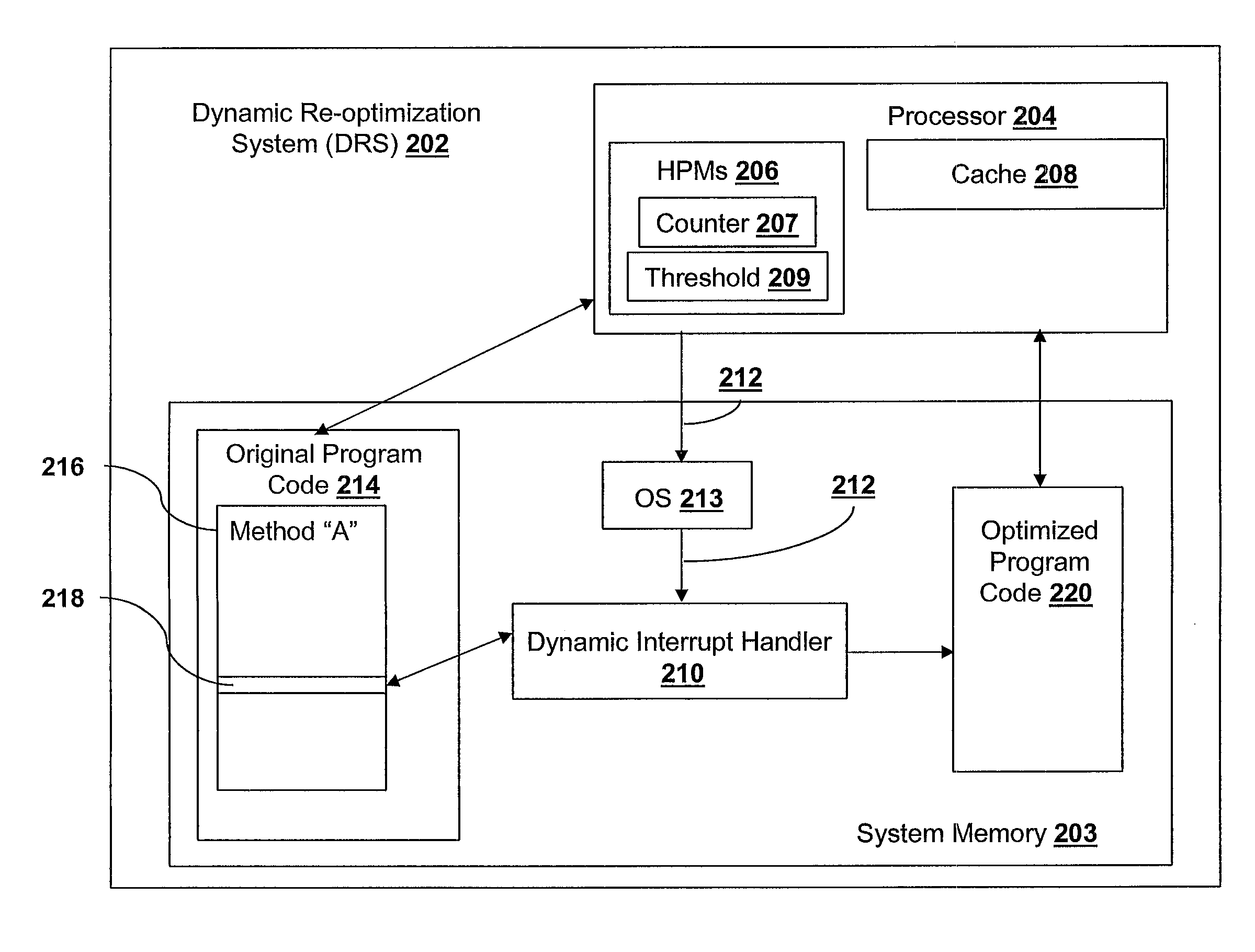

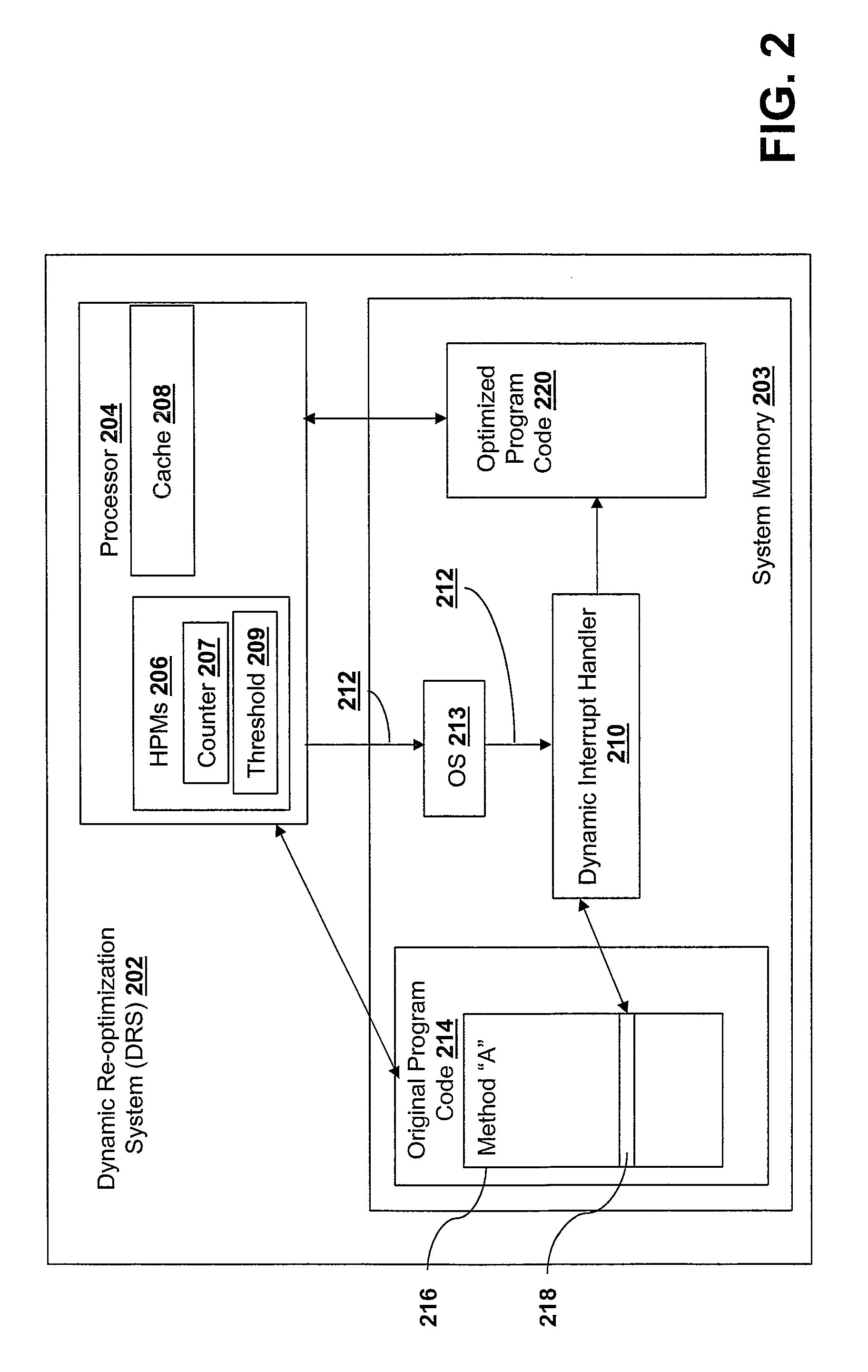

Using hardware interrupts to drive dynamic binary code recompilation

InactiveUS20090271772A1Specific program execution arrangementsMemory systemsComputerized systemDynamic recompilation

A method, computer system, and computer program product for using one or more hardware interrupts to drive dynamic binary code recompilation. The execution of a plurality of instructions is monitored to detect a problematic instruction. In response to detecting the problematic instruction, a hardware interrupt is thrown to a dynamic interrupt handler. A determination is made whether a threshold for dynamic binary code recompilation is satisfied. If the threshold for dynamic code recompilation is satisfied, the dynamic interrupt handler optimizes at least one of the plurality of instructions.

Owner:IBM CORP

Method and apparatus to preserve trace data

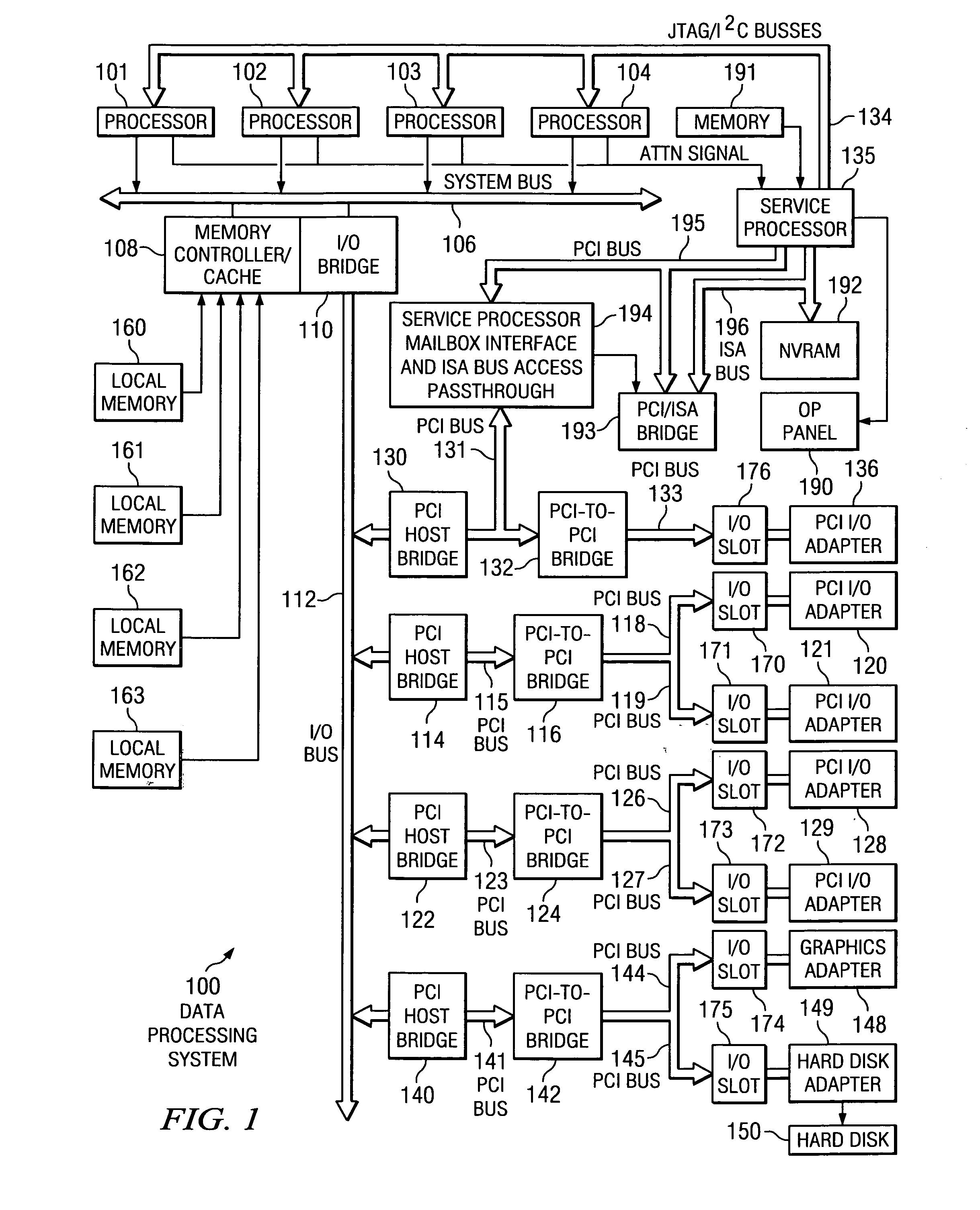

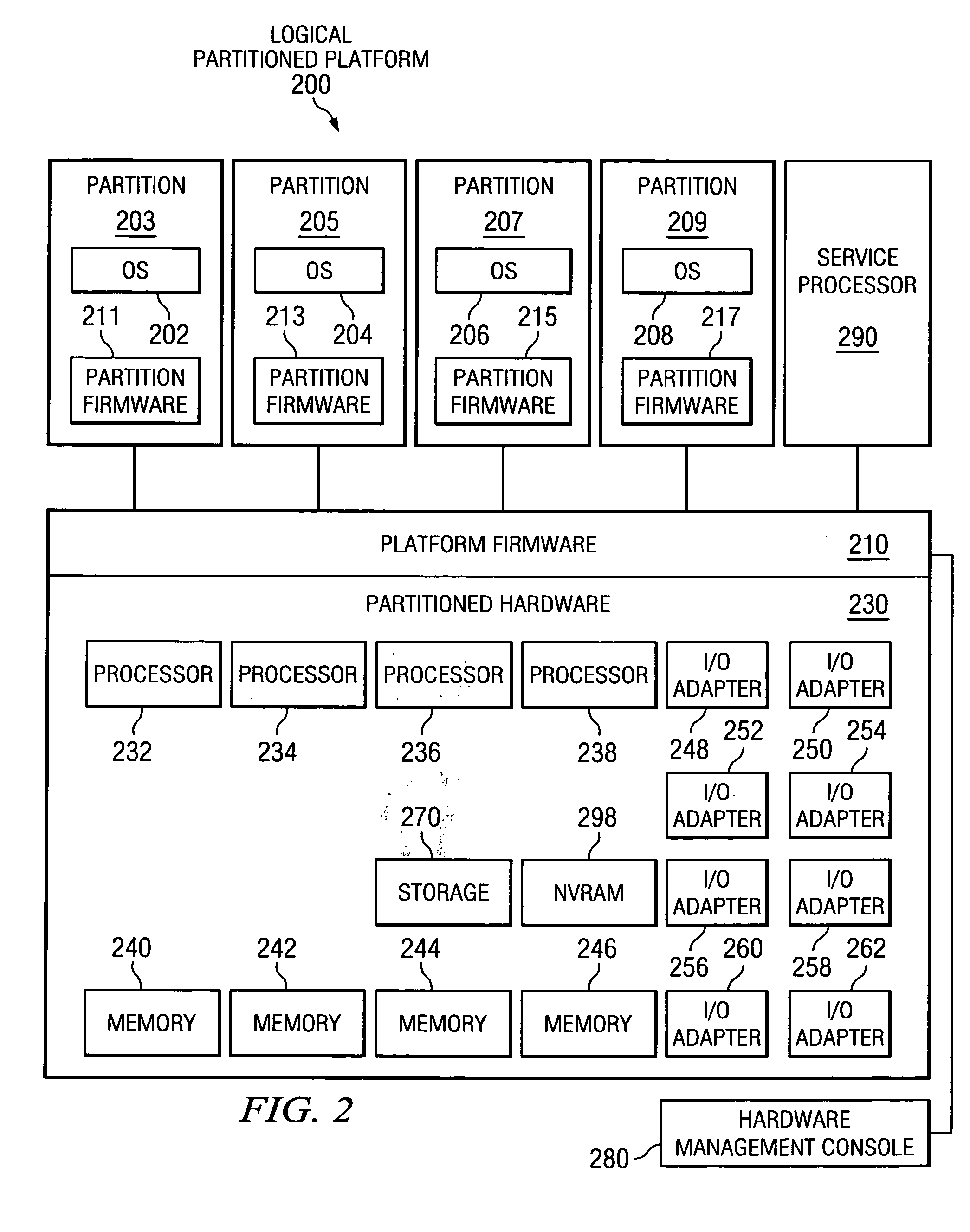

InactiveUS20050278574A1Program initiation/switchingHardware monitoringData processing systemInterrupt handler

A method, apparatus, and computer instructions for processing trace data in a logical partitioned data processing system. A partition causing an exception is identified in response to detecting the exception. The partition is one within a set of partitions in the logical partitioned data processing system. The trace data for the identified partition is stored in an error log or other data structure for a machine check interrupt handler.

Owner:IBM CORP

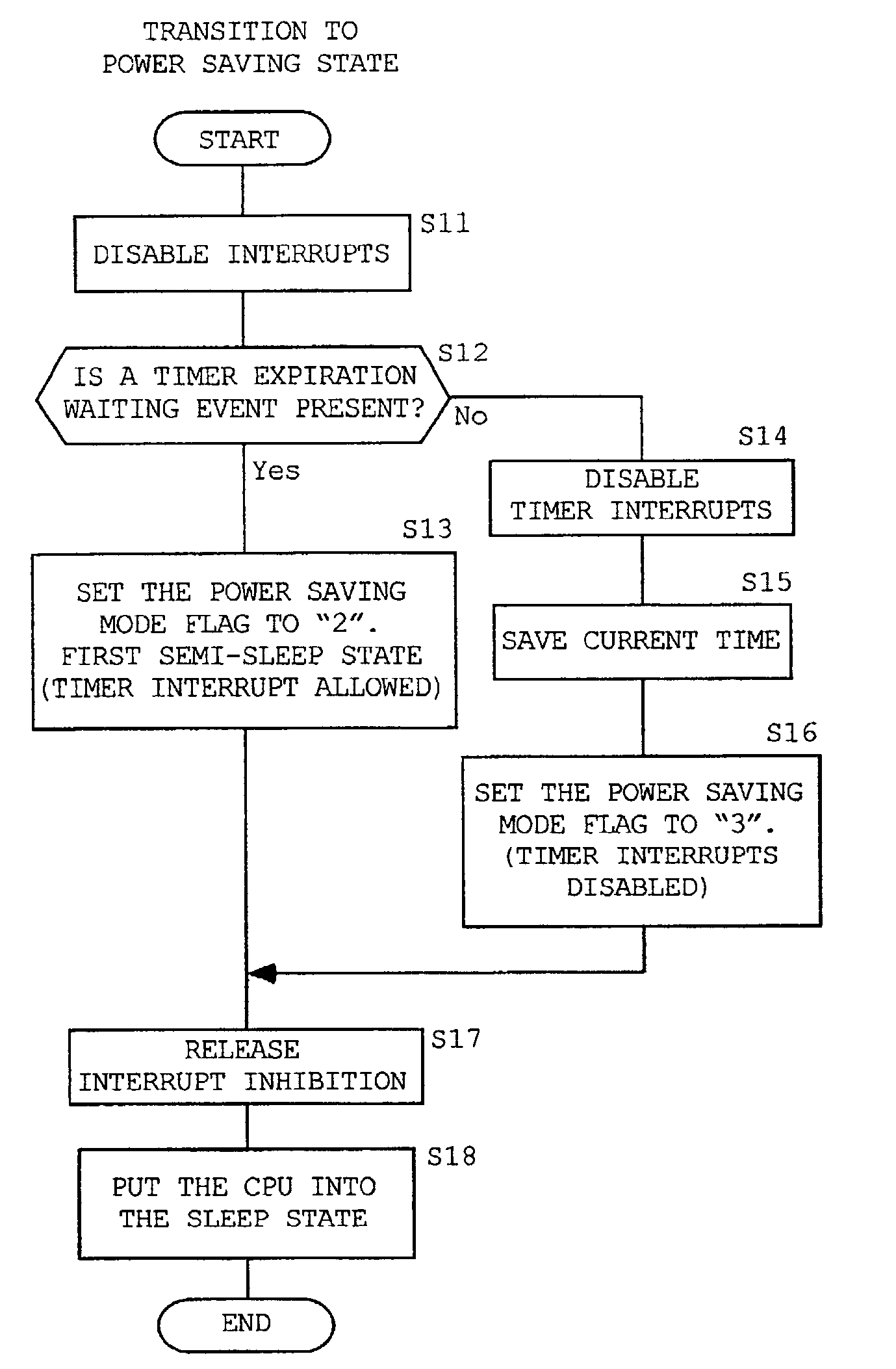

System and method for switching a computer system to a first or second power saving mode based on whether or not there exists a timer-expiration-waiting event in an event queue

InactiveUS7007180B2More powerPower Loss MinimizationEnergy efficient ICTVolume/mass flow measurementComputerized systemOperation mode

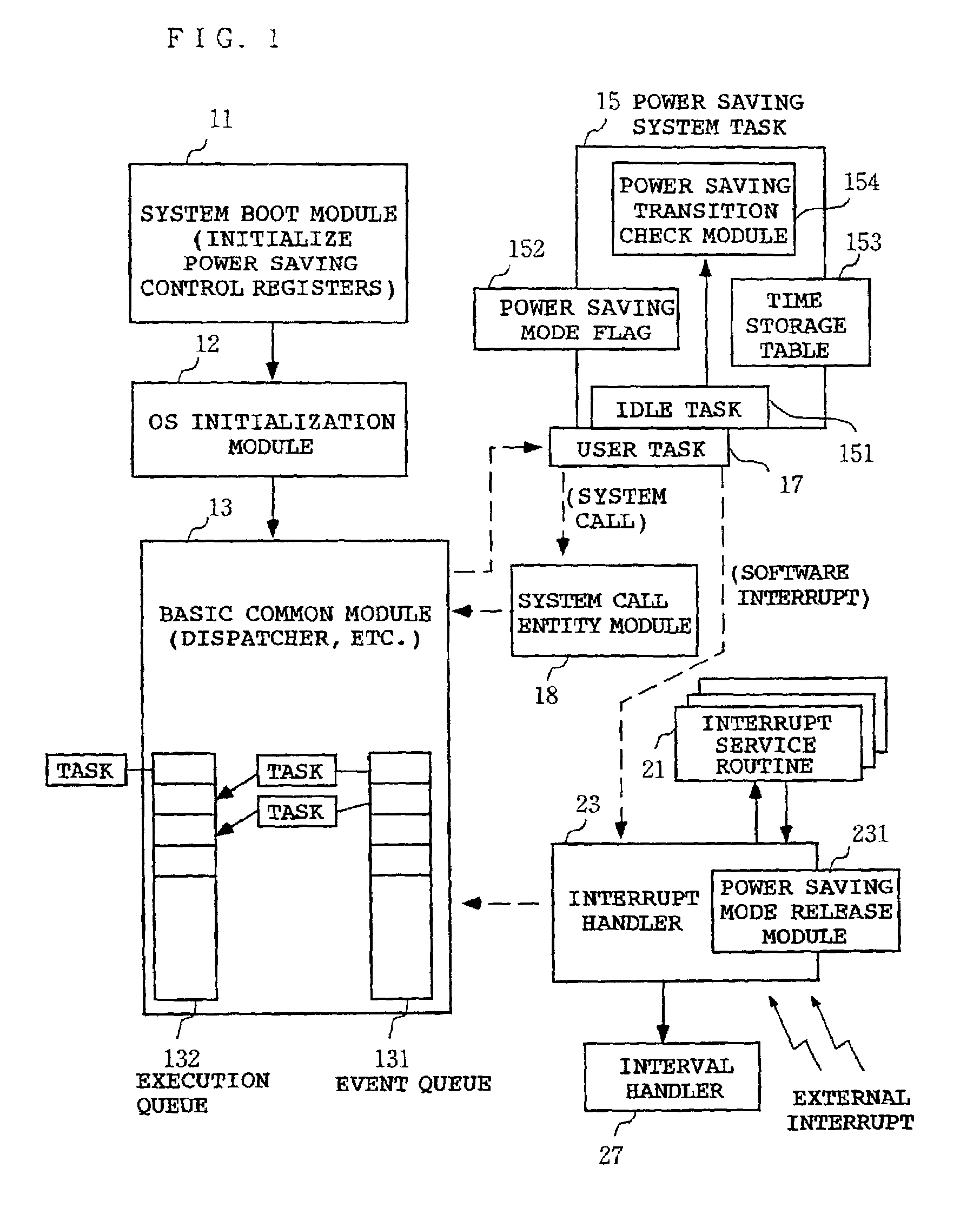

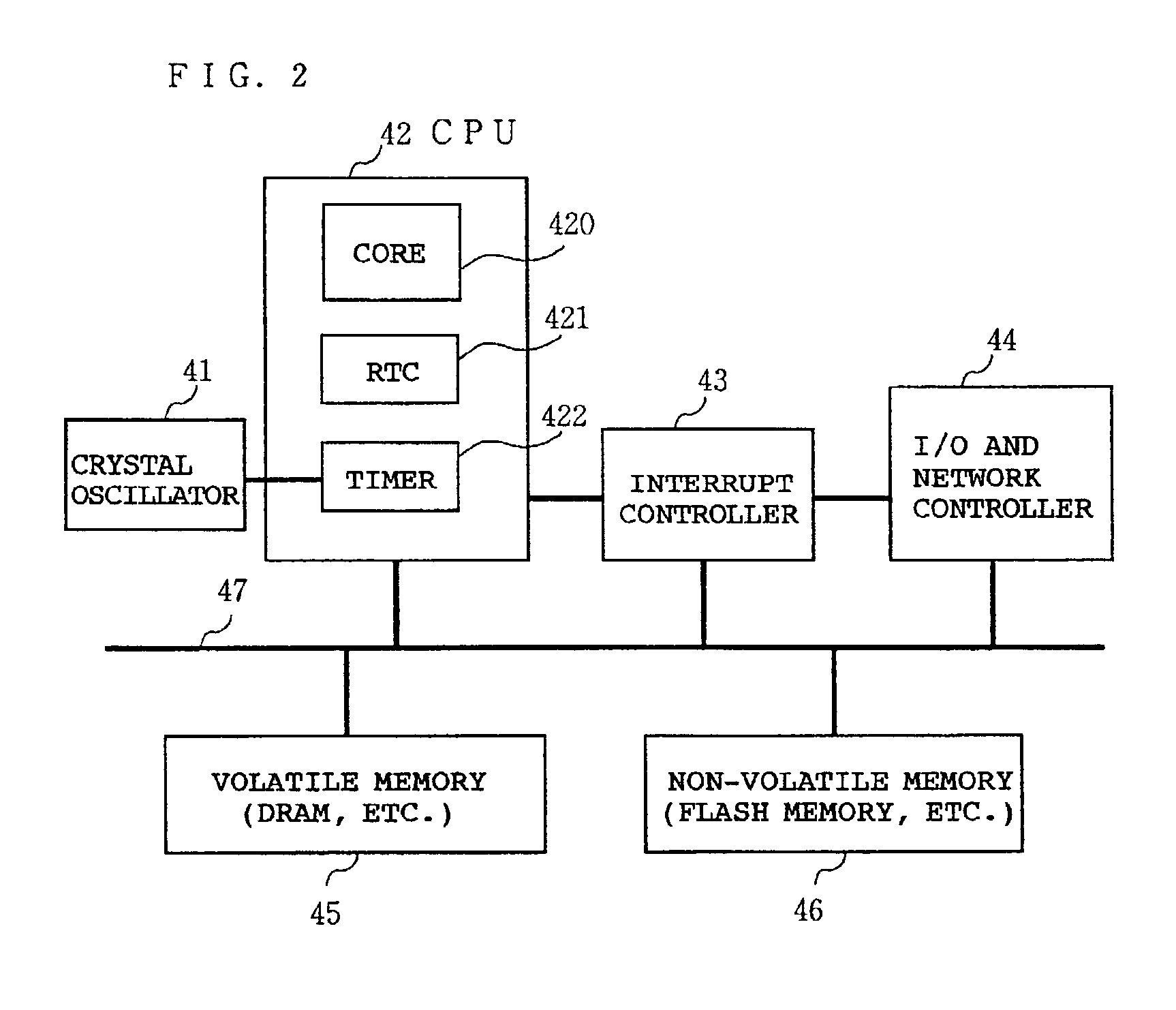

A power saving method and device capable of dynamically select an appropriate power saving mode according to operation states of a computer system. When a power saving system task 15 detects that an execution queue 132 does not contain any executable user task and the computer system has entered an idle state, a power saving transition check module 154 checks if an event queue 131 contains a timer-expiration-waiting event. Depending upon whether or not the timer-expiration-waiting event is present, the computer system moves from a normal operation mode to a first or a second power saving operation mode, each power saving operation mode having its own power saving effect. A power saving mode release module 231 of an interrupt handler 23 returns the system from the first or second power saving operation mode to the normal operation mode in response to an occurrence of an interrupt. For example, in the first power saving operation mode, the CPU operation clock is stopped. In the second power saving operation mode, the CPU operation clock is stopped and, at the same time, a timer interrupt operation is disabled.

Owner:ACCESS

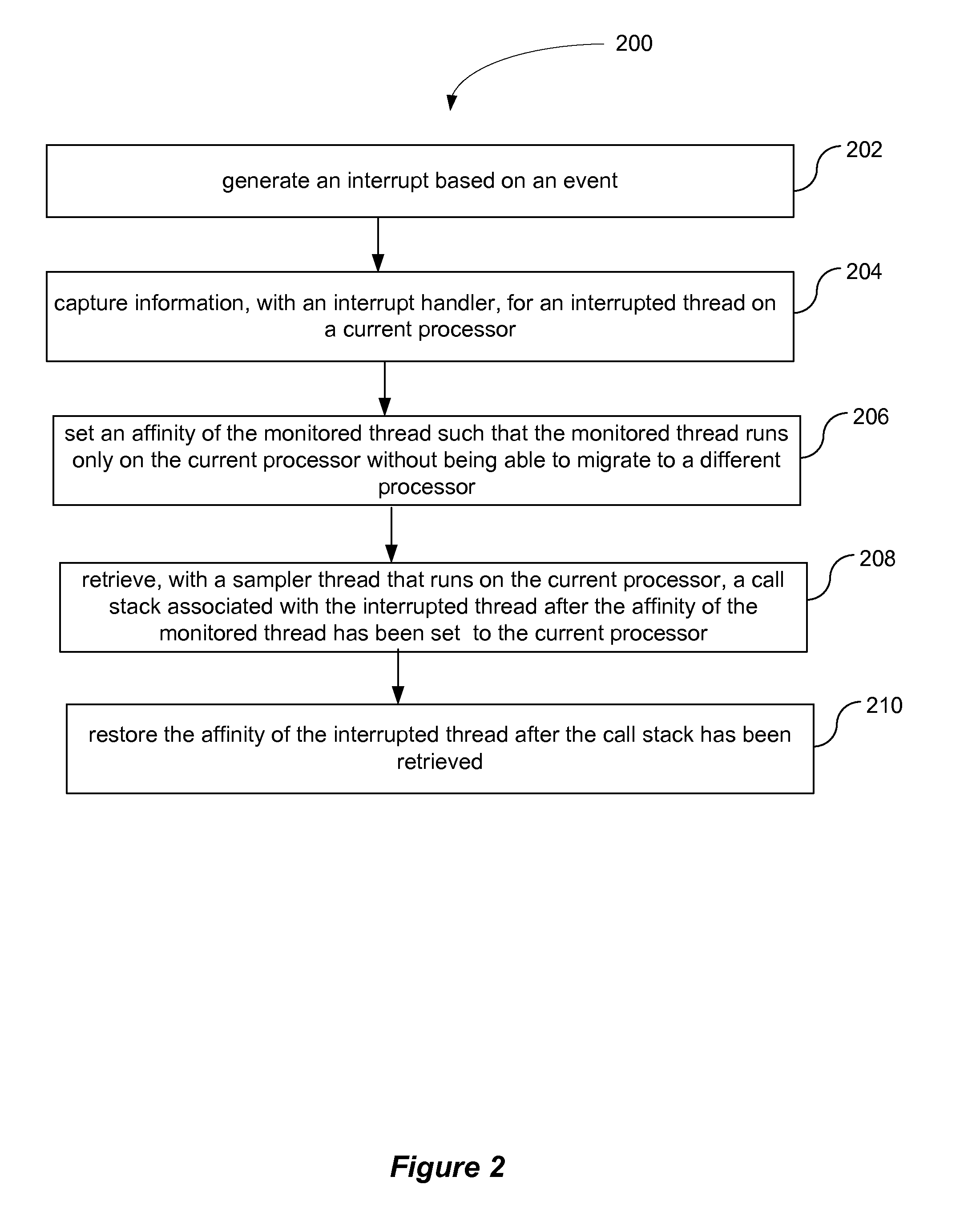

Performing call stack sampling by setting affinity of target thread to a current process to prevent target thread migration

A sample is generated based on an event. Further, an interrupt handler captures information for an interrupted thread on a current processor. In addition, an affinity of the interrupted thread is set such that the interrupted thread runs only on the current processor without being able to migrate to a different processor. A sampler thread that runs on the current processor retrieves a call stack associated with the interrupted thread after the affinity of the interrupted thread has been set to the current processor. The affinity of the interrupted thread is restored after the call stack has been retrieved.

Owner:INT BUSINESS MASCH CORP