Patents

Literature

38 results about "Bus error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

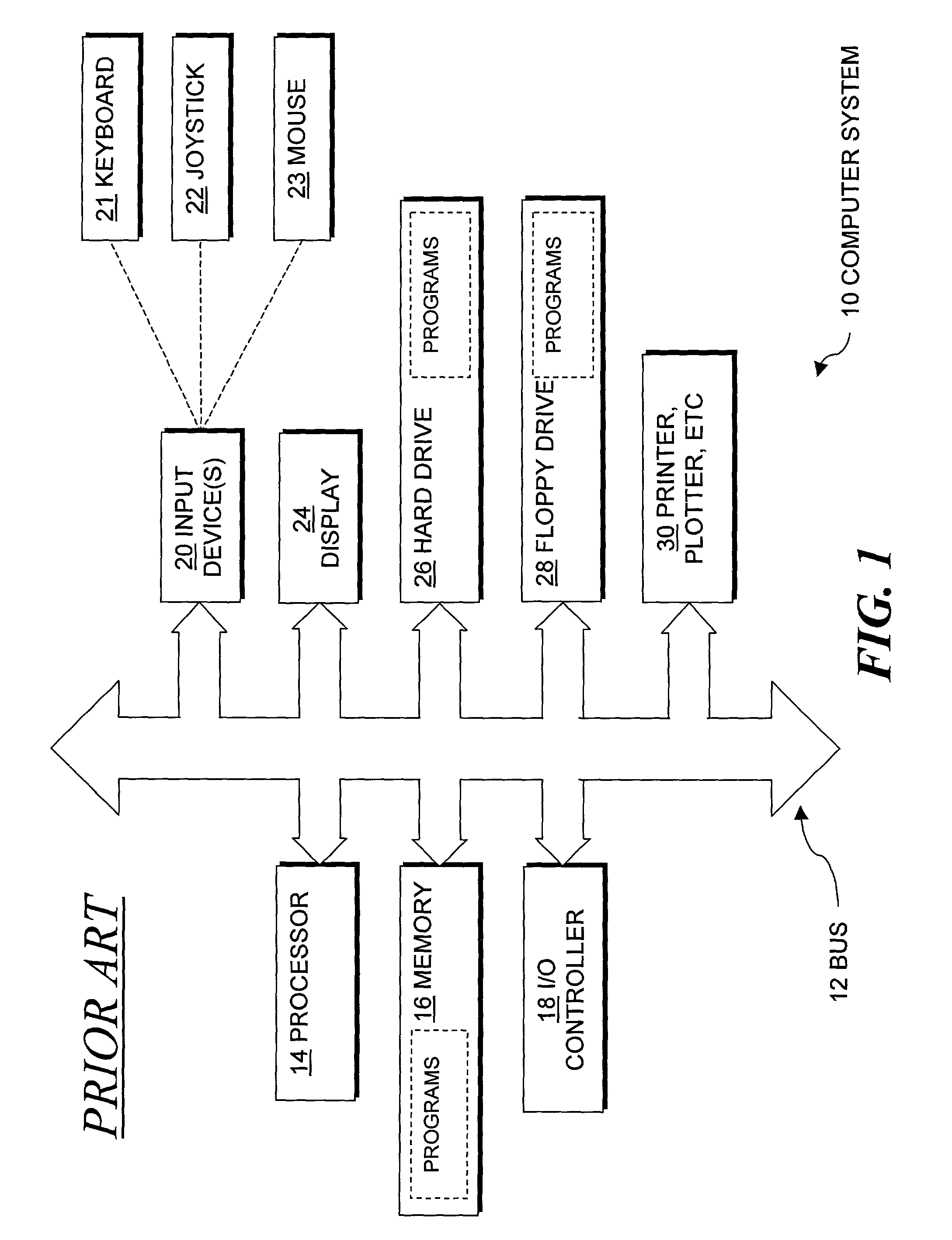

In computing, a bus error is a fault raised by hardware, notifying an operating system (OS) that a process is trying to access memory that the CPU cannot physically address: an invalid address for the address bus, hence the name. In modern use on most architectures these are much rarer than segmentation faults, which occur primarily due to memory access violations: problems in the logical address or permissions.

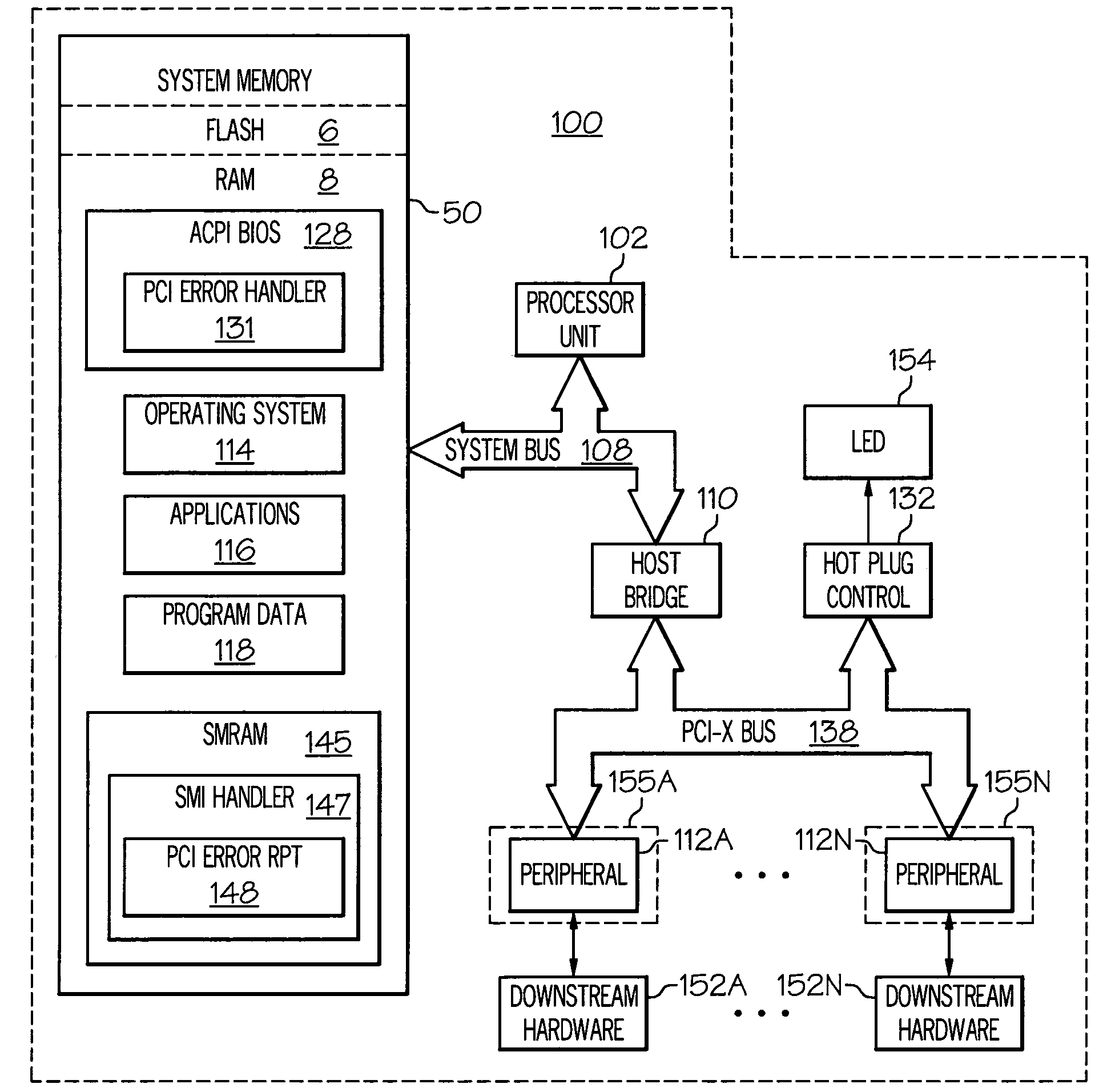

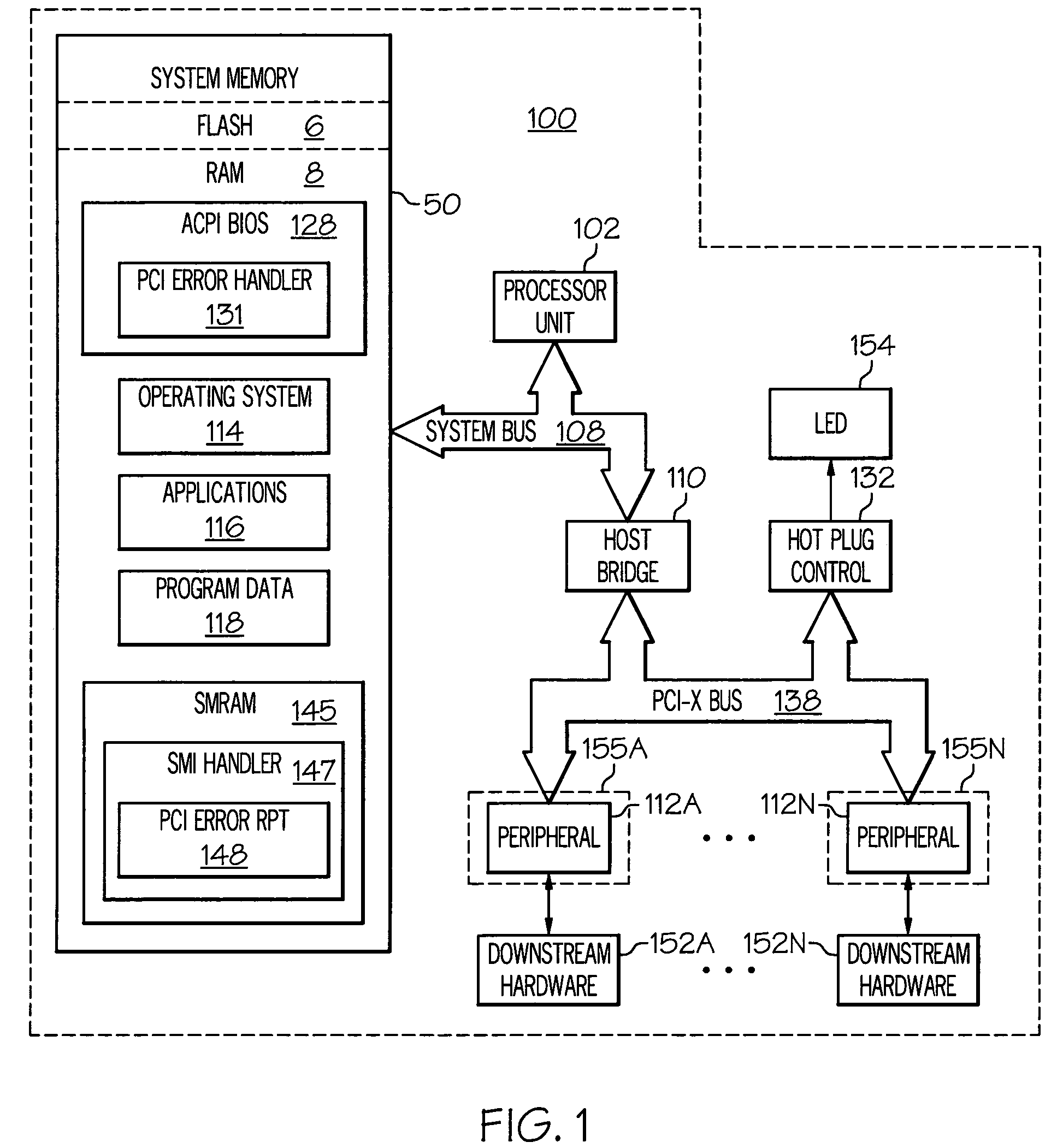

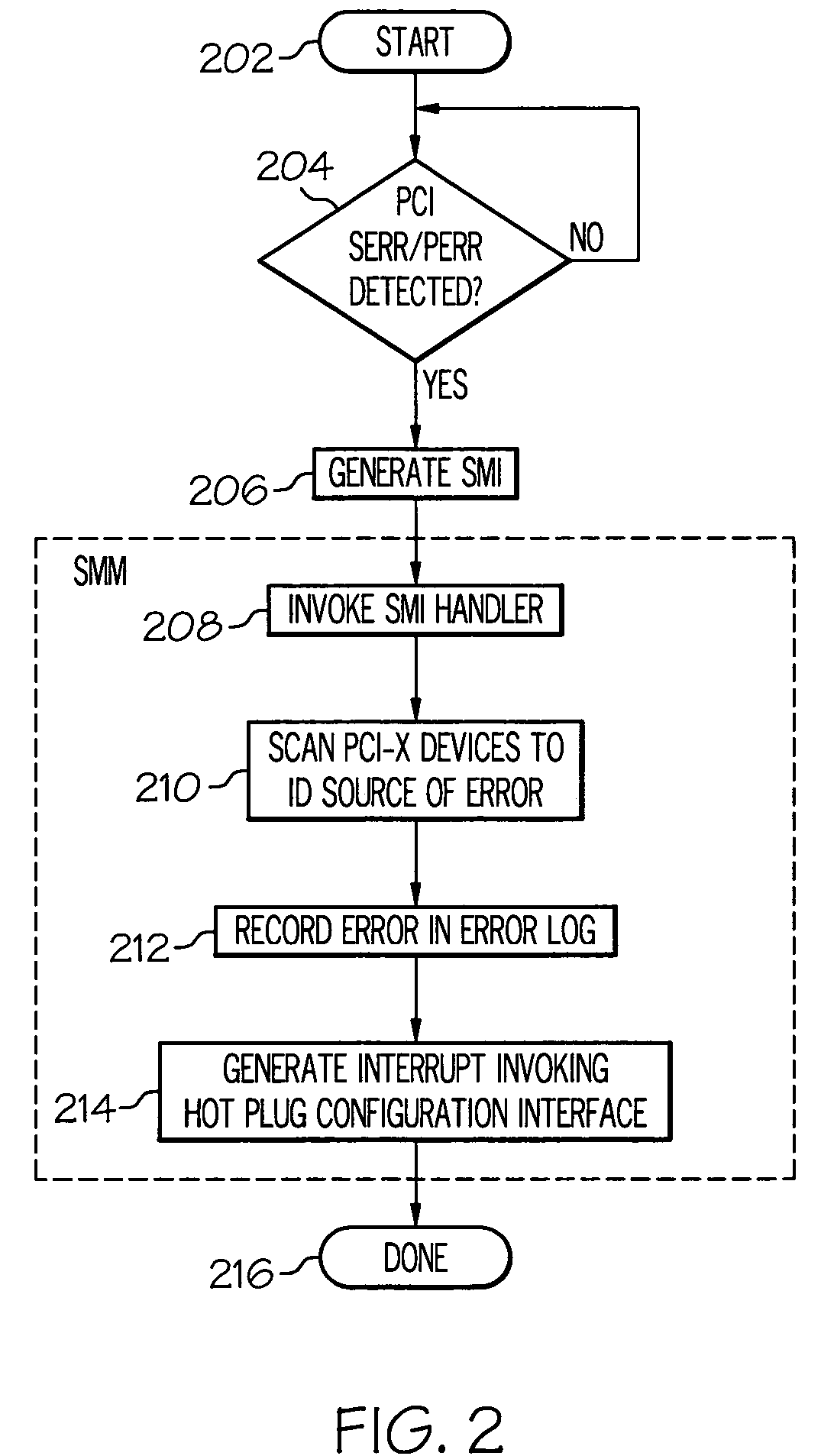

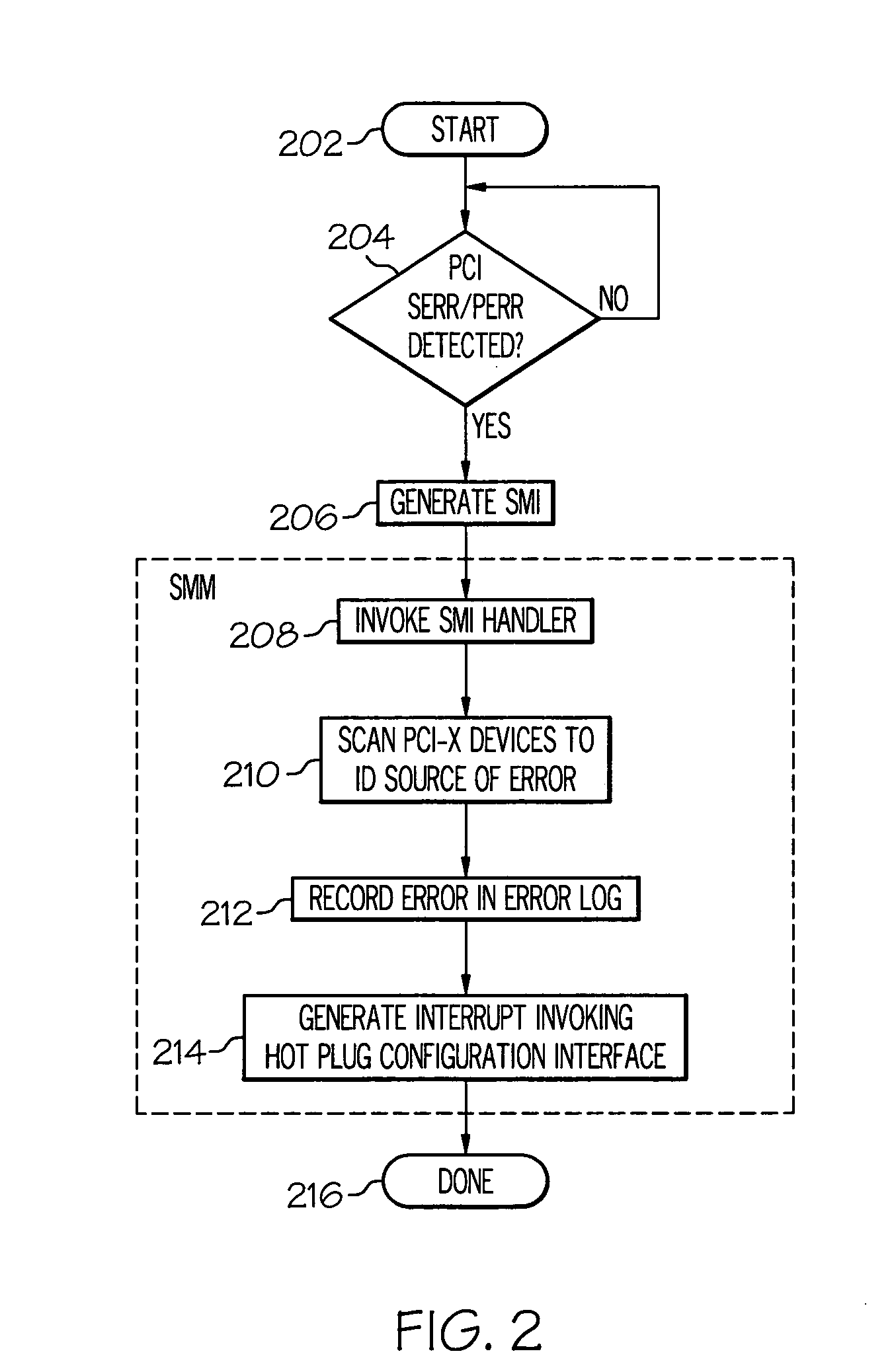

System and method for using hot plug configuration for PCI error recovery

InactiveUS7447934B2Non-redundant fault processingAdvanced Configuration and Power InterfaceOperational system

Owner:LENOVO GLOBAL TECH INT LTD

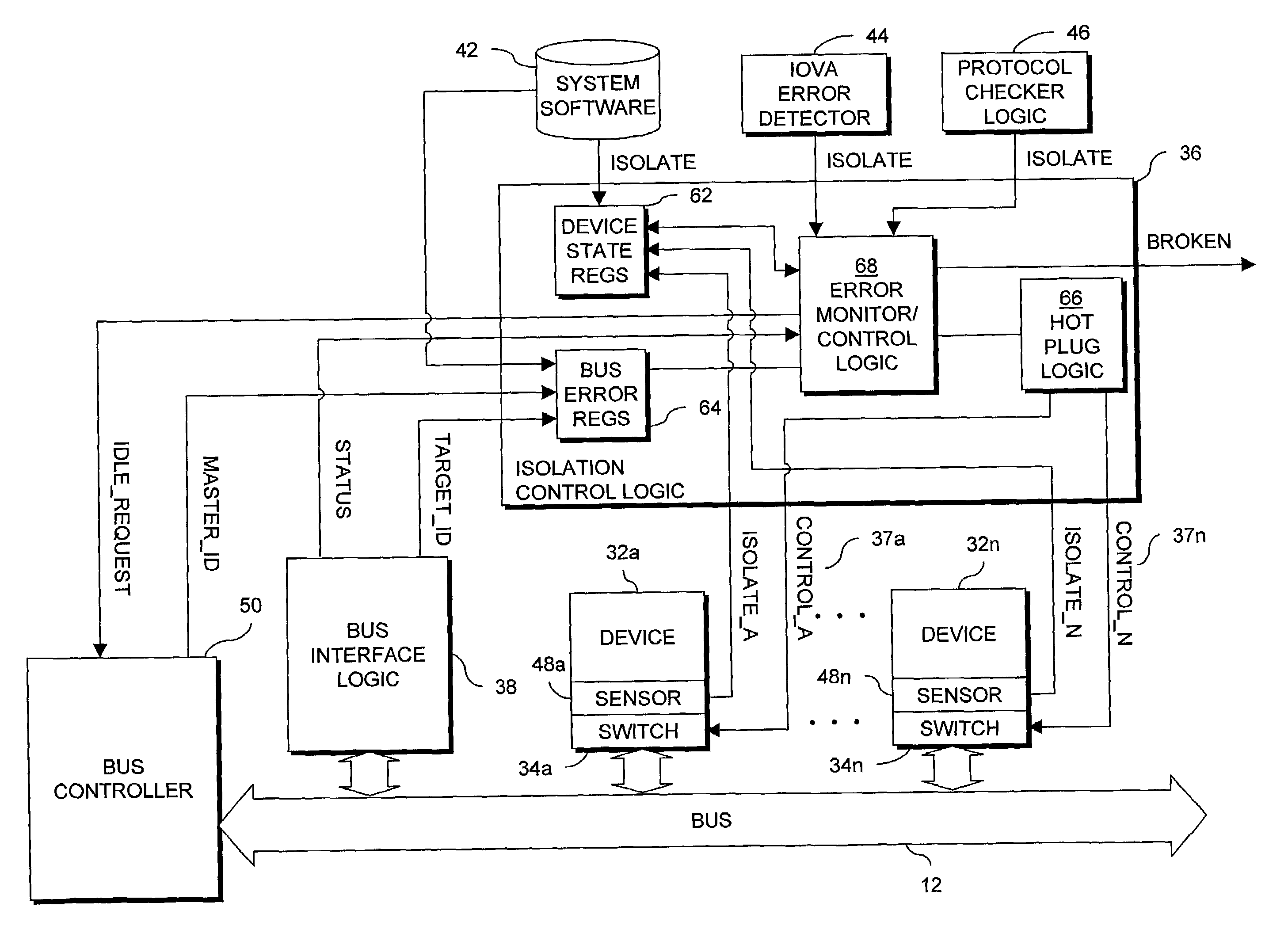

Methods and apparatus for computer bus error termination

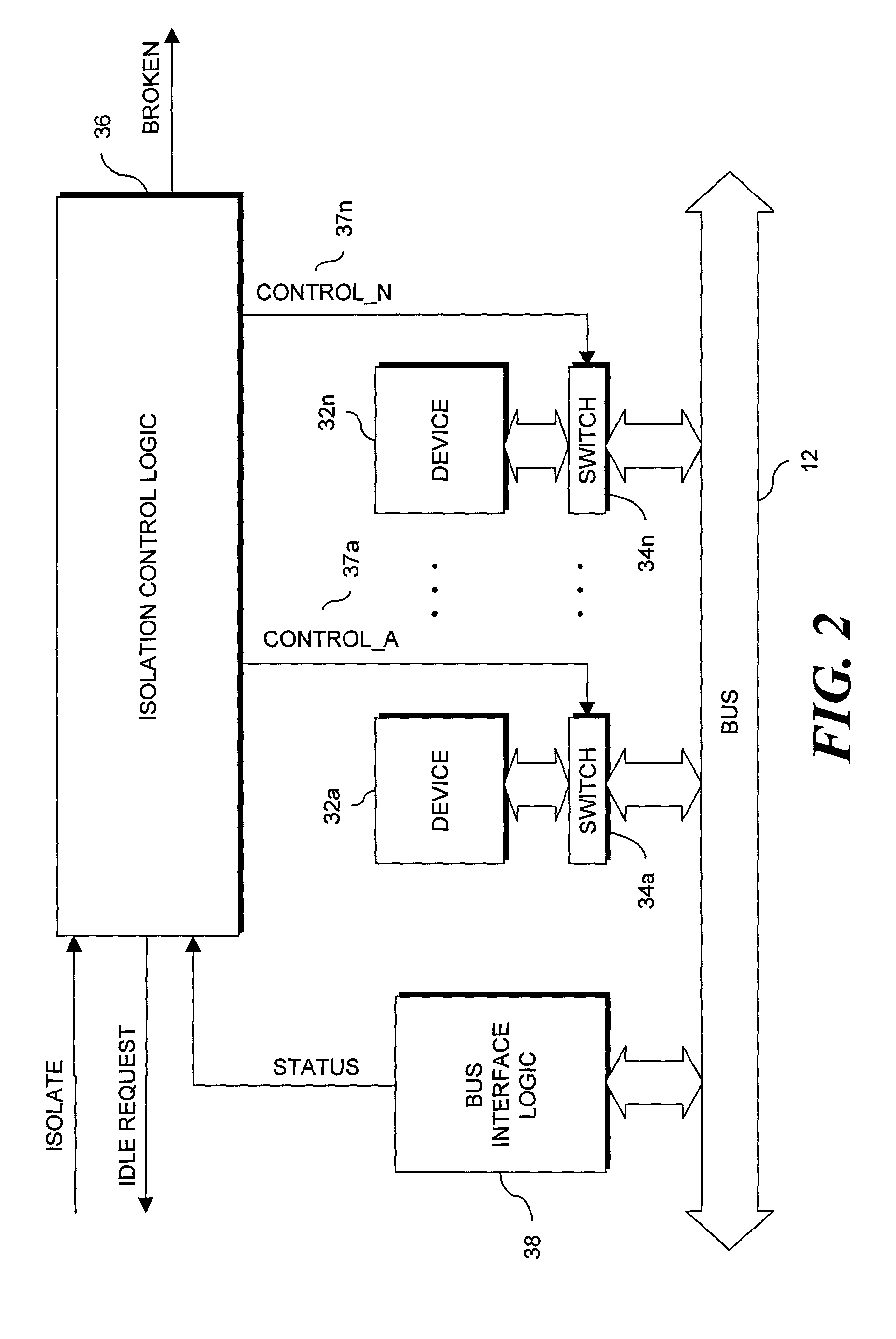

In a computer system having a bus architecture, a system and process for isolating a device from a bus without interrupting system operation is described, the system including bus interface logic monitoring and reporting activity on the bus, isolation control logic receiving error signals from error detectors, and isolation switches through which devices are interconnected to the bus, the isolation switches allowing for the isolation of the devices from the bus. The isolation control logic determines the devices to be isolated responsive to the reported error and, in turn, transmits an isolation switch control signal to the isolation switch(es) associated with the identified device(s) to isolate those device(s) from the bus. In some embodiments, errors are reported by system software, input / output virtual address error detectors for systems using virtual memory addressing, protocol error detectors, and sensors sensing the physical removal of a bus-connected device from its bus interface slot.

Owner:STRATUS TECH IRELAND LTD

System and method for using hot plug configuration for PCI error recovery

InactiveUS20070011500A1Non-redundant fault processingAdvanced Configuration and Power InterfaceOperational system

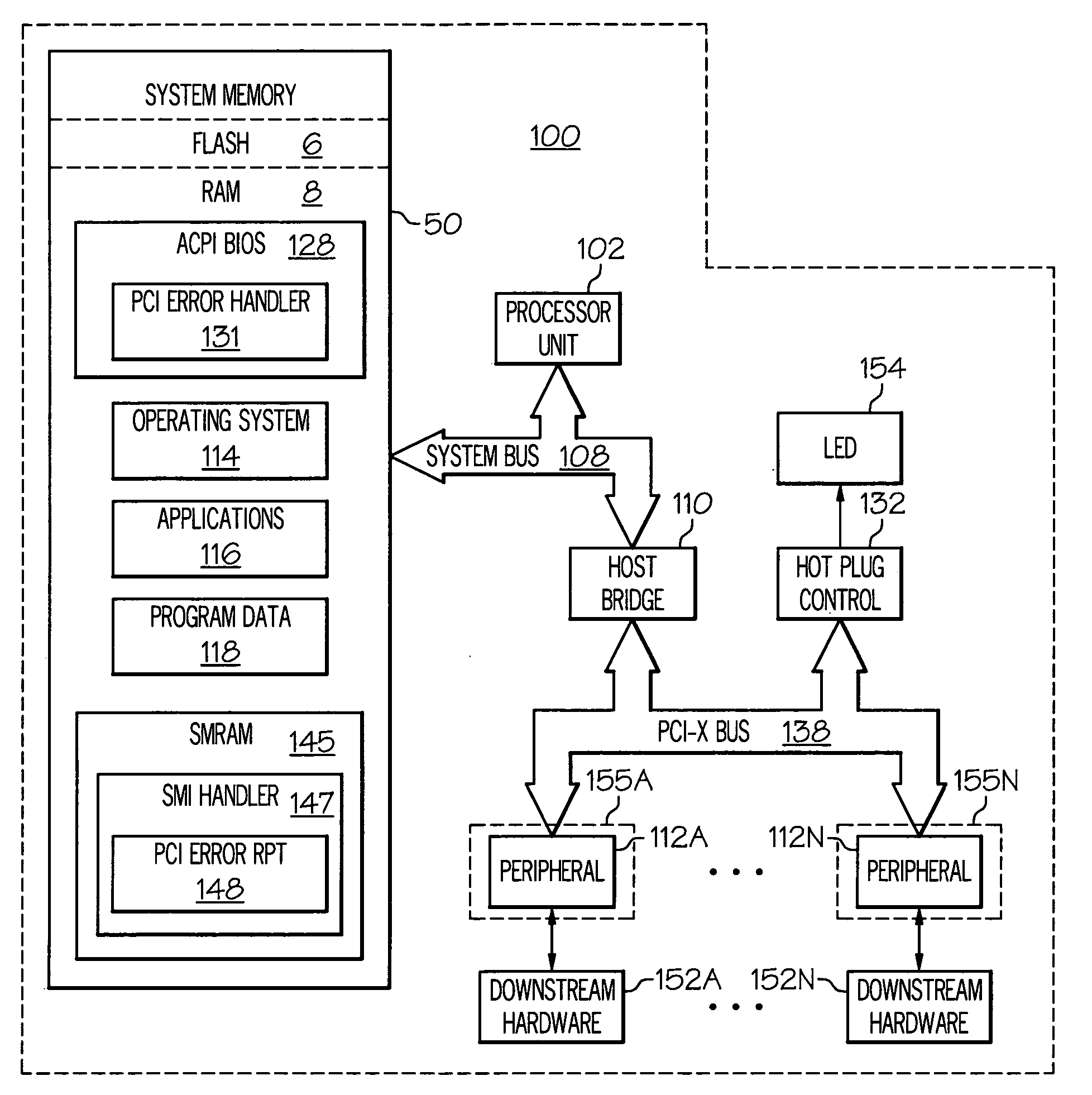

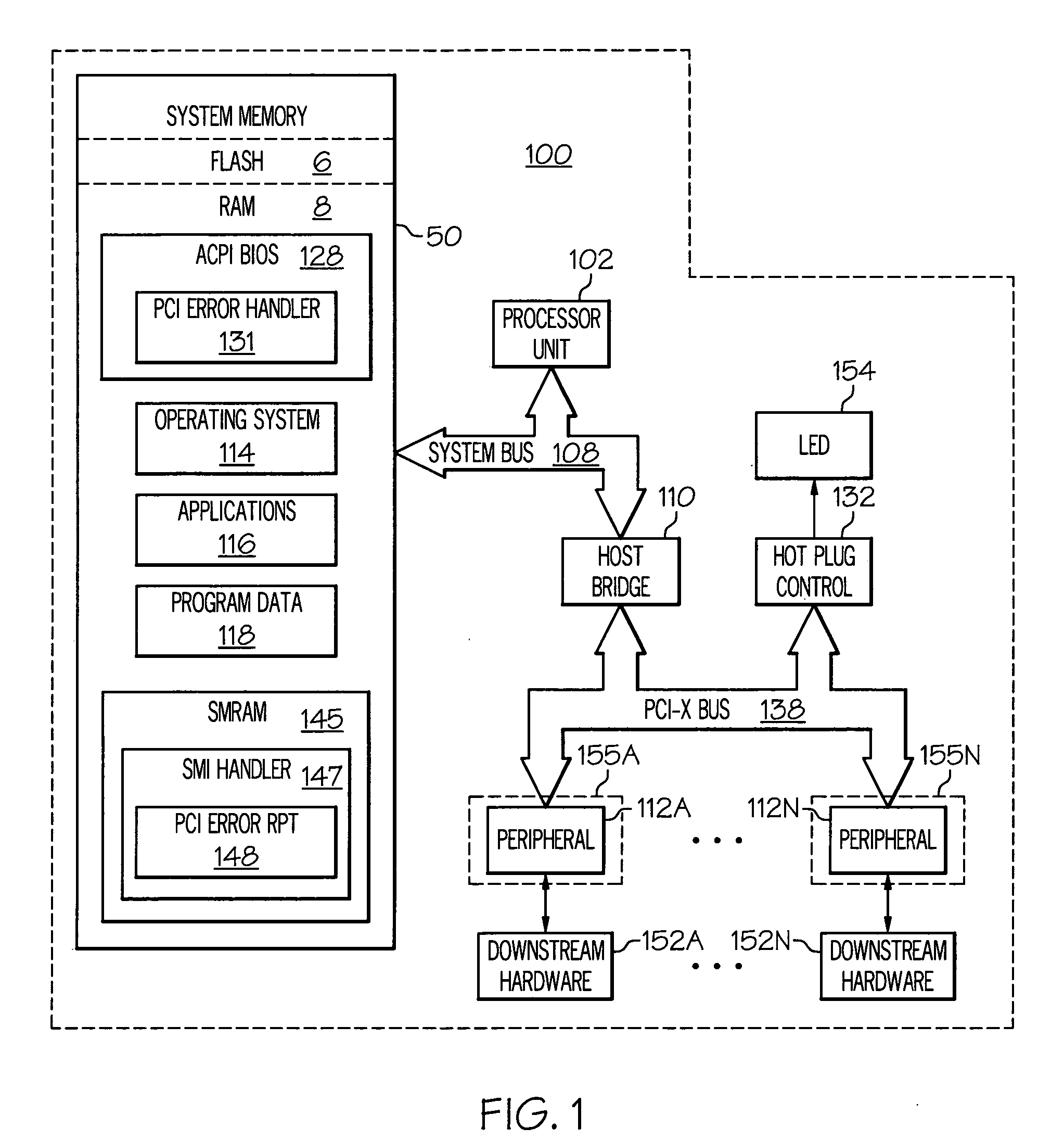

A method, system, and program product for recovering from a bus error in a computer system having a hot plug interface. In accordance with the method of the present invention, an operating system transparent interrupt, such as a system management interrupt, is generated in response to a bus error. Responsive to the operating system transparent interrupt, the hot pluggable bus is scanned and a device associated with the error is identified by an interrupt handler invoked by the interrupt. Finally, a hot plug configuration manager, such as an advanced configuration and power interface is utilized to remove the identified device from system operations without having to restart the system.

Owner:LENOVO GLOBAL TECH INT LTD

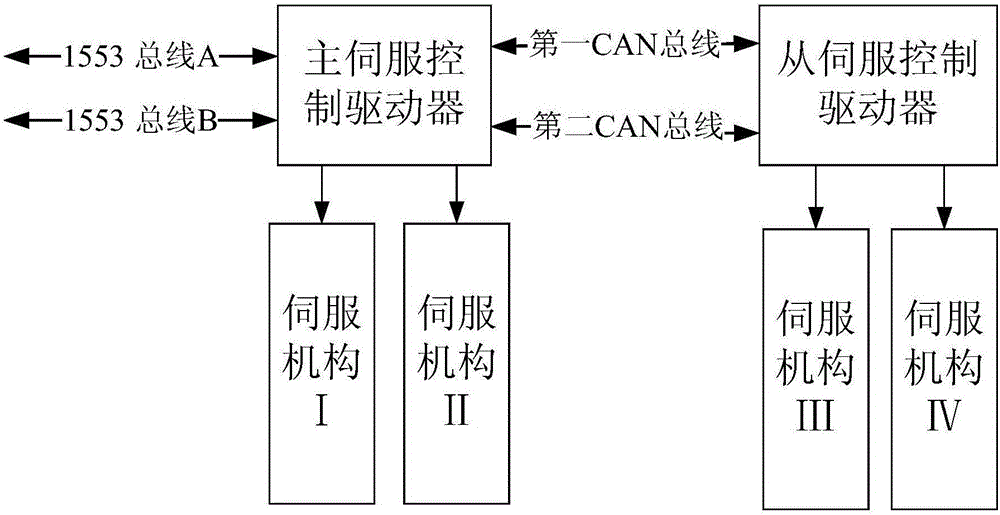

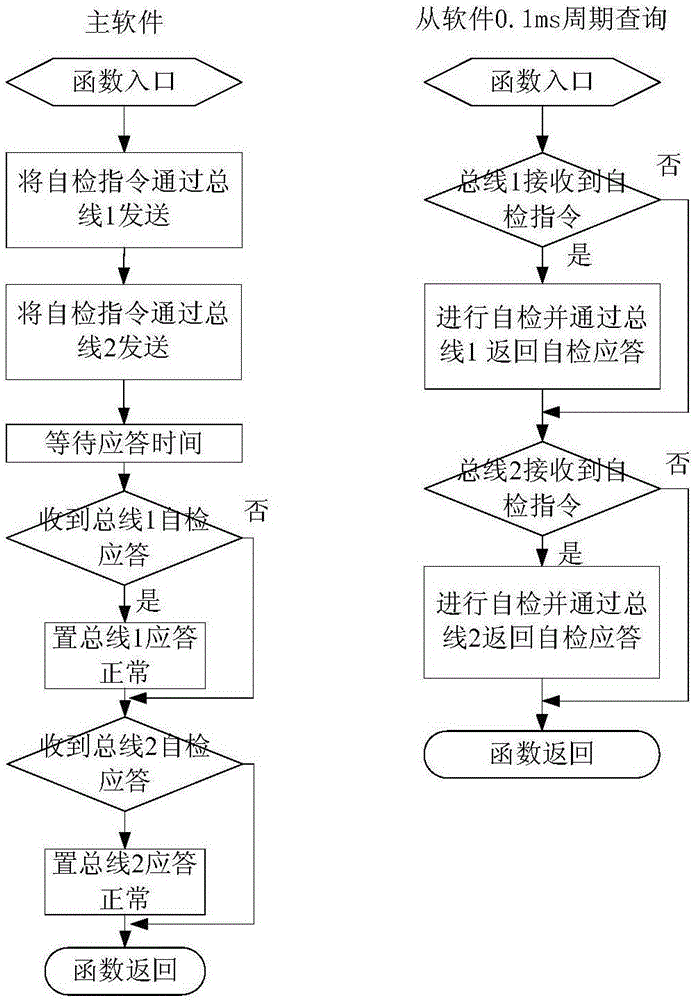

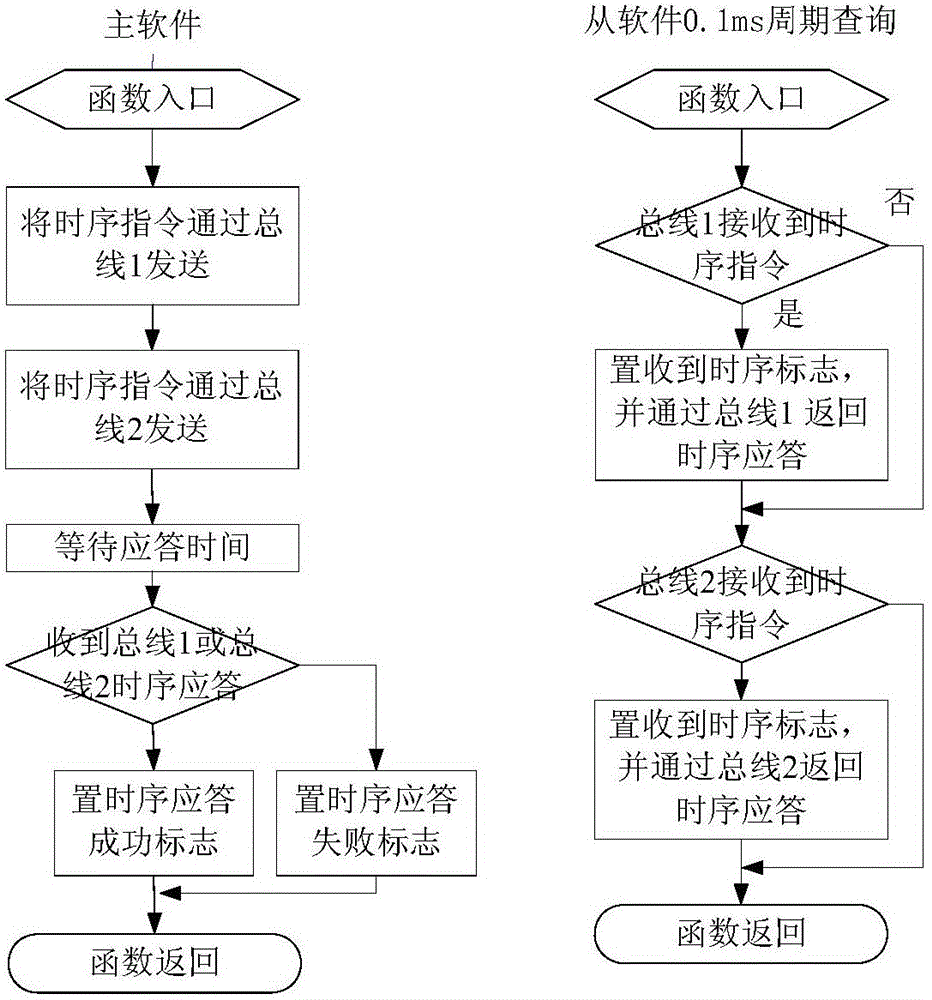

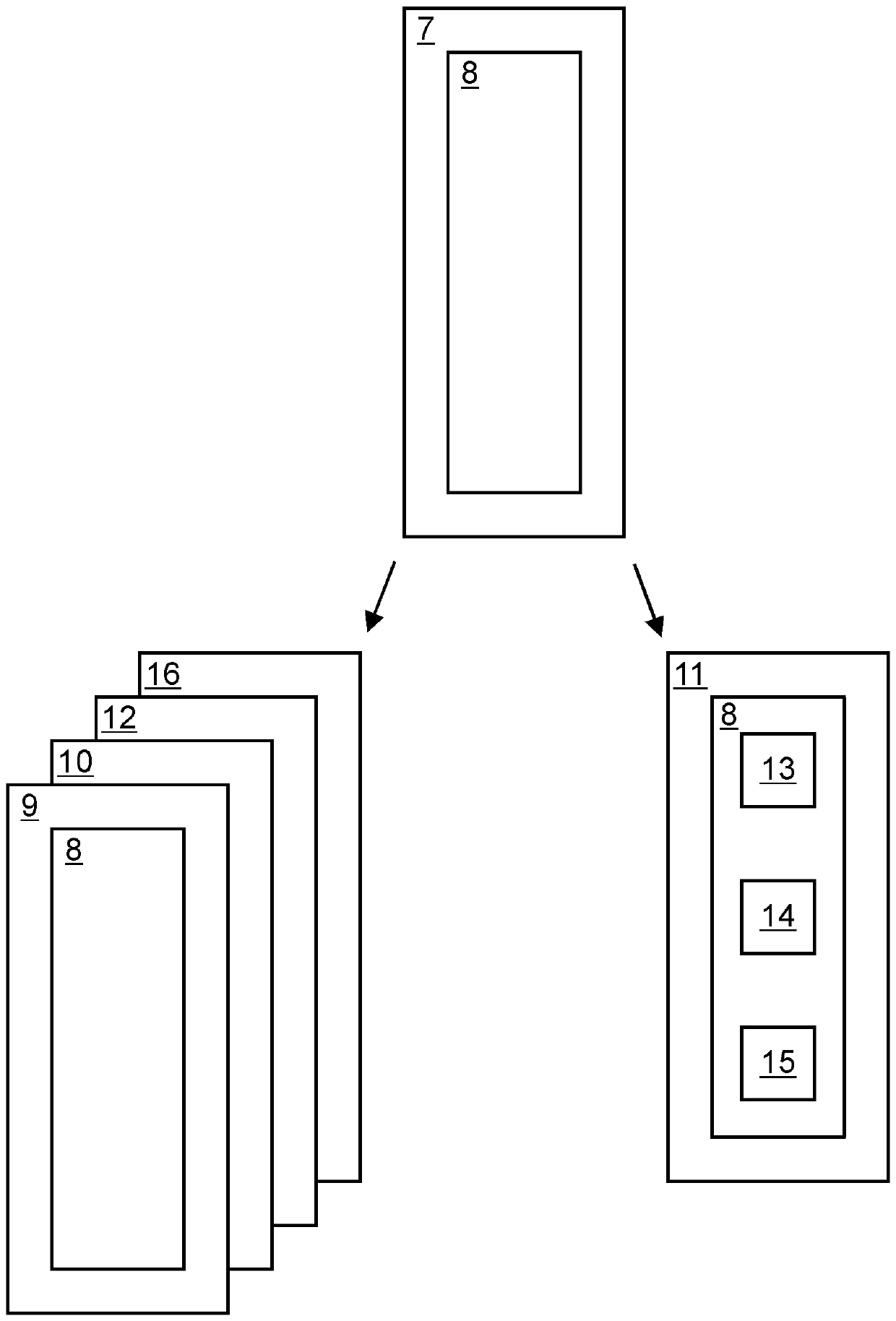

Multi-intelligent stand-alone servo control system based on dual redundant CAN bus communication

ActiveCN106444713AAchieve coordinationSolve the problem of distributed control requirementsProgramme controlElectric testing/monitoringSelf recoveryRocket

The invention relates to a multi-intelligent stand-alone servo control system based on dual redundant CAN bus communication. A main servo control drive receives the instruction of a host computer, so as to carry out corresponding operation. The instruction received by the host computer is redundantly sent to a servo control drive through a first CAN bus and a second CAN bus, wherein the first CAN bus and the second CAN bus are peer to each other. An instruction operation result and measurement parameters are fed back to the host computer, wherein the instruction operation result and the measurement parameters are sent by the main servo control drive in the system and an auxiliary servo control drive. Without increasing additional data transmission, bus error self-diagnosis and bus state self-diagnosis are carried out on the dual redundant CAN buses are in real time. When communication bus abnormities are found through self-diagnosis, corresponding self-recovery measures are taken for self-recovery. The system is used for the communication of different intelligent stand-alones of a rocket flight control servo system, realizes highly reliable communication with relatively low cost, has the functions of self-diagnosis and self-recovery, and ensures the high reliability of a rocket and other flight control systems.

Owner:BEIJING RES INST OF PRECISE MECHATRONICS CONTROLS +1

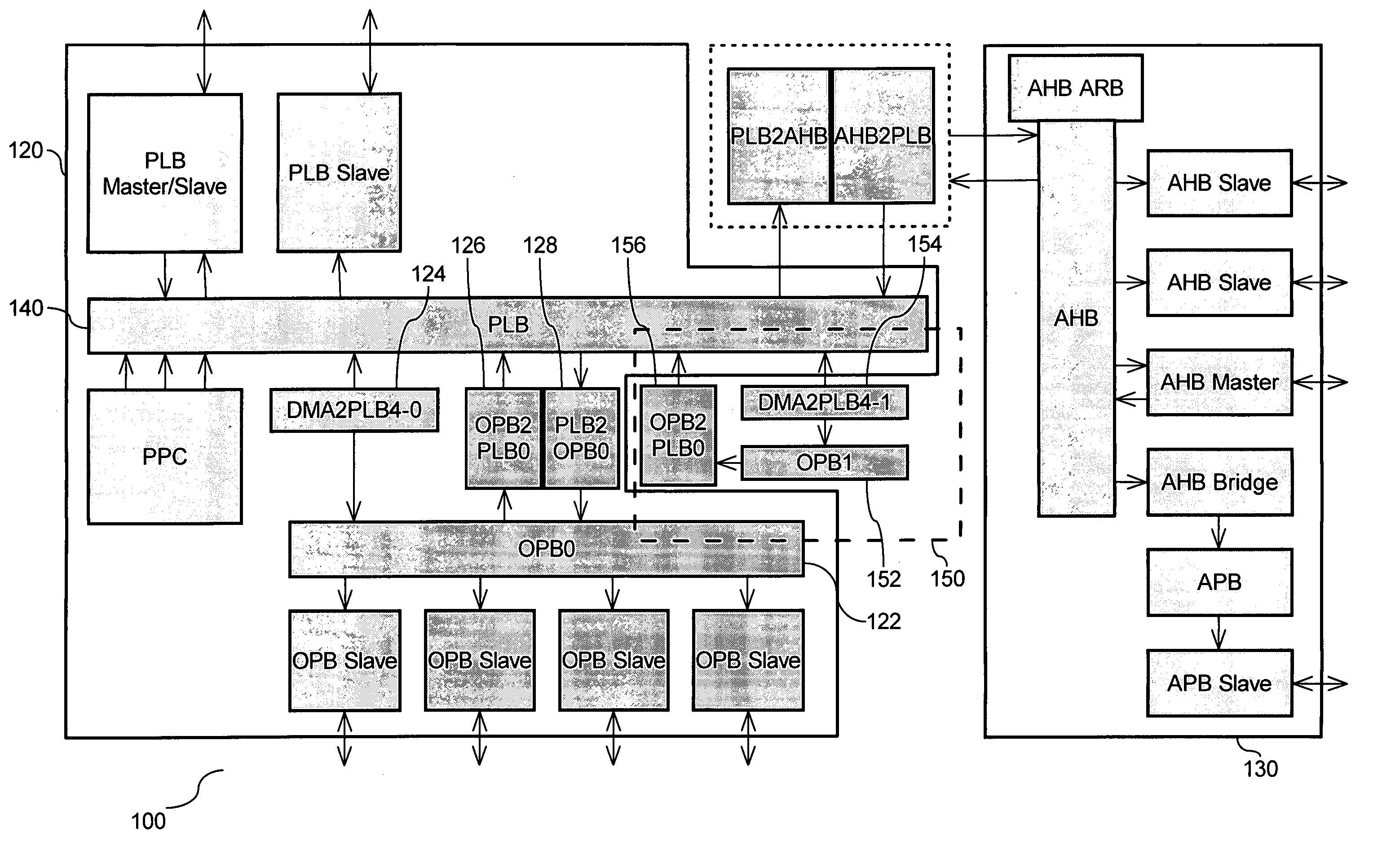

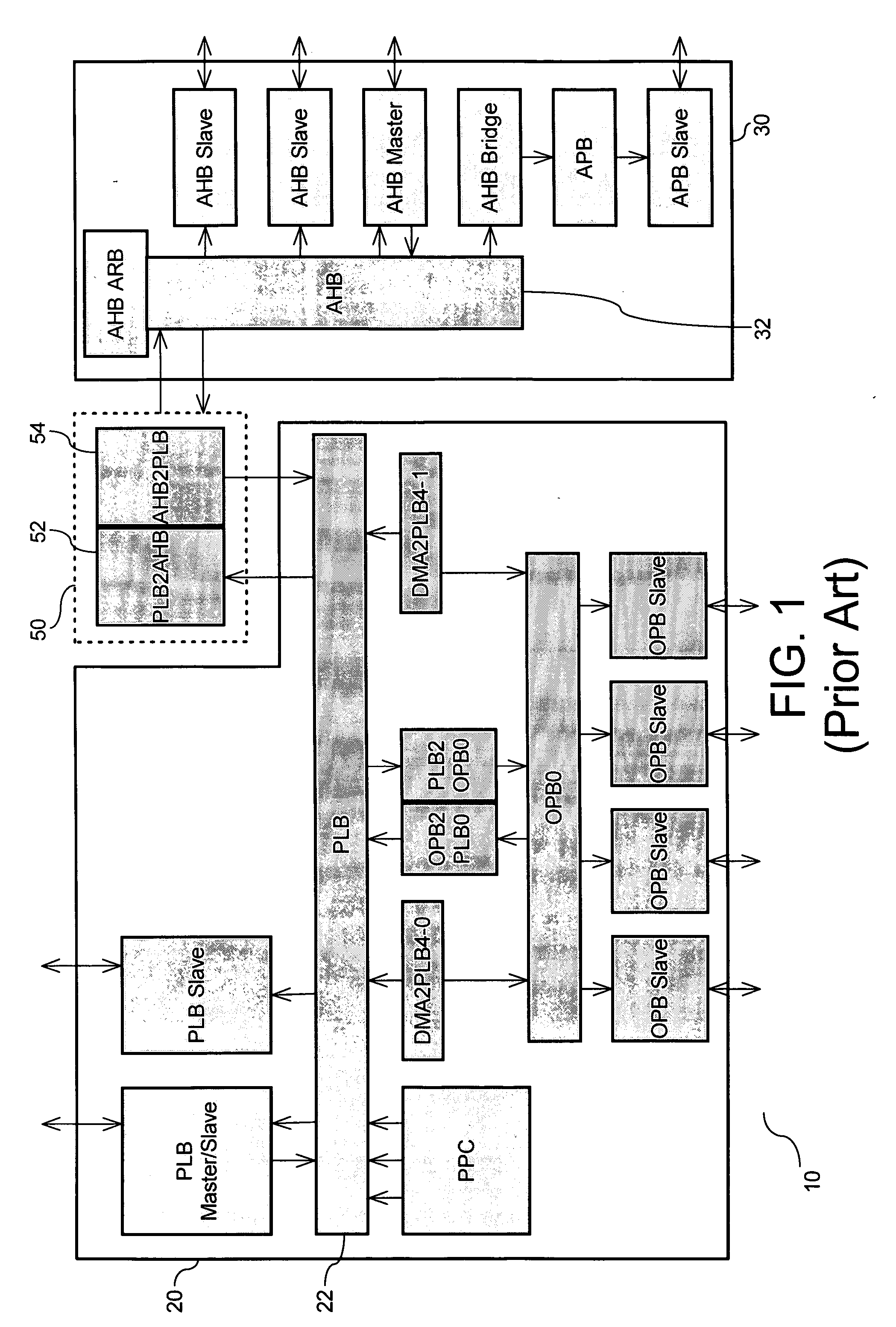

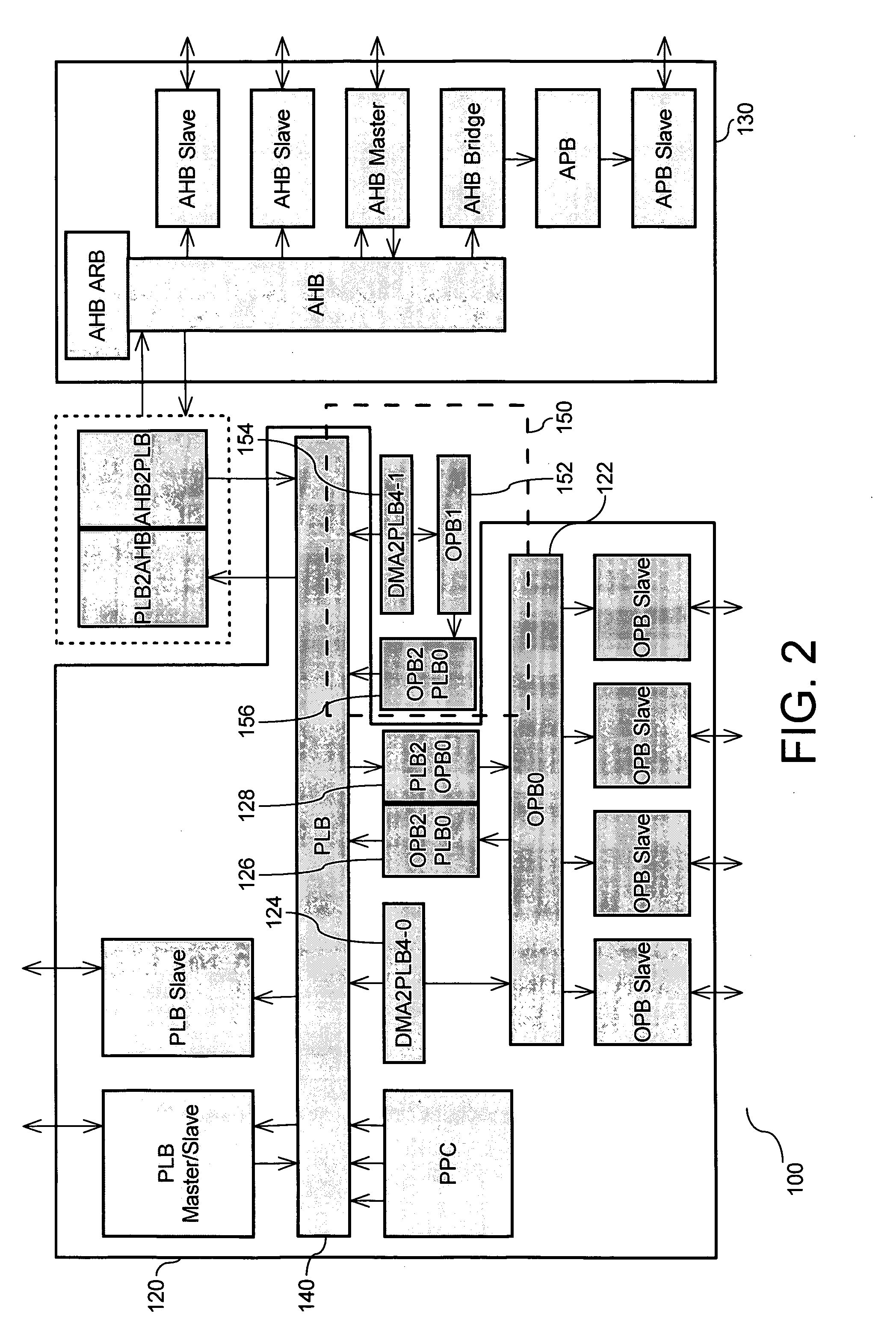

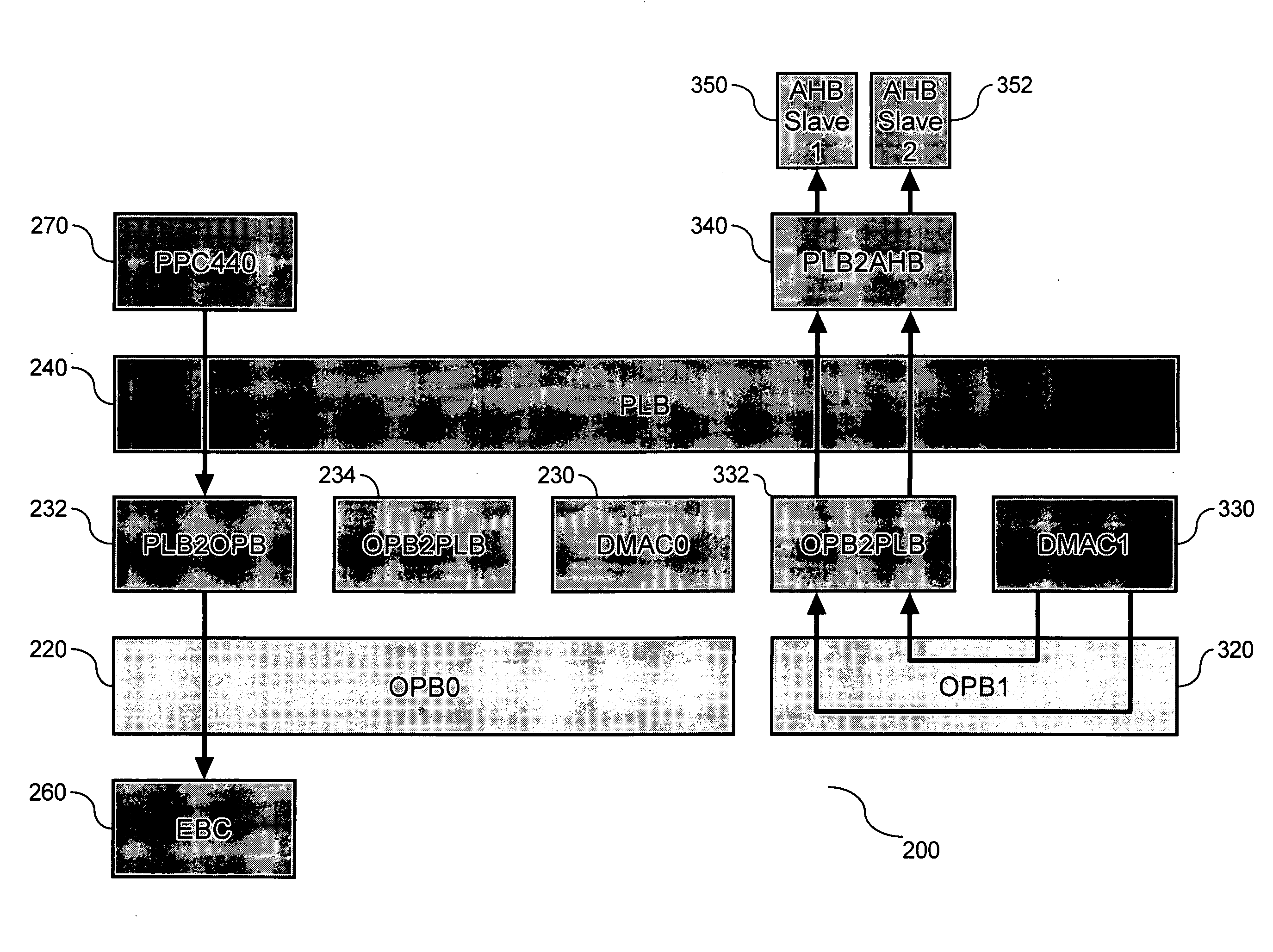

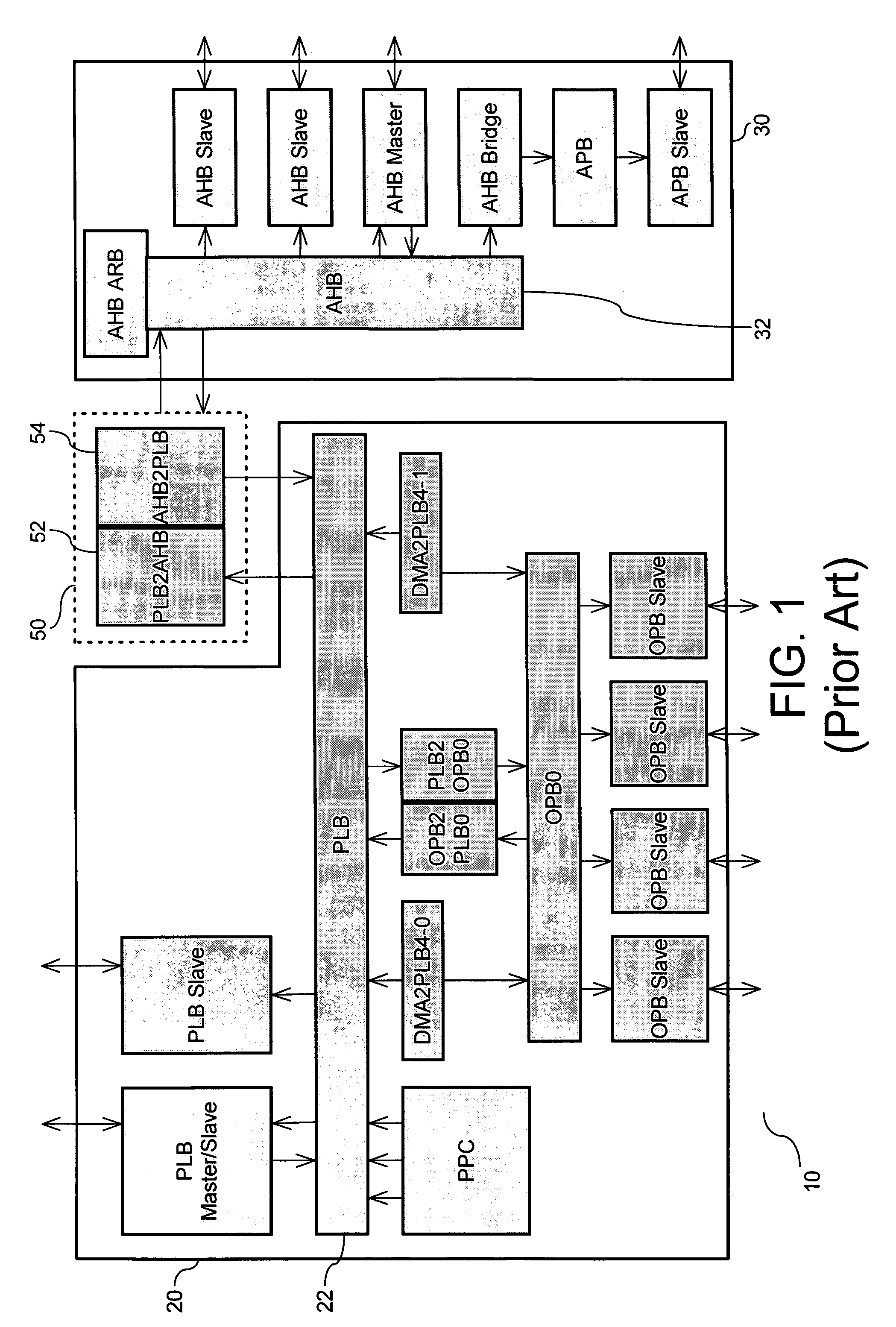

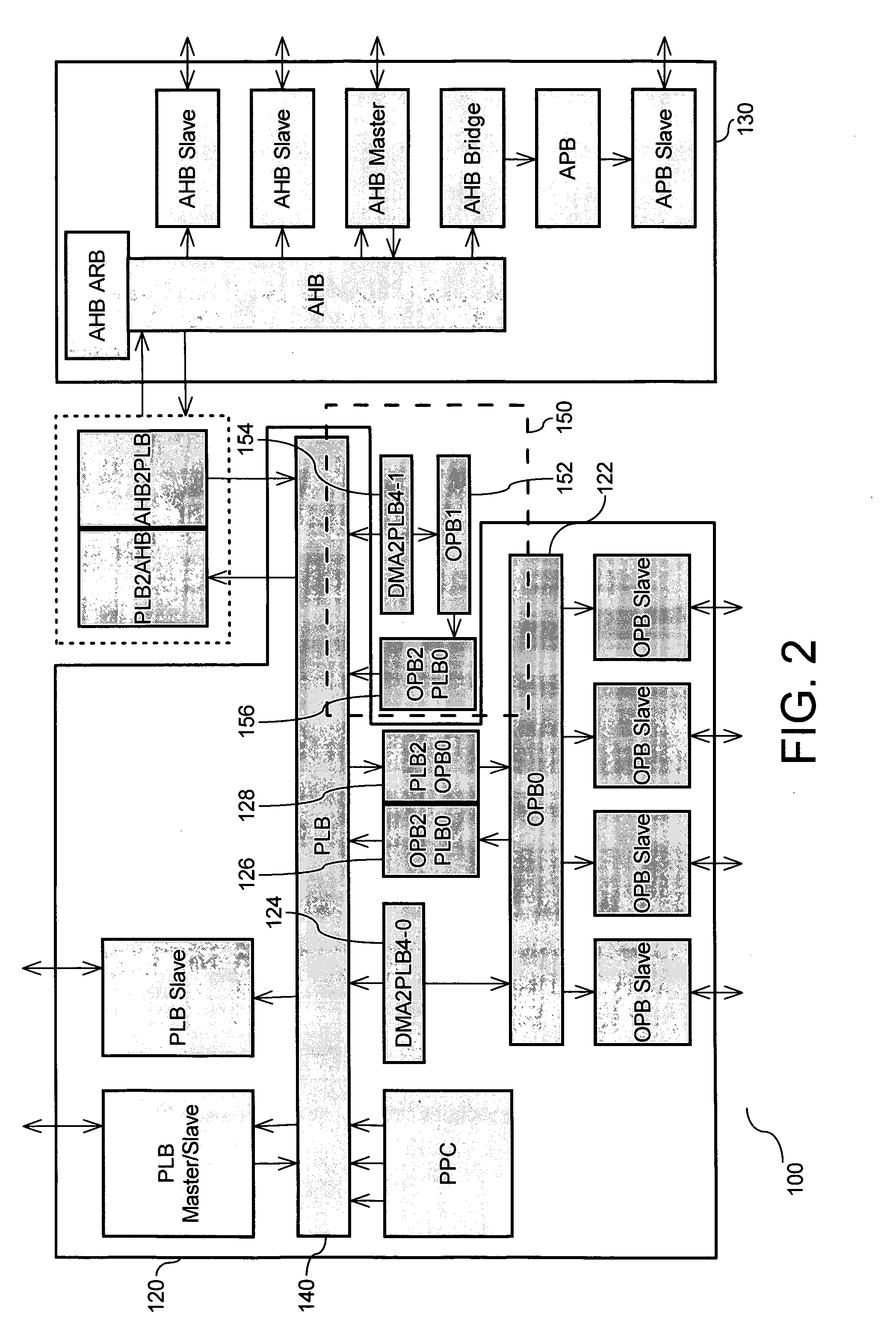

System-On-a-Chip mixed bus architecture

InactiveUS20070130409A1Mitigates bus errorCommunication is limitedGeneral purpose stored program computerMemory systemsData transmissionBus error

A mixed architecture system on chip is provided by combining a CoreConnect system on chip architecture with an AMBA system on chip architecture. To eliminate data transfer and bus error that could occur in the mixed architecture, an additional peripheral bus and bridge are provided to manage communication with AHB resources.

Owner:IBM CORP

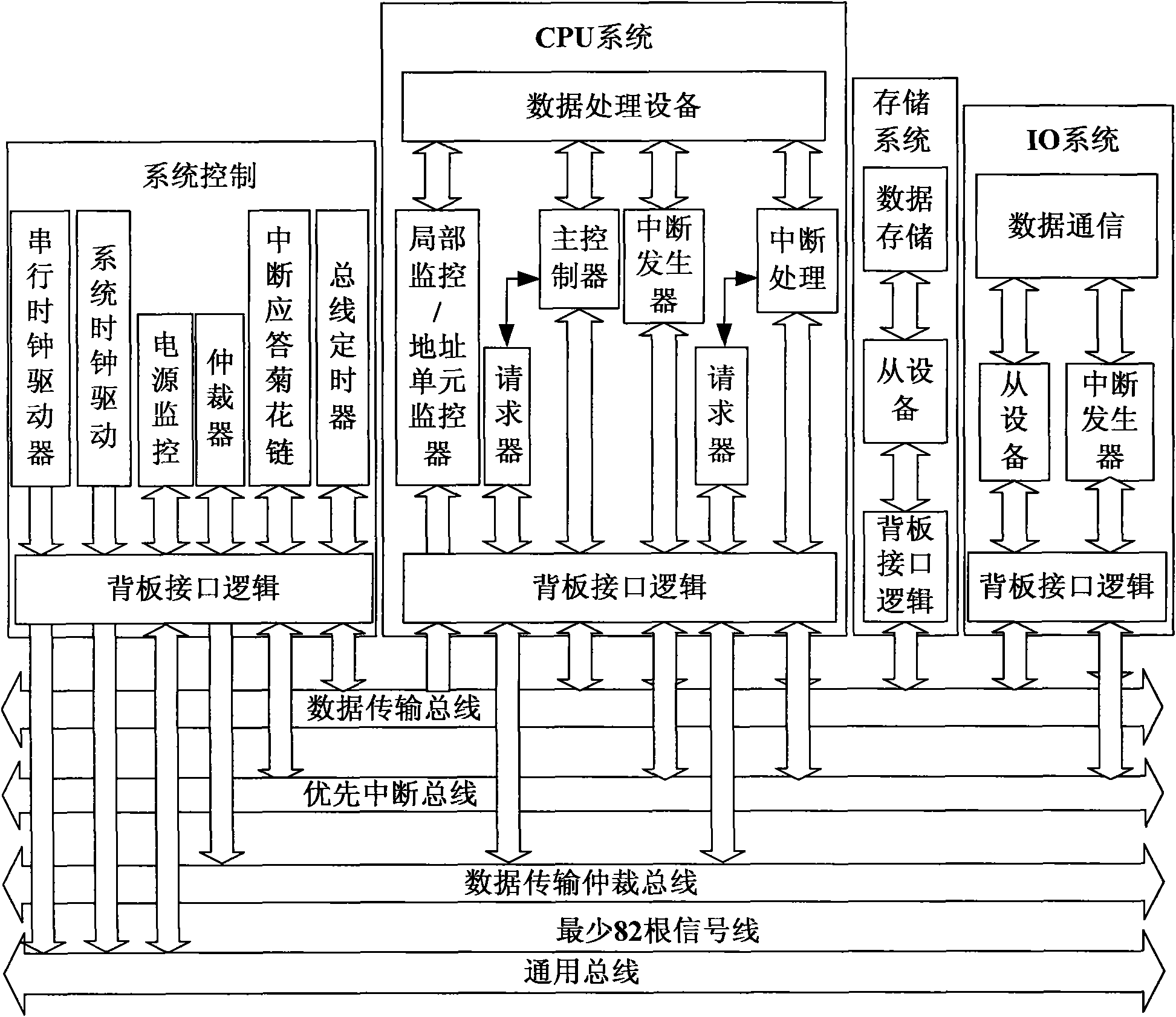

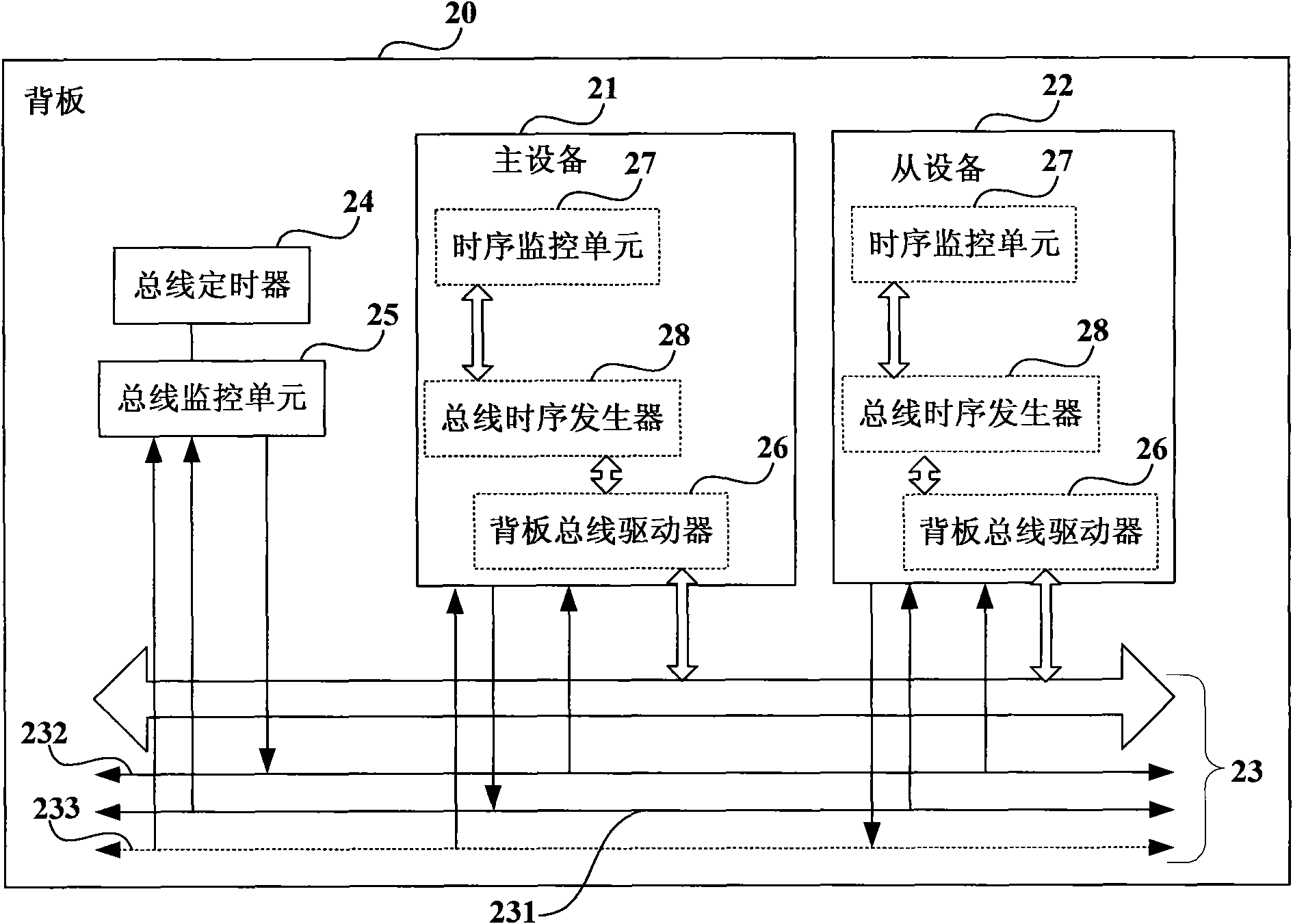

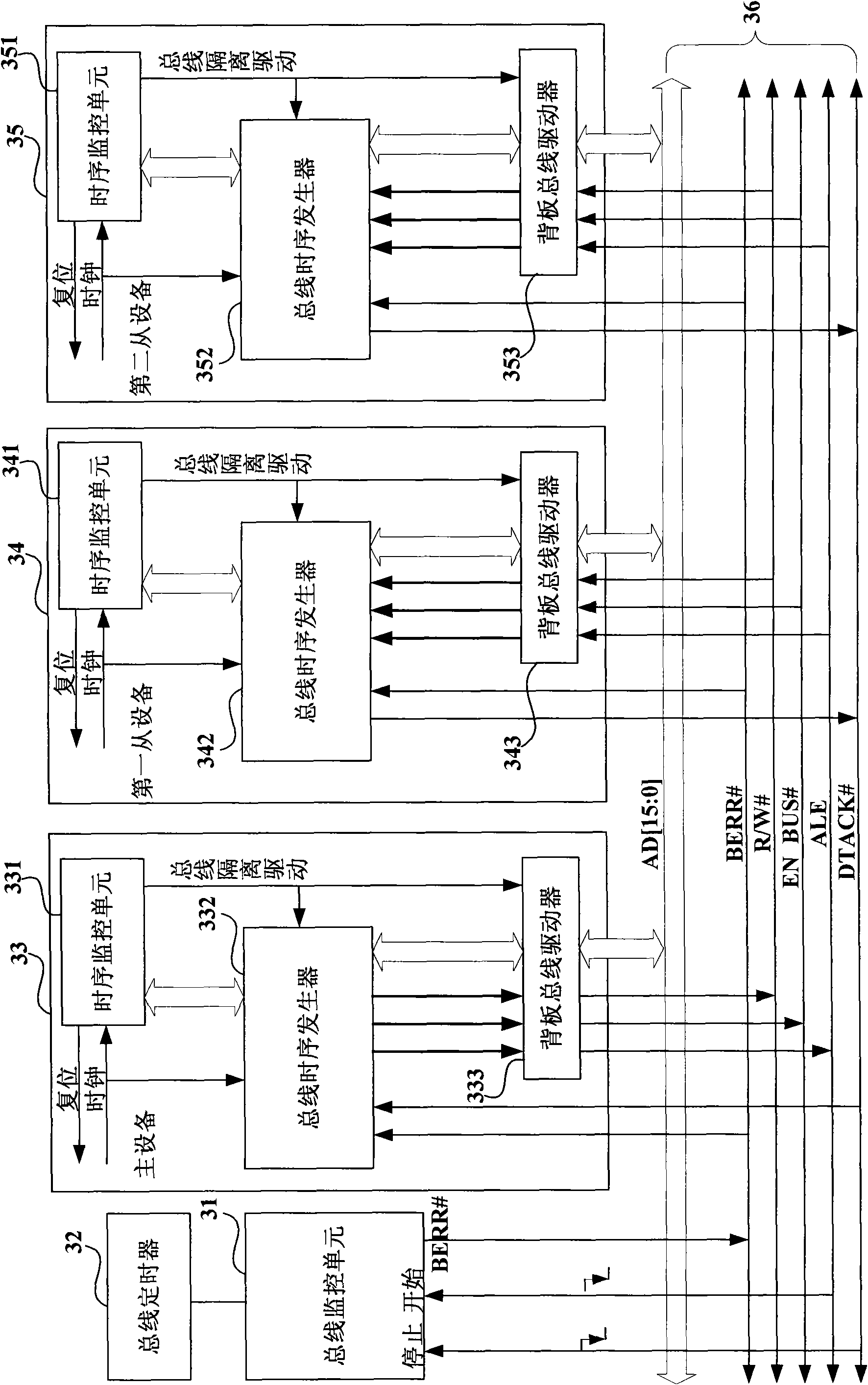

Computer system and method for monitoring bus of same

InactiveCN101667152AReduce in quantityRealize bus data transmissionHardware monitoringComputerized systemTimer

The invention relates to a computer system and a method for monitoring a bus of the computer system. The system comprises a master device, a slave device, a back plate bus and a bus timer, wherein themaster device is connected with the slave device by the back plate bus. The back plate bus comprises an address latch enabling signal line and a bus error signal line, wherein the address latch enabling signal line is used for transmitting an address latch enabling signal, and the bus error signal line is used for transmitting a bus error signal. The computer system also comprises a bus monitoring unit, wherein the bus monitoring unit is connected with the address latch enabling signal line and the bus error signal line and used for starting the bus timer to time when receiving the bus address latch enabling signal by the address latch enabling signal line and for transmitting the bus error signal by the bus error signal line when the bus timer is overtime.

Owner:HUAWEI TECH CO LTD

System-on-a-chip mixed bus architecture

InactiveUS7475182B2Mitigates bus errorCommunication is limitedGeneral purpose stored program computerMemory systemsData transmissionBus error

A mixed architecture system on chip is provided by combining a CoreConnect system on chip architecture with an AMBA system on chip architecture. To eliminate data transfer and bus error that could occur in the mixed architecture, an additional peripheral bus and bridge are provided to manage communication with AHB resources.

Owner:INT BUSINESS MASCH CORP

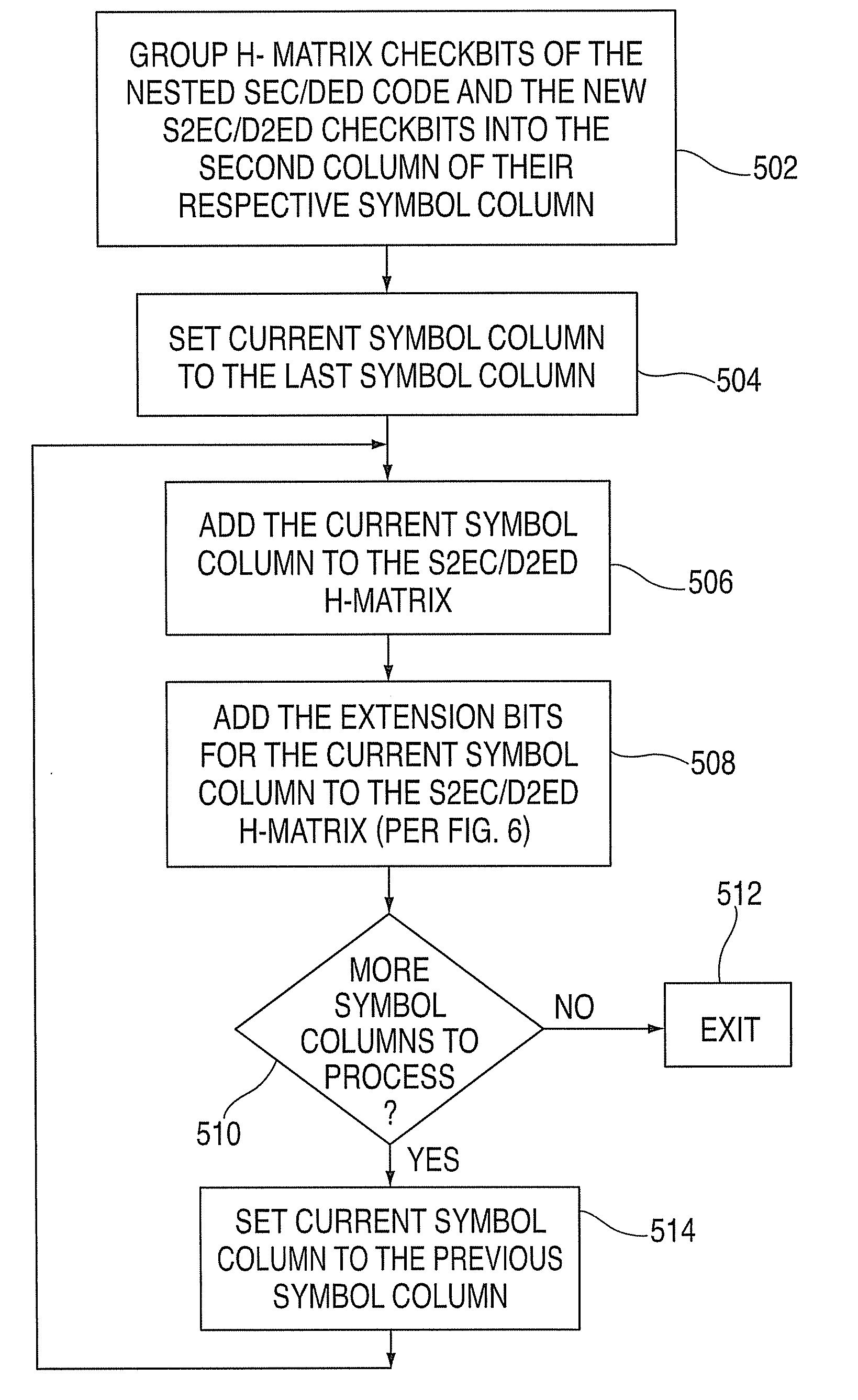

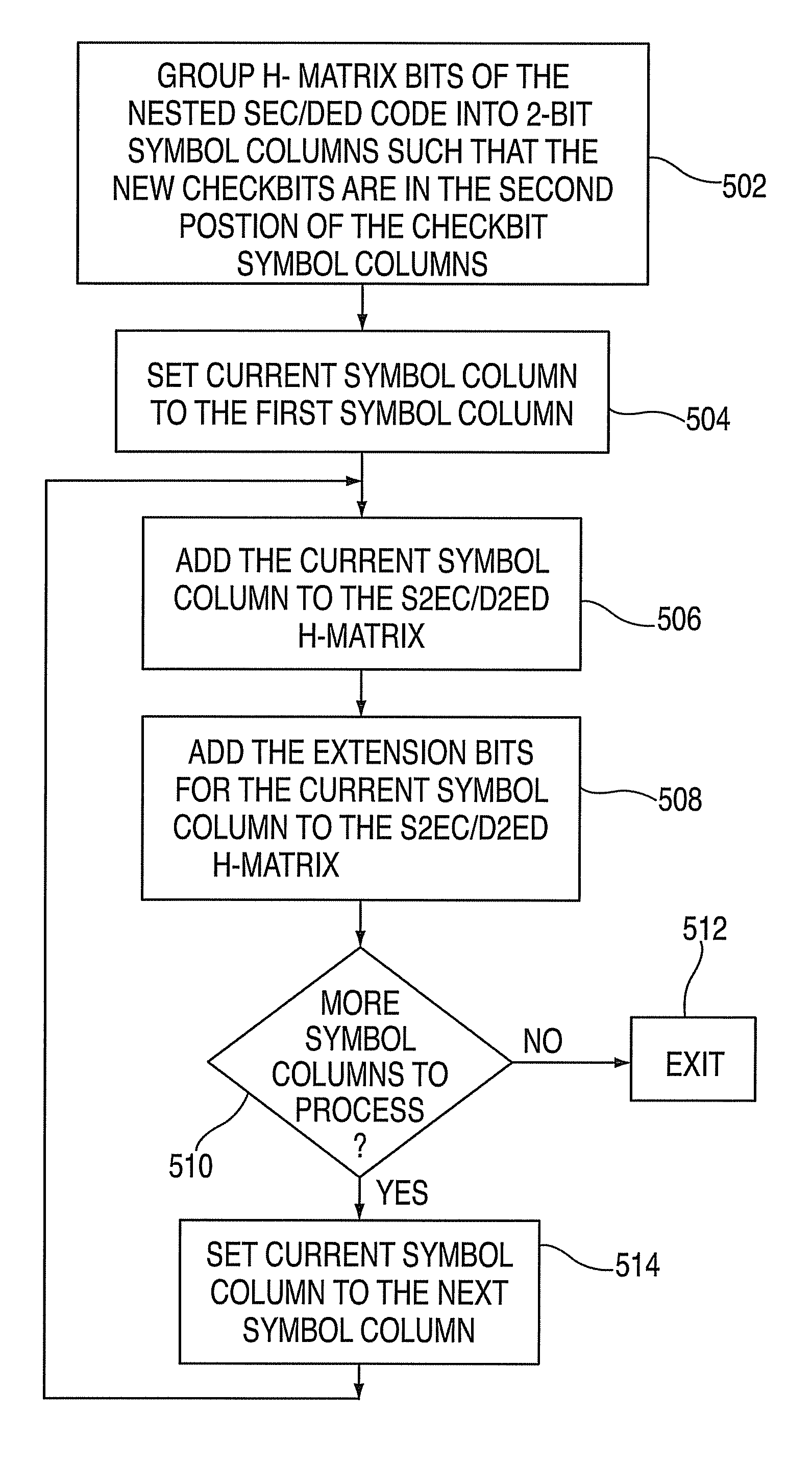

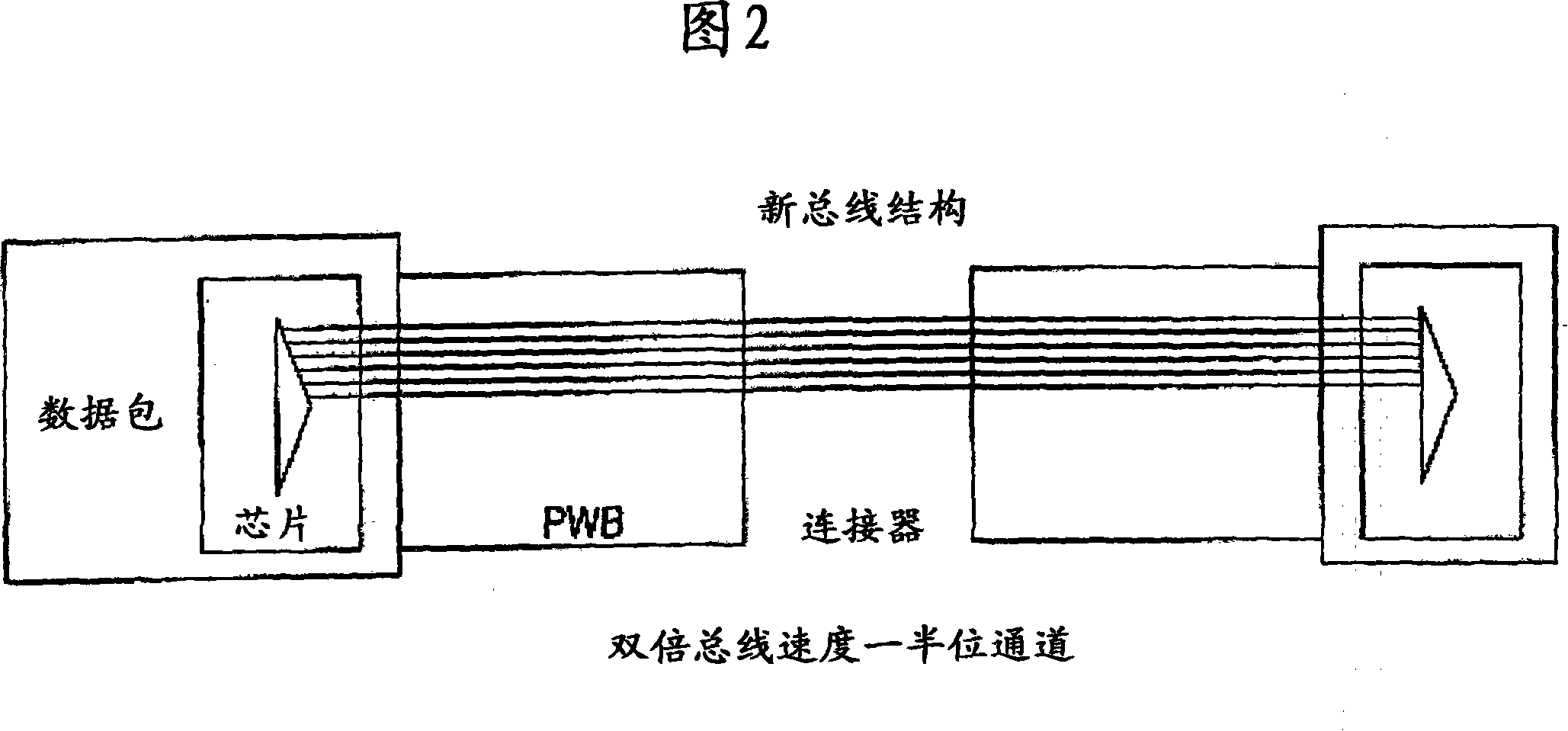

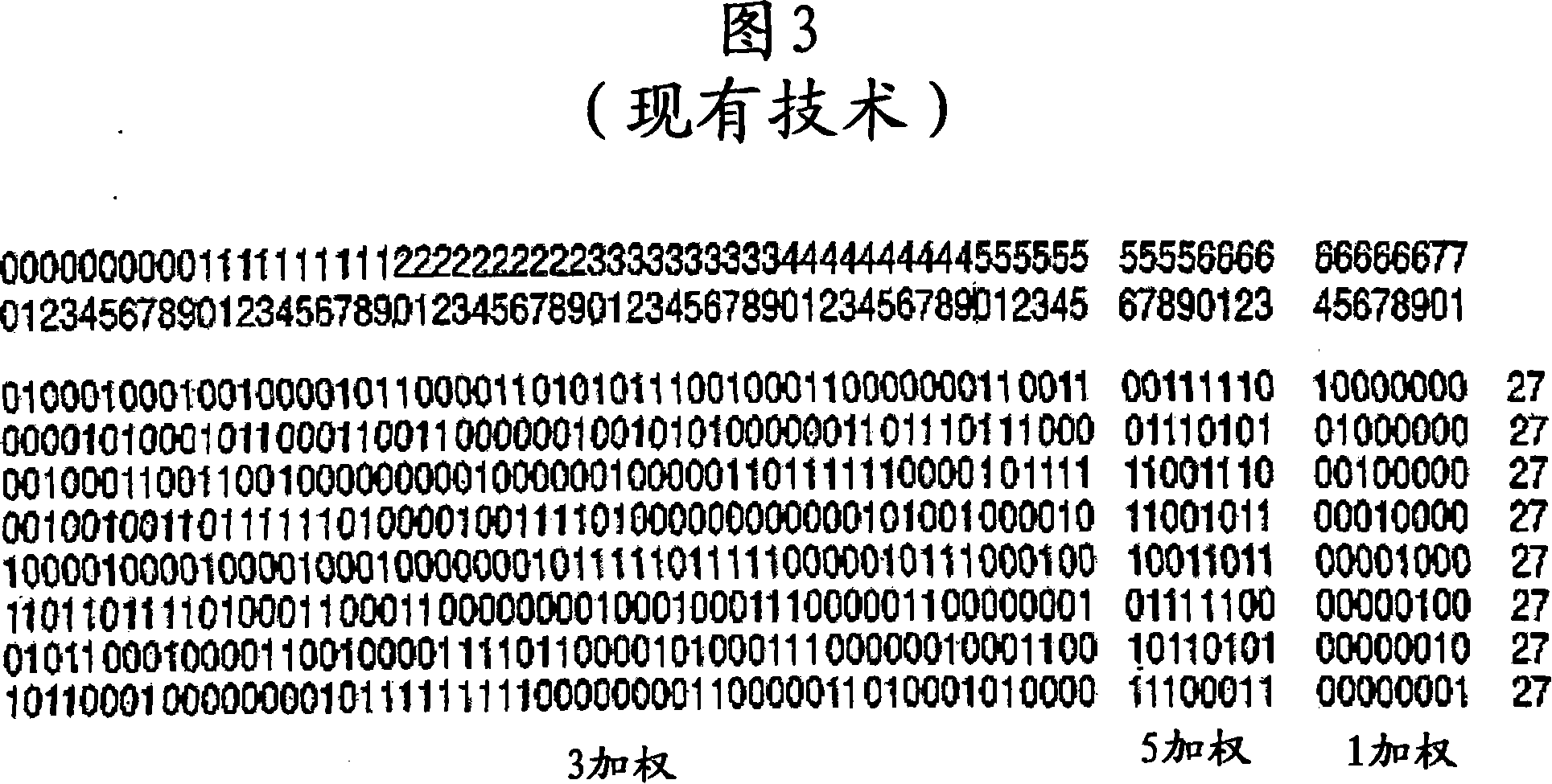

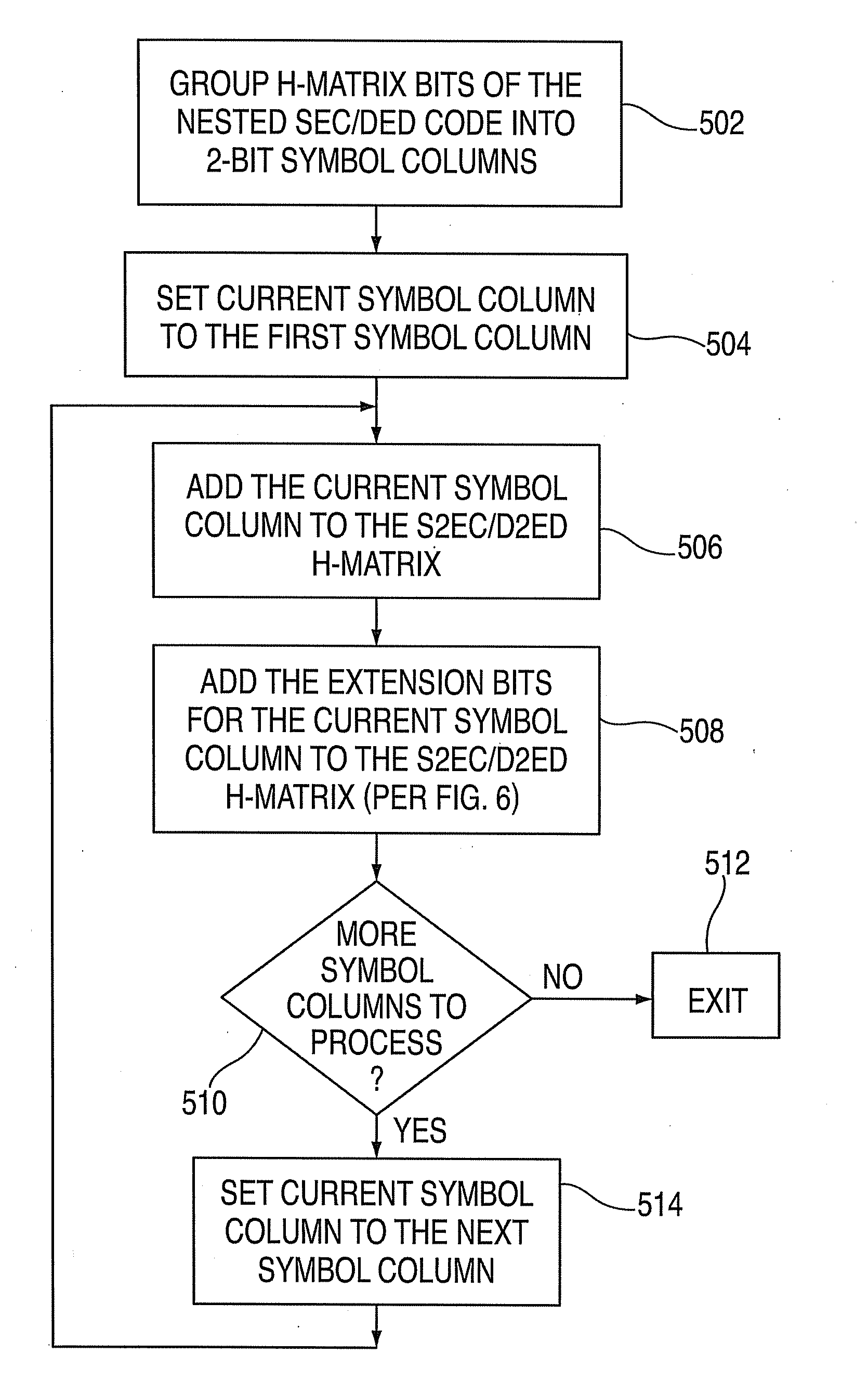

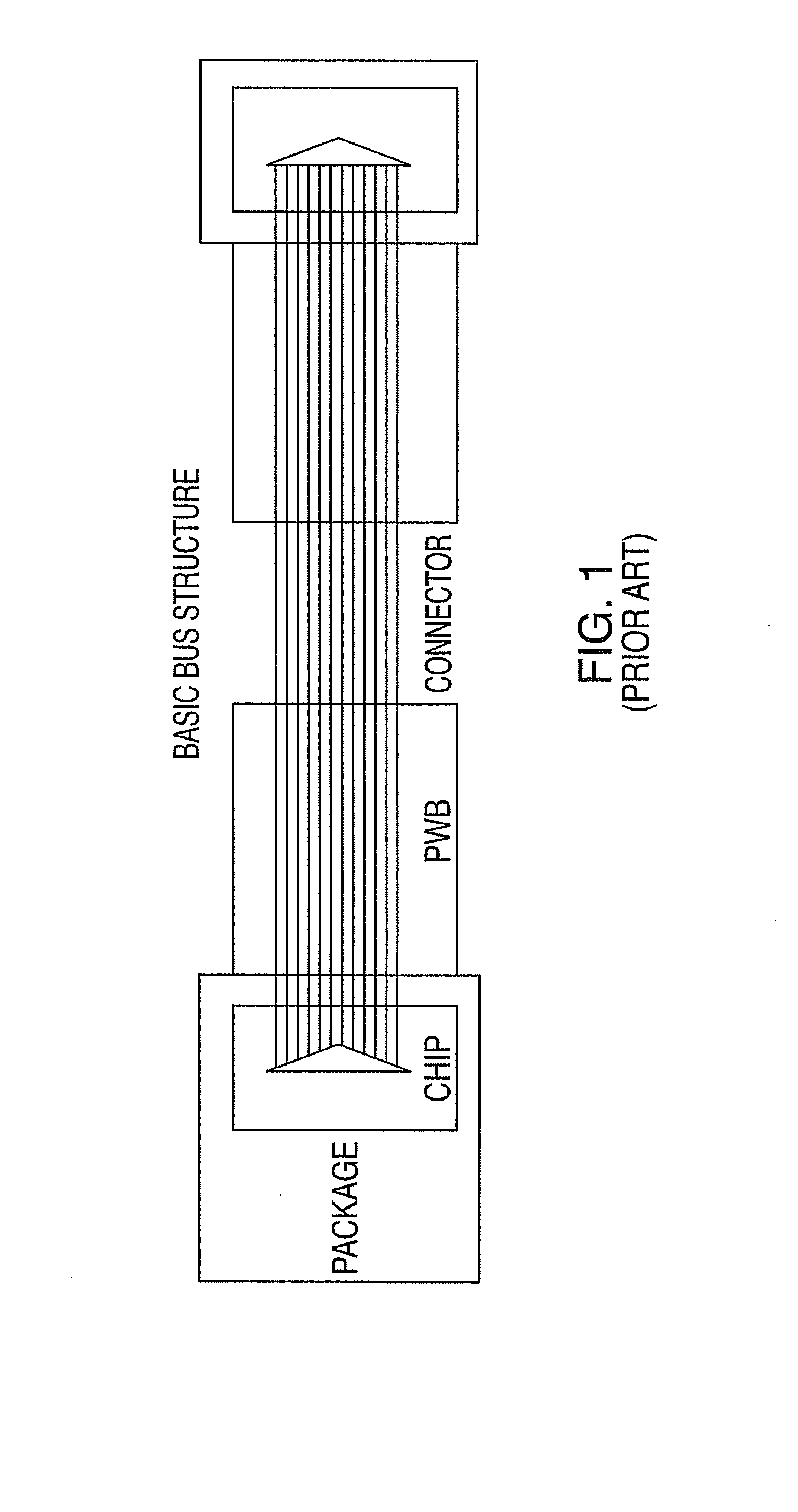

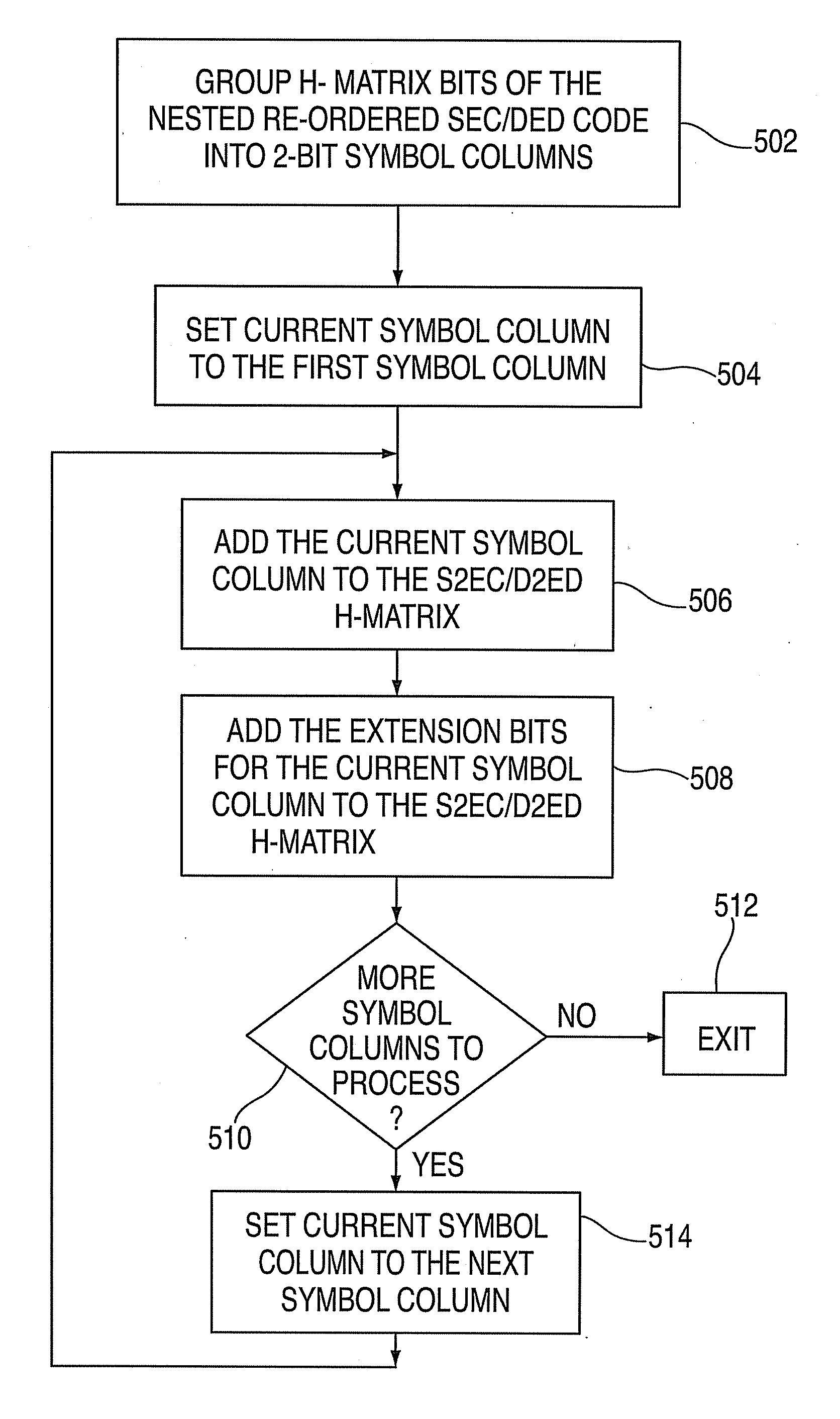

Systems, methods, and computer program products for providing a two-bit symbol bus error correcting code with all checkbits transferred last

Systems, method, and computer program products for providing a nested two-bit symbol bus error correcting code scheme for transfer over a bus in two or more transfers. Methods include constructing a nested error correcting code (ECC) scheme. The method includes receiving a Hamming distance n code including original checkbits. A symbol correcting code H-matrix framework is defined including specifying bit positions for the original checkbits and for additional checkbits associated with a symbol correcting code. The bit positions are specified such that the original checkbits and the additional checkbits are in bit positions that are transferred over a bus in a transfer subsequent to a first transfer. A symbol correcting code H-matrix is created using the bit positions indicated by the framework by iteratively adding rows of H-matrix bits on a symbol column basis such that the symbol correcting code H-matrix describes the symbol correcting code, and the Hamming distance n code is preserved as a subset of the symbol correcting code H-matrix.

Owner:IBM CORP

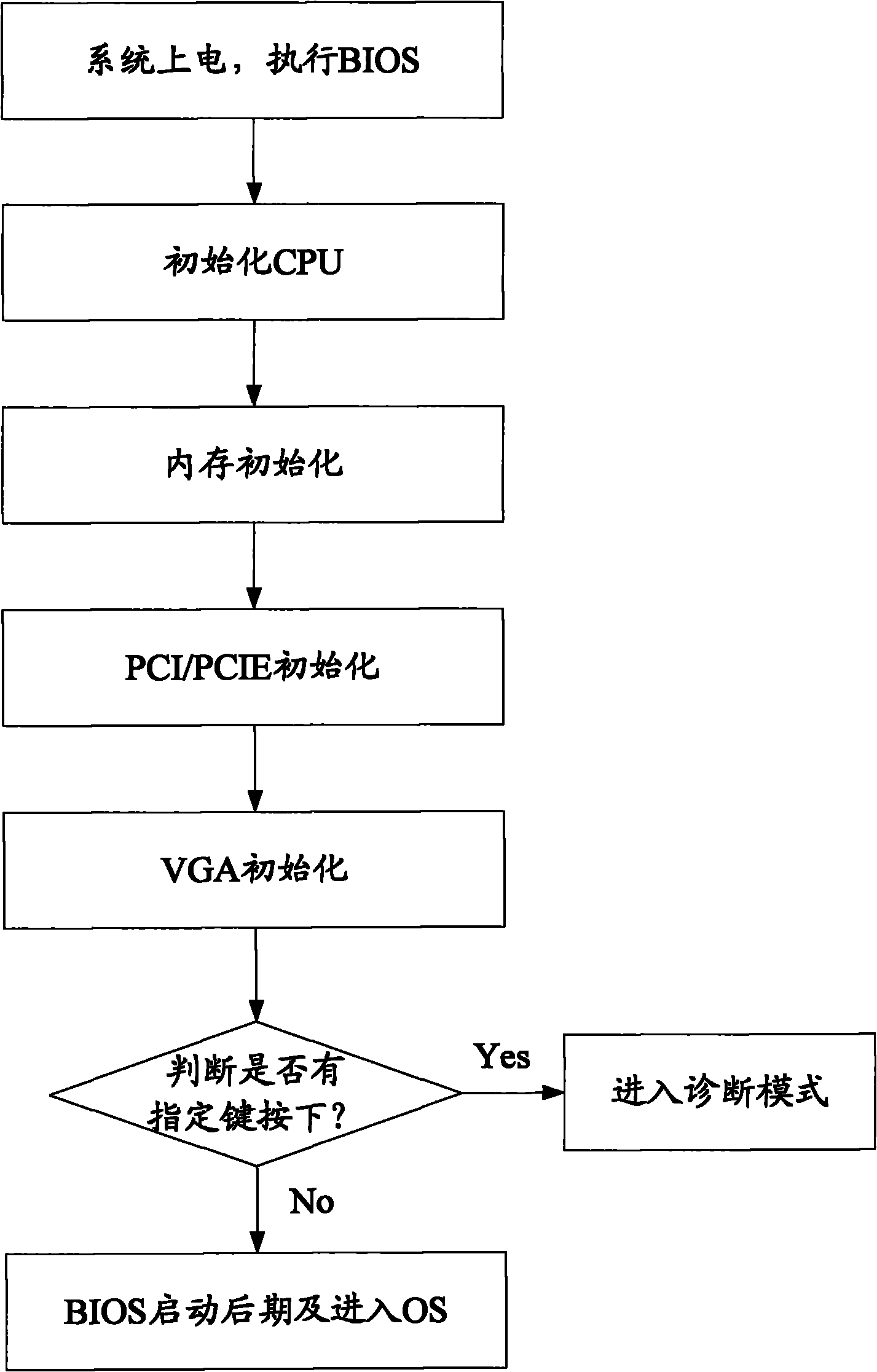

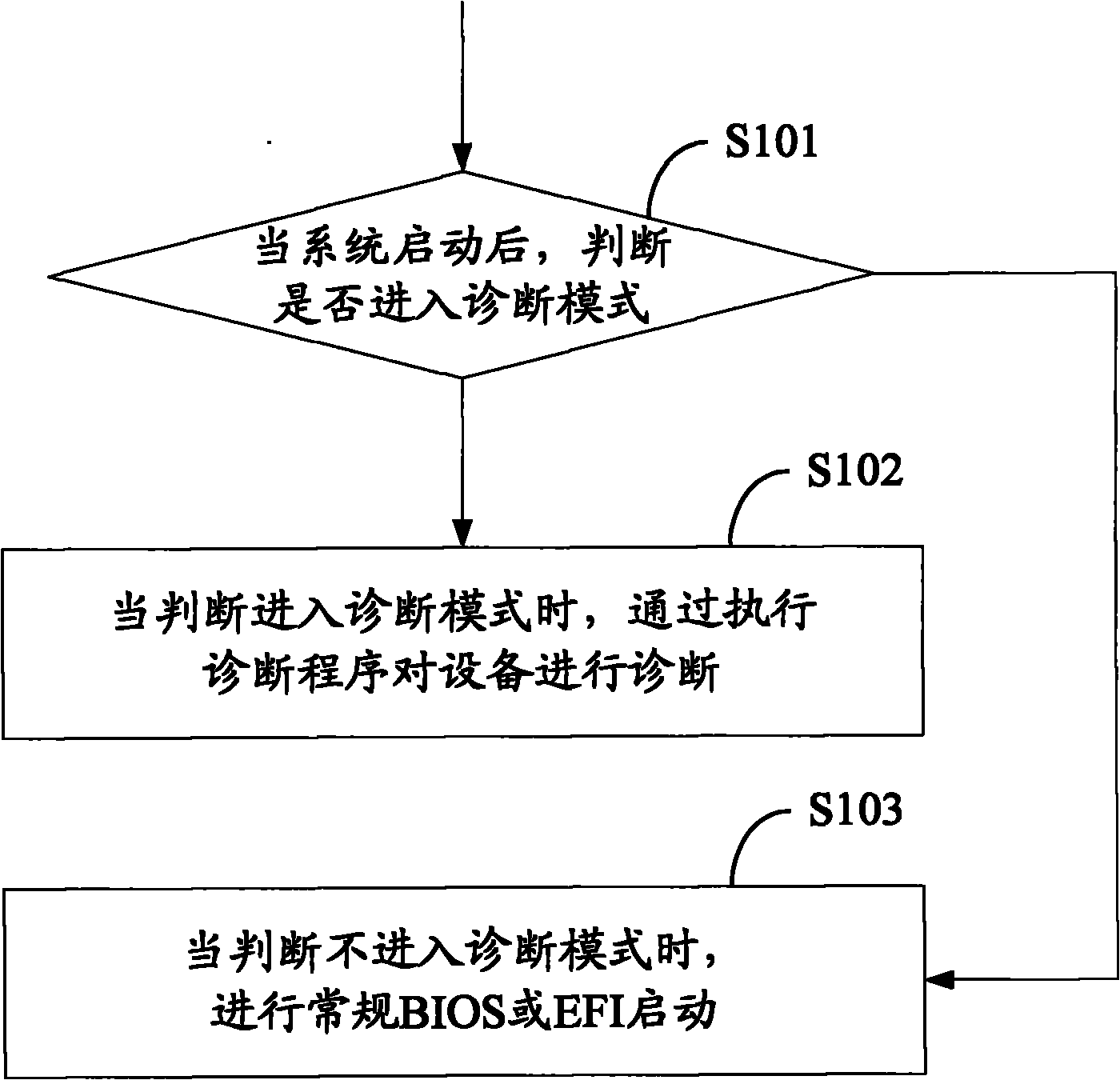

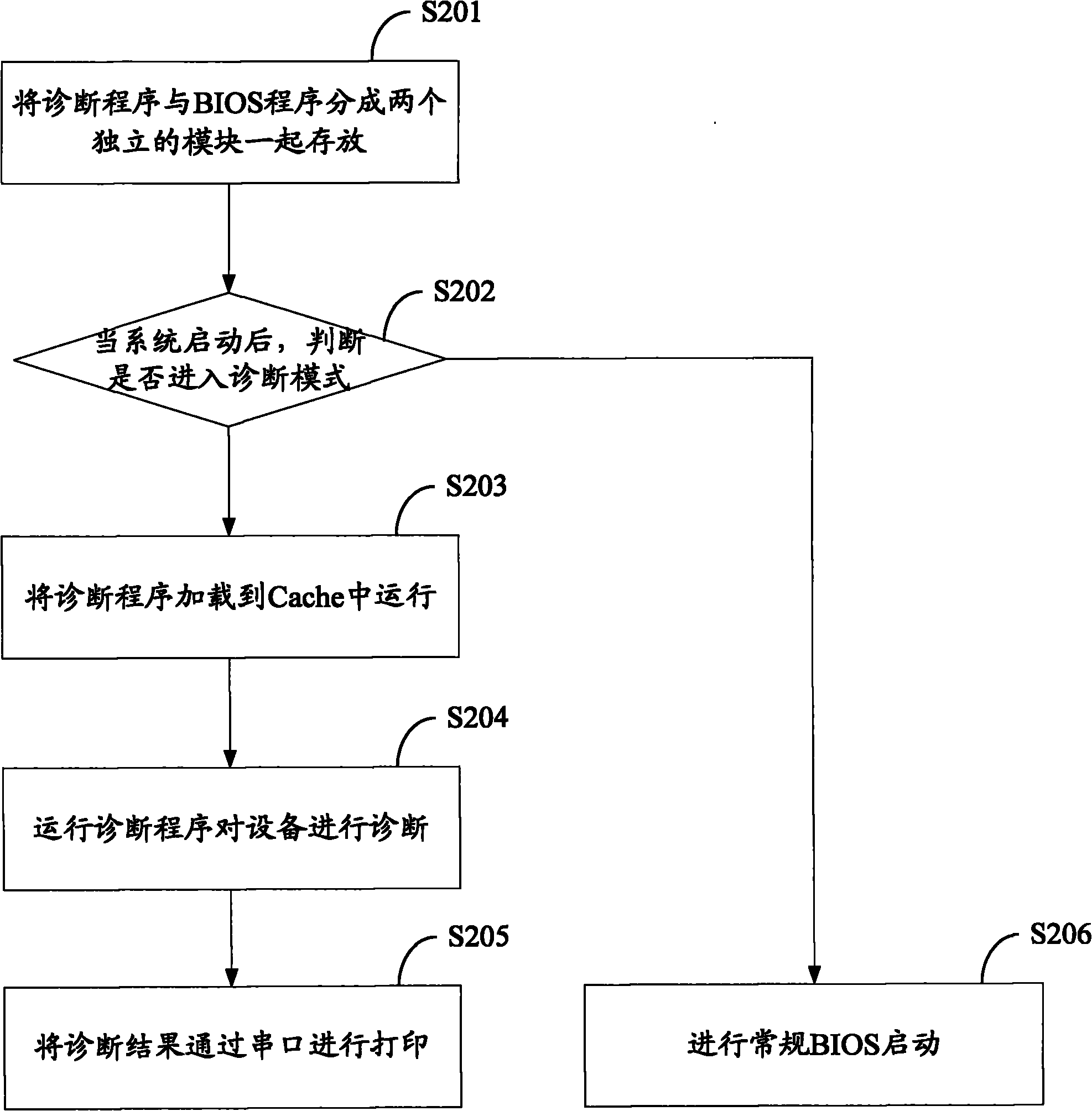

Equipment diagnosis method and system

InactiveCN102081562AAccurate judgmentAccurate diagnosisDetecting faulty hardware by power-on testDiagnostic programDiagnosis methods

The embodiment of the invention discloses an equipment diagnosis method and system. The equipment diagnosis method comprises: when a system is started, judging whether the system enters a diagnosis mode; when the system enters the diagnosis node, diagnosing the equipment by performing a diagnosis program; when the system does not enter the diagnosis node, carrying out normal basic input output system (BIOS) or extensible firmware interface (EFI) startup. In the embodiment of the invention, whether the system enters the diagnosis node or not is firstly judged after the system is started, if yes, the diagnosis node is started, and if no, the normal BIOS or EFI startup is continuously performed to realize accurate diagnosis on equipment; and if the memory or peripheral component interconnect / peripheral component interface express (PCI / PCIE) bus errors happen in the equipment, the fault can be diagnosed because the diagnosis program is loaded before BIOS startup.

Owner:HUAWEI TECH CO LTD

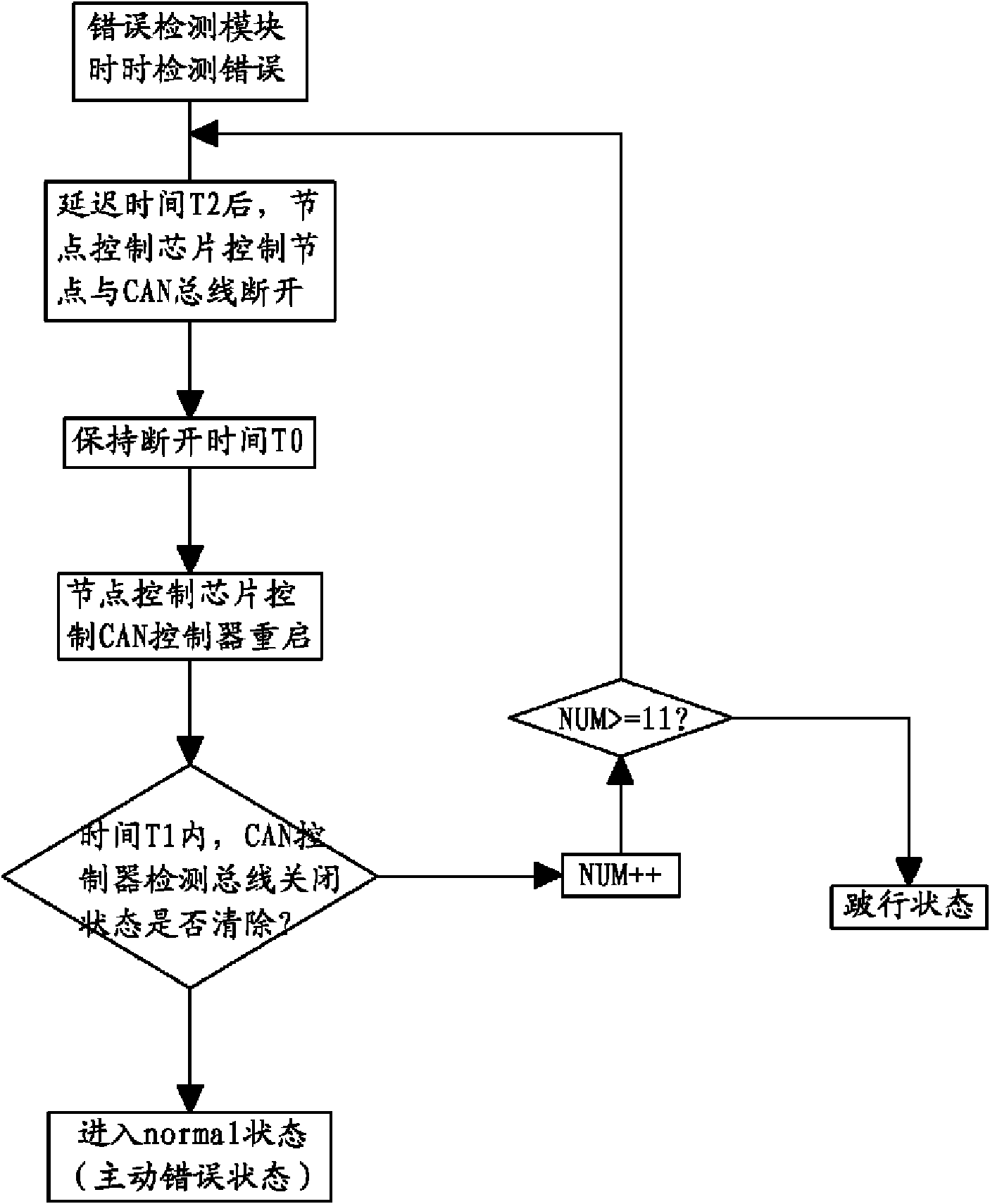

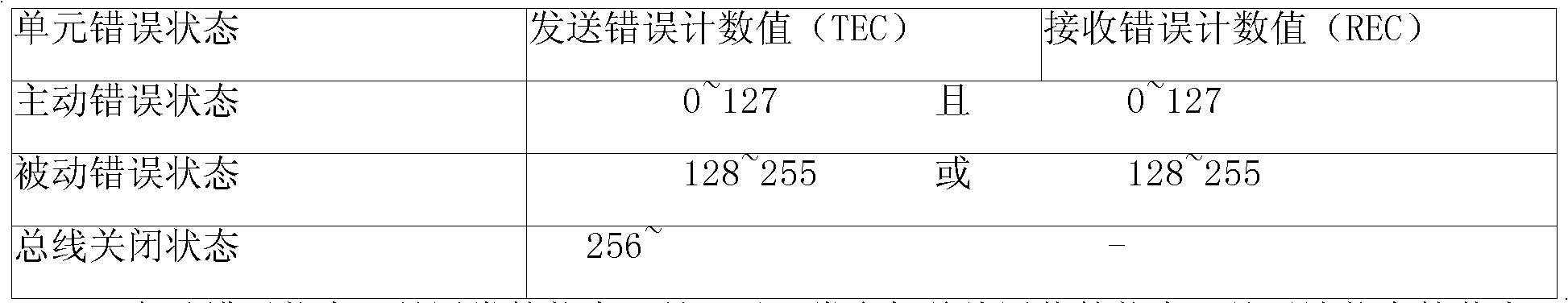

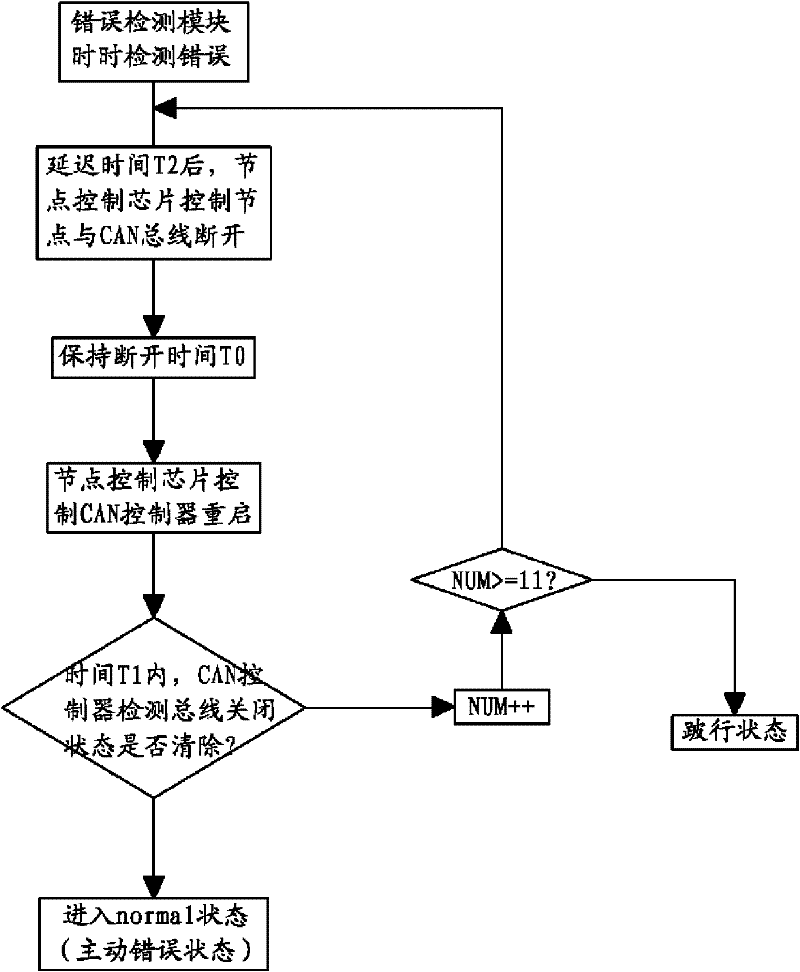

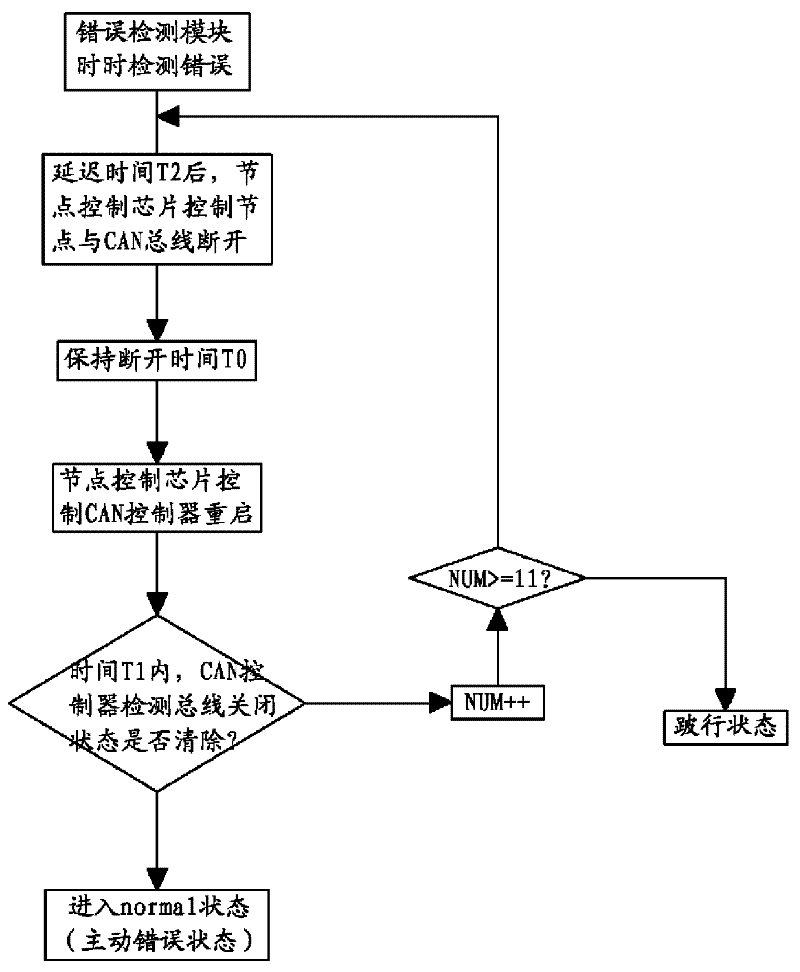

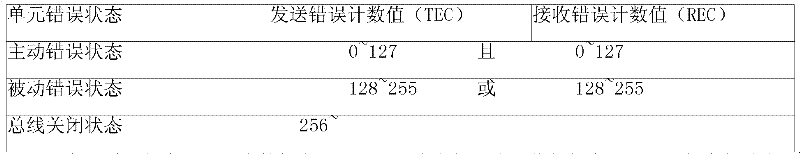

Bus error recovery processing method

The invention provides a bus error recovery processing method, which belongs to the technical field of CAN buses. The invention solves the problem that when the existing bus node enters a bus-off state by error, the bus node is difficult to recover to a normal operation state. In the bus error recovery processing method, the node detects the error and enters the 'bus-off state' to carry out error recovery processing operation which comprises the following steps: a, an error detection module detects error from time to time, and meanwhile, an error handling module controls the node to be in a corresponding state according to the counted error detected by the error detection module; b, a main controller controls the node to be disconnected with the CAN bus; c, the disconnection time T0 is kept, and when the time T0 is up, the step d is carried out; d, the main controller controls a CAN controller to be restarted up; and e, the CAN controller monitors the level signal of the CAN bus. The bus error recovery processing method has the advantage of timely eliminating the error detected on the node.

Owner:HUAWEI TEHCHNOLOGIES CO LTD

Systems, methods, and computer program products for providing a two-bit symbol bus error correcting code

Systems, methods and computer program products for providing a nested two-bit symbol bus error correcting code. Methods include constructing a nested error correcting code (ECC) scheme. The method includes receiving a Hamming distance n code. A symbol correcting code H-matrix is created by iteratively adding rows of H-matrix bits on a symbol column basis such that the symbol correcting code H-matrix describes a symbol correcting code, and the Hamming distance n code is preserved as a subset of the symbol correcting code H-matrix.

Owner:IBM CORP

Systems, methods, and computer program products for providing a two-bit symbol bus error correcting code with bus timing improvements

Owner:INT BUSINESS MASCH CORP

Systems, methods, and computer program products for providing a two-bit symbol bus error correcting code with bus timing improvements

Systems, method, and computer program products for providing a nested two-bit symbol bus error correcting code scheme for transfer over a bus in two or more transfers. Methods include constructing a nested error correcting code (ECC) scheme. The method includes receiving a Hamming distance n code including original checkbits. A symbol correcting code H-matrix framework is defined including specifying bit positions for the original checkbits and for additional checkbits associated with a symbol correcting code. The bit positions are specified such that the additional checkbits are in bit positions that are transferred over a bus in a transfer subsequent to a first transfer. A symbol correcting code H-matrix is created using the bit positions indicated by the framework by iteratively adding rows of H-matrix bits on a symbol column basis such that the symbol correcting code H-matrix describes the symbol correcting code, and the Hamming distance n code is preserved as a subset of the symbol correcting code H-matrix.

Owner:IBM CORP

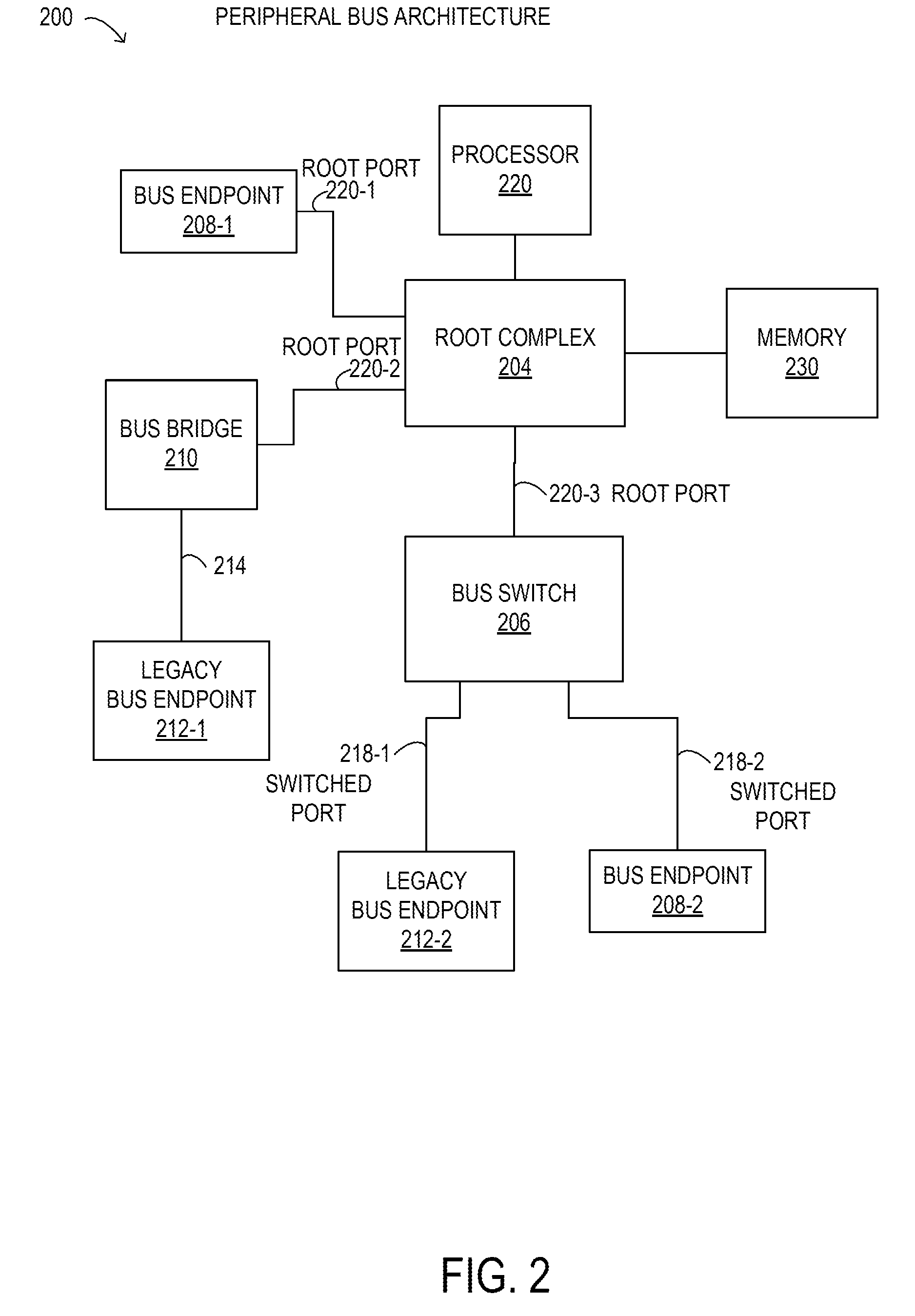

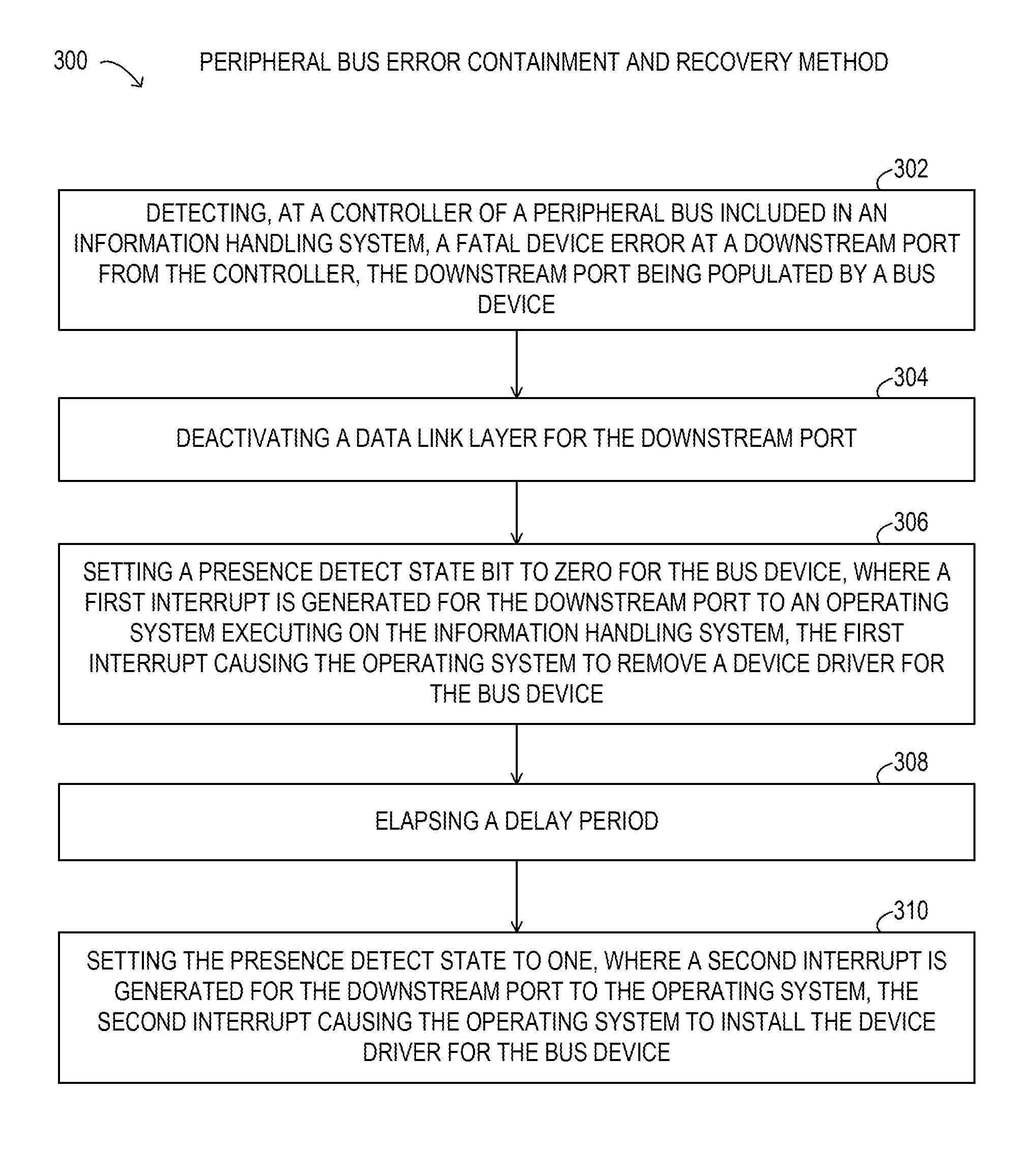

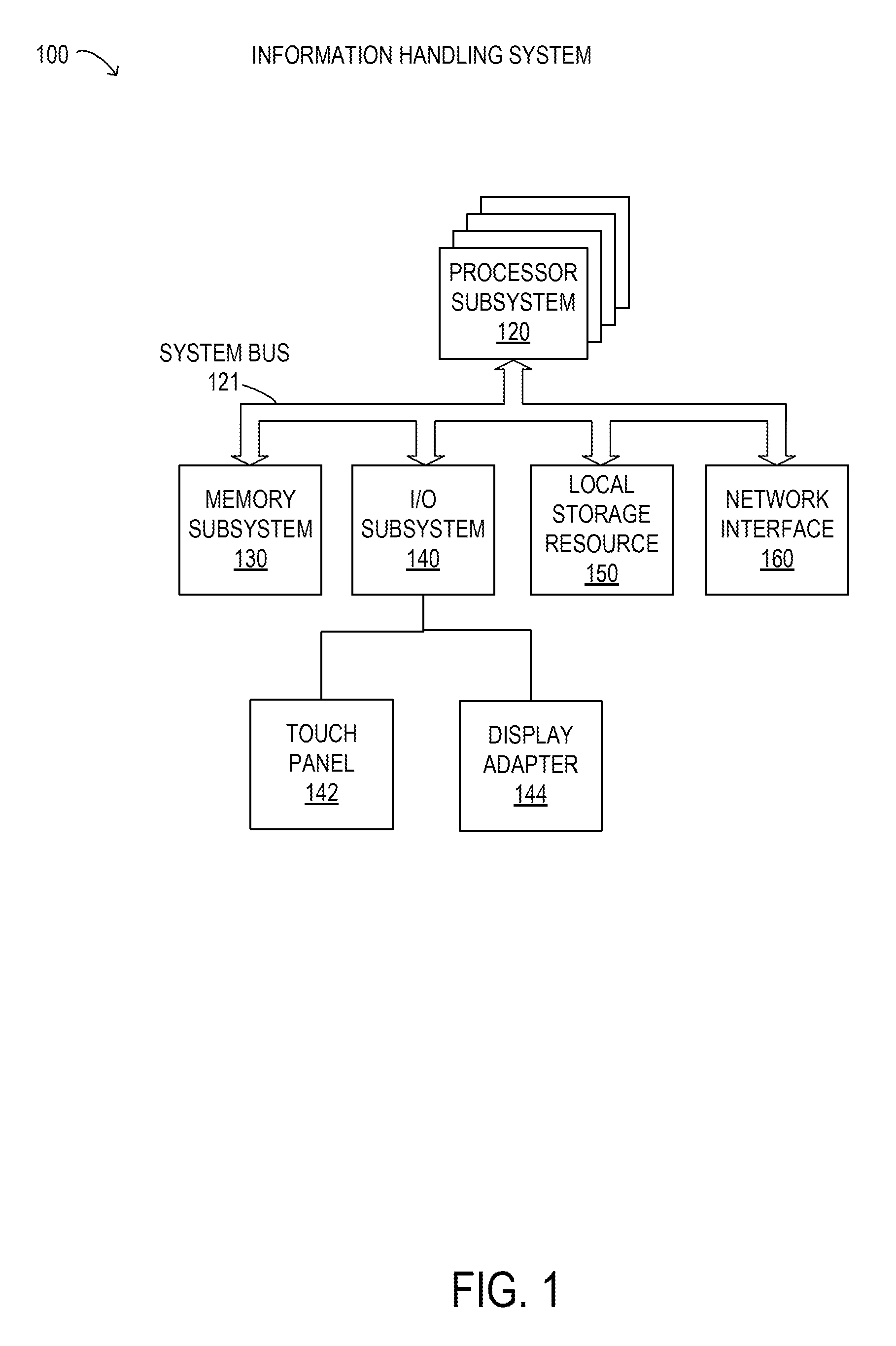

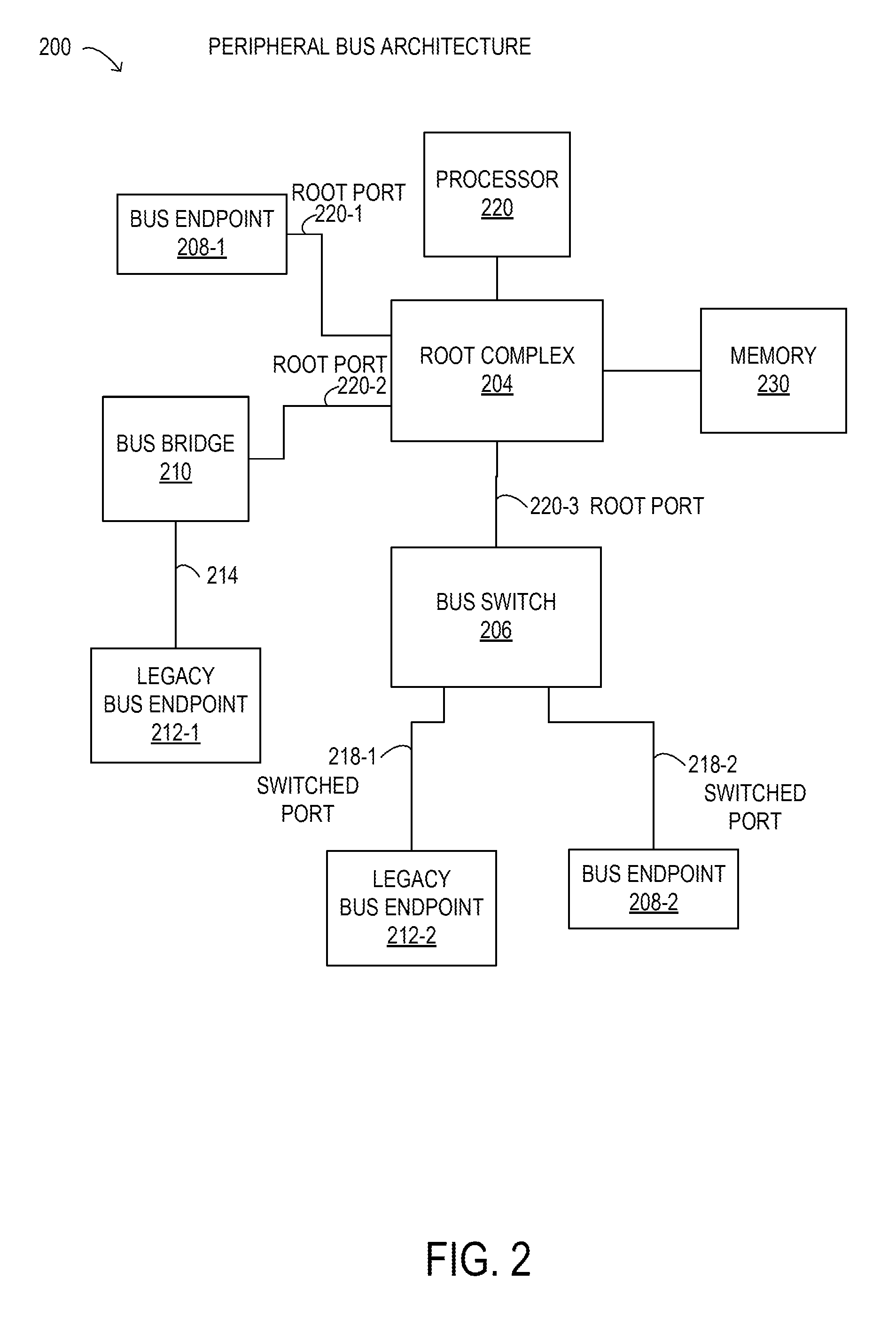

Peripheral bus error containment and recovery

ActiveUS20160132395A1Non-redundant fault processingRedundant operation error correctionOperational systemBus mastering

A peripheral bus error containment and recovery system enables a bus device to experience a fatal bus error and recover without stopping execution of an operating system. When a fatal bus error is detected at the bus device, a bus controller may deactivate a data link layer for a downstream port populated by the bus device, causing an operating system device driver to be uninstalled for the bus device. Then, the operating system device driver may be reinstalled without physically removing the bus device.

Owner:DELL PROD LP

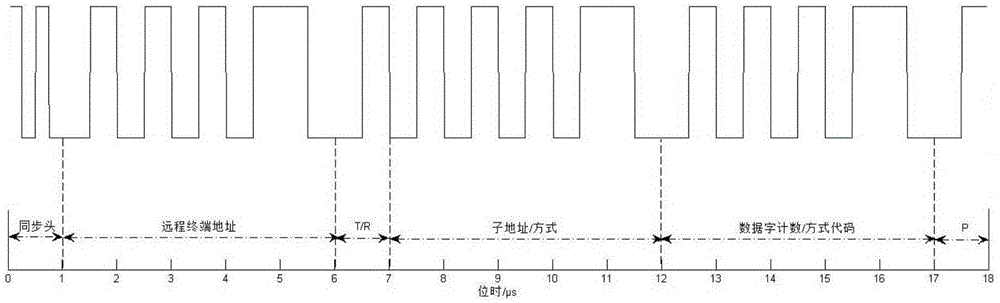

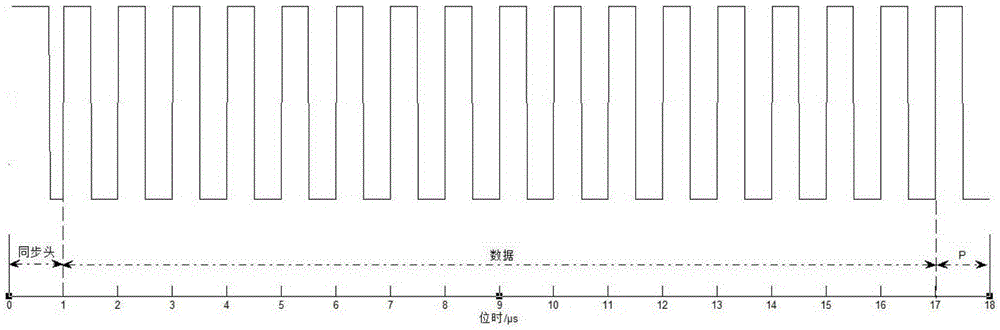

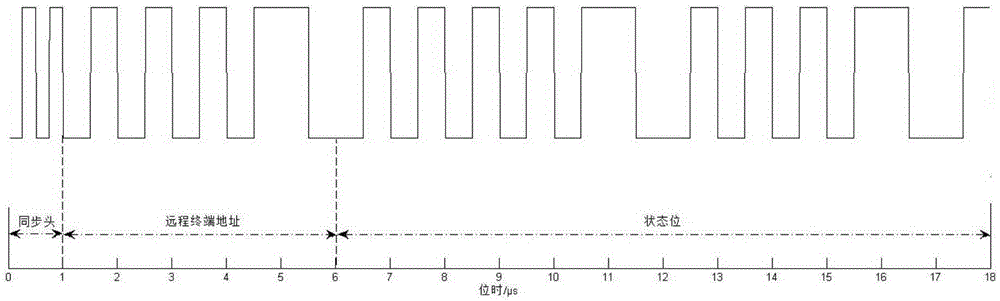

High-integrity coding method of 1553B bus

ActiveCN105406943AImprove bit error detection rateReduce time uncertainty and other issuesError preventionBus networksProblem of timeConfusion

The invention discloses a high-integrity coding method of a 1553B bus, and is used to solve the technical problem of poor integrity of an existing 1553B bus coding method. According to the technical scheme, a synchronous head coding mode of an instruction character and a state character of the 1553B bus is improved, a BM clearly distinguishes the instruction character and the state character from different code identification angles, a message interface is divided easily, determinacy of a bus semantic rule is achieved, a confusion identification problem of a 1553B bus monitor for the bus instruction character and the state character is solved, implementation technology is simple, and the difficulty is small. Optimization design of a vertical odd parity character of a 1553B bus message is increased, so the bit error detection rate of bus transmission is improved, the problems of time indeterminacy and the like which exist when bus error retransmission is performed are reduced, and integrity of a transmission content is improved. The method improves the integrity of the 1553B bus and the effective throughput rate of the 1553B bus at the same time, and shortens message delay transmission efficiency.

Owner:陕西钧磐数据科技有限公司

Systems, methods, and computer program products for providing a two-bit symbol bus error correcting code with bus diagnostic features

Systems, method, and computer program products for providing a nested two-bit symbol bus error correcting code for transfer over a bus in two or more transfers Methods include constructing a nested error correcting code (ECC) scheme. The method includes receiving a Hamming distance n code including original checkbits. A symbol correcting code H-matrix framework is defined including specifying bit positions for the original checkbits and for additional checkbits associated with a symbol correcting code. The bit positions are specified such that the additional checkbits are in bit positions that are transferred over a bus in a transfer subsequent to a first transfer. A symbol correcting code H-matrix is created using the bit positions indicated by the framework by iteratively adding rows of H-matrix bits on a symbol column basis such that the symbol correcting code H-matrix describes the symbol correcting code, and the Hamming distance n code is preserved as a subset of the symbol correcting code H-matrix.

Owner:GLOBALFOUNDRIES INC

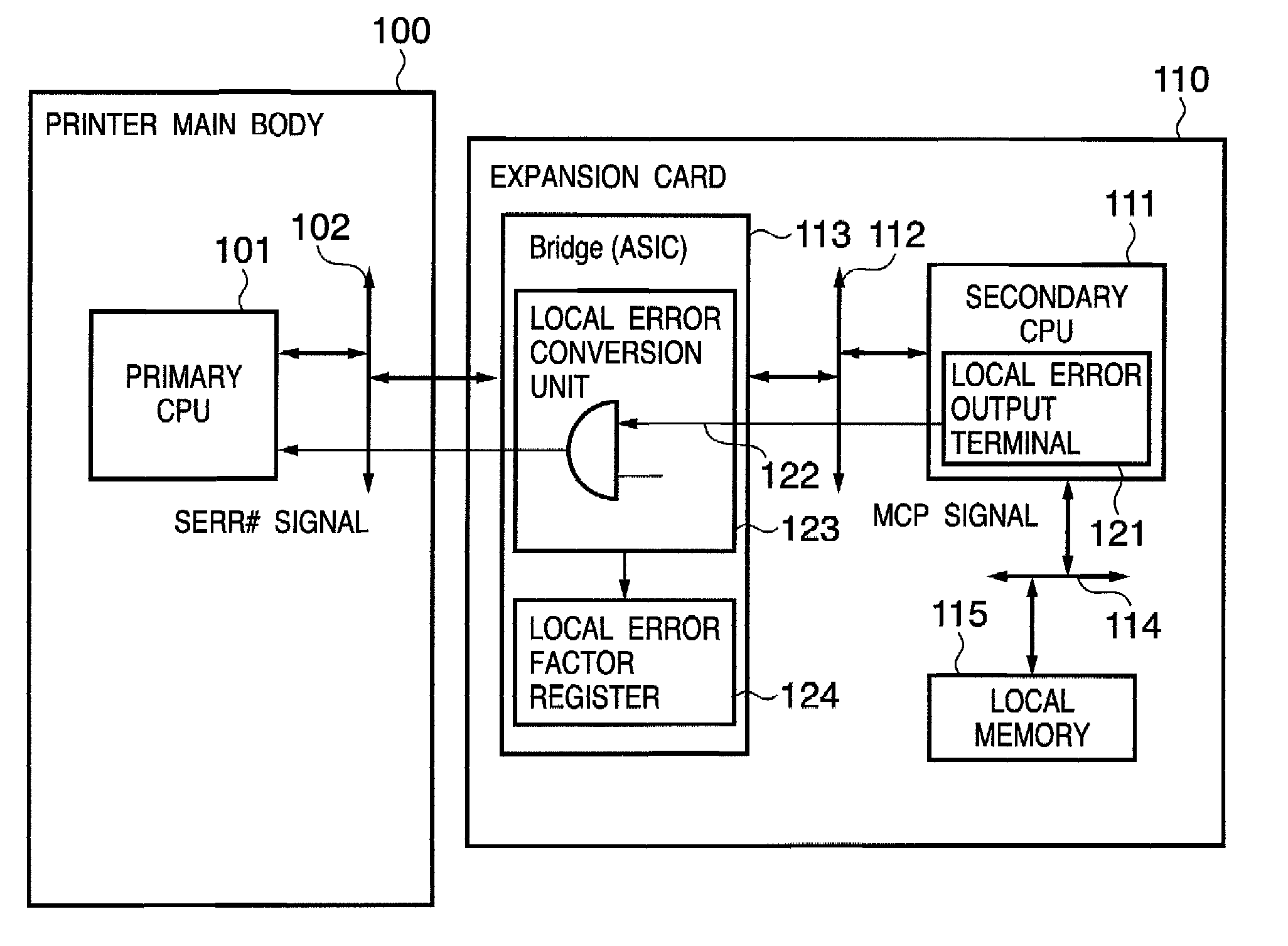

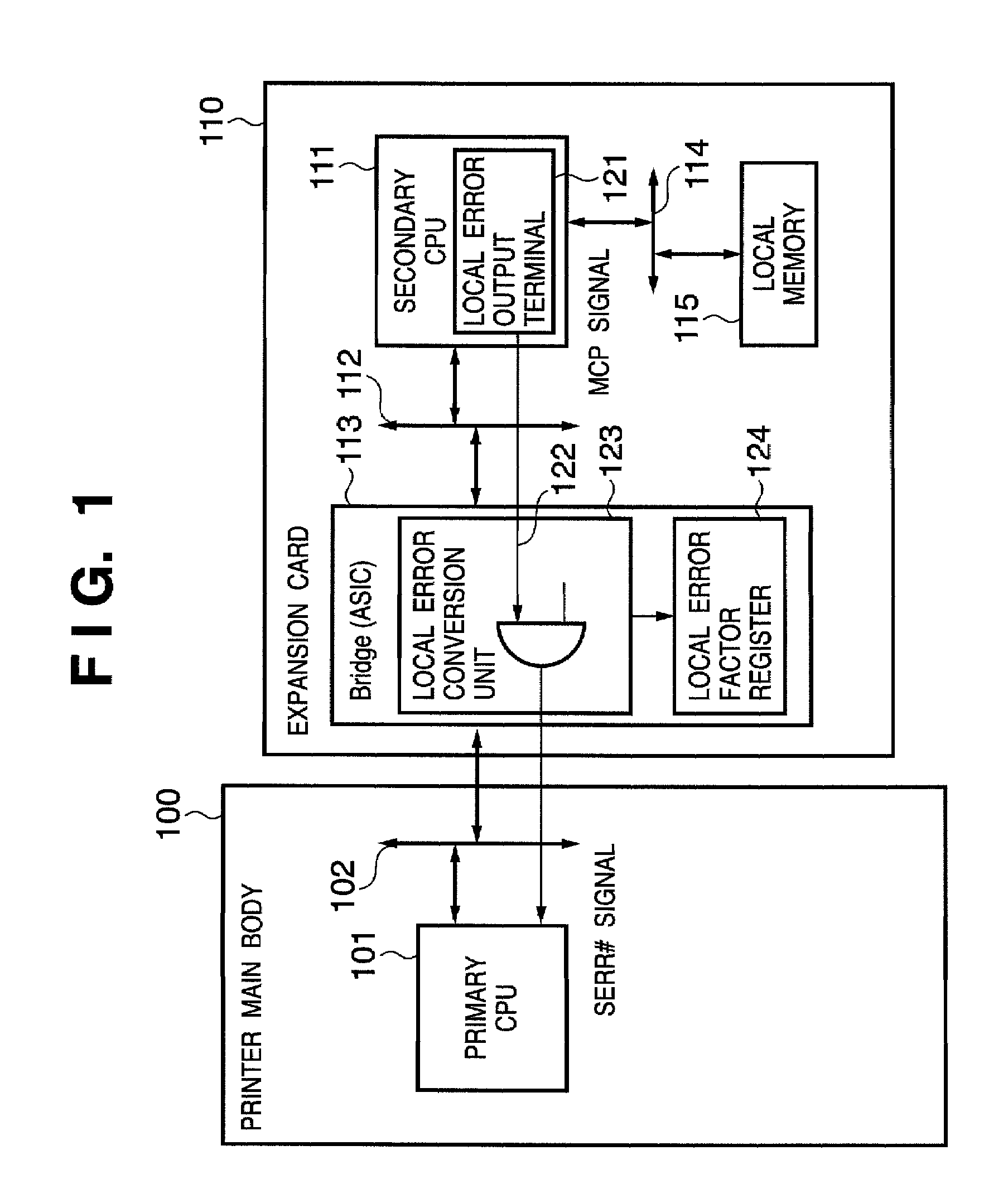

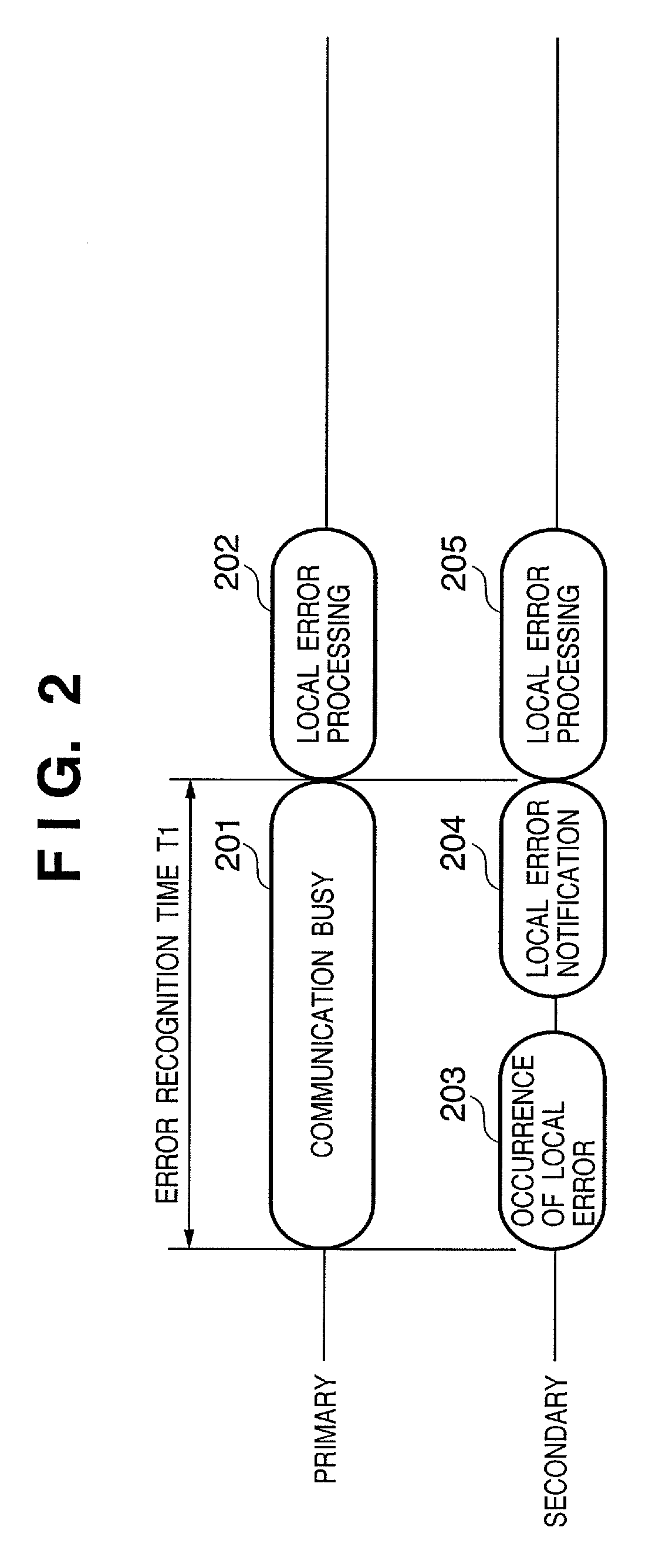

Error processing method and information processing apparatus

ActiveUS8032794B2Appropriately processedRedundant data error correctionInformation processingError processing

An error processing method processes an error generated on a bus of a CPU, by inputting a bus error that is generated on at least one of an instruction bus and a data bus of the CPU to the CPU by a bus error input part, counting the bus error by a bus error counter part of the CPU, and specifying a region of a memory part that is coupled to the CPU based on a value of the bus error counter part.

Owner:CYPRESS SEMICON CORP

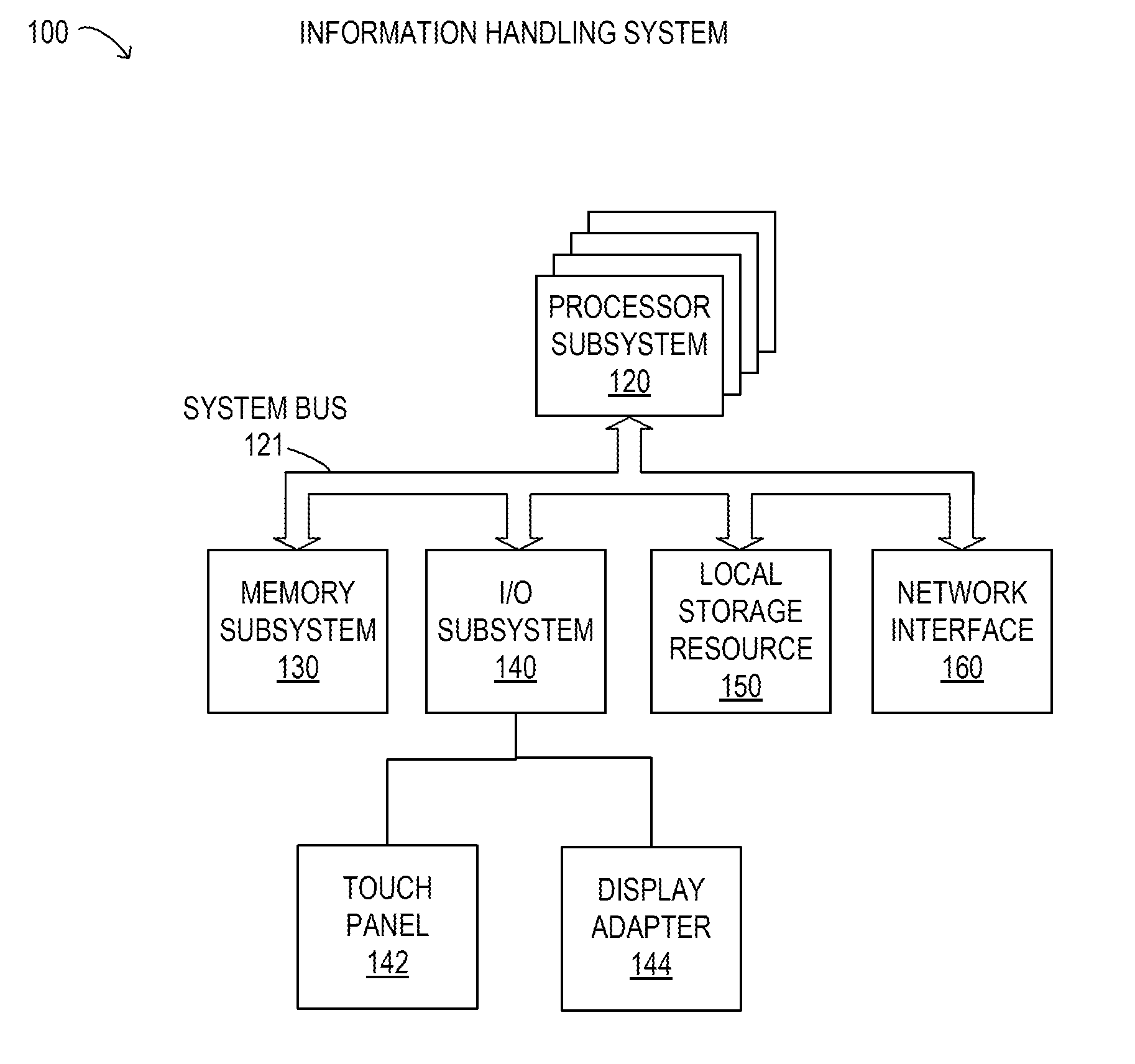

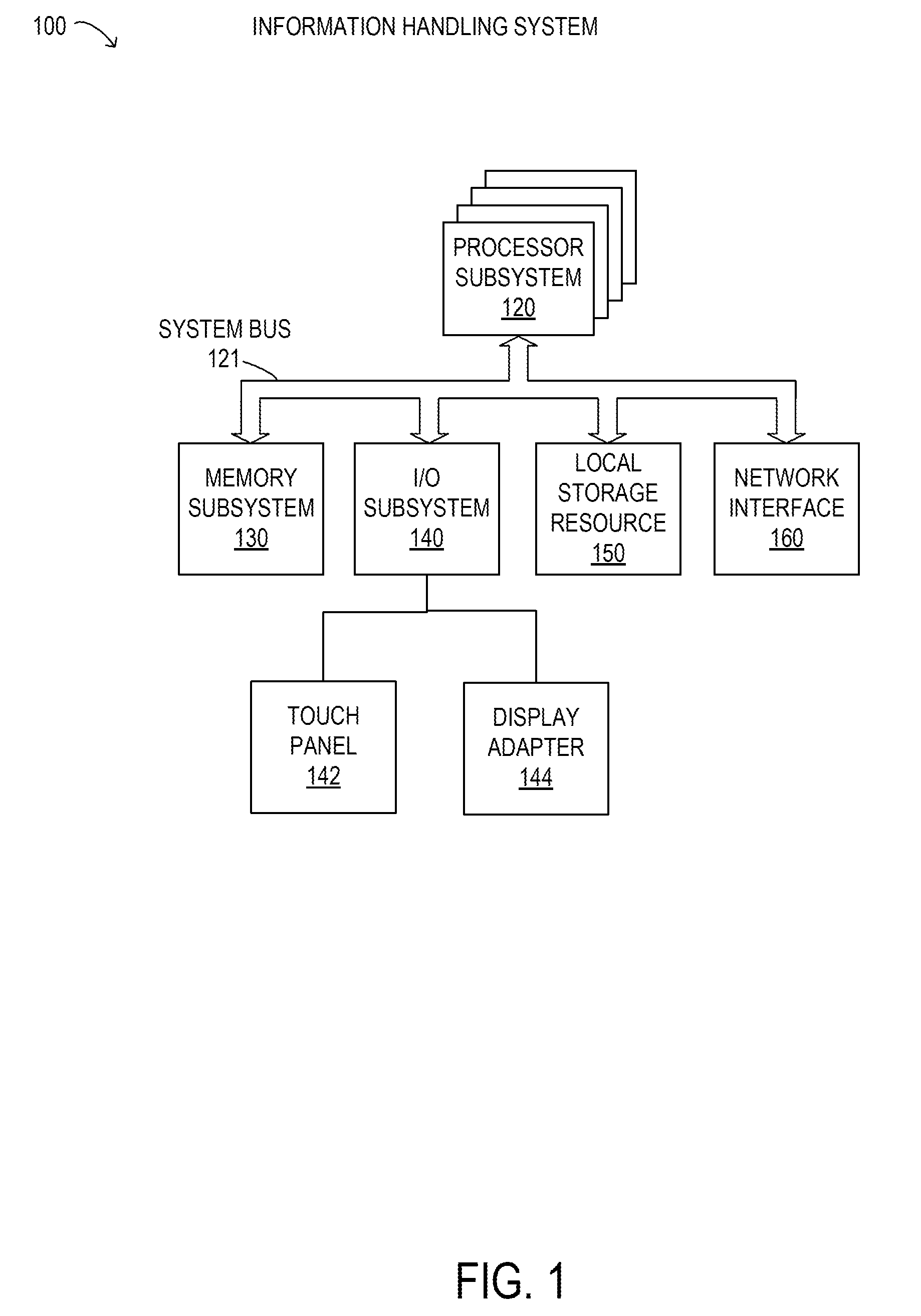

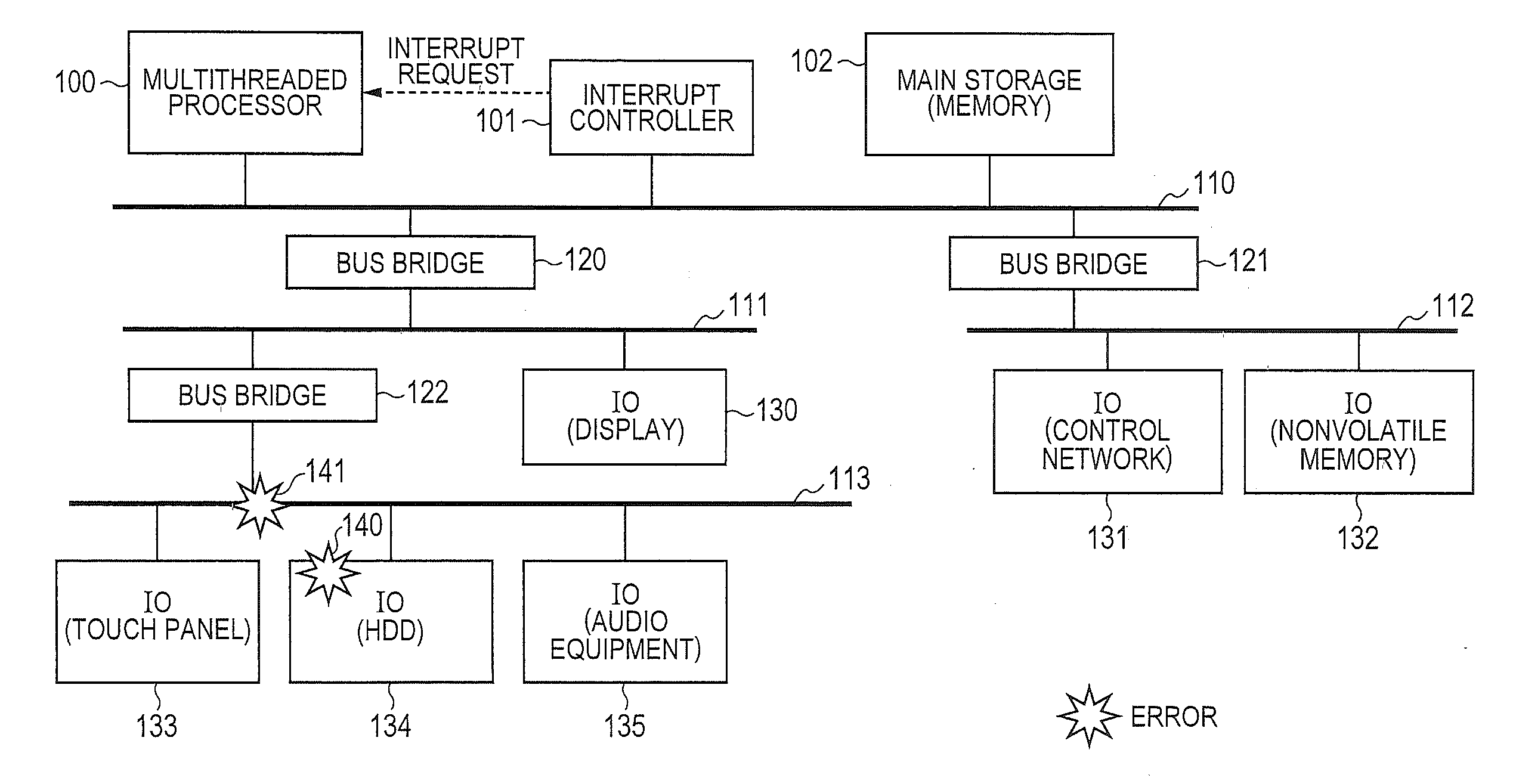

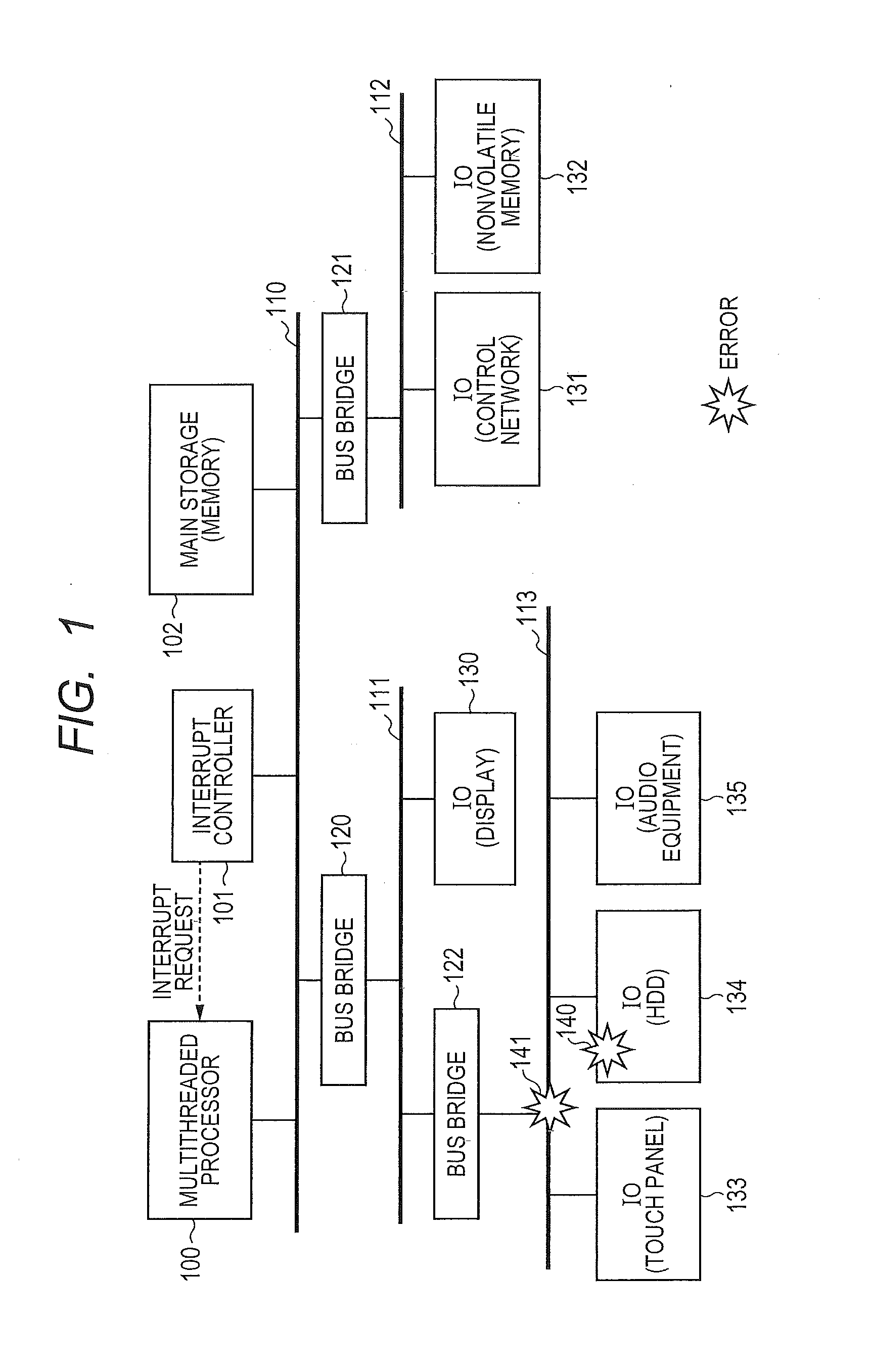

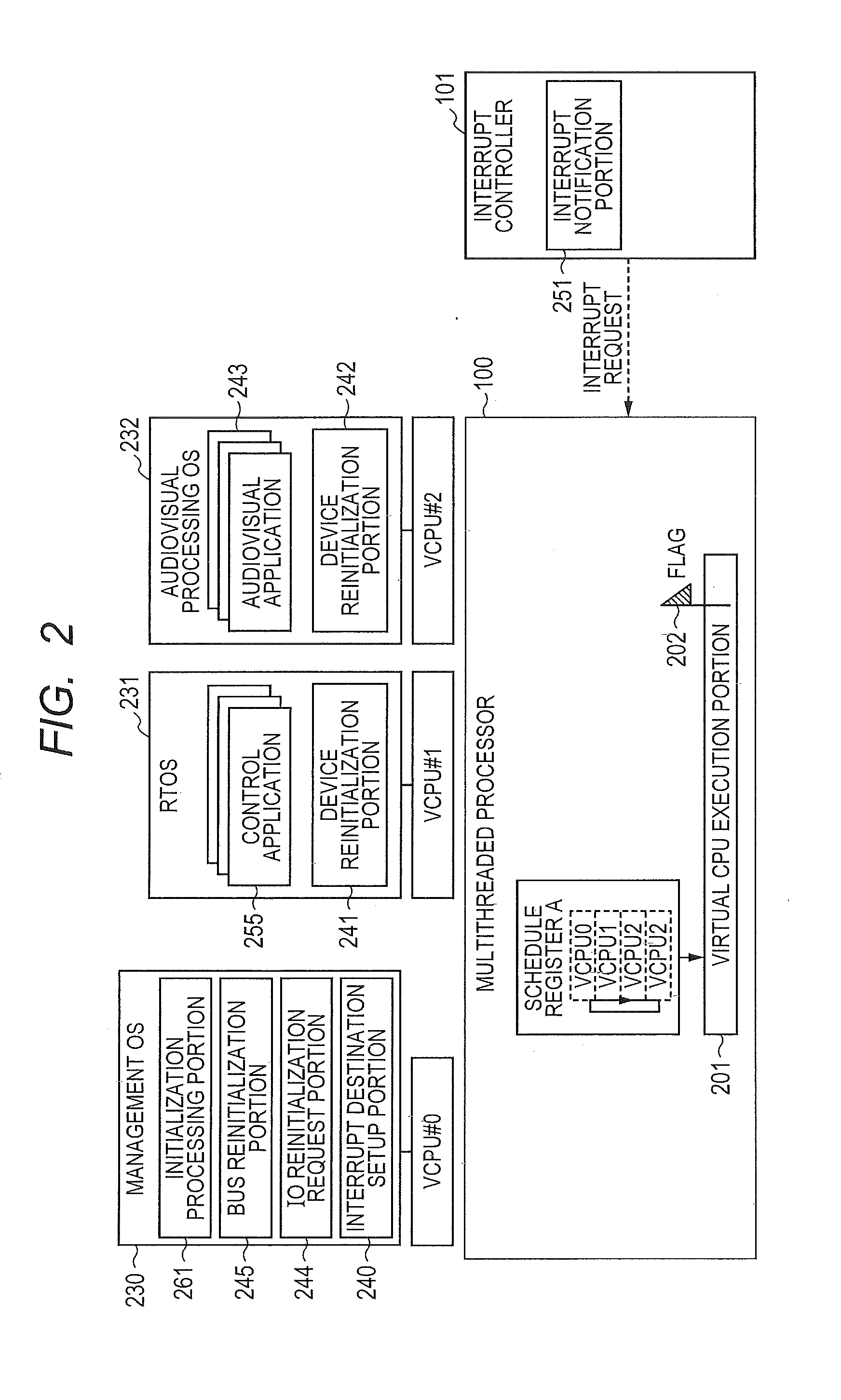

Computer system

ActiveUS20160041883A1Hardware monitoringNon-redundant fault processingMultithreadingOperating system

A computer system includes an interrupt controller to notify a bus error occurrence, and a multithreaded processor. The multithreaded processor includes a schedule register that settles a sequence of performing a plurality of virtual CPUs and stores data for virtual CPUs to be performed, and a virtual CPU execution portion that performs virtual CPUs according to a sequence settled by the schedule register. Virtual CPUs operate different operating systems (OS's) and include a first virtual CPU that operates a management OS to manage other OS's. When notified of bus error occurrence, the virtual CPU execution portion operates only the first virtual CPU regardless of an execution sequence settled in the schedule register. The first virtual CPU reinitializes a bus where an error occurred.

Owner:RENESAS ELECTRONICS CORP

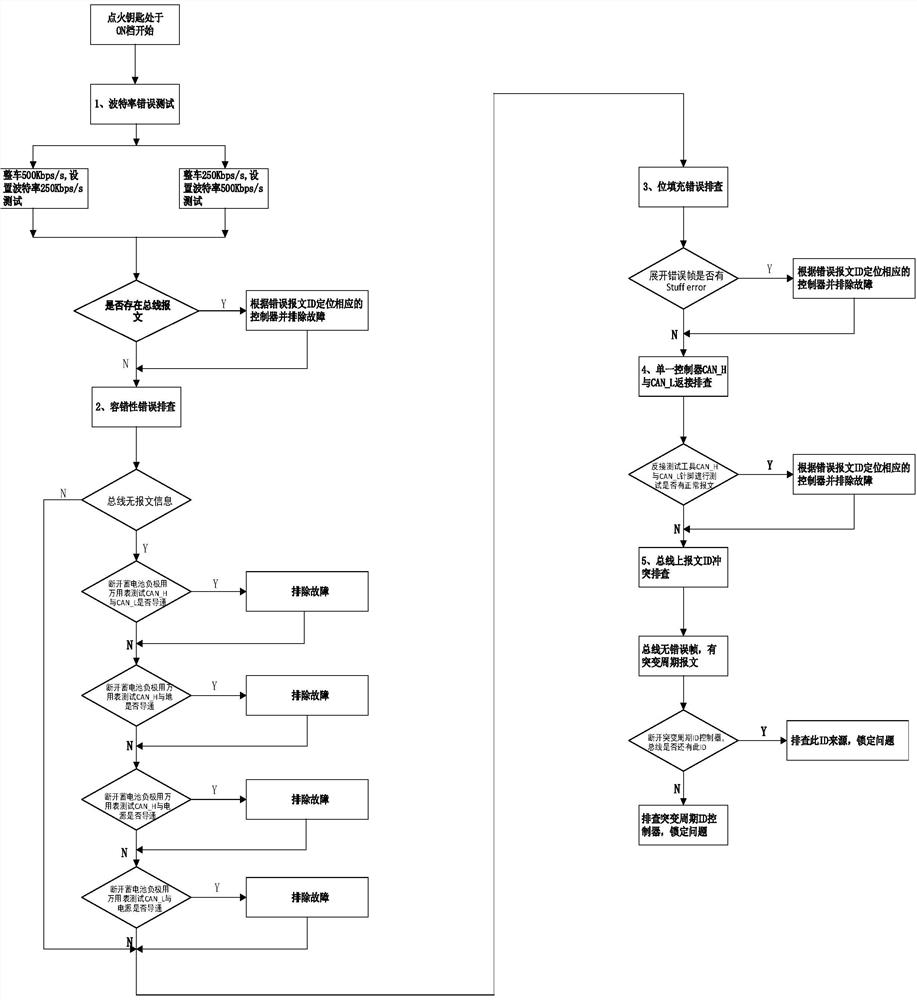

Method for quickly checking error frames of CAN bus of whole vehicle

PendingCN112835343AImprove detection efficiencyProgramme controlElectric testing/monitoringArea networkReverse connection

The invention discloses a method for quickly checking error frames of a CAN (Controller Area Network) bus of a whole vehicle. The method is characterized by comprising the following steps of: step 1, checking bus baud rate mismatch; step 2, checking fault-tolerant error frames; step 3, checking bit filling error frames; step 4, performing reverse connection troubleshooting on the single controller CAN_H and the single controller CAN_L; and step 5, checking bus ID conflicts. According to the method, the fault can be judged when an error is detected in any one of the steps 1-4, the whole process does not need to be completed, and the detection efficiency is high.

Owner:DONGFENG AUTOMOBILE COMPANY

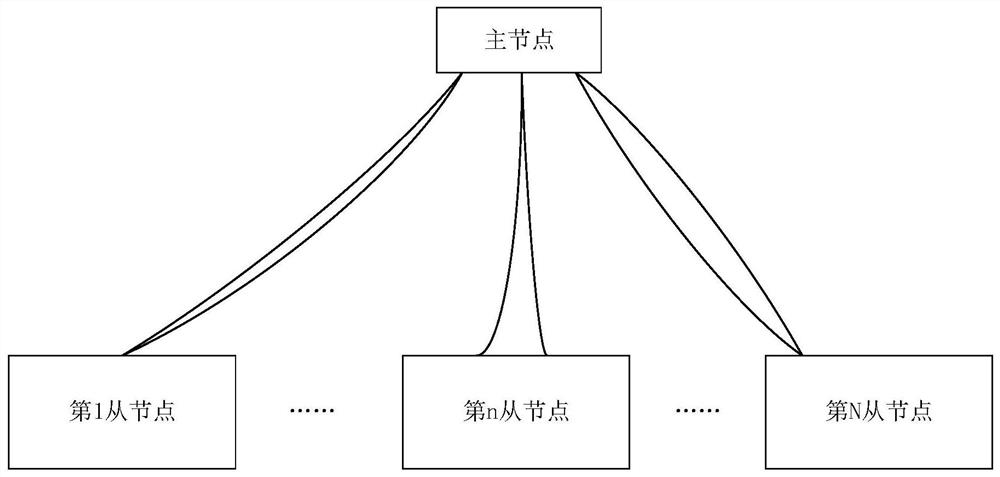

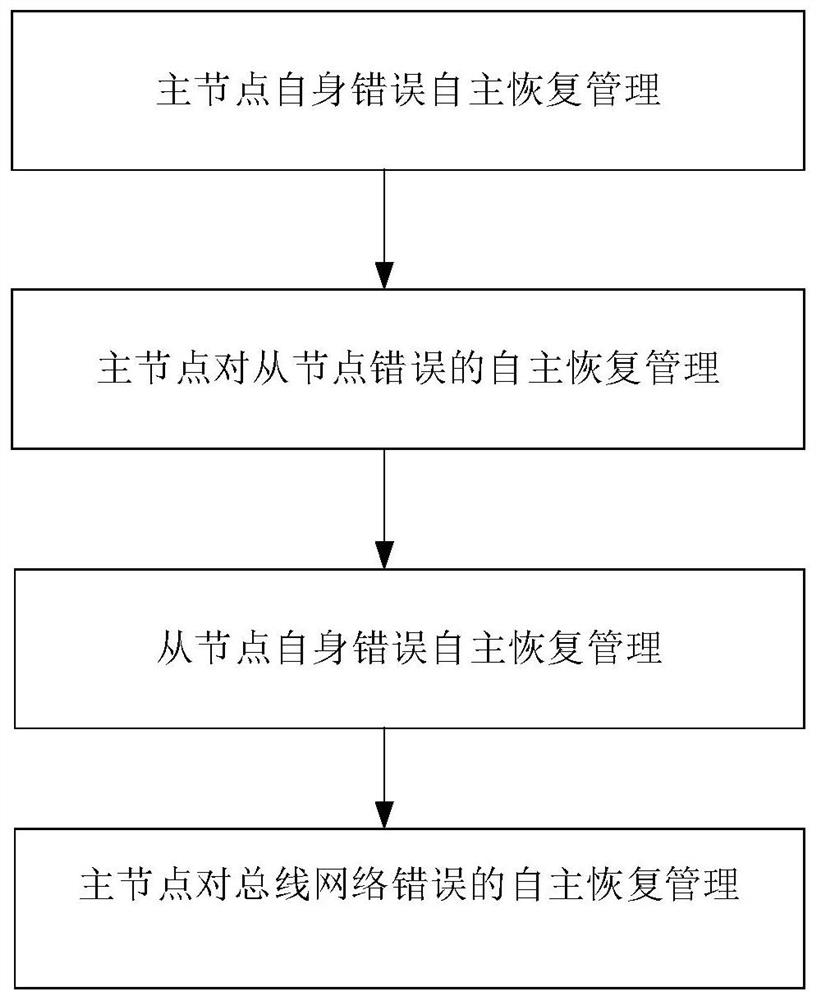

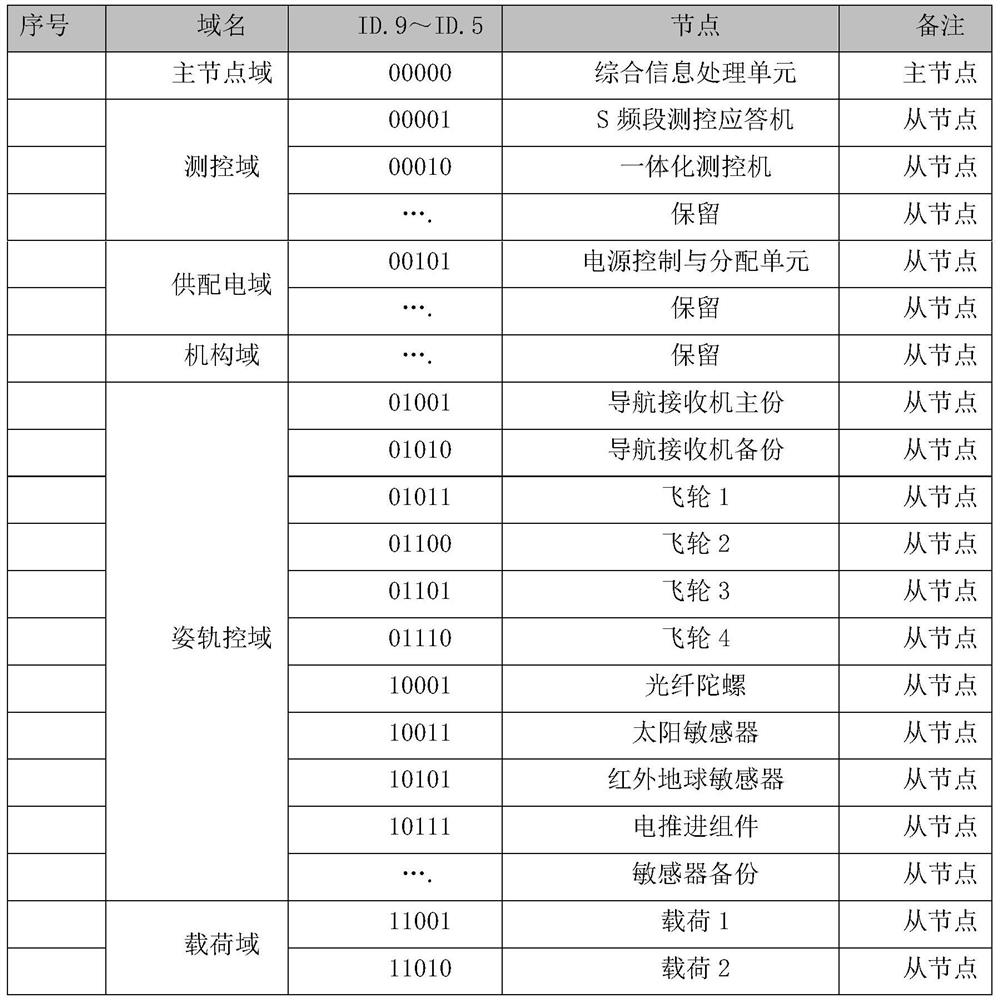

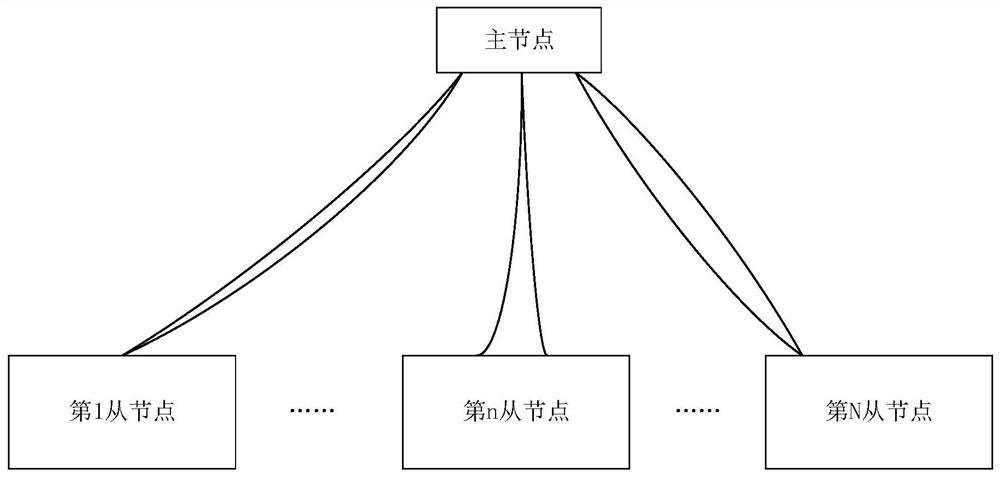

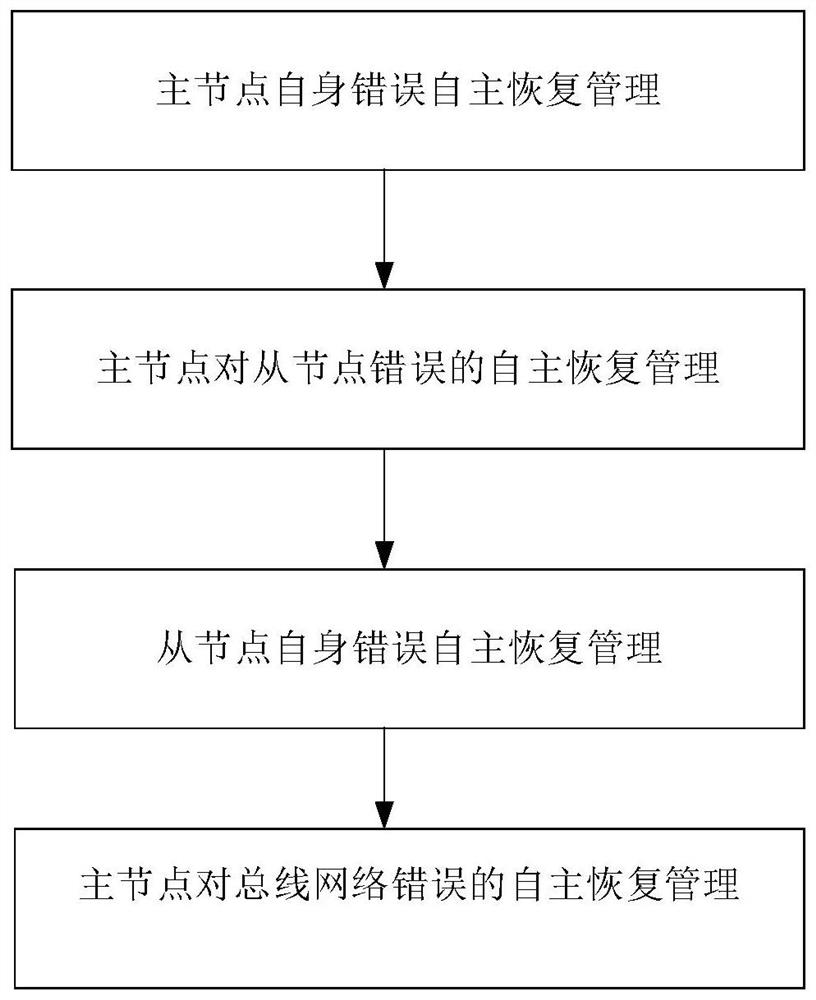

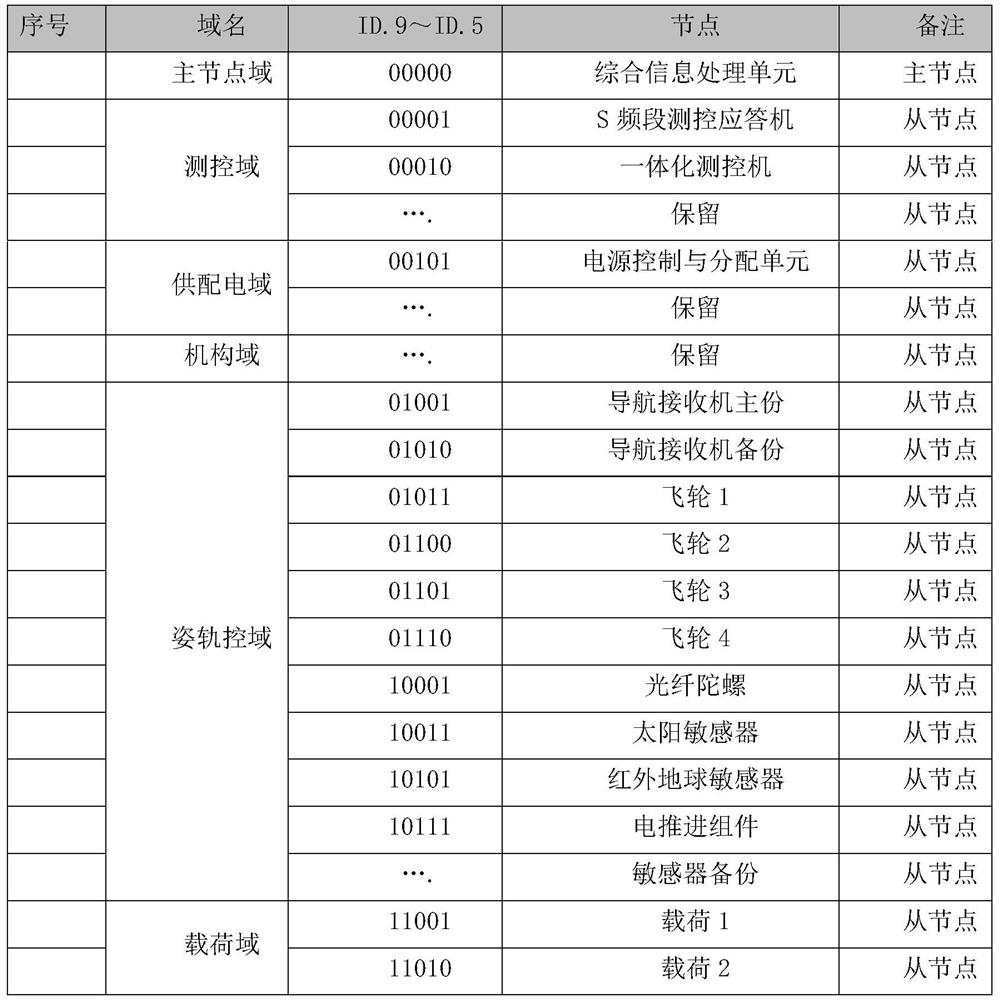

Autonomous error correction management method for CAN bus of spacecraft

ActiveCN112859713AHigh self-management practicalityEasy to operateProgramme controlComputer controlFlight vehicleEngineering

The invention discloses an autonomous error correction management method for a CAN bus of a spacecraft. The CAN bus is composed of a master node and N slave nodes. The method comprises the steps: performing autonomous recovery management on bus errors by the master node, performing autonomous recovery management on the bus errors by the slave nodes, and performing autonomous recovery management on bus network errors by the master node, wherein the autonomous recovery management on the bus errors by the master node refers to that the main node regularly detects all channel buses and autonomously corrects errors of the channel buses which do not meet the standard; the autonomous recovery management on the bus errors by the slave nodes refers to that the slave nodes detect the own channel bus and performs autonomous error correction on the channel bus which finds the errors; and the autonomous recovery management on the bus errors by the master node refers to that the master node sends an instruction to start fault processing diagnosis when the proportion of the slave nodes which are monitored by the master node in the communication period T5 and have continuous communication abnormity is higher than a standard proportion.

Owner:航天科工空间工程发展有限公司

Peripheral bus error containment and recovery

ActiveUS9547557B2Non-redundant fault processingRedundant operation error correctionOperational systemBus mastering

A peripheral bus error containment and recovery system enables a bus device to experience a fatal bus error and recover without stopping execution of an operating system. When a fatal bus error is detected at the bus device, a bus controller may deactivate a data link layer for a downstream port populated by the bus device, causing an operating system device driver to be uninstalled for the bus device. Then, the operating system device driver may be reinstalled without physically removing the bus device.

Owner:DELL PROD LP

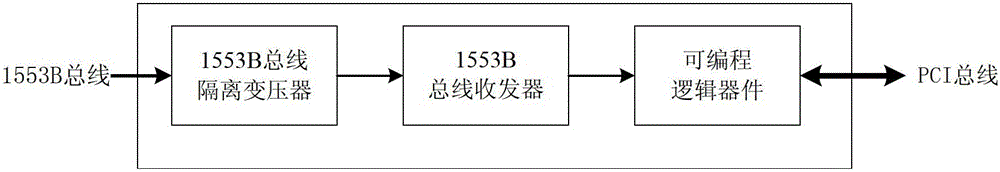

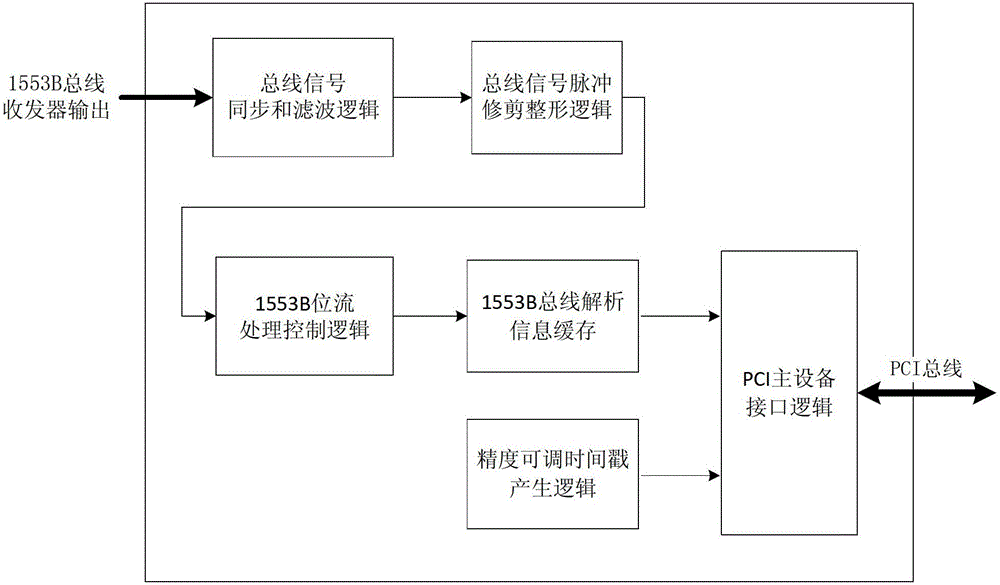

A 1553b bus monitoring system

ActiveCN103346931BComprehensive and Complete DocumentationAccurately determine the transfer timeBus networksTime informationTransceiver

The invention discloses a 1553B bus monitoring system which comprises a 1553B bus isolation transformer, a 1553B bus transceiver and a programmable logic device. After a 1553B bus passes through the 1553B bus isolation transformer and the 1553B bus transceiver, a pair of logically complementary digital signals are output; filter shaping, code stream extraction and protocol analysis and processing are conducted on the input digital signals through the programmable logic device and extracted word information and timestamp information of the 1553B bus are written in a computer memory. With regard to normal 1553B bus transmission, all command word information, control word information, data word information and interval time information of the adjacent words can be monitored and recorded by the monitoring system, wherein the command word information, the control word information, the data word information and the interval time information of the adjacent words are transmitted on the 1553B bus. With regard to abnormal 1553B bus transmission, when a bus transmission abnormality occurs, a bus fault type, a fault occurrence time point and recorded position information when a fault occurs can be monitored and recorded by the monitoring system.

Owner:BEIJING AEROSPACE AUTOMATIC CONTROL RES INST +1

A method for autonomous error correction management of space vehicle CAN bus

ActiveCN112859713BHigh self-management practicalityEasy to operateProgramme controlComputer controlFlight vehicleBus

The invention discloses an autonomous error correction management method for a CAN bus of a space vehicle. The CAN bus is composed of a master node and N slave nodes; Autonomous recovery management and autonomous recovery management of bus network errors by the master node; the autonomous recovery management of bus errors by the master node means that the master node regularly detects all channel buses and performs autonomous error correction on channel buses that do not meet the standards; The self-recovery management of the bus error by the slave node refers to that the slave node detects its own channel bus and performs autonomous error correction on the channel bus that finds an error; the self-recovery management of the bus error by the master node refers to The proportion of slave nodes with continuous communication abnormality detected in the period T5 is higher than the standard proportion, and an instruction is sent to start troubleshooting and diagnosis.

Owner:航天科工空间工程发展有限公司

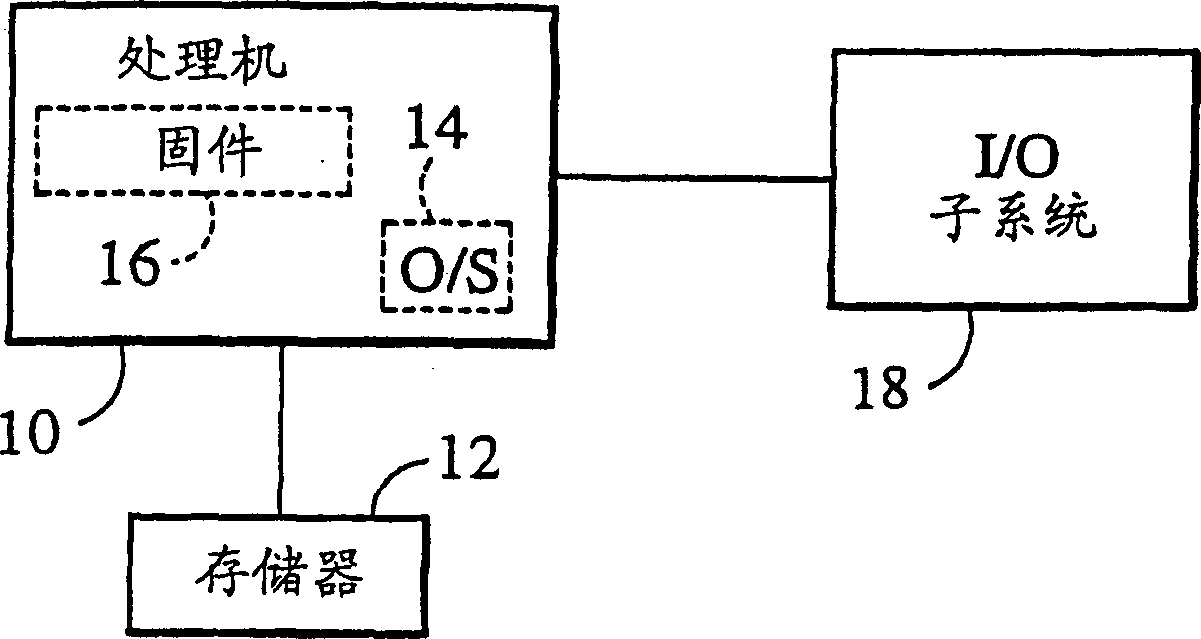

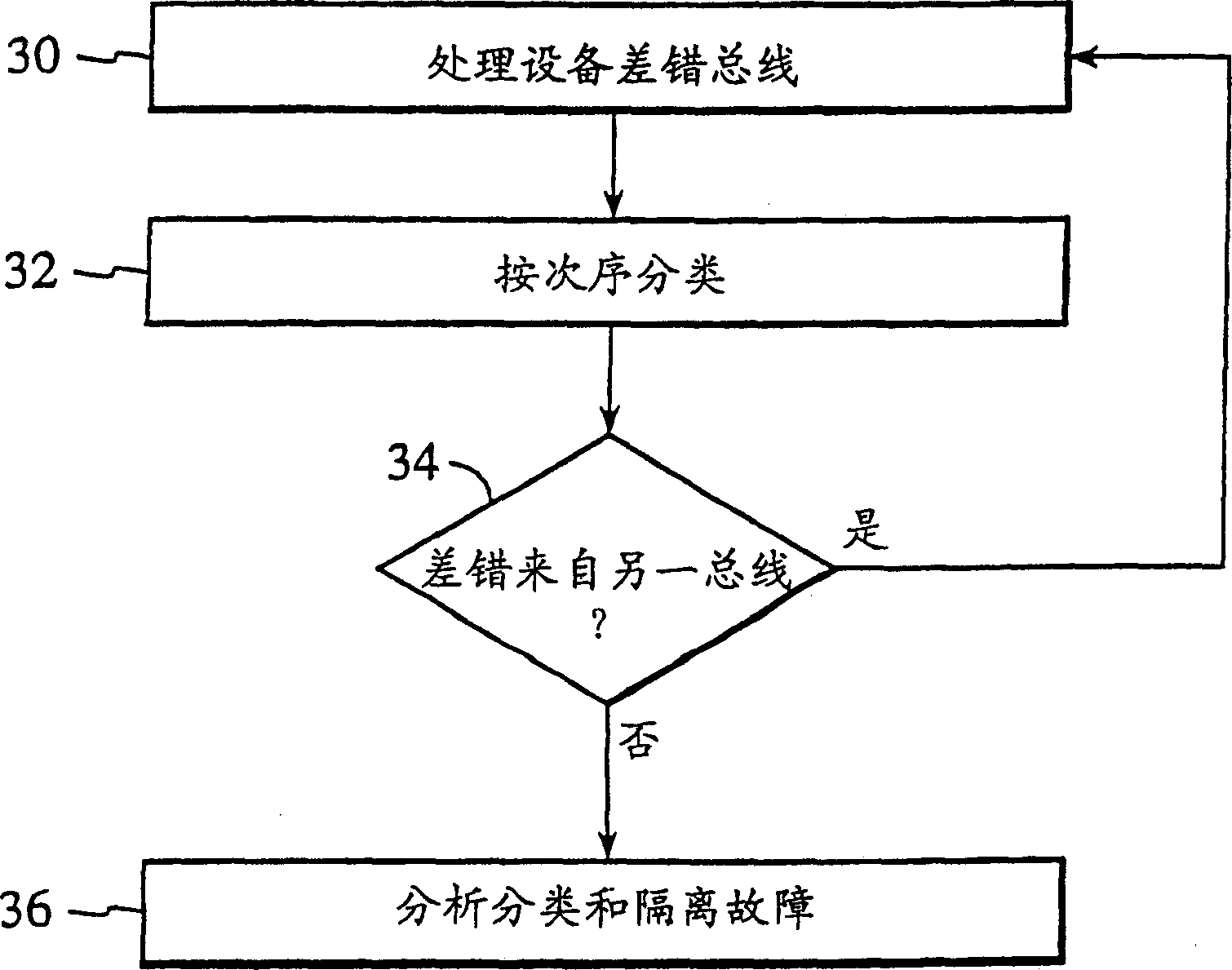

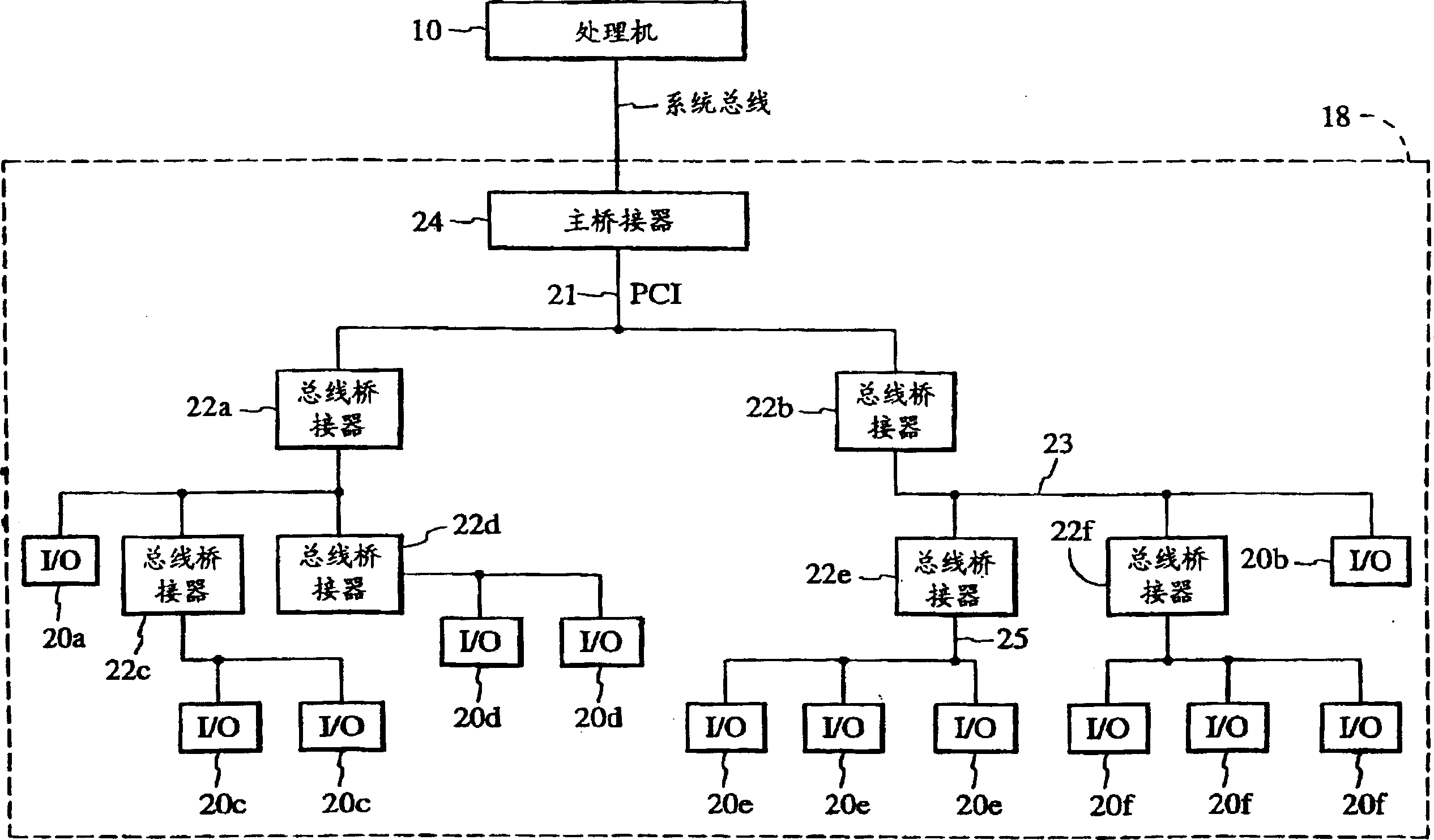

Method and system for fault isolation for PCI bus errors

Method and system aspects for fault isolation on a bus are provided. In a method aspect, a method for isolating a fault condition on a bus of a computer system, the computer system including an input / output (I / O) subsystem formed by a plurality of I / O devices communicating via the bus, includes categorizing, in a recursive manner, the I / O subsystem, and isolating a source of an error condition within the I / O subsystem. Further, the I / O subsystem communicates via a peripheral component interconnect, PCI, bus. In a system aspect, a computer system for isolating a fault condition on a PCI bus includes a processing mechanism, and an input / output mechanism, coupled to the processing mechanism.

Owner:IBM CORP

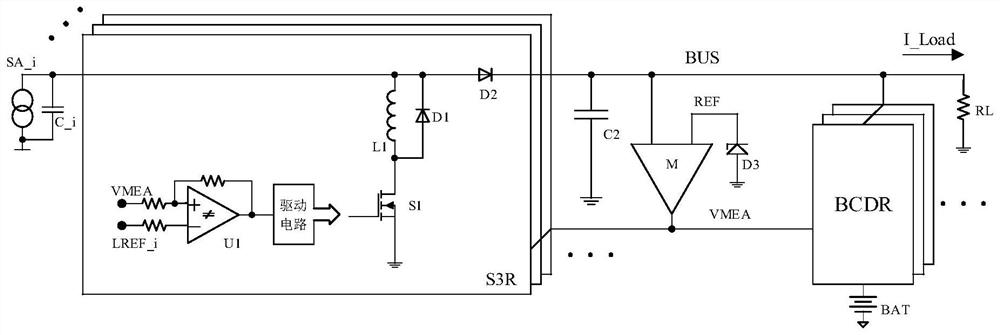

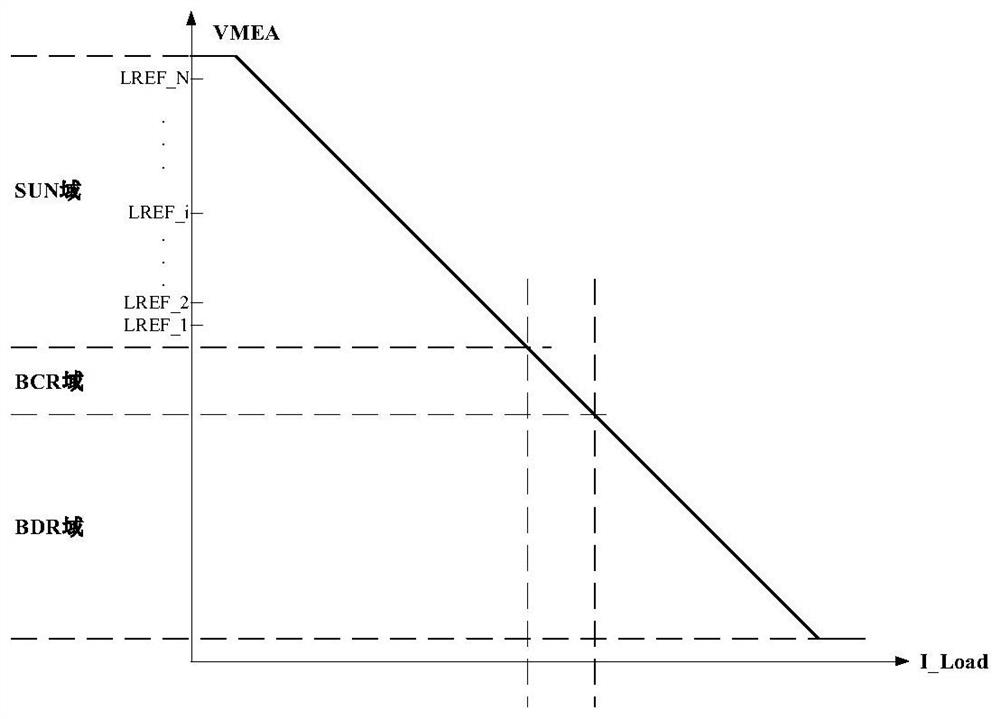

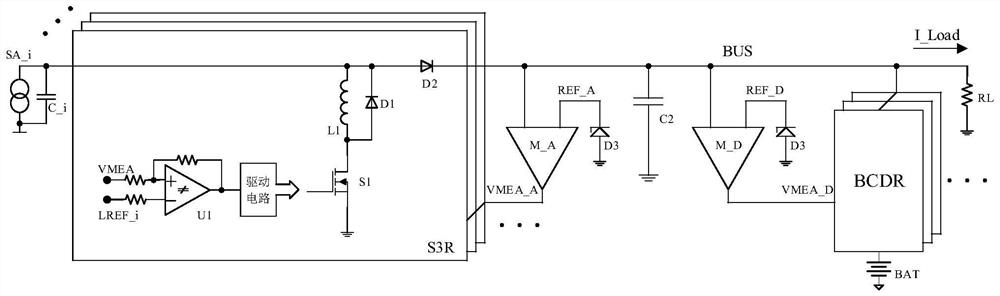

Power supply controller and direct grid-connected control method

PendingCN114336830AImprove dynamic characteristicsImprove dynamic stabilityBatteries circuit arrangementsDc-dc conversionControl engineeringLoop design

The invention provides a power supply controller and a direct grid-connected control method, the power supply controller comprises an S3R, a BCDR and a bus error amplifier, the S3R is connected with a first bus error amplifier, and the BCDR is connected with a second bus error amplifier. The method has the advantages that the BCDR and the S3R are provided with the independent bus error amplifiers, loop design decoupling of the BCDR and the S3R is achieved, the design is more flexible, the dynamic characteristic and stability of the bus are improved, and the power expansion capacity is enhanced; through the direct grid-connected control method of the dual power supply controllers, the power expansion capability of the power supply controllers is further improved, the grid-connected method does not need to add an independent grid-connected controller single machine, so that power expansion can be performed under the condition of not additionally increasing the weight of the whole satellite, and the method can be expanded and applied to grid-connected control of multiple power supply controllers.

Owner:SHENZHEN AEROSPACE NEW POWER TECH

A bus error recovery processing method

Owner:HUAWEI TEHCHNOLOGIES CO LTD

Method for handling errors in bus communication and bus communications system

PendingCN110635964AEfficient analysisFaulty hardware testing methodsError identificationCommunications systemError processing

The invention relates to a method for error handling during bus communication between a first and a second bus member according to a bus protocol. The bus protocol in the method defines at least one bus error code for an error and a bus message having a bus data field. If the first bus member identifies an error, the following steps are performed. The first bus member stores an error identification of the error supplemented with a bus error code in the first bus member, generates a first bus message and writes the bus error code into a bus data field of the first bus message. The second bus member generates a second bus message triggered by the bus error code, which has a request for transmitting an error identification. The first bus member generates a third bus message triggered by the request and writes the stored error identification into the bus data field of the third bus message. The second bus member identifies the error by analyzing the bus error code and the error identification.

Owner:KROHNE MESSTECHNICK GMBH & CO KG

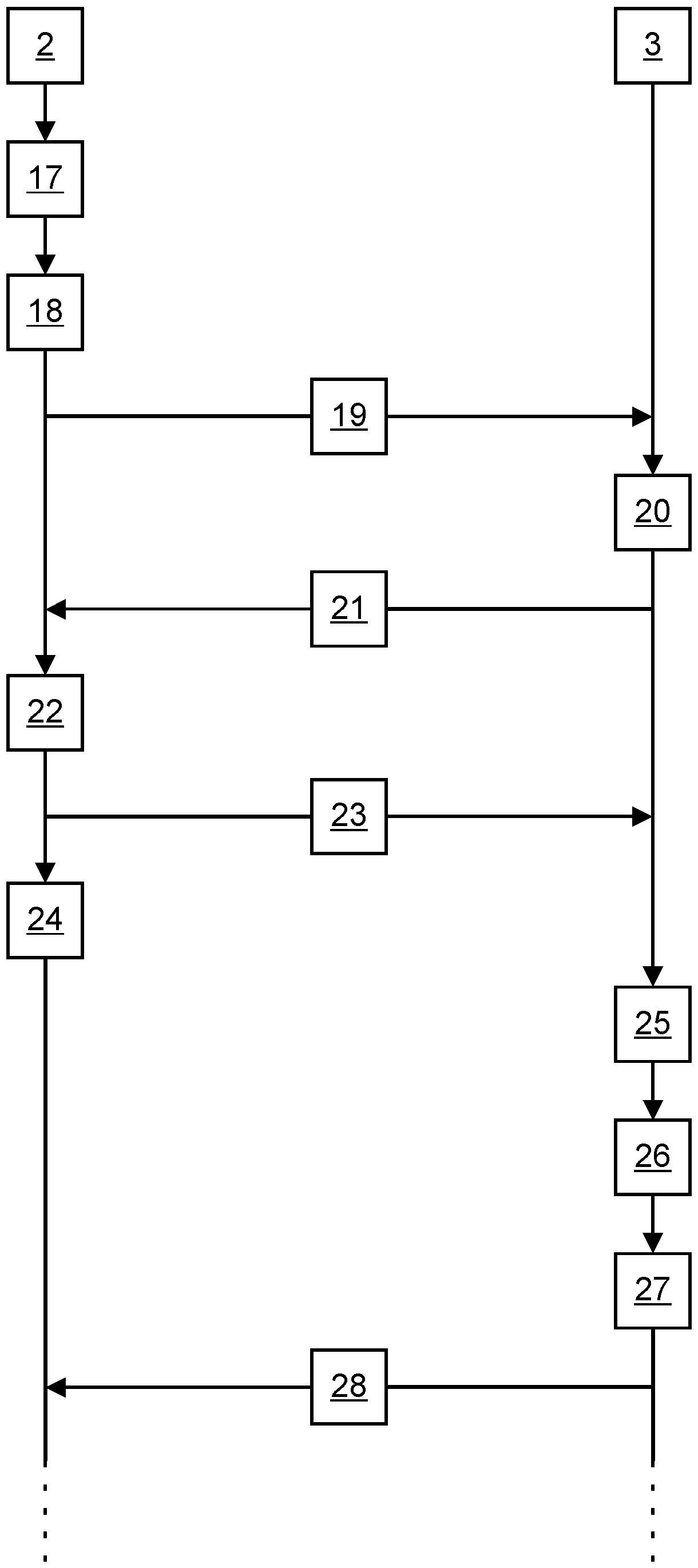

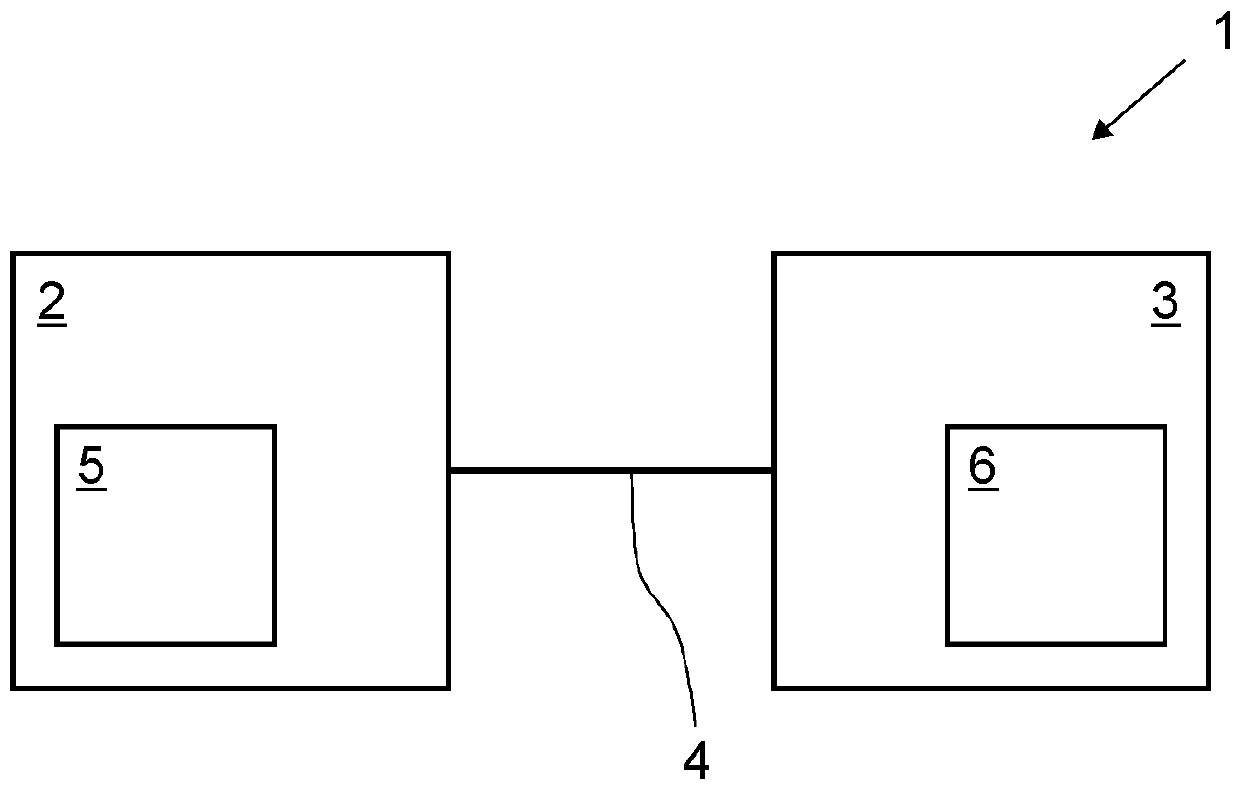

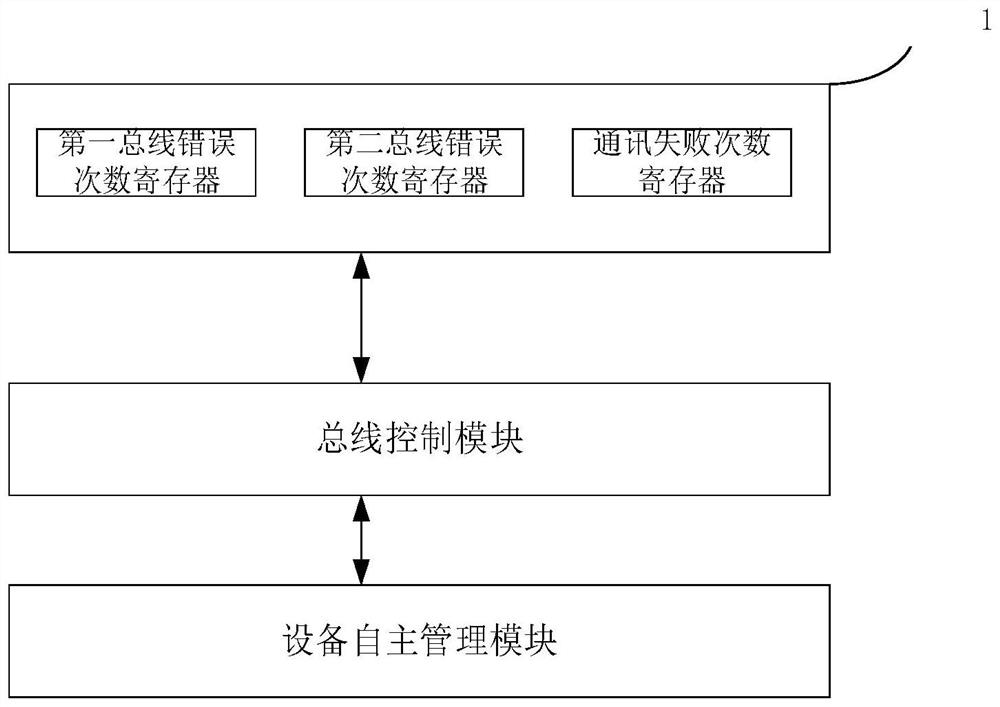

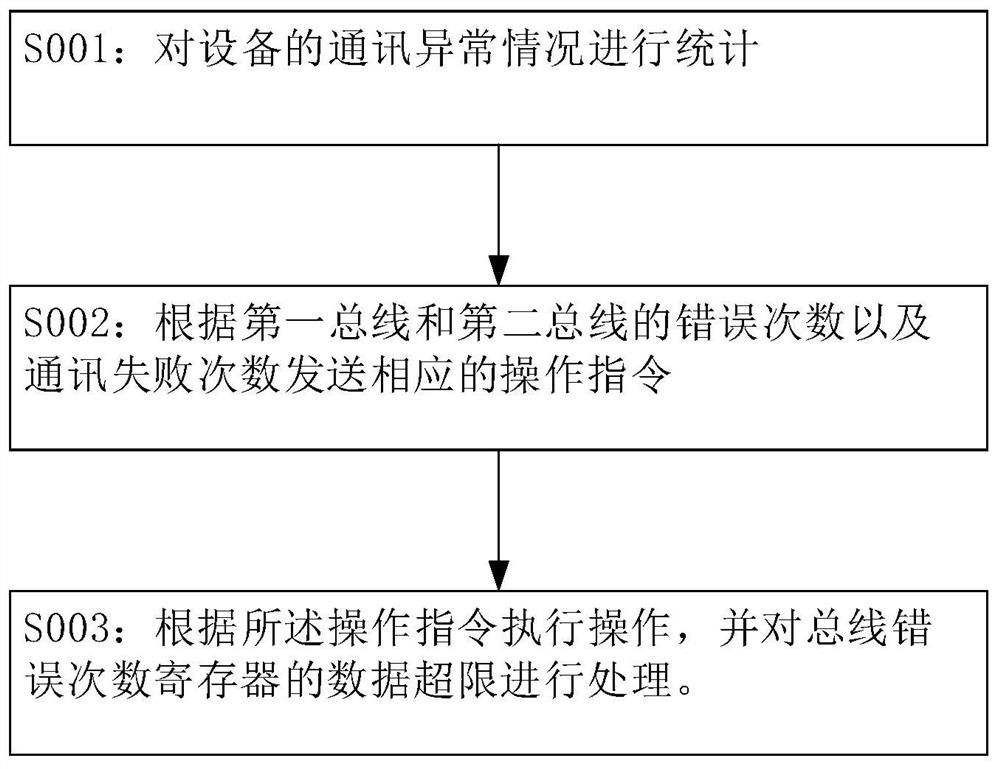

A system and method for autonomous switching processing of a space vehicle CAN bus

ActiveCN112859711BImprove fault toleranceEffectively respond to abnormal communication statusProgramme controlComputer controlComputer hardwareFlight vehicle

The invention discloses a CAN bus autonomous switching processing system and method of a space vehicle. The system includes a bus error counting module, a bus control module and an equipment autonomous management module. The bus error counting module is used to record the number of communication errors and the number of communication failures of the first bus and the second bus and send them to the bus control module; the bus control module is used to record the number of communication errors and communication failures according to the bus. Perform processing operations on the bus; the device autonomous management module is configured to receive a processing operation instruction sent by the bus control module, and execute the instruction.

Owner:航天科工空间工程发展有限公司