Method and system for fault isolation for PCI bus errors

A PCI bus, error technology, applied in the field of fault isolation, can solve the problems of difficult fault isolation, wide performance range, large number, etc., to achieve the effect of reducing fuzzy judgment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention relates to fault isolation for PCI architectures. The following description is written to enable one of ordinary skill in the art to make and use the invention, and is written in accordance with the terms and requirements of the patent application. Those skilled in the art will readily appreciate that various modifications can be made to the preferred embodiment and that the general principles herein can be applied to other embodiments. Therefore, the present invention is not limited to the embodiments presented here, and its application scope is extremely wide according to the basic principles and performances described here.

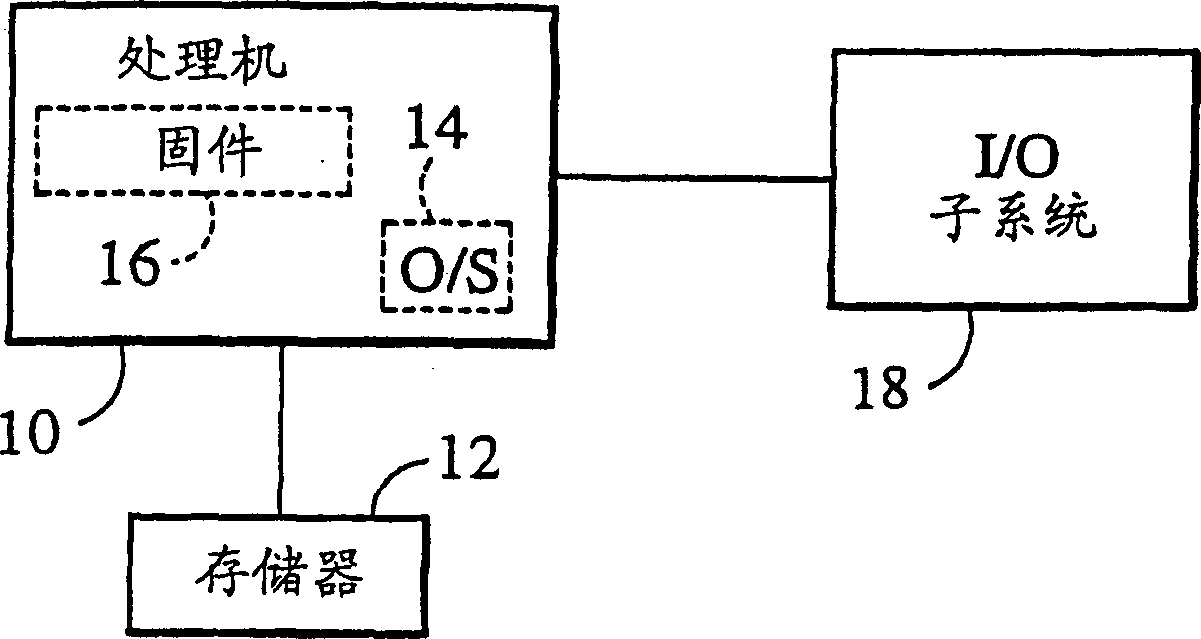

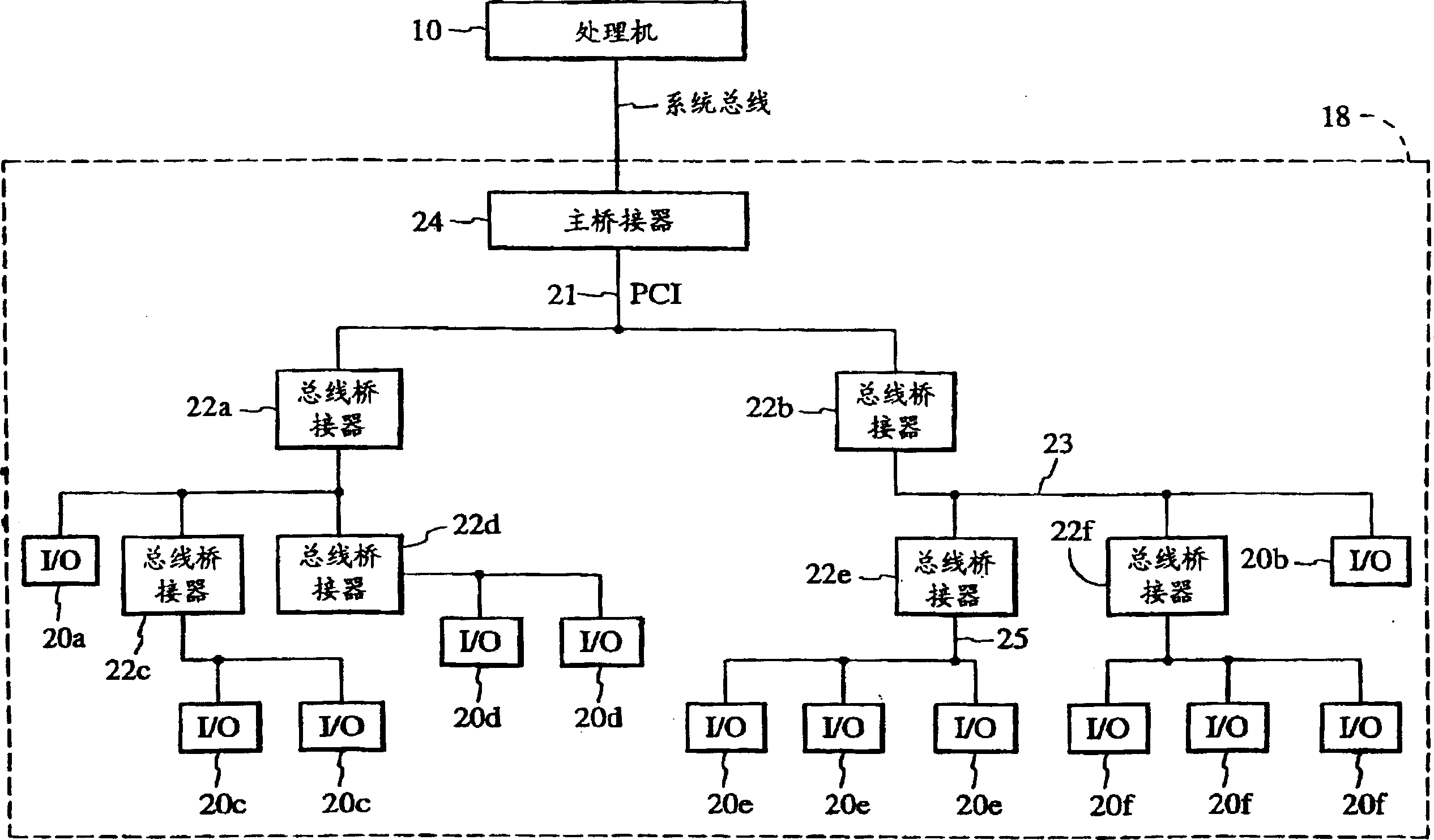

[0017] figure 1 A basic block diagram of a general purpose computer system to which the invention may be applied is shown. As shown in the figure, the computer system of the present invention has a processor 10 (such as a Power PC processor produced by IBM Corporation) coupled to memory 12, namely RAM (Random Access Memor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More