Embedded static random access memory (SRAM) test structure and test method based on institute of electrical and electronics engineers (IEEE) 1500

A technology of memory testing and testing methods, applied in static memory, instruments, etc., can solve the problems of system design efficiency impact, inability to effectively solve the problem of embedded SRAM test multiplexing, etc., and achieve the effect of improving integration efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The specific implementation manners of the present invention will be described in detail below in conjunction with the accompanying drawings and embodiments.

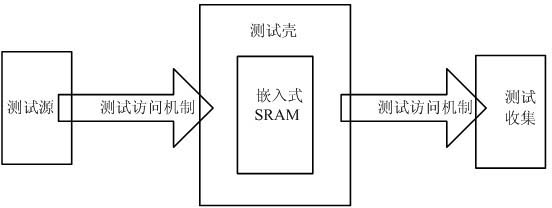

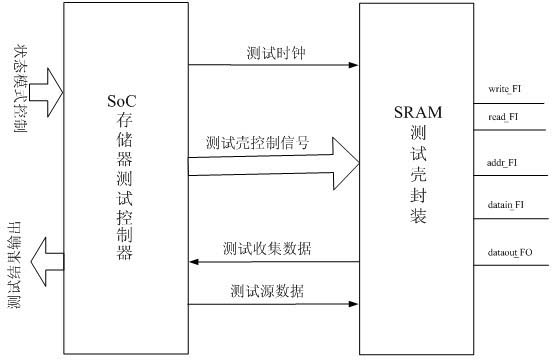

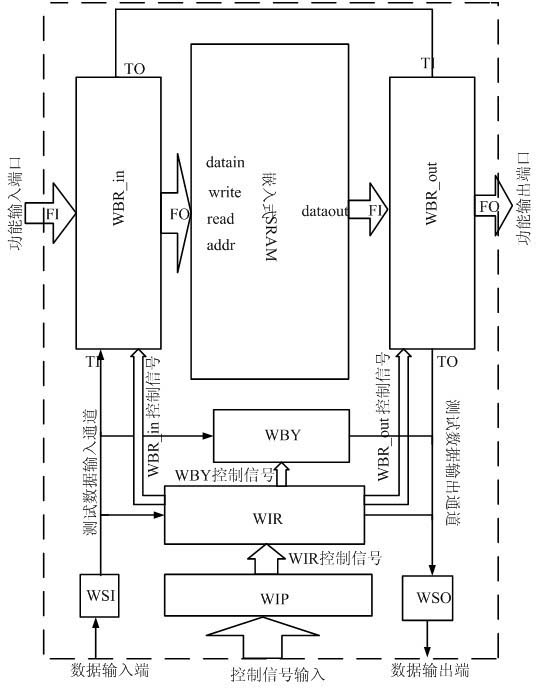

[0030] like figure 2 As shown, an embedded SRAM memory test structure based on IEEE 1500, including a BIST test controller and an embedded SRAM packaged test shell based on IEEE 1500 standards, the test shell receives control signals and command signals sent by the BIST test controller , test address data, test stimulus data, and test response The data is output to the BIST test controller, and the test shell Wrapper surrounds the tested embedded SRAM. The components in the test shell conform to the functional description of the IEEE 1500 standard; the BIST test controller has a clock signal, a state mode control signal port, and a test controller The control signal output port of the test shell Wrapper is connected to the corresponding port of the test shell; the data output port WSO of the test shell is conn...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More