Patents

Literature

1457 results about "Time windows" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

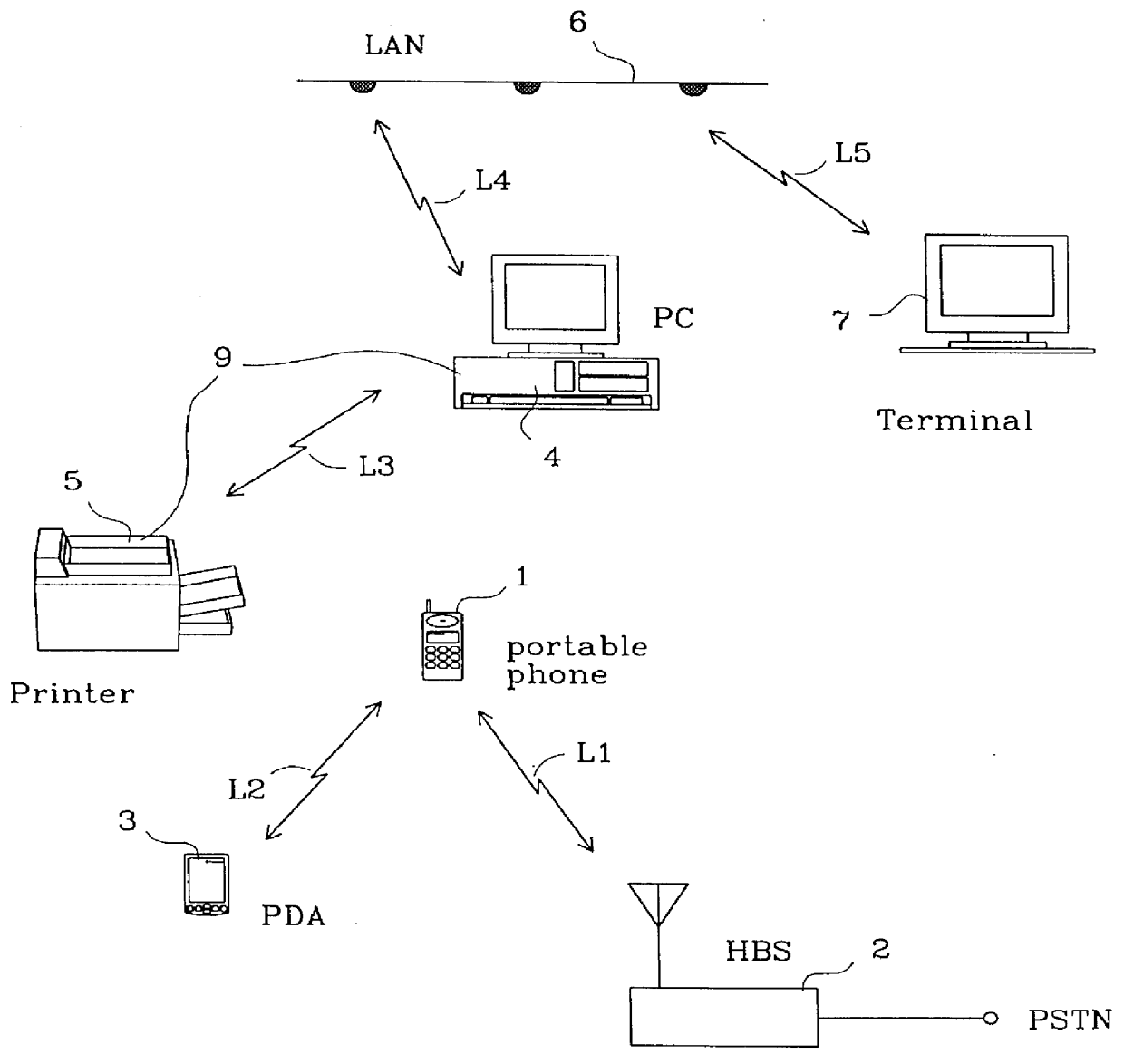

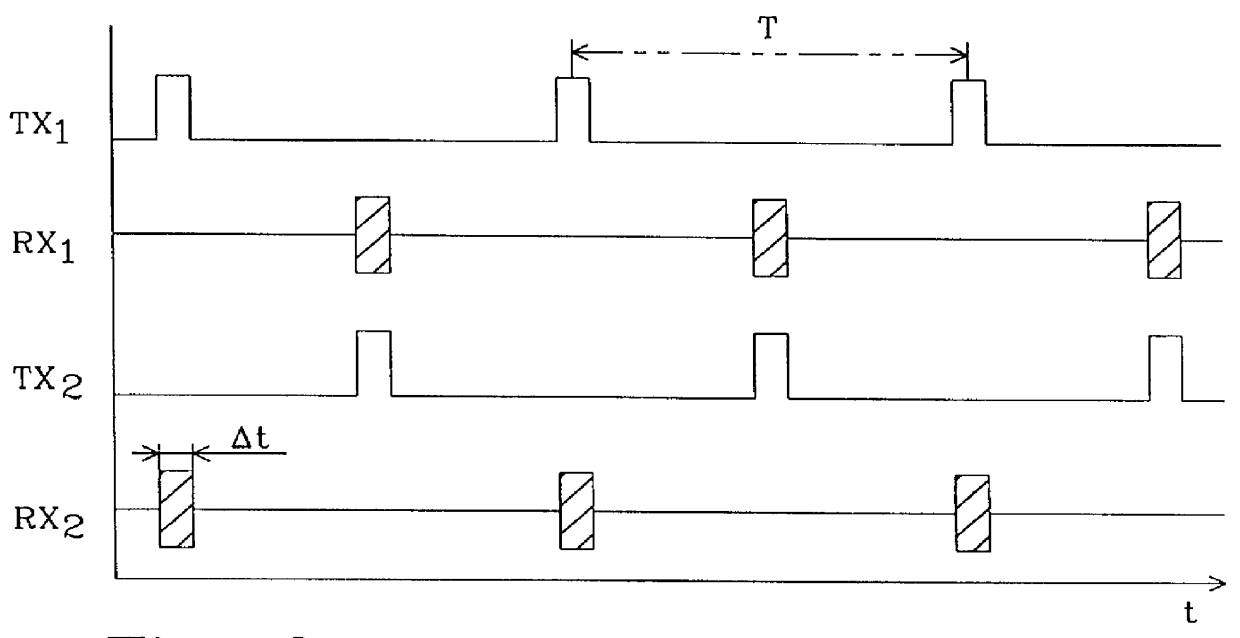

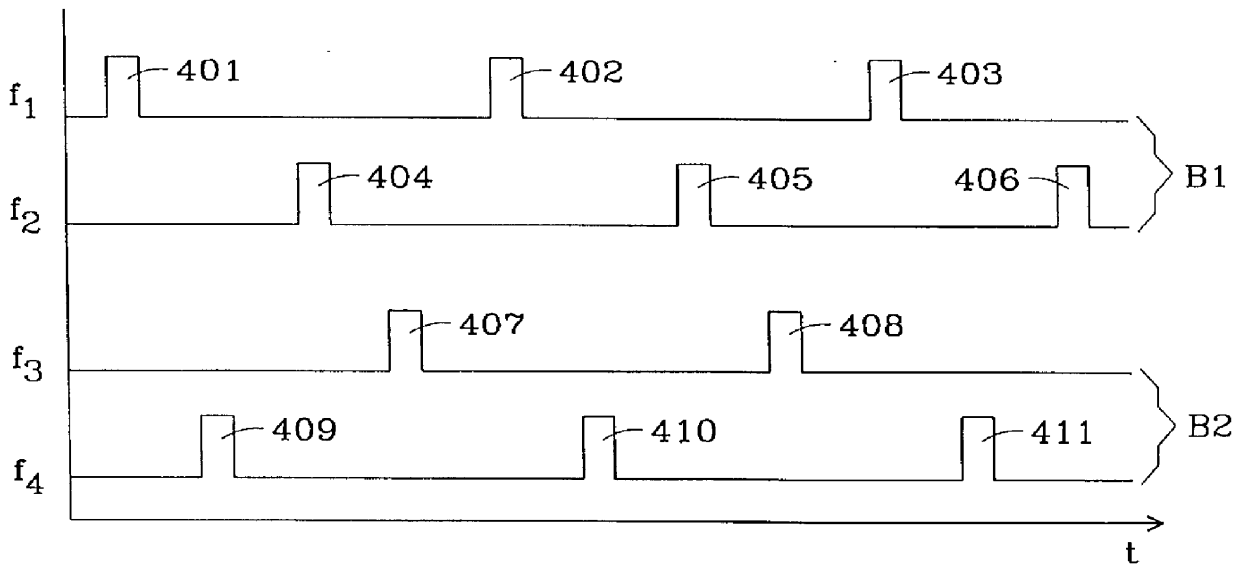

Method and arrangement for radio communication

InactiveUS6028853ATime-division multiplexRadio transmission for post communicationTime windowsAir interface

The present invention relates to a method and arrangement in an ad-hoc network for synchronizing a multiple of radio transceiver arrangements with different characteristics that make use of a common air interface. Each transceiver arrangement comprises at least two transceivers which mutually communicate via a radio transmission link. All transceivers synchronize to a common synchronization signal comprising two staggered beacon pulse series signals (TX1, TX2) which have the same repetition rate. The transceivers synchronize their internal timers which control the signal transmission from the transceivers, to the strongest one of the two beacon pulse series signals (TX1, TX2) by listening during one of the corresponding sets of time windows (RX1, RX2). Between the reception of two beacon pulses, each transceiver transmits beacon pulses itself, thus contributing to the generation of the other beacon pulse series signal, on which other transceivers can lock.

Owner:TELEFON AB LM ERICSSON (PUBL)

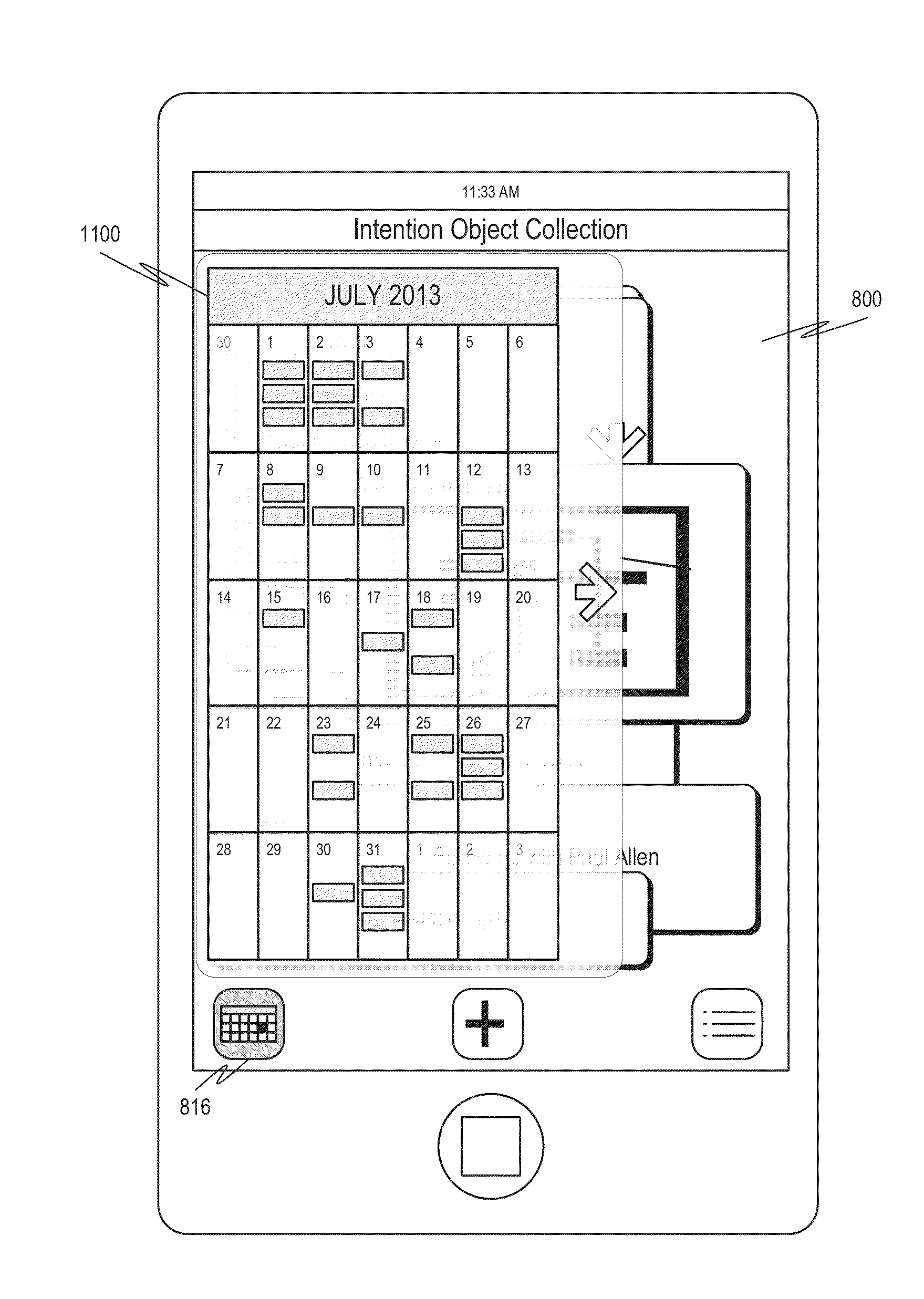

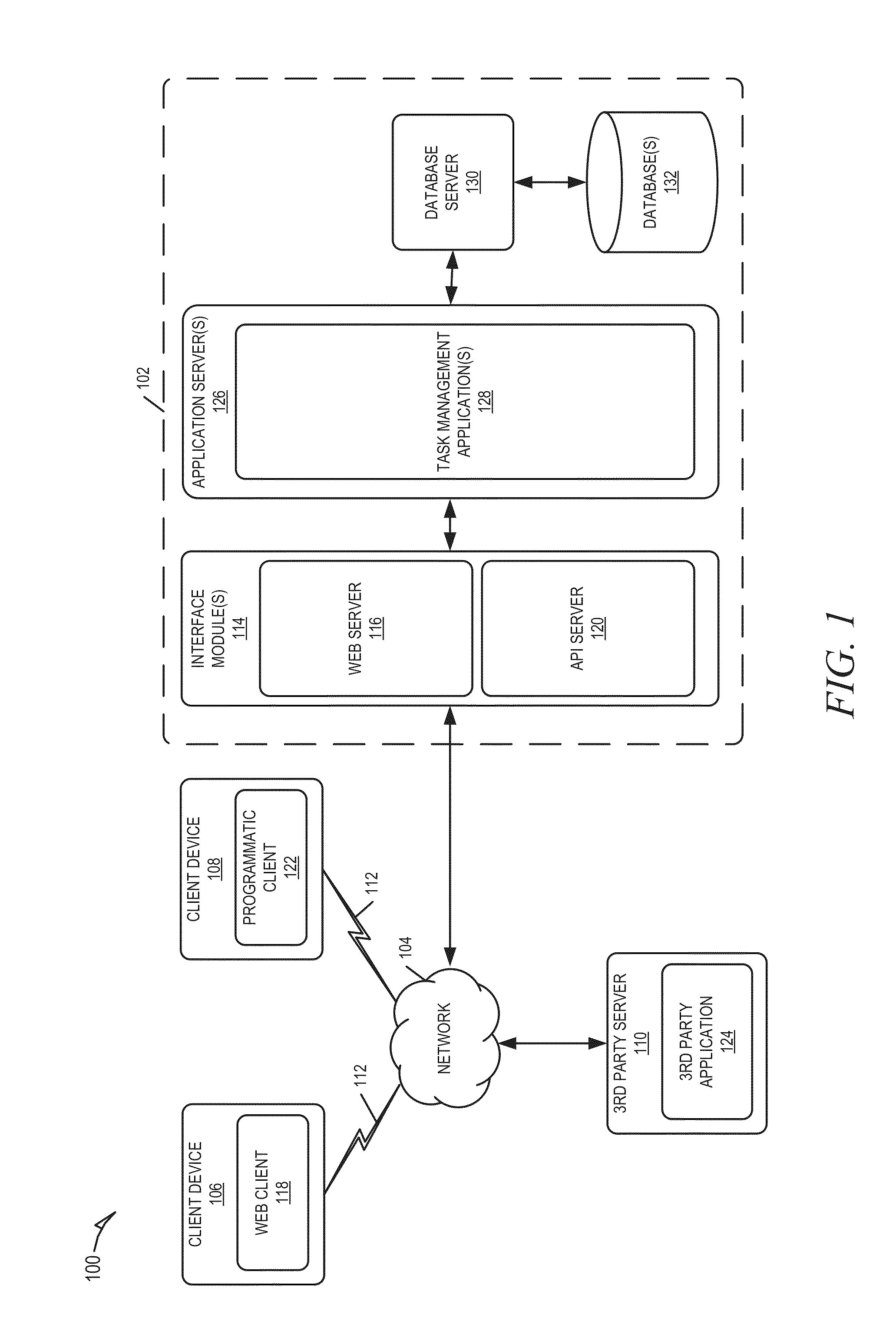

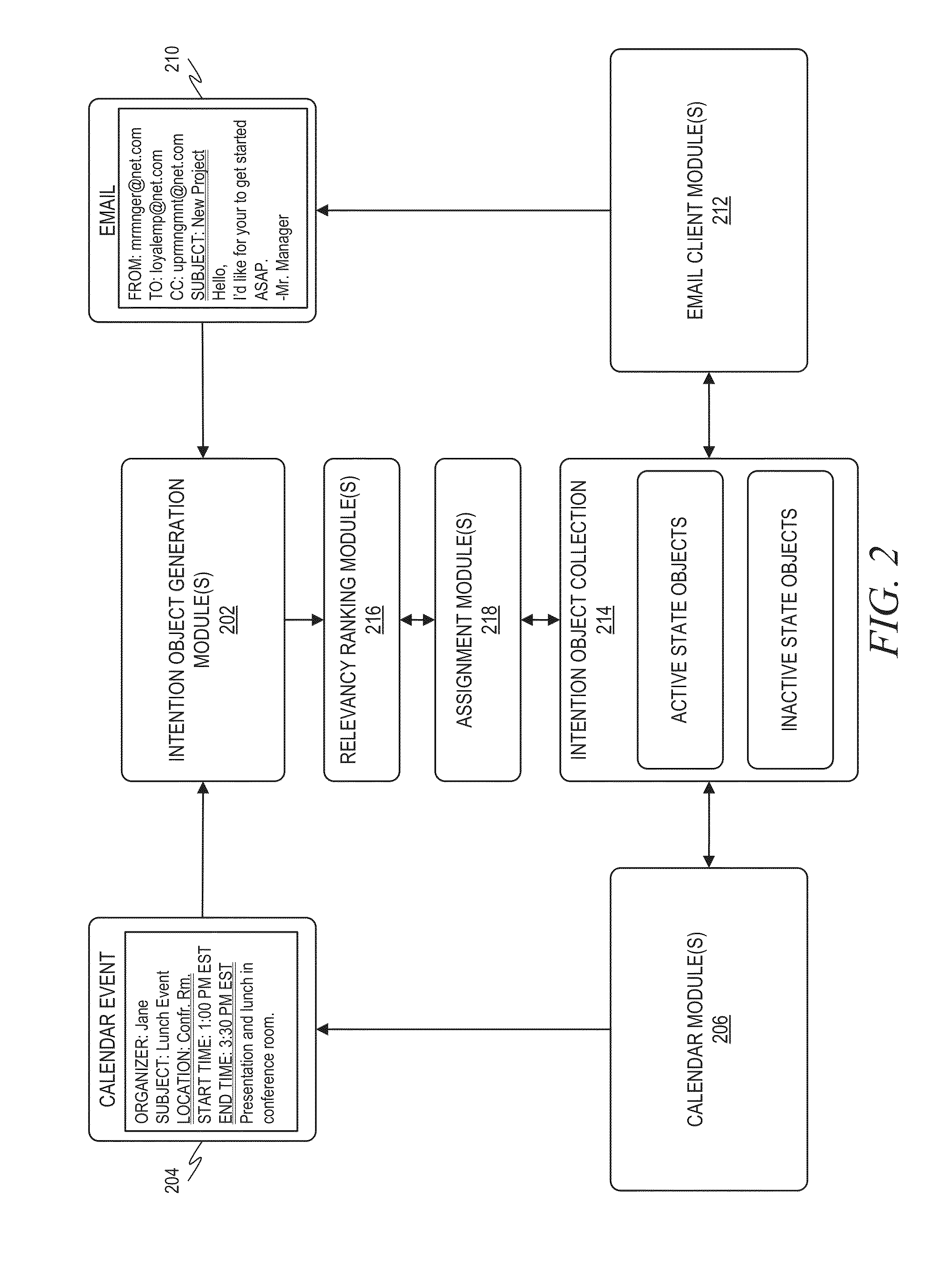

System and method for activity management presentation

ActiveUS20150135085A1Input/output processes for data processingEngineeringHuman–computer interaction

A system, computer-readable storage medium storing at least one program, and computer-implemented method for presenting a set of intention objects arranged by coarse time windows is disclosed. In example embodiments, the method may include accessing a set of intention objects belonging to a user. Each of the intention objects may define the intention of the user to undertake an intention and each object may comprise a data structure including a plurality of activity attributes of the intended activity. The method may further include assigning particular intention objects of the set of intention objects to a coarse time window based on the attributes of the respective intention objects. The method may further include presenting at least a portion of the set of intention objects to a user in a day view that is arranged based on the assigned coarse time windows.

Owner:GOOGLE LLC

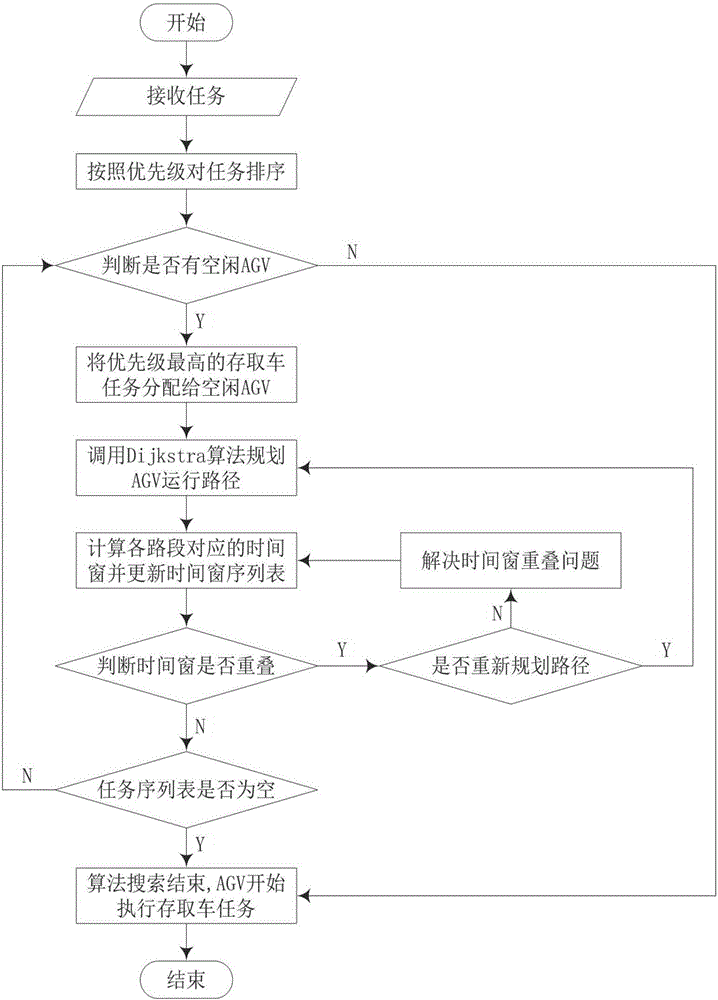

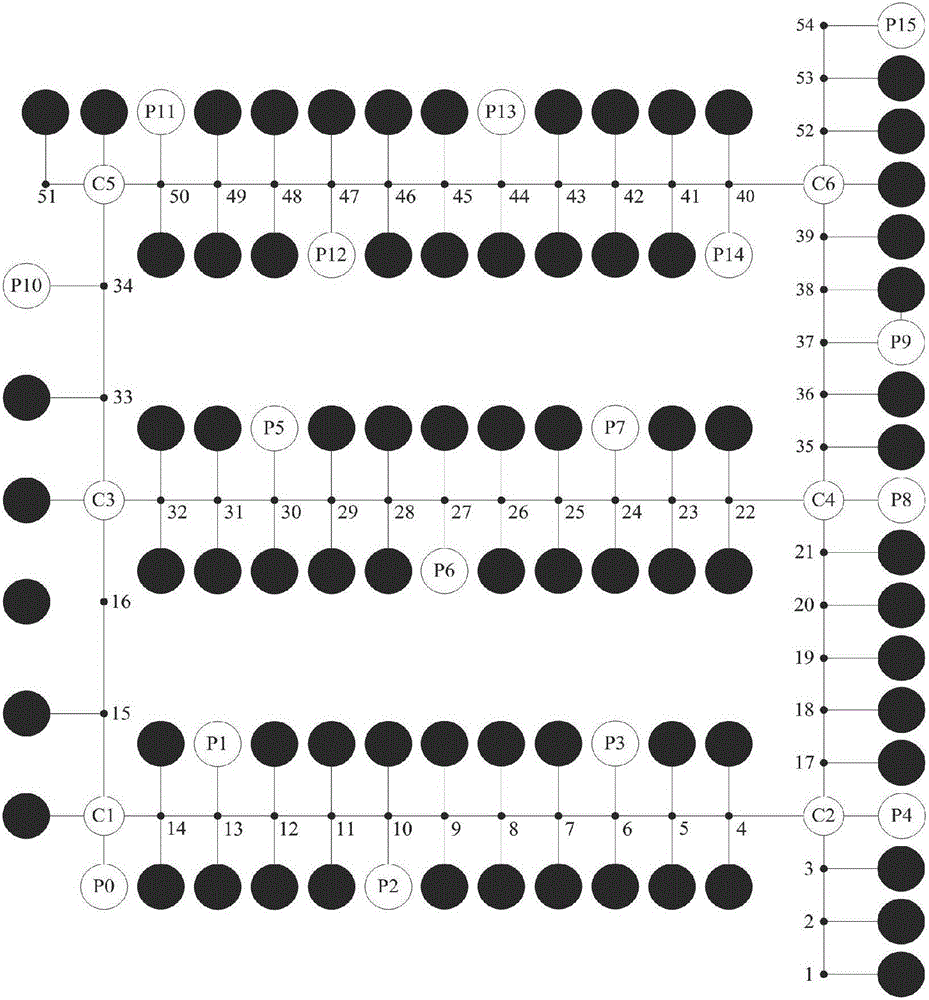

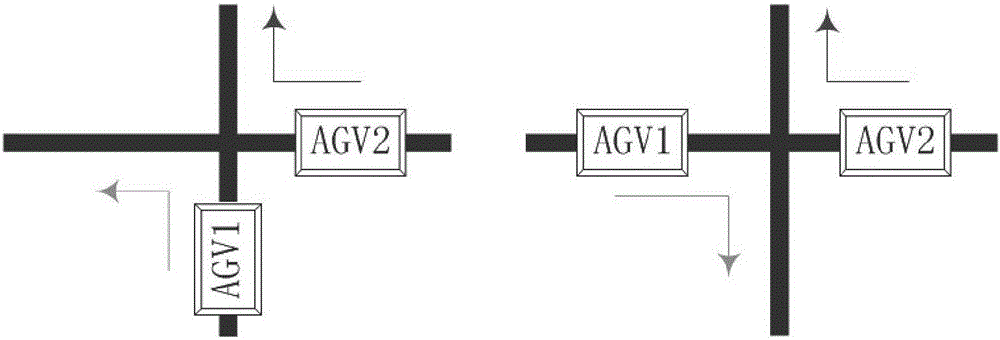

Parking system path planning method based on dynamic time windows

The invention discloses a parking system path planning method based on dynamic time windows, and belongs to the technical field of path planning. The method is characterized by comprising the following steps: S1, building a work environment model of AGVs in an intelligent garage in a topological method; S2, setting priority for each AGV and each car parking / picking task according to different evaluation criteria; S3, using a Dijkstra algorithm to plan a shortest possible path for an AGV accepting a task; S4, arranging feasible path time windows; S5, designing conflict resolution strategies according to different types of conflicts; and S6, planning a conflict-free optimal path for the AGV using a parking system path planning algorithm based on dynamic time windows. A time-sharing use strategy is used, and the Dijkstra algorithm and a time window method are combined effectively, so that the problem that the existing multi-AGV path planning is of poor flexibility and is prone to deadlock or collision conflict is solved effectively, and a shortest conflict-free optimal path can be planned for an AGV accepting a task. In addition, the overall operation efficiency of an intelligent three-dimensional parking system can be improved effectively, and the car parking / picking waiting time can be reduced for social members.

Owner:JIANGSU MARITIME INST

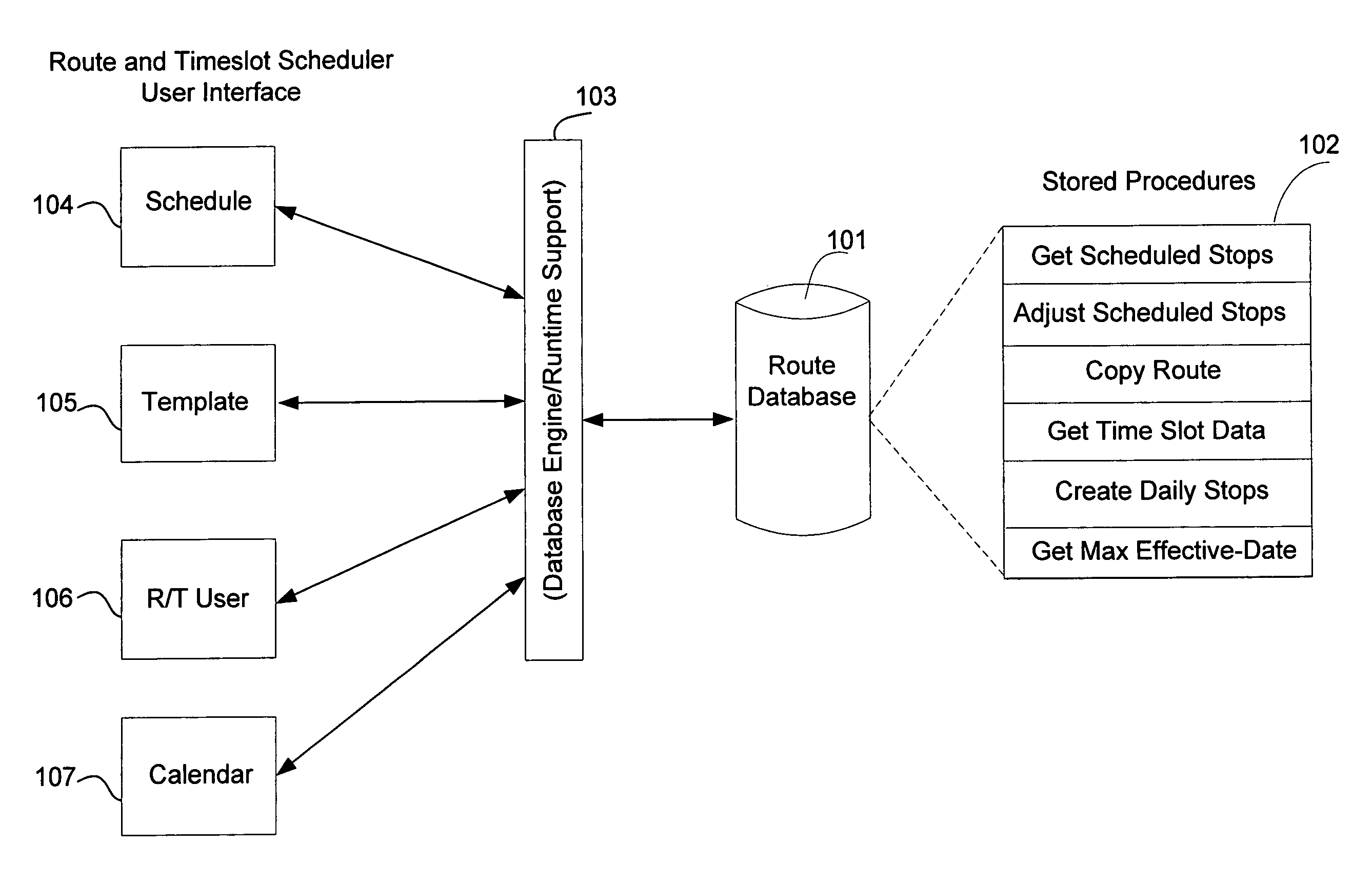

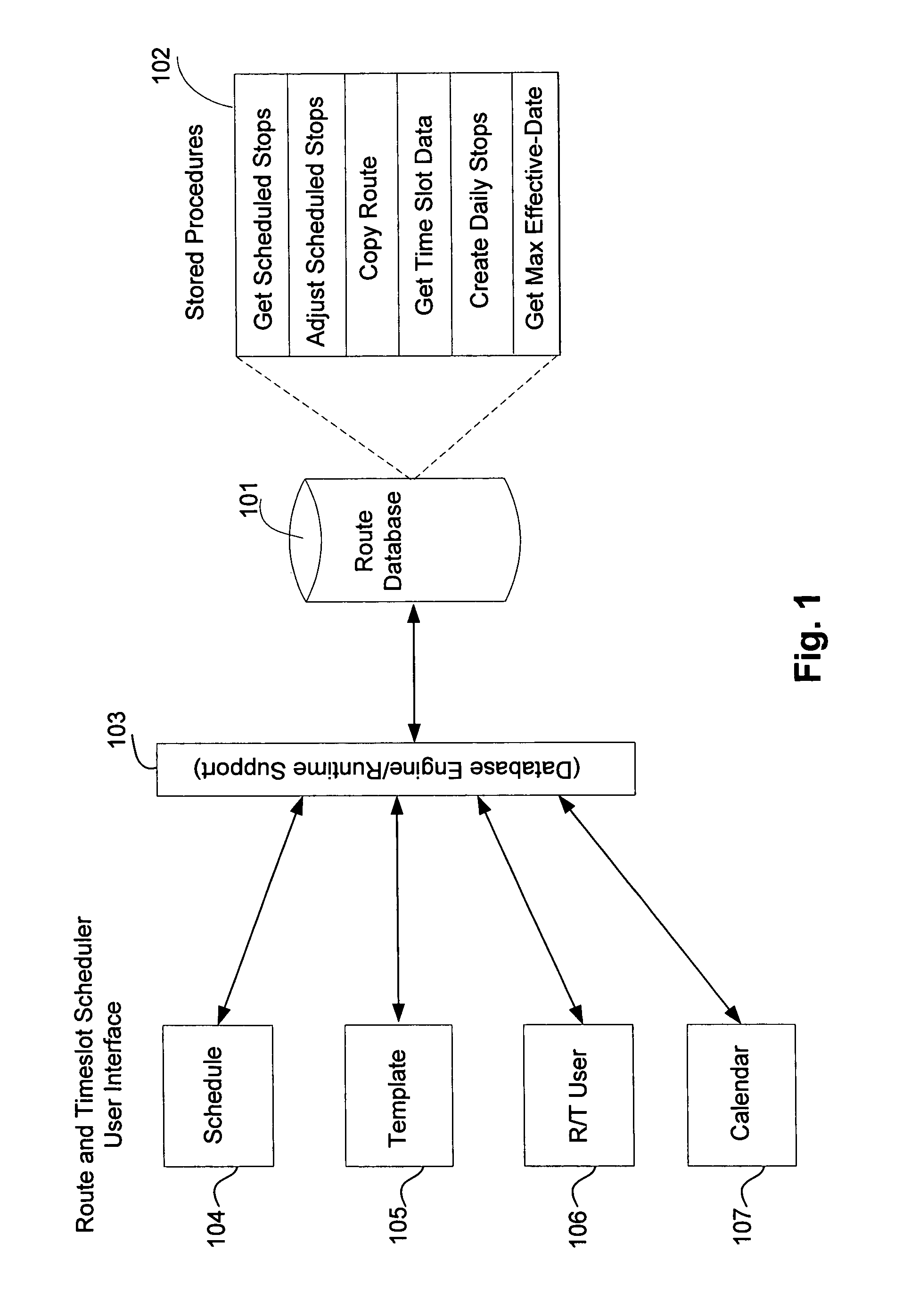

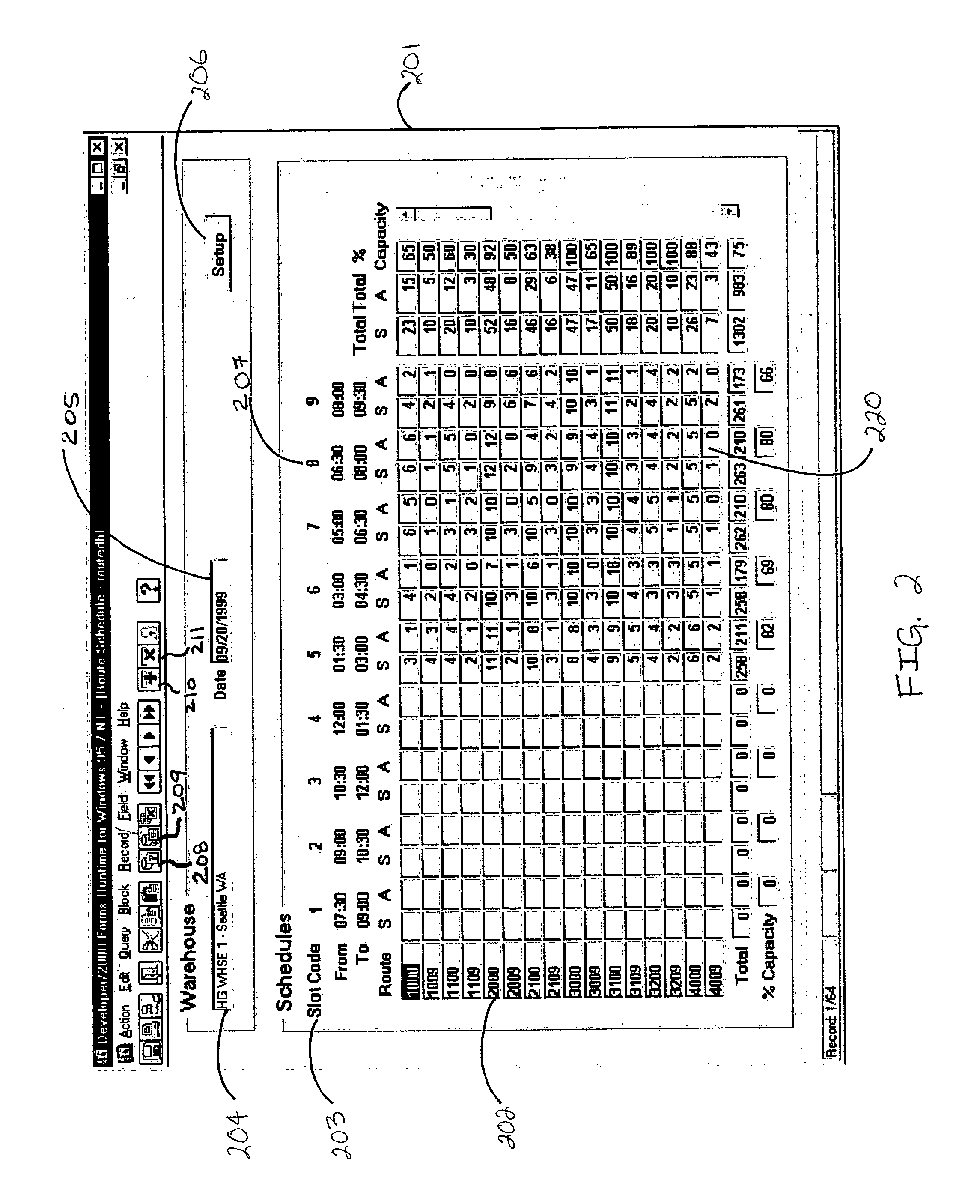

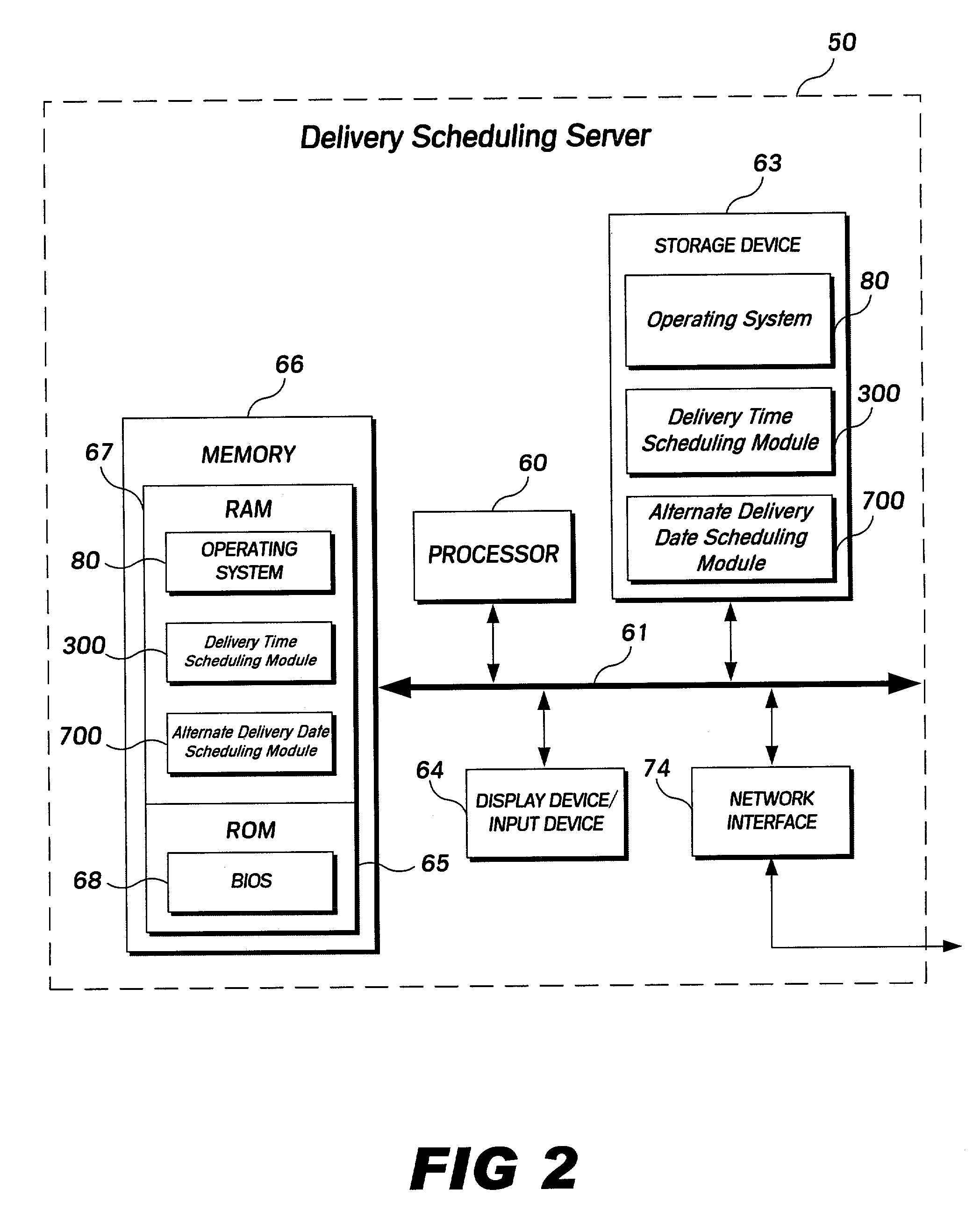

Method and system for scheduling distribution routes and timeslots

Computer-based methods and systems for dynamically scheduling the distribution of products and services among a system of routes and timeslots are provided. Exemplary embodiments provide a Route and Timeslot Scheduler (the “RTS”), which controls the creation, quantity, and allocation of schedule stops (or events) for each timeslot of each route based upon a calendar and template system. Each route typically represents a geographic area to which products can be delivered. Each timeslot typically represents a window of time, during which delivery stops (or events) can be scheduled. Scheduled stops / events are created based upon defaults which are specified in the template system. A calendar system is provided to specify which routes and timeslots, which would otherwise be available based upon the template system, are actually applicable to be scheduled on a given calendar day. The RTS creates scheduled stops for a designated point.

Owner:JUNE RAY

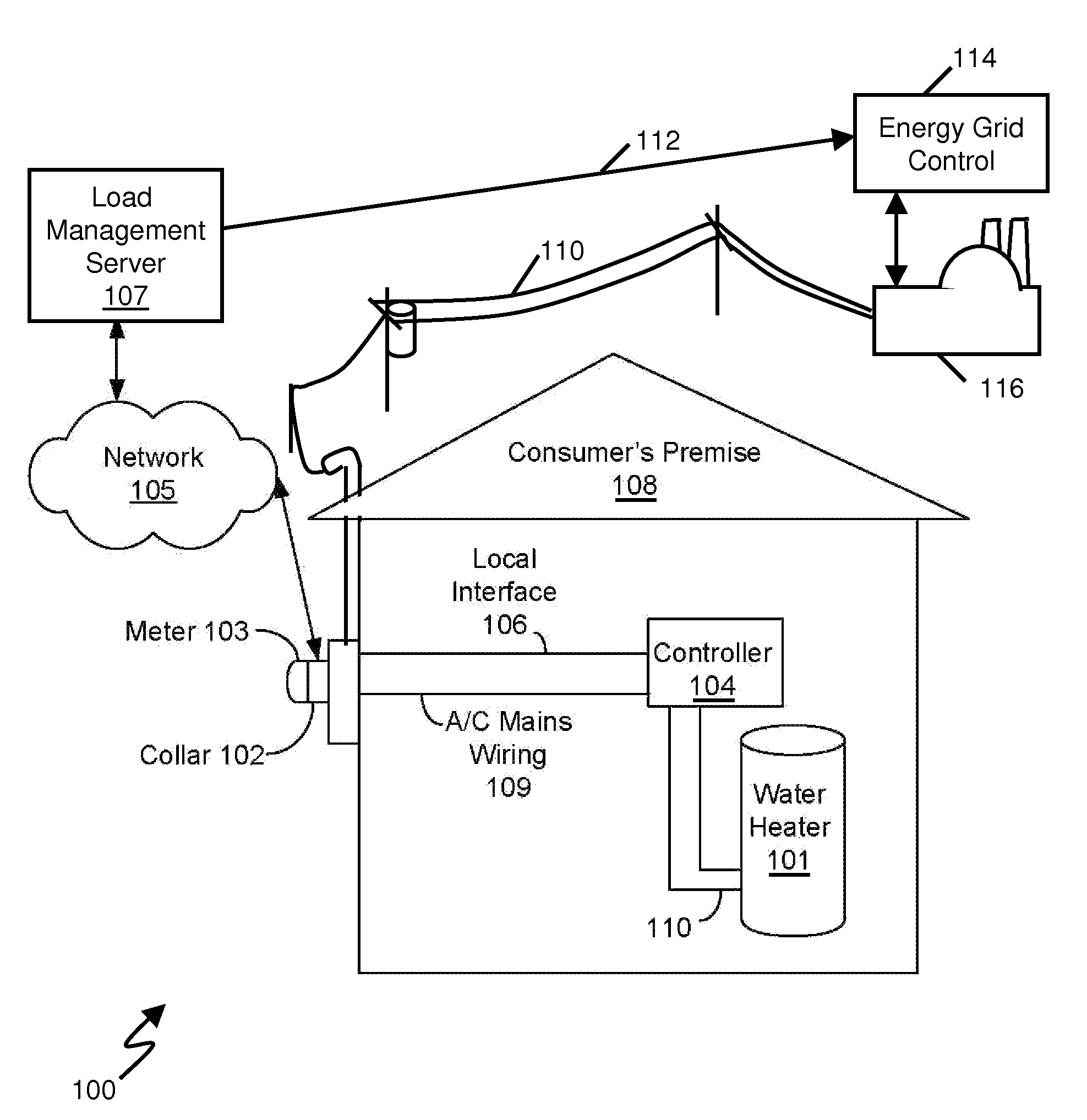

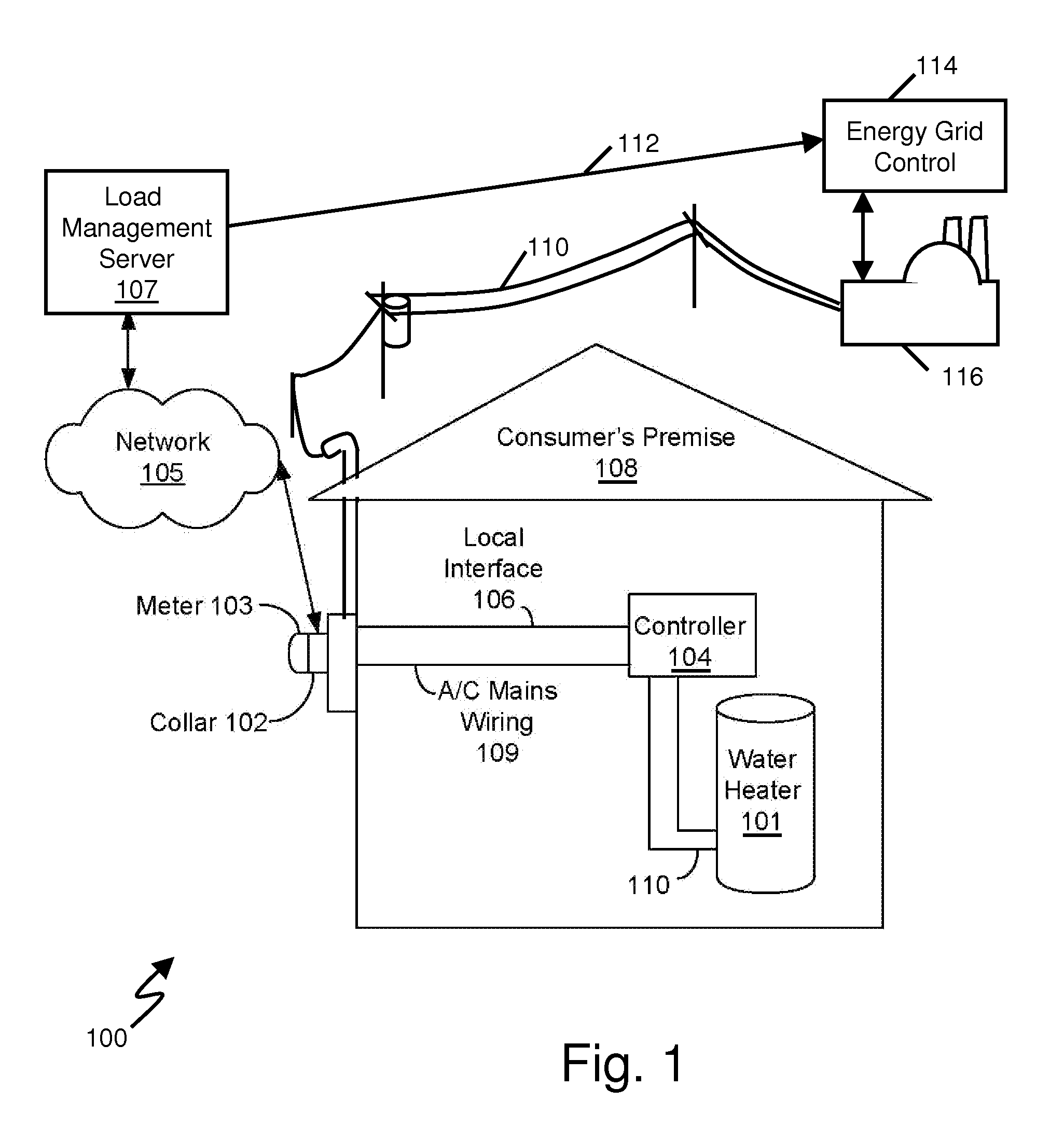

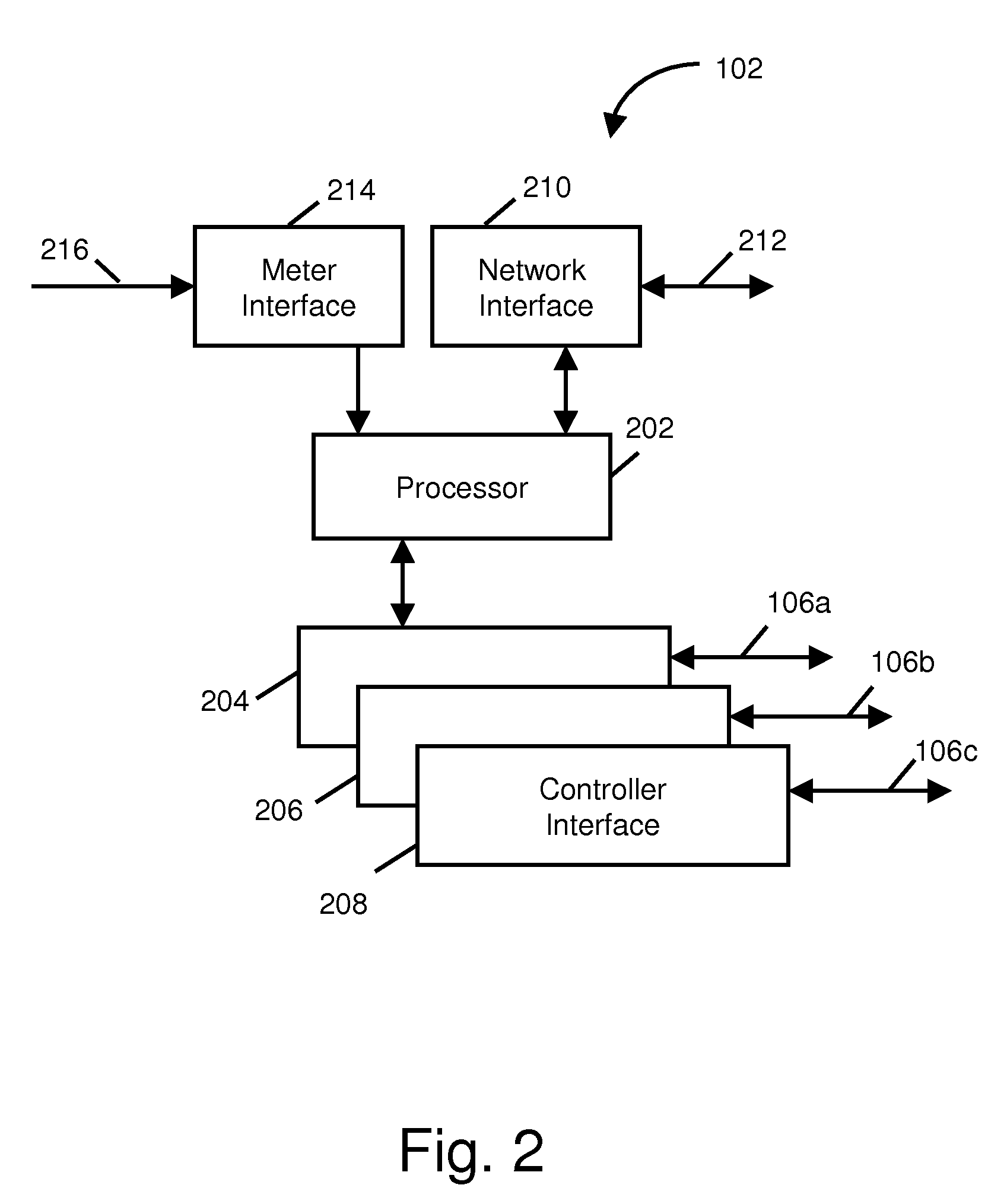

Water Heater Demand Side Management System

ActiveUS20100004790A1Reduce network trafficLevel controlVolume/mass flow measurementQuality of serviceEngineering

A system for shifting energy demand from on-peak time windows to off-peak time windows by using hot water heater load shifting, while providing the end user with the level of service (i.e., availability of hot water) according to the user's customary use described by service quality criteria. The shift is accomplished by a controller located at the end user establishment and in communication with a central control server. The controller monitors local water heater upper and / or lower temperature and controls upper and / or lower water heater heating elements in accordance with a demand shift process commanded by the central control server. The controller may determine usage and remaining capacity for reporting back to the central control server. A volumetric capacity and usage determination is disclosed. The control server may select water heaters according to use patterns and / or measured capacity. One embodiment is adapted for use with existing water heaters without disrupting safety features of the existing water heater.

Owner:CARINA TECH +1

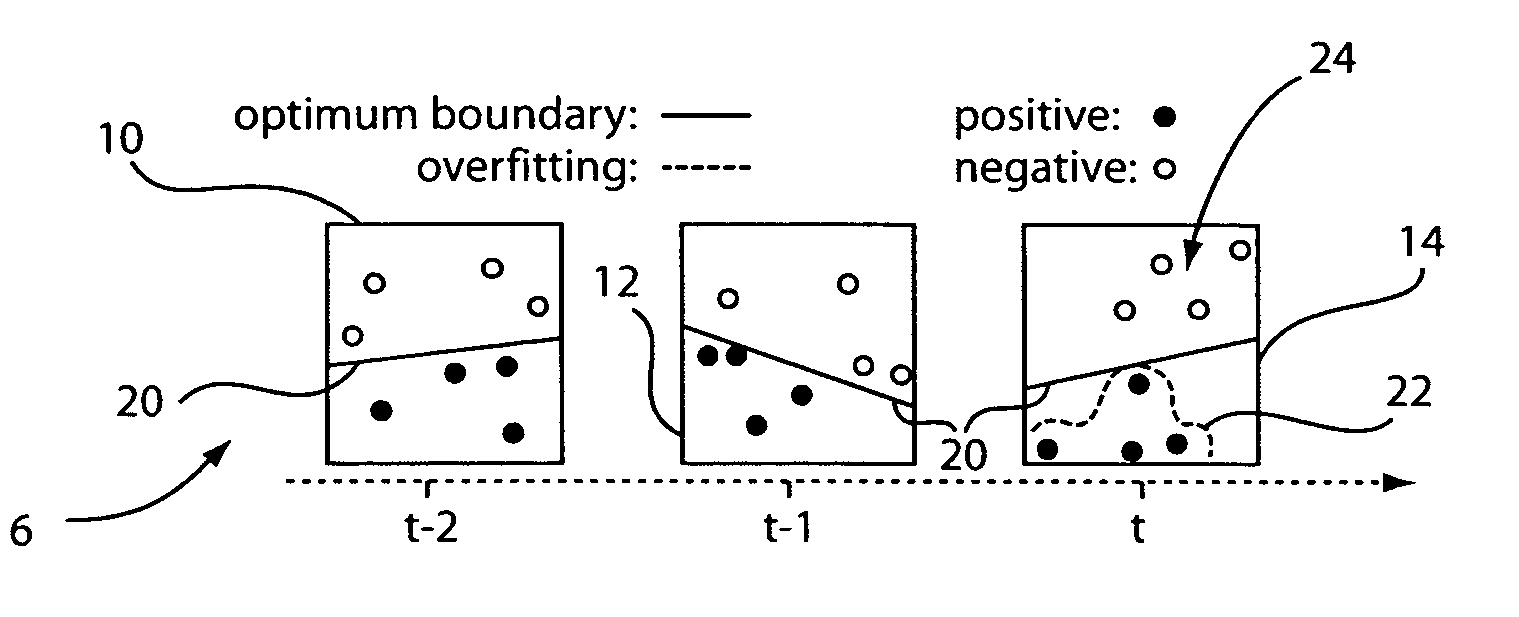

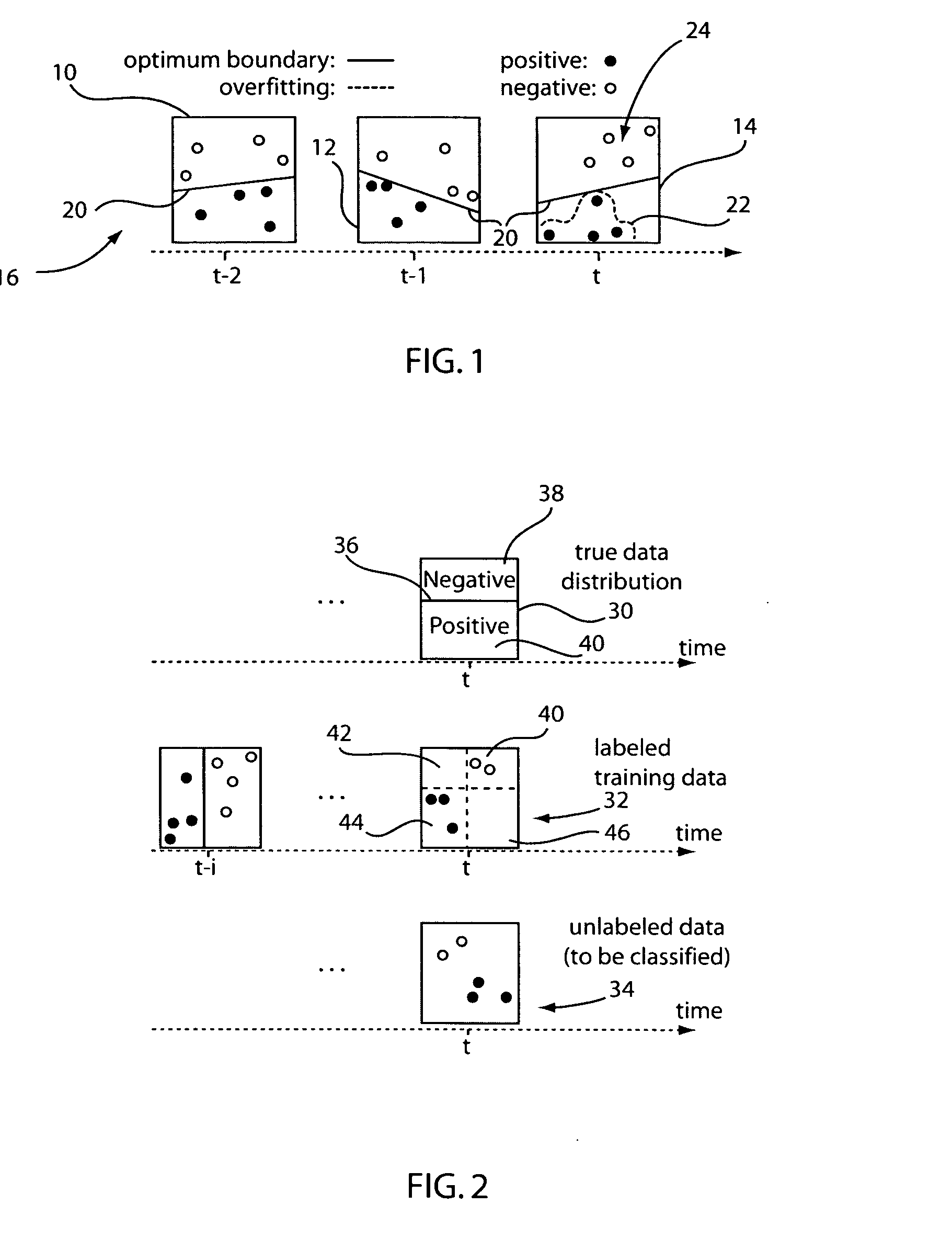

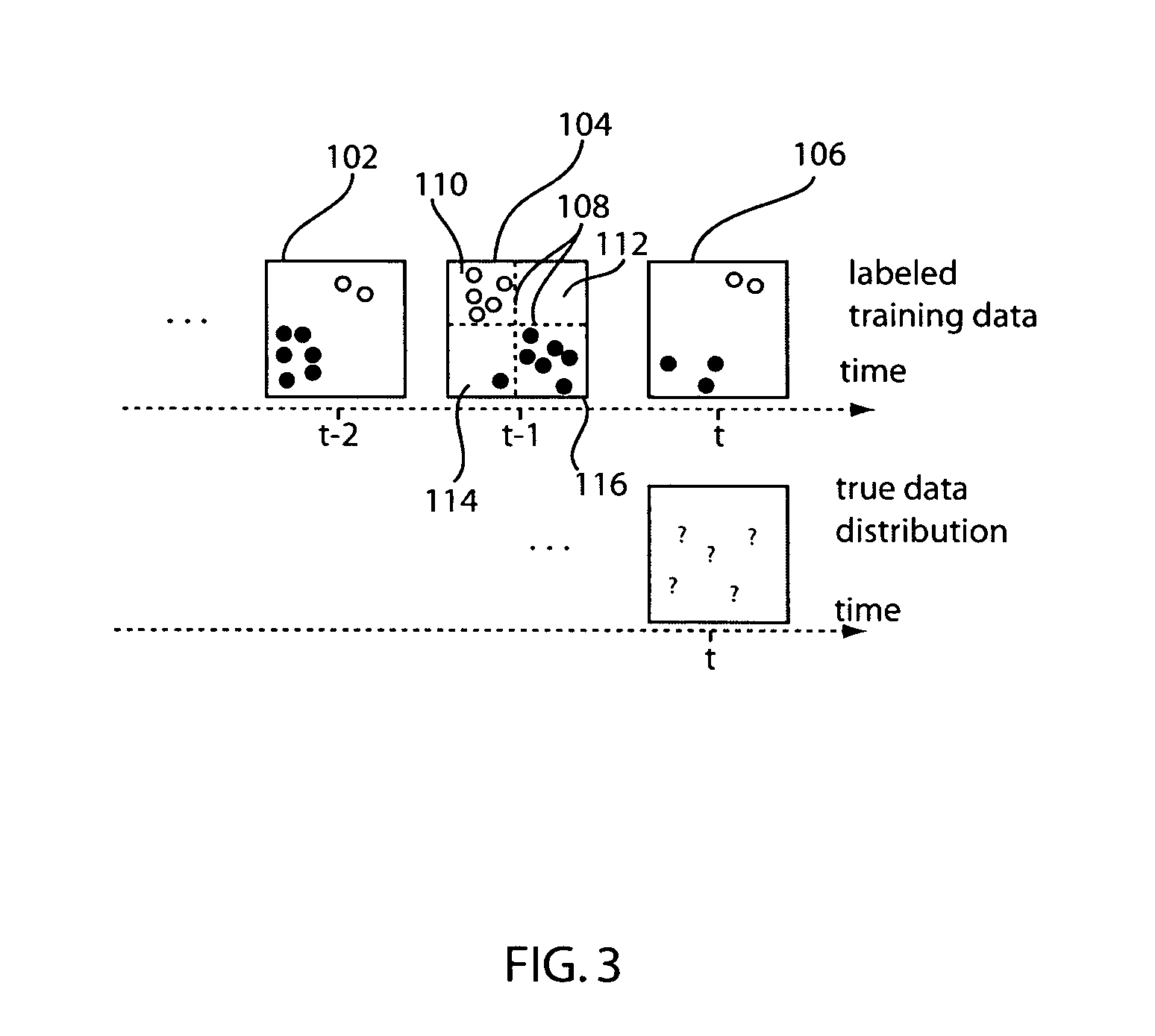

System and method for learning models from scarce and skewed training data

InactiveUS20080071721A1Adjustable weightEnsemble learningKnowledge representationConcept driftMachine learning

A system and method for learning models from scarce and / or skewed training data includes partitioning a data stream into a sequence of time windows. A most likely current class distribution to classify portions of the data stream is determined based on observing training data in a current time window and based on concept drift probability patterns using historical information.

Owner:IBM CORP

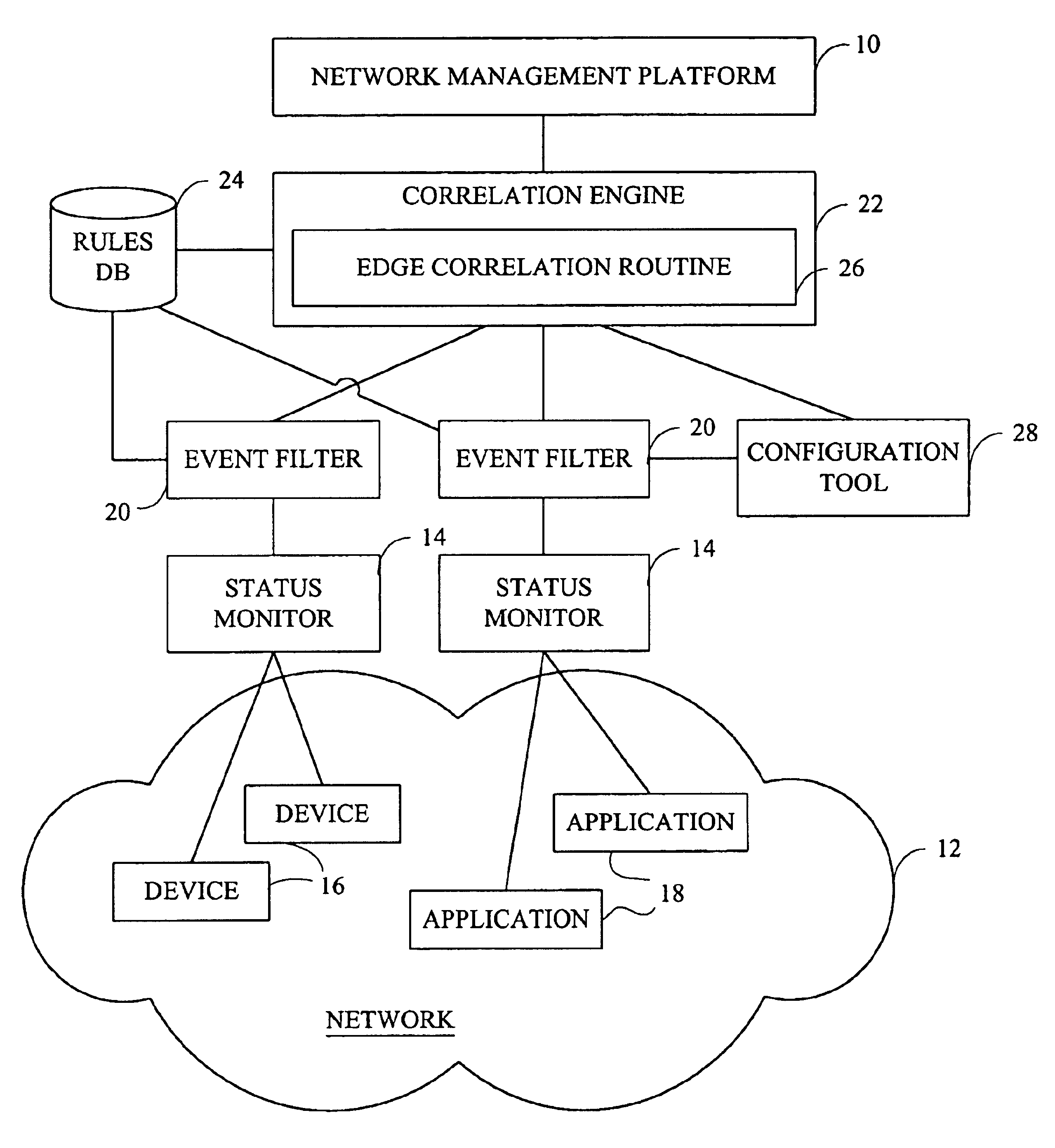

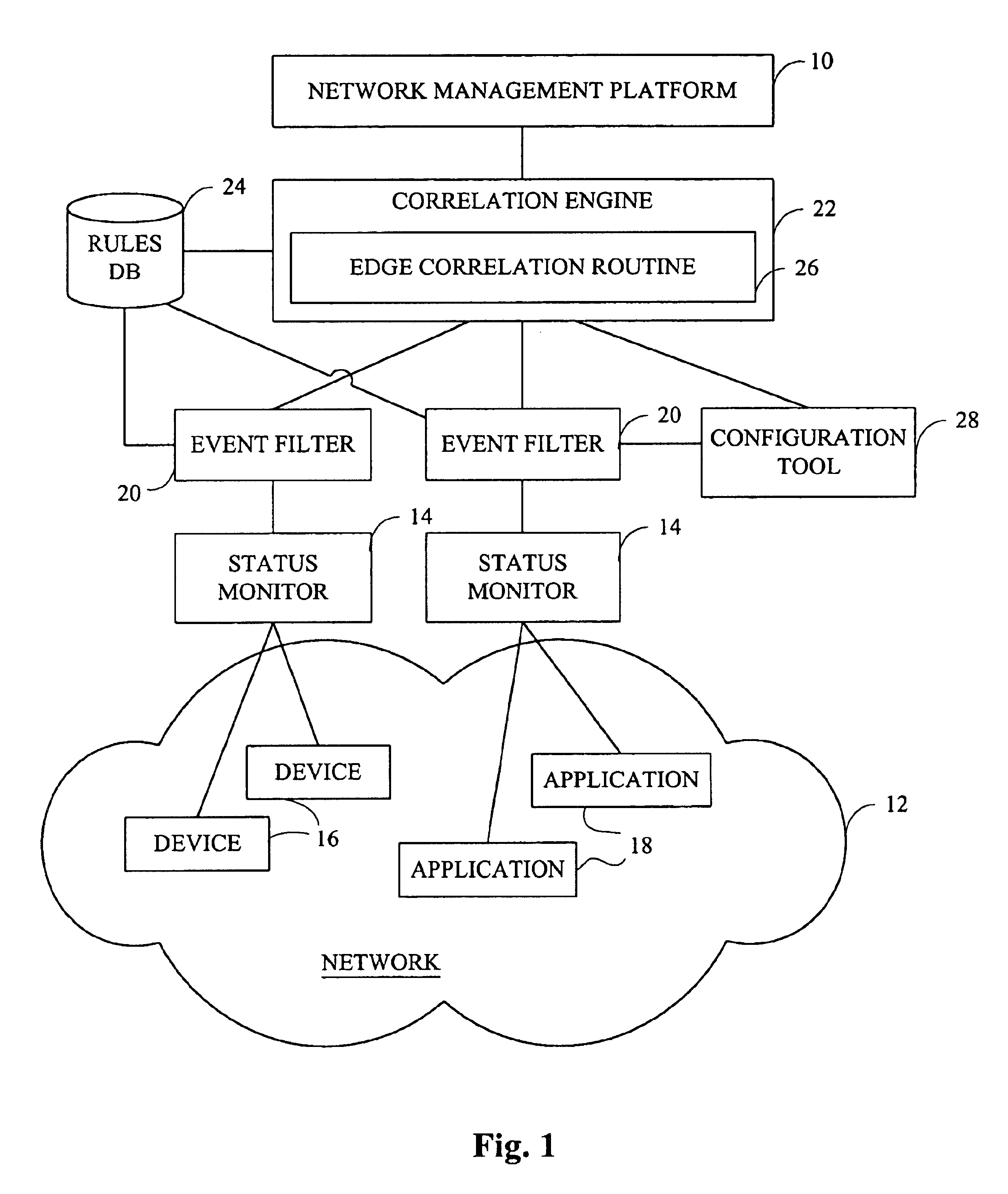

Method and system for reducing false alarms in network fault management systems

InactiveUS6966015B2Reducing false alarmReduce the possibilityError detection/correctionData switching networksFault managementRule-based system

Methods and systems are described for reducing the number of false alarms in fault correlation software used to detect and diagnose faults in computer networks and similar systems. The fault correlation software includes rules that monitor a number of indicators that, if occurring together over a window of time, are known to cause or reflect the occurrence of a fault. The method involves monitoring the transition of these indicators from one state to another over the time window and determining the extent of the correlation of the transitions of the indicators. The determination that indicators monitored by a rule do not correlate closely in their transitions is used to reduce the likelihood of the rule finding correlation of the indicators as a whole. This in turn reduces the number of false alarms which the rule-based system might otherwise have transmitted.

Owner:IBM CORP

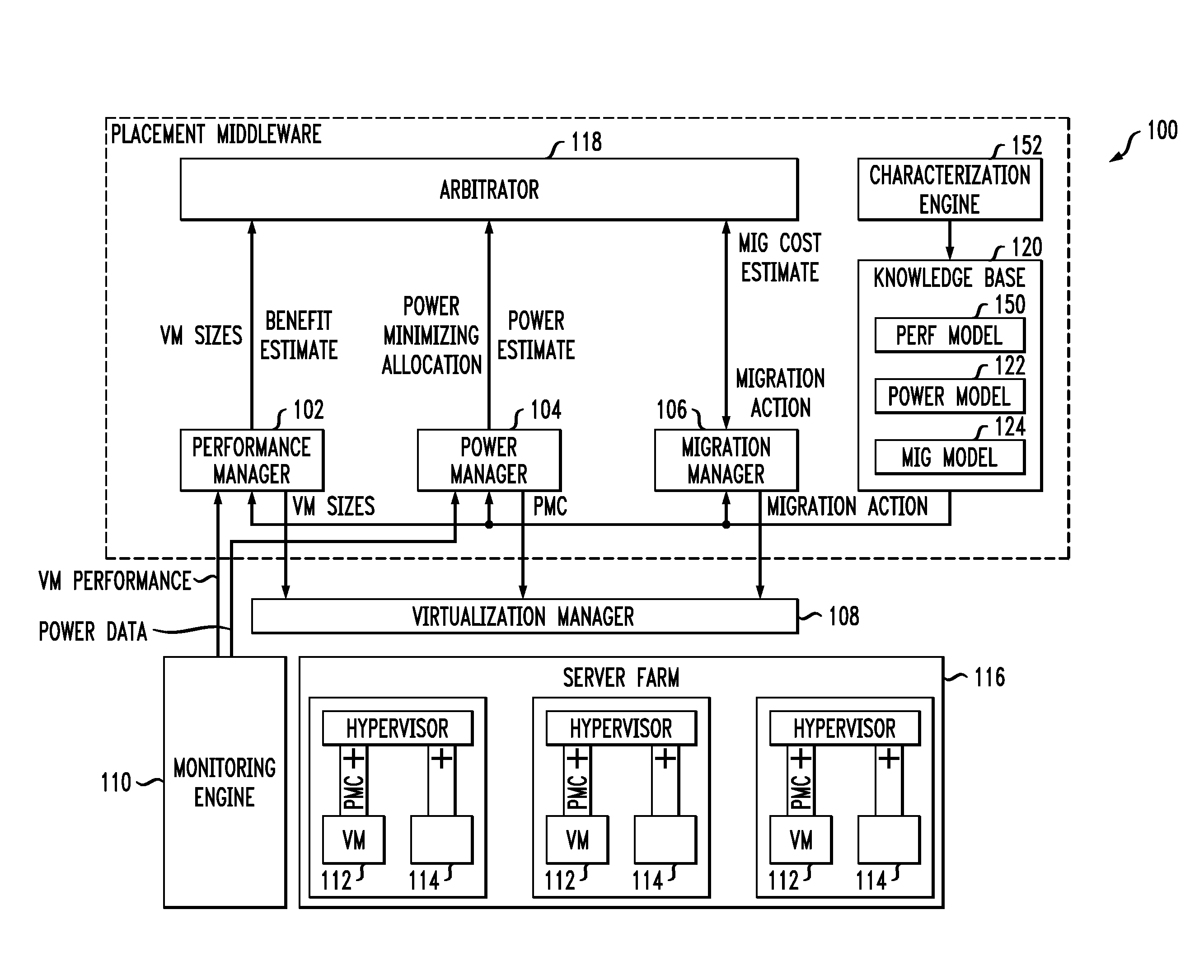

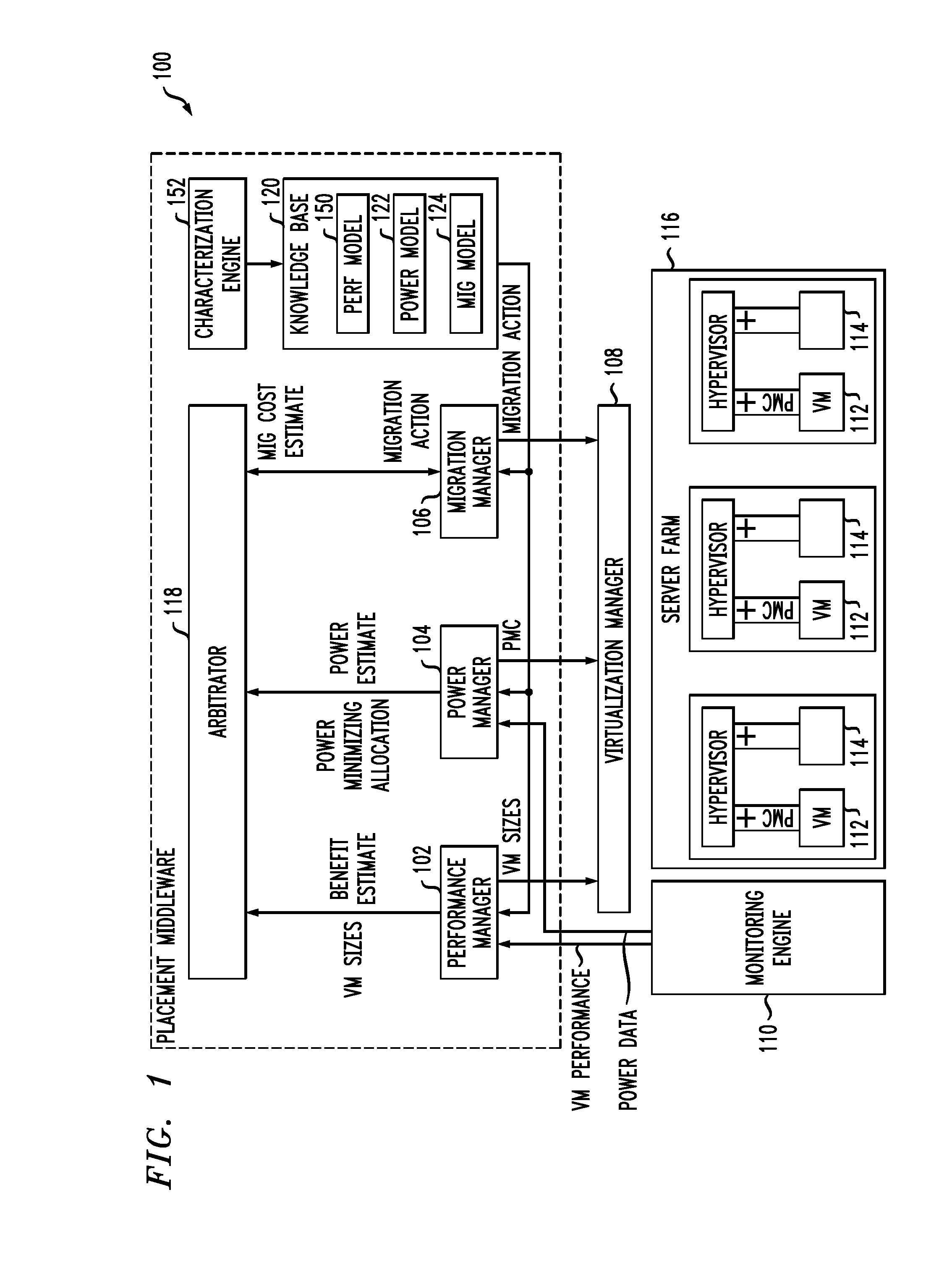

Techniques for placing applications in heterogeneous virtualized systems while minimizing power and migration cost

ActiveUS20100180275A1Minimizing migrationMinimize powerVolume/mass flow measurementPower supply for data processingVirtualizationN application

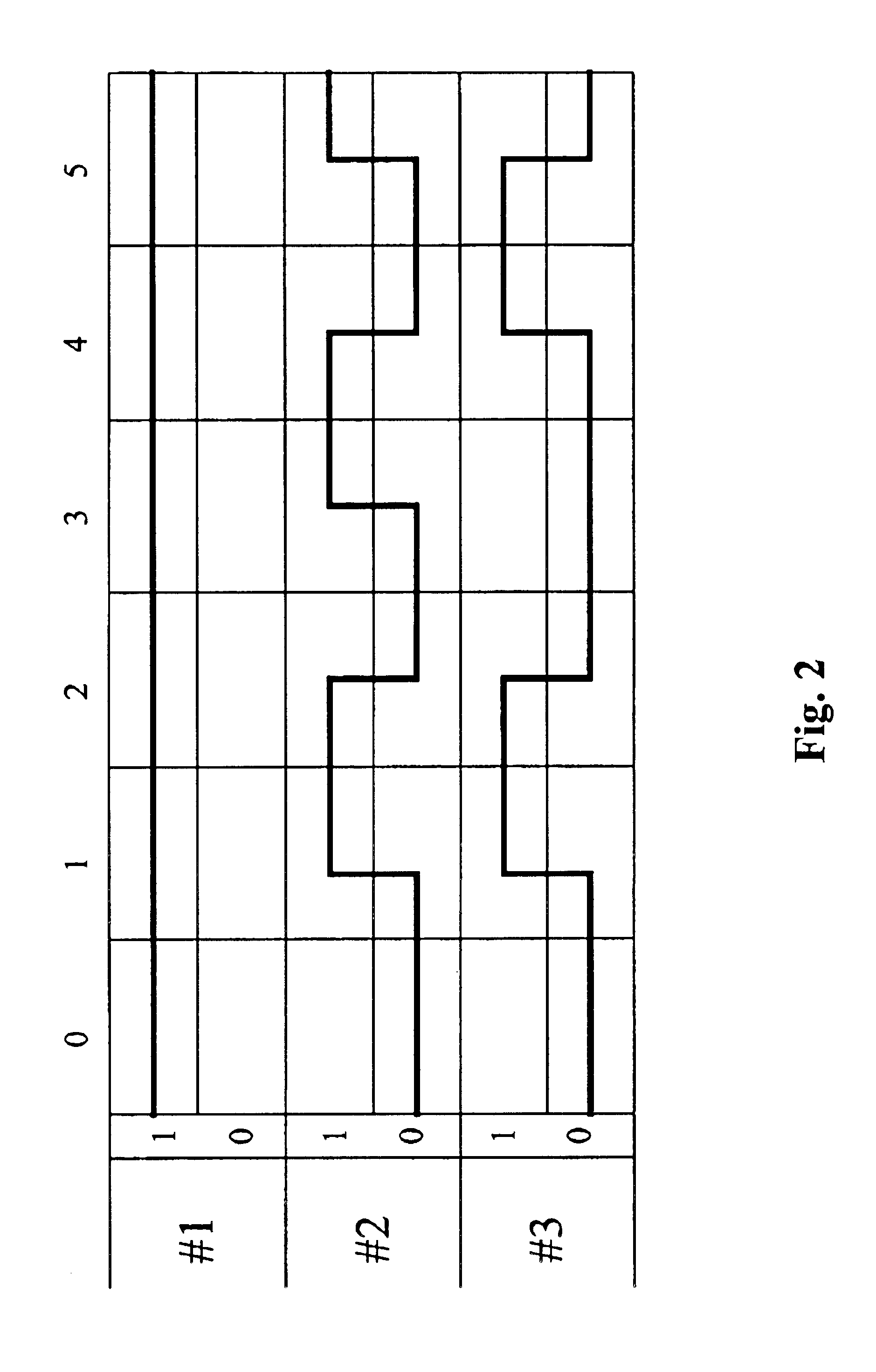

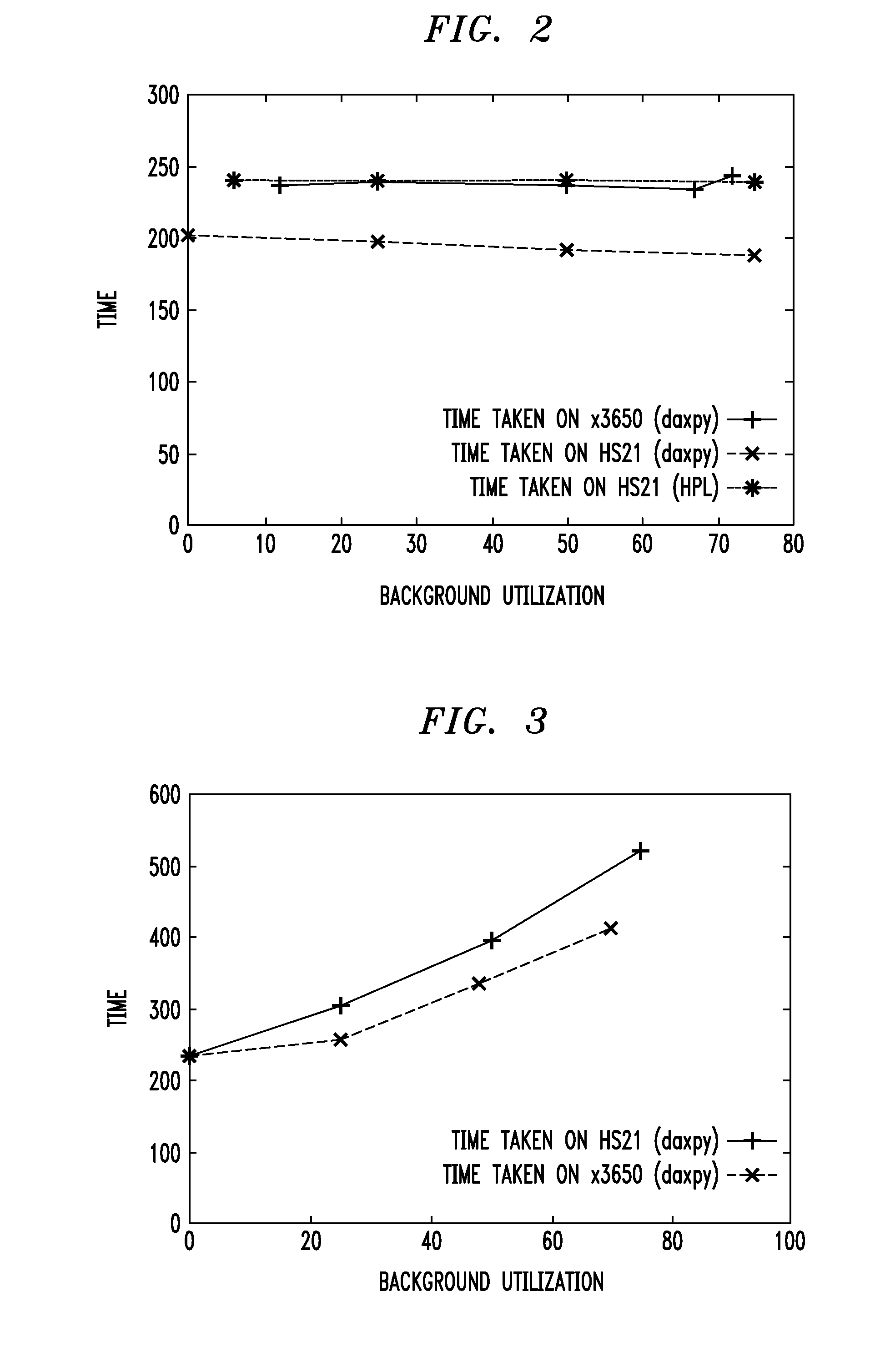

N applications are placed on M virtualized servers having power management capability. A time horizon is divided into a plurality of time windows, and, for each given one of the windows, a placement of the N applications is computed, taking into account power cost, migration cost, and performance benefit. The migration cost refers to cost to migrate from a first virtualized server to a second virtualized server for the given one of the windows. The N applications are placed onto the M virtualized servers, for each of the plurality of time windows, in accordance with the placement computed in the computing step for each of the windows. In an alternative aspect, power cost and performance benefit, but not migration cost, are taken into account; there are a plurality of virtual machines; and the computing step includes, for each of the windows, determining a target utilization for each of the servers based on a power model for each given one of the servers; picking a given one of the servers with a least power increase per unit increase in capacity, until capacity has been allocated to fit all the virtual machines; and employing a first fit decreasing bin packing technique to compute placement of the applications on the virtualized servers.

Owner:IBM CORP

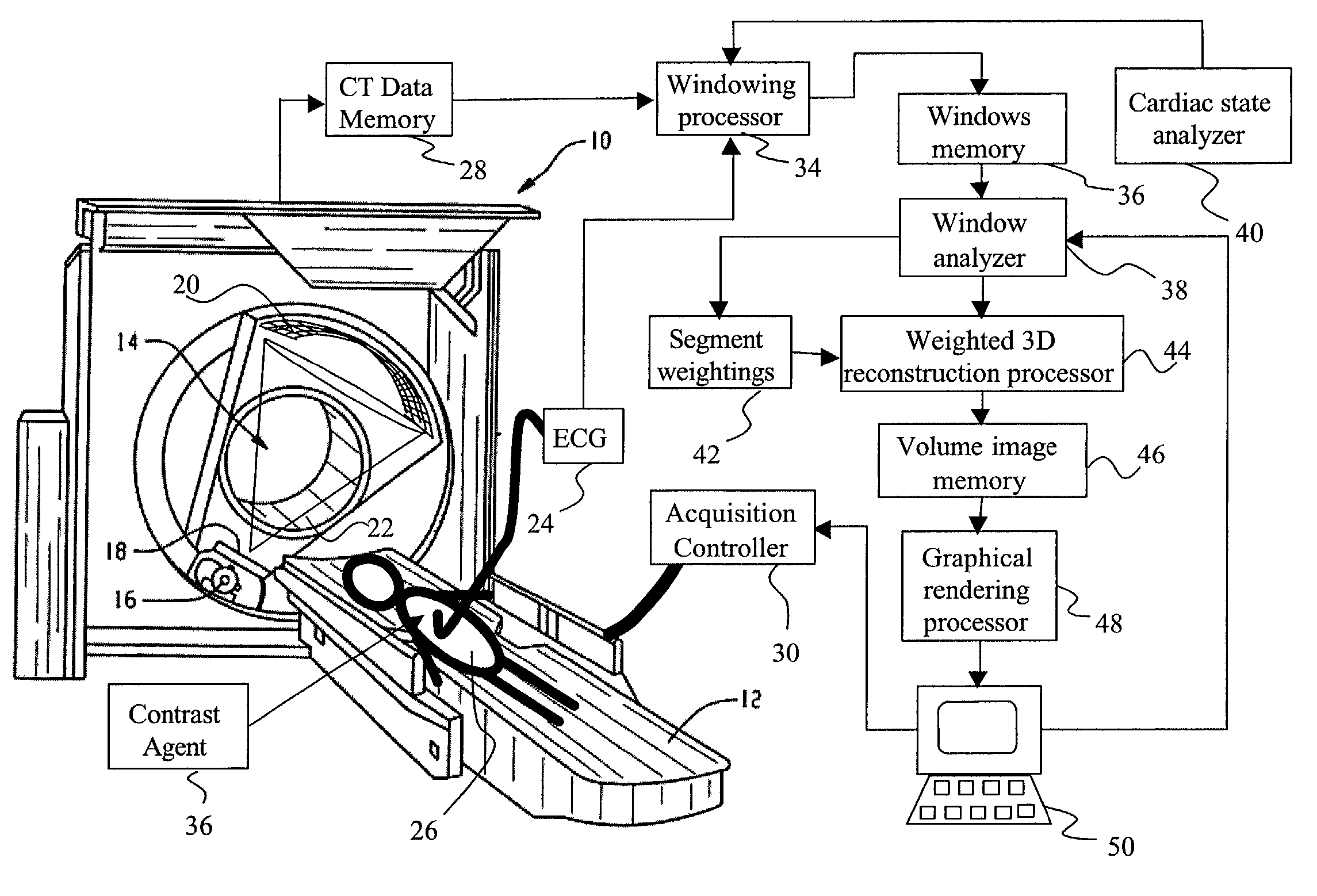

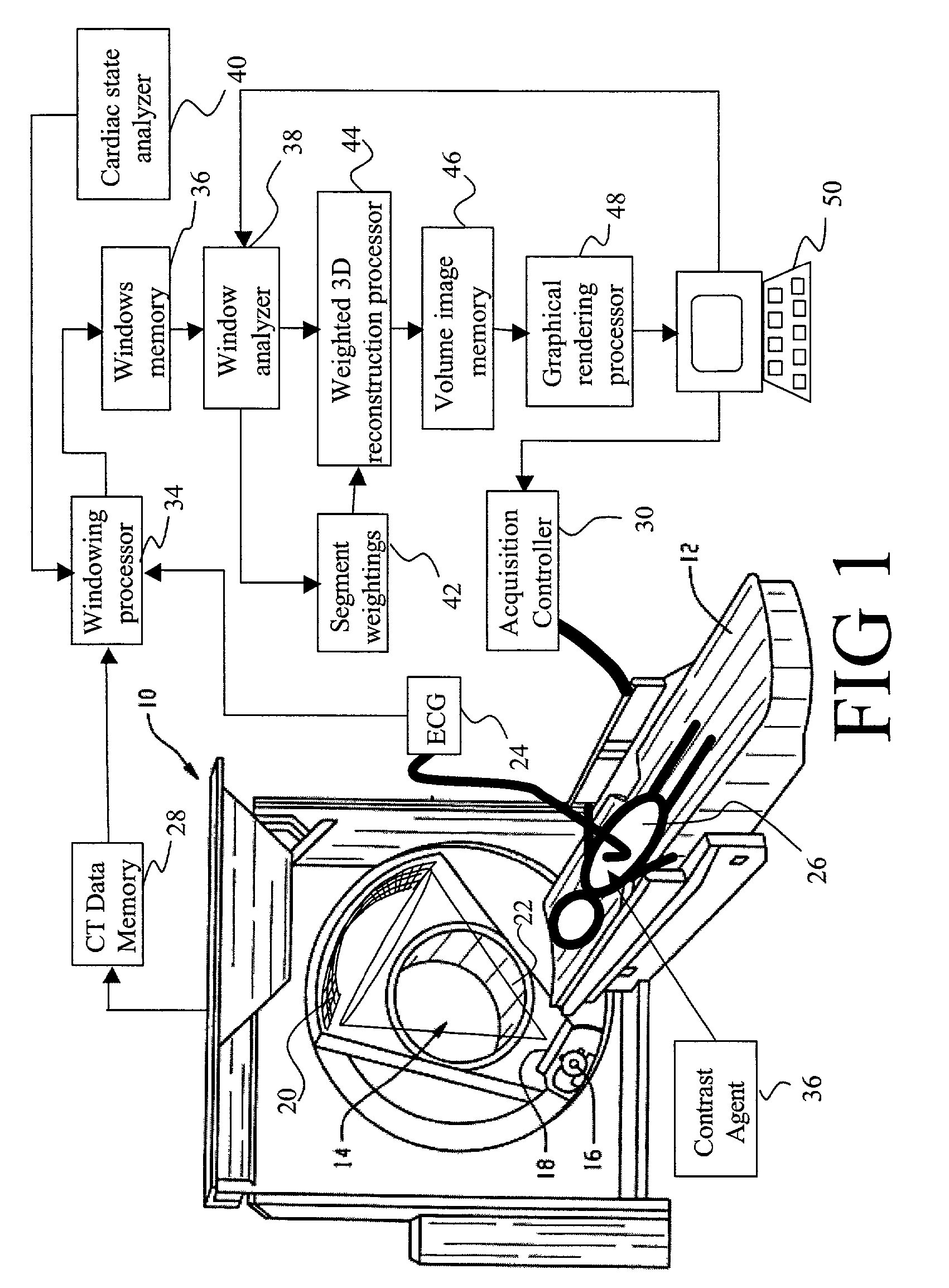

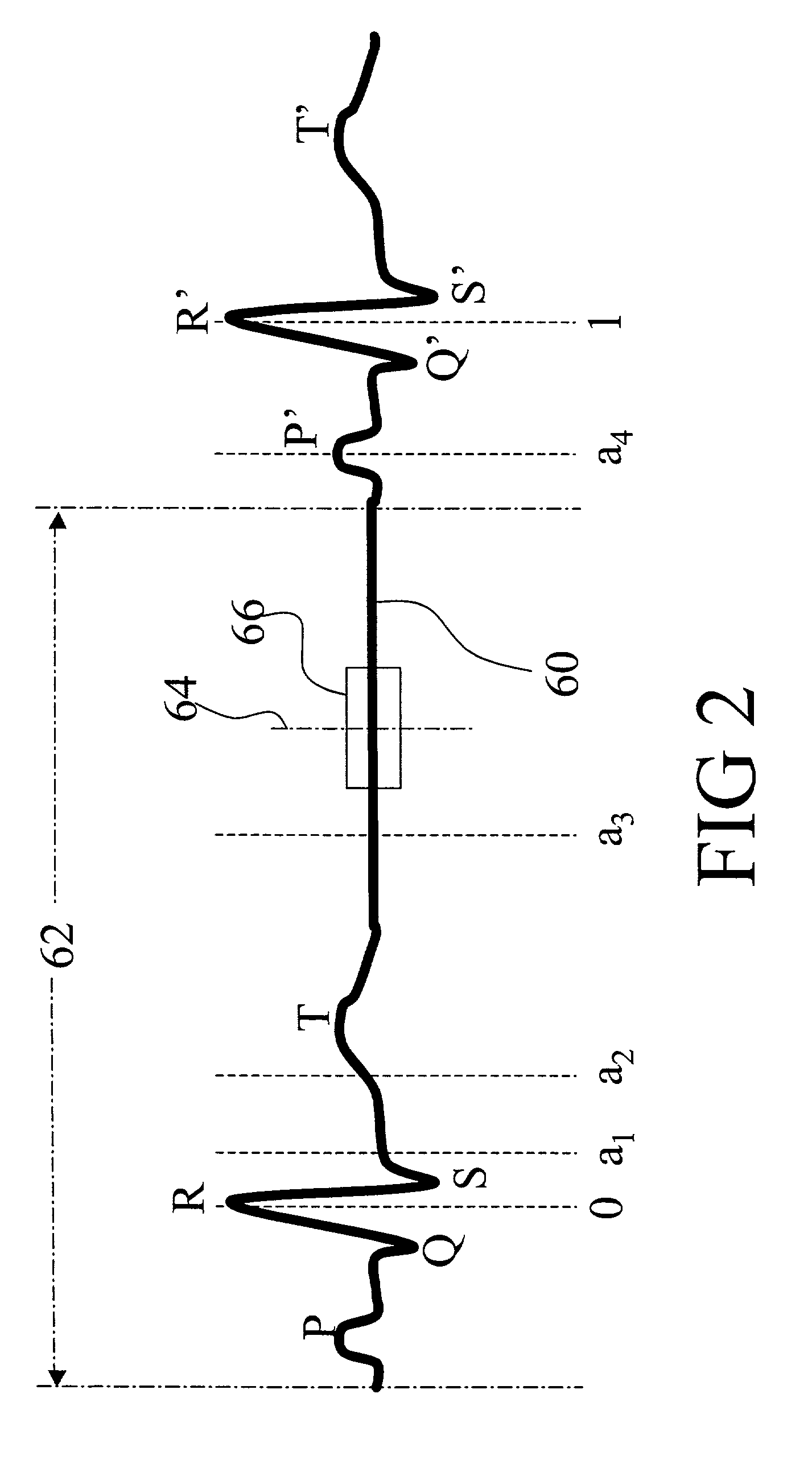

Dynamic computed tomography imaging using positional state modeling

InactiveUS7058440B2Improves temporalImprove spatial resolutionElectrocardiographyMaterial analysis using wave/particle radiationData segmentData set

An apparatus for computed tomography (CT) imaging of a cyclically moving organ includes a positional state monitor (24, 40) that monitors a positional state of the cyclically moving organ such as the heart. A cone-beam CT scanner (10) acquires image data at least within a plurality of time windows. Each time window is centered about an occurrence of a selected positional state of the organ. A window analyzer (38) selects a data segment within each time window such that the data segments combine to form a complete data set covering a selected angular range. A reconstruction processor (44) reconstructs the selected data segments into an image representation.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

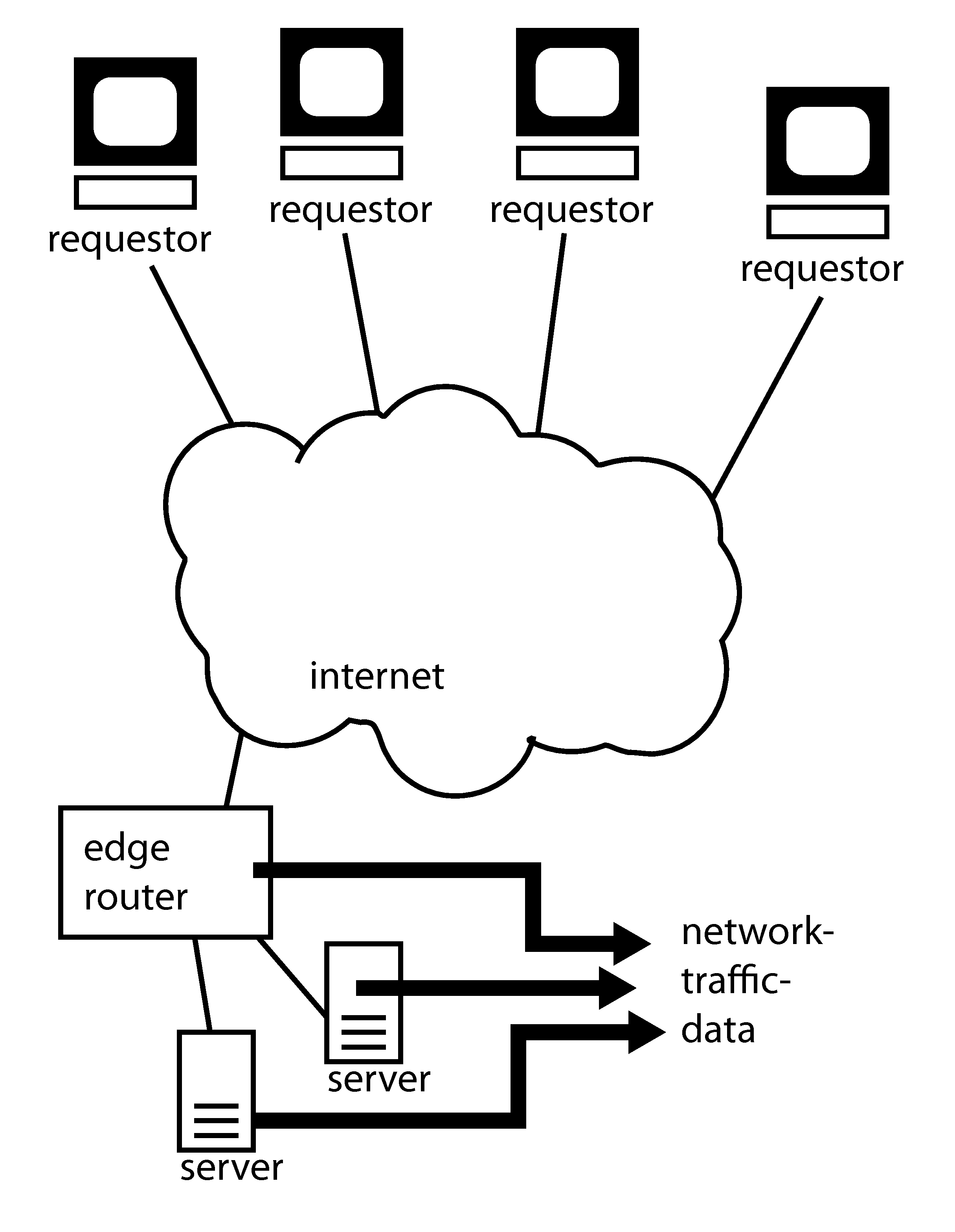

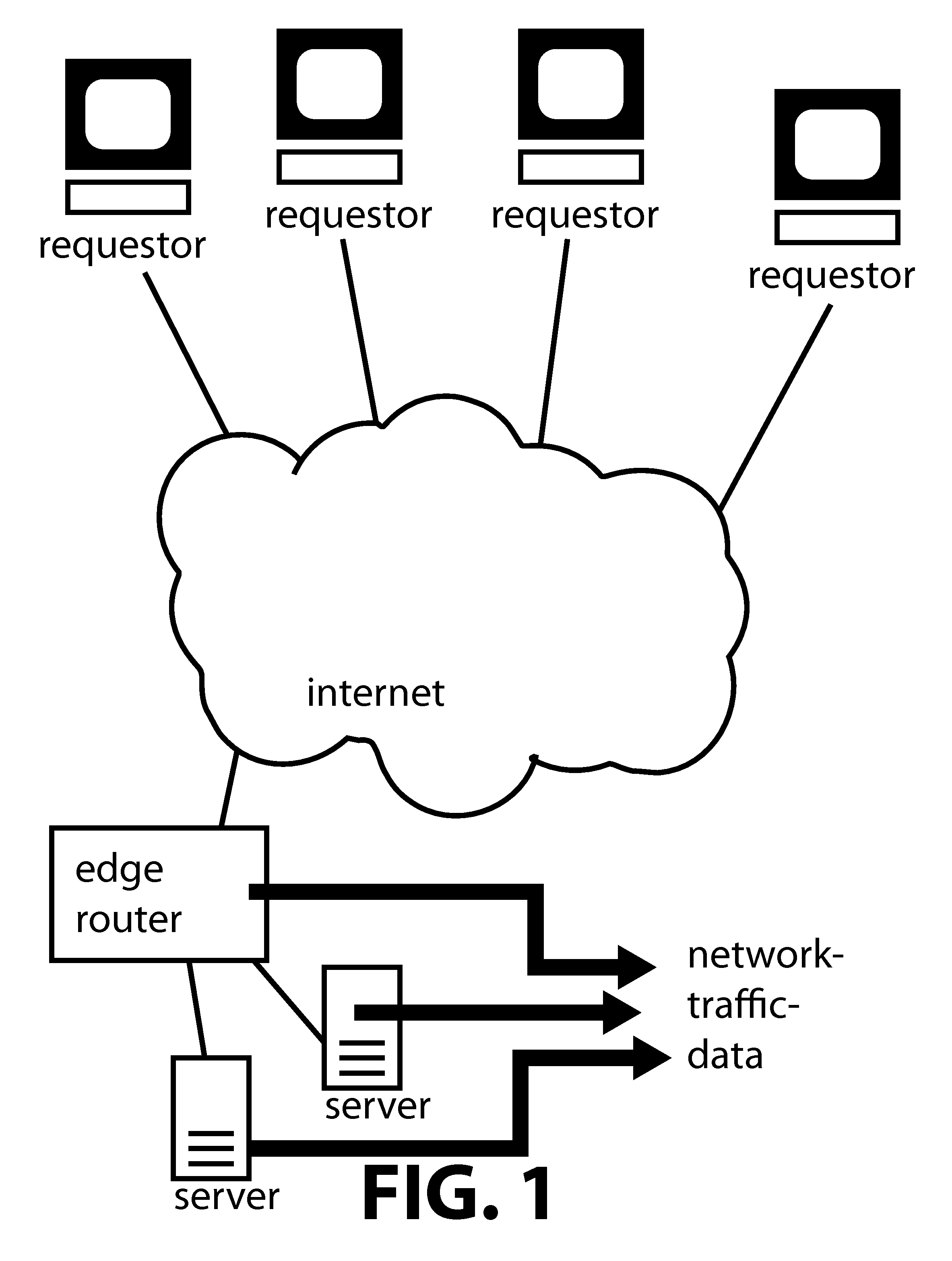

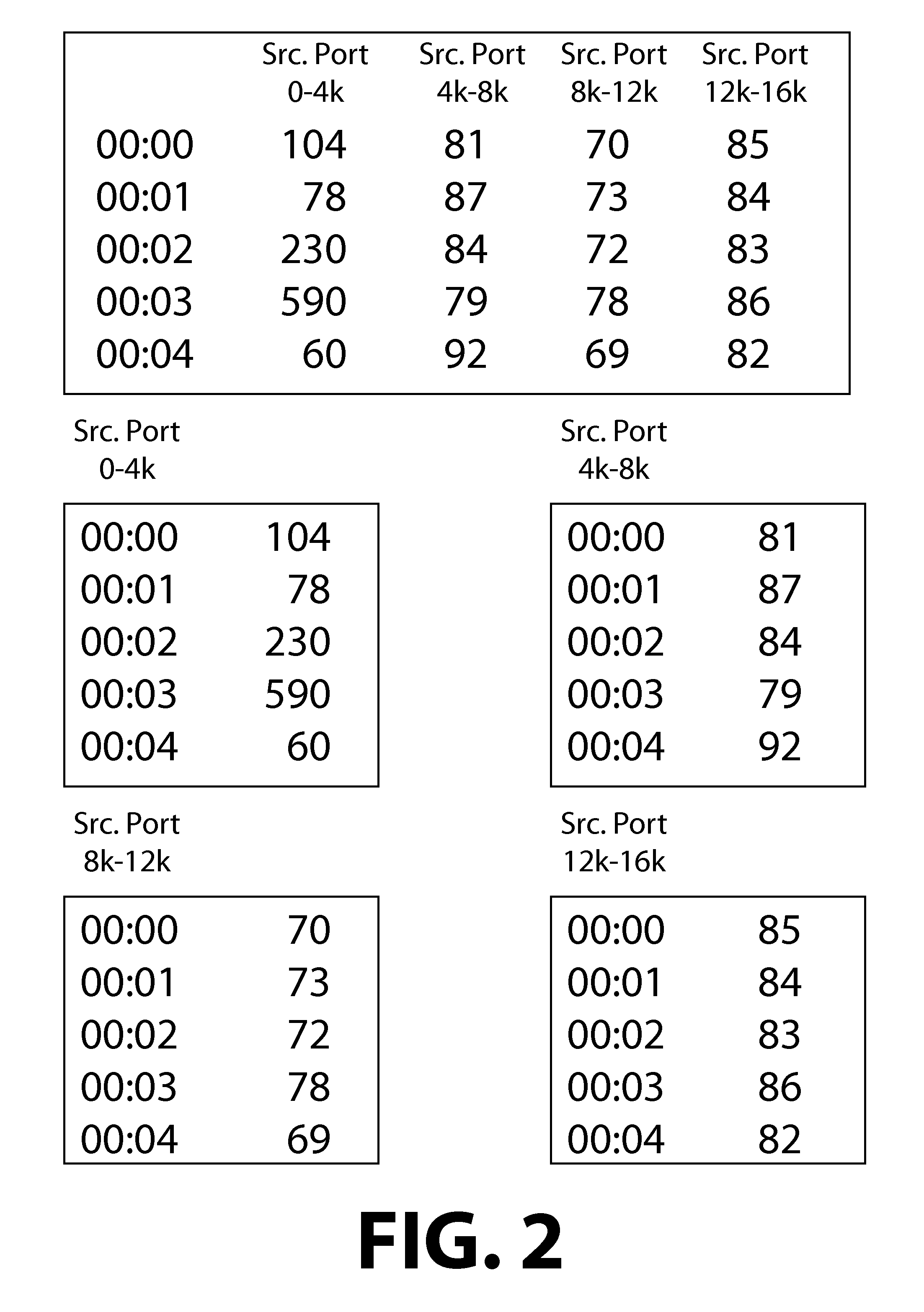

Detecting and mitigating denial of service attacks

InactiveUS20120174220A1Memory loss protectionError detection/correctionRate ratioReal-time computing

Embodiments of this invention provide methods for detecting a denial of service attack (DoS) and isolating traffic that relates to the attack. The method may begin by collecting network traffic data by observing individual packets carried over the network. The data may then be compiled into a time series comprising network traffic data relating successive time-intervals. A difference value based upon the entry in the time series for a large time-window and for a small time-window. A deviation score may then be determined by calculating the ratio of the difference values. The deviation score may indicate whether an attack occurred. In an embodiment of the invention, an attack is deemed to occur if the deviation score is between 0.6 and 1.4.

Owner:VERISIGN

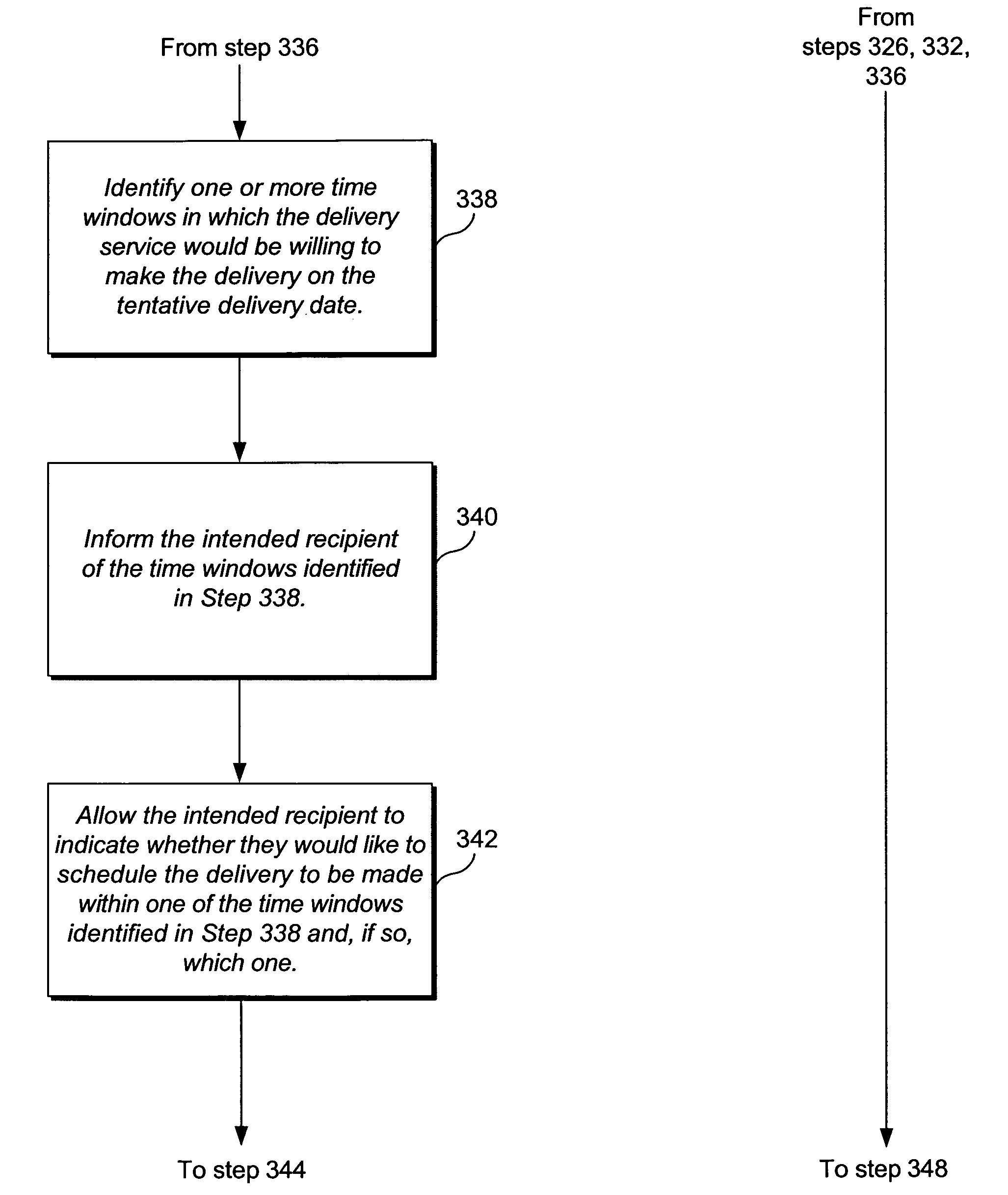

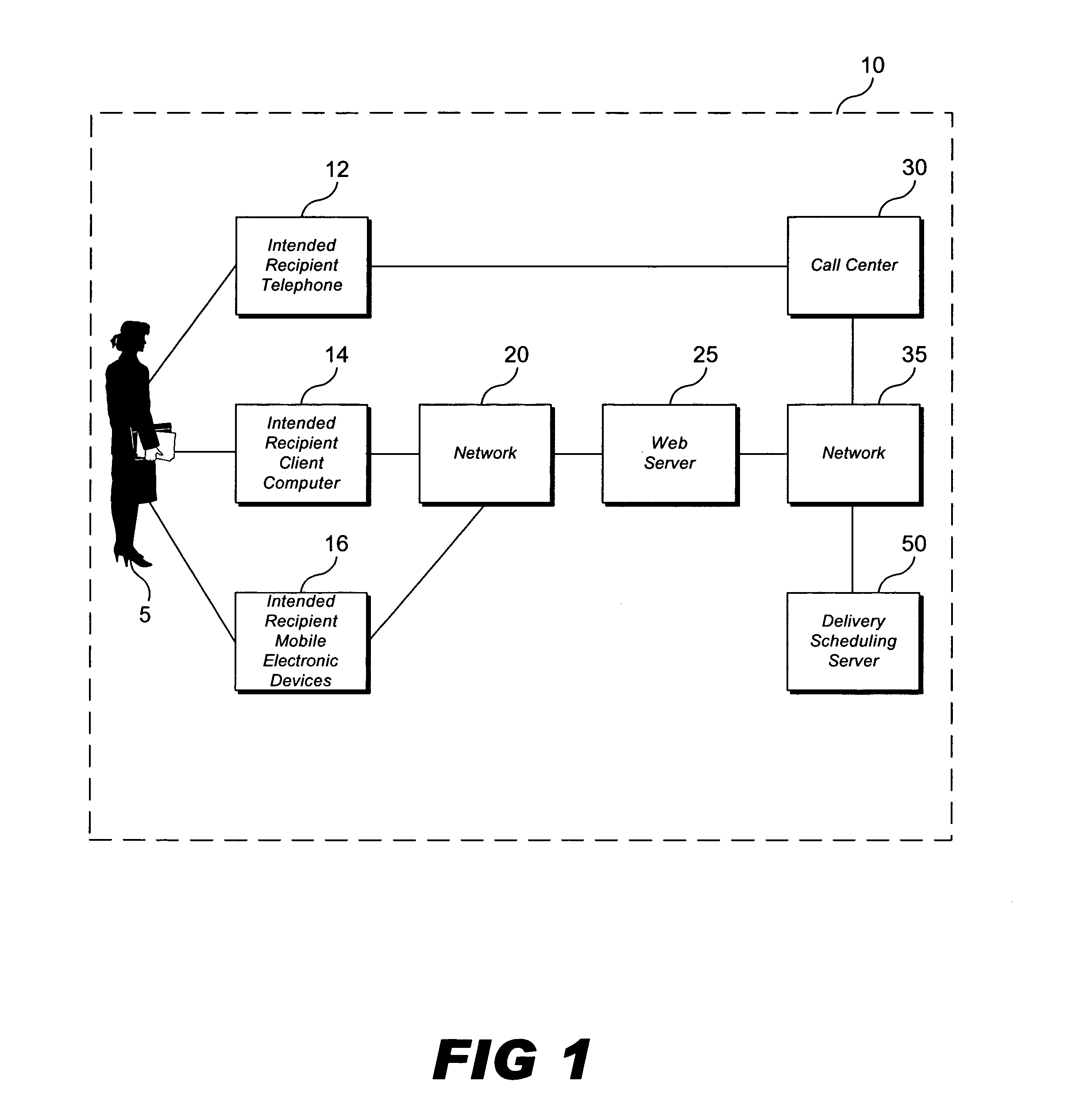

Parcel or service delivery with partially scheduled time windows

InactiveUS7233907B2Reduce deliveryMinimize any diversionRegistering/indicating time of eventsOptical signalsComputer networkEngineering

A delivery scheduling system that is configured for scheduling the delivery of an item or service from a sender to an intended recipient. After receiving a signal indicating that, for example, a particular package is to be delivered to an intended recipient, the system attempts to establish interactive contact with the recipient either by direct contact with the recipient, or by leaving the recipient a message to establish direct contact with the system at a convenient time. Upon establishing contact with the recipient, the system allows the intended recipient to schedule delivery of the package. More particularly, the recipient may schedule the package to be delivered: (1) within a particular time window; (2) before or after a particular time of day; or (3) on a particular day.

Owner:UNITED PARCEL SERVICE OF AMERICAN INC

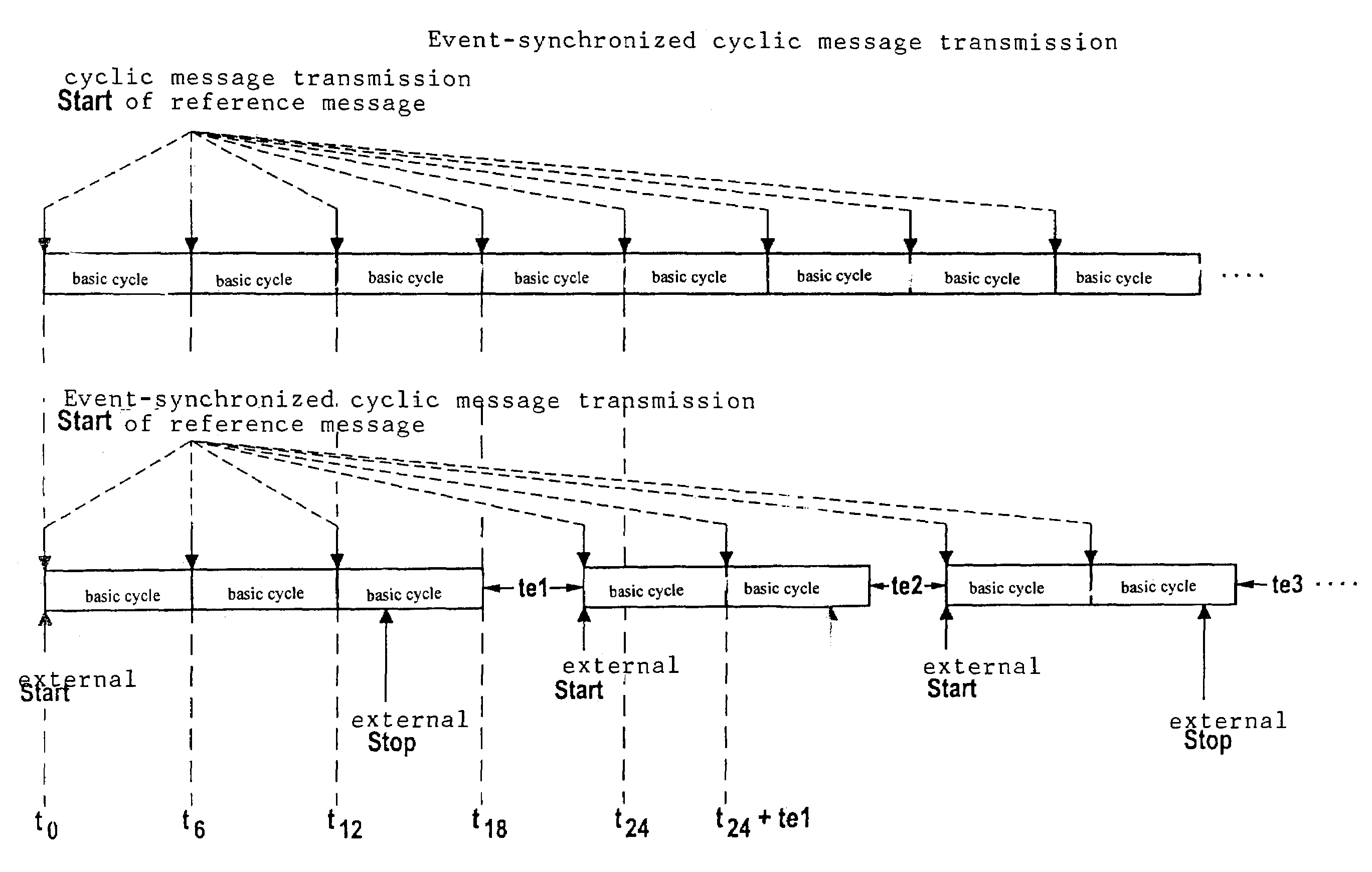

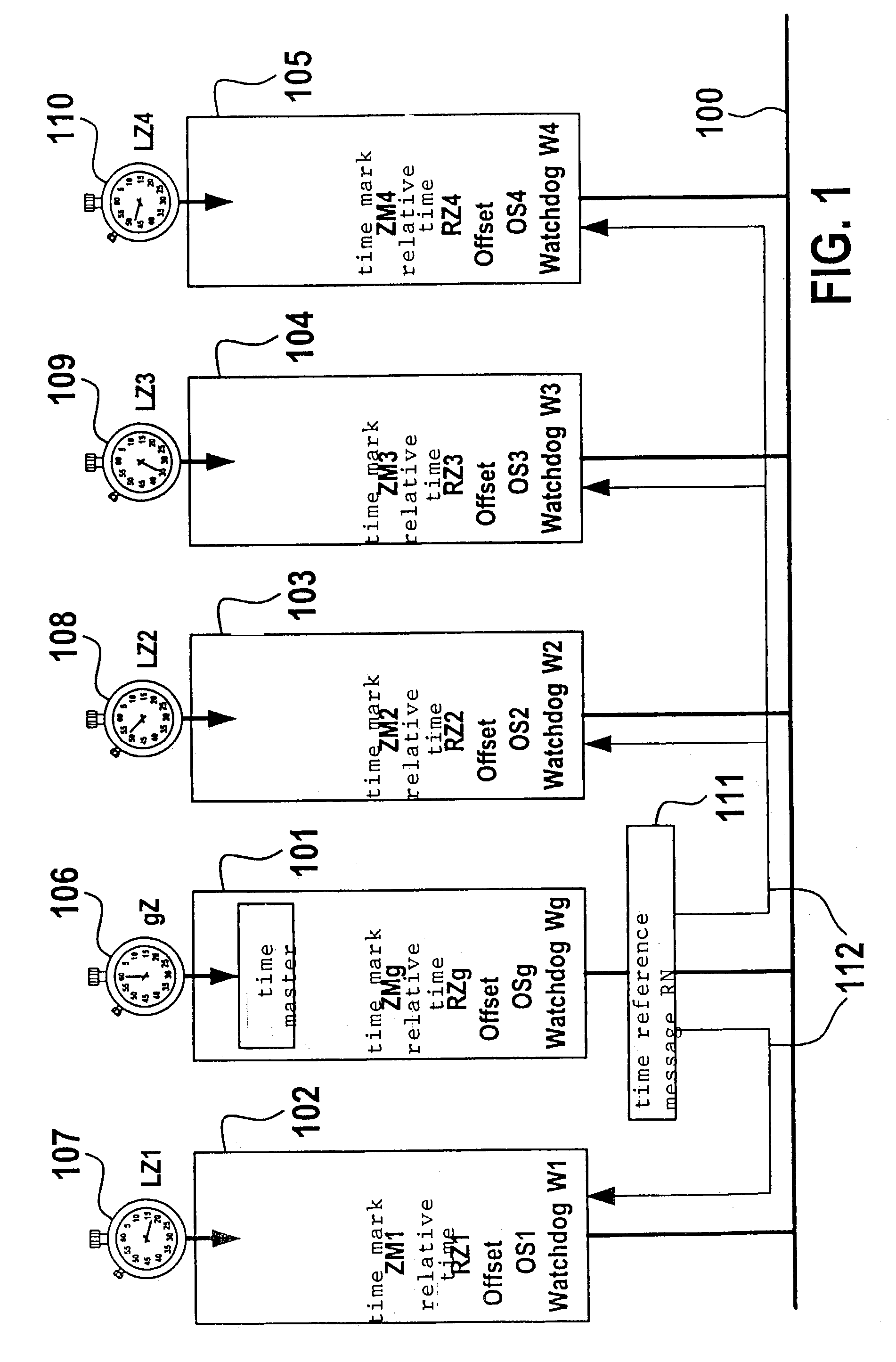

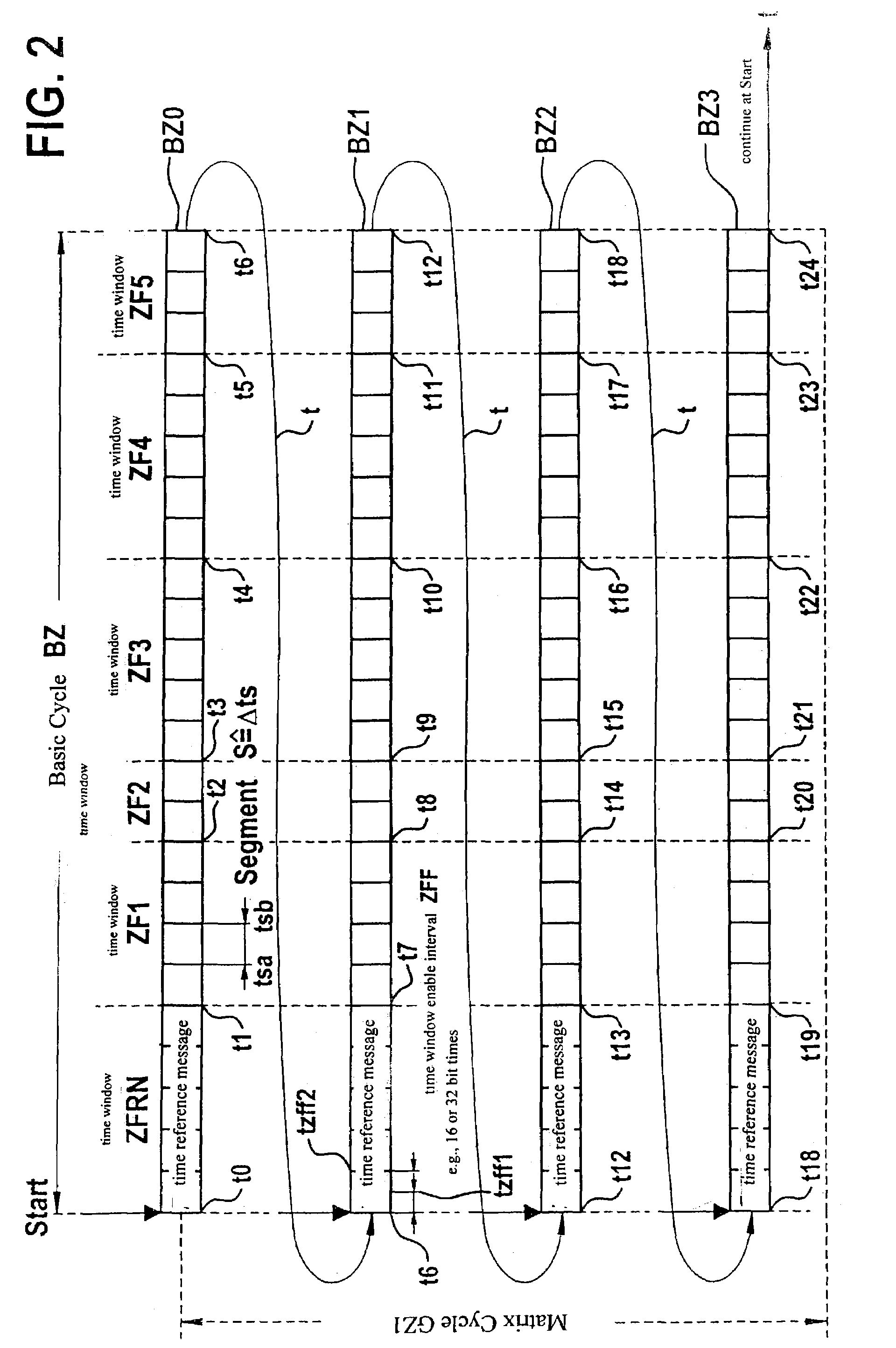

Method and device for exchanging data between at least two stations connected via a bus system

InactiveUS7171579B2Quick checkBroadcast transmission systemsTime-division multiplexTime controlTime windows

A method and a device for exchanging data in messages between at least two stations connected via a bus system, the messages containing the data being transmitted by the stations over the bus system and the messages being controlled over time by a first station in such a manner that the first station repeatedly transmits a reference message over the bus at at least one specifiable time interval and the time interval is divided into time windows of specifiable length, the messages being transmitted in the time windows, a reference message and the subsequent time windows until the next reference message being combined into a first cycle, and the first station interrupting the transmission at the end of a first cycle due to a stop request, in particular, a message of the at least second station.

Owner:ROBERT BOSCH GMBH

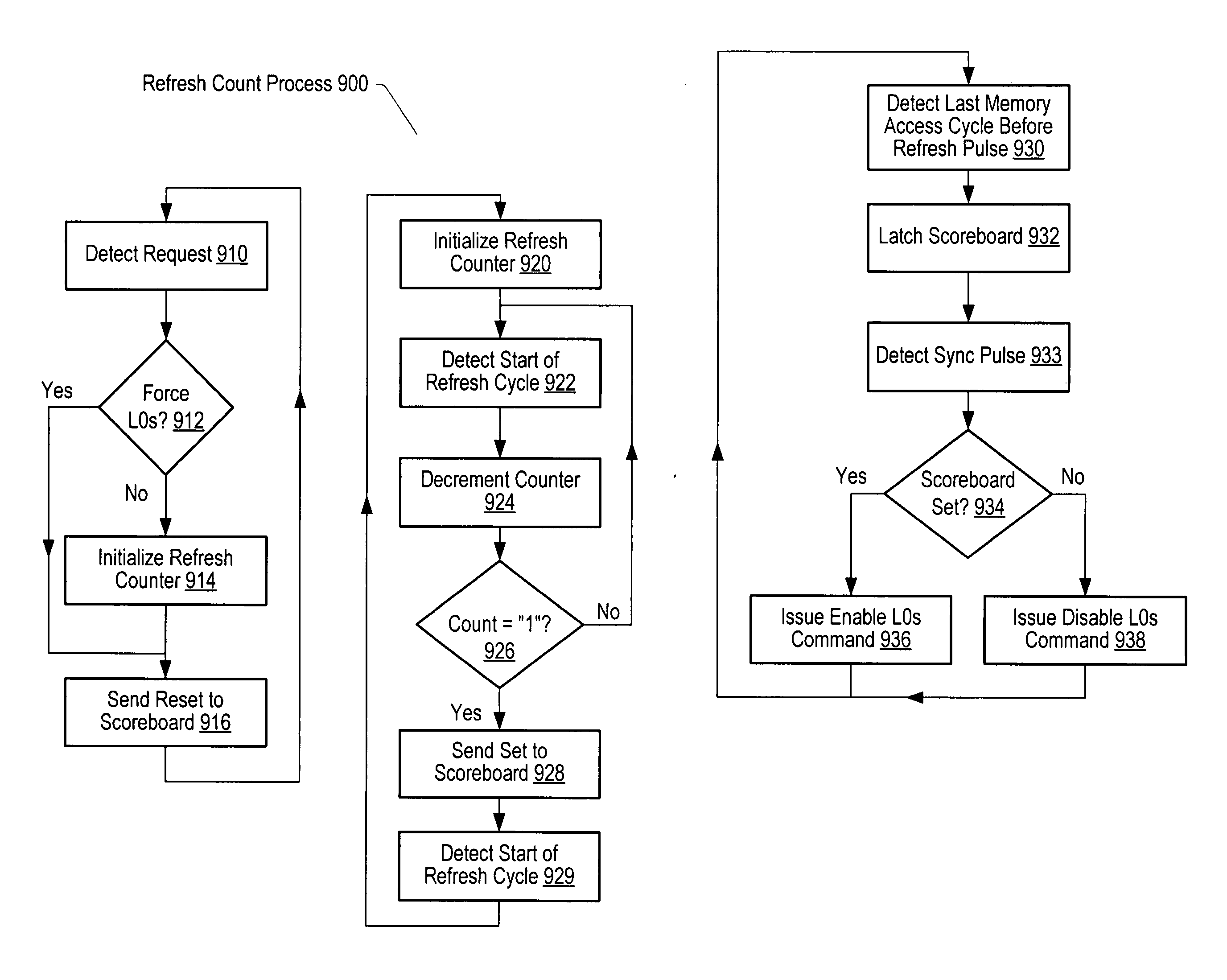

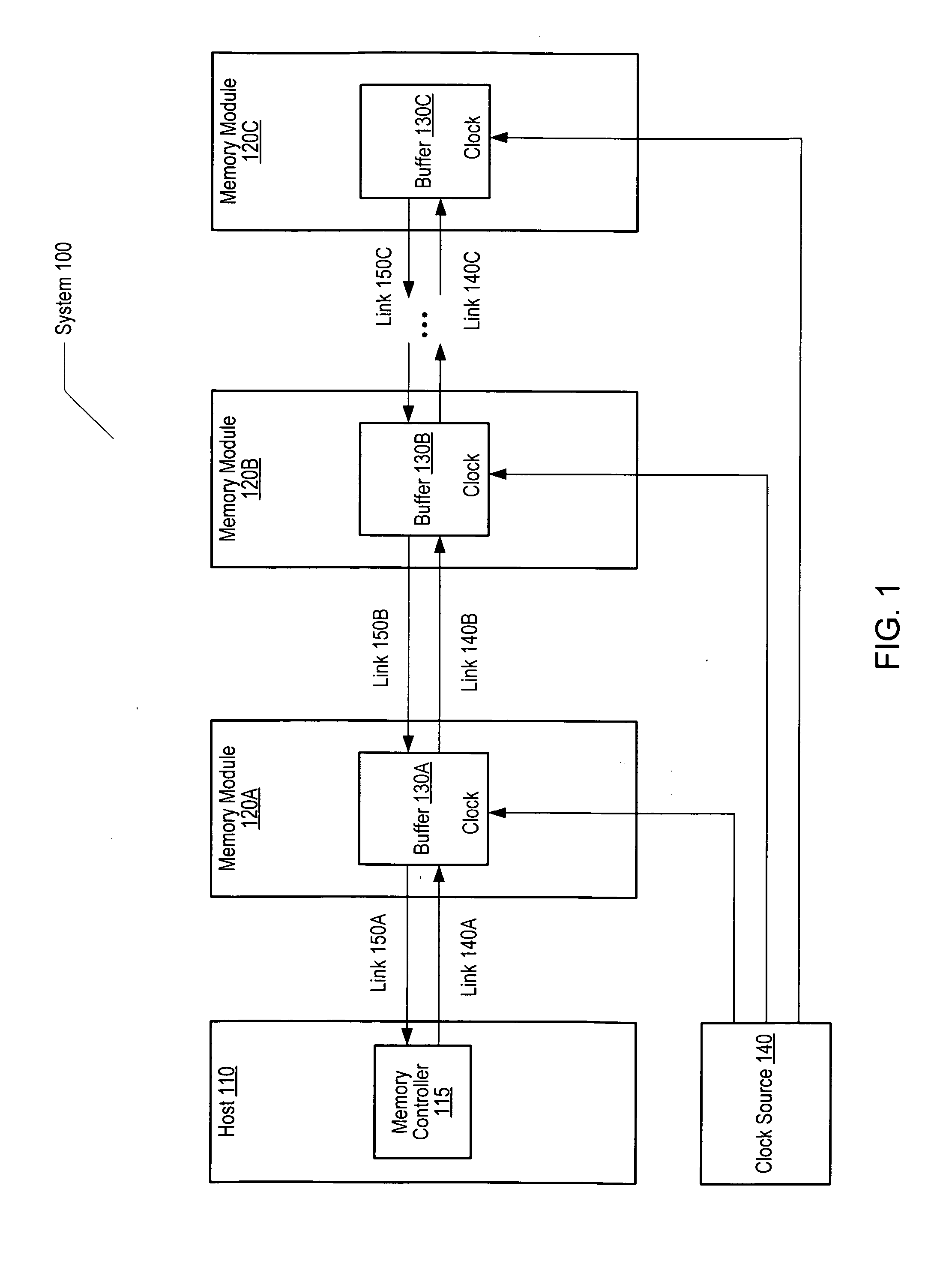

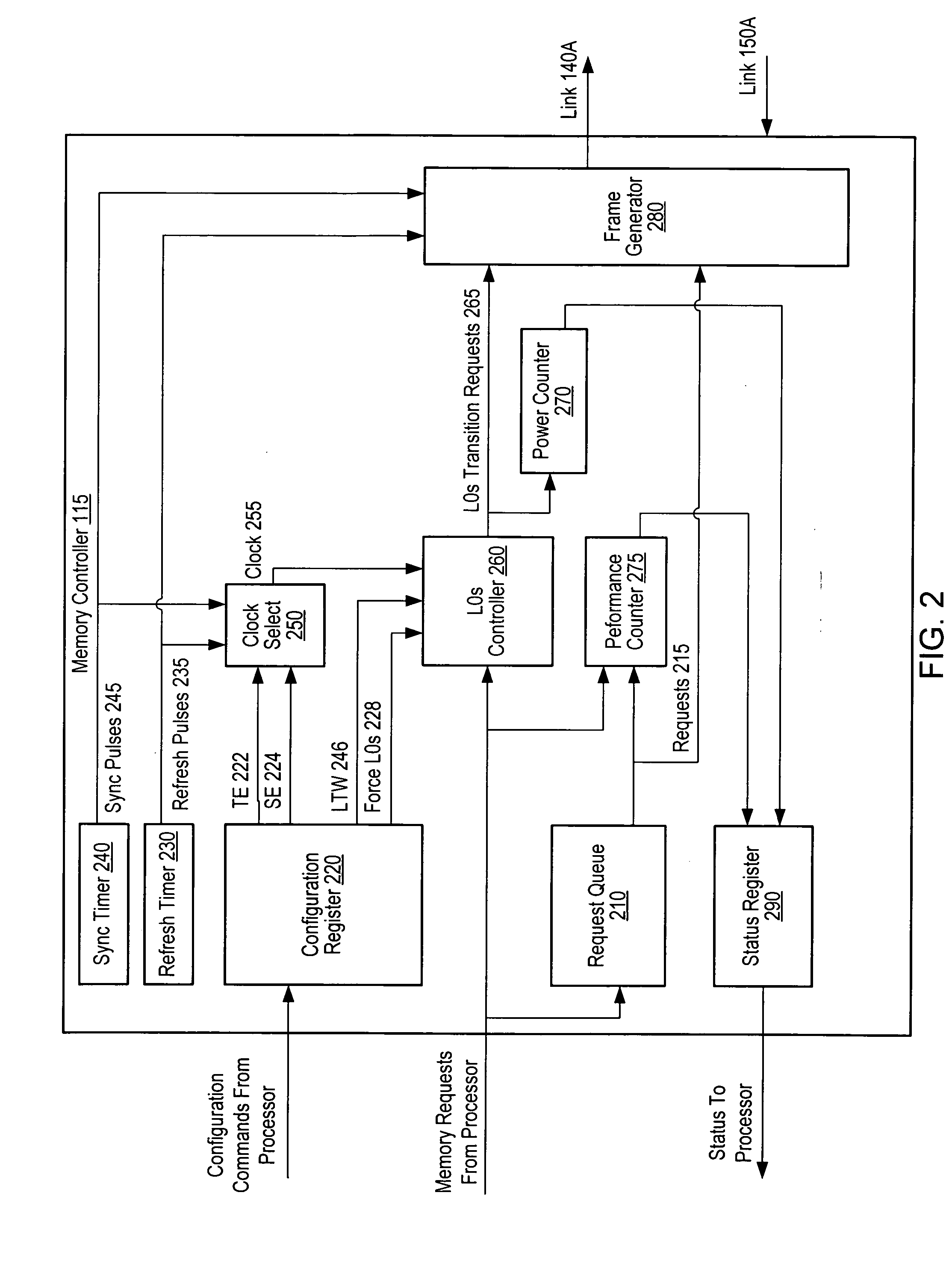

Power throttling in a memory system

ActiveUS20070083701A1Low power stateEnergy efficient ICTVolume/mass flow measurementTerm memorySnubber

A memory system is disclosed. The memory system includes a memory controller coupled to one or more memory modules, at least one of the memory modules including a buffer. The memory controller is configured to convey a command to at least one of the memory modules in response to detecting that no memory requests addressed to the at least one of the memory modules have been received during a specified window of time. In response to the command, the buffer of the at least one of the memory modules is configured to enter a reduced power state. The specified window of time may be either a specified number of memory refresh intervals or buffer sync intervals. The memory controller maintains a count of memory refresh or buffer sync intervals.

Owner:ORACLE INT CORP

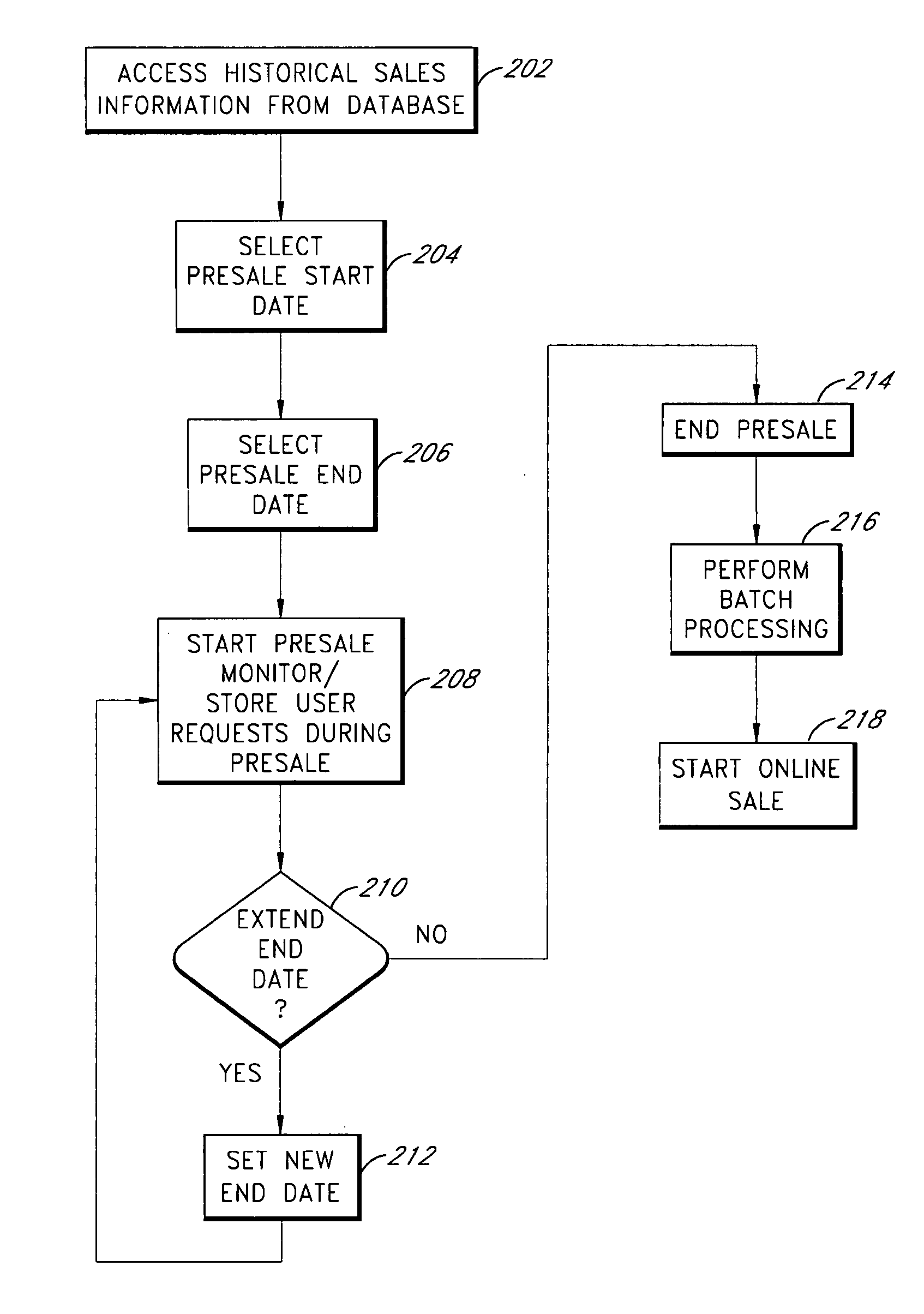

Methods and systems for reducing burst usage of a networked computer system

ActiveUS20070245351A1Reducing burst usageResource allocationReservationsBatch processingTime windows

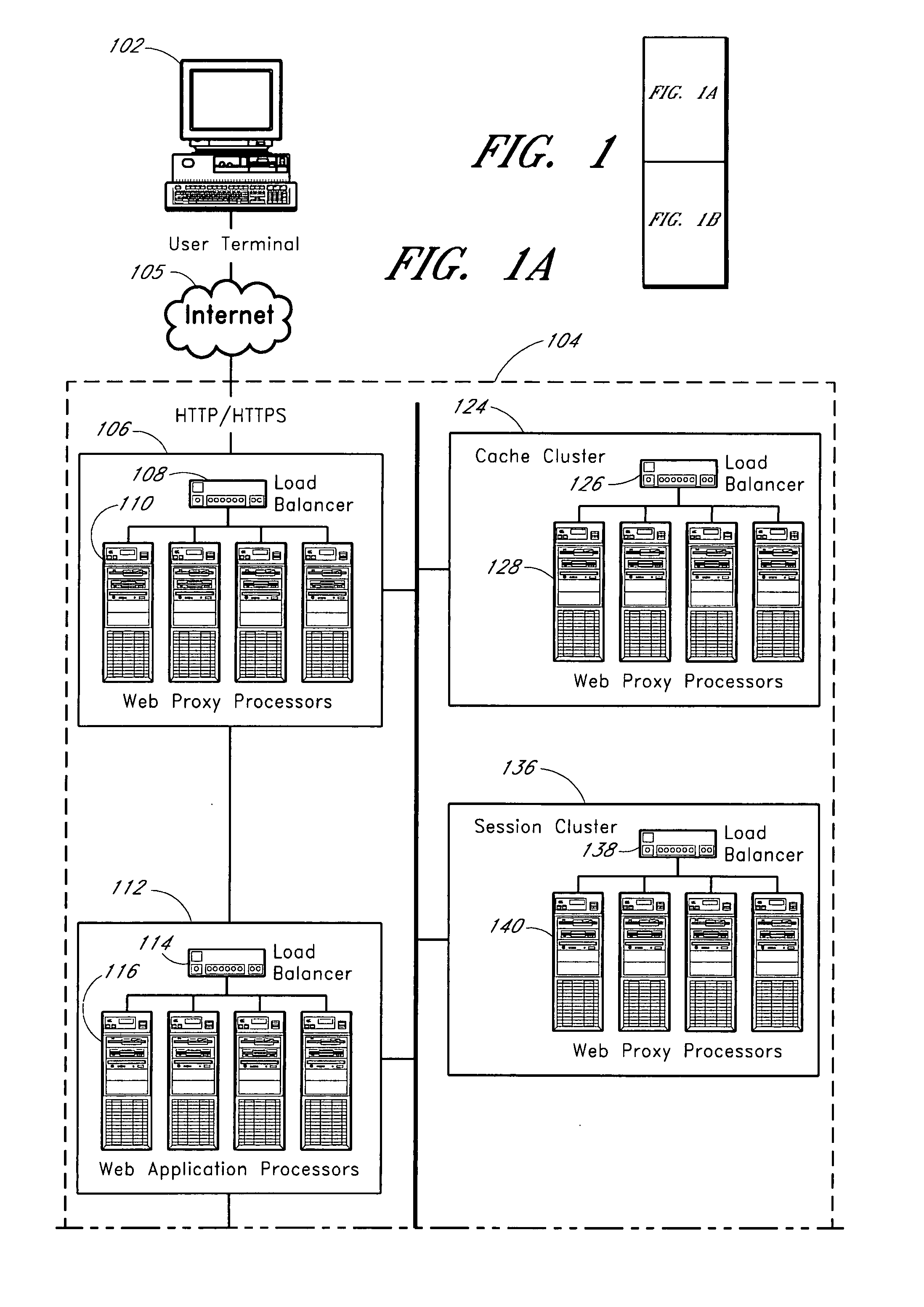

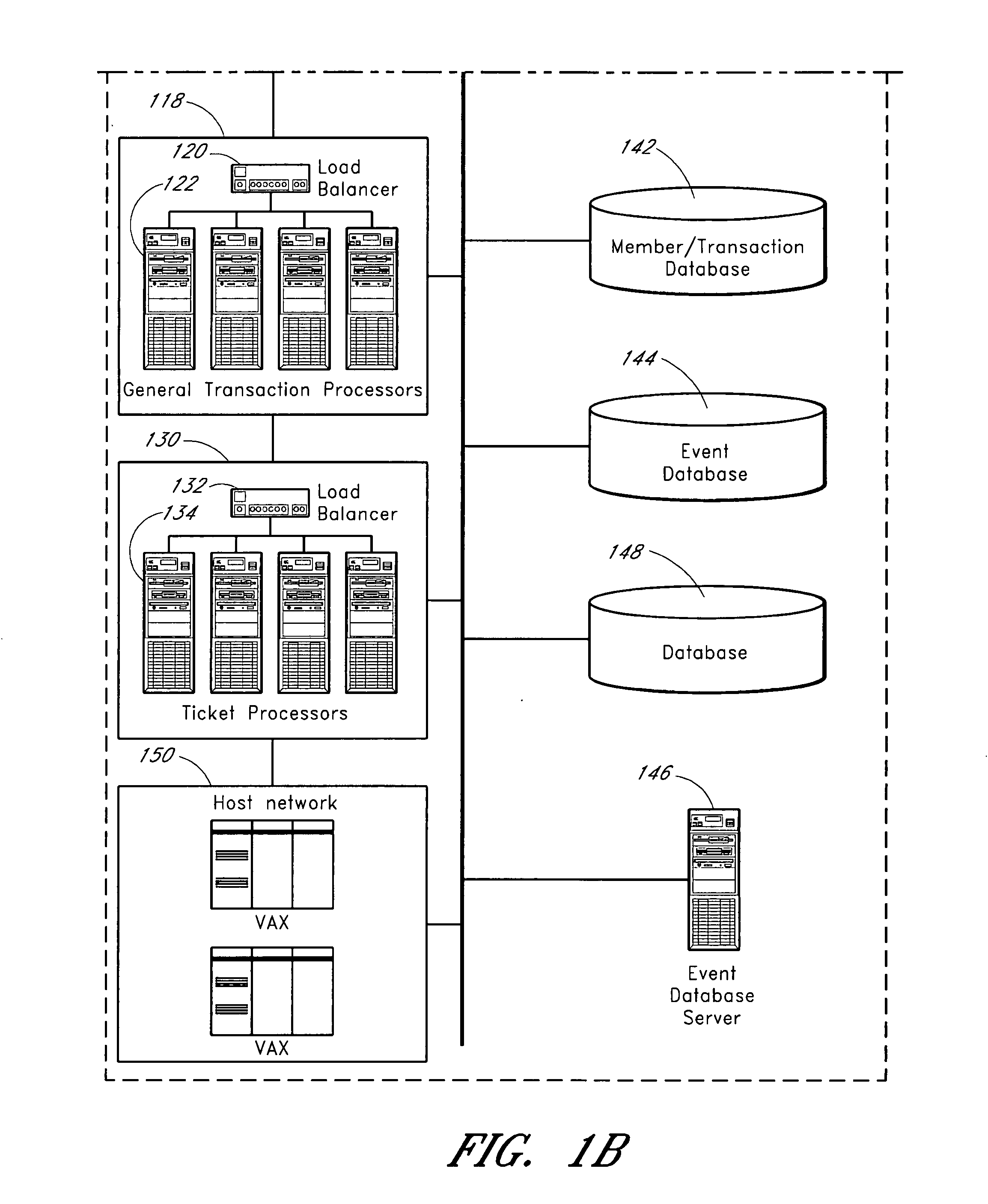

Methods and systems for reducing burst usage of a networked computer system are described herein. In an embodiment, resource requesters can request, within a time window, resources over a computer network before the resources are available. The resources can then be allocated in batch mode when the resources are available. Thus, resource requests do not have to be processed in real-time, and resource requests can be received before the resources are available.

Owner:LIVE NATION ENTERTAINEMENT INC

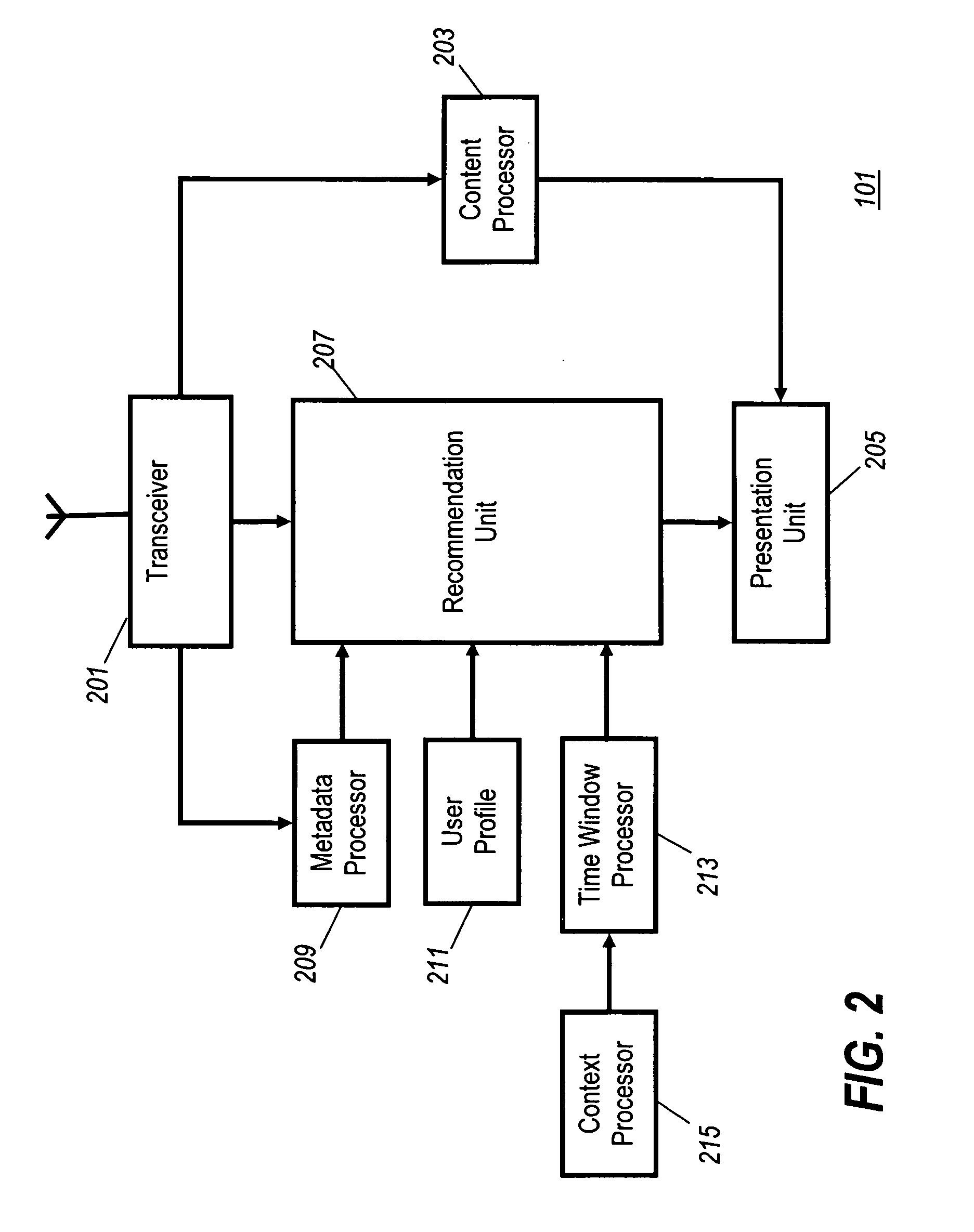

Apparatus and method for generating content program recommendations

InactiveUS20090158342A1Improve user experienceIncrease contentTelevision system detailsColor television detailsMobile contentContext data

An apparatus for generating content program recommendations comprises a meta-data processor (209) which provides characterising data for a plurality of content programs. A context processor (215) provides first context data for a user and a time window processor (213) determines a content consumption time window for the user in response to the first context data. The content consumption time window represents an estimated time window available to the user for consuming content. A recommendation unit (207) then generates a content program recommendation comprising in response to the content consumption time window and the characterising data. The invention may be particularly advantageous for mobile content program distribution services, such as a mobile television service, as recommendations may be generated that take into account the particular characteristics of the mobile user environment. Specifically, the recommendation can take into account the increased probability of a disruption to the consumption experience caused by external factors.

Owner:MOTOROLA MOBILITY LLC

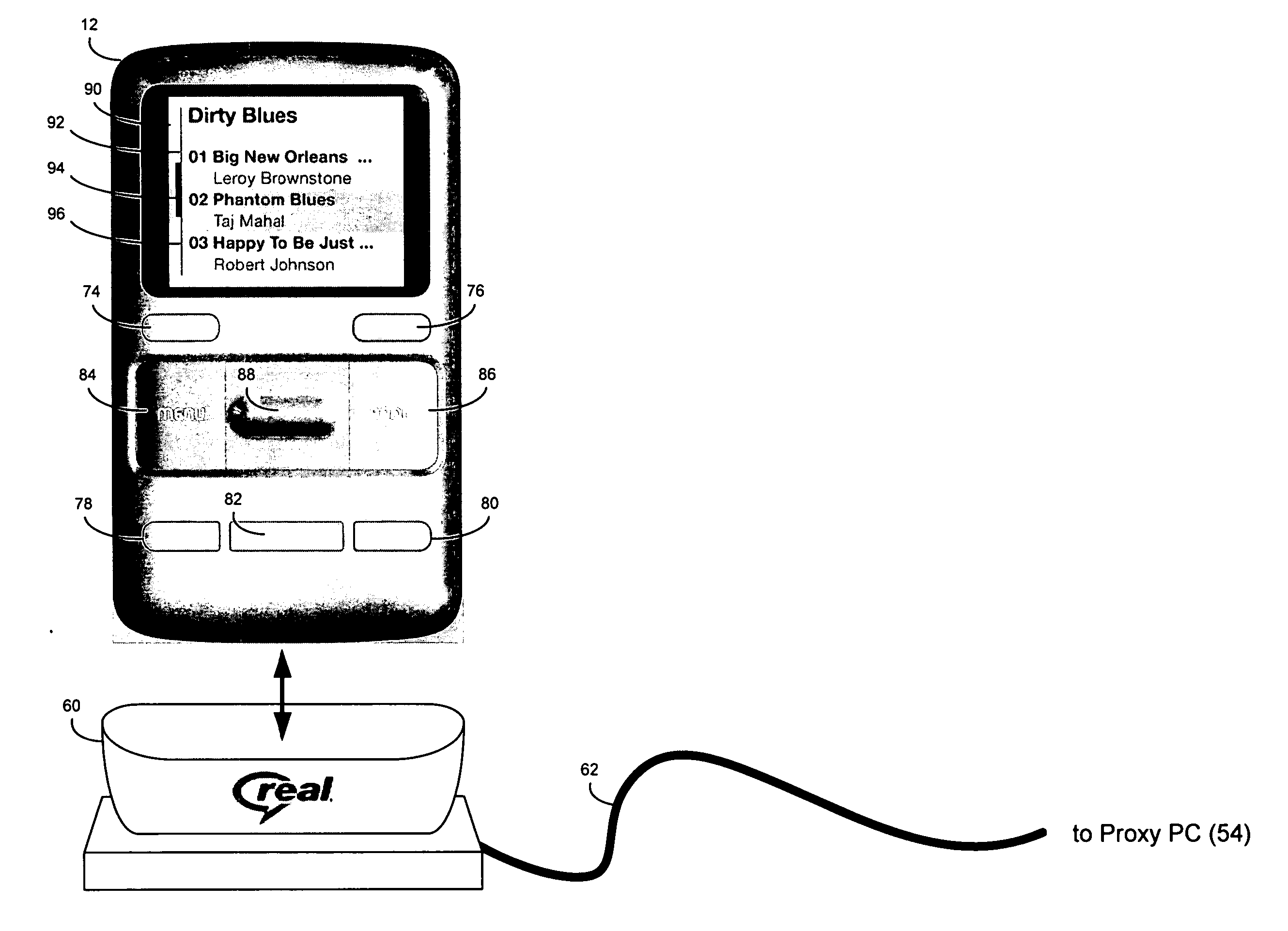

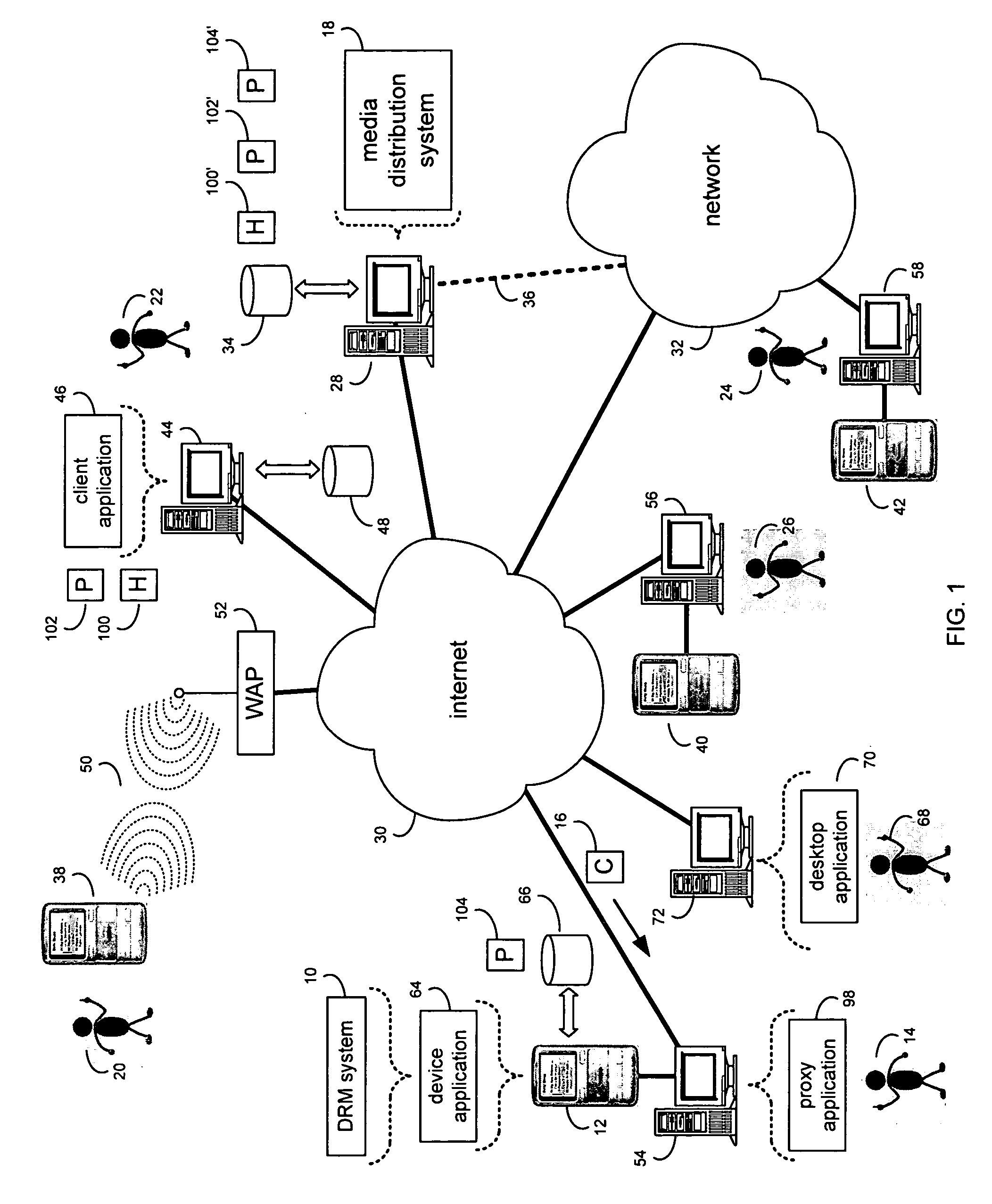

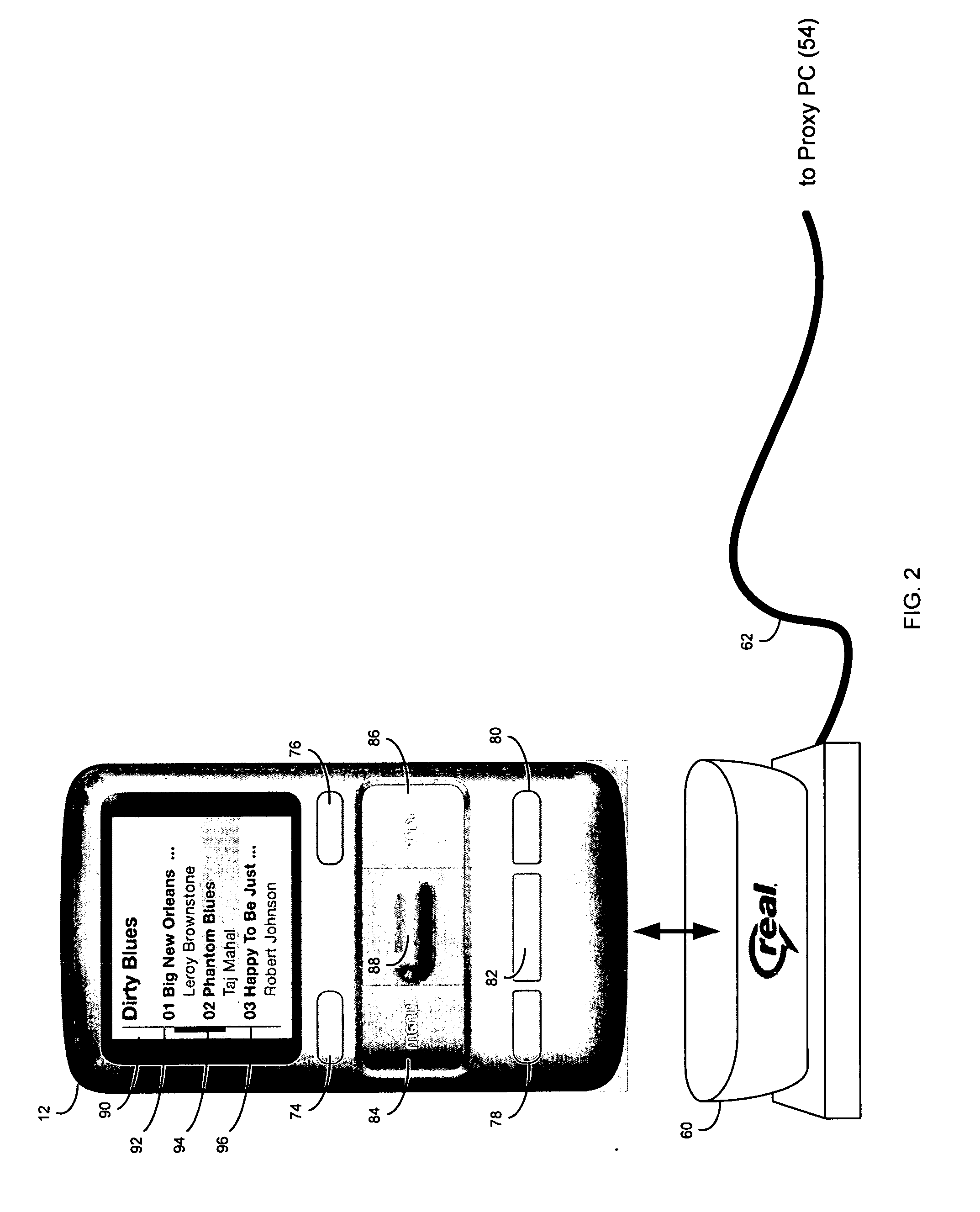

System and method for chronologically presenting data

InactiveUS20070061759A1Metadata audio data retrievalSpecial data processing applicationsTime windowsWorld Wide Web

A method, computer program product and computing device for associating at least one historical event with at least one media content event based, at least in part, upon a chronological relationship. A chronological representation of the at least one historical event and the at least one media content event is displayed within a window of time. A user selection of an informational item displayed within the chronological representation is received, and the chronological representation is updated based on the selected informational item.

Owner:REALNETWORKS INC

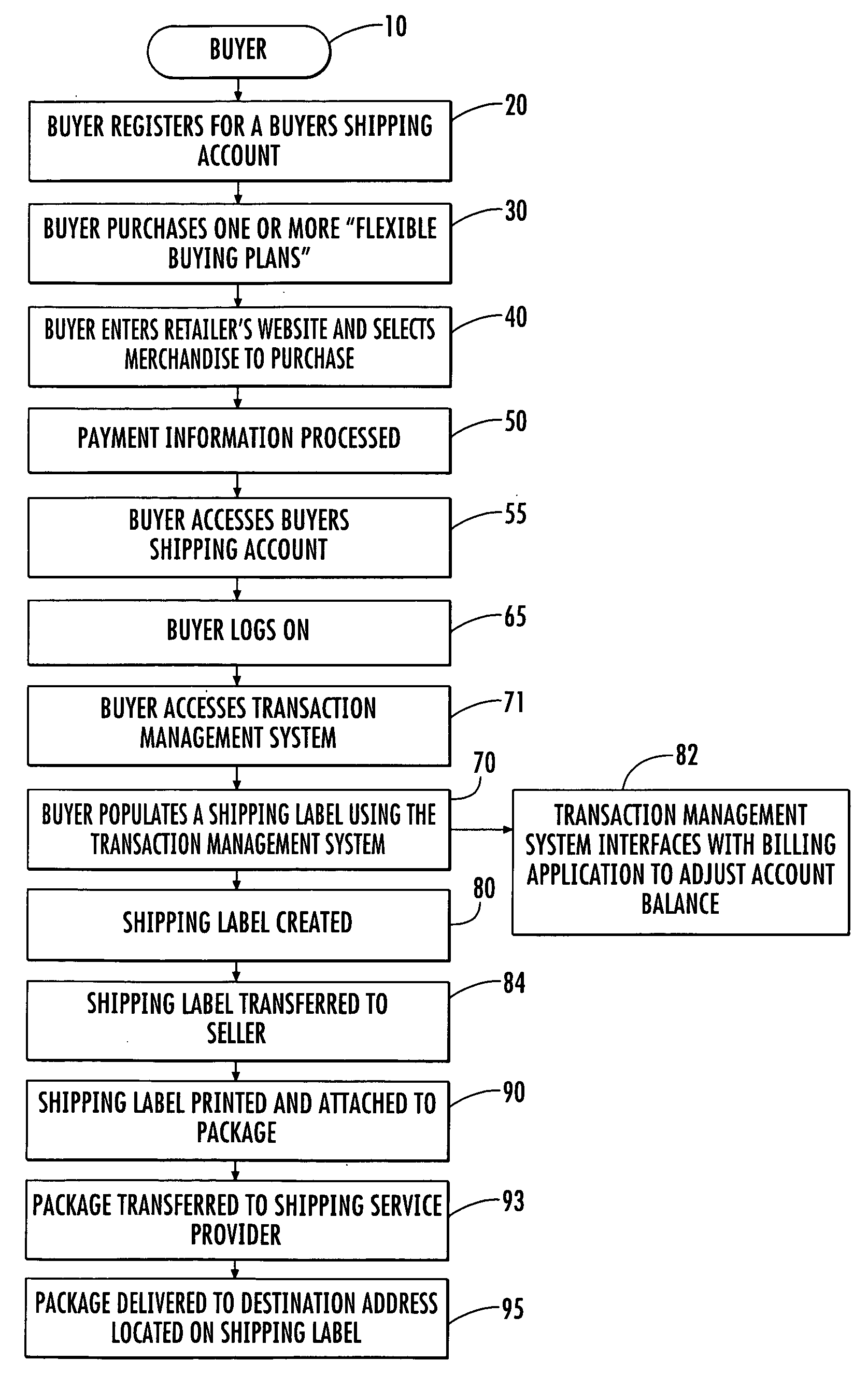

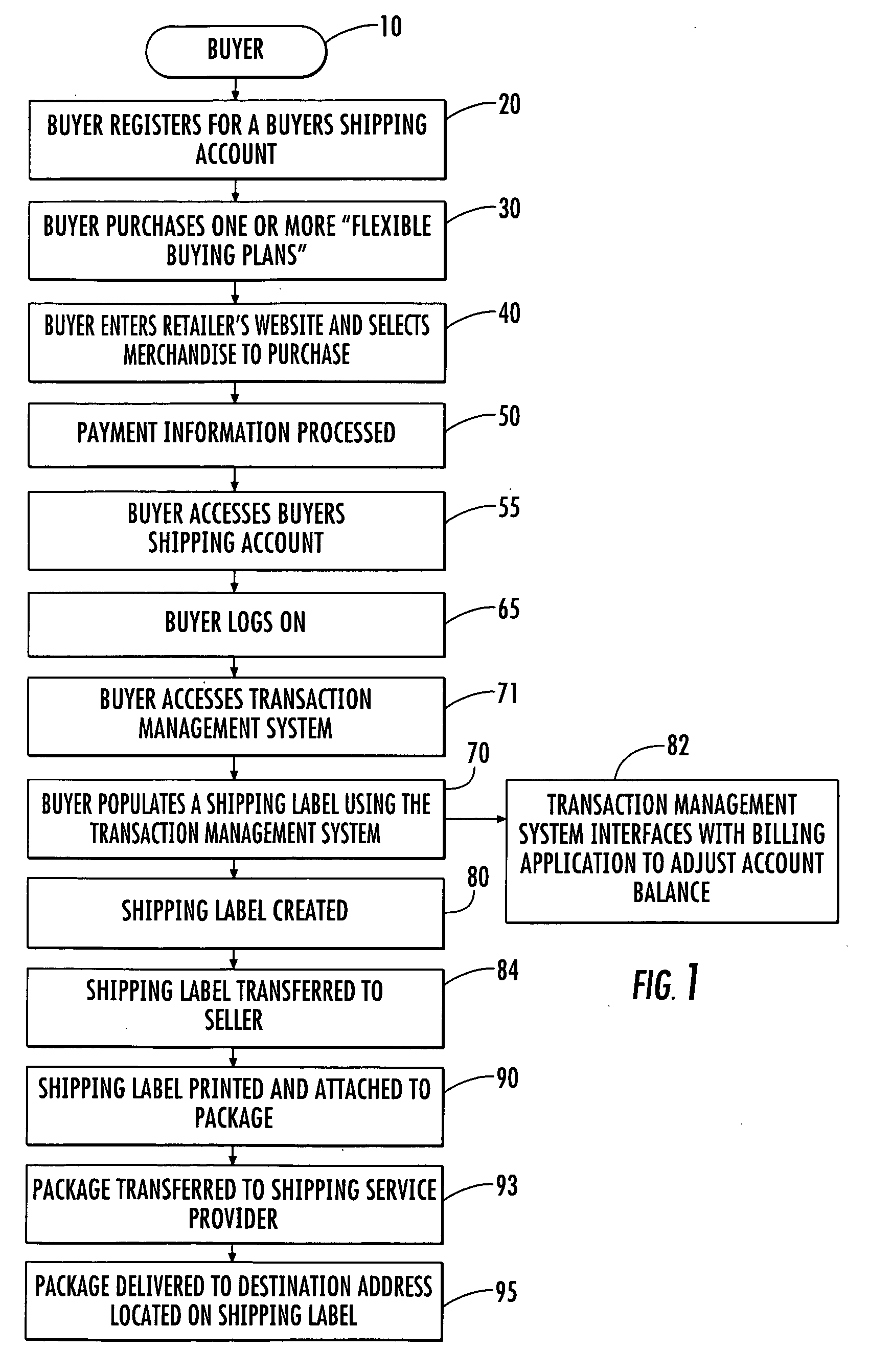

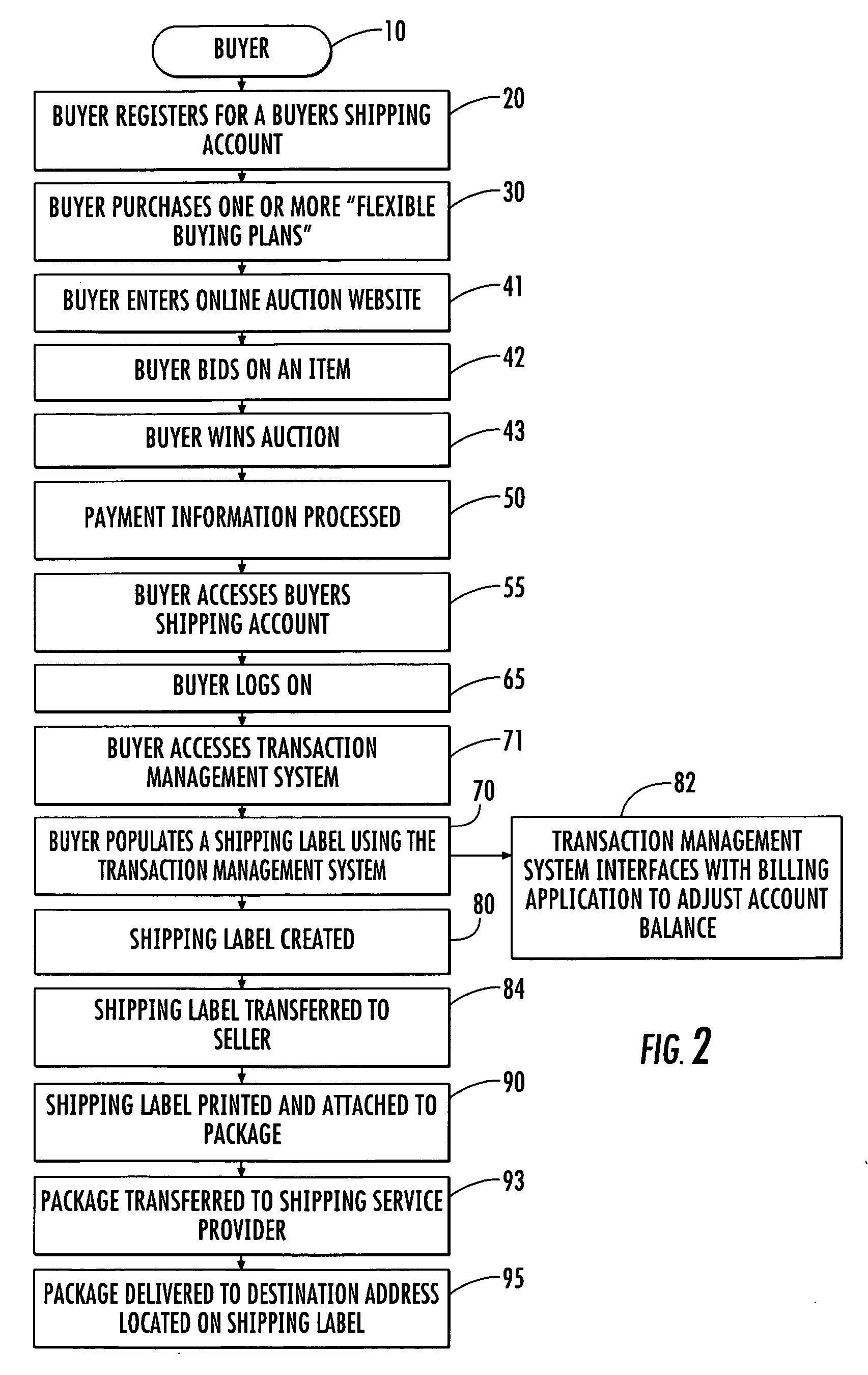

Buyer-initiated shipping system

A system and method in which a buyer registers for a buyer's shipping account and uses the shipping account to pay shipping costs associated with purchases made over the Internet. When a buyer purchases merchandise over the Internet from either a retailer's website or from an individual through an online auction, the buyer is capable of controlling the shipping process by logging on to their buyer's shipping account. Among other things, the buyer can use their shipping account to select the desired type of shipping service (overnight air or ground) and populate a shipping label with shipping information such as delivery address, return address, and preferred delivery time windows. Once the shipping label has been populated and verified, the shipping label is electronically transferred to the seller for use in shipping the package. The system and methods of the present invention allow the buyer greater control over the shipping process. In many cases, the present invention will also help buyers / receivers control costs by eliminating the shipper's shipping and handling fee.

Owner:UNITED PARCEL SERVICE OF AMERICAN INC

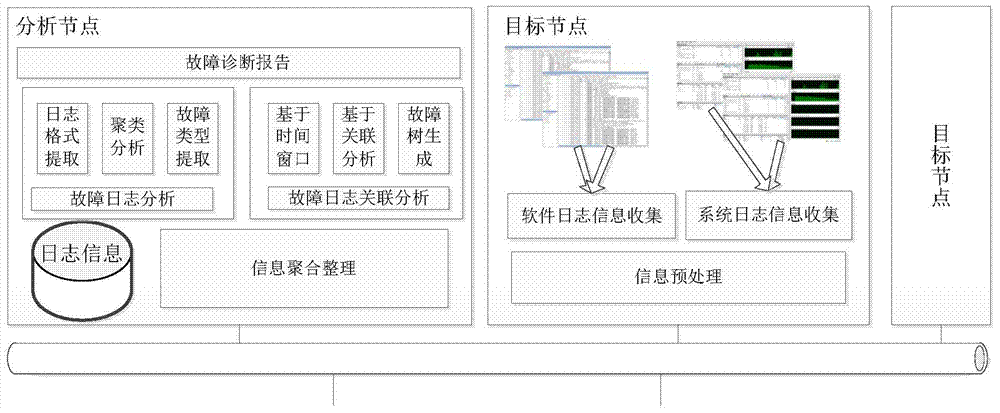

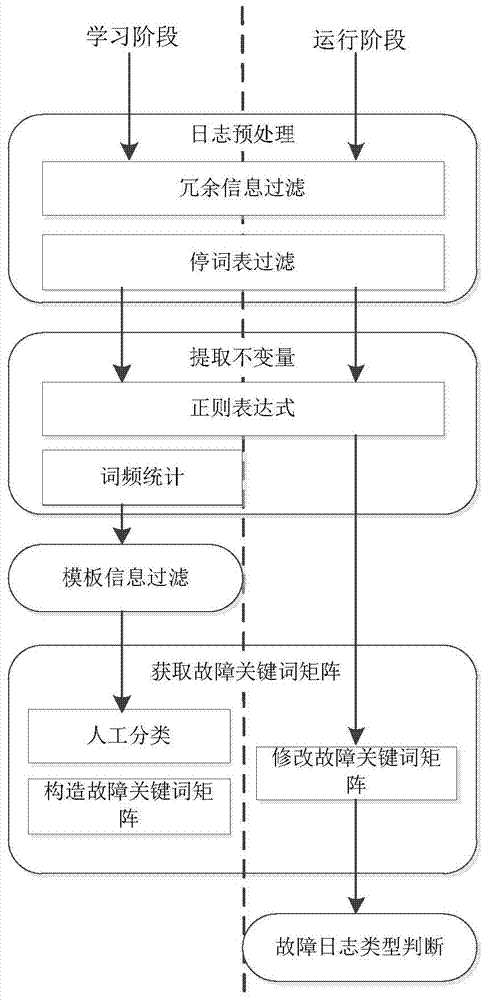

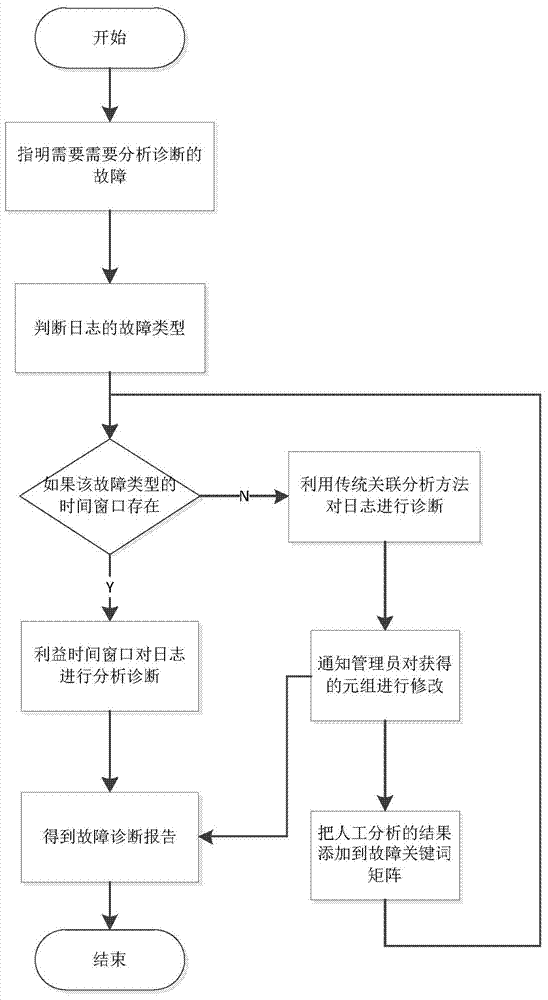

Log based computer system fault diagnosis method and device

InactiveCN103761173AConvenient and rapid fault classificationProcessing speedDetecting faulty computer hardwareHardware monitoringProcess systemsLog management

The invention discloses a log management and fault diagnosis method and device under multiple hosts. The method comprises fault log collection, fault log analysis and fault log correlation analysis. Fault log collection comprises collecting fault logs of all hardware and software in the cluster and storing the logs in a log server uniformly. Fault log analysis comprises filtering the fault logs, extracting log template information and classifying the logs according to log types. Fault log correlation analysis comprises performing fault reason analysis by using log analysis results and combining time windows, clustering the related faults caused by the same fault into a category and trying to find the root of the type of the faults. The method and the device are capable of analyzing the system operation condition effectively, assisting administrators to process system faults and improving the fault type determination accuracy.

Owner:HUAZHONG UNIV OF SCI & TECH

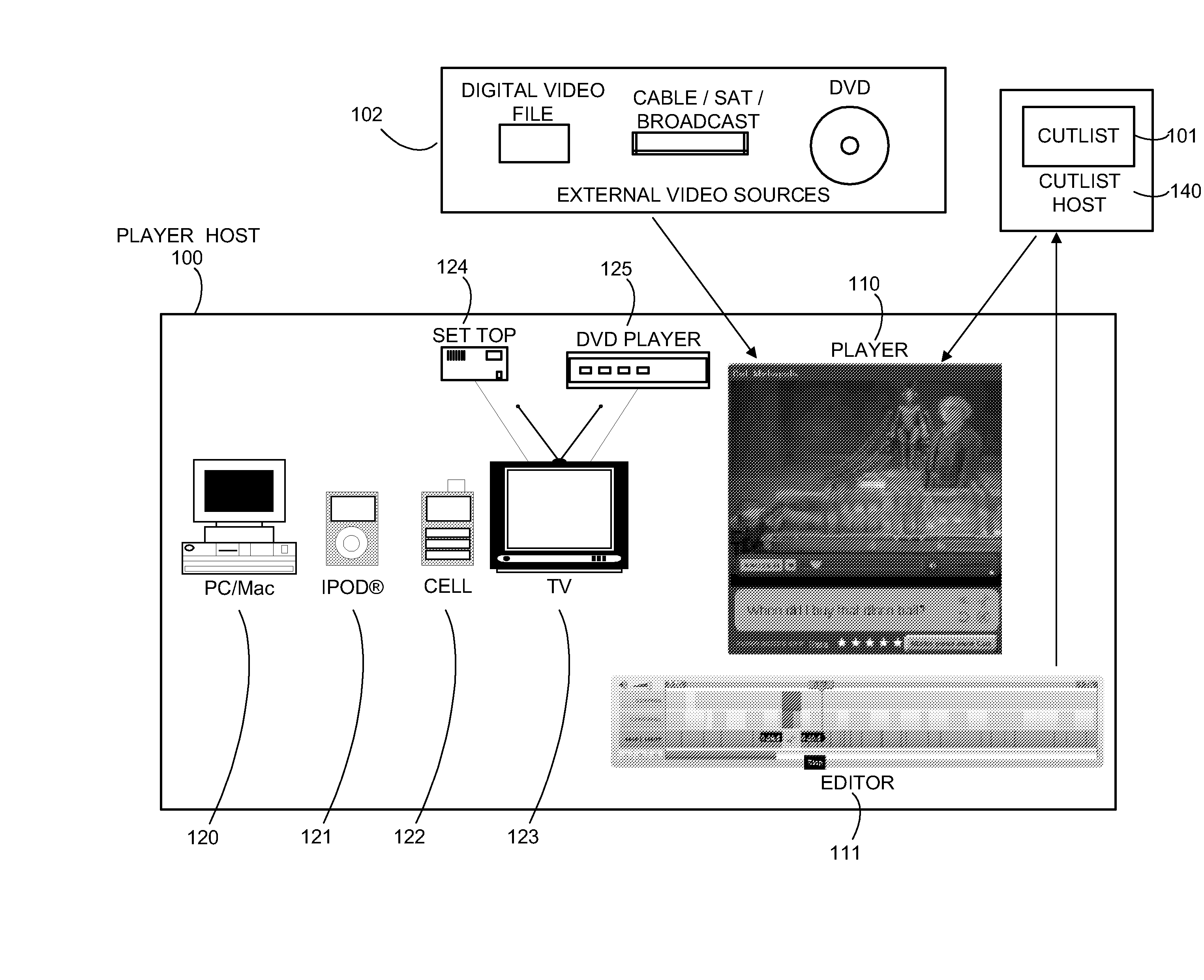

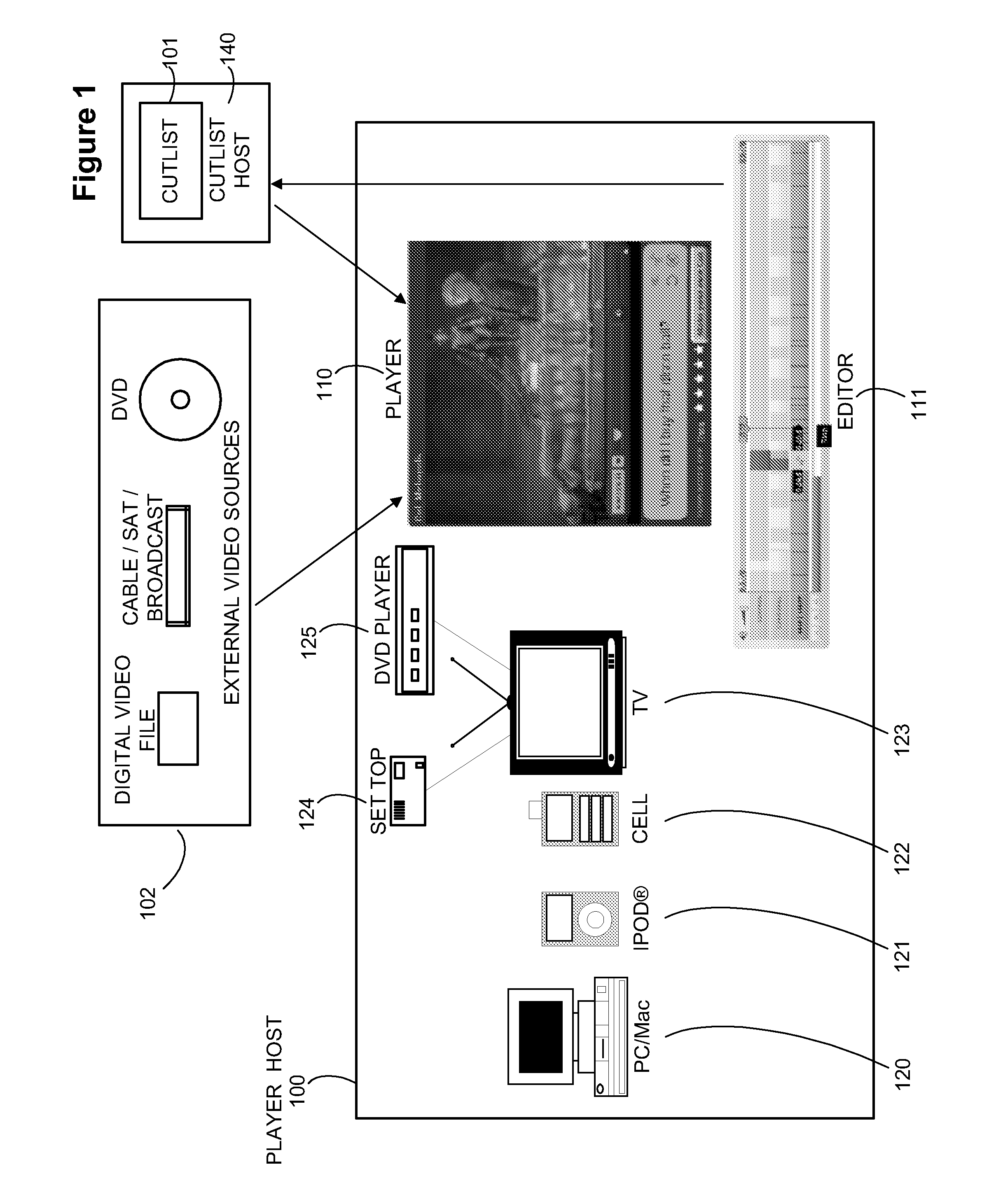

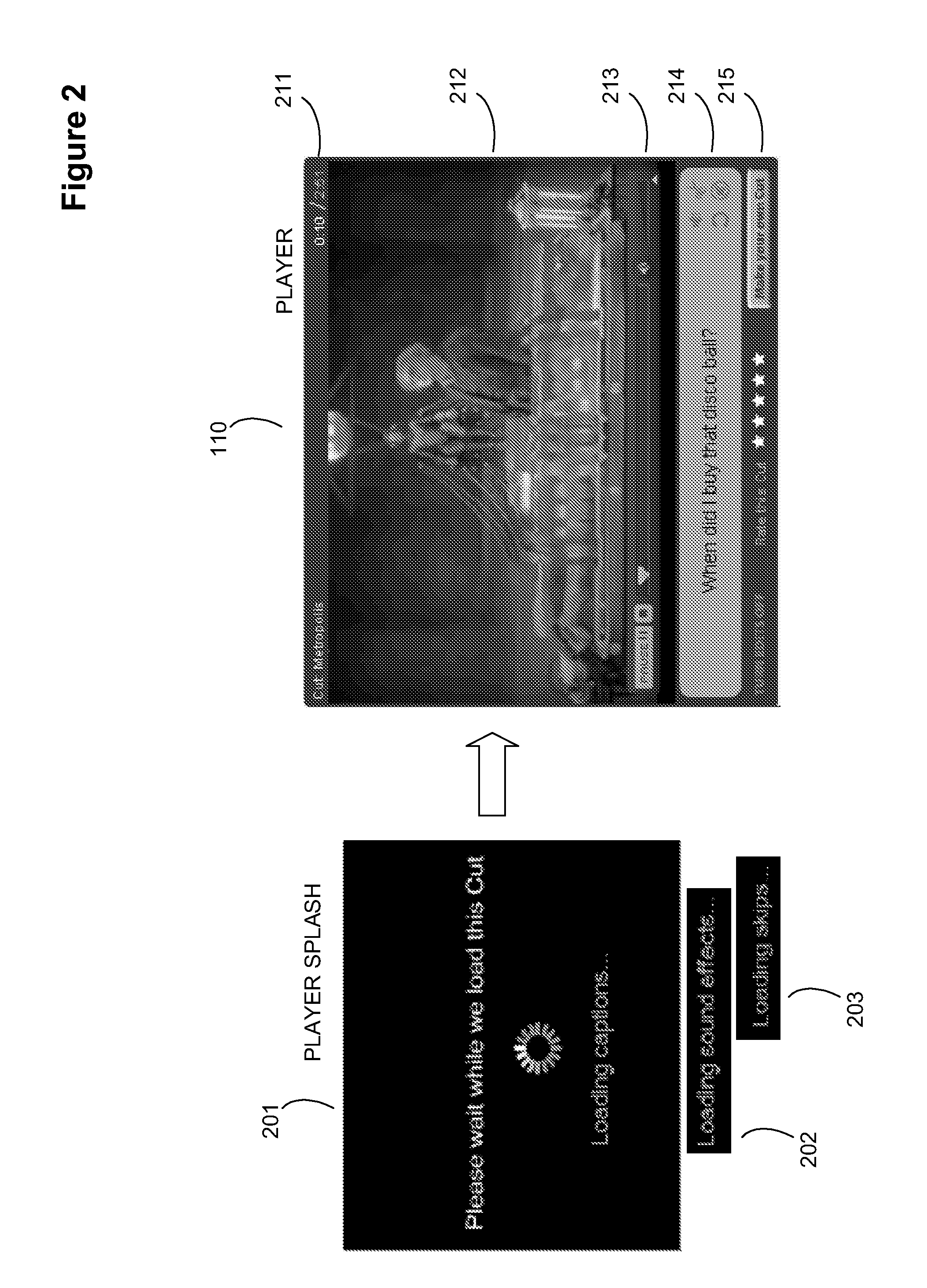

Personalized cutlist creation and sharing system

InactiveUS20070297755A1Television system detailsElectronic editing digitised analogue information signalsPersonalizationGraphics

Plays videos in conjunction with a “cutlist” utilized to modify the video. Videos include any visual media such as online or streaming video, broadcast television or movies, digital media files having a video component or DVDs. The videos may originate from any location such as online, on YOUTUBE.COM®, cable television, or a local resource such as a digital media file or DVD. Cutlists may include “mashups” and “cuts”. Mashups add content and include additional user generated input such as text, audio, commentary, graphics, avatar overlays, advertisements or other video. Cuts allow skipping of video and are time windows or scenes that are not to be viewed. The modified video may be viewed on any device associated with a video display. Cutlists may be shared among users to modify the performance of original video source without modifying the video itself, therein bypassing any copyright issues.

Owner:LEGEND FILMS INC

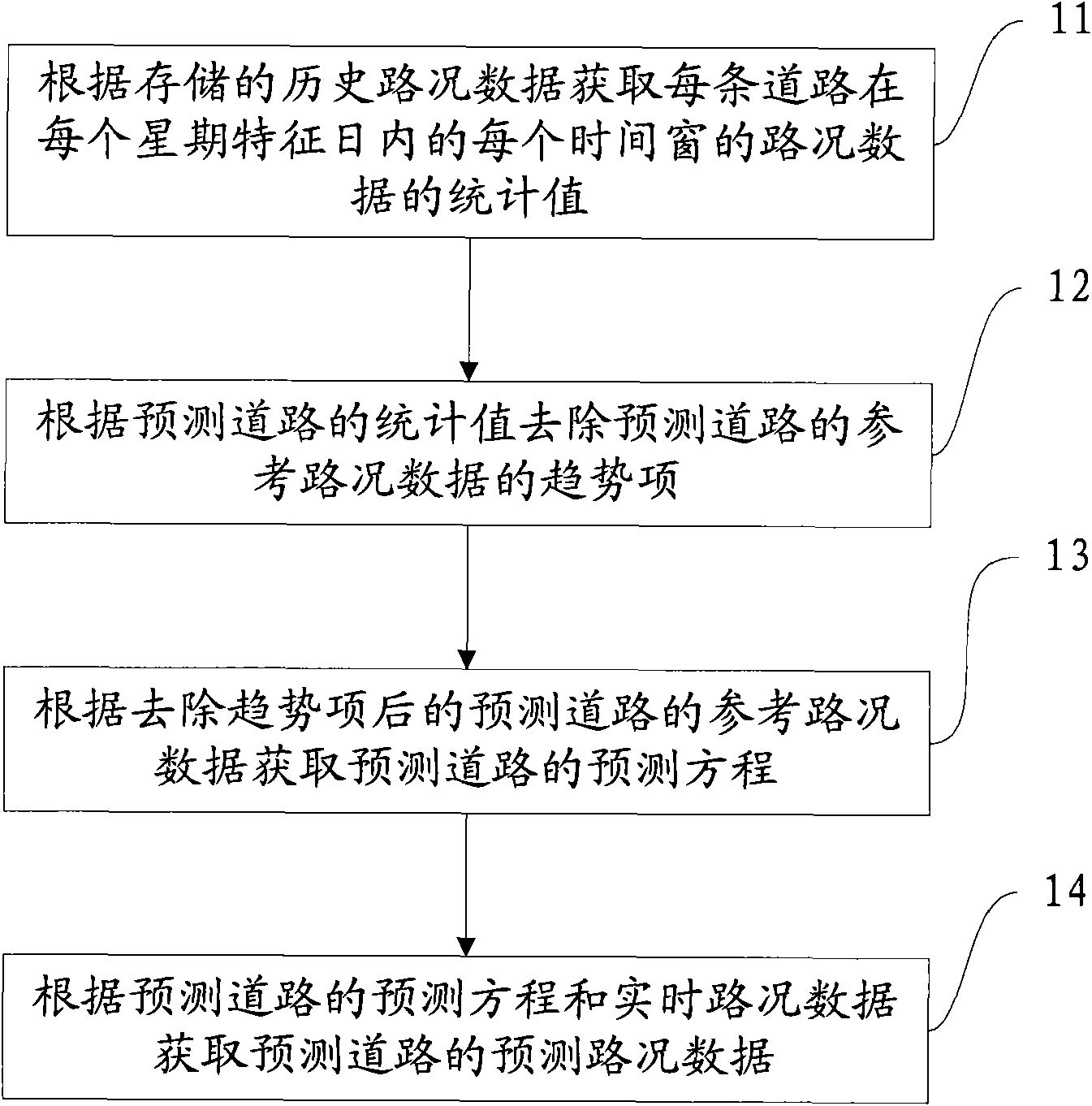

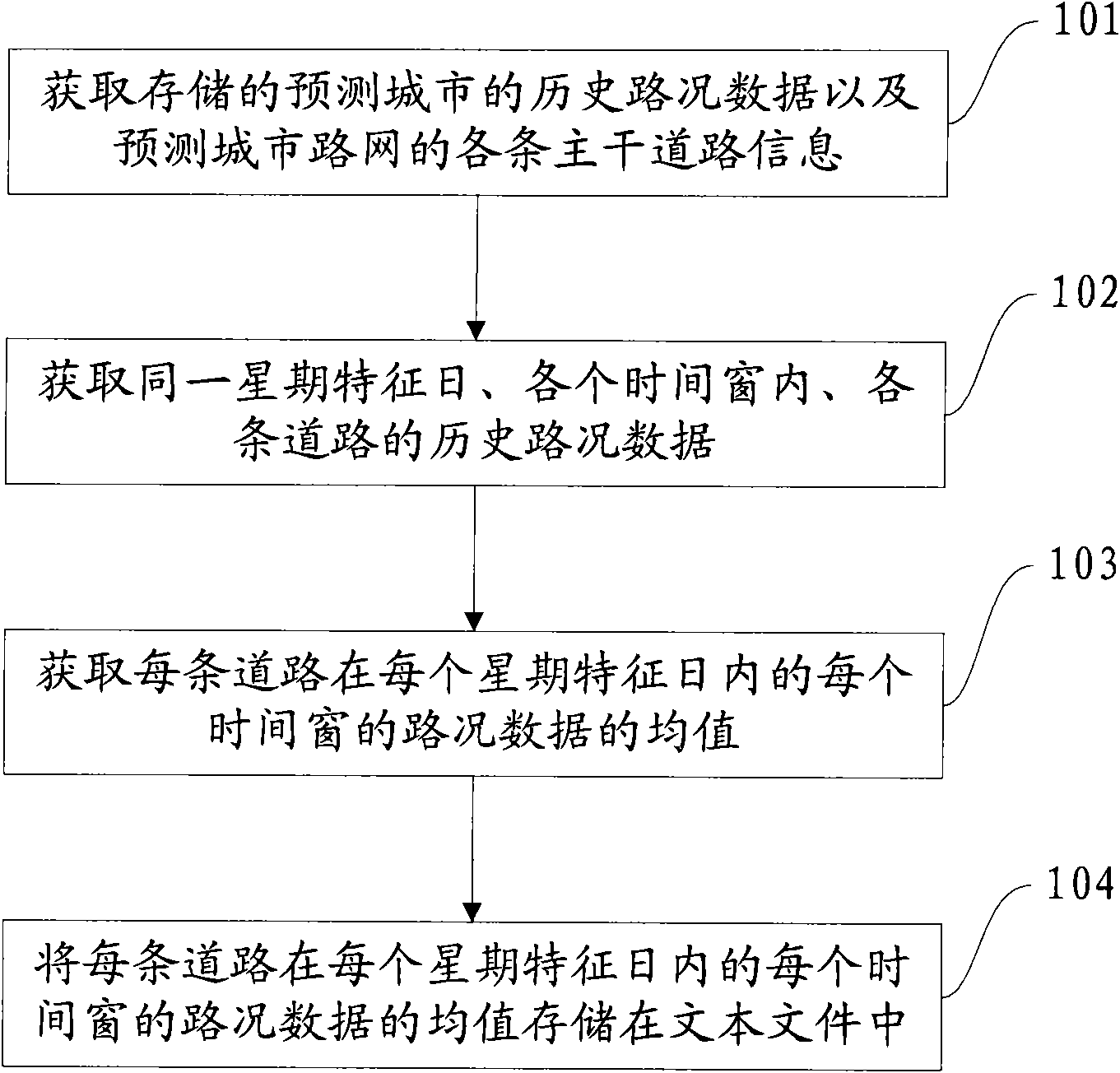

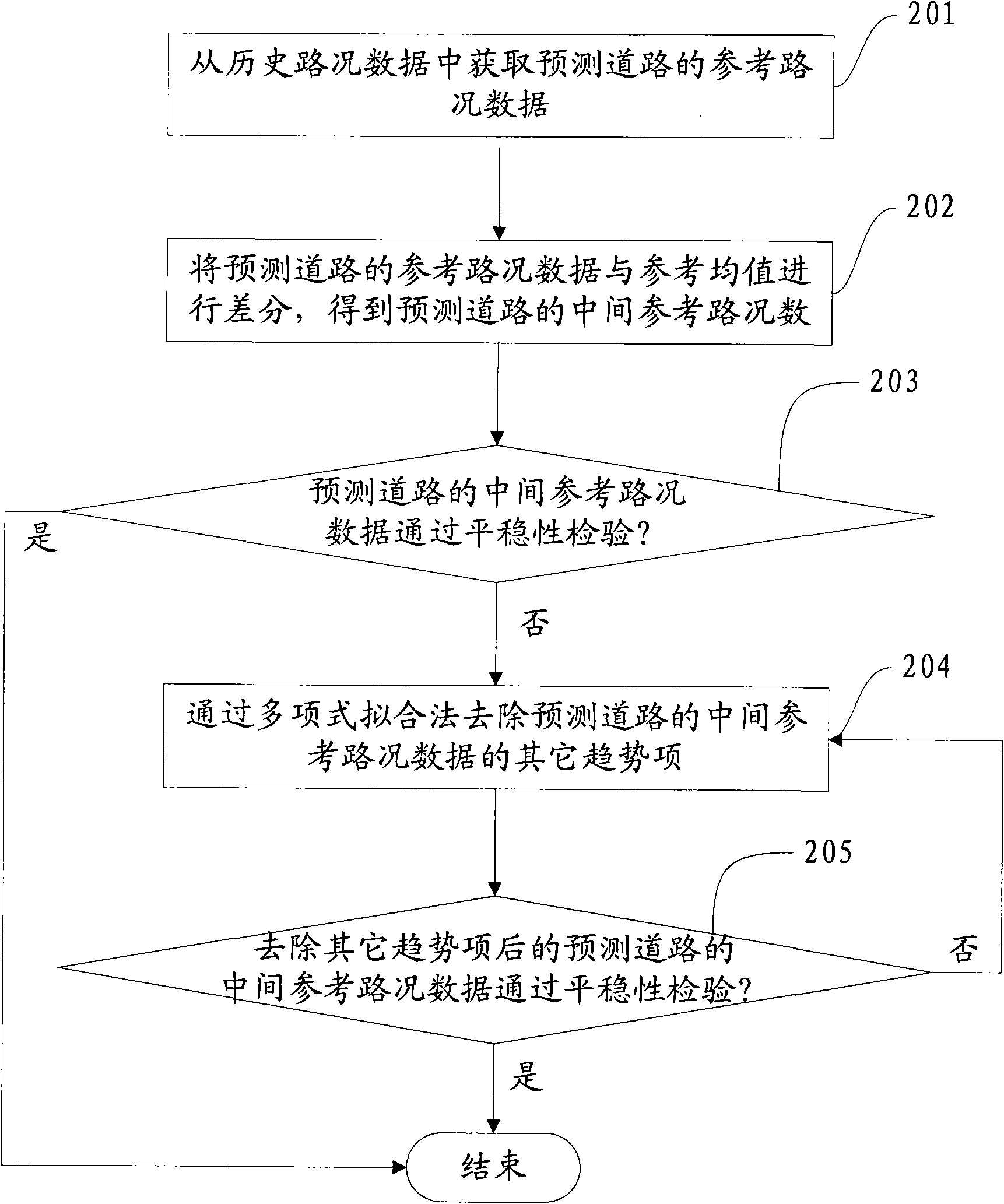

Traffic information predicting method based on time series and device thereof

ActiveCN101673463ACyclical Trend CancellationMeet the time-varying characteristicsArrangements for variable traffic instructionsPredictive methodsTime windows

The embodiment of the invention discloses a traffic information predicting method based on time series and a device thereof, relating to the communication field. In order to fast, effectively and accurately predict the traffic information, the technical scheme of the invention comprises the following steps: obtaining a statistic value of road condition data of each time window of each road in characteristic days every week according to memorized history road condition data; removing a trend term of reference road condition data of a predictive road according to the statistic value of the predictive road; obtaining a predictive equation of the predictive road according to the reference road condition data of the predictive road after removing the trend term; and obtaining predictive road condition data of the predictive road according to the predictive equation of the predictive road and real-time road condition data of the predictive road.

Owner:CENNAVI TECH

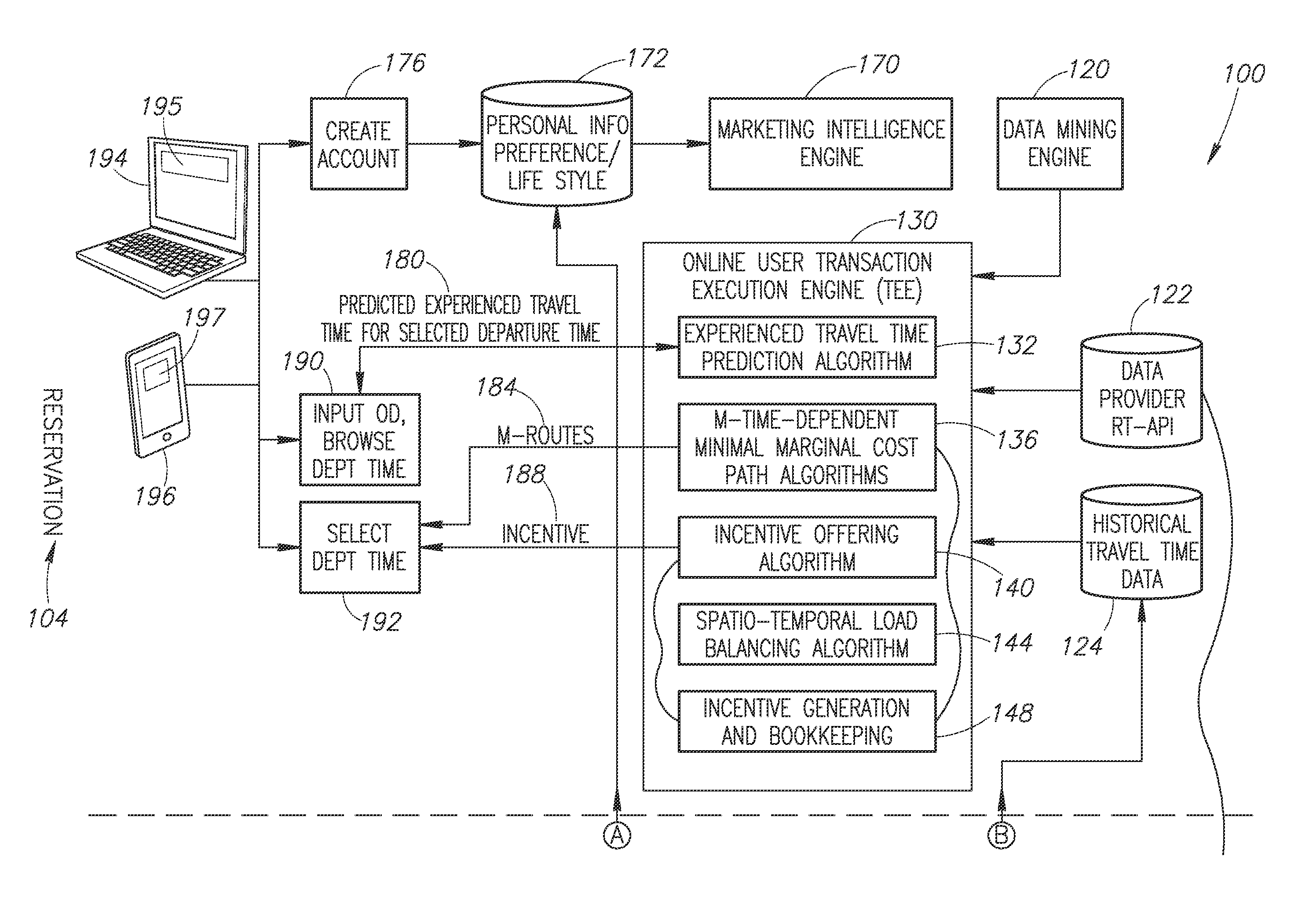

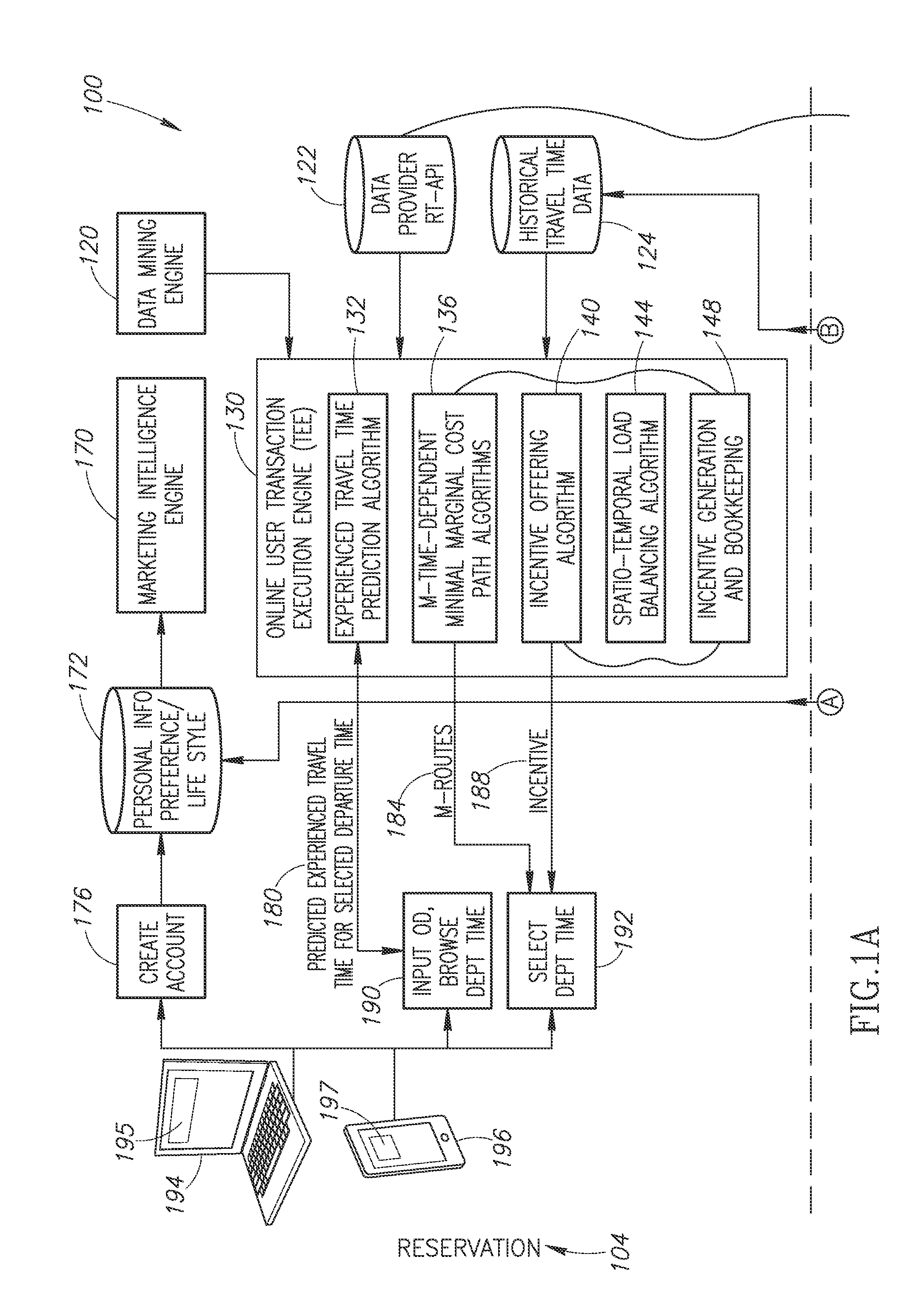

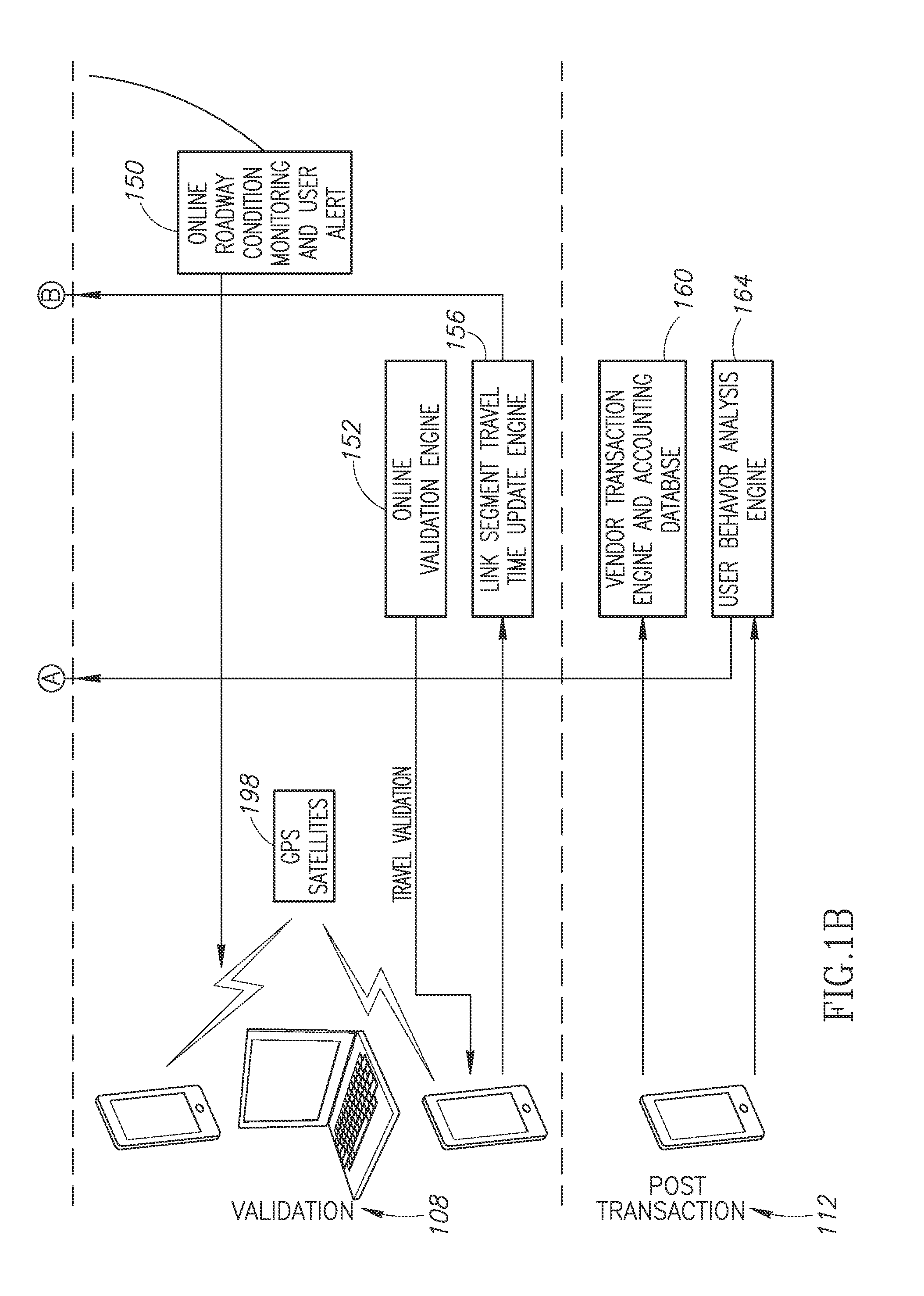

Active traffic and demand management system

ActiveUS20120226434A1Analogue computers for vehiclesArrangements for variable traffic instructionsRequirements managementSoftware system

Systems and methods for providing incentives for the public to travel during time windows and routes that help alleviate traffic congestion. The systems described herein include at least two components: a computer server software system that includes various algorithms and database sub-systems; and a mobile device application. Generally, a user may enter an origin, destination, and preferred time of travel for an intended trip into the mobile device application, which transmits the information to a remote server. The server computes a route for the trip and provides the user with available incentives for traveling the route at one or more departure time windows. The user's mobile device transmits GPS data to the server, which allows the server to verify whether the user has traveled the route during the specified time window. If so, the server then provides the incentive to the user via the user's mobile device or through email.

Owner:THE ARIZONA BOARD OF REGENTS ON BEHALF OF THE UNIV OF ARIZONA

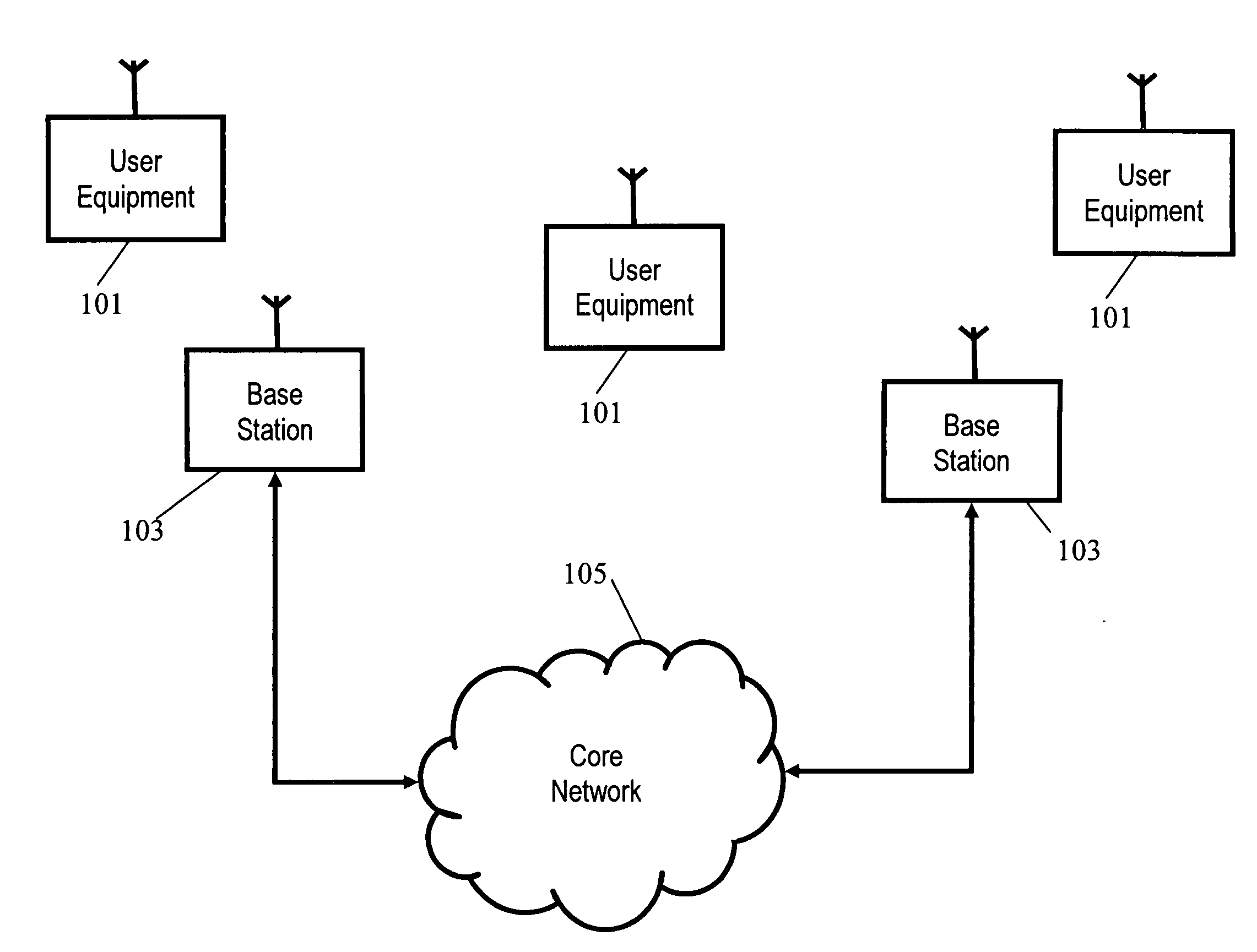

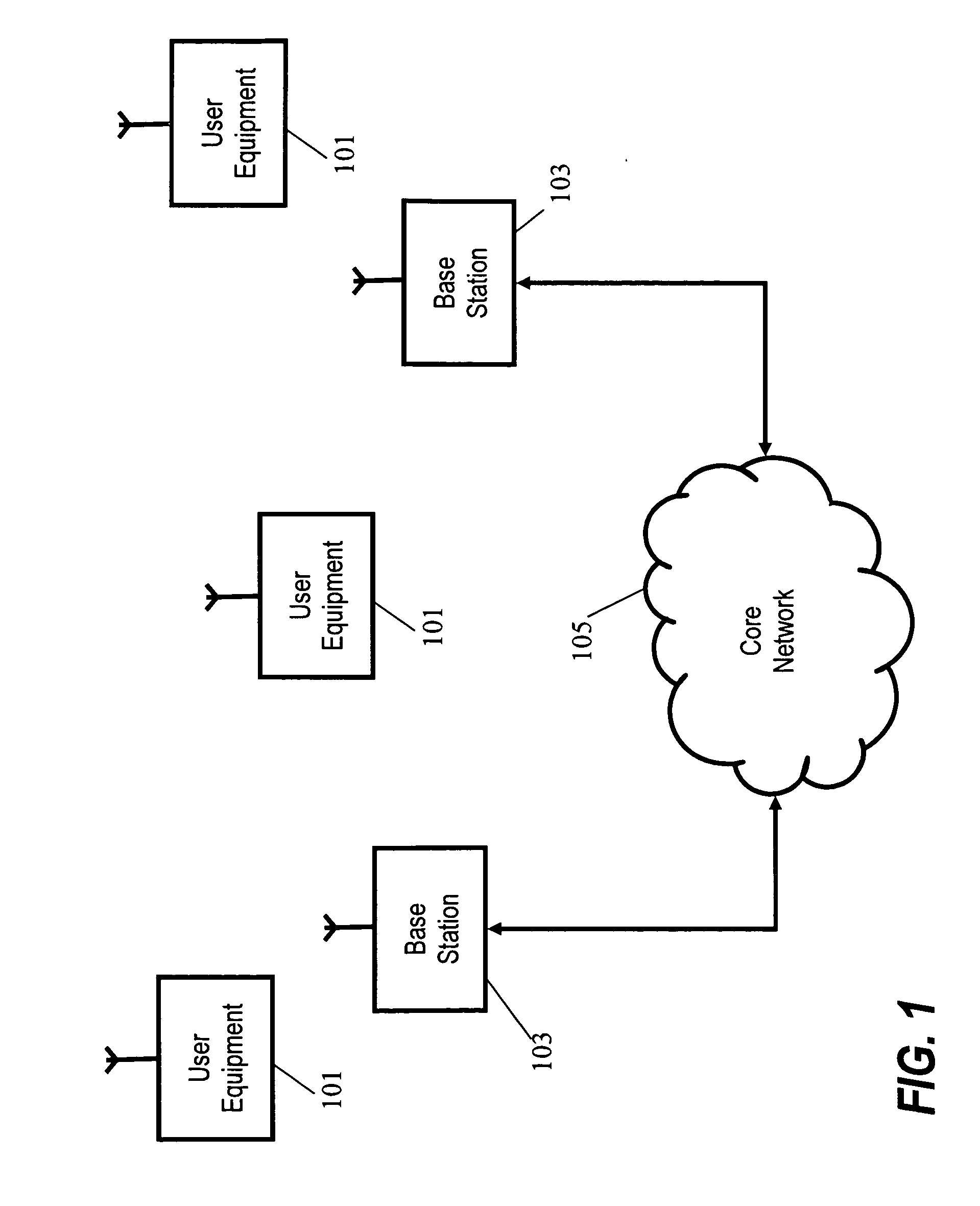

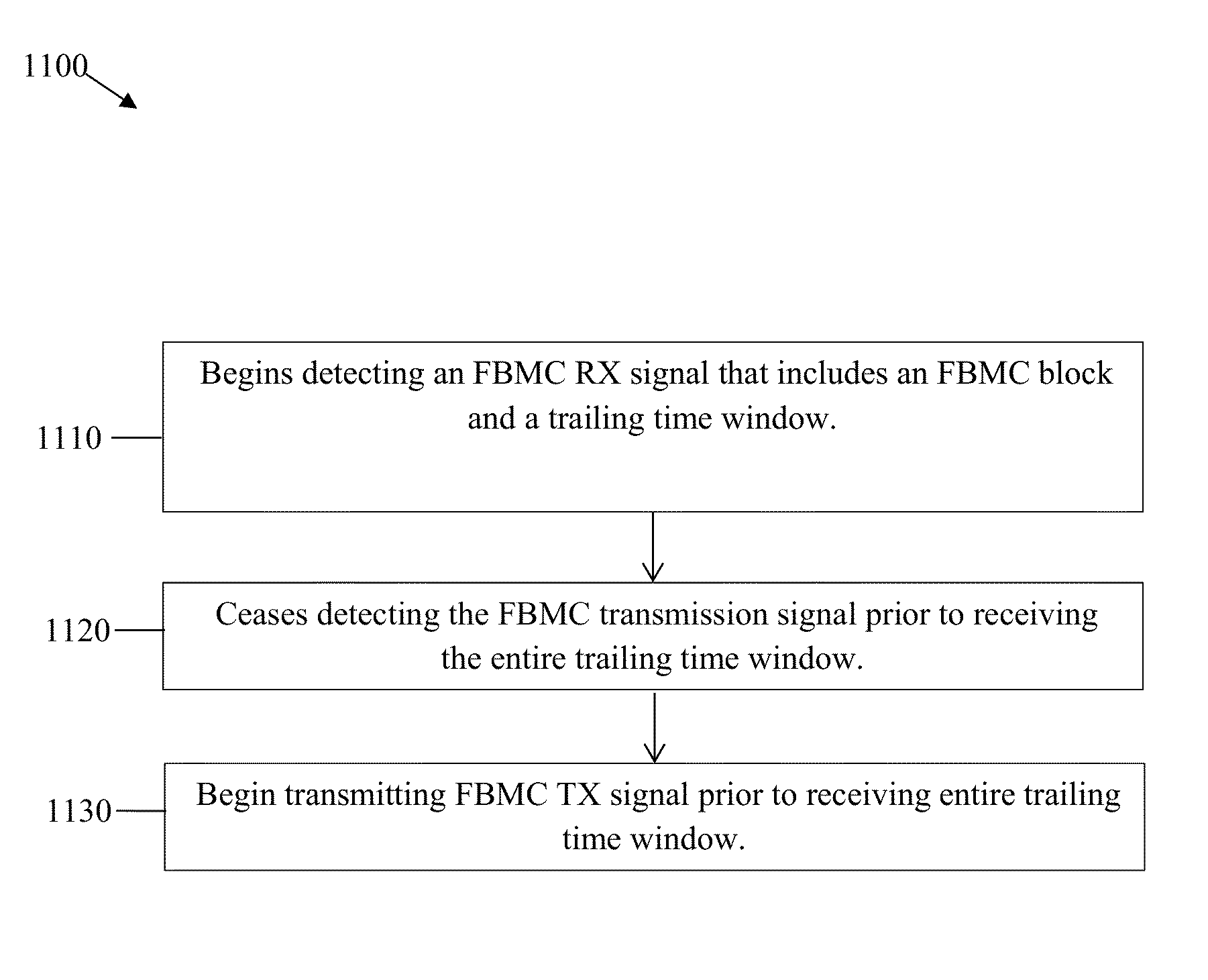

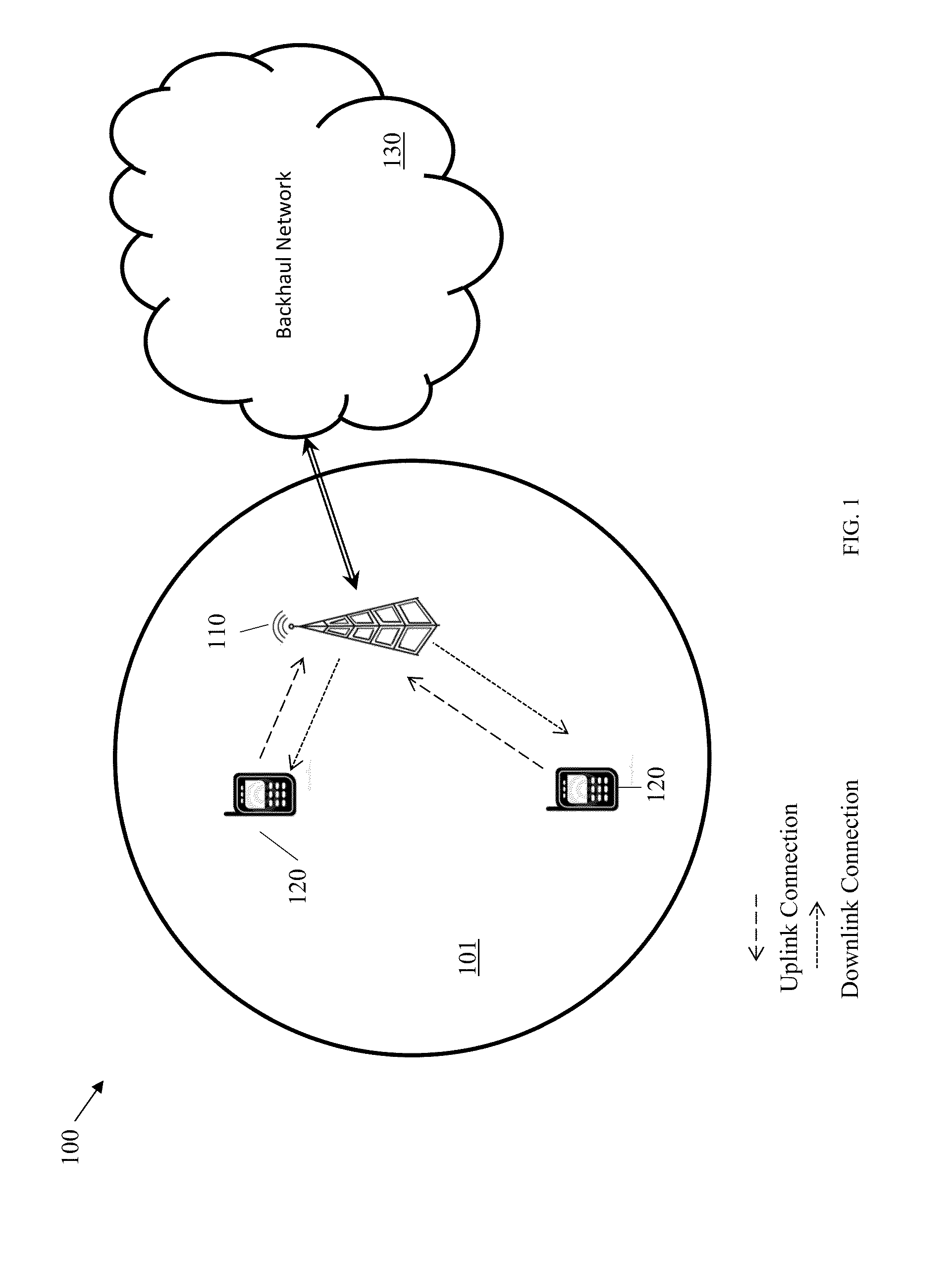

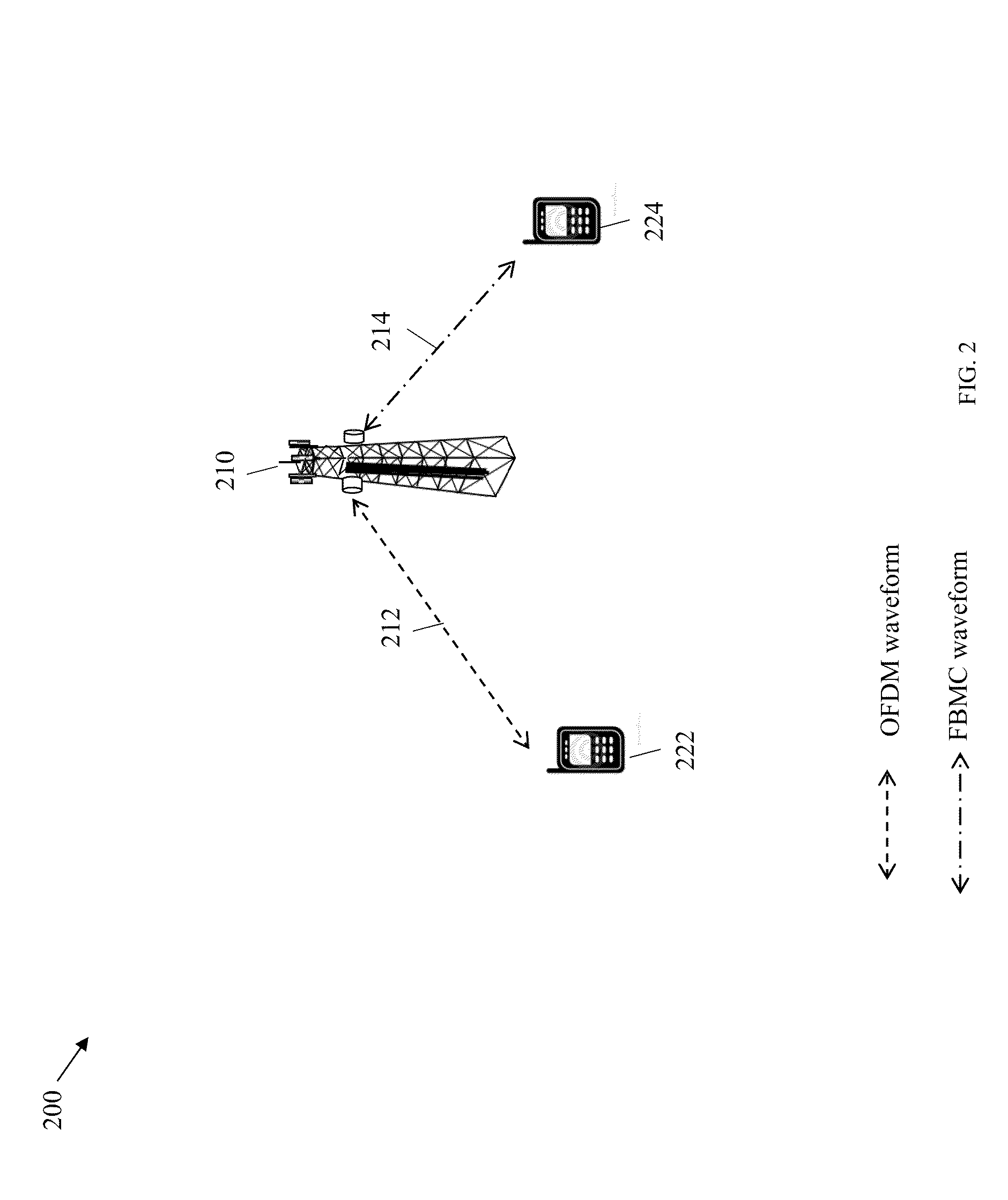

Frame Structure for Filter Bank Multi-Carrier (FBMC) Waveforms

ActiveUS20140233437A1Reduce overhead timeSynchronisation arrangementModulated-carrier systemsTime domainTelecommunications

A unified frame structure for filter bank multi-carrier (FBMC) and orthogonal frequency division multiplexed (OFDM) waveforms may allow FBMC and OFDM frames to be communicated over a common channel without significant inter-frame gaps. The unified frame structure may set an FBMC frame duration to an integer multiple of an OFDM frame element duration to enable alignment of FBMC frames and OFDM frames in the time domain. The unified frame structure may also map control channels in the FBMC and OFDM frames to common resource locations so that the respective control channels are aligned in the time and / or frequency domains. The unified frame structure may also share synchronization channels between FBMC and OFDM frames. Additionally, overhead in an FBMC time division duplexed (TDD) communications channel can be reduced by overlapping time windows appended to FBMC blocks.

Owner:HUAWEI TECH CO LTD

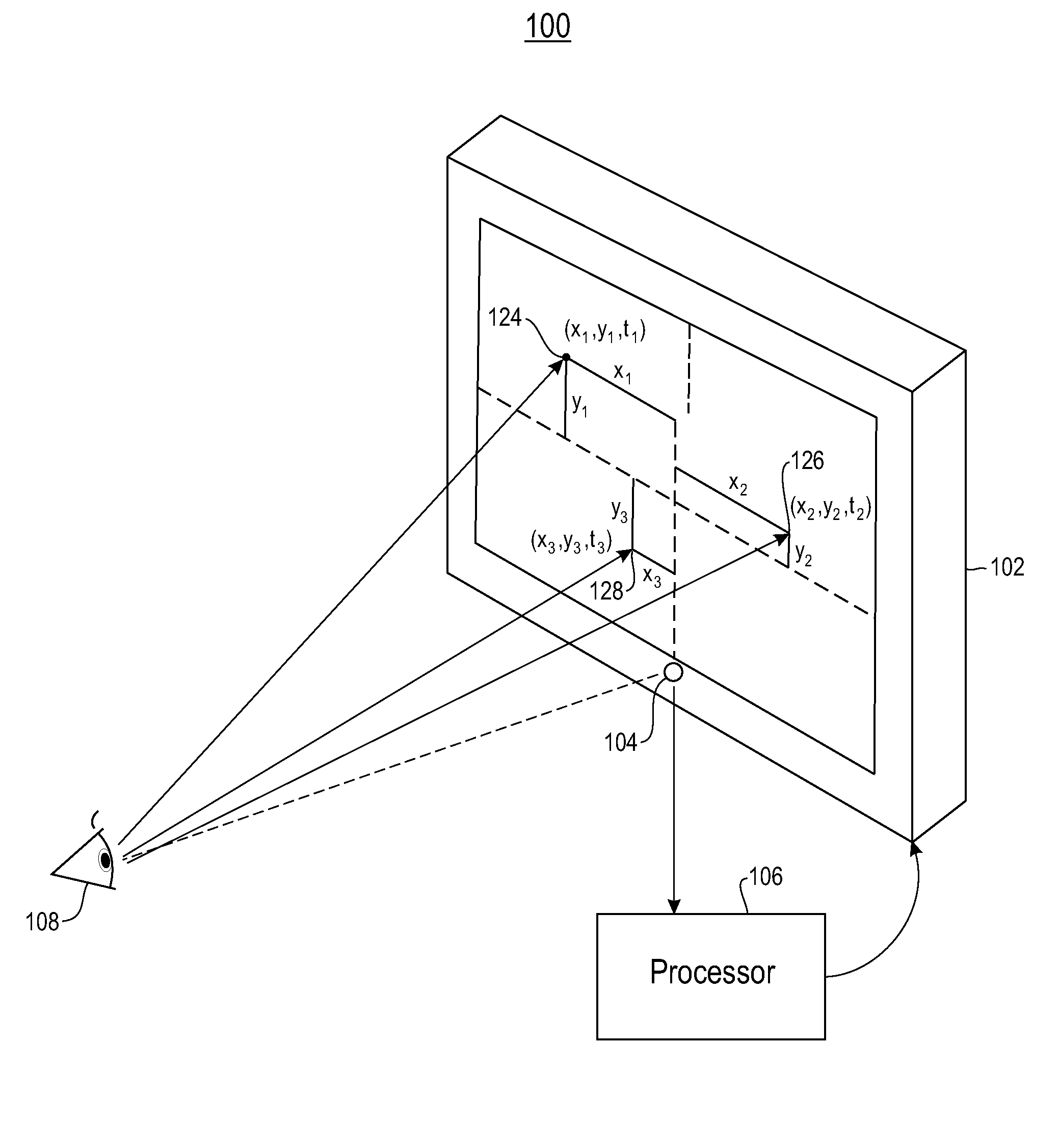

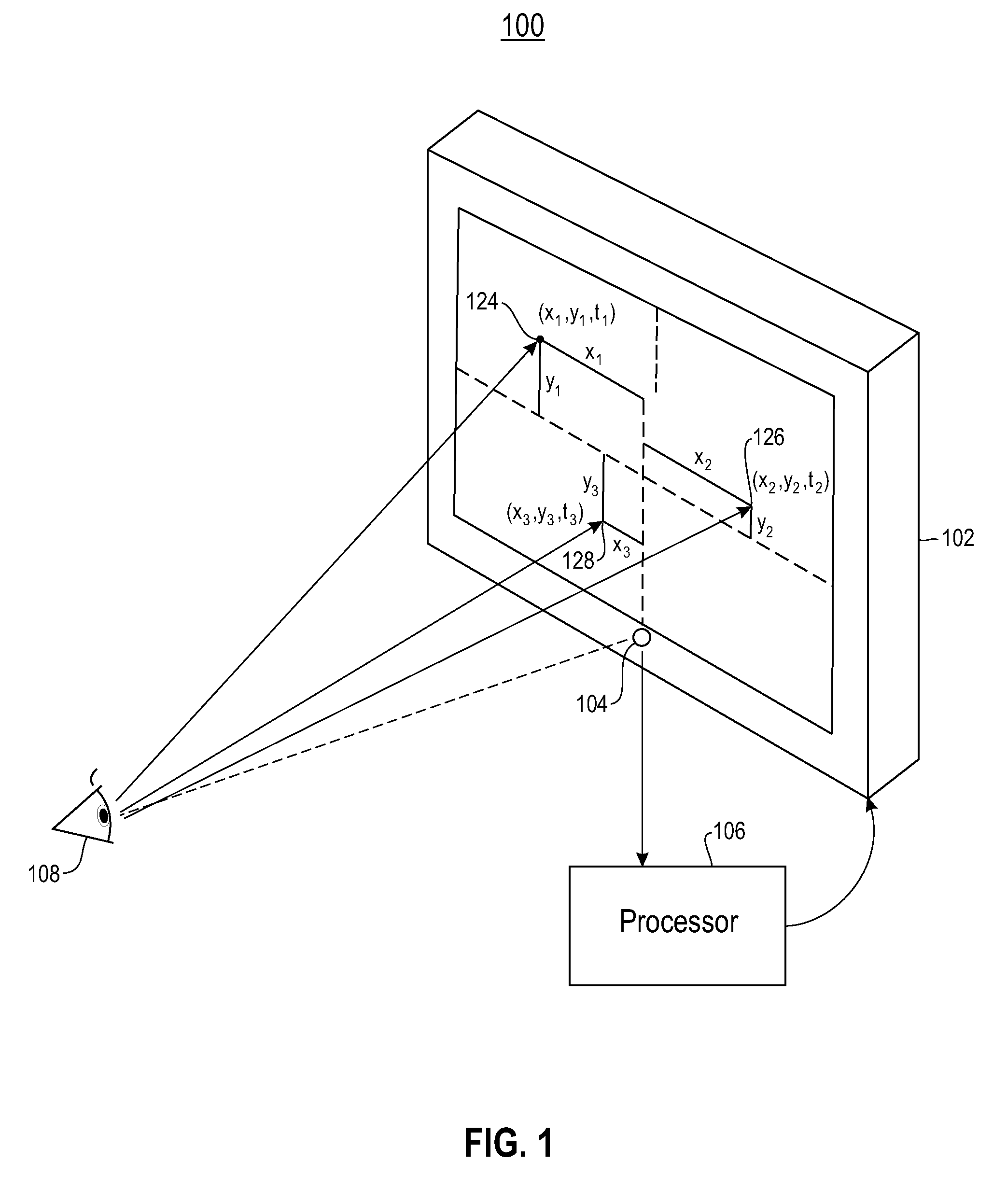

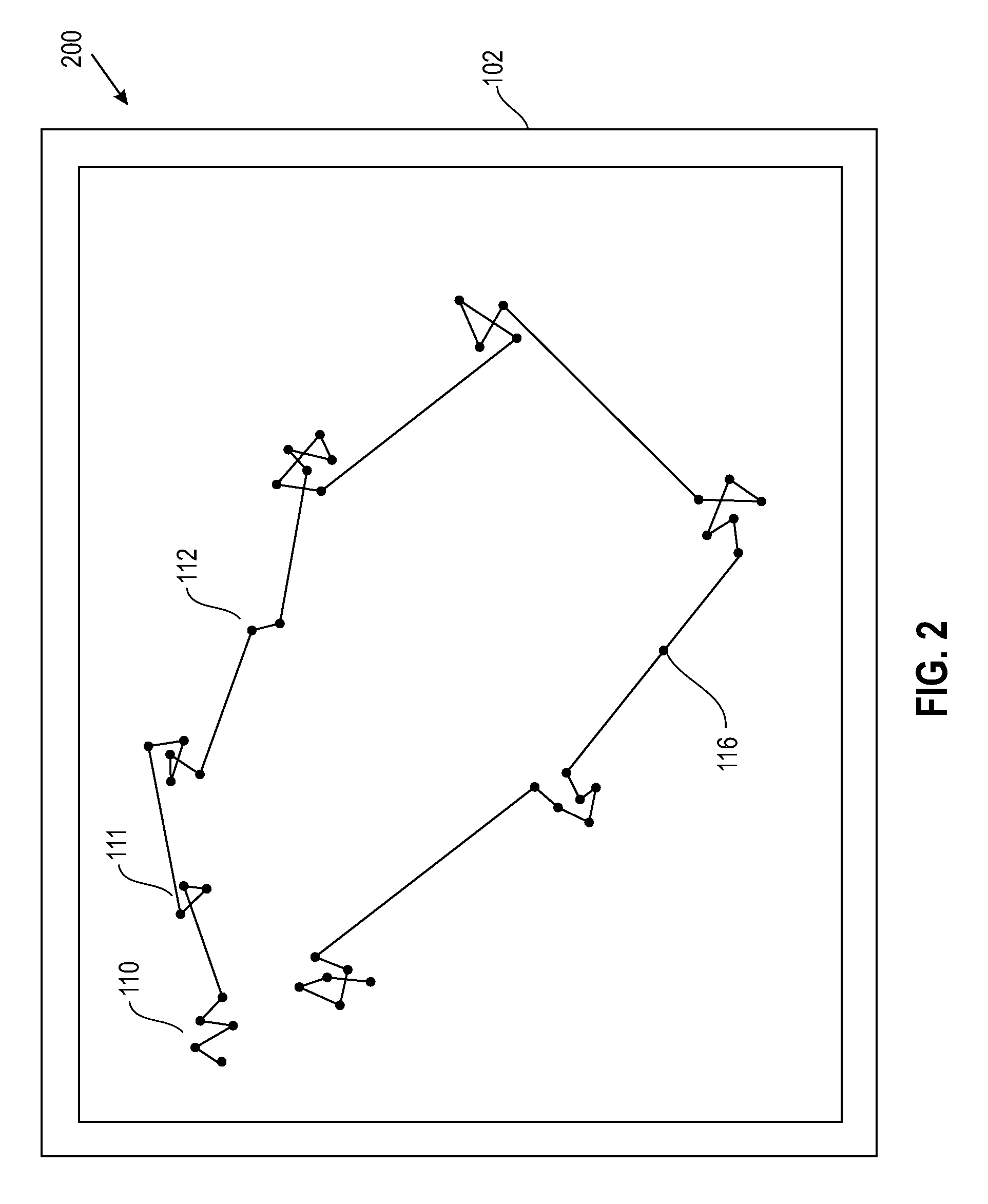

System and method of detecting eye fixations using adaptive thresholds

A system and method of adaptively establishing fixation thresholds for eye-gaze tracking data and identifying fixations within the eye-gaze tracking data are disclosed. Eye-gaze tracking data is collected. A saccade estimate may be calculated using a percentile statistic of the changes in eye-gaze position. Fixations may be determined by comparing the saccade estimates with the changes in eye-gaze positions over time windows.

Owner:GOOGLE LLC

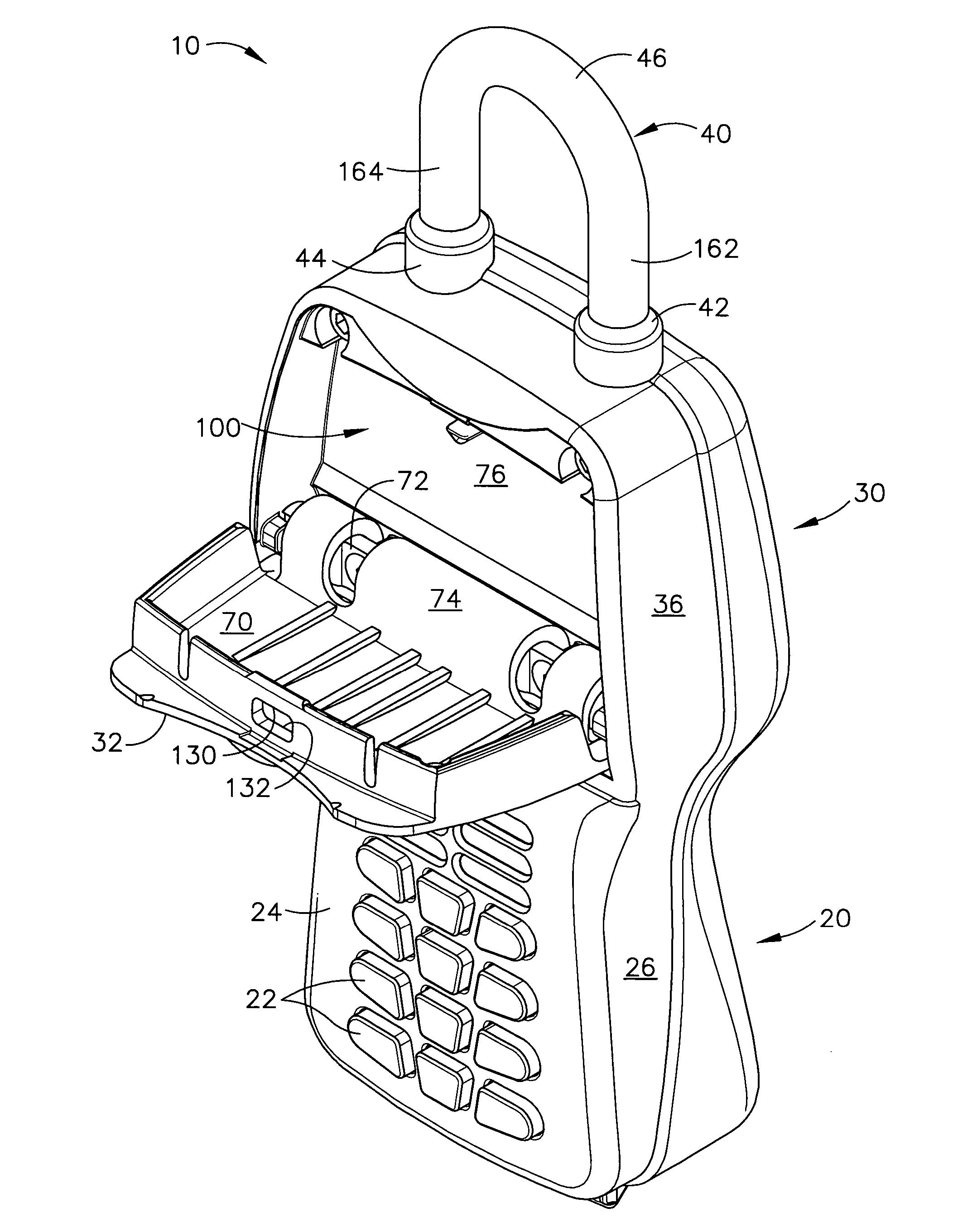

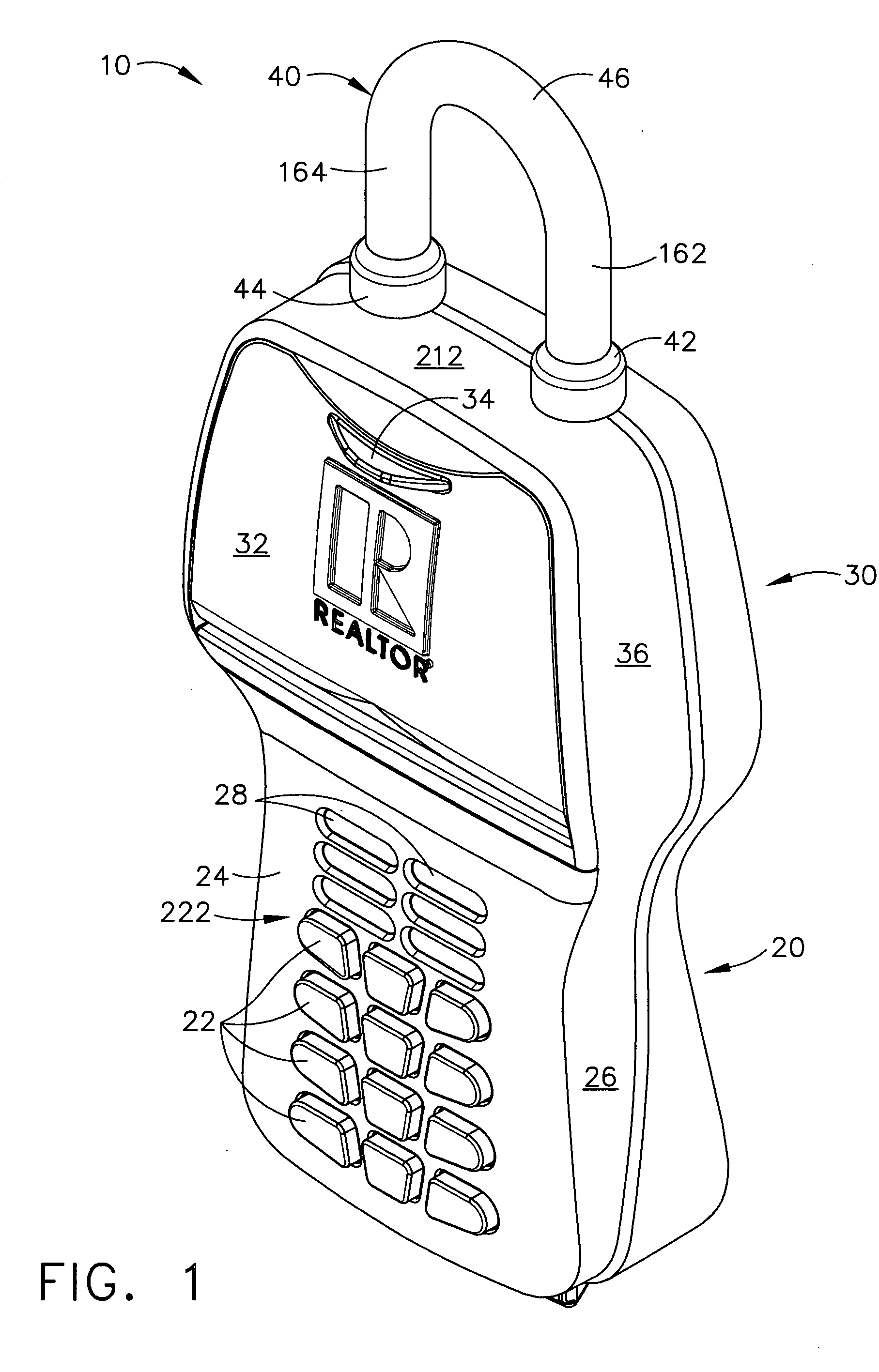

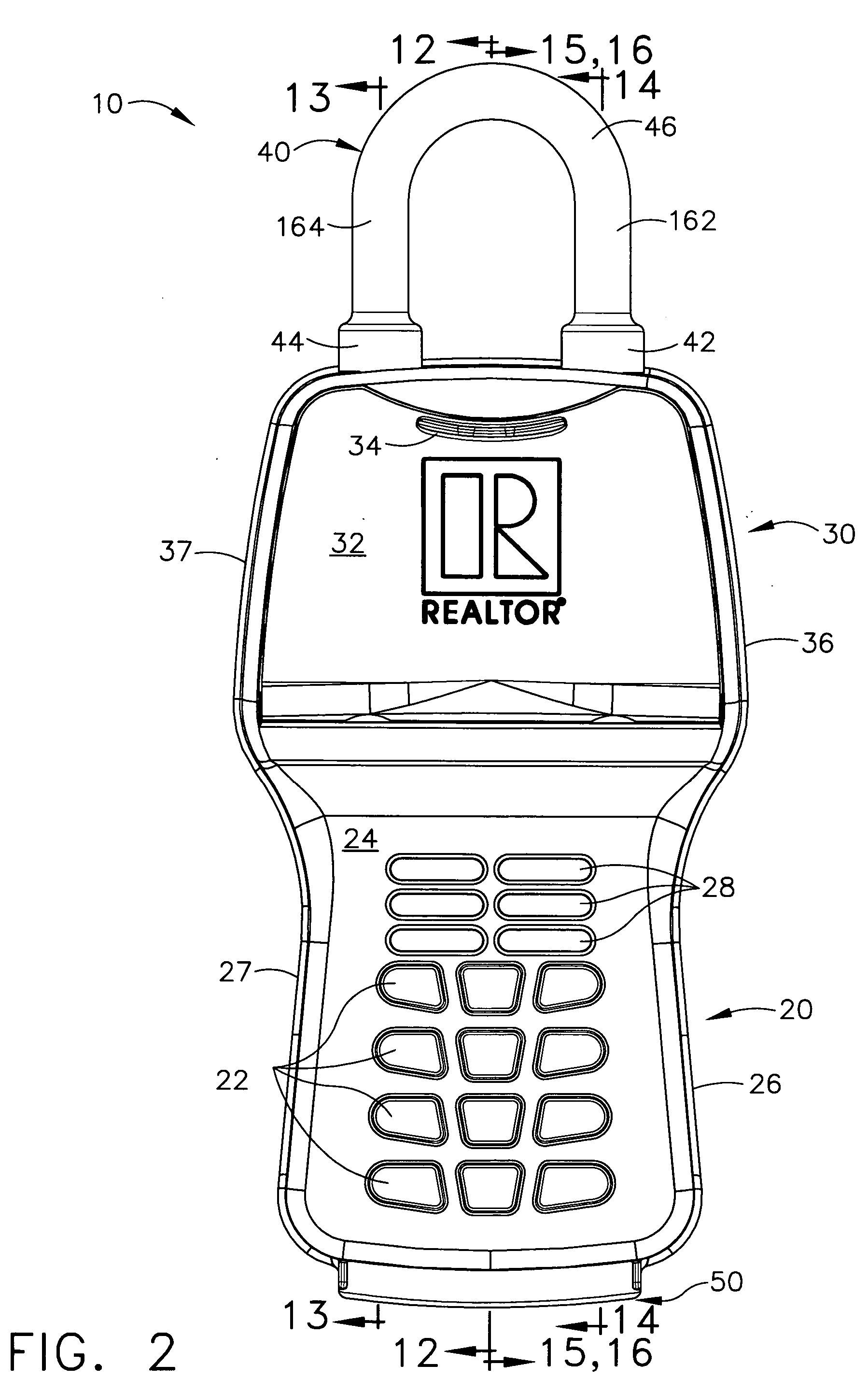

Electronic lock box with multiple modes and security states

InactiveUS20050206499A1Avoid damageProlong lifeElectric signal transmission systemsMultiple keys/algorithms usageSecure stateMultiple modes

An electronic lock box contains a secure compartment for storing keys to a structure. A linear actuator moves in one direction opening the door to the secure compartment, and moves in the opposite direction releasing a shackle that holds the lock box to the structure. A lock box system uses an encryption algorithm to diversify user PIN data at a central computer, and stores that diversified information on a memory card for later use when the user attempts to access a lock box. The central computer and electronic lock box both keep track of system “epoch time,” and the memory card must be presented to the electronic lock box within a correct epoch time window for the diversified PIN data to be successfully decrypted and compared to the user's PIN data that is entered on a keypad of the electronic lock box.

Owner:SENTRILOCK

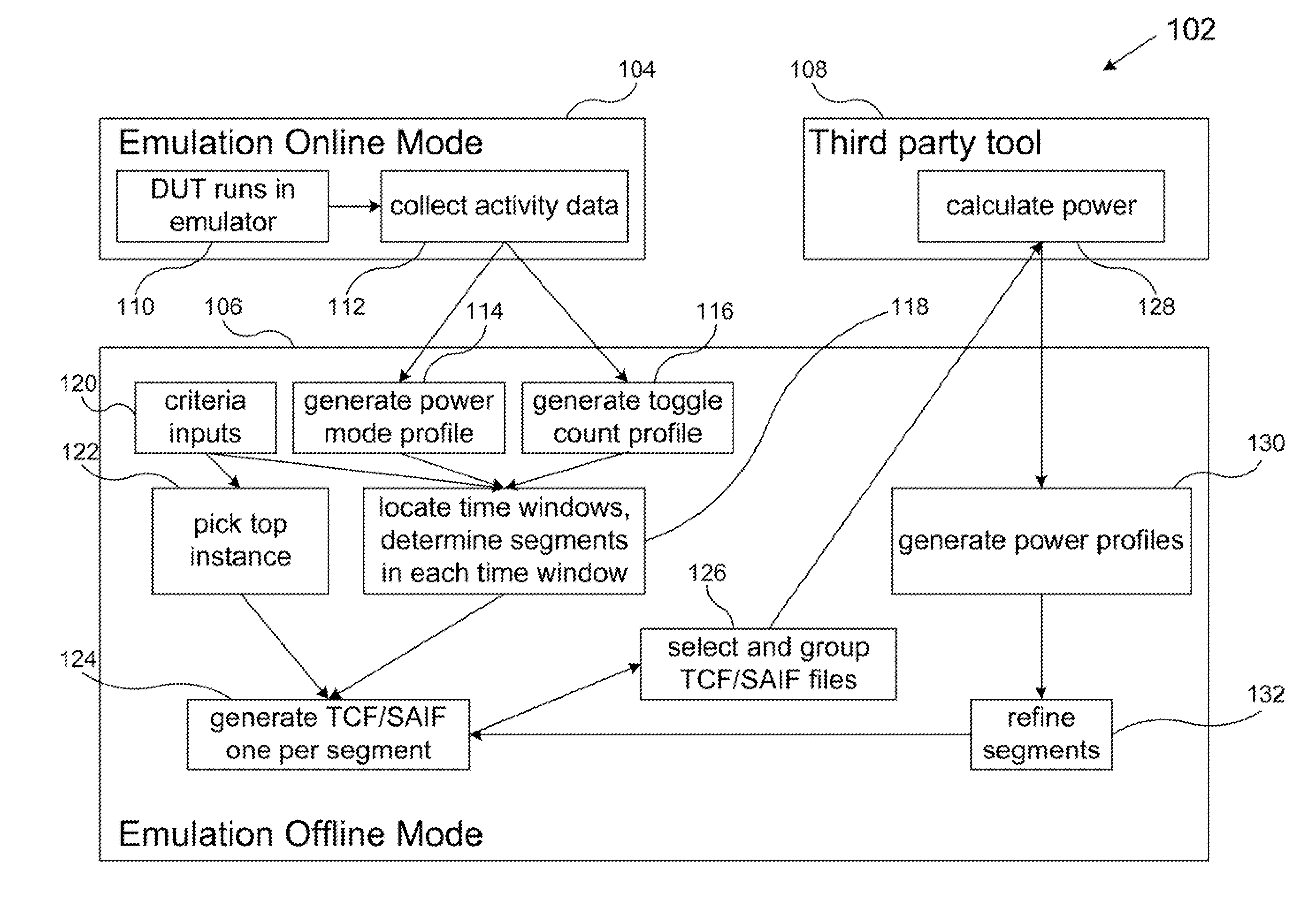

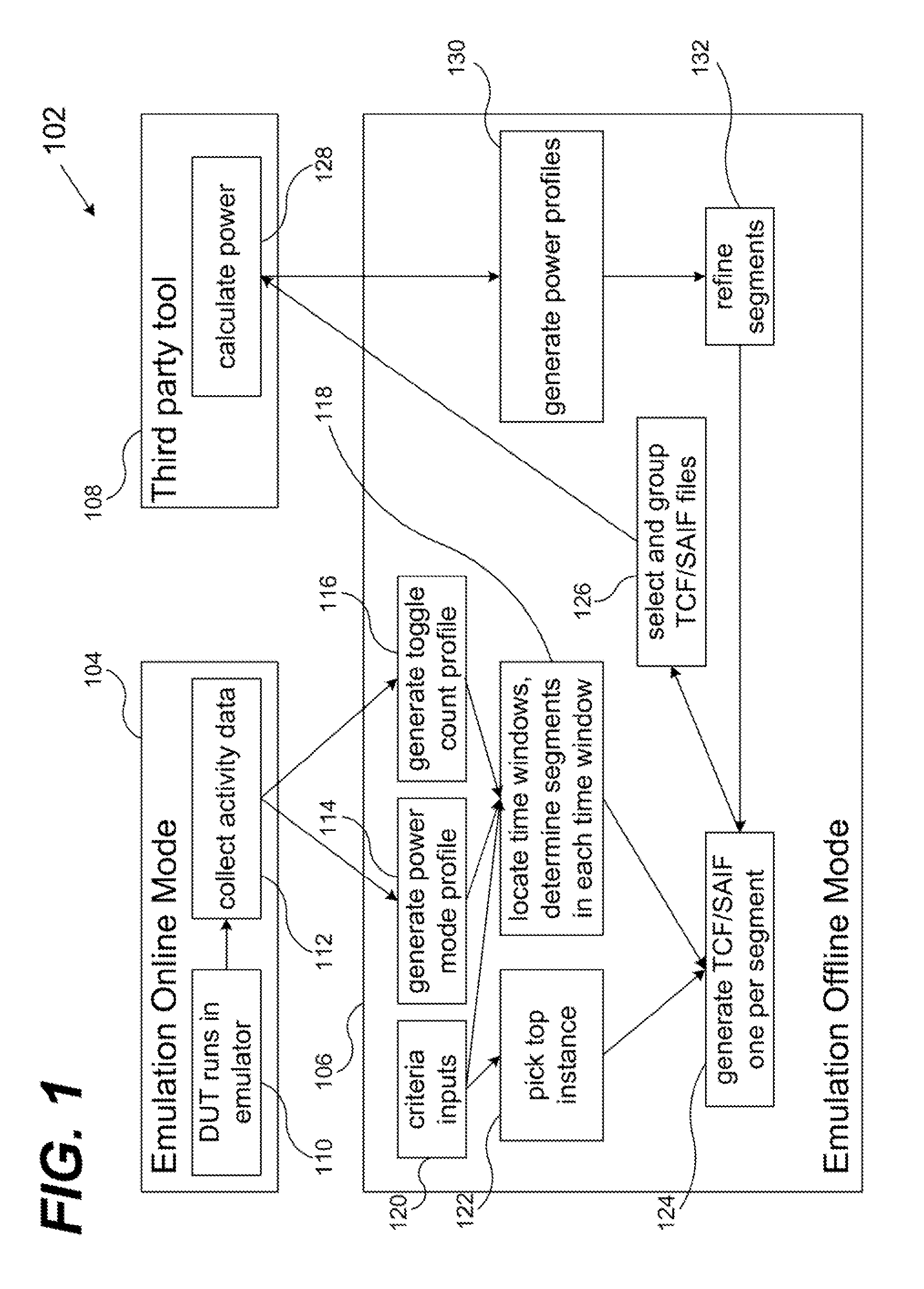

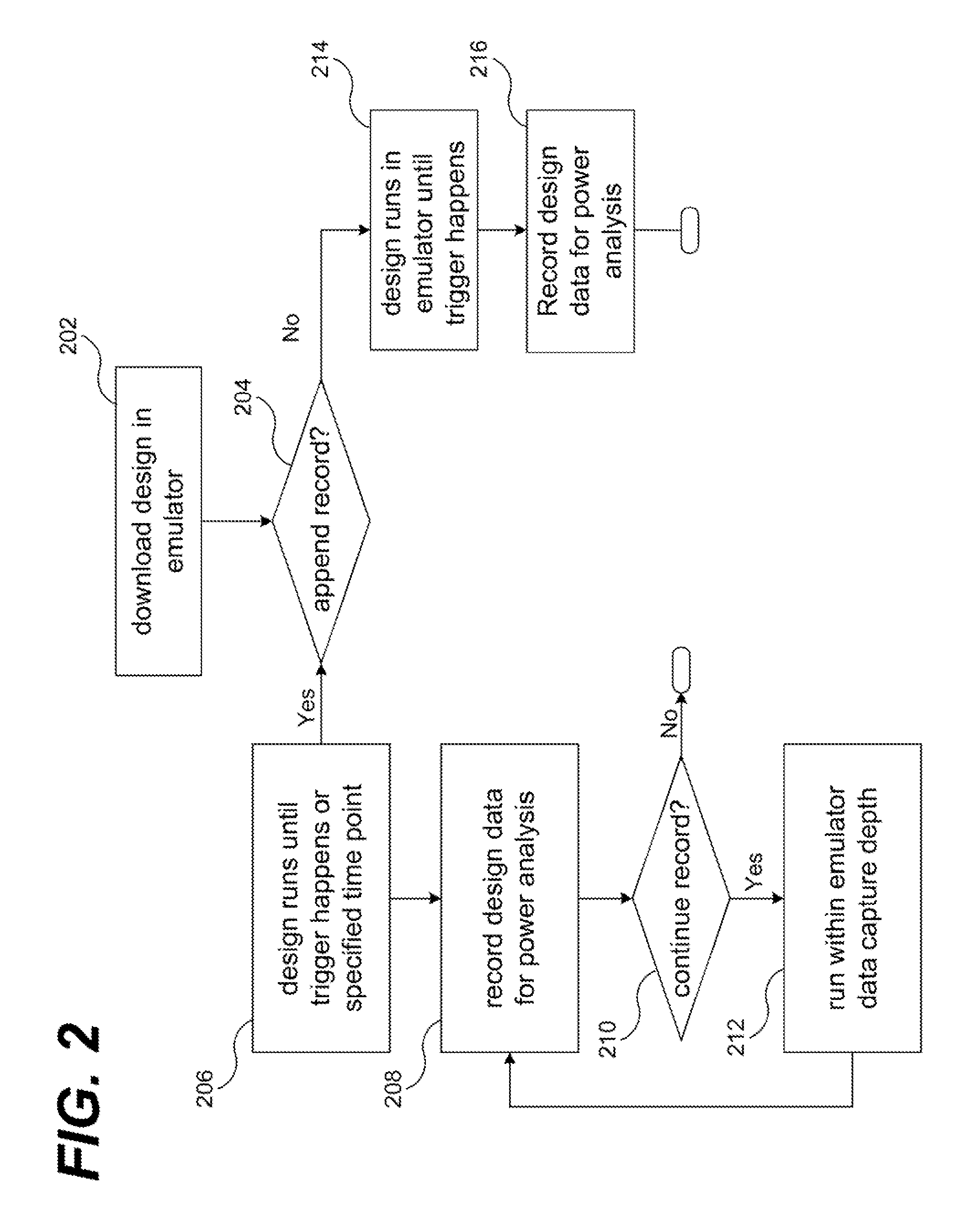

Peak power detection in digital designs using emulation systems

ActiveUS20090271167A1High activityIncrease valueAnalogue computers for nuclear physicsComputer aided designElectronic systemsPeak value

A method of analyzing power consumption for a DUT (device under test) that includes an integrated circuit or an electronic system includes: providing emulation data for states of the DUT in one or more time windows; determining operational mode values from the emulation data and a selection of operational modes that characterize circuit behavior in the one or more time windows; dividing each time window into one or more segments based on at least one power criterion; determining power-activity values for the one or more segments; determining power-consumption values for the one or more segments from the power-activity values; using the power-activity values and the power-consumption values to determine relative power activity across the one or more segments and adjusting the one or more segments to target high power activity over operational modes in the one or more time windows; and saving one or more values for power activity of the DUT in a computer-readable medium.

Owner:CADENCE DESIGN SYST INC

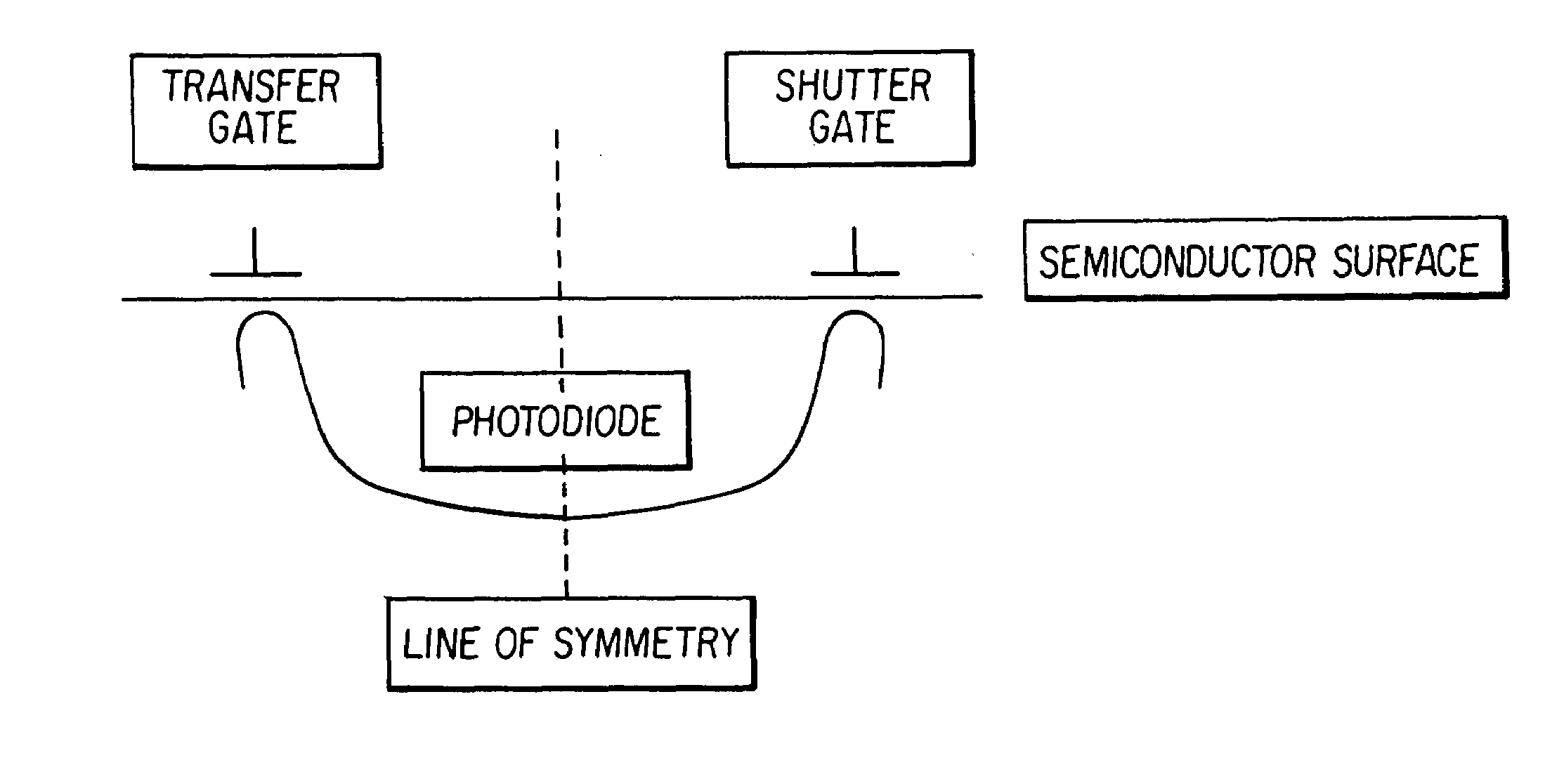

Image sensor pixel for global electronic shuttering

InactiveUS7129979B1Television system detailsTelevision system scanning detailsCMOS sensorPixel density

A pixel design for CMOS image sensors that has a high frame rate potential and, therefore, provides motion capture capabilities. The pixel is designed for global electronic shuttering so every pixel is exposed simultaneously to images incident upon the pixel array plane. The present invention has the advantages of: (1) Allowing the accommodation of changes in the pixel output groupings for different monochrome output format or CFA patterns with only changes in metal routing layers; (2) allowing true electronic shuttering to image moving scene with all the pixels having the same capture time windows; and (3) providing a symmetric global shutter gate and transfer gate to minimize pixel related fixed pattern noise. The pixel architecture provides for a CMOS based, active pixel image sensor comprising an array of pixels formed in rows and columns, with each of the pixels containing at least one active circuit element. There are a plurality of output channels formed such that each of the output channels are operatively connected to a subset of pixels wherein each of the pixel have an attribute that is the same. The pixel architecture also provides an output gate region and a shutter gate region that are symmetric about the center of the pixel. By arranging the shutter and transfer gates, a symmetric manner about the center of the pixel, a more efficient transfer of electrons to these gates is provided. A Pixel Output Bus structure allows configurable connections to column-wise signal busses that provide parallel output channels.

Owner:OMNIVISION TECH INC

Method and apparatus for demixing of degenerate mixtures

InactiveUS6430528B1Reduce environmental noiseAccurately determineDigital computer detailsHearing aids signal processingChannel parameterTime windows

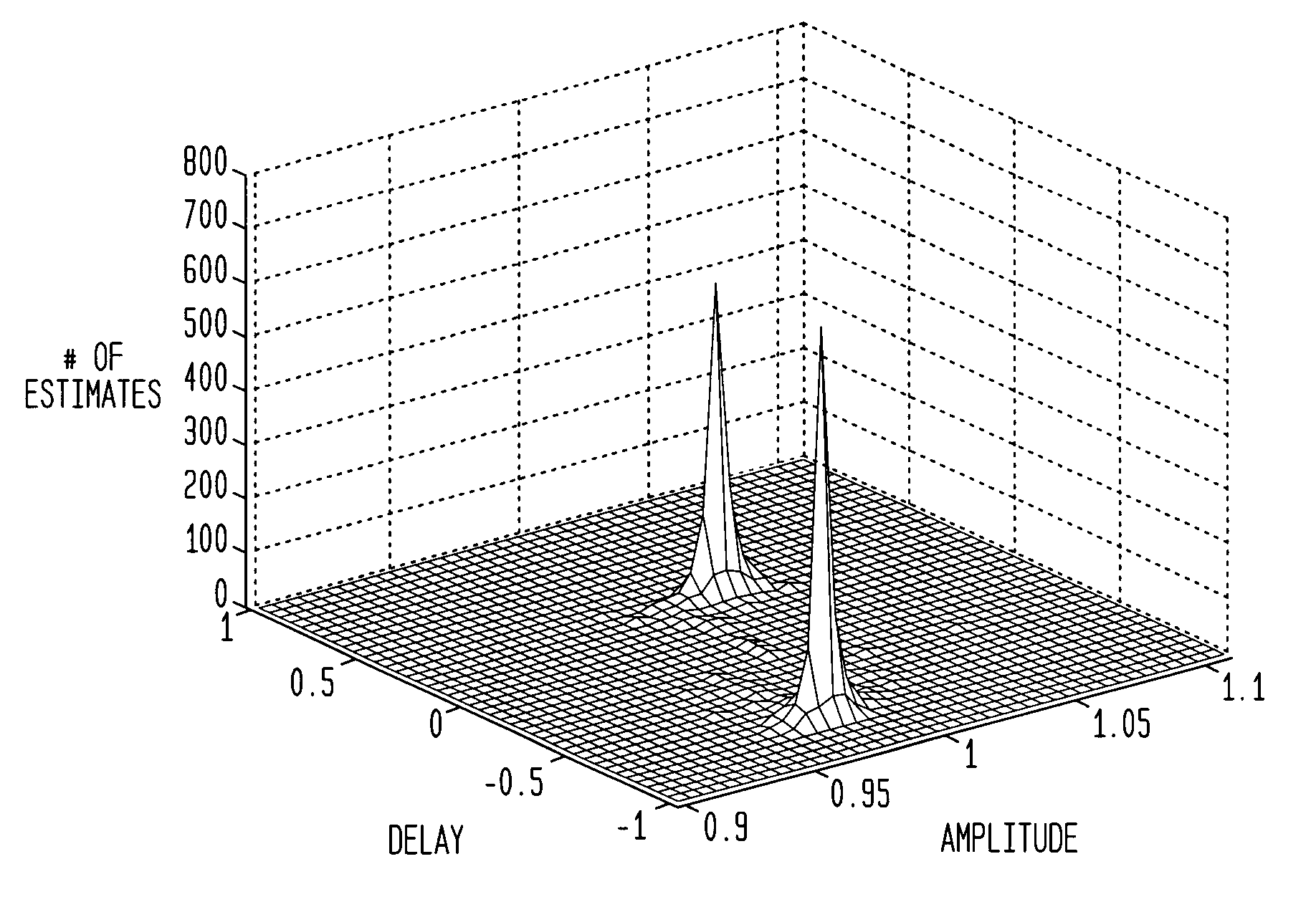

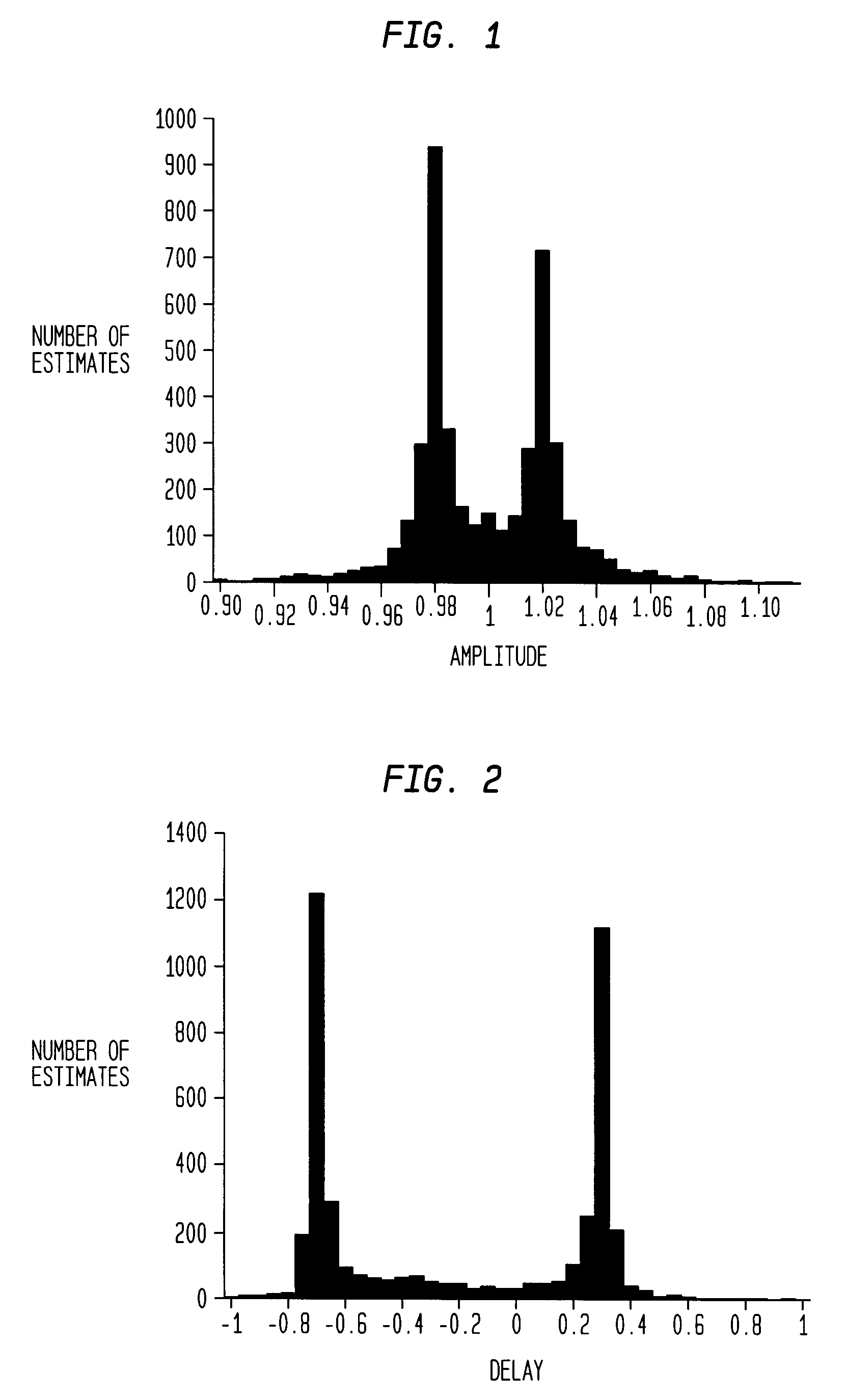

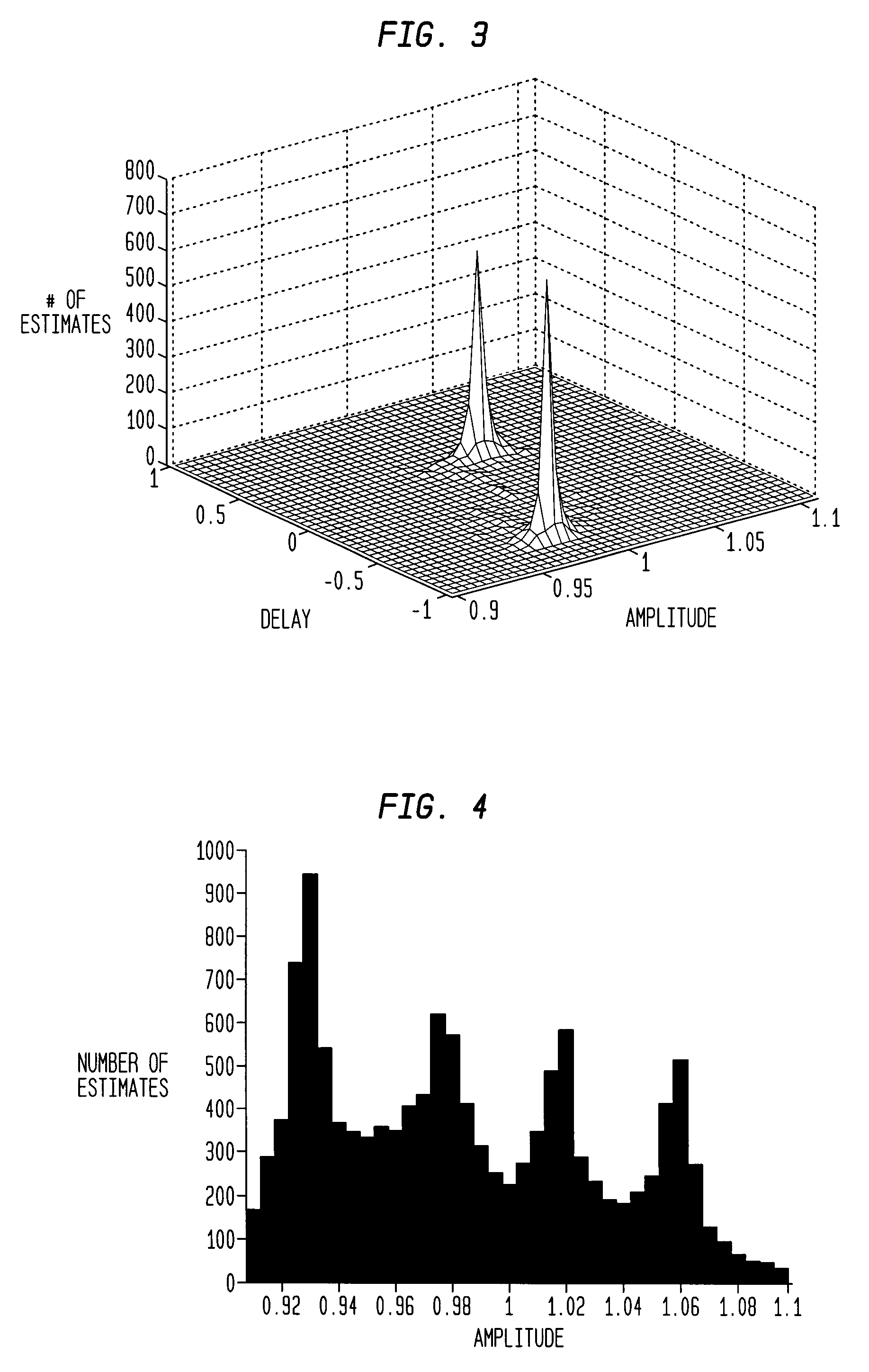

A method and system for blind channel estimation comprises acquiring two mixtures of at least one at least weakly W-disjoint orthogonal source signal, calculating point-by-point ratios of a transform of a time-window of each of said mixture signals, determining channel parameter estimates from said ratios, constructing a histogram of said channel parameter estimates, repeating the calculating, determining and constructing steps for successive time windows of the mixture signals, and selecting as estimates of said channel parameters those estimates associated with identified peaks on said histogram.

Owner:SIEMENS CORP

Vision-aided system and method for guiding a vehicle

ActiveUS20060149472A1Instruments for road network navigationAnalogue computers for trafficQuality dataVisual perception

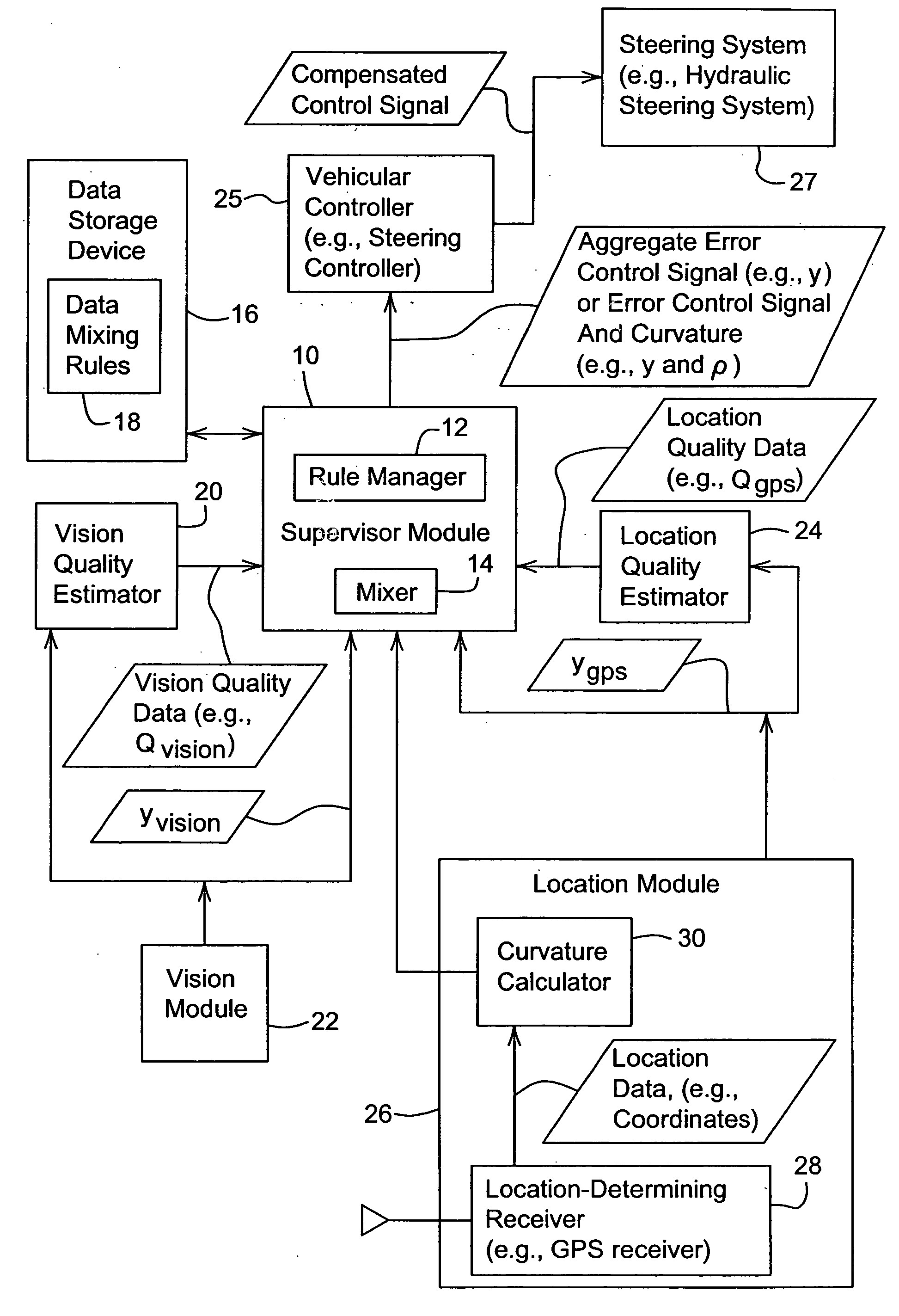

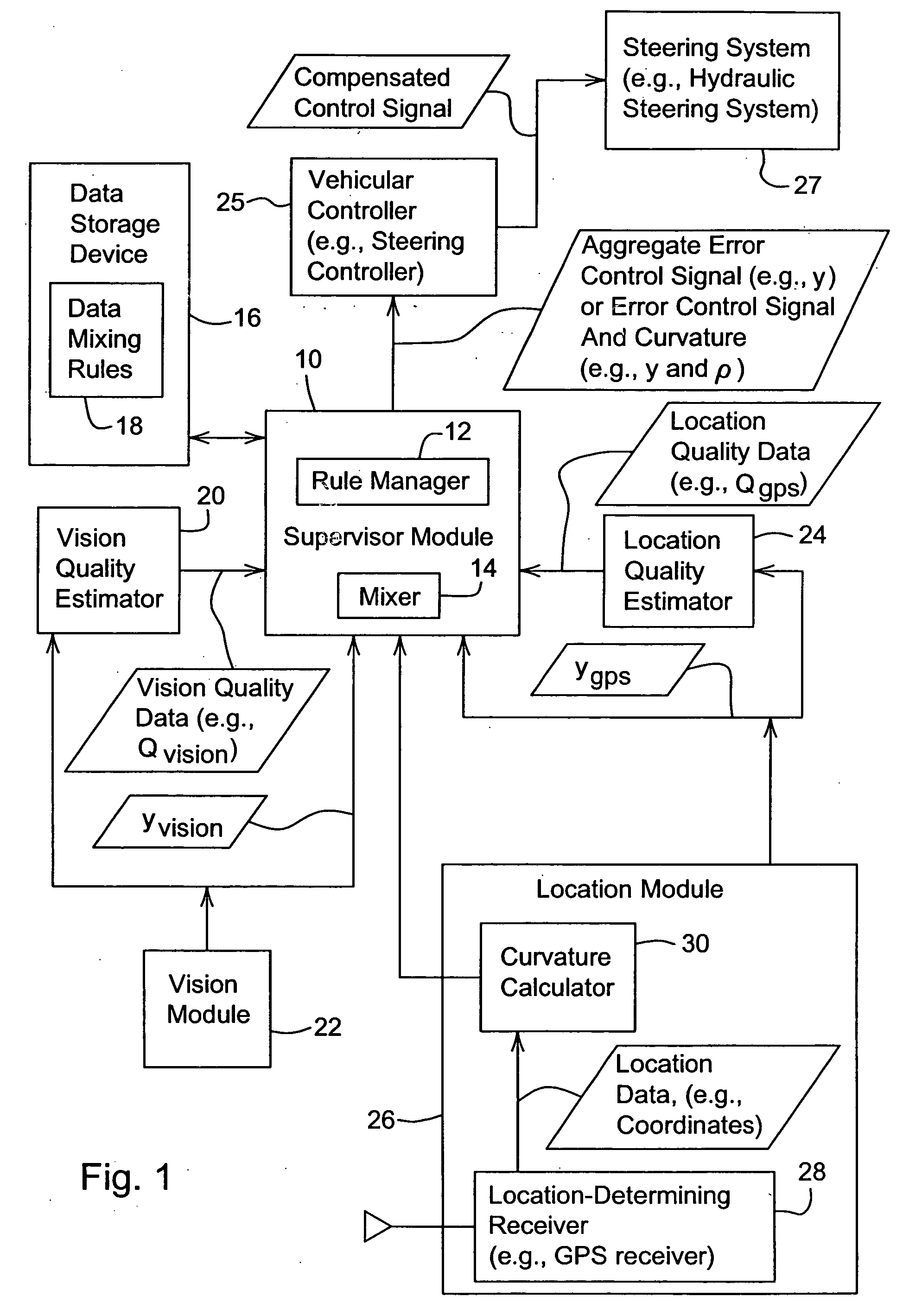

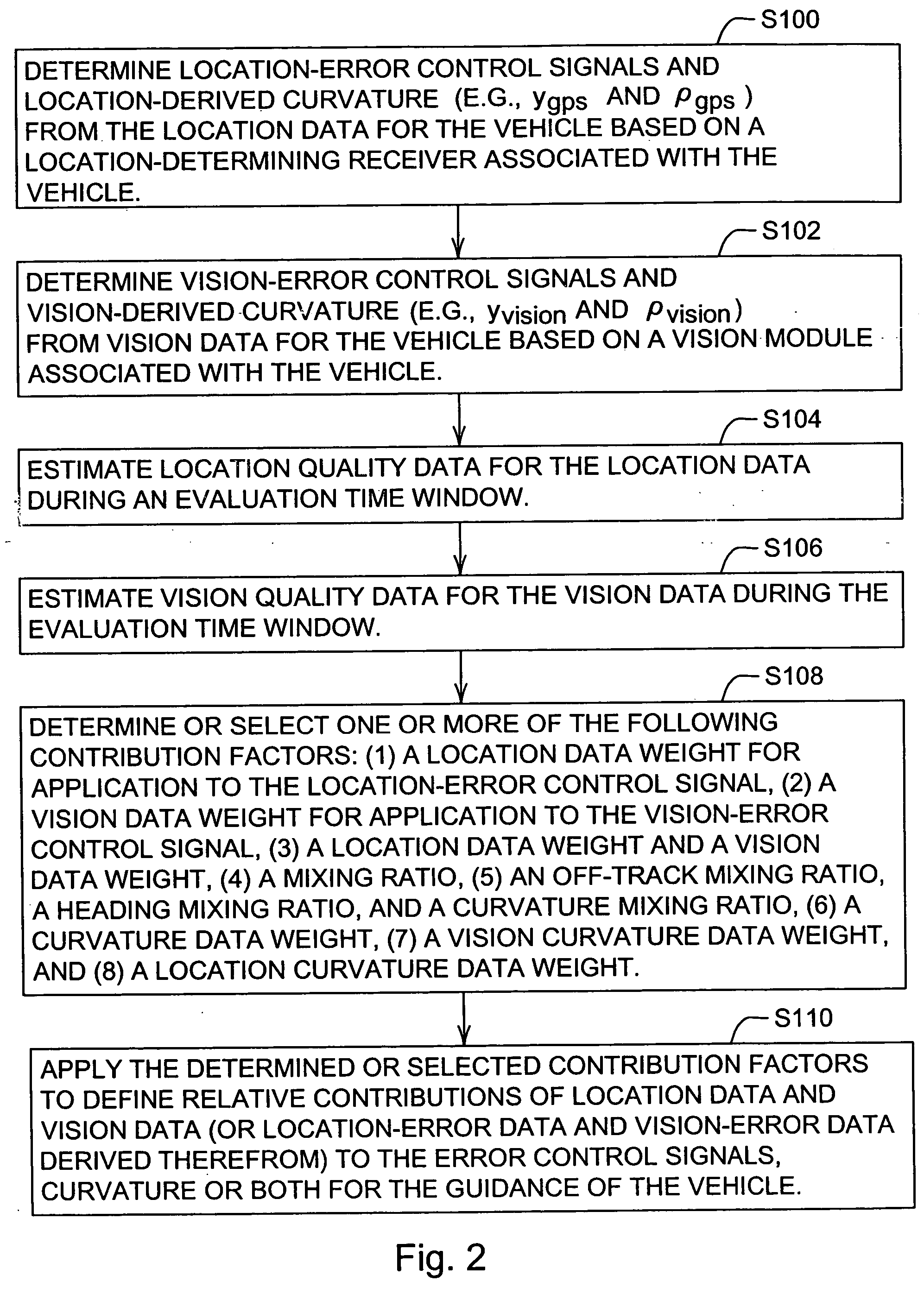

A method and system for guiding a vehicle comprises a location determining receiver for collecting location data for the vehicle. A vision module collects vision data for the vehicle. A location quality estimator estimates the location quality data for the location data during an evaluation time window. A vision module estimates vision quality data for the vision data during the evaluation time window. A supervisor module selects at least one of a location data weight and a vision data weight based on the quality data.

Owner:DEERE & CO

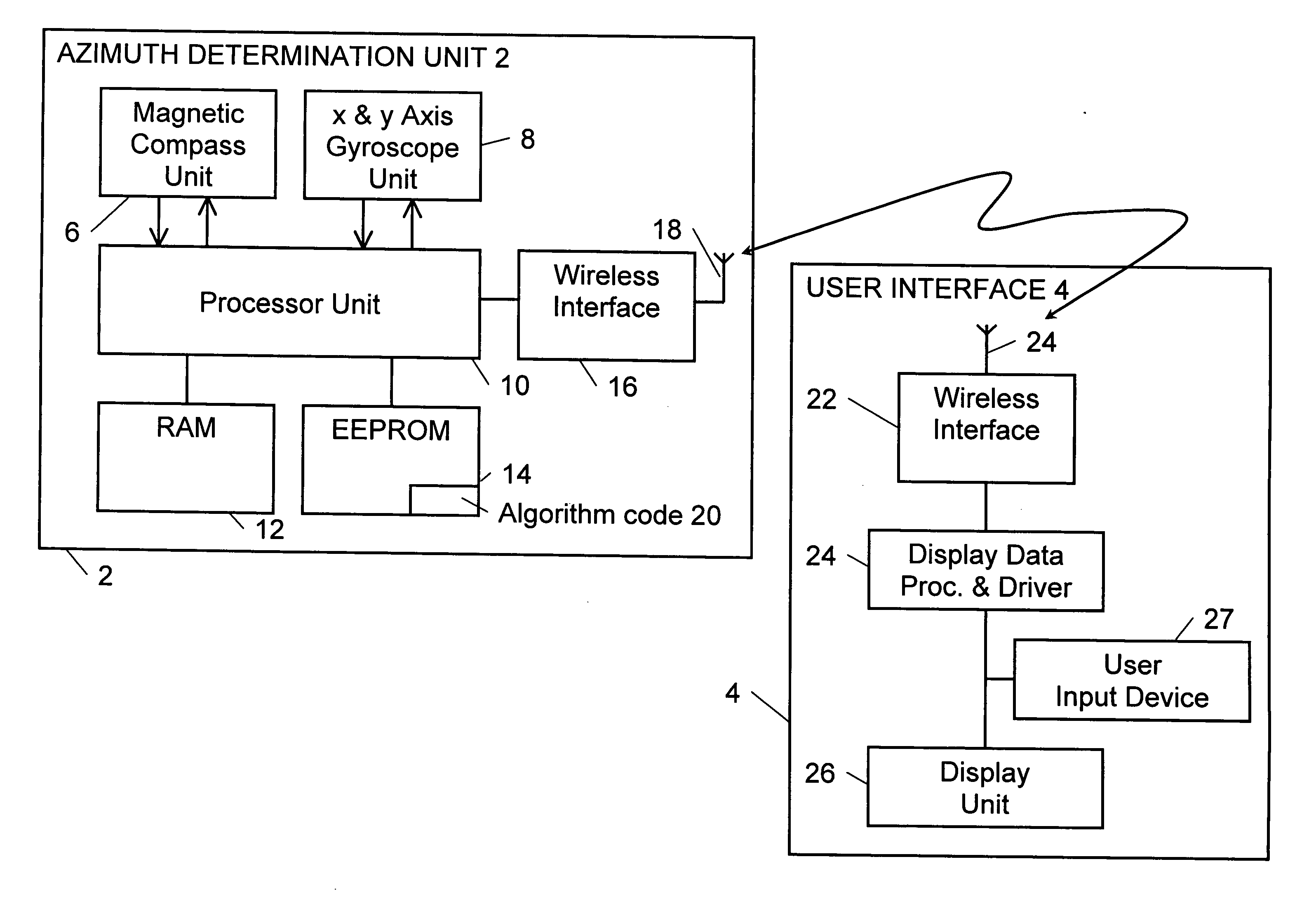

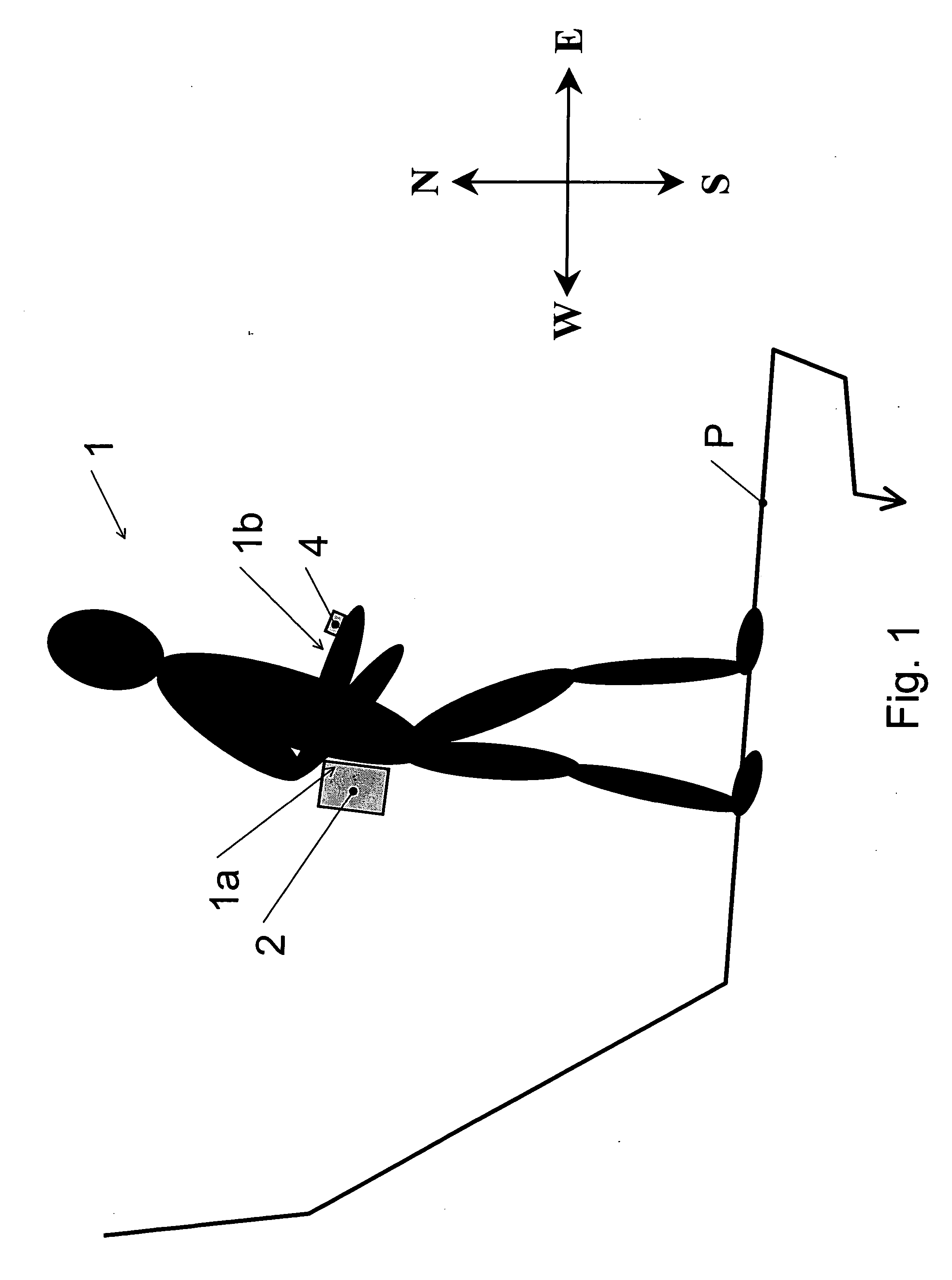

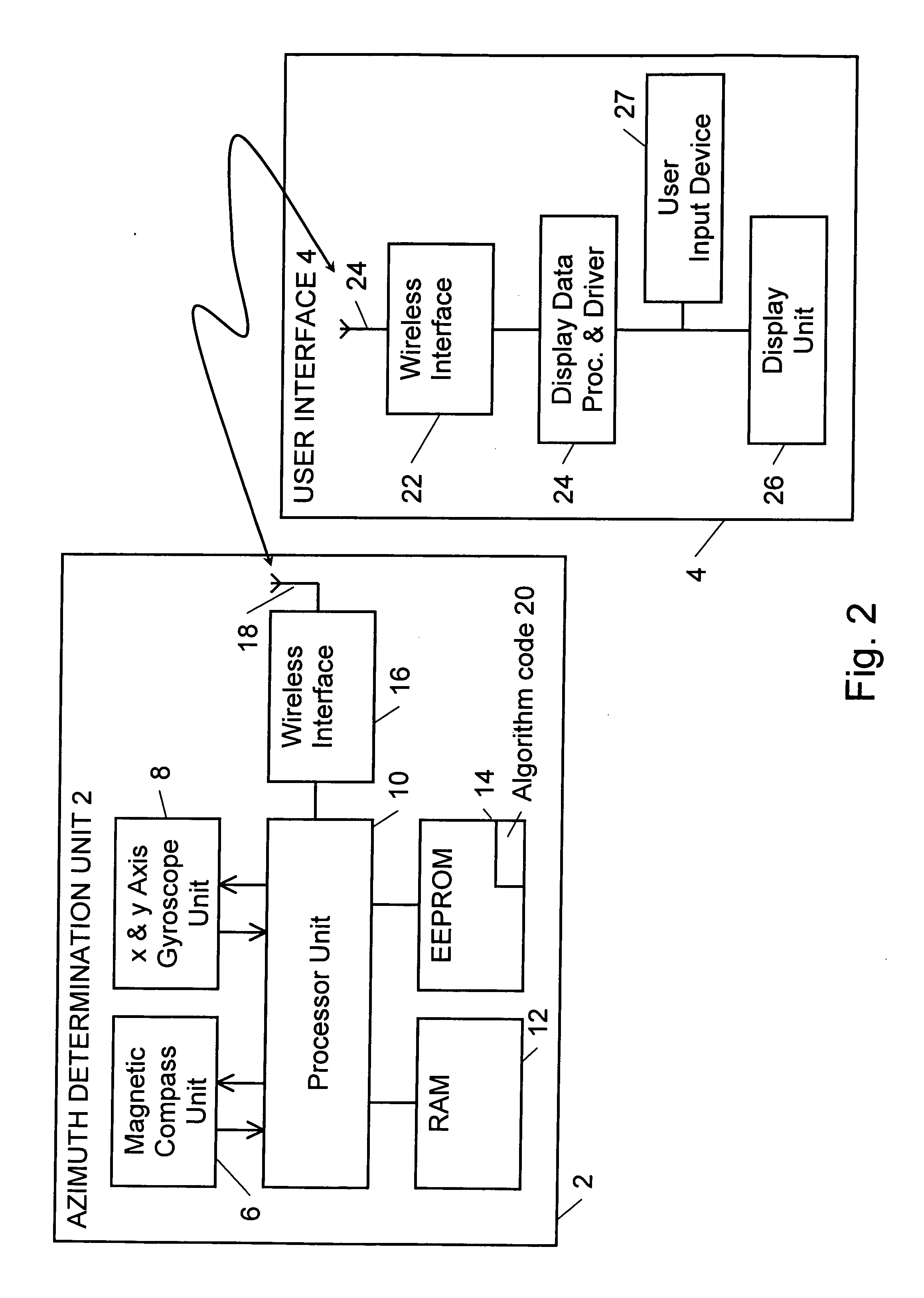

Method, apparatus and computer program for azimuth determination e.g. for autonomous navigation applications

InactiveUS20060195254A1Navigational calculation instrumentsNavigation by speed/acceleration measurementsMagnetic disturbanceGyroscope

For an observer equipped with a first azimuth data source responsive to a magnetic field to deliver first azimuth data, such as a compass, and with a second azimuth data source delivering second azimuth data and which is independent of magnetic fields, such as a gyroscope. The azimuth is determined by: analyzing the first and second azimuth data to determine whether a magnetic disturbance is present, and determining azimuth selectively on the basis of: the first azimuth data, the second azimuth data, or a combination of the first and second azimuth data, as a function of the result of the comparing step. In an embodiment, the choices of azimuth data source and events such as magnetic disturbances, sensor updates, types of trajectory deduced, are stored as a history sequence over successive time windows, by analogy with a DNA sequence, and is exploited for optimizing azimuth or navigation results.

Owner:VECTRONIX AG

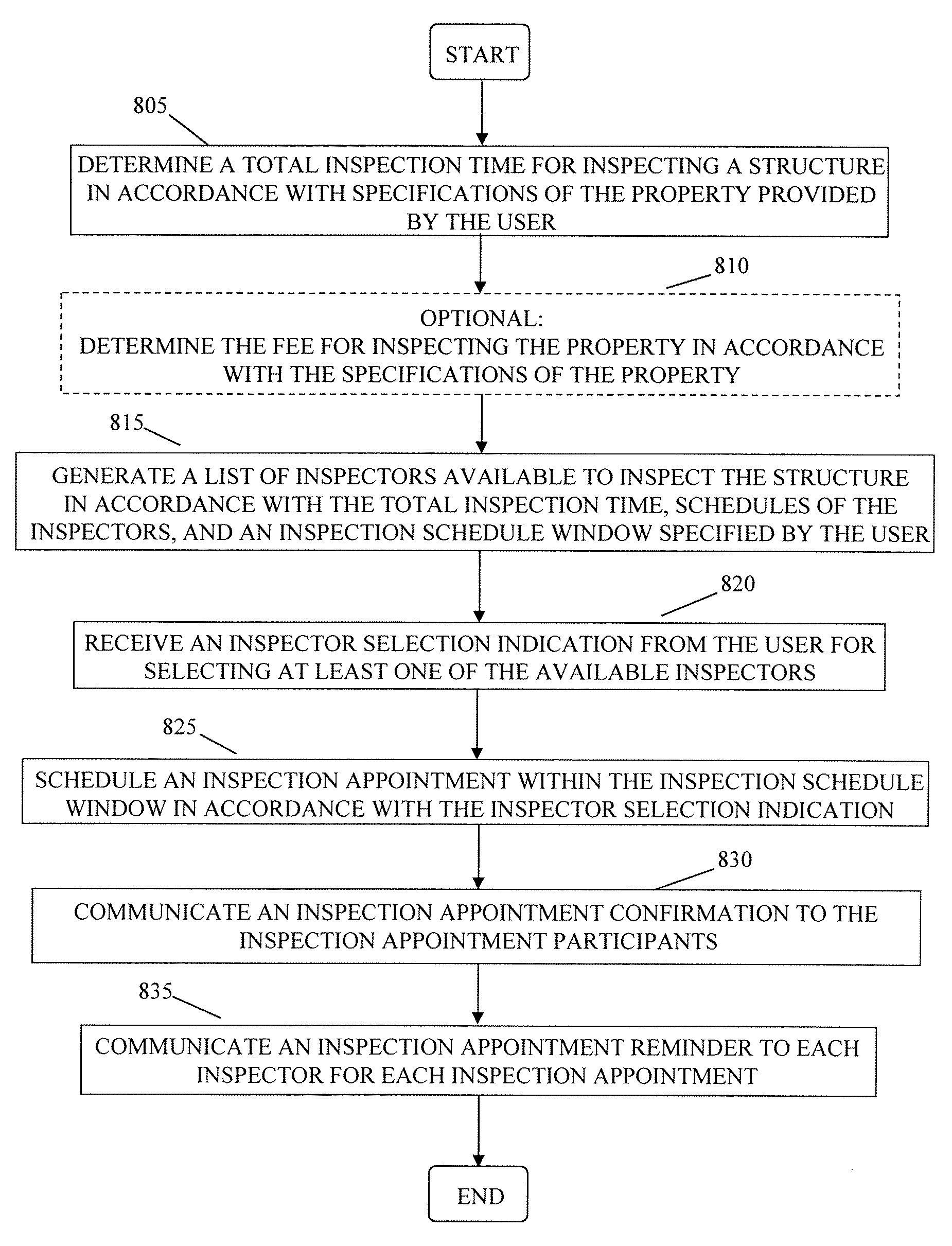

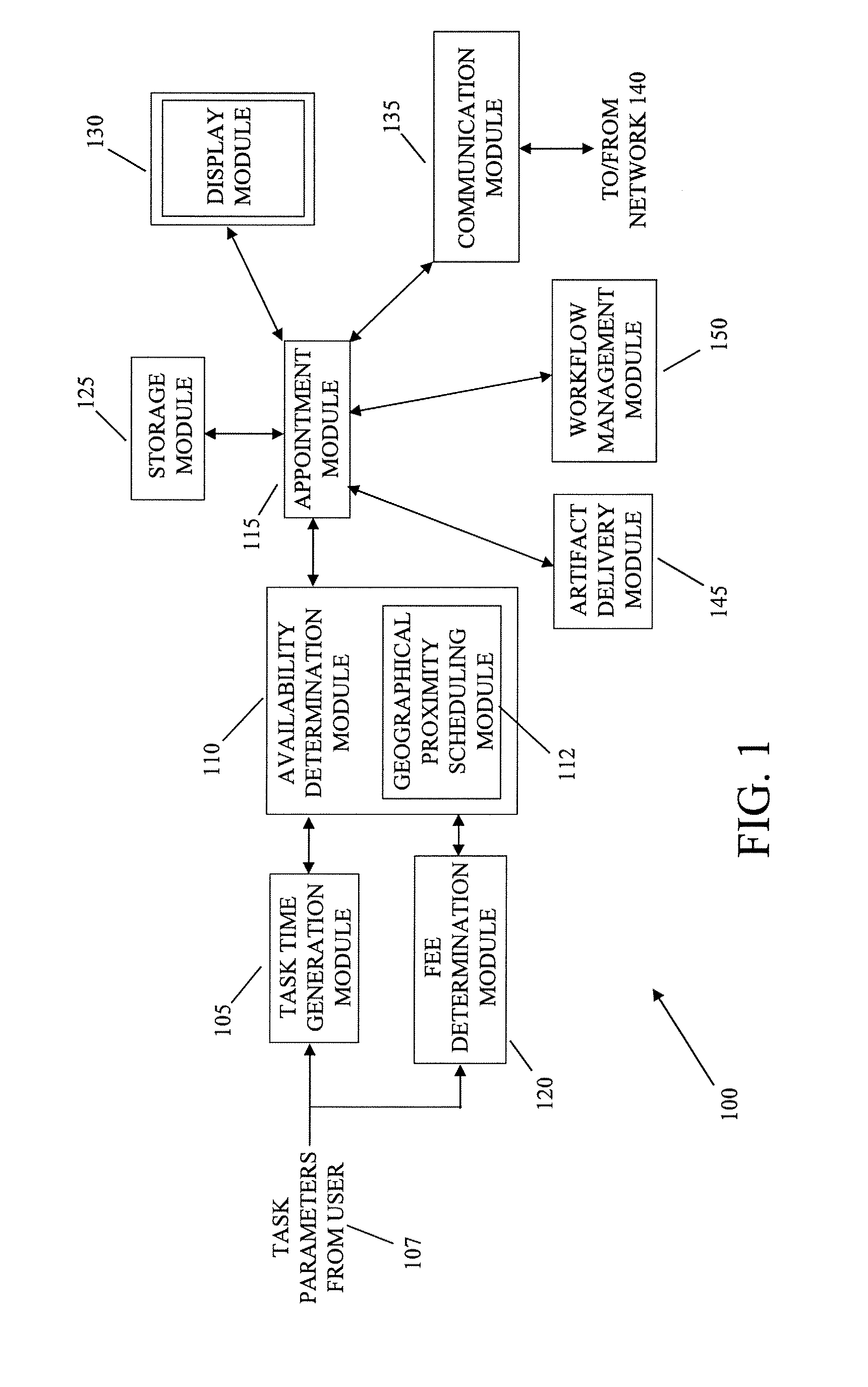

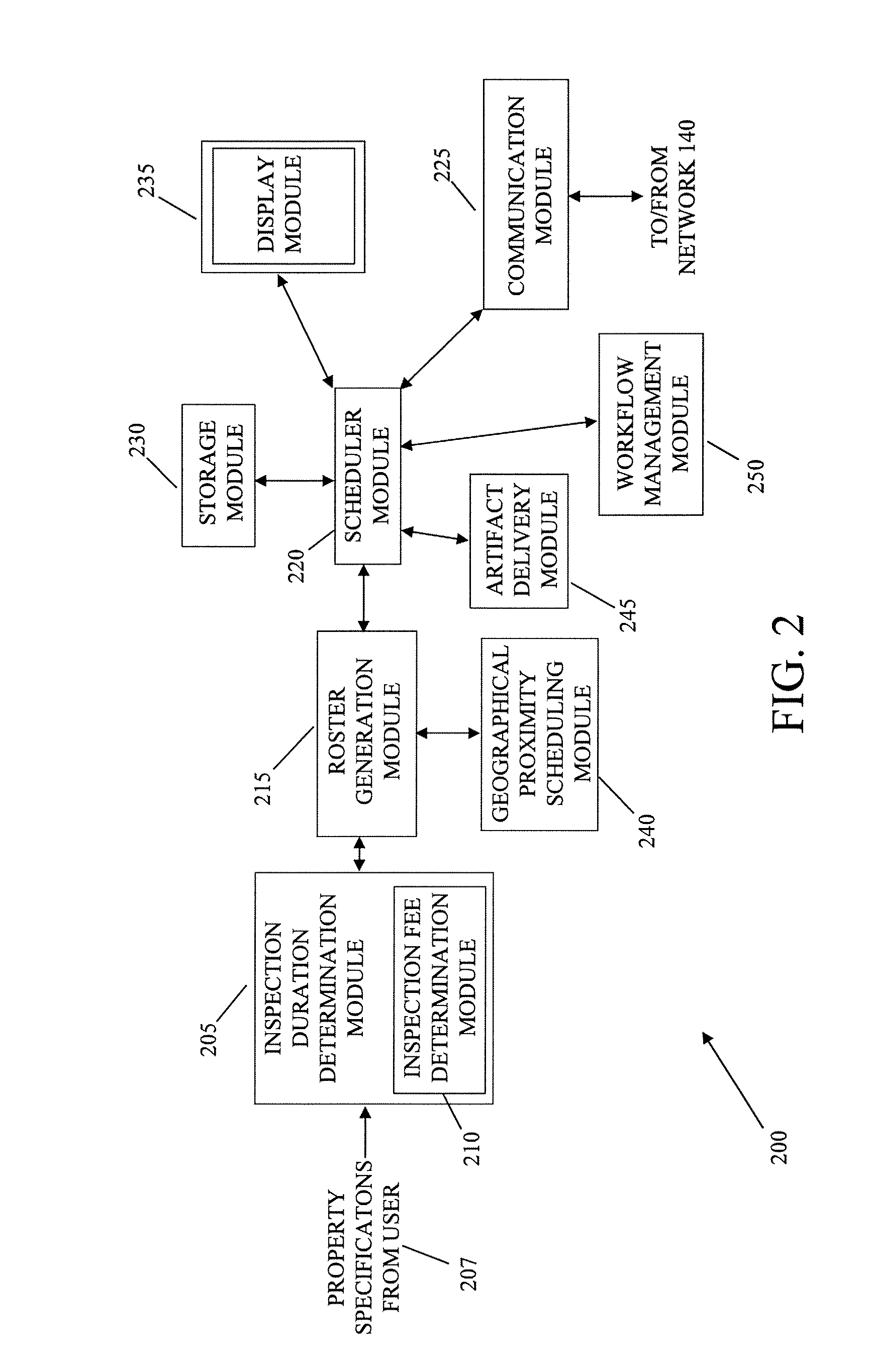

Parameter-based appointment scheduling system and method

A system for automatically scheduling an appointment for performing a task includes a task time generation module configured to calculate a total time for performing the task in accordance with task parameters provided by a user. The system includes an availability determination module in communication with the task time generation module. The availability determination module is configured to generate a list of entities available for performing the task in accordance with the total time for performing the task, schedules of each entity, and a date / time window specified by the user. The system includes an appointment module in communication with the availability determination module. The appointment module is configured to schedule the appointment for performing the task within the date / time window in accordance with a user selection of at least one entity from the list of available entities.

Owner:INSPECTION MANAGEMENT SYST