Patents

Literature

107 results about "Test pattern generators" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and system for providing a smart memory architecture

ActiveUS20140157065A1High rateHigh error rateError detection/correctionDigital computer detailsMemory chipSmart memory

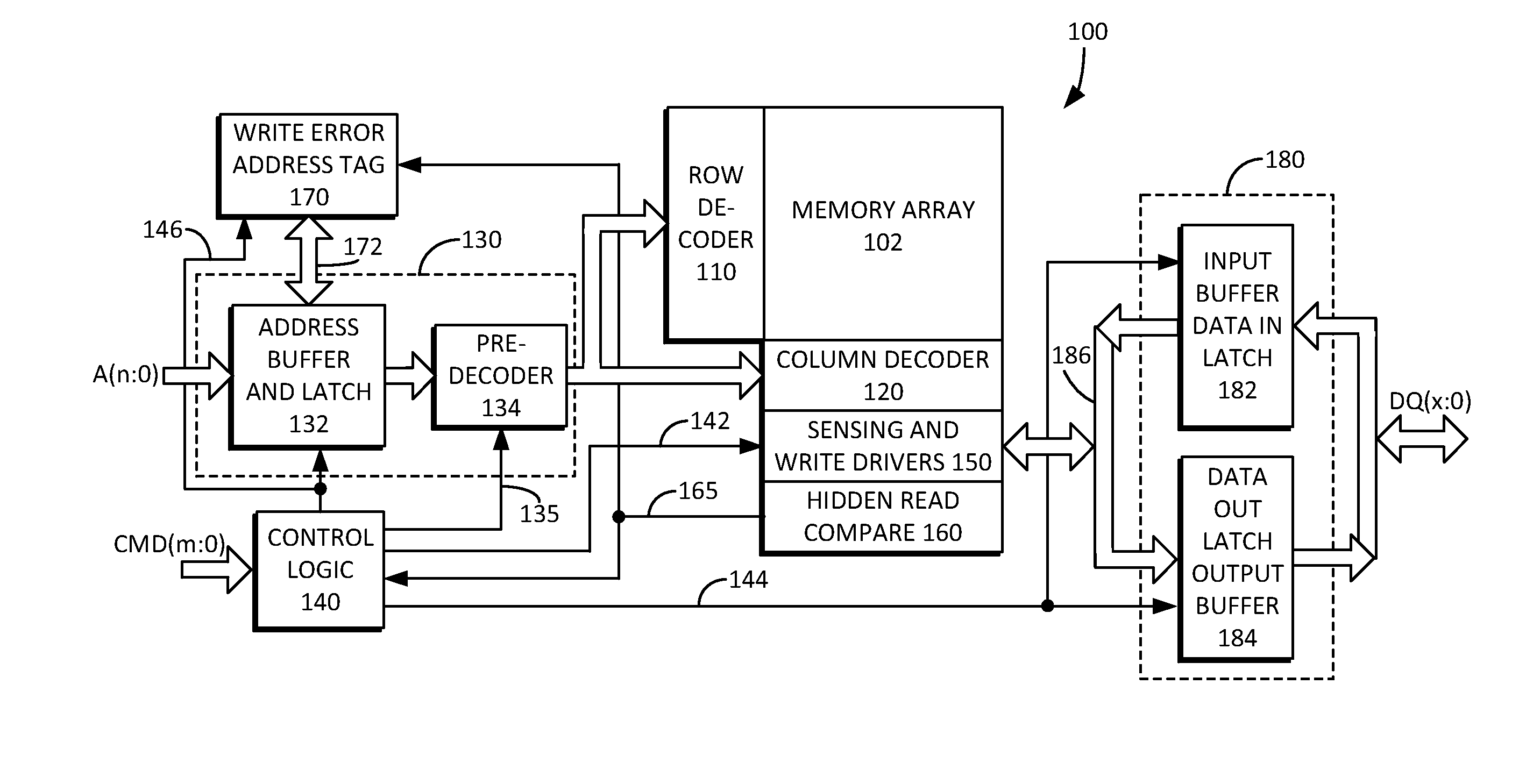

A smart memory system preferably includes a memory including one or more memory chips, and a processor including one or more memory processor chips. The system may include a smart memory controller capable of performing a bit error rate built-in self test. The smart memory control may include bit error rate controller logic configured to control the bit error rate built-in self test. A write error rate test pattern generator may generate a write error test pattern for the bit error rate built-in self test. A read error rate test pattern generator may generate a read error test pattern for the built-in self test. The smart memory controller may internally generate an error rate timing pattern, perform built-in self test, measure the resulting error rate, automatically adjust one or more test parameters based on the measured error rate, and repeat the built-in self test using the adjusted parameters.

Owner:SAMSUNG ELECTRONICS CO LTD

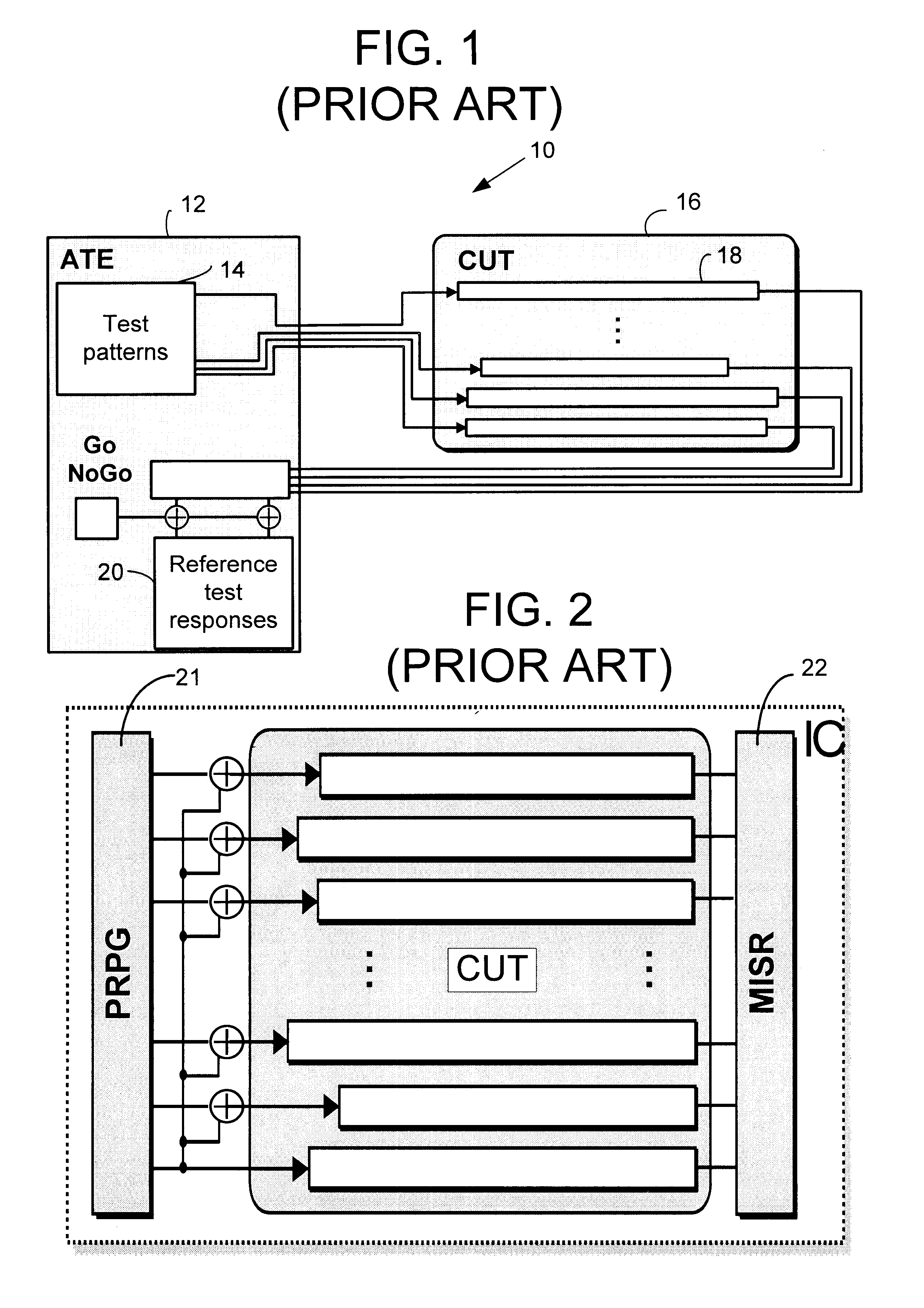

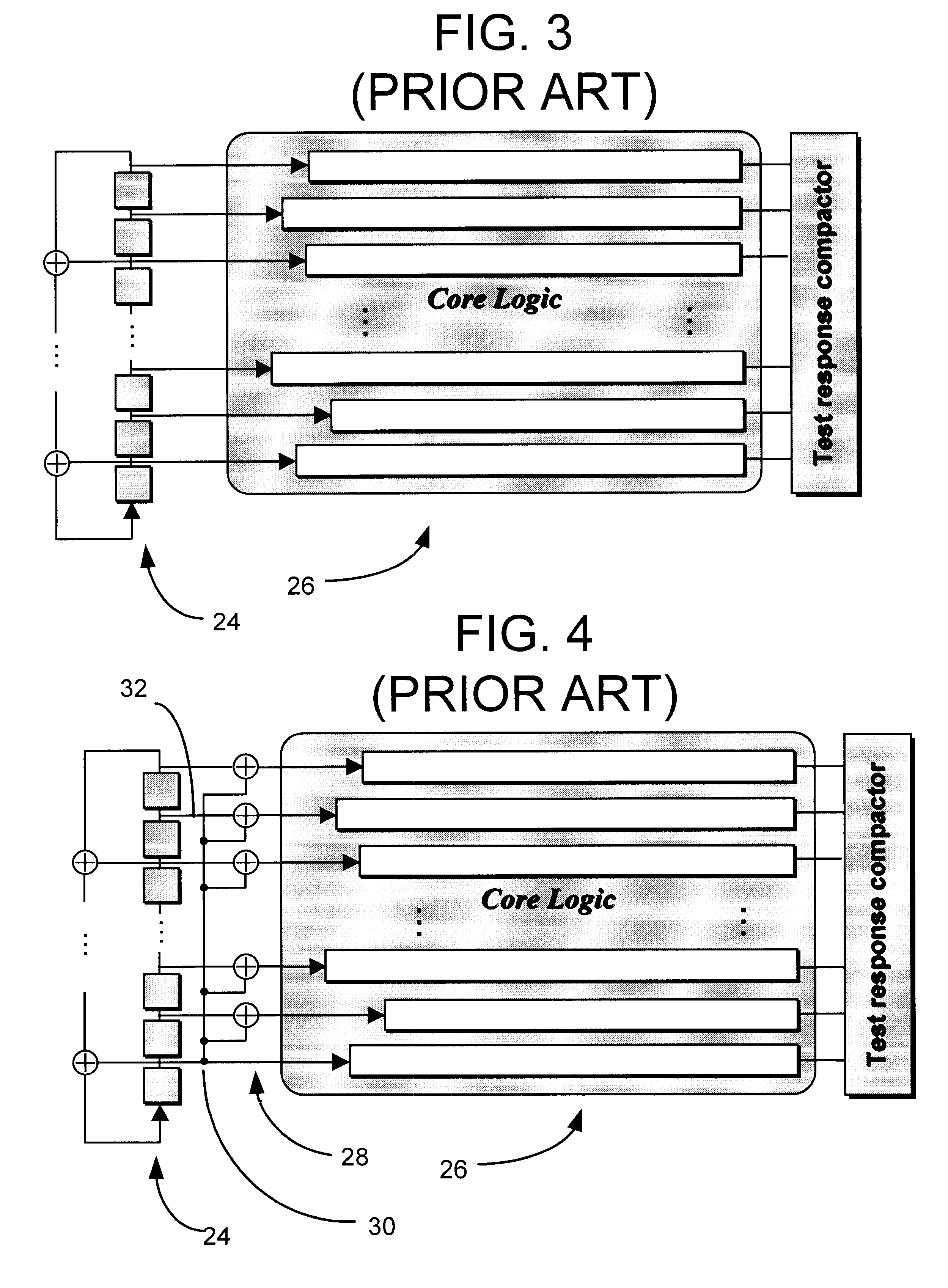

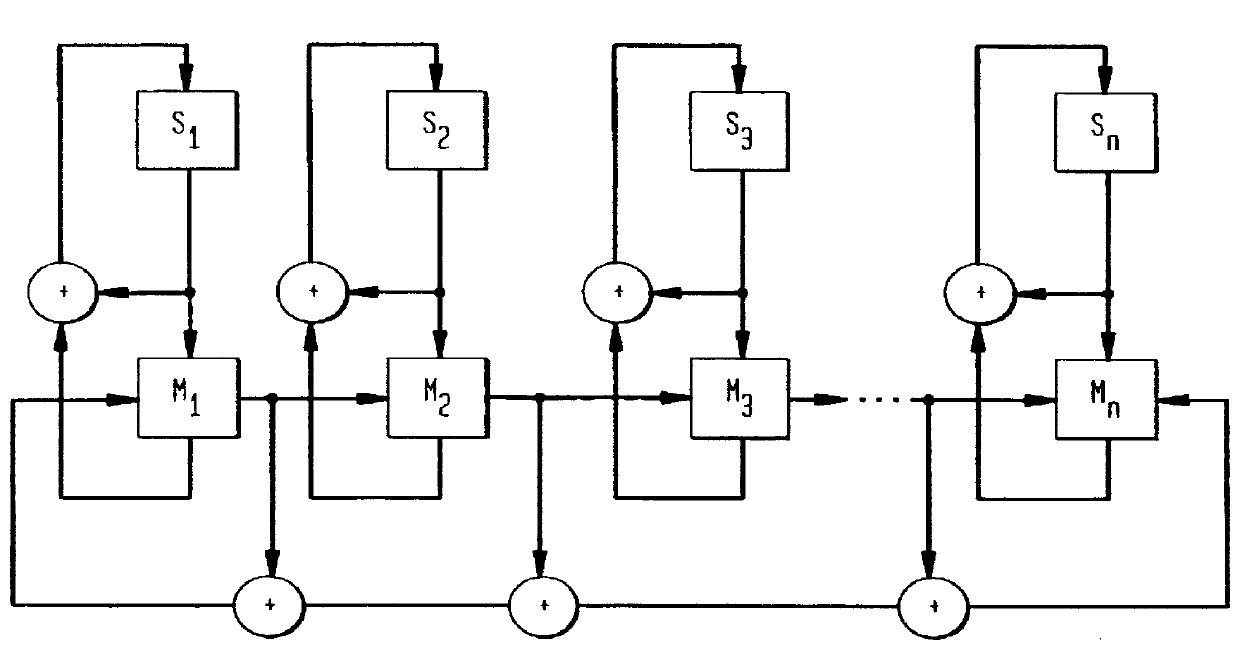

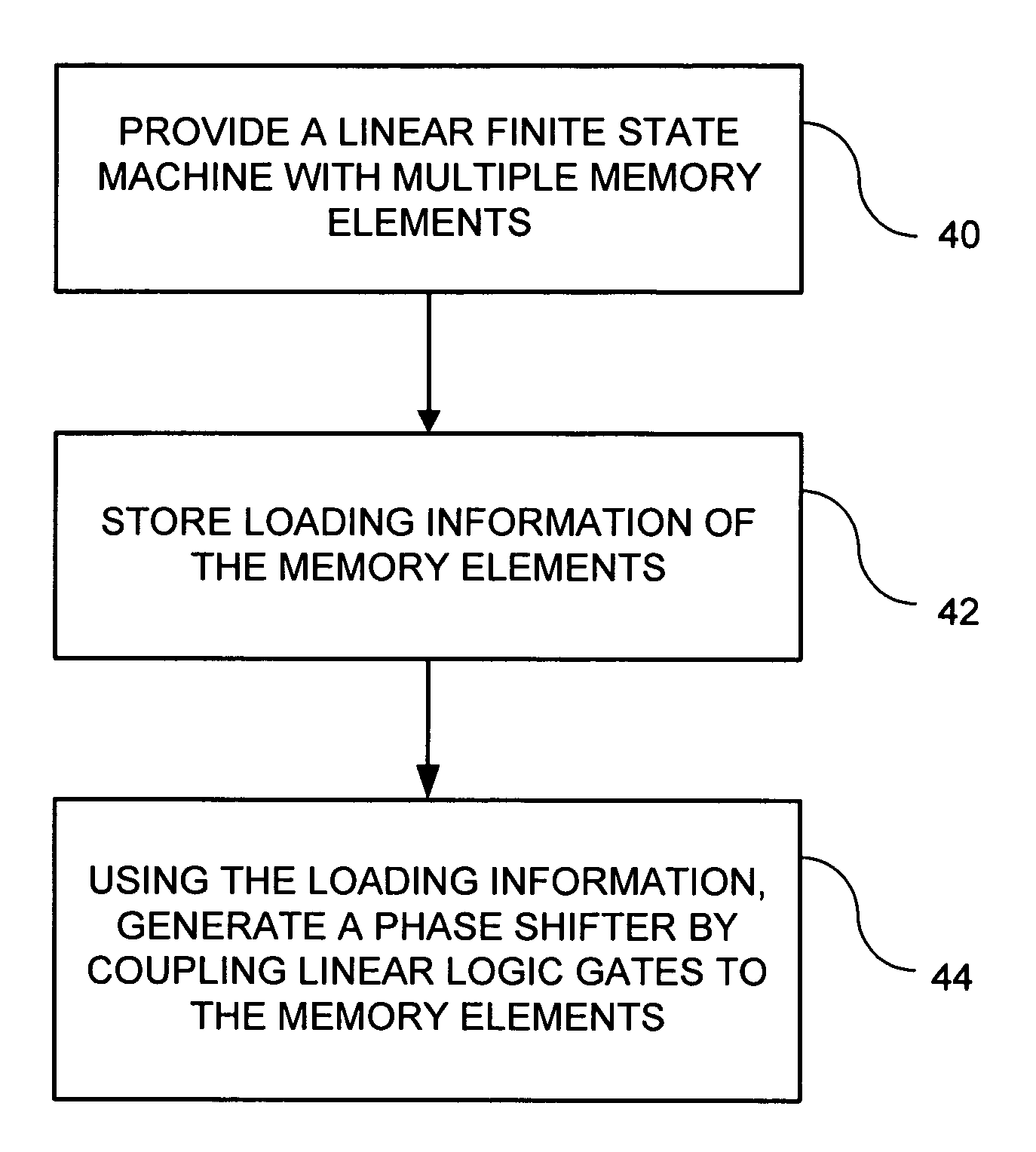

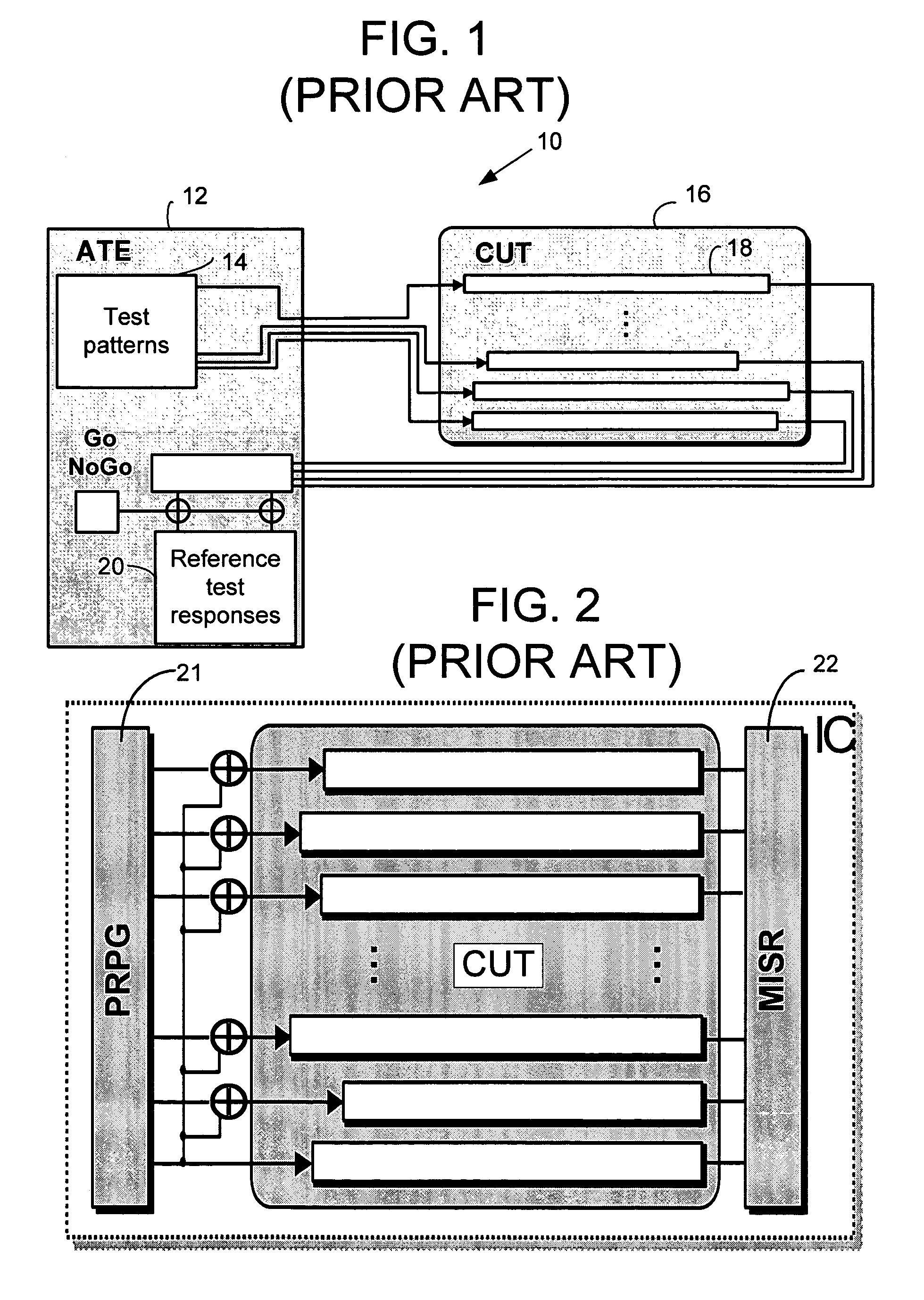

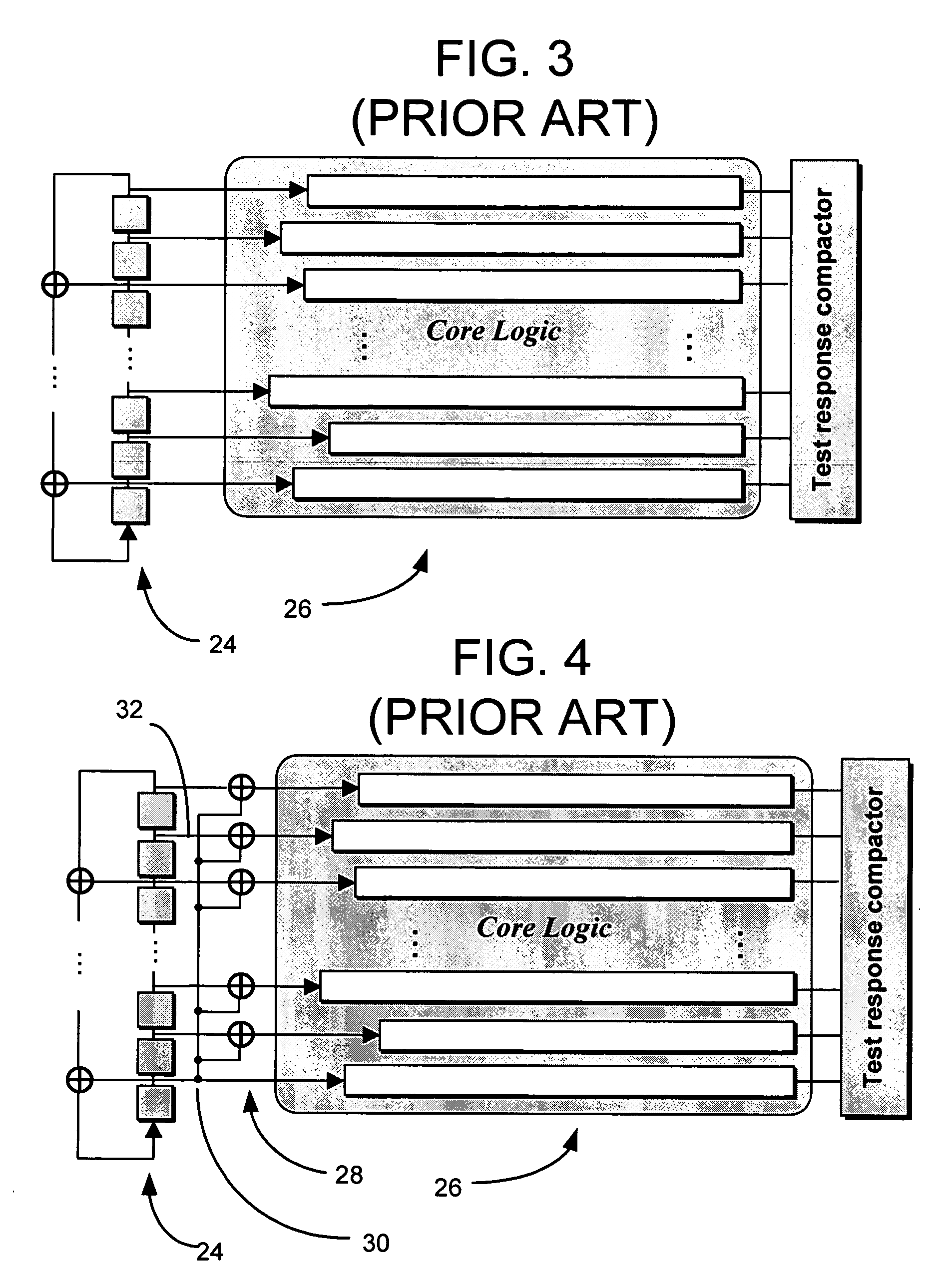

Phase shifter with reduced linear dependency

InactiveUS6874109B1Electronic circuit testingError detection/correctionCircuit complexityLinear dependency

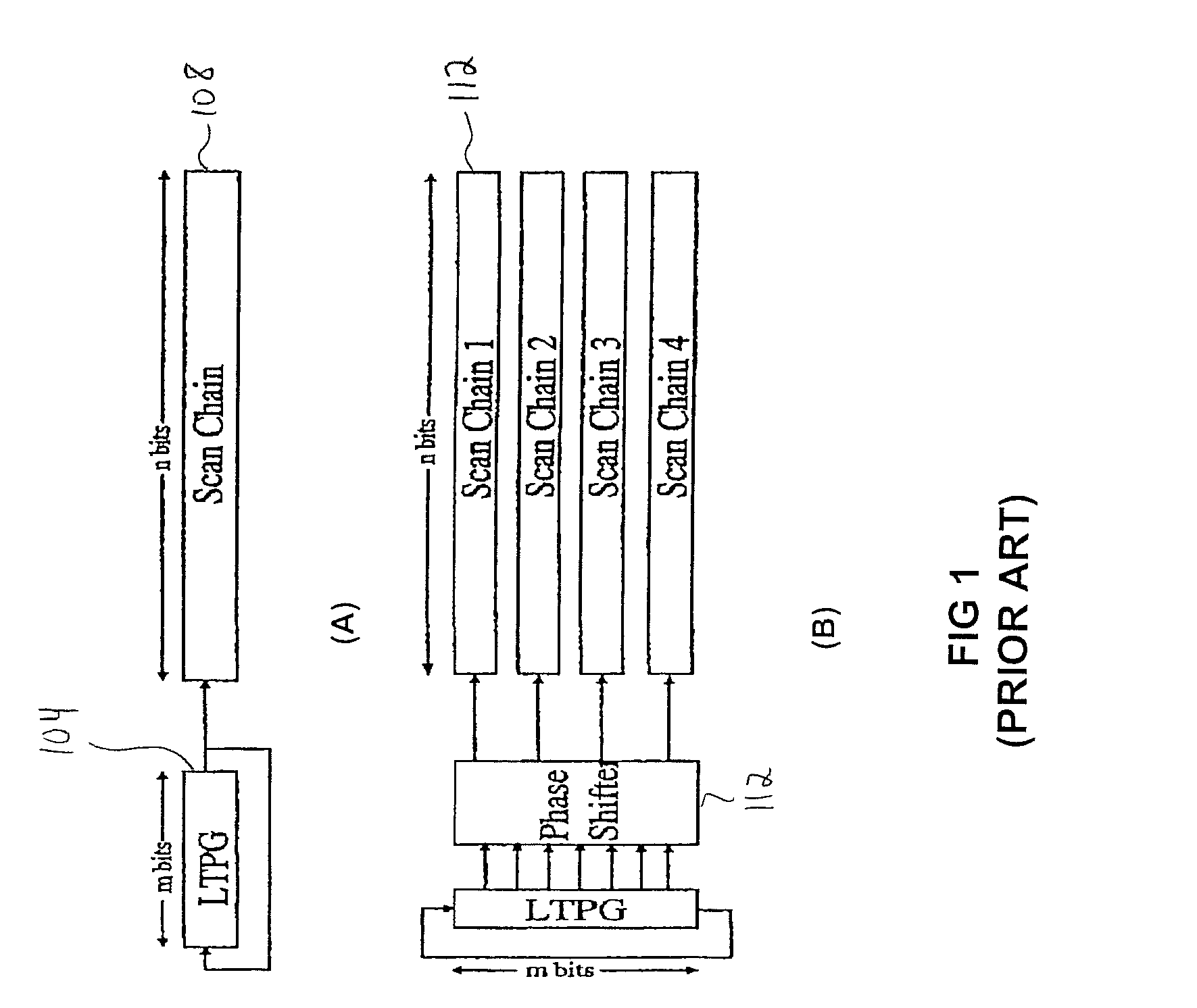

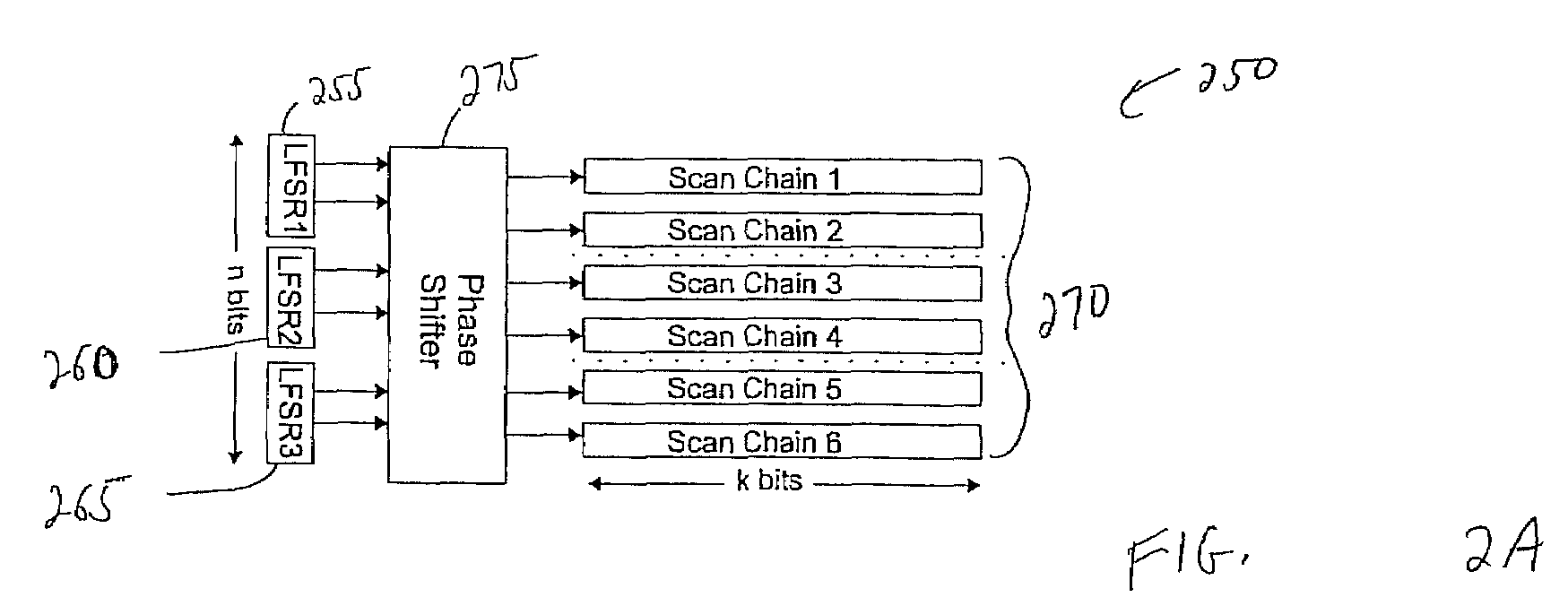

A method is disclosed for the automated synthesis of phase shifters. Phase shifters comprise circuits used to remove effects of structural dependencies featured by pseudo-random test pattern generators driving parallel scan chains. Using a concept of duality, the method relates the logical states of linear feedback shift registers (LFSRs) and circuits spacing their inputs to each of the output channels. The method generates a phase shifter network balancing the loads of successive stages of LFSRs and satisfying criteria of reduced linear dependency, channel separation and circuit complexity.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

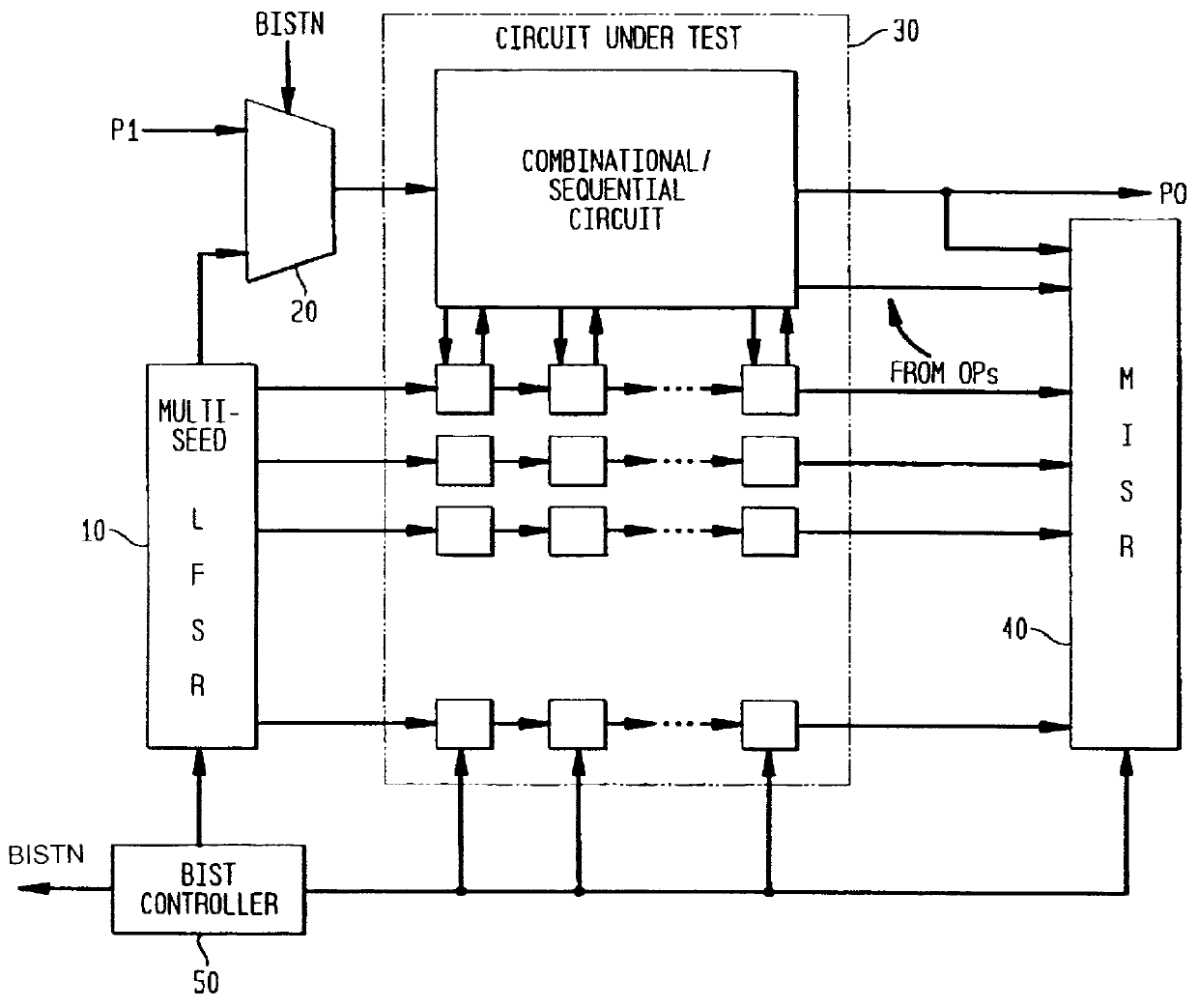

Bist architecture for detecting path-delay faults in a sequential circuit

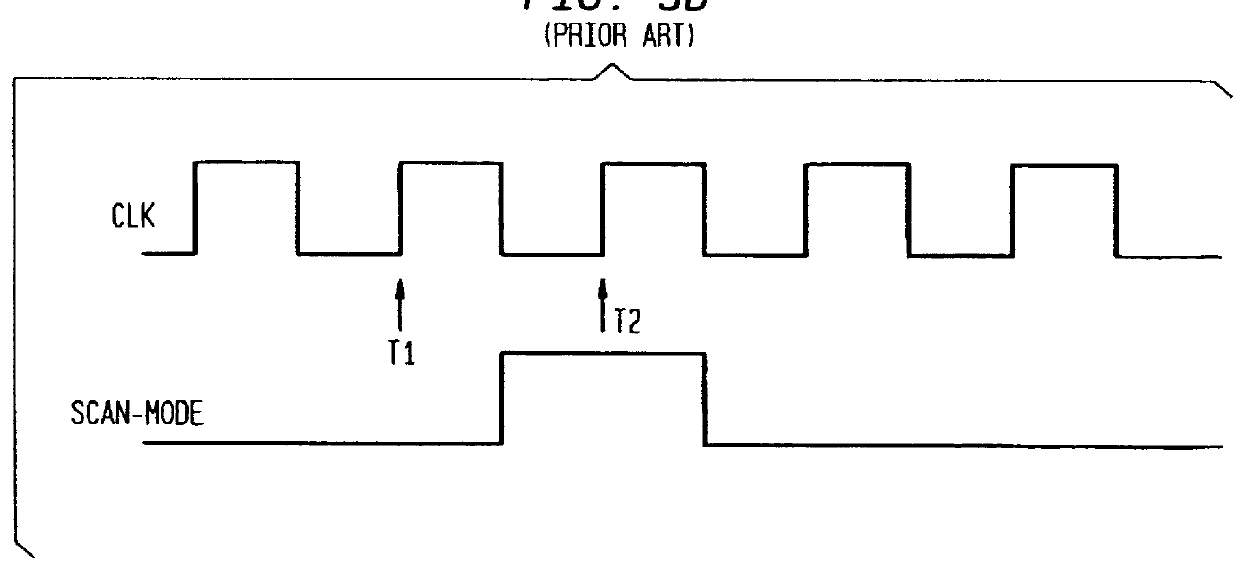

A scan-based BIST architecture for detecting path-delay faults in a sequential circuit converted to a combinational circuit or a less complex sequential circuit including a combinational portion and a plurality of scan flip-flops. The BIST structure includes a test pattern generator for generating two test patterns and a controller for generating a clock signal and an extended scan mode signal which is held high for two clock cycles while the output response of the combinational portion to the first and second test vectors is latched into the scan flip-flops in order to detect a signal transition. The invention is further directed to a method for detection of path-delay faults using this scan-based BIST architecture. To improve the fault coverage for path-delay faults, observation points may be inserted at the inputs of selected scan flip-flops. A predetermined number of scan flip-flops having the highest activation frequency are selected as the observation points.

Owner:LUCENT TECH INC +1

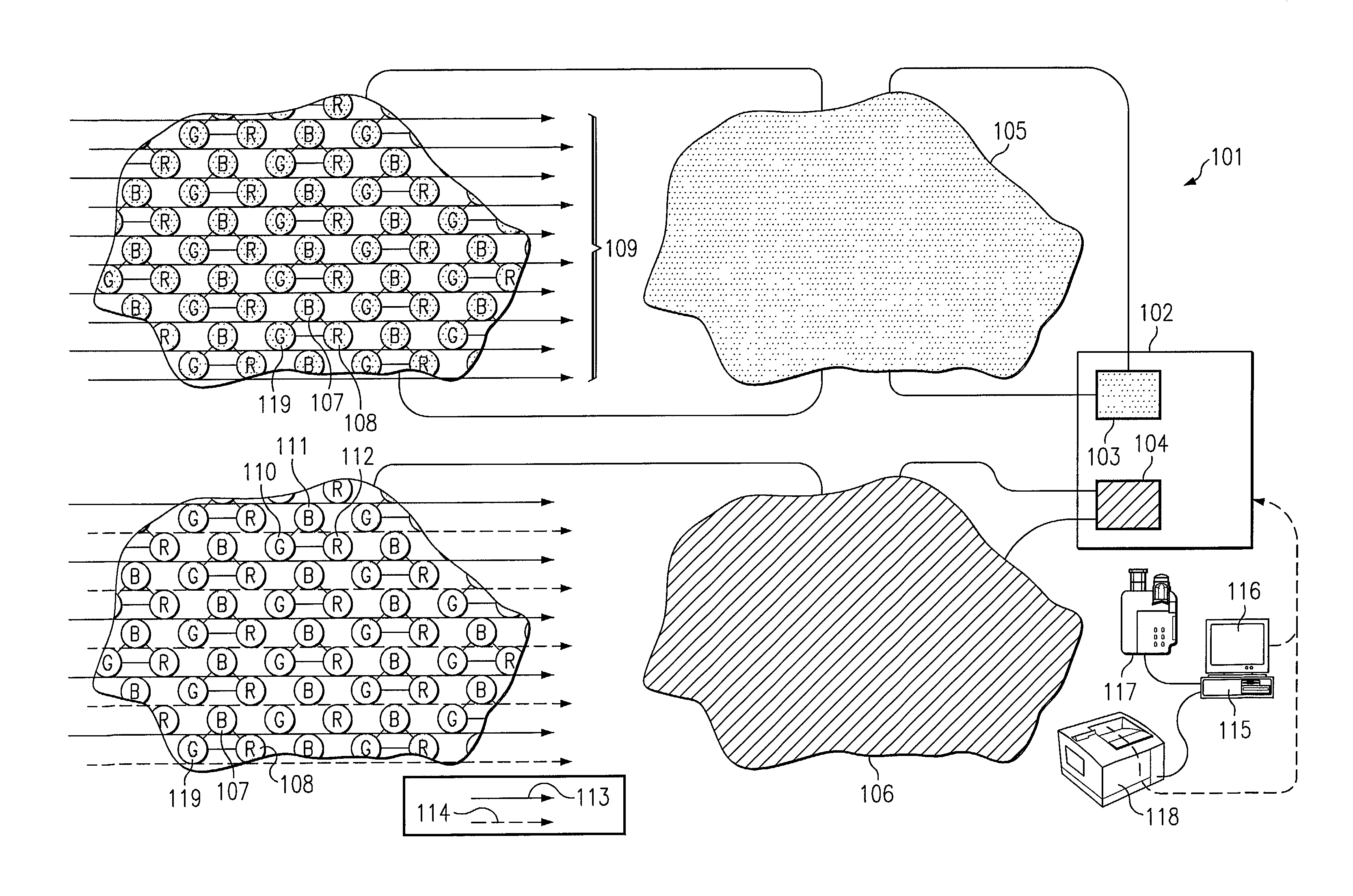

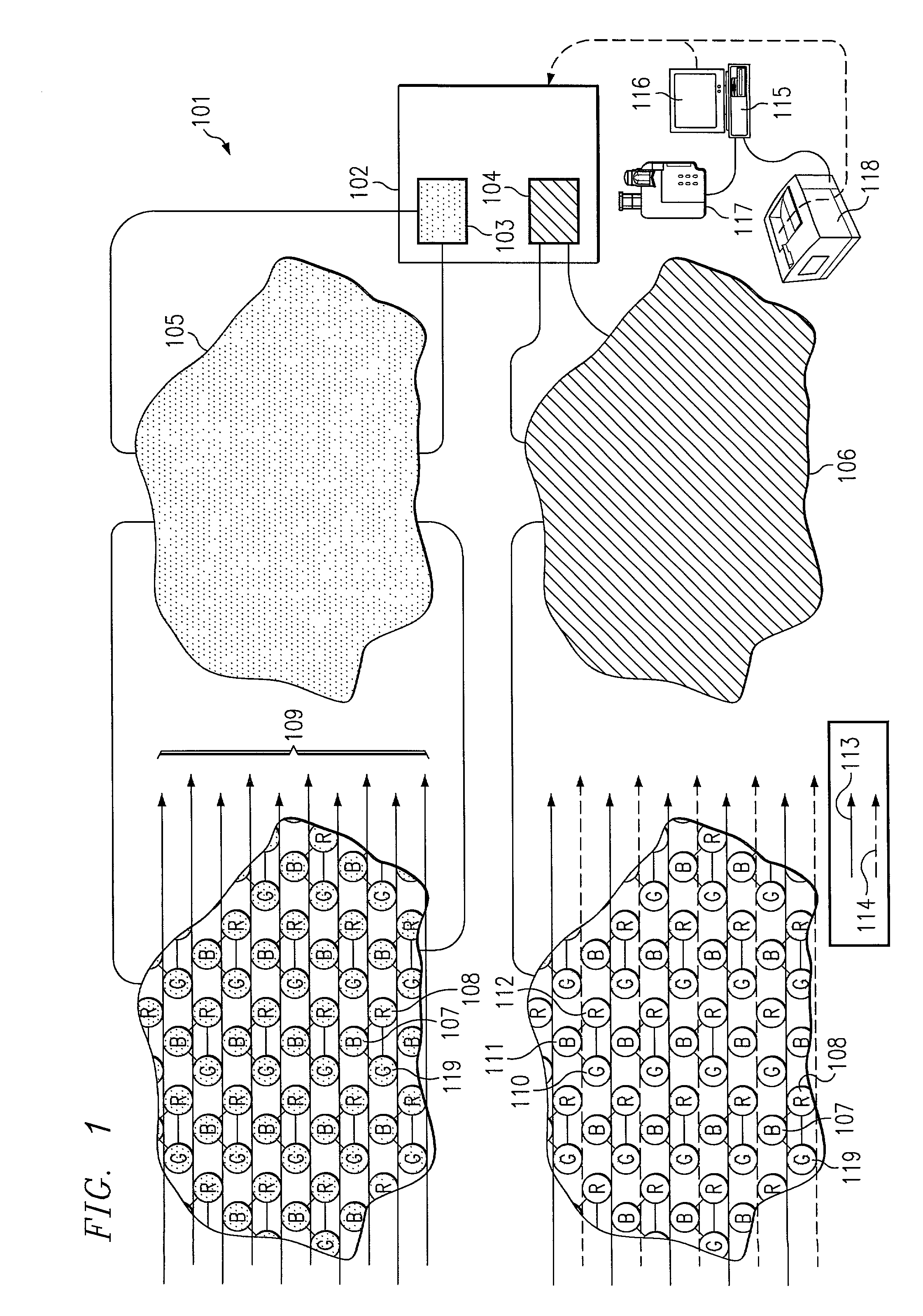

System and method of in-service testing of compressed digital broadcast video

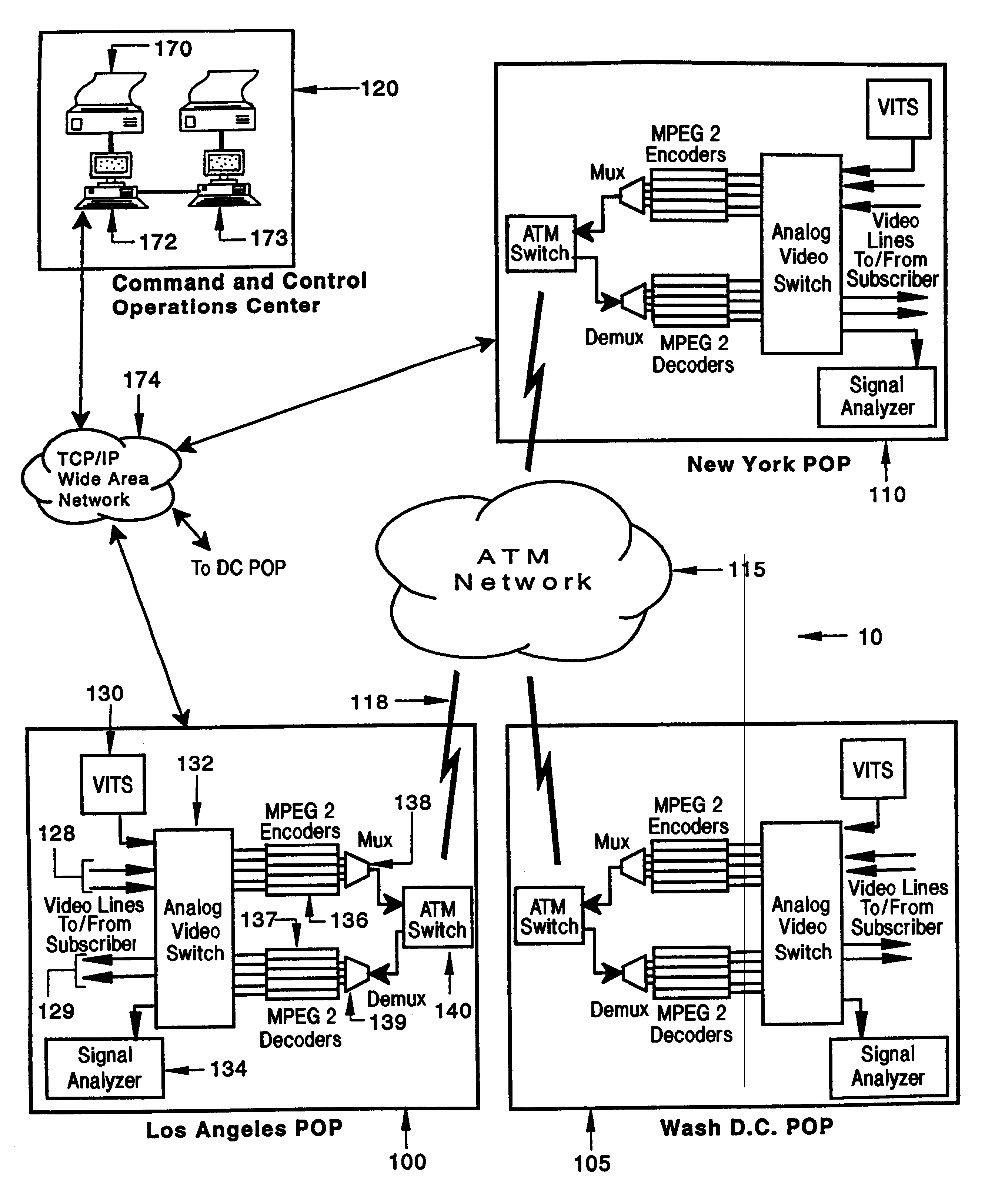

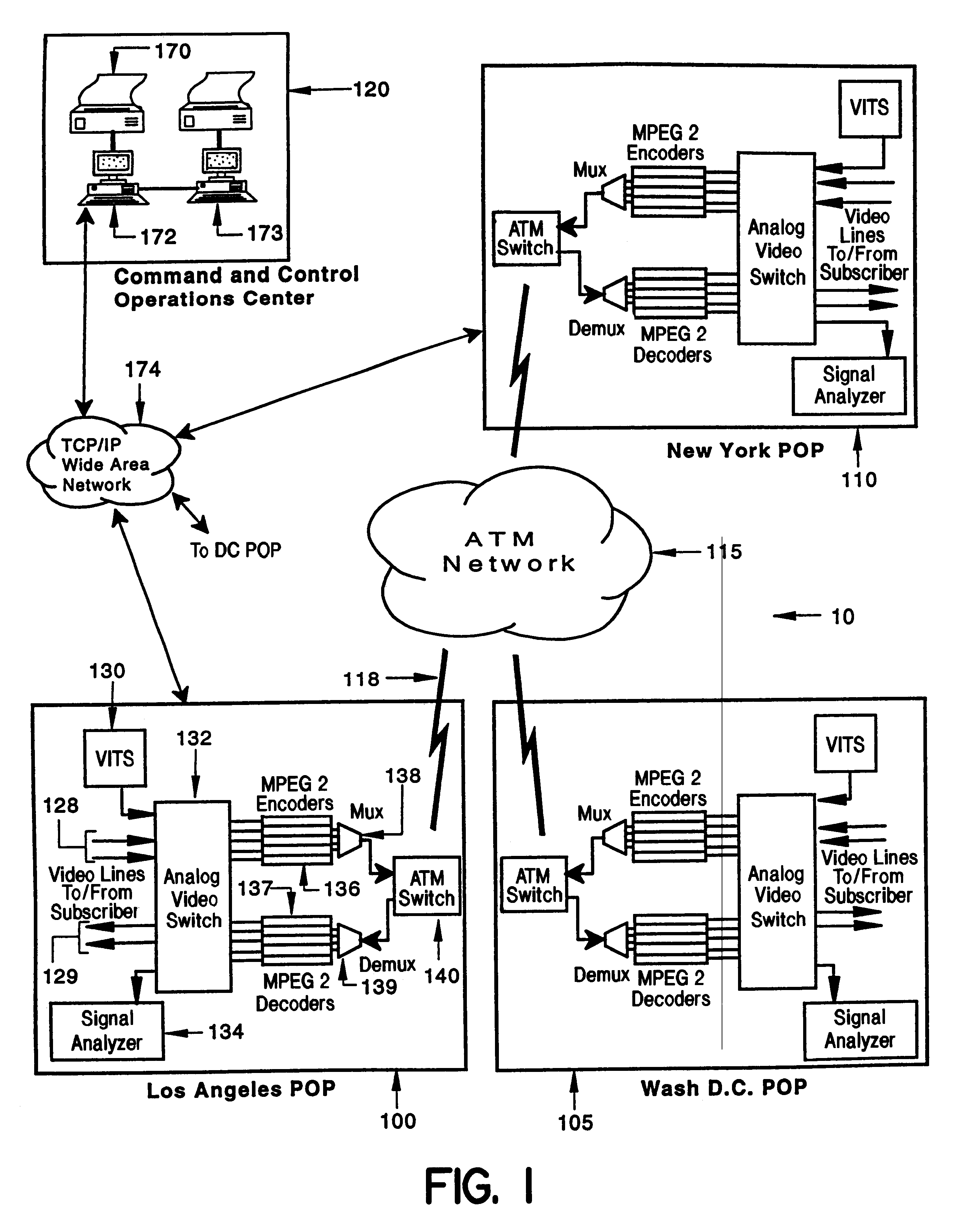

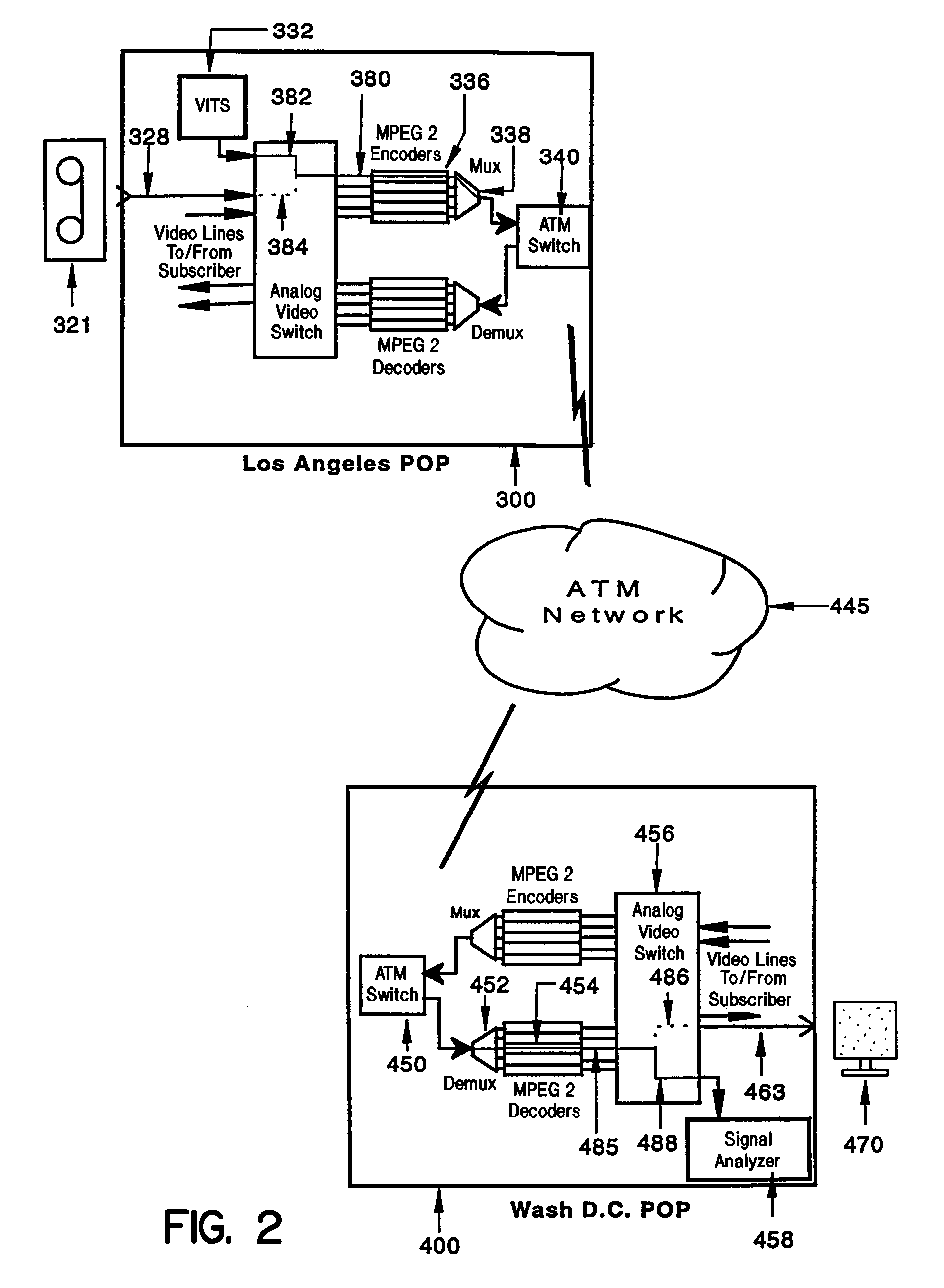

A switched digital video broadcast network provides in-service testing of digitized broadcast video signals subject to analog-to-digital and digital-to-analog conversion. The network includes a plurality of gateways, each gateway coupled to video signal sources and sink. Video frames transmitted on the network are subject to analog-to-digital and digital-to-analog conversion and compression in an MPEG 2 encoder / decoder. Each gateway and includes a test pattern generator and test measurement analyzer for in-service testing of the video signals. The test pattern generator inserts a test signal on pre-selected lines (22, 23 or 261,262) in a Video Blanking Interval (VBI) and time periods of a video frame. The test signal may be dynamically placed at any location in the frame using concealment techniques The video lines are not seen by television viewers. The test pattern generator and test measurement analyzer are synchronized using vertical integral time code and a trigger packet sent by the transmitting station. The test signals enable both in-service and out-of-service testing to be performed for the entire suite of EIA / TIA 250C standard video tests.

Owner:IBM CORP

Phase shifter with reduced linear dependency

InactiveUS20050015688A1Electronic circuit testingRecord information storageCircuit complexityLinear correlation

A method is disclosed for the automated synthesis of phase shifters. Phase shifters comprise circuits used to remove effects of structural dependencies featured by pseudo-random test pattern generators driving parallel scan chains. Using a concept of duality, the method relates the logical states of linear feedback shift registers (LFSRs) and circuits spacing their inputs to each of the output channels. The method generates a phase shifter network balancing the loads of successive stages of LFSRs and satisfying criteria of reduced linear dependency, channel separation and circuit complexity.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

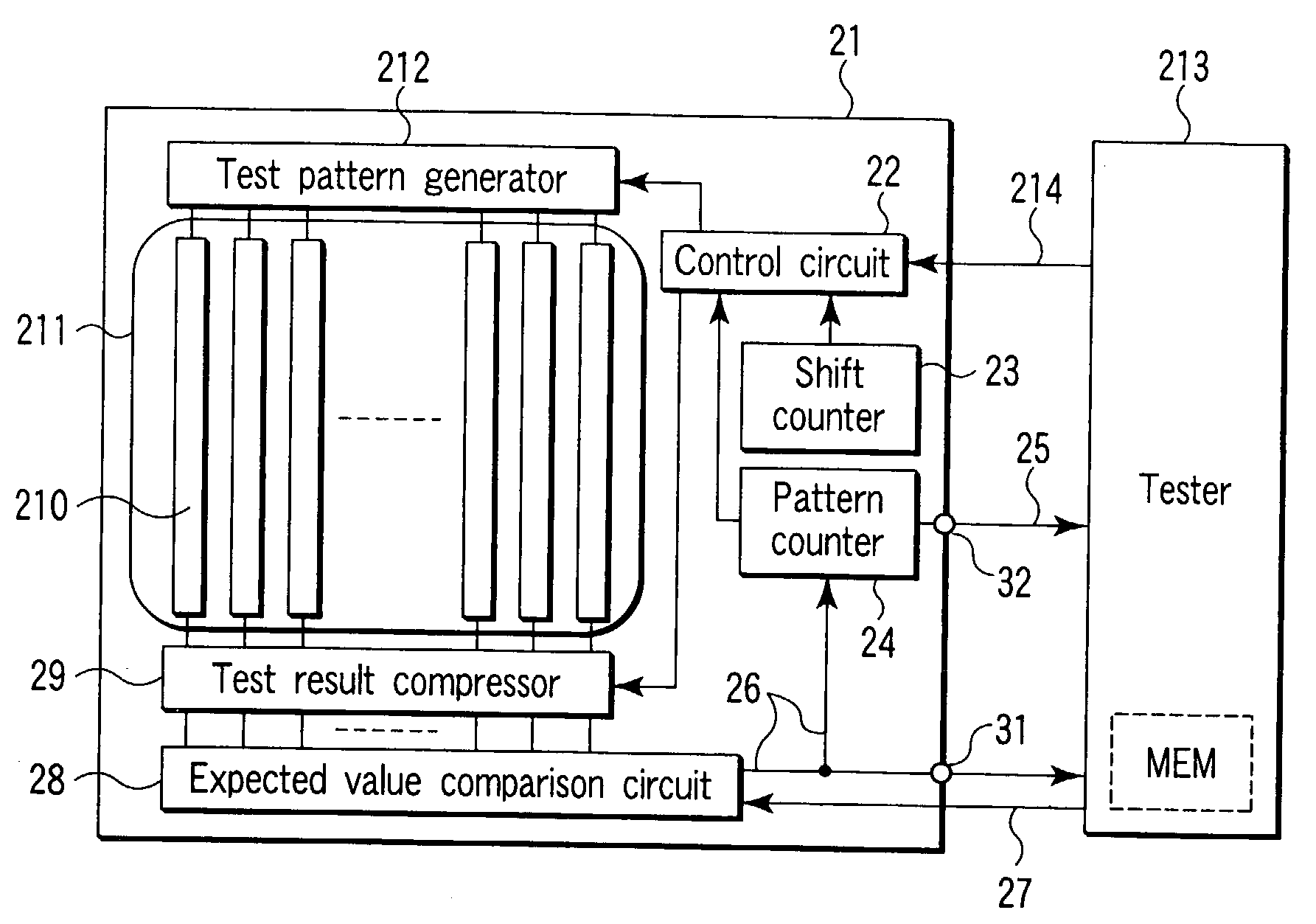

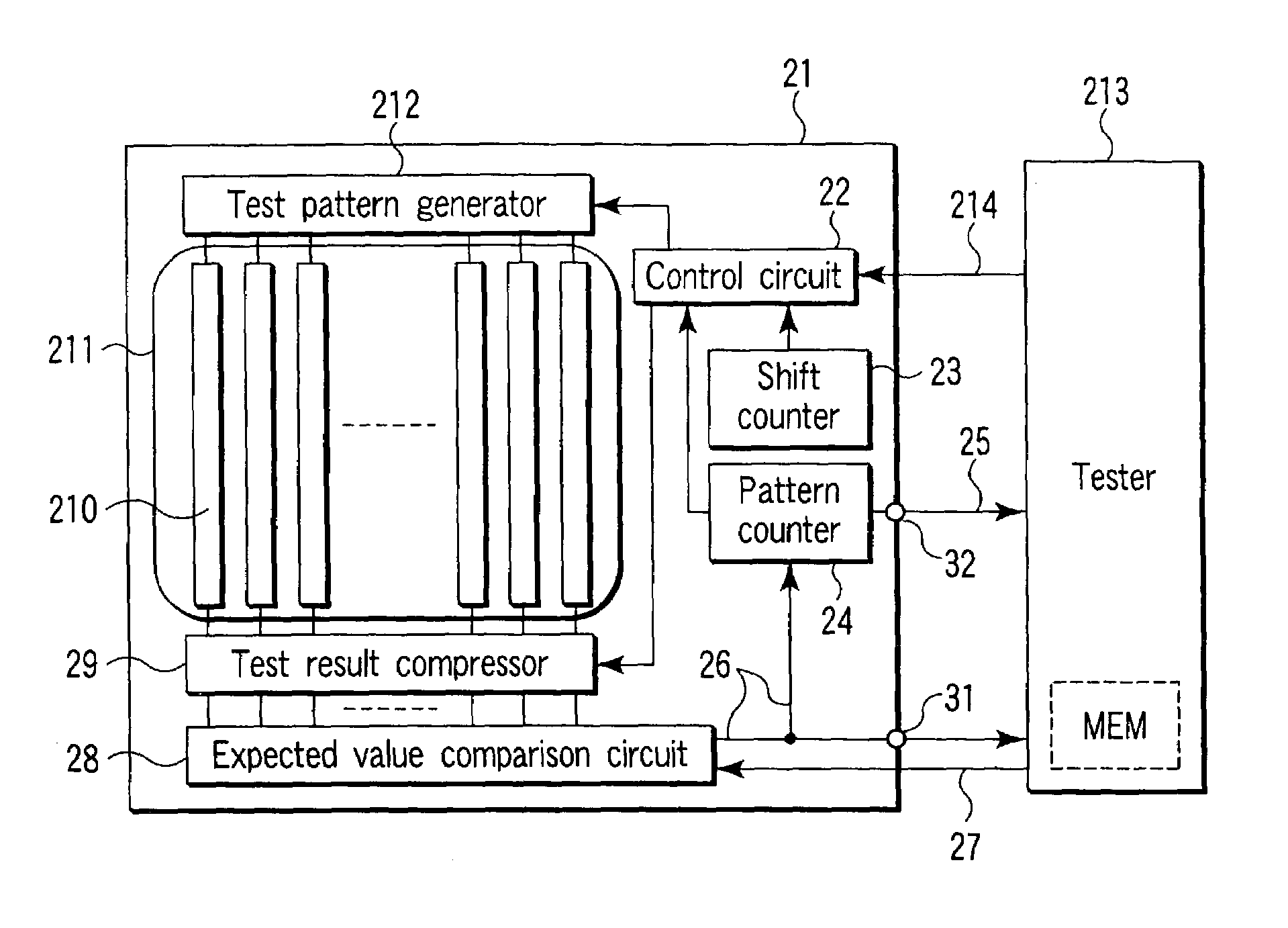

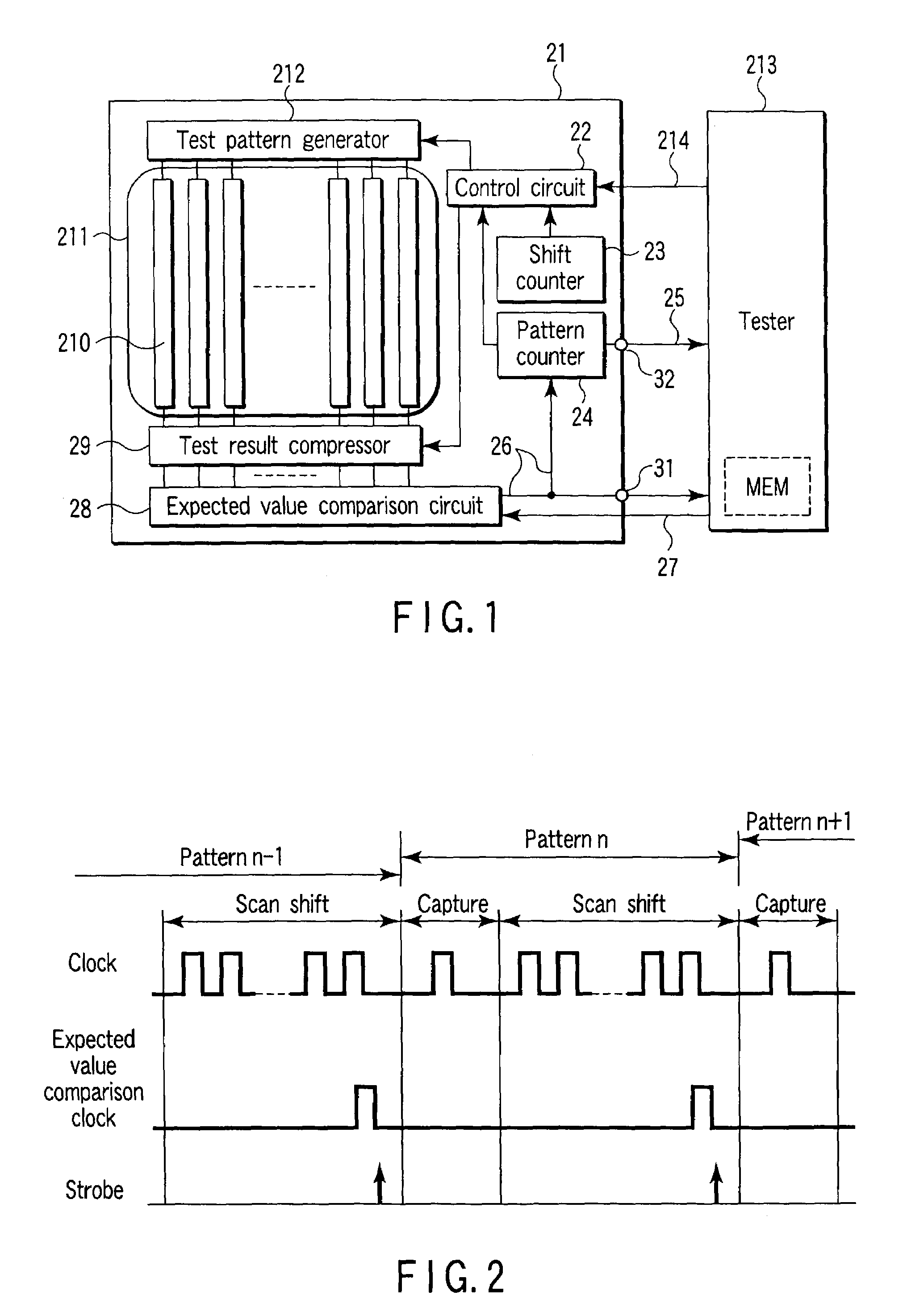

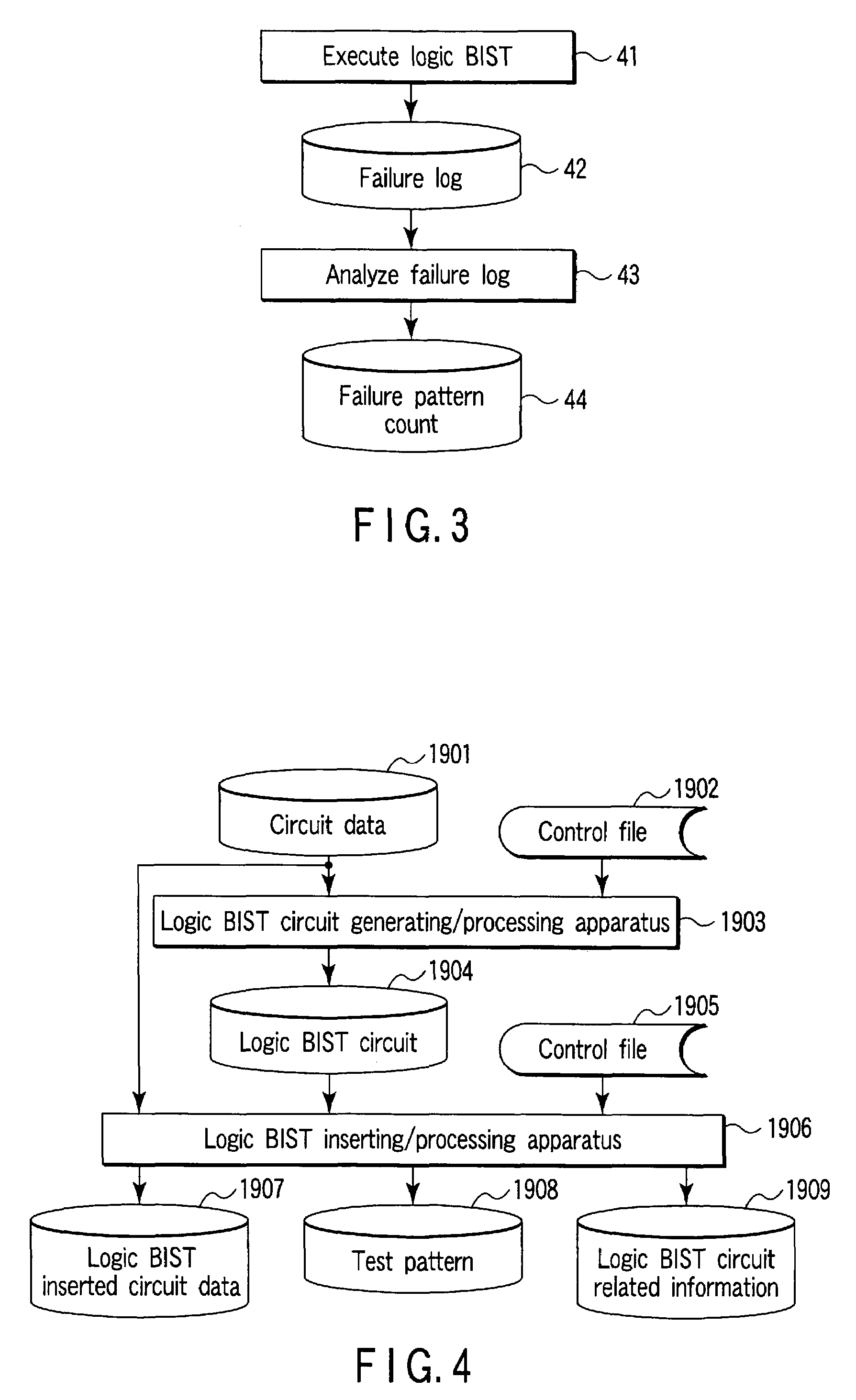

Semiconductor integrated circuit, design support apparatus, and test method

InactiveUS20030229886A1Electronic circuit testingSolid-state devicesBuilt-in self-testLogic circuitry

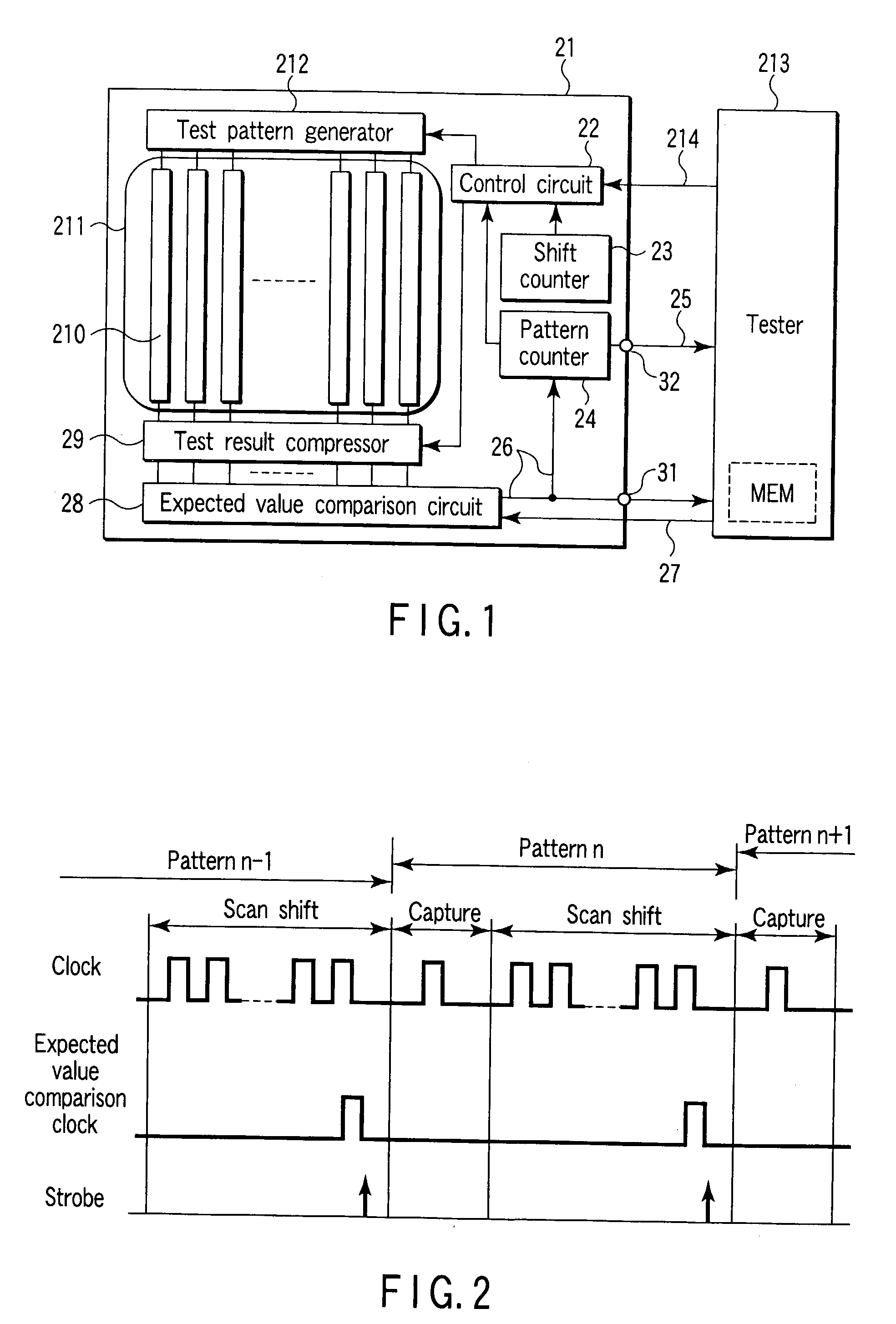

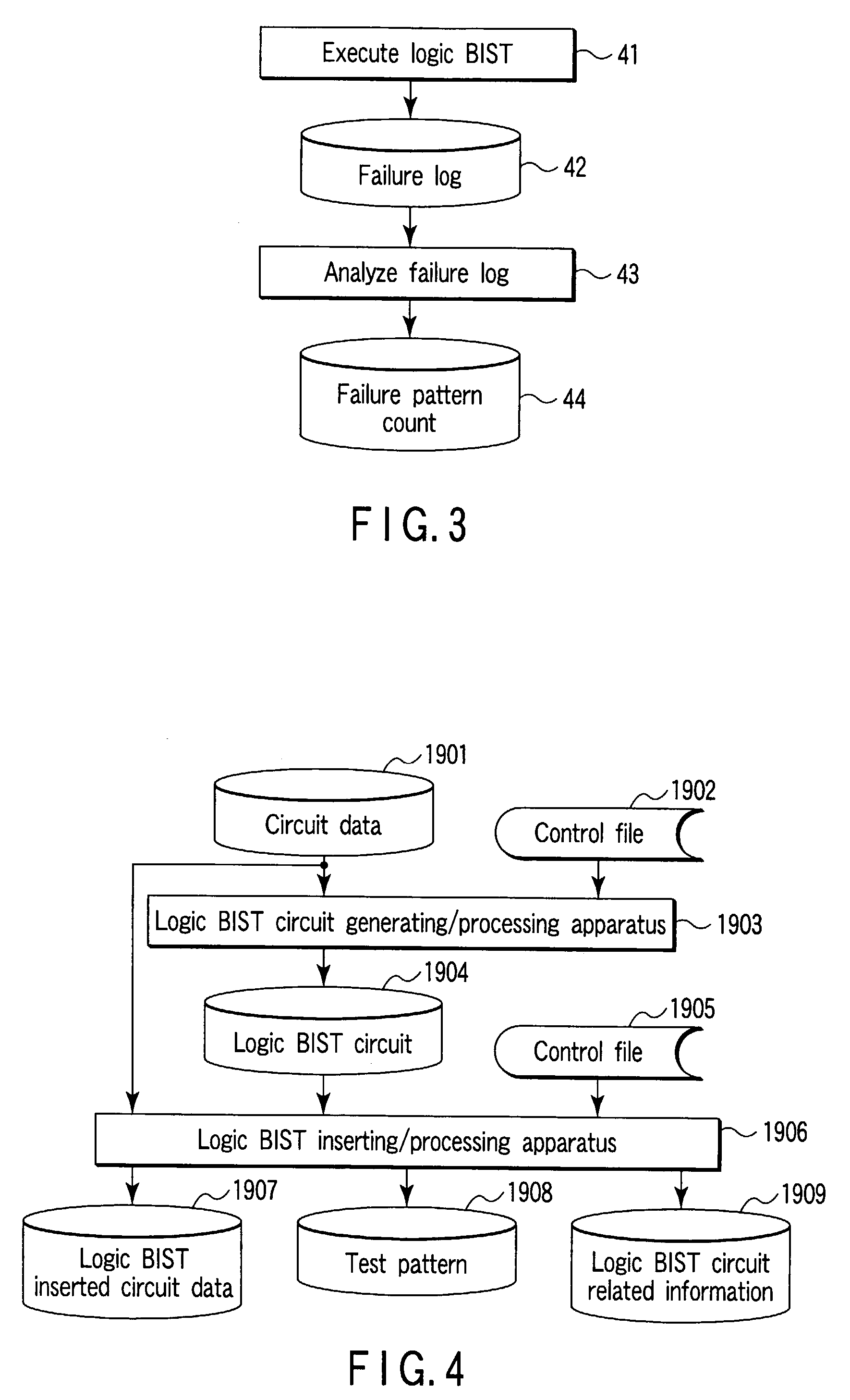

There is disclosed a semiconductor integrated circuit comprising a logic BIST circuit which includes a test pattern generator and test result compressor and which performs a built-in self test (logic BIST) of a logic circuit, a pattern counter which counts test patterns during the logic BIST, an expected value comparison circuit which compares a compressed value output of the test result compressor with an expected value input from an external tester for each test pattern and which outputs a failure flag at a mismatch detection time, an external terminal which outputs the failure flag from the LSI, and an external terminal which outputs from the LSI a pattern count signal at a time when the pattern counter receives the failure flag.

Owner:KK TOSHIBA

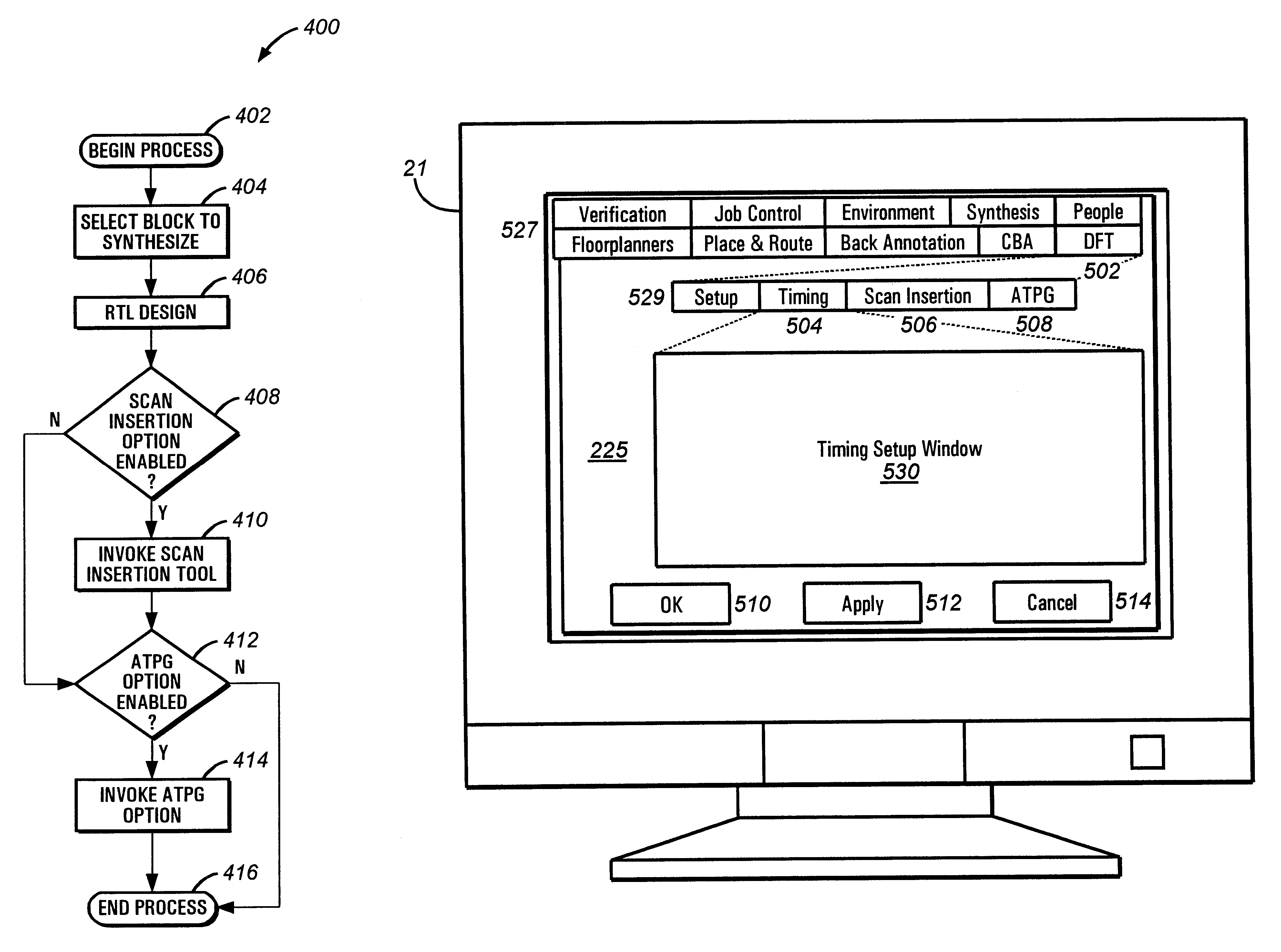

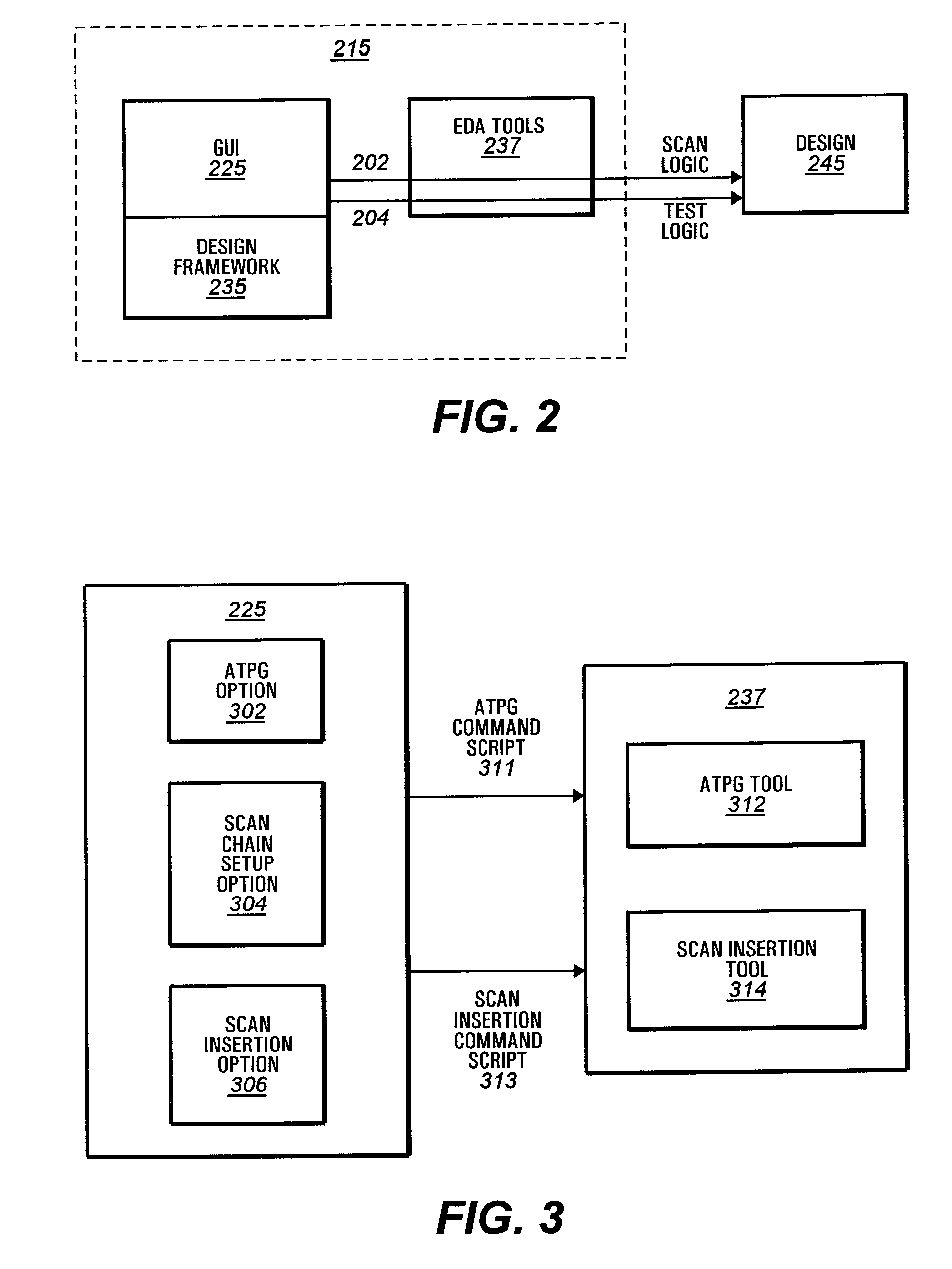

Graphical user interface for testability operation

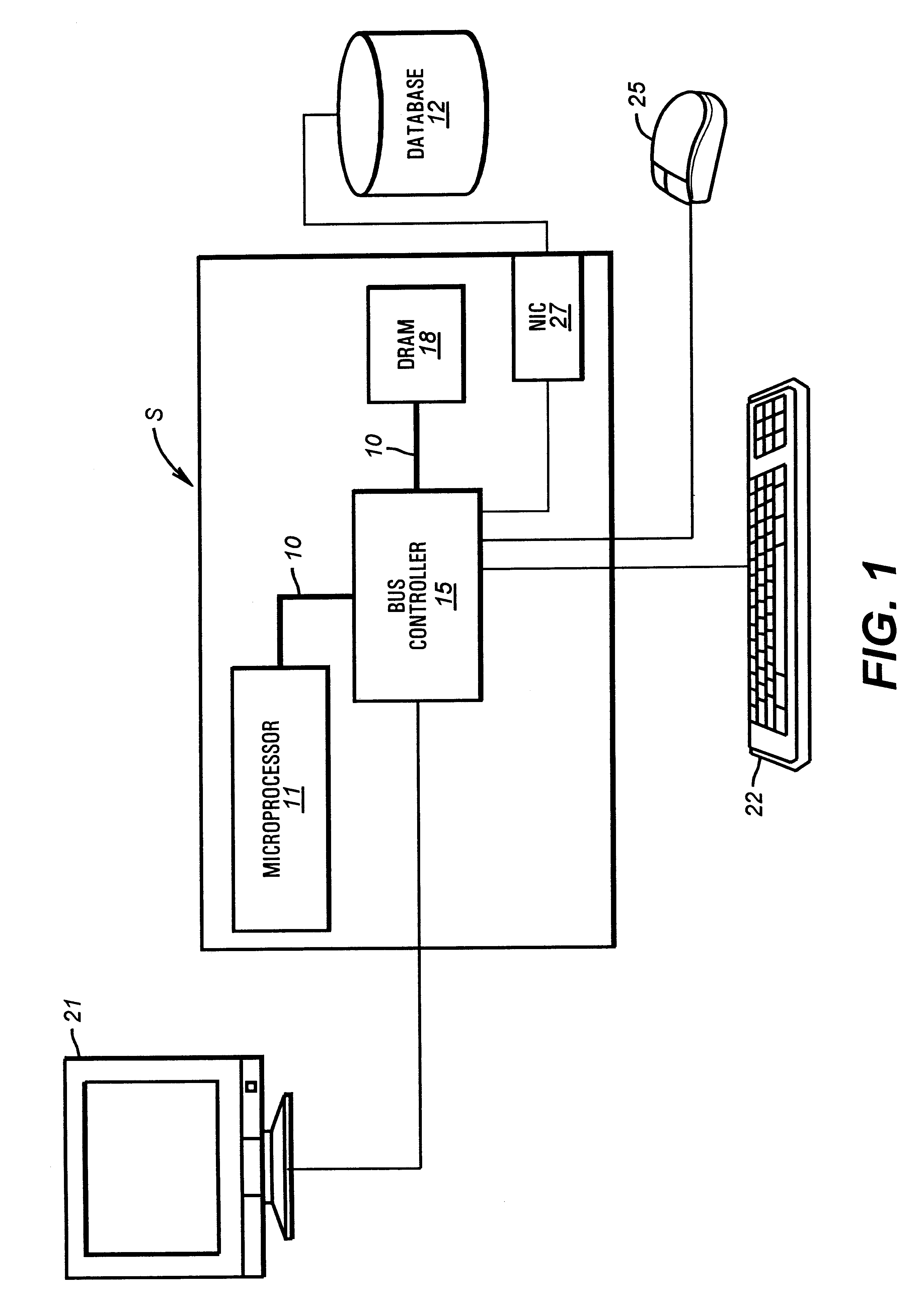

InactiveUS6341361B1Accurate analysisQuickly and efficiently and accurately testabilityElectronic circuit testingFunctional testingFault coverageGraphics

A graphical user interface (GUI) provides a design engineer the capability of automatically inserting scan logic and test logic into a design. The graphical user interface includes a scan insertion option for a design engineer to invoke a scan insertion tool to check the design for testability. The graphical user interface also permits the design engineer to invoke a test generation tool such as an automatic test pattern generator (ATPG) tool to check the design for fault coverage. The graphical user interface, which can serve as a front end for a design framework, enables a design engineer to efficiently increase testability while still in a design phase.

Owner:ADVANCED MICRO DEVICES INC

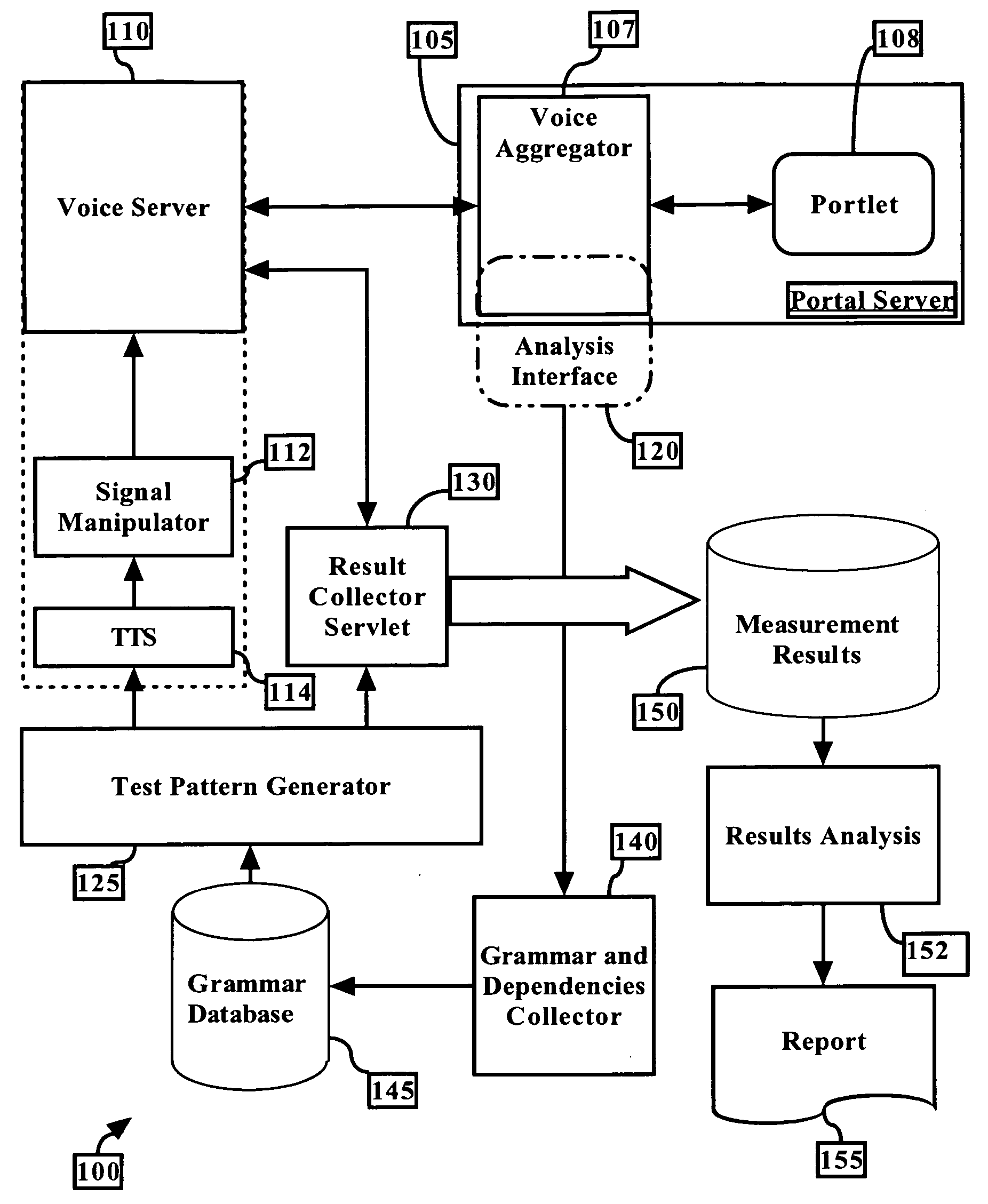

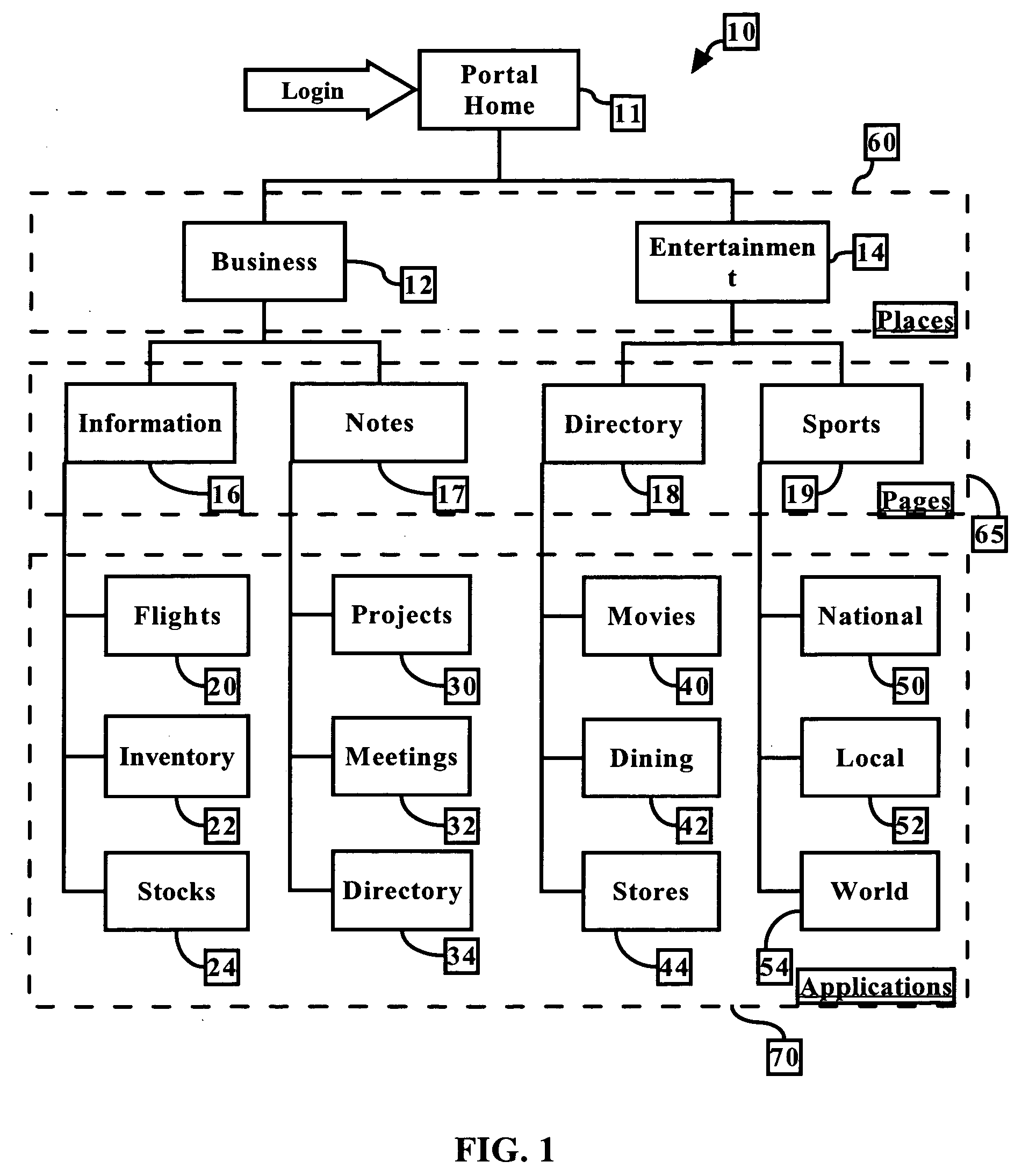

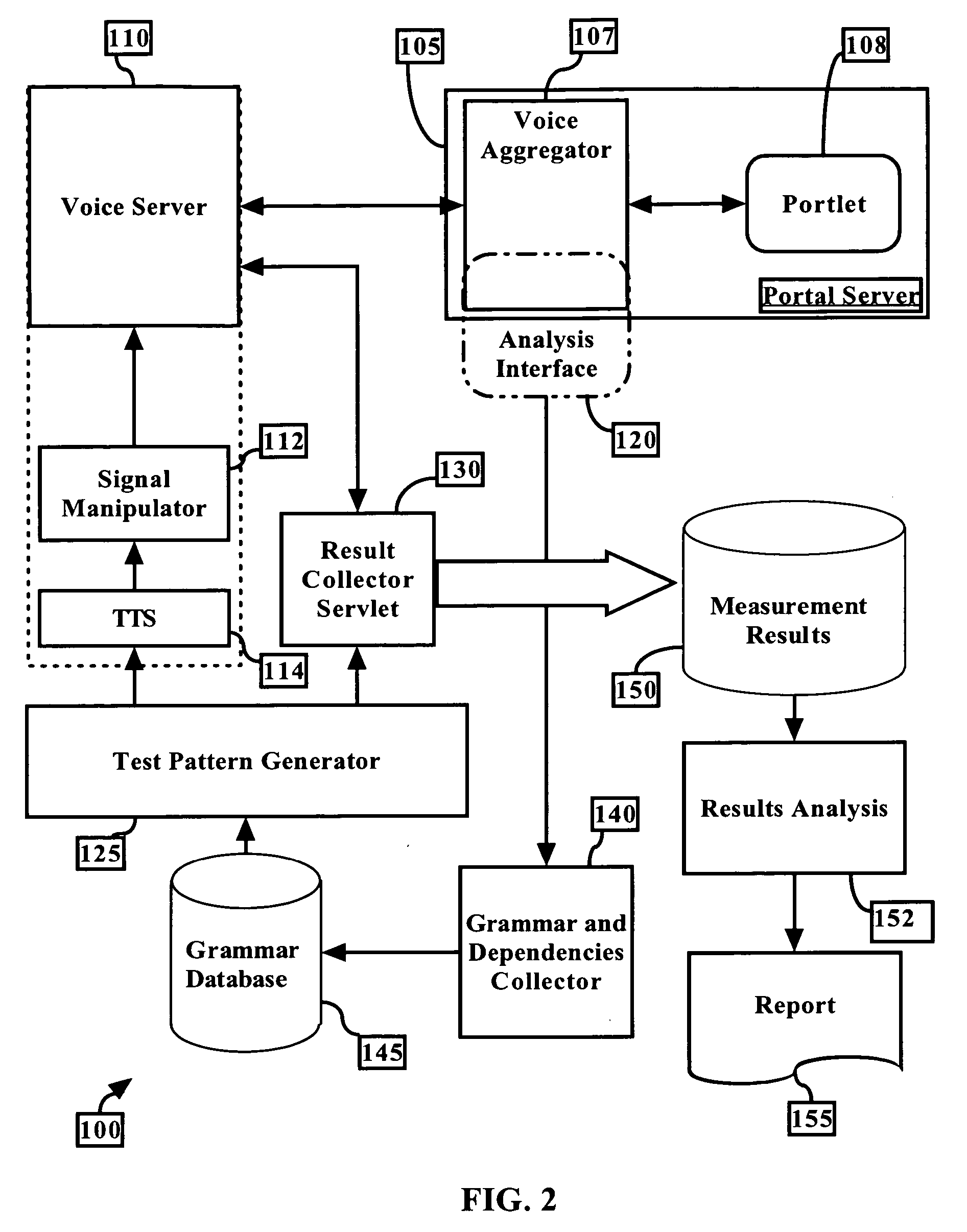

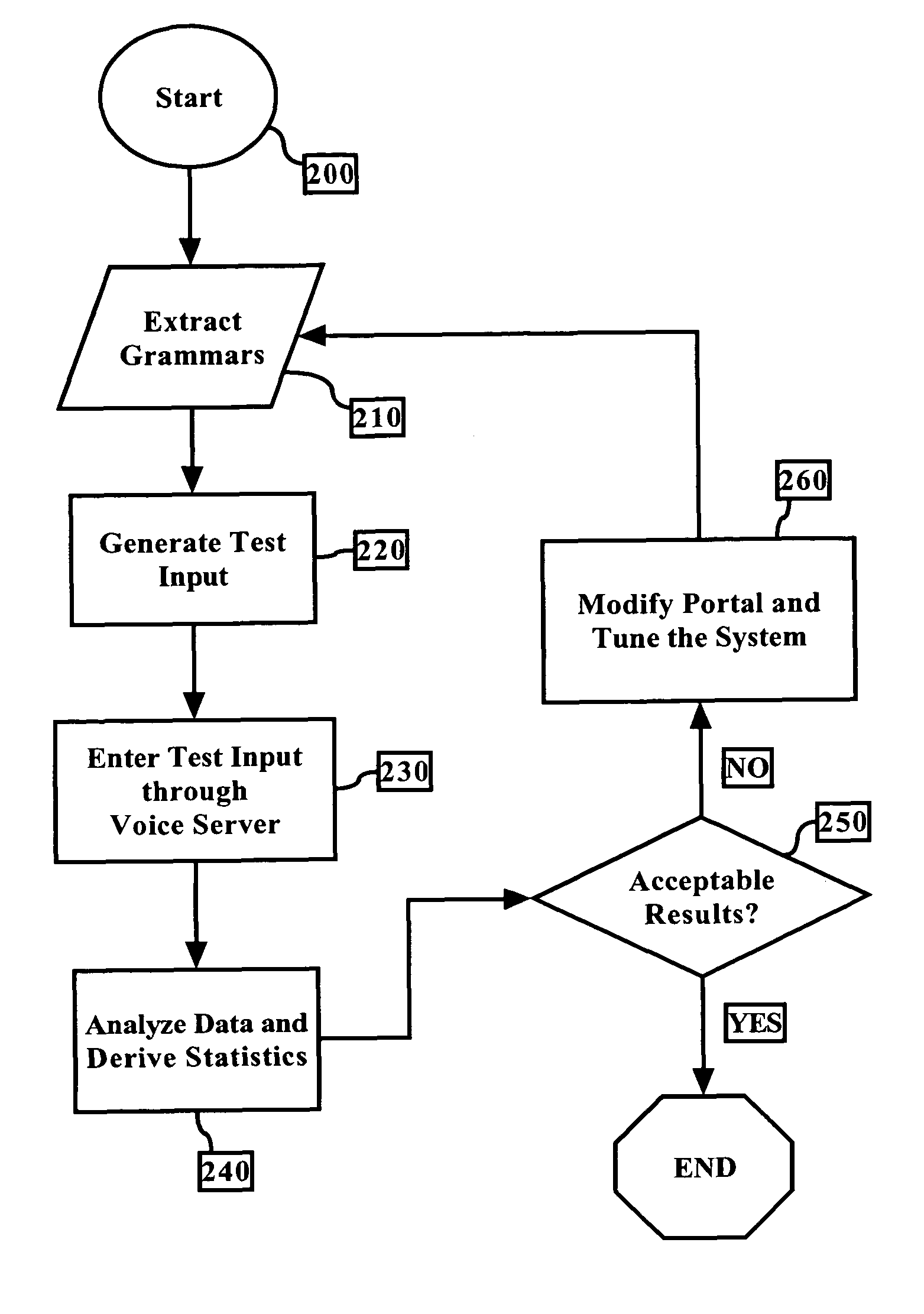

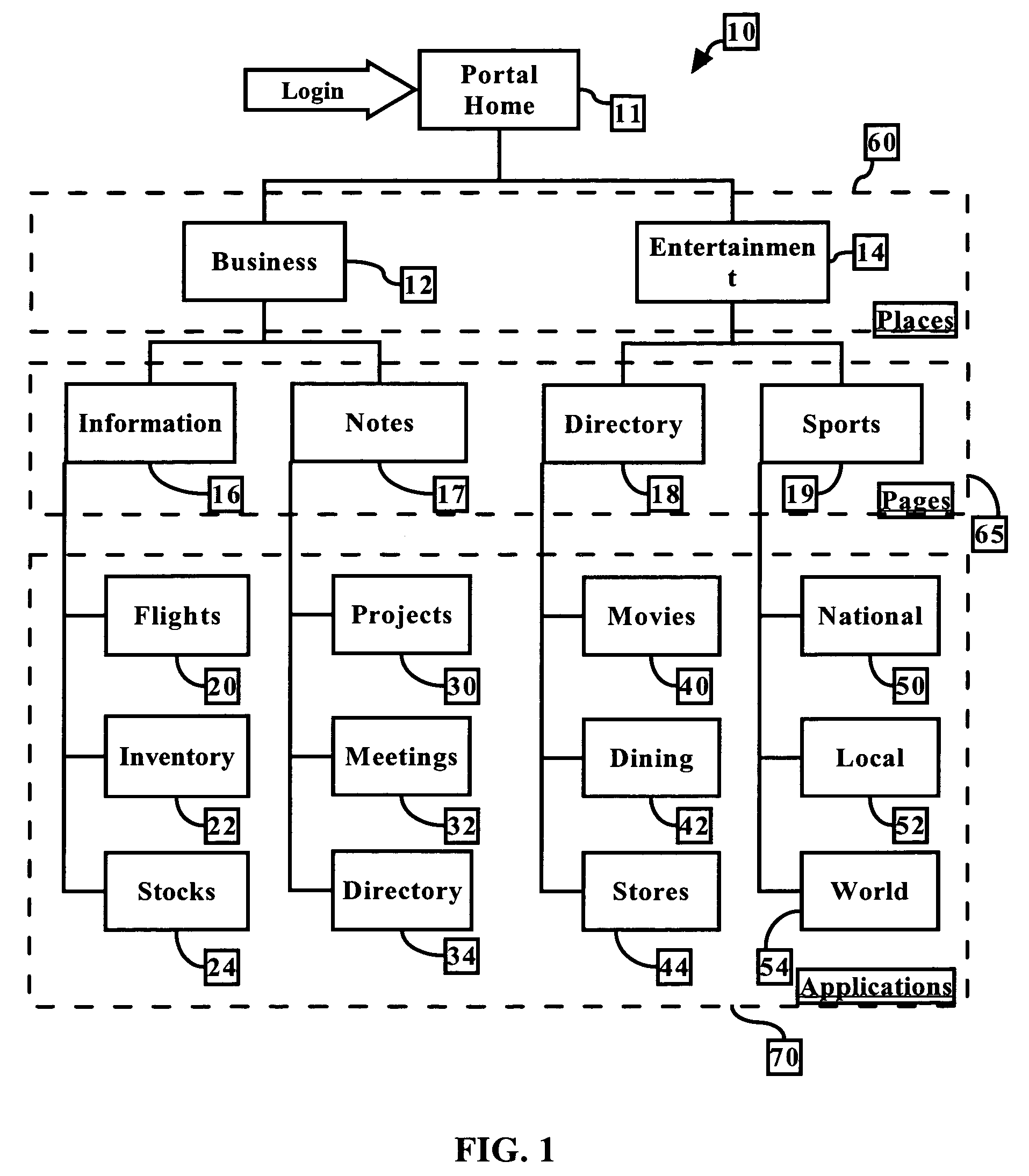

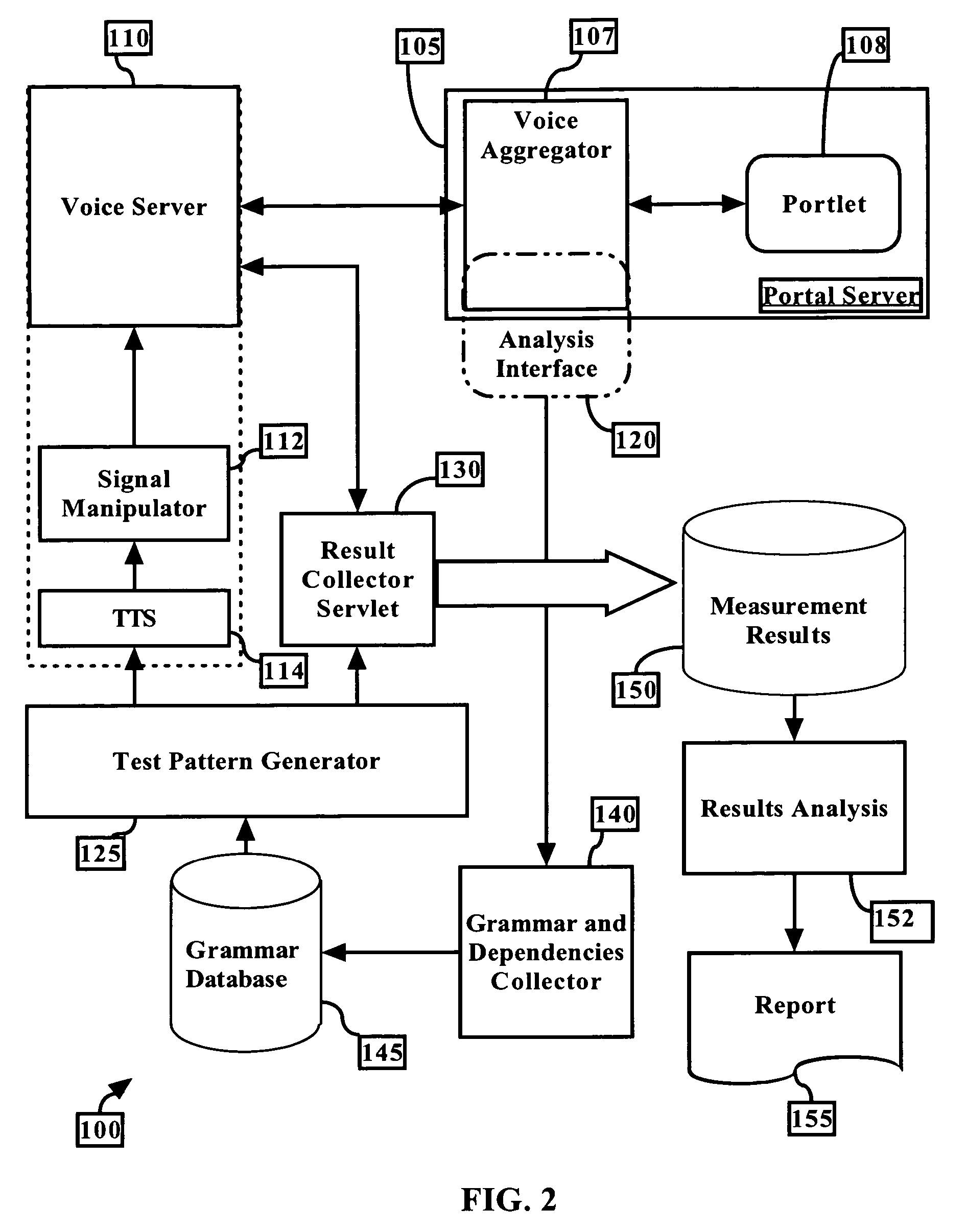

Quality evaluation tool for dynamic voice portals

ActiveUS20050131676A1Automatic call-answering/message-recording/conversation-recordingSpeech recognitionTest inputSystems analysis

A method and system for evaluating the quality of voice input recognition by a voice portal is provided. An analysis interface extracts a set of current grammars from the voice portal. A test pattern generator generates a test input for each current grammar. The test input includes a test pattern and a set of active grammars corresponding to each current grammar. The system further includes a text-to-speech engine for entering each test pattern into the voice server. A results collector analyzes each test pattern entered into the voice server with the speech recognition engine against the set of active grammars corresponding to the current grammar for said test pattern. A results analyzer derives a set of statistics of a quality of recognition of each current grammar.

Owner:NUANCE COMM INC

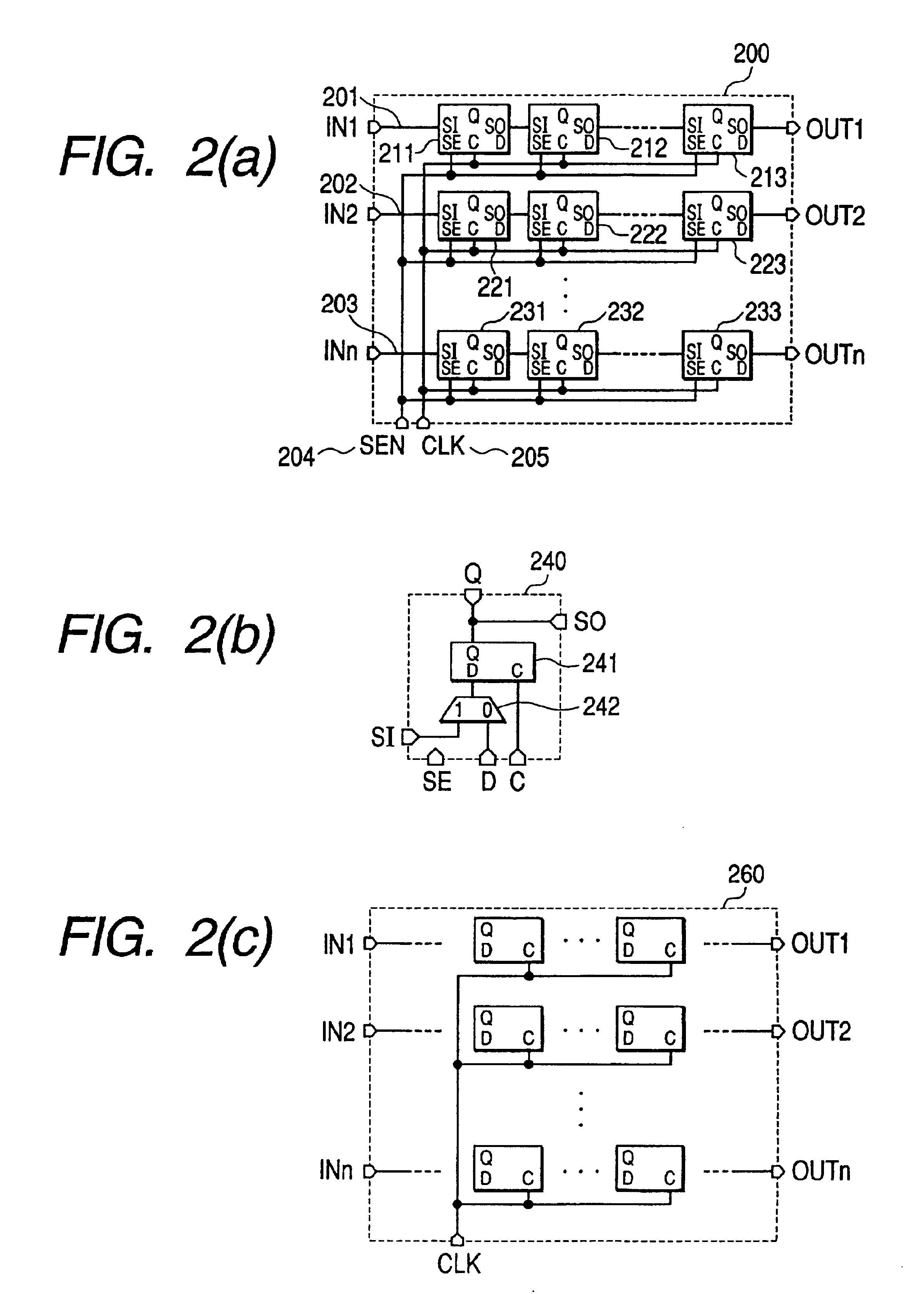

Electronic system with self-test function and simulation circuit for electronic system

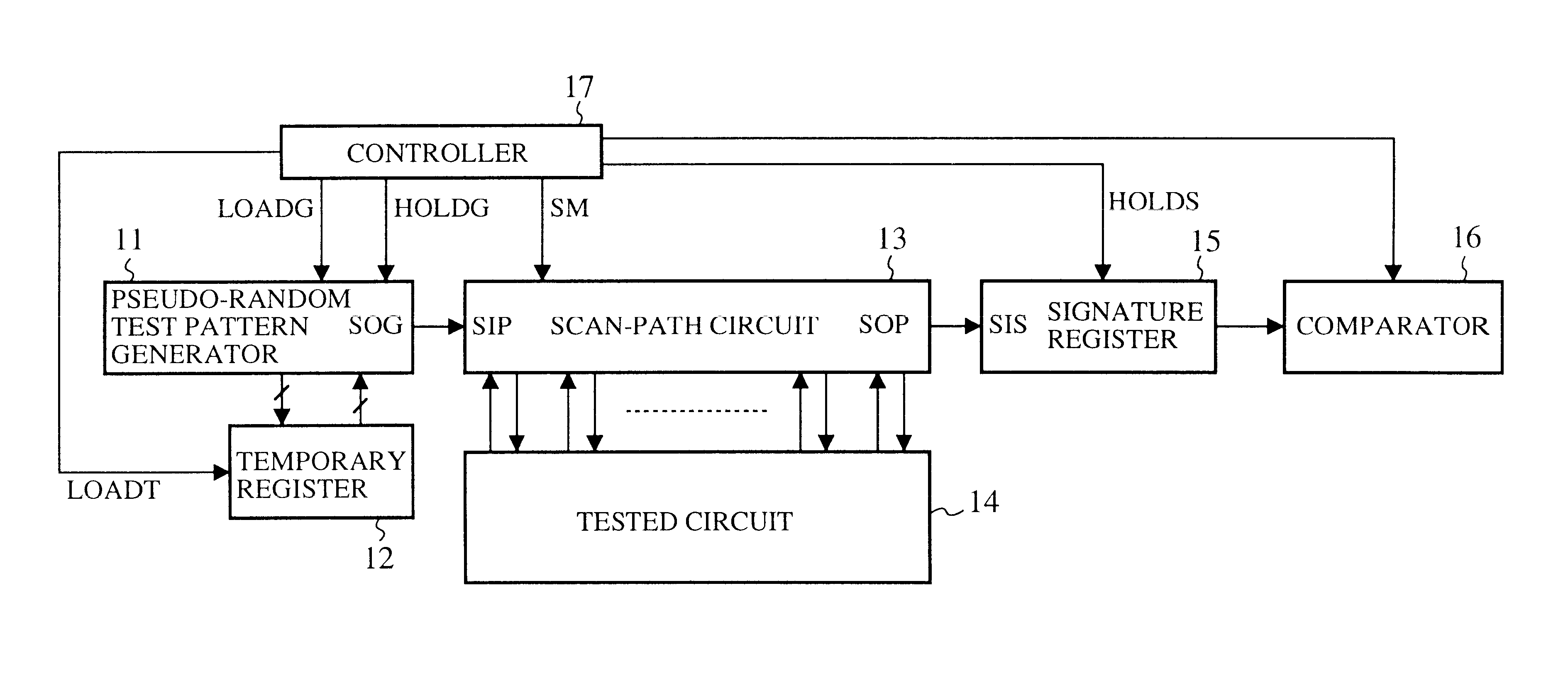

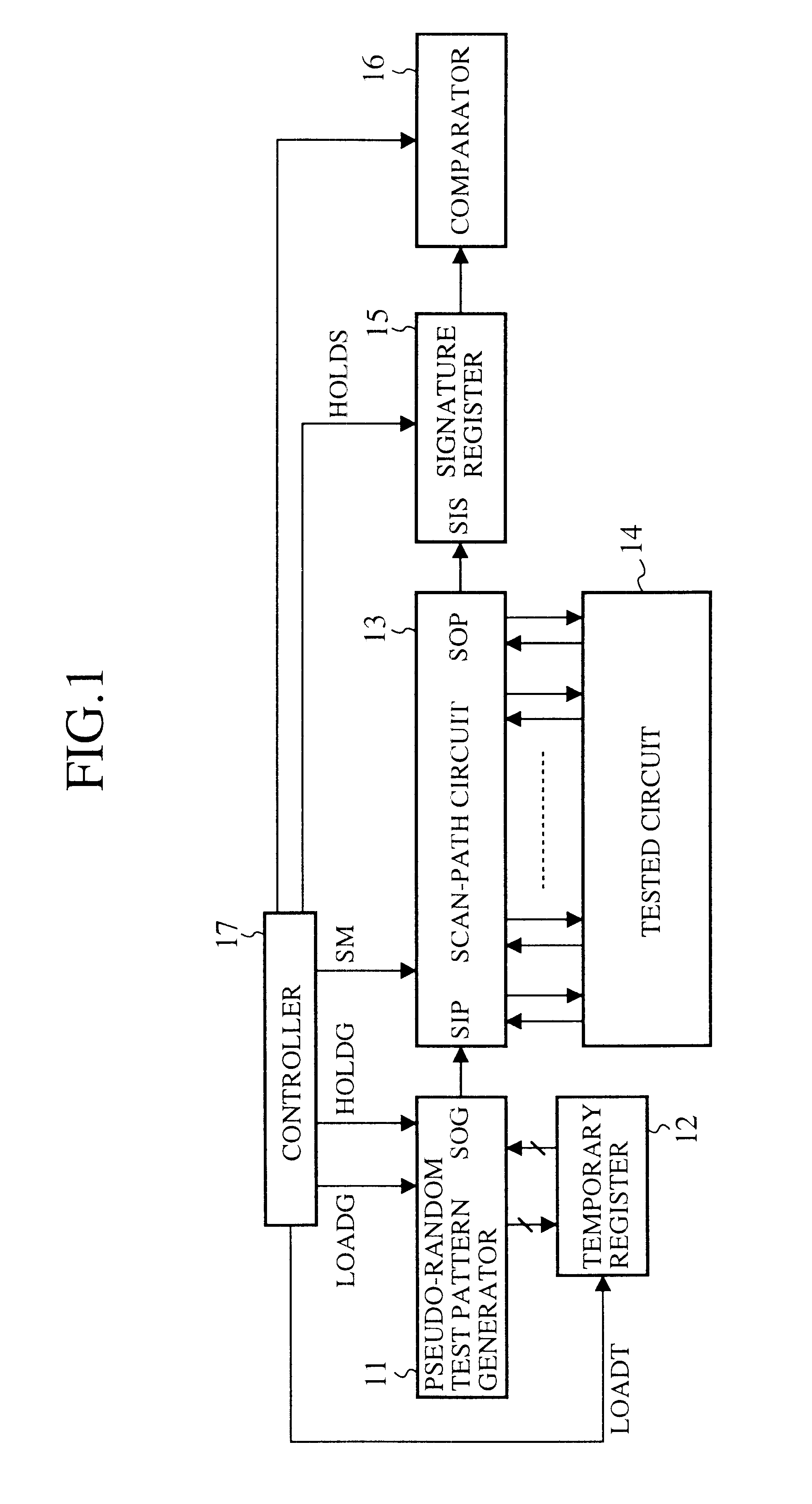

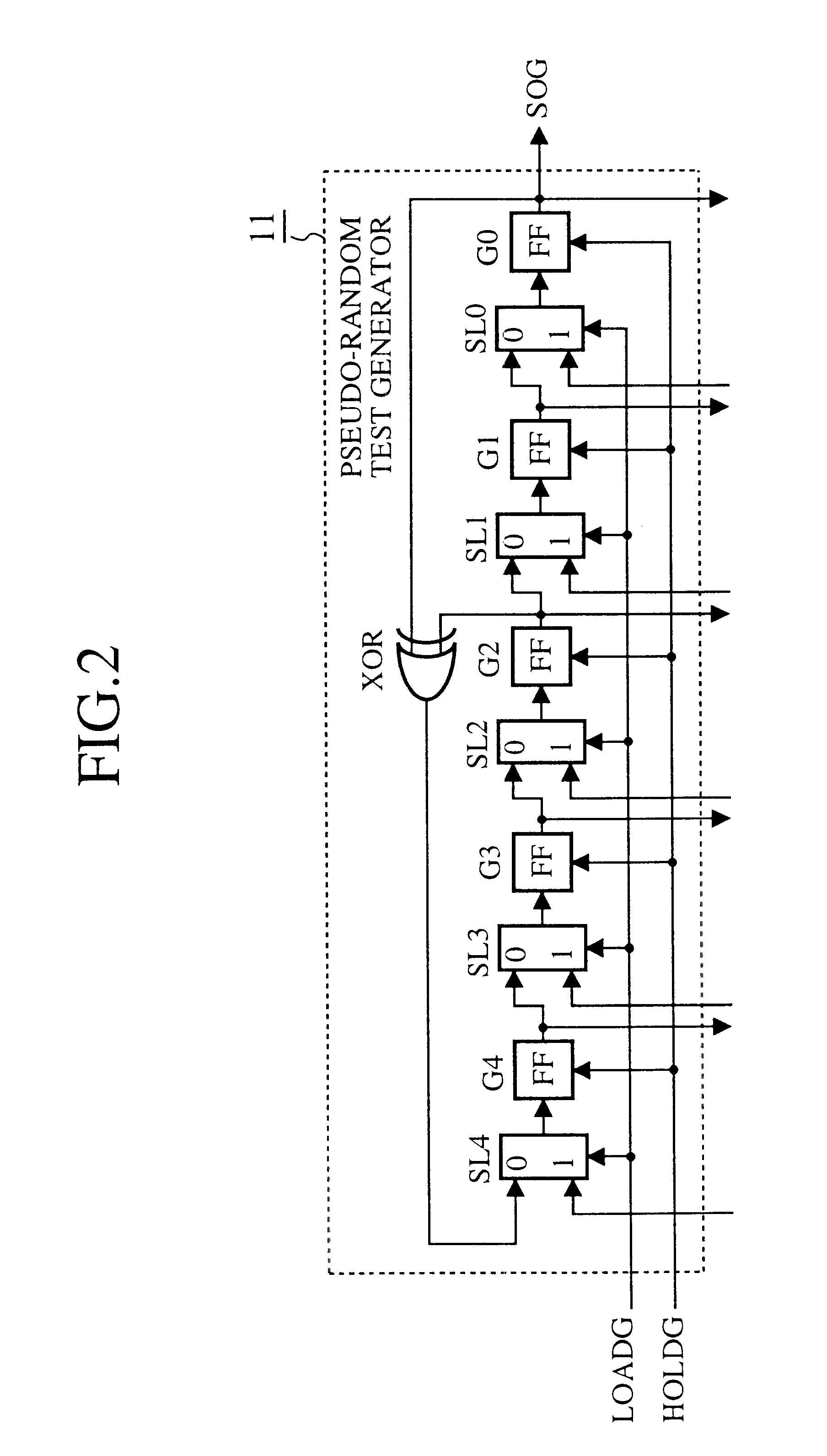

InactiveUS6401226B1Electronic circuit testingError detection/correctionElectronic systemsEngineering

An electronic system with a self-test function has a pseudo-random test pattern generator that serially generates data constituting a pseudo-random test pattern, and stores a 1-bit shifted pseudo-random test pattern obtained by shifting the pseudo-random test pattern by one bit. When a scan-path circuit supplies the pseudo-random test pattern to a tested circuit which carries out an operation based on the pseudo-random test pattern, and then loads an operation result of the tested circuit, the 1-bit shifted pseudo-random test pattern is supplied to the tested circuit as the next pseudo-random test pattern. This makes it possible to solve a problem of a conventional electronic system in that it takes a long time to evaluate the operation results of the tested circuit because it takes at least (1+n)xm clock cycles, where m is the number of pseudo-random test patterns supplied to the tested circuit and n is the number of stages of the scan-path circuit.

Owner:MITSUBISHI ELECTRIC CORP

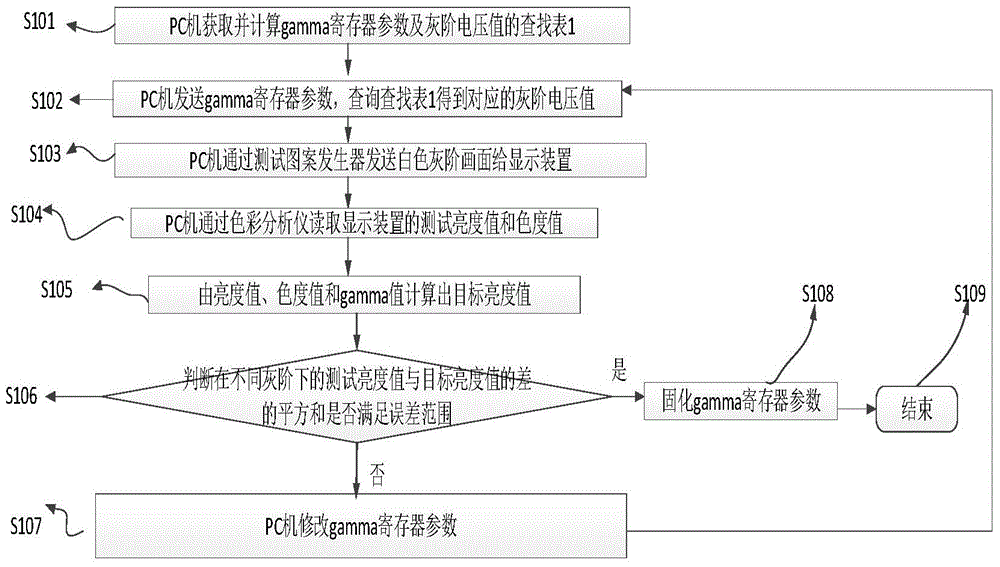

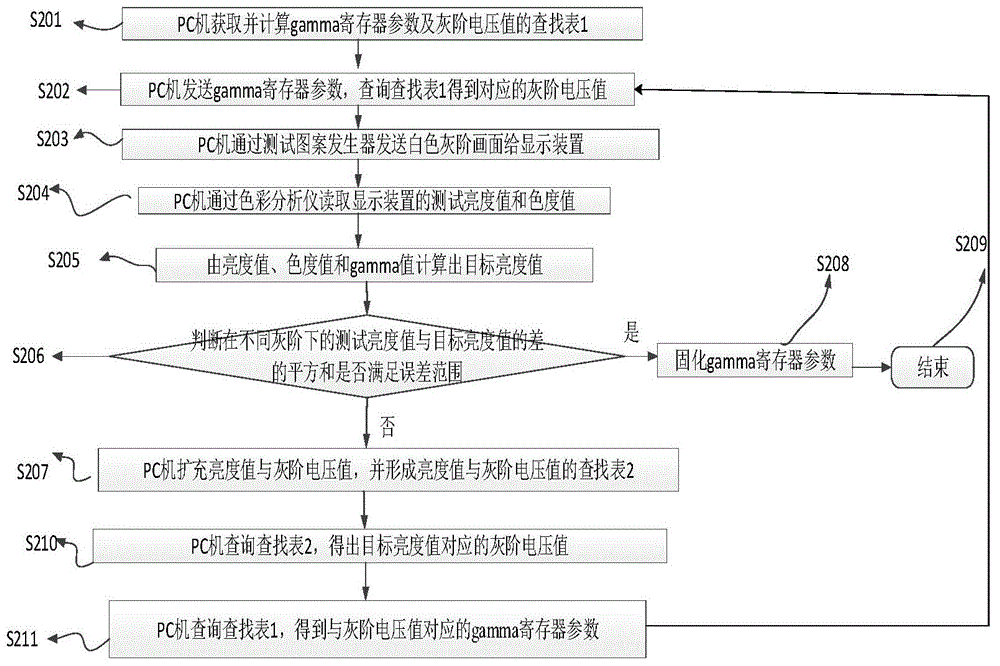

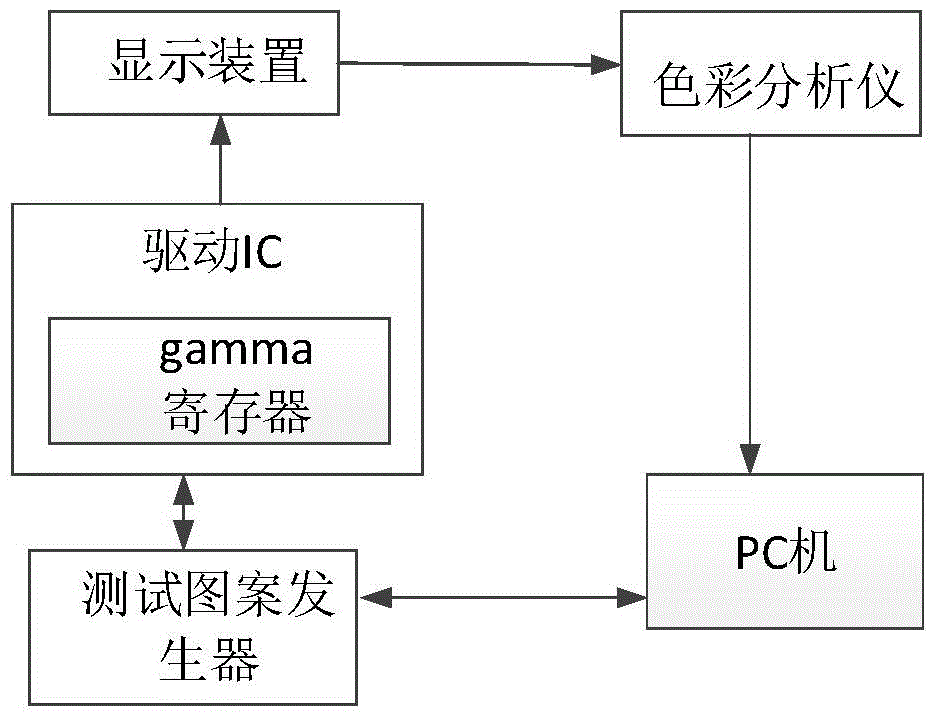

Automatic gamma and white balance correction method and device for display device

ActiveCN104809974AWill not be affected by subjective judgmentImprove Calibration AccuracyCathode-ray tube indicatorsElectricityGray level

The invention relates to a correction method and device, in particular to an automatic gamma and white balance correction method and a device for a display device. The automatic gamma and white balance correction device comprises a display device, a color analysis meter, a PC (Personal Computer) and a test pattern generator which are sequentially connected electrically; the test pattern generator is electrically connected with the display device through a driving IC (Integrated Circuit). According to the automatic gamma and white balance correction device, whether the quadratic sum of difference between luminance values under different gray levels and target luminance values satisfies an error range or not is judged, correction is finished after solidification of gamma register parameters in a gamma register of the driving IC, the gamma register parameters are modified if not, and recalibration is performed until the quadratic sum of the difference between the luminance values and the targeted luminance values satisfies the error range; a calibration result is automatically judged after calibration of gamma and white balance and the calibration result is not influenced by subjective judgment of tested person.

Owner:TRULY HUIZHOU SMART DISPLAY

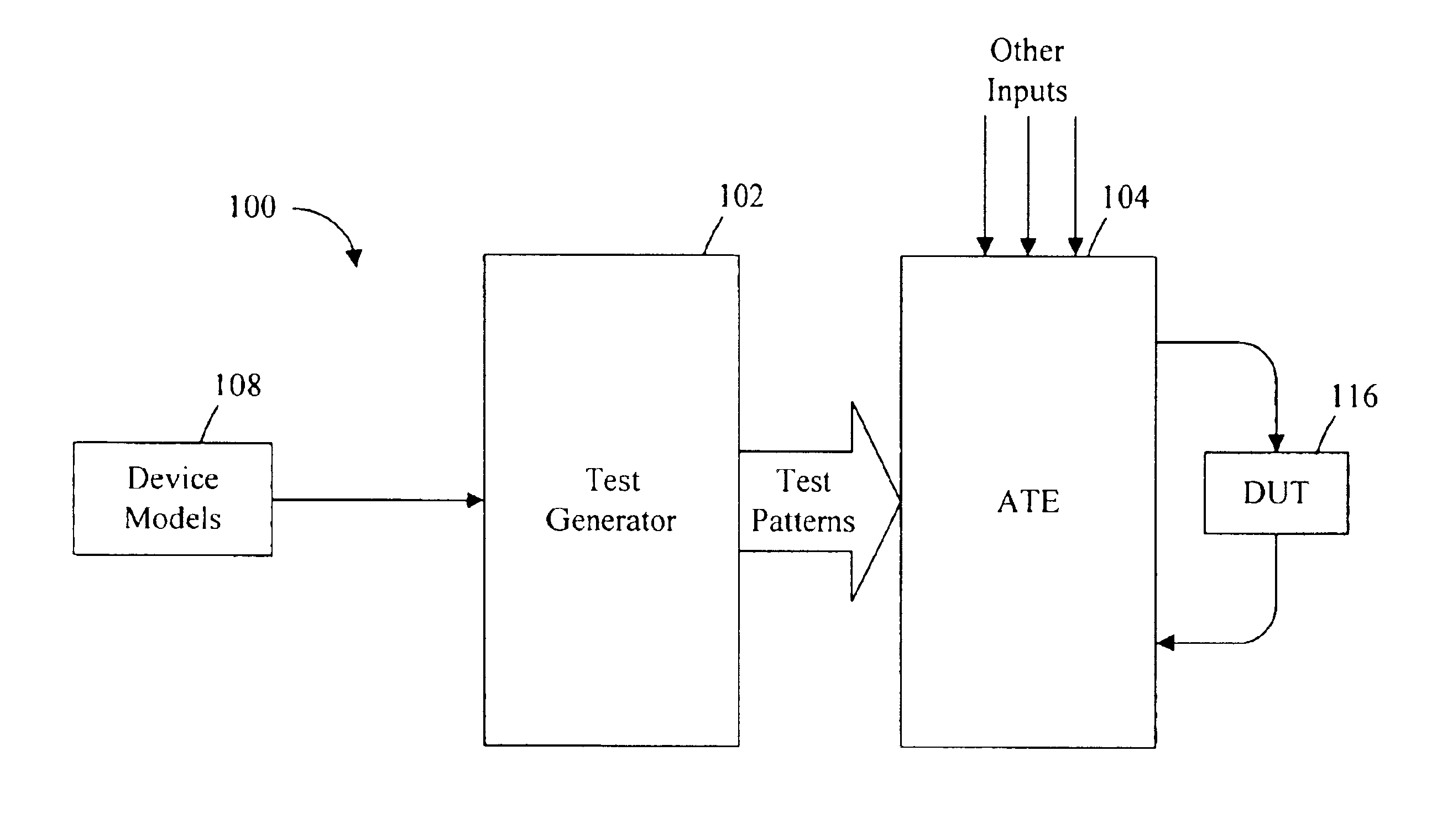

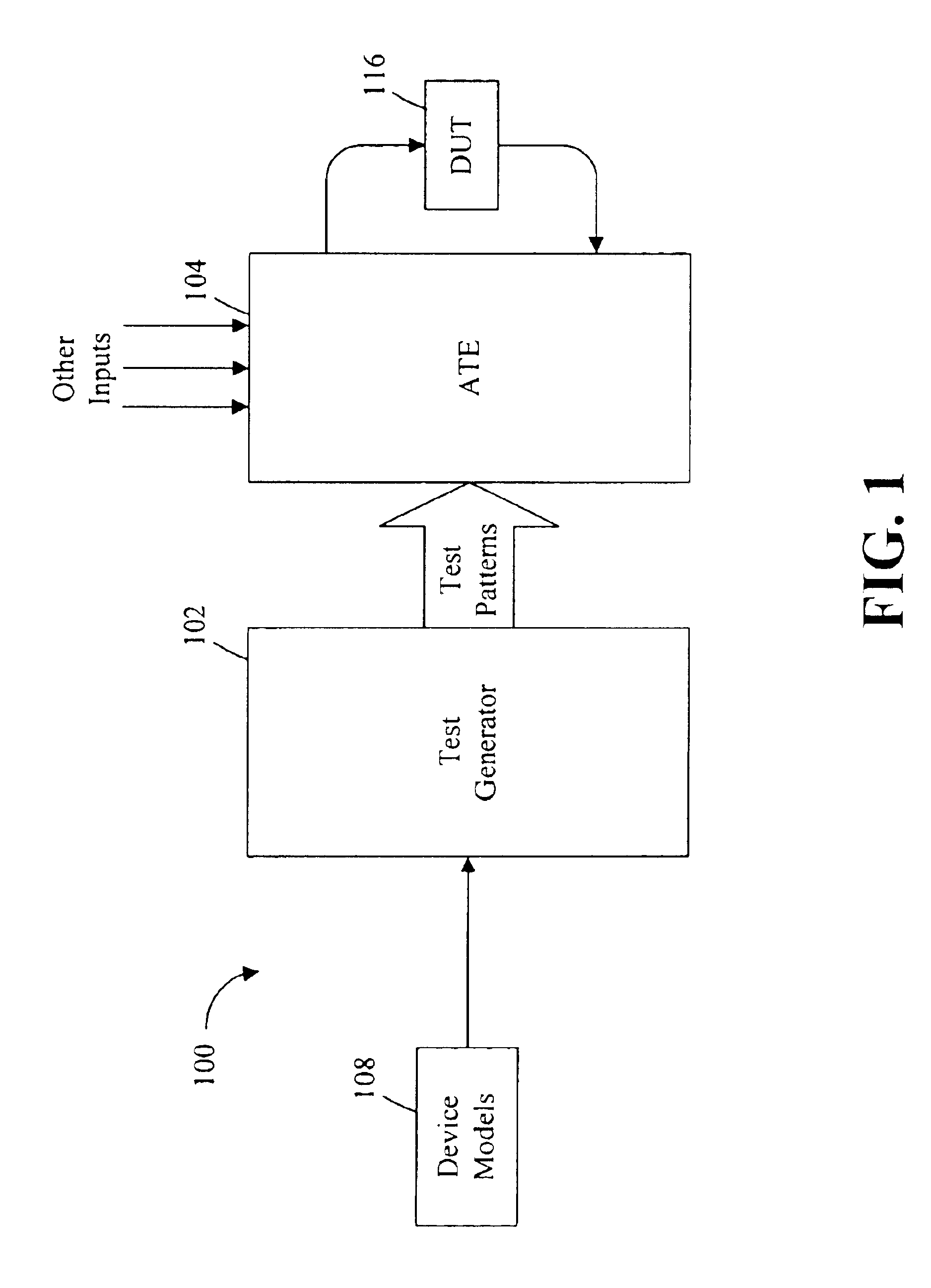

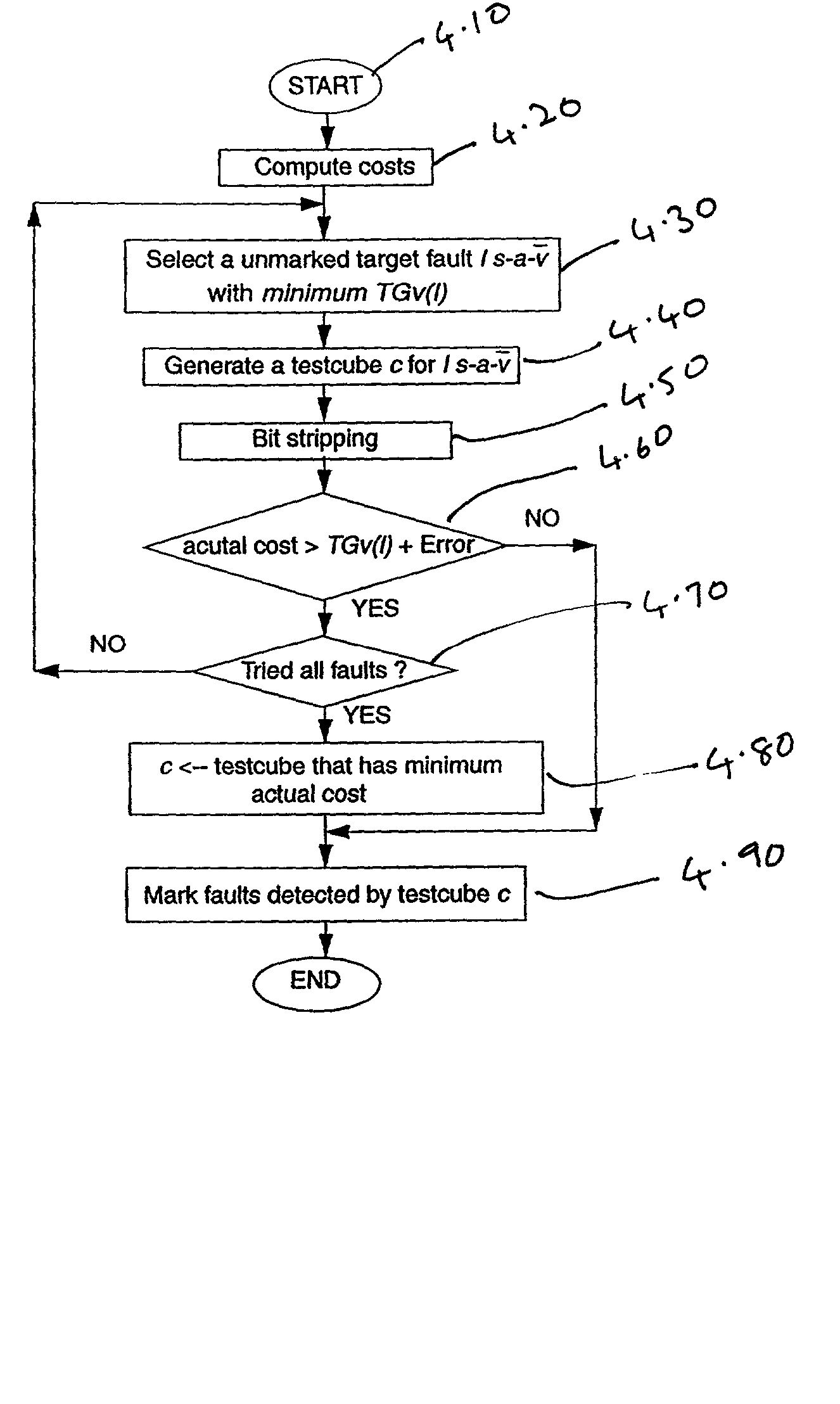

Apparatus and method for generating a set of test vectors using nonrandom filling

The present invention is generally directed to an improved automatic test pattern generator for generating test patterns that are used by an integrated circuit testing device. In accordance with one aspect of the invention, a method is provided for generating a set of test vectors for testing an integrated circuit, each test vector of the set of test vectors containing a plurality of bits defining test inputs for the integrated circuit. The method includes the steps of defining a list of faults for the integrated circuit, and generating at least one test vector that defines values for those inputs necessary to detect at least one target fault selected from the list of faults, the values comprising only a portion of the bits of the at least one test vector, wherein a remainder of the bits in the at least one test vector are unspecified bit positions. The method further includes the step of setting the values of a plurality of the unspecified bit positions using a non-random filling methodology.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

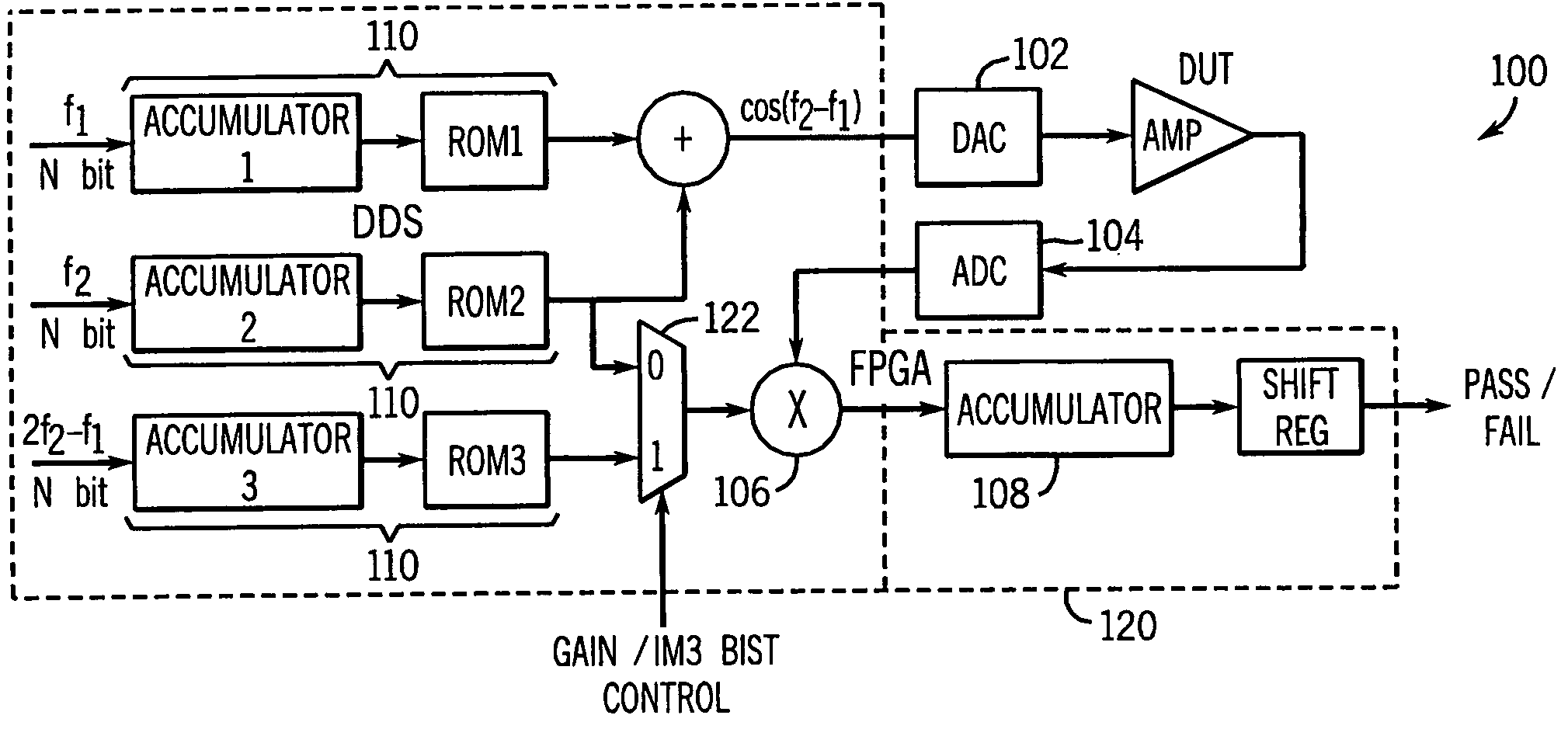

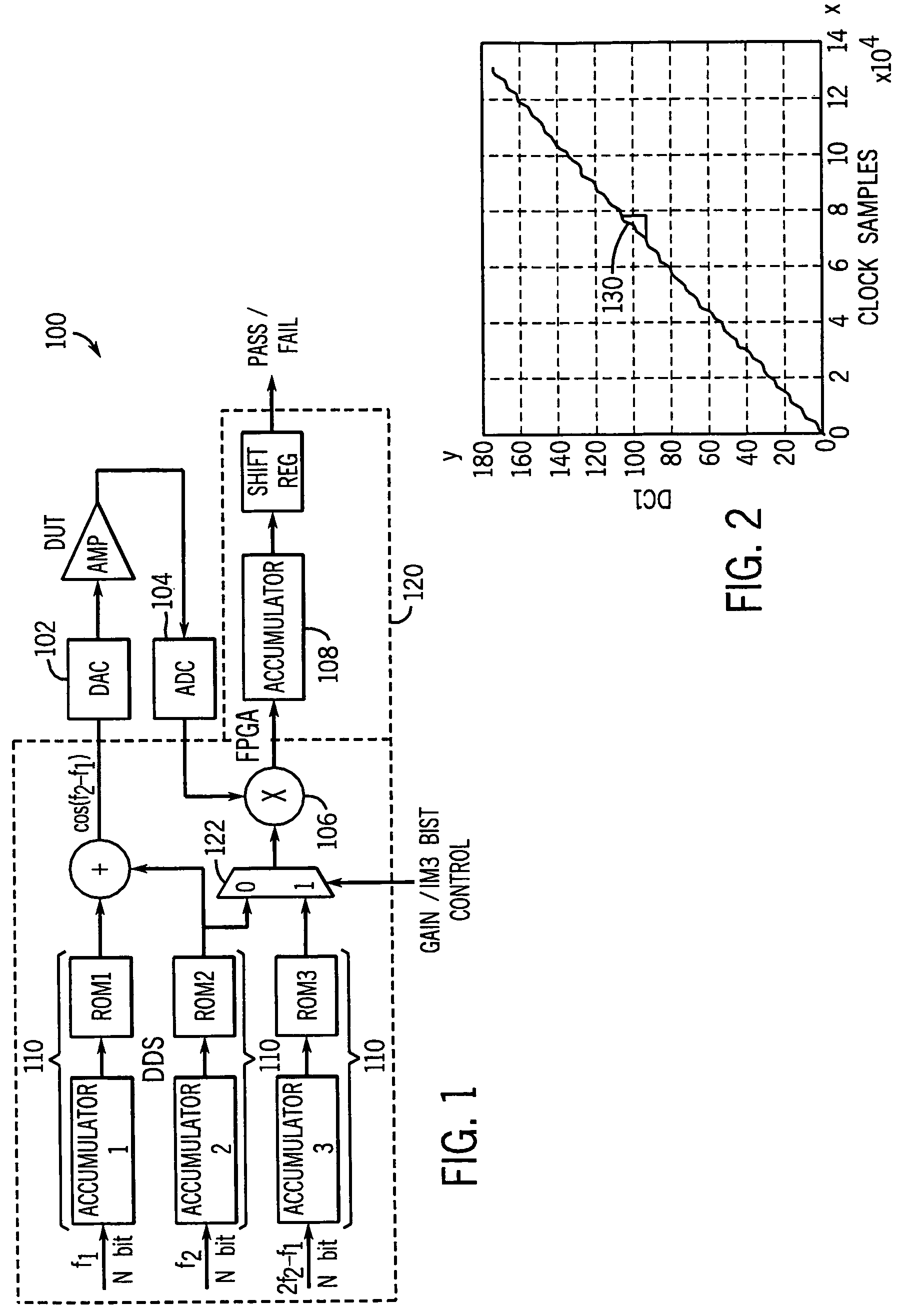

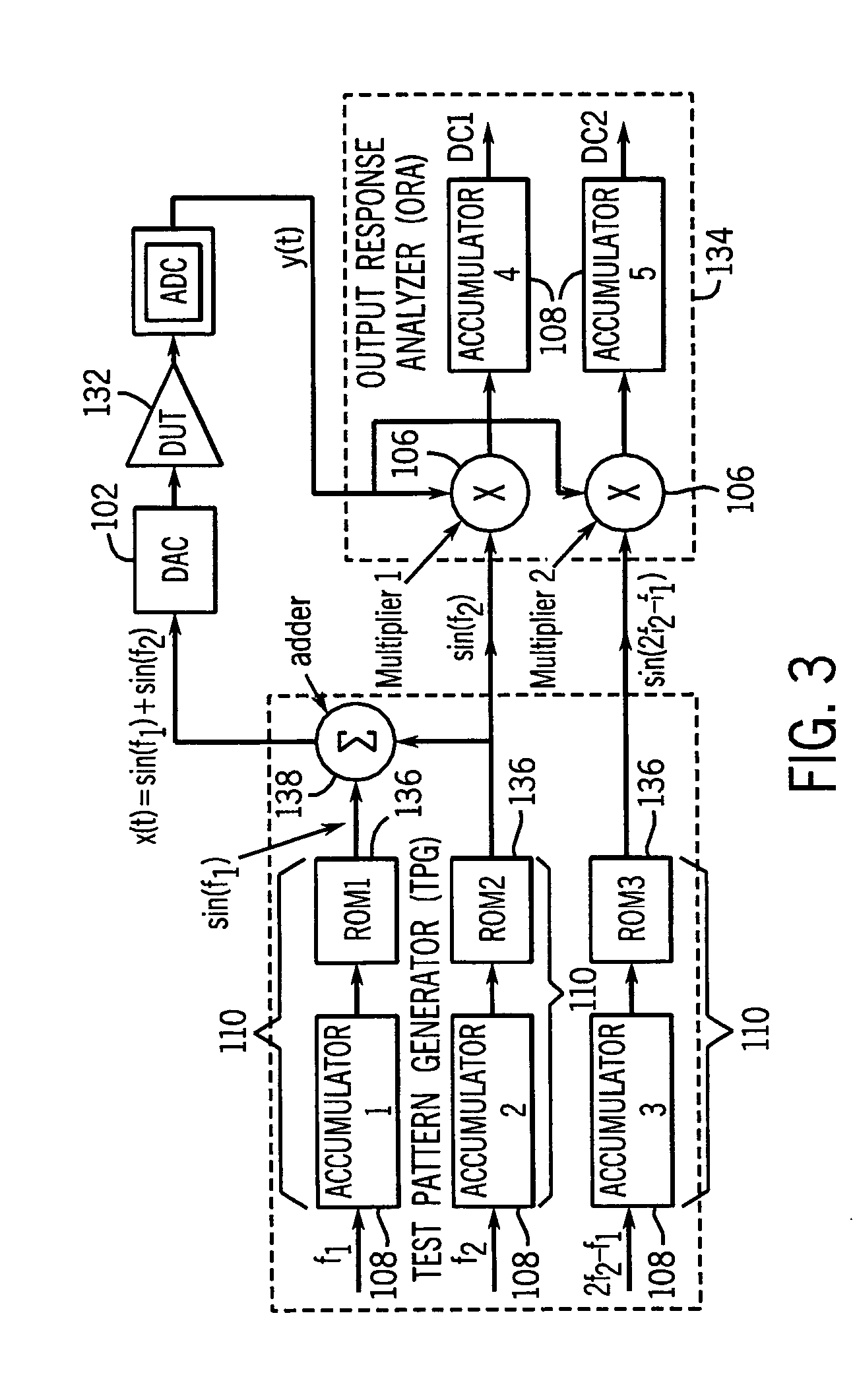

Automatic analog test & compensation with built-in pattern generator & analyzer

ActiveUS20060020865A1Electronic circuit testingError detection/correctionFrequency spectrumEngineering

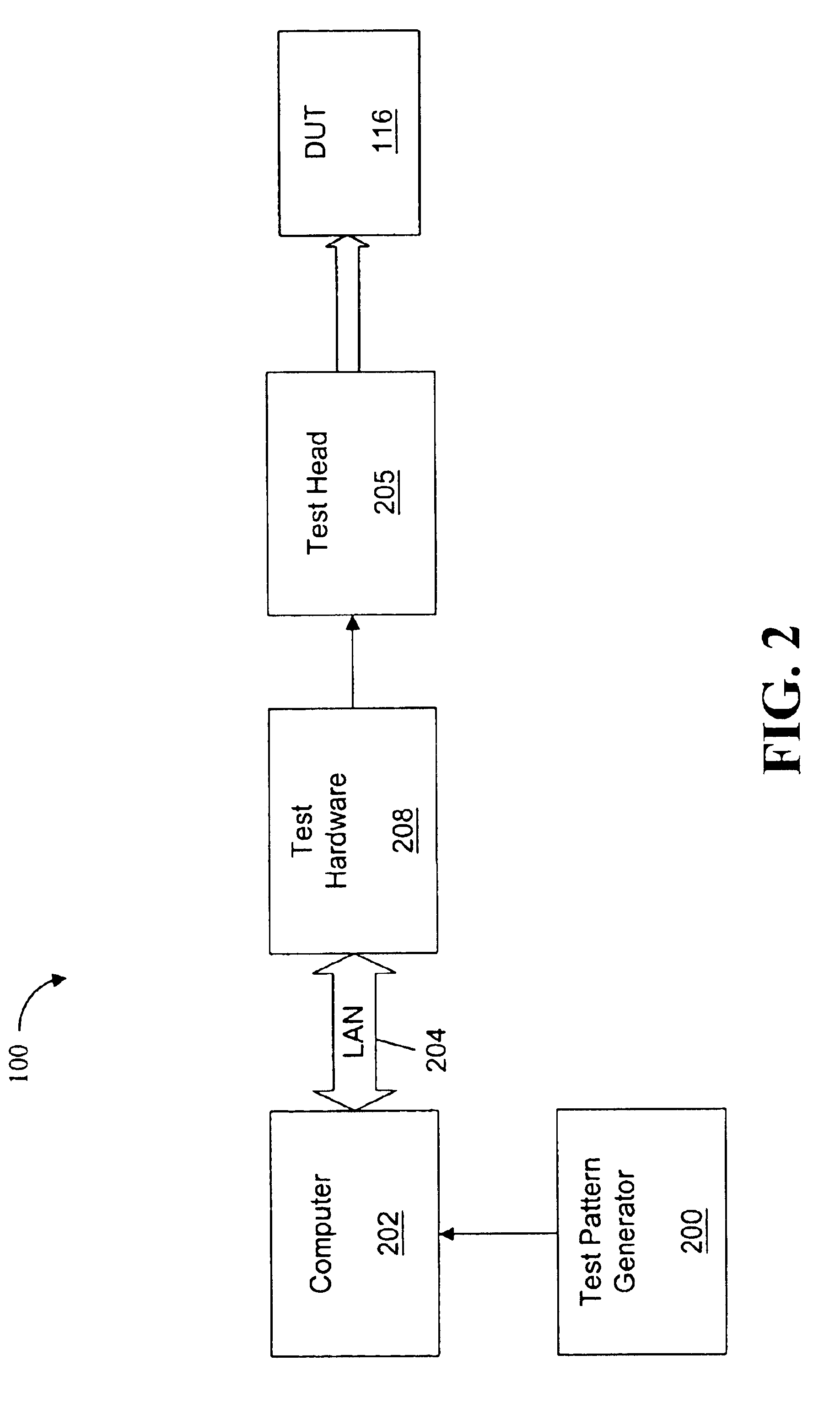

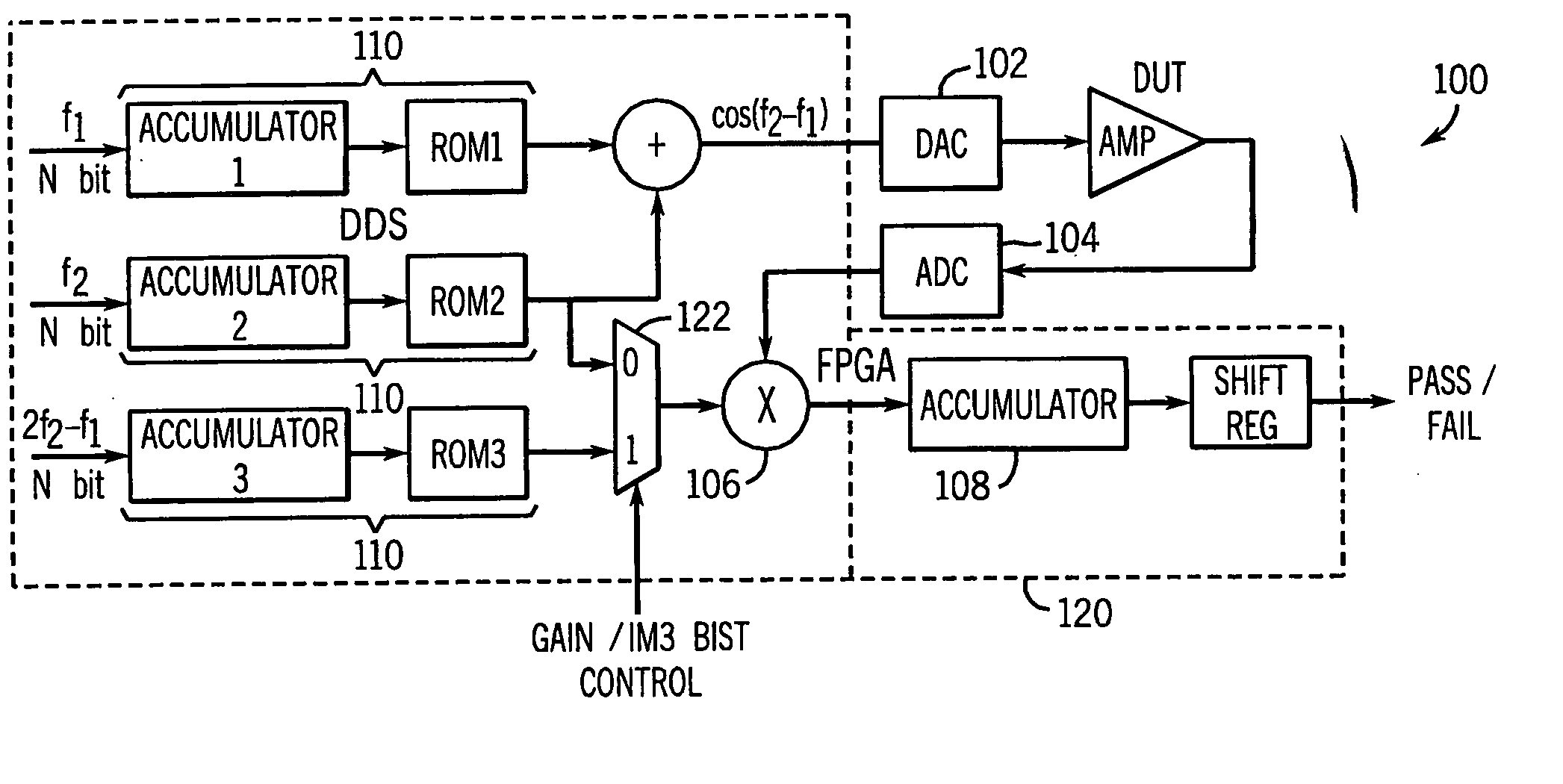

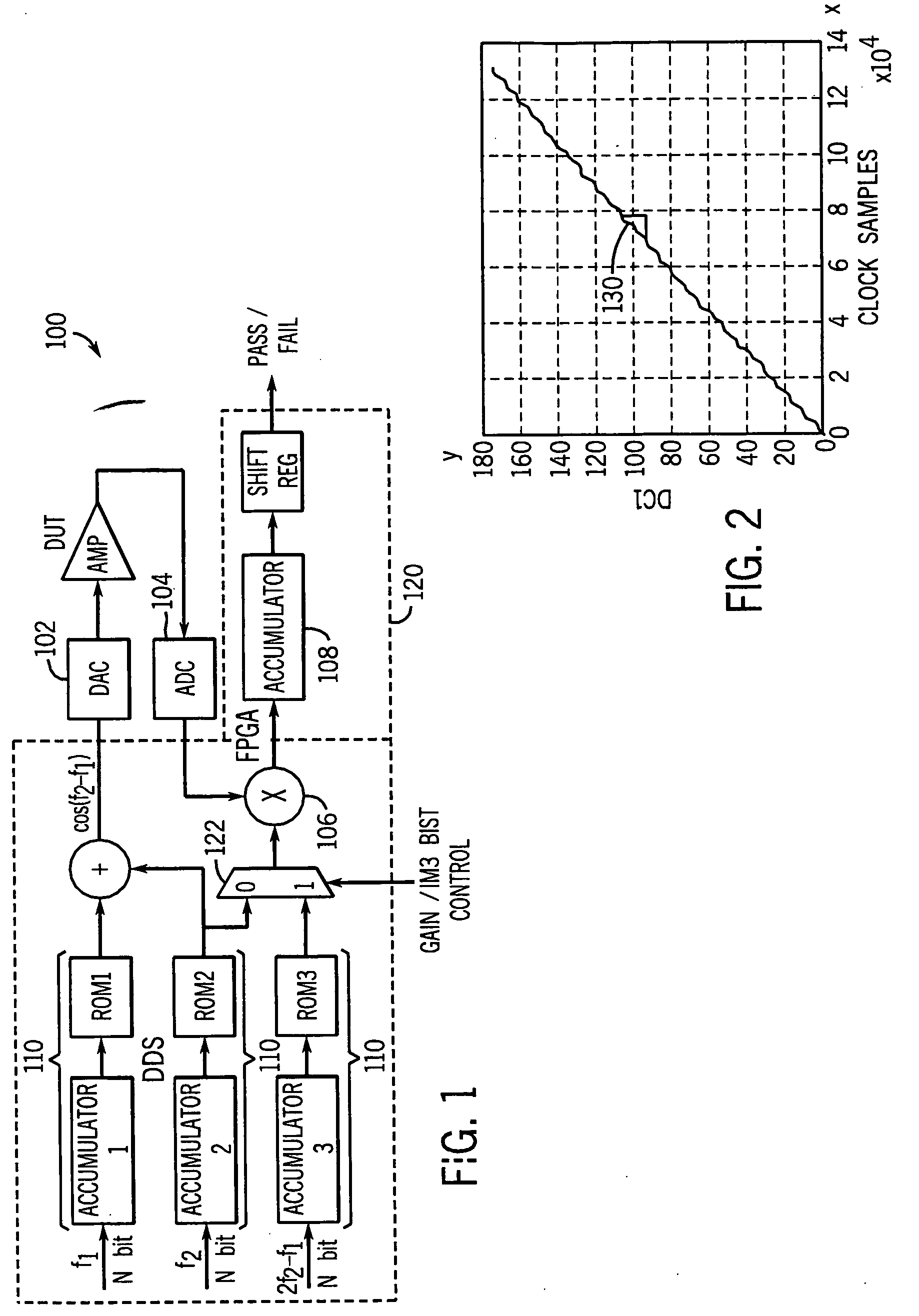

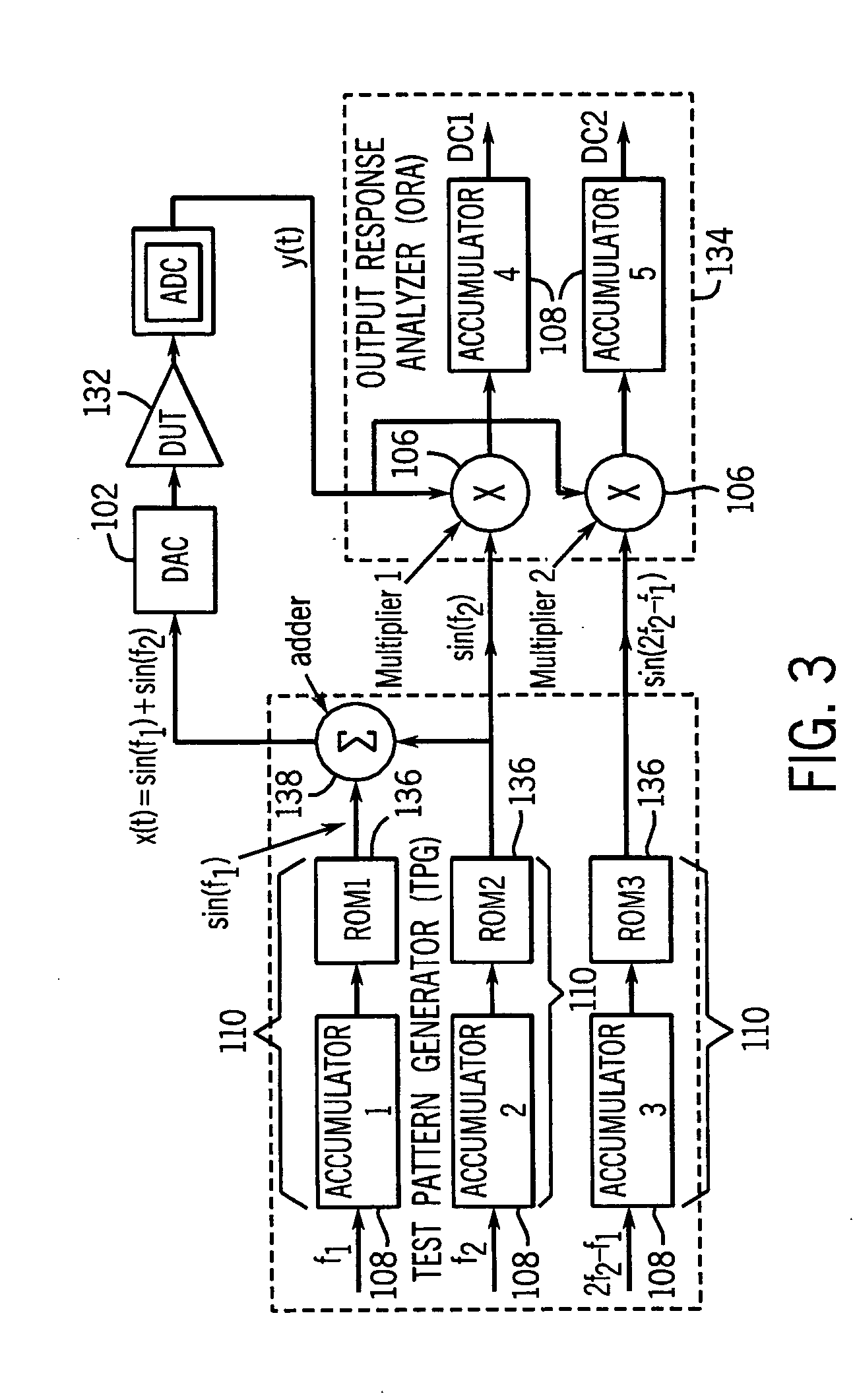

A built-in-self test (BIST) scheme for analog circuitry functionality tests such as frequency response, gain, cut-off frequency, signal-to-noise ratio, and linearity measurement. The BIST scheme utilizes a built-in direct digital synthesizer (DDS) as the test pattern generator that can generate various test waveforms such as chirp, ramp, step frequency, two-tone frequencies, sweep frequencies, MSK, phase modulation, amplitude modulation, QAM and other hybrid modulations. The BIST scheme utilizes a multiplier followed by an accumulator as the output response analyzer (ORA). The multiplier extracts the spectrum information at the desired frequency without using Fast Fourier Transform (FFT) and the accumulator picks up the DC component by averaging the multiplier output.

Owner:AUBURN UNIV

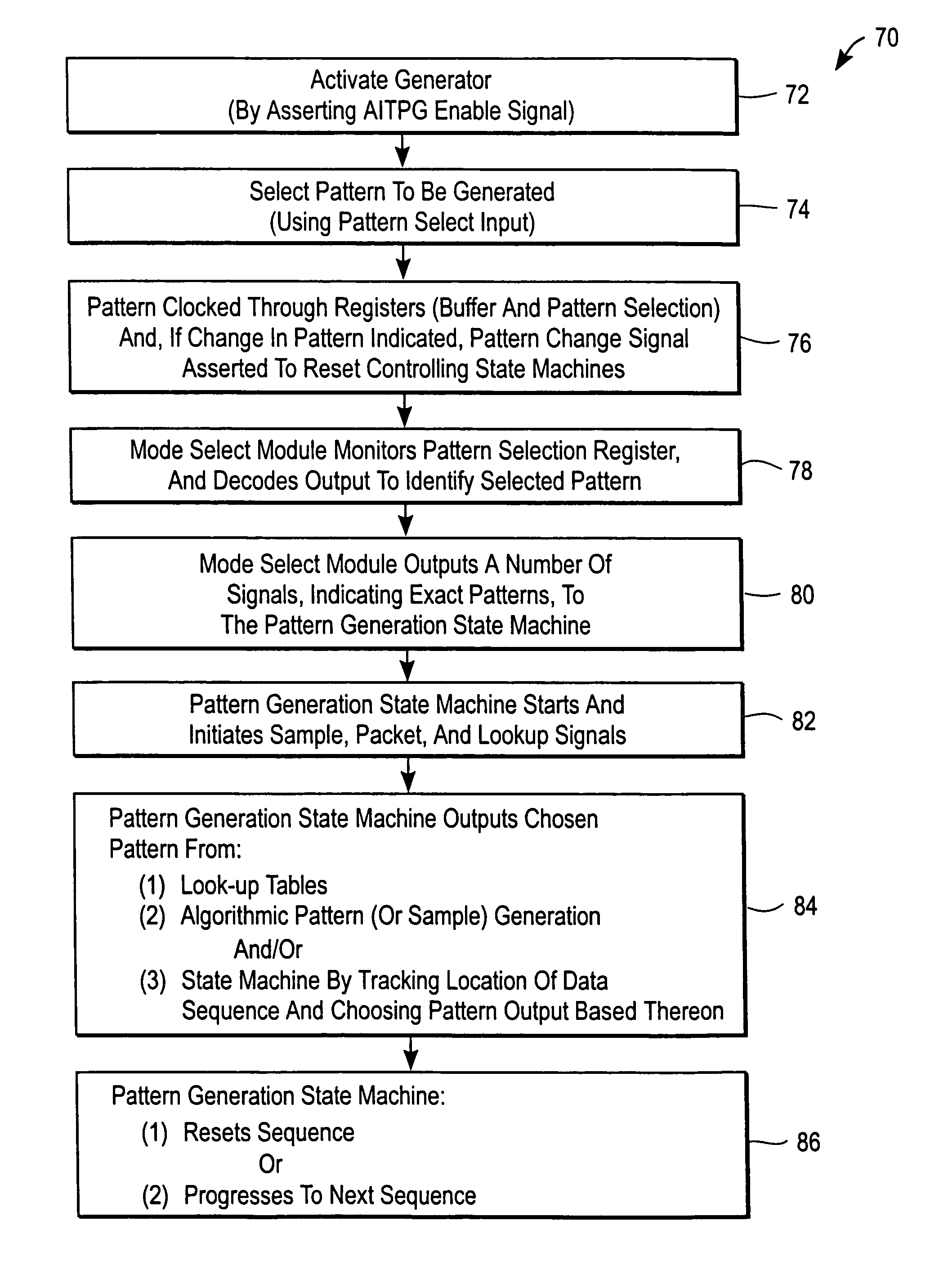

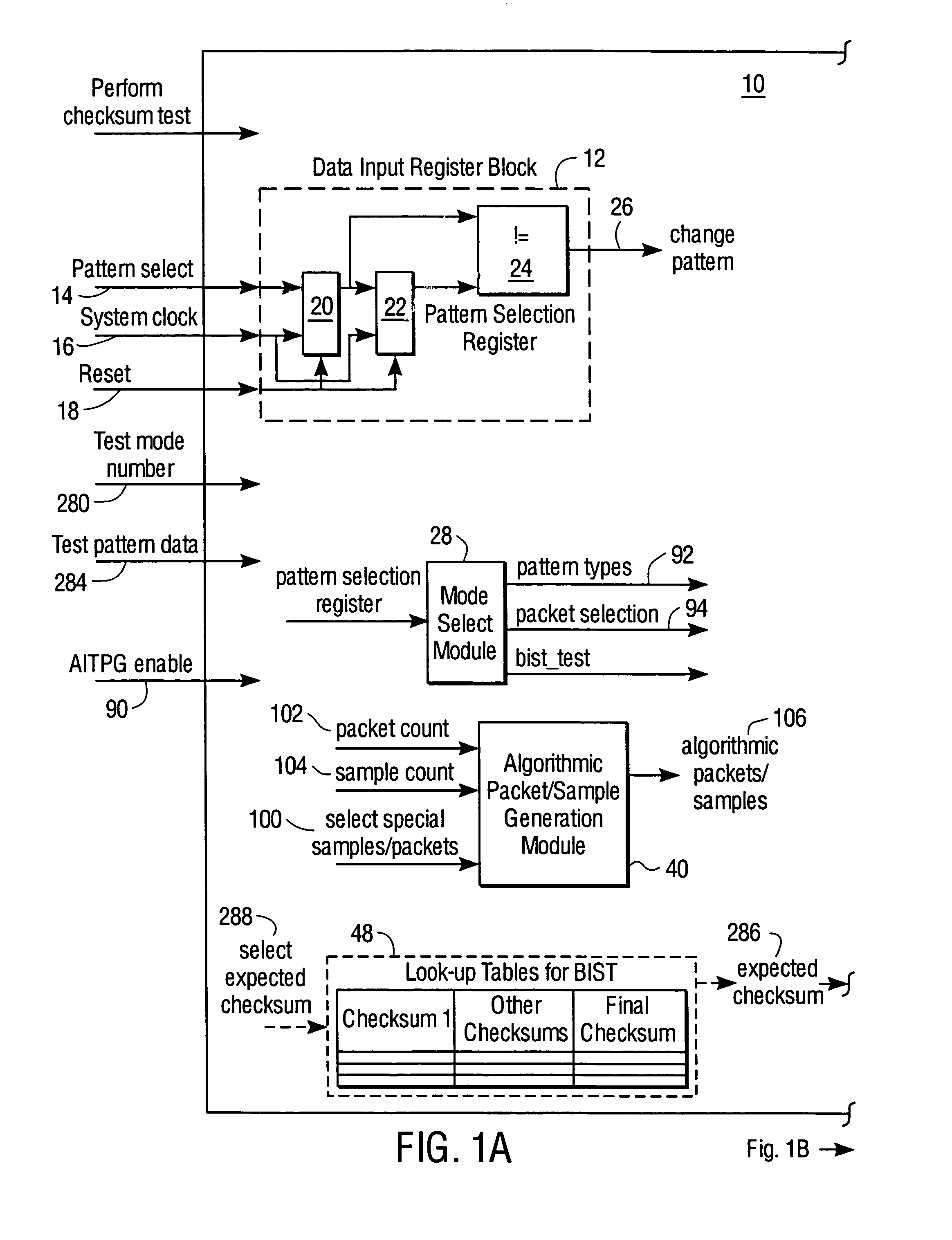

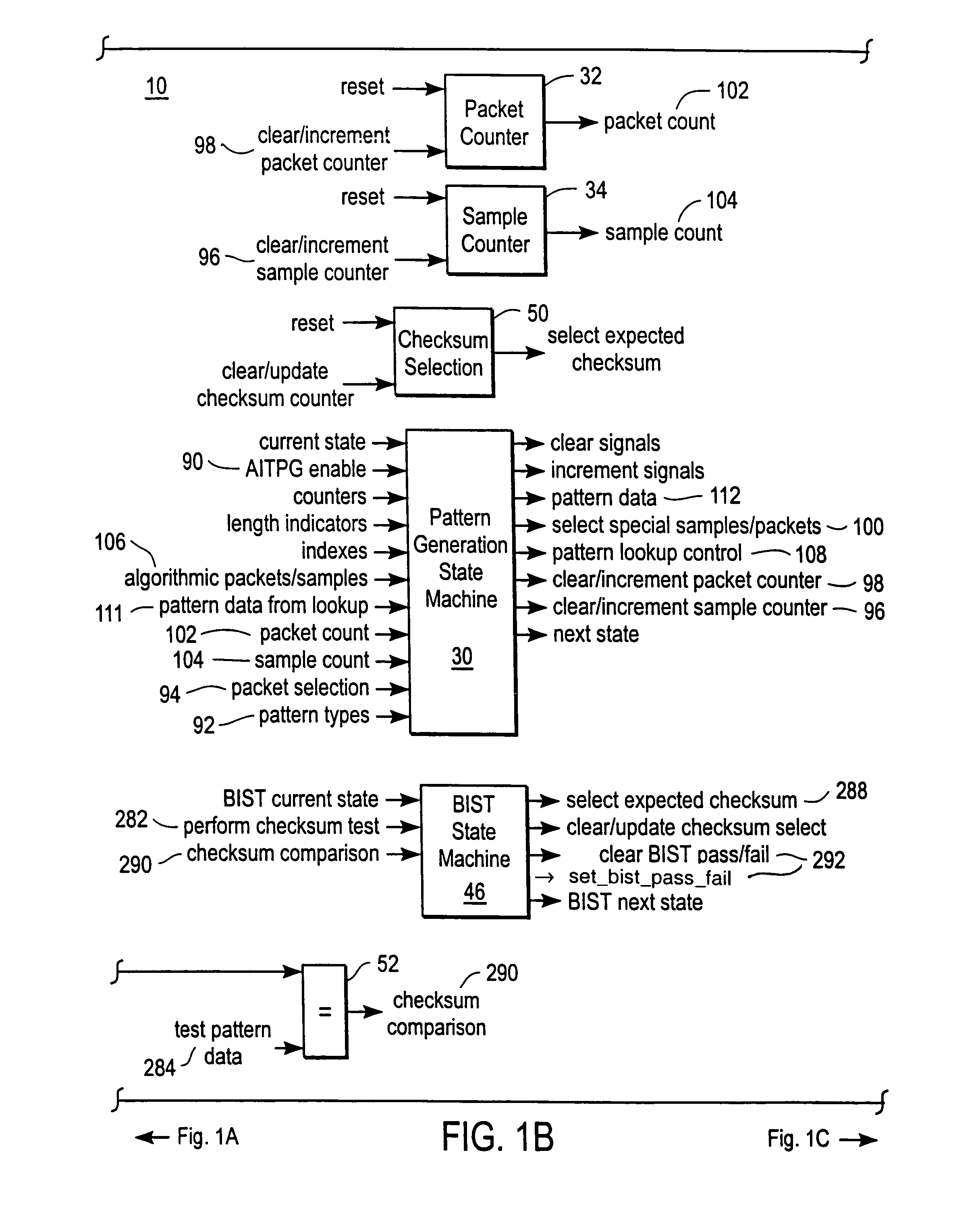

Algorithmic test pattern generator, with built-in-self-test (BIST) capabilities, for functional testing of a circuit

InactiveUS7062696B2Electronic circuit testingError detection/correctionComputer hardwareFunctional testing

A test system includes a test data generator to provide test data (e.g., a test pattern) to a subject circuit (e.g., a digital television video circuit). The test data is functionally to verify the subject circuit. The functional verification of the subject circuit is performed utilizing an output of the subject circuit generated responsive to the test data in accordance with an operational functionality of the subject circuit. The test data generator is also coupled to provide the test data to a built-in self-test (BIST) circuit so as to enable the built-in self-test circuit to receive the test data.

Owner:NAT SEMICON CORP

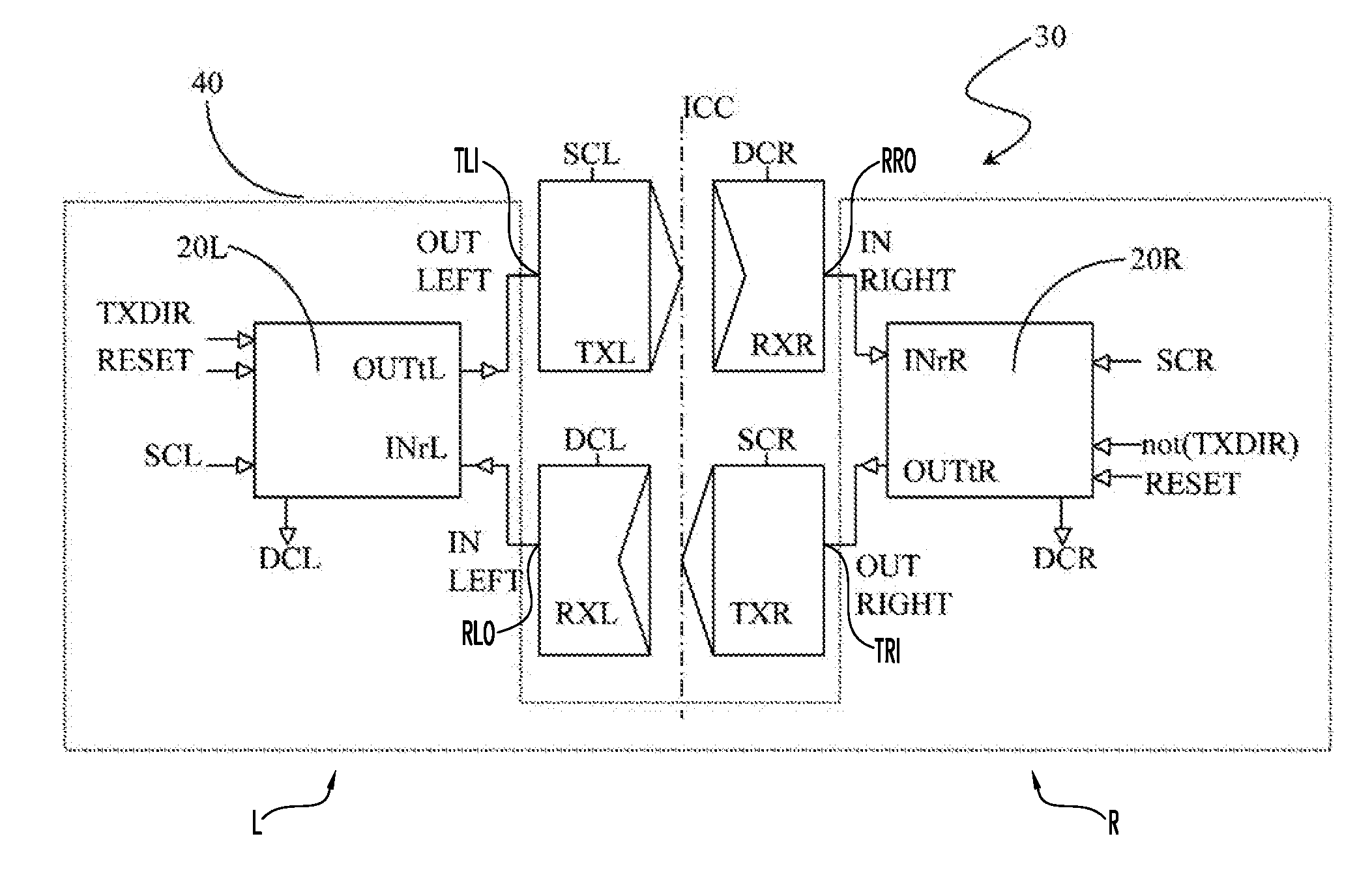

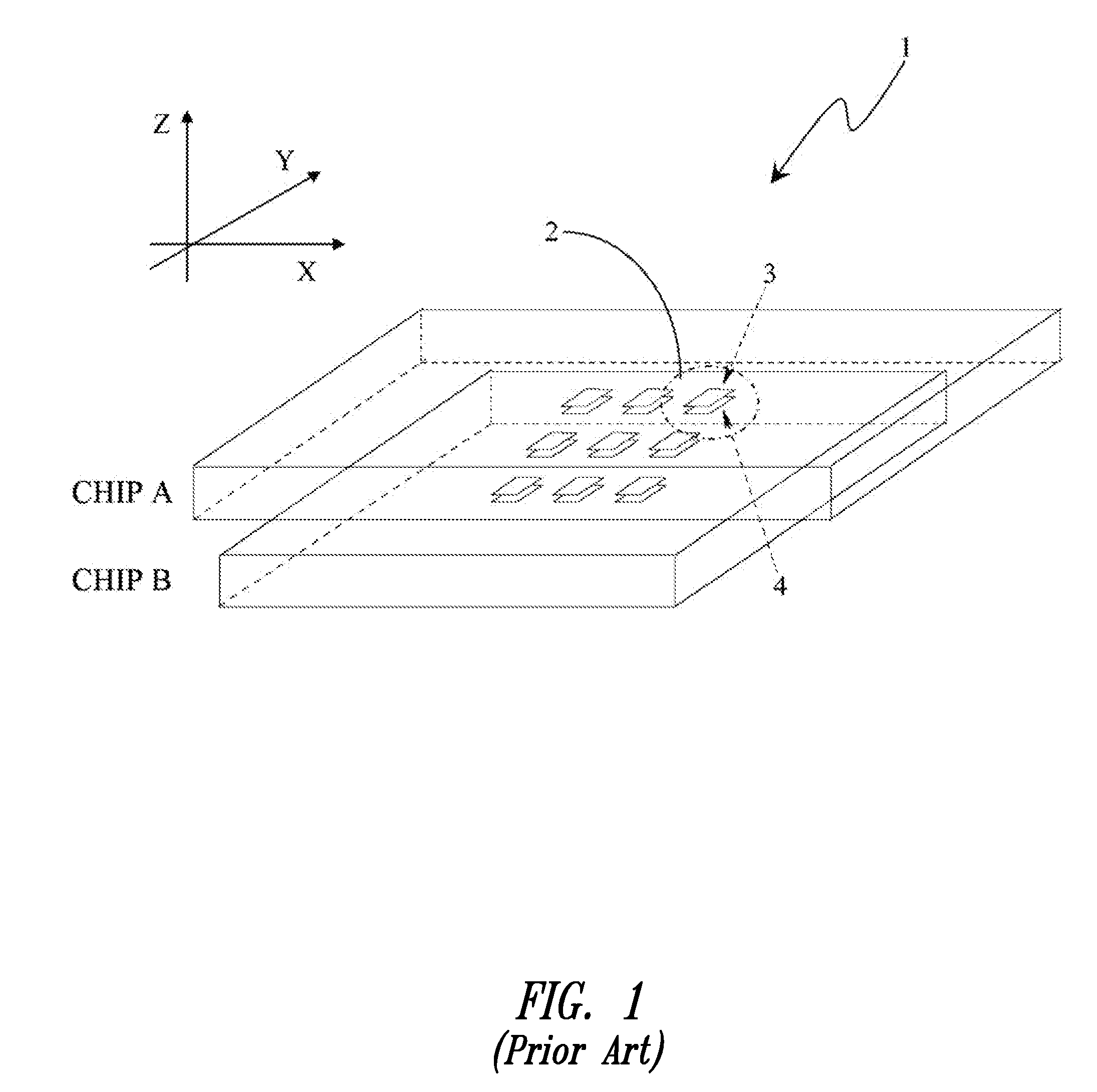

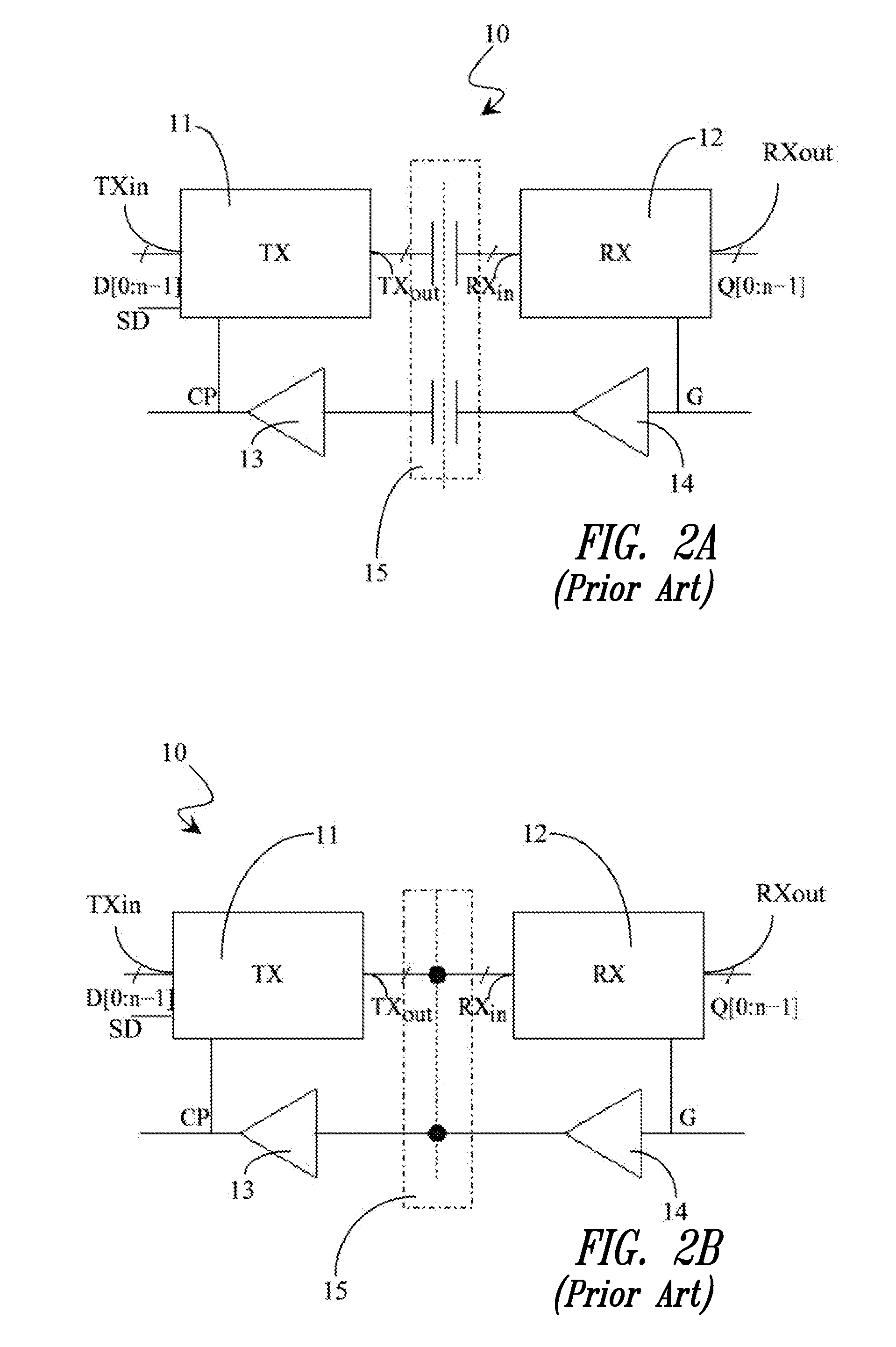

Communication system between a first and a second synchronous device that are uncorrelated in time

ActiveUS20090168860A1Guaranteed to workSynchronisation signal speed/phase controlTransmission monitoringCommunications systemEngineering

A communication system includes first and second independently clocked devices, comprising, for each device, a transmitter and a receiver connected to each other in a crossed way in correspondence of an inter-chip communication channel. The communication system further comprises a synchronizer in turn including at least a first and a second synchronization block, having respective input terminals connected to the receivers and respective output terminals connected to the transmitters and comprising at least: a test pattern generator that generates a programmable test pattern signal; a pattern detector to check a matching between stored and received test pattern signals and thus lock corresponding clock phases of the synchronization blocks in case of positive result of this check; and a delay block able to change the clock phases until a synchronized condition of the synchronization blocks is verified, this synchronized condition corresponding to a matching between stored and received test pattern signals.

Owner:STMICROELECTRONICS SRL

Quality evaluation tool for dynamic voice portals

InactiveUS8050918B2Automatic call-answering/message-recording/conversation-recordingSpeech recognitionConsequence analysisTest input

A method and system for evaluating the quality of voice input recognition by a voice portal is provided. An analysis interface extracts a set of current grammars from the voice portal. A test pattern generator generates a test input for each current grammar. The test input includes a test pattern and a set of active grammars corresponding to each current grammar. The system further includes a text-to-speech engine for entering each test pattern into the voice server. A results collector analyzes each test pattern entered into the voice server with the speech recognition engine against the set of active grammars corresponding to the current grammar for said test pattern. A results analyzer derives a set of statistics of a quality of recognition of each current grammar.

Owner:NUANCE COMM INC

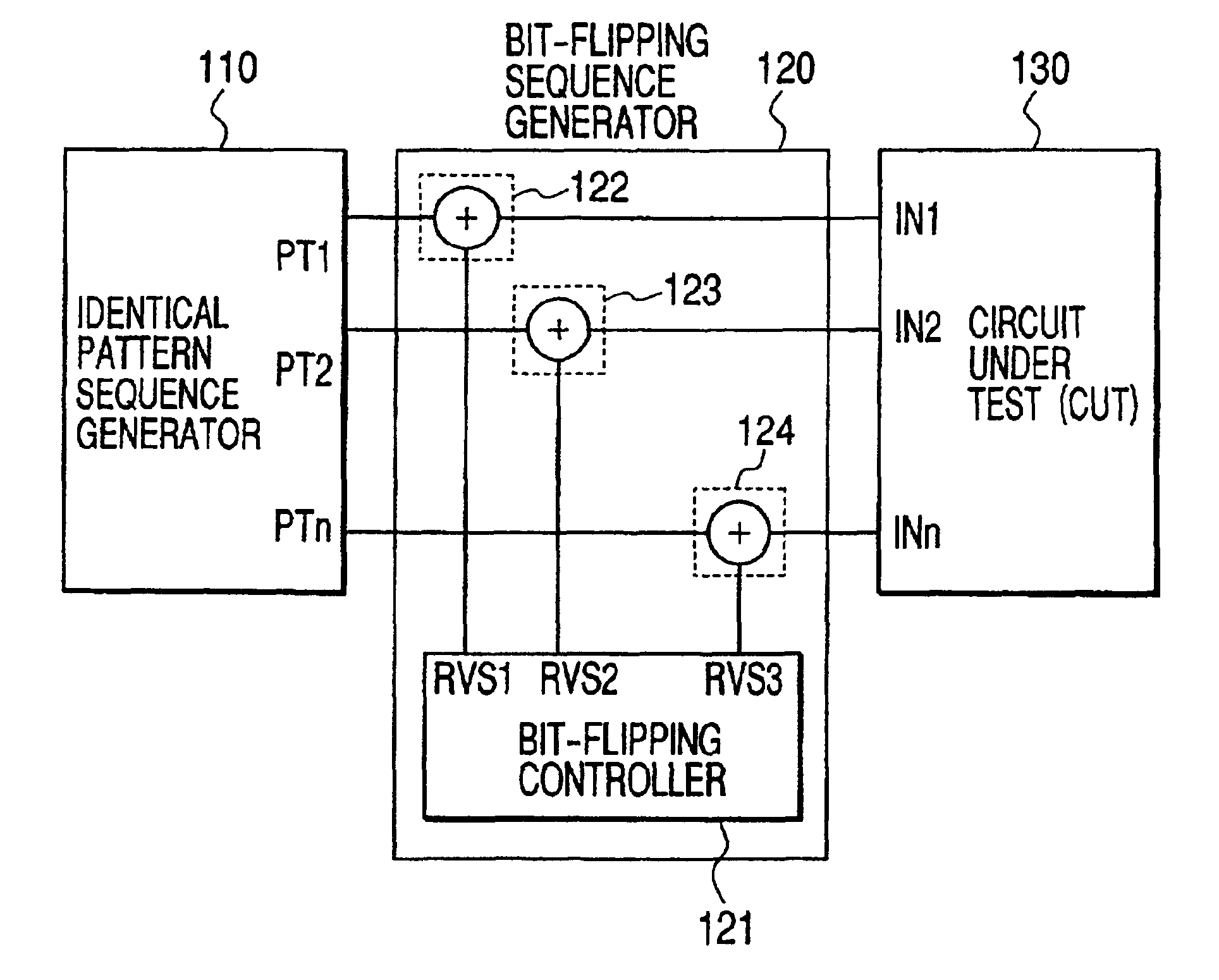

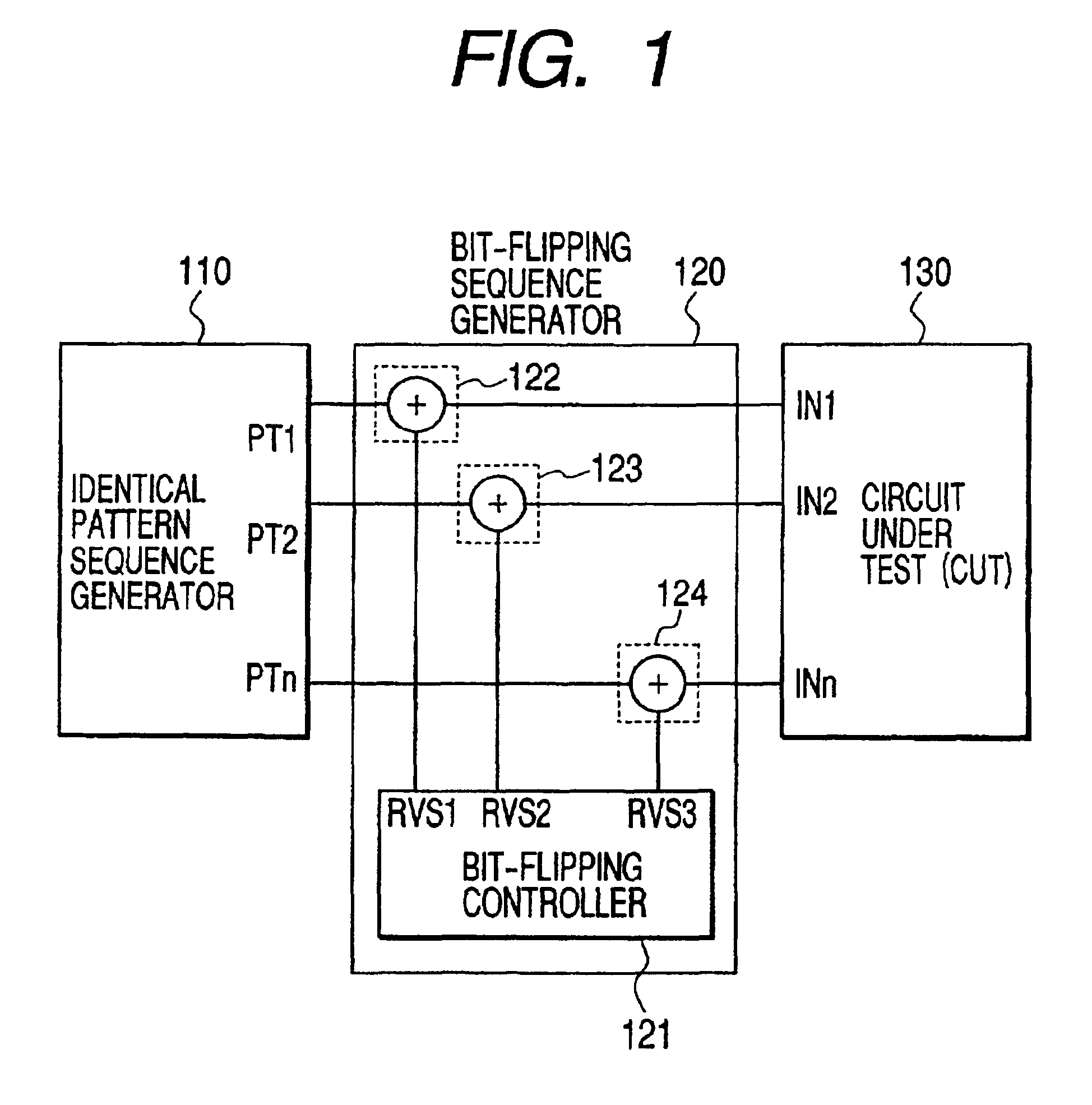

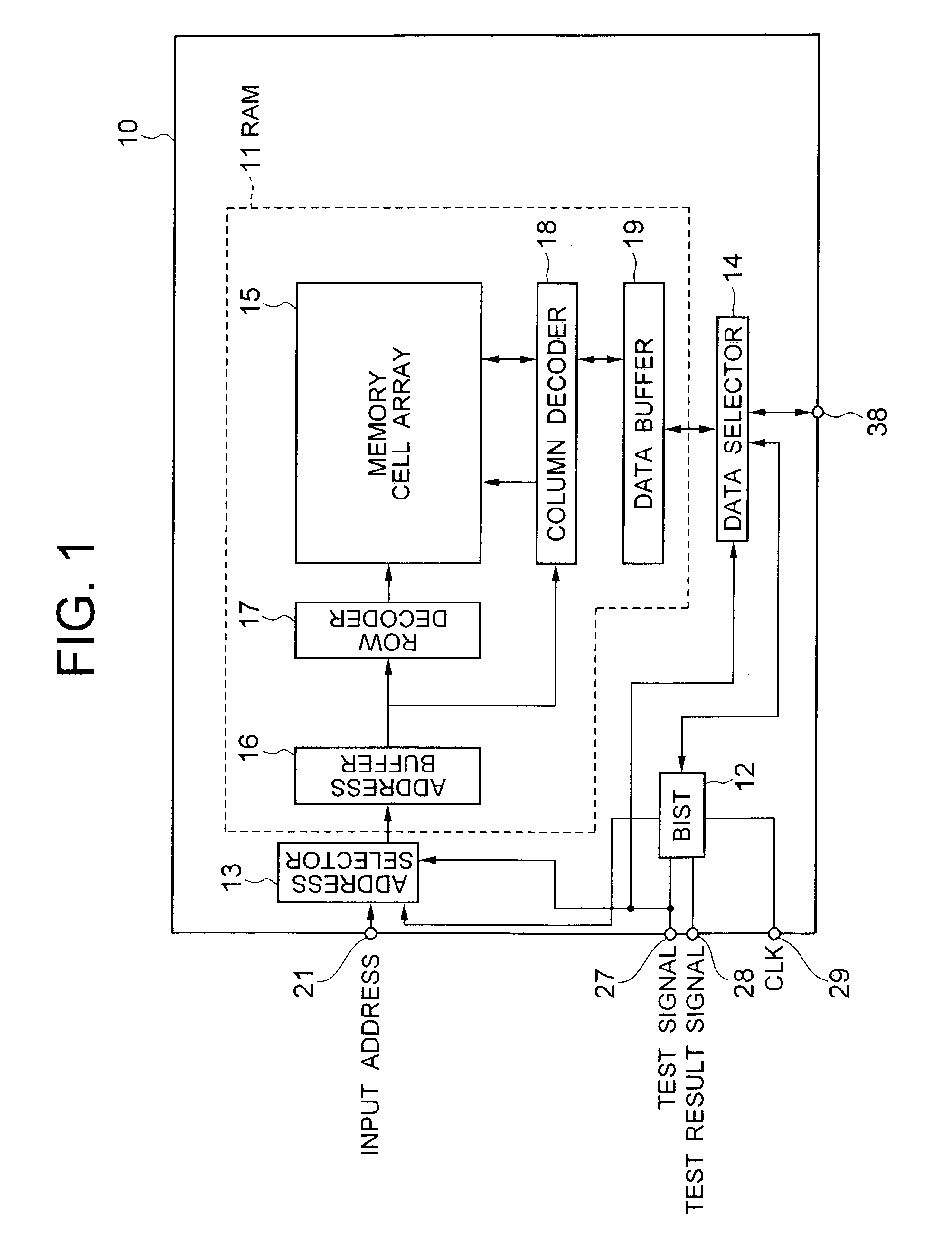

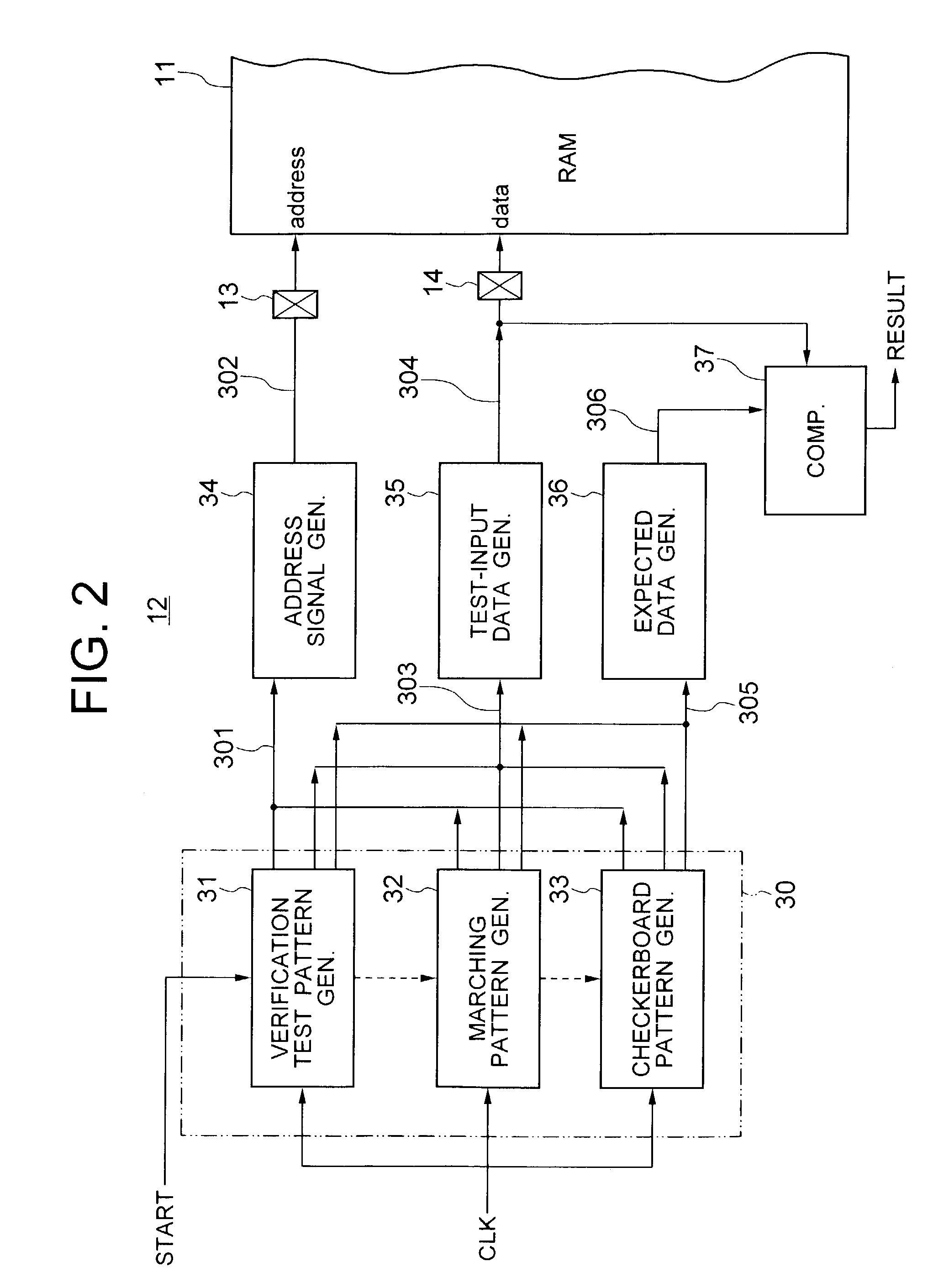

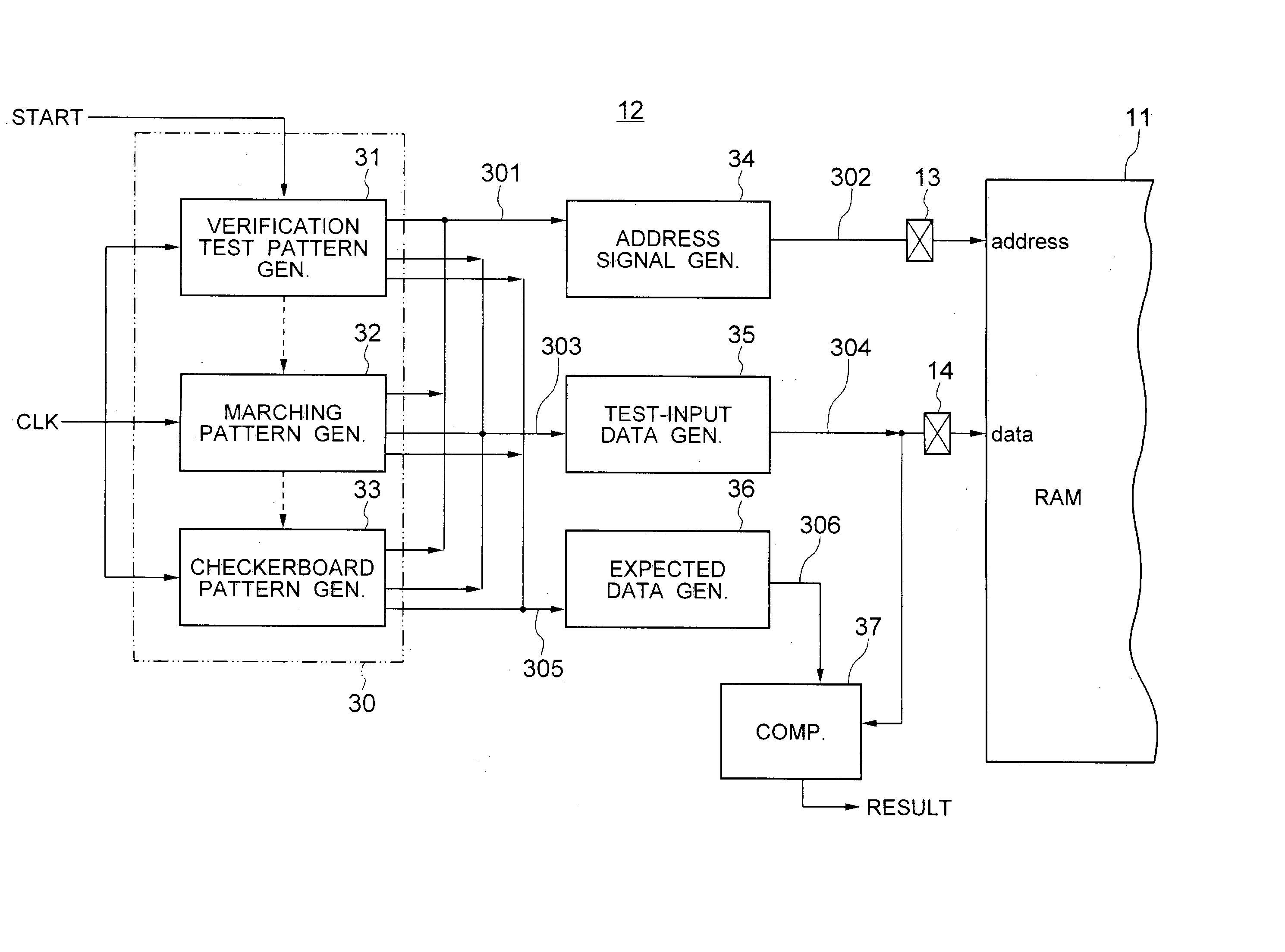

Test method of semiconductor intergrated circuit and test pattern generator

InactiveUS6922803B2Avoid problemsEliminate overheadElectronic circuit testingDetecting faulty computer hardwareFault coverageGraphics

A semiconductor integrated circuit test method which reduces the required data volume for testing and efficiently detects faults in a circuit to be tested, the method comprising means 110 to generate identical pattern sequences repeatedly and means 120 to control flipped bits in pattern sequences, in order to generate neighborhood pattern sequences and use the neighborhood patterns to test the circuit under test 130. The neighborhood patterns include, in whole or in part, such pattern sequences as ones without flipped bits, ones with all or some flipped bits in one pattern and ones with all or some flipped bits in consecutive patterns or patterns at regular intervals, the interval being equivalent to a given number of patterns. Because a test pattern generator is provided independently of the circuit to be tested, the problem of a prolonged design period can be eliminated, a loss in the operating speed of the circuit under test is minimized and a high fault coverage can be achieved with less hardware overhead and a smaller volume of test data.

Owner:HITACHI LTD

Low hardware overhead scan based 3-weight weighted random BIST architectures

InactiveUS6886124B2Reduce signalingMinimize the numberError preventionTransmission systemsHemt circuitsTest sequence

Owner:NEC CORP

Method and apparatus for testing logic circuit designs

InactiveUS7484151B2Electronic circuit testingError detection/correctionLogic circuit designEngineering

Owner:NEC CORP

Digital camera for image device calibration

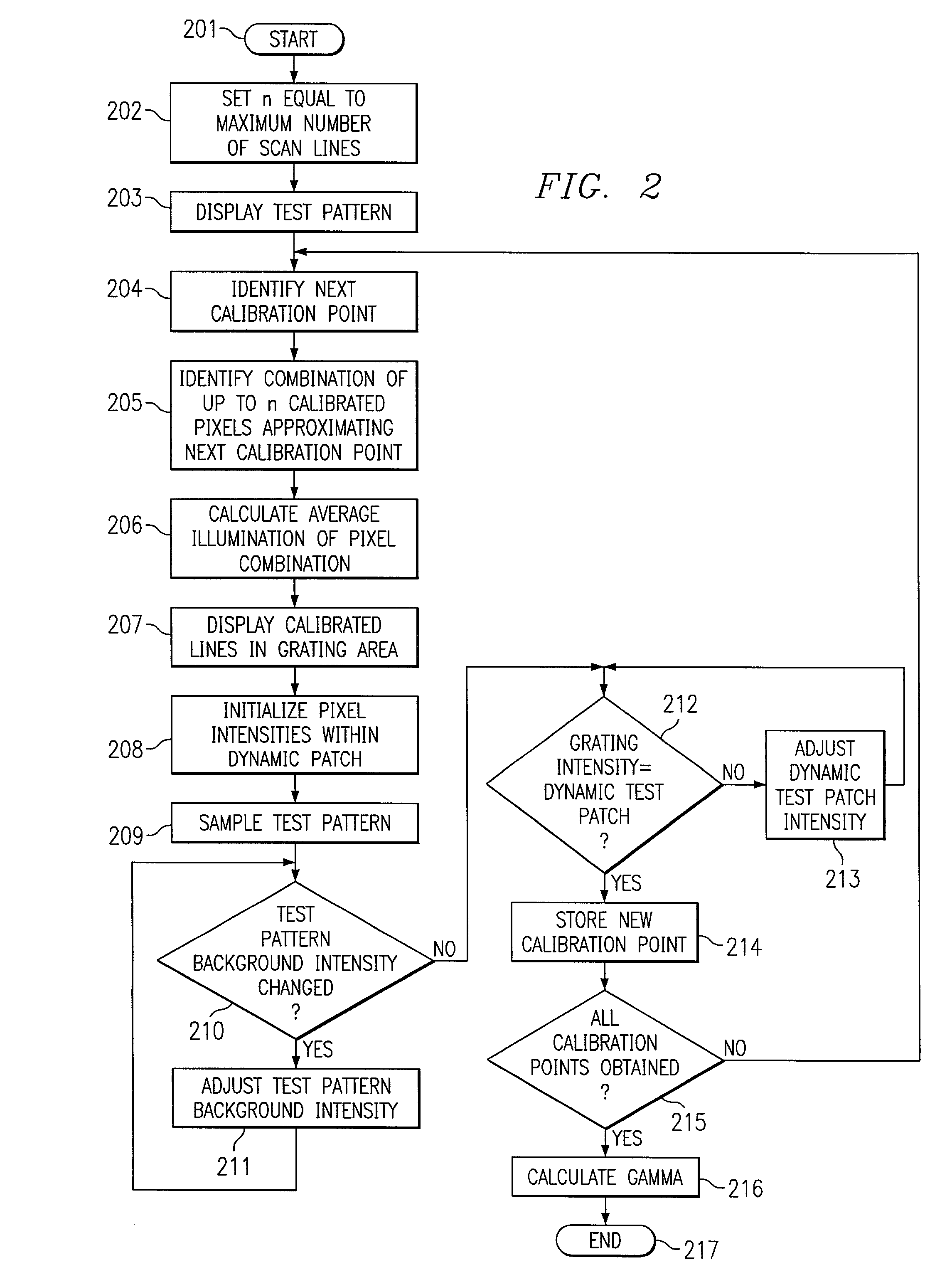

InactiveUS7133148B2Electric signal transmission systemsDigitally marking record carriersGraphicsGrating

The invention is directed to an apparatus for calibrating an output of an image output device, comprising an image input device configured to image an output of the image output device; and a test pattern generator having an output of a dynamic test patch area and a grating area connected to an input of the image output device and responsive to the image input device for adjusting an intensity level of the dynamic test patch area to match an average intensity level of the grating area.

Owner:HEWLETT PACKARD DEV CO LP

Semiconductor integrated circuit, design support apparatus, and test method

A semiconductor integrated circuit includes a self-testing circuit having a test circuit which is incorporated in a logic circuit to test the logic circuit. The test circuit has a test pattern generator to generate a test pattern and a compressor to compress a test result output. The logic circuit includes a plurality of scan chains including a plurality of serial connected registers and the compressor includes a through output portion. The semiconductor integrated circuit also includes a pattern counter which counts the test pattern at a test time of the logic circuit, a shift counter which counts the number of shifts in the scan chain in the logic circuit at the test time, and a failure information output circuit which is connected to the test circuit and which outputs step information of the test pattern corresponding to a failure to an integrated circuit external terminal when the failure is detected at the test time.

Owner:KK TOSHIBA

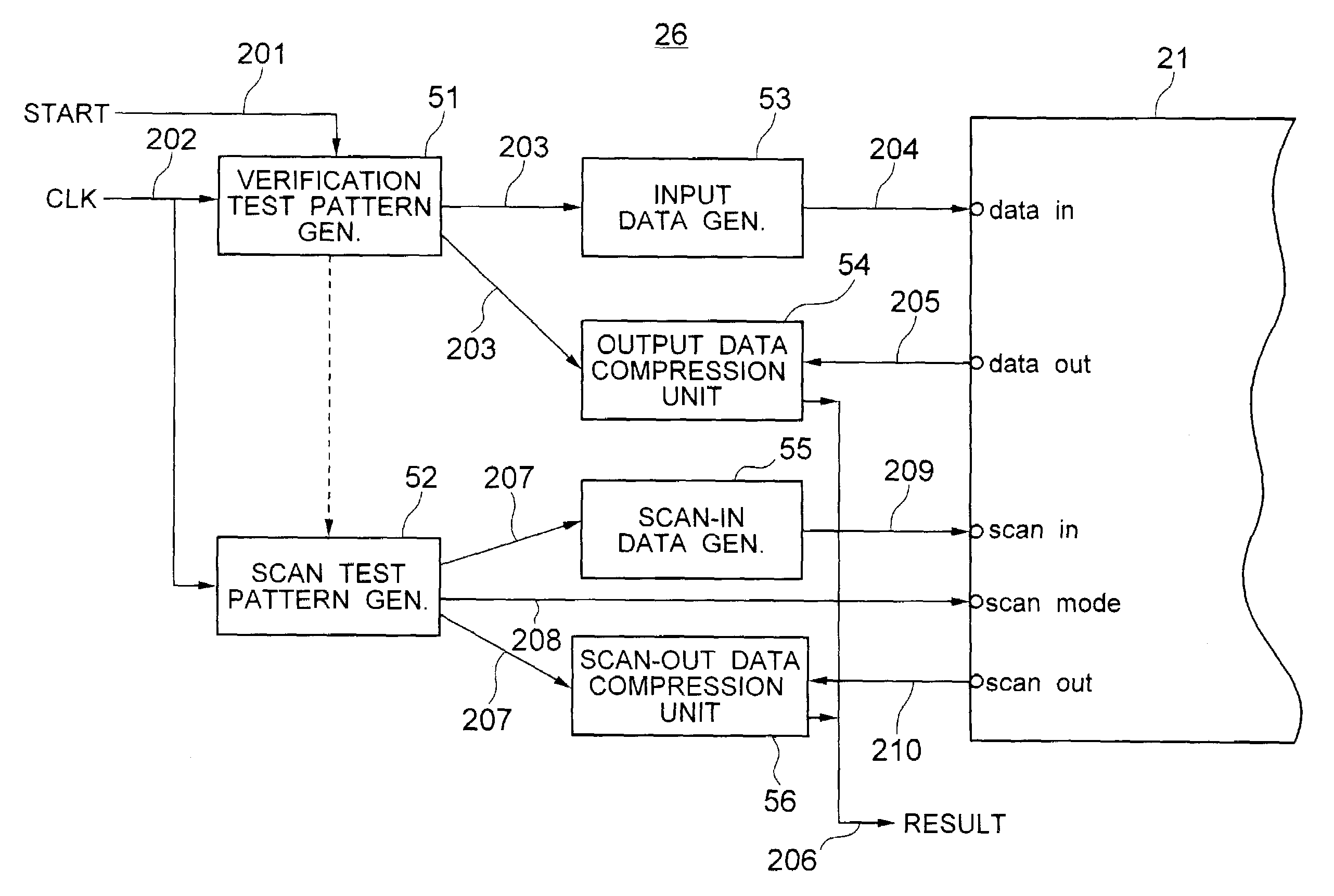

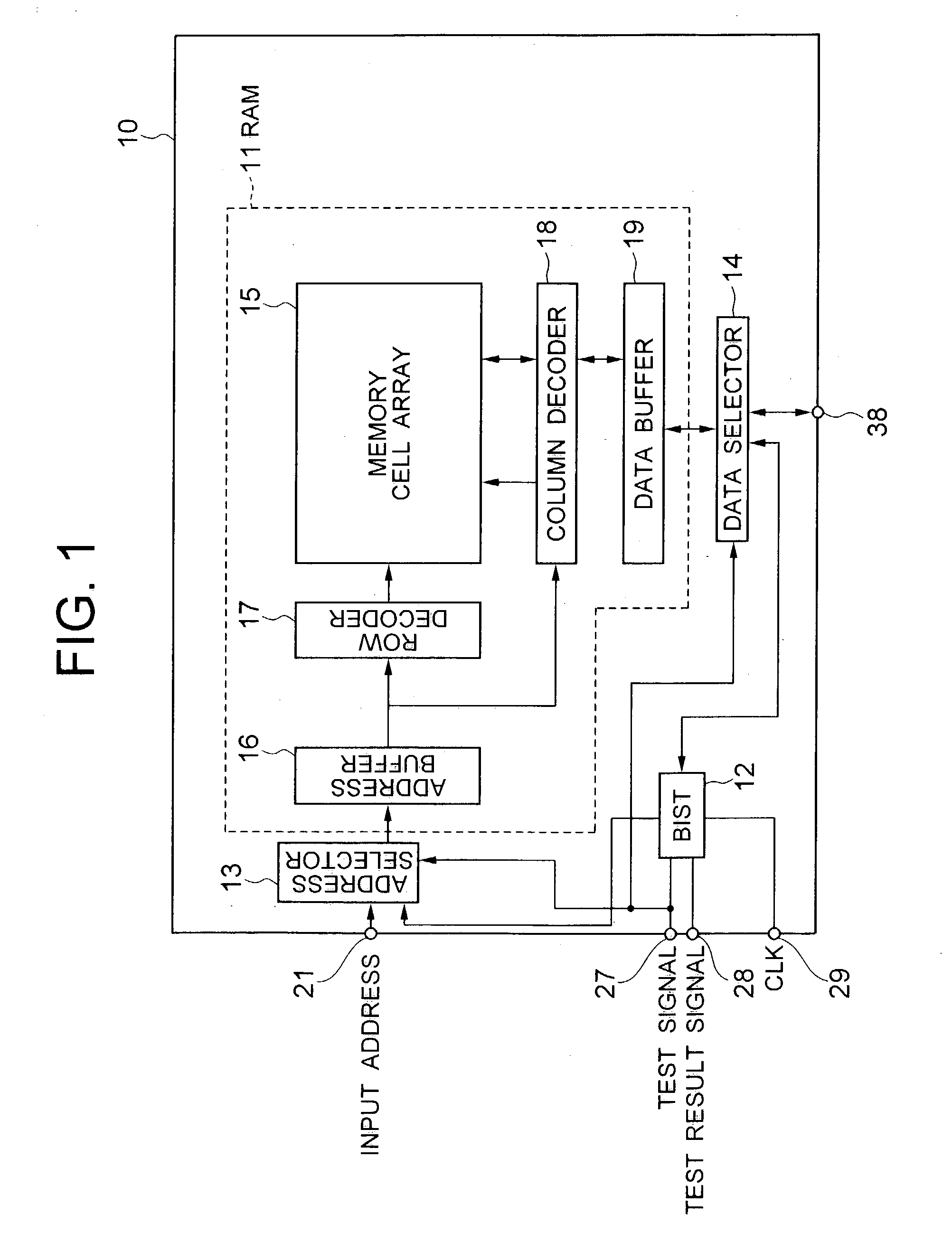

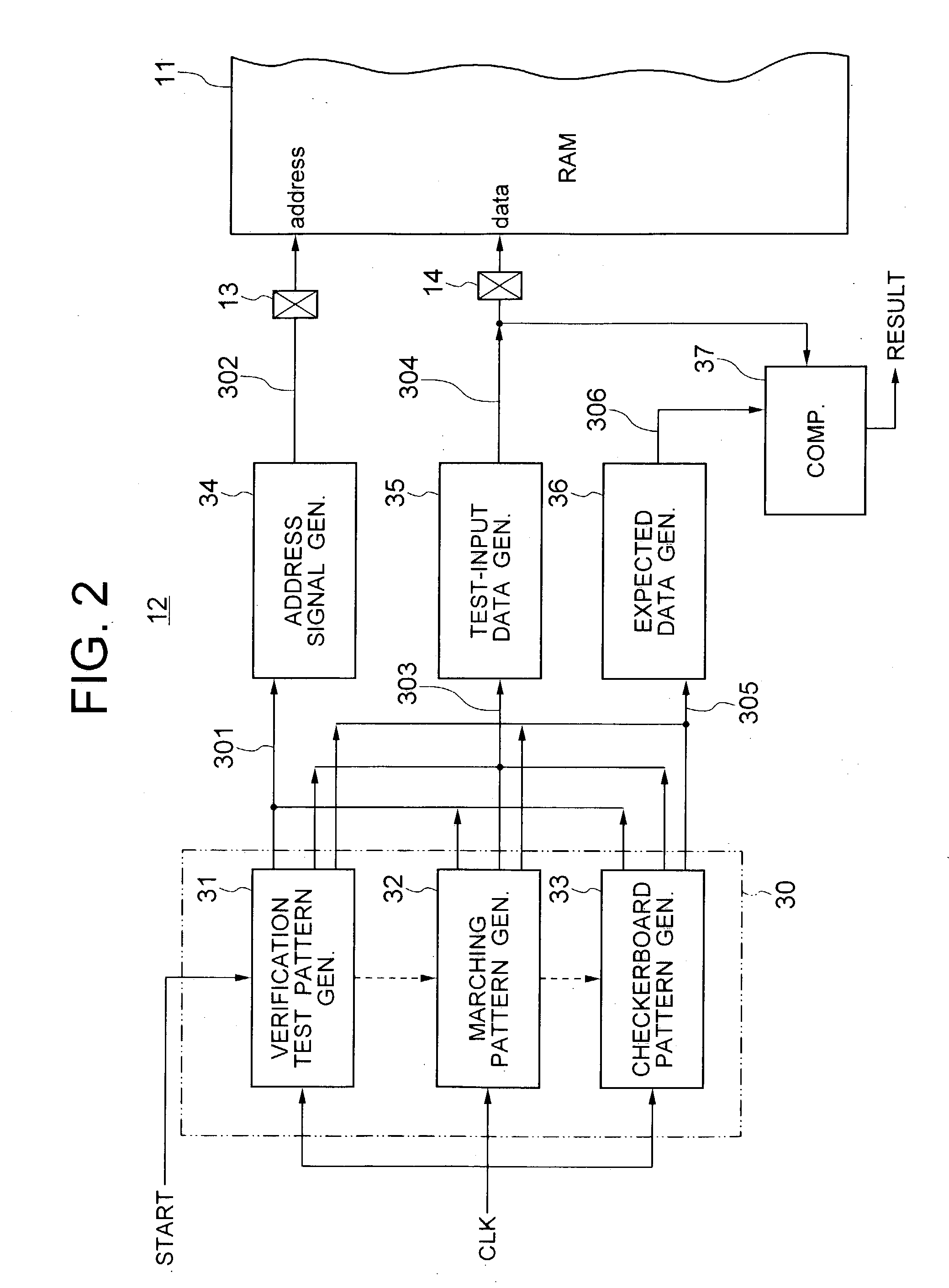

Built-in self test circuit

InactiveUS7360116B2Short timeReduce overall man-hoursElectronic circuit testingError detection/correctionDesign stageValidation testing

A built-in self test circuit (BIST circuit) in an LSI includes a verification test pattern generator for generating verification test pattern which is used for verifying the connections in the LSI including the BIST circuit in the design stage thereof, and another test pattern generator which is used to test the function of the LSI.

Owner:RENESAS ELECTRONICS CORP

Built-in self test circuit

InactiveUS20030191998A1Reduce testingShort timeElectronic circuit testingSolid-state devicesDesign stageValidation testing

A built-in self test circuit (BIST circuit) in an LSI includes a verification test pattern generator for generating verification test pattern which is used for verifying the connections in the LSI including the BIST circuit in the design stage thereof, and another test pattern generator which is used to test the function of the LSI.

Owner:RENESAS ELECTRONICS CORP

Automatic analog test and compensation with built-in pattern generator and analyzer

A built-in-self test (BIST) scheme for analog circuitry functionality tests such as frequency response, gain, cut-off frequency, signal-to-noise ratio, and linearity measurement. The BIST scheme utilizes a built-in direct digital synthesizer (DDS) as the test pattern generator that can generate various test waveforms such as chirp, ramp, step frequency, two-tone frequencies, sweep frequencies, MSK, phase modulation, amplitude modulation, QAM and other hybrid modulations. The BIST scheme utilizes a multiplier followed by an accumulator as the output response analyzer (ORA). The multiplier extracts the spectrum information at the desired frequency without using Fast Fourier Transform (FFT) and the accumulator picks up the DC component by averaging the multiplier output.

Owner:AUBURN UNIV

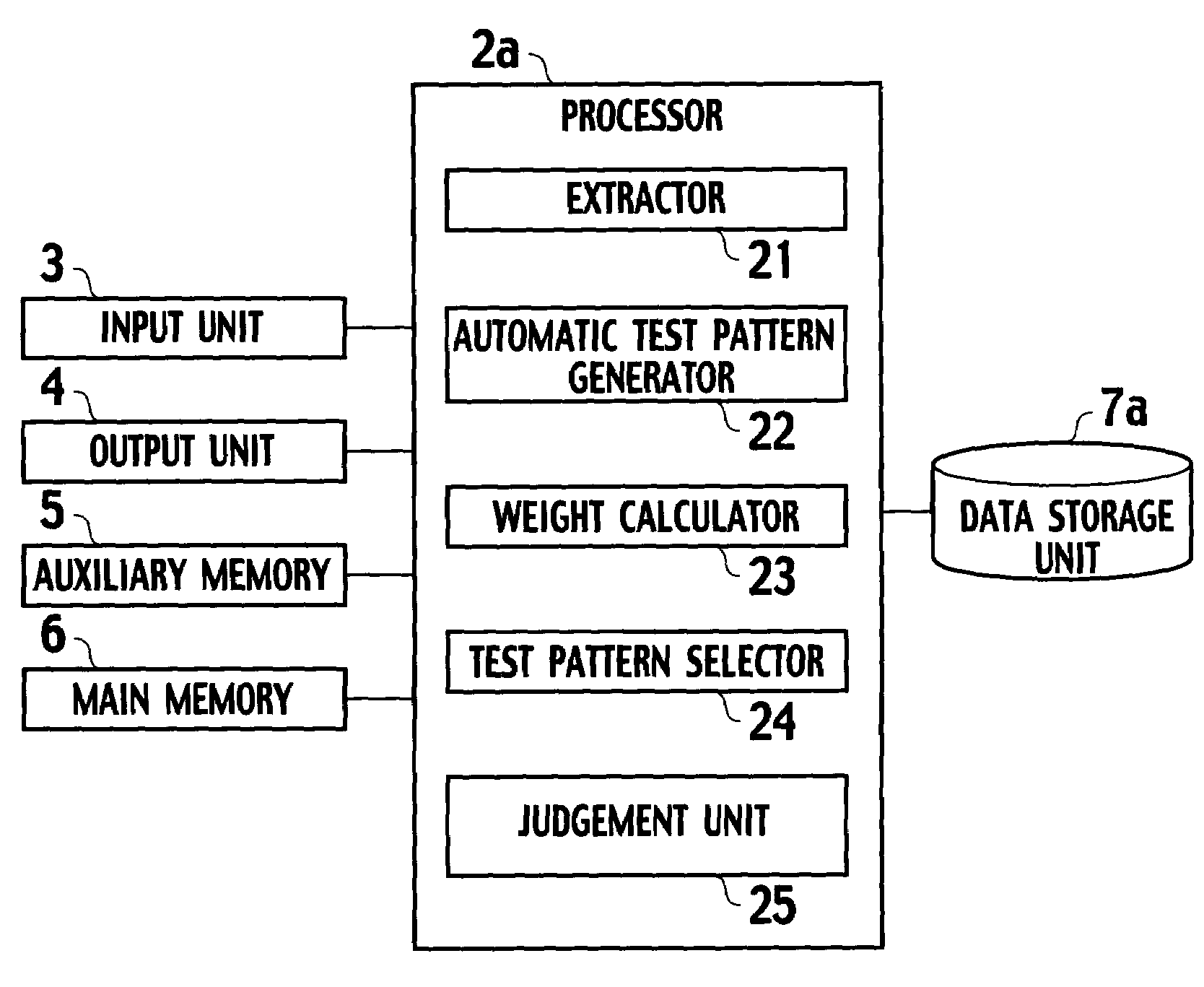

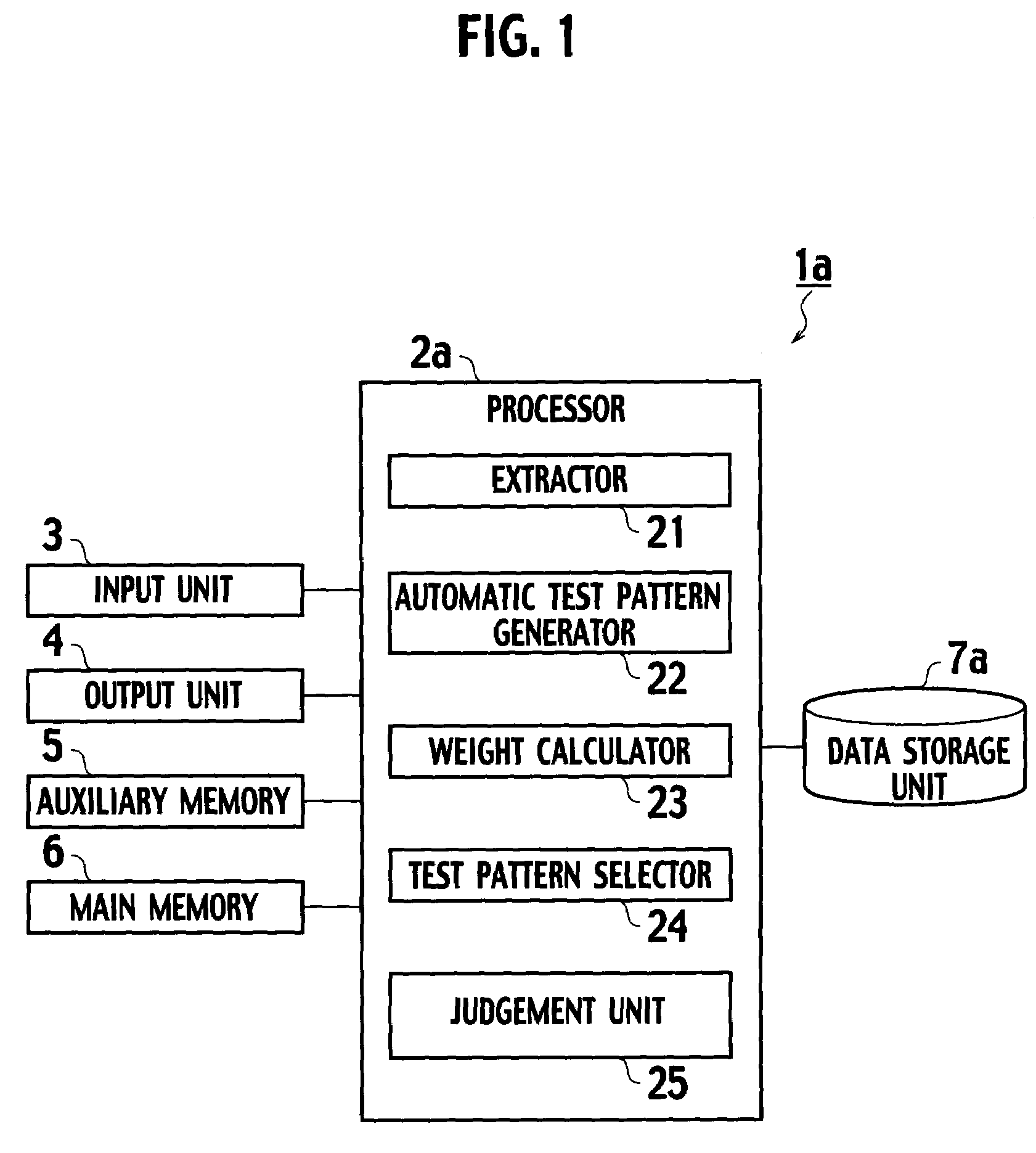

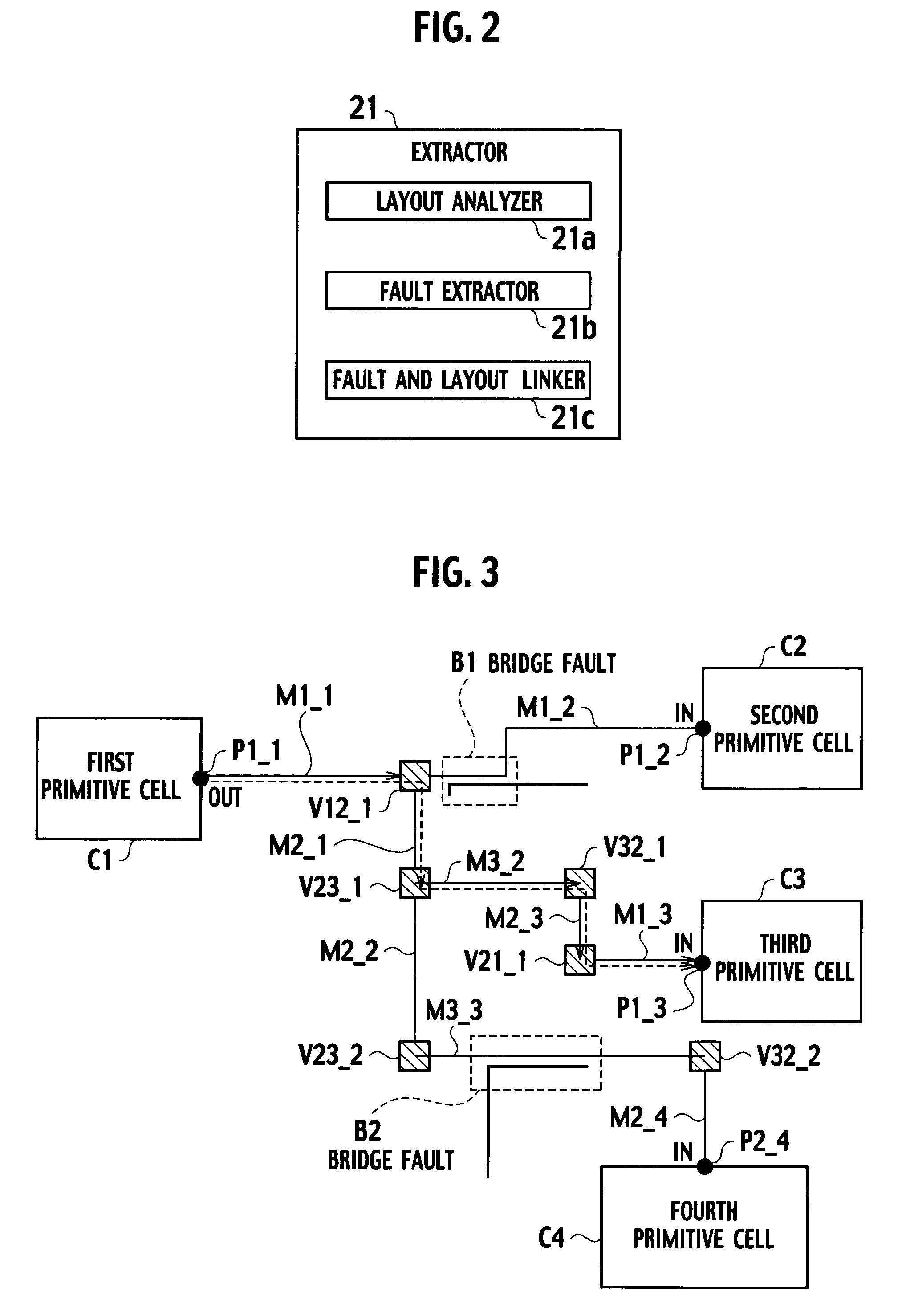

Test pattern generating apparatus, method for automatically generating test patterns and computer program product for executing an application for a test pattern generating apparatus

InactiveUS7406645B2Electronic circuit testingError detection/correctionCircuit under testProcess failure

A test pattern generating apparatus includes an extractor configured to extract a plurality of layout parameters (elements) of a circuit under test based on gate net information and layout information of the circuit, and to link the layout parameters (elements) with corresponding fault models respectively. A weight calculator is configured to calculate a weight for each fault model linked with the layout parameters (elements) for both a plurality of undetected faults of the fault model and a plurality of faults detected by a plurality of test patterns, based on process failure (defect) information and layout parameter (element) information. An automatic test pattern generator is configured to generate the test patterns in accordance with the weight of each fault model linked with the layout parameters (elements).

Owner:KK TOSHIBA

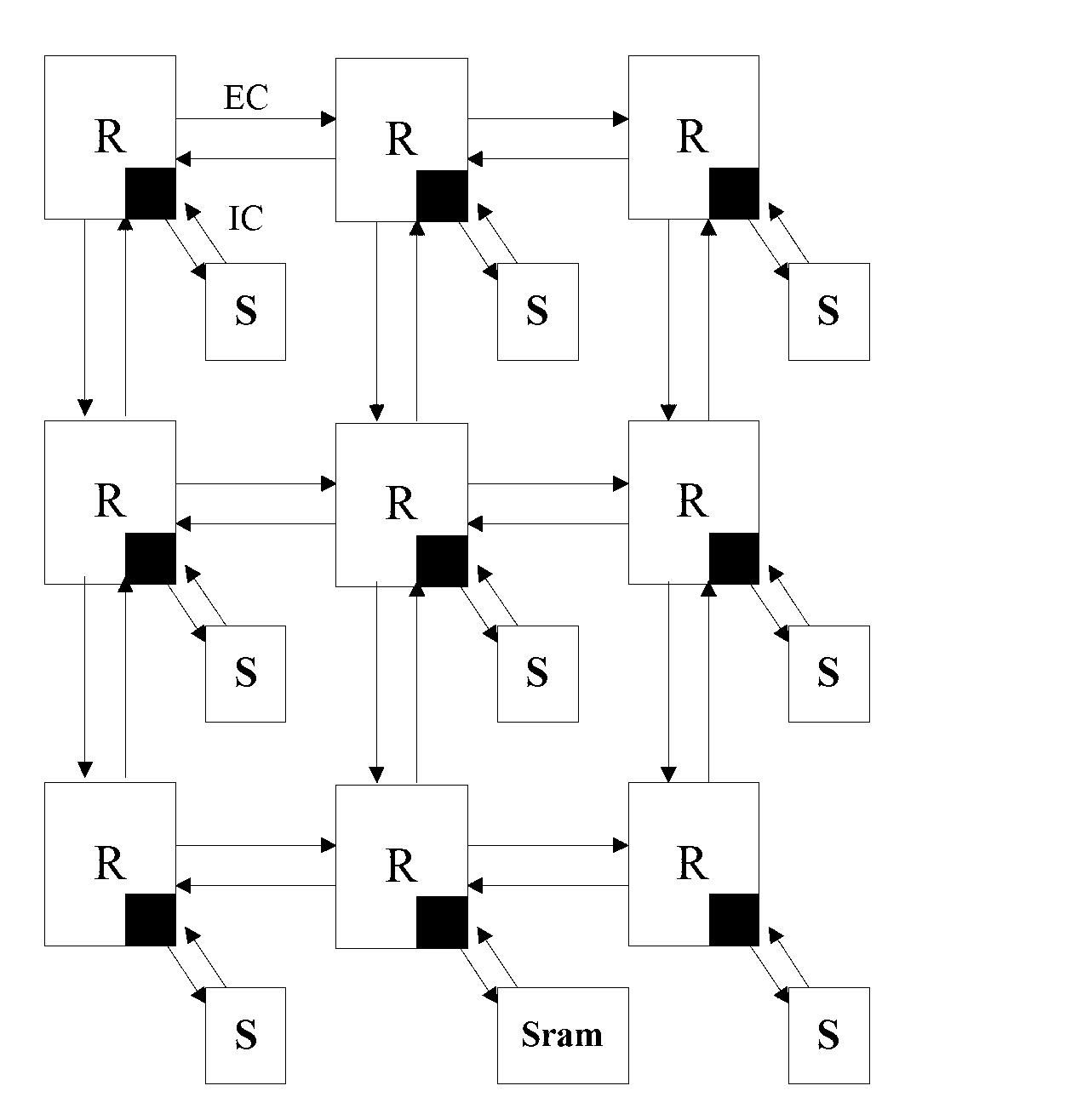

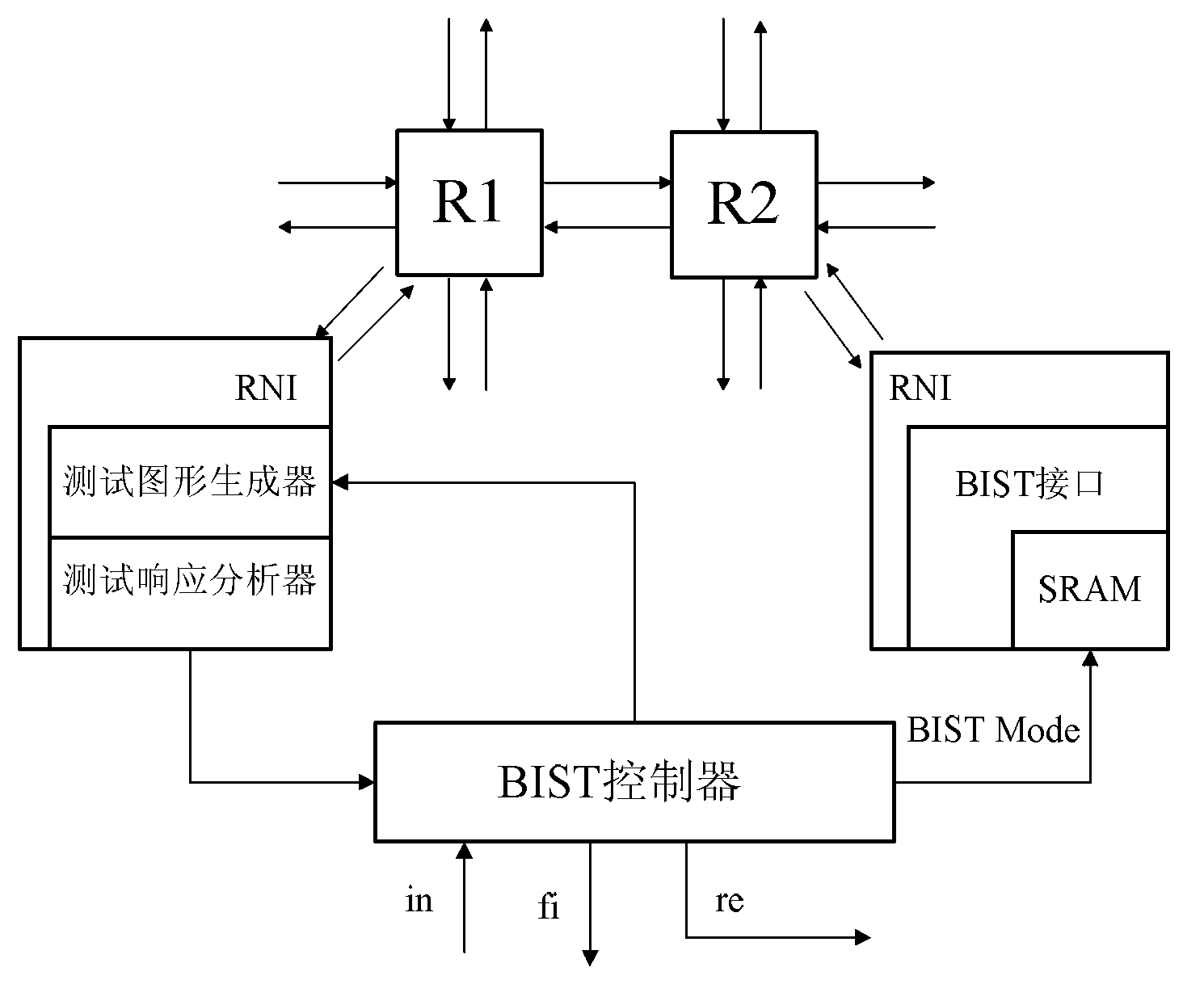

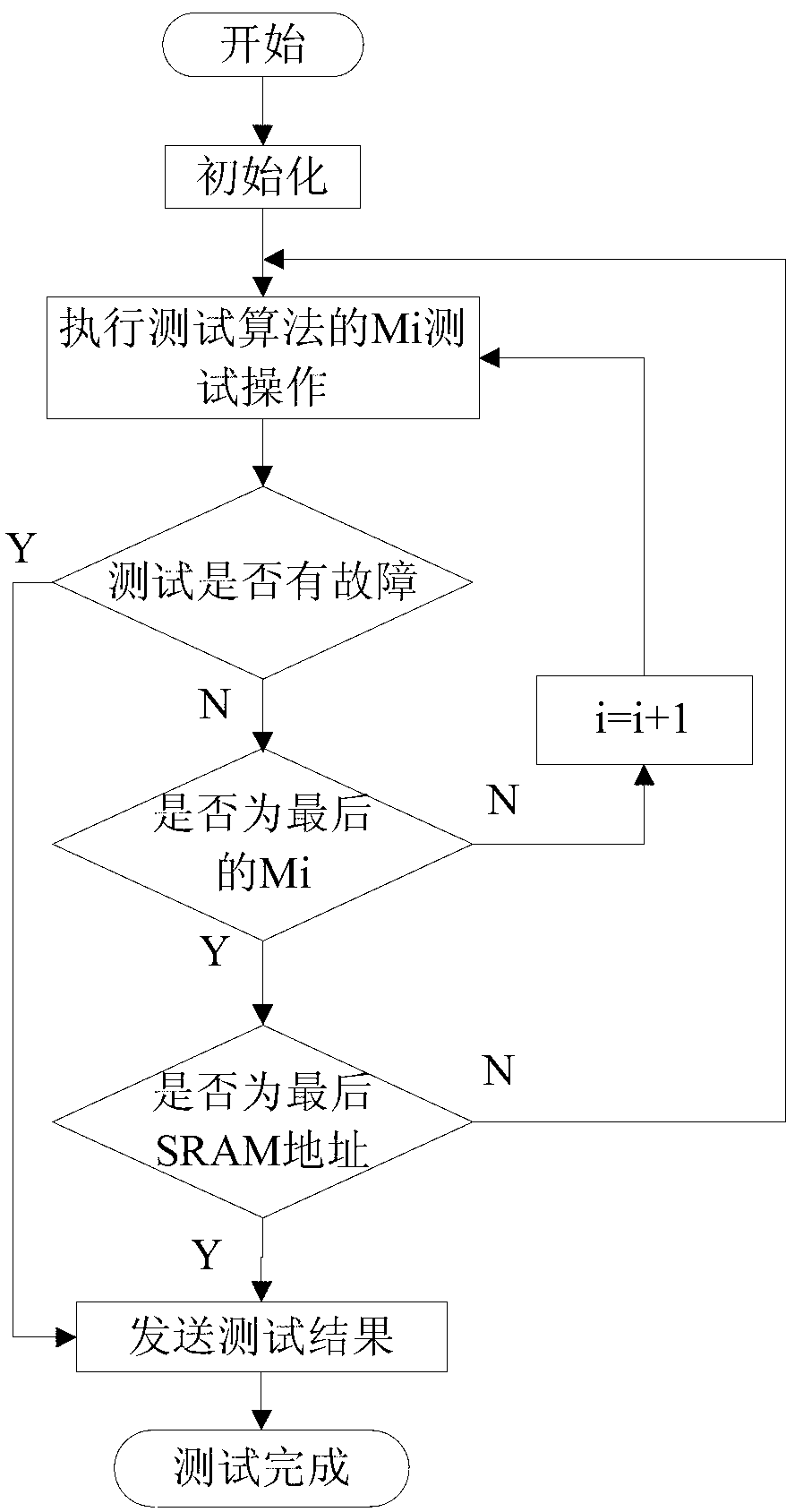

Built-in self-test structure and method for on-chip network resource node storage device

ActiveCN103310850AReduce areaSmall area overheadStatic storageStatic random-access memoryTest algorithm

The invention discloses a built-in self-test structure and method for an on-chip network resource node storage device. The built-in self-test structure comprises a built-in self-test (BIST) controller arranged on a field programmable gate array (FPGA) chip, a resource network interface and a BIST interface which are embedded into corresponding routers, a test pattern generator and a test response analyzer, wherein the BIST controller is connected with external test equipment through an external interface. The built-in self-test method comprises the following steps that: the external test equipment sends an instruction start test program to the BIST controller; the BIST controller sends an enabling signal and a state selection signal to each test module according to a March C+ test algorithm program, performs read-write operation on each address of a static random access memory (SRAM) under each test state, and stops sending the signals if failures are found out. A test result is sent to the external test equipment. According to the built-in self-test structure and method, the test time is reduced by 50 percent; a routing network of a network operation center (NoC) is reused as a test data route; data transmission is reliable and safe; a chip area is low in expense; the failure coverage rate is high.

Owner:GUILIN UNIV OF ELECTRONIC TECH

Low hardware overhead scan based 3-weight weighted random BIST architectures

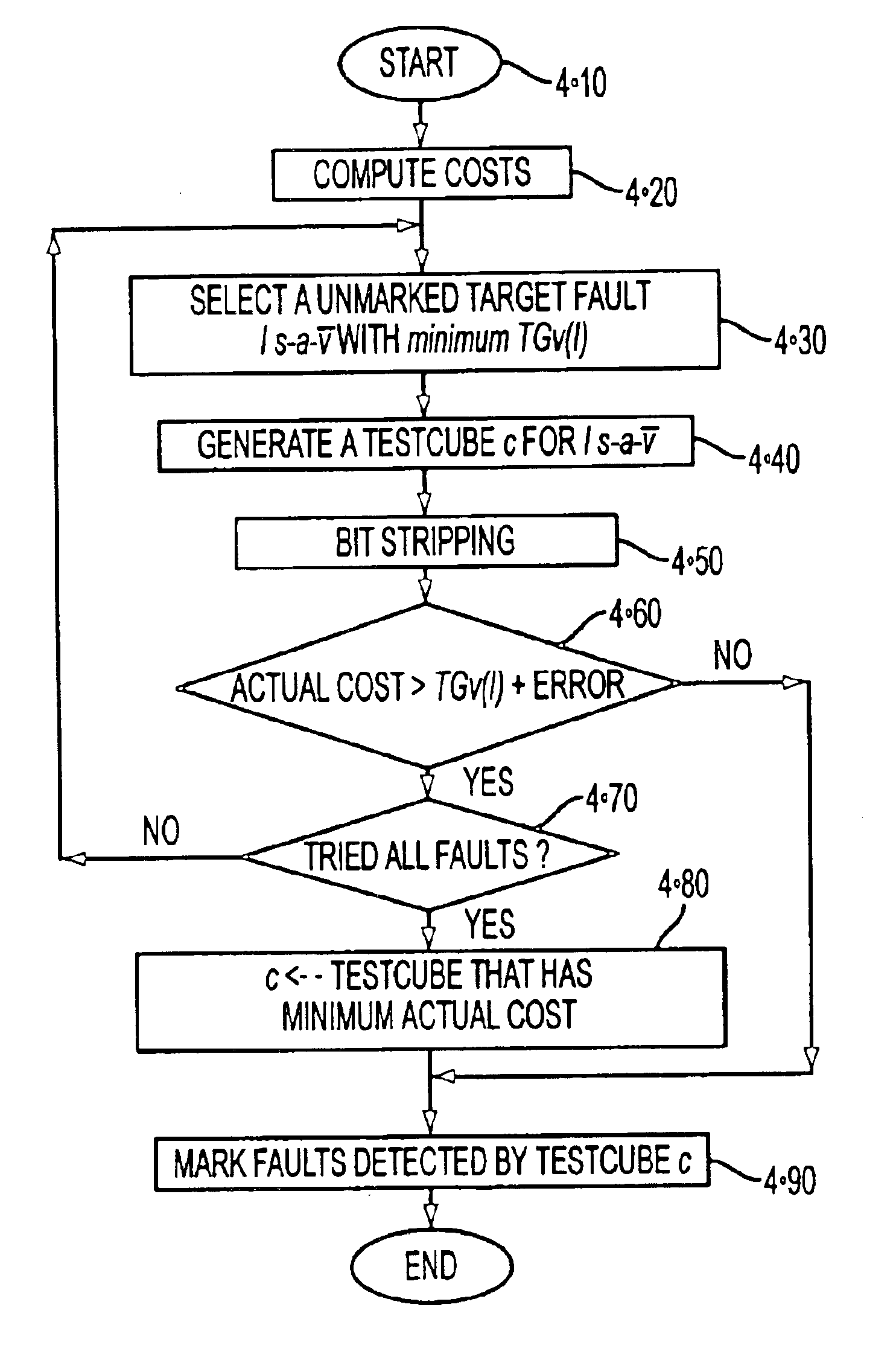

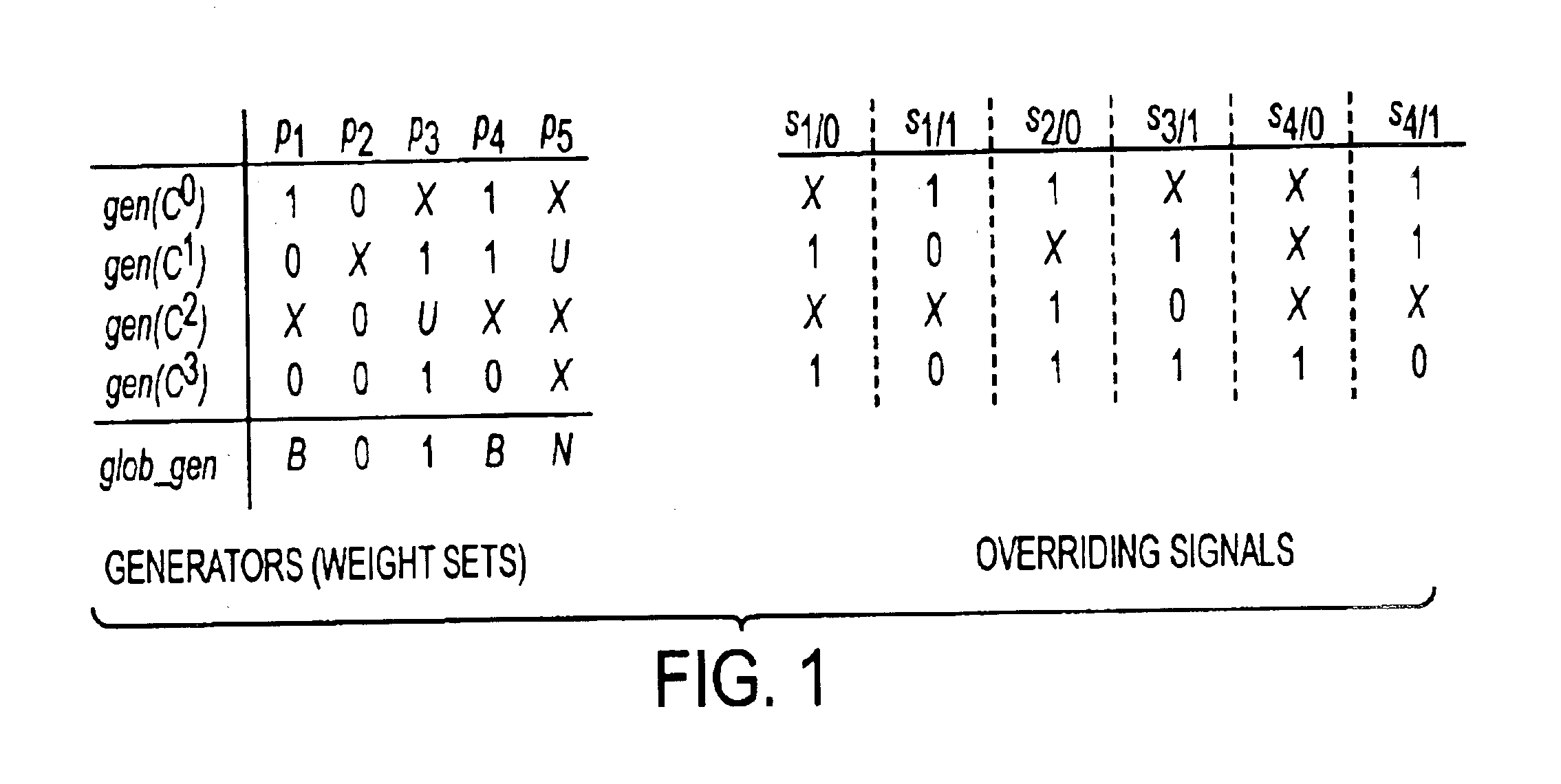

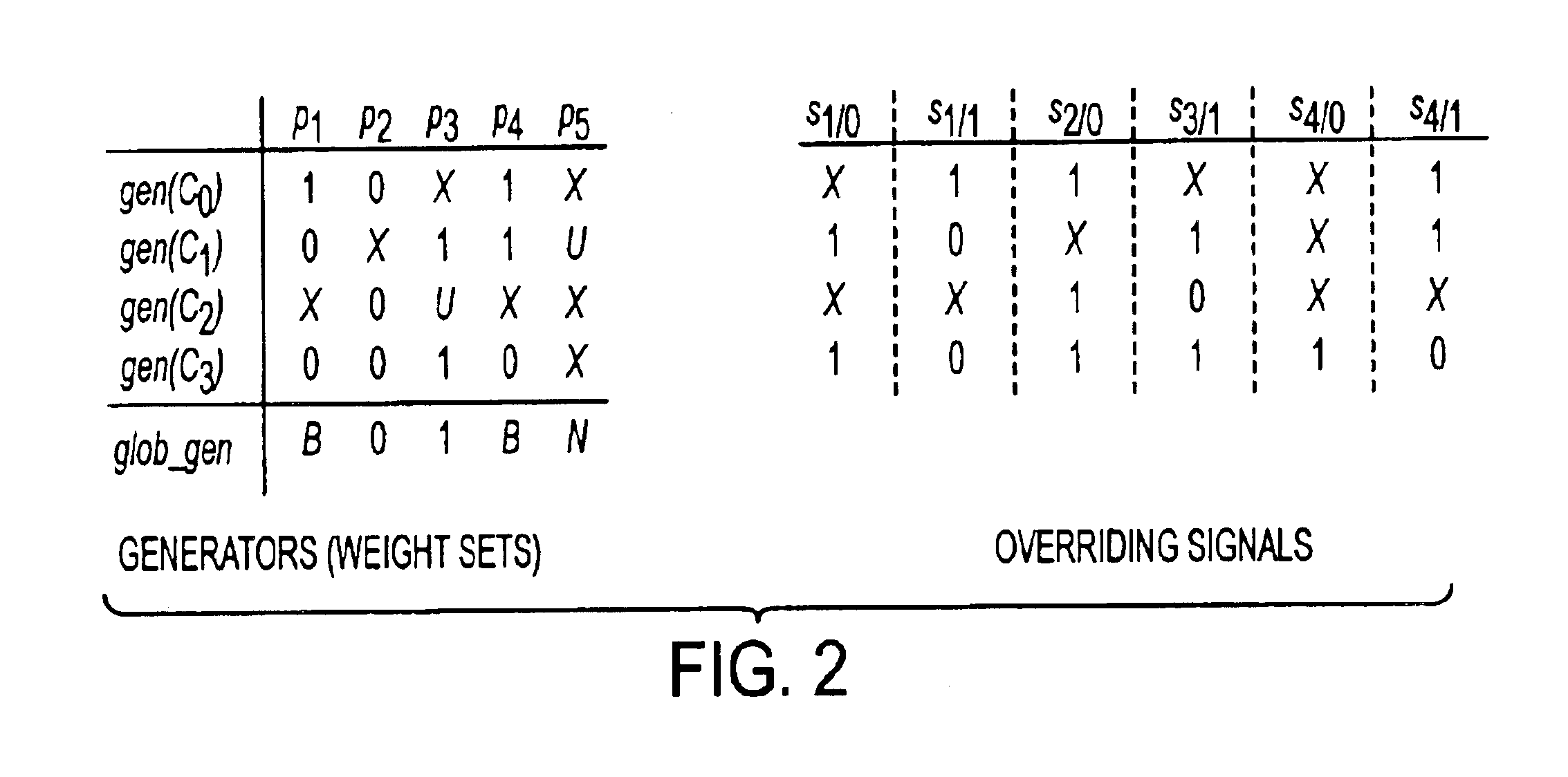

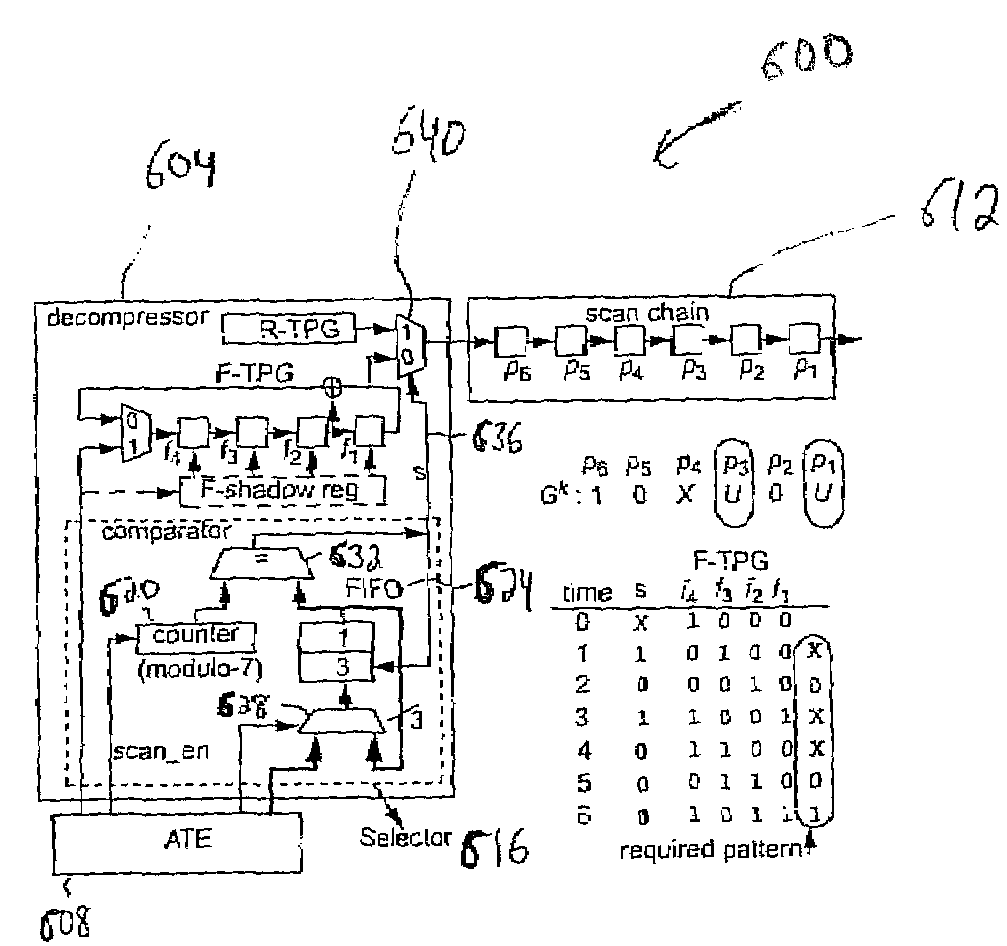

InactiveUS20030149927A1Reducing signalMinimize the numberError preventionTransmission systemsComputer hardwareTest fixture

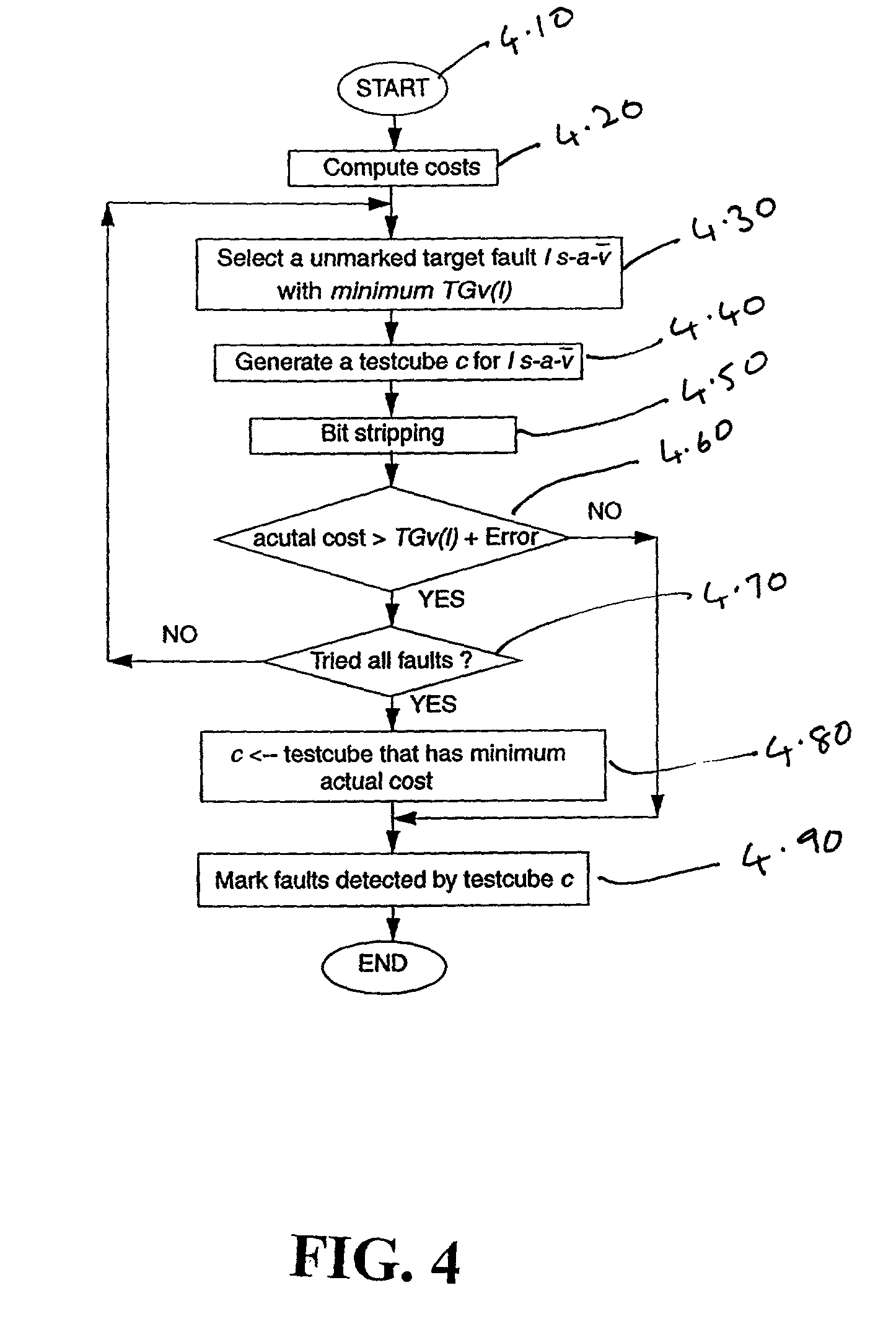

Techniques for generating a test set for hard to detect faults is disclosed. A set of hard to detect faults is identified. A test set for the hard to detect faults is generated by using an improved automatic test pattern generator. The improved automatic test pattern generator is adapted to consider hardware overhead and test sequence lengths, the hardware overheads being incurred when each new testcube is added to the test set. Parallel and serial type test per scan built-in self test circuits designed and adapted to use the disclosed improved automatic test pattern generator are also disclosed.

Owner:NEC CORP

Method and apparatus for collecting and displaying bit-fail-map information

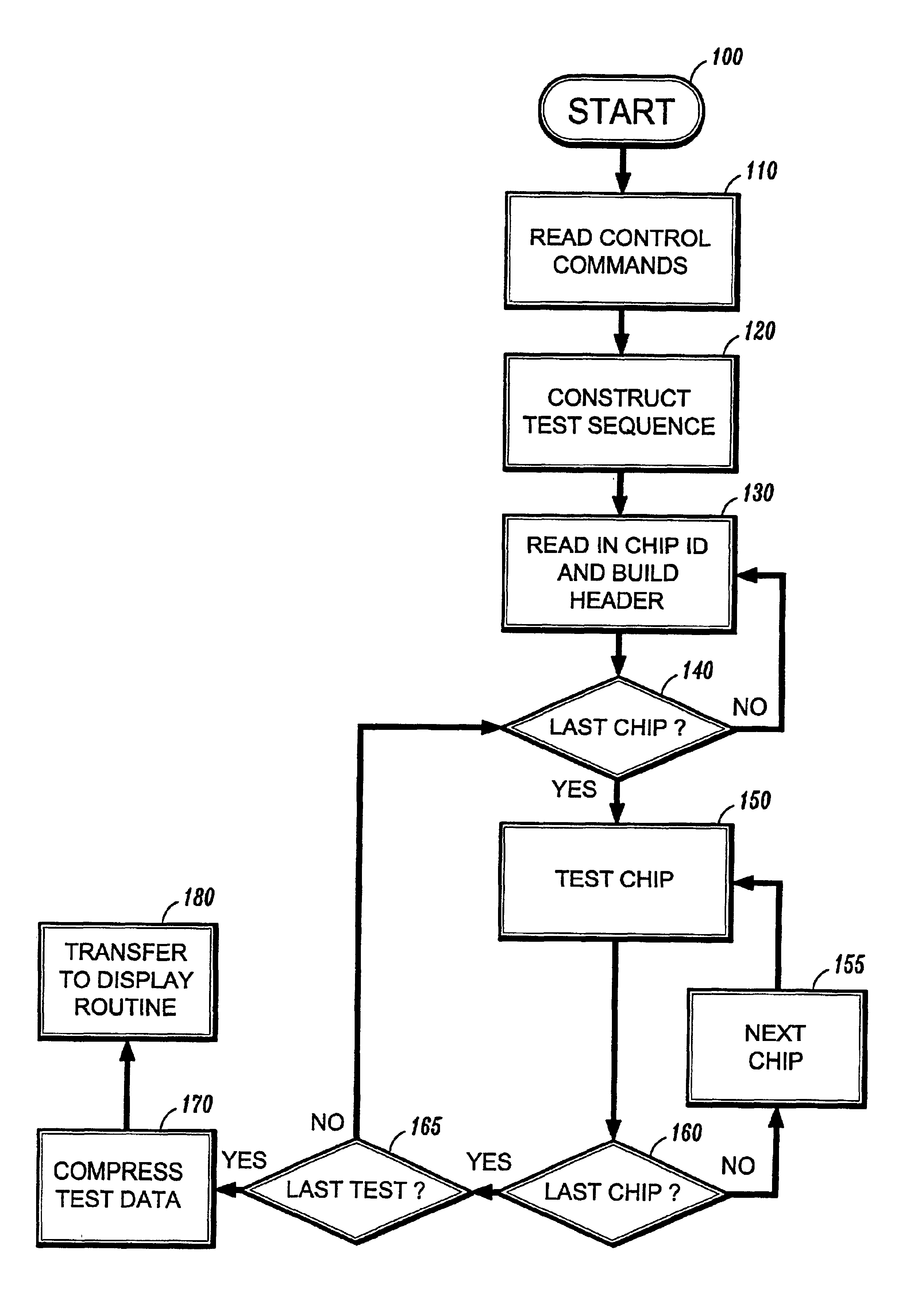

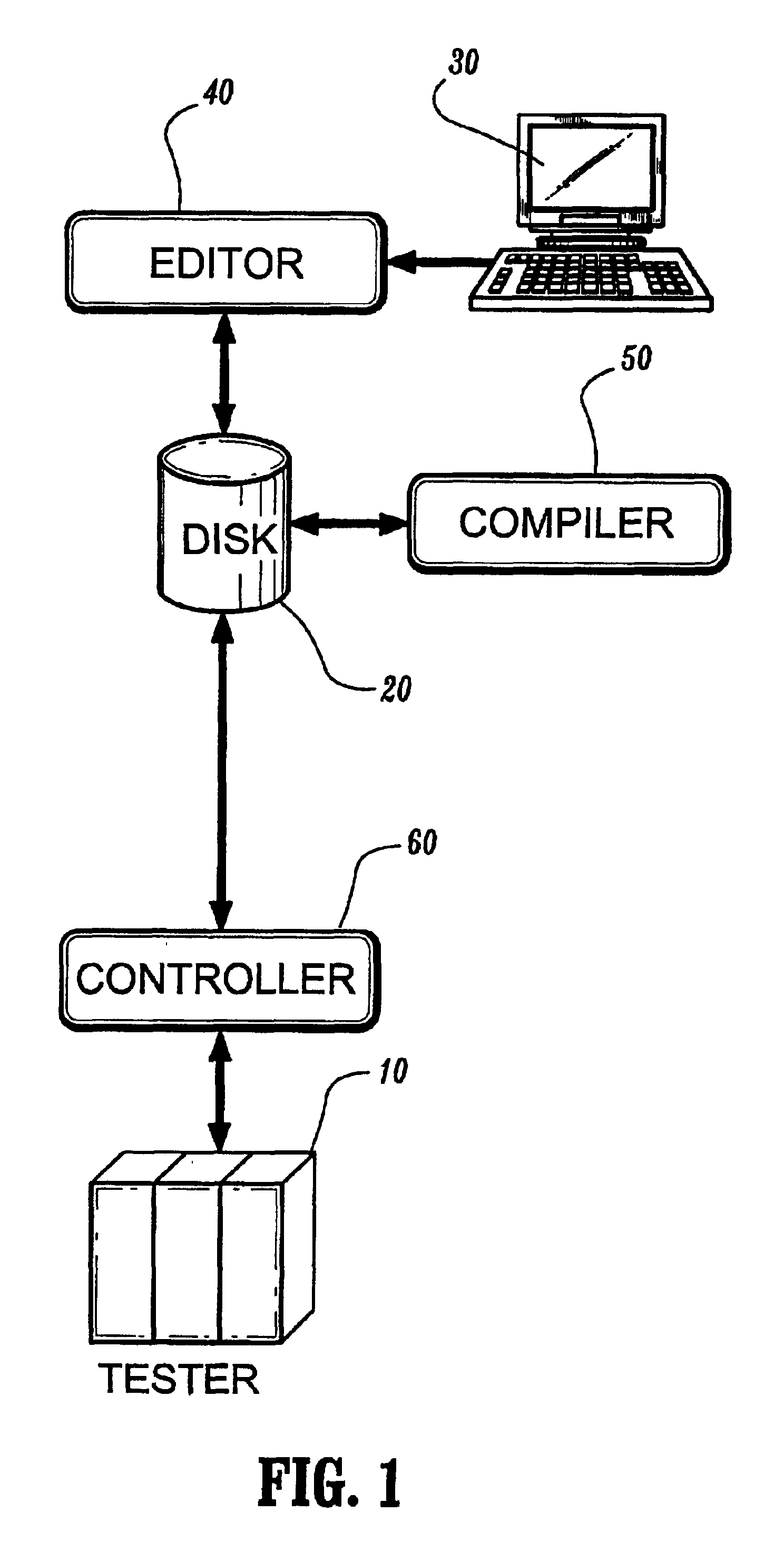

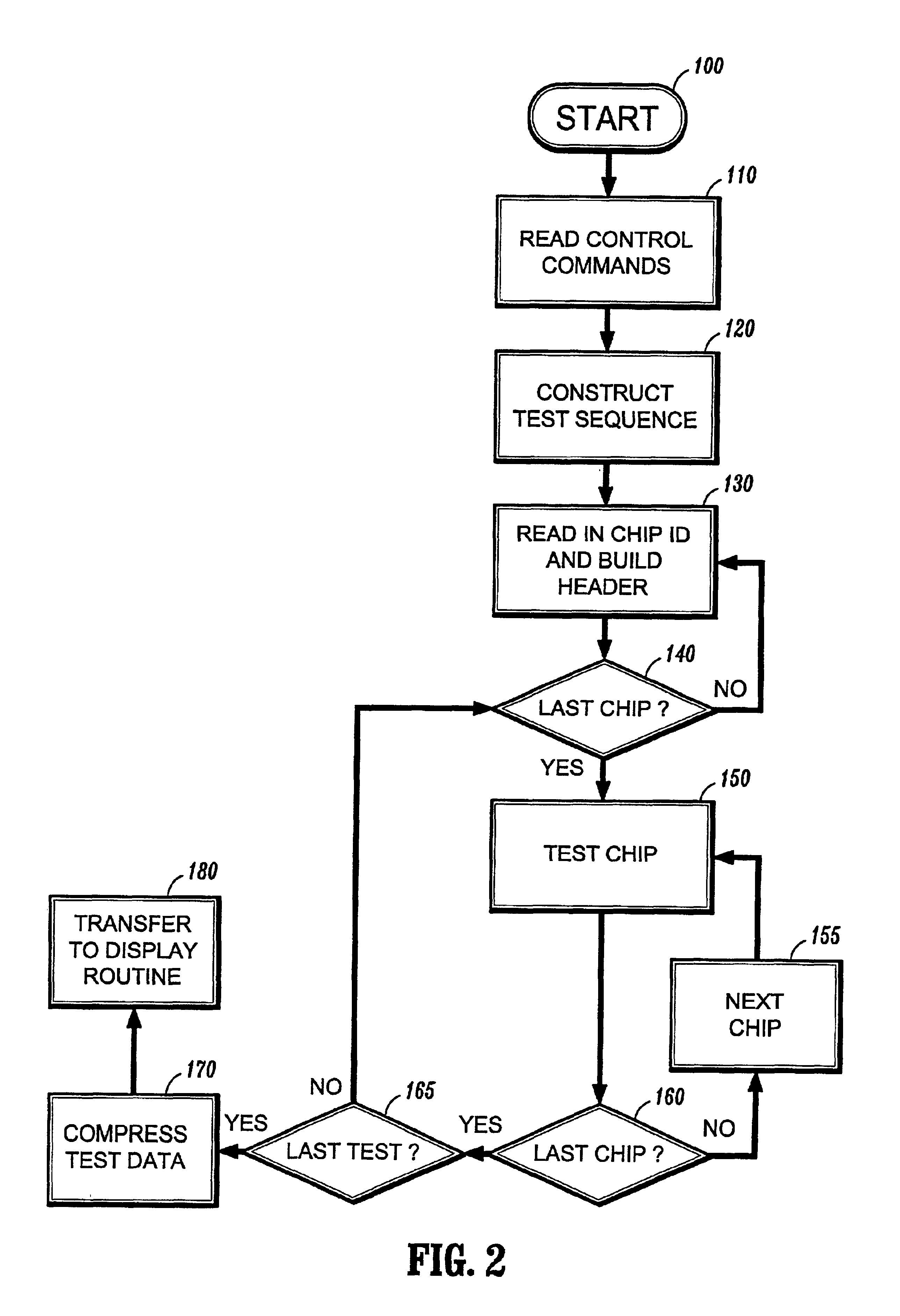

Disclosed is a method of testing memory, comprising providing one or more semiconductor wafers having one or more semiconductor chips thereon, each said chip comprising one or more memory cells, providing a programmable testing apparatus comprising at least one test pattern generators and a test bed adapted to receive said one or more wafers in communicative contact so as to address individual memory cells, chips, and wafers and transmit information thereto and receive information therefrom, receiving one or more test commands, constructing a test sequence of one or more commanded tests from said test commands, constructing at least one header comprising location information for each said wafer, chip and memory cell, testing said memory cells with a test pattern generated by said test pattern generator, collecting the results of said testing and passing them to a display device, passing said location information to said display device, constructing and displaying a graphical representation of said test results using said location information.

Owner:POLARIS INNOVATIONS

System and method for predicting iwarx and stwcx instructions in test pattern generation and simulation for processor design verification/validation in interrupt mode

InactiveUS20090024894A1Electronic circuit testingError detection/correctionPattern generationProcessor design

During a test pattern build, a test pattern generator pseudo-randomly selects an address for a selected lwarx instruction and builds the lwarx instruction using the pseudo-random address into a test pattern. Subsequently, the test pattern generator builds a store instruction after the lwarx instruction using the pseudo-random address. The store instruction is adapted to store the pseudo-random address in a predetermined memory location. The test pattern generator also builds an interrupt service routine that services an interrupt associated with the interrupt request; checks the predetermined memory location; determines that the pseudo-random address is located in the predetermined memory location; and executes a subsequent lwarx instruction using the pseudo-random address.

Owner:IBM CORP

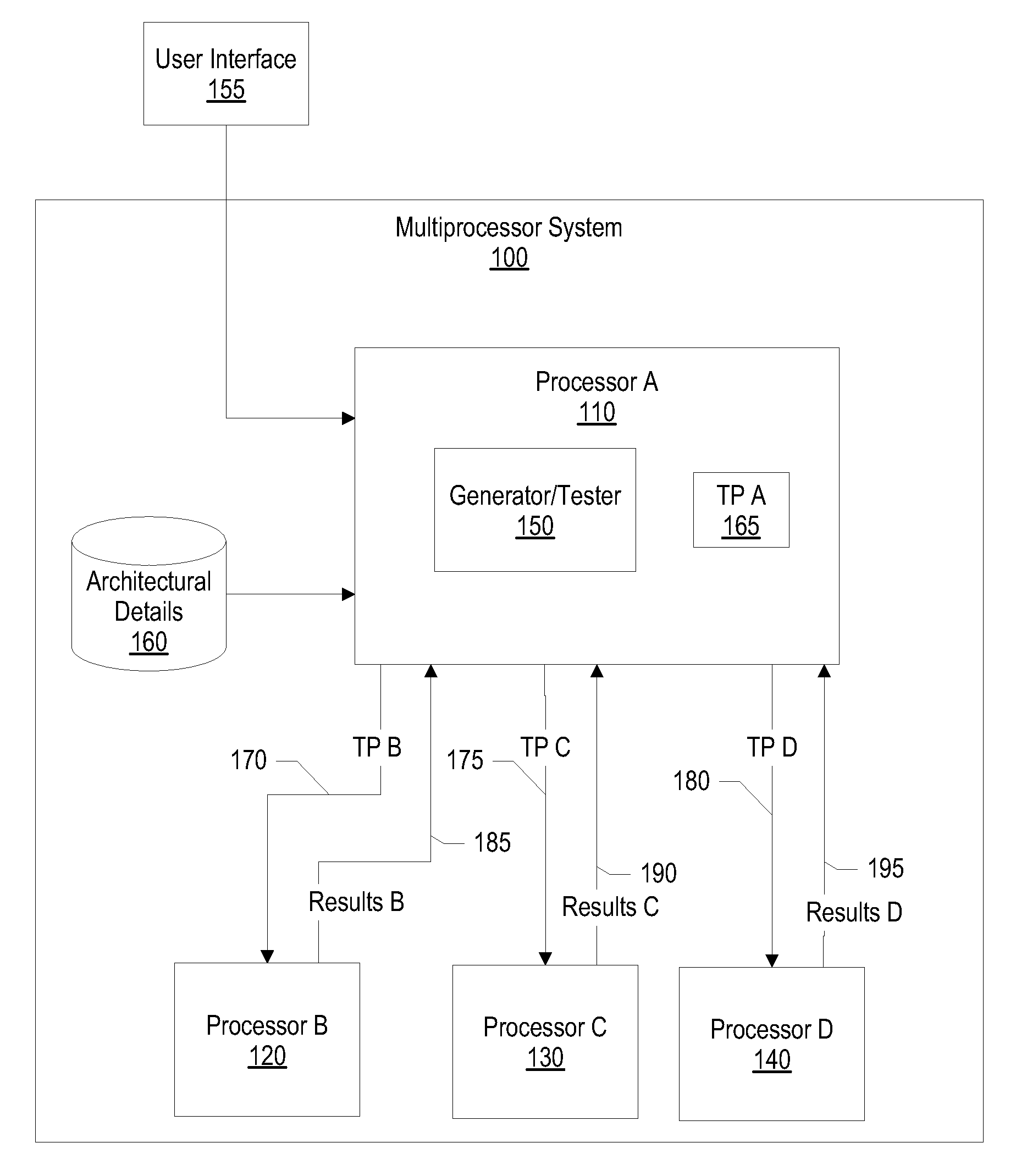

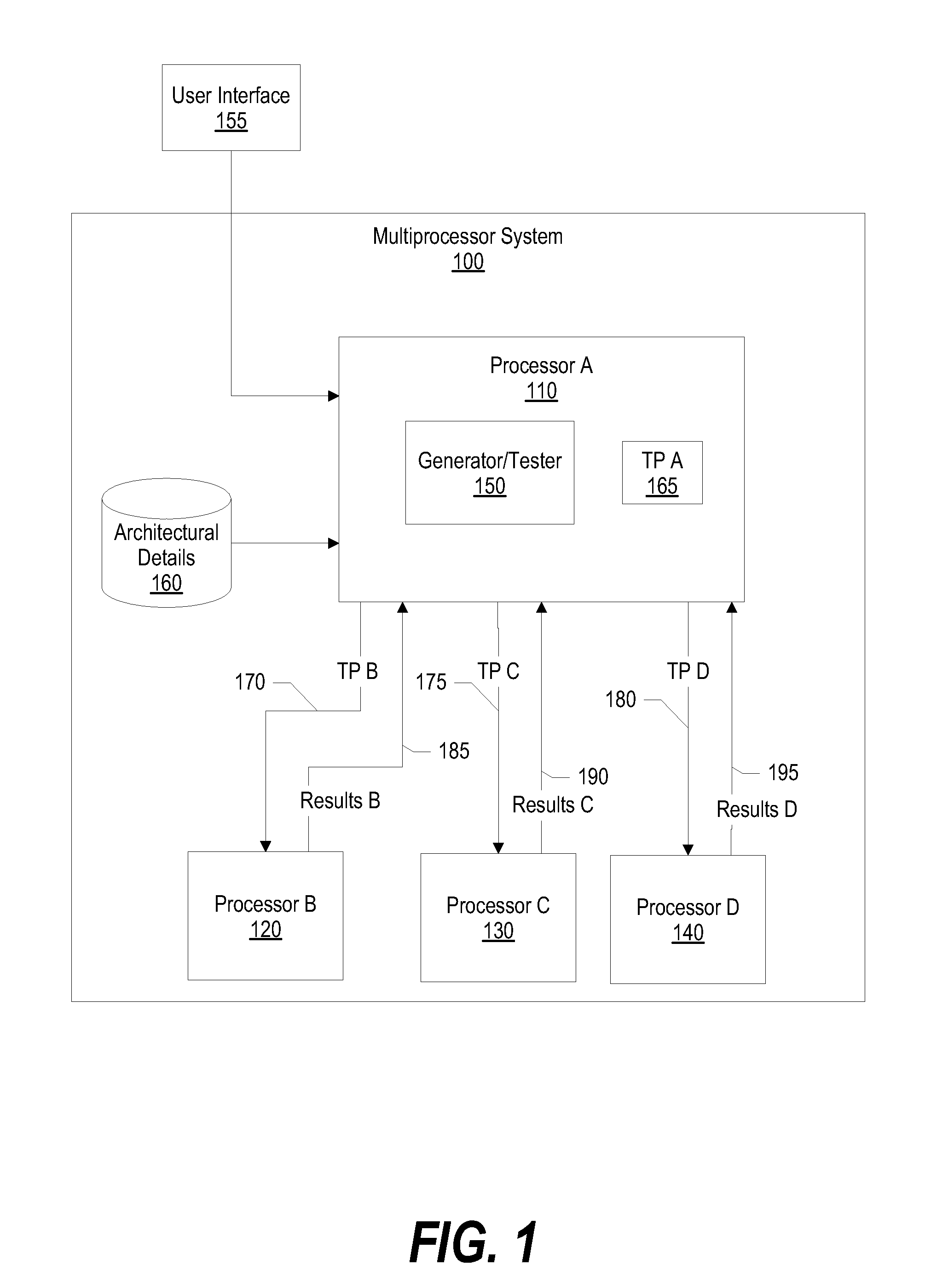

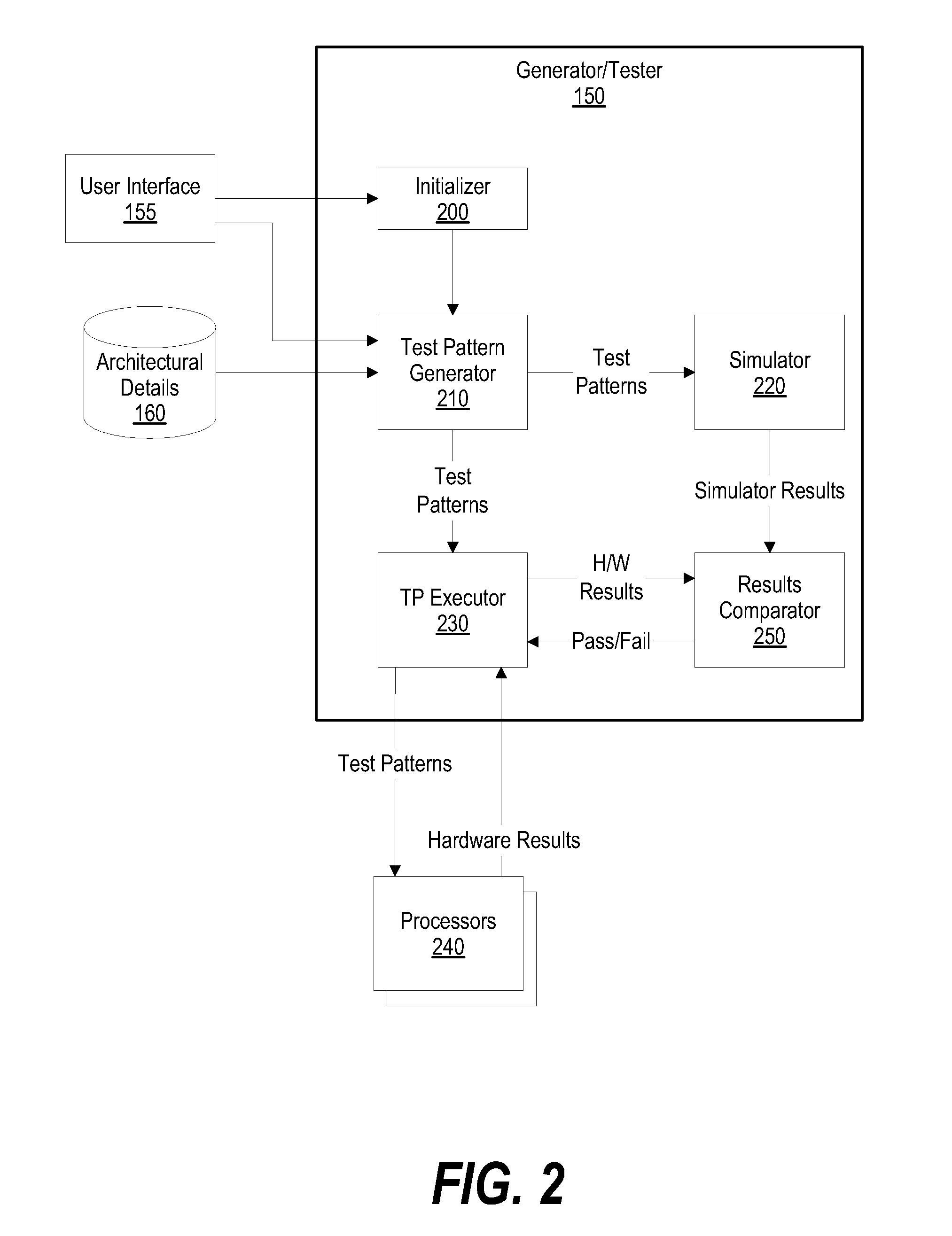

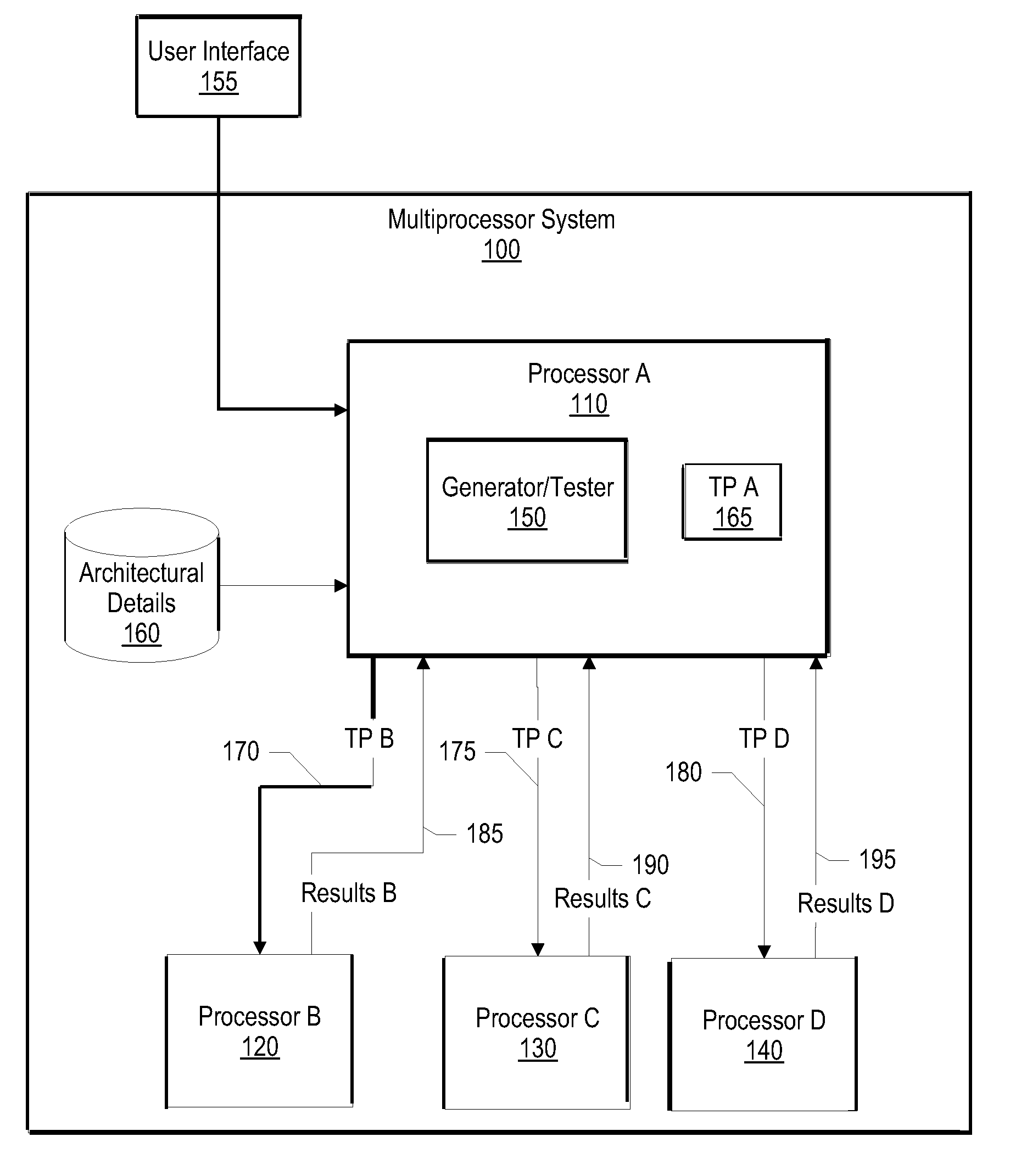

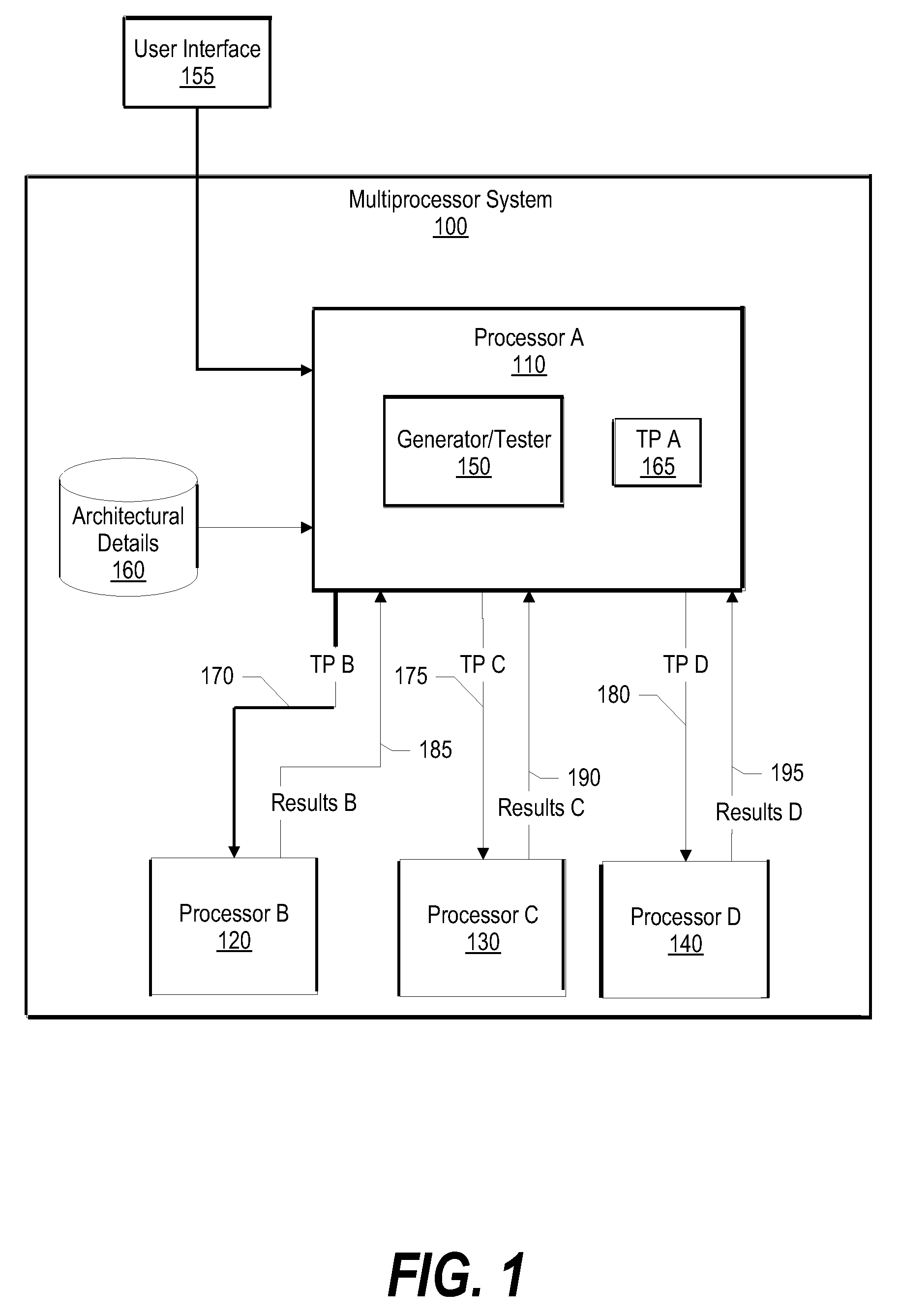

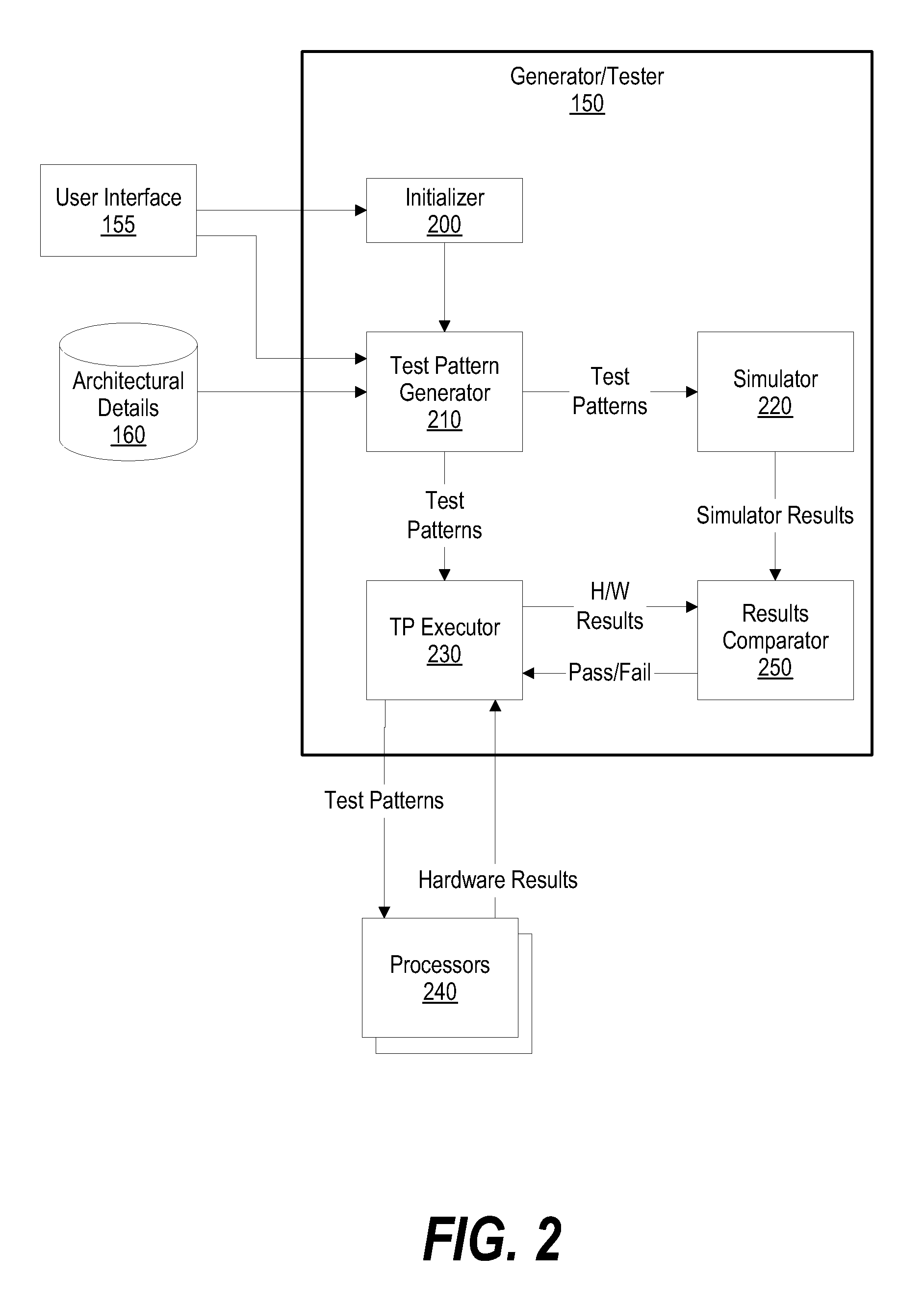

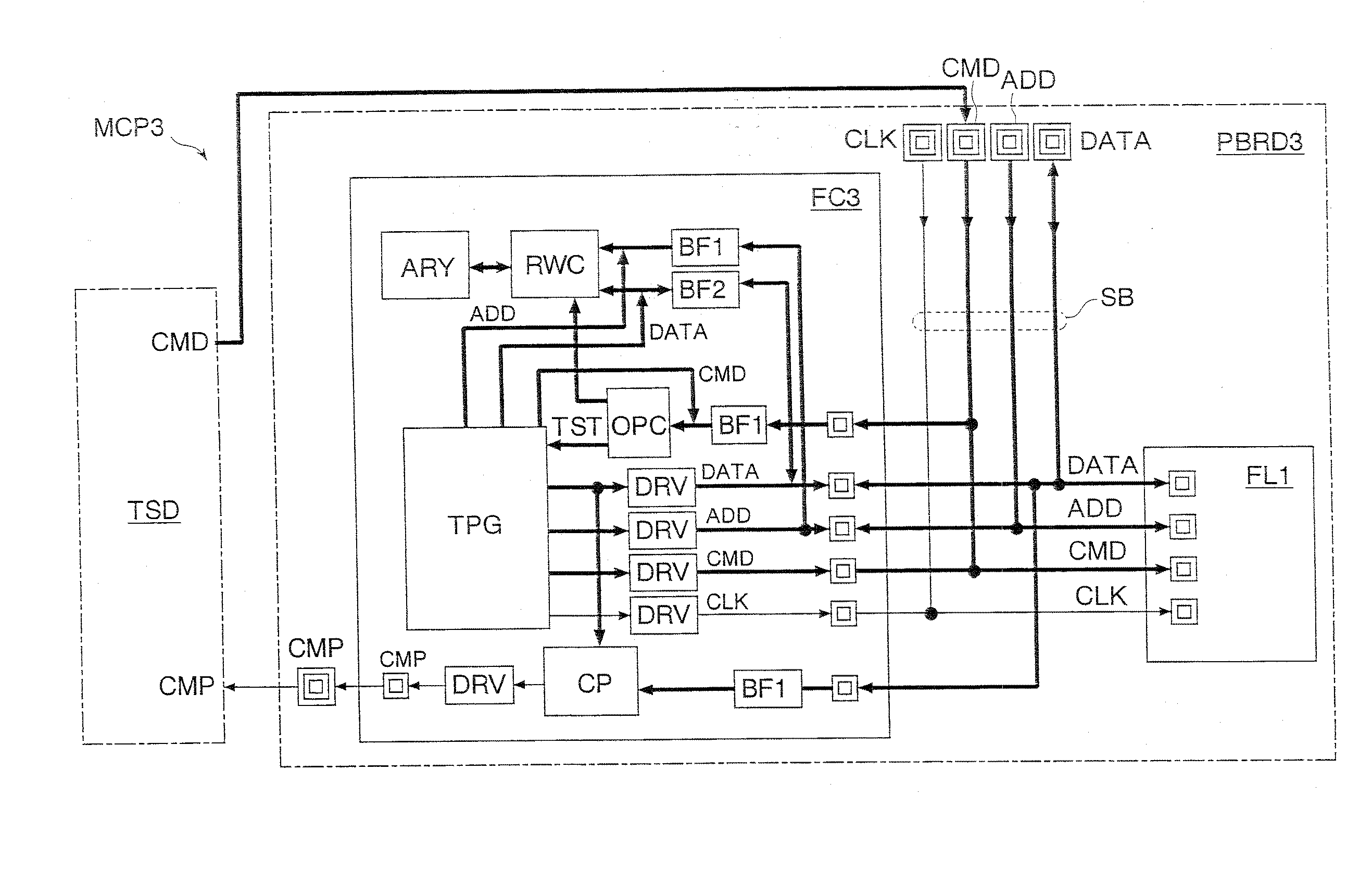

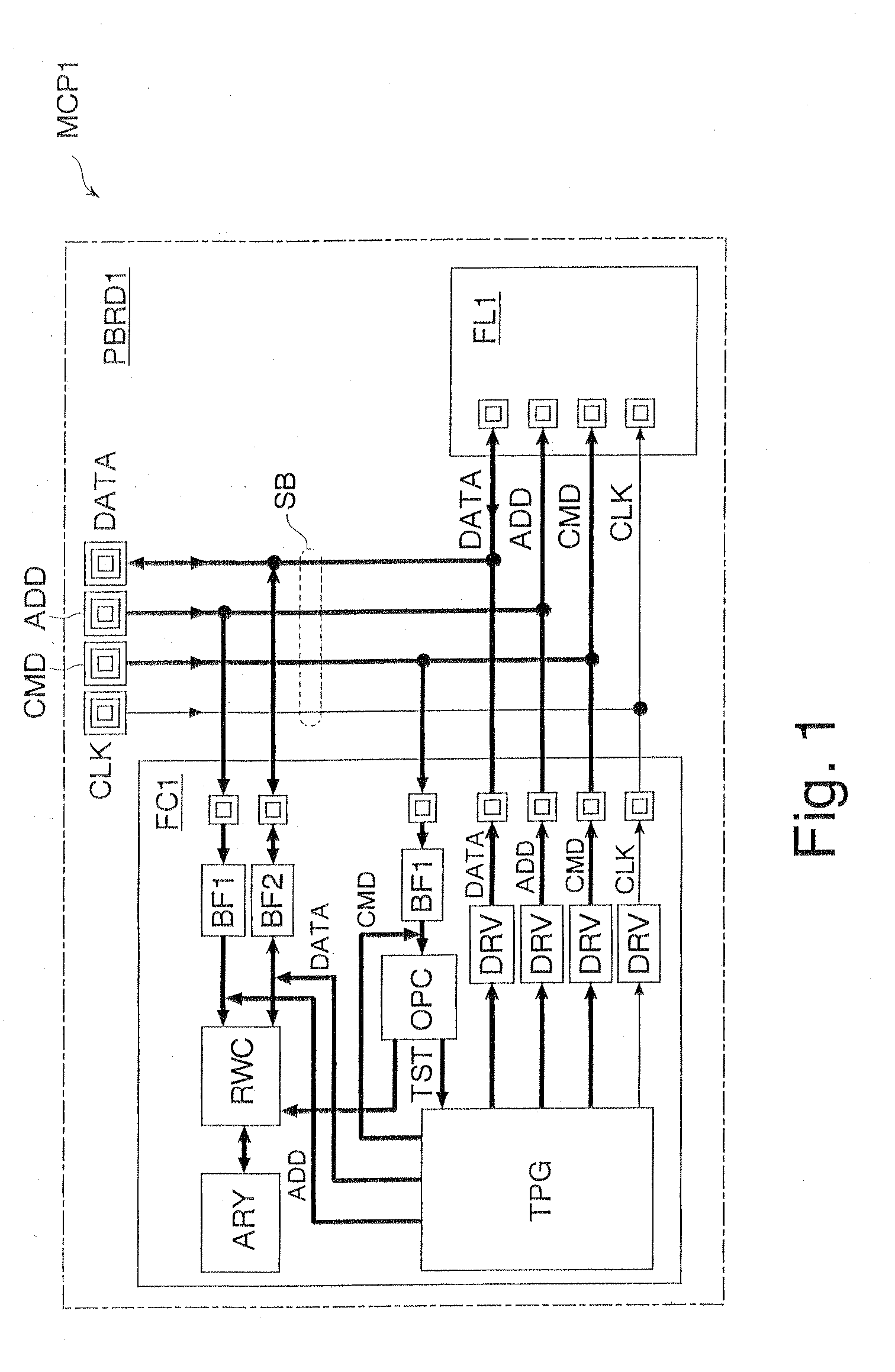

System and method for creating different start cache and bus states using multiple test patterns for processor design verification and validation

ActiveUS7747908B2Increase coverageElectronic circuit testingError detection/correctionMulti processorBroadband

A system and method for creating different start cache and bus states using multiple test patterns for processor design verification and validation is presented. A test pattern generator / tester re-uses test patterns in different configurations that alter cache states and translation lookaside buffer (TLB) states, which produces different timing scenarios on a broadband bus. The test pattern generator / tester creates multiple test patterns for a multi-processor system and executes the test patterns repeatedly in different configurations without rebuilding the test patterns. This enables a system to dedicate more time executing the test patterns instead of building the test patterns. By repeatedly executing the same test patterns in a different configuration, the invention described herein produces different start cache states, different TLB states, along with other processor units, each time the test patterns execute that, in turn, changes the bus timing.

Owner:TWITTER INC

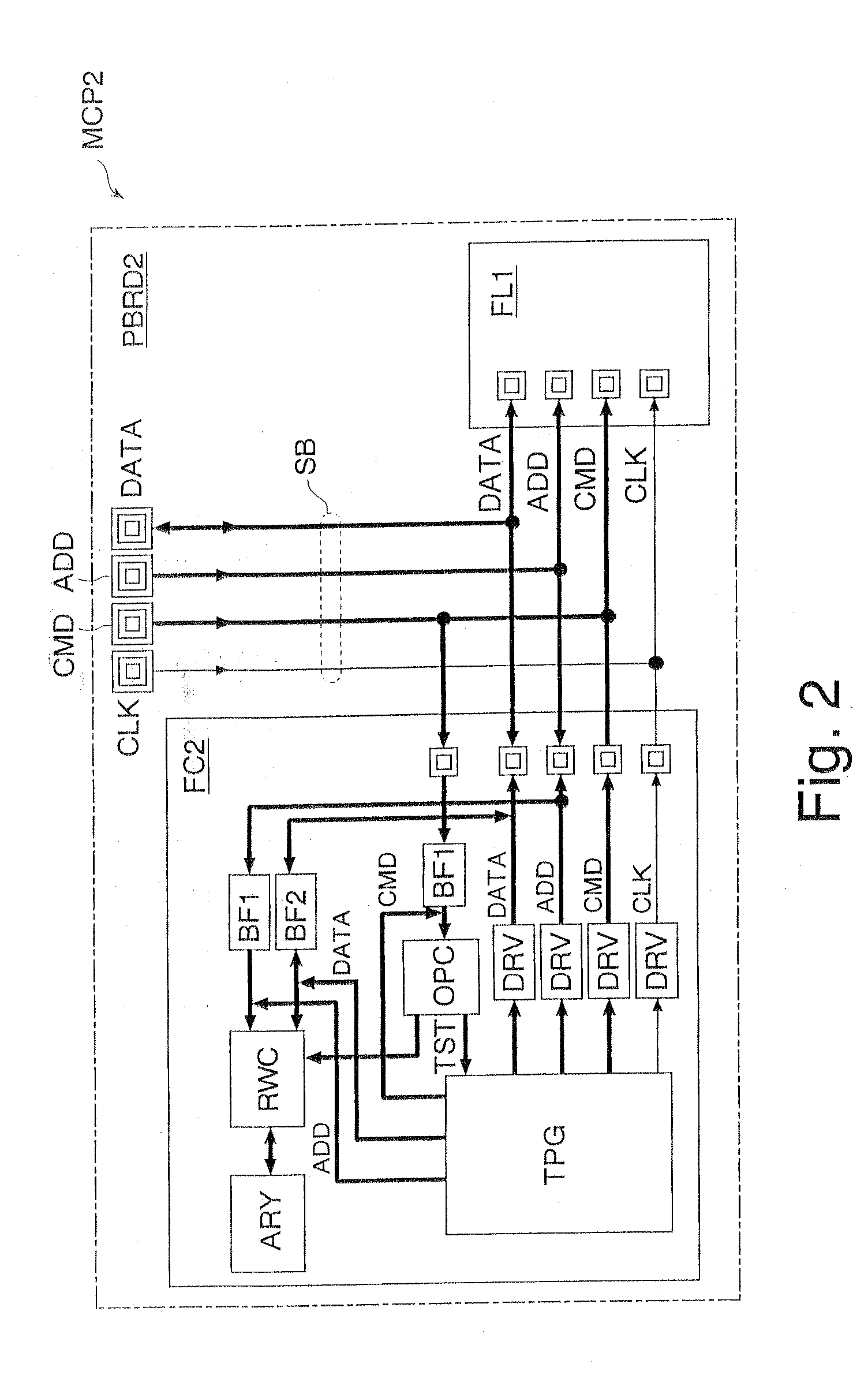

Semiconductor memory, system, testing method for system

InactiveUS20080104458A1Reduce testing costsReduce system costError detection/correctionStatic storageMemory chipSystem testing

A plurality of test patterns generated by a test pattern generator is output from a first memory chip to test a second memory chip, which is of a different type from the first memory chip and mounted in the same package. Therefore, when different types of memory chips are mounted in the same package, the memory chip is tested even no terminal of the memory chip is connected to an external terminal of a system. Since there is no need to form any useless terminal in the system, system cost is reduced. Since a testing apparatus generating complicated test patterns is made unnecessary, test cost is reduced. The test pattern generator is constructed using nonvolatile logic and therefore, tests can be carried out without preparing test patterns in advance. Consequently, a user who purchases the first and second memory chips to construct a system can also carry out tests easily.

Owner:FUJITSU MICROELECTRONICS LTD