Patents

Literature

38 results about "Pseudo random testing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

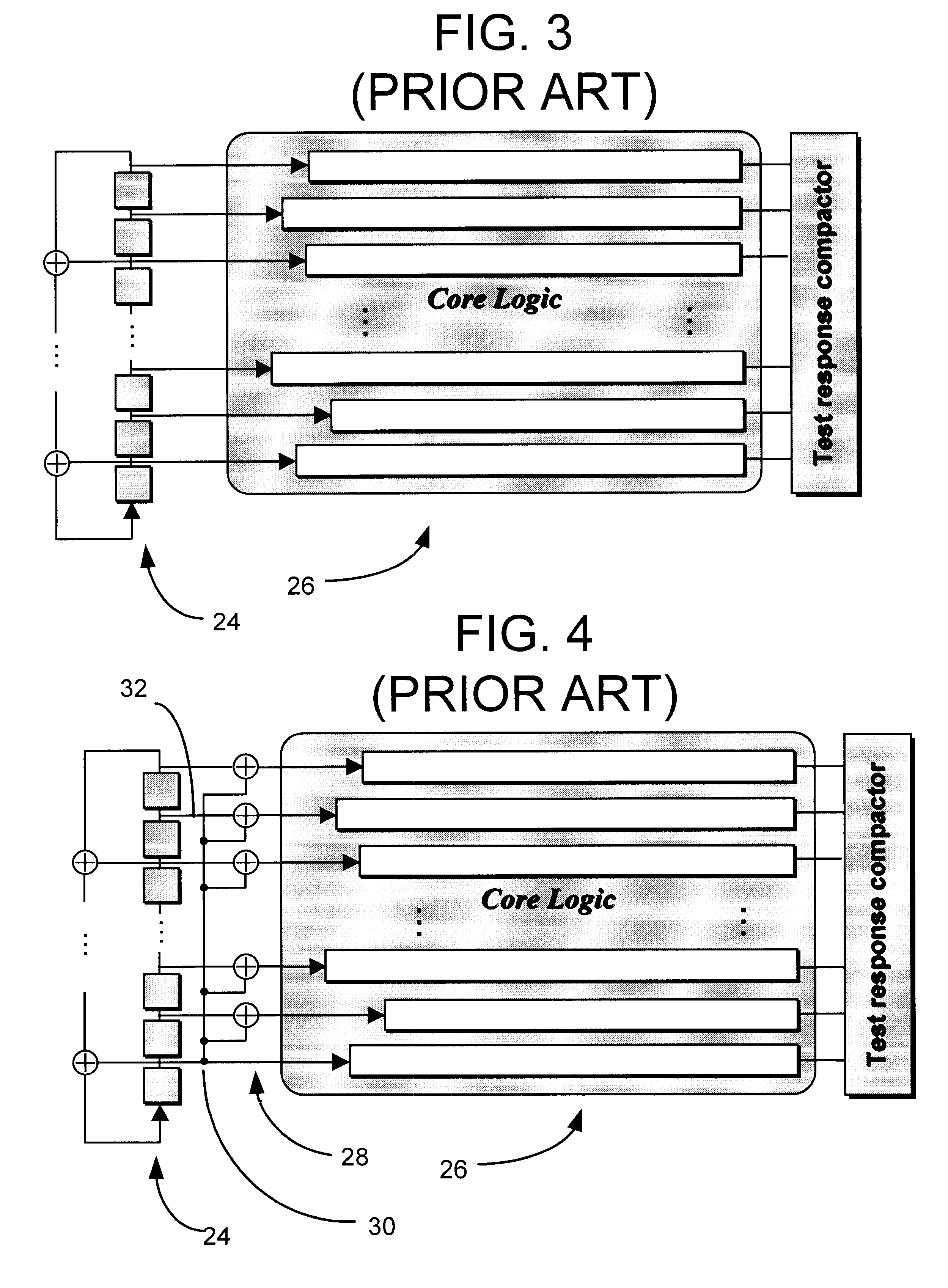

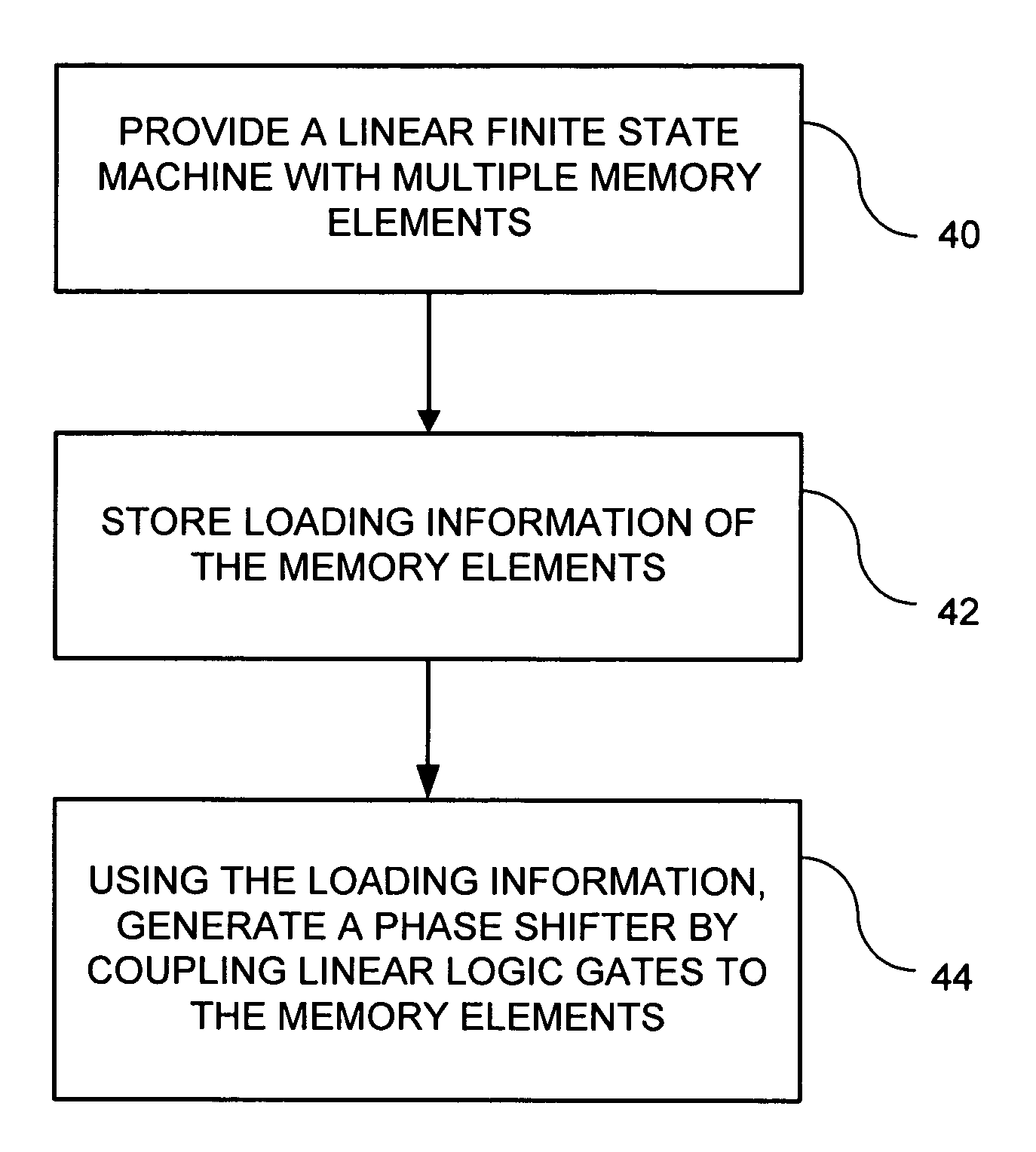

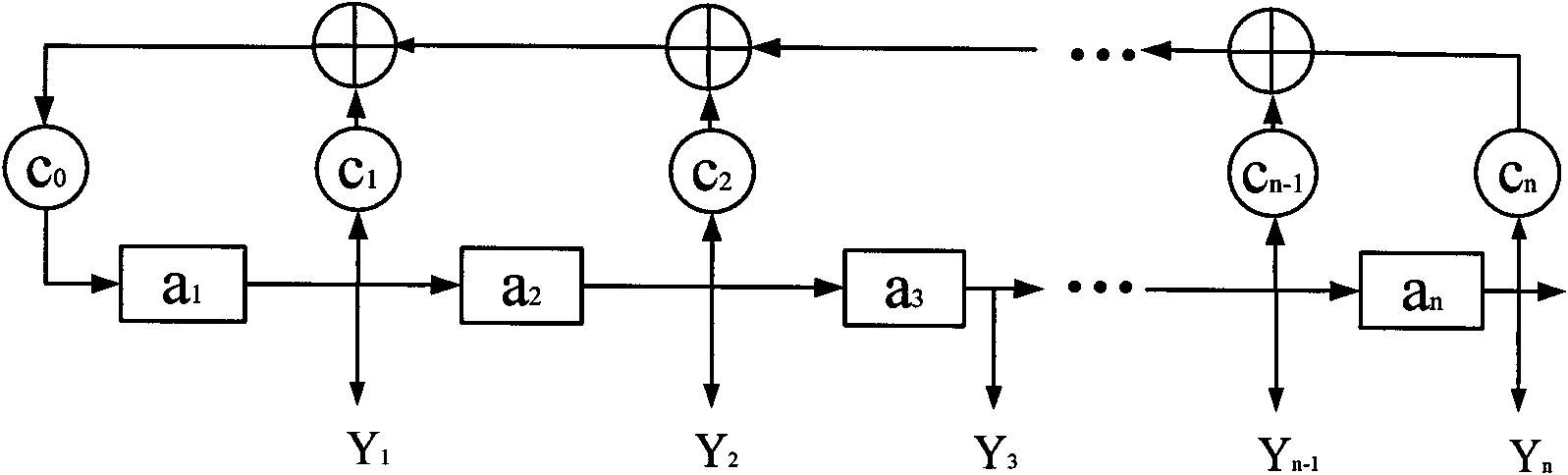

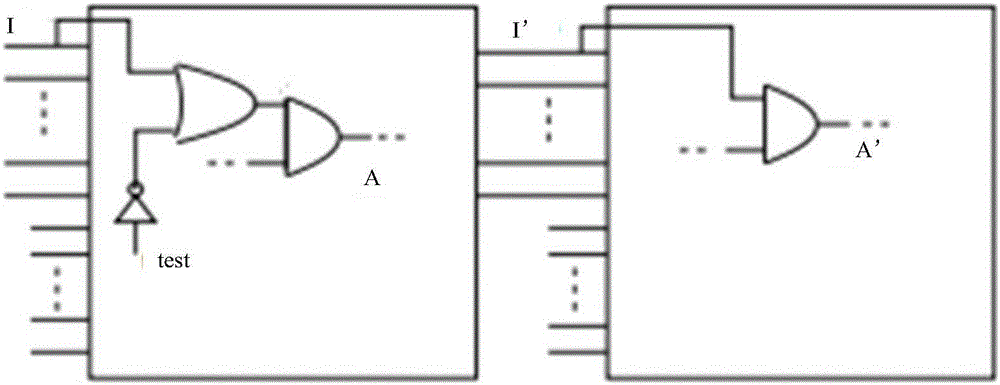

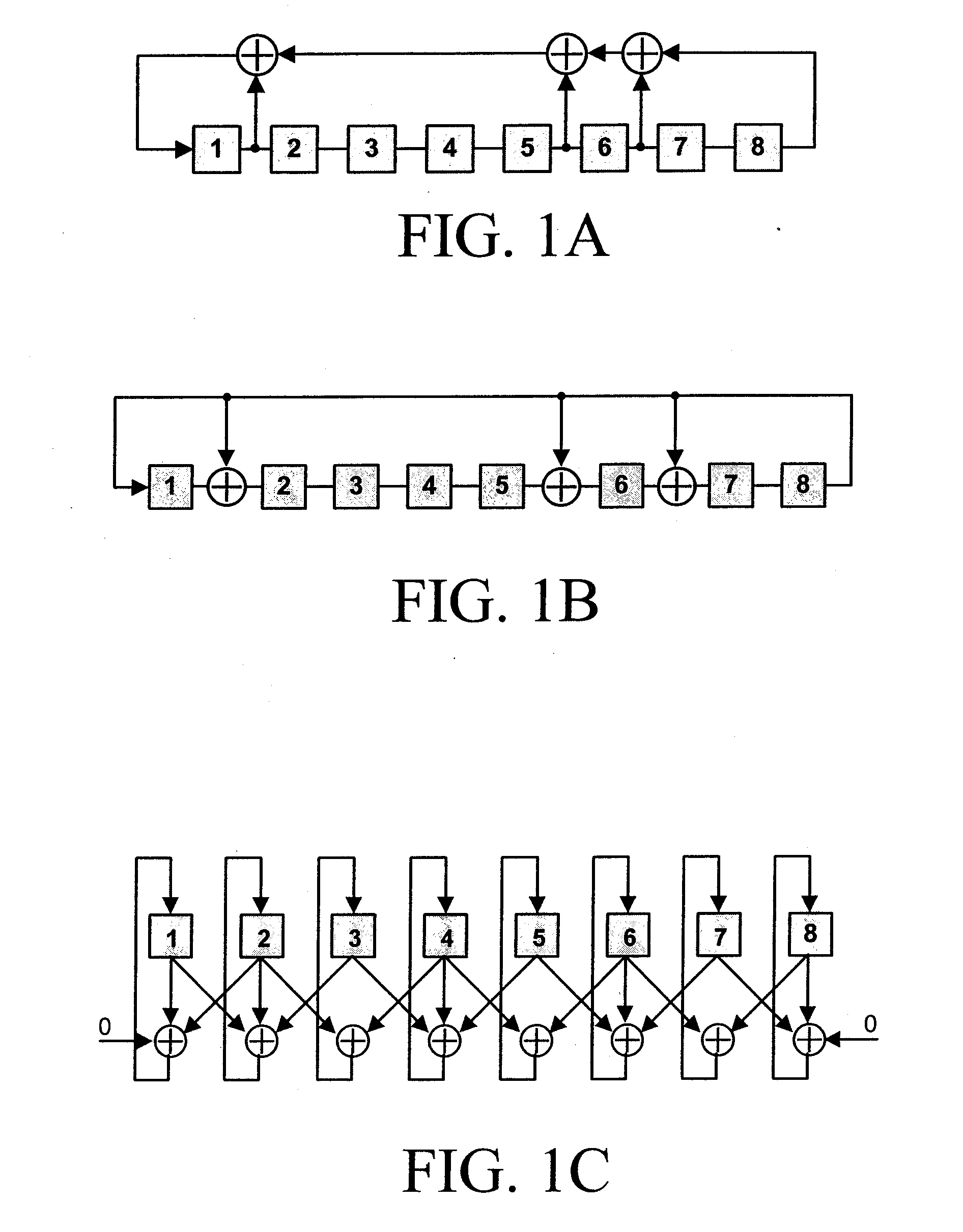

Phase shifter with reduced linear dependency

InactiveUS6874109B1Electronic circuit testingError detection/correctionCircuit complexityLinear dependency

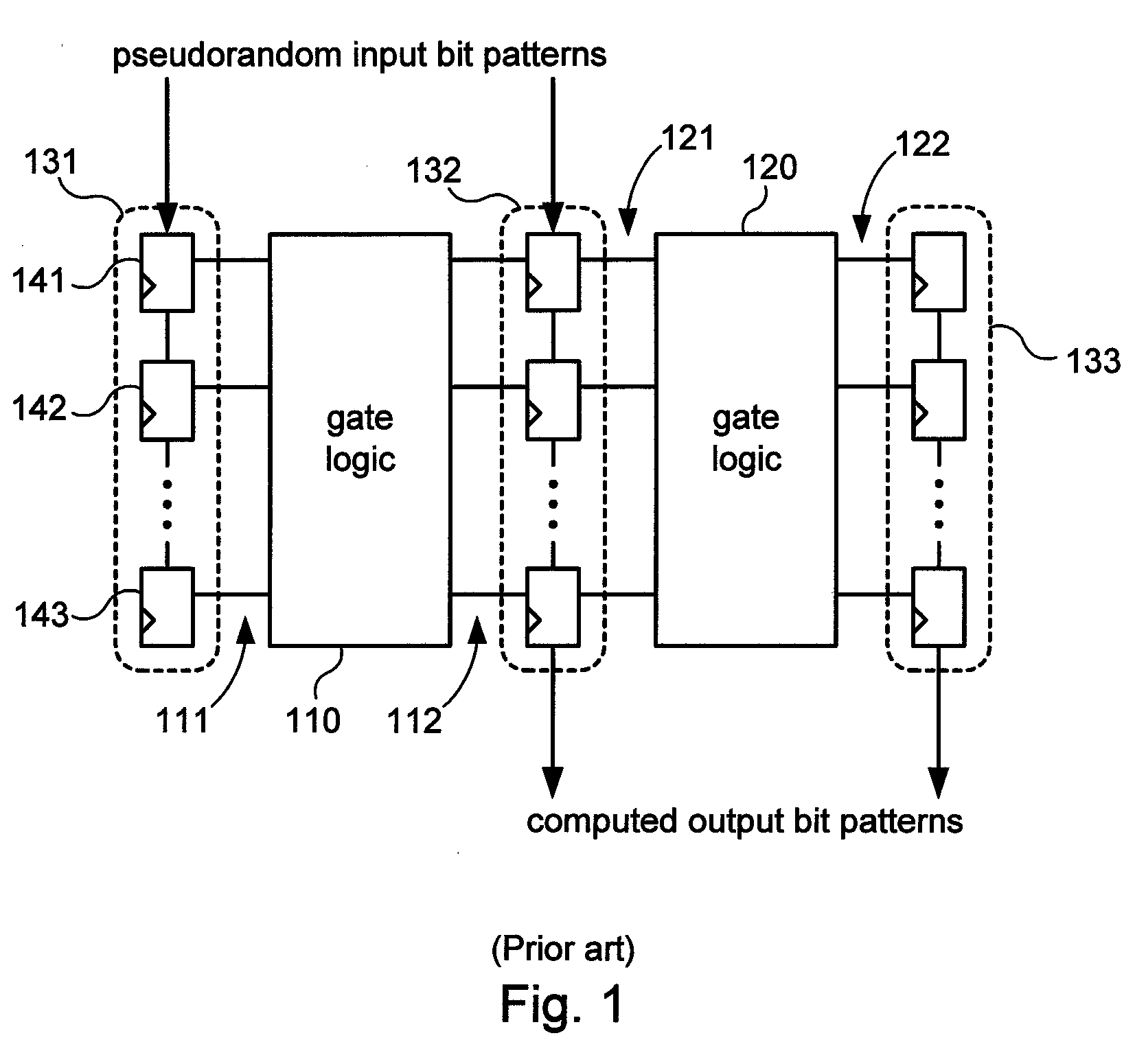

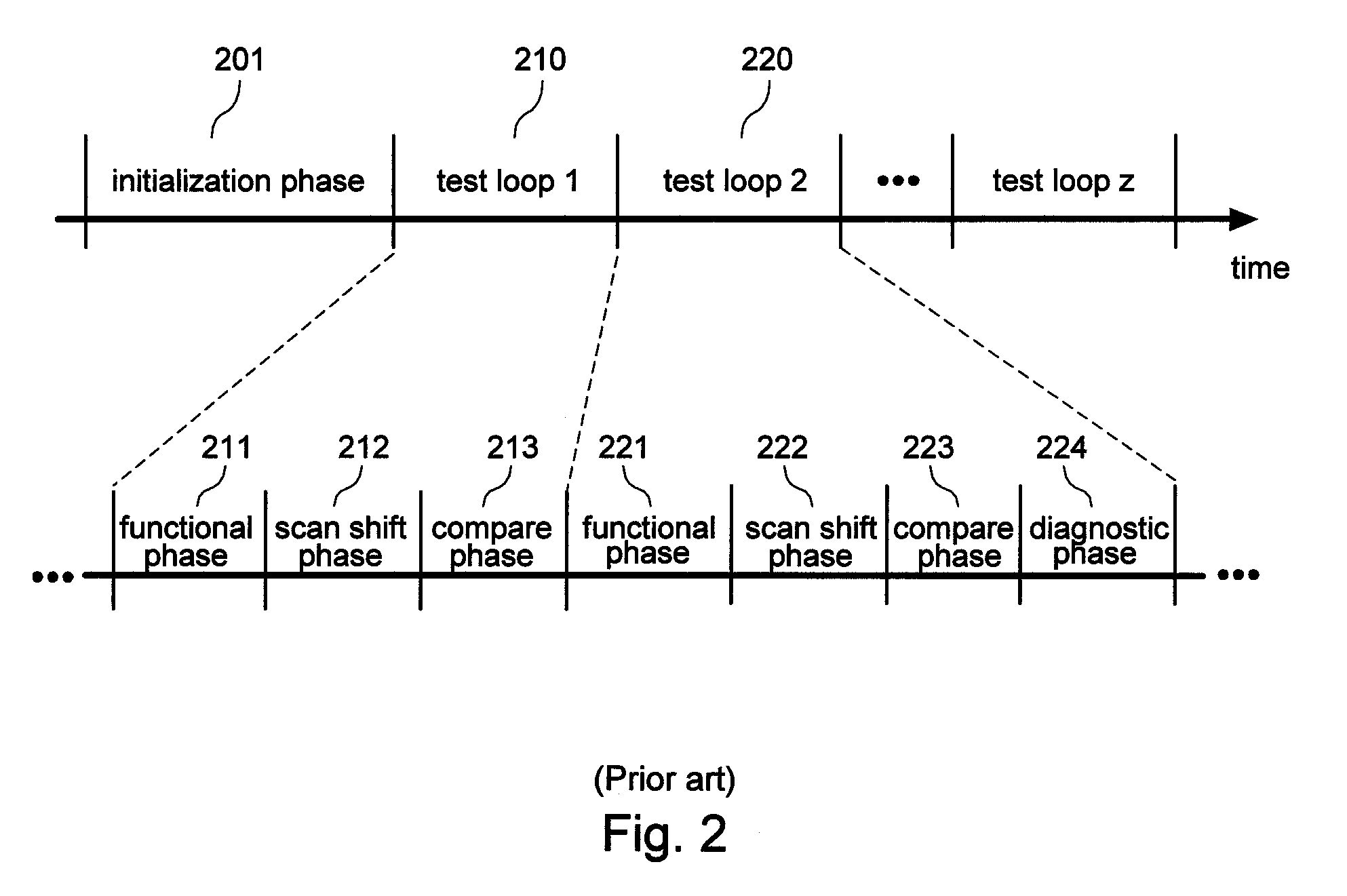

A method is disclosed for the automated synthesis of phase shifters. Phase shifters comprise circuits used to remove effects of structural dependencies featured by pseudo-random test pattern generators driving parallel scan chains. Using a concept of duality, the method relates the logical states of linear feedback shift registers (LFSRs) and circuits spacing their inputs to each of the output channels. The method generates a phase shifter network balancing the loads of successive stages of LFSRs and satisfying criteria of reduced linear dependency, channel separation and circuit complexity.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

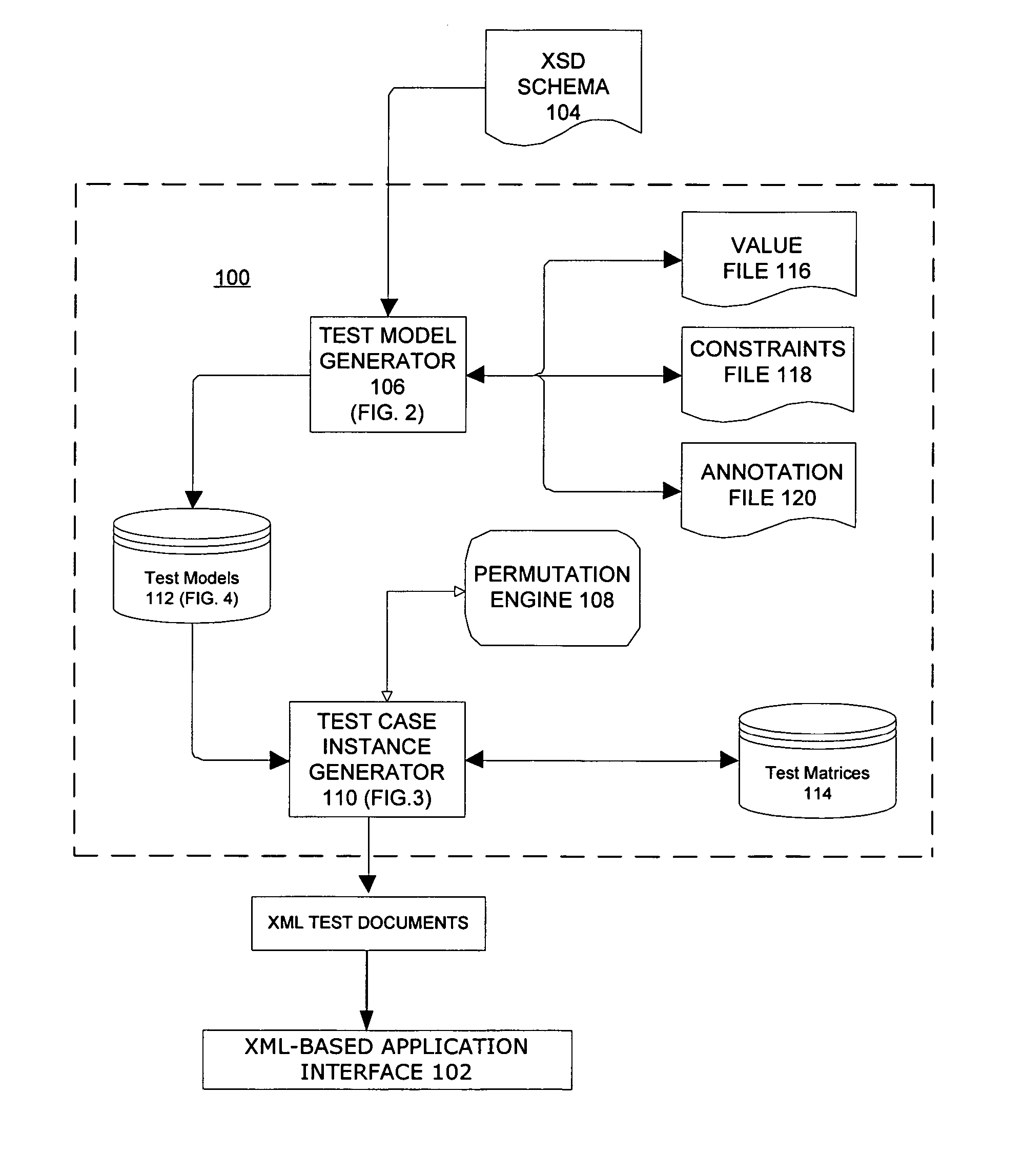

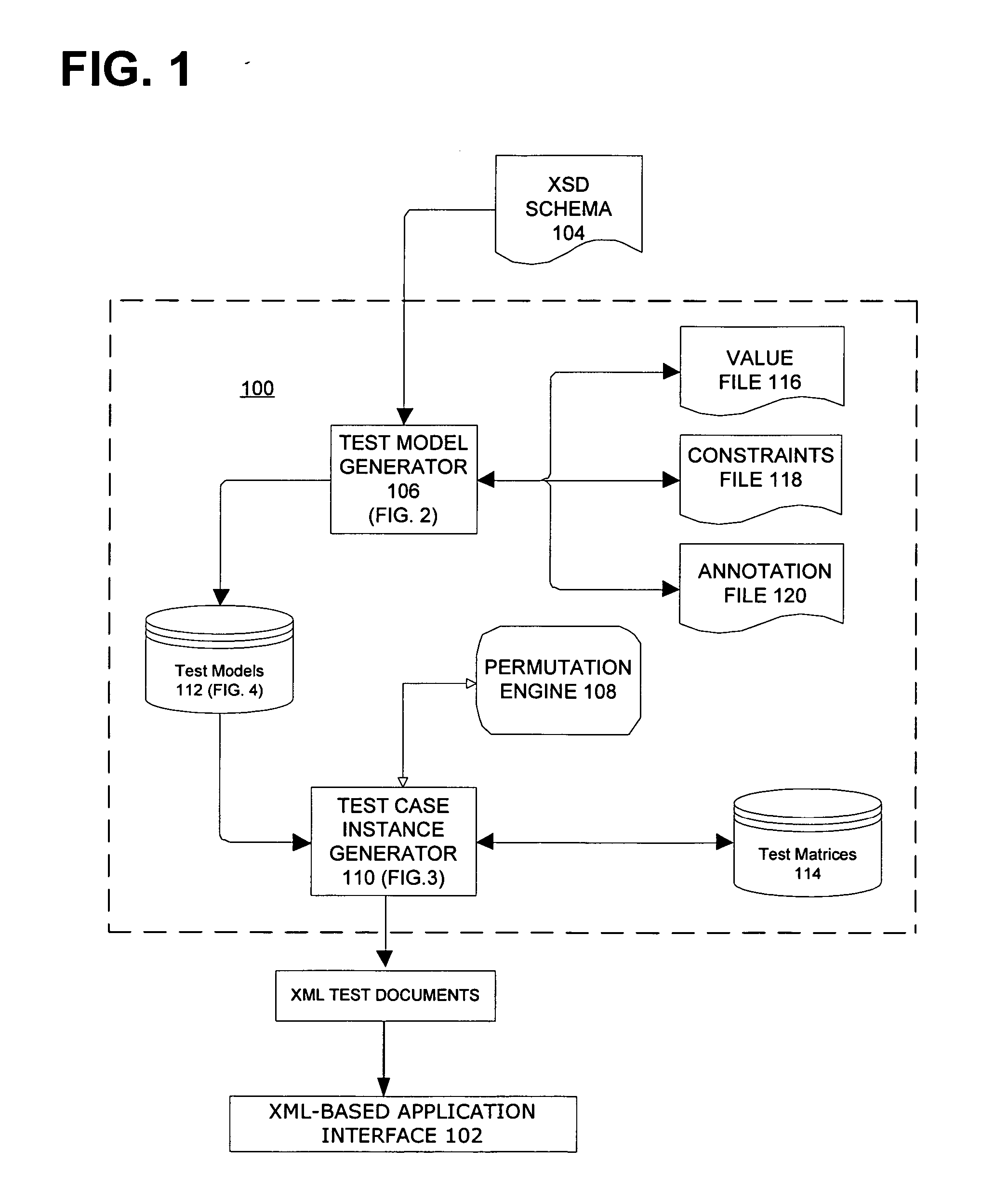

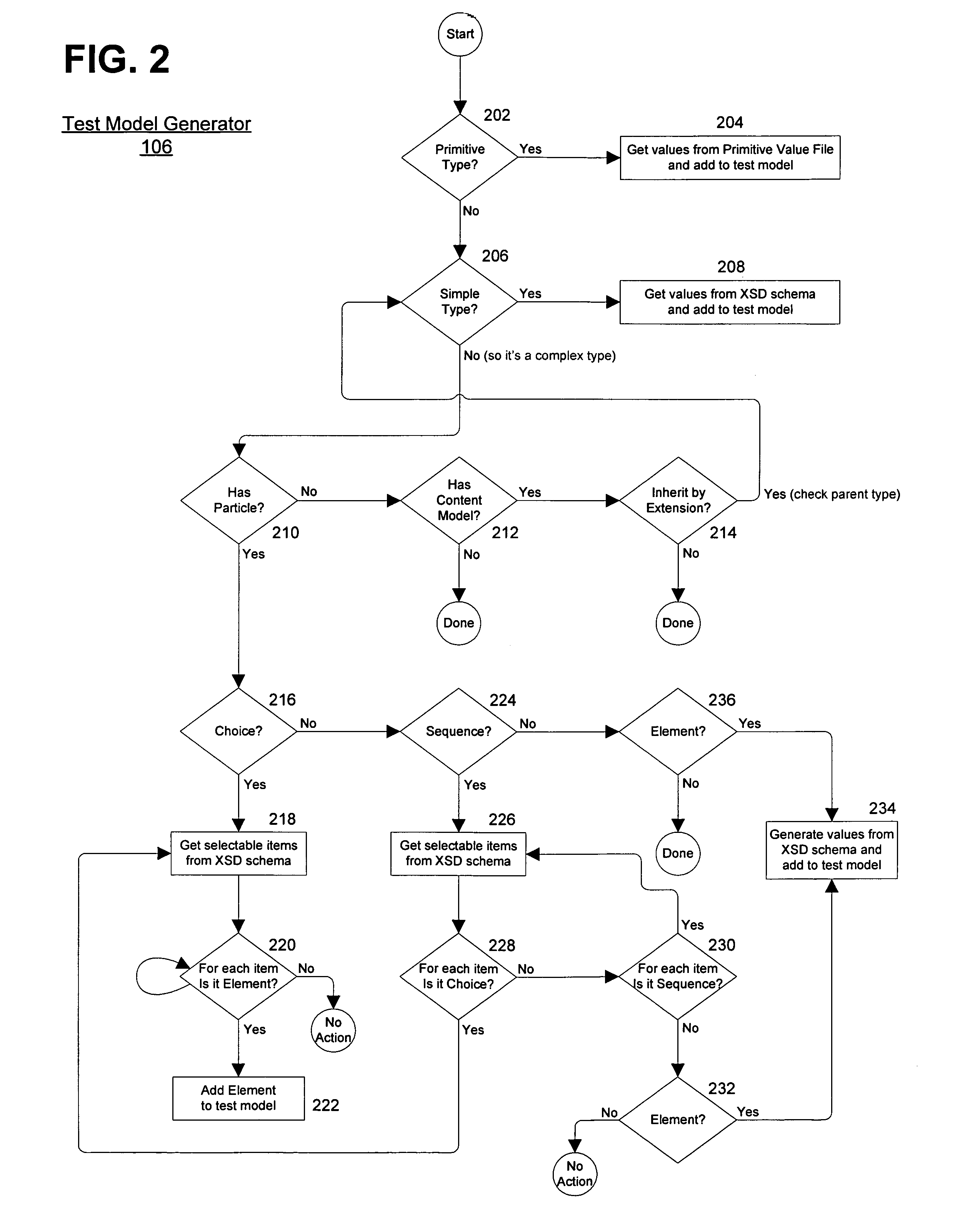

Pseudo-random test case generator for XML APIs

InactiveUS20060101397A1Improve software testing efficiencyMinimize revenue lossError detection/correctionSpecific program execution arrangementsTheoretical computer scienceApplication software

A test case generator including a test model generator for generating test models. A test case instance generator uses a permutation engine to generate test matrices from the tests models and generates XML documents from the test matrices. The documents are applied to an XML-based application interface to test the interface.

Owner:MICROSOFT TECH LICENSING LLC

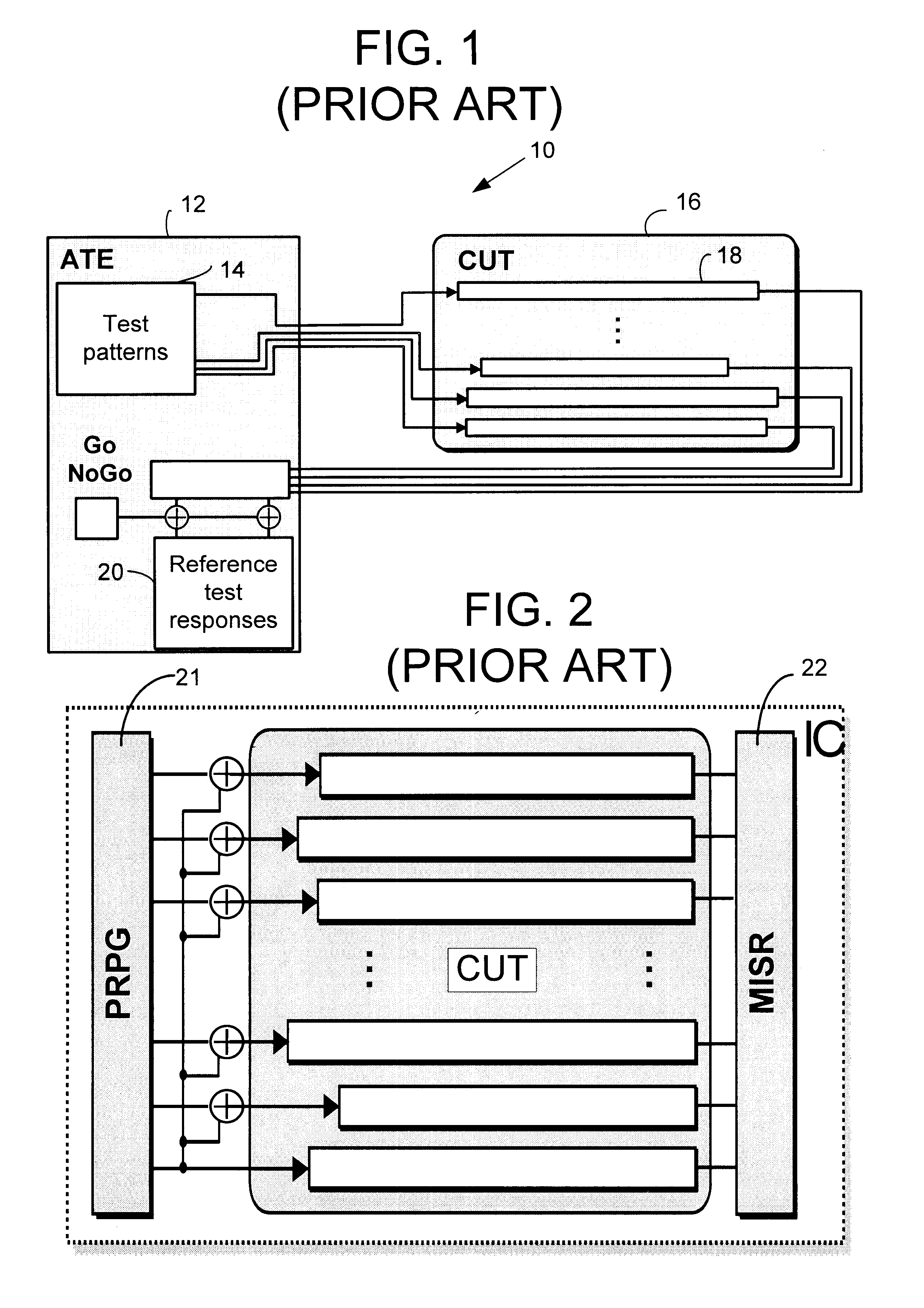

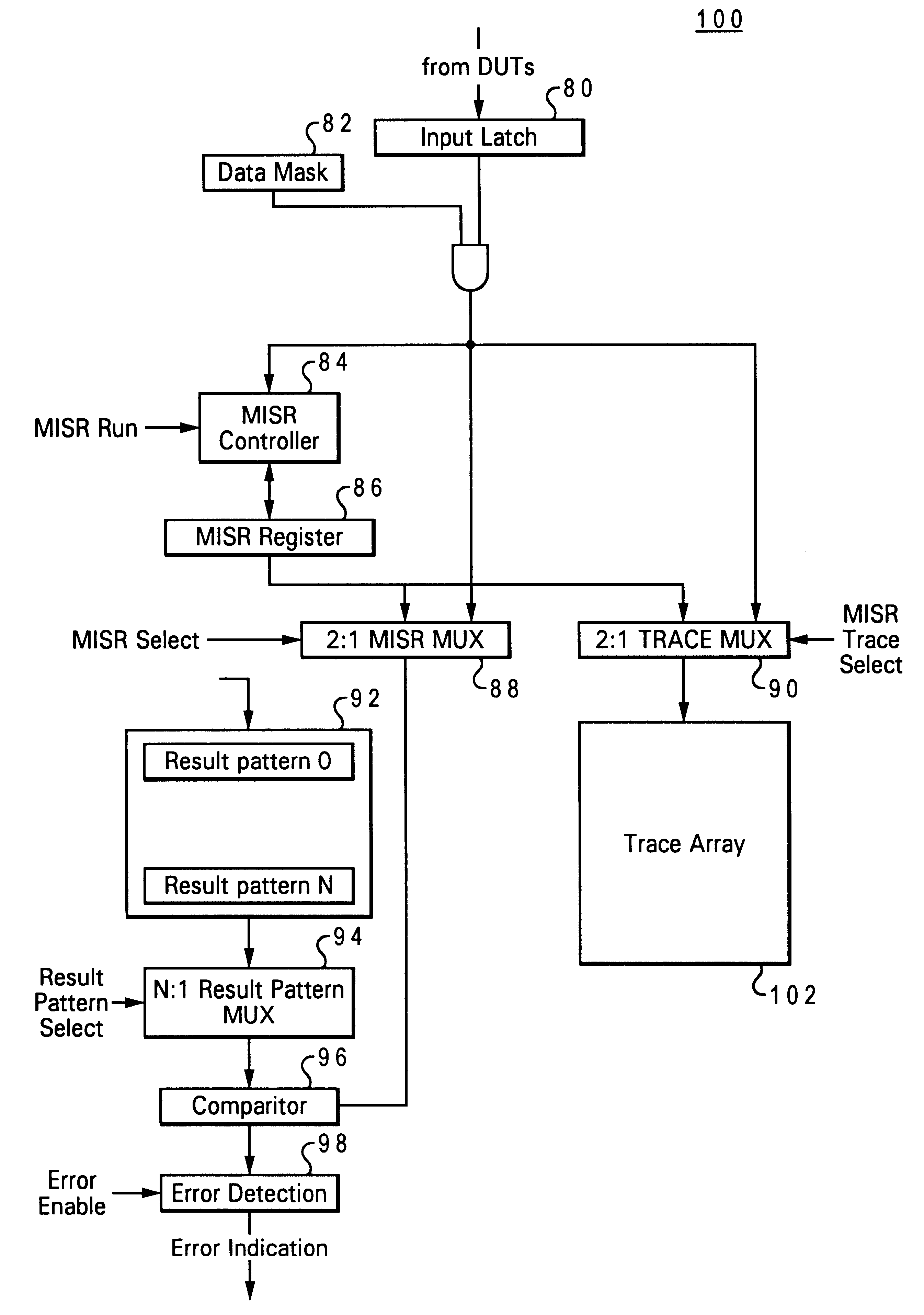

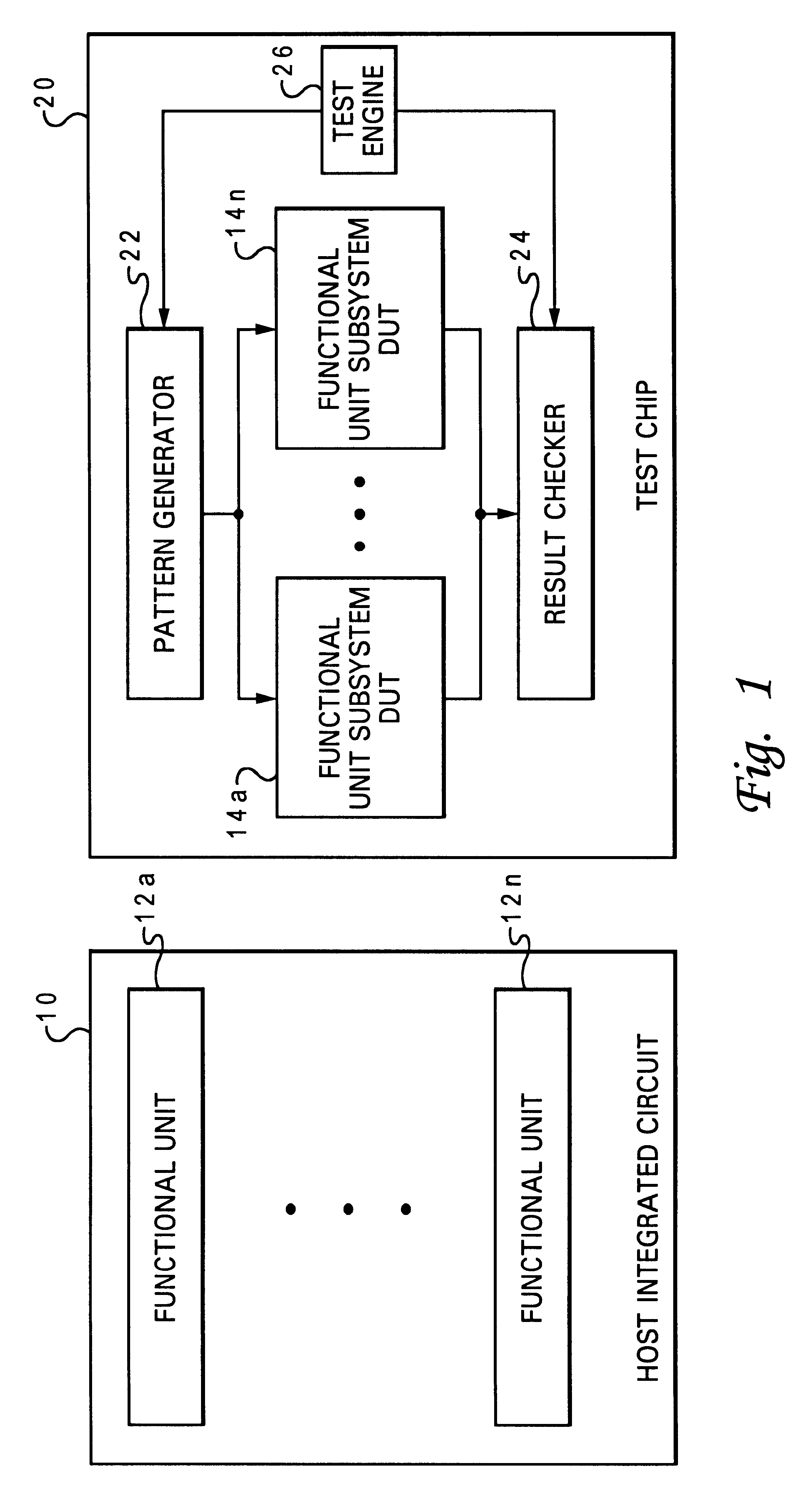

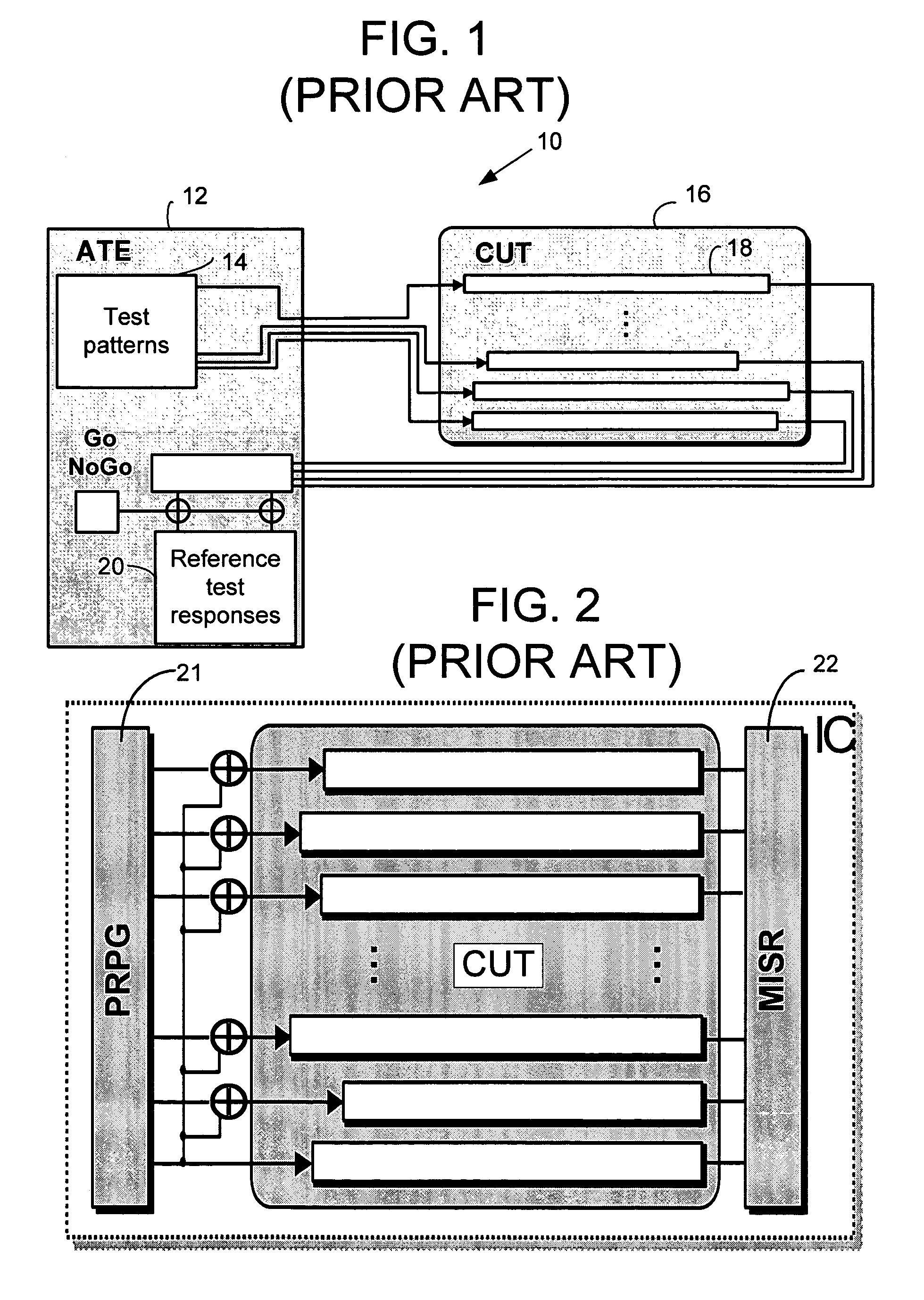

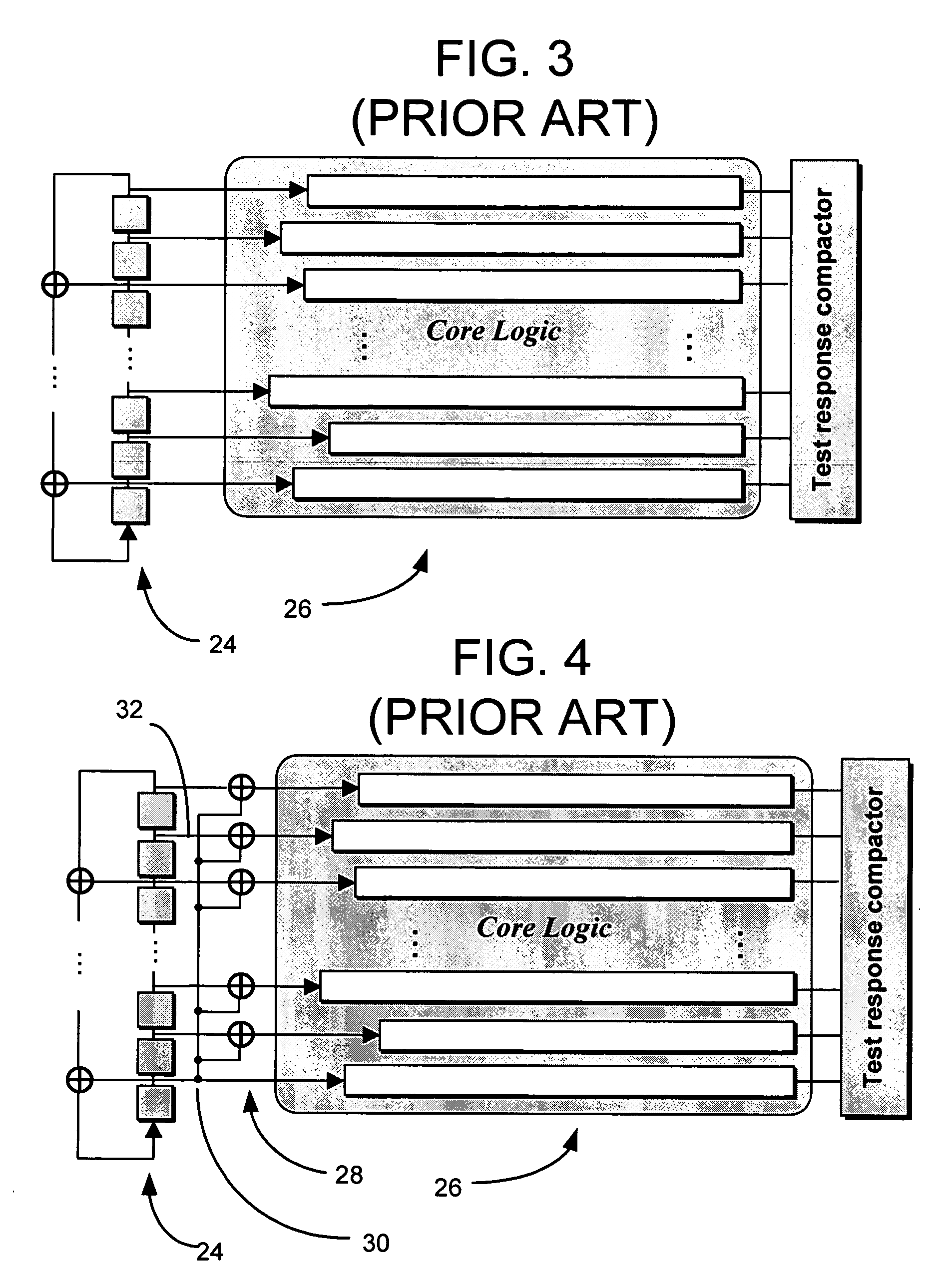

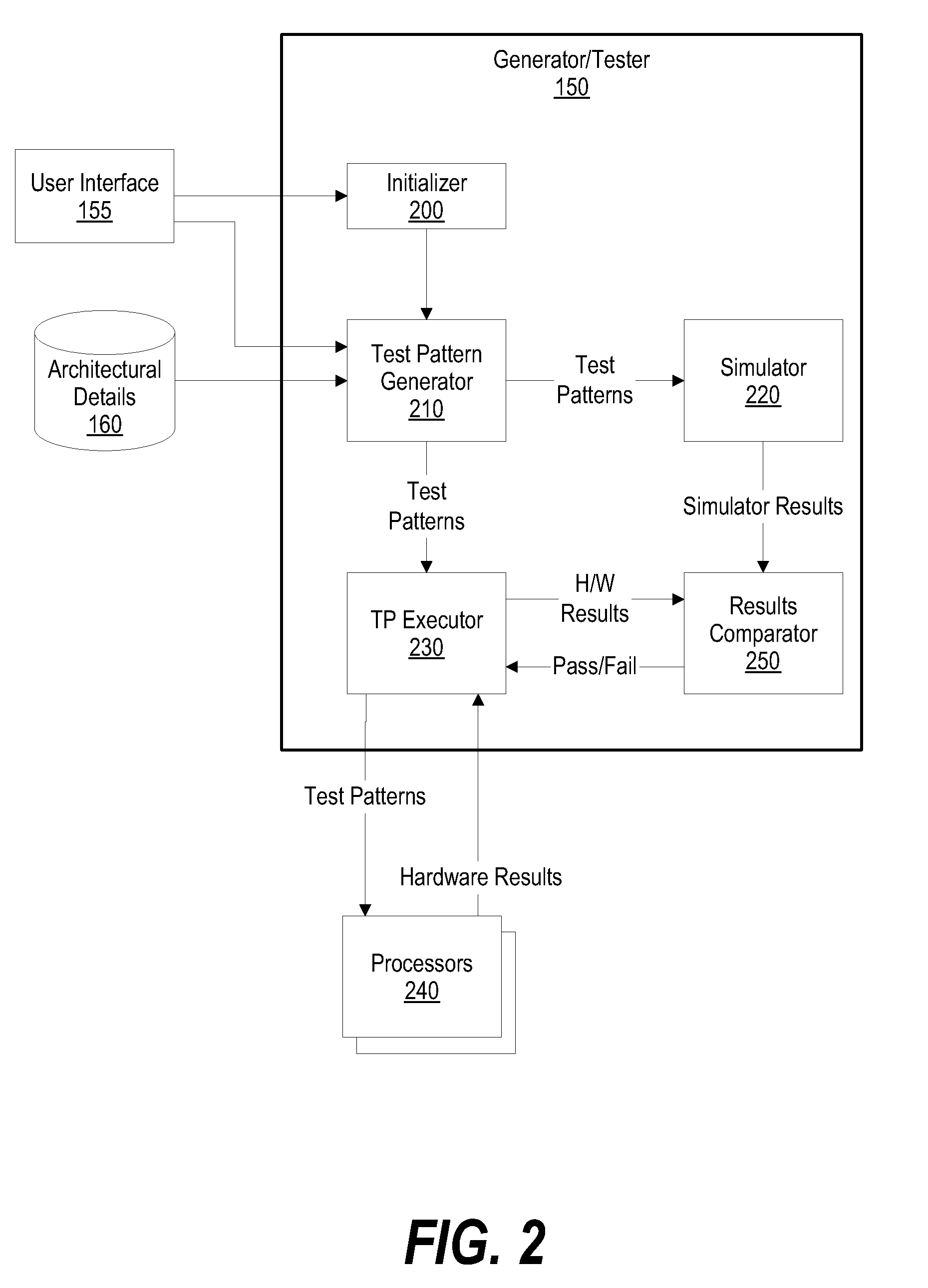

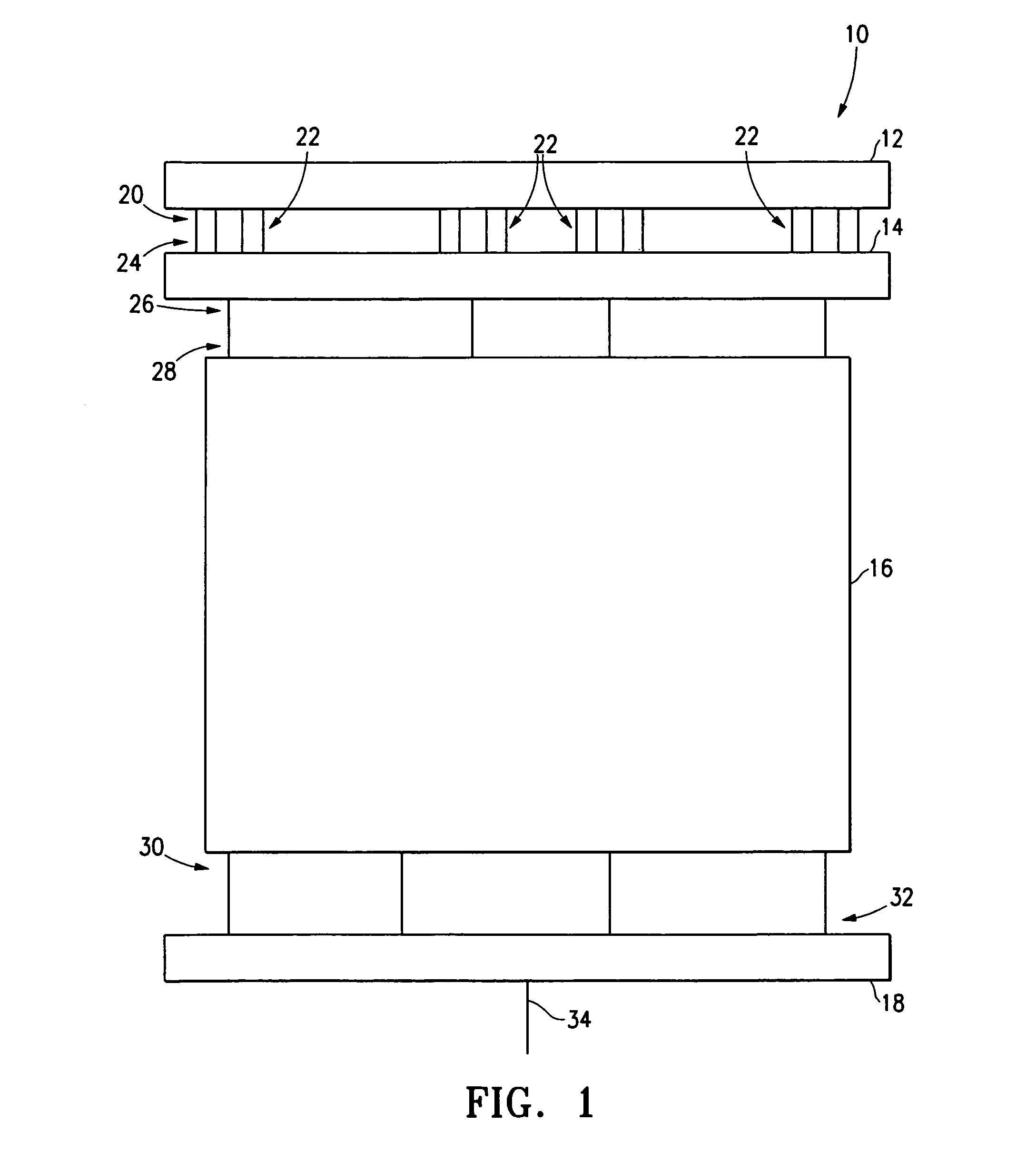

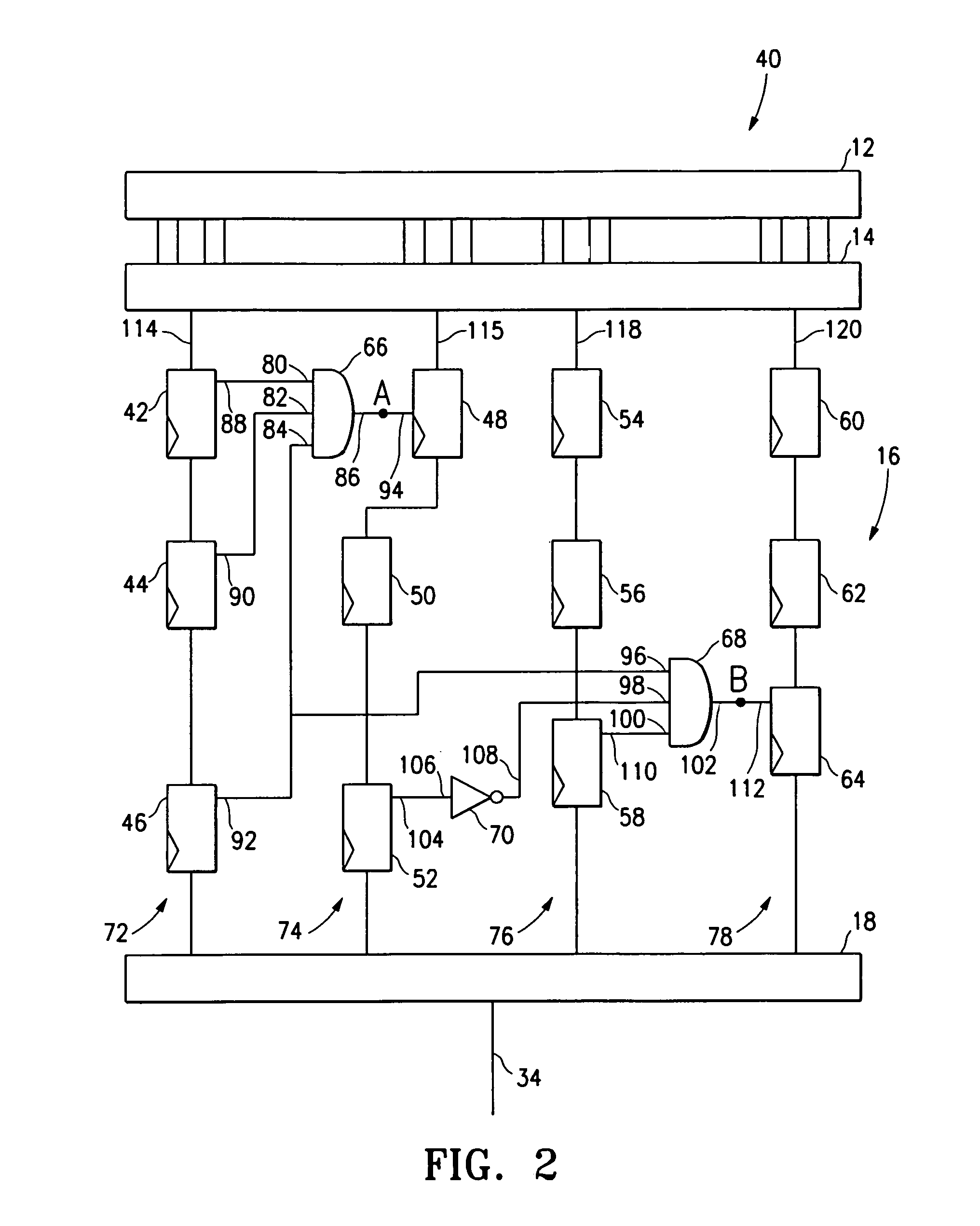

Method and system for performing pseudo-random testing of an integrated circuit

InactiveUS6393594B1Electronic circuit testingError detection/correctionEngineeringIntegrated circuit

A method and system for testing an integrated circuit. A test substrate is provided which is manufactured by the same particular production technology for which the integrated circuit is designed. A pattern generator for generating test data and a result checker for comparing output data are embedded on the test substrate. Isolated portions of circuitry of the integrated circuit are selectively embedded onto the test substrate. Test data from the pattern generator is applied to the isolated portions of circuitry under a first operating condition. The data output from the isolated portions of circuitry is selectively recorded into the result checker. The isolated portions of circuitry are then subjected to testing by applying test data from the pattern generator to the isolated portions of circuitry under a second operating condition. Errors in the isolated portions of circuitry are detected with the result checker by comparing data output from the isolated portions of circuitry with the selectively recorded data output, such that the integrated circuit is tested by subsets, independently of testing the integrated circuit in its entirety.

Owner:IBM CORP

Phase shifter with reduced linear dependency

InactiveUS20050015688A1Electronic circuit testingRecord information storageCircuit complexityLinear correlation

A method is disclosed for the automated synthesis of phase shifters. Phase shifters comprise circuits used to remove effects of structural dependencies featured by pseudo-random test pattern generators driving parallel scan chains. Using a concept of duality, the method relates the logical states of linear feedback shift registers (LFSRs) and circuits spacing their inputs to each of the output channels. The method generates a phase shifter network balancing the loads of successive stages of LFSRs and satisfying criteria of reduced linear dependency, channel separation and circuit complexity.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

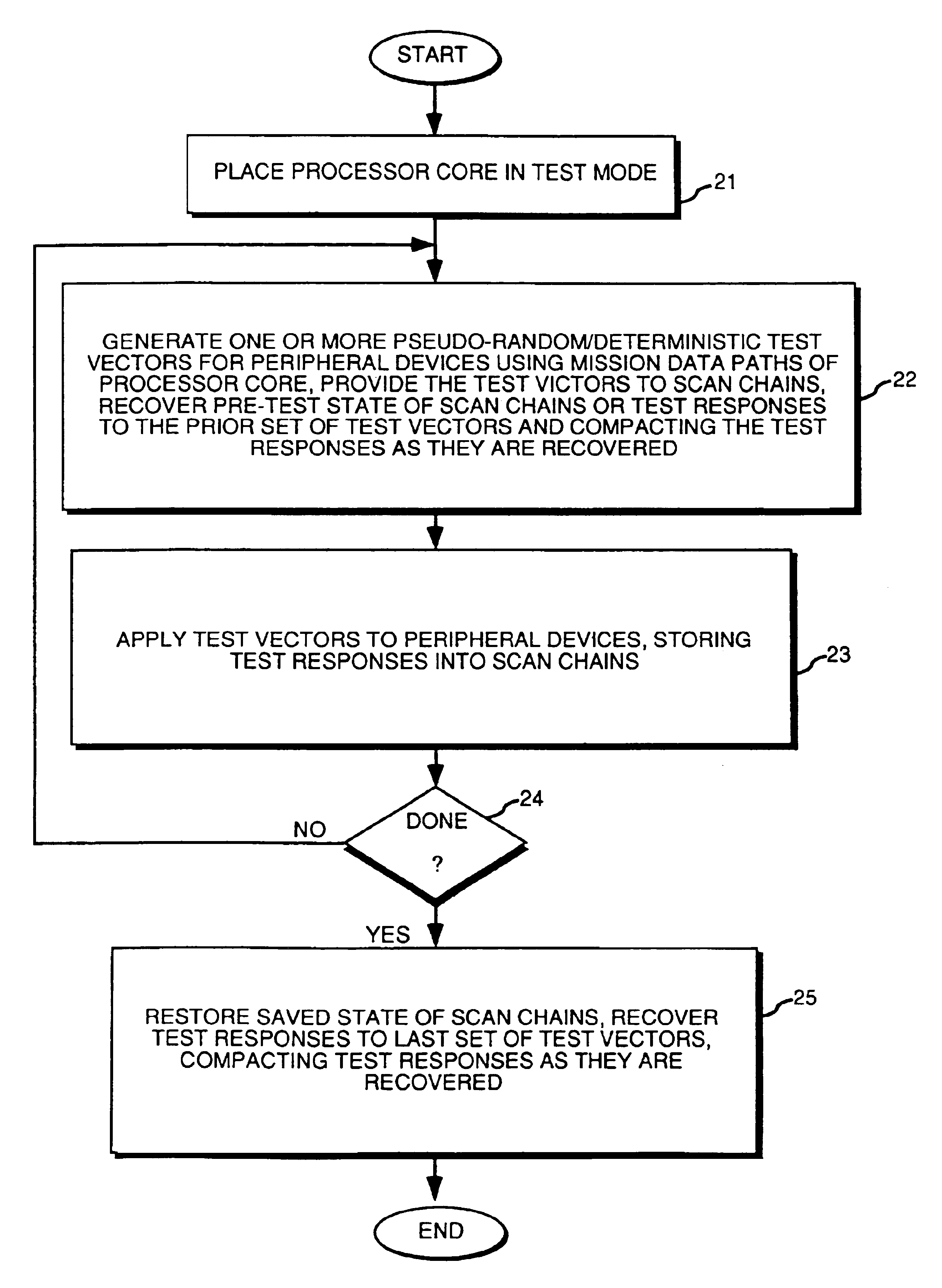

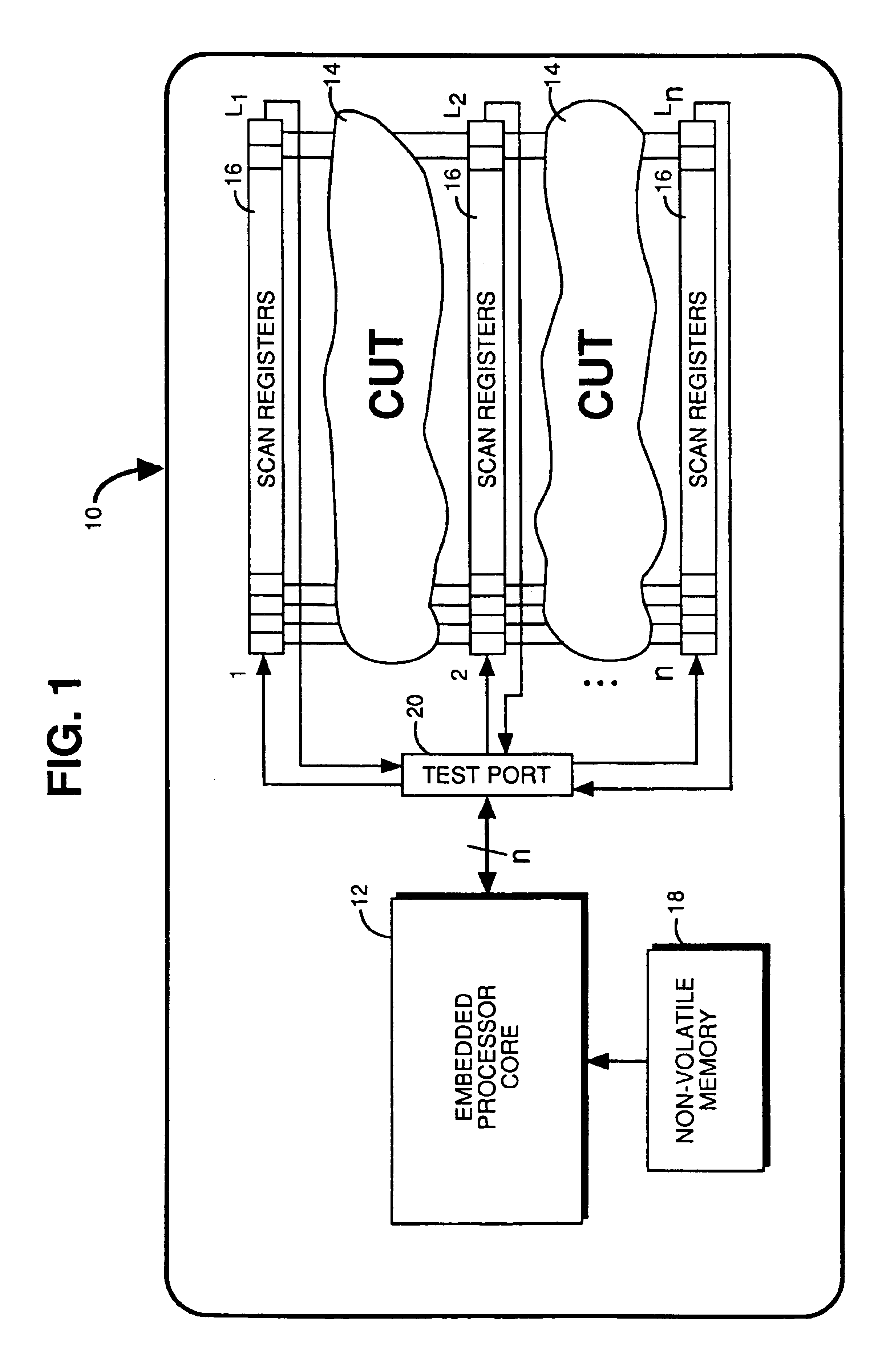

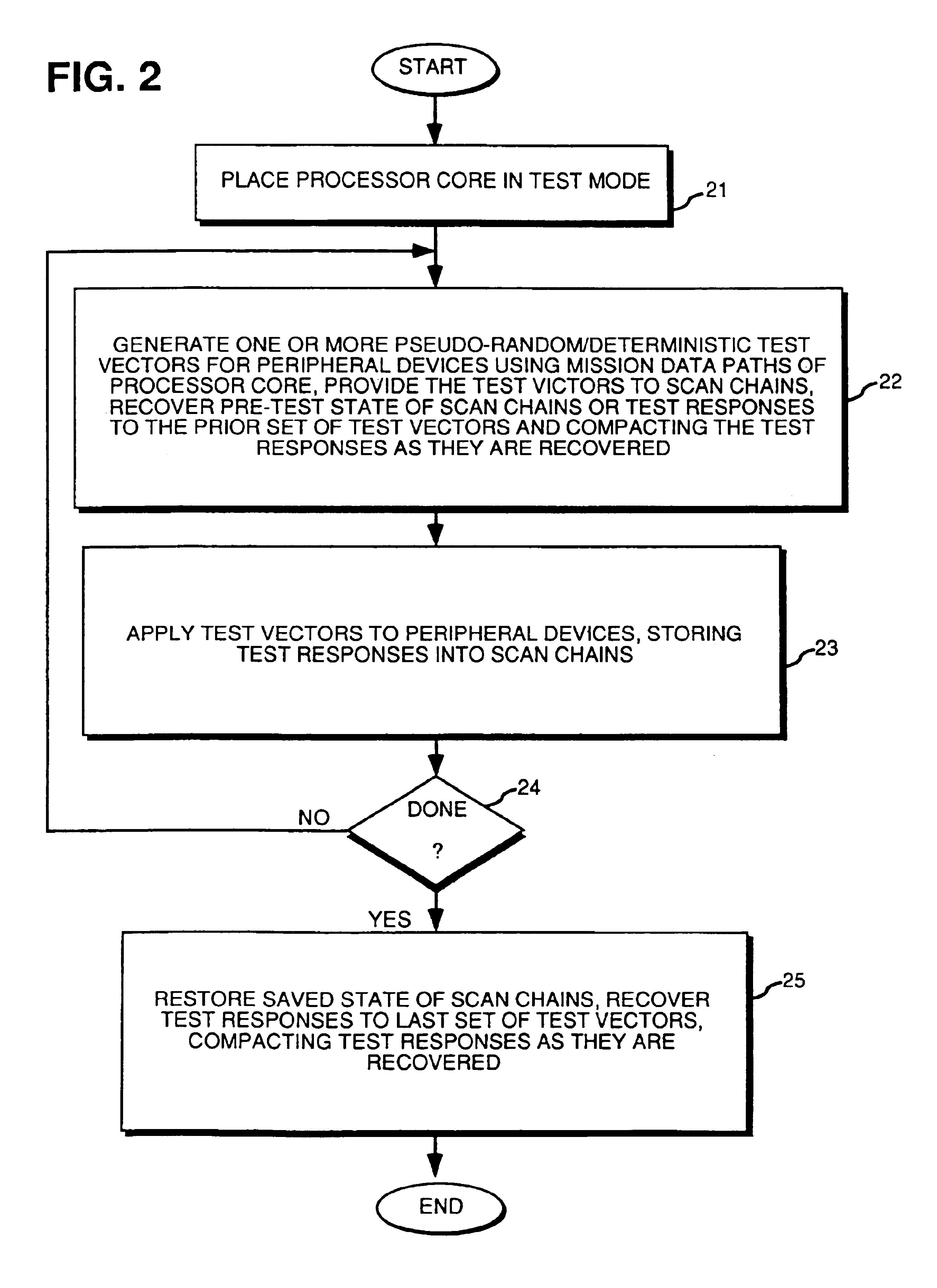

Arithmetic built-in self-test of multiple scan-based integrated circuits

InactiveUS6954888B2Reduce error impactElectronic circuit testingHardware monitoringProcessor registerLeast significant bit

Owner:MENTOR GRAPHICS CORP

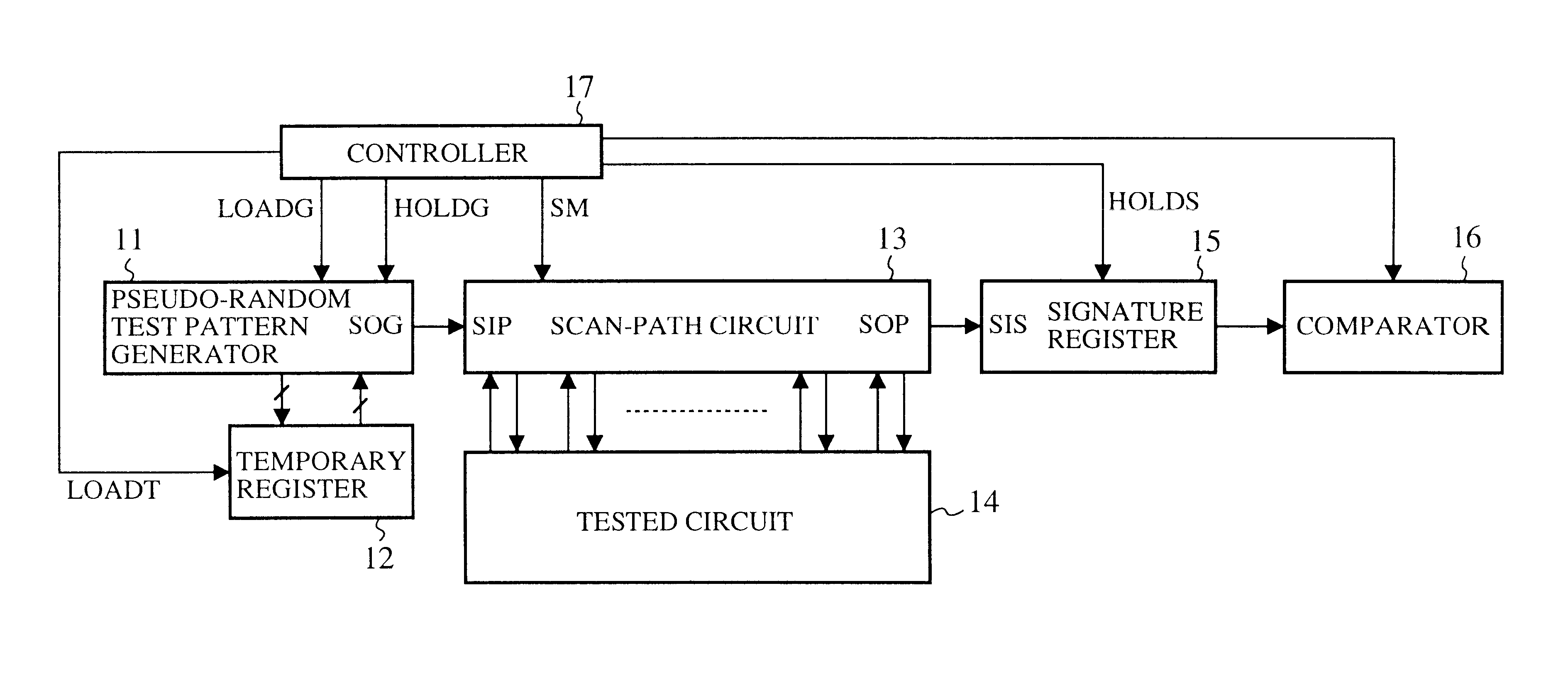

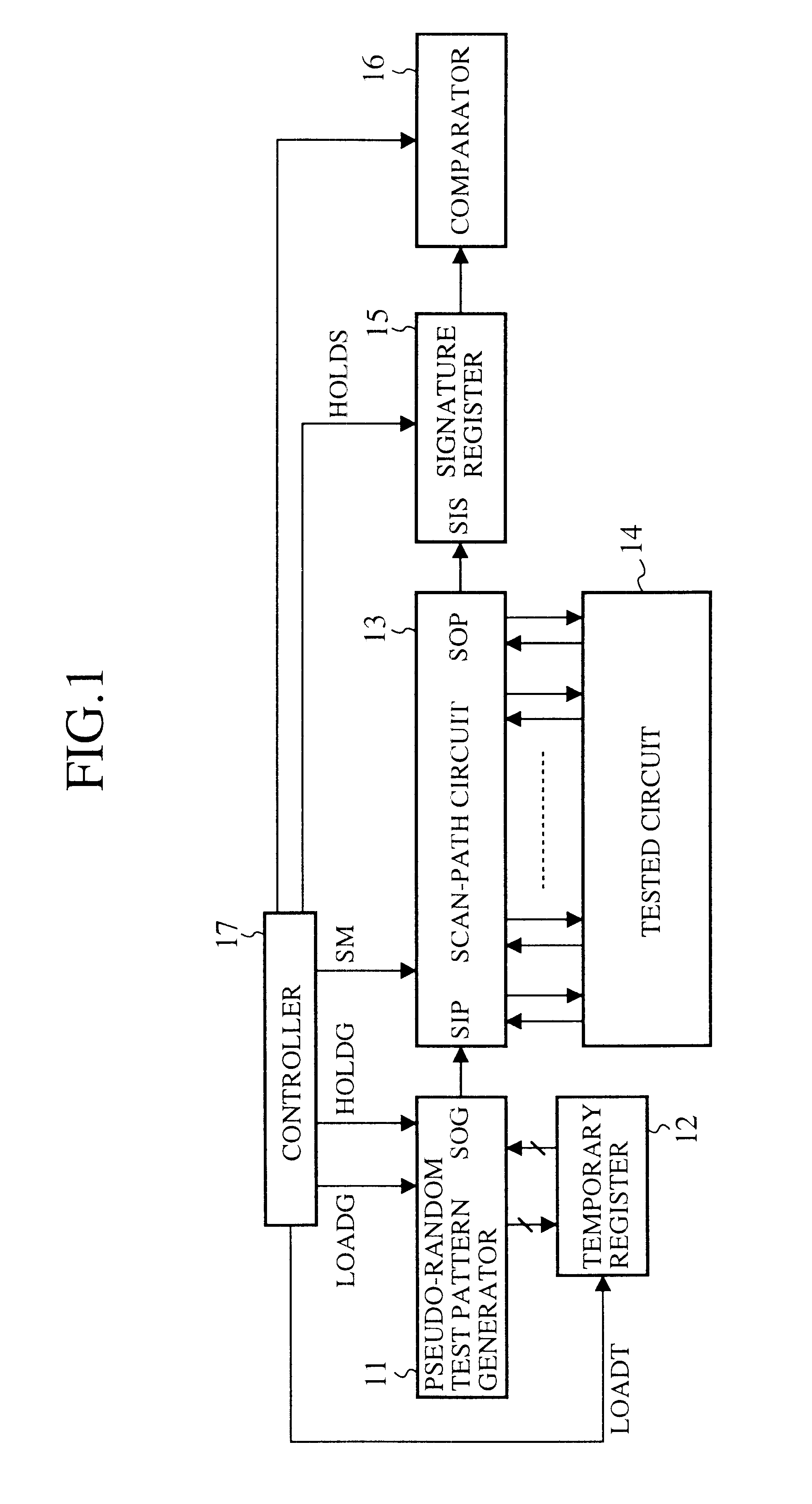

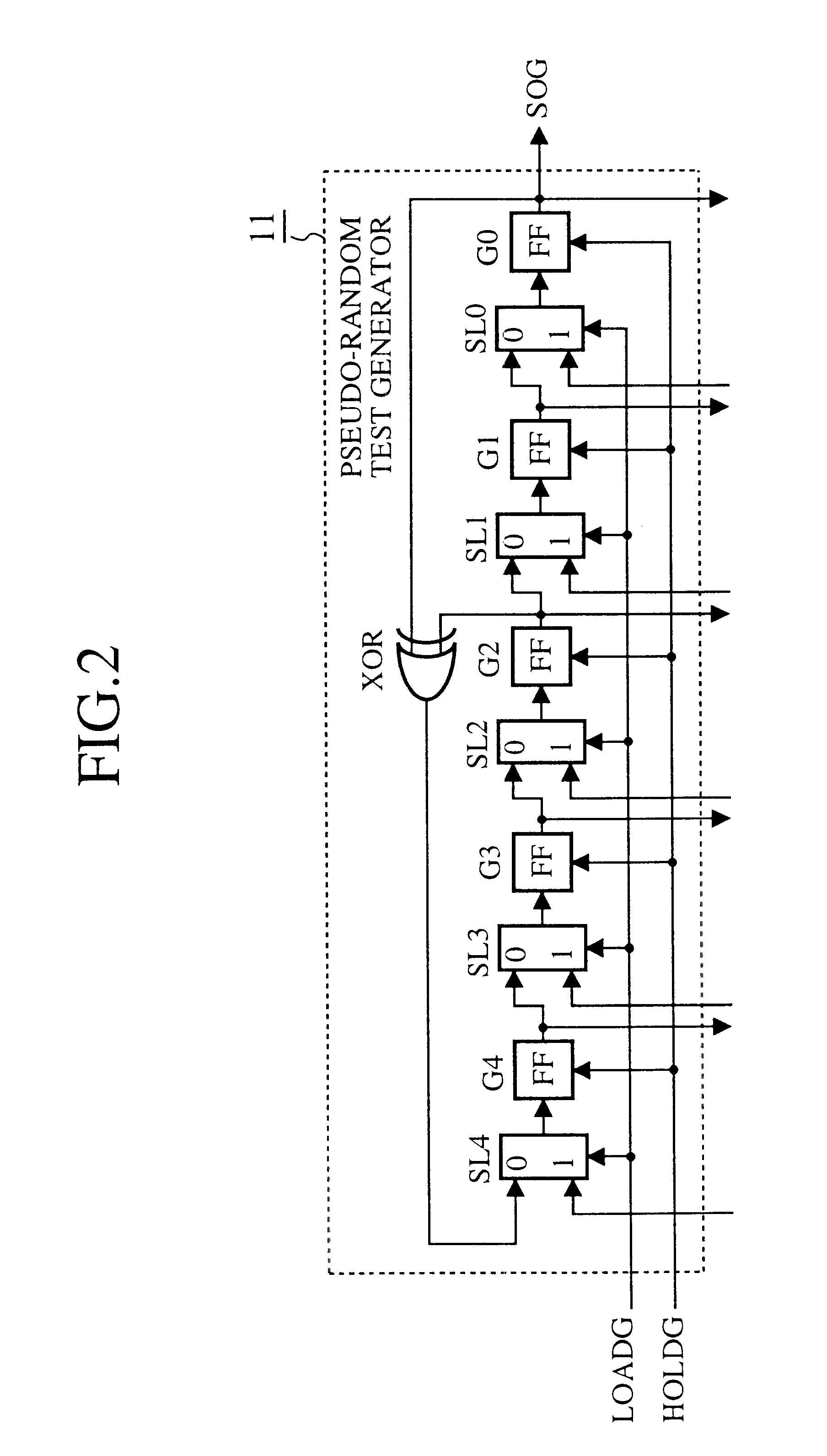

Electronic system with self-test function and simulation circuit for electronic system

InactiveUS6401226B1Electronic circuit testingError detection/correctionElectronic systemsEngineering

An electronic system with a self-test function has a pseudo-random test pattern generator that serially generates data constituting a pseudo-random test pattern, and stores a 1-bit shifted pseudo-random test pattern obtained by shifting the pseudo-random test pattern by one bit. When a scan-path circuit supplies the pseudo-random test pattern to a tested circuit which carries out an operation based on the pseudo-random test pattern, and then loads an operation result of the tested circuit, the 1-bit shifted pseudo-random test pattern is supplied to the tested circuit as the next pseudo-random test pattern. This makes it possible to solve a problem of a conventional electronic system in that it takes a long time to evaluate the operation results of the tested circuit because it takes at least (1+n)xm clock cycles, where m is the number of pseudo-random test patterns supplied to the tested circuit and n is the number of stages of the scan-path circuit.

Owner:MITSUBISHI ELECTRIC CORP

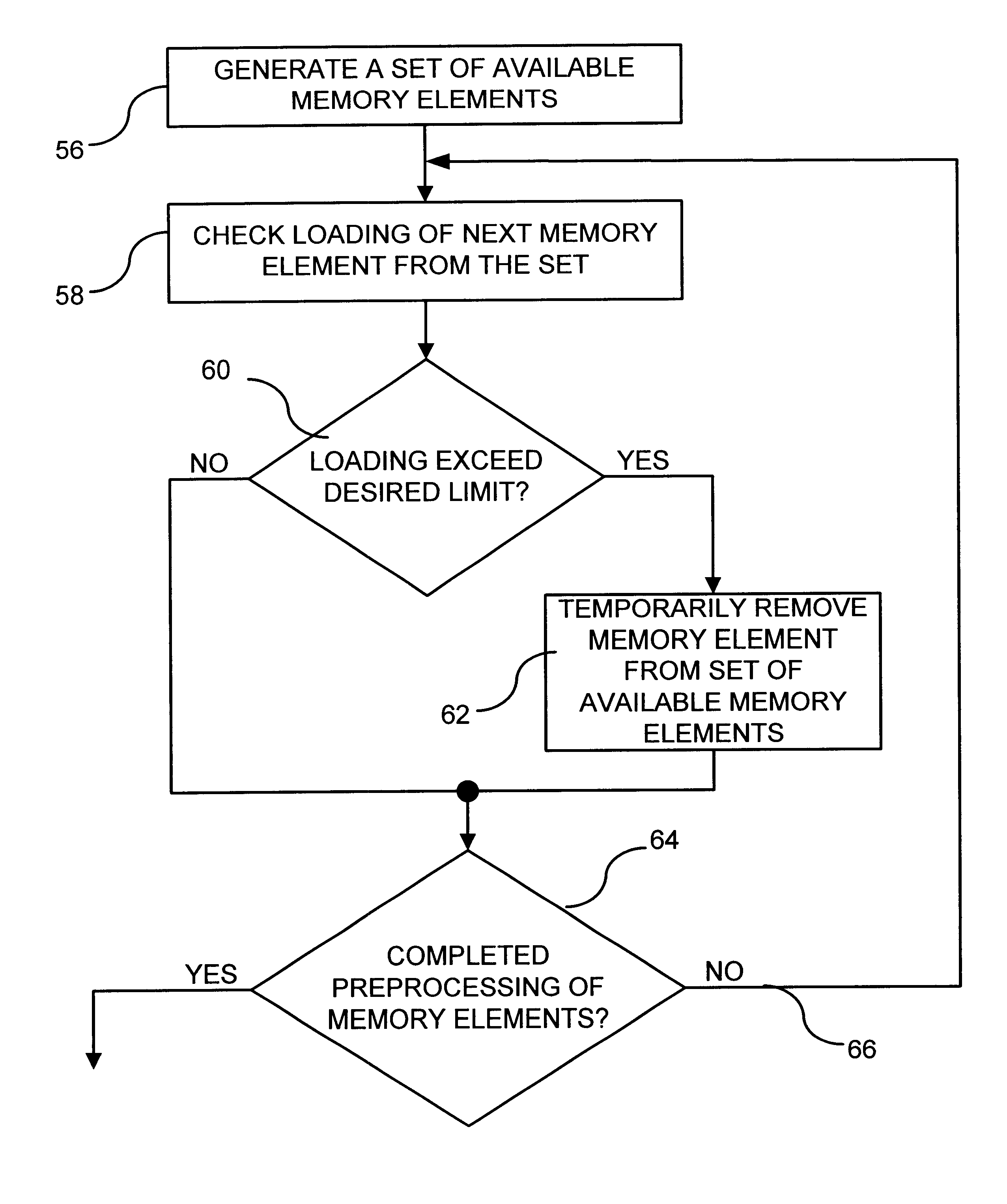

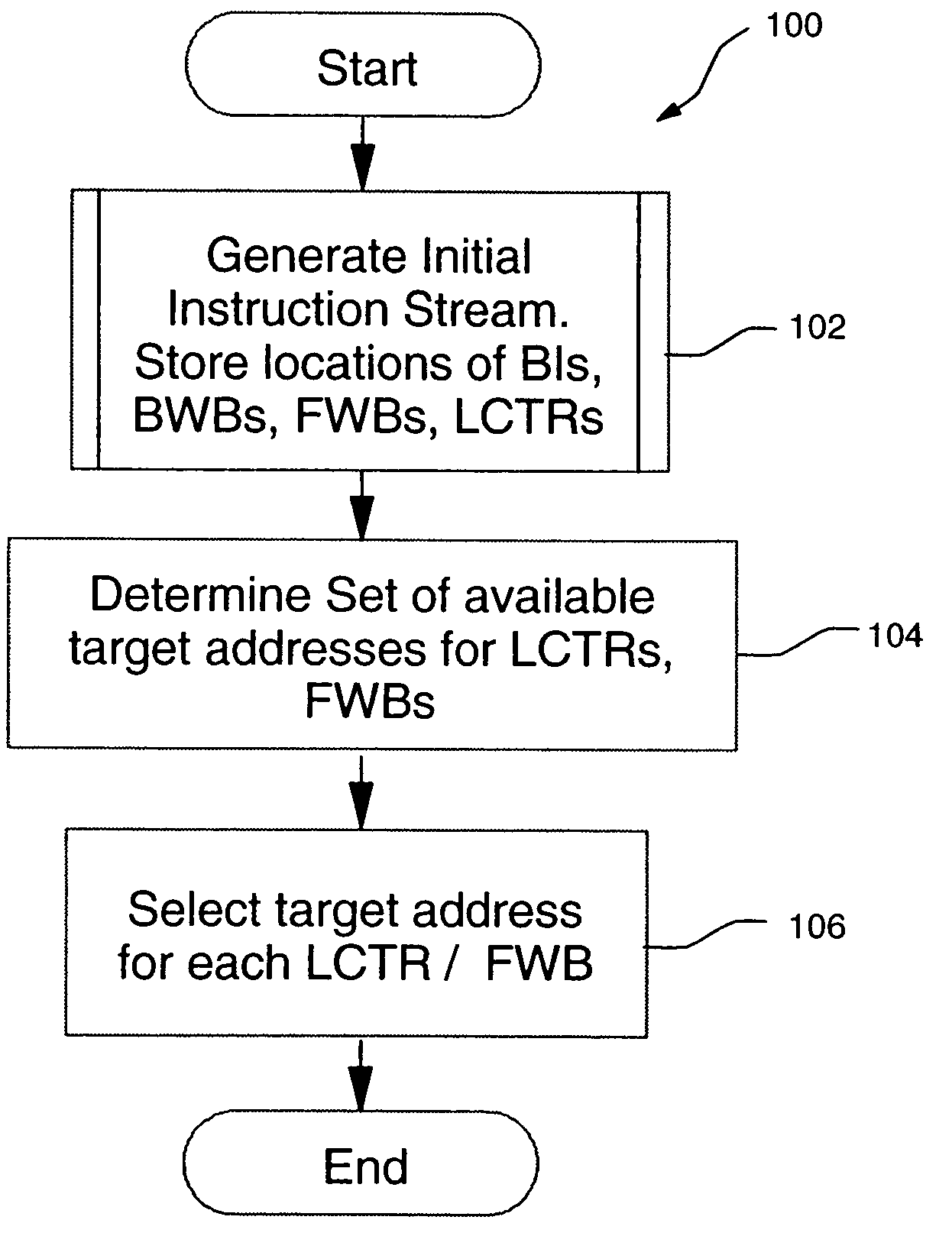

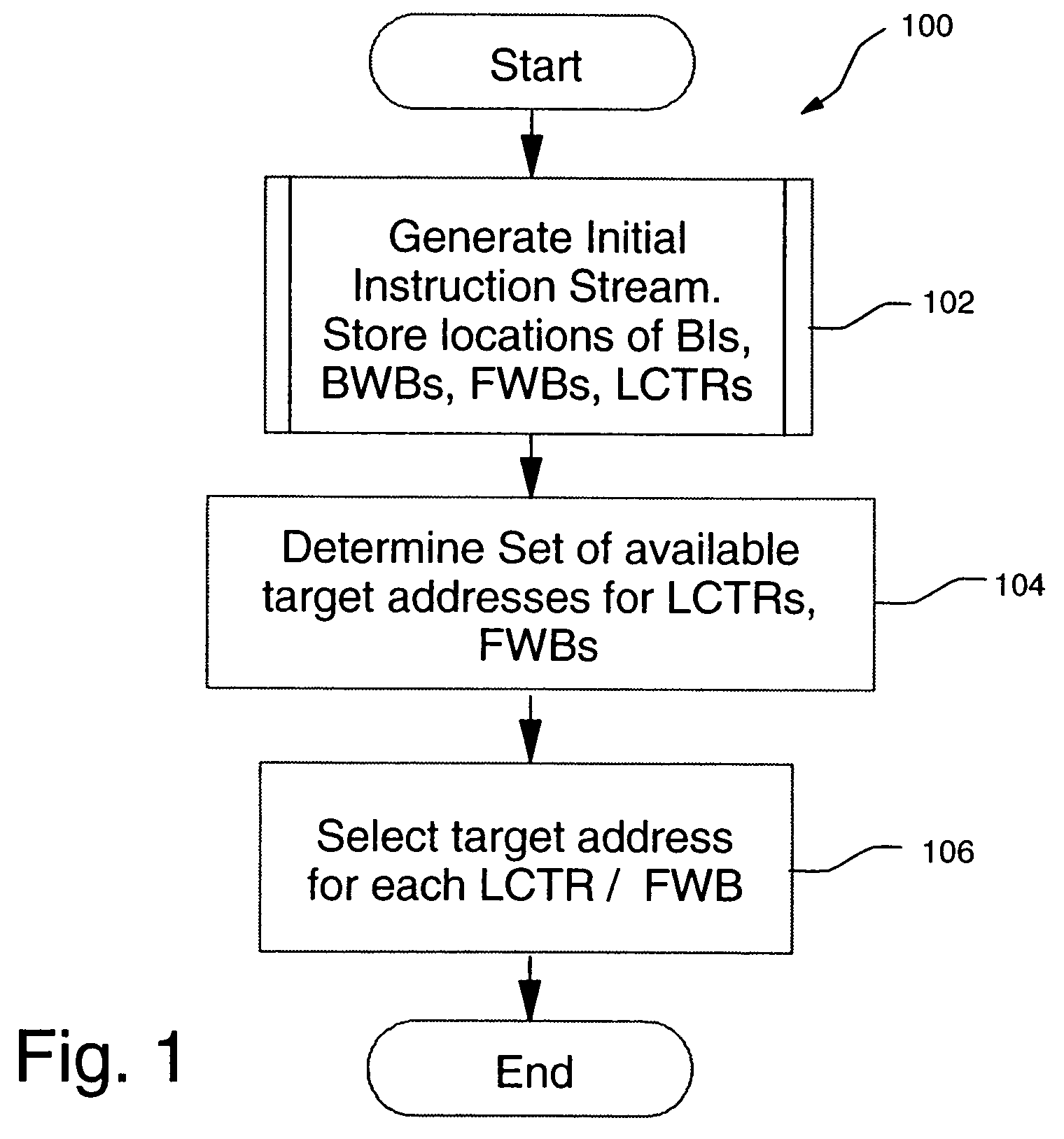

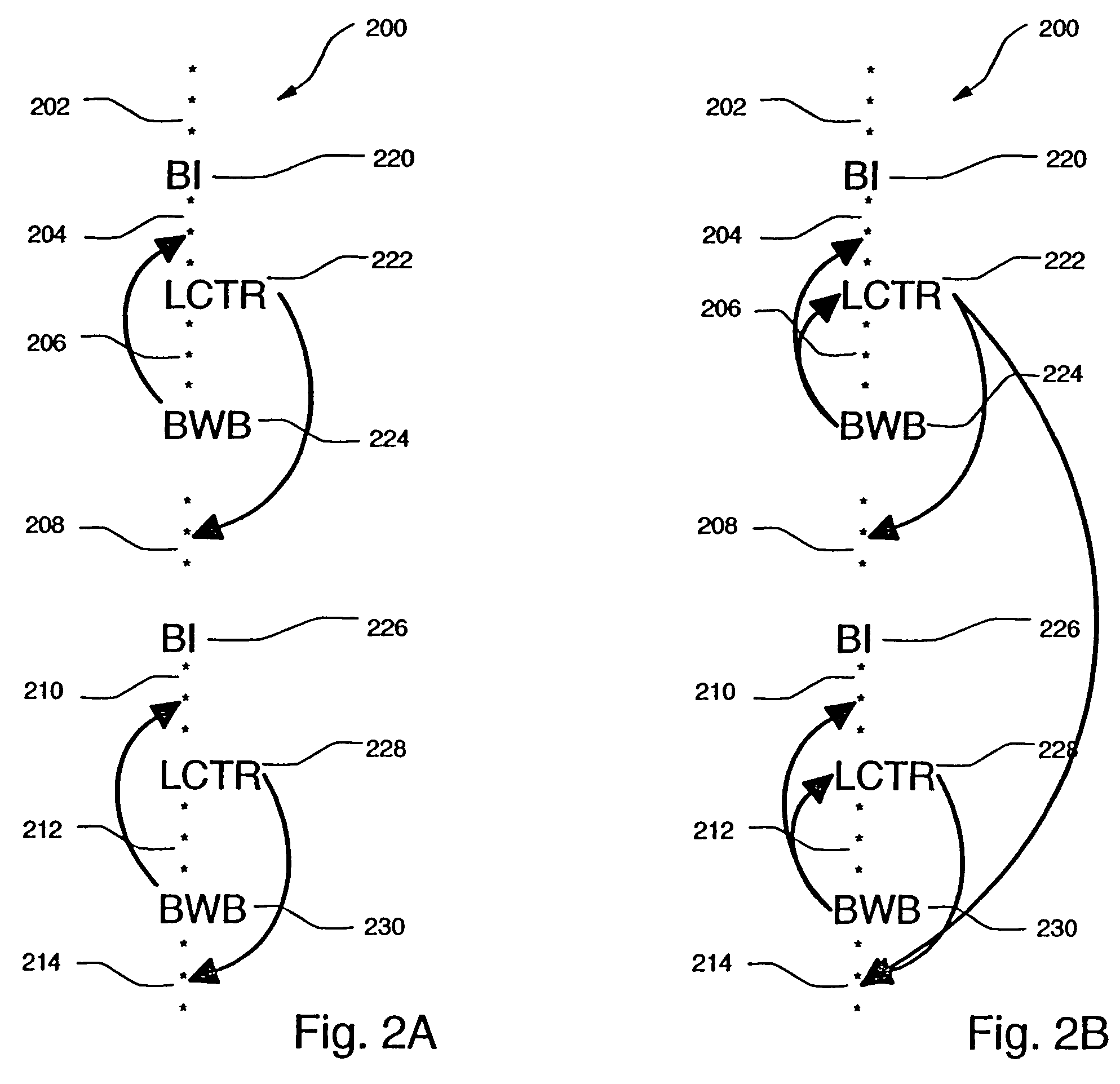

Method, system, and computer program product to generate test instruction streams while guaranteeing loop termination

InactiveUS7877742B2Error detection/correctionDigital computer detailsInstruction streamPseudo random testing

A method, system, and computer program product for generating terminating, pseudo-random test instruction streams, including forward and backward branching instructions. A first instruction stream is generated, including at least one backward branching instruction and at least one forward branching instruction. Each backward branching instruction is preceded by at least one forward branching instruction, which is used to guarantee termination of the loop formed by the backward branching instruction. Backward branching targets are resolved when the backward branching instruction is inserted into the first instruction stream. Forward branching targets remain unresolved in the first instruction stream. A set of potential branch targets is determined for each forward branching instruction. For each forward branching instruction, a branch target is randomly selected from the set of potential branch targets for that forward branching instruction. The final terminating instruction stream consists of the first stream, with all forward branch targets resolved.

Owner:IBM CORP

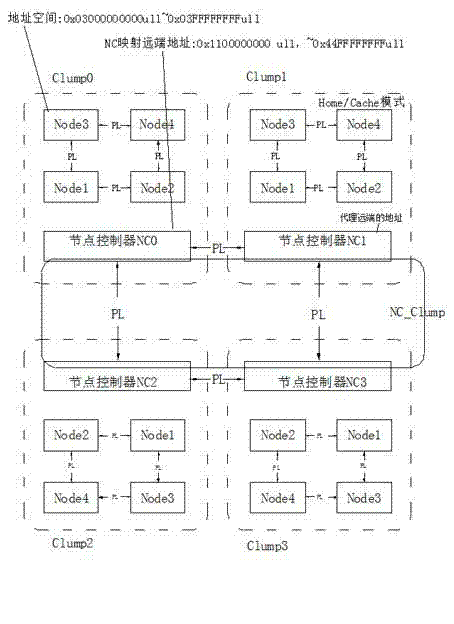

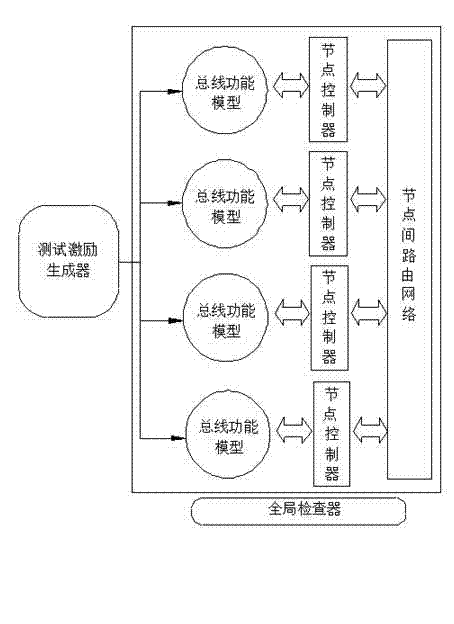

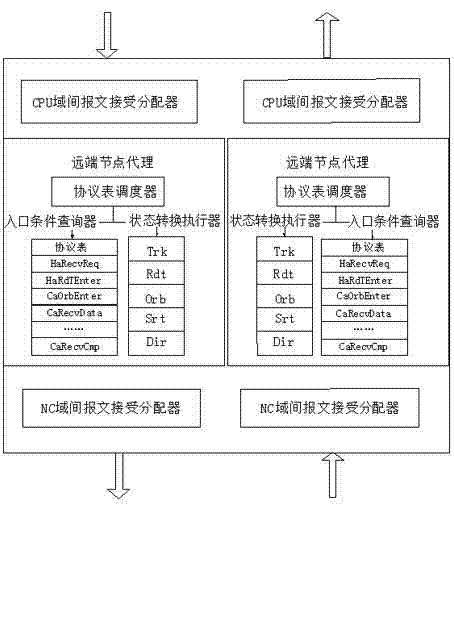

Software simulation verification method based on Cache coherence protocol

InactiveCN102880537AEasy diagnosisSpeed up the debugging processFunctional testingTheoretical computer scienceLogisim

The invention provides a software simulation verification method based on a Cache coherence protocol. According to the method, pseudo random test which is capable of compiling constraint models and also carrying out band constraint in a manual mode is subject to software simulation and verification; specific objects are verified, and the accuracy and defect of the protocols are fed back. The method based on software simulation comprises the following steps of: firstly determining a multi-stage coherence description mode based on an expanded Cache Coherence protocol; and subsequently realizing the software simulation verification method, counting the coverage rate and carrying out error report. With the adoption of the method, the Cache Coherence protocol in multi-stage domains in a multi-state space can be verified effectively so as to enable a protocol table to realize the establishment of corresponding logic relationship, judge whether the state transition of a system in accordance with the protocol table accords with the coherence definition through an overall checker, and primarily judge whether a mode established in accordance with the protocol table has expected properties. The model system has the remarkable advantages that counter-examples can be generated automatically so as to assist in debugging errors of the system and accelerating system diagnosis and debugging.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

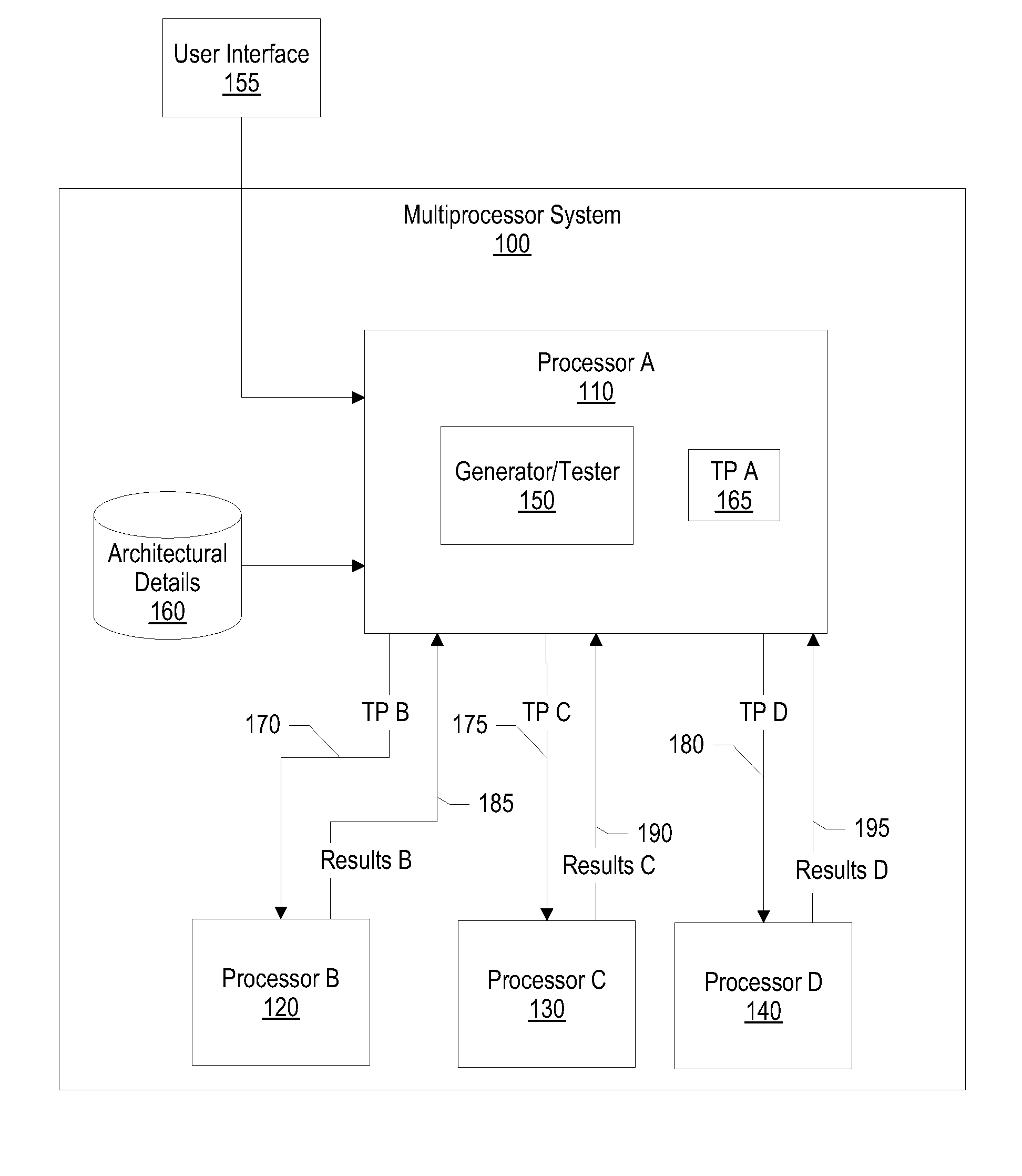

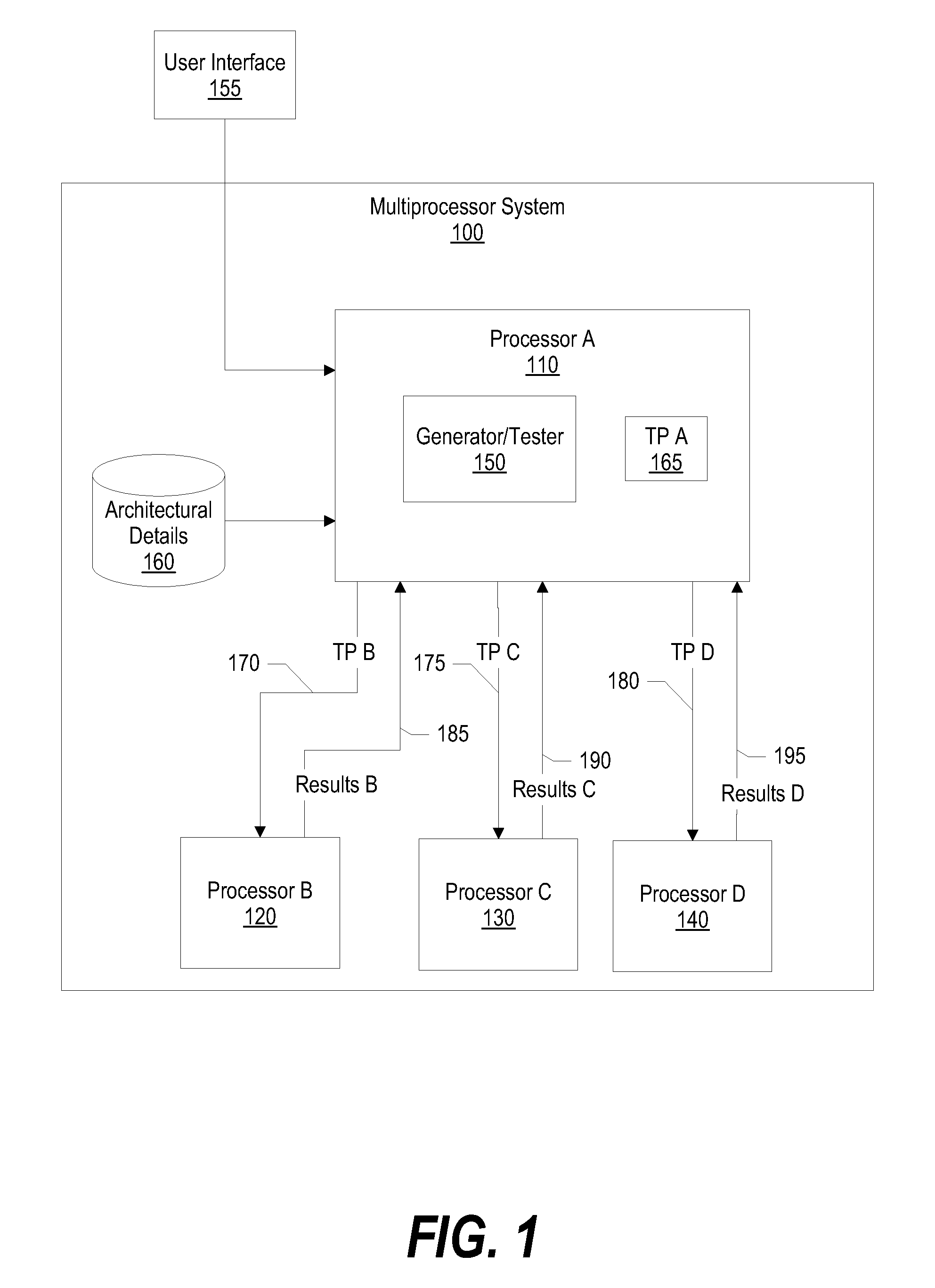

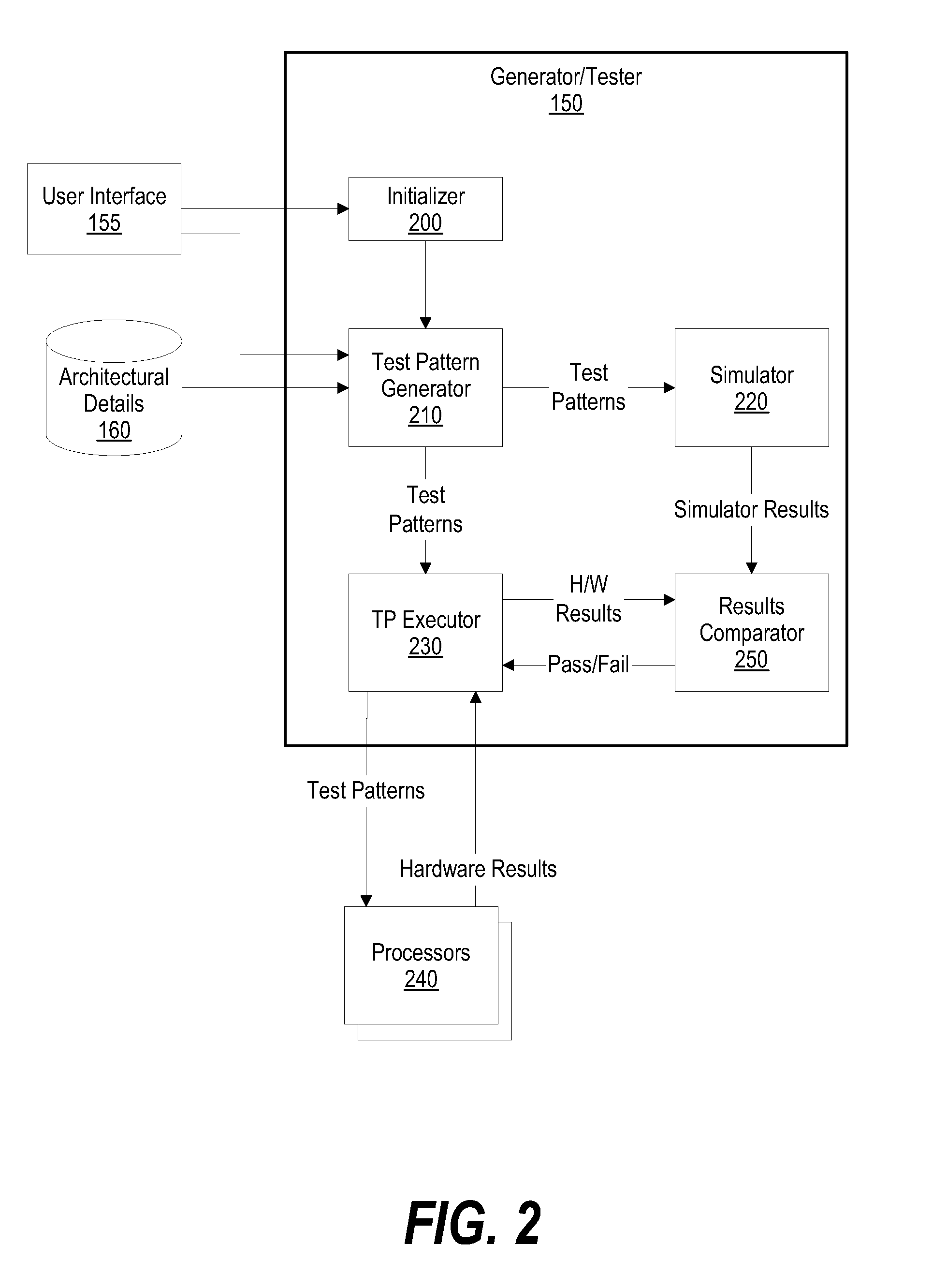

System and Method for Pseudo-Random Test Pattern Memory Allocation for Processor Design Verification and Validation

InactiveUS20090024891A1Efficient testingElectronic circuit testingHardware monitoringPage tableFalse sharing

A system and method for pseudo-randomly allocating page table memory for test pattern instructions to produce complex test scenarios during processor execution is presented. The invention described herein distributes page table memory across processors and across multiple test patterns, such as when a processor executes “n” test patterns. In addition, the page table memory is allocated using a “true” sharing mode or a “false” sharing mode. The false sharing mode provides flexibility of performing error detection checks on the test pattern results. In addition, since a processor comprises sub units such as a cache, a TLB (translation look aside buffer), an SLB (segment look aside buffer), an MMU (memory management unit), and data / instruction pre-fetch engines, the test patterns effectively use the page table memory to test each of the sub units.

Owner:IBM CORP

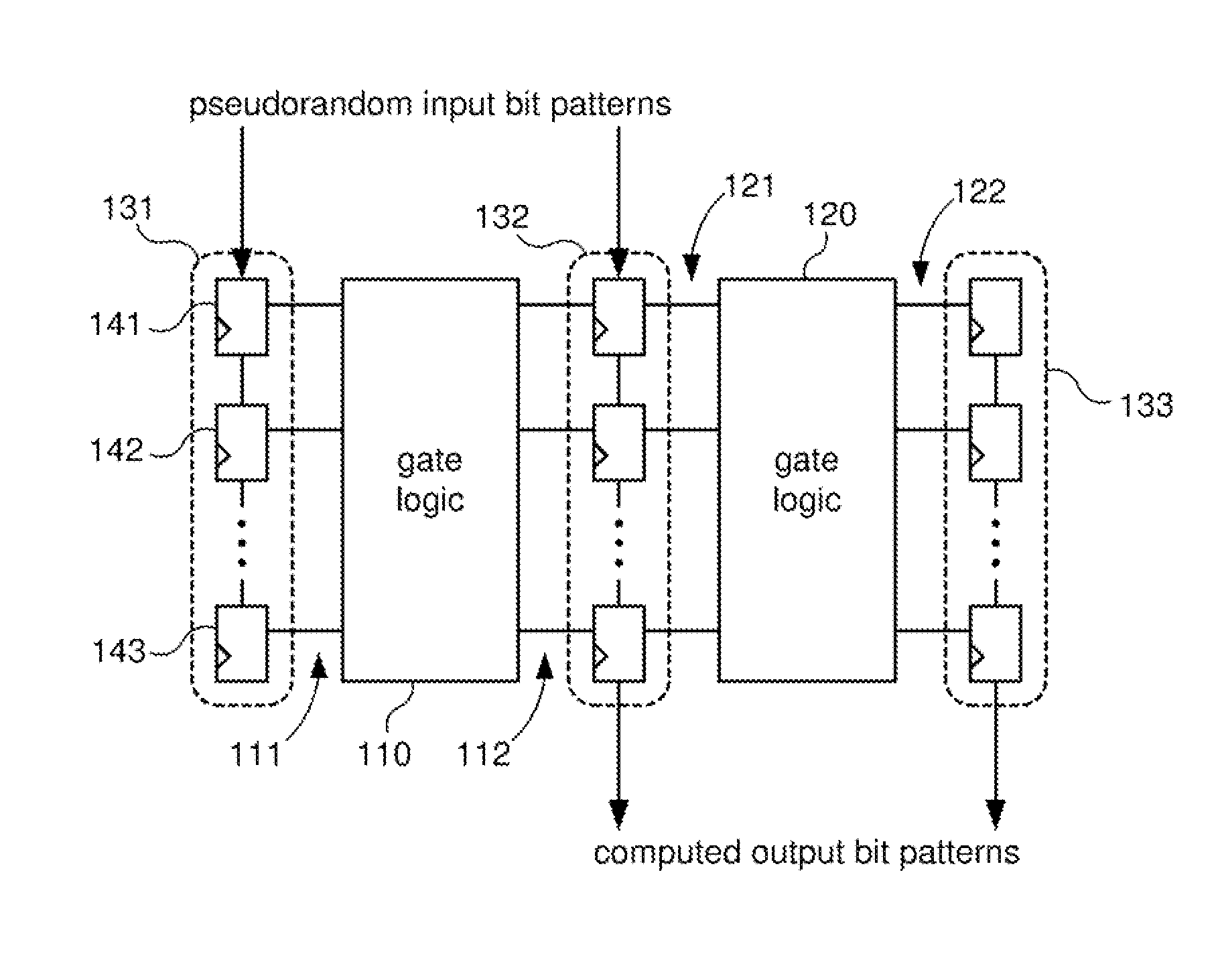

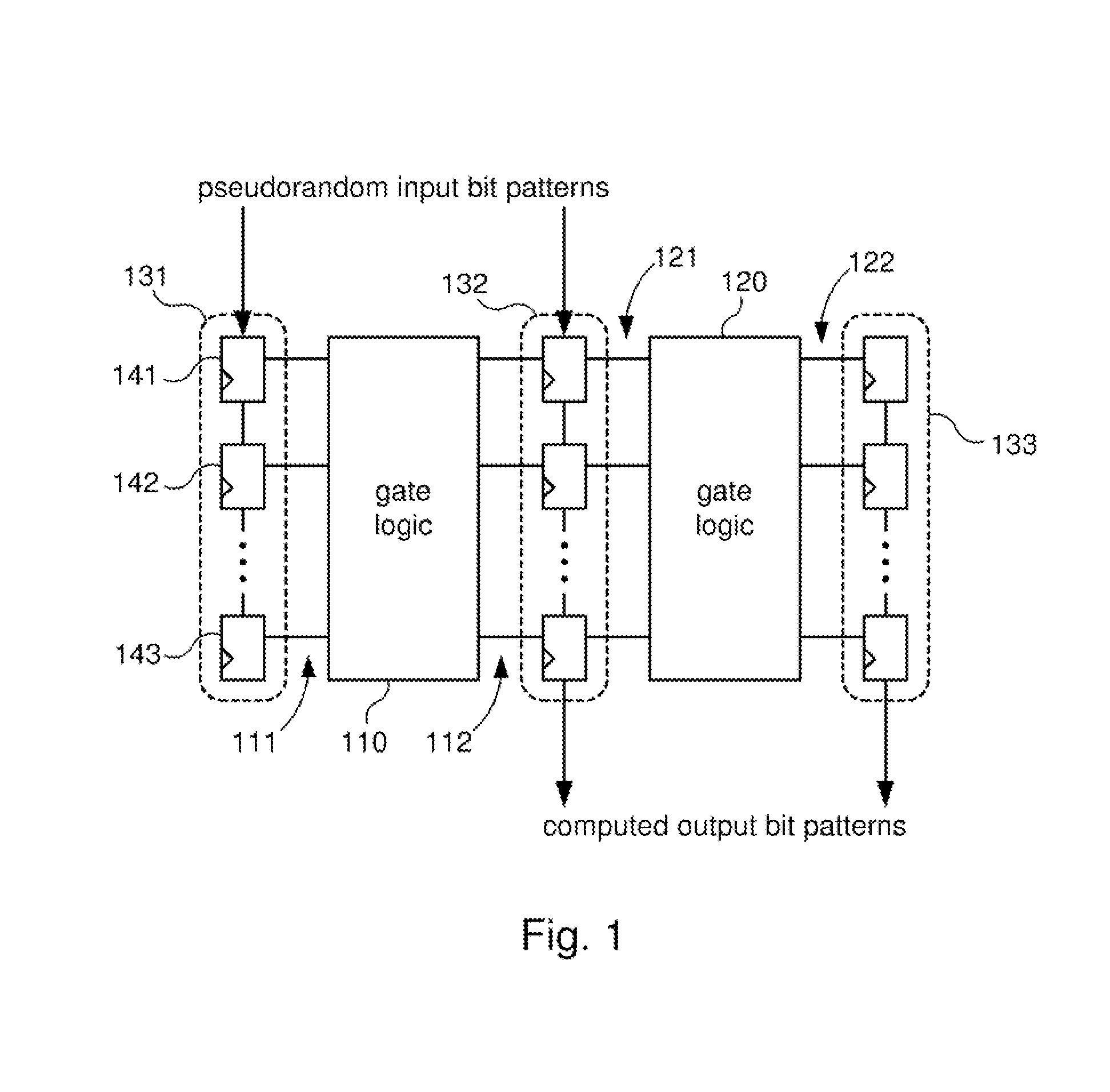

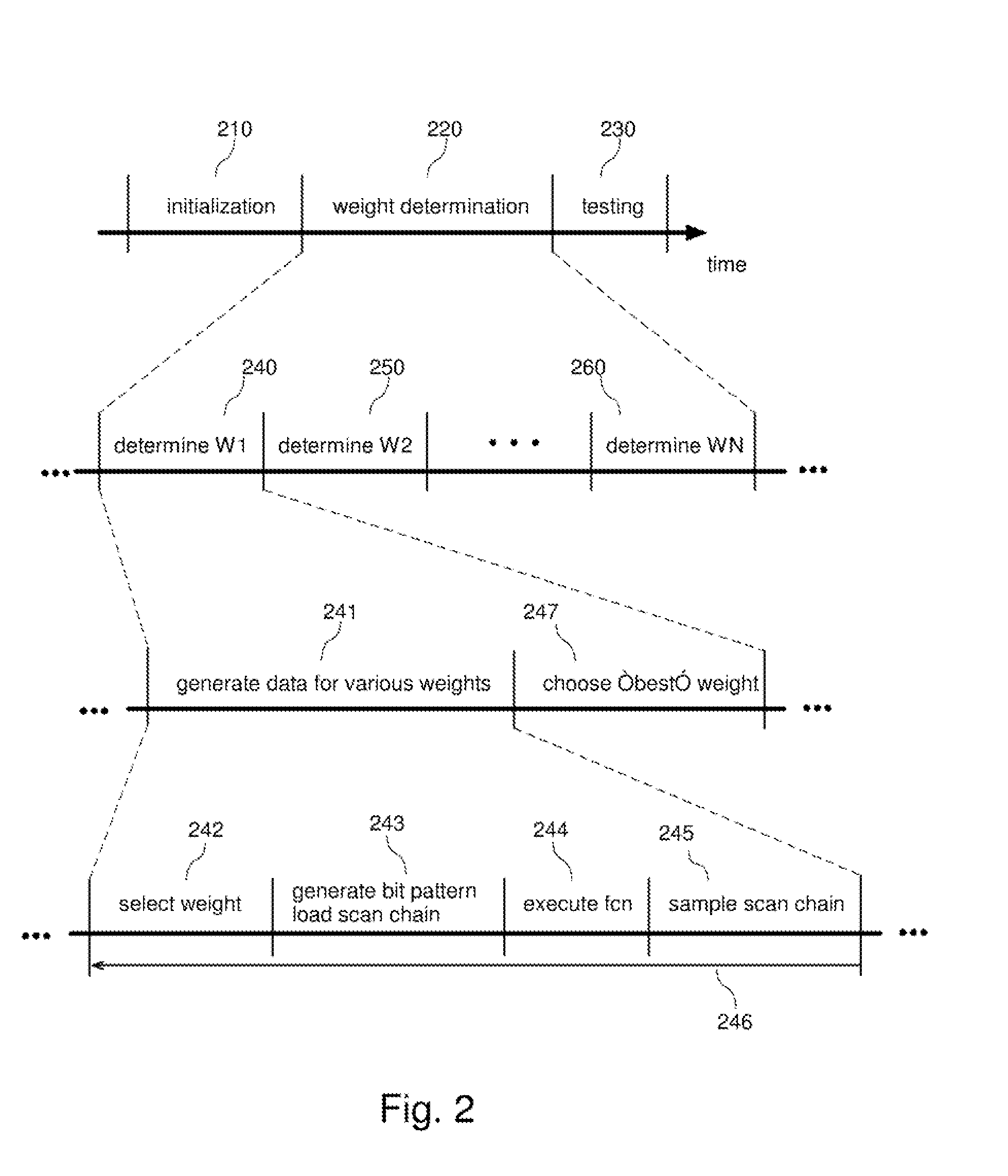

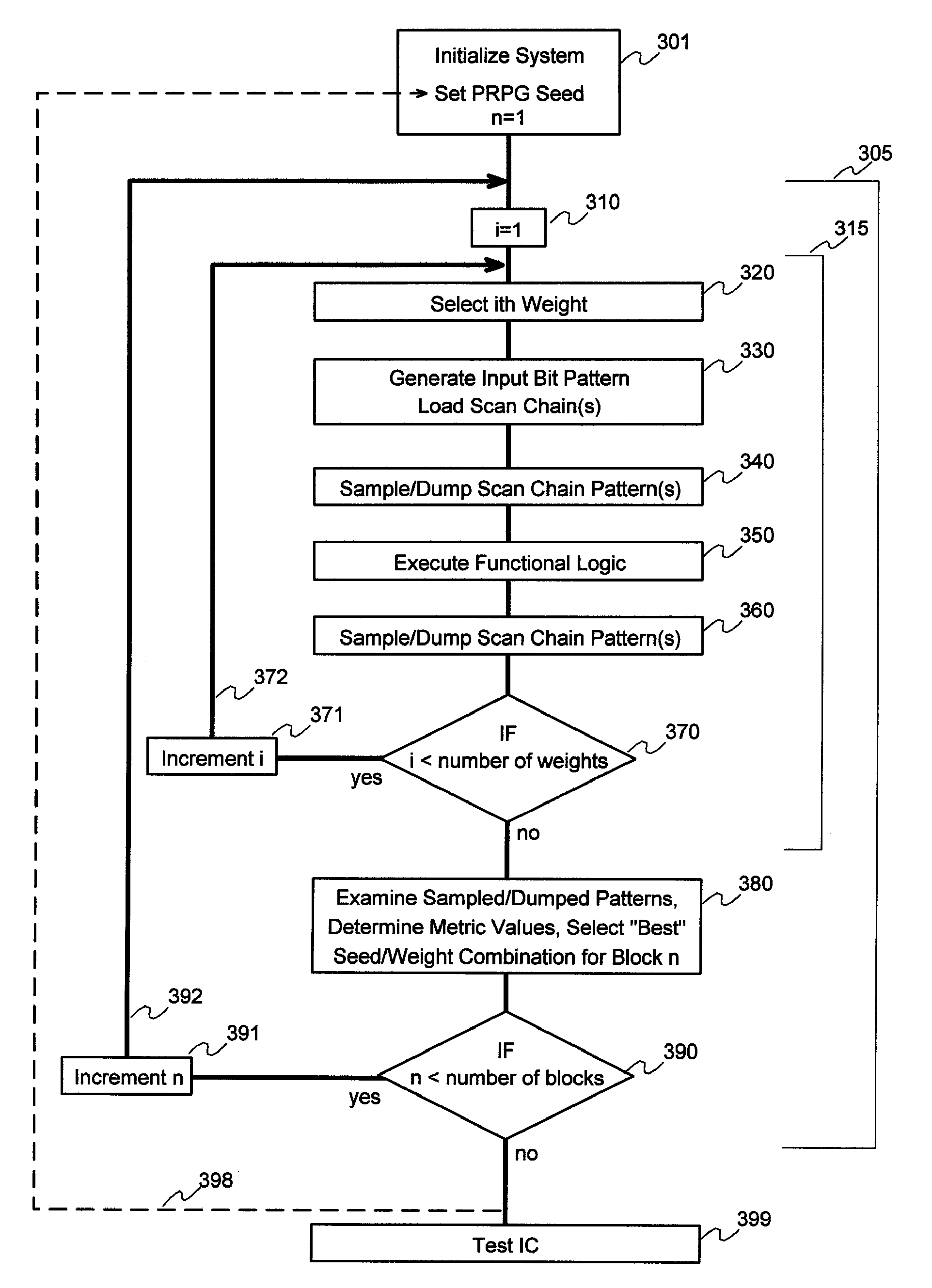

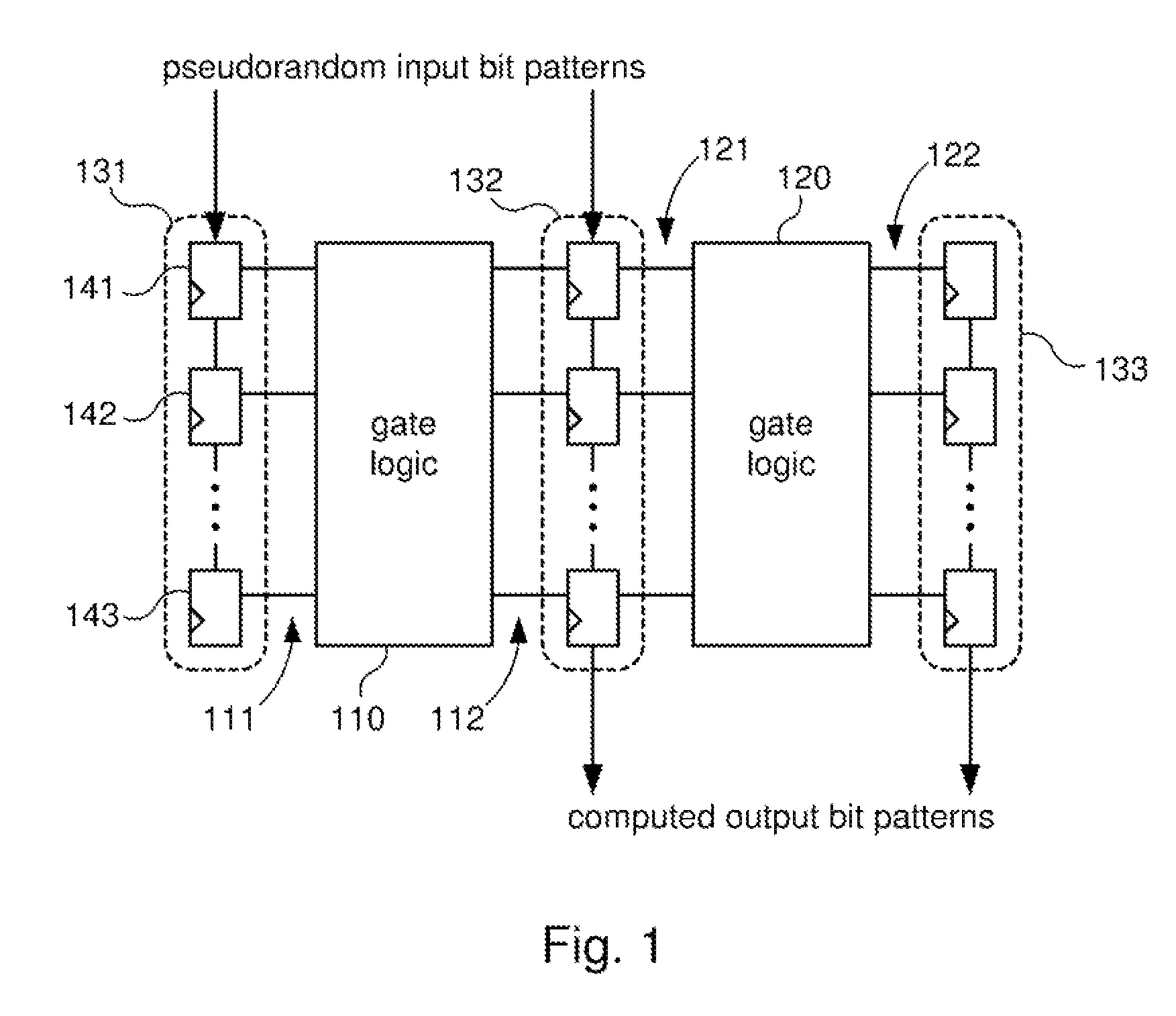

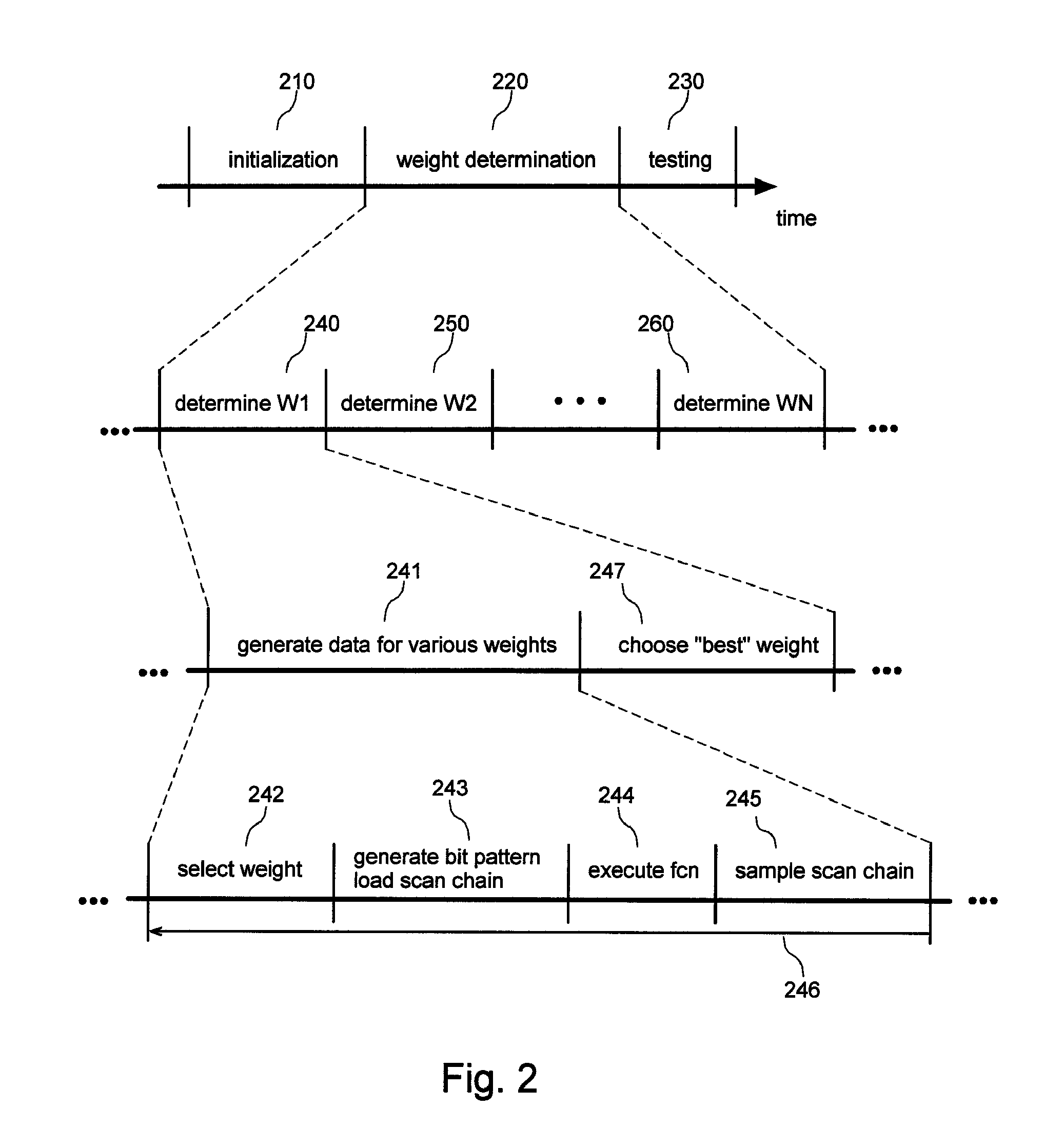

Systems and Methods for Improved Fault Coverage of LBIST Testing

InactiveUS20070273401A1Improve fault coverageReduce in quantityElectronic circuit testingError detection/correctionFault coverageEngineering

Systems and methods for improved fault coverage of logic built-in-self-tests (LBISTs) in integrated circuits (ICs) by determining weighting and / or seed values to be used in generating pseudorandom test bit patterns for each channel to optimize fault coverage. In one embodiment, a method includes generating a pseudorandom sequence of bits, applying a weighting value to the sequence, propagating the weighted sequence through one or more levels of logic, and capturing the resulting data. Metrics are then applied to the captured data to determine the suitability or optimality of the weighting value, and an optimal weighting value is selected. This may be performed for a plurality of trial values for each of a number of channels to obtain a set of weighting values for the different LBIST channels. The method may also include determining a seed value for the pseudorandom bit pattern generator.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

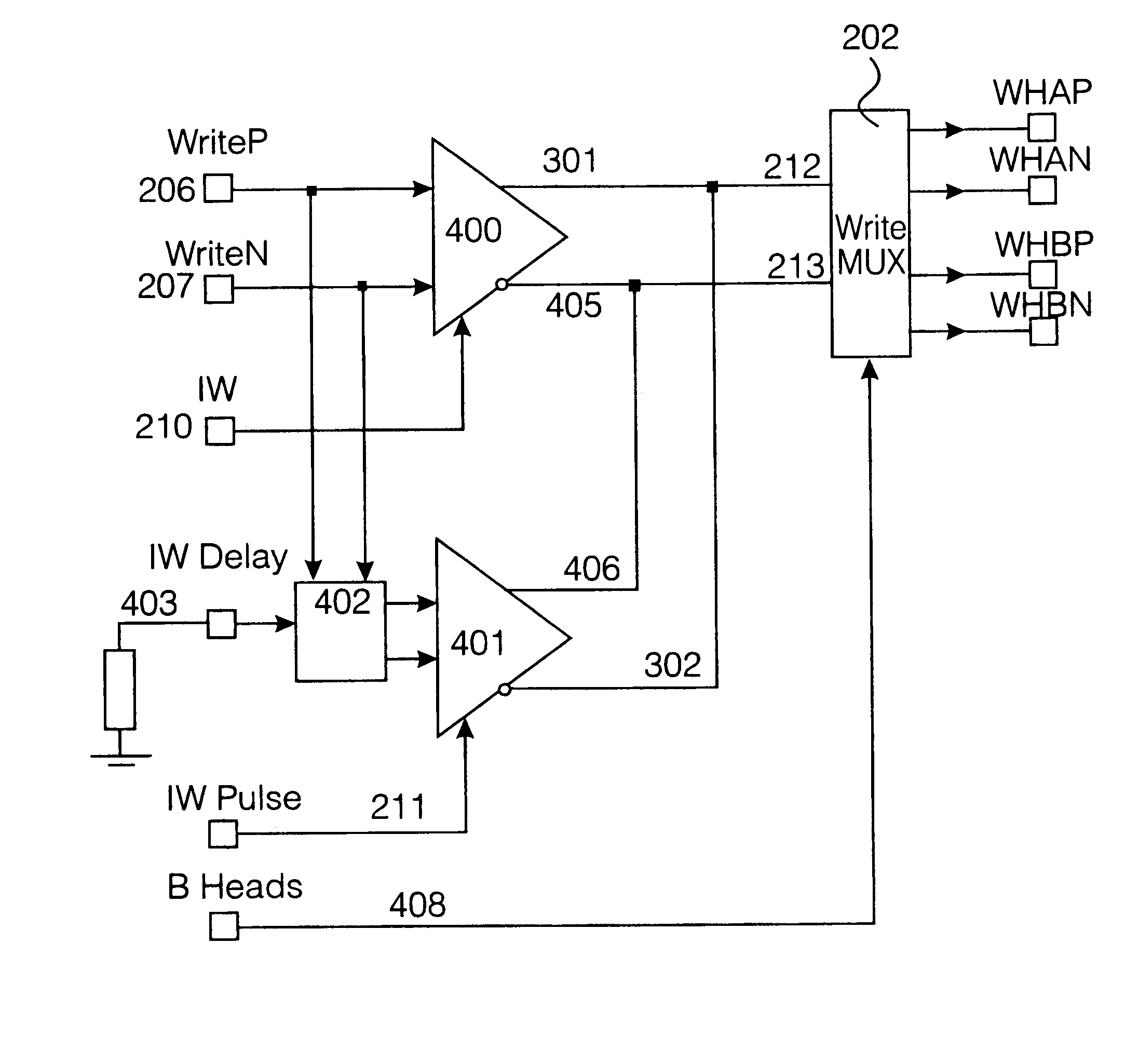

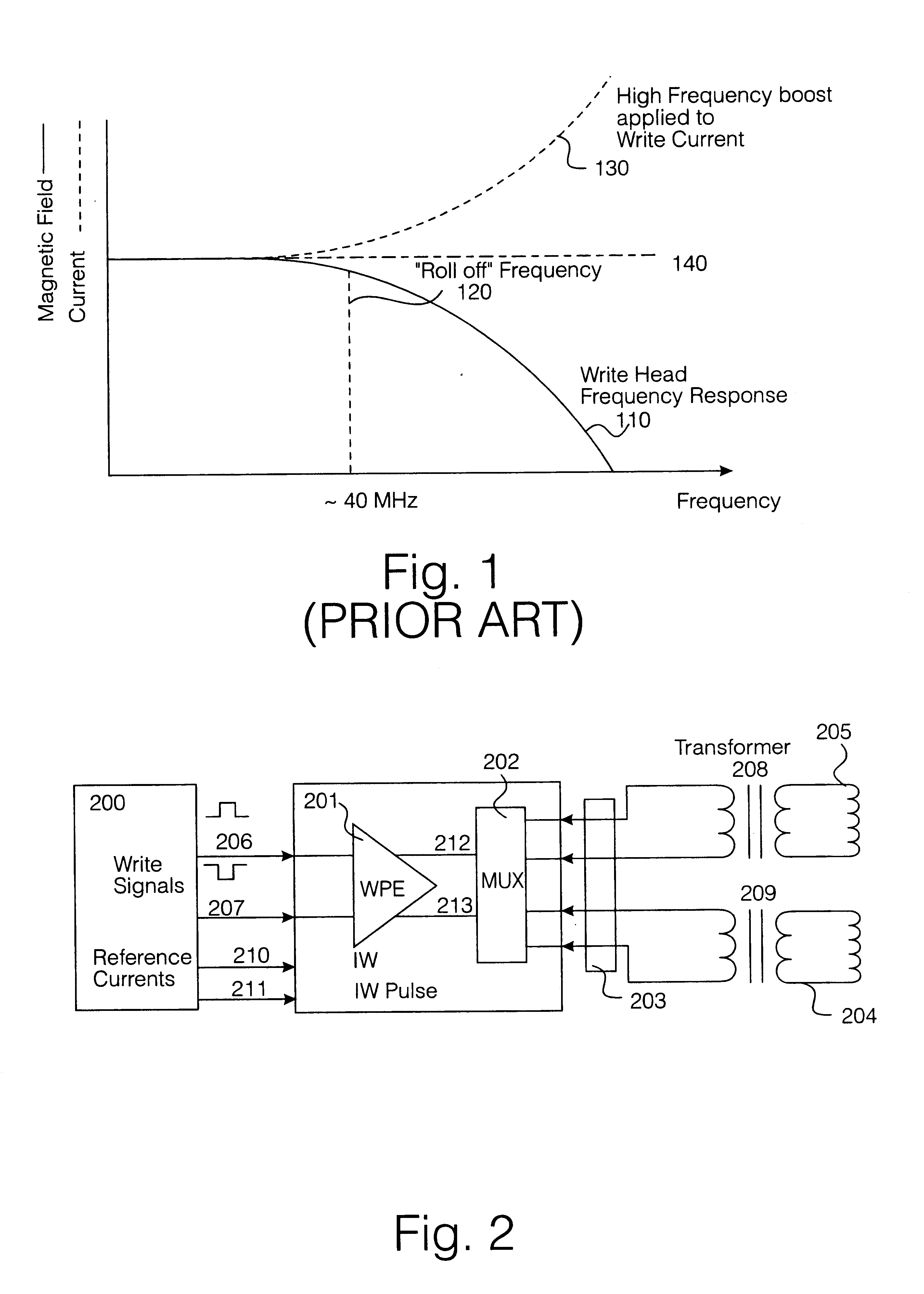

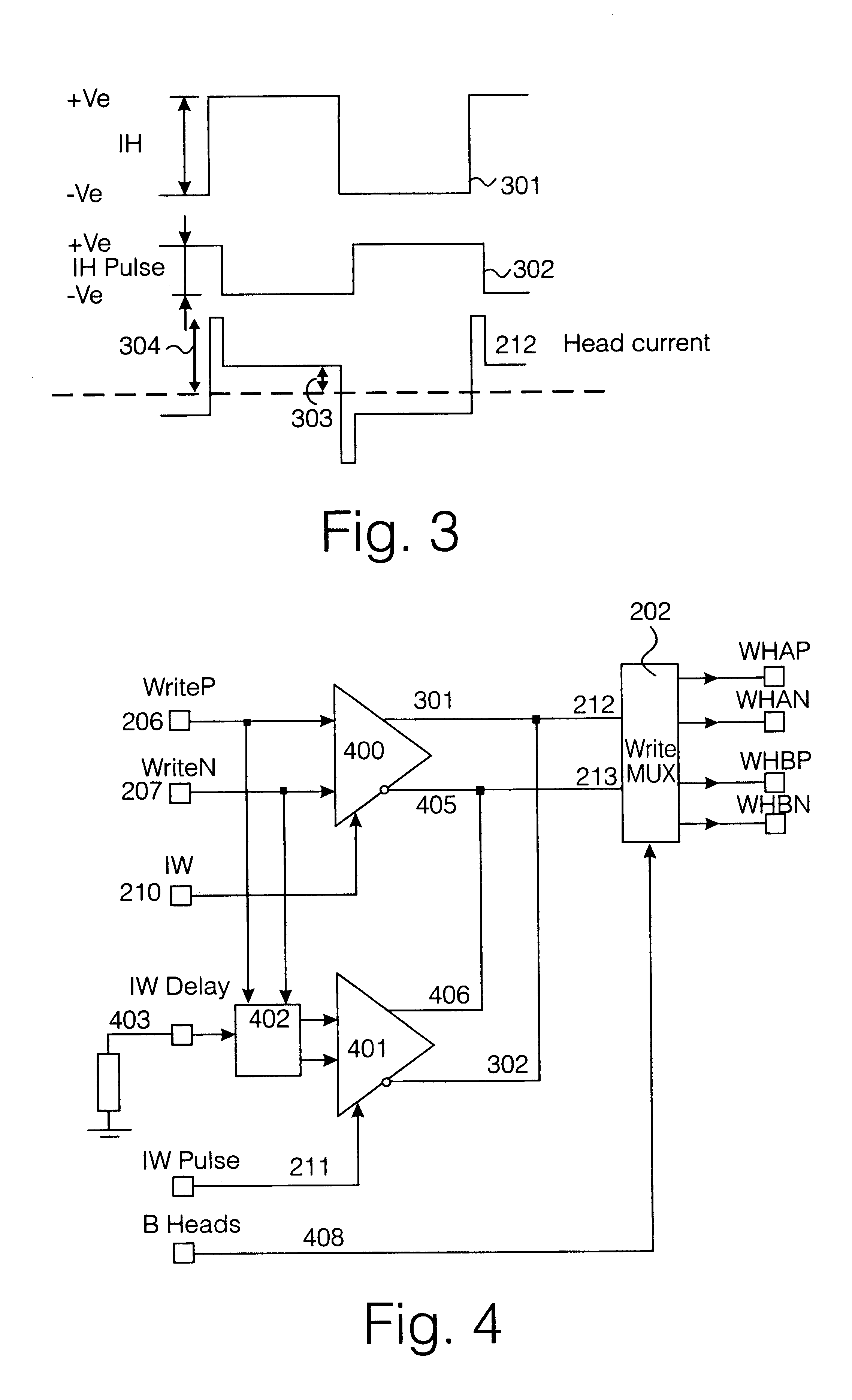

Calibrating write pre-equalization in a data storage device

A method is described of calibrating a write pre-equalization circuit in the write channel of a magnetic data storage device which maximizes the rate at which the write channel can write to a data storage medium. The method includes the steps of: setting an amplitude of a delayed current to a minimum value ; setting a delay period of the delayed current to a minimum value; setting an amplitude of a main driver current to a minimum value; recording a low frequency test signal to the data storage medium; reading the low frequency test signal from the data storage medium; monitoring a quality metric of the low frequency test signal; varying the amplitude of the main driver current over a range of amplitudes; selecting an optimum amplitude of the main driver current; setting the delay period of the delayed signal to a predetermined value; recording a pseudo-random test signal to the data storage medium; reading the pseudo-random test signal from the data storage medium; monitoring a quality metric of the read pseudo-random test signal; varying the amplitude of the delayed current over a range of amplitudes; and selecting an optimum value of the delayed current, depending on the monitored quality metric.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

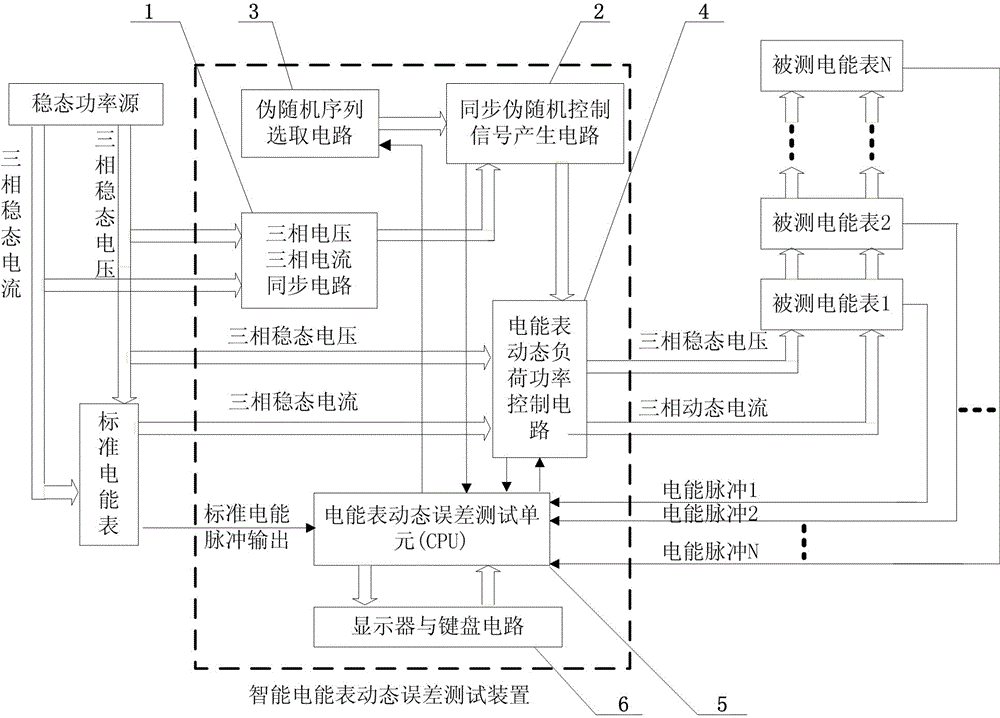

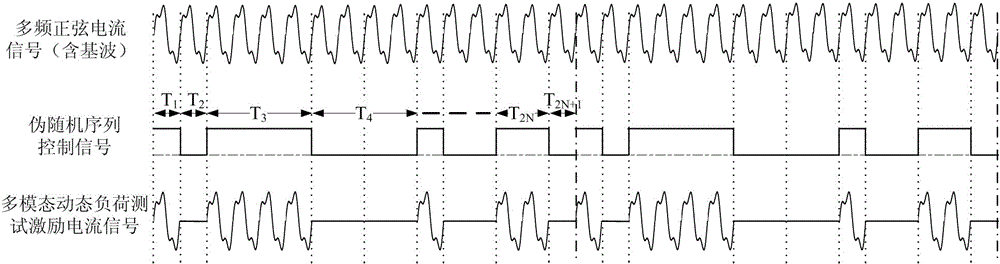

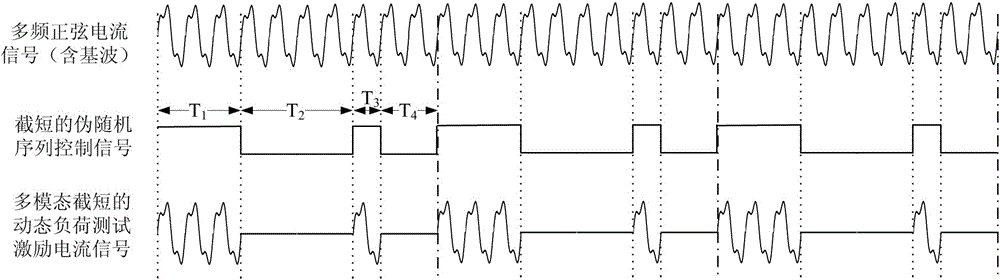

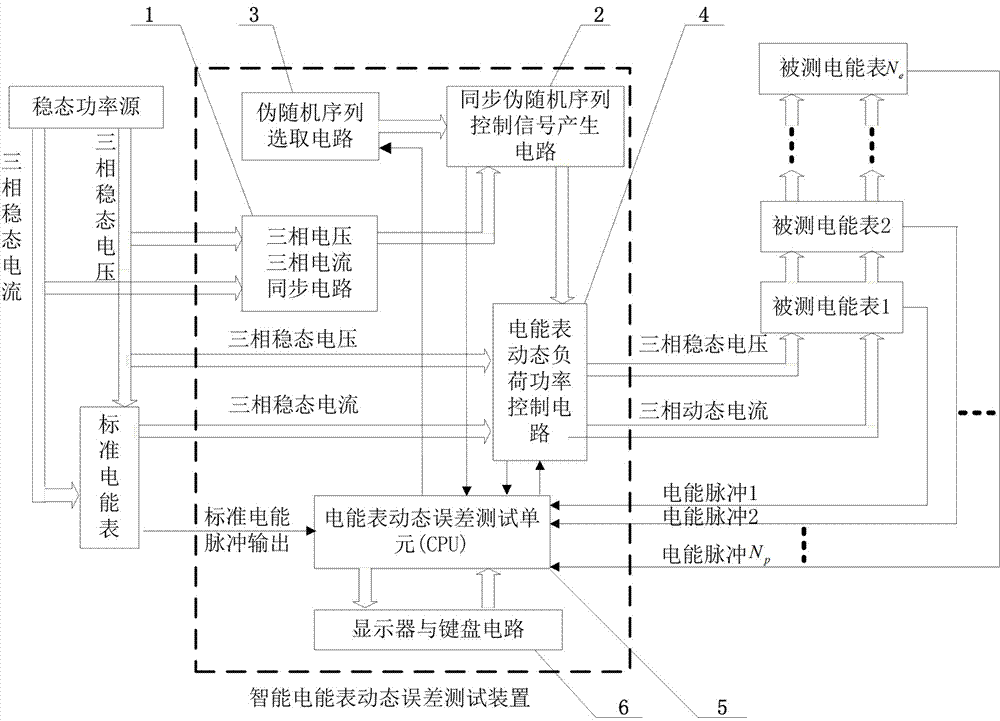

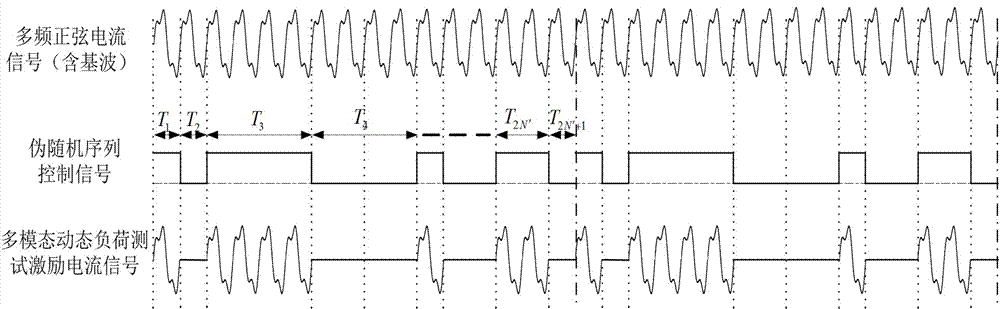

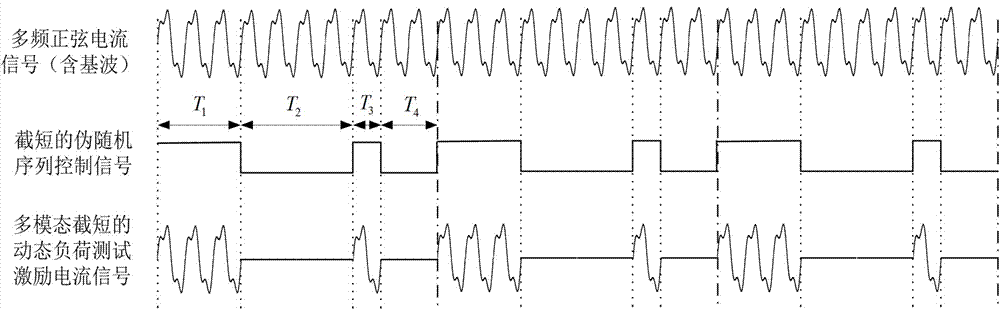

Dynamic error testing method and device for intelligent ammeter

ActiveCN104569900AImplement dynamic error testingSolve the problem of comprehensive testing of dynamic error characteristicsElectrical measurementsModal testingControl signal

The invention relates to a dynamic error testing method and device for an intelligent ammeter. The device consists of a synchronous circuit with a three-phase voltage and / or a three-phase current, a synchronous pseudo random sequence control signal generating circuit, a pseudo random sequence selecting circuit, an ammeter dynamic load power control circuit, an ammeter dynamic error testing unit, a display and keyboard unit and a dynamic error measuring algorithm. The method and device can effectively generate multi-modal pseudo random testing excitation current and power and effectively reflect randomness of change of the dynamic load current and the power, thereby tracing the source from dynamic load electric energy value to a dynamic load electric energy value of the pseudo random change and fully testing the dynamic error characteristic of the ammeter under multi-modal testing excitation; the method and device solve the problem that exiting determined testing excitation current and power cannot reflect randomness of the dynamic load change and solve the problem of tracing the source of the dynamic load electric energy value and testing the dynamic error under dynamic load of the pseudo random change; the method and device can be widely used in a dynamic error testing system of the intelligent ammeter.

Owner:BEIJING UNIV OF CHEM TECH

Bit-error rate tester with pattern generation

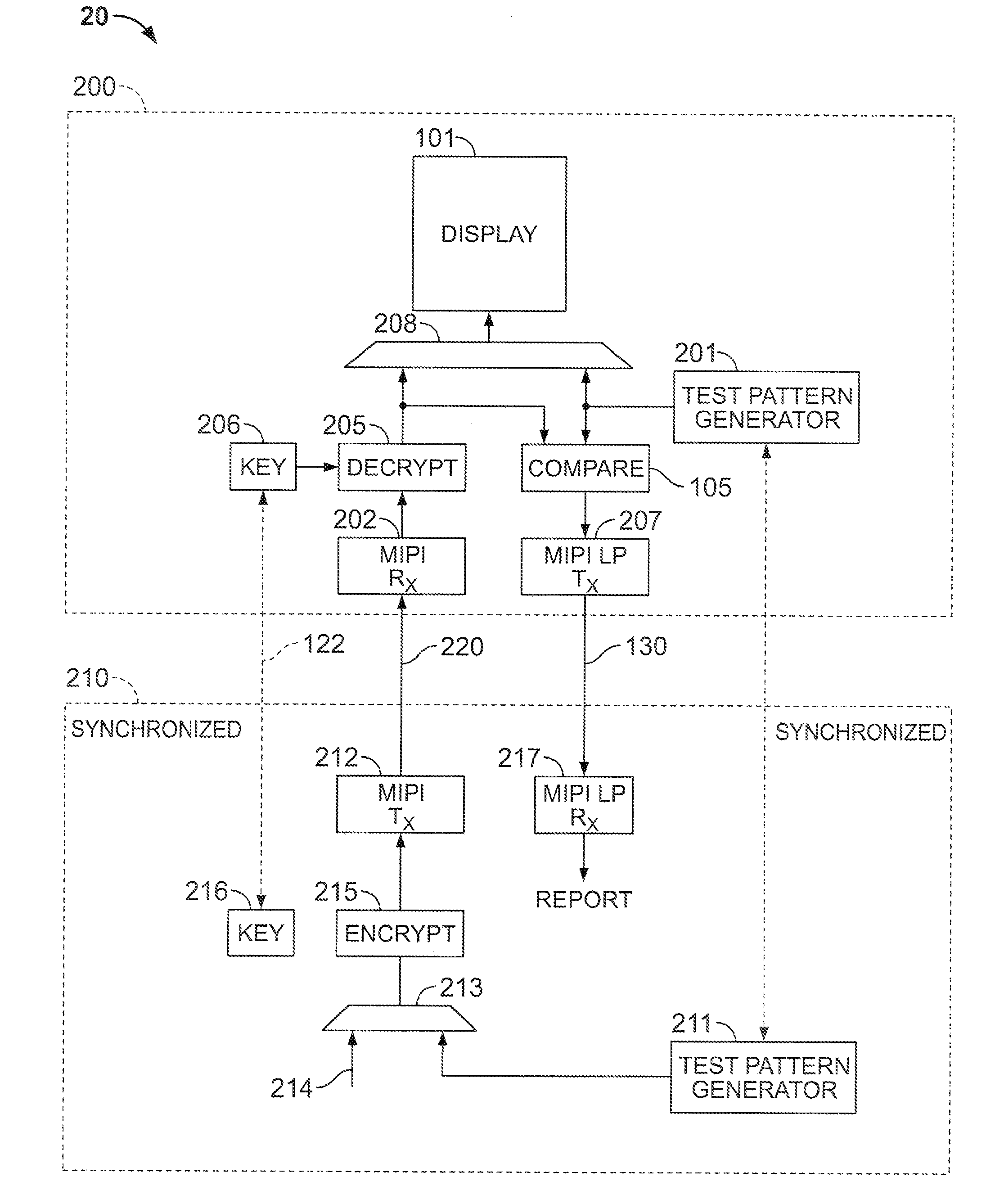

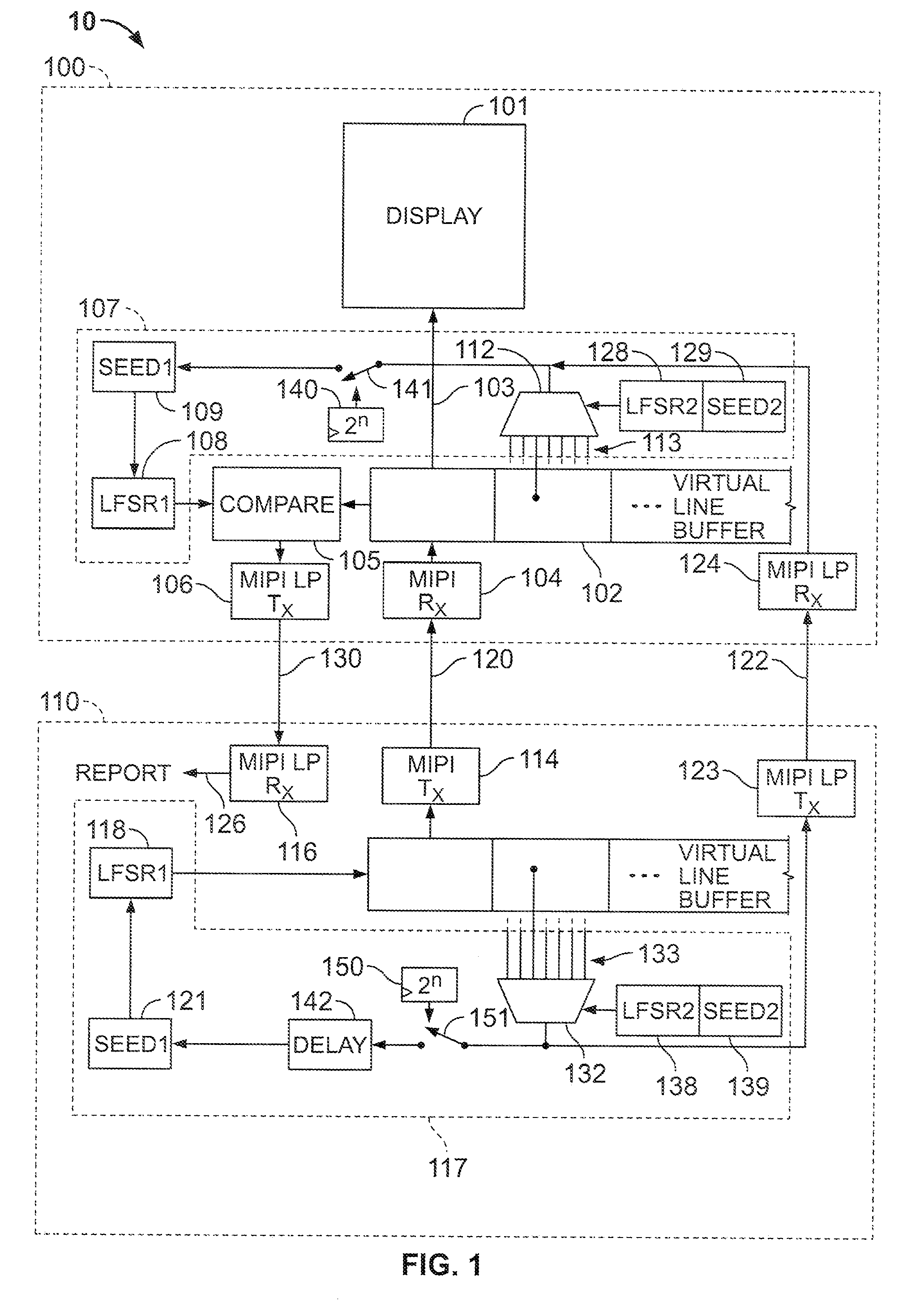

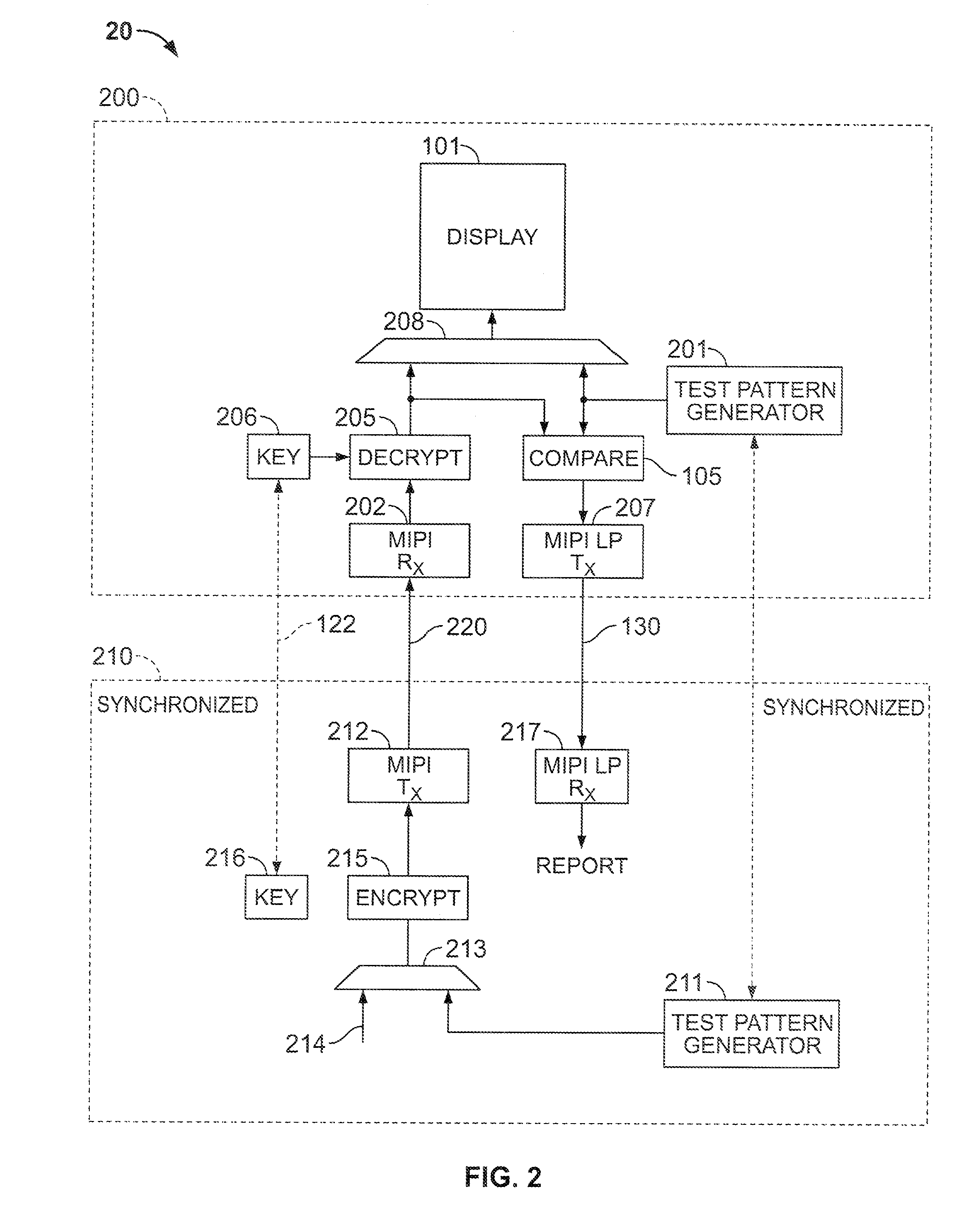

InactiveUS20100077211A1Synchronising transmission/receiving encryption devicesUser identity/authority verificationComputer moduleEngineering

Identical random, or pseudorandom, test patterns in a peripheral device (“receiver”) to be tested, and in a transmitter that sends the test pattern to the receiver, are generated by using pattern generation circuitry in both the transmitter and the receiver that operates identically based on a pattern input value, or seed. The same seed is input to both the transmitter and the receiver. The pattern generation circuitry can be a linear-feedback shift register (“LFSR”), which generates pseudorandom numbers, and identical LFSRs in both the transmitter and the receiver are provided with the same seed. The LFSR may be reseeded periodically. The new seed can be an output of the LFSR itself, or a second LFSR is provided whose output is used to determine the new seed for the first LFSR. Alternatively, cryptographic modules are used in the transmitter and the receiver to generate the test pattern based on identical keys.

Owner:APPLE INC

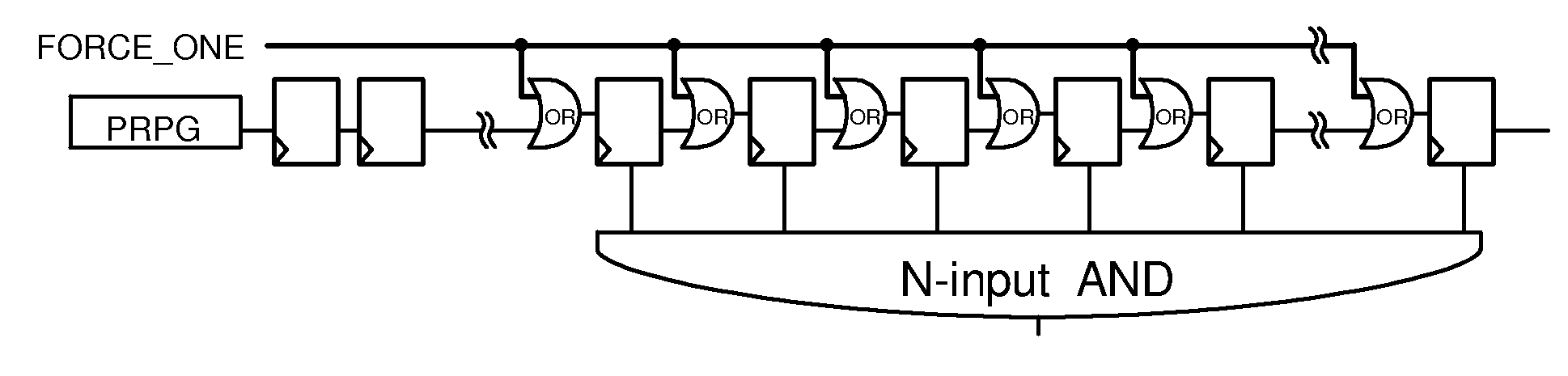

Systems and methods for improved scan testing fault coverage

Systems and methods for improved fault coverage of logic built-in-self-tests (LBISTs) in integrated circuits (ICs) which ensure testing of specific logic by forcing specific values into scan latches that contain otherwise pseudorandom test bit patterns. In one embodiment, an LBIST system comprises a plurality of scan latches and forcing logic coupled to a first set of the scan latches which provide inputs to selected target logic. The forcing logic is configured to overwrite values stored in the first set of scan latches with desired values. In one embodiment, the forcing logic includes a bypass path that enables shifting of unaltered bit patterns around the first set of scan latches. Bits in the bypass path may be inverted when the bypass path is not being used in order to help detect errors in the operation of the bypass path.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

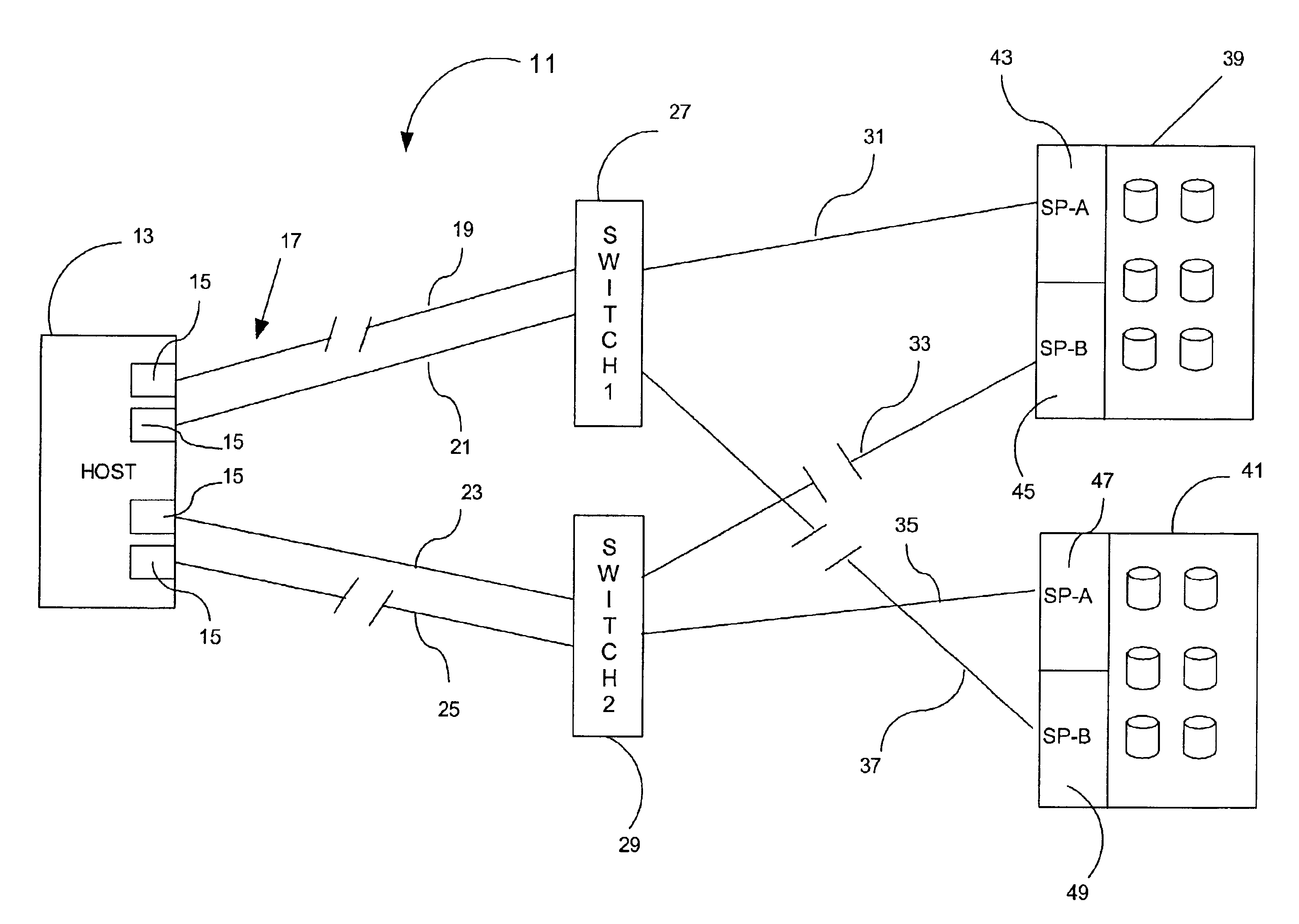

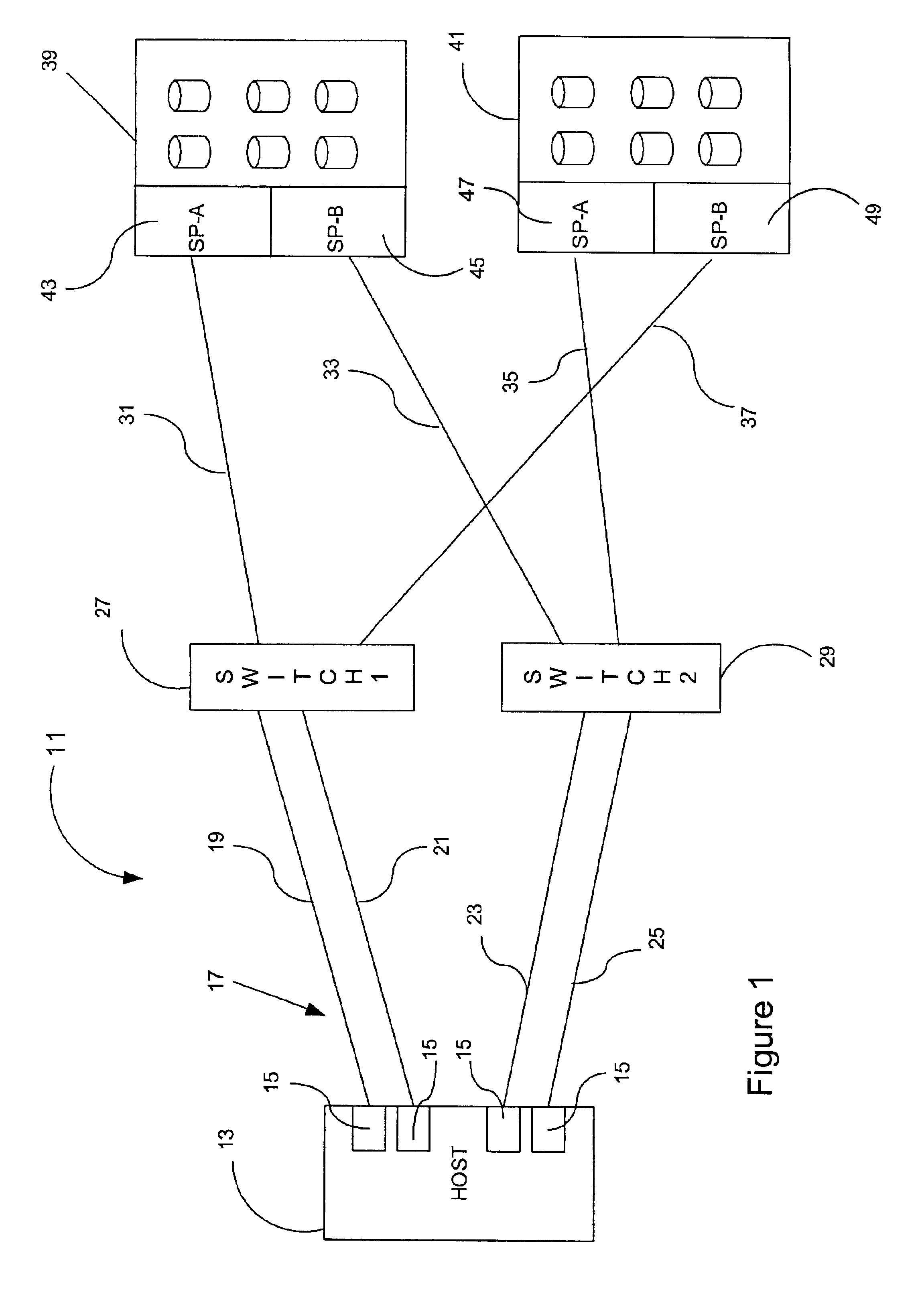

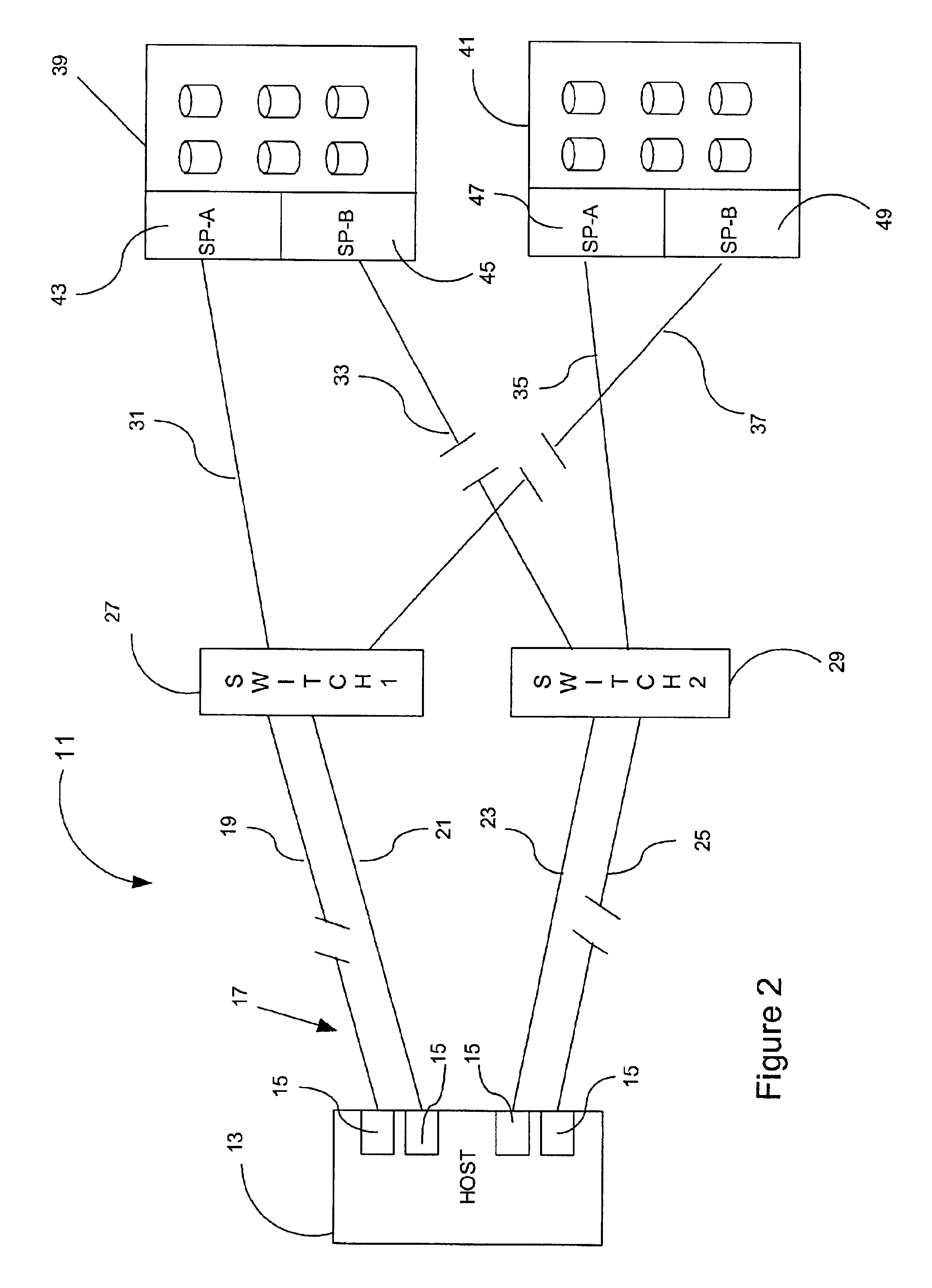

Method and system for pseudo-random testing a fault tolerant network

A method and system for pseudo-random testing a fault tolerant network for determining the network's response to failure includes generating an image of the network on a host. At least one path of the network is selected to be physically failed through the use of a random number generator such that the selection is done pseudo-randomly. The part is then failed and the network's response to the failure is detected and all attempts to repair the failure logged up to and including the first successful attempt to repair the failure. In the event of a failure to repair a path occurs, the test is stopped, a repair effected, and the test restarted at the point the failure to repair occurred.

Owner:EMC IP HLDG CO LLC

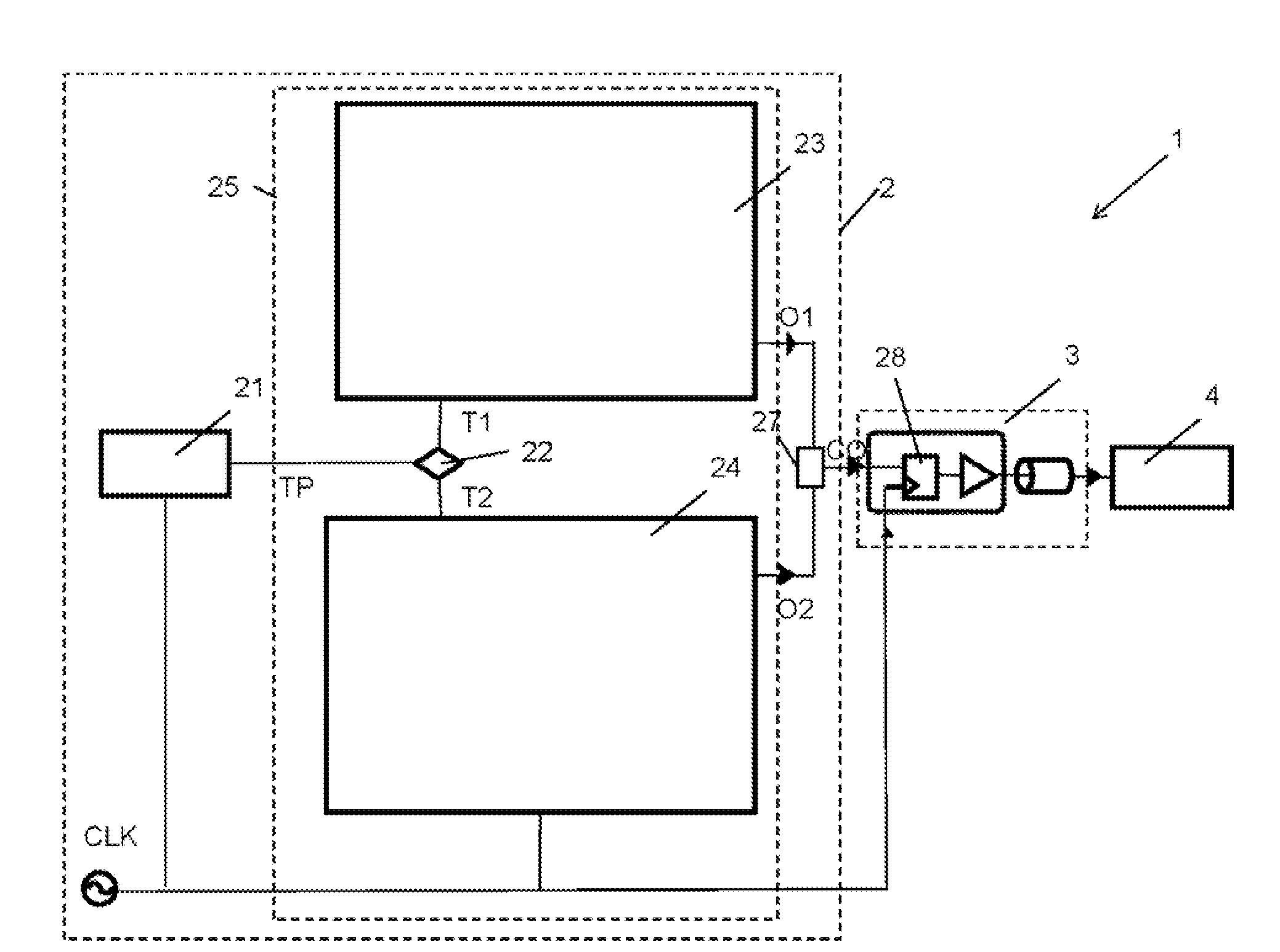

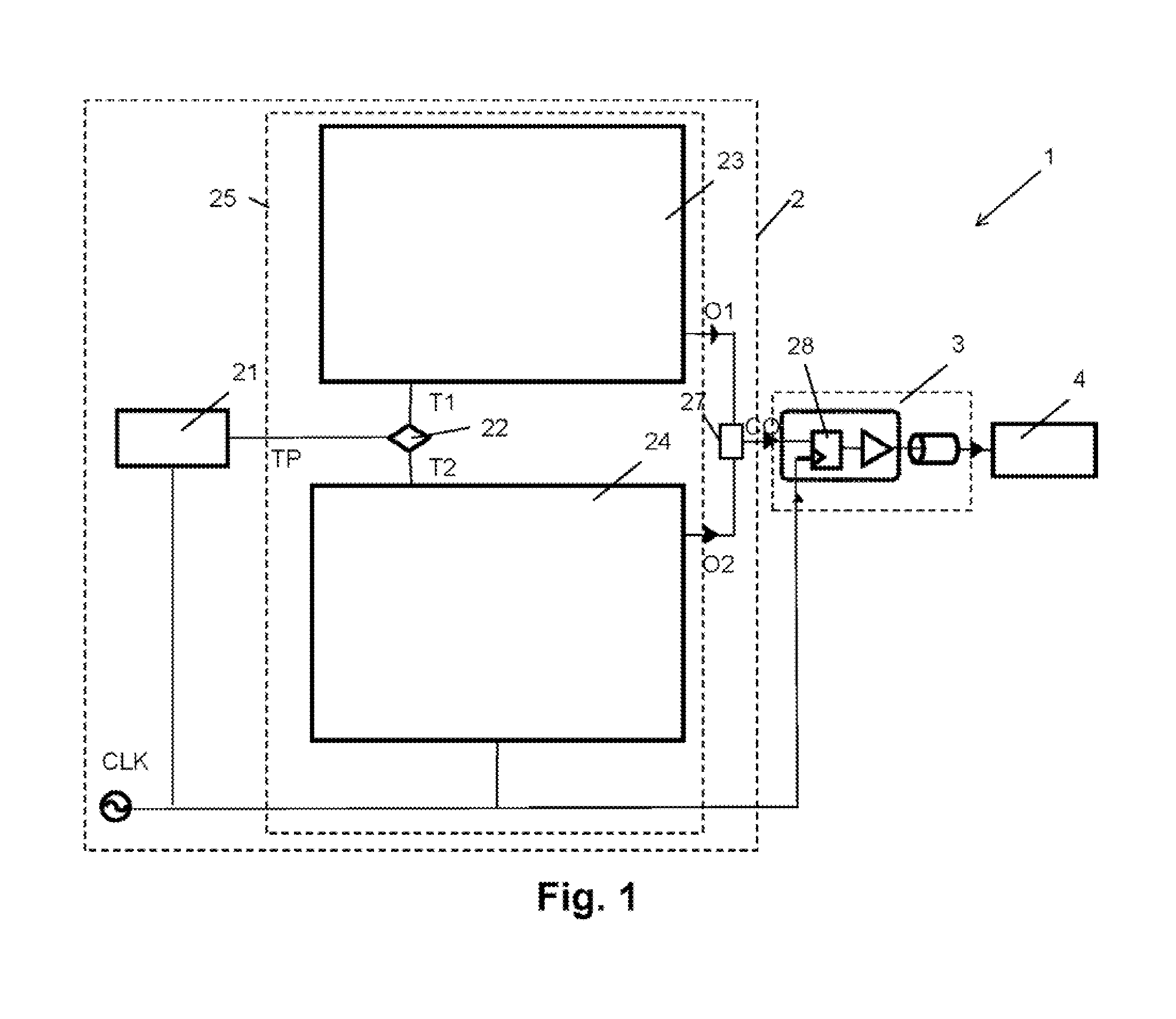

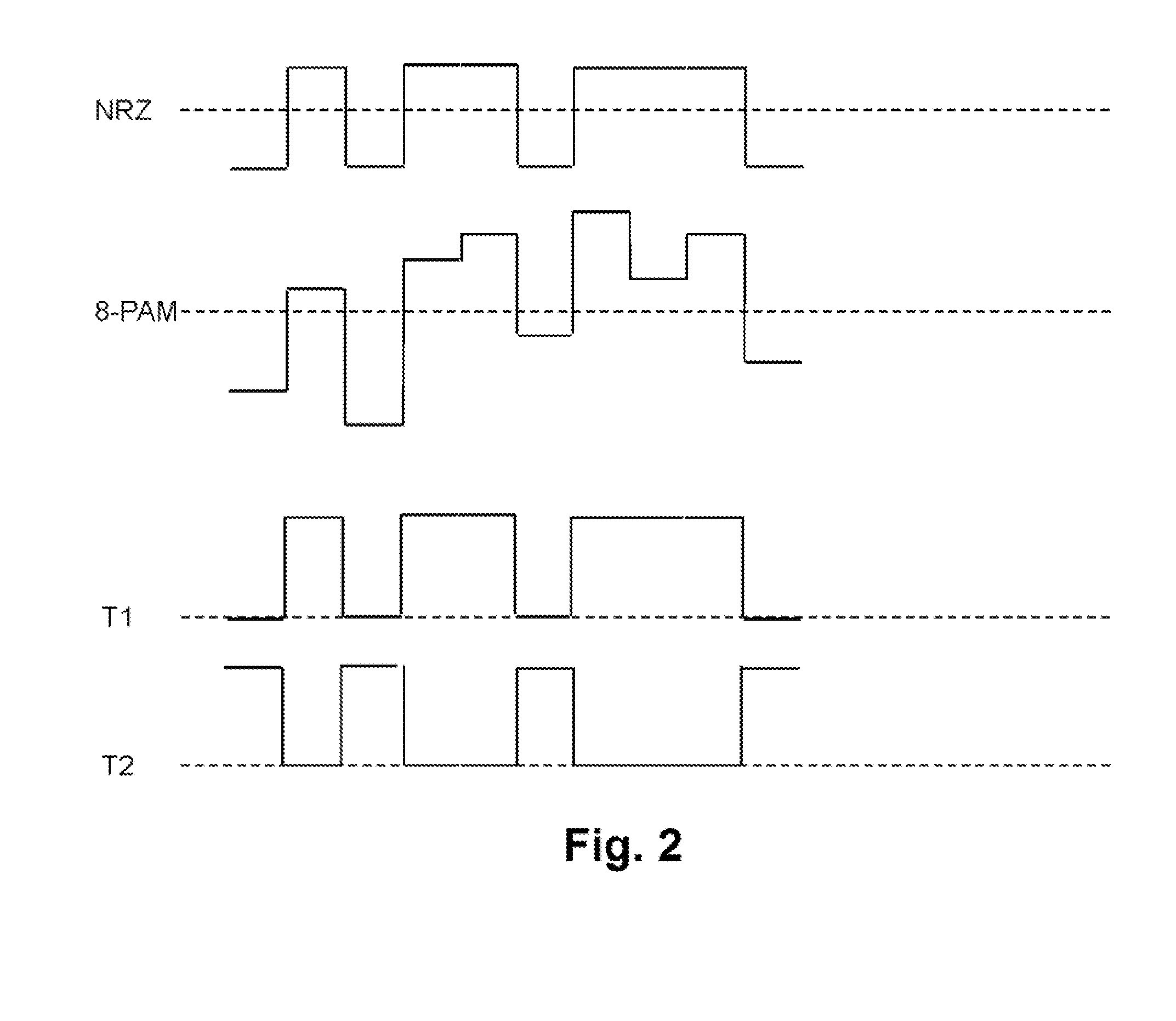

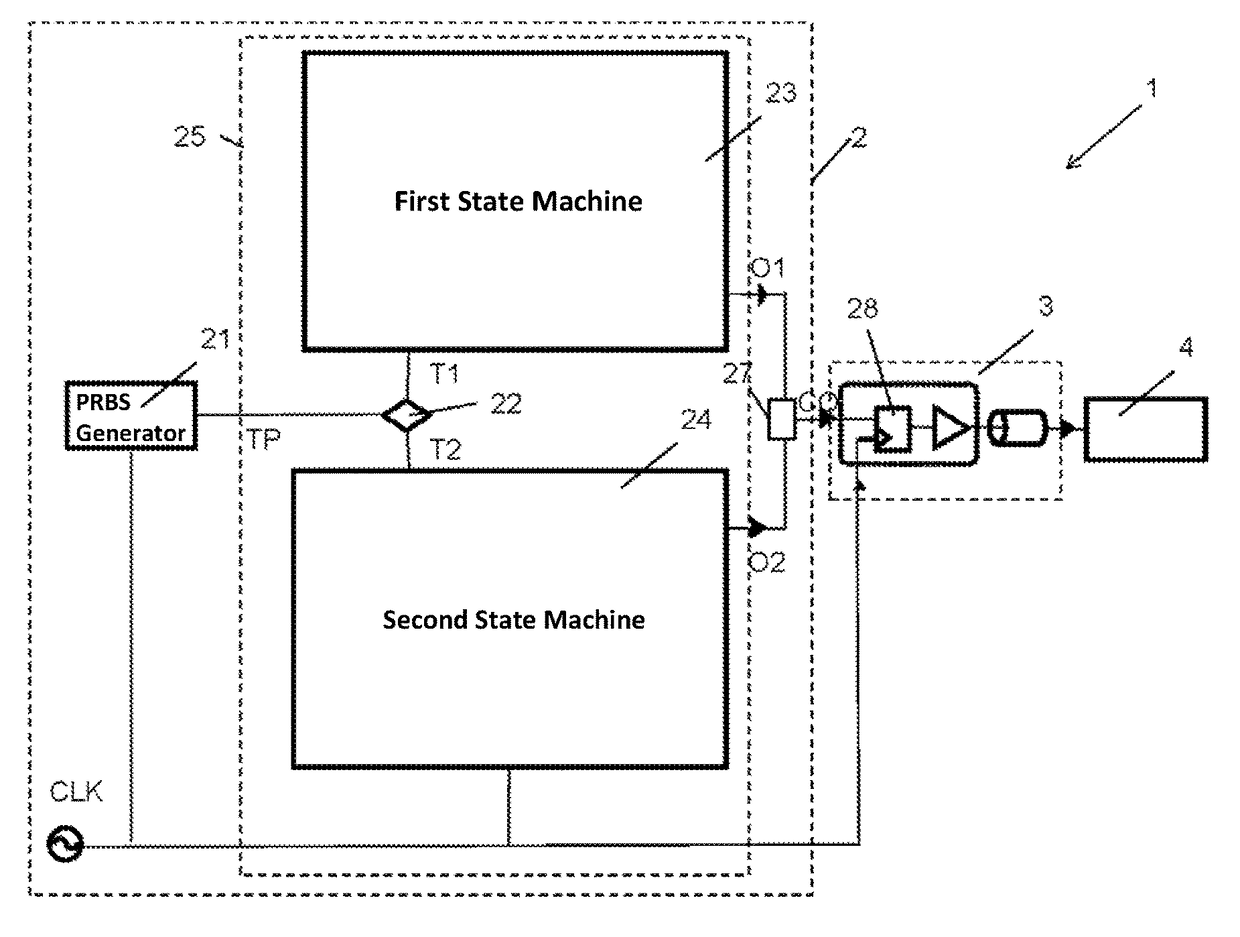

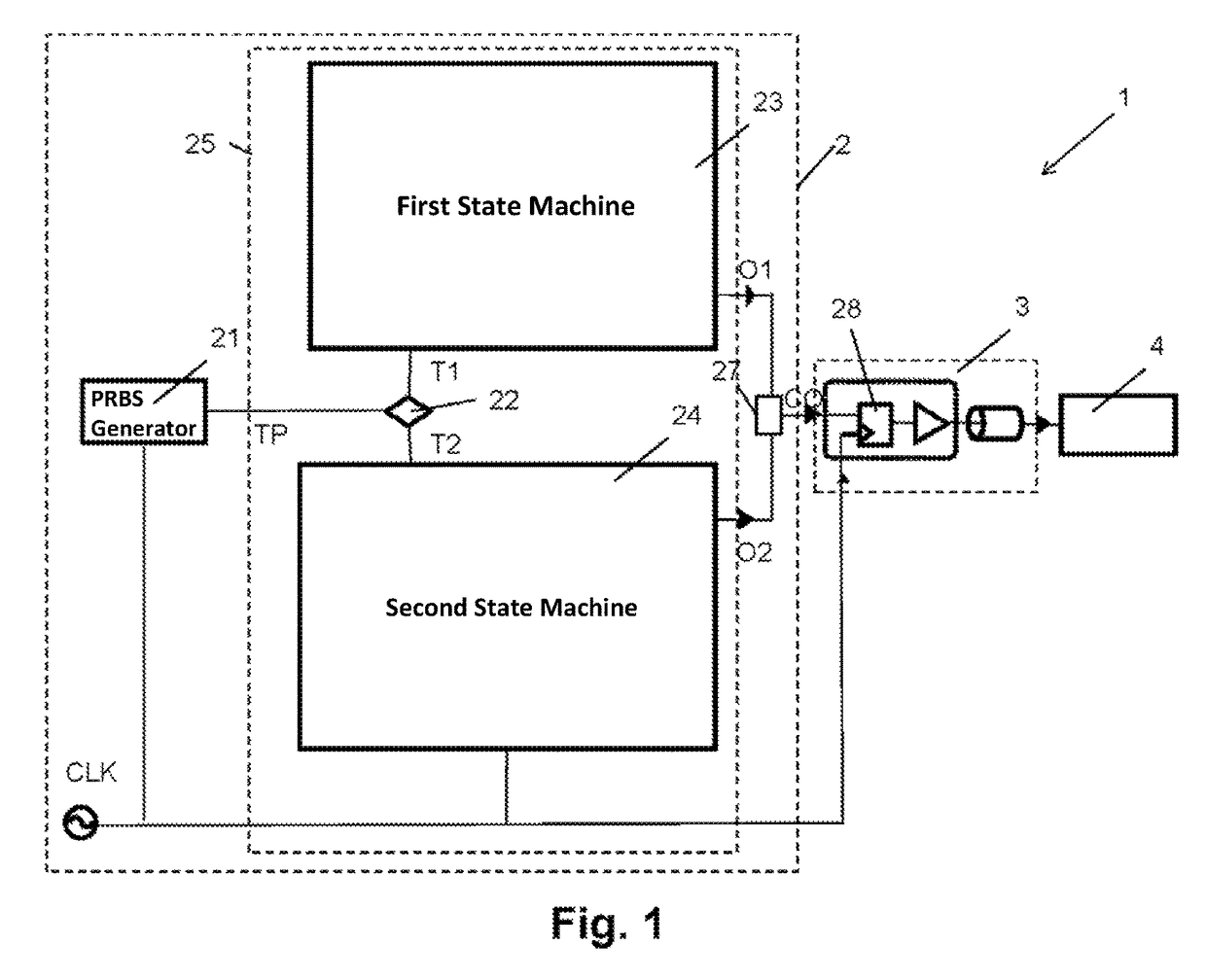

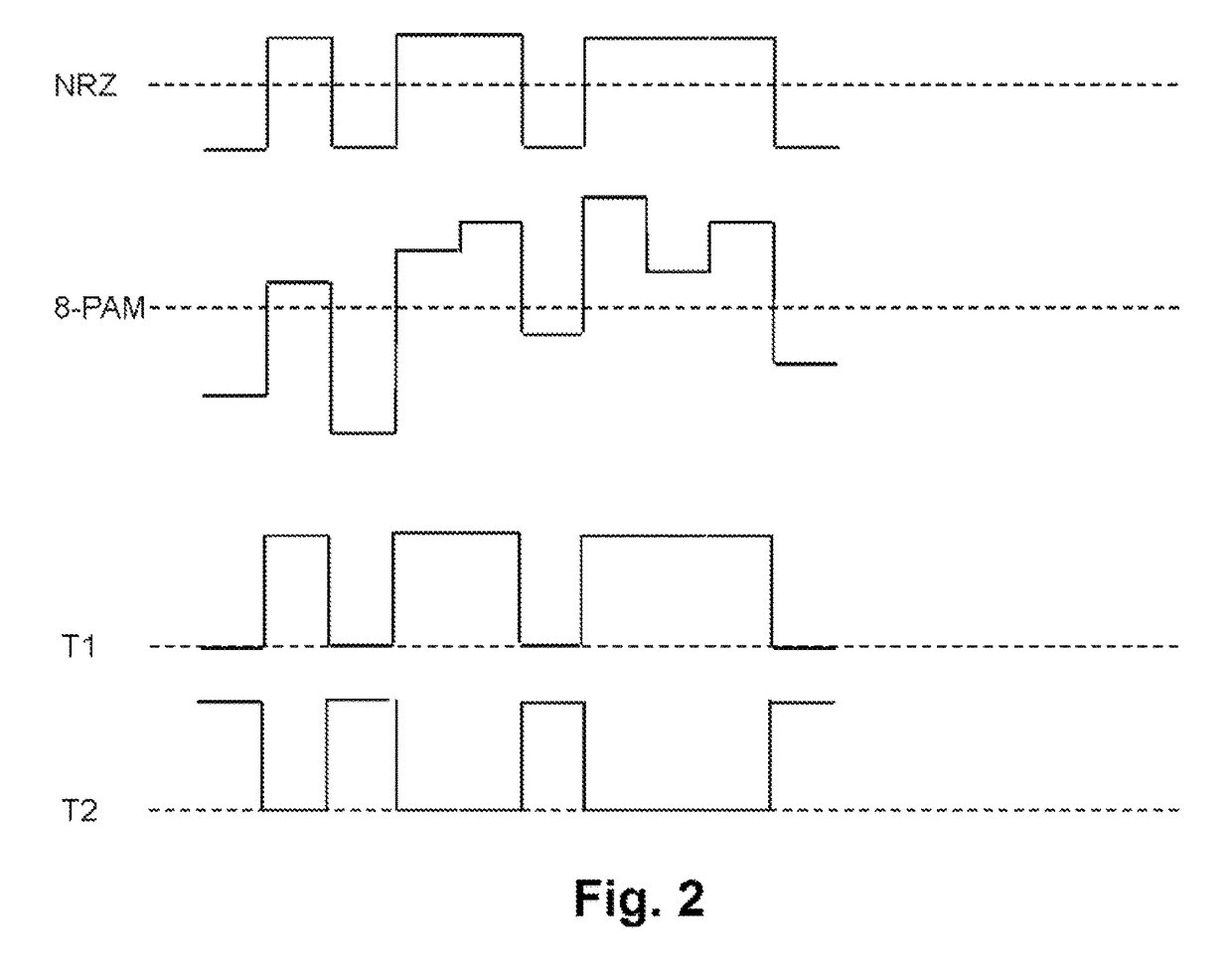

Method and apparatus for generating a multi-level pseudo-random test signal

InactiveUS20160087822A1Evenly distributedThe testing process is simpleElectrical testingTransmission monitoringPattern sequenceAlgorithm

The present invention relates to a method for generating multi-level PRBS patterns for testing purposes, wherein the method includes the steps of providing a binary PRBS signal with a binary bit pattern sequence and mapping each bit of the binary bit pattern sequence to a symbol of a multilevel output.

Owner:IBM CORP

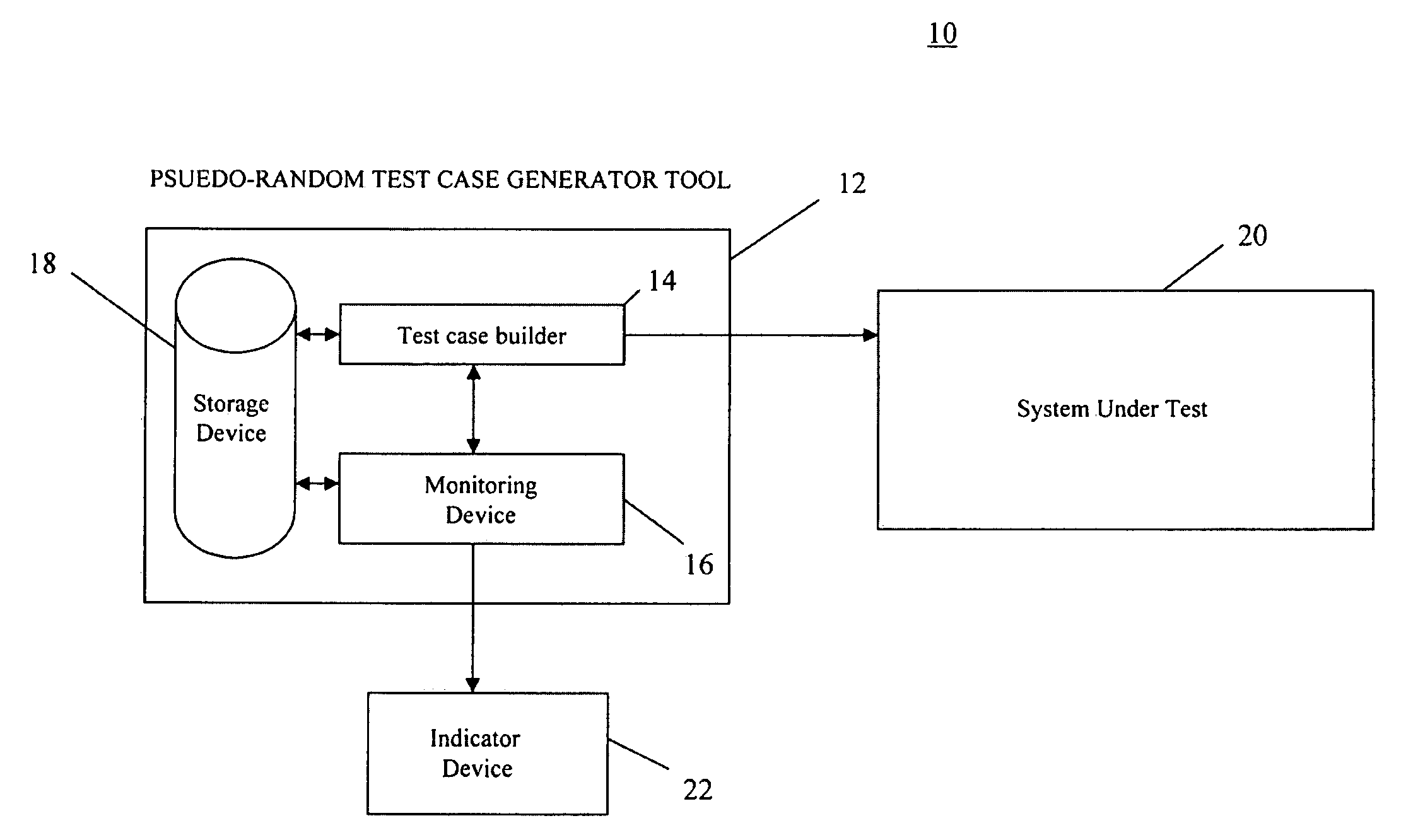

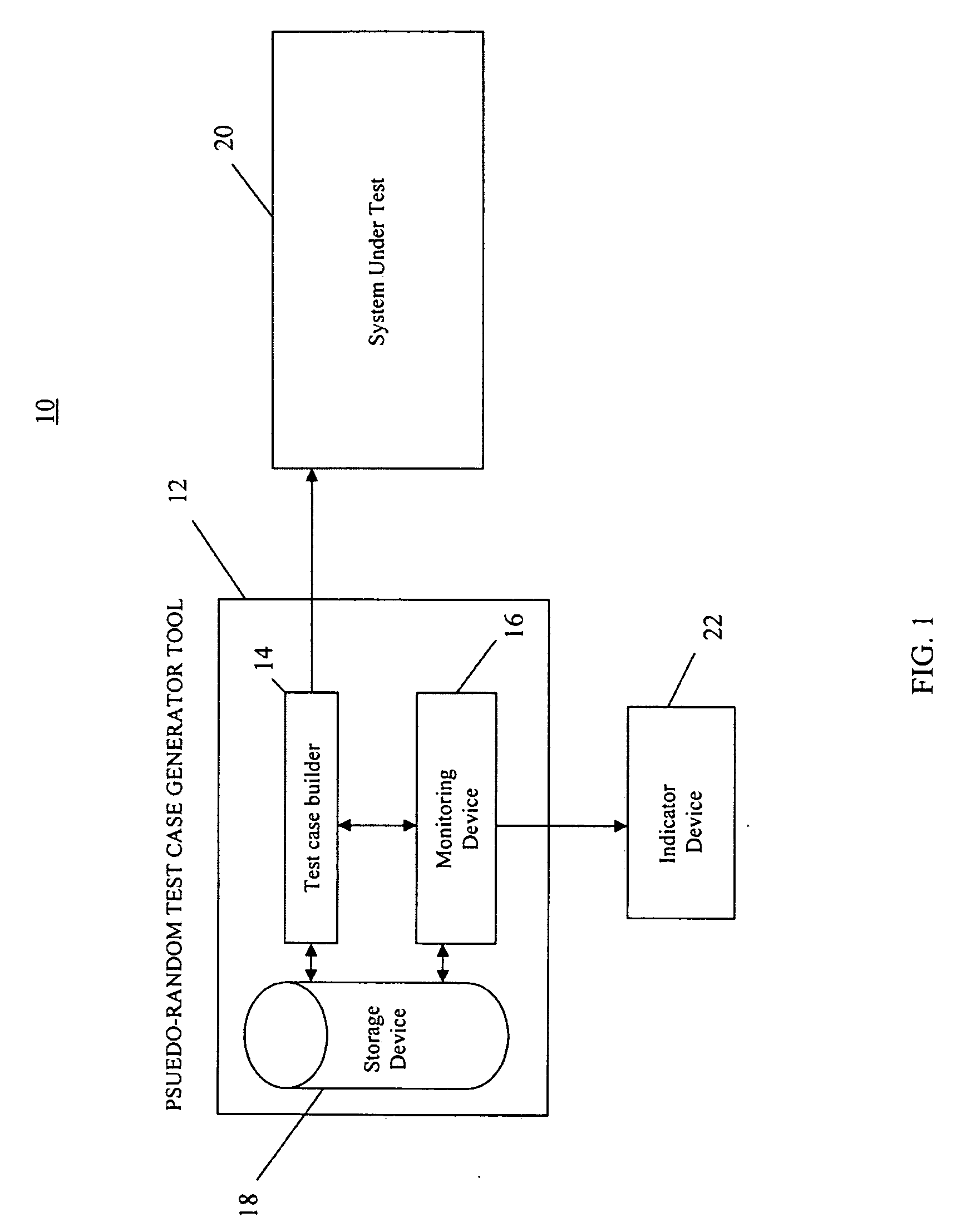

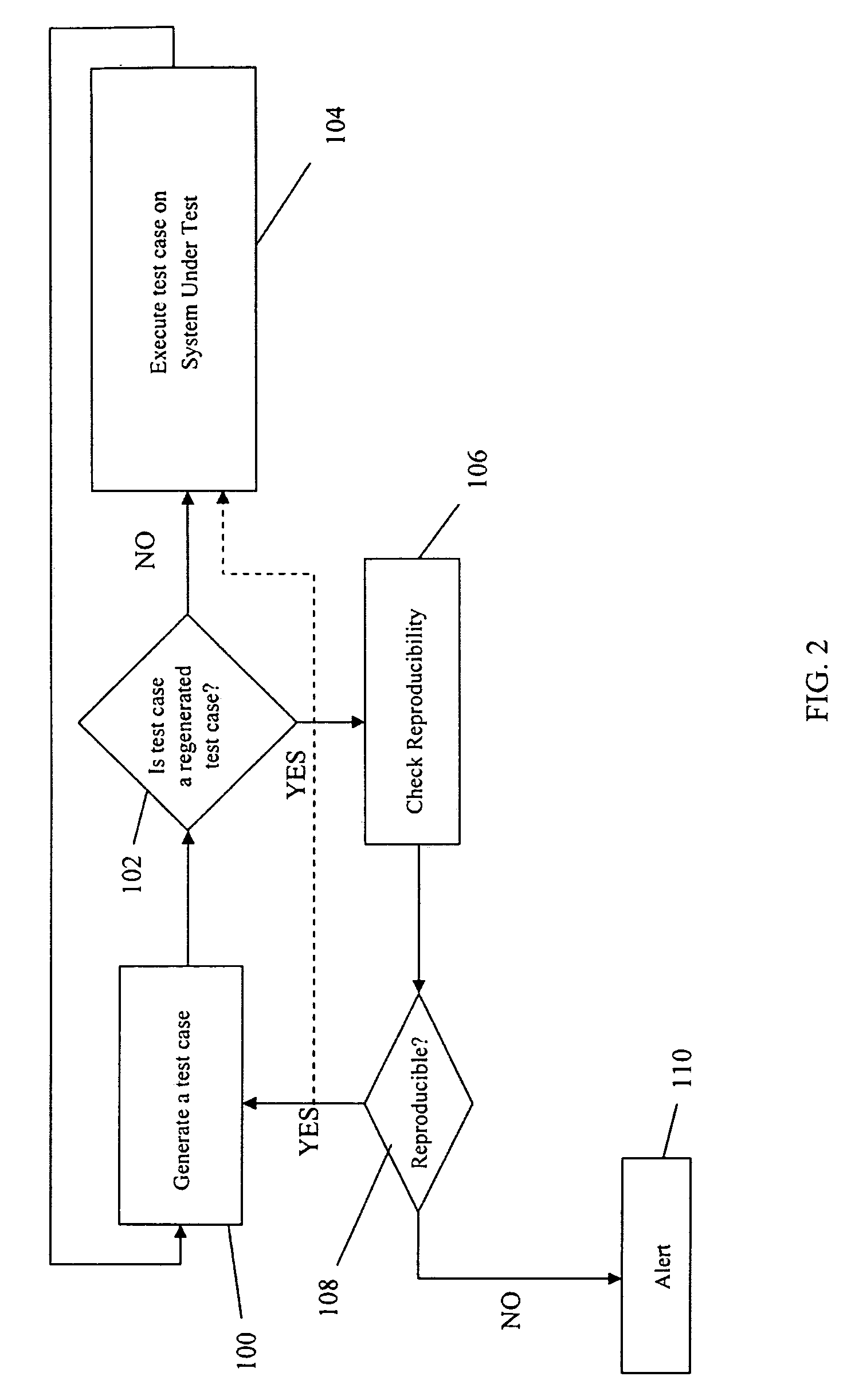

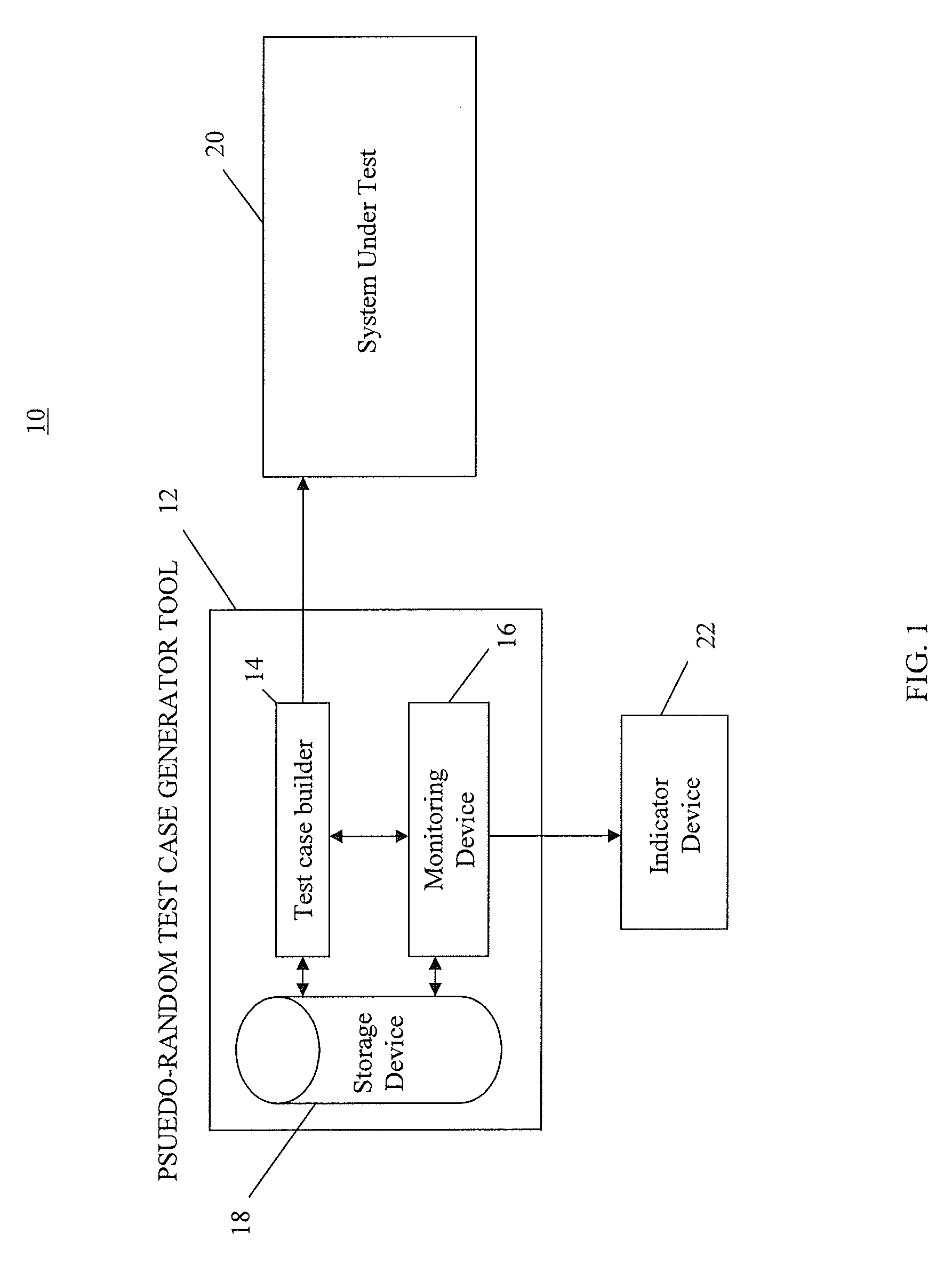

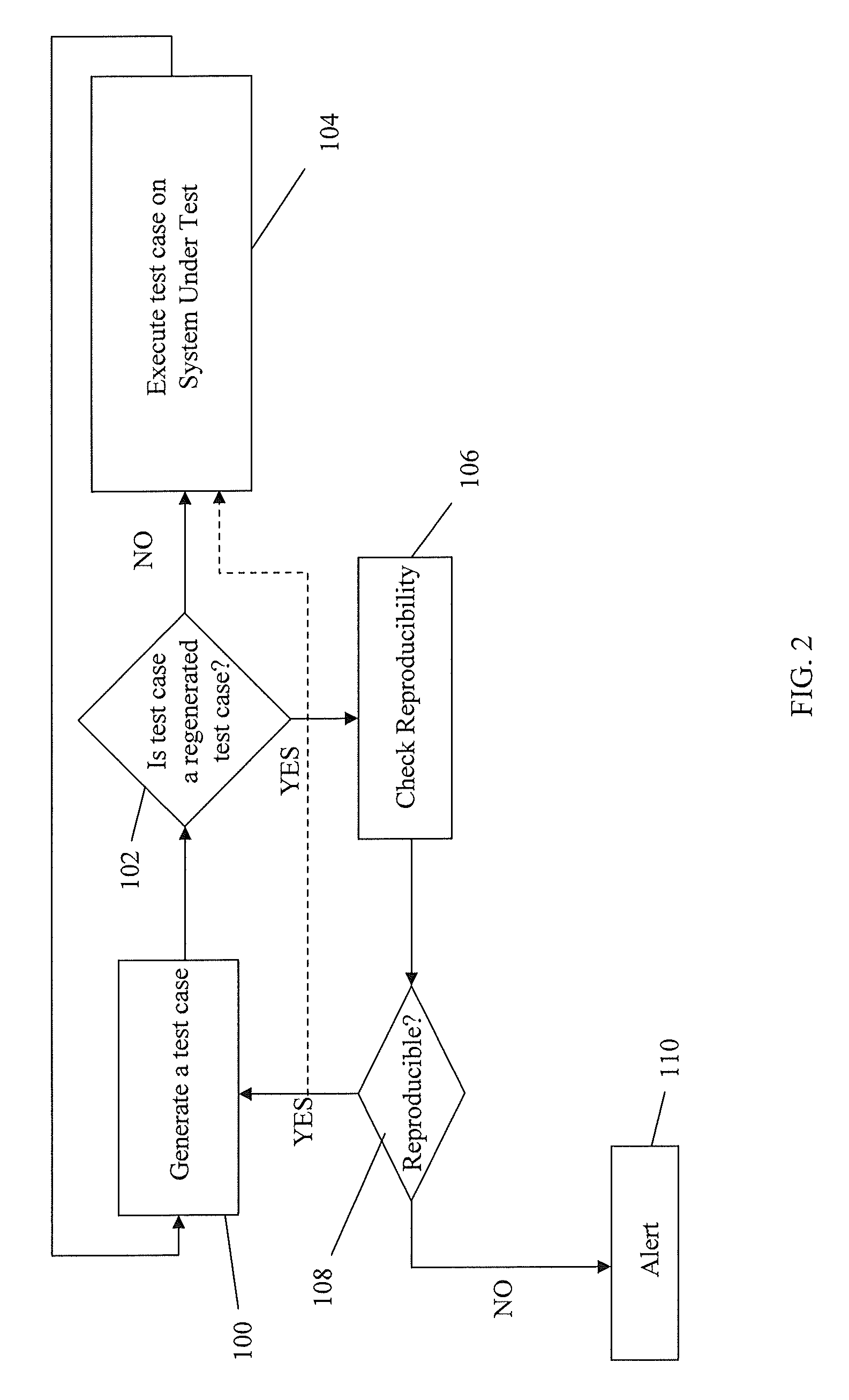

System and method for detecting non-reproducible pseudo-random test cases

InactiveUS20090222696A1Electronic circuit testingError detection/correctionTest case generatorAdemetionine

A method for monitoring a test case generator system by detecting non-reproducible pseudo-random test cases, comprising: building a first pseudo-random test case having a first sequence of seeds comprising a first starting seed and a first ending seed through the test case generator system; reproducing the first sequence of seeds of the first pseudo-random test case by building a second pseudo-random test case having a second sequence of seeds comprising a second starting seed and a second ending seed through the test case generator system when the test case generator system is operating in a reproduction mode, the first starting seed being used as the second starting seed of the second sequence of seeds; and comparing the first ending seed in the first sequence of seeds to the second ending seed in the second sequence of seeds.

Owner:IBM CORP

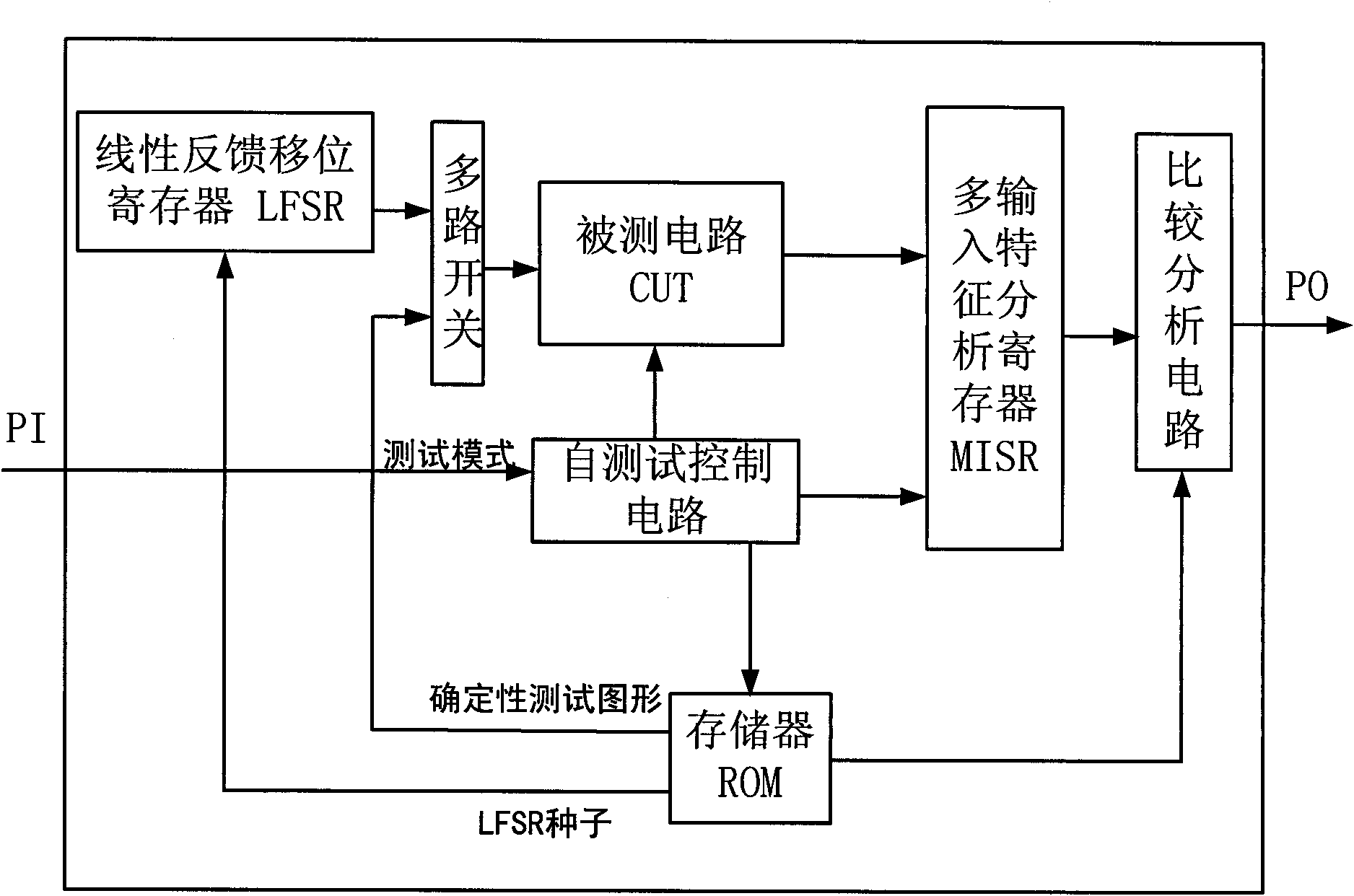

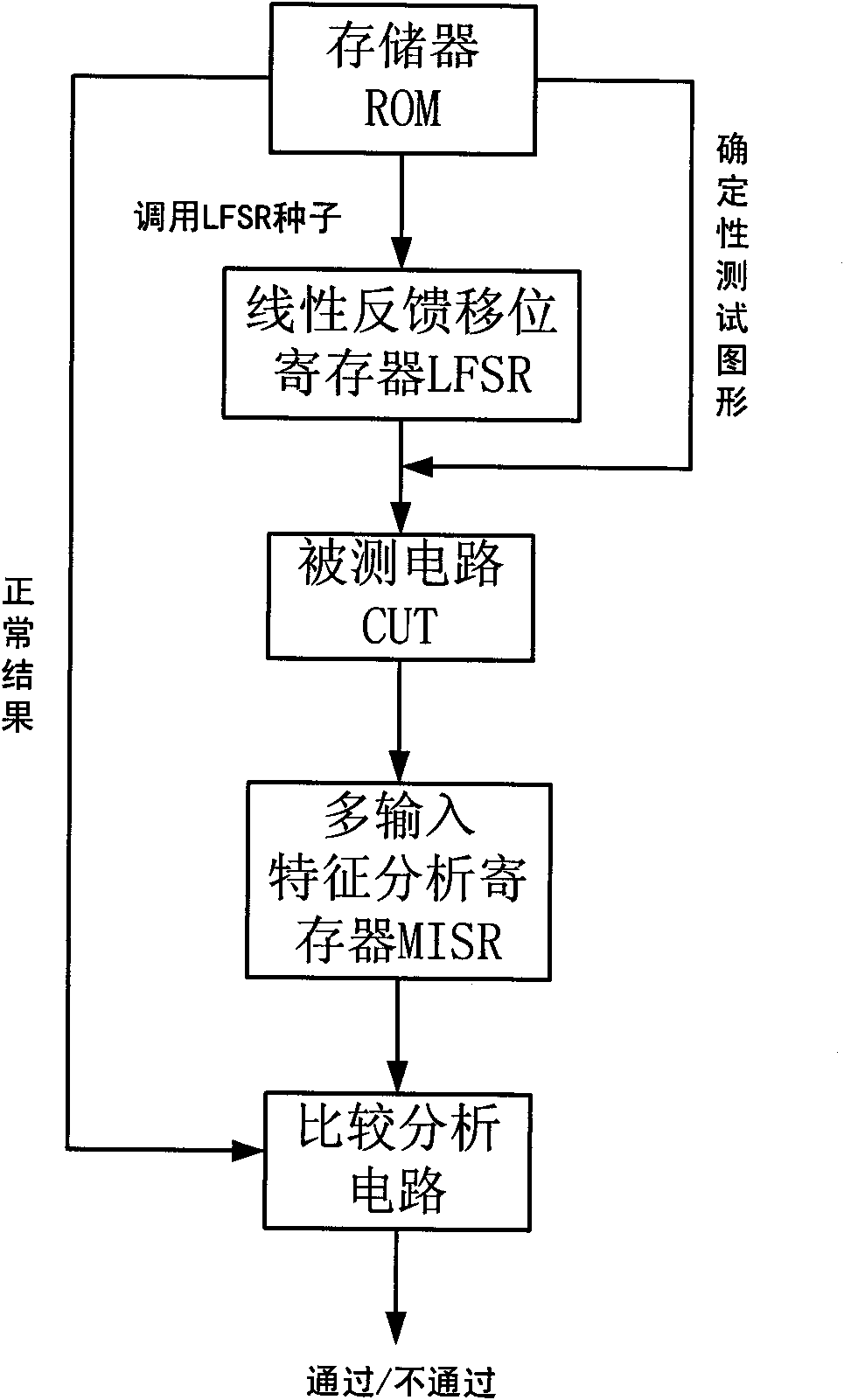

Built-in self-testing system and method thereof with mixed mode

InactiveCN101881812AImprove fault coverageReduce test power consumptionElectrical testingMulti inputFault coverage

The invention relates to a built-in self-testing system and a method thereof with a mixed mode. The testing system comprises a circuit (CUT) to be tested, a self-testing control circuit, a multi-input feature analysis register (MISR), a memory (ROM) and a comparative analysis circuit. The invention has the improvement that the built-in self-testing system also comprises a linear feedback shift register (LFSR) which is used for generating a pseudo-random testing figure and a multi-way switch; the input end of the linear feedback shift register (LFSR) is connected with the memory (ROM), one input end of the multi-way switch is connected with the output end of the linear feedback shift register (LFSR), the other input end of the multi-way switch is connected with the memory (ROM), and the output end of the multi-way switch is connected to the input end of the circuit (CUT) to be tested; and the testing method of the built-in self-testing system is a built-in self-testing method which is based on a pseudo-random method and a determinacy generation method and has a mixed mode. The invention has the advantage that the self-testing system and the method thereof have high fault-coverage rate, short testing time, low testing power consumption and simple structure.

Owner:NO 63908 TROOPS PLA

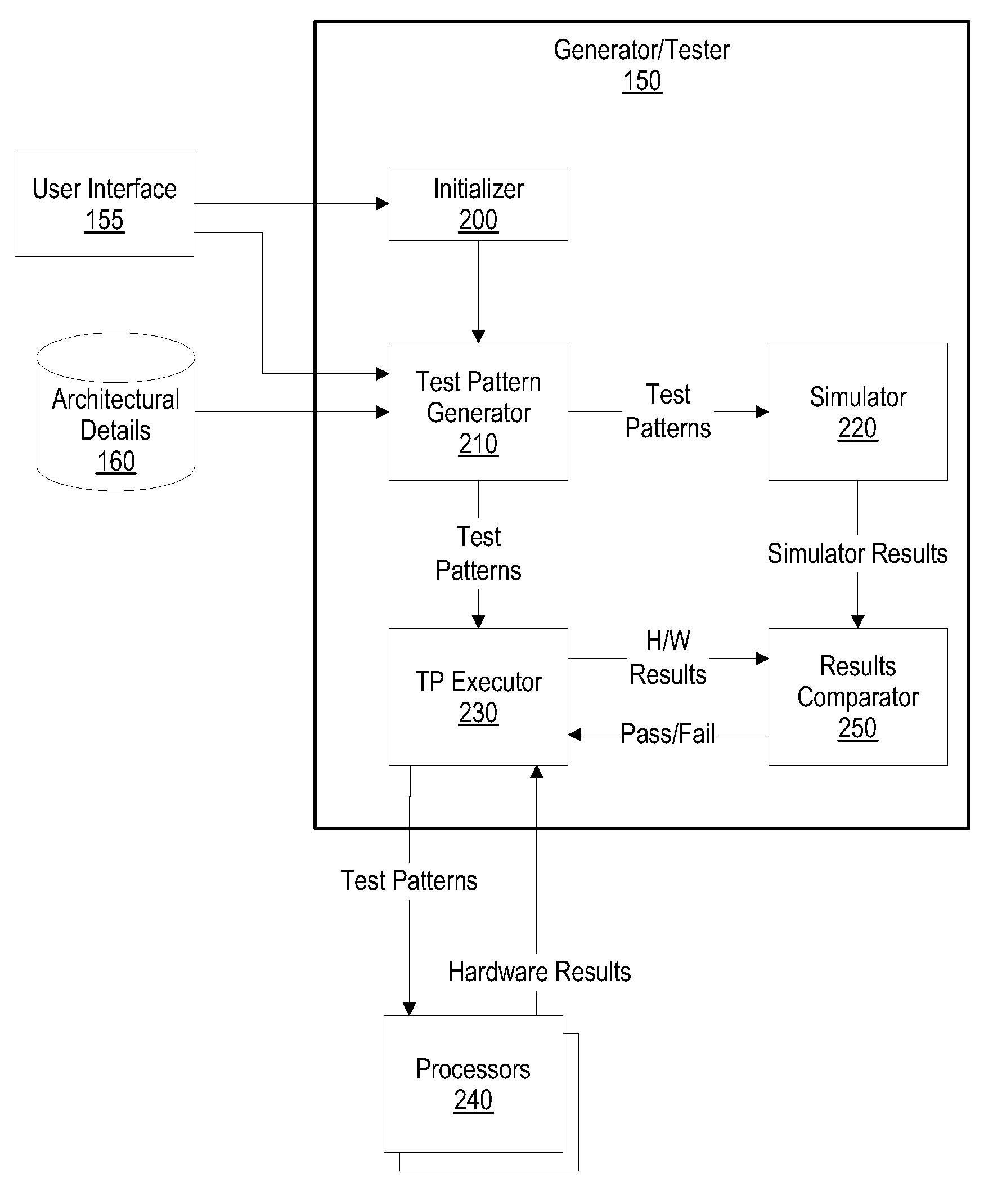

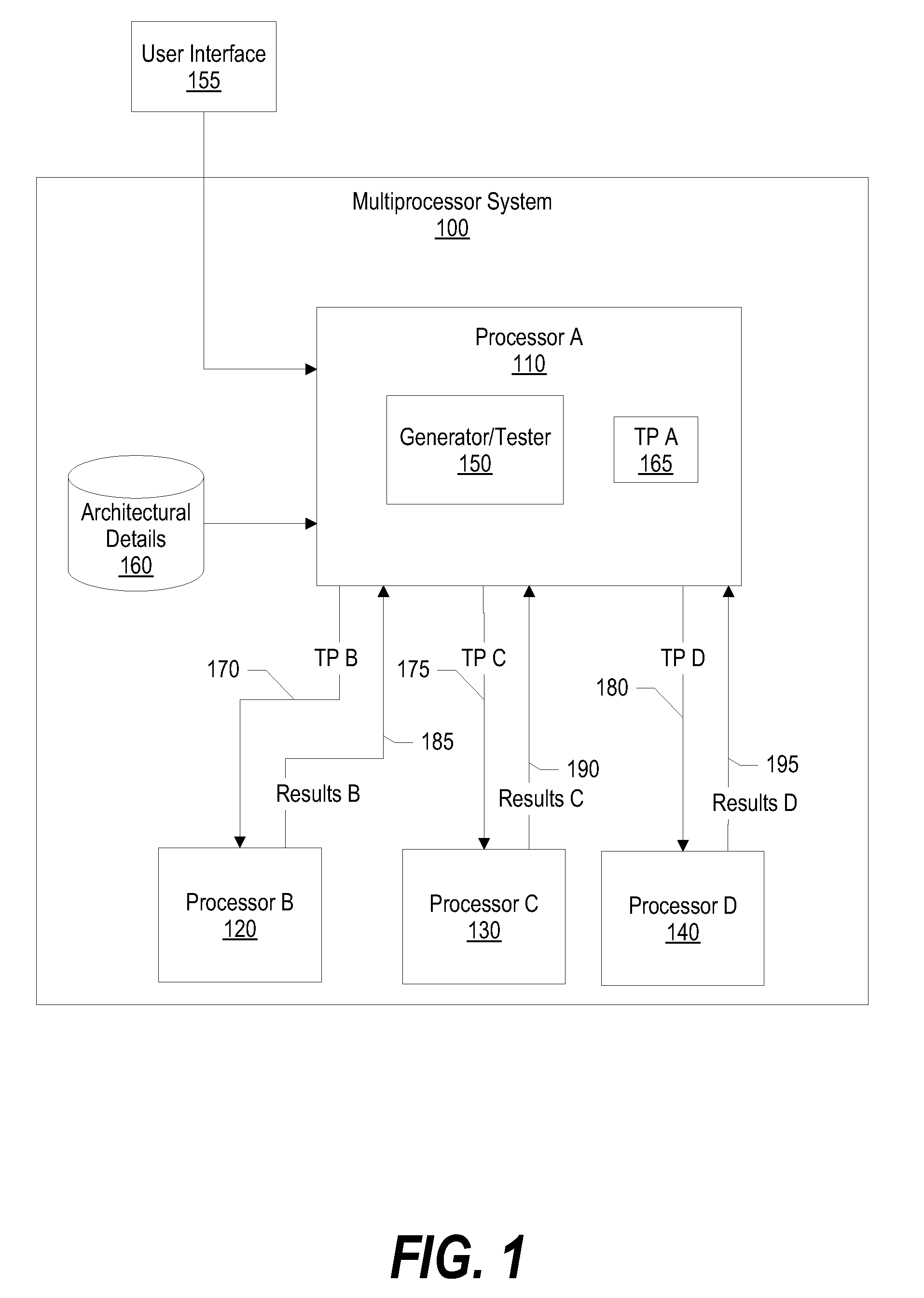

System and method for pseudo-random test pattern memory allocation for processor design verification and validation

InactiveUS7584394B2Efficient testingElectronic circuit testingError detection/correctionPage tableVerification and validation

A system and method for pseudo-randomly allocating page table memory for test pattern instructions to produce complex test scenarios during processor execution is presented. The invention described herein distributes page table memory across processors and across multiple test patterns, such as when a processor executes “n” test patterns. In addition, the page table memory is allocated using a “true” sharing mode or a “false” sharing mode. The false sharing mode provides flexibility of performing error detection checks on the test pattern results. In addition, since a processor comprises sub units such as a cache, a TLB (translation look aside buffer), an SLB (segment look aside buffer), an MMU (memory management unit), and data / instruction pre-fetch engines, the test patterns effectively use the page table memory to test each of the sub units.

Owner:IBM CORP

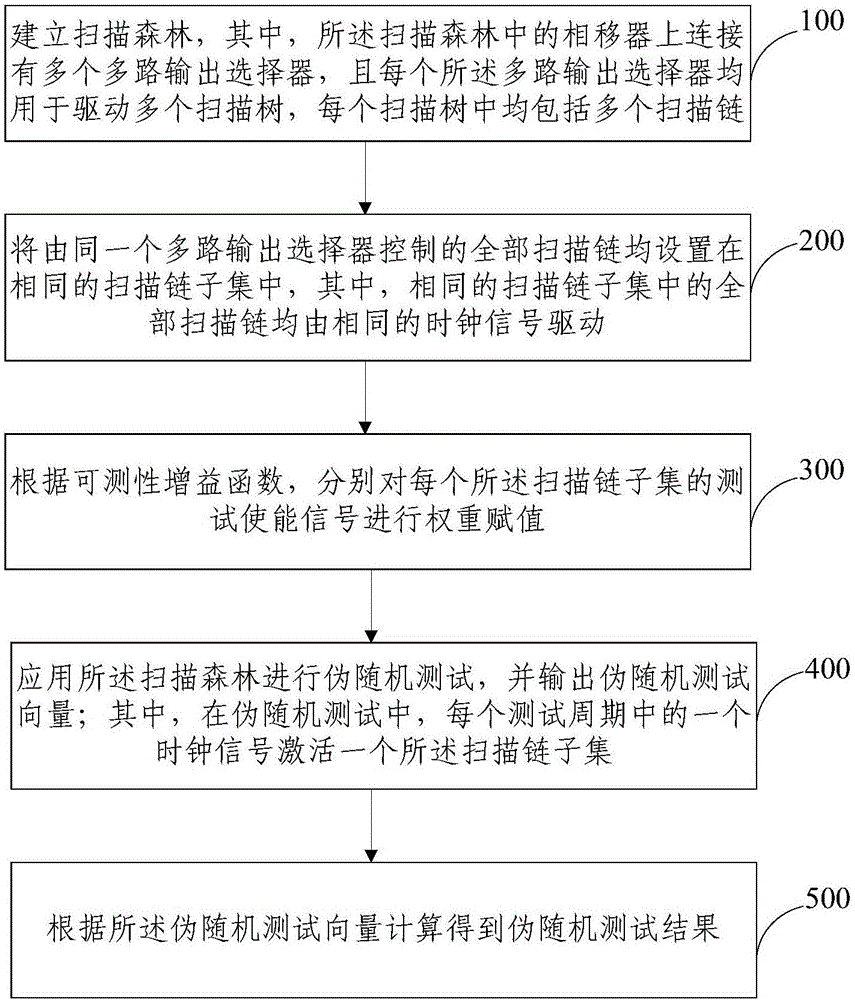

Low-power consumption weighted pseudo-random test method, system, device and storage medium

ActiveCN107526019AReduce overheadIncrease overheadElectronic circuit testingFault coverageComputer science

Owner:TSINGHUA UNIV

Systems and methods for improved fault coverage of LBIST testing

InactiveUS7681098B2Improve fault coverageReduce in quantityElectronic circuit testingError detection/correctionFault coverageLogic built-in self-test

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS

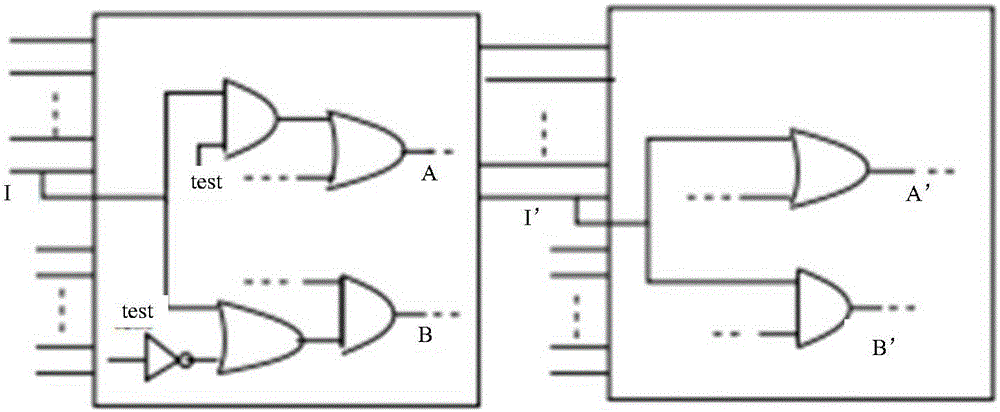

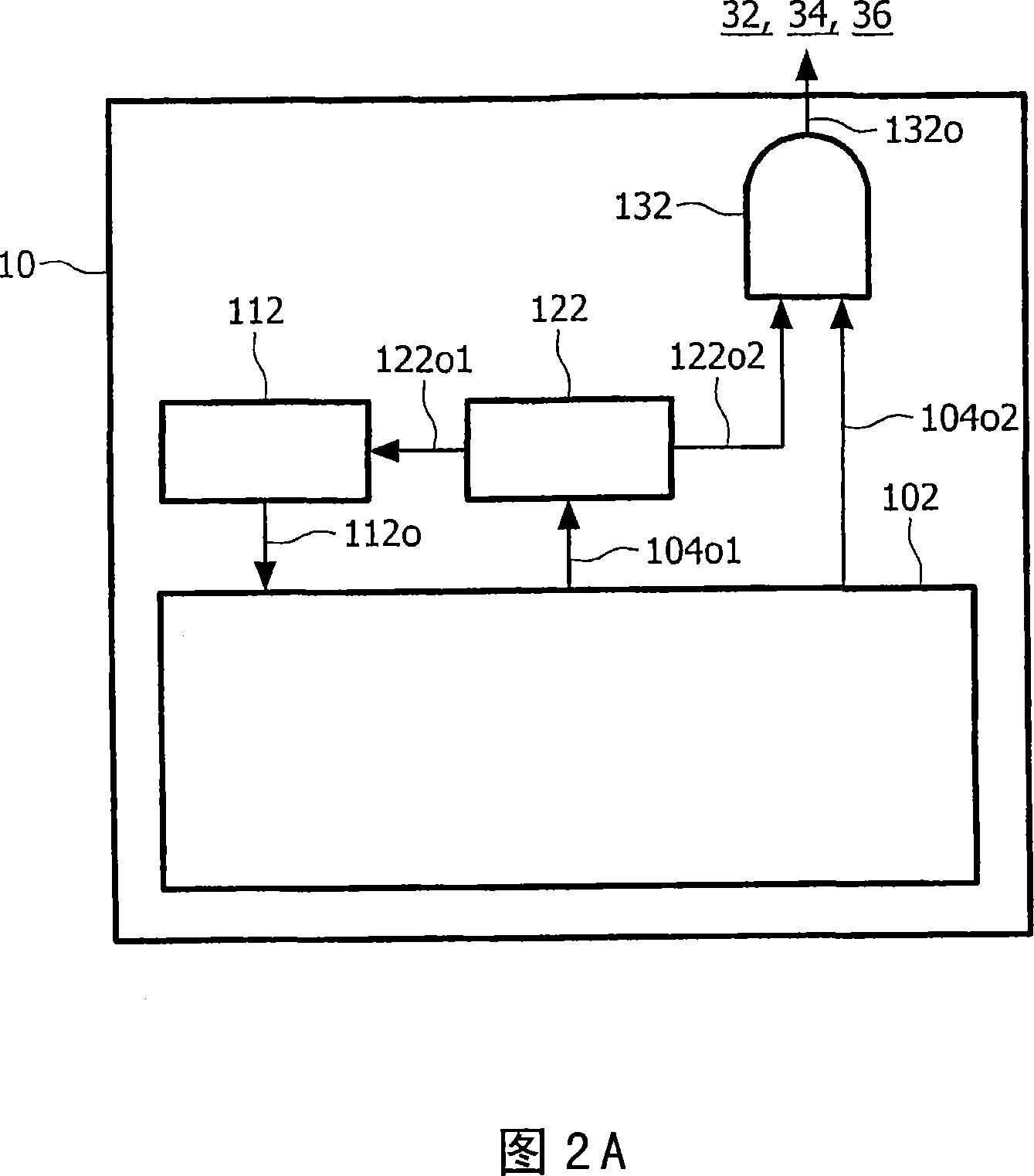

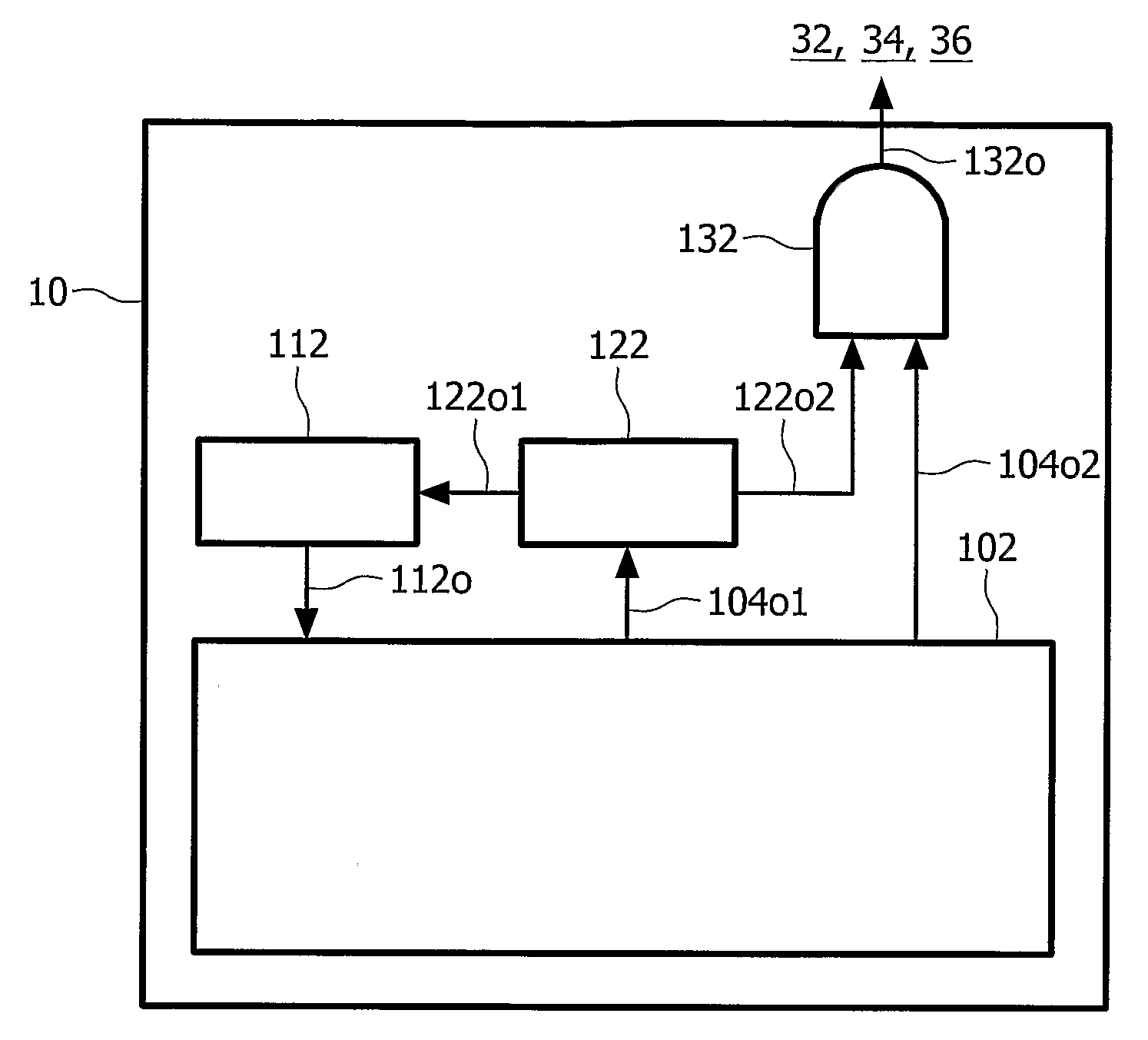

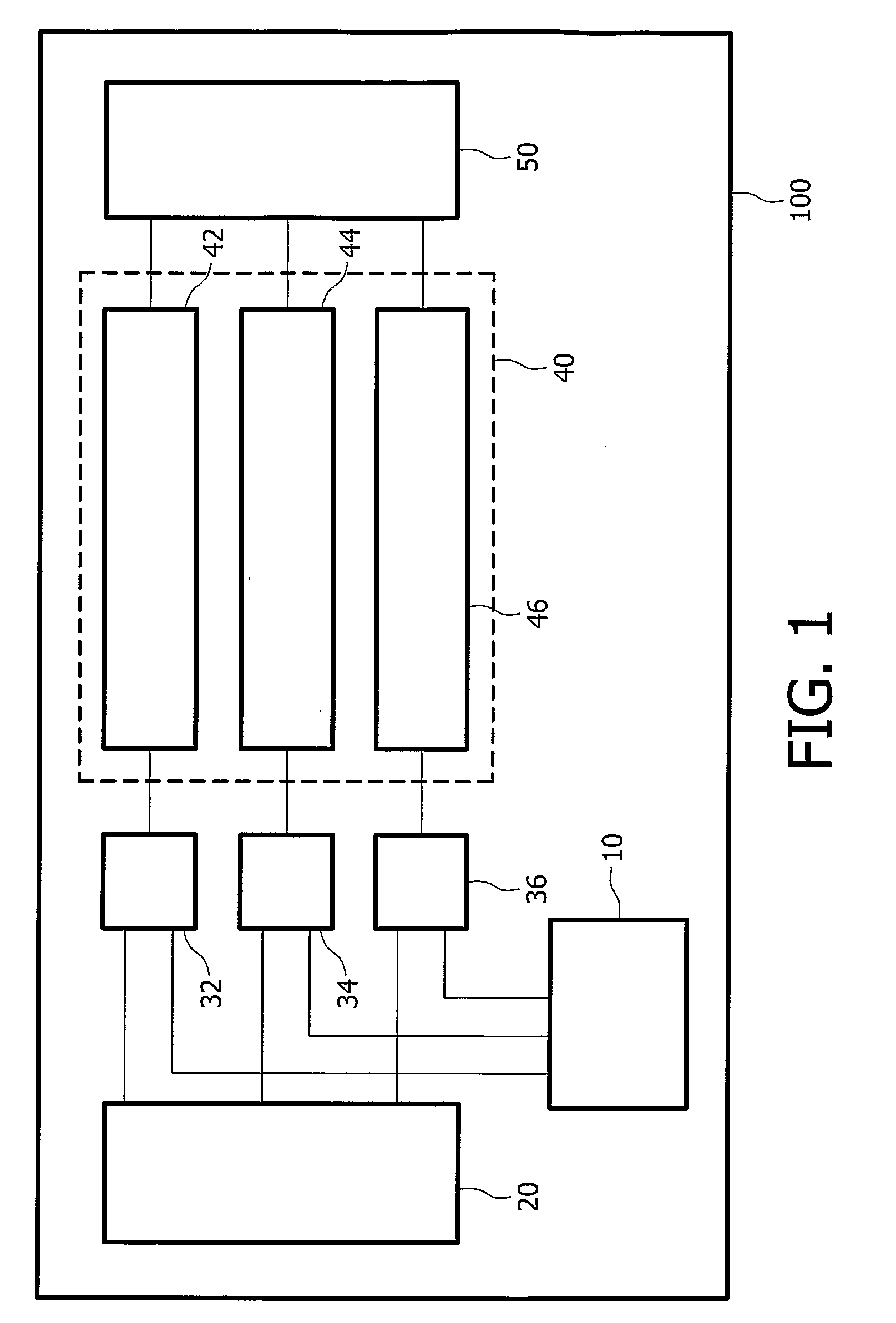

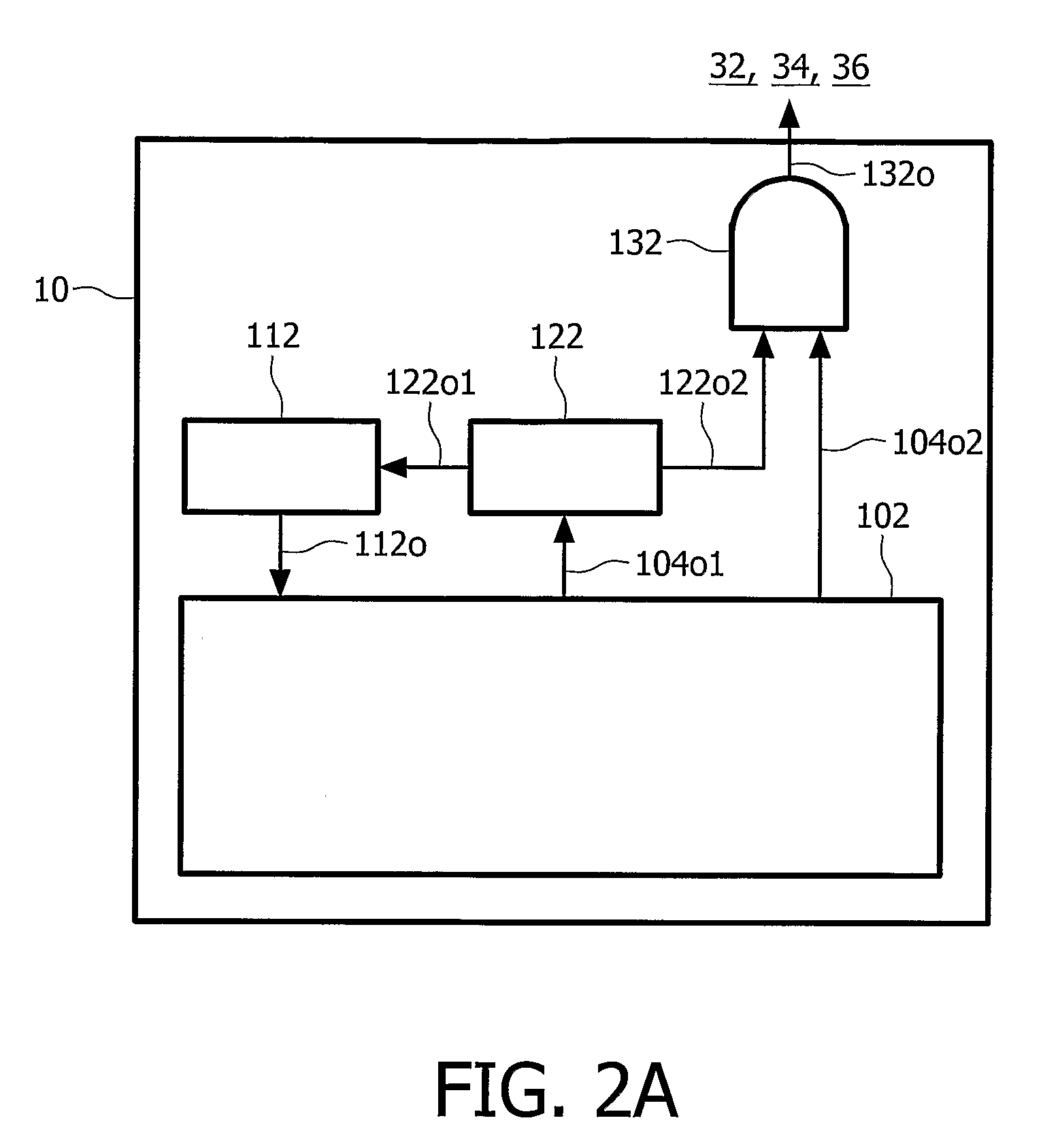

Circuit arrangement and method of testing an application circuit provided in said circuit arrangement

InactiveCN101014869AImproved error coverageLow costElectrical testingSoftware engineeringHemt circuits

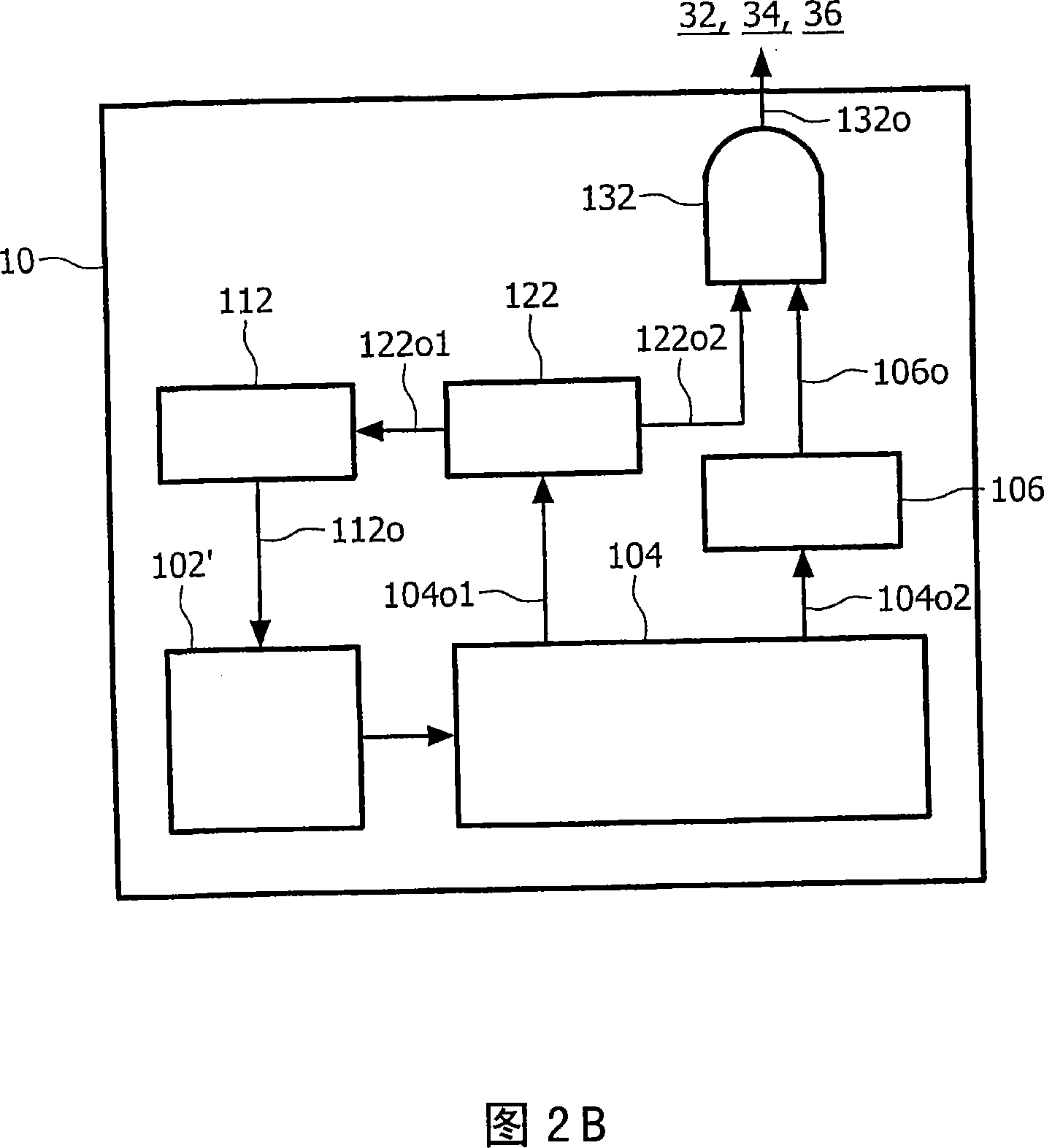

The object is to develop an integrated circuit arrangement (100) with at least one application circuit (40) to be tested. In addition, with at least one self-test circuit (10, 20, 32, 34, 36, 50) provided for testing the application circuit (40) and generating at least one pseudo-random test sample, wherein the said pseudo-random test sample can be converted into at least one test vector that is programmable and / or deterministic. Moreover, that can be supplied to the application circuit (40) for testing purposes via at least one logic gate (32, 34, 36). And by means of at least one signal that can be applied to said logic gate (32, 34, 36), and wherein the output signal arising in dependence on the deterministic test vector can be evaluated by the application circuit (40) by means of at least one signature register (50). As well as a method of testing the application circuit (40) present in the integrated circuit arrangement (100) by means of the self-test circuit (10, 20, 32, 34, 36, 50) further such that the BIST [build in self test] hardware connected to the additional deterministic logic can be reduced. It is suggested that the signal to be supplied to the logic gate (32, 34, 36) can be made available by a BFF [bit flipping function] logic circuit (10) based on at least one.

Owner:NXP BV

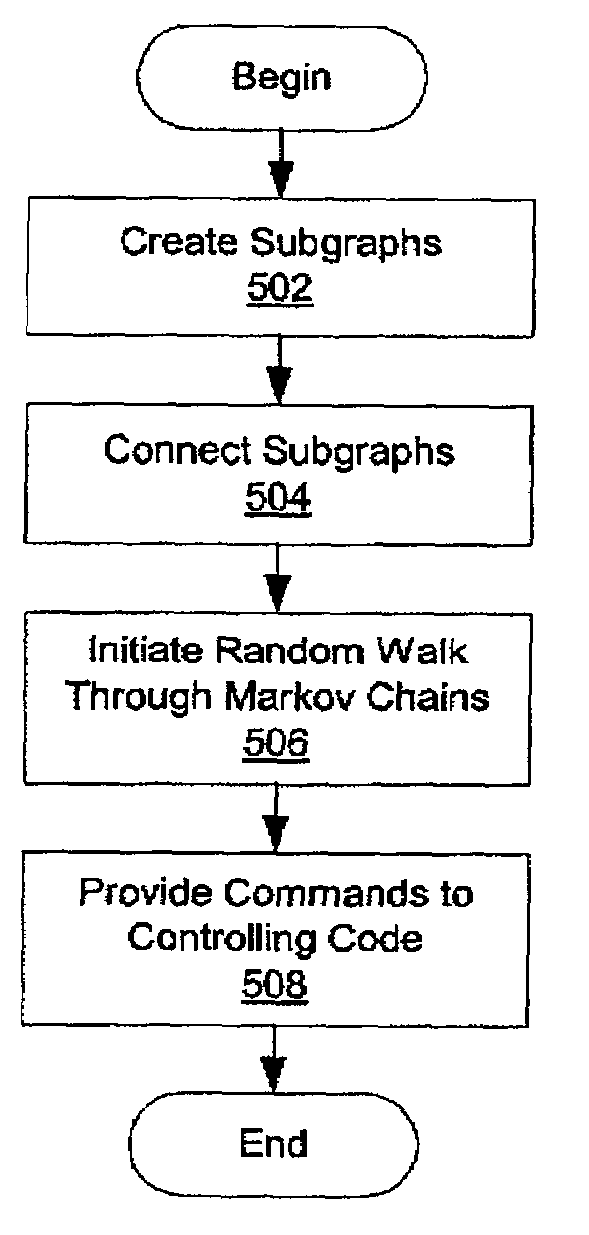

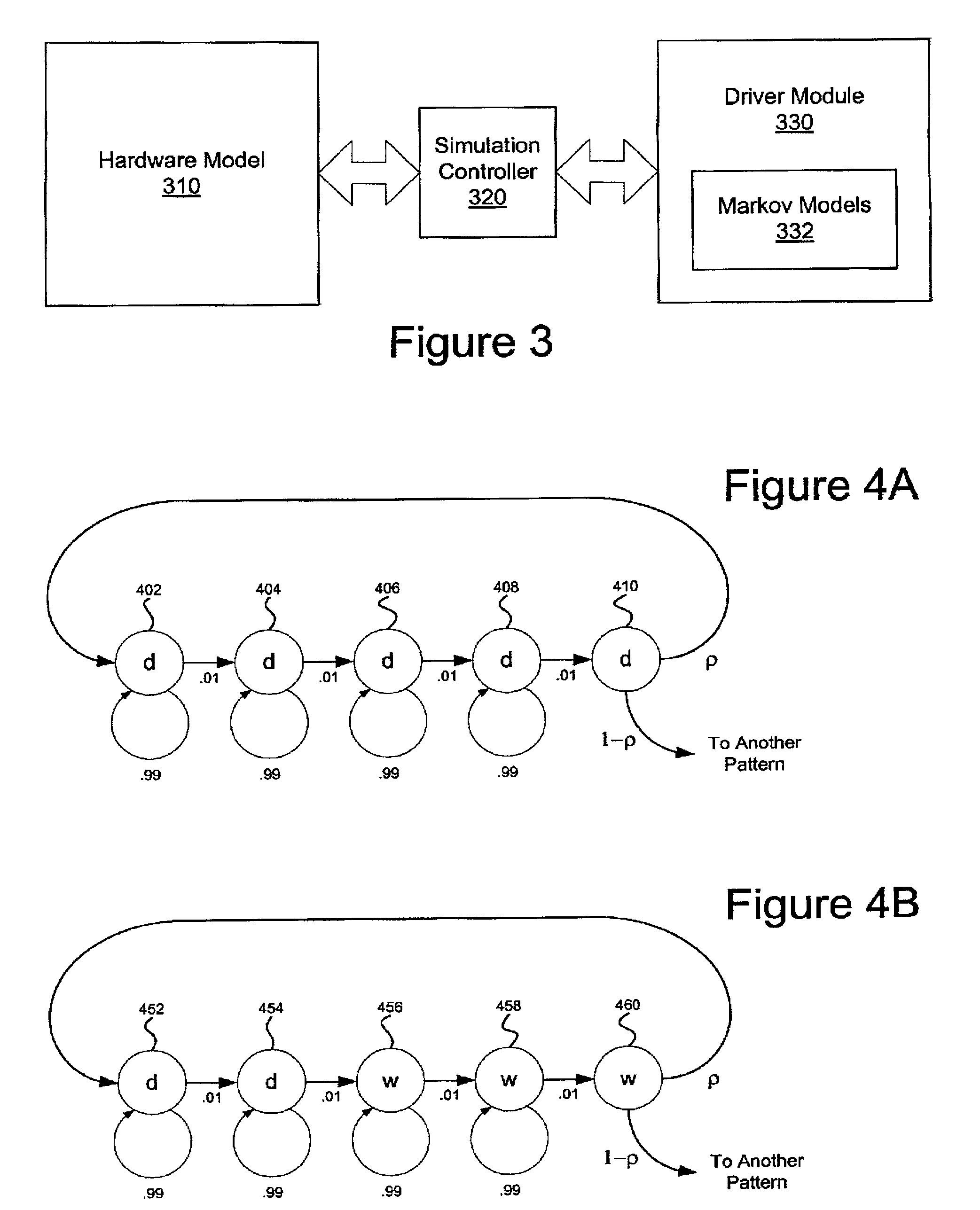

Pseudo random test pattern generation using Markov chains

InactiveUS6965852B2Electronic circuit testingAnalogue computers for electric apparatusMarkov chainPattern generation

A driver module is provided that generates test patterns with desired tendencies. The driver module provides these test patterns to controlling code for simulation of a hardware model. The test patterns are generated by creating and connecting subgraphs in a Markov chain. The Markov model describes a plurality of states, each having a probability of going to at least one other state. Markov models may be created to determine whether to drive an interface in the hardware model and to determine the command to drive through the interface. Once the driver module creates and connects the subgraphs of the Markov models, the driver module initiates a random walk through the Markov chains and provides the commands to the controlling code.

Owner:INT BUSINESS MASCH CORP

Circuit Arrangement and Method of Testing an Application Circuit Provided in Said Circuit Arrangement

InactiveUS20080195907A1Clear surfaceLow costElectronic circuit testingLogical operation testingTest sampleProcessor register

The object being to develop an integrated circuit arrangement (100) with at least one application circuit (40) to be tested, and with at least one self-test circuit (10, 20, 32, 34, 36, 50) provided for testing the application circuit (40) and generating at least one pseudo-random test sample, wherein said pseudo-random test sample can be converted into at least one test vector that is programmable and / or deterministic and that can be supplied to the application circuit (40) for testing purposes via at least one logic gate (32, 34, 36) and by means of at least one signal that can be applied to said logic gate (32, 34, 36), and wherein the output signal arising in dependence on the deterministic test vector can be evaluated by the application circuit (40) by means of at least one signature register (50), as well as a method of testing the application circuit (40) present in the integrated circuit arrangement (100) by means of the self-test circuit (10, 20, 32, 34, 36, 50) further such that the B[uild-]I[n]S[elf-]T[est] hardware connected to the additional deterministic logic can be reduced, it is suggested that the signal to be supplied to the logic gate (32, 34, 36) can be made available by a B[it]F[lipping]F[unction] logic circuit (10) based on at least one

Owner:NXP BV

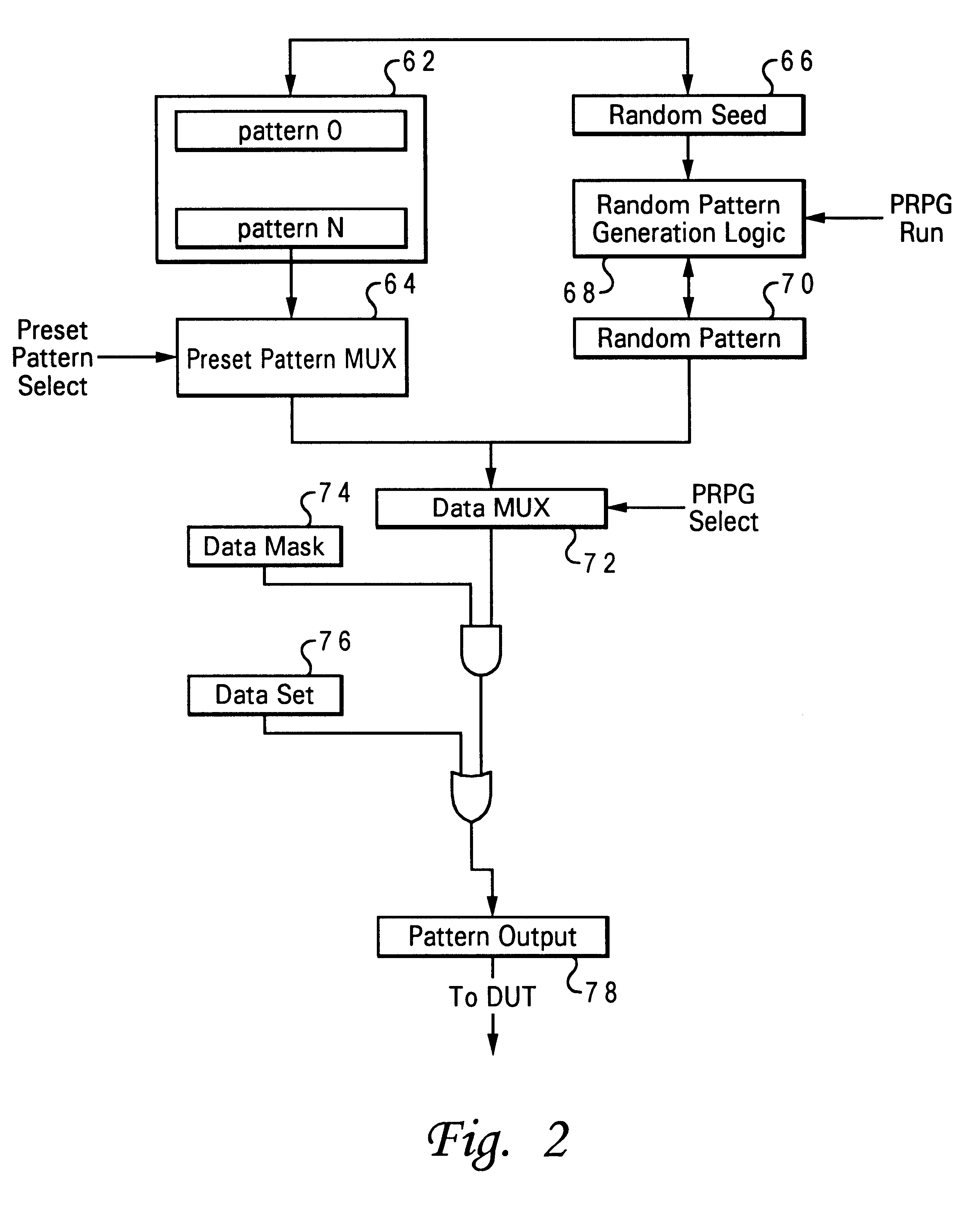

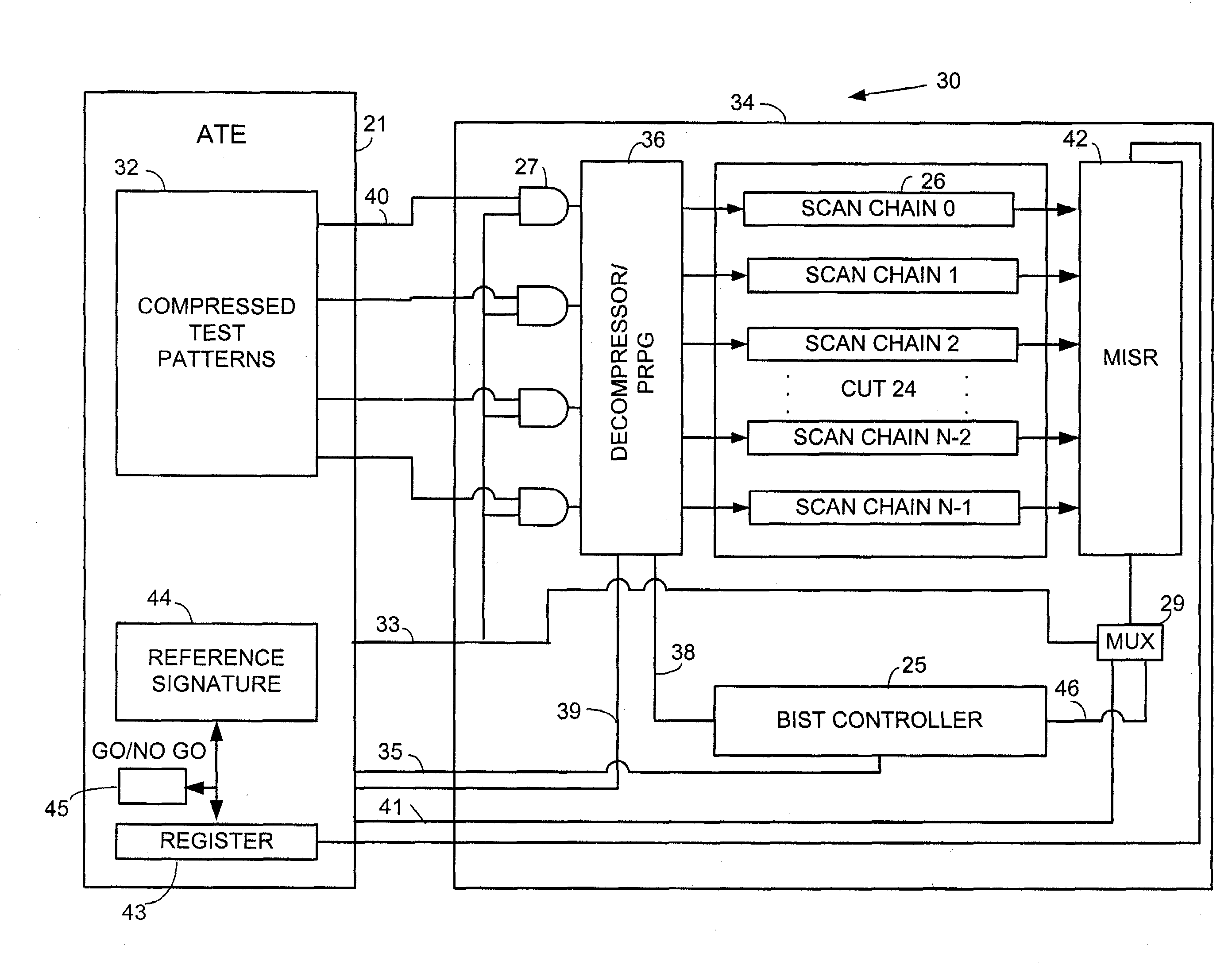

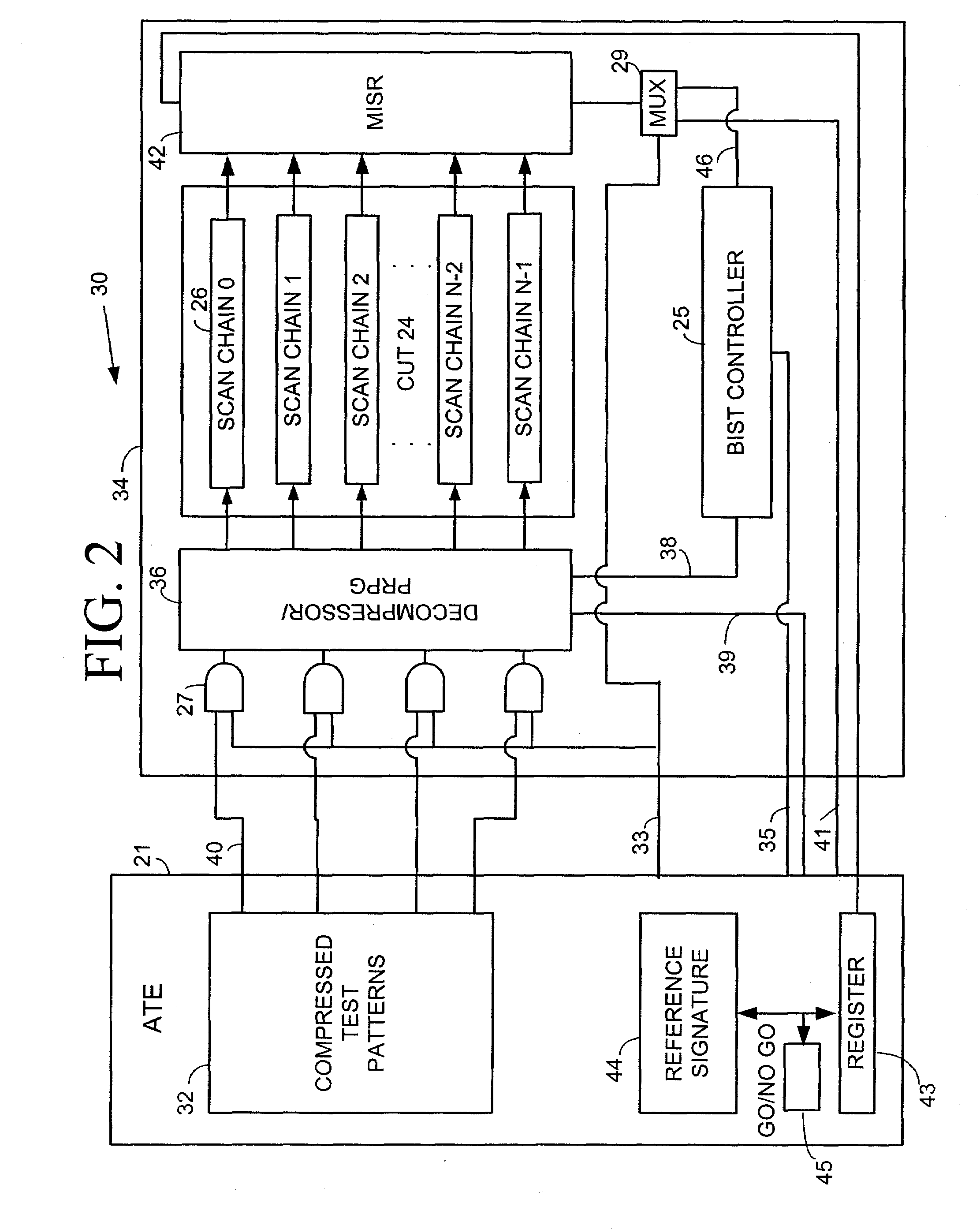

Decompressor/prpg for applying pseudo-random and deterministic test patterns

InactiveUS20090177933A1Semiconductor/solid-state device testing/measurementElectronic circuit testingFault coverageCircuit under test

A novel decompressor / PRPG on a microchip performs both pseudo-random test pattern generation and decompression of deterministic test patterns for a circuit-under-test on the chip. The decompressor / PRPG has two phases of operation. In a pseudo-random phase, the decompressor / PRPG generates pseudo-random test patterns that are applied to scan chains within the circuit-under test. In a deterministic phase, compressed deterministic test patterns from an external tester are applied to the decompressor / PRPG. The patterns are decompressed as they are clocked through the decompressor / PRPG into the scan chains. The decompressor / PRPG thus provides much better fault coverage than a simple PRPG, but without the cost of a complete set of fully-specified deterministic test patterns.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

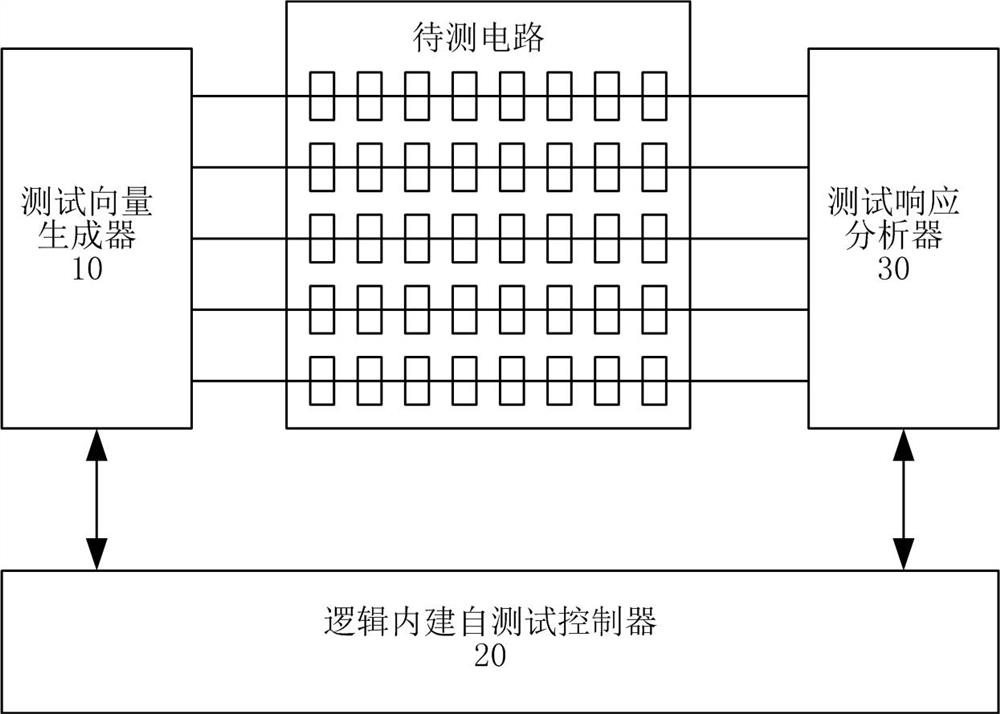

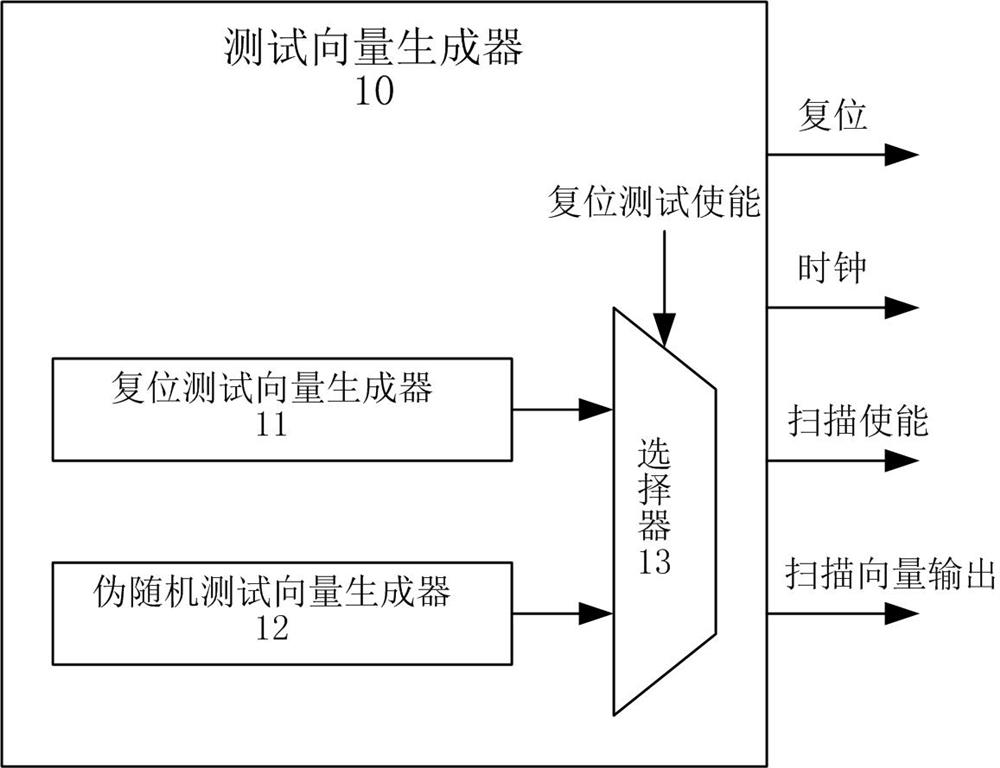

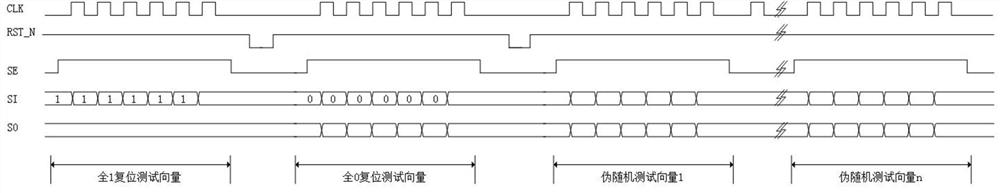

Reset circuit test system and method for logic built-in self-test

ActiveCN114360622ASolve problems that cannot be coveredMany test vectorsStatic storageFault coverageControl engineering

A logic built-in self-test reset circuit test system comprises a test vector generator, a logic built-in self-test controller and a test response analyzer, the test vector generator generates a reset test vector and a pseudo-random test vector, receives an instruction of the logic built-in self-test controller, and analyzes the reset test vector and the pseudo-random test vector according to the instruction of the logic built-in self-test controller. The reset signal, the clock signal, the scanning enable signal and the scanning vector output signal are output to a circuit to be tested; the logic built-in self-test controller is used for respectively controlling the signal output of the test vector generator and controlling the test response analyzer to test the circuit to be tested; and the test response analyzer receives an instruction of the logic built-in self-test controller and tests the circuit to be tested. The invention also provides a reset circuit test method for logic built-in self-test, which solves the problem that the reset signal cannot be highly covered in the traditional logic built-in self-test by using less logic, and improves the fault coverage rate.

Owner:NANJING SEMIDRIVE TECH CO LTD

System and method for detecting non-reproducible pseudo-random test cases

InactiveUS7774668B2Electronic circuit testingError detection/correctionTest case generatorComputer science

A method for monitoring a test case generator system by detecting non-reproducible pseudo-random test cases, comprising: building a first pseudo-random test case having a first sequence of seeds comprising a first starting seed and a first ending seed through the test case generator system; reproducing the first sequence of seeds of the first pseudo-random test case by building a second pseudo-random test case having a second sequence of seeds comprising a second starting seed and a second ending seed through the test case generator system when the test case generator system is operating in a reproduction mode, the first starting seed being used as the second starting seed of the second sequence of seeds; and comparing the first ending seed in the first sequence of seeds to the second ending seed in the second sequence of seeds.

Owner:IBM CORP

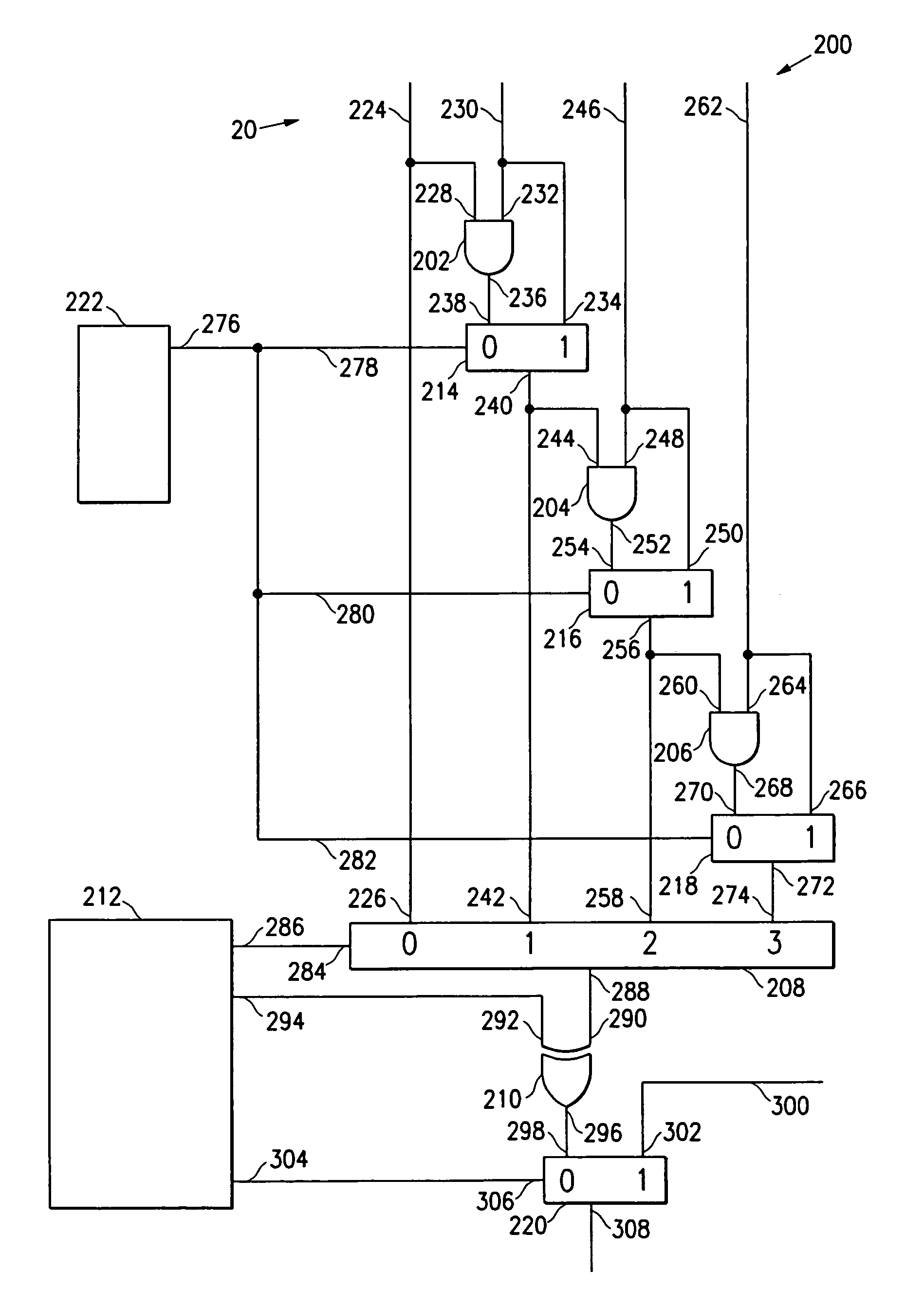

Circuit apparatus and method for testing integrated circuits using weighted pseudo-random test patterns

A method for testing an electronic circuit includes selecting an input signal using a first multiplexer, selecting a signal to be input to the first multiplexer using at least one other multiplexer, and controlling the at least one other multiplexer using a selection signal output from a control circuit.

Owner:TOSHIBA AMERICA ELECTRONICS COMPONENTS +2

Smart Energy Meter Dynamic Error Test Device

ActiveCN104569900BImplement dynamic error testingSolve the problem of comprehensive testing of dynamic error characteristicsElectrical measurementsSequence controlModal testing

A dynamic error testing device for an intelligent electric energy meter, which consists of a synchronous circuit for three-phase voltage and / or three-phase current, a synchronous pseudo-random sequence control signal generation circuit, a pseudo-random sequence selection circuit, a dynamic load power control circuit for electric energy meters, and a dynamic load power control circuit for electric energy meters. Composed of error test unit, display and keyboard unit, and dynamic error measurement algorithm; it can effectively generate multi-mode pseudo-random test excitation current and power, effectively reflect the randomness of dynamic load current and power changes, and realize pseudo-random dynamic load changes The traceability of the electric energy value to the steady-state load electric energy value realizes the comprehensive test of the dynamic error characteristics of the electric energy meter under the multi-mode test excitation; solves the randomness problem that the current deterministic test excitation current and power cannot reflect the dynamic load change; It solves the problem of traceability and dynamic error test of dynamic load electric energy value under pseudo-randomly changing dynamic load; it has a wide range of applications in the dynamic error test system of smart electric energy meters.

Owner:BEIJING UNIV OF CHEM TECH

Method and apparatus for generating a multi-level pseudo-random test signal

InactiveUS9882752B2The testing process is simpleElectrical testingWireless communicationPattern sequenceAlgorithm

The present invention relates to a method for generating multi-level PRBS patterns for testing purposes, wherein the method includes the steps of providing a binary PRBS signal with a binary bit pattern sequence and mapping each bit of the binary bit pattern sequence to a symbol of a multilevel output.

Owner:IBM CORP