Patents

Literature

167 results about "Process failure" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A process failure refers to anything that create a process or quality abnormality that necessitates shutting a plant down.

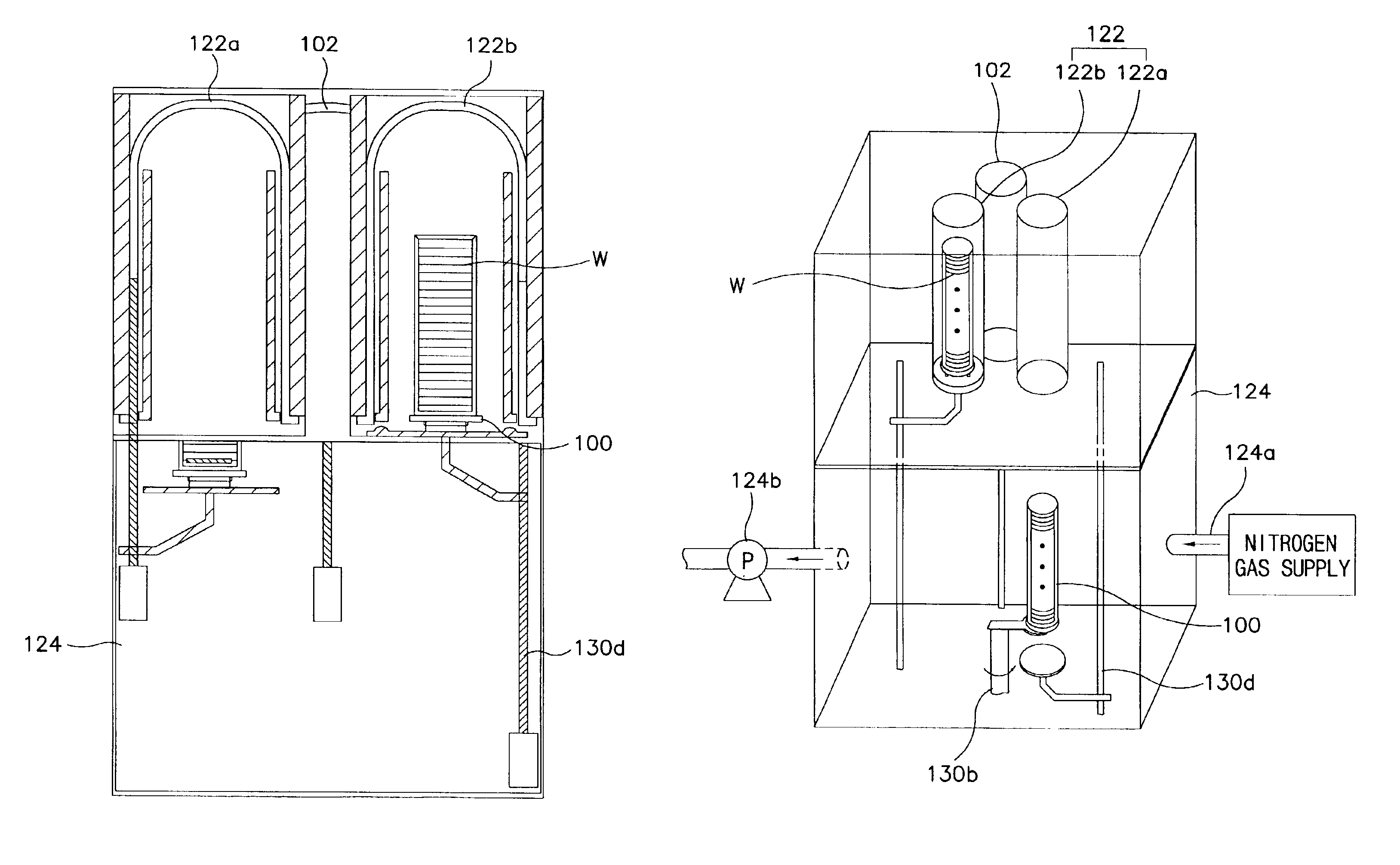

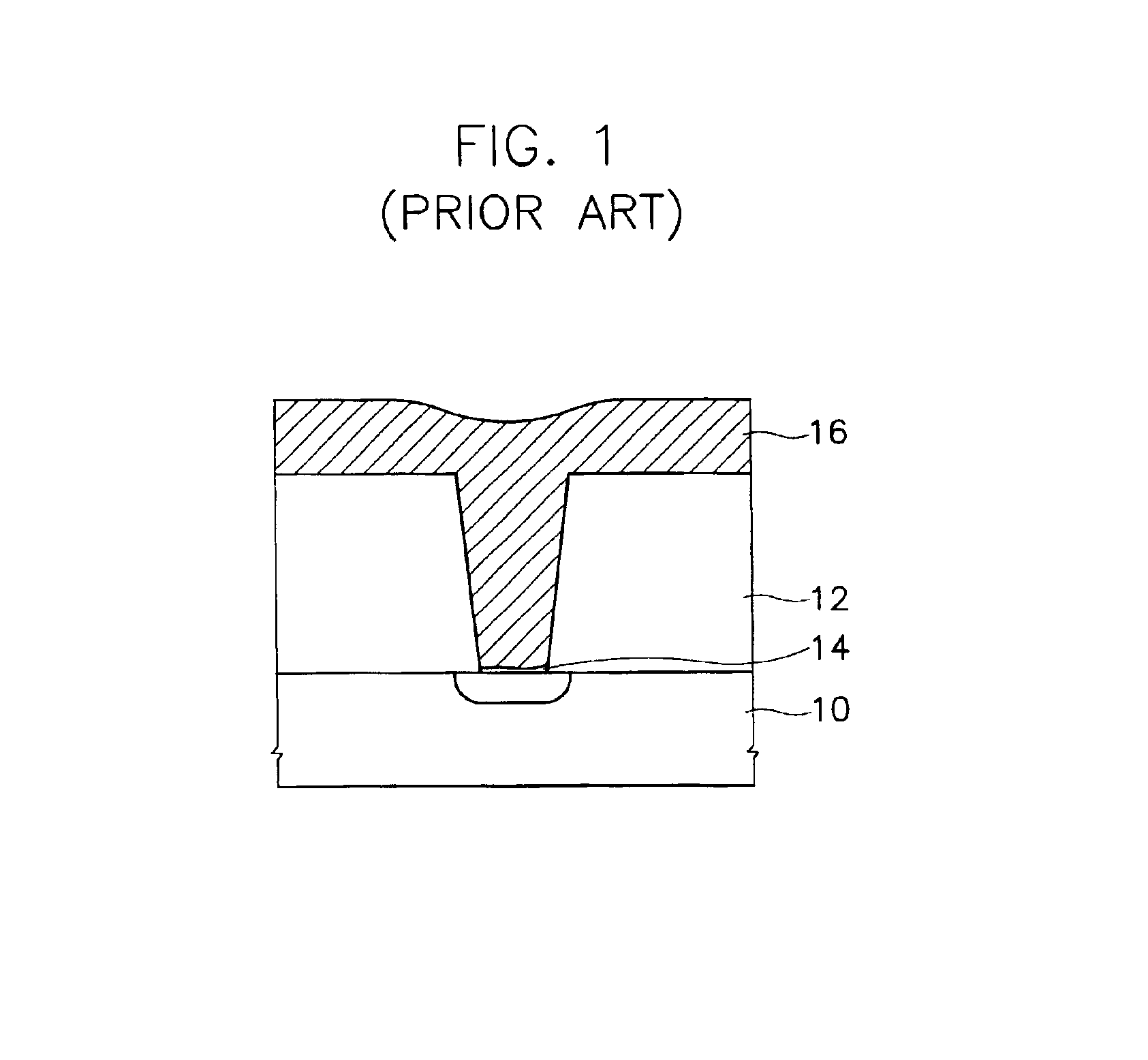

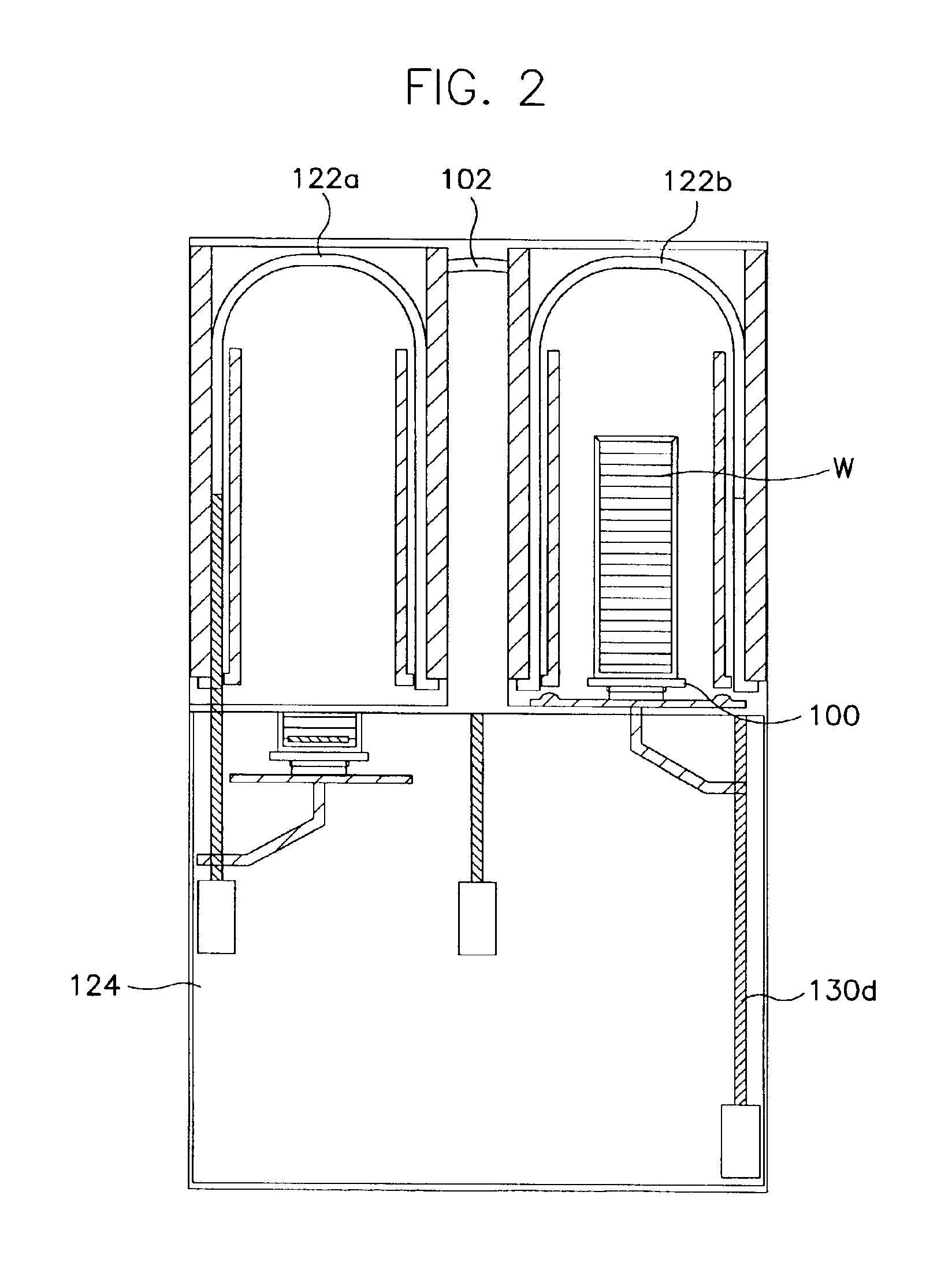

Method of and apparatus for performing sequential processes requiring different amounts of time in the manufacturing of semiconductor devices

InactiveUS6911112B2Without need for significant downtimeHigh productSemiconductor/solid-state device manufacturingCharge manipulationProduction rateDevice material

A method of manufacturing a semiconductor device includes first and second processes, the latter requiring more processing time. An apparatus for performing the semiconductor manufacturing process includes a first reactor, and a plurality of second reactors for each first reactor. A first group of wafers are subjected to the first process within the first reactor, and are then transferred into a second reactor as isolated from the outside air. The first group of wafers is subjected to the second process within the second reactor. At the same time, a second group of wafers are subjected to the first process within the first reactor. After the first process is completed, the second group of wafers is transferred into an unoccupied one of the second reactors as isolated from the outside air. There, the second group of wafers is subjected to the second process. Accordingly, process failures otherwise due to the exposure of the wafers are minimized, and productivity is high despite the difference in the processing times.

Owner:SAMSUNG ELECTRONICS CO LTD

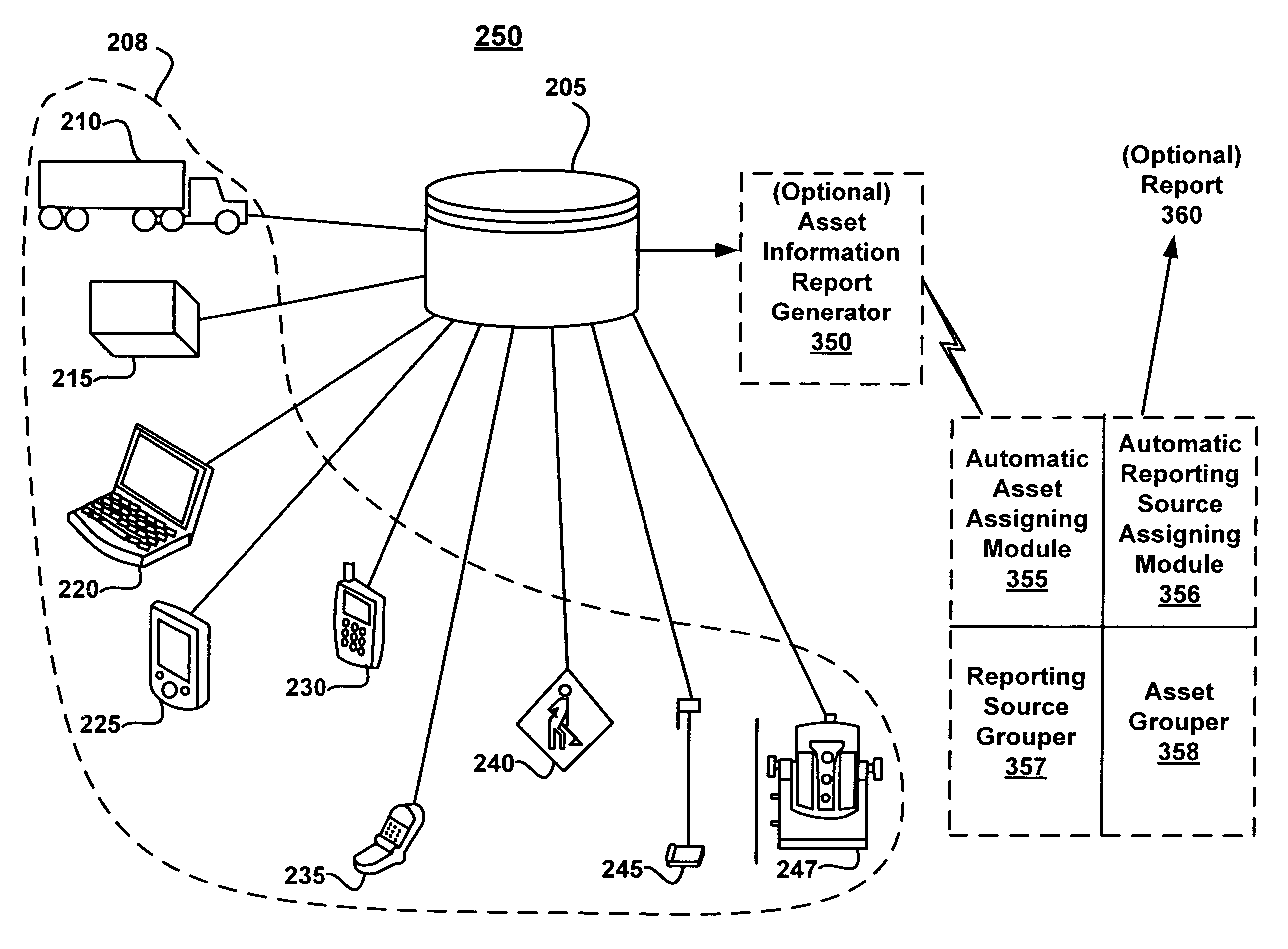

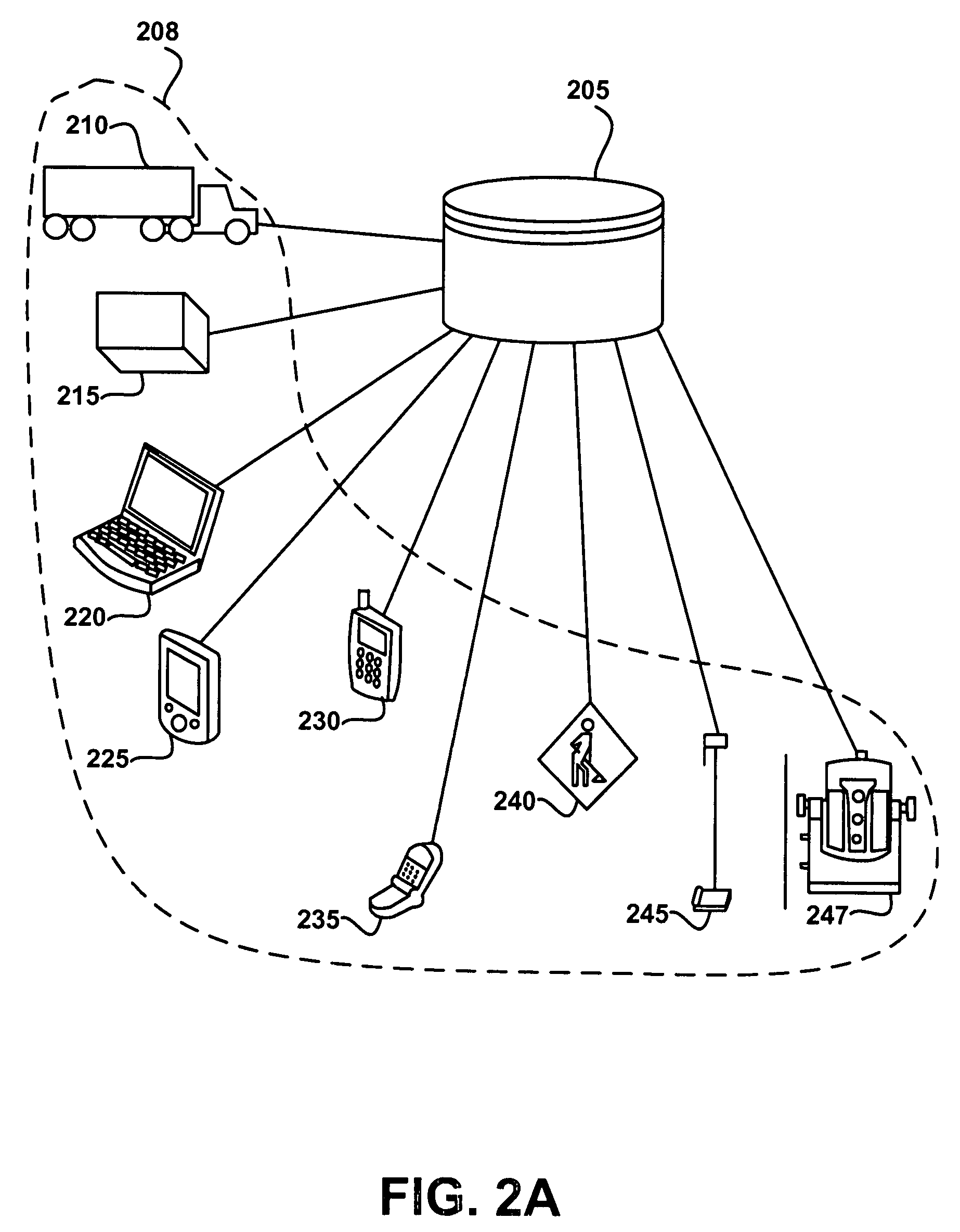

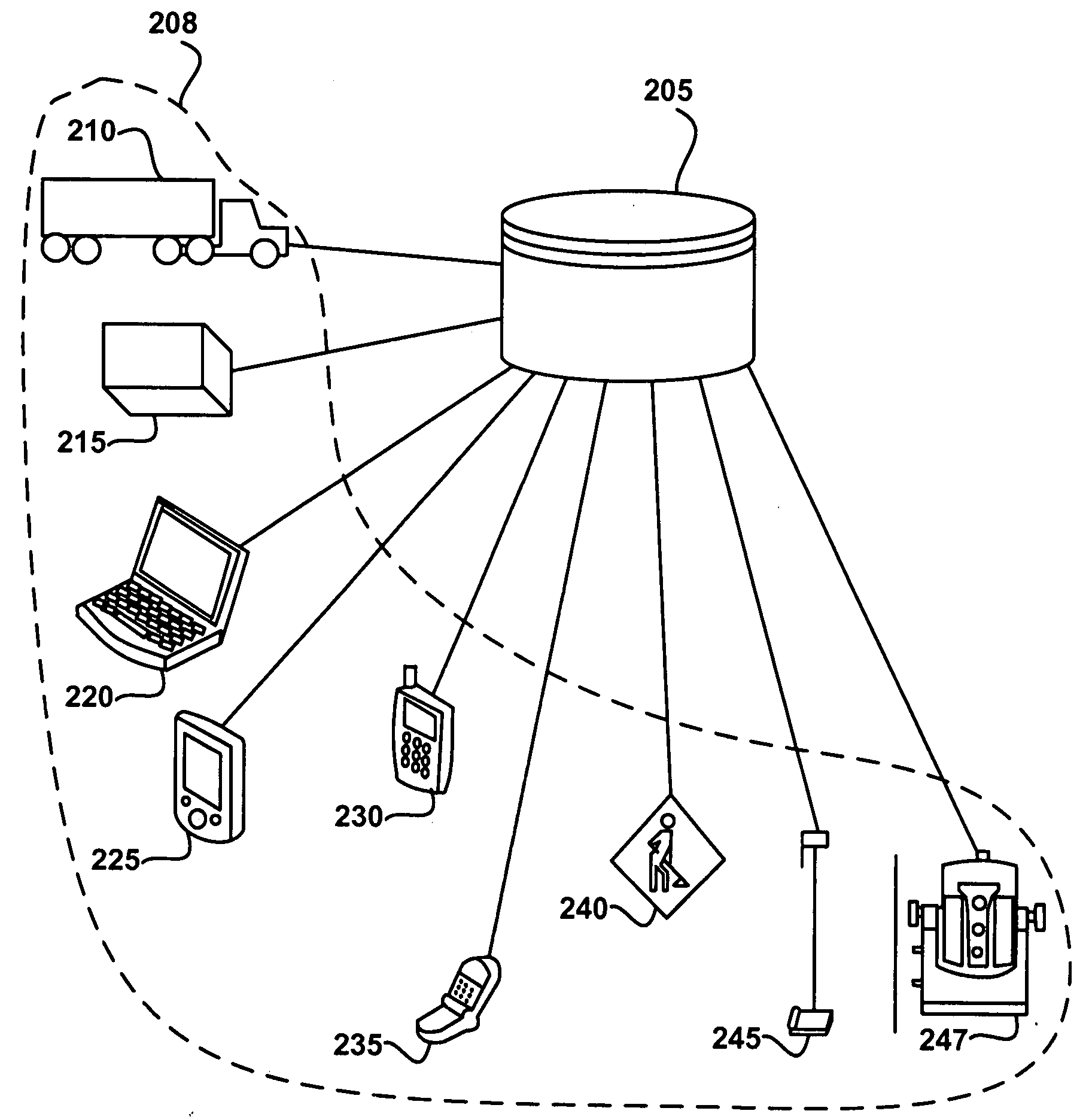

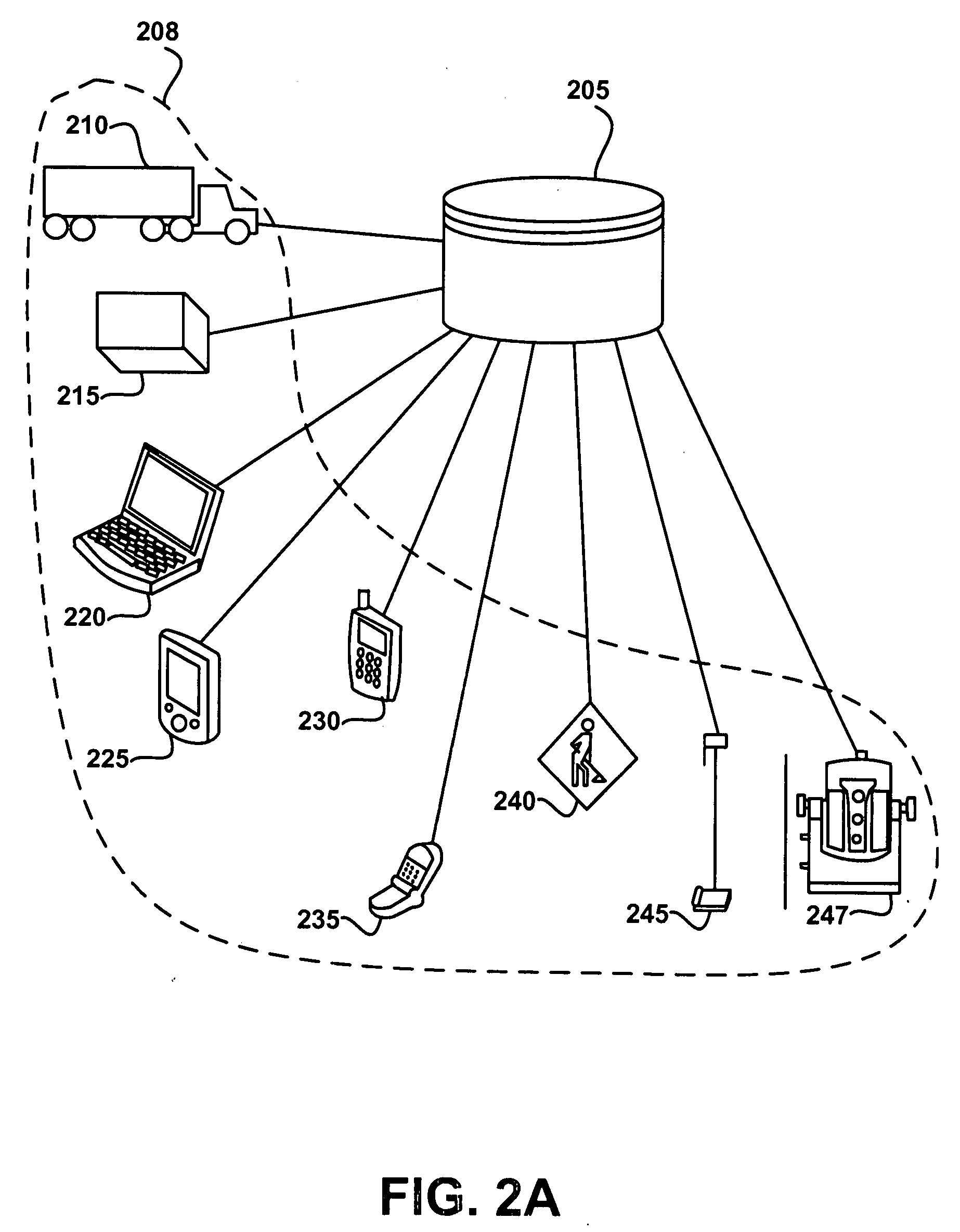

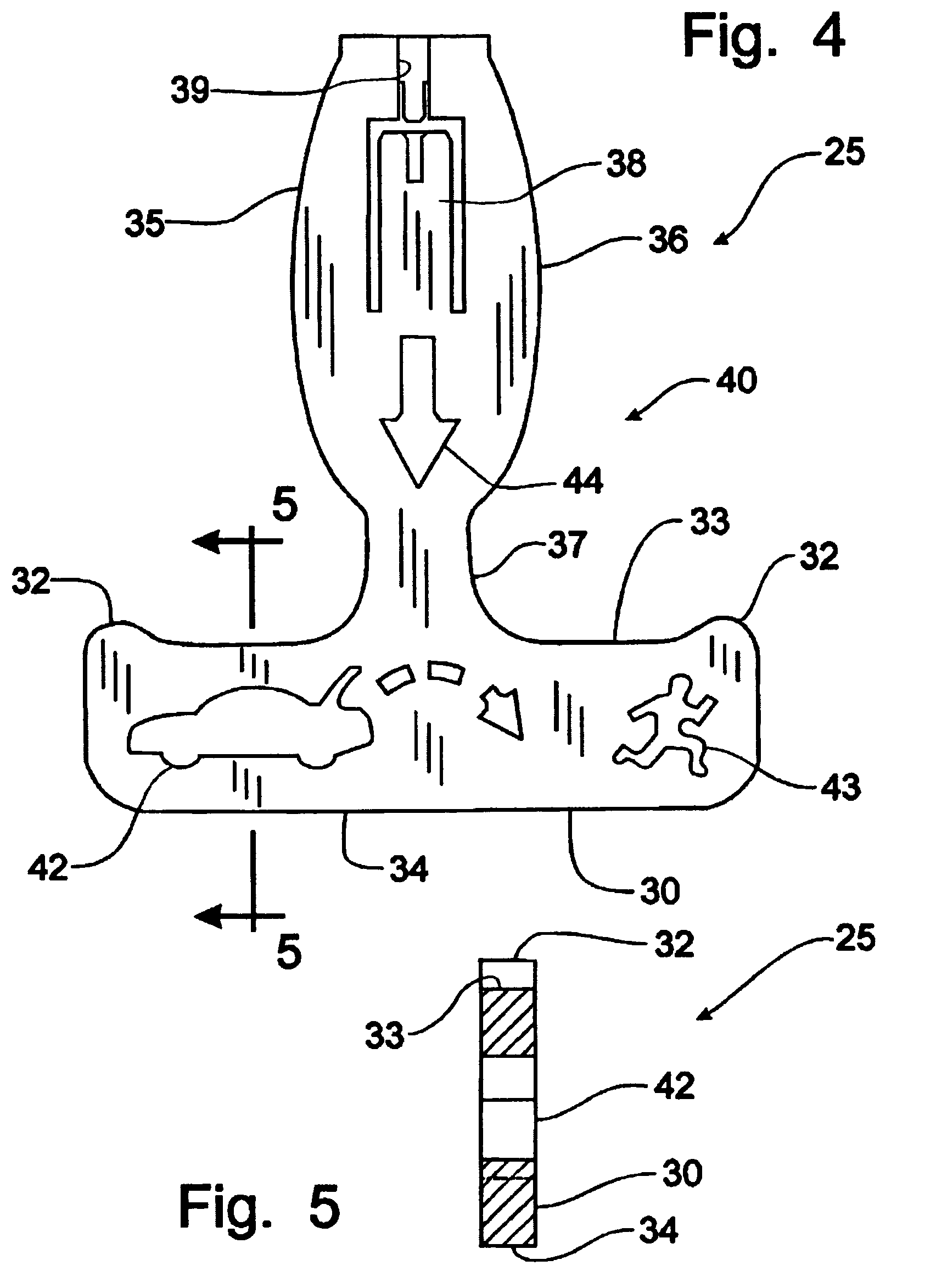

Detecting construction equipment process failure

ActiveUS7898403B2Analogue computers for trafficRegistering/indicating working of vehiclesReporting sourceProcess failure

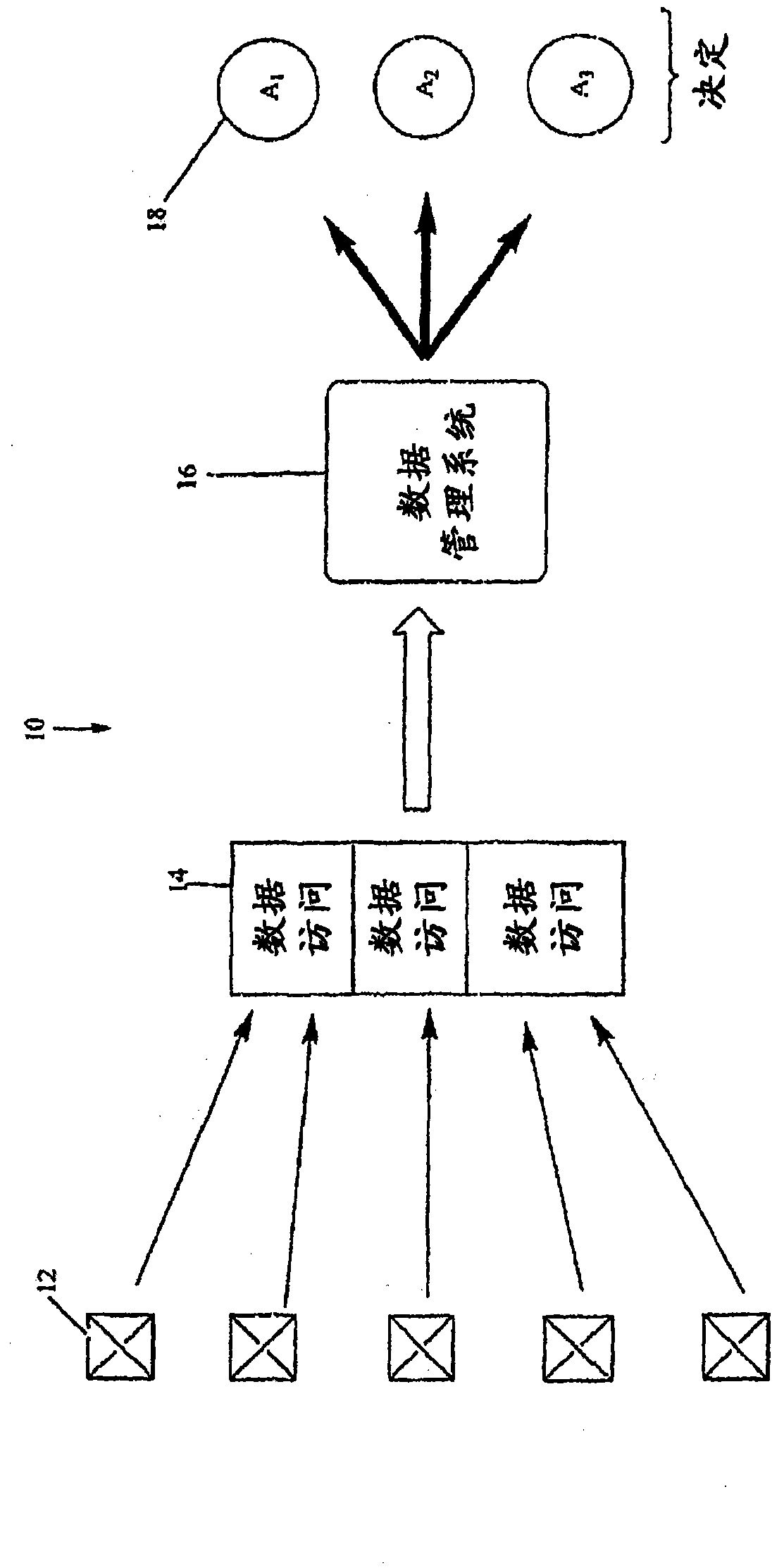

A method and system for detecting construction equipment process failure are disclosed. According to one embodiment, information about a construction equipment asset from a reporting source is received. A database is then populated with the information. A process failure report is provided if the construction equipment asset is operated in a manner which violates a process norm assigned to the construction equipment asset.

Owner:TRIMBLE NAVIGATION LTD

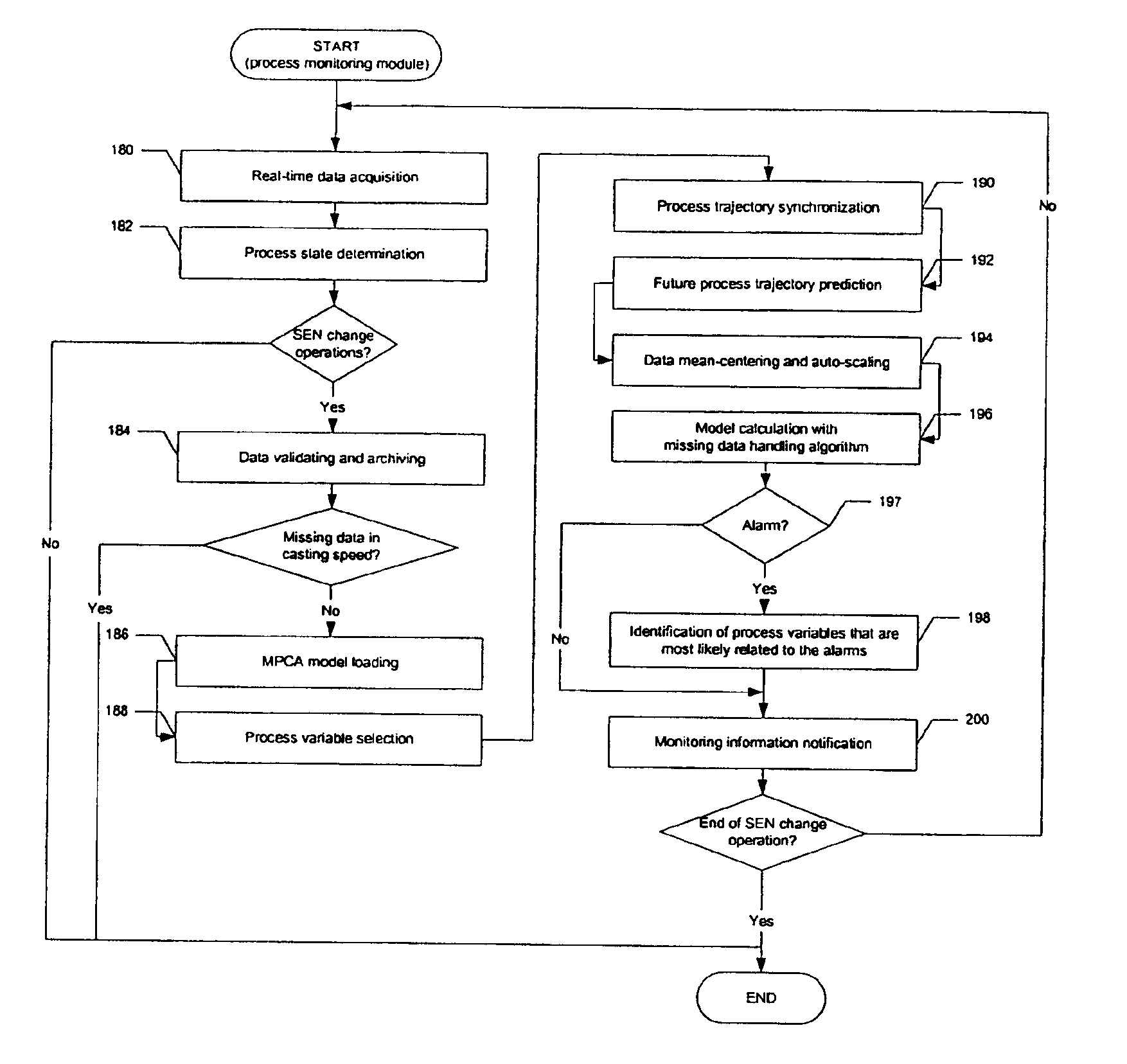

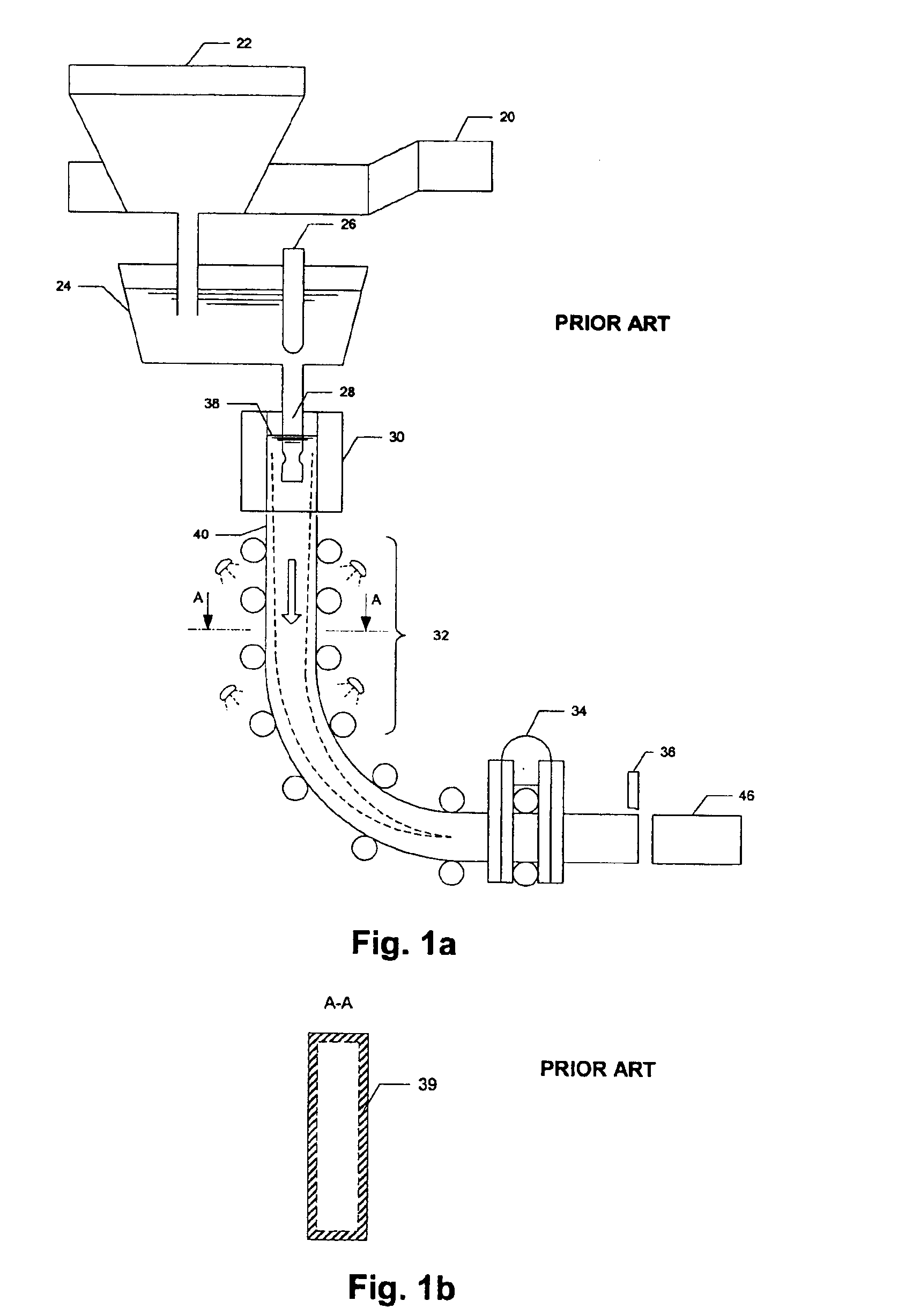

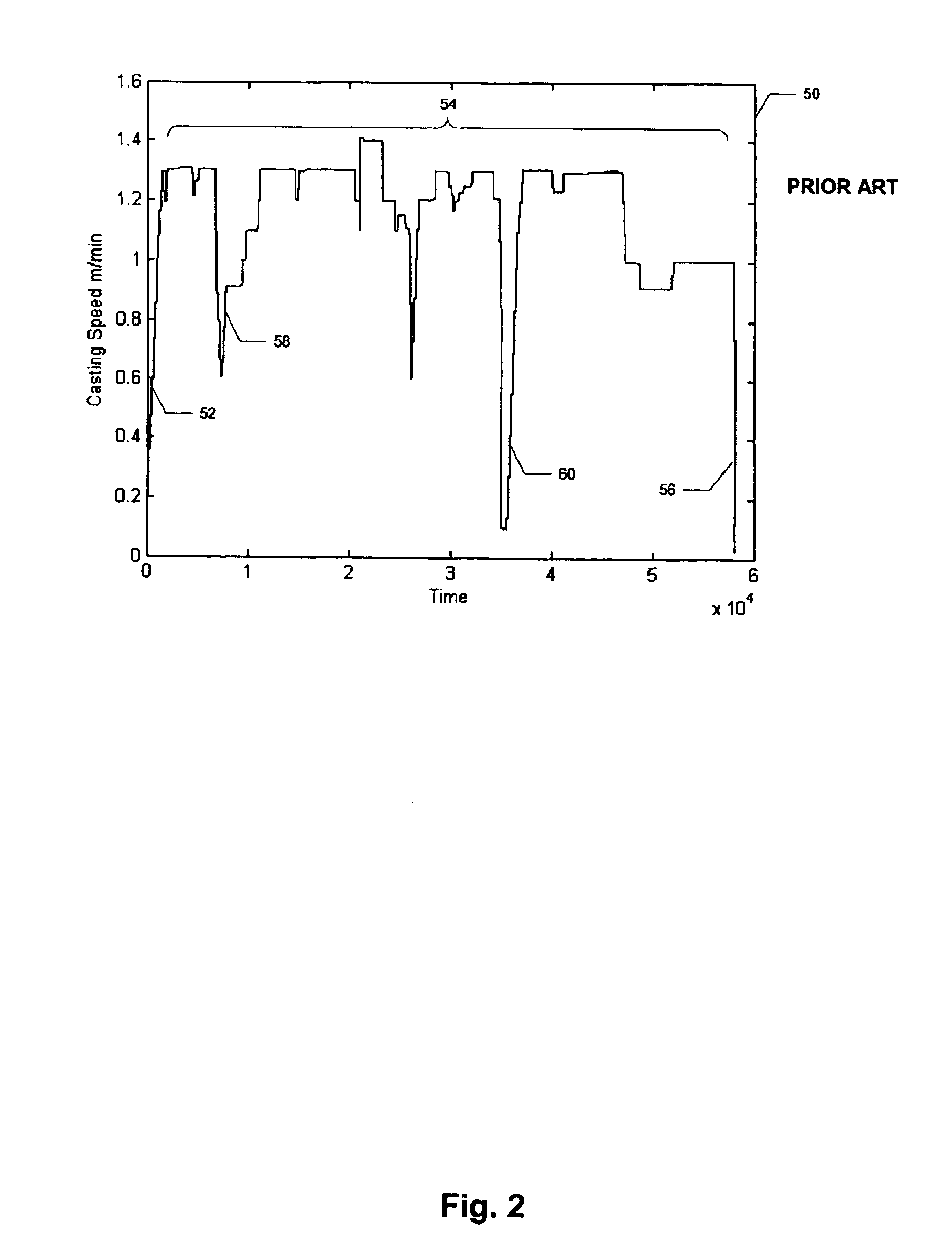

Real-time system and method of monitoring transient operations in continuous casting process for breakout prevention

ActiveUS6885907B1Testing/monitoring control systemsMoulding machine componentsPrincipal component analysisMultivariate statistical

A real-time system and method for online monitoring a transient operation in a continuous casting process. The transient operation refers to, but is not limited to, submerged entry nozzle changes, flying tundish changes, product grade changes, etc. This invention treats the aforementioned transient operations as batch processes and utilizes multiway principal component analysis to develop a multivariate statistical model to characterize normal process transitions based on carefully selected historical process data. Such a model is used by an online monitoring system to determine if a continuous caster transient operation is normal. This monitoring system can further be used to predict an impending breakout, one type of catastrophic process failures which may occur in a continuous casting process, during the transient operation. Process variables that are most likely related to the predicted breakout are identified by the system such that appropriate control actions can be taken to prevent an actual breakout occurrence.

Owner:DOFASCO INC

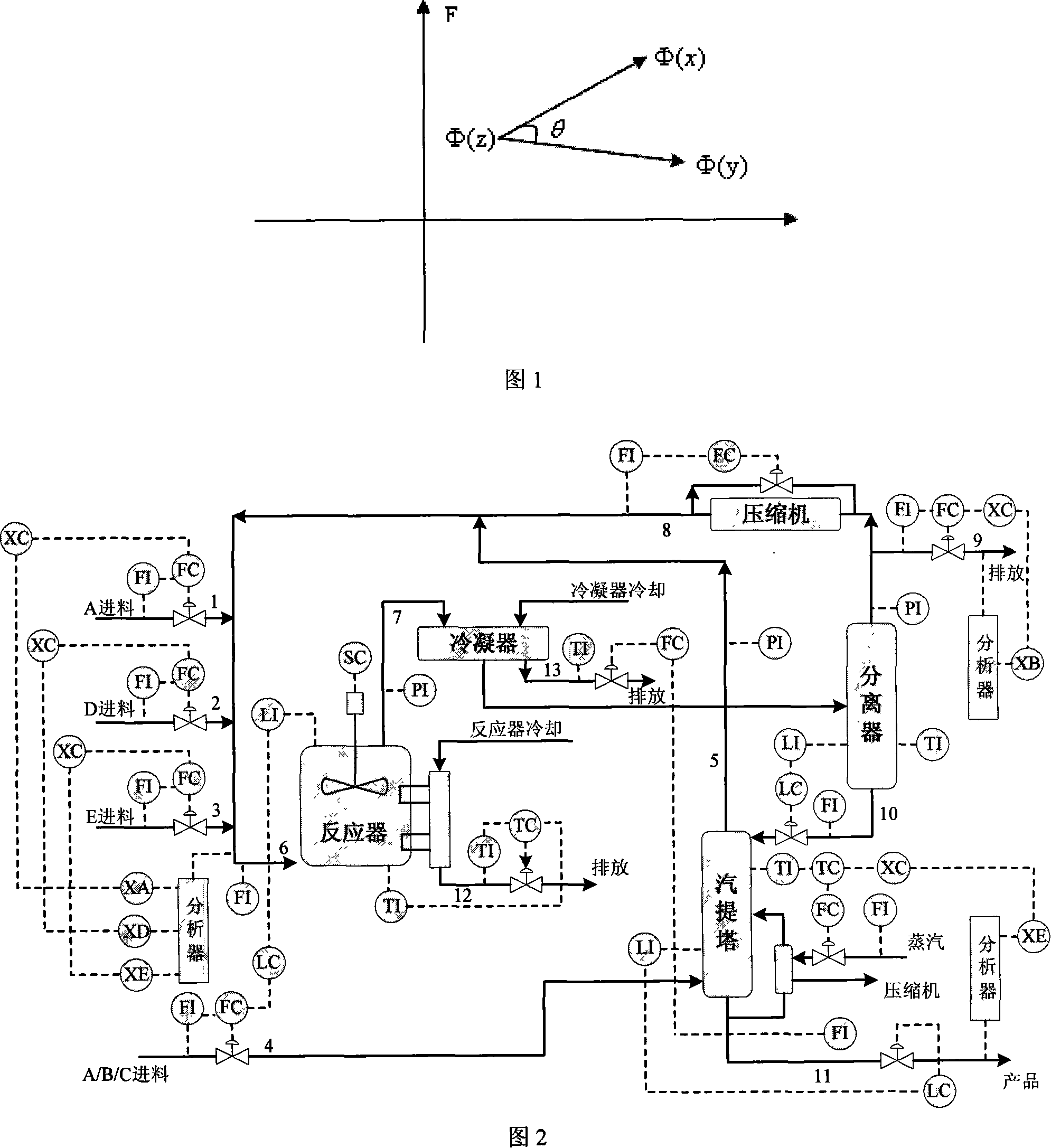

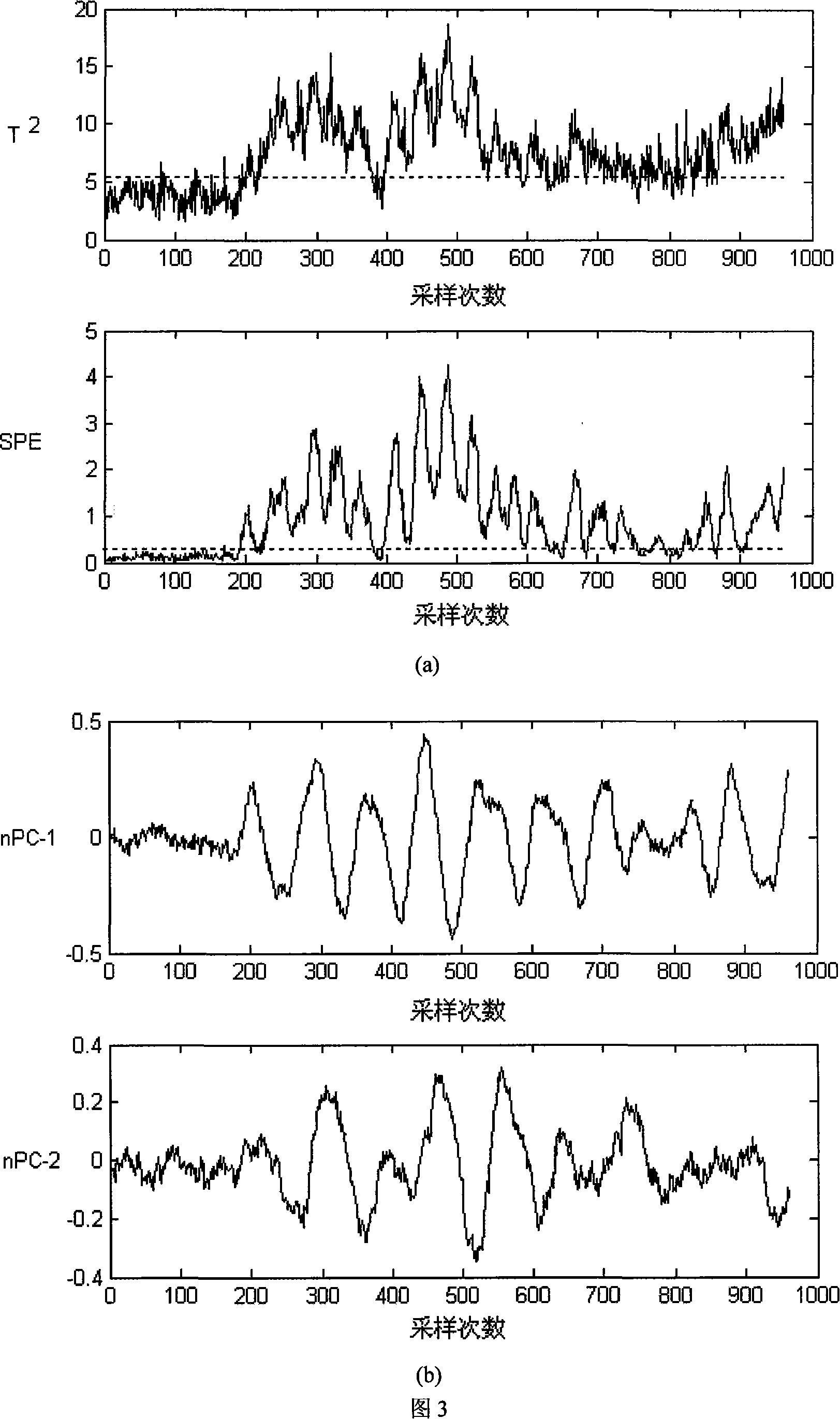

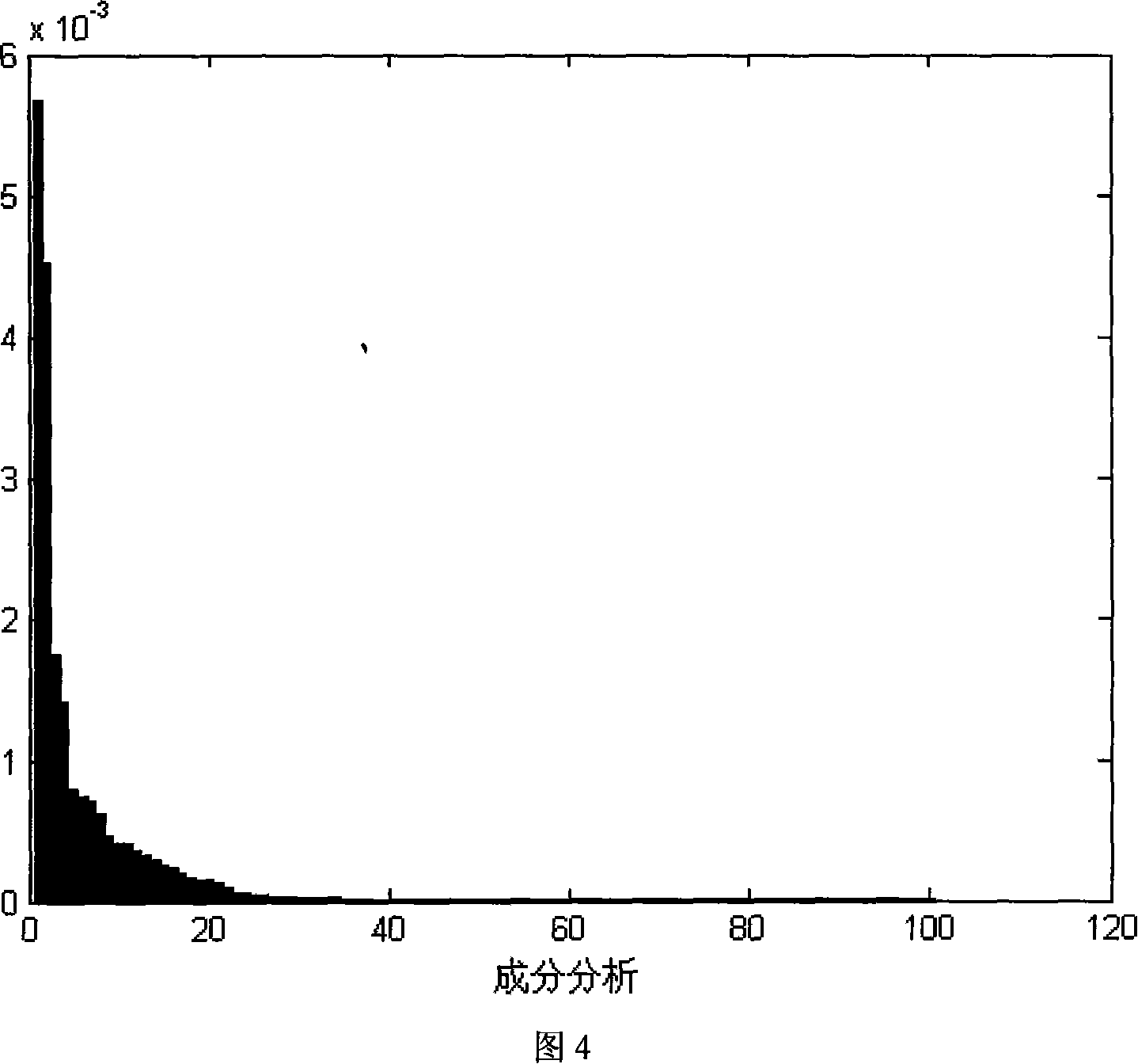

Non-linearity process failure diagnosis method

InactiveCN101158873AExert grasping abilityUse classification abilityElectric testing/monitoringKernel principal component analysisData acquisition

The invention relates to a nonlinear process fault diagnosis method, comprising the steps such as data acquisition, similar analysis, whitening process to the data by utilizing kernel principal component analysis, solving of observation variable z after whitening, independent component exaction by modifying an ICA analysis, and fault detection and diagnosis analysis by utilization of T<2> and SPE statistics and LS-SVM. The invention puts forward the nonlinear dynamic process fault diagnosis technique, combines the advantages of Kernel, ICA and LS-SVM, that is, the exerts the kernel-to-nonlinear express ability, and at the same plays the master ability of ICA to the dynamic characteristic as well as LS - SVM classification ability.

Owner:NORTHEASTERN UNIV

Detecting construction equipment process failure

ActiveUS20080084332A1Analogue computers for trafficRegistering/indicating working of vehiclesReporting sourceProcess failure

A method and system for detecting construction equipment process failure are disclosed. According to one embodiment, information about a construction equipment asset from a reporting source is received. A database is then populated with the information. A process failure report is provided if the construction equipment asset is operated in a manner which violates a process norm assigned to the construction equipment asset.

Owner:TRIMBLE NAVIGATION LTD

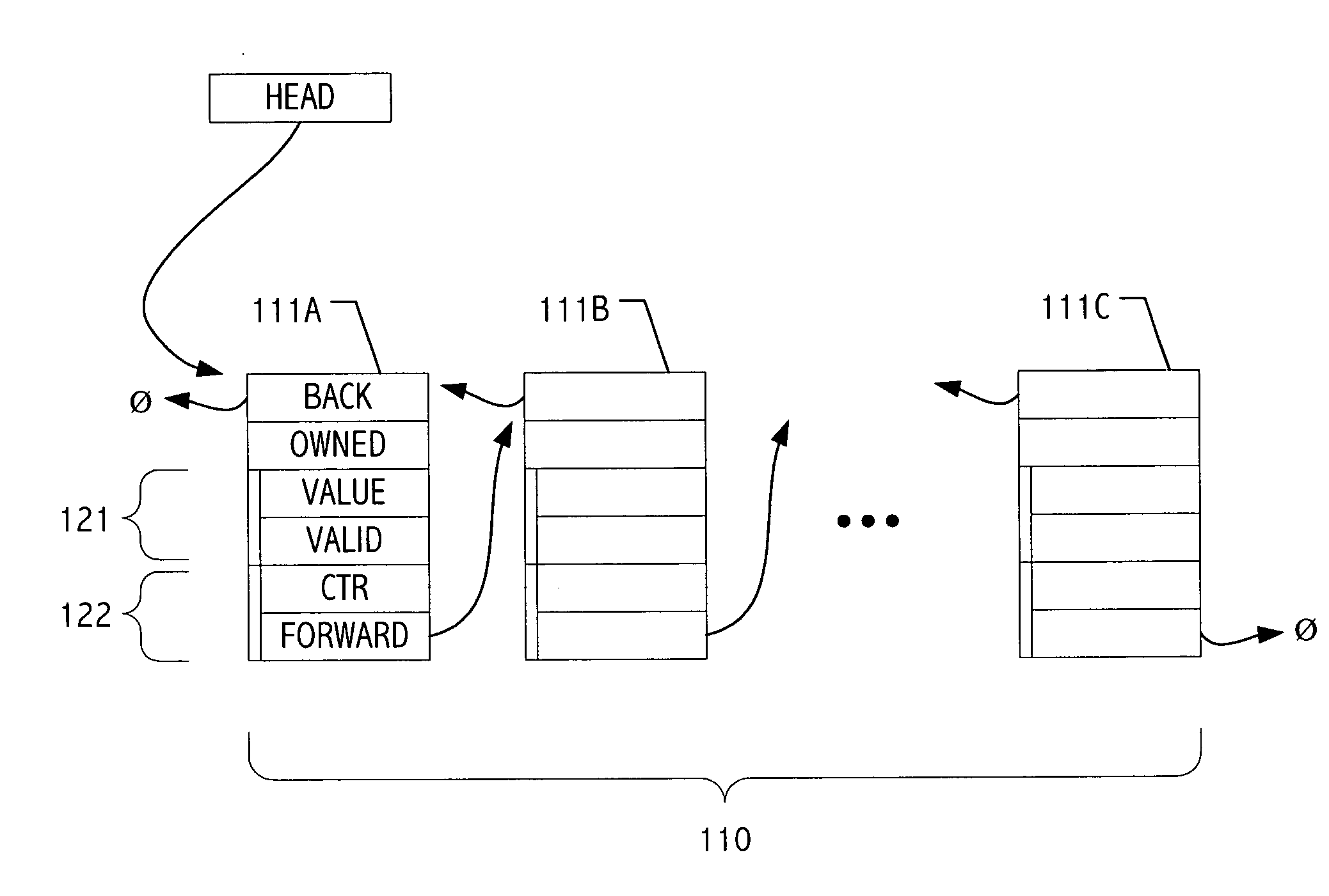

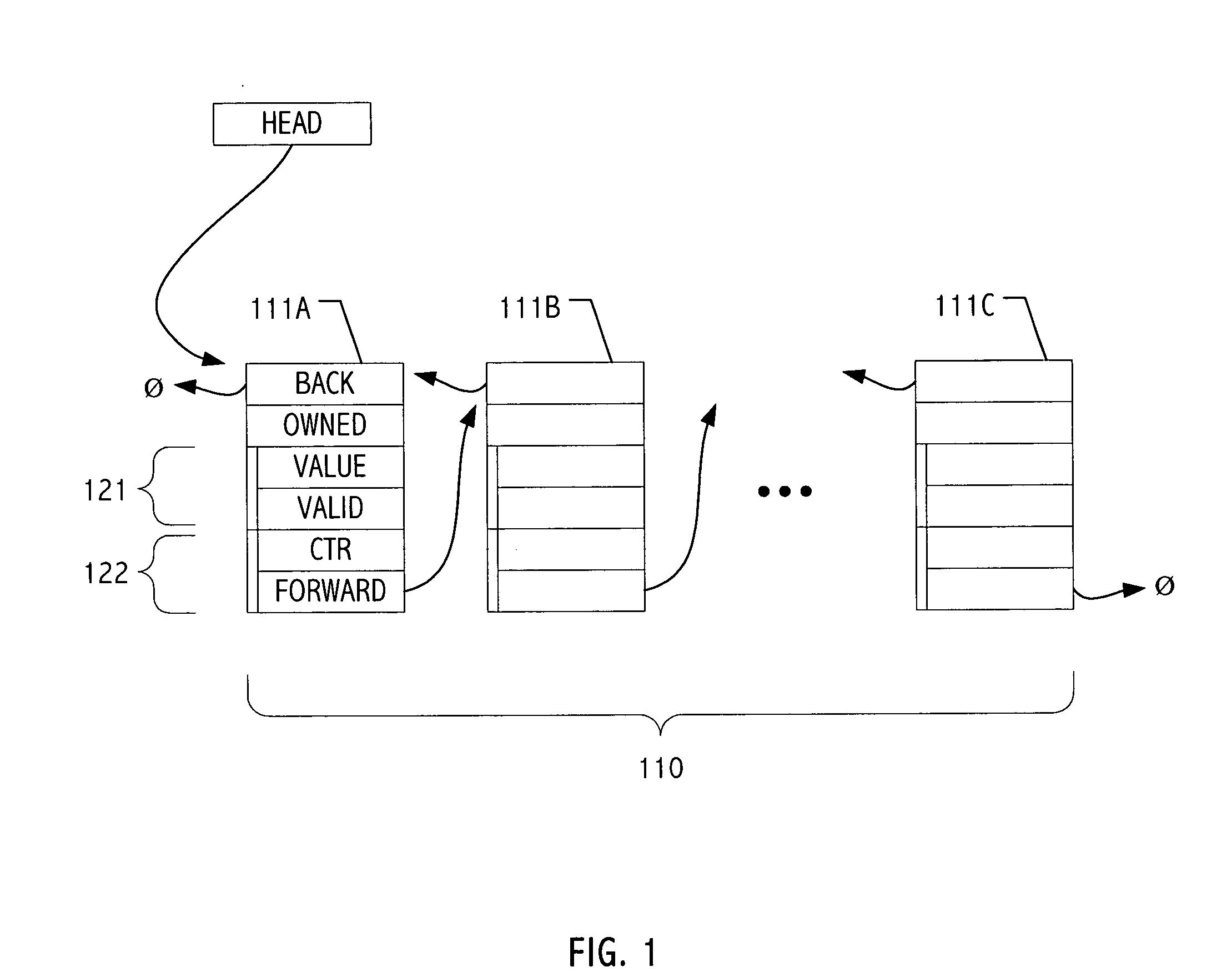

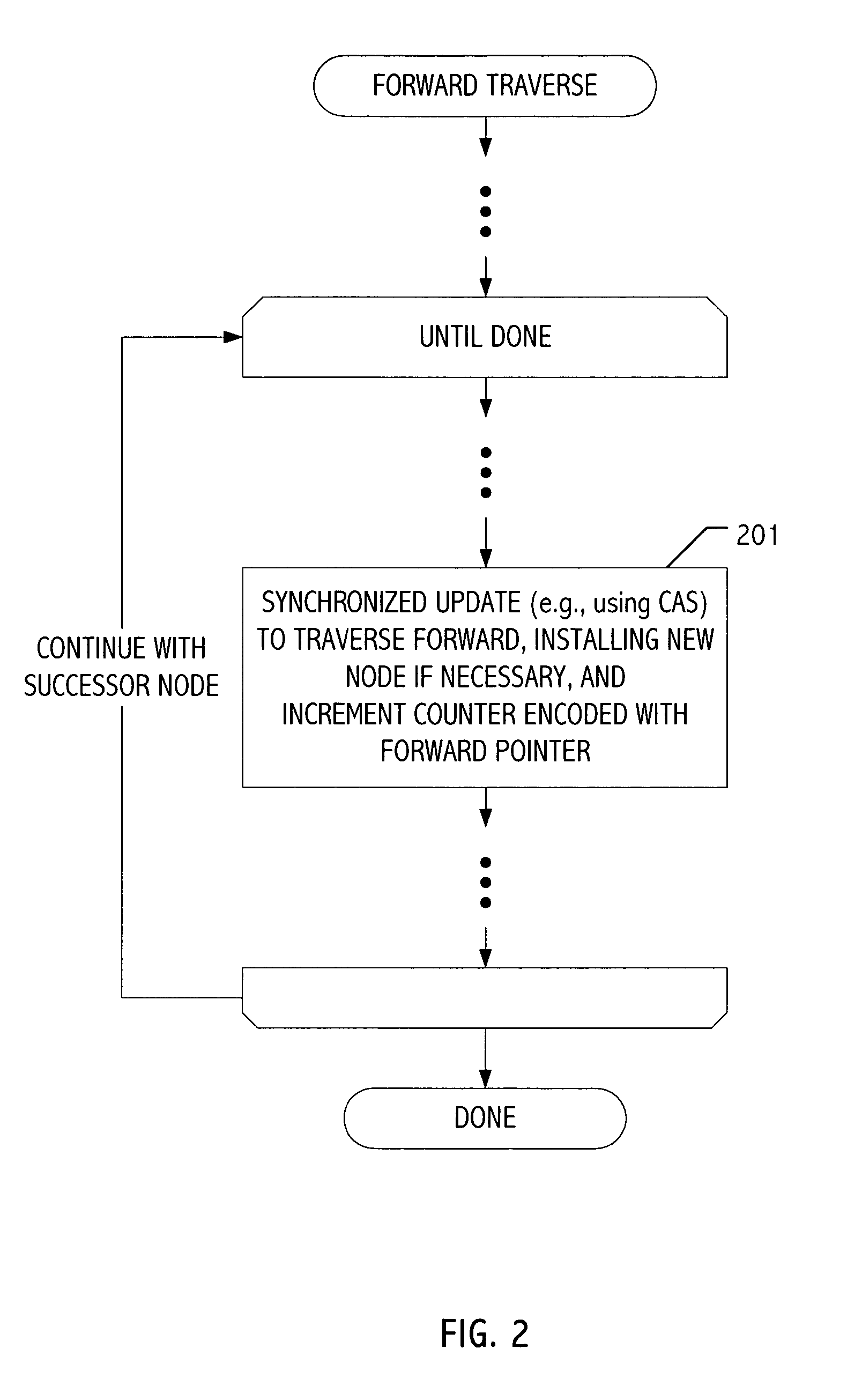

Space- and time-adaptive nonblocking algorithms

ActiveUS20040153687A1Data processing applicationsError preventionNon-blocking algorithmTheoretical computer science

We explore techniques for designing nonblocking algorithms that do not require advance knowledge of the number of processes that participate, whose time complexity and space consumption both adapt to various measures, rather than being based on predefined worst-case scenarios, and that cannot be prevented from future memory reclamation by process failures. These techniques can be implemented using widely available hardware synchronization primitives. We present our techniques in the context of solutions to the well-known Collect problem. We also explain how our techniques can be exploited to achieve other results with similar properties; these include long-lived renaming and dynamic memory management for nonblocking data structures.

Owner:ORACLE AMERICAN INC

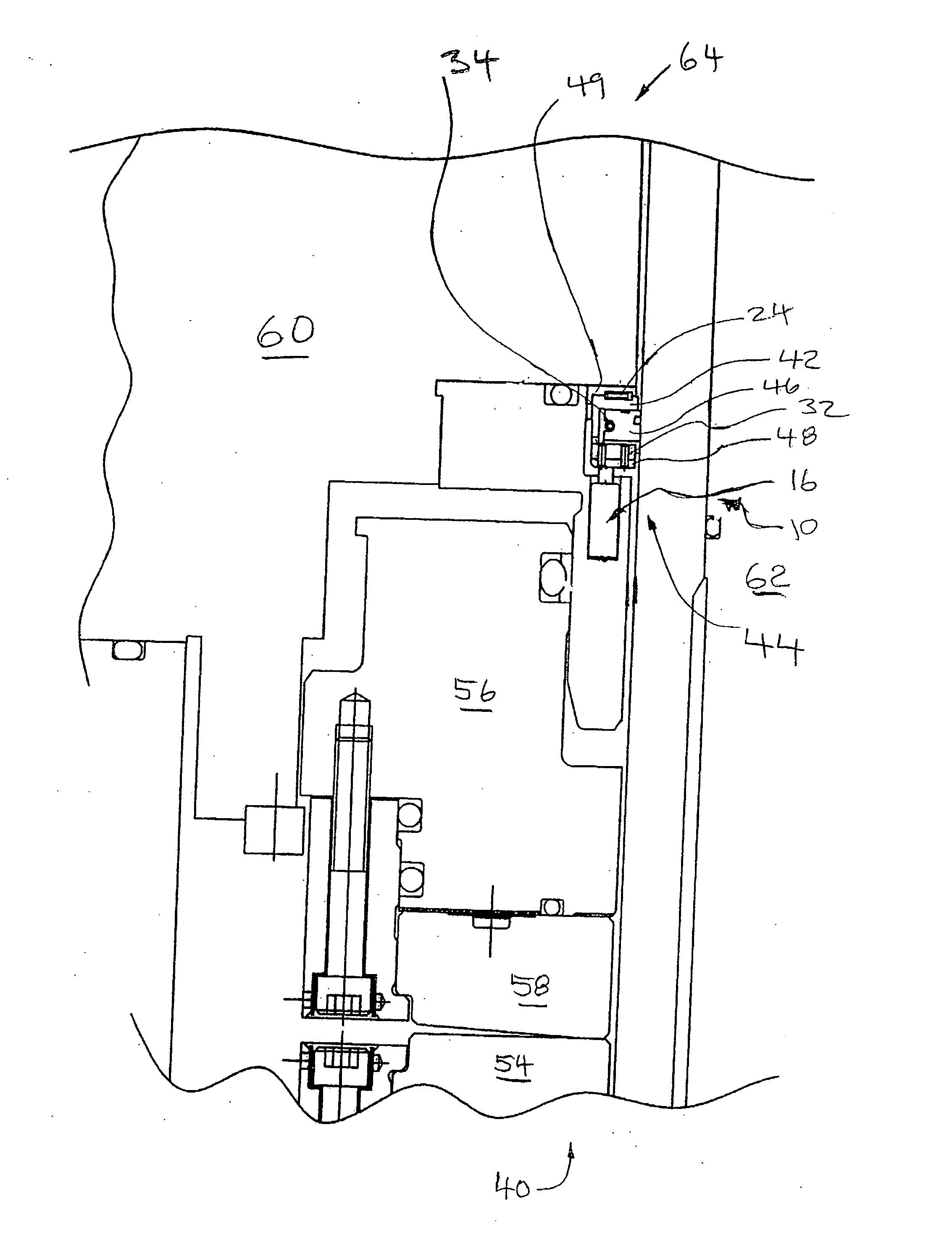

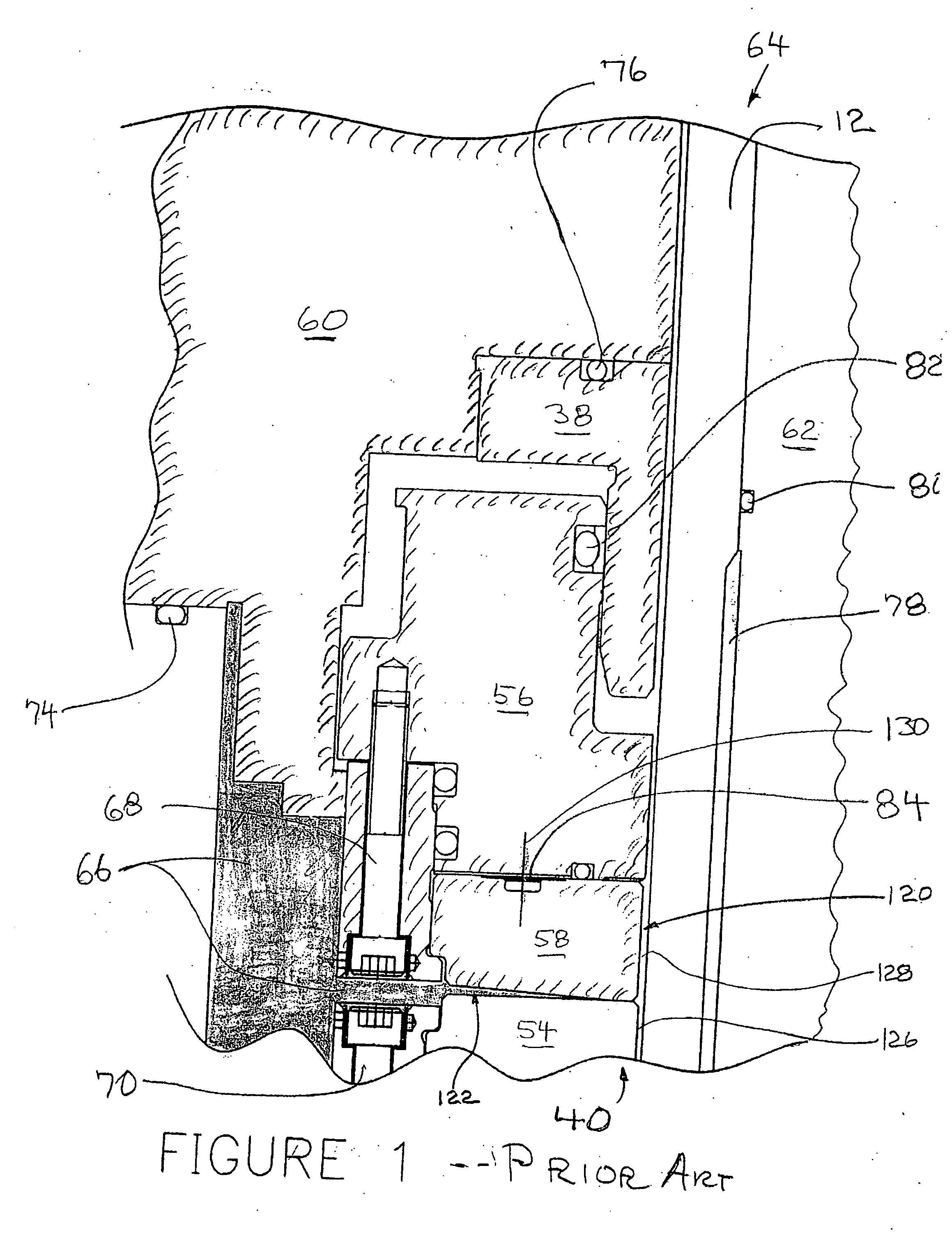

Shutdown seal for reactor coolant pump

InactiveUS20070140877A1Big impactMinimal effectSpecific fluid pumpsEngine sealsCoolant flowProcess failure

A thermally actuated shutdown seal provides a shutdown seal usable in a pump having a primary seal assembly positioned circumferentially about a rotating shaft for separating a region of high pressure coolant fluid from the shaft. The shutdown seal includes a two-piece interlocked housing which encompasses carbon graphite ring segments positioned circumferentially about the shaft, a garter spring and a series of compression springs. The replaceable insert with machined recess contains the shutdown seal assembly and is biased axially with a wave spring and held with the annular recess by a closure ring. The seal is designed with coolant fluid flow directly in contact with such ring segments and specially designed paths around the ring segments during normal pump operation. The seal requires a thermally actuated means for moving the two-piece interlocked housing axially into a blocking position within the coolant flow path to shutdown and minimize fluid flow bypassing the ring segments and between the ring segments and the pump shaft, upon occurrence of a process failure in the facility served by the pump and consequent temperature rise of the fluid being pumped.

Owner:STEIN SEAL +1

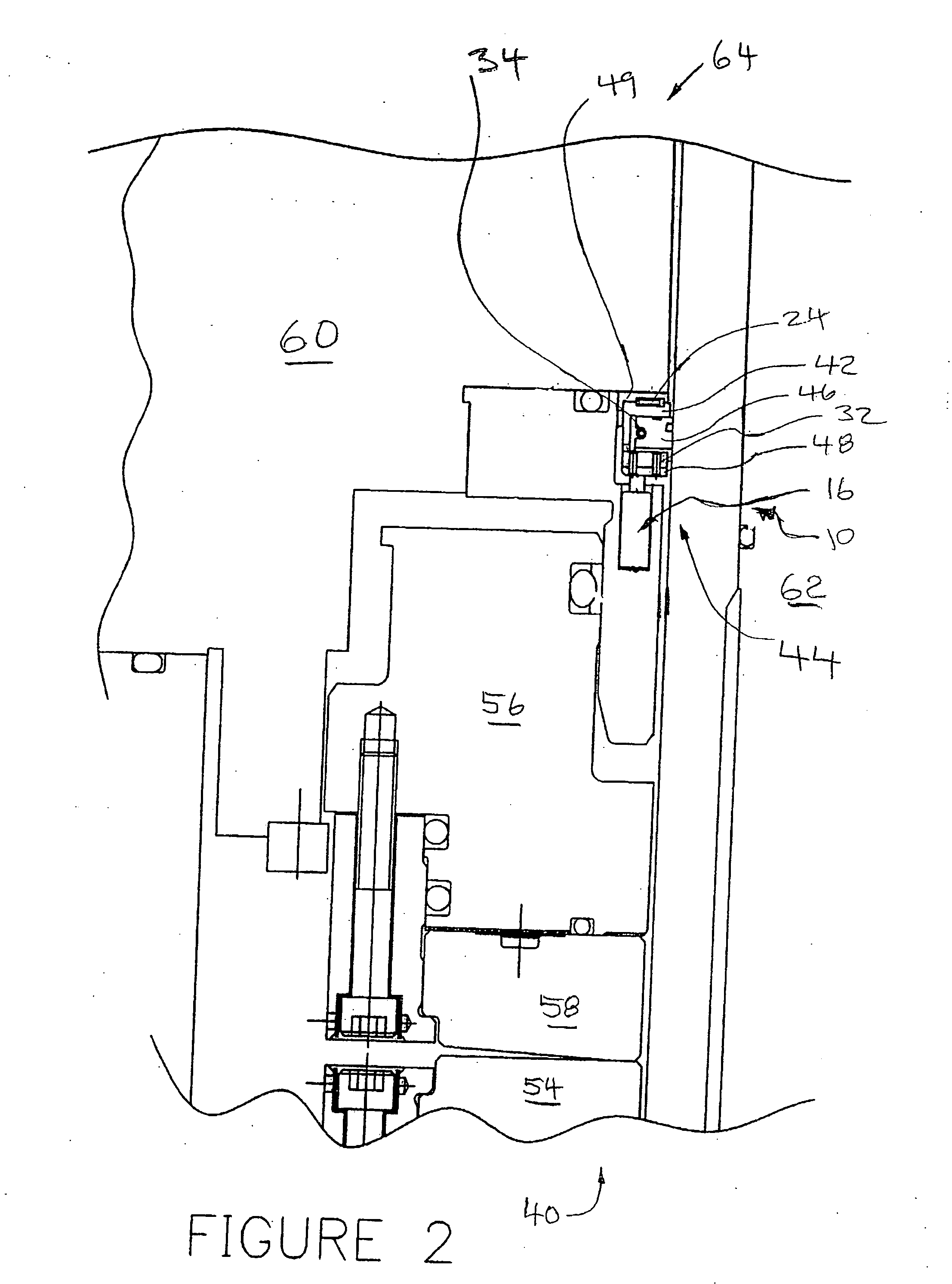

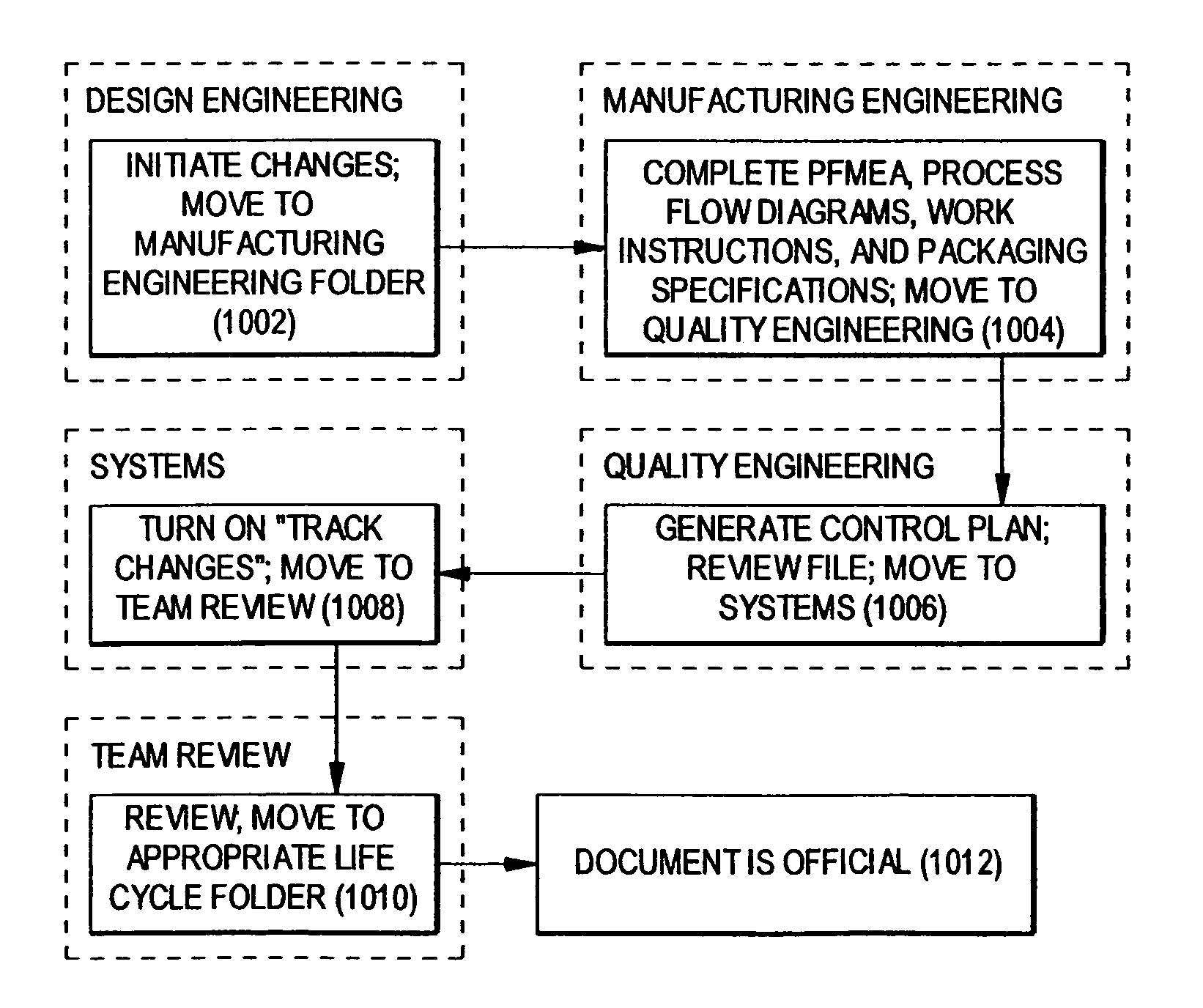

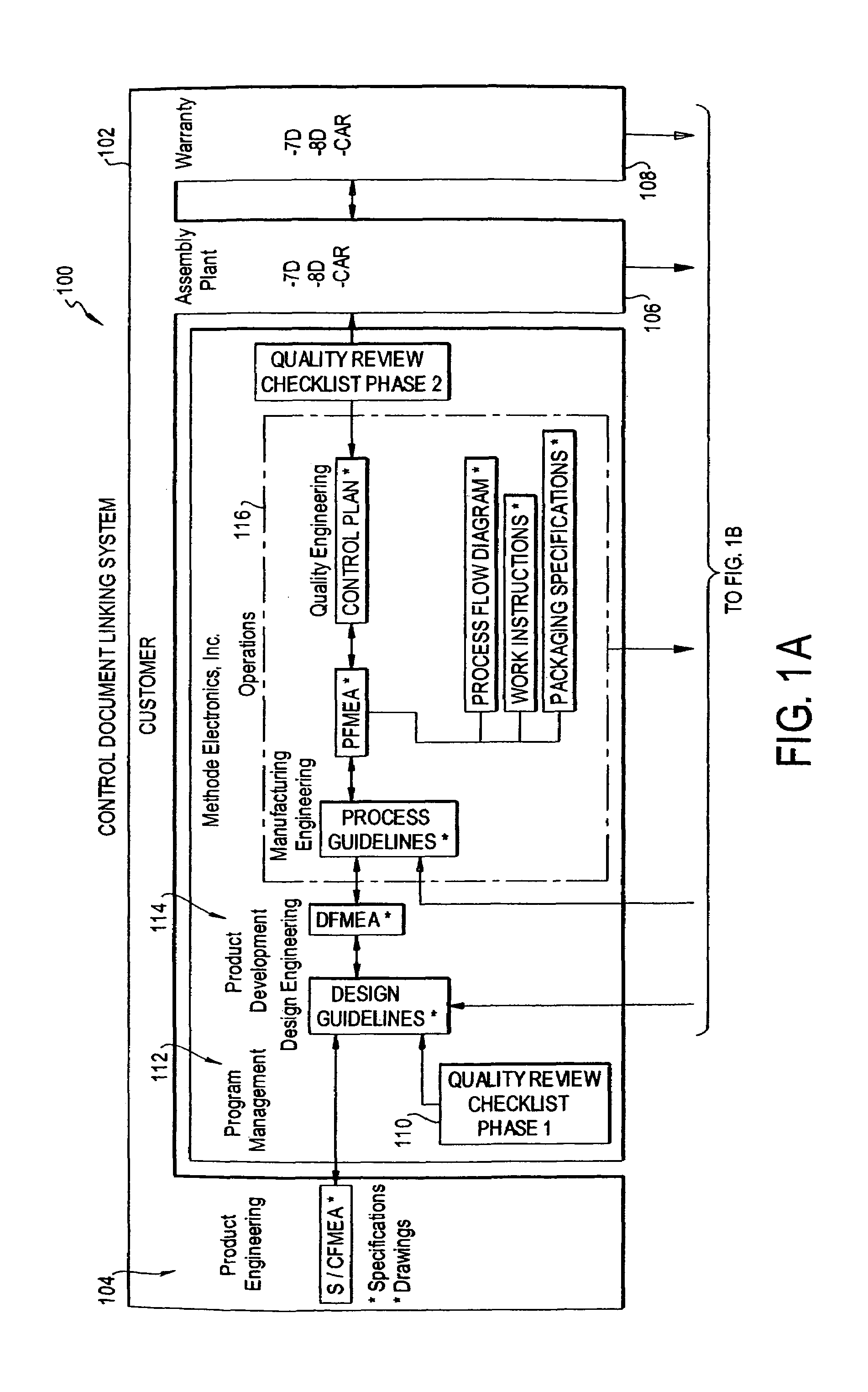

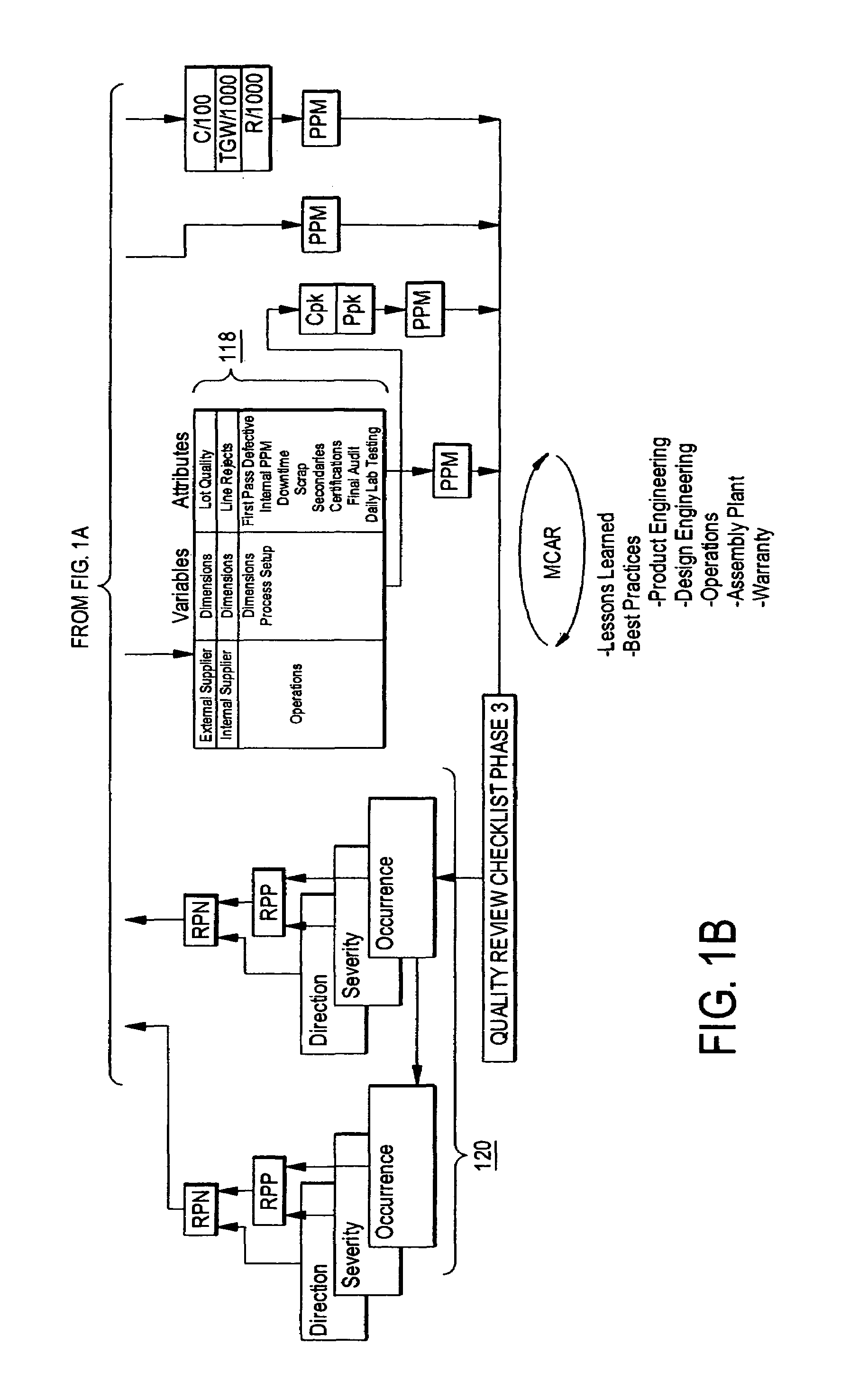

Design control document linking template

InactiveUS7096082B1Facilitate consistent entryWork lessFinanceAnimal feeding devicesOriginal dataElectronic form

A control document template streamlines the creation of control documents and facilitates consistent entry of data. A multi-page spreadsheet file incorporates the design and process failure mode effects analysis pages, the control plan, tools for forming the process flow diagram, the work instructions, and the packaging specifications. A macro sorts the failure mode effects analysis pages by risk priority number without overwriting the original data.

Owner:METHODE ELETRONICS INC

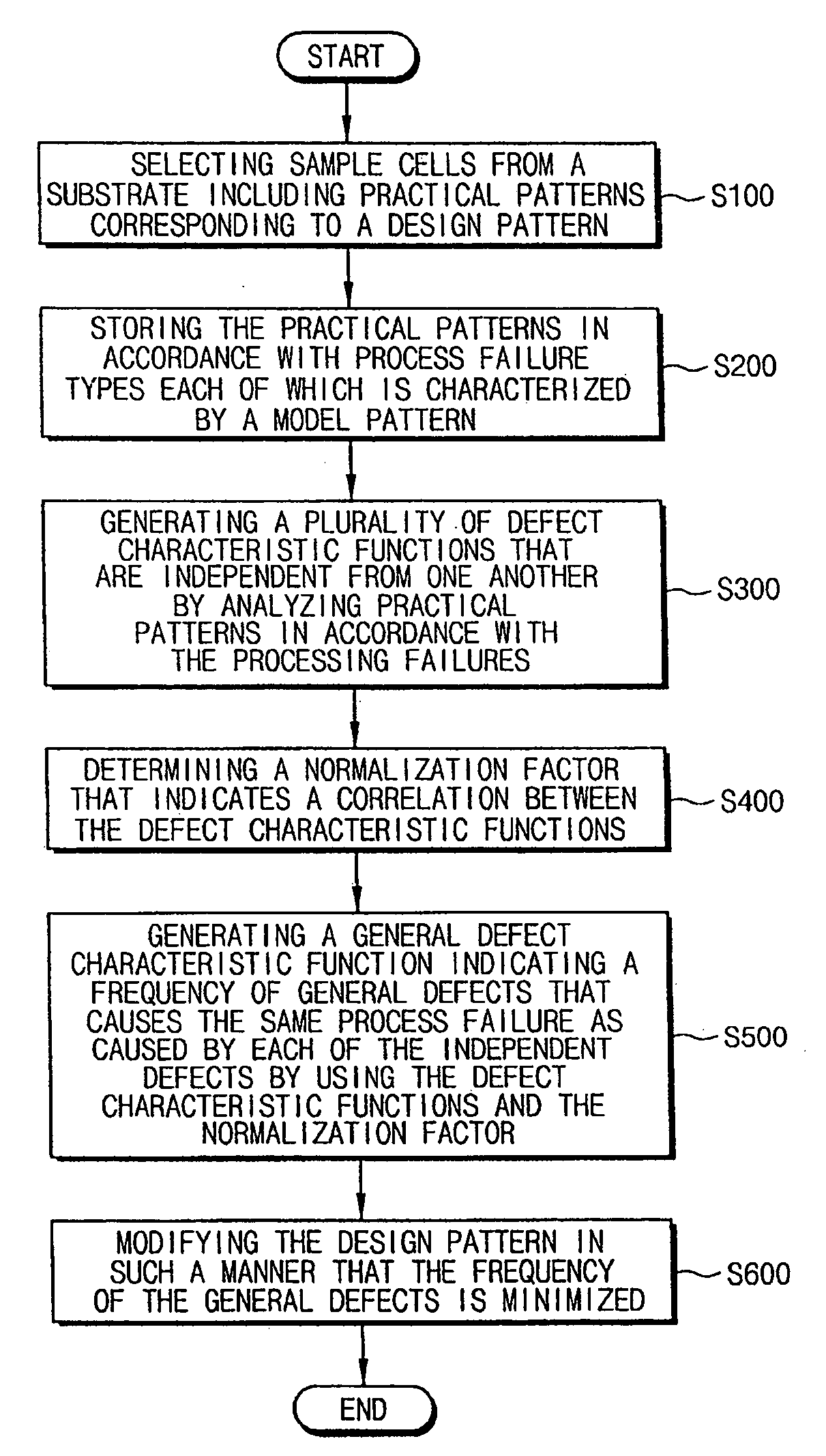

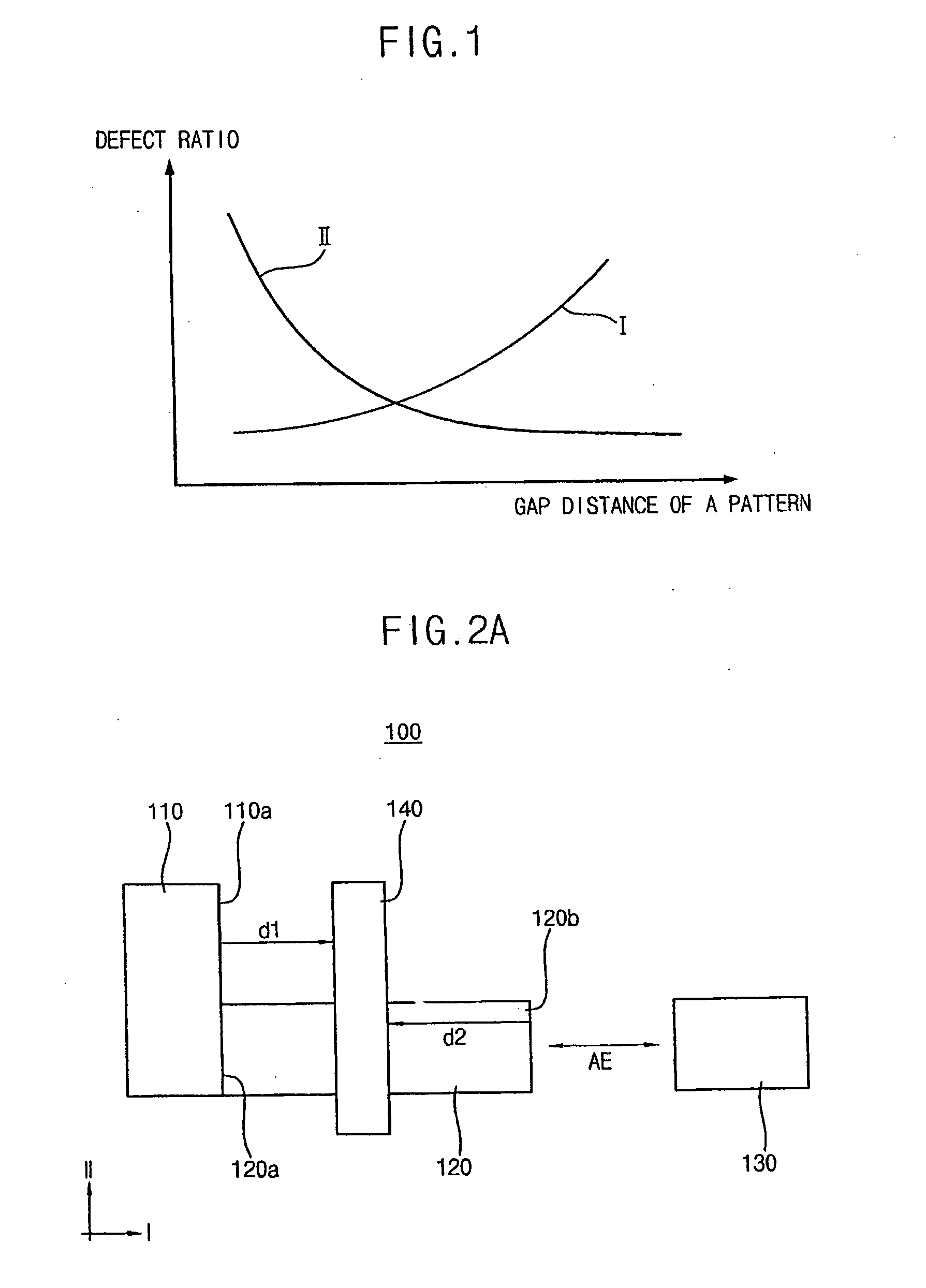

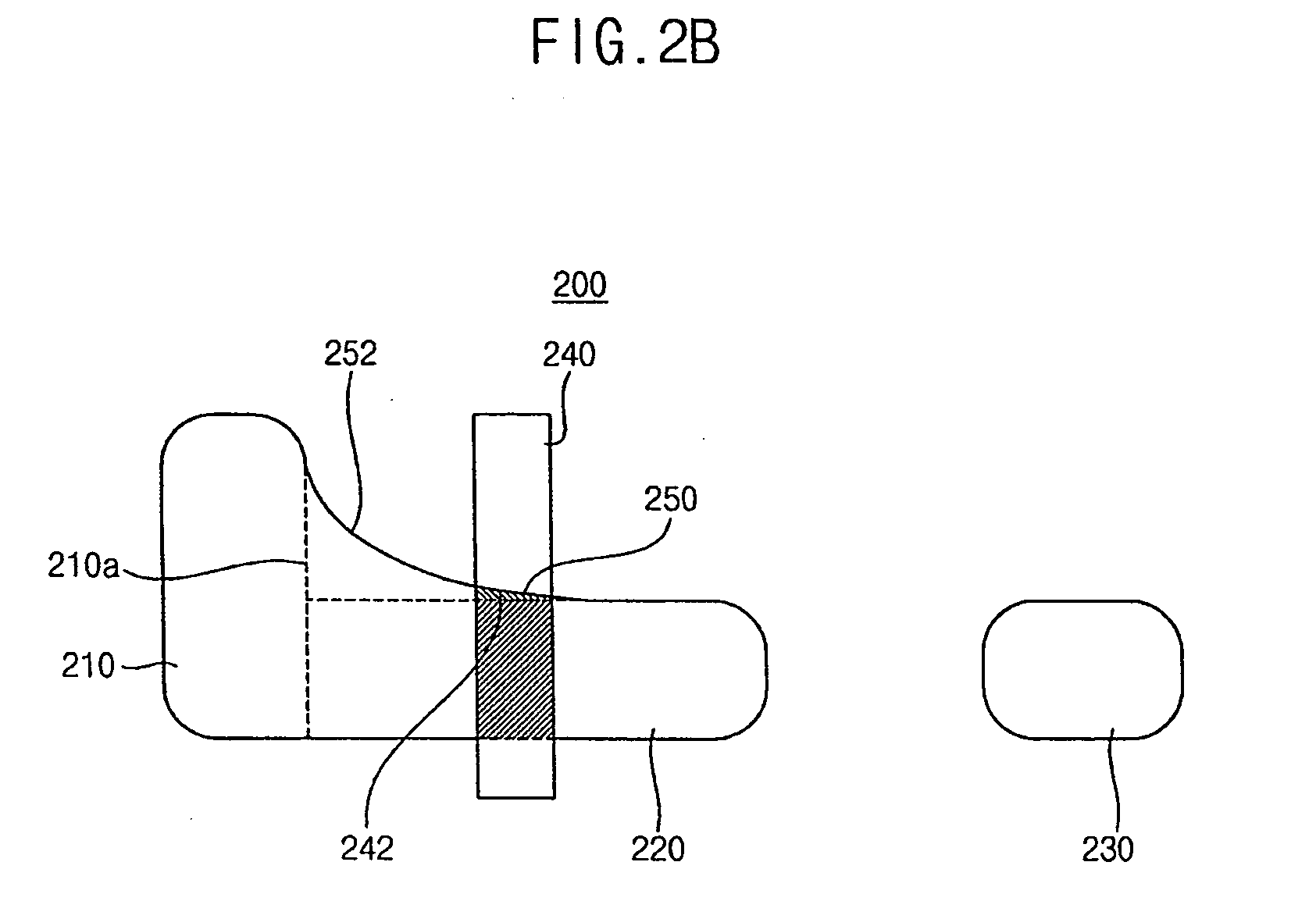

Method of correcting a design pattern for an integrated circuit and an apparatus for performing the same

ActiveUS20080250361A1Minimizing different kinds of defectsMinimize the differenceSolid-state devicesPhotomechanical apparatusProcess failureIntegrated circuit layout

In an apparatus and method for automatically correcting a design pattern in view of different process defects, defect characteristic functions that indicate frequencies of each process defect independent from one another are generated, and a normalization factor that indicates relationships between the defect characteristic functions is determined. A general defect characteristic function indicating a frequency of general defects is generated using the defect characteristic functions and the normalization factor. The general defect causes the same process failure as caused by each of the process defects. The design pattern is modified using the general defect characteristic function in such a manner that the frequency of the general defects is minimized when at least one portion of the design pattern corresponding to the model pattern is transcribed on the substrate. Accordingly, the whole design pattern may be automatically corrected based on the general defect characteristic function.

Owner:SAMSUNG ELECTRONICS CO LTD

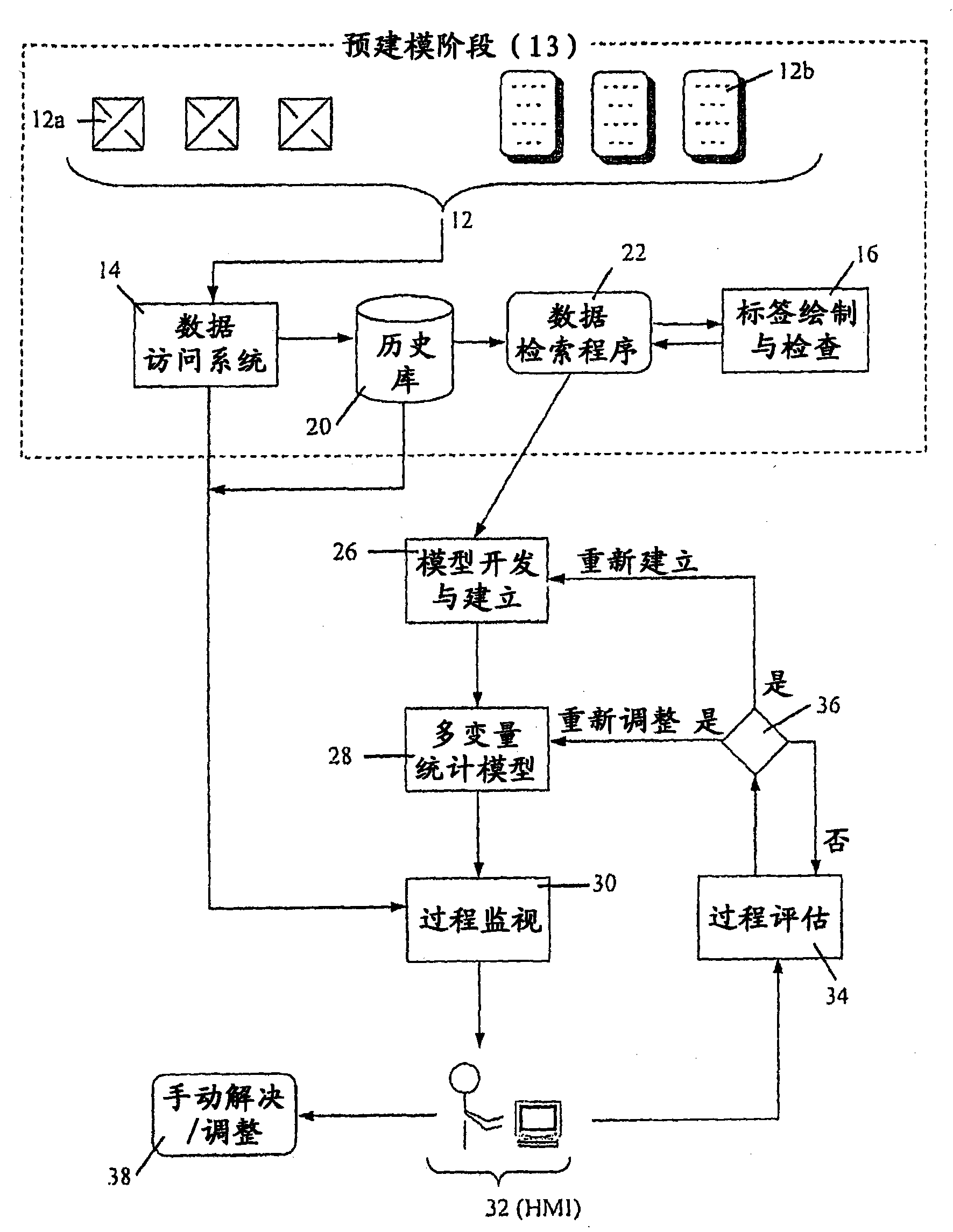

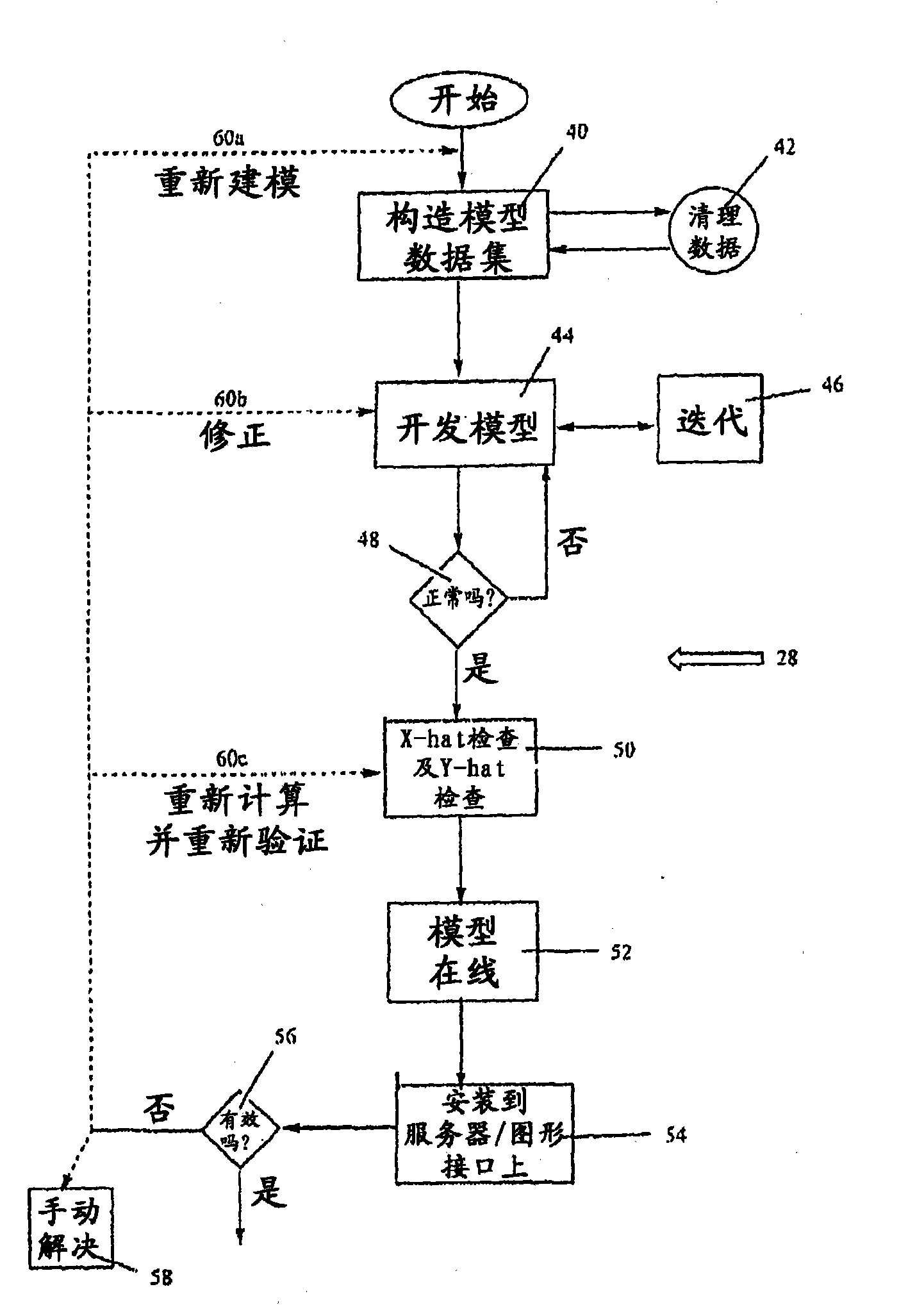

System and methods for continuous, online monitoring of a chemical plant or refinery

A near real-time system and method for continuous online monitoring of a plurality of operations in a continuous chemical process facility is described. The method of monitoring the operations is based on a multivariate statistical model developed using off-line, selected process-specific historical process data. Such a model is used by an online monitoring system to monitor the continual operation of a chemical manufacturing facility or refinery in real-time from a remote location. Such real-time monitoring allows for determination of whether one or more of the plurality of operations are operating within their normal operational parameters. This real-time, continuous monitoring system can further be used to predict impending failures or trouble-spots within the continuous production process, or to minimize catastrophic process failures which may occur in a continuous chemical manufacturing process. Process variables, or ''tags'', that are most likely related to predicted process failures can be identified by the model system, such that appropriate control actions can be taken to prevent an actual process failure occurrence, which can lead to costly production down times.

Owner:SHELL INT RES MAATSCHAPPIJ BV

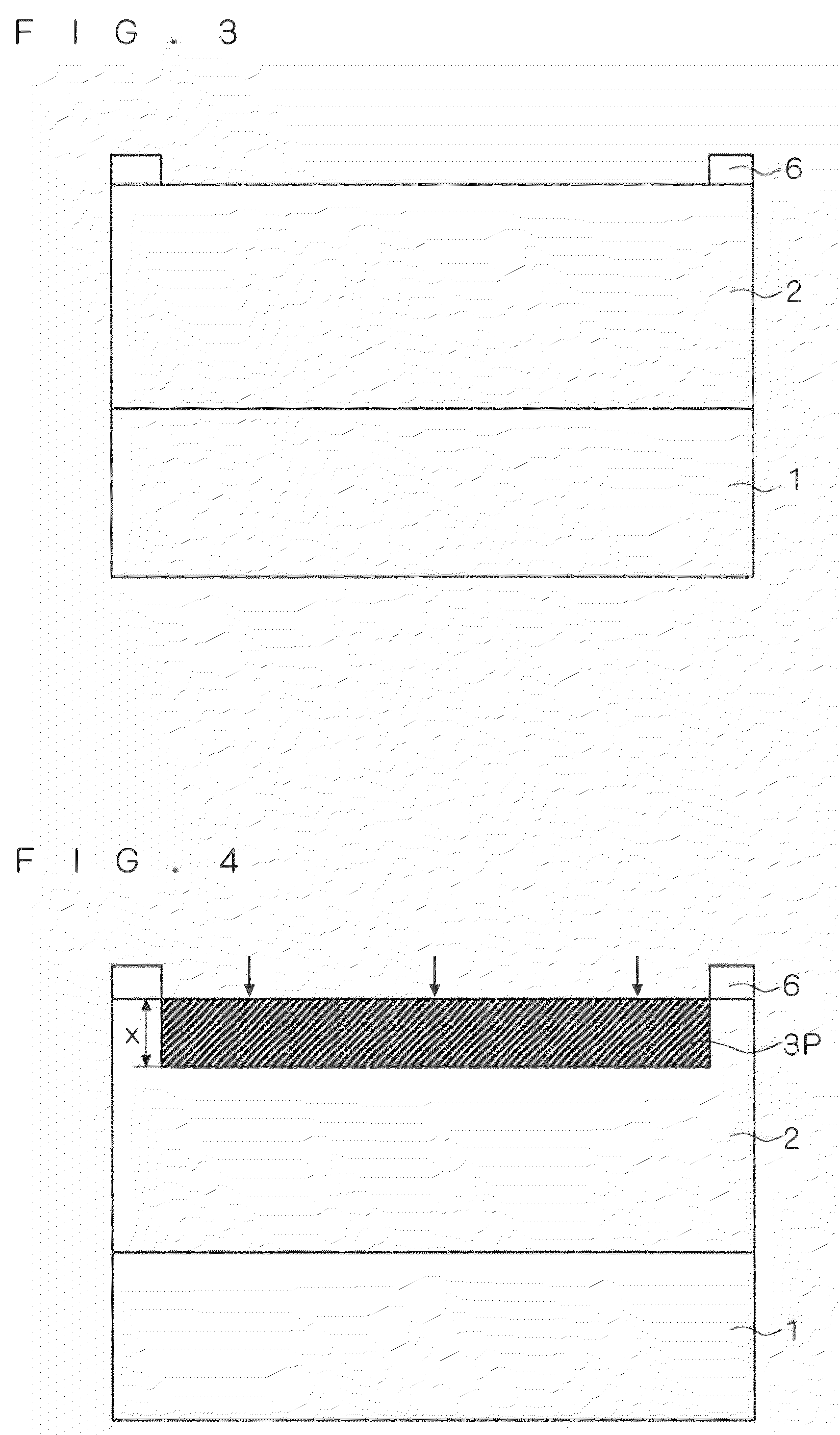

Silicon carbide semiconductor device comprising silicon carbide layer and method of manufacturing the same

ActiveUS20090250705A1Semiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationDevice material

A p base ohmic contact of a silicon carbide semiconductor device consists of a p++ layer formed by high-concentration ion implantation and a metal electrode. Since the high-concentration ion implantation performed at the room temperature significantly degrades the crystal of the p++ layer to cause a process failure, a method for implantation at high temperatures is used. In terms of switching loss and the like of devices, it is desirable that the resistivity of the p base ohmic contact should be lower. In well-known techniques, nothing is mentioned on a detailed relation among the ion implantation temperature, the ohmic contact resistivity and the process failure. Then, in the ion implantation step, the temperature of a silicon carbide wafer is maintained in a range from 175° C. to 300° C., more preferably in a range from 175° C. to 200° C. The resistivity of the p base ohmic contact using a p++ region formed by ion implantation at a temperature in a range from 175° C. to 300° C. becomes lower than that in a case where the p++ region is formed by ion implantation at a temperature over 300° C. Further, this can avoid any process failure.

Owner:MITSUBISHI ELECTRIC CORP

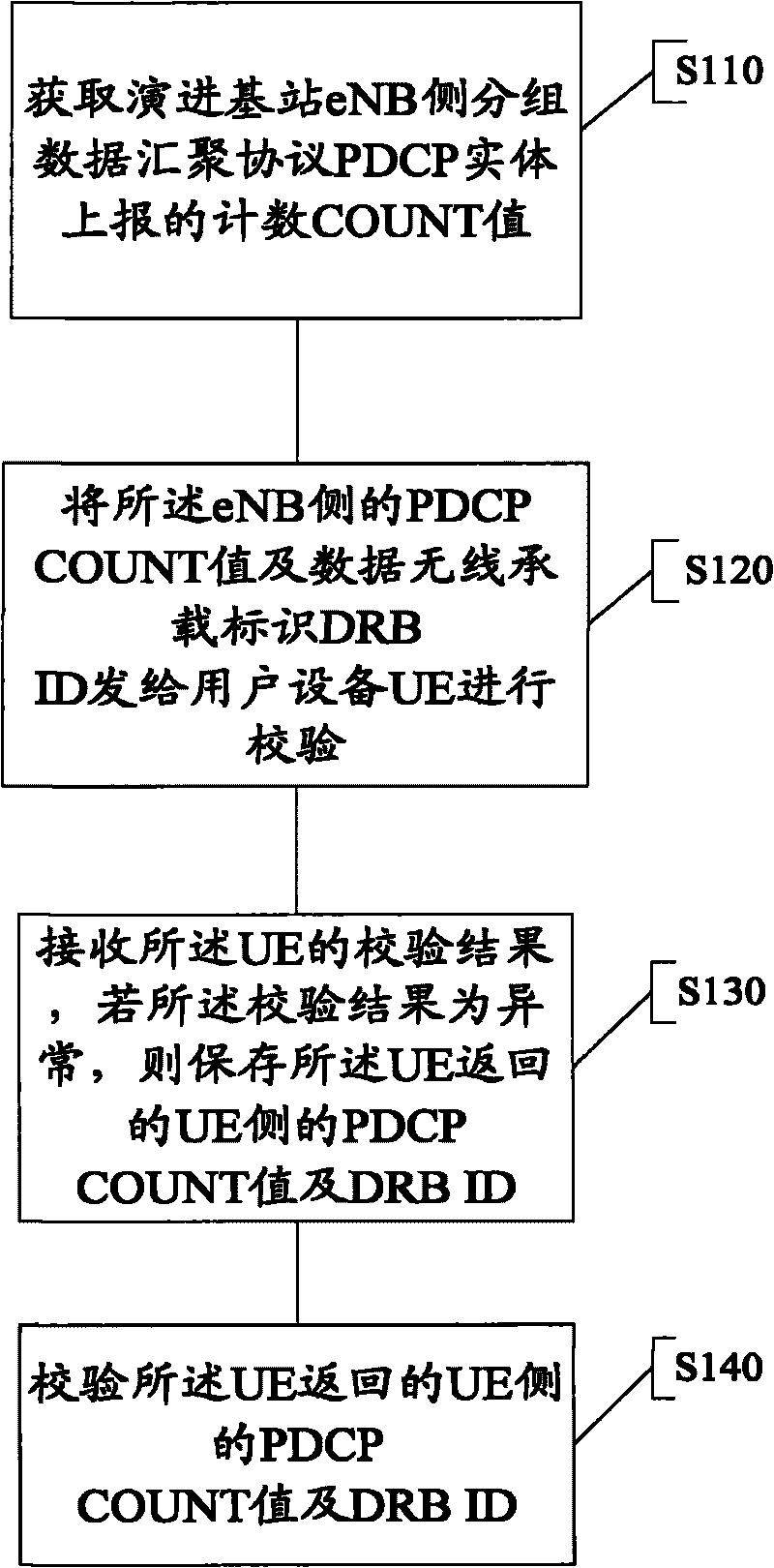

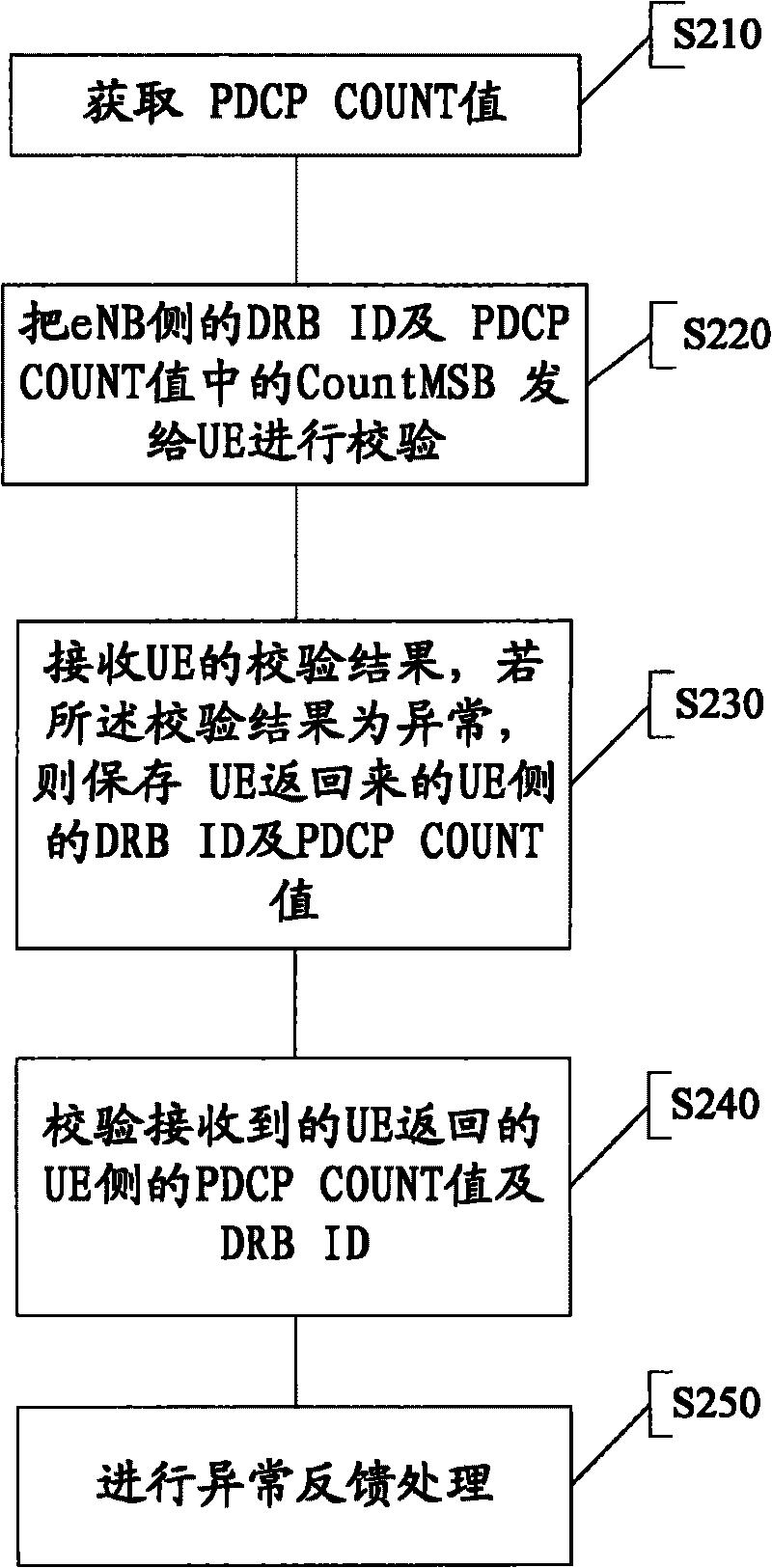

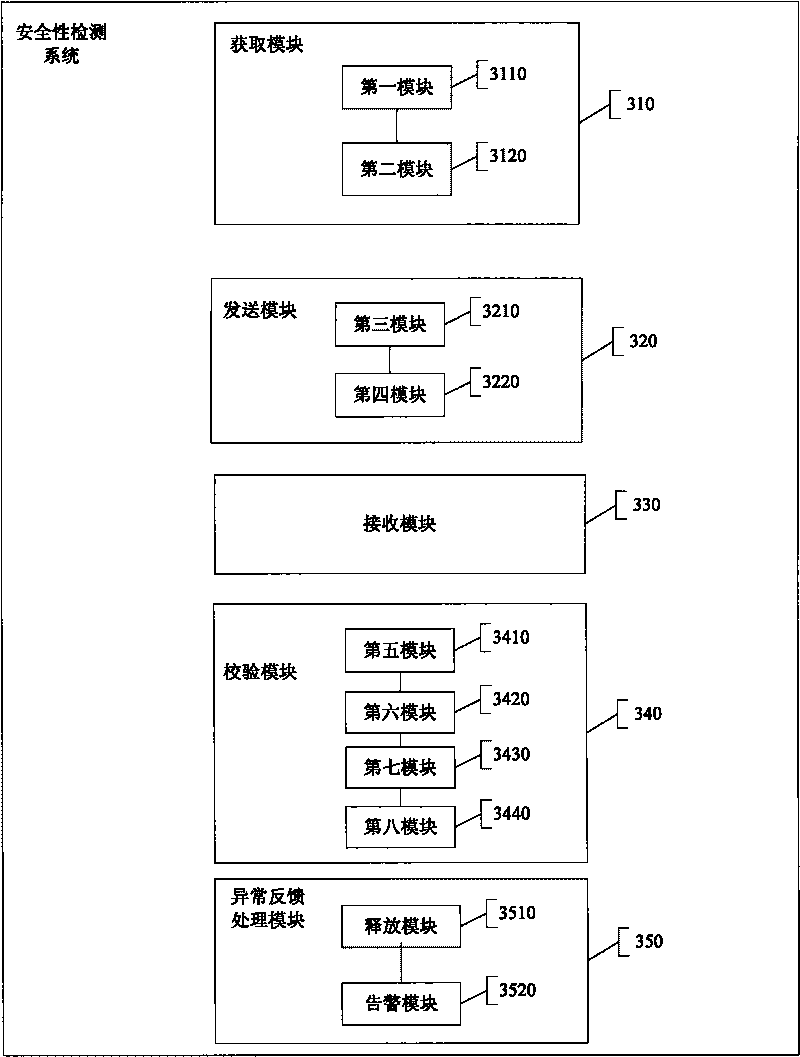

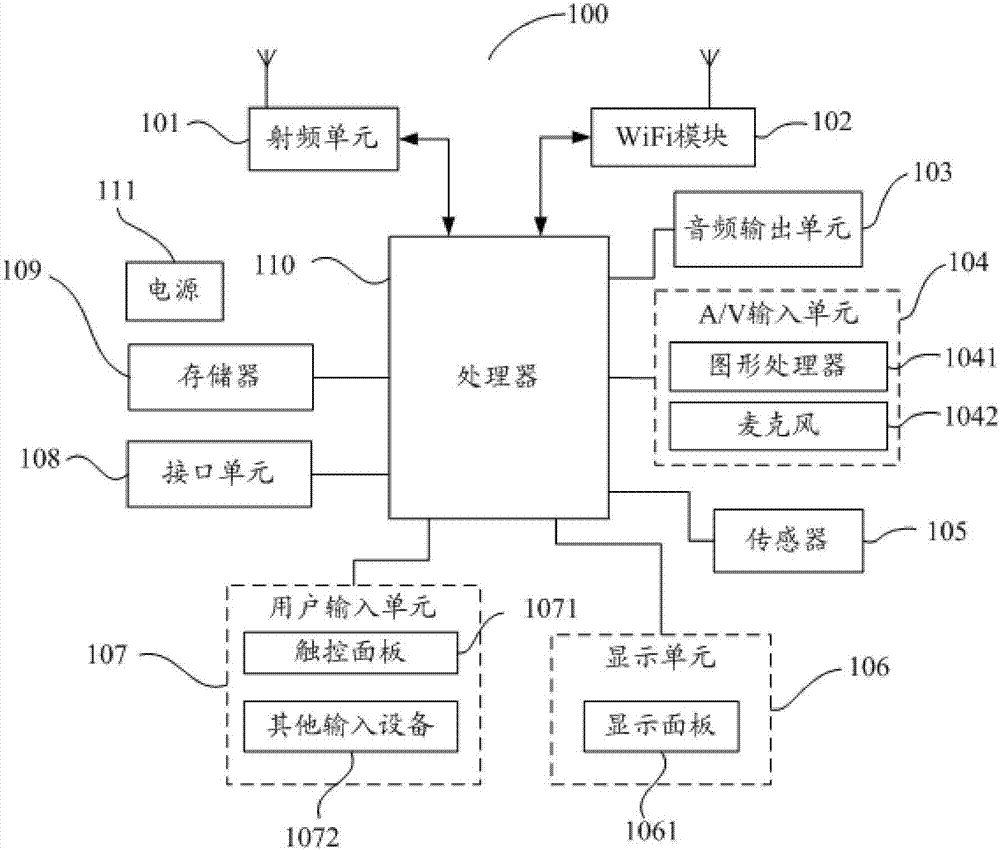

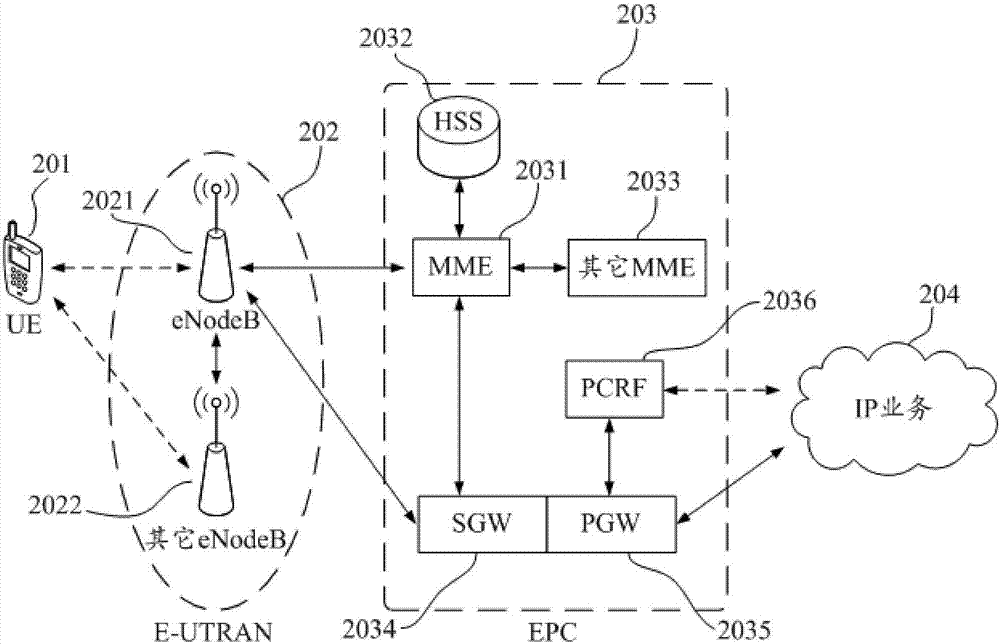

Method and system for safety detection

The embodiment of the invention discloses a method and a system for safety detection. The method is that a COUNT value is obtained; the COUNT value and a DRB ID are transmitted to an UE for check; the check result is received and the COUNT value and the DRB ID on the side of the UE are saved if abnormality occurs; and the COUNT value and the DRB ID on the side of the UE are checked. The system comprises an acquisition module 310, a transmitter module 320, a receiver module 330 and a check module, wherein the acquisition module 310 is used to acquire the COUNT value; the transmitter module 320is used to transmit the COUNT value and the DRB ID on the side of an eNB to the UE for check; the receiver module 330 is used to receive the check result of the UE and the COUNT value and the DRB ID on the side of the UE are saved if abnormality occurs; and the check module 340 is used to check the COUNT value and the DRB ID on the side of the UE. The method and the system for safety detection can overcome the problem of counter check process failure caused by realization differences of different manufacturers and can improve the reliability of the counter check process.

Owner:HUAWEI TECH CO LTD

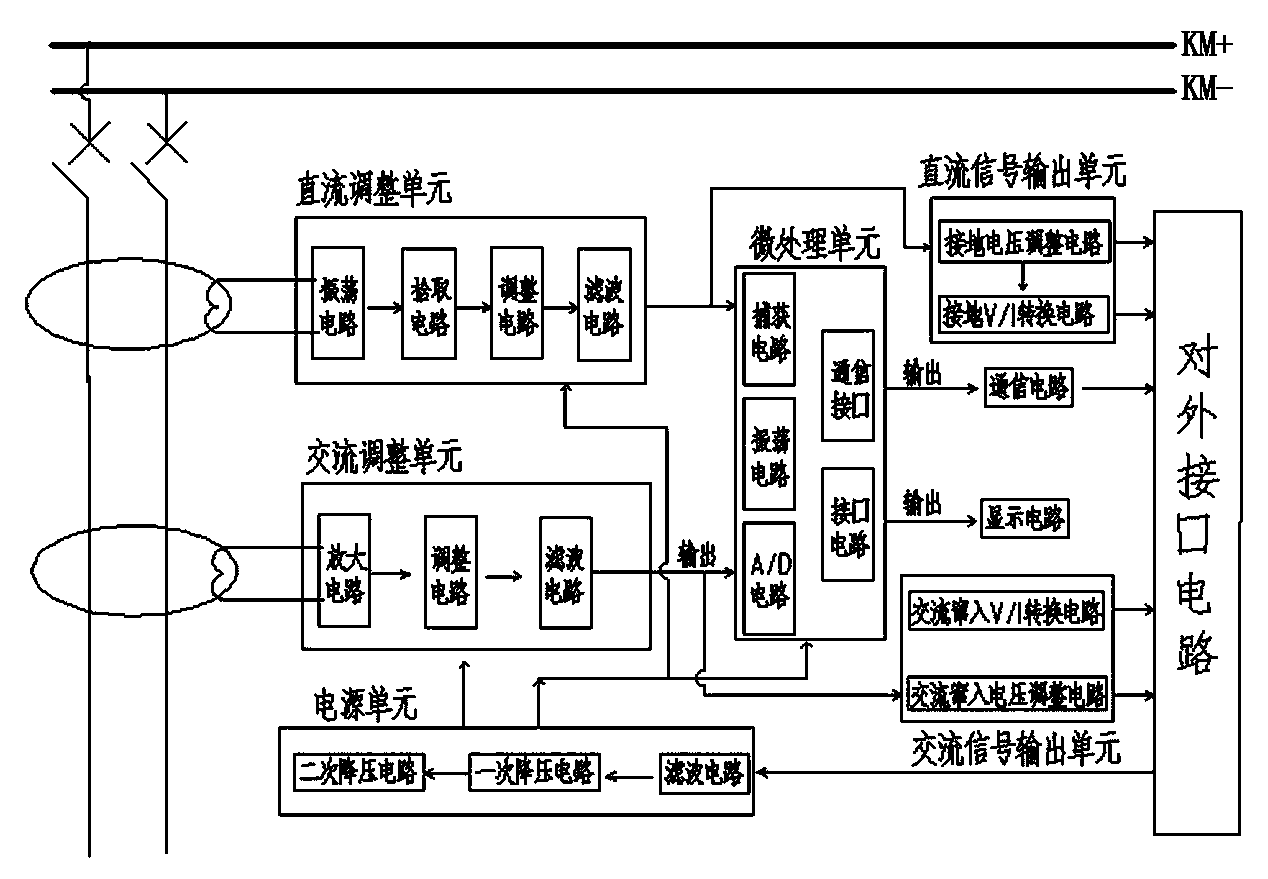

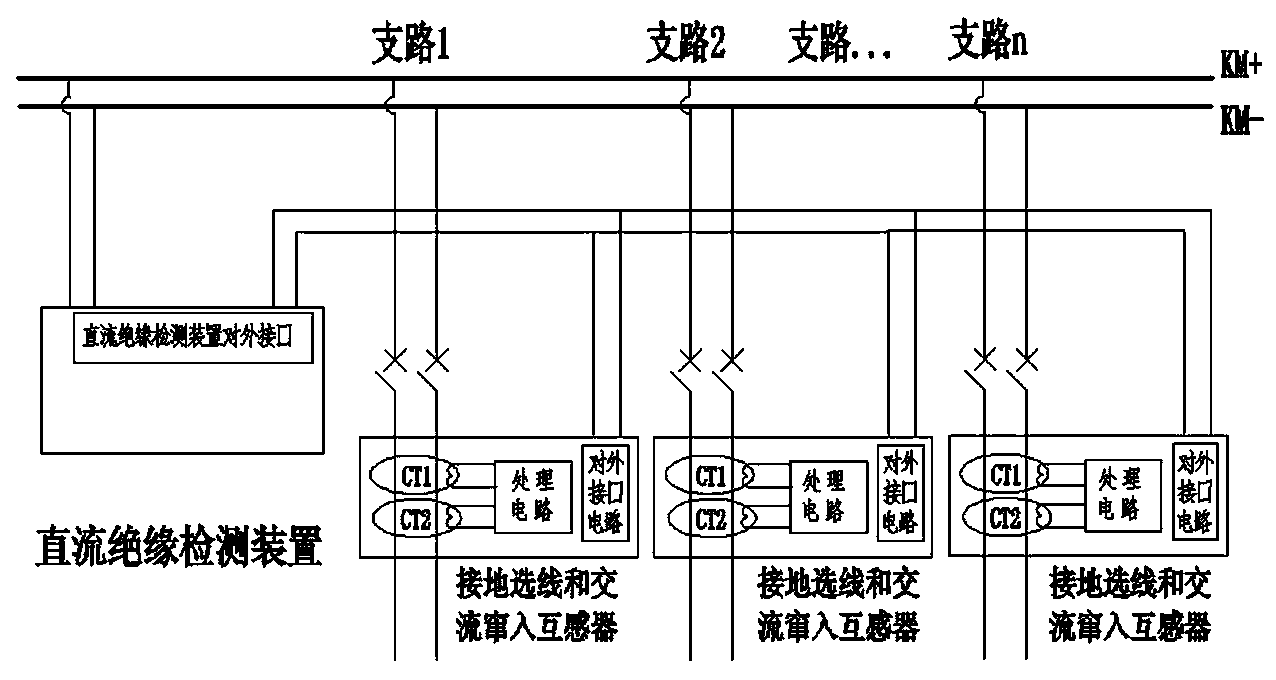

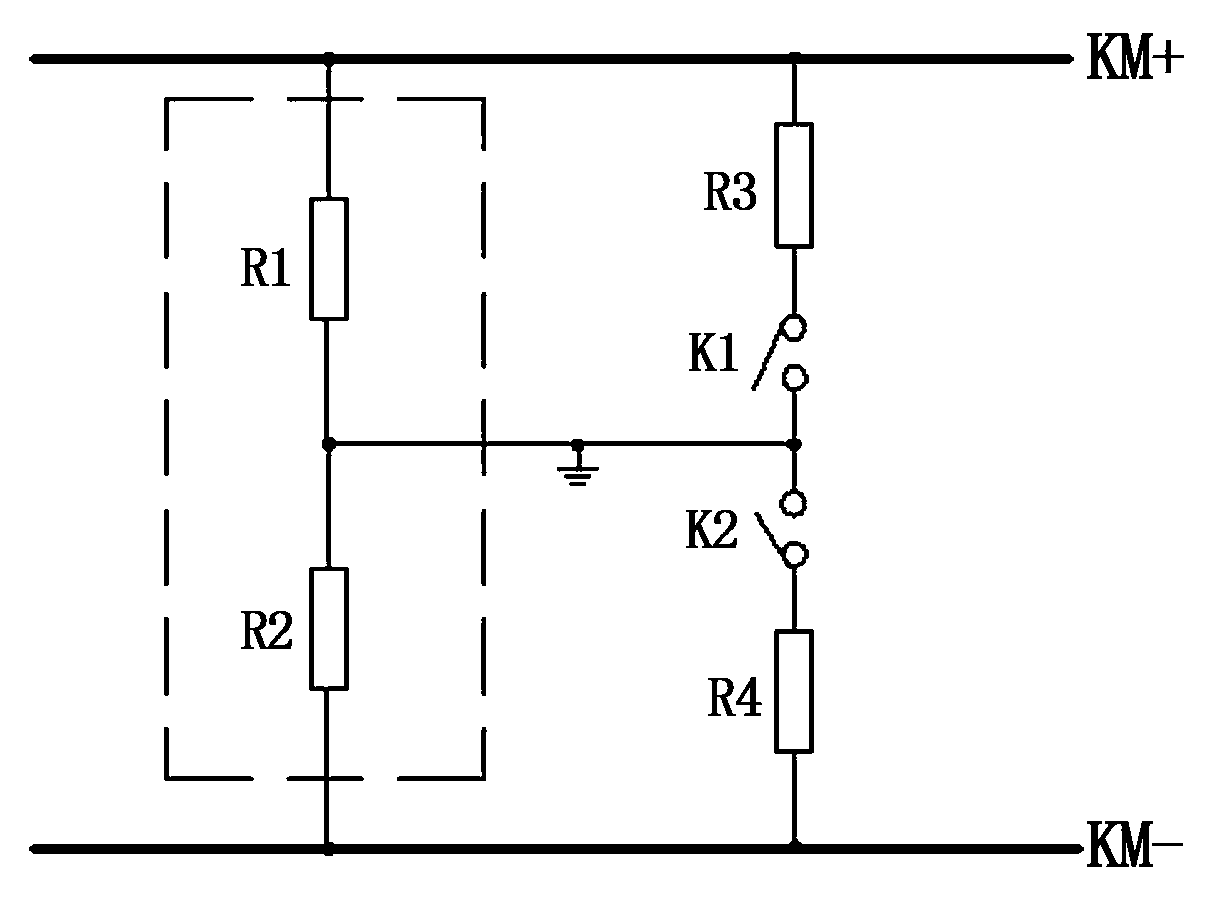

Sensor for direct current fault line selection and alternating current interlarding line selection

InactiveCN103558507AStable, safe and reliable operationImpedence measurementsFault locationSignal conditioningProcess failure

The invention relates to a sensor for direct current fault line selection and alternating current interlarding line selection. The sensor comprises at least one magnetic core or iron core for sensing a direct current or an alternating current, and a sensing signal of the magnetic core or iron core passes through a current signal conditioning unit and a micro-processing unit to be transmitted to an external interface circuit. The sensor can detect a fault branch circuit in time, provide basis for troubleshooting for overhaul personnel, enable a user to conveniently process failures as soon as possible and provide a powerful guarantee for safe, reliable and stable operation of a direct current power system.

Owner:STATE GRID CORP OF CHINA +2

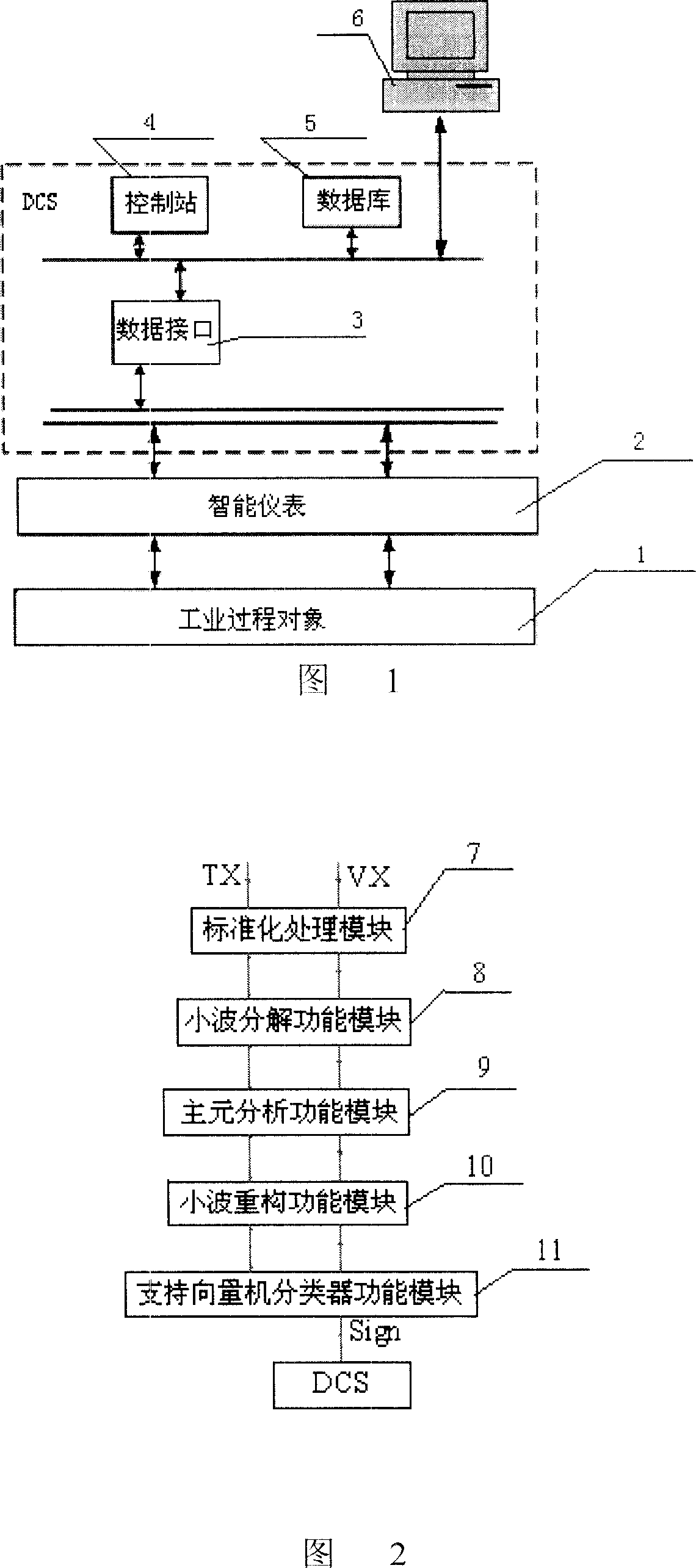

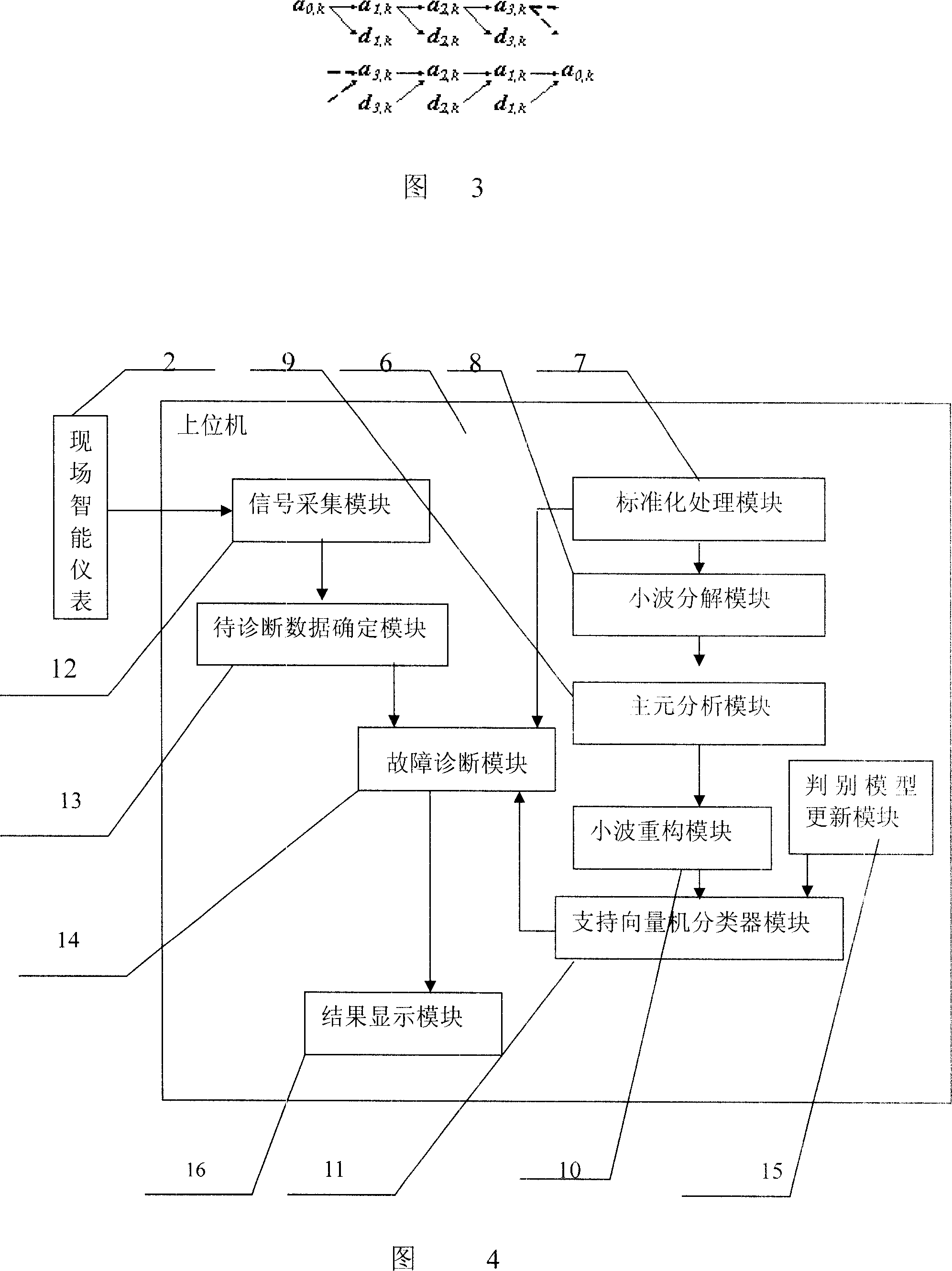

Industrial process fault diagnosis system and method based on wavelet analysis

InactiveCN1996190ASolving nonlinear classification problemsGuide production wellTotal factory controlProgramme total factory controlSupport vector machine classifierProcess failure

An industrial production process diagnostic system based on small wave analysis comprises industrial process object connected on site intelligent meter, DCS system and its upper position control machine with the DCS system made of data interface, control station, data base, the intelligent meter, DCS system and the upper position control machine connected sequentially, with the said upper position control machine composed of standardized handling module, small wave dissolving module, pivot element analysis function module, small wave restructuring module, support vector machine classifier module and diagnostic judging module. It also puts forward a failure diagnostic method. It provides an industrial production process failure diagnostic system and method with good diagnostic effect based on small wave analysis.

Owner:ZHEJIANG UNIV

Consumption method based on consumption queue, terminal and computer readable storage medium

InactiveCN107197017AAvoid missingGuaranteed successful consumptionInterprogram communicationData switching networksProcess failureCurrent consumption

The invention discloses a consumption method based on a consumption queue, a terminal and a computer readable storage medium, and relates to the technical field of communication. The consumption method based on the consumption queue comprises the following steps: obtaining current consumption information from the consumption queue of a Redis remote dictionary server; and monitoring the consumption condition of the current consumption information, and returning consumption failure information to the Redis in the case of processing failure of the current consumption information, so that the Redis adds the current consumption information to the consumption queue again. According to the consumption method disclosed by the invention, the consumption terminal monitors the consumption condition of each piece of consumption information and returns the consumption failure information to the Redis in the case of consumption failure of the consumption information, the Redis adds the information subjected to consumption failure to the consumption queue again and performs consumption processing again, until the consumption information is successfully processed. The leakage of the consumption information subjected to processing failure can be avoided, and the successful consumption of each piece of consumption information can be guaranteed.

Owner:NUBIA TECHNOLOGY CO LTD

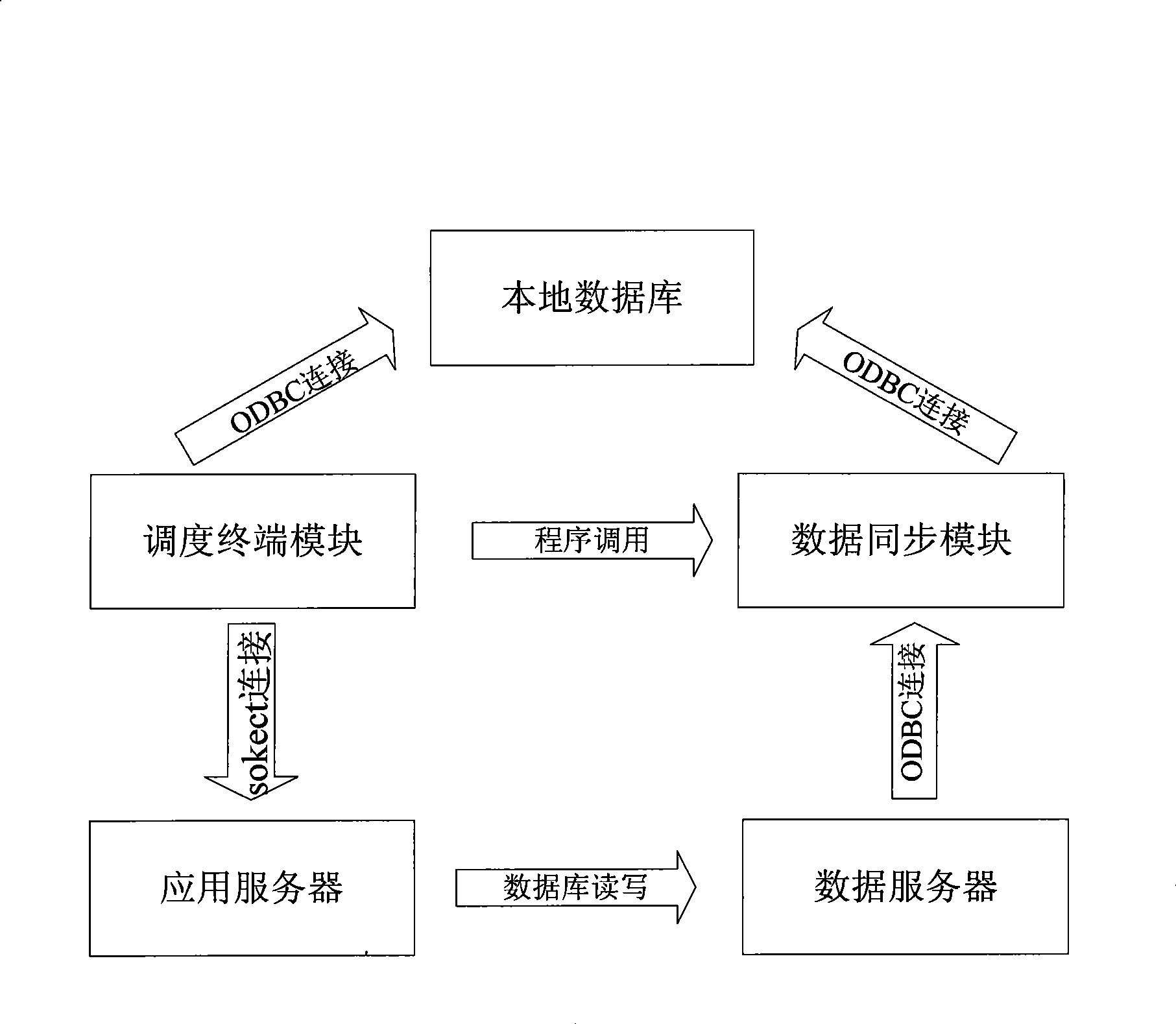

Dispatch and command emergency system of dispatching terminal and control method thereof

InactiveCN101397024AEnsure safetyReduce work stressAutomatic systemsData synchronizationApplication server

The invention relates to a dispatching and commanding emergency system of a dispatching platform. The system comprises a local database, a dispatching terminal module, an application server, a data server and a data synchronization module; the dispatching terminal module is respectively connected with the local database, the application server and the data synchronization module; the application server is connected with the data server; the data server is connected with the data synchronization module; the data synchronization module is connected with the local database. Compared with the prior art, the dispatching and commanding emergency system of a dispatching platform can dispatch and read in-time running data according to the data in the local database after failure and can carry out dispatching work even if being under an off-line state, thus improving the working efficiency, ensuring the smooth running of each dispatching section in a railway bureau as well as the safety of railway transportation, playing the role of emergency assisting on the existing TDCS (train dispatching centralized system) and making up the blank of domestic railway transportation system during processing failure emergency.

Owner:CASCO SIGNAL

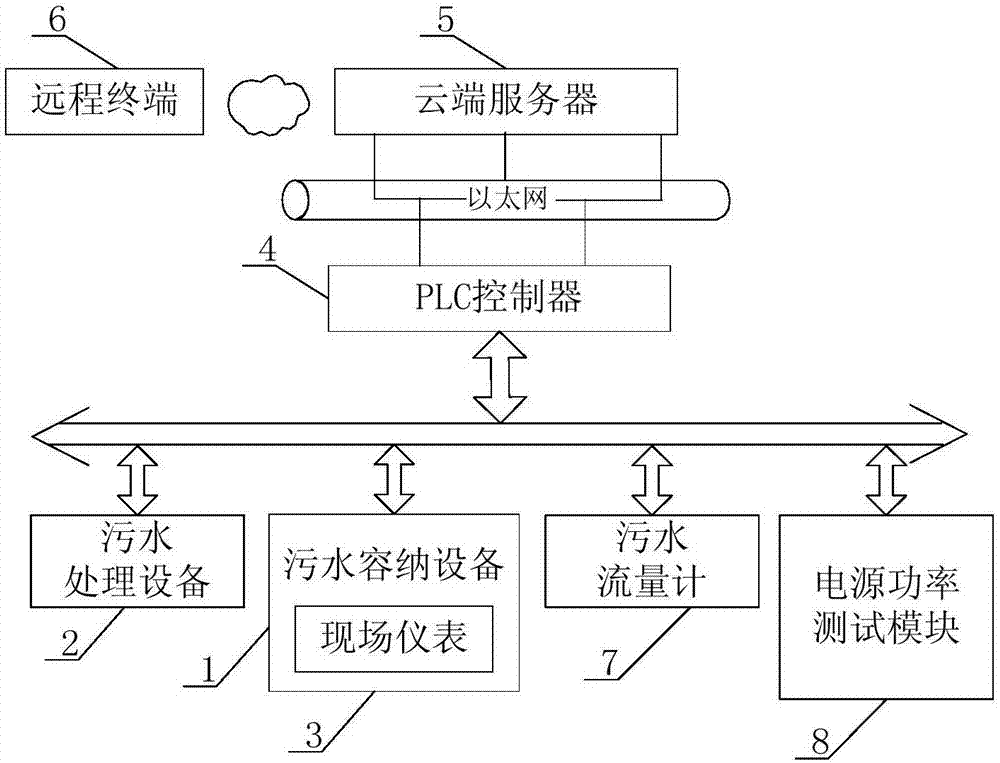

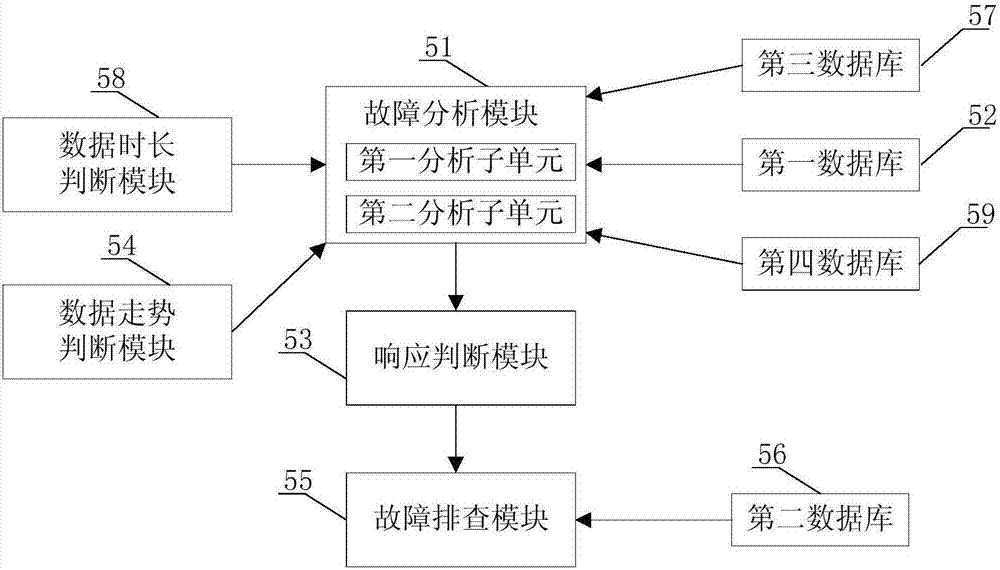

Sewage processing system based on cloud data monitoring

ActiveCN107357243AEasy to operateEasy to understand the real-time situationProgramme control in sequence/logic controllersProcess failureSewage

The invention discloses a sewage processing system based on cloud data monitoring. The sewage processing system based on the cloud data monitoring comprises a sewage processing device, an on-site instrument, a PLC controller, a cloud server and a remote terminal. The cloud server comprises a fault analysis module, a response determination module, a data trend determination module and a data checking module. The sewage processing system based on cloud data monitoring is more intelligent, easy to operate and is convenient for working staff to process failures as quickly as possible. The technical staff can monitor a production state on site without going to the site personally, can perform real-time tracking and maintenance on site, can timely check and maintain when the sewage processing device is failed, and guarantees normalization of the device operation.

Owner:苏州冉生电气自动化科技有限公司

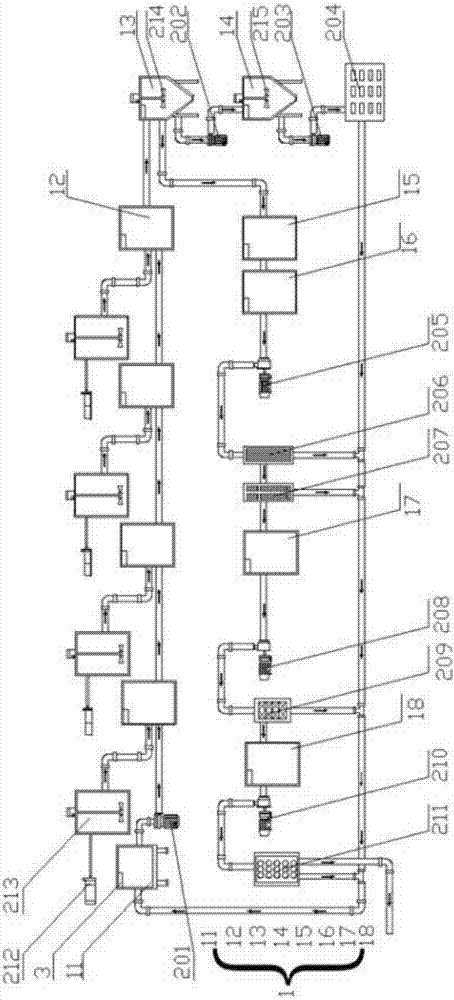

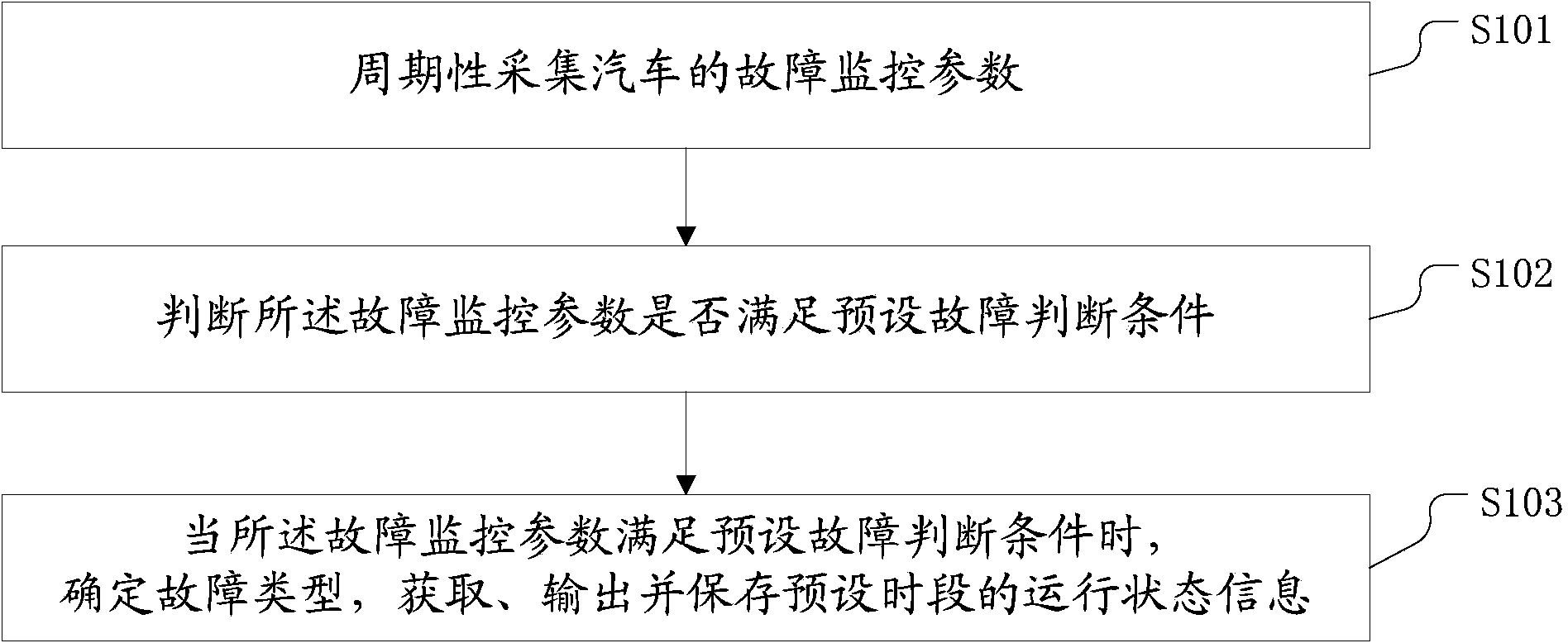

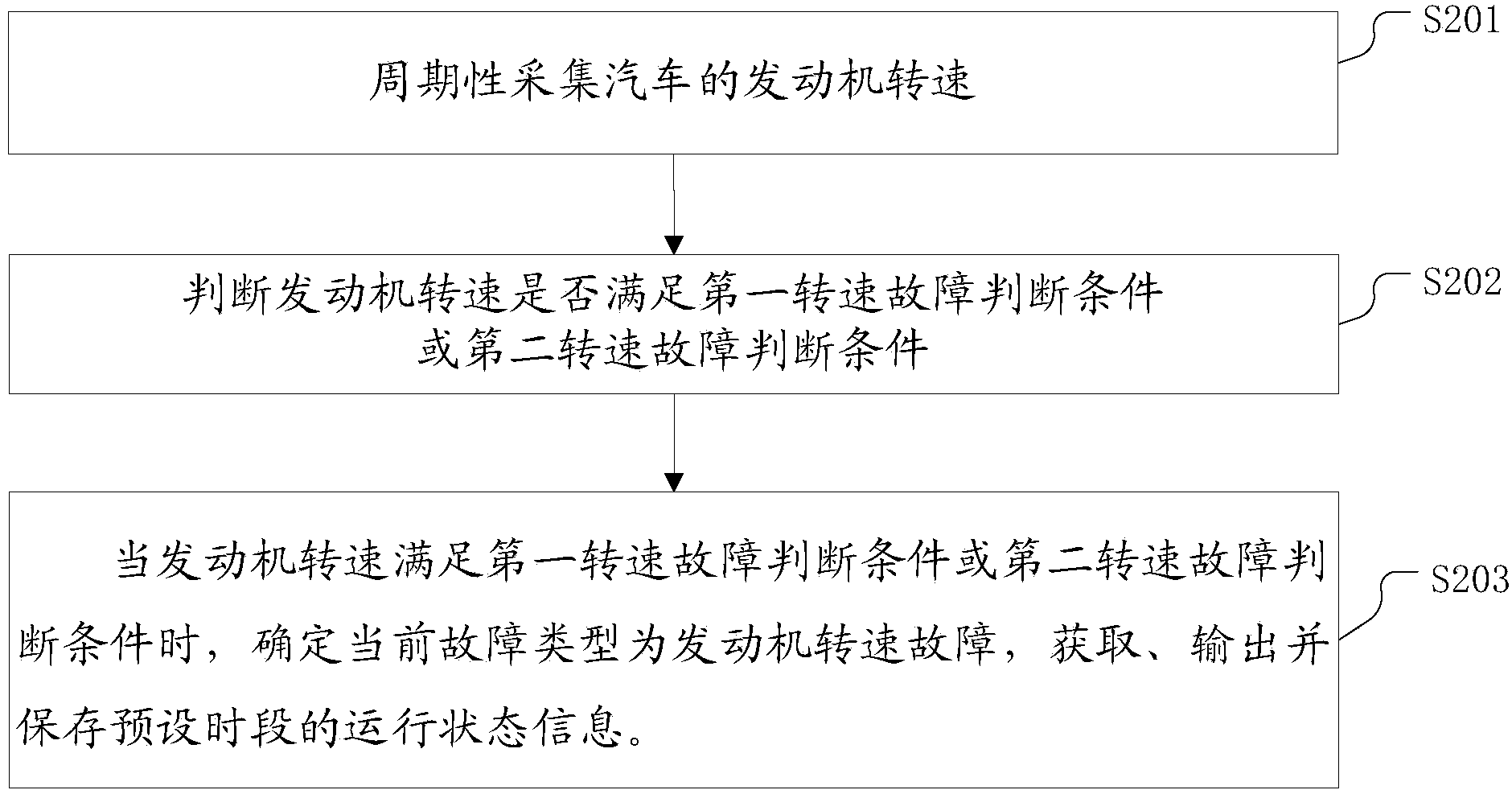

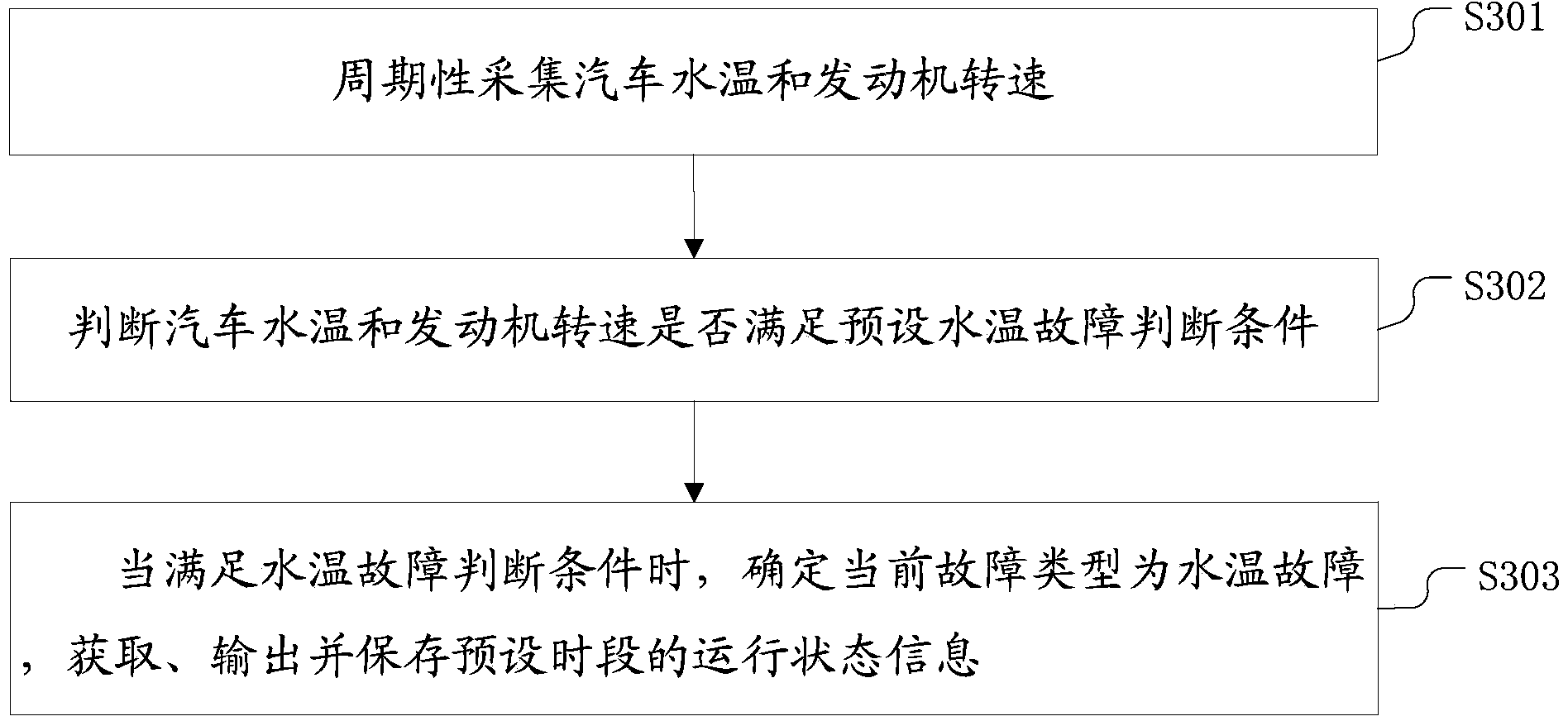

Method and device for detecting vehicle failure

The invention discloses a method and a device for detecting a vehicle failure. Whether a failure monitoring parameter satisfies a preset failure judging condition or not is judged by acquiring the failure monitoring parameter of a vehicle, a failure type is determined when the failure monitoring parameter satisfies the preset failure judging condition, and the running state information within a preset time interval is acquired, output and stored, wherein the failure monitoring parameter comprises one of engine rotation speed, vehicle water temperature, travelling speed and engine oil pressure. By the technical scheme, the corresponding failure type can be determined when a failure takes place, i.e. when the failure monitoring parameter satisfies the preset failure judging condition, and the running state information within the related time interval is output and stored, so that related equipment or technical staff can accurately position a failure by analyzing the running state information, the corresponding measure can be quickly taken to remove the failure, and the problems of the prior art are solved.

Owner:BEIJING JINGWEI HIRAIN TECH CO INC

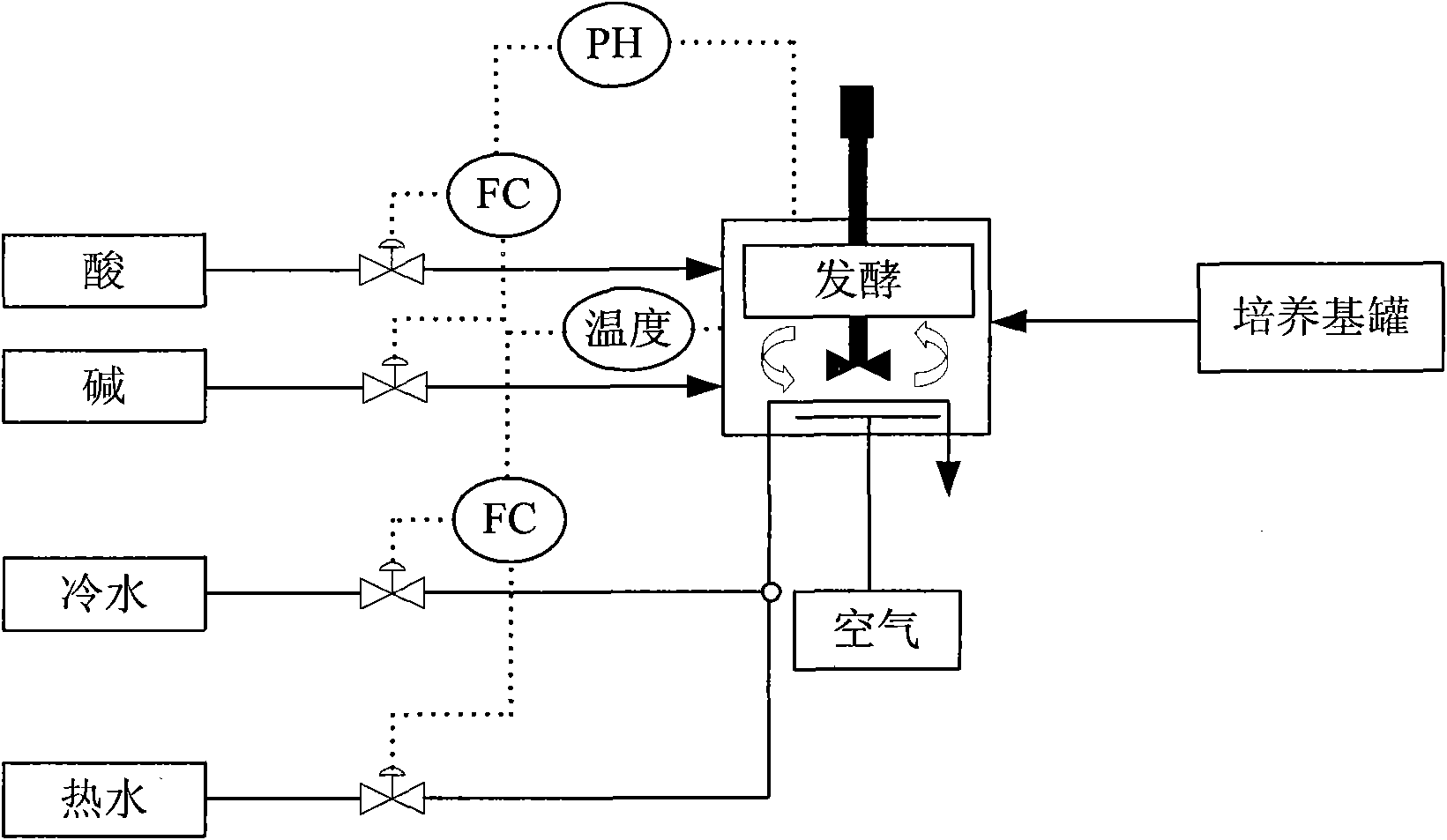

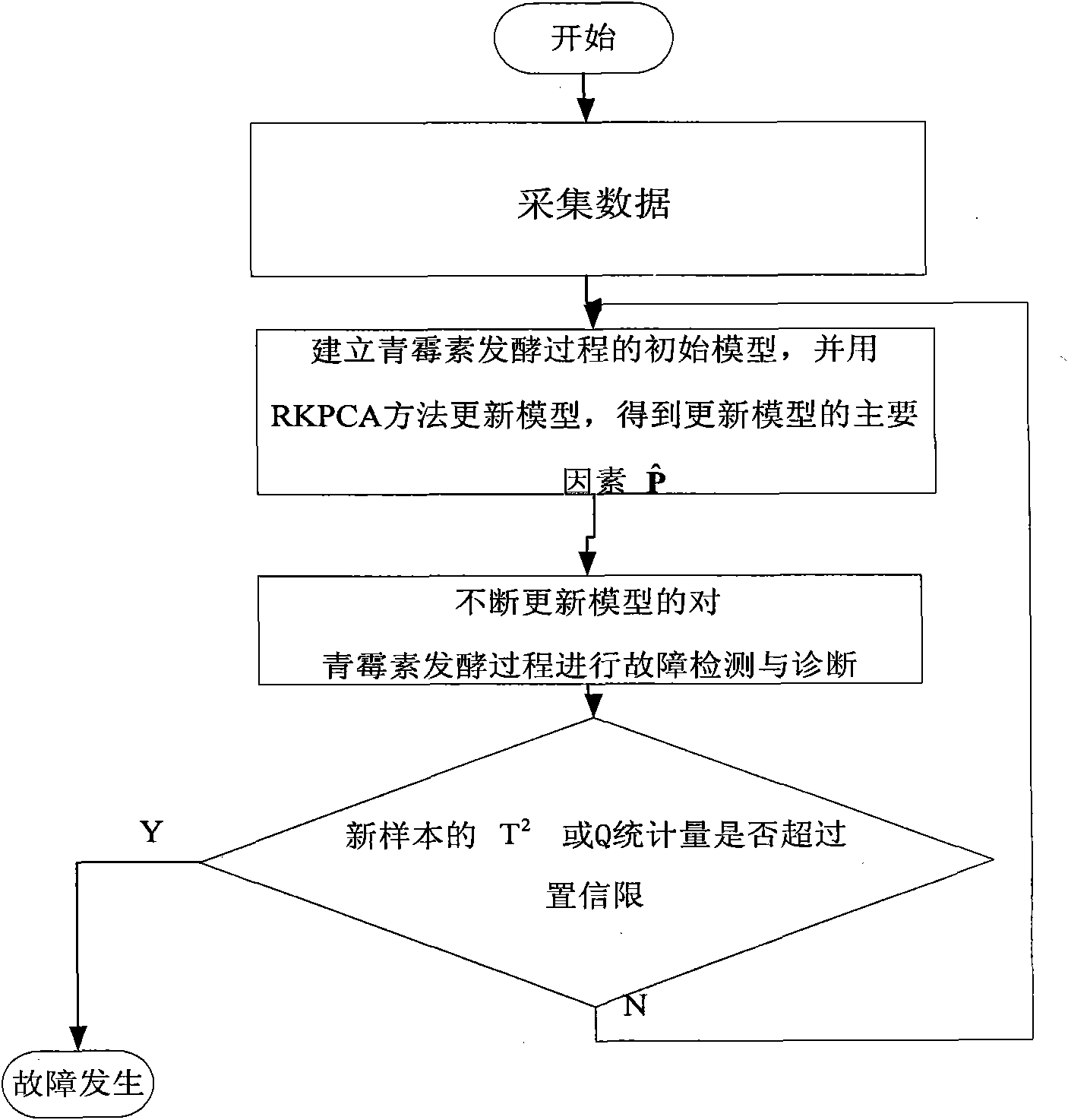

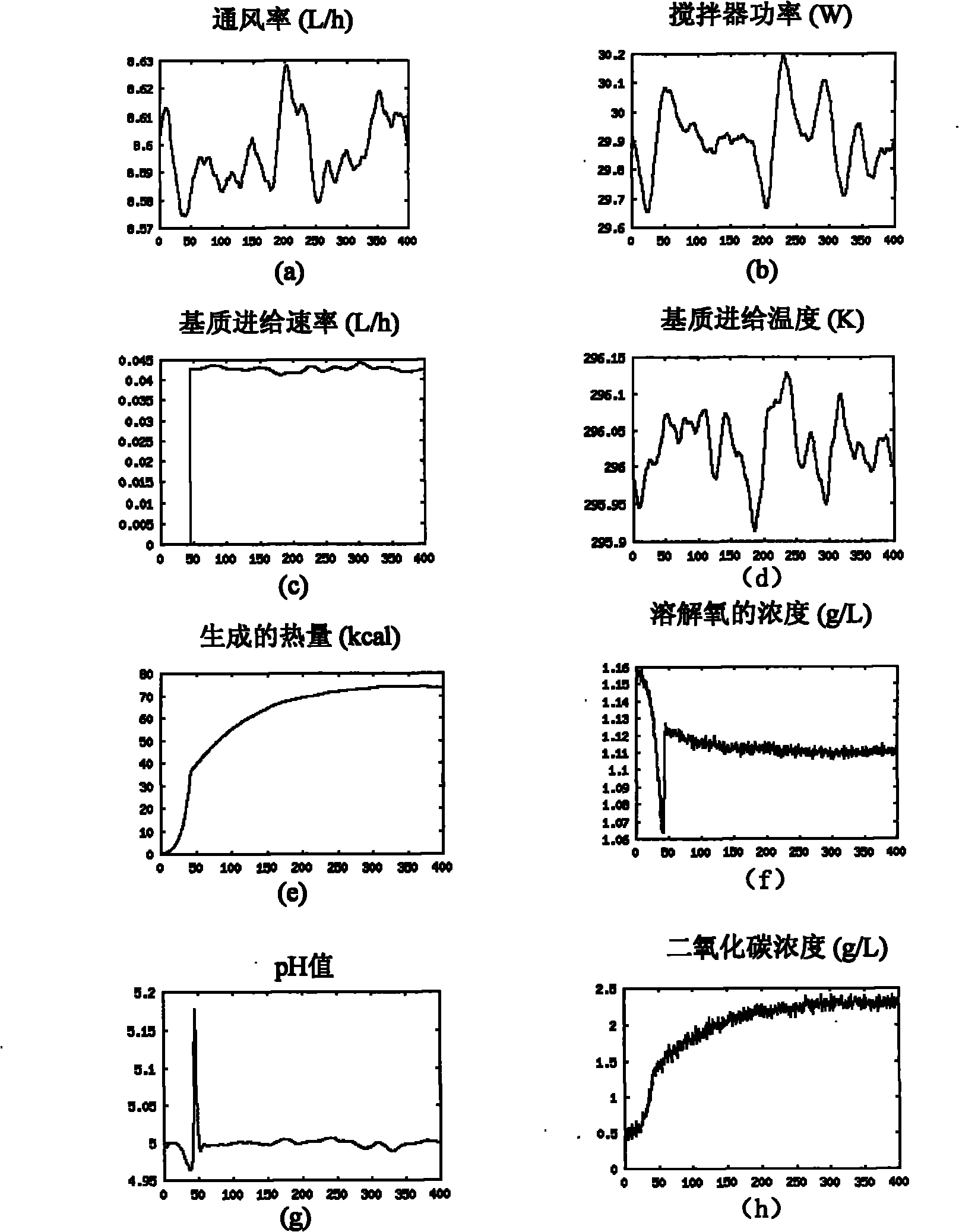

Penicillin fermentation process failure monitoring method based on recursive kernel principal component analysis

InactiveCN101964021ASolve nonlinear problemsReduce false alarmsSpecial data processing applicationsCovarianceRecursive computation

The invention relates to a penicillin fermentation process failure monitoring method based on recursive kernel principal component analysis (RKPCA), which belongs to the technical field of failure monitoring and diagnosis. The method comprises the following steps: acquiring the ventilation rate, stirrer power, substrate feed rate, substrate feed temperature, generated heat quantity, concentrationof dissolved oxygen, pH value and concentration of carbon dioxide; and establishing an initial monitoring model by using the first N numbered standardized samples, updating the model by a RKPCA method, and computing the characteristic vectors to detect and diagnose the failure in the process of continuous annealing, wherein when the T2 statistics and SPE statistics exceed the respective control limit, judging that a failure exists, and otherwise, judging that the whole process is normal. The method mainly solves the problems of data nonlinearity and time variability; and the RKPCA method is used for updating the model by carrying out recursive computation on the characteristic values and characteristic vectors of the training data covariance. The result indicates that the method can greatly reduce the false alarm rate and enhance the failure detection accuracy.

Owner:NORTHEASTERN UNIV

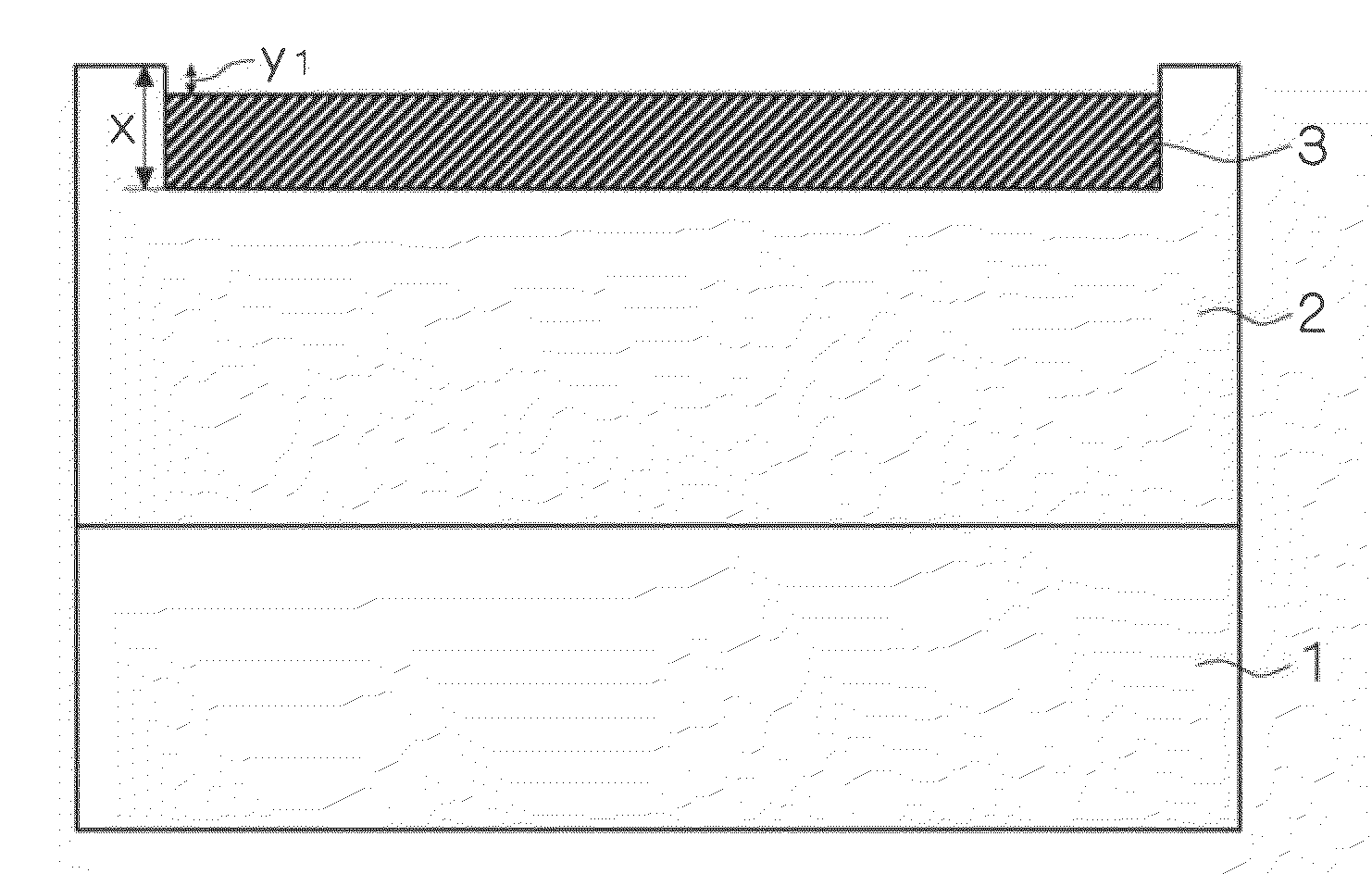

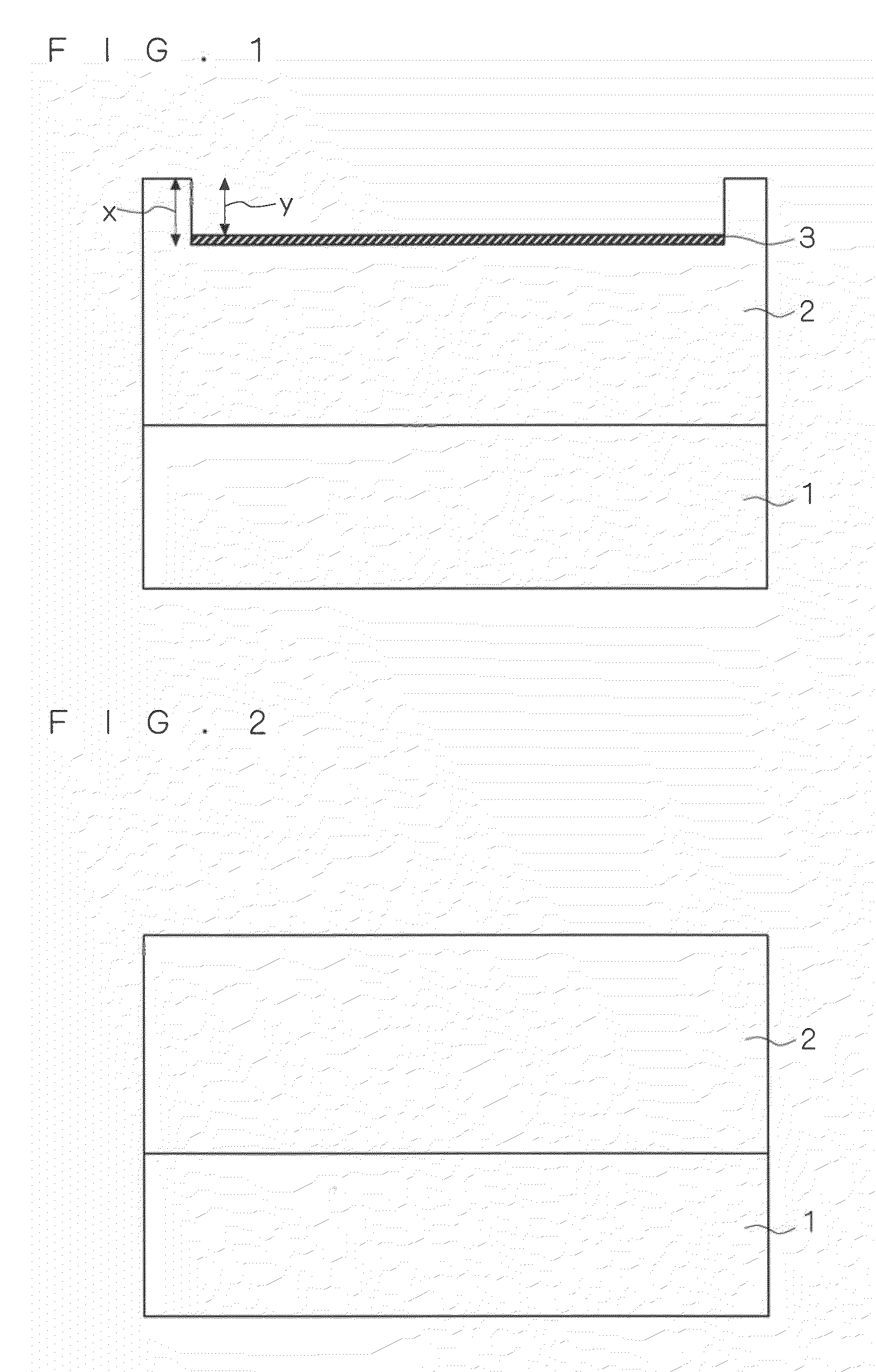

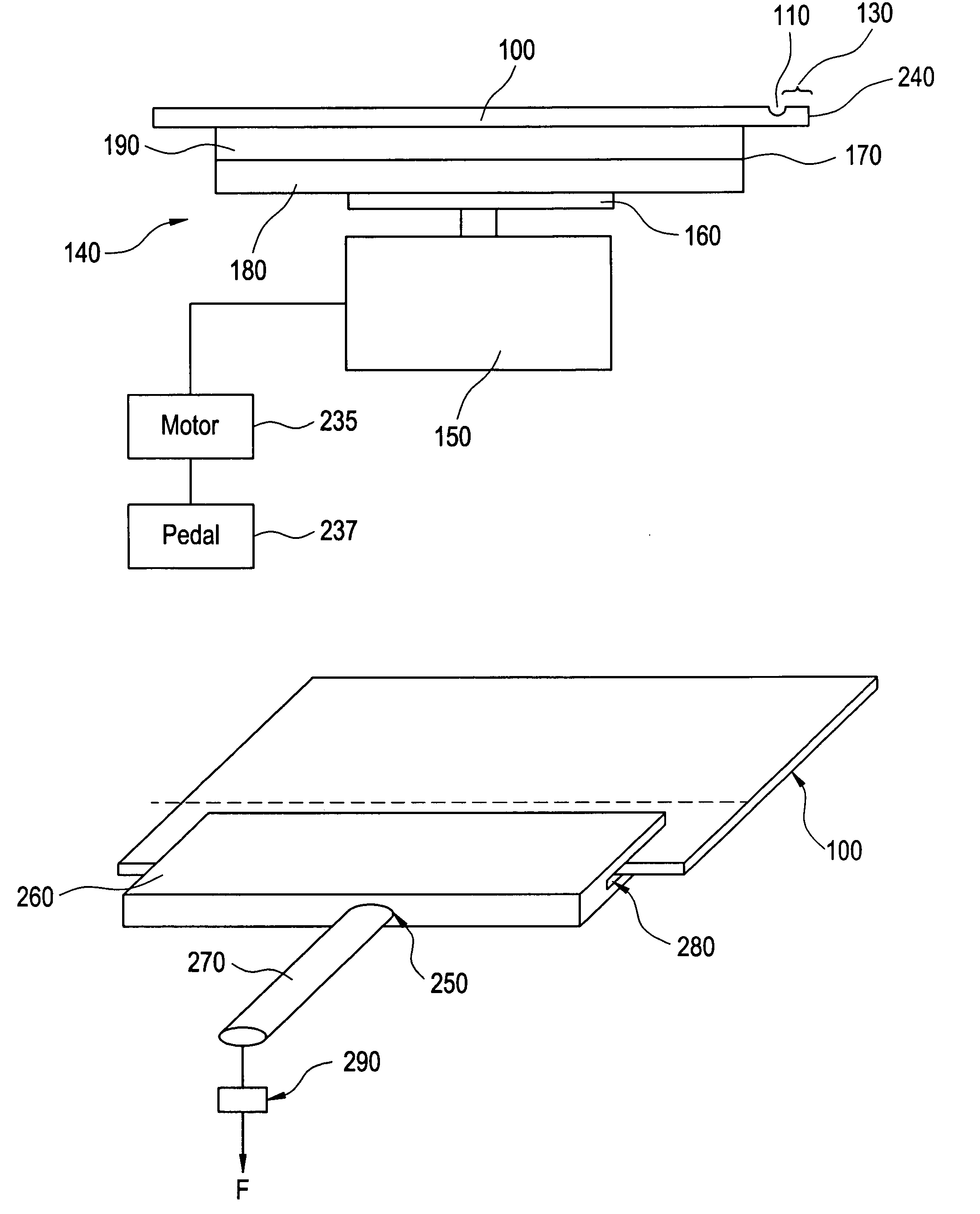

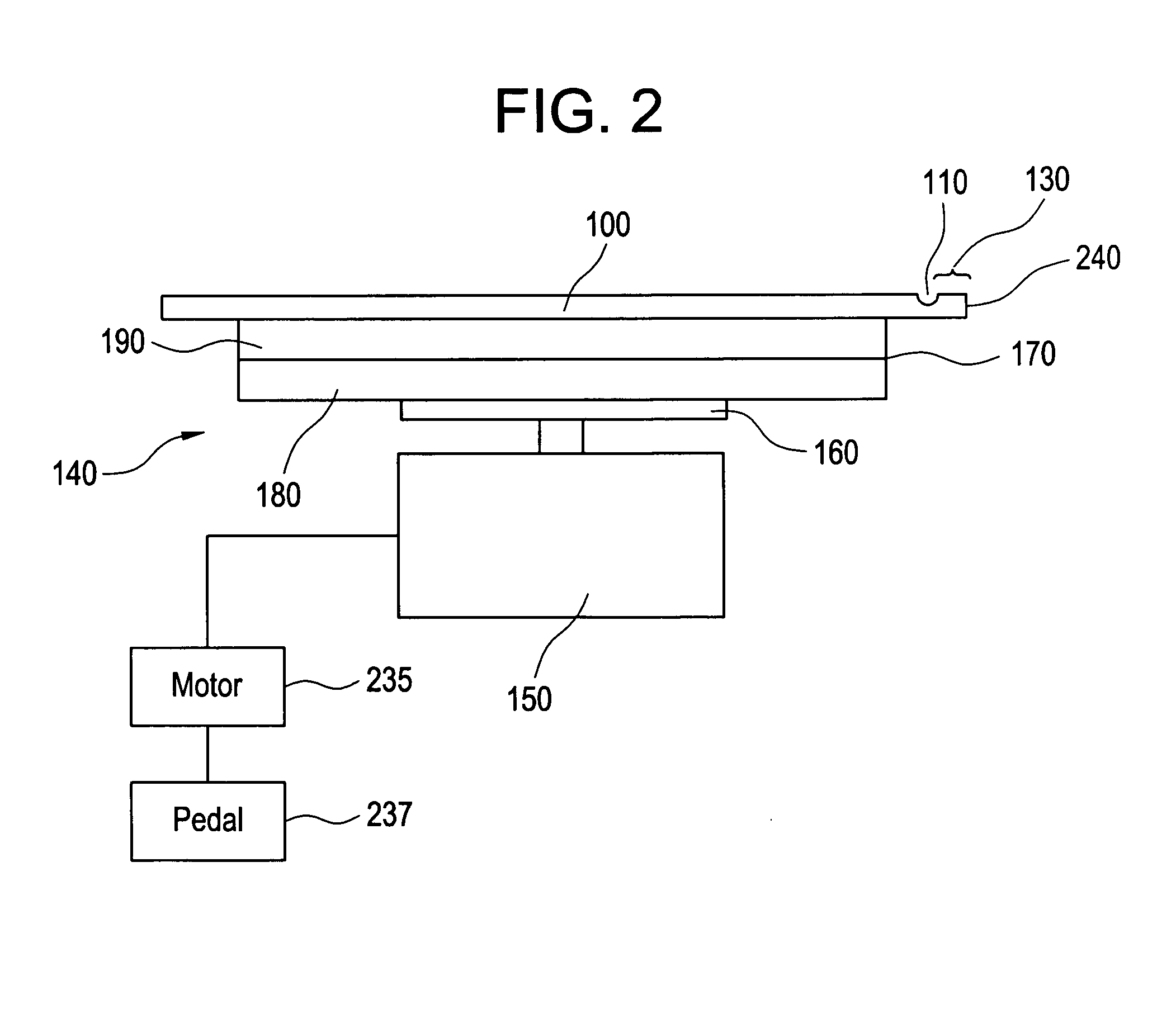

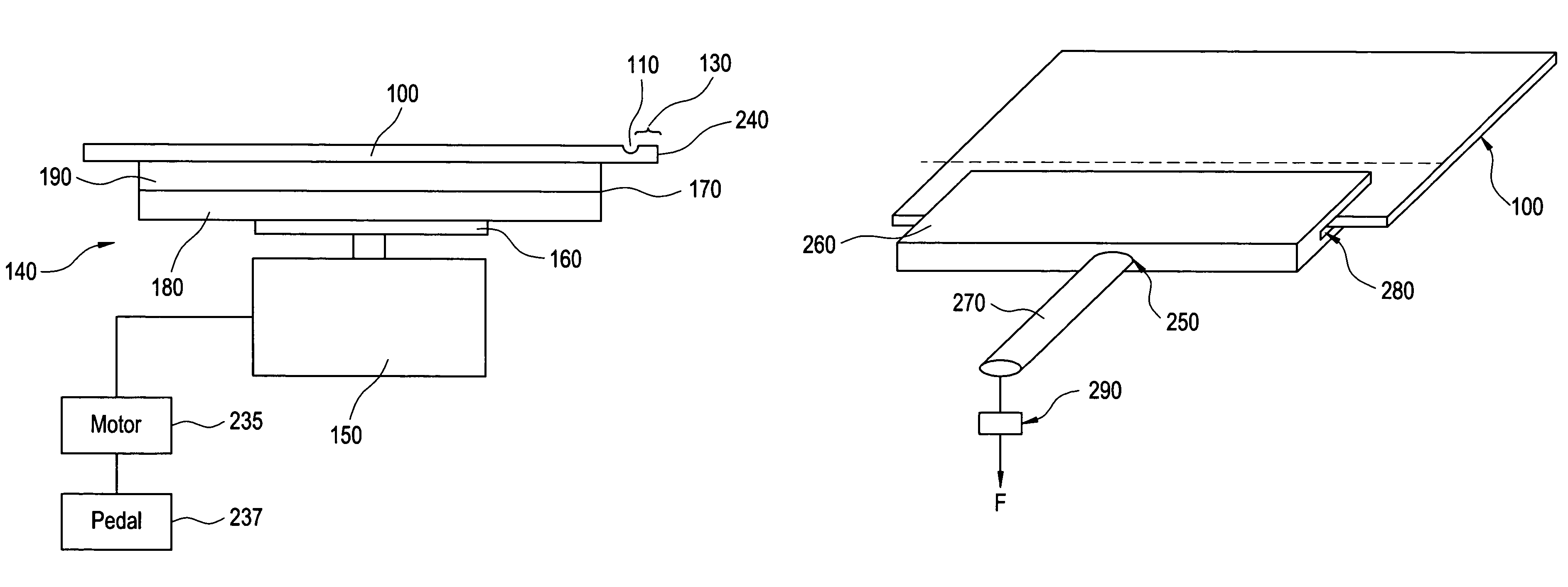

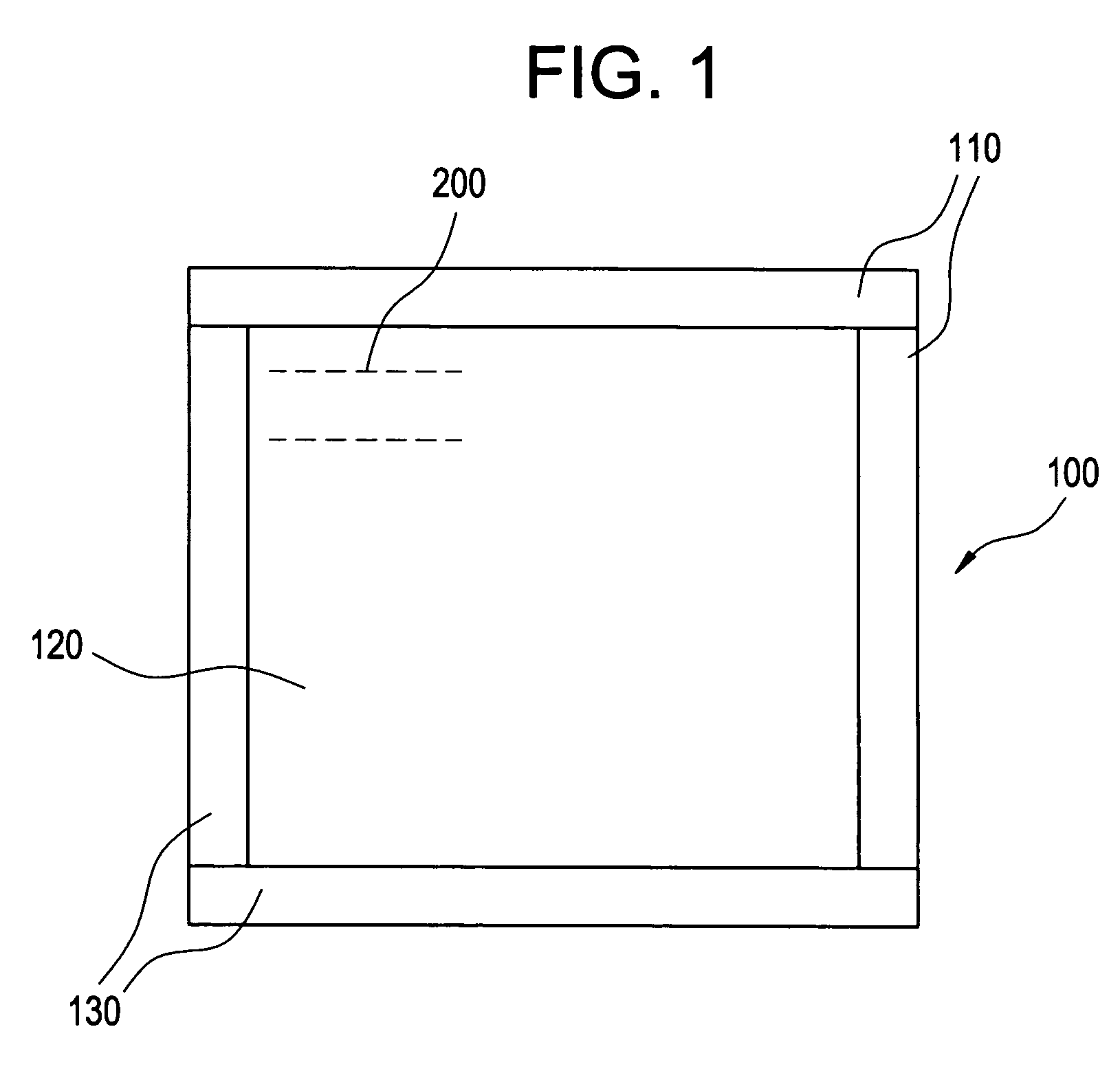

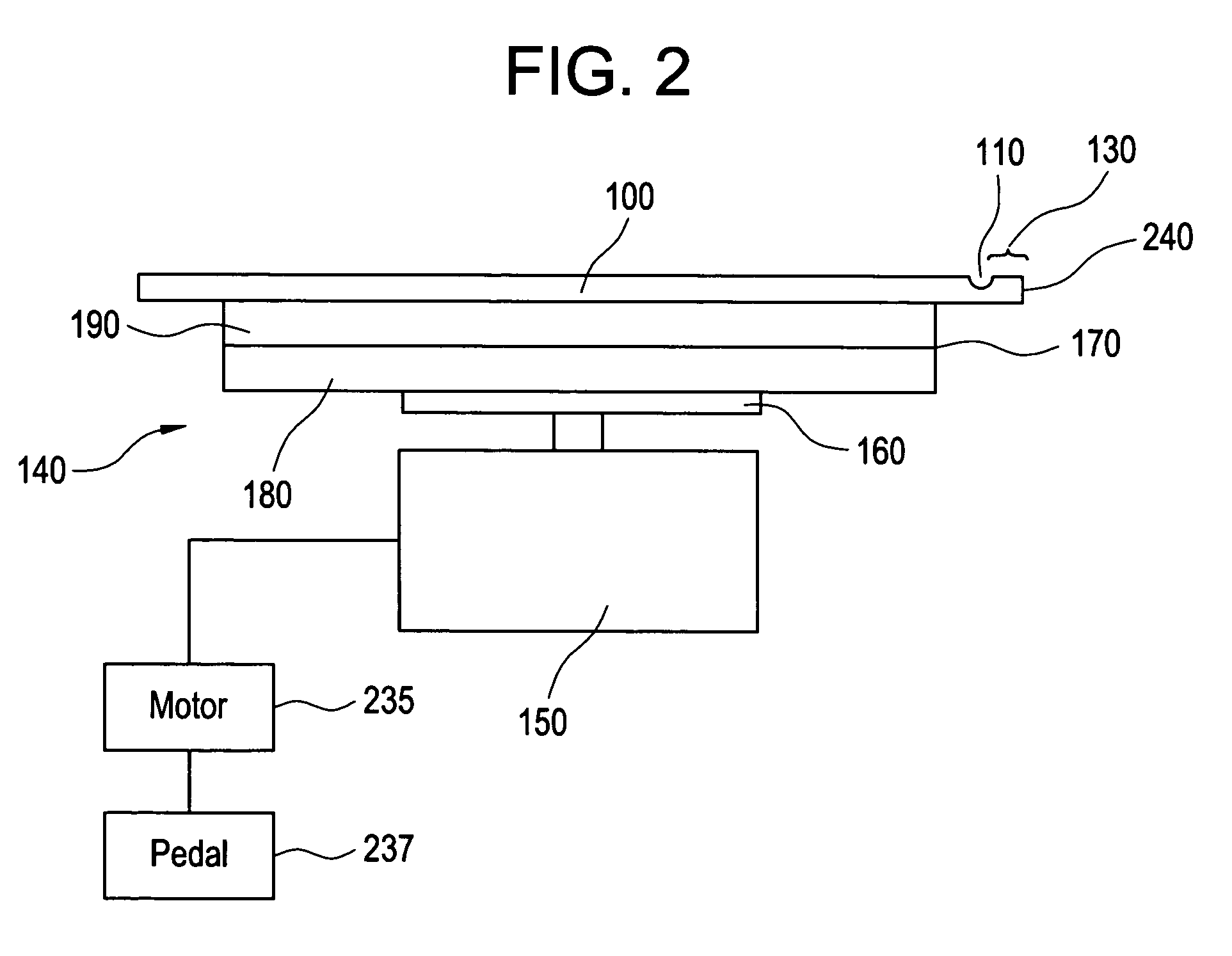

Apparatus and method for glass separation for flat panel displays

InactiveUS6962279B1Minimize separation defectMore separatedConveyorsGlass severing apparatusDisplay deviceProcess failure

A method and apparatus for separating glass panels that minimizes process failures and improves separation process consistency by utilizing a separation handle which applies the minimal pressure necessary to remove the edge portion from the glass panel. The glass panel is cut along the score line, which outlines the edge portions of the glass panel to be removed. The panel is placed upon the separating apparatus, which pumps nitrogen along the underside of the glass panel, causing the glass panel to float above the apparatus. Locating pins are inserted to position the panel on the stage. Once the glass panel is in place, a vacuum sucks the panel against the stage, holding the panel tightly against the stage. The separation handle is then inserted over the edge portion to be removed. A measured force is applied to the handle, with the force incrementally increased until the slow, controllable separation of the edge is achieved. This level of force is maintained until separation is complete.

Owner:GE MEDICAL SYST GLOBAL TECH CO LLC

Method for printing bar codes on iridescent paper

InactiveCN101973169AReduce sheddingReduce accumulationPhotomechanical apparatusOther printing apparatusInfrared lampBarcode

The invention discloses a method for printing bar codes on iridescent paper. The method comprises the following steps of: making films with the bar code pattern into a PS (Photoshop) printing plate; making a on-the-spot bar code pattern 1 to 2 mm longer than each side of the bar code pattern and making a photosensitive resin flexographic plate with the on-the-spot bar code pattern; printing a layer of UV (Ultra Voilet) base oil on the iridescent paper by utilizing an offset press and a polishing set and irradiating the printed UV base oil for drying through an infrared lamp; printing a layer of bar codes at the position the UV base oil printed on the surface of the iridescent paper by utilizing an offset press first set and irradiating for solidification and drying through an ultraviolet lamp; and printing a layer of UV gloss oil or UV matt oil on the solidified and dried surface of the bar codes, and solidifying and drying the printed UV gloss oil or the UV matt oil through the ultraviolet lamp to obtain the iridescent paper printed with the bar codes. The method has the characteristic of less printing process failure; and the bar codes printed on the iridescent paper according to the method has the characteristics of smooth ink layers, good hand touch and easy recognition.

Owner:SHAANXI UNIV OF SCI & TECH

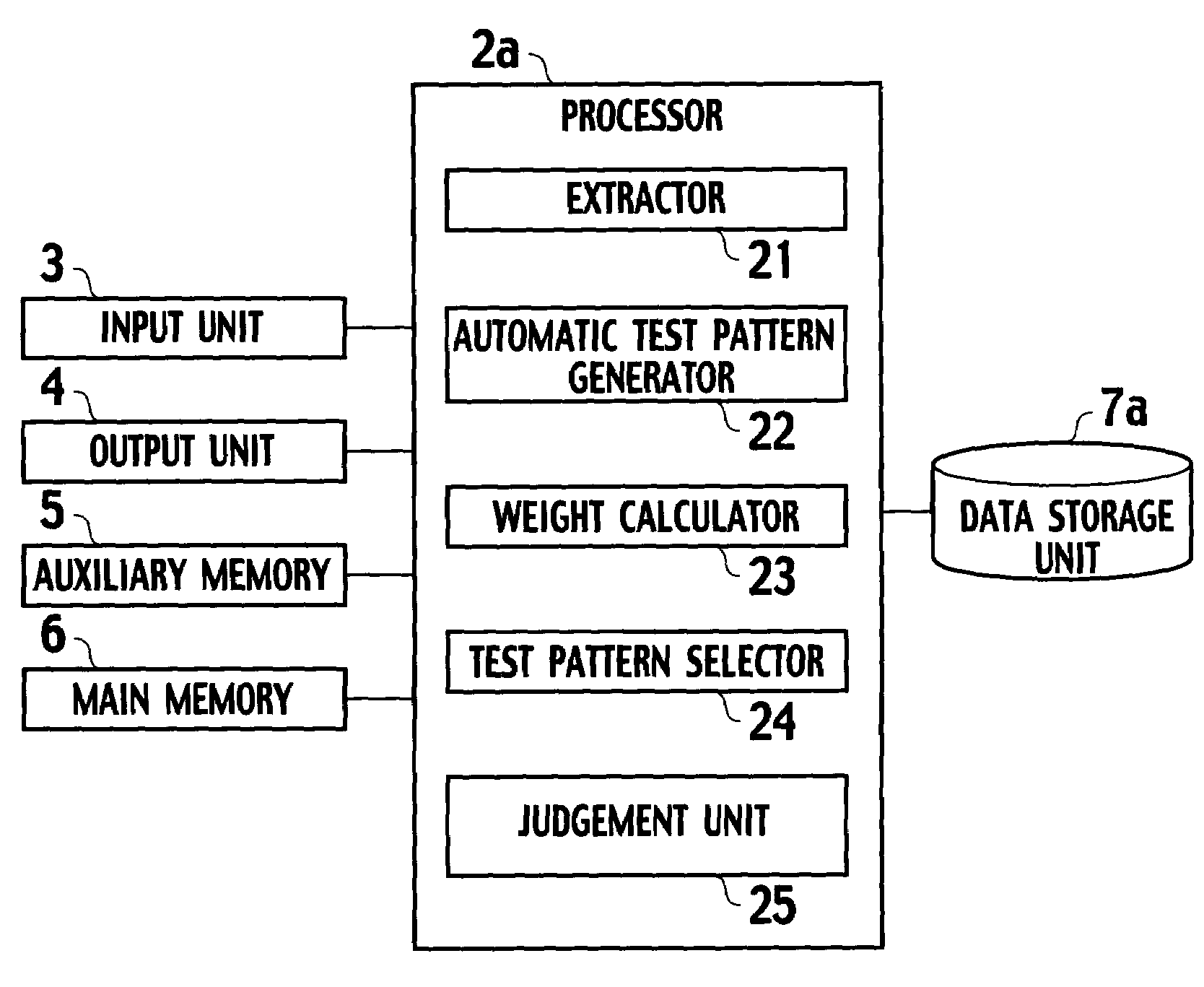

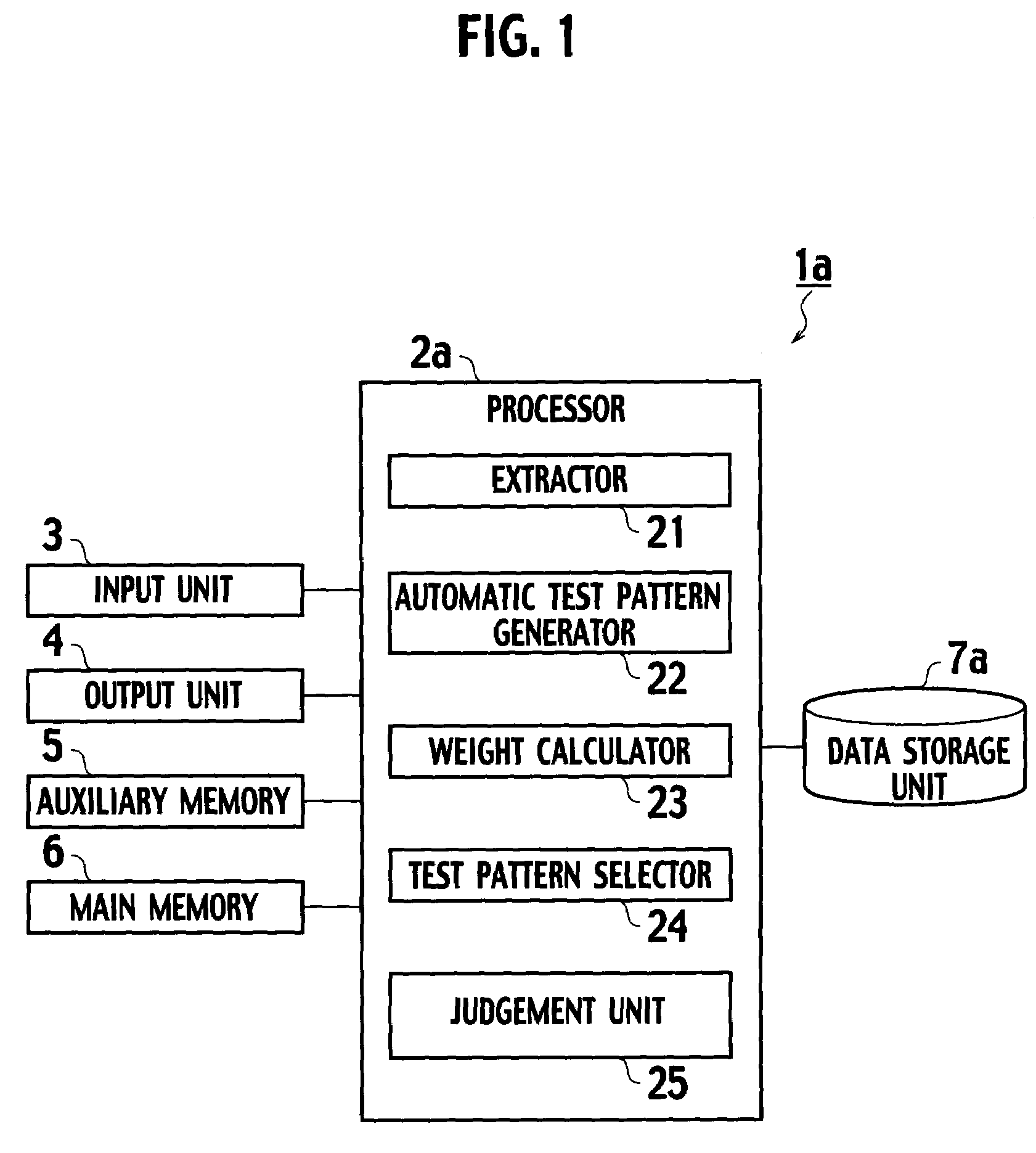

Test pattern generating apparatus, method for automatically generating test patterns and computer program product for executing an application for a test pattern generating apparatus

InactiveUS7406645B2Electronic circuit testingError detection/correctionCircuit under testProcess failure

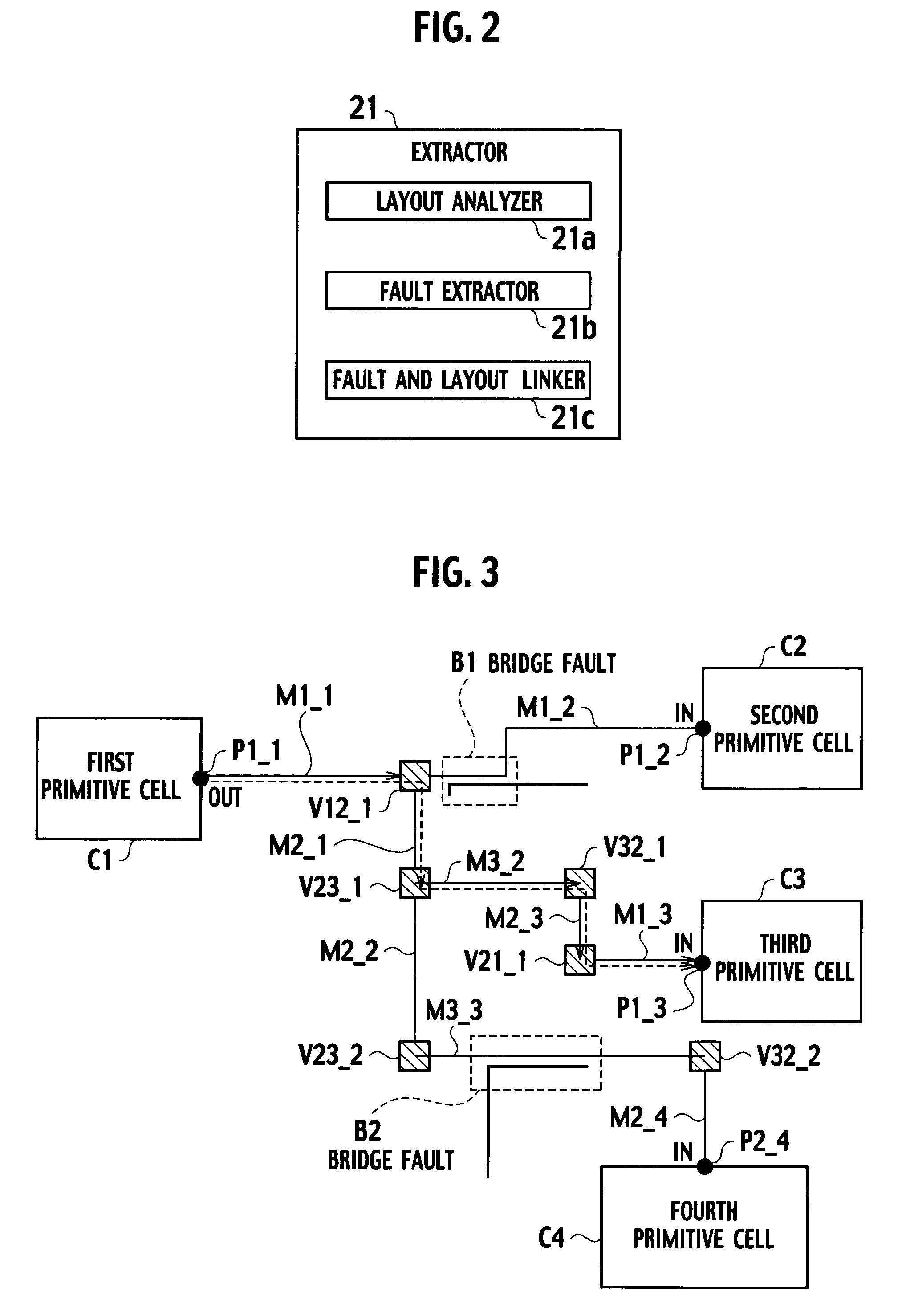

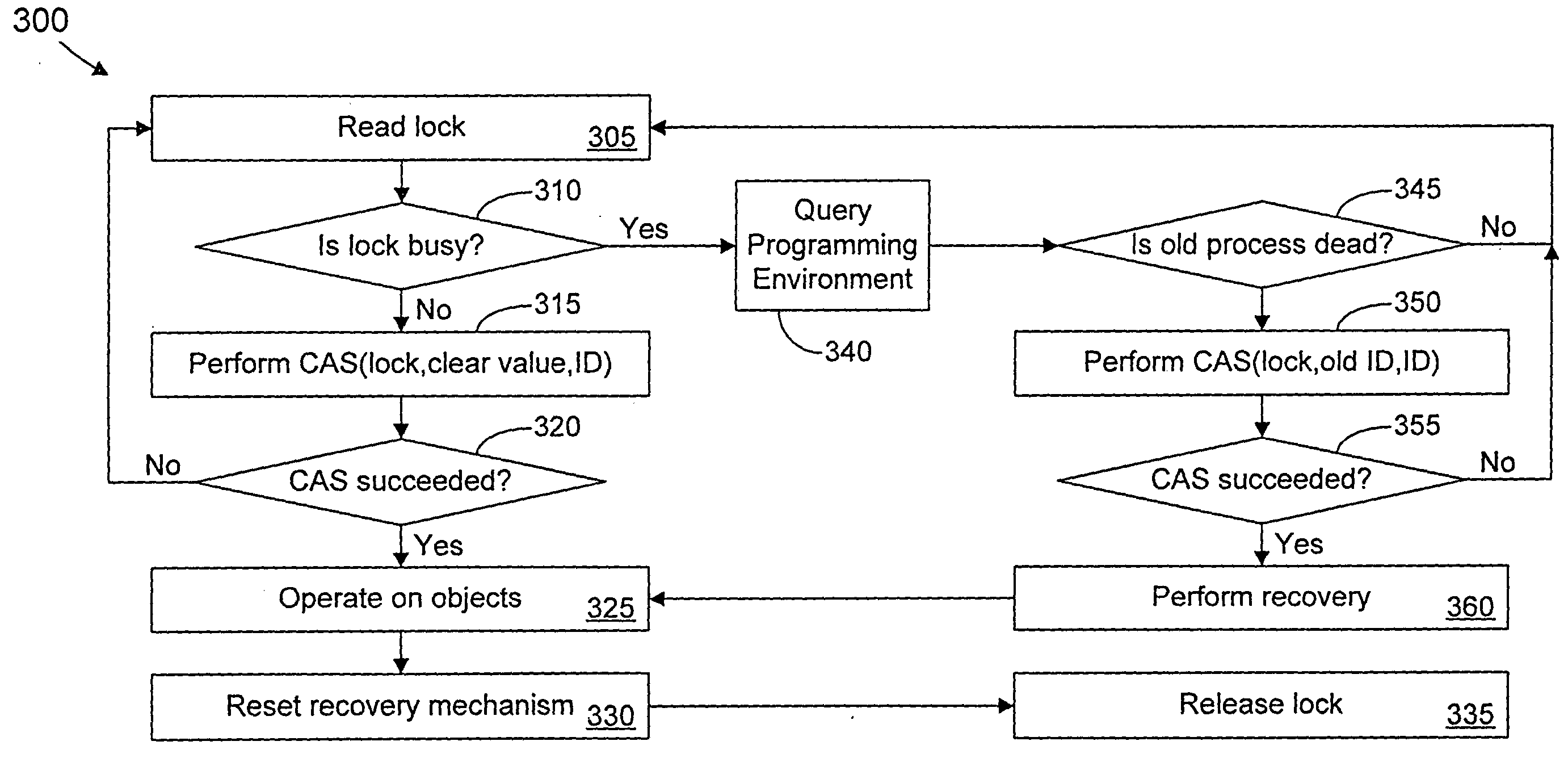

A test pattern generating apparatus includes an extractor configured to extract a plurality of layout parameters (elements) of a circuit under test based on gate net information and layout information of the circuit, and to link the layout parameters (elements) with corresponding fault models respectively. A weight calculator is configured to calculate a weight for each fault model linked with the layout parameters (elements) for both a plurality of undetected faults of the fault model and a plurality of faults detected by a plurality of test patterns, based on process failure (defect) information and layout parameter (element) information. An automatic test pattern generator is configured to generate the test patterns in accordance with the weight of each fault model linked with the layout parameters (elements).

Owner:KK TOSHIBA

Fault tolerant mutual exclusion locks for shared memory systems

InactiveUS20050066064A1Unauthorized memory use protectionMultiprogramming arrangementsProcess failureUnavailability

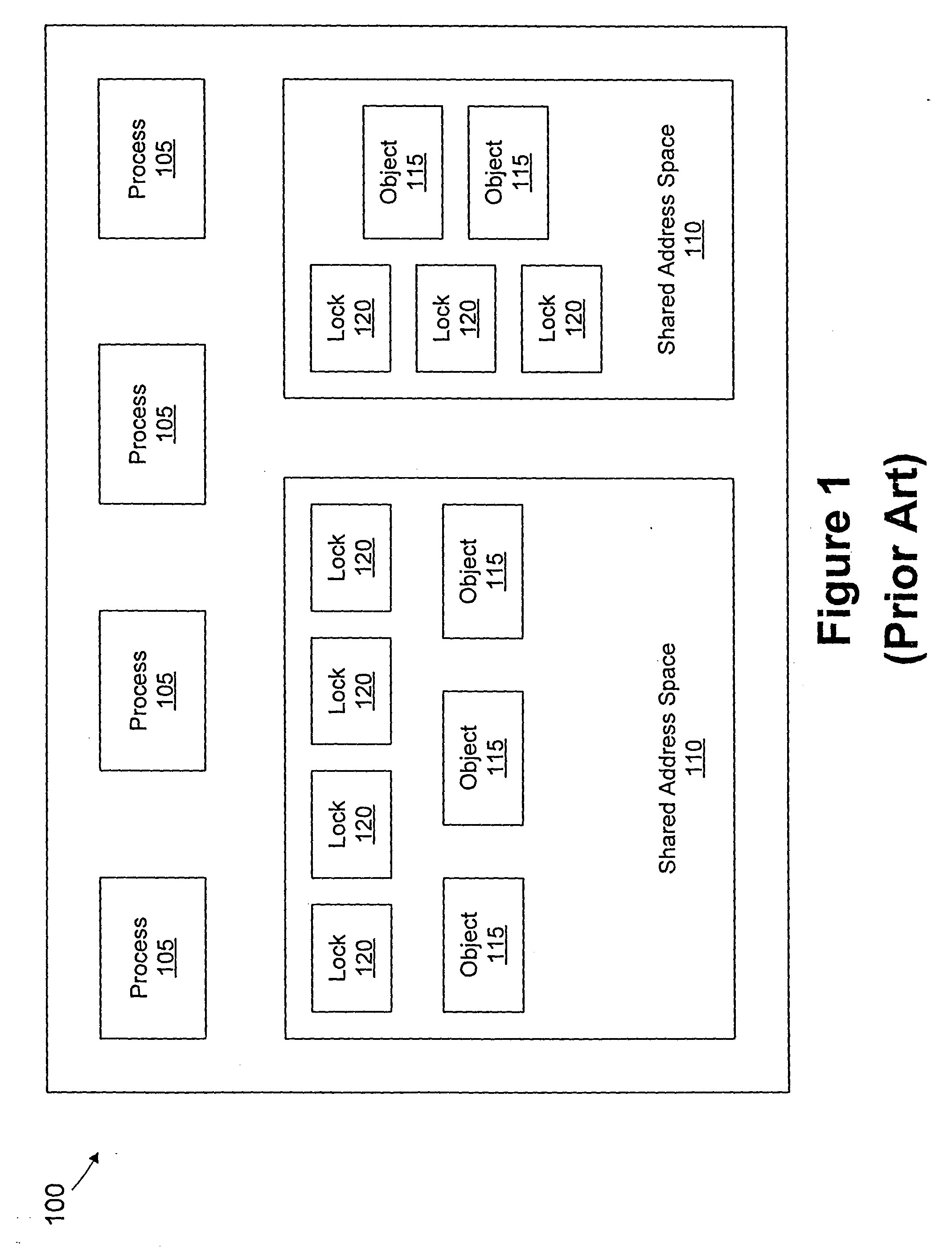

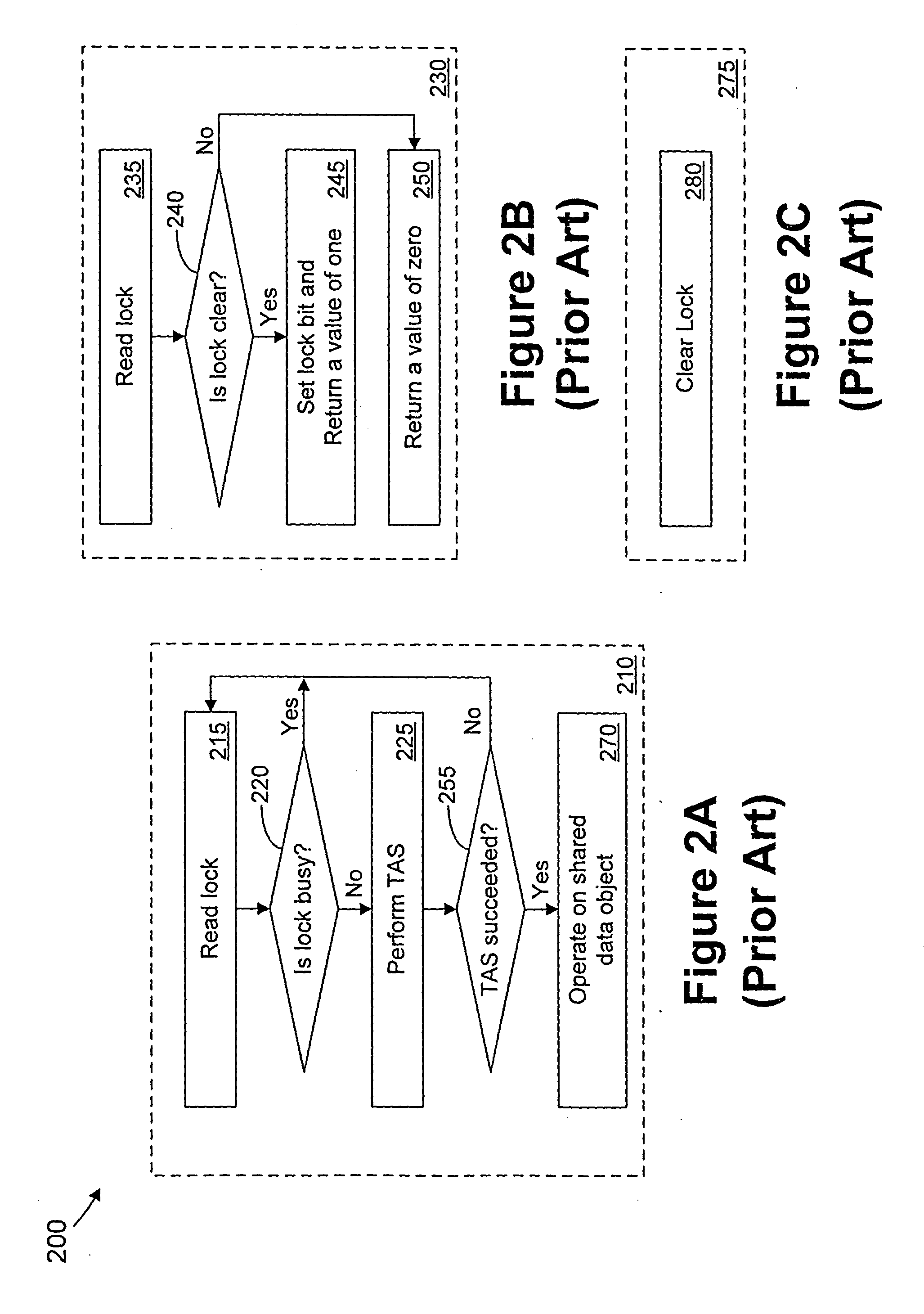

The present invention provides a method of implementing a fault-tolerant mutual exclusion lock. The present invention records in a lock structure the IDs of all processes whose failure can lead to the permanent unavailability of the lock. When a process finds the lock unavailable and suspects a permanent failure, it queries the programming environment about the status of all or some of the processes that could have caused the lock's unavailability. If the programming environment determines that these processes have failed, the live process tries to usurp the lock. If it succeeds, it executes some recovery mechanism and frees the lock or proceeds to operate on the objects protected by the lock. The method guarantees recovery from process failures. Furthermore, more sophisticated implementations are provided that apply to queue-based locks where more than one process can cause the lock to be permanently unavailable, as well as implementations that balance the speed of recovery while minimizing the frequency of queries to the programming environment, as these queries may be costly in execution time.

Owner:GLOBALFOUNDRIES INC

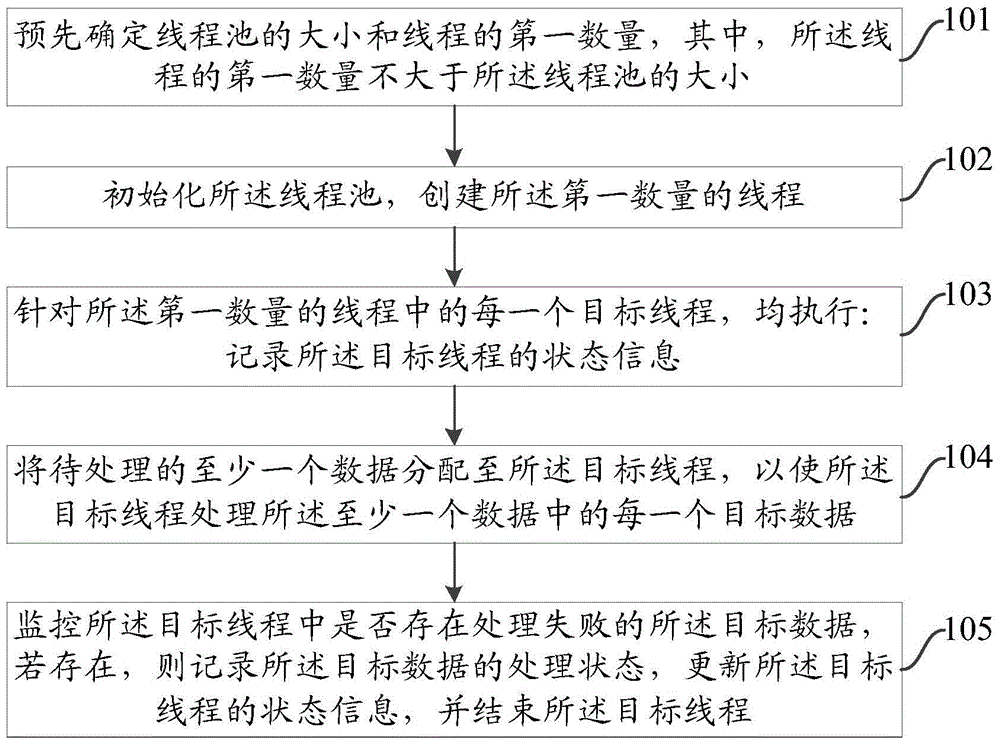

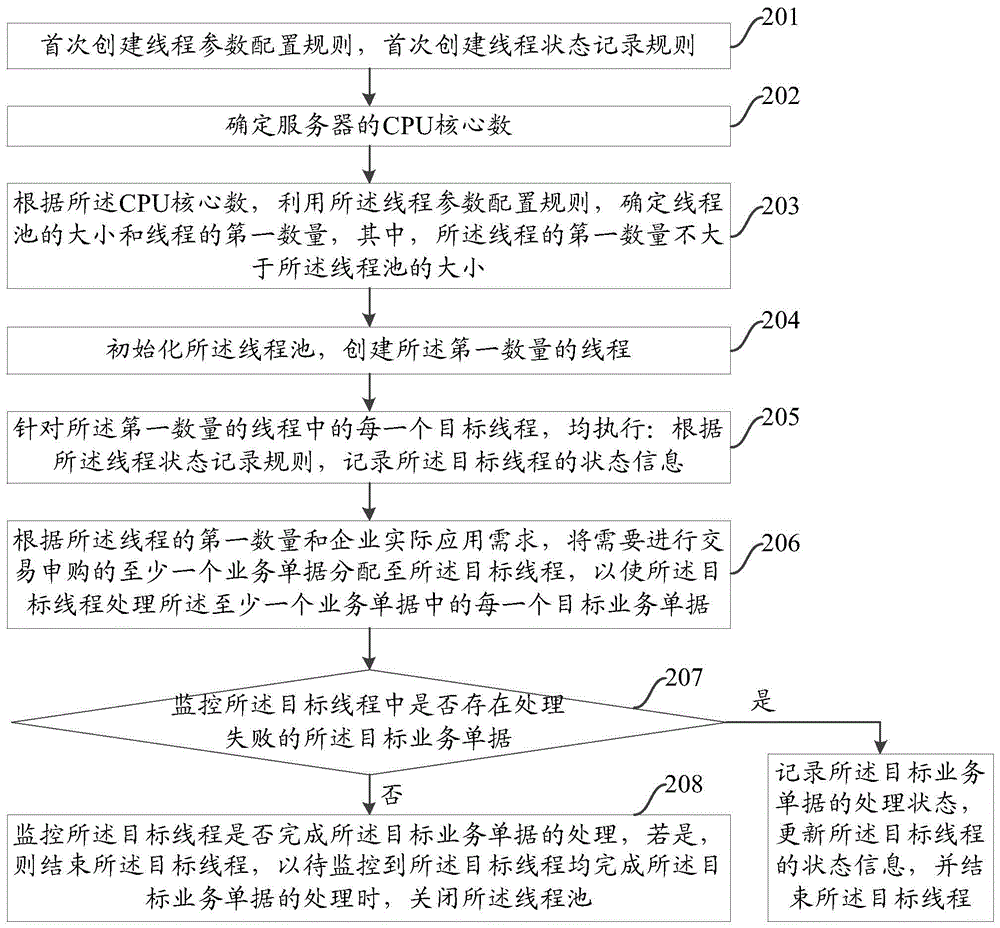

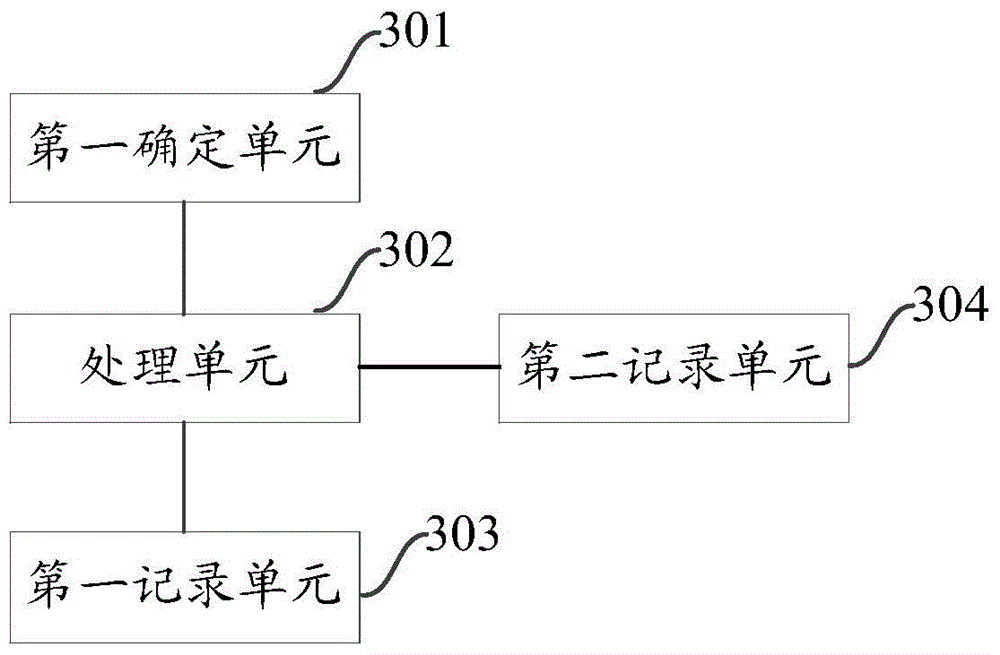

Multithread processing data method and device

The invention provides a multithread processing data method and device; the method comprises the following steps: determining the quantity of threads used for processing data, building threads of corresponding quantity, and recording state information of each built thread; distributing to-be processed data to each thread, so each thread can process corresponding data; monitoring a data processing process, when process failure data is monitored in a random thread, the processing state is recorded, the state information of the thread is updated, and the thread is finished. The method and device use a multithread mode to process data, thus improving data processing efficiency.

Owner:INSPUR COMMON SOFTWARE

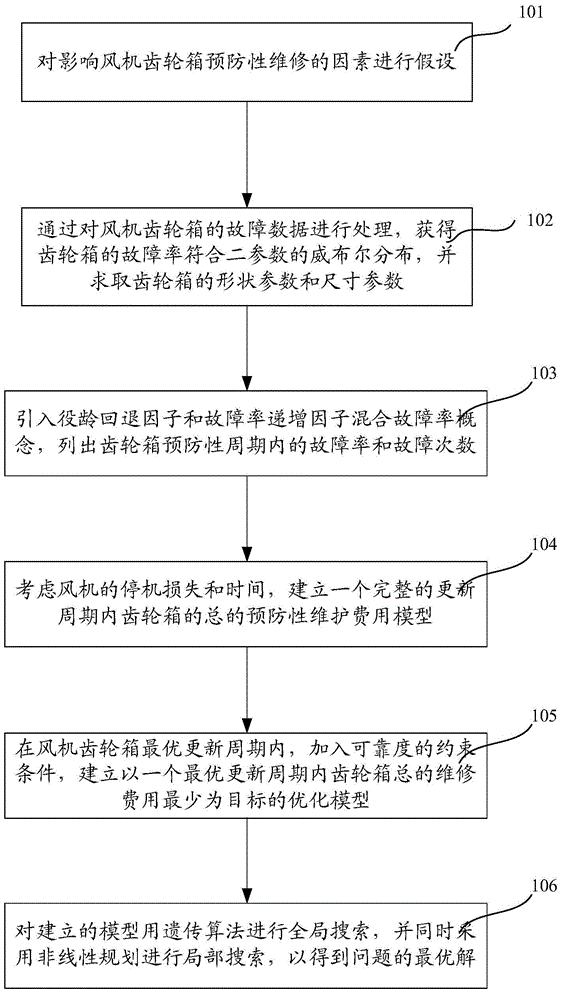

Preventative maintenance method of fan gear case

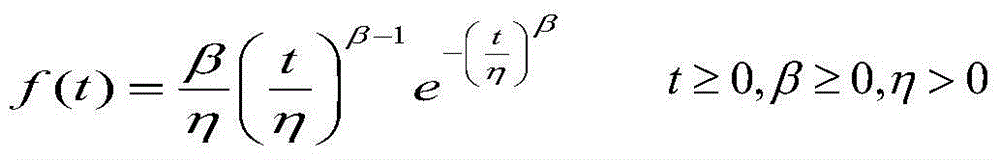

InactiveCN104899455AGenetic modelsSpecial data processing applicationsFailure rateEstimation methods

The invention discloses a preventative maintenance method of a fan gear case. The preventative maintenance method of the fan gear case includes: assuming factors which influence preventative maintenance of the fan gear case; obtaining failure rate of the fan gear case, which conforms to two parameter Weibull distribution, by processing failure data on the fan gear case, and using a maximum likelihood estimation method to figure out shape parameters and dimension parameters of the fan gear case; introducing a service age reduction factor and failure rate progressive increase factor mixing failure rate concept, and listing the failure rate and the failure number of the fan gear case in a preventative period; fully considering halt loss and halt time of a fan, and building a total preventative maintenance cost model of the fan gear case in a complete update cycle; adding constraint conditions of reliability in the optimum update cycle of the fan gear case, and building an optimum model which aims at minimizing total maintenance cost of the fan gear case in the optimum update cycle; using a genetic algorithm to perform a global search on the established optimum model, and using a nonlinear plan to perform a local search so as to obtain an optimum solution of a problem.

Owner:SHANGHAI DIANJI UNIV

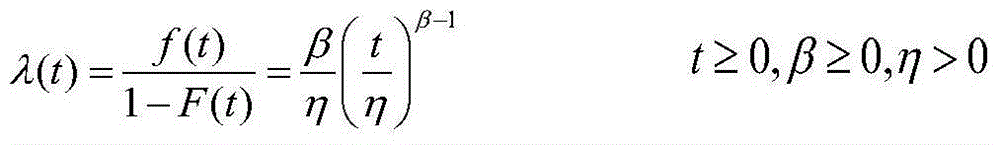

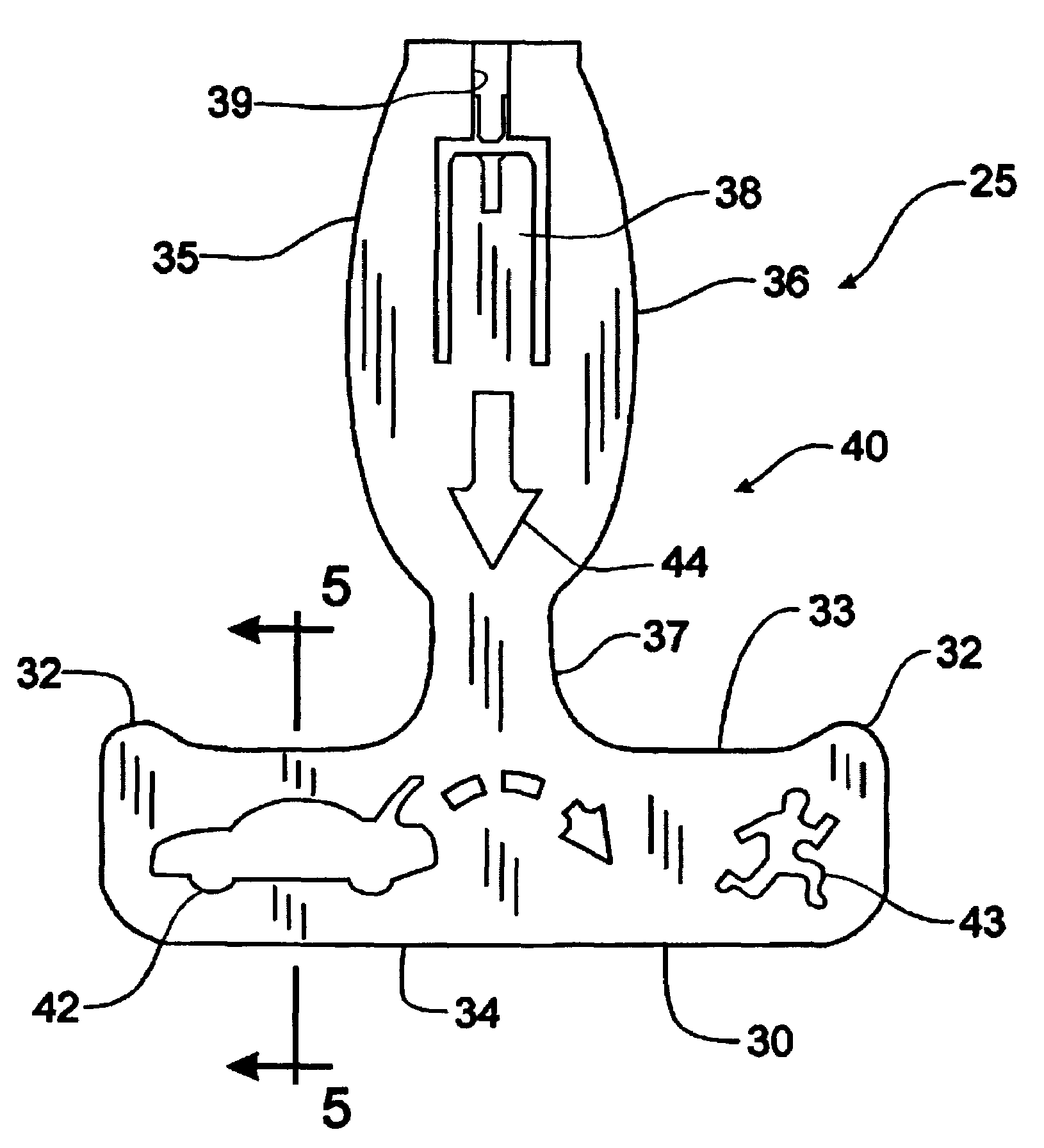

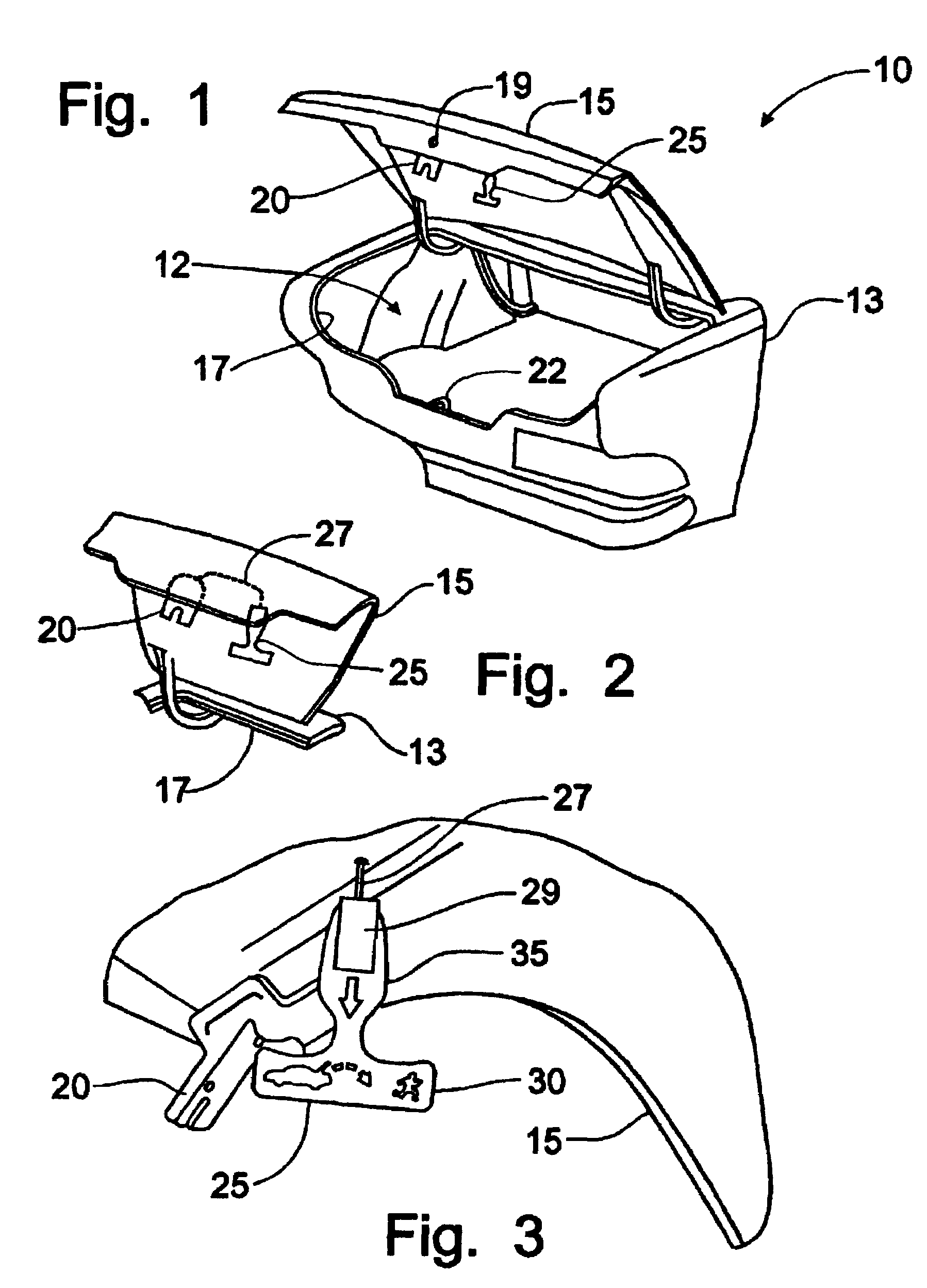

Trunk release handle for automobiles

ActiveUS7029138B2Visibility of providingHigh degreeVehicle locksOptical signallingVisibilityGraphics

An emergency trunk release handle for an automobile displays the graphics explaining the use and function of the handle by cutting out the material from the handle. Forming the emergency release handle from a phosphorescent plastic material that can be formed by a molding process, such as injection molding, the cut-out graphics show as darkened areas, when viewed in the dark confines of an automobile trunk, to provide a high degree of visibility for the graphics. The graphics are also visible when seen against the dark carpet in the interior of an opened trunk cavity. The formation of the graphics is accomplished by coring the mold in the configuration of the desired graphics and by forming the plastic material in the mold around the cores. The resultant handle structure is thus formed in a cost effective manner that reduces the process failure potential during the manufacturing of the handle.

Owner:FORD GLOBAL TECH LLC

Method for glass separation for flat panel displays

InactiveUS7204400B2Minimize separation defectMore separatedConveyorsGlass severing apparatusDisplay deviceProcess failure

A method and apparatus for separating glass panels that minimizes process failures and improves separation process consistency by utilizing a separation handle which applies the minimal pressure necessary to remove the edge portion from the glass panel. The glass panel is cut along the score line, which outlines the edge portions of the glass panel to be removed. The panel is placed upon the separating apparatus, which pumps nitrogen along the underside of the glass panel, causing the glass panel to float above the apparatus. Locating pins are inserted to position the panel on the stage. Once the glass panel is in place, a vacuum sucks the panel against the stage, holding the panel tightly against the stage. The separation handle is then inserted over the edge portion to be removed. A measured force is applied to the handle, with the force incrementally increased until the slow, controllable separation of the edge is achieved. This level of force is maintained until separation is complete.

Owner:GE MEDICAL SYST GLOBAL TECH CO LLC

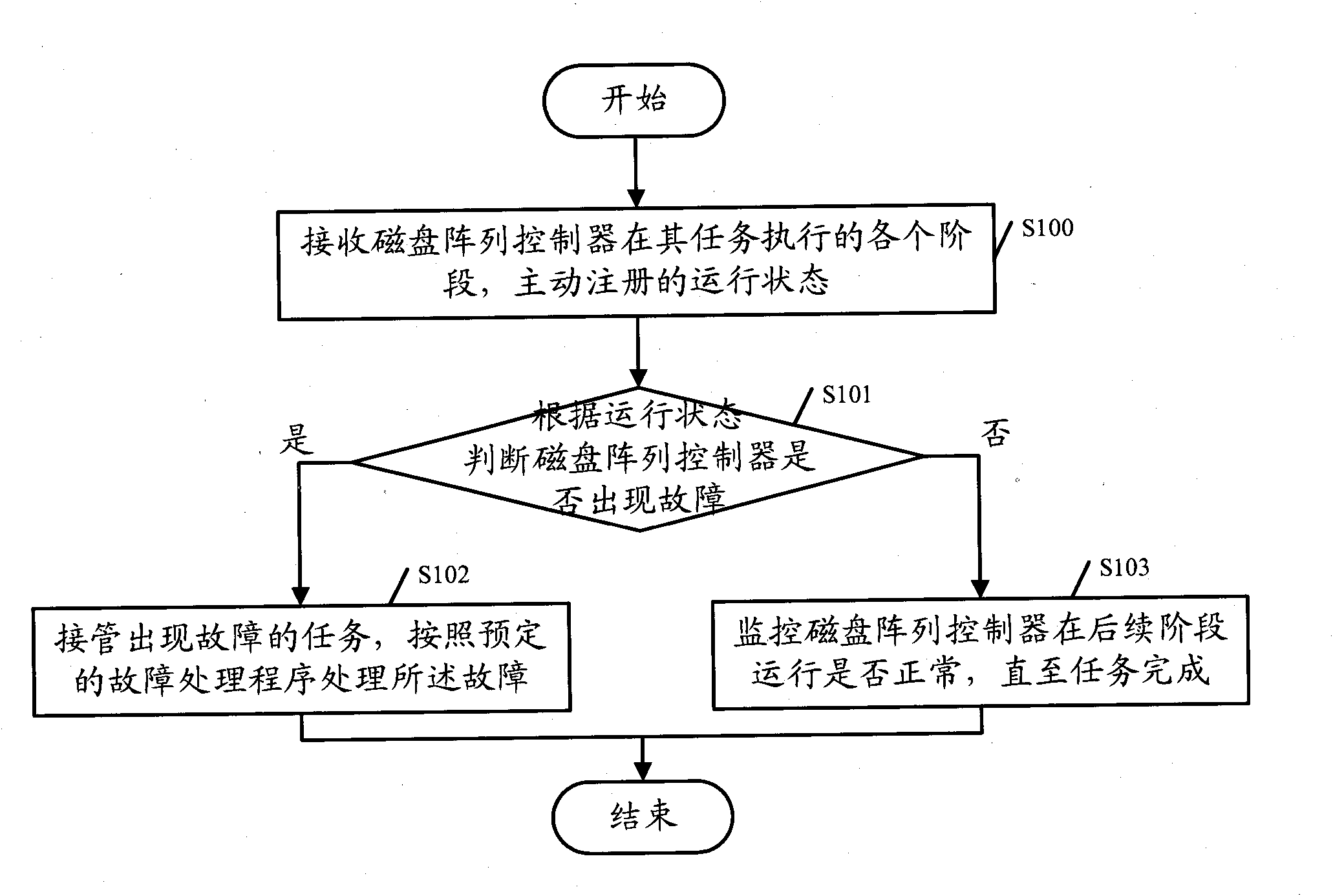

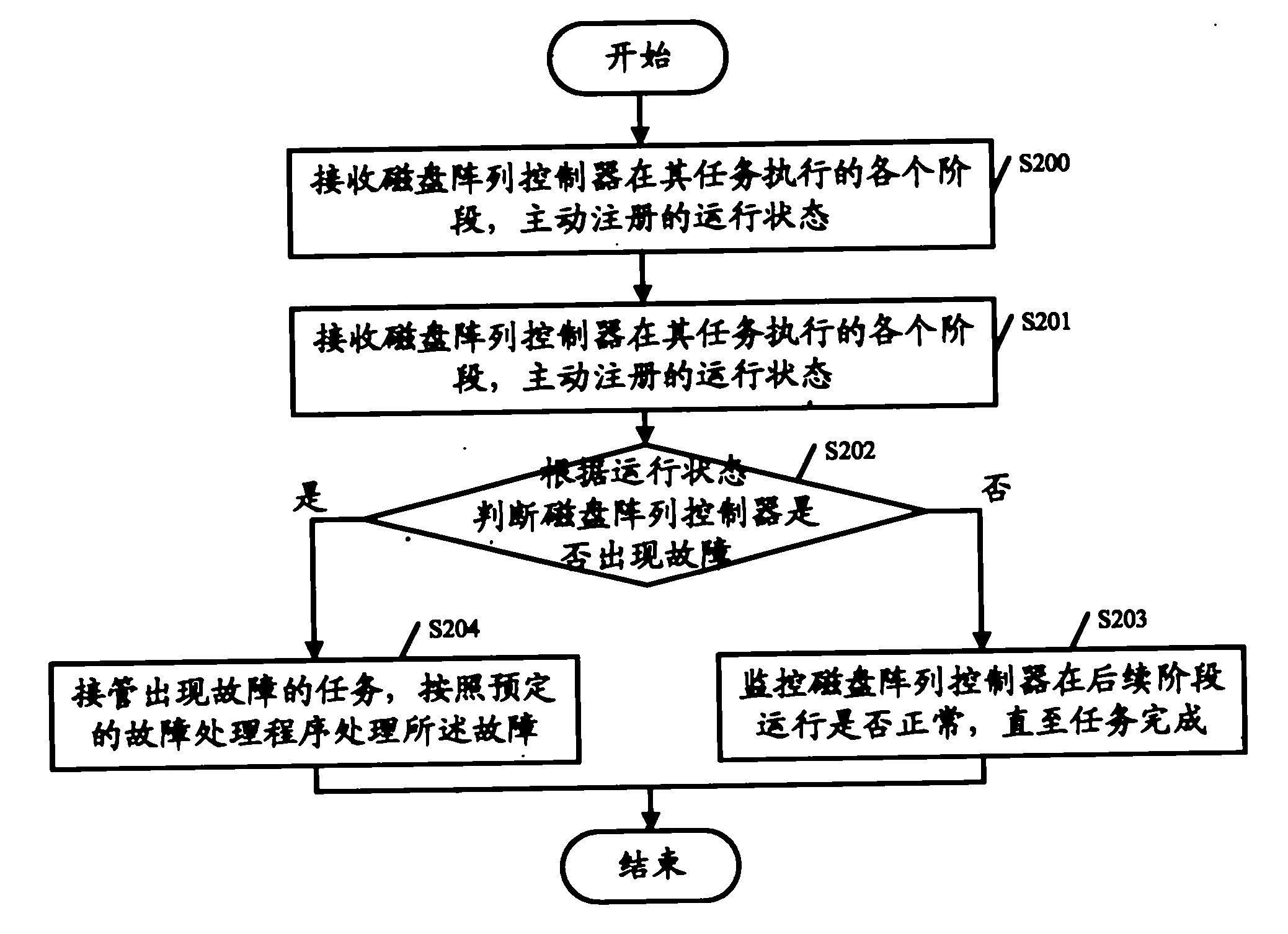

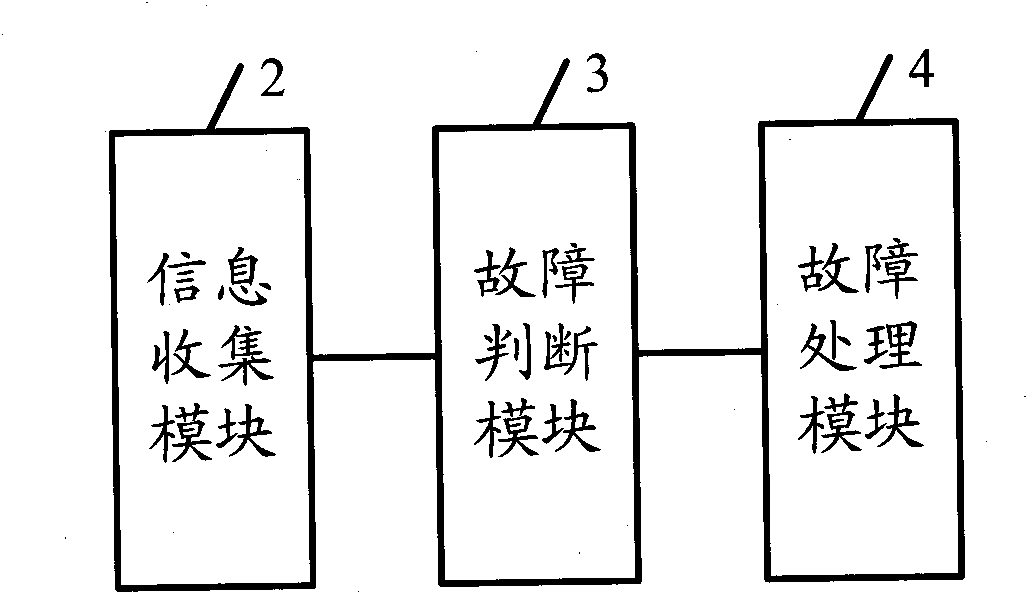

Method and system for processing failure of redundant array of independent disk controller

InactiveCN101887386AMonitor the running processTroubleshooting in timeInput/output to record carriersFault responseDisk controllerProcess failure

The invention discloses a method and a system for processing a failure of a redundant array of independent disk (RAID) controller. The method comprises the following steps of: receiving running states which are actively registered by the RAID controller at every task execution stage of the RAID controller; judging whether the RAID controller goes wrong in the process of executing tasks according to the running states of the RAID controller; and if the RAID controller goes wrong in the process of executing the tasks, taking over the tasks and processing the failure according to a preset failure processing program. The method and the system for processing the failure of the RAID controller can independently and actively monitor a running process of the RAID controller, actively detect the failures of the RAID controller and timely process the failure. And simultaneously, when the RAID controller goes wrong, the system for processing the failure of the RAID controller can ensure that the RAID controller does not cause resource leak, module failure even shutdown and other errors due to failures.

Owner:深圳市迪菲特科技股份有限公司

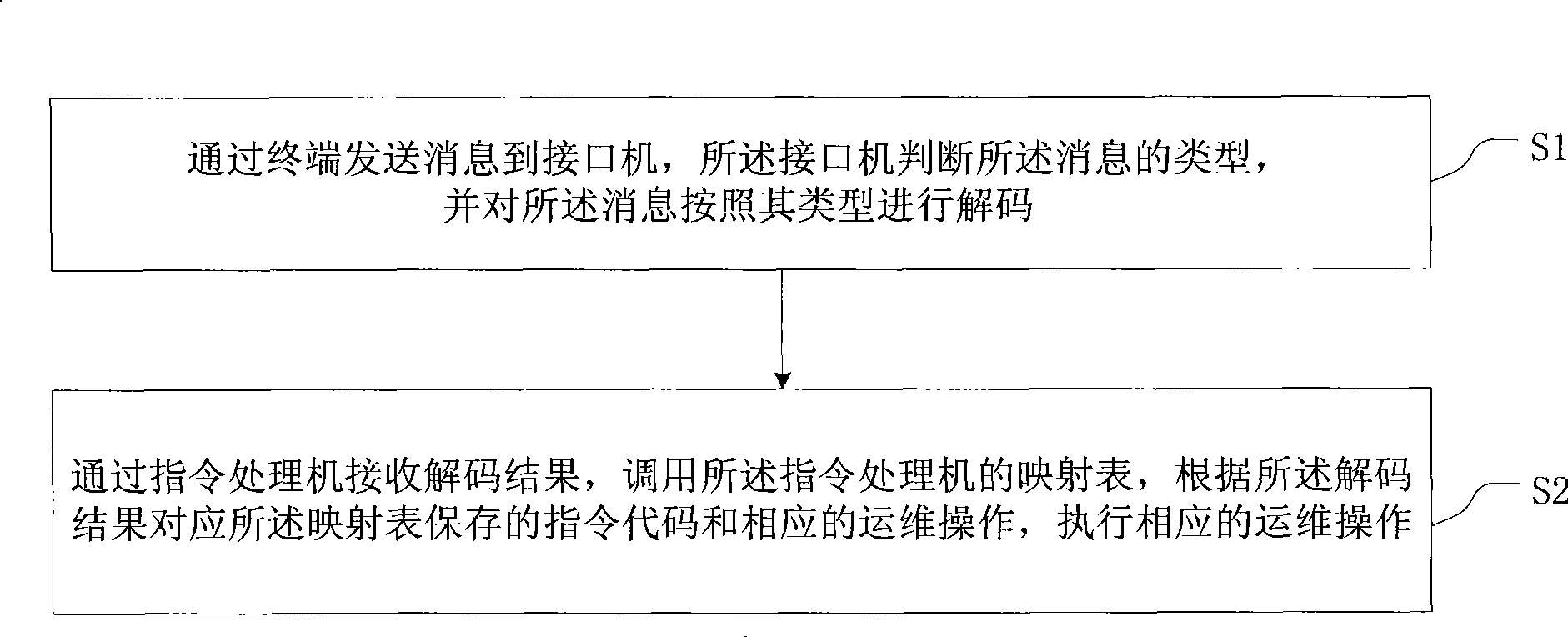

Novel maintenance system and method

InactiveCN101483836AEasy to handleTimely operation and maintenanceWireless network protocolsMessaging/mailboxes/announcementsTime limitMessage type

The invention discloses a remote operation and maintenance system and a method thereof; wherein the remote operation and maintenance system comprises a terminal, an interface message processor and an instruction processor; wherein the terminal is used for sending message to the interface message processor; the interface message processor is used for judging message type, decoding the messages according to the type and sending the decoding result to the instruction processor; the instruction processor which is provided with a mapping table comprises instruction codes and the corresponding operation and maintenance operation, and the instruction processor is used for receiving the decoding result of the interface message processor; the decoding result is corresponding to the instruction codes; the instruction processor is also used for executing the corresponding operation and maintenance of the instruction codes according to the decoding result and sending the operation and maintenance result to the terminal through the interface message processor. The remote operation and maintenance system and the method can execute operation and maintenance in time through various modes, thus achieving the purposes of being free from area and time limit and quickly processing failure without the personal presence of operators.

Owner:ZTE CORP

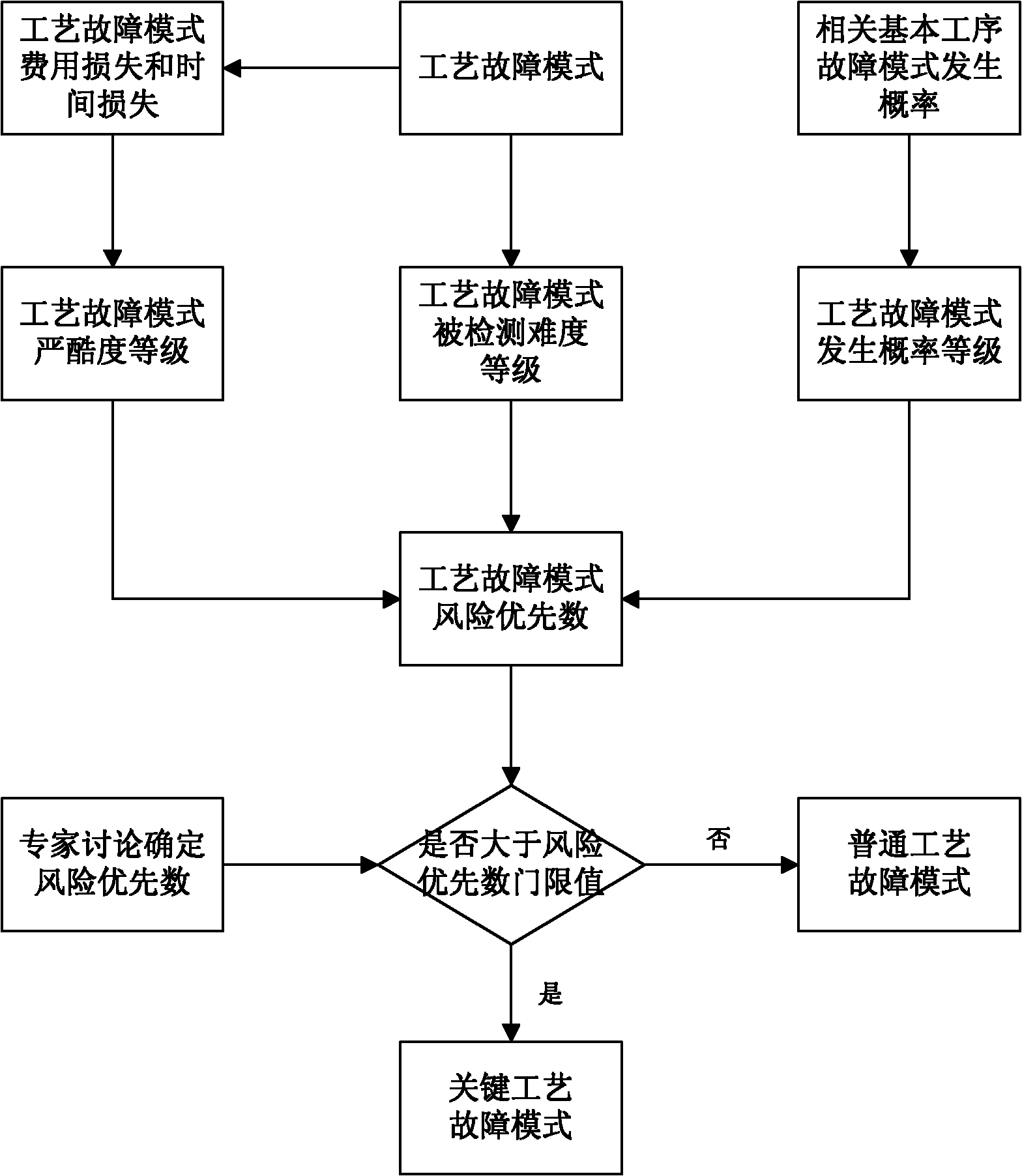

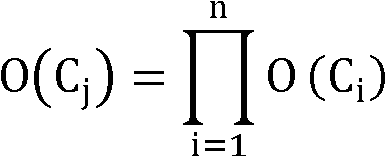

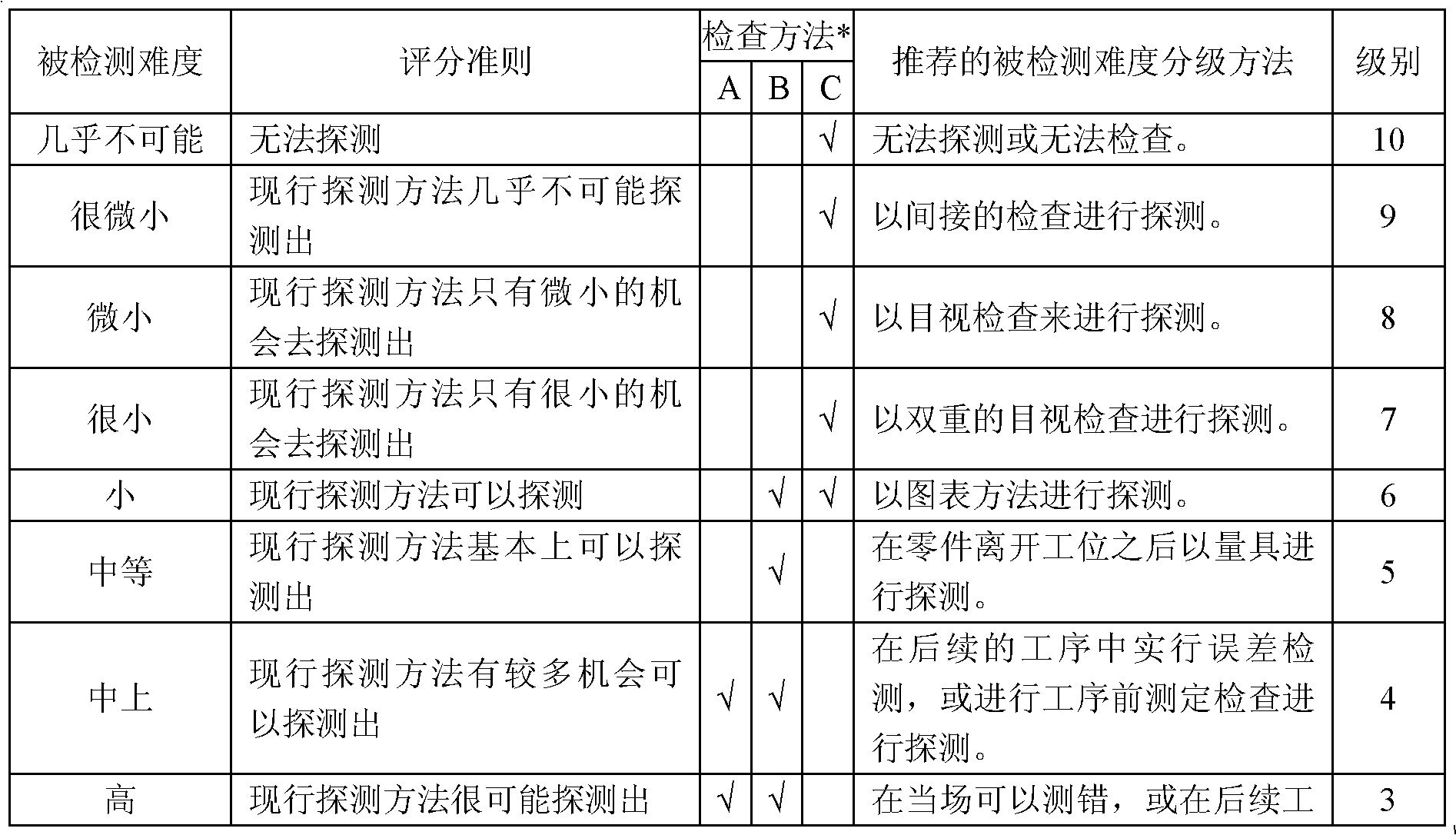

Method for analyzing harmfulness of mechanical assembly process

InactiveCN102156820AEasy to operateEasy accessSpecial data processing applicationsProcess failureOperability

The invention provides a method for analyzing harmfulness of a mechanical assembly process, comprising the following five steps of: step I, determining the grade of severity of a process failure model; step II, determining the grade of occurrence probability of a process failure model; step III, determining the grade of tested difficulty of a process failure mode; step Iv, calculating the risk priority number of process failure mode; and step V, determining the failure mode of a critical process. The method for analyzing harmfulness of a mechanical assembly process has the advantages that the grade of severity, the grade of occurrence probability and the grade of tested difficulty of a process failure mode are subjected to mathematical analysis and determination by means of a quantification method on the basis of the existing process harmfulness analysis method, the maneuverability is strong, the combination of required parameters and data and the practice is close, the obtaining is convenient, the operation is easy, and the method is suitable for popularizing in the technical field of process reliability engineering.

Owner:BEIHANG UNIV