Test circuit of on-chip multicore processor and design method of testability

A multi-core processor and test circuit technology, applied in the direction of measuring electricity, measuring electrical variables, instruments, etc., can solve the problems of different test excitation and response vectors, increase test overhead and cost, prolong chip test time, etc., to reduce extra costs. Power consumption overhead, reduced test cost, and the effect of shortened test time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

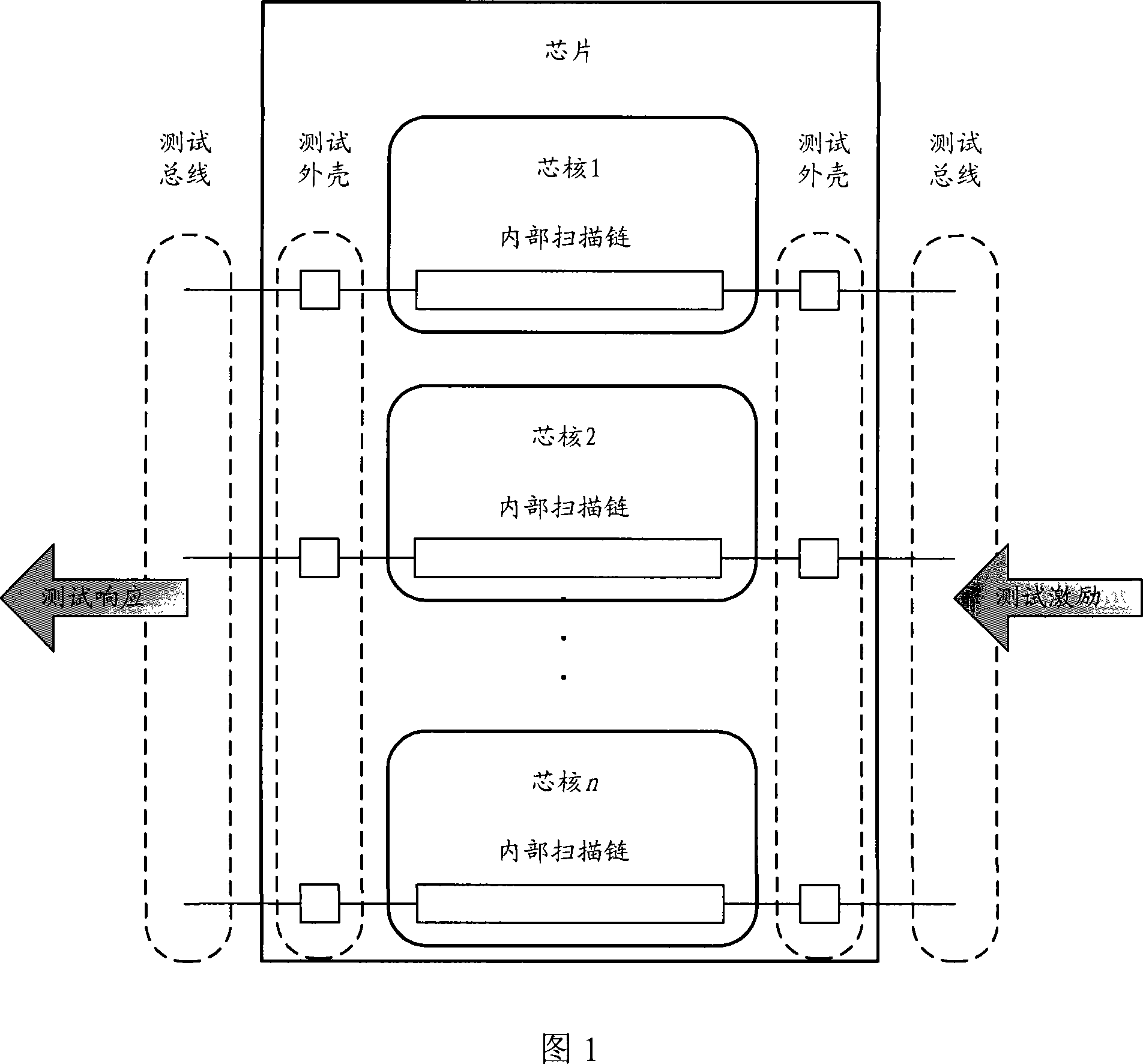

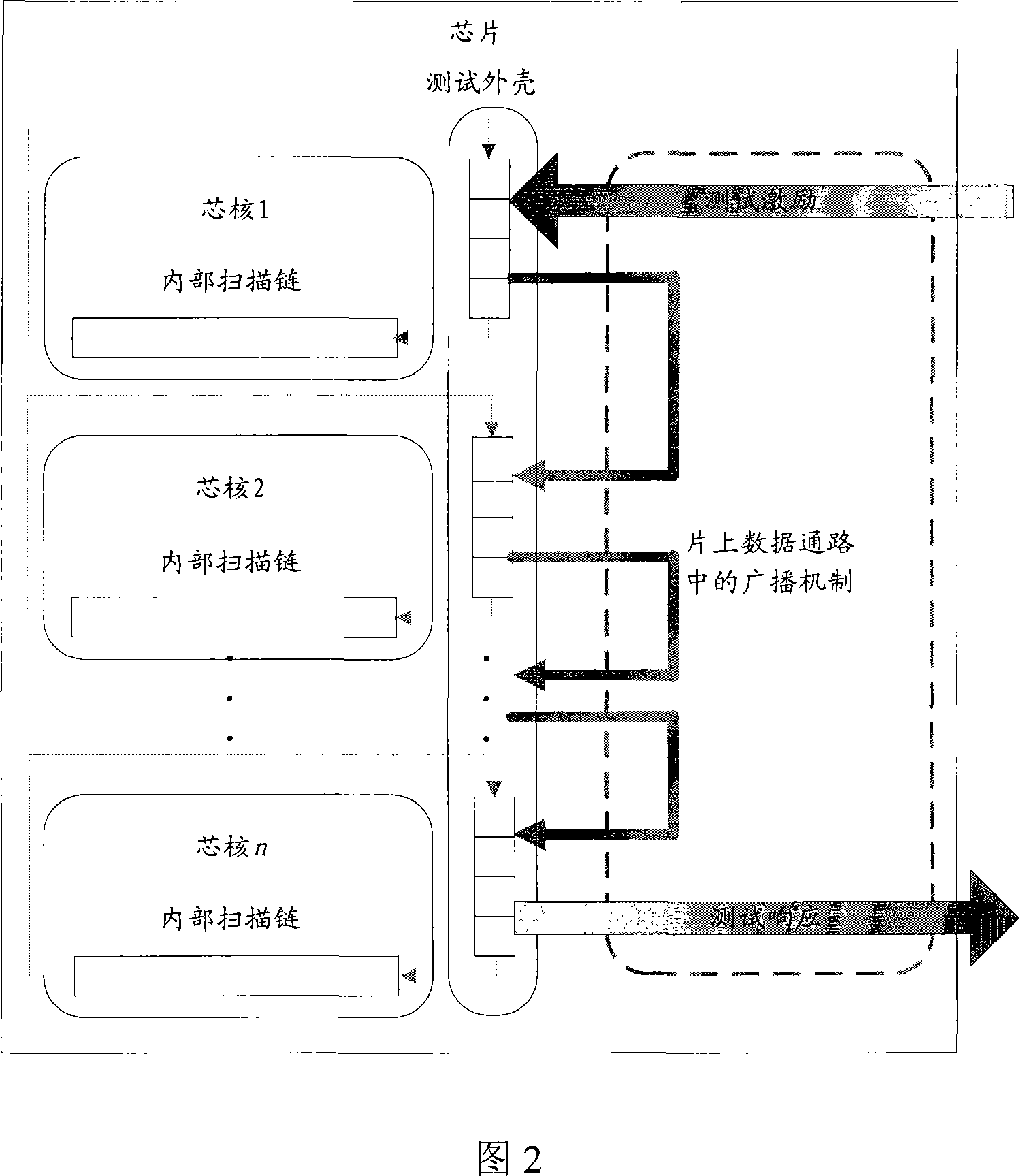

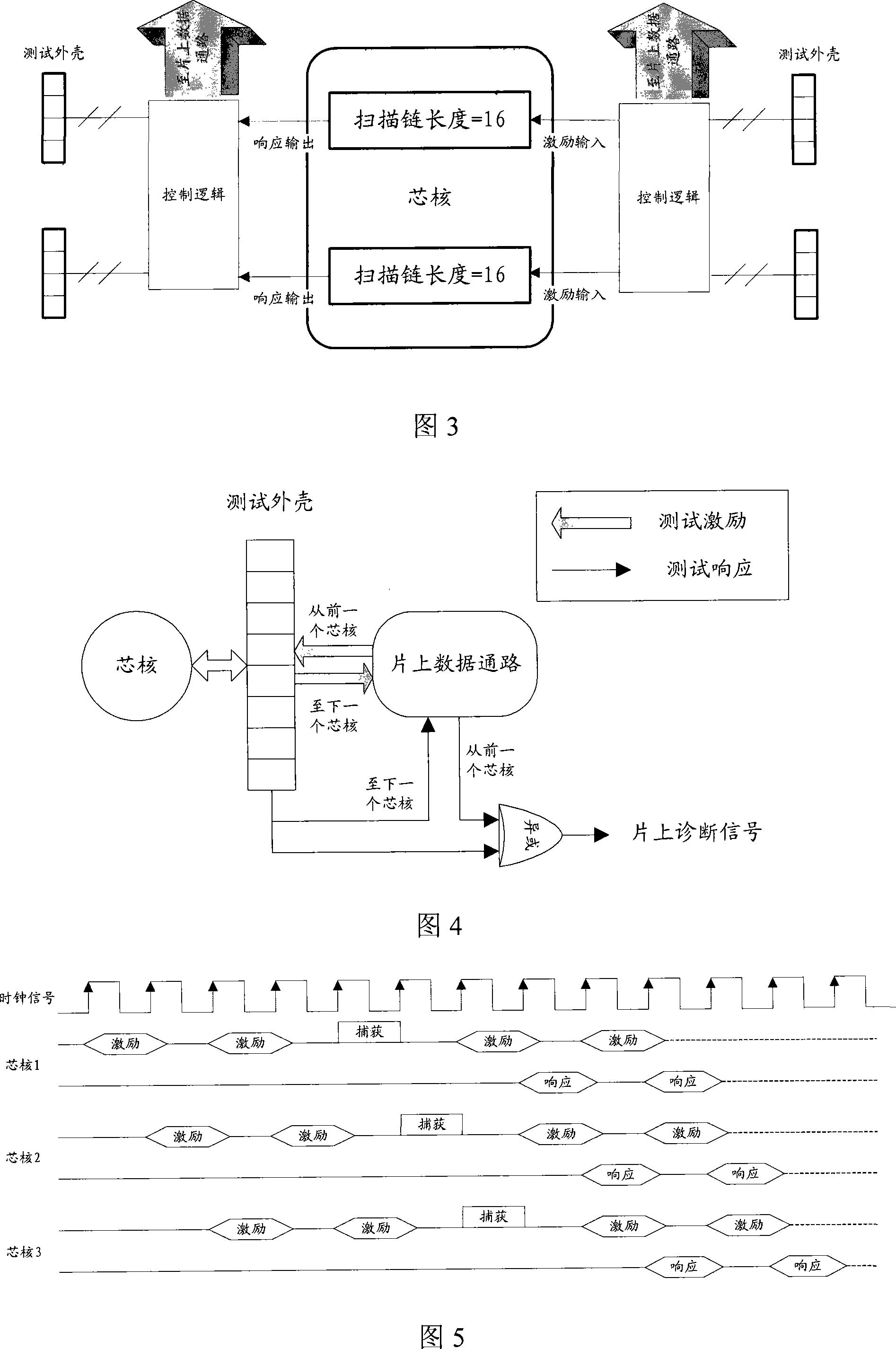

[0046] As shown in Figure 2, Figure 2 is a schematic diagram of the testability design scheme for the on-chip multi-core processor provided by the present invention, and the circuit includes two components: at least one test shell register for buffering core test data to be tested chain, and the interconnection circuit between the test shell register chain and the core core to be tested and the on-chip data path.

[0047] Among them, the test shell register chain used for caching the core test data to be tested is generally divided into multiple groups, and the specific number of groups is determined by the core scanning structure. The determination method will be described in detail below and omitted here temporarily. The test shell register chain is composed of a plurality of registers connected in series, through the interconnection circuit between the test shell register chain and the core core to be tested, and the interconnection circuit between the test shell register ch...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More