On-chip memory debugging method and device based on memory built-in self-test

An on-chip memory, built-in self-test technology, applied in static memory, instruments, etc., can solve the problem of not being able to collect on-chip memory array read data, etc., to reduce debugging time, debug access logic is simple and efficient, and increase the success rate. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

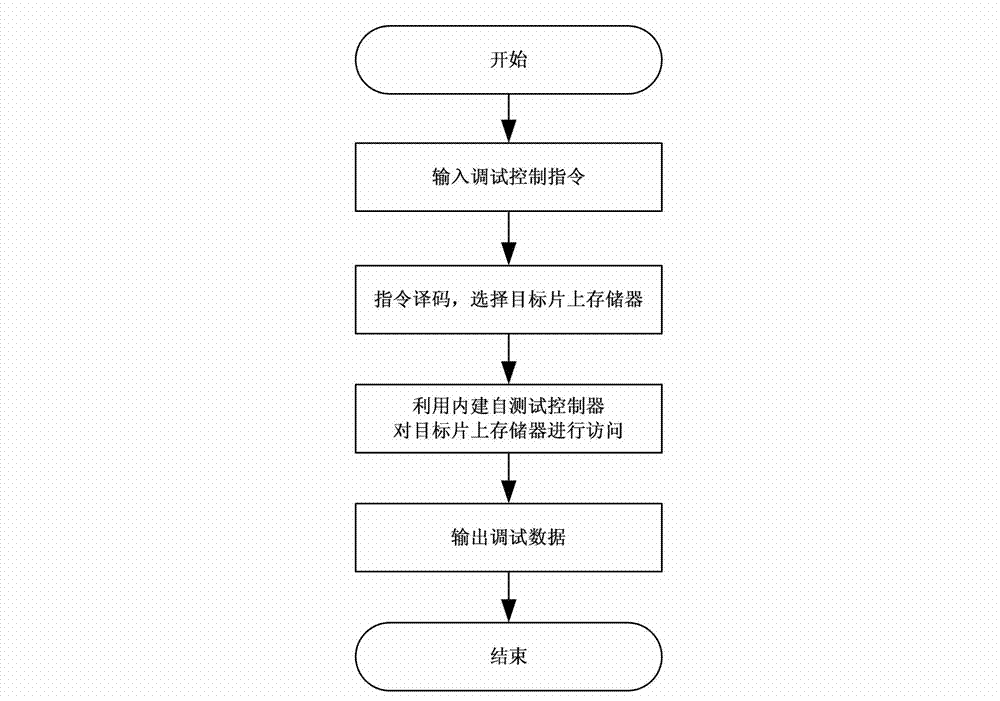

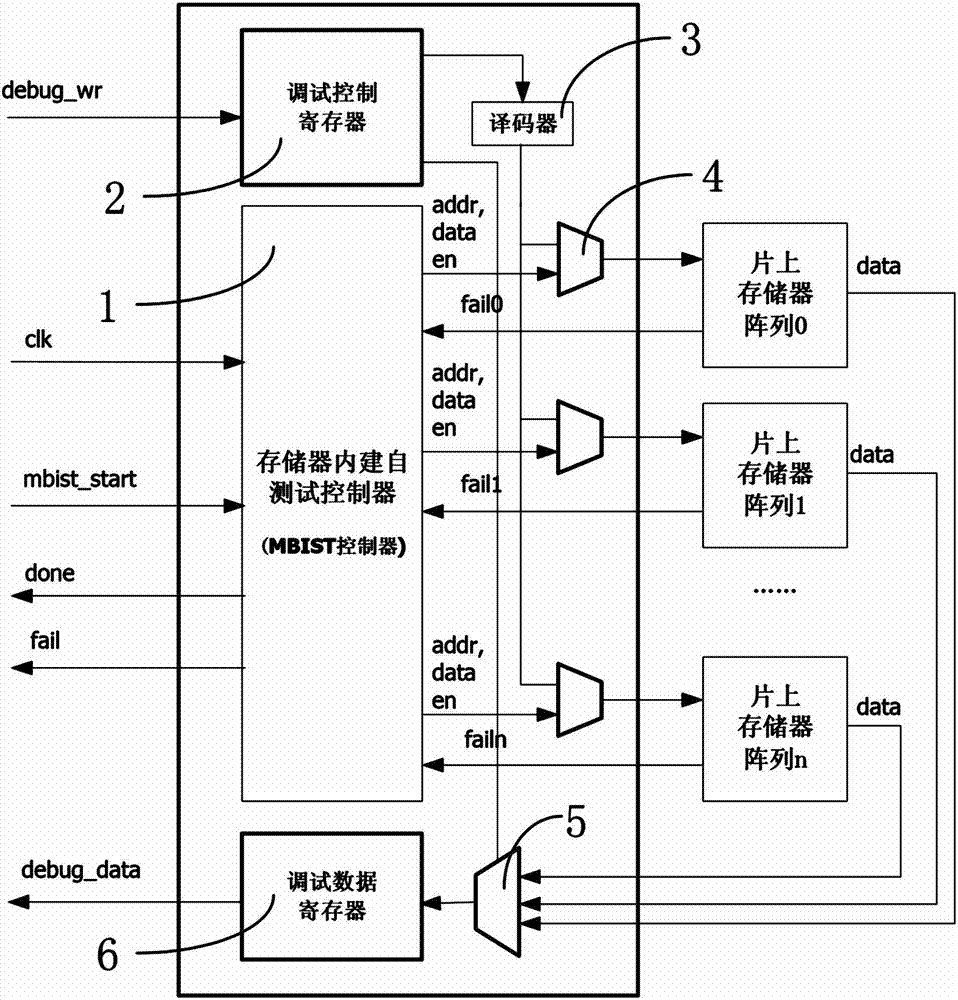

[0029] like figure 2 As shown, the implementation steps of the on-chip memory debugging method based on memory built-in self-test in this embodiment are as follows:

[0030] 1) Enter the debug control command to start memory debugging, the debug control command includes the number of the target on-chip memory to be debugged and the read area to be debugged;

[0031] 2) Decode the number of the debugging control command, and select the target on-chip memory according to the decoding signal;

[0032] 3) Under the control of the memory built-in self-test controller, access the selected target on-chip memory according to the read area to be debugged in the debug control instruction;

[0033] 4) Cache the read data of the target on-chip memory into the debug data register, and output the data of the debug data register as the debug result data of the debug control instruction.

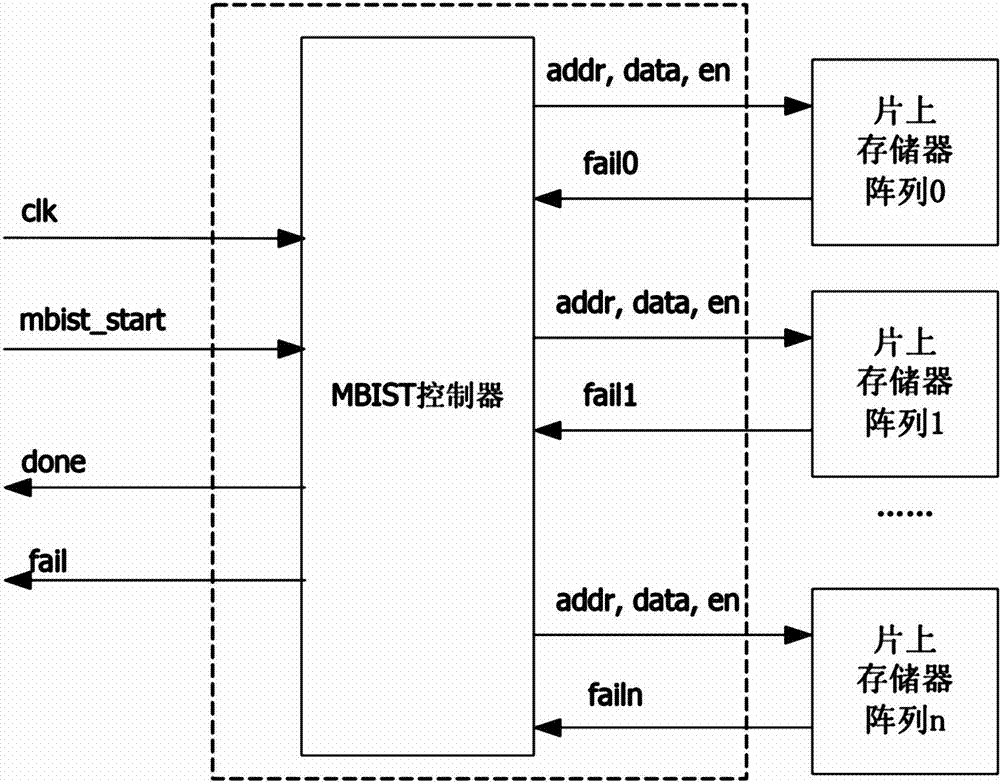

[0034]The memory built-in self-test circuit already has the control function of reading and writing t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More