Patents

Literature

194results about How to "Reduce power overhead" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Configuration method applied to coarse-grained reconfigurable array

InactiveCN102508816AReduce the amount of informationReduce visitsProgram controlArchitecture with single central processing unitConfiguration generationEngineering

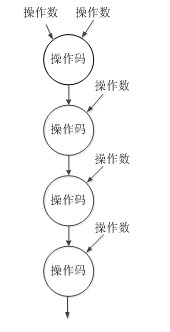

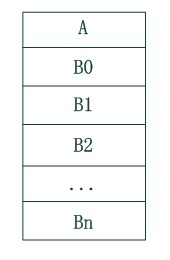

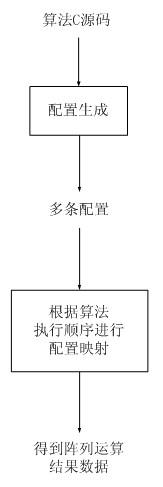

The invention discloses a configuration method applied to a coarse-grained reconfigurable array, which aims at a coarse-grained reconfigurable array with a certain scale, and comprises a configuration defining scheme taking data links as basic description objects, a corresponding configuration generating scheme and a corresponding configuration mapping scheme. The configuration defining scheme includes that a program corresponds to a plurality of configurations, each configuration corresponds to one data link, and each data link consists of a plurality of reconfigurable cells with data dependence relations. Compared with a traditional scheme taking RCs (reconfigurable cells) as basic description objects, the configuration defining scheme is capable of concealing interlinking information among the RCs and providing a larger configuration information compression space, thereby being beneficial to decrease of the total amount of configuration and time for switching configuration. Besides, the configuration of one description data link consists of a route, a functional configuration and one or more data configurations, the data configurations share one route and functional configuration information, and switching of one configuration includes one-time or multiple switching of the data configuration after one-time switching of the corresponding route and the functional configuration.

Owner:SOUTHEAST UNIV

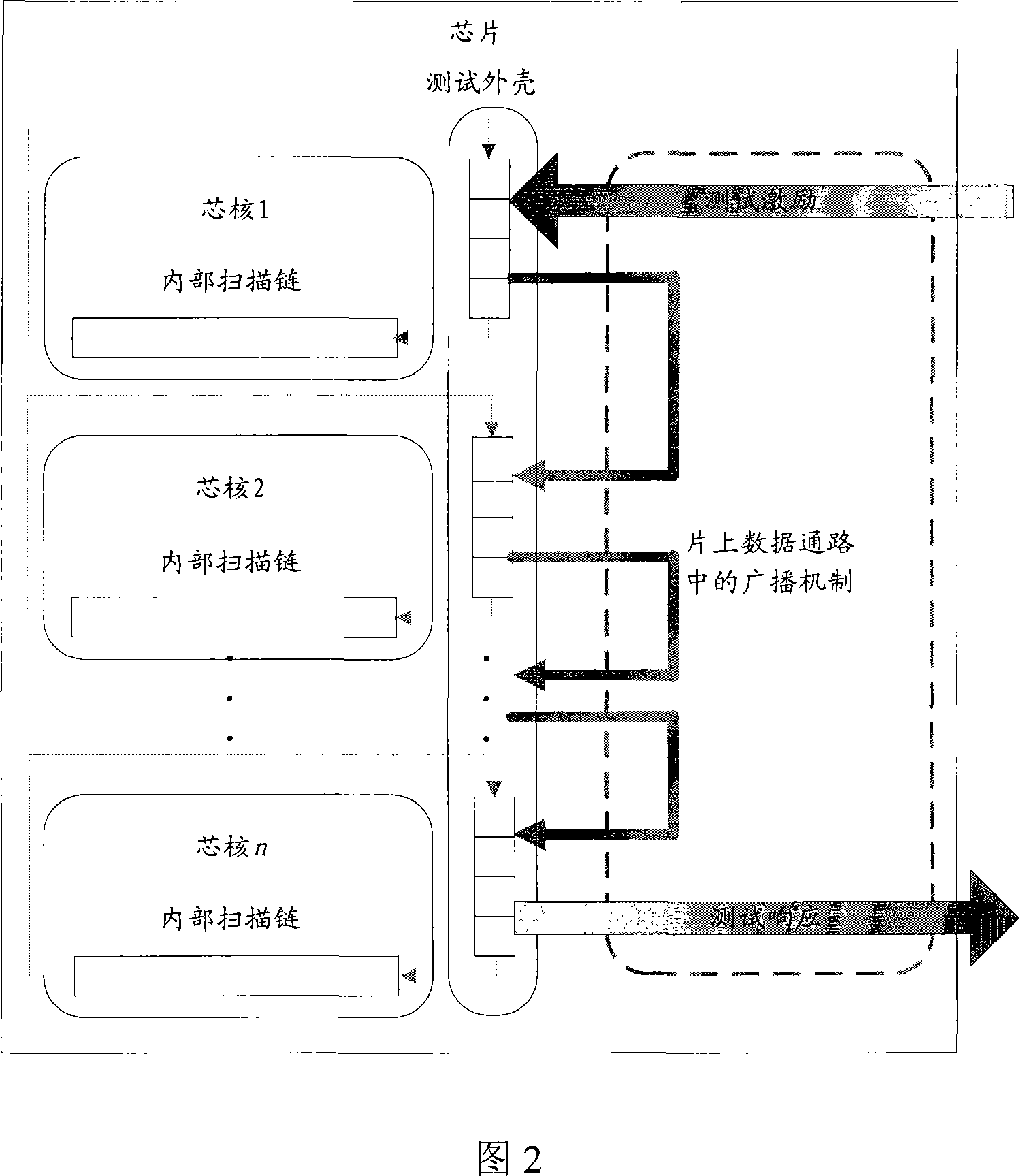

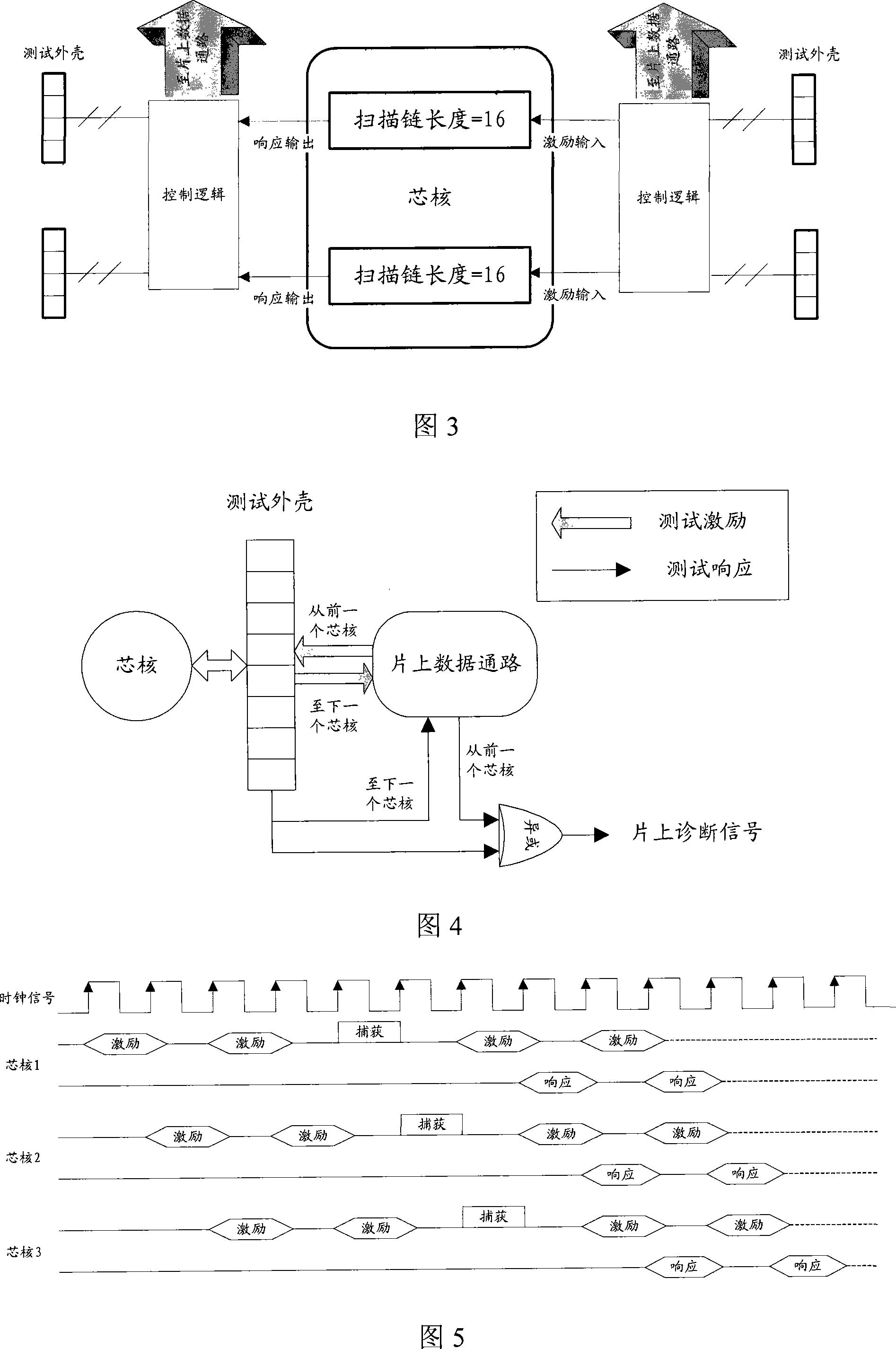

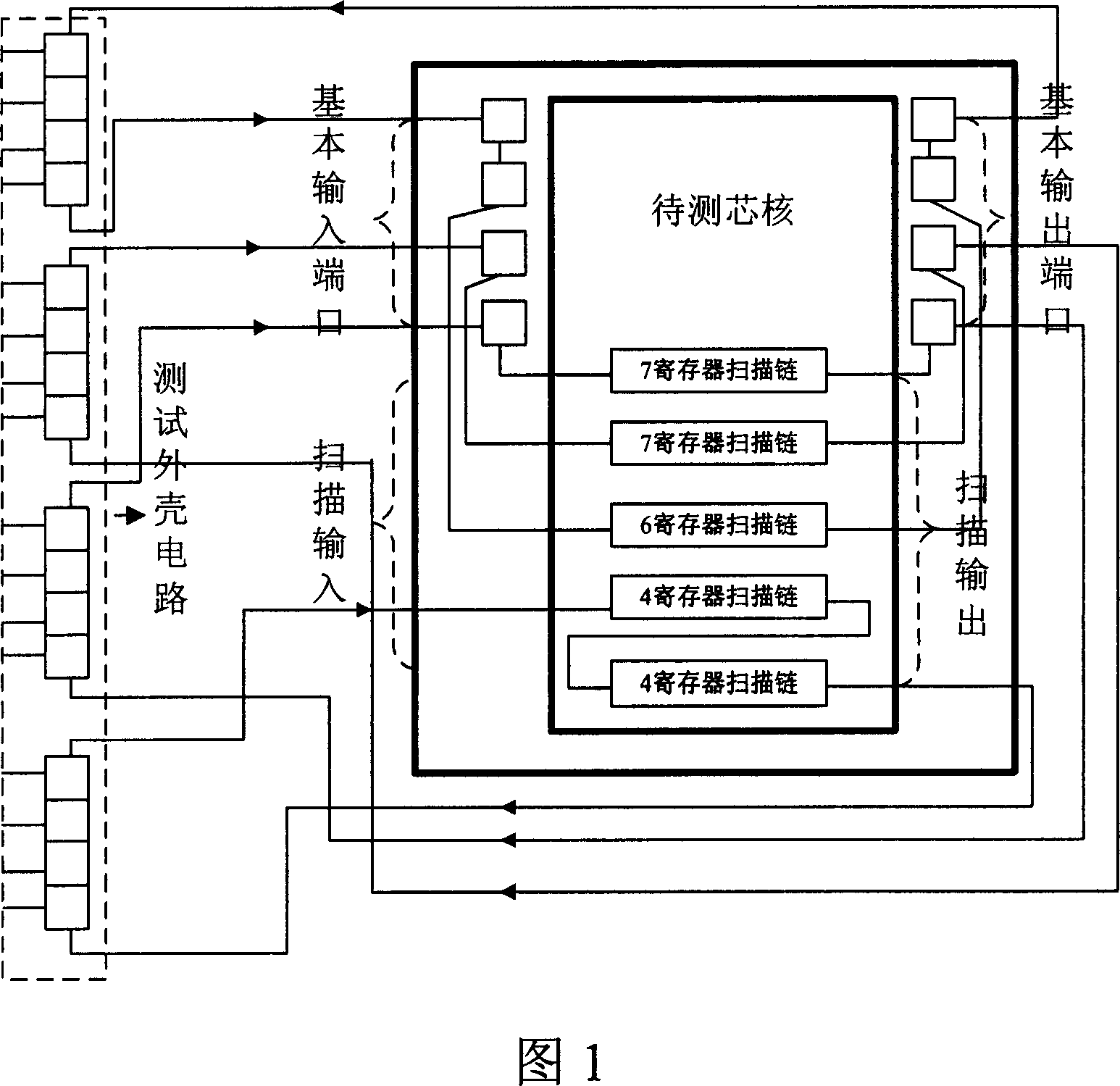

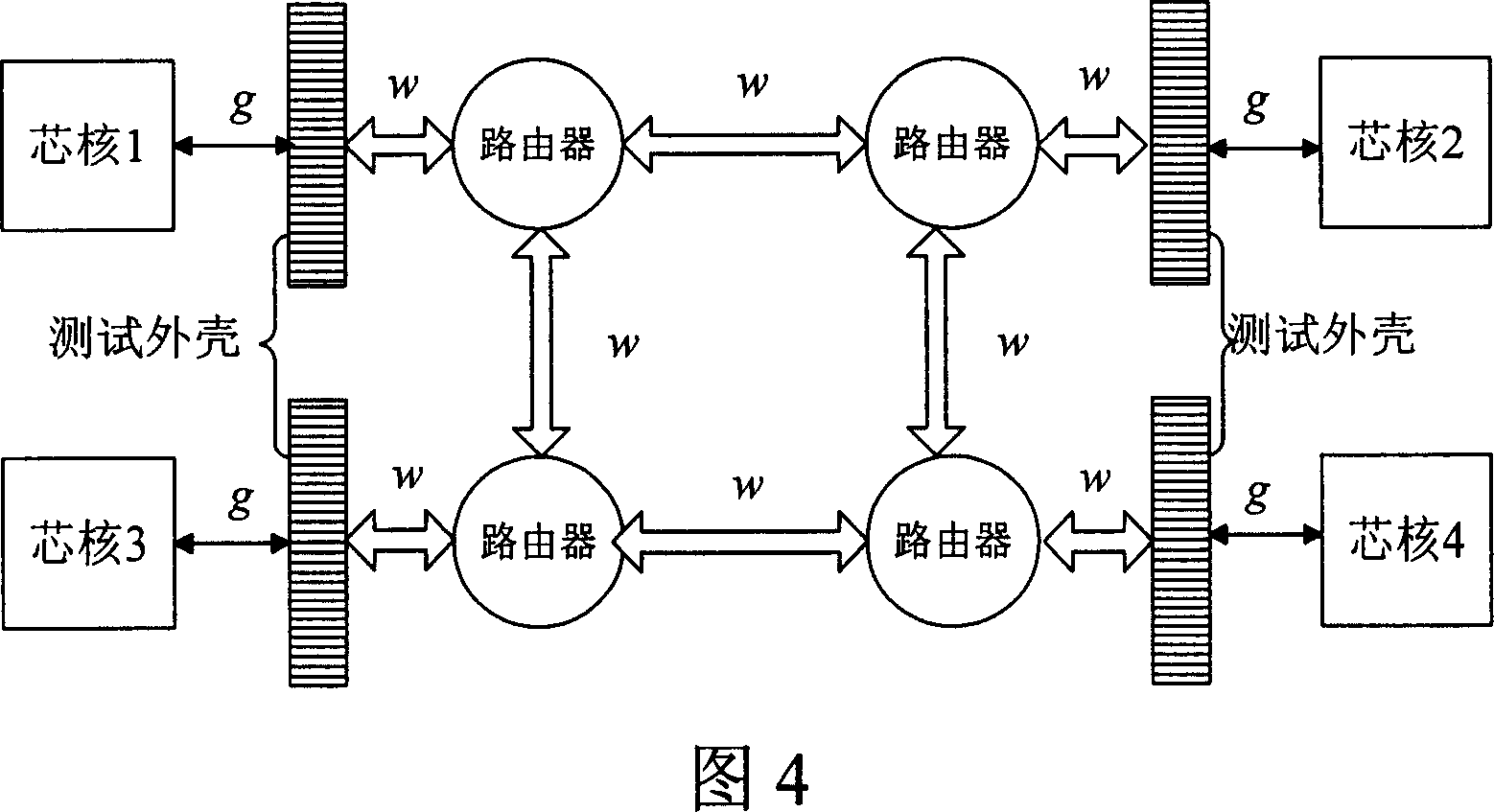

Test circuit of on-chip multicore processor and design method of testability

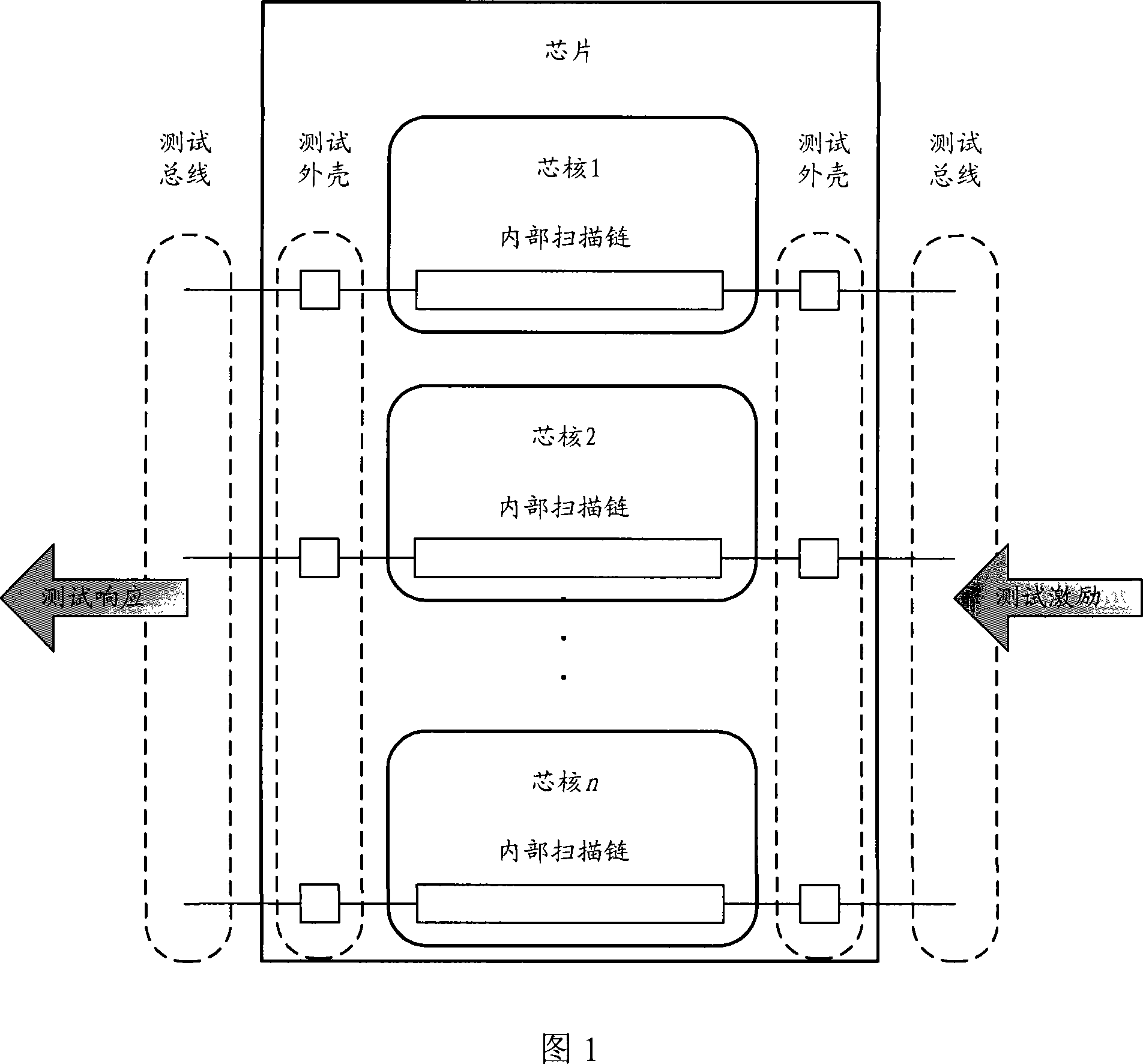

The present invention provides a testing circuit and a testability design method thereof for an on-chip multinuclear processor; wherein, the testing circuit comprises a testing shell register chain, a chip core connecting circuit waiting to be tested, an on-chip data path connecting circuit and a control logic circuit. The chip core connecting circuit waiting to be tested is an interconnection circuit, which is connected between the testing shell register chain and the chip core waiting to be tested. The on-chip data path connecting circuit is the interconnection circuit which is connected between the testing shell register chain and the on-chip data path. The control logic circuit controls the data flow direction of the chip core connecting circuit waiting to be tested and the on-chip data path connecting circuit. The present invention conducts an optimum design according to the characteristics of the on-chip multinuclear processor. The bandwidth of the on-chip data path is fully used. The testing cost is reduced and the amount of a transmission data packet in the on-chip data path is reduced. So an extra power spending caused by mass active data packet is greatly reduced and the testing time is greatly shortened.

Owner:INST OF COMPUTING TECHNOLOGY - CHINESE ACAD OF SCI

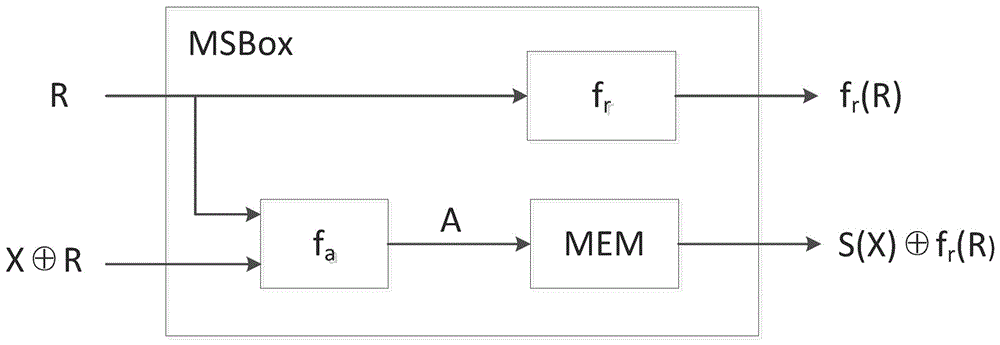

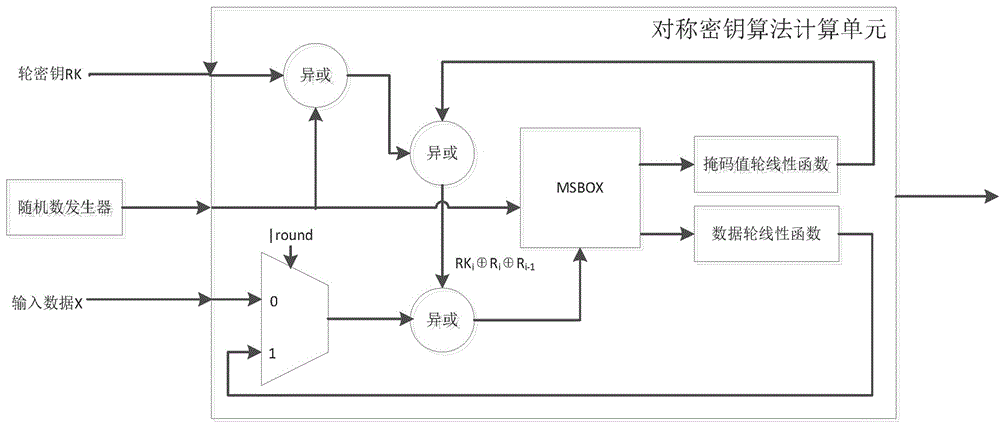

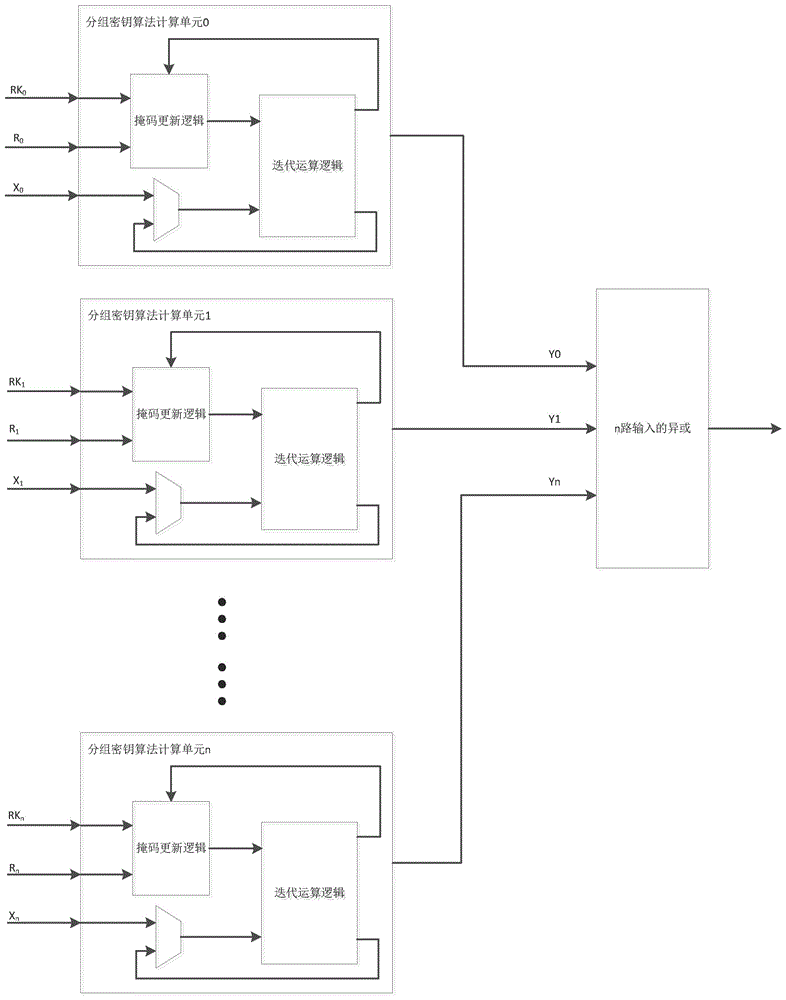

Mask S box, packet key calculation unit, apparatus and corresponding construction method

ActiveCN106788974AHigh reusabilityIncreased complexityEncryption apparatus with shift registers/memoriesDigital data processing detailsS-boxComputer module

The present invention discloses a mask S box, a packet key calculation unit, an apparatus and corresponding construction method. The mask S box comprises an input module, an address mapping processing module, and an output module. The input module receives and uses a random number and input data masked by the random number as two inputs of the mask S box. The address mapping processing module performs one-to-one mapping on the two inputs and corresponding storage addresses in a memory of the mask S box. The output module performs linear processing on the random number by using a linear equation so as to obtain and uses the random number after linear conversion as one output of the mask S box. The storage address is obtained after the random number undergone linear conversion masks the output of the original S box, and is used as another output of the mask S box. The mask S box is safe, and further, the mask S box is easy to implement, is low in power consumption and small in area, and is optimized and expanded to realize the anti-high order DPA encryption device.

Owner:SHENZHEN STATE MICRO TECH CO LTD

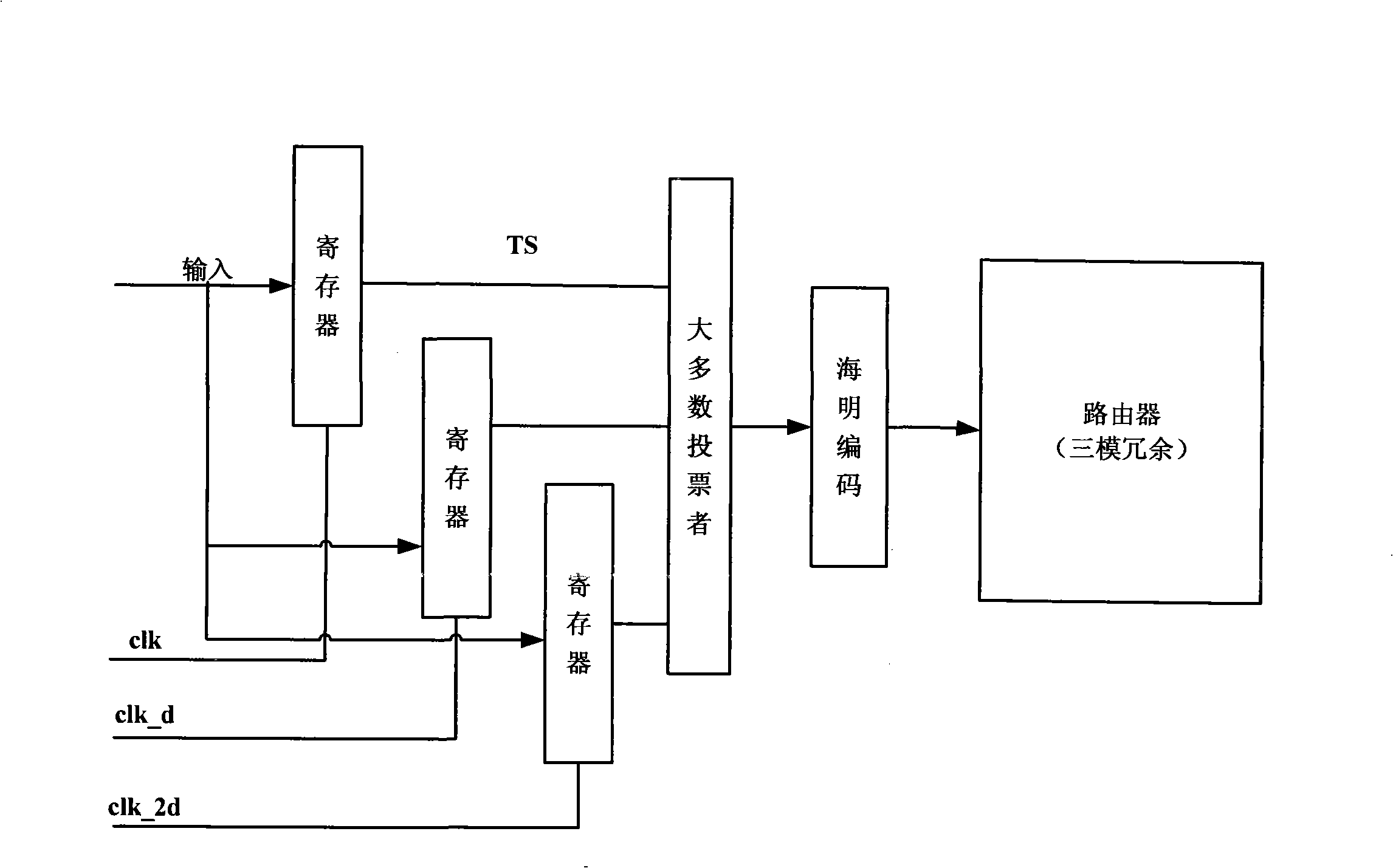

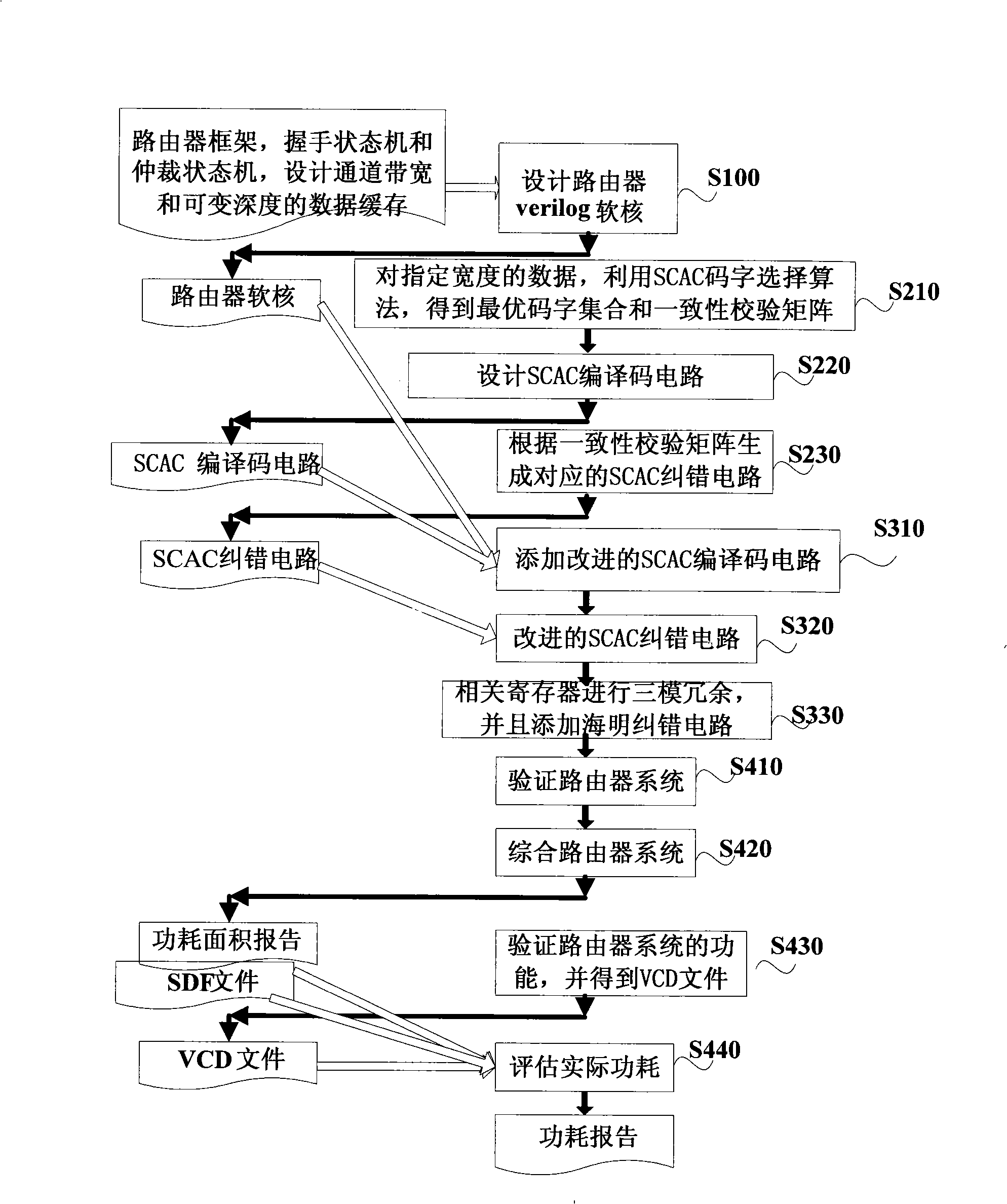

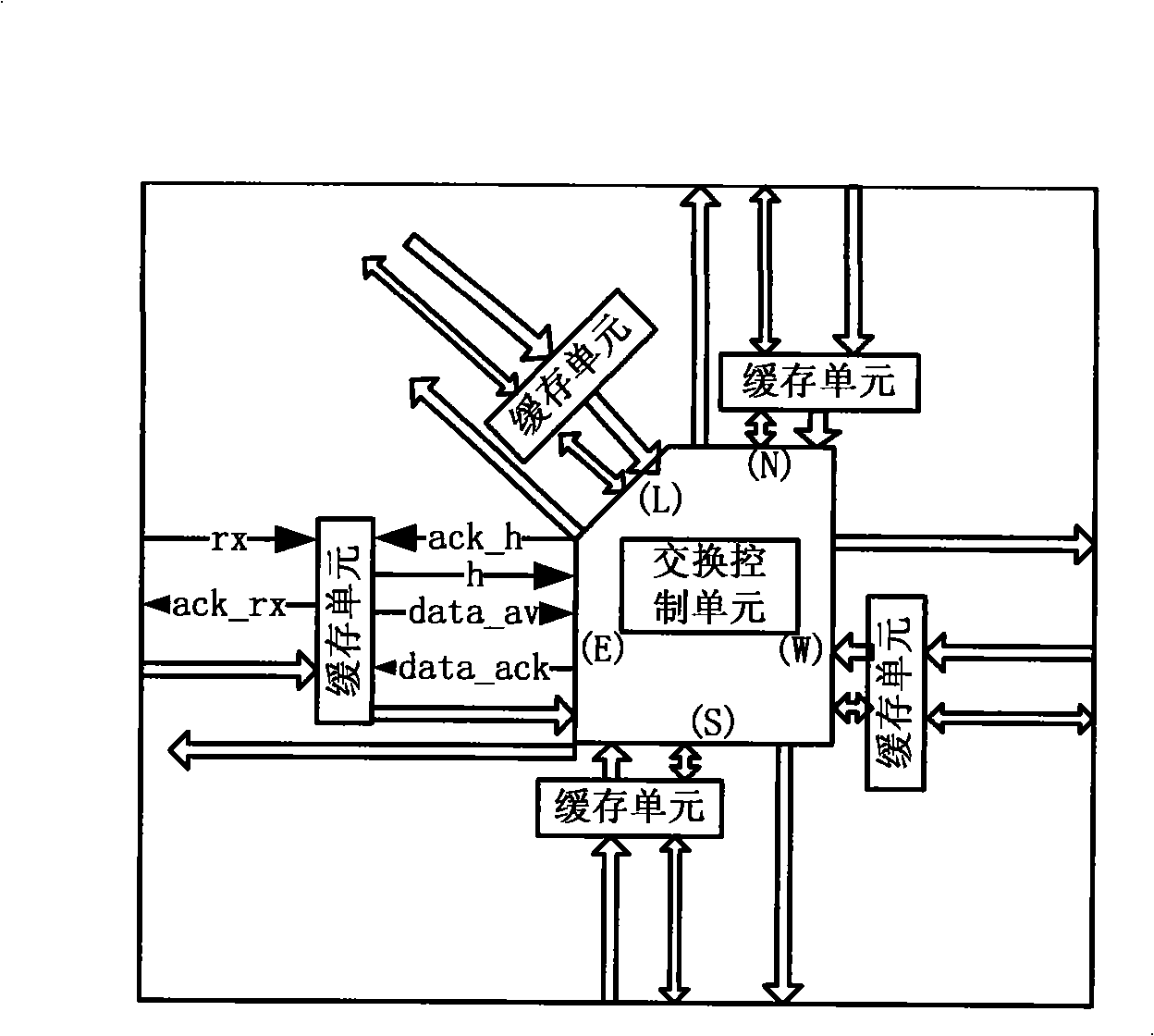

Highly reliable network server system on chip and design method thereof

ActiveCN101335606AReduce areaReduce power overheadError preventionData switching networksFault toleranceTime delays

The invention discloses an on-chip network router system with high reliability and a design method thereof, wherein, the design method of the on-chip network router system with high reliability comprises the steps that: a router soft core based on a wormhole routing swap mode and a rotation routing selection mode is designed; a corresponding SCAC coding circuit, an SCAC decoding circuit and an SCAC error correction circuit are designed for data with a specified width; and the SCAC error correction circuit is added into the router; the SCAC coding circuit and the SCAC decoding circuit are connected with the router so as to from a framework of the router system; an SCAC-TMR fault tolerance proposal is designed for the framework of the router system and the on-chip network router system with high reliability is realized; the functions of the on-chip network router system with high reliability are tested and verified and the performance of the on-chip network router system with high reliability is evaluated. The on-chip network router system with high reliability of the invention can reduce the area, the energy consumption and the expenses of the on-chip network, ensure the reliable data transmission of the on-chip network and prevent a signal jumping with a relatively long time delay from appearing on the channel, thus being more applicable to the design of fault-tolerant and multi-core processors in the future.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

Differential reference voltage buffer

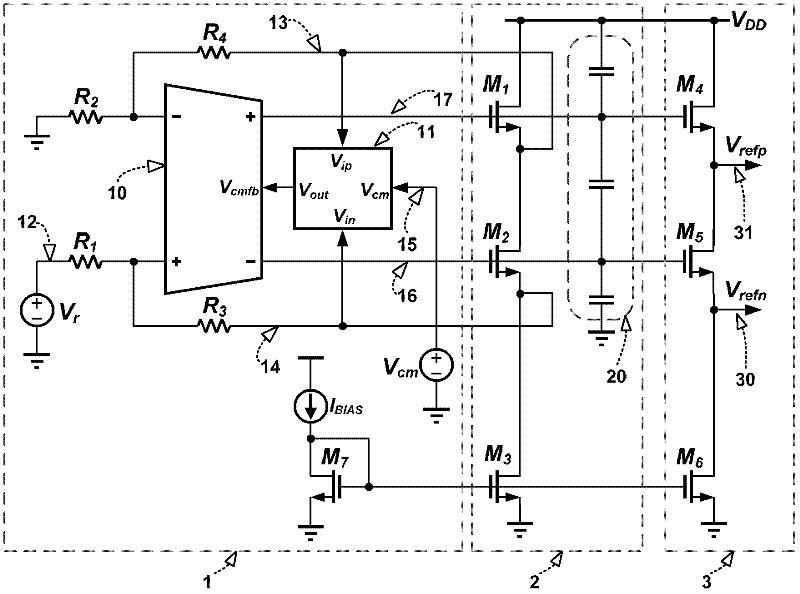

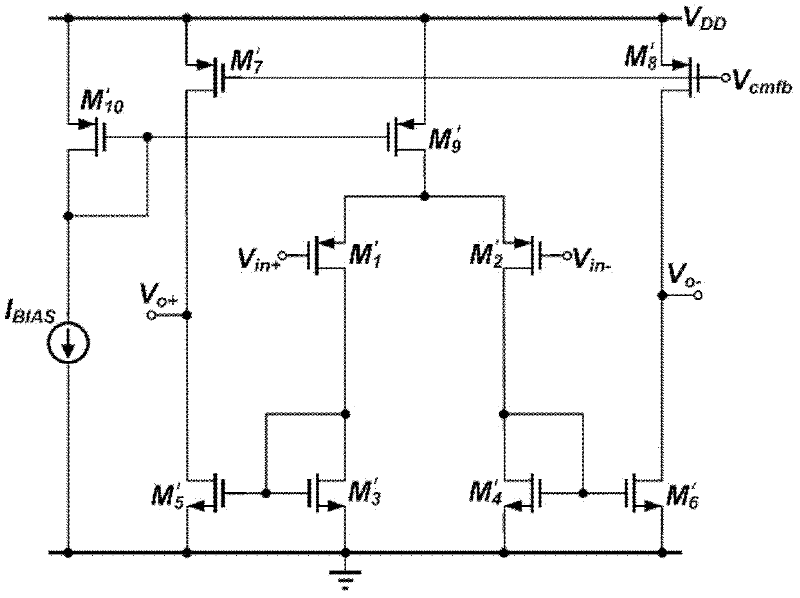

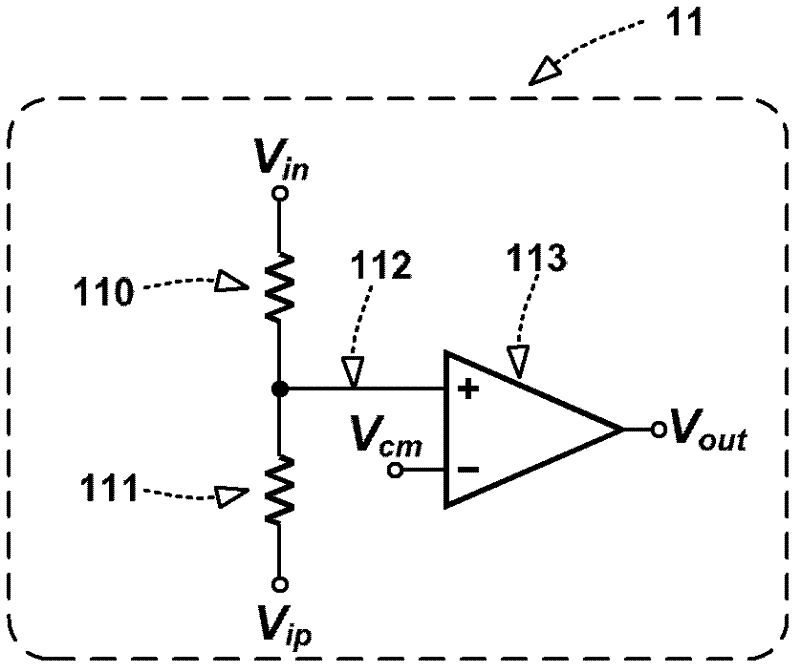

ActiveCN102412824AQuick responseStrong capacitive drive capabilityReliability increasing modificationsLogic circuit coupling/interface arrangementsLow noiseVoltage reference

The invention provides a differential reference voltage buffer, which comprises a control section, a copy buffer section, and a main buffer section connected in series between the control section and the copy buffer section, wherein the control section comprises a full differential operational amplifier and a common-mode feedback circuit, and an output end the common-mode feedback circuit is connected to a common-mode feedback input end of the full differential operational amplifier; the main buffer section comprises a first transistor and a second transistor sharing bias current on a same branch, an output end of the full differential operational amplifier is connected to grid electrodes of the first and second transistors, and source electrodes of the first and second transistors are connected to an input end of the common-mode feedback circuit; and the copy buffer section comprises a fourth transistor and a fifth transistor sharing bias current on a same branch, grid electrodes of the fourth and fifth transistors are respectively connected to the grid electrodes of the first and second transistor, and source electrodes of the fourth and fifth transistors respectively output a reference voltage. The differential reference voltage buffer provided by the invention has fast response speed, low noise and low power consumption, and can increase the performance and precision of a data converter.

Owner:SHANGHAI BEILING

Optimal energy efficiency-based antenna selection method for multi-user and large-scale antenna relay system

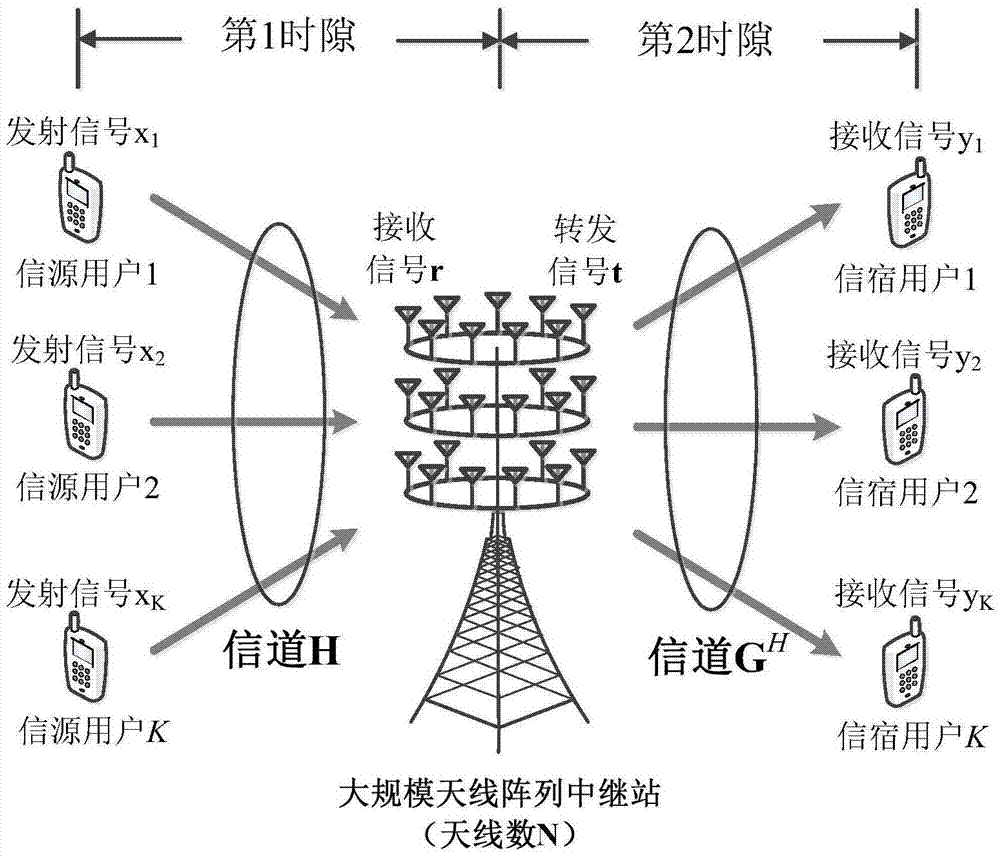

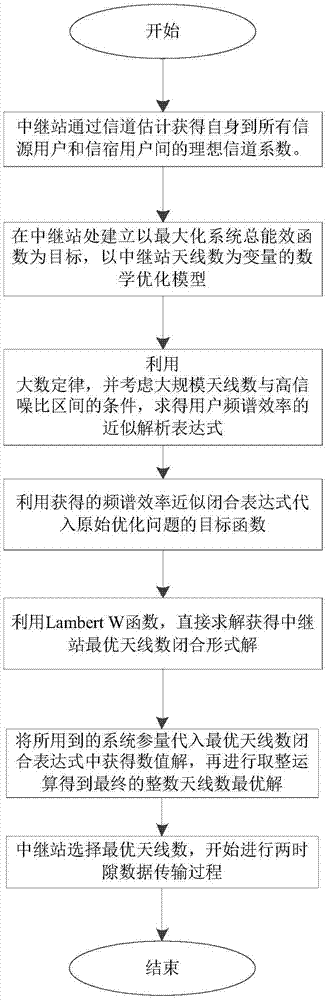

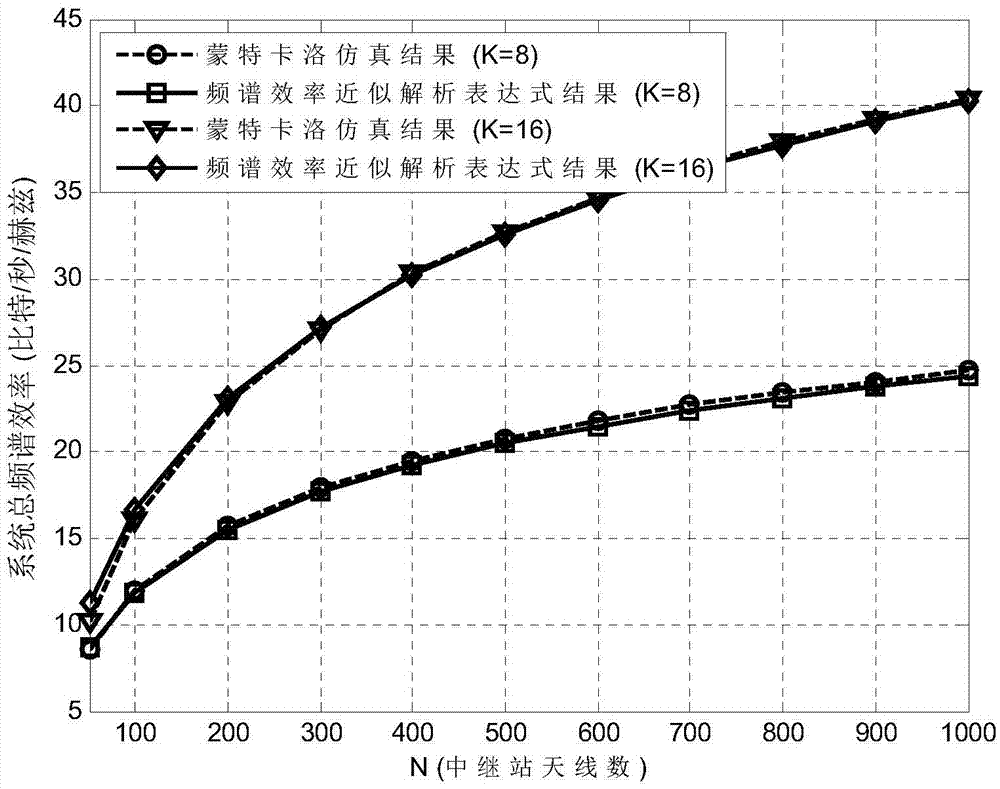

InactiveCN105450275AReduce power overheadReduce complexitySpatial transmit diversityHigh level techniquesMathematical modelPairwise coupling

The present invention discloses an optimal energy efficiency-based antenna selection method for a multi-user and large-scale antenna relay system. The system comprises a plurality of information source users, a plurality of information sink users and a relay station, wherein the number of the information source users is equal to the number of the information sink users. The information source users and the information sink users are pairwise coupled and the information transmission between the information source users and the information sink users is realized via the relay station within two time slots. All information source users and information sink users in the system are respectively provided with a single antenna. The relay station is provided with an antenna array of a large-scale number illustrated in the drawings of the abstract. According to the technical scheme of the invention, in order to realize that the energy efficiency of the system is maximal, the antenna number of the relay station is adopted as an optimization variable for the establishment of a mathematical model. Since no clear analytical expression is available for a target function of the above optimization problem, an approximately accurate analytical expression for the target function of the optimization problem is figured out firstly based on the law of large numbers in the large dimensional random matrix theory. After that, based the quasi-concave characteristics of the optimization variable in the analytical expression, an optimal antenna number closed-form solution for realizing the optimal energy efficiency is finally solved out by means of the Lambert W function at the same time.

Owner:SOUTHEAST UNIV

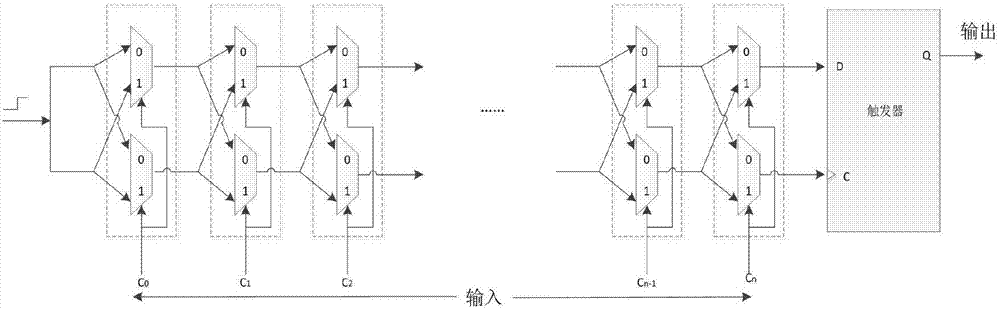

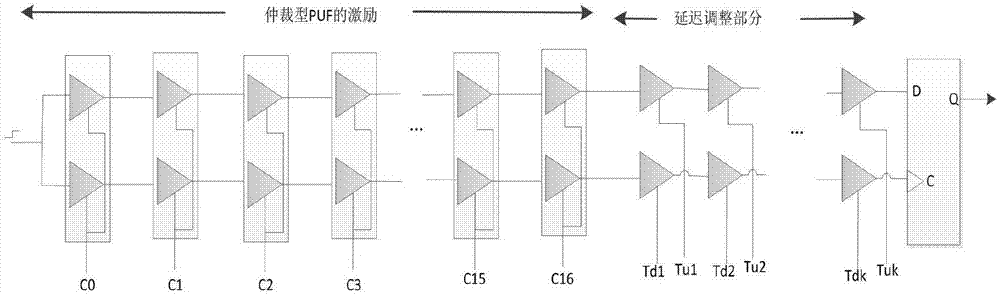

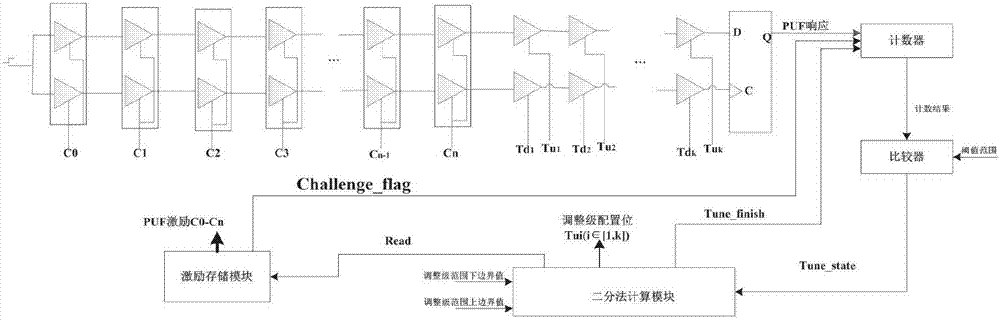

Wiring delay deviation fast calibration method of arbitration-type PUF based on FPGA

ActiveCN107103144AReduce power overheadReduce time overheadCAD circuit designSpecial data processing applicationsComputer moduleComputer science

The invention discloses a wiring delay deviation fast calibration method of an arbitration-type PUF based on an FPGA. According to the technical scheme, fast calibration of delay deviation is achieved by an automatic adjusting circuit which is composed of one counter, one comparator, one dichotomy computing module and one excitation storage module. After input read signals become effective, the excitation storage module outputs stored excitations to the PUF from the first excitation to the last excitation, and afterwards sets excitation marking signals connected with the counter to be effective. When input adjusting completion signals become effective, the counter conducts zero clearing, and begins to conduct accumulative counting on responses of the PUF, and when the excitation marking signals become effective, the counter stops counting, and outputs transfers a counting result to the comparator, the comparator outputs adjusting marking signals for calculating the next adjustment stage to a dichotomy module according to the relation between the counting result and a given threshold value range. In the dichotomy computing module, the next adjustment stage is calculated, and the corresponding adjustment stage is output to be configured and applied in a delay adjustment block of the PUF. Then under the adjustment stage, excitations are input to the PUF again to conduct the next round of adjustment till a counting result is in a threshold value range in the comparator, and then the comparator outputs adjustment stage number marking signals. According to the wiring delay deviation fast calibration method of the arbitration-type PUF based on the FPGA, time consumed in the adjusting process of the PUF can be effectively shortened.

Owner:BEIJING UNIV OF CHEM TECH

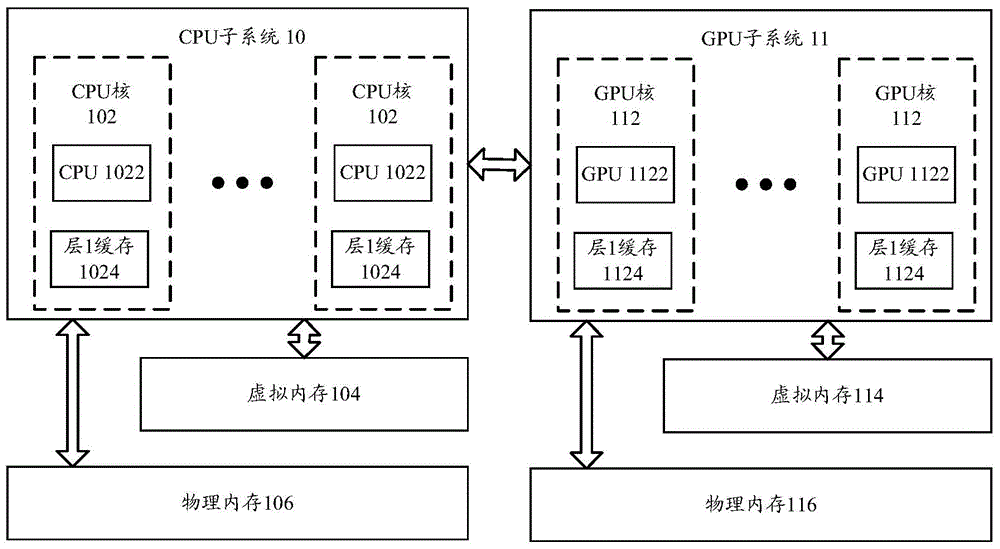

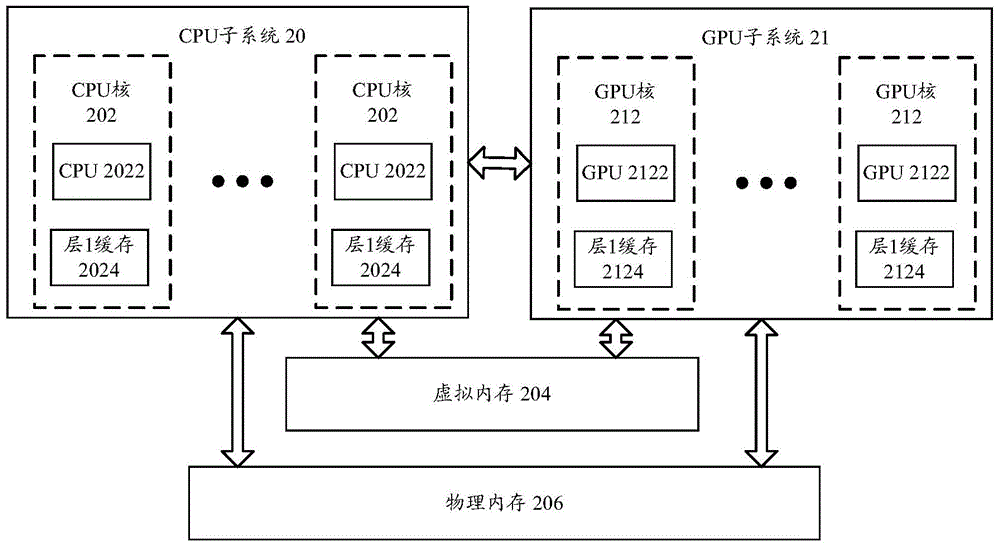

System on chip and memory access management method thereof

InactiveCN105302765ASmall footprintSmall area overheadMemory adressing/allocation/relocationDigital computer detailsMemory sharingAccess management

The invention provides a system on chip SOC and a memory access management method thereof, and aims at realizing the memory sharing of different processor subsystems in the SOC, and carrying out consistency management on a shared memory among the processor subsystems, so as to reduce the area and the power consumption of the SOC and realize the uniform management of the shared memory. The system on chip comprises the processor subsystems, the shared memory and a system memory management unit MMU, wherein the system MMU is connected between the processor subsystems and the shared memory and used for managing the access from the processor subsystems to the shared memory.

Owner:CHINA ACAD OF TELECOMM TECH

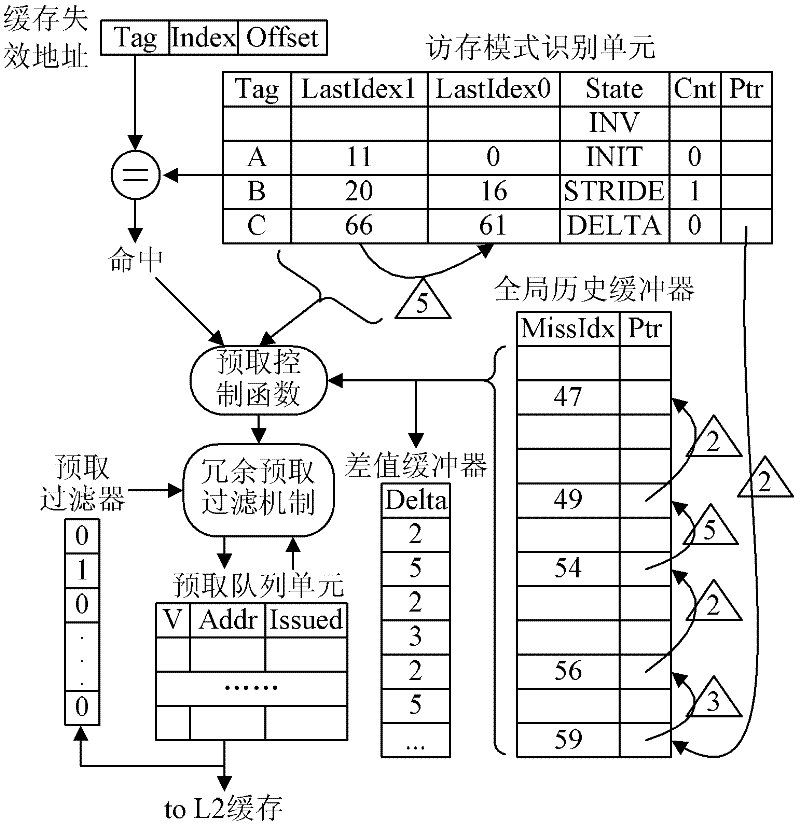

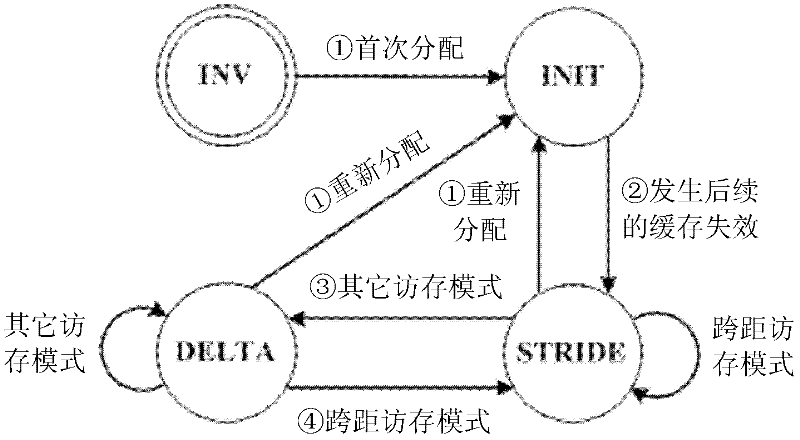

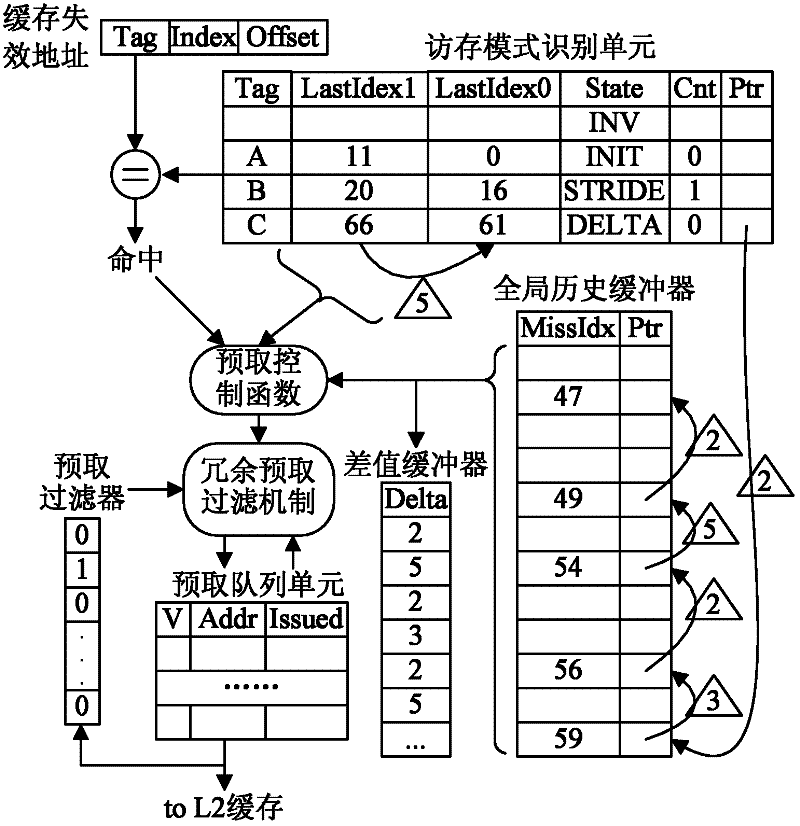

Method and device for realizing data pre-fetching

ActiveCN102521158AImprove optimization performanceReduce bandwidth requirementsMemory architecture accessing/allocationEnergy efficient ICTLocal failureBandwidth requirement

The invention provides a method and a device for realizing data pre-fetching. A pre-fetcher device comprises: a memory access mode recognition unit divides a global failure address flow into a local failure address flow, records information of two addresses with caching failure happening lately in the local failure address flow as history memory access information according to a time sequence, and captures a spanning memory access mode according to the record and generates a corresponding pre-fetching address. According to the invention, the storage utilization efficiency of a difference value related pre-fetcher is improved and the redundancy pre-fetching having no contribution to pre-fetcher performance improvement is reduced, so that the pre-fetcher can obtain a better performance optimization effect under the condition of same storage expense, and the cached bandwidth requirement and power consumption expense on a pre-fetcher access sheet are reduced effectively.

Owner:BEIJING PKUNITY MICROSYST TECH

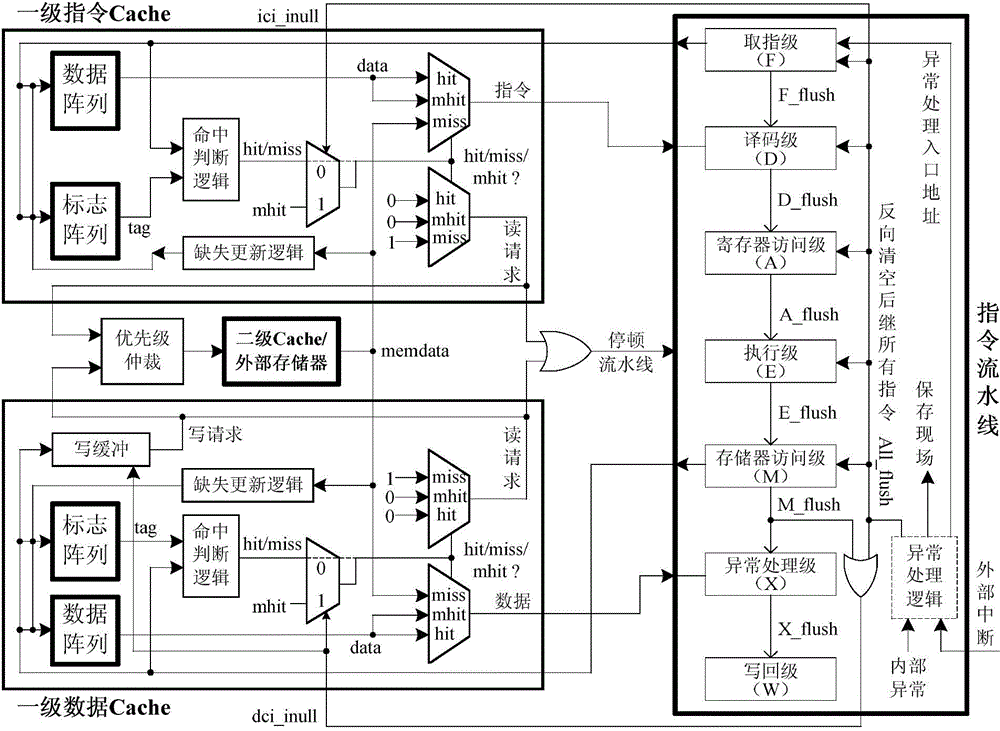

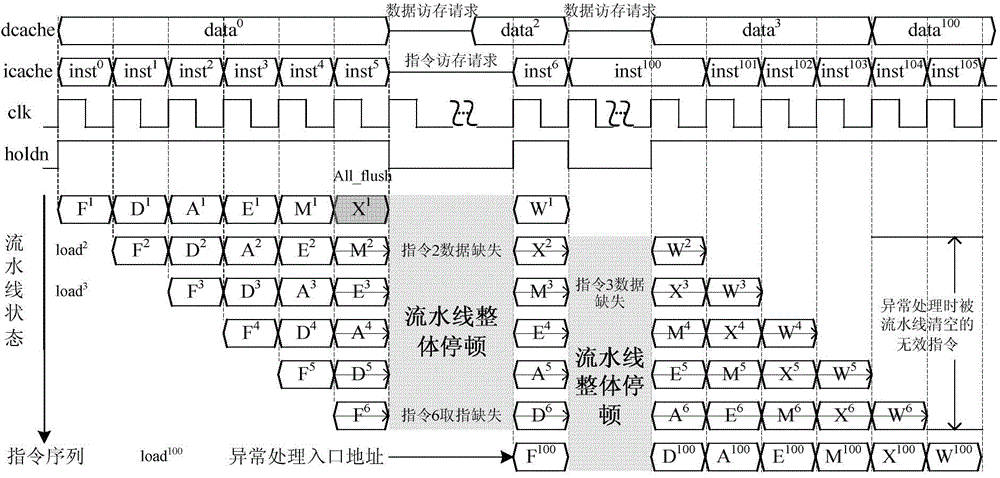

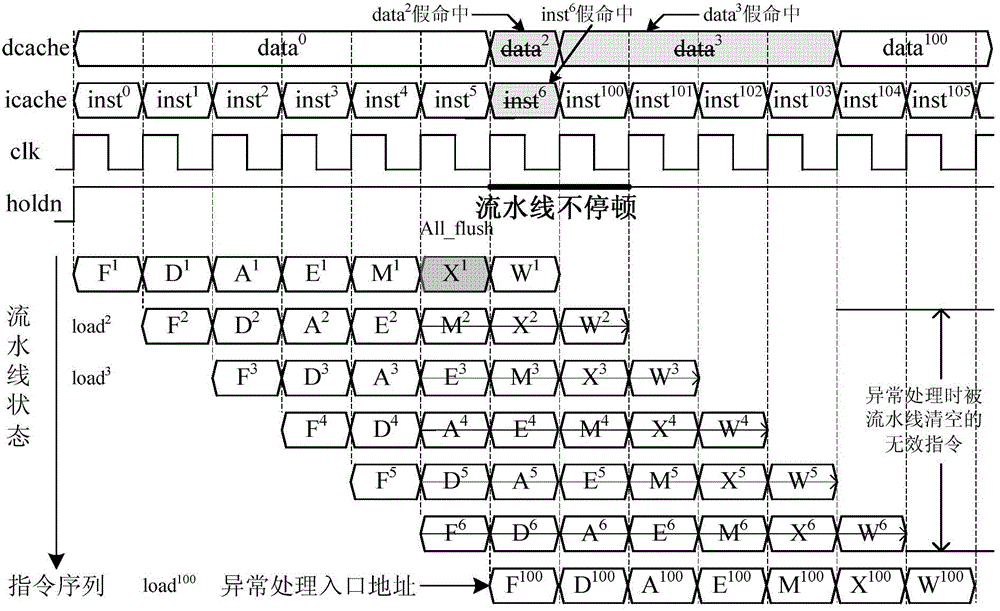

Exception handling method and structure tolerant of missing cache and capable of emptying assembly line quickly

ActiveCN104461758AEliminate pausesHigh speedFault responseMachine execution arrangementsAssembly lineException handling

The invention provides an exception handling method and structure tolerant of missing cache and capable of emptying an assembly line quickly. The exception handling method includes the steps that firstly, a false hit state is defined, and the access result of the cache by invalid commands emptied by the assembly line is marked; correct command codes or data words are not guaranteed by the cache under the false hit state, and the corresponding cache information of access addresses is output directly; an assembly line emptying signal is directly acted on the command cache in the command taking operation in the false hit state to enable the false hit state to be selected when the invalid commands have access to the cache; when exception handling begins, data cache is selected and controlled through the assembly line emptying signal and the or logic of a storage access level invalid marking signal; when an exception occurs, the cache enters the false hit state to enable the assembly line to advance continuously. The invention further discloses the structure applying the exception handling method. By means of the exception handling method and structure tolerant of missing the cache and capable of emptying the assembly line quickly, the exception handling speed can be increased, and the real-time performance of the system is improved.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

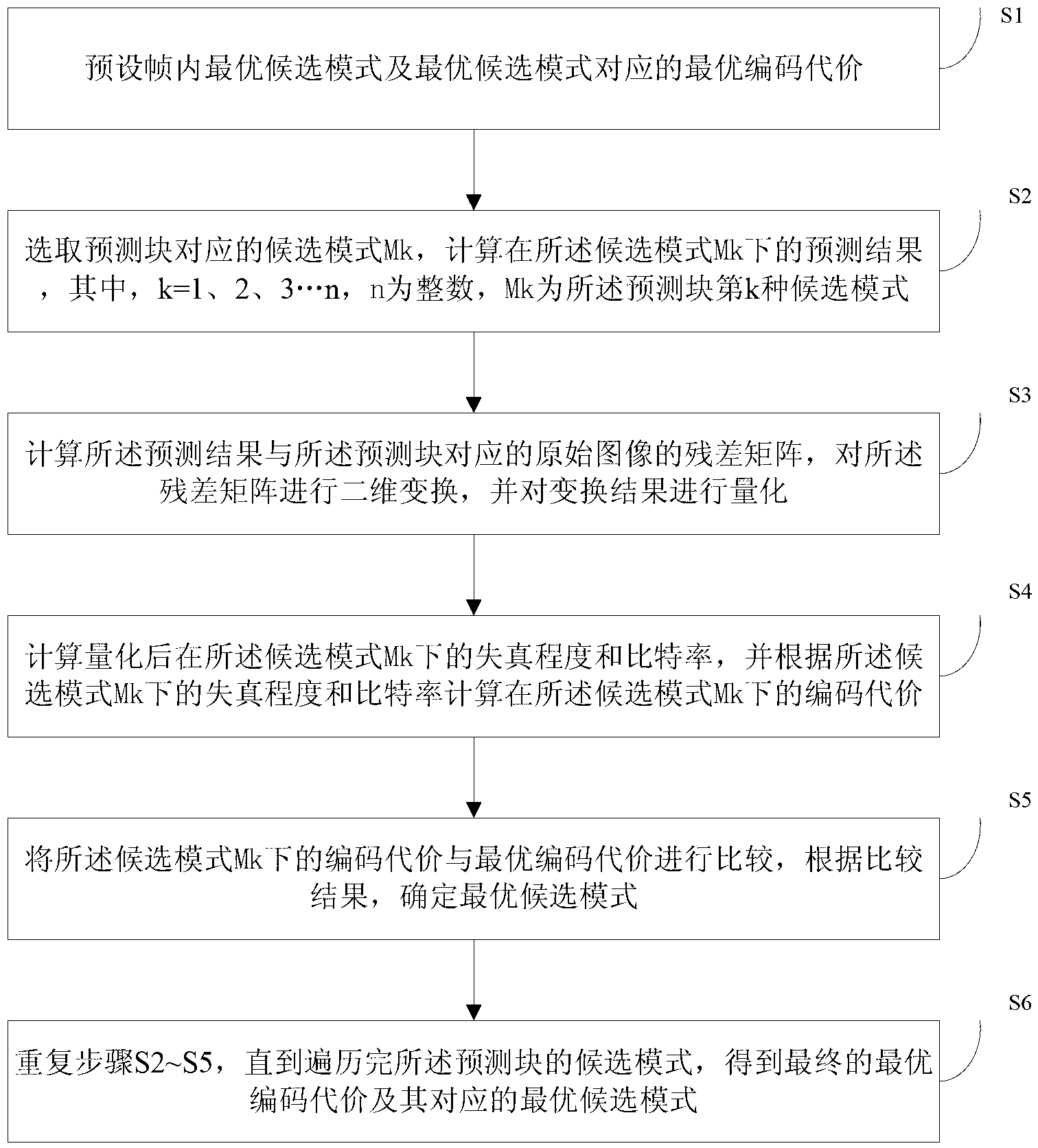

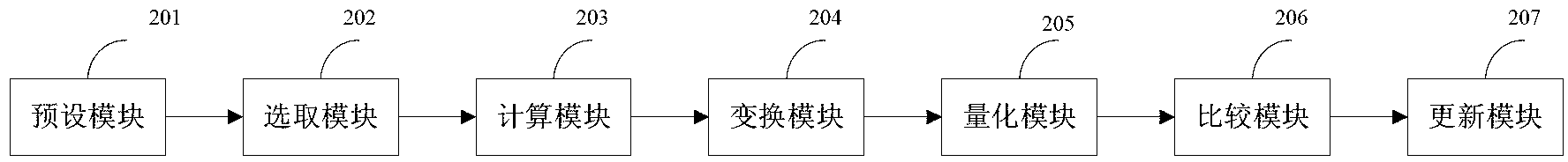

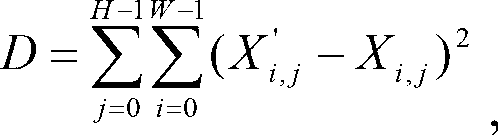

Method and device for intra-frame mode prediction based on two-dimensional Hadamard transformation

ActiveCN103024392AThe calculation process is simpleReduce power overheadTelevision systemsDigital video signal modificationAlgorithmResidual matrix

The invention provides a method and a device for intra-frame mode prediction based on two-dimensional Hadamard transformation. The method includes: S1, presetting an optimal coding cost Jbest; S2, selecting a candidate mode Mk corresponding to a prediction block, and computing a predication result under the candidate mode Mk; S3, computing a residual matrix of an original image corresponding to the predication result and the predication block, performing two-dimensional transformation for the residual matrix and quantifying a transformation result; S4, computing the distortion degree and the distortion rate under the candidate mode Mk after quantification, and computing the coding cost Jk under the candidate mode Mk; S5, comparing the Jk with the Jbest, if the Jk< the Jbest, the Jbest= the Jk, and the Mk serves as the optimal candidate mode, and if the Jk>=the Jbest, the Jbest and the optimal candidate mode corresponding to the Jbest are unchanged; and S6, repeating the steps from S2 to S5 until candidate modes of the predication block are traversed, so that the final optimal coding cost and the optimal candidate mode corresponding to the optimal coding cost are obtained. By the method, power consumption expenses and hardware area are reduced.

Owner:TSINGHUA UNIV +1

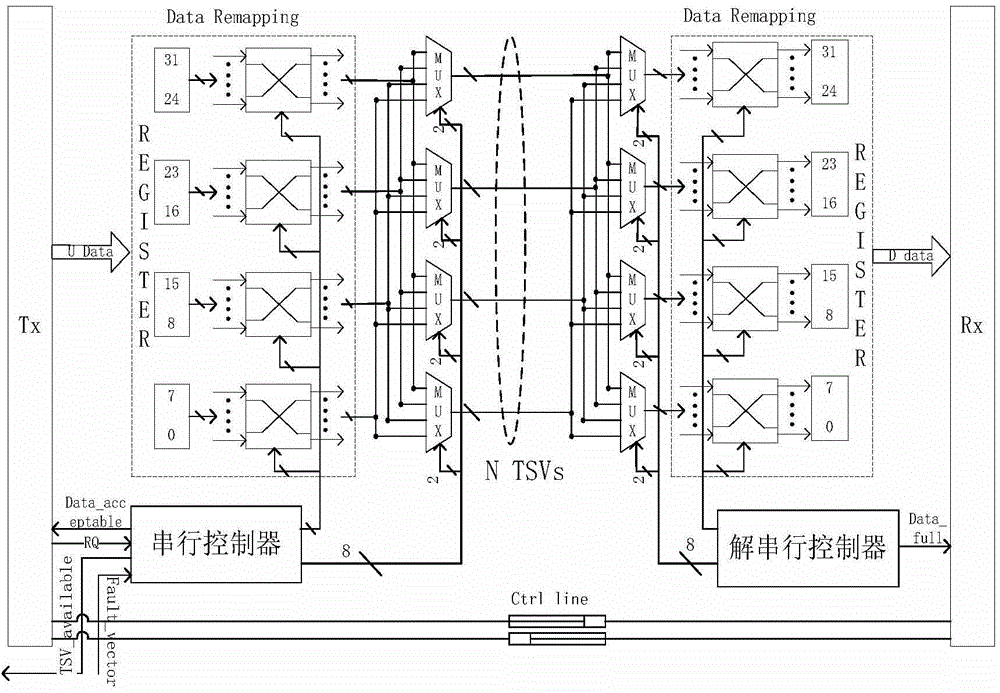

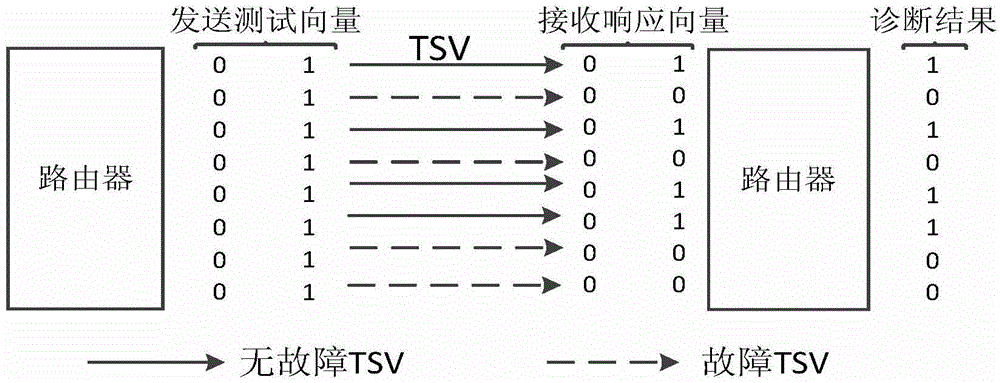

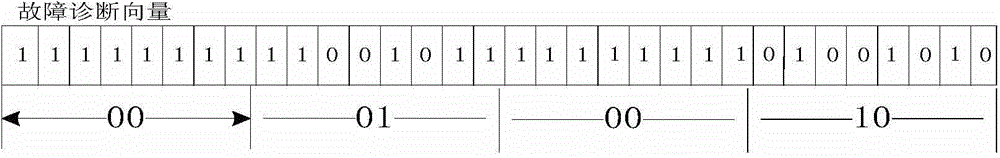

Fault-tolerant method aiming at TSV fault grading in 3D NoC

ActiveCN104133732AReduce congestionGuaranteed reliabilityFault responseSerial transferNetwork packet

The invention discloses a fault-tolerant method aiming at TSV (Through Silicon Via) fault grading in 3D NoC (Network on Chip). According to the method, TSVs and data bits are respectively divided into four groups; if a TSV fault state value is within 6, the serial transmission among the groups and among data bits in the groups can be realized by using rest available TSVs; and otherwise, a localized fault-tolerant routing algorithm is used, and the address of the optimum TSV is found out from a locally stored TSV state table and is used as a temporary target address to be added to a data packet header for completing interlayer communication. According to the scheme of the method provided by the invention, the corresponding fault-tolerant method is selected through judging the fault grade of TSV links; higher reliability of the system is ensured; and meanwhile, the waste of available resources is reduced.

Owner:黄山市开发投资集团有限公司

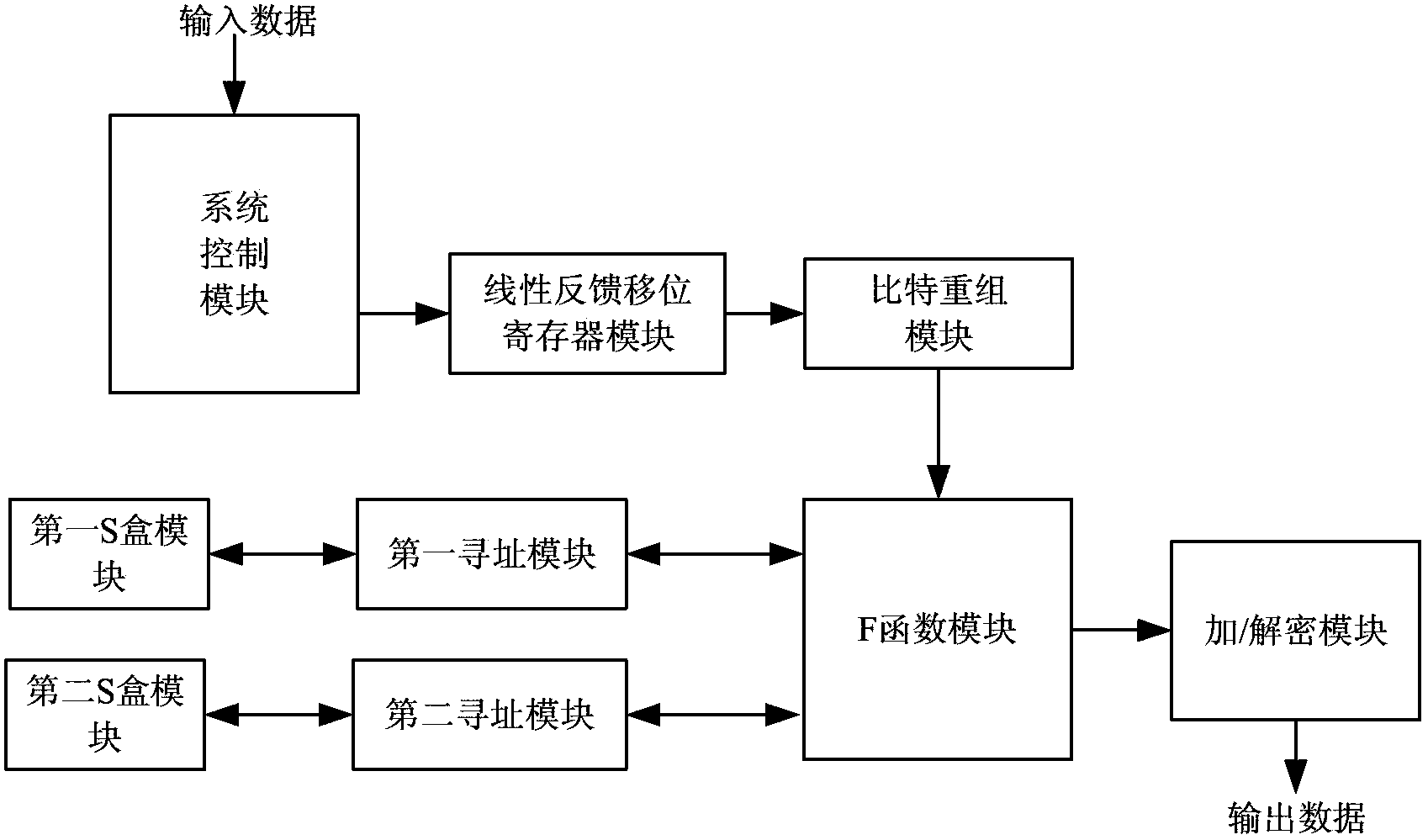

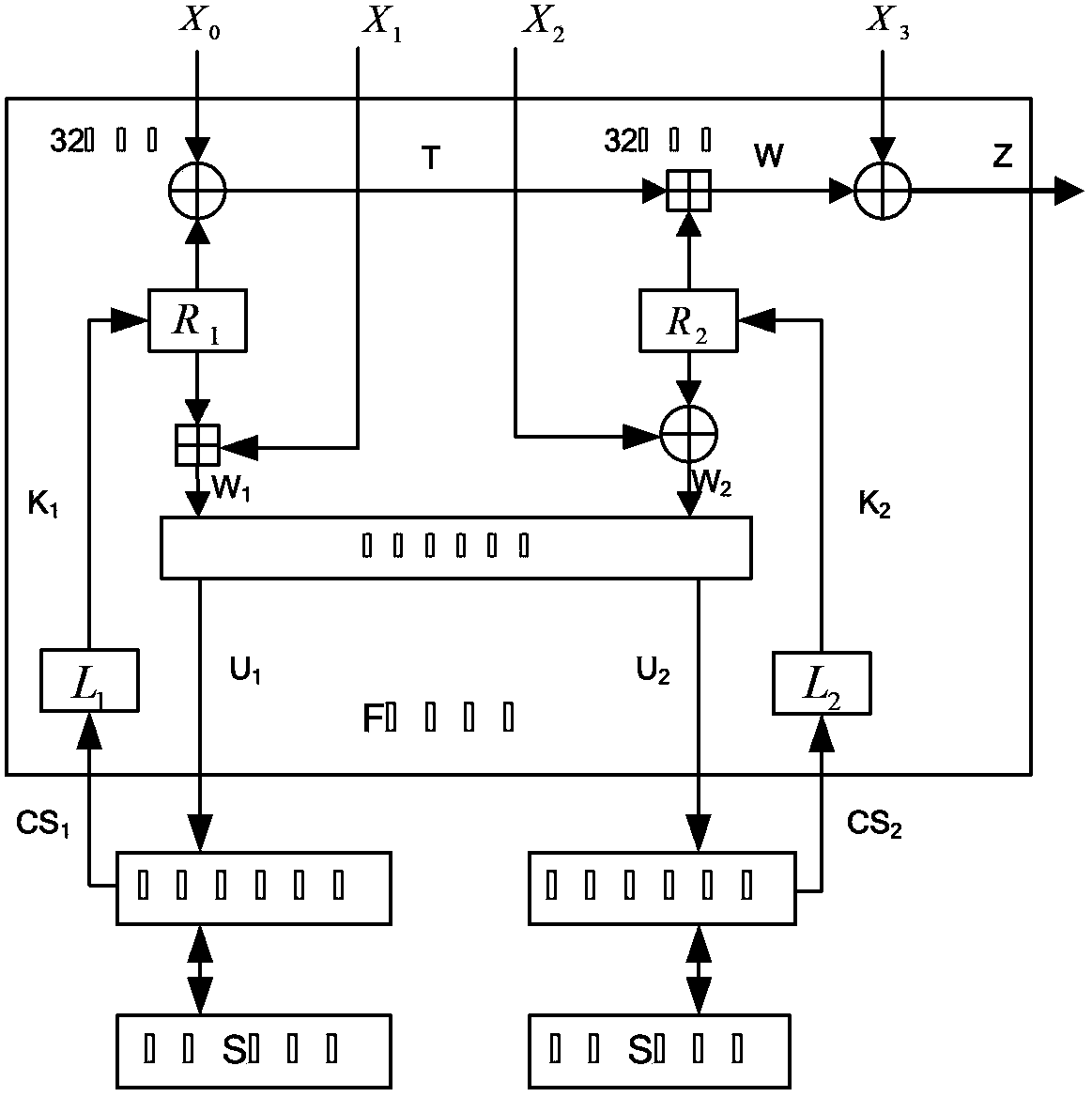

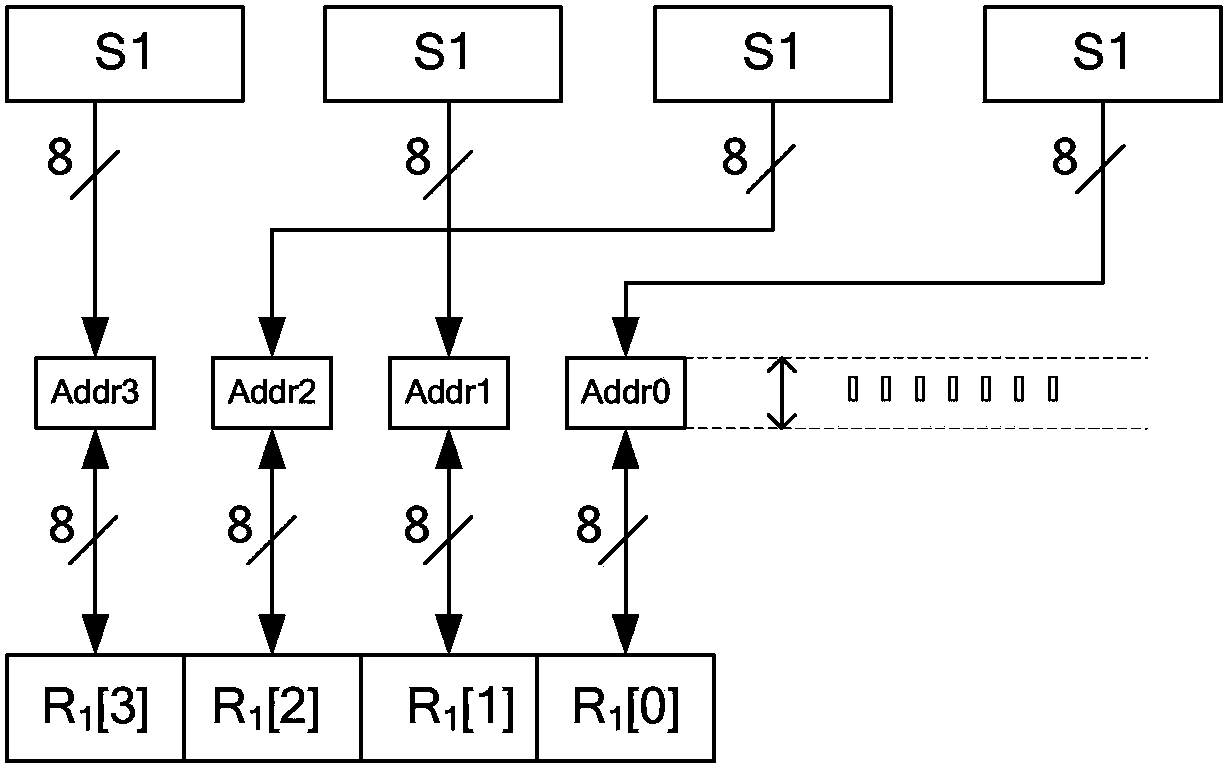

System and method for achieving ZUC

ActiveCN103731822AReduce resource overheadReduce power overheadKey distribution for secure communicationSecurity arrangementS-boxCommunications system

The invention discloses a system and method for achieving the ZUC, and belongs to the technical field of communication system encryption. The system comprises a system control module, a linear feedback shift register module, a bit recombination module, an F function module, a first addressing module, a second addressing module, a first S box module, a second S box module and an encryption / decryption module. According to the system and method, the resource cost of the system can be greatly reduced by optimizing parallel addressing logic of the ZUC, and meanwhile the power consumption cost of the system can be reduced by optimizing an achievement structure, based on a lookup table, of an S box.

Owner:中科芯未来微电子科技成都有限公司

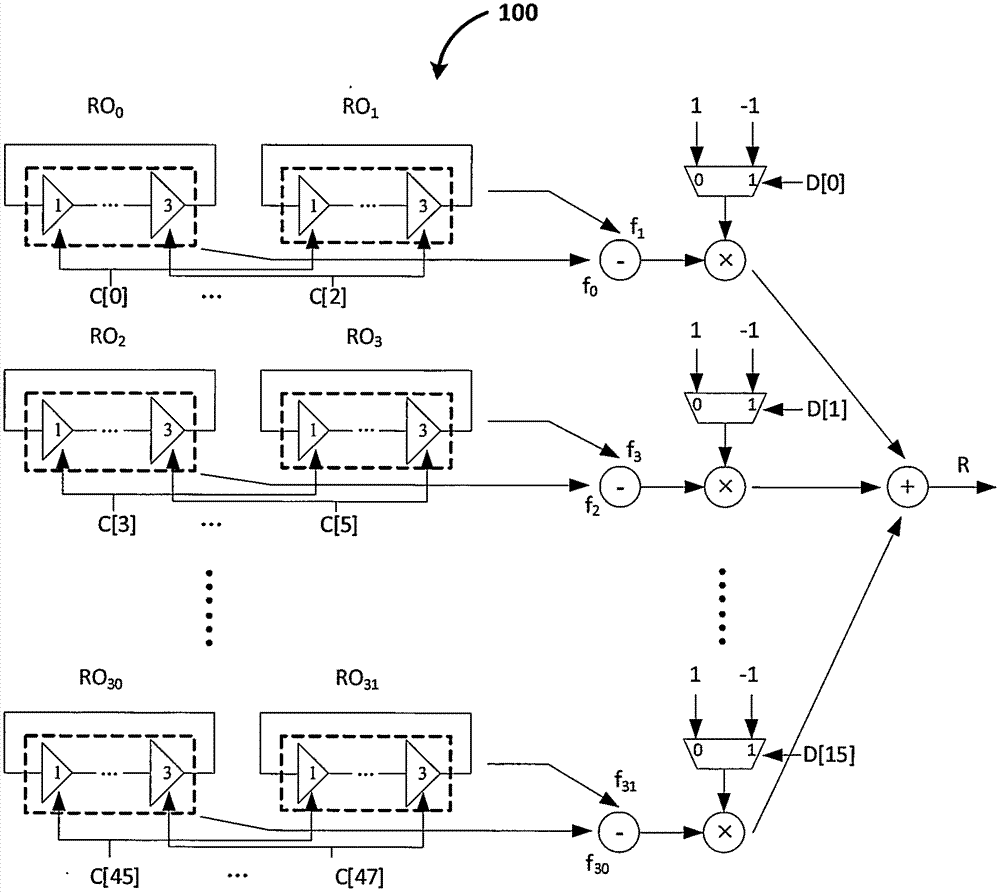

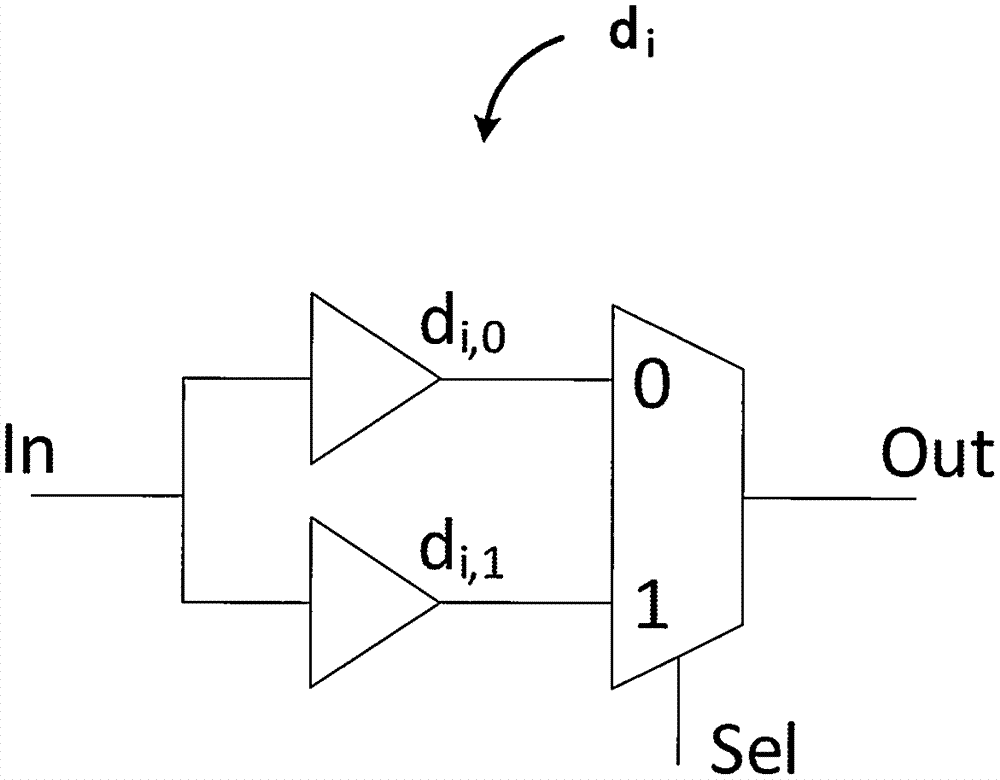

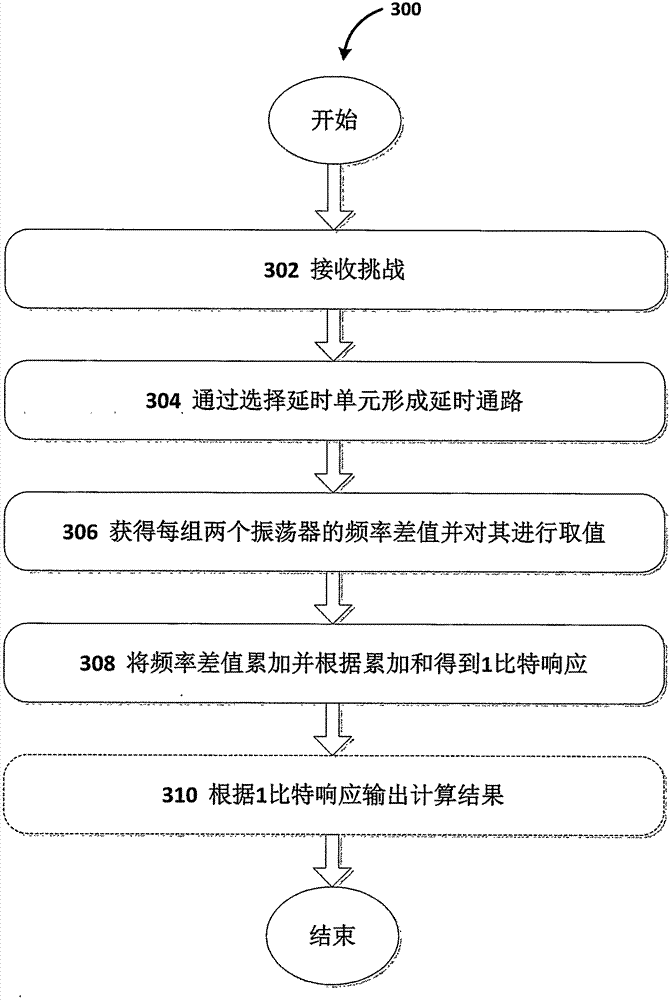

Circuit used for realizing physical unclonable function and corresponding operation method

ActiveCN106919860AReduce areaReduce power overheadInternal/peripheral component protectionTime delaysPhysical unclonable function

The invention relates to a circuit used for realizing a physical unclonable function. The circuit comprises n pieces of oscillators of which the time delay paths are configurable, wherein n is an even number; the oscillators independently have the frequencies of f0, f1...fn-2 and fn-1; n pieces of oscillators are divided into n / 2 groups, and each group comprises two oscillators; and each oscillator comprises m pieces of time delay unit groups, and each time delay unit group comprises at least two time delay units. The circuit is configured as follows: receiving challenges; selecting the time delay unit to form the time delay path; obtaining the frequency difference value of two oscillators in each group, and carrying out evaluation on the frequency difference value; and carrying out accumulation on the frequency difference value, and obtaining a bit response according to an accumulated sum. In addition, the invention also relates to a method for operating the circuit.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

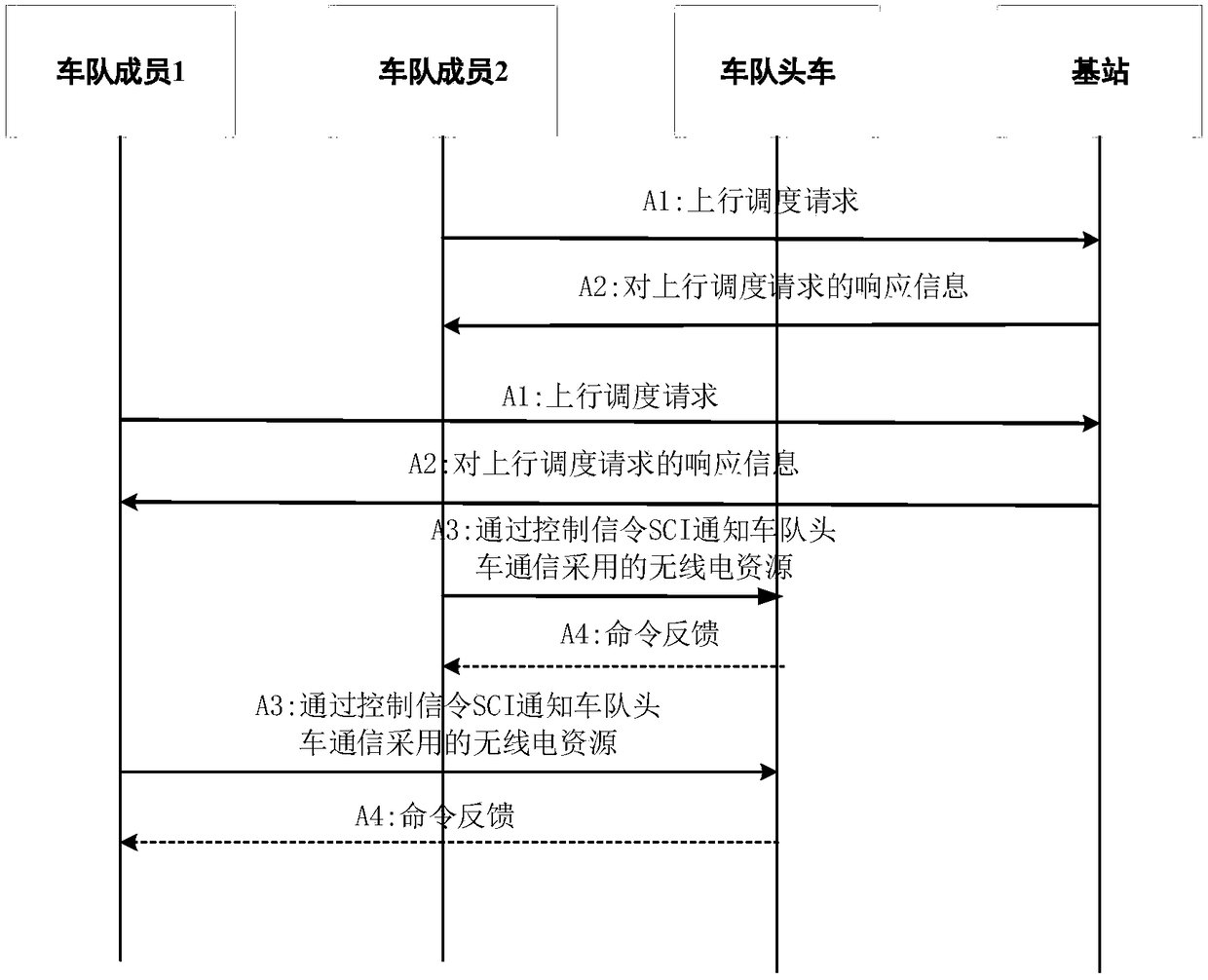

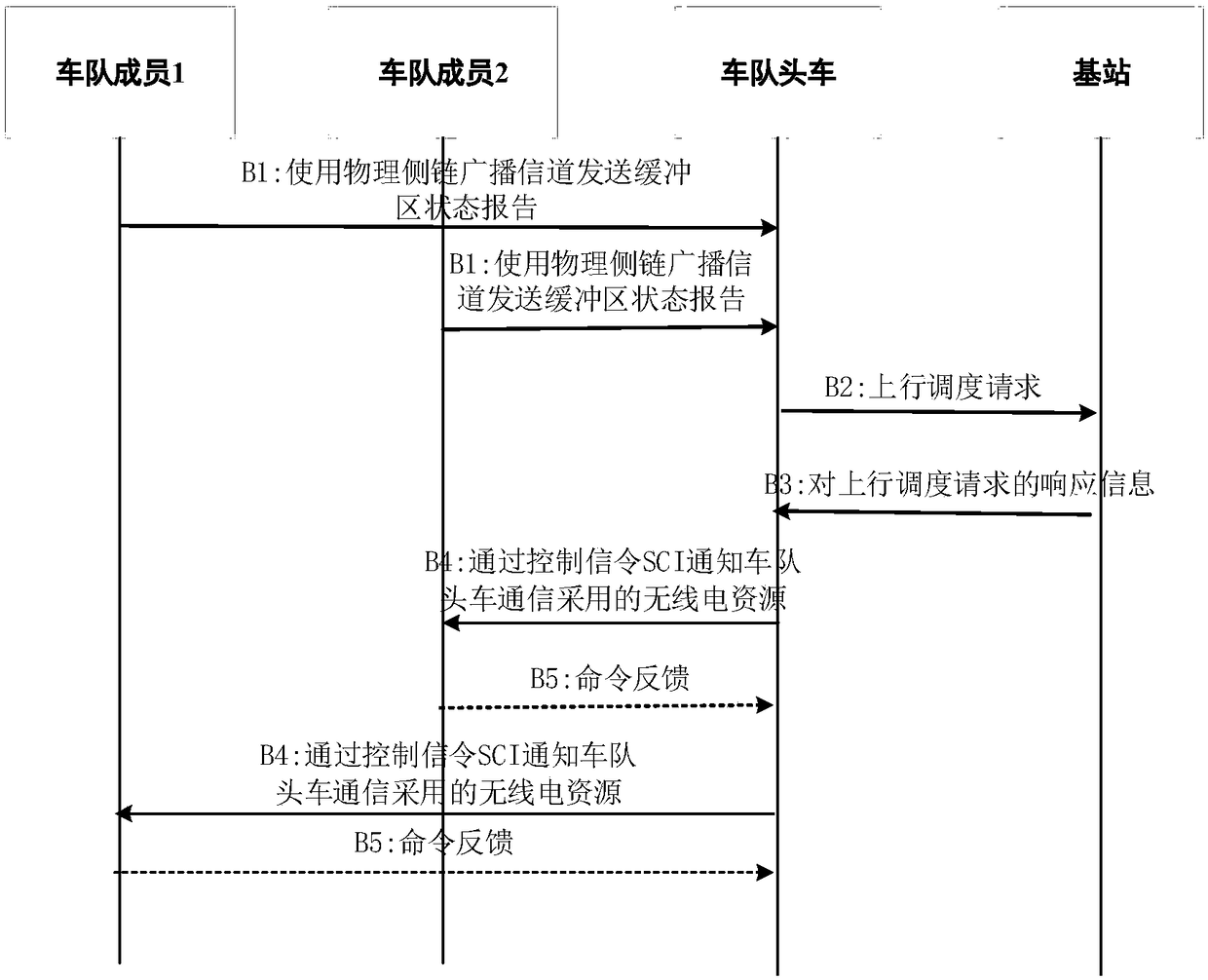

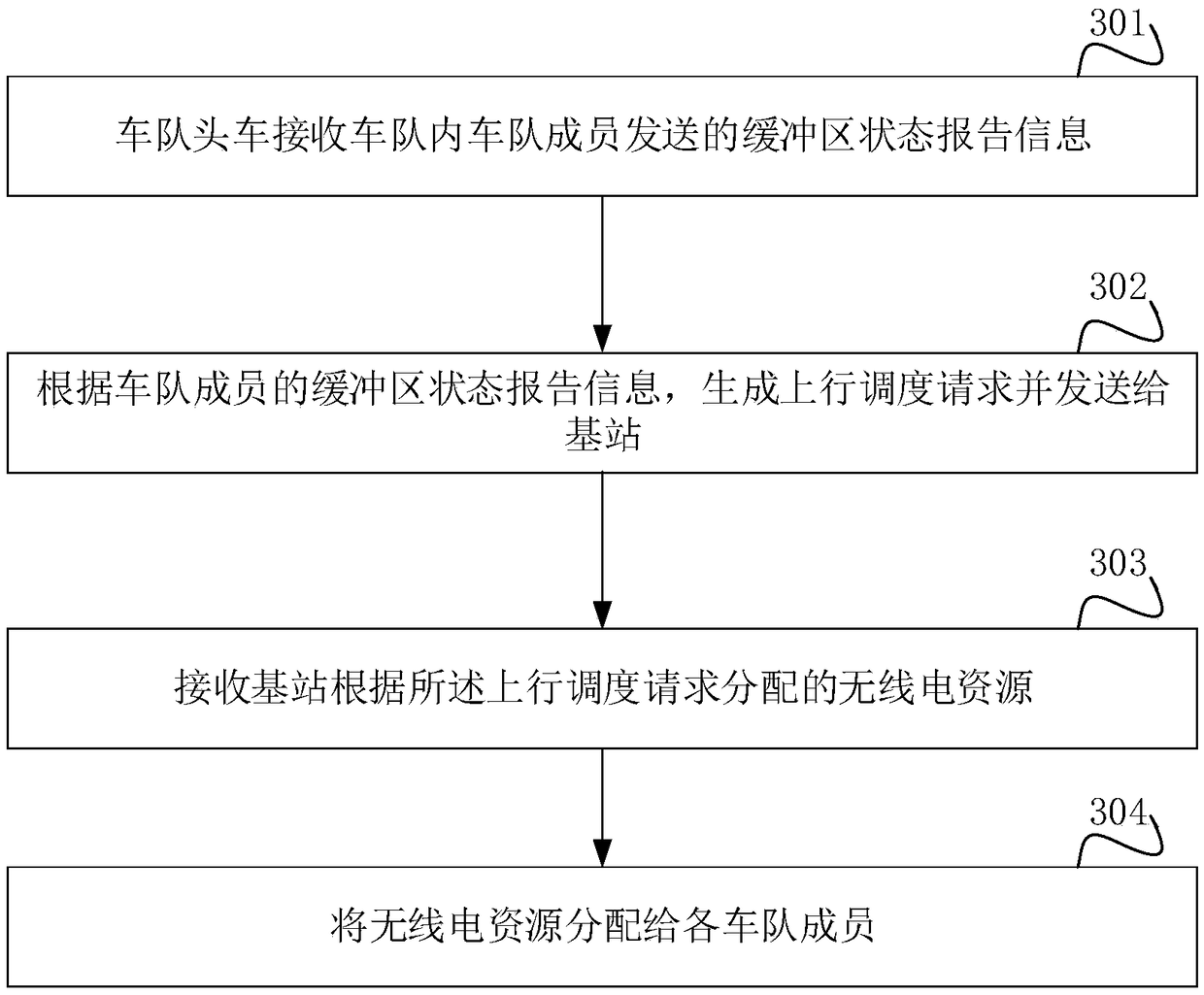

Vehicle networking resource allocation method, device, computing device and storage medium

InactiveCN109041248AReduce signaling interactionReduce power overheadParticular environment based servicesSignal allocationVehicle networksEngineering

The invention discloses a vehicle networking resource allocation method, a device, a computing device and a storage medium, which relate to the vehicle networking field and are used for solving the problem that the power consumption of a fleet member is large due to the signaling interaction between the fleet member and a base station. In the method, a fleet member sends buffer status report information to a fleet head vehicle through a link side broadcast channel, and the fleet head vehicle sends an uplink scheduling request to a base station, thereby reducing the signaling interaction between the fleet member and the base station and reducing the power consumption overhead of the fleet member. At the same time, by transmitting the position information of the fleet head car and the virtual member of each fleet to the base station, the base station can allocate resources among each fleet, and the resources among each fleet can be reused, and the unnecessary signaling overhead can be reduced.

Owner:HISENSE

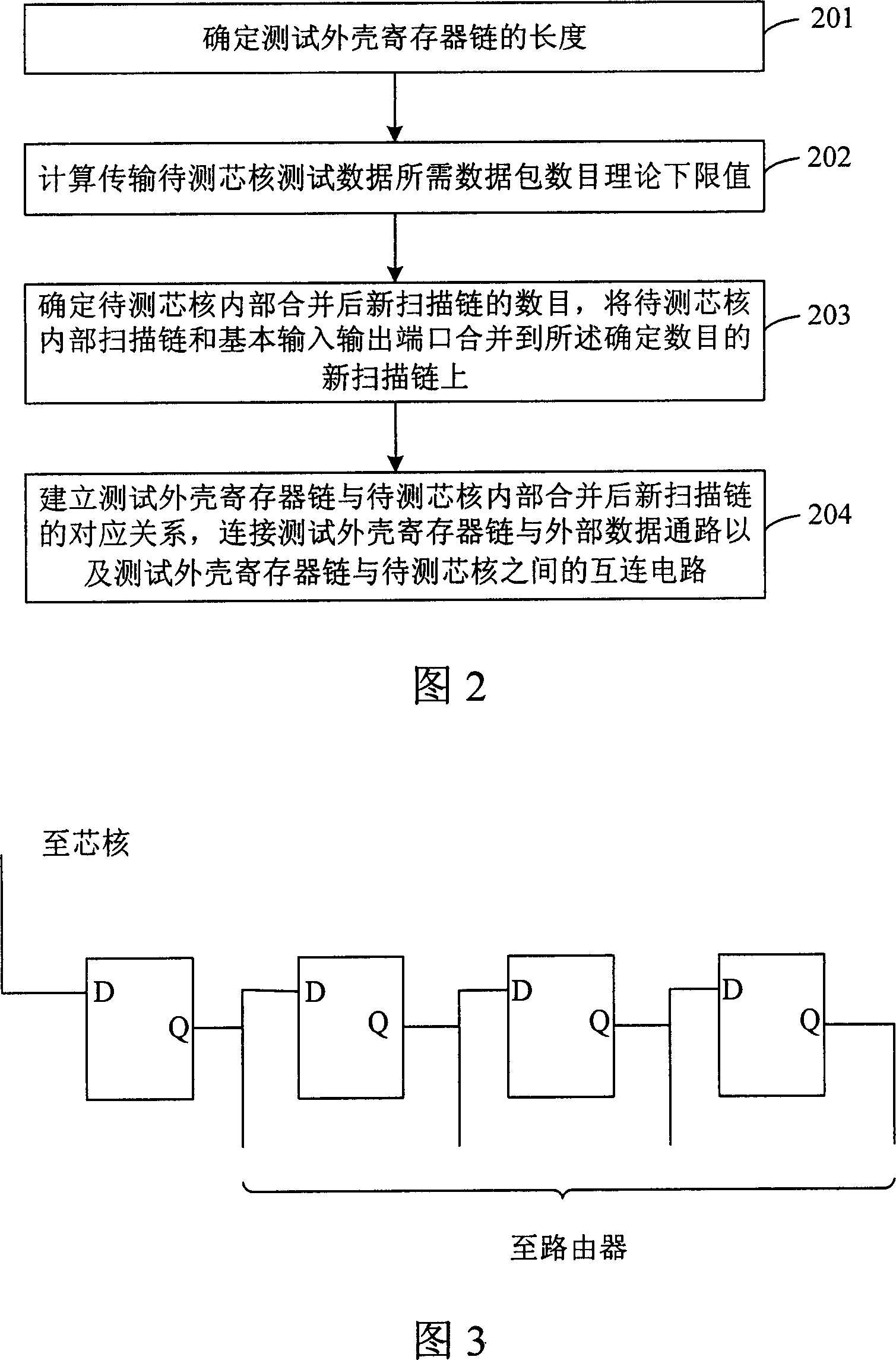

A test shell circuit and its design method

ActiveCN101102232AMake the most of your bandwidthRealize the designSupervisory/monitoring/testing arrangementsData switching networksProcessor registerExternal data

The invention comprises: at least one test enclosure register chain used for testing the core to be tested; an interconnection circuit for connecting said test enclosure register chain to the core to be tested; an interconnection circuit for connecting said test enclosure register chain to the external data channel. The invention also reveals a method for designing the test enclosure circuit.

Owner:INST OF COMPUTING TECH CHINESE ACAD OF SCI

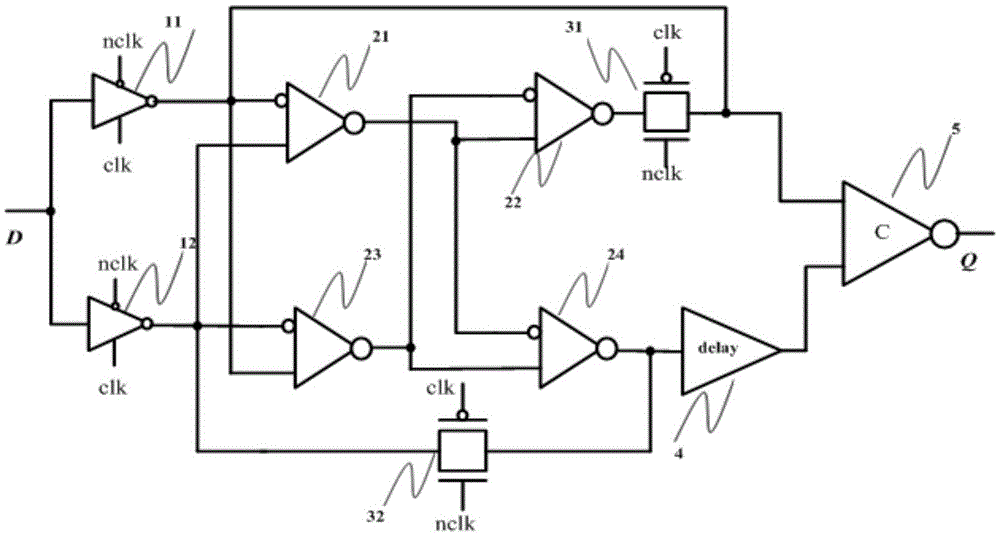

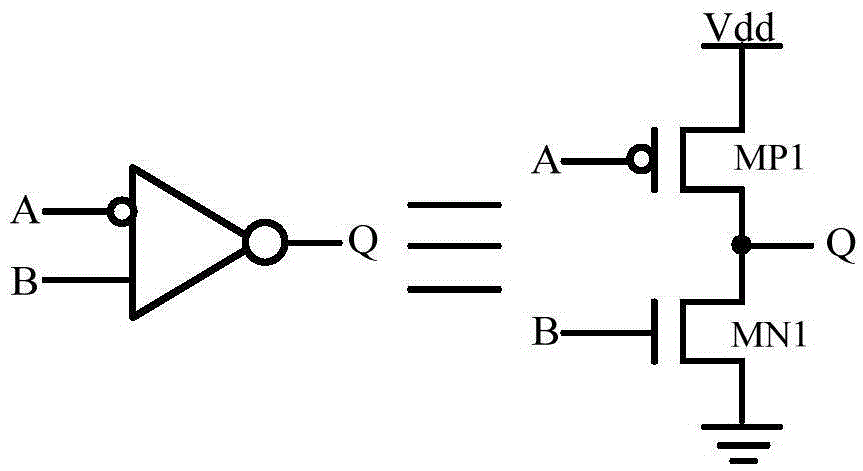

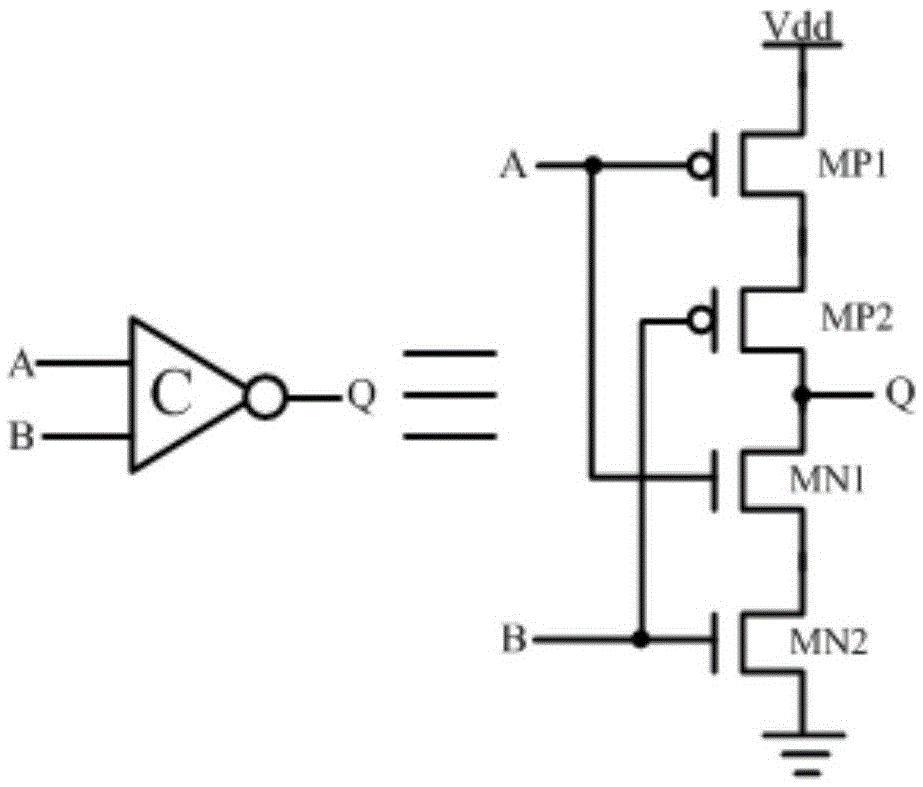

Self-recovery single particle resistance latch register structure based on time-delay unit

InactiveCN105577160AWith self-recovery functionSimple structureReliability increase in field effect transistorsSelf recoveryDual mode

The invention discloses a self-recovery single particle resistance latch register structure based on a time-delay unit, comprising two clock-control inverter structures, four dual-input inverter structures, two transmission gate structures, one time delay unit and a C unit structure; the four dual-input inverter structures constitute a dual-mode interlocking structure to realize self-recovery of the single event upset (SEU); the time delay unit structure and an C unit constitute a filtering structure to block the single event transient (SET) coming from the combination logic circuit. The invention can tolerate the SEU happened in the latch register structure and the SET transmitted from the logic circuit, has the self-recovery function, has a simple circuit, reduces the consumption of the area, reduces the power consumption and improves the system reliability.

Owner:HEFEI UNIV OF TECH

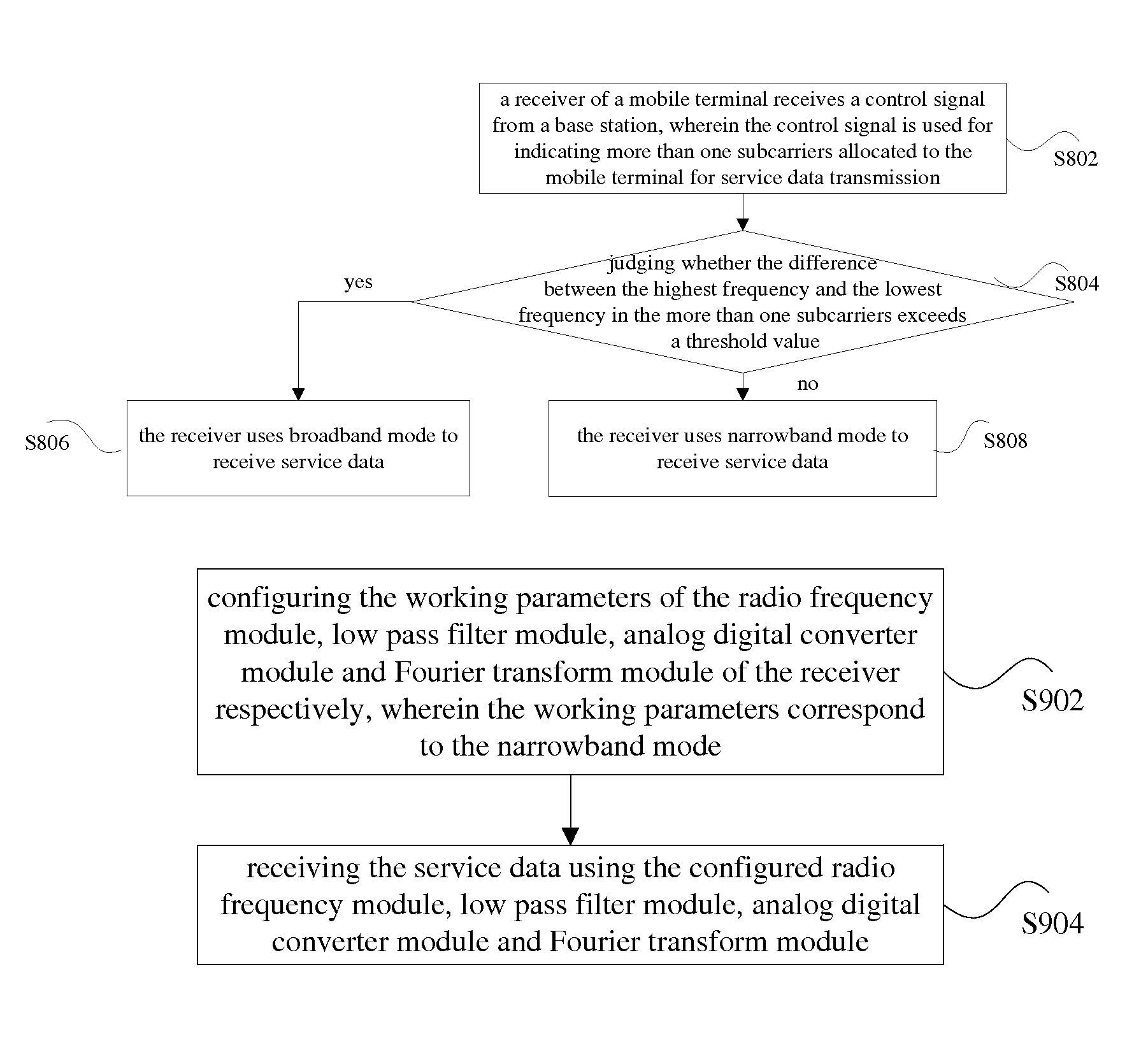

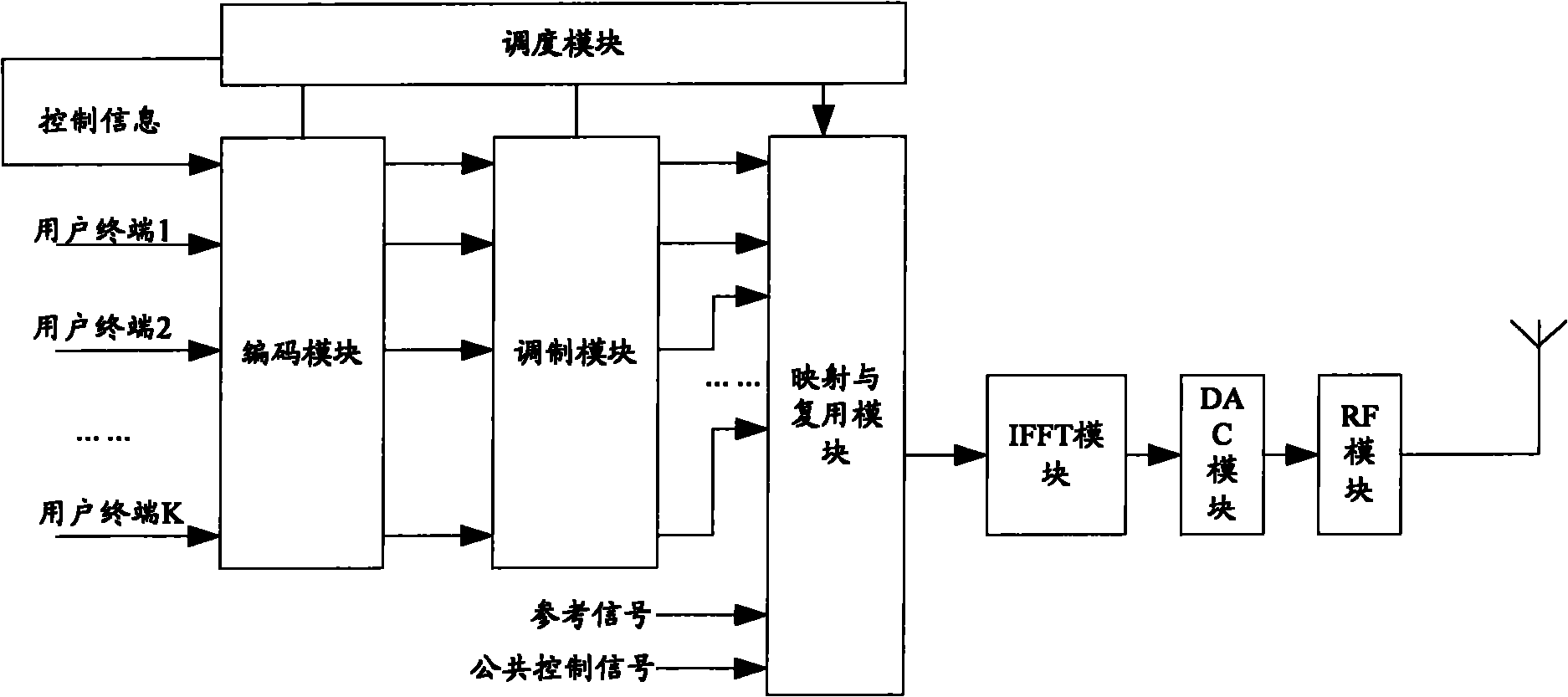

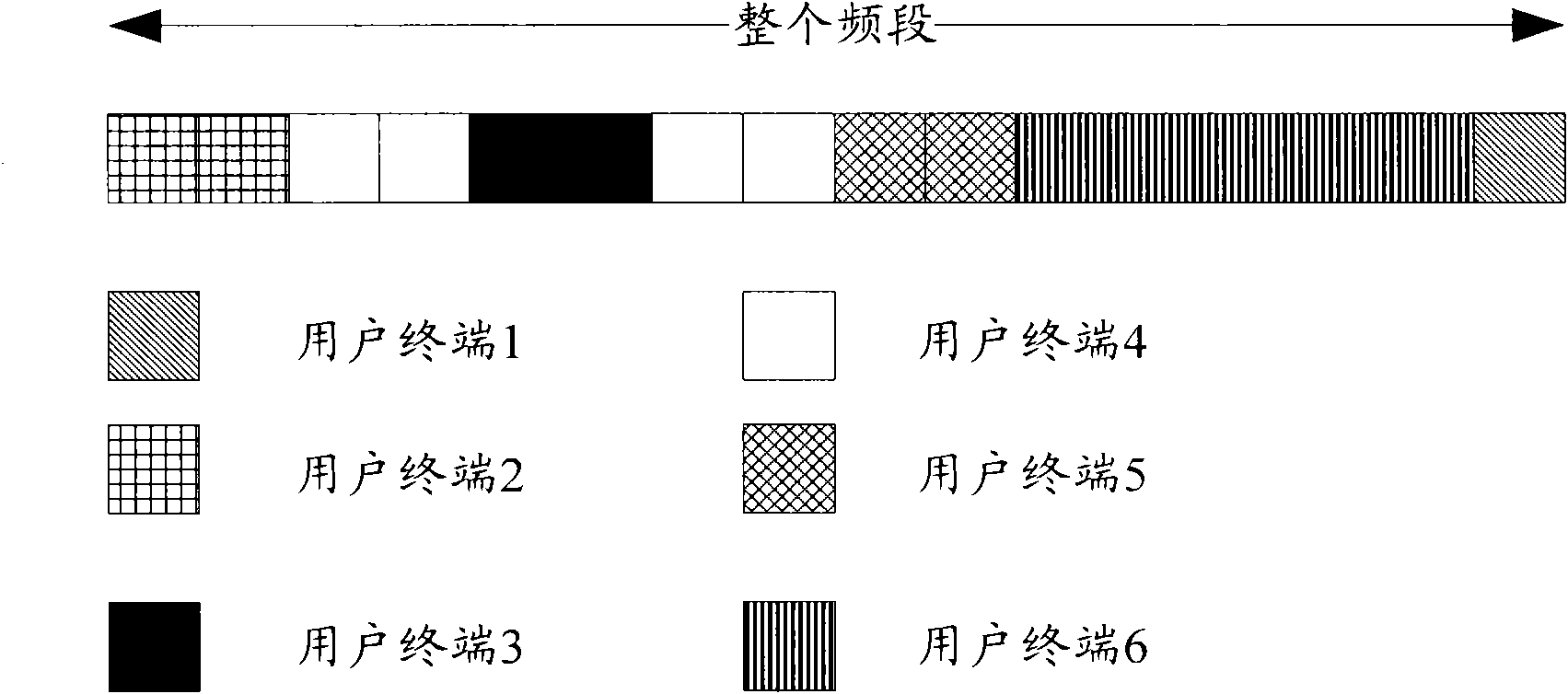

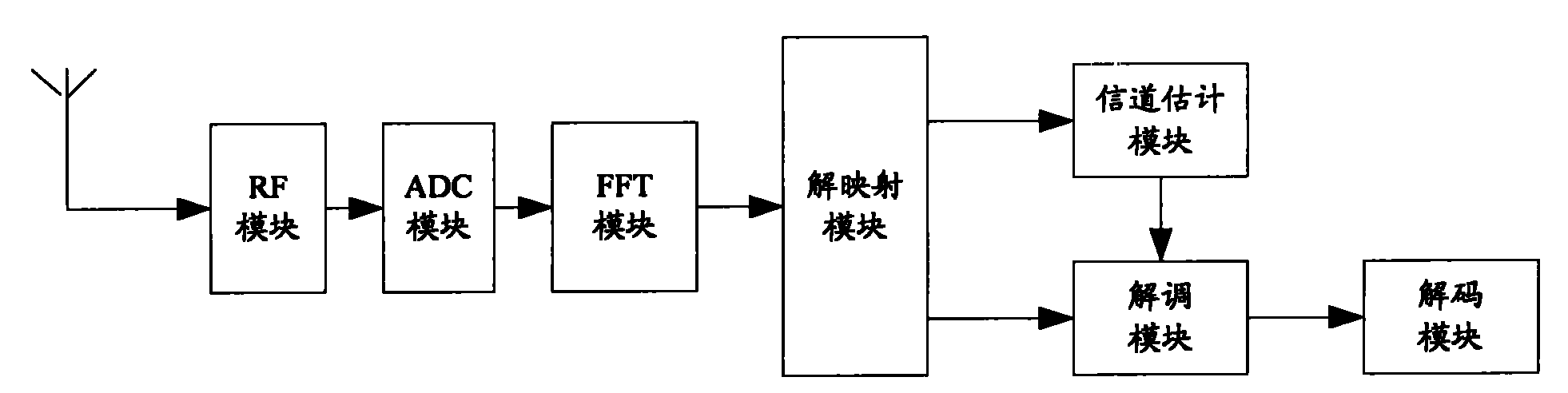

Method for service data transmission, a receiver, a mobile terminal, a transmitter and a base station

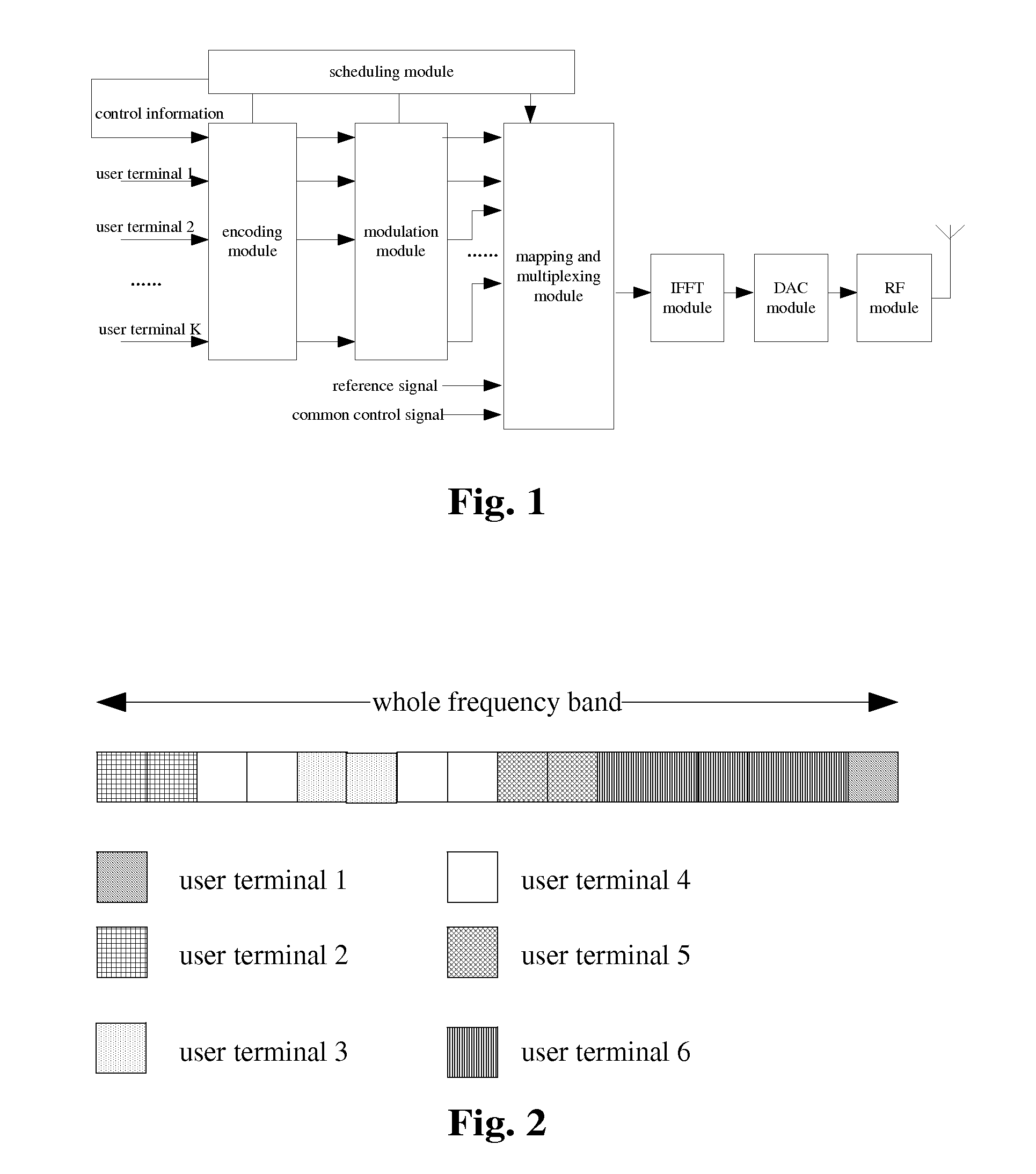

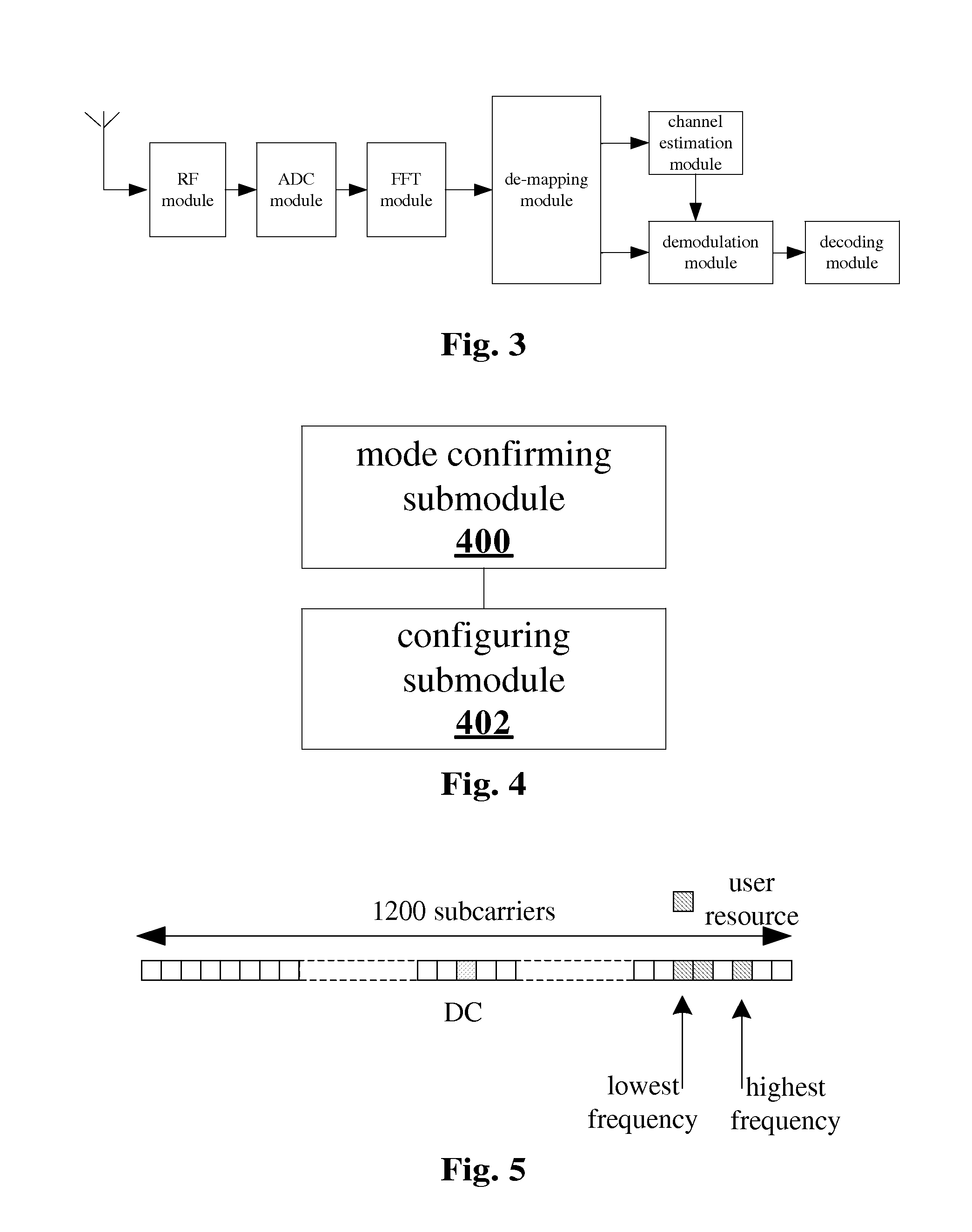

ActiveUS8923192B2Reduce power overheadReduce power consumptionError preventionFrequency-division multiplex detailsControl signalCarrier signal

The present invention discloses a method for service data transmission, a receiver, a mobile terminal, a transmitter and a base station. In the above method, a receiver of a mobile terminal receives a control signal sent by a base station, wherein the control signal is used for indicating more than one subcarriers allocated to the mobile terminal and the more than one subcarriers are used for service data transmission; it is judged whether the difference between the highest frequency FREHigh and the lowest frequency FRELow in the more than one subcarriers exceeds a threshold value THB; if not exceed, then the receiver receives service data using a narrowband mode, otherwise receives the service data using a broadband mode. By way of the technical solution of the present invention, the signal bandwidth processed by the receiver can become narrow, the digital sampling rate becomes lower, the calculation amount of the FFT module and relevant storage are reduced, thus achieving the effect of reducing the power consumption overhead of the mobile terminal.

Owner:SANECHIPS TECH CO LTD

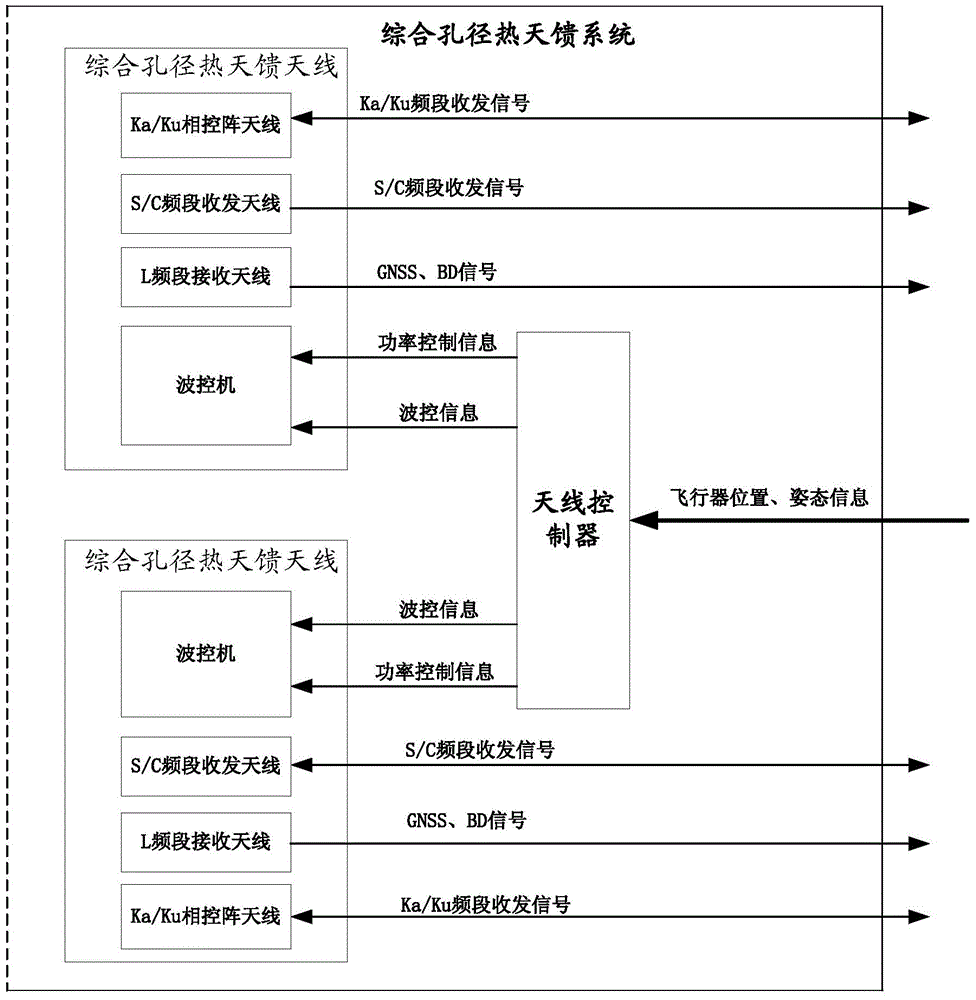

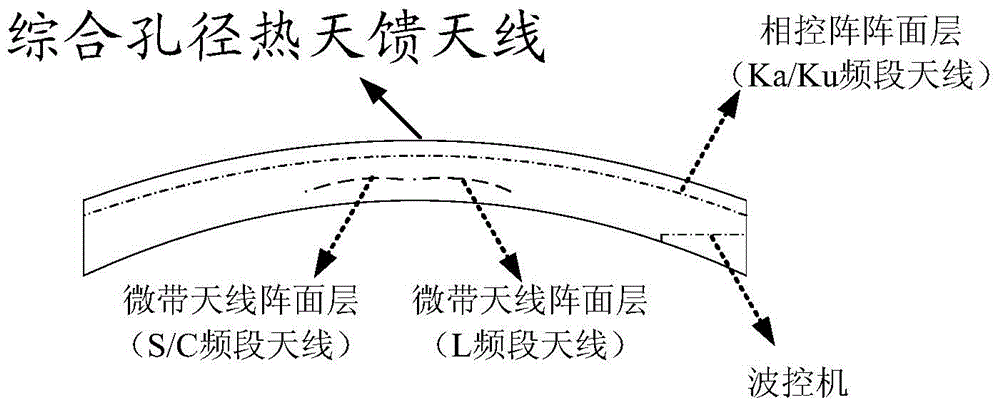

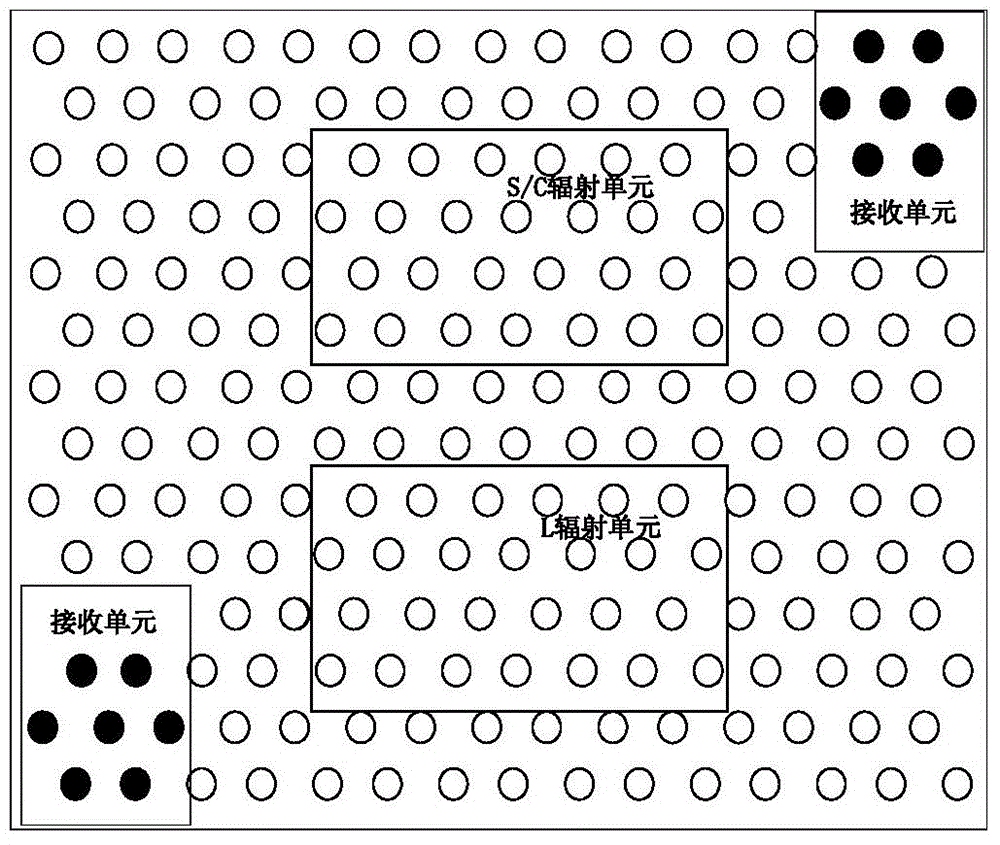

Synthesis aperture heat antenna feeder system suitable for large posture changes

ActiveCN104466351AReduce typesReduce in quantityAntenna adaptation in movable bodiesIndependent non-interacting antenna combinationsMulti bandArray element

The invention discloses a synthesis aperture heat antenna feeder system suitable for large posture changes. The synthesis aperture heat antenna feeder system is composed of two synthesis aperture heat antenna feeder antennas and an antenna controller. The synthesis aperture heat antenna feeder antennas are installed on an air vehicle in a vertically-opposite mode. The multi-band frequency conformal cold-heat-integrated phased array design mode is adopted for the synthesis aperture heat antenna feeder antennas, multi-band frequency antennas are embedded into phased-array array faces in a layered mode, and transmitting and receiving of Ka / Ku frequency band signals, S / C frequency band signals and L frequency band signals can be completed through the single synthesis aperture heat antenna feeder antenna. The phased-array array faces and antenna heat protection covers of the synthesis aperture heat antenna feeder antennas are integrally designed in a synthesis mode, and the amplitudes and the phase positions of the antennas can be corrected by adjusting phased-array antenna parameters. The antenna controller obtains the angle and the distance between the air vehicle and an object according to position information and posture information of the air vehicle, and the number of working transmitting array elements and the number of working receiving array elements of the synthesis aperture heat antenna feeder antennas are dynamically adjusted; meanwhile, the synthesis aperture heat antenna feeder antennas suitable for communication are selected according to the angle information, and beam control is completed.

Owner:CHINA ACAD OF LAUNCH VEHICLE TECH

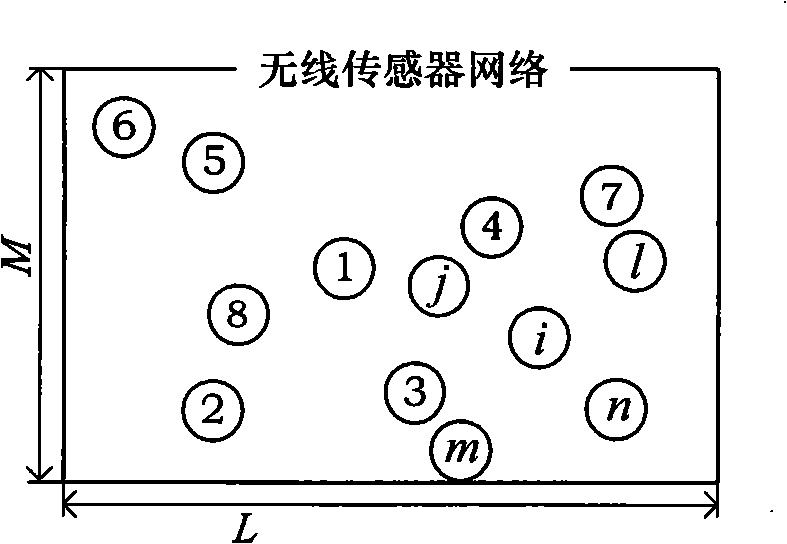

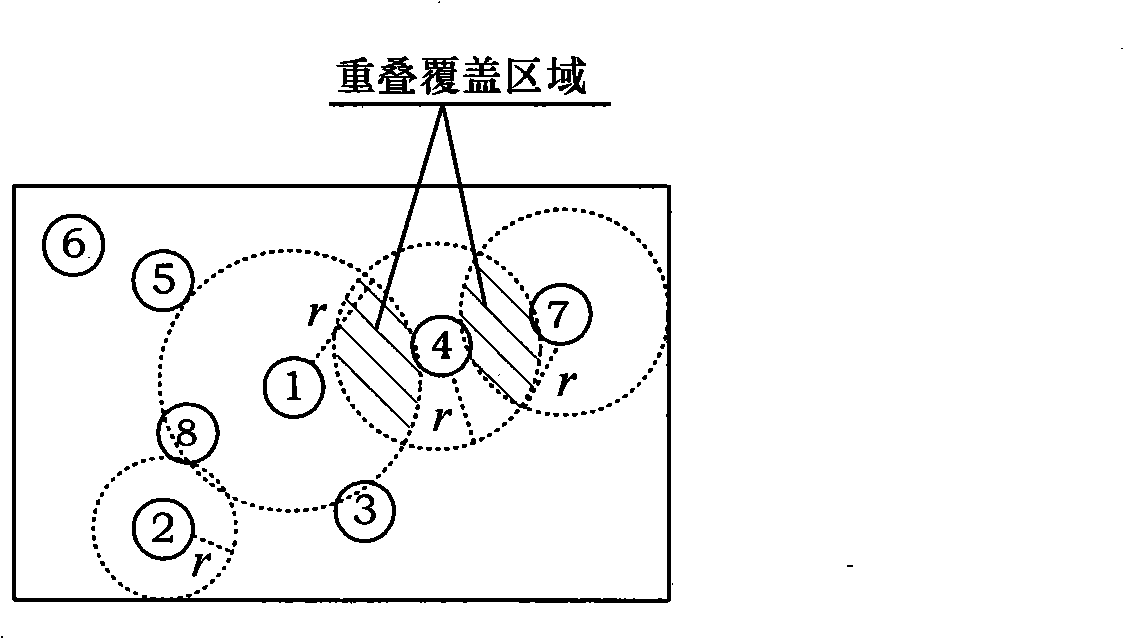

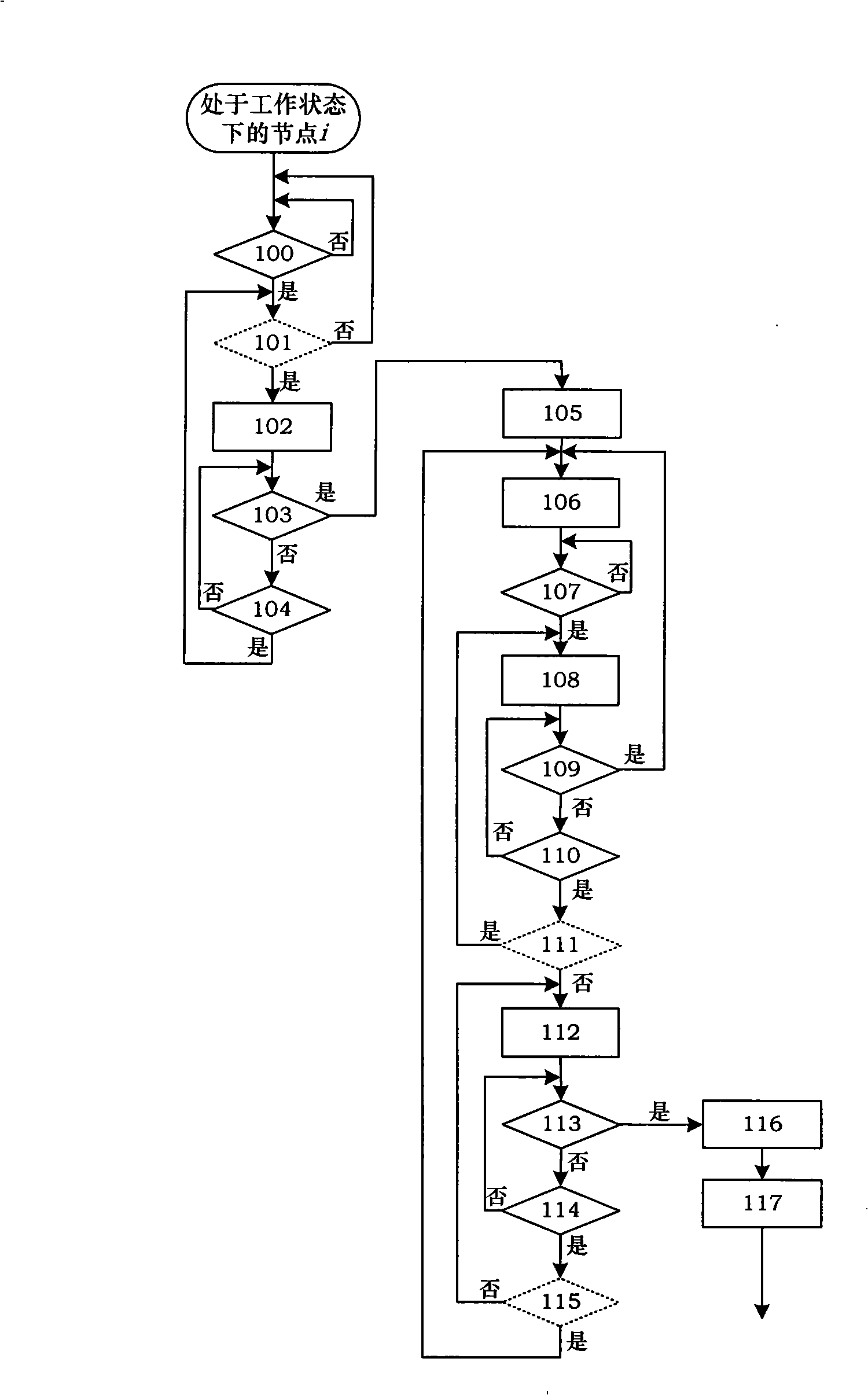

Control method for shrouding wireless sensor network using multiplex intersection point shrouding discrimination

InactiveCN101350831APrecise screeningReliable Coverage ControlData switching by path configurationSleep controlWireless mesh network

The invention discloses a covering and controlling method of the wireless sensor network which adopts the covering judgment of multiple intersection points. The method carries out the distributed type node dynamic sleep control on the wireless sensor network via a redundancy judgment rule of the covering degree of the multiple intersection points. At the initial period of the network operation, each node is at the working status and periodically broadcasts the working message to the neighboring node, simultaneously collects the working information of all neighboring nodes; when one node receives the information from the neighboring node, the node carries out the redundancy qualification judgment, and keeps or transforms the status according to the judgment result for realizing the distributed type node dynamic sleep control of the sensor network. The method judges the redundancy of the network node according to the necessary and sufficient condition for avoiding the occurrence of the blind spot of covering, simultaneously enables the number of the active nodes to decrease to the minimum, decreases the power consumption of the system, prolongs the service life of the network, and realizes the coverage-configurable network covering and controlling which has the advantages of completeness, reliability and high efficiency.

Owner:BEIHANG UNIV

Service data transmission method, receiver, mobile terminal, transmitter and base station

ActiveCN102256339AReduce the amount of calculationReduce storagePower managementModulated-carrier systemsControl signalCarrier signal

The invention discloses a service data transmission method, a receiver, a mobile terminal, a transmitter and a base station. The method comprises the following steps of: receiving a control signal from the base station by the receiver of the mobile terminal, wherein the control signal is used for indicating a plurality of sub-carriers distributed for the terminal and used for transmitting service data; and judging whether the difference between the highest frequency FREHigh and the lowest frequency FRELow in the plurality of sub-carriers exceeds a threshold value THB, if not, receiving the service data by the receiver in a narrow-band mode, or else, receiving the data service in a broadband mode. According to the technical scheme provided by the invention, the signal bandwidth processed by the receiver can be narrowed, the digital sampling rate can be lowered, the calculated quantity and the relative storage of an FFT (Fast Fourier Transform) module can be reduced, and the effect of reducing power consumption of the mobile terminal can be further reduced.

Owner:SANECHIPS TECH CO LTD

Network processor and network operation method

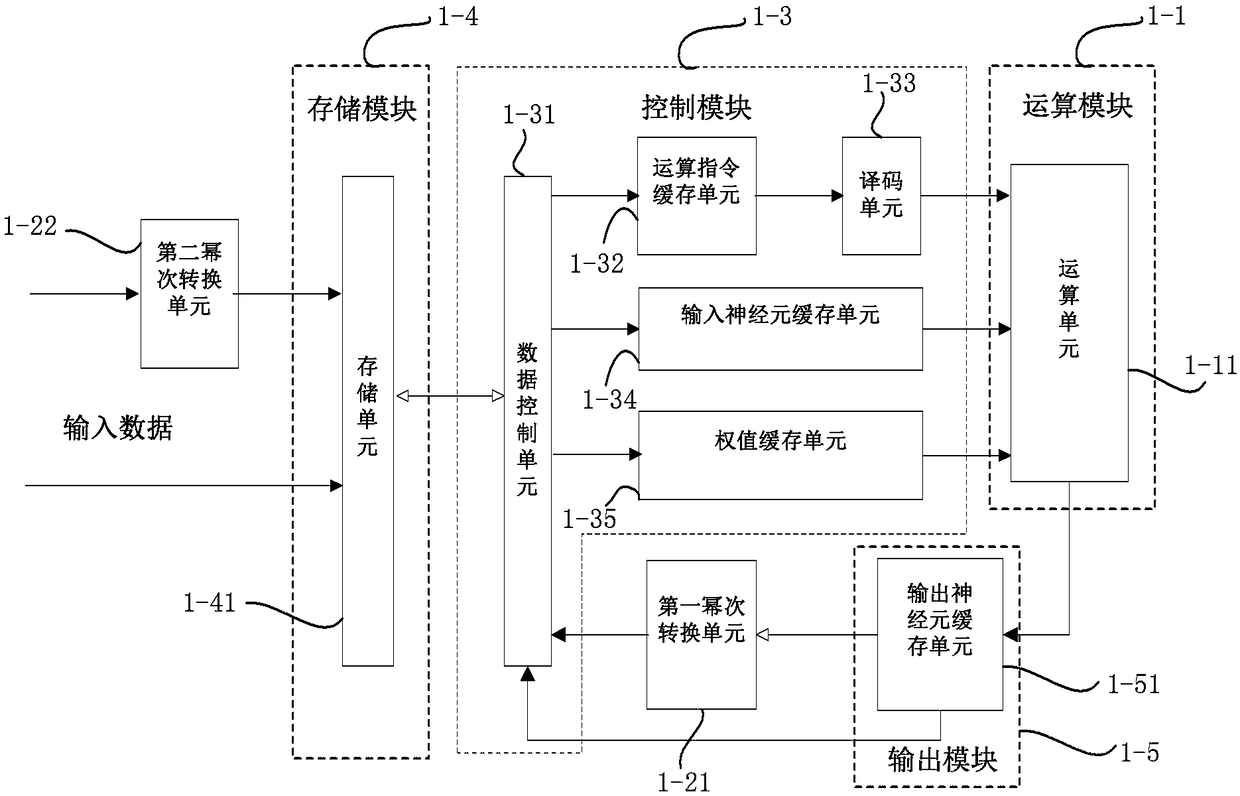

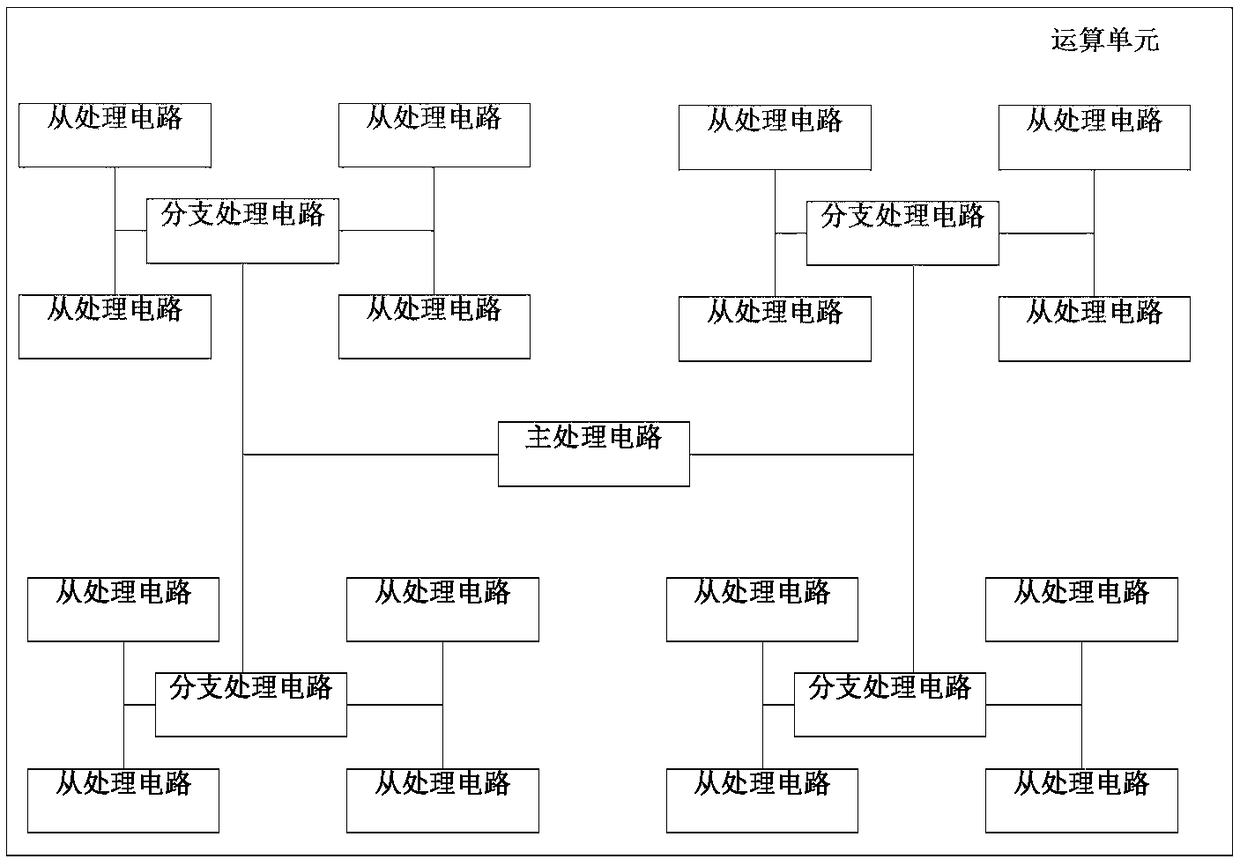

PendingCN109359736ASave storage spaceSimplify the multiplication operationGeometric image transformationProcessor architectures/configurationMemory busParallel computing

The invention provides a network processor and a network operation method. The network processor comprises a memory, a high speed temporary memory and a heterogeneous core. Wherein the memory is usedfor storing data and instructions of neural network operation; The high-speed temporary memory is connected with the memory through a memory bus; The heterogeneous kernel is connected with the high-speed temporary memory through a high-speed temporary memory bus, reads the data and instructions of the neural network operation through the high-speed temporary memory, completes the neural network operation, sends the operation result back to the high-speed temporary memory, and controls the high-speed temporary memory to write the operation result back to the memory. The network processor and the network operation method disclosed by the invention can reduce the power consumption overhead of the network calculation and can fully utilize the parallelism of the network, thereby reducing the cost of the network operation and improving the efficiency of the network operation.

Owner:SHANGHAI CAMBRICON INFORMATION TECH CO LTD

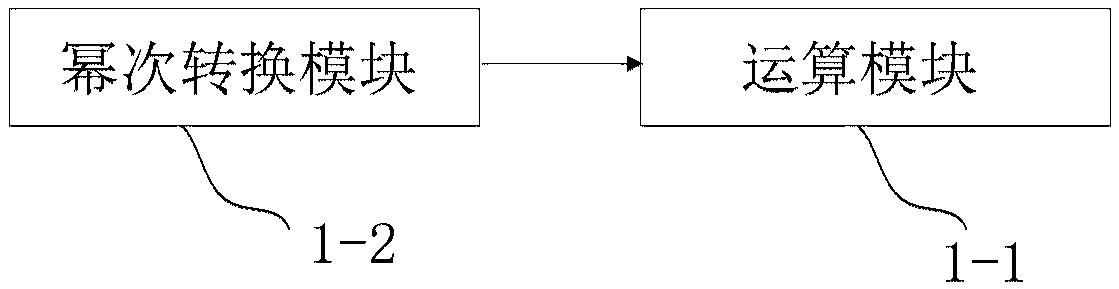

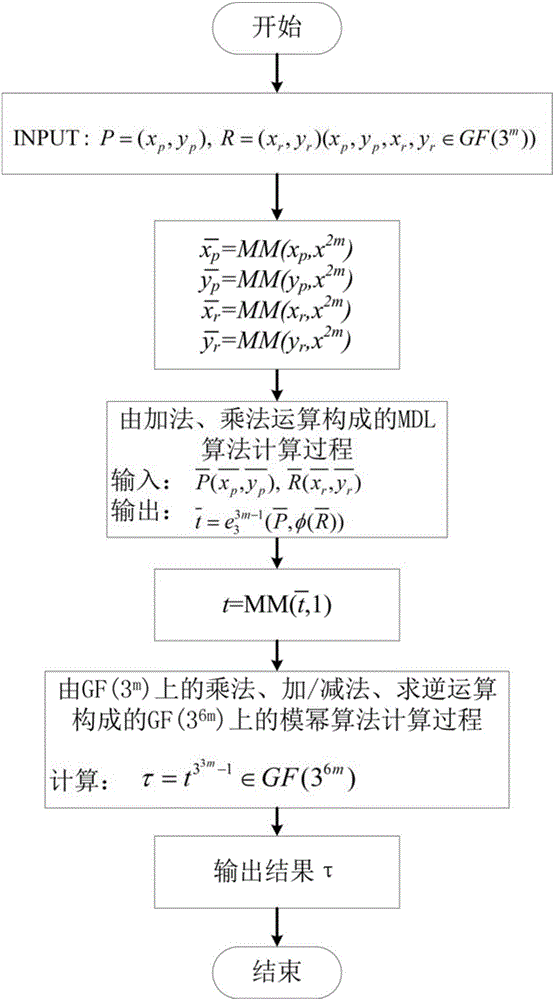

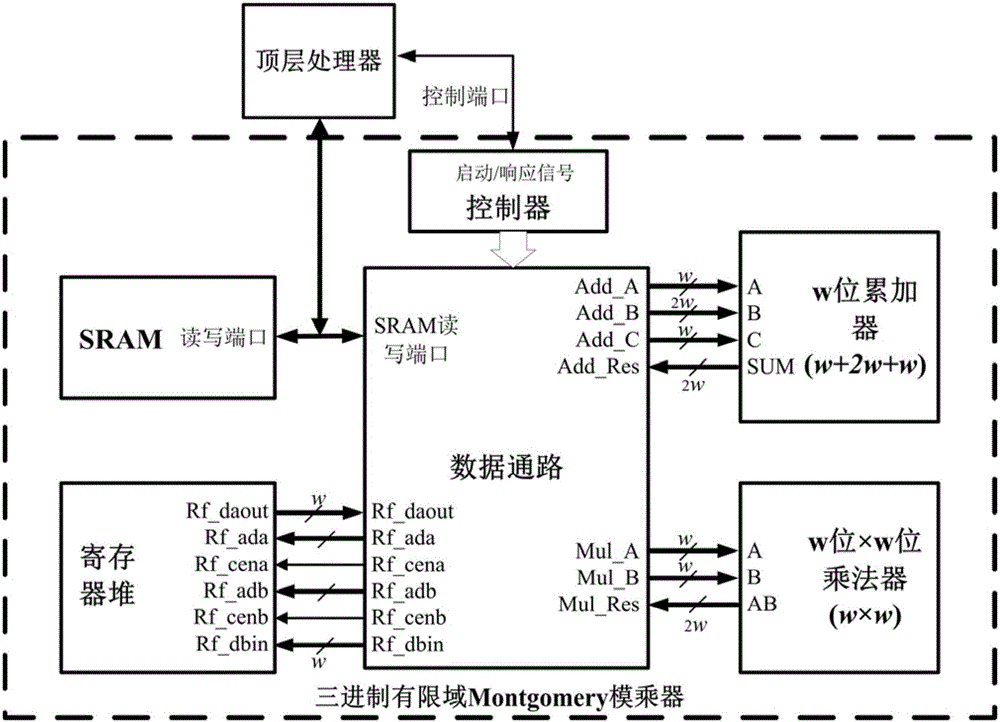

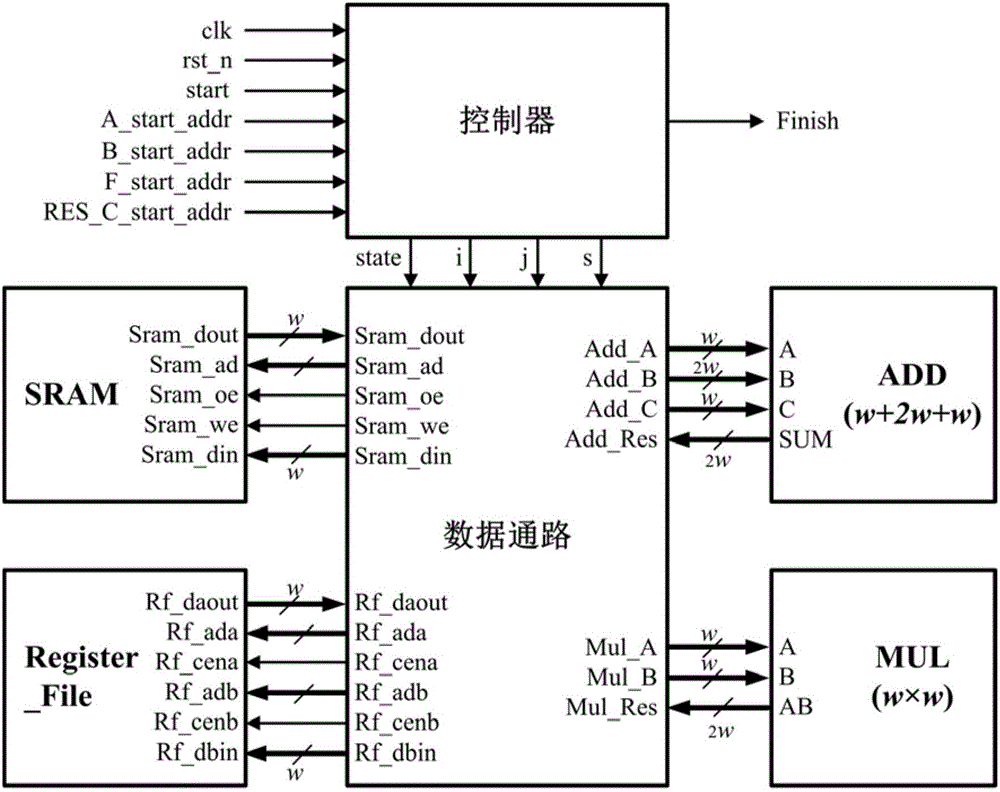

Montgomery modular multiplication based Tate pairing algorithm and hardware structure therefor

ActiveCN105068784AReduce hardware overheadReduce power overheadDigital data processing detailsHardware structureStatic random-access memory

The invention belongs to the technical field of realization of cryptographic algorithms of embedded systems and particularly relates to a ternary finite field Montgomery modular multiplication based Tate pairing algorithm and a hardware structure for realizing the algorithm. The algorithm comprises: converting X coordinates and Y coordinates of two input points P and R on an elliptic curve to a Montgomery domain from a defined GF(3m) domain; according to an MDL (minimum description length) algorithm procedure taking multiplication, addition / subtraction and cubic operation on GF(3m) as basic operations, performing operation in the Montgomery domain; and converting a calculation result to the GF(3m) domain from the Montgomery domain, and performing 33m-1-power modular exponentiation on the calculation result. The hardware structure comprises a top-level processor, a controller, a ternary accumulator, a ternary multiplier, a register file and an SRAM (static random access memory), wherein the controller is used for controlling input of the ternary accumulator and the ternary multiplier and read-write operation of the SRAM and the register file so as to control data transmission of the whole circuit.

Owner:TSINGHUA UNIV

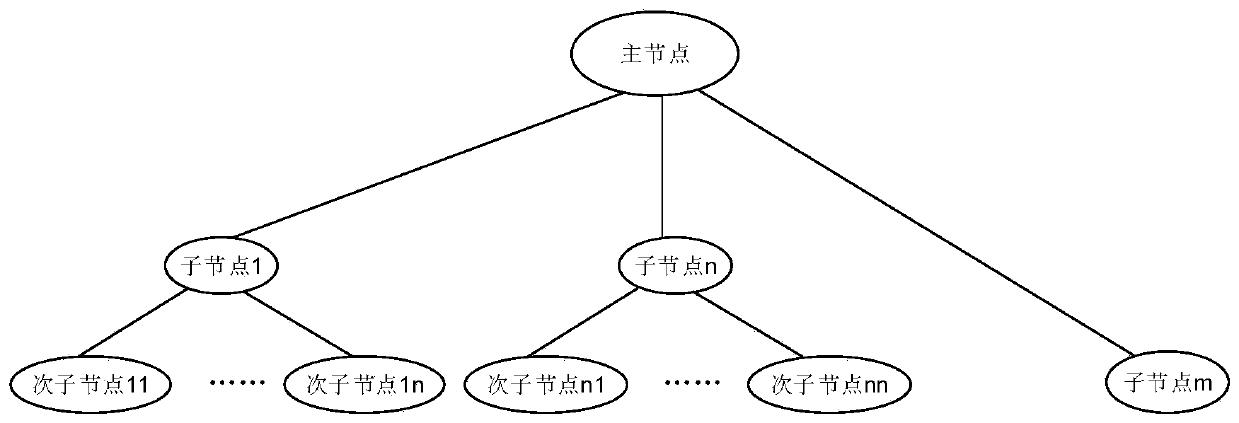

Internet of Things data transmission method and system

InactiveCN110138672AGuaranteed availabilityImprove data transfer efficiencyNetwork traffic/resource managementStar/tree networksThe InternetData loss

The invention relates to the technical field of Internet of Things data transmission, in particular to an Internet of Things data transmission method and system, and the method comprises the followingsteps: S1, enabling a main node to transmit a data packet to a next-level sub-node directly connected with the main node; each stage of sub-node transmits a data packet to the next stage of sub-nodewhich is directly connected with the sub-node after completing data receiving; S2, enabling the main node to calculate the number proportion of the child nodes completing data receiving, and transmitdata packets to all levels of child nodes not completing data receiving after the number proportion reaches a preset value of the number proportion, wherein the to-be-transmitted data is upgraded data, and version upgrading is carried out after all levels of child nodes receive the upgraded data. According to the Internet of Things data transmission method and system provided by the invention, theproblems of network congestion, data loss and the like caused by the fact that the Internet of Things equipment distributes data to the network in the whole network can be solved, and the data transmission efficiency of the network is improved.

Owner:WU QI TECH INC +1

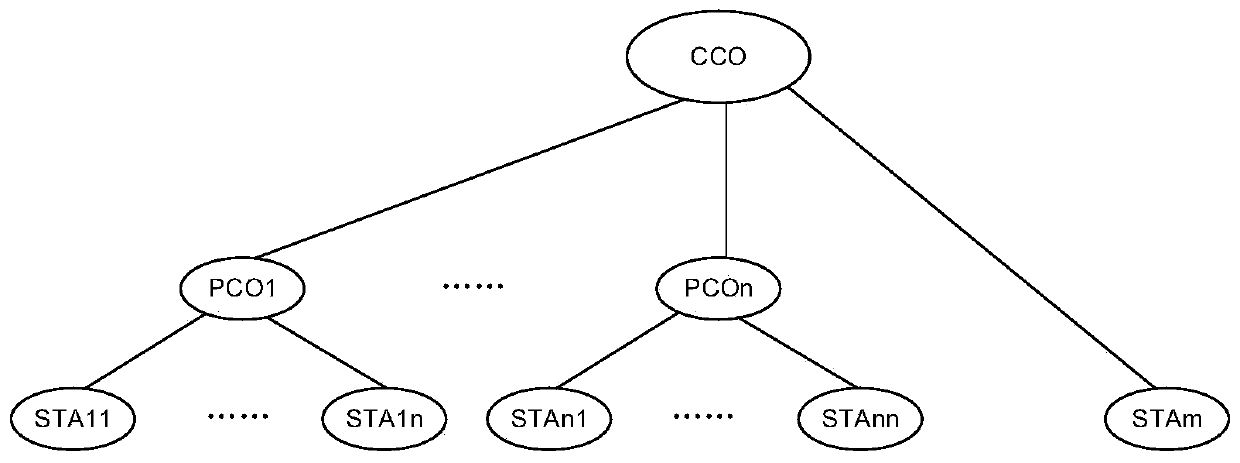

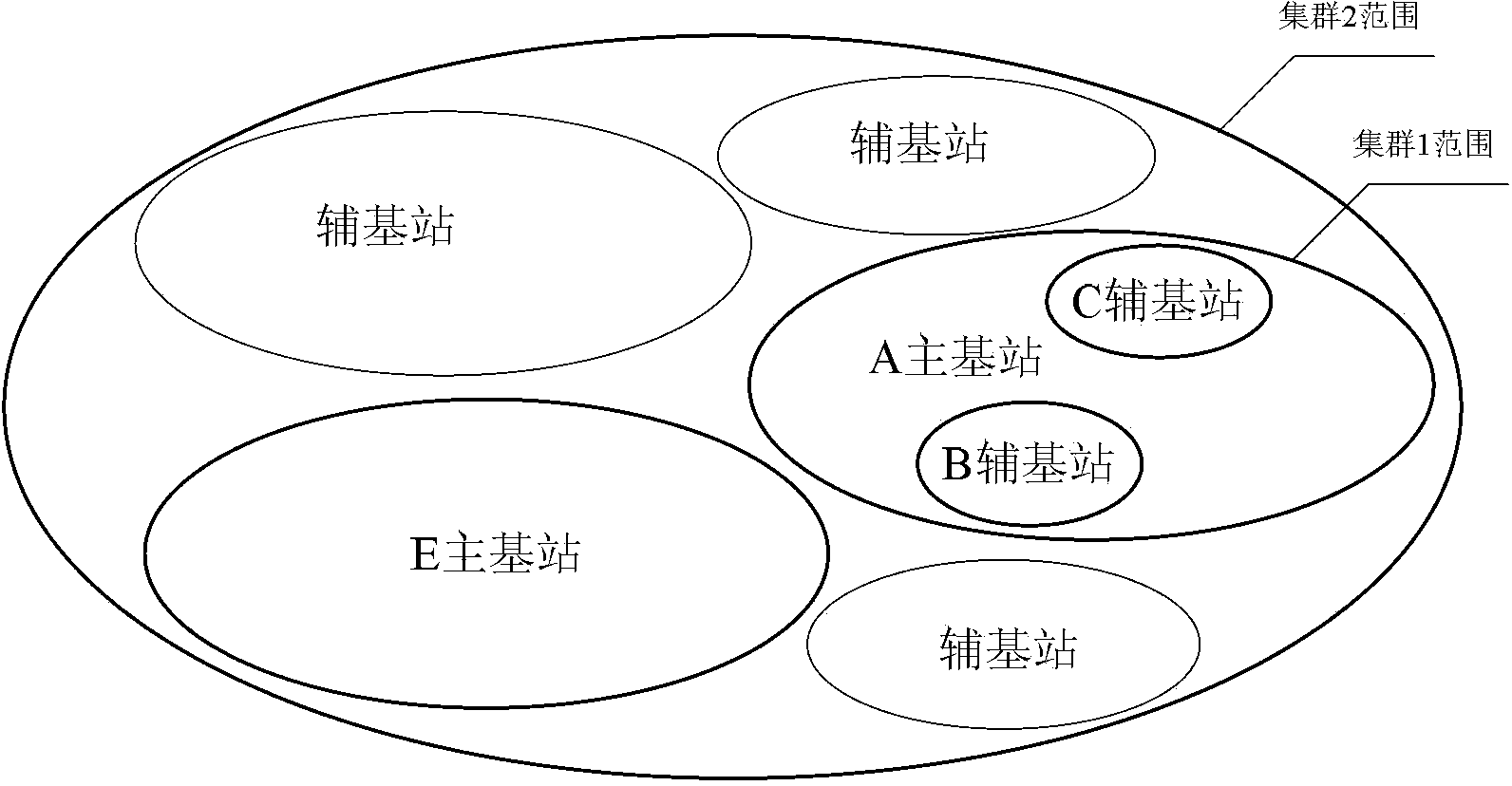

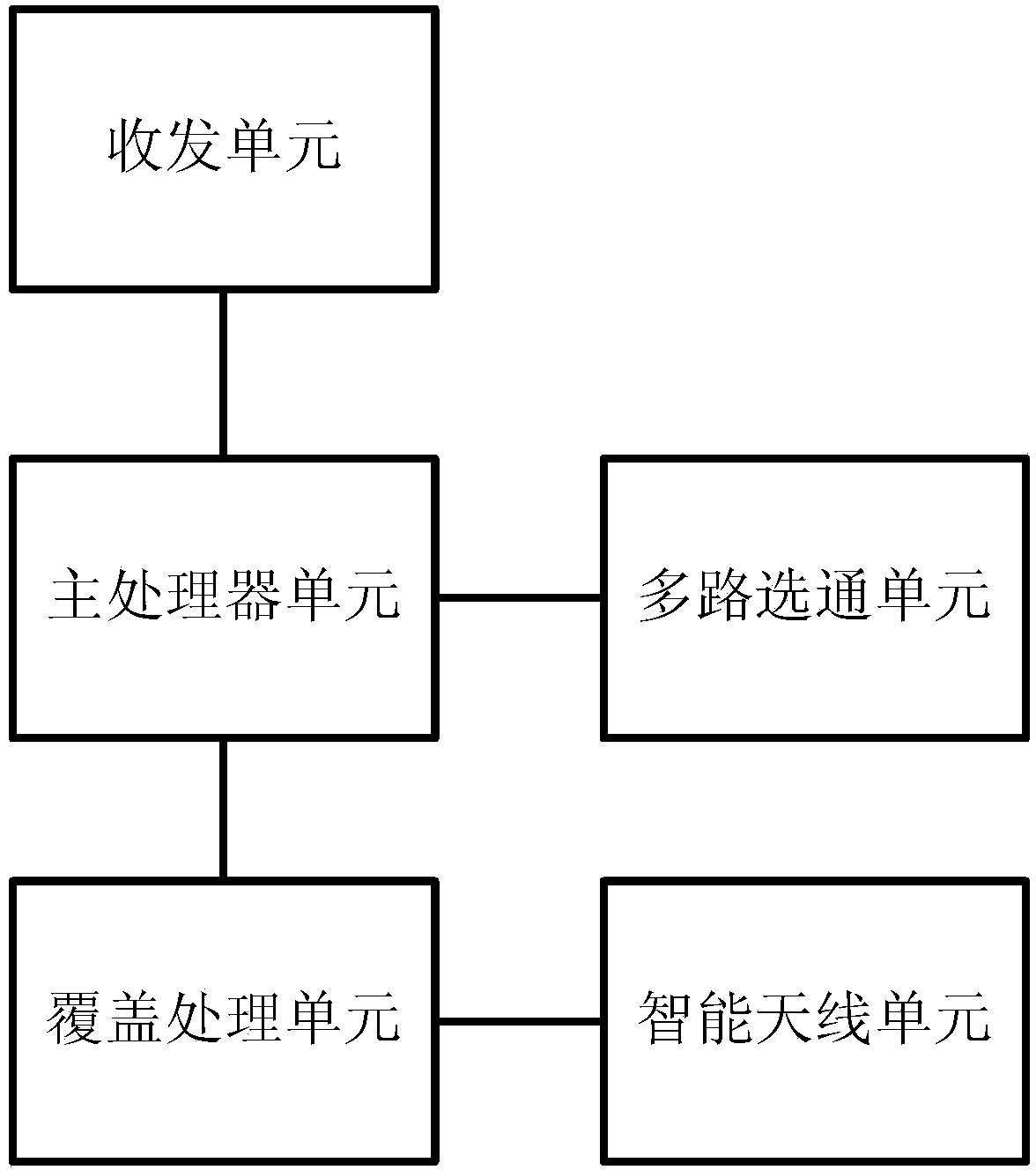

Multi-base-station coordinating method and system applied to honeycomb system, and base stations

InactiveCN104284345AIncrease power consumptionImprove interferencePower managementNetwork planningHoneycombTransfer operation

A multiple base station collaboration method, system and base station for use in cellular systems, relating to the field of wireless communications. Said multiple base station collaboration method comprises: during cellular system planning, forming a cluster out of a group of neighboring base stations, configuring one of same to be a primary base station and configuring the rest to be auxiliary base stations; during normal cellular system operation, monitoring devices corresponding to each of the auxiliary base stations update, in real time, statistics regarding the service volume of the cell areas corresponding to a given auxiliary base station, and upload the statistical service volume information to the primary base station; when the primary base station determines that the reported service volume received from the auxiliary base station is lower than a preconfigured first threshold value, service transfer operations are initiated for said auxiliary base station; after service transfer operations are complete, the primary base station uses the controller corresponding to said auxiliary base station to shut down said auxiliary base station. The above technical solution improves wireless system power consumption and interference and achieves significant gains in efficiency.

Owner:ZTE CORP

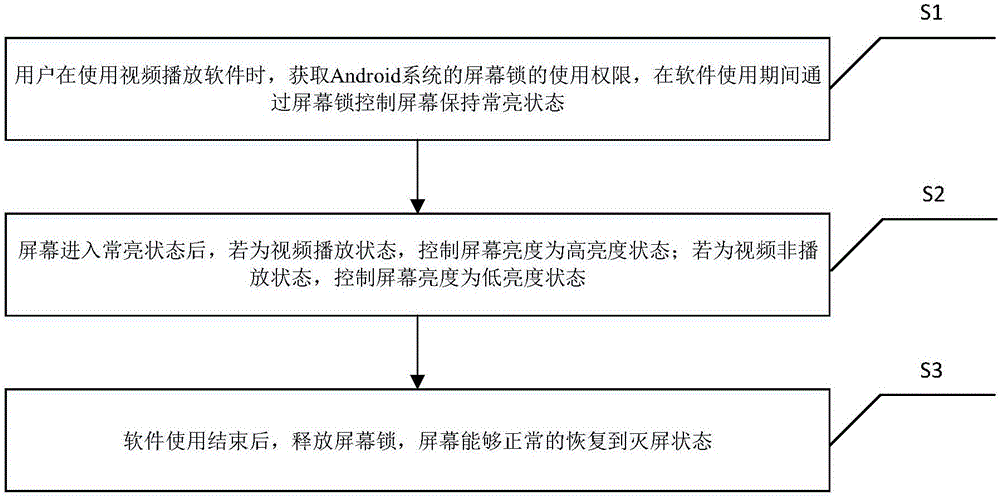

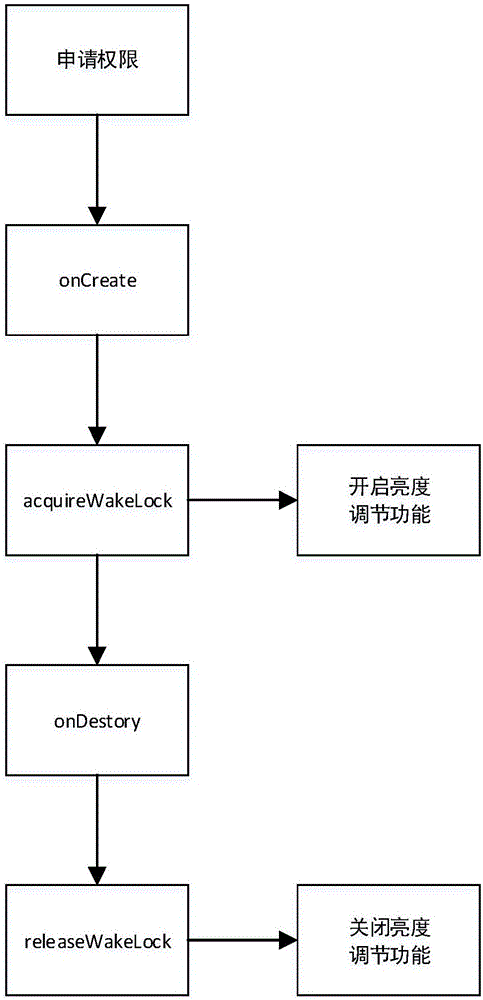

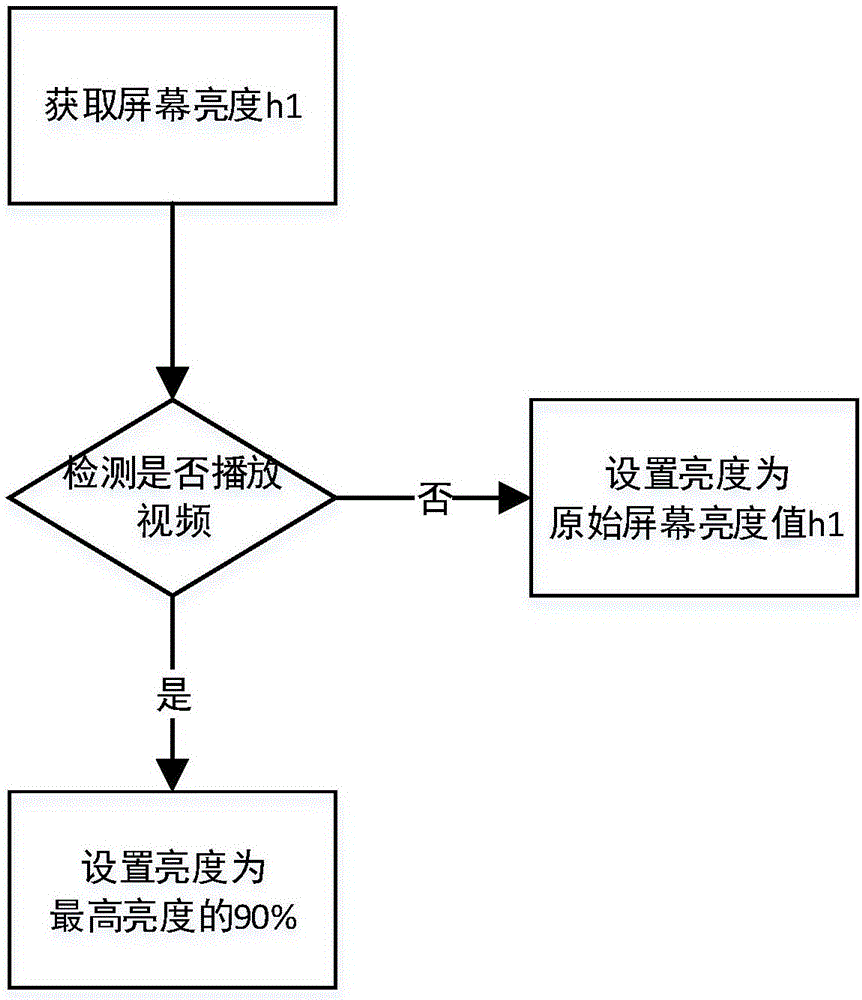

Android screen always-on and energy-saving control method and system based on dynamic brightness adjustment

ActiveCN106453892AIncrease or decrease brightnessReduce power overheadCurrent supply arrangementsCathode-ray tube indicatorsEmbedded systemSoftware

The invention discloses an Android screen always-on and energy-saving control method and system based on dynamic brightness adjustment. The method comprises the following steps: S1, when a user uses video play software, acquiring the using permission of a screen lock of an Android system, and controlling a screen to be in an always-on state in the use period of the software via the screen lock; S2, after the screen enters the always-on state, controlling the brightness of the screen in a high brightness state if the Android system is in a video playing state, or controlling the brightness of the screen in a low brightness state if the Android system is in a non-video playing state; and S3, unlocking the screen lock after use of the software is finished, so that the screen can recover a screen-off state normally. According to the method and the system, the brightness of the screen can be improved or lowered according to different video use conditions, so that power consumption can be reduced, and the standby time of a mobile phone can be prolonged; and the method can improve user experience.

Owner:WUHAN DOUYU NETWORK TECH CO LTD

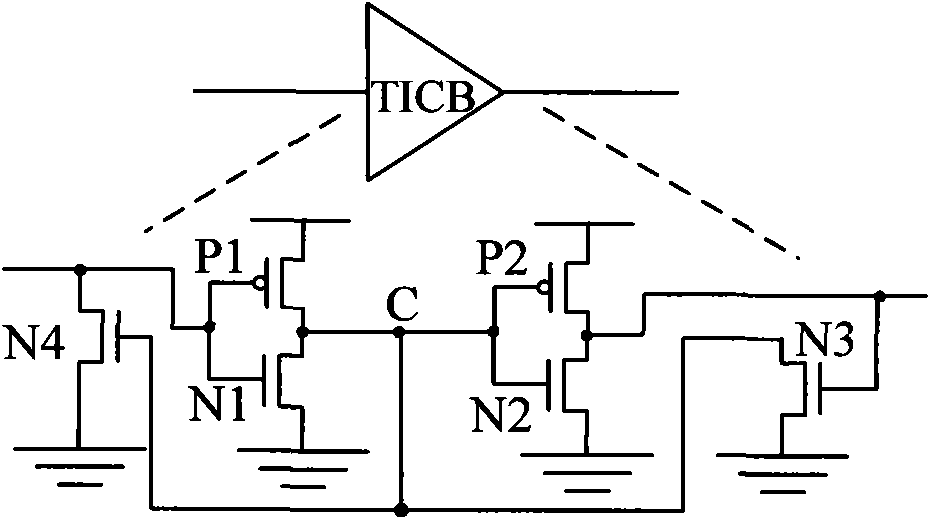

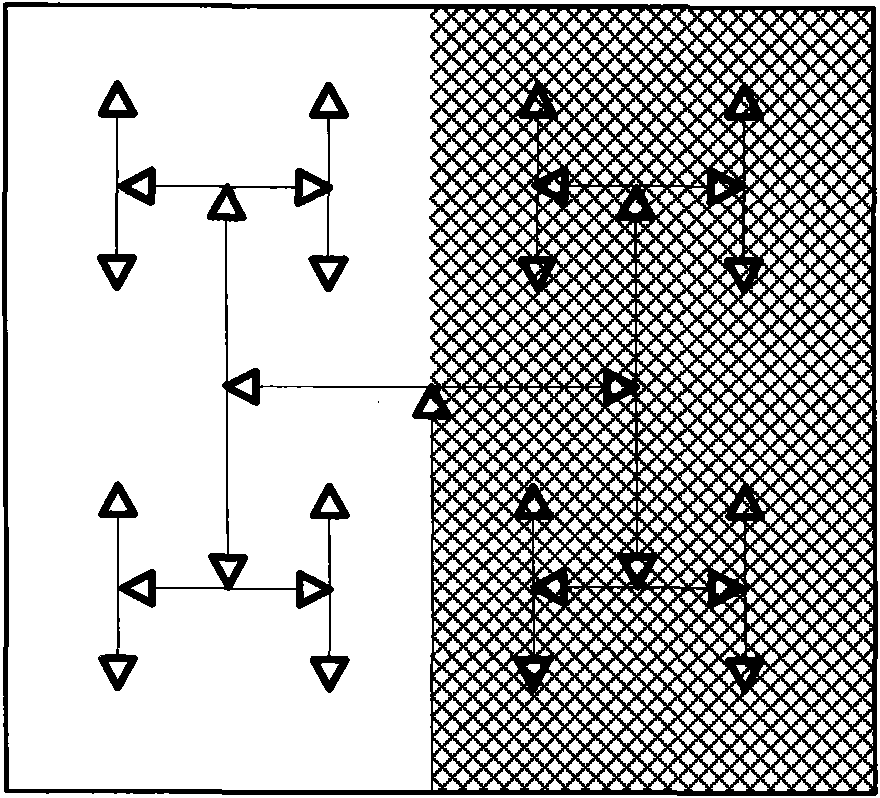

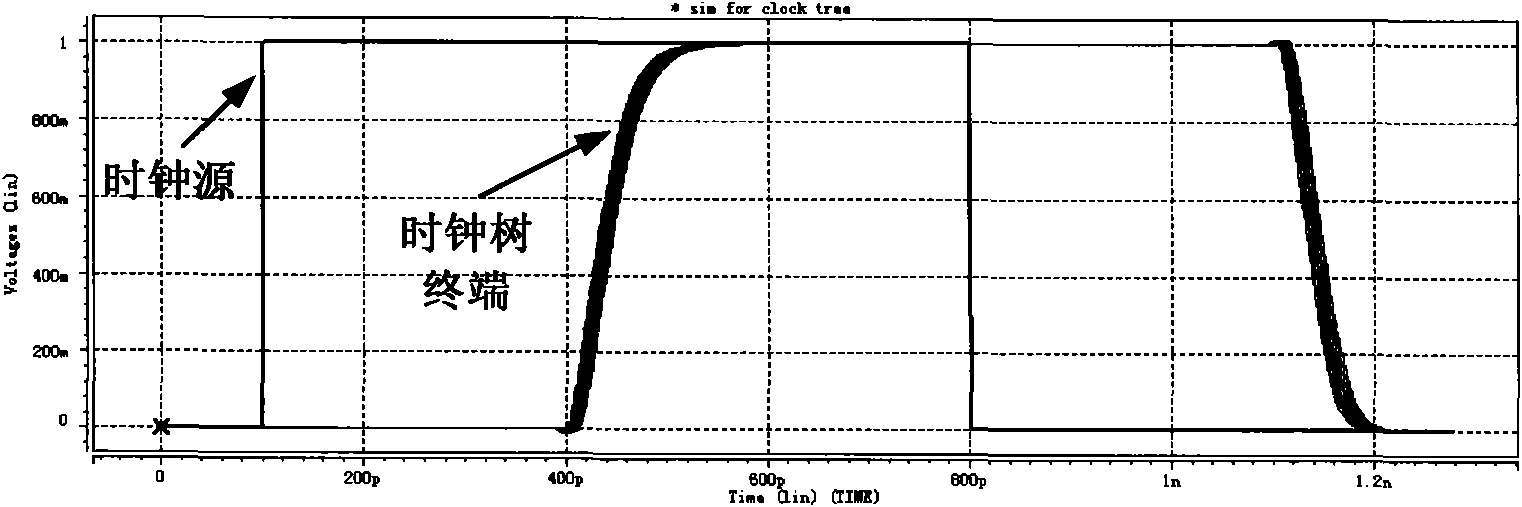

Temperature-insensitive clock buffer and H-shaped clock tree circuit

ActiveCN101888227AReduce areaReduce power overheadSingle output arrangementsIntegrated circuitEngineering

The invention provides a temperature-insensitive clock buffer (TICB) and an H-shaped clock tree circuit. The TICB comprises a first phase inverter, a second phase inverter, a first NMOS tube and a second NMOS tube, wherein the output end of the first phase inverter is connected with the input end of the second phase inverter; the input end of the first phase inverter is used as the input end of the TICB, and the output end of the second phase inverter is used as the output end of the TICB; the drain of the first NMOS tube is connected with the input end of the first phase inverter, the grid of the first NMOS tube is connected with the output end of the first phase inverter, and the source of the first NMOS tube is connected with a low level; and the drain of the second NMOS tube is connected with the input end of the second phase inverter, the grid of the second NMOS tube is connected with the output end of the second phase inverter, and the source of the second NMOS tube is connected with the low level. The H-shaped clock tree circuit comprises a plurality of TICBs. The technical scheme of the invention can resist temperature deviation and reduce clock skew caused by non-uniform temperature distribution, thereby ensuring the performance of an integrated circuit.

Owner:BEIJING PKUNITY MICROSYST TECH

Video processing method and device, terminal and storage medium

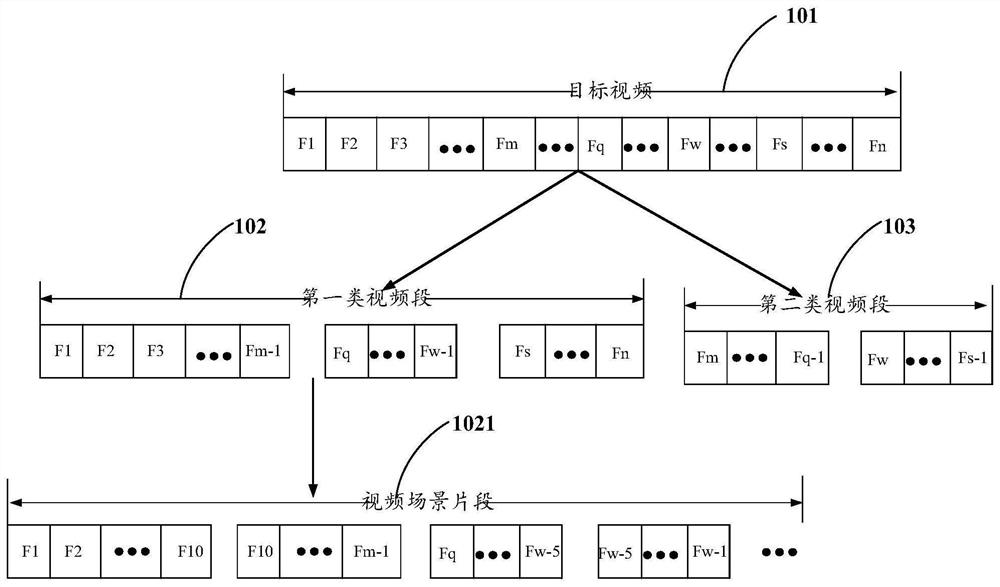

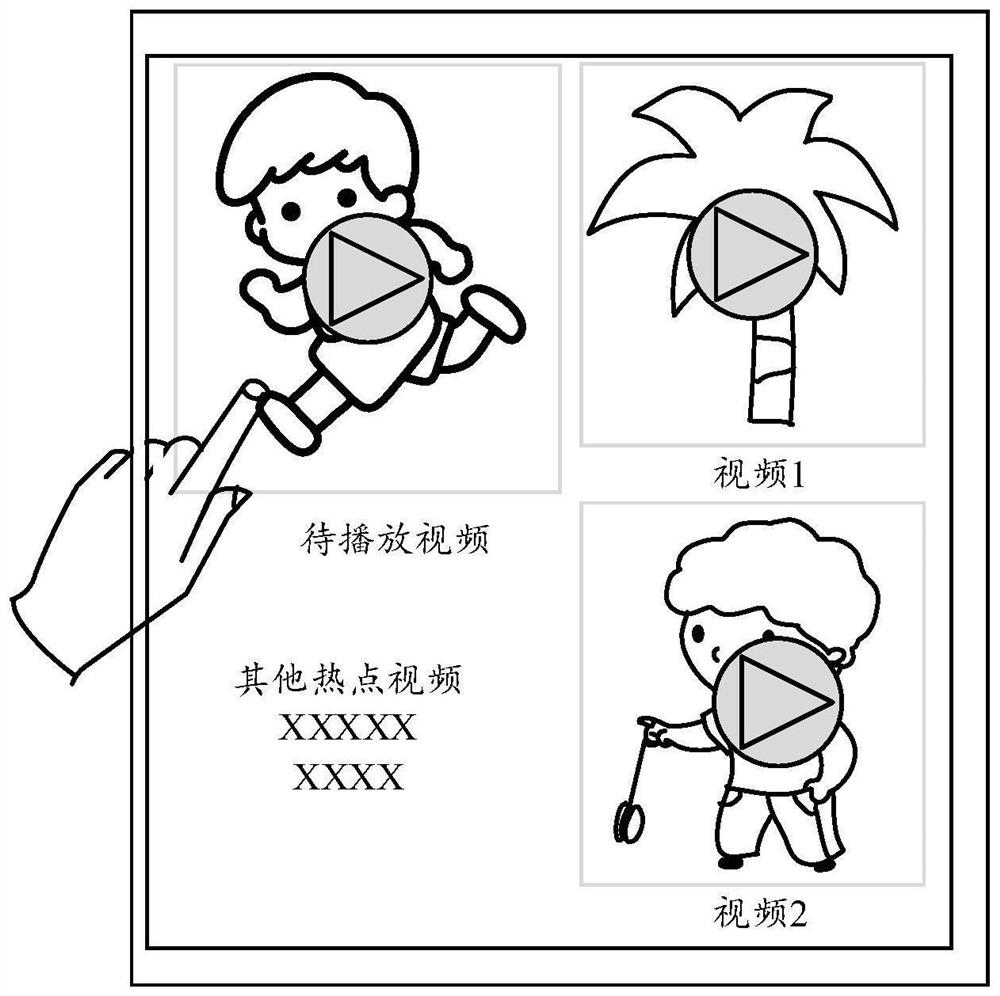

ActiveCN112153462AShorten the durationReduce power overheadSelective content distributionComputer graphics (images)Video processing

The embodiment of the invention discloses a video processing method and device, a terminal and a storage medium. The method comprises the following steps: determining a first type of video segments from a target video; dividing the first type of video segments into a video scene segment set according to the similarity between the image frames included in the first type of video segments, wherein the similarity between the image frames included in the video scene segments in the video scene segment set meets a similarity condition; performing duration compression processing on each video scenesegment according to the duration threshold; and splicing the video scene segments subjected to the duration compression processing to obtain a compressed first-type video segment, and splicing a second-type video segment included in the target video and the compressed first-type video segment according to a video playing sequence to obtain a compressed target video. According to the embodiment ofthe invention, intelligent duration compression processing on the target video is realized.

Owner:TENCENT TECH (SHENZHEN) CO LTD

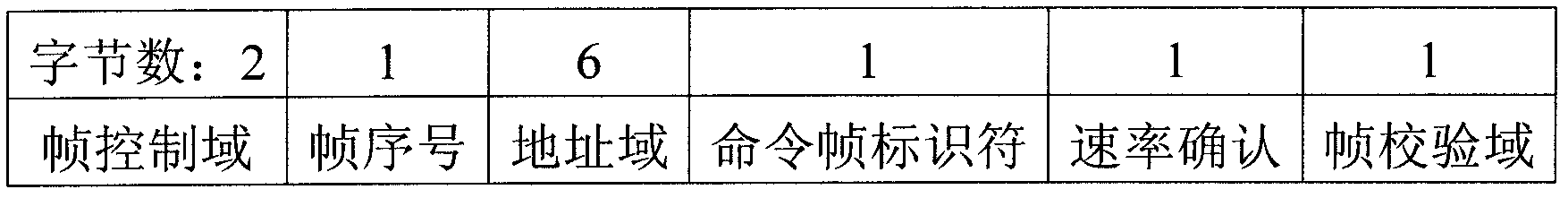

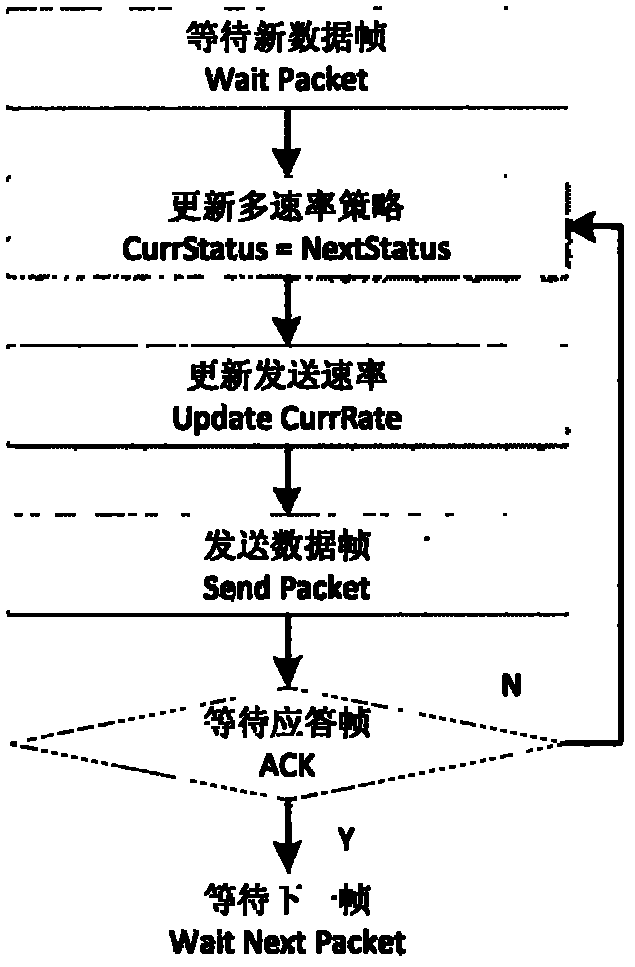

Adaptive and multirate channel adjusting method suitable for wireless sensor network

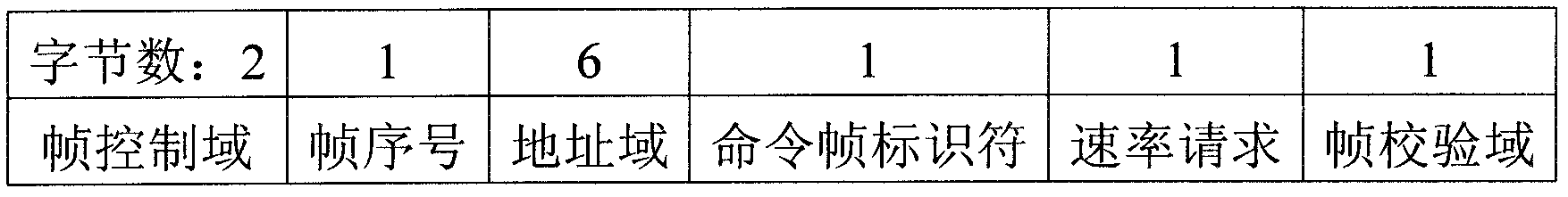

ActiveCN102368859AReduce power overheadAvoid transmission delaysError preventionNetwork traffic/resource managementWireless mesh networkNetwork packet

The invention discloses an adaptive and multirate channel adjusting method suitable for a wireless sensor network. The method is characterized in that: the adjusting method is a mixed multirate adjusting strategy, which comprises a fast channel adjusting strategy and a slow channel strategy. On the basis of statistics on sending situations, when there is a fast-changing channel strategy mode, if a plurality of continuous data packets are sent successfully at a same rate, the mode is switched to a slow-changing channel strategy mode; and when there is the slow-changing channel strategy mode, if data transmission failures continuously occur and the transmission failures can not be solved by reducing transmission rates, the mode is switched to a fast channel strategy mode. When there is a fast channel strategy state, transmit-receive sides decide an optimum transmission rate by a handshake decision; and when there is a slow channel strategy state, the sending side selects an optimum transmission rate according to historical transmission statistical information. According to the method provided in the invention, a defect that adaptive channel changing can not be carried out in the current multirate adjusting method is overcome; meanwhile, a problem that power consumption is sensitive when a wireless sensor network employs a traditional multirate adjusting method is solved.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

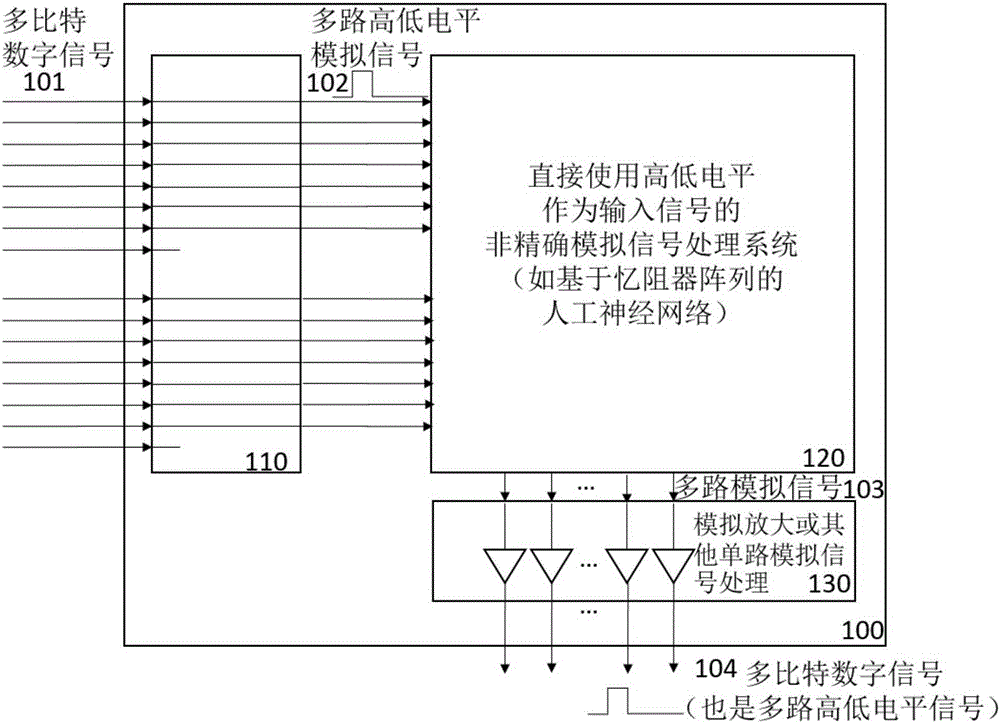

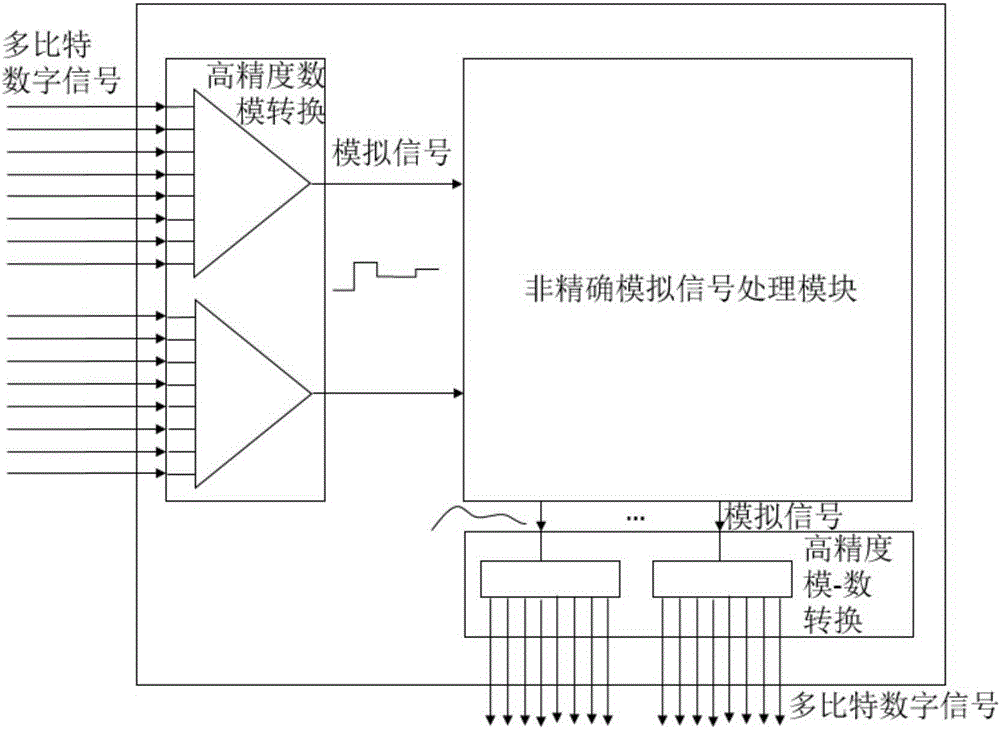

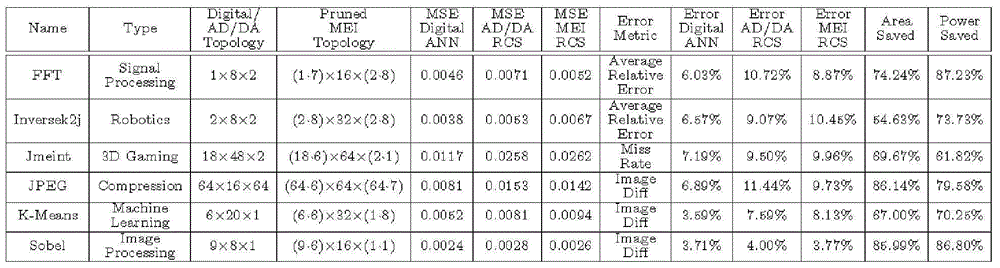

Digital-analog mixed signal processing system for imprecise computation

ActiveCN105184365AReduced area and power overheadSimplify interface designPhysical realisationInterface designDigital input

The invention discloses a digital-analog mixed signal processing system for imprecise computation, comprising an input module used for decomposing A B-bit digital input signals into A*B single-bit high- and low-level signals and sending the high- and low-level signals to a signal processing module as analog input signals, the signal processing module used for calculating the analog input signals to obtain C analog output signals and sending the analog output signals to an output module, and the output module used for converting the analog output signals into D high- and low-level signals and outputting the D high- and low-level signals as E F-bit digital signals, wherein D, E and F are natural numbers, and D=E*F. The digital-analog mixed signal processing system for imprecise computation has the advantages as follows: the area and power consumption of a computing system on a conversion interface are reduced effectively, and interface design is greatly simplified; and the area is reduced by more than 50%, the energy consumption is reduced by more than 60%, and the application space of the system of the type is significantly improved.

Owner:TSINGHUA UNIV