A test shell circuit and its design method

A technology for testing enclosures and design methods, applied in the directions of monitoring/monitoring/test arrangement, electrical components, transmission monitoring, etc., can solve problems such as the influence of the total test time of the chip, mismatches, etc., to reduce the number of transmitted data packets and optimize the design. , improve the effect of parallelism

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

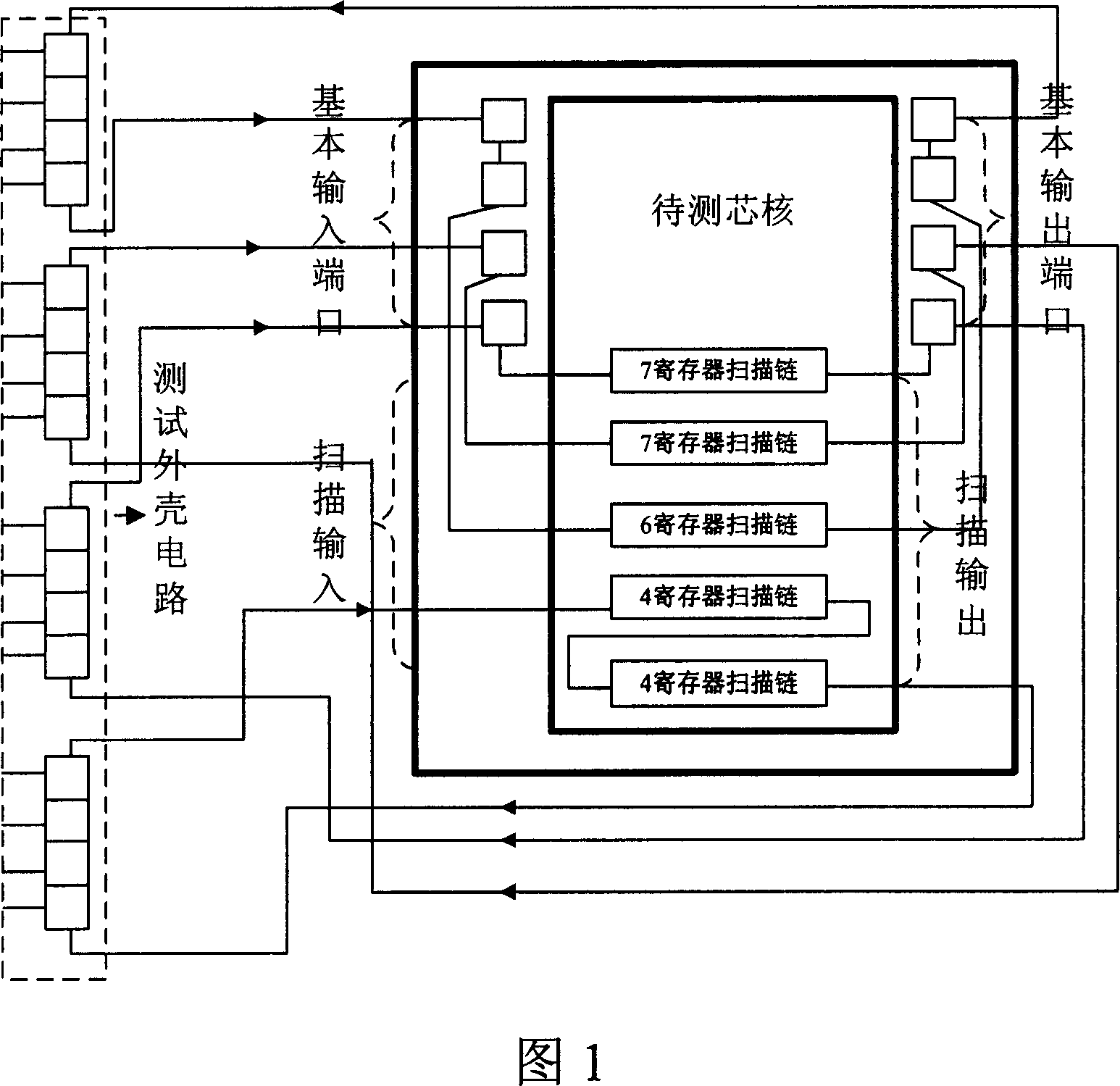

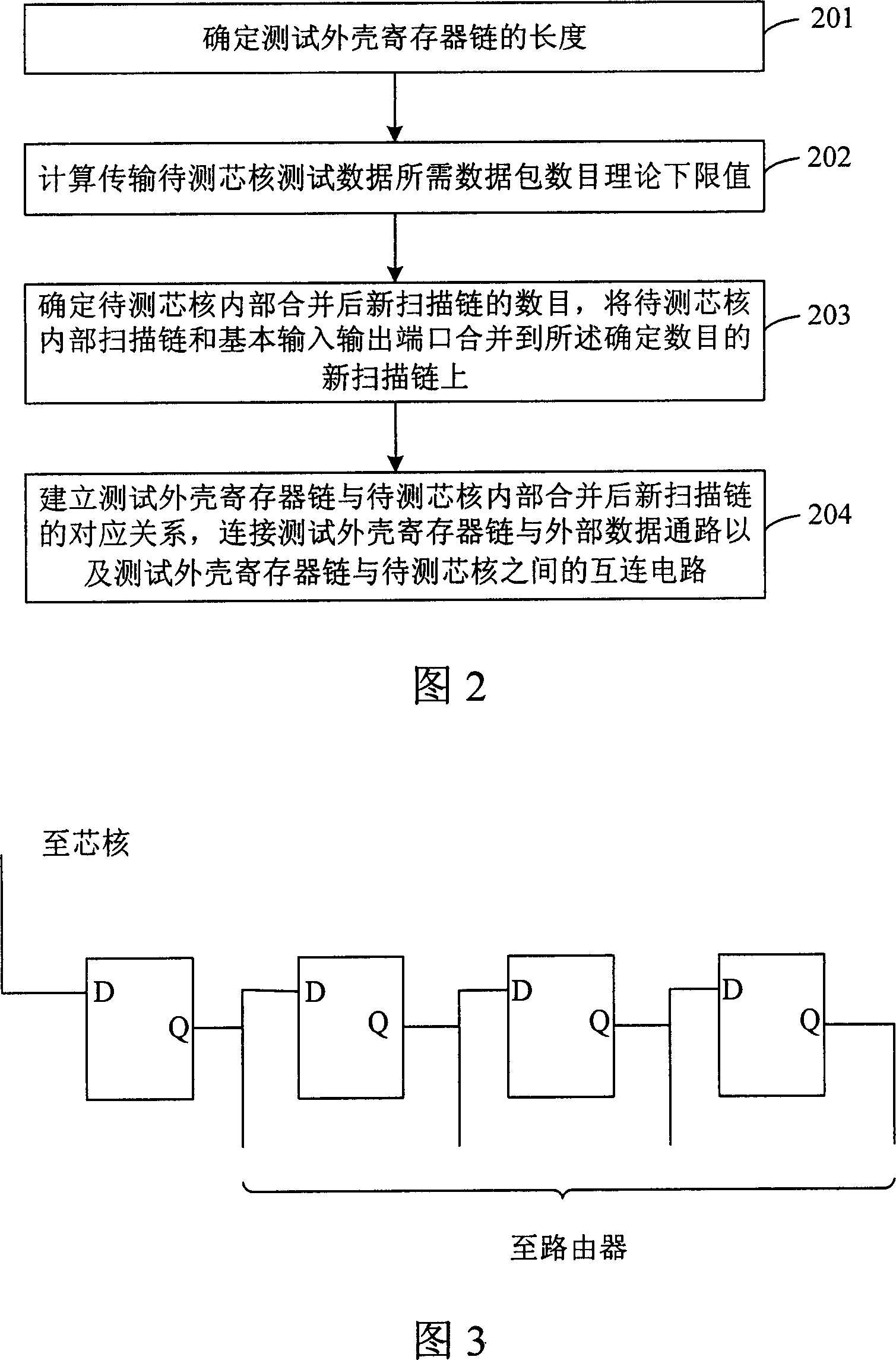

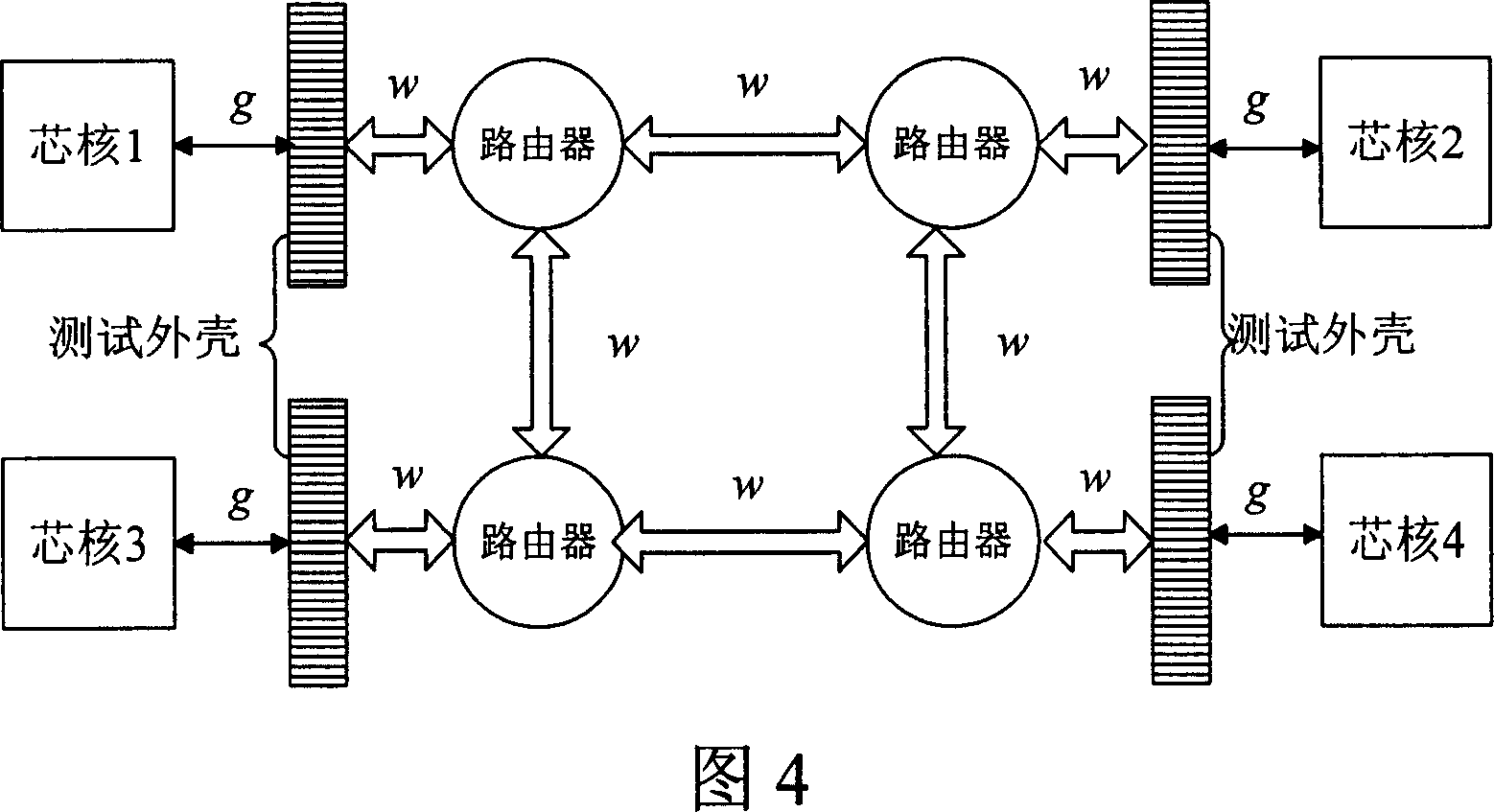

[0073] In this embodiment, it is assumed that a core to be tested contains 15 scan chains containing 45 registers, 5 scan chains containing 20 registers, and 108 input / output ports, 108 being the number of input ports and output ports The maximum value between the numbers, the bandwidth w of the data path is 16, then according to the total number N of the test shell registers is equal to the bandwidth w of the data path, it can first be determined that the total number N of the test shell registers is 16.

[0074] Then, calculate the theoretical lower limit of the number of data packets required to transmit the core test data to be tested according to formula (1):

[0075]

[0076] Then, since w=16, try to allocate the test shell registers to g groups in the order of {16, 8, 4, 2, 1}.

[0077] First, assuming g=16, the number of registers l on each new scan chain including the added basic input and output ports shall not exceed (N / g)×n p =(16 / 16)×56=56. On the premise tha...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More