Patents

Literature

98results about How to "Reduce hardware overhead" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

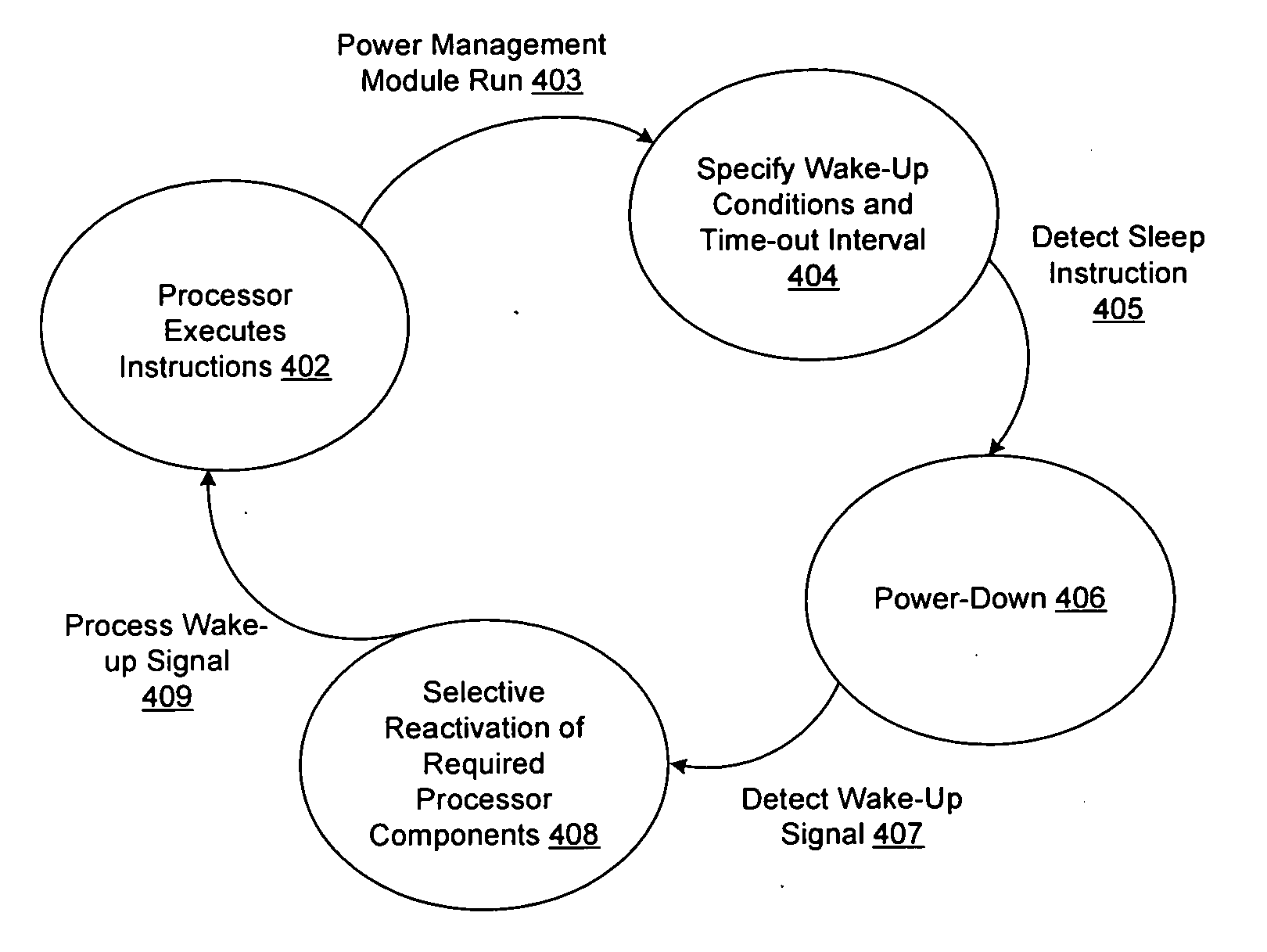

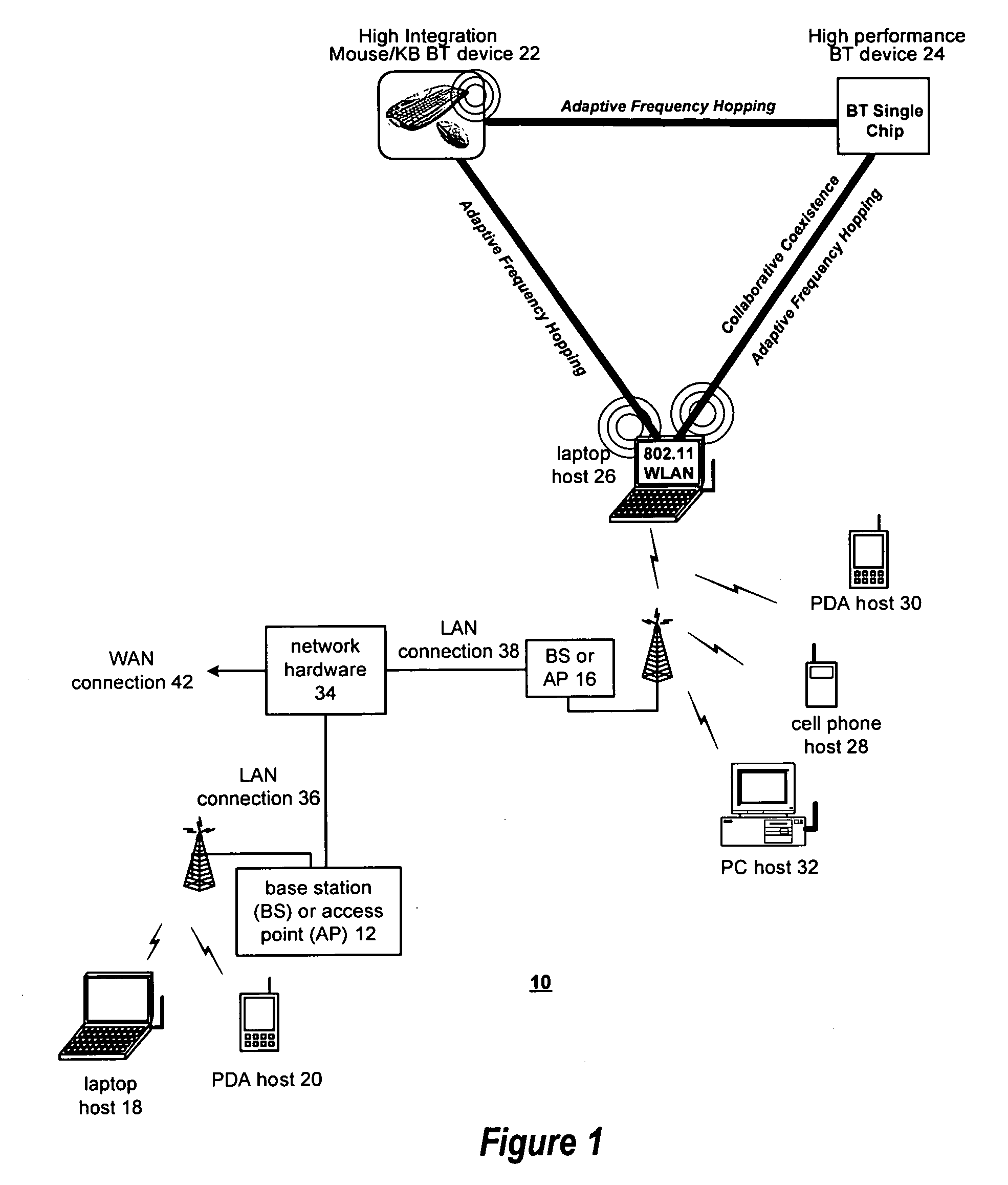

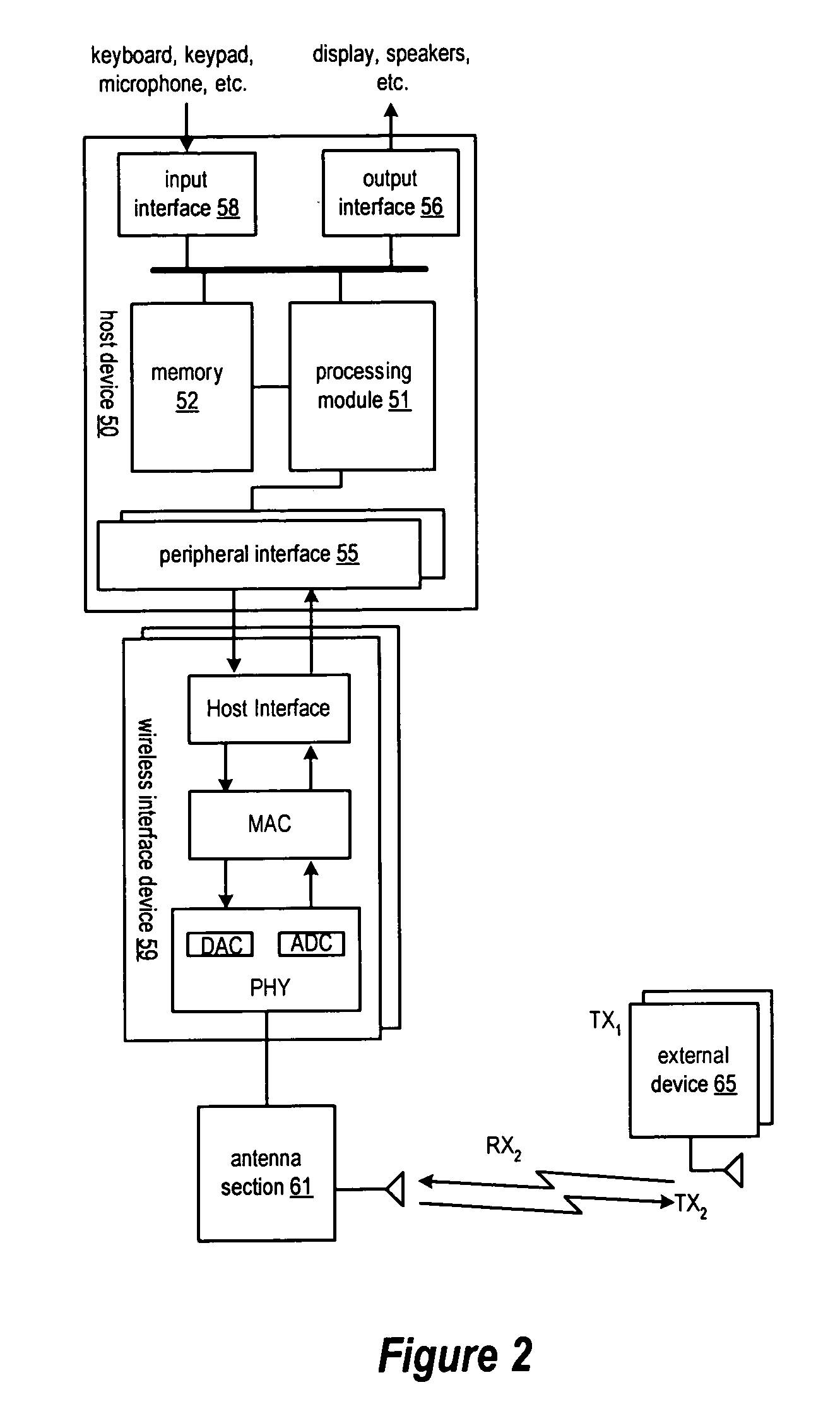

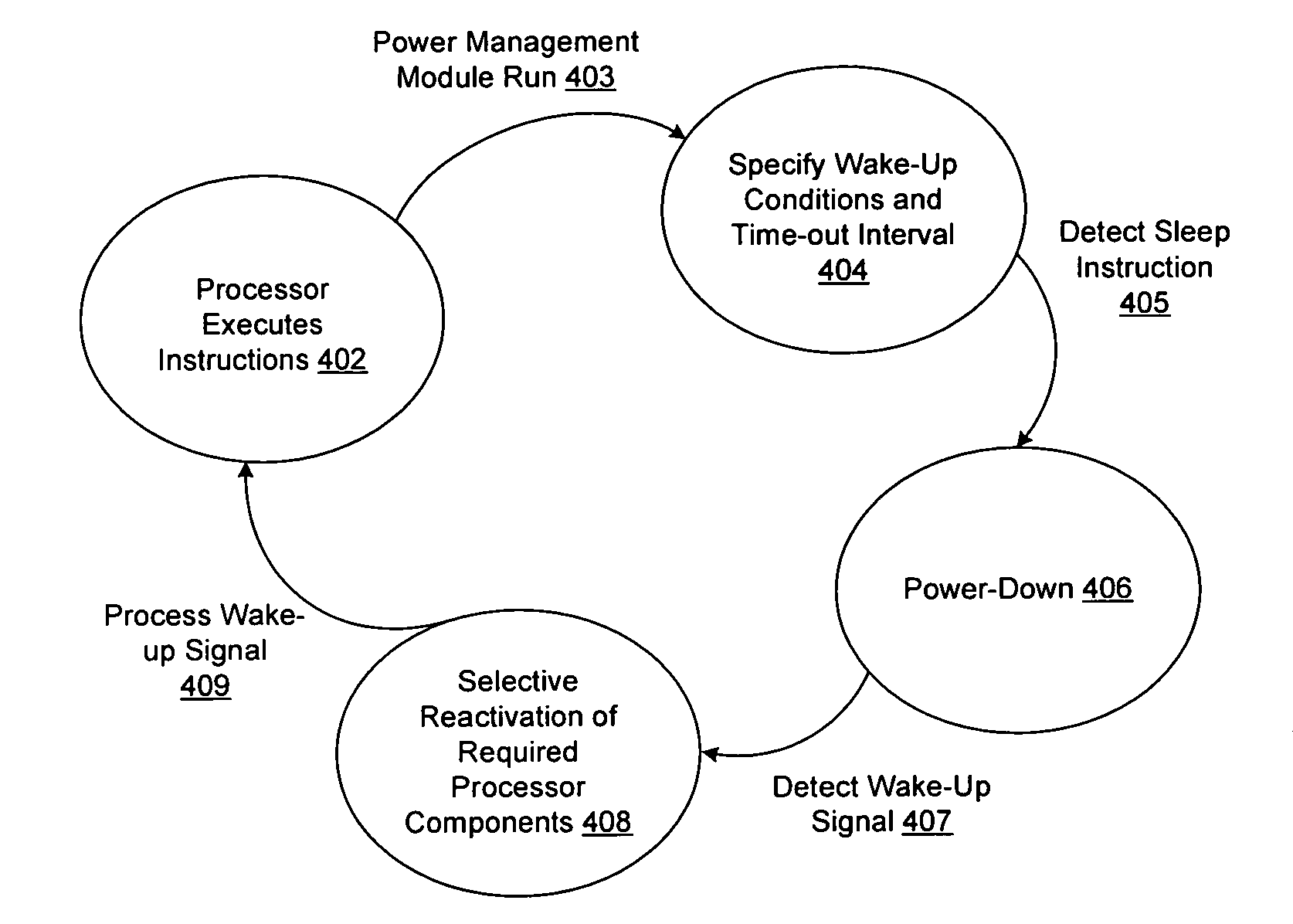

MAC controlled sleep mode/wake-up mode with staged wake-up for power management

ActiveUS20050215274A1Fast power onEfficiently reactivatedEnergy efficient ICTPower managementCMOSEngineering

A power management scheme for a wireless communications device processor substantially implemented on a single CMOS integrated circuit is described. By incorporating controls for sleep and wake-up mode transitions in the processor's control logic, improved power savings with reduced latency is provided, obviating the need for hardware-focused solutions with elaborate signaling mechanisms. A fully integrated power management with staged wake-up operations controlled by the MAC solution consumes less power than the conventional wireless LAN solutions in standby mode.

Owner:AVAGO TECH INT SALES PTE LTD

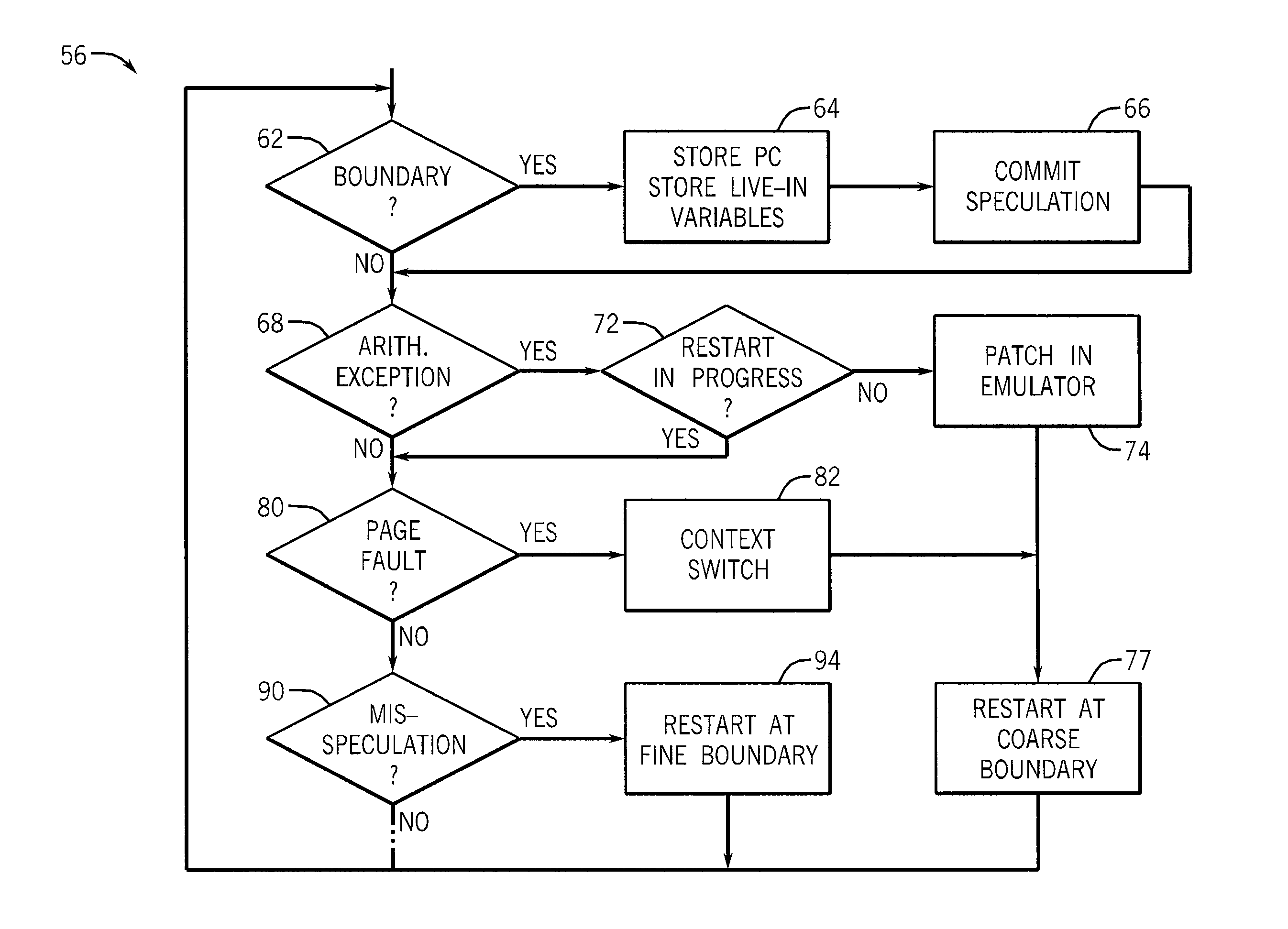

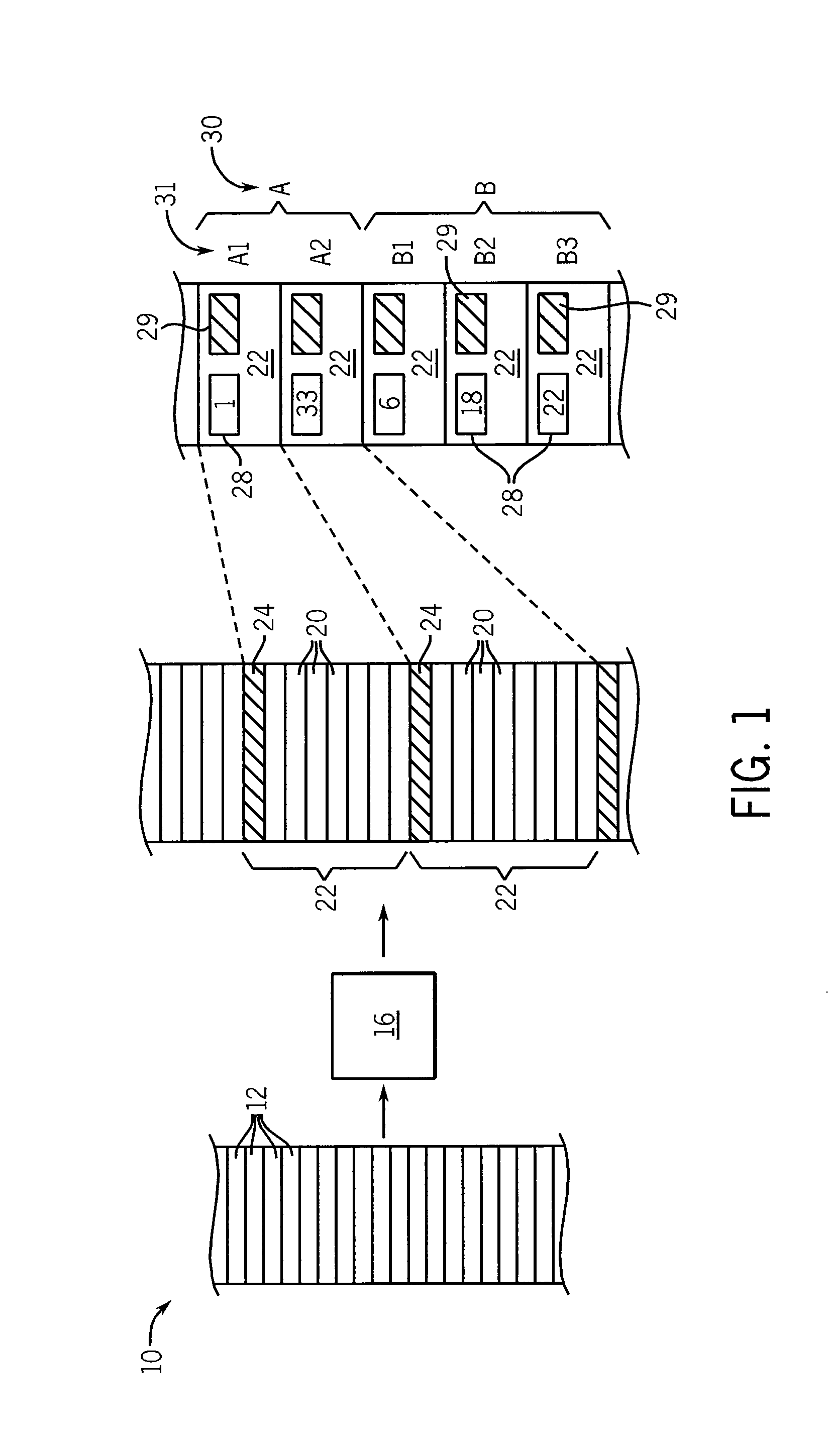

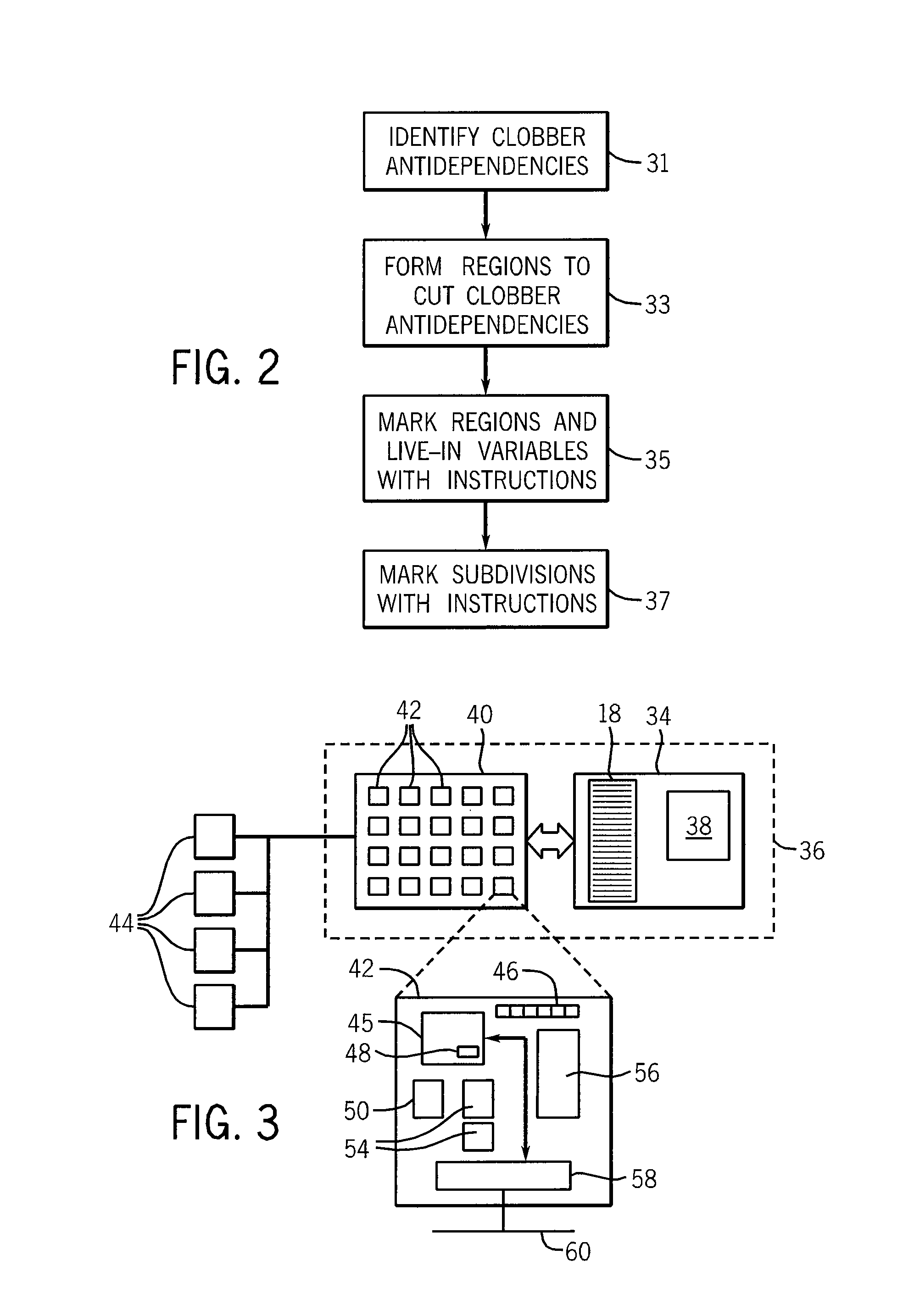

Computer Processor Providing Exception Handling with Reduced State Storage

ActiveUS20140019735A1Reduce hardware overheadSimple methodInstruction analysisDigital computer detailsArchitecture of Integrated Information SystemsException handling

A computer architecture allows for simplified exception handling by restarting the program after exceptions at the beginning of idempotent regions, the idempotent regions allowing re-execution without the need for restoring complex state information from checkpoints. Recovery from mis-speculation may be provided by a similar mechanism but using smaller idempotent regions reflecting a more frequent occurrence of mis-speculation. A compiler generating different idempotent regions for speculation and exception handling is also disclosed.

Owner:WISCONSIN ALUMNI RES FOUND

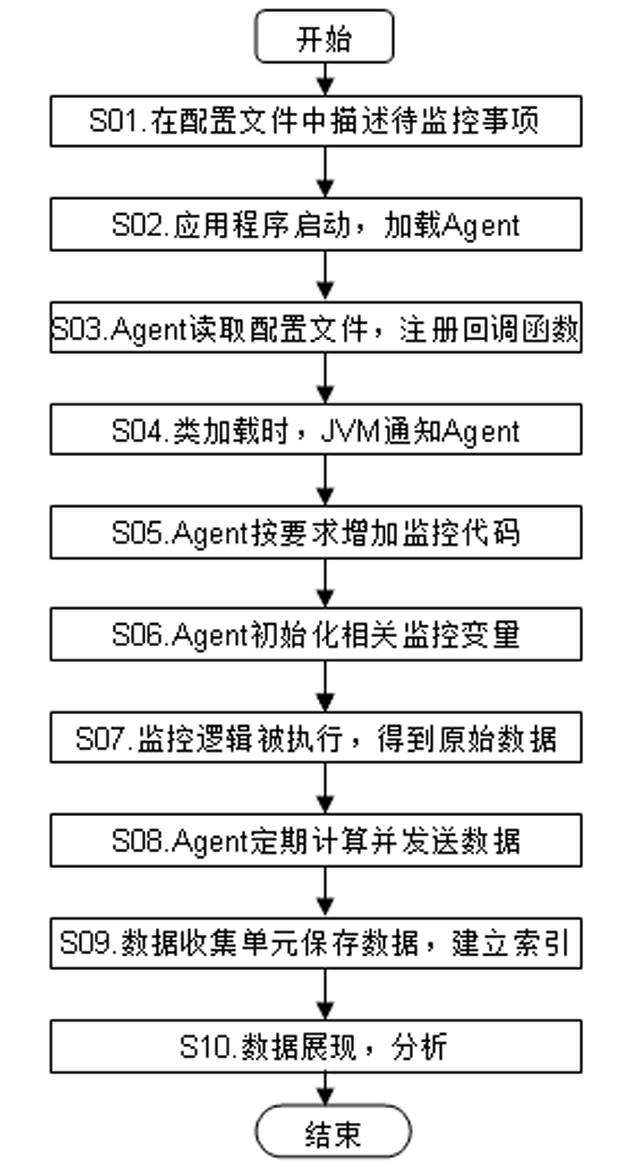

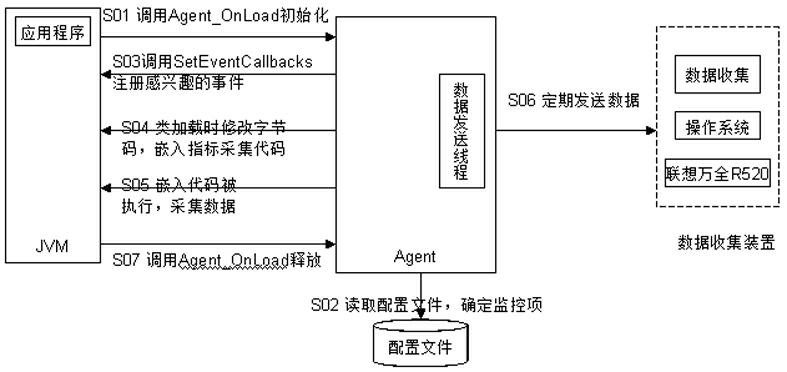

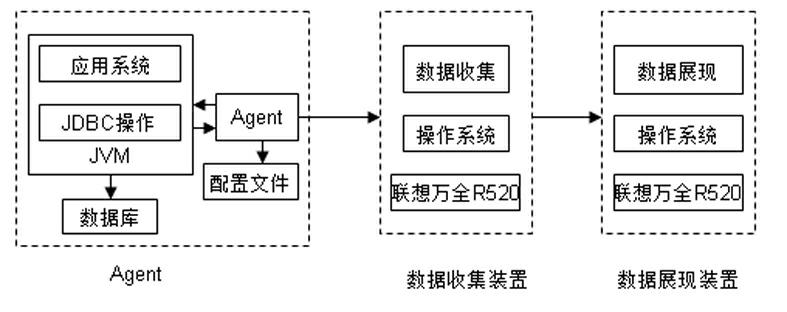

Monitoring method and device of JAVA application system in running

InactiveCN102122263AReduce hardware overheadDoes not affect normal operationHardware monitoringOriginal dataConfigfs

The invention discloses a monitoring method and device of a JAVA application system in running. The JAVA application system monitoring method mainly comprises the steps of: describing a monitored class or method and a monitor control index through a configuration file; (2) modifying starting parameters of an application program, and loading Agent when a JVM (Java Virtual Machine) is started; (3) reading the configuration file by the Agent, and registering an event to be noticed according to a monitoring requirement; (4) obtaining a notice by the Agent when the application program runs and a specified class is loaded; (5) modifying a bytecode of a corresponding class by the Agent, and adding a logic required in monitoring; (6) initializing relevant index variable by the Agent; (7) automatically executing the monitoring logic when the monitored method is called, and obtaining the original data of the relevant index; and (8) computing the value of the relevant index by the Agent according to the description of the configuration file. By applying the JAVA application system monitoring method disclosed by the invention, the ability of an IT (Information Technology) operation and maintenance staff for diagnosing, analyzing, positioning and solving faults of an IT system can be improved remarkably.

Owner:勤智数码科技股份有限公司

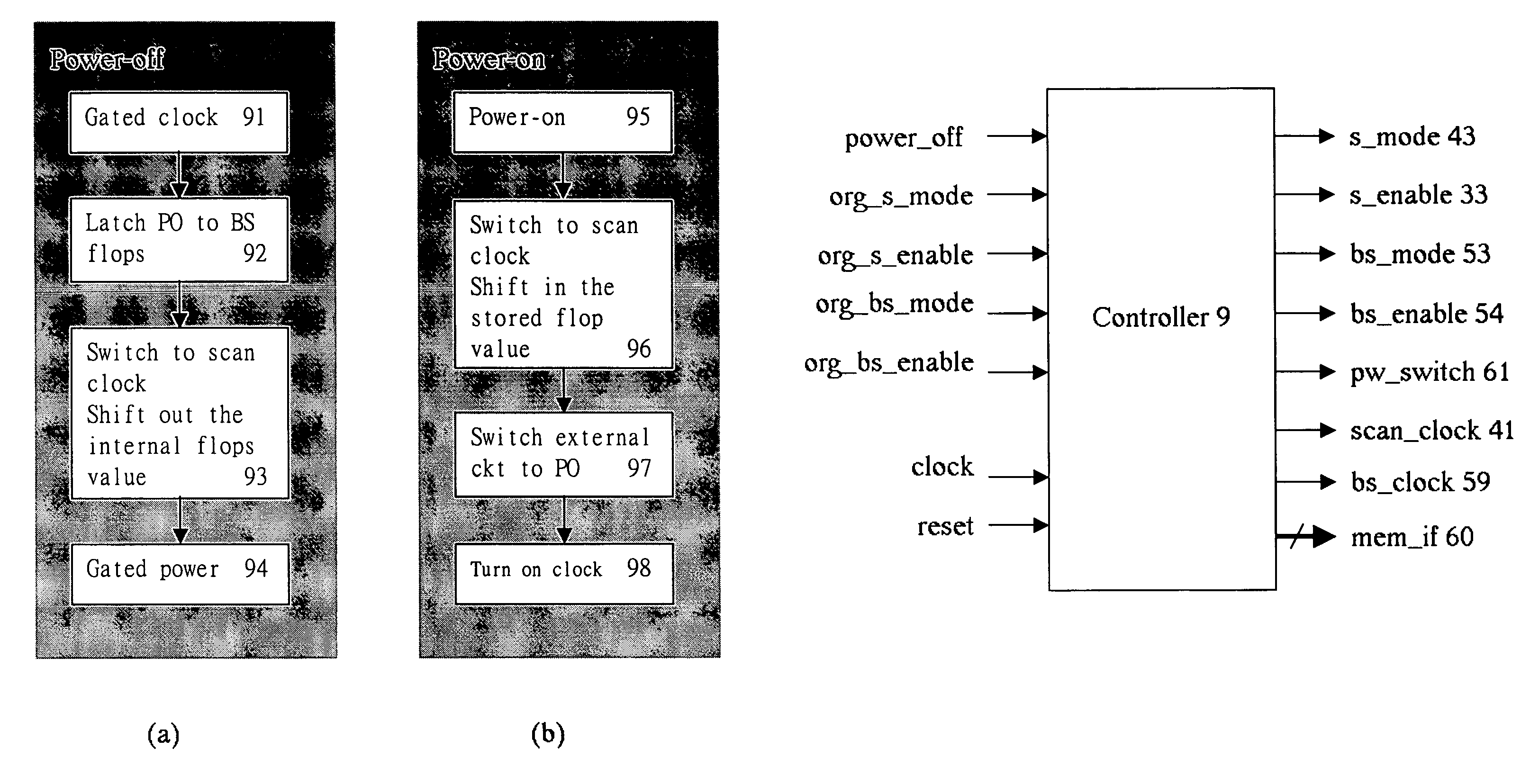

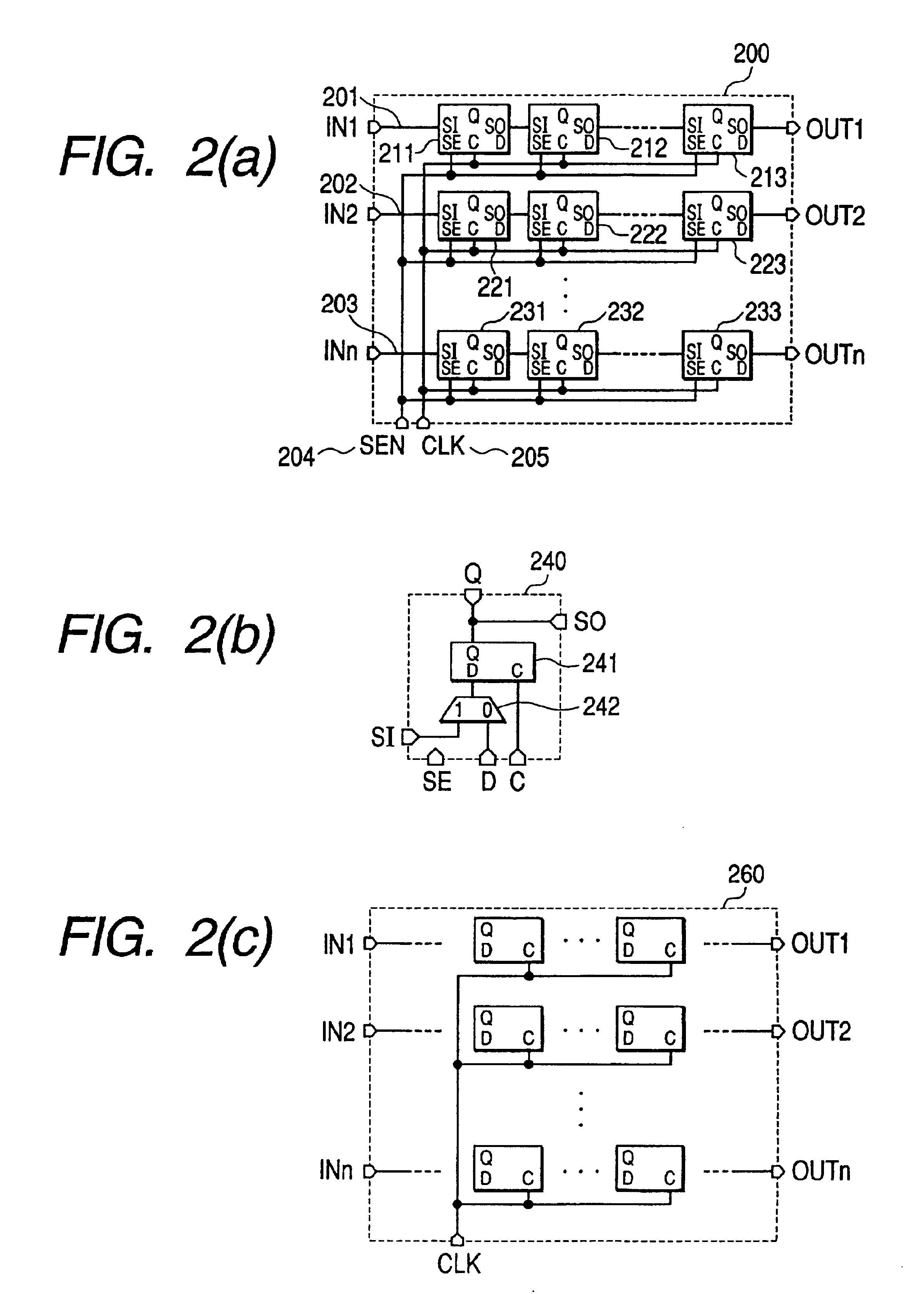

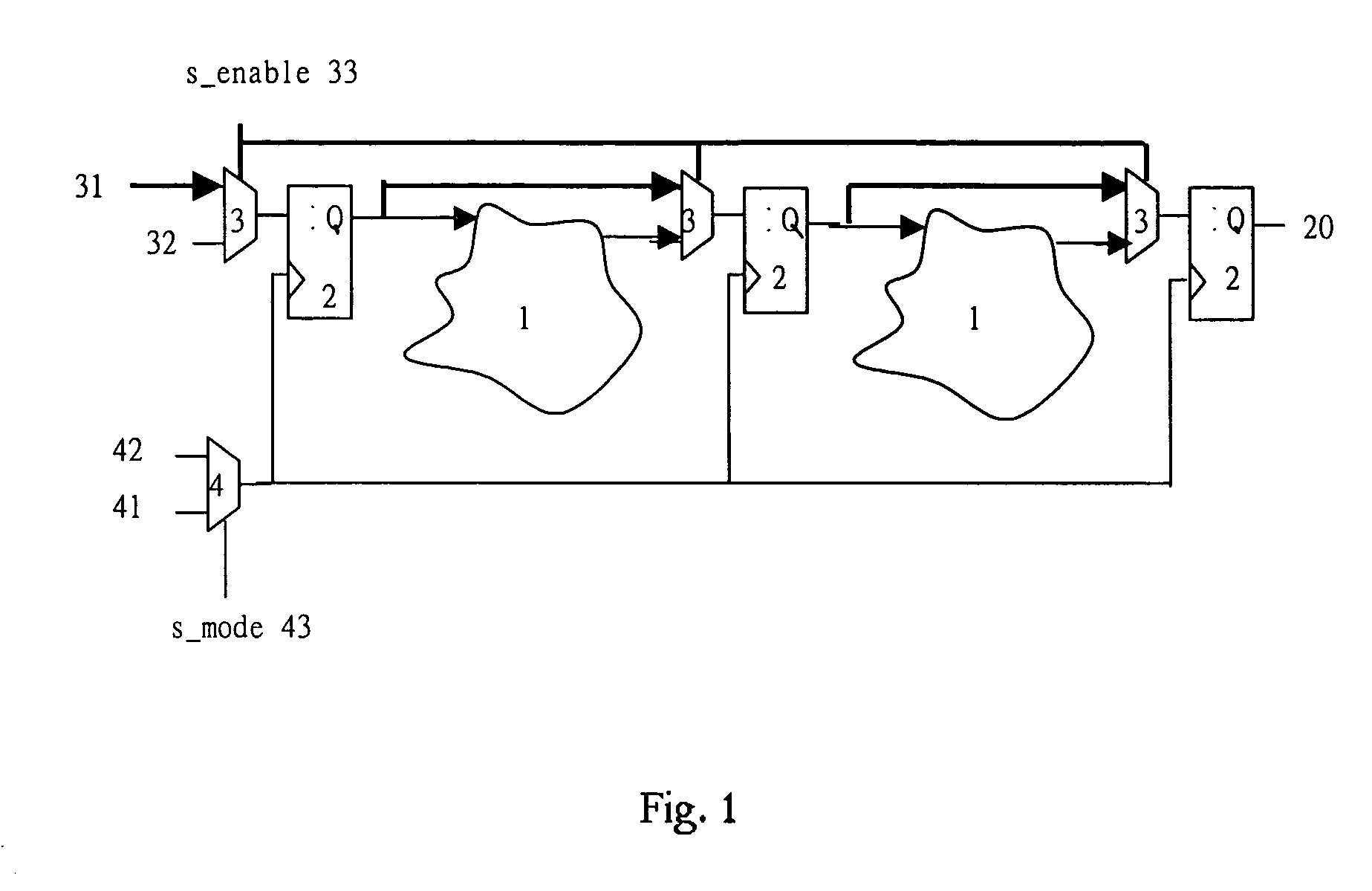

Method of using scan chains and boundary scan for power saving

InactiveUS7392447B2Reduce hardware overheadSave powerEnergy efficient ICTElectronic circuit testingInternal memoryExternal storage

Owner:PRINCETON TECH CORP

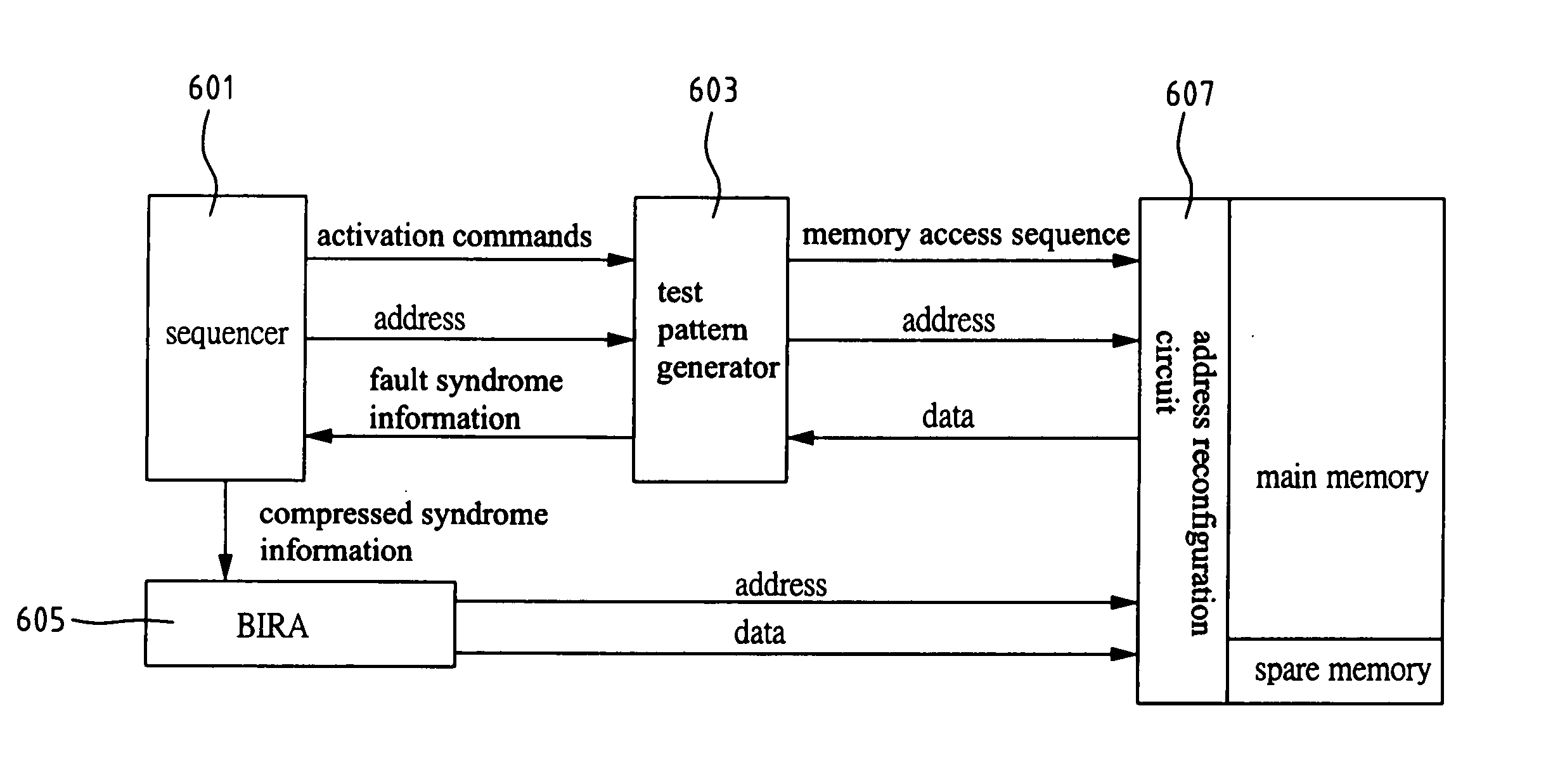

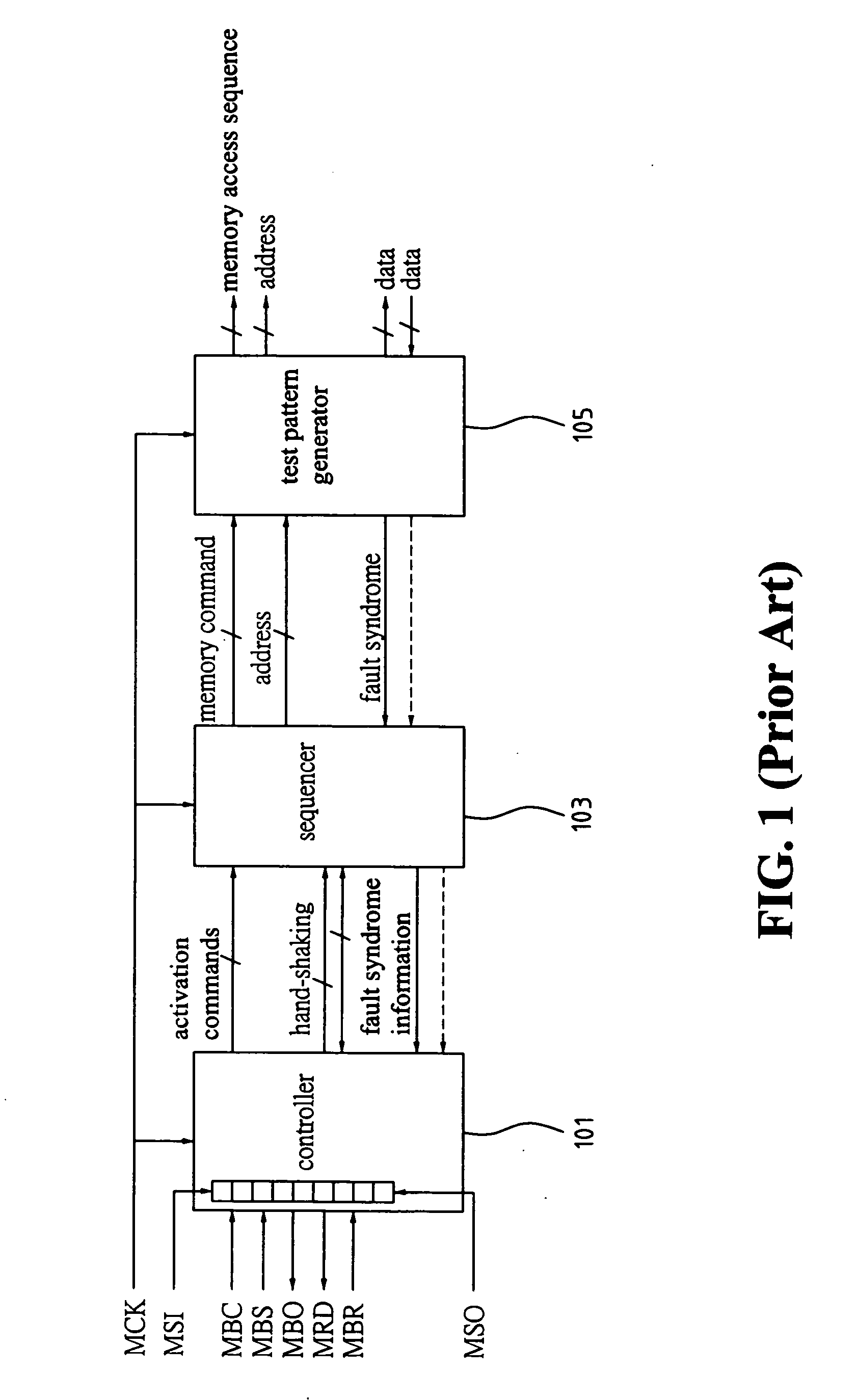

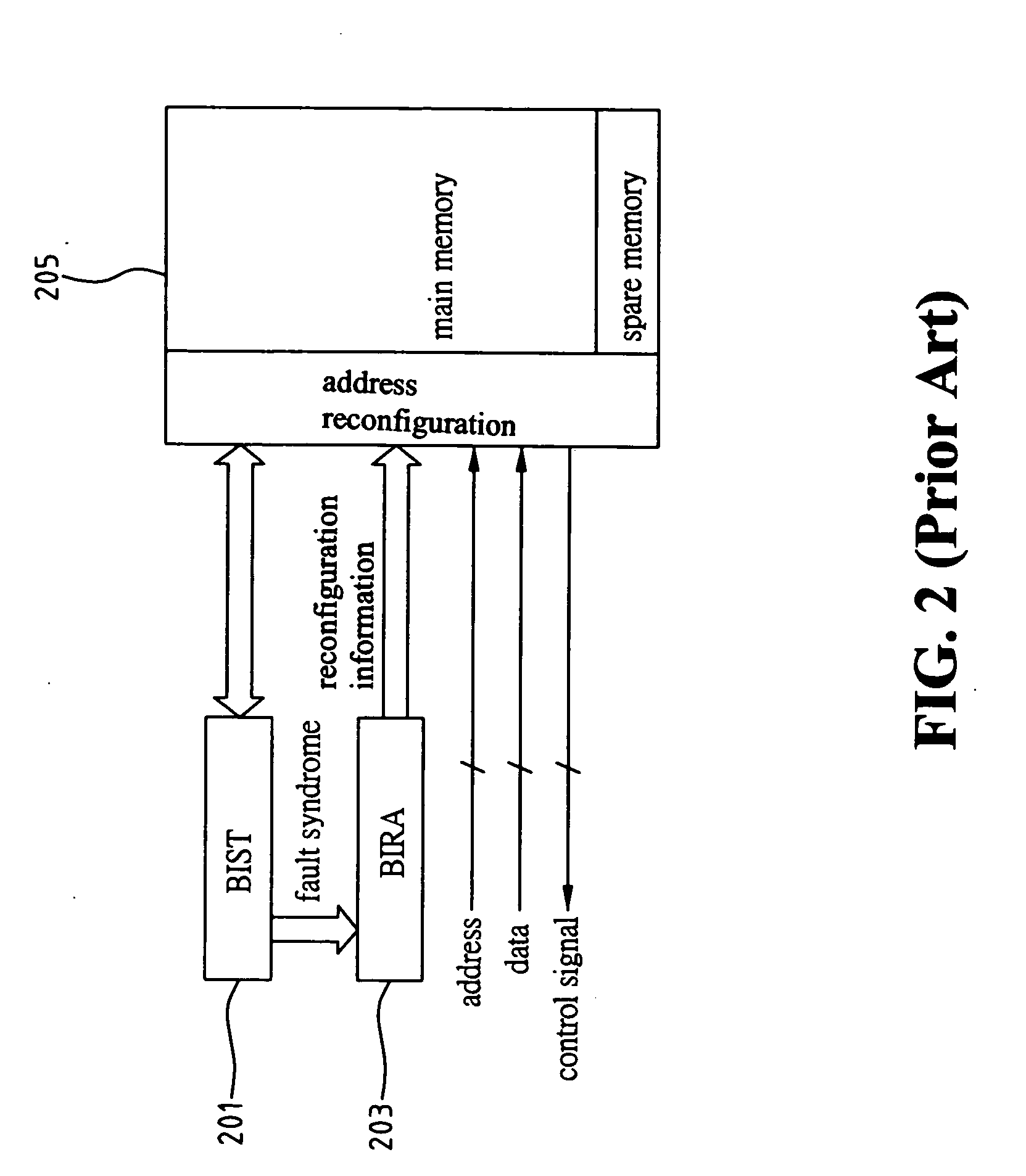

Method and apparatus of build-in self-diagnosis and repair in a memory with syndrome identification

ActiveUS20060064618A1Easy to analyzeHardware overhead is low and decreaseElectronic circuit testingDigital storageAutomatic test equipmentComputer science

The present invention provides a method and apparatus for a memory build-in self-diagnosis and repair with syndrome identification. It uses a fail-pattern identification and a syndrome-format structure to identify faulty rows, faulty columns and single faulty word in the memory during the testing process, then exports the syndrome information. Based on the syndrome information, a redundancy analysis algorithm is applied to allocate the spare memory elements repairing the faulty memory cells. It has a sequencer with enhanced fault syndrome identification, a build-in redundancy-analysis circuit with improved redundancy utilization, and an address reconfigurable circuit with reduced timing penalty during normal access. The invention reduces the occupation time and the required capture memory space in the automatic test equipment. It also increases the repair rate and reduces the required area overhead.

Owner:IND TECH RES INST

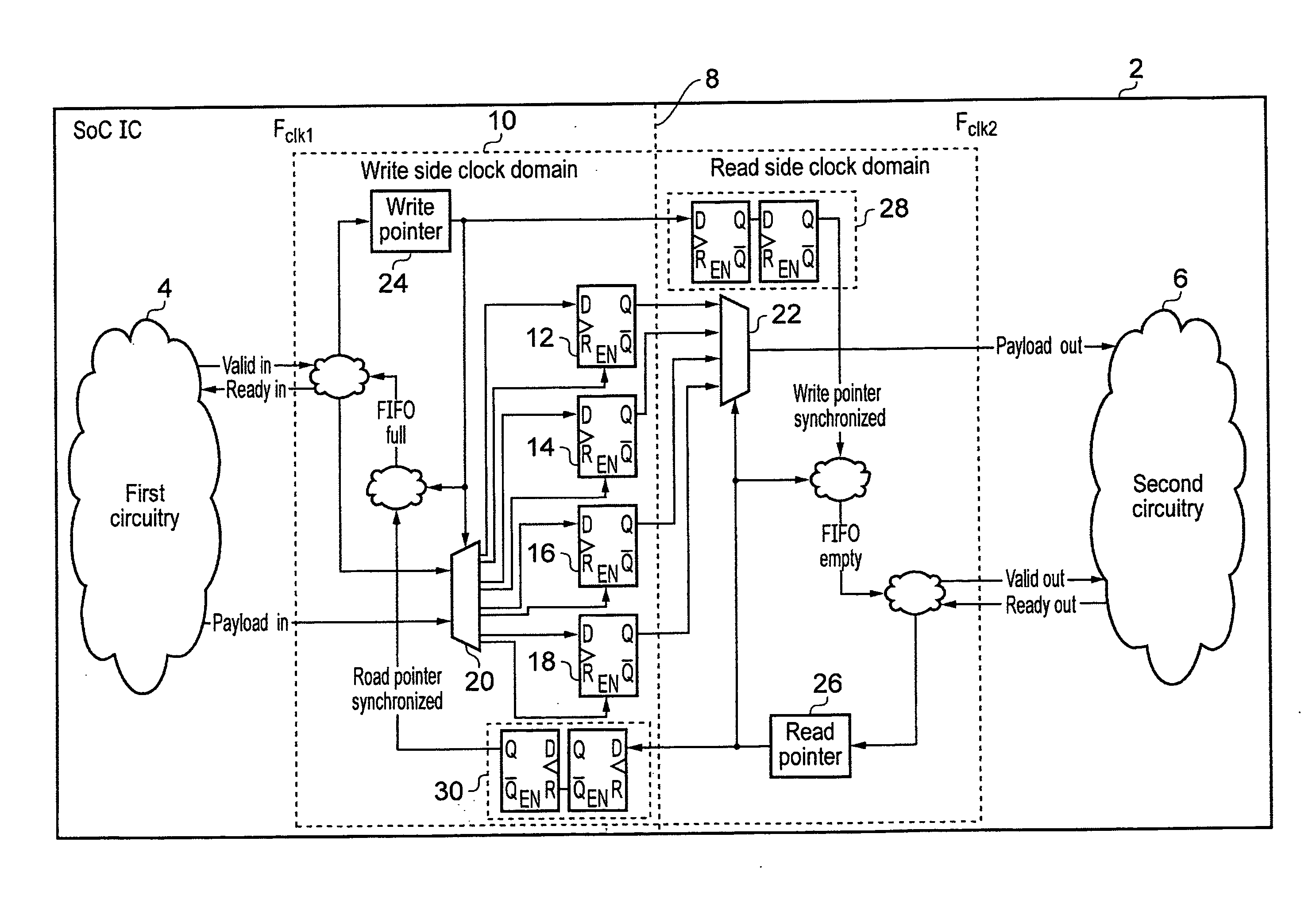

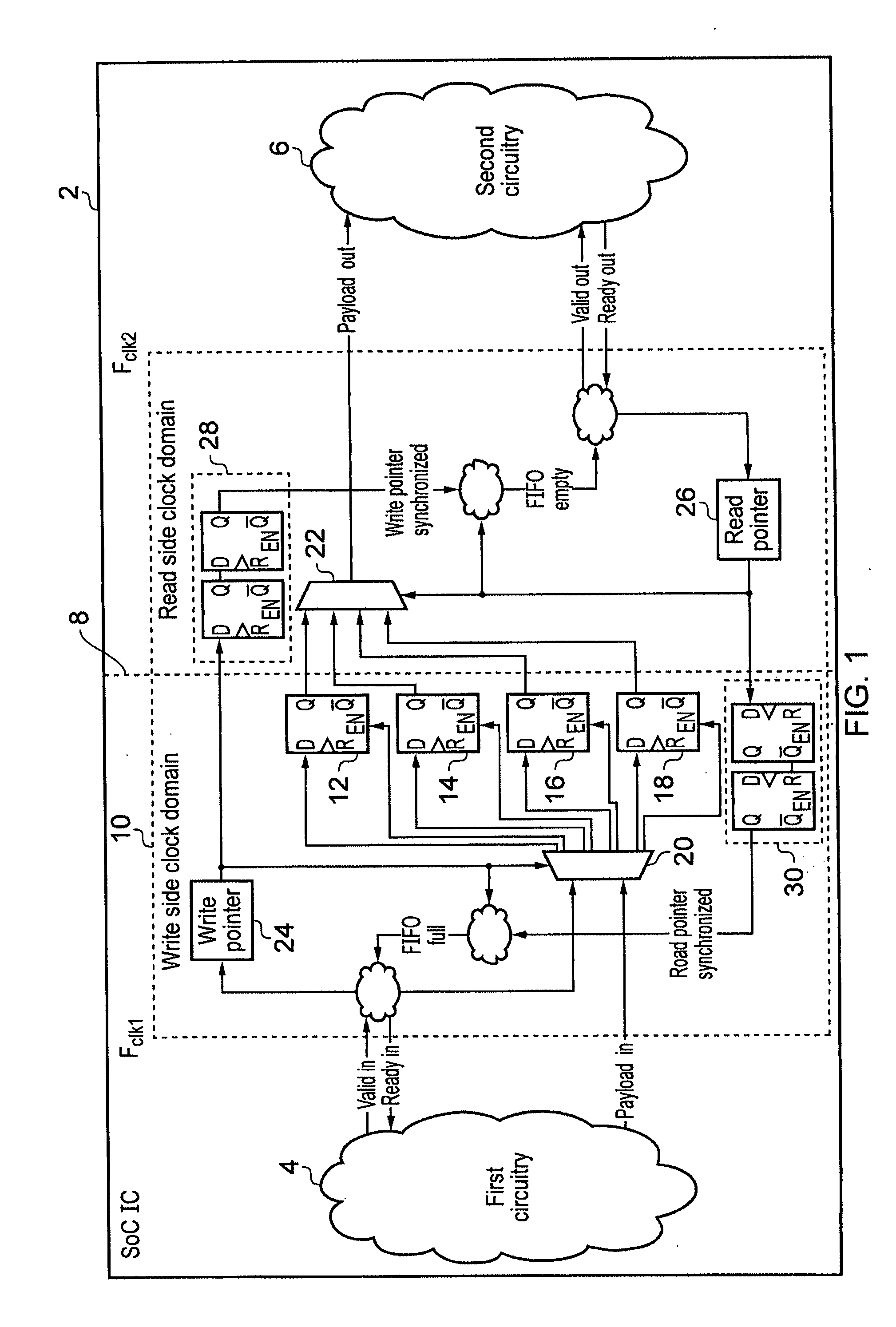

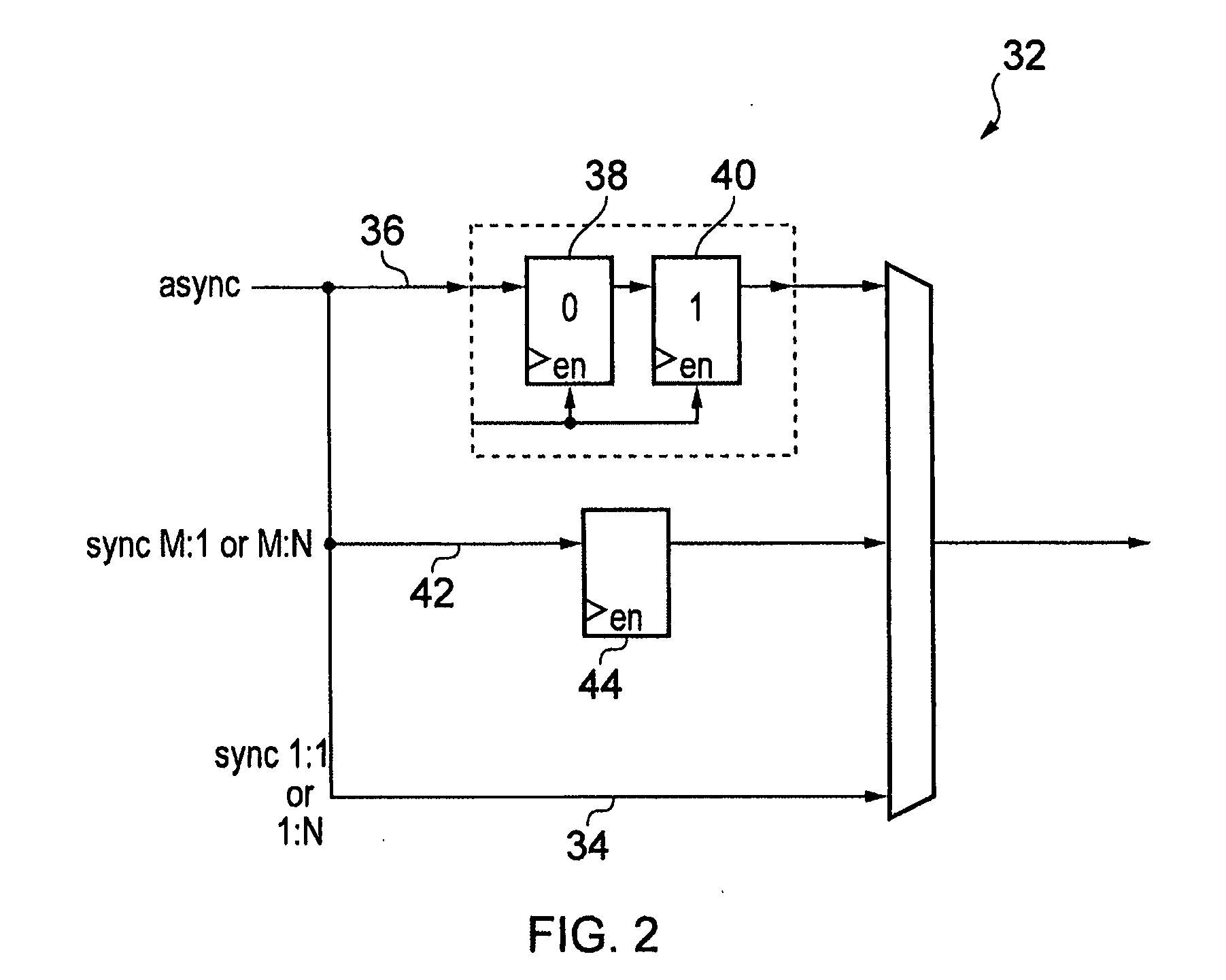

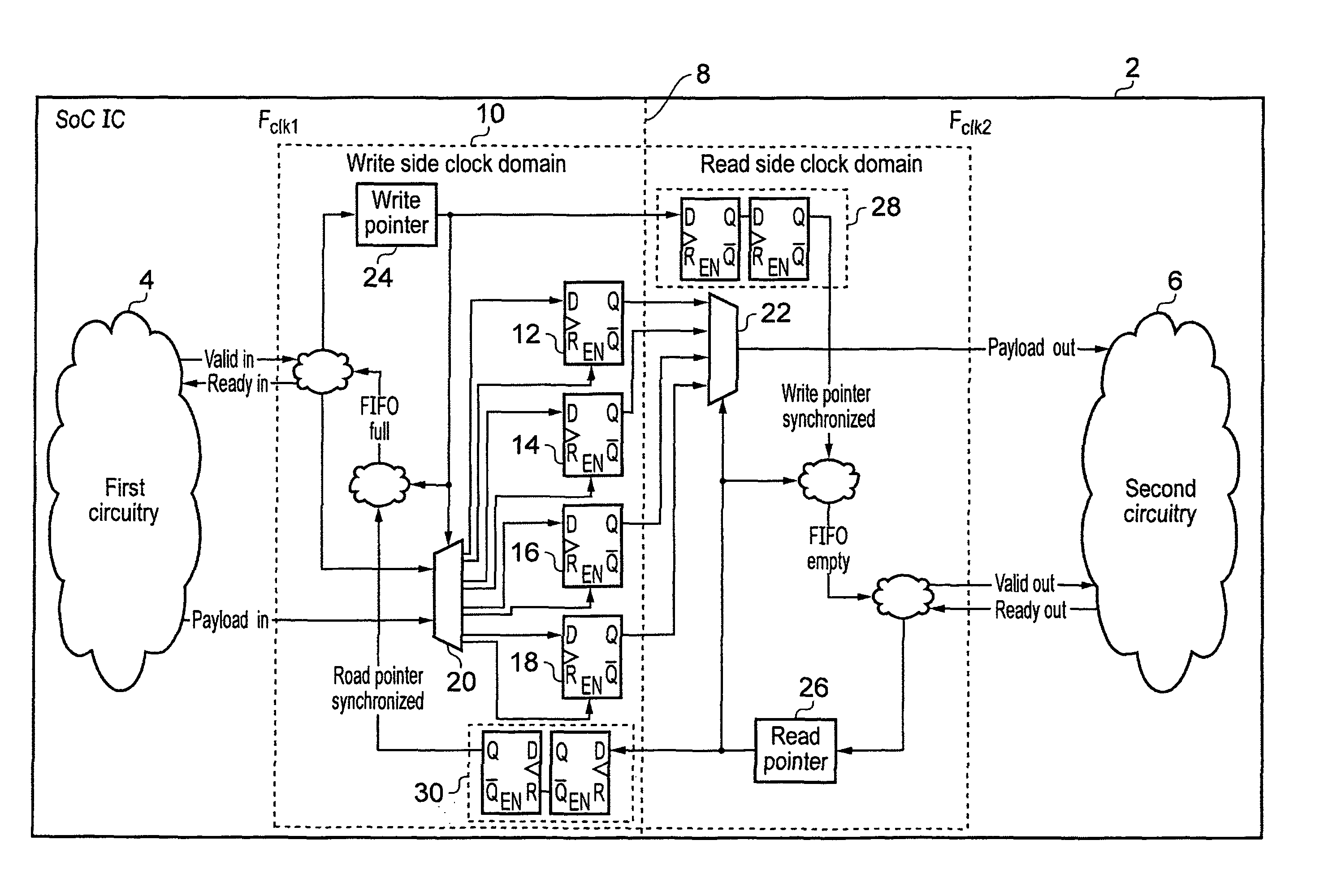

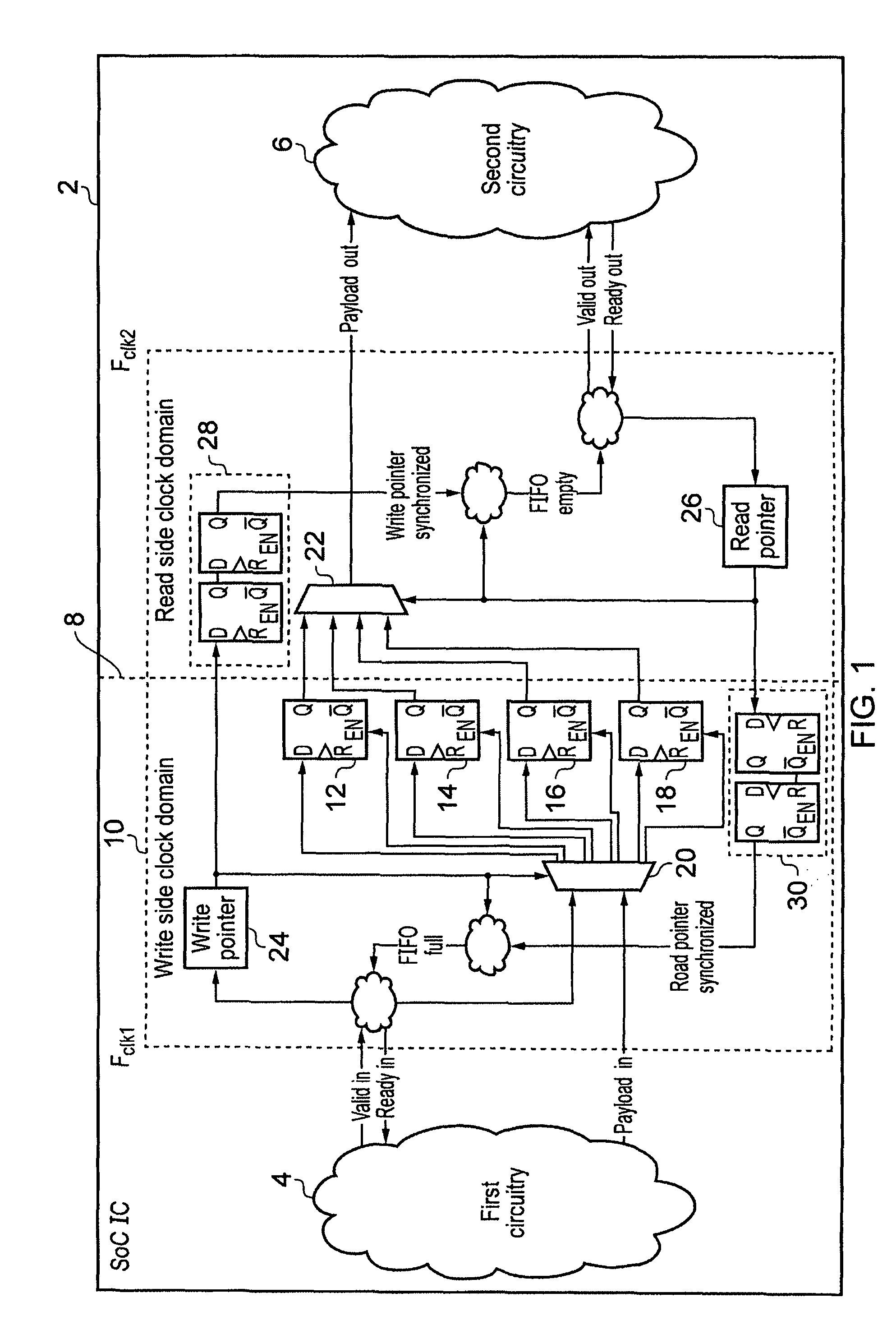

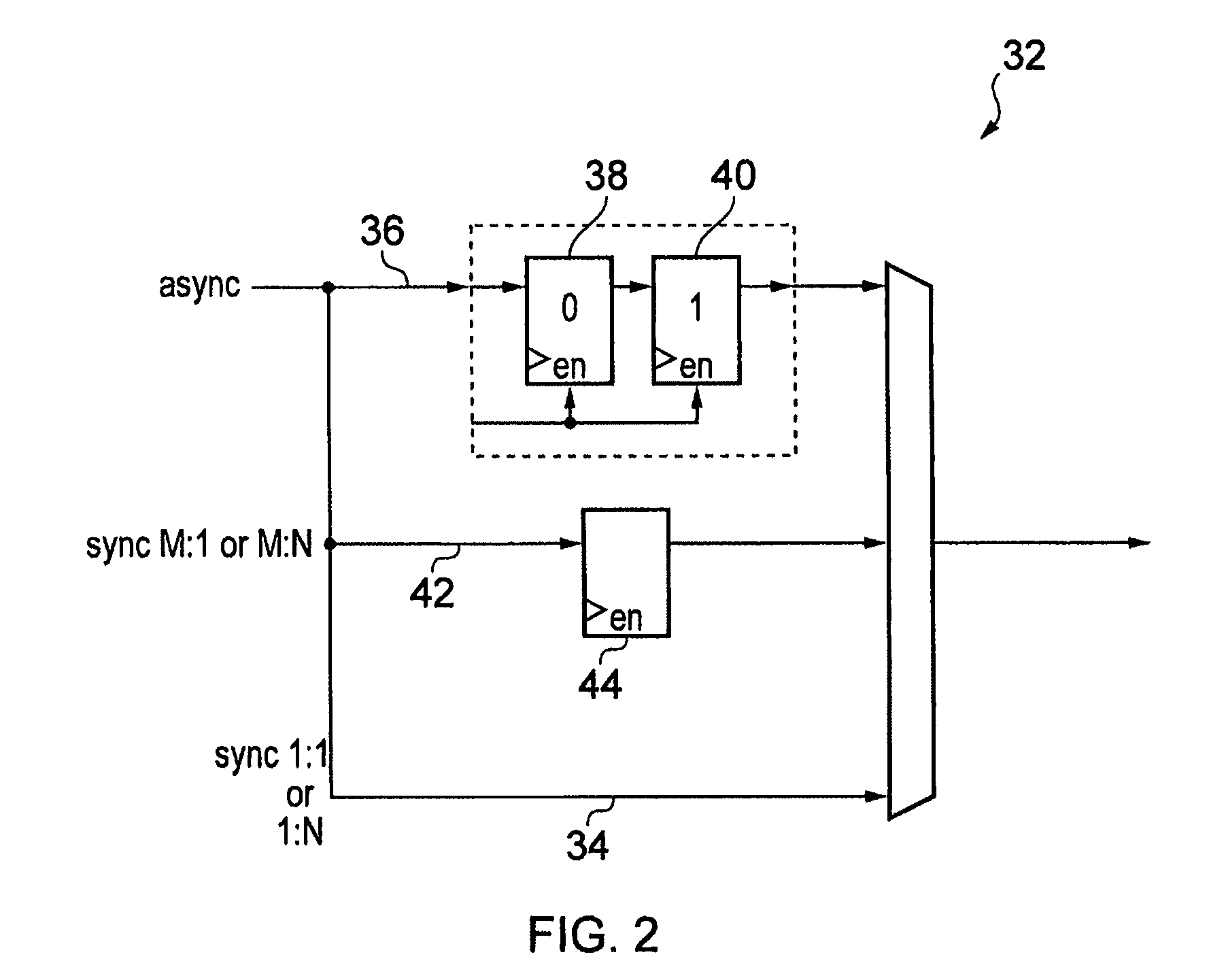

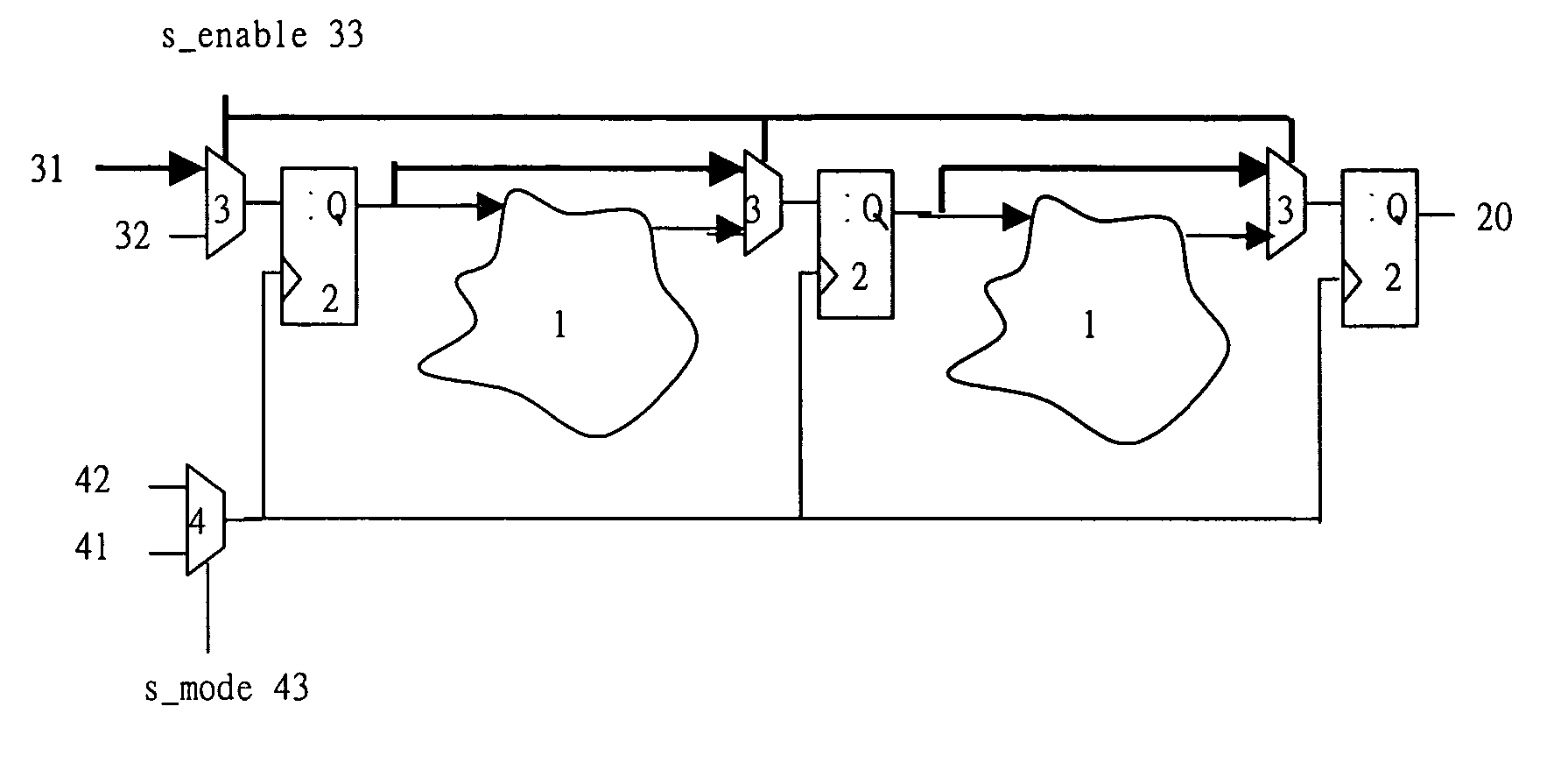

Synchronising between clock domains

ActiveUS20110116337A1Reduce hardware overheadIncrease in synchronisation delayDigital storageGenerating/distributing signalsProcessor registerClock rate

An integrated circuit 2 is provided with multiple clock domains separated by a clock boundary 8. Data values are passed across the clock boundary 8 using a first-in-first-out memory (FIFO), a read pointer and a write pointer for the FIFO are passed across the clock boundary 8 and must be synchronised to the receiving clock frequency. The clocks being used on either side of the clock boundary 8 may be switched and have a variable relationship therebetween. Multiple synchronisation paths are provided within pointer synchronising circuitry 32 which are used depending upon the particular relationship between the clocks on either side of the clock boundary 8. A pre-switch pointer value is held in a transition register 44 until a post-switch pointer value is available from the new synchronising path 36 when a switch in clock mode is made which requires an increase in synchronisation delay.

Owner:ARM LTD

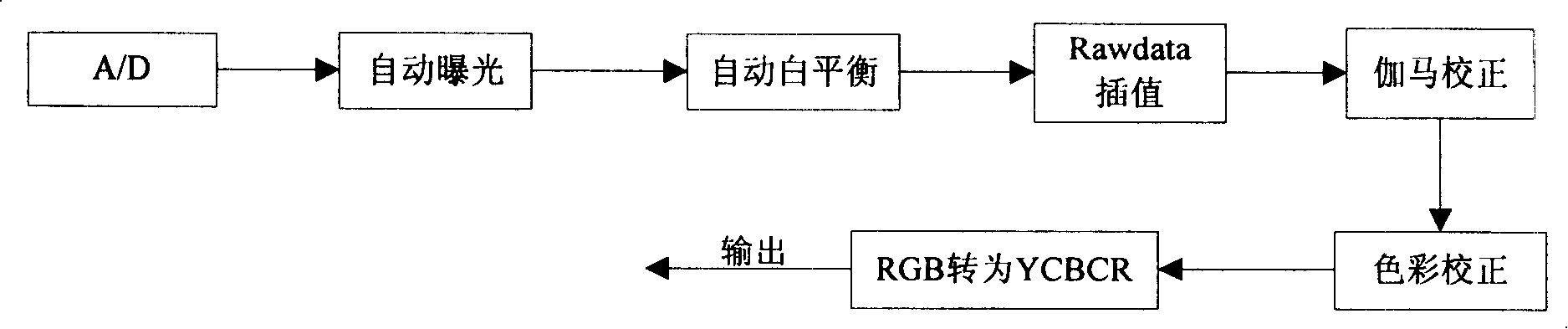

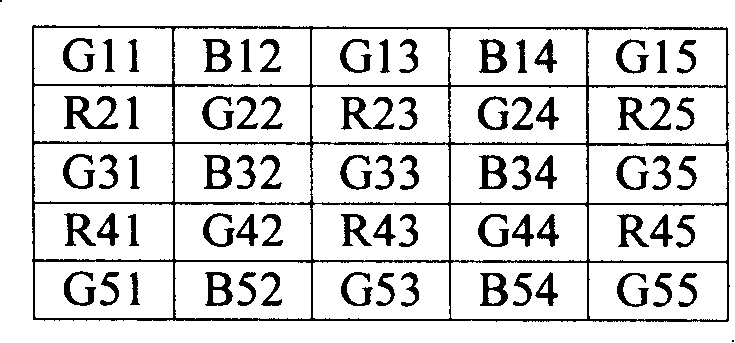

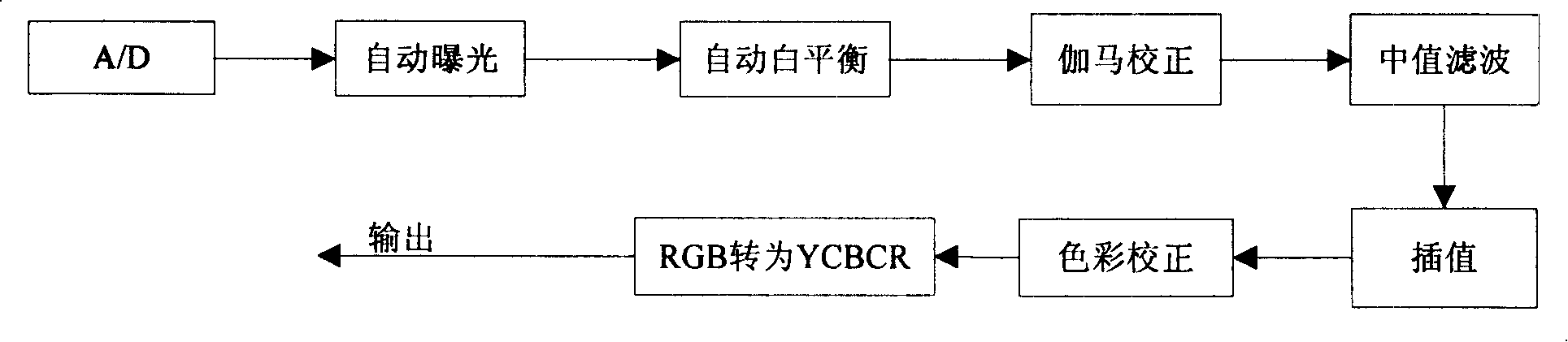

Image processing device and method for image sensor

InactiveCN101193314AQuality improvementReduce hardware overheadColor signal processing circuitsPicture signal generatorsSignal-to-noise ratio (imaging)Imaging processing

The invention provides a device for processing the image of an image sensor and a method thereof. The device mainly includes a gamma correction module, a median filter module and an interpolation module. The method mainly includes the following steps: image data of red, green or blue channels collected by the image sensor is processed by means of nonlinear transforming; according to the magnitude of signal-to-noise ratio of the image data processed by nonlinear transforming, the image data is processed by corresponding median filtering; and the image data of the red, green or blue channels processed by the median filtering is processed by means of interpolatory calculation to obtain the image data of the red, green, blue three channels and the obtained image data is outputted. By using the invention, hardware overhead of the image sensor can be saved and the signal-to-noise ratio of image output of the image sensor can be improved.

Owner:BEIJING SUPERPIX MICRO TECHNOLOGY CO LTD

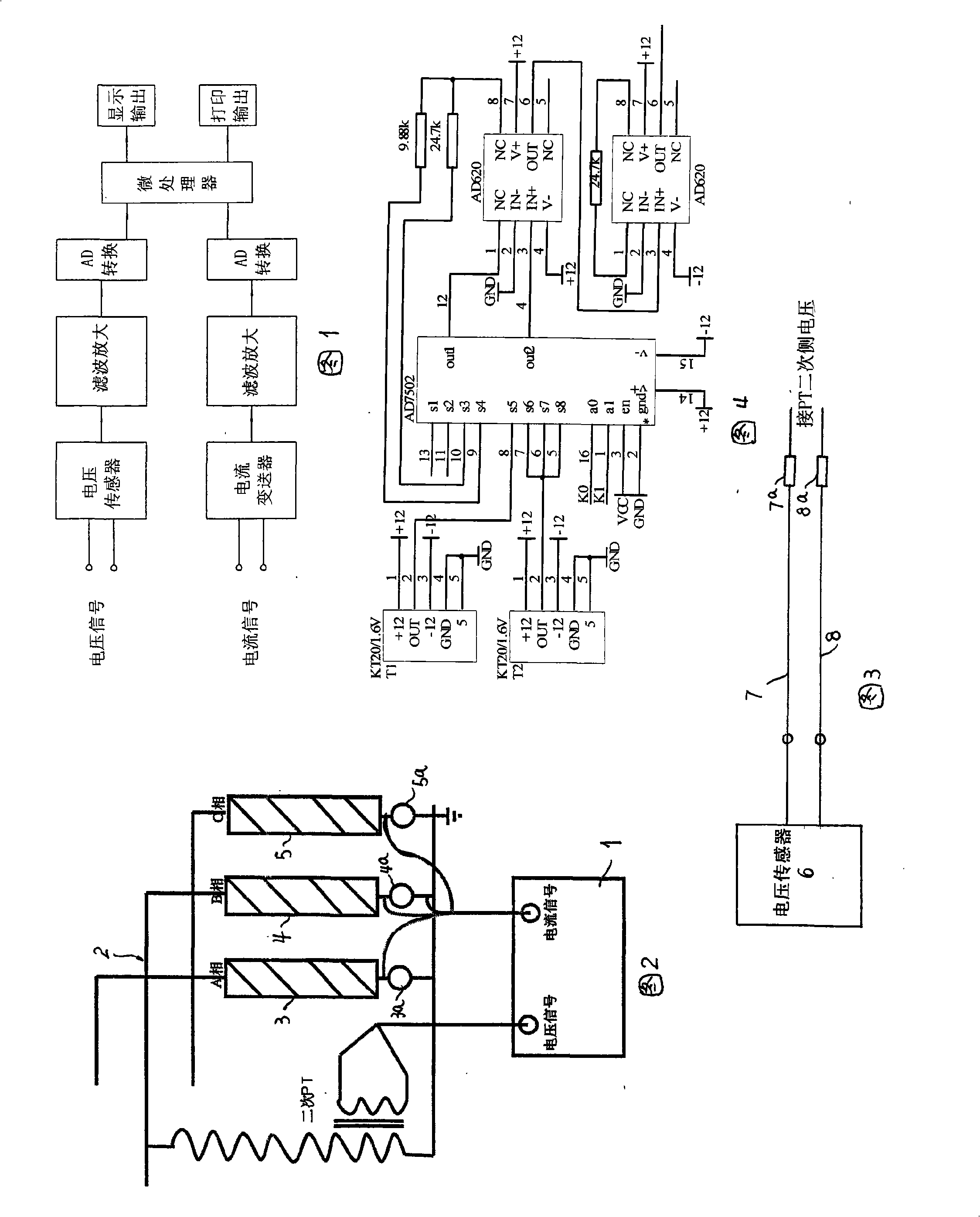

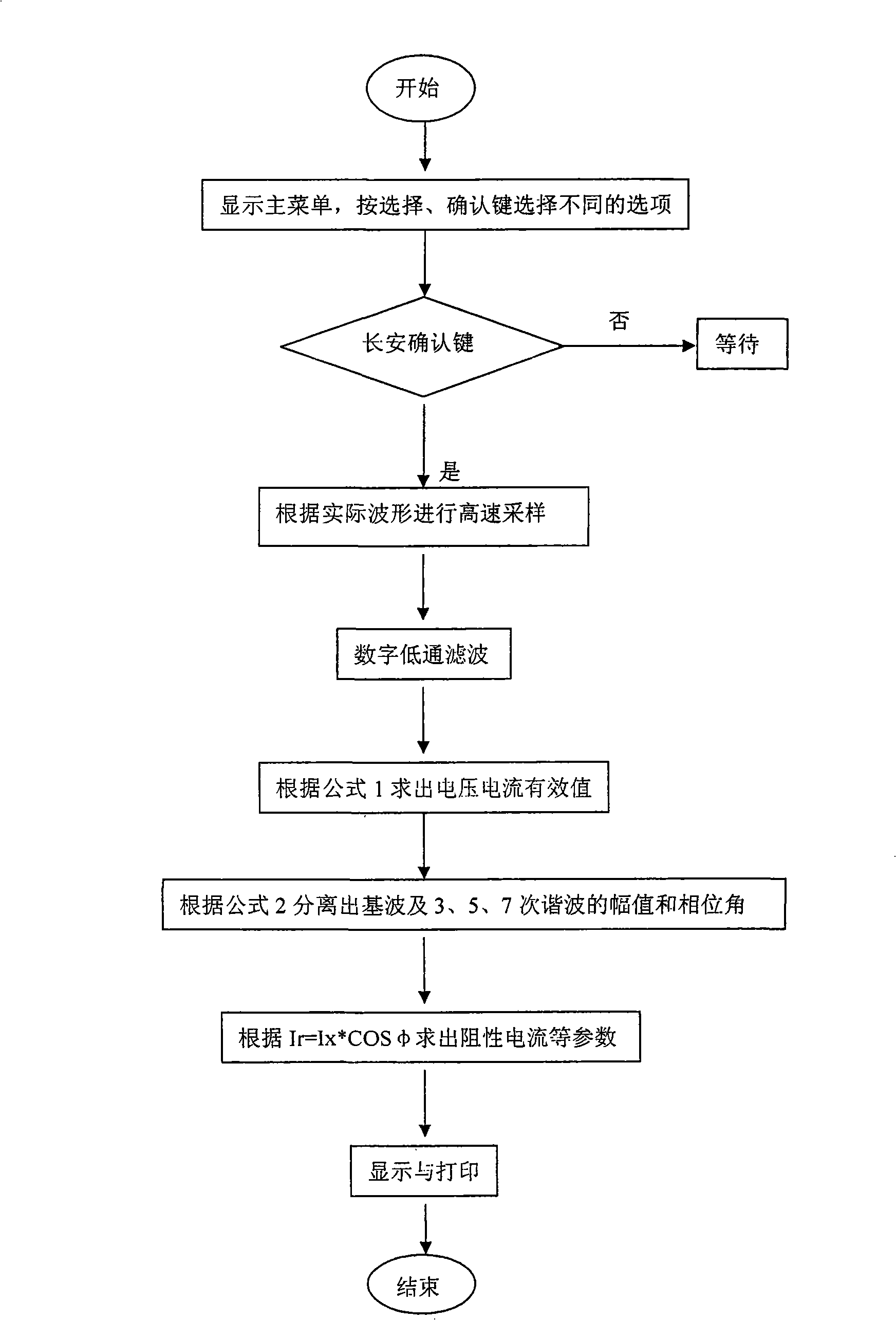

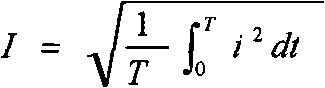

Resistive current tester for great current zinc oxide lightning arrester

ActiveCN101403777AReduce hardware overheadReliable equipmentElectrical testingMeasurement using digital techniquesVoltage sensorZinc

The invention provides a large-current ZnO arrester resistant current testing instrument, comprising a digital signal processor. A voltage channel is formed by the sequential cascading of a voltage sensor, a filter amplification circuit and an AD converter, a voltage signal is led out from a PT secondaly side by a voltage testing wire and is transmitted to the digital signal processor after processing; a current passage is formed by the sequential cascading of a current transmitter, a filter amplification circuit and an AD converter, a current signal is taken out from a discharging counter at the lower end of the arrester and is transmitted the current signal to the digital signal processor after processing. The current testing instrument has the advantages of high testing precision, convenient usage and safety and reliability.

Owner:STATE GRID SICHUAN ELECTRIC POWER CORP ELECTRIC POWER RES INST +2

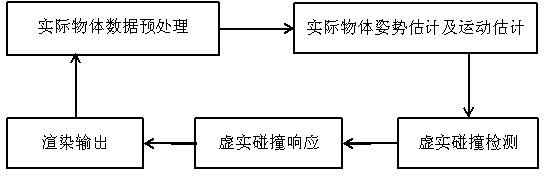

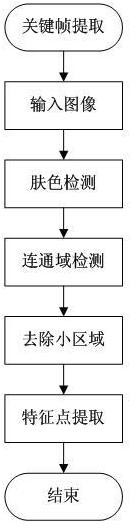

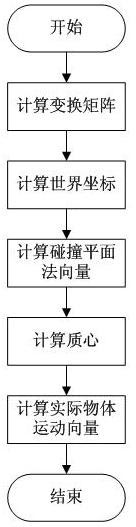

Method for detecting and responding false-true collision based on augmented reality

InactiveCN102194248ASmall amount of calculationReduce hardware overhead3D-image rendering3D modellingCharacteristic pointCollision response

The invention discloses a method for detecting and responding false-true collision based on augmented reality, which comprises the following steps: 1) preprocessing an actual object acquired by a camera; 2) performing posture estimation and motion estimation on the actual object; 3) performing the false-true collision detection according to a position relationship between a mass center of a virtual object and a collision plane; 4) responding to the false-true collision according to a detection result; and 5) modifying an virtual image, rendering and outputting the virtual image. According to the method, a relative true three-dimensional false-true collision response effect can be achieved by using the three-dimensional collision detection method for only calculating four characteristic points of the actual object. The calculation complexity is low. The monocular vision three-dimensional false-true collision detection and response are realized.

Owner:SHANGHAI UNIV

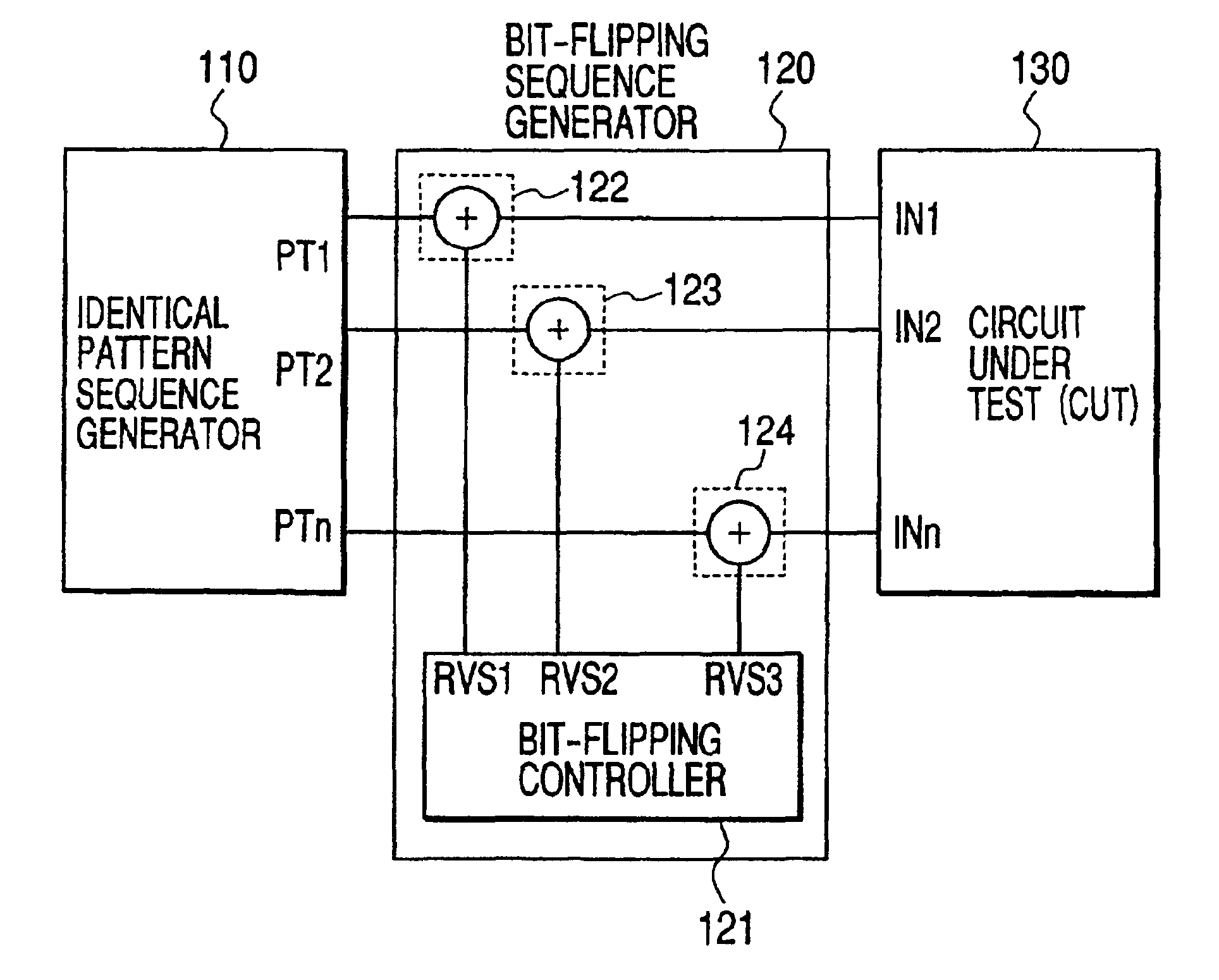

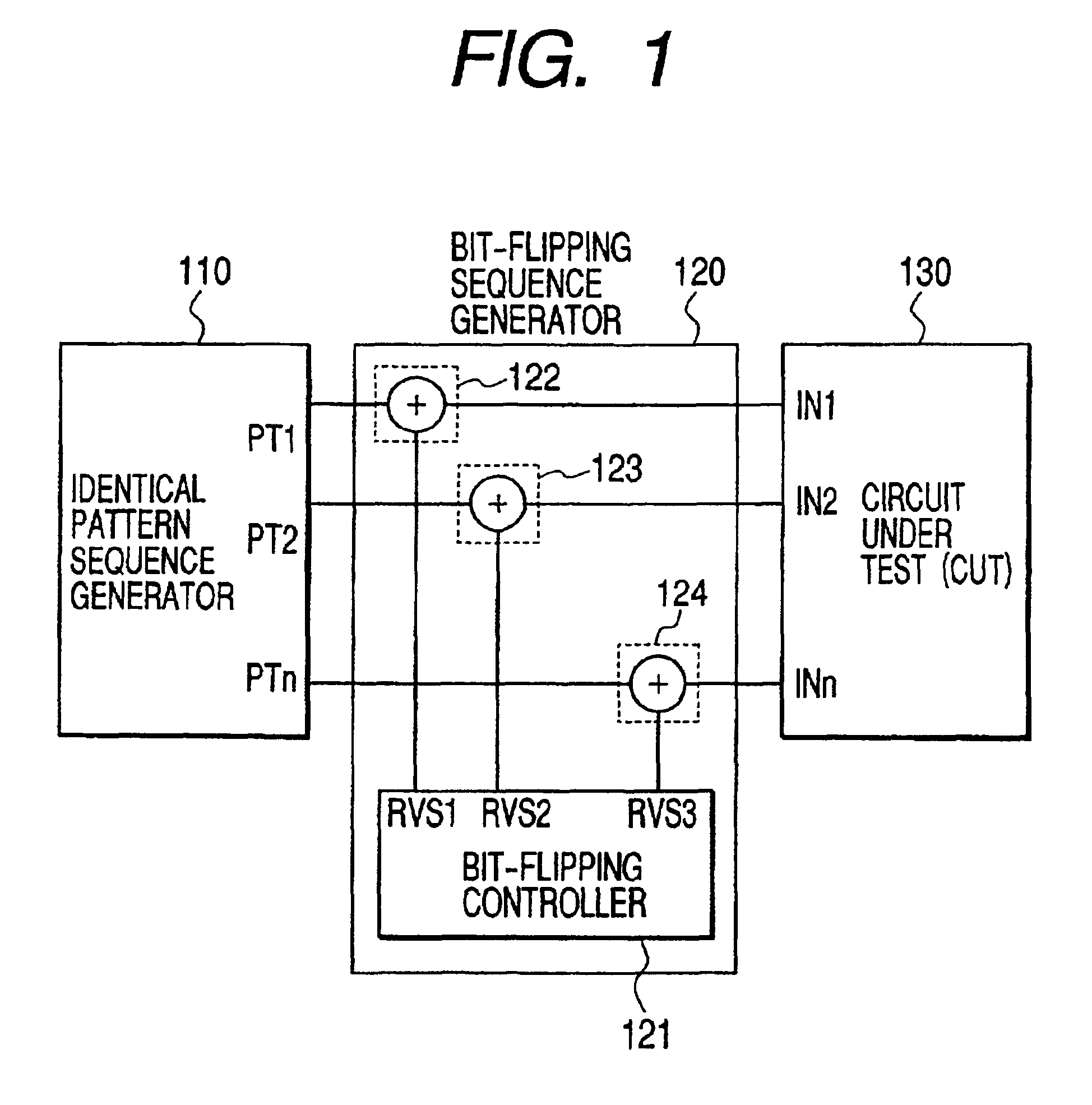

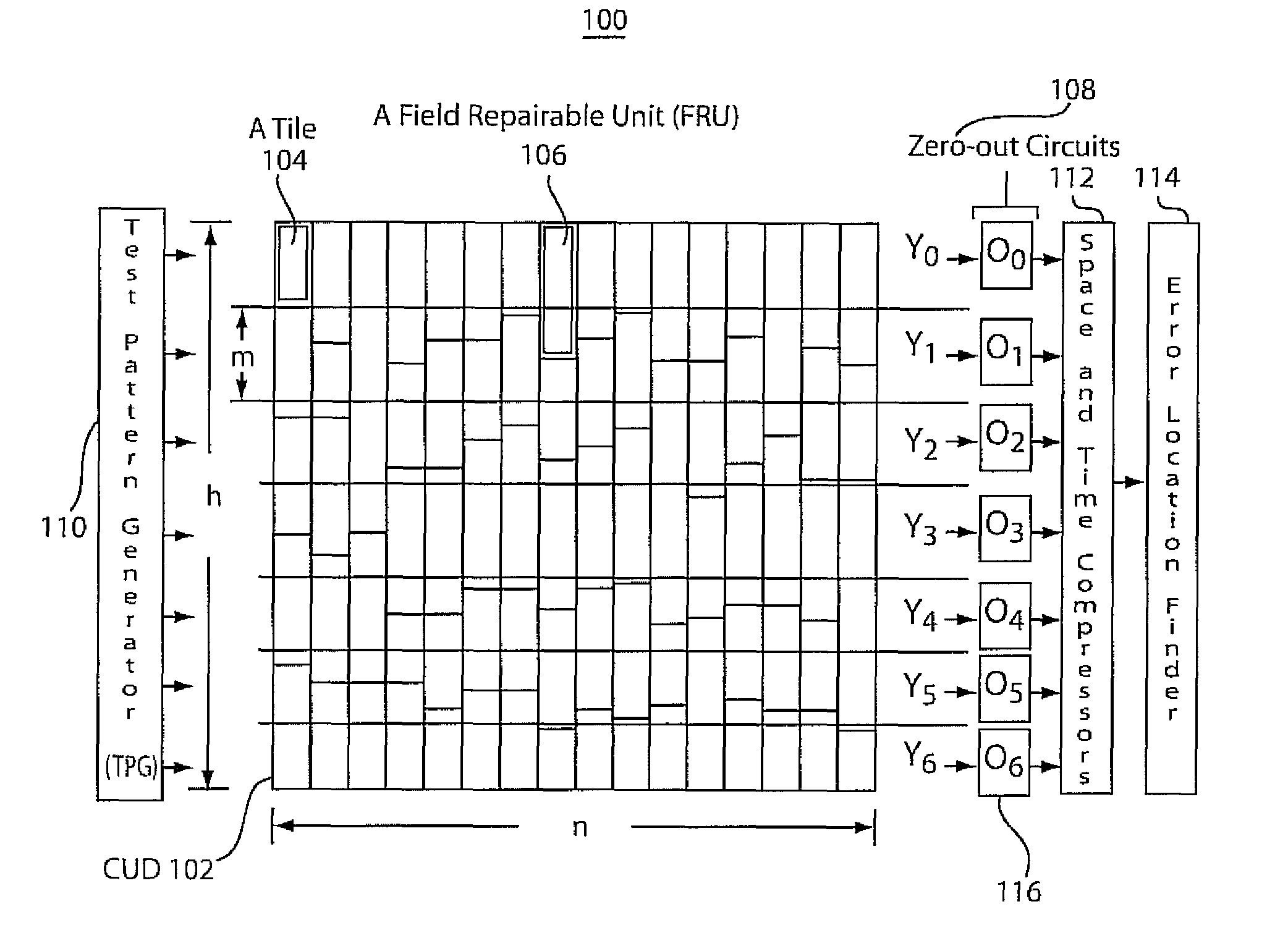

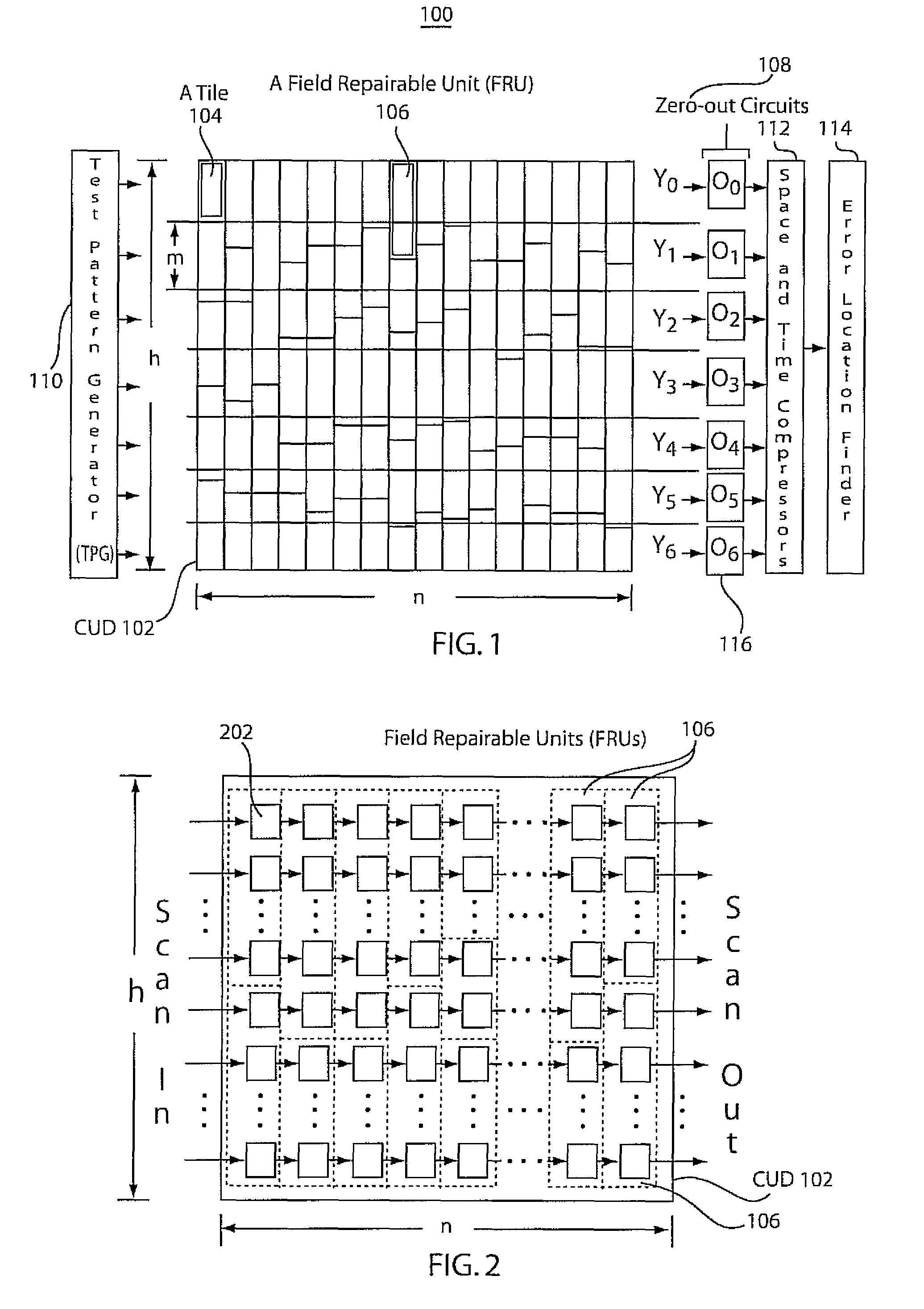

Test method of semiconductor intergrated circuit and test pattern generator

InactiveUS6922803B2Avoid problemsEliminate overheadElectronic circuit testingDetecting faulty computer hardwareFault coverageGraphics

A semiconductor integrated circuit test method which reduces the required data volume for testing and efficiently detects faults in a circuit to be tested, the method comprising means 110 to generate identical pattern sequences repeatedly and means 120 to control flipped bits in pattern sequences, in order to generate neighborhood pattern sequences and use the neighborhood patterns to test the circuit under test 130. The neighborhood patterns include, in whole or in part, such pattern sequences as ones without flipped bits, ones with all or some flipped bits in one pattern and ones with all or some flipped bits in consecutive patterns or patterns at regular intervals, the interval being equivalent to a given number of patterns. Because a test pattern generator is provided independently of the circuit to be tested, the problem of a prolonged design period can be eliminated, a loss in the operating speed of the circuit under test is minimized and a high fault coverage can be achieved with less hardware overhead and a smaller volume of test data.

Owner:HITACHI LTD

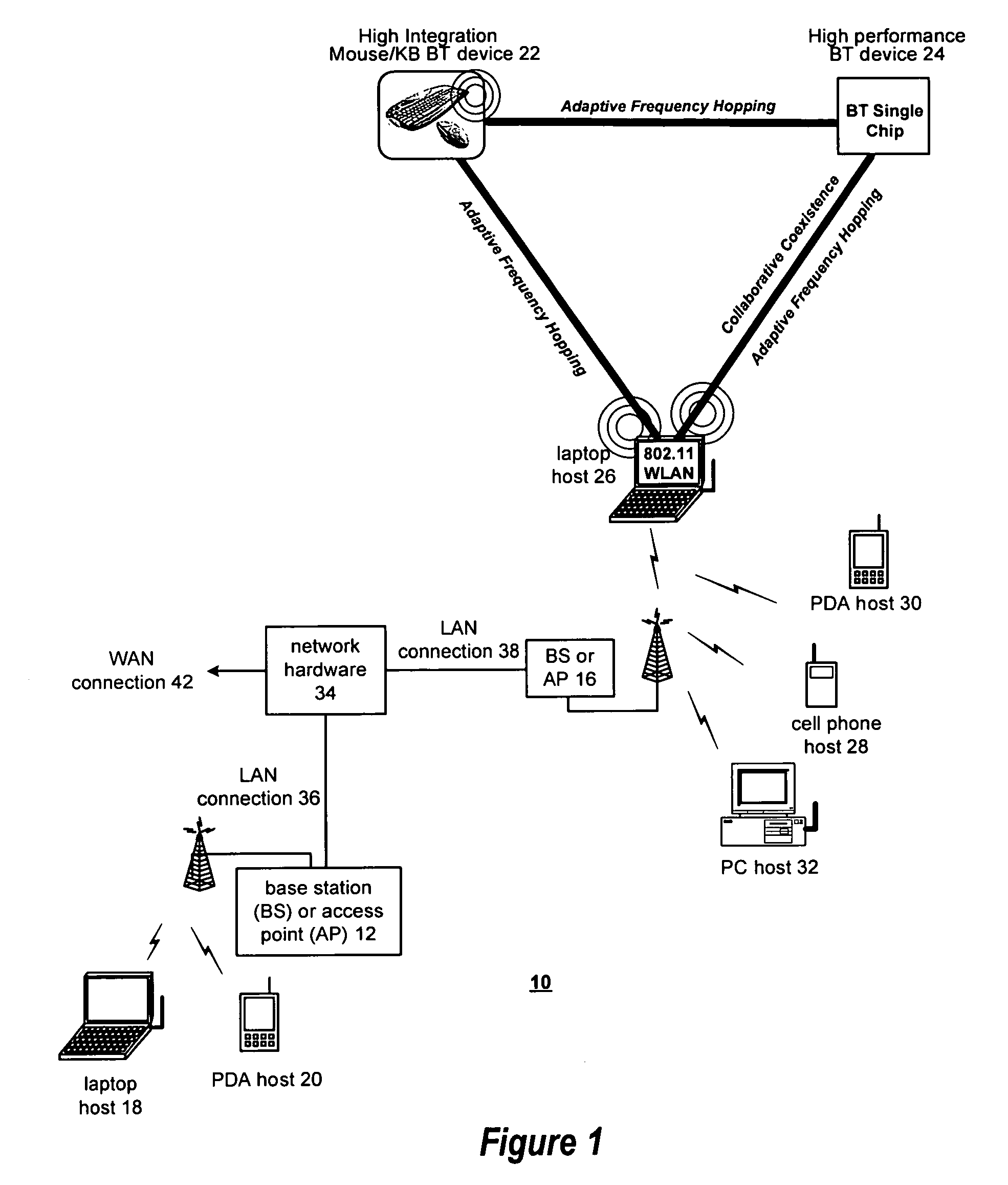

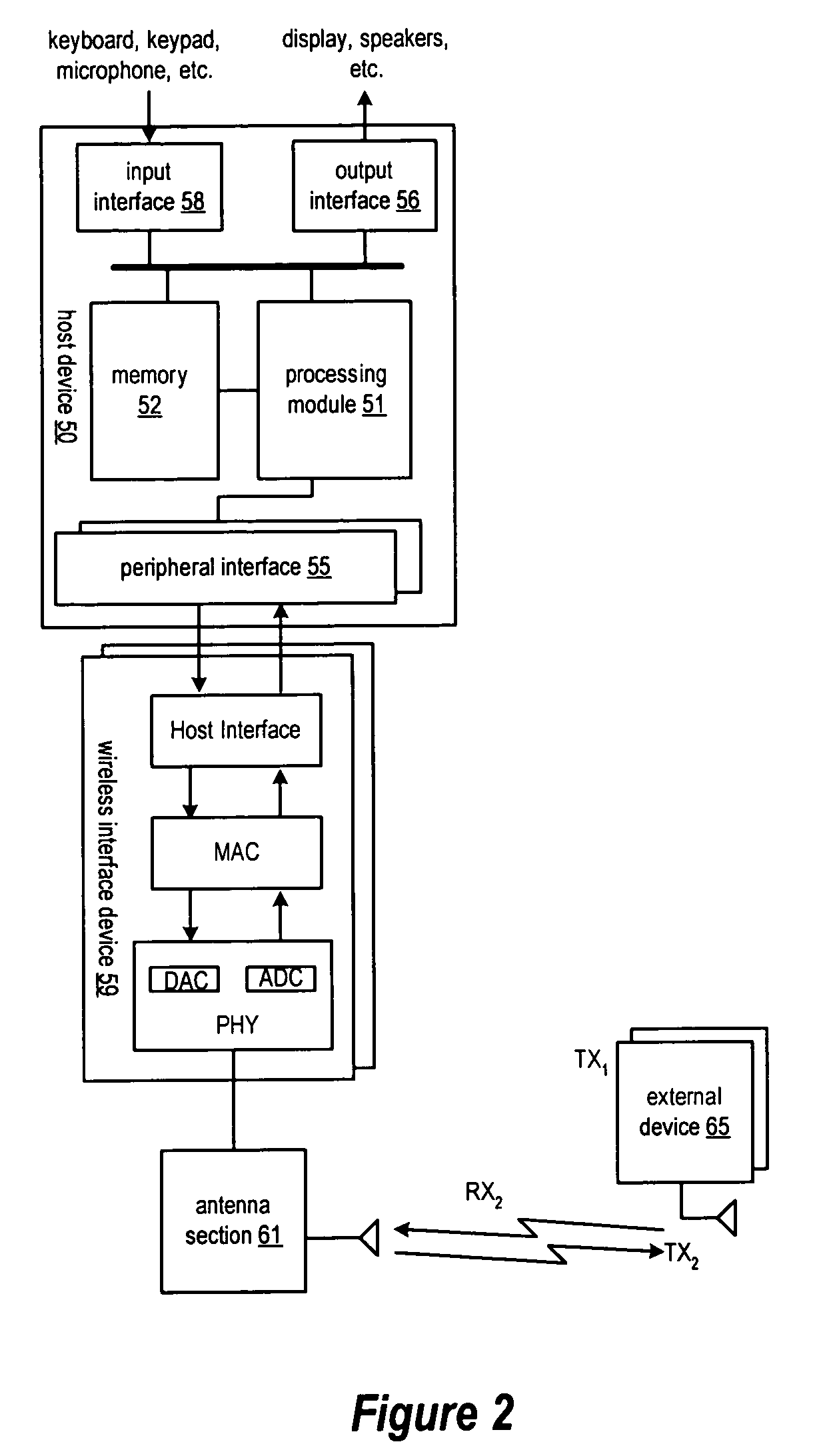

MAC controlled sleep mode/wake-up mode with staged wake-up for power management

ActiveUS7583985B2Fast power onEfficiently reactivatedEnergy efficient ICTPower managementCMOSEngineering

A power management scheme for a wireless communications device processor substantially implemented on a single CMOS integrated circuit is described. By incorporating controls for sleep and wake-up mode transitions in the processor's control logic, improved power savings with reduced latency is provided, obviating the need for hardware-focused solutions with elaborate signaling mechanisms. A fully integrated power management with staged wake-up operations controlled by the MAC solution consumes less power than the conventional wireless LAN solutions in standby mode.

Owner:AVAGO TECH INT SALES PTE LTD

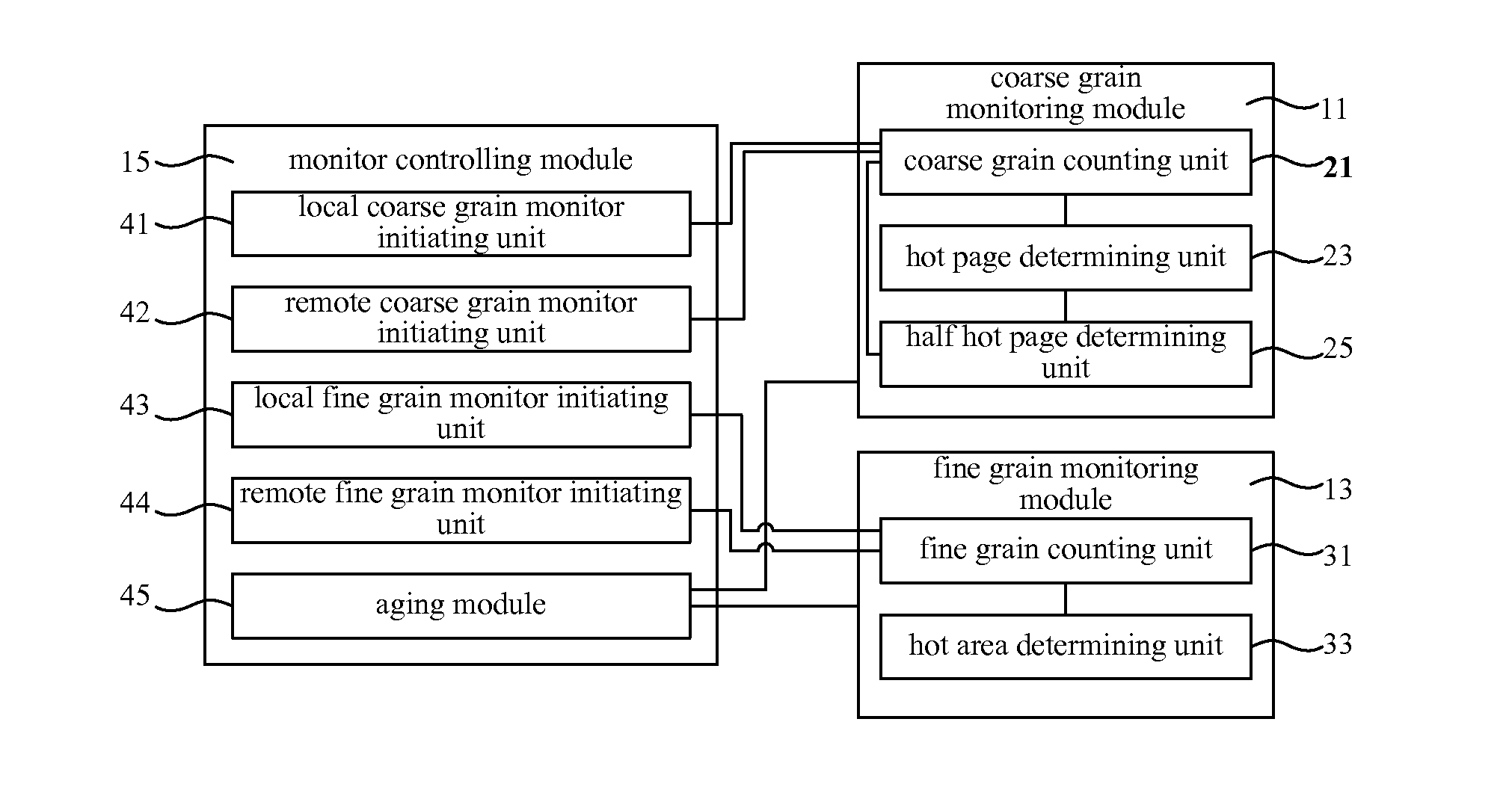

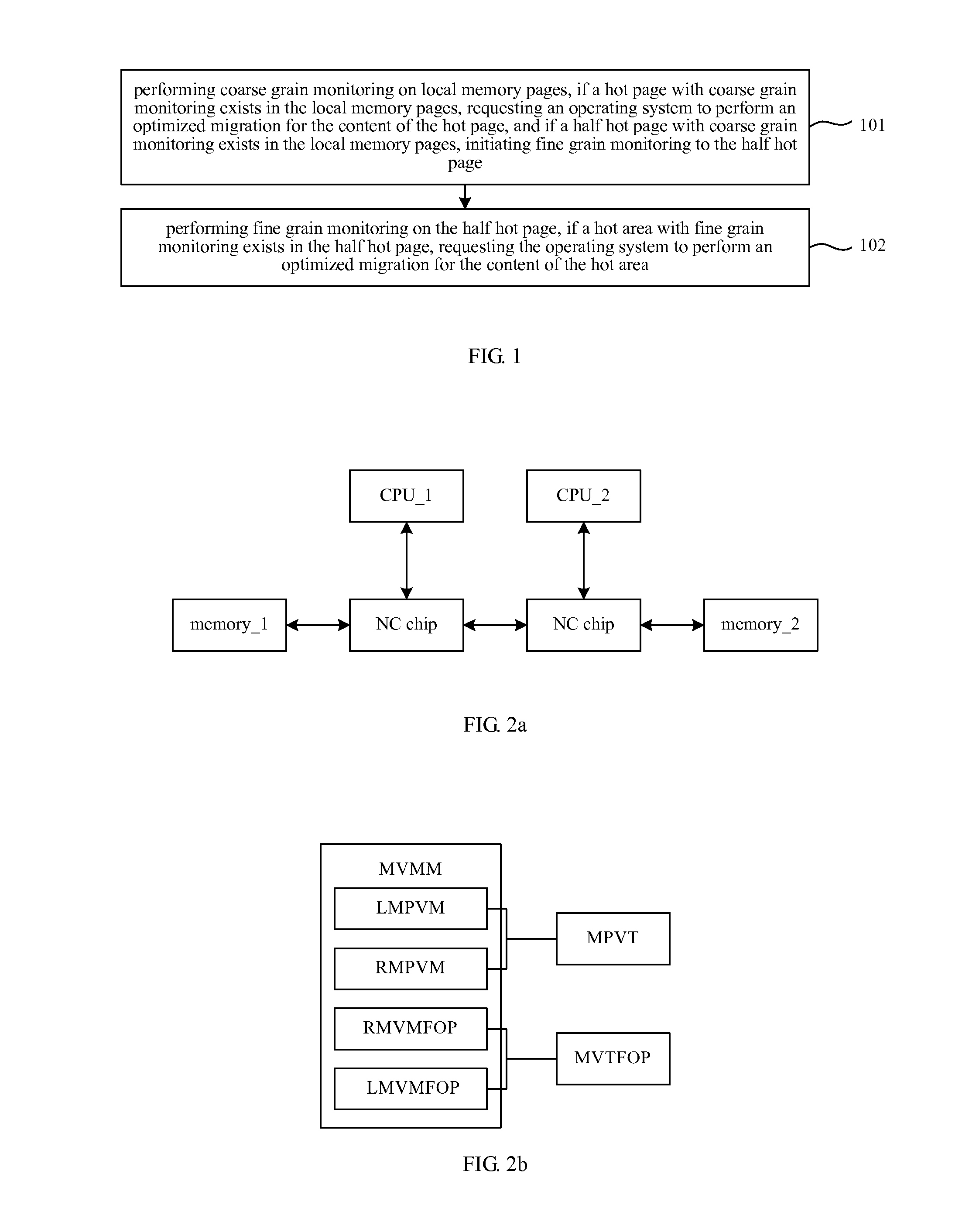

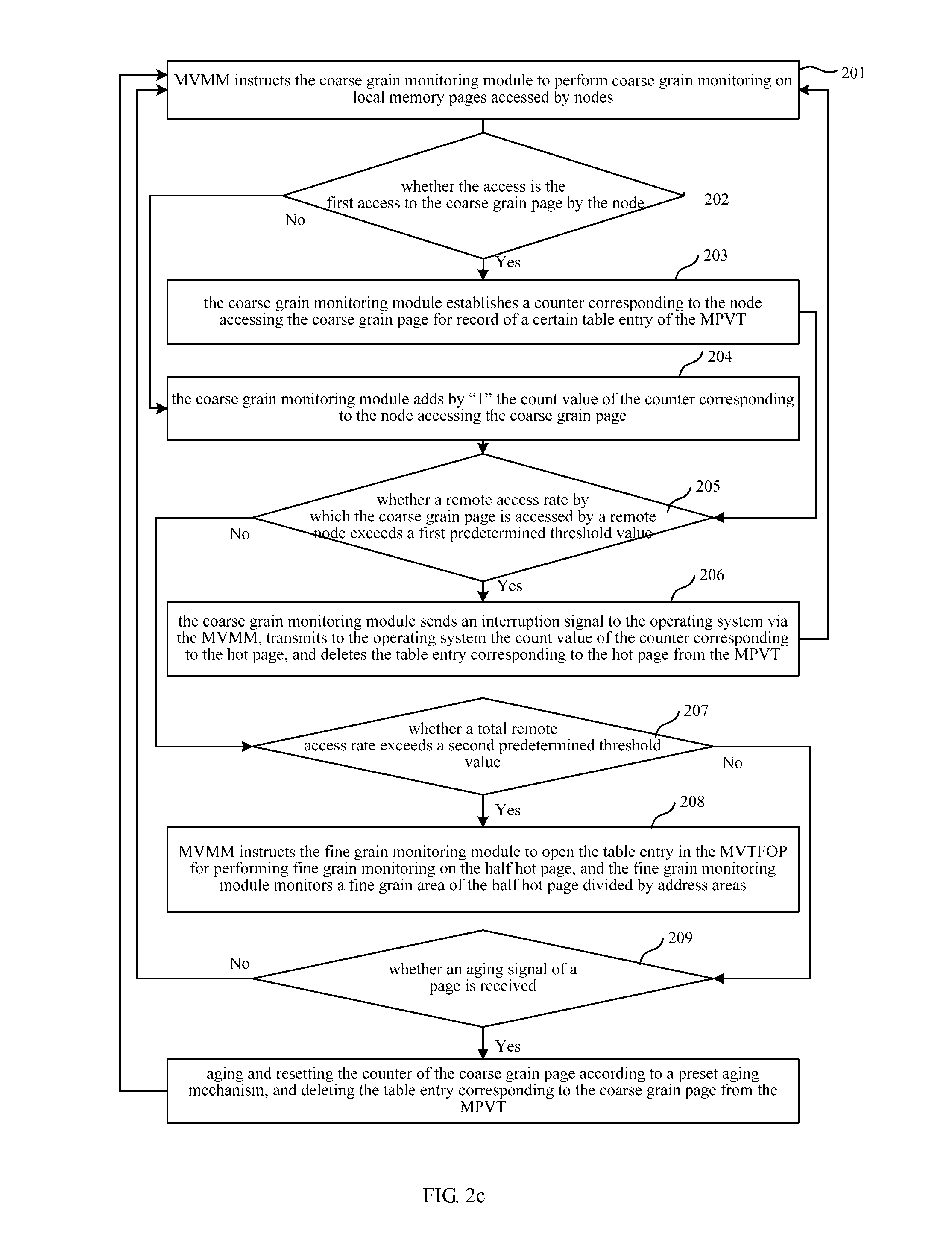

Memory access monitoring method and device

ActiveUS20120272029A1Reduce in quantityReduce hardware overheadMemory architecture accessing/allocationError detection/correctionOperational systemMonitoring methods

A memory access monitoring method and a memory access monitoring method device are disclosed, The method comprises: performing coarse grain monitoring on local memory pages, if a hot page with coarse grain monitoring exists in the local memory pages, requesting an operating system to perform an optimized migration for the content of the hot page, and if a half hot page with coarse grain monitoring exists in the local memory pages, initiating fine grain monitoring to the half hot page; and performing fine grain monitoring on the half hot page, if a hot area with fine grain monitoring exists in the half hot page, requesting the operating system to perform an optimized migration for the content of the hot area.

Owner:HUAWEI TECH CO LTD

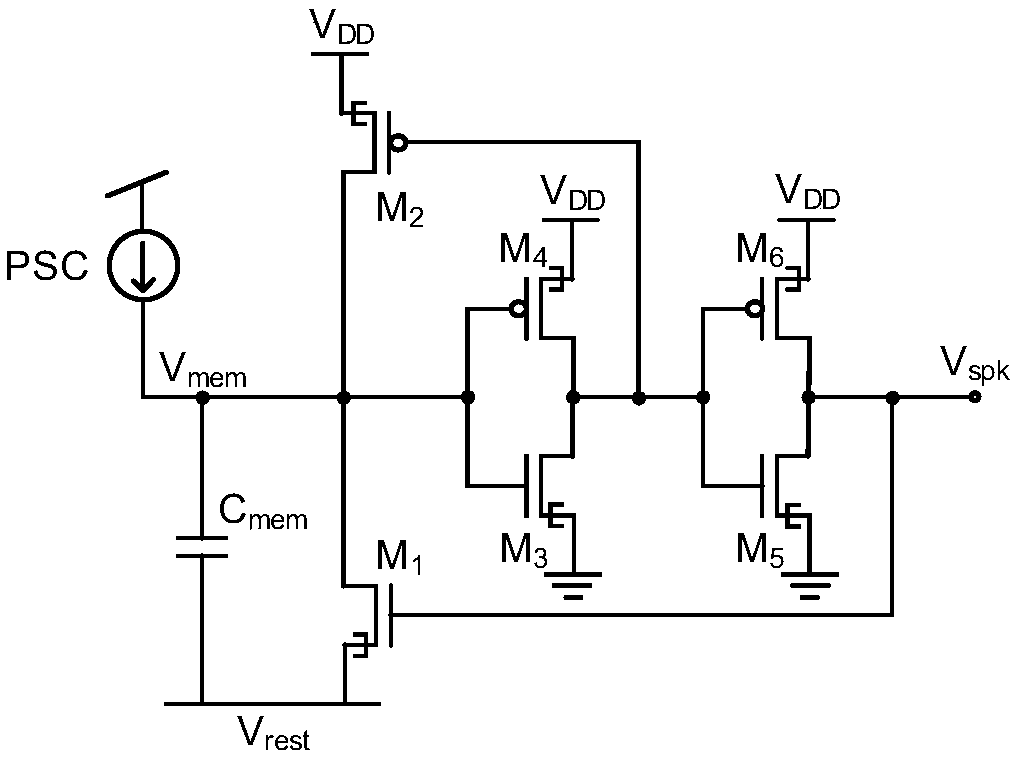

Pulse neuron circuit based on tunneling field effect transistor

ActiveCN108880529AReduce hardware overheadReduce short-circuit energy consumptionPhysical realisationLogic circuitsCapacitanceNeuron

The invention provides a pulse neuron circuit based on a tunneling field effect transistor, and belongs to the technical field of pulse neuron in neuromorphic calculation. The circuit comprises a capacitor, a leakage and reset tube, a positive feedback tube, and two stages of inverters connected in series, wherein the capacitor is used for simulating the cytomembrane capacitance of a biological neuron and accumulating charges caused by the input post-synaptic current; the leakage and reset tube is an N type TFET device that provides a leakage and reset path for the charges accumulated on the capacitor; the positive feedback tube is a P type TFET device that supplements charges for the capacitor when the input of a first stage of inverter approaches to a logic threshold level thereof; and the two stages of inverters connected in series are composed of complementary TFETs for amplifying the voltage change at an input end. Compared with the implementation mode based on the traditional MOSFET, the pulse neuron circuit provided by the invention has lower hardware overhead, and can effectively reduce the short circuit energy consumption every time when the circuit releases the pulse, sothat the circuit has higher energy efficiency.

Owner:PEKING UNIV

Synchronising between clock domains

ActiveUS8301932B2Lower latencyLittle latencyGenerating/distributing signalsTransmission path multiple useProcessor registerClock rate

An integrated circuit 2 is provided with multiple clock domains separated by a clock boundary 8. Data values are passed across the clock boundary 8 using a first-in-first-out memory (FIFO), a read pointer and a write pointer for the FIFO are passed across the clock boundary 8 and must be synchronized to the receiving clock frequency. The clocks being used on either side of the clock boundary 8 may be switched and have a variable relationship therebetween. Multiple synchronization paths are provided within pointer synchronizing circuitry 32 which are used depending upon the particular relationship between the clocks on either side of the clock boundary 8. A pre-switch pointer value is held in a transition register 44 until a post-switch pointer value is available from the new synchronizing path 36 when a switch in clock mode is made which requires an increase in synchronization delay.

Owner:ARM LTD

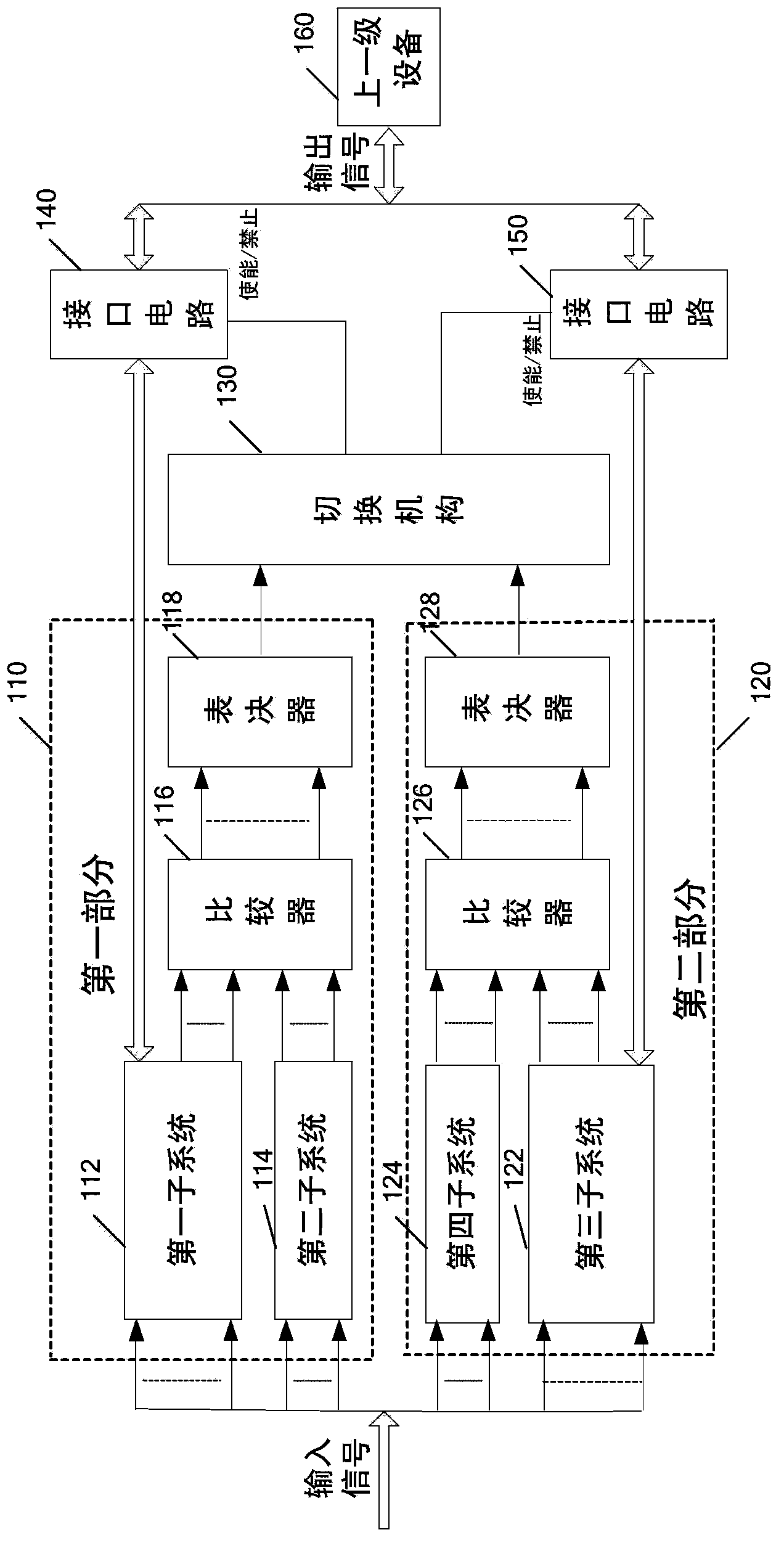

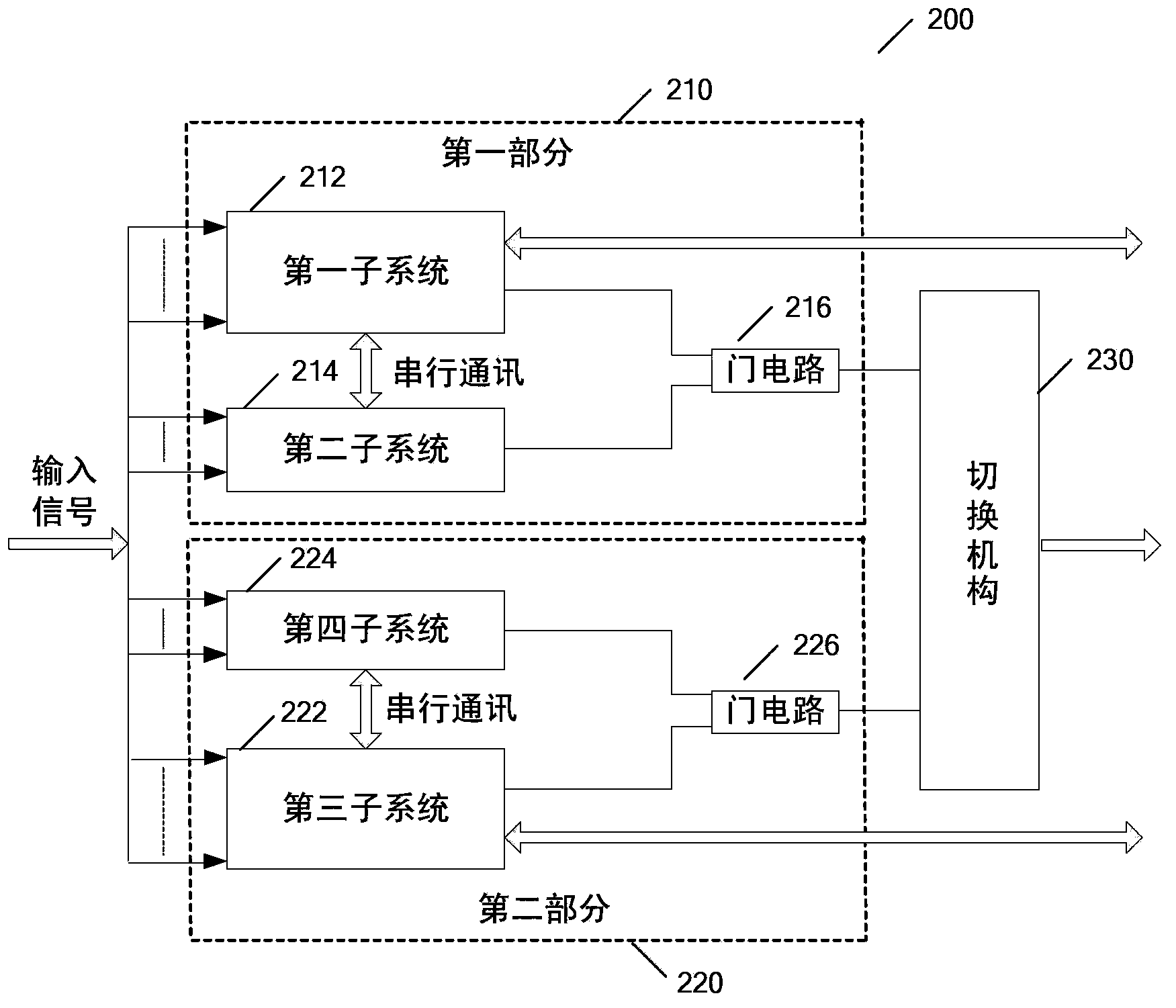

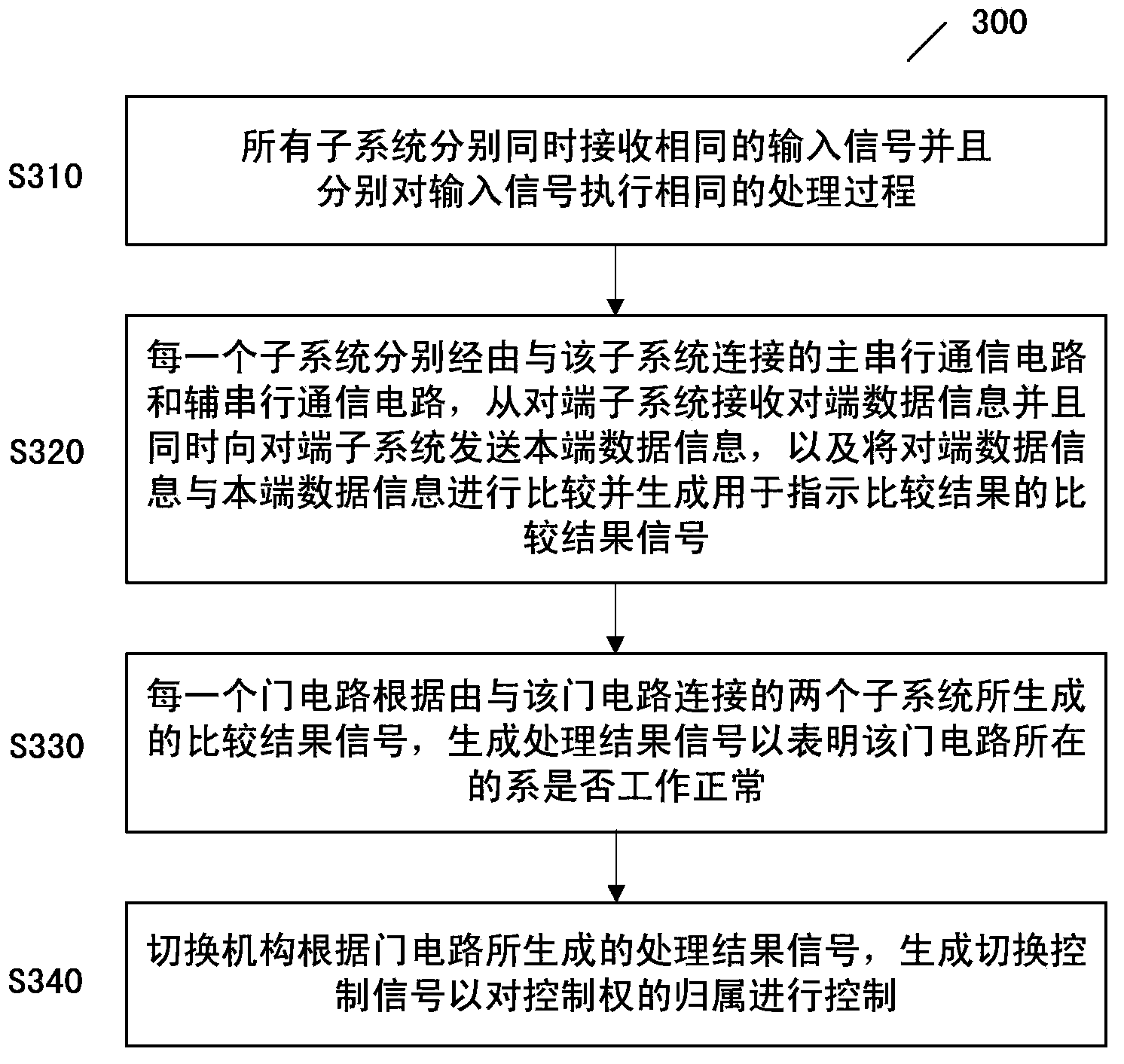

Double 2-vote-2 redundant system and method

ActiveCN103678031AReduce hardware overheadLow costRedundant operation error correctionData informationSystems design

The invention provides a double 2-vote-2 redundant system and method. The system comprises a first part, a second part and a switching mechanism, wherein the first part comprises a first subsystem, a second subsystem and a first gate circuit, the first subsystem and the second subsystem are connected through a first main serial communication circuit and a first auxiliary serial communication circuit, the second part comprises a third subsystem, a fourth subsystem and a second gate circuit, and the third subsystem and the fourth subsystem are connected through a second main serial communication circuit and a second auxiliary serial communication circuit; all the subsystems receive the same input signal at the same time and conduct the same processing, each subsystem receives opposite-end data information from the corresponding subsystem at the opposite end through the corresponding main serial communication circuit and auxiliary serial communication circuit, sends local-end data information to the subsystem at the opposite end, and compares the opposite-end data information with the local-end data information and generates a comparison result signal, each gate circuit generates processing result signals according to the comparison result signals generated by the subsystems, and the switching mechanism generates switching control signals according to the processing result signals generated by the gate circuits. According to the double 2-vote-2 redundant system and method, more advanced double 2-vote-2 redundant system design is realized.

Owner:SIEMENS SIGNALLING

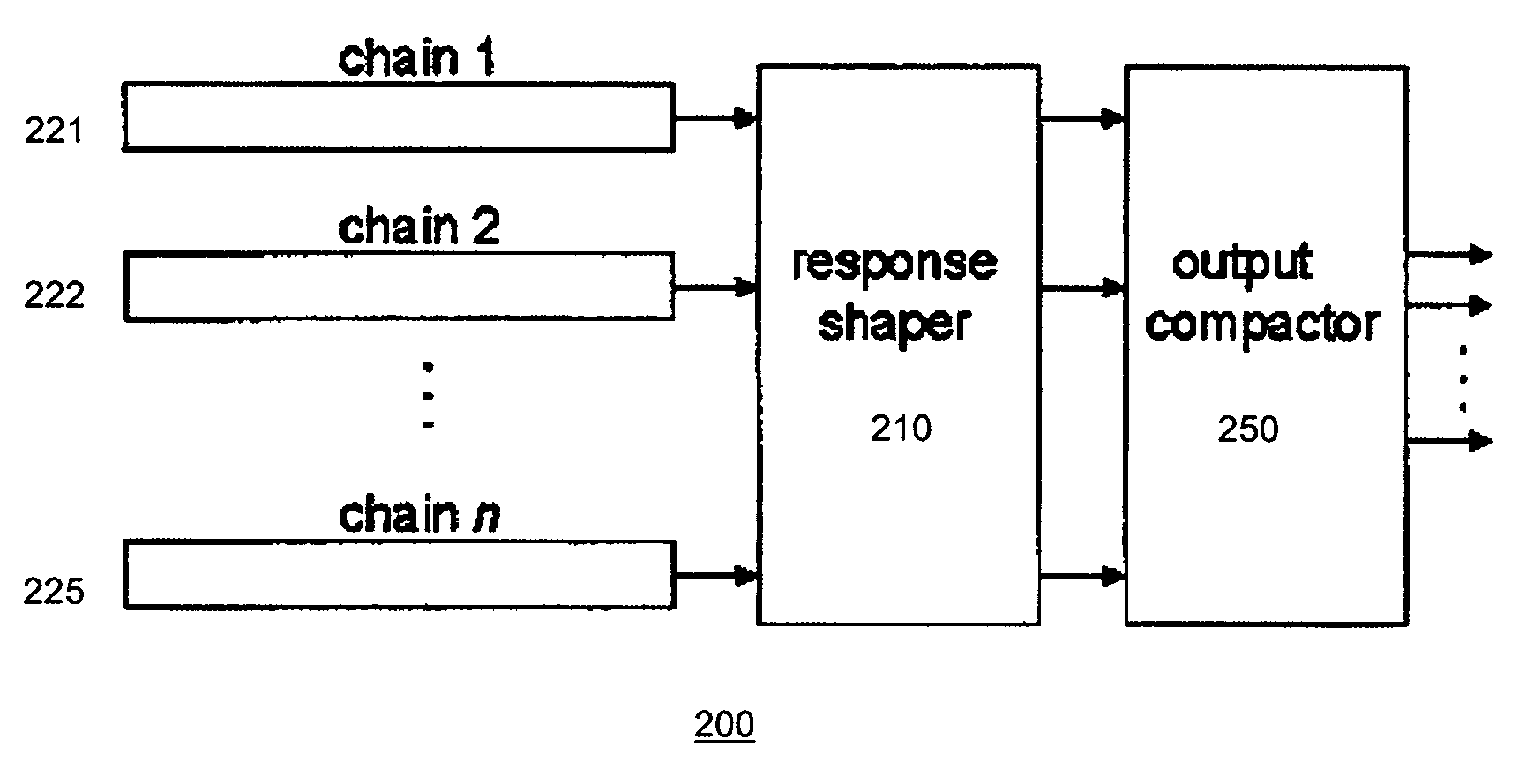

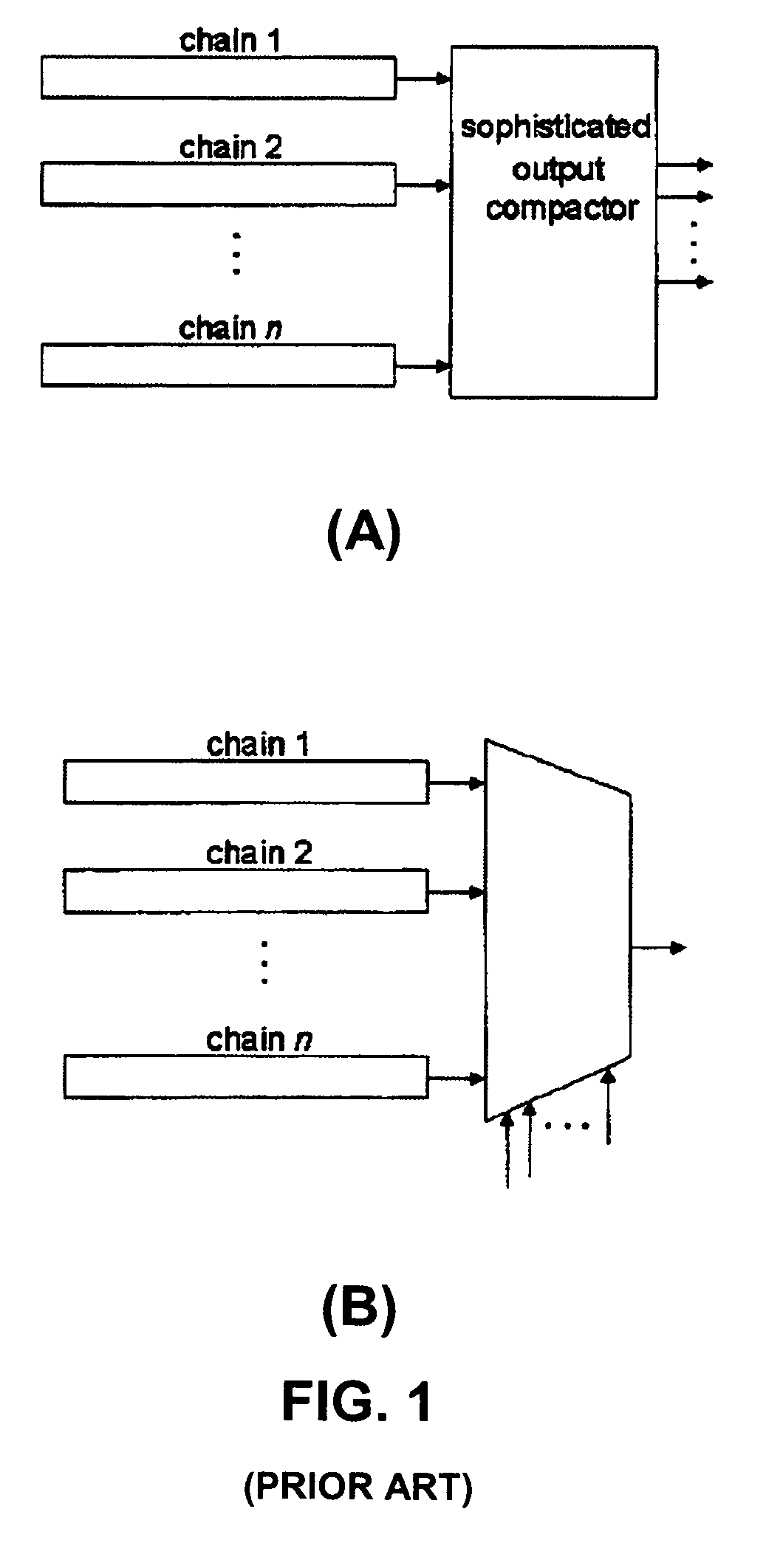

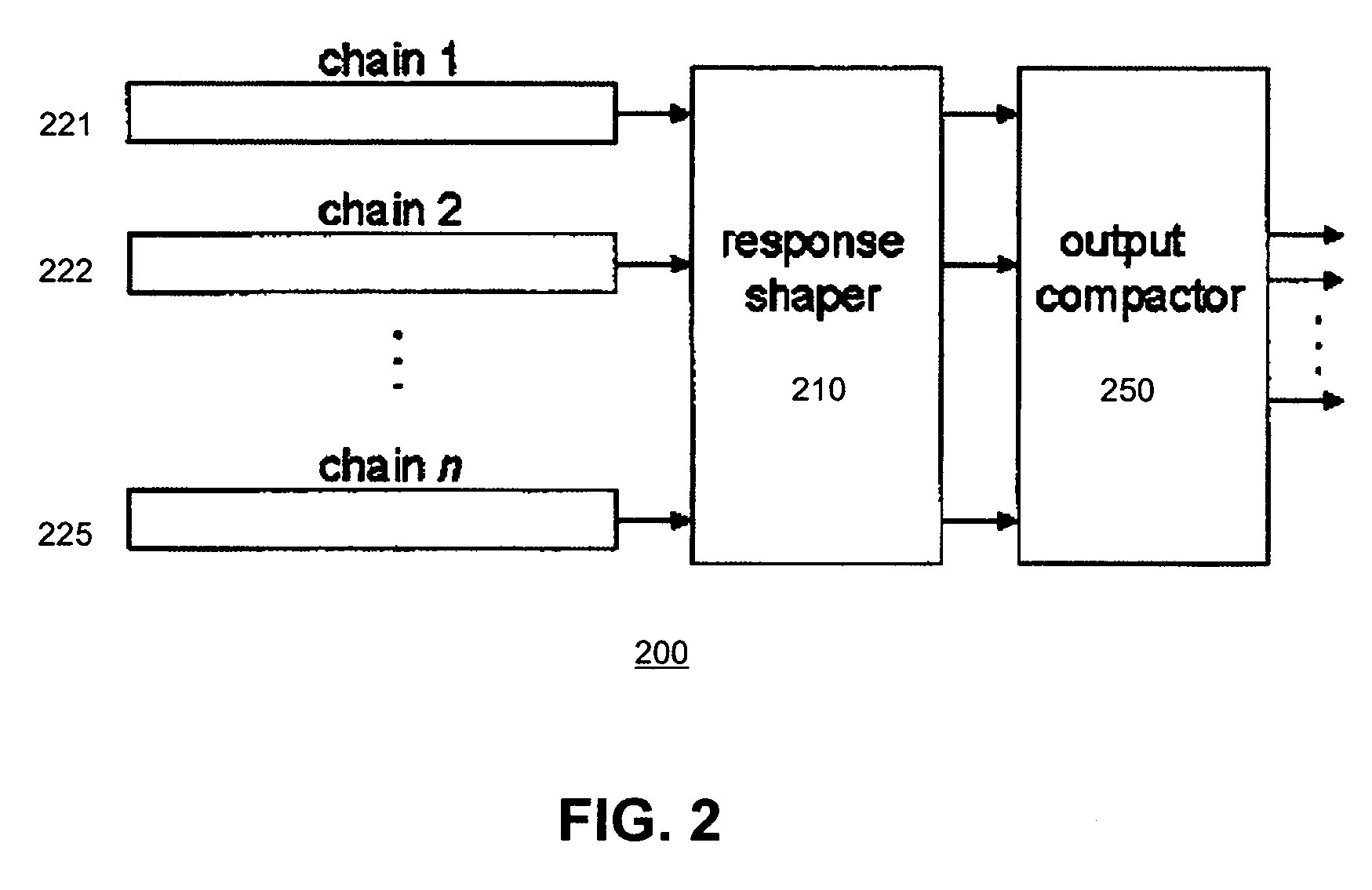

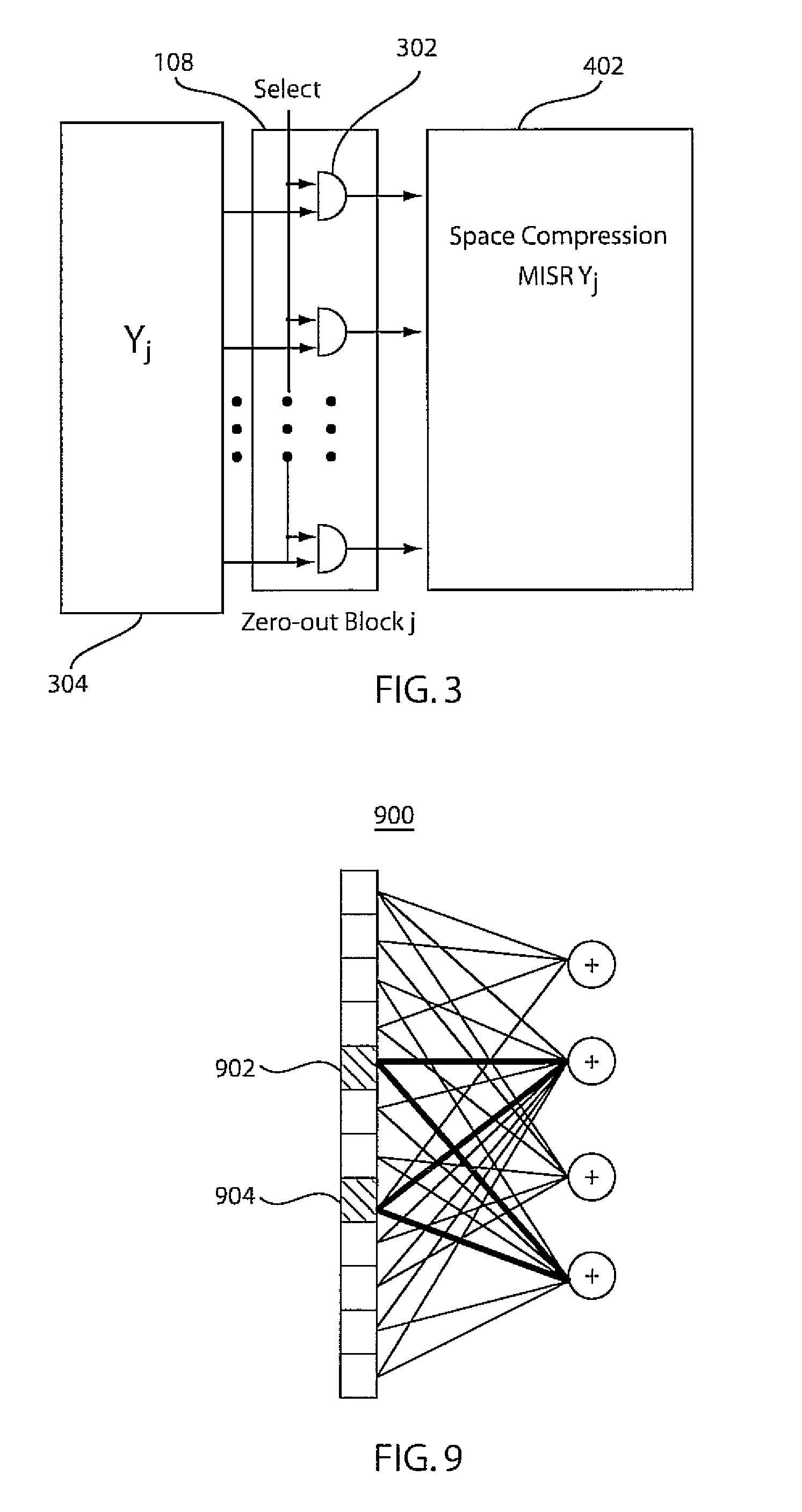

Test output compaction using response shaper

InactiveUS7222277B2Minimize maskingMinimizes such masking of faultsElectronic circuit testingEngineeringScan chain

A test output compaction architecture and method that takes advantage of a response shaper in order to minimize masking of faults during compaction. A response shaper is inserted between a plurality of scan chains and an output compactor. The response shaper receives output responses from scan chains and reshapes the output responses in a manner that minimizes masking of faults by the output compactor.

Owner:NEC CORP

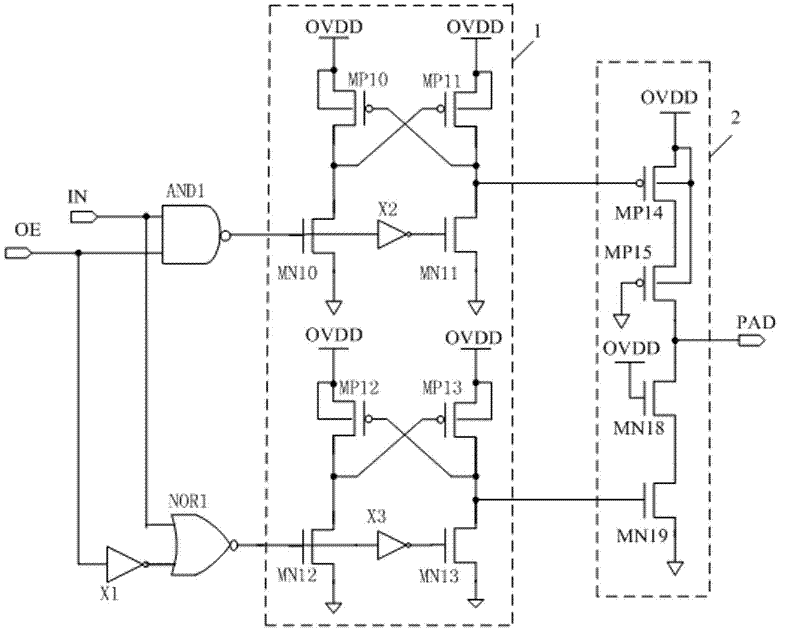

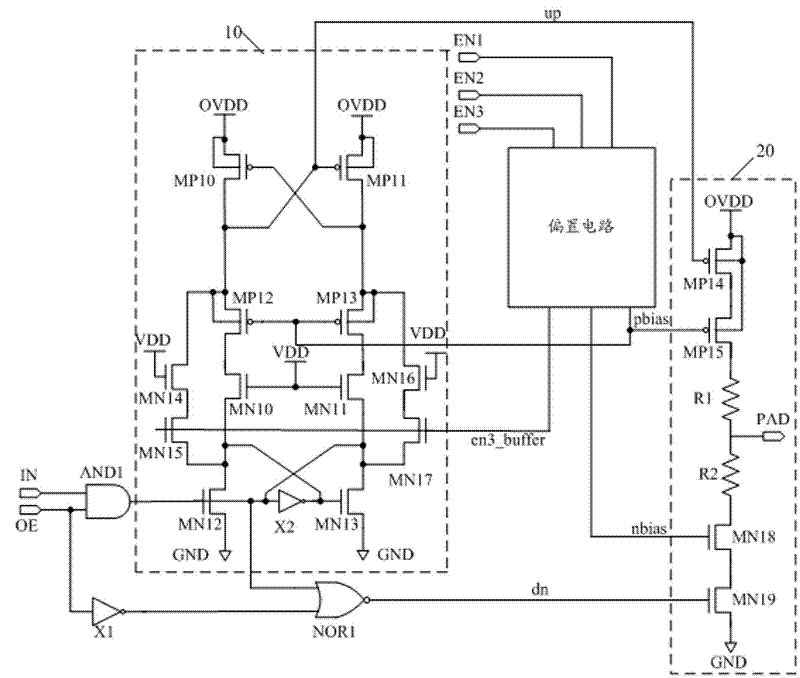

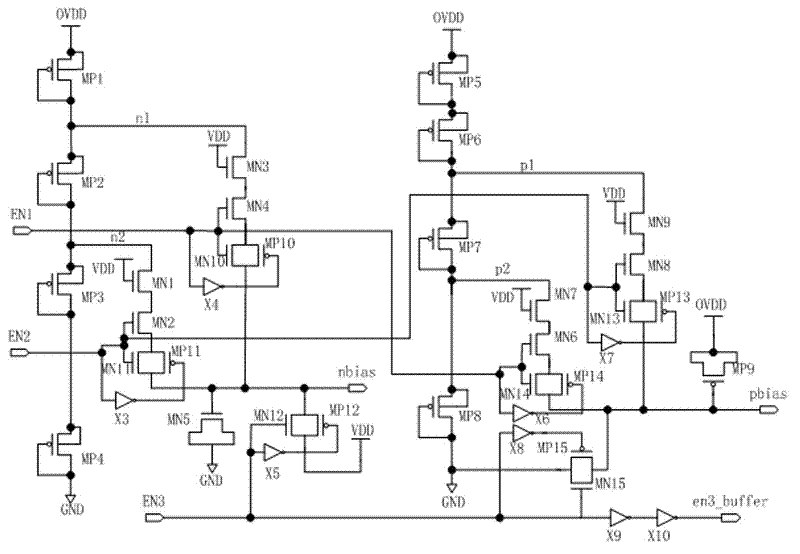

Input output (IO) interface output circuit in microprocessor

InactiveCN102521176AReduce hardware overheadReduce overheadElectric digital data processingInput/outputEngineering

The invention discloses an input output (IO) interface output circuit in a microprocessor, which comprises a level switch circuit used for converting a core power supply VDD in the microprocessor into an IO power supply OVDD with different voltage, a biasing circuit used for generating and outputing biasing signals pbias and nbias and a bypass enable signal and a driving circuit used connecting the biasing signal pbias and the biasing signal nbias. The level switch circuit comprises a switch network and a bypass circuit both connected with the core power supply VDD. The biasing signal pbias and the bypass enable signal are respectively output to the switch network and the bypass circuit, the switch network adapts to the IO power supply OVDD with different voltage by changing voltage of the biasing signal pbias, and the bypass enable signal controls connection of the bypass circuit when the IO power supply OVDD is equal to the core power supply VDD. The IO interface output circuit outputs the biasing signal pbias and nbias with different voltage through the biasing circuit, enables an IO circuit to have different driving capability and greatly saves hardware expense in design of the circuit.

Owner:SHENZHEN STATE MICROELECTRONICS CO LTD

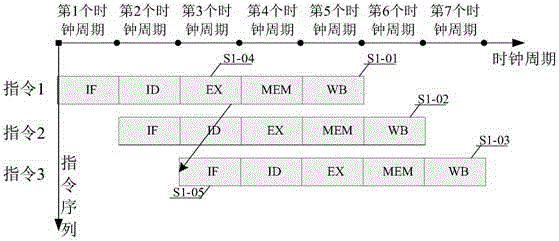

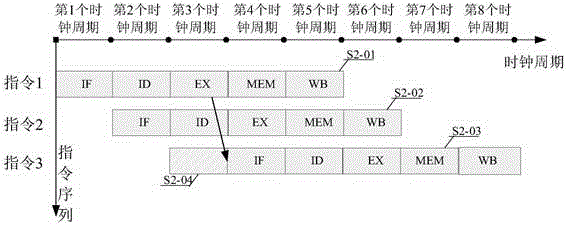

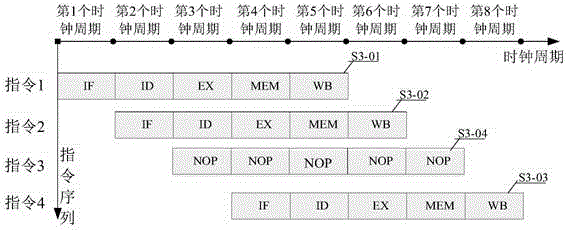

Method and device for realizing flow line of processing instructions and processor

ActiveCN105975252AImprove efficiencyReduce usageConcurrent instruction executionInstruction memoryParallel computing

The invention provides a method and a device for realizing a flow line of processing instructions and a processor. The flow line of the processing instructions comprises an instruction acquisition stage, a decoding stage and an execution stage. The method comprises the following steps of acquiring a predetermined number of to-be-processed instructions from an instruction memory in the instruction acquisition stage; judging an instruction type of each instruction in the predetermined number of instructions, computing a skip target address when judging that the current instruction is a skip instruction, acquiring a skip target instruction from the instruction memory according to the skip target address and decoding a delay slot instruction after the current instruction and the skip target instruction in the decoding stage; and executing the decoded delay slot instruction and the decoded skip target instruction in sequence in the execution stage. According to the method and the device for realizing the flow line of the processing instructions and the processor, the efficiency of the flow line can be improved; and meanwhile, the hardware cost and the possible delay cost and power consumption cost can be saved.

Owner:LOONGSON TECH CORP

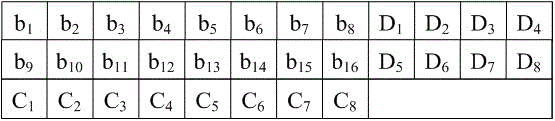

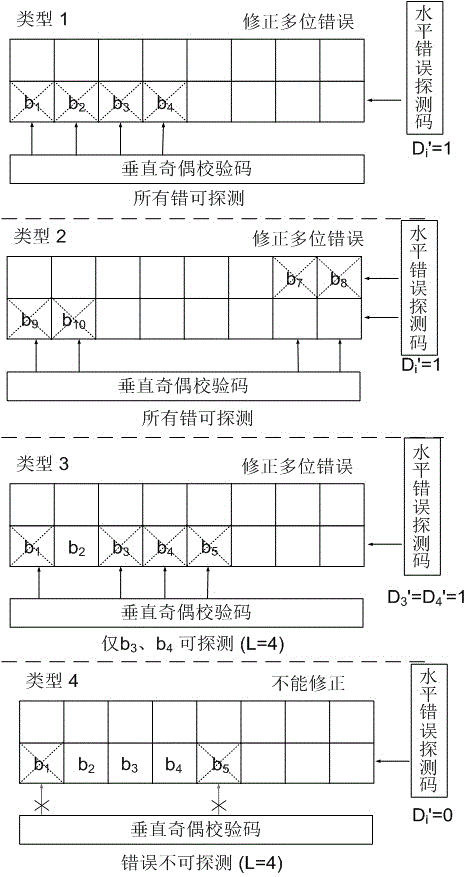

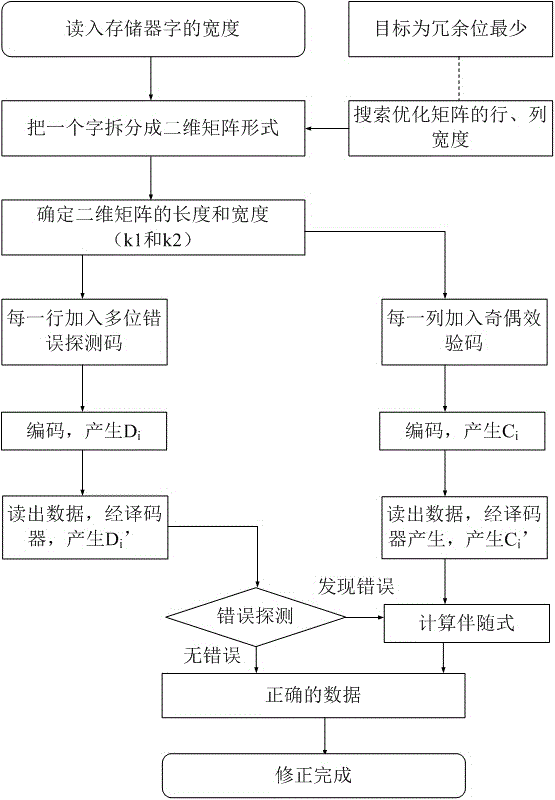

Novel two-dimensional coding reinforcing method and circuit arrangement for aerospace memory

InactiveCN104409103AReduce hardware overheadSuppress multiple bit flipsStatic storageParity check codeLow complexity

A two-dimensional coding reinforcing method for aerospace memories. Low-complexity multiple bit error detection and correction method is introduced into the reinforcing method, and the multiple bit error detection and correction method can carry out detection and correction on arbitrary multiple bit error. The reinforcing method comprises the following steps: 1, reading the word width of the memory, and logically converting a word with width N into a (k1, k2) two-dimensional matrix form; 2, determining the line number k1 and the column number k2 of the two-dimensional matrix; 3, adding a horizontal error detection code in each line, adding a vertical parity check code in each column; 4, when a word in the memory occurs multiple bit upsets, indicating the row and column the error respectively by the horizontal error detection code and the vertical parity check code; and when the interval of discontinuous multiple bit errors is less than L, giving a wrong signal by the horizontal error detection code; and 5, according to the amendment information bit, amending the information bits, and completing the amendment.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

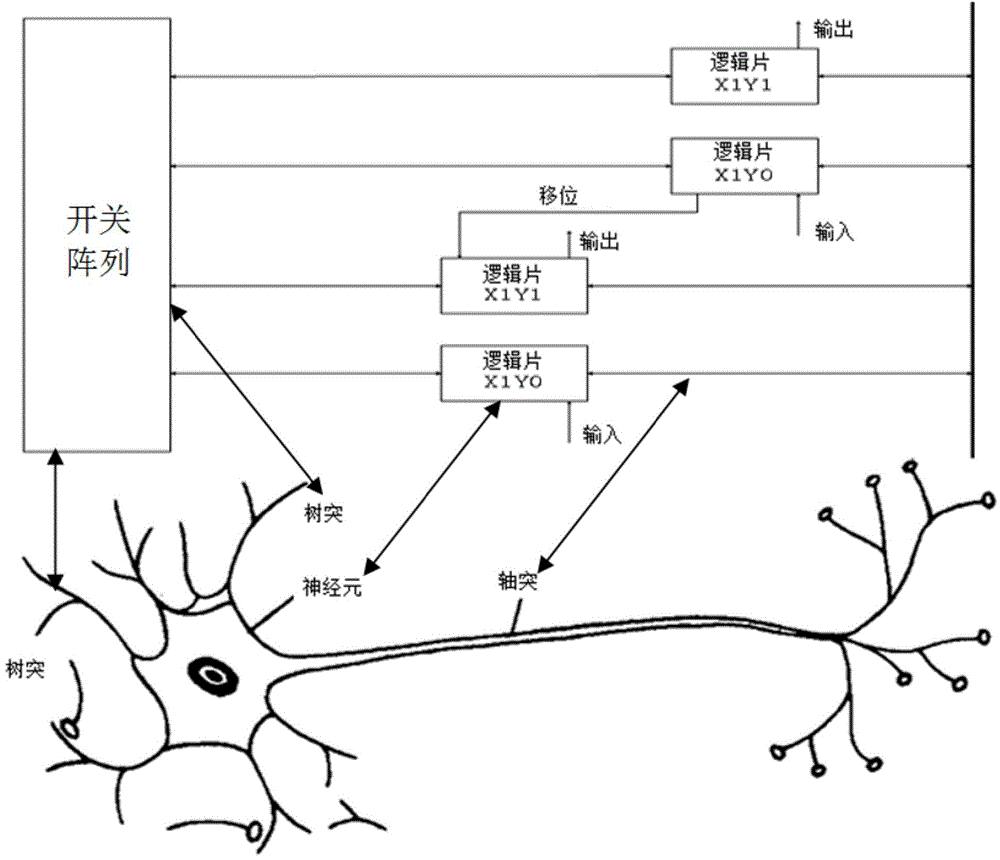

Method for achieving neural network calculation based on field-programmable gate array

ActiveCN104915195AReduce hardware overheadReduce the learning cycleBiological neural network modelsSpecific program execution arrangementsRound complexityMachine learning

The invention relates to a method for achieving neural network calculation based on a field-programmable gate array (FPGA) and belongs to the technical field of neural network calculation. Firstly, the mapping relation between basic logic units in the FPGA and all components of a neural network is established, functions of the basic logic units of the FPGA are described through a programming language, models of the basic logic units in the FPGA are established, the neural network is stimulated through the mapping relation between the FPGA and a neural network structure, and a self-learning process of the network is completed through reconfiguration of the interconnection relation between the basic logic units of the FPGA and operational capacity of the network. Compared with a method pursuing a neural network structure consistent with a true neural network structure in the current stage, hardware expenditure can be greatly reduced while the neural network of the same complexity is stimulated. Secondarily, the learning process of the neural network is completed on an FPGA software model, the learning period is greatly shortened, and time cost is saved.

Owner:TSINGHUA UNIV

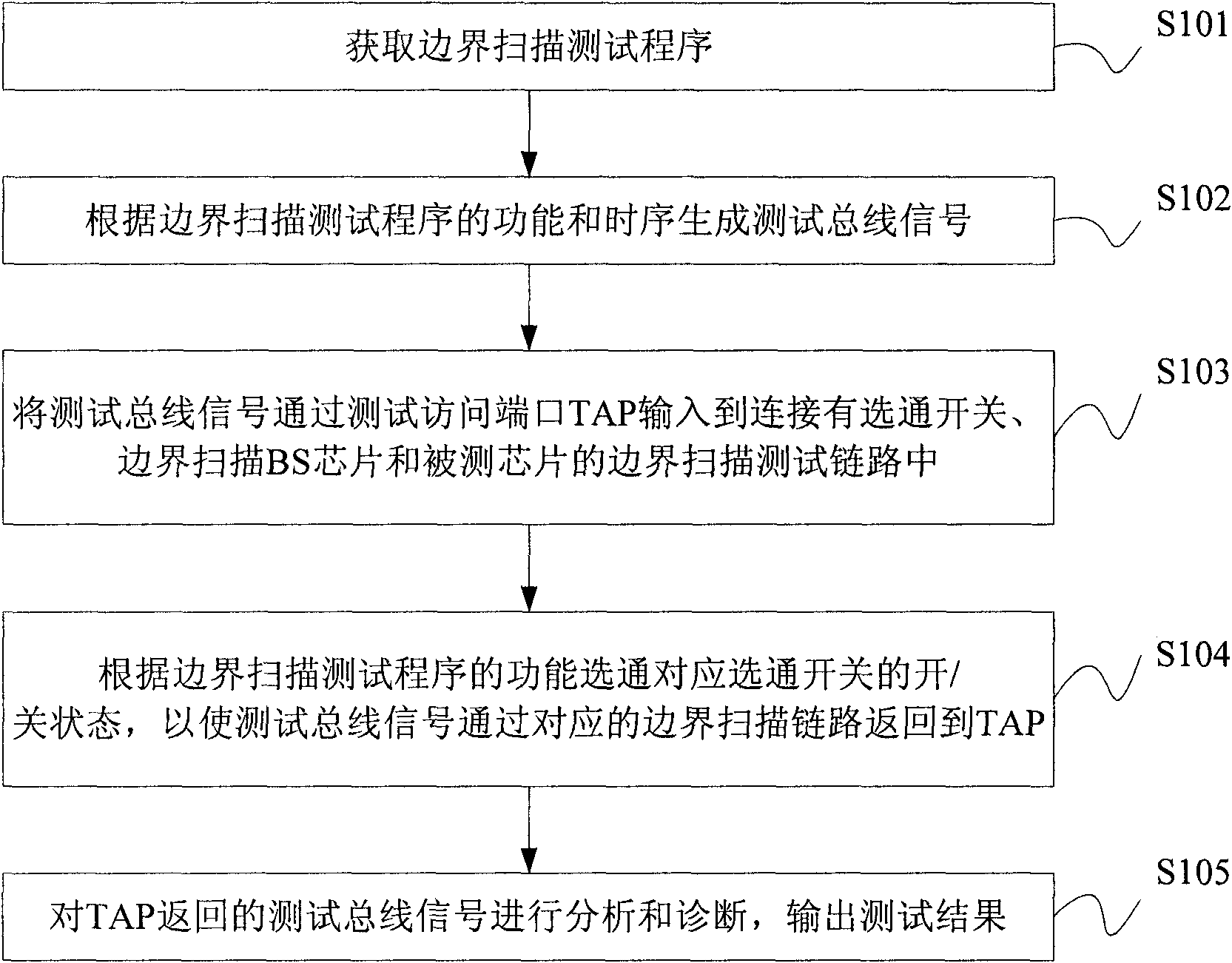

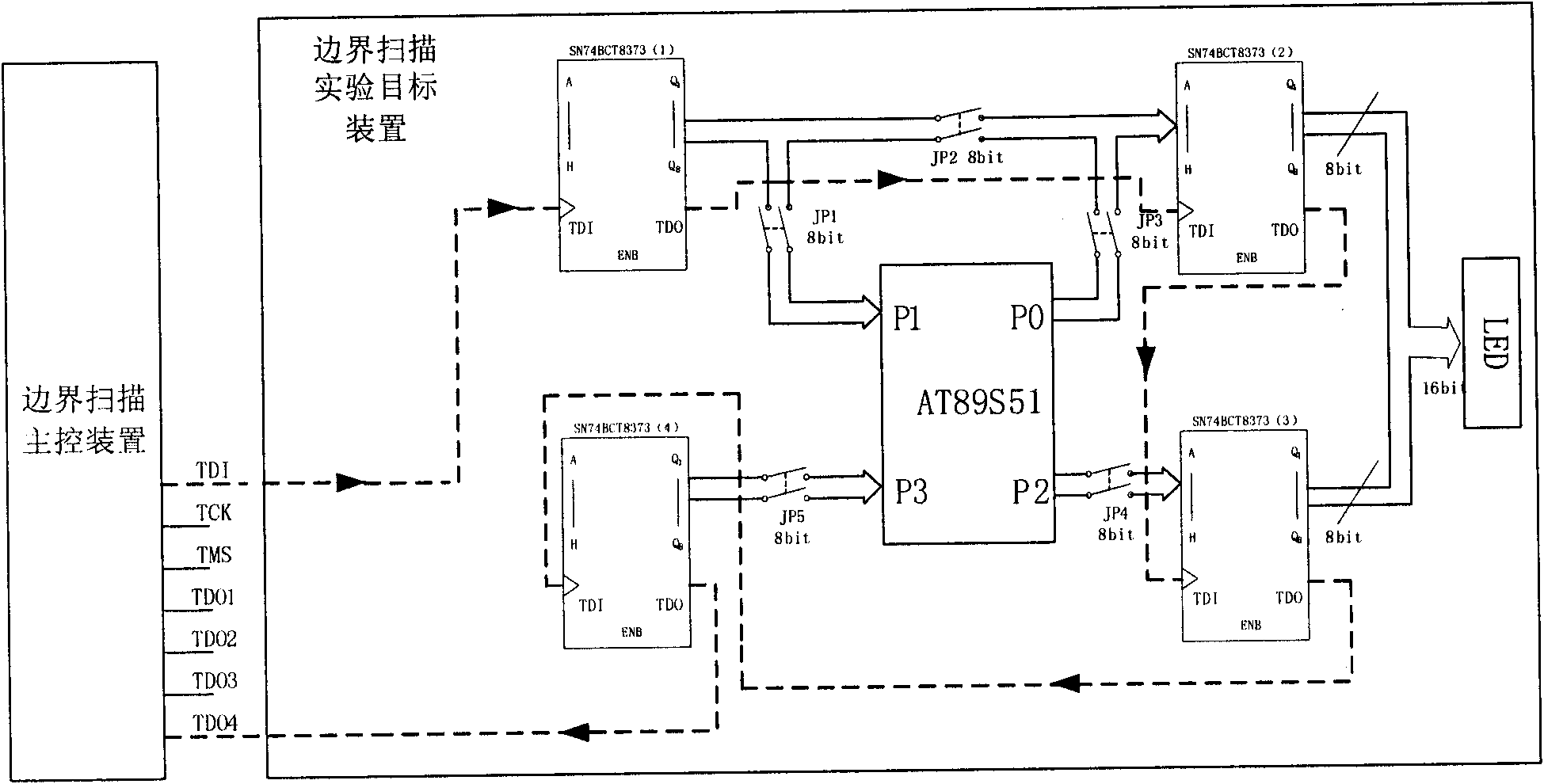

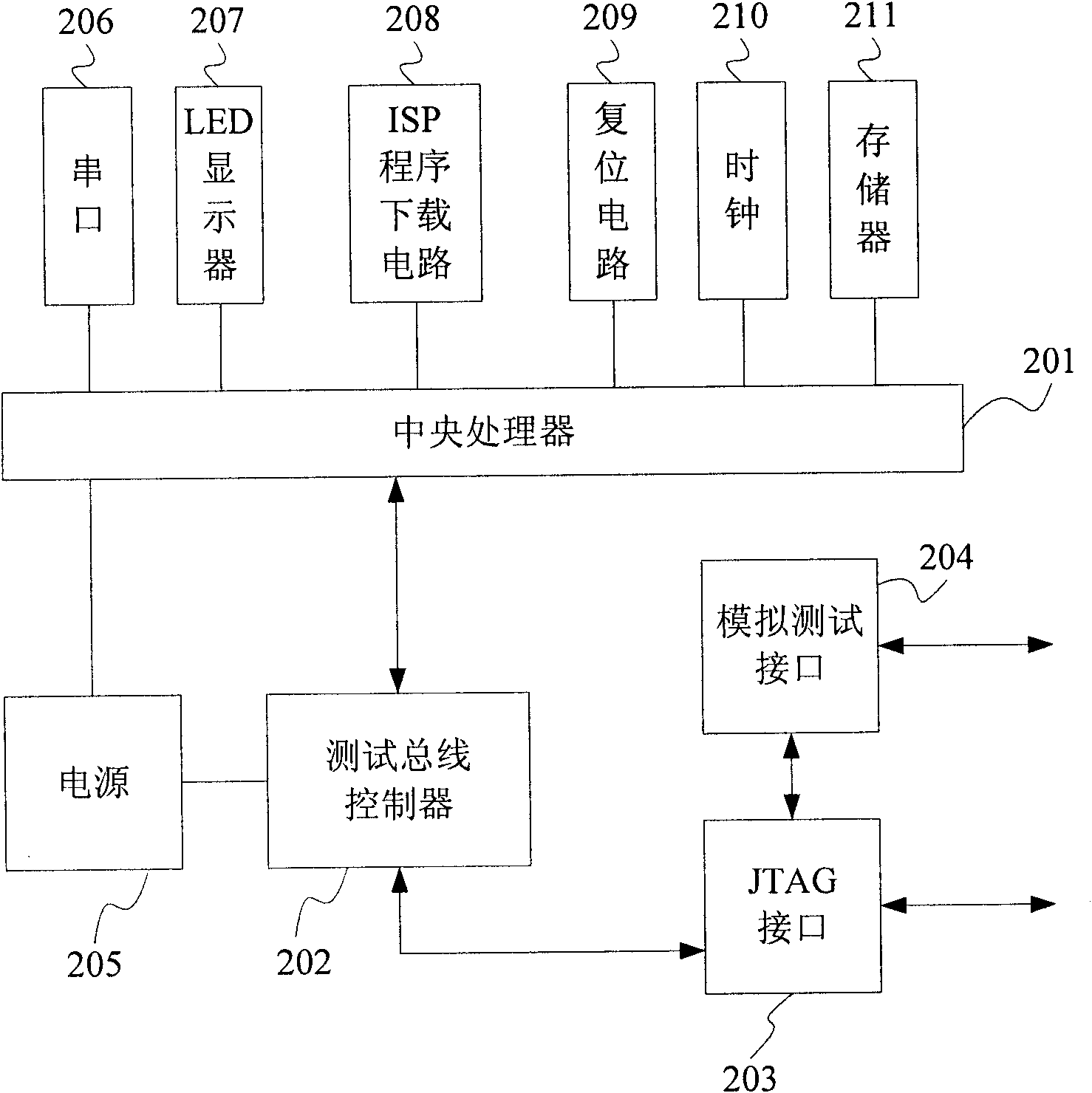

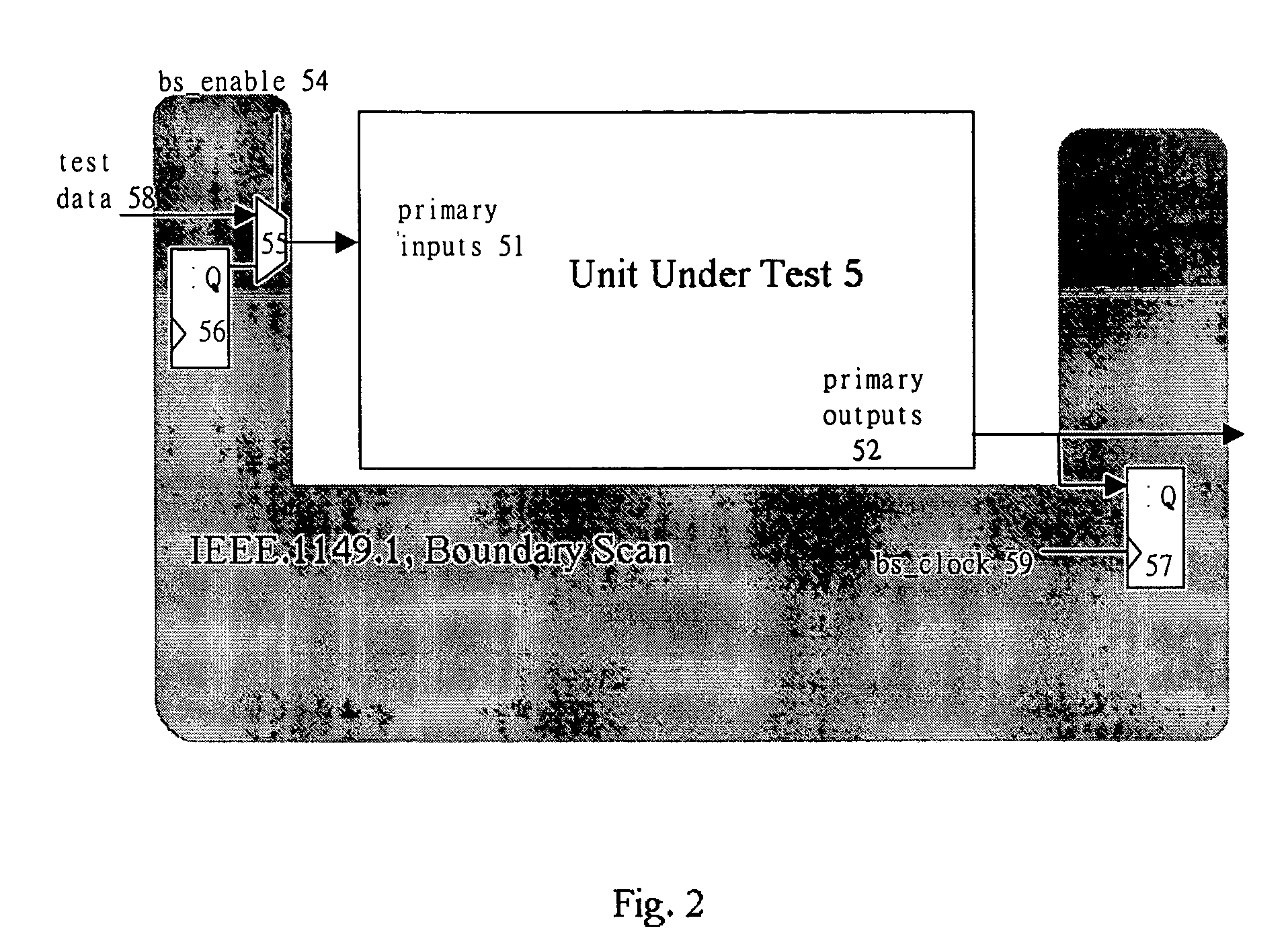

Method, system and target device for boundary scan experiment

InactiveCN101819250AReduce hardware overheadReduce overheadElectronic circuit testingEducational modelsBoundary scan testingEngineering

The invention provides a method, a system and a target device for boundary scan experiment. The test target device comprises a TAP input end, a BS chip slot, a slot for a chip to be tested an a TAP output end, wherein the TAP input end is used for receiving externally input TAP test bus signals; the BS chip slot is connected with the TAP input end and is used for bearing a BS chip; the slot for the chip to be tested is connected with the BS chip slot through a jumper switch and is used for bearing the chip to be tested; and the TAP output end is connected with the BS chip slot and is used forfeeding back test signals to an external TAP. The invention provides an experiment platform for learning and practicing to learners of the boundary scan technique, and can provide experiment of multiple test patterns based on all the boundary scan test standards.

Owner:徐磊 +2

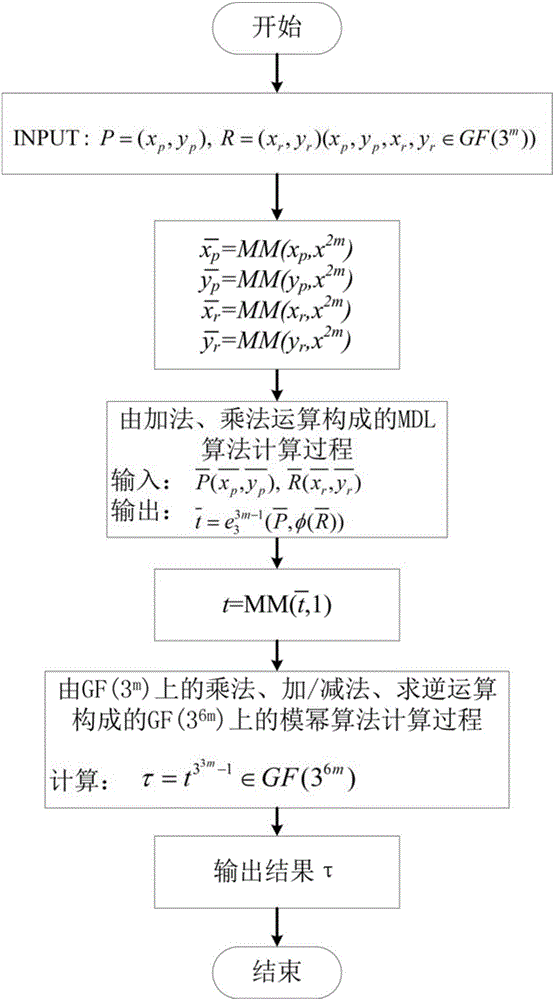

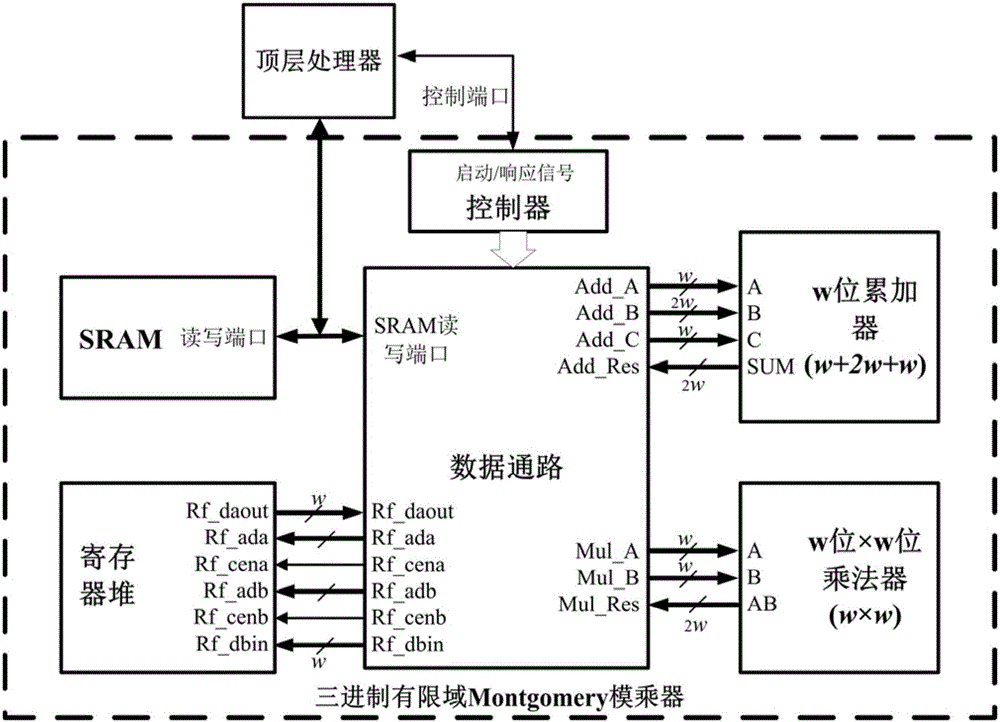

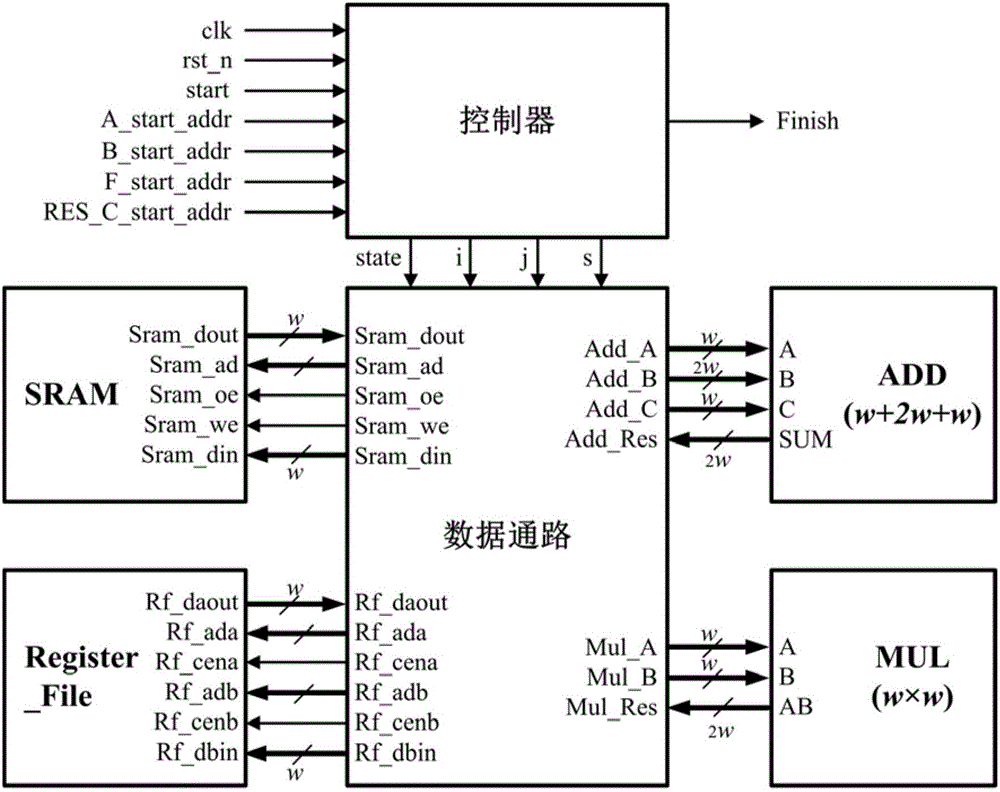

Montgomery modular multiplication based Tate pairing algorithm and hardware structure therefor

ActiveCN105068784AReduce hardware overheadReduce power overheadDigital data processing detailsHardware structureStatic random-access memory

The invention belongs to the technical field of realization of cryptographic algorithms of embedded systems and particularly relates to a ternary finite field Montgomery modular multiplication based Tate pairing algorithm and a hardware structure for realizing the algorithm. The algorithm comprises: converting X coordinates and Y coordinates of two input points P and R on an elliptic curve to a Montgomery domain from a defined GF(3m) domain; according to an MDL (minimum description length) algorithm procedure taking multiplication, addition / subtraction and cubic operation on GF(3m) as basic operations, performing operation in the Montgomery domain; and converting a calculation result to the GF(3m) domain from the Montgomery domain, and performing 33m-1-power modular exponentiation on the calculation result. The hardware structure comprises a top-level processor, a controller, a ternary accumulator, a ternary multiplier, a register file and an SRAM (static random access memory), wherein the controller is used for controlling input of the ternary accumulator and the ternary multiplier and read-write operation of the SRAM and the register file so as to control data transmission of the whole circuit.

Owner:TSINGHUA UNIV

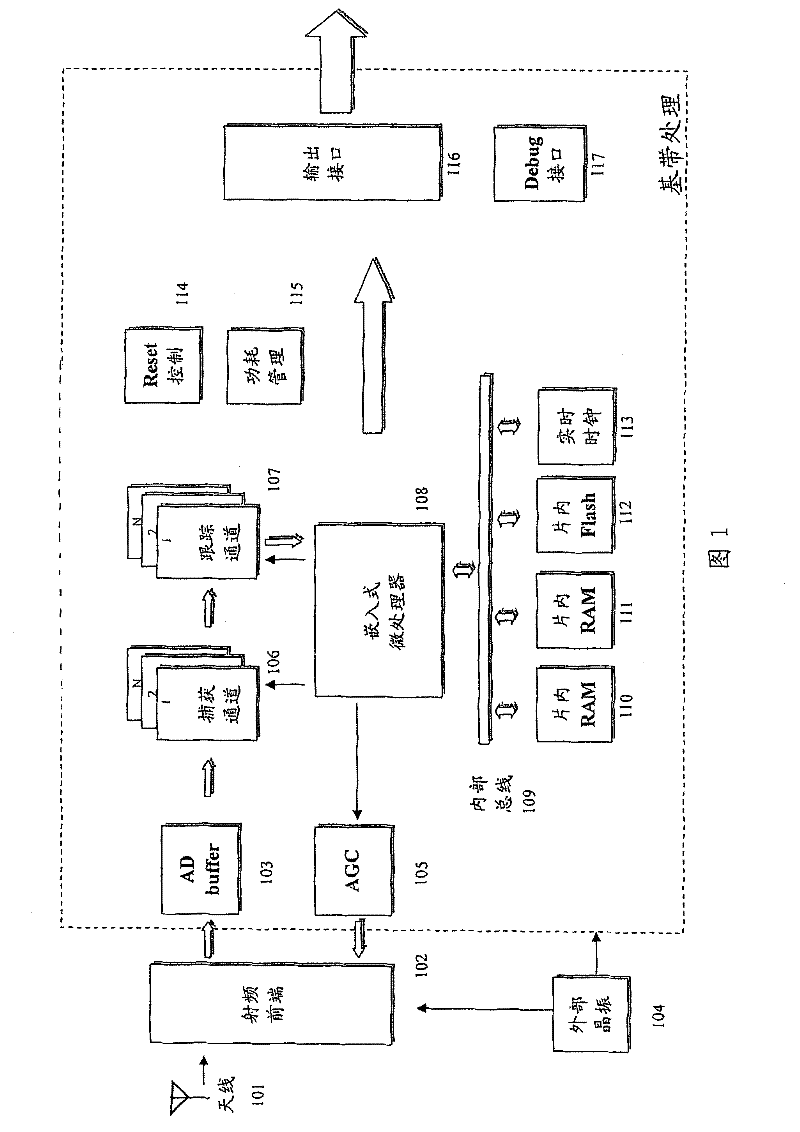

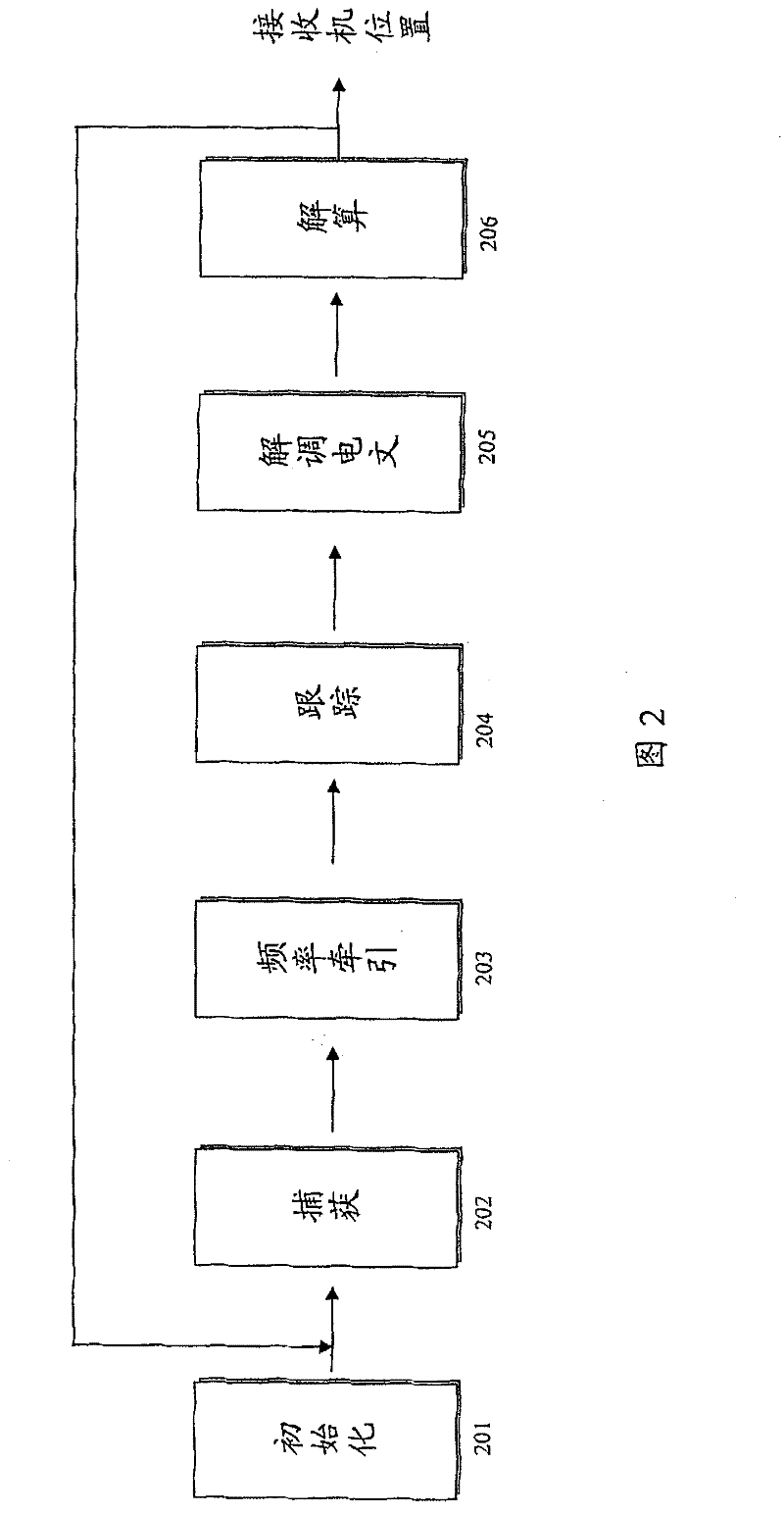

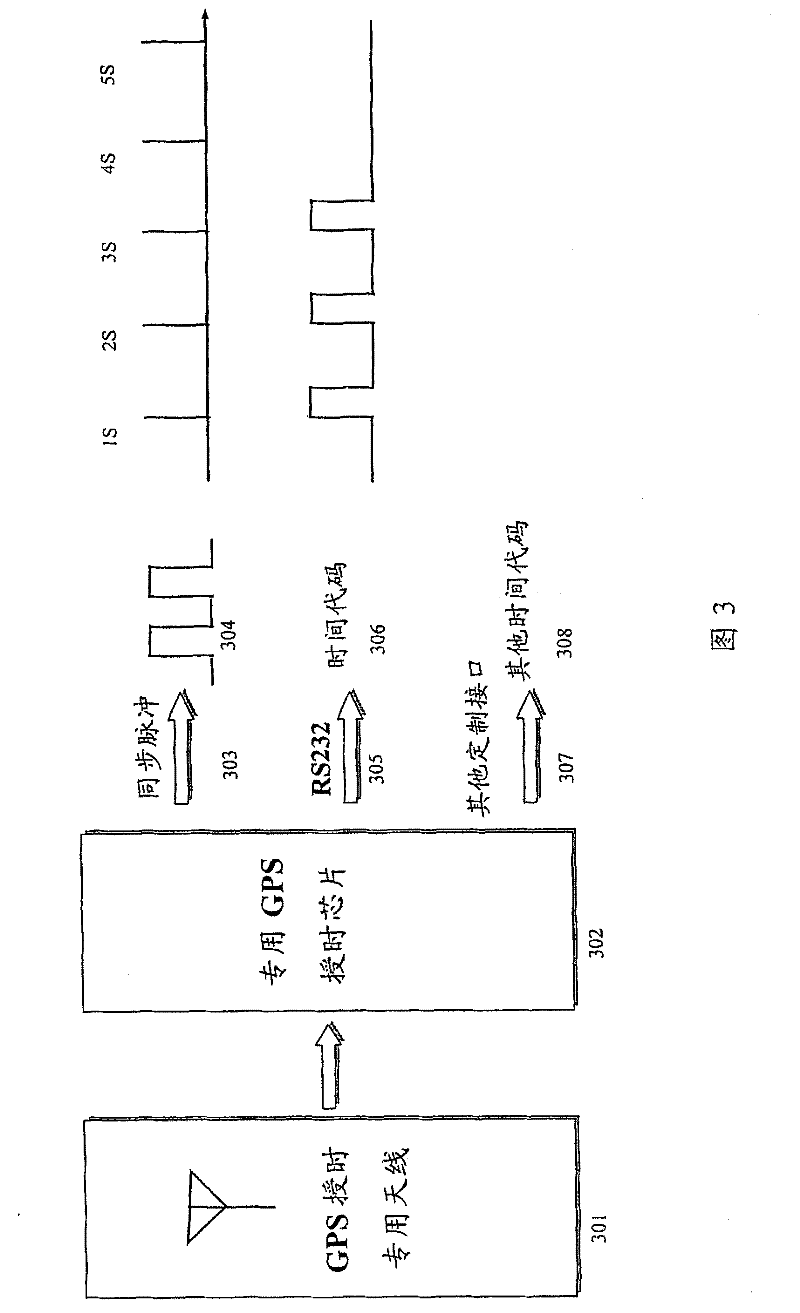

Low-cost timing and synchronization method and device for global positioning system receiver

InactiveCN101430372BReduce overheadSimple designPulse automatic controlPosition fixationSystems designGps receiver

The present invention is a low-cost timing and synchronization method and equipment for a global positioning system receiver, which relates to the field of time granting and synchronization, and in particular to a baseband processing chip based on a global positioning system, such as the global positioning system (GPS) of the United States. Low-cost timing and synchronization domains implemented at the level. The invention improves the timing and synchronization method based on the global positioning system, and realizes it based on the global positioning system baseband processing chip device. The invention performs soft calibration on the crystal oscillator through the coordinated universal time calculated by the global positioning system, realizes time service to external equipment through the combination of time code and synchronous pulse signal, and uses low-cost crystal oscillator to realize high-precision time service. At the same time, the invention does not need to calibrate the crystal oscillator in the form of hardware, greatly simplifies the system design, reduces the cost, and has the advantages of small hardware overhead, strong scalability, and high reliability.

Owner:北京中科引航科技有限公司

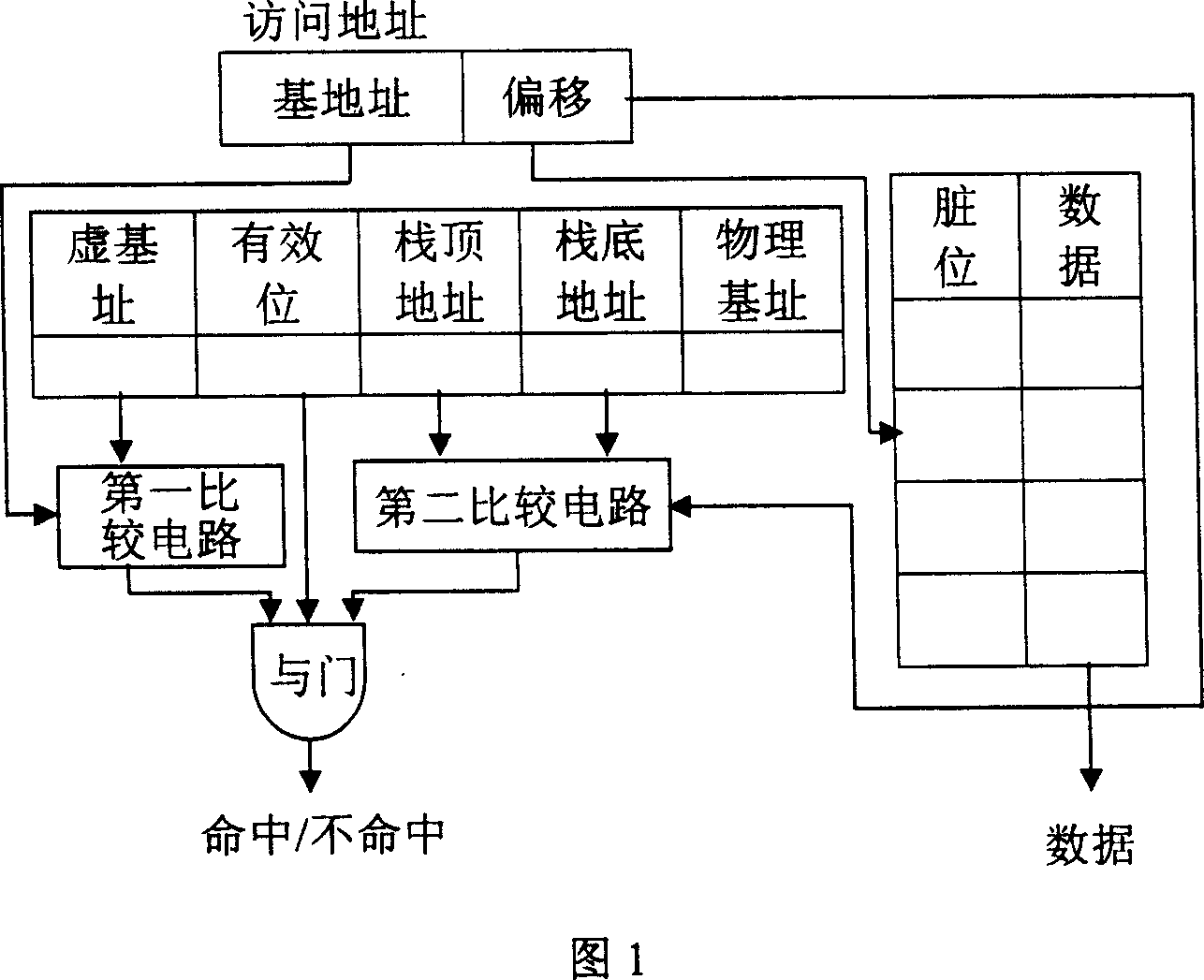

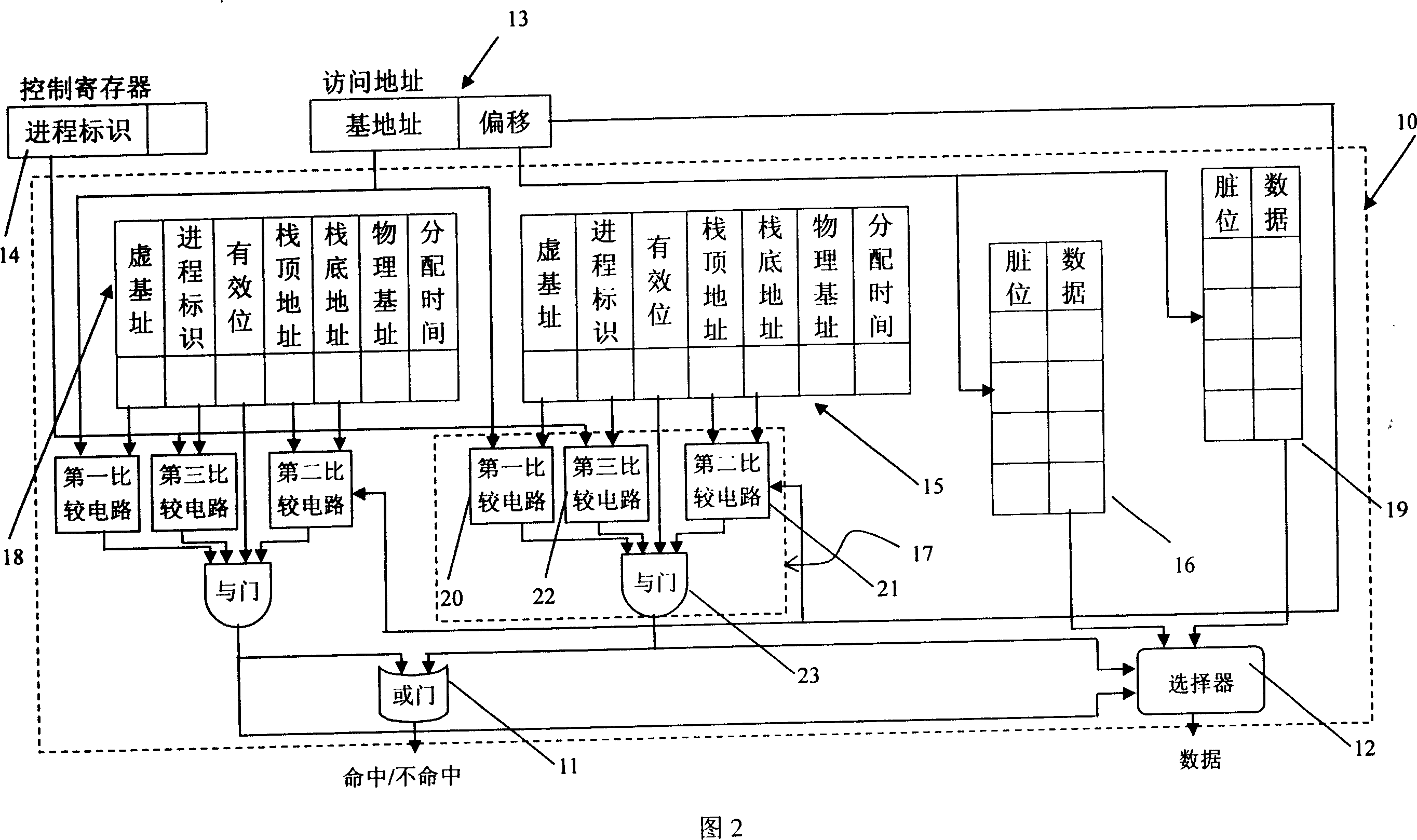

Stack cache memory applied for context switch and buffer storage method

ActiveCN1963789AReduce hardware overheadSimple controlMemory adressing/allocation/relocationAddress spaceMemory block

This invention discloses one shed high buffer memory and its buffer memory method suitable for upper and down text switch, which comprises at least two shed high speed buffer blocks; one or gate circuit, one selector, wherein, the shed buffer memory block is composed of label part, data part and control part; the said shed high speed buffer block is composed of at least three comparing circuits and one and gate circuit. The method comprises the following steps: a, initiating shed; b, aligning shed space; c, recycling shed space; comparing label to determine whether to shot of shed high buffer.

Owner:LOONGSON TECH CORP

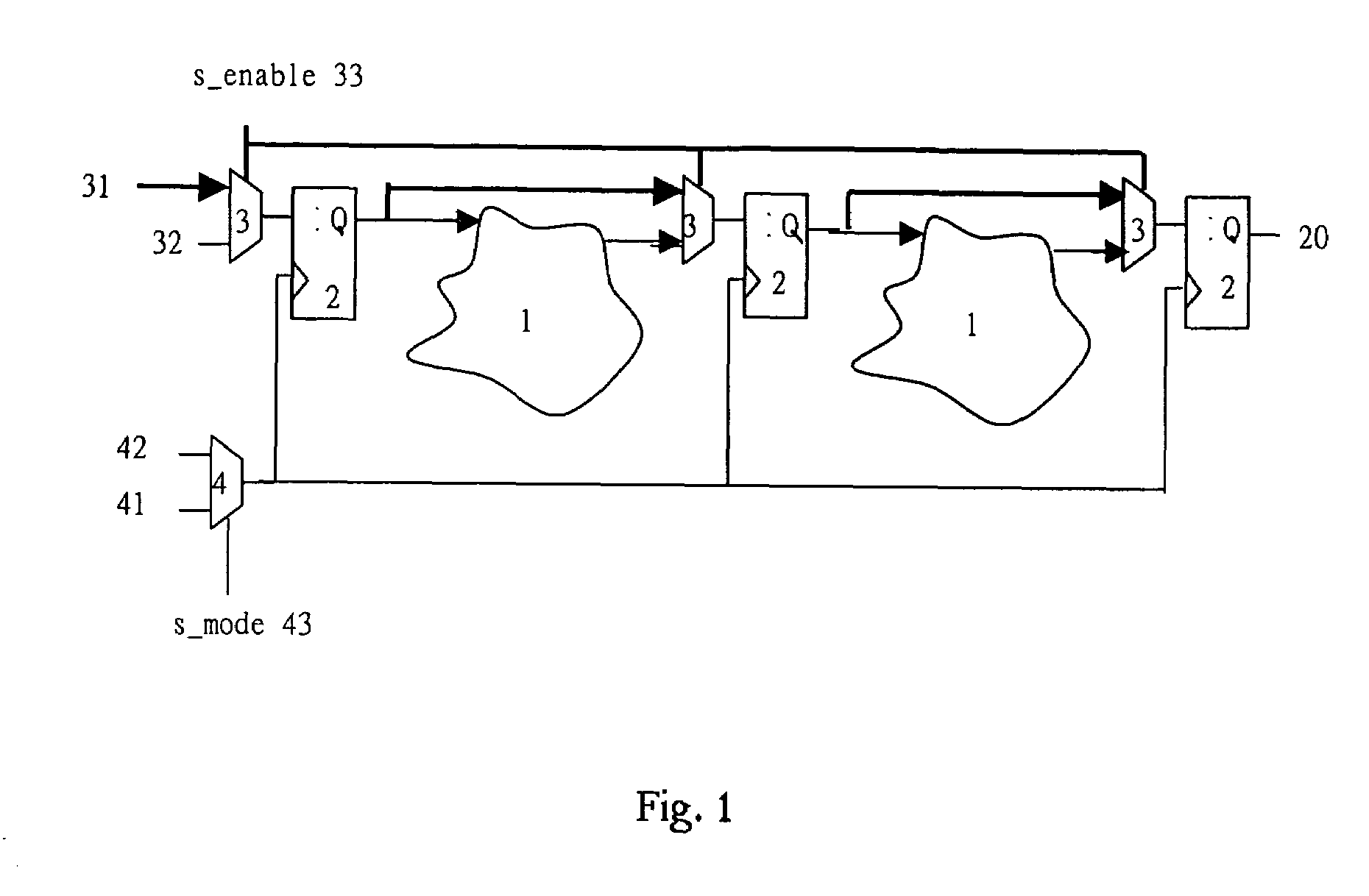

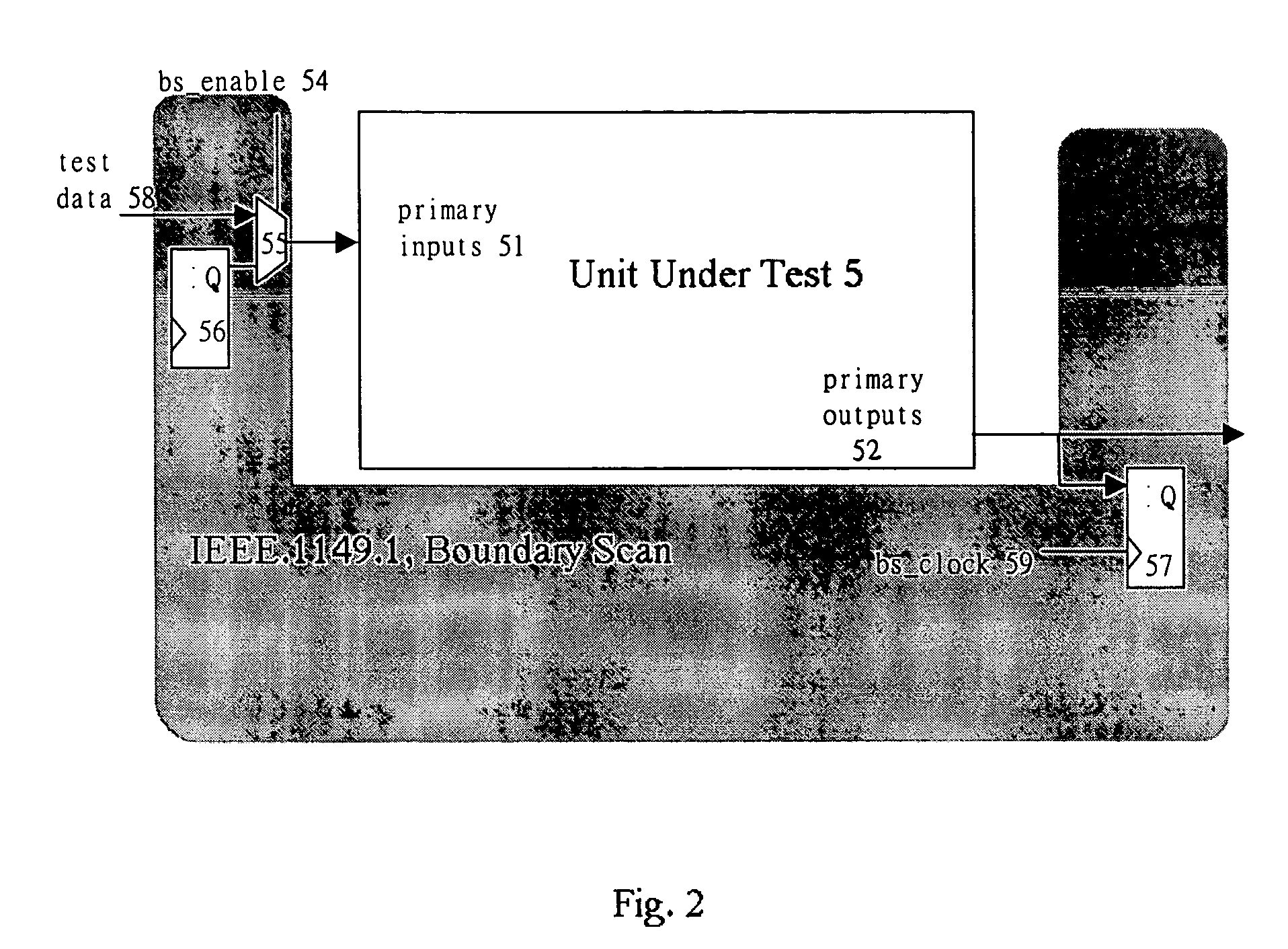

Method of using scan chains and boundary scan for power saving

InactiveUS20060107074A1Reduce hardware overheadSave powerEnergy efficient ICTElectronic circuit testingLow overheadPower saving

The invention provides a method and circuitry to save power in a synchronous logic ASIC with low overhead. The scan chain(s) and boundary scan mechanism of the synchronous logic ASIC are used and modified for shifting out current states of internal memory devices of the synchronous logic ASIC to an external memory and for retaining the power-off blocks' primary output values to the memory devices of the boundary scan circuit, so the proposed gated power method is efficient and low overhead in the synchronous, flop-based, logic circuit design.

Owner:PRINCETON TECHNOLOGY

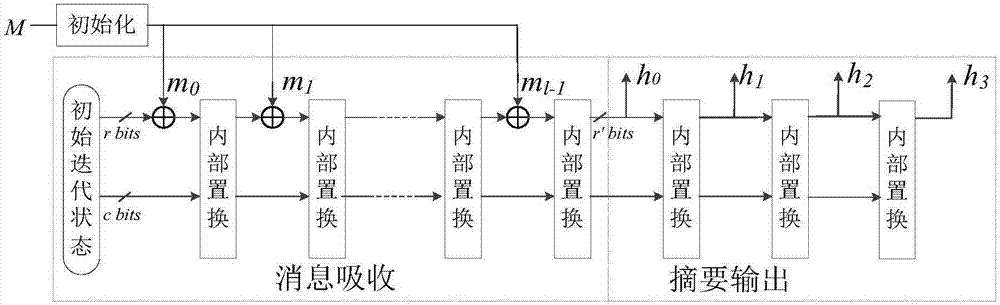

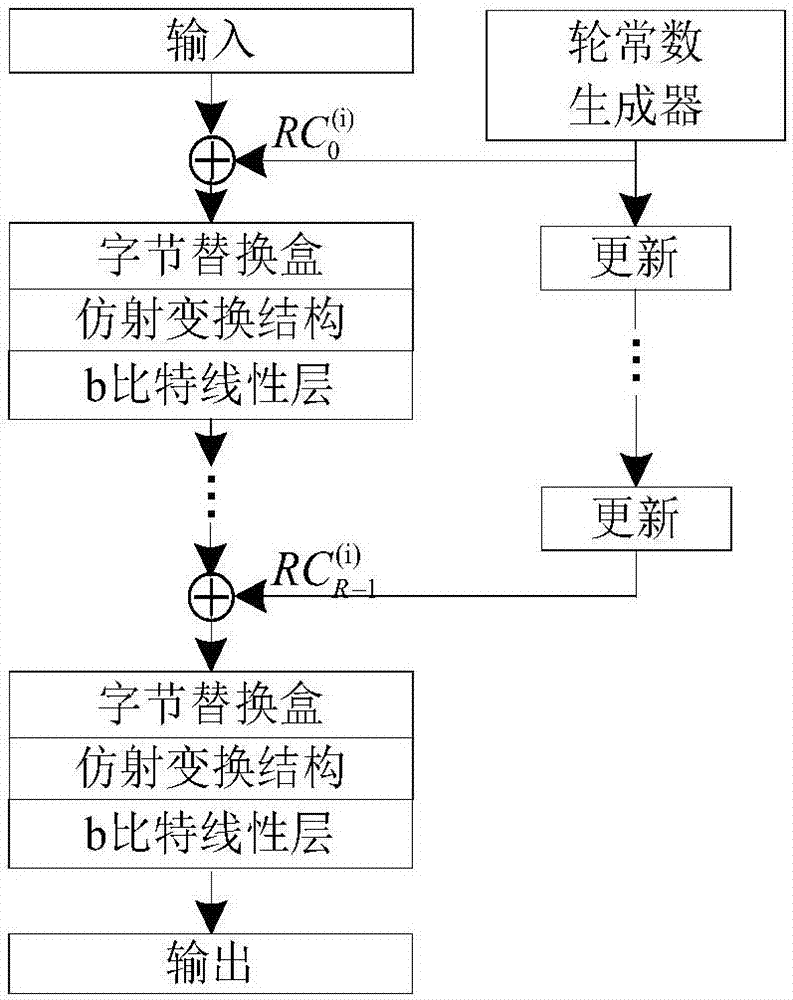

Affine transformation subbytes box-based lightweight hash method

ActiveCN107124264AIncreases resistance to stat saturationIncrease aggressivenessEncryption apparatus with shift registers/memoriesComputer hardwareHash function

The invention relates to an affine transformation subbytes box-based lightweight hash method. The method comprises the following steps of a message initializing stage, a message absorption stage, and an abstract output stage. The method has the advantages that first, the method uses a sponge structure externally, has a computable security boundary, provides three versions of parameter combination so as to meet application demands of different environments, and can provide from anti-collision of 40 bit to first preimage security of 128 bit; second, the affine transformation S box with an internal replacement structure is added with linearity layer confusion, so that the defect that the linearity layer of a similar PRESENT structure is too simple is overcome, the anti-statistical saturation attack ability of the internal replacement structure is enhanced, therefore, the overall security of the lightweight hash method is improved; and third, a non-linearity layer of the internal replacement structure adopts an S box of three bit with good differential characteristic, and the S box of three bit is lower in hardware overhead compared with an S box of four bit of a same type of lightweight hash function family.

Owner:BEIHANG UNIV

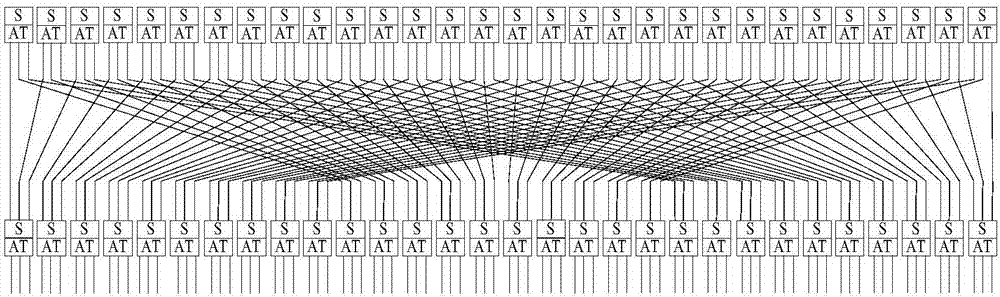

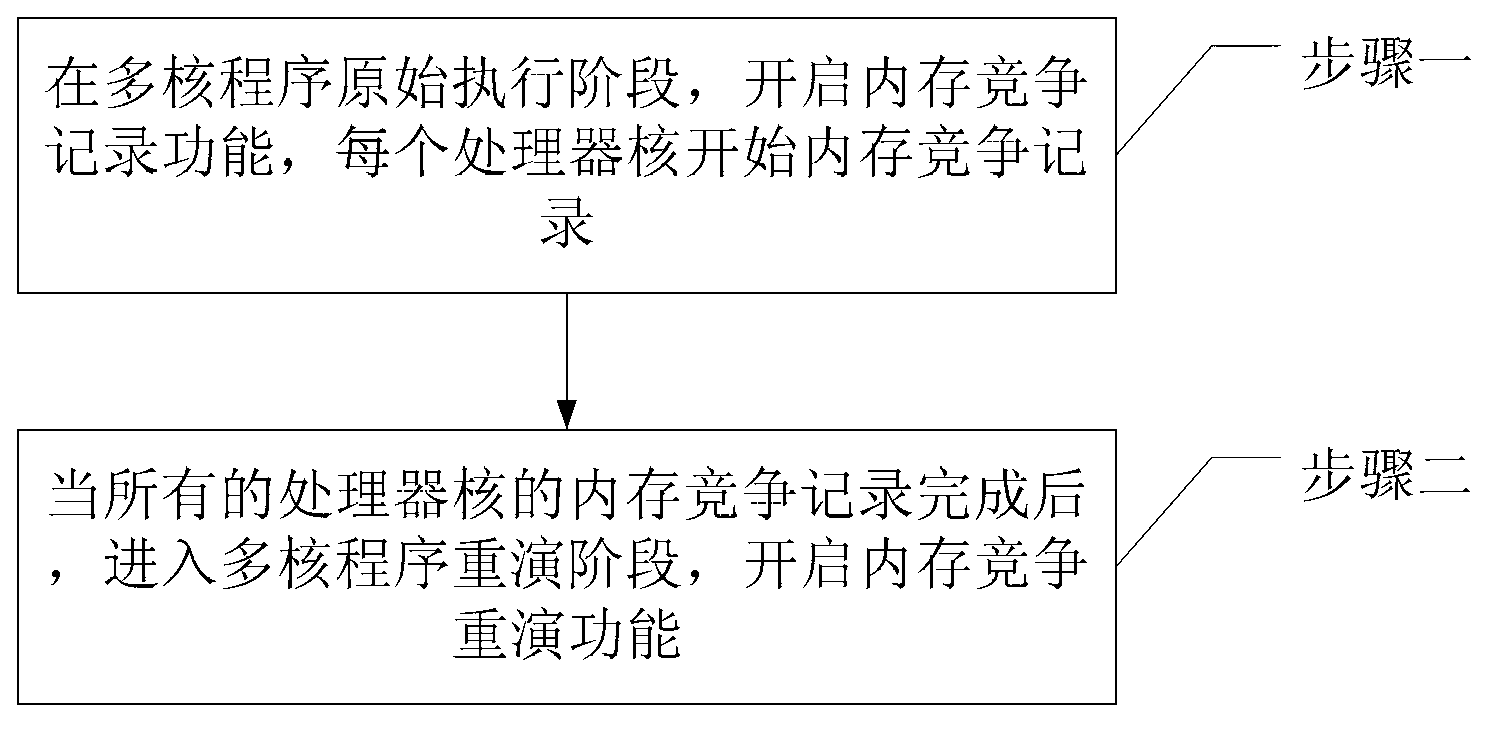

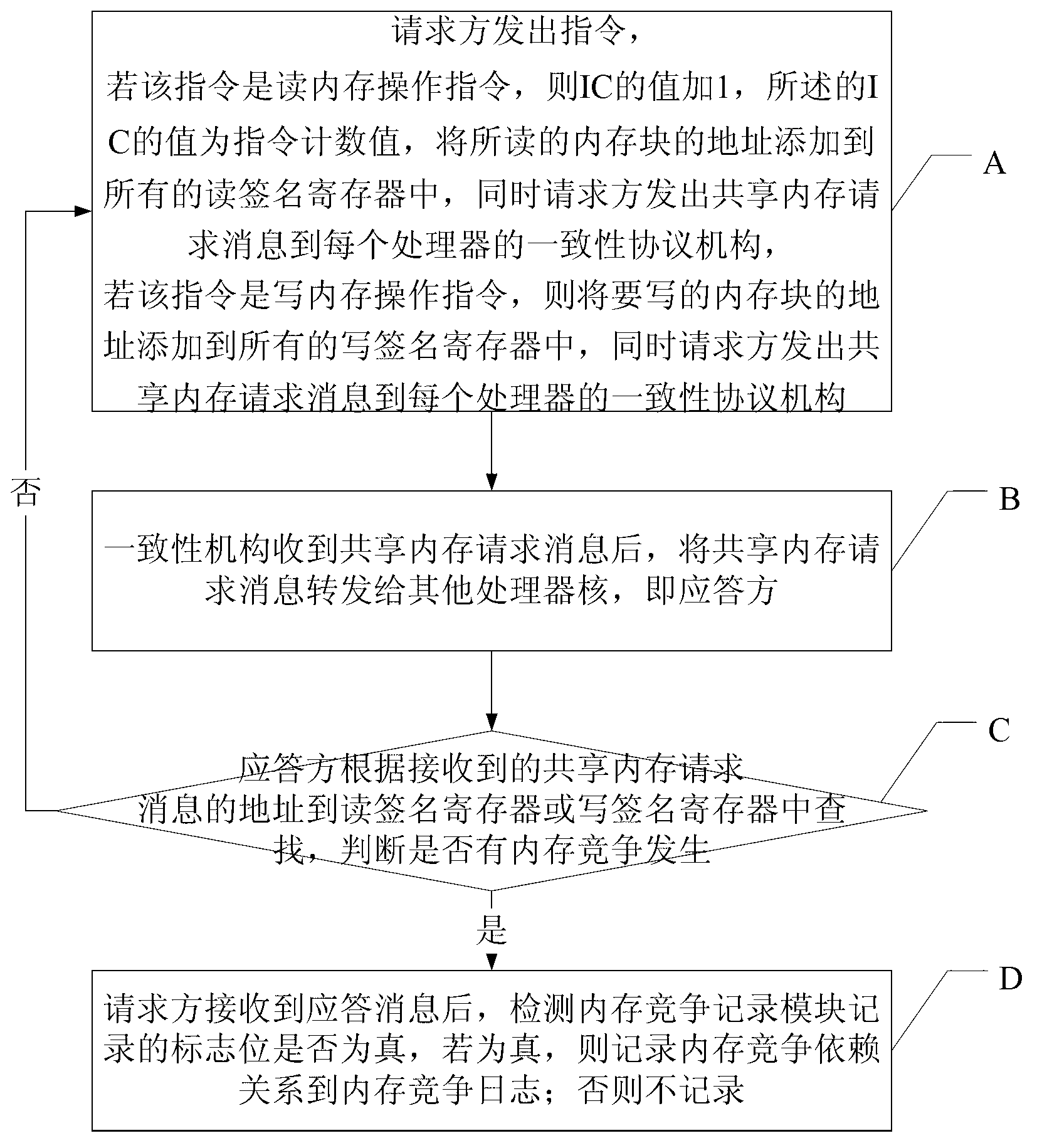

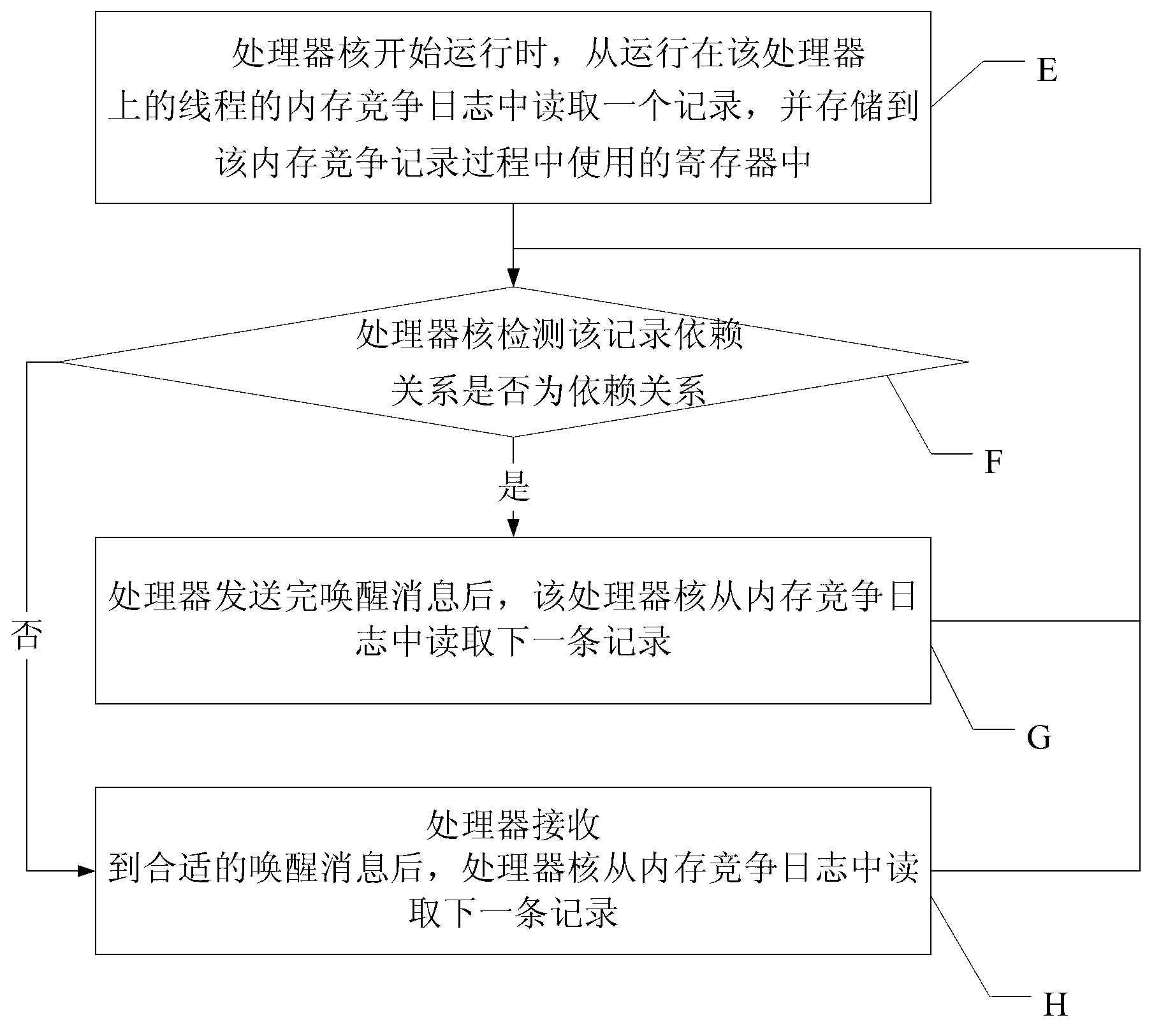

Multi-core program memory competition recording and replaying method realized by signature

InactiveCN103019829AReduce hardware overheadImprove efficiencyResource allocationFault toleranceNeglect

The invention relates to a multi-core program memory competition recording and replaying method realized by a signature, and solves the problem of low replaying efficiency due to neglect of memory competition replaying performance and only emphasis of memory competition recording performance in the conventional multi-core program determinacy replaying method based on hardware. The method comprises the steps as follows: 1, performing a memory competition recording function during the initial execution phase of a multi-core program, and starting memory competition recording operation by each processor core; and 2, after finishing the memory competition recording operations of all the processor cores, performing a memory competition replaying function during the multi-core program replaying period. The method is applied to the fields of multi-core program debugging, intrusion detection, fault tolerance and the like.

Owner:HARBIN INST OF TECH

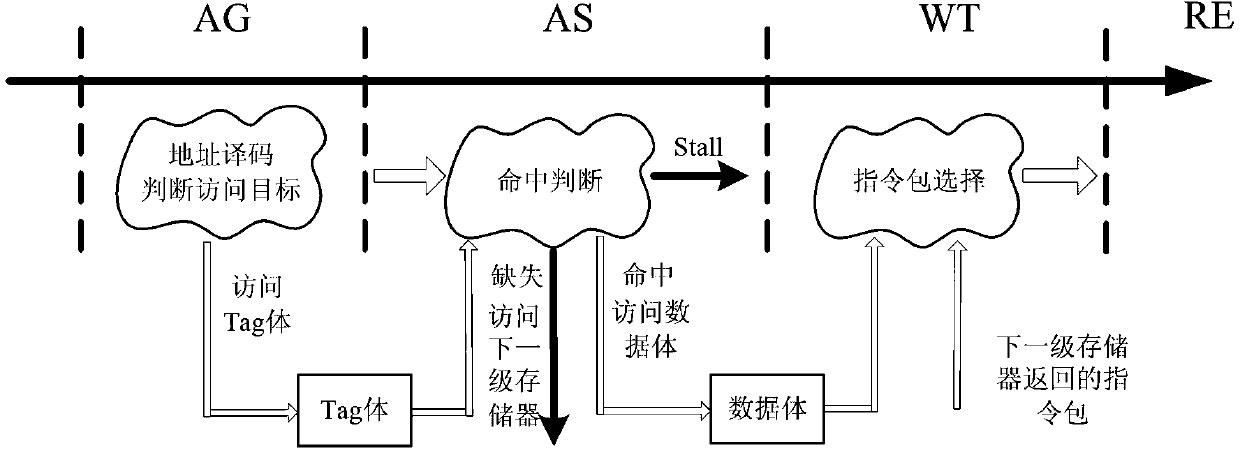

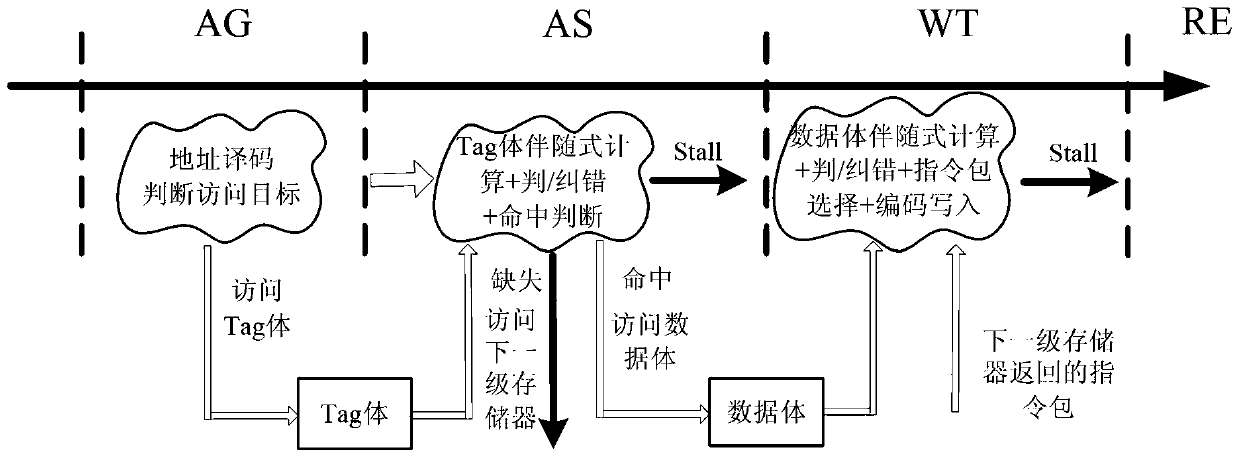

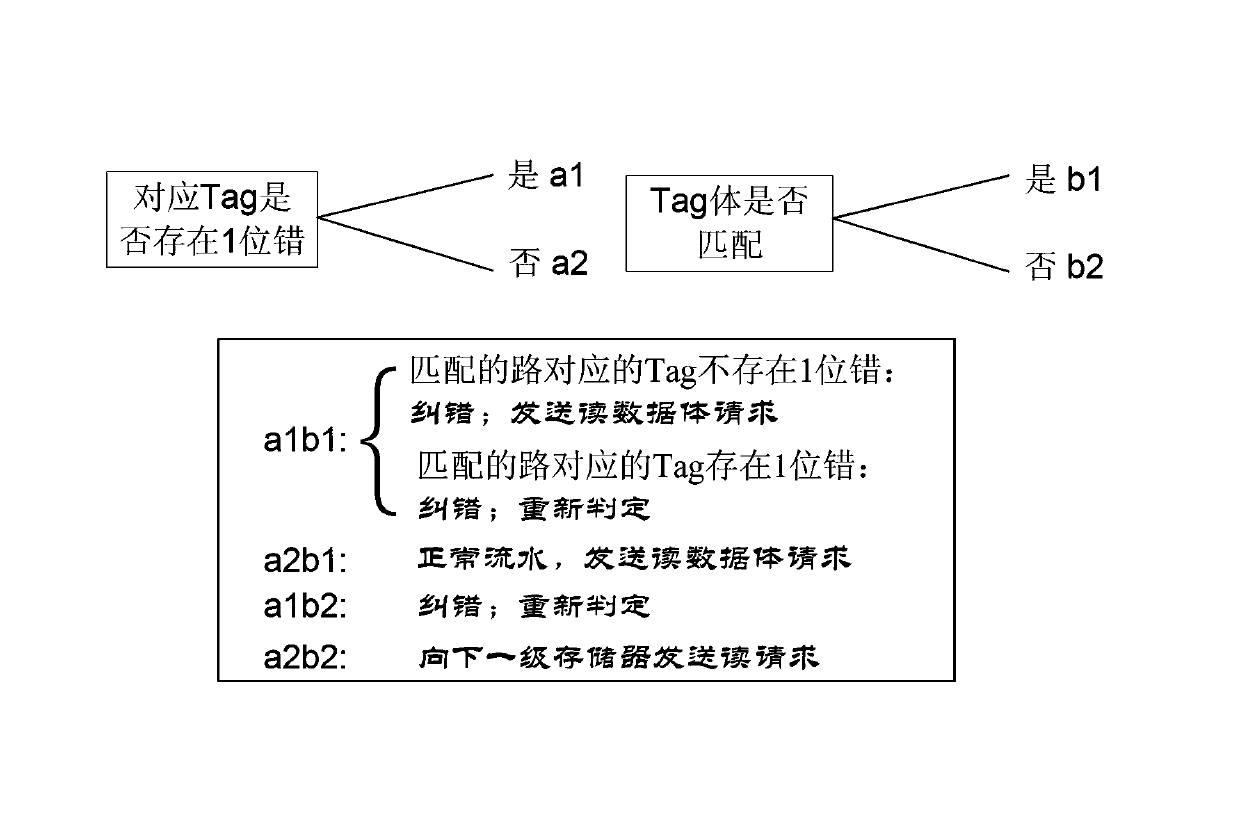

Efficient fetch production line supporting synchronous EDAC inspection

ActiveCN103279329ALower latencyEfficientConcurrent instruction executionRedundant data error correctionProduction lineError correcting

The invention discloses an efficient fetch production line supporting synchronous EDAC inspection. The procedure comprises the steps: (1) program address generate (AG), (2) program address send (AS), wherein the AS is used for receiving returned data from a Tag body, conducting hitting judgment, conducting Tag body accompany computation, judging whether errors occur in the Tag body and correcting the first stage errors, the production line is stopped when errors occur in the Tag body information which is received by the AS, the AS corrects the errors, then conducts the hitting judgment and judges whether to read a next stage memorizer or not, (3) program access ready wait (WT), wherein the WT is used for waiting for an instruction packet returned from a data body or the next memorizer, making judgment, conducting data body accompany computation, judging whether errors occur in the data body, correcting the first stage error and writing in the EDAC codes of the Tag body and the data body, and (4) program fetch packet receive (RE). The efficient fetch production line supporting synchronous EDAC inspection has the advantages of being efficient, strong in error correcting capability, little in hardware cost, transparent to a programmer and the like.

Owner:NAT UNIV OF DEFENSE TECH

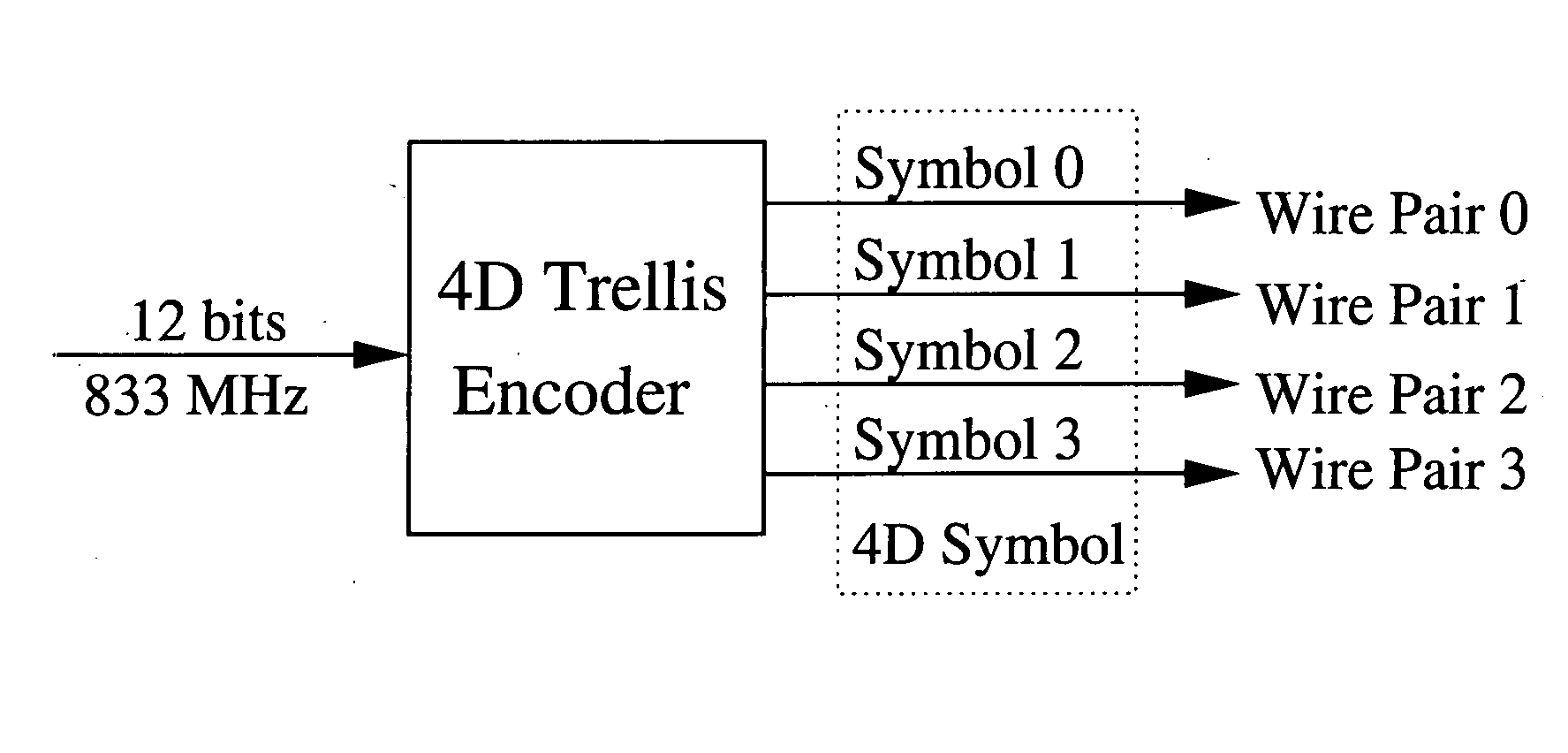

Interleaved trellis coded modulation and decoding

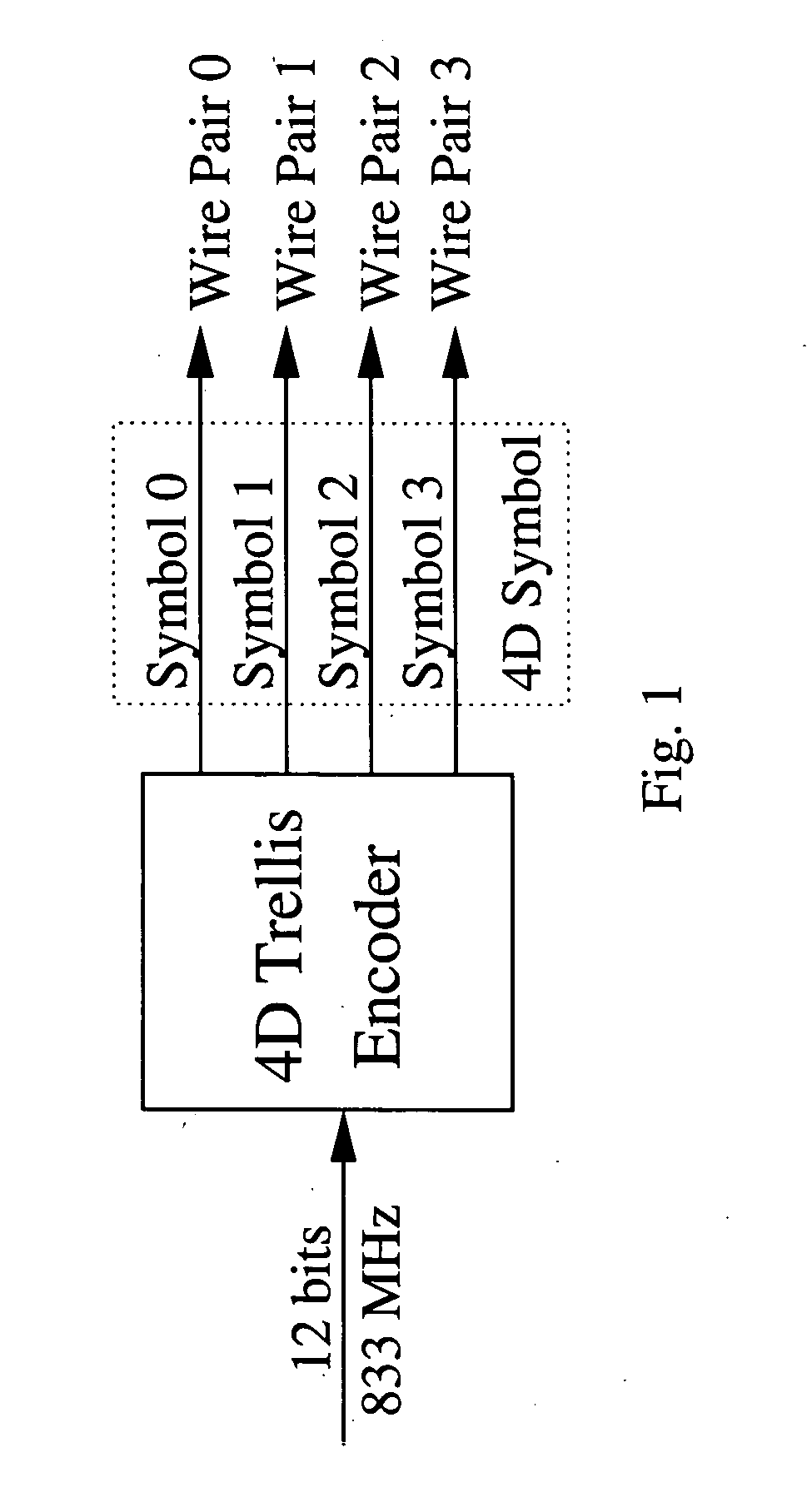

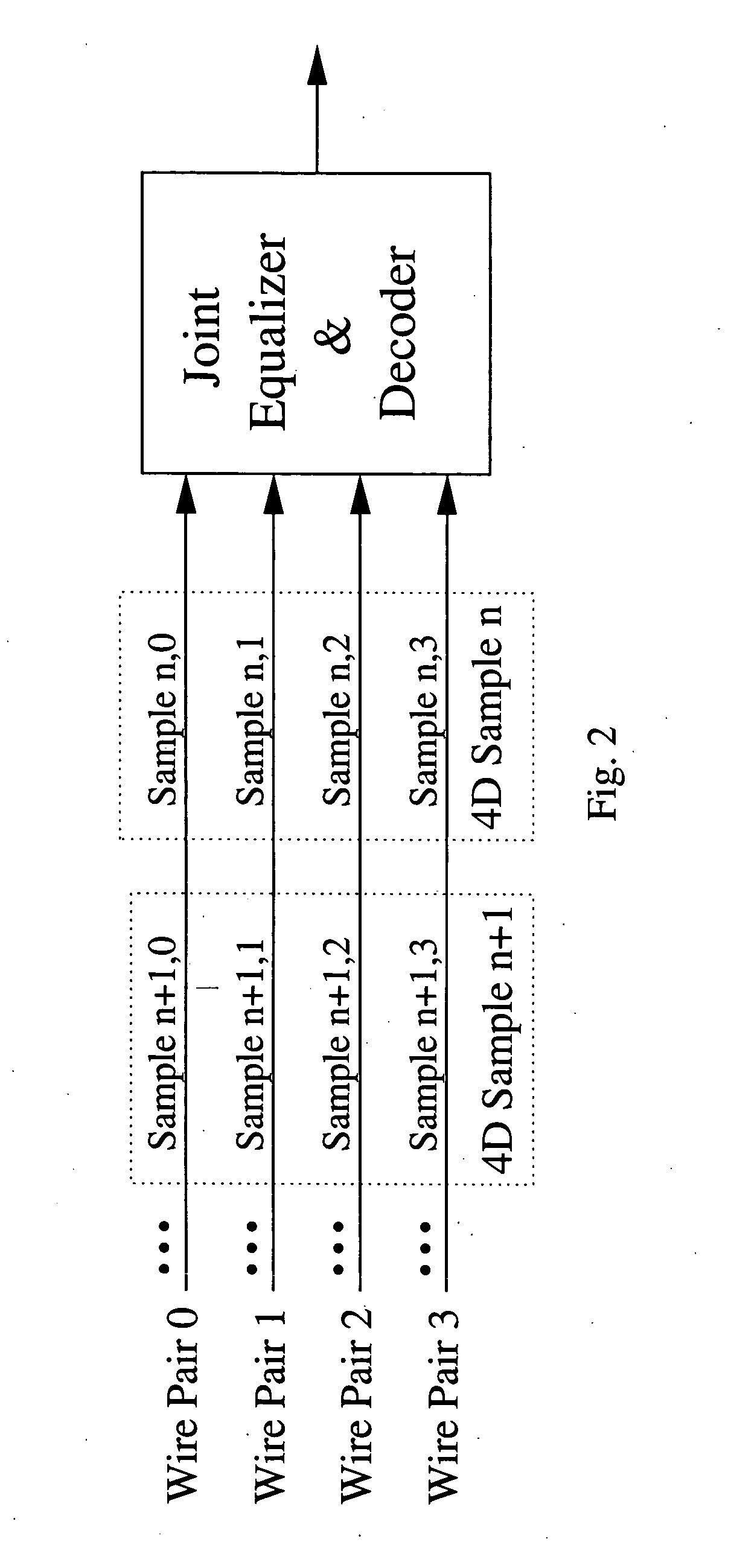

InactiveUS20050018786A1Reduce hardware overheadHigh throughputChannel dividing arrangementsForward error control useParallel channelCoded modulation

Digital communications systems employ trellis coded modulation schemes. A K-dimensional trellis coded modulated symbol is transmitted over M channels in K / M cycles (where M divides K). K / M consecutive data units are transmitted serially in a time multiplexed manner in K / M consecutive cycles over one channel. If M=1, then each symbol is transmitted over one channel in K cycles in a time-multiplexed manner. At the receiver, a symbol is formed by grouping the data received from M channels in K / M cycles and this symbol is then decoded by a joint equalizer and decoder. If the number of parallel channels is N, then N / M trellis coded modulators and N / M decoders can be used in parallel. The advantage of this approach is an increase in speed by factor N / M. The N / M trellis coded modulation and joint equalization and decoding operations can also be implemented by using fewer hardware trellis coded modulators and decoders using folding technique where multiple operations are time-multiplexed to the same hardware modulator or decoder which are operated by higher clock speed.

Owner:PARHI KESHAB K +1