Method for achieving neural network calculation based on field-programmable gate array

A neural network and gate array technology, applied in the field of neural network computing, can solve problems such as waste of resources, and achieve the effects of saving time and cost, reducing learning cycles, and reducing hardware overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] The method that the present invention proposes based on field programmable gate array and realizes neural network calculation comprises the following steps:

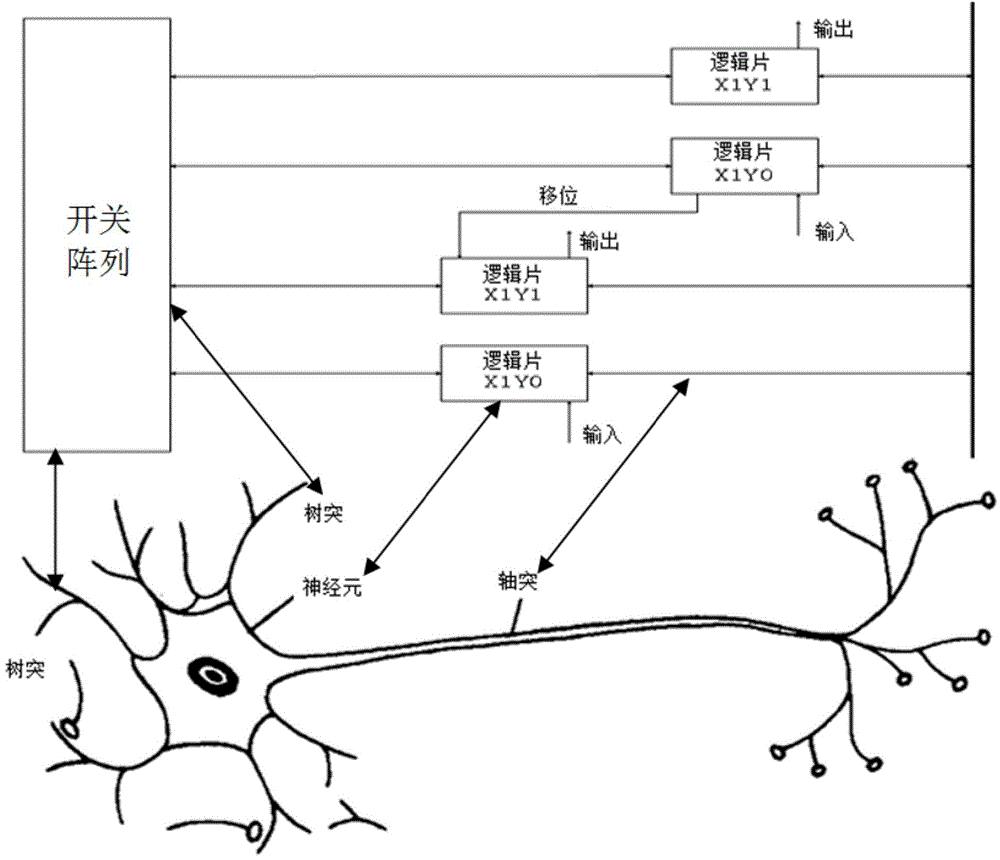

[0015] (1) Establish the mapping relationship between the basic logic unit in the field programmable gate array and each component of the neural network; for example, regard the logic slice unit (Slice) in the field programmable gate array as a neuron in the neural network, and The switch matrix unit (Switch Matrix) in the field programmable gate array is regarded as multiple synapses in the neural network, and the internal wiring of the field programmable gate array is regarded as the axon in the neural network, such as figure 1 shown.

[0016] (2) Use a programming language, such as C language, to describe the functions of each basic logic unit of the field programmable gate array, establish a model of all the basic logic units in the field programmable gate array, and analyze each basic logic unit of the field ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More