Novel two-dimensional coding reinforcing method and circuit arrangement for aerospace memory

A two-dimensional code and memory technology, which is applied in the field of novel space-use memory two-dimensional code reinforcement and circuit devices, can solve the problem of long memory word and column selection wiring, inability to correct errors, area, data access time and power consumption Influence and other issues, to achieve the effect of reducing hardware overhead, improving reliability, and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

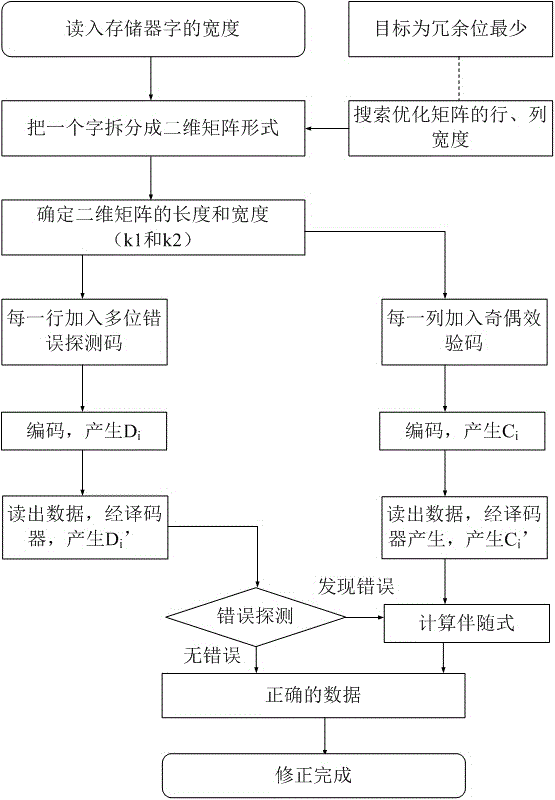

[0031] The present invention will be further described below in conjunction with the accompanying drawings and embodiments.

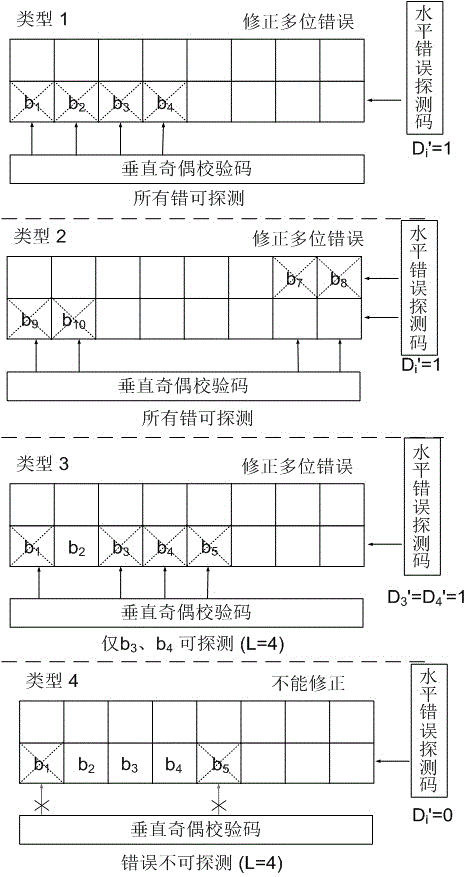

[0032] The present invention proposes a two-dimensional code reinforcement method for aerospace memory, the reinforcement method introduces a low-complexity multi-bit error detection and correction method, and the multi-bit error detection and correction method can correct any multi-bit errors Detect and correct.

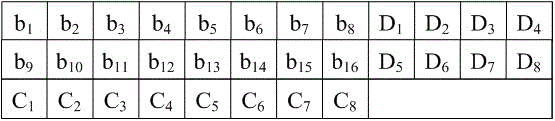

[0033] The multi-bit error detection and correction method is specifically: the maximum number of errors caused by a radiation event is L , then the memory system needs to use the detection capability as L vertical error detection code. for a person with N word of bits, the detection bits of the horizontal error detection code D i It can be obtained by the following detection bit calculation formula:

[0034]

[0035] in, The symbol stands for XOR, i , L and K Take a positive integer, and K The value satisfies , b i Represe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More